MOSFET and its manufacture

A metal oxide half-field and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem that the anisotropic etching method is not easy to control, affects device performance, and deteriorates the surface properties of the channel region and other issues, to achieve the effect that the conditions of the production method are easy to control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

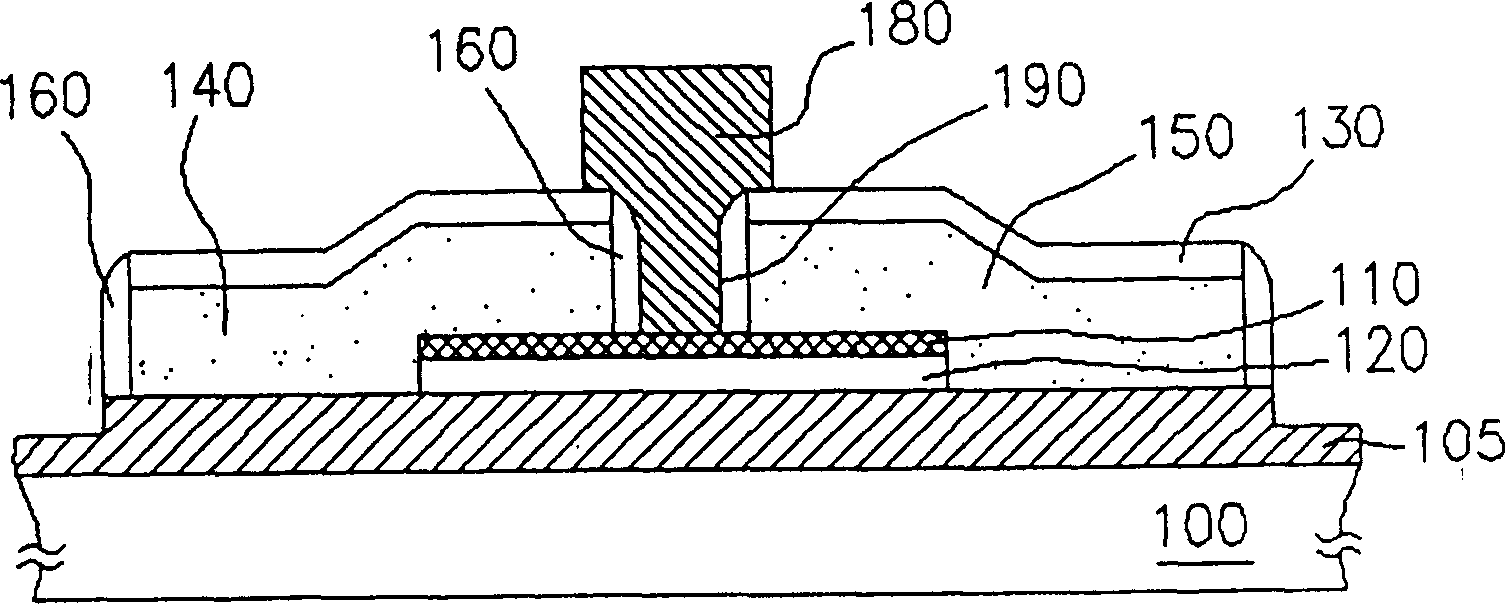

[0031] In order to make the above-mentioned objects, features and advantages of the present invention more obvious and easy to understand, a preferred embodiment is given below, and described in detail with the accompanying drawings as follows:

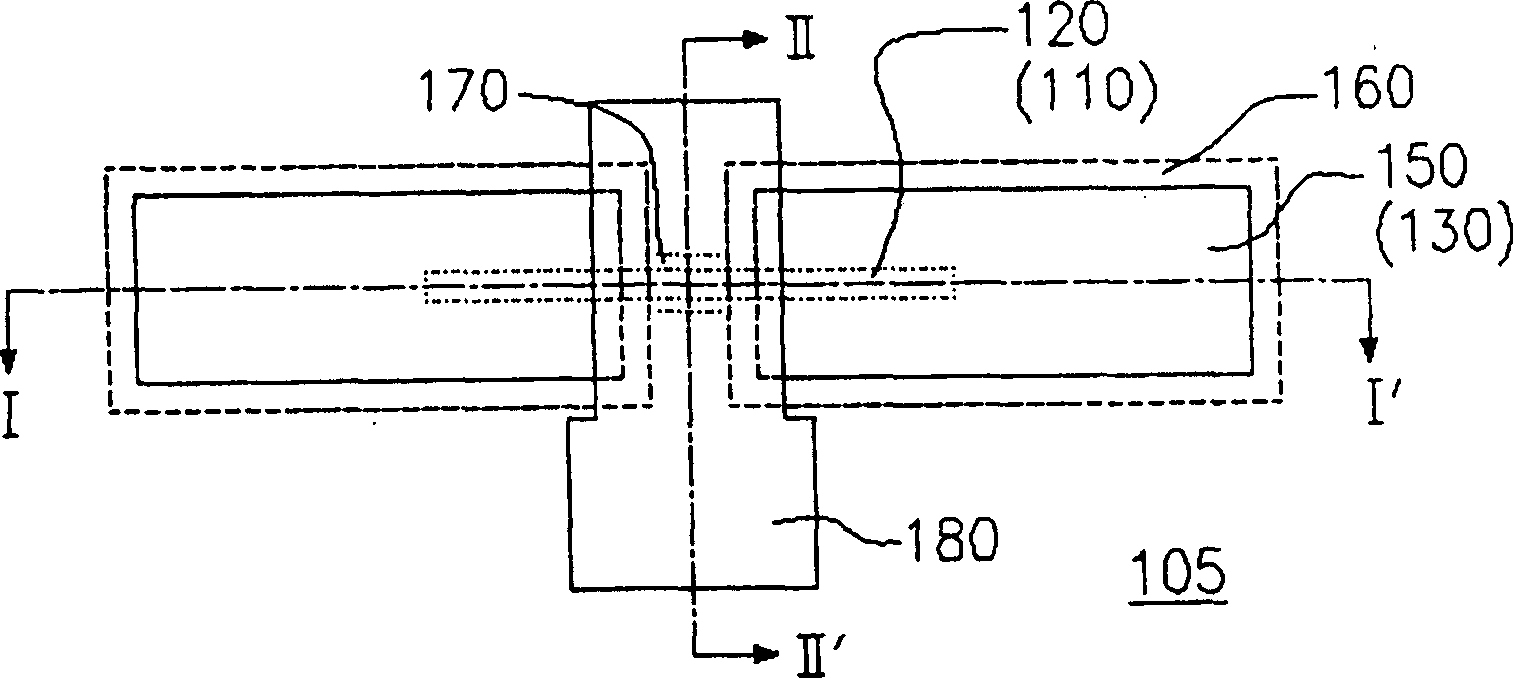

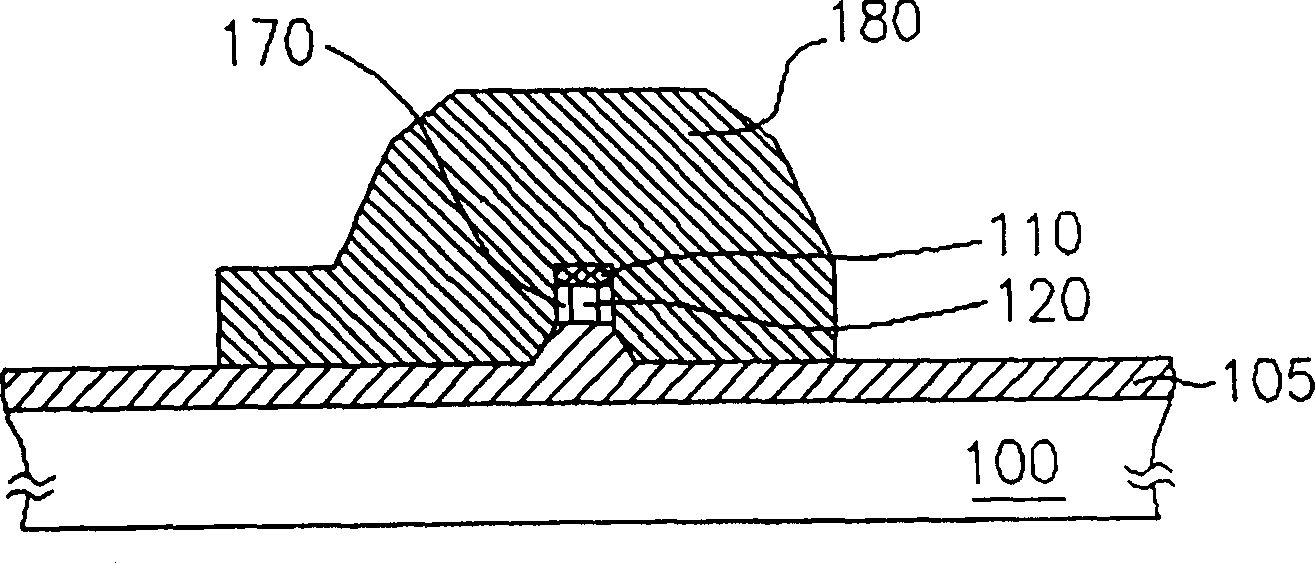

[0032] Please refer to figure 2 --9, is a sectional view of the manufacturing process of the MOSFET according to the preferred embodiment of the present invention; and please refer to Figure 2-1 , 5-1 , 6-1, 8-1, which are respectively figure 2 , 5 , 6, 8 top view, namely figure 2 , 5 , 6, and 8 are respectively Figure 2-1 , 5-1 , 6-1, 8-1 sectional view of the cutting line III-III'. in addition Figure 8-2 for Figure 8-1 Sectional view of cutting line IV-IV'.

[0033] Please refer to figure 2 , 2 -1, first provide a semiconductor substrate 200, such as a bulk silicon substrate, and then form a circular Shallow Trench Isolation (STI) and a shallow channel region (Channel Region) thereon. The material of the trench ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More