Patents

Literature

142results about How to "Increase parasitic capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

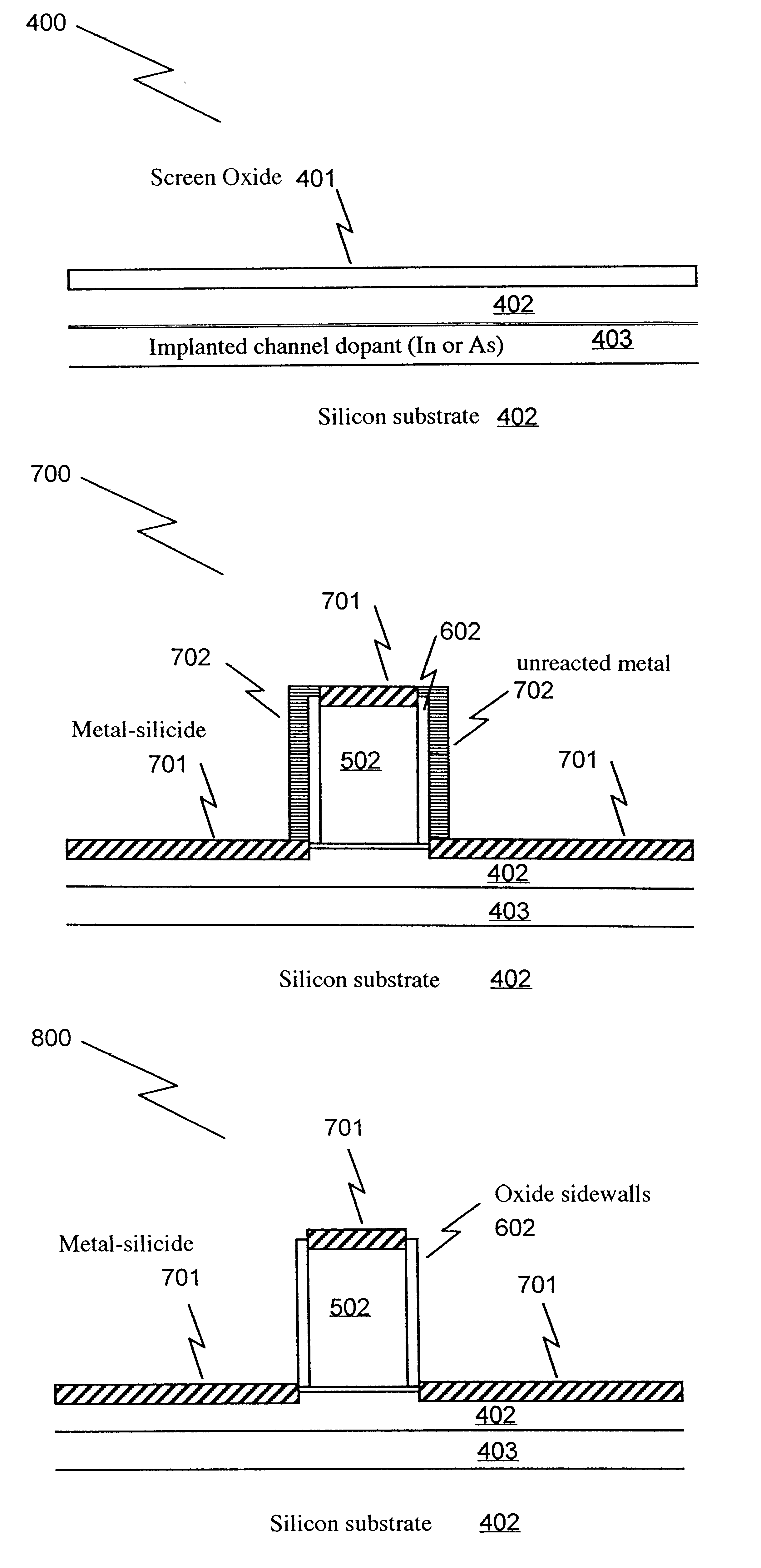

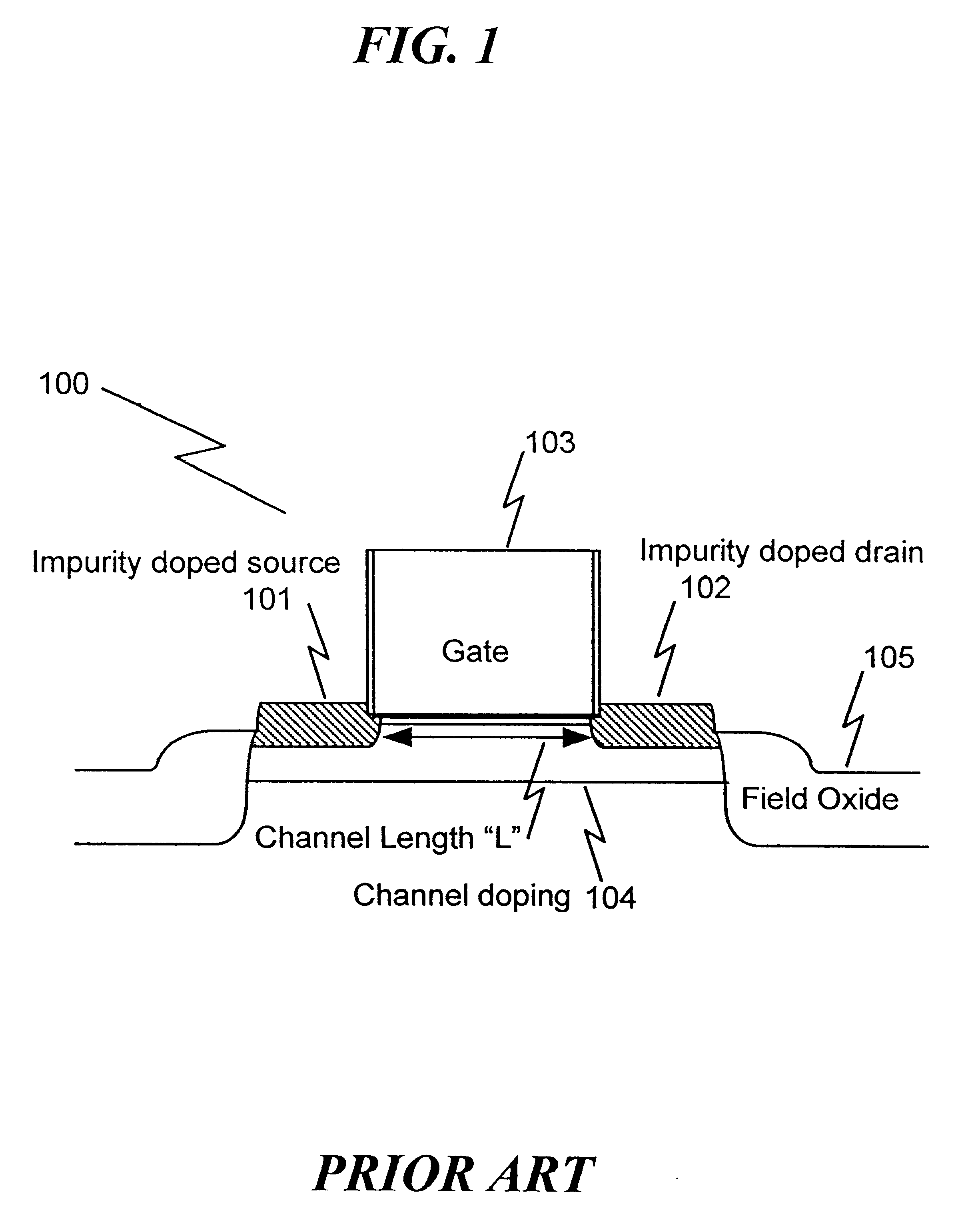

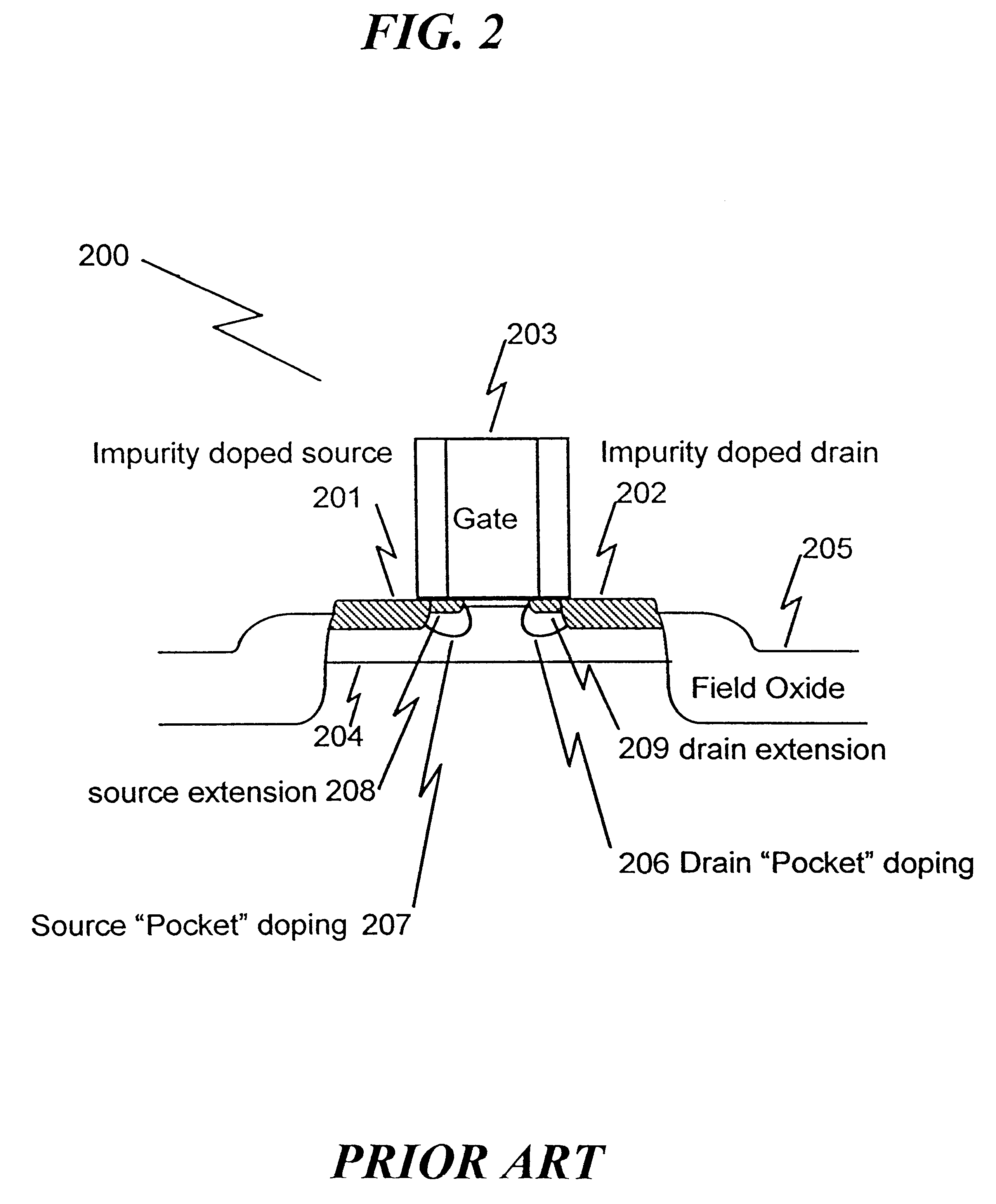

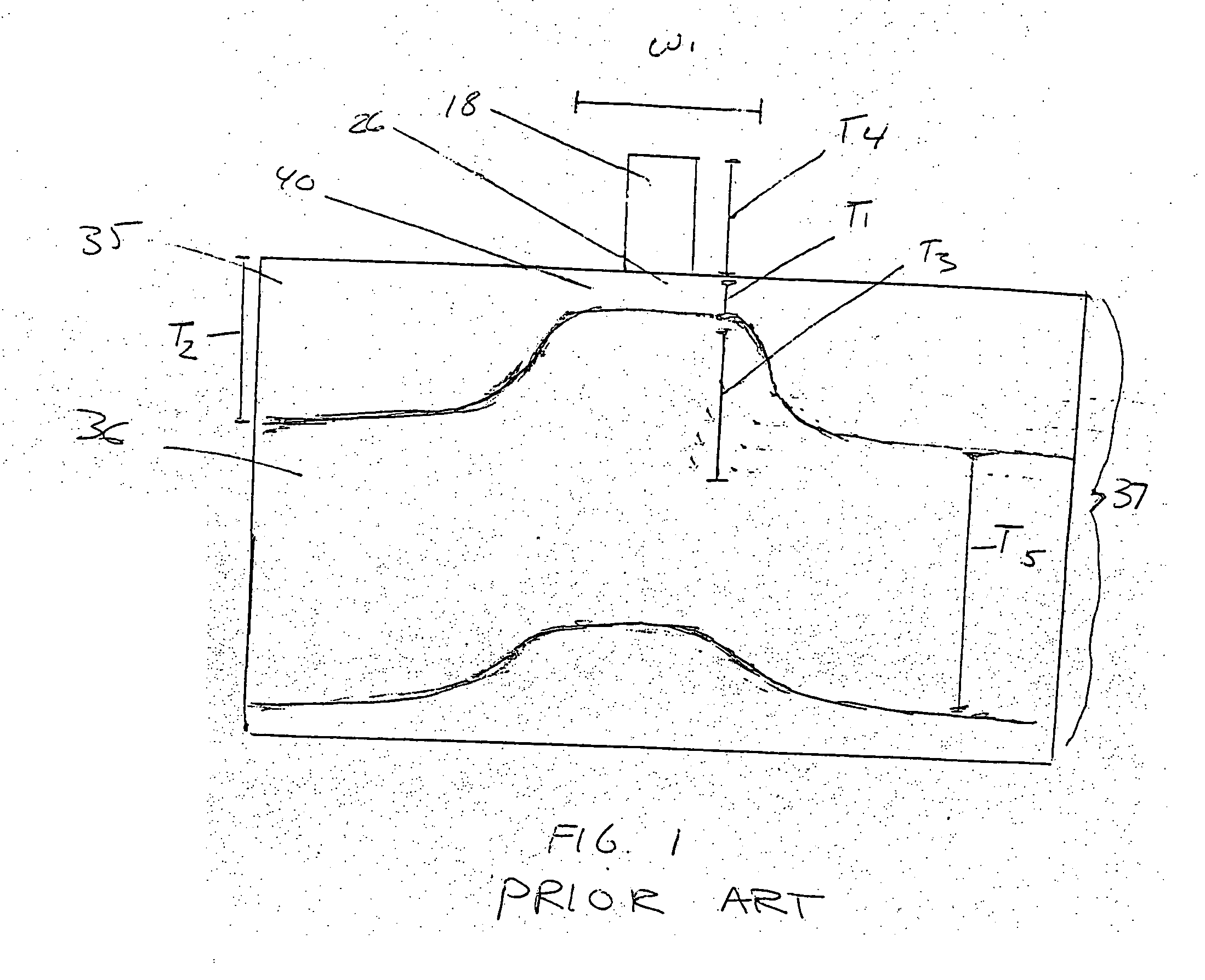

Method of manufacturing a short-channel FET with Schottky-barrier source and drain contacts

InactiveUS6303479B1Without add parasitic capacitanceReduce manufacturingTransistorSolid-state devicesEngineeringDopant

The present invention Is a fabrication method for a short-channel Schottky-barrier field-effect transistor device. The method of the present invention includes introducing channel dopants into a semiconductor substrate such that the dopant concentration varies in the vertical direction and is generally constant in the lateral direction. A gate electrode is formed on the semiconductor substrate, and source and drain electrodes are formed on the substrate to form a Schottky or Schottky-like contact to the substrate.

Owner:AVOLARE 2 LLC

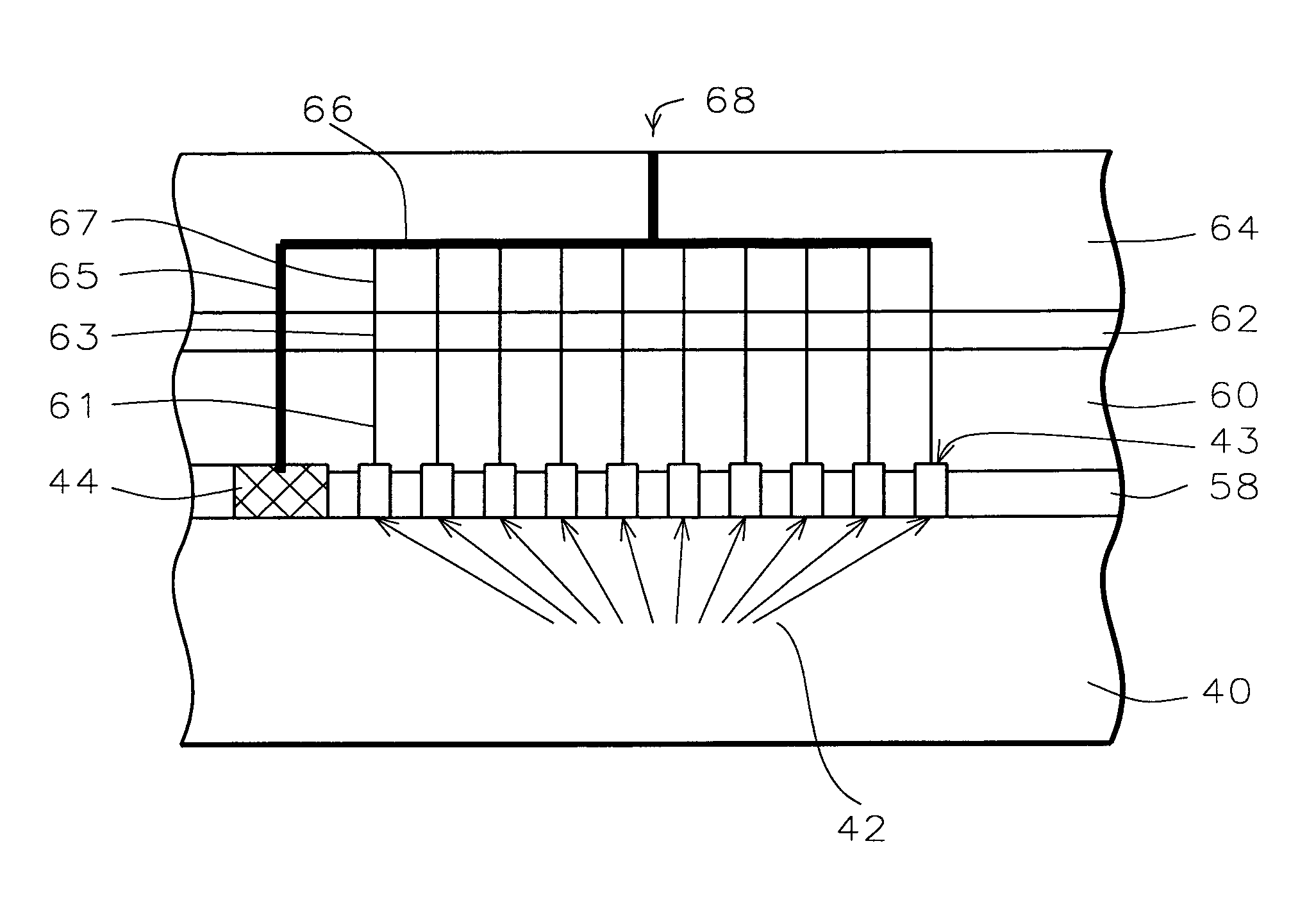

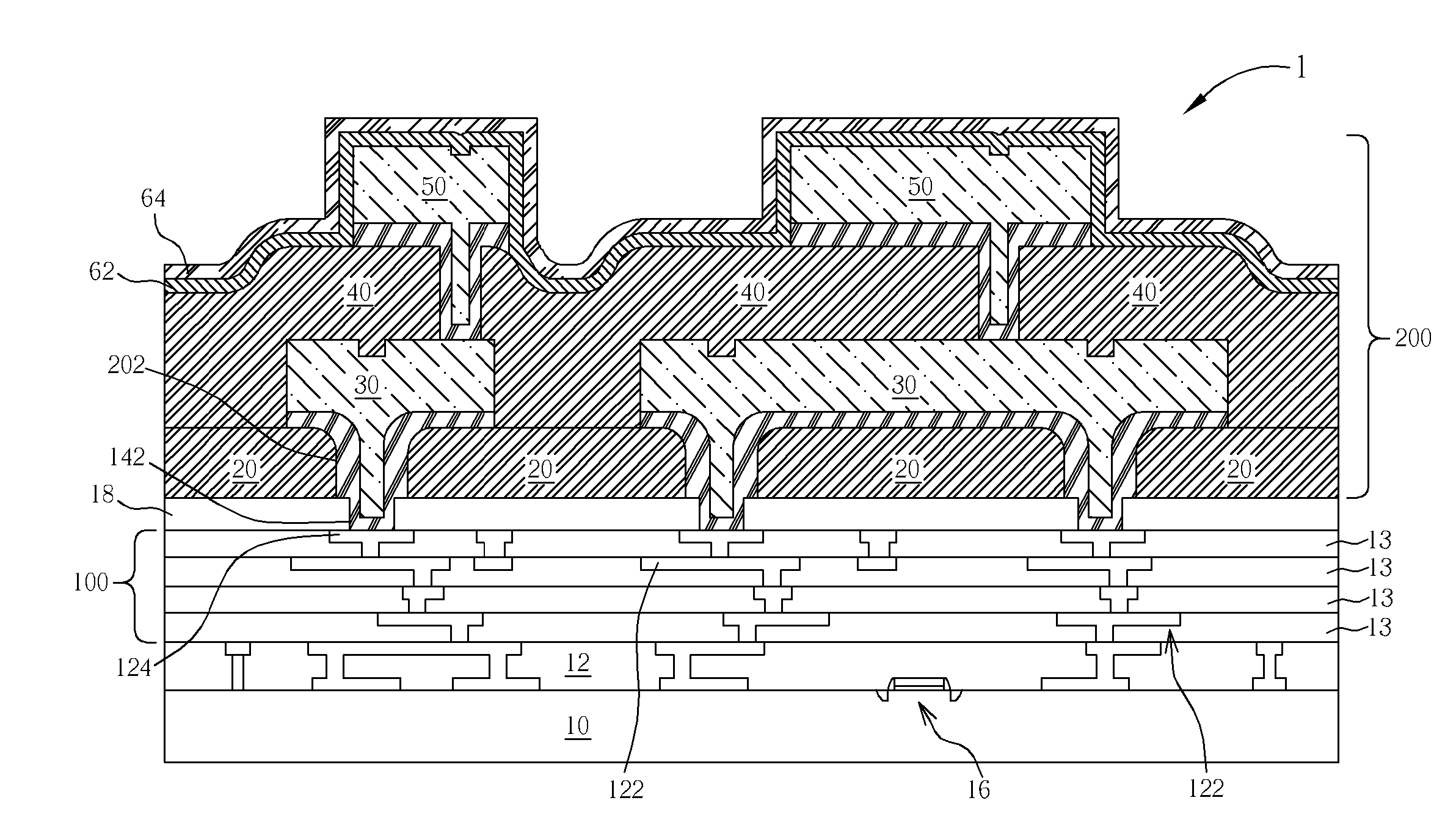

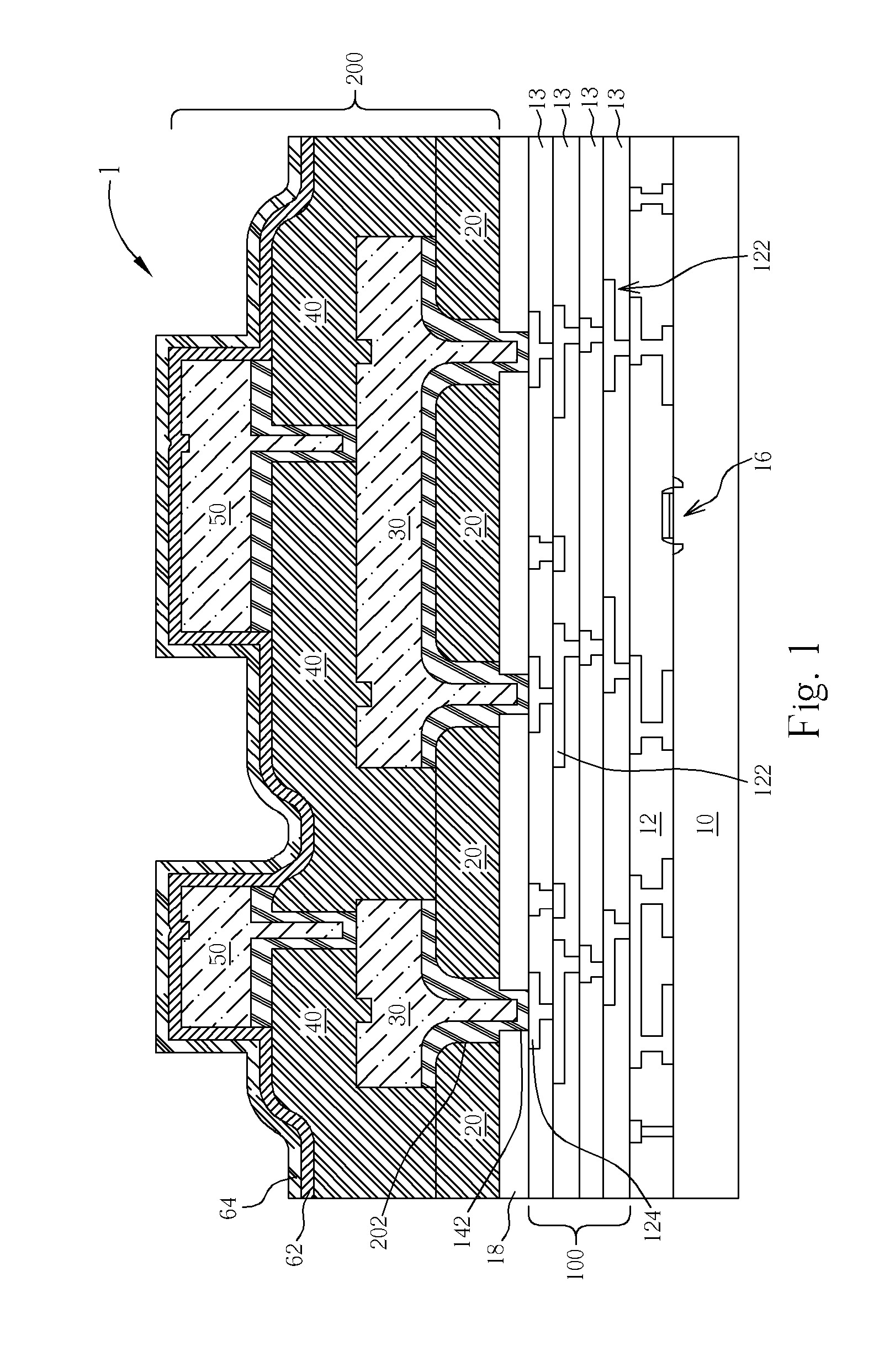

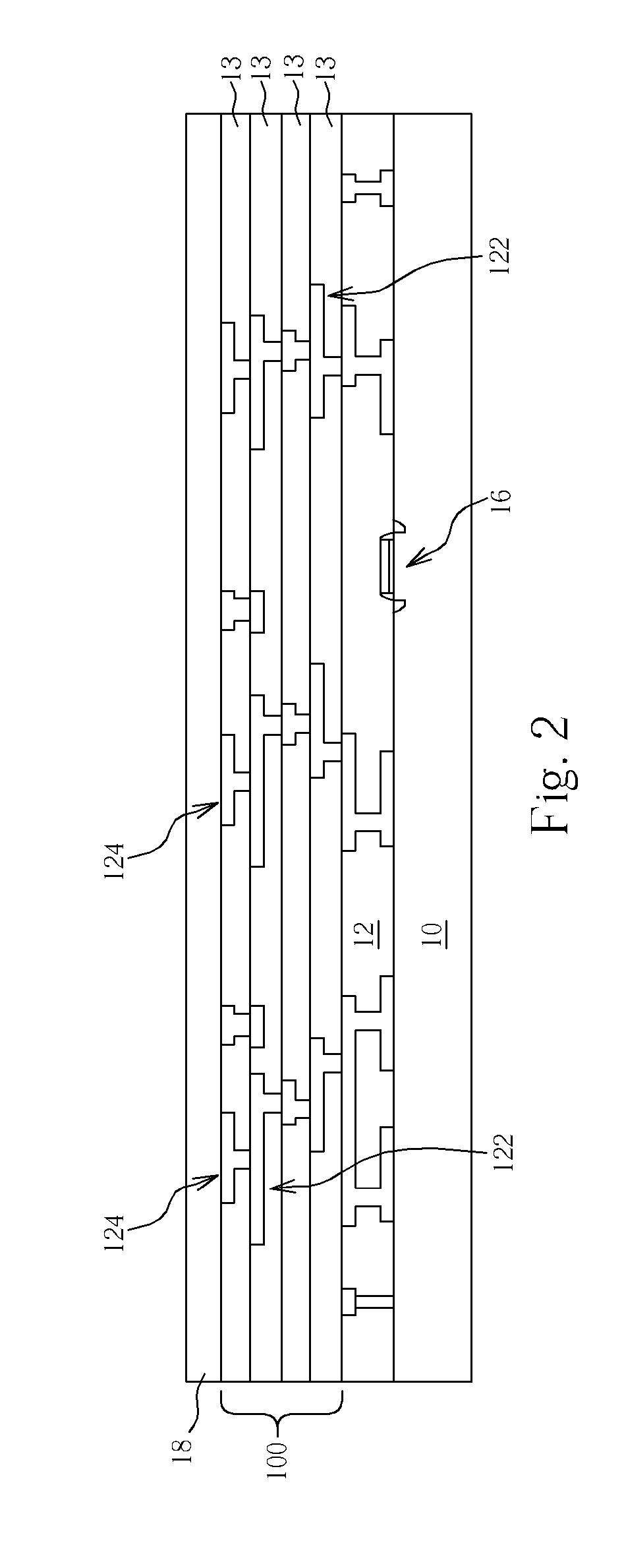

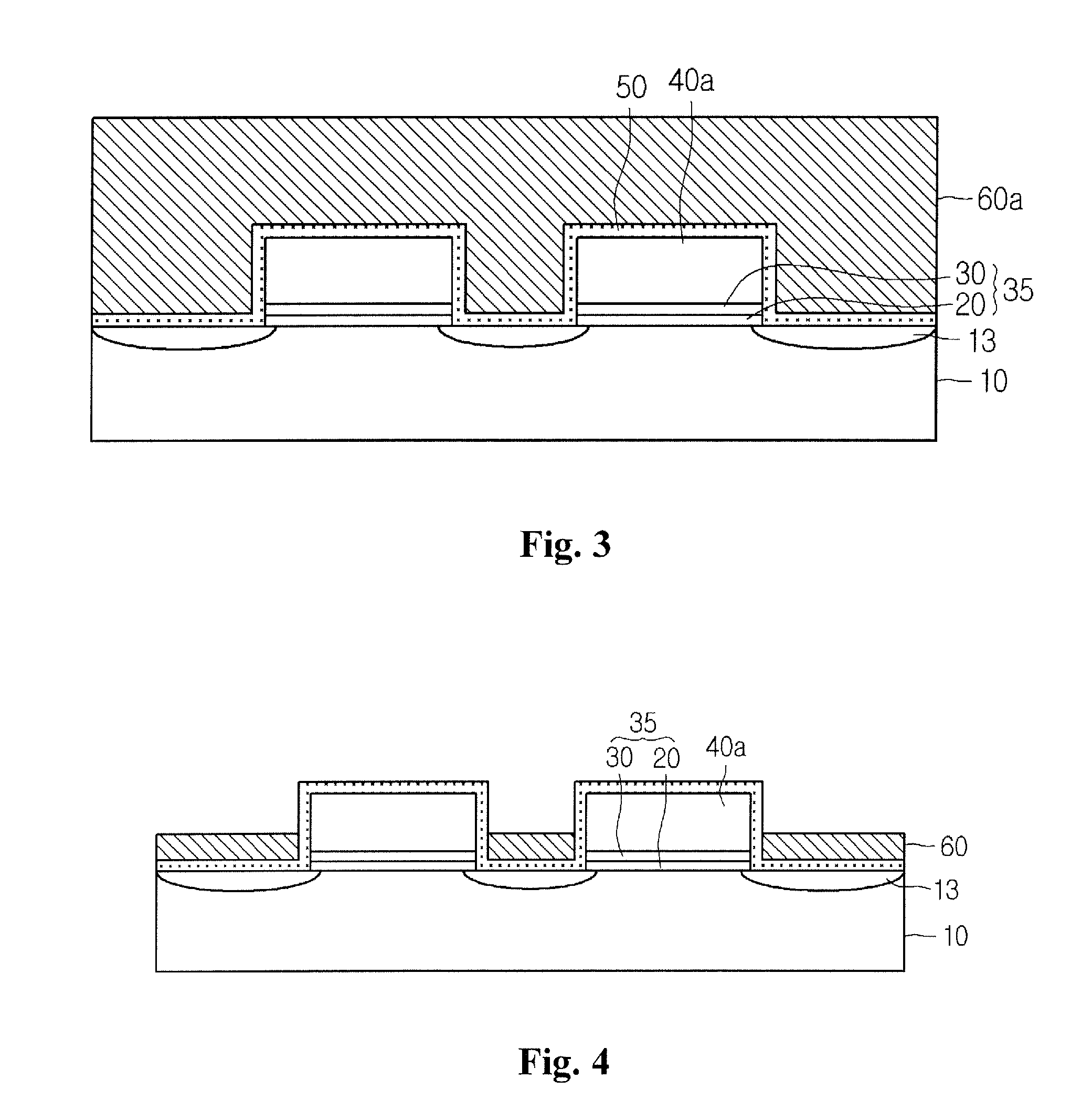

Post passivation interconnection schemes on top of the IC chips

InactiveUS7230340B2High resistivityRemove restrictionsSemiconductor/solid-state device detailsSolid-state devicesFine lineDielectric

A new method is provided for the creation of interconnect lines. Fine line interconnects are provided in a first layer of dielectric overlying semiconductor circuits that have been created in or on the surface of a substrate. A layer of passivation is deposited over the layer of dielectric, a thick second layer of dielectric is created over the surface of the layer of passivation. Thick and wide interconnect lines are created in the thick second layer of dielectric. The first layer of dielectric may also be eliminated, creating the wide thick interconnect network on the surface of the layer of passivation that has been deposited over the surface of a substrate.

Owner:QUALCOMM INC

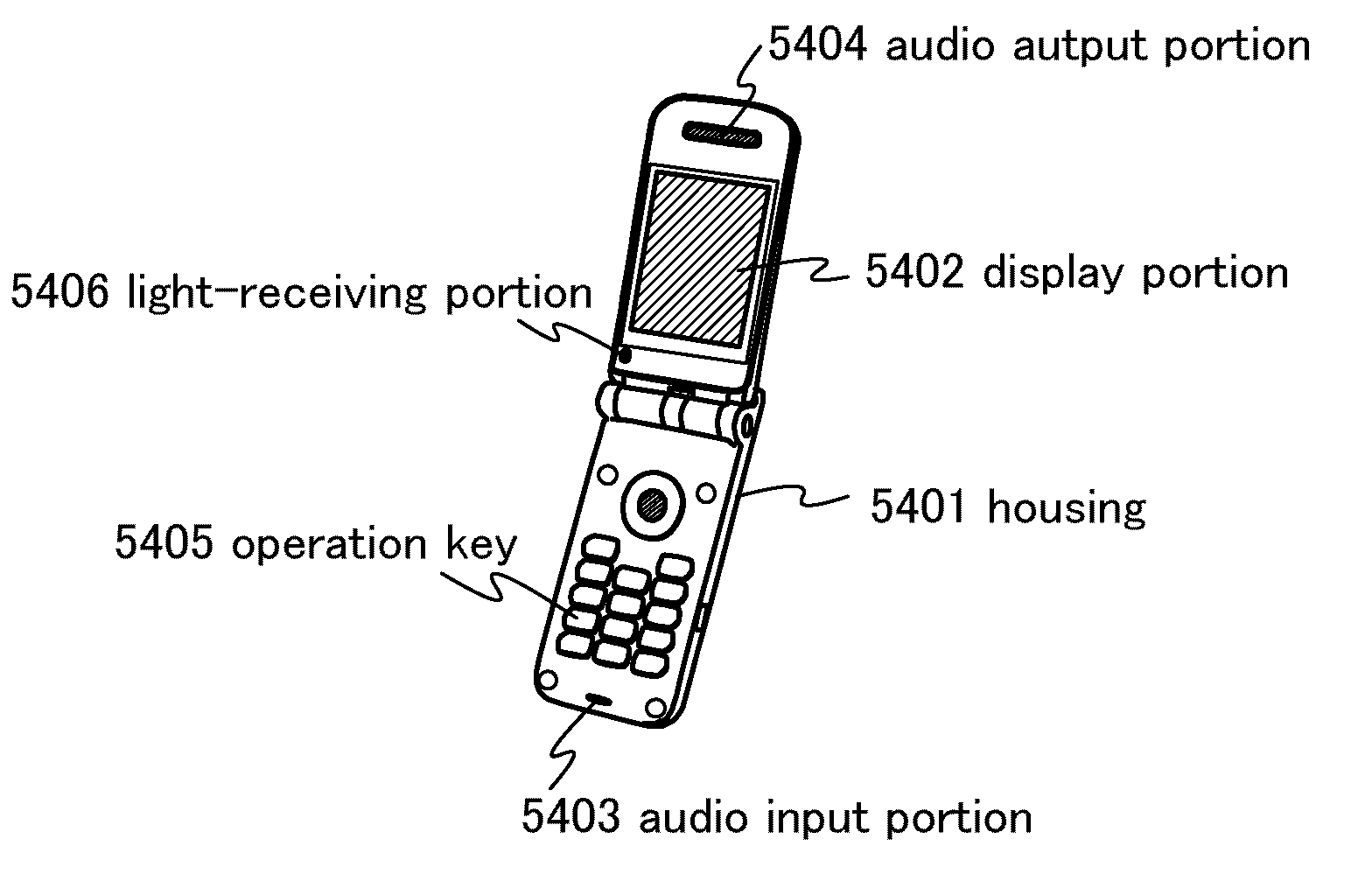

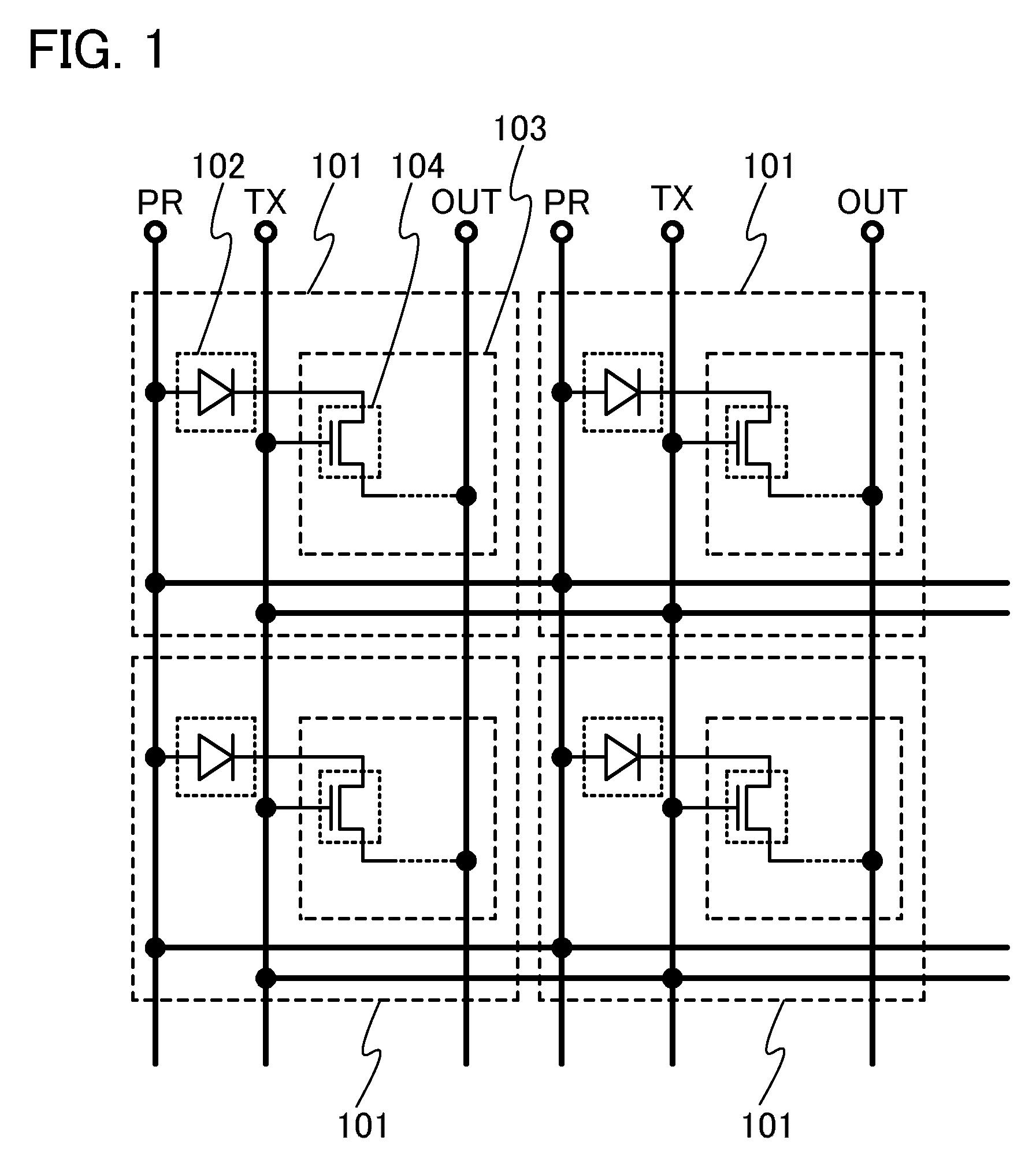

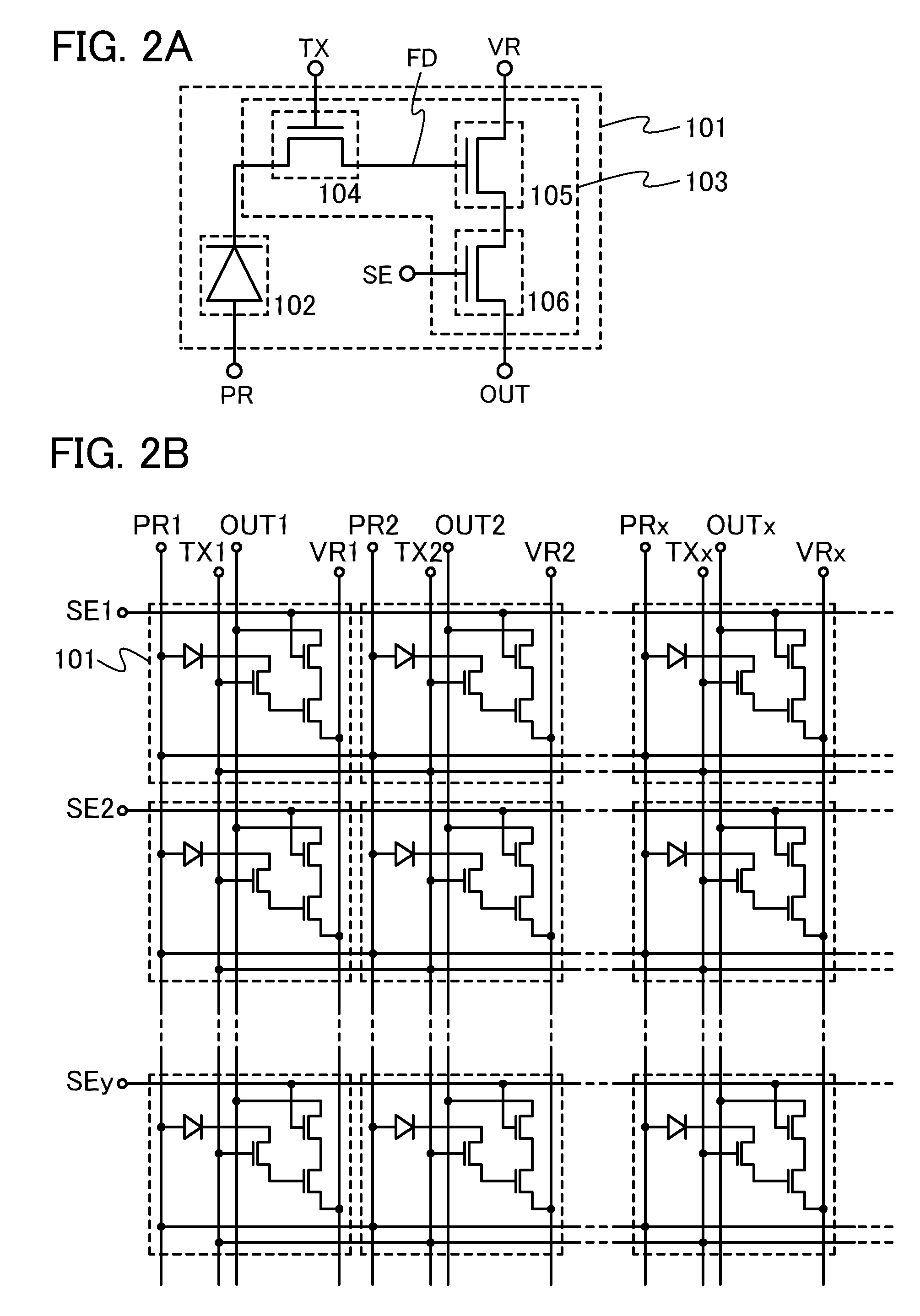

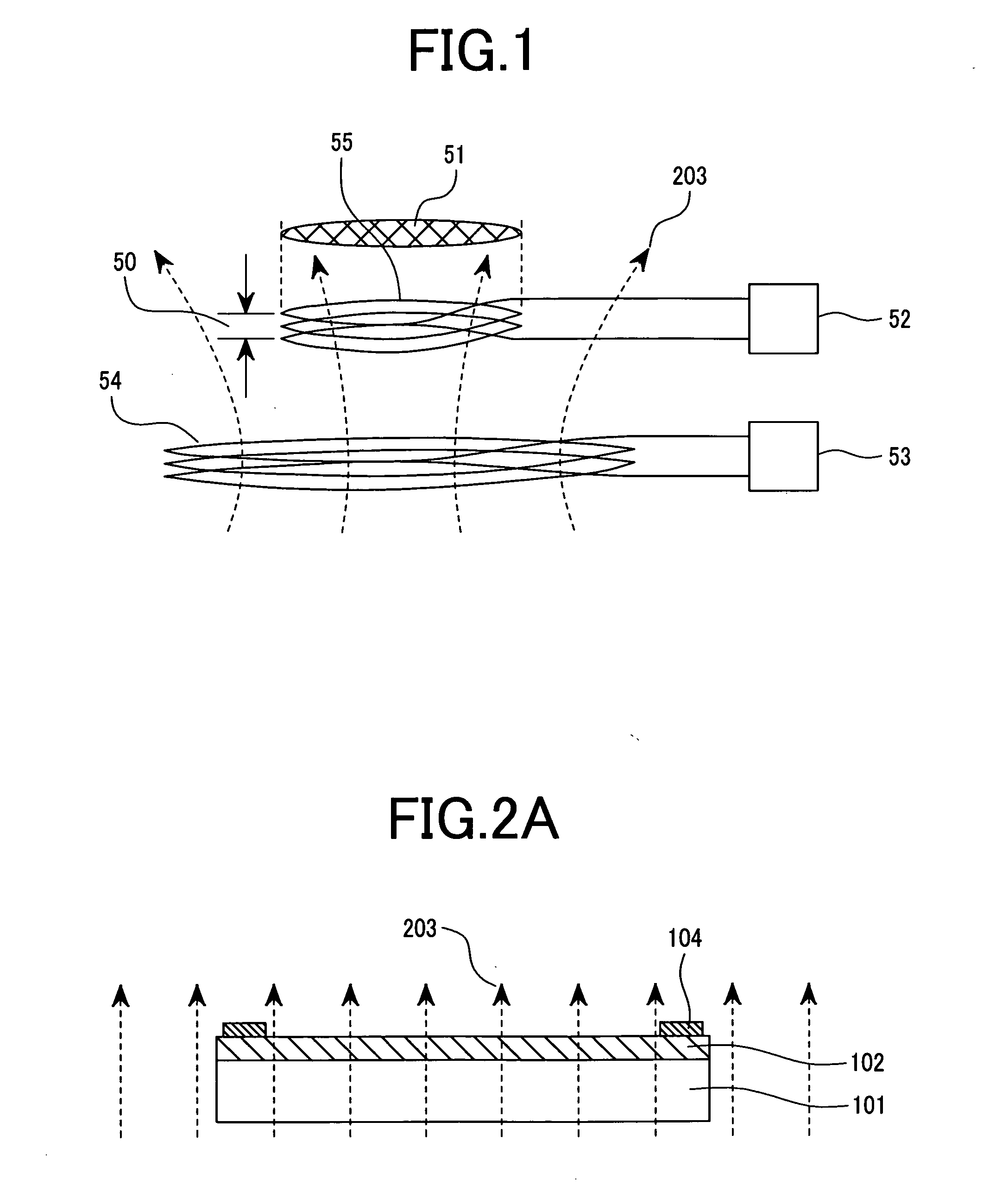

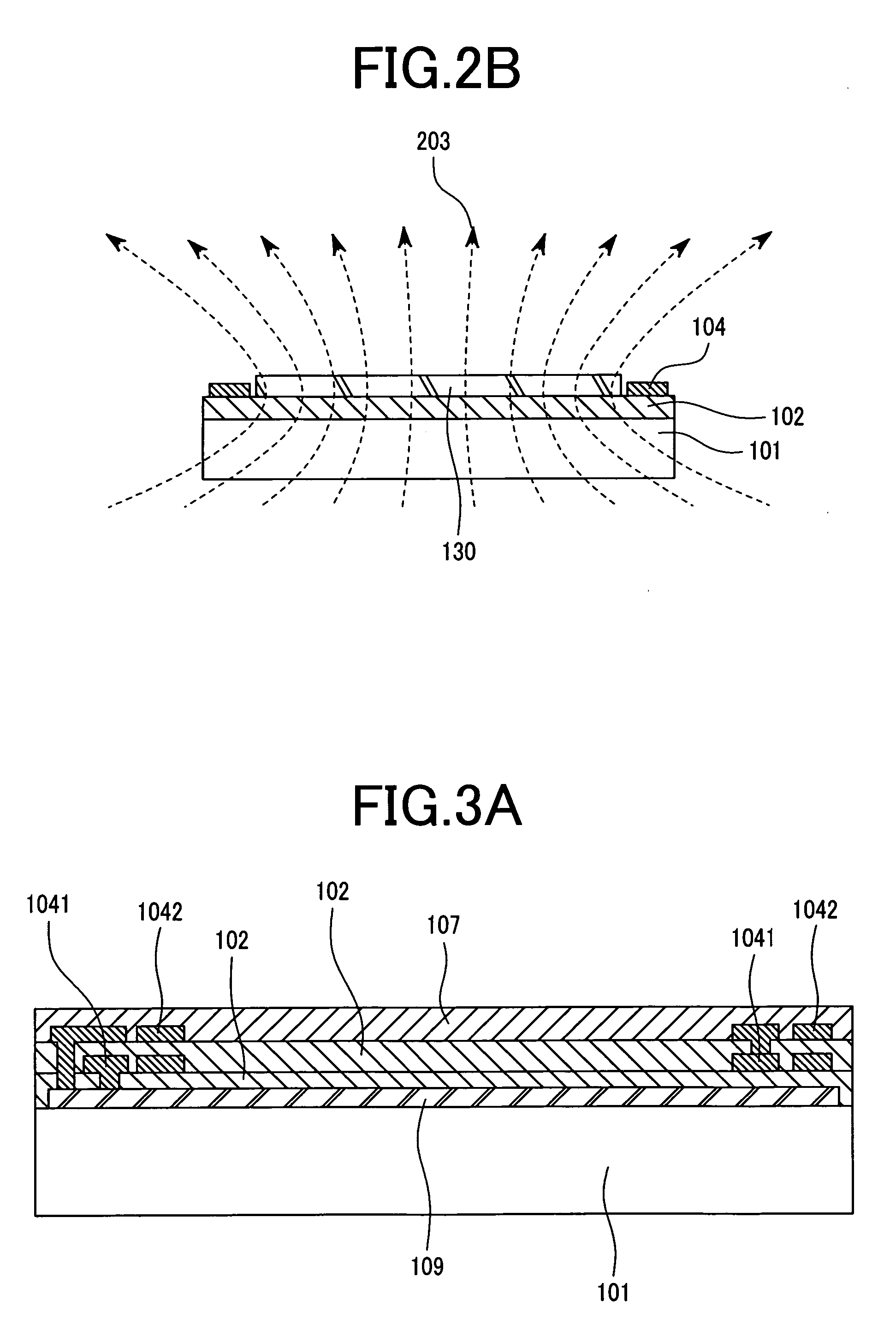

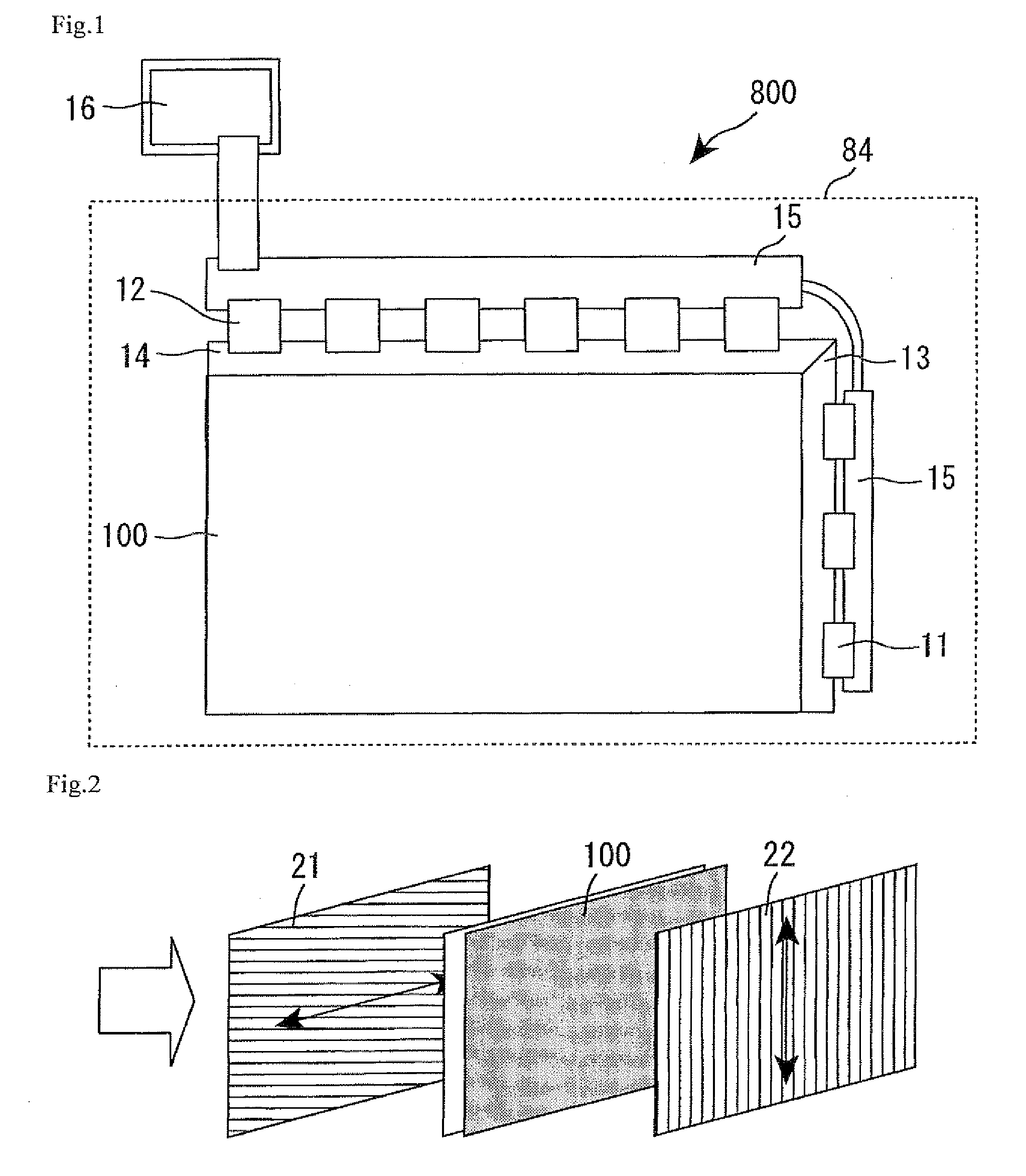

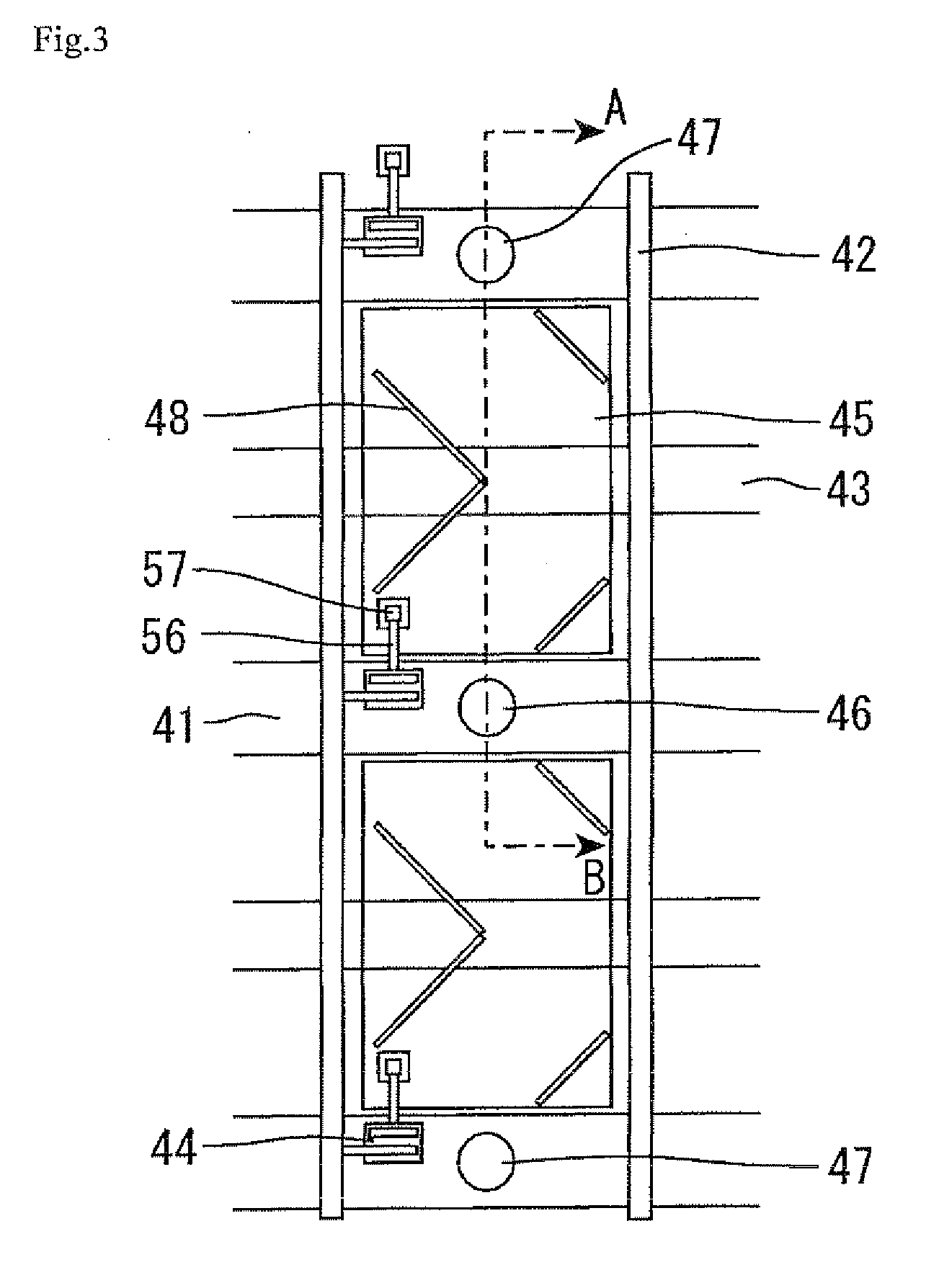

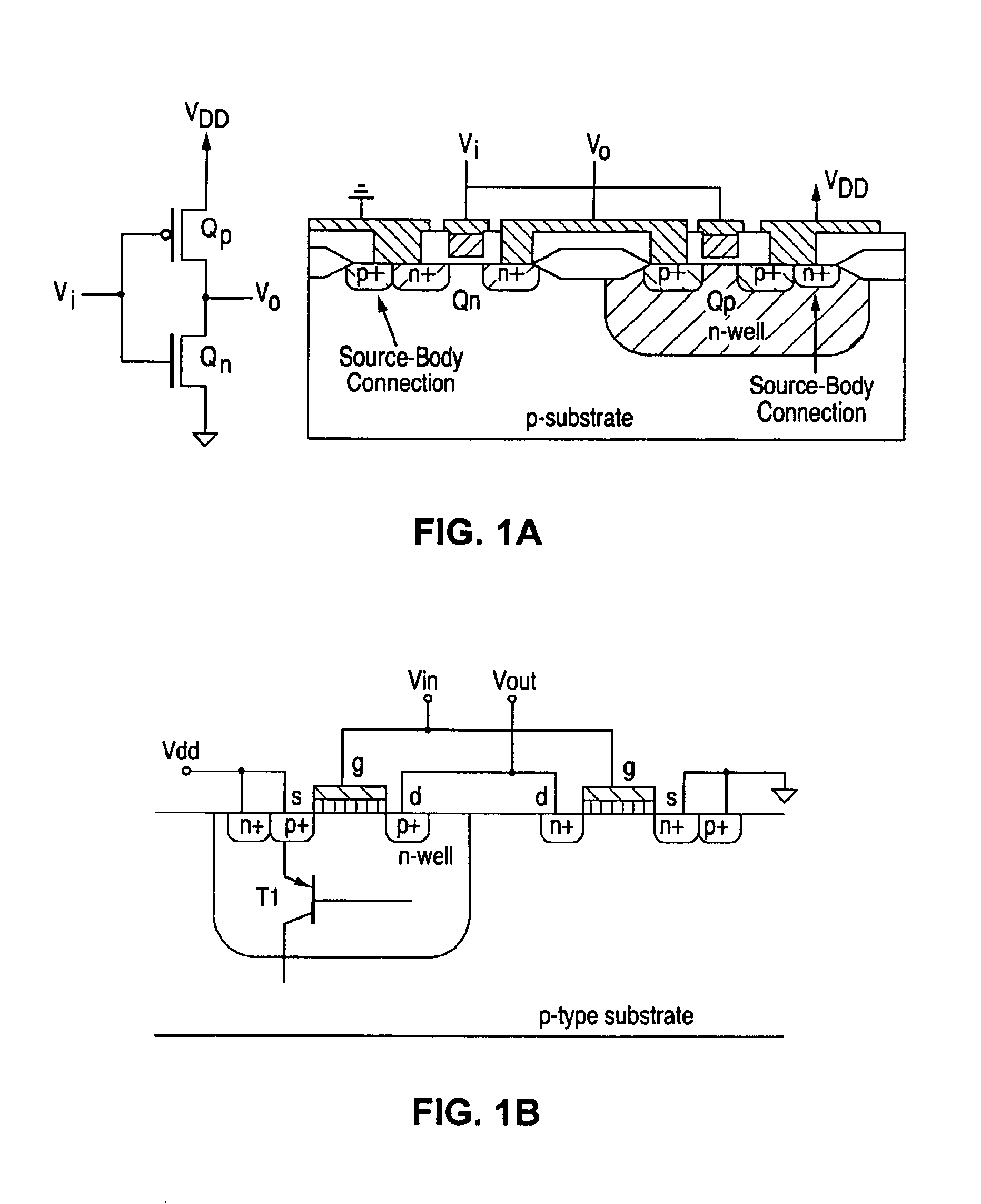

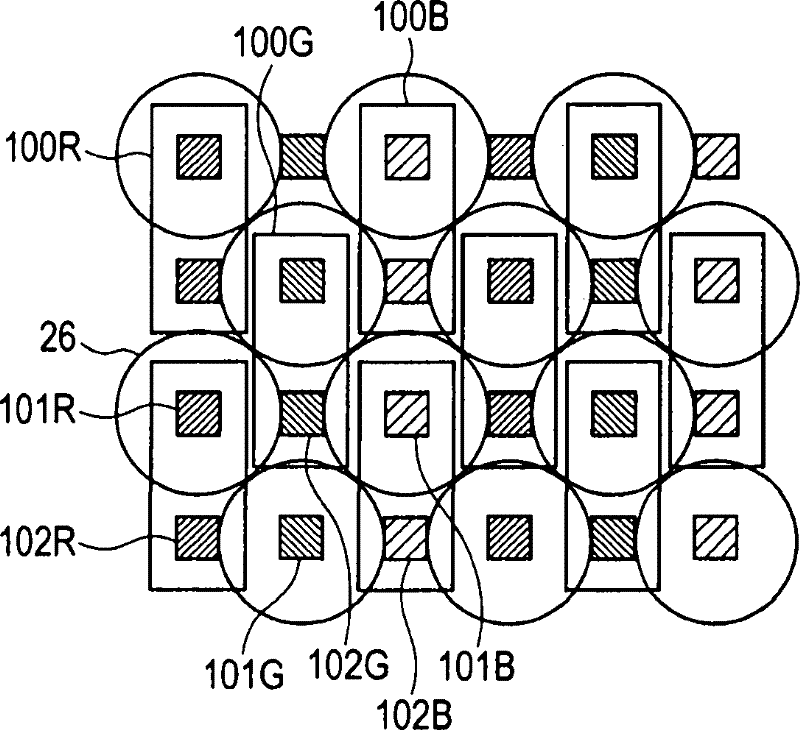

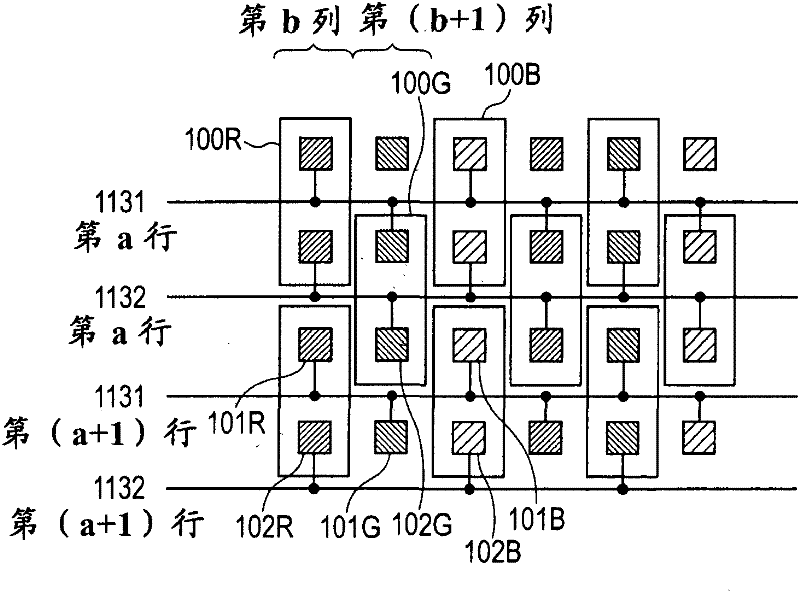

Solid-state imaging device and semiconductor display device

ActiveUS20120002090A1Suppress potential decreaseSuppress signal delayTelevision system detailsTelevision system scanning detailsDisplay deviceEngineering

An object is to provide a solid-state imaging device or a semiconductor display device with which a high-quality image can be taken. By performing operation using a global shutter method, a potential for controlling charge accumulation operation can be shared by all pixels. In addition, a first photosensor group includes a plurality of photosensors connected to a wiring supplied with an output signal, and a second photosensor group includes a plurality of photosensors connected to another wiring supplied with the output signal. A wiring for supplying a potential or a signal for controlling charge accumulation operation to the first photosensor group is connected to a wiring for supplying the potential or signal to the second photosensor group.

Owner:SEMICON ENERGY LAB CO LTD

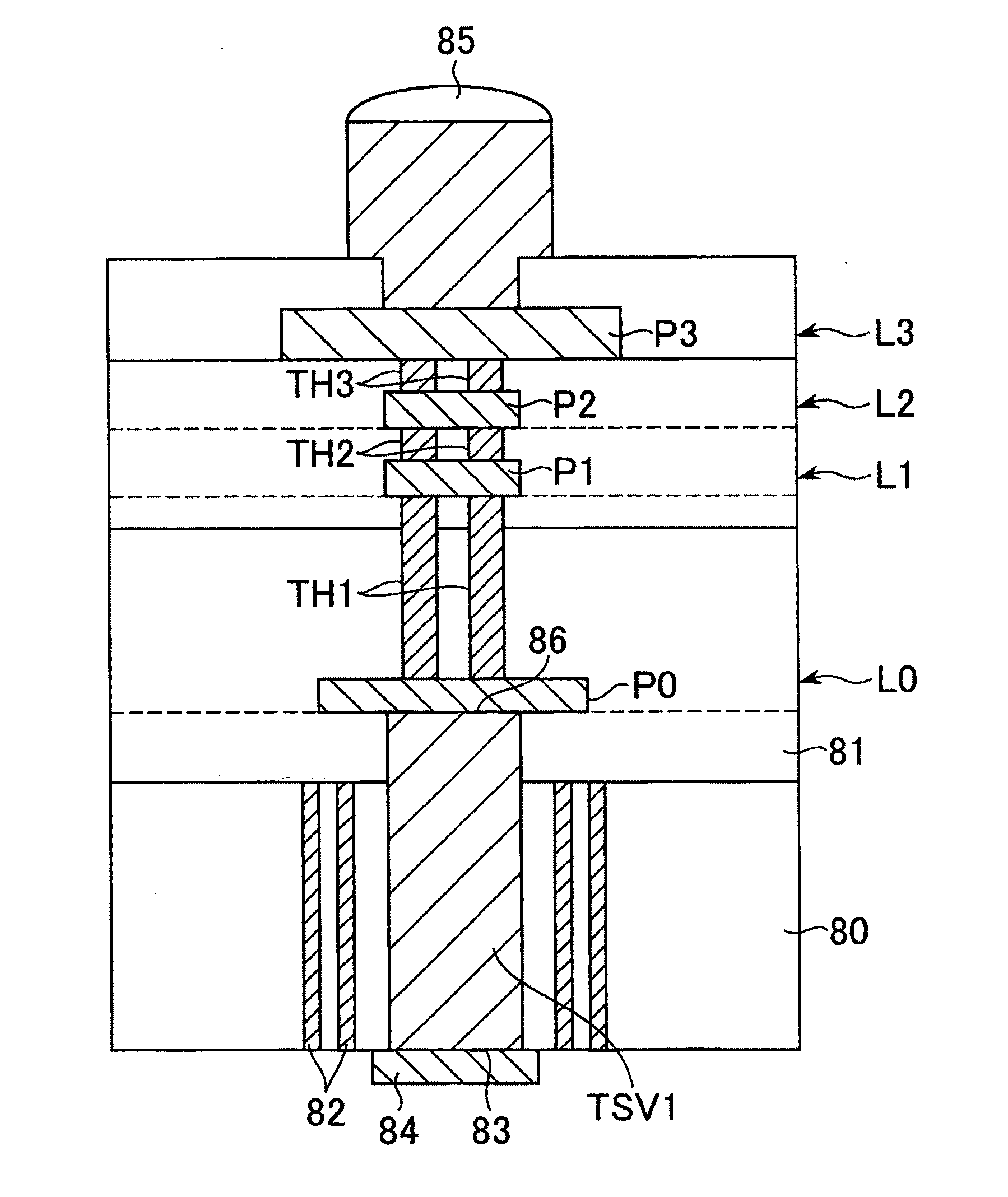

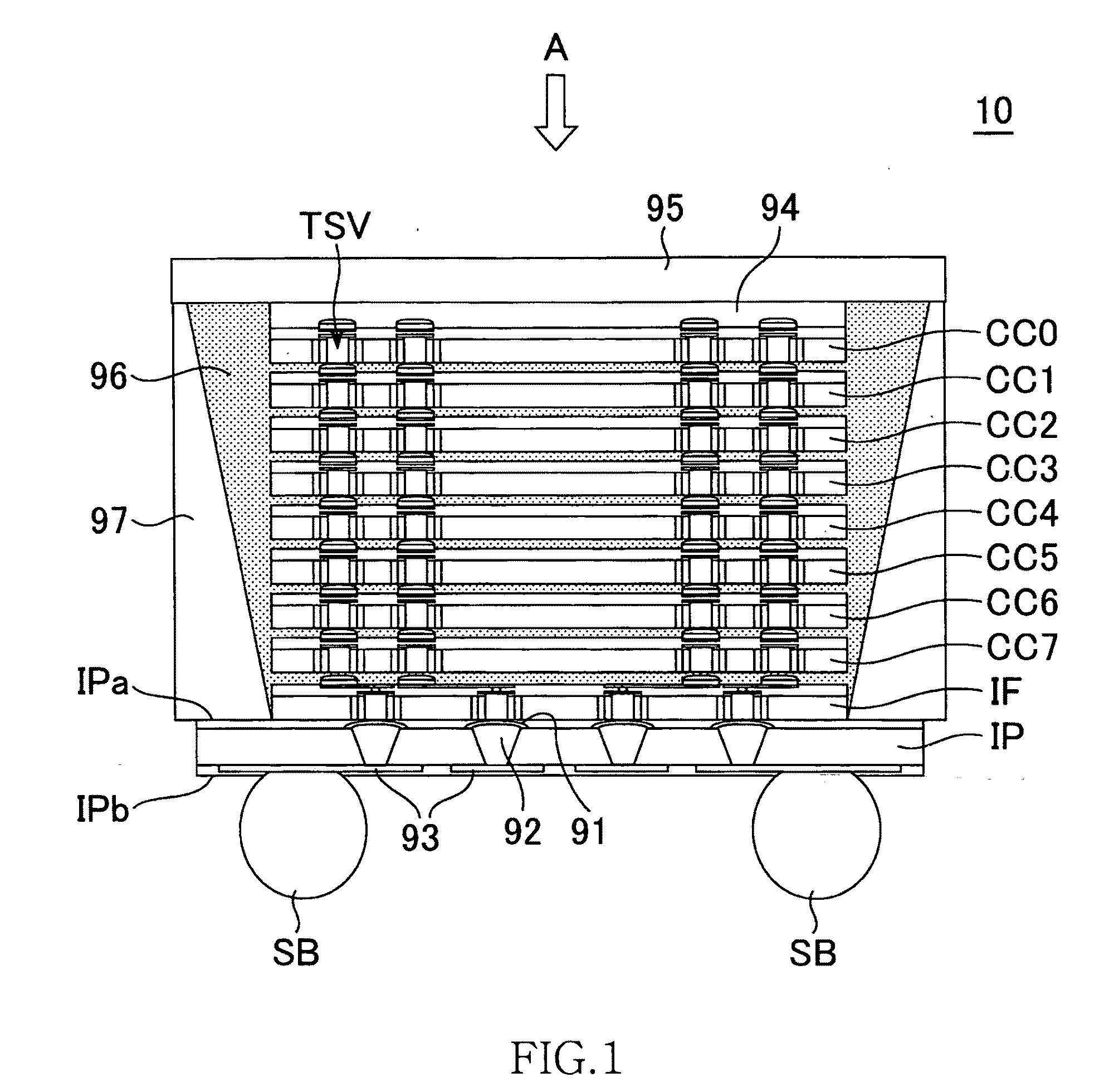

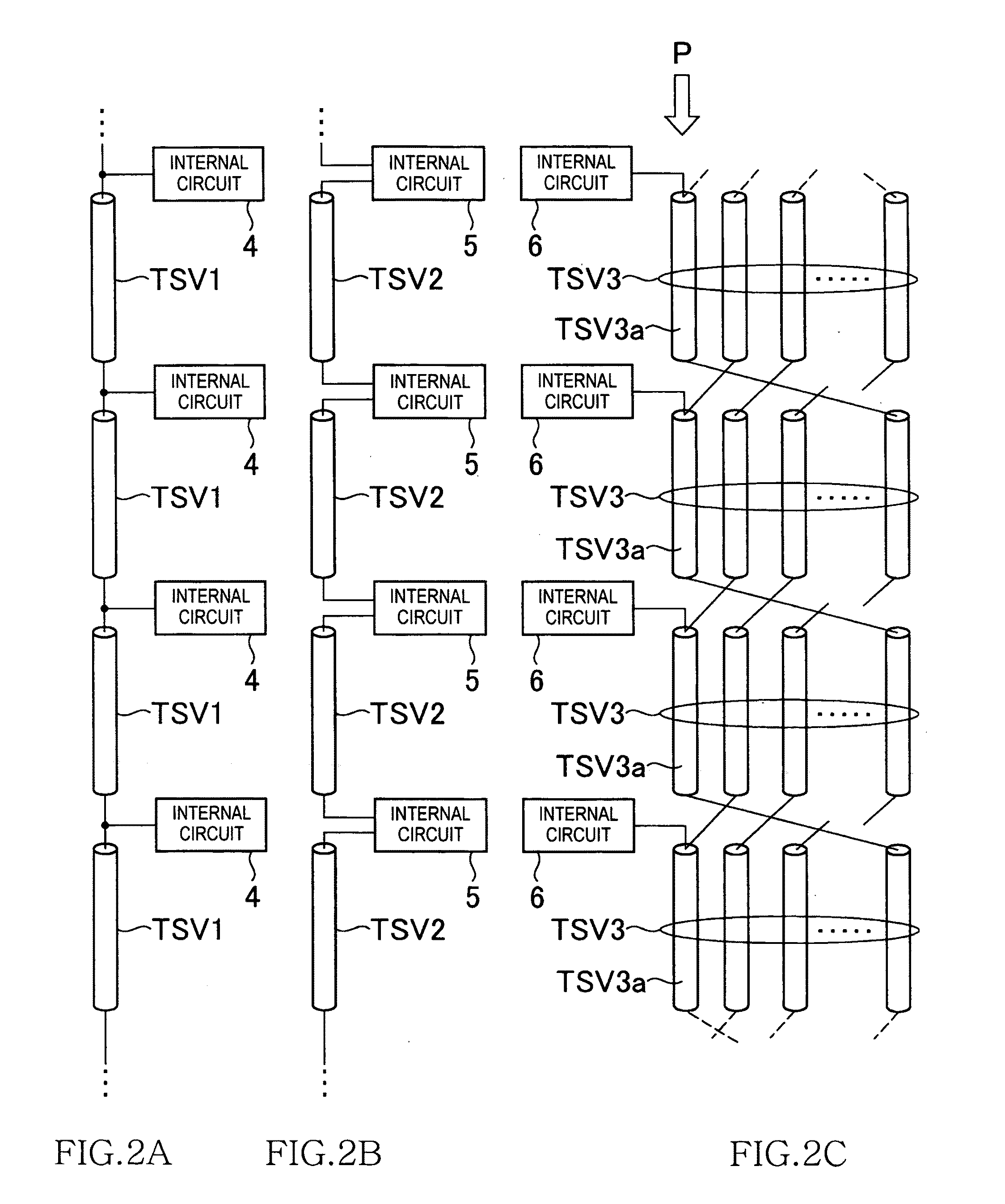

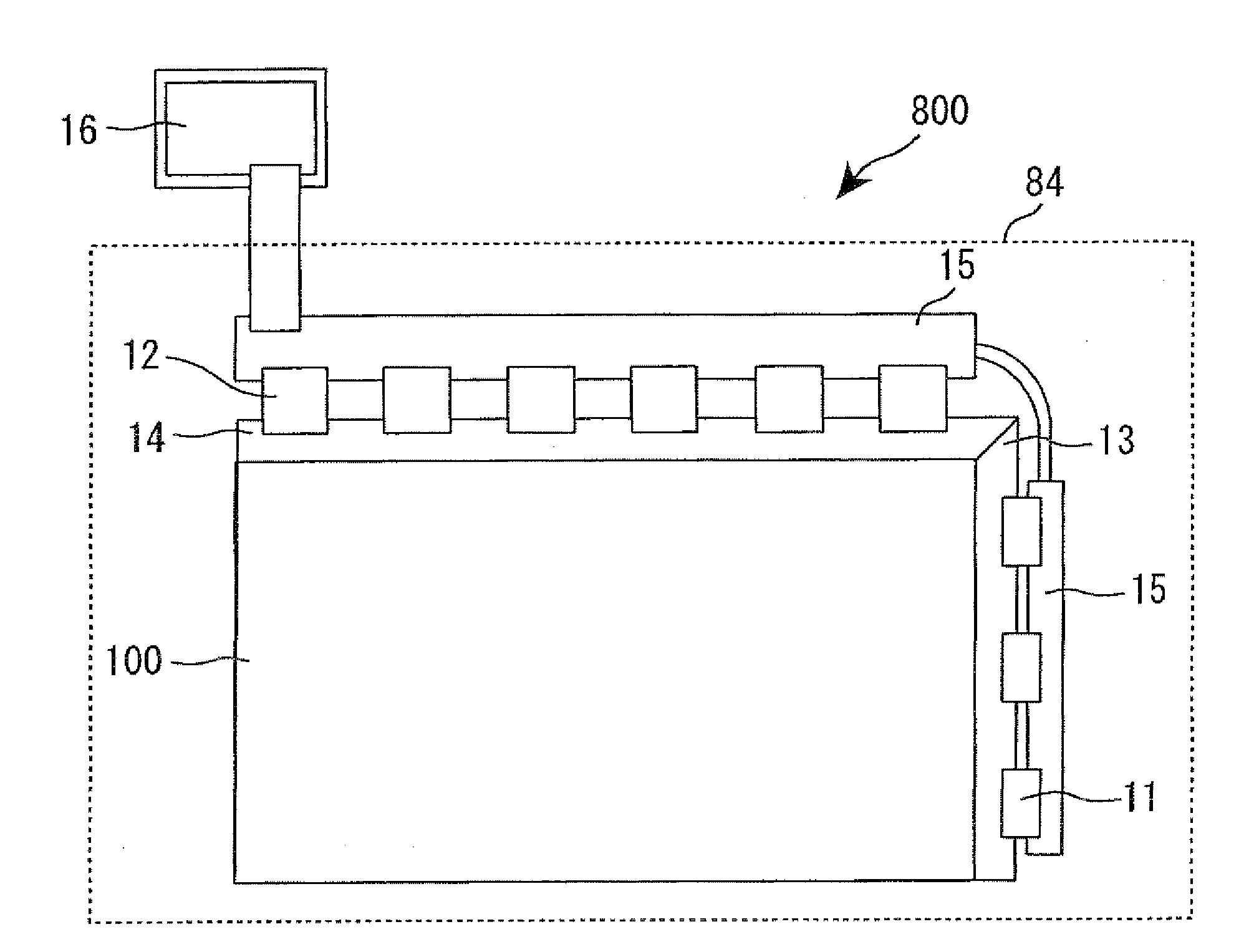

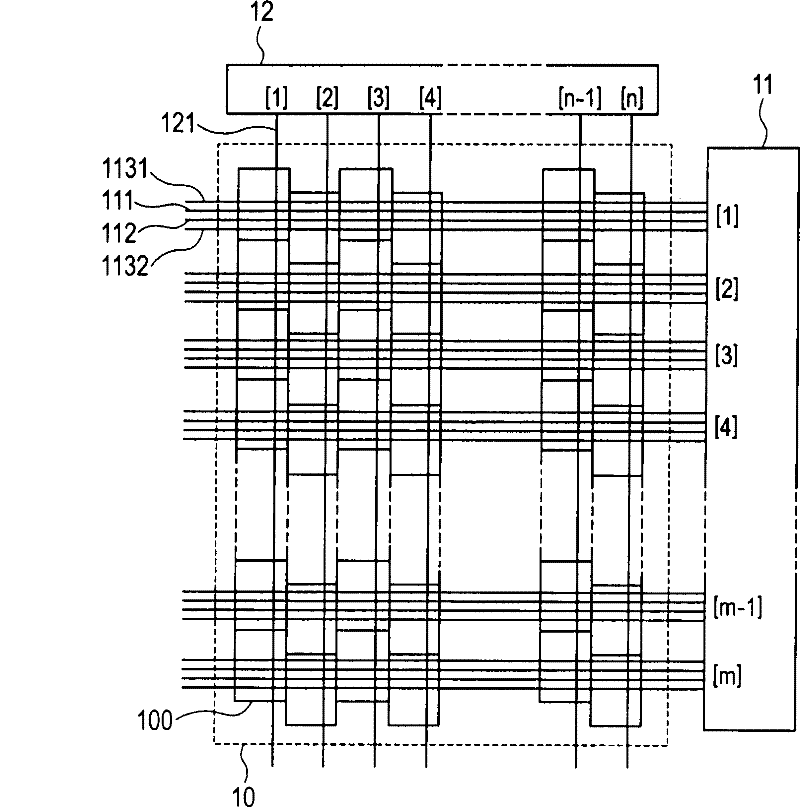

Semiconductor device and information processing system including the same

ActiveUS20110084385A1Large capacitance componentImprove signal qualitySemiconductor/solid-state device detailsPrinted electric component incorporationInformation processingParasitic capacitance

A semiconductor device includes a plurality of core chips and an interface chip that controls the core chips. Each of the core chips and the interface chip includes plural through silicon vias that penetrate a semiconductor substrate and plural pads respectively connected to the through silicon vias. The through silicon vias include a through silicon via of a power source system to which a power source potential or a ground potential is supplied, and a through silicon via of a signal system to which various signals are supplied. Among the pads, at least an size of a pad connected to the through silicon via of the power source system is larger than a size of a pad connected to the through silicon via of the signal system. Therefore, a larger parasitic capacitance can be secured.

Owner:LONGITUDE LICENSING LTD

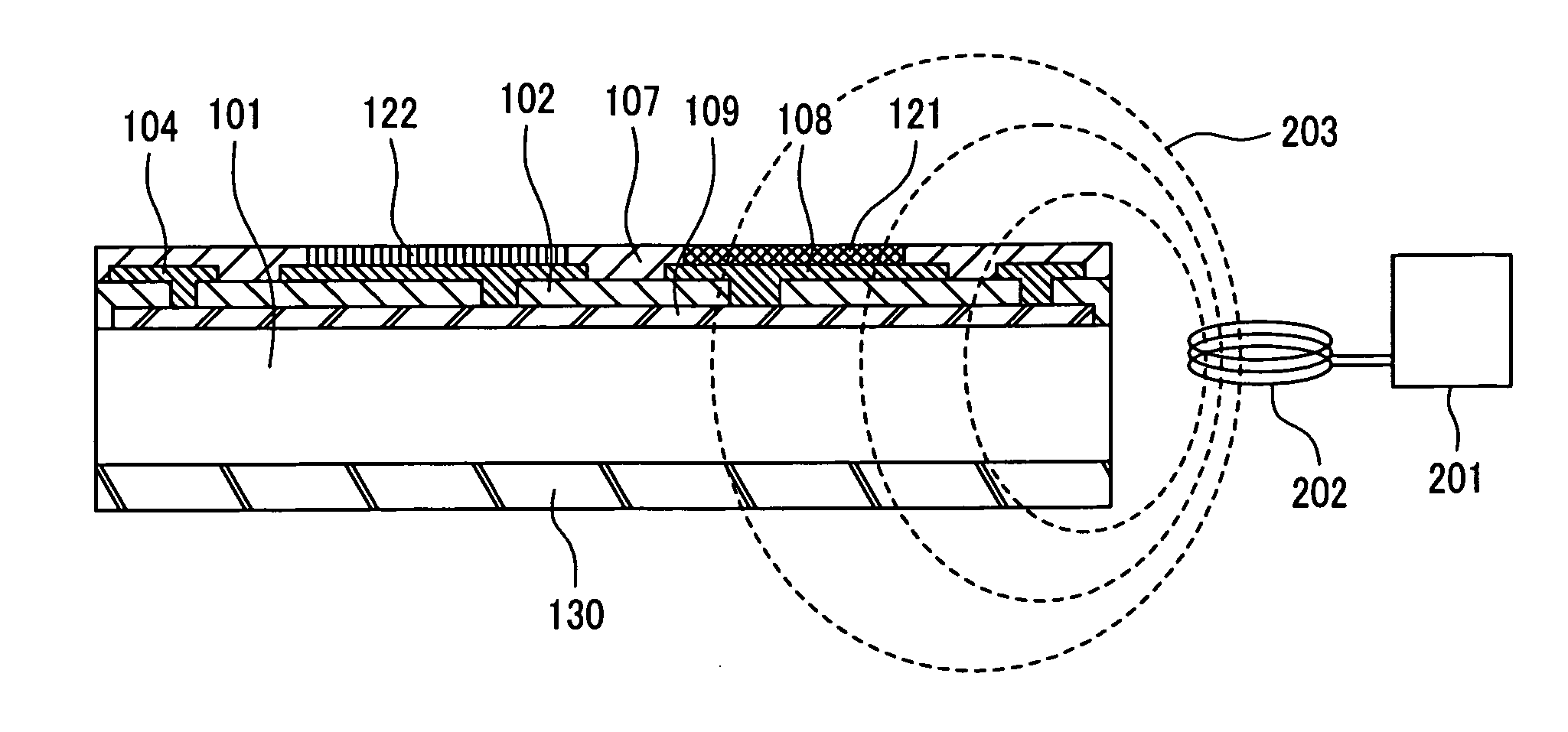

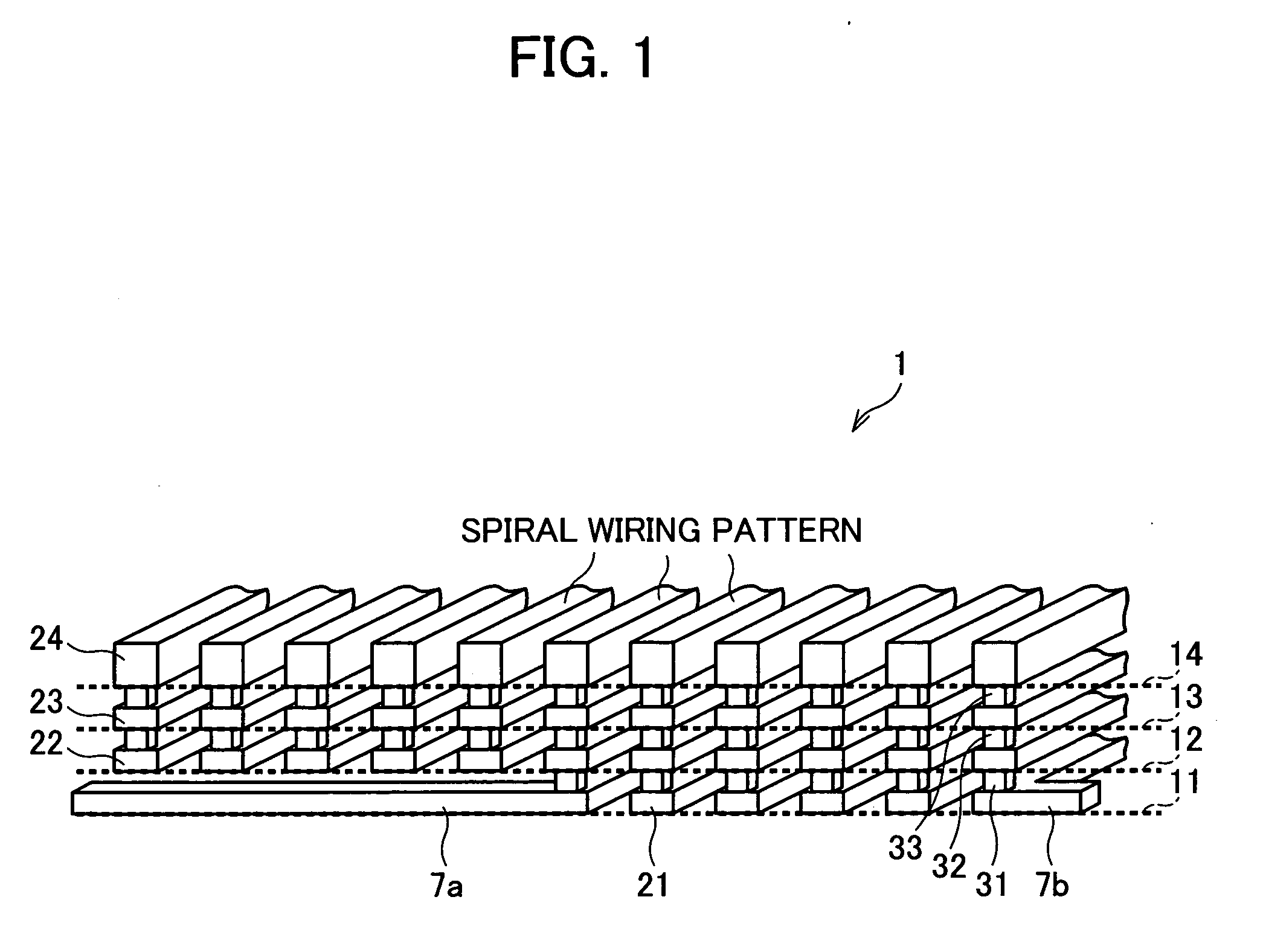

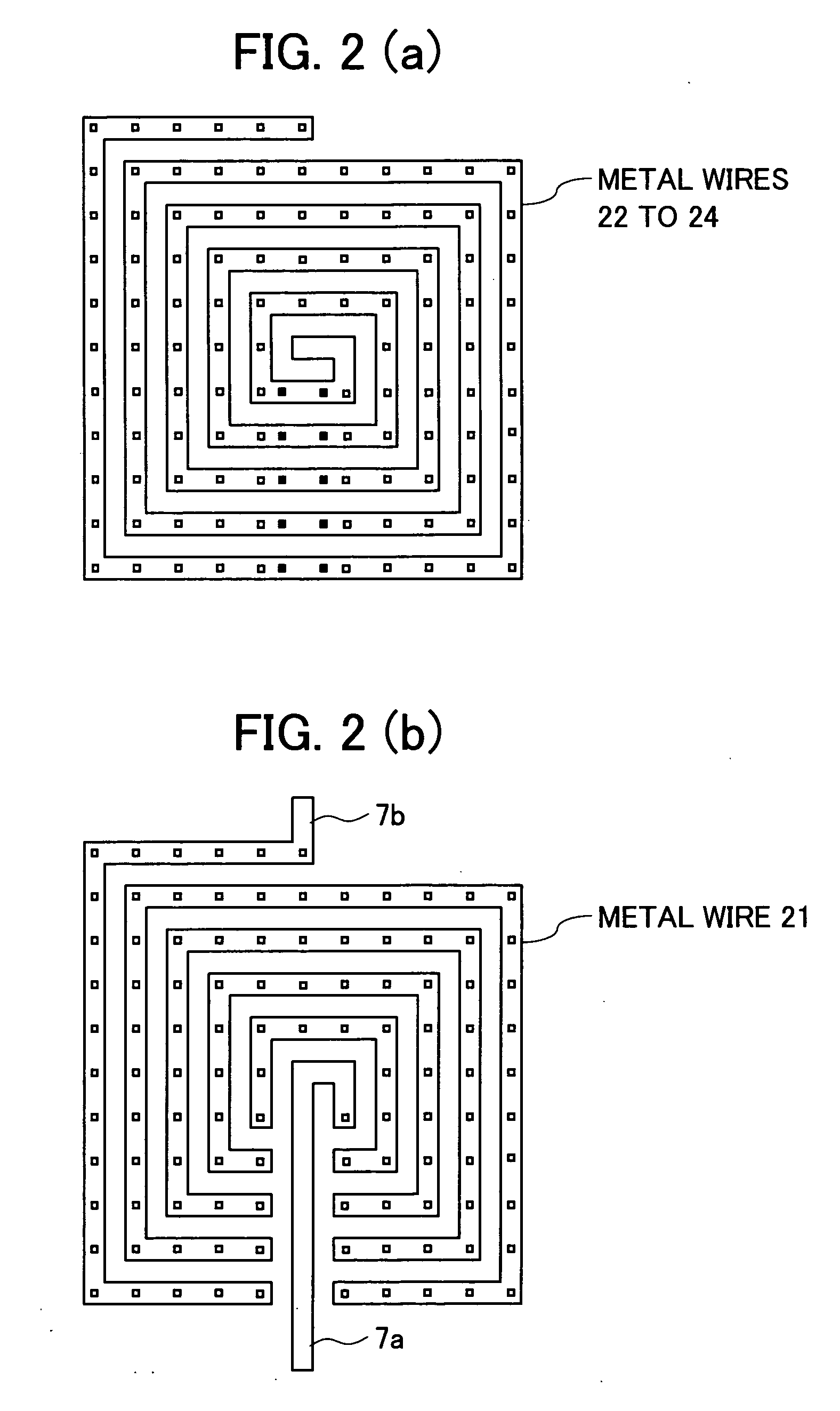

Semiconductor chip with coil antenna and communication system

InactiveUS20050173532A1Good communication characteristicsIncrease parasitic capacitanceLoop antennas with ferromagnetic coreAntenna supports/mountingsElectromagnetic couplingElectrical conductor

The present invention intends to prevent the communication distance from becoming shorter with a reduction in size of a coil antenna to the chip size and with a consequent decrease of an induced voltage. According to the present invention there is provided a semiconductor chip having a coil antenna and a circuit surface and adapted to transmit and receive signals by radio to and from an external device. The semiconductor chip has a configuration for increasing an electromagnetic coupling coefficient between the coil antenna and the external device. According to a concrete example thereof, a magnetic material is disposed, the coil antenna is formed by a stacked structure comprising plural conductor layers and insulating layers superimposed one on another, or the coil antenna is disposed outside an external form of a circuit of the semiconductor chip.

Owner:HITACHI LTD

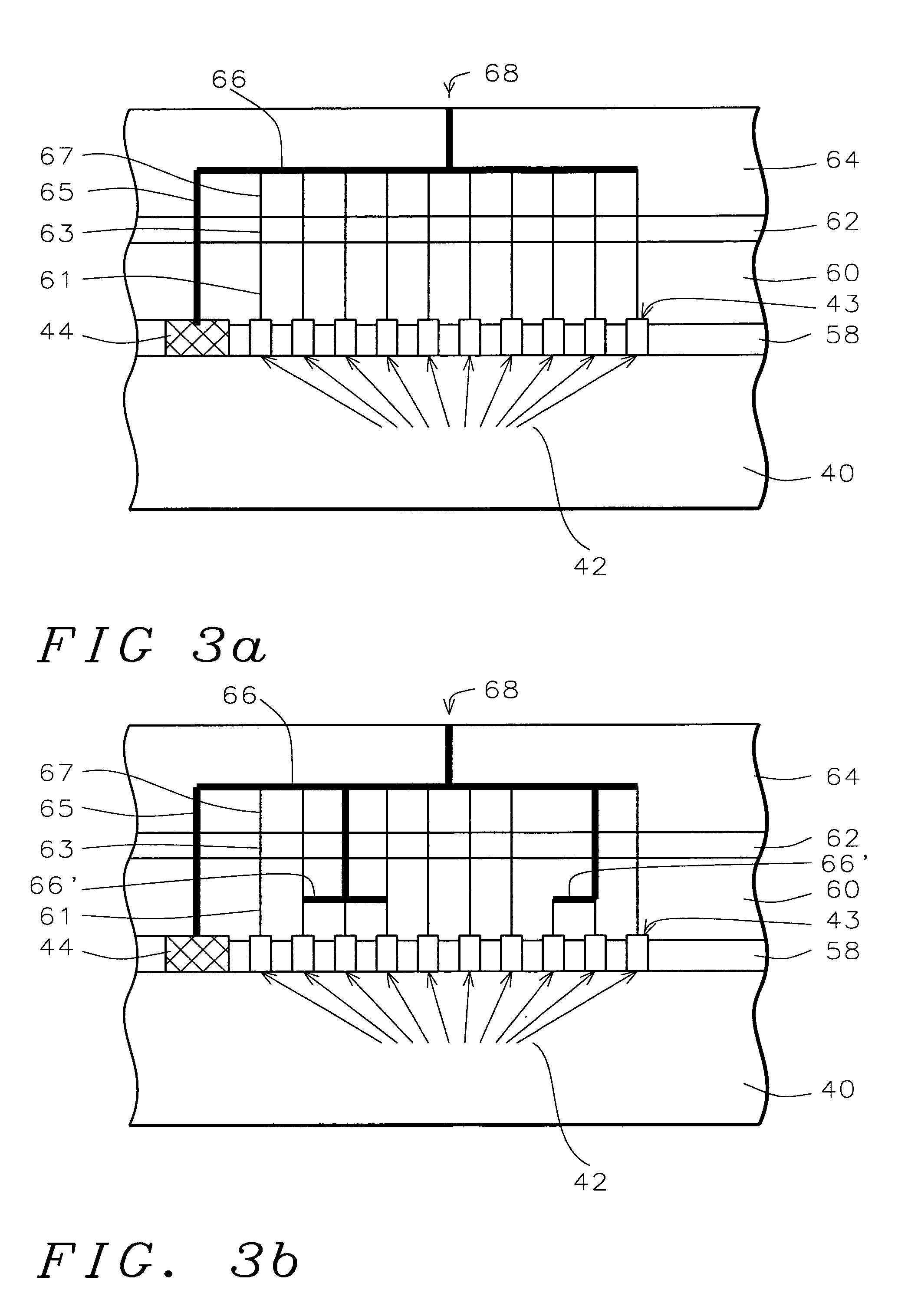

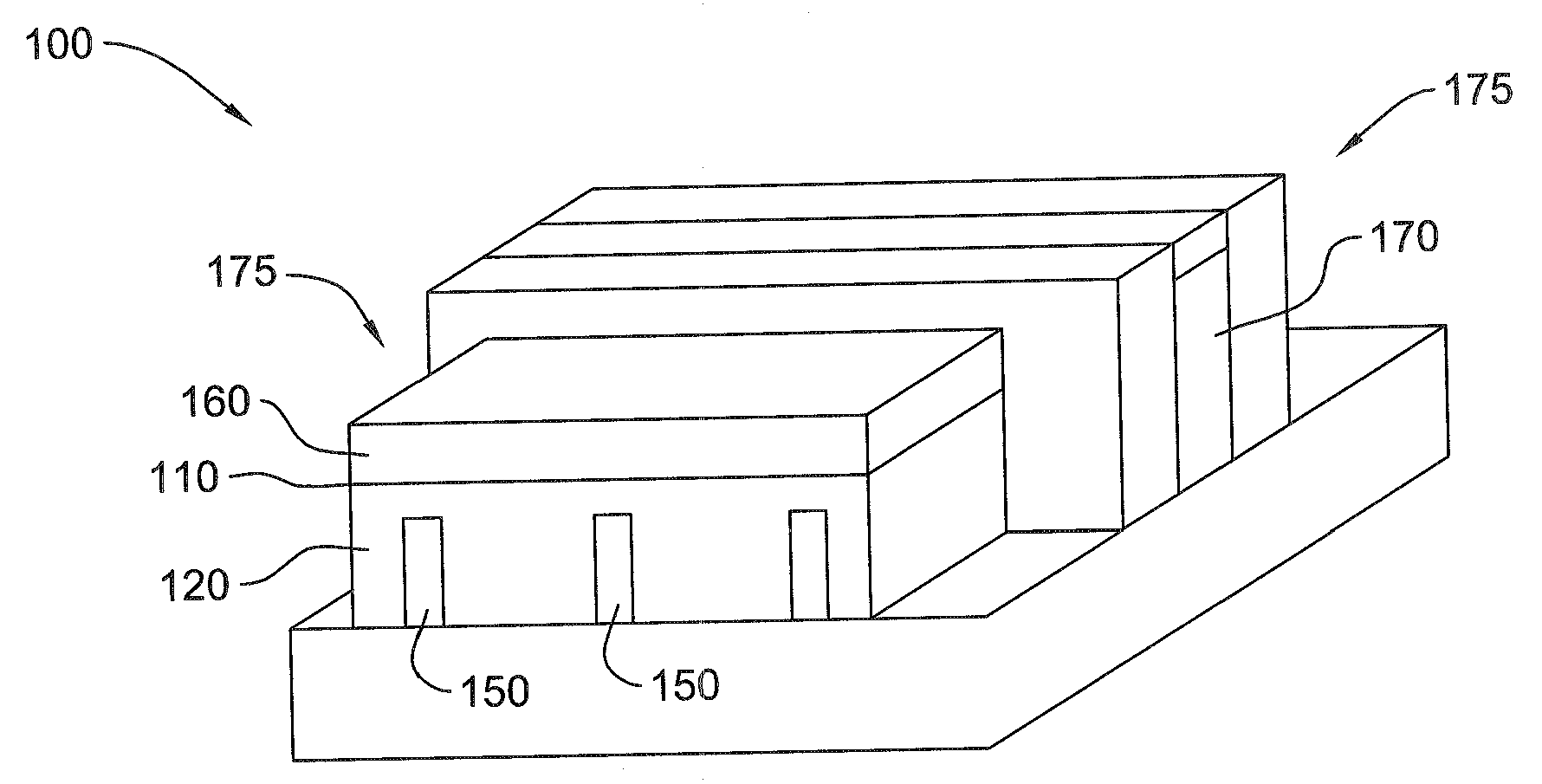

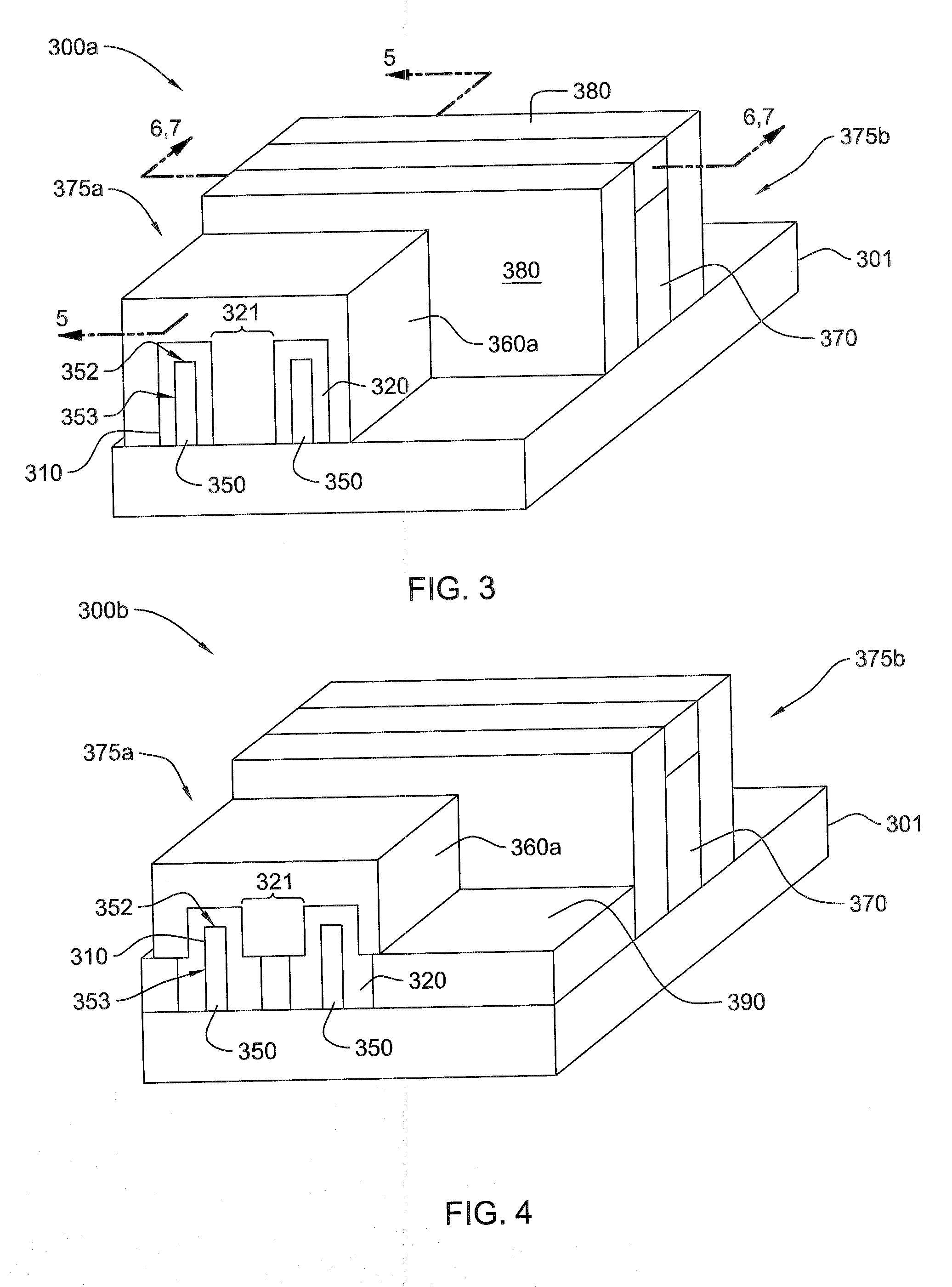

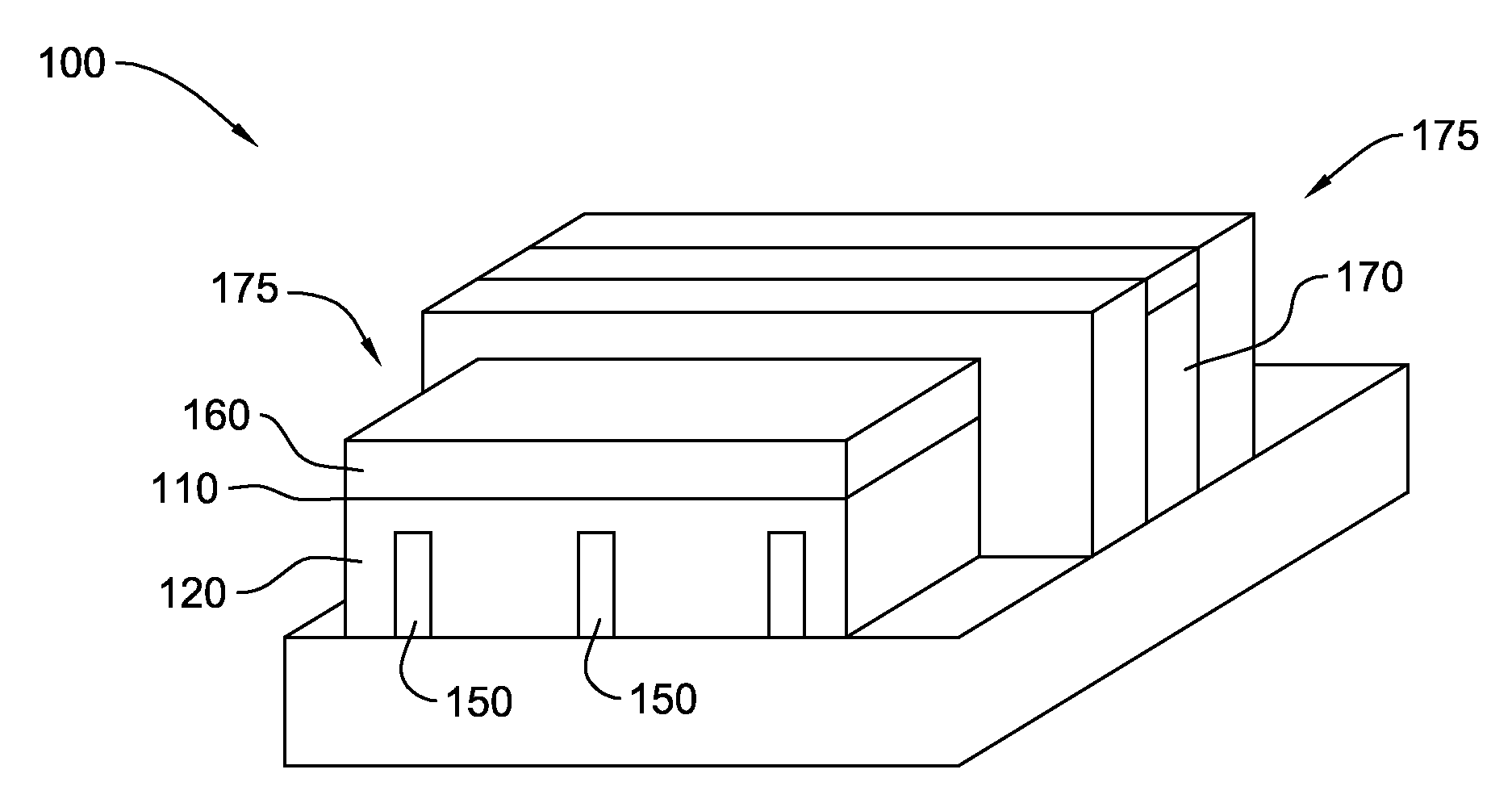

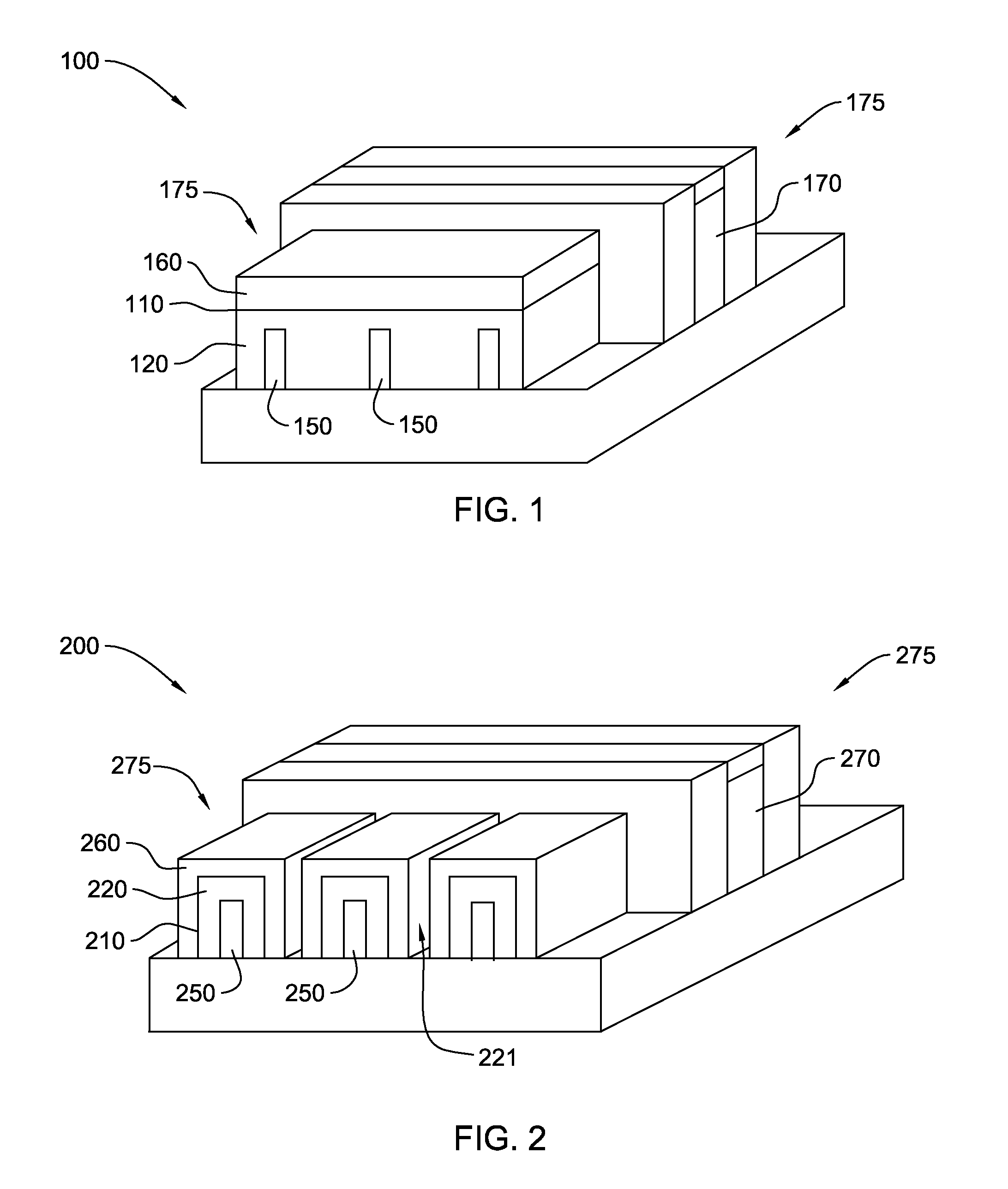

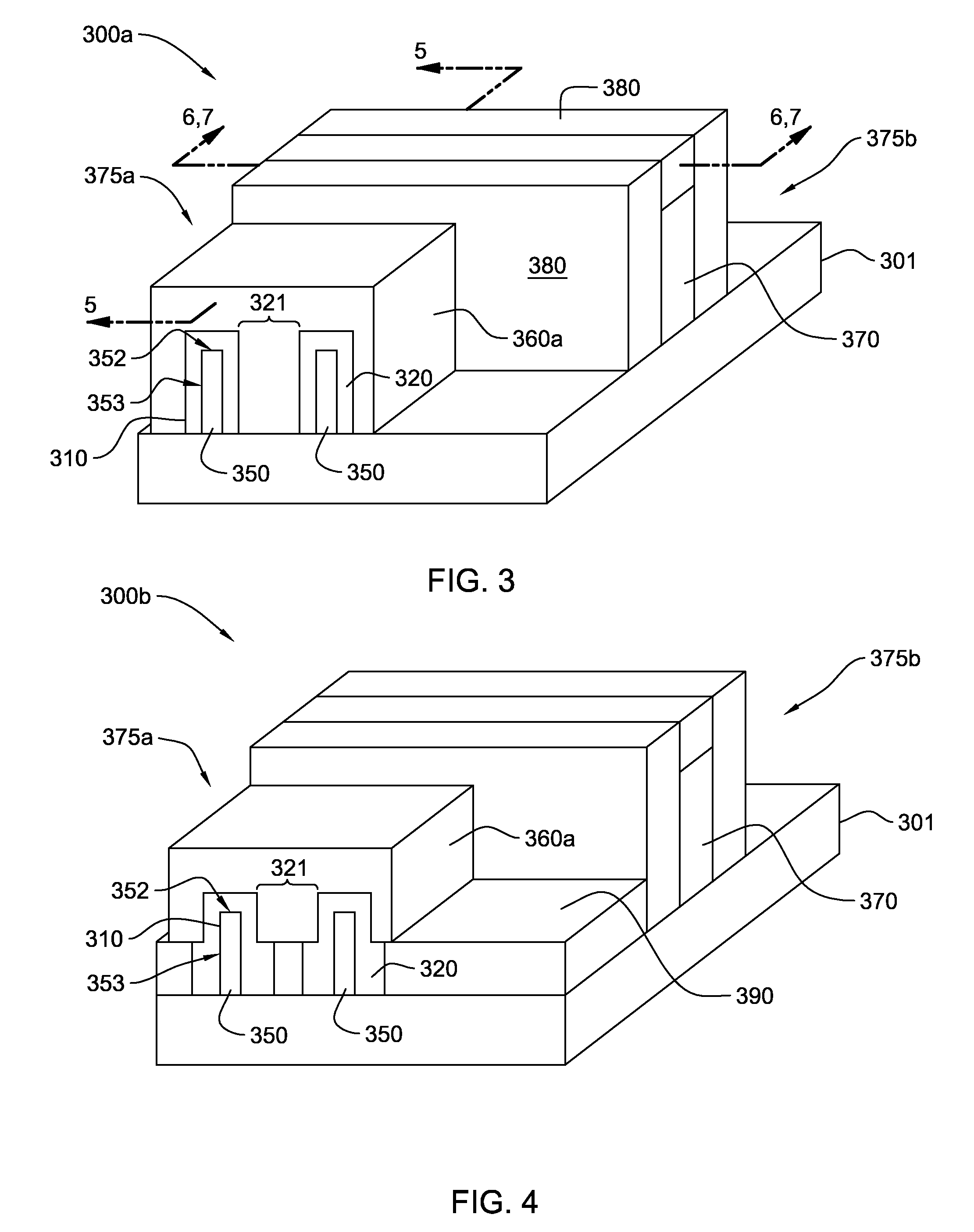

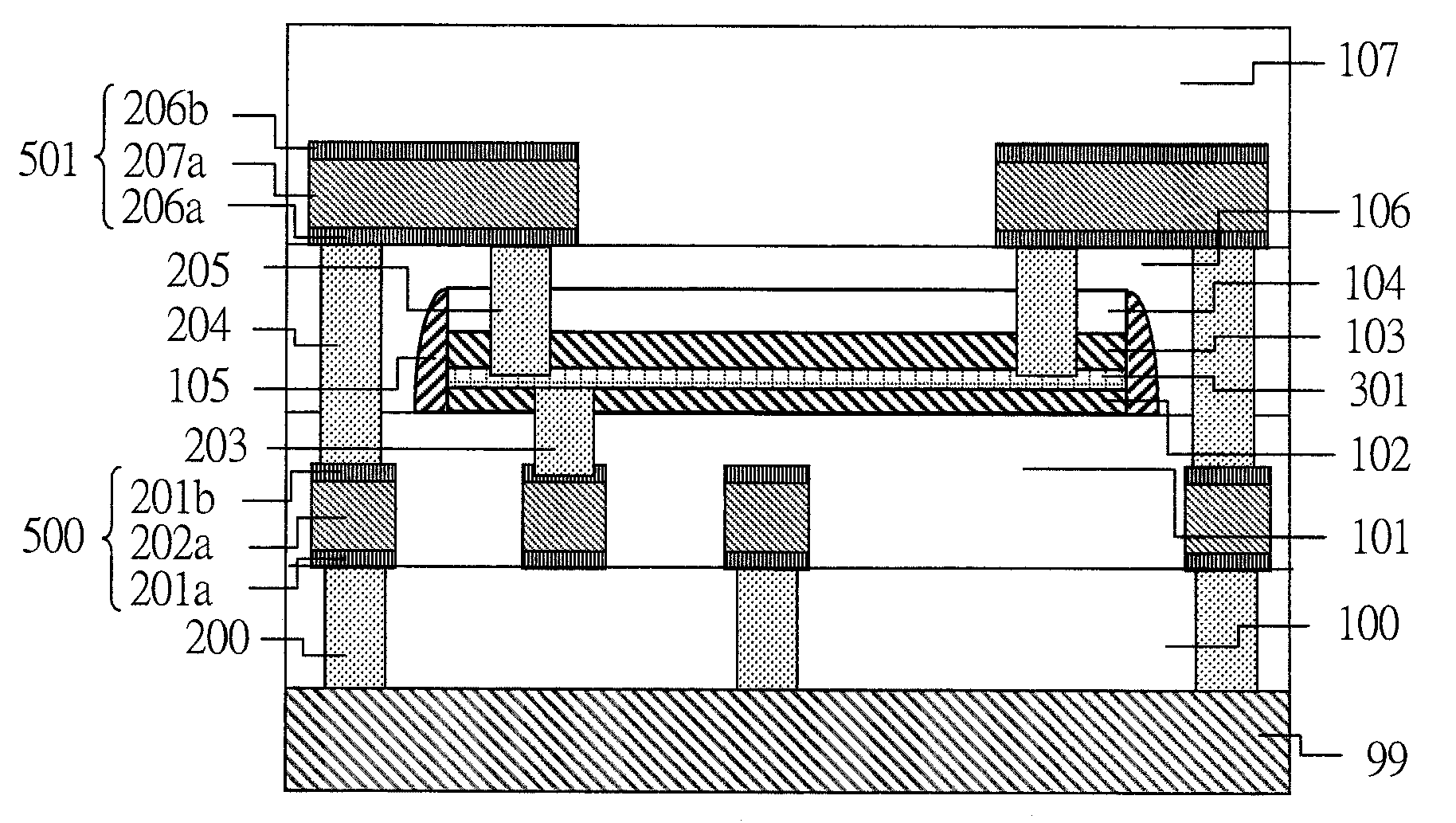

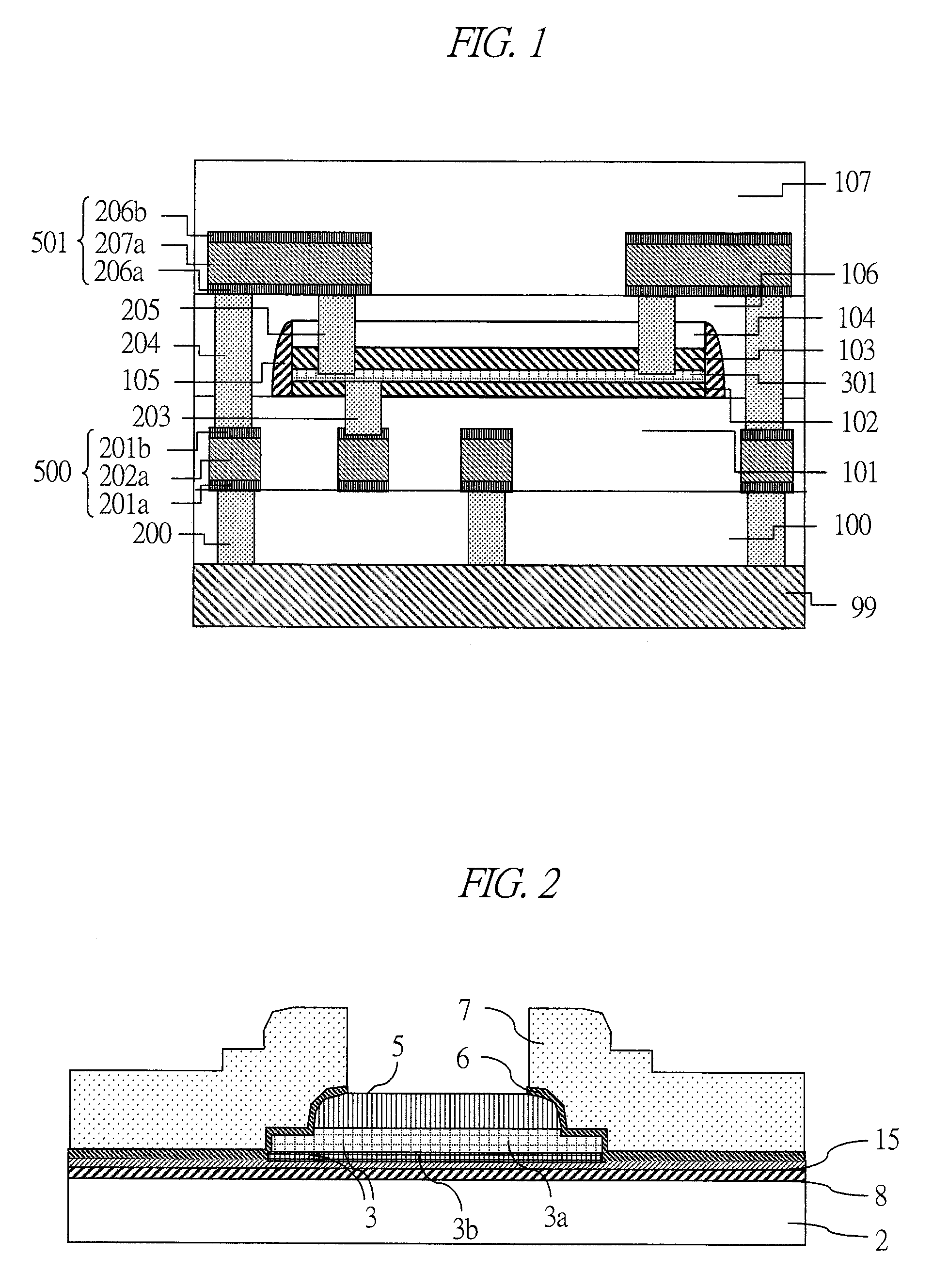

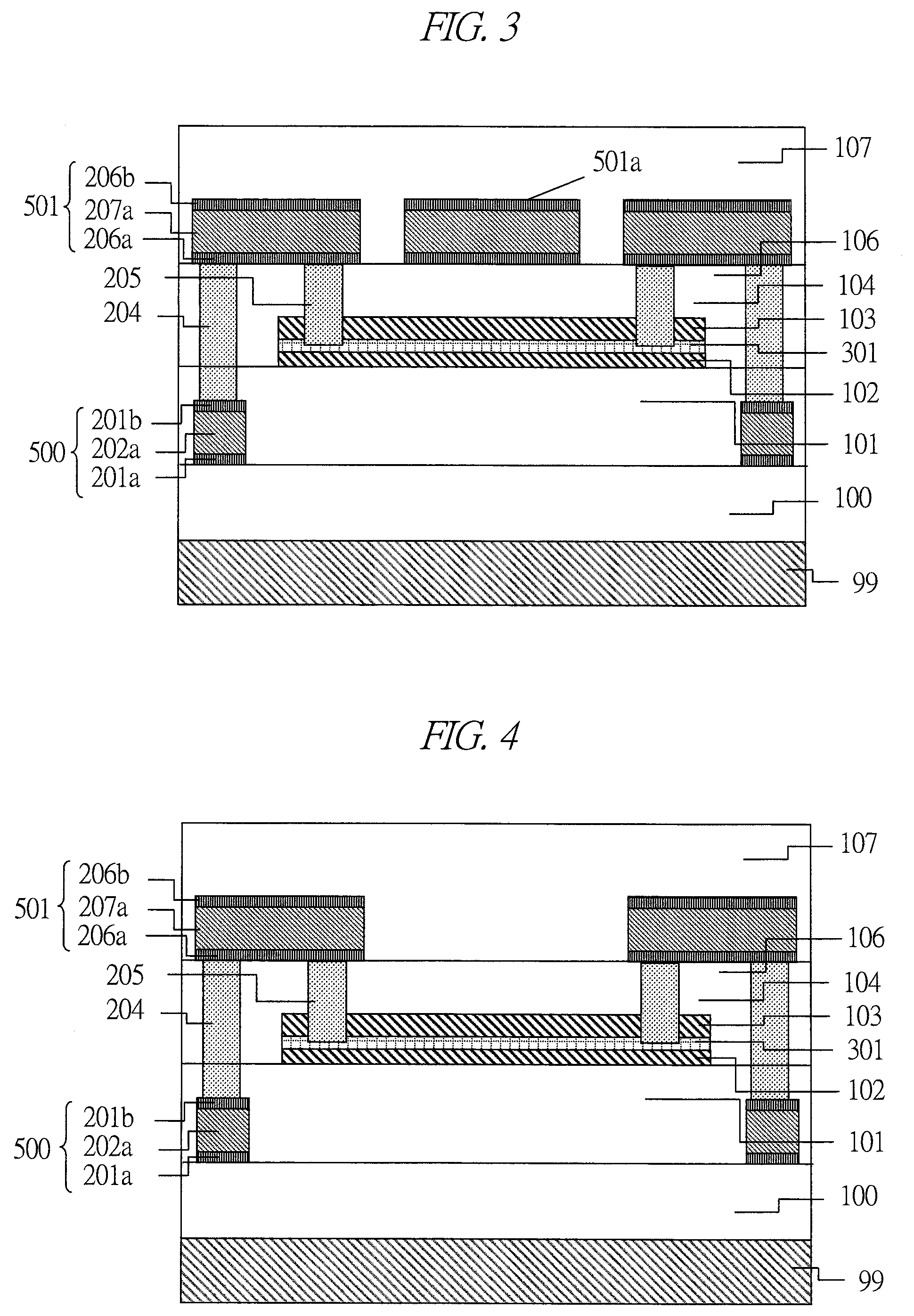

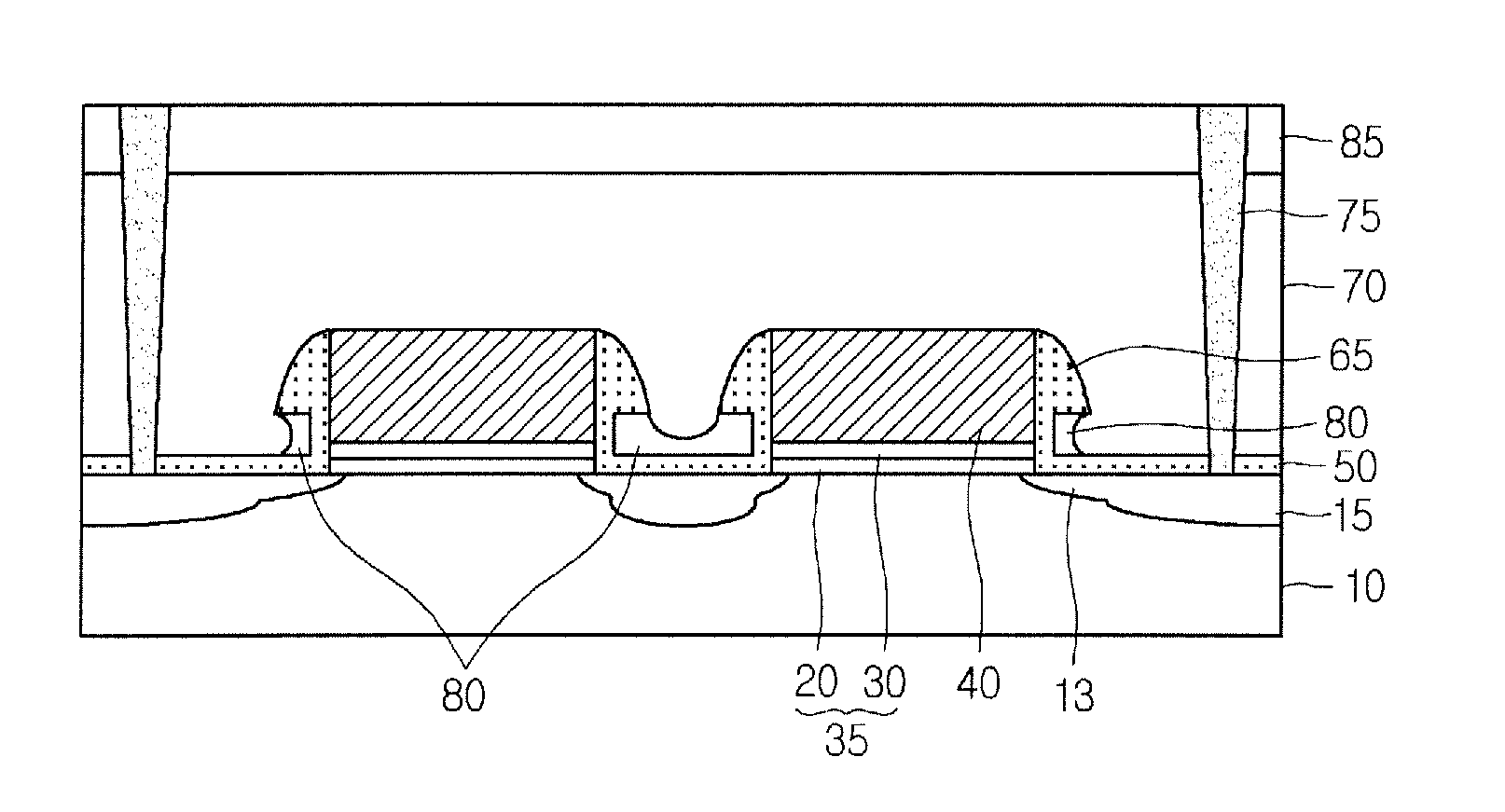

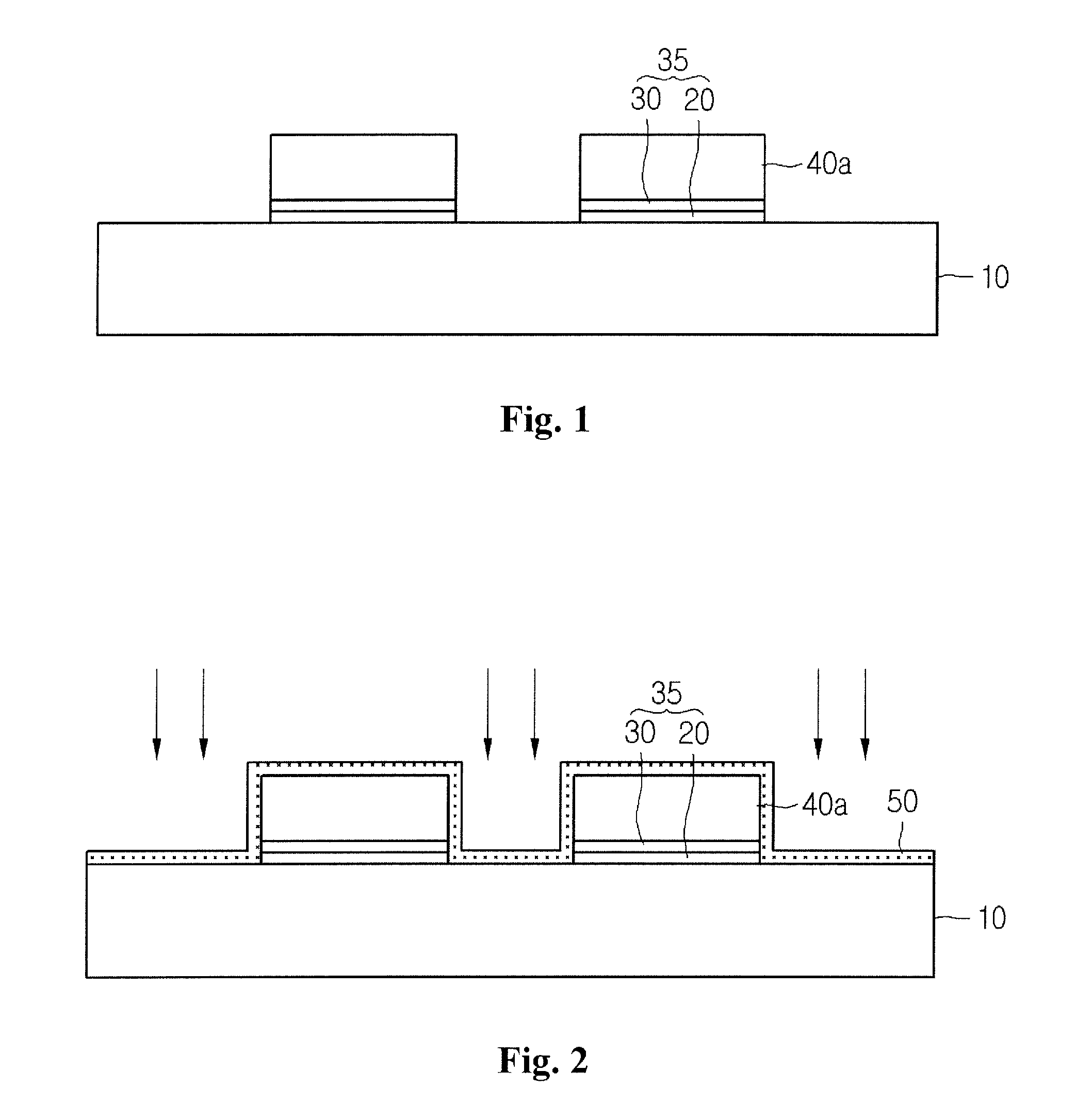

Fin-type field effect transistor structure with merged source/drain silicide and method of forming the structure

ActiveUS20090101978A1Increase parasitic capacitanceSeries resistance is minimizedSemiconductor devicesMetal silicideParasitic capacitance

Disclosed herein are embodiments of a design structure of a multiple fin fin-type field effect transistor (i.e., a multiple fin dual-gate or tri-gate field effect transistor) in which the multiple fins are partially or completely merged by a highly conductive material (e.g., a metal silicide). Merging the fins in this manner allow series resistance to be minimized with little, if any, increase in the parasitic capacitance between the gate and source / drain regions. Merging the semiconductor fins in this manner also allows each of the source / drain regions to be contacted by a single contact via as well as more flexible placement of that contact via.

Owner:GLOBALFOUNDRIES US INC

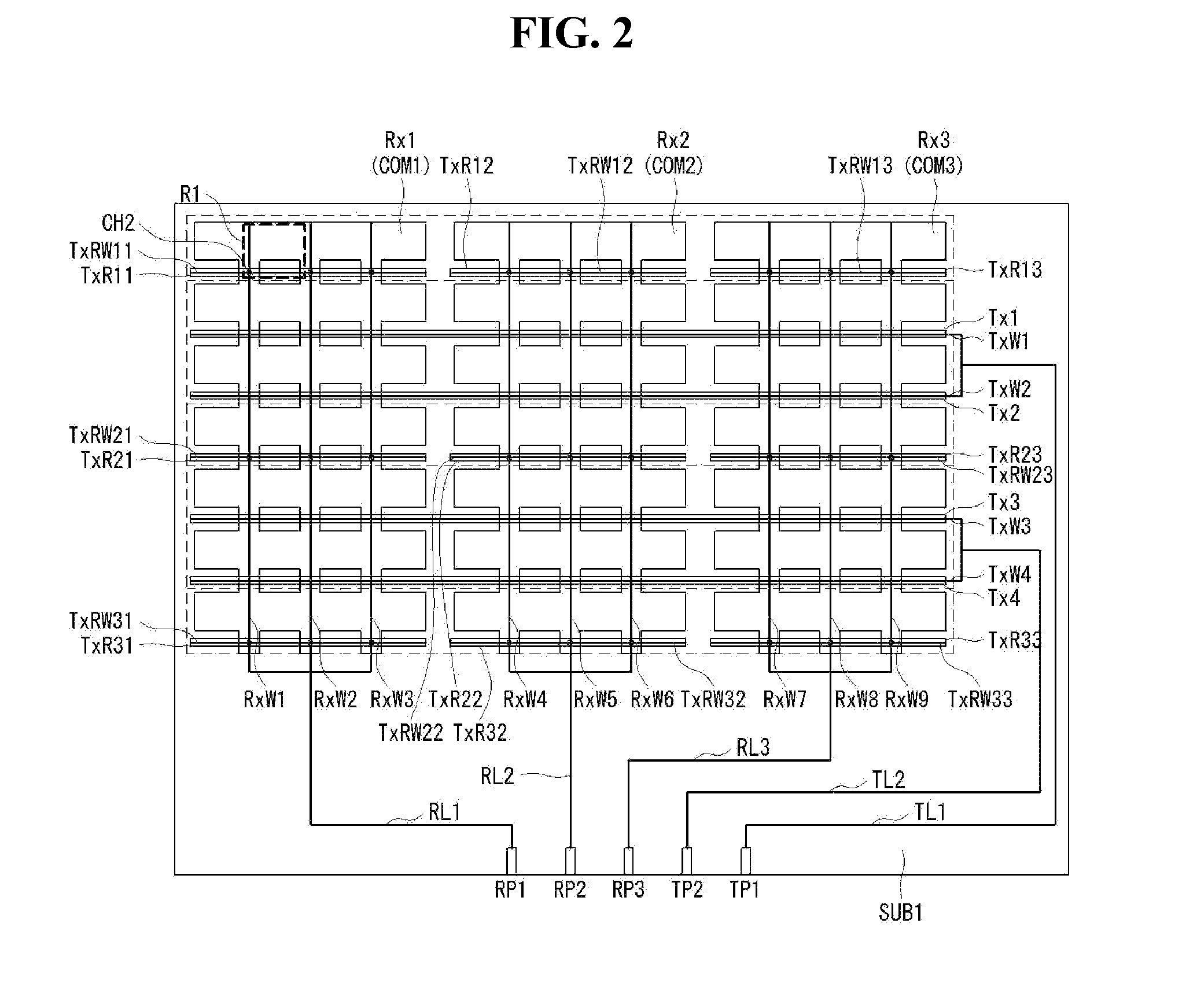

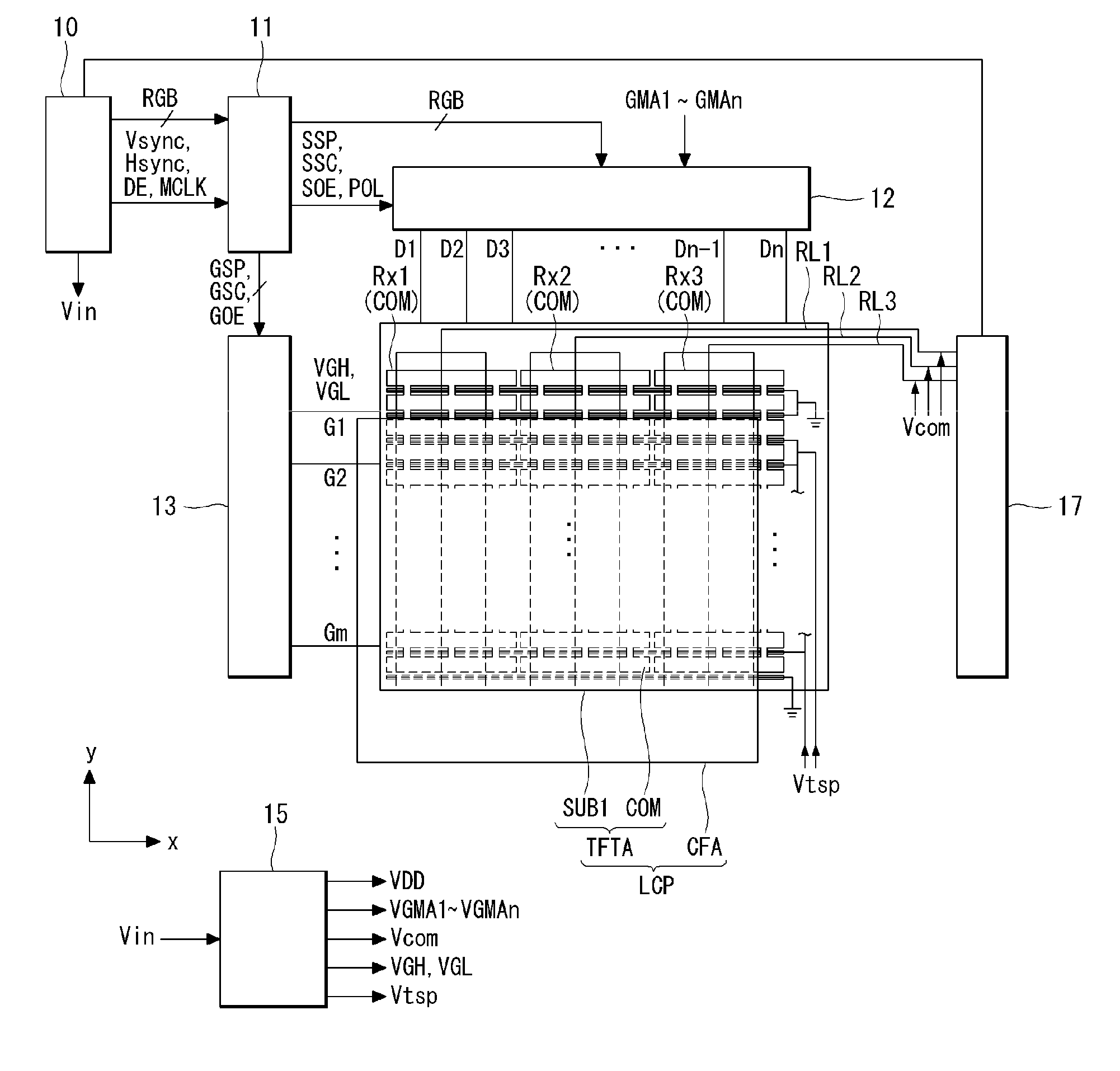

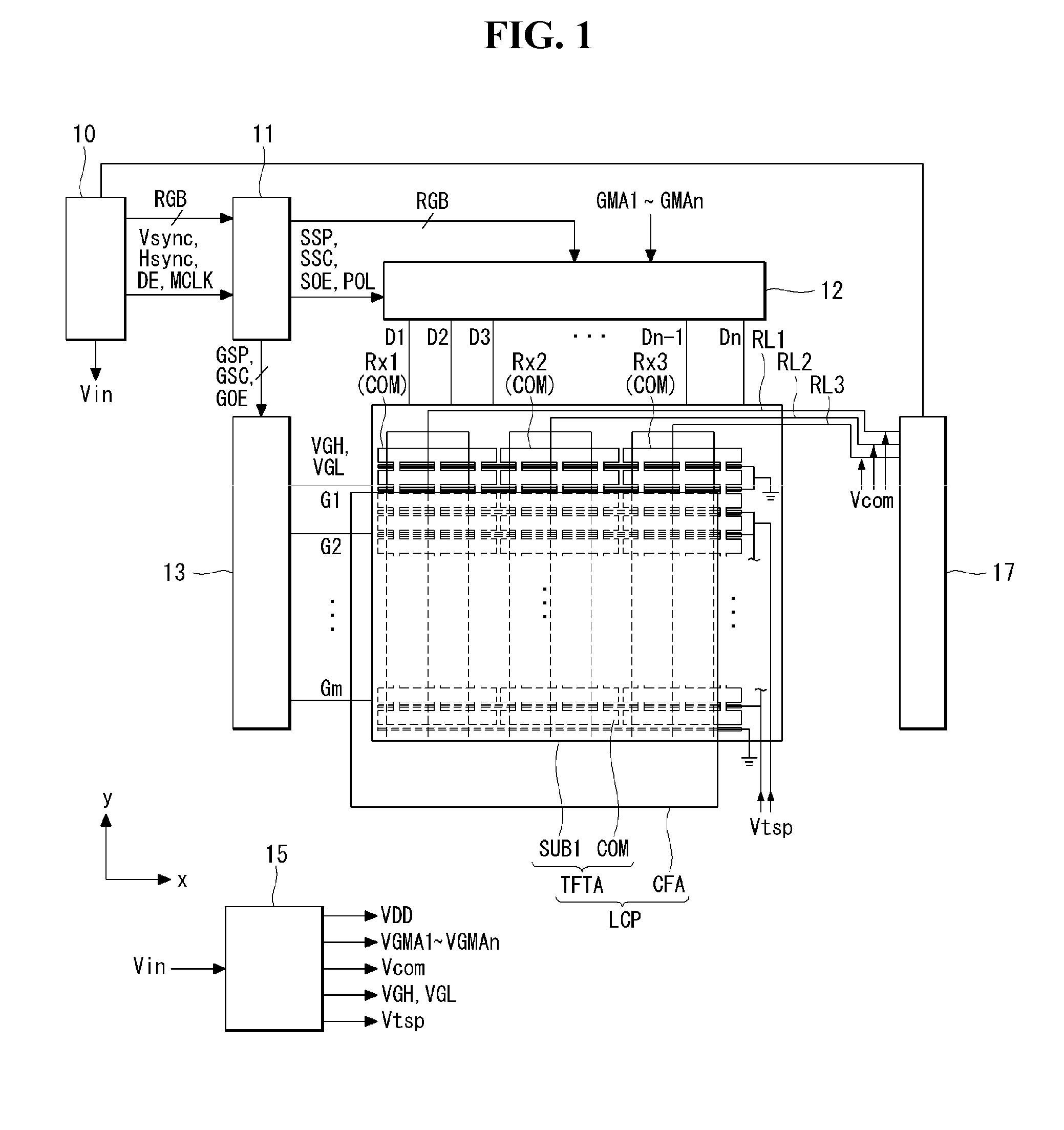

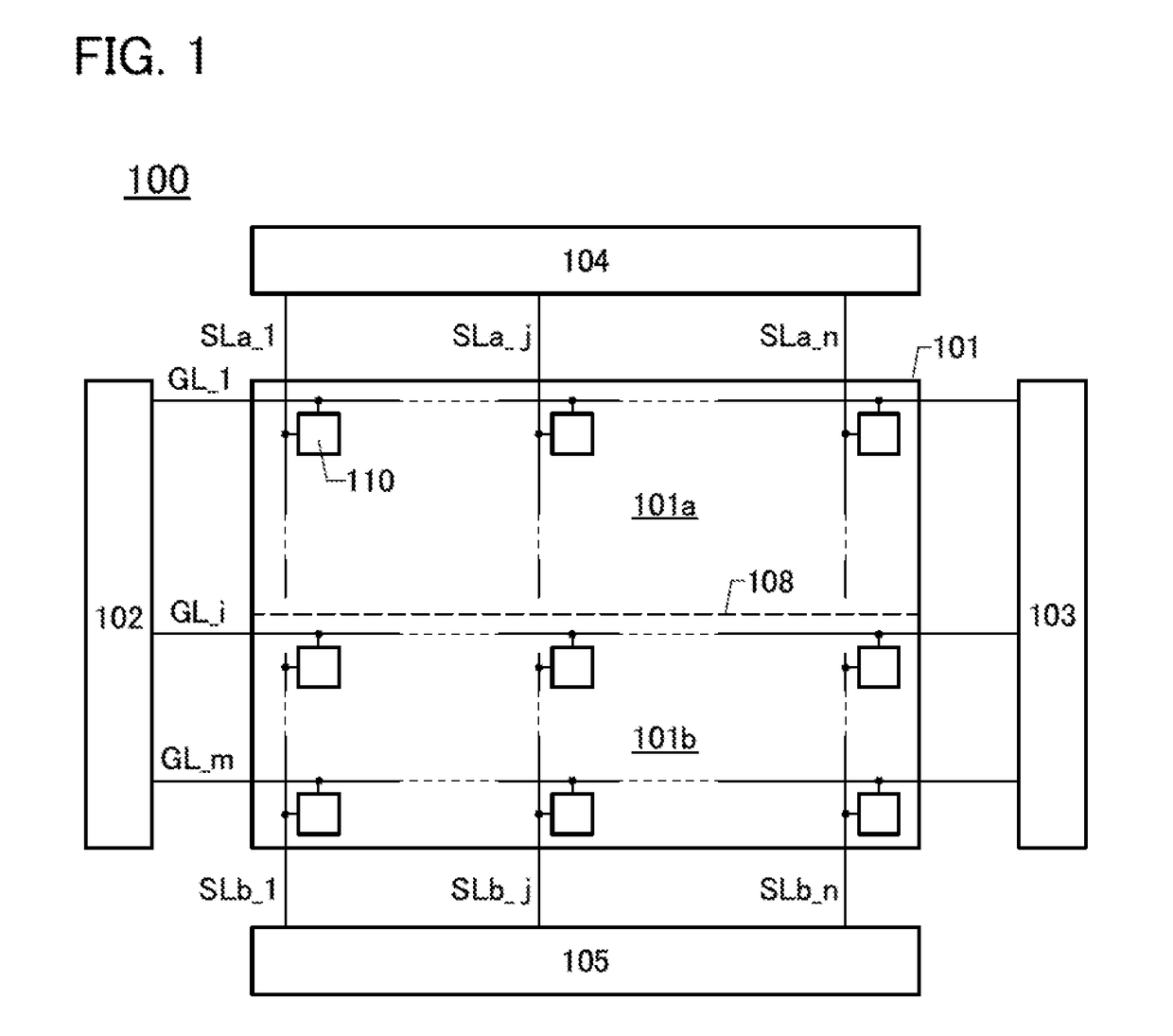

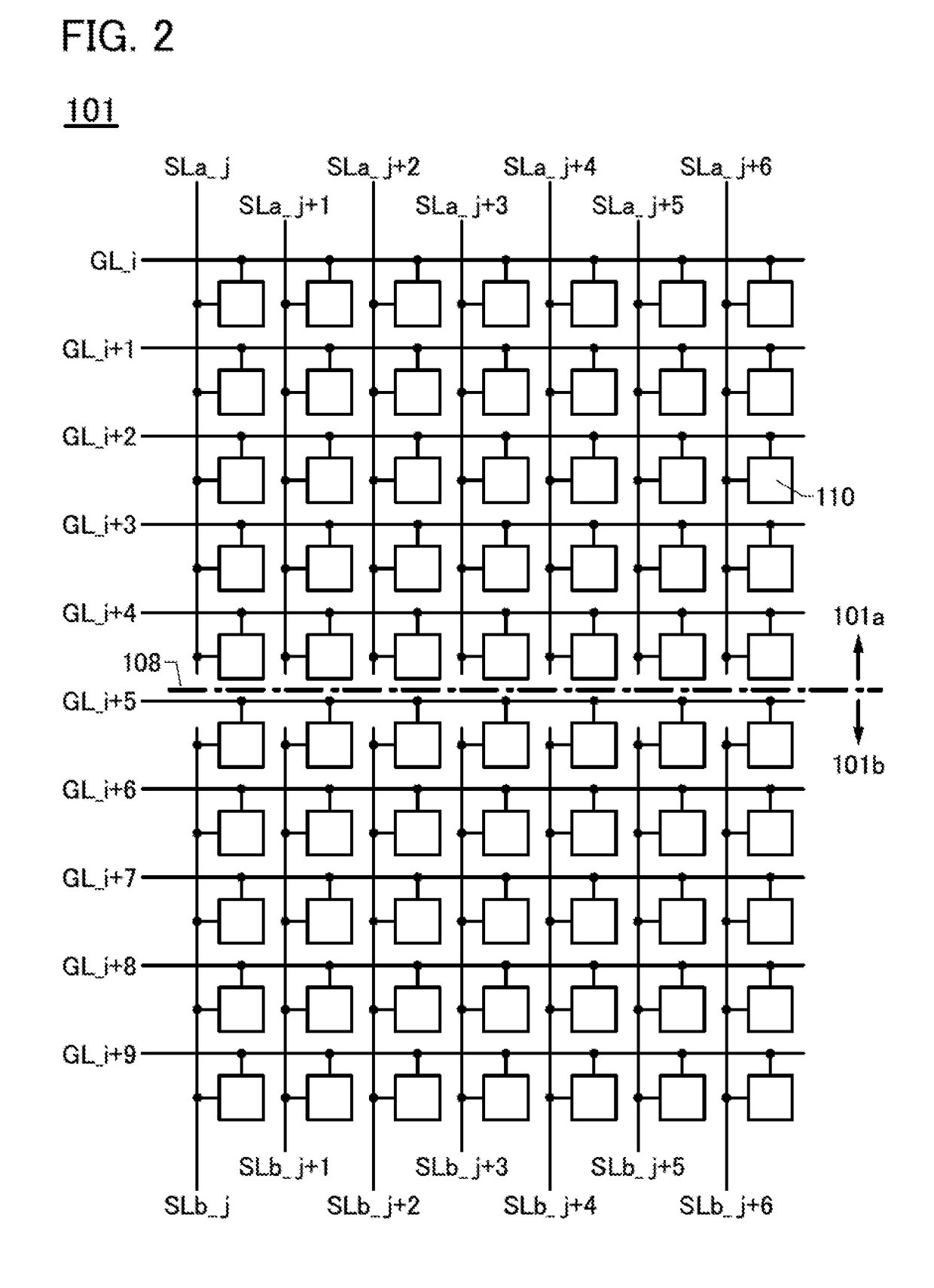

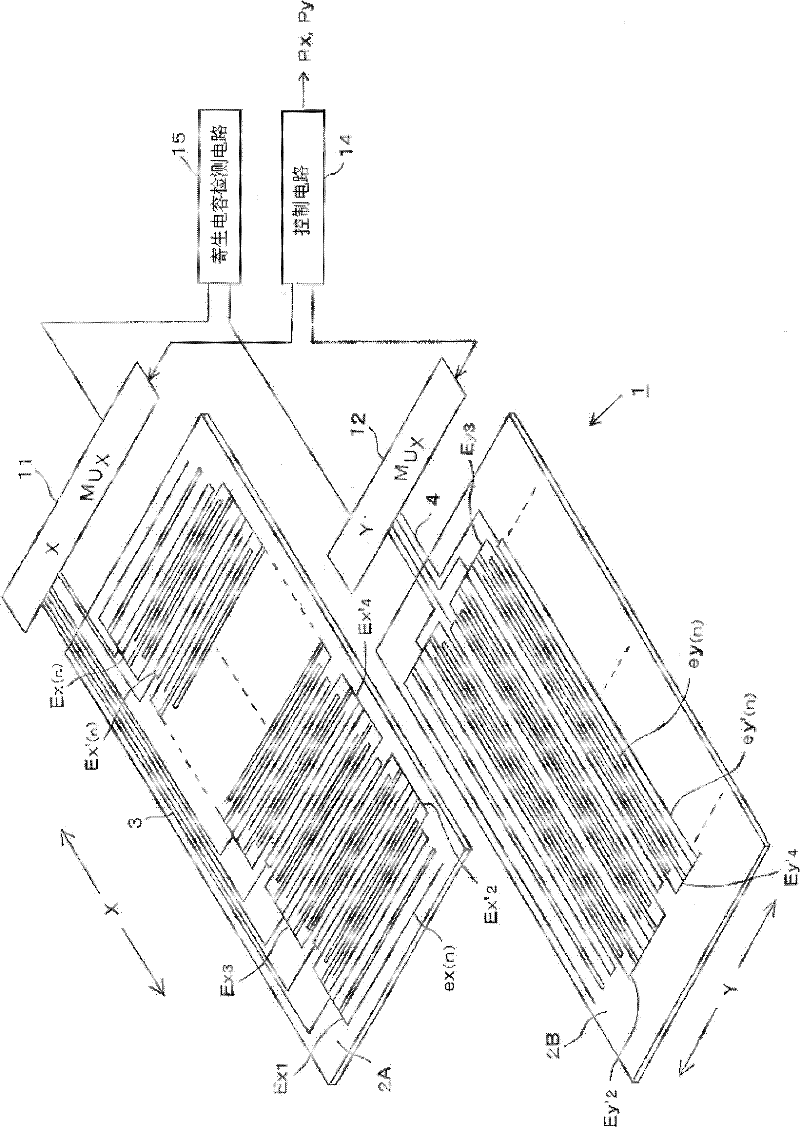

Touch sensor integrated type display device

ActiveUS20140168537A1Prevent in touch sensitivityIncrease parasitic capacitanceNon-linear opticsInput/output processes for data processingDisplay devicePhysics

A touch sensor integrated type display device includes gate lines and data lines; a plurality of pixel electrodes respectively formed in pixel areas defined by crossings of the gate and data lines; a first electrode formed between first pixel electrodes and in parallel with a first gate line of the gate lines, the first pixel electrodes being adjacent to each other with the first gate line interposed therebetween; second electrodes formed between second pixel electrodes and arranged in a line in parallel with a second gate line adjacent to the first gate line, the second pixel electrodes being adjacent to each other with the second gate line interposed therebetween; and third electrodes, each of which is formed in parallel with the data lines and contacts the second electrodes, at least a portion of each of the third electrodes overlapping the first and second pixel electrodes.

Owner:LG DISPLAY CO LTD

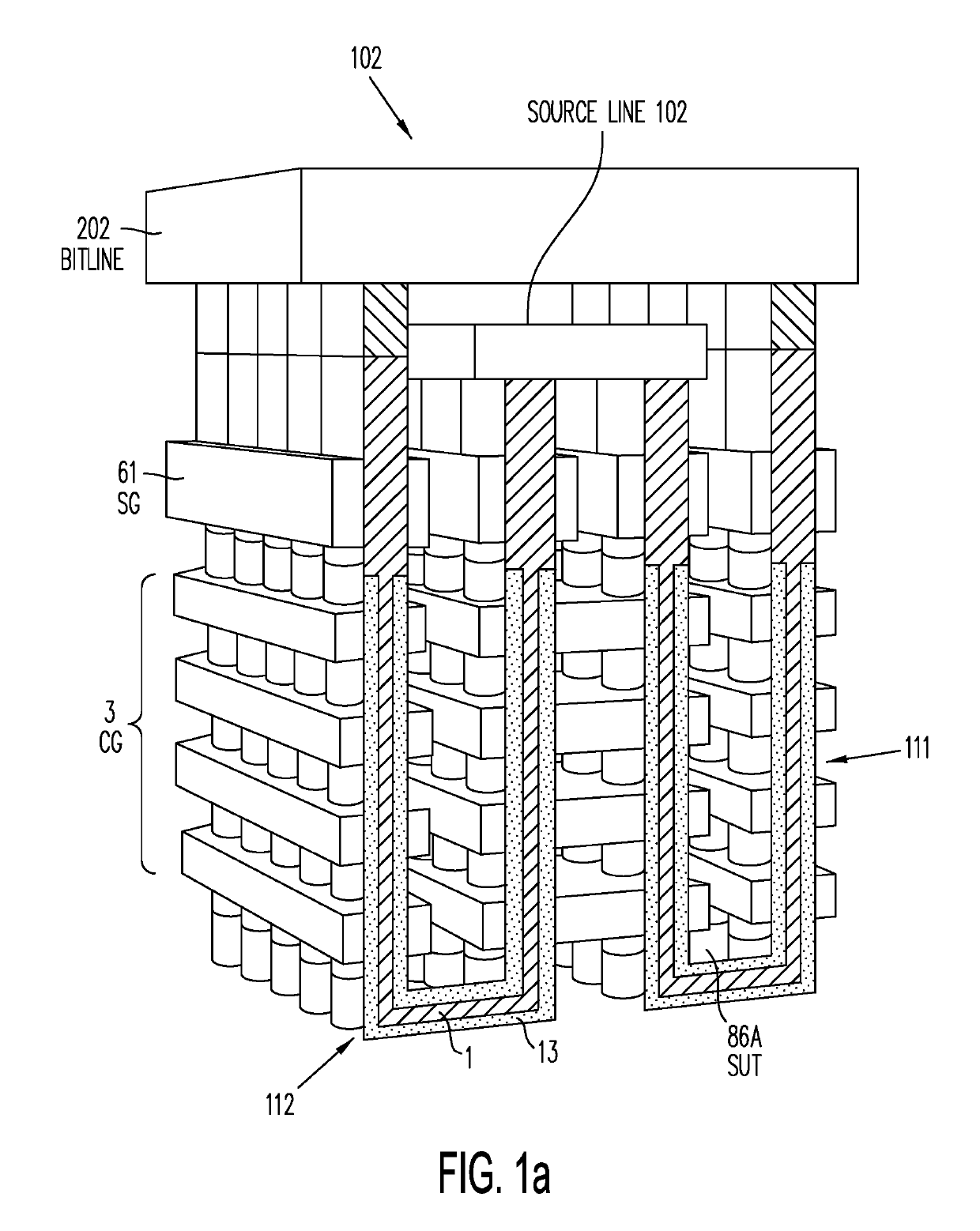

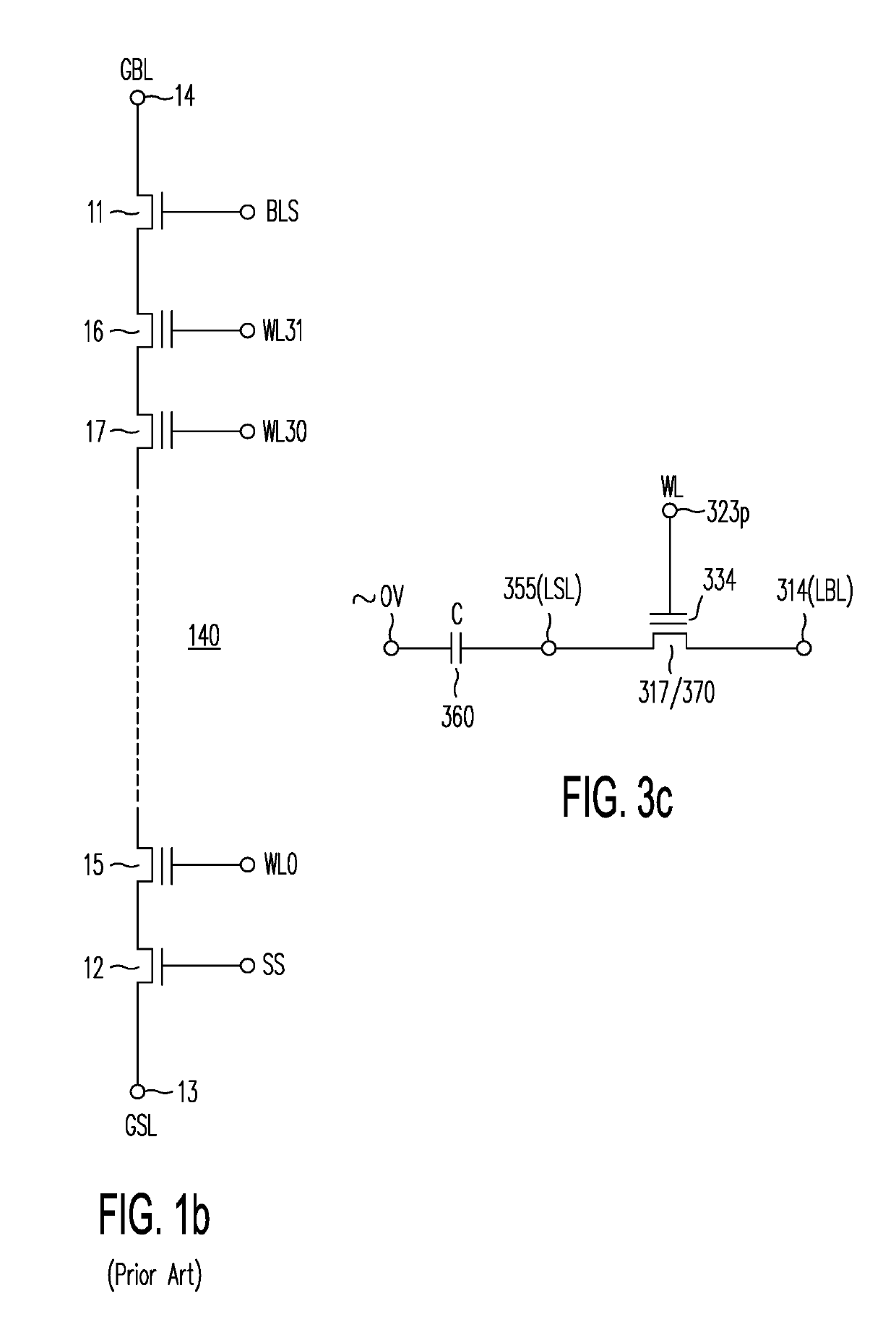

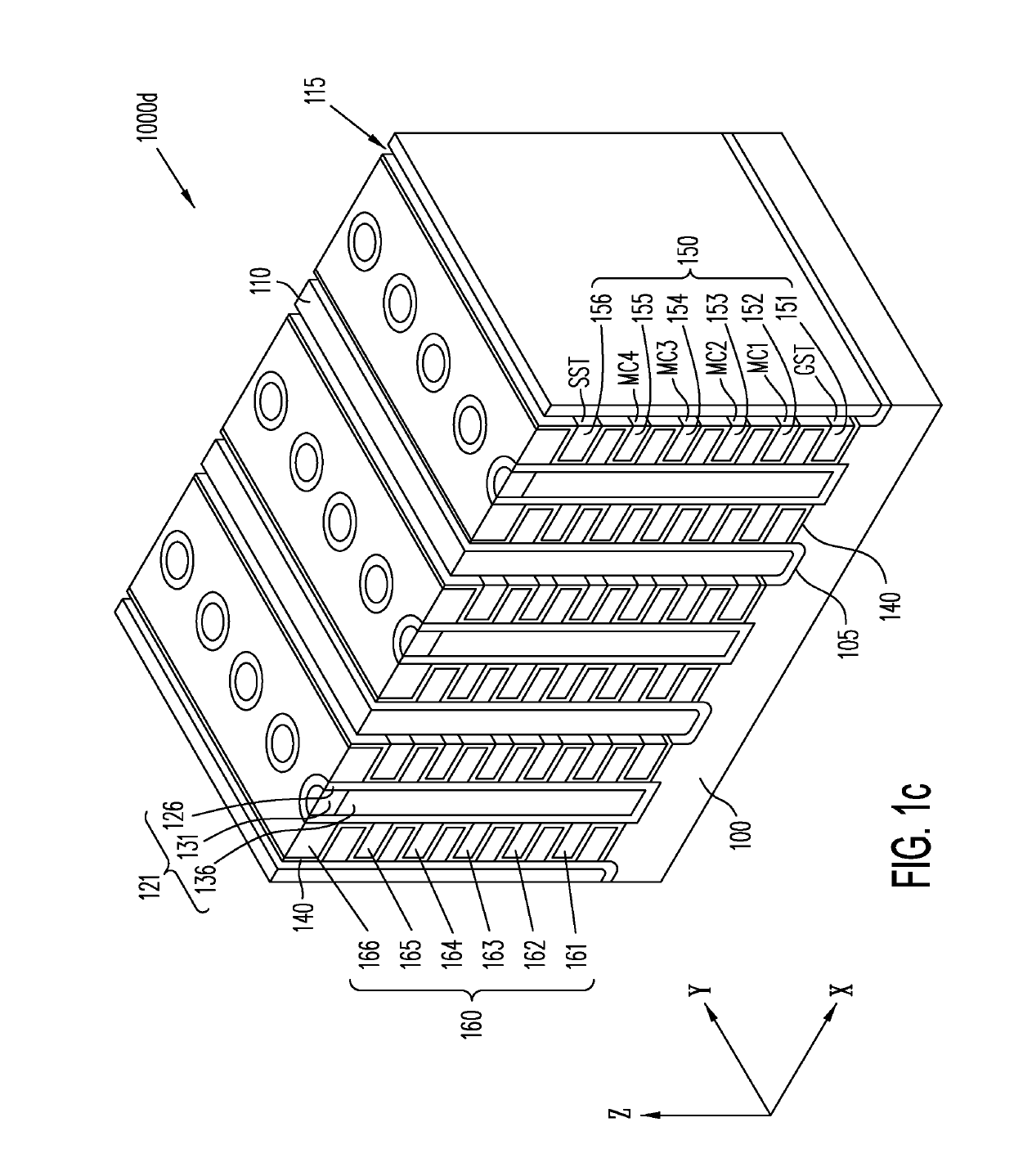

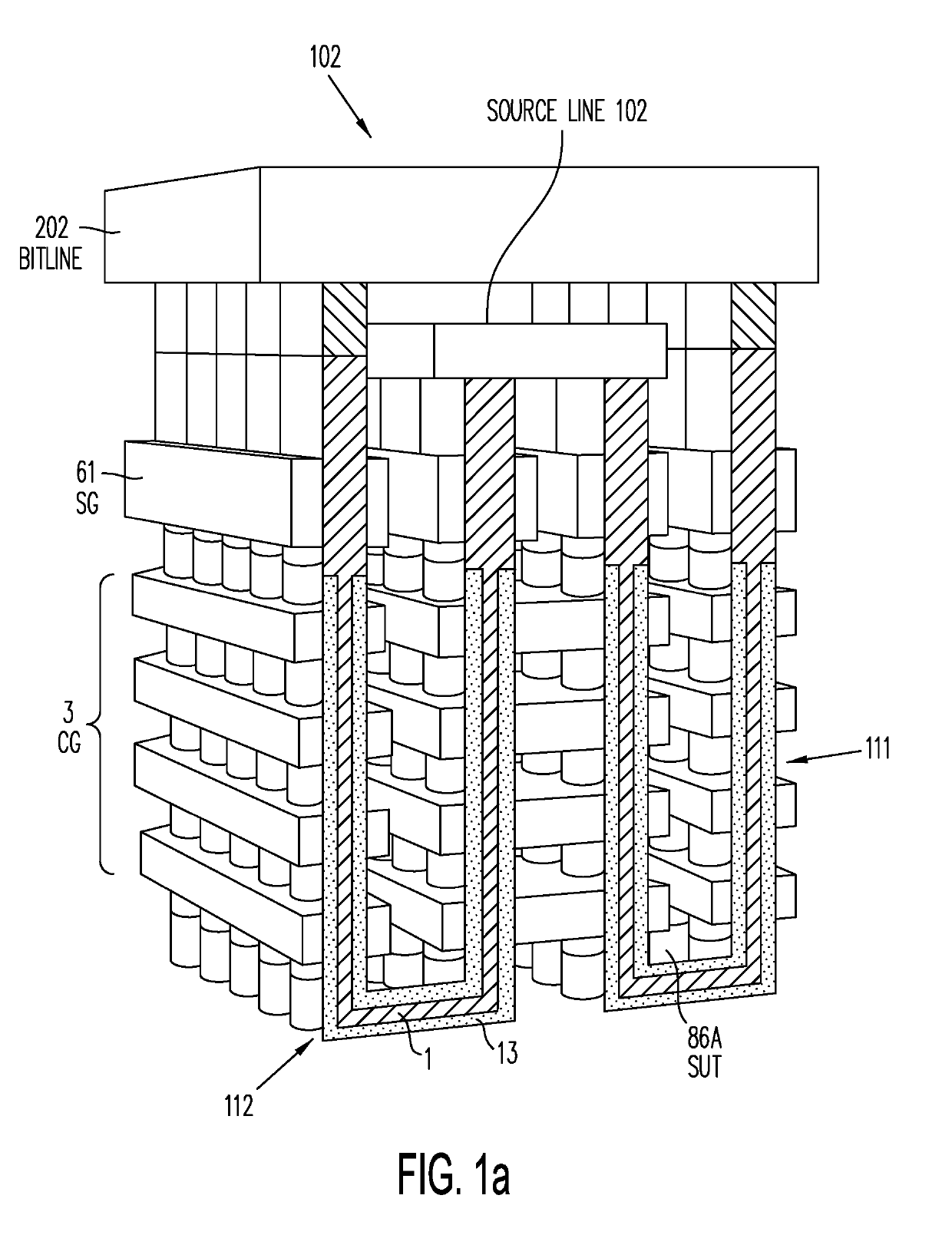

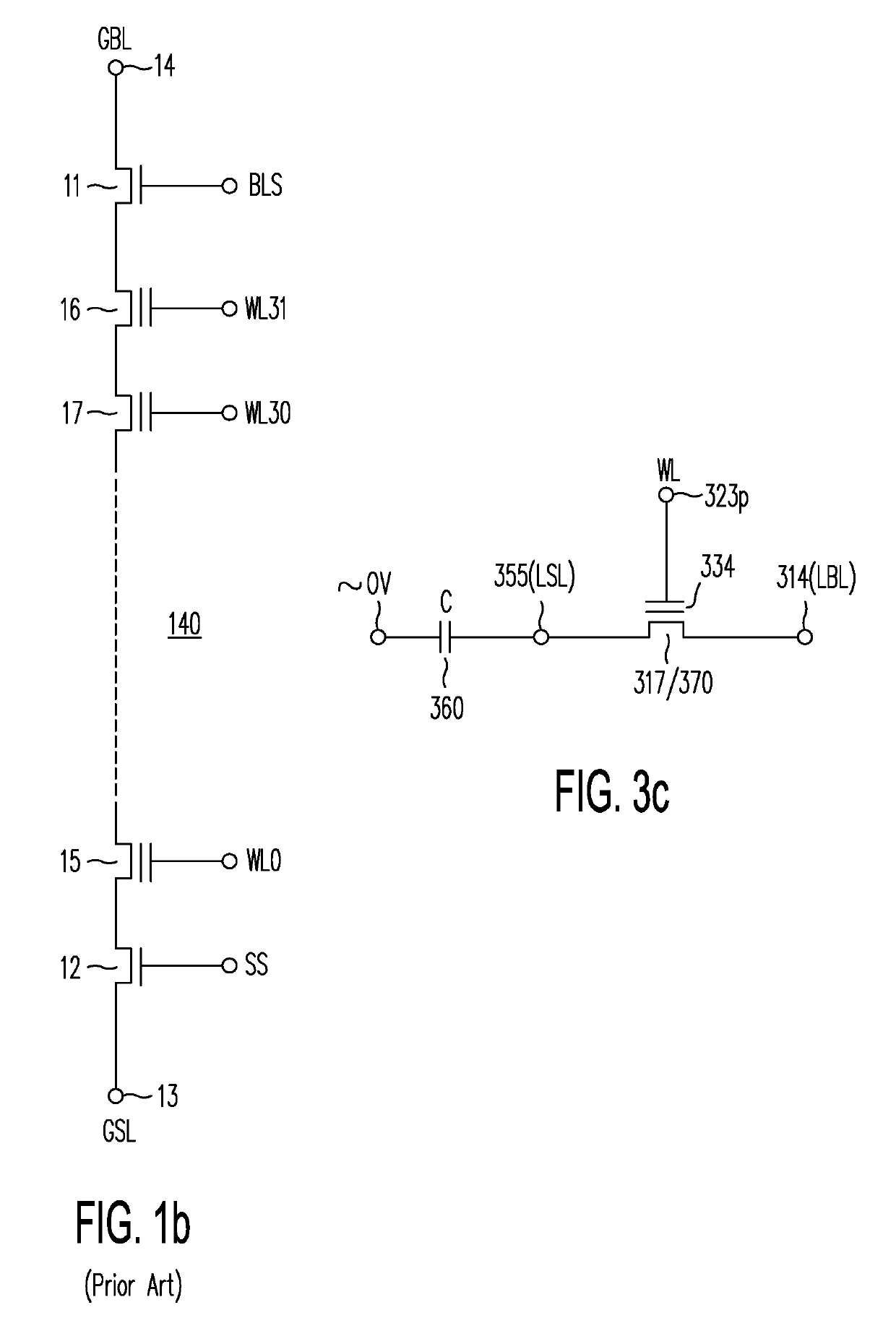

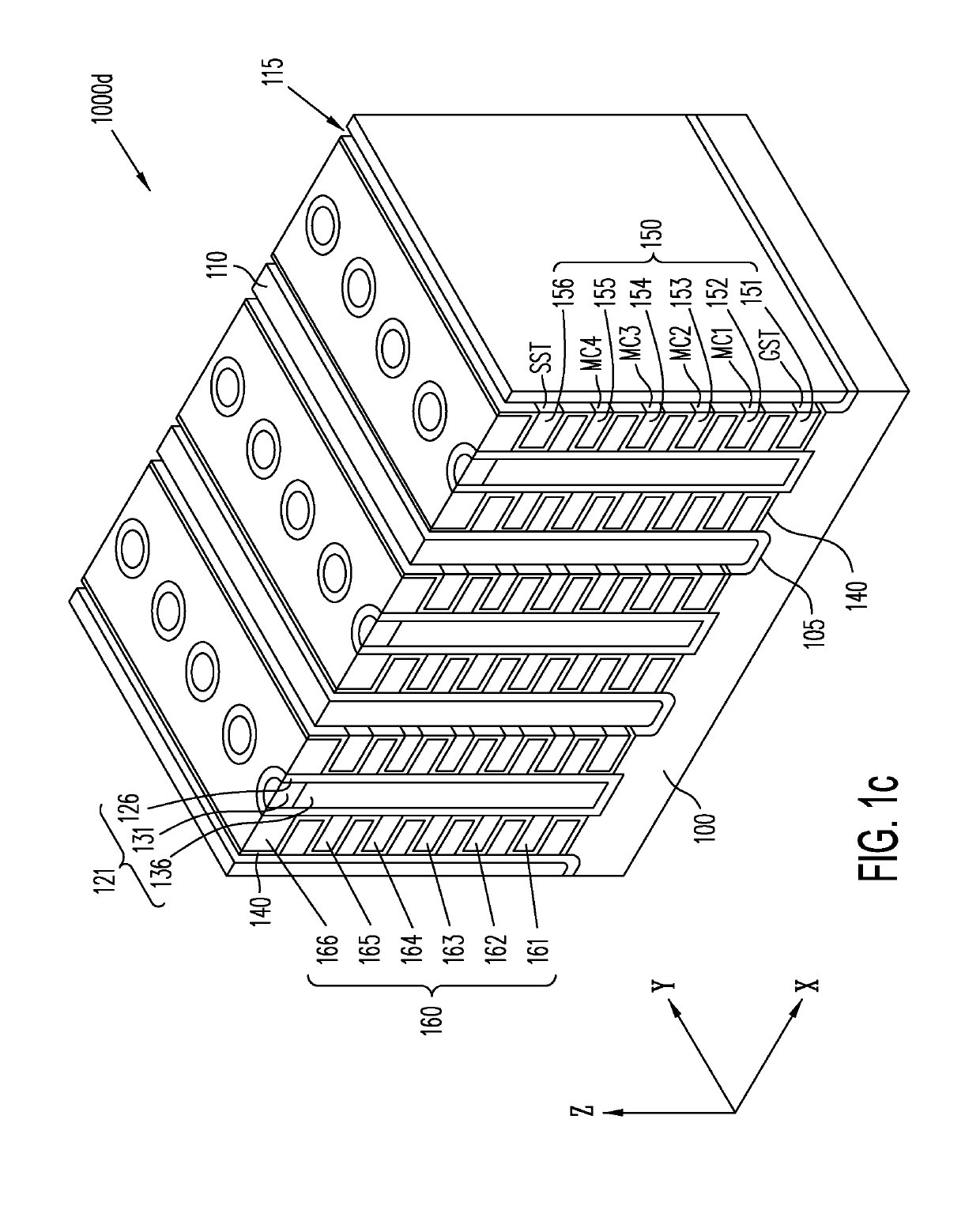

Three-dimensional vertical NOR Flash Thin-Film Transistor Strings

ActiveUS20190319044A1Lower read latencyReduce sensitivityTransistorSemiconductor/solid-state device detailsAudio power amplifierEngineering

A memory structure, includes active columns of polysilicon formed above a semiconductor substrate, each active column includes one or more vertical NOR strings, with each NOR string having thin-film storage transistors sharing a local source line and a local bit line, the local bit line is connected by one segment of a segmented global bit line to a sense amplifier provided in the semiconductor substrate.

Owner:SUNRISE MEMORY CORP

Three-dimensional vertical NOR Flash Thin-Film Transistor Strings

ActiveUS20190244971A1Lower read latencyReduce sensitivityTransistorSemiconductor/solid-state device detailsSemiconductorSense amplifier

A memory structure, includes active columns of polysilicon formed above a semiconductor substrate, each active column includes one or more vertical NOR strings, with each NOR string having thin-film storage transistors sharing a local source line and a local bit line, the local bit line is connected by one segment of a segmented global bit line to a sense amplifier provided in the semiconductor substrate.

Owner:SUNRISE MEMORY CORP

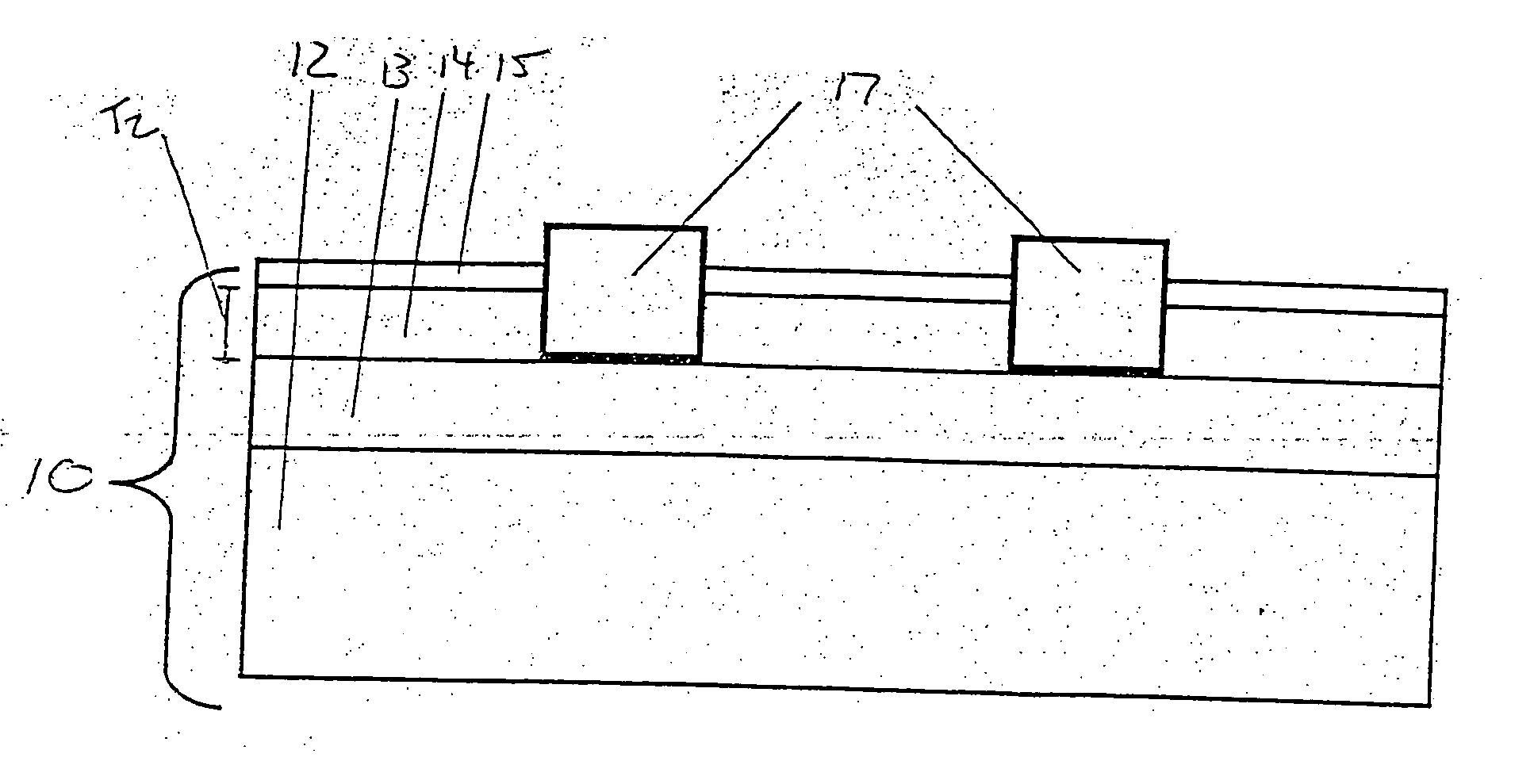

High performance integrated circuit device and method of making the same

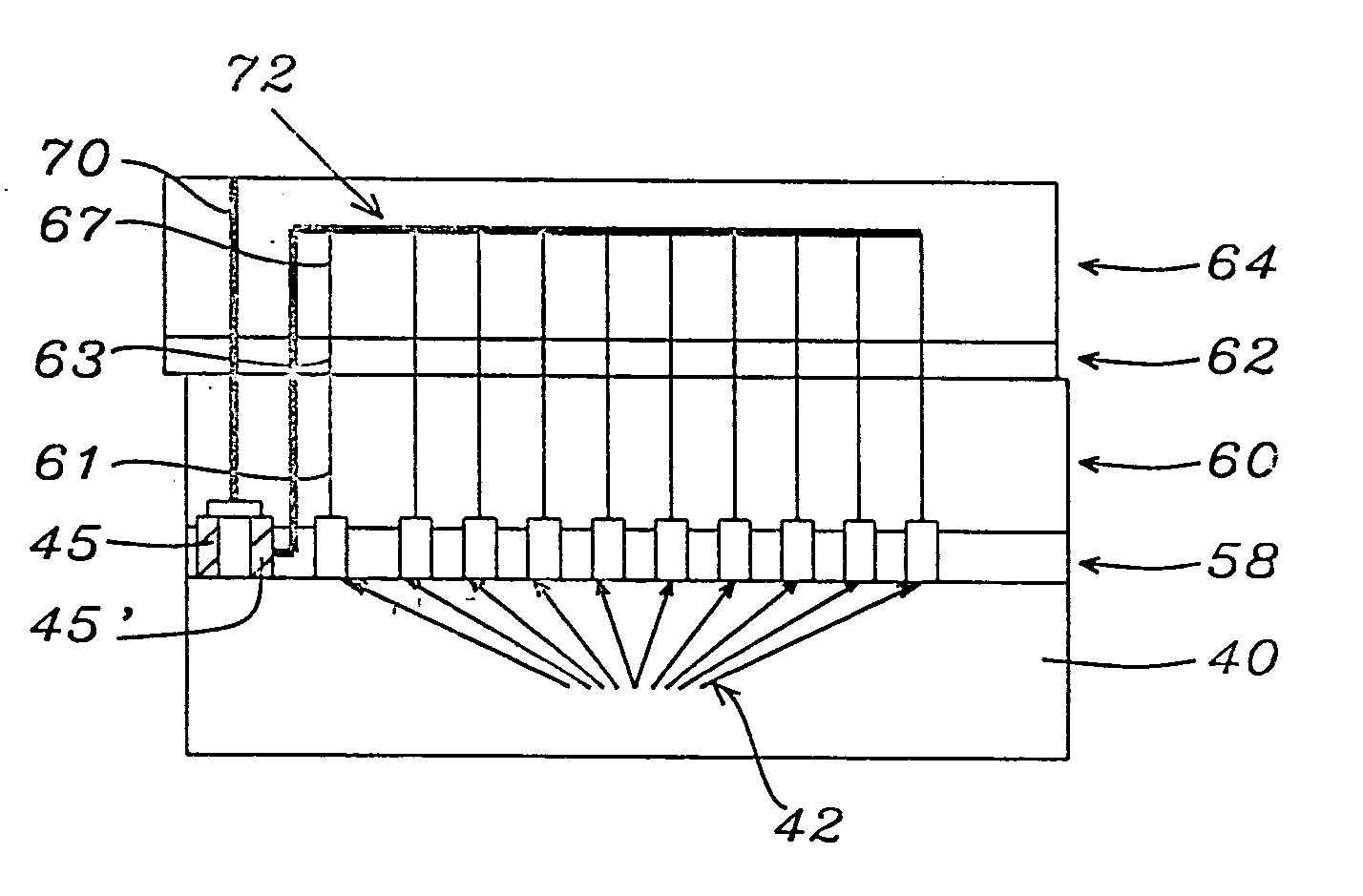

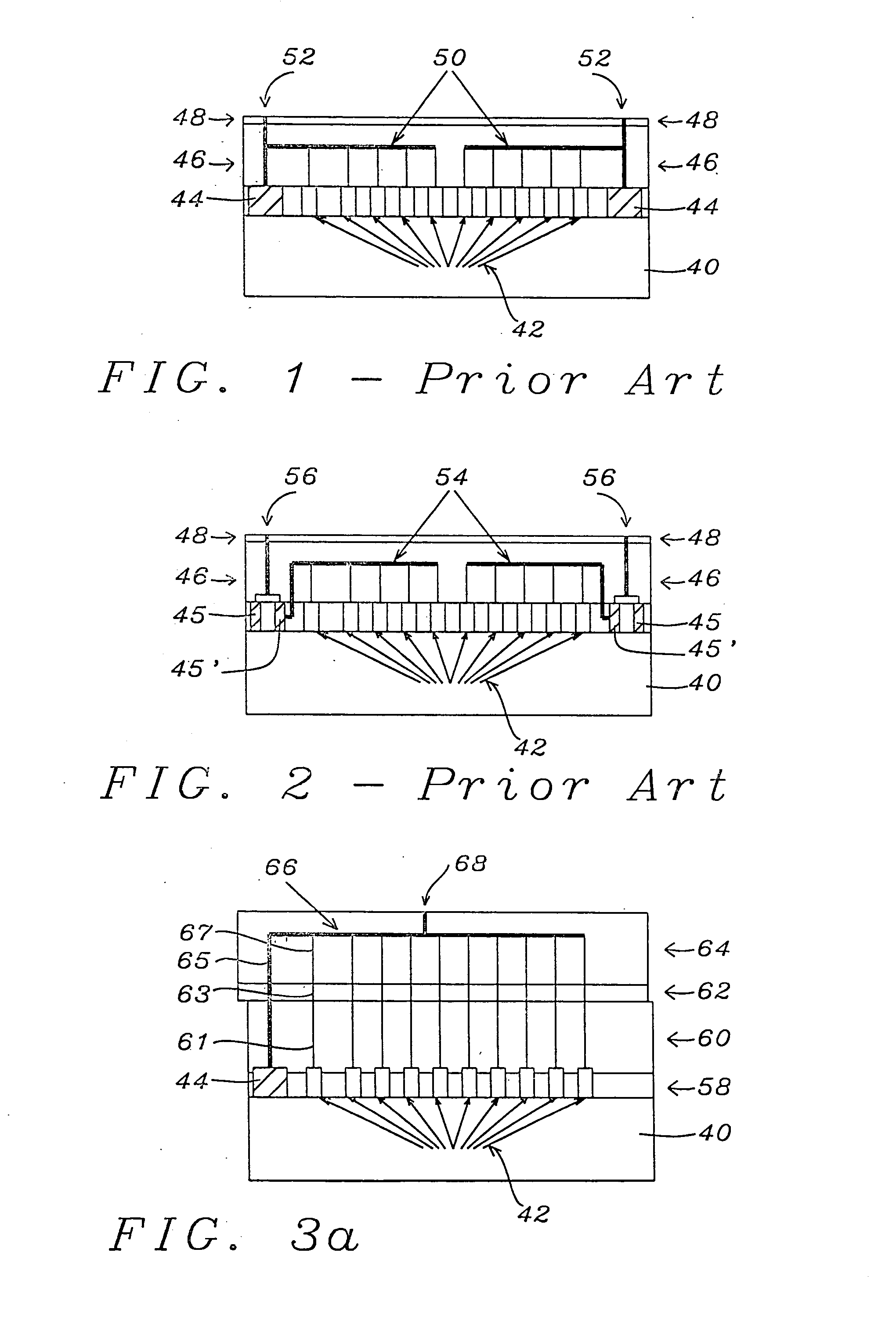

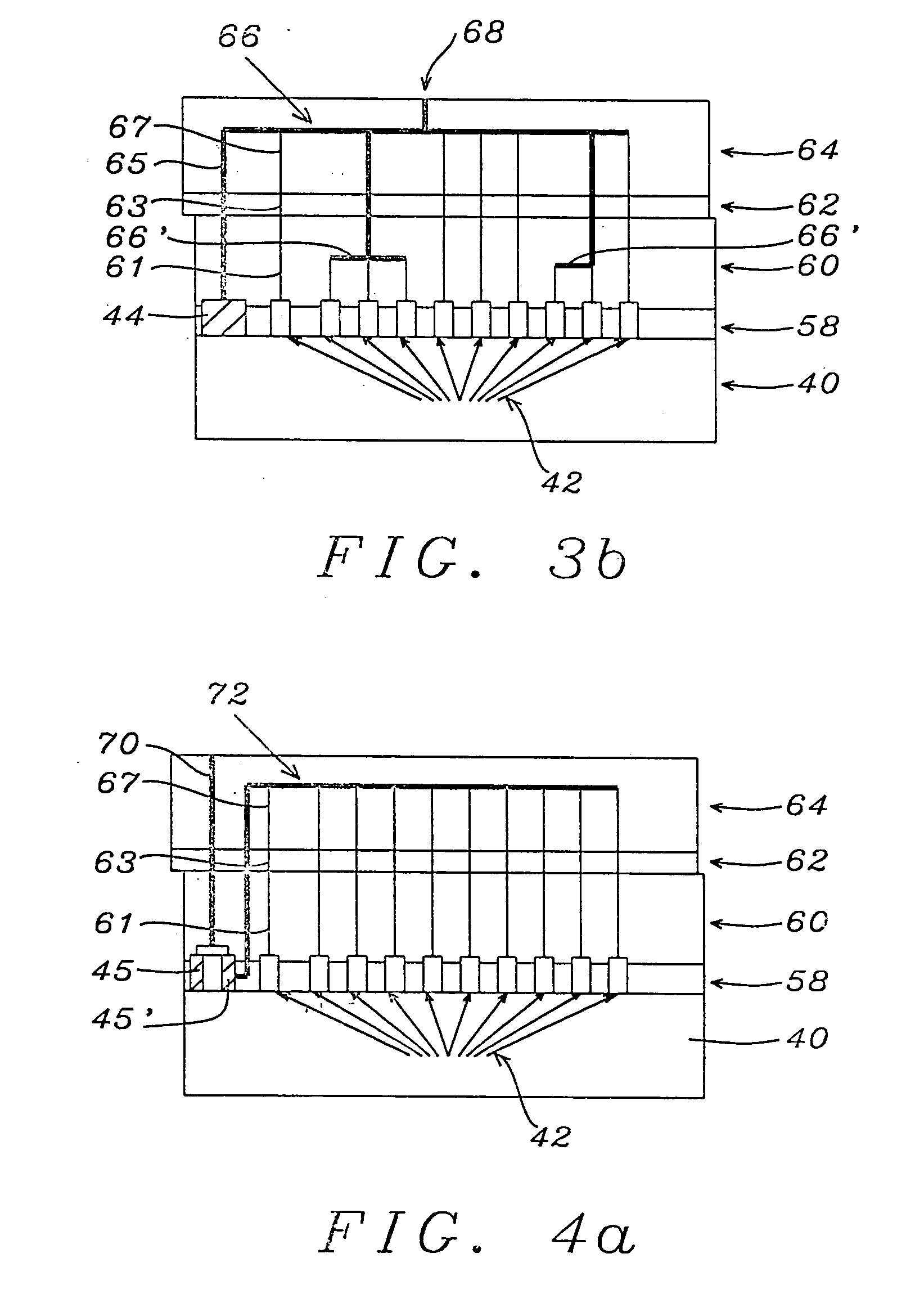

InactiveUS20060267198A1Increase resistanceIncrease parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesFine lineInterconnection

A new interconnection scheme is described, comprising both coarse and fine line interconnection schemes in an IC chip. The coarse metal interconnection, typically formed by selective electroplating technology, is located on top of the fine line interconnection scheme. It is especially useful for long distance lines, clock, power and ground buses, and other applications such as high Q inductors and bypass lines. The fine line interconnections are suited for local interconnections. The combined structure of coarse and fine line interconnections forms a new interconnection scheme that not only enhances IC speed, but also lowers power consumption.

Owner:QUALCOMM INC

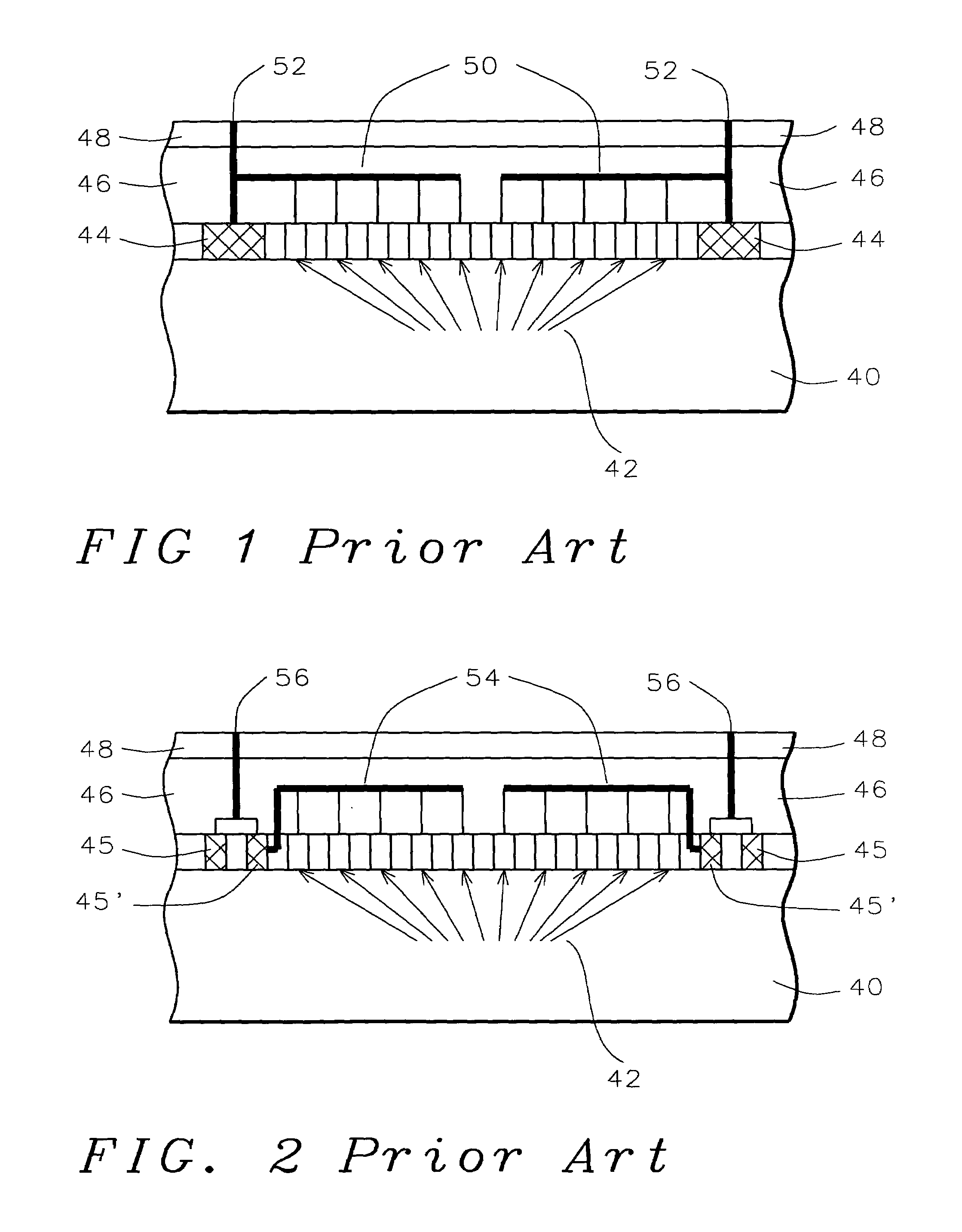

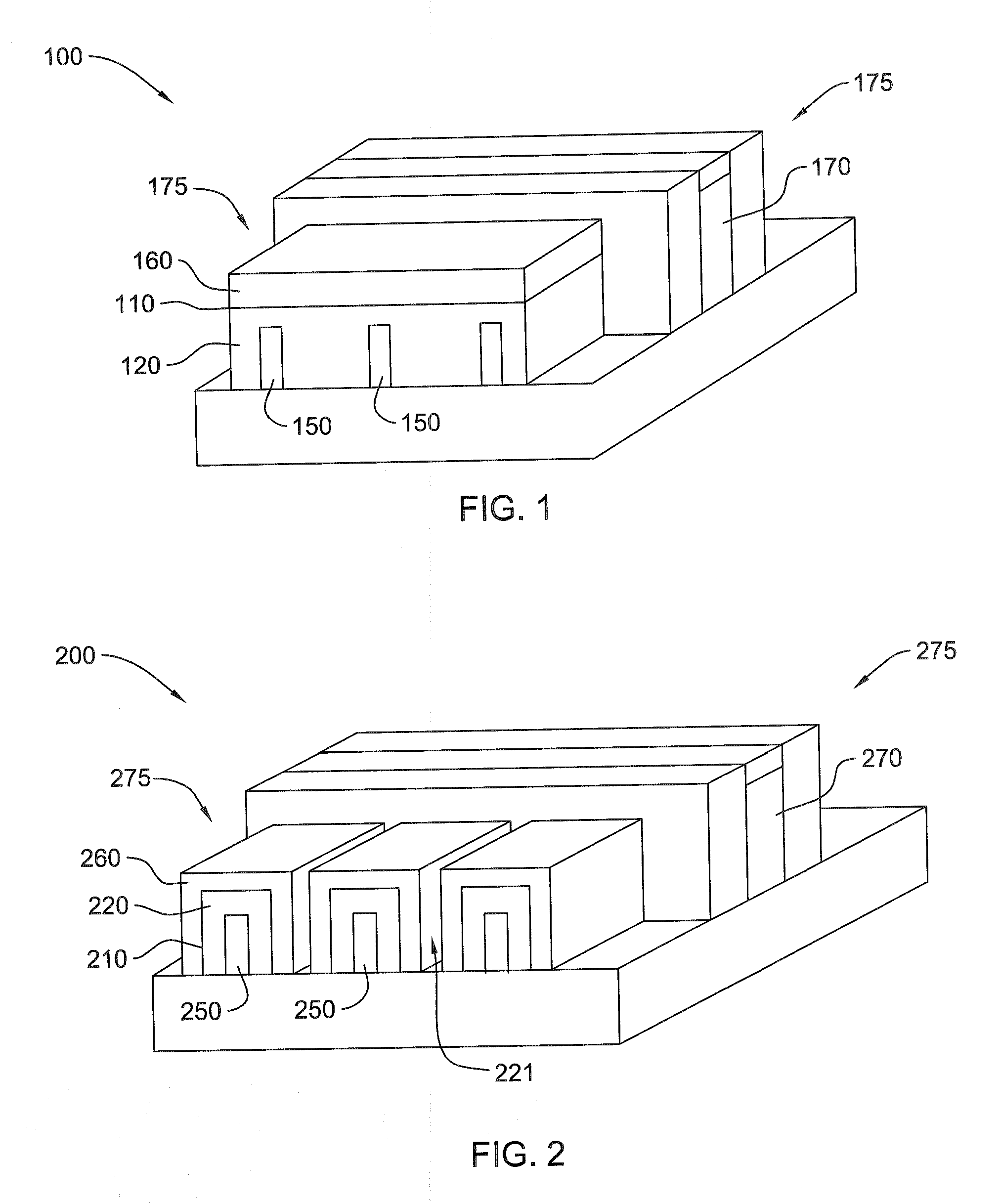

Fin-type field effect transistor structure with merged source/drain silicide and method of forming the structure

ActiveUS20090020819A1Increase parasitic capacitanceSeries resistance be minimizeTransistorSolid-state devicesField-effect transistorMetal silicide

Disclosed herein are embodiments of a multiple fin fin-type field effect transistor (i.e., a multiple fin dual-gate or tri-gate field effect transistor) in which the multiple fins are partially or completely merged by a highly conductive material (e.g., a metal silicide). Merging the fins in this manner allow series resistance to be minimized with little, if any, increase in the parasitic capacitance between the gate and source / drain regions. Merging the semiconductor fins in this manner also allows each of the source / drain regions to be contacted by a single contact via as well as more flexible placement of that contact via.

Owner:GLOBALFOUNDRIES US INC

Touch sensor integrated type display device

ActiveUS20140168149A1Reduce thicknessPrevent in touch sensitivityInput/output processes for data processingDisplay deviceEngineering

A touch sensor integrated type display device includes gate lines and data lines crossing over each other, pixel electrodes respectively formed in areas defined by crossing the gate lines and the data lines, first electrodes, each of which is formed between the pixel electrodes and in parallel with the gate line, the pixel electrodes being adjacent to each other with the gate line interposed therebetween, second electrodes formed in parallel with the data lines to overlap the pixel electrode, first routing wires connecting some of the first electrodes to form first electrode groups arranged in a first direction, second routing wires connecting another some of the first electrodes to form second electrode groups arranged in the first direction; and third routing wires connecting some of the second electrodes to form third electrode groups arranged in a second direction.

Owner:LG DISPLAY CO LTD

Post passivation interconnection schemes on top of the IC chips

InactiveUS20060038231A9Increase resistanceIncrease parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesFine lineDielectric

A new method is provided for the creation of interconnect lines. Fine line interconnects are provided in a first layer of dielectric overlying semiconductor circuits that have been created in or on the surface of a substrate. A layer of passivation is deposited over the layer of dielectric, a thick second layer of dielectric is created over the surface of the layer of passivation. Thick and wide interconnect lines are created in the thick second layer of dielectric. The first layer of dielectric may also be eliminated, creating the wide thick interconnect network on the surface of the layer of passivation that has been deposited over the surface of a substrate.

Owner:QUALCOMM INC

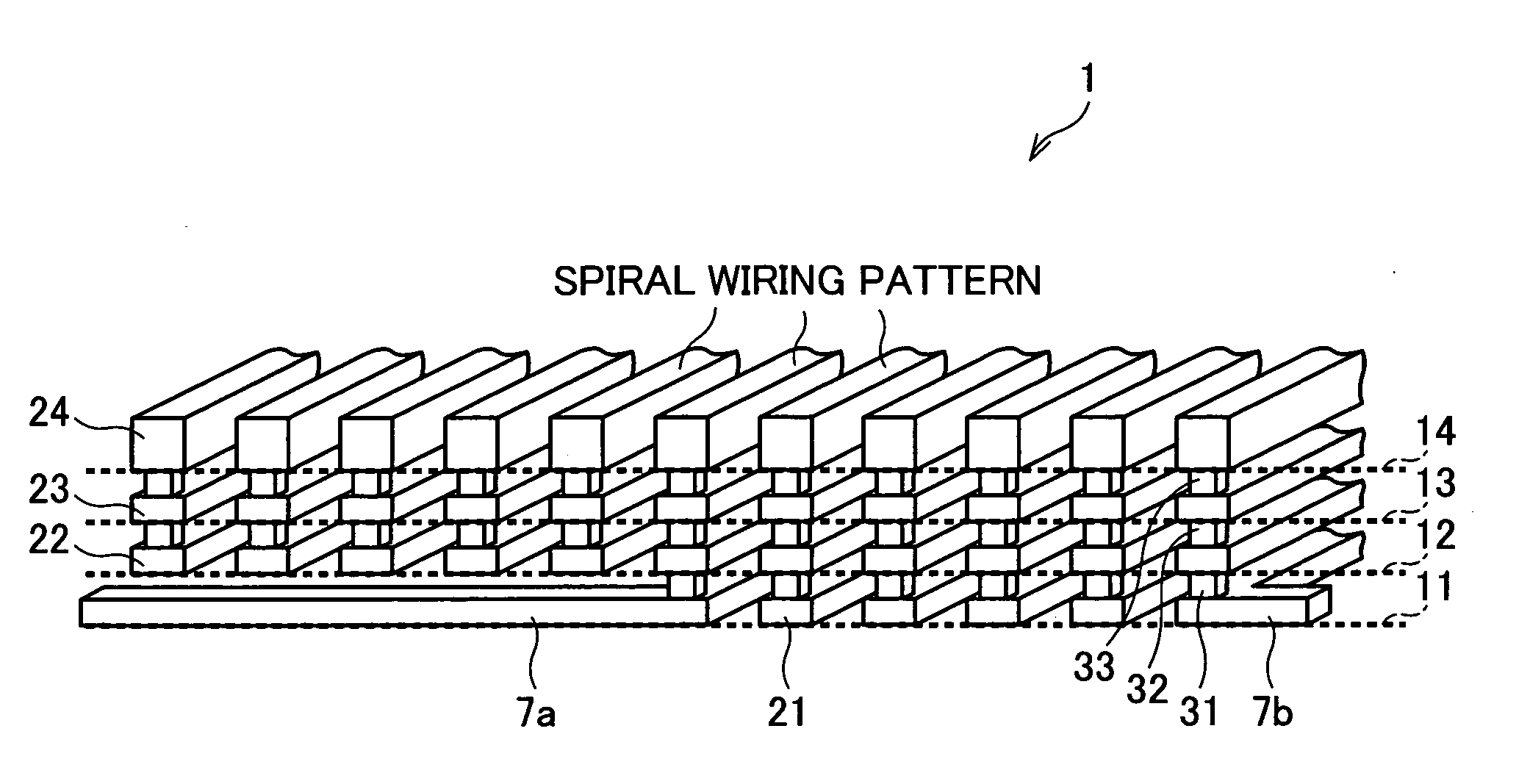

Inductor, resonant circuit, semiconductor integrated circuit, oscillator, and communication apparatus

InactiveUS20060125589A1Increase parasitic capacitanceHigh QTransformers/inductances coils/windings/connectionsOscillations generatorsEngineeringInductor

An inductor of the present invention includes a plurality of insulating layers being stacked and coil patterns respectively provided on predetermined layers of the insulating layers. The coil patterns are provided on at least two of the insulating layers, and electrically connected to each other. With this arrangement, it is possible to improve Q of the inductor without increasing the size of the inductor.

Owner:SHARP KK

Ultra-thin Si MOSFET device structure and method of manufacture

InactiveUS20050118826A1Slow circuit performanceIncrease parasitic capacitanceTransistorSolid-state devicesMOSFETOxide

The present invention comprises a method for forming an ultra-thin channel MOSFET and the ultra-thin channel MOSFET produced therefrom. Specifically, the method comprises providing an SOI substrate having a buried insulating layer underlying an SOI layer; forming a pad stack atop the SOI layer; forming a block mask having a channel via atop the pad stack; providing a localized oxide region in the SOI layer on top of the buried insulating layer thereby thinning a portion of the SOI layer, the localized oxide region being self-aligned with the channel via; forming a gate in the channel via; removing at least the block mask; and forming source / drain extensions in the SOI layer abutting the thinned portion of the SOI layer. Providing the localized oxide region further comprises implanting oxygen dopant through the channel via into a portion of the SOI layer; and annealing the dopant to create the localized oxide region.

Owner:GLOBALFOUNDRIES INC

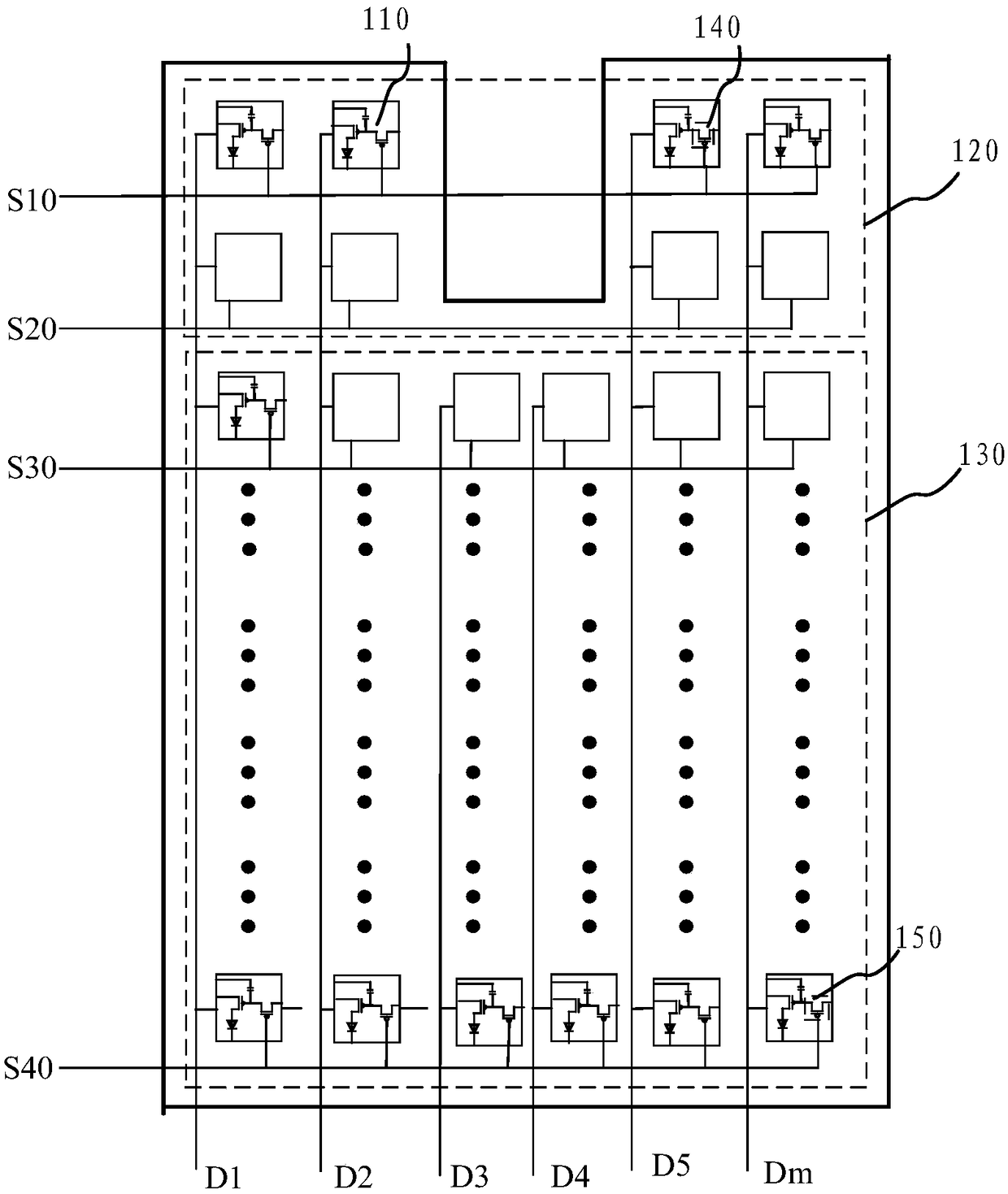

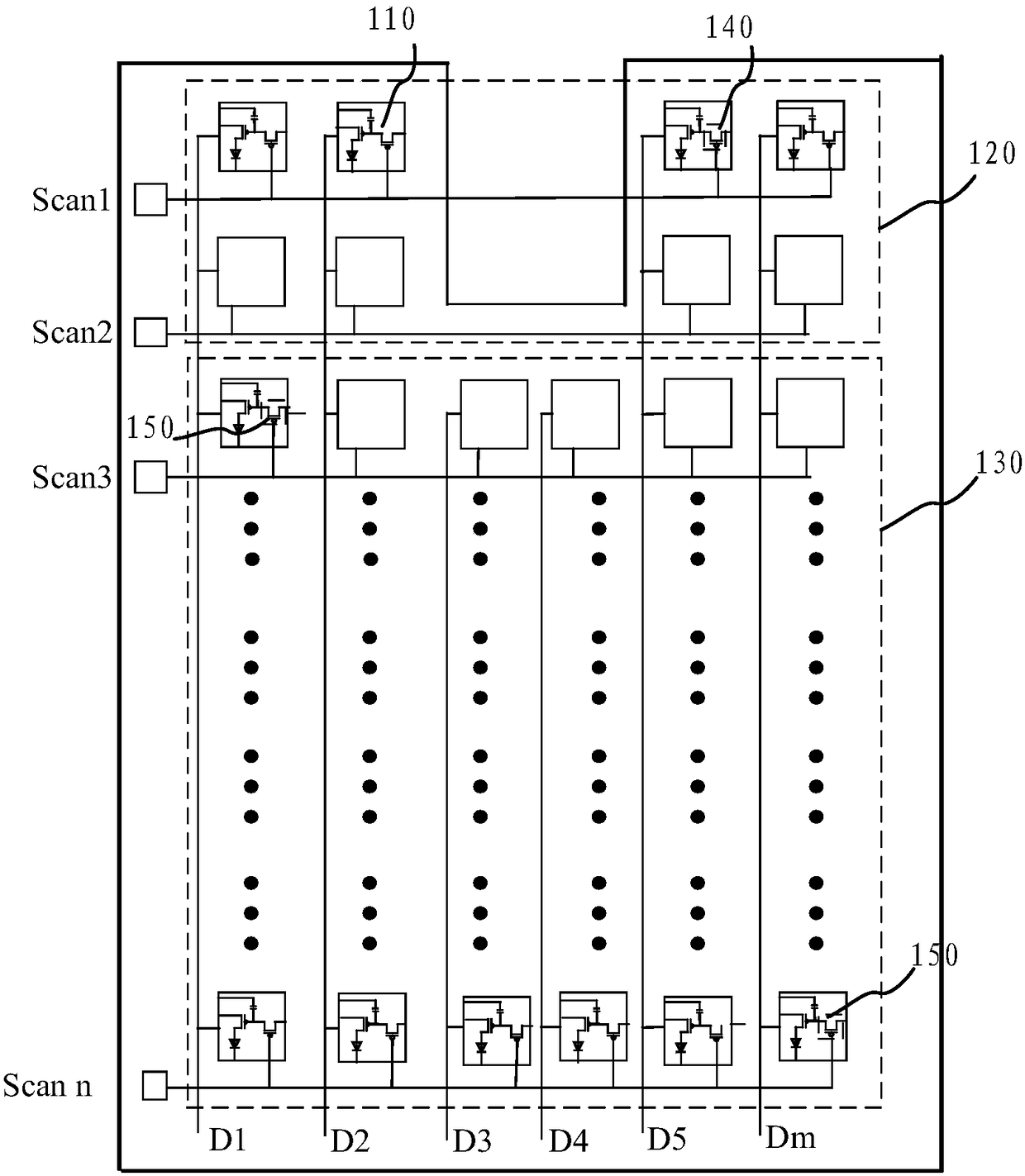

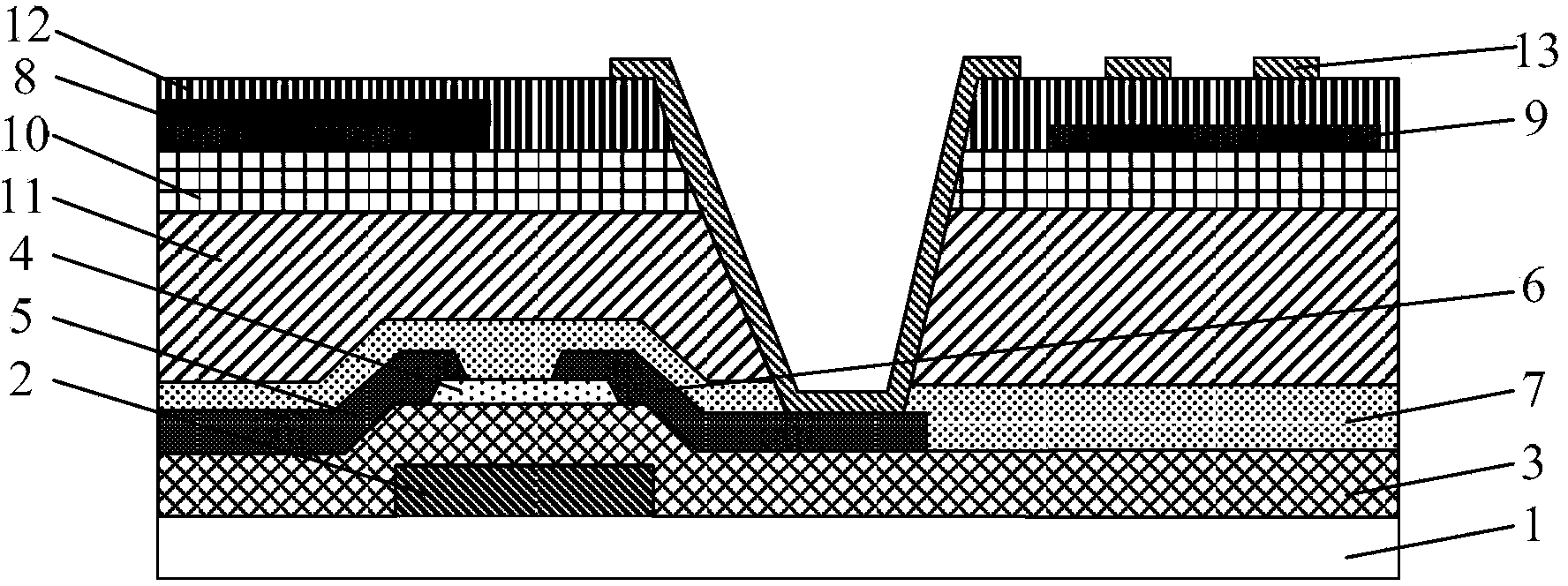

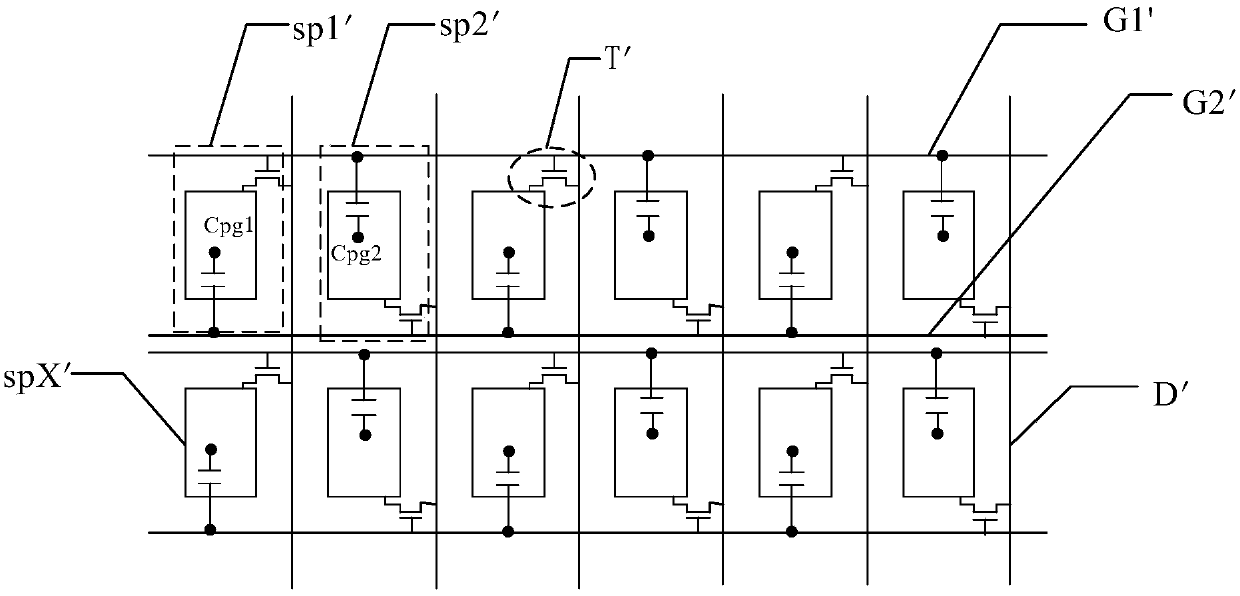

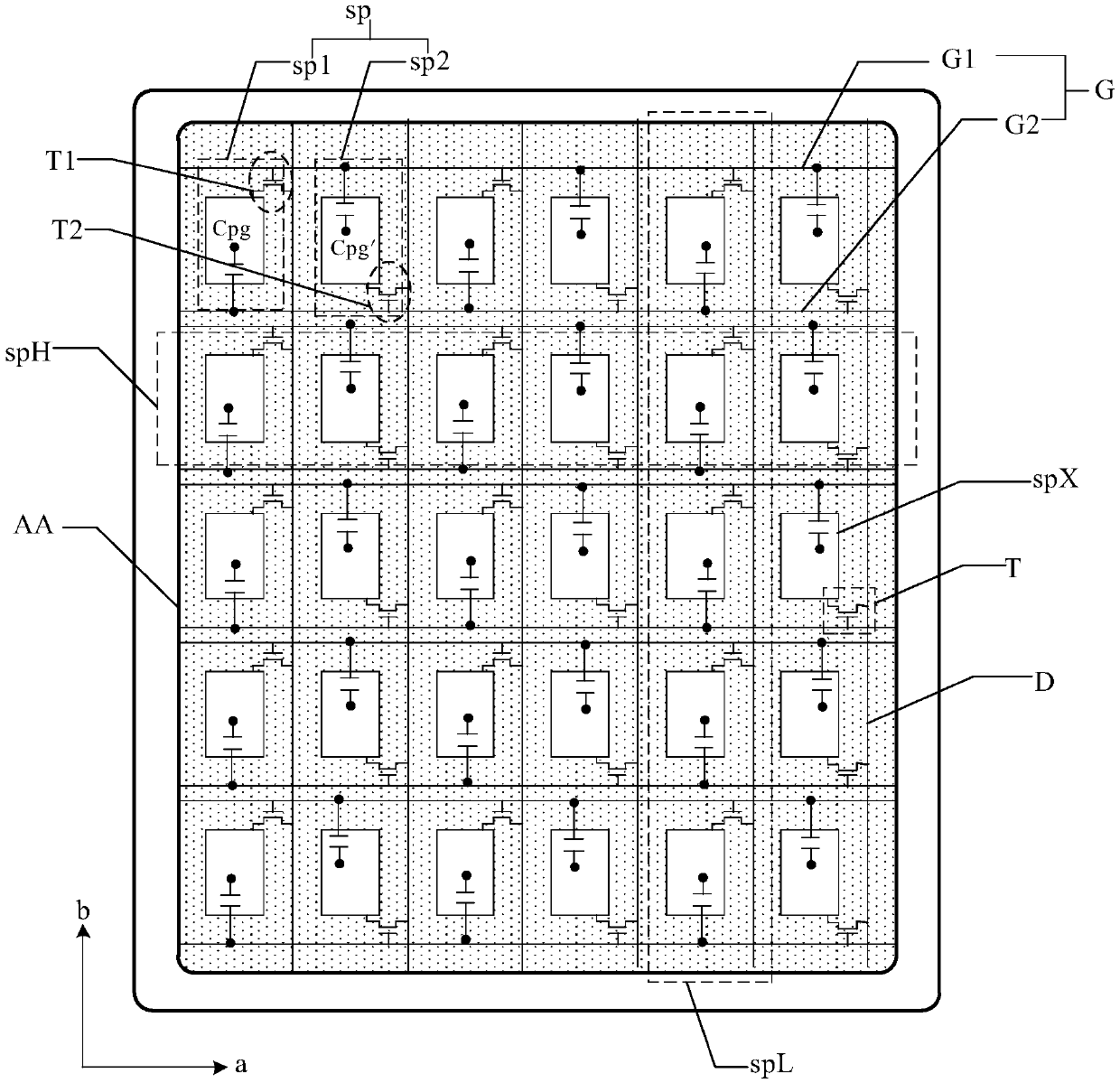

Array substrate, display screen and display device

ActiveCN108417172AIncrease parasitic capacitanceSolve the technical problem of uneven image brightnessStatic indicating devicesDisplay deviceComputer science

The invention relates to an array substrate, a display screen and a display device. The array substrate comprises a substrate body, at least one first switch transistor and at least one second switchtransistor, a corresponding display area on the substrate body comprises pixels in array distribution and is divided into a special-shaped display area and a non-special-shaped display area, the number of the pixels in each row of the special-shaped display area is smaller than that in any row of the non-special-shaped display area, the first switch transistors are positioned in the special-shapeddisplay area and correspond to the pin the special-shaped display area, and the second switch transistors are positioned in the non-special-shaped display area and correspond to the pixels in the non-special-shaped display area; width-length ratio of the first switch transistors is equal to that of the second switch transistor, and grid area of the first switch transistors is greater than that ofthe second switch transistors. The technical problem that displayed images are nonuniform in brightness caused by load difference in the special-shaped display area and the non-special-shaped displayarea is solved, and display effect is improved.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

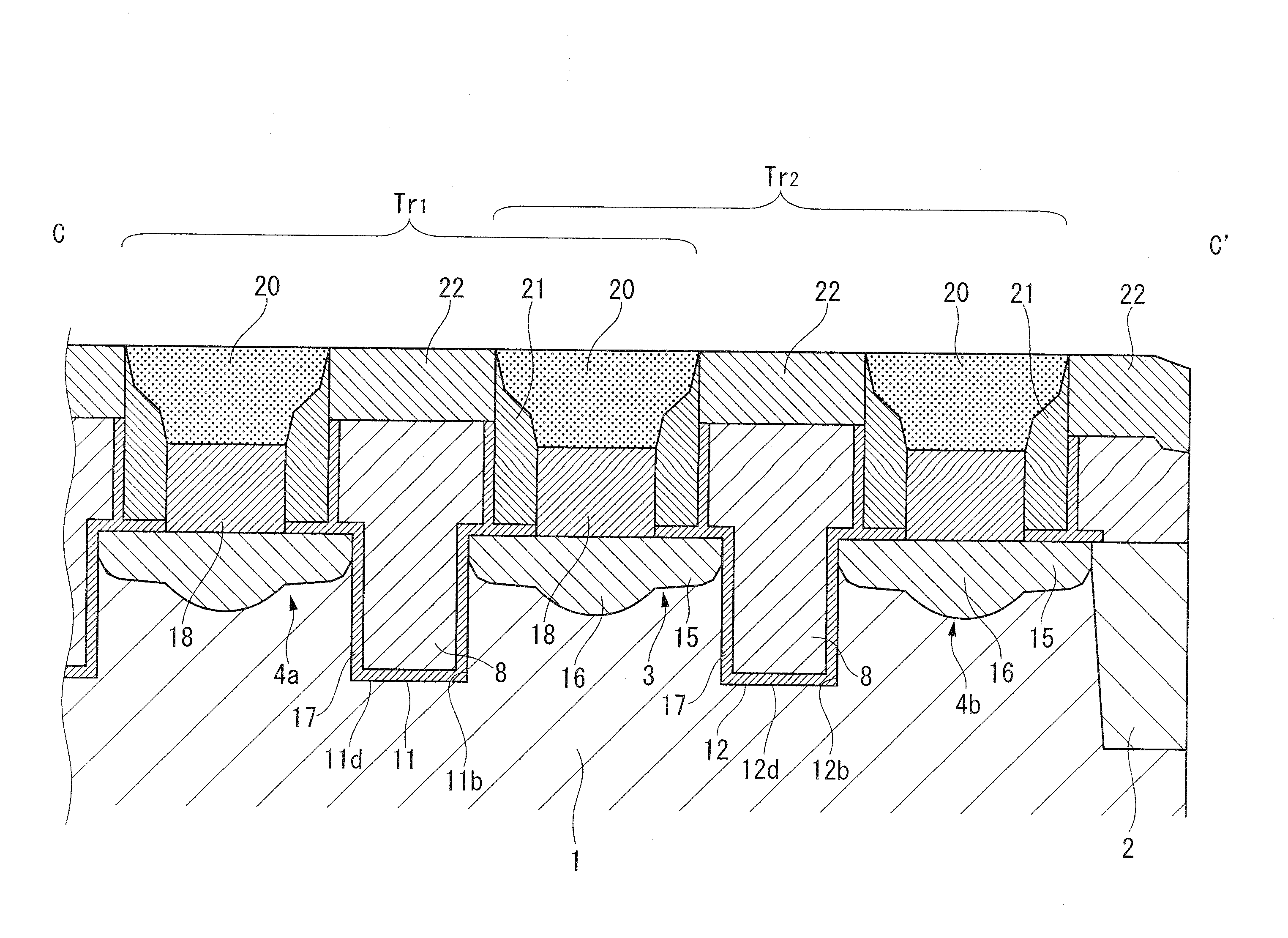

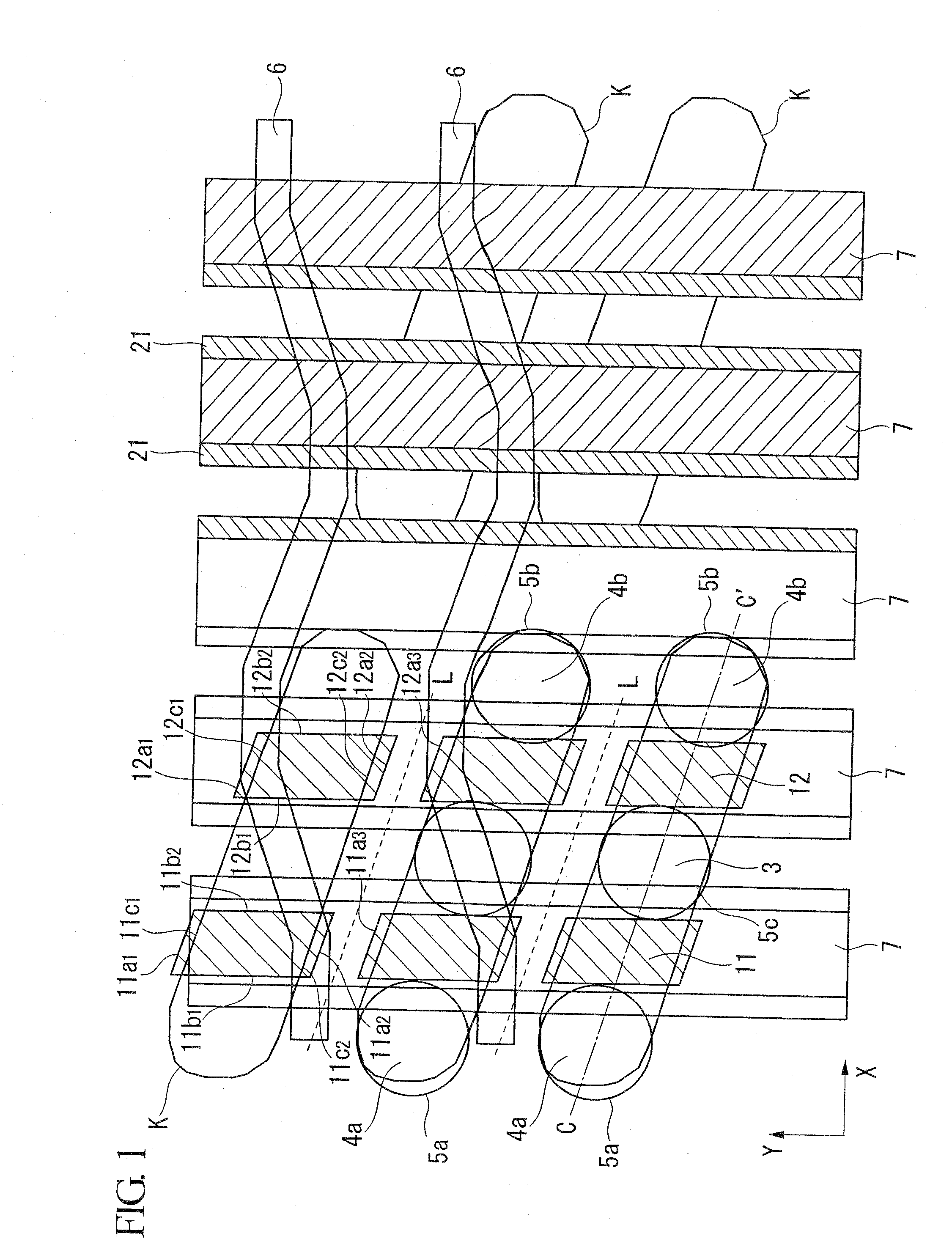

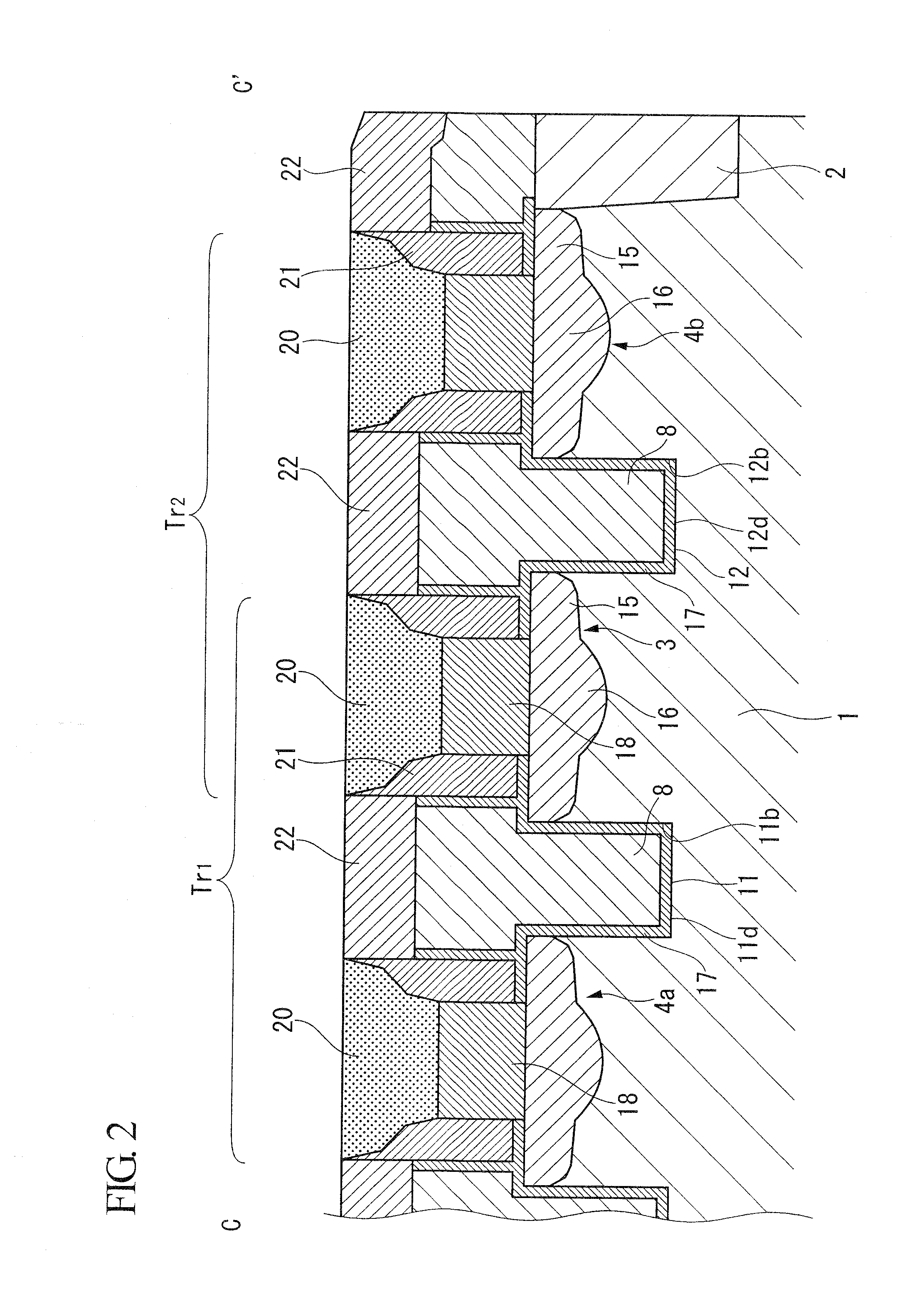

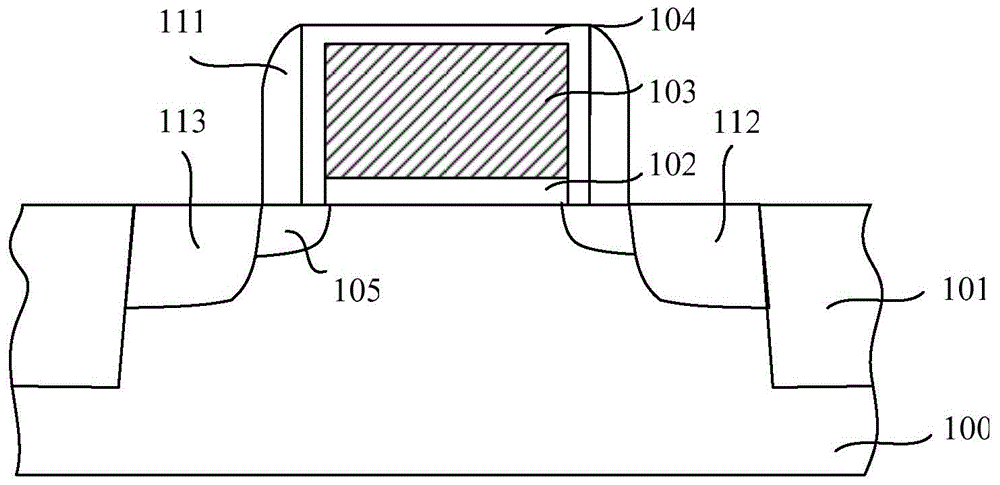

Semiconductor device and method of forming the same

InactiveUS20080073708A1Increase channel lengthIncrease parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringTrench gate

A semiconductor device and a method of forming the semiconductor device are provided. The semiconductor device may include, but is not limited to, a semiconductor substrate and a third array of semiconductor elements. The semiconductor substrate may include a first array of separate grooves, a second array of separate active regions, and at least an isolating region, the isolating region separating the separate active regions from each other. Each separate groove extends in the separate active region and does not extend over the isolating region. The third array of semiconductor elements is provided on the semiconductor substrate. Each of the semiconductor elements has an electrically conductive portion that is provided in the separate groove. The semiconductor element may be a trench gate transistor, and the electrically conductive portion may be a gate electrode.

Owner:ELPIDA MEMORY INC

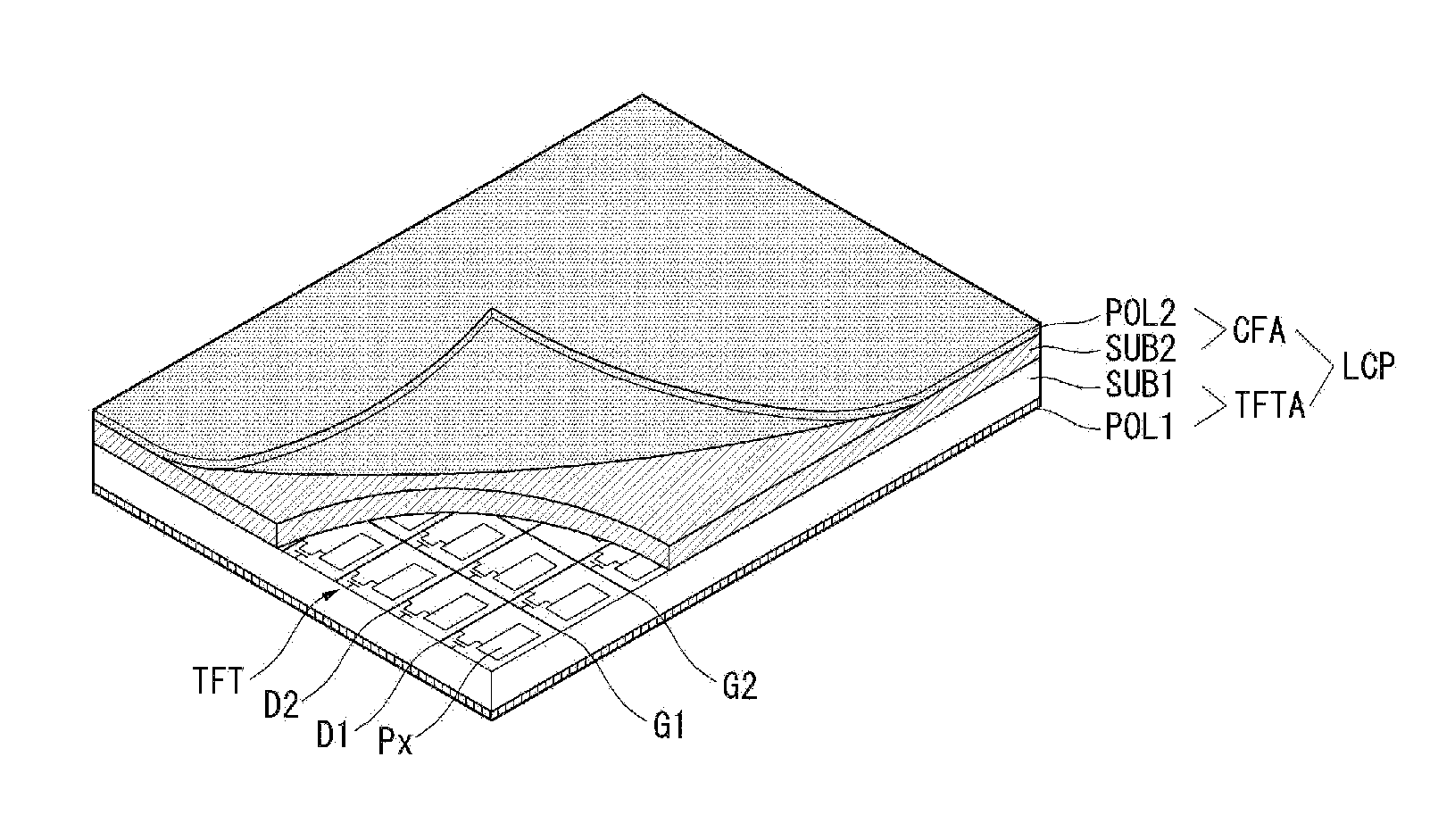

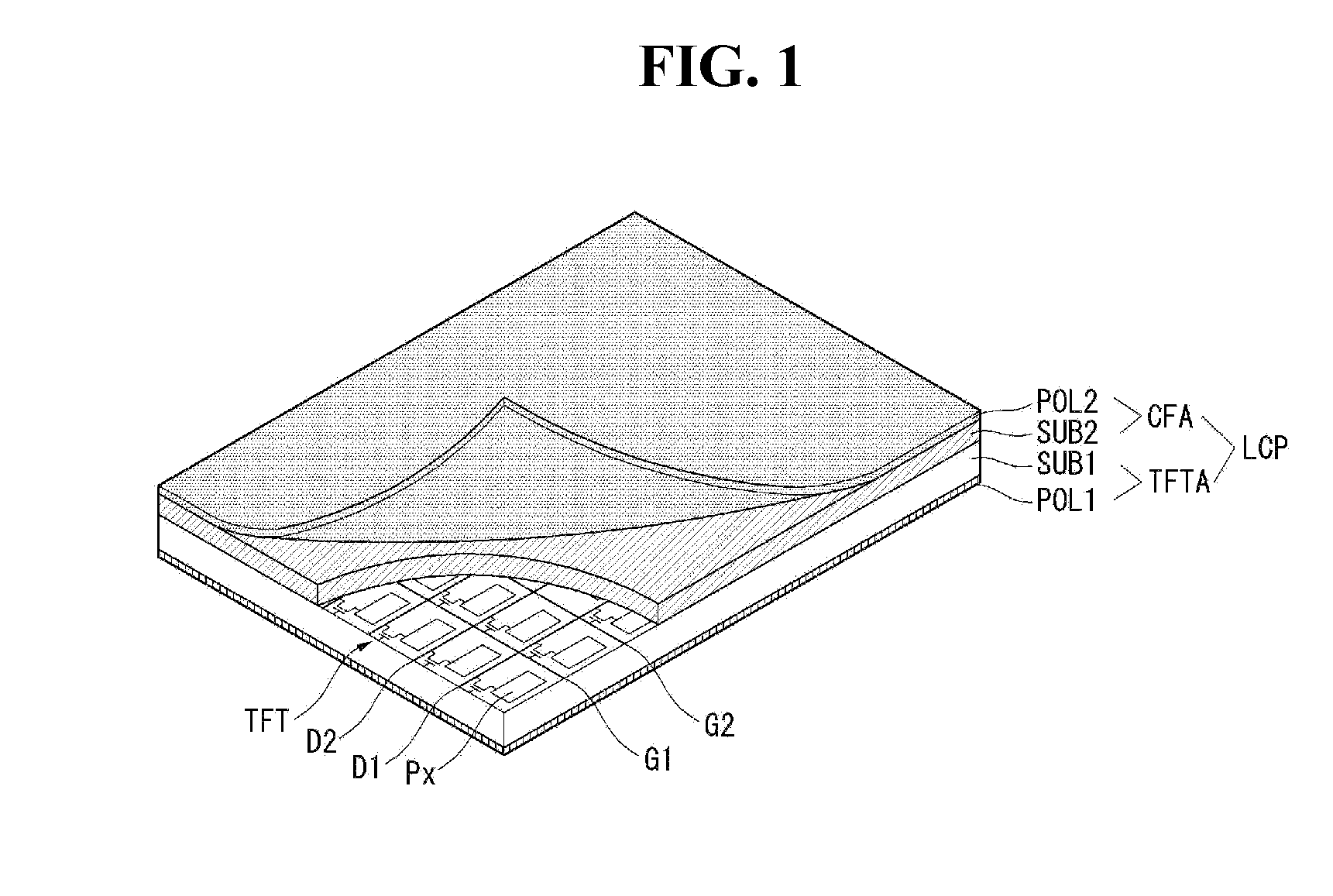

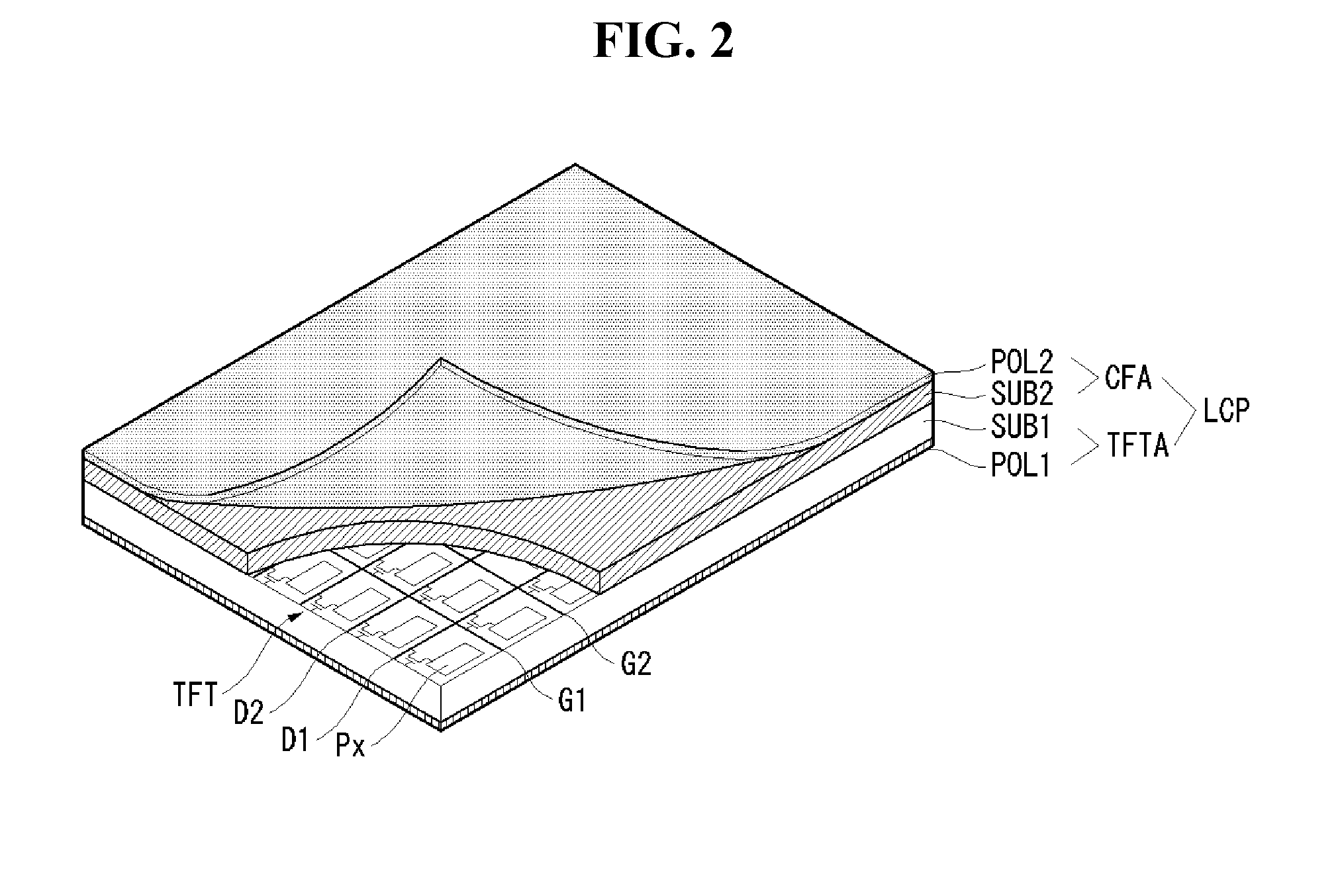

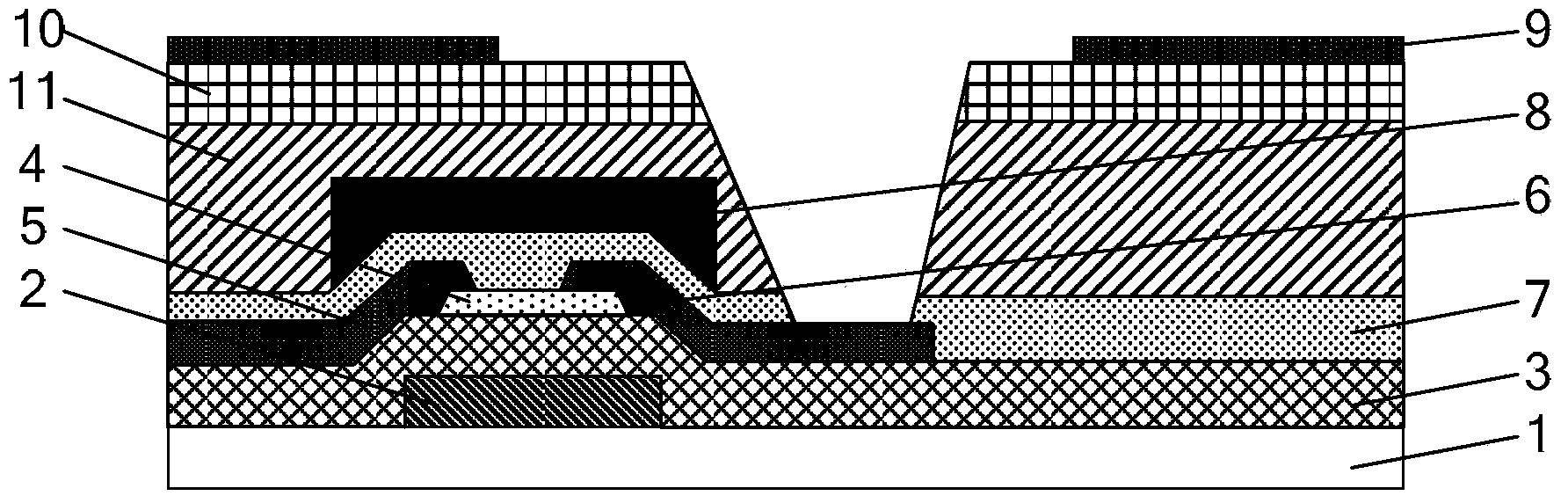

Active matrix substrate, liquid crystal display panel, liquid crystal display element, liquid crystal display device, and substrate for liquid crystal display panels

ActiveUS20100045906A1High display qualityIncrease in screen sizeNon-linear opticsLiquid-crystal displayEngineering

The present invention has an object to provide an active matrix substrate, a liquid crystal display panel, a liquid crystal display element, a liquid crystal display device, and a substrate for liquid crystal display panel, each capable of suppressing generation of uneven cell gap without increase in a parasitic capacitance of a wiring. The active matrix substrate of the present invention is an active matrix substrate including a spacer on a substrate, wherein the spacer includes a base layer and a covering layer, the base layer being buried in the covering layer.

Owner:SHARP KK

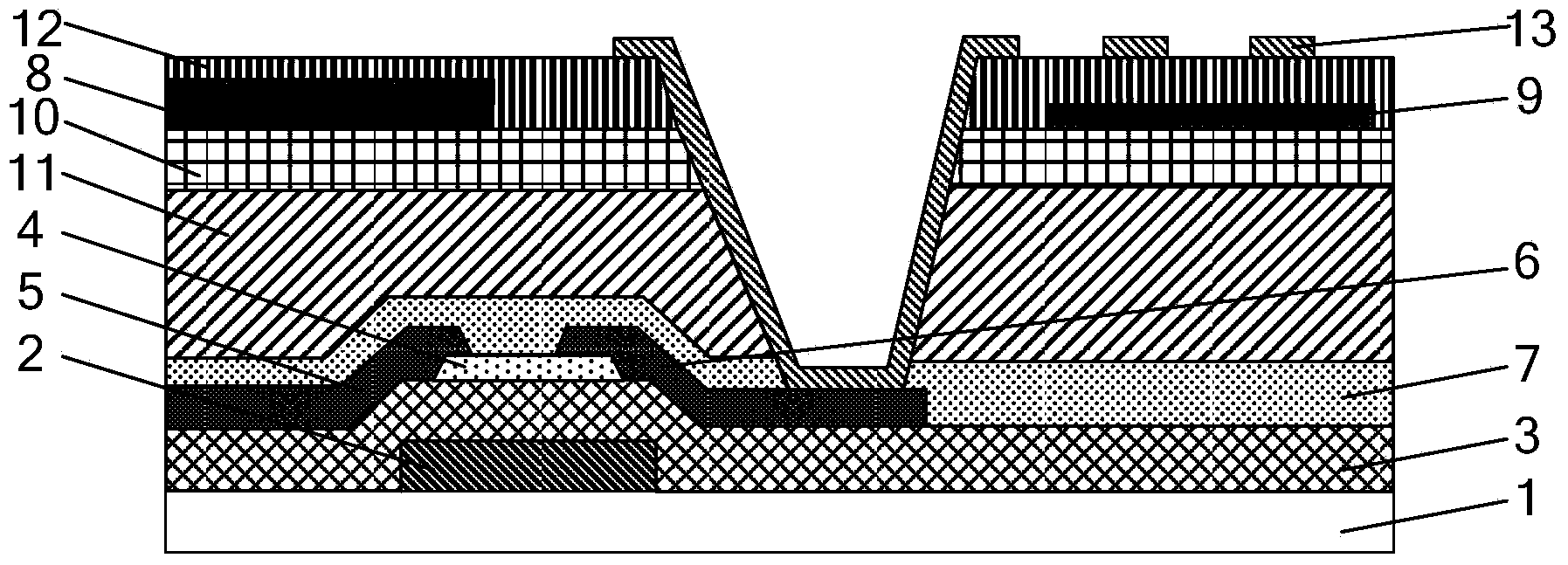

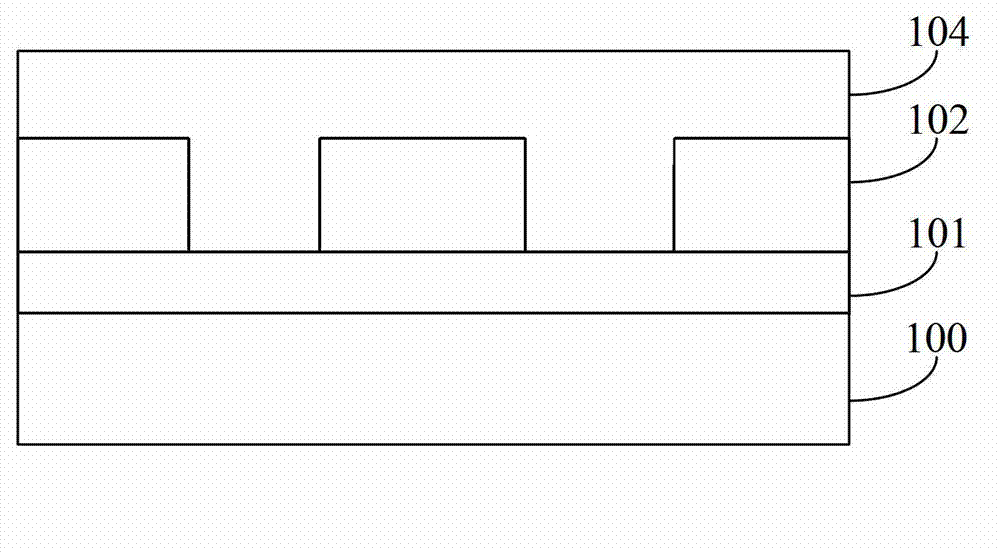

COA (color filter on array) substrate, production method thereof and display device

InactiveCN104317097AIncrease parasitic capacitanceSolve the problem of large parasitic capacitanceSolid-state devicesNon-linear opticsParasitic capacitanceDisplay device

An embodiment of the invention provides a COA (color filter on array) substrate, a production method thereof and a display device and relates to the technical field of display. By the aid of the COA substrate, the production method thereof and the display device, the problem that large parasitic capacitance can be generated between a common electrode and a grid line and / or between the common electrode and a data line in the prior art is solved, signal delay is avoided, normal transmission of signals is guaranteed, and the display quality of pictures of the display device is improved. The COA substrate comprises a grid line, a data line, a common electrode layer and a black matrix, wherein the black matrix is arranged between the grid line and the common electrode layer and / or between the data line and the common electrode layer and is made of metal materials. The COA substrate, the production method thereof and the display device are applied to the display device production technology.

Owner:BOE TECH GRP CO LTD

Semiconductor device and manufacturing method of the same

ActiveUS20090302993A1Increase parasitic capacitanceIncrease the resistance valueSemiconductor/solid-state device detailsSolid-state devicesSurface oxidationParasitic capacitance

A semiconductor device according to the present invention includes: a lower-surface oxidation preventing insulating film formed on a lower surface of a metal resistor element; an upper-surface oxidation preventing insulating film formed on an upper surface of the metal resistor element; and a side-surface oxidation preventing insulating film formed only near a side surface of the metal resistor element by performing anisotropic etching after being deposited on a whole surface of a wafer in a process separated from the lower-surface oxidation preventing insulating film and the upper-surface oxidation preventing insulating film. According to the present invention, it is possible to prevent the increase of the resistance value due to the oxidation of the metal resistor element and also to prevent the increase of the parasitic capacitance between metal wiring layers without complicating the fabrication process.

Owner:HITACHI LTD

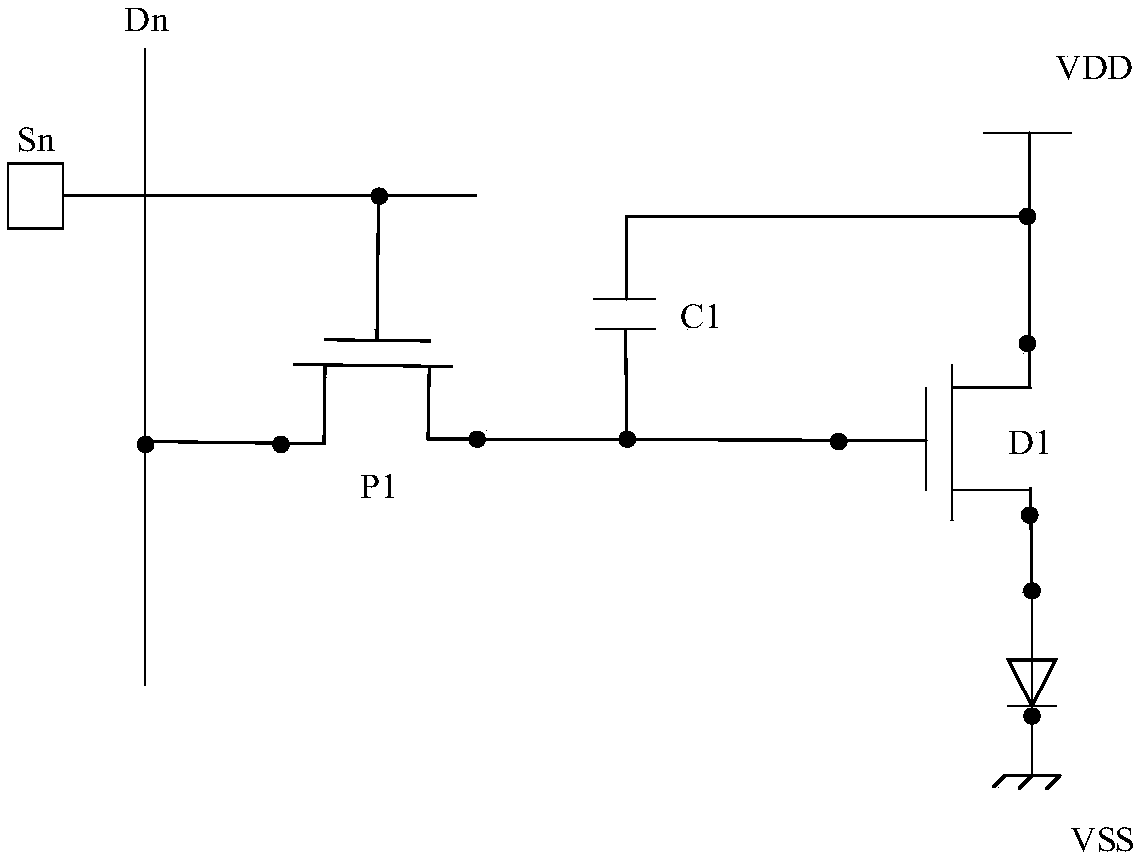

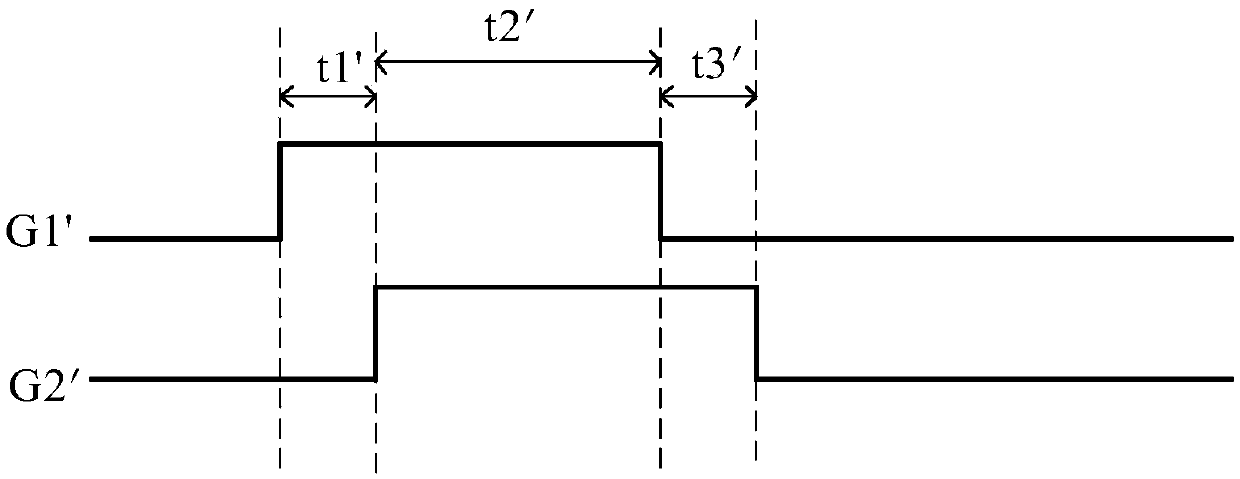

Display panel and display device

PendingCN109521616AIncrease parasitic capacitanceReduce voltageNon-linear opticsParasitic capacitanceDisplay device

The invention discloses a display panel and a display device, and belongs to the technical field of display. The display panel comprises a display area, wherein the display area includes a plurality of data lines and a plurality of pixel electrode; first sub-pixels and second sub-pixels in the display area are alternately arranged to form pixel rows, one pixel row is driven by a first scanning line and a second scanning line together, and the time when a scanning signal is inputted into the first scanning line and the time when a scanning signal is inputted into the second scanning line are overlapped when the first scanning line and the second scanning line drive the same pixel row; each sub-pixel includes a pixel electrode; each first sub-pixel includes a first transistor, and each second sub-pixel includes a second transistor; the parasitic capacitance between a source electrode and a grid electrode in the first transistor is the first parasitic capacitance, the parasitic capacitance between a source electrode and a grid electrode in the second transistor is the second parasitic capacitance, and the second parasitic capacitance is greater than the first parasitic capacitance. The display panel can ensure that the brightness of the second sub-pixels and the brightness of the first sub-pixels tend to be the same and improve the display uniformity.

Owner:SHANGHAI AVIC OPTOELECTRONICS

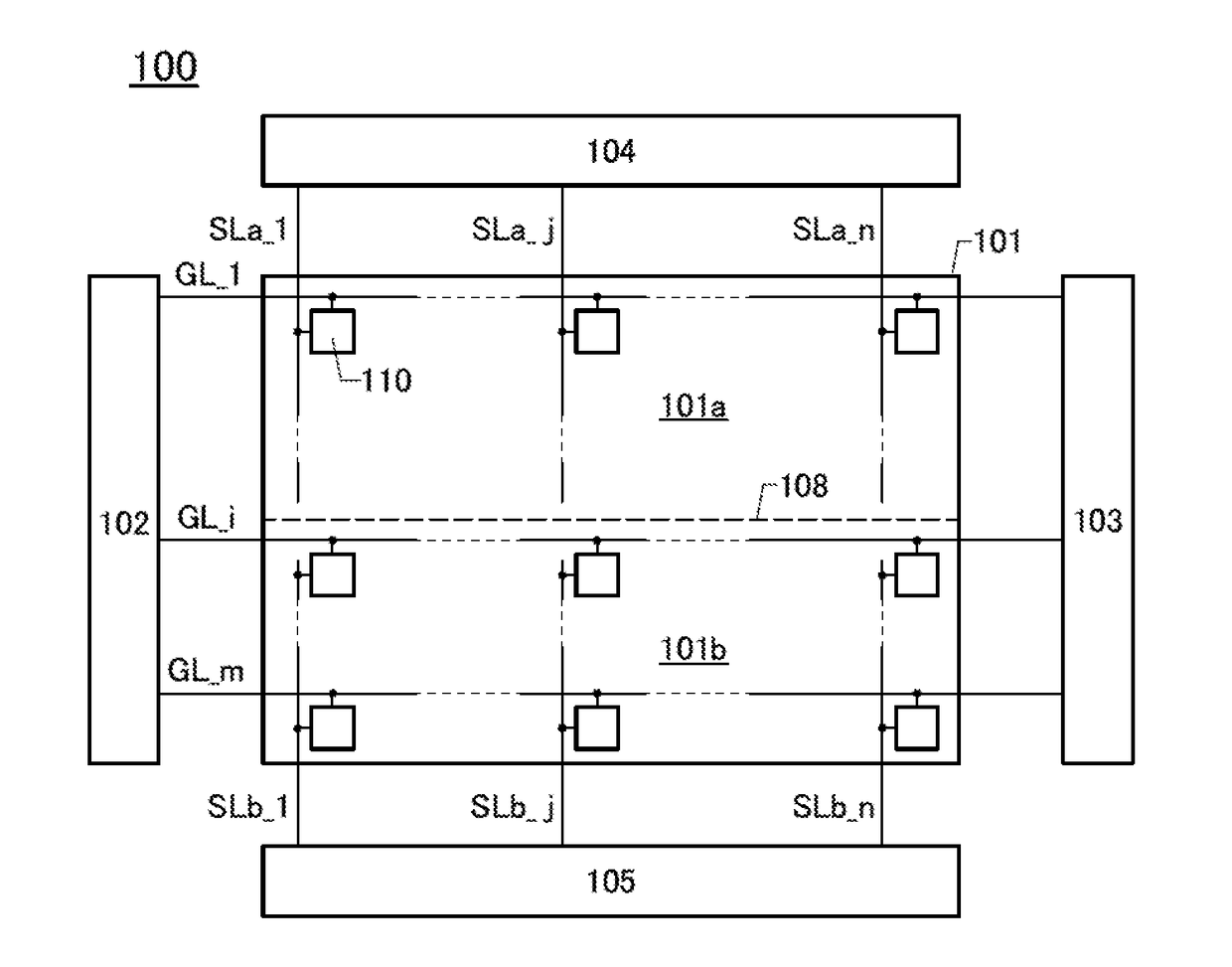

Display device

ActiveUS20180204532A1Avoid display qualityImprove the immunityStatic indicating devicesDigital data processing detailsDisplay deviceEngineering

A display device with favorable display quality is provided. A display portion where a plurality of pixels is arranged in a matrix is divided into Region A and Region B, i.e., regions on the upstream side and the downstream side of a scanning direction. A signal line for supplying an image signal is provided in each of Region A and Region B. Region A and Region B adjoin each other such that a boundary line showing the boundary between the regions is bent. Bending the boundary line suppresses formation of a stripe in a boundary portion. For example, in a given column, the total number of pixels electrically connected to a signal line in Region A is made different from the total number of pixels electrically connected to a signal line in Region B.

Owner:SEMICON ENERGY LAB CO LTD

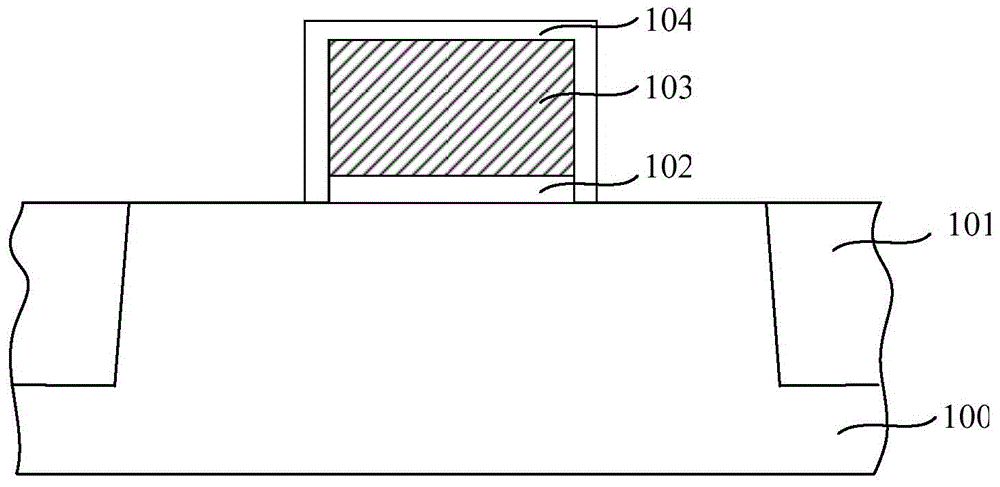

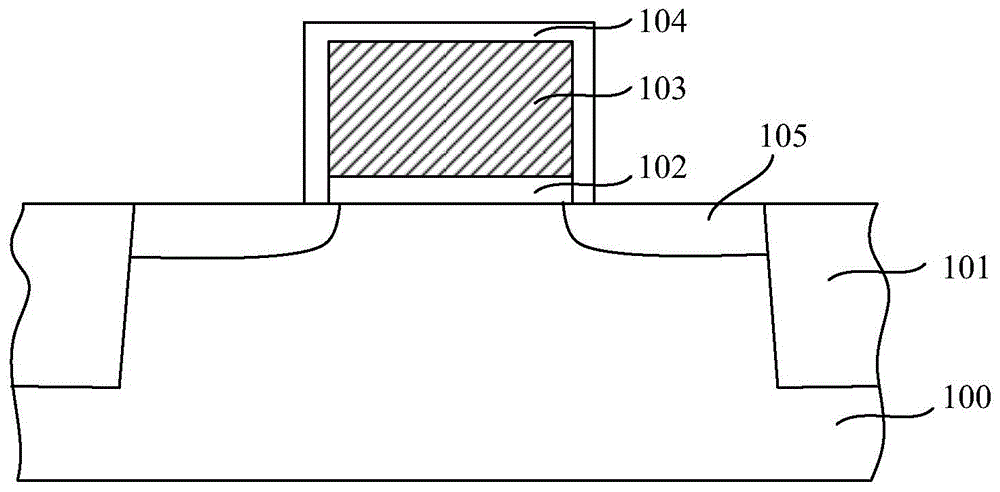

Semiconductor Device and Method for Fabricating the Same

InactiveUS20080283937A1Increase parasitic capacitanceReduce operating speedSolid-state devicesSemiconductor/solid-state device manufacturingDielectricGate dielectric

Provided are a semiconductor device and a method for fabricating the same. The semiconductor device can include a transistor structure, including a gate dielectric on a substrate, a gate electrode on the gate dielectric, a spacer at sidewalls of the gate electrode, and source / drain regions in the substrate; and an interlayer dielectric on the transistor structure where an air gap is provided in a region between the spacer, the interlayer dielectric, and the source / drain region of the substrate.

Owner:DONGBU HITEK CO LTD

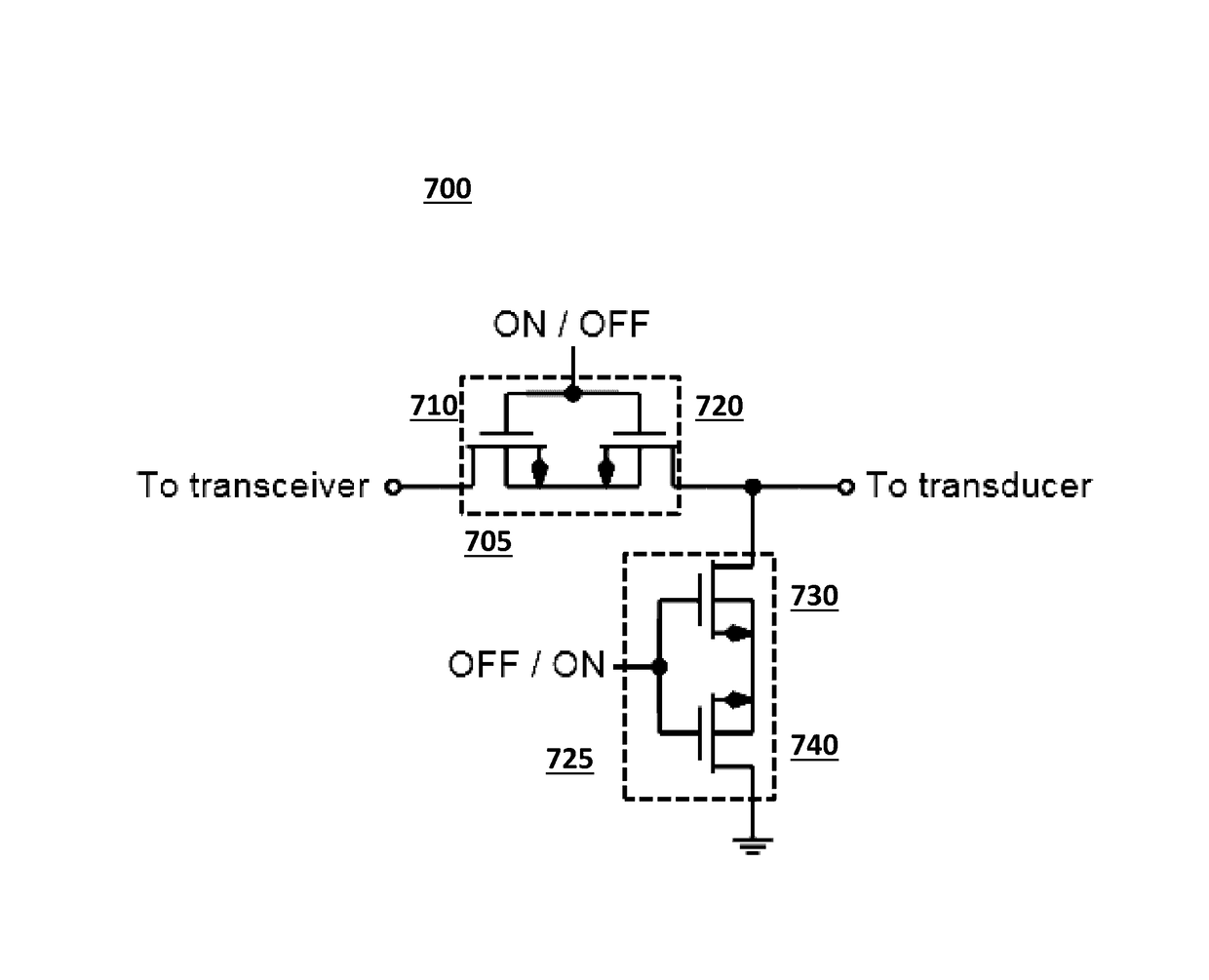

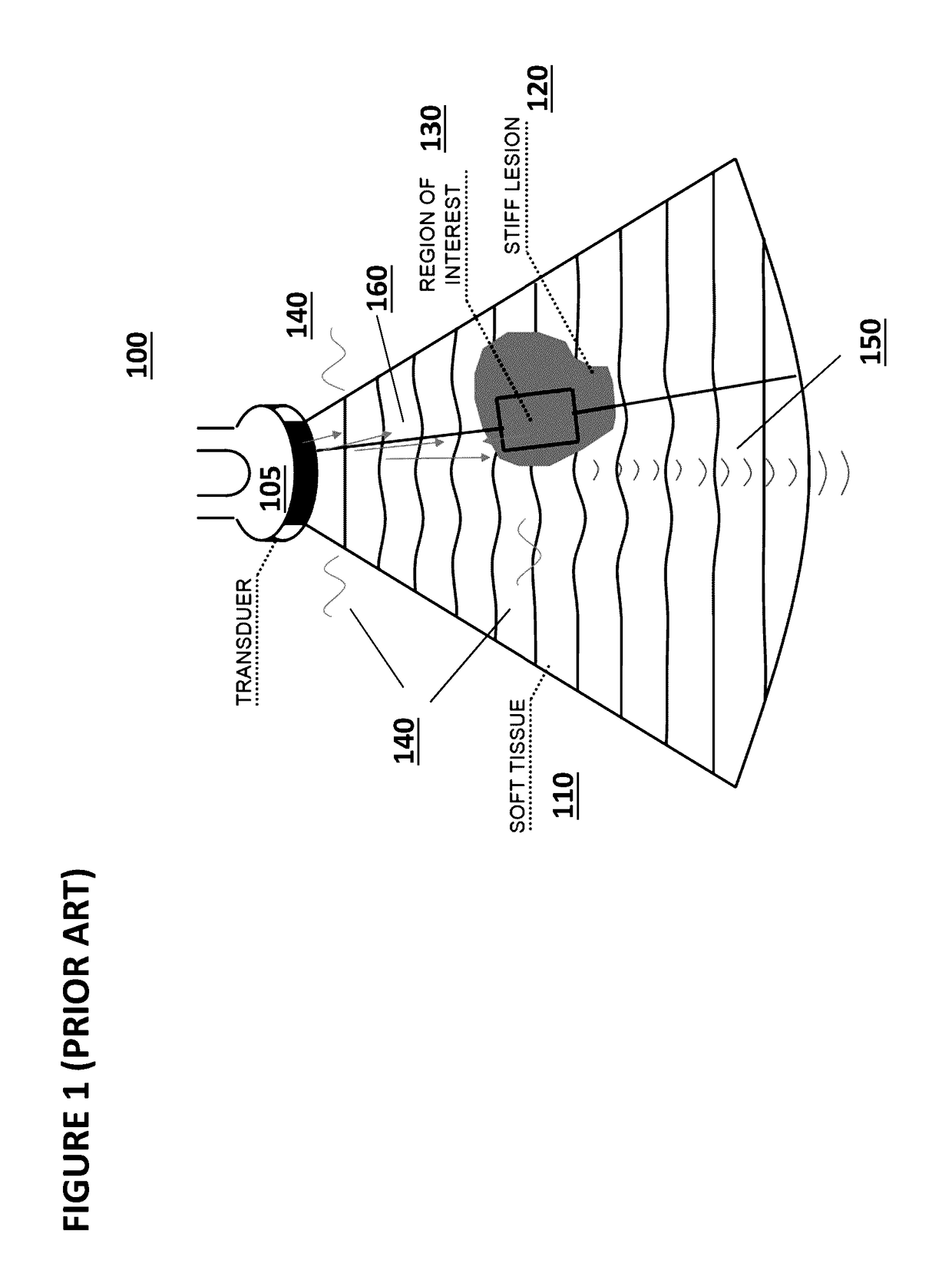

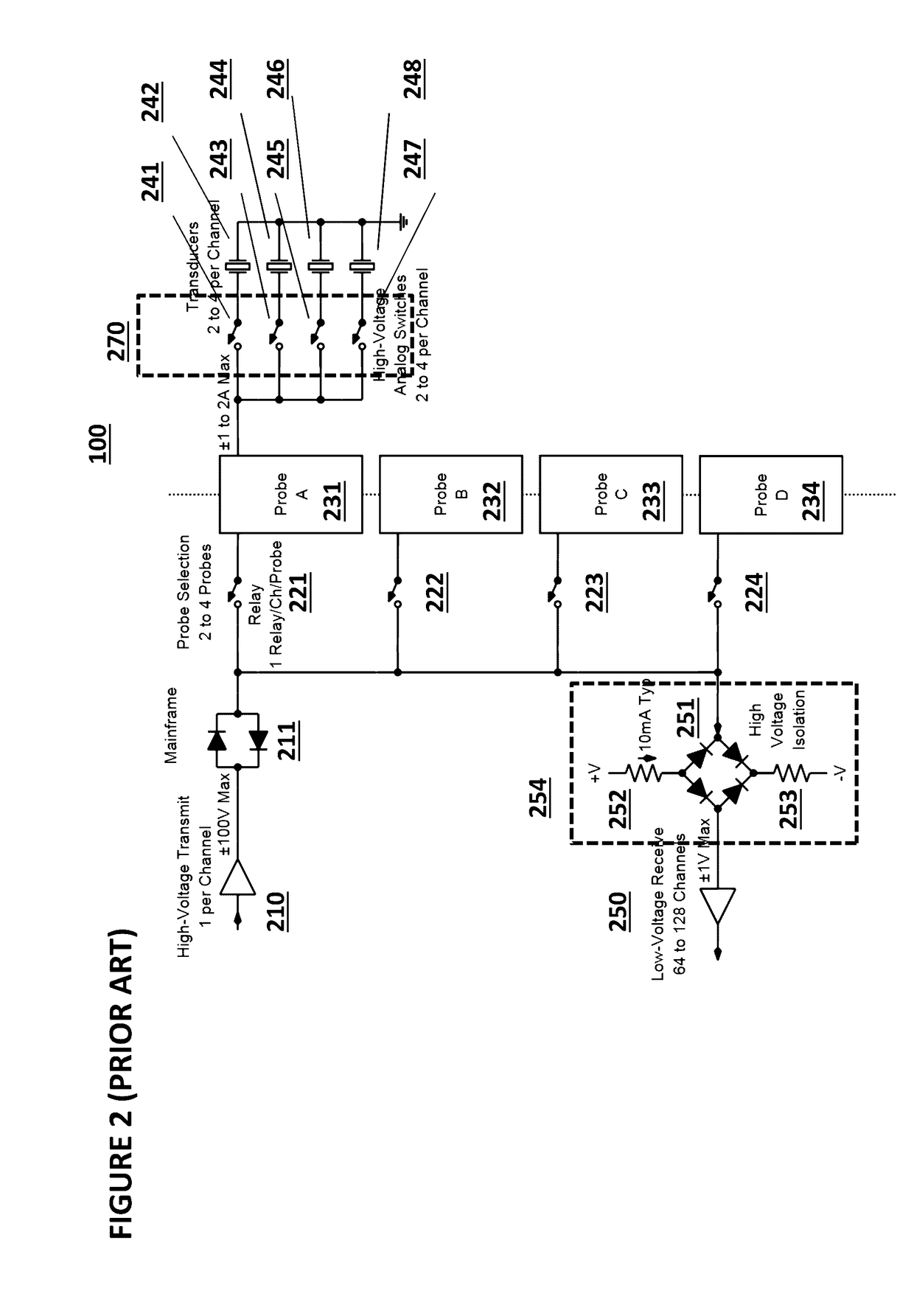

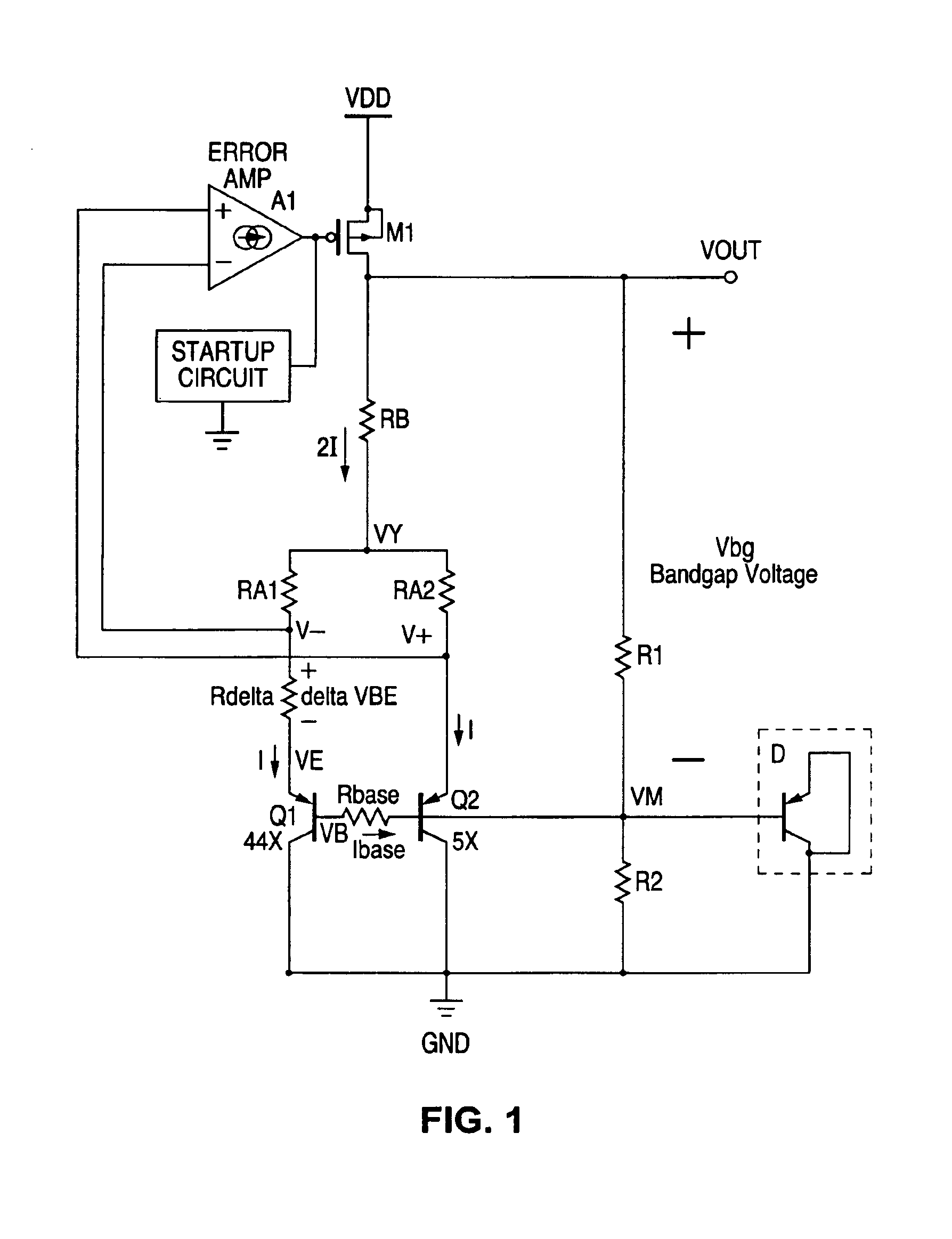

Optimized CMOS Analog Switch

ActiveUS20170104481A1Increase parasitic capacitanceImplementation is particularly straightforwardOrgan movement/changes detectionElectronic switchingCMOSSonification

An improved analog switch for use in an ultrasound elastography probe is disclosed. The improved analog switch results in less heat dissipation compared to prior art analog switches.

Owner:MICROCHIP TECH INC

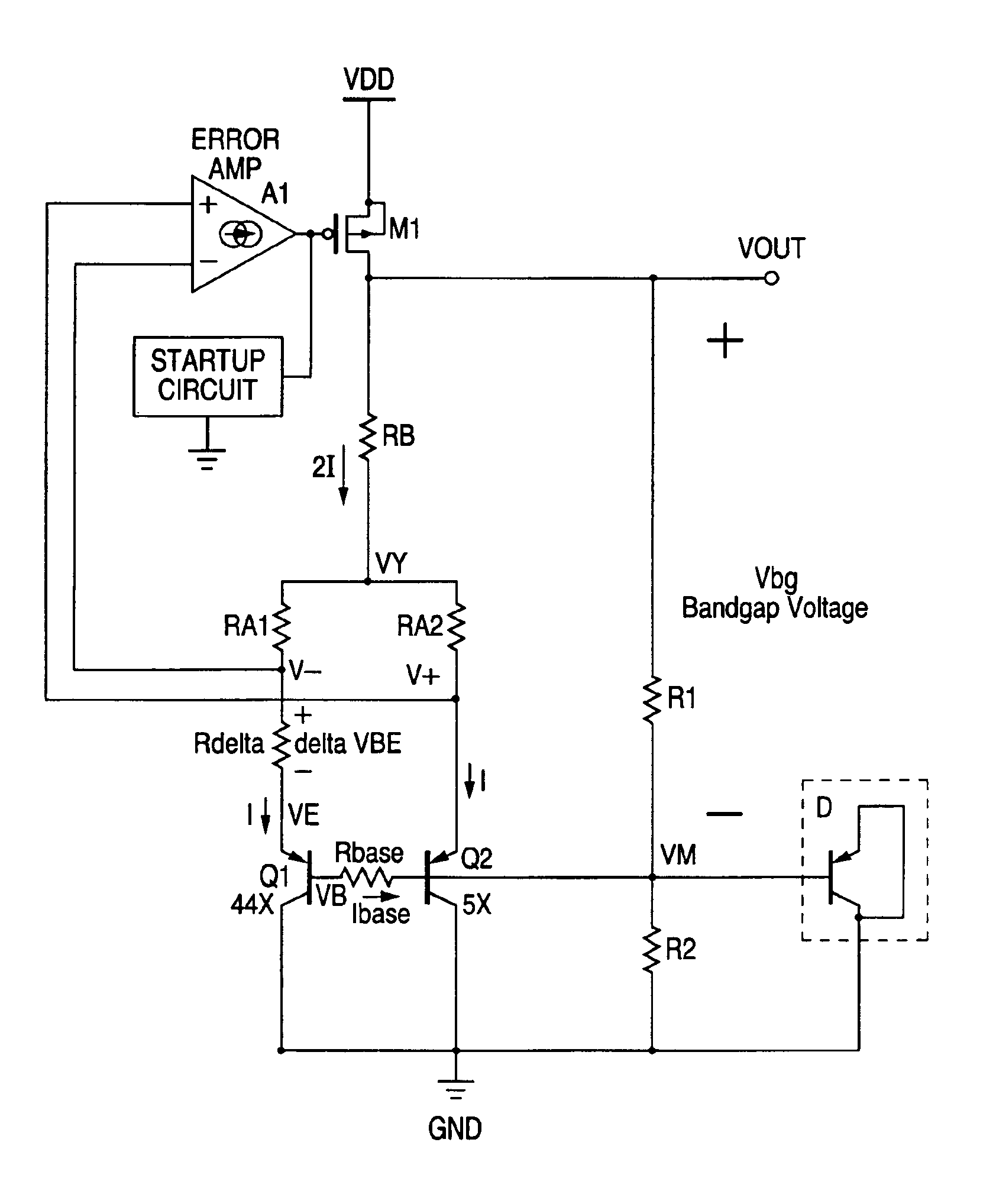

Metal oxide semiconductor (MOS) bandgap voltage reference circuit

ActiveUS6858917B1Increase parasitic capacitanceImprove referenceTransistorSolid-state devicesParasitic capacitanceSemiconductor

A metal oxide semiconductor (MOS) bandgap voltage reference circuit with a plurality of dummy bipolar junction transistors (BJTs) coupled to the mismatched parasitic substrate BJTs for improving parasitic capacitance matching, thereby improving startup behavior of the bandgap reference circuitry.

Owner:NAT SEMICON CORP

Organic el display apparatus

InactiveCN102479484AIncrease front brightnessReduce power consumptionStatic indicating devicesComputer scienceView angle

Provided is an organic EL display apparatus in which, depending on a situation in which a user uses the organic EL display apparatus, display with high light use efficiency and high front luminance (luminous efficiency)or display with large view angle is selectable. Pixels each include subpixels having different optical characteristics from each other, and the pixels and the subpixels are respectively arranged in a staggered pattern. Further, the subpixels are independently controlled.

Owner:CANON KK

Interconnection line structure and forming method thereof

ActiveCN103077921AAdd depthIncrease in sizeSemiconductor/solid-state device detailsSolid-state devicesParasitic capacitanceEngineering

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

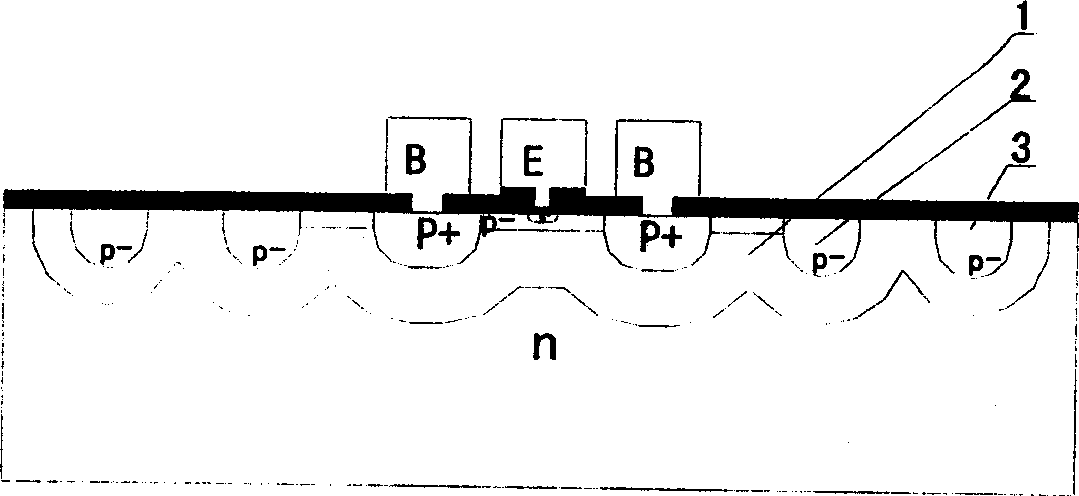

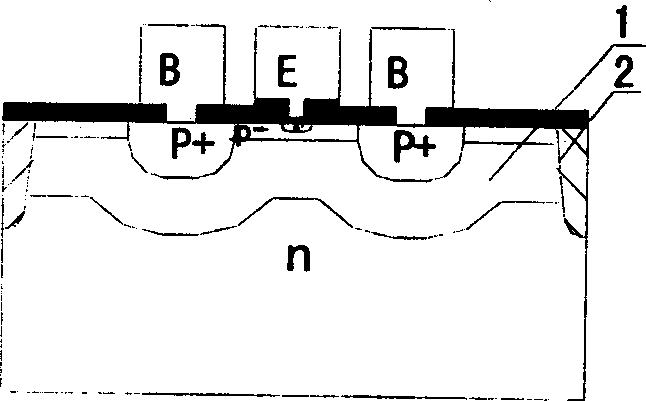

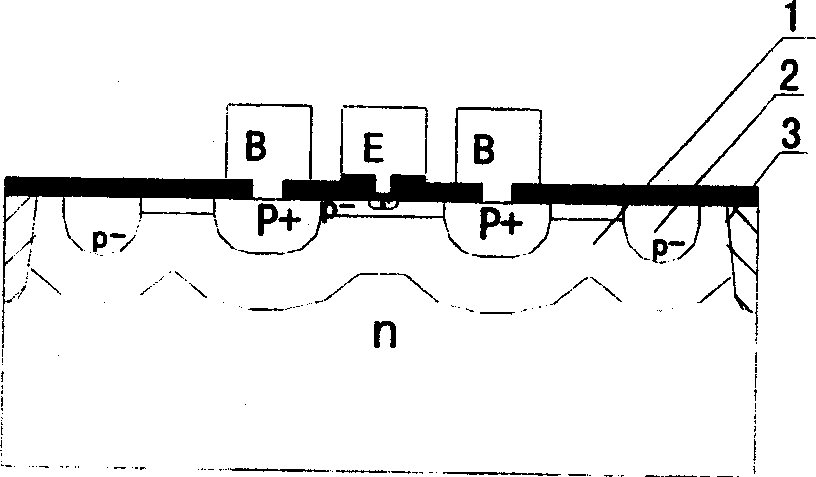

Semiconductor platform technology

InactiveCN1794432AHigh collector junction breakdown voltageLower junction capacitanceSemiconductor/solid-state device manufacturingCapacitanceMicrowave

This invention relates to a platform technology of semiconductors combining advantages of the plane and mesa technologies to diffuse a deep junction at the edge of the PN junction to let it have a most possible high break-over voltage and erode silicon in the width sphere of an exhaust region of the outside of said junction to form a mesa structure, which can bear rather high break-over voltage to block the further expansion of the exhaust areas and reduce the capacitance of the PN junction, so the total break-over voltage of the collector junction of the transistor is increased due to the sum voltage shared by the mesa and the PN junction.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Capacitive touch panel

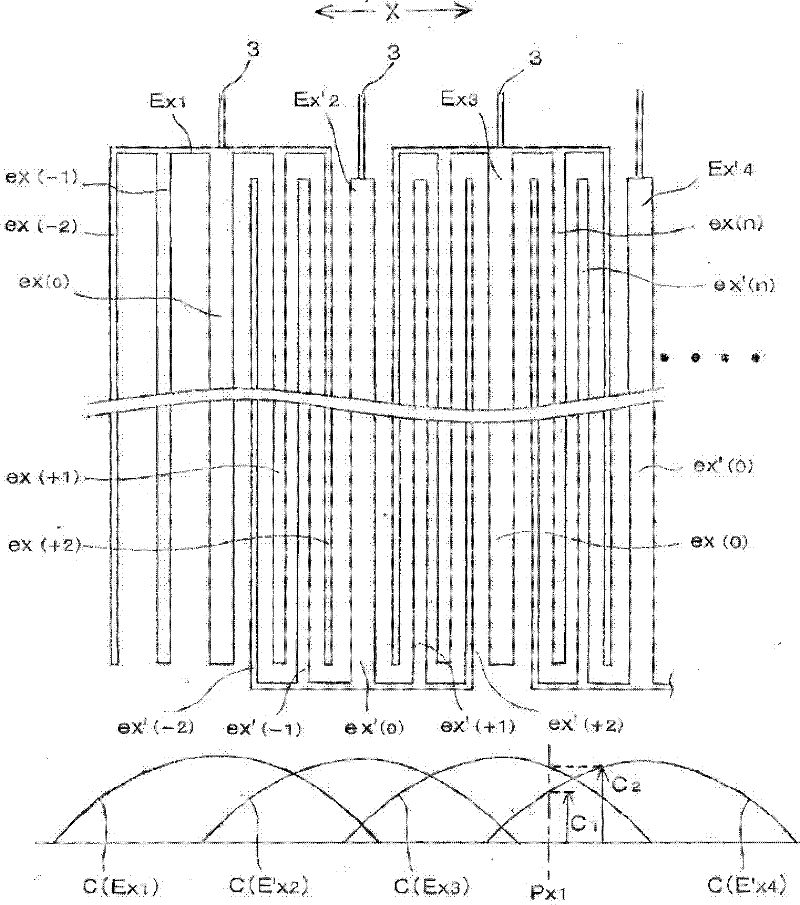

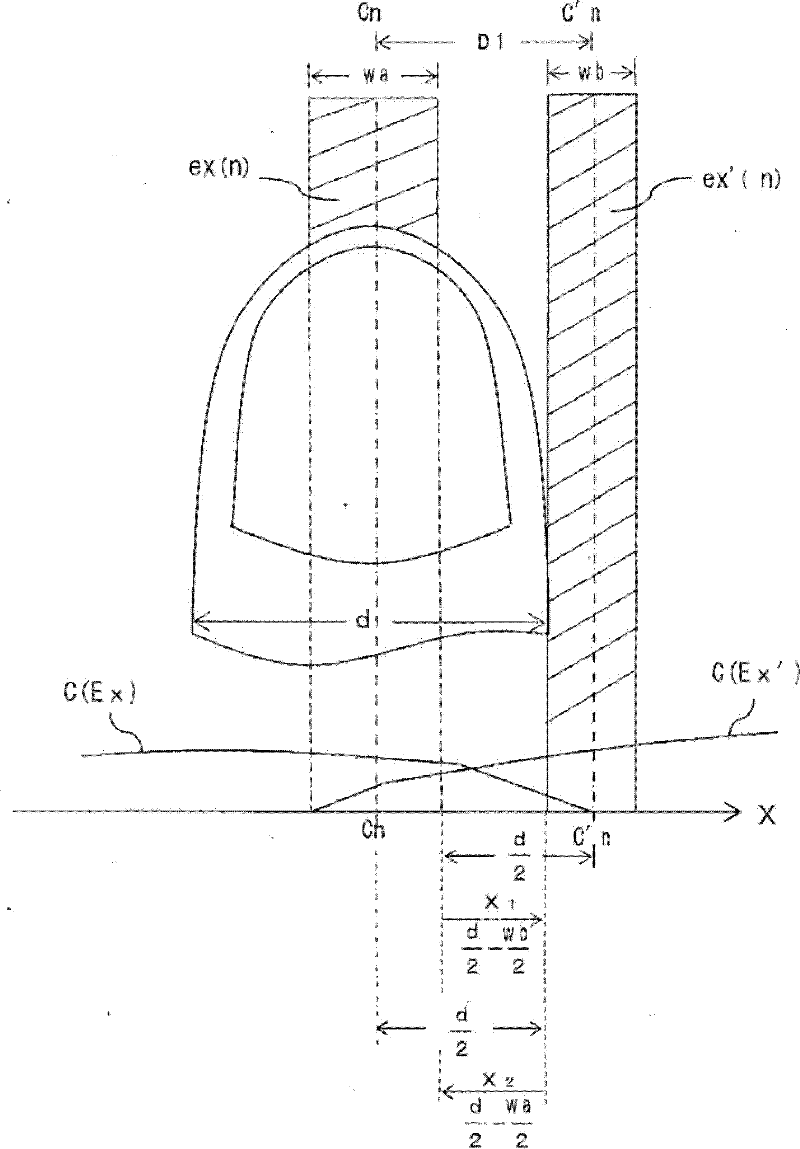

InactiveCN102541369AInput operation area expandedReduce detection errorInput/output processes for data processingParasitic capacitanceEngineering

A capacitive touch panel that detects an input position accurately with a limited number of sensing electrodes is provided. First and second sensing electrodes adjacent to each other in a detecting direction are arranged such that among a plurality of branch patterns of the first sensing electrode a branch pattern closer to the second sensing electrode, and among a plurality of branch patterns of the second sensing electrode a branch pattern closer to the first sensing electrode are alternately arranged in the detecting direction. The widths in the detecting direction of the plurality of branch patterns of each sensing electrode are set such that the branch patterns on the opposite sides in the detecting direction have the smallest width, and the width of a branch pattern gradually becomes greater as the branch pattern gets closer to a branch pattern at the center.

Owner:SMK CO LTD

Transistor and method of forming same

ActiveCN105448916AIncrease switching speedReduce contact areaTransistorSemiconductor/solid-state device manufacturingParasitic capacitanceSemiconductor

A transistor and a method of forming the same are disclosed. The method of forming the transistor comprises the steps of providing a semiconductor substrate consisting of a first region, a second region and a third region which are adjacent to one another; carrying out well region ion implantation, and forming a well region in the semiconductor substrate; carrying out channel ion implantation, and forming a first doped region in the surface of the well region in the first region; forming a gate structure on the semiconductor substrate and in the first region, the gate structure covering the first doped region in the first region; carrying out shallow doped ion implantation, forming a shallow doped source region in the semiconductor substrate and in the second region at one side of the gate structure, and forming a shallow doped drain region in the semiconductor substrate and in the third region at the other side of the gate structure; and forming an elevated source region on the shallow doped source region, and forming an elevated drain region on the shallow doped drain region. The method of the invention reduces the parasitic capacitance between the source and drain regions and the channel region and the substrate.

Owner:SEMICON MFG INT (SHANGHAI) CORP