Interconnection line structure and forming method thereof

An interconnection wire and semiconductor technology, applied in the field of interconnection wire structure and the formation of interconnection wire structure, can solve the problems of small parasitic capacitance and the effect of parasitic capacitance is no longer obvious, and achieve the reduction of parasitic capacitance and dielectric constant Small, improve the effect of RC delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

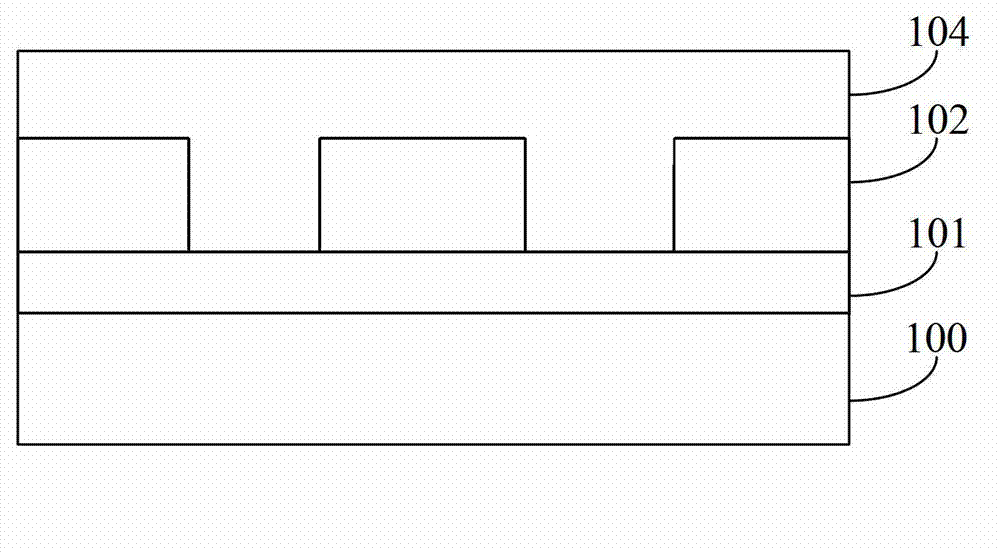

[0037] The inventor researched the existing metal interconnection structure forming method and found that, referring to Figure 4 , as the distance between adjacent metal interconnection lines becomes smaller, an air gap 105 is formed in the intermetallic dielectric layer 104 between adjacent metal interconnection lines. The inventor further studied the problem of the air gap, and realized that the air gap 105 will not increase the parasitic capacitance between adjacent metal interconnection lines, but will reduce the parasitic capacitance. Forming an air gap (air gap) between adjacent metal interconnection lines can be used as an effective method to reduce parasitic capacitance between metal interconnections.

[0038] Therefore, how to form an air gap in the intermetallic dielectric layer between adjacent metal interconnection lines, or even form a larger volume of air gap, has become the research focus of the inventors.

[0039] Through creative work, the inventor obtained ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More