Patents

Literature

34results about How to "Improve RC delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

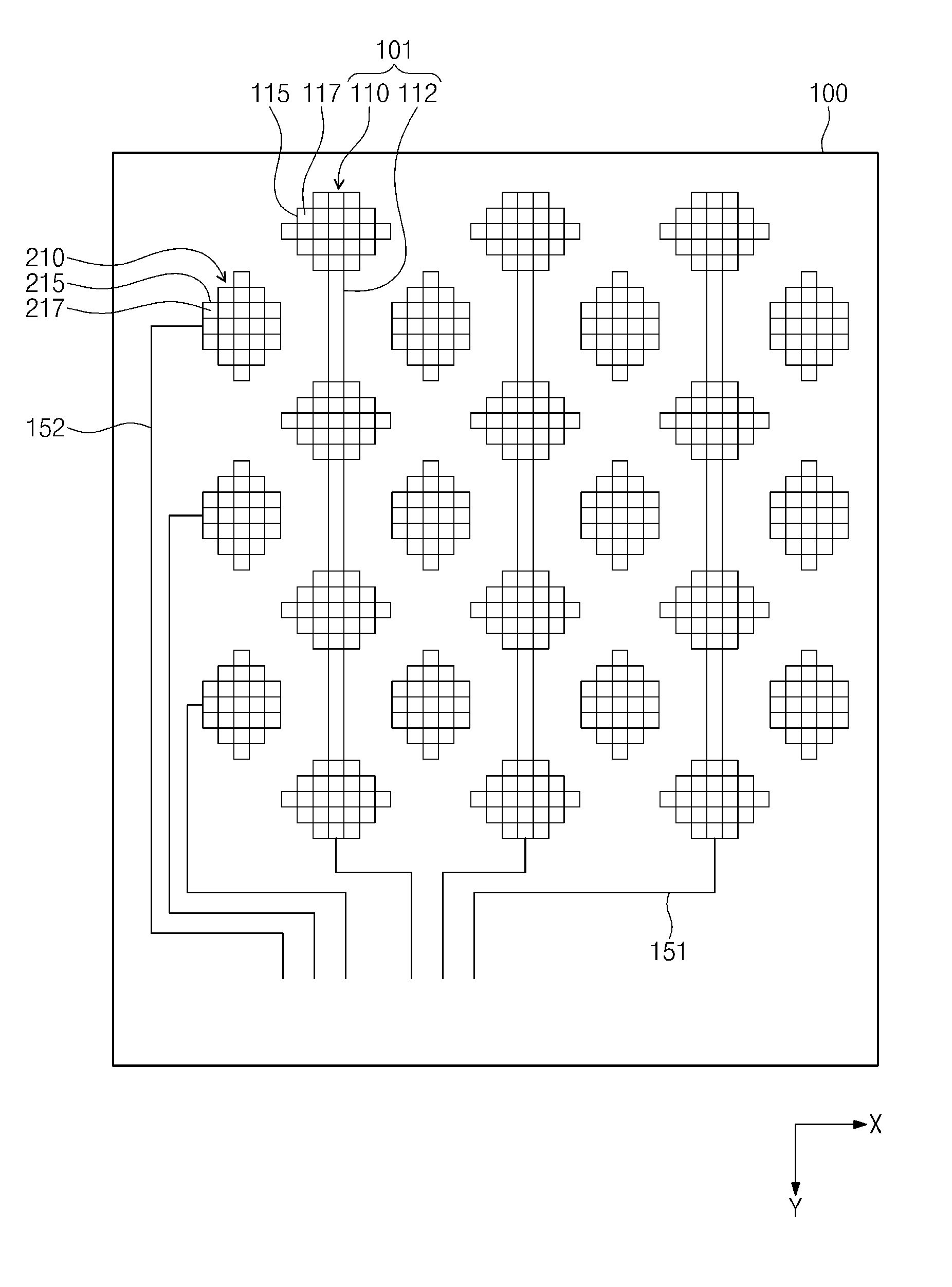

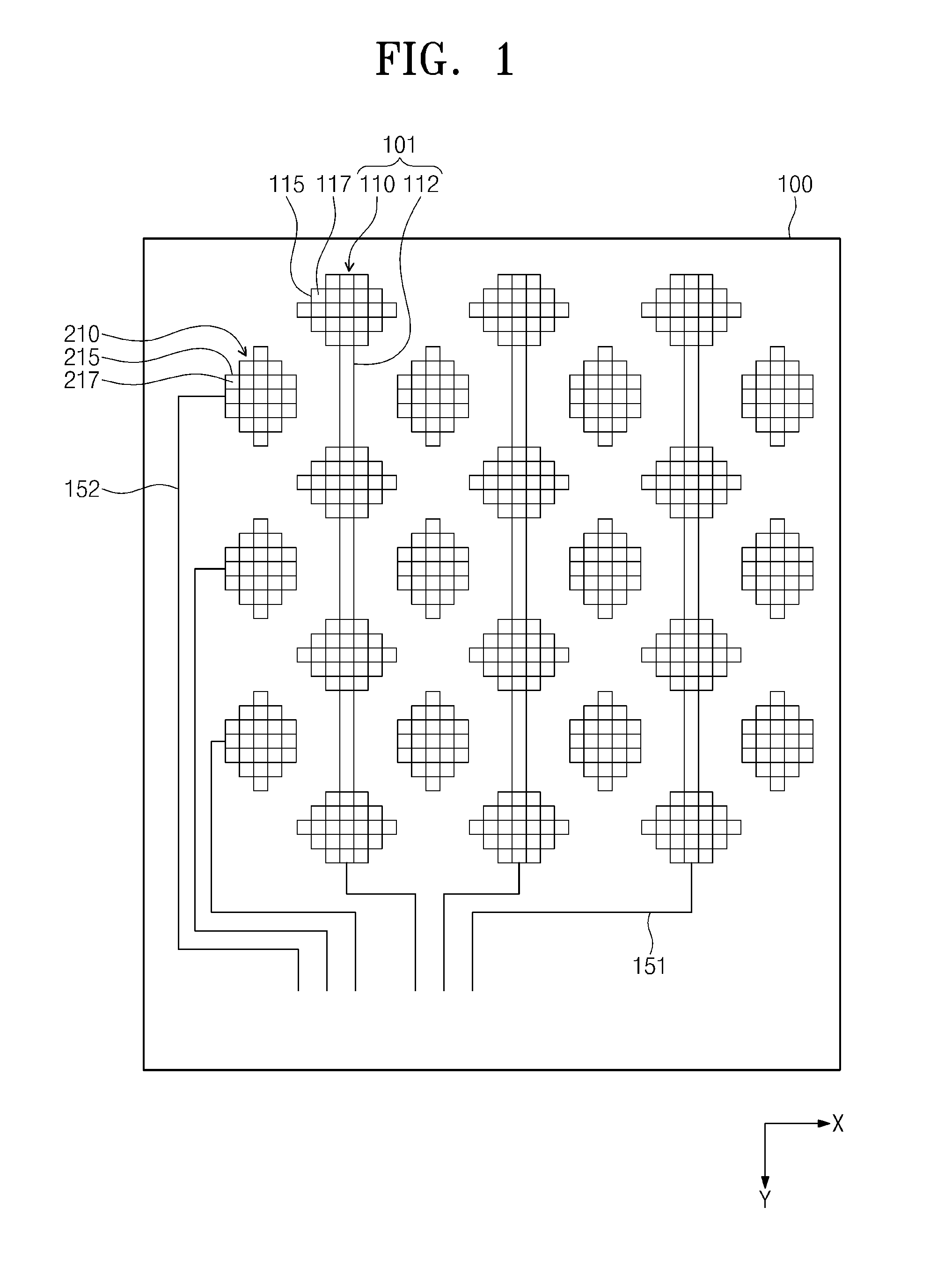

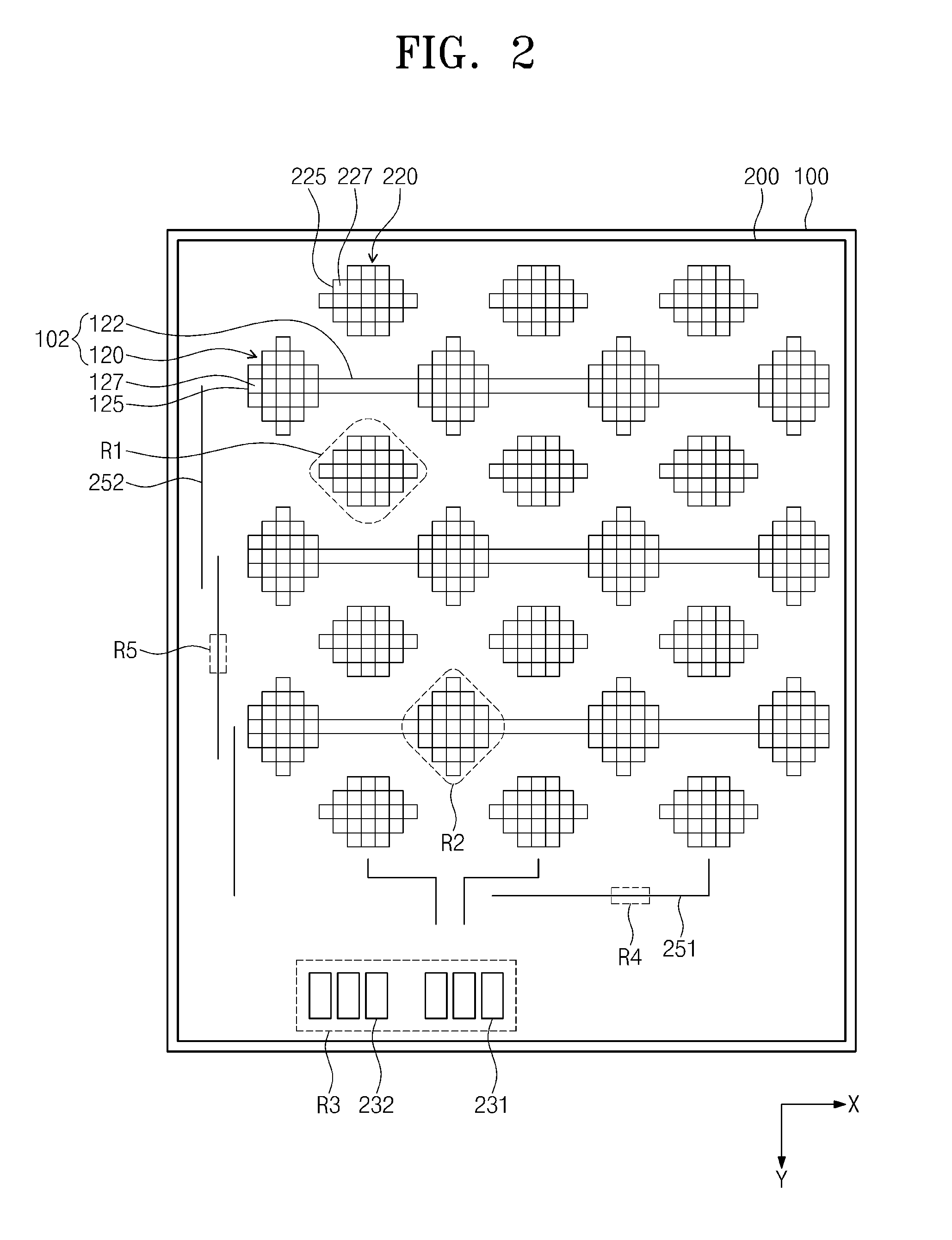

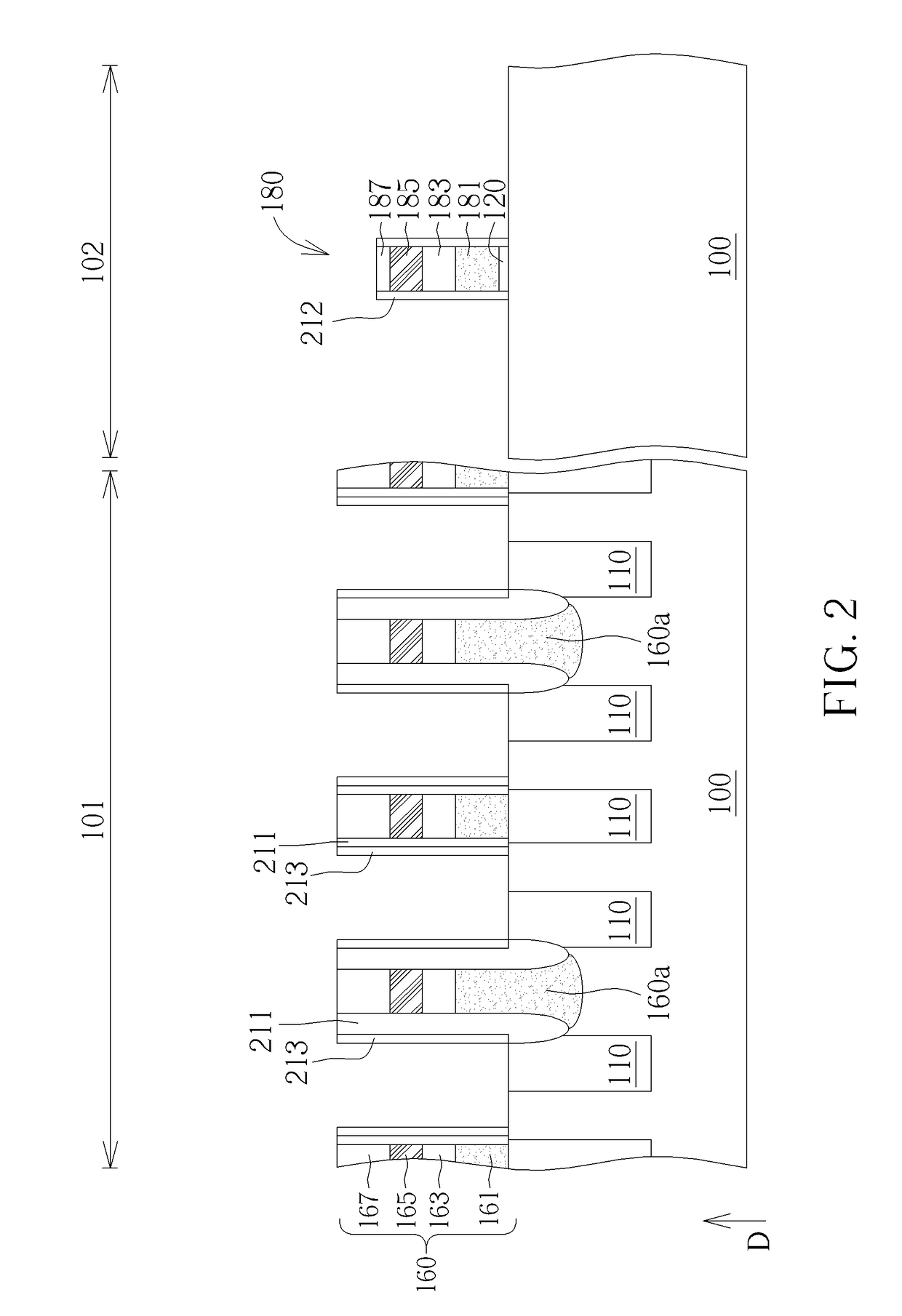

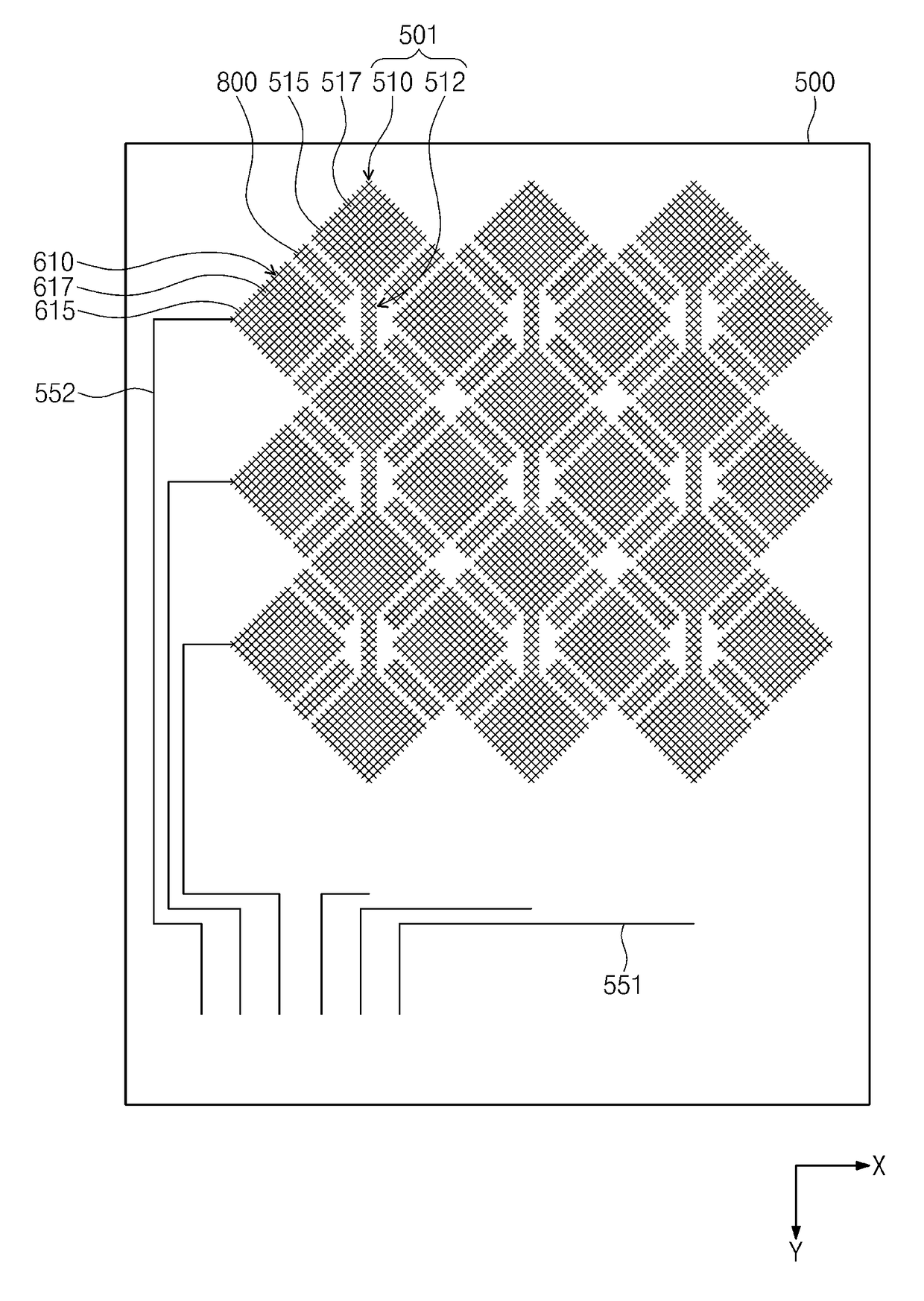

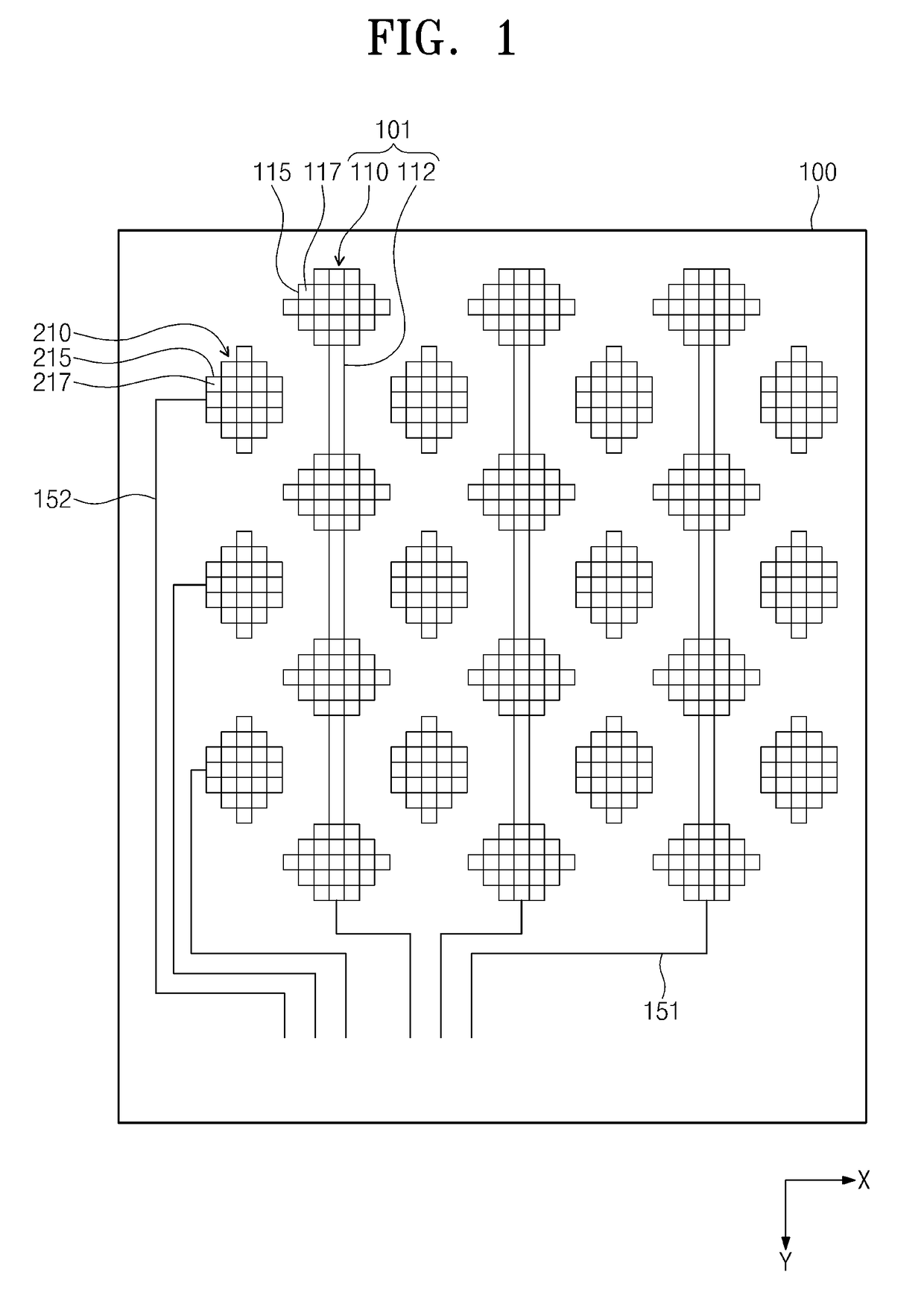

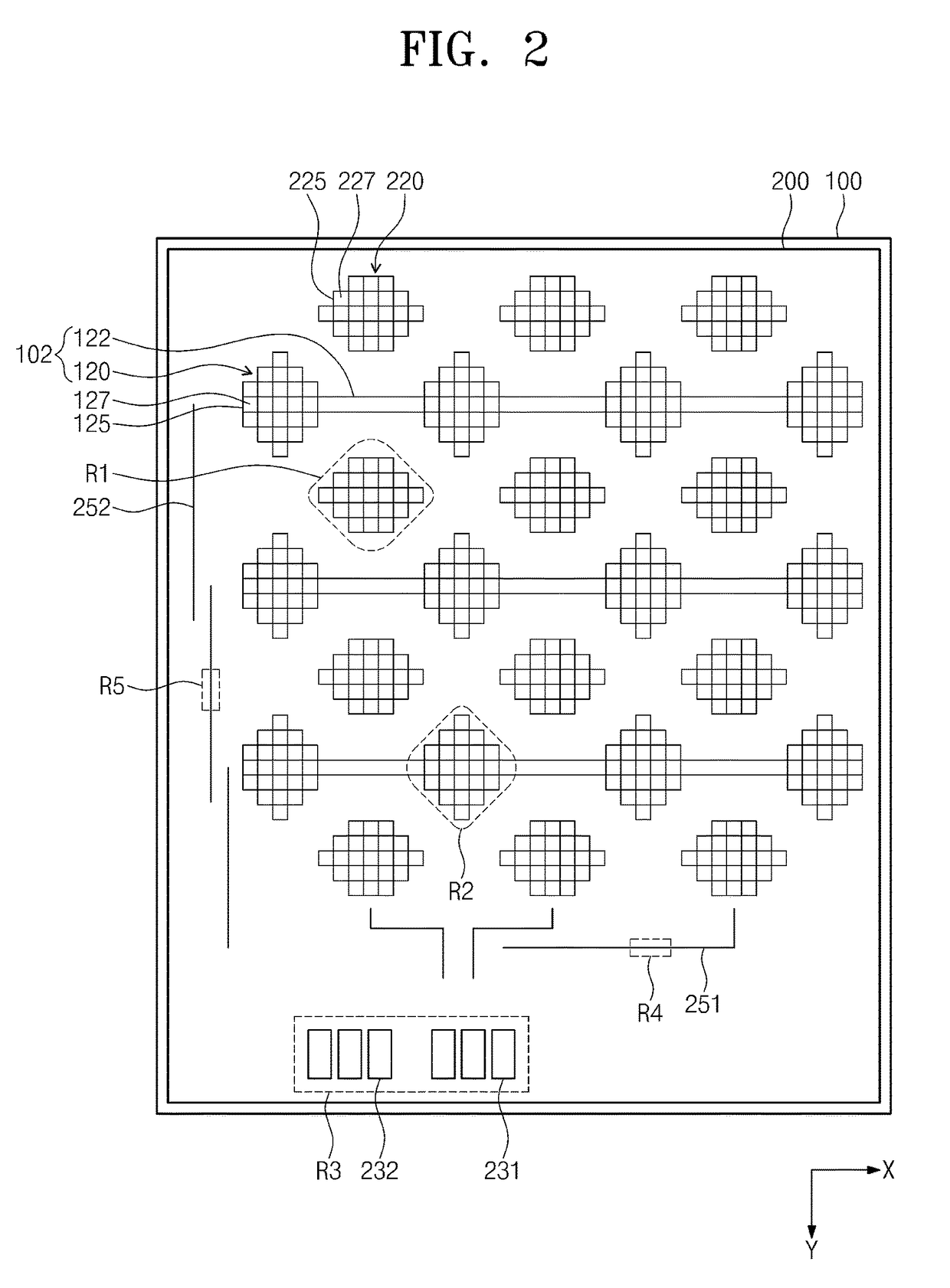

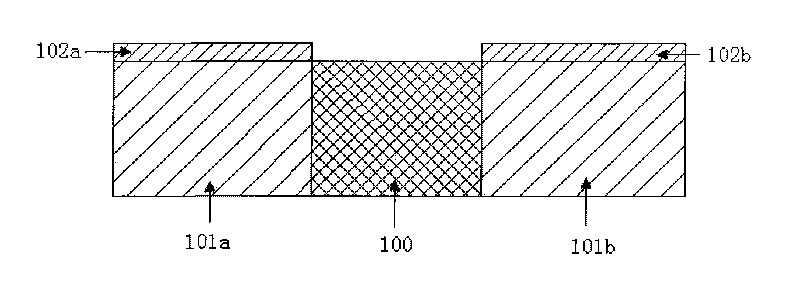

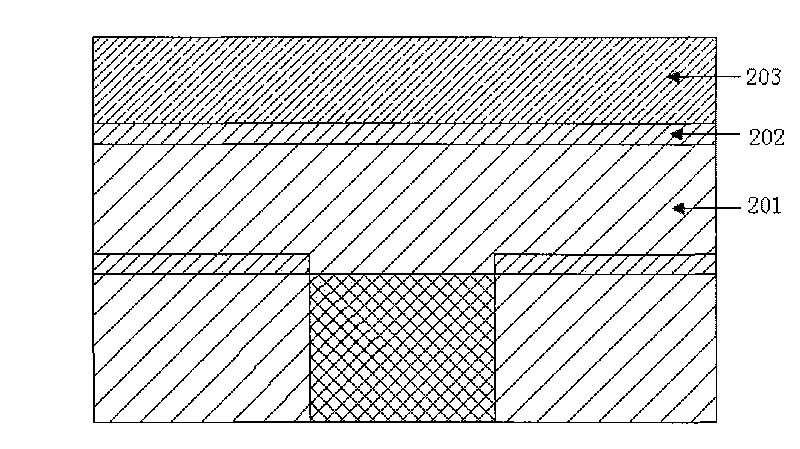

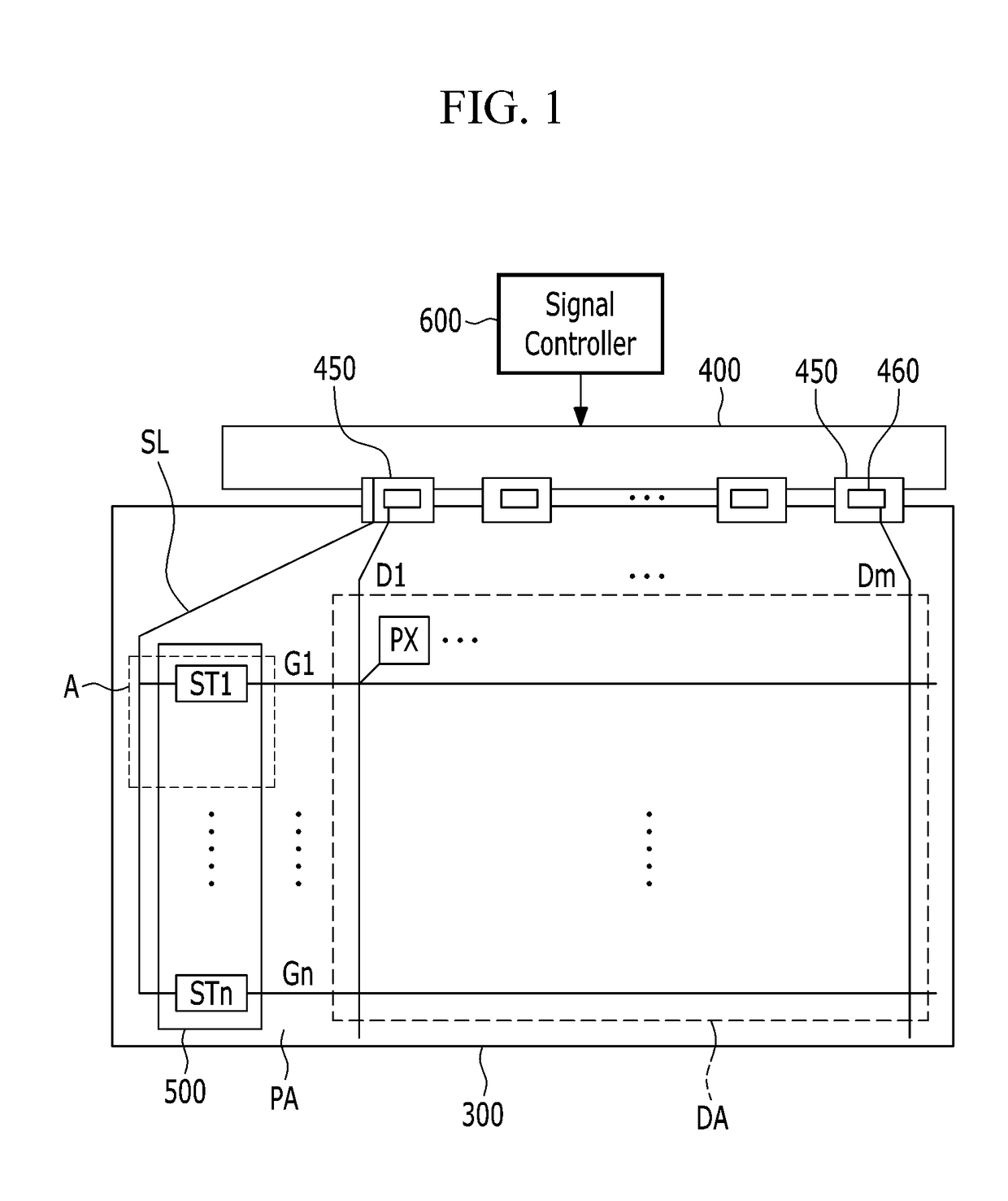

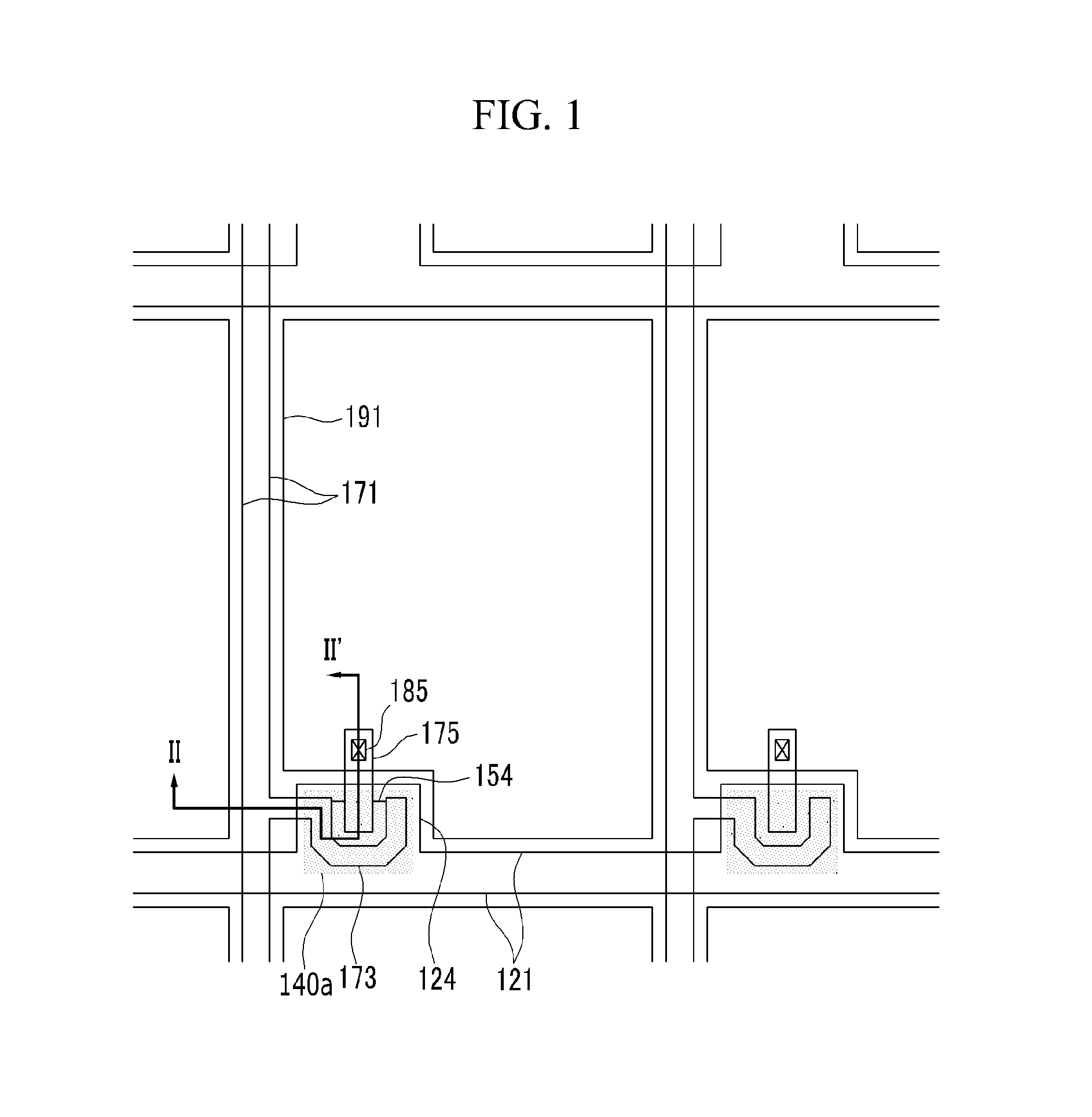

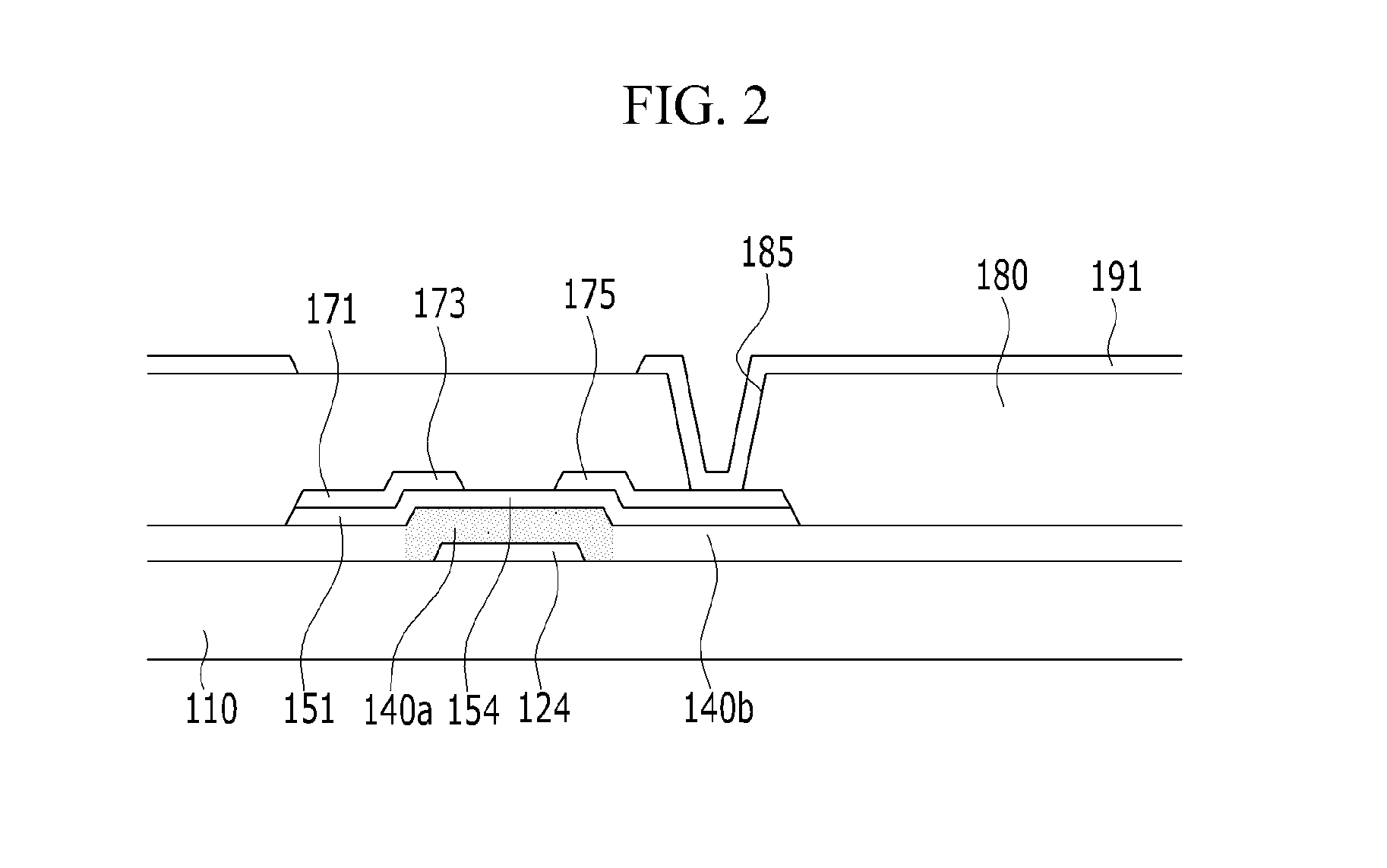

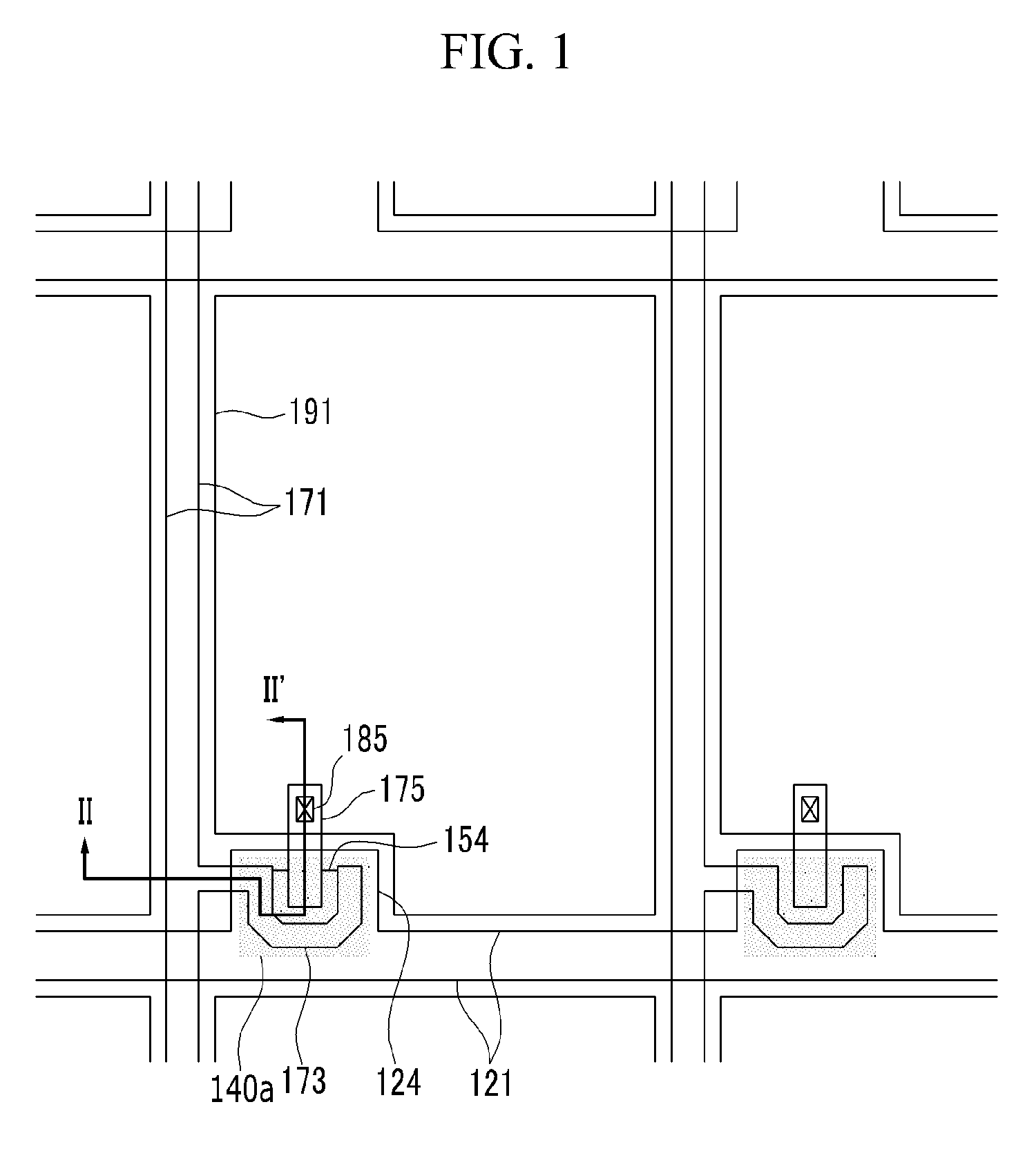

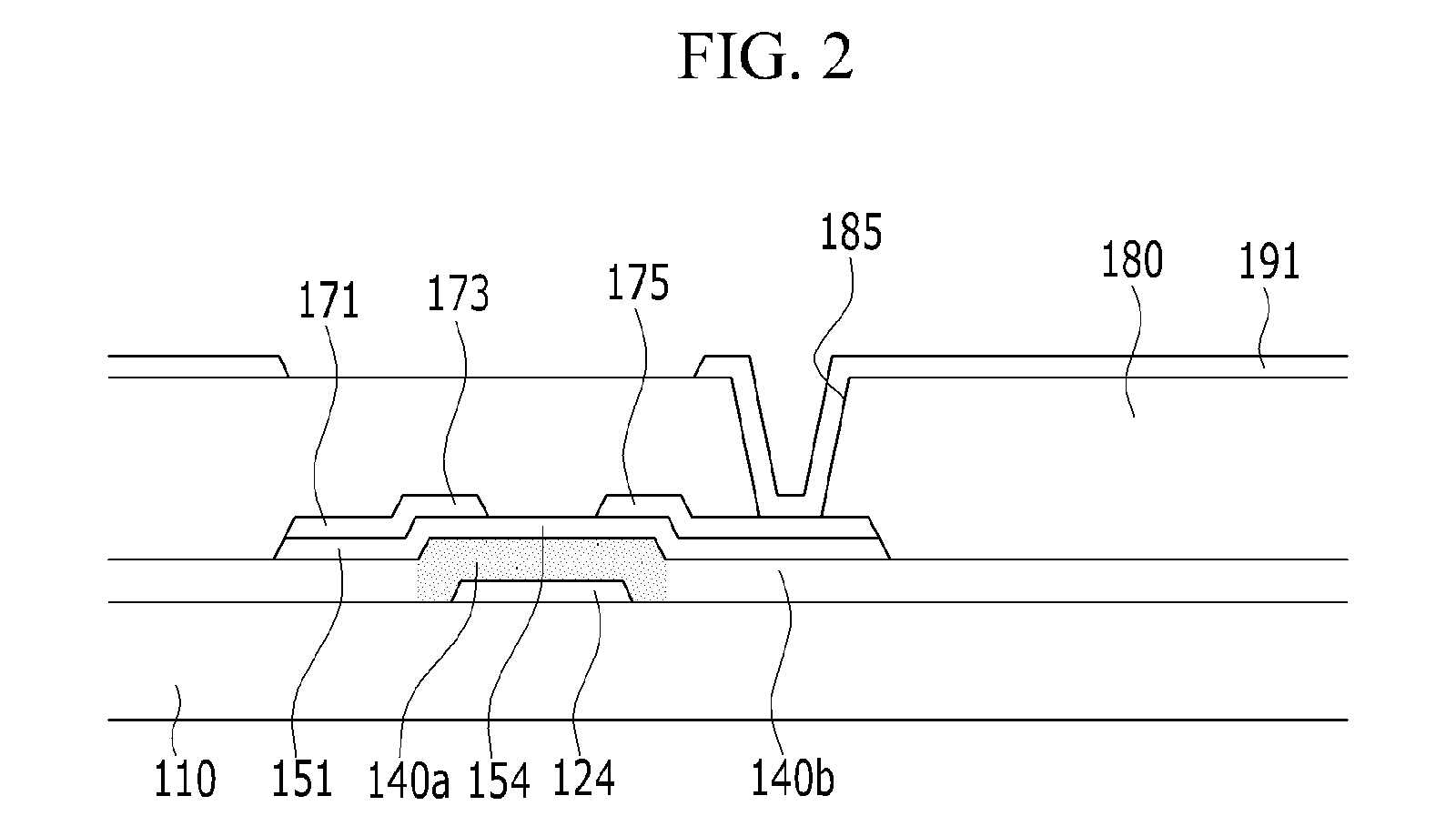

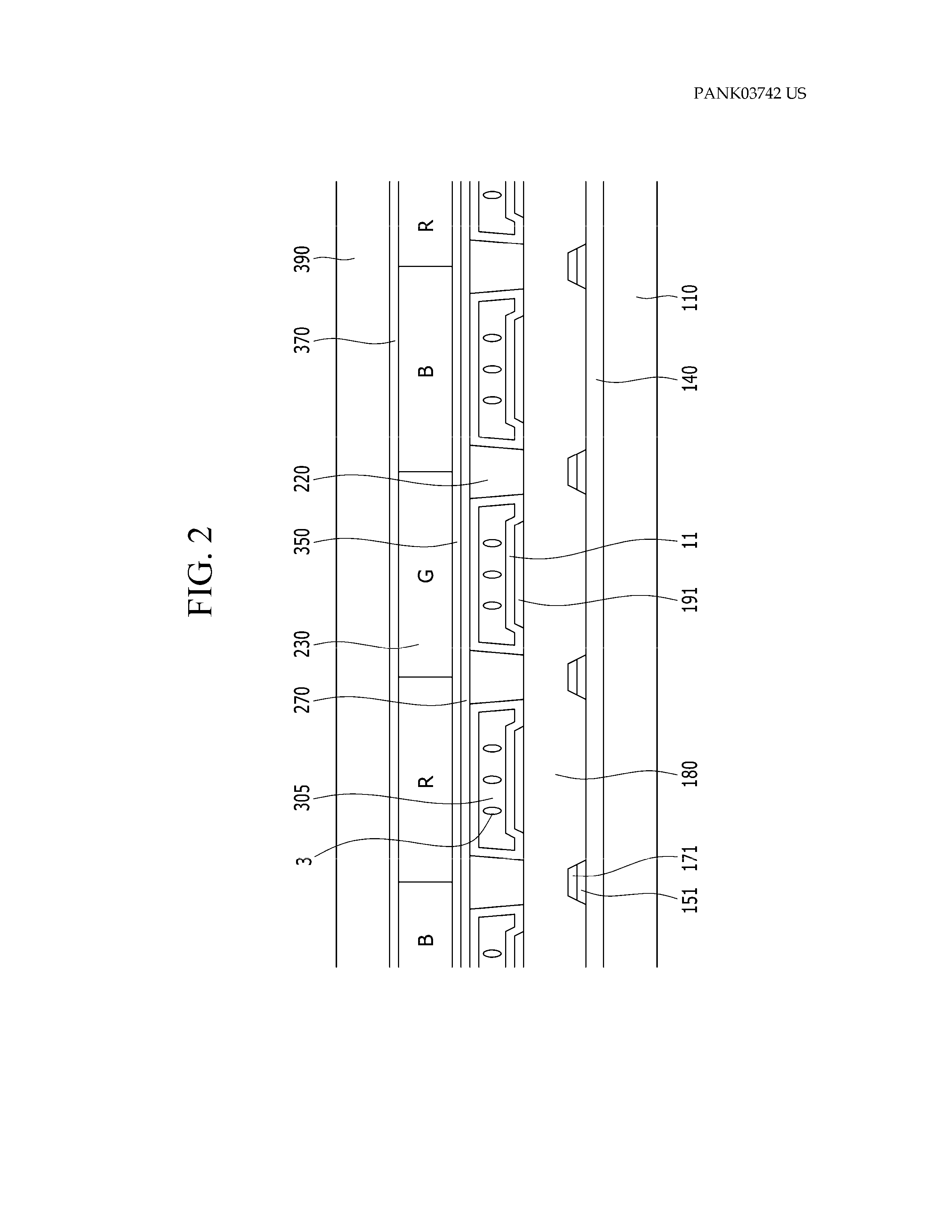

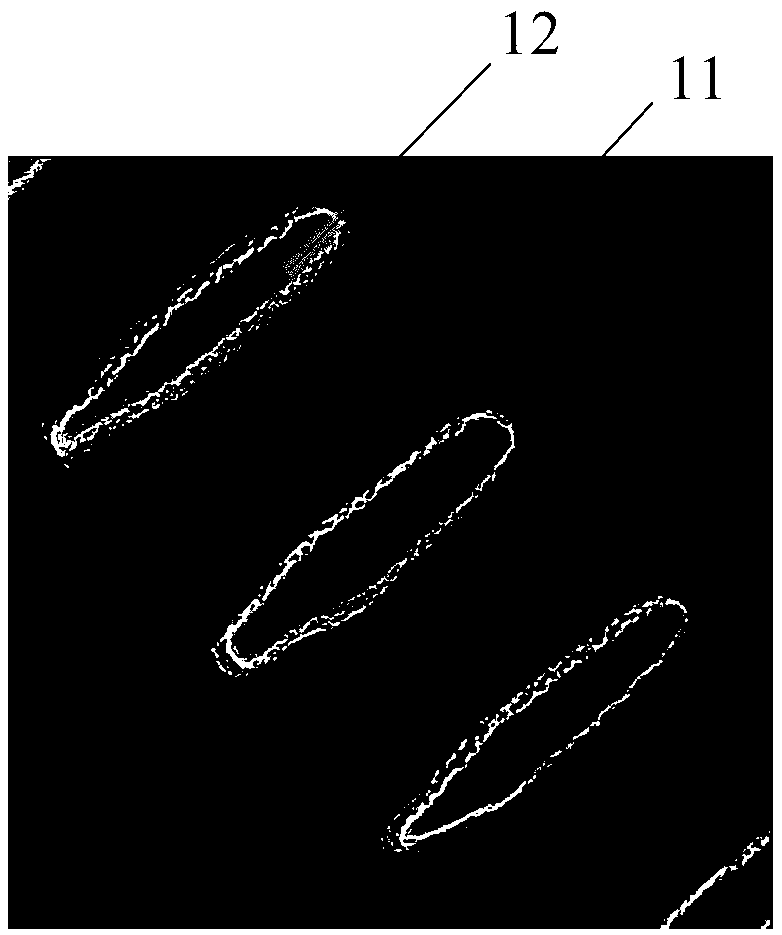

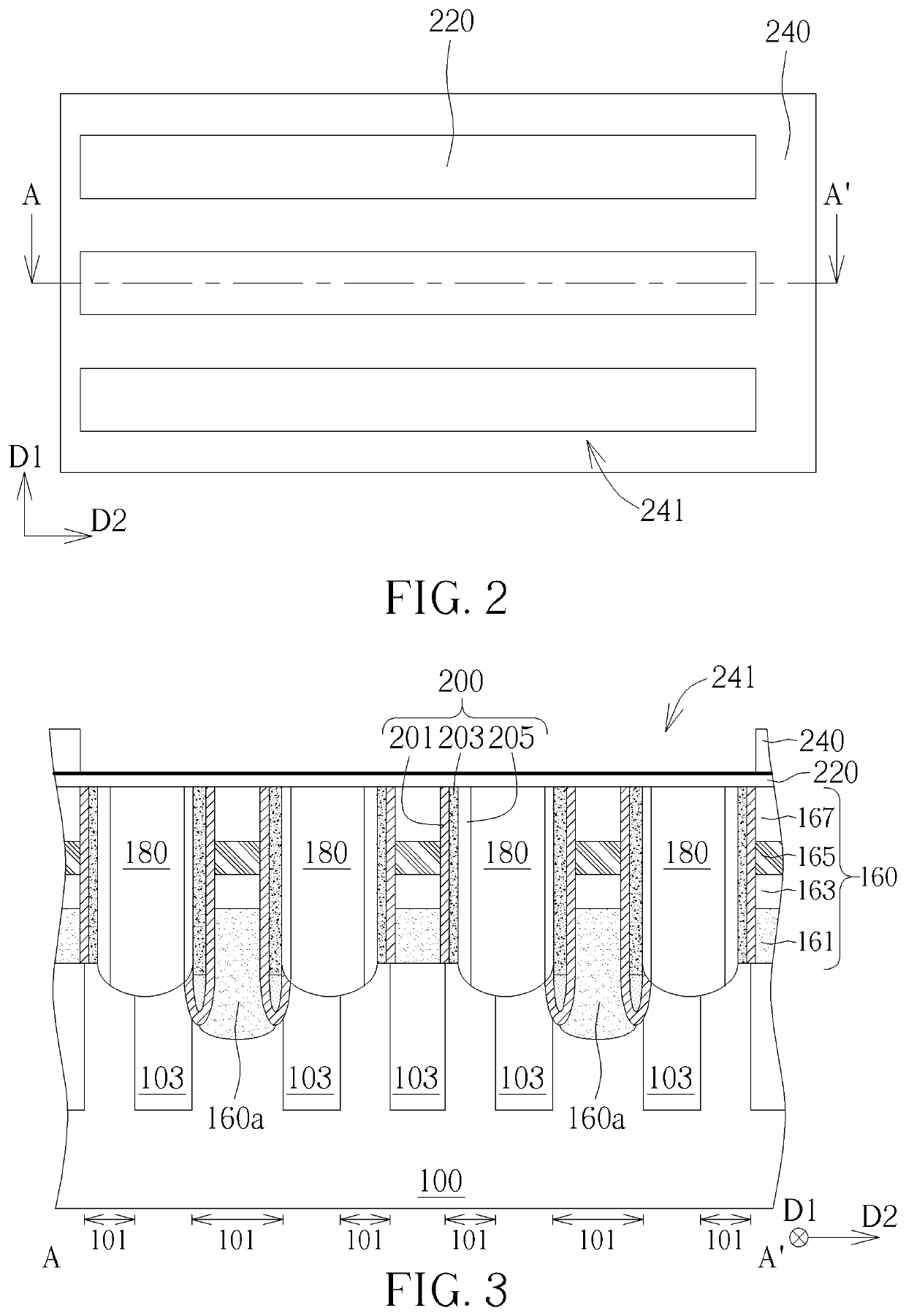

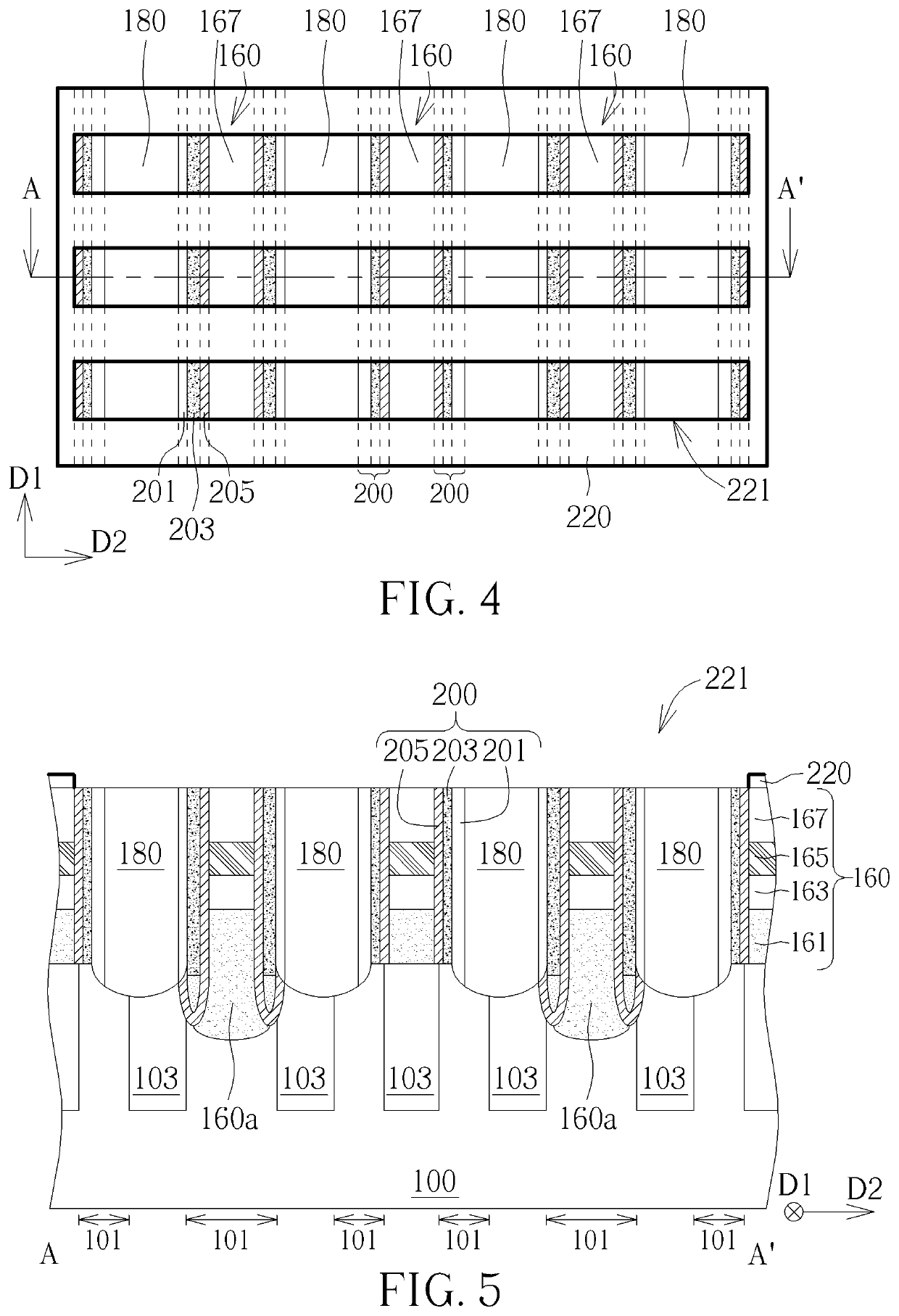

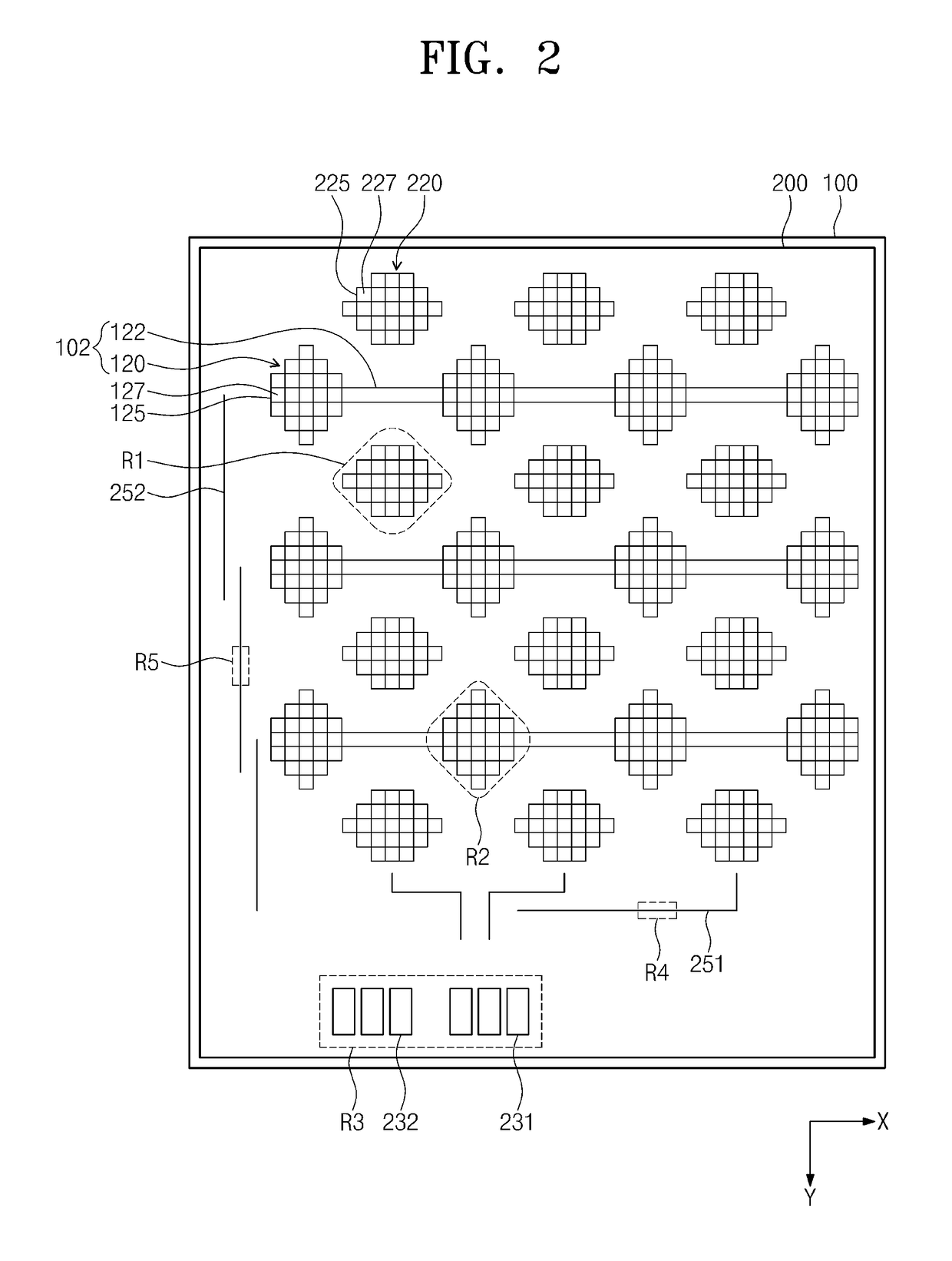

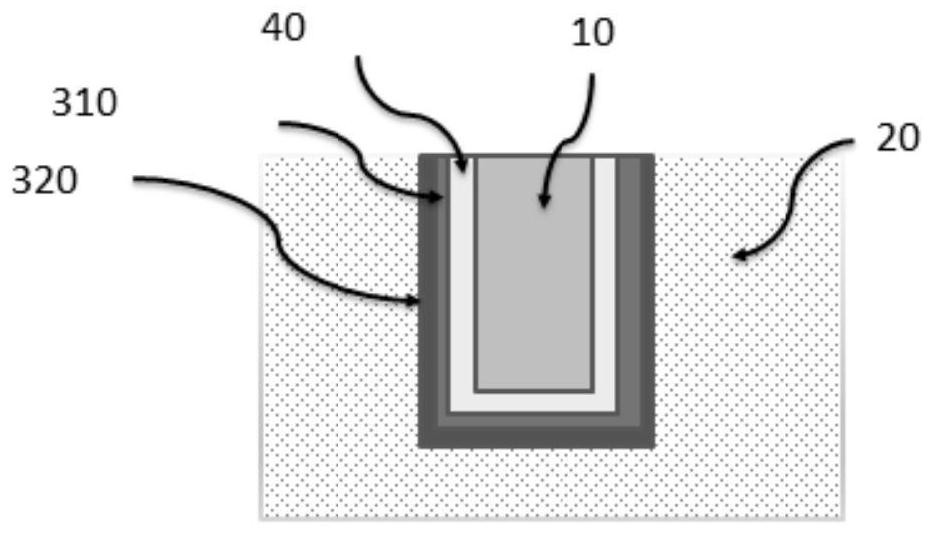

Touch panel and display apparatus including the same

ActiveUS20160048248A1Reduce resistanceImprove RC delayCathode-ray tube indicatorsInput/output processes for data processingInsulation layerEngineering

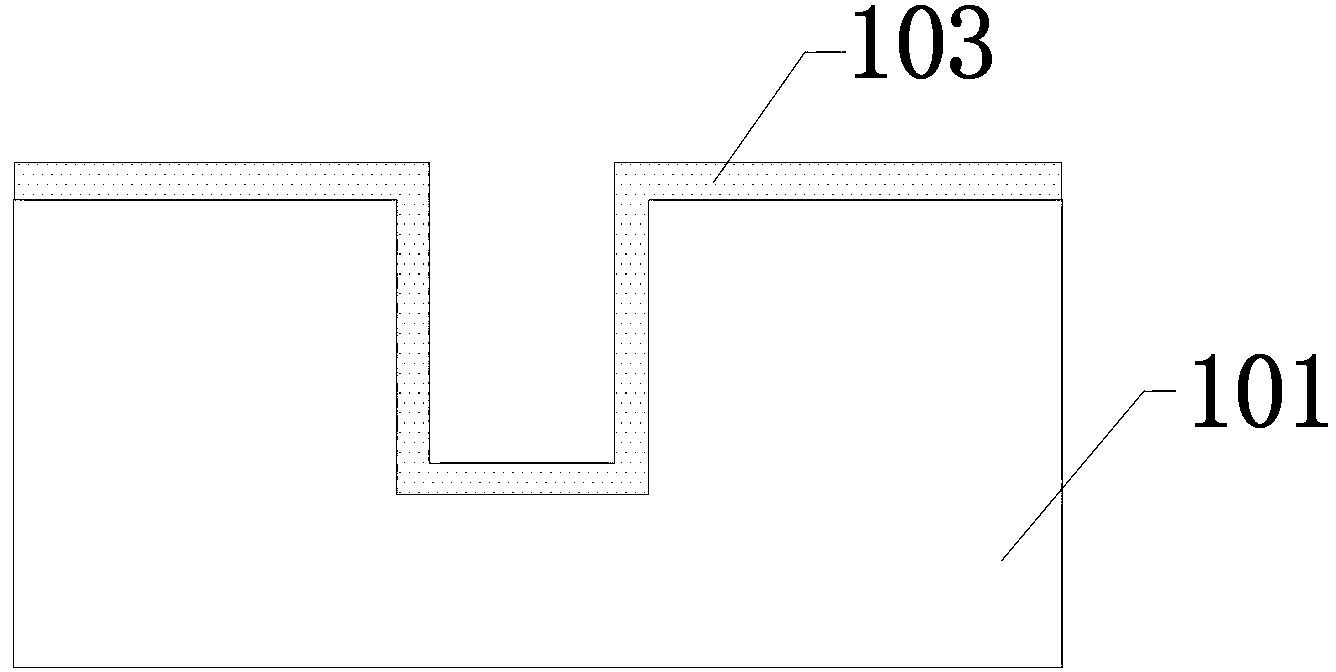

A touch panel including a substrate, first touch electrodes, each of the first touch electrodes including first mesh patterns disposed on the substrate, an insulation layer disposed on the first touch electrodes, second touch electrodes, each of the second touch electrodes including second mesh patterns disposed on the insulation layer, first auxiliary mesh electrodes disposed on the substrate, the first auxiliary mesh electrodes being electrically connected to at least a portion of the corresponding second mesh patterns, and second auxiliary mesh electrodes disposed on the insulation layer, the second auxiliary mesh electrodes being electrically connected to at least a portion of the corresponding first mesh patterns.

Owner:SAMSUNG DISPLAY CO LTD

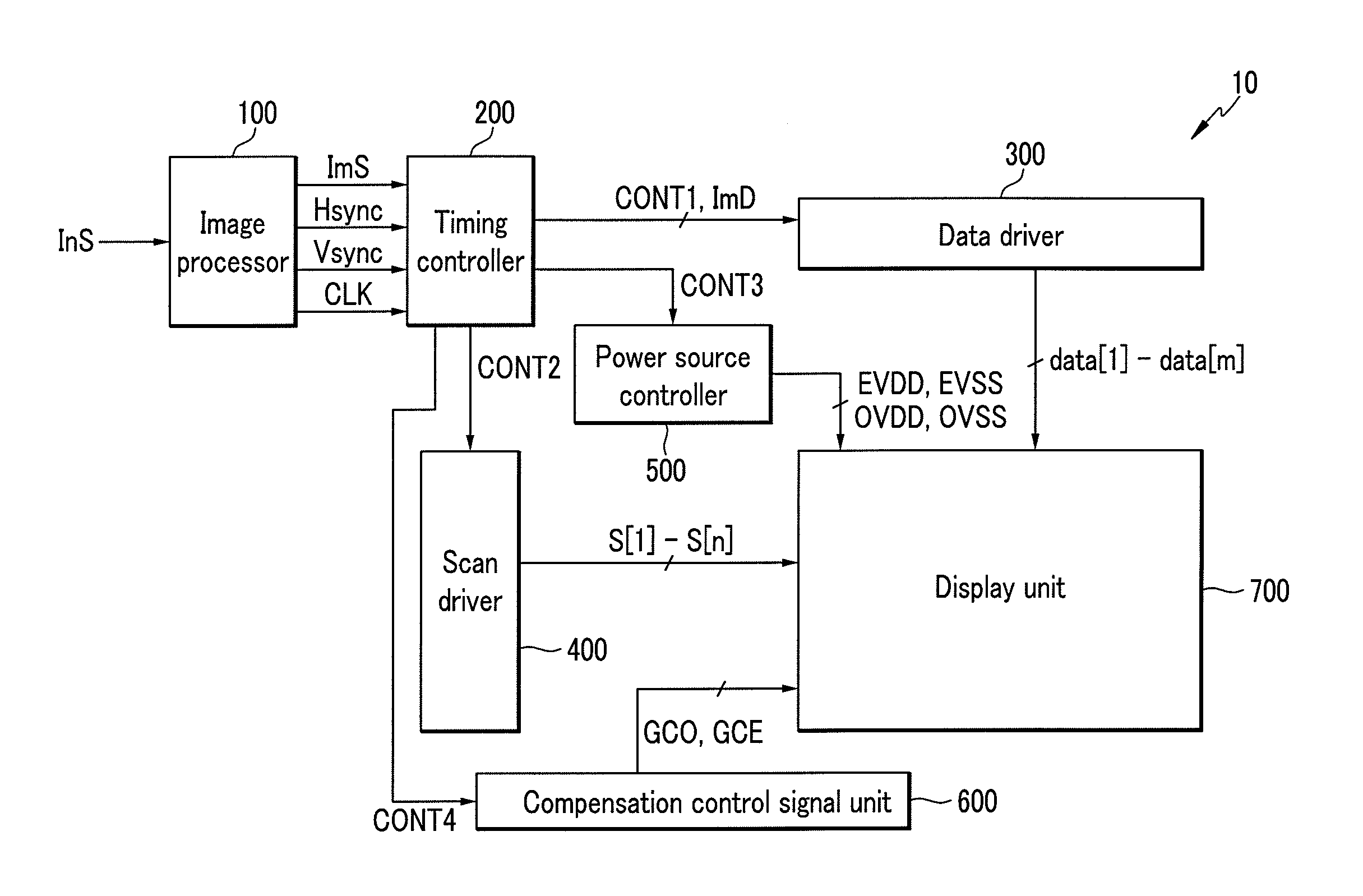

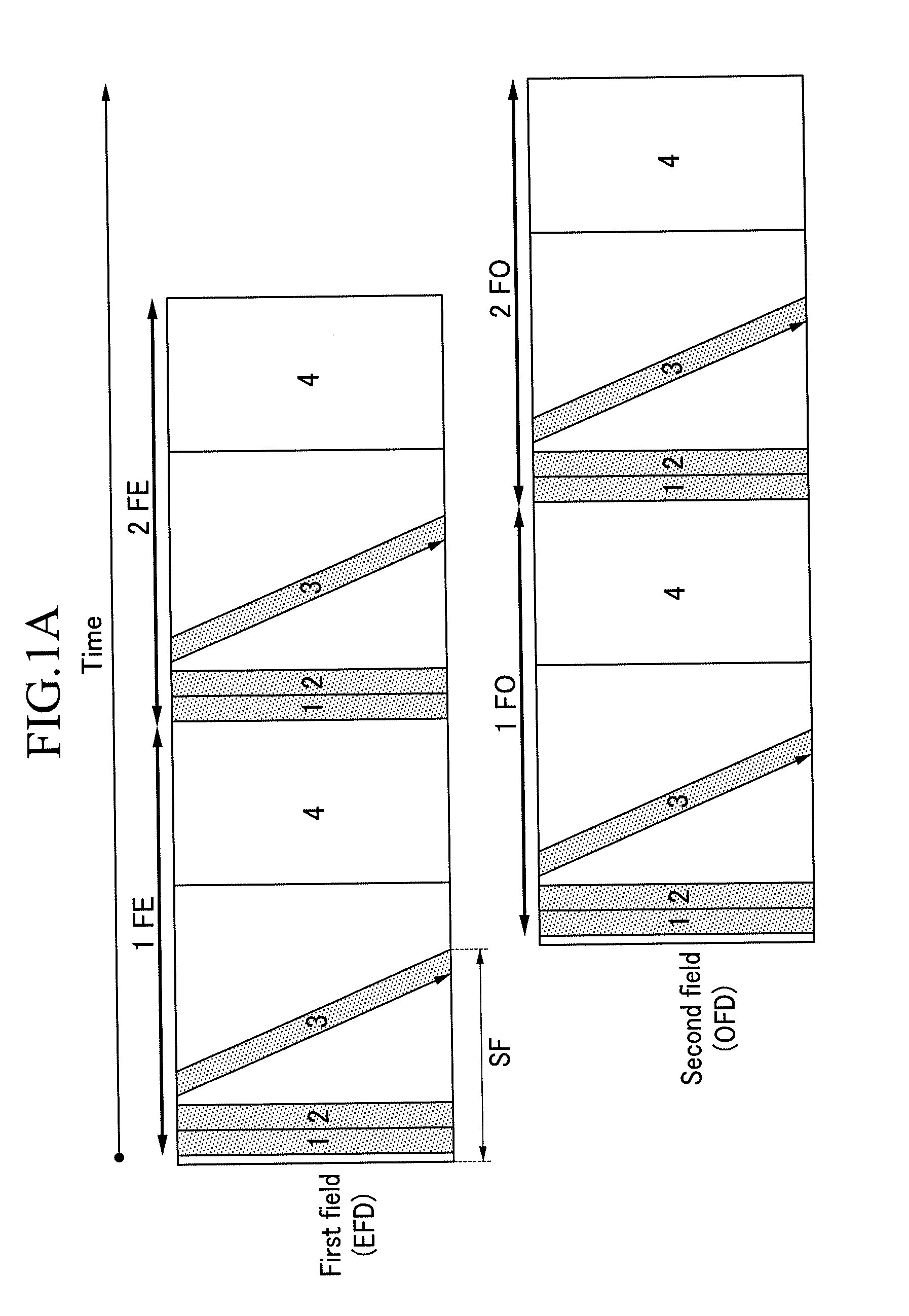

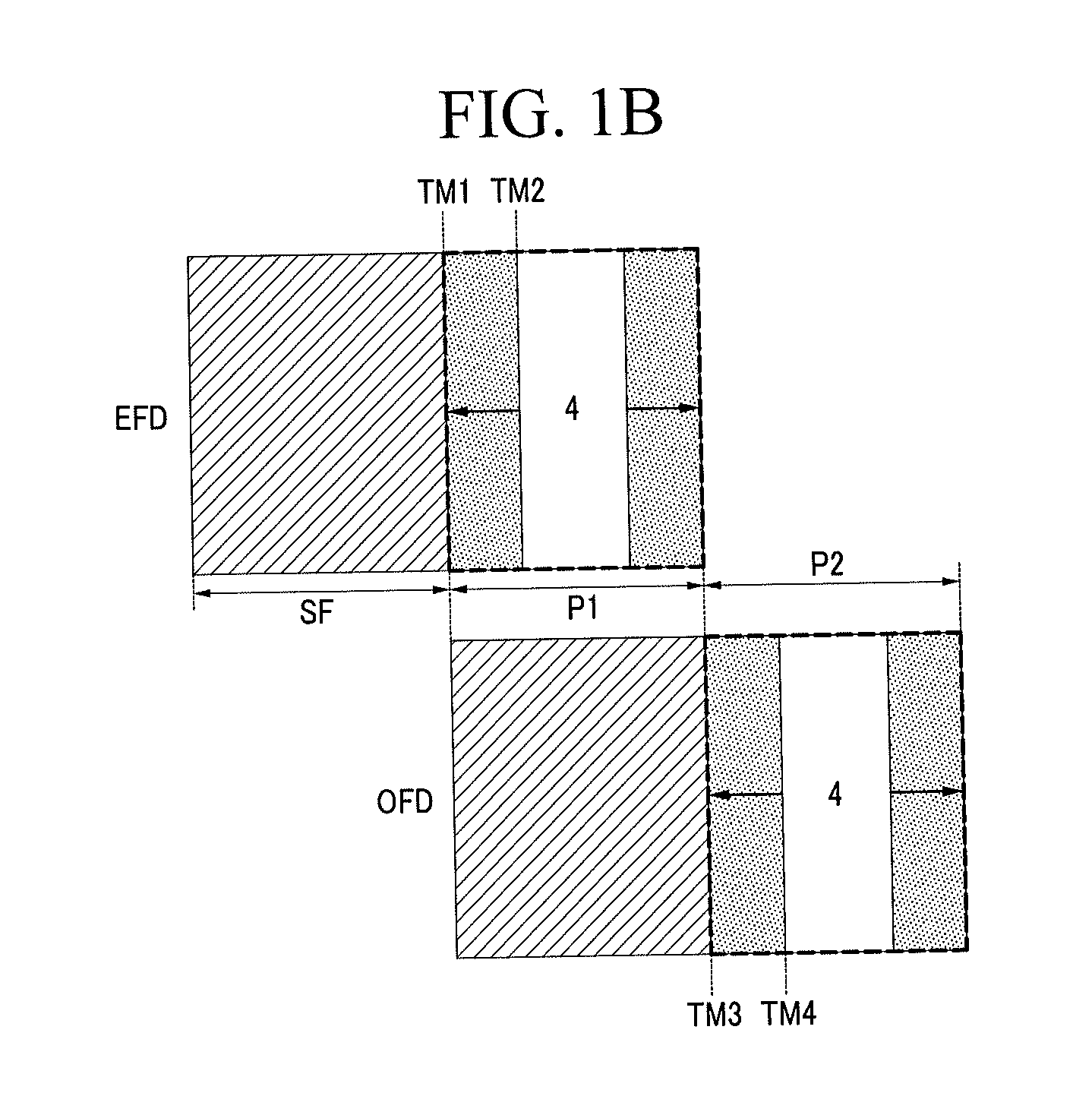

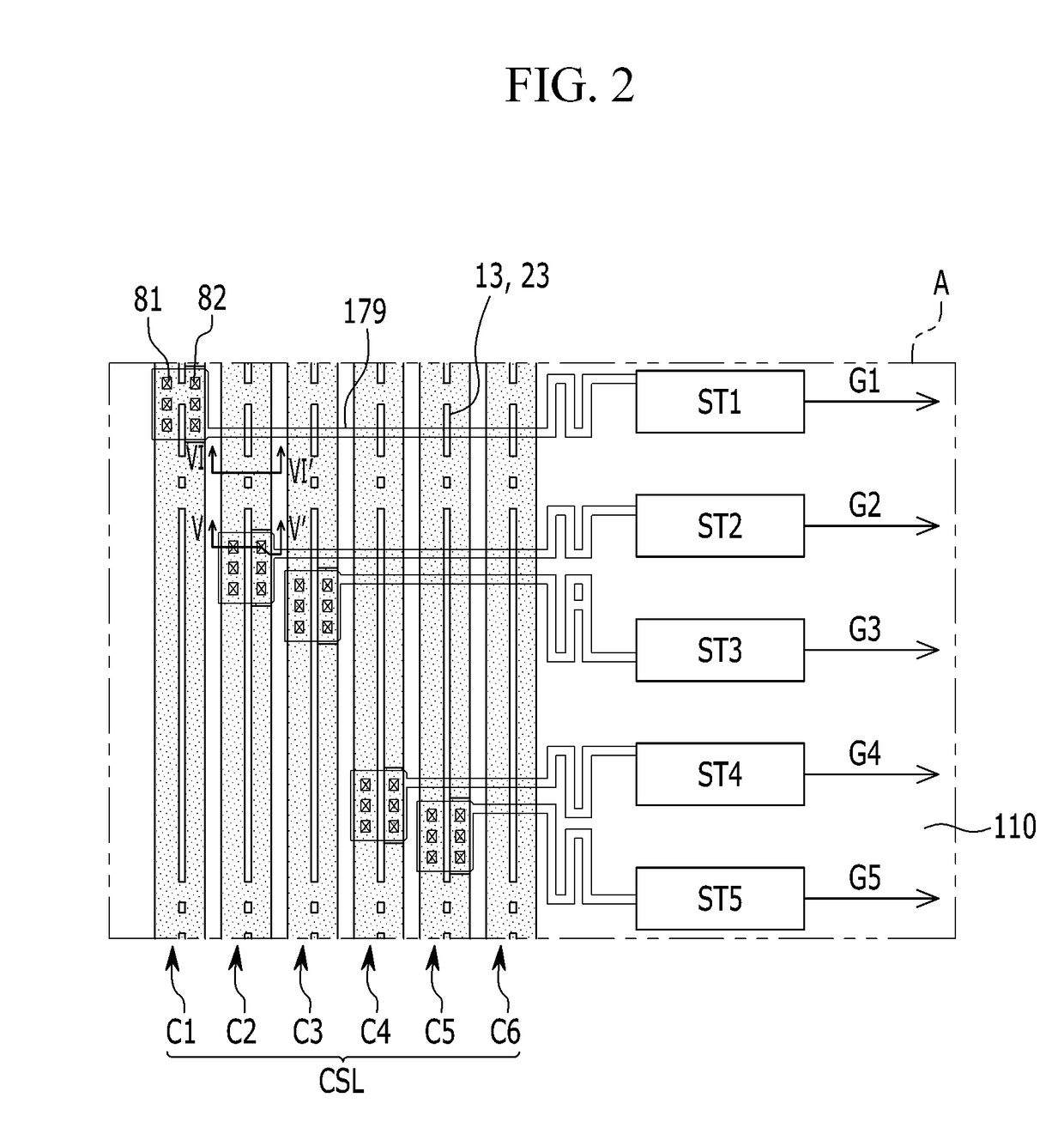

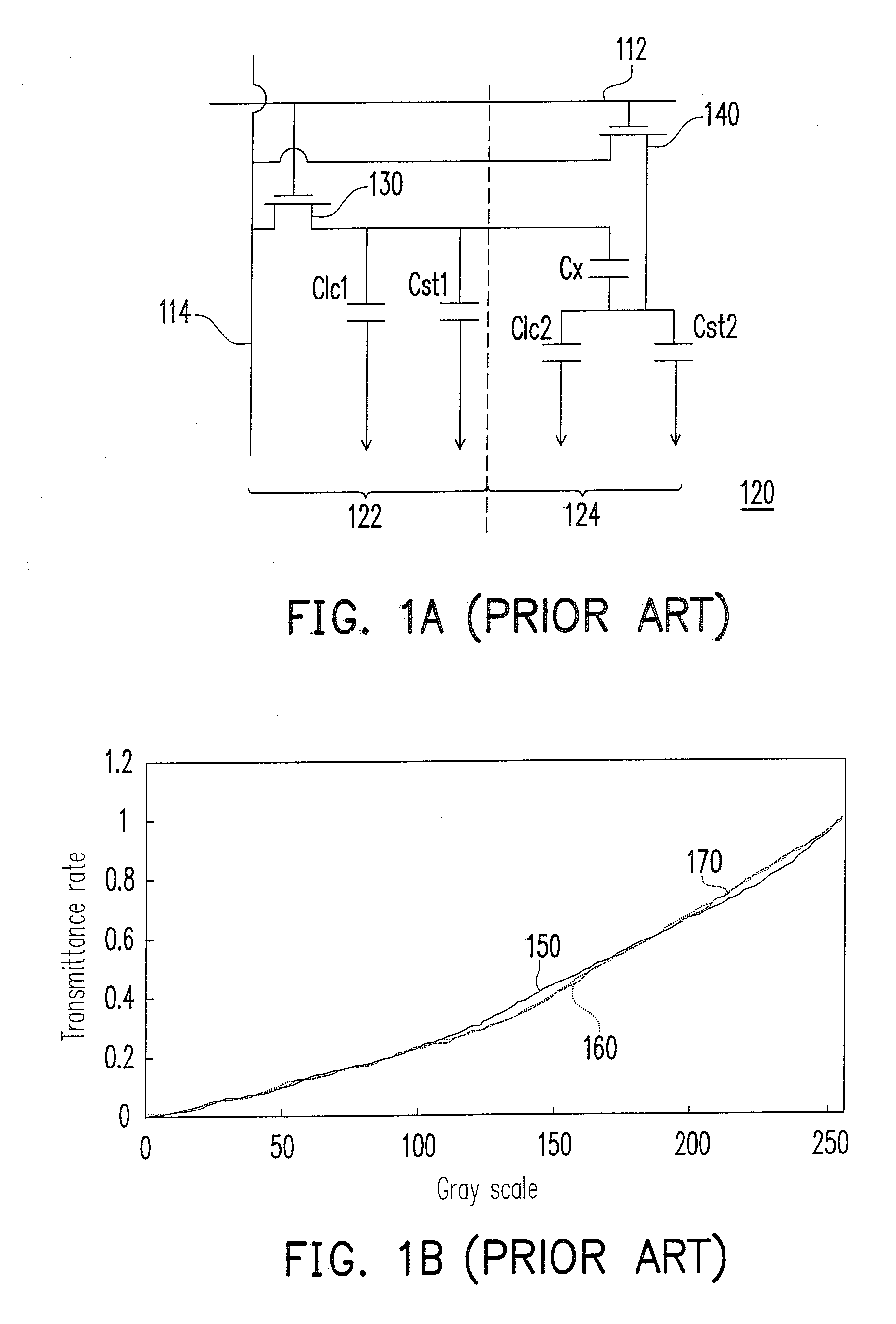

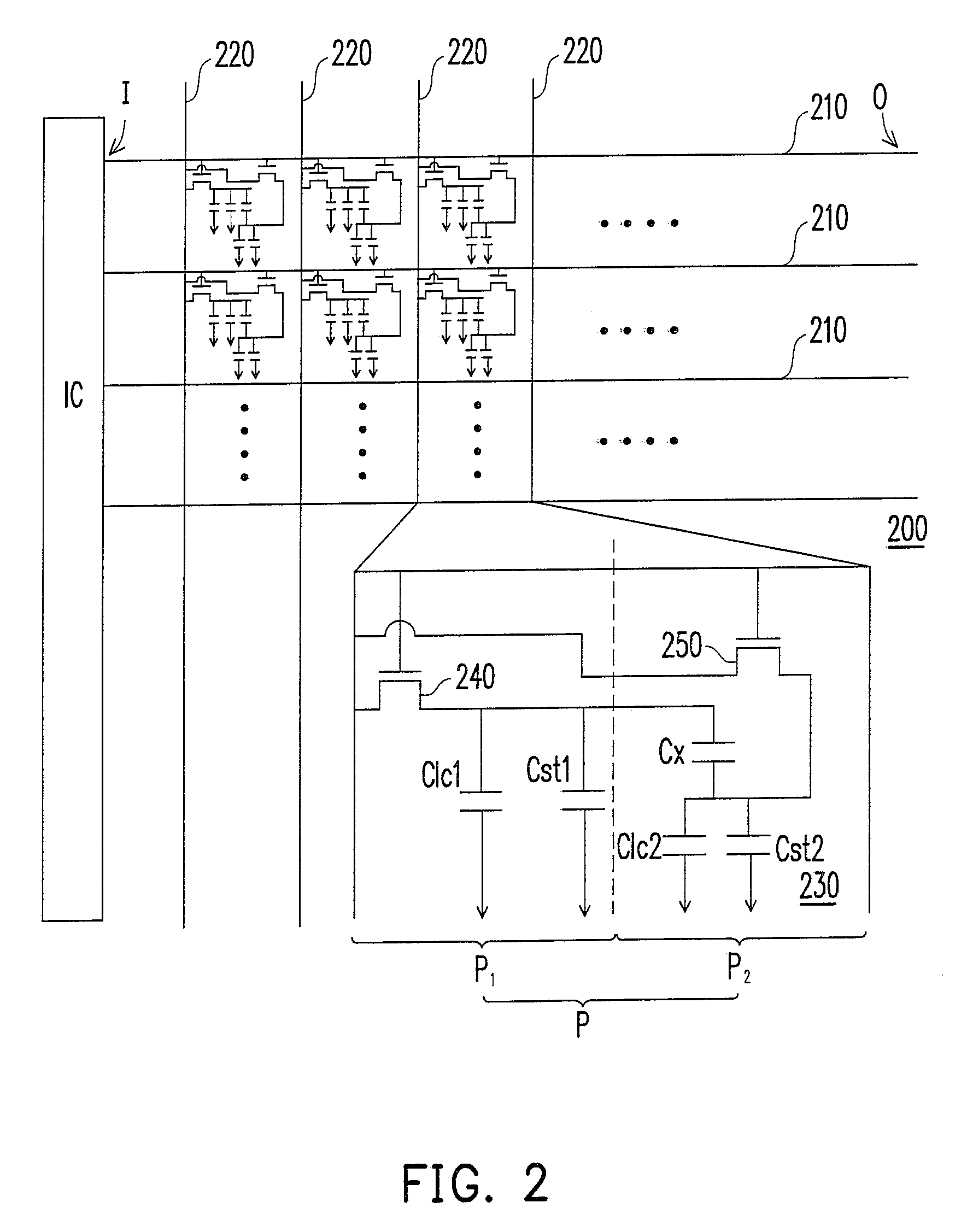

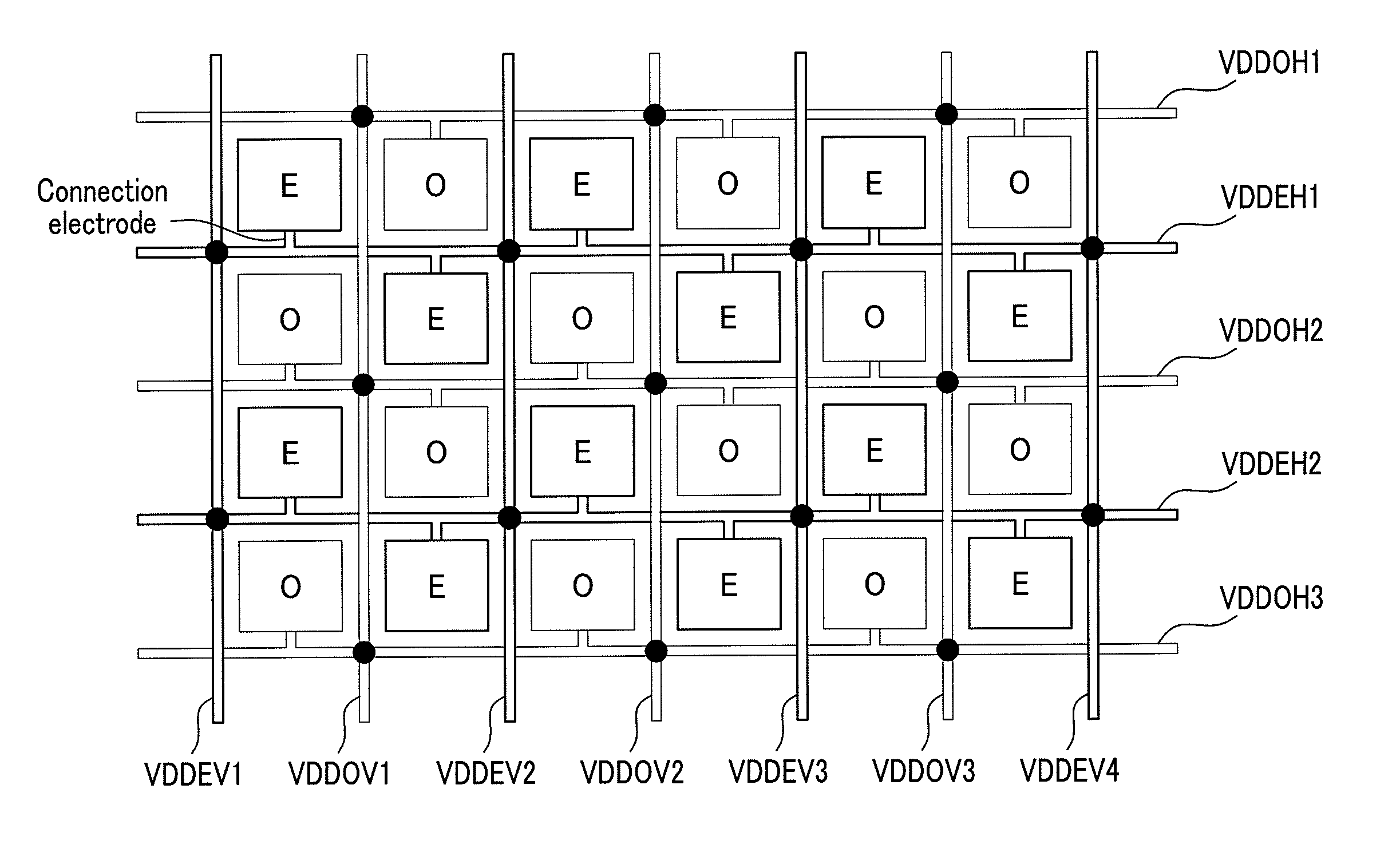

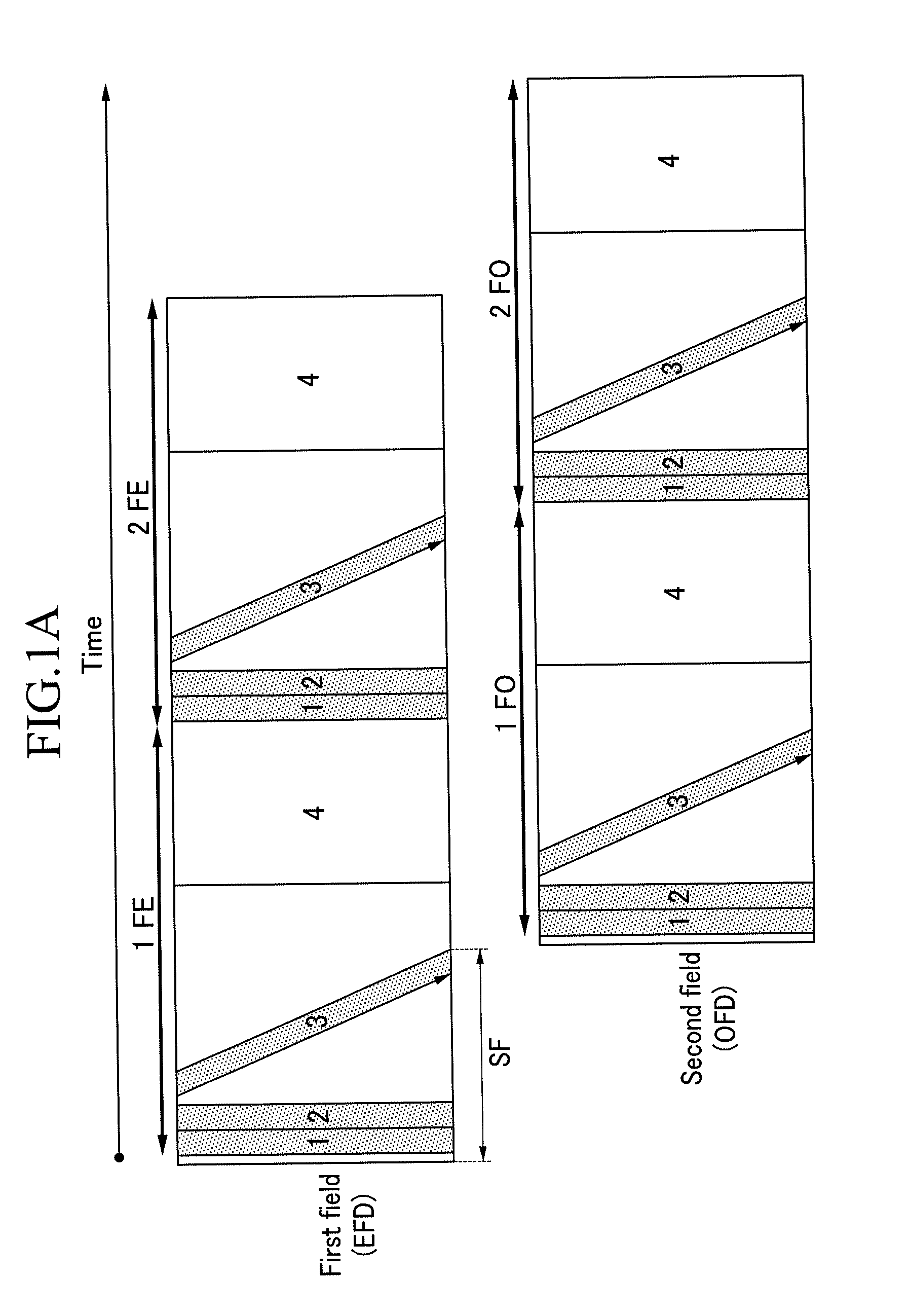

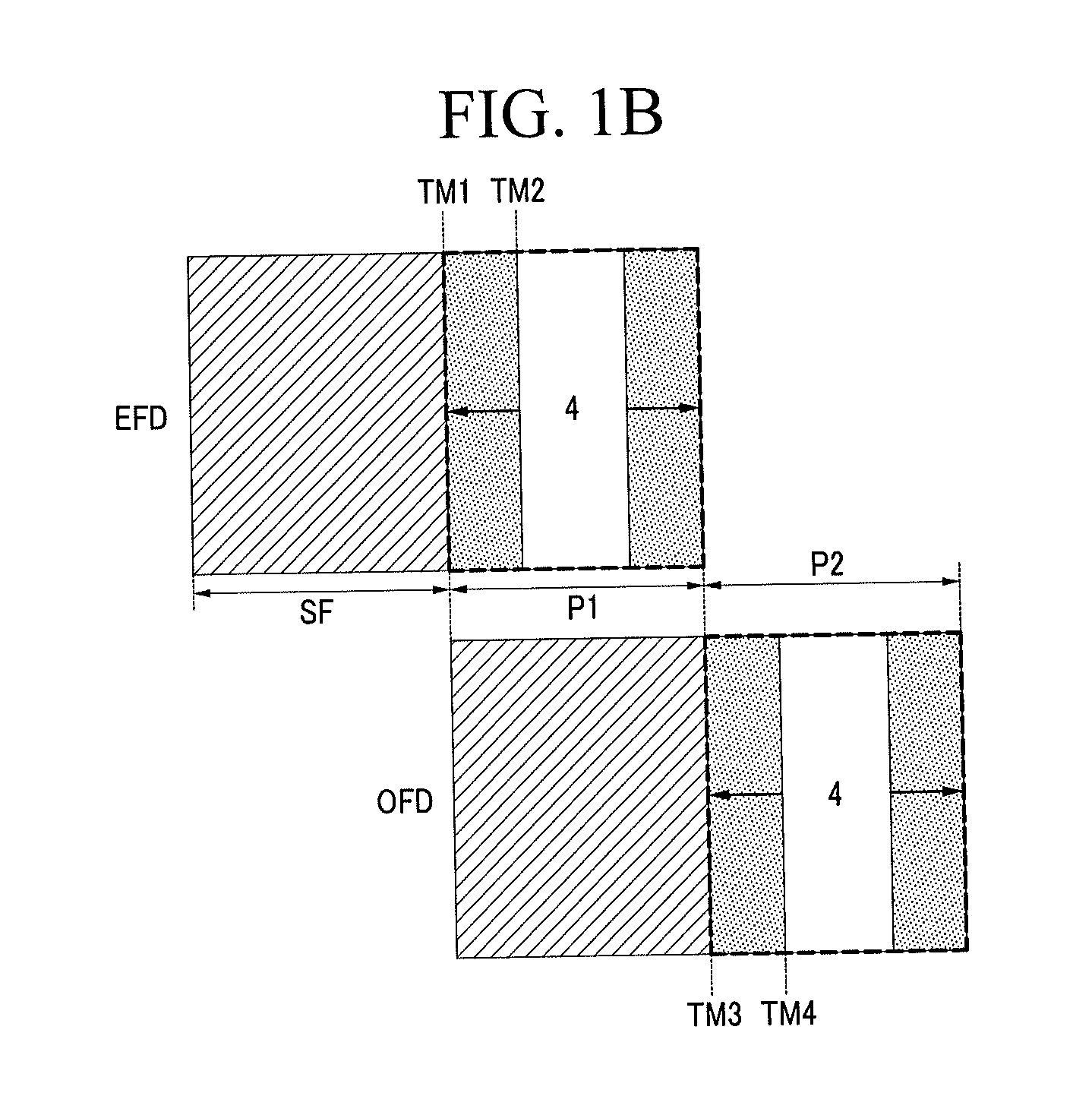

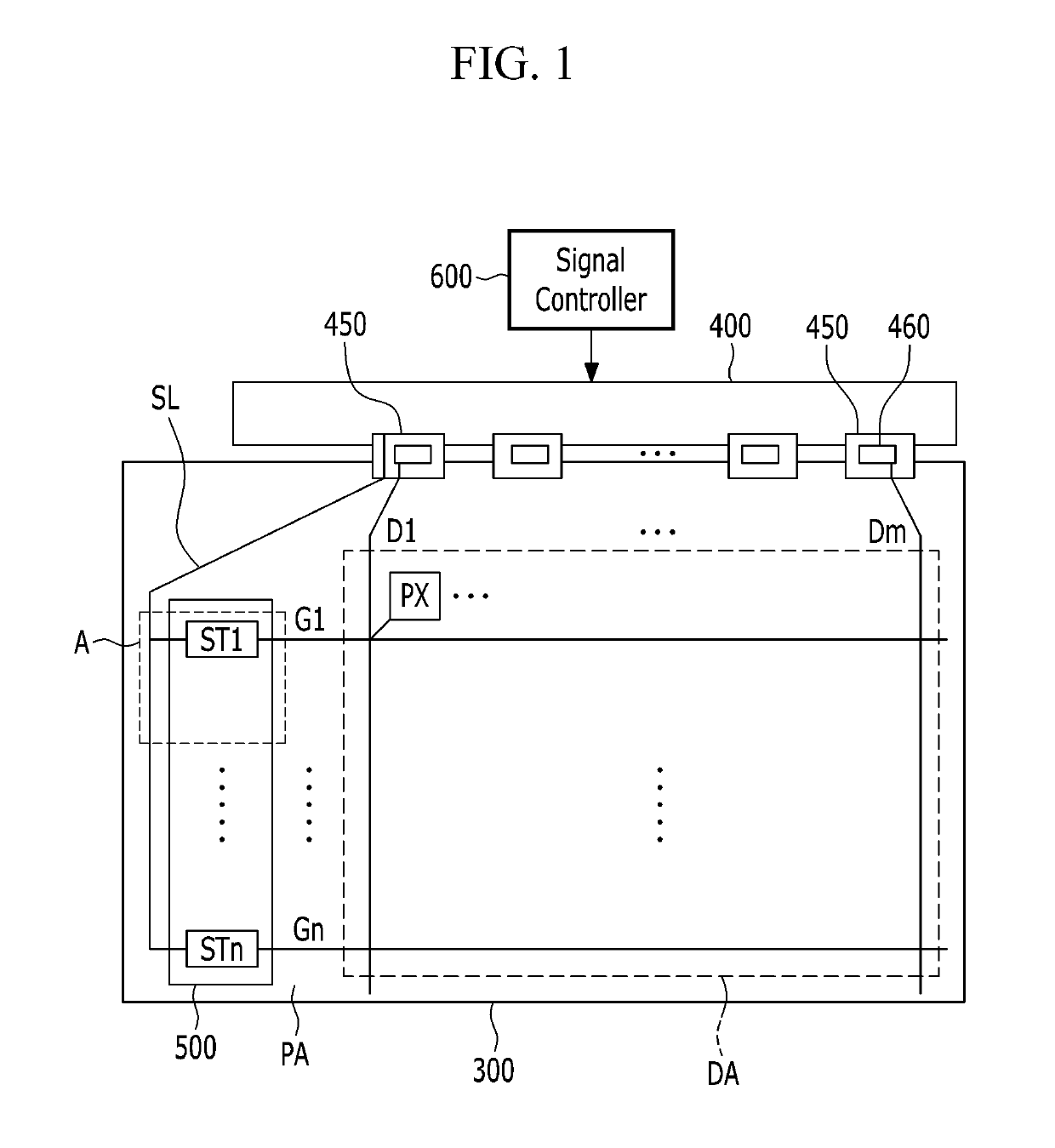

Display device and driving method thereof

ActiveUS20120249615A1Increase drive frequencyIncrease production costCathode-ray tube indicatorsSteroscopic systemsData signalDisplay device

A method of driving a display device including a plurality of pixels, the method including transmitting a plurality of data signals to first group pixels during a first scan period, simultaneously emitting light through the first group pixels according to a programmed data signal during a first light emitting period adjacent to the first scan period, transmitting a plurality of data signals to second group pixels, different from the first group pixels, during a second scan period, and simultaneously emitting light through the second group pixels according to a programmed data signal during a second light emitting period adjacent to the second scan period. A first field including the first scan period and the first light emitting period and a second field including the second scan period and the second light emitting period are temporally divided.

Owner:SAMSUNG DISPLAY CO LTD

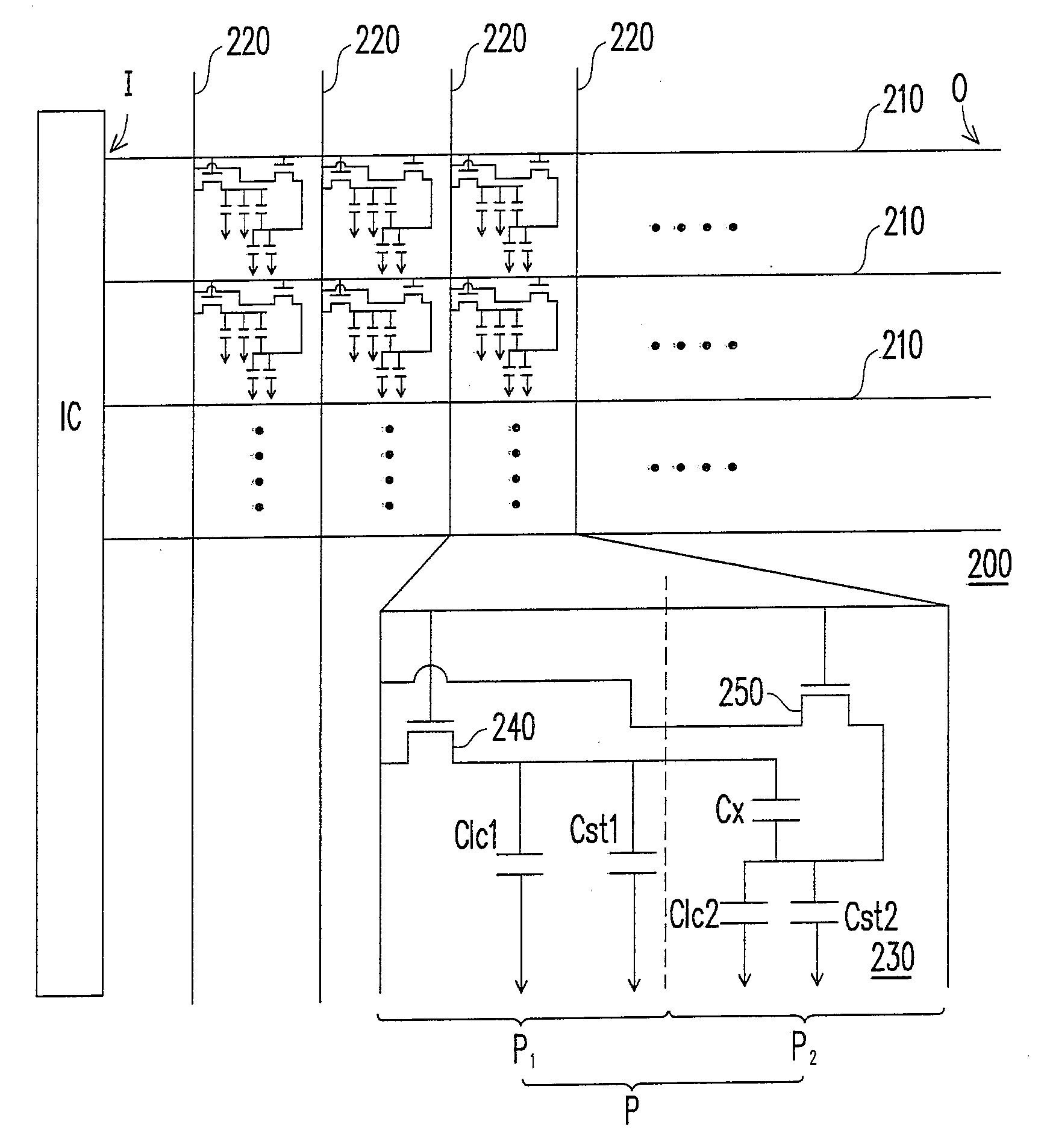

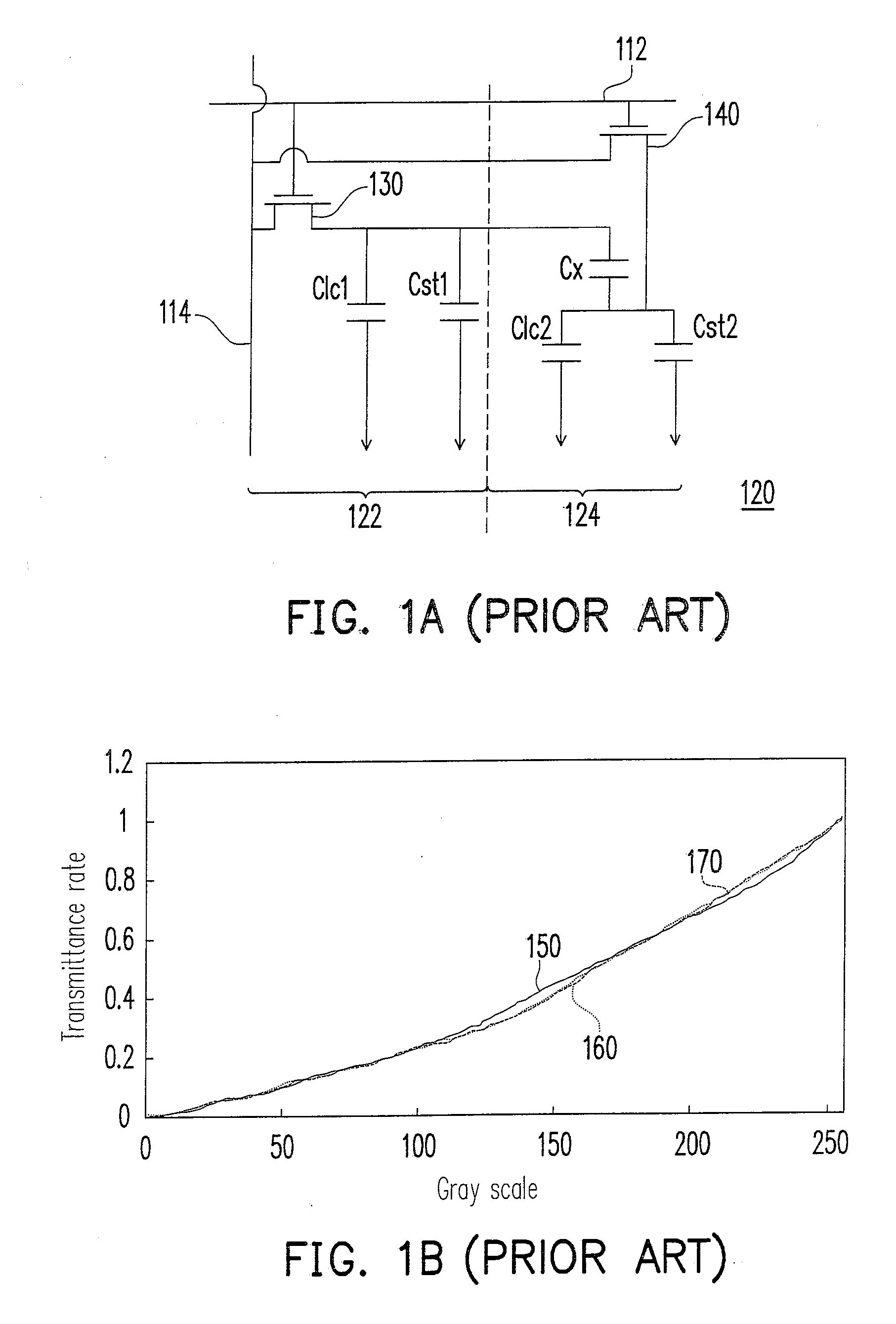

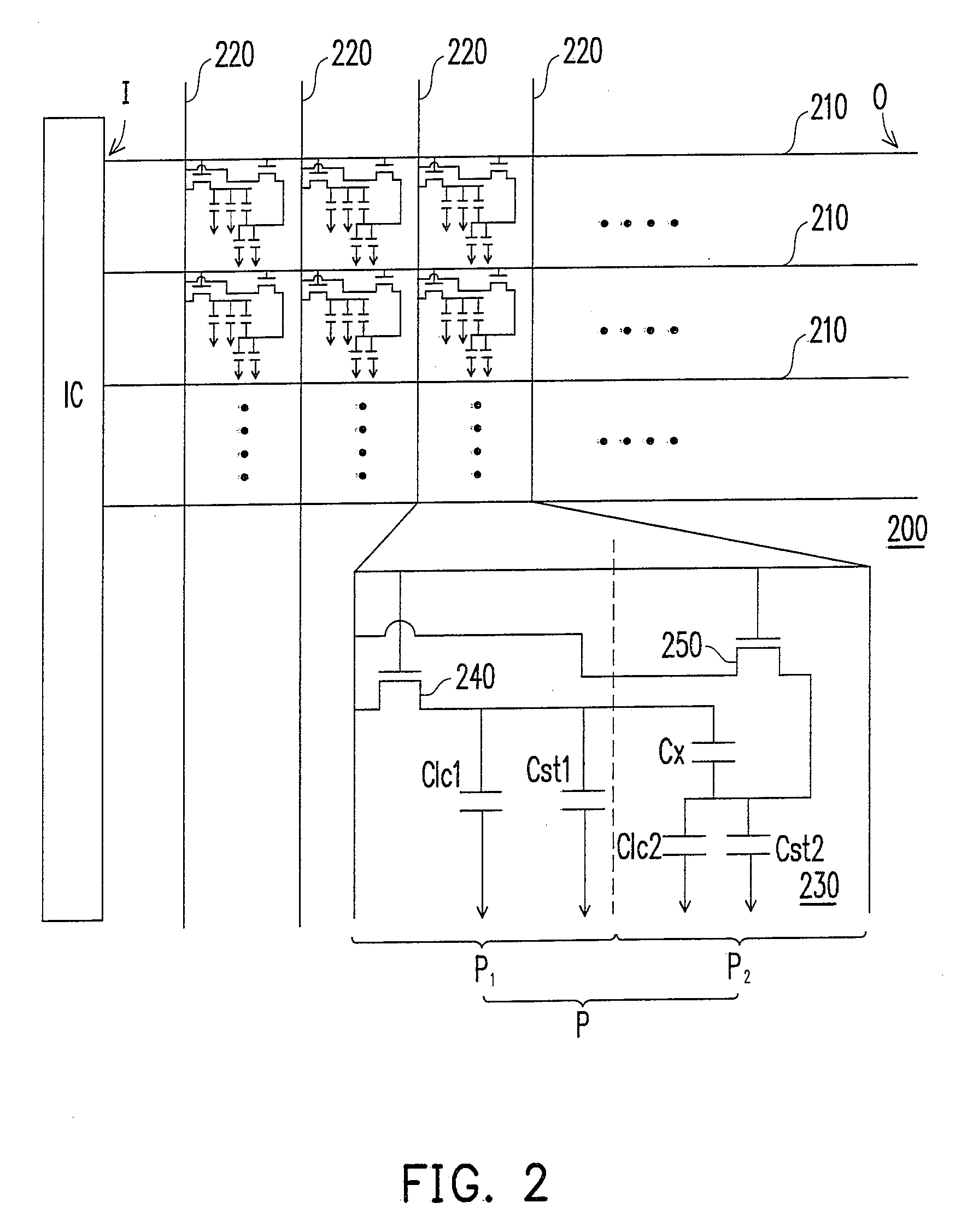

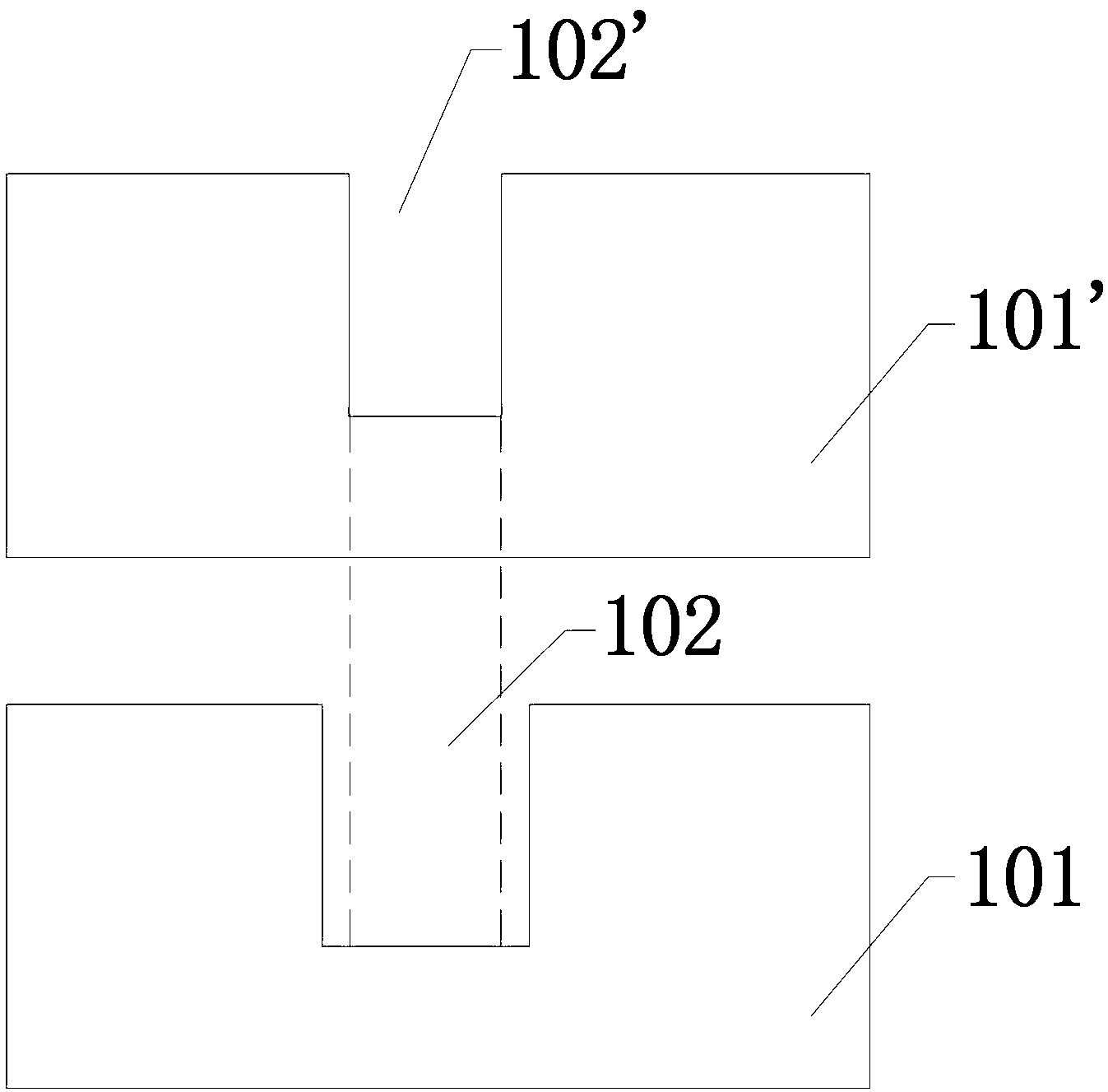

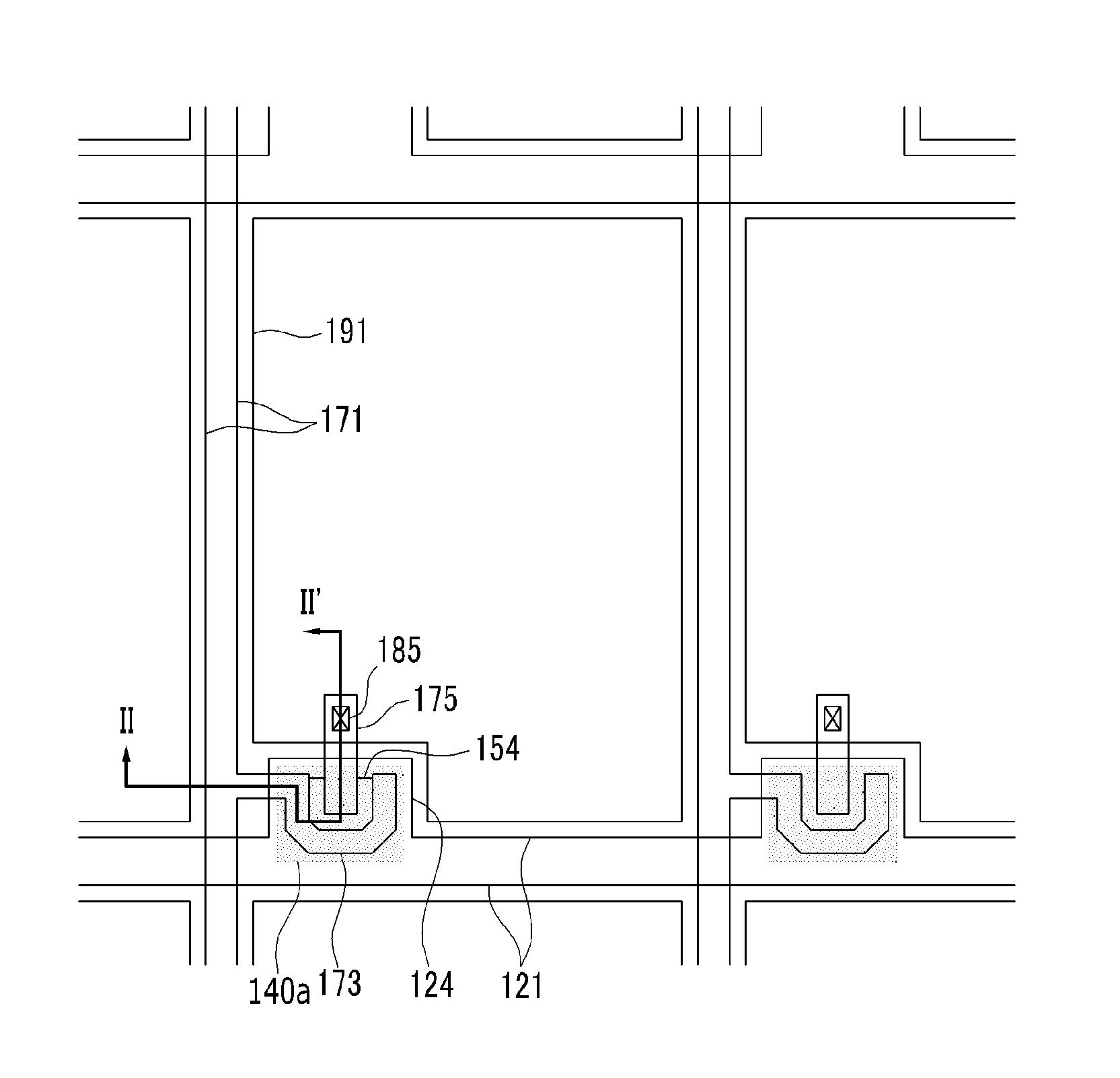

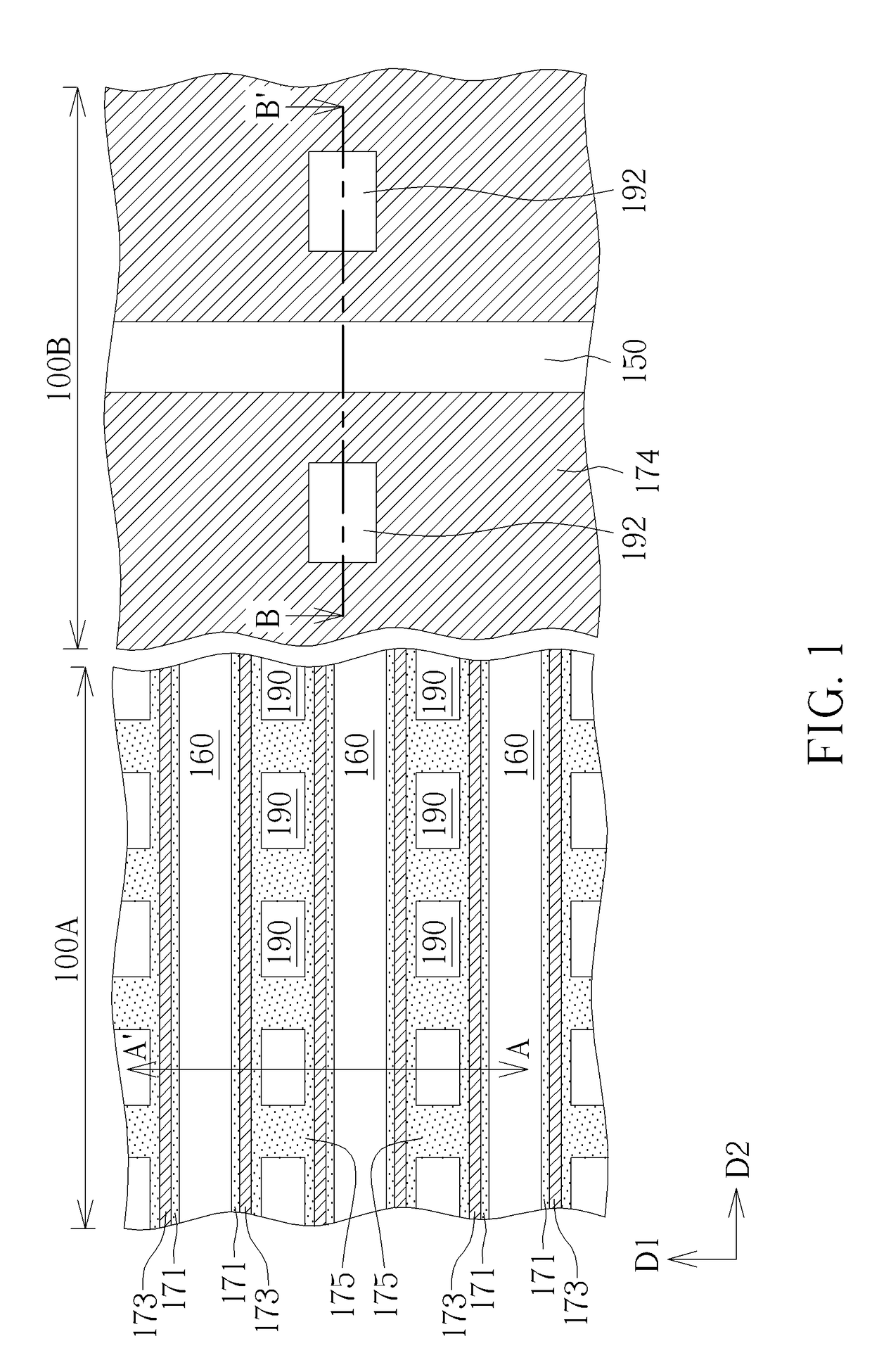

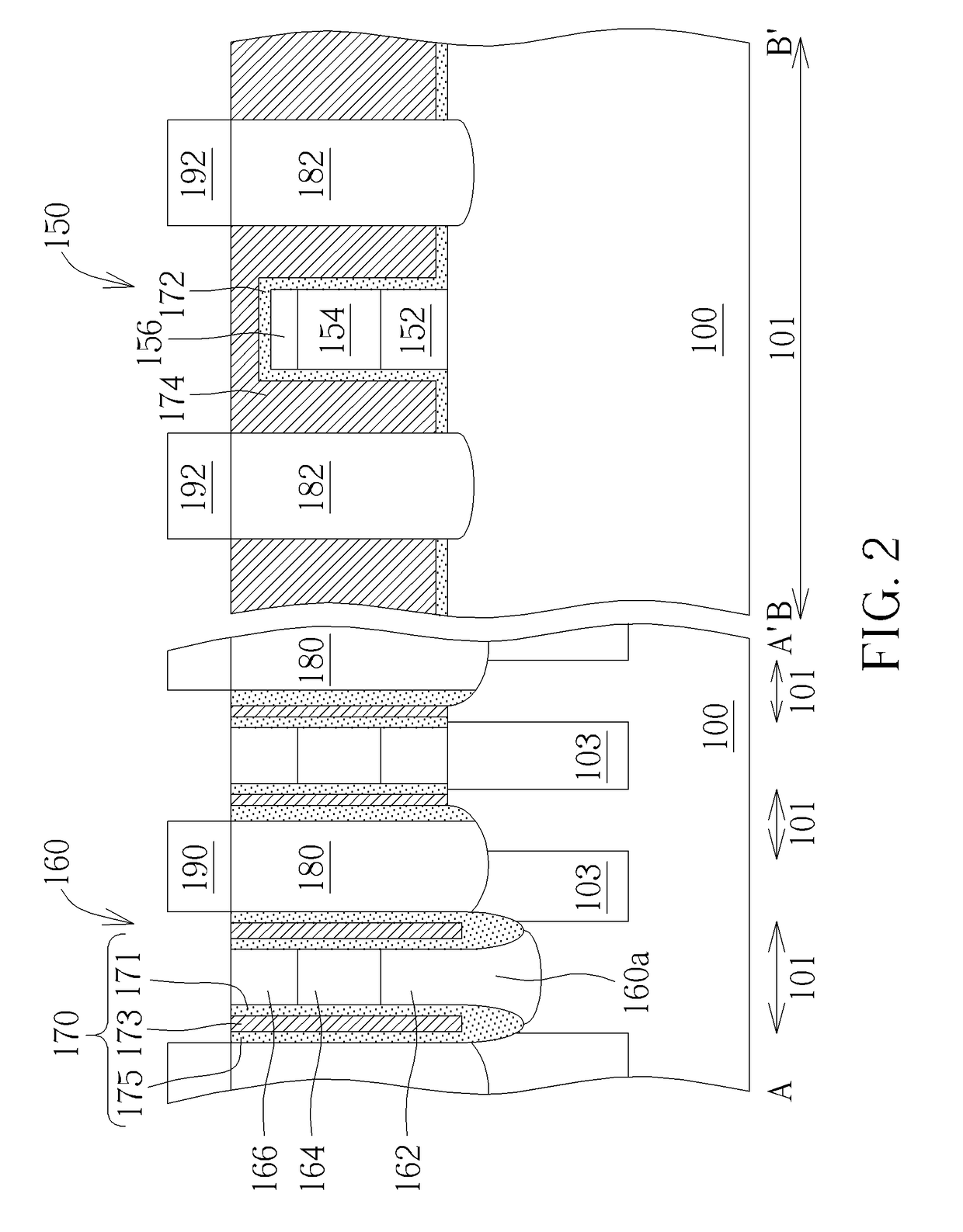

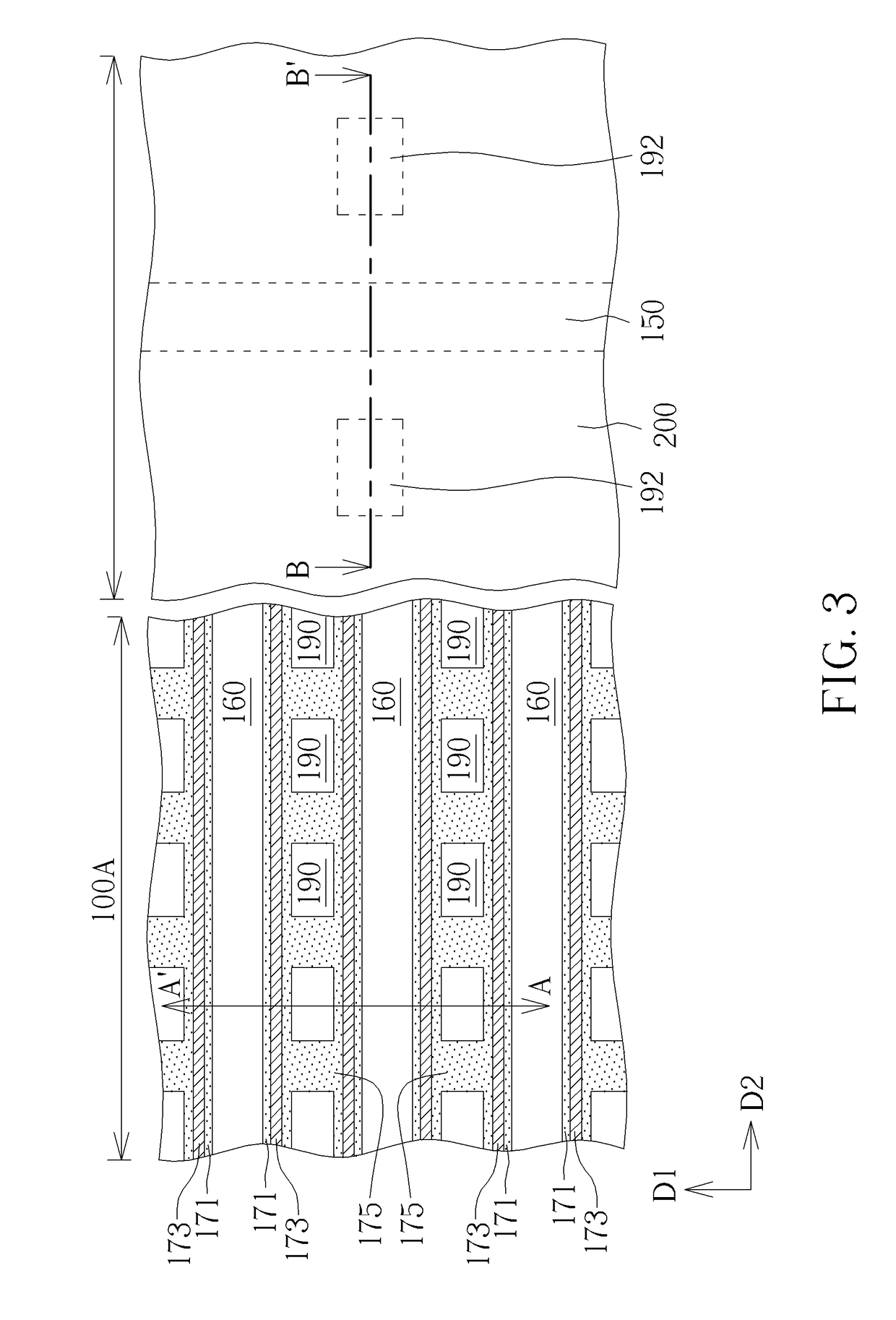

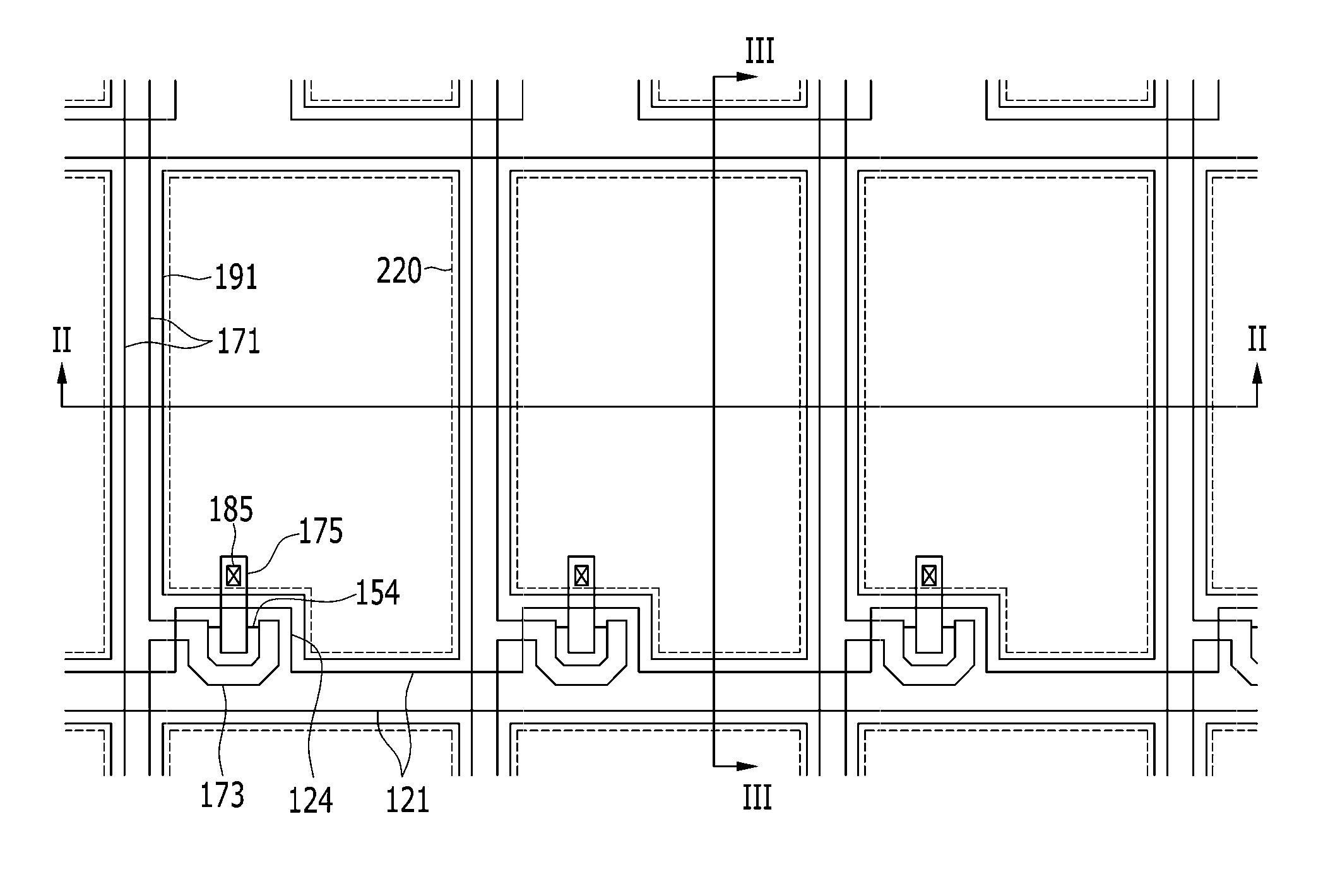

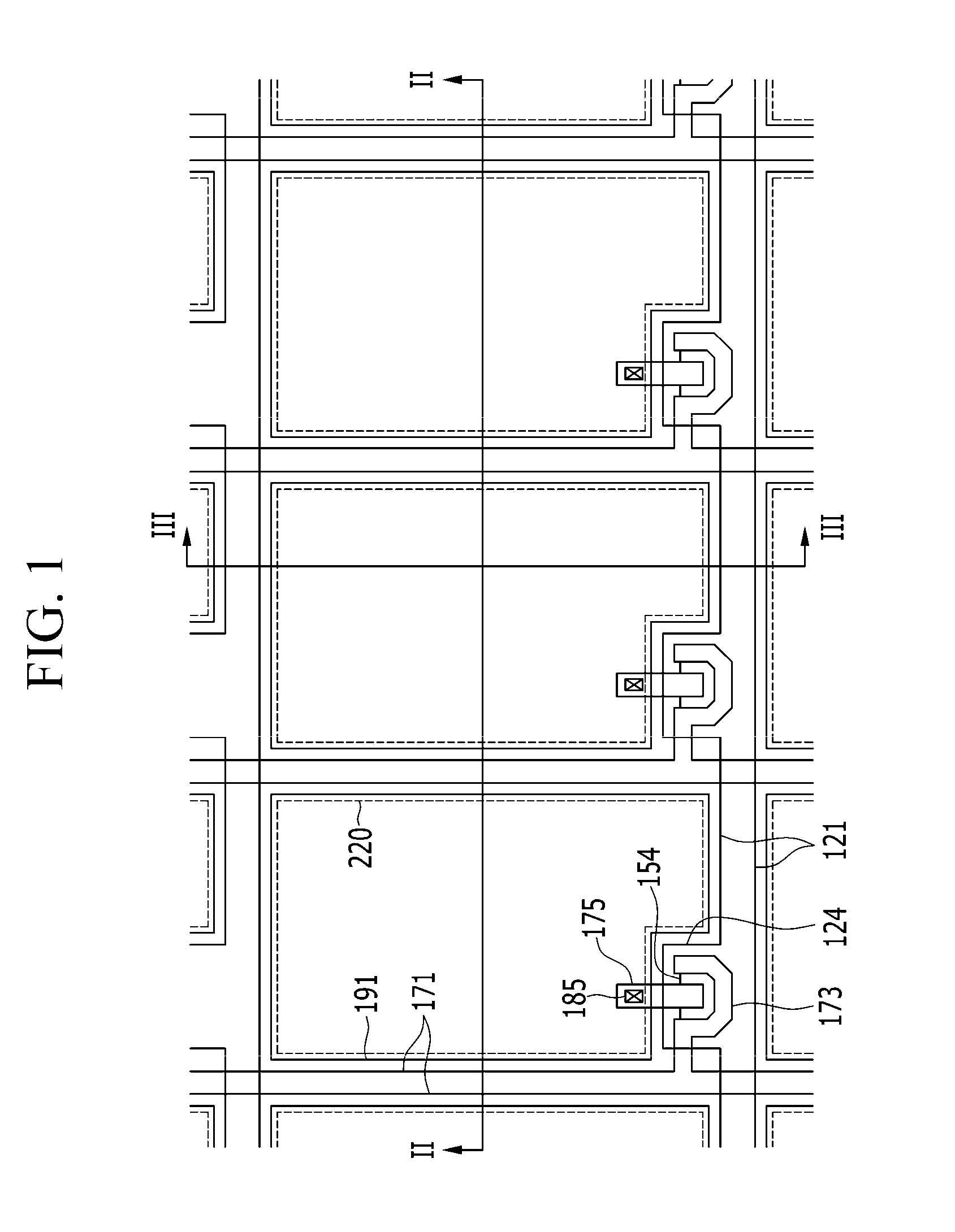

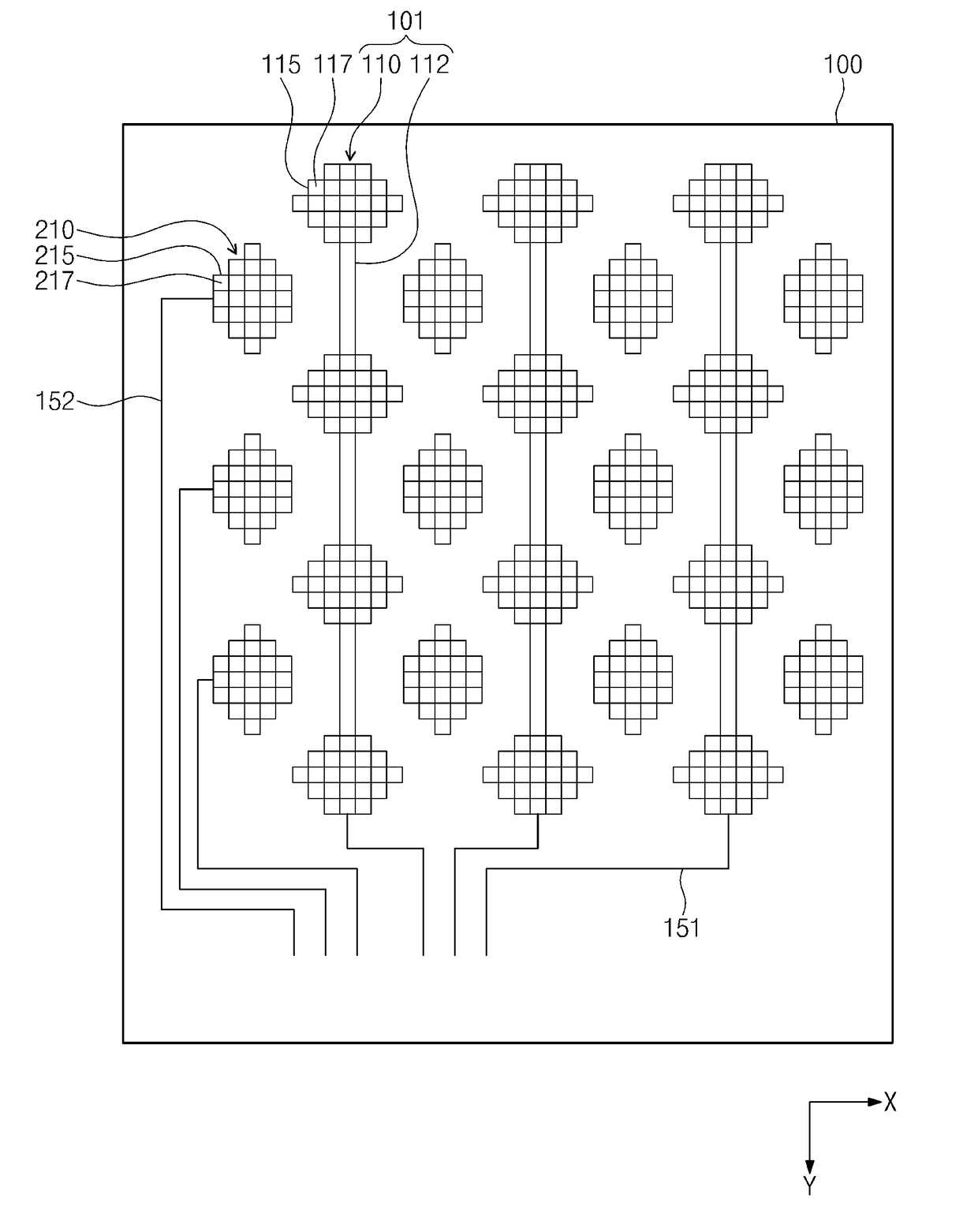

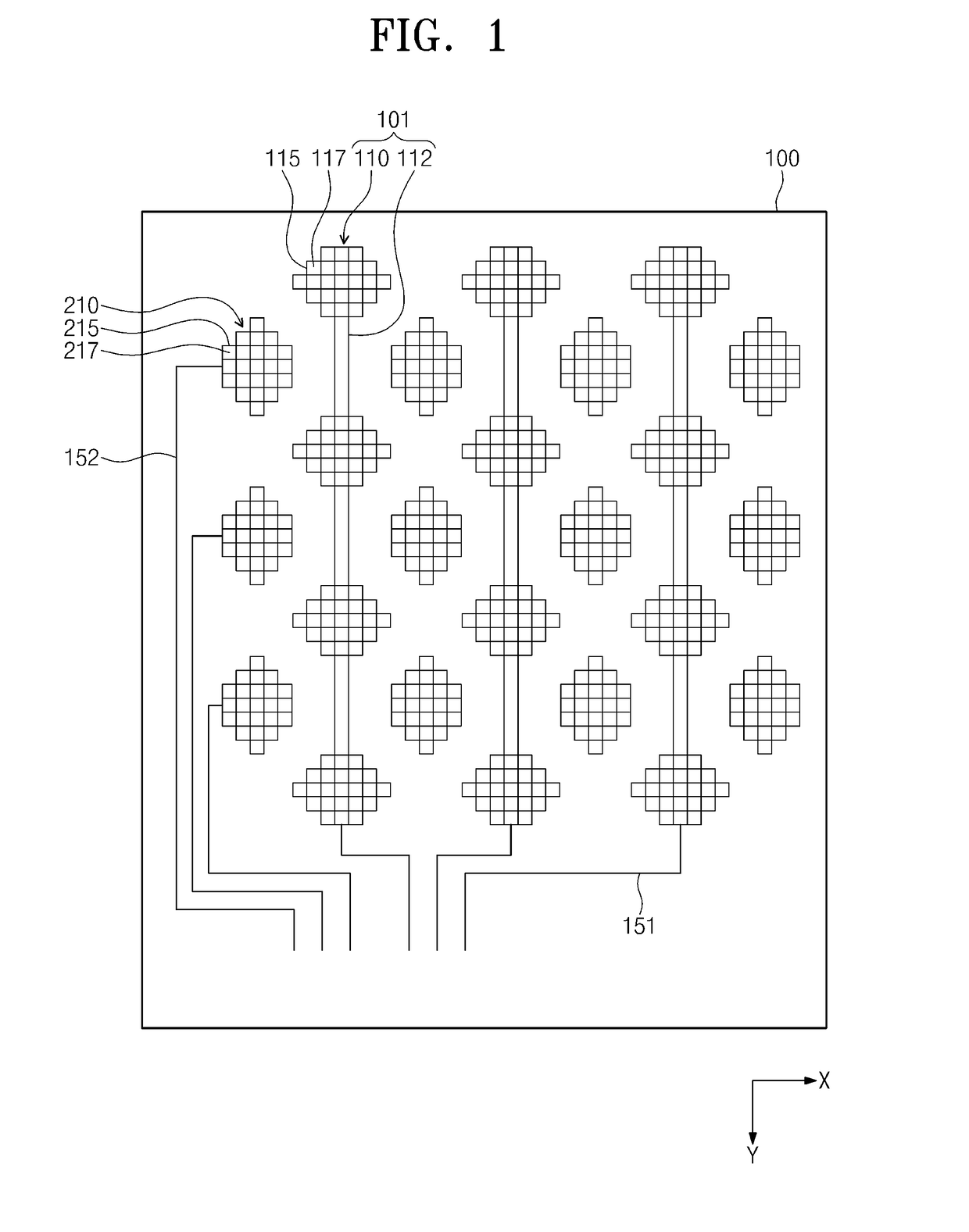

Thin film transistor array substrate and pixel structure

A thin film transistor (TFT) array substrate including a substrate, scan lines and data lines both disposed on the substrate, and pixel structures is provided. A plurality of pixel areas is defined by the scan lines and the data lines on the substrate. Each scan line has a driving signal input terminal and an end terminal. Each pixel area includes a first sub-pixel area and a second sub-pixel area. The pixel structures are respectively disposed in the pixel areas and driven by the scan lines and the data lines. Each pixel structure in the respective pixel area includes a first TFT corresponding to the first sub-pixel area and a second TFT corresponding to the second sub-pixel area. Besides, ratios of a channel width to a channel length of the second TFTs connected to the same scan line increase gradually from the driving signal input terminal to the end terminal.

Owner:AU OPTRONICS CORP

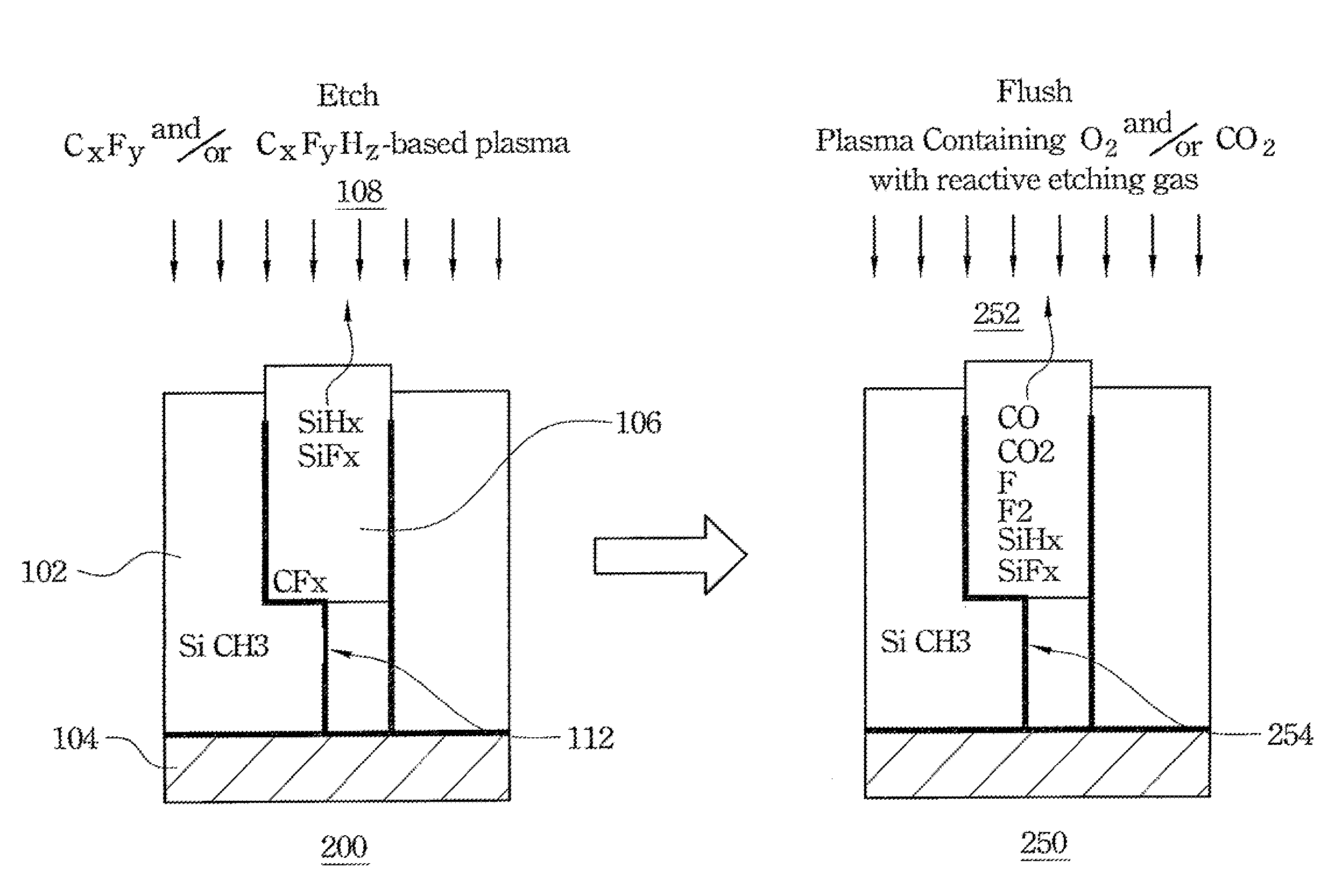

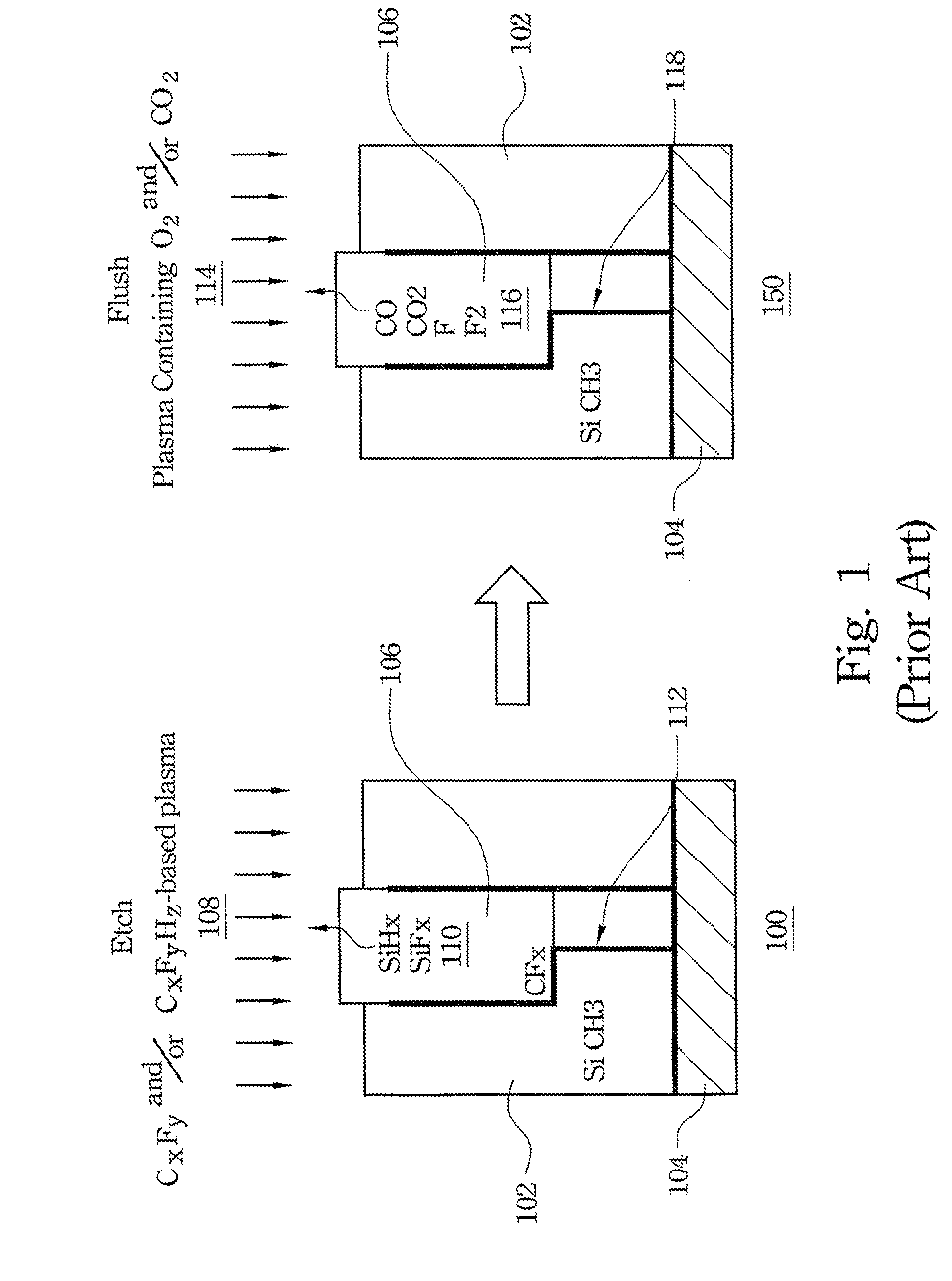

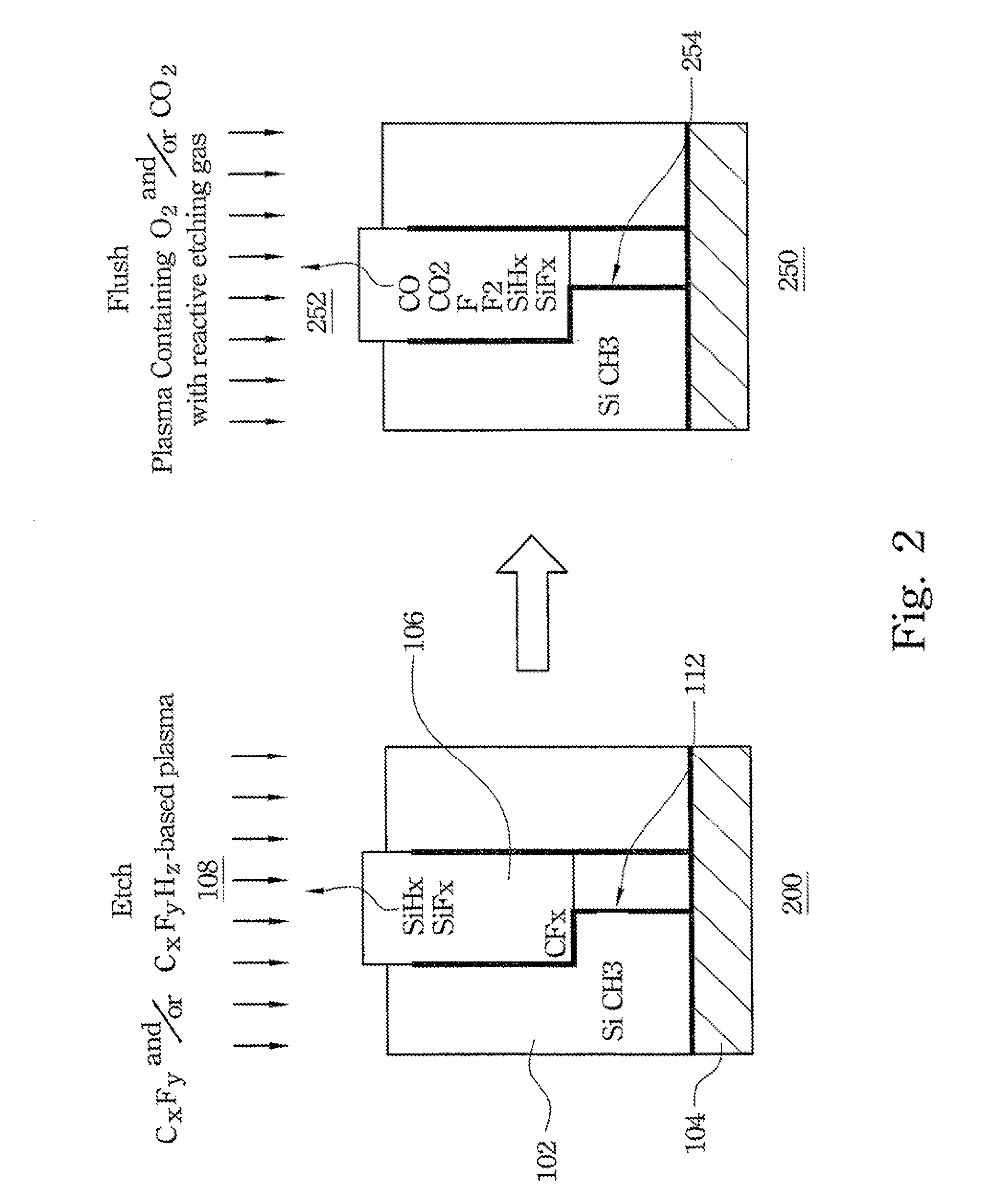

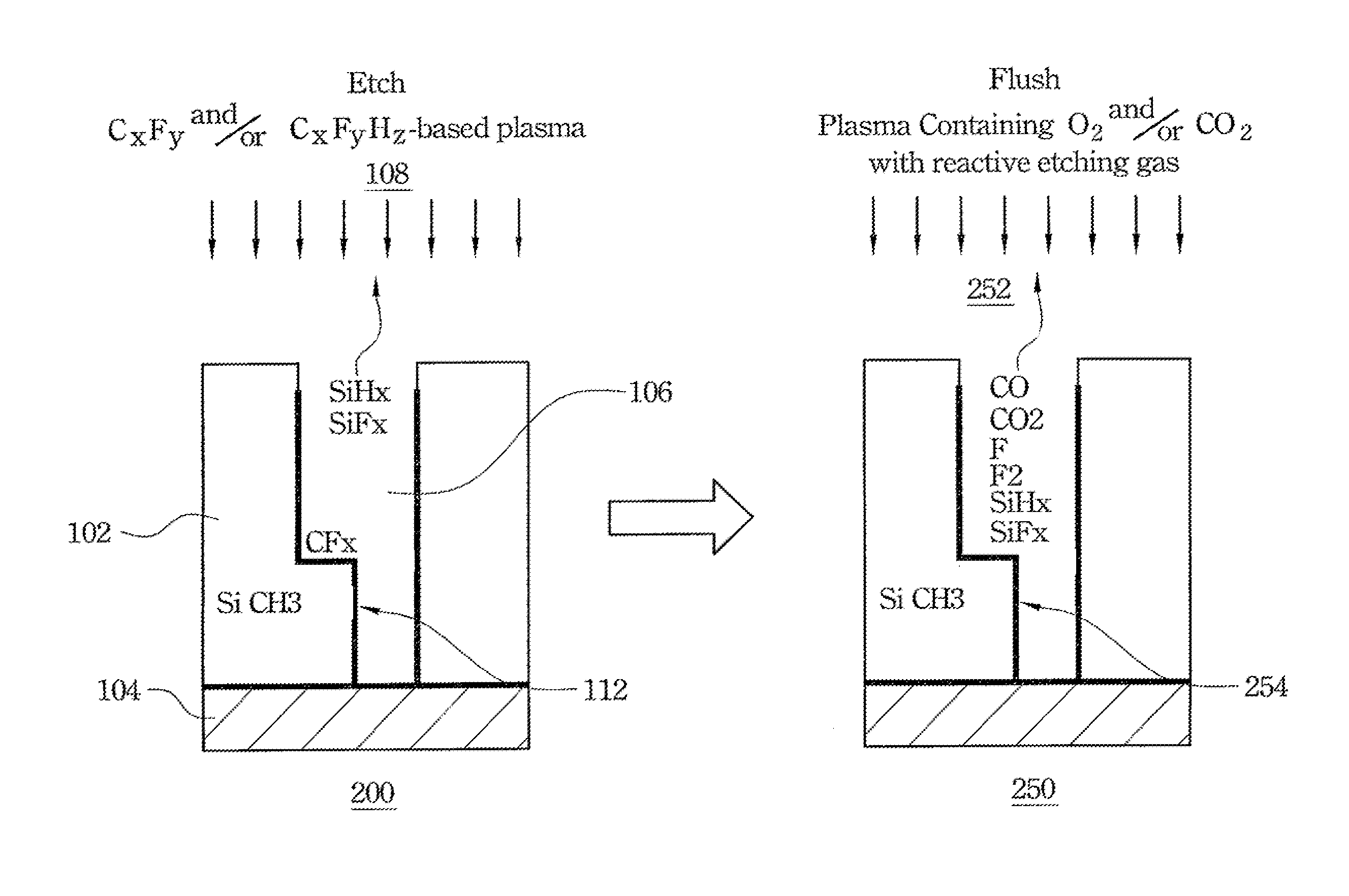

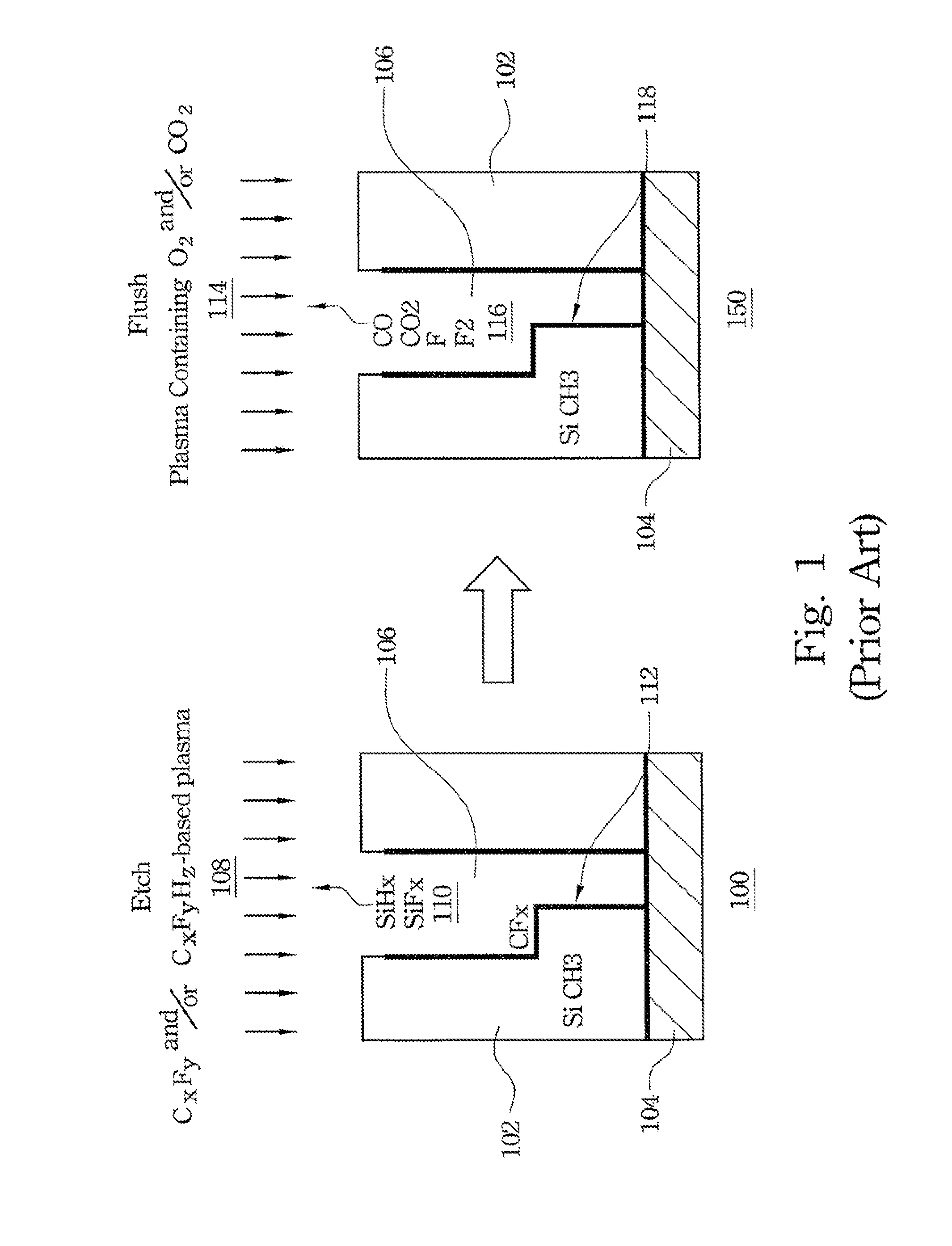

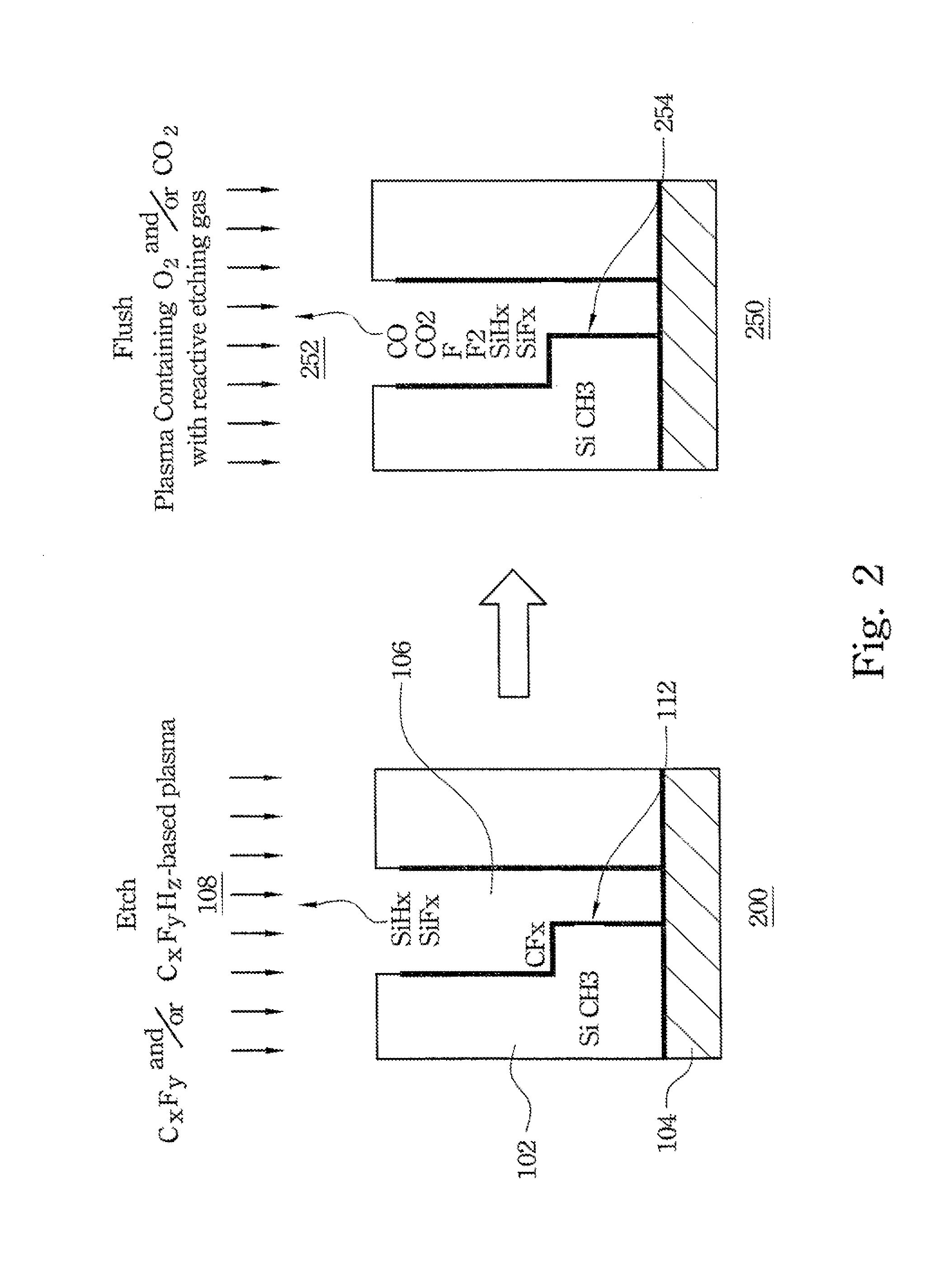

Method for Fabricating Low-k Dielectric and Cu Interconnect

ActiveUS20080311756A1Increase capacitanceImprove RC delaySemiconductor/solid-state device manufacturingDelayed timeIntegrated circuit

A system and method for improving the performance of an integrated circuit by lowering RC delay time is provided. A preferred embodiment comprises adding a reactive etch gas to the ash / flush plasma process following a low-k dielectric etch. The illustrative embodiments implement a removal of the damage layer that is formed during a low-k dielectric etch.

Owner:TAIWAN SEMICON MFG CO LTD

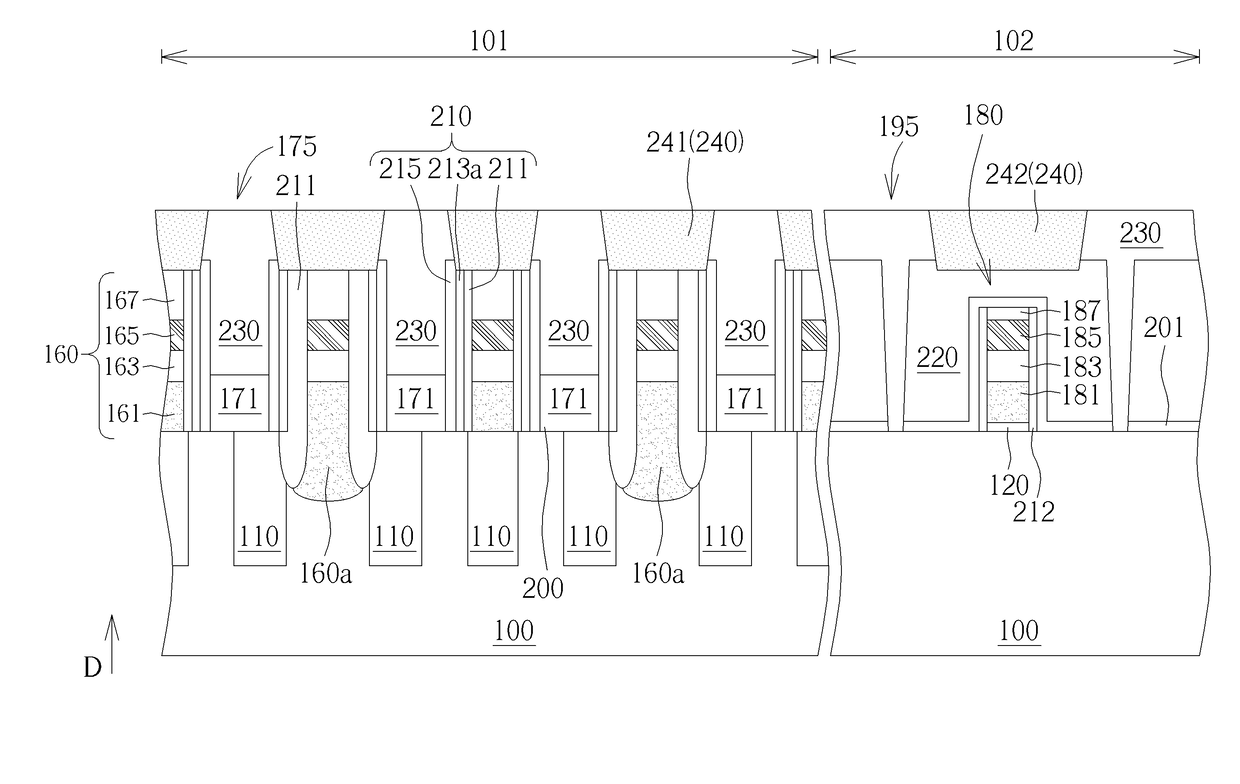

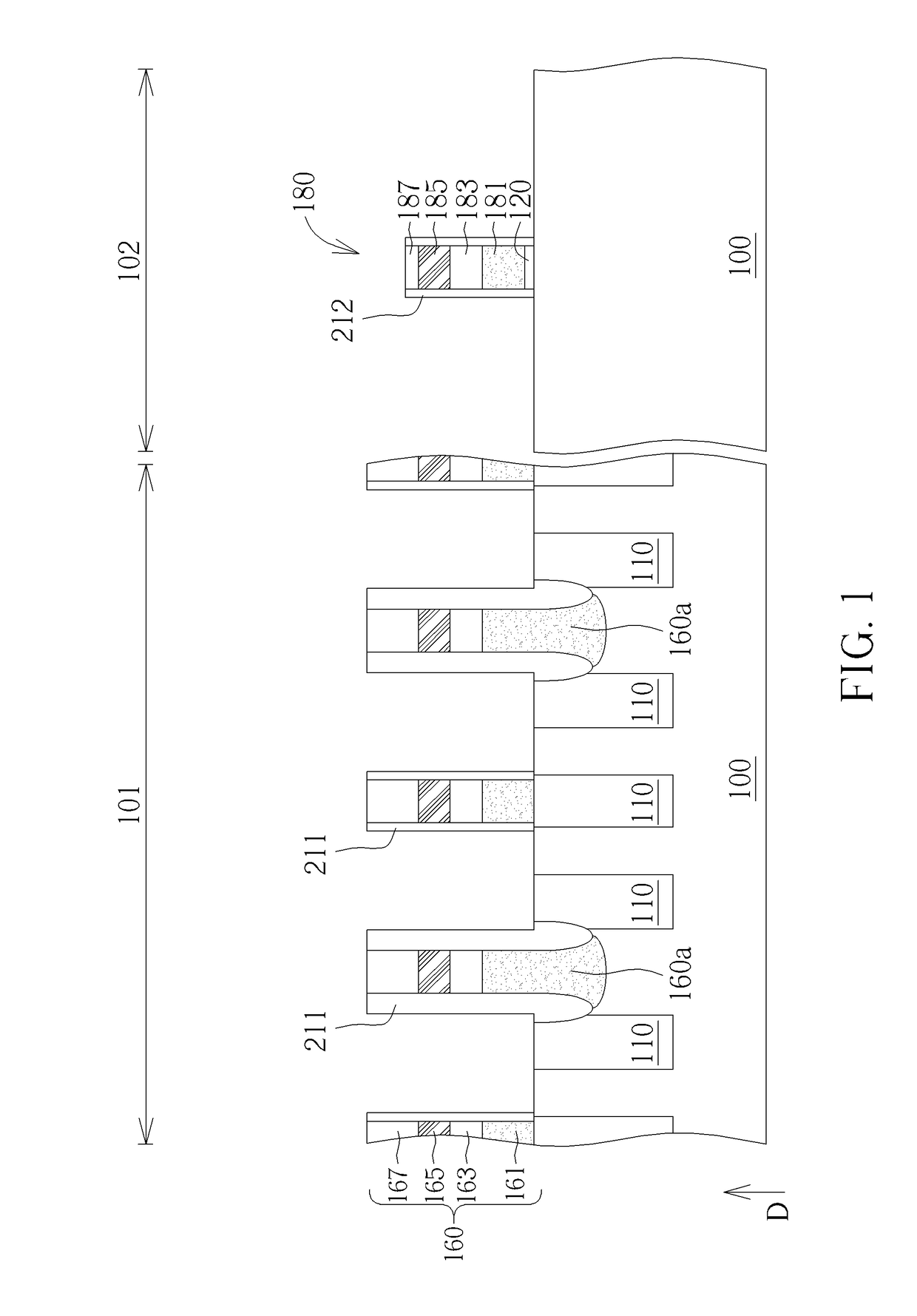

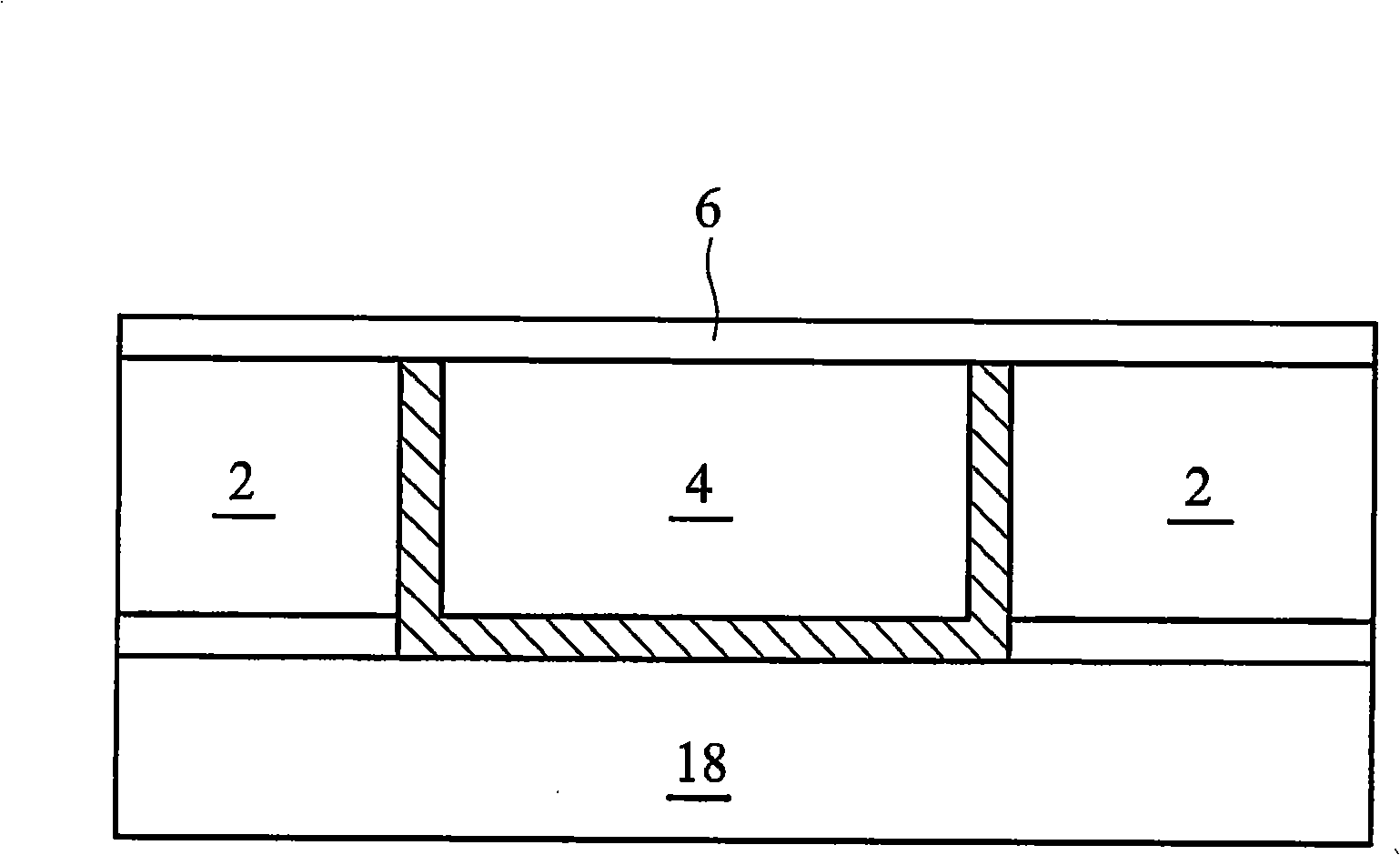

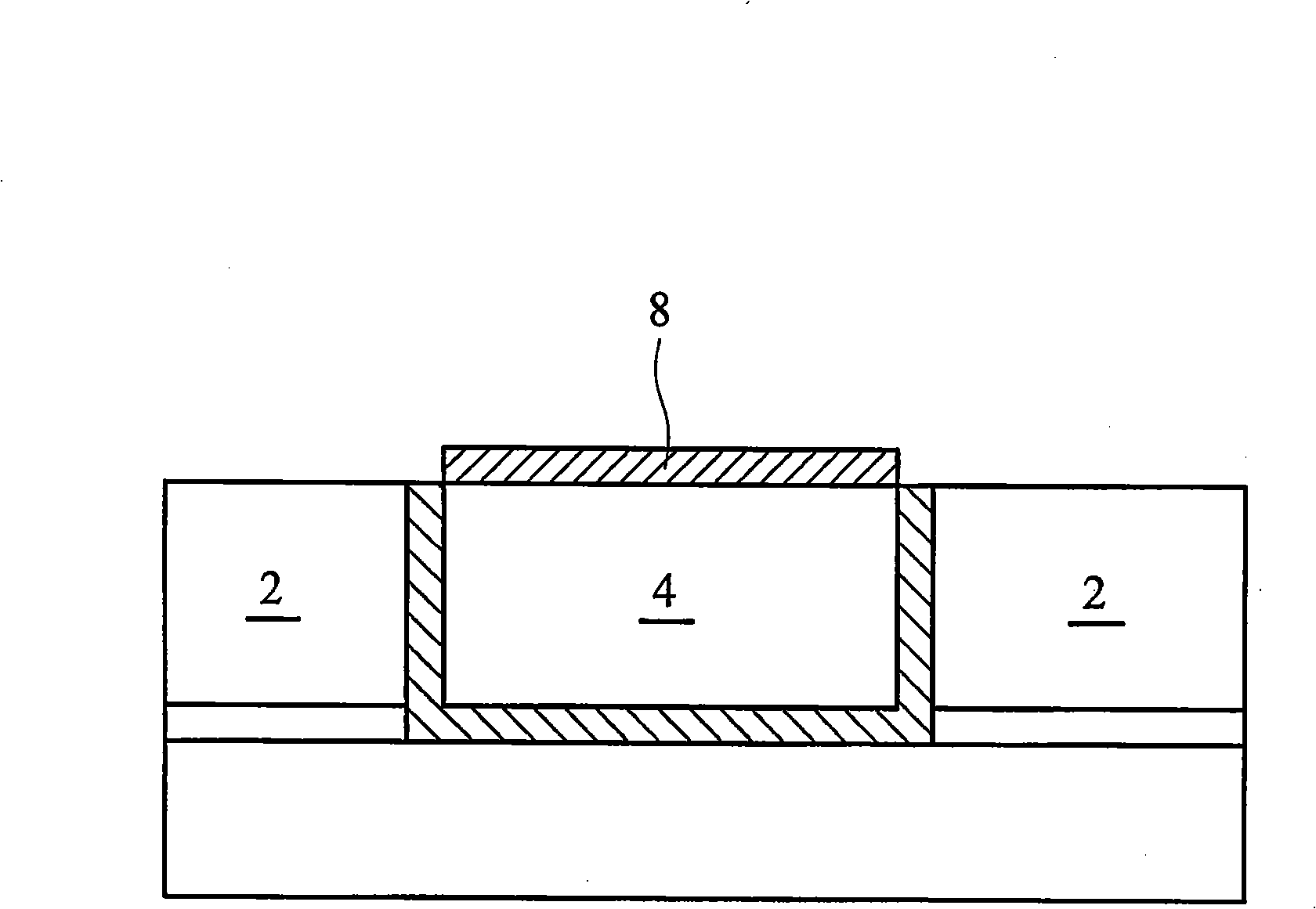

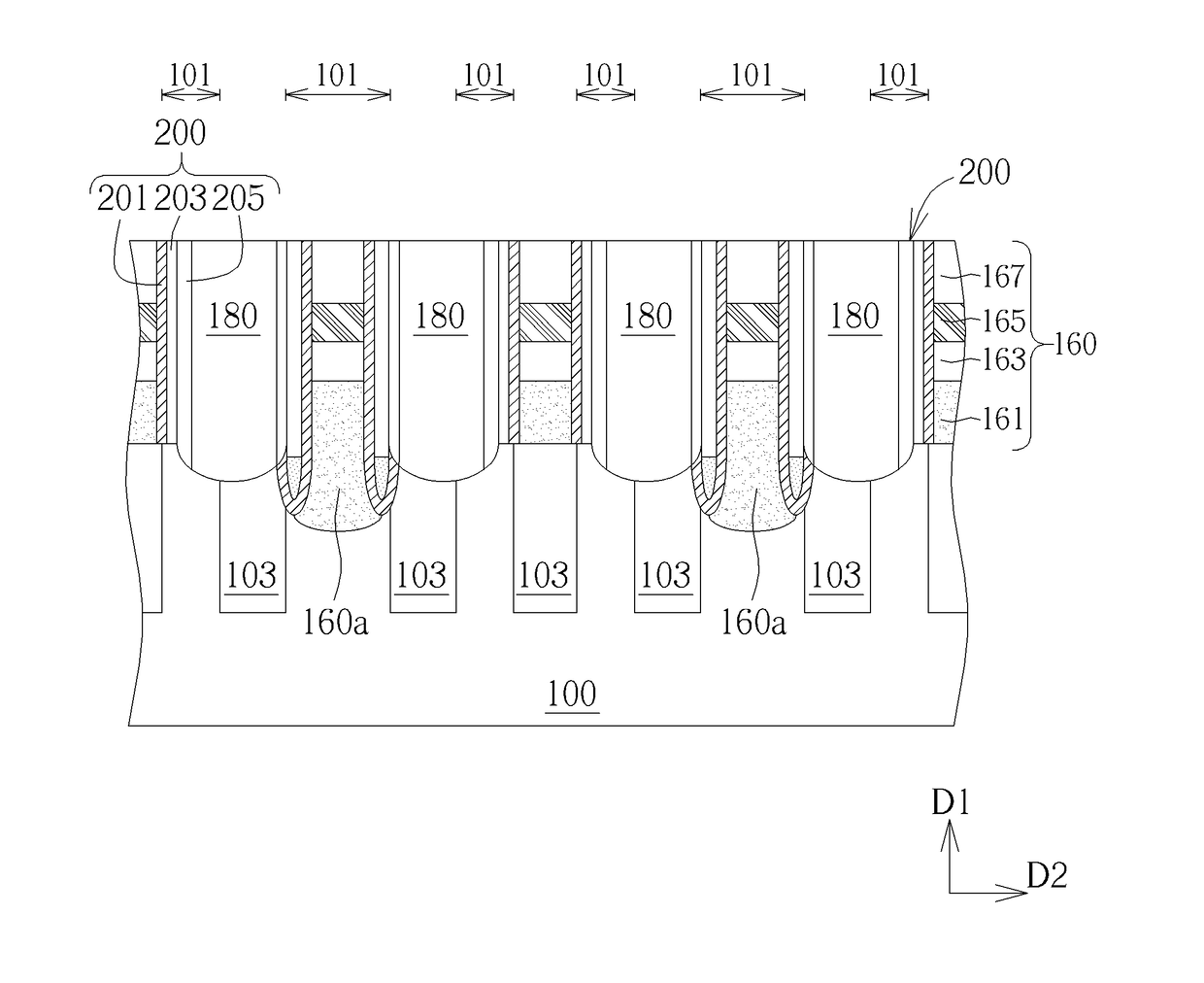

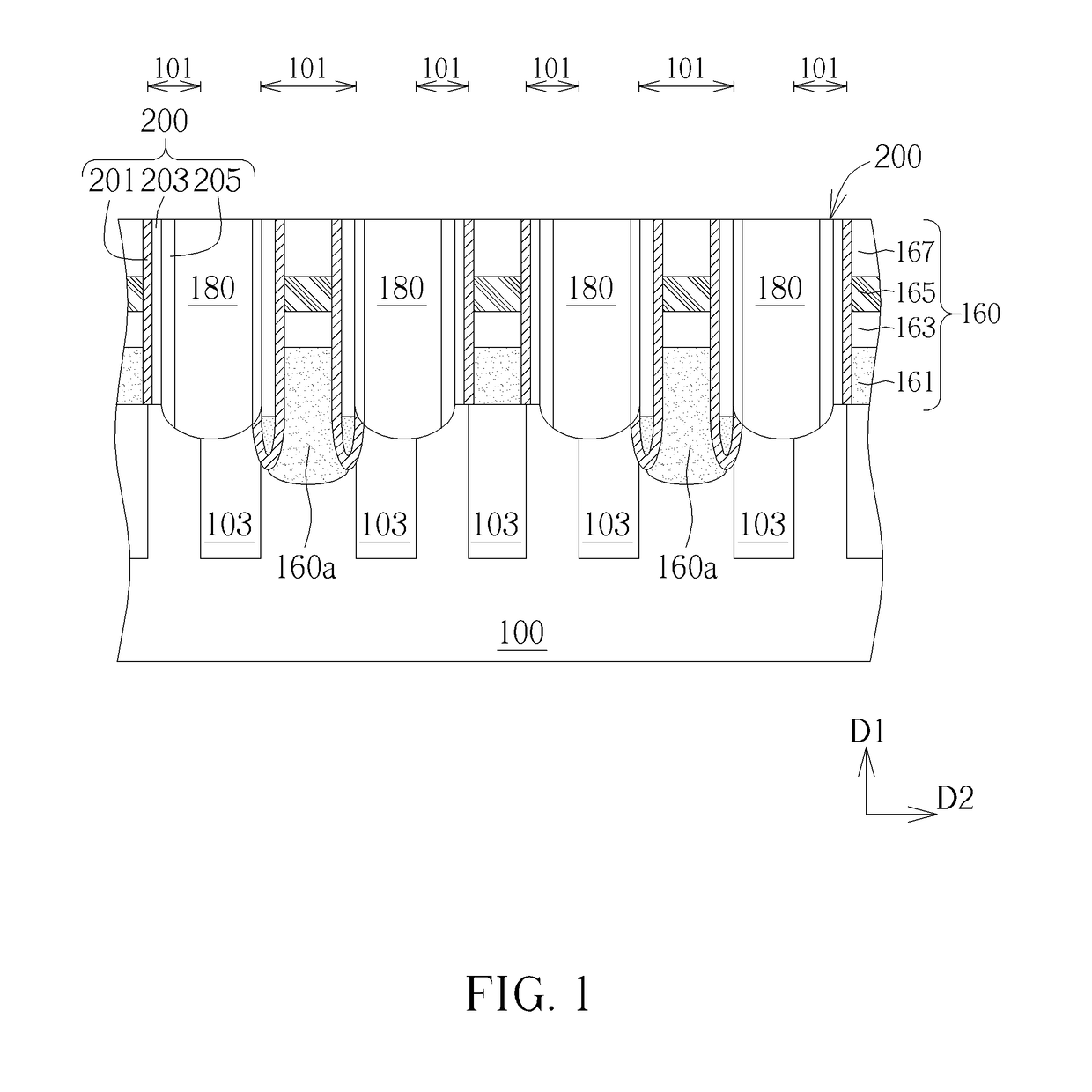

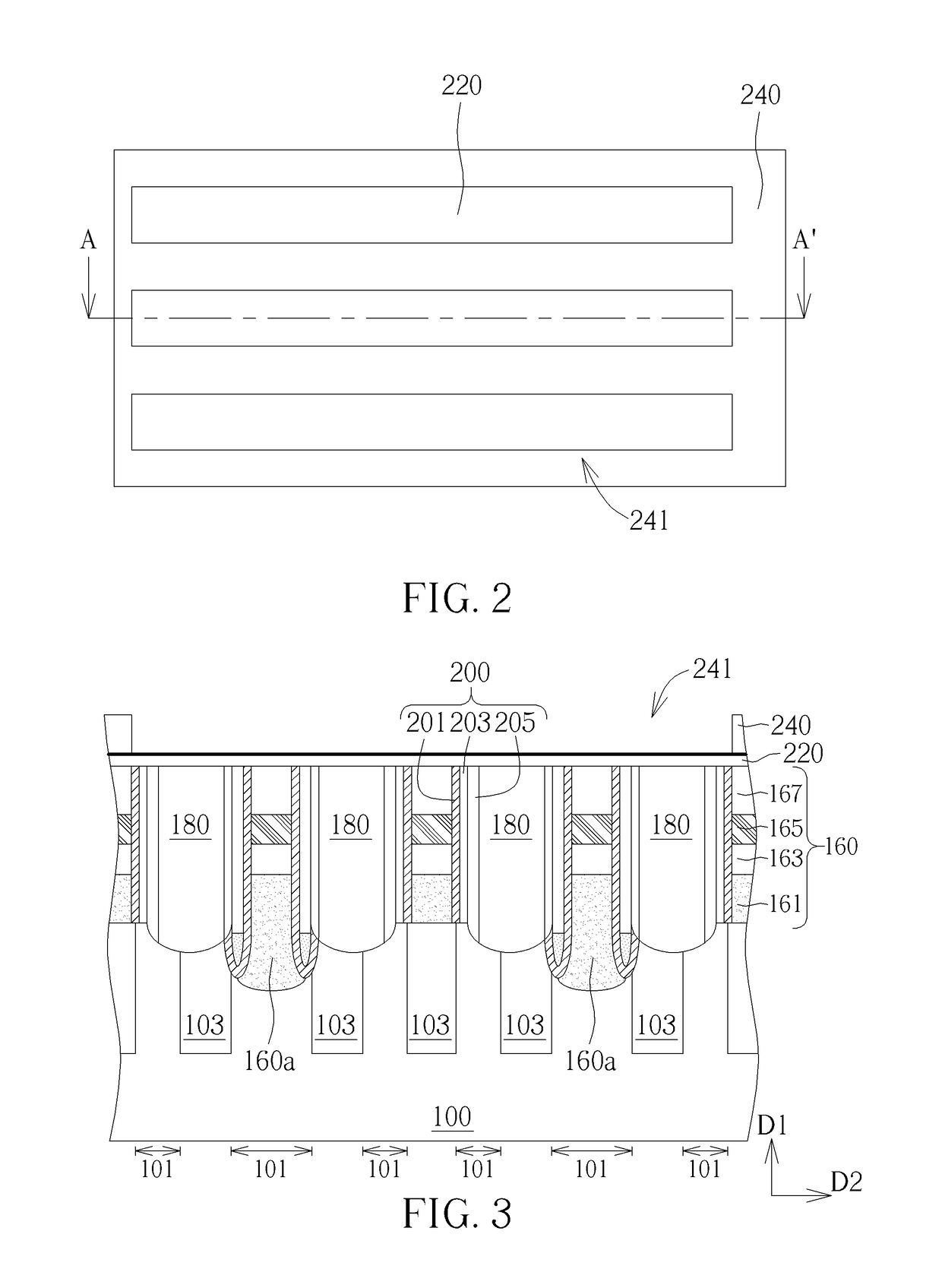

Semiconductor device and method of forming the same

A semiconductor device and method of forming the same, the semiconductor device includes bit lines, a transistor, a dielectric layer, plugs and a capping layer. The bit lines are disposed on a substrate within a cell region thereof, and the transistor is disposed on the substrate within a periphery region. The plugs are disposed in the dielectric layer, within the cell region and the periphery region respectively. The capping layer is disposed on the dielectric layer, and the capping layer disposed within the periphery region is between those plugs. That is, a portion of the dielectric layer is therefore between the capping layer and the transistor.

Owner:UNITED MICROELECTRONICS CORP +1

Touch panel and display apparatus including the same

ActiveUS9927939B2Reduce resistanceImprove RC delayCathode-ray tube indicatorsInput/output processes for data processingInsulation layerEngineering

A touch panel including a substrate, first touch electrodes, each of the first touch electrodes including first mesh patterns disposed on the substrate, an insulation layer disposed on the first touch electrodes, second touch electrodes, each of the second touch electrodes including second mesh patterns disposed on the insulation layer, first auxiliary mesh electrodes disposed on the substrate, the first auxiliary mesh electrodes being electrically connected to at least a portion of the corresponding second mesh patterns, and second auxiliary mesh electrodes disposed on the insulation layer, the second auxiliary mesh electrodes being electrically connected to at least a portion of the corresponding first me patterns.

Owner:SAMSUNG DISPLAY CO LTD

Method for selectively depositing diffusion barrier for copper interconnection

InactiveCN101692437AImprove RC delayReduce contact resistanceSemiconductor/solid-state device manufacturingInterconnectionDiffusion barrier

The invention belongs to the technical field of integrated circuits and particularly discloses a method for selectively depositing a diffusion barrier for copper interconnection, which comprises a step of before depositing the diffusion barrier, coating a layer of organic group on an exposed copper surface to prevent the absorption of a precursor on the copper surface in an atomic layer depositing process to selectively deposit the diffusion barrier. In the method, the deposition of the diffusion barrier in places except for the bottom of a copper interconnection hole is realized, so the unnecessary diffusion barrier in the copper through hole is removed and the contact resistance in the through hole is reduced. Thus, the resistance of the system is reduced and consequentially the RC delay of the whole circuit is reduced.

Owner:FUDAN UNIV

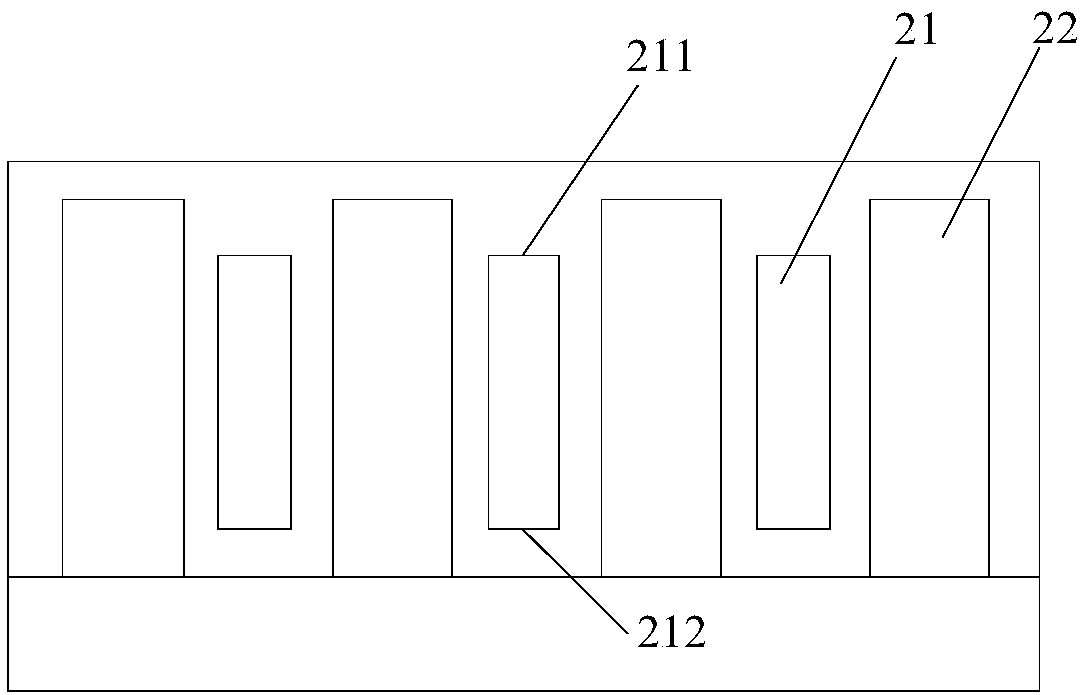

Interconnection line structure and forming method thereof

ActiveCN103077921AAdd depthIncrease in sizeSemiconductor/solid-state device detailsSolid-state devicesParasitic capacitanceEngineering

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

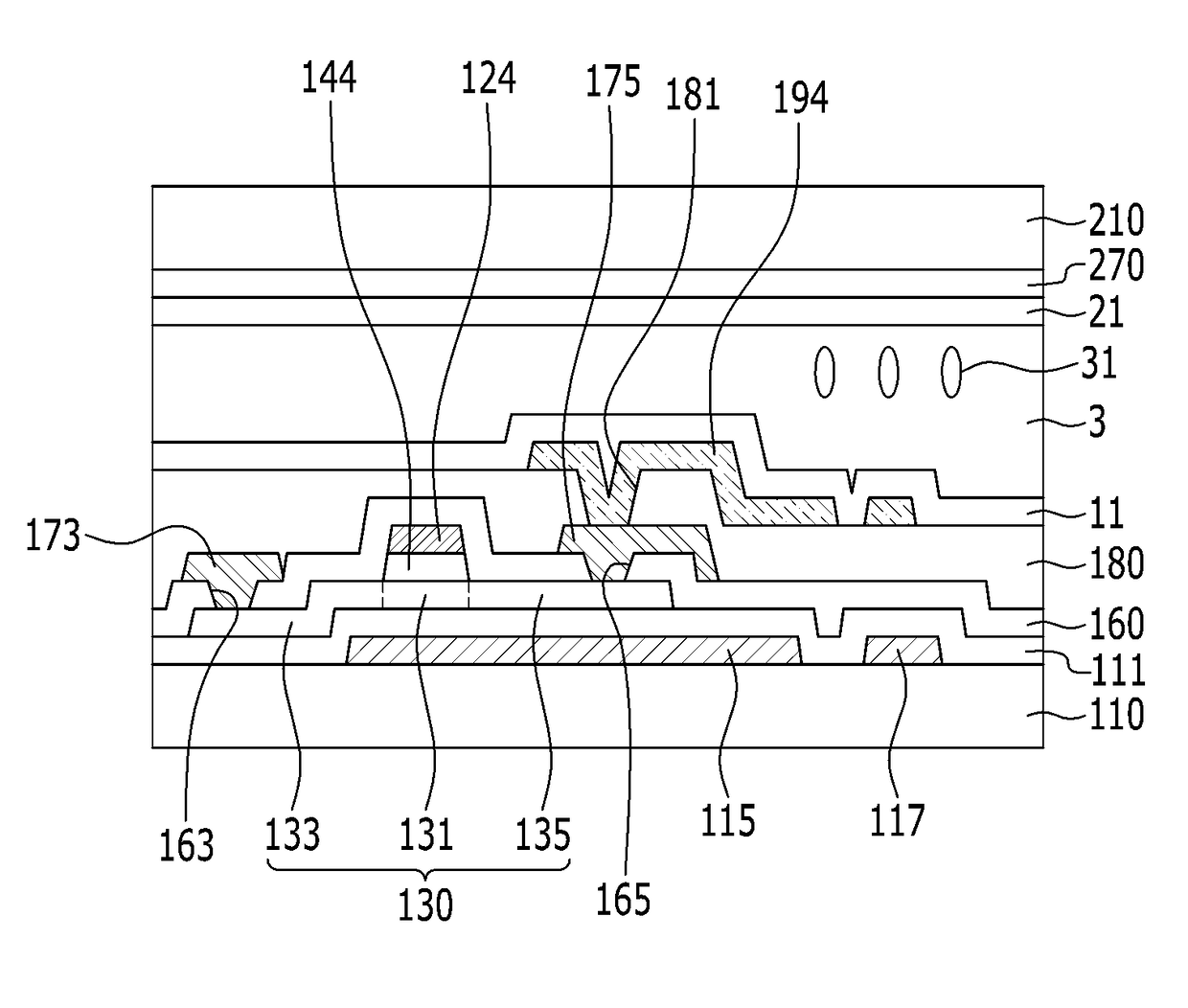

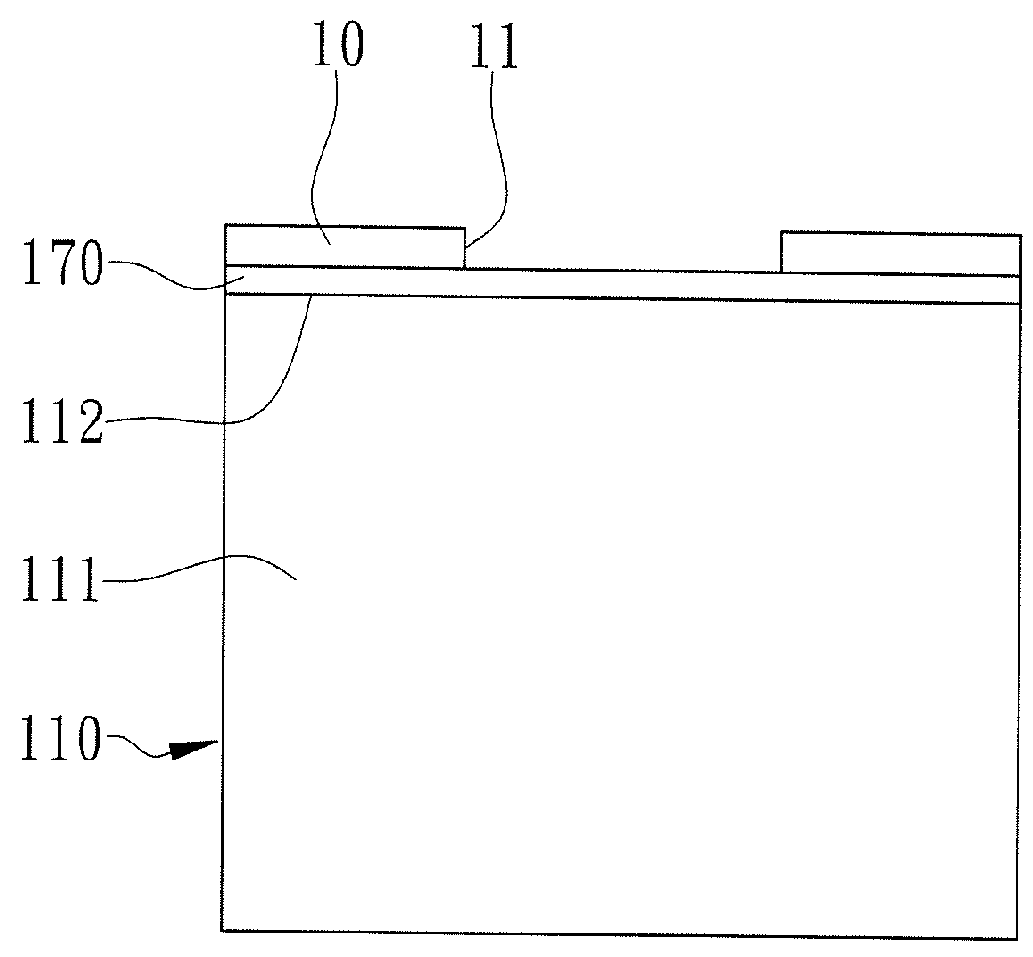

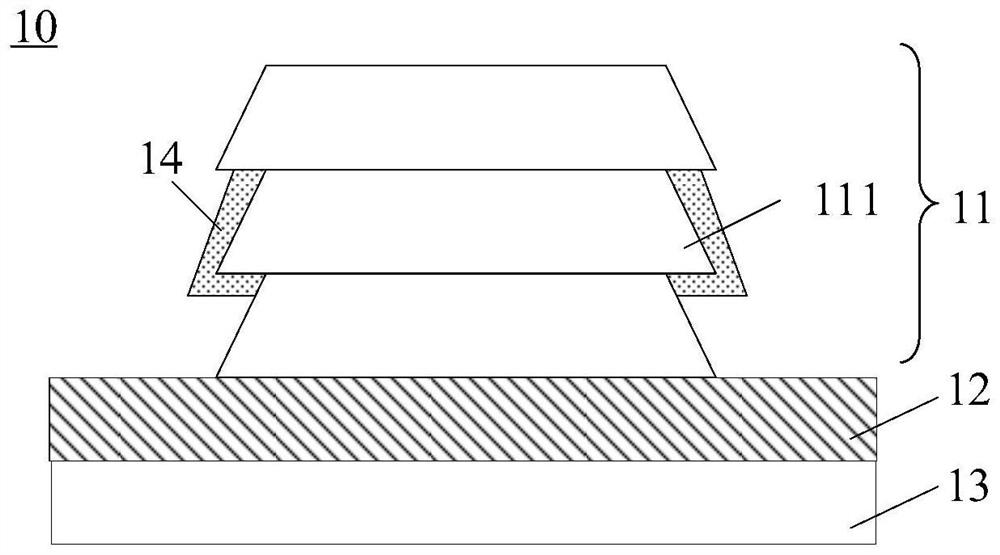

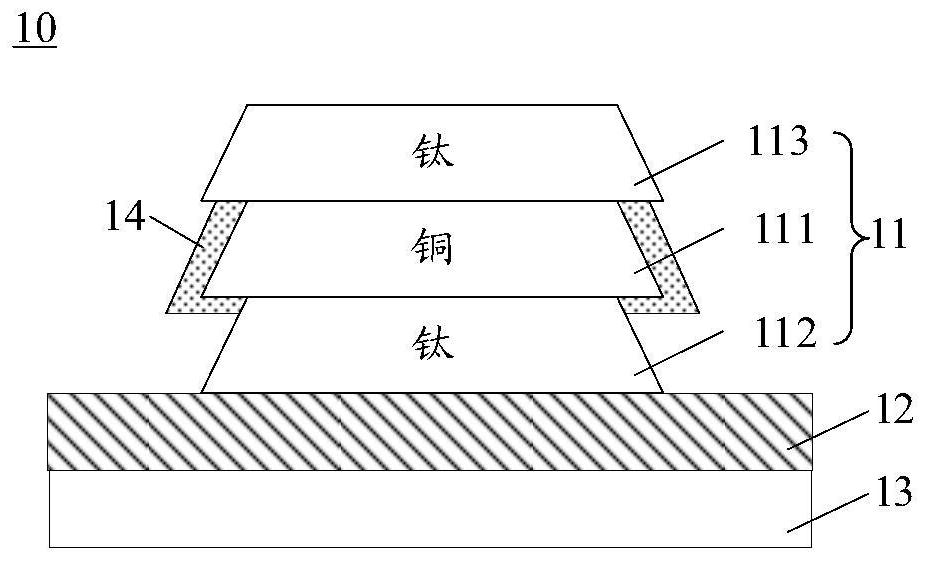

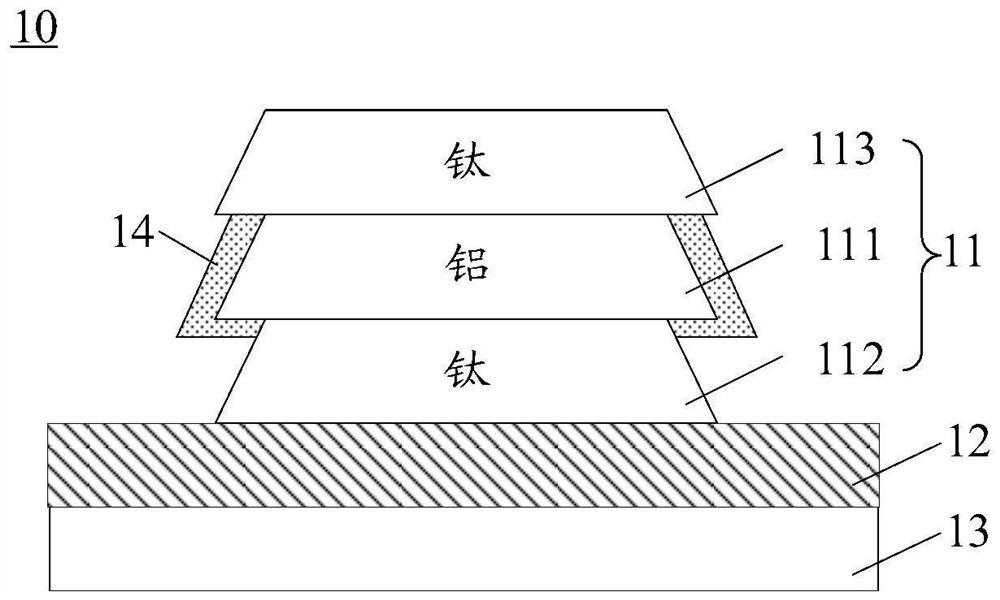

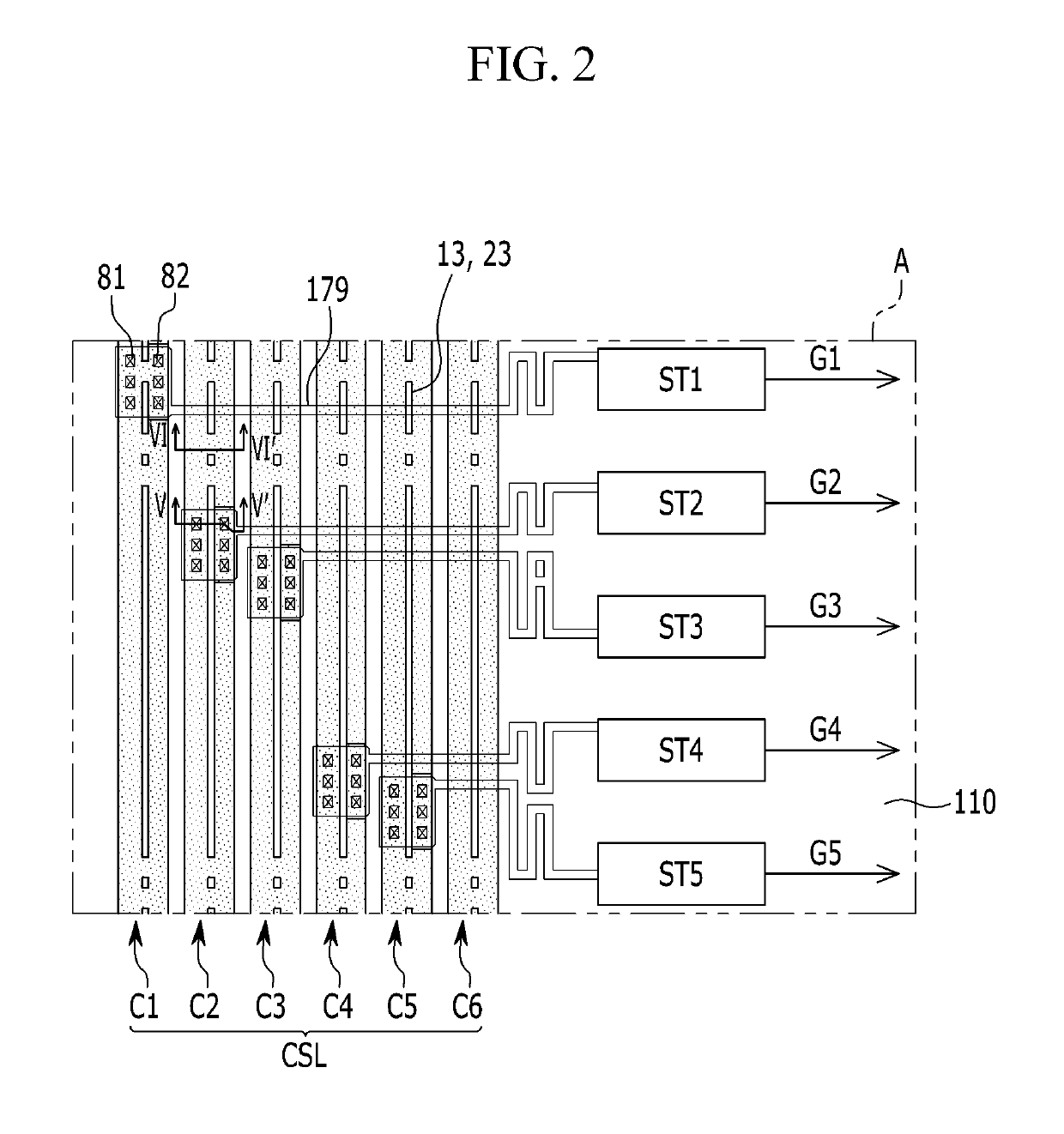

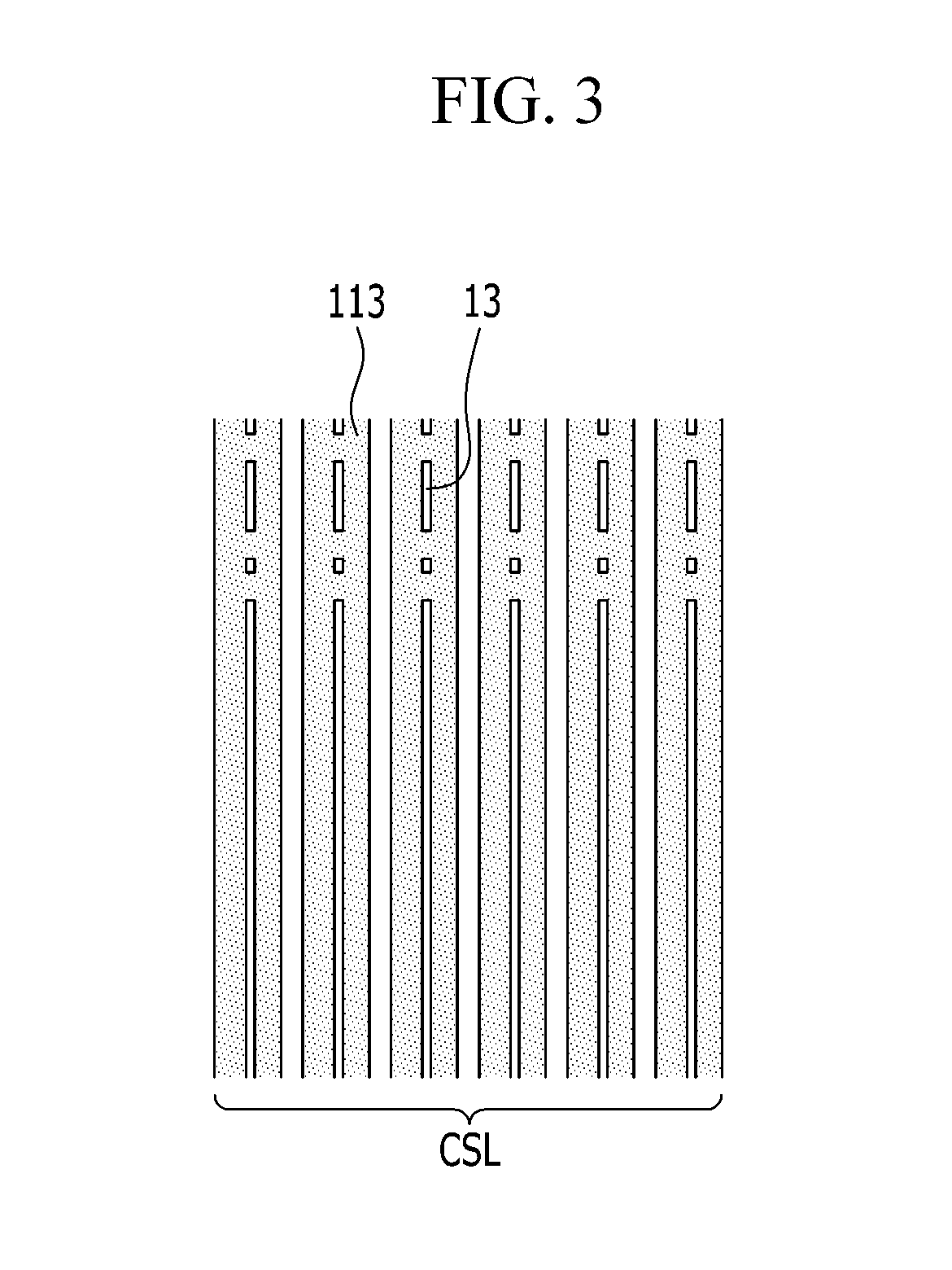

Display device and manufacturing method thereof

ActiveUS20170309242A1Reduce resistanceUndesirable delayTransistorStatic indicating devicesDisplay deviceEngineering

A display device including a substrate, a gate driver disposed on the substrate and including a plurality of stages, a clock signal line disposed on the substrate, and transmitting a clock signal to at least one of the stages, a transistor disposed on the substrate, and a light blocking layer disposed between the substrate and the transistor and overlapping the transistor. The clock signal line includes a first conductive line and a second conductive line overlapping the first conductive line, and the first conductive line is disposed in the same layer as the light blocking layer.

Owner:SAMSUNG DISPLAY CO LTD

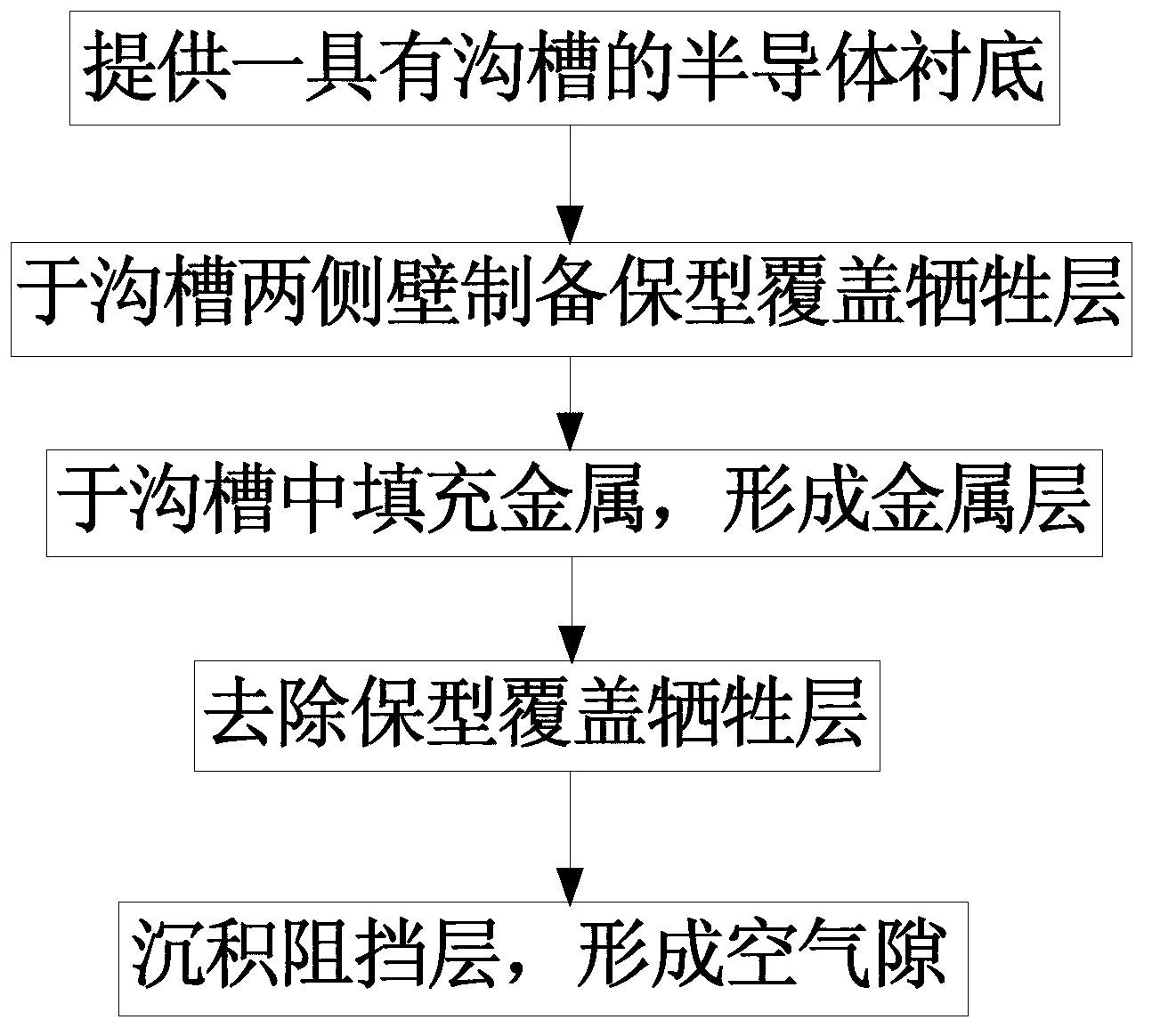

Air gap forming method

InactiveCN103325728AThe process steps are simpleLess consumablesSemiconductor/solid-state device manufacturingMaterial consumptionEngineering

The invention discloses an air gap forming method. According to the method, the critical size of a cannelure is required to be larger than the critical size required by technology requirements when technological design of the cannelure is carried out, a mould-keeping covering layer is deposited in the cannelure in a large critical size, a mould-keeping covering layer on the bottom of the cannelure and a mould-keeping covering layer on the upper surface of a semiconductor substrate are removed, a mould-keeping covering sacrificial layer is reserved, the subsequent filling process is continued, and finally the mould-keeping covering sacrificial layer is removed and a blocking layer is deposited on the top of the cannelure to obtain an air gap structure. According to the air gap forming method, the number of processing steps is small, material consumption is low, critical sizes of a through hole and the cannelure are increased during photoetching and etching while RC delay is improved, technological difficulty is reduced, production efficiency is improved, and production cost is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

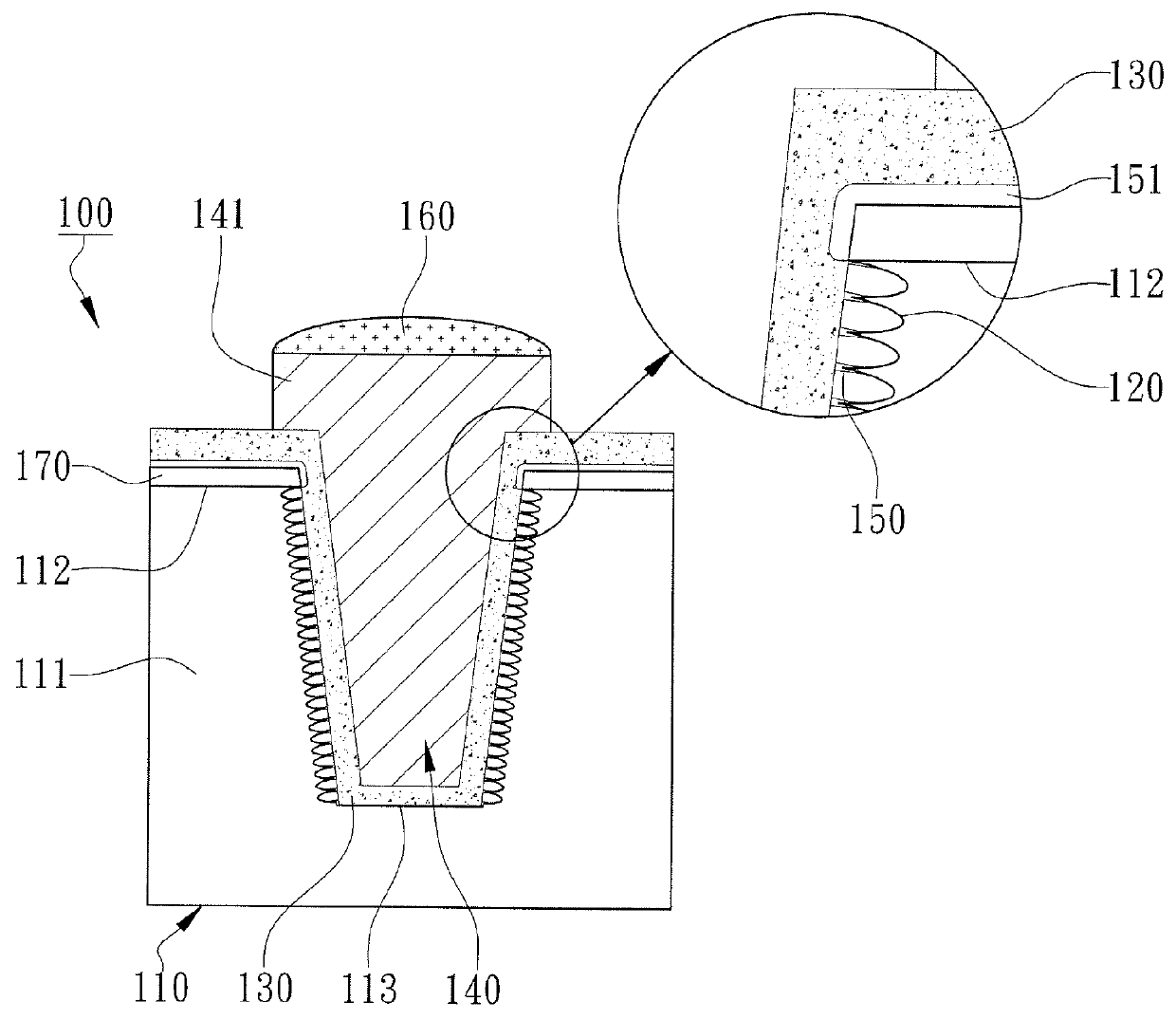

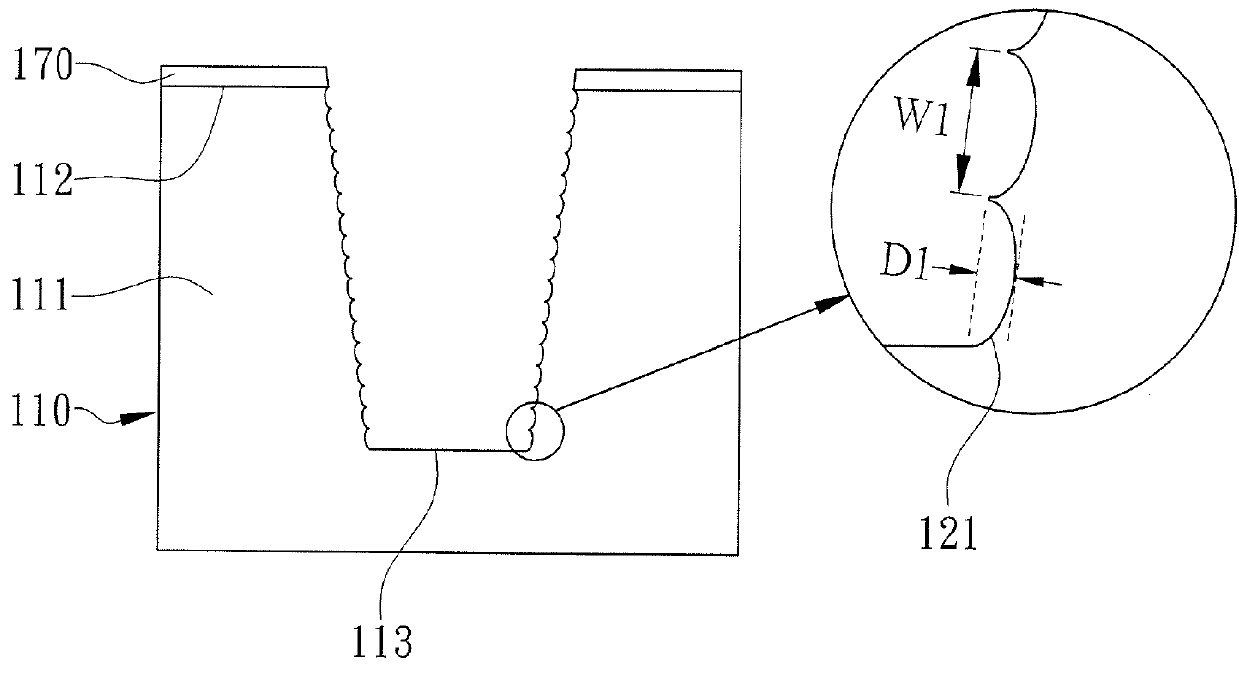

TSV structure having insulating layers with embedded voids

ActiveUS9379043B1Improve RC delayTime delay issueSemiconductor/solid-state device detailsSolid-state devicesSemiconductorWidth ratio

Disclosed is a TSV structure having insulating layers with embedded voids, including a chip layer, a dielectric liner and a conductive filler. There is at least a via reentrant from one surface of the semiconductor body of the chip layer. A plurality of air-gap cavities are formed on the sidewall of the via where the cavities have a depth-to-width ratio not less than one. The dielectric liner covers the sidewall of the via without filling into the air-gap cavities. The conductive filler is disposed in the via without filling into the air-gap cavities due to the isolation of the dielectric liner so as to form an air insulating layer with a plurality of enclosed voids embedded between the semiconductor body and the dielectric liner. Accordingly, RC Delay of the TSV structure can be improved.

Owner:POWERTECH TECHNOLOGY

Semiconductor structure and its manufacture method

ActiveCN101286494AGuaranteed qualityImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor structure

An integrated circuit structure includes a semiconductor substrate; a dielectric layer over the semiconductor substrate; a conductive wiring in the dielectric layer; and a metal carbide cap layer over the conductive wiring.

Owner:TAIWAN SEMICON MFG CO LTD

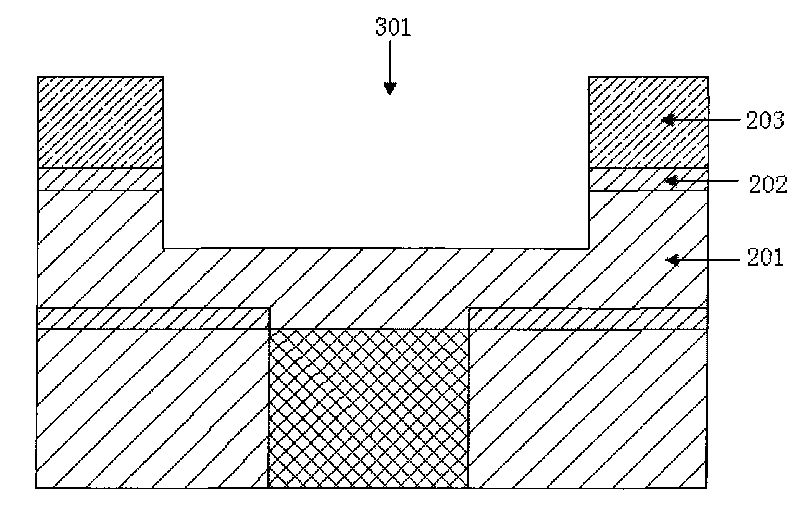

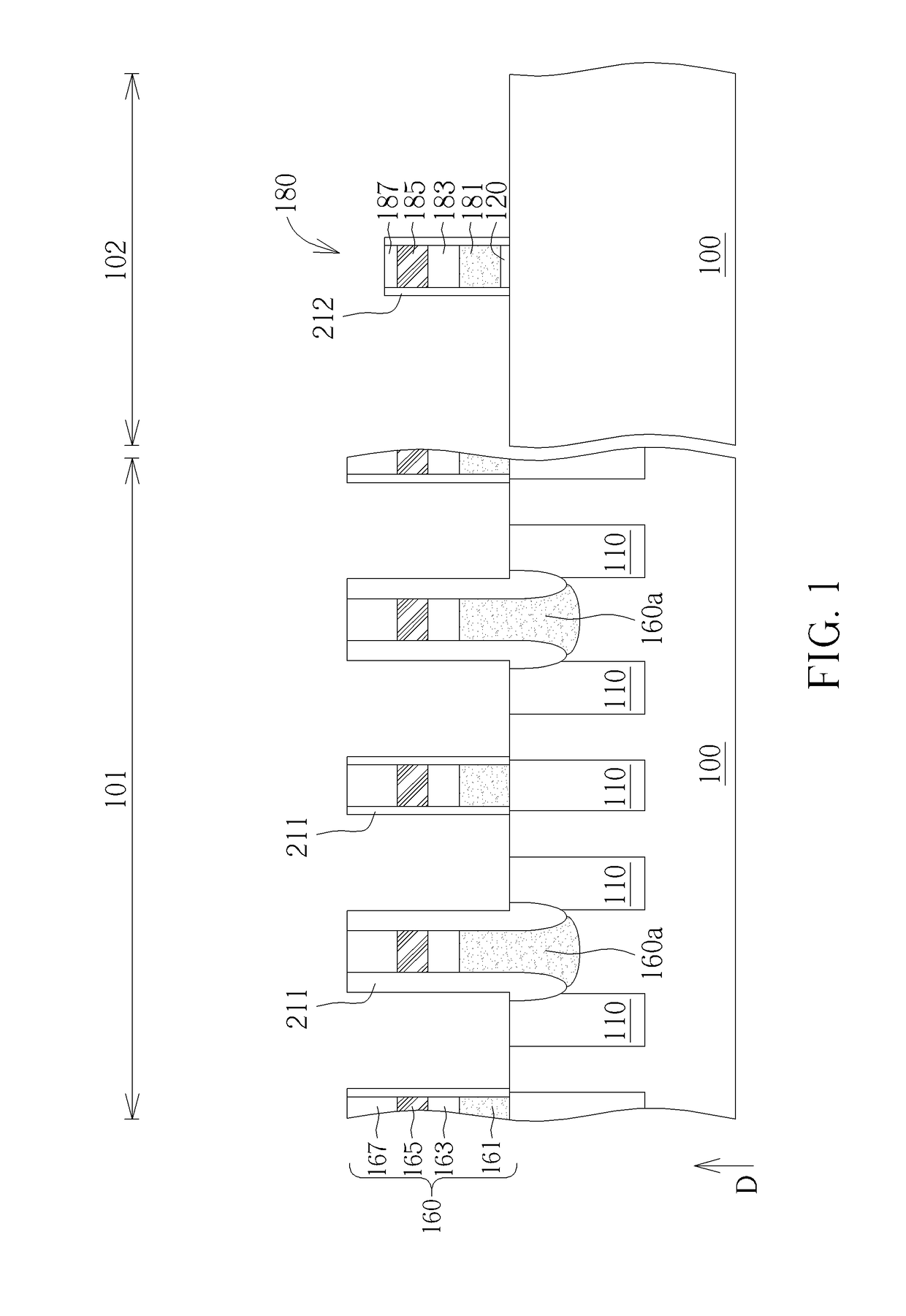

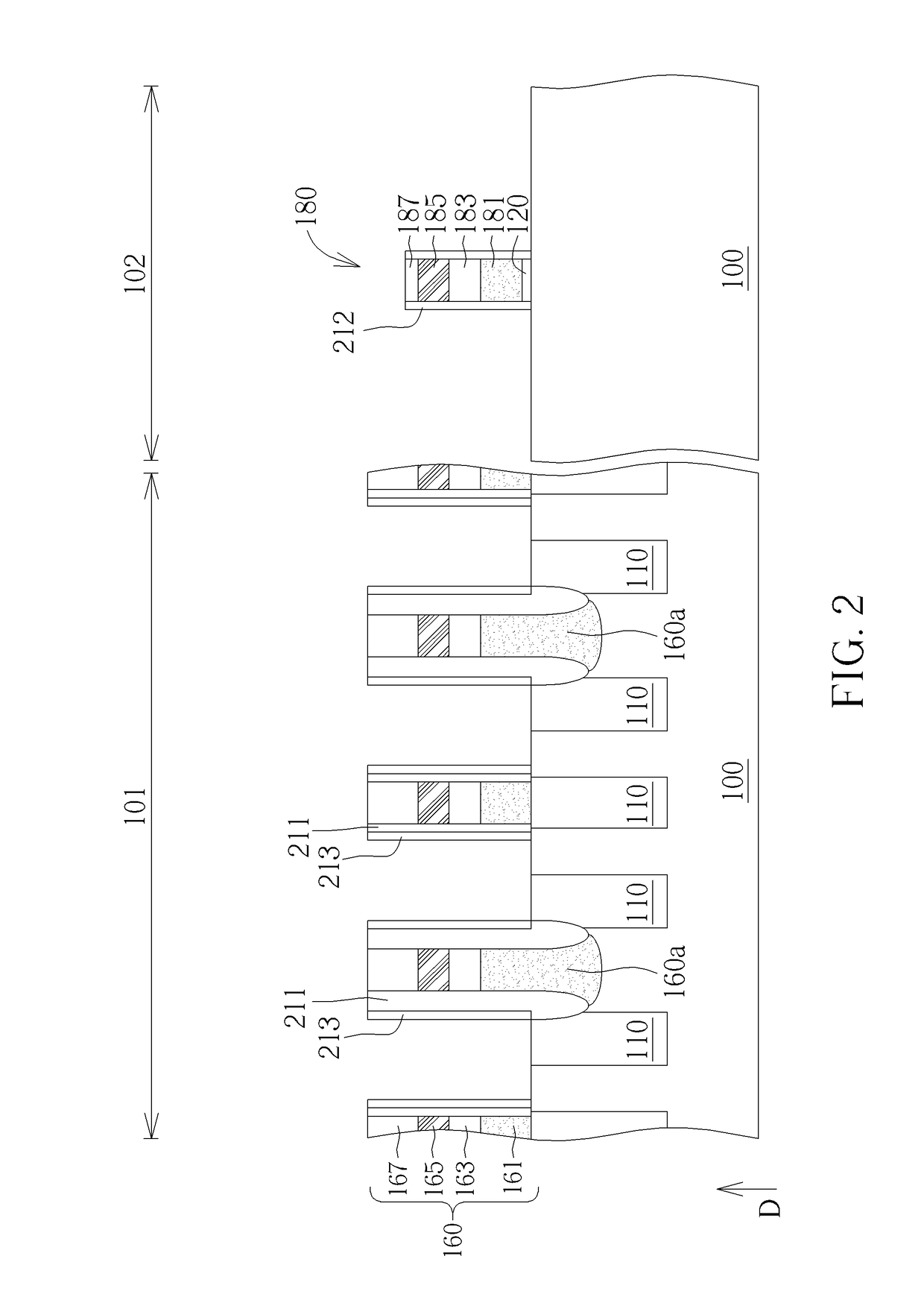

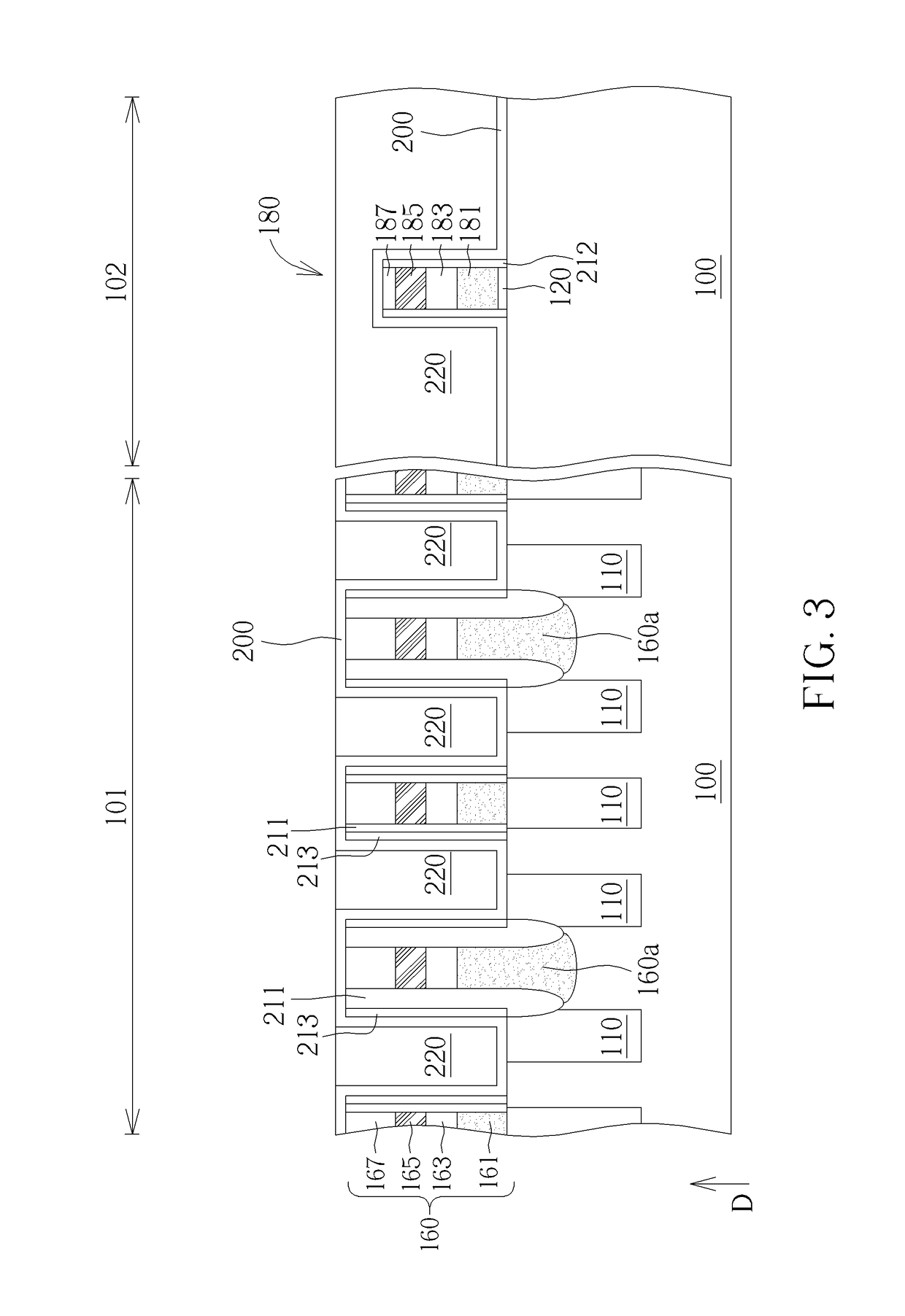

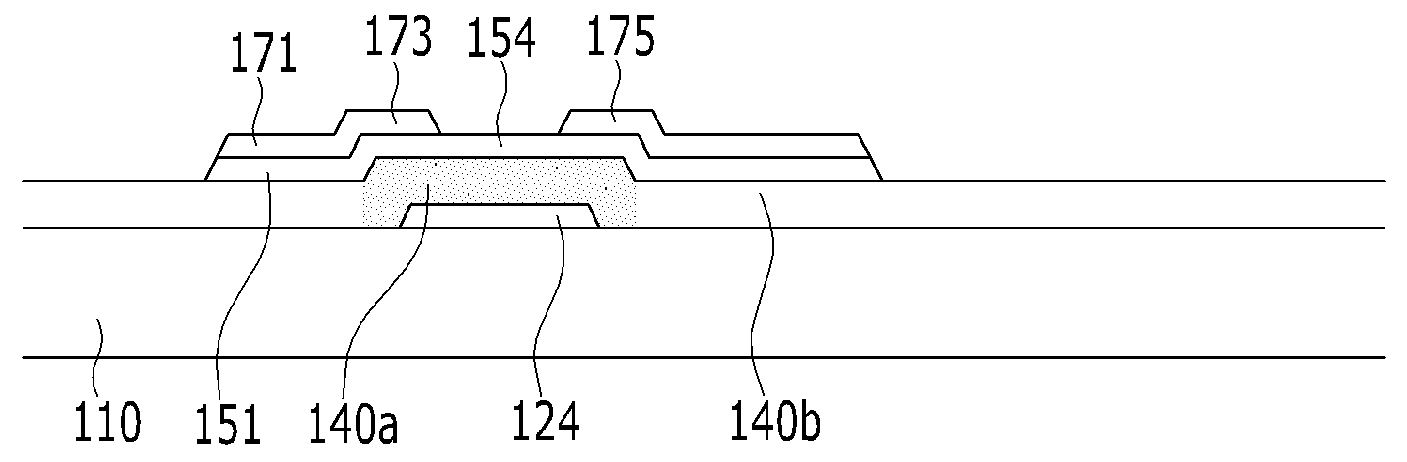

Thin film transistor and manufacturing method thereof

ActiveUS20130056828A1Improve RC delayIncrease currentTransistorSolid-state devicesSiliconSemiconductor

A thin film transistor is provided. A thin film transistor according to an exemplary embodiment of the present invention includes: a substrate; a gate line disposed on the substrate and including a gate electrode; a semiconductor layer disposed on the substrate and including at least a portion overlapping the gate electrode; a gate insulating layer disposed between the gate line and the semiconductor layer; and a source electrode and a drain electrode disposed on the substrate and facing each other over a channel region of the semiconductor layer. The gate insulating layer includes a first region and a second region, the first region corresponds to the channel region of the semiconductor layer, the first region is made of a first material, the second region is made of a second material, and the first material and the second material have different atomic number ratios of carbon and silicon.

Owner:SAMSUNG DISPLAY CO LTD

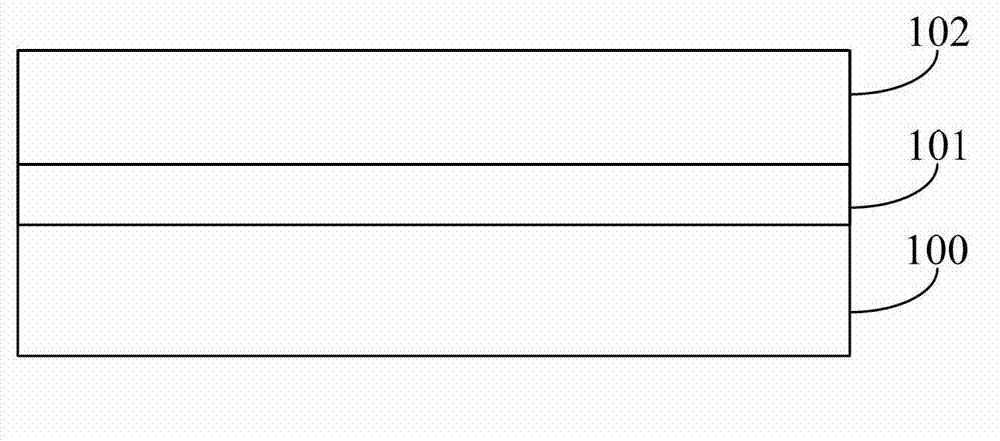

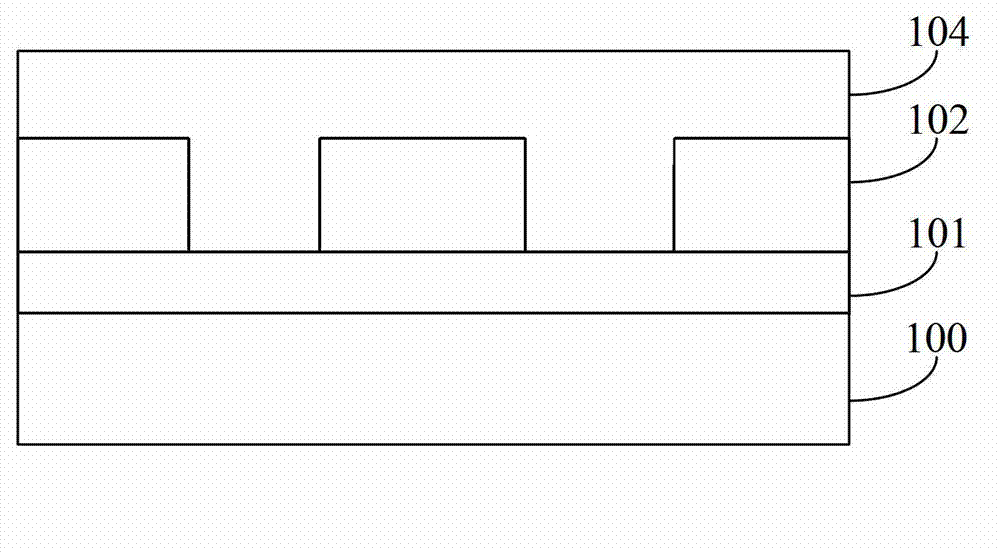

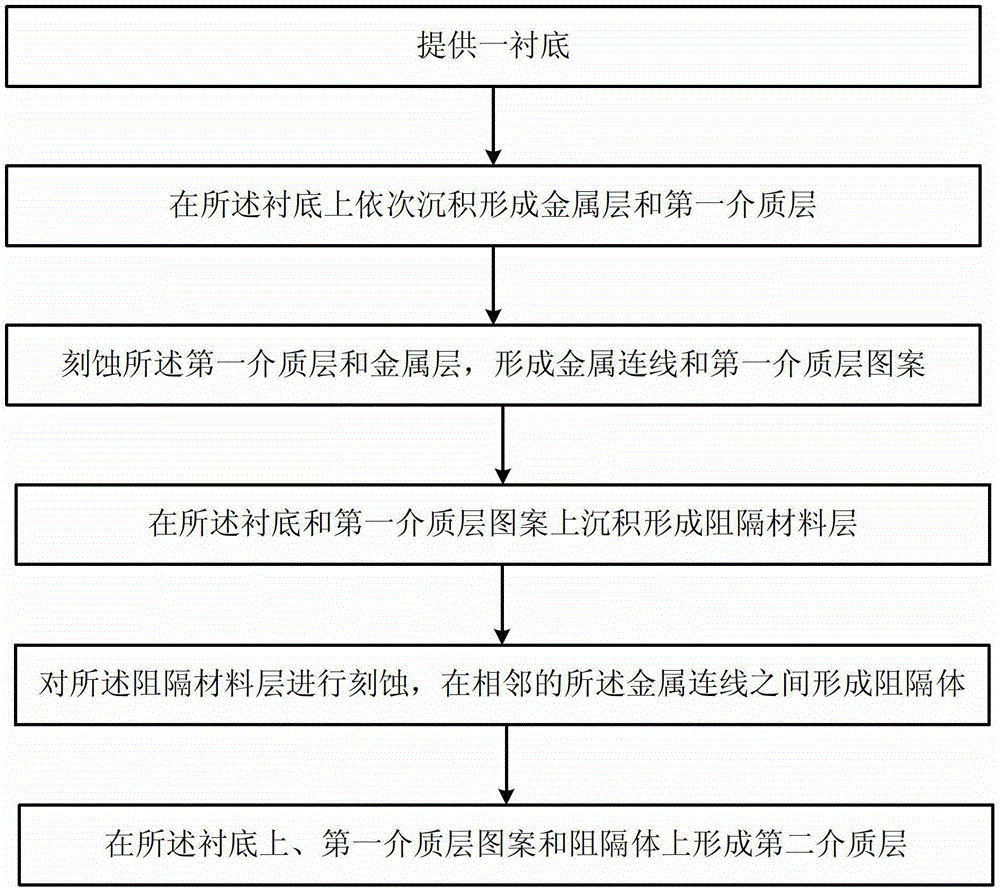

A manufacturing method for a semiconductor device

ActiveCN103337474ALow dielectric constantReduce parasitic capacitanceSemiconductor/solid-state device manufacturingParasitic capacitanceDeposition process

The invention provides a manufacturing method for a semiconductor device. The manufacturing method of the invention comprises the following steps: firstly, a substrate is provided; secondly, a metal layer and a first dielectric layer are sequentially formed on the substrate through a deposition process; thirdly, the first dielectric layer and the metal layer are etched, and metal wires and first dielectric layer patterns on the metal wires are formed, and a part of the substrate is exposed; fourthly, an obstruction material layer is formed through a deposition process on the substrate and the first dielectric layer pattern; fifthly, the obstruction material layer is etched, and at least one obstruction body is formed between the adjacent metal wires; sixthly, a second dielectric layer is formed on the substrate, the first dielectric layer patterns, and the obstruction body, and gaps are formed between the metal wires and the obstruction body and / or in the second dielectric layer between the adjacent obstruction bodies. Through the adoption of the above method, the gaps can be formed in the second dielectric layer between the metal wires, and the dielectric constant of the second dielectric layer can be effectively reduced. A parasitic capacitance between the metal wires can be reduced and the condition of a RC delay of the interconnected metal wires is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Semiconductor device and method of forming the same

A semiconductor device and method of forming the same, the semiconductor device includes bit lines, a transistor, a dielectric layer, plugs and a capping layer. The bit lines are disposed on a substrate within a cell region thereof, and the transistor is disposed on the substrate within a periphery region. The plugs are disposed in the dielectric layer, within the cell region and the periphery region respectively. The capping layer is disposed on the dielectric layer, and the capping layer disposed within the periphery region is between those plugs. That is, a portion of the dielectric layer is therefore between the capping layer and the transistor.

Owner:UNITED MICROELECTRONICS CORP +1

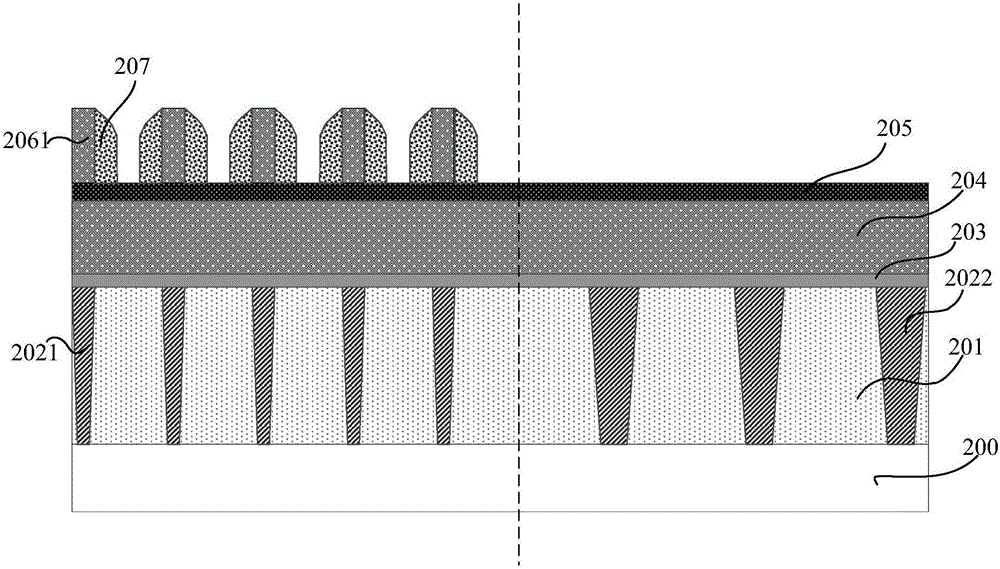

Thin film transistor and manufacturing method thereof, array substrate, display panel and equipment

PendingCN111834466AReduce sheet resistanceImprove stabilityTransistorSolid-state devicesThin membraneEngineering

The invention relates to the technical field of display, and particularly discloses a thin film transistor and a manufacturing method thereof, an array substrate, a display panel and an electronic device. The thin film transistor comprises a grid electrode, a grid electrode insulating layer, an active layer and a protective layer. The active layer is arranged on one side of the gate insulation layer, the gate is arranged on the other side, deviating from the active layer, of the gate insulation layer, the square resistance value of the gate is smaller than or equal to a preset square resistance value, and the gate at least comprises a first metal layer. The protective layer at least covers the exposed surface of the first metal layer to prevent the first metal layer from being oxidized. Inthis way, RC delay on the grid electrode can be reduced, and the problem that a display device is uneven in image flickering is solved.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Thin film transistor and manufacturing method thereof

A thin film transistor is provided. A thin film transistor according to an exemplary embodiment of the present invention includes: a substrate; a gate line disposed on the substrate and including a gate electrode; a semiconductor layer disposed on the substrate and including at least a portion overlapping the gate electrode; a gate insulating layer disposed between the gate line and the semiconductor layer; and a source electrode and a drain electrode disposed on the substrate and facing each other over a channel region of the semiconductor layer. The gate insulating layer includes a first region and a second region, the first region corresponds to the channel region of the semiconductor layer, the first region is made of a first material, the second region is made of a second material, and the first material and the second material have different atomic number ratios of carbon and silicon.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor device, manufacturing method therefor, and electronic device

ActiveCN107527913AImprove performanceImprove RC delaySolid-state devicesSemiconductor devicesCapacitancePower semiconductor device

The invention provides a semiconductor device, a manufacturing method therefor and an electronic device, and relates to the technical field of semiconductors. The semiconductor substrate comprises a substrate which comprises a core region and is provided with an interlayer dielectric layer; a plurality of first bit lines which are disposed on the interlayer dielectric layer in the core region at intervals; a first dielectric layer which covers the first bit lines and the interlayer dielectric layer in the core region, wherein each part, between the adjacent first bit lines in the core region, of the first dielectric layer is provided with an air gap. According to the invention, the air gaps are disposed between the adjacent bit lines of the semiconductor devices, thereby reducing the capacitance of the bit lines, and reducing the coupling noise between the bit lines. Also, units with the uniform performances can be obtained, such as a unit with the uniform threshold voltage (Vt) and a unit with the uniform random telegraph noise. Moreover, the device improves the RC delay of the bit lines, and is enabled to have better performances.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

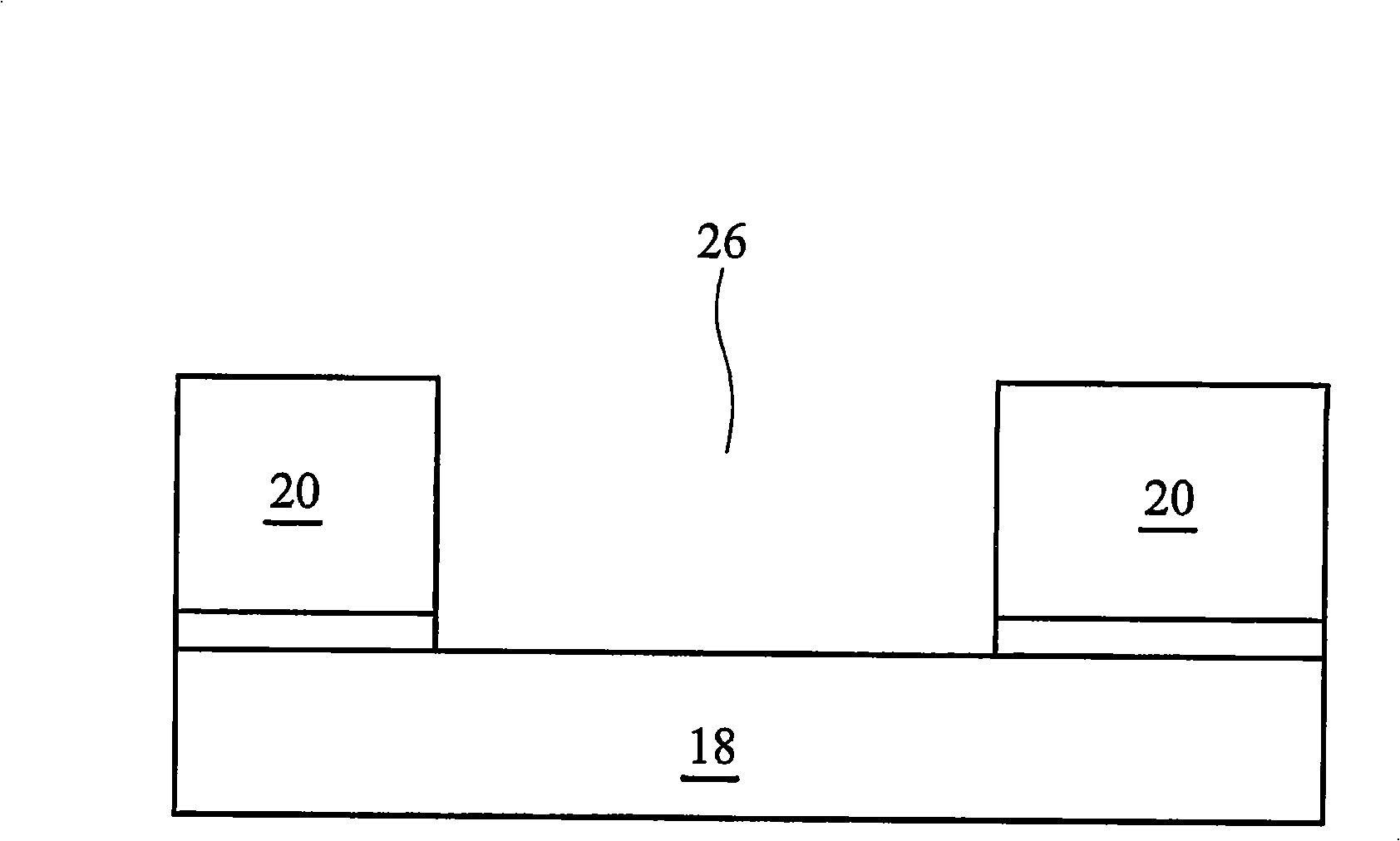

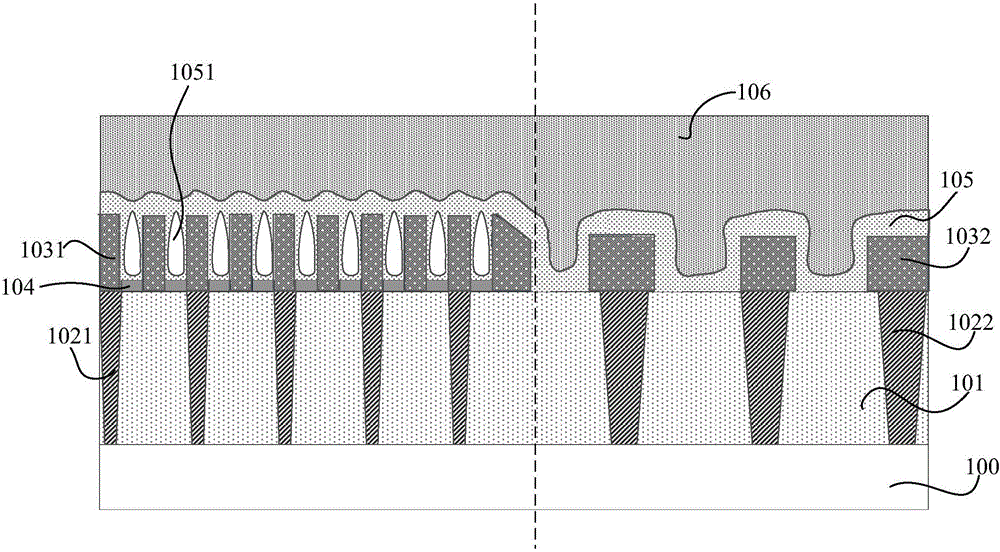

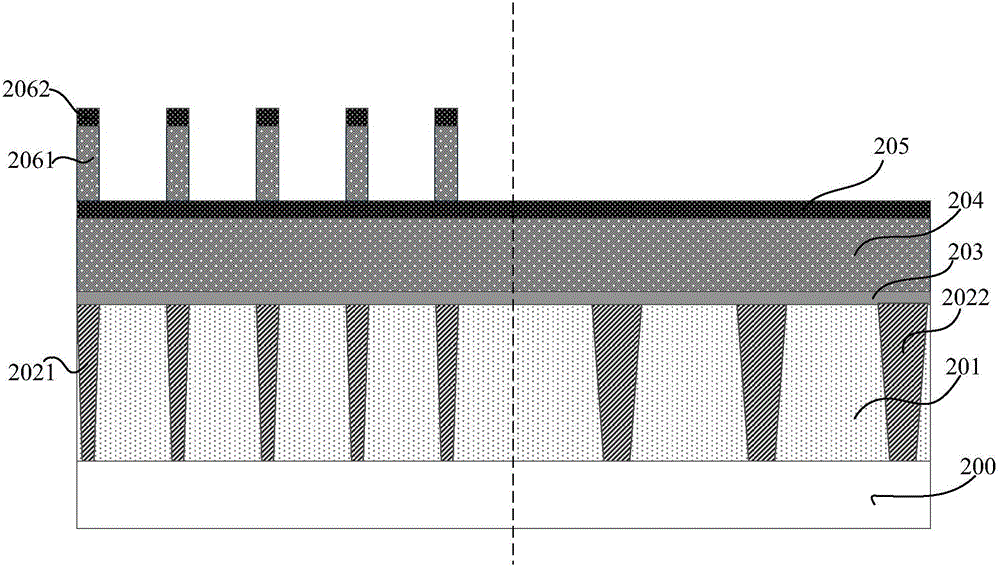

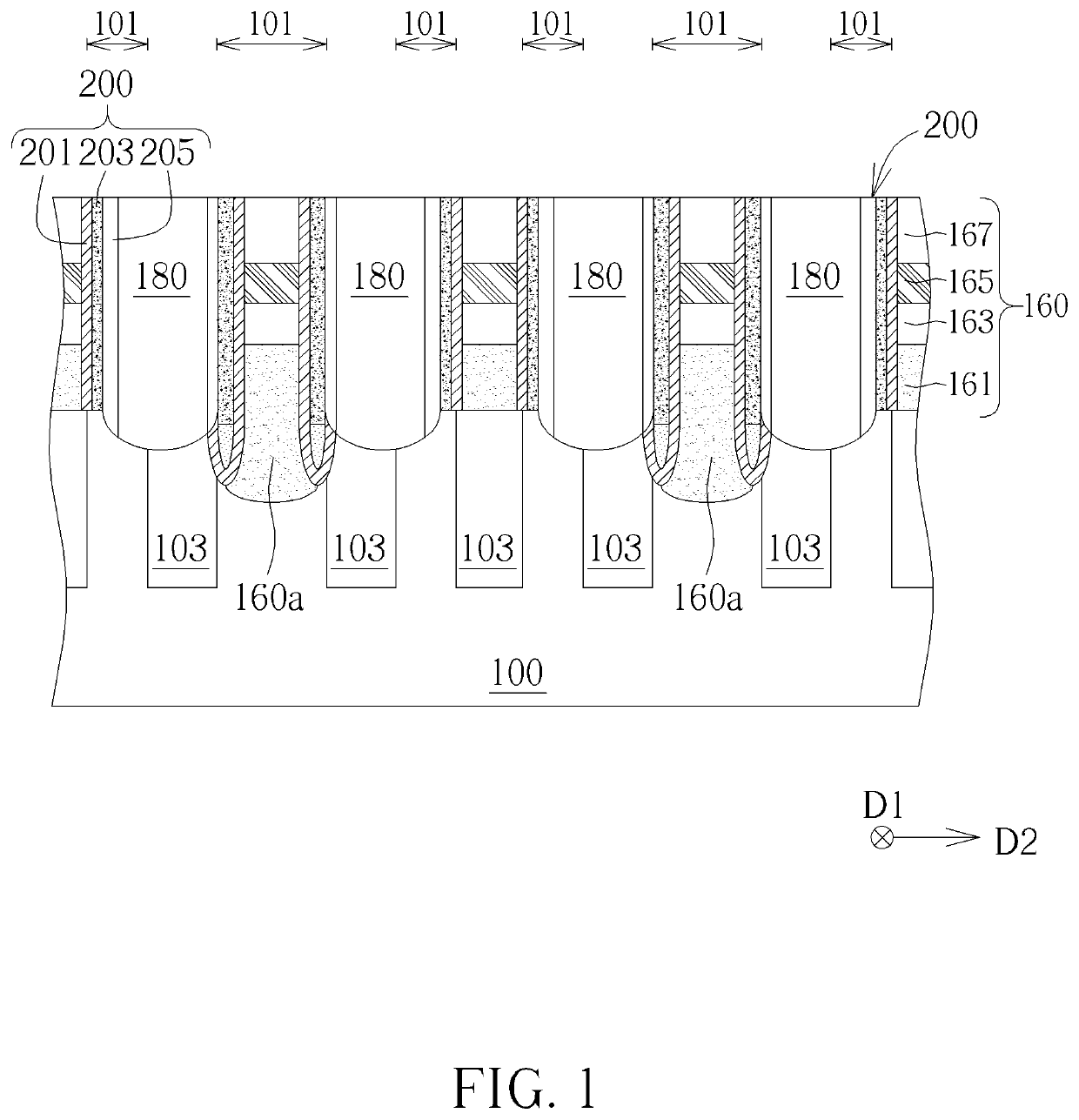

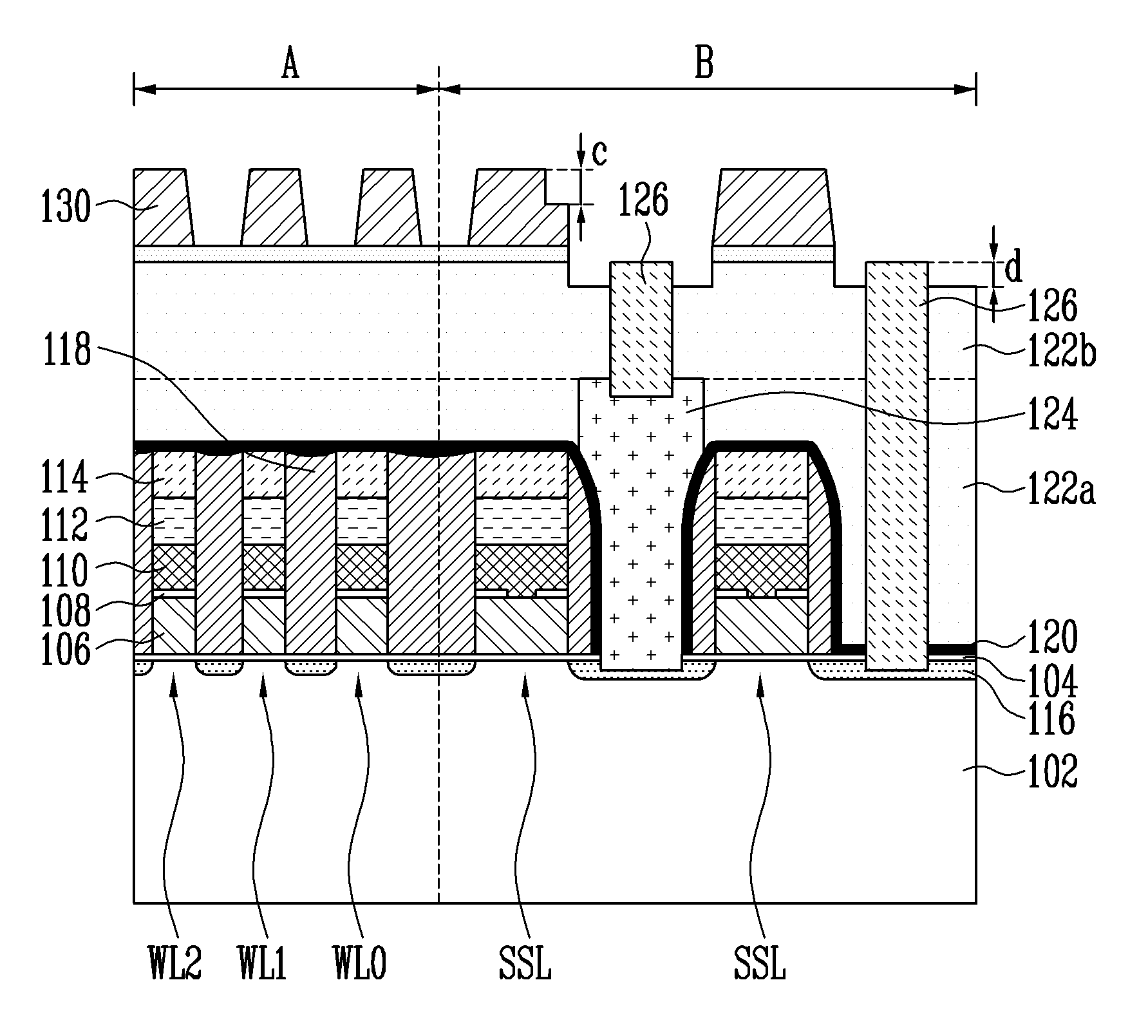

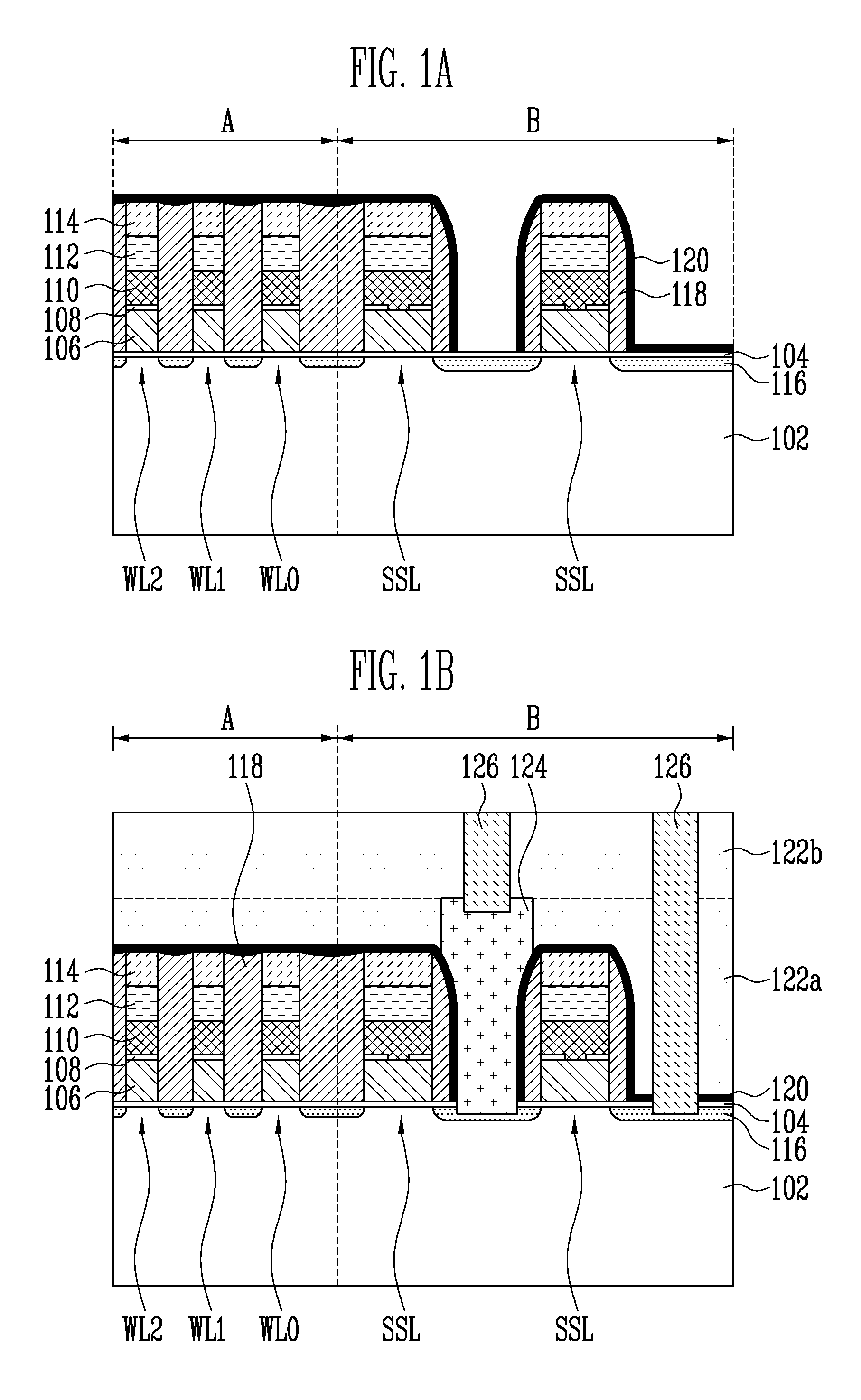

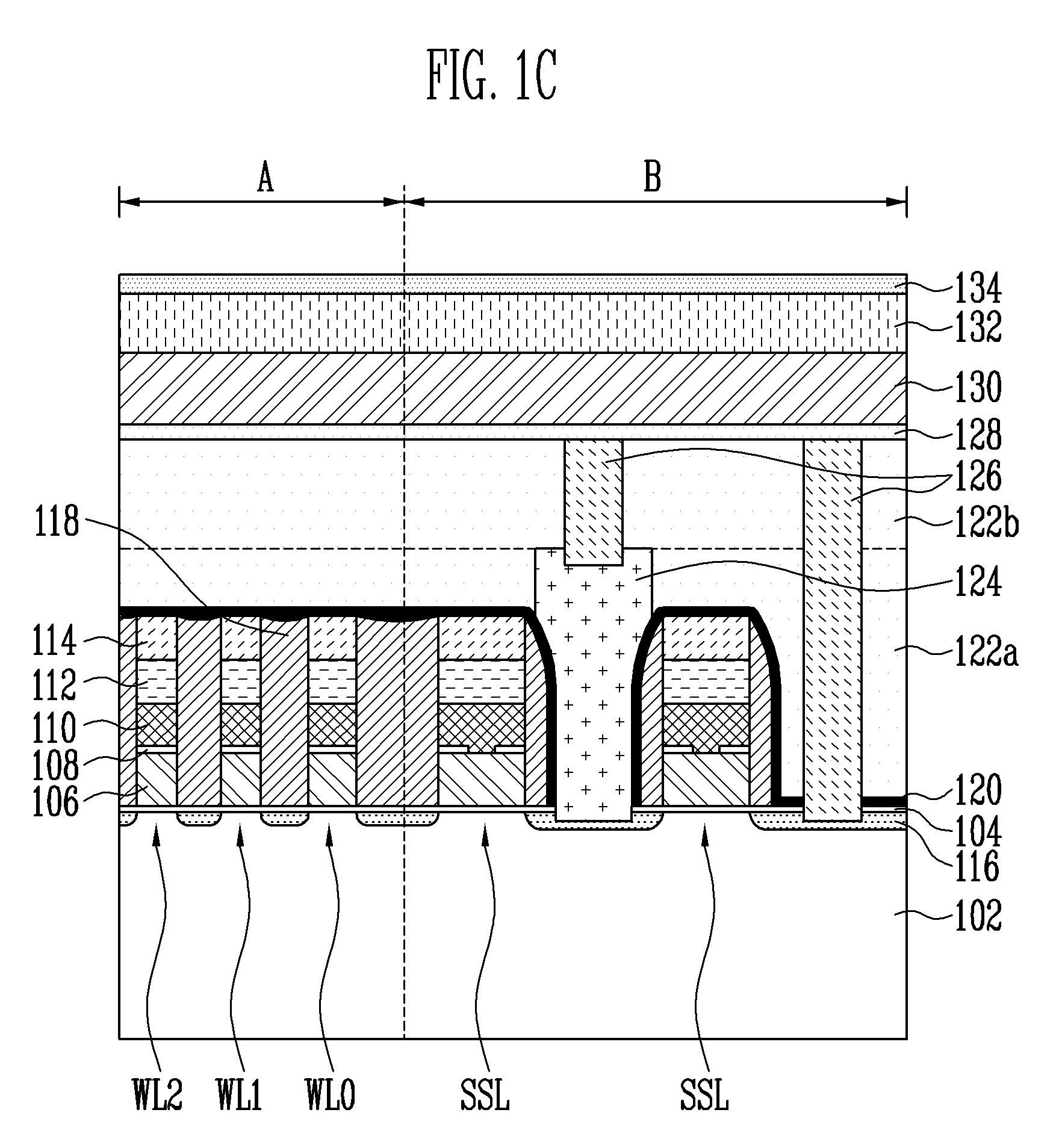

Method of forming semiconductor memory device

ActiveUS20190013321A1Improve RC delaySimple processTransistorSolid-state devicesBit lineChemical reaction

A method of forming semiconductor memory device includes the following steps. Firstly, a substrate is provided and the substrate includes a cell region. Then, plural bit lines are disposed within the cell region along a first direction, with each of the bit line includes a tri-layered spacer structure disposed at two sides thereof. Next, plural of first plugs are formed within the cell region, with the first plugs being disposed at two sides of each bit lines. Furthermore, plural conductive patterns are formed in alignment with each first plugs. Following theses, a chemical reaction process is performed to modify the material of a middle layer of the tri-layered spacer structure, and a heat treatment process is performed then to remove the modified middle layer, thereto form an air gap layer within the tri-layered spacer structure.

Owner:UNITED MICROELECTRONICS CORP +1

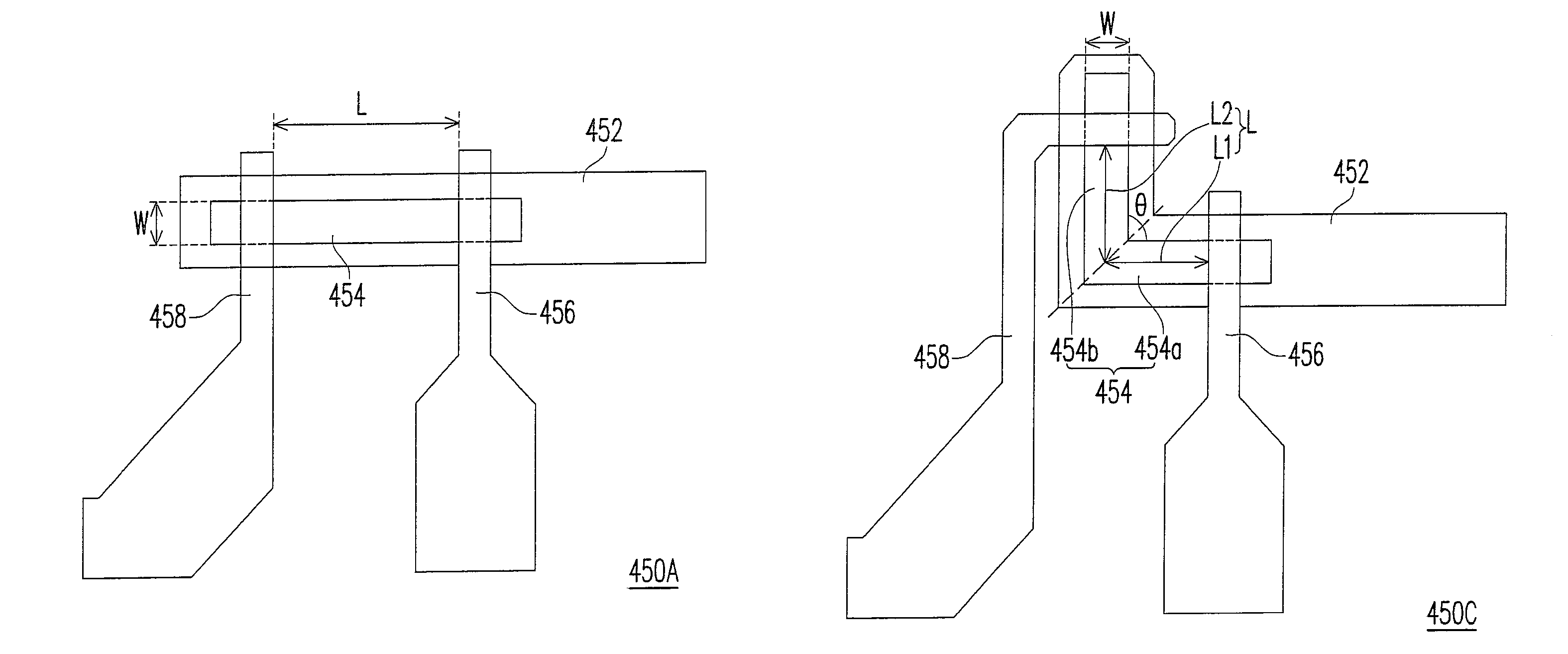

Thin film transistor array substrate and pixel structure with TFT having varying included angle of channel layer

A thin film transistor (TFT) array substrate including a substrate, scan lines and data lines both disposed on the substrate, and pixel structures is provided. A plurality of pixel areas is defined by the scan lines and the data lines on the substrate. Each scan line has a driving signal input terminal and an end terminal. Each pixel area includes a first sub-pixel area and a second sub-pixel area. The pixel structures are respectively disposed in the pixel areas and driven by the scan lines and the data lines. Each pixel structure in the respective pixel area includes a first TFT corresponding to the first sub-pixel area and a second TFT corresponding to the second sub-pixel area. Besides, ratios of a channel width to a channel length of the second TFTs connected to the same scan line increase gradually from the driving signal input terminal to the end terminal.

Owner:AU OPTRONICS CORP

Display device and driving method thereof

ActiveUS9584799B2Increase drive frequencyIncrease production costCathode-ray tube indicatorsSteroscopic systemsDisplay deviceData signal

A method of driving a display device including a plurality of pixels, the method including transmitting a plurality of data signals to first group pixels during a first scan period, simultaneously emitting light through the first group pixels according to a programmed data signal during a first light emitting period adjacent to the first scan period, transmitting a plurality of data signals to second group pixels, different from the first group pixels, during a second scan period, and simultaneously emitting light through the second group pixels according to a programmed data signal during a second light emitting period adjacent to the second scan period. A first field including the first scan period and the first light emitting period and a second field including the second scan period and the second light emitting period are temporally divided.

Owner:SAMSUNG DISPLAY CO LTD

Liquid crystal display and method for manufacturing the same

InactiveUS20160109772A1Reduce weightReduce thicknessTransistorSolid-state devicesLiquid-crystal displayEngineering

A liquid crystal display is presented. The liquid crystal display includes: a gate line and a data line formed on a substrate and extending in directions that are substantially perpendicular to each other; a thin film transistor positioned in a region where the gate line and the data line cross each other; a pixel electrode connected to one terminal of the thin film transistor; a liquid crystal layer filling a plurality of microcavities positioned on the pixel electrode; a common electrode positioned on the liquid crystal layer; a partition wall portion positioned between the plurality of adjacent microcavities; and a roof layer positioned on the common electrode and the partition wall portion and including color filters, in which the partition wall portion is formed of a material having a lower dielectric constant than the roof layer.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor device and method of forming the same

ActiveUS20180211964A1Low dielectric constantStable supportTransistorSolid-state devicesPower semiconductor deviceEngineering

A semiconductor device and method of forming the same, the semiconductor device includes plural bit lines, plural conductive patterns, plural conductive pads and a spacer. The bit lines are disposed on a substrate, along a first direction. The conductive patterns are disposed on the substrate, along the first direction, wherein the conductive patterns and the bit lines are alternately arranged in a second direction perpendicular to the first direction. The conductive pads are arranged in an array and disposed over the conductive patterns and the bit lines. The spacer is disposed between the bit lines and the conductive patterns, under the conductive pads, wherein the spacers includes a tri-layered structure having a first layer, a second layer and a third layer, and the second layer includes a plurality of air gaps separated arranged along the first direction.

Owner:UNITED MICROELECTRONICS CORP +1

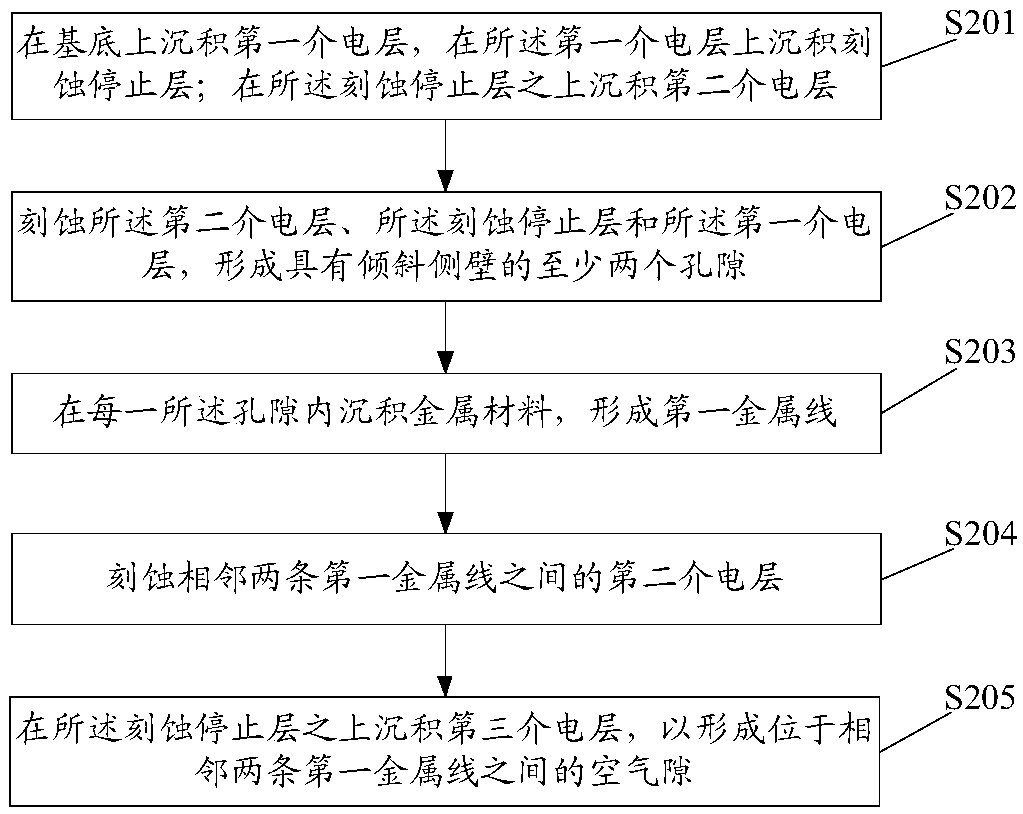

Forming method of semiconductor device and semiconductor device

InactiveCN109585363AImprove RC delaySemiconductor/solid-state device detailsSolid-state devicesDielectric layerSemiconductor

The embodiment of the invention discloses a forming method of a semiconductor device and a semiconductor device. The method comprises steps: depositing a first dielectric layer on a substrate, and depositing an etching stop layer on the first dielectric layer; depositing a second dielectric layer on the etching stop layer; etching the second dielectric layer, the etching stop layer and the first dielectric layer to form at least two pores with inclined side walls; depositing a metal material in each hole to form a first metal line; Etching the second dielectric layer between two adjacent firstmetal wires; a third dielectric layer is deposited over the etch stop layer to form an air gap between two adjacent first metal lines.

Owner:YANGTZE MEMORY TECH CO LTD

Method of forming semiconductor device

ActiveUS20210043684A1Improve RC delayImprove the possible collapse issuesTransistorSolid-state devicesBit lineDevice material

A semiconductor device and method of forming the same, the semiconductor device includes plural bit lines, plural conductive patterns, plural conductive pads and a spacer. The bit lines are disposed on a substrate, along a first direction. The conductive patterns are disposed on the substrate, along the first direction, wherein the conductive patterns and the bit lines are alternately arranged in a second direction perpendicular to the first direction. The conductive pads are arranged in an array and disposed over the conductive patterns and the bit lines. The spacer is disposed between the bit lines and the conductive patterns, under the conductive pads, wherein the spacers includes a tri-layered structure having a first layer, a second layer and a third layer, and the second layer includes a plurality of air gaps separated arranged along the first direction.

Owner:UNITED MICROELECTRONICS CORP +1

Touch panel and display apparatus including the same

ActiveUS20180188859A1Reduce resistanceImprove RC delayCathode-ray tube indicatorsInput/output processes for data processingEngineeringTouch panel

A touch panel including a substrate, first touch electrodes, each of the first touch electrodes including first mesh patterns disposed on the substrate, an insulation layer disposed on the first touch electrodes, second touch electrodes, each of the second touch electrodes including second mesh patterns disposed on the insulation layer, first auxiliary mesh electrodes disposed on the substrate, the first auxiliary mesh electrodes being electrically connected to at least a portion of the corresponding second mesh patterns, and second auxiliary mesh electrodes disposed on the insulation layer, the second auxiliary mesh electrodes being electrically connected to at least a portion of the corresponding first mesh patterns.

Owner:SAMSUNG DISPLAY CO LTD

Display device and manufacturing method thereof

ActiveUS10504467B2Reduce resistanceUndesirable delayTransistorStatic indicating devicesDisplay deviceEngineering

A display device including a substrate, a gate driver disposed on the substrate and including a plurality of stages, a clock signal line disposed on the substrate, and transmitting a clock signal to at least one of the stages, a transistor disposed on the substrate, and a light blocking layer disposed between the substrate and the transistor and overlapping the transistor. The clock signal line includes a first conductive line and a second conductive line overlapping the first conductive line, and the first conductive line is disposed in the same layer as the light blocking layer.

Owner:SAMSUNG DISPLAY CO LTD

Method of forming damascene patterns of semiconductor devices

ActiveUS7759232B2Deep unityMinimize changesTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

A method of forming damascene patterns of semiconductor devices comprise forming a first insulating layer and contact plugs, formed in the first insulating layer, over a semiconductor substrate, forming an etch barrier layer and a second insulating layer over the first insulating layer, forming damascene patterns in the second insulating layer, forming a mask layer over the second insulating layer of other region except a region in which the contact plugs are formed so that the damascene patterns are exposed through the region in which the contact plugs are formed, removing the etch barrier layer under the exposed damascene patterns using an etching process employing the mask layer, and removing the mask layer.

Owner:SK HYNIX INC

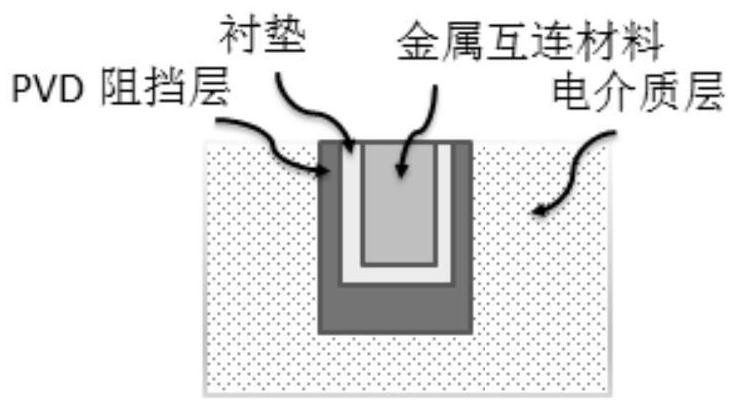

Barrier layer for interconnection structure and preparation method thereof

PendingCN113675171AImprove adhesionImprove high impedance problemSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectHemt circuits

The invention discloses a barrier layer for an interconnection structure. The barrier layer is arranged between a metal interconnection material and a dielectric layer of an interconnection structure, and comprises a first barrier layer and a second barrier layer, wherein the first barrier layer surrounds the outer layer of the metal interconnection material, and the second barrier layer surrounds the outer side of the first barrier layer. The barrier layer provided by the invention comprises the two barrier layers formed by atomic layer precipitation, the two barrier layers are made of different materials, and the adhesive force between the original barrier layer and the metal interconnection material can be improved by utilizing the material with stable metal performance and good adhesive force, so that the problems that an existing single barrier layer is poor in performance and high impedance is caused by double barrier layers formed by ALD and PVD can be solved so as to reduce the heat from the interconnection current to the damage of the integrated circuit, improve the RC delay of the IC circuit is improved and improve the yield of IC production.

Owner:广东汉岂工业技术研发有限公司

Method for fabricating low-k dielectric and Cu interconnect

InactiveUS7998873B2Improve performanceReduce carbon consumptionSemiconductor/solid-state device manufacturingDelayed timeIntegrated circuit

Owner:TAIWAN SEMICON MFG CO LTD