Method for selectively depositing diffusion barrier for copper interconnection

A technology for depositing copper and barrier layers, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of increasing circuit RC interconnection delay, contact resistance and interconnection resistance increase, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

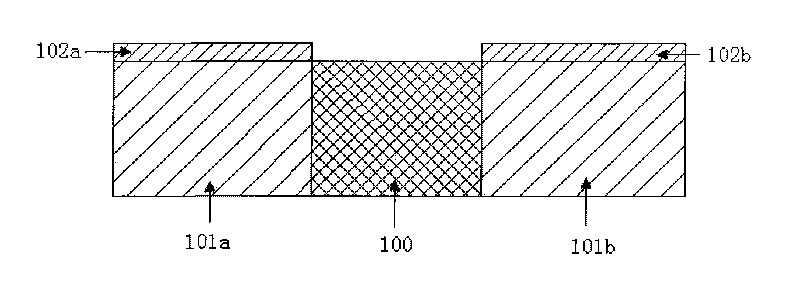

[0028] Step 1: Please refer to figure 1 , providing an integrated circuit substrate in which a certain level of wiring of an interconnection structure has been completed, the material 100 is copper, the materials 101a and 101b are low dielectric constant dielectrics, and the materials 102a and 102b are silicon nitride or other etching barrier materials .

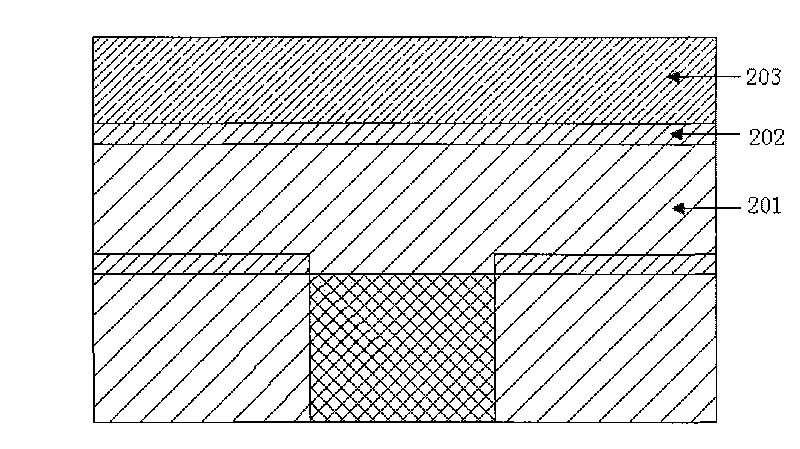

[0029] Step 2: Please refer to figure 2 A thin film 201, a thin film 202 and a thin film 203 are sequentially formed on the provided substrate, the thin film 201 is a low dielectric constant medium, the thin film 202 is silicon nitride or other etching barrier materials, and the thin film 203 is a photoresist layer.

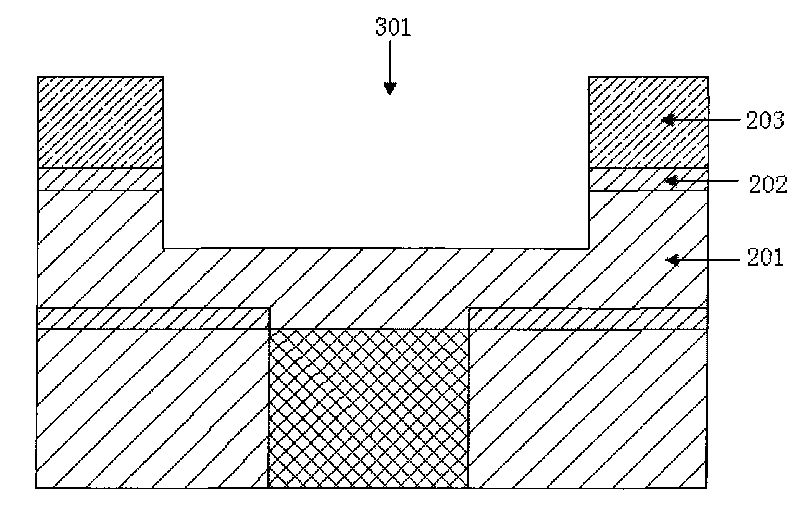

[0030] Step 3: Please refer to image 3 , after determining the position of the interconnect groove, an opening 301 is formed in the film 203 , the film 202 and the film 201 ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More