Patents

Literature

152 results about "Ic production" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

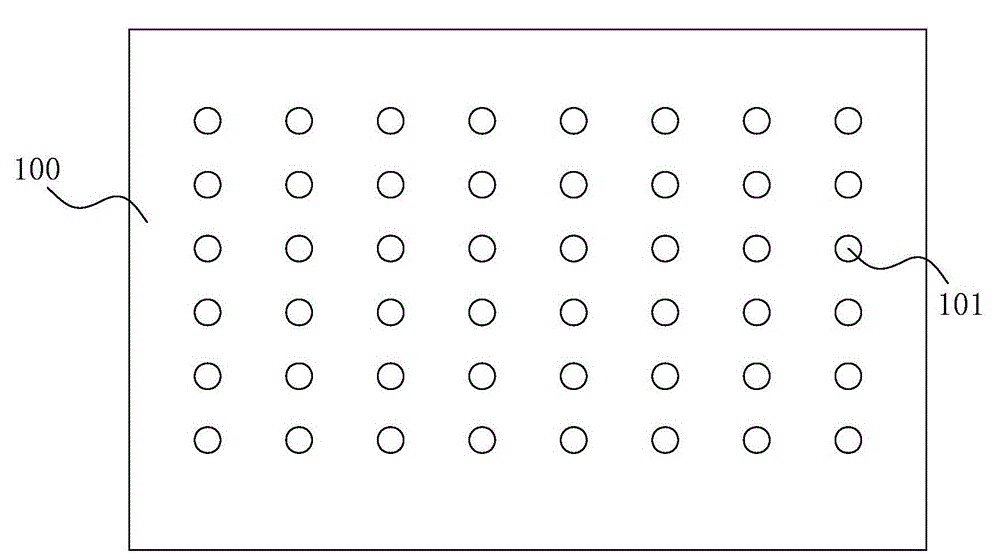

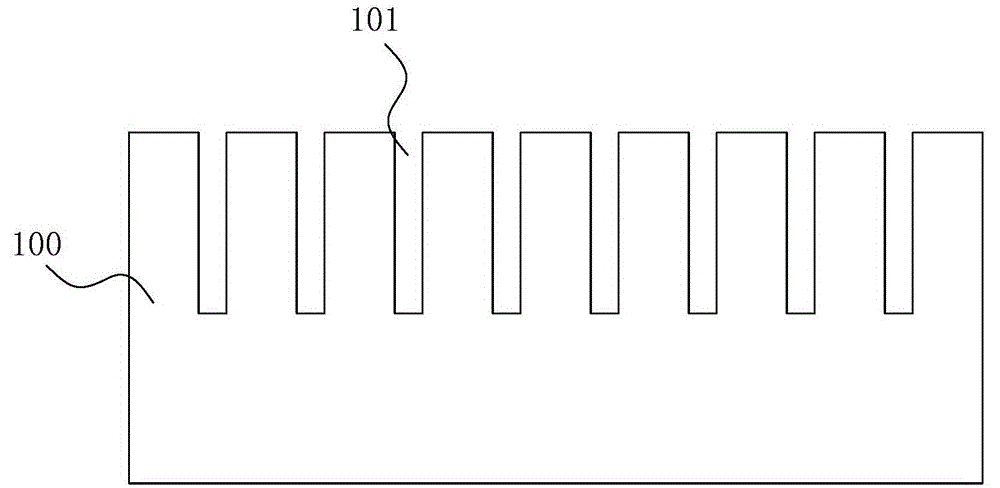

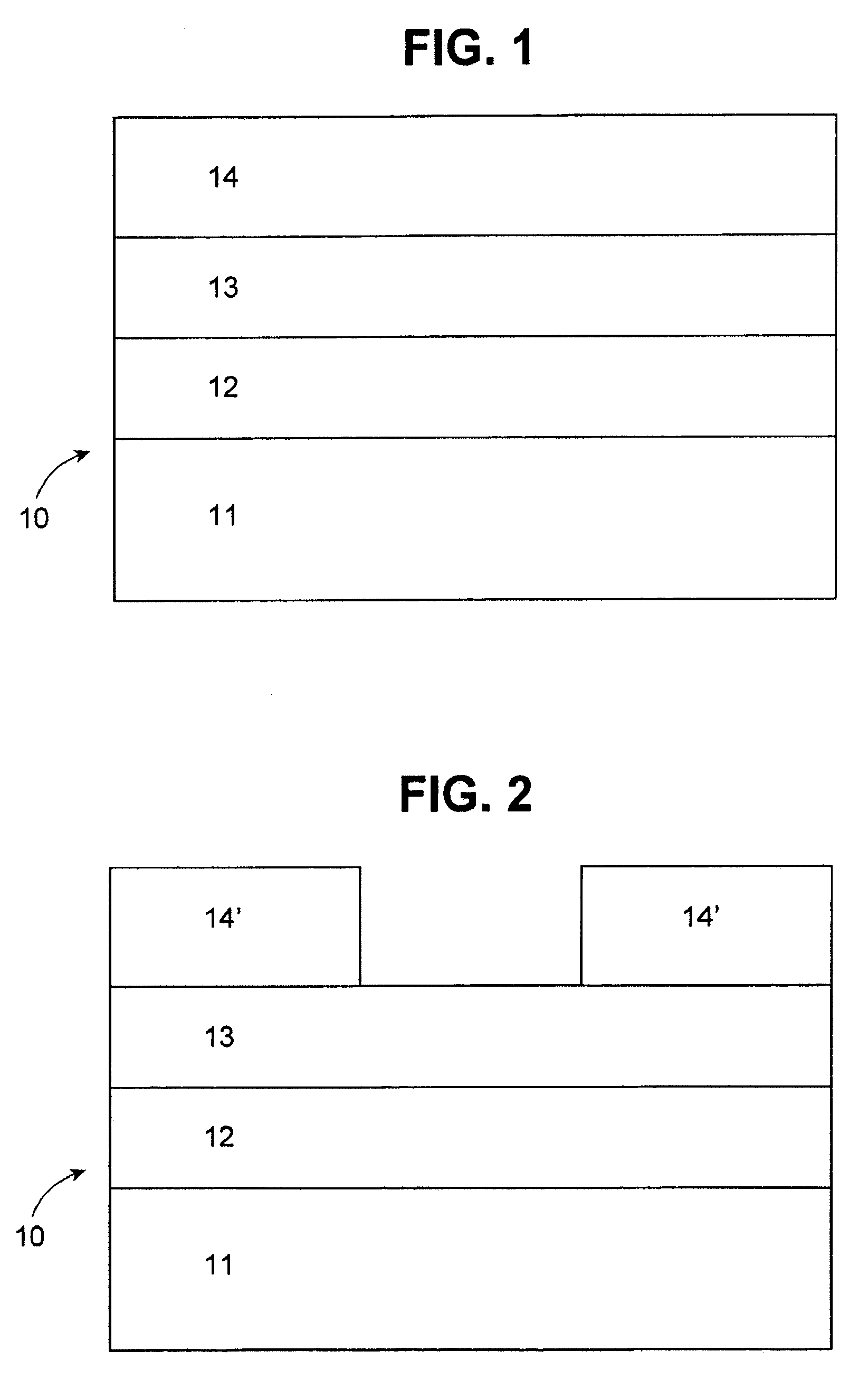

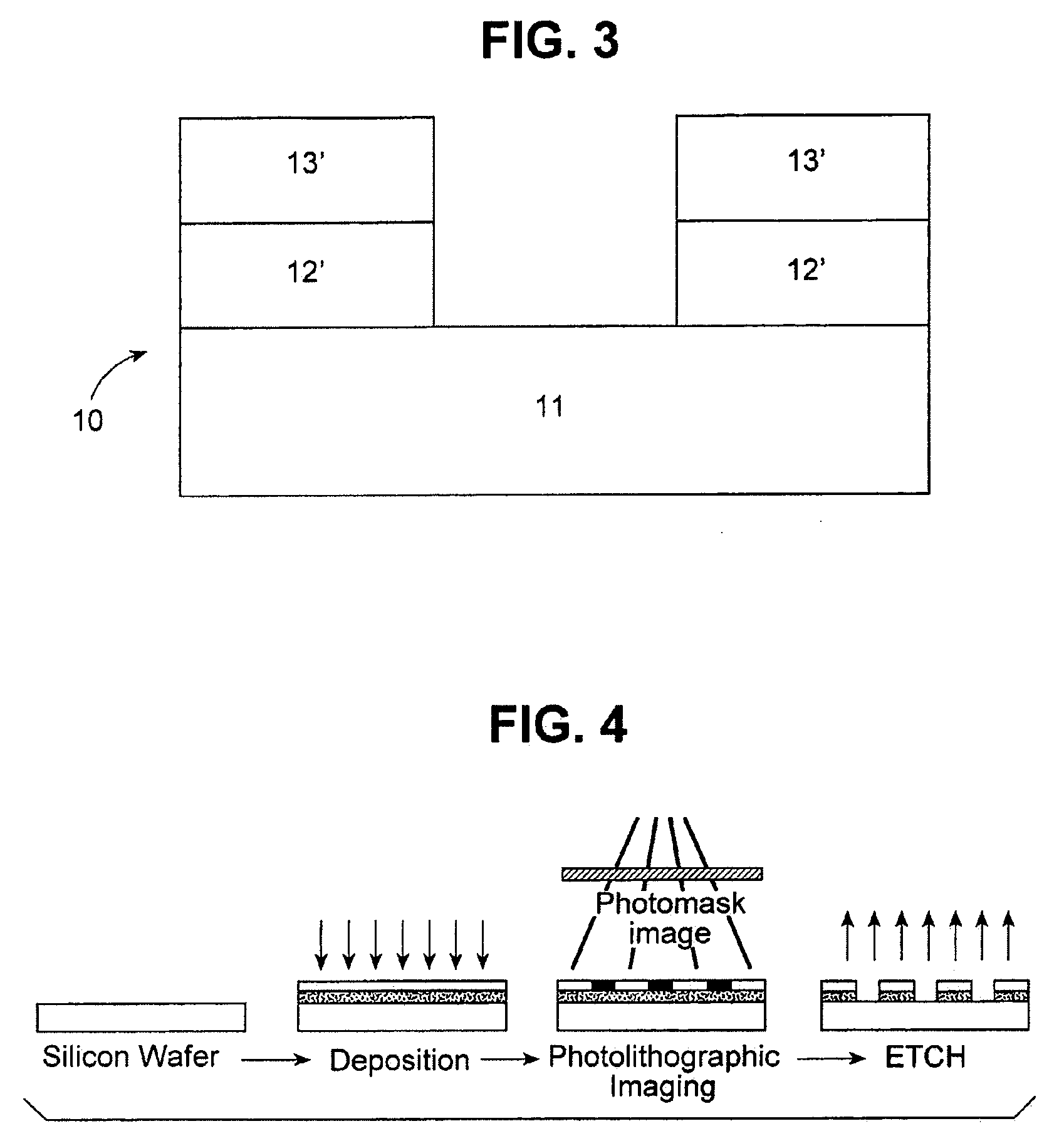

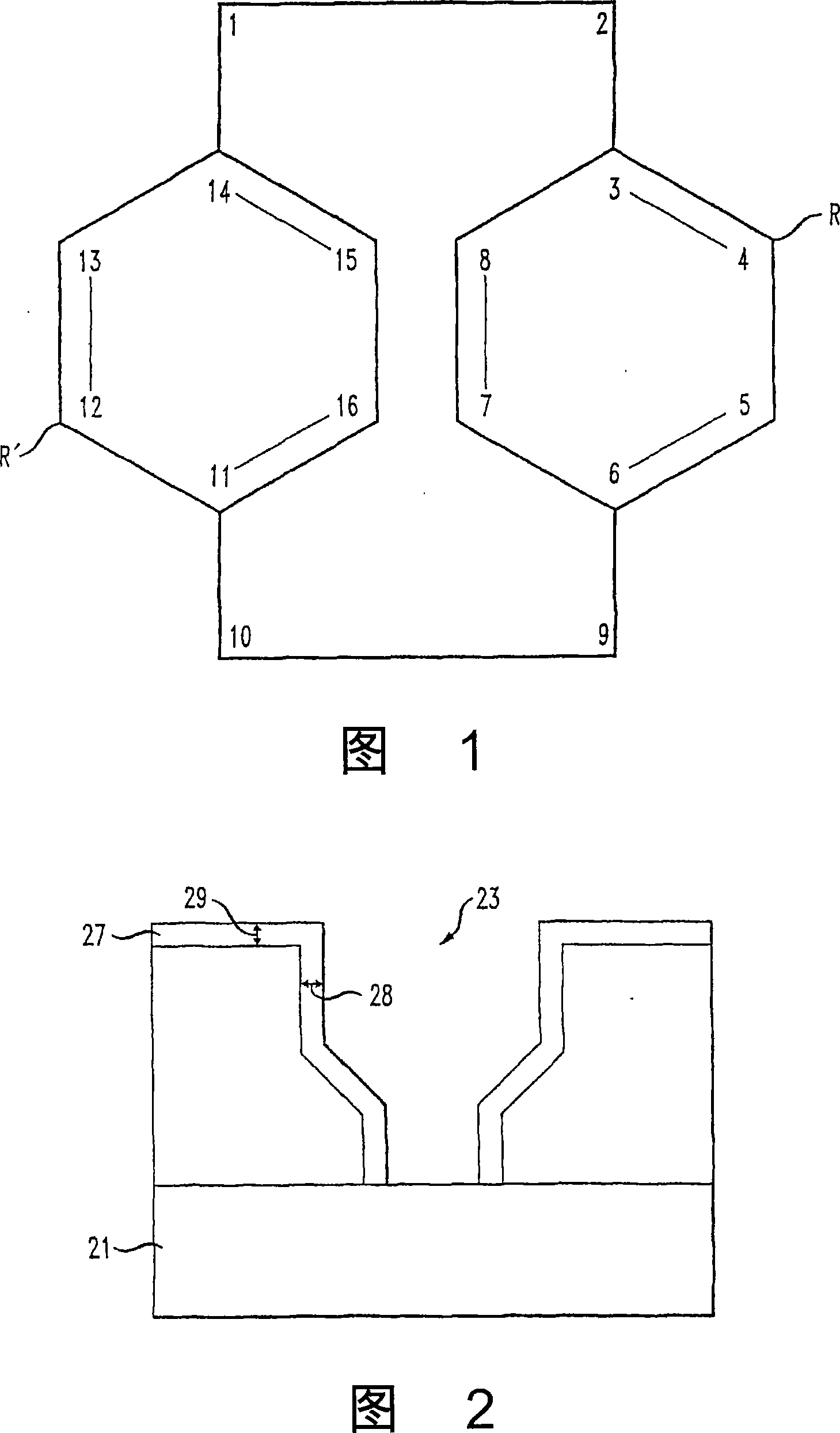

Method of IC production using corrugated substrate

ActiveUS7265008B2Improve performance consistencyImprove performanceLaser detailsSolid-state devicesMOSFETPerformance enhancement

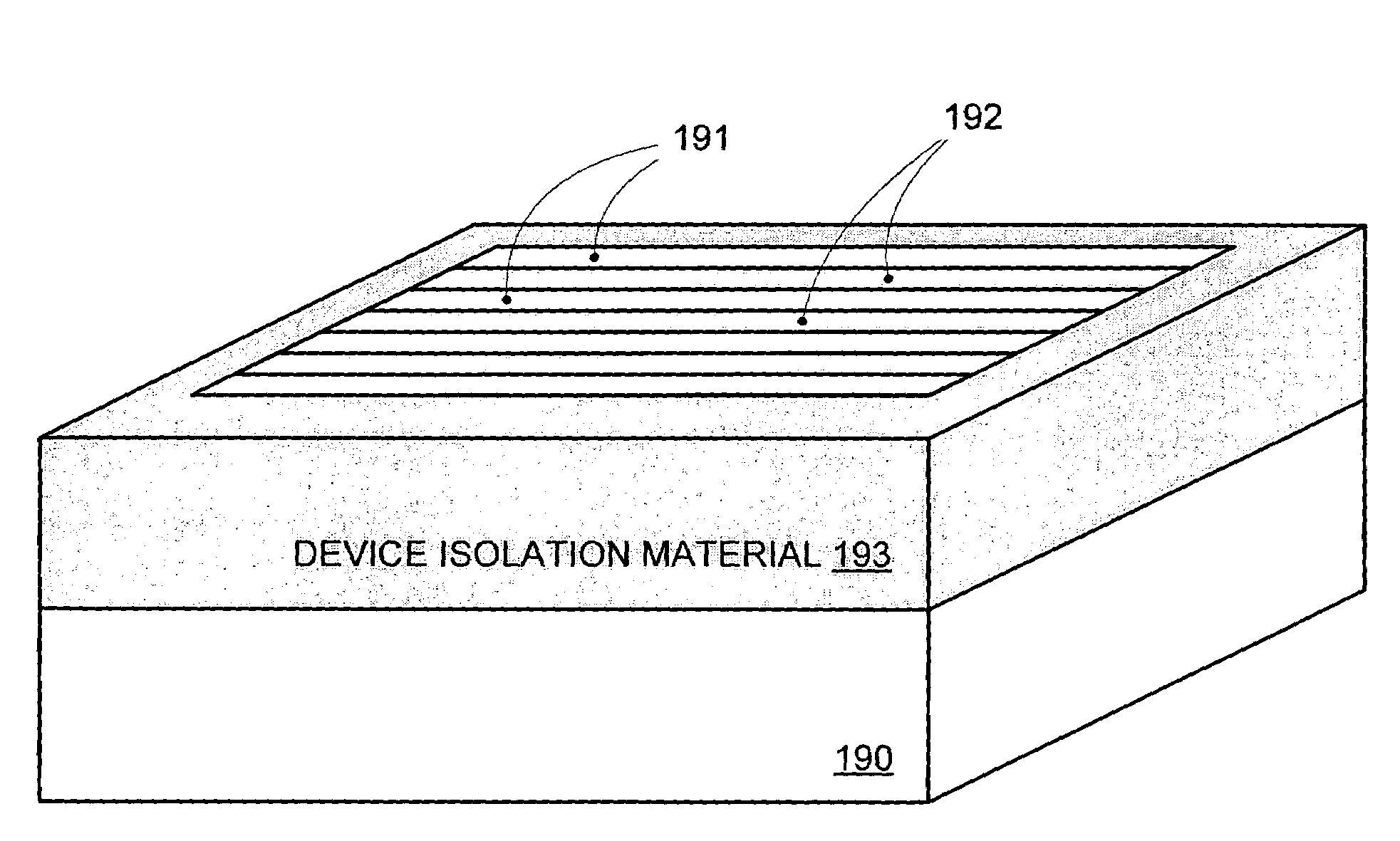

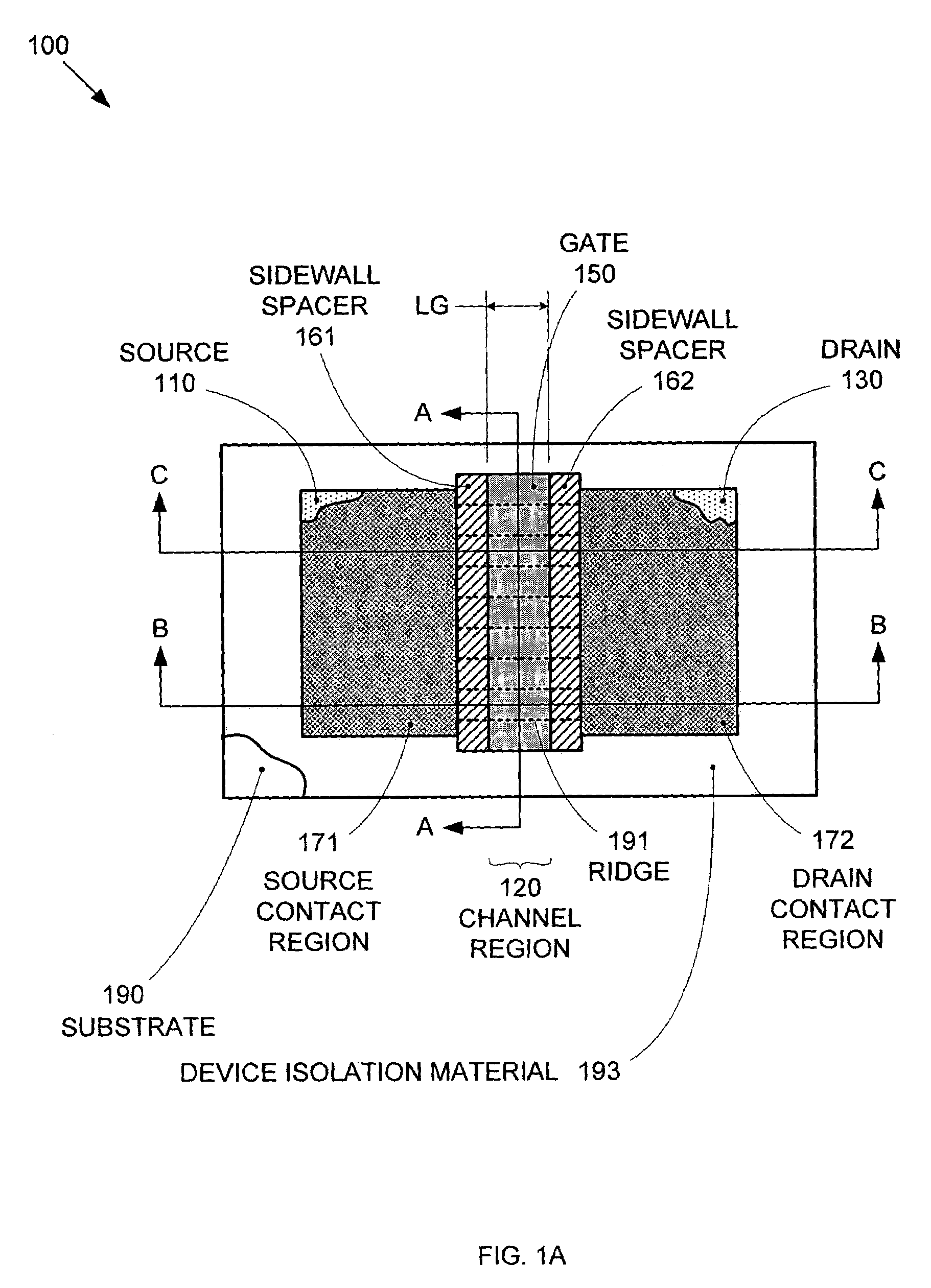

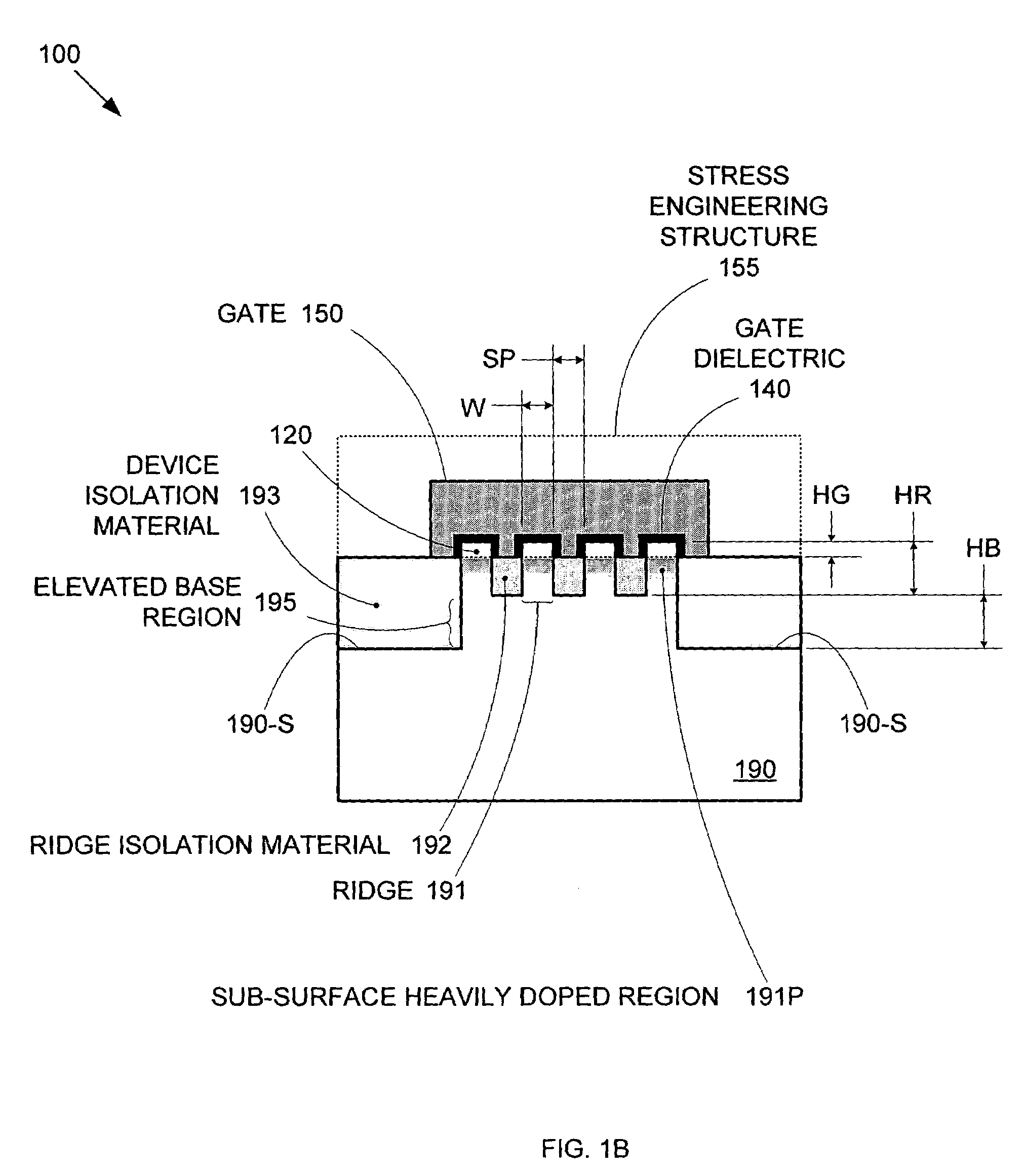

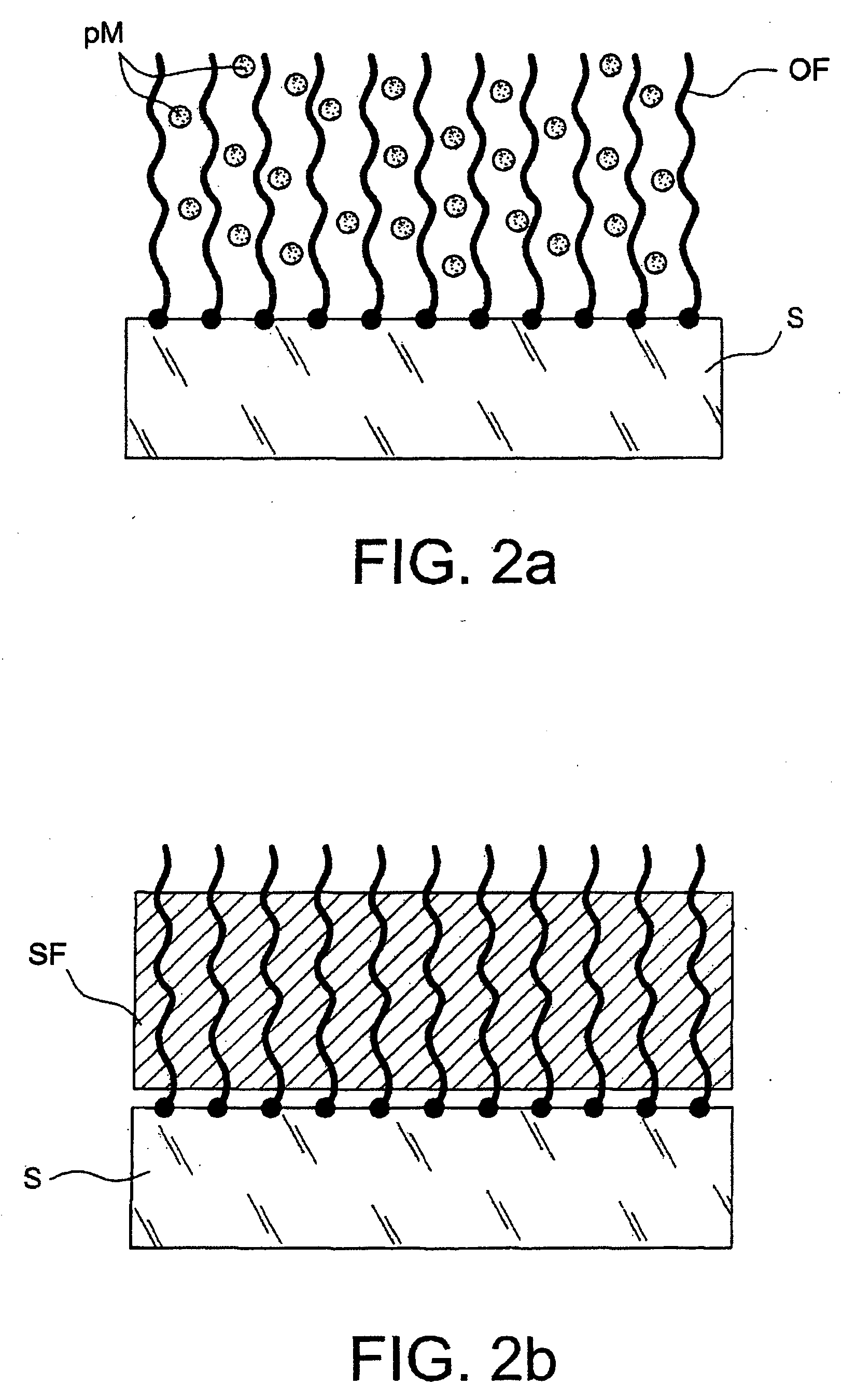

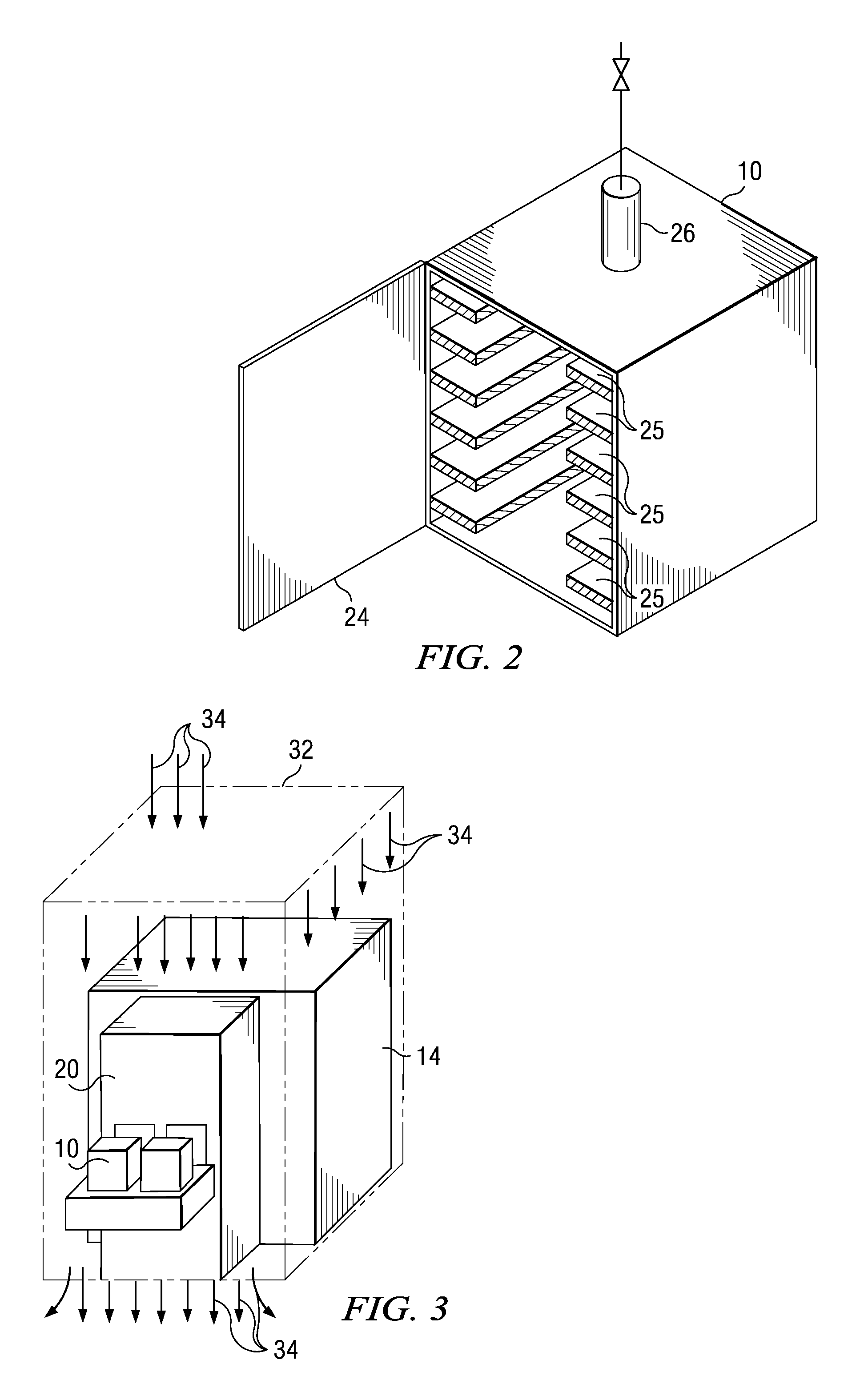

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

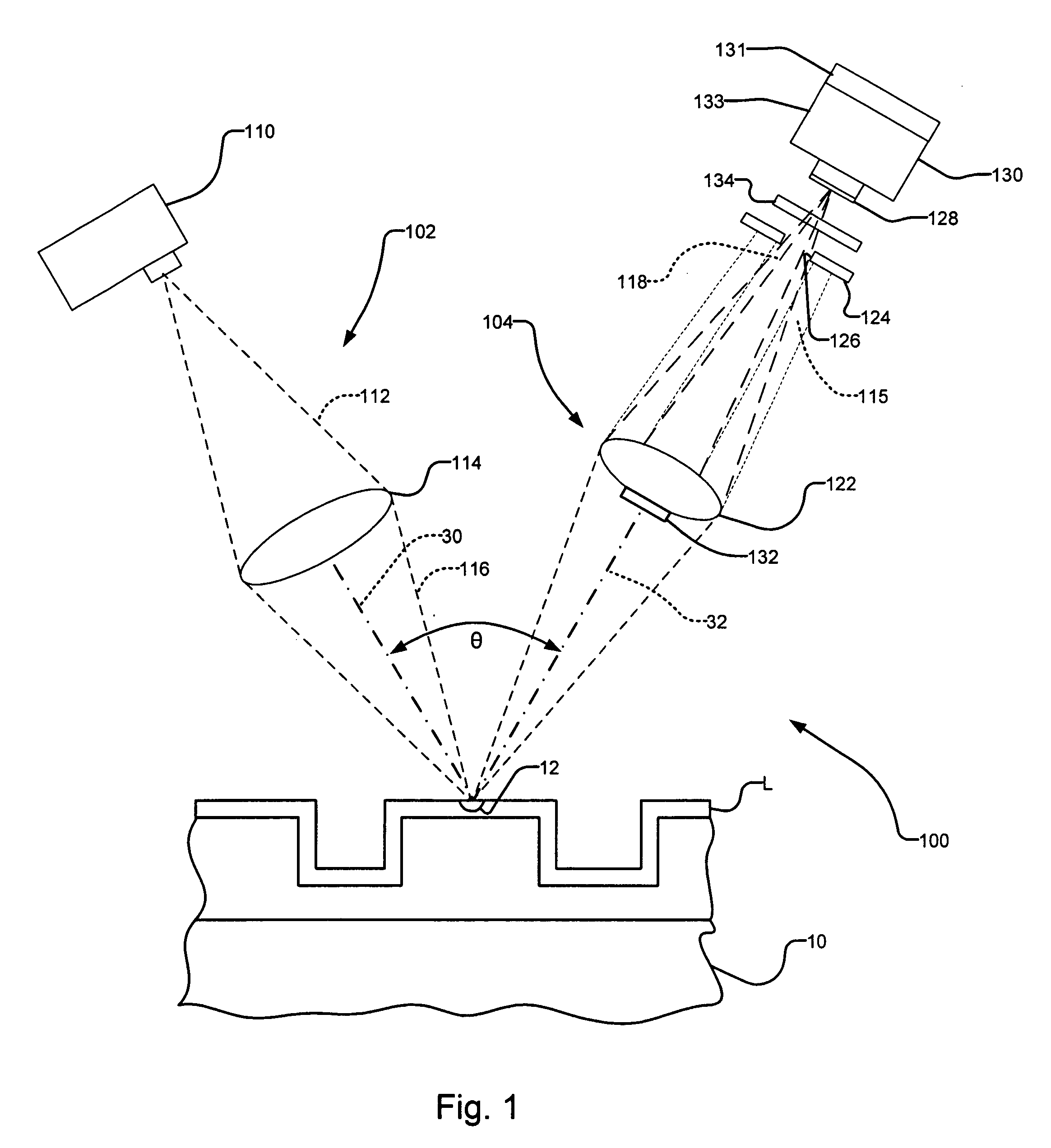

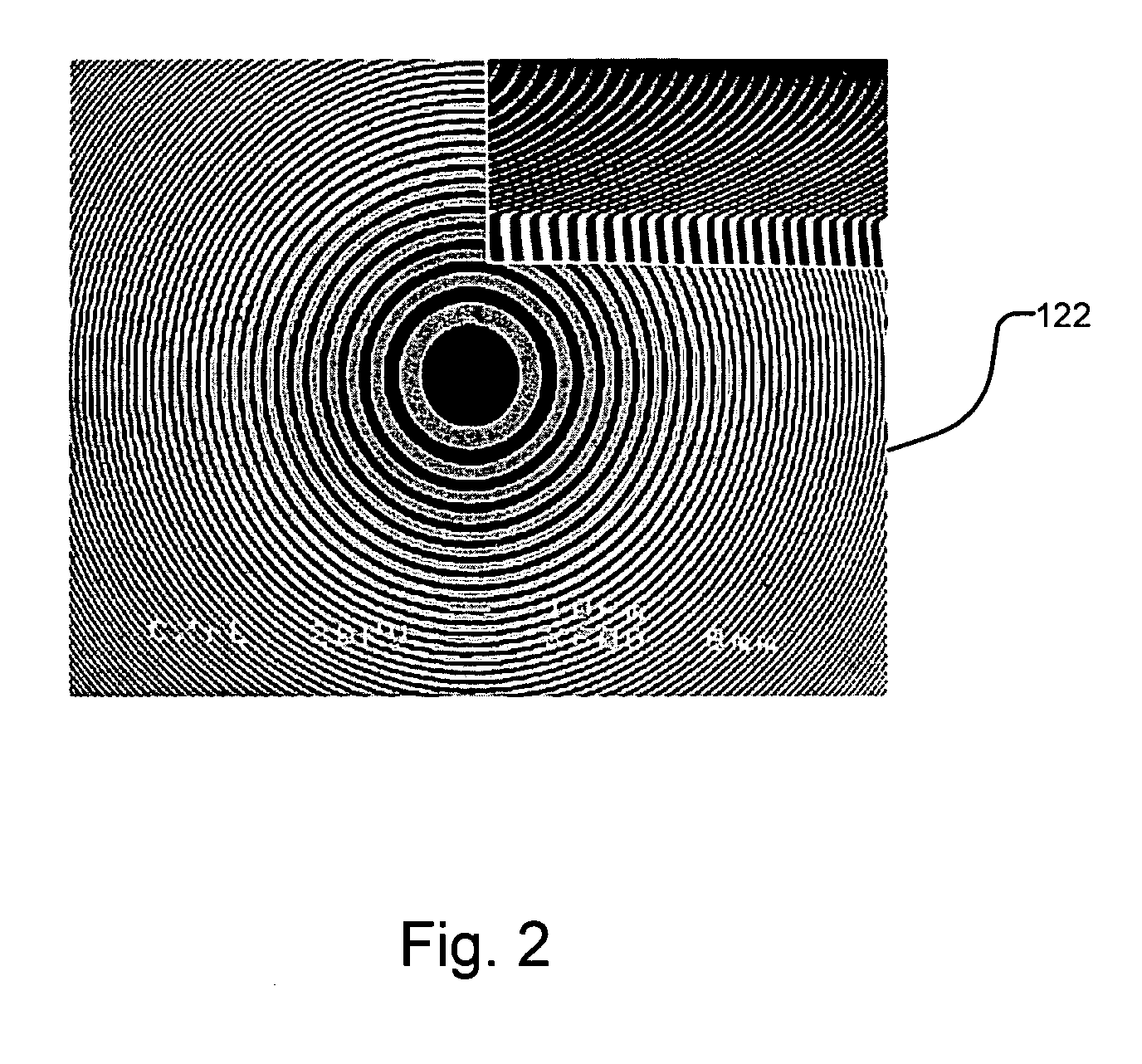

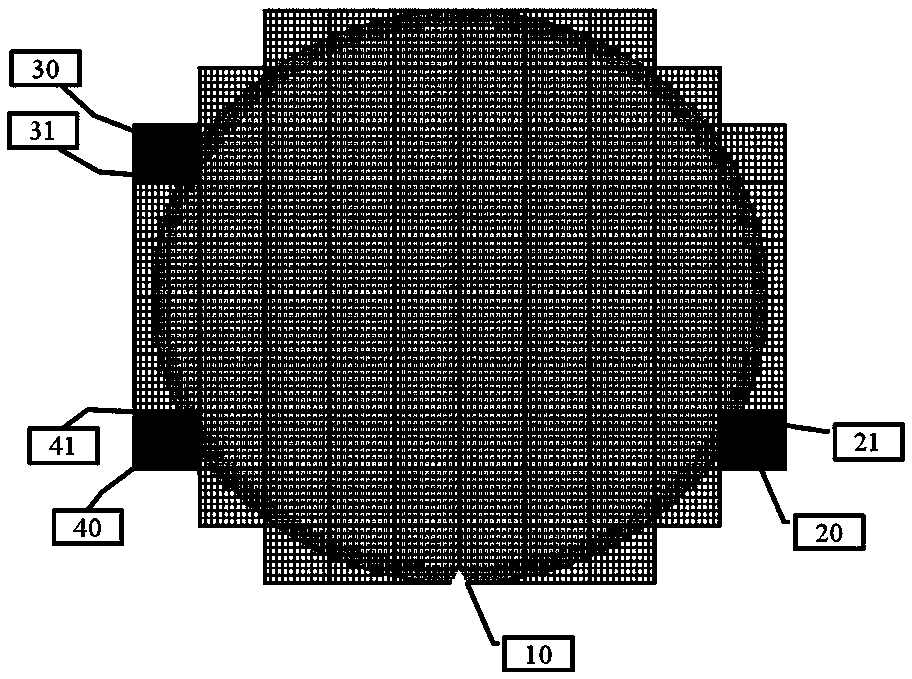

Back-end-of-line metallization inspection and metrology microscopy system and method using x-ray fluorescence

InactiveUS20050282300A1Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementCopper interconnectMetrology

Systems and methods for performing inspection and metrology operations on metallization processes such as on back-end-of-line (BEOL) metallization thickness and step coverage are disclosed. Specific examples include measurements of thickness and uniformity of barrier layers, including tantalum for example, and seed layers, including copper for example, in Damascene, including dual-Damascene, trenches during the interconnect fabrication steps of integrated circuit production. The invention also relates to the detection and measurement of void formation during and after copper electroplating. The invention utilizes x-ray fluorescence to measure the absolute thicknesses and the thickness uniformity of the barrier layers in the trenches, the copper seed layers for electroplating, and the final copper interconnects.

Owner:XRADIA

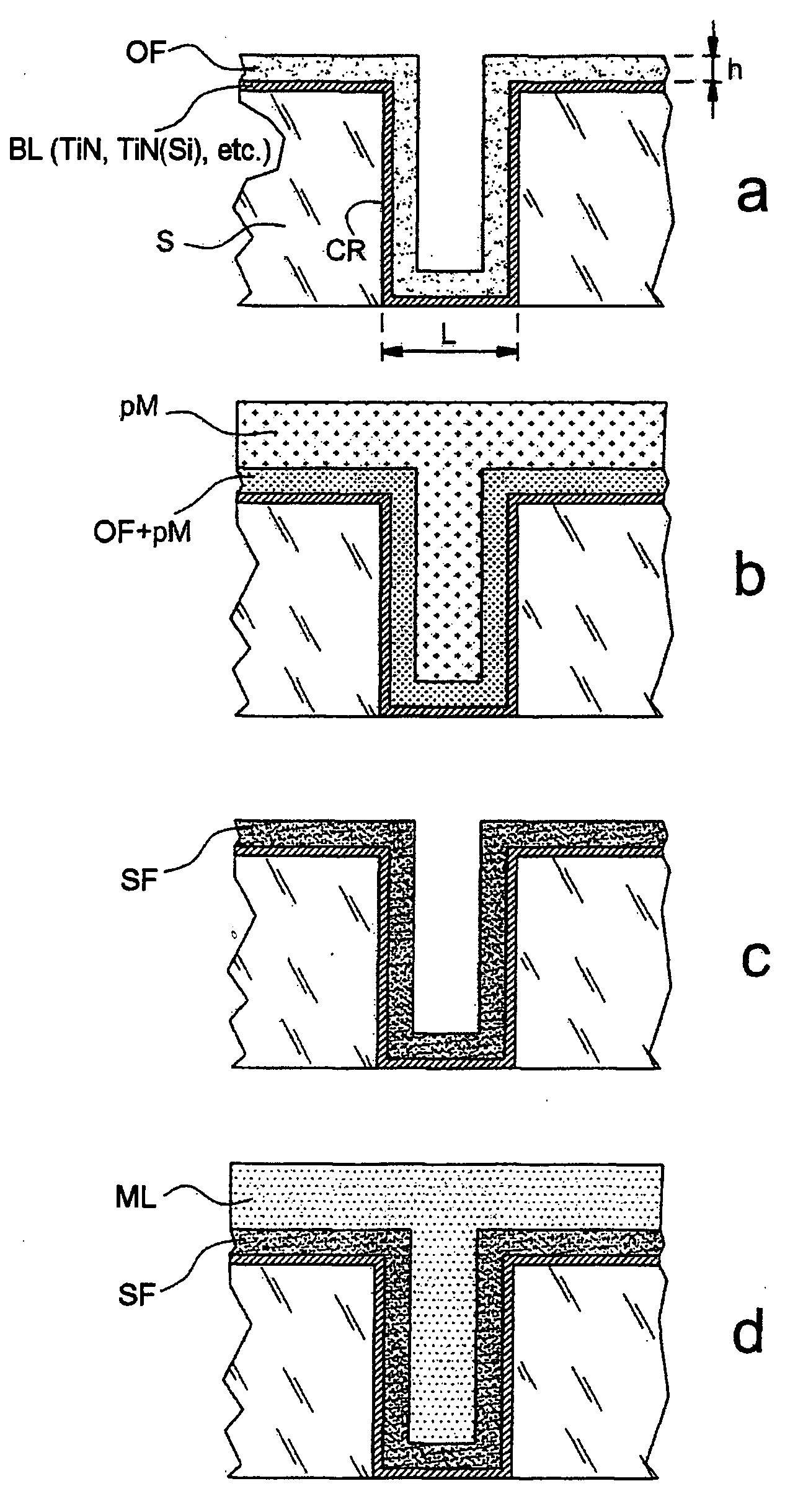

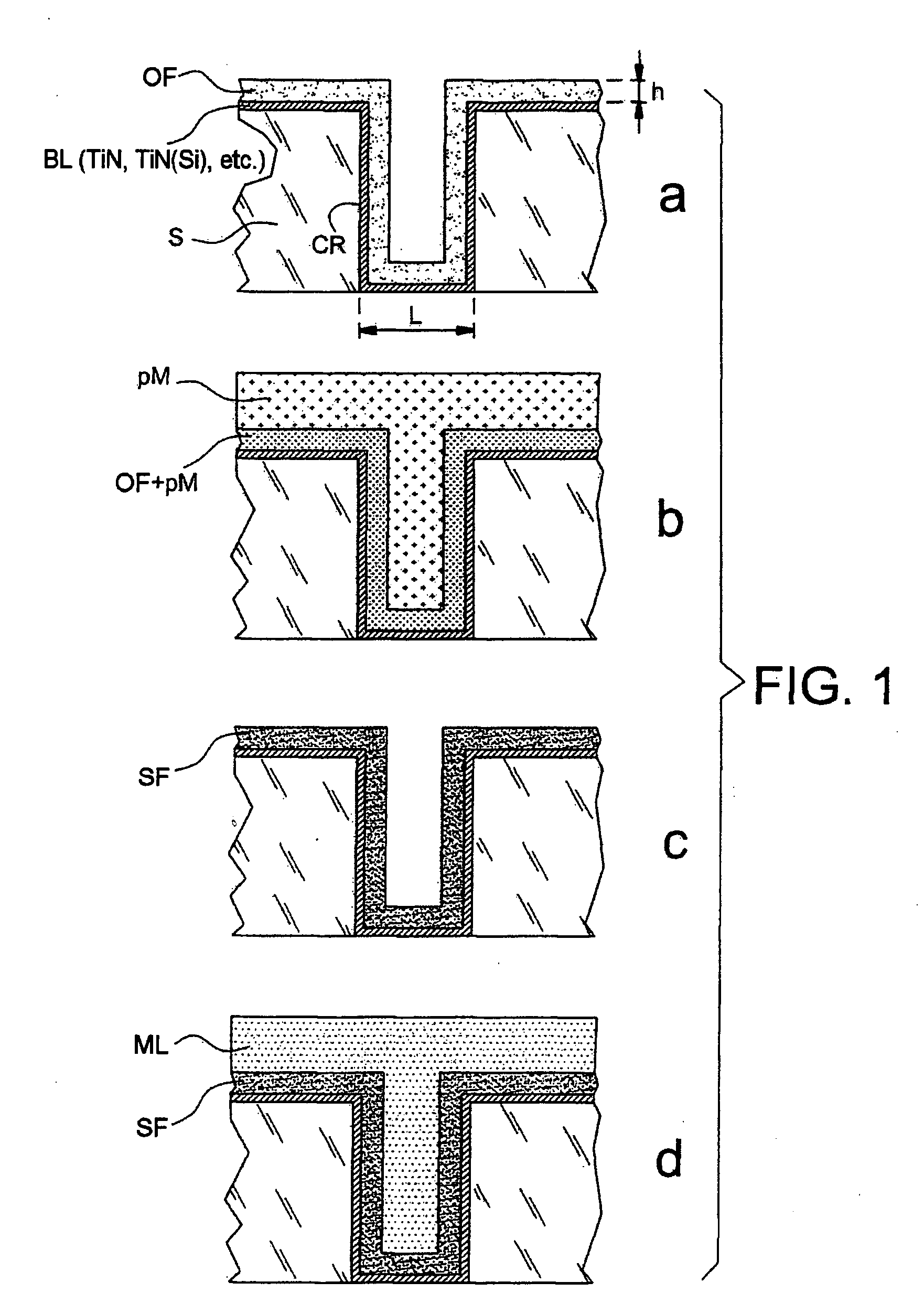

Surface-coating method, production of microelectronic interconnections using said method and integrated circuits

InactiveUS20060211236A1Overcome irregularitiesFacilitated releaseSemiconductor/solid-state device manufacturingLiquid/solution decomposition chemical coatingOrganic filmMetallic materials

The present invention relates to a process for coating a surface of a substrate with a seed film of a metallic material, the said surface being an electrically conductive or semiconductive surface and having recesses and / or projections. The process comprises the following: an organic film is placed on the said surface, the said film having a thickness such that the free face of this film conformally follows the recesses and / or projections of the said electrically conductive or semiconductive surface on which it is placed; a precursor of the metallic material is inserted within the said organic film placed on the said surface at the same time as, or after, the step consisting in placing the said organic film on the said surface; and the said precursor of the metallic material inserted within the said organic film is converted into the said metallic material. This process allows integrated circuits, interconnects in microelectronics and microsystems to be fabricated.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

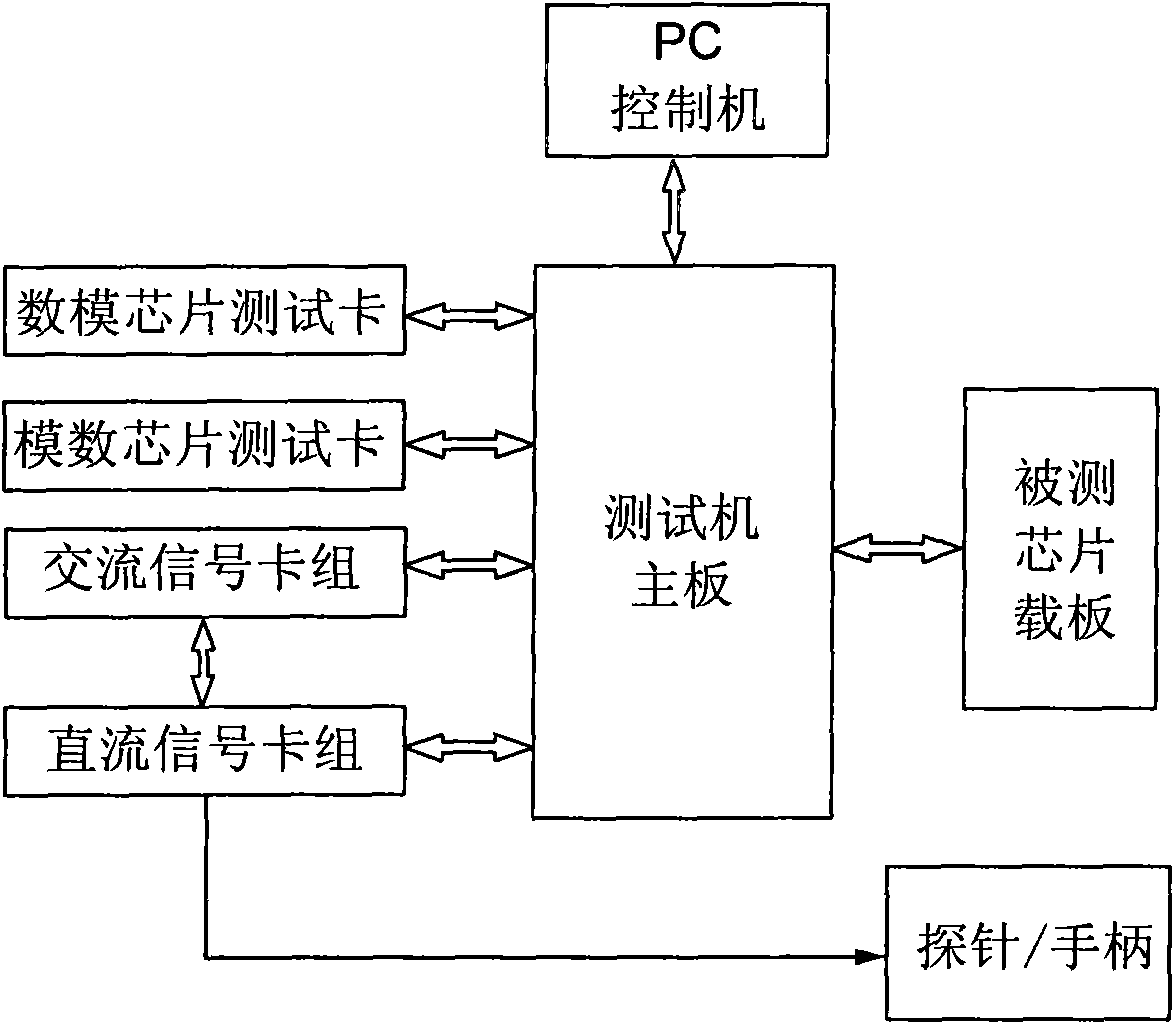

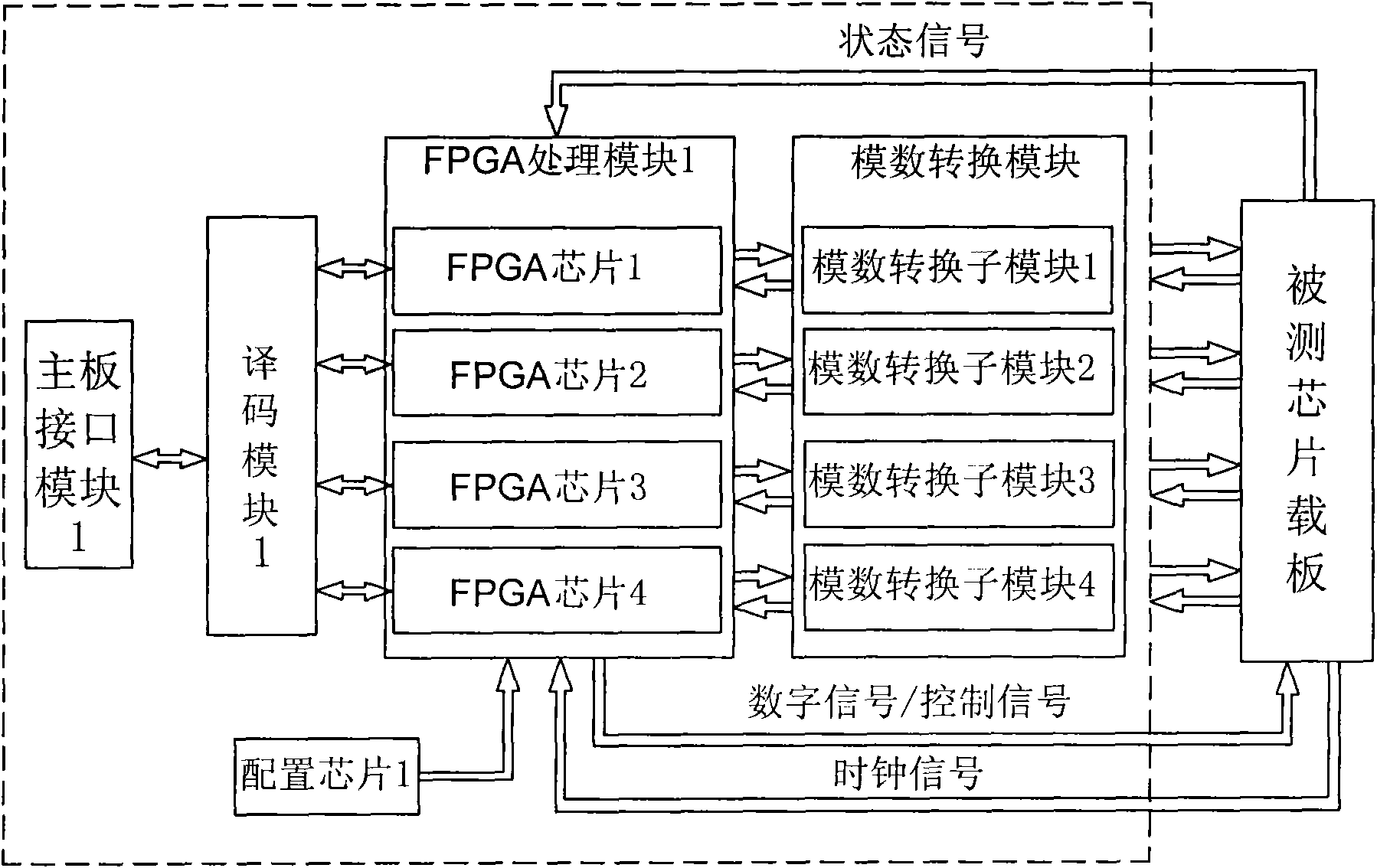

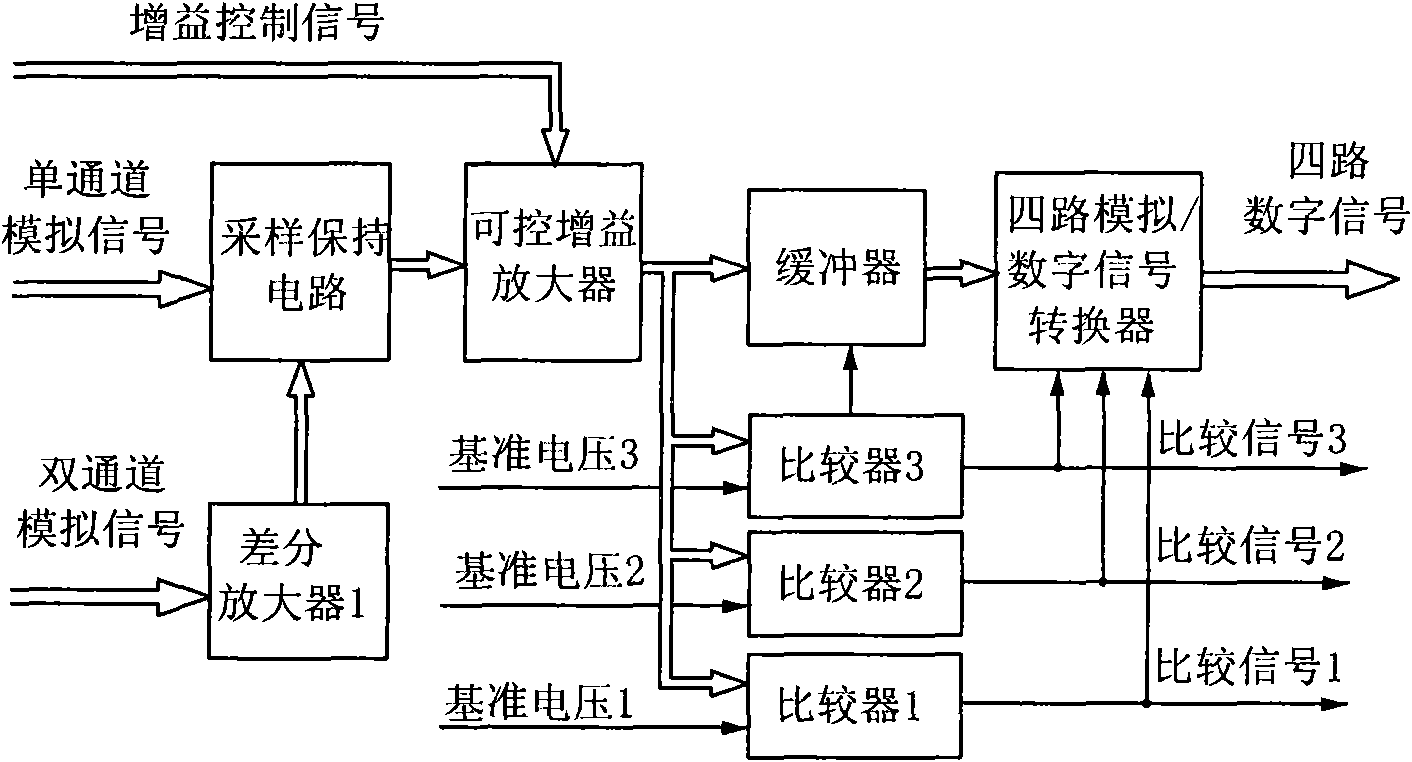

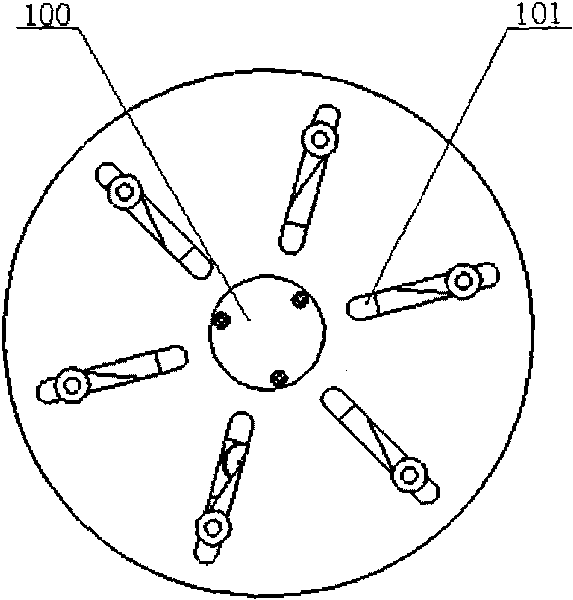

Multi-functional integrated circuit chip testing machine

ActiveCN101587167AExpand the scope of testingAdd test functionElectronic circuit testingAnalog chipIc production

The present invention relates to a multi-functional integrated circuit chip testing machine which comprises the following components: a casing, an inner testing machine mainboard, an AC signal card group and a DC signal card group. The AC signal card group and the DC signal card group are connected with each other and are respectively installed on the testing machine mainboard. The testing machine mainboard is respectively connected with a PC controlled and a tested chip carrier plate. The multi-functional integrated circuit chip testing machine is technically characterized in that the testing machine mainboard is also installed with a digital / analog chip testing card and an analog / digital chip testing card. The multi-functional integrated circuit chip testing machine of the invention is reasonably designed, realizes the test function to different types of integrated circuit chip, reduced device investment of the integrated circuit manufacturer and saves the operation and maintenance cost of the device. Furthermore the multi-functional integrated circuit chip testing machine of the invention has the characteristics of wide testing range, stable performance, high testing speed, high efficiency, flexible and convenient using, etc.

Owner:天津津能易安泰科技有限公司

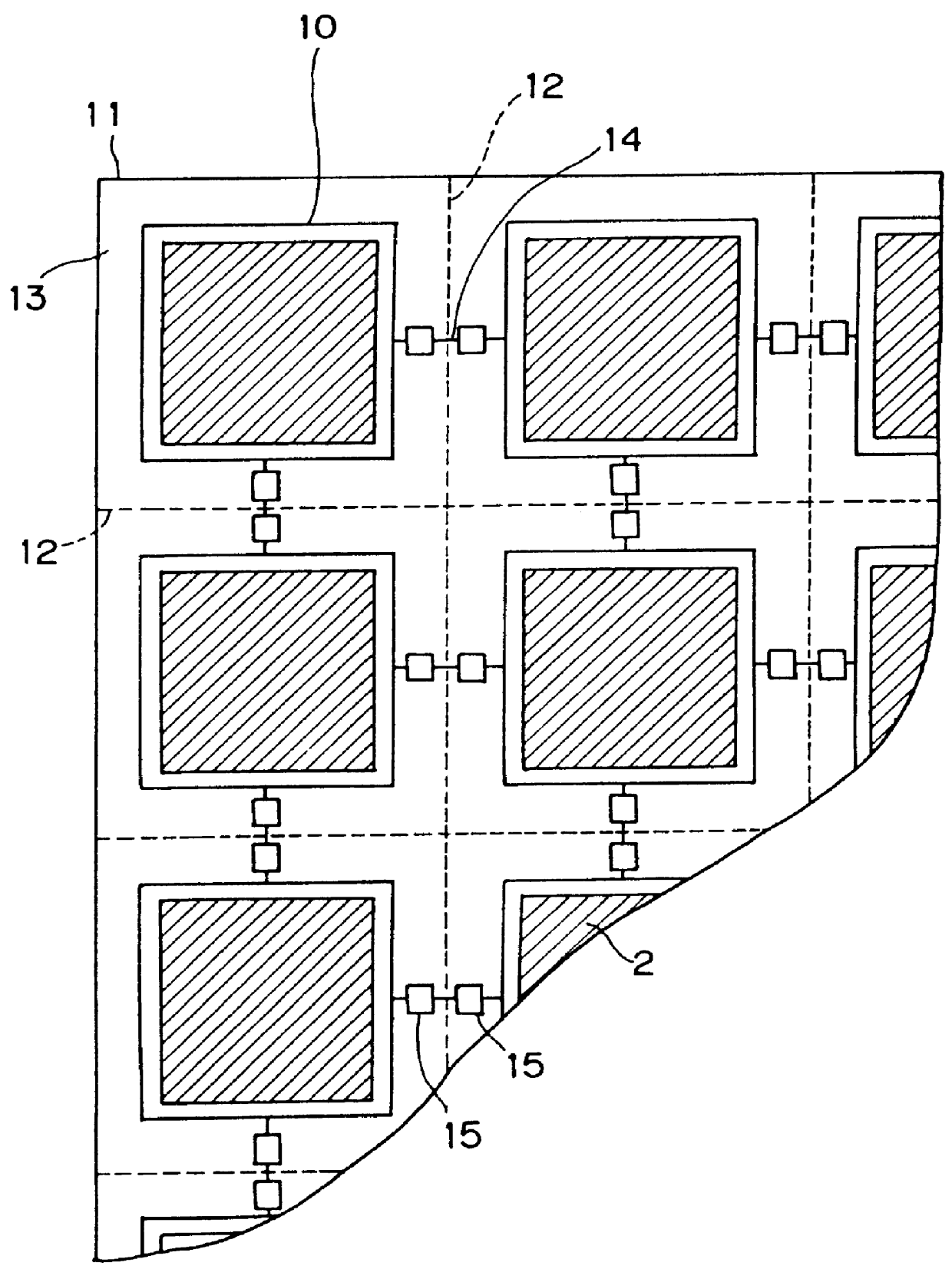

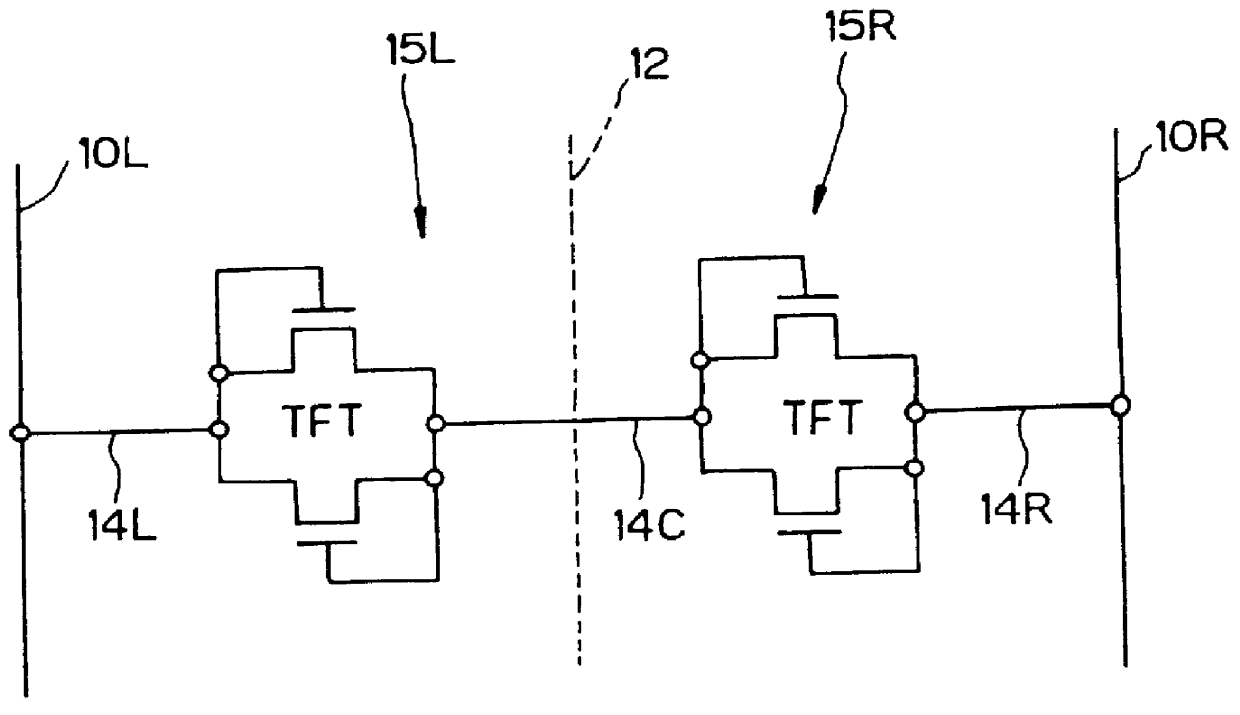

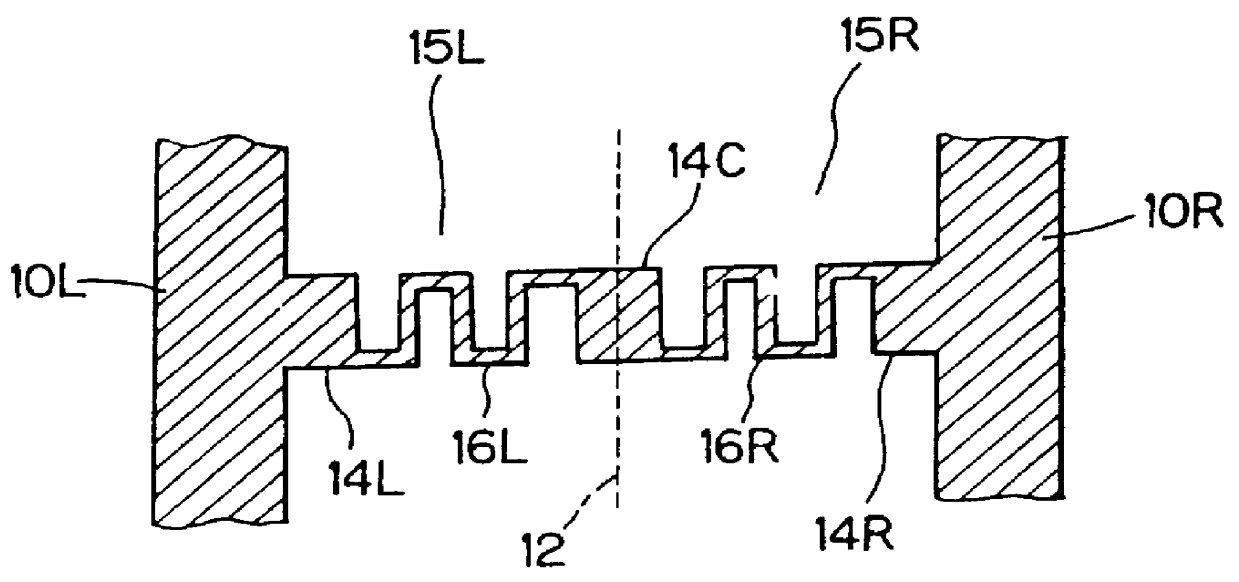

Semiconductor aggregate substrate and semiconductor device with fuse structure to prevent breakdown

Electrostatic breakdown is avoided during fabrication of individual semiconductor devices using a semiconductor aggregate substrate. The semiconductor aggregate substrate is comprised of a large wafer. A plurality of sections are provided on the surface of the wafer, which are divided by division lines. A display active matrix circuit is integrally formed in each of the segments through normal IC production processing. Guard ring patterns are provided so that they surround the individual display active matrix circuits. A connection pattern is also provided for commonly connecting the guard ring patterns adjoining each other through the division lines. The connection pattern has opening structures for dealing with an external overcurrent on both sides of the division lines. The opening structures are constituted by, for example fuse patterns.

Owner:SONY CORP

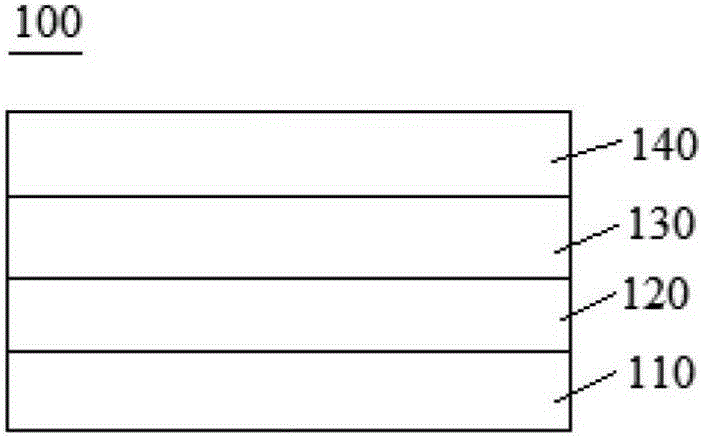

Composite single crystal thin film and method for manufacturing composite single crystal thin film

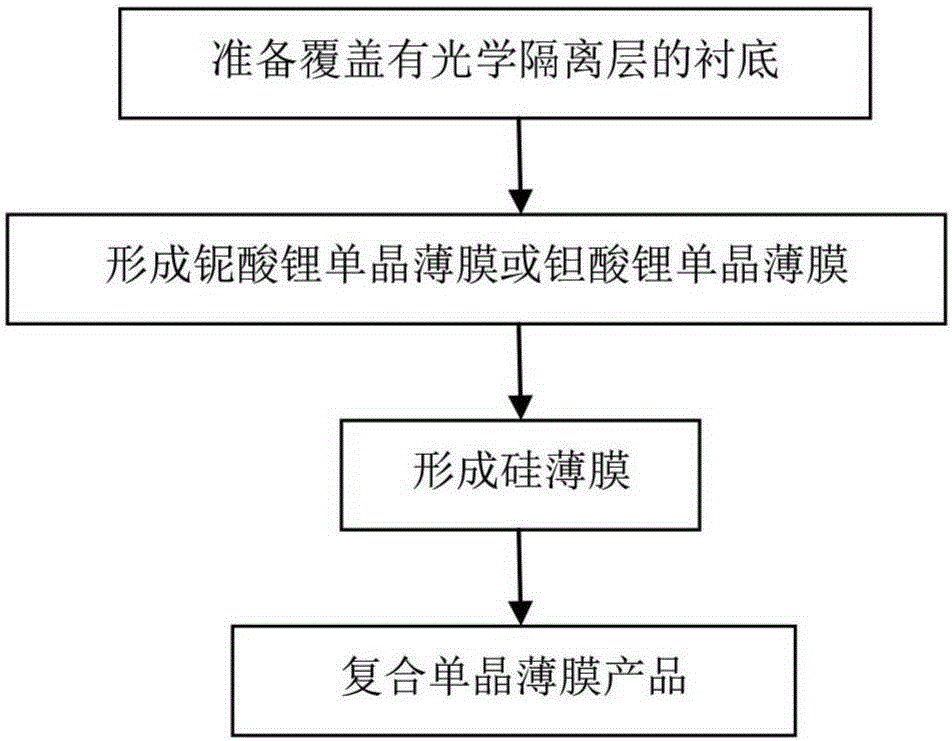

InactiveCN105321806APerfectly compatibleGood nonlinear opticsFinal product manufactureSemiconductor/solid-state device manufacturingIsolation layerSingle crystal

The invention discloses a composite single crystal thin film and a method for manufacturing the composite single crystal thin film. The composite single crystal thin film comprises a substrate, an optical isolation layer, a lithium niobate single crystal thin film or a lithium tantalate single crystal thin film and a silicon thin film, wherein the optical isolation layer is located on a substrate; the lithium niobate single crystal thin film or the lithium tantalate single crystal thin film is located on the optical isolation layer; and the silicon thin film is located on the lithium niobate single crystal thin film or the lithium tantalate single crystal thin film. The composite single crystal thin film disclosed by the invention has good nonlinear optical effect, acousto-optical effect, electro-optic effect and the like of a lithium niobate or lithium tantalite material, and simultaneously has the characteristic of a mature processing technology of a silicon material, so that the composite single crystal thin film disclosed by the invention can achieve relatively good compatibility with an existing IC production technology and has a broad industrial prospect. In addition, stable and effective industrial production can be achieved according to the method for manufacturing the composite single crystal thin film disclosed by the invention.

Owner:JINAN JINGZHENG ELECTRONICS

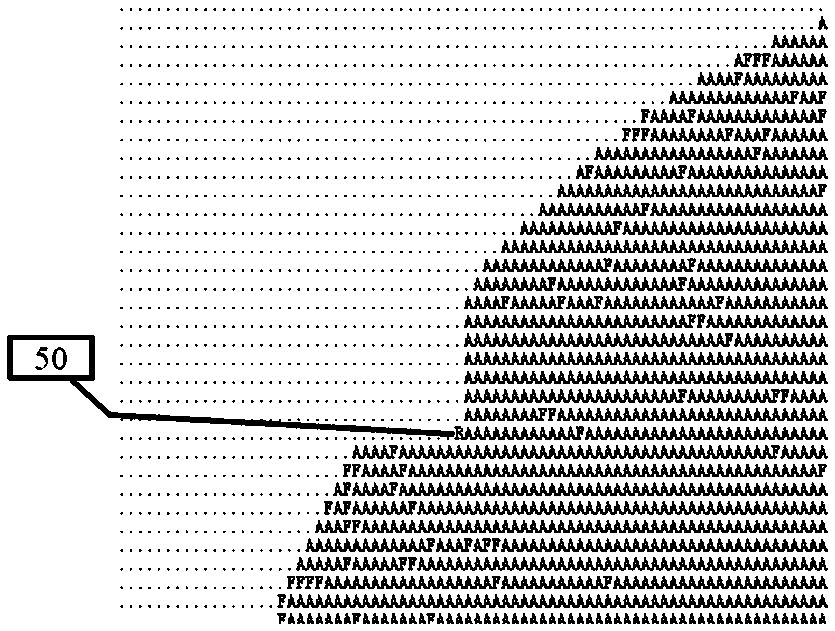

Method for correcting layering optical proximity effect

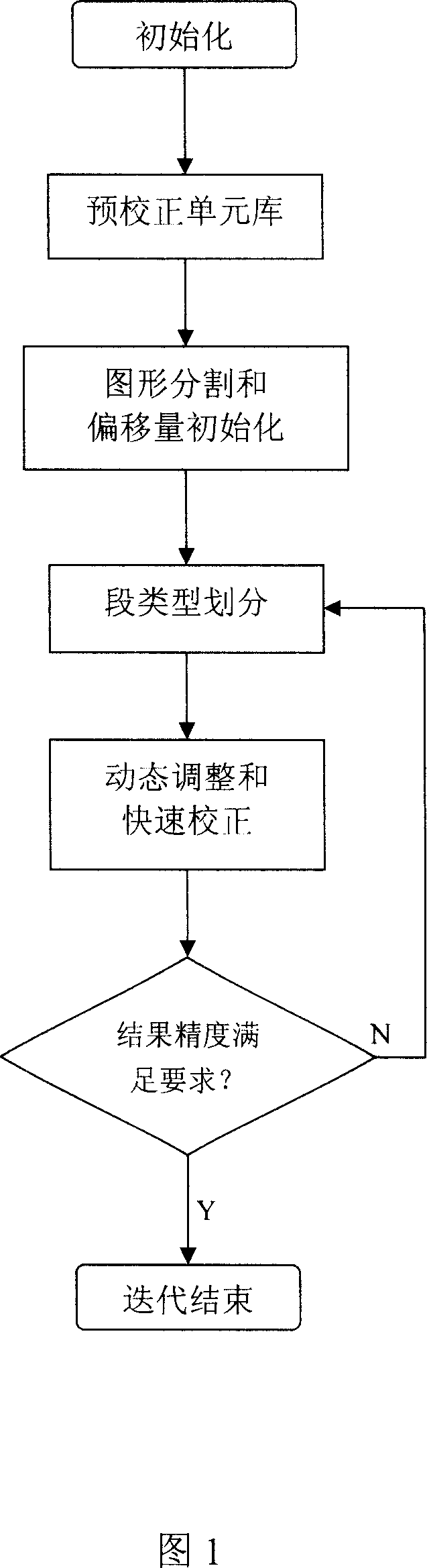

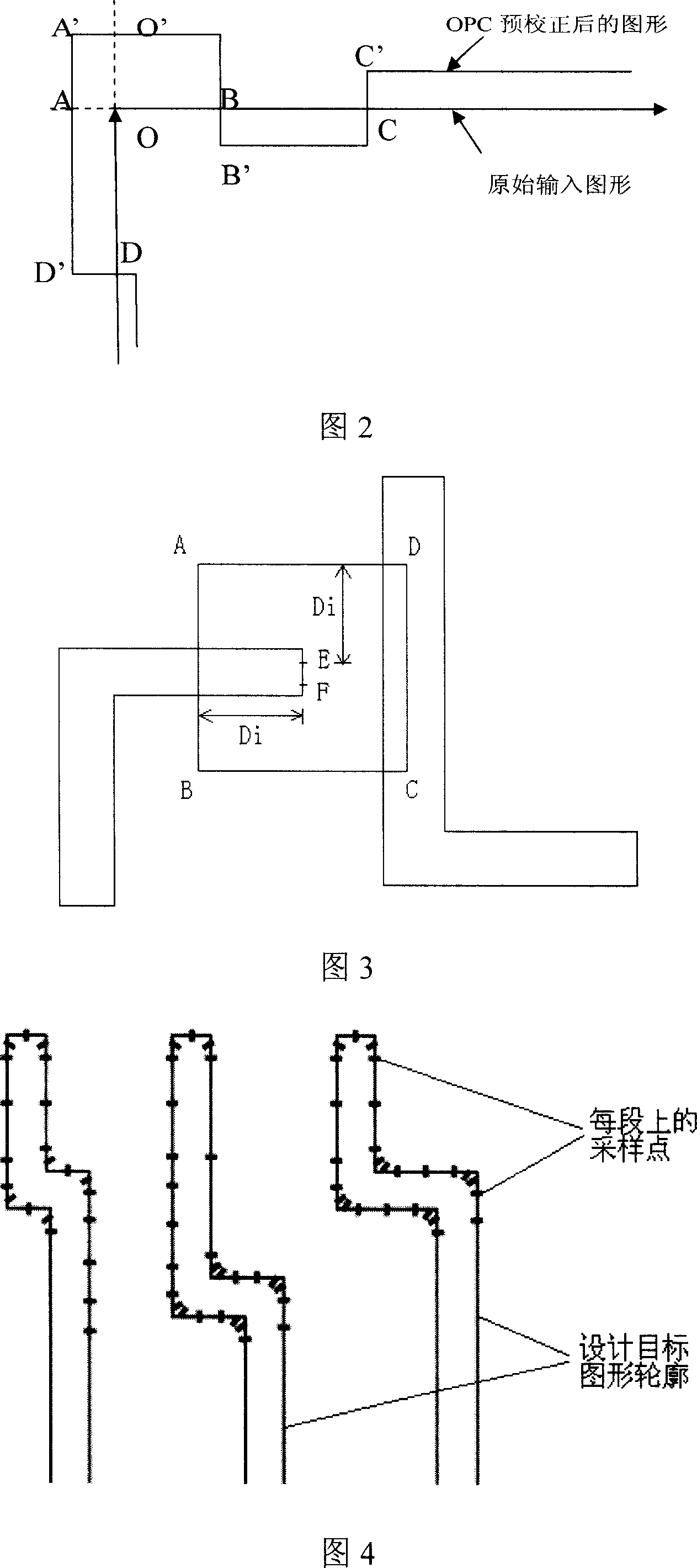

InactiveCN101013271AHigh speedImprove predictabilitySemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusGraphicsDesign engineer

The invention discloses a hierarchical optical proximity effect correction method, including the preparation of the pre-correction module library, the initialization of the mask graphic offset and the step using dynamic adjustment algorithm for rapid computation, and it provides a method to make full use of the territory hierarchical structure in the optical proximity effect correction, and under the deep submicron conditions, the high precision mask process is considered as high costs for too big calculation quantities, and the computational complexity can be greatly reduced under the help of the new algorithm, and meanwhile, the new approach provides the module library with pre-correction results to IC design process, making the design engineer more flexible and effective to check the design. The method of the invention can be used for aided high-precision IC mask board, to increase the results predictability in IC design process, and OPC correction computational speed, lower costs, and increase IC production yield and reduce production cycle.

Owner:ZHEJIANG UNIV

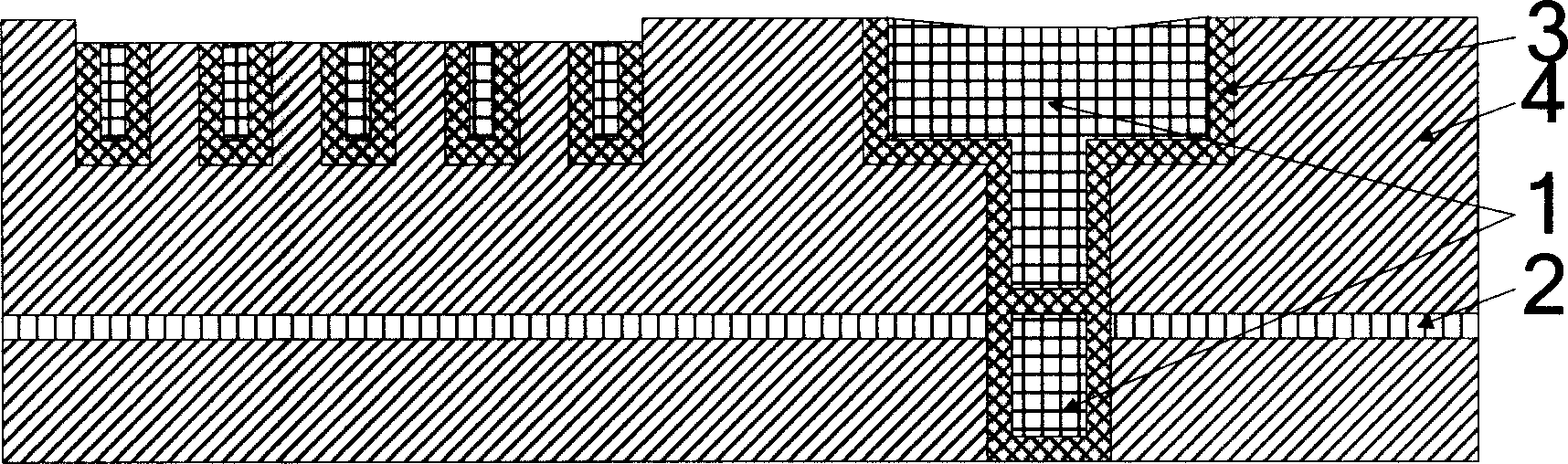

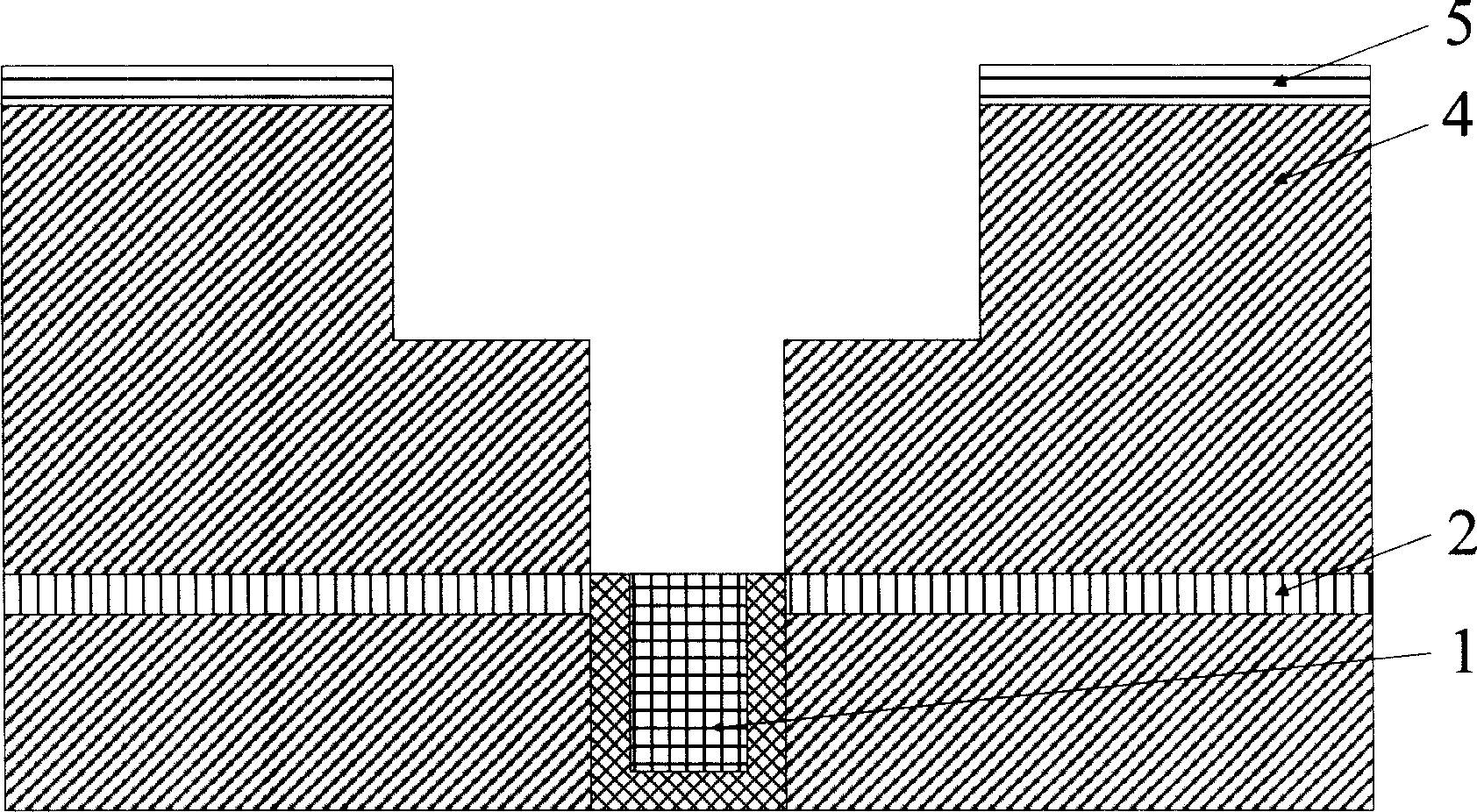

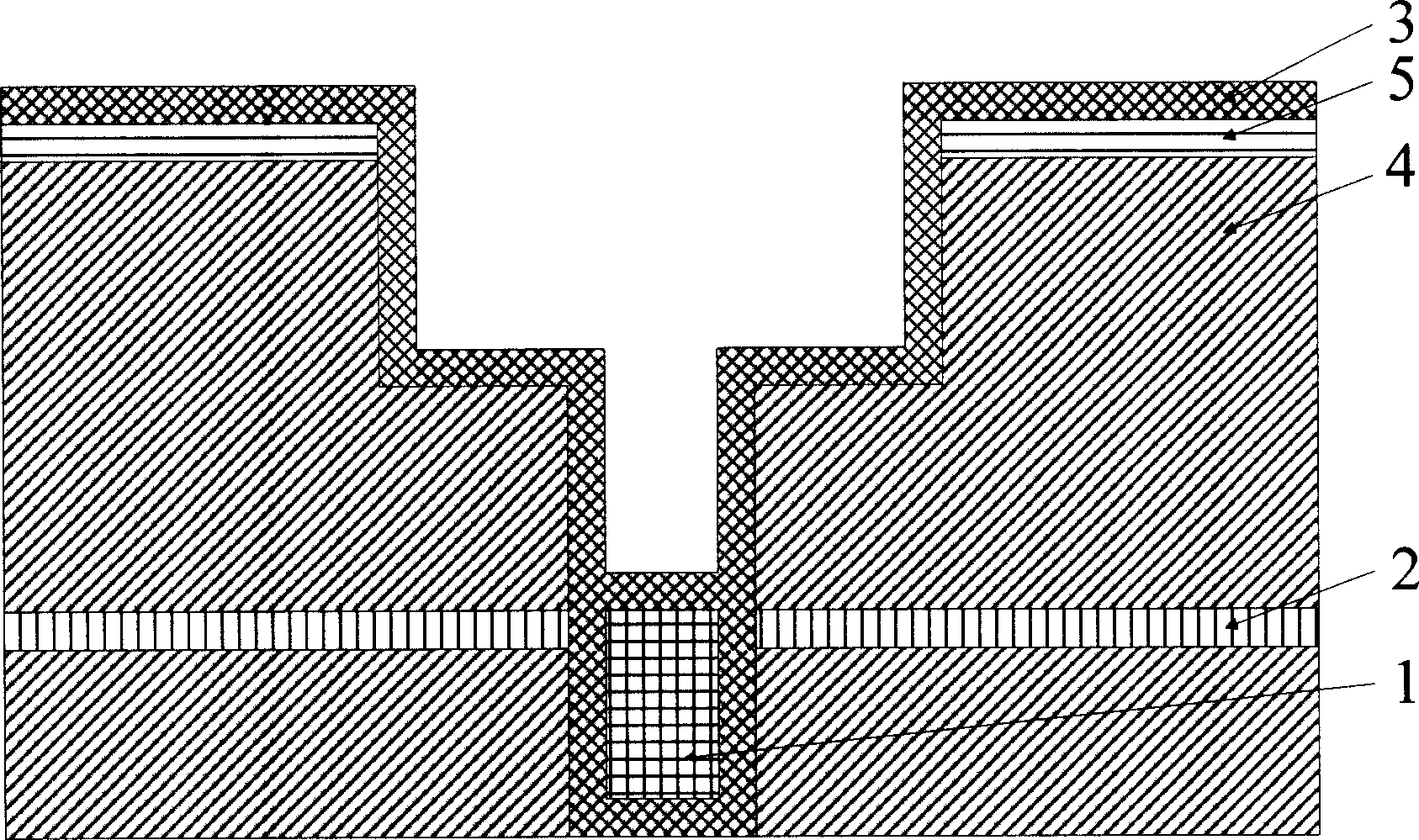

Processing method of capacitor type MEMS sensor and sensor structure

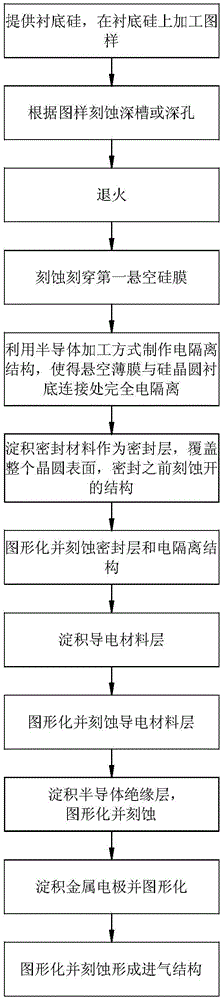

ActiveCN105036059AAvoid investmentAdjust the rangeDecorative surface effectsChemical vapor deposition coatingCapacitanceProduction line

The invention provides a processing method of a capacitor type MEMS sensor and the capacitor type MEMS sensor. The method adopts a SON (silicon-on-nothing) technology to perform single-faced processing to obtain two layers of silicon films to be used as two electrodes of a capacitor, and measures pressure by utilizing capacitance change brought by shape change after the lower silicon film is pressed. The processing method can be implemented with an IC production line and does not need extra equipment or non-CMOS production line technology, such as anodic bonding. The processing method of the invention facilitates the control of the consistence of the performance of sensors on a whole wafer.

Owner:GUANGDONG HEWEI INTEGRATED CIRCUIT TECH

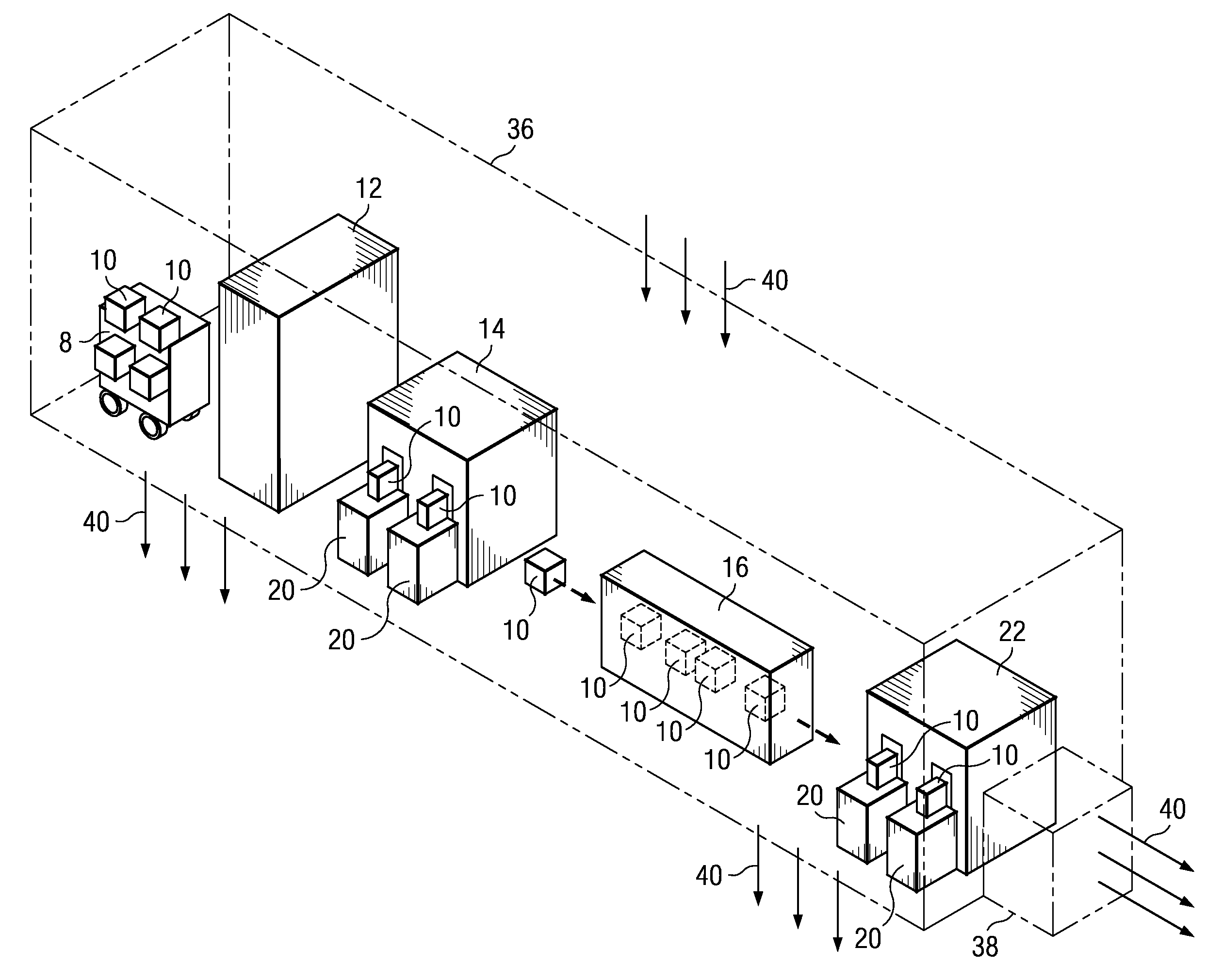

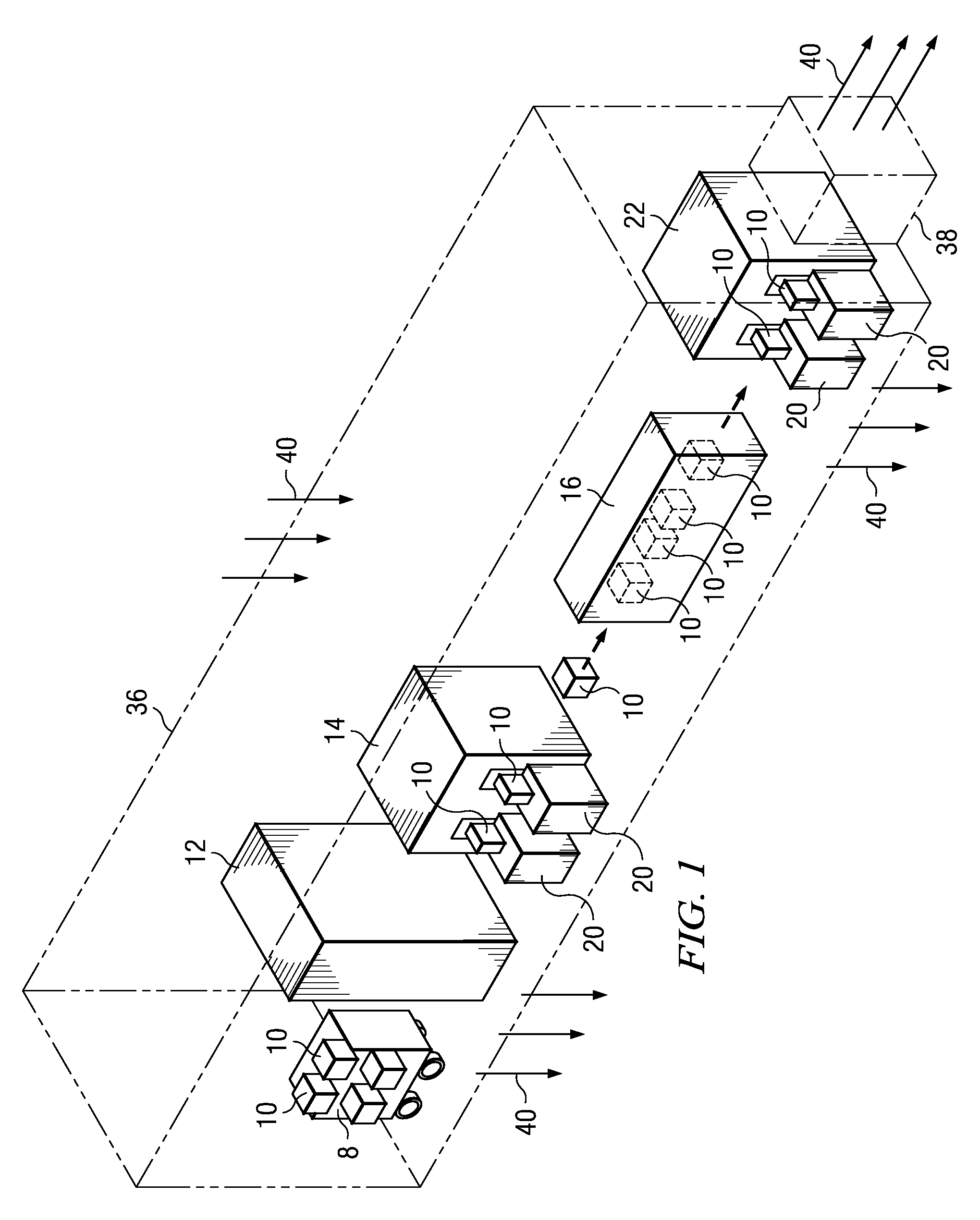

Preventing Contamination in Integrated Circuit Manufacturing Lines

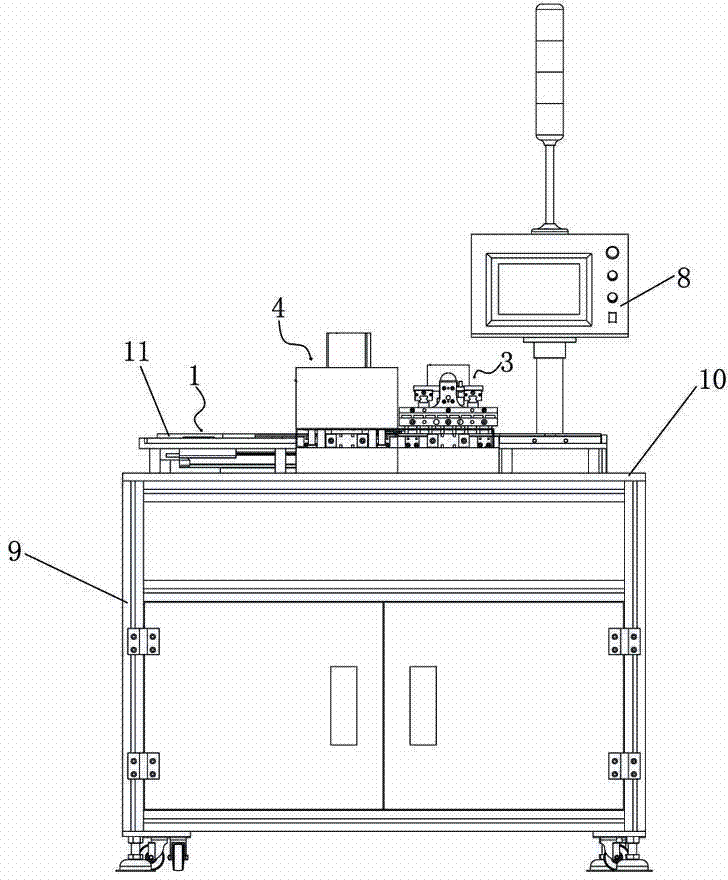

ActiveUS20080304944A1Reduce exposureImprove performanceDust-free enclosuresSemiconductor/solid-state device manufacturingIntegrated circuit manufacturingEngineering

A semiconductor manufacturing line includes an inert environment selected from the group consisting essentially of an inert airtight wafer holder, an inert wafer transport channel, an inert production tool, an inert clean room, and combinations thereof.

Owner:TAIWAN SEMICON MFG CO LTD

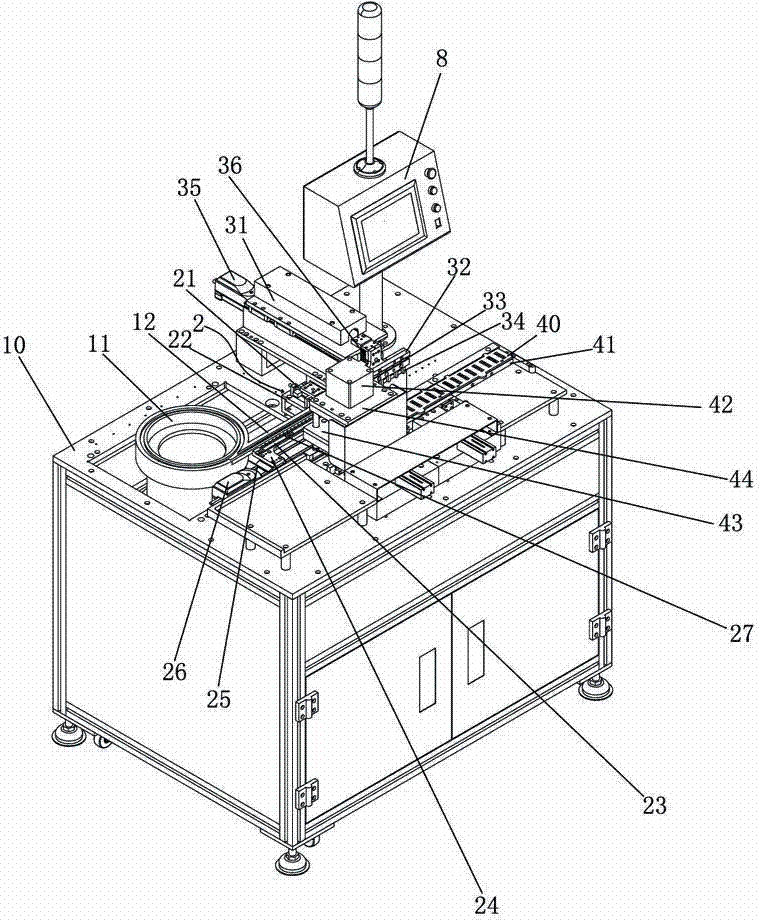

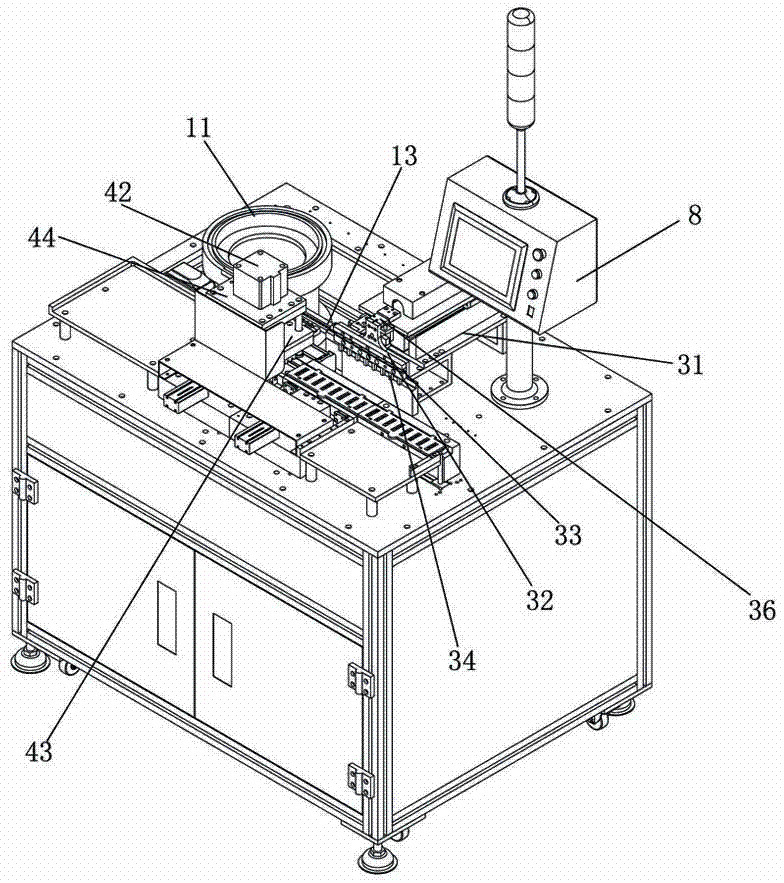

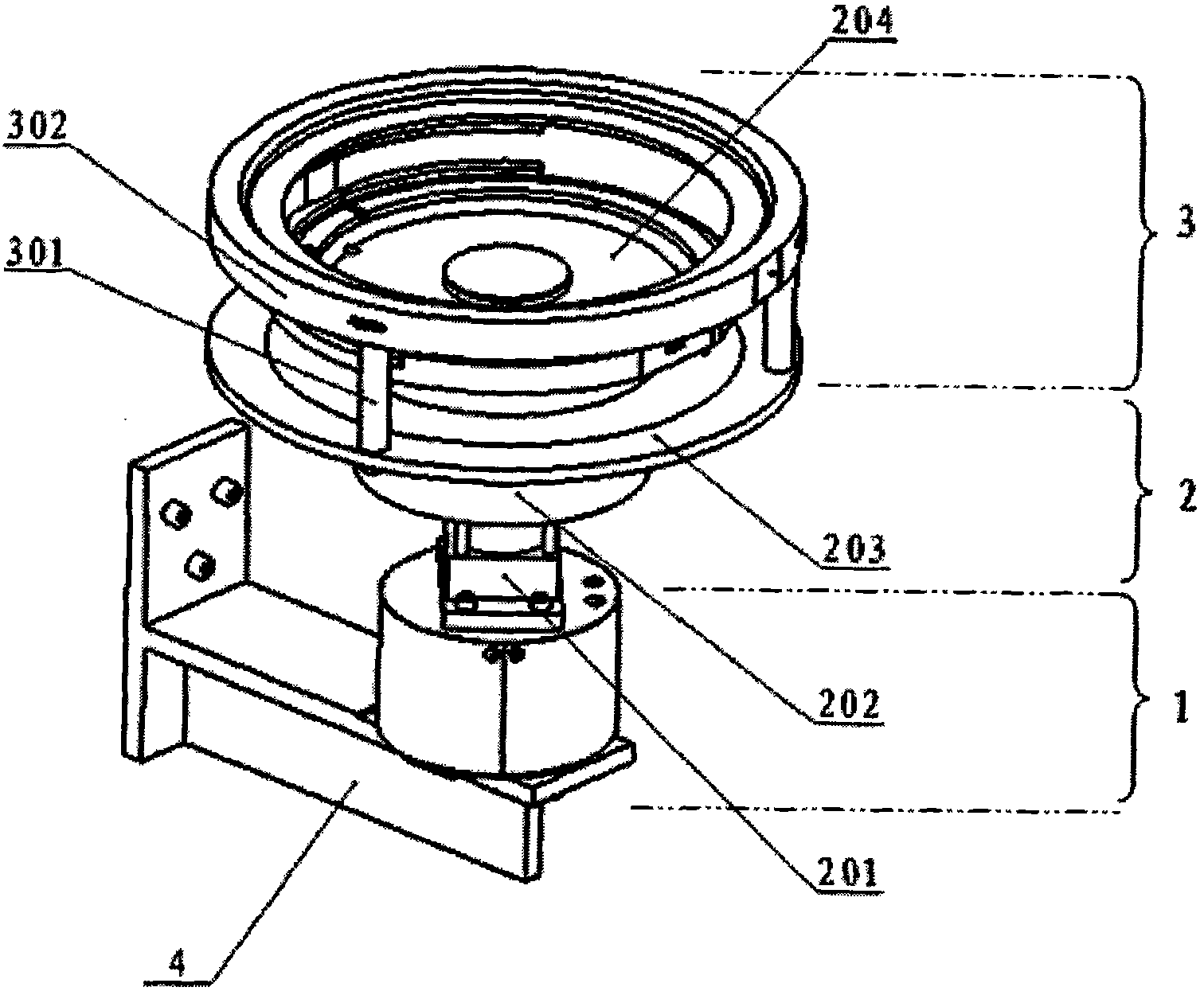

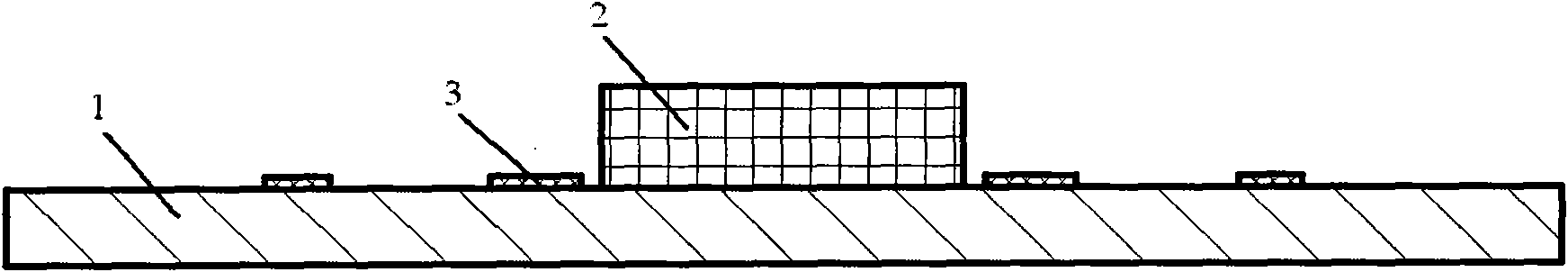

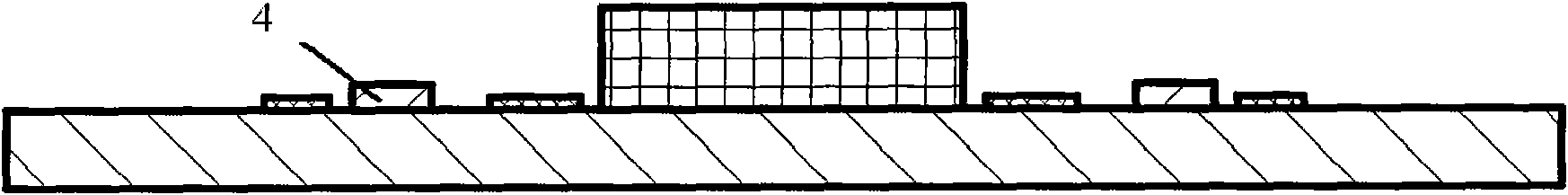

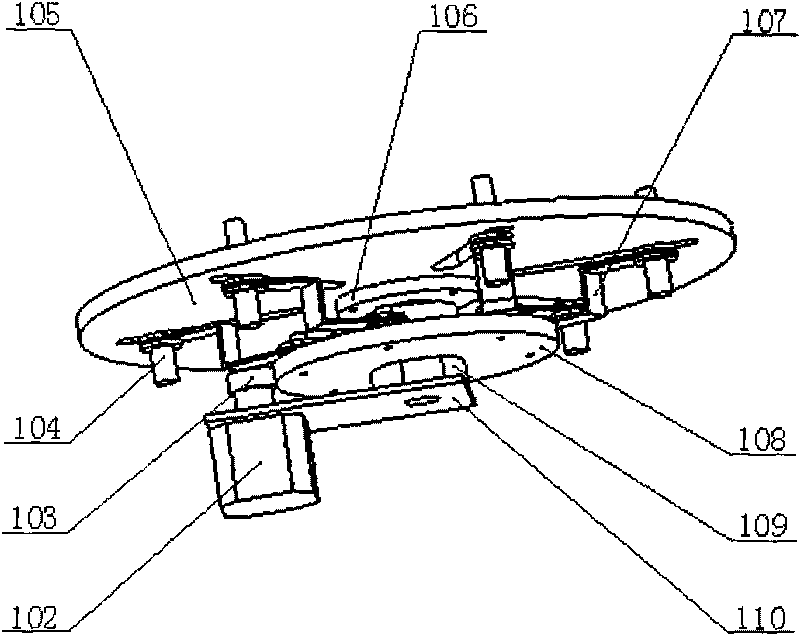

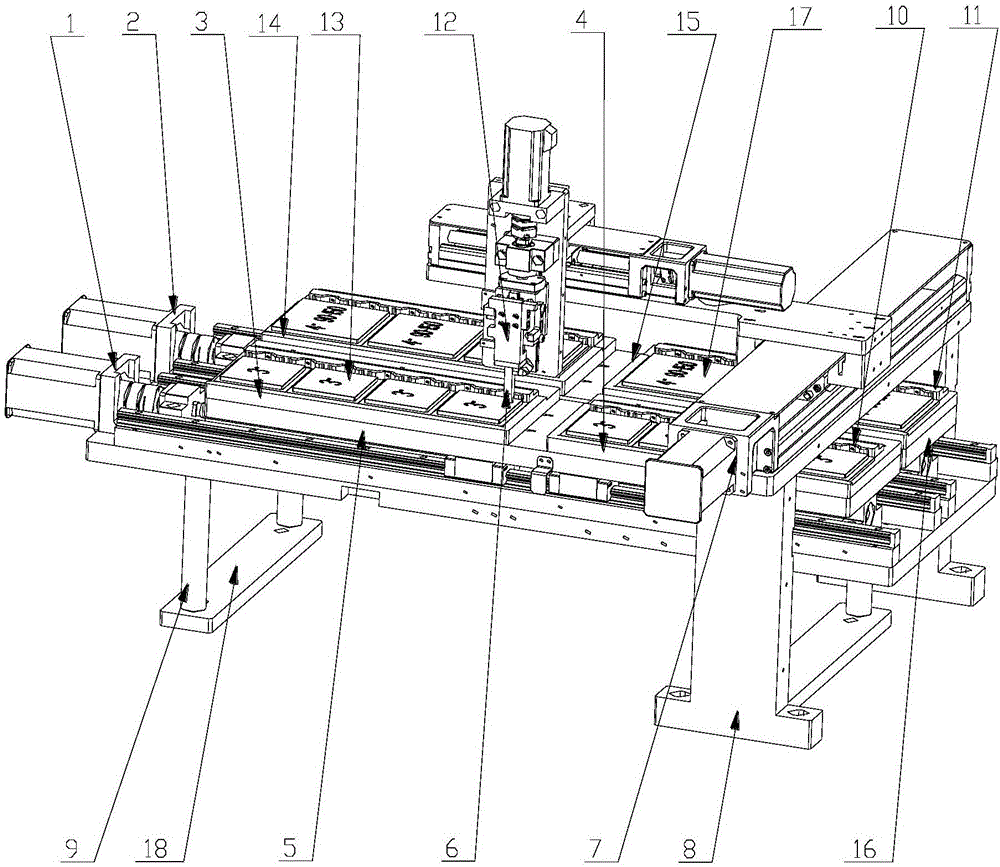

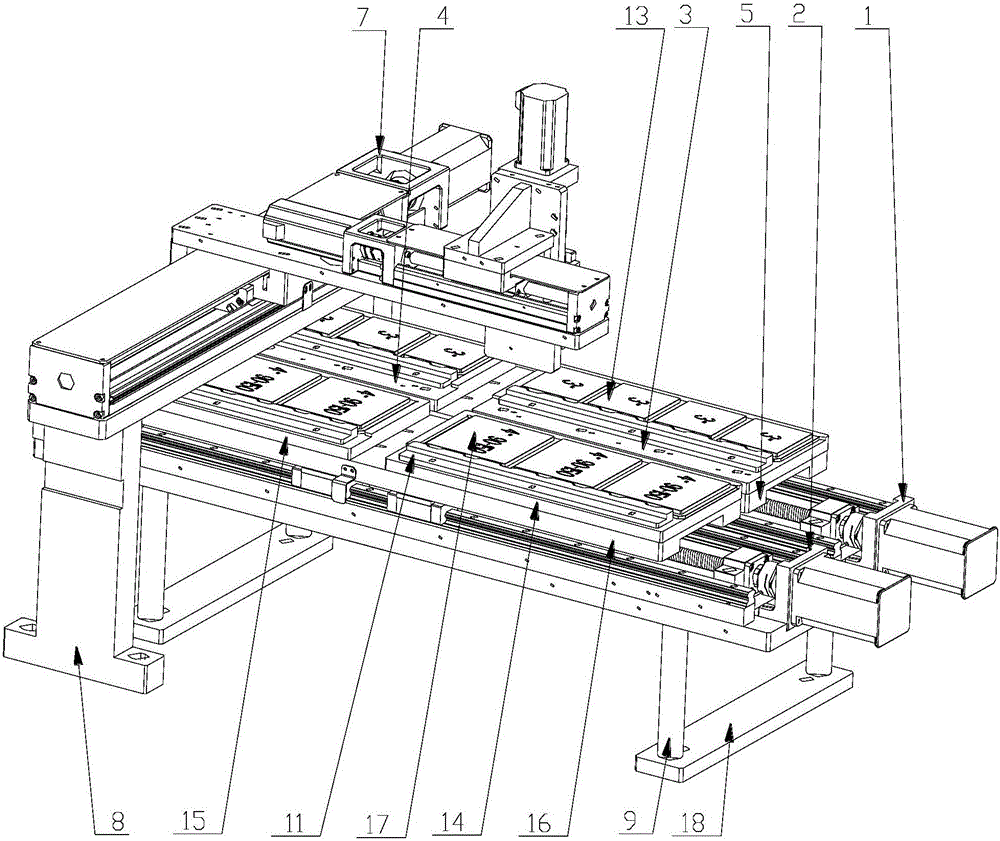

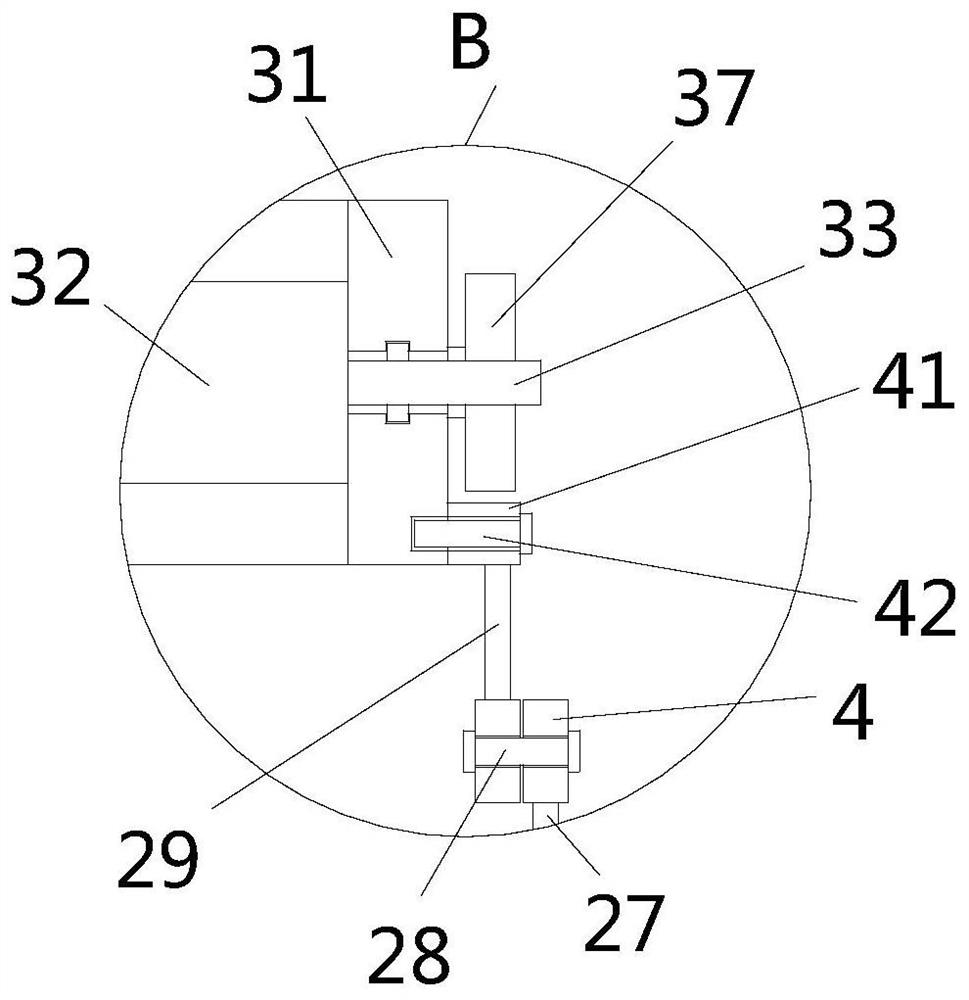

Automatic cover mounting machine for photoelectric IC production

The invention discloses an automatic cover mounting machine for photoelectric IC production. The machine comprises a machine frame and a working platform arranged on the machine frame, wherein an automatic feeding mechanism, a conveying mechanism, an absorbing displacement mechanism and a press-fit mechanism are arranged on the working platform, the conveying mechanism is arranged at the discharging end of the automatic feeding mechanism, the absorbing displacement mechanism is arranged between the conveying mechanism and the press-fit mechanism, action elements in the automatic feeding mechanism, the conveying mechanism, the absorbing displacement mechanism and the press-fit mechanism are all connected with a display control device, and the display control device controls the work of the automatic feeding mechanism, the conveying mechanism, the absorbing displacement mechanism and the press-fit mechanism, and the press-fit mechanism is used for mounting a cover on a photoelectric IC. The automatic cover mounting machine for photoelectric IC production has the advantages of being capable of achieving automatic operation, high in efficiency, high in qualified rate of products and the like.

Owner:DONGGUAN GAOJING ELECTRONICS TECH

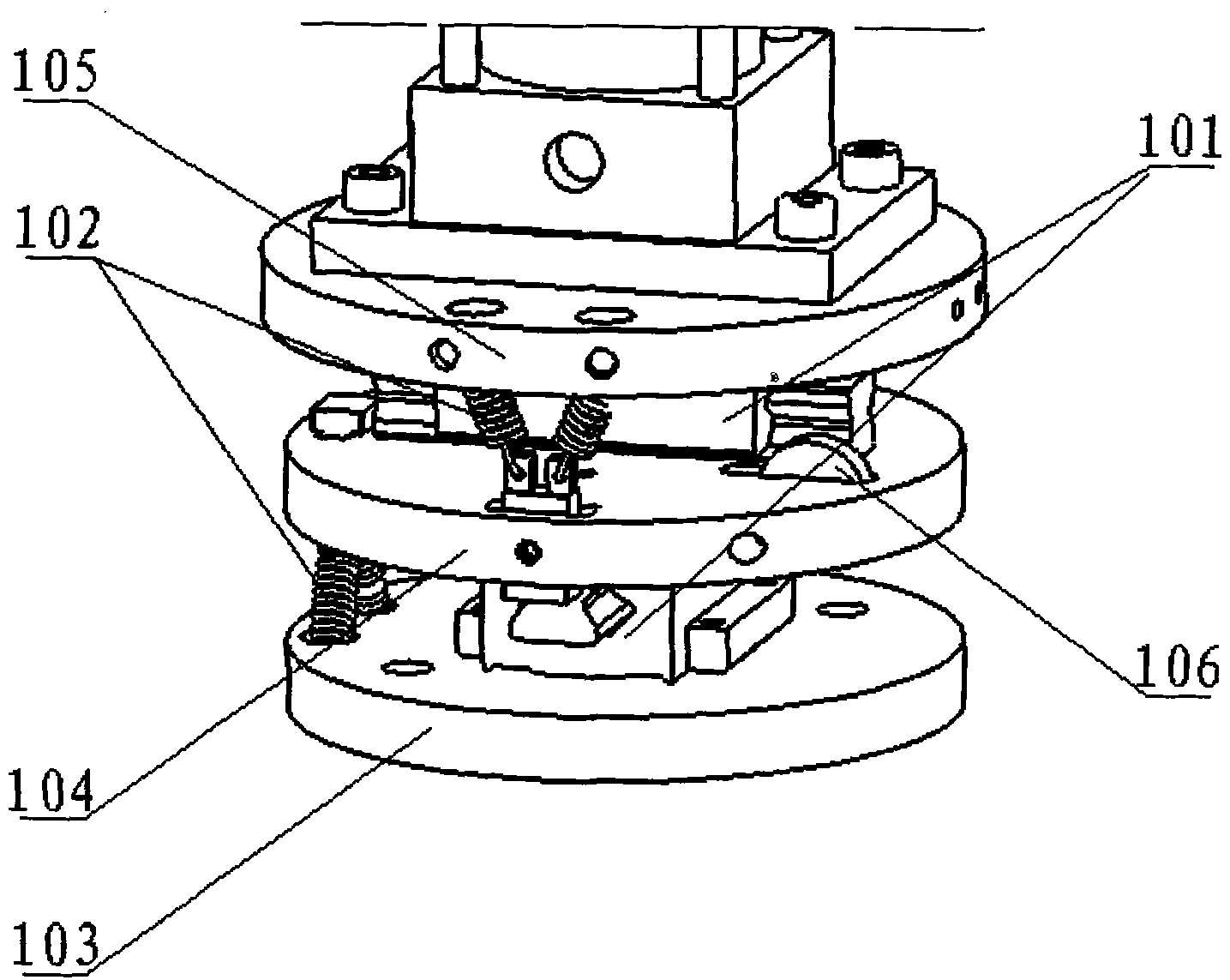

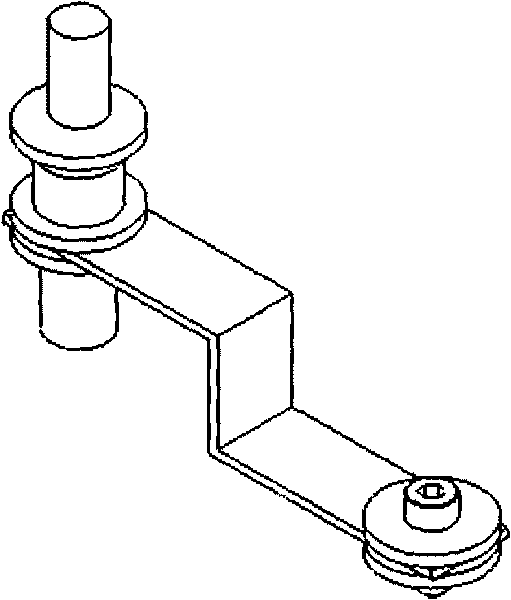

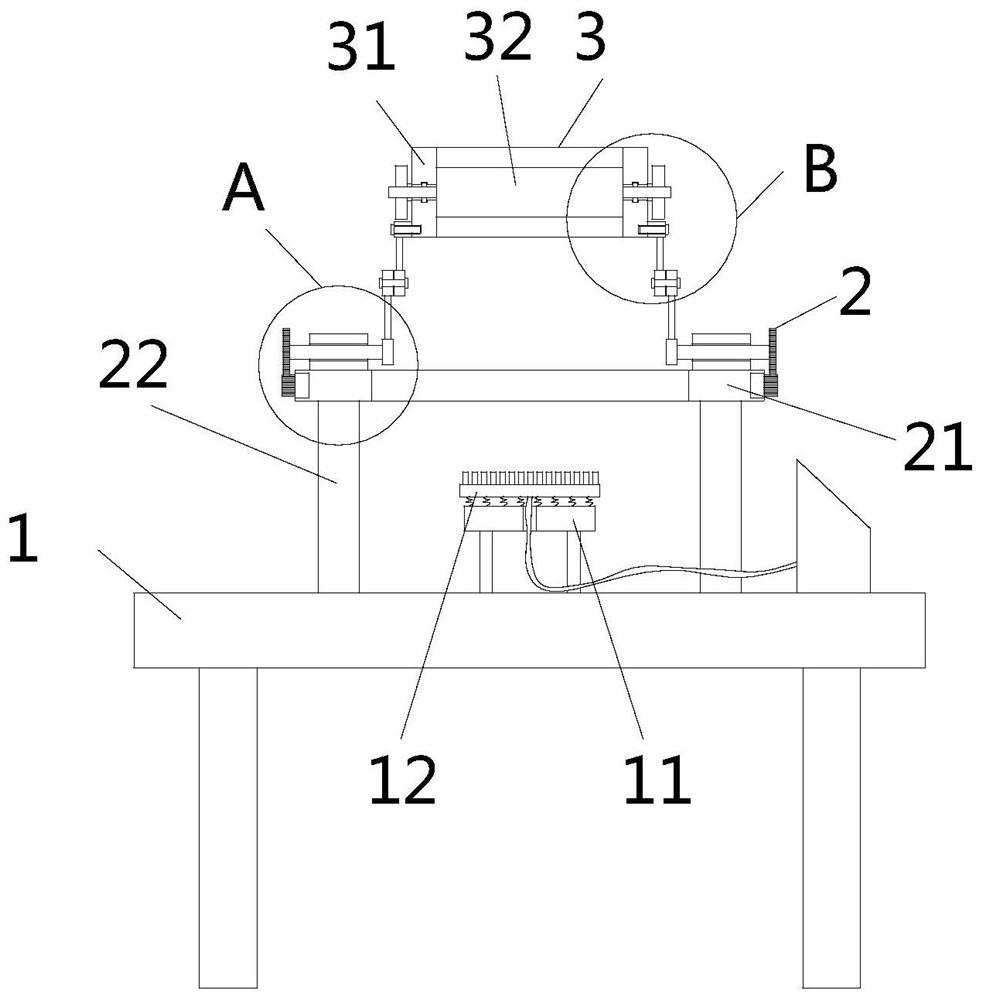

Silicon wafer positioning and loading device applied to chemical mechanical polishing equipment

ActiveCN102371535AFacilitate automatic loadingImprove loading efficiencySemiconductor/solid-state device manufacturingLapping machinesButt jointEngineering

The invention provides a silicon wafer positioning and loading device applied to chemical mechanical polishing equipment and relates to the technical field of silicon-wafer chemical mechanical polishing equipment. A base plate of the positioning and loading device is connected to a loading guide ring on the base plate through a supporting rod; a stretching part on a lifting driving mechanism is fixedly connected to a silicon wafer fixture thereon; the silicon wafer fixture is connected to a silicon wafer guide ring outside the silicon wafer fixture; a butt-joint guiding mechanism of a silicon wafer loading device and a silicon wafer resisting-joint guiding mechanism are arranged on the loading guide ring; and an automatic displacement adjusting mechanism and an automatic resetting mechanism are arranged on the base plate or the lower part of the lifting driving mechanism. The positioning and loading device can accurately position a silicon wafer and convey the silicon wafer to a loader for processing. The positioning and loading device has the advantages of simple structure, accurate positioning, loading safety, reliable property and operation convenience, and is beneficial to realizing the automatic loading of the silicon wafer and promoting the efficiencies for positioning, loading and processing the silicon wafer. The positioning and loading device is especially suitable for the loading of the silicon wafer in the chemical mechanical polishing equipment and also can be used for loading wafers during production processes of a transistor and an integrated circuit.

Owner:THE 45TH RES INST OF CETC

Production process of silicon wafter for solar cell with waste IC chips

InactiveCN1810394ALess impuritiesImprove photoelectric conversion efficiencyWaste processingSolid waste disposalMetal silicideSilicon oxide

The production process of silicon chip for solar cell with waste integrated circuit chips includes the following steps: treating waste integrated circuit chips with HCl and H2SO4 to eliminate Mg, Al, Mn, Zn, Cr, Fe, Ni, Sn, Pb and other metals with activity higher than hydrogen; treating with HNO3 to eliminate Cu, Hg, Ag and other transition metals; treating with mixed acid of HF and HNO3 to eliminate metal silicide, silicon oxide and silicon nitride; single-side thinning and double-side thinning to eliminate active area and silicon chip with original resistivity; cleaning, classifying, detecting and grading to obtain silicon chip for solar cell. The process can obtain silicon chip with less impurity and intact crystal structure for producing solar device with high photoelectronic conversion efficiency.

Owner:浙江东源电子有限公司

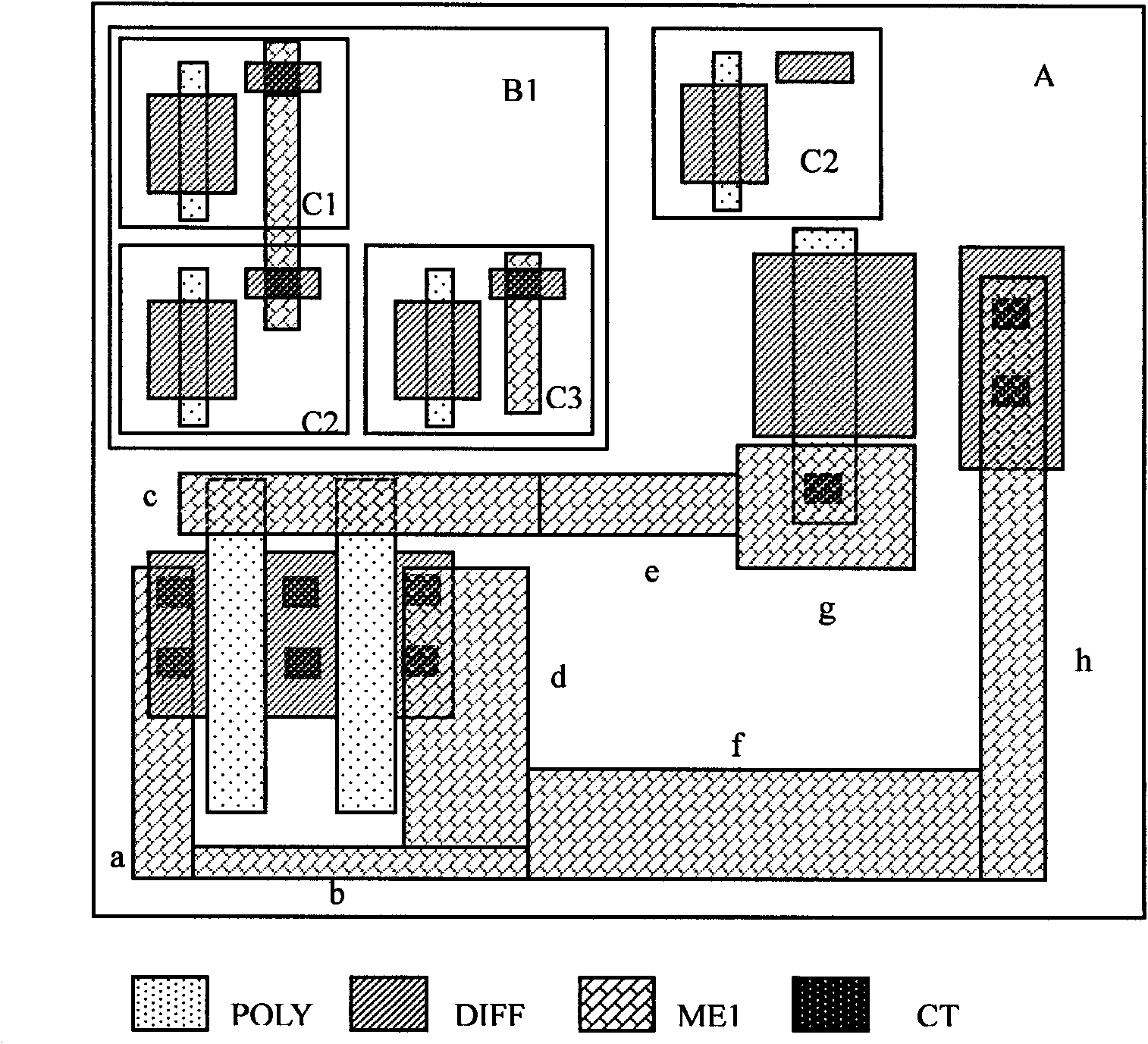

Method for quickly extracting critical area of layout

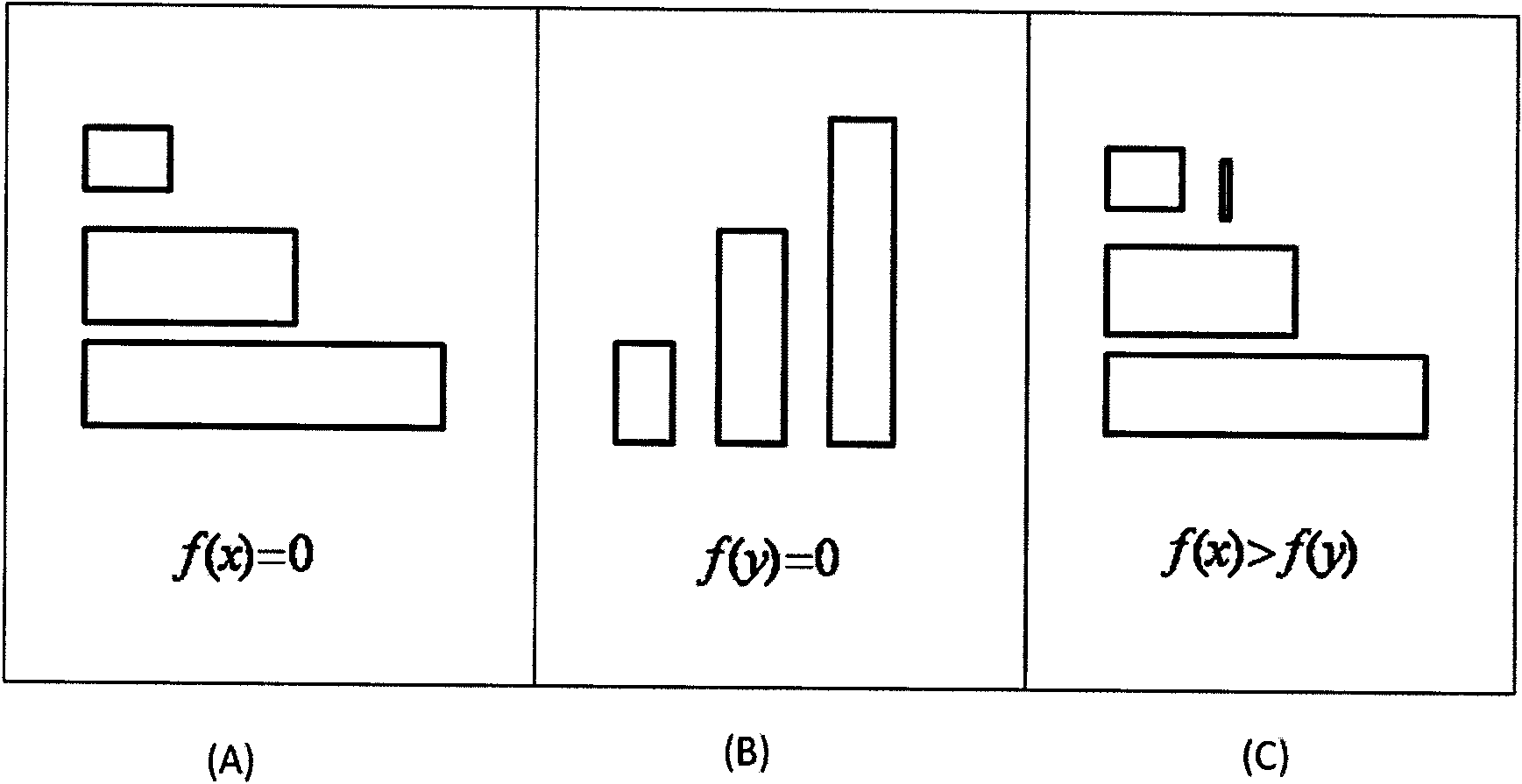

InactiveCN101789048ADoes not affect the data structureQuick extractionSpecial data processing applicationsGraphicsIntegrated circuit layout

The invention discloses a method for quickly extracting the critical area of a layout, which includes the following steps that: layout information is extracted; a blocked ordered multi-level indexed table is established; the defects of the production technique are simulated at random, and the affection is statistically analyzed; and the blocked ordered multi-level indexed table is utilized to calculate the critical area. By utilizing the method which first classifies basic pattern units of the integrated circuit layout and then hierarchically traverses a layout tree to extract all the patterns superposed with defective polygons, the invention can quickly extract all the patterns superposed with defective polygons in a layout tree with great depth and extension within an effective time and space range and calculate the critical area of the layout, and is used for directing the practical integrated circuit production to increase the yield.

Owner:ZHEJIANG UNIV

Wafer-grade vacuum encapsulation process for micro-electro-mechanical system

InactiveCN101554987ALow seal qualityLarge package sizeDecorative surface effectsChemical vapor deposition coatingEngineeringWafer bonding

A wafer-grade vacuum encapsulation process for a micro-electro-mechanical system belongs to an encapsulation method for a micro-electro-mechanical system and solves the problems of the film deposition-based vacuum encapsulation process that the deposited film is thin, has small chamber and is easy to be damaged and the encapsulation device has leaked vacuum and reduced service life. The process sequentially comprises a step of depositing an air absorbent, a step of depositing a thin sacrificial layer, a step of depositing a cushion chamber sacrificial layer, a step of depositing thick sacrificial layer, a step of preparing an encapsulation cover, a step of etching a releasing hole, a step of removing sacrificial layer and a step of sealing. The process solves the problems that the existing encapsulation method has short vacuum retaining time, low sealing quality, large encapsulation dimension, incompatibility between the process and the standard IC process and high cost, thus ensuring the air pressure in the inner-most chamber; and simultaneously, the cost of the process is less than that of the vacuum encapsulation based on wafer-bonding process, and the process can realize production in general IC production factories and greatly promote the development and generalization of wafer-grade MEMES vacuum encapsulation technology.

Owner:HUAZHONG UNIV OF SCI & TECH

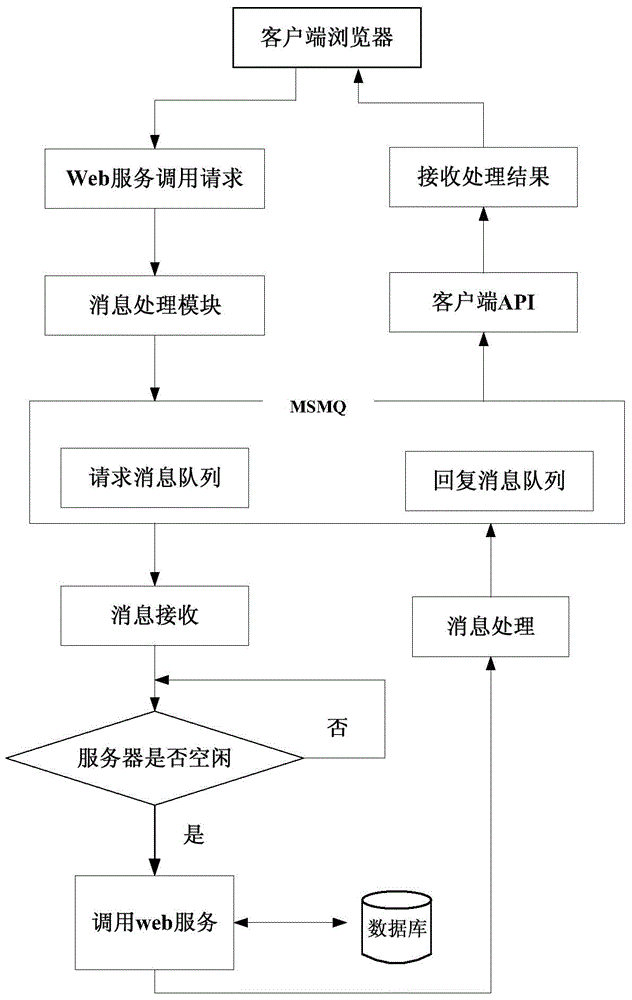

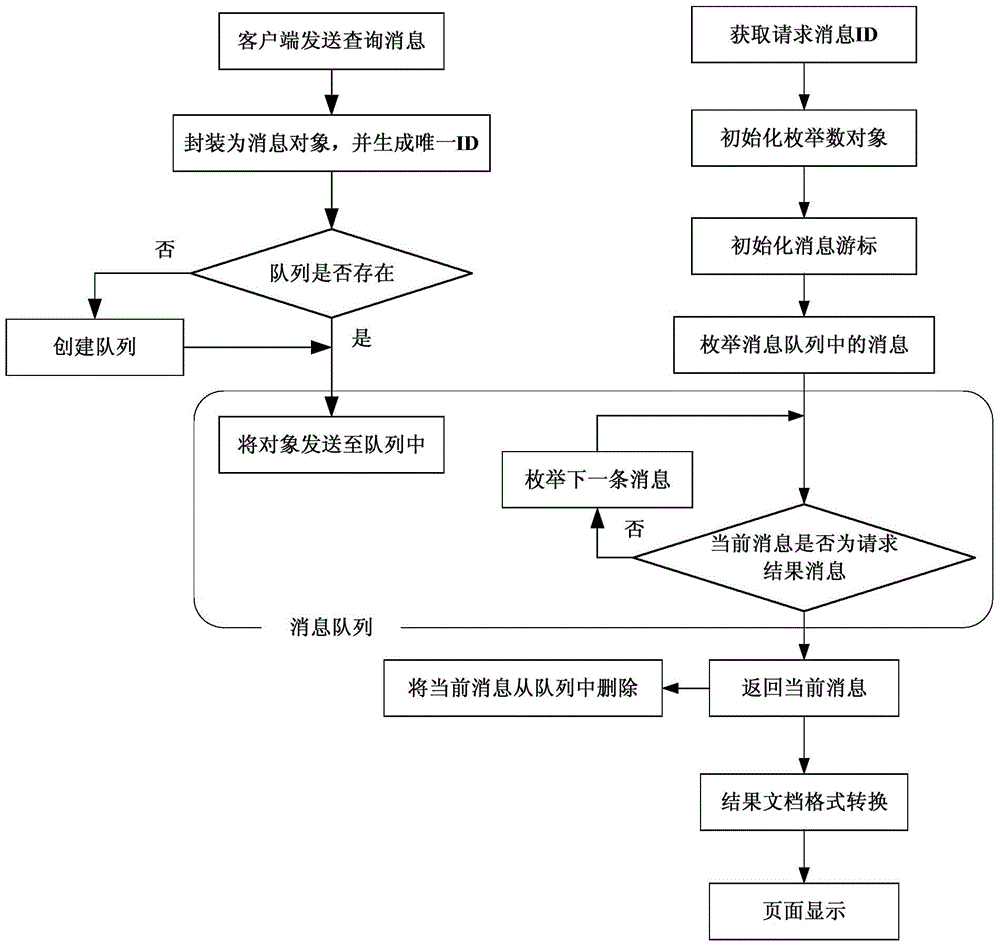

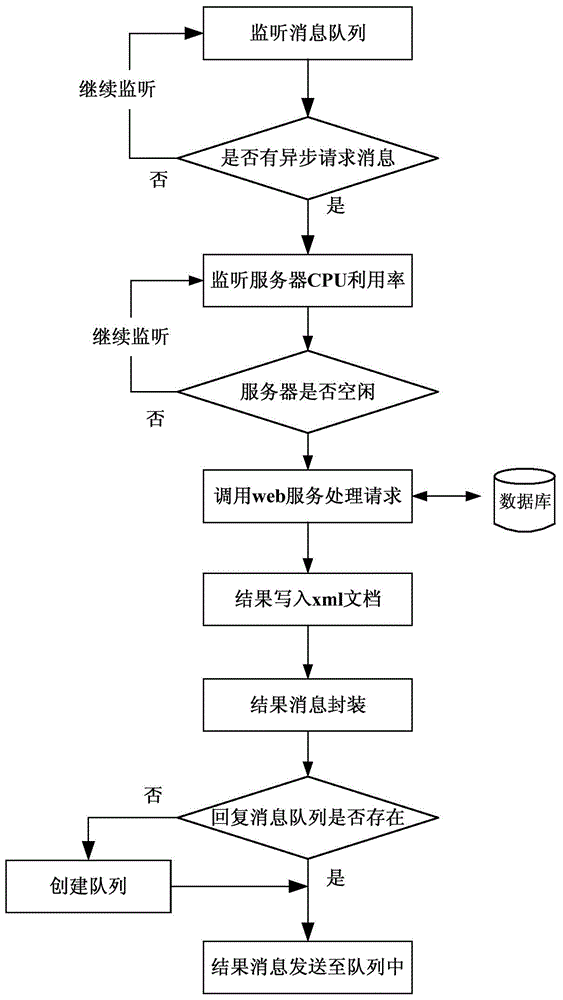

Asynchronous calling method applied to integrated circuit production line monitoring system

InactiveCN104378221AEasy to operateDo not block stop other responsesData switching networksComputer hardwareWeb service

The invention discloses an asynchronous calling method applied to an integrated circuit production line monitoring system. The asynchronous calling method includes the following steps that firstly, a client side request message is packaged into a message object, an unique ID is generated, and the message object is sent into a request message queue and waits for being processed by a server; secondly, when a server side monitors that an asynchronous request message exists in the request queue and the server is in an idle state, a web service corresponding to an asynchronous request is called; thirdly, after the asynchronous request is processed, a result message is sent to a replay message queue, and the content of the message is the ID of the request and a processing result; fourthly, a client side assembly finds the corresponding result message according to the ID of the request; fifthly, the result message is converted into a format required by a user. According to the method, asynchronous data transmission between a client side and the server in the integrated circuit production line monitoring system is achieved and instantaneity and effectiveness of the system are improved.

Owner:MICROCYBER CORP

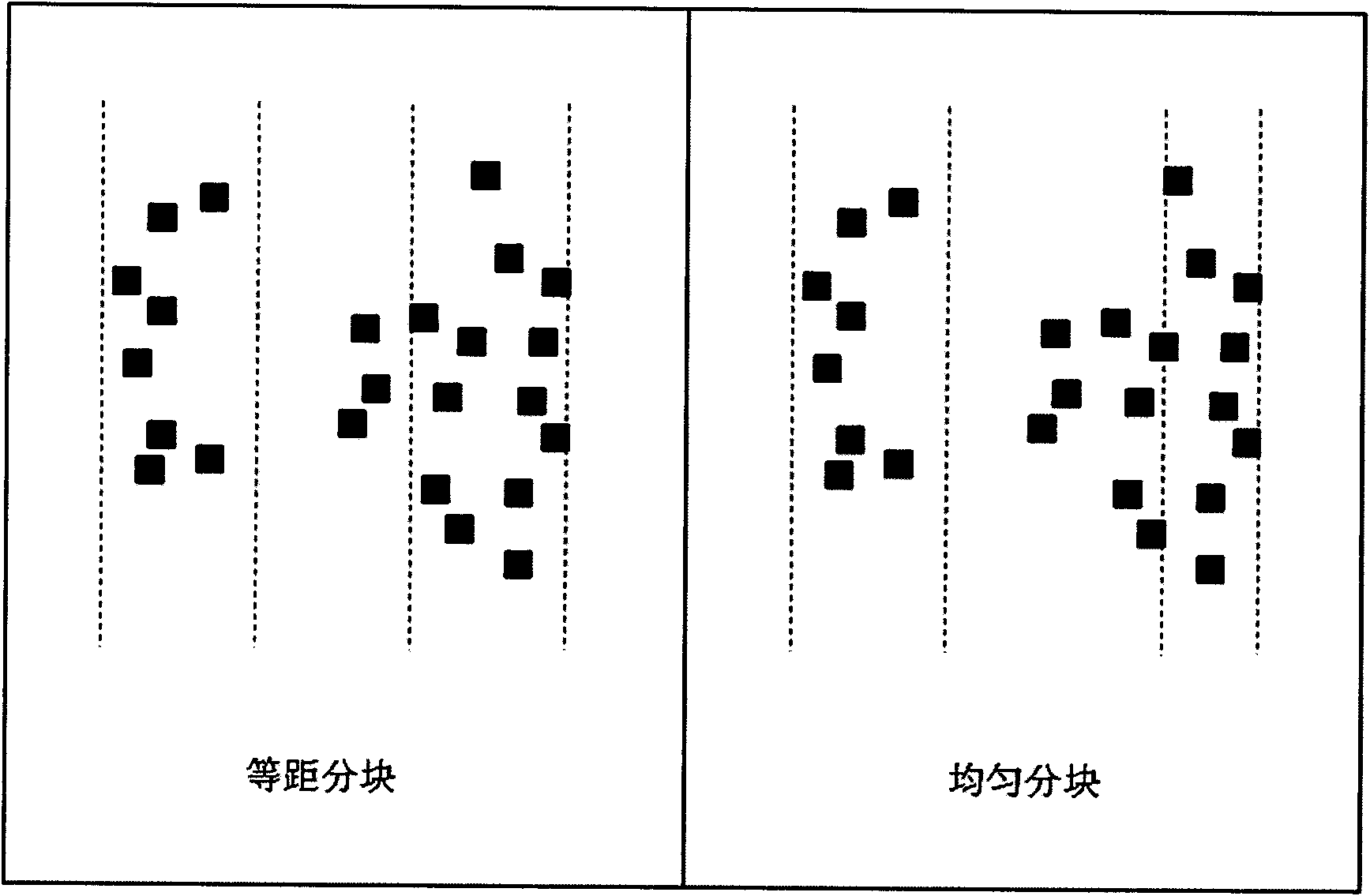

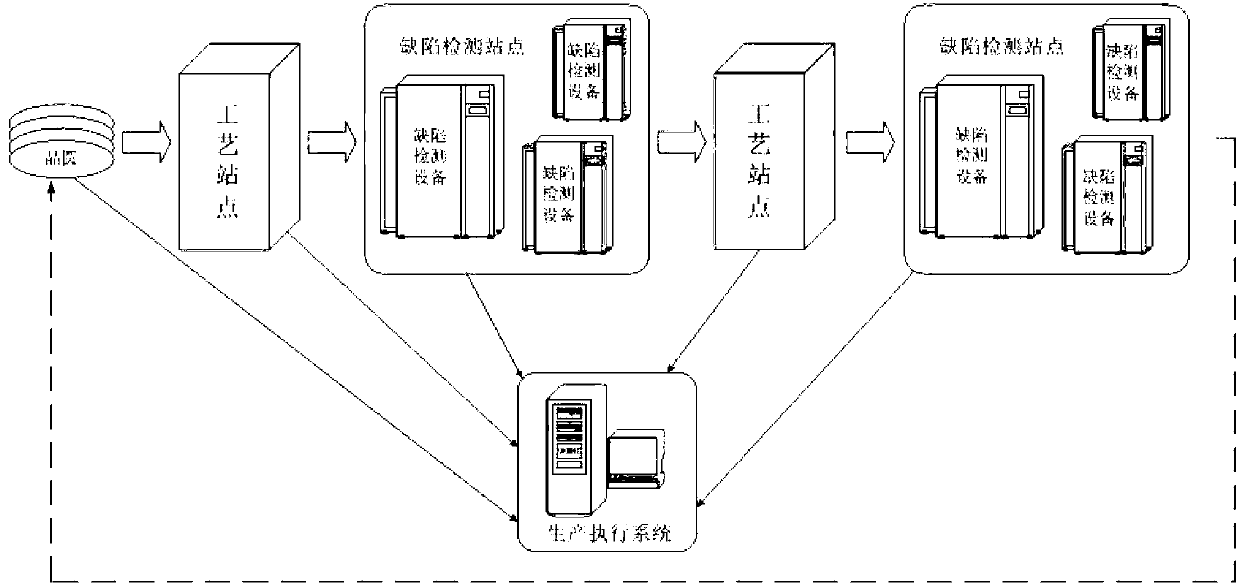

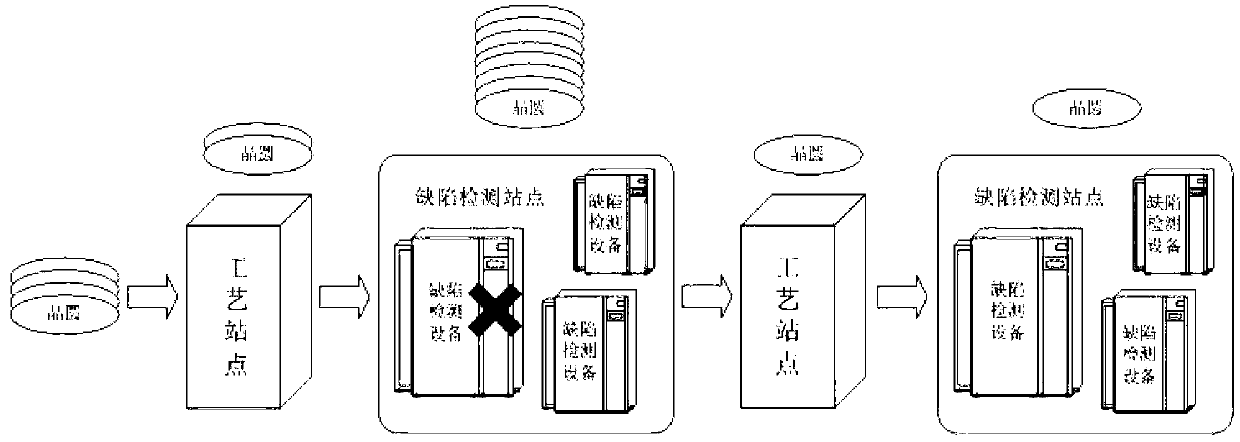

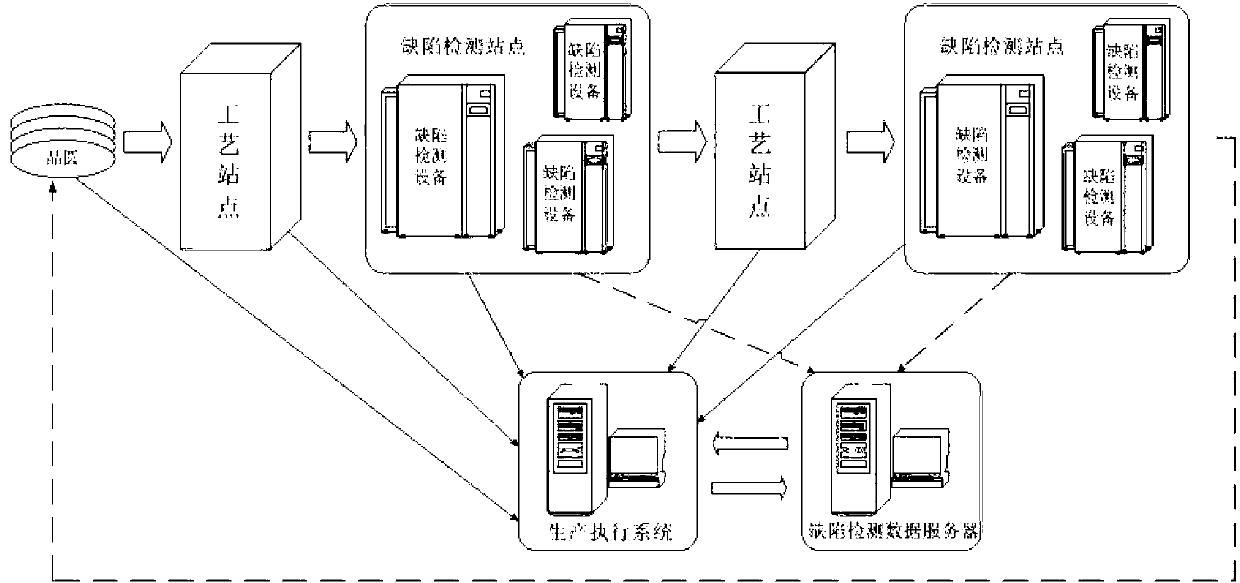

Defect casual inspection method capable of dynamically adjusting according to technology wafer number load

ActiveCN103346105AAvoid accumulationHigh speedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingIc productionComputer science

The invention discloses a defect casual inspection method capable of dynamically adjusting according to the technology wafer number load. The method comprises the following steps: presetting a defect detection data server; inputting and storing standard casual inspection frequency of a defect detection station and operation speed ratios of different defect detection procedures at normal production time into the defect detection data server; the defect detection data server calculating the real-time capacity of the defect detection station according to the real-time state of each defect detection device in the defect detection station, and automatically upgrading the standard casual inspection frequency of the defect detection station. By the adoption of the method, the problem that dynamic changes of the defect detection capacity cause production speed to become slow and production cost to be increased is effectively avoided. The frequency of defect casual inspection is adjusted according to the dynamic changes of the technology wafer number load, so that integrated circuit production speed is effectively improved, the production period is shortened, and the production cost is eventually reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

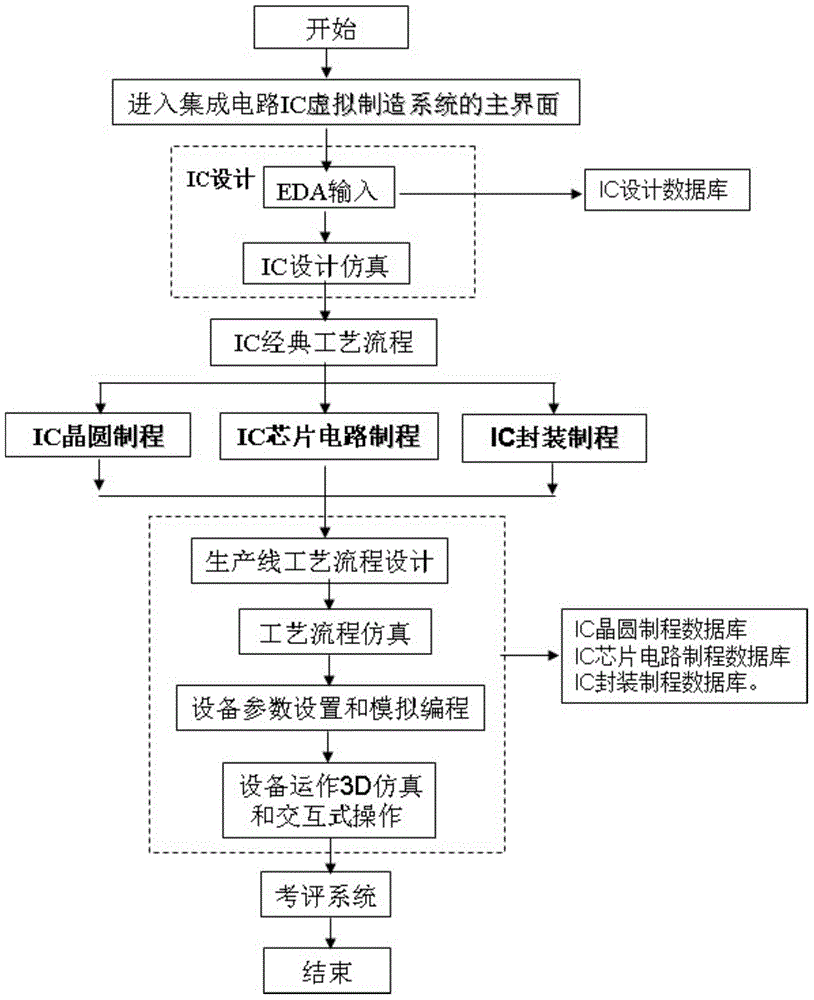

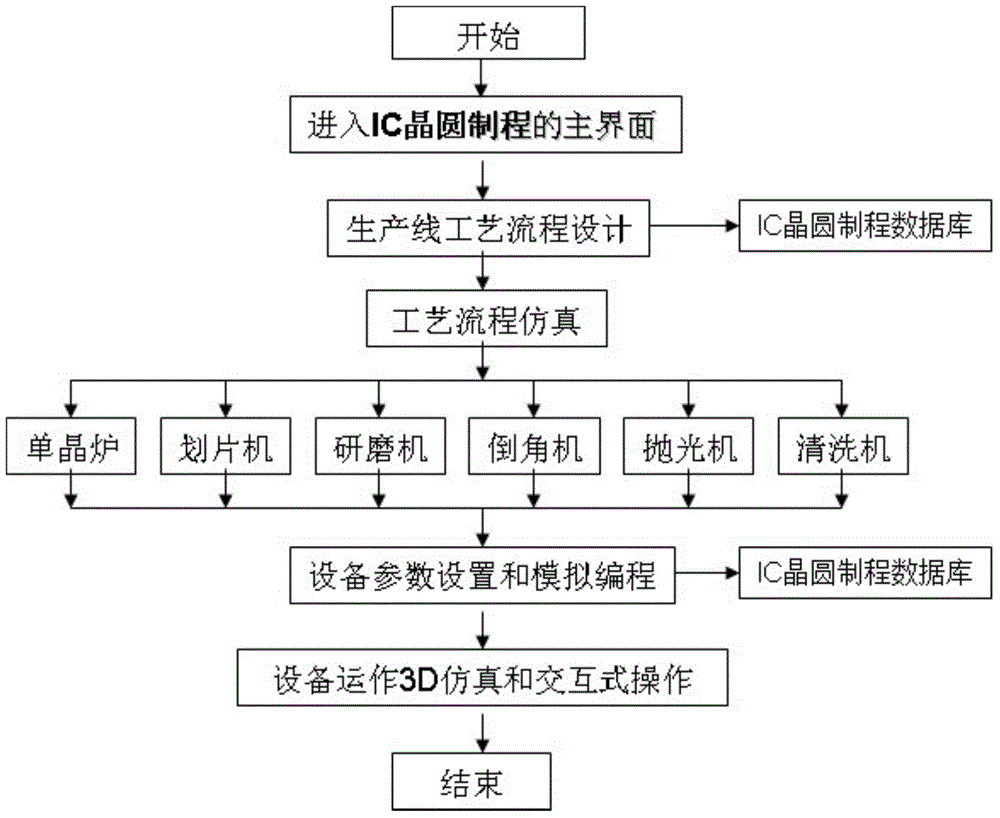

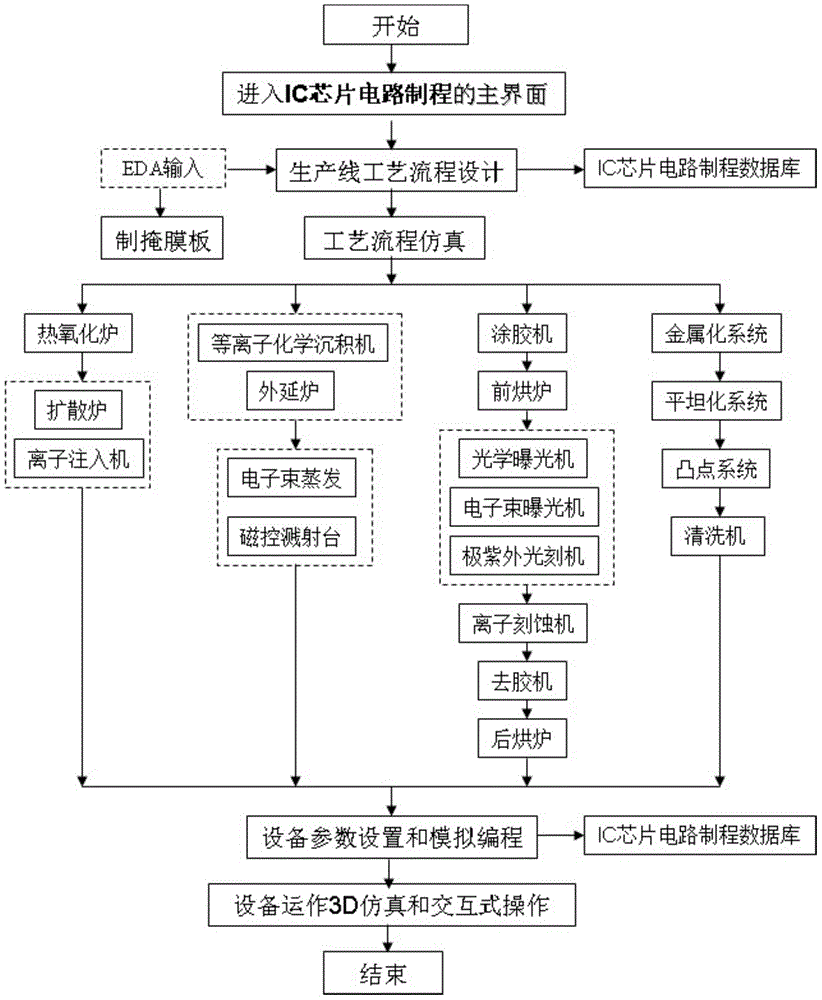

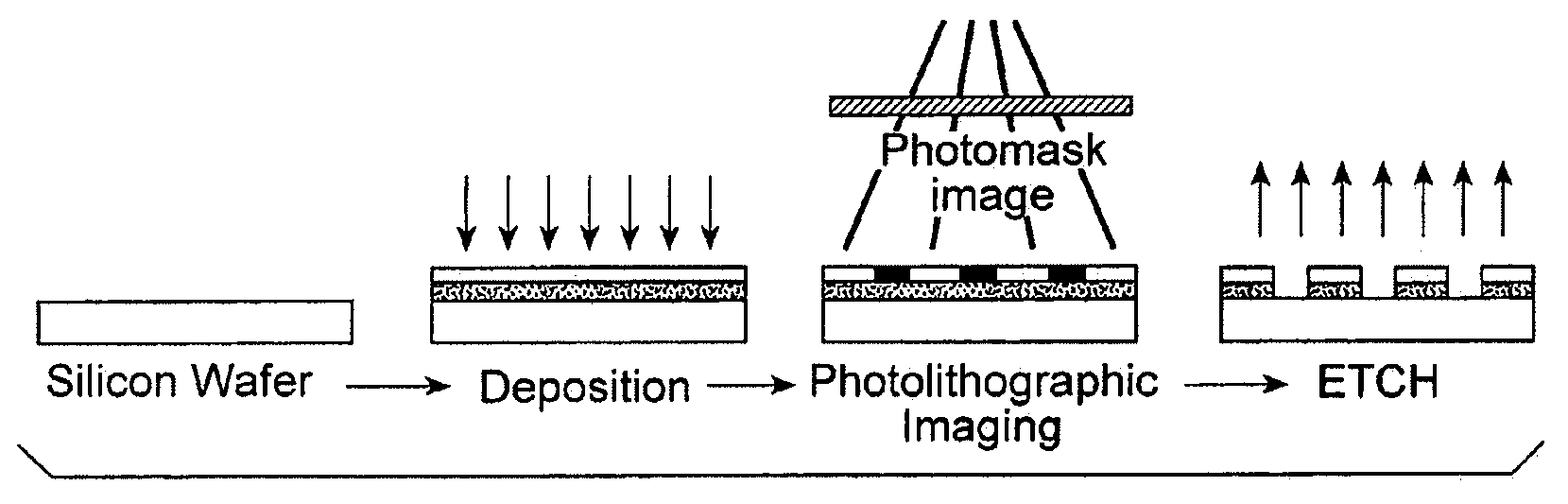

IC (integrated circuit) virtual manufacturing system and implementing method thereof

InactiveCN104657560AImprove technical levelShort development cycleSpecial data processing applicationsIntegrated circuit layoutDigital manufacturing

The invention relates to an IC (integrated circuit) virtual manufacturing system and an implementing method thereof. The implementing method comprises the following steps of according to an EDA (electronic design automation) design document, designing the technological process of an IC production line, wherein the IC production line comprises an IC wafer manufacturing process, an IC chip circuit manufacturing process and an IC packaging manufacturing process; displaying the technological process of the IC production line in a 3D (three-dimensional) cartoon way; performing the parameter setting and programming simulating on key equipment of the IC production line, and inputting the data into a database; automatically performing the mechanism working process 3D simulating and interactive operation on the key equipment of the IC production line by an object orienting technique and a Unity technique under the VC++6.0 environment. The implementing method has the advantages that the intuitive reference is provided for the data modifying of the technological design of the IC production line and the key equipment within the shortest period, so as to realize the purposes of short development cycle, low cost and high production efficiency; the training, examination and technical qualification certifying examination can be performed on IC technicians and engineers.

Owner:CHANGZHOU AUTOSMT INFORMATION TECH

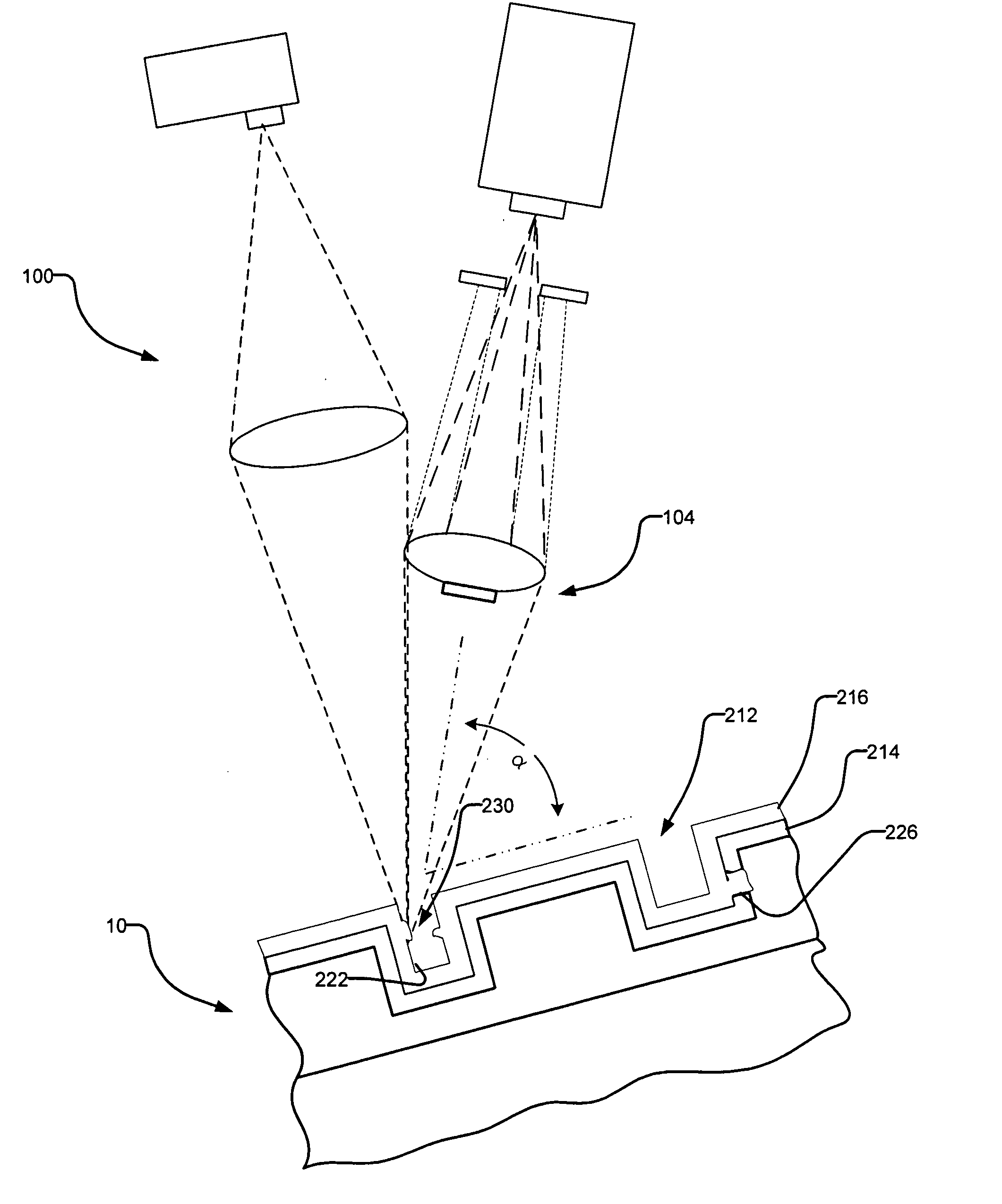

Photomask with detector for optimizing an integrated circuit production process and method of manufacturing an integrated circuit using the same

ActiveUS20080261127A1Semiconductor/solid-state device manufacturingPhotomechanical exposure apparatusSource imageIc production

A photomask for integrated circuit production for development of integrated circuit components, where the integrated circuit production uses a radiation source that generates a source image, includes a substrate with one or more layers disposed thereon; a source separator element that separates the source image into one or more duplicate source images; one or more polarizing elements each corresponding to one of the one or more duplicate source images; and one or more sensors each corresponding to one of the one or more polarizing elements, the one or more sensors sensing one or more radiation characteristics of the radiation source.

Owner:PHOTRONICS INC

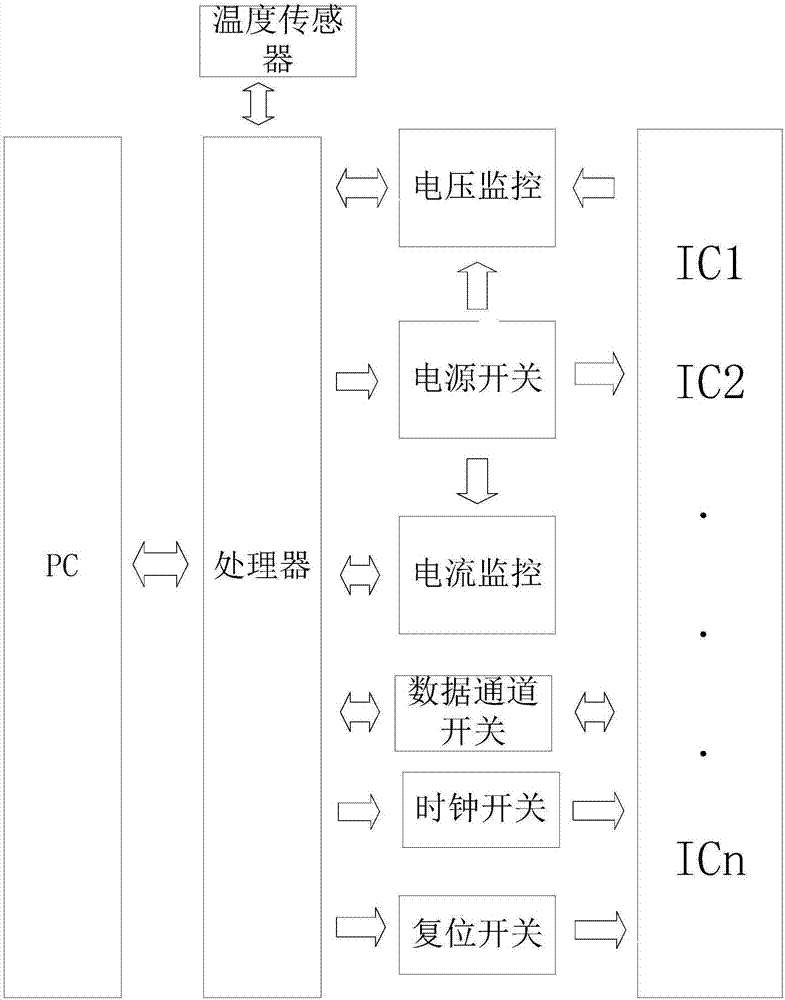

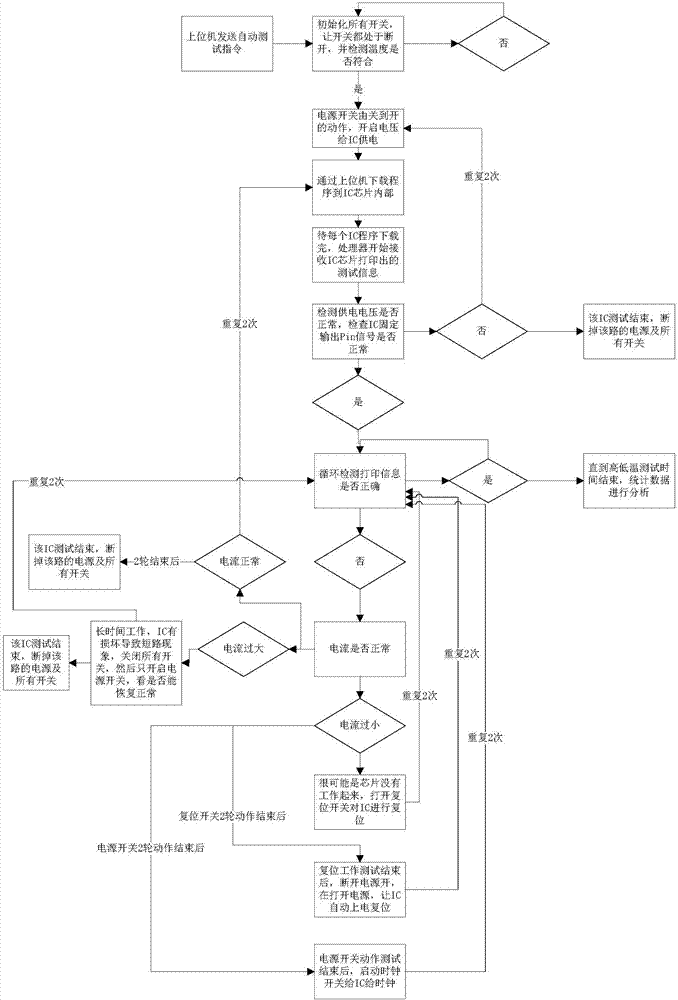

High and low temperature test device for IC testing

The invention relates to a high and low temperature test device for IC testing, so that technical problems that abnormity elimination and correction can not be carried out on a single abnormal integrated circuit while a high-and-low-temperature box is not opened and the power of the integrated circuit that can not be corrected or has been tested can not be cut off completely to enter a silence state in the prior art can be solved. The test device is composed an upper computer, a hardware circuit connected with the upper computer, and a plurality of ICs connected with the hardware circuit. The hardware circuit includes a processor, a power supply module, a current monitoring module, a voltage monitoring module and a switch module, wherein the power supply module, the current monitoring module, the voltage monitoring module and the switch module are connected with the processor. Therefore, the problems can be solved well. The test device can be applied to the industrial IC production.

Owner:张家港市欧微自动化研发有限公司

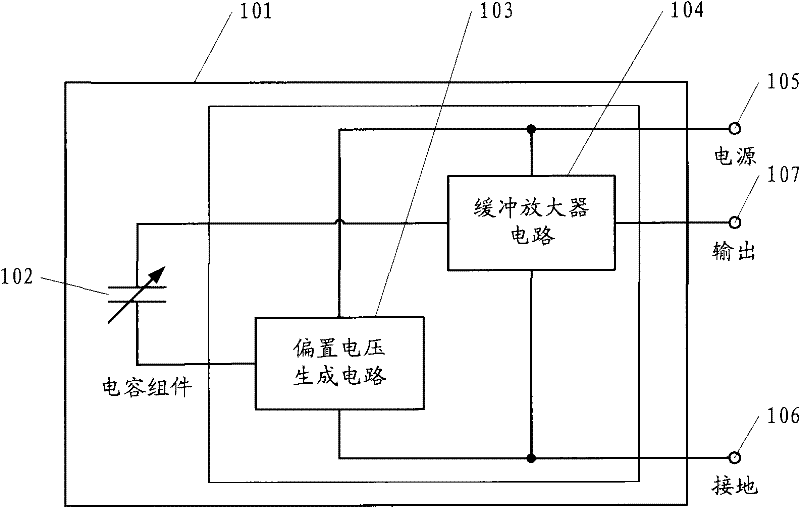

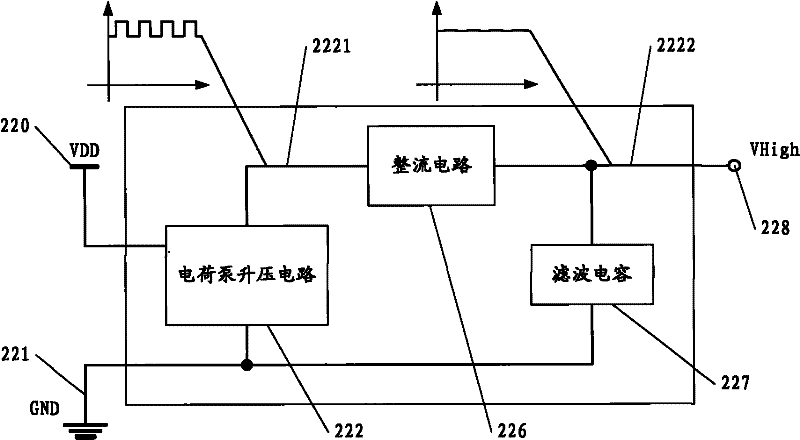

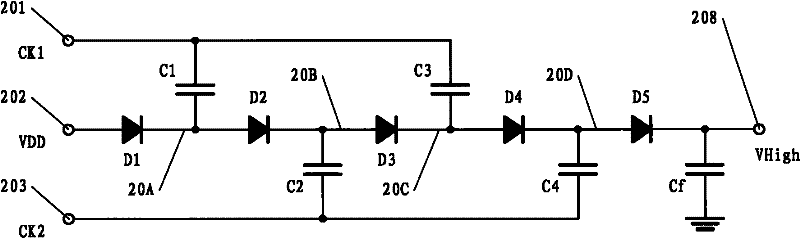

An integrated microphone bias voltage control method and bias voltage generation circuit

ActiveCN102271300AIncrease output impedanceSmall fluctuationTransducer acoustic reaction preventionElectric variable regulationCMOSBicmos integrated circuits

The invention discloses an integrated microphone offset voltage control method and an offset circuit. The method is implemented based on the CMOS (complementary metal-oxide-semiconductor) or BiCMOS (bipolar complementary metal oxide semiconductor) integrated circuit production process, and is applied to an offset voltage generating circuit of a silicon microphone which comprises a charge pump booster circuit, a rectifier circuits and a filter circuits. According to the method, the relationship between output voltages and input currents of the offset voltage generating circuit is controlled, so that the circuit is within a neighboring region with zero current, the input currents of output nodes of the circuit are increased with the increase of output voltages, and the increasing slope rises rapidly with the increase in voltage. The circuit is implemented by connecting a compensation circuit in parallel between the output terminal and the ground terminal of the rectifier circuit; and the compensation circuit has the following functions: in the region of almost zero current and close to the voltage of offset voltage working points of the microphone, the input currents of the output nodes are increased with the increase of voltages applied to the two ends of the compensation circuit, and the current increase rate is higher than the voltage increase rate.

Owner:SHANDONG GETTOP ACOUSTIC

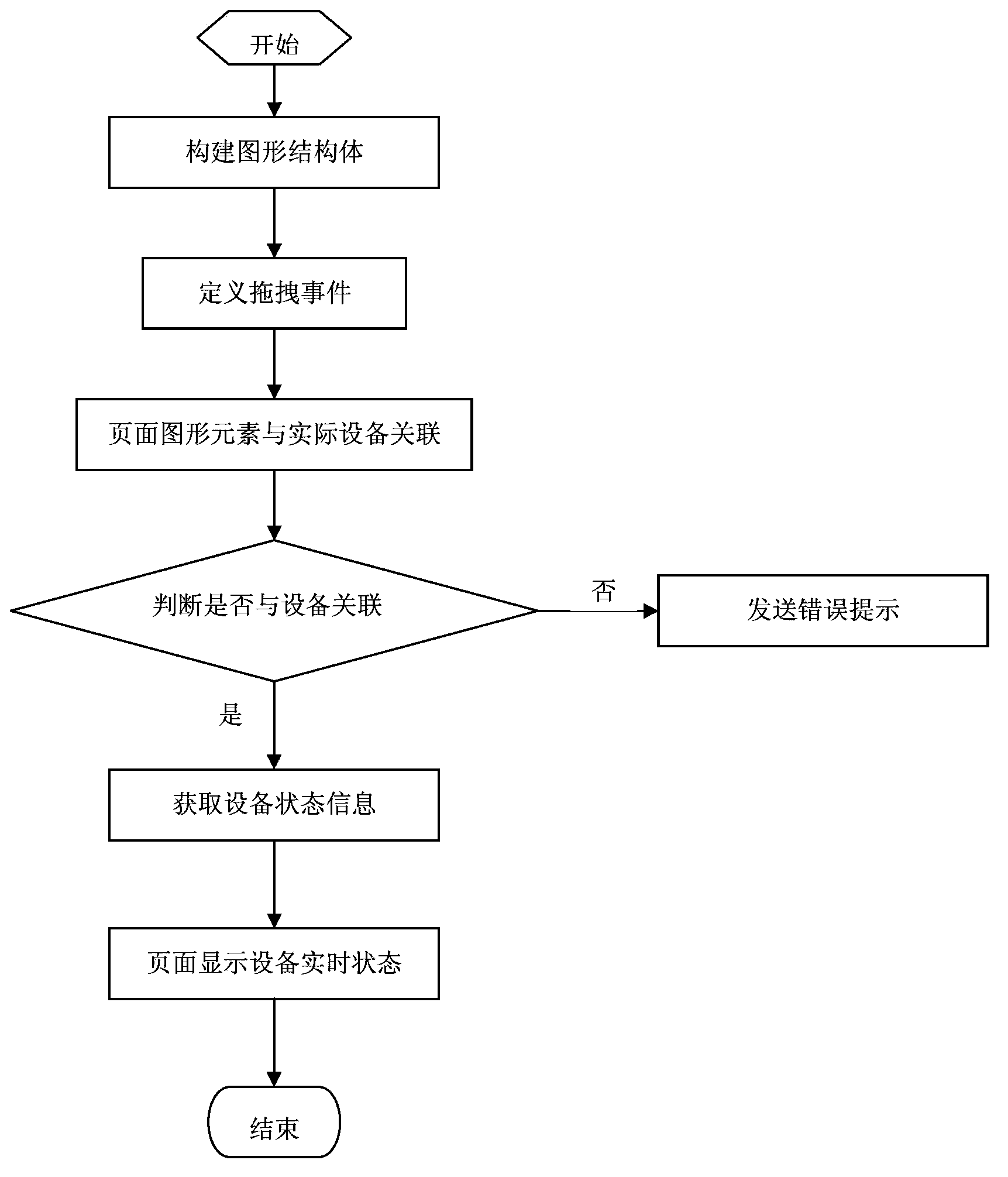

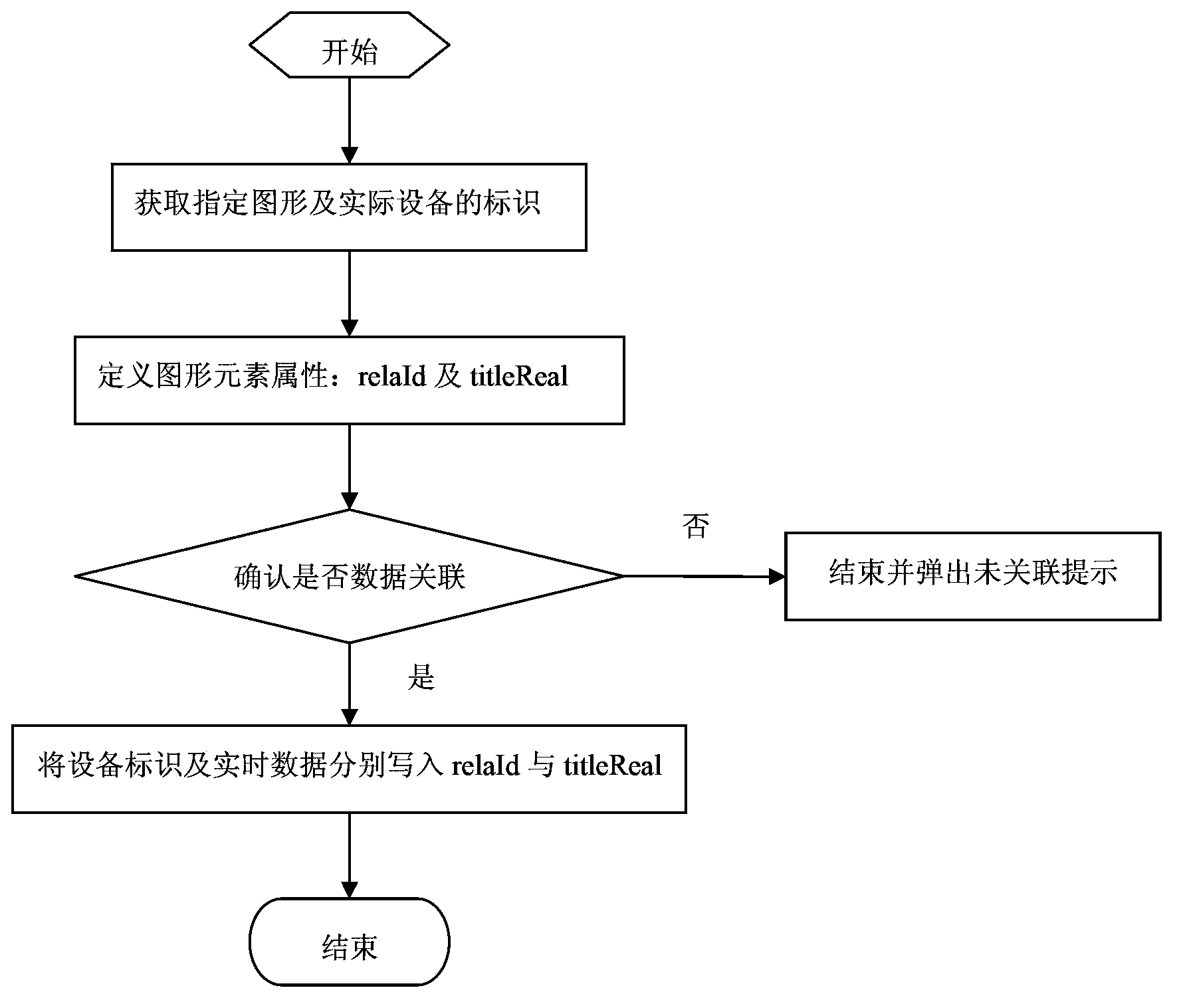

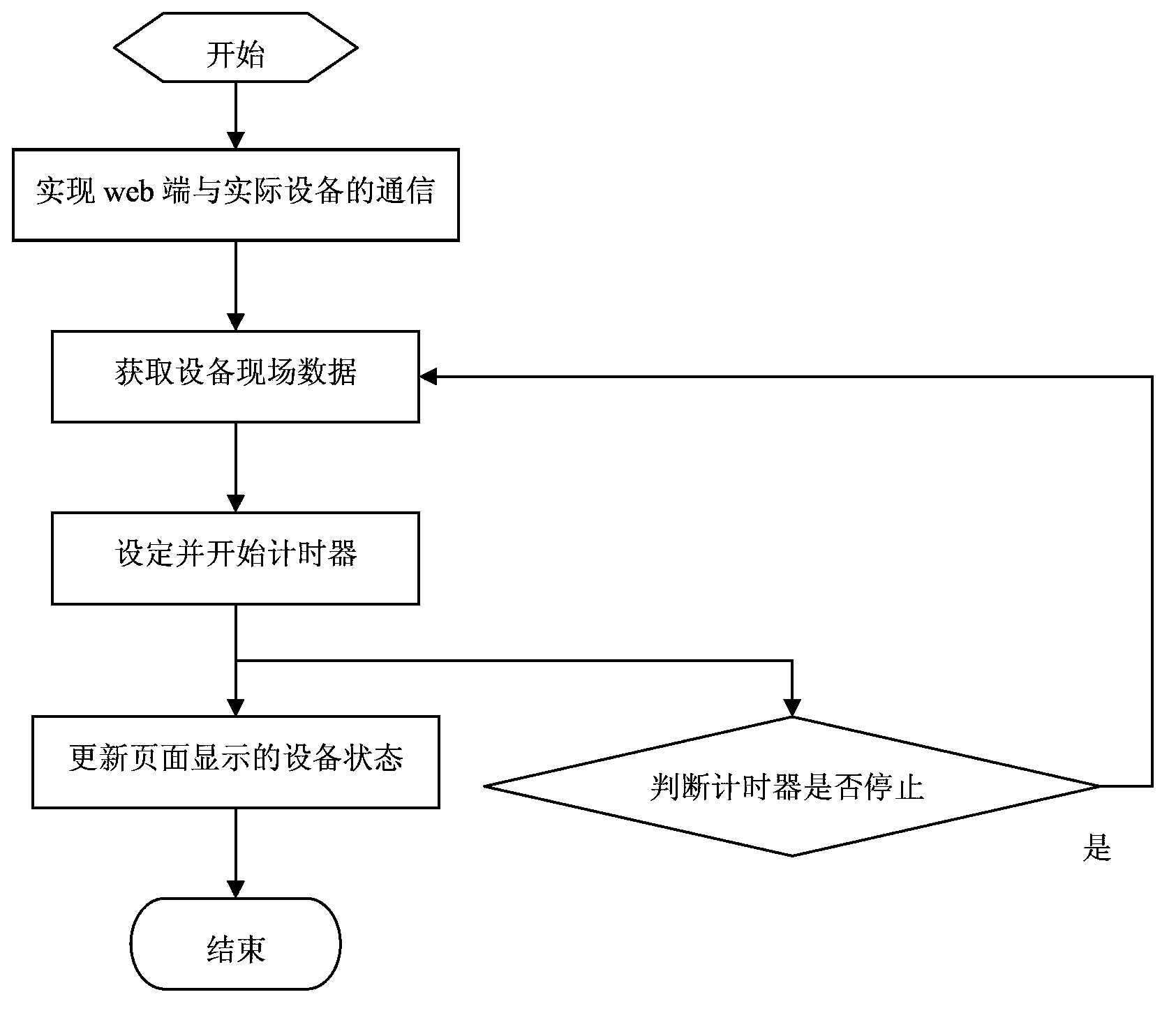

Visual configuration method for integrated circuit production line monitoring system

InactiveCN104142897AEasy to operateInput/output processes for data processingProduction lineGraphics

The invention discloses a visual configuration method for an integrated circuit production line monitoring system. The visual configuration method has the effect of monitoring the integrated circuit production line in real time by the details of realizing connection with a device through serial communication, acquiring real-time production status of device and displaying the status on a web page. The visual configuration method includes the steps of 1, building a graph structural body which includes a graphic edit too bar and a graphic edit area; 2, defining events which are selected, dragged and placed through dragging actions; 3, performing visual configuration, building relation between graph elements at the page end and the actual device; and 4, acquiring real-time status of the device and updating information displayed in the page in real time. The device configuration is achieved by means of dragging, and accordingly the visual configuration method has the advantages of operational convenience, high speed, visual display and the like.

Owner:MICROCYBER CORP

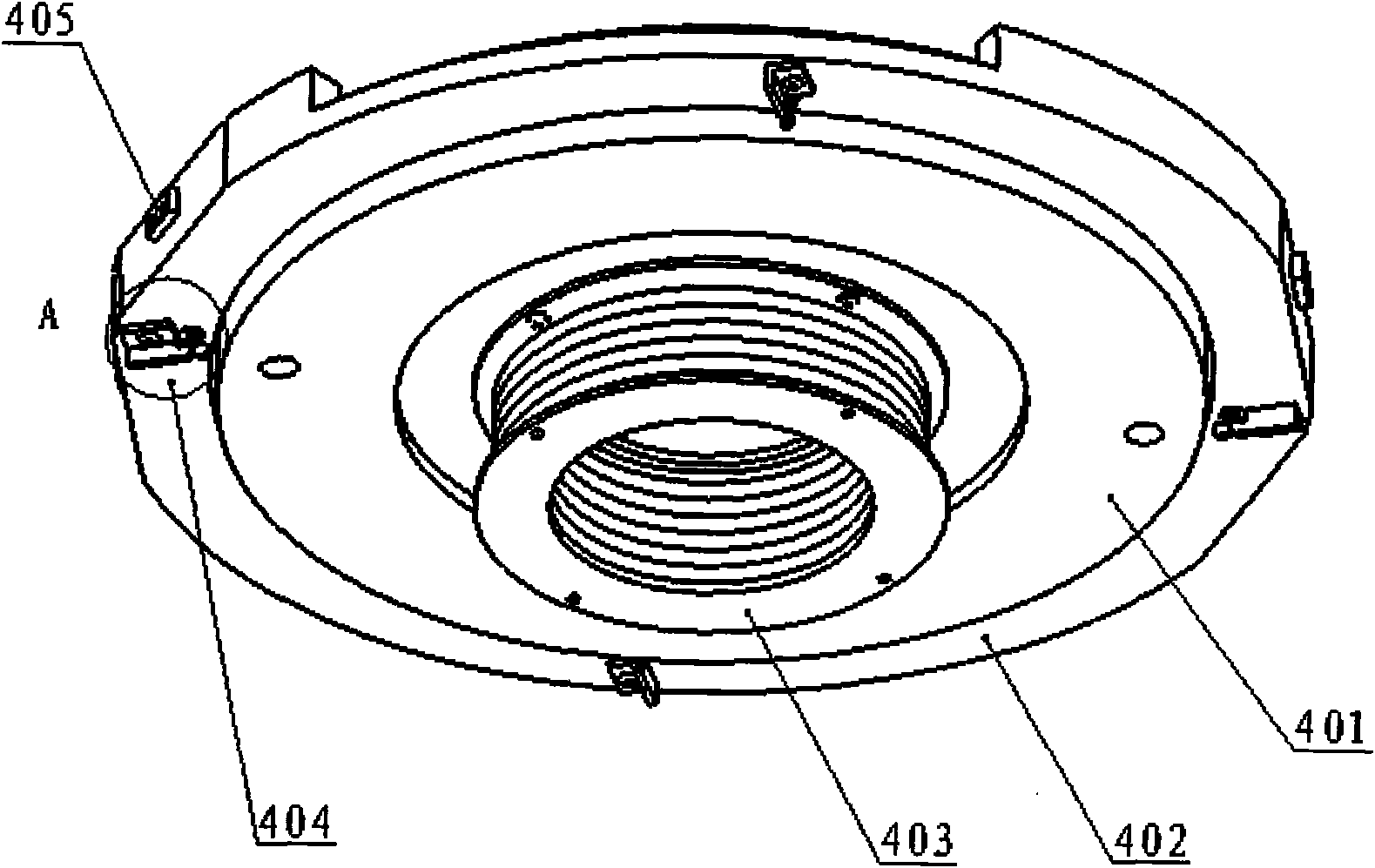

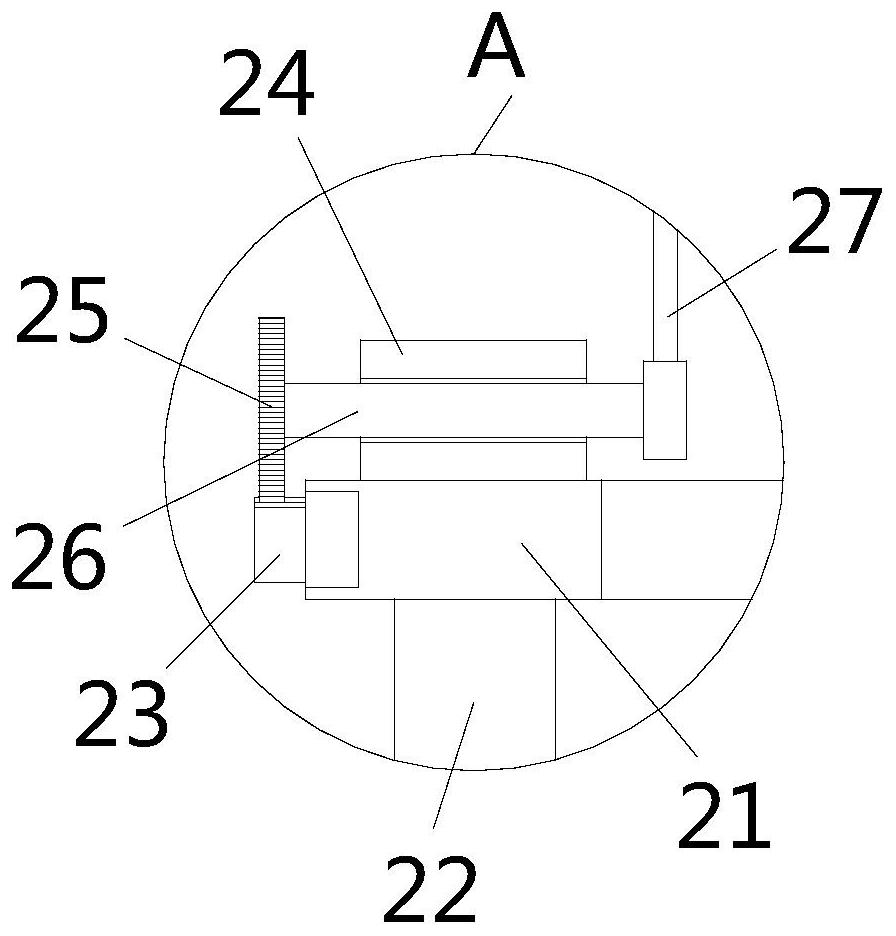

Silicon chip cleaning device of chemical and mechanical polishing equipment

ActiveCN101716585APrecise positioningEasy to cleanCleaning processes and apparatusEngineeringUnresolved Issue

The invention provides a silicon chip cleaning device of chemical and mechanical polishing equipment, relating to the technical field of the chemical and mechanical polishing equipment. The silicon chip cleaning device of the chemical and mechanical polishing equipment is provided with a silicon chip positioning support which is fixed on a central plate, and a silicon chip positioning supporting and resetting device and a silicon chip rotating device are arranged on the central plate. The invention favorably solves the unsolved problems existing in the prior art for a long term. By adopting the silicon chip cleaning device, silicon chips can be accurately positioned as well as reliably cleaned and reset so that the silicon chips obtain high cleanliness and high-efficiency cleaning effect with less abandonment and cost reduction. The silicon chip cleaning device has wide purpose, is suitable for cleaning the silicon chip in each producing procedure of transistors and integrated circuits, is particularly suitable for cleaning the silicon chips polished by using a chemical and mechanical method, can greatly enhance the cleanliness of the surfaces of the polished silicon chips, and can be preferably used for the end point detection after polishing.

Owner:THE 45TH RES INST OF CETC

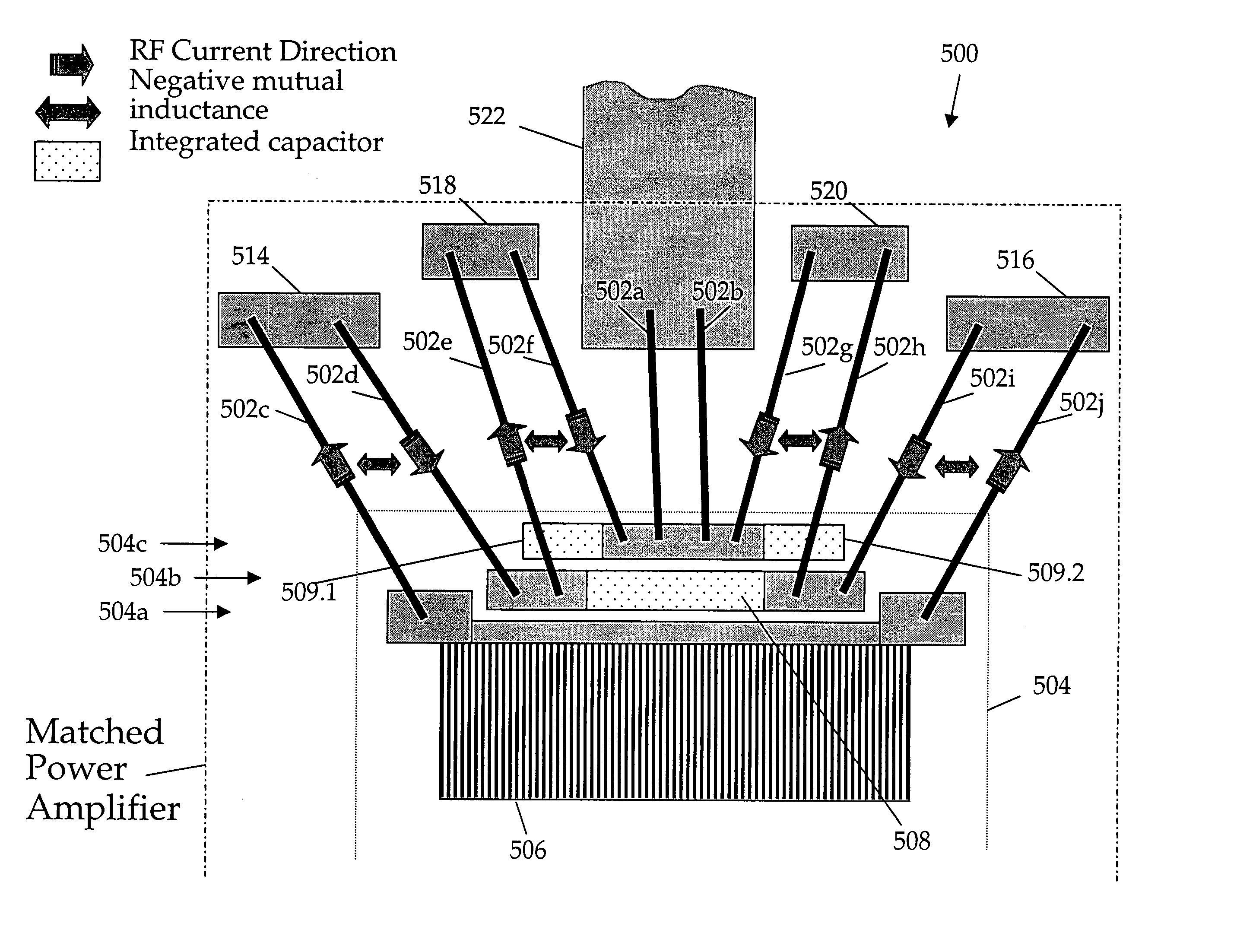

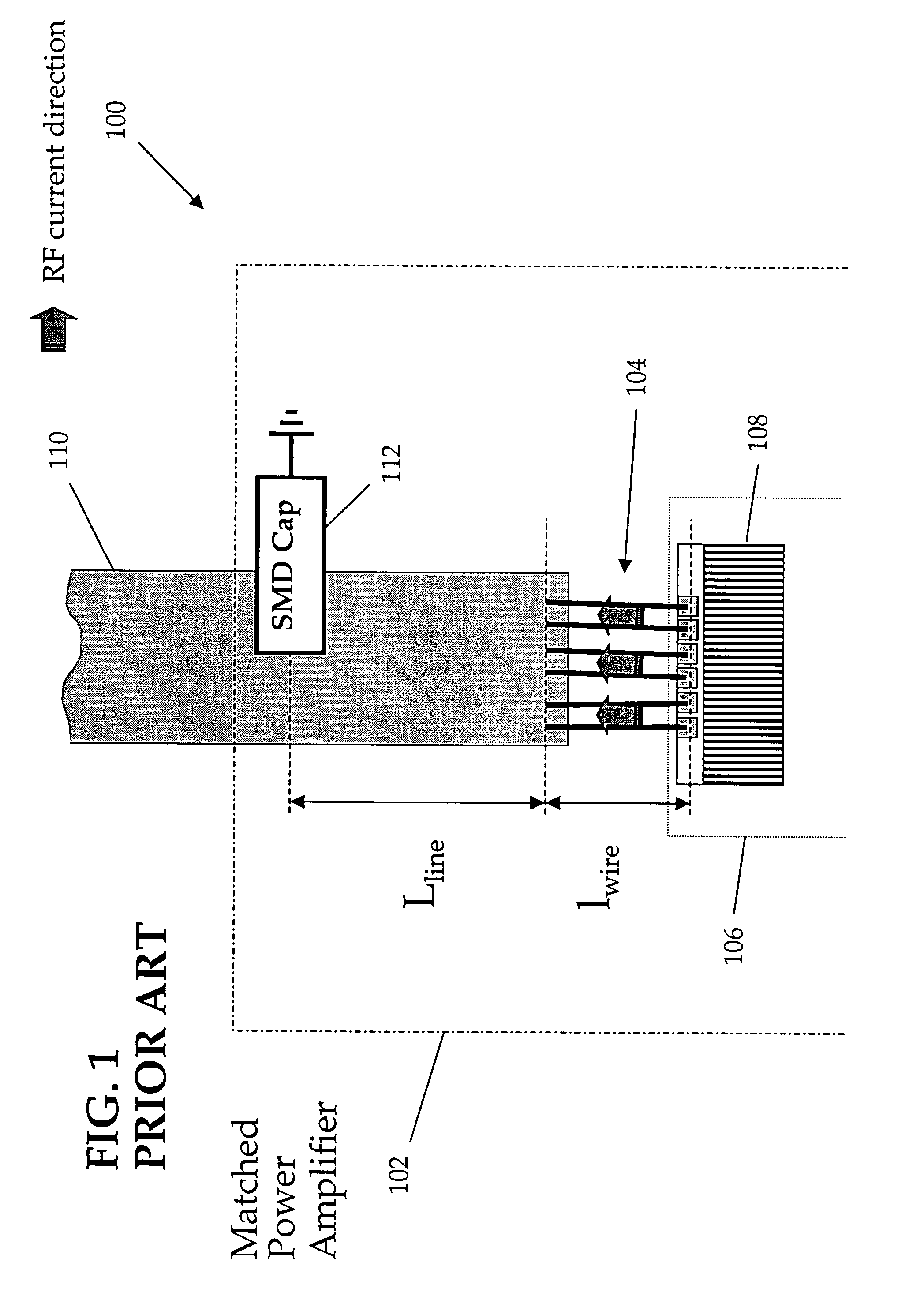

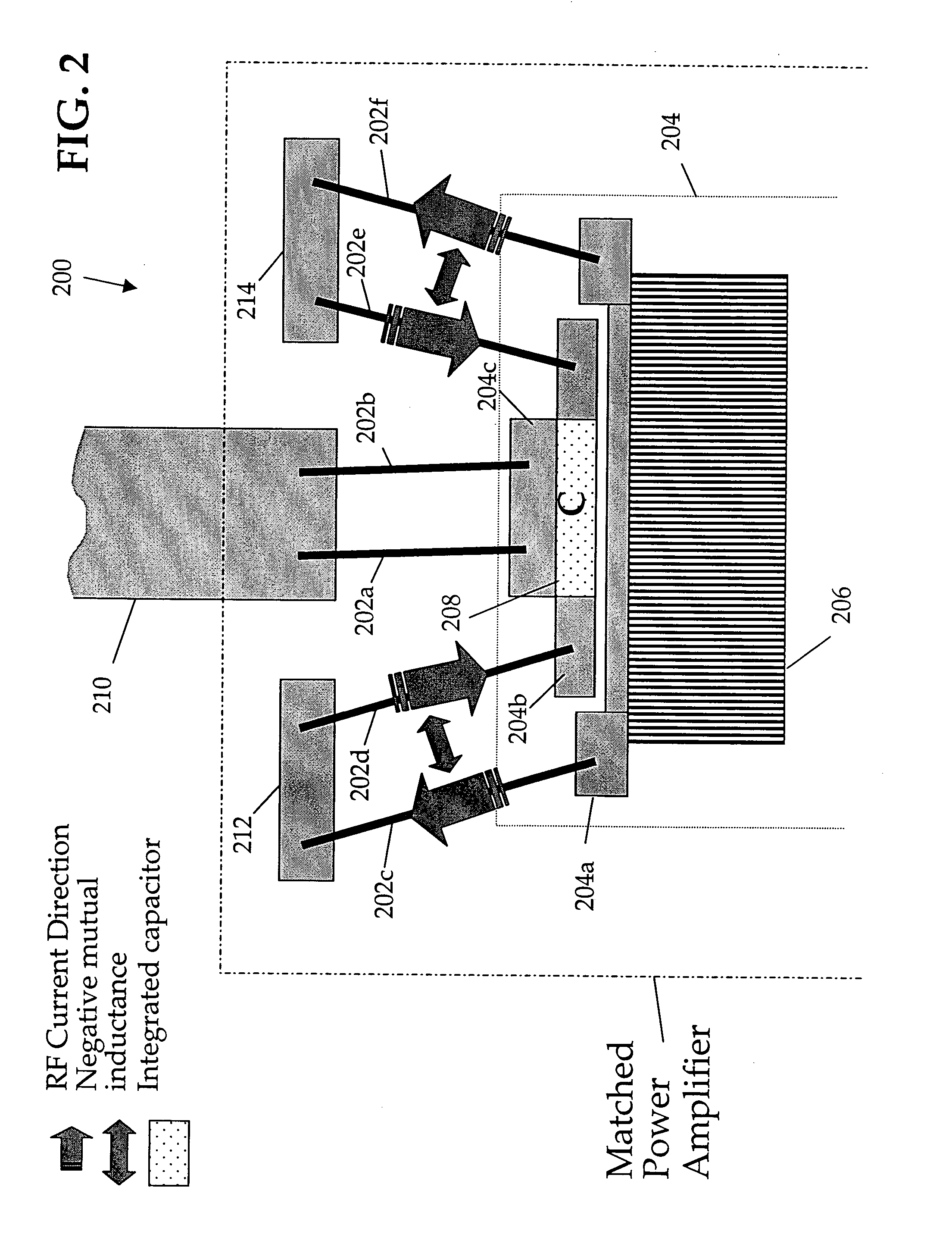

Arrangement and method impedance matching

InactiveUS7113054B2Increase in sizeReduce in quantityImpedence matching networksMultiple-port networksElectrical conductorChip size

An arrangement and method for impedance matching (e.g., for a power amplifier) comprising a first node (204a) for receiving an output current to be impedance matched; a second node (212, 214) for receiving output current from the first node; a first current conductor (202c) for carrying current from the first node to the second node; a third node (204b) for receiving output current from the second node; and a second current conductor (202d) for carrying current from said second node to said third node, whereby the first and second current conductors are closely positioned so that their inductance is the sum of their self-inductances and the negative sum of their mutual inductance. The current conductors may be wire bonds, the arrangement may include a capacitor integrated in a power amplifier IC module, in which the capacitor may be provided in a separate IC from the power amplifier, the arrangement may utilise a plurality of impedance matching cells, and the wire bonds may be interdigitated across the semiconductor die. This provides the following advantages: easy to implement; increased accuracy of matching; requires few external components; easy to manufacture; no need for dedicated design flow; requires only standard IC production and test tools; uses low loss matching networks; involves only a small increase in die size (due to integration of capacitor), but the total size of the solution may be significantly reduced (e.g., by 50%) because of the reduced number of external components.

Owner:NXP USA INC

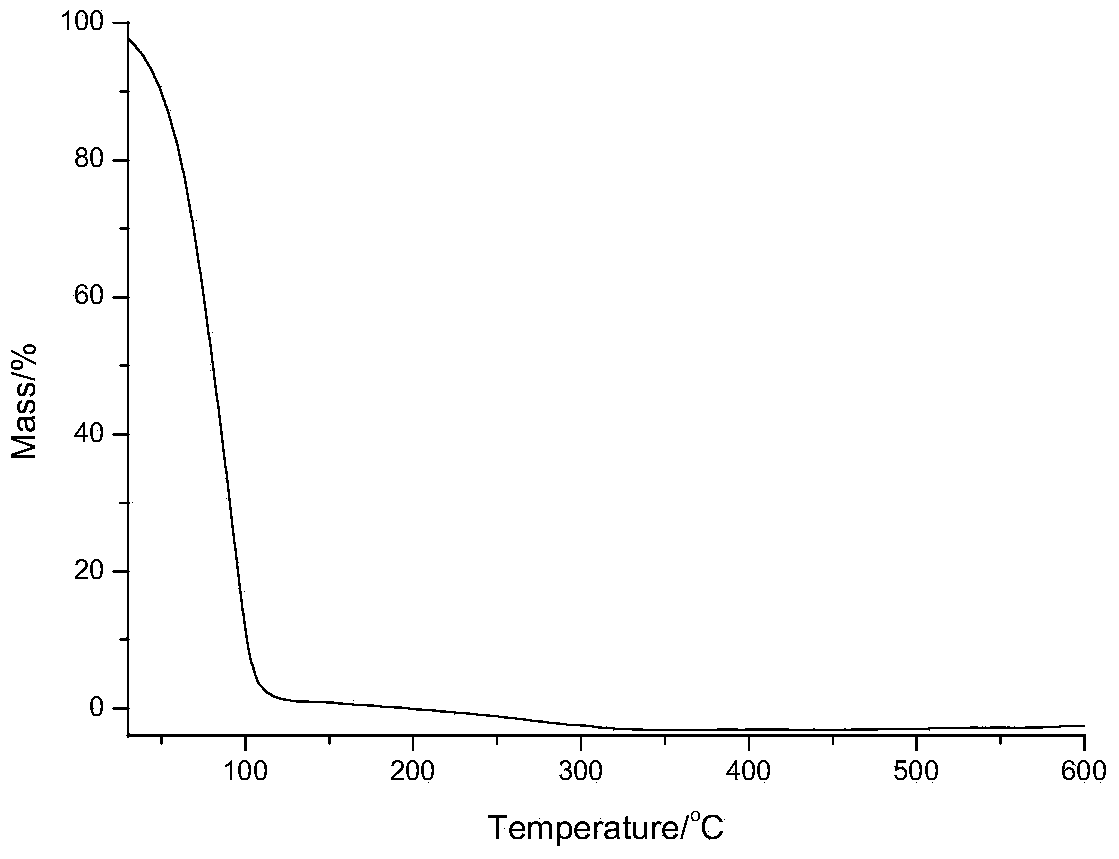

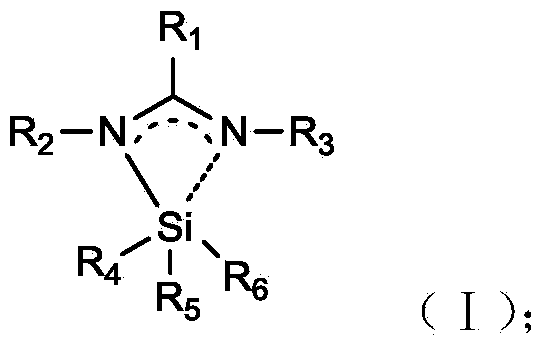

Compound containing N amidino-silicon and application thereof

ActiveCN104341447ALower synthesis costSynthetic conditions are mildSilicon organic compoundsChemical vapor deposition coatingSolventIntegrated circuit

The invention relates to a compound containing N amidino-silicon. The compound is prepared according to the following methods: (1) dissolving carbodiimide or derivatives thereof into a reaction solvent, adding an alkyl / amido lithium solution, aminopyridine or derivatives thereof and alkyl / amido lithium under the stirring condition of -78 DEG C to 0 DEG C according to the molar ratio of 1 to (1-1.2), restoring to room temperature, and then further stirring and reacting for 0.5-3 hours to obtain a reaction mixture; (2) filtering the reaction mixture obtained in the step (1) to obtain lithium salt solid, and dissolving the lithium salt solid into an organic solvent to obtain a lithium salt solution; (3) dropwise adding a silicon-containing reactant or a solution thereof to the lithium salt solution at -78 DEG C to 0 DEG C according to the molar ratio of lithium salt to silicon-containing reactant being (1-4) to (1-1.1), rising to a certain temperature and reacting for 3-10 hours; (4) filtering the reaction mixture obtained in the step (3), concentrating and crystallizing filtrate, or distilling at reduced pressure to obtain a silicon compound containing an amidine ligand. The compound disclosed by the invention can be applied to production of integrated circuits to prepare films of silicon nitride, carbon-containing silicon nitride and the like.

Owner:JIANGNAN UNIV

Use of copper Dimashg process in production of integrated circuits

InactiveCN1855417AImprove yieldReduce adverse reactionsSemiconductor/solid-state device manufacturingGas phaseTantalum nitride

The method comprises: based on the flat surface of photosensitive material and the polysilicon etch-back technology, a selective etch is made for the tantalum nitride and tantalum metal layer deposited with physical vapour deposition process; a one time metal copper chemical mechanical polishing is used to replace the original two times polishing process, copper chemical mechanical polishing and tantalum nitride / tantalum metal layer polishing. The invention reduces the dishing of metal wire and the erosion of insulation media caused by over-polishing from multi times of chemical mechanical polishing.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +2

Deposition of polymeric materials and precursors therefor

Substituted paracyclophanes are particularly useful as precursors in the formation of a cross-linkable polymer on a deposition substrate such as an electronic device being processed. The paracyclophane precursor including a cross-linkable substituent such as an alkynyl is cracked at the phenyl linkages. The substrate is subjected to the*cracked precursor. As a result, an organic polymer is formed on the substrate. Cross-linking of the polymer through reaction, e.g. thermally induced reaction, of the cross-linkable substituents produces a thermally stable cross-linked polymer. The deposition of such cross-linked polymer is particularly useful for sealing ultra low k dielectric materials used in the damascene process in the production of integrated circuits. Alternatively the polymer is also advantageous as an adhesive in wafer-to-wafer bonding. Alternatively, the polymer is useful as a hardmask to replace silicon nitride and silicon carbide in the back-end-of-the-line processing of electronic devices.

Owner:BREWER SCI

Positioning method for packaging and picking up chips

ActiveCN105374726ASolve the problem of ineffective one-to-one correspondenceEasy to operateSemiconductor/solid-state device detailsSolid-state devicesIc productionIntegrated circuit

The invention discloses a positioning method for packaging and picking up chips. The method comprises steps of: using triangular unexposed regions on the edge of a wafer as positioning regions in an integrated circuit production design process; in an integrated circuit chip manufacture process, selecting one or two of the triangular unexposed regions, not exposing or etching the one or two triangular unexposed regions, and selecting a positioning point in order to achieve pickup positioning; in an integrated circuit testing flow, bypassing the triangular unexposed regions, marking good or bad chips in wafer map file, and marking untested chips as invalid chips; and in an integrated circuit chip packing and picking process, picking up chips by using a wafer map and enabling positioning marks in the wafer map to correspond to special positioning patterns on entity wafers so that one-to-one correspondence between the wafer map file and the entity wafers is achieved and a problem of erroneously picking up a chip is prevented in a packaging process.

Owner:唐山捷准芯测信息科技有限公司

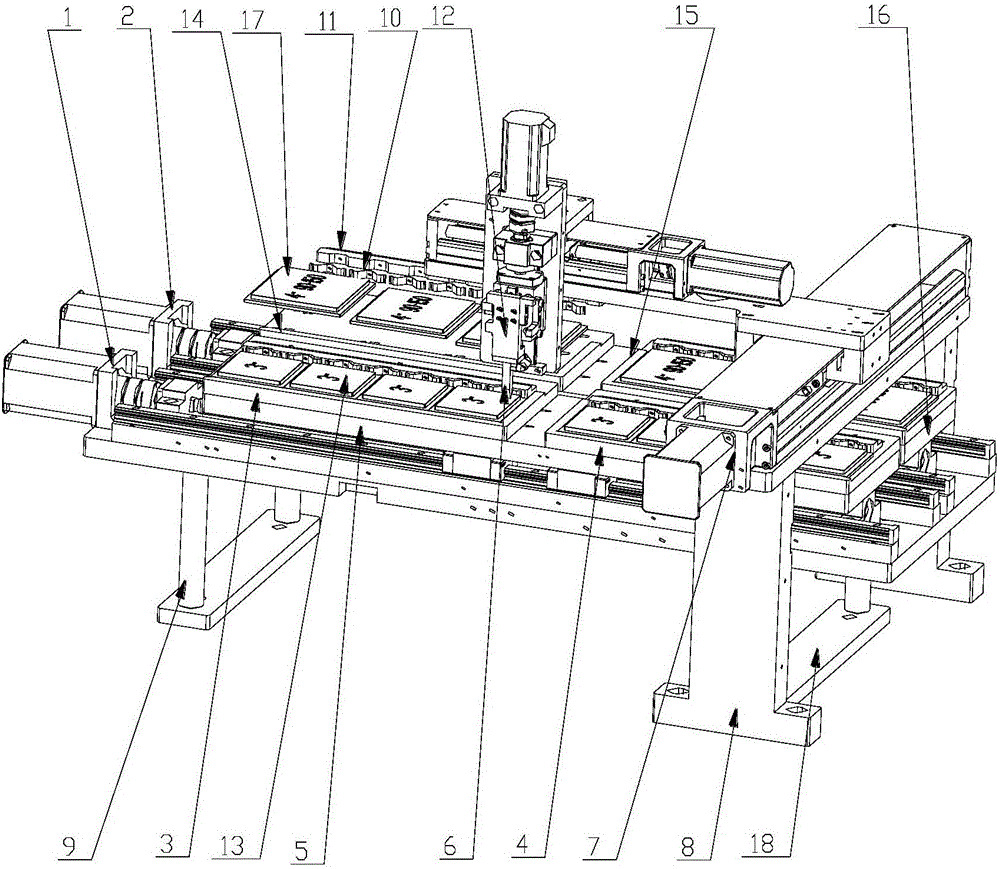

Non-shutdown various-IC picking device

InactiveCN106629037AIncrease flexibilityGuaranteed stabilityConveyor partsShortest distanceControl theory

The invention discloses a non-shutdown various-IC picking device which comprises an IC picking mechanism, a servo motor X-Y-Z-direction work platform, servo motor X-Y-Z-direction work platform mounting racks, a feeding mechanism and a servo motor X-direction work platform A and B mounting rack base. The IC picking mechanism is mounted on the servo motor X-Y-Z-direction work platform; the servo motor X-Y-Z-direction work platform is mounted on the servo motor X-Y-Z-direction work platform mounting racks; and the feeding mechanism is mounted on the servo motor X-direction work platform A and B mounting rack base. The non-shutdown various-IC picking device is used for picking ICs in a small fixed area, the stability and success rate of IC picking are guaranteed, IC picking in the shortest distance is guaranteed, the IC picking time is shortened, and the efficiency of the device is improved; and stable non-shutdown same-type IC production is achieved by means of left area feeding and right area feeding, and stable non-shutdown IC production can be achieved as long as movable IC feeding mechanism bodies are additionally arranged.

Owner:SHENZHEN COMWIN AUTOMATION TECH

Semiconductor integrated circuit test equipment

InactiveCN112964978AImprove positioning test efficiencyHigh precisionElectronic circuit testingIc productionSemiconductor

The invention relates to the technical field of integrated circuit production and processing, and discloses semiconductor integrated circuit test equipment. The semiconductor integrated circuit test equipment comprises a workbench, wherein a test board is fixedly installed at the center of the top part of the workbench, a probe board is arranged at the top part of the test board, a lifting mechanism is arranged at the top part of the workbench, and the lifting mechanism comprises a lifting table. According to the semiconductor integrated circuit test equipment, a rotating ring rotates in one direction on the outer wall of the lifting table, so that a positioning frame is driven by four groups of moving rods and four groups of linkage rods to continuously reciprocate up and down in a hollow part in the middle of the lifting table, the positioning frame drives a circuit board limited in a cavity of the positioning frame to reciprocate up and down, when the positioning frame moves to the lowest part of the lifting platform, the circuit board is in extrusion contact with a probe on the top part of the probe plate, and the circuit board is accurately butted with the probe on the probe plate up and down. The positioning test efficiency of a semiconductor integrated circuit board is improved.

Owner:北京瓢虫星球信息技术有限公司

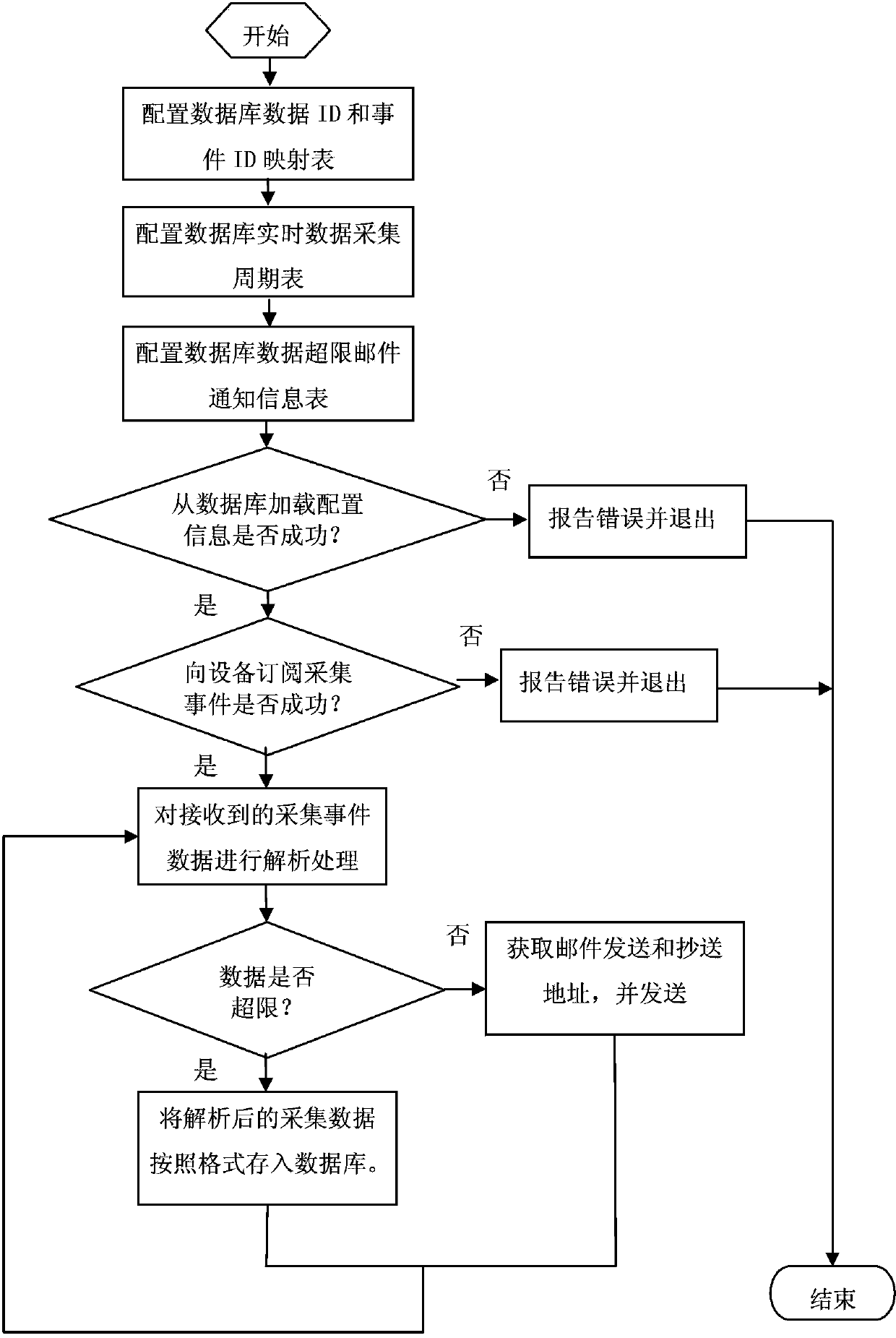

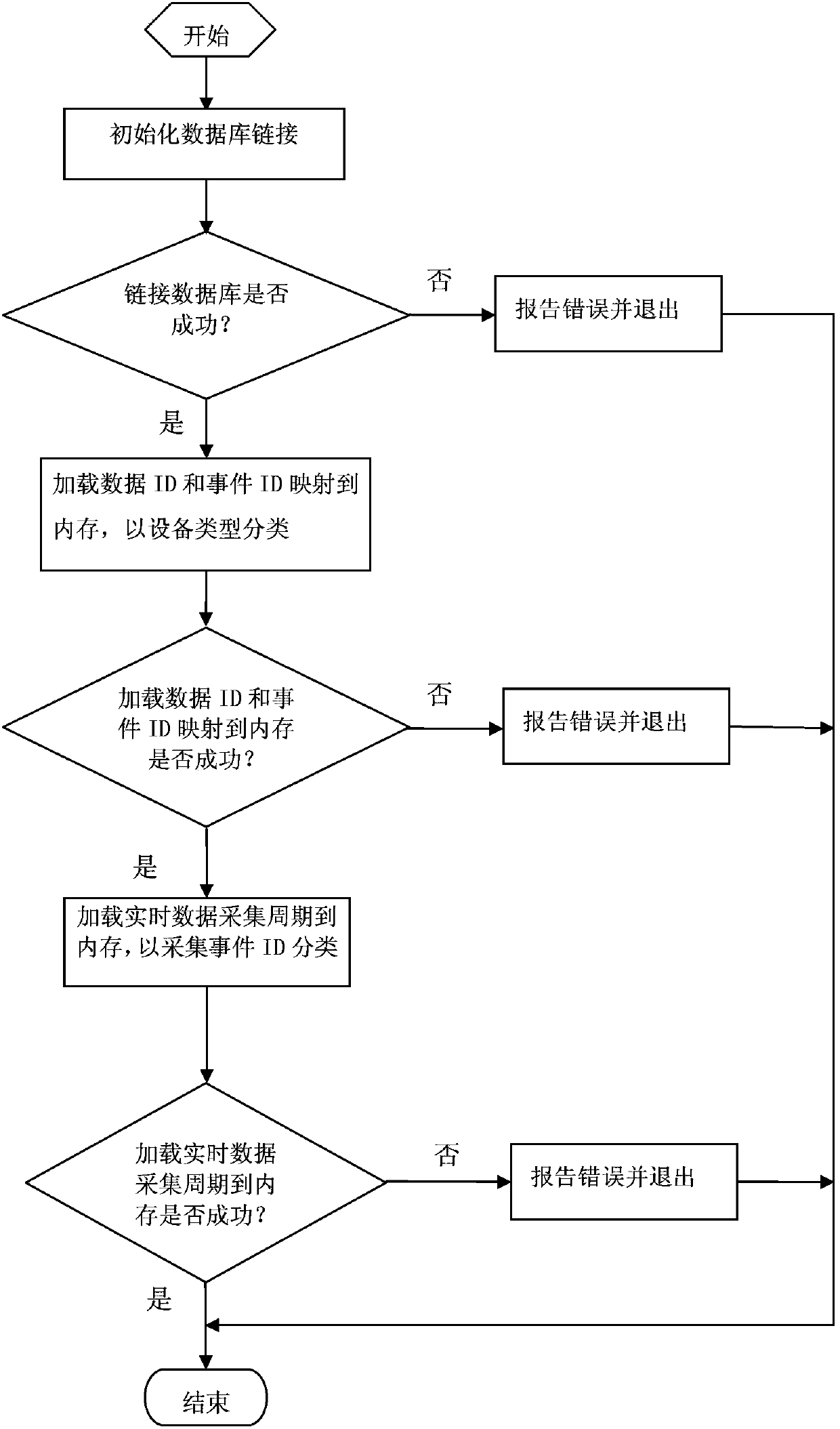

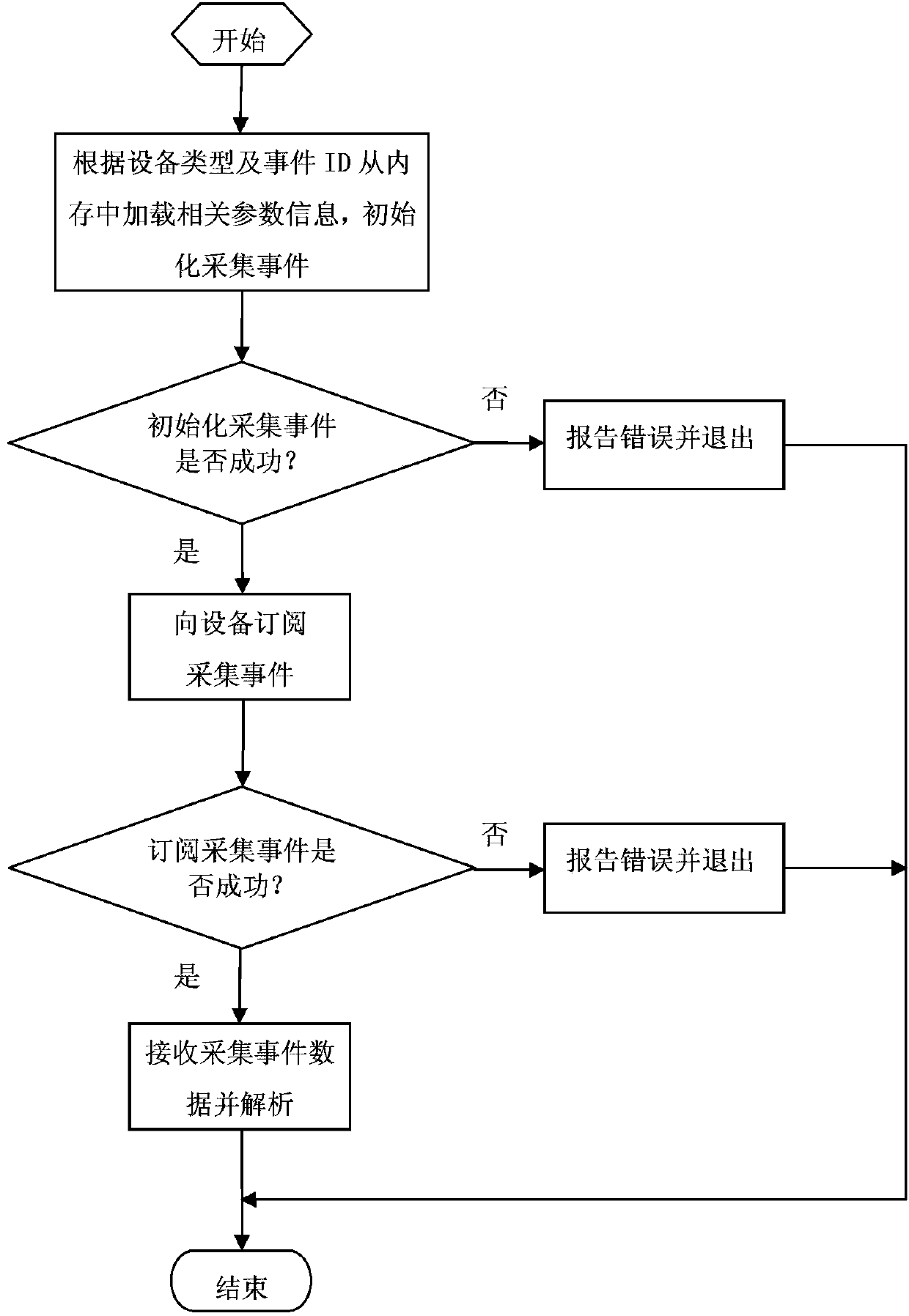

Rapid collecting and distributing method of real-time data for integrated circuit production equipment

InactiveCN103399881AEasy to update dynamicallyImprove development efficiencySpecial data processing applicationsReal-time dataIc production

The invention discloses a rapid collecting and distributing method of real-time data for integrated circuit production equipment, aiming to distribute the real-time data collected by different types of integrated circuit production equipment. The rapid collecting and distributing method includes steps of 1), configuring a data collection ID of database management and an event ID mapping table; 2), configuring a real-time data-collecting periodic table of the database management; 3), configuring a notification information table of data-overrun emails for a control section that the equipment of the database management belongs to; 4), loading configuration information from the database; 5), customizing the collected events from the integrated circuit production equipment; 6), subjecting the received data of the collected events to analytical processing; 7), subjecting the collected and analyzed data to distributing processing. By the rapid collecting and distributing method, the real-time data collected by the different types of the integrated circuit production equipment can be subjected to distributing processing which can be customized by customers, so that flexibility and adaptability of software are improved.

Owner:MICROCYBER CORP