Patents

Literature

1242 results about "Guard ring" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

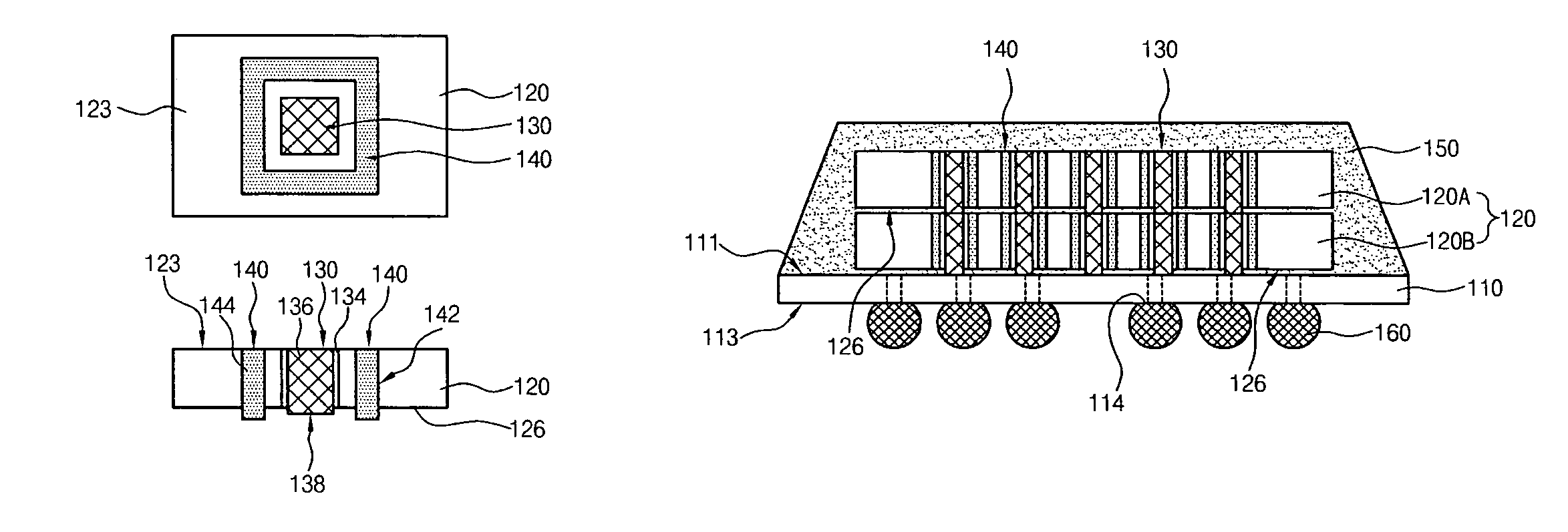

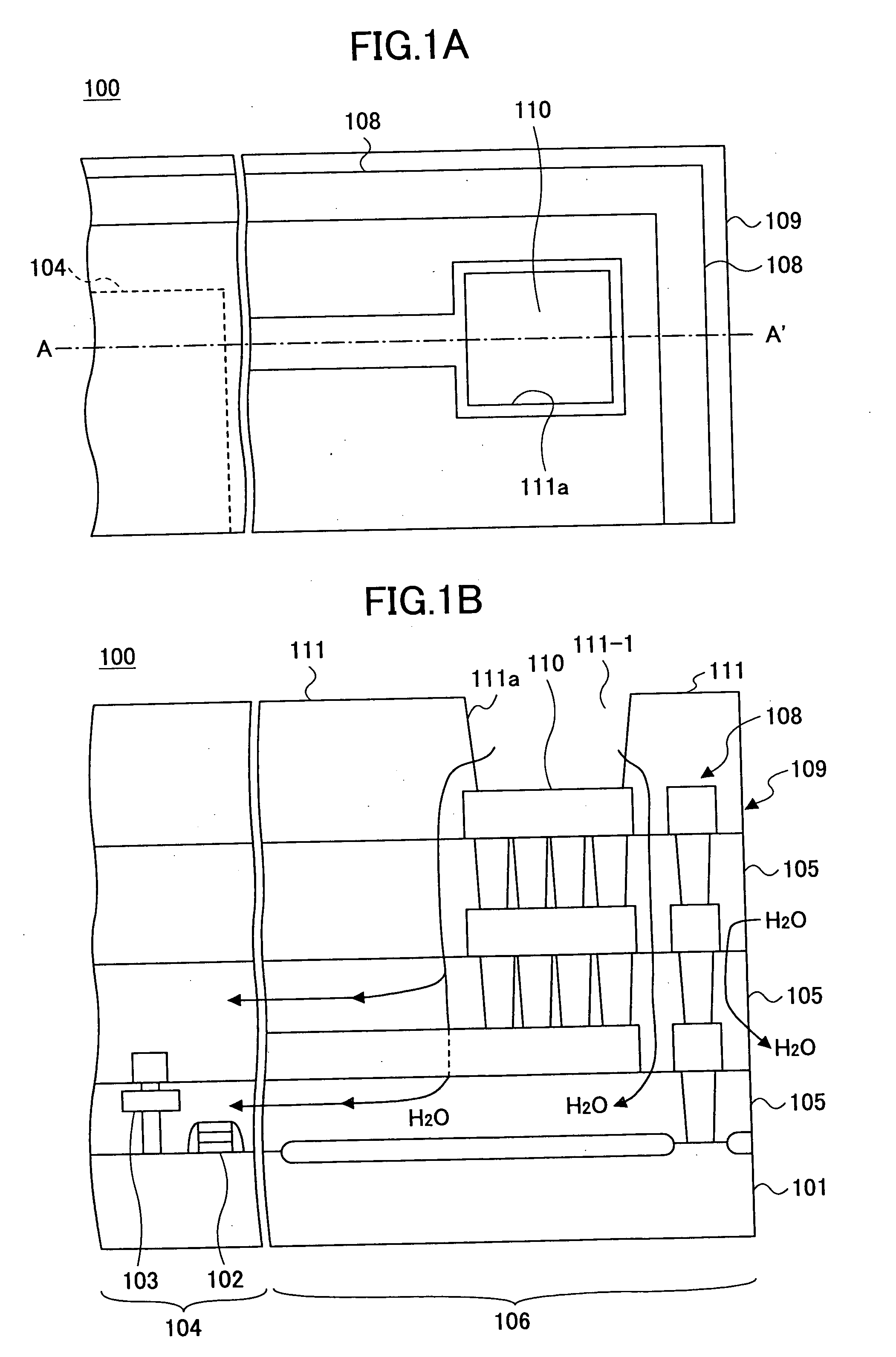

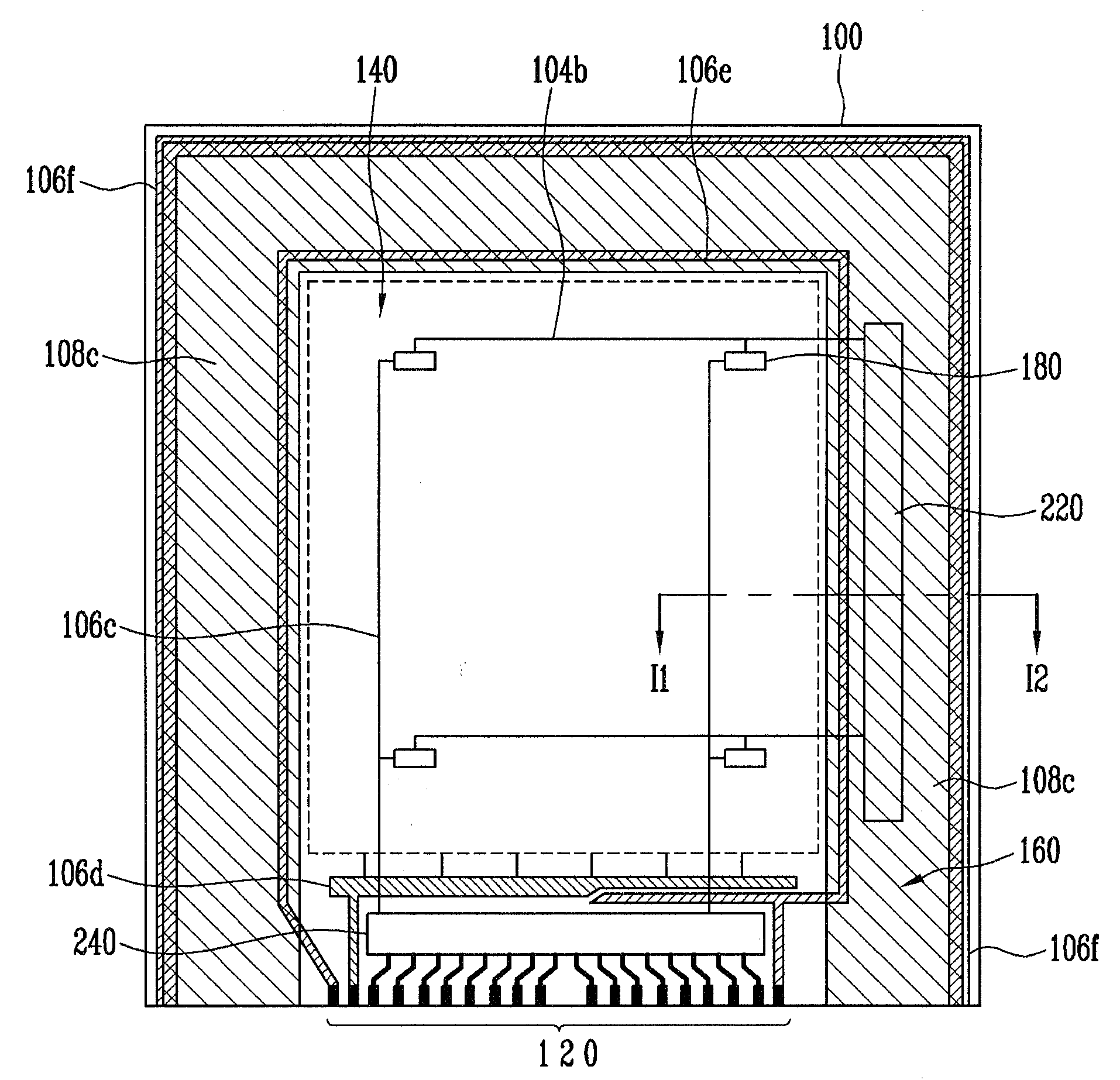

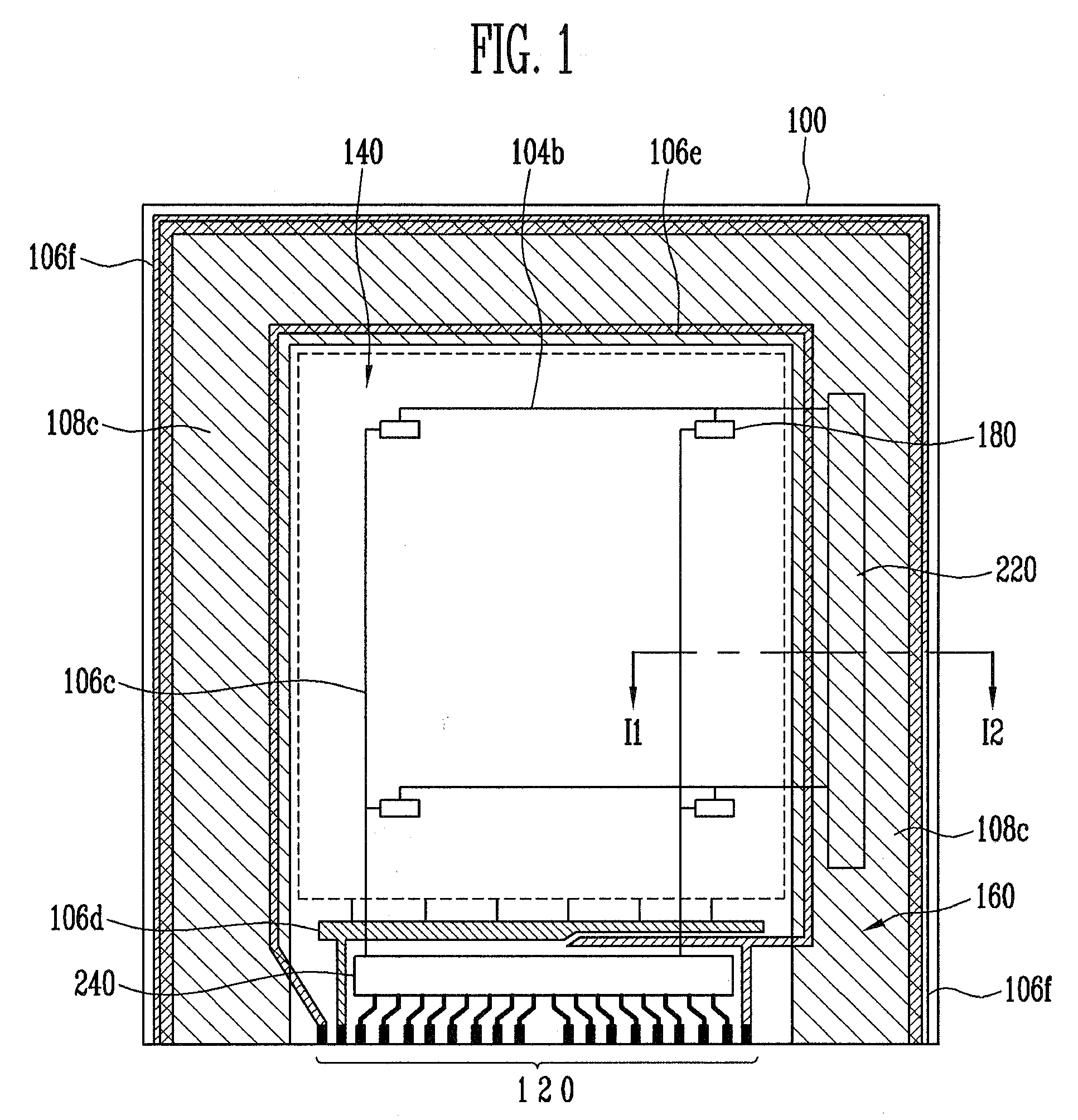

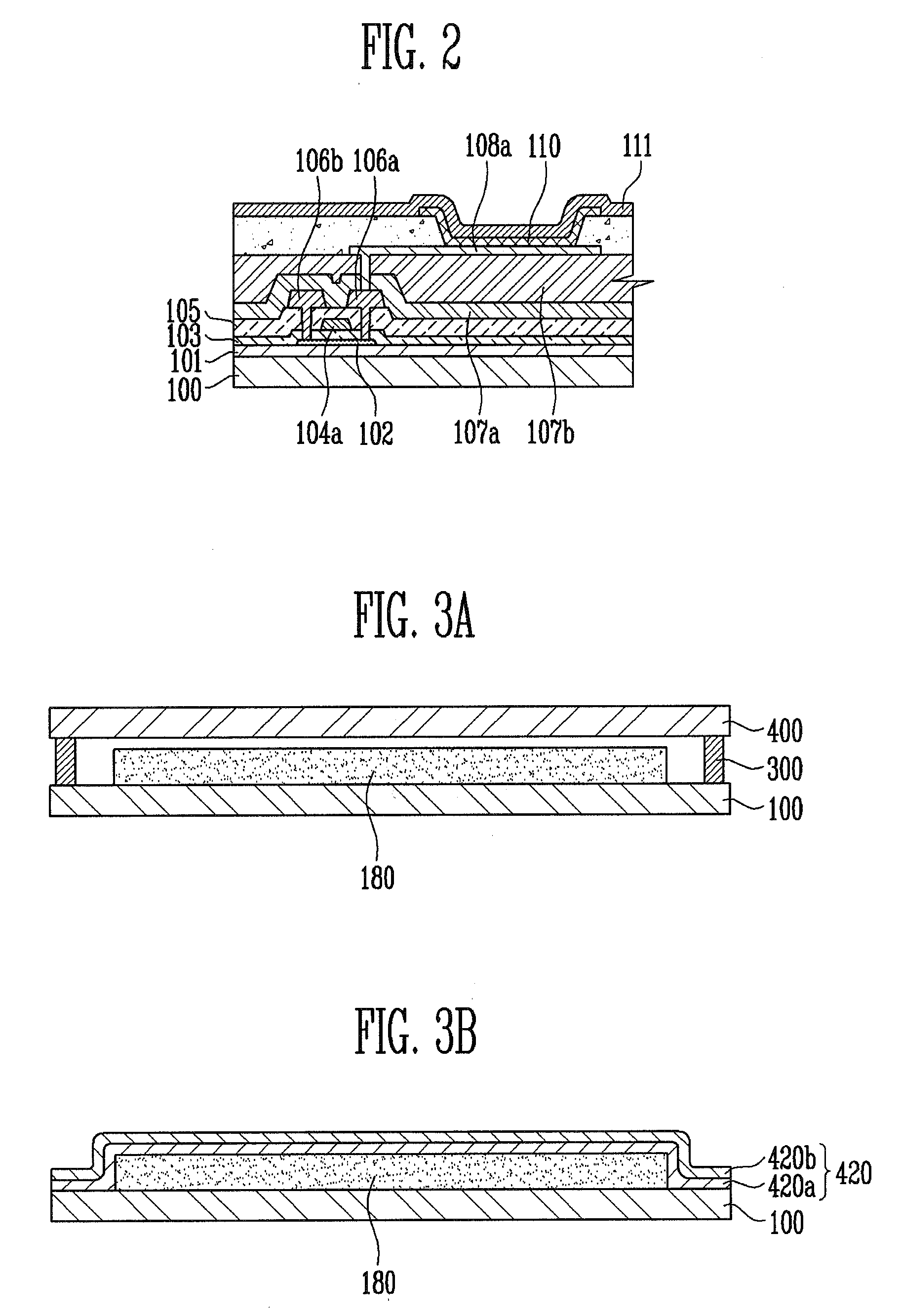

Stack package having guard ring which insulates through-via interconnection plug and method for manufacturing the same

ActiveUS7525186B2Avoid crackingAvoid disconnectionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSolder ball

A stack package comprises a substrate having a circuit pattern; at least two semiconductor chips stacked on the substrate, having a plurality of through-via interconnection plugs and a plurality of guard rings which surround the respective through-via interconnection plugs, and connected with each other by the medium of the through-via interconnection plugs; a molding material for molding an upper surface of the substrate including the stacked semiconductor chips; and solder balls mounted to a lower surface of the substrate.

Owner:SK HYNIX INC

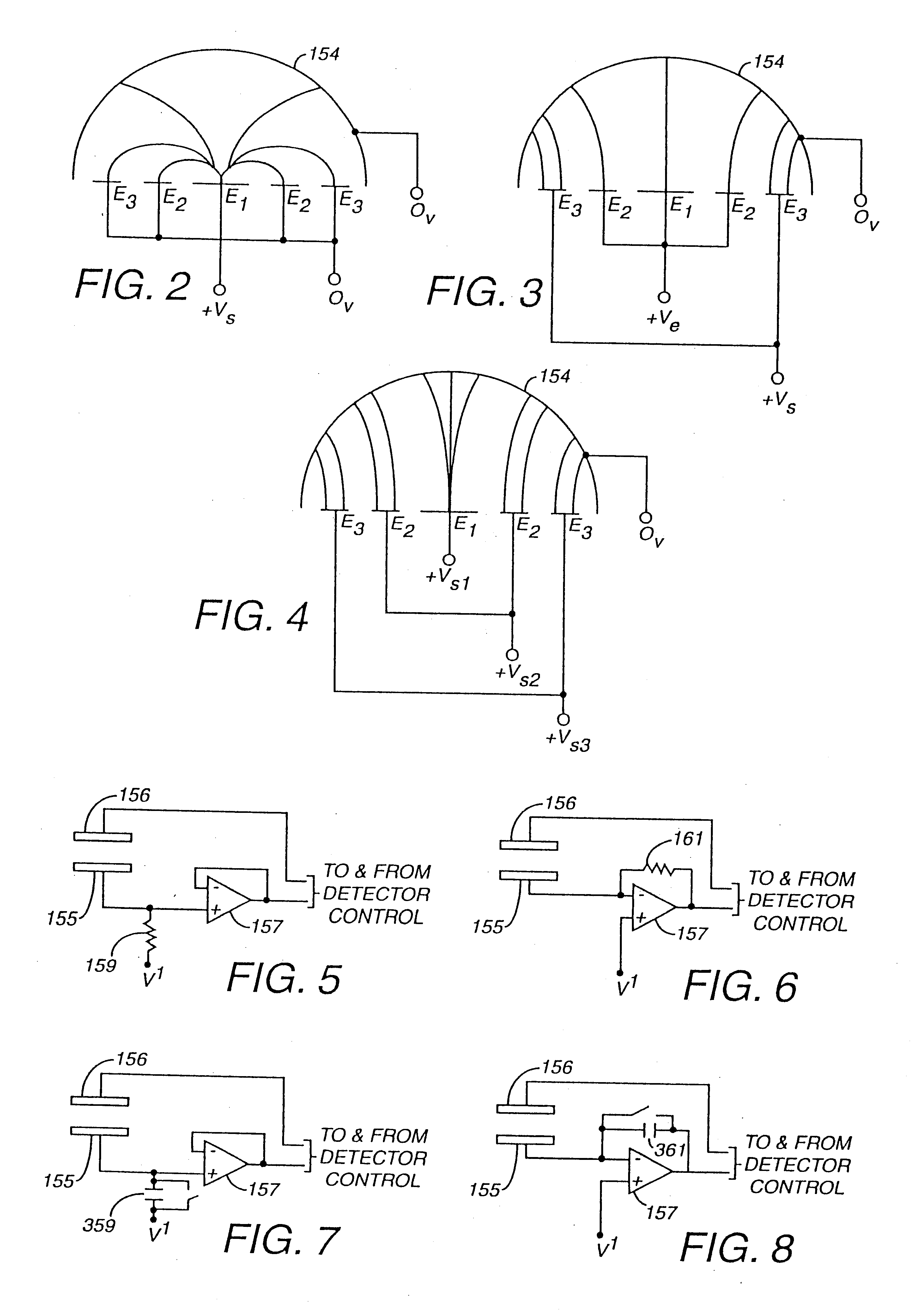

Electronic circuit

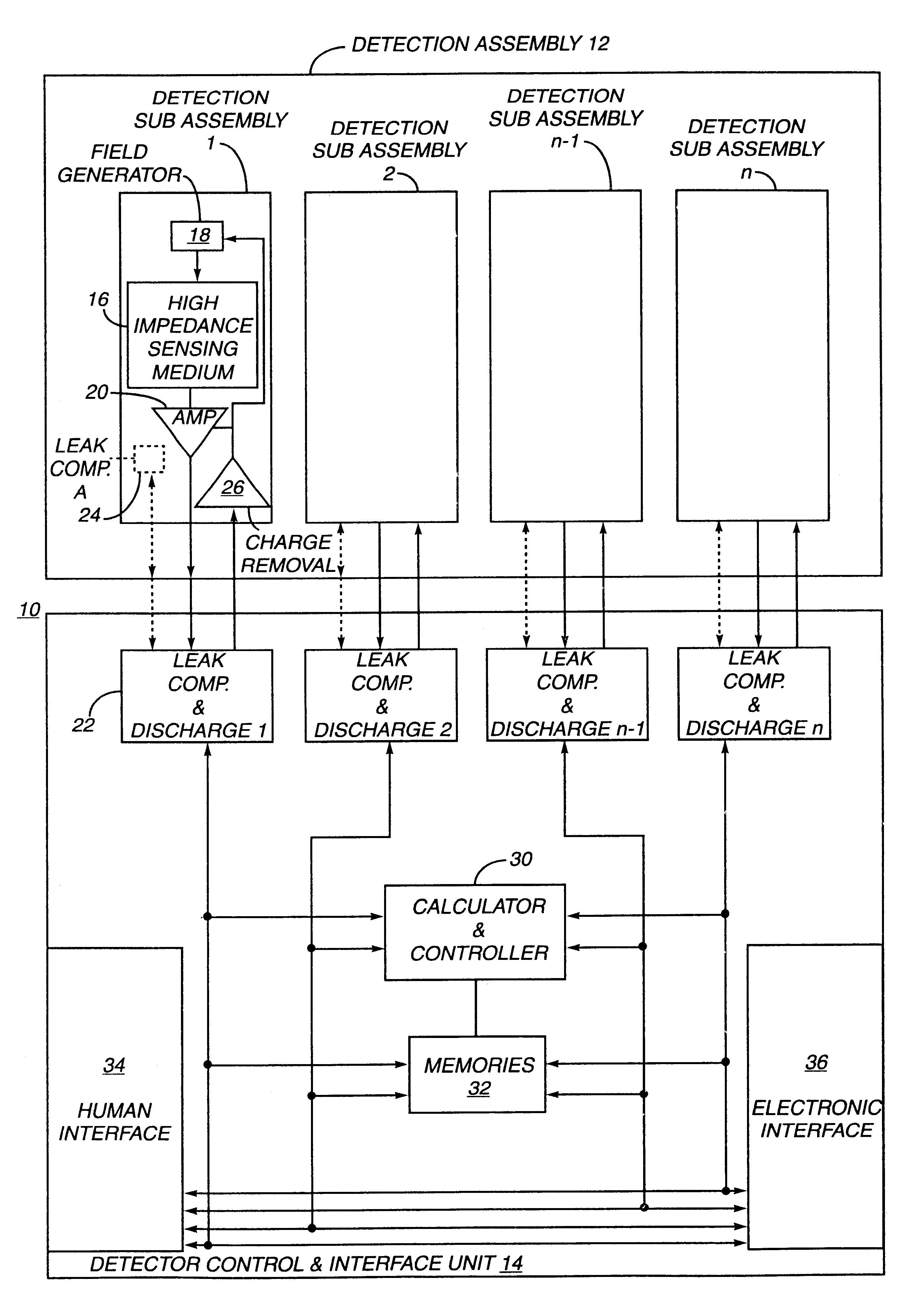

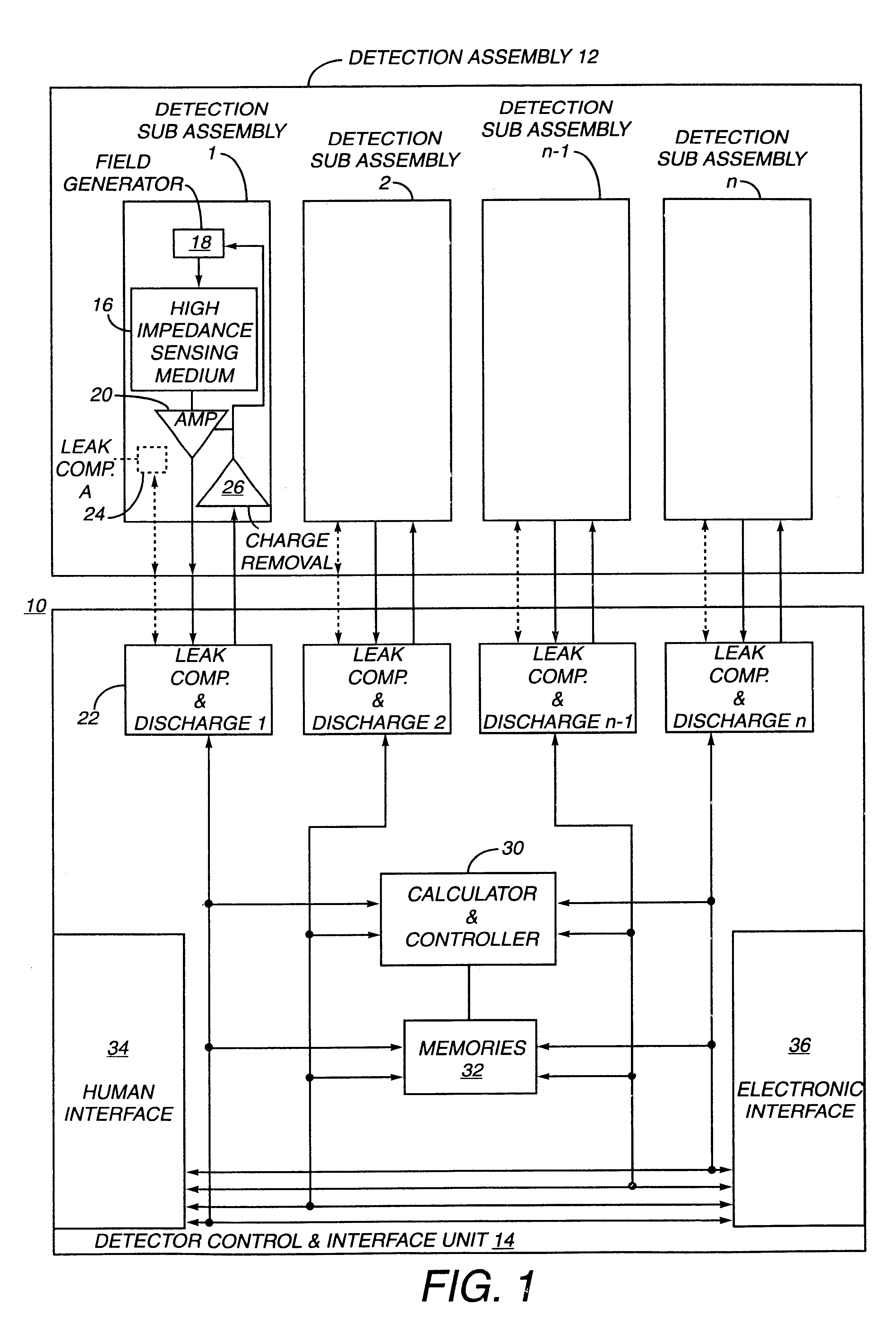

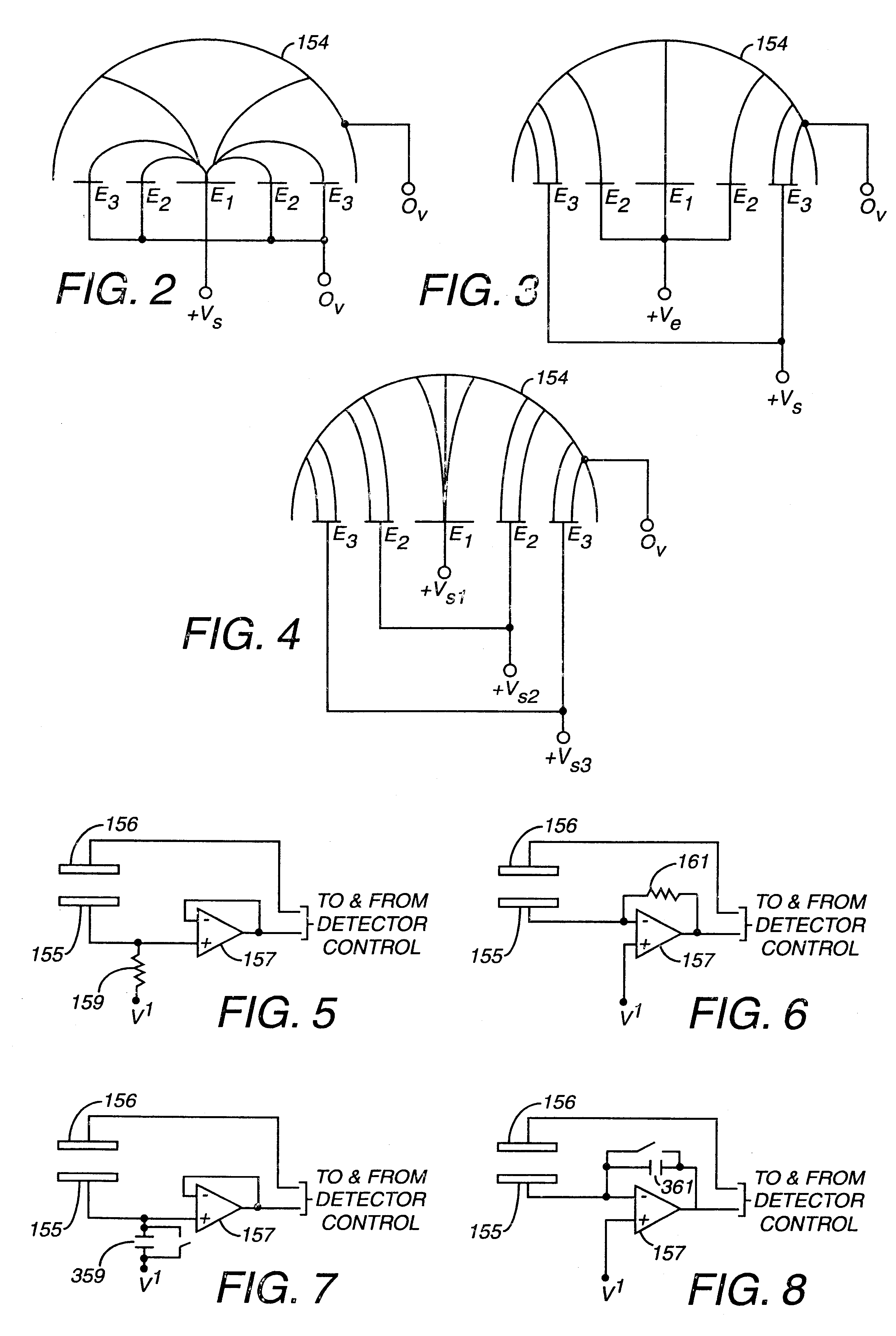

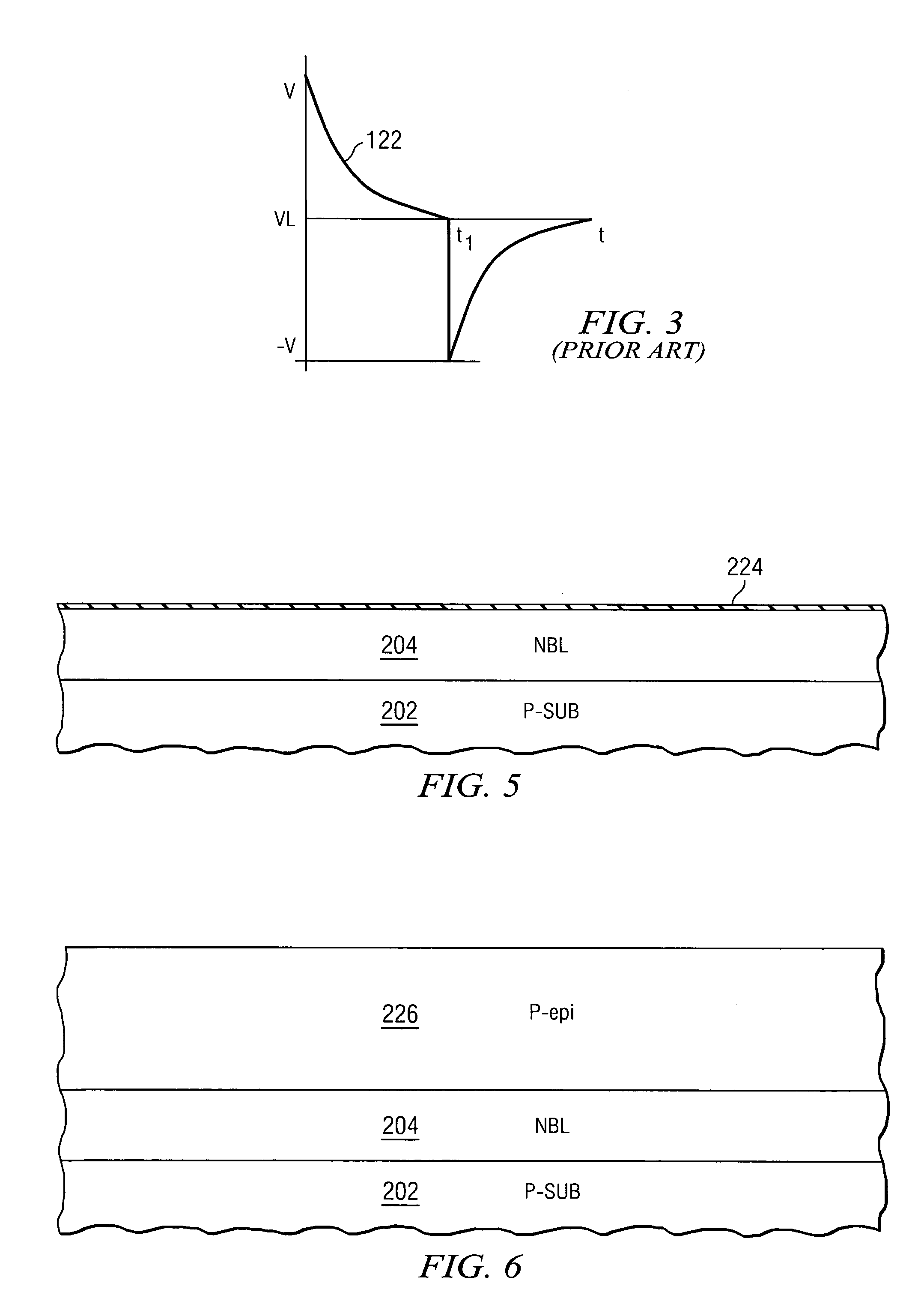

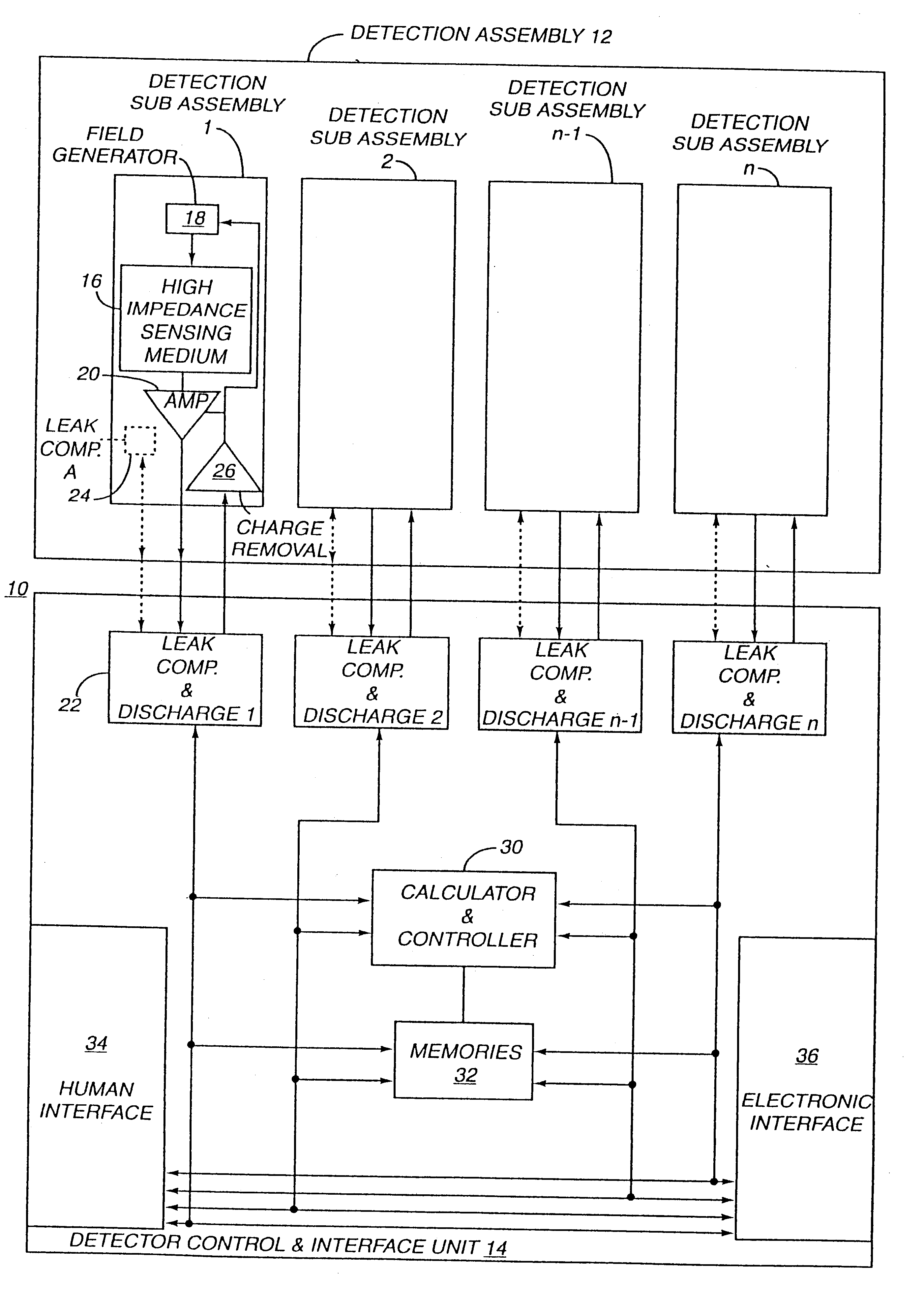

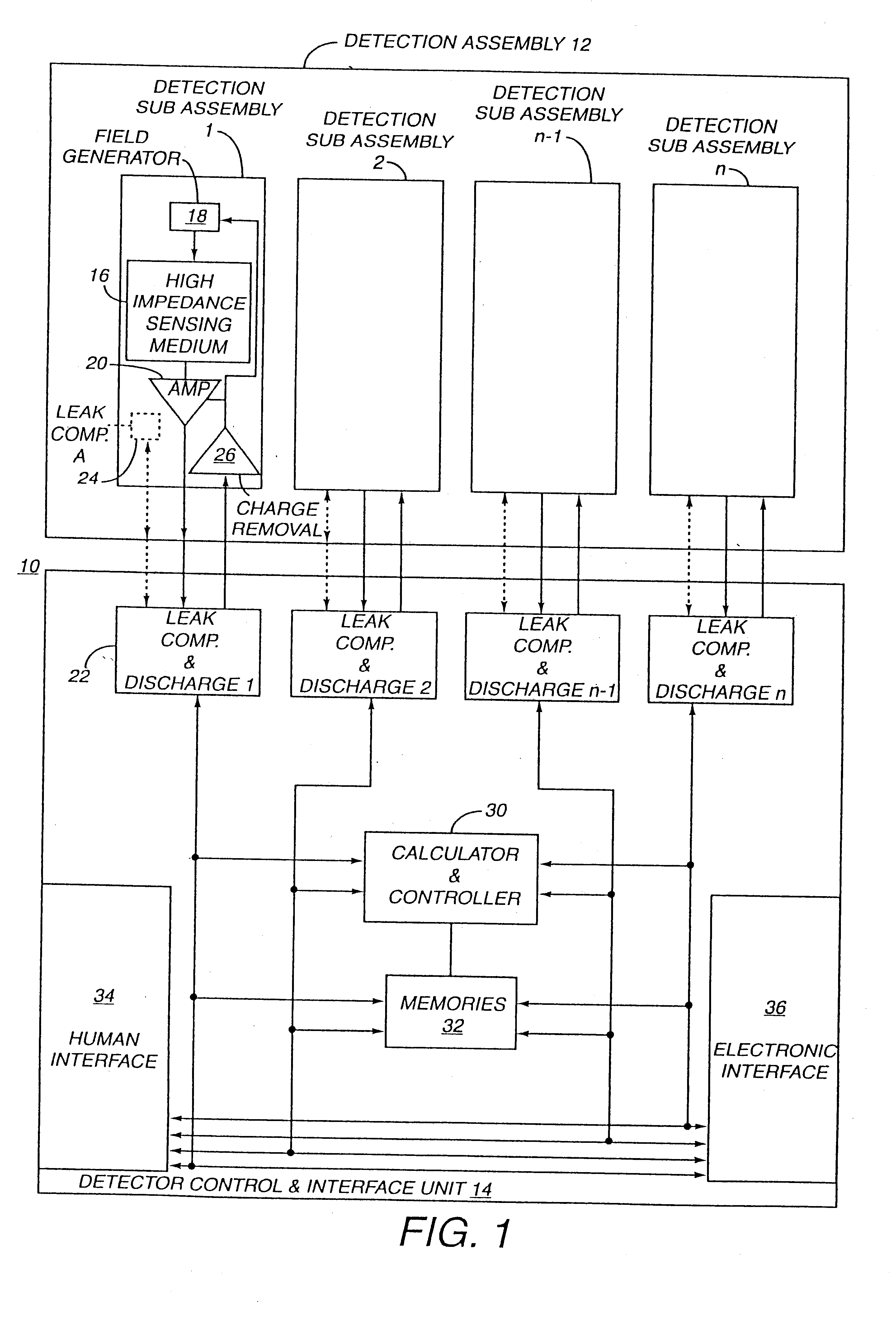

InactiveUS6353324B1Improve performanceLimits of linearityPhotometry electrical circuitsMeasurement using digital techniquesCapacitanceEngineering

The present invention relates to an electronic circuit and an array of such circuits for precisely measuring small amounts or small changes in the amount of charge, voltage, or electrical currents. One embodiment of the present invention provides an electronic circuit for measuring current or charge that can be used with a variety of sensing media (including high impedance sensing media) that produce a signal by either charge or current production or induction in response to physical phenomena occurring within the sensing media. In another embodiment, the voltage level (bias) of either the sensing or reference electrode can be switched relative to the other upon receipt of a triggering pulse. This changes the polarity of the electric field to cause charge of the opposite polarity to be driven to the sensing electrode, thereby eliminating the need to electrically connect a discharge path to the sensing electrode to clear the charge accumulated at the sensing electrode. This can be supplemented by capacitively coupling a compensation signal to the sensing electrode to cause the amplifier output signal to lessen in magnitude below a threshold level that permits additional charge or current measurements of the same polarity before performing bias reversal. Alternately or in combination with bias reversal and capacitive compensation, sensor performance can be improved by minimizing inaccuracies caused by leakage currents or current drawn from the sensor. Other described methods of reducing leakage currents that can be used alone or in combination with the aforementioned features include the use of guard rings, physical switches or relays, the controlled creation of charges or currents of a specific polarity in a specific region of the sensing medium, controlled leakage over the surface of an insulator, and controlling the environment in which the circuit operates.

Owner:BRIDGE SEMICON

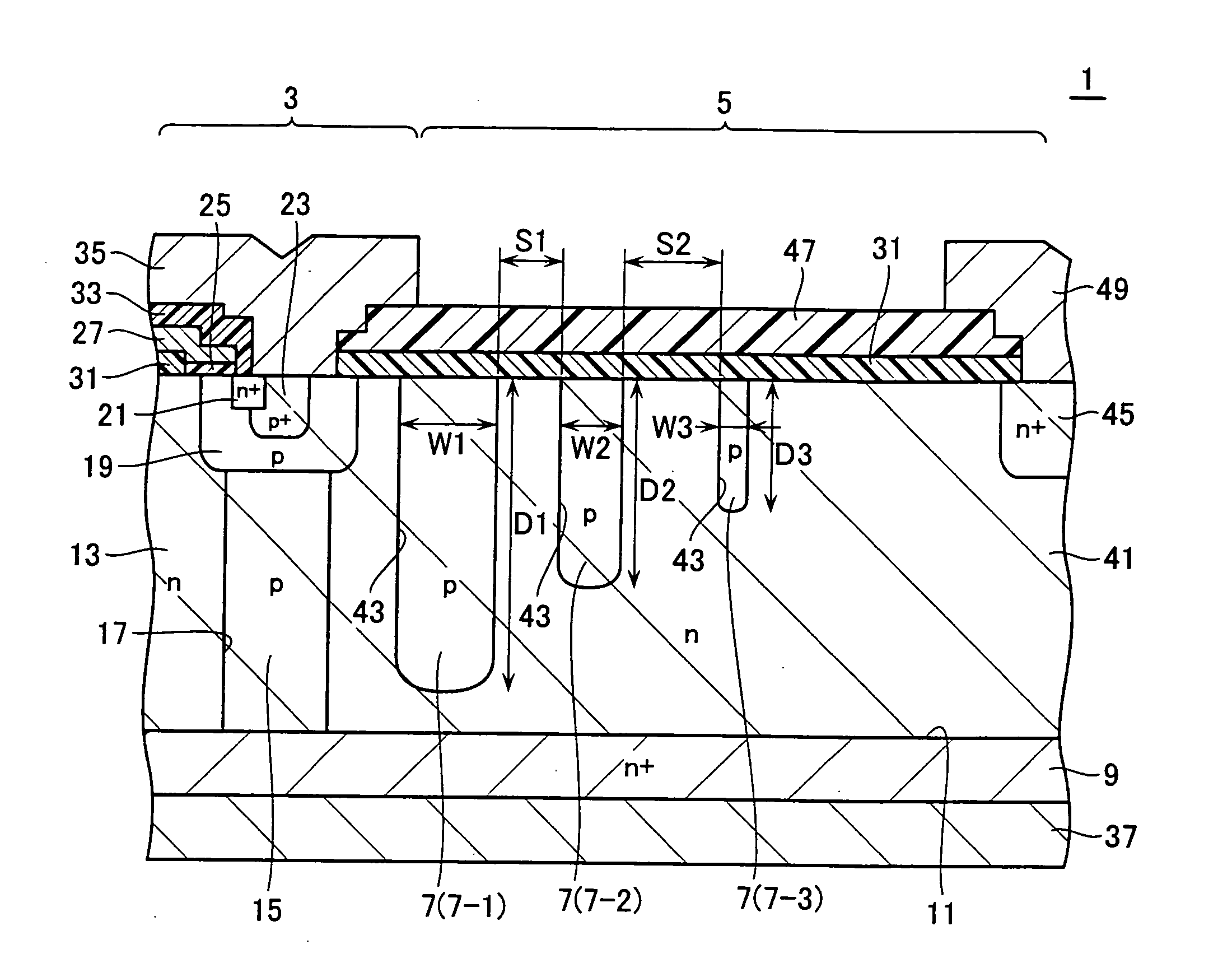

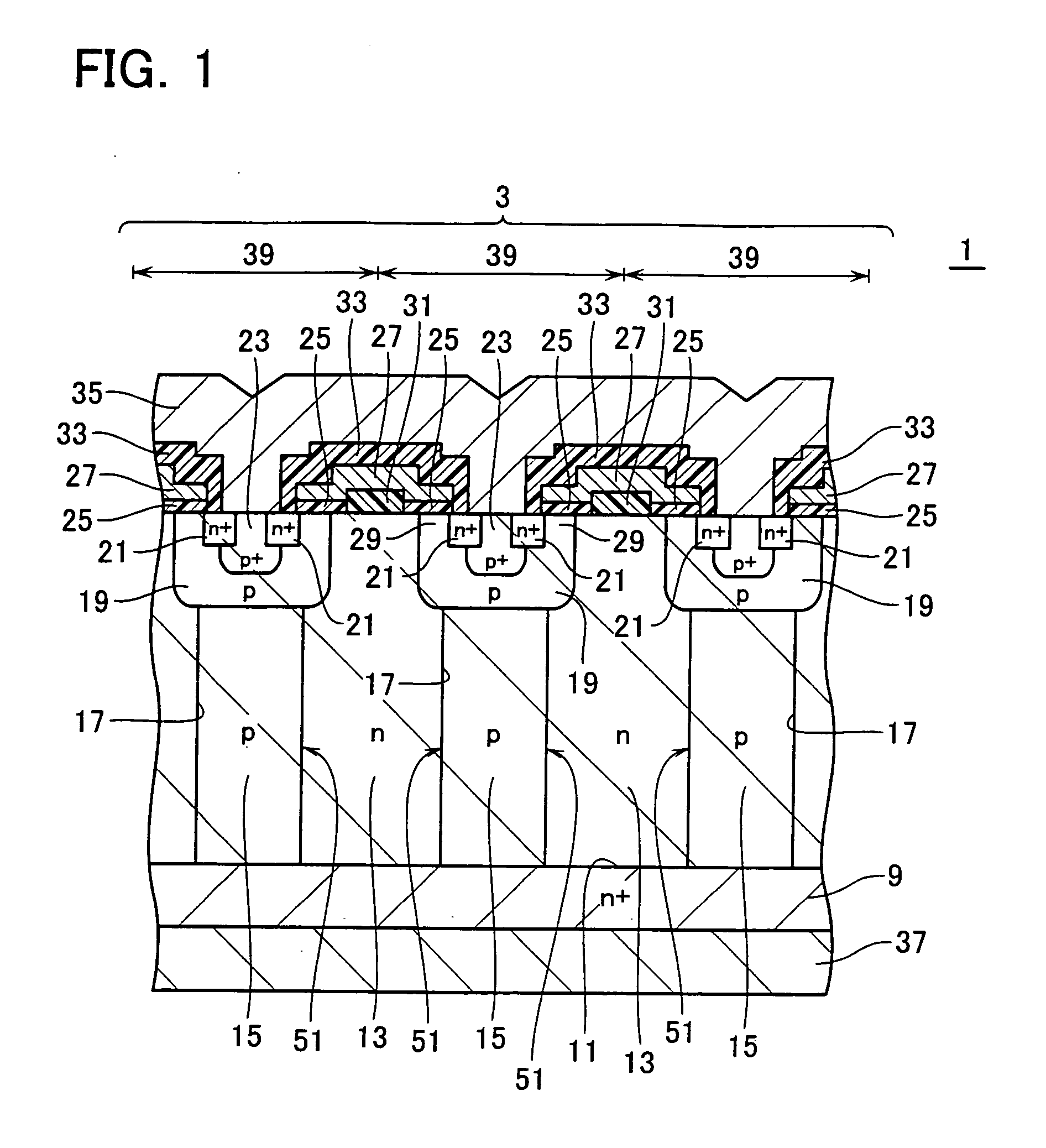

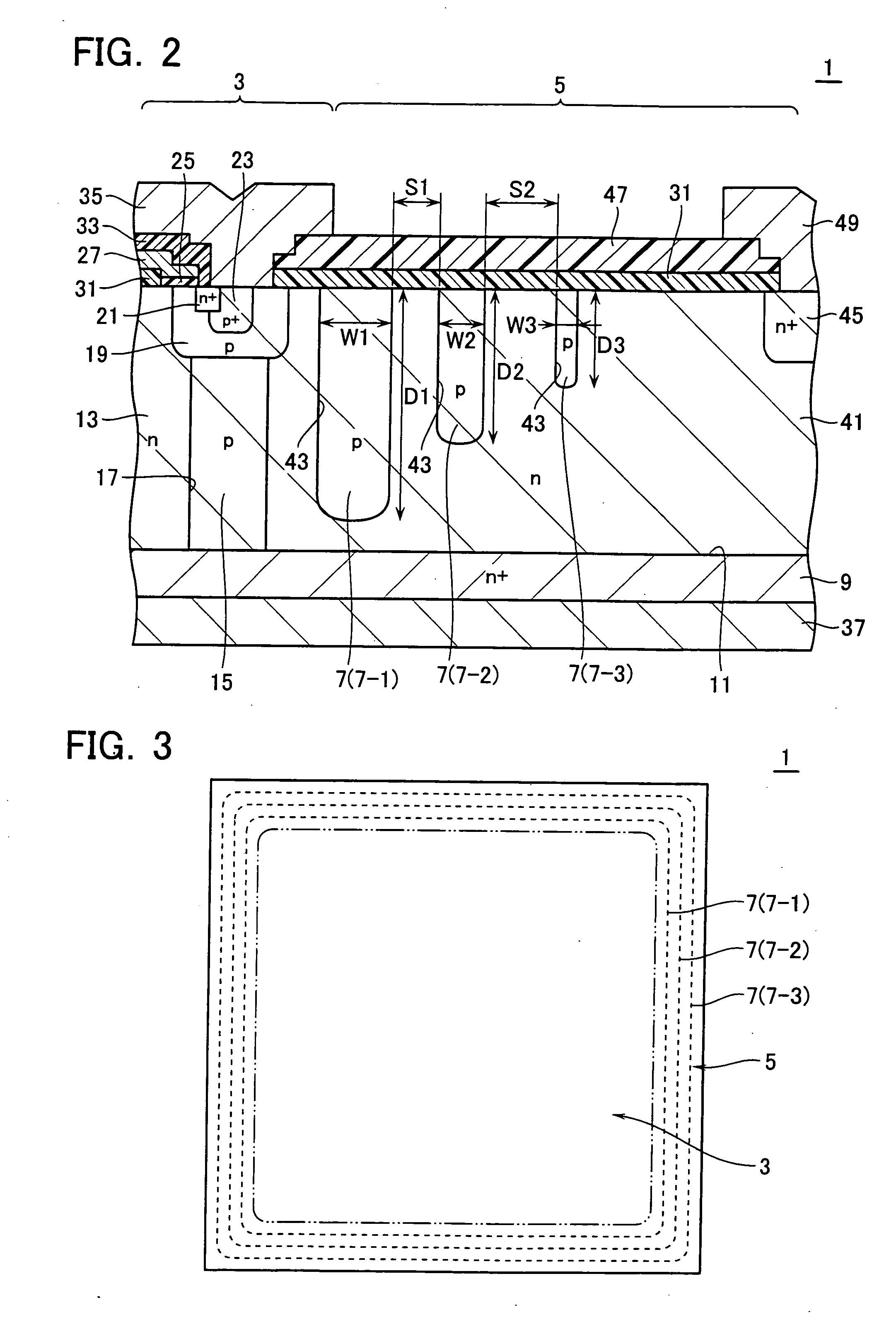

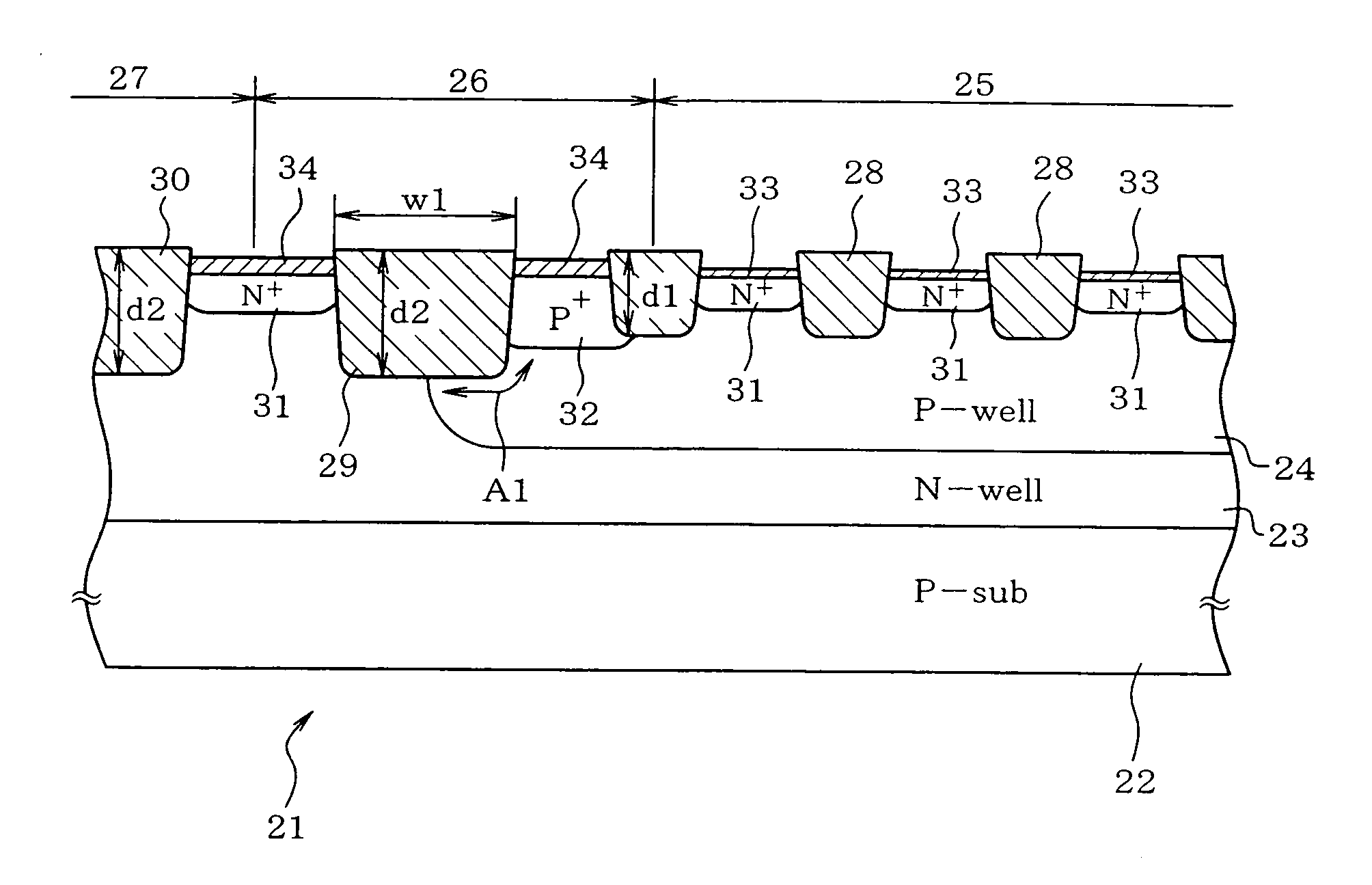

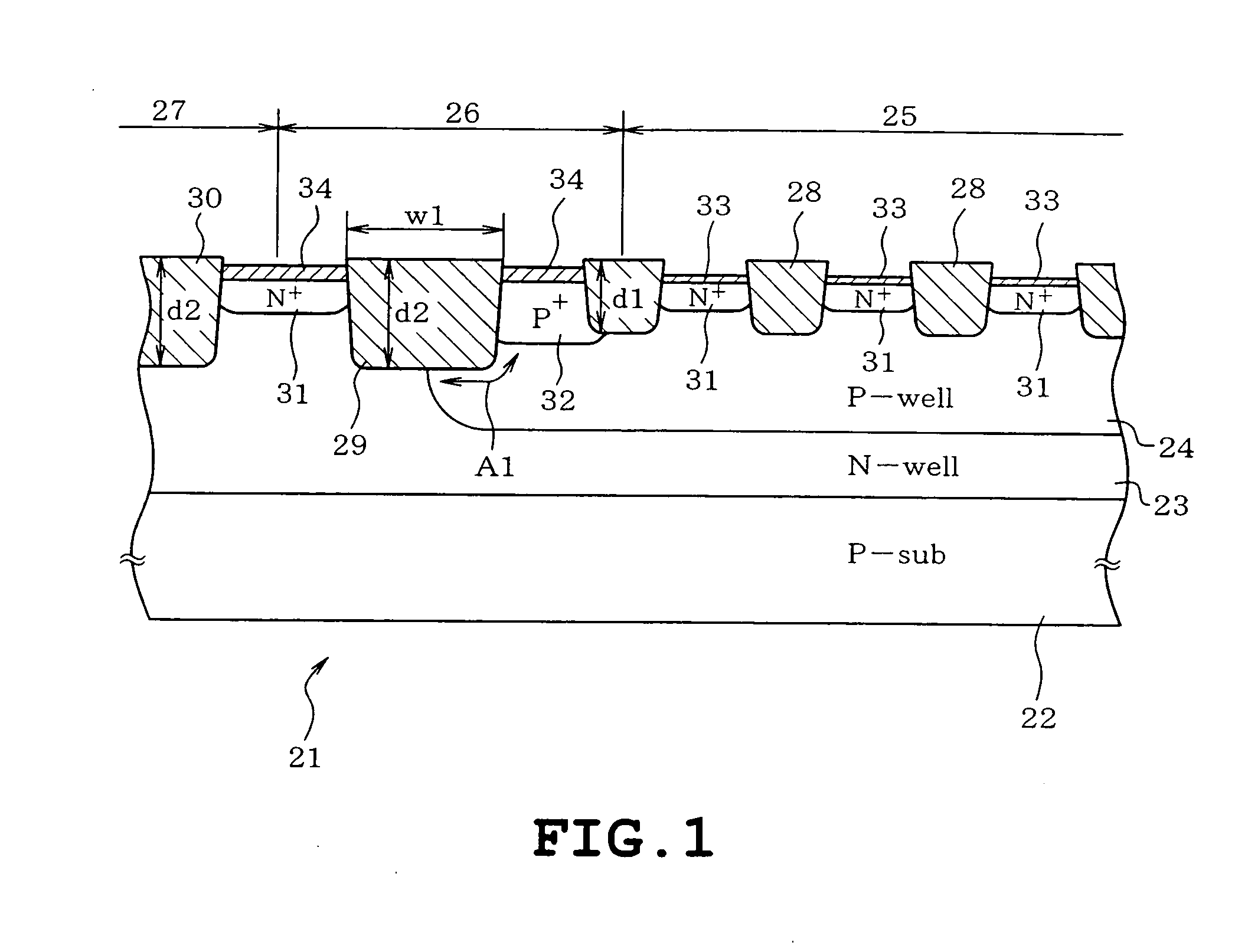

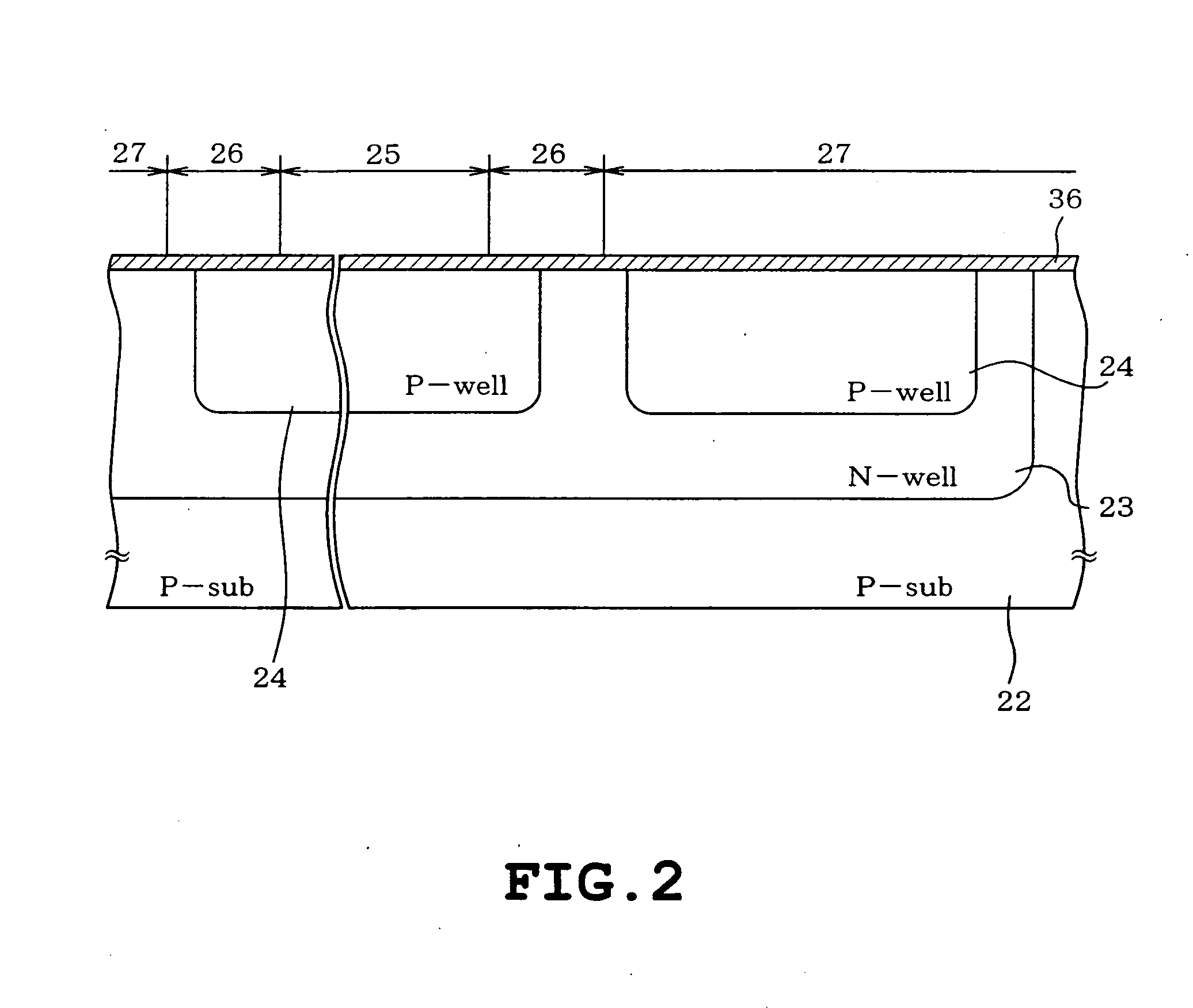

Semiconductor device and fabrication method of the same

InactiveUS20060043480A1Small widthSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

A semiconductor device comprises a semiconductor layer which includes a terminate end part and a cell formation part that is surrounded by this end part, and a plurality of guard rings each of which is formed at the end part to surround the cell formation part. These guard rings are made shallower and smaller in width as they get near to the guard ring that resides at the outside position.

Owner:KK TOSHIBA

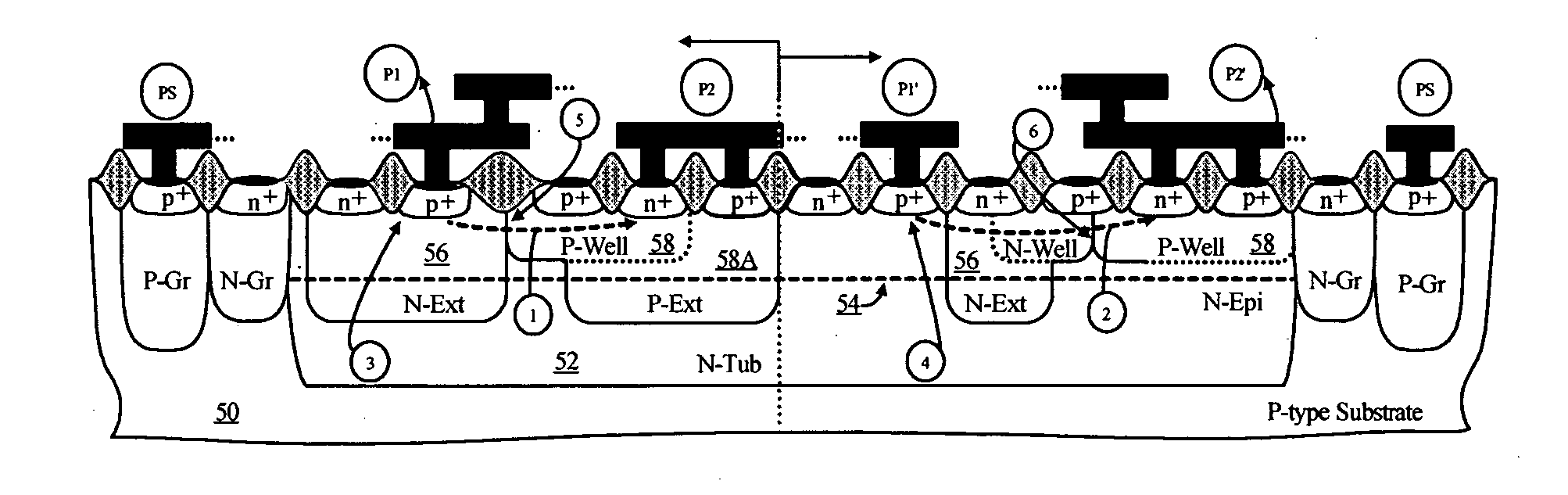

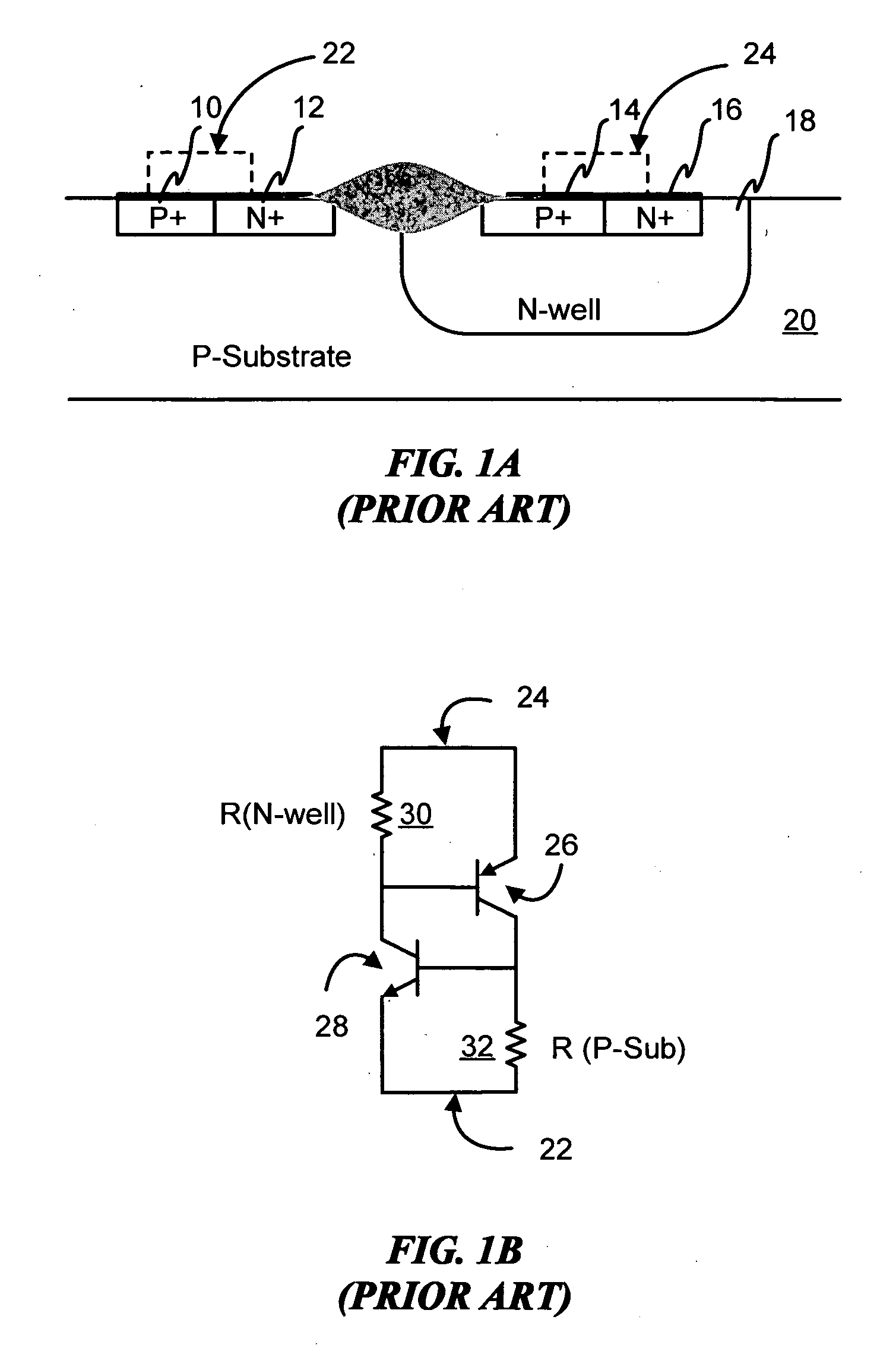

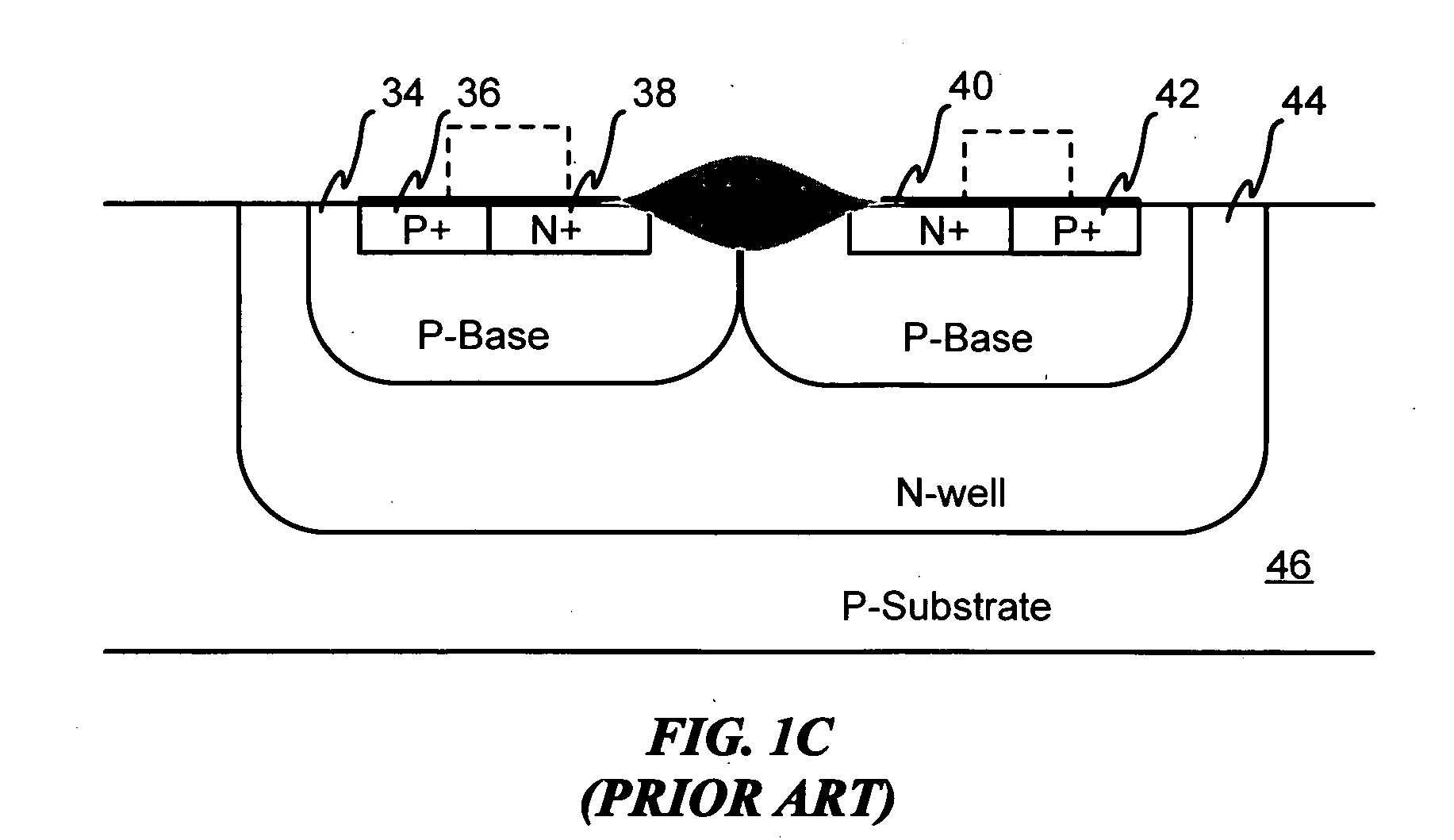

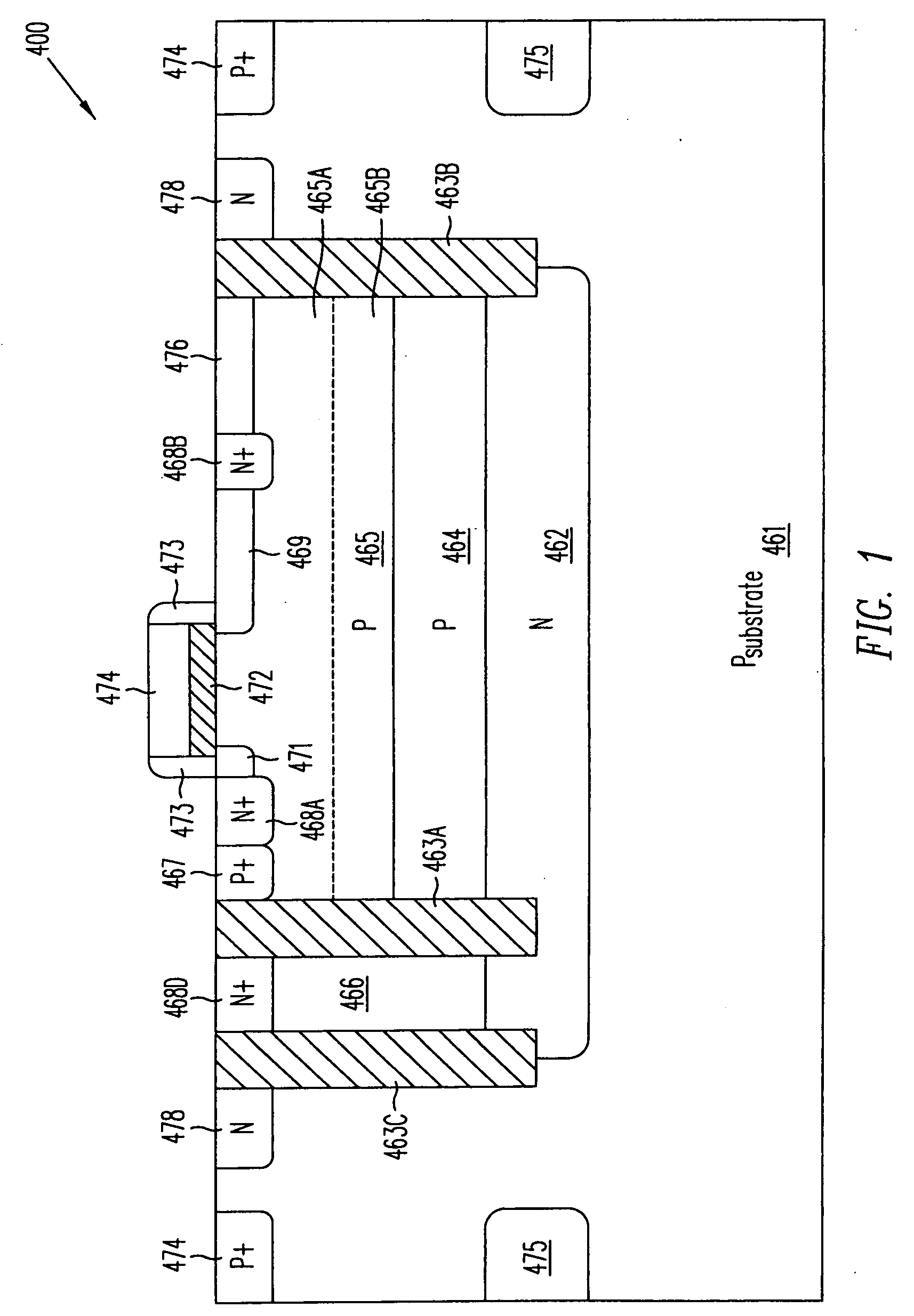

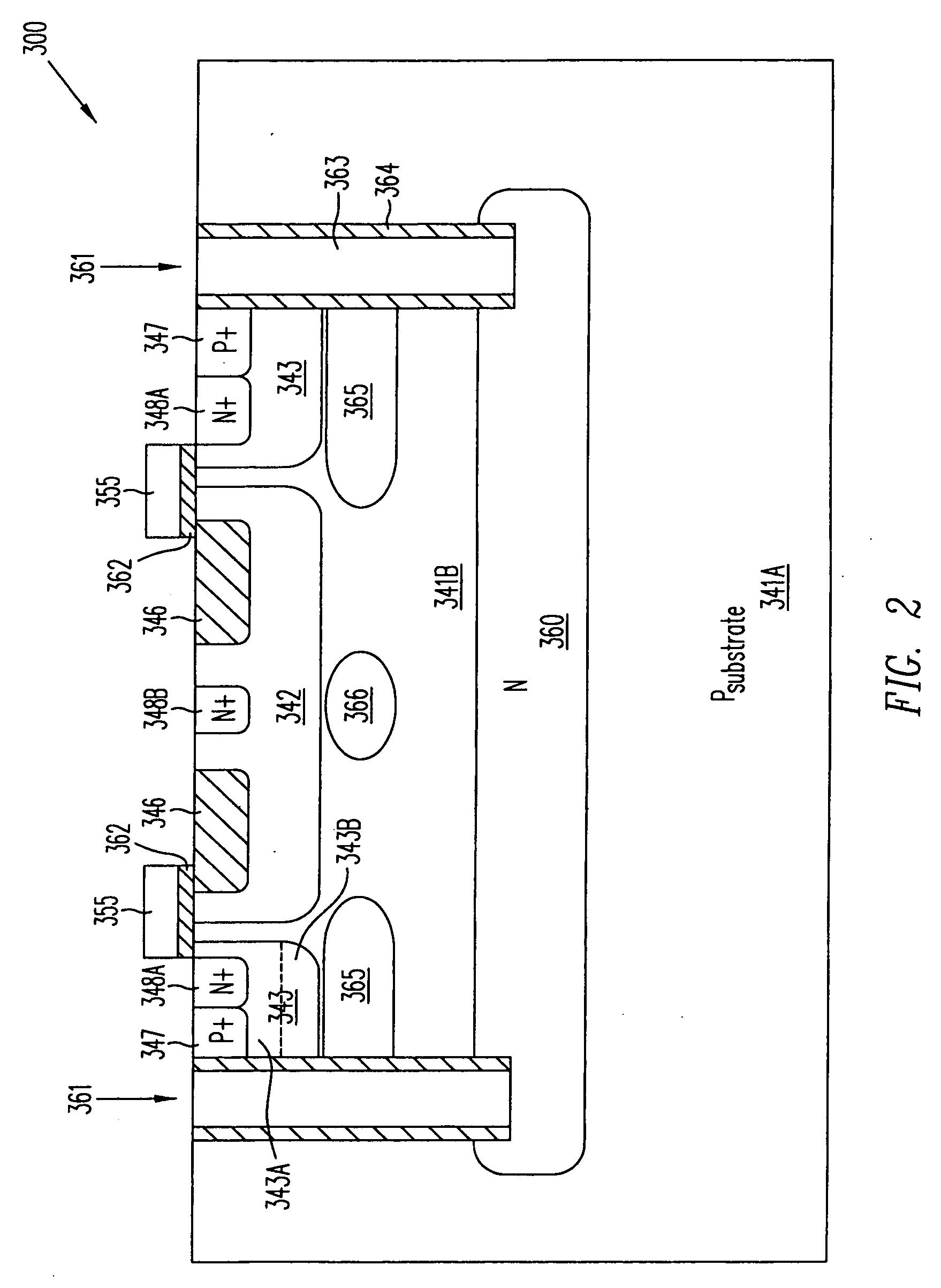

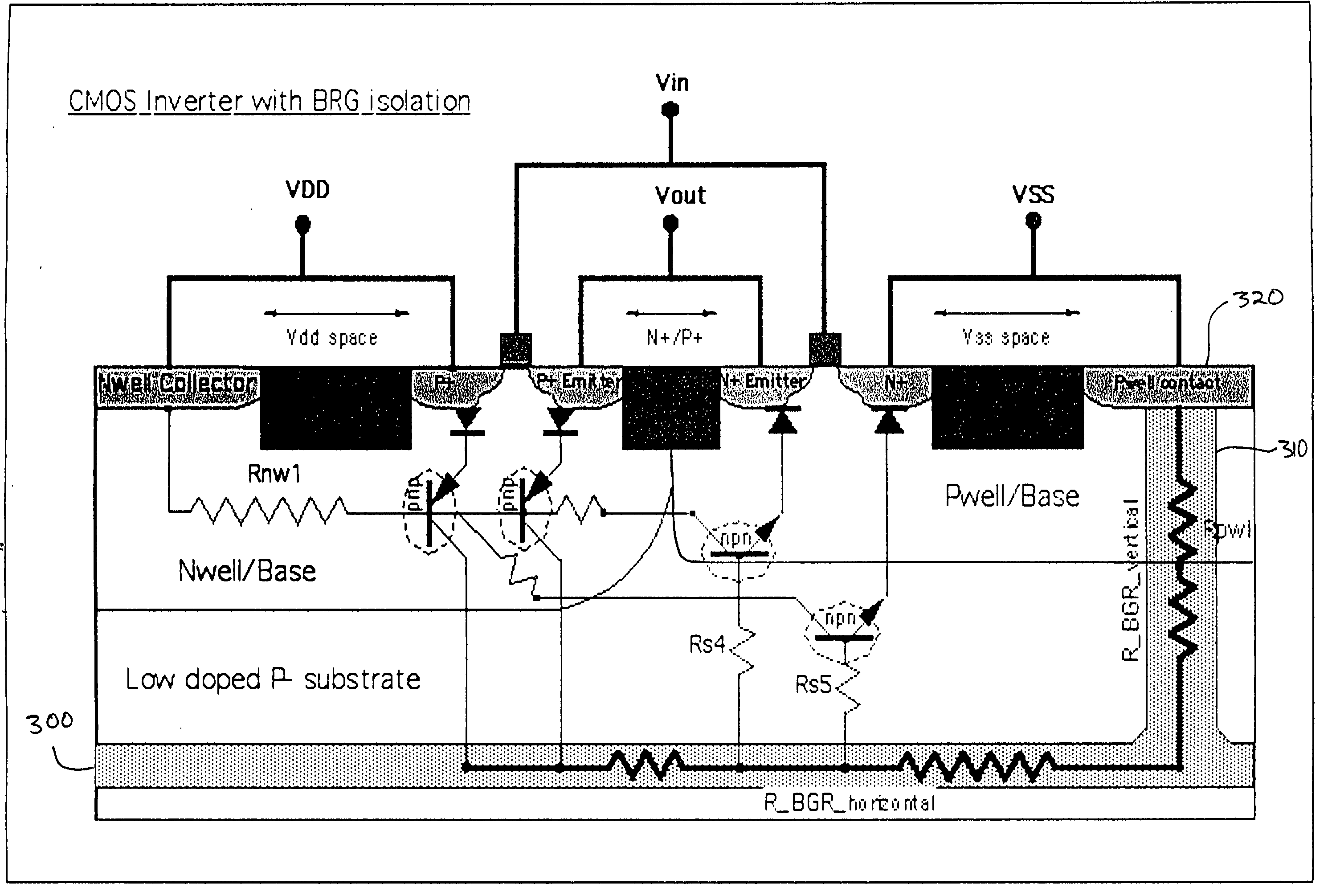

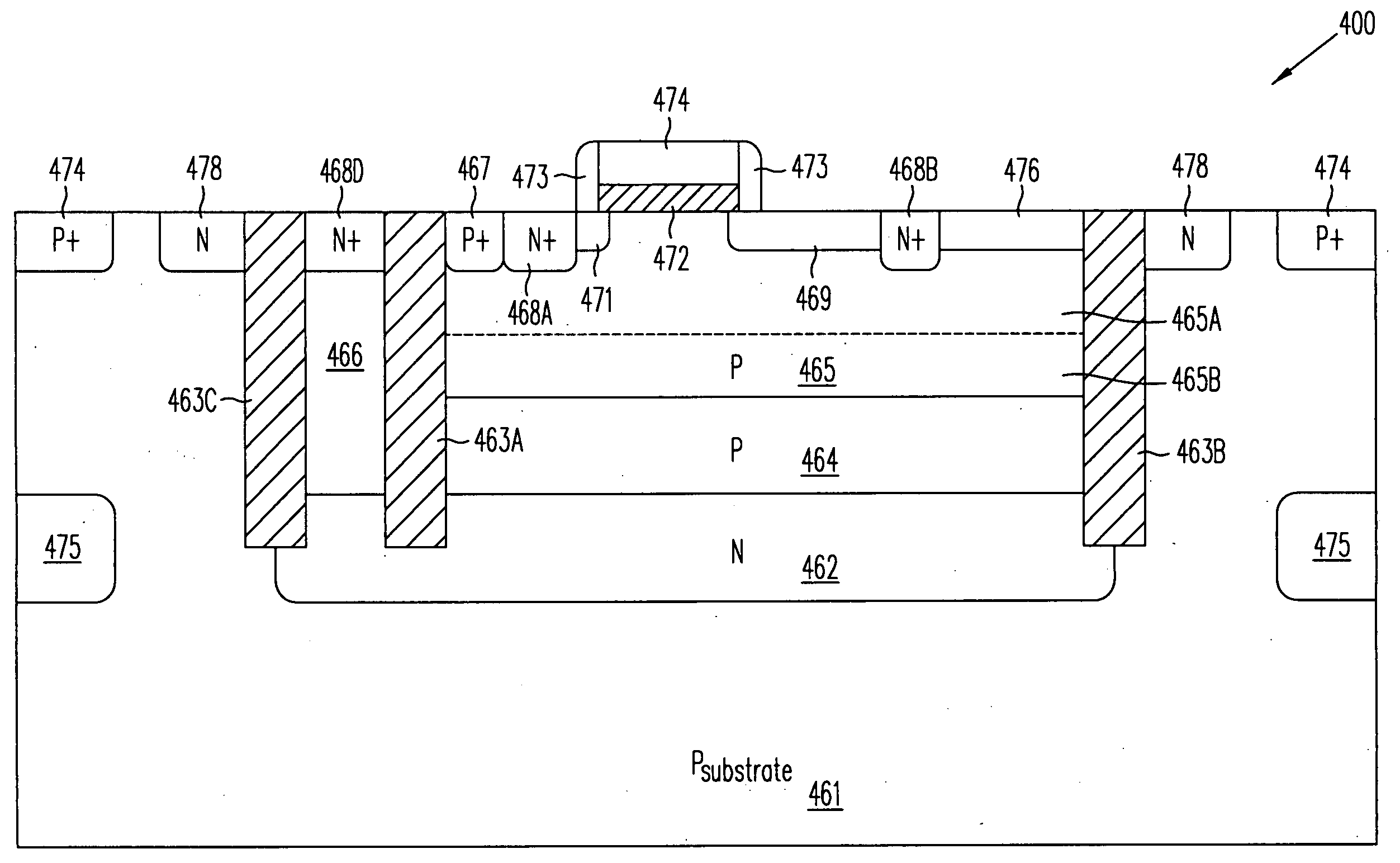

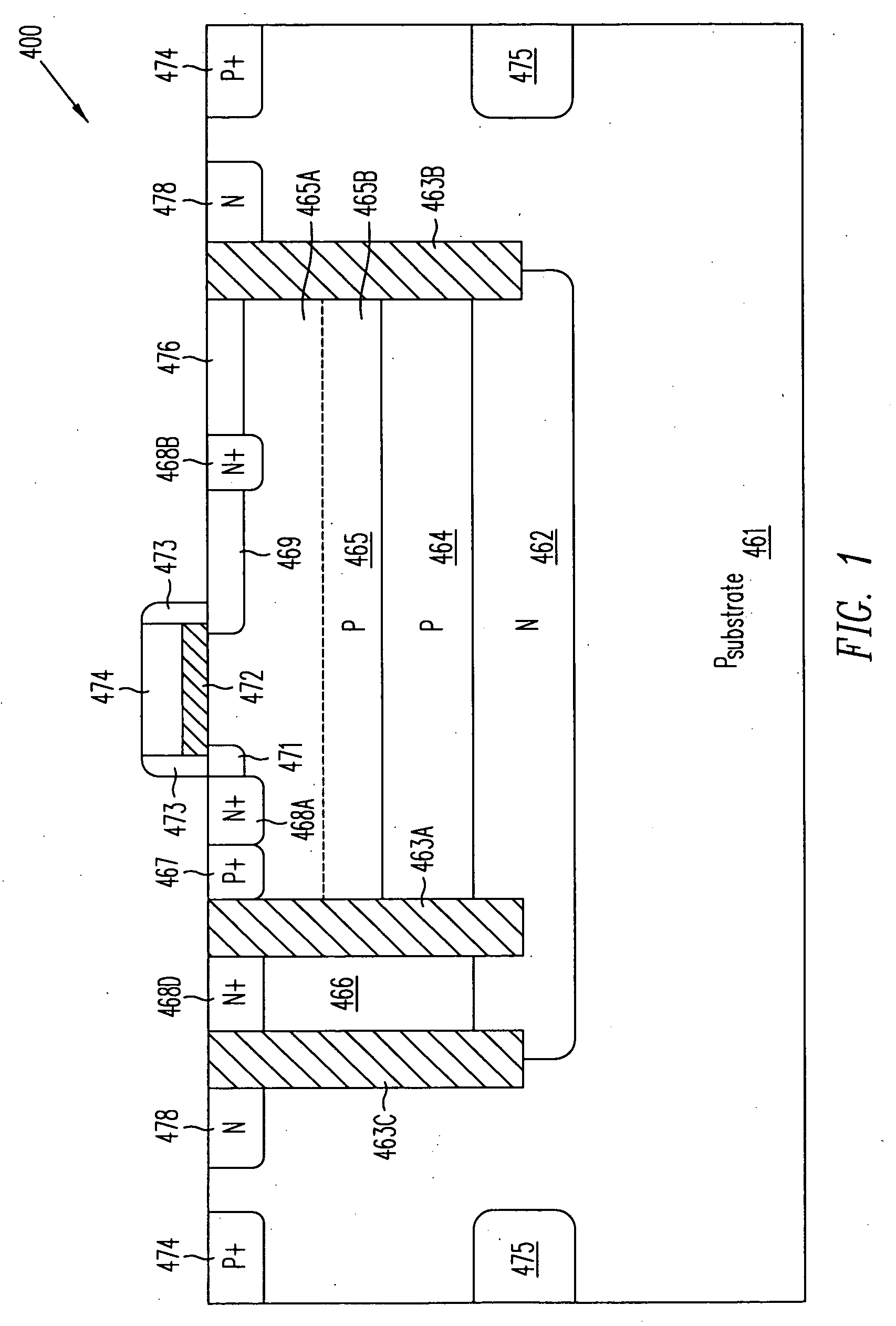

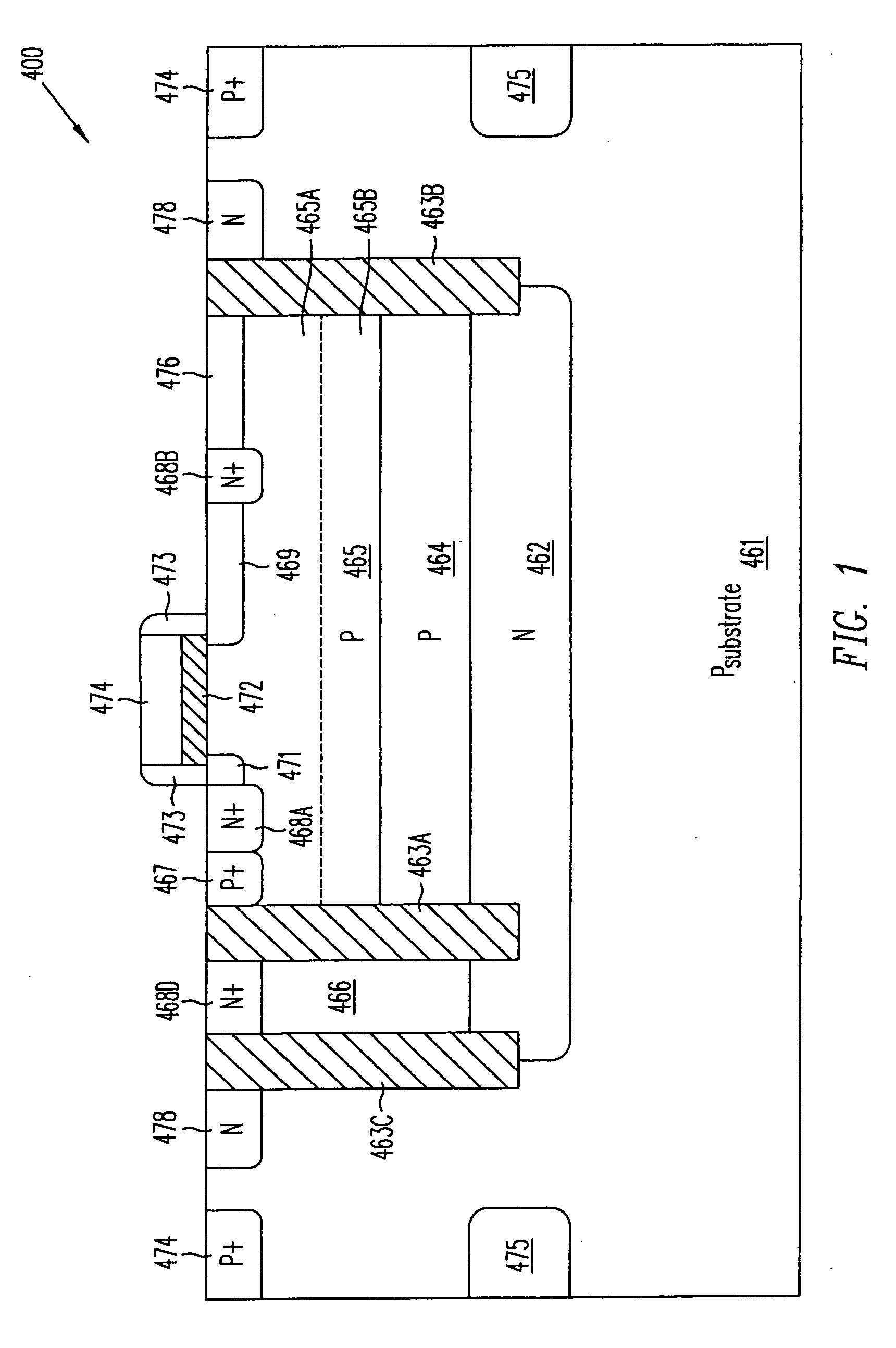

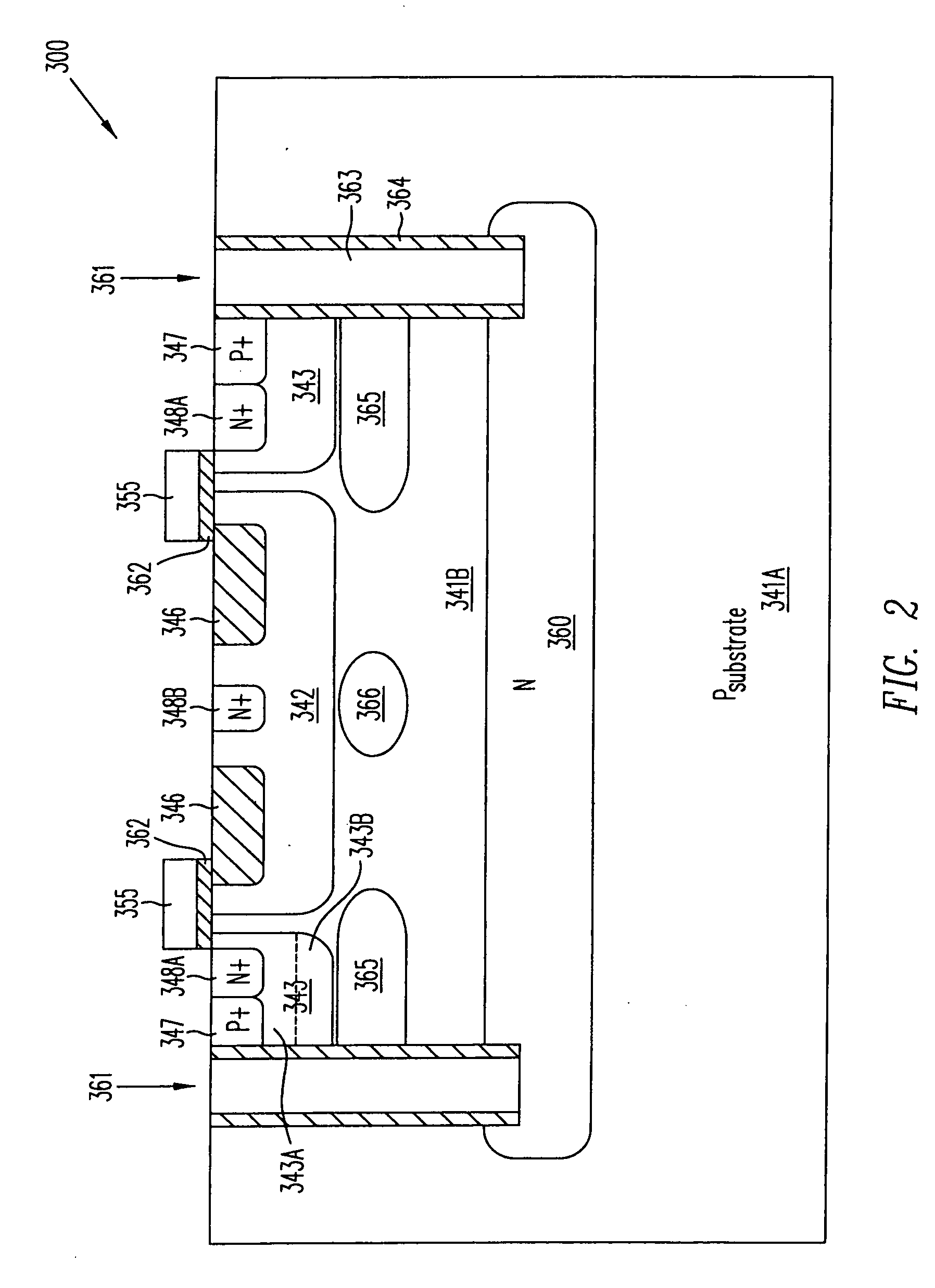

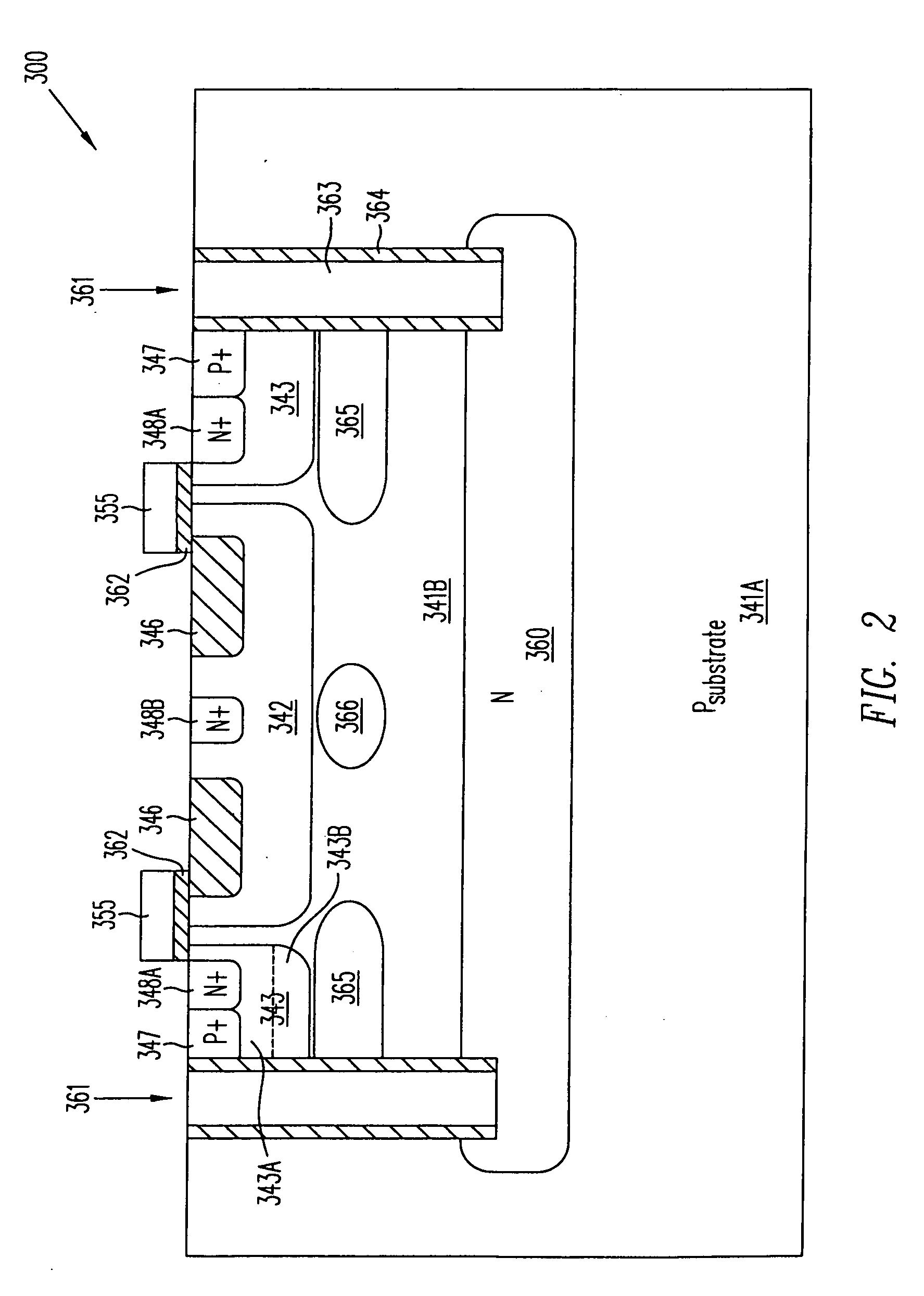

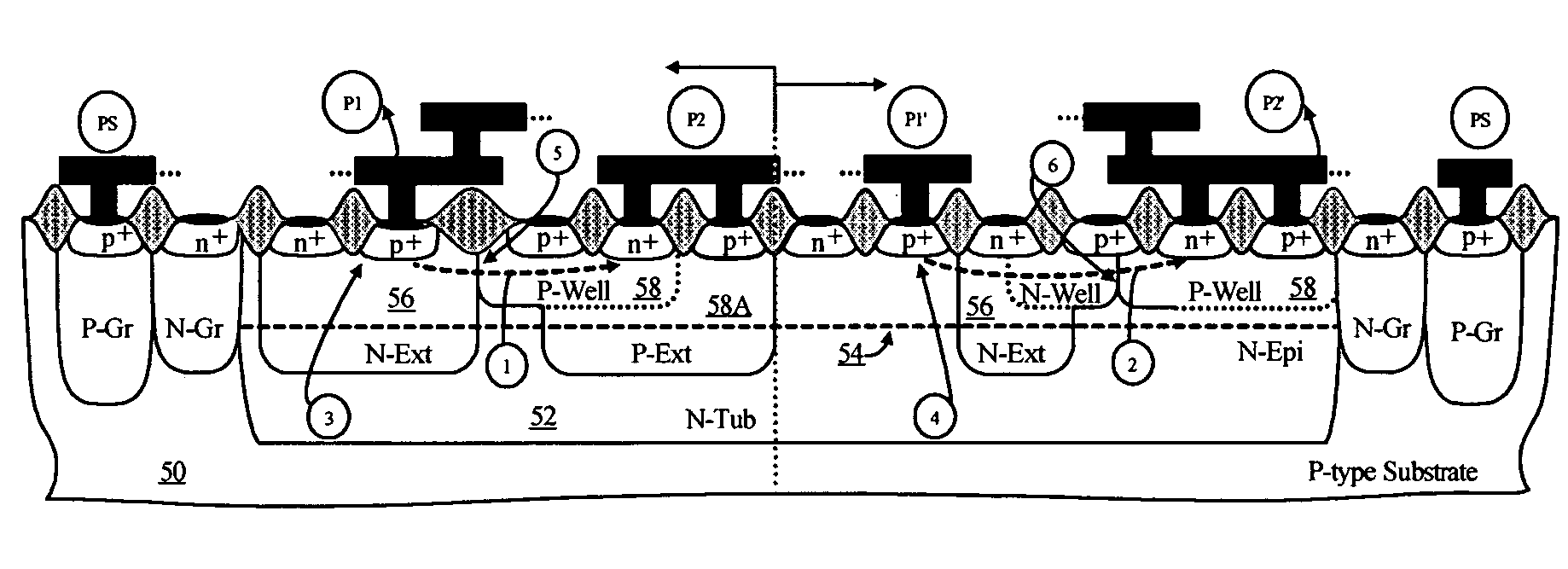

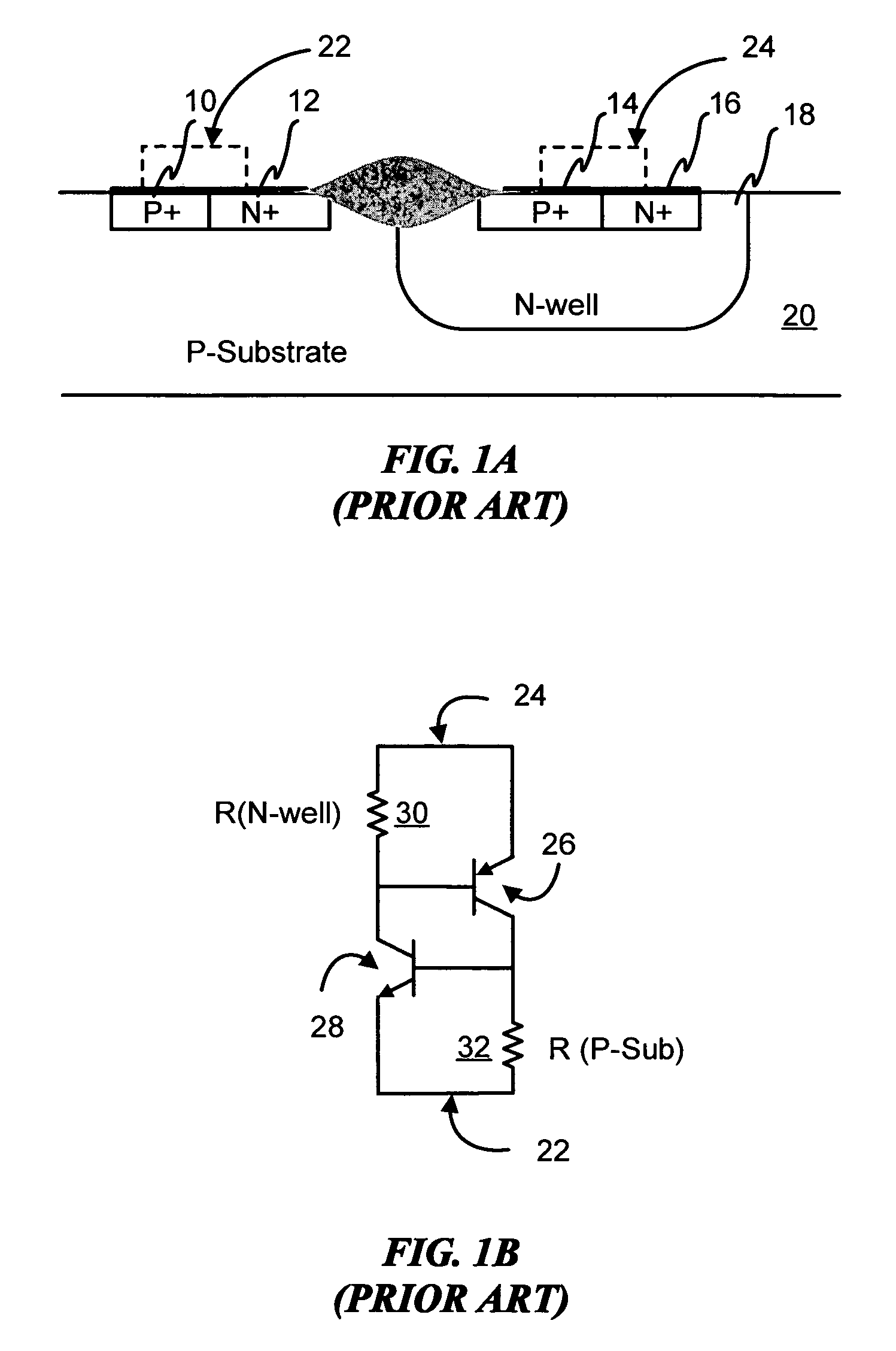

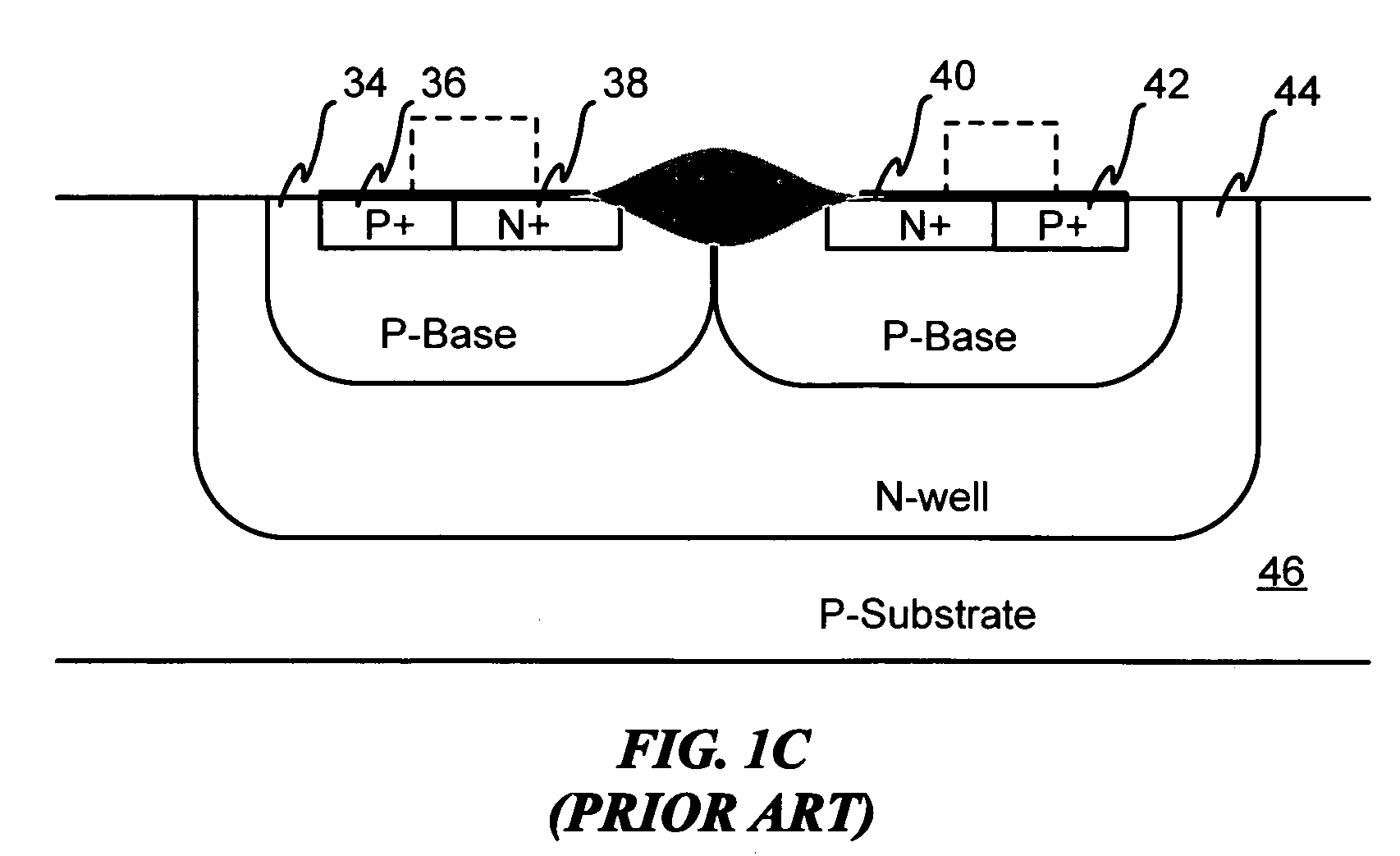

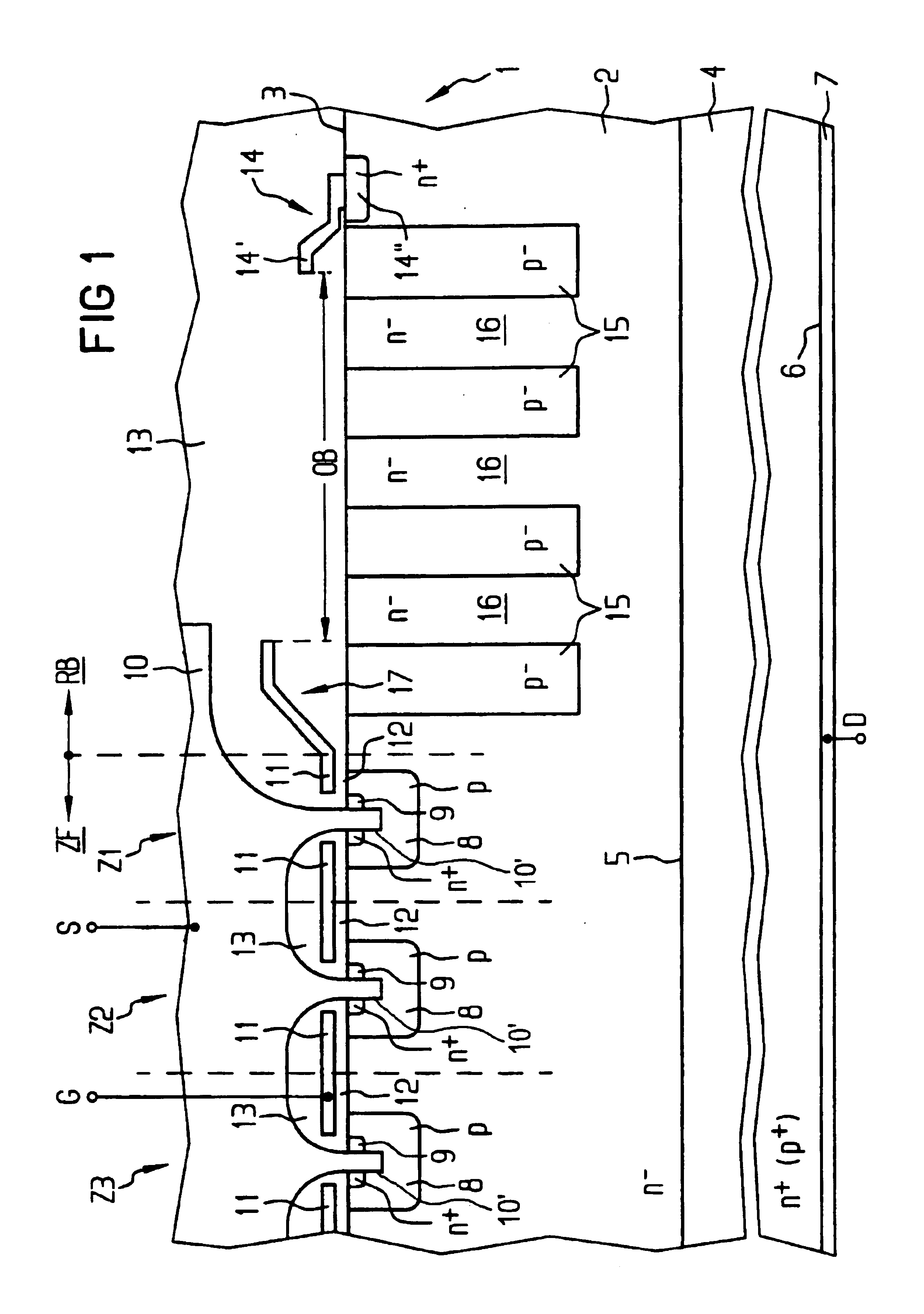

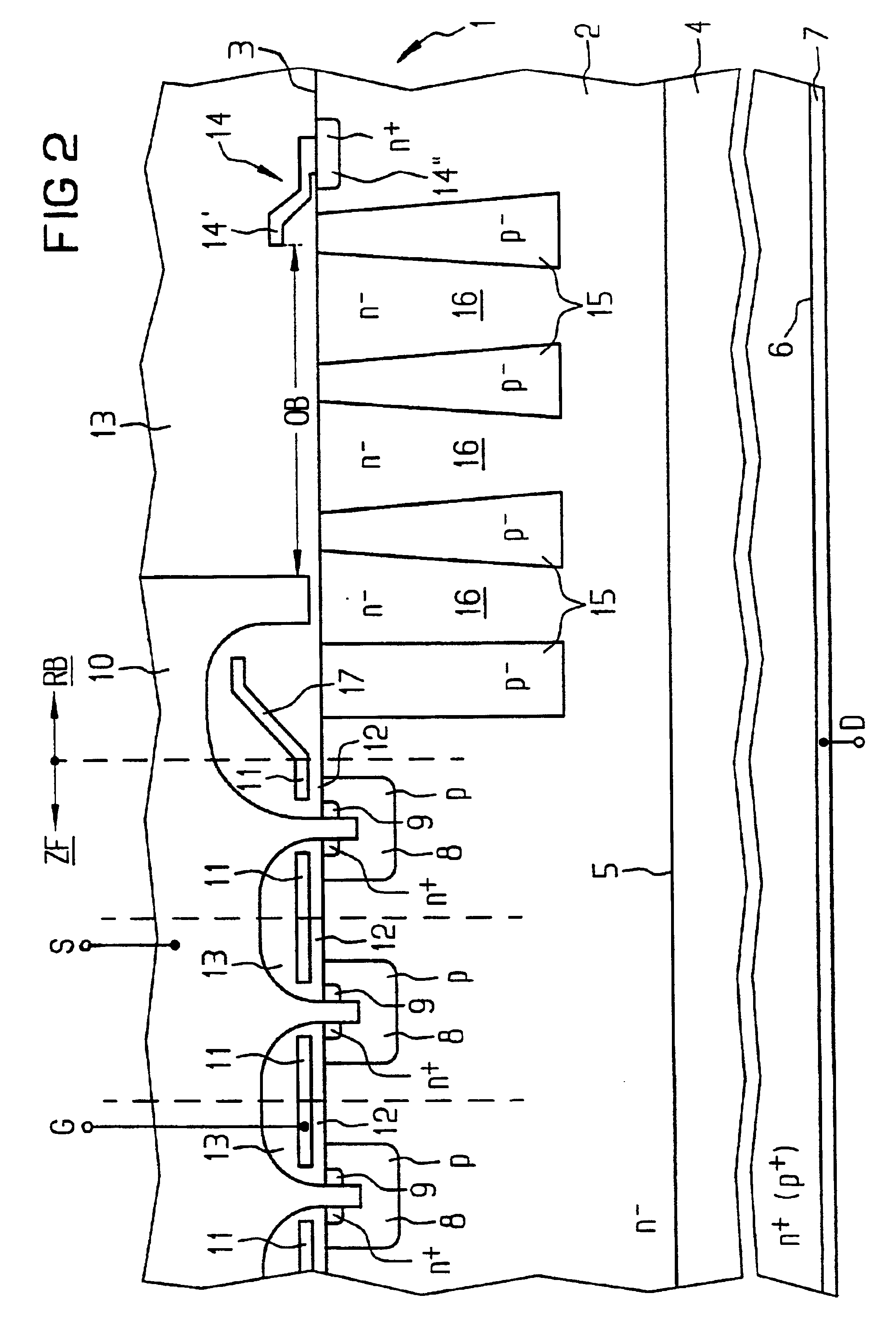

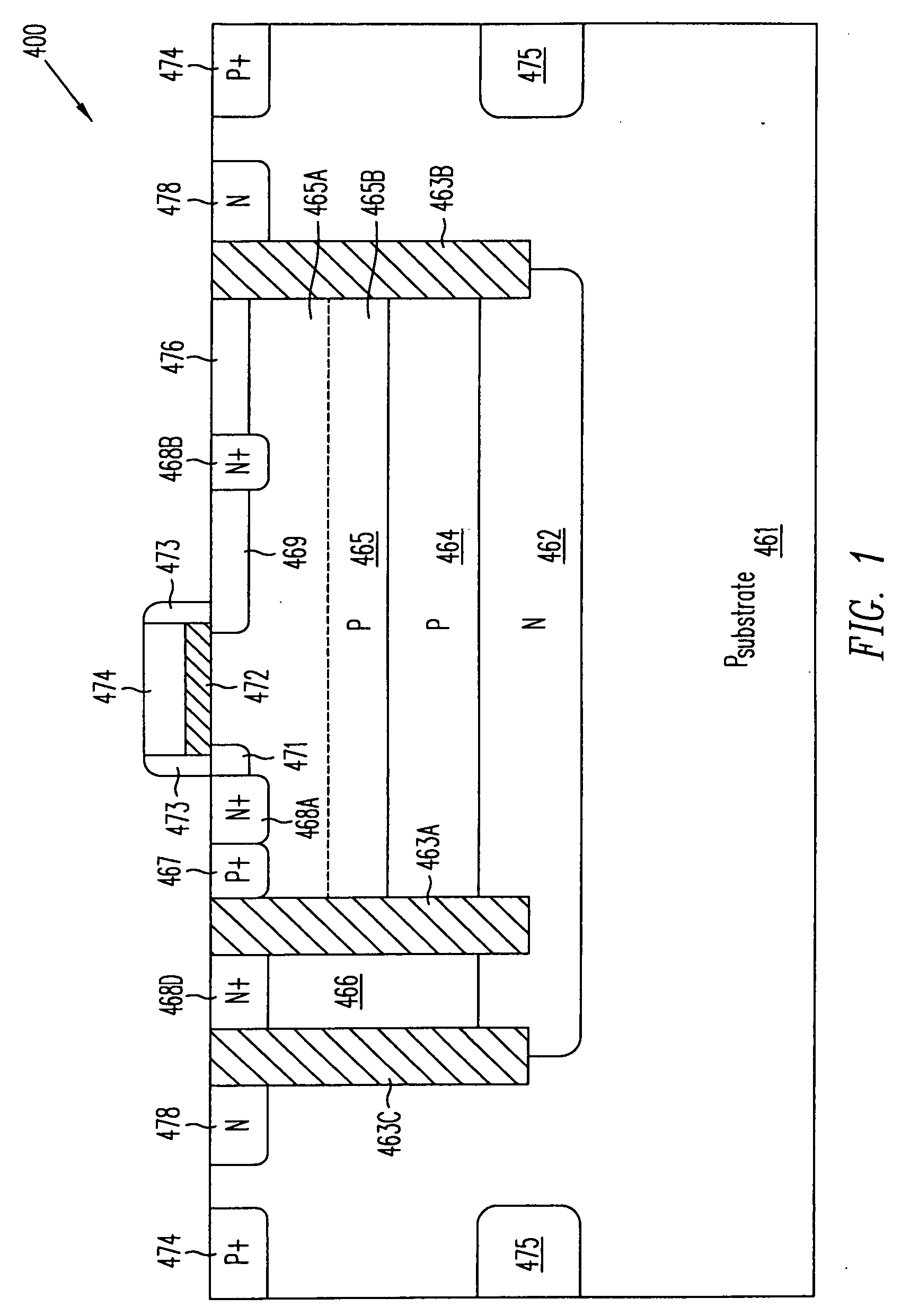

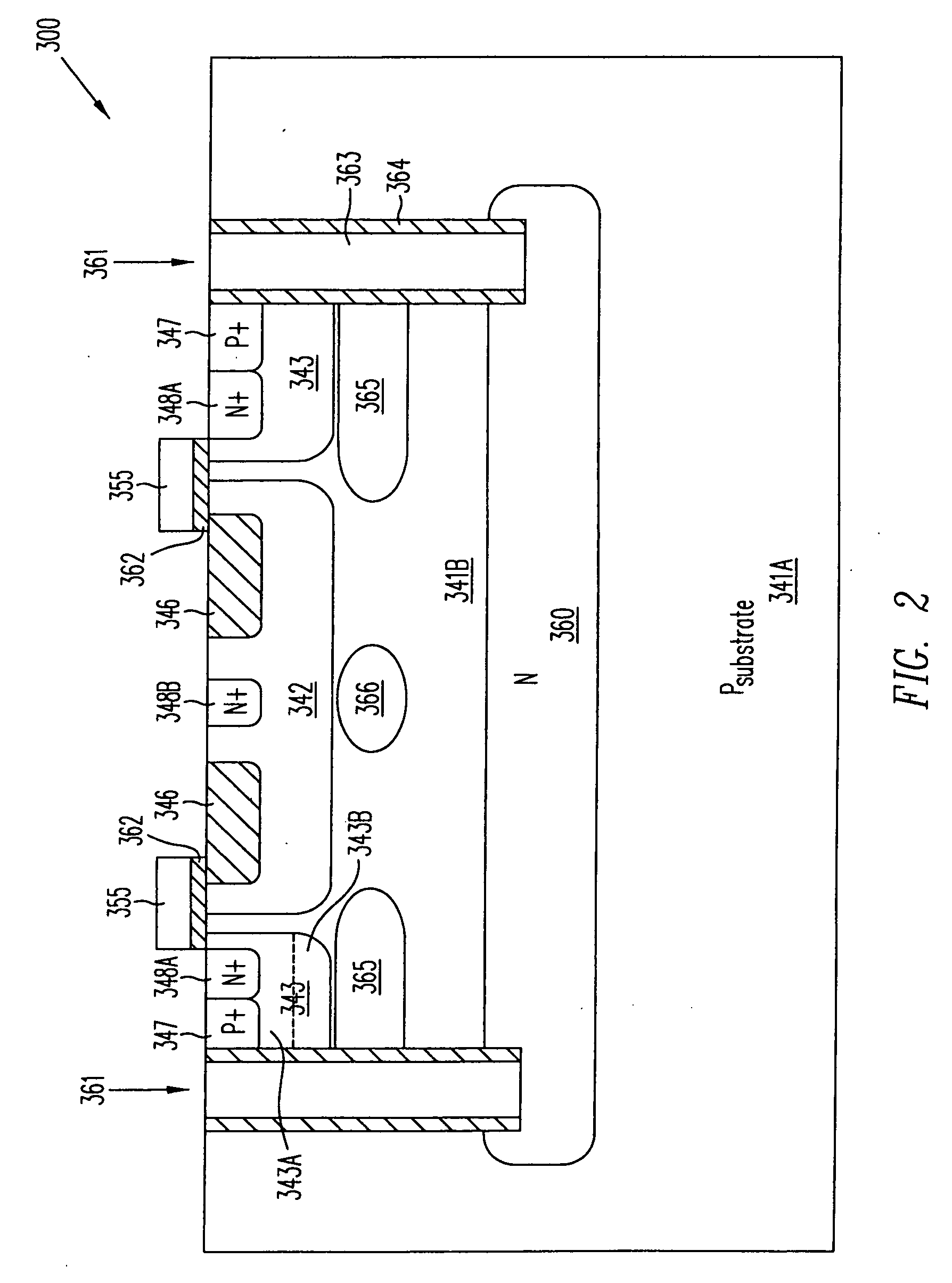

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

InactiveUS20070007545A1Impaired immunityHigh protection levelTransistorThyristorNon symmetricTransmission-line pulse

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

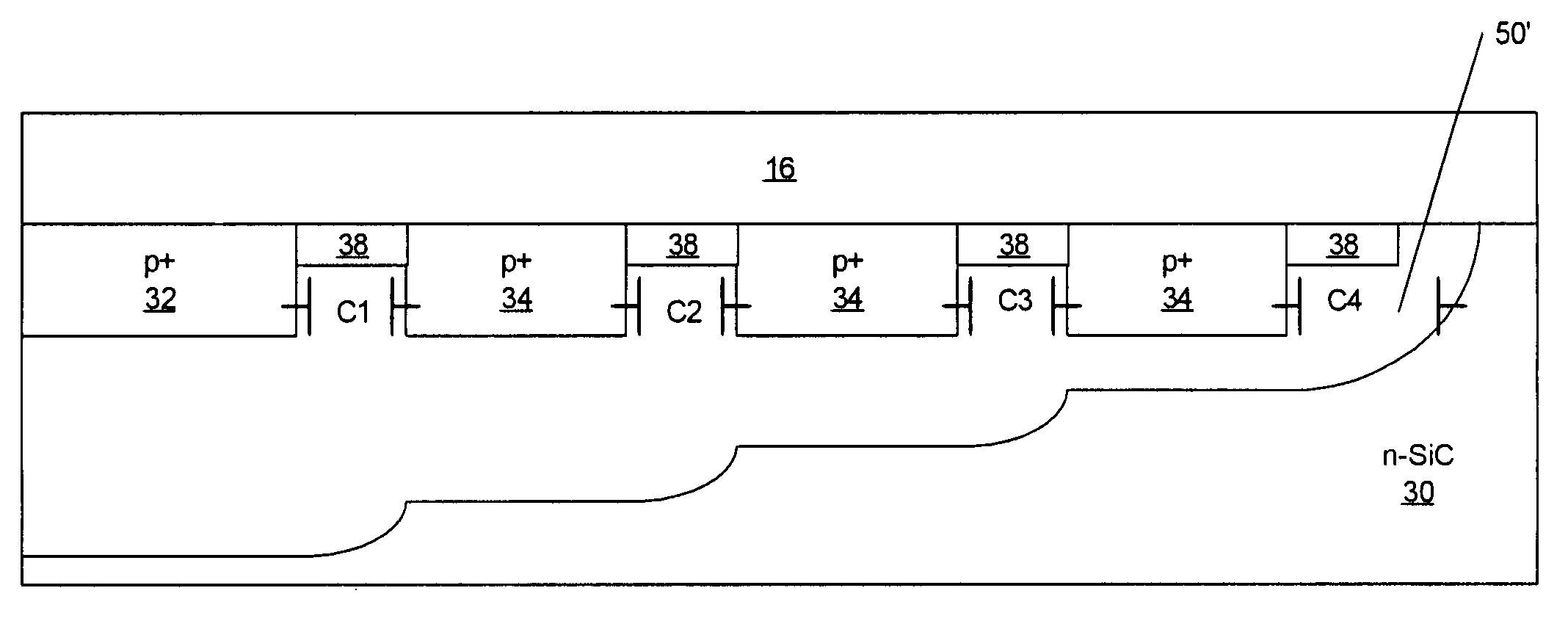

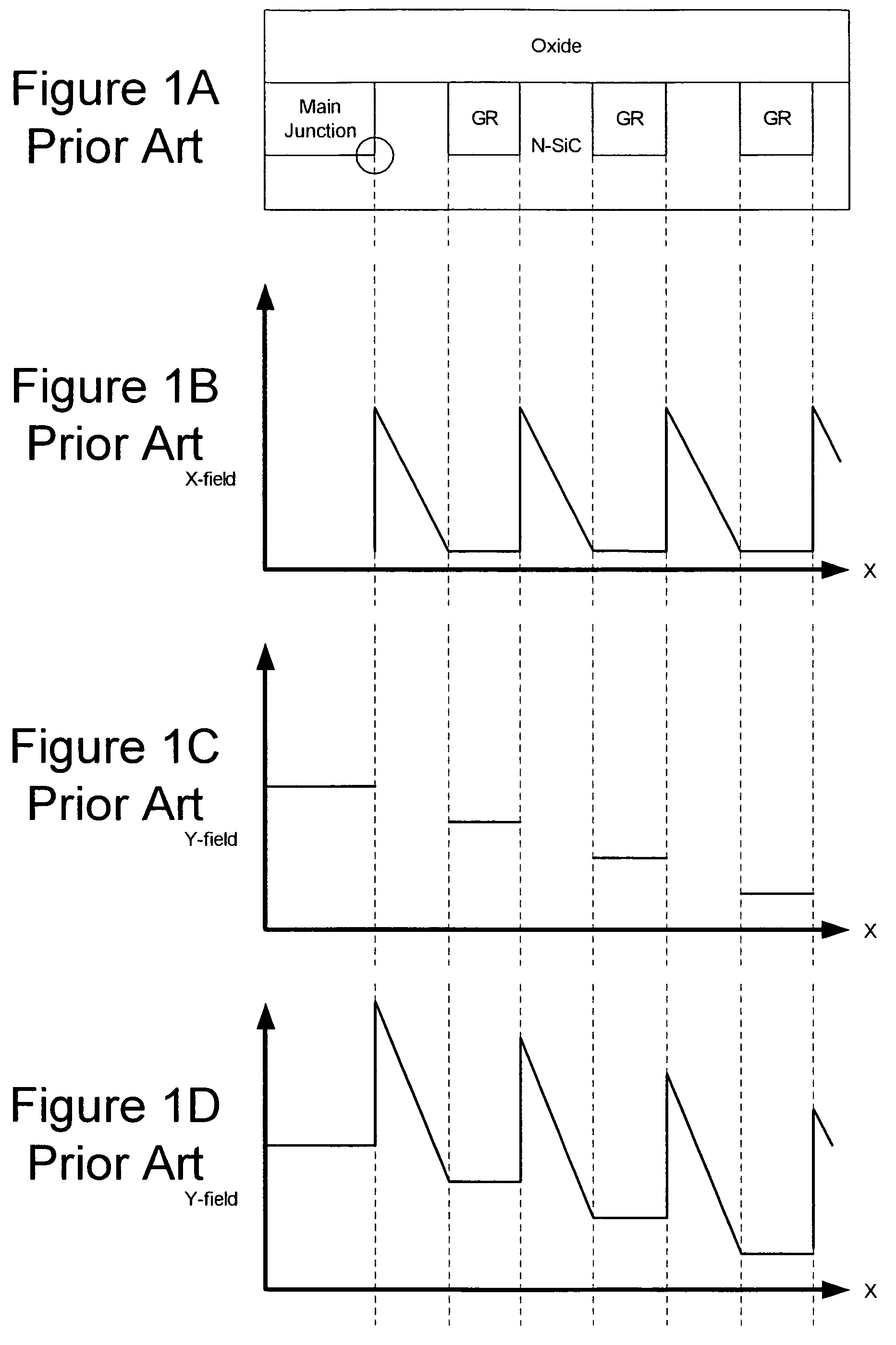

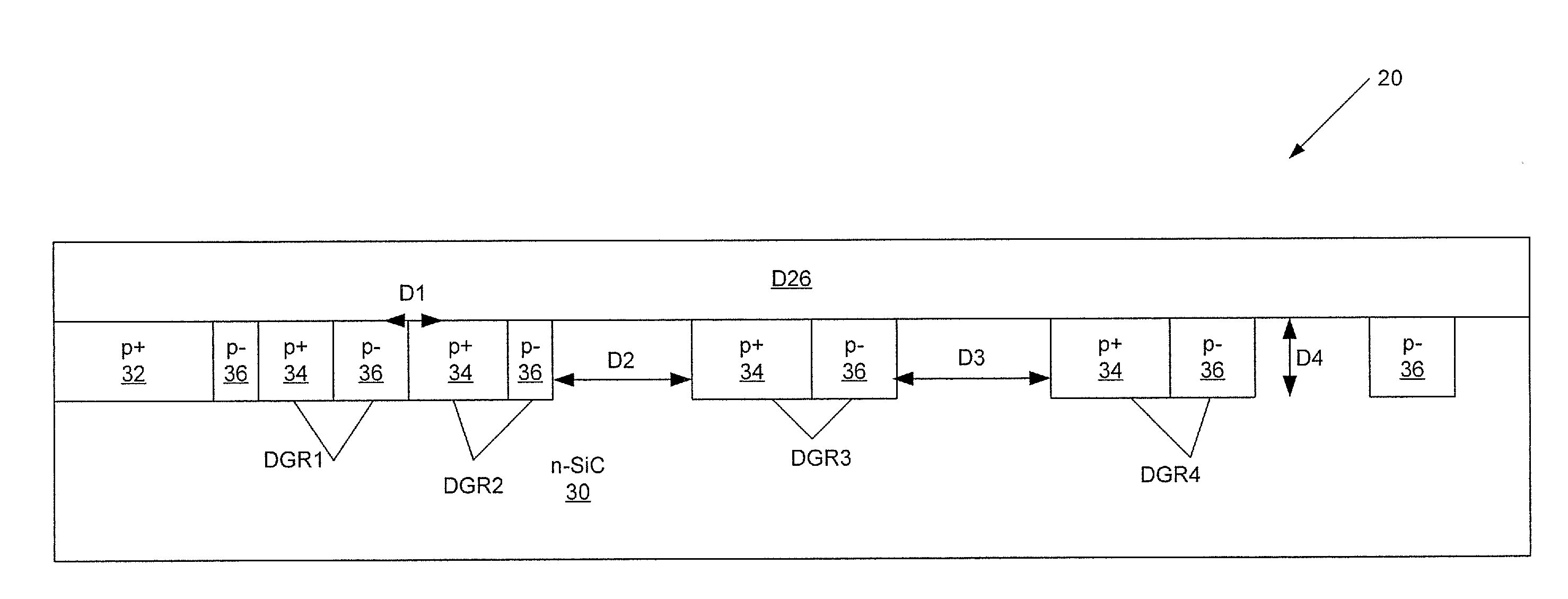

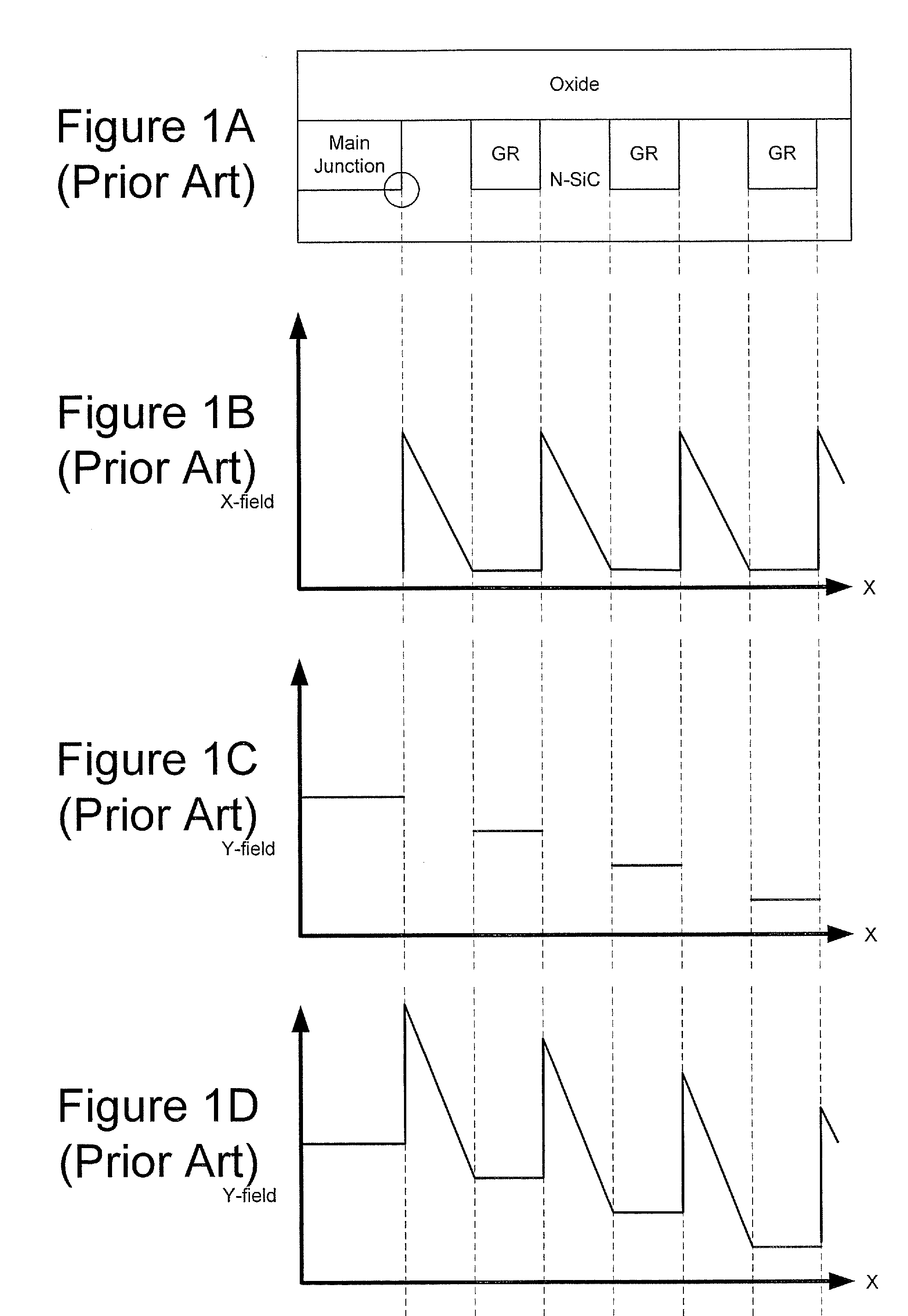

Multiple floating guard ring edge termination for silicon carbide devices

ActiveUS7026650B2Semiconductor/solid-state device manufacturingSemiconductor devicesSurface chargesSemiconductor

Edge termination for silicon carbide devices has a plurality of concentric floating guard rings in a silicon carbide layer that are adjacent and spaced apart from a silicon carbide-based semiconductor junction. An insulating layer, such as an oxide, is provided on the floating guard rings and a silicon carbide surface charge compensation region is provided between the floating guard rings and is adjacent the insulating layer. Methods of fabricating such edge termination are also provided.

Owner:CREE INC

Isolated quasi-vertical DMOS transistor

Various integrated circuit devices, in particular a quasi-vertical DMOS transistor, are formed inside an isolation structure which includes a floor isolation region and a trench extending from the surface of the substrate to the floor isolation region. The trench may be filled with a dielectric material or may have a conductive material in a central portion with a dielectric layer lining the walls of the trench. Various techniques for terminating the isolation structure by extending the floor isolation region beyond the trench, using a guard ring, and a forming a drift region are described.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

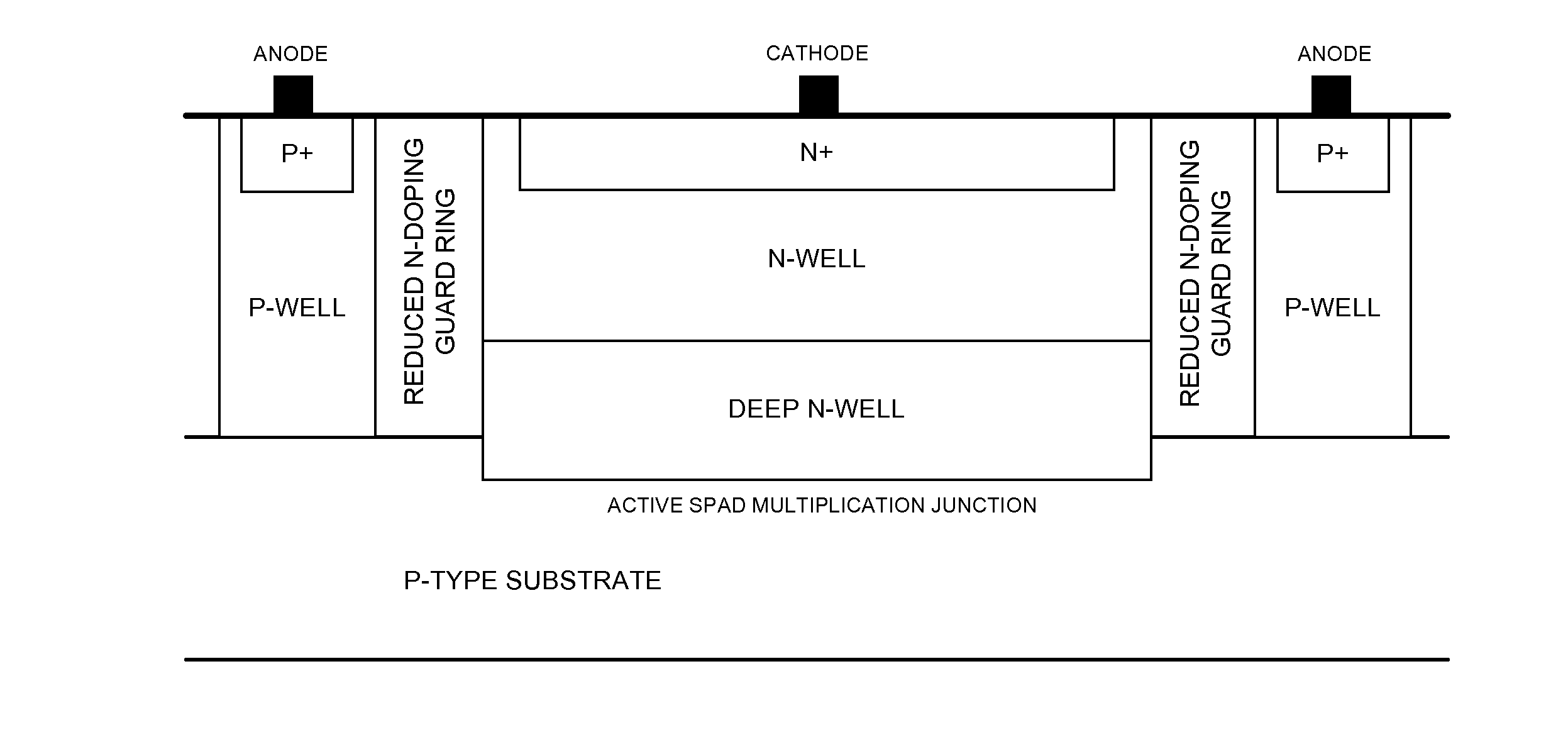

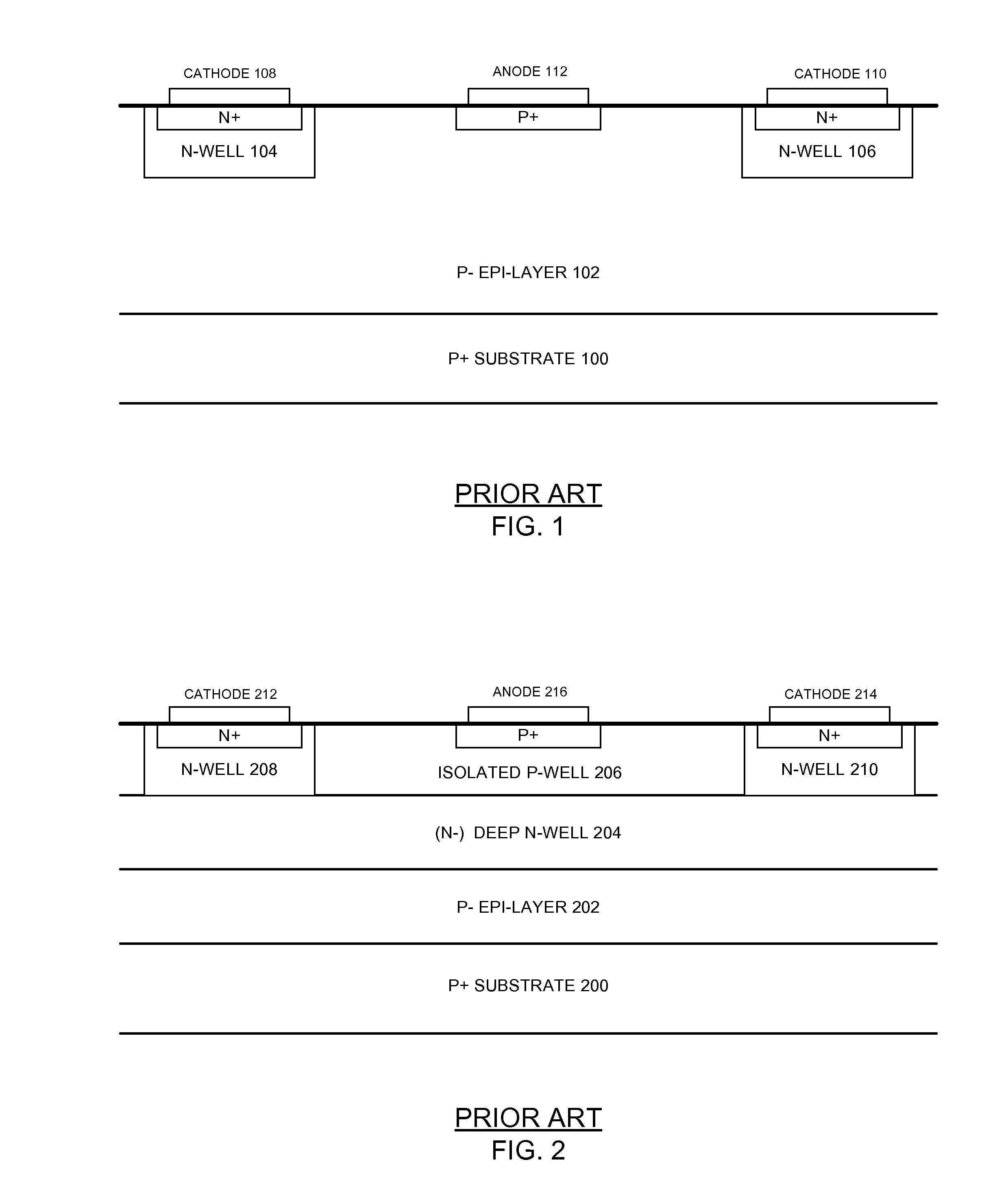

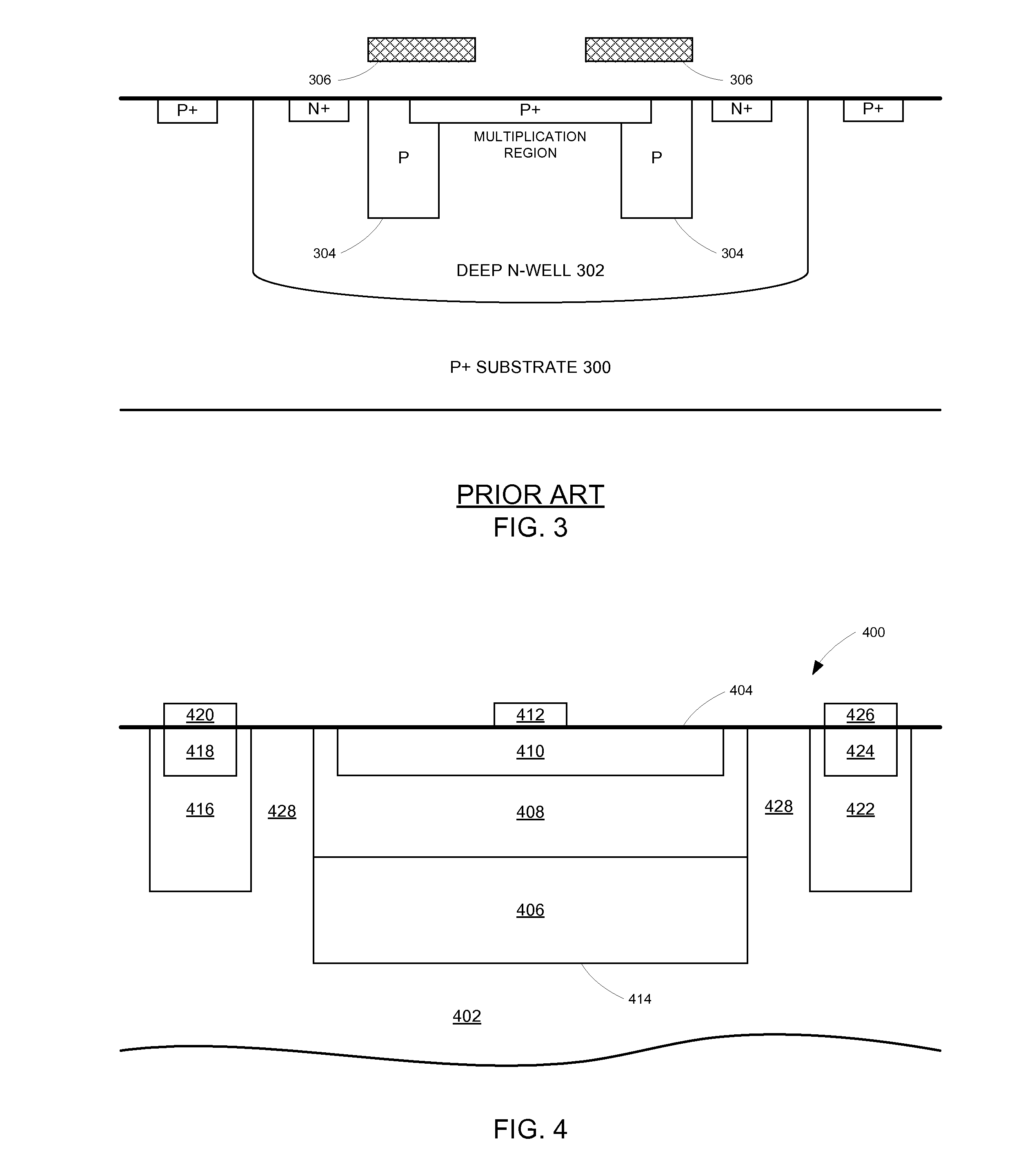

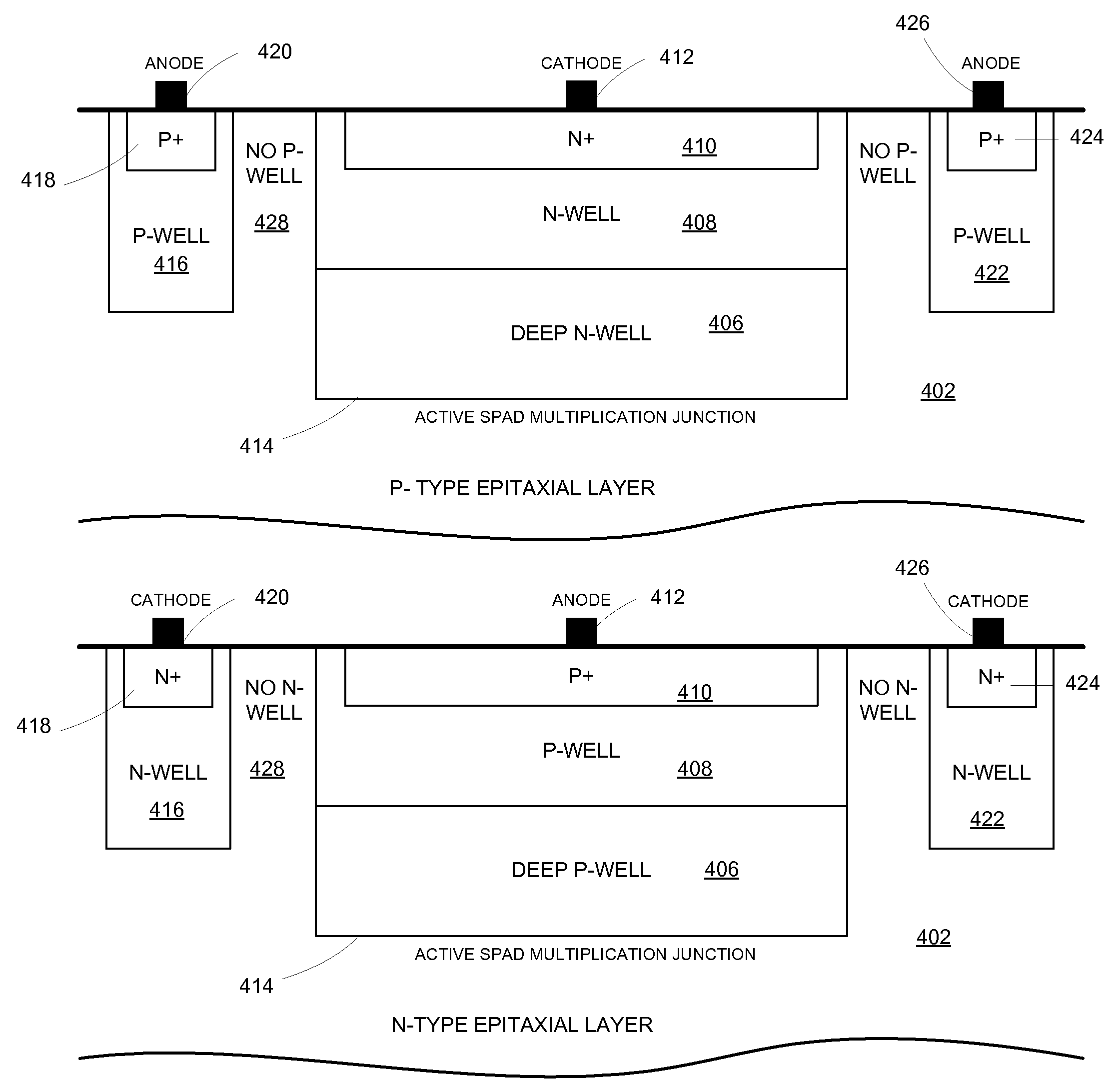

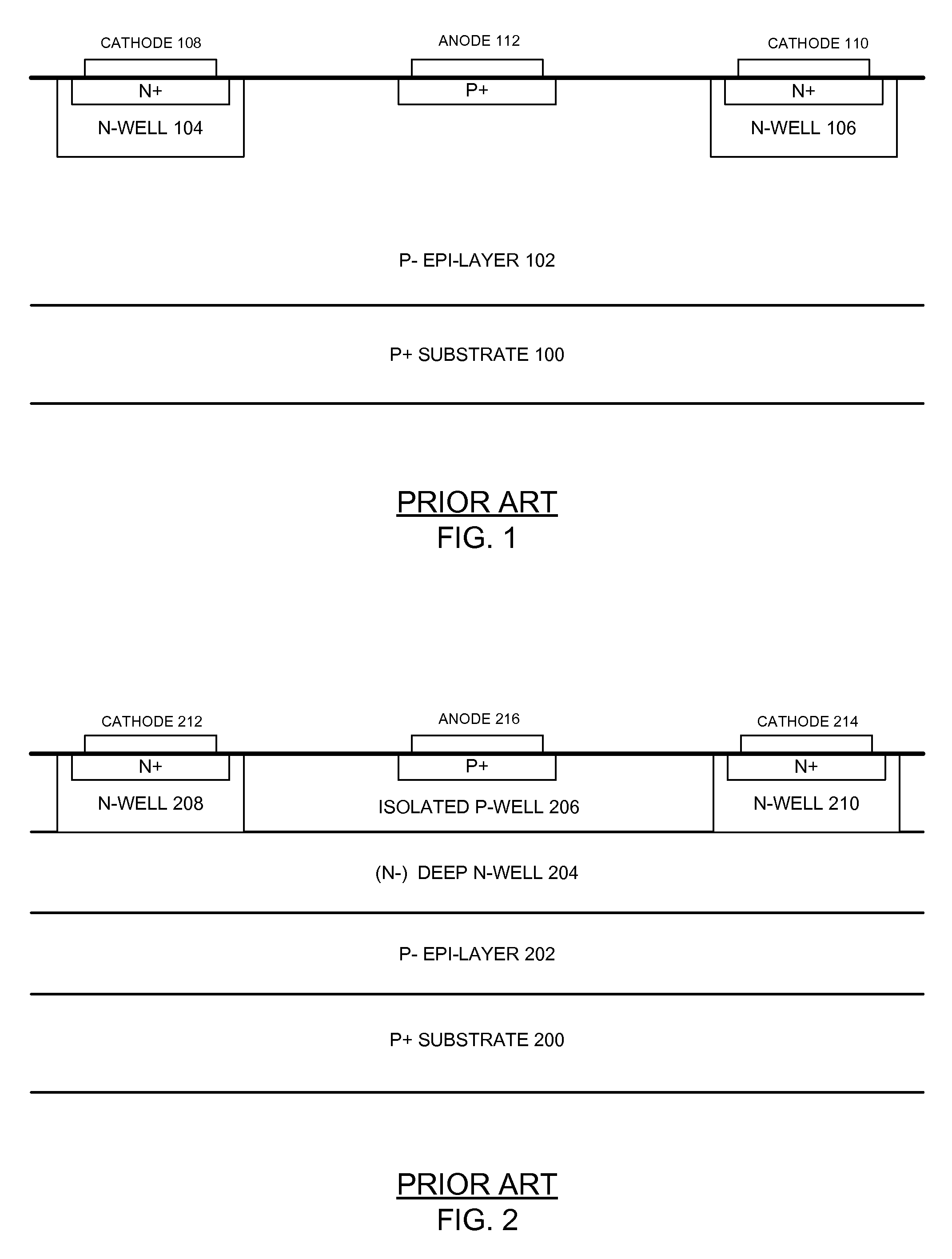

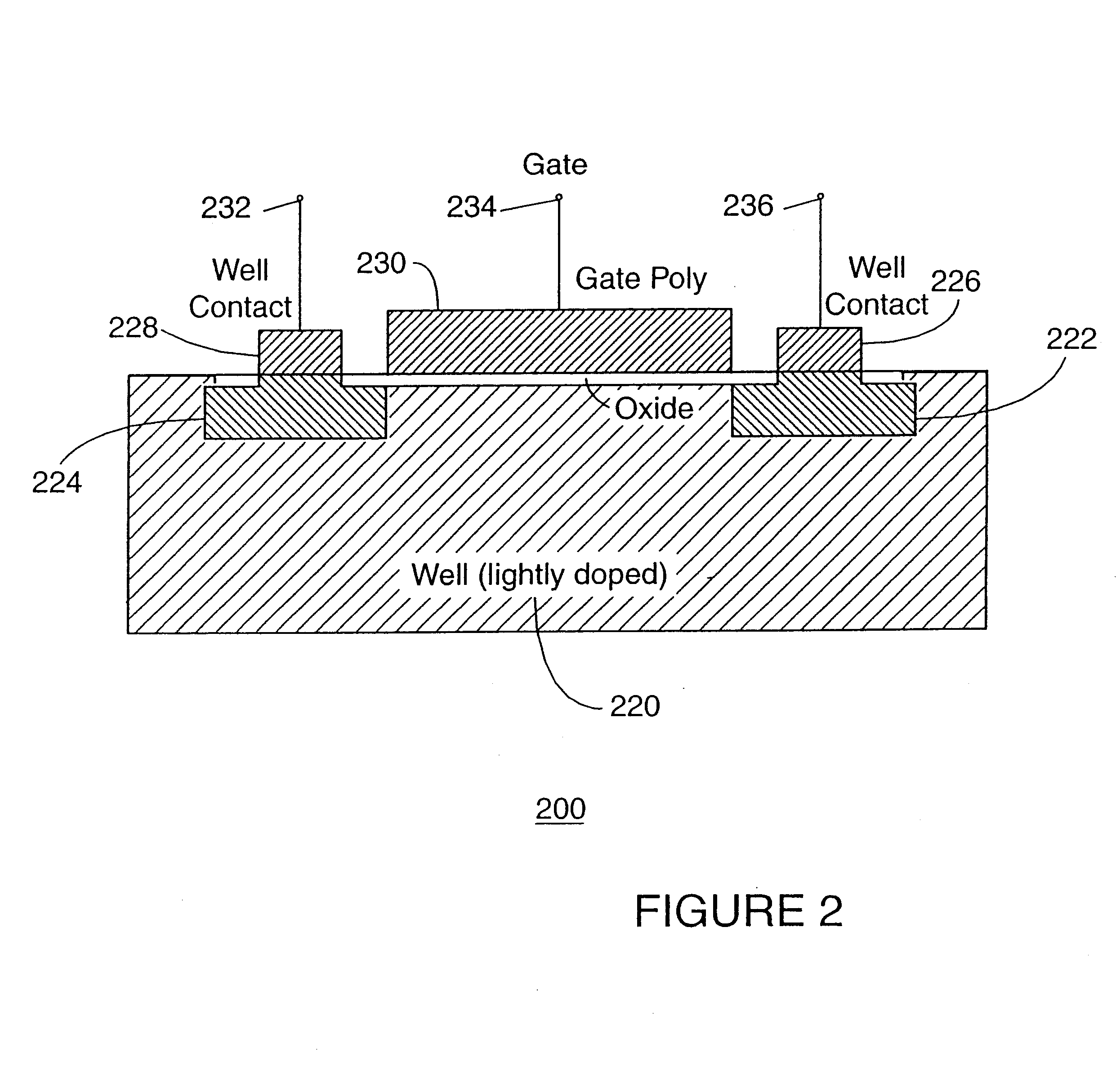

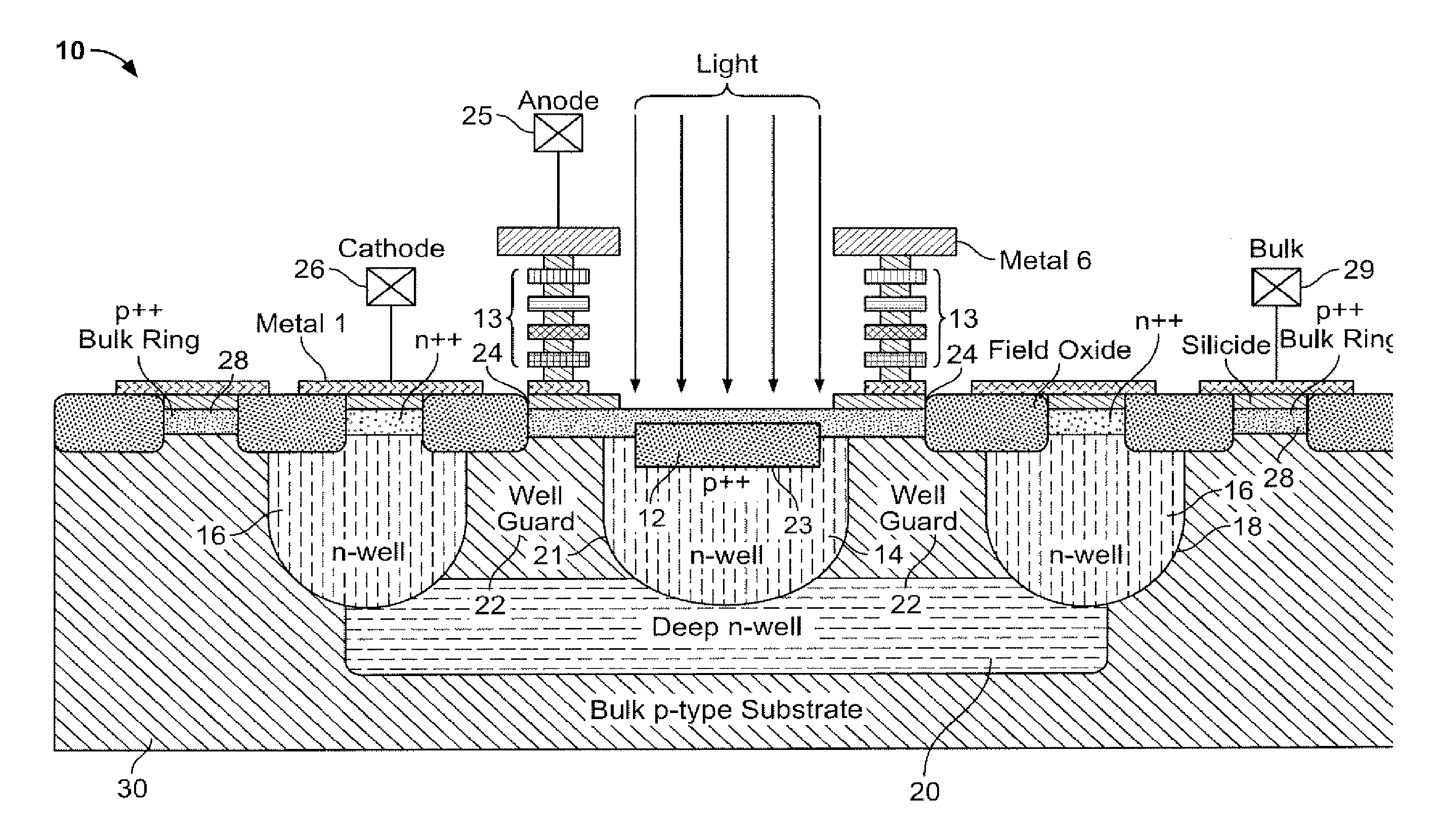

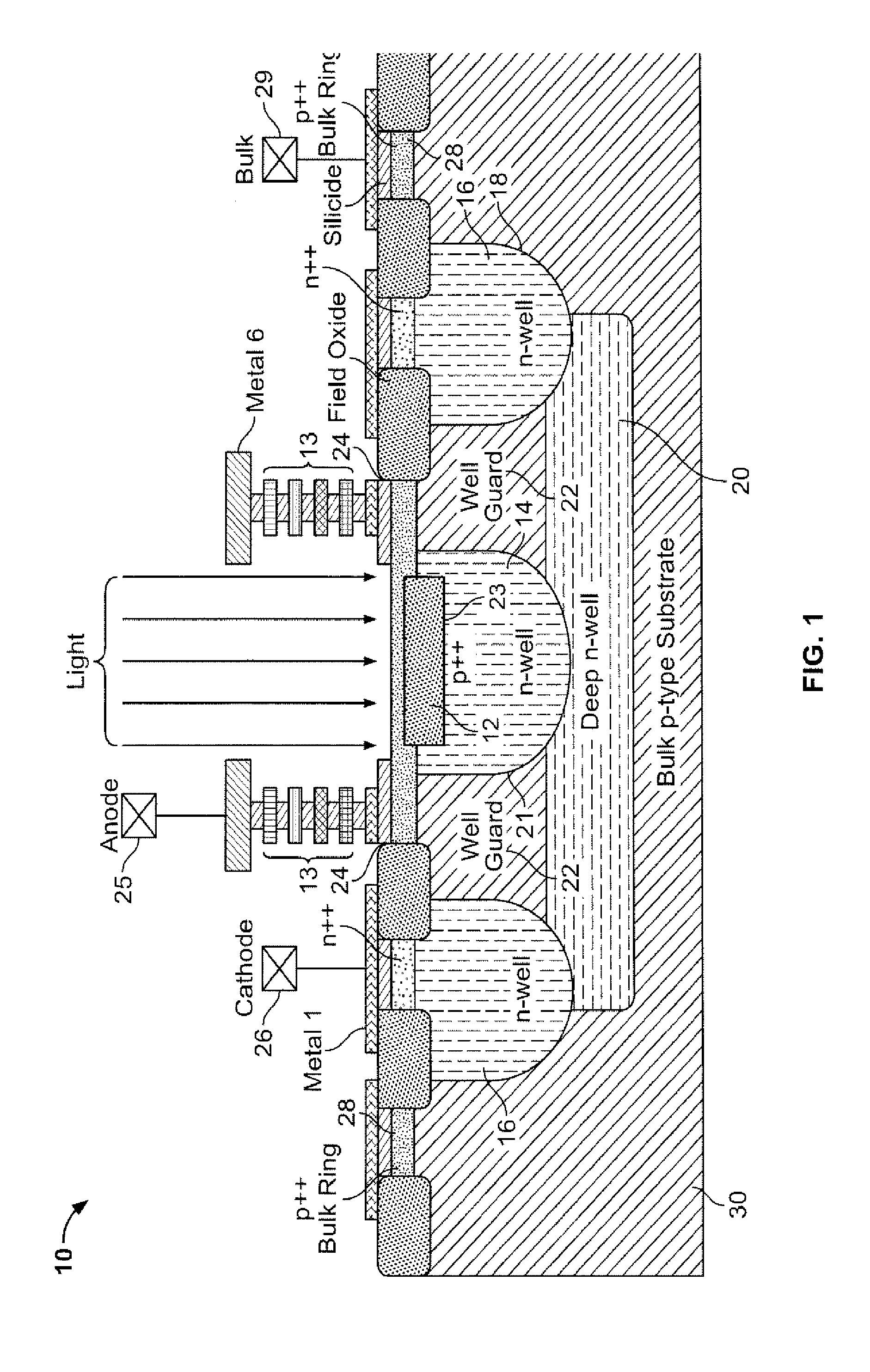

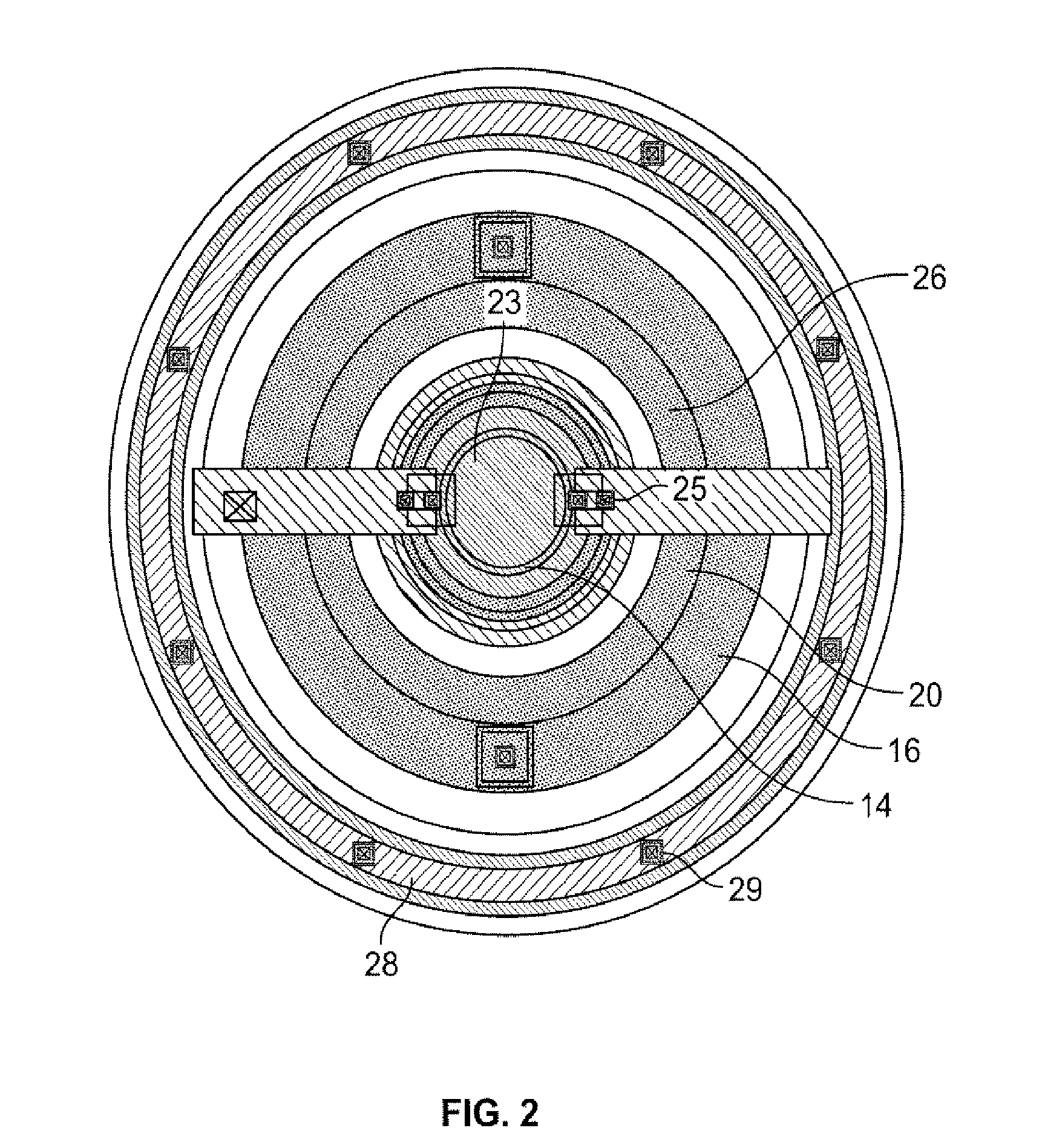

Single photon avalanche diode for CMOS circuits

ActiveUS20130193546A1Improves blue responseImproved broad spectrum sensitivityFinal product manufactureSolid-state devicesCMOSSingle-photon avalanche diode

A single photon avalanche diode for use in a CMOS integrated circuit includes a deep n-well region formed above a p-type substrate and an n-well region formed above and in contact with the deep n-well region. A cathode contact is connected to the n-well region via a heavily doped n-type implant. A lightly doped region forms a guard ring around the n-well and deep n-well regions. A p-well region is adjacent to the lightly doped region. An anode contact is connected to the p-well region via a heavily doped p-type implant. The junction between the bottom of the deep n-well region and the substrate forms a multiplication region when an appropriate bias voltage is applied between the anode and cathode and the guard ring breakdown voltage is controlled with appropriate control of the lateral doping concentration gradient such that the breakdown voltage is higher than that of the multiplication region.

Owner:STMICROELECTRONICS RES & DEV +1

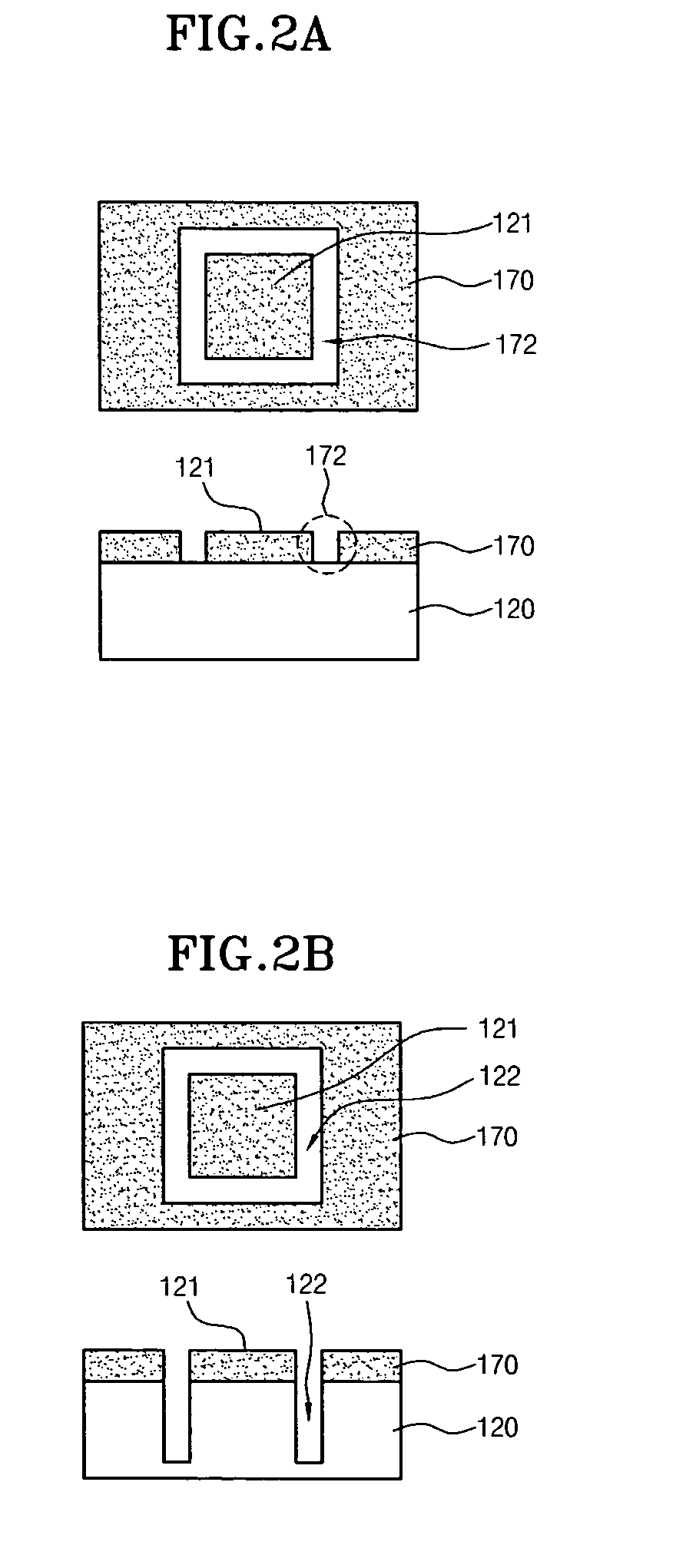

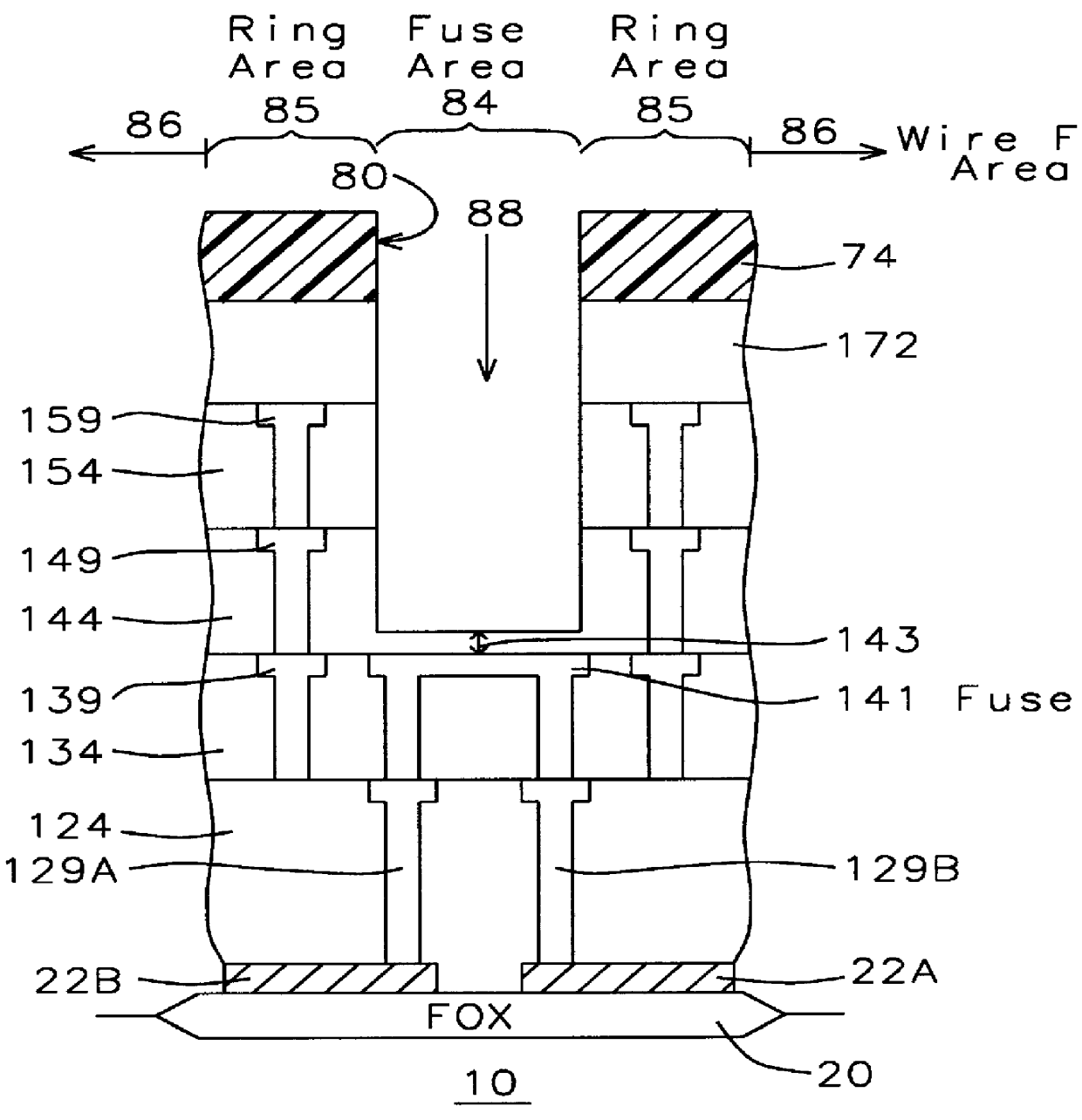

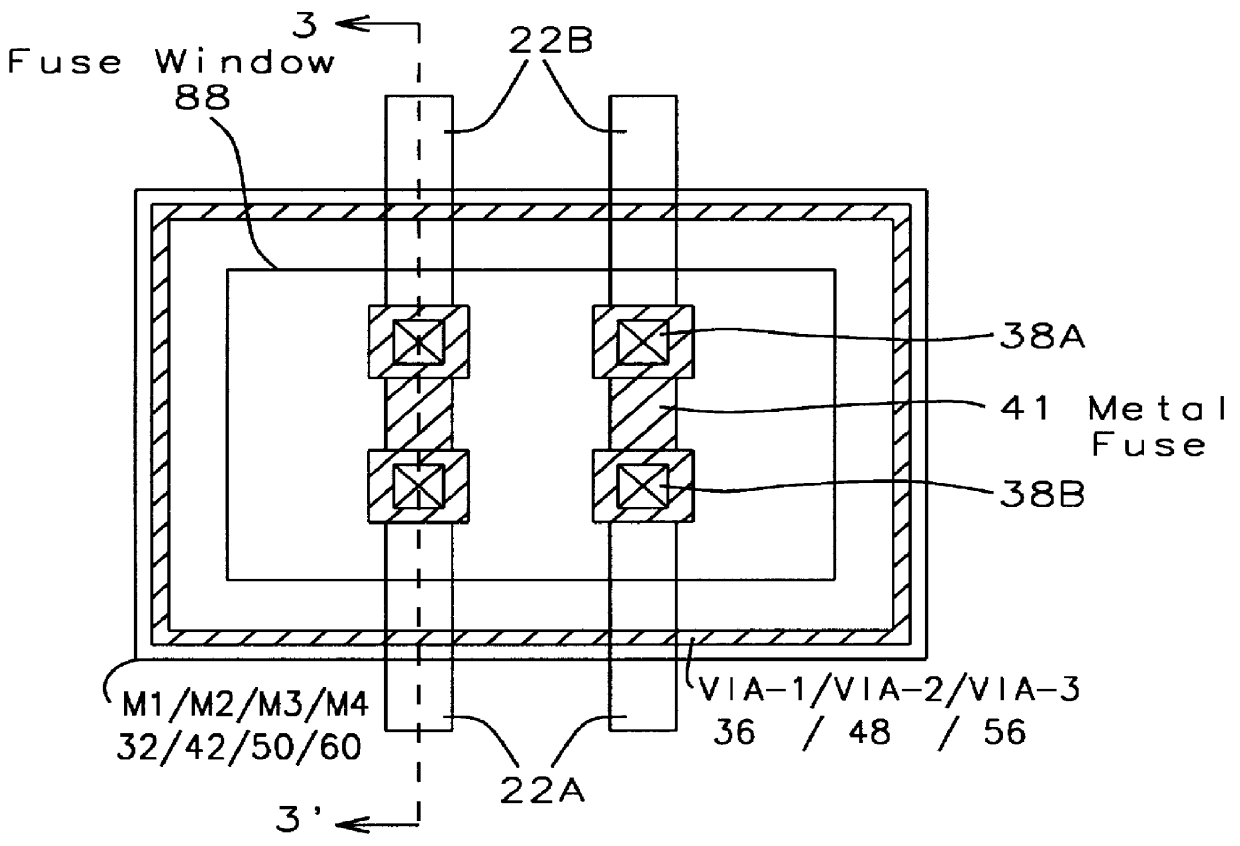

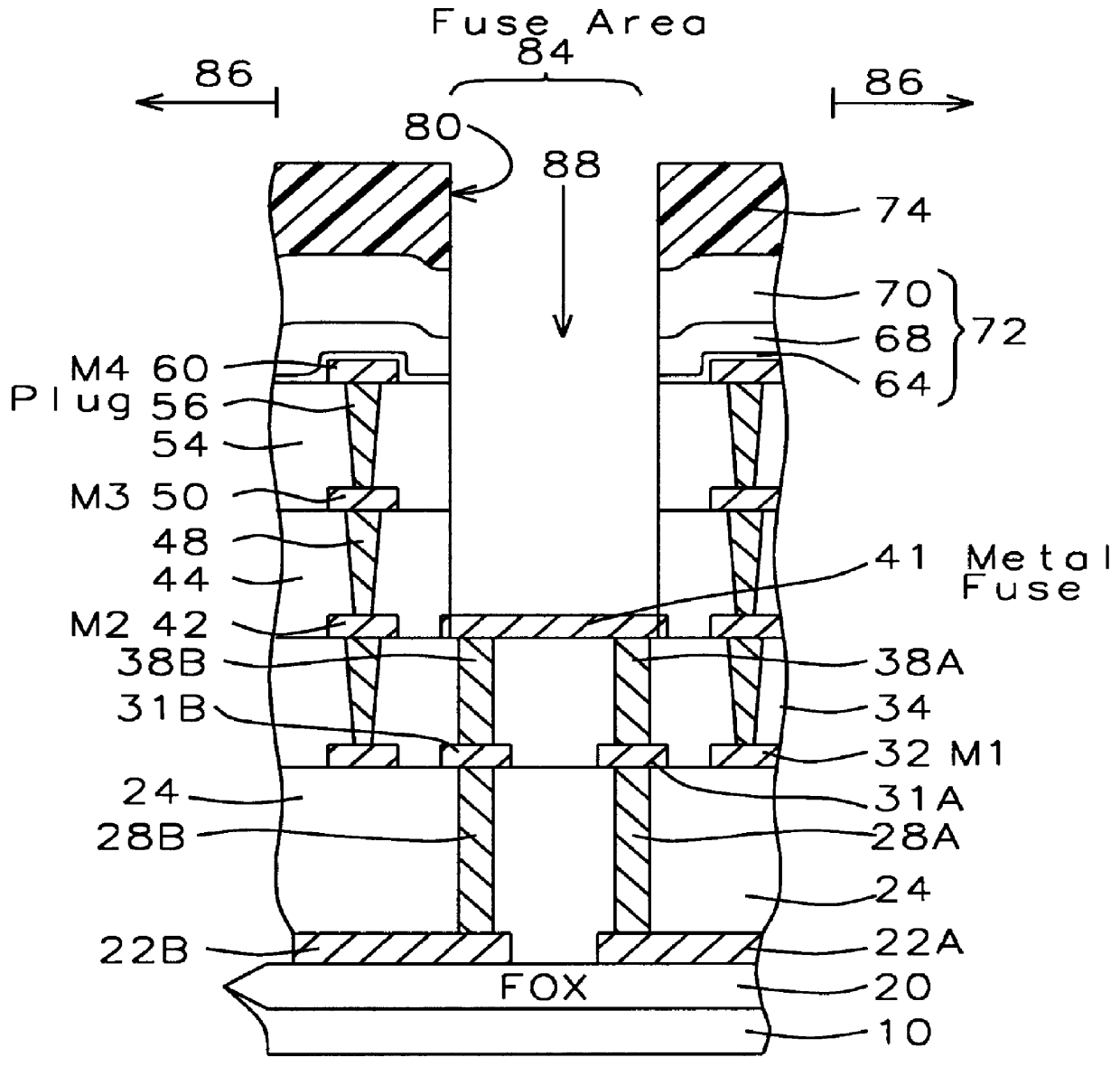

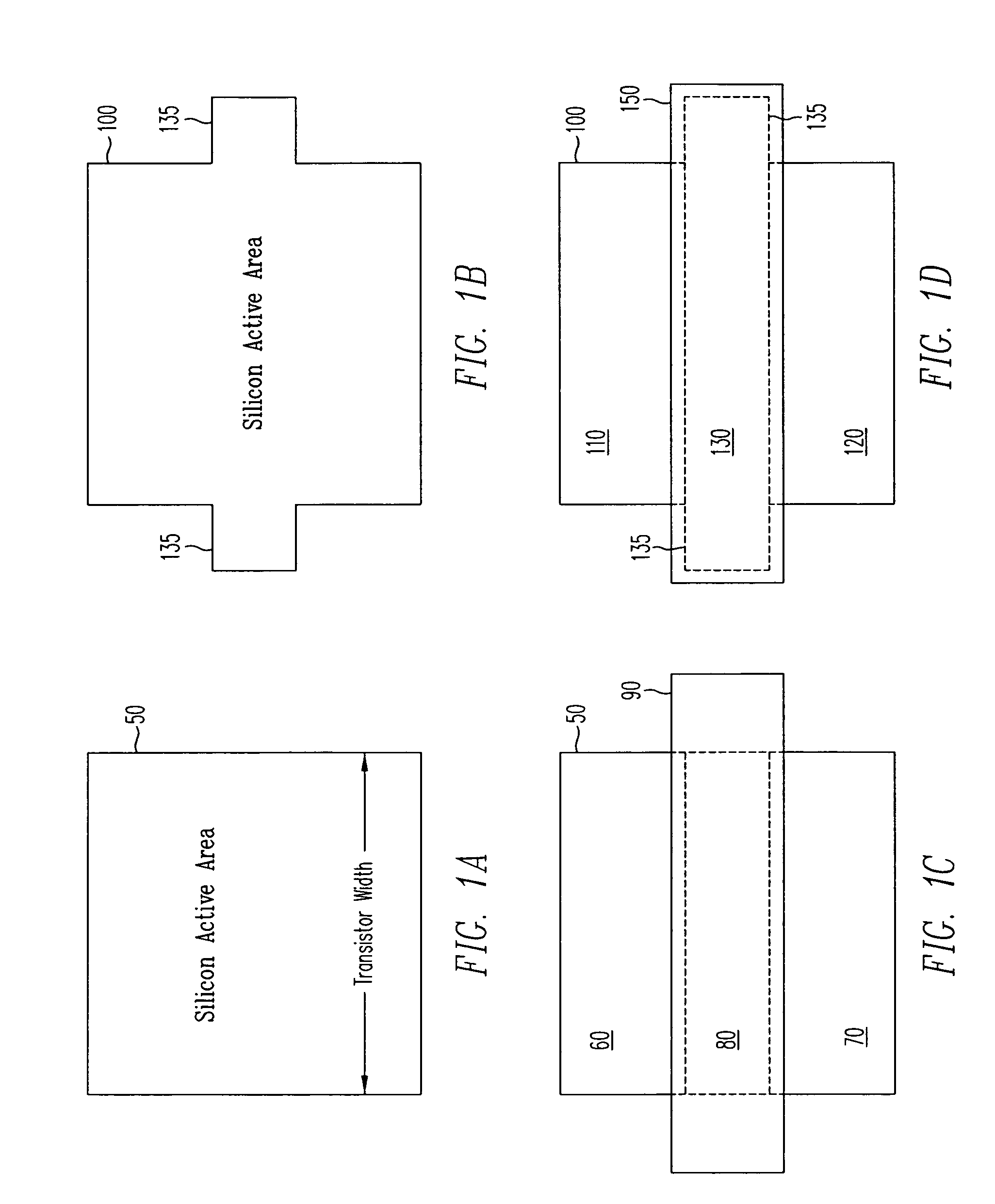

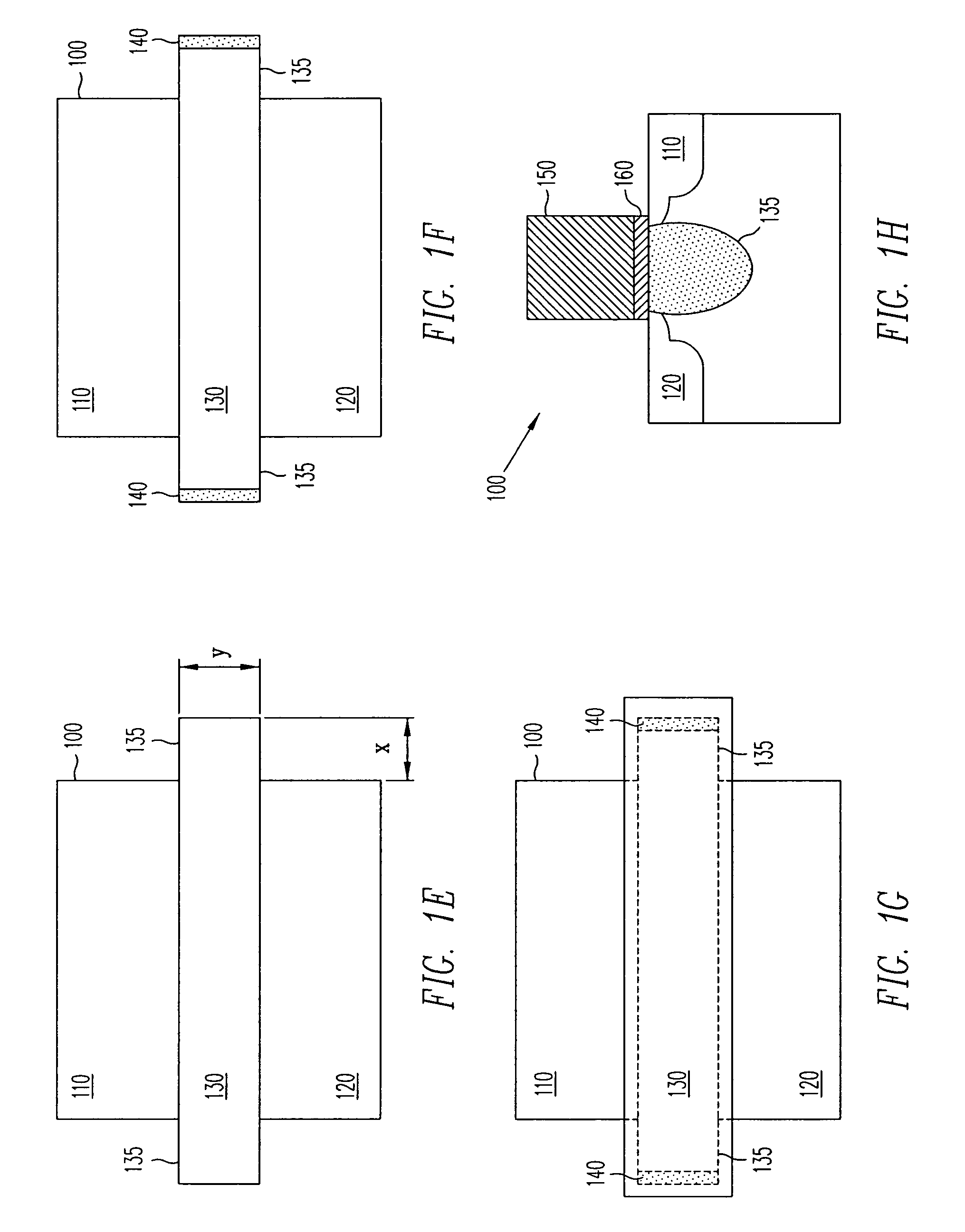

Fabrication of metal fuse design for redundancy technology having a guard ring

InactiveUS6100118ASemiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

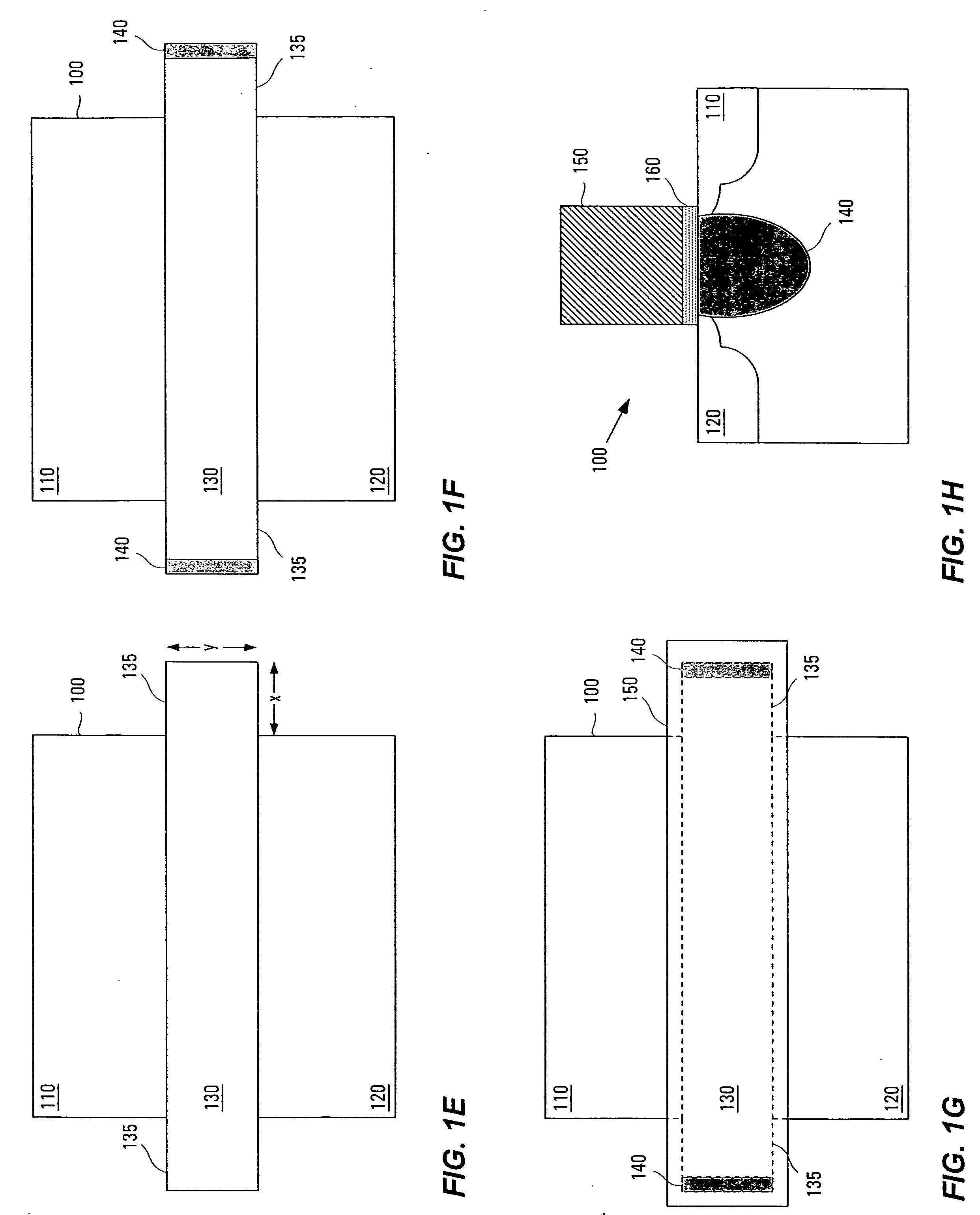

A method of fabricating a metal guard ring (e.g., 139 149 159) around for a metal fuse 141 and fuse opening 88. The metal fuse 41 is formed from a second metal layer (M2) (or M3 or M4, etc.) and is connected to an underlying polysilicon layer 22 by fuse interconnections 129A 129B. The method comprises: a) forming a first polysilicon line 22A and a second polysilicon line 22B over at least the fuse area 84 insulated (e.g., 20) from a substrate 10; b) forming one or more levels of fuse interconnects (129A 129B) electrically connected to the first polysilicon line 22A and the second polysilicon line 22B; the fuse interconnects 129A 129B passing through vias in one or more insulating layers 24 34; c) simultaneously forming a metal fuse 141 connecting the polysilicon interconnects 129A 129B over the fuse area 84 and forming a first guard ring 139 around a fuse area 84; d) forming an dielectric layer 144 over the metal fuse 141 and the first guard ring 139; e) forming a guard ring around the fuse areas 84; the guard ring composed of a plurality of metal wiring layers 149 159 formed on and through vias in a plurality of dielectric layers 144 154; and f) forming a fuse opening 88 through at least a portion of the plurality of dielectric layers 144 154 172 in the fuse area.

Owner:TAIWAN SEMICON MFG CO LTD

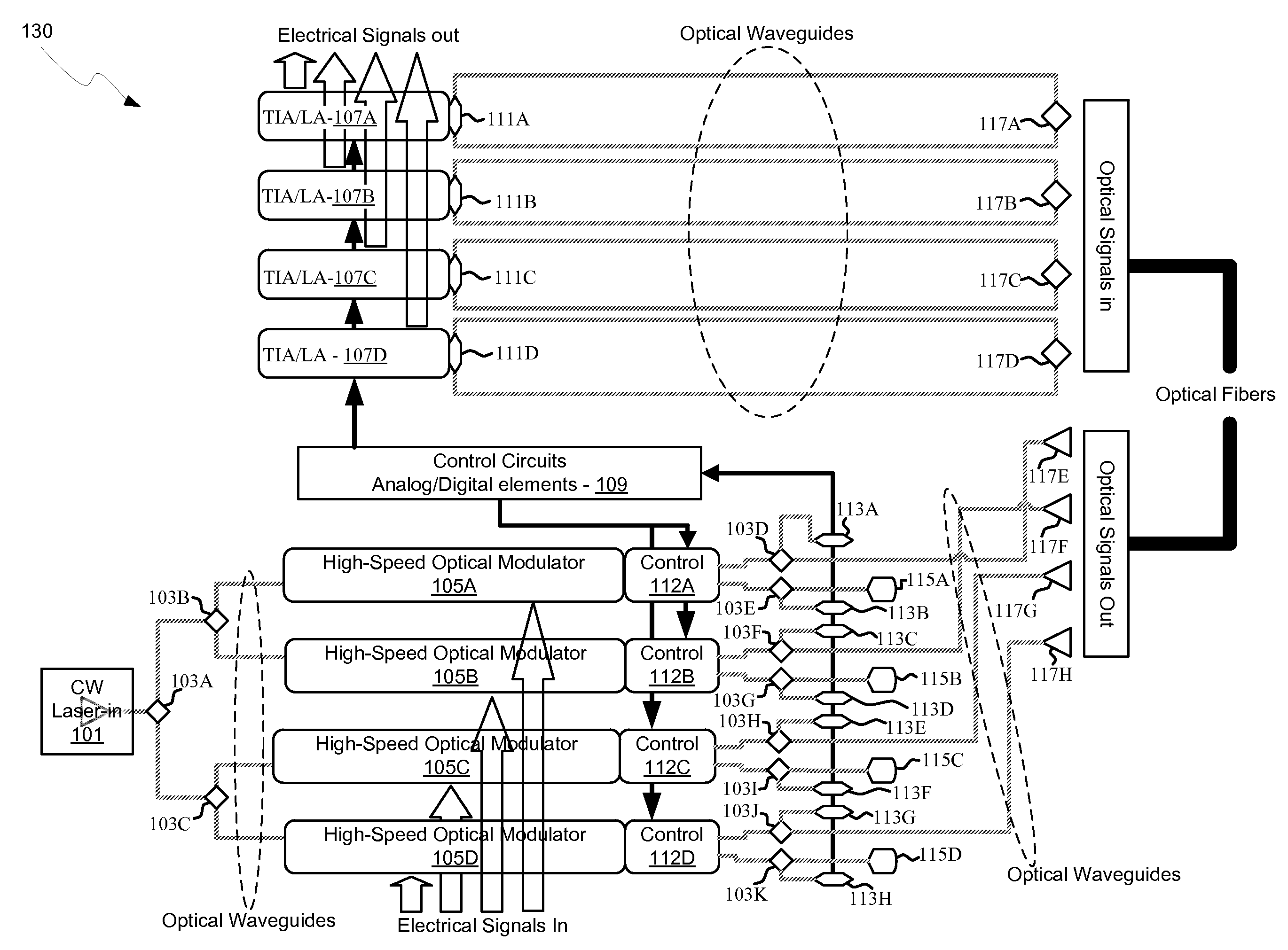

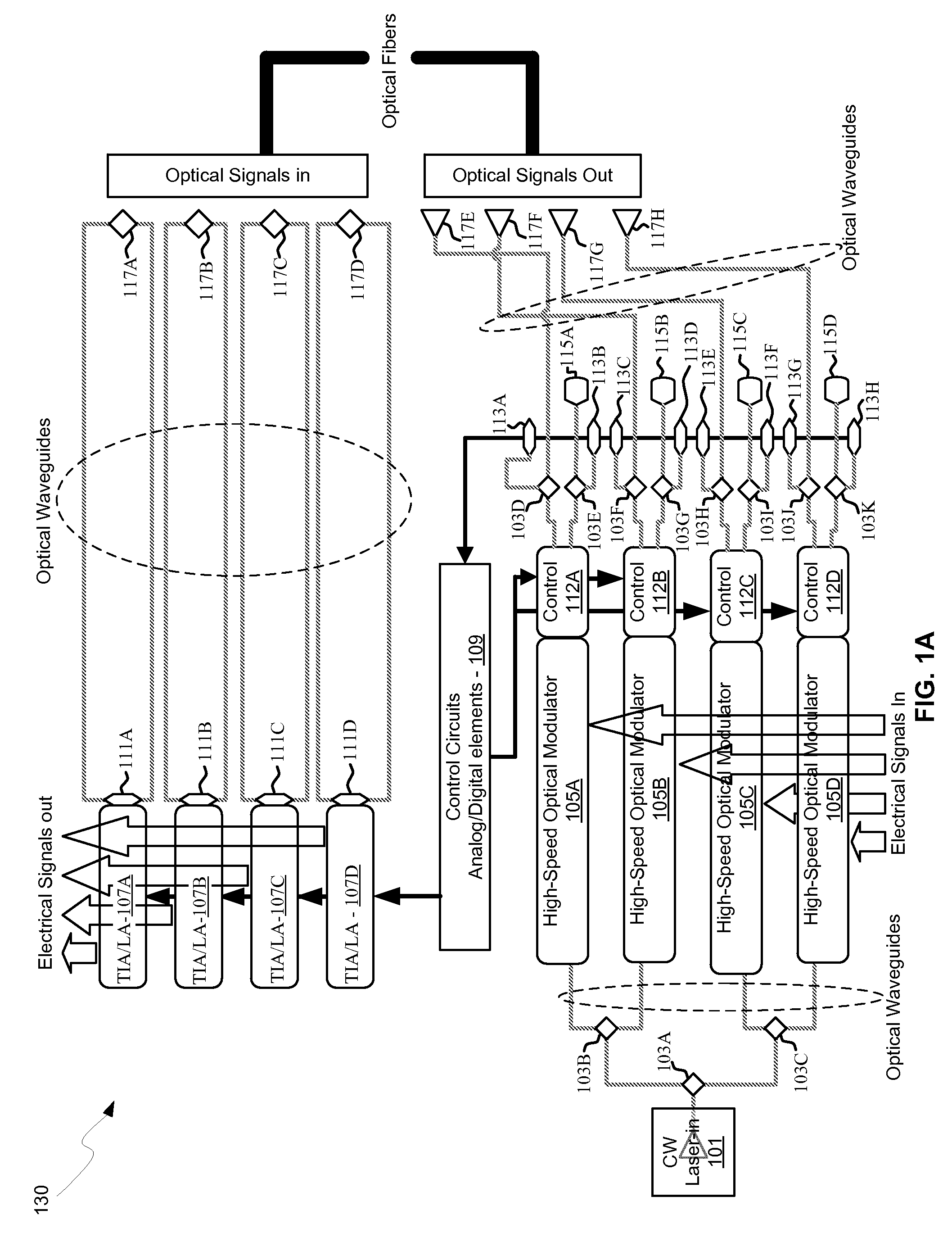

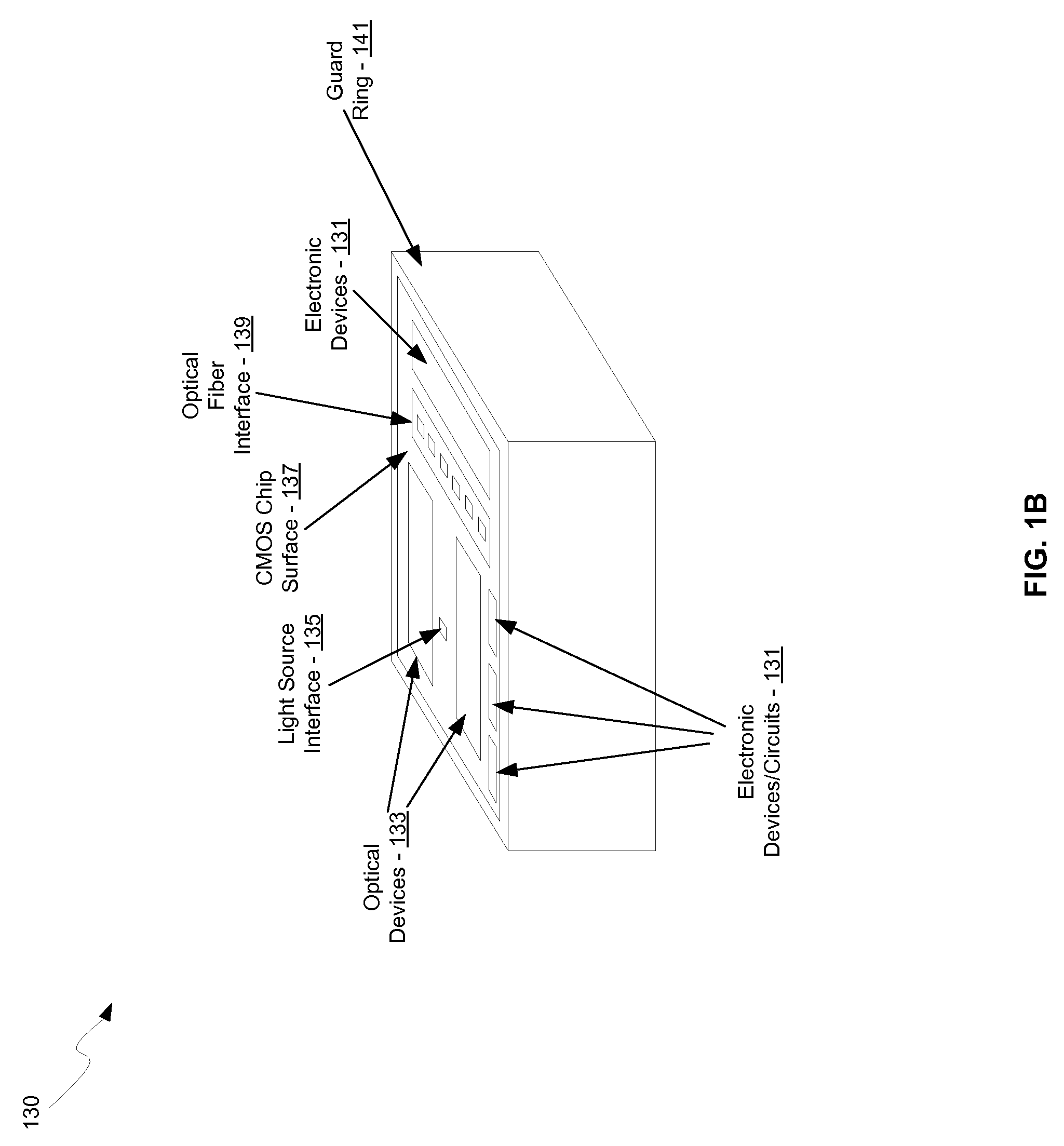

Method and system for optoelectronics transceivers integrated on a CMOS chip

Methods and systems for optoelectronics transceivers integrated on a CMOS chip are disclosed and may include receiving optical signals from optical fibers via grating couplers on a top surface of a CMOS chip, which may include a guard ring. Photodetectors may be integrated in the CMOS chip. A CW optical signal may be received from a laser source via grating couplers, and may be modulated using optical modulators, which may be Mach-Zehnder and / or ring modulators. Circuitry in the CMOS chip may drive the optical modulators. The modulated optical signal may be communicated out of the top surface of the CMOS chip into optical fibers via grating couplers. The received optical signals may be communicated between devices via waveguides. The photodetectors may include germanium waveguide photodiodes, avalanche photodiodes, and / or heterojunction diodes. The CW optical signal may be generated using an edge-emitting and / or a vertical-cavity surface emitting semiconductor laser.

Owner:CISCO TECH INC

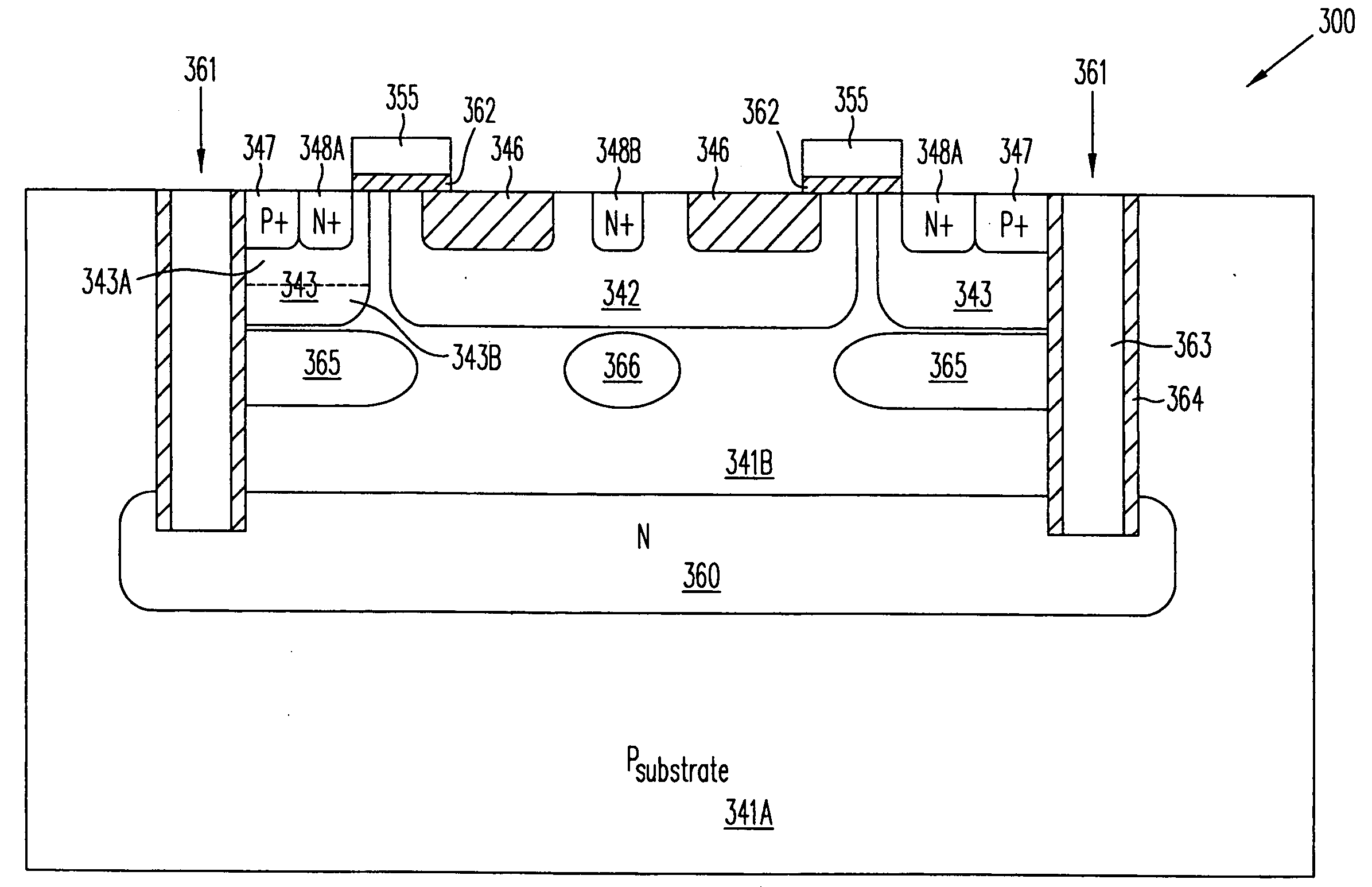

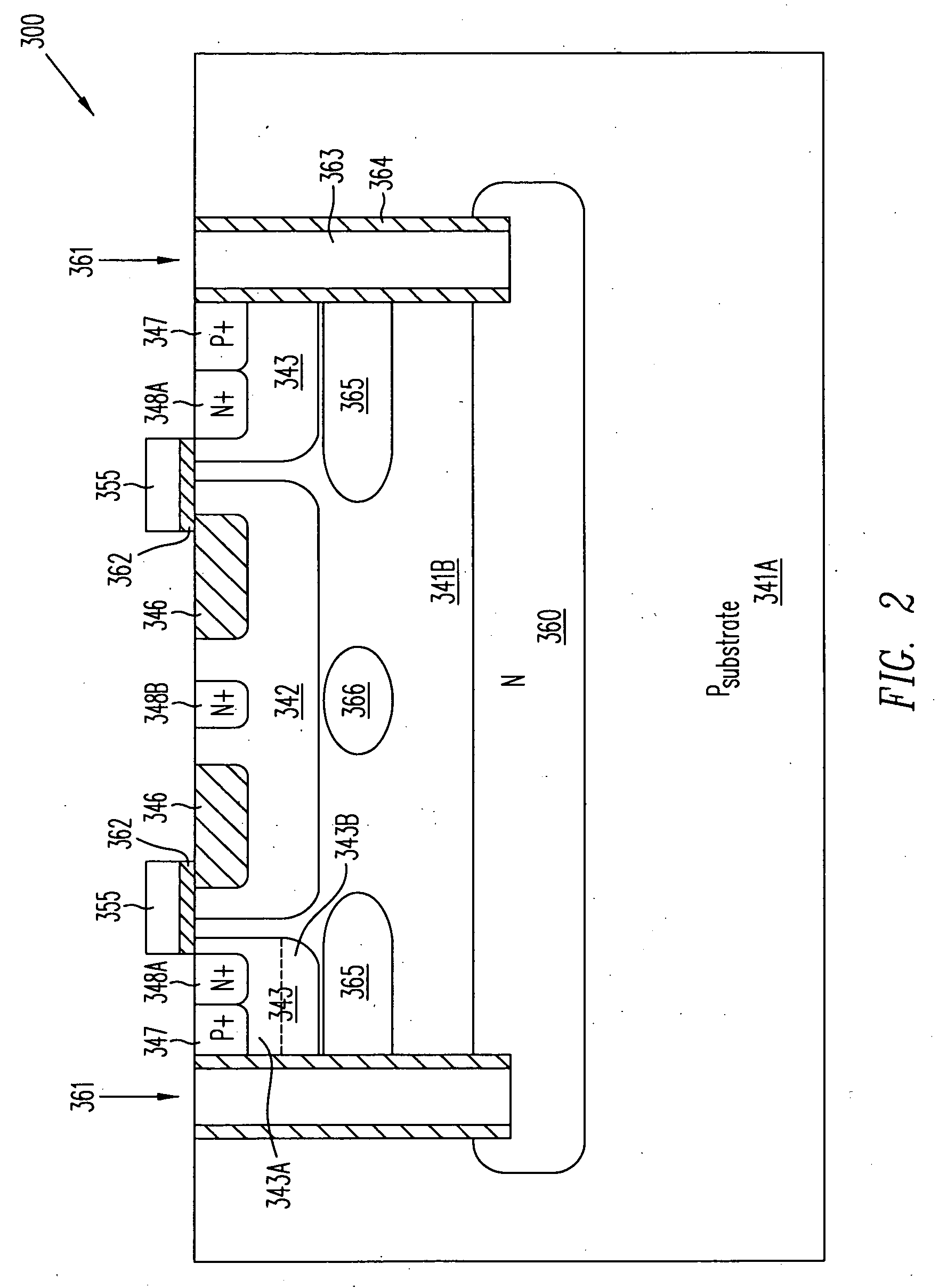

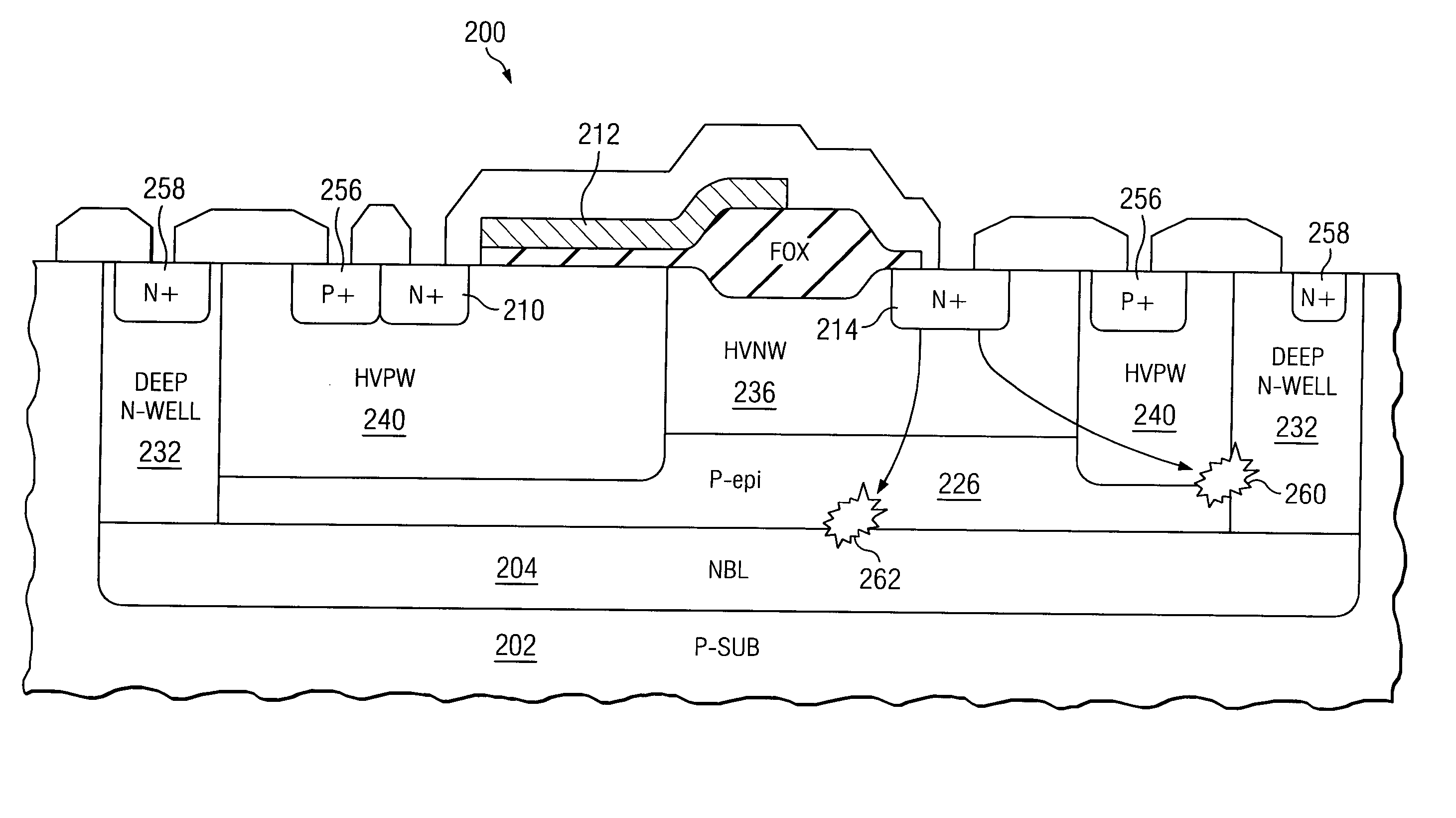

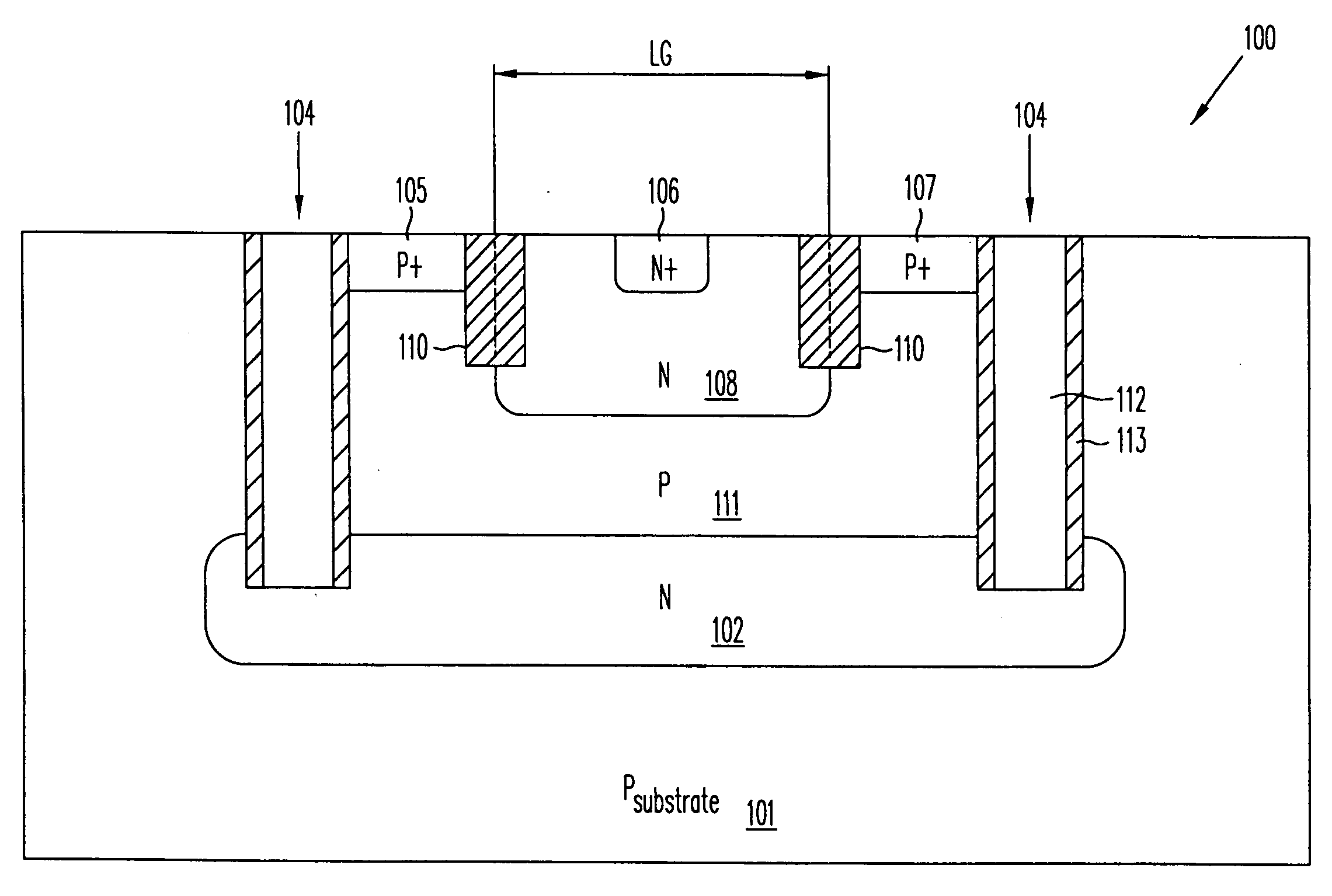

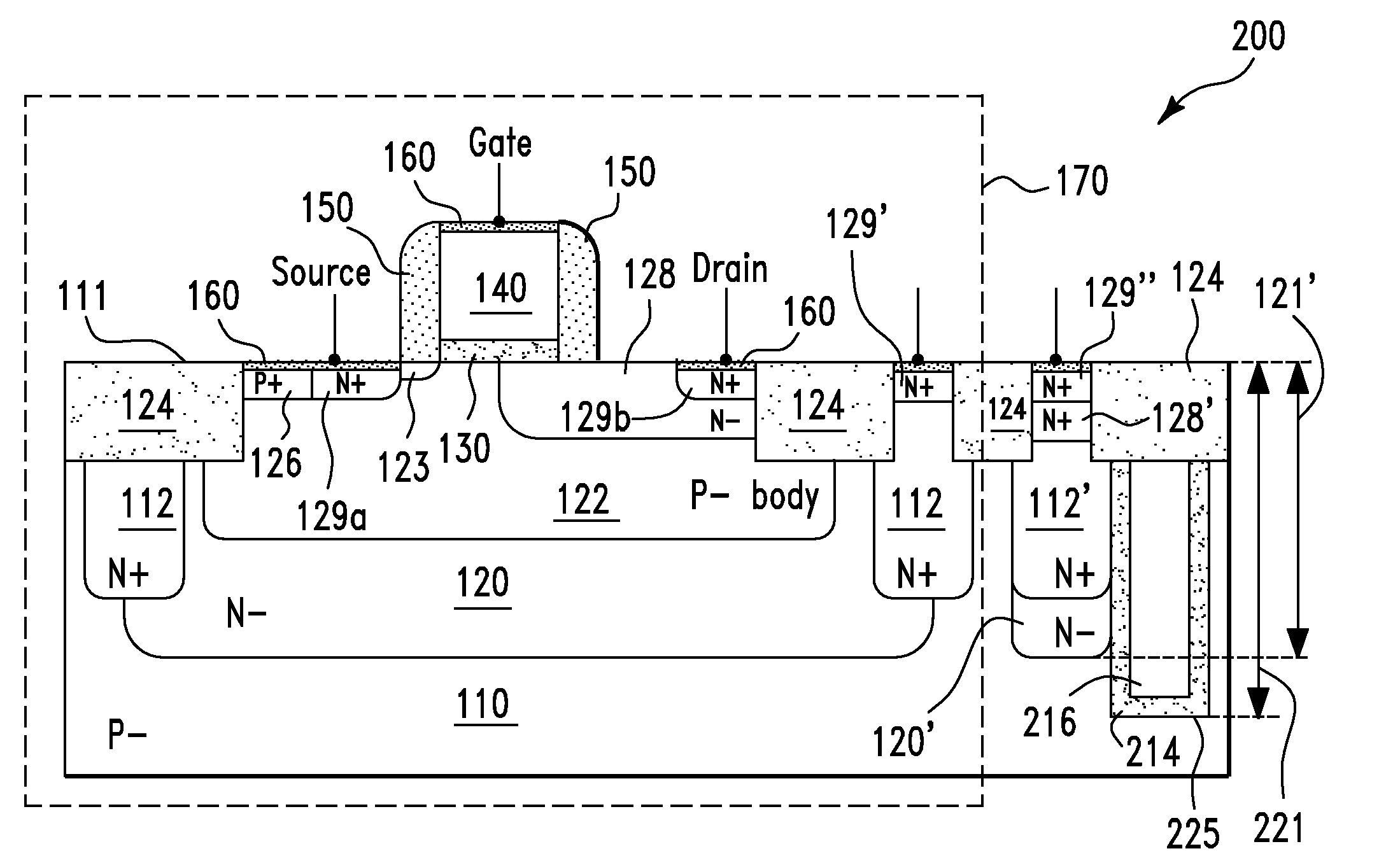

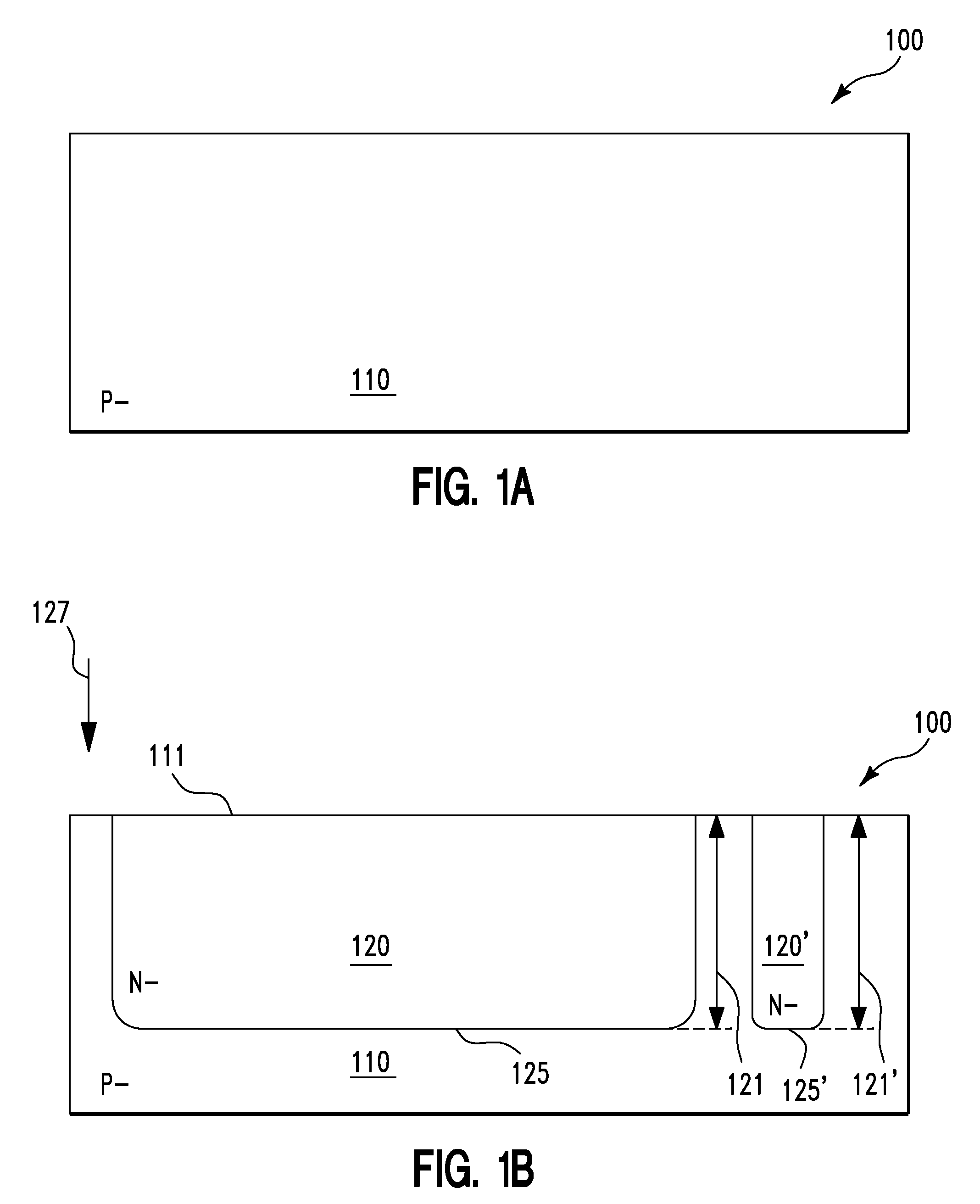

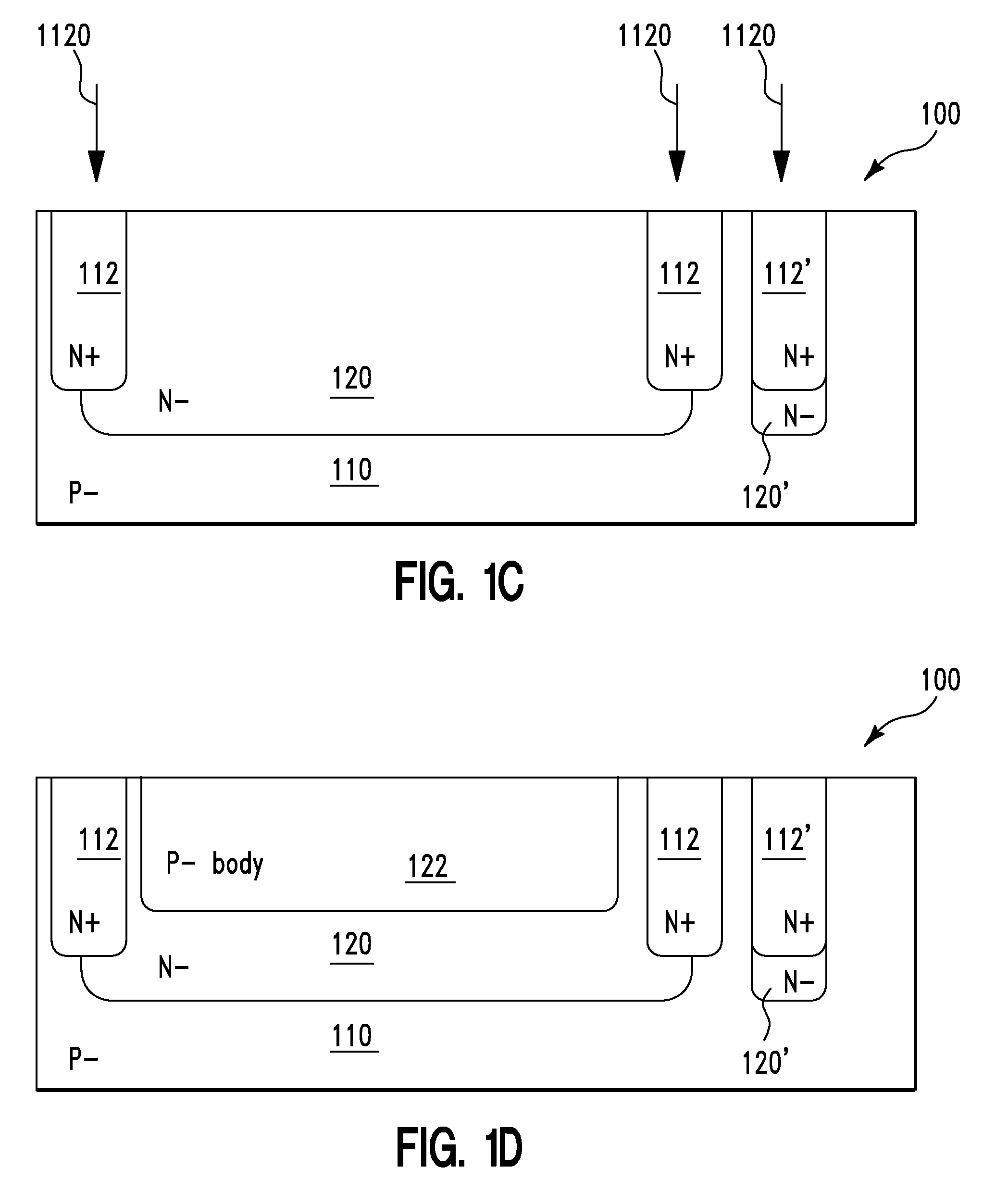

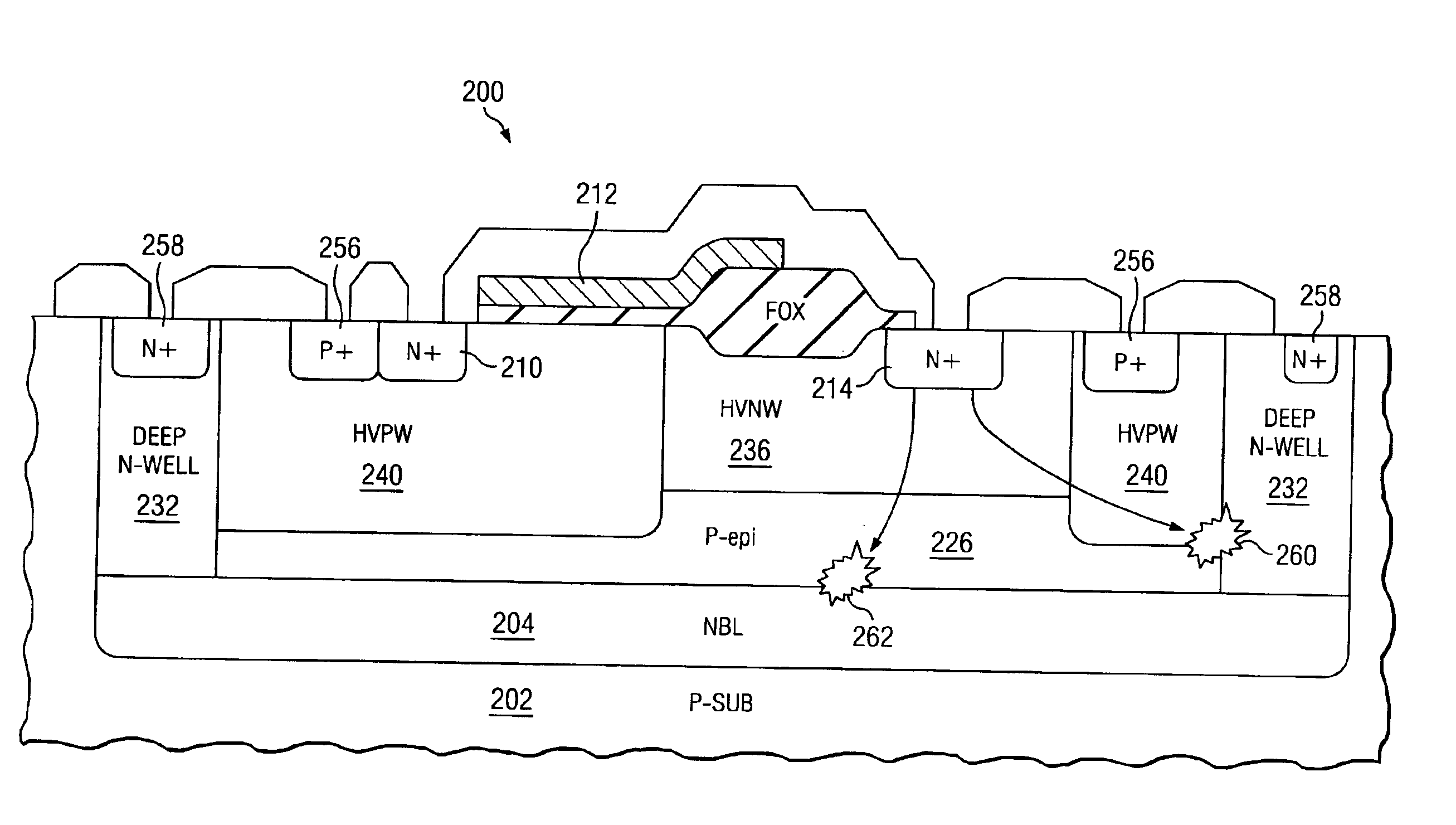

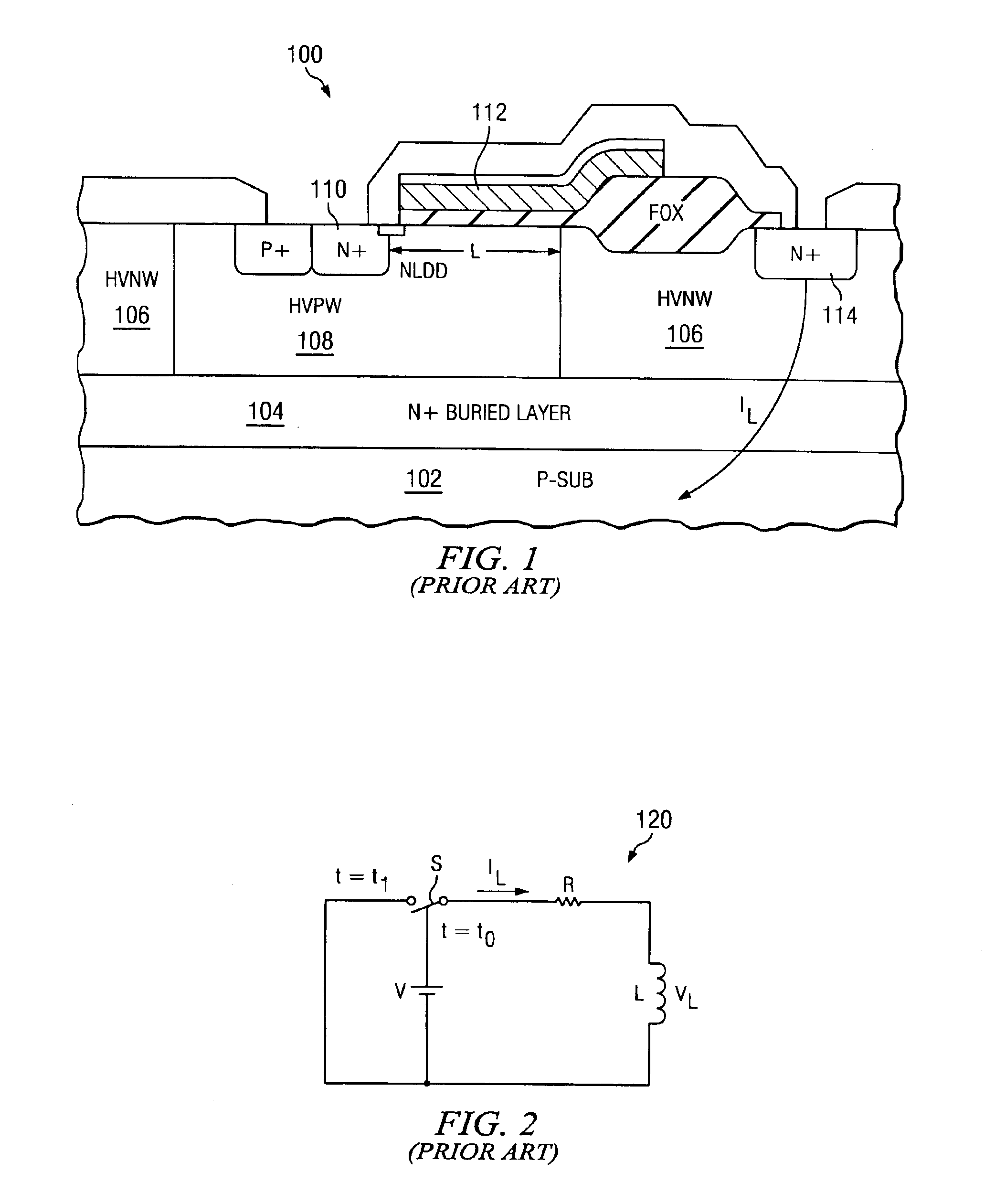

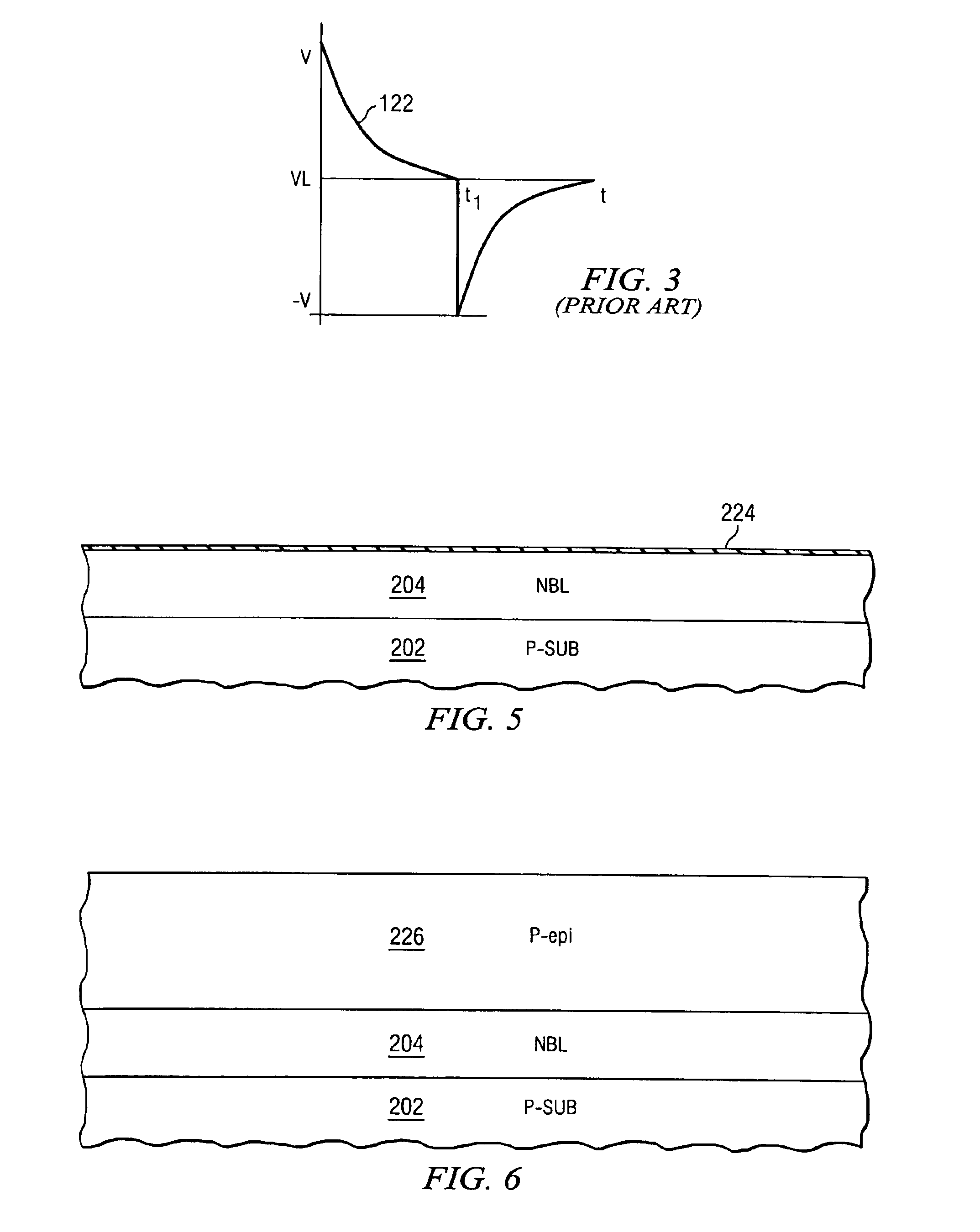

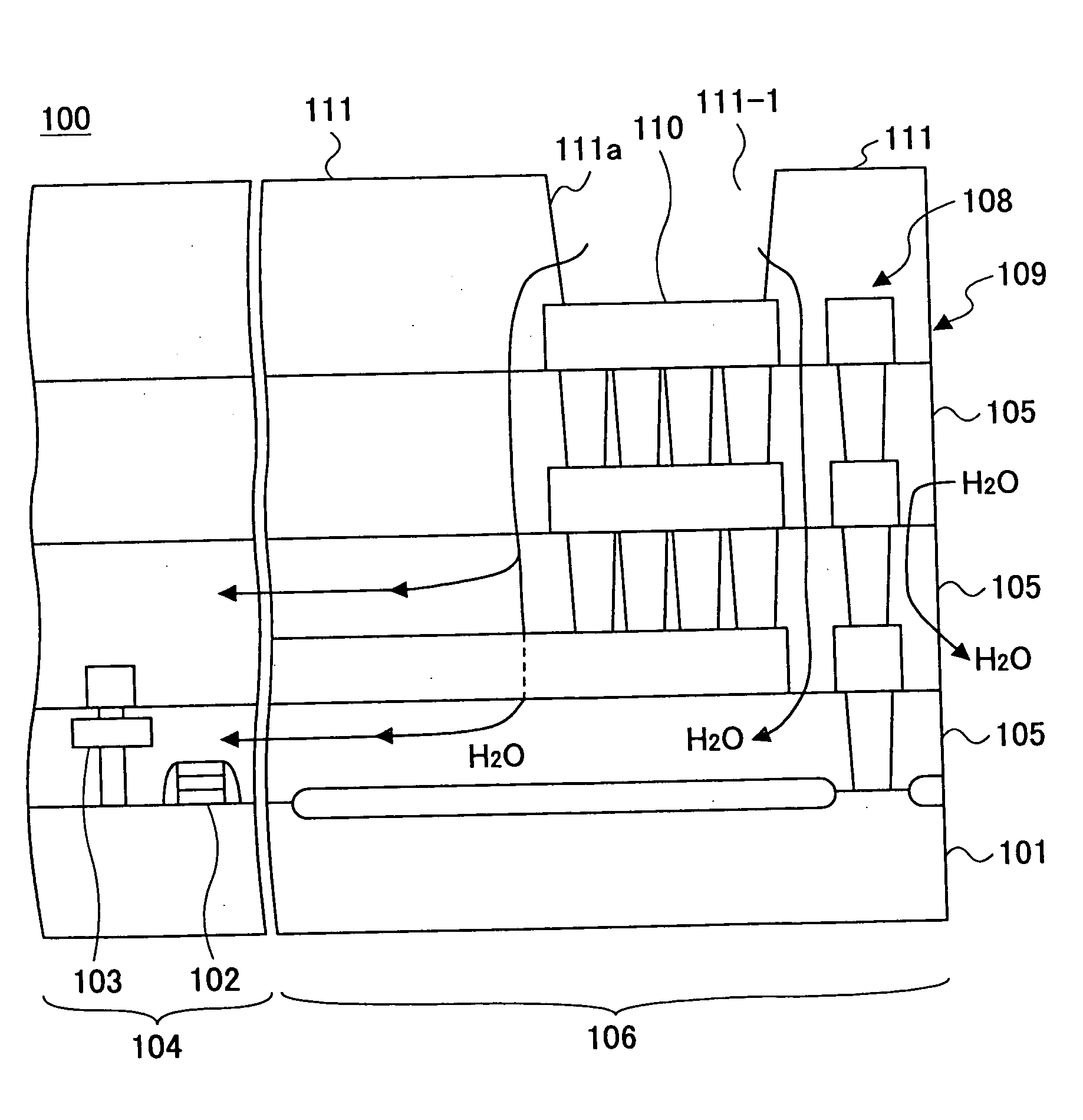

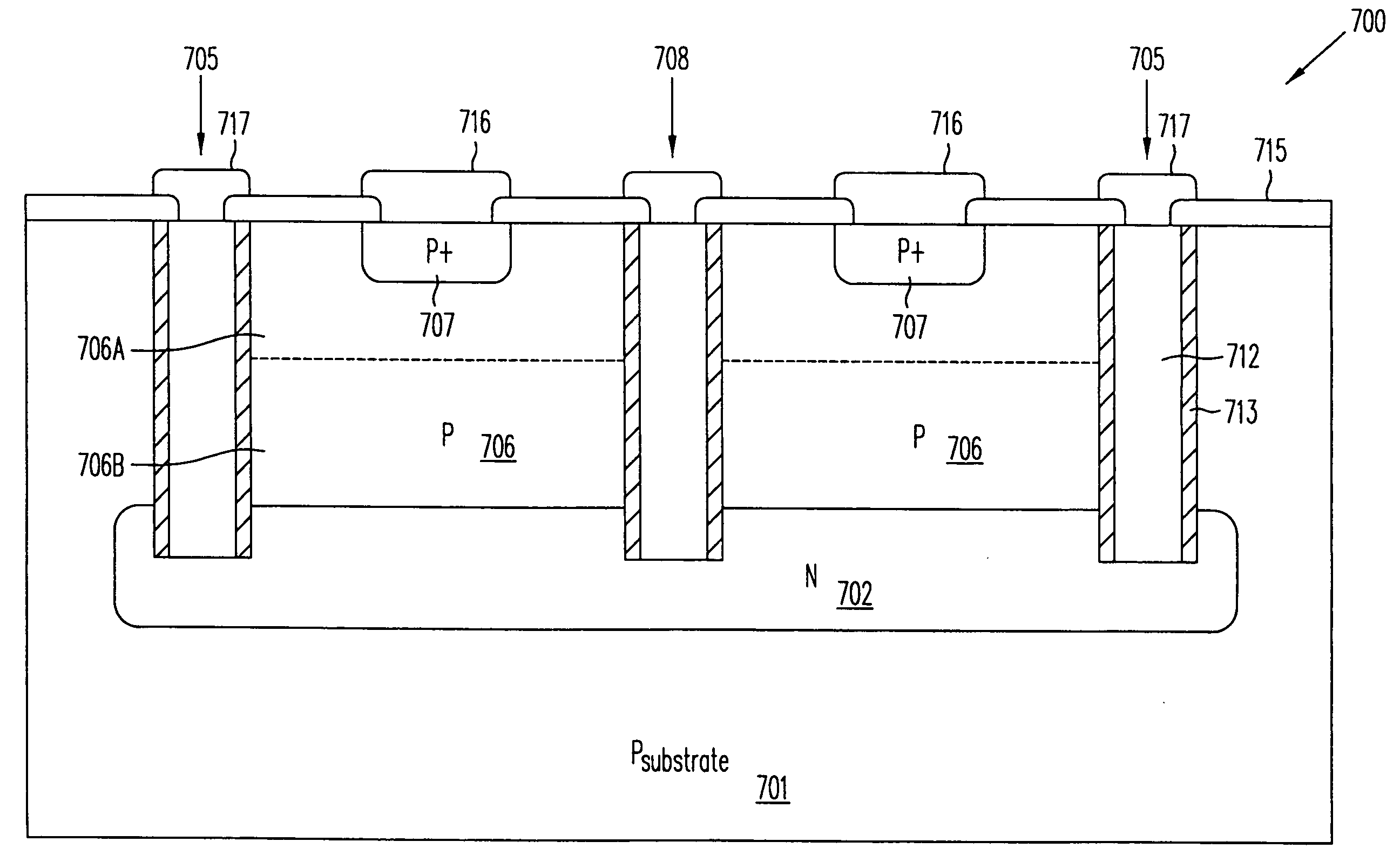

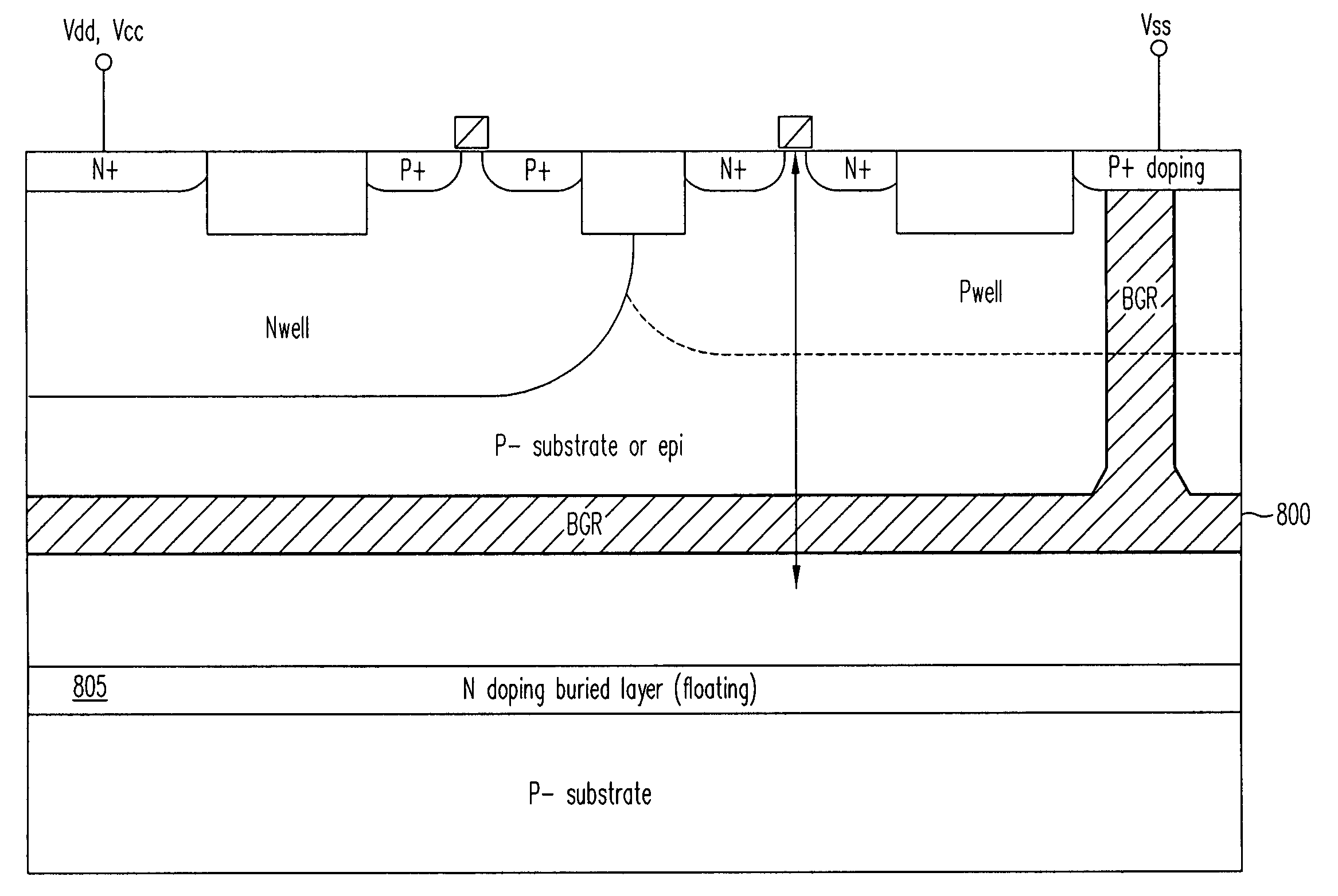

Buried guard ring and radiation hardened isolation structures and fabrication methods

ActiveUS20050179093A1Reduce and eliminate detrimental effectLow costTransistorSemiconductor/solid-state device detailsManufacturing technologyDevice material

Semiconductor devices can be fabricated using conventional designs and process but including specialized structures to reduce or eliminate detrimental effects caused by various forms of radiation. Such semiconductor devices can include the one or more parasitic isolation devices and / or buried guard ring structures disclosed in the present application. The introduction of design and / or process steps to accommodate these novel structures is compatible with conventional CMOS fabrication processes, and can therefore be accomplished at relatively low cost and with relative simplicity.

Owner:SILICON SPACE TECH

Isolated transistor

InactiveUS20080191277A1Reduce chargeReducing other time-dependent surface-related phenomenonTransistorThyristorConductive materialsDielectric layer

Various integrated circuit devices, in particular a transistor, are formed inside an isolation structure which includes a floor isolation region and a trench extending from the surface of the substrate to the floor isolation region. The trench may be filled with a dielectric material or may have a conductive material in a central portion with a dielectric layer lining the walls of the trench. Various techniques for terminating the isolation structure by extending the floor isolation region beyond the trench, using a guard ring, and a forming a drift region are described.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

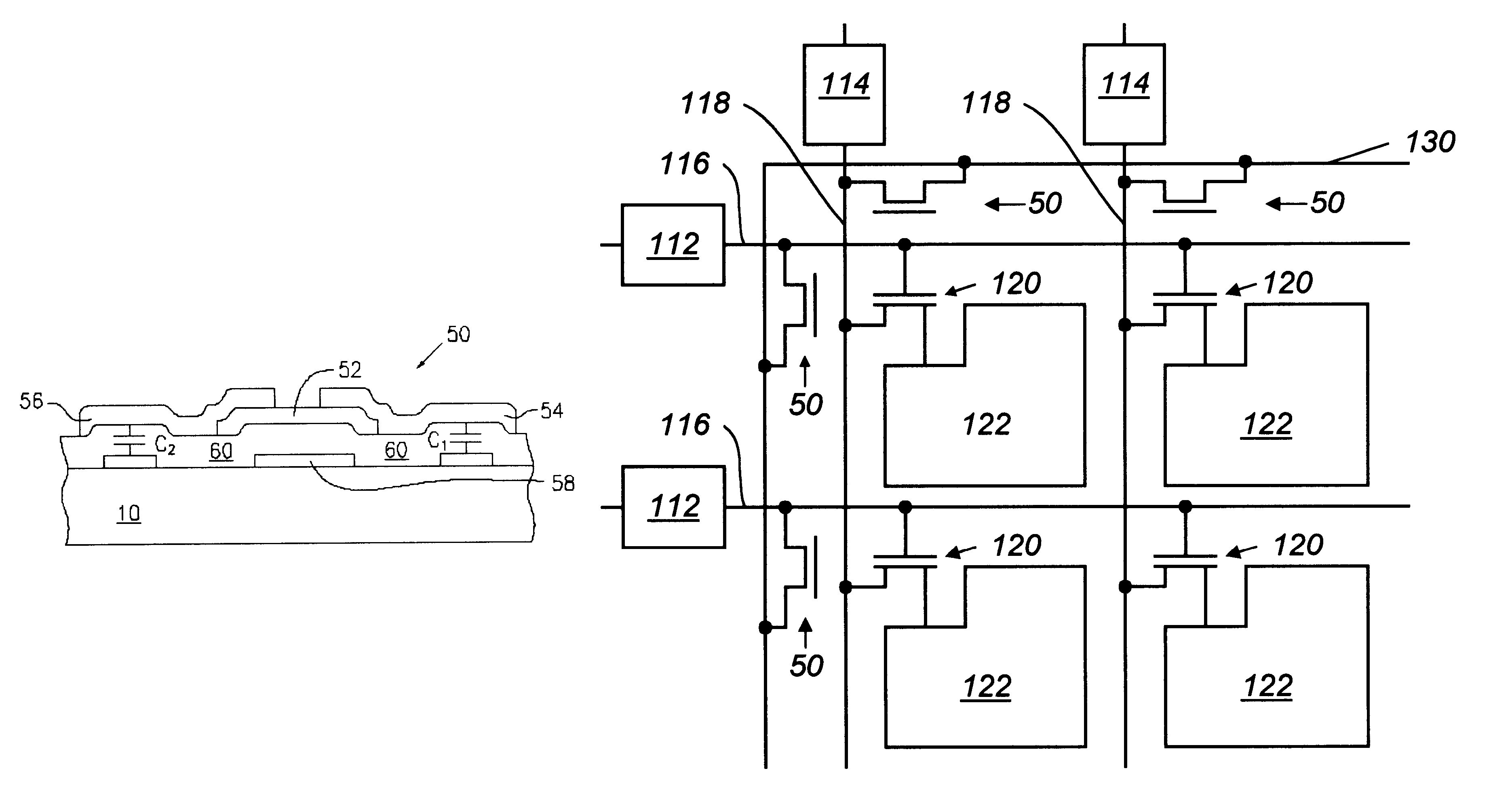

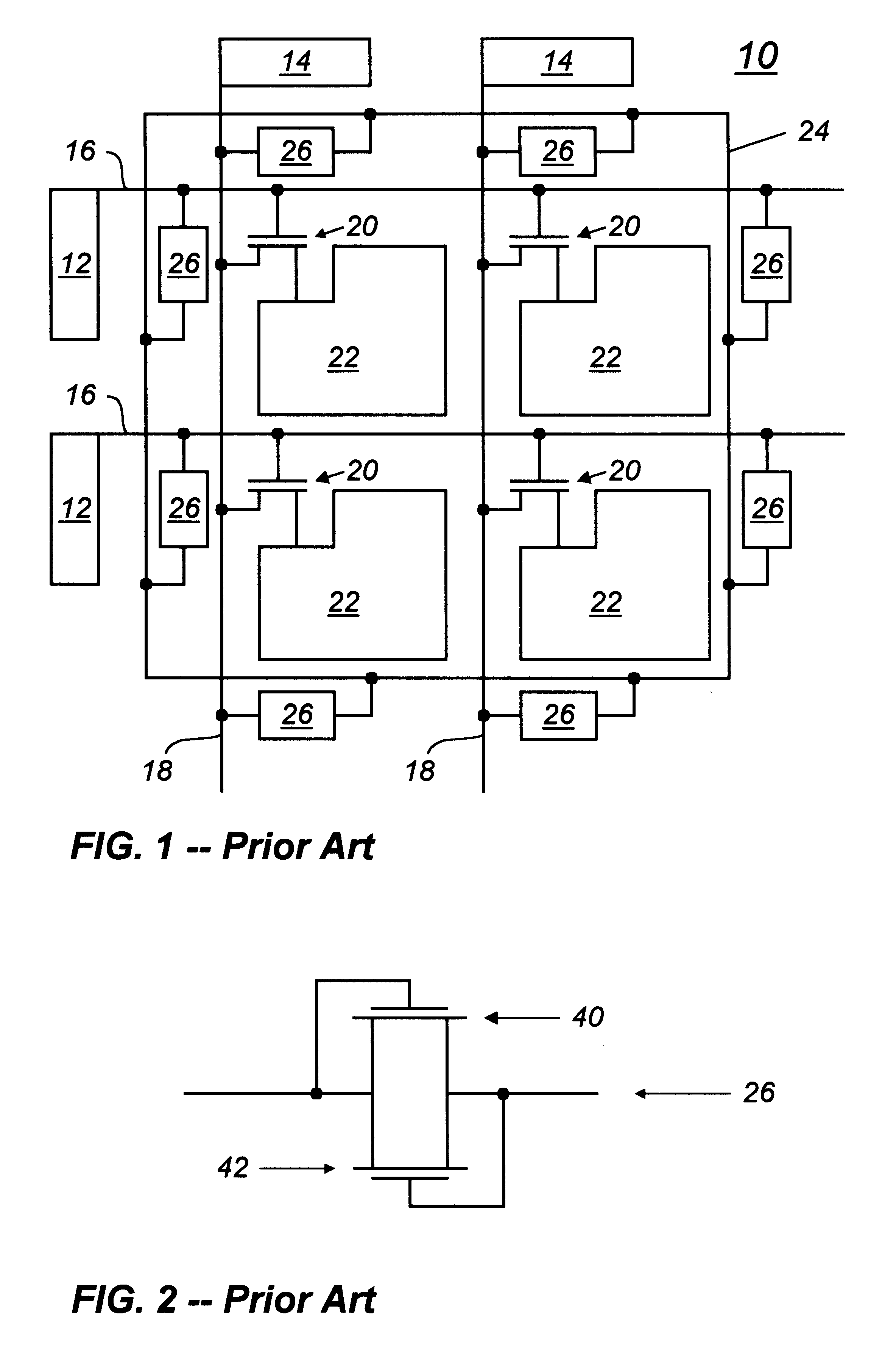

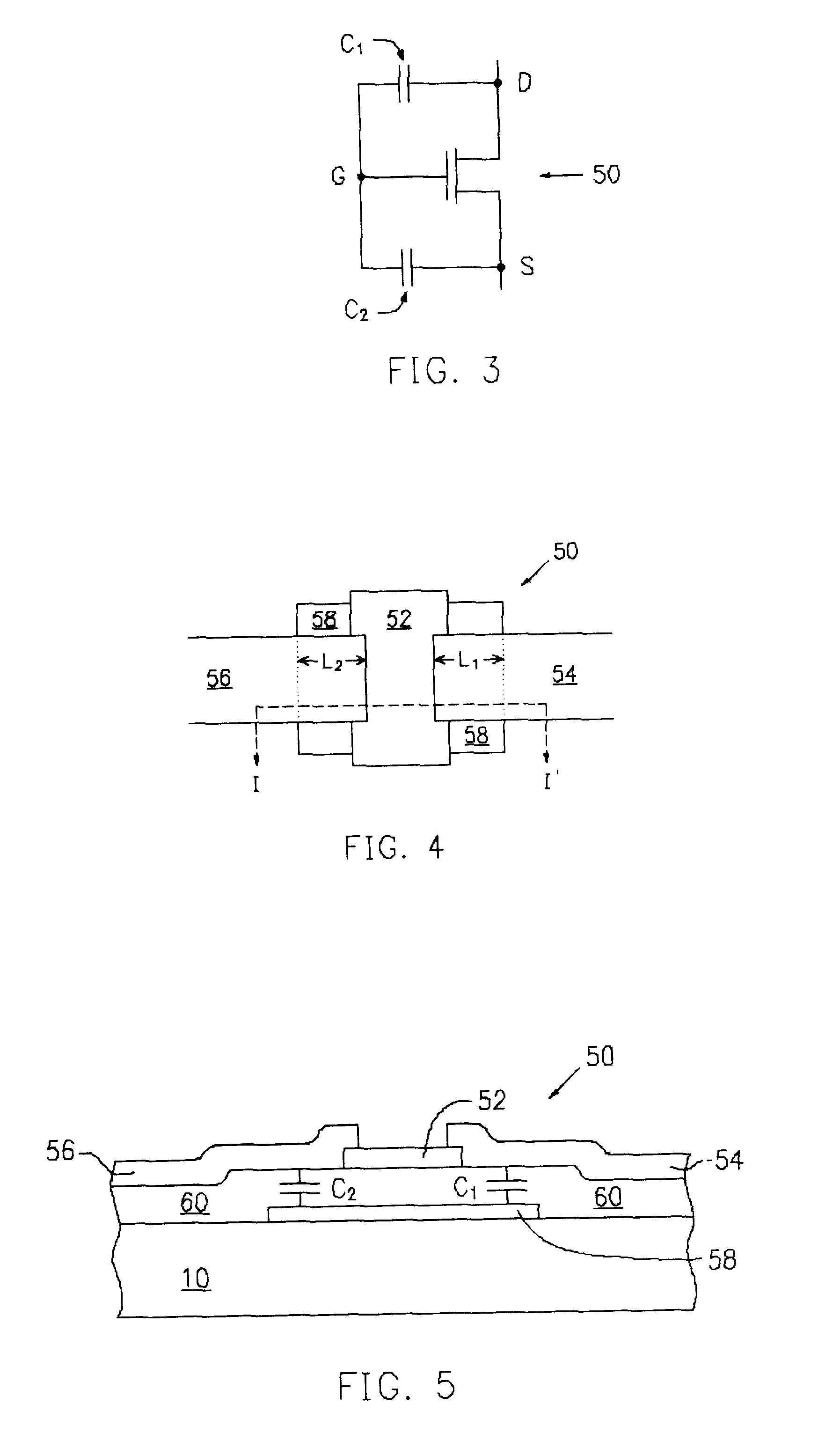

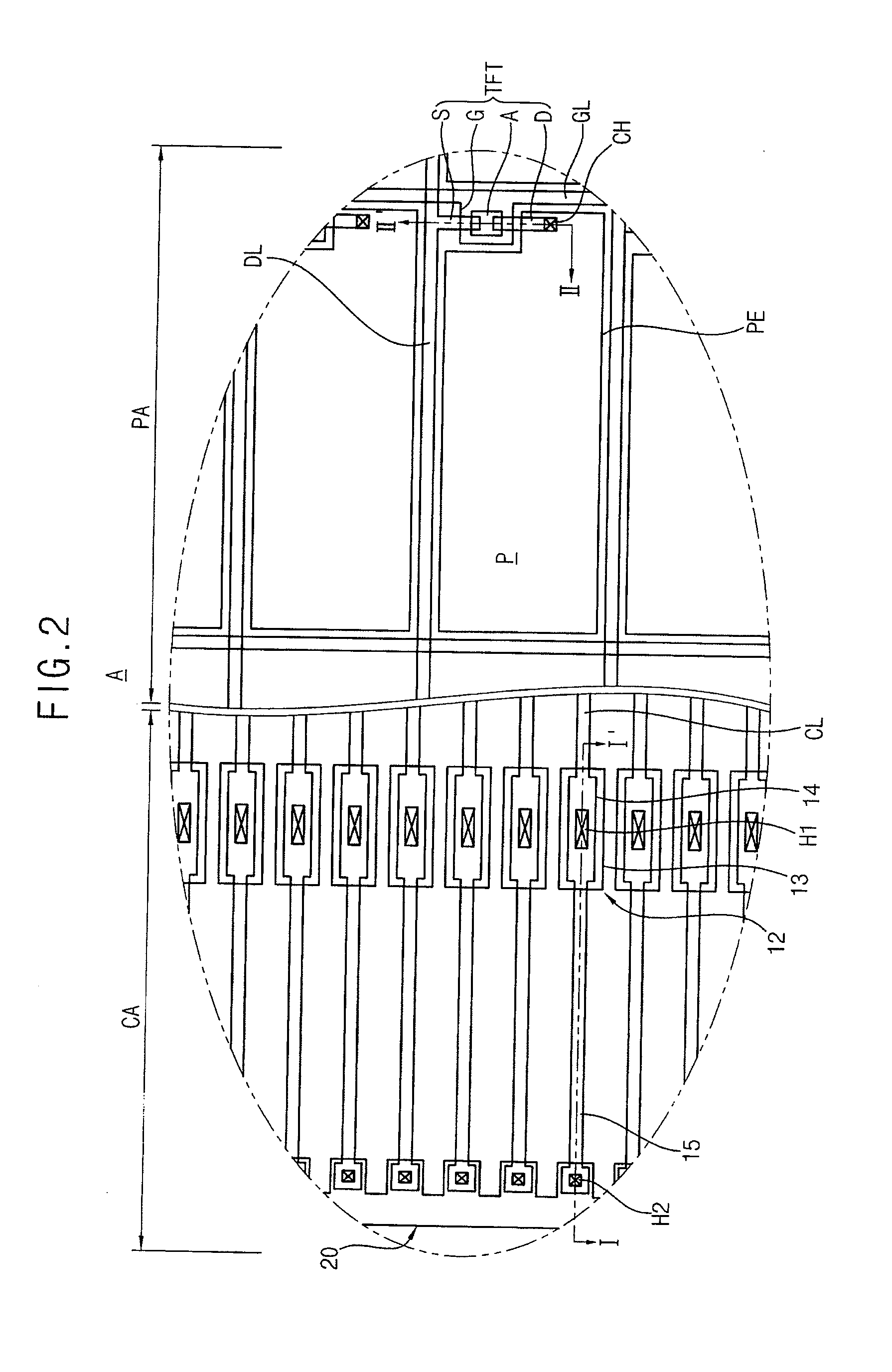

Capacitively coupled field effect transistors for electrostatic discharge protection in flat panel displays

A flat panel display includes a plurality of parallel row select lines and a plurality of column drive lines, with the row select lines and the column drive lines intersecting to define a matrix of pixel locations. Signals are provided to contact pads located on the periphery of the display and the signals flow over the row select lines and the column drive lines to thin film transistors located adjacent a pixel electrode at each of the pixel locations. The signals provided to each thin film transistor cause the transistor to charge a corresponding pixel electrode to control a pixel of the display. ESD protection for the display comprises a guard ring adjacent the contact pads. Capacitively coupled field effect transistors (CCFETs) connect the row select lines to the guard ring and connect the column drive lines to the guard ring. A CCFET is formed as a thin film transistor and typically has a floating gate capacitively coupled to the drain and source of the thin film transistor.

Owner:AU OPTRONICS CORP

Single photon avalanche diode for CMOS circuits

ActiveUS9178100B2Reduce cost and complexityLong wavelength detection propertyFinal product manufactureSolid-state devicesCMOSSingle-photon avalanche diode

Owner:STMICROELECTRONICS (RES & DEV) LTD +1

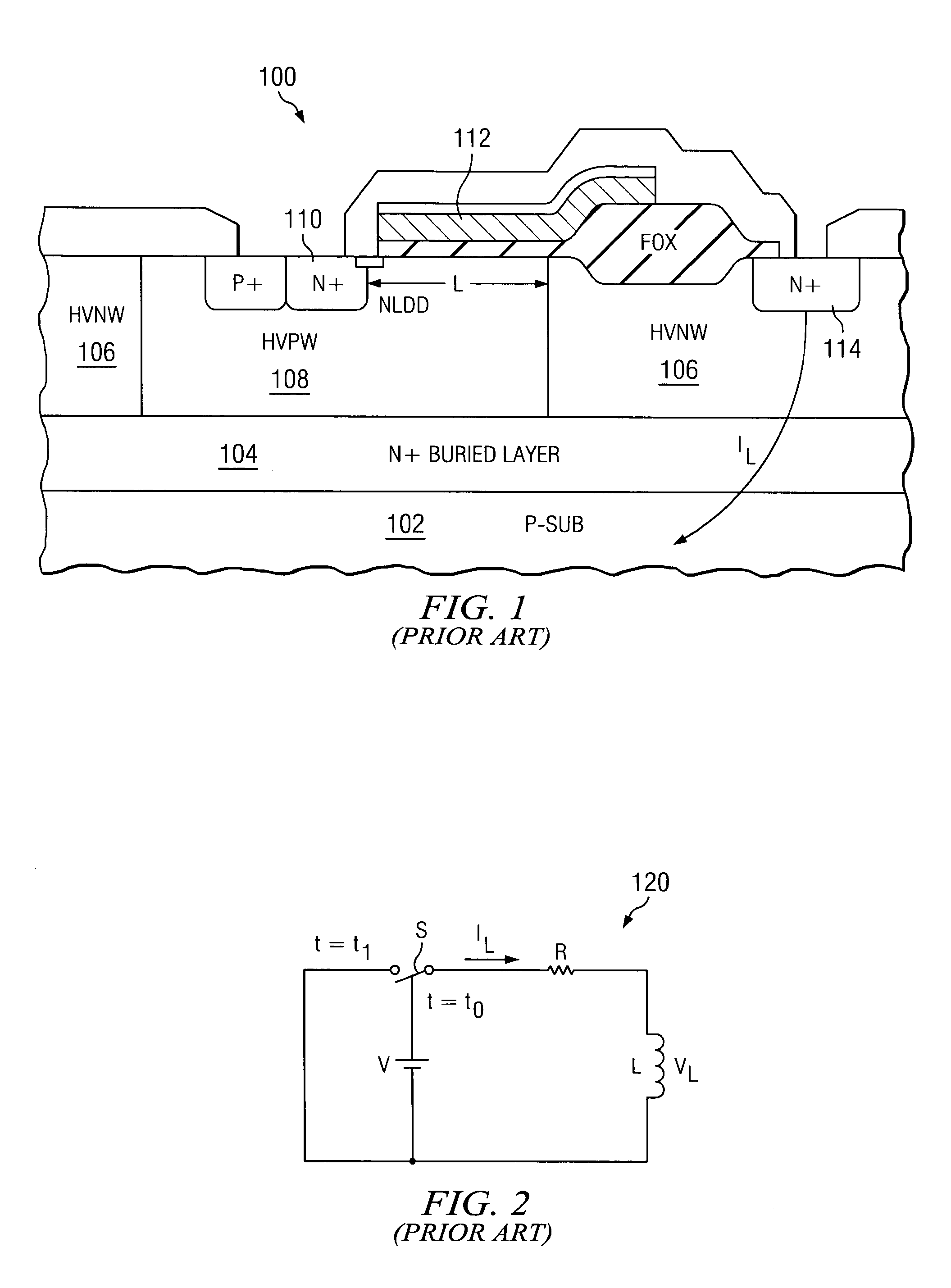

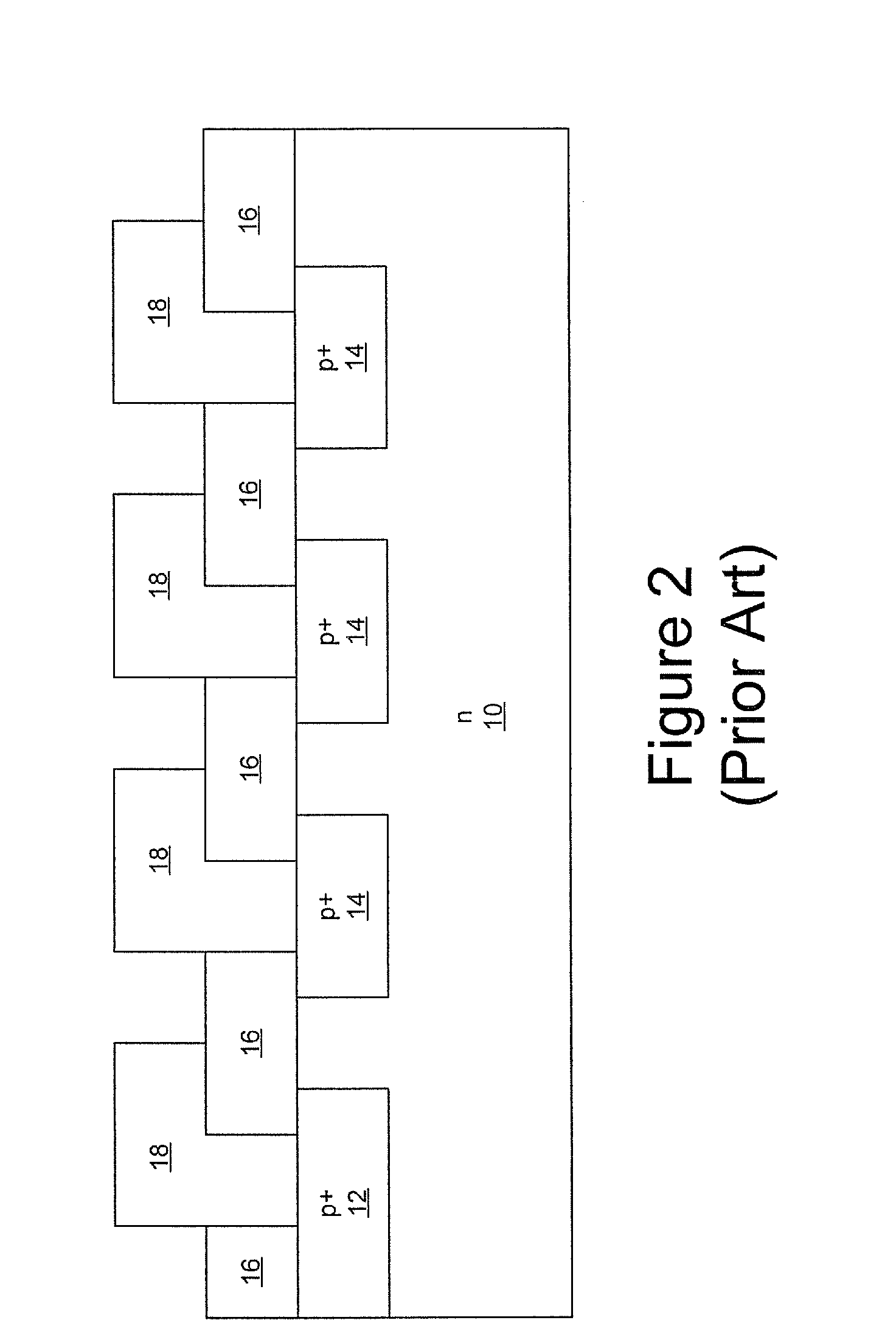

Ldmos device with isolation guard rings

InactiveUS20050073007A1Avoid leakage currentLatch-up, early breakdown and reliability issues are preventedSemiconductor/solid-state device detailsSolid-state devicesLDMOSDevice material

A method of forming a LDMOS semiconductor device and structure for same. A preferred embodiment comprises forming a first guard ring around and proximate the drain of a LDMOS device, and forming a second guard ring around the first guard ring. The first guard ring comprises a P+ base guard ring, and the second guard ring comprises an N+ collector guard ring formed in a deep N-well, in one embodiment. The first guard ring and second guard ring prevent leakage current from flowing from the drain of the LDMOS device to the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

Isolated junction field-effect transistor

Various integrated circuit devices, in particular a junction field-effect transistor (JFET), are formed inside an isolation structure which includes a floor isolation region and a trench extending from the surface of the substrate to the floor isolation region. The trench may be filled with a dielectric material or may have a conductive material in a central portion with a dielectric layer lining the walls of the trench. Various techniques for terminating the isolation structure by extending the floor isolation region beyond the trench, using a guard ring, and a forming a drift region are described.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

Isolation and termination structures for semiconductor die

InactiveUS20080197445A1Reduce chargeReducing other time-dependent surface-related phenomenonTransistorThyristorMOSFETSemiconductor chip

Various integrated circuit devices, including a lateral DMOS transistor, a quasi-vertical DMOS transistor, a junction field-effect transistor (JFET), a depletion-mode MOSFET, and a diode, are formed inside an isolation structure which includes a floor isolation region and a trench extending from the surface of the substrate to the floor isolation region. The trench may be filled with a dielectric material or may have a conductive material in a central portion with a dielectric layer lining the walls of the trench. Various techniques for terminating the isolation structure by extending the floor isolation region beyond the trench, using a guard ring, and a forming a drift region are described.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

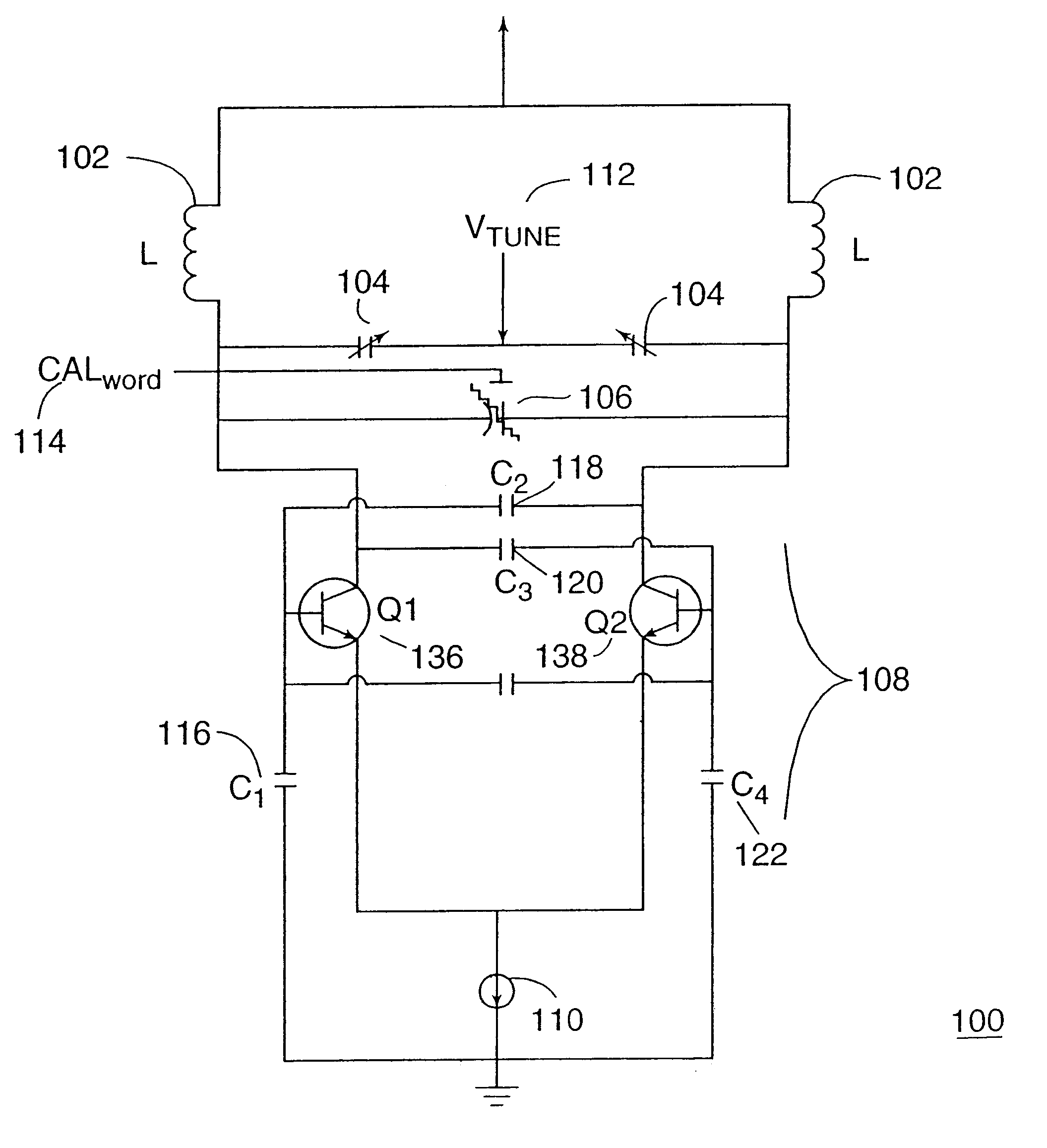

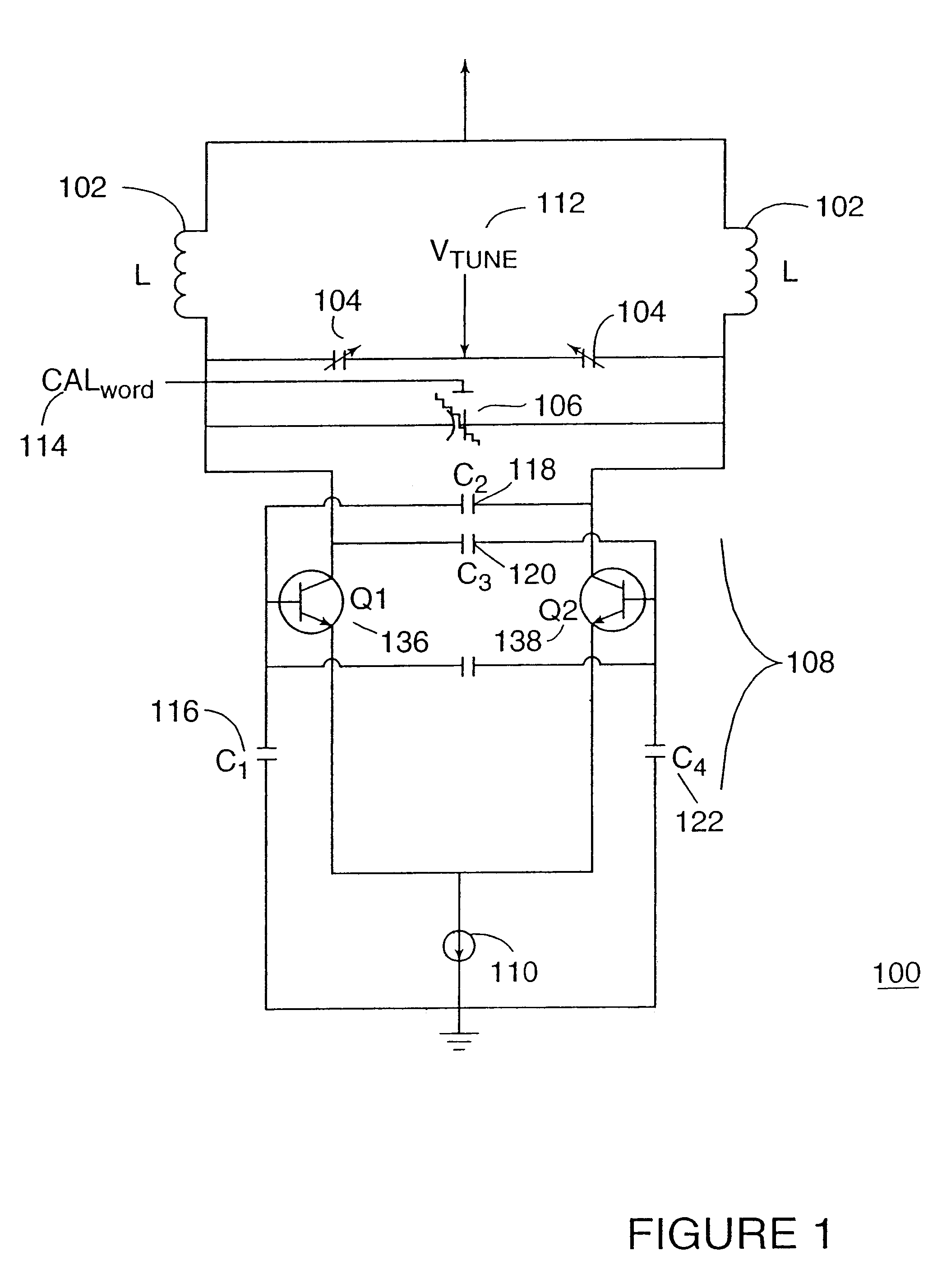

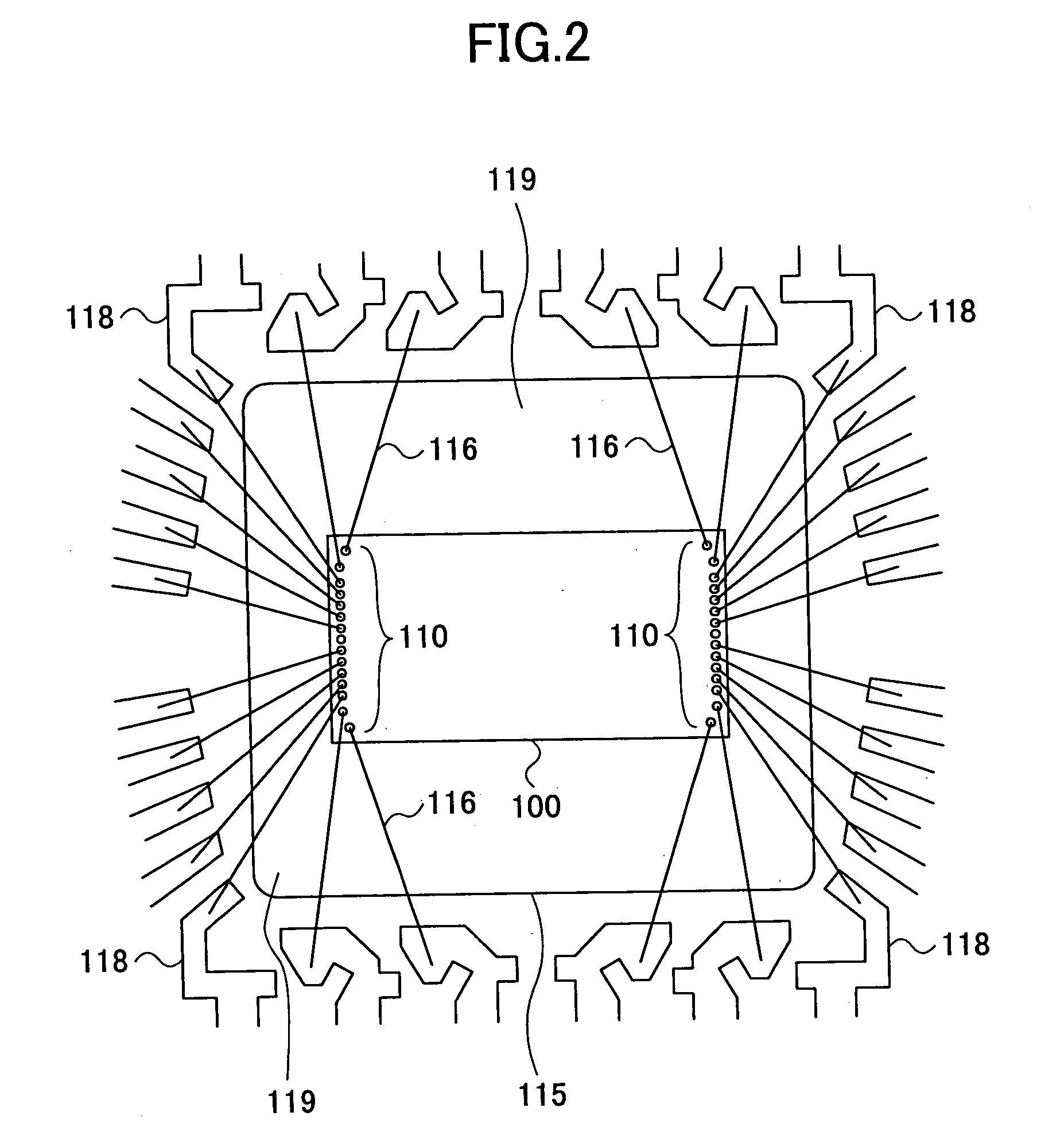

Method and apparatus for fully integrating a voltage controlled oscillator on an integrated circuit

InactiveUS6268778B1Wide tuning capacitance rangeReduce parasitic capacitanceAngle modulation by variable impedencePulse automatic controlLc resonatorSelf resonance

A method and apparatus for fully integrating a Voltage Controlled Oscillator (VCO) on an integrated circuit. The VCO is implemented using a differential-mode circuit design. The differential-mode implementation of the VCO preferably comprises a differential mode LC-resonator circuit, a digital capacitor, a differential pair amplifier, and a current source. The LC-resonator circuit includes at least one tuning varactor and two high Q inductors. The tuning varactor preferably has a wide tuning capacitance range. The tuning varactor is only used to "fine-tune" the center output frequency f0 of the VCO. The center output frequency f0 is coarsely tuned by the digital capacitor. The VCO high Q inductors comprise high gain, high self-resonance, and low loss IC inductors. The IC VCO is fabricated on a high resistivity substrate material using a trench isolated guard ring. The guard ring isolates the fully integrated VCO, and each of its component parts, from RF signals that may be introduced into the IC substrate by other devices. By virtue of the improved performance characteristics provided by the digital capacitor, the analog tuning varactor, the high Q inductor, and the trench isolated guard ring techniques, the inventive VCO is fully integrated despite process variations in IC fabrication.

Owner:CSR TECH INC

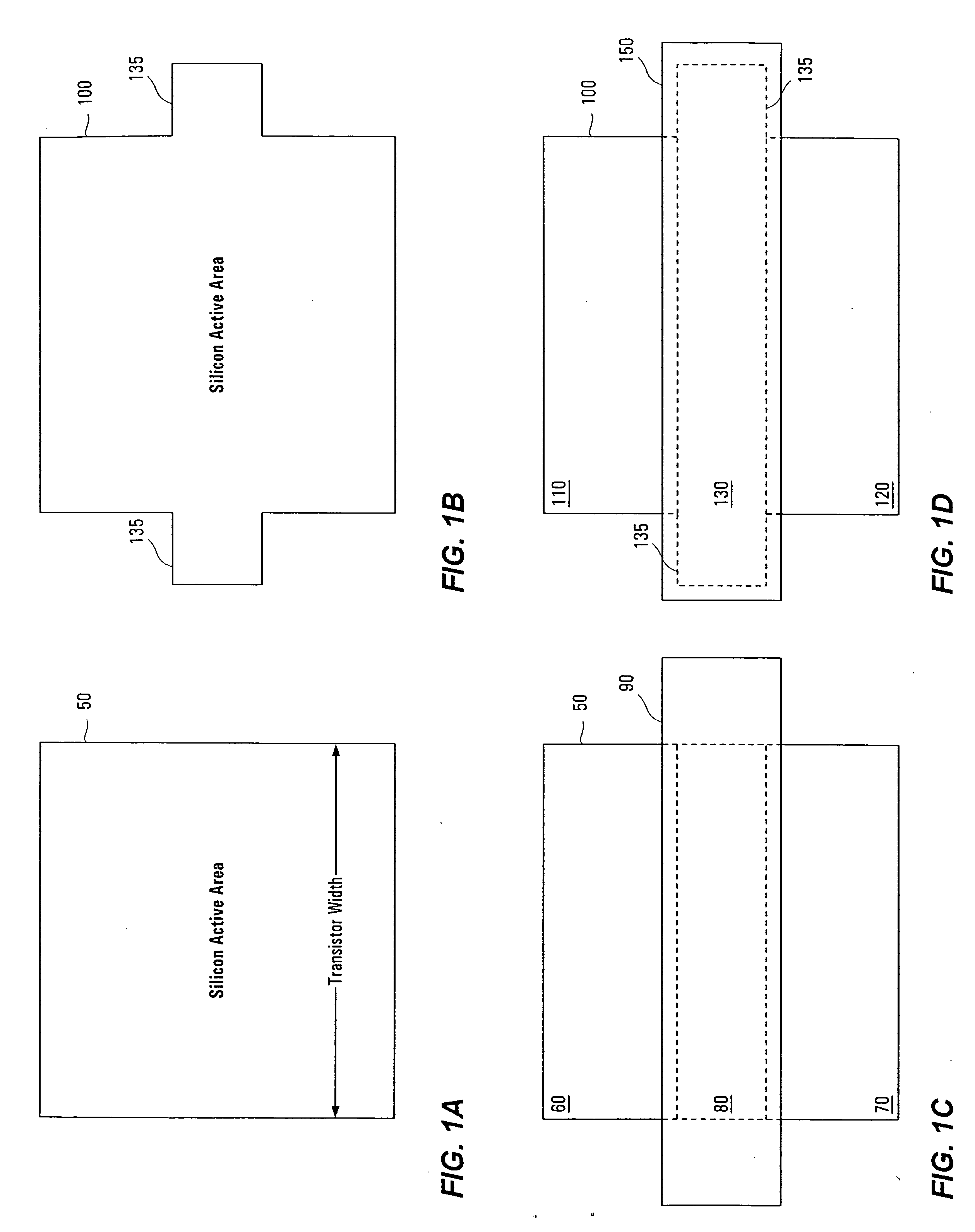

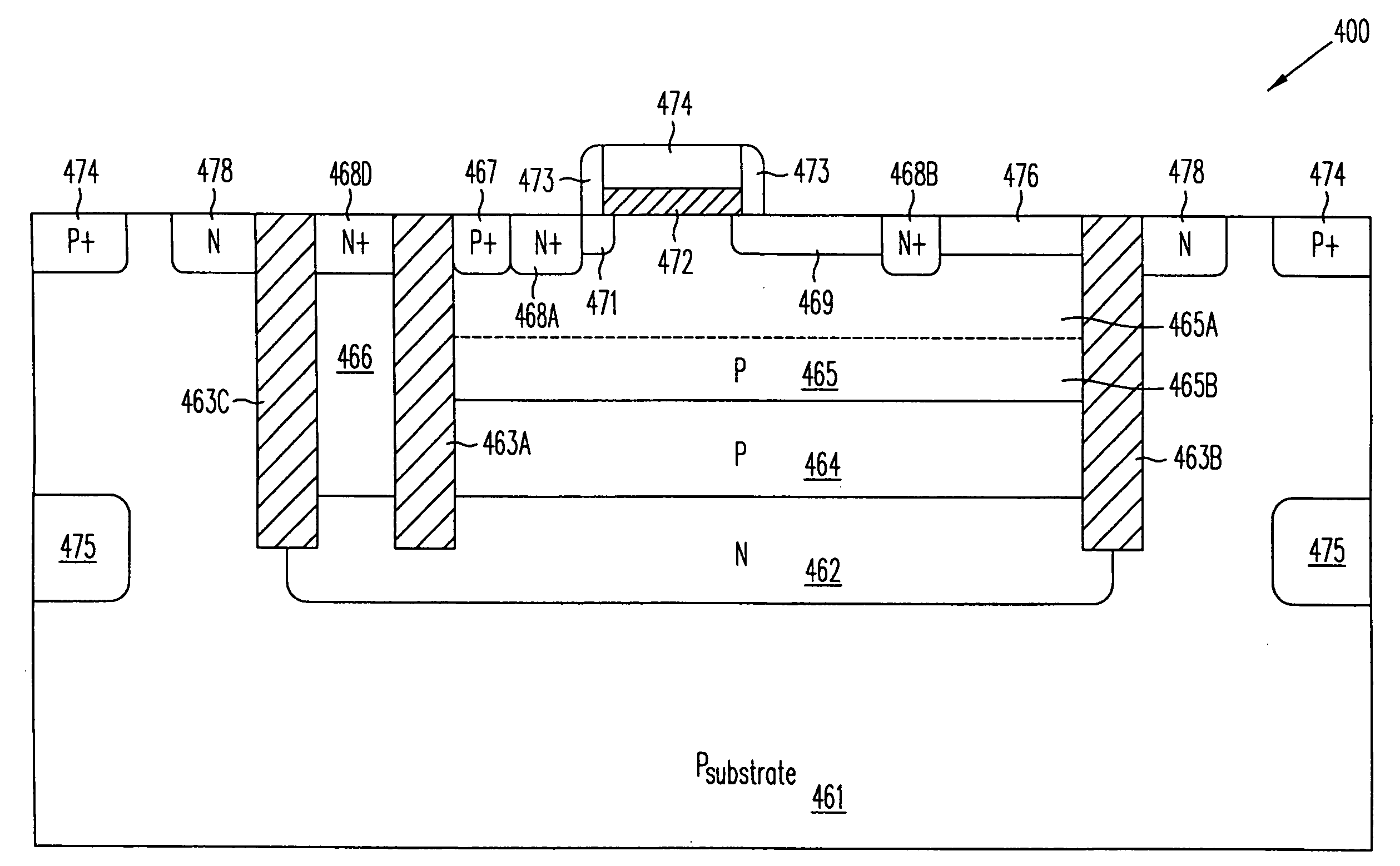

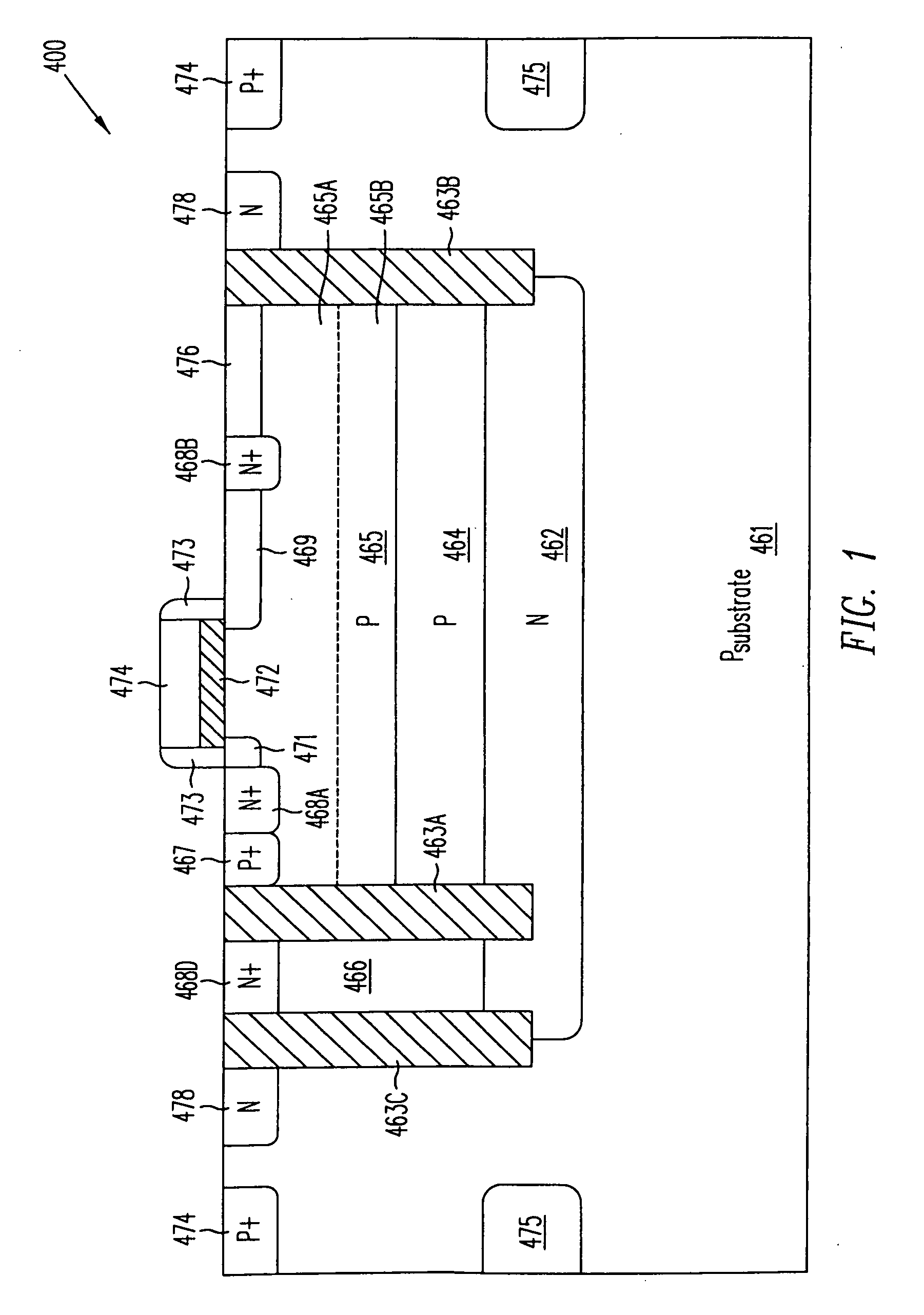

Guard ring structures for high voltage CMOS/low voltage CMOS technology using ldmos (lateral double-diffused metal oxide semiconductor) device fabrication

A semiconductor structure and a method for forming the same. The method includes providing a semiconductor structure. The semiconductor structure includes a semiconductor substrate. The method further includes simultaneously forming a first doped transistor region of a first transistor and a first doped guard-ring region of a guard ring on the semiconductor substrate. The first doped transistor region and the first doped guard-ring region comprise dopants of a first doping polarity. The method further includes simultaneously forming a second doped transistor region of the first transistor and a second doped guard-ring region of the guard ring on the semiconductor substrate. The second doped transistor region and the second doped guard-ring region comprise dopants of the first doping polarity. The second doped guard-ring region is in direct physical contact with the first doped guard-ring region. The guard ring forms a closed loop around the first and second doped transistor regions.

Owner:GLOBALFOUNDRIES INC

LDMOS device with isolation guard rings

InactiveUS6924531B2Avoid leakage currentLatch-up, early breakdown and reliability issues are preventedSemiconductor/solid-state device detailsSolid-state devicesLDMOSEngineering

A method of forming a LDMOS semiconductor device and structure for same. A preferred embodiment comprises forming a first guard ring around and proximate the drain of a LDMOS device, and forming a second guard ring around the first guard ring. The first guard ring comprises a P+ base guard ring, and the second guard ring comprises an N+ collector guard ring formed in a deep N-well, in one embodiment. The first guard ring and second guard ring prevent leakage current from flowing from the drain of the LDMOS device to the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

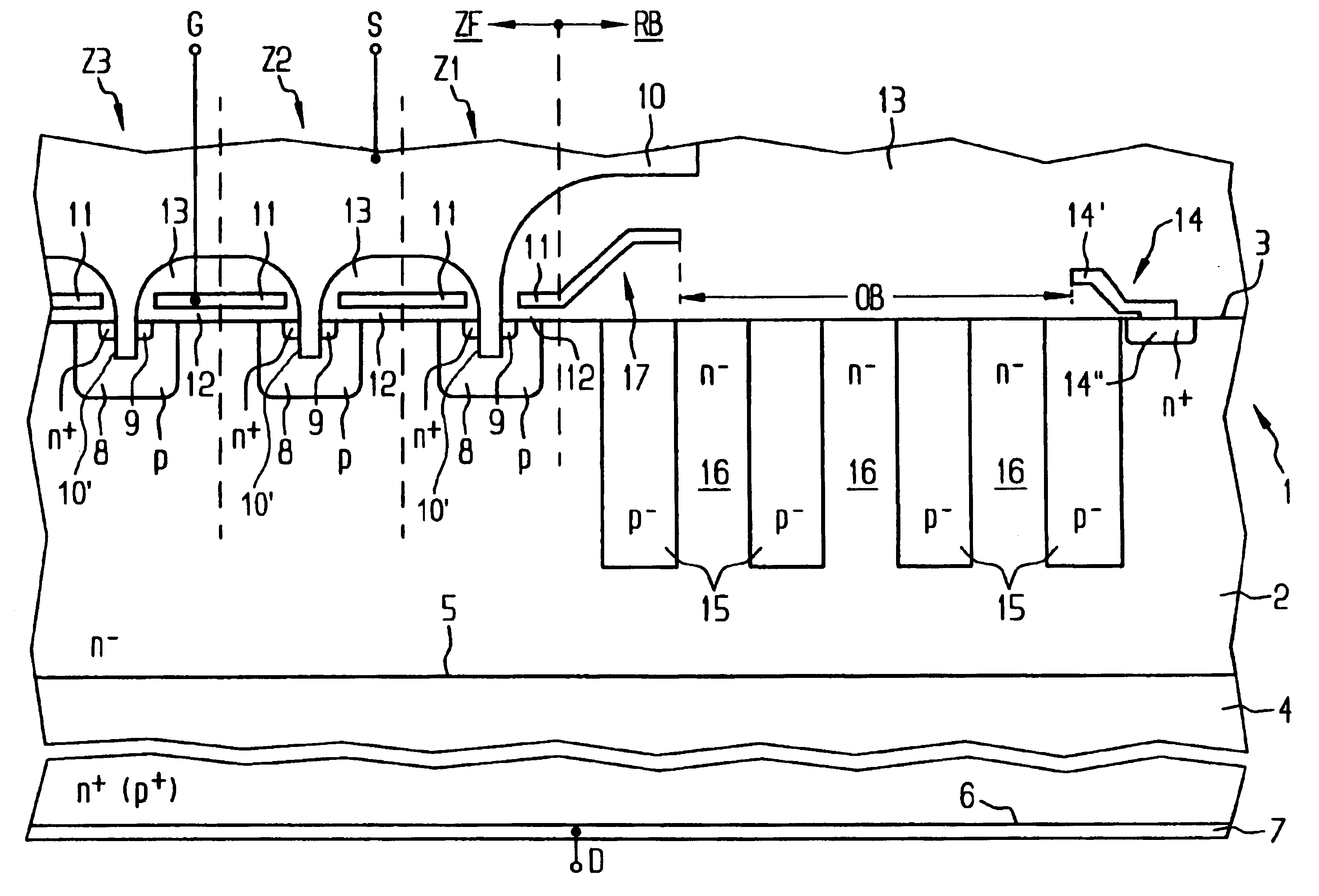

High voltage resistant edge structure for semiconductor components

The invention relates to a high voltage resistant edge structure in the edge region of a semiconductor component which has floating guard rings of the first conductivity type and inter-ring zones of the second conductivity type which are arranged between the floating guard rings, wherein the conductivities and / or the inter-ring zones are set such that their charge carriers are totally depleted when blocking voltage is applied. The inventive edge structure achieves a modulation of the electrical field both at the surface and in the volume of the semiconductor body. If the inventive edge structure is suitably dimensioned, the field intensity maximum can easily be situated in the depth; that is, in the region of the vertical p-n junction. Thus, a suitable edge construction which permits a “soft” leakage of the electrical field in the volume can always be provided over a wide range of concentrations of p and n doping.

Owner:INFINEON TECH AG

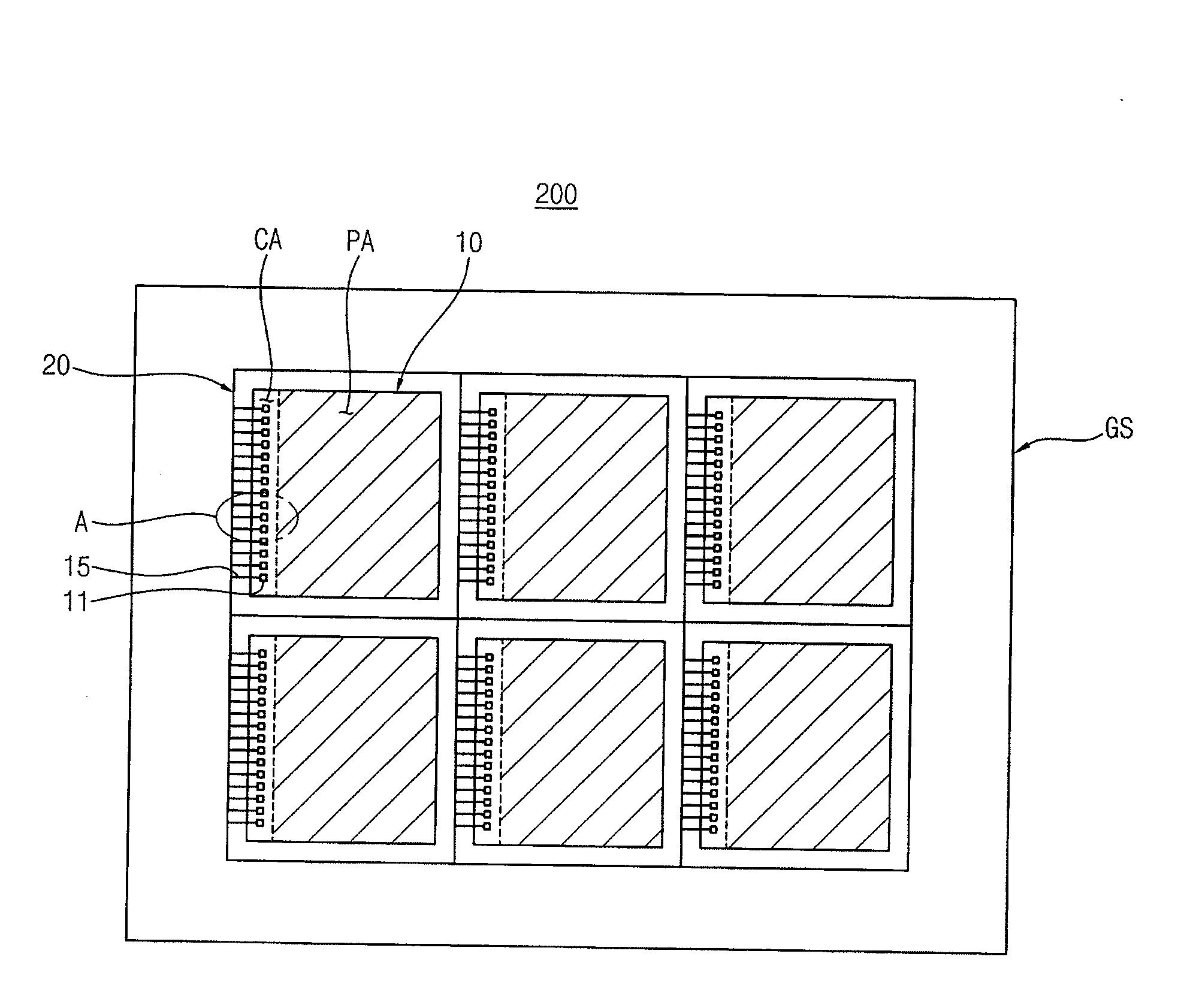

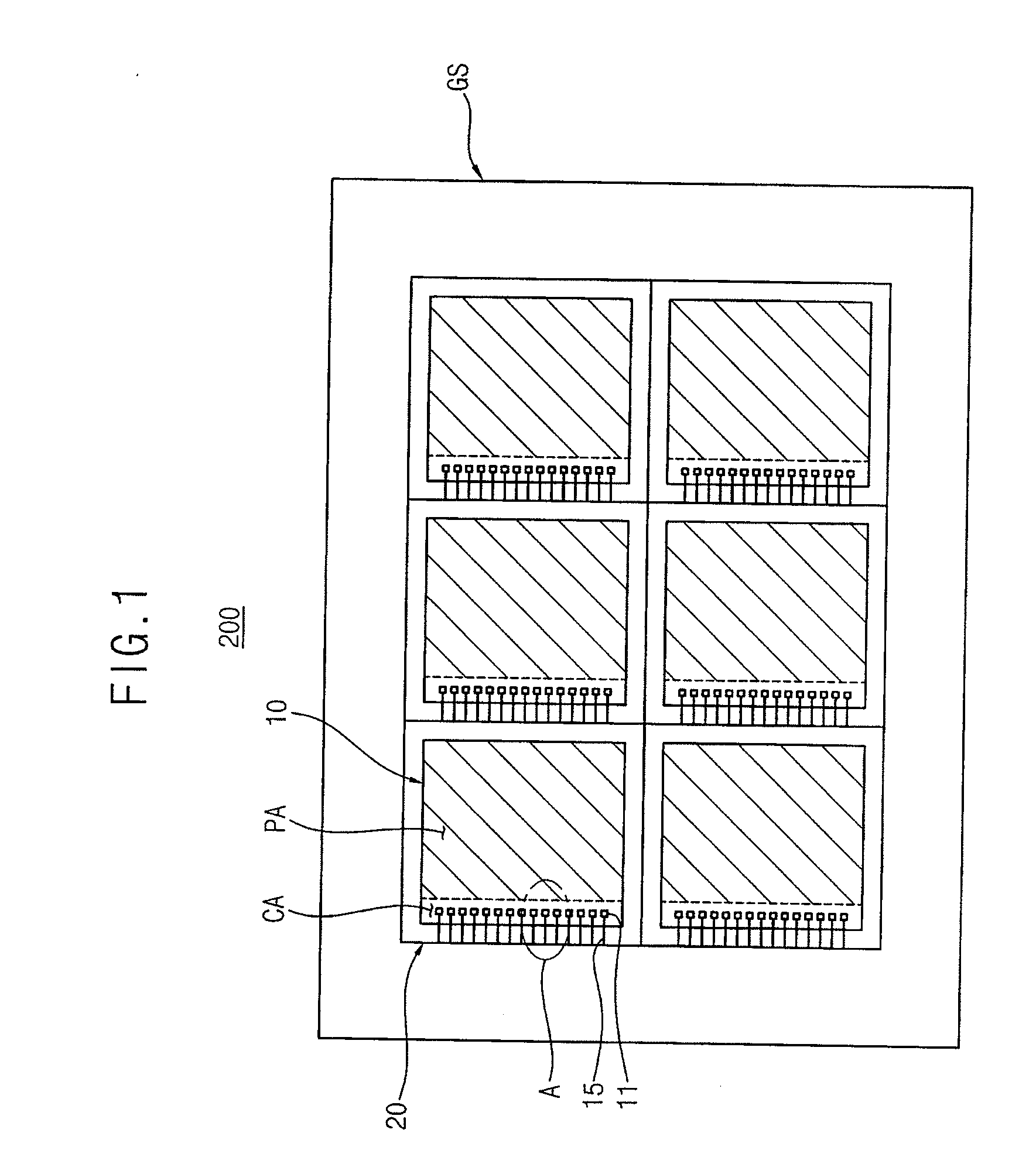

Display substrate, method for manufacturing the same, and display apparatus having the same

InactiveUS20080204618A1Efficiently dissipatedShort circuitStatic indicating devicesNon-linear opticsElectricityEngineering

A display substrate includes a substrate, a guard ring and a connecting line. The substrate includes a plurality of active areas, and each of the active areas has a pixel area and a peripheral area. The guard ring is formed on the substrate to enclose each of the active areas, and is formed from substantially the same layer as a pixel electrode that is formed in a unit pixel. The connecting line is formed from a different layer than the guard ring, to electrically connect the guard ring with pads. The connecting line is formed before forming an organic insulating layer, and thus the frequency and / or severity of patterning defects of the connecting line may be reduced or prevented. Accordingly, short circuits between the pads may be prevented, and the corrosion resistance of the display apparatus may be increased.

Owner:SAMSUNG ELECTRONICS CO LTD

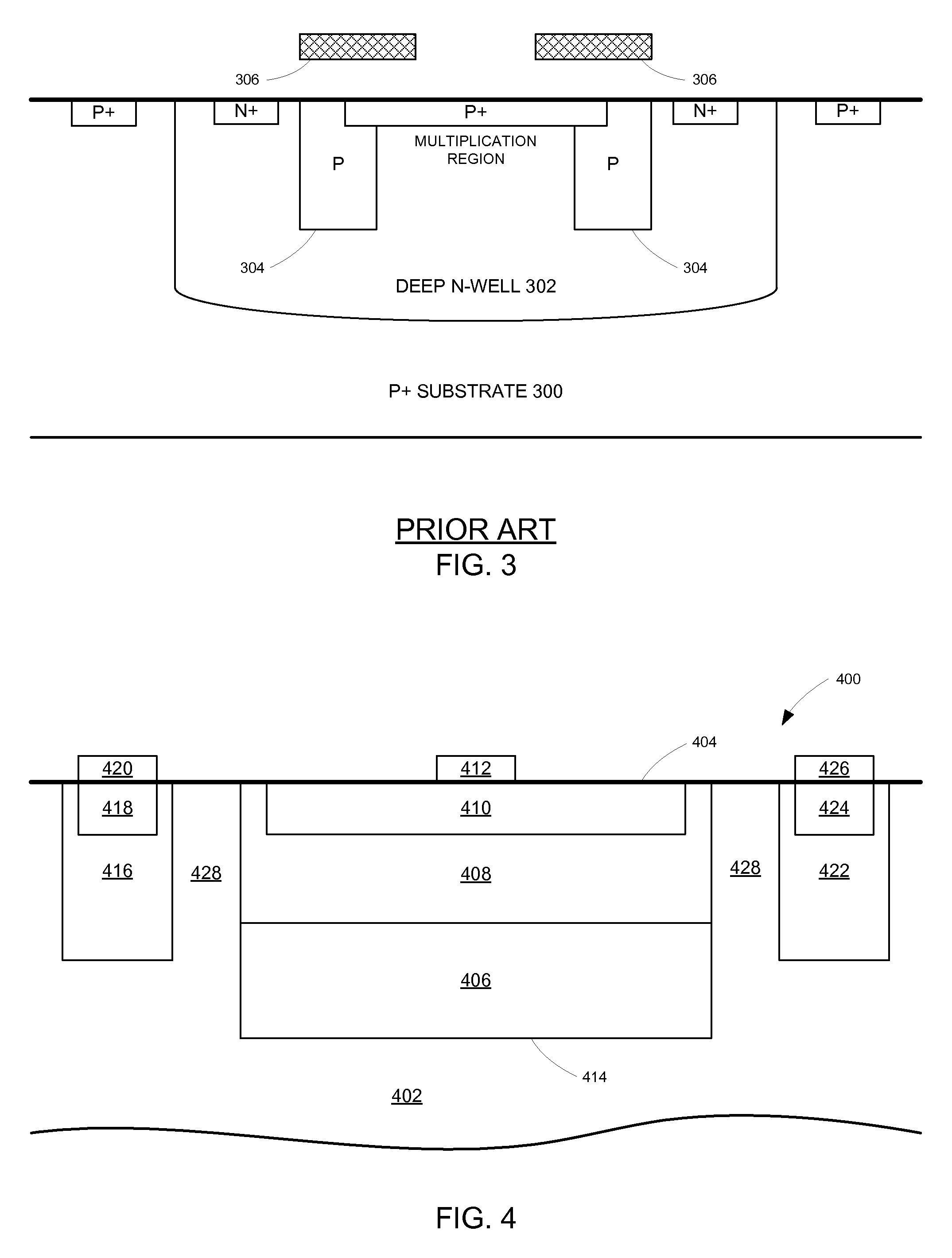

Deep submicron and NANO CMOS single photon photodetector pixel with event based circuits for readout data-rate reduction communication system

ActiveUS20100245809A1Solid-state devicesMaterial analysis by optical meansSensor arrayCommunications system

An avalanche photodiode and a sensor array comprising an array of said avalanche photodiodes is disclosed. Then avalanche photodiode comprises a substrate of a first conductivity type; a first well of a second conductivity type formed within the substrate; a second well of the second conductivity type formed substantially overlying and extending into the first well; a heavily doped region of the first conductivity type formed substantially overlying and extending into the first well, the junction between the heavily doped region and the second well forming an avalanche multiplication region; a guard ring formed from a first conductivity material positioned substantially about the periphery of the multiplication region at least partially underlying the heavily doped region; and an outer well ring of the second conductivity type formed about the perimeter of the deep well and the guard ring. The sensor array comprises a plurality of pixel elements, each of the pixel elements being configured to operate on discrete value continuous time (DVCT) basis. Each of the pixel elements can include the avalanche photodiode previously described.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

Semiconductor device and method of fabricating the same

InactiveUS20050127473A1Increase in the chip area and occurrence of dishing or the like can be preventedTransistorSolid-state devicesHigh densityP–n junction

A semiconductor device includes a semiconductor substrate of a first conduction type, a first well of a second conduction type formed on the semiconductor substrate, a plurality of second wells of the first conduction type provided in the first well for forming memory cells and a peripheral circuit respectively, each second well having a first depth, a first trench isolating region formed so as to isolate an element within the second well for the memory cells and having a first depth, a guard-ring diffusion region of the first conduction type provided in the vicinity of a peripheral edge of each second well for the memory cells and doped with a high density impurity so as to encompass a forming region of the memory cells, a second trench isolating region formed so that a p-n junction of each second well terminates on a bottom thereof in the vicinity of an outside of the guard-ring diffusion region, the second trench isolating region having a second depth larger than the first depth of each second well, and a third trench isolating region isolating an element formed in each second well for the peripheral circuit, the third trench isolating region having the second depth.

Owner:KK TOSHIBA

Semiconductor device and fabrication method thereof

ActiveUS20050127395A1Improve reliabilityReduce performanceThyristorVehicle arrangementsDevice materialEngineering

A semiconductor device includes a semiconductor substrate, a circuit part formed on and above the semiconductor substrate, a passivation film covering the circuit part, an electrode pad provided outside the circuit part in such a manner that the electrode pad is exposed from the passivation film, and a guard ring pattern provided between the electrode pad and the circuit part such that the guard ring pattern surrounds the circuit part substantially. The guard ring pattern extends from a surface of the semiconductor substrate to the passivation film.

Owner:FUJITSU SEMICON LTD

Isolated diode

InactiveUS20080197446A1Reduce chargeReducing other time-dependent surface-related phenomenonTransistorSolid-state devicesConductive materialsEngineering

Various integrated circuit devices, in particular a diode, are formed inside an isolation structure which includes a floor isolation region and a trench extending from the surface of the substrate to the floor isolation region. The trench may be filled with a dielectric material or may have a conductive material in a central portion with a dielectric layer lining the walls of the trench. Various techniques for terminating the isolation structure by extending the floor isolation region beyond the trench, using a guard ring, and a forming a drift region are described.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

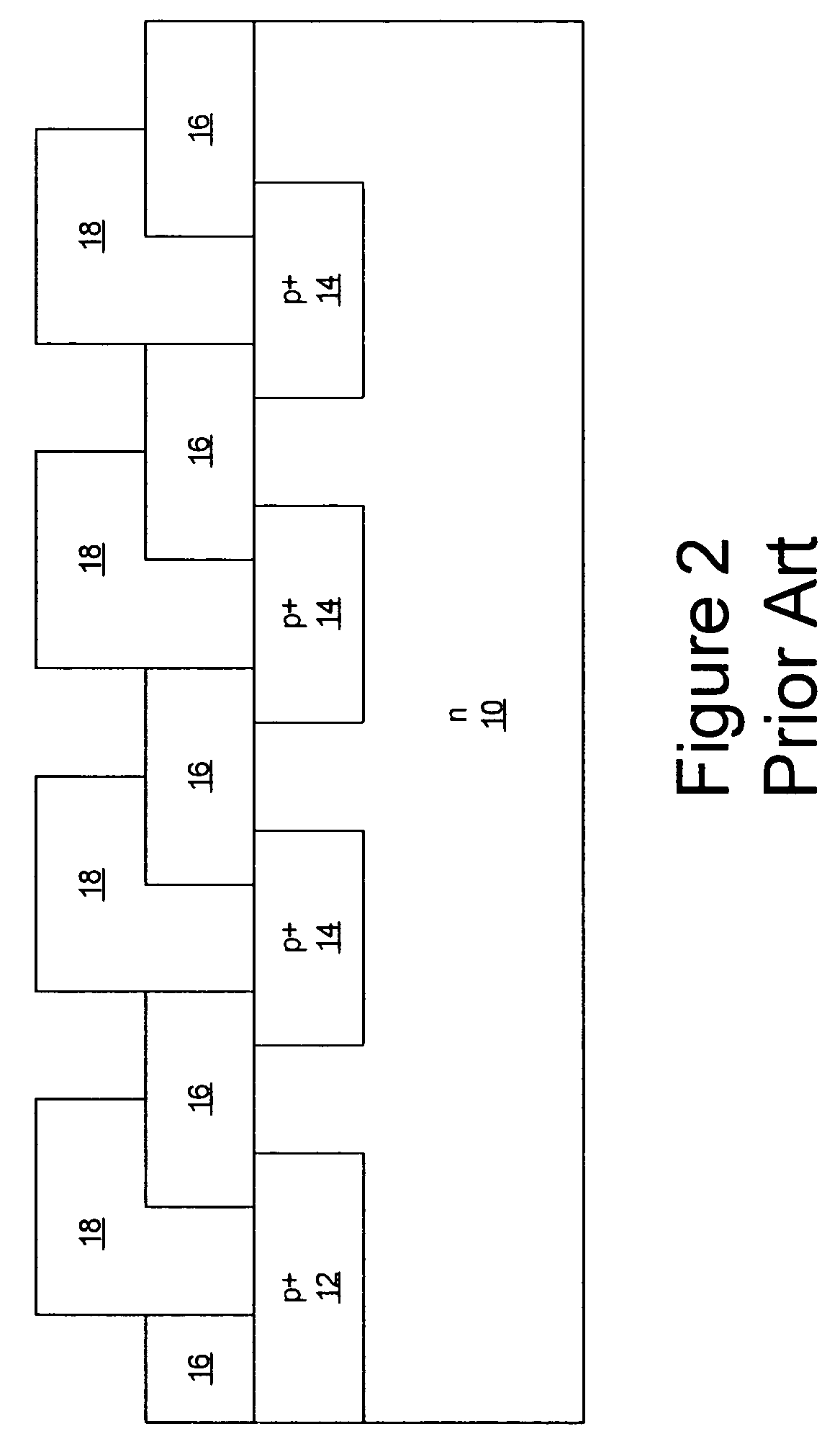

Double Guard Ring Edge Termination for Silicon Carbide Devices and Methods of Fabricating Silicon Carbide Devices Incorporating Same

ActiveUS20090212301A1Reduce doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

Edge termination structures for semiconductor devices are provided including a plurality of spaced apart concentric floating guard rings in a semiconductor layer that at least partially surround a semiconductor junction. The spaced apart concentric floating guard rings have a highly doped portion and a lightly doped portion. Related methods of fabricating devices are also provided herein.

Owner:CREE INC

Organic light emitting display and method of manufacturing the same

ActiveUS20090026932A1Avoid damageSimple methodDischarge tube luminescnet screensElectroluminescent light sourcesThin layerDisplay device

An organic light emitting display and a method of manufacturing the same. The light emitting display includes a substrate having a pixel region and a non-pixel region; an organic light emitting diode (OLED) in the pixel region and including a first electrode, an organic thin layer, and a second electrode; a driving circuit unit in the non-pixel region and for driving the OLED; a shielding layer in the non-pixel region and on the driving circuit unit, the shielding layer being electrically coupled to a ground power source; and an insulating layer interposed between the driving circuit unit and the shielding layer. The shielding layer effectively protects the driving circuit unit in the non-pixel region form electrostatic discharge (ESD). Also, the light emitting display may include a guard ring at an edge portion of the non-pixel region and electrically coupled to the shielding layer to further protect the driving circuit from ESD.

Owner:SAMSUNG DISPLAY CO LTD

Buried guard ring and radiation hardened isolation structures and fabrication methods

ActiveUS7304354B2Reduce and eliminate effectLow costTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

Semiconductor devices can be fabricated using conventional designs and process but including specialized structures to reduce or eliminate detrimental effects caused by various forms of radiation. Such semiconductor devices can include the one or more parasitic isolation devices and / or buried guard ring structures disclosed in the present application. The introduction of design and / or process steps to accommodate these novel structures is compatible with conventional CMOS fabrication processes, and can therefore be accomplished at relatively low cost and with relative simplicity.

Owner:SILICON SPACE TECH

Electronic circuit

InactiveUS6414318B1Improve performanceLimits of linearityElectric discharge tubesSolid-state devicesCapacitanceEngineering

The present invention relates to an electronic circuit for measuring small amounts of charge or small electrical currents. One embodiment of the present invention provides an electronic circuit for measuring current or charge that can be used with a variety of sensing media (including high impedance sensing media) that produce a signal by either charge or current production or induction in response to physical phenomena occurring within the sensing media. In another embodiment, the voltage level (bias) of either the sensing or reference electrode can be switched relative to the other upon receipt of a triggering pulse. This changes the polarity of the electric field to cause charge of the opposite polarity to be driven to the sensing electrode, thereby eliminating the need to electrically connect a discharge path to the sensing electrode to clear the charge accumulated at the sensing electrode. This can be supplemented by capacitively coupling a compensation signal to the sensing electrode to cause the amplifier output signal to lessen in magnitude below a threshold level that permits additional charge or current measurements of the same polarity before performing bias reversal. Alternately or in combination with bias reversal and capacitive compensation, sensor performance can be improved by minimizing inaccuracies caused by leakage currents or current drawn from the sensor. Other methods of reducing leakage currents that can be used alone or in combination with the aforementioned features include the use of guard rings, physical switches or relays, the controlled creation of charges or currents of a specific polarity in a specific region of the sensing medium, controlled leakage over the surface of an insulator, and controlling the environment in which the circuit operates.

Owner:BRIDGE SEMICON