Patents

Literature

428results about How to "Reduce doping concentration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

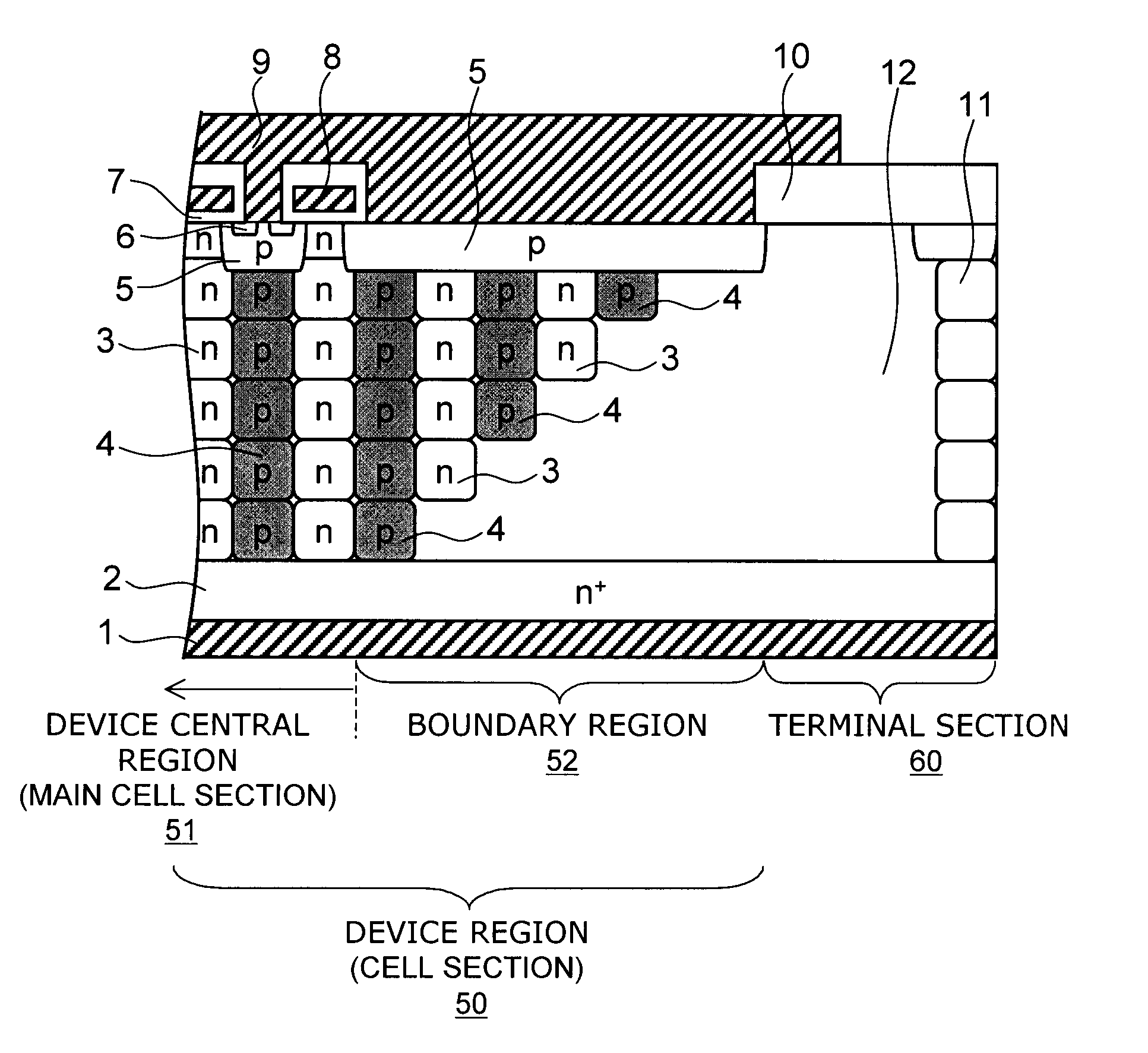

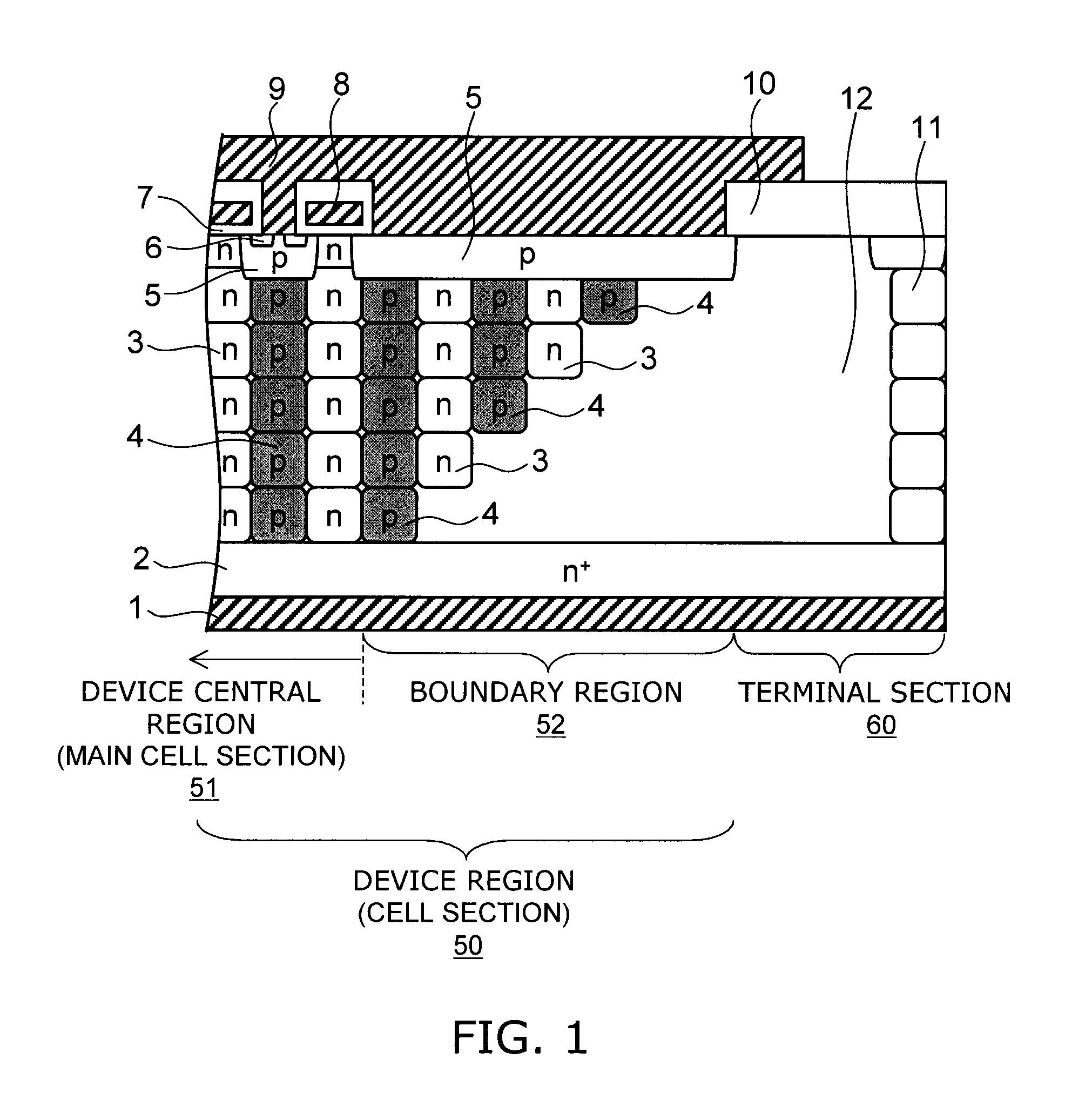

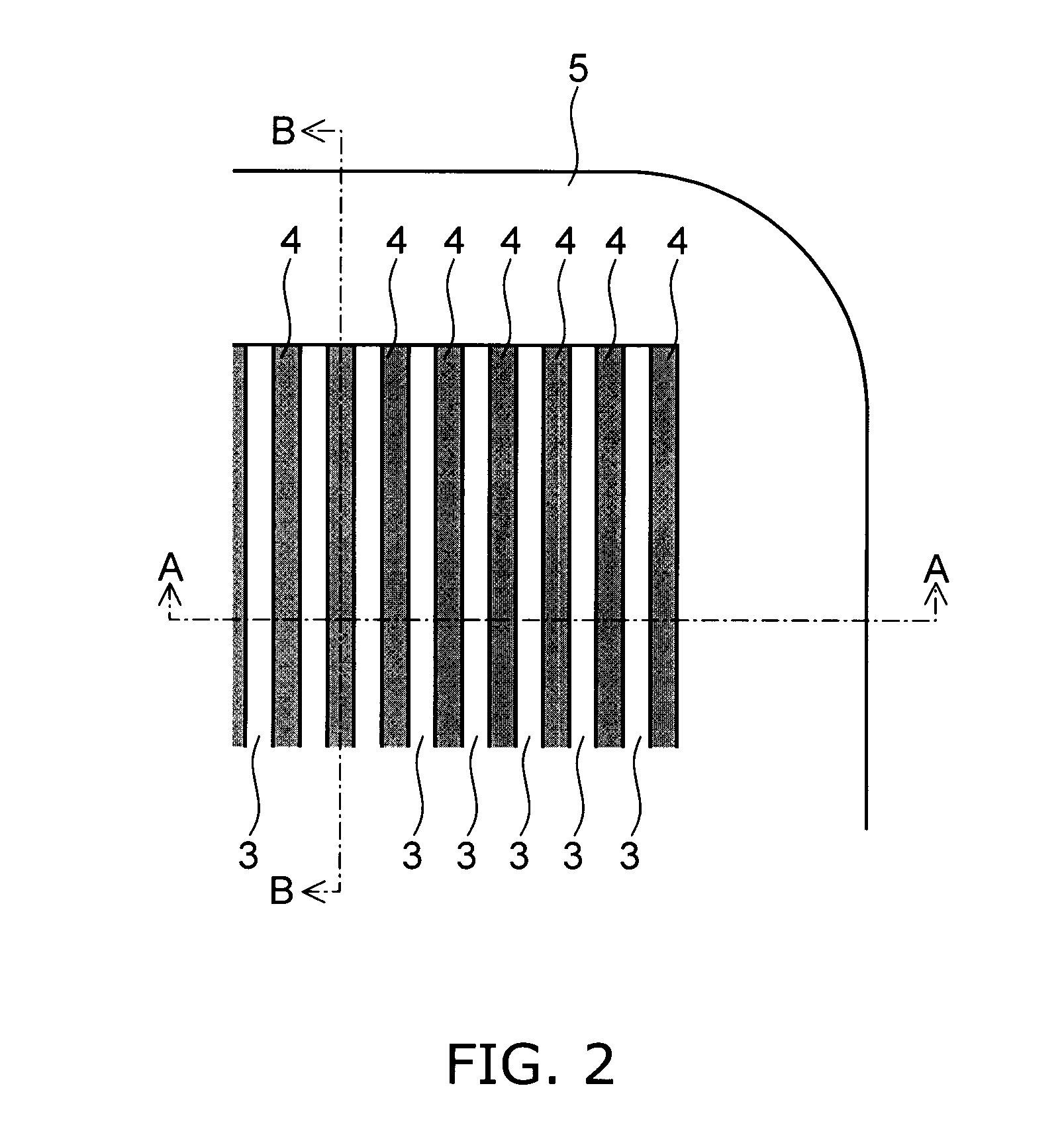

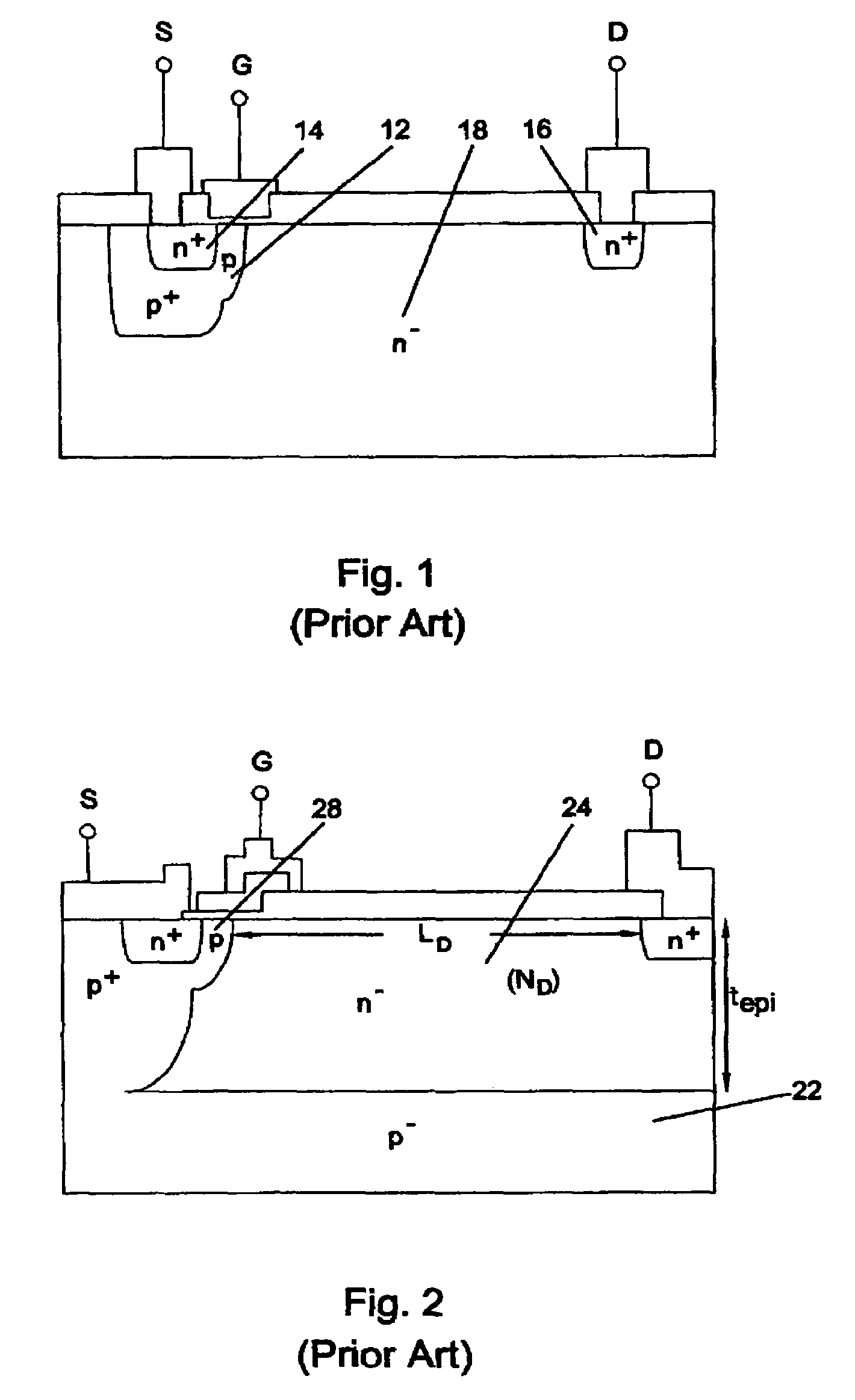

Semiconductor device

InactiveUS20070272979A1Reduce doping concentrationSemiconductor/solid-state device manufacturingDiodeHigh resistanceDopant

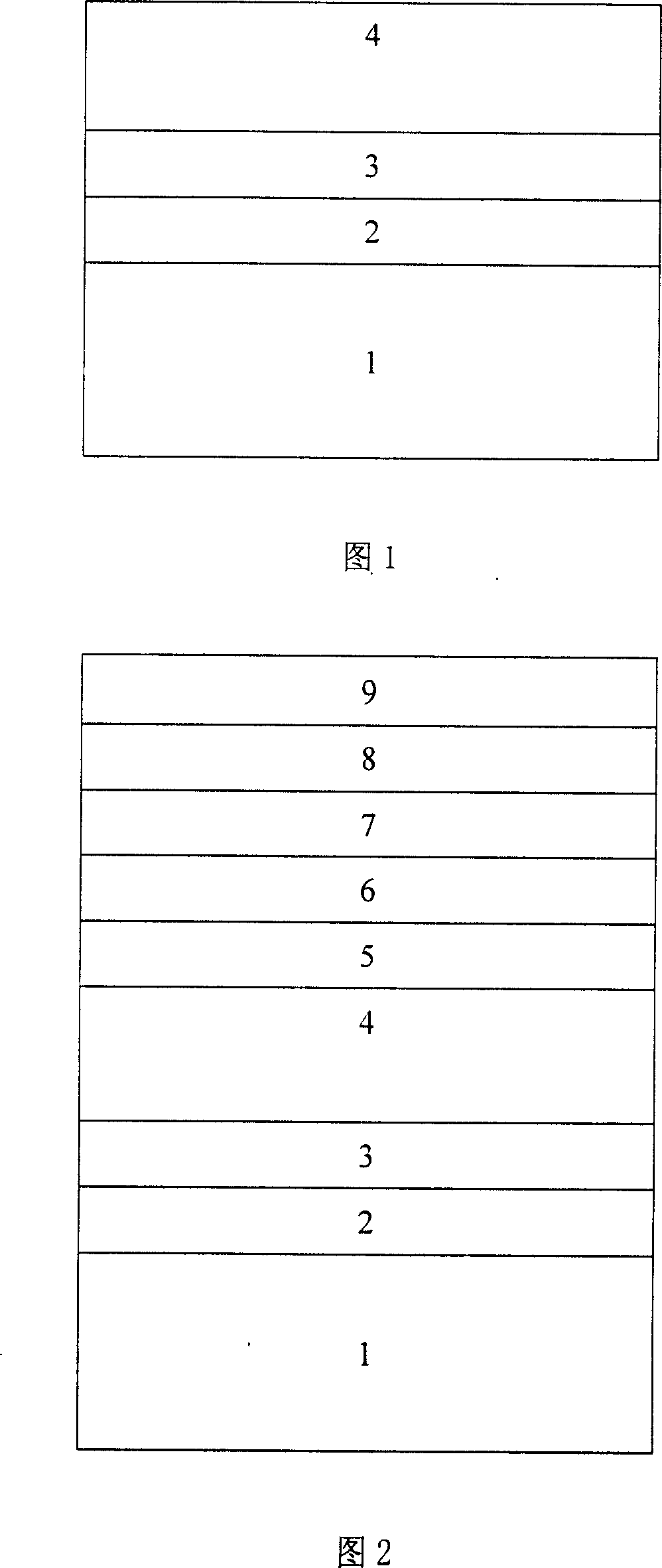

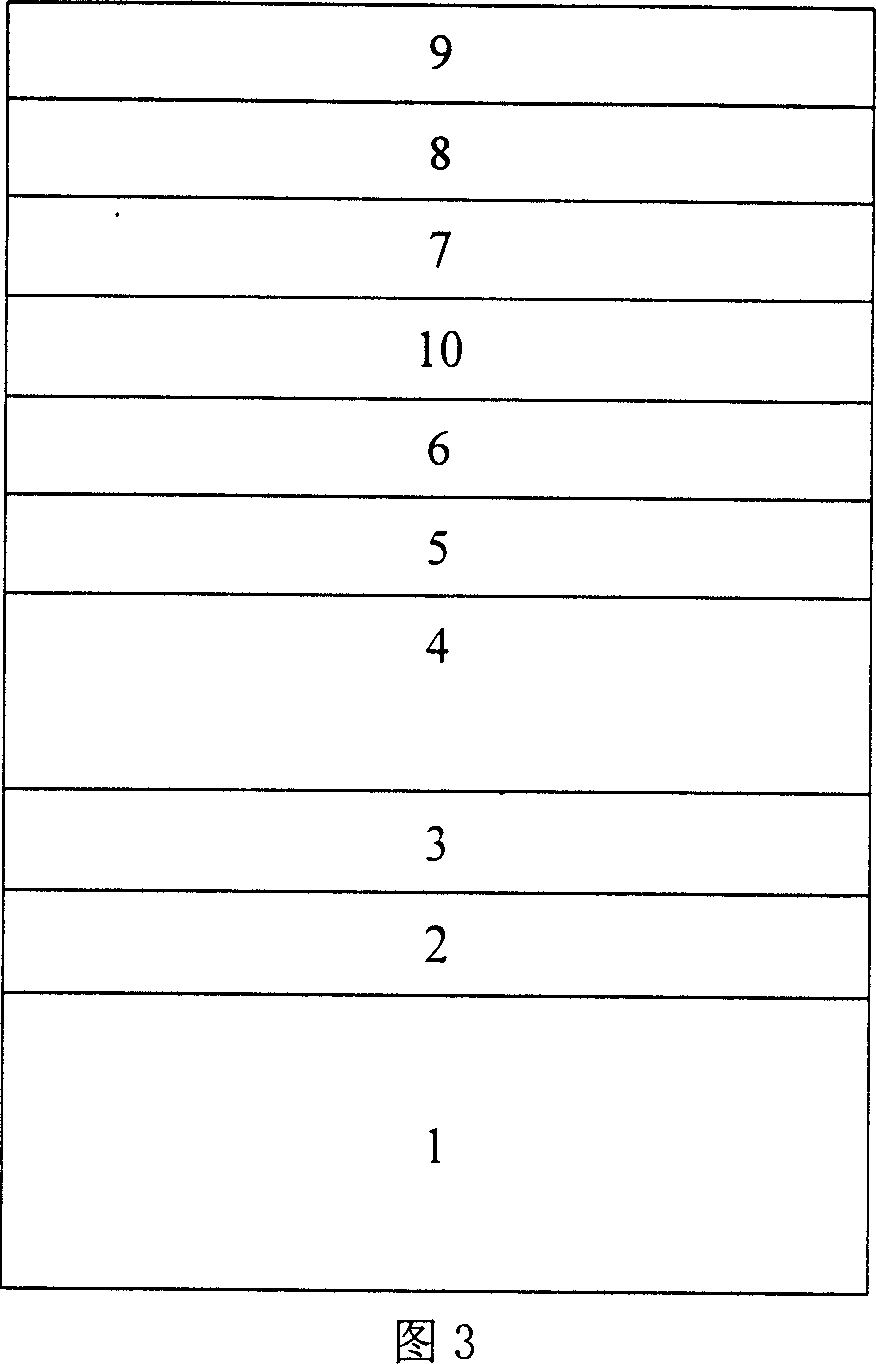

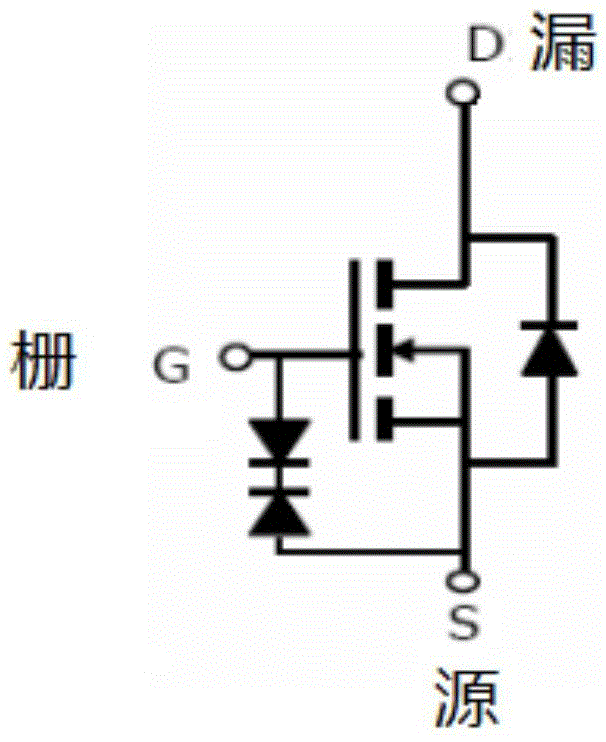

A semiconductor device includes: a semiconductor layer of a first conductivity type; a first semiconductor pillar region of the first conductivity type provided on a major surface of the semiconductor layer; a second semiconductor pillar region of a second conductivity type provided adjacent to the first semiconductor pillar region on the major surface of the semiconductor layer, the second semiconductor pillar region forming a periodic arrangement structure substantially parallel to the major surface of the semiconductor layer together with the first semiconductor pillar region; a first main electrode; a first semiconductor region of the second conductivity type; a second semiconductor region of the first conductivity type; a second main electrode; a control electrode; and a high-resistance semiconductor layer provided on the semiconductor layer in an edge termination section surrounding the first semiconductor pillar region and the second semiconductor pillar region. The high-resistance semiconductor layer has a lower dopant concentration than the first semiconductor pillar region. A boundary region is provided between a device central region and the edge termination section. The first semiconductor pillar region and the second semiconductor pillar region adjacent to the high-resistance semiconductor layer in the boundary region have a depth decreasing stepwise toward the edge termination section.

Owner:KK TOSHIBA

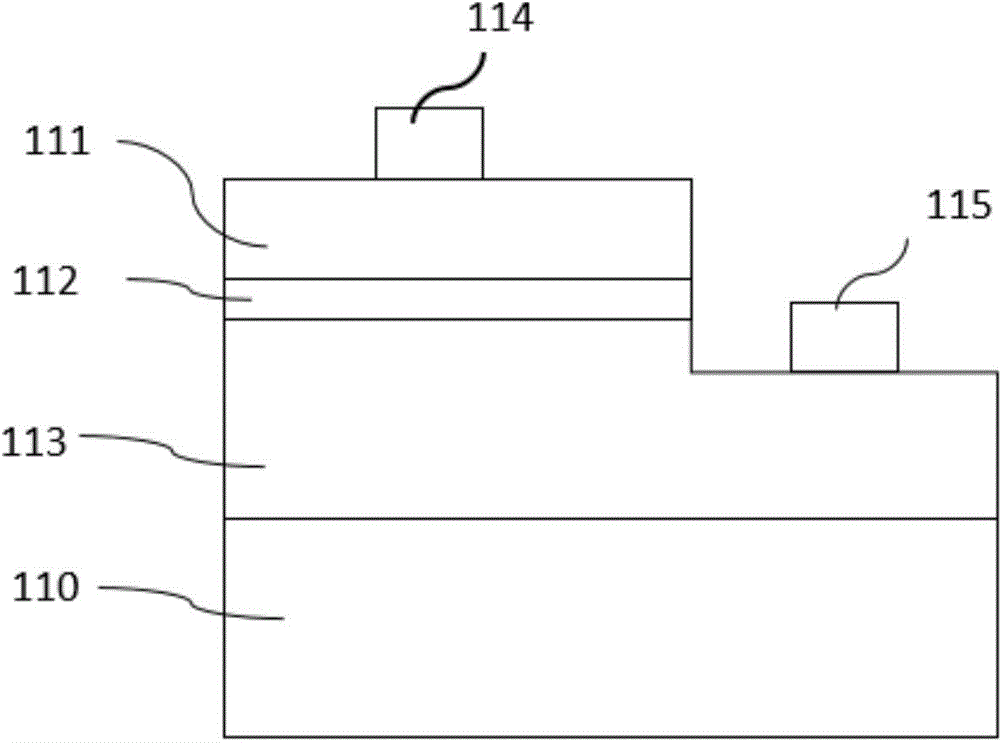

Non polarity A side nitride film growing on the silicon(102) substrate and its making method and use

InactiveCN101009347AEasy to separateIncrease overlapLaser detailsFinal product manufactureSolar batteryLight-emitting diode

The invention relates to a nonpolar A side nitride film that comprises a silicon (102) underlay, metal layer which grows upon the silicon underlay sequentially, InGaAlN initial growth layer and the first InGaAlN buffer layer, it characterized in that: said silicon underlay is Si underlay which adopts the (102) side or offset angle. The nonpolar a side nitride film which grows on the silicon underlay can be used in LBD, laser, solar battery. The component extension configuration is adopted according to different component, for example the LBD and laser, and using the mature silicon craft further to produce relative diprosopia electrode component or peeling off component. The advantages of the invention are: the invention can increase the growth quality of nonpolar GaN base material, and decrease the cost; the craft of current component can be simplified greatly, the cost can be decreased, and increase the elimination efficiency and lightening efficiency greatly.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

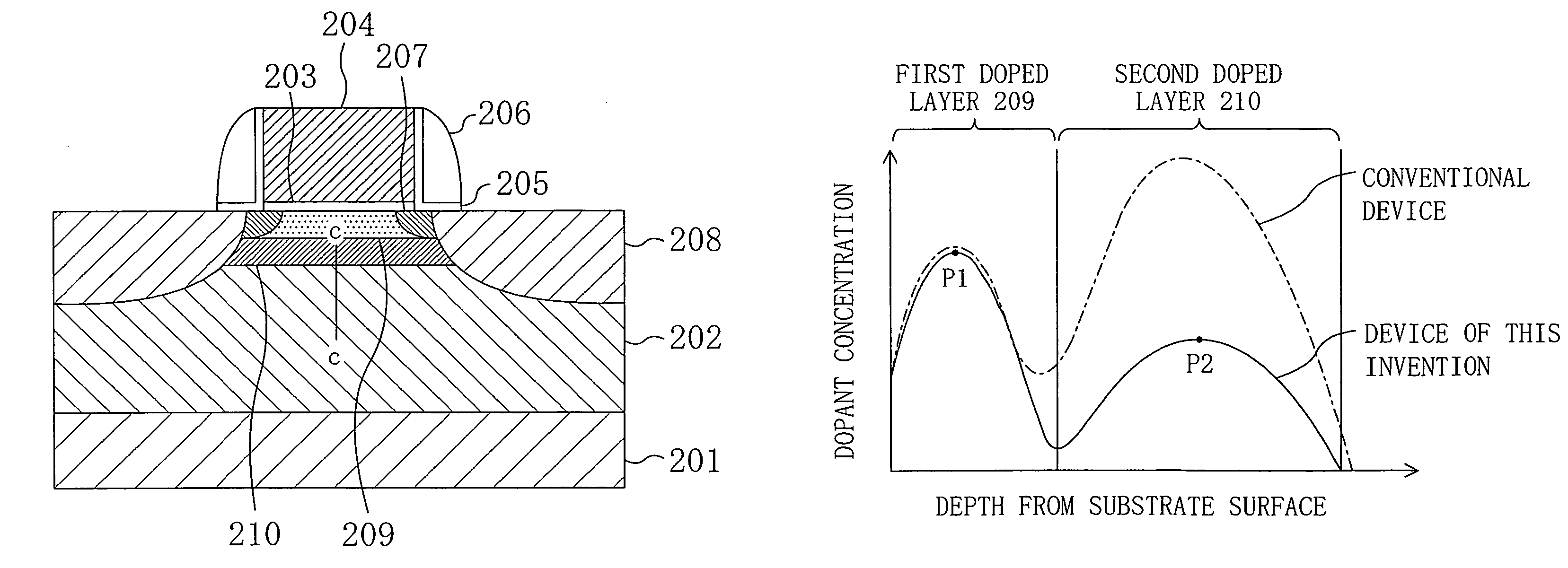

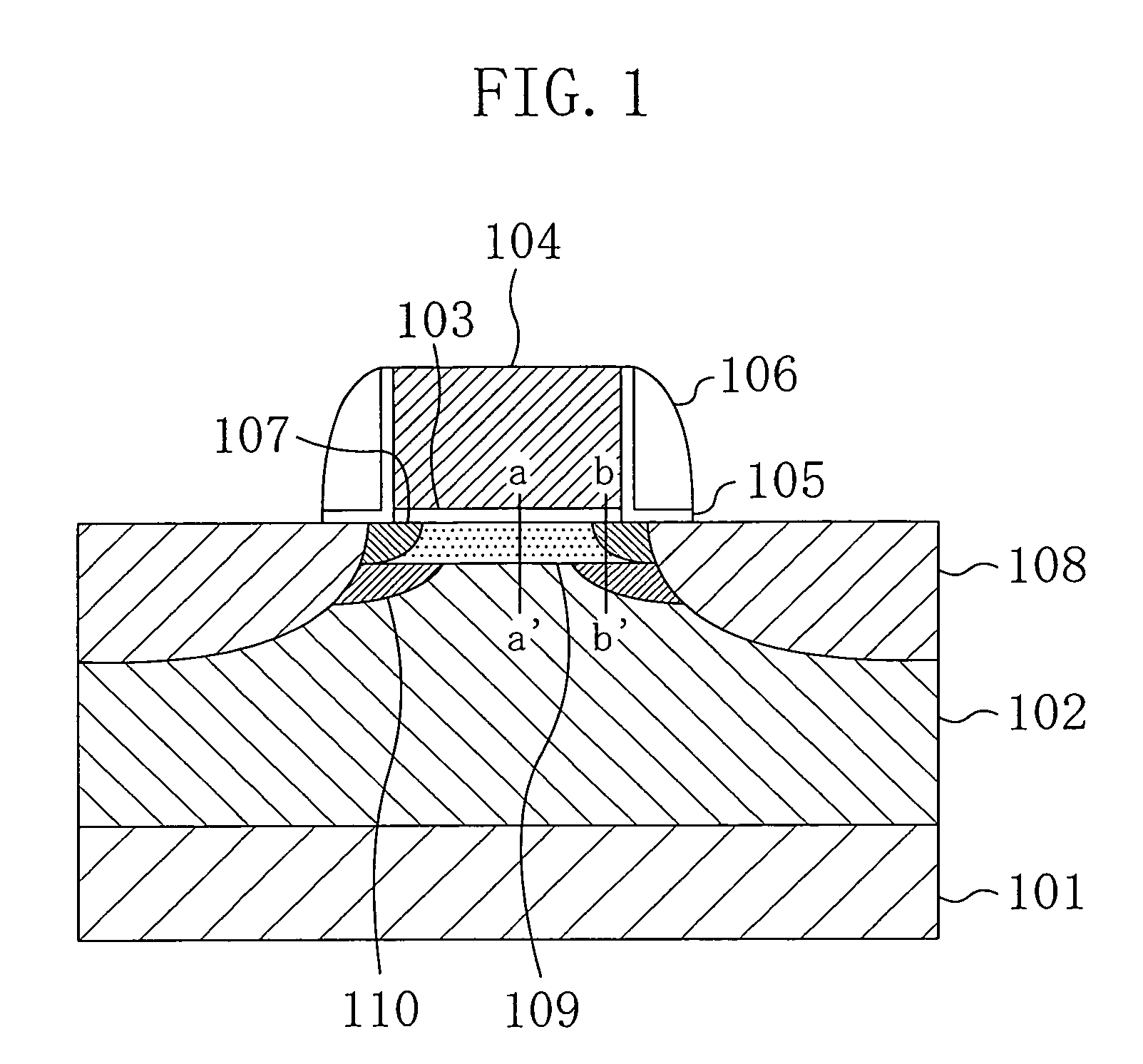

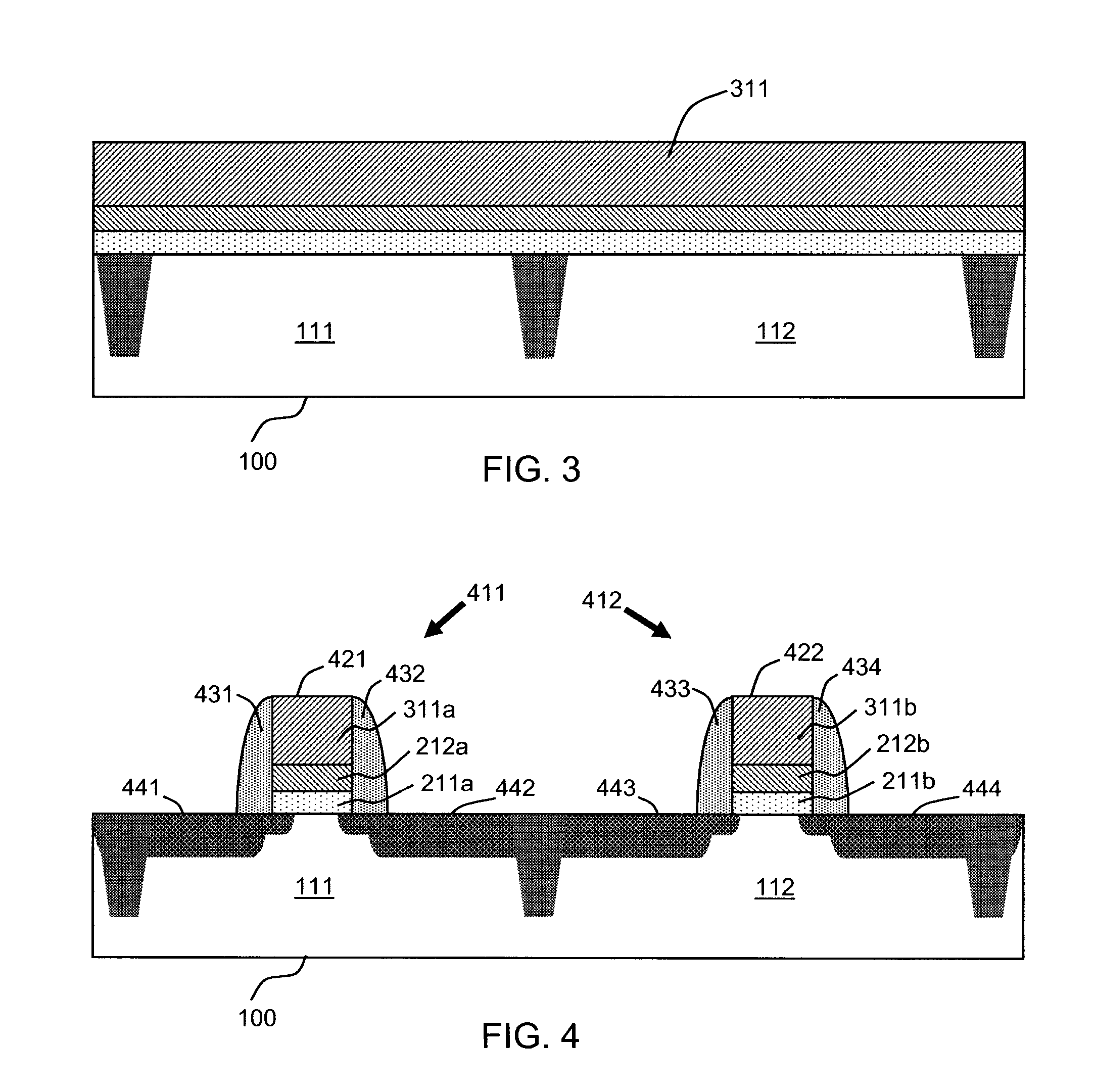

Semiconductor device and method for fabricating the same

ActiveUS7301208B2Increase powerImprove leakage currentTransistorSemiconductor/solid-state device manufacturingDopantPeak value

A first doped layer of a conductivity type opposite to that of source / drain regions is formed in a semiconductor substrate under a gate electrode. A second doped layer of the conductivity type opposite to that of the source / drain regions is formed in the semiconductor substrate below the first doped layer. The first doped layer has a first peak in dopant concentration distribution in the depth direction. The first peak is located at a position shallower than the junction depth of the source / drain regions. The second doped layer has a second peak in dopant concentration distribution in the depth direction. The second peak is located at a position deeper than the first peak and shallower than the junction depth of the source / drain regions. The dopant concentration at the first peak is higher than that at the second peak.

Owner:GK BRIDGE 1

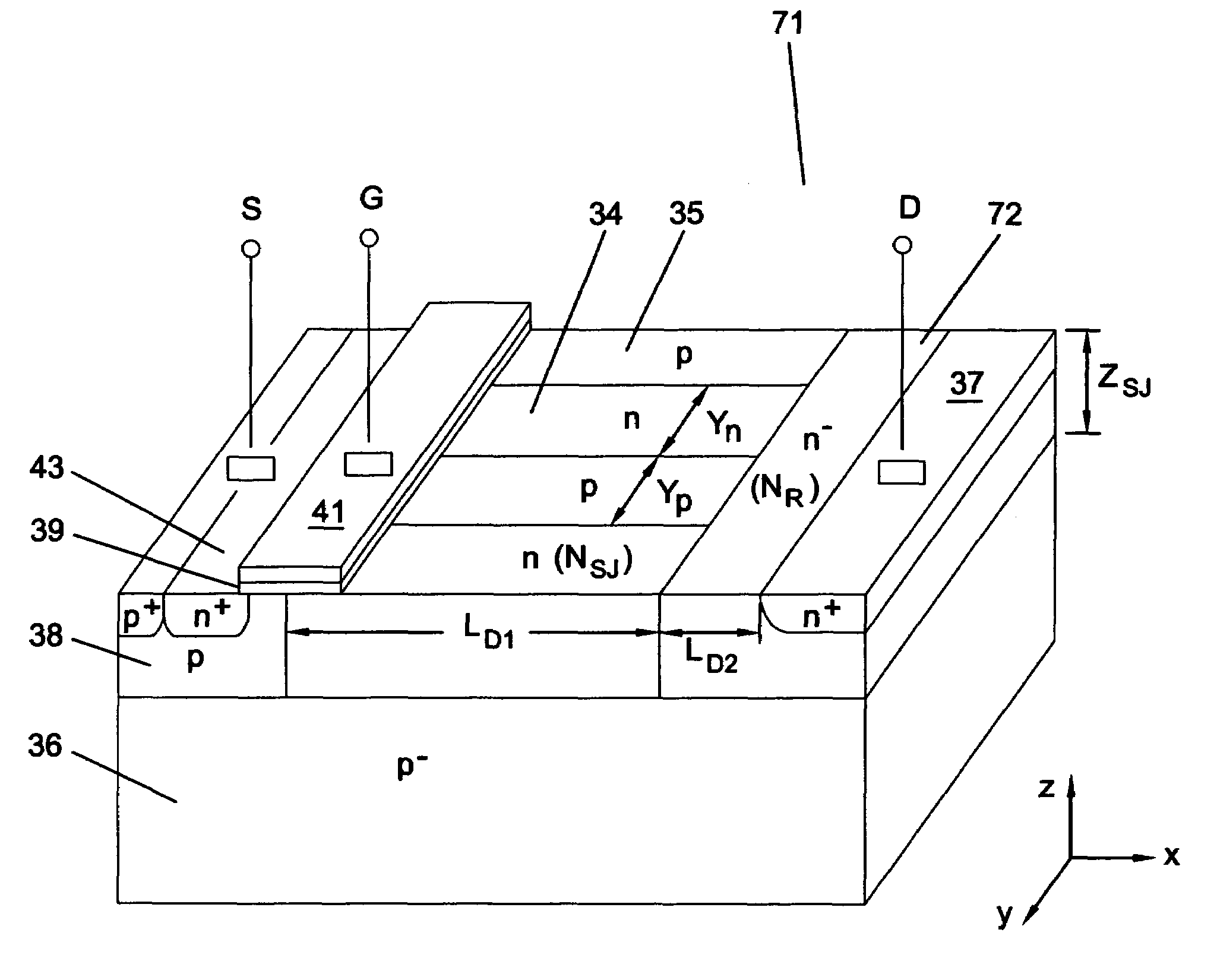

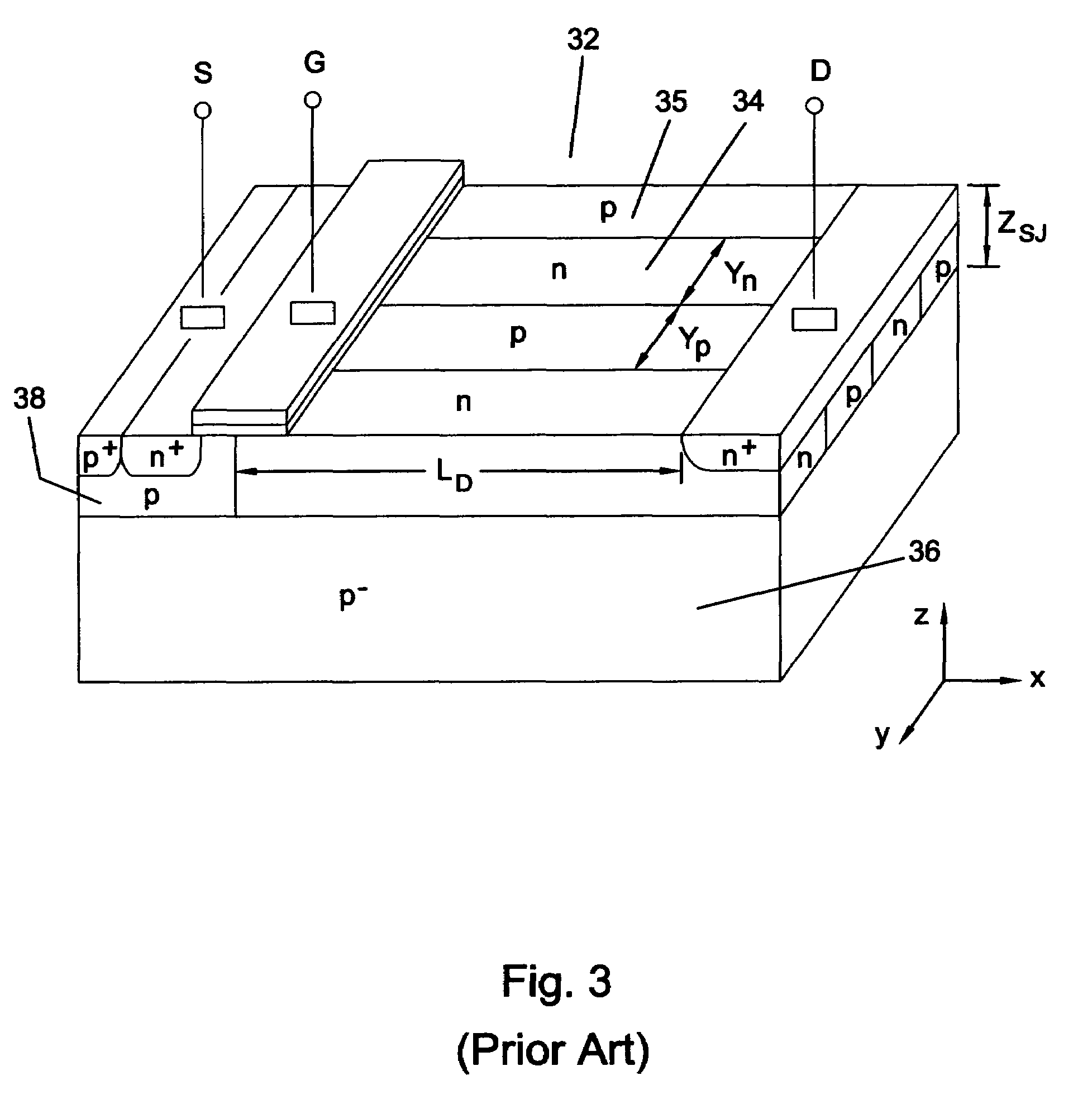

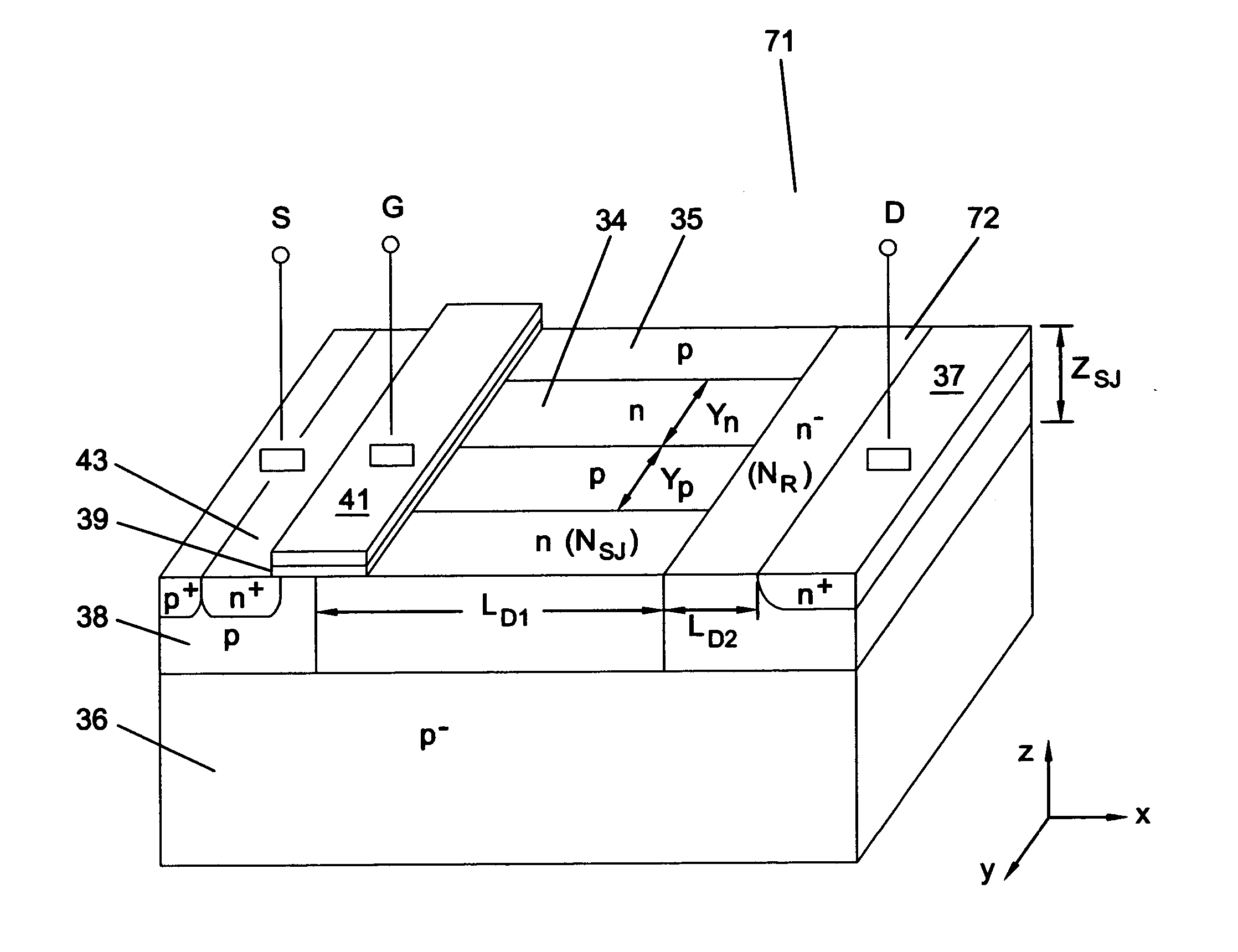

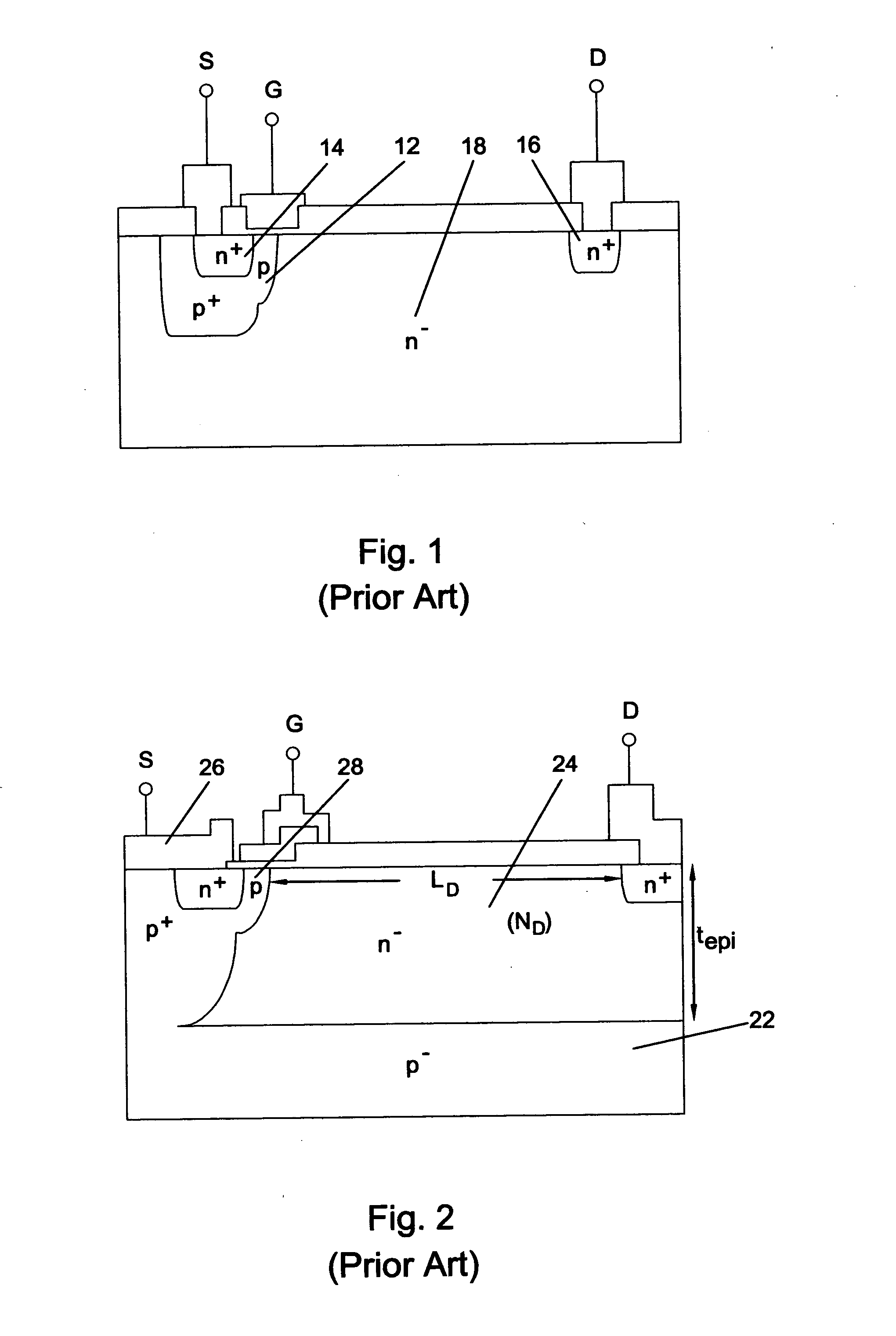

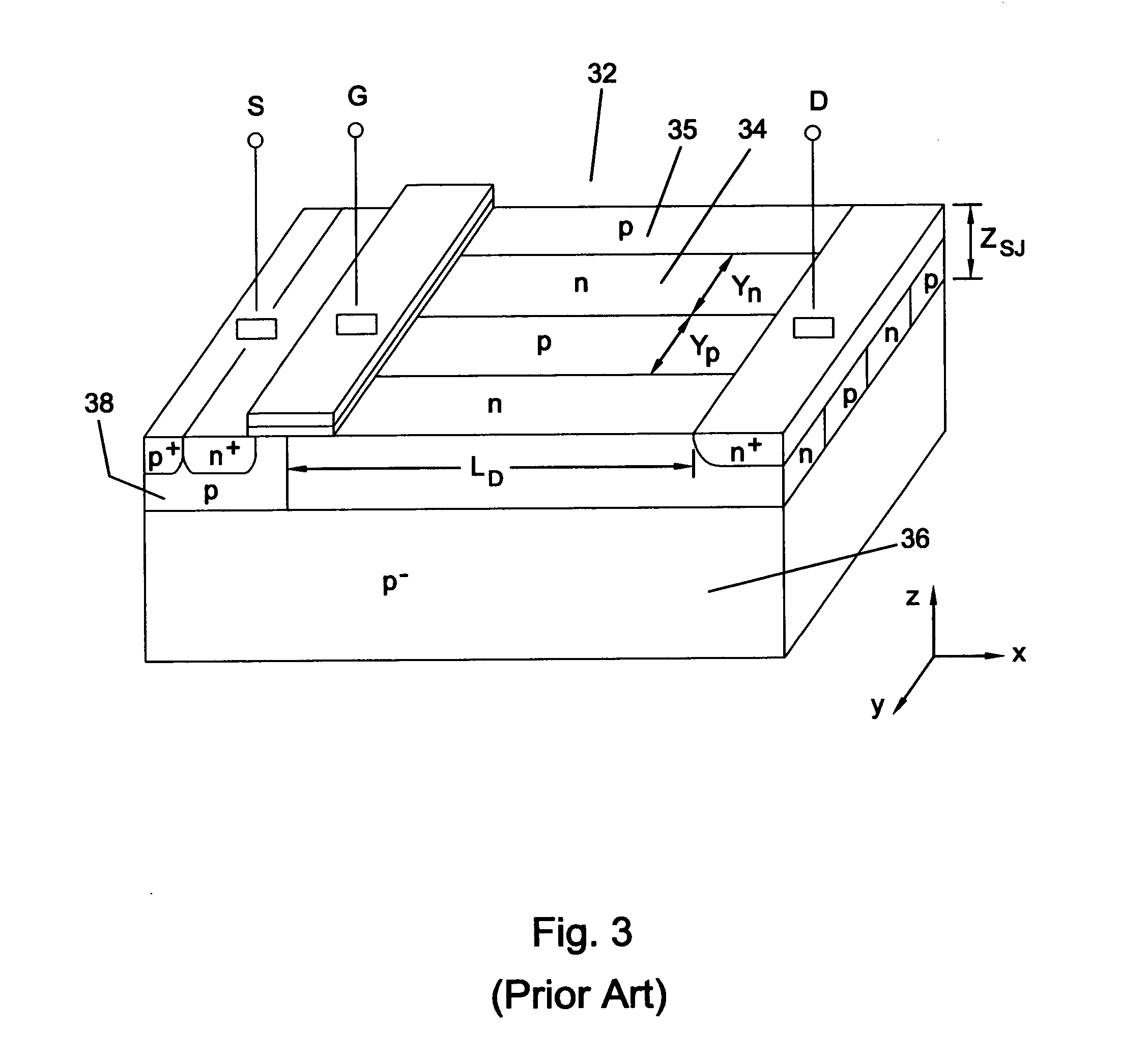

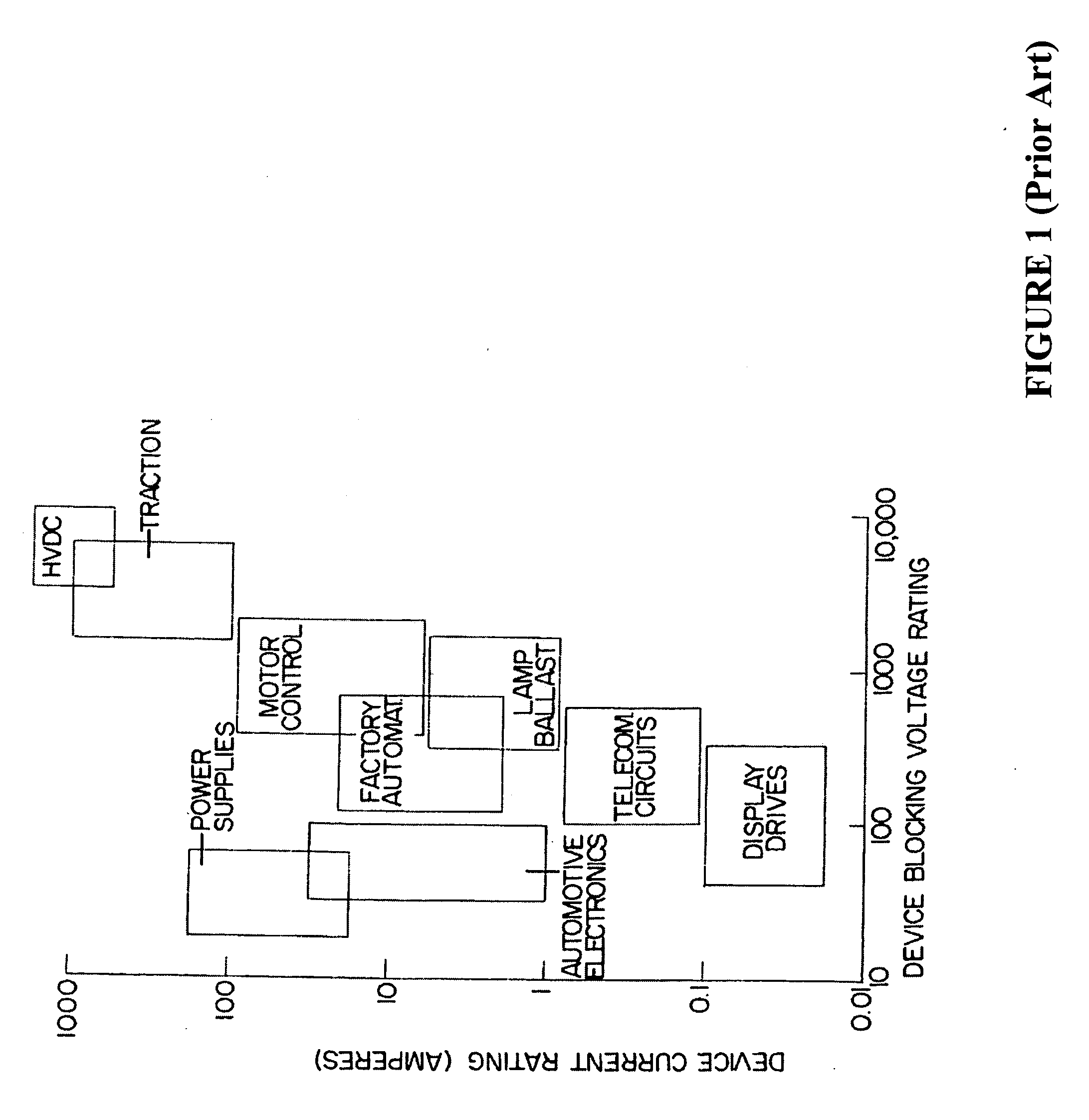

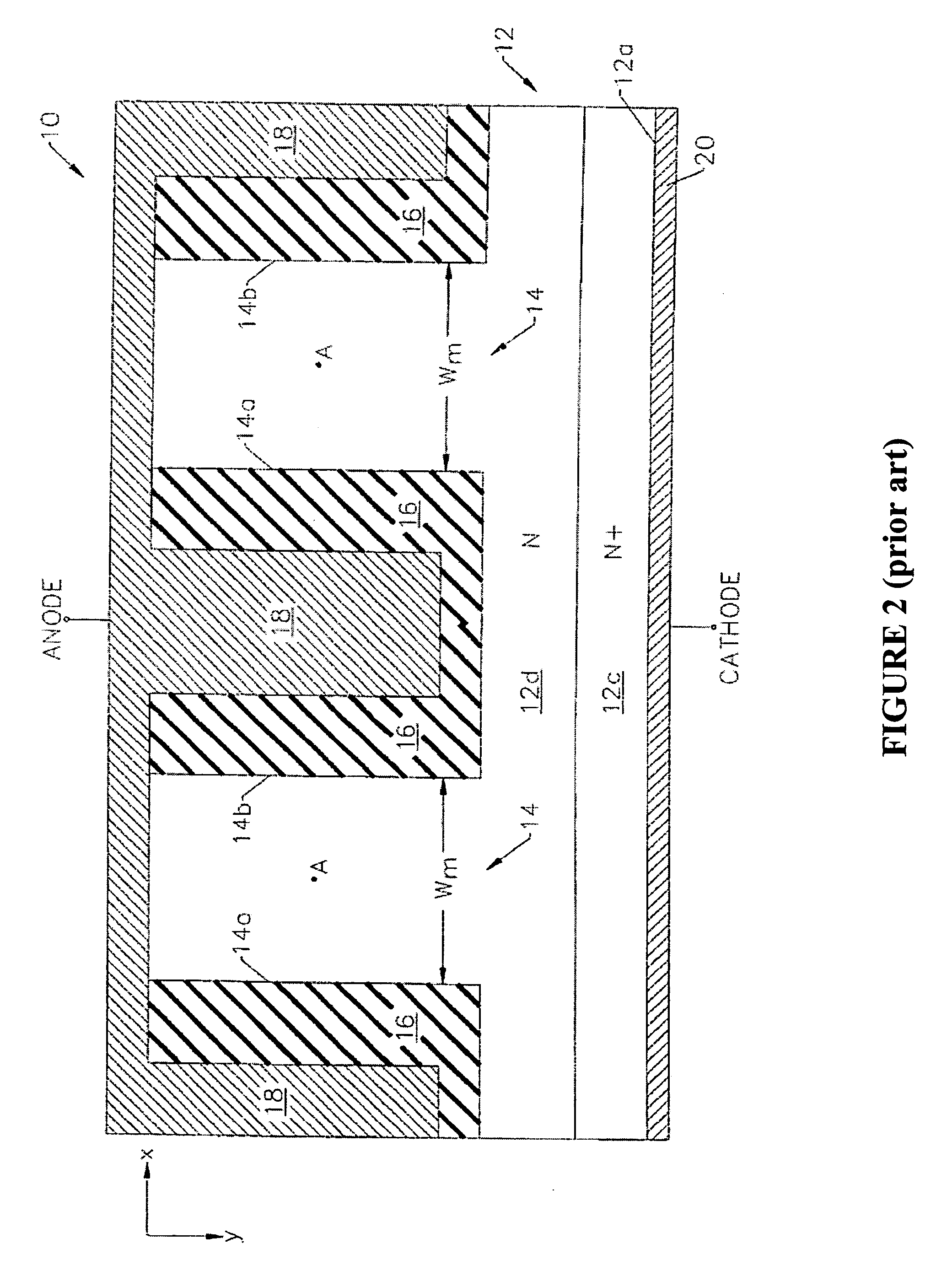

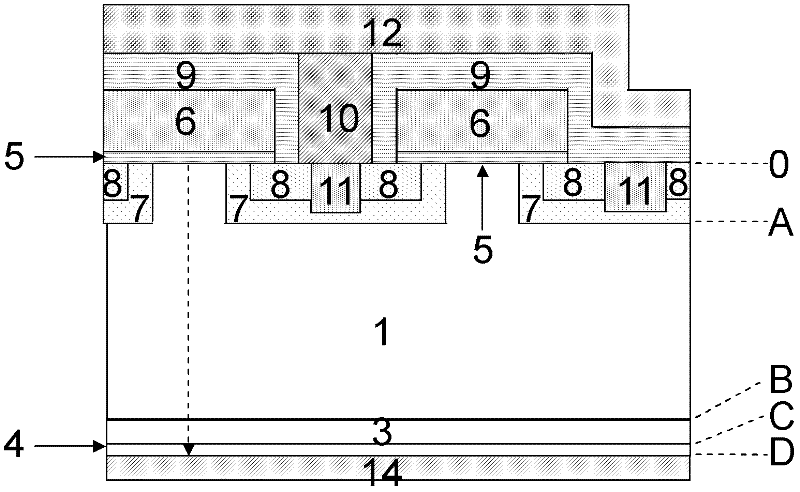

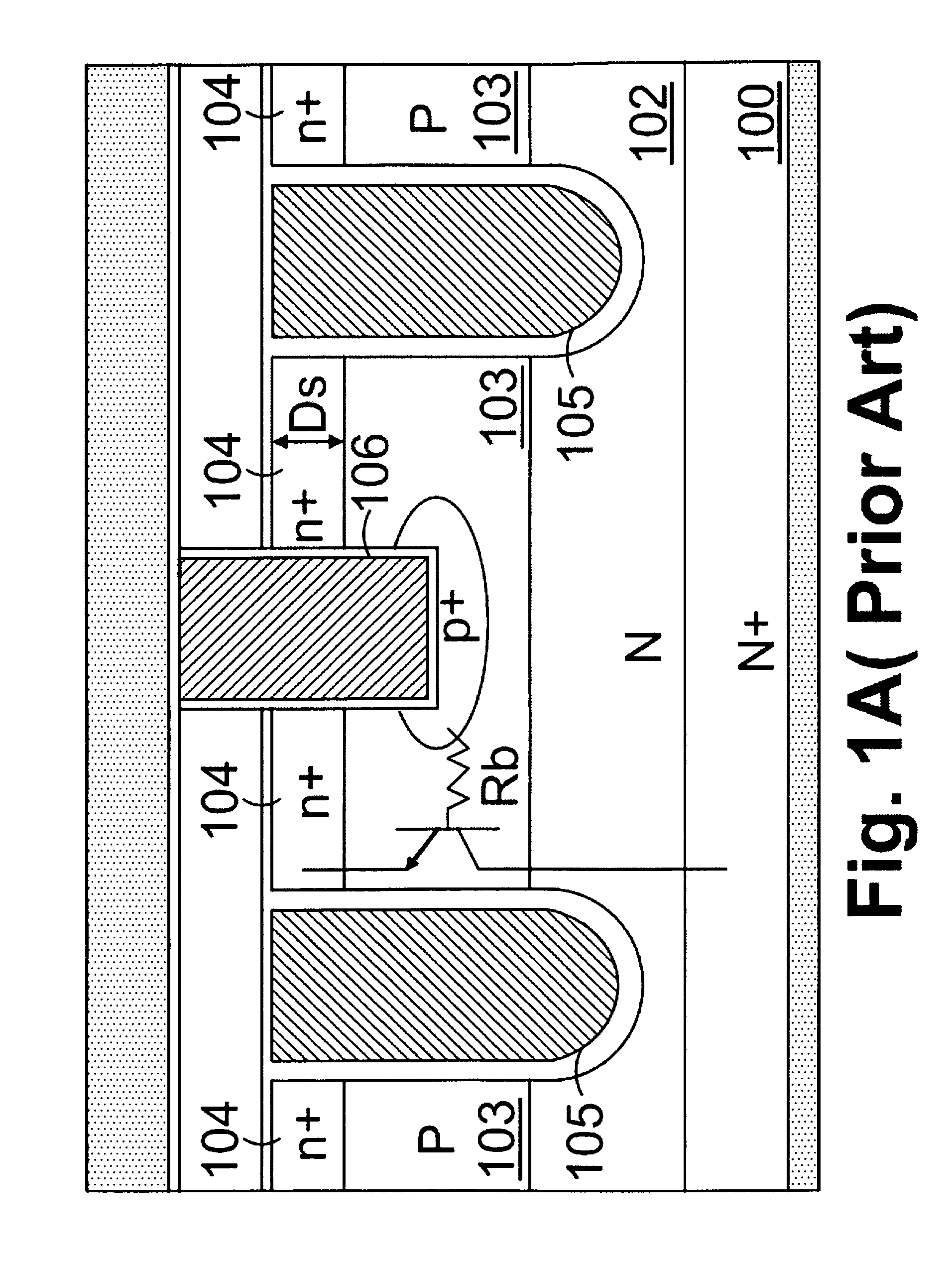

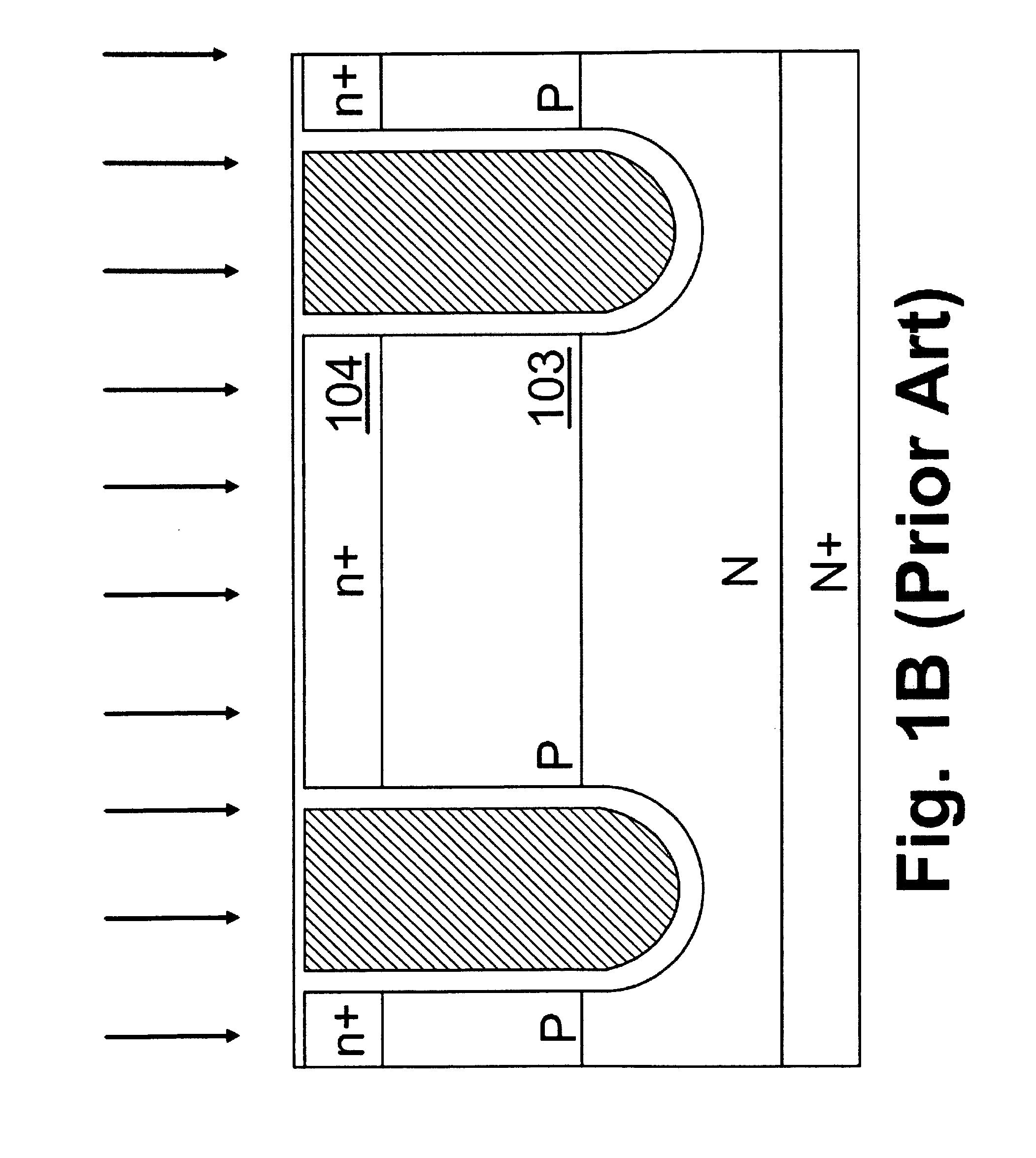

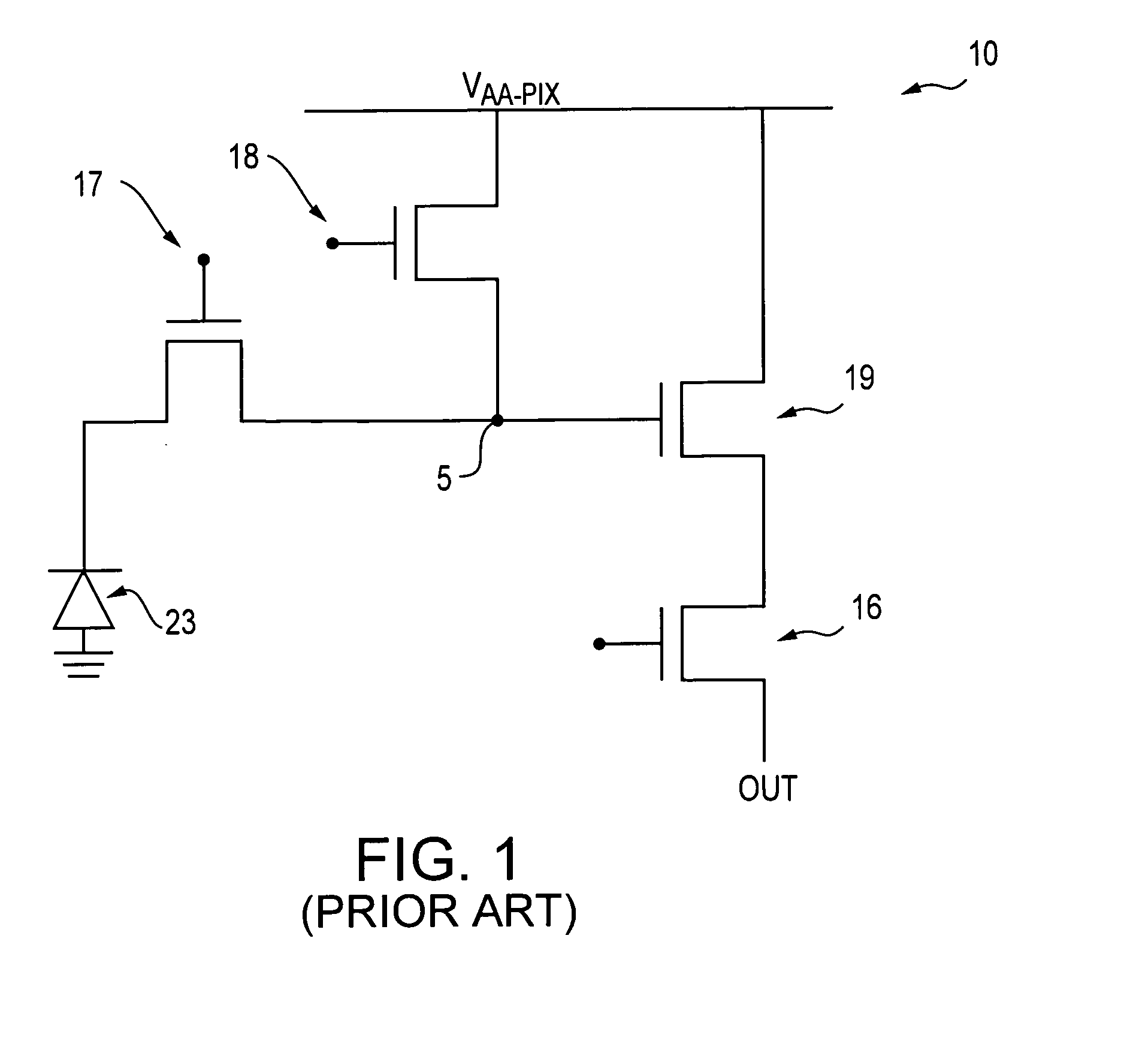

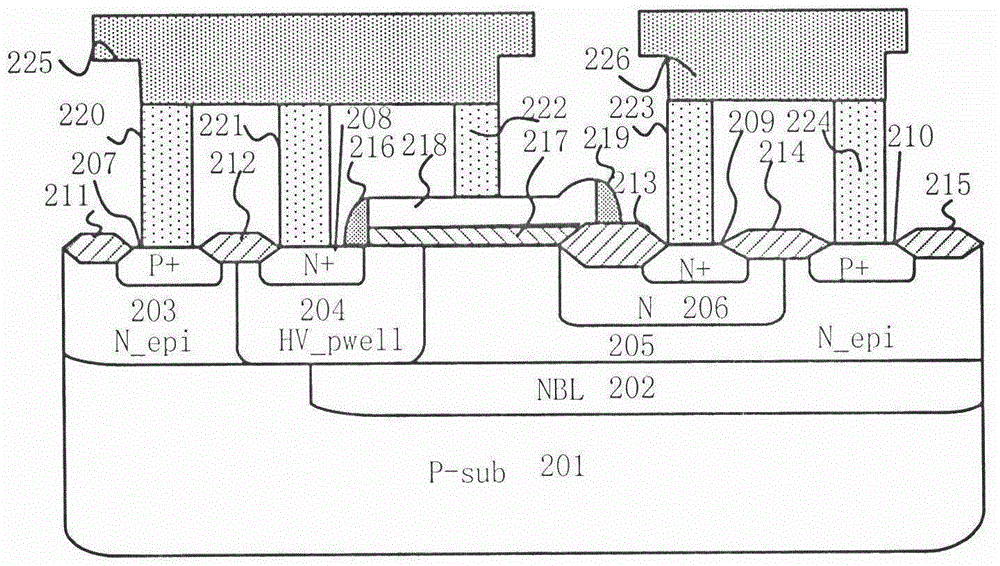

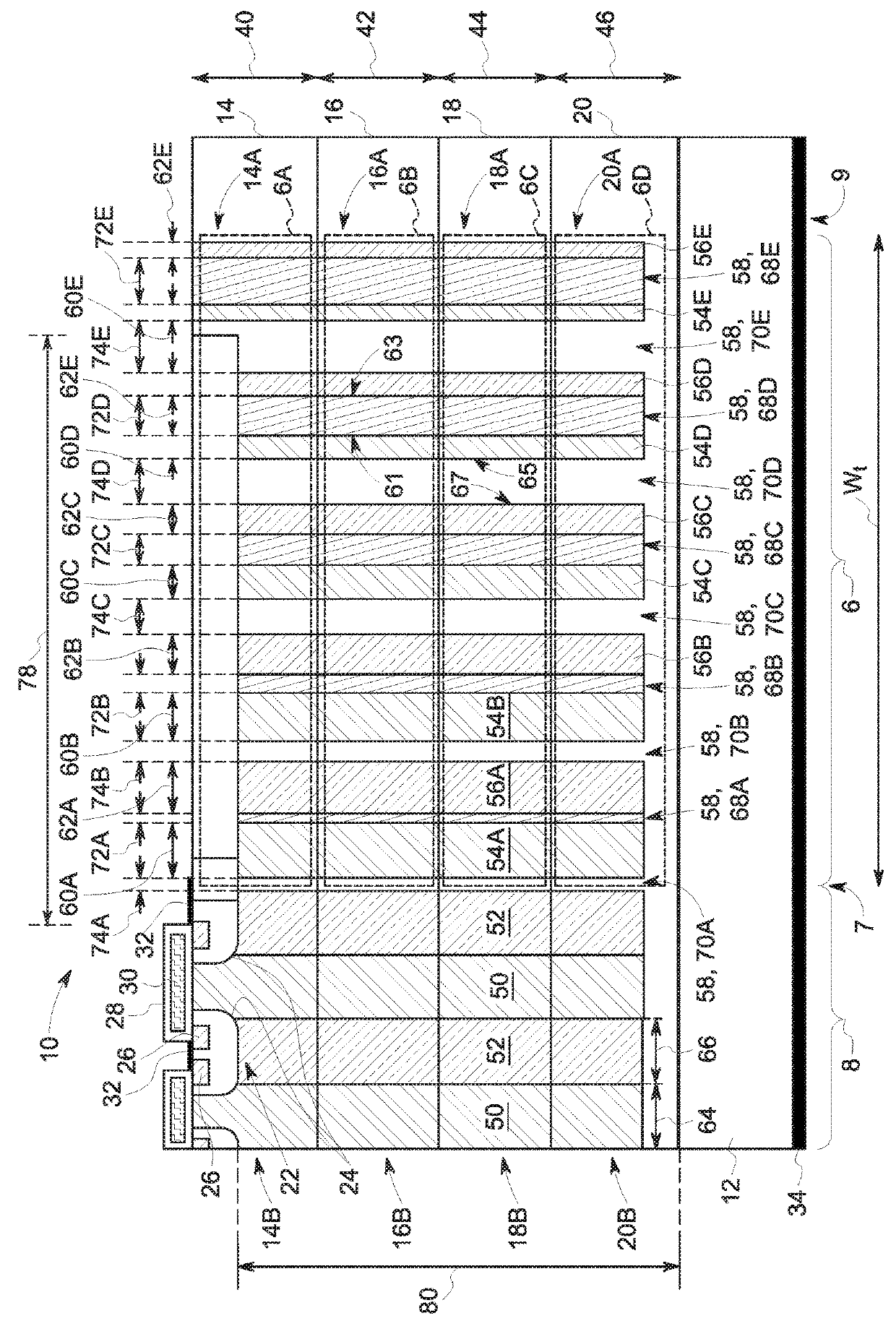

Super junction / resurf LDMOST (SJR-LDMOST)

InactiveUS7023050B2Reduce doping concentrationBreakdown voltage of deviceSemiconductor devicesMOSFETDisplay device

A lateral double diffused MOSFET (LDMOST) incorporates both the reduced surface field (RESURF) and super junction (SJ) in a split-drift region to significantly improve the on-state, off-state and switching characteristics in junction-isolated (JI) technology. The structure effectively suppresses substrate-assisted-depletion which is the main problem encountered when applying the SJ concept to lateral power devices. The device structure features a split-drift region formed of two parts: a SJ structure that extends over most of the drift region, and a terminating RESURF region occupying a portion of the drift region next to the drain. The structure offers improved breakdown voltage and reduced specific on resistance as compared to convention structures, and is useful in power integrated circuits suitable for a variety of applications including flat plasma panel display, automotive electronics, motor control, power supply and high voltage lamp ballasts.

Owner:SALAMA C ANDRE T +1

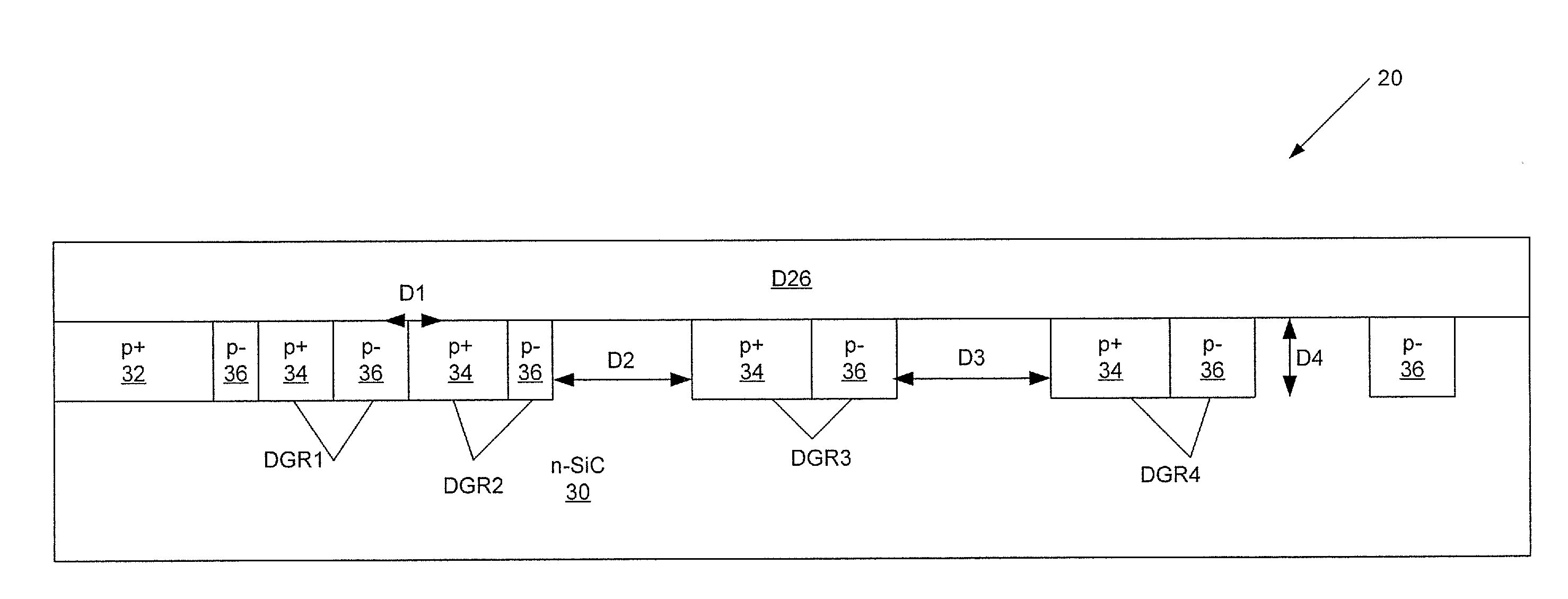

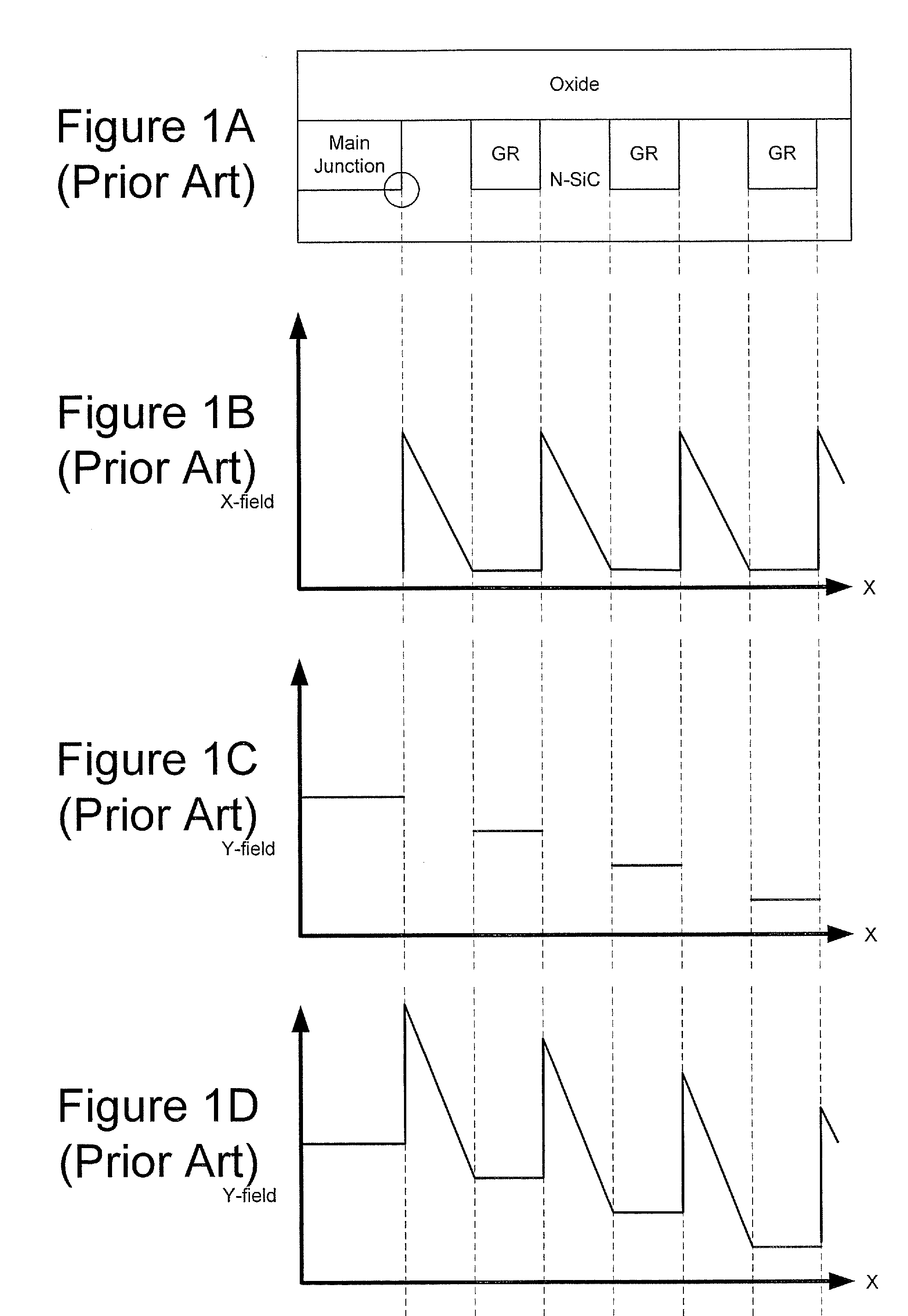

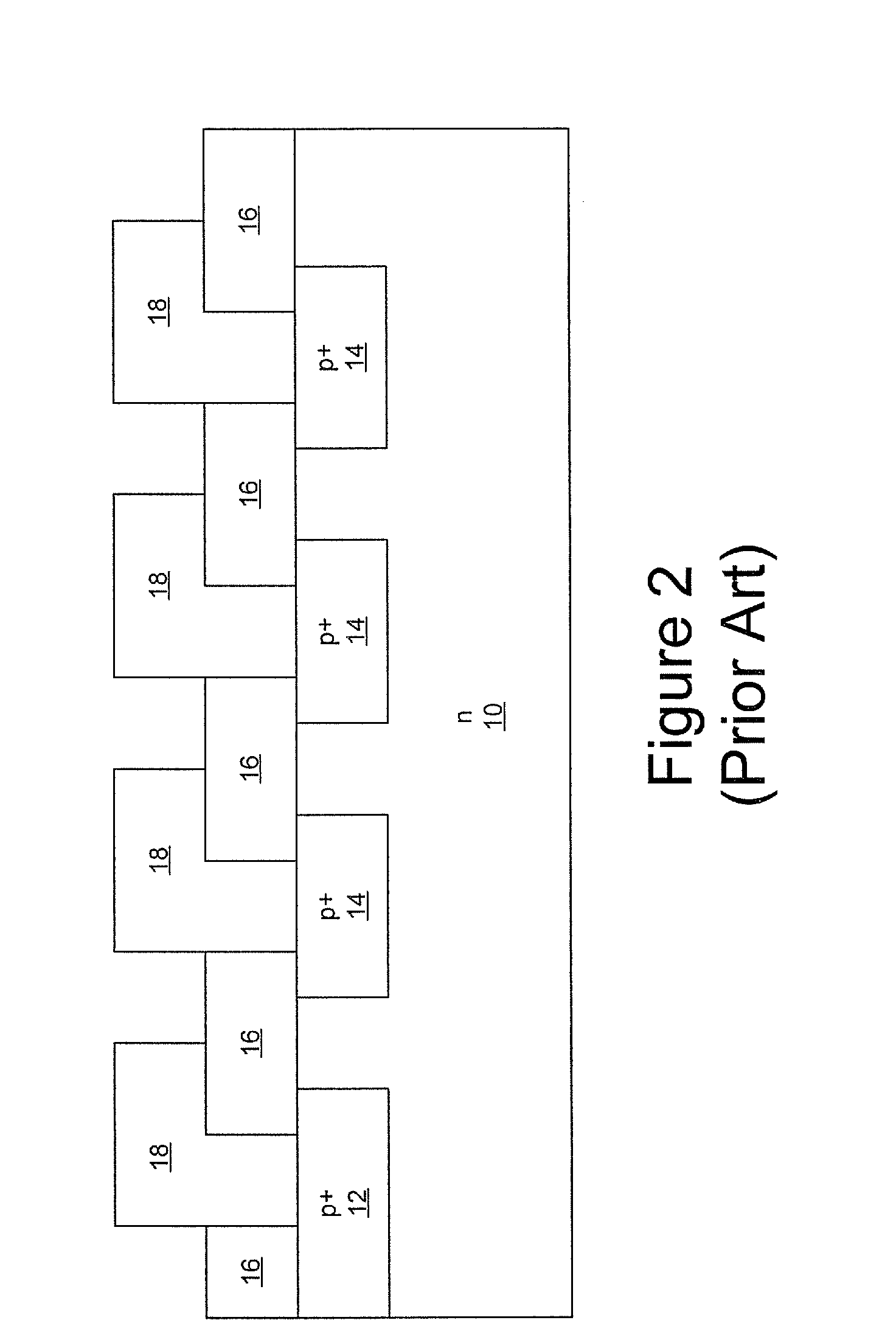

Double Guard Ring Edge Termination for Silicon Carbide Devices and Methods of Fabricating Silicon Carbide Devices Incorporating Same

ActiveUS20090212301A1Reduce doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

Edge termination structures for semiconductor devices are provided including a plurality of spaced apart concentric floating guard rings in a semiconductor layer that at least partially surround a semiconductor junction. The spaced apart concentric floating guard rings have a highly doped portion and a lightly doped portion. Related methods of fabricating devices are also provided herein.

Owner:CREE INC

Super junction / resurf ldmost (sjr-LDMOST)

InactiveUS20050017300A1Reduce doping concentrationBreakdown voltage of deviceSemiconductor devicesMOSFETElectrical ballast

A lateral double diffused MOSFET (LDMOST) incorporates both the reduced surface field (RESURF) and super junction (SJ) in a split-drift region to significantly improve the on-state, off-state and switching characteristics in junction-isolated (JI) technology. The structure effectively suppresses substrate-assisted-depletion which is the main problem encountered when applying the SJ concept to lateral power devices. The device structure features a split-drift region formed of two parts: a SJ structure that extends over most of the drift region, and a terminating RESURF region occupying a portion of the drift region next to the drain. The structure offers improved breakdown voltage and reduced specific on resistance as compared to convention structures, and is useful in power integrated circuits suitable for a variety of applications including flat plasma panel display, automotive electronics, motor control, power supply and high voltage lamp ballasts.

Owner:SALAMA C ANDRE T +1

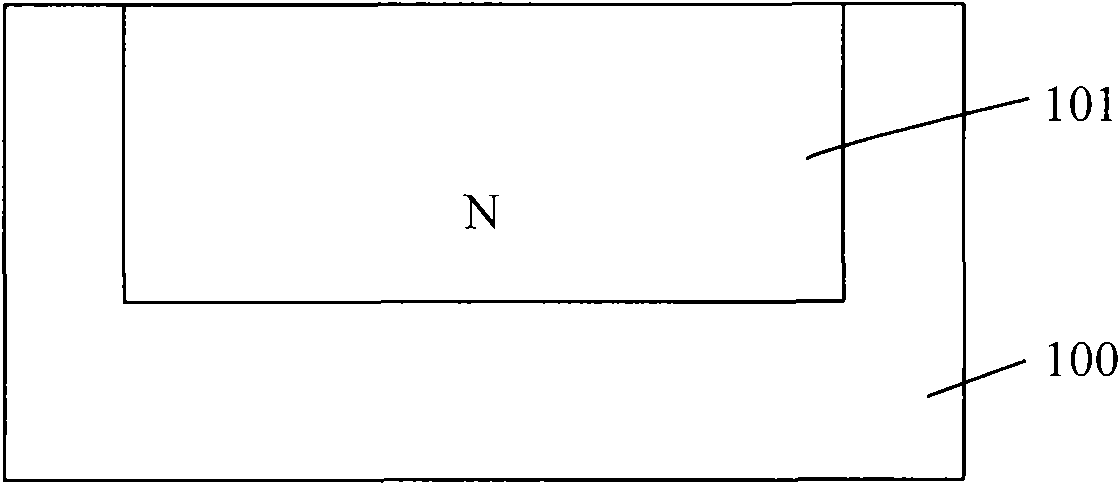

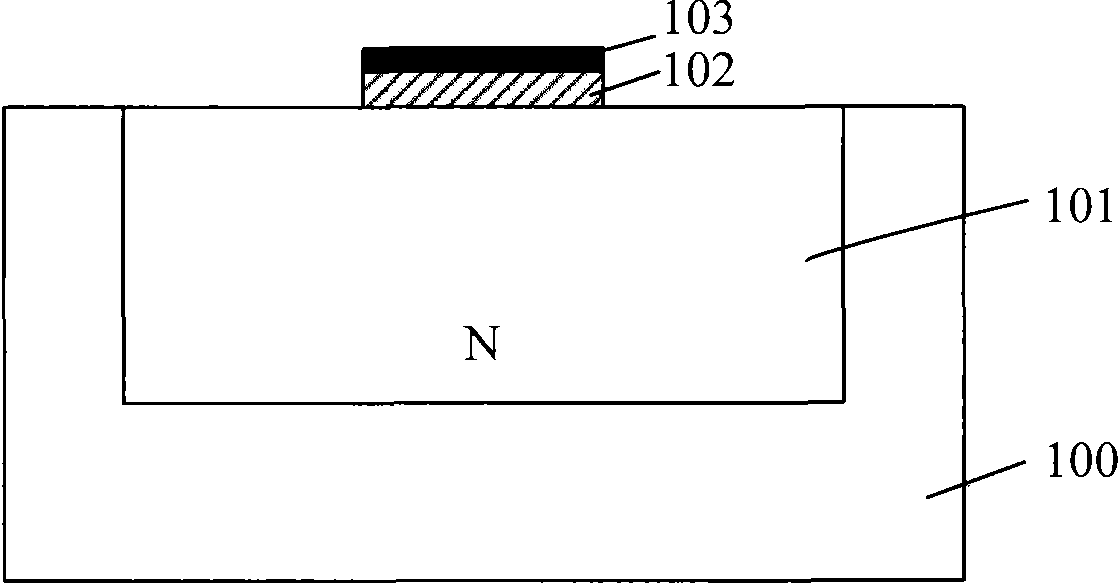

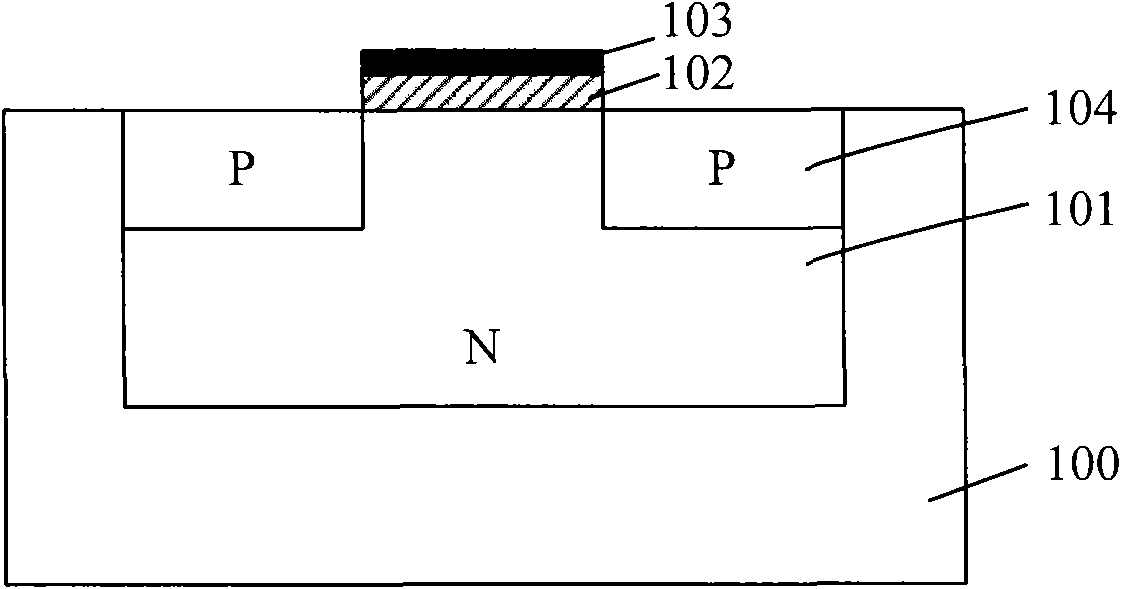

Metal oxide semiconductor (MOS) transistor and formation method thereof

InactiveCN101789447AAvoid affecting basic performanceReduce doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceIon implantation

The invention provides a metal oxide semiconductor (MOS) transistor and a formation method thereof. The formation method of the transistor comprises the following steps of: forming an isolated well on a semiconductor substrate through repeated ion injection; carrying out reversed-phase ion injection on the isolated well; and forming a grid electrode, a source region and a drain region of the MOS transistor on the isolated well. The invention reduces the doping concentration nearby the interface of the source and the drain regions and the isolated well so as to weaken the junction capacitance and further reduce the influence of the parasitic junction capacitance on transistor devices, and also keeps the doping concentration on the surface of the isolated well and nearby the interface of the isolated well and the substrate so as to avoid affecting the original properties of the transistor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

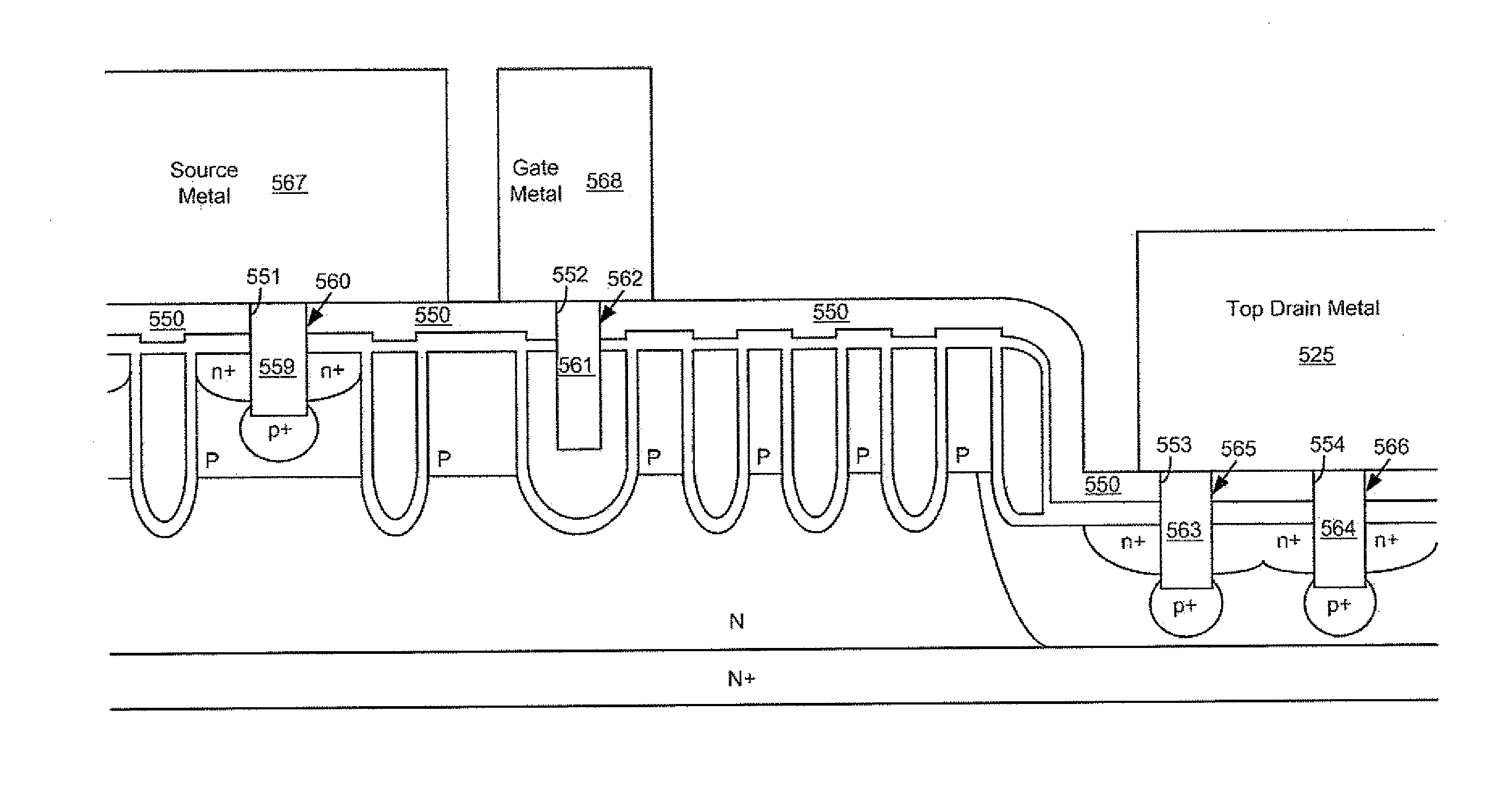

Trench mosfet having a top side drain

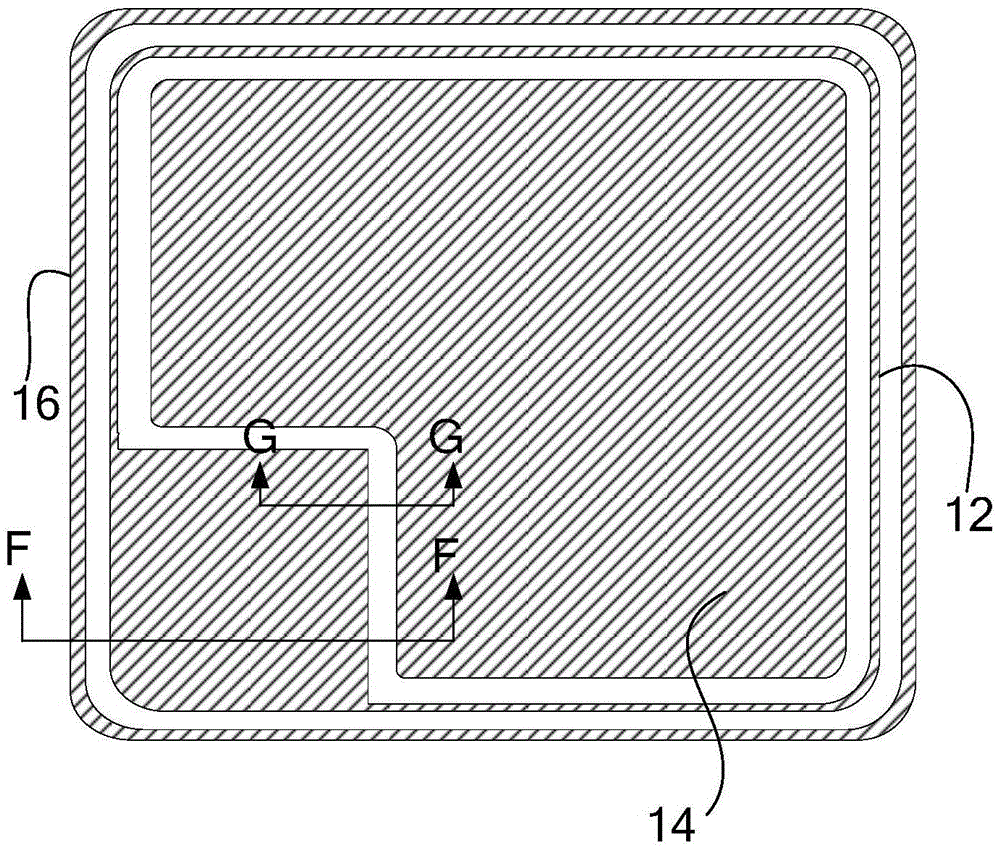

ActiveUS20130207172A1Increase the doping concentrationGreat junction depthTransistorSolid-state devicesTrench mosfetBody contact

This invention discloses a trench MOSFET comprising a top side drain region in a wide trench in a termination area besides a BV sustaining area, wherein said top side drain comprises a top drain metal connected to an epitaxial layer and a substrate through a plurality of trenched drain contacts, wherein the wide trench is formed simultaneously when a plurality of gate trenches are formed in an active area, and the trenched drain contacts are formed simultaneously when a trenched source-body contact is formed in the active area.

Owner:FORCE MOS TECH CO LTD

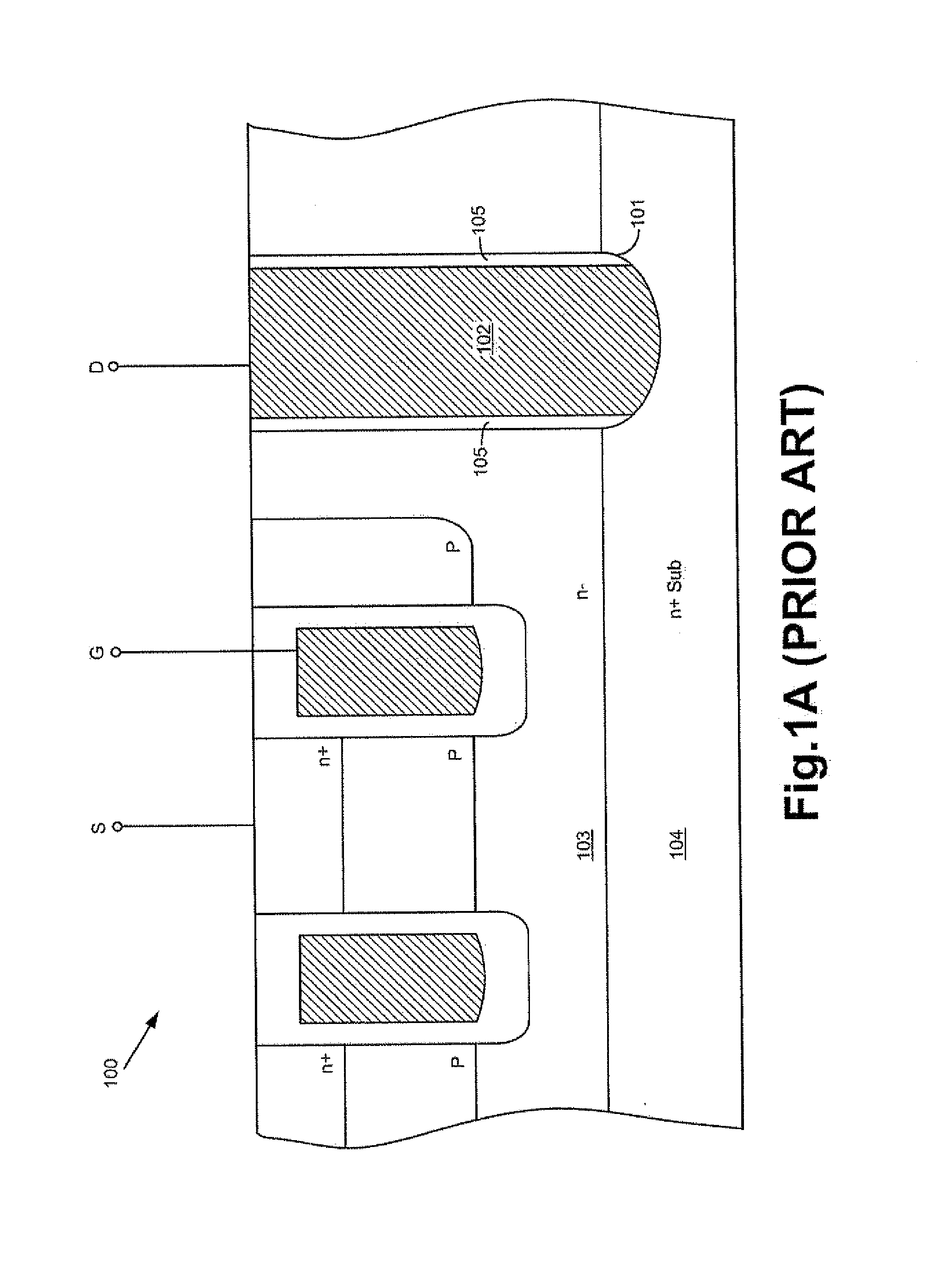

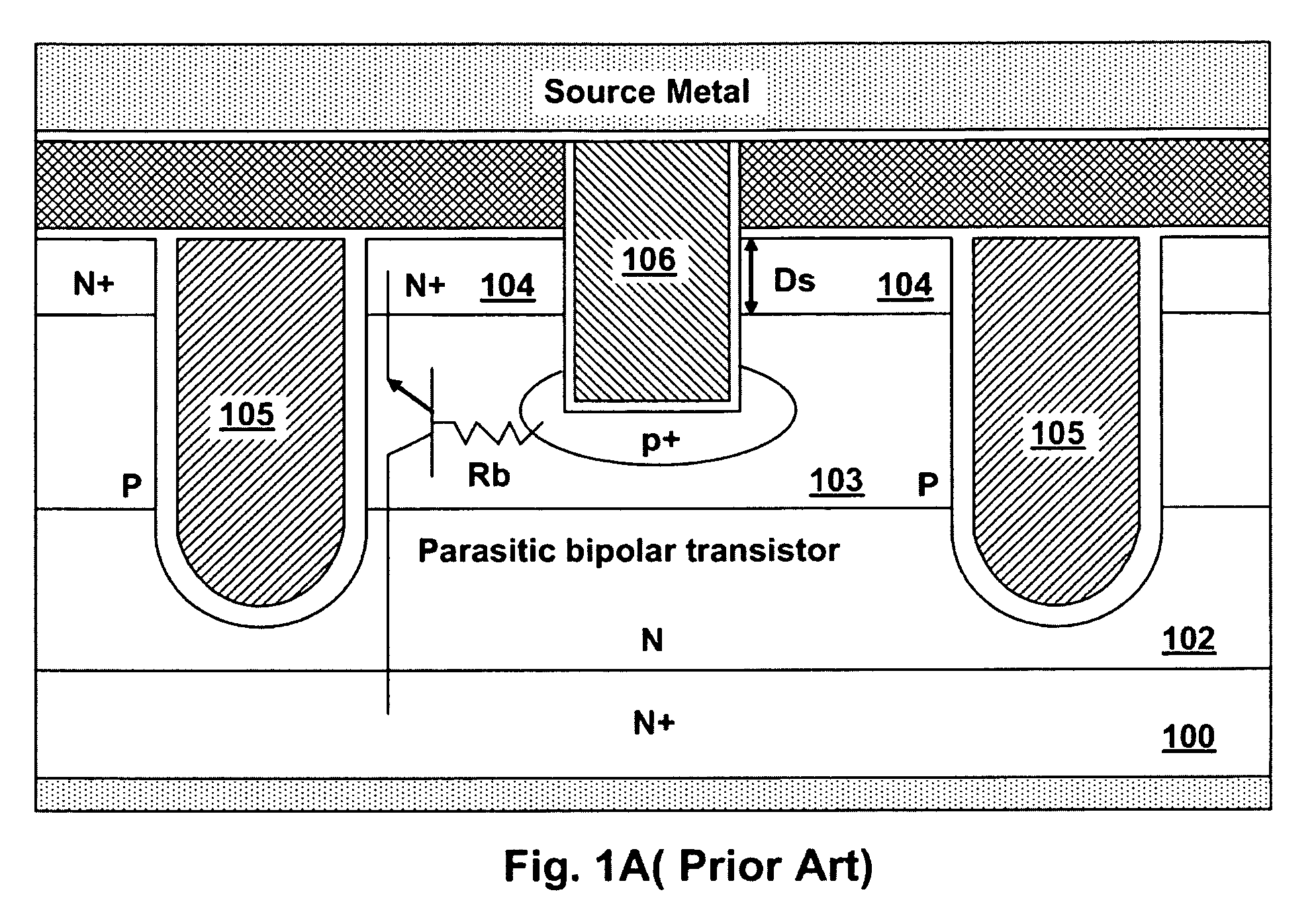

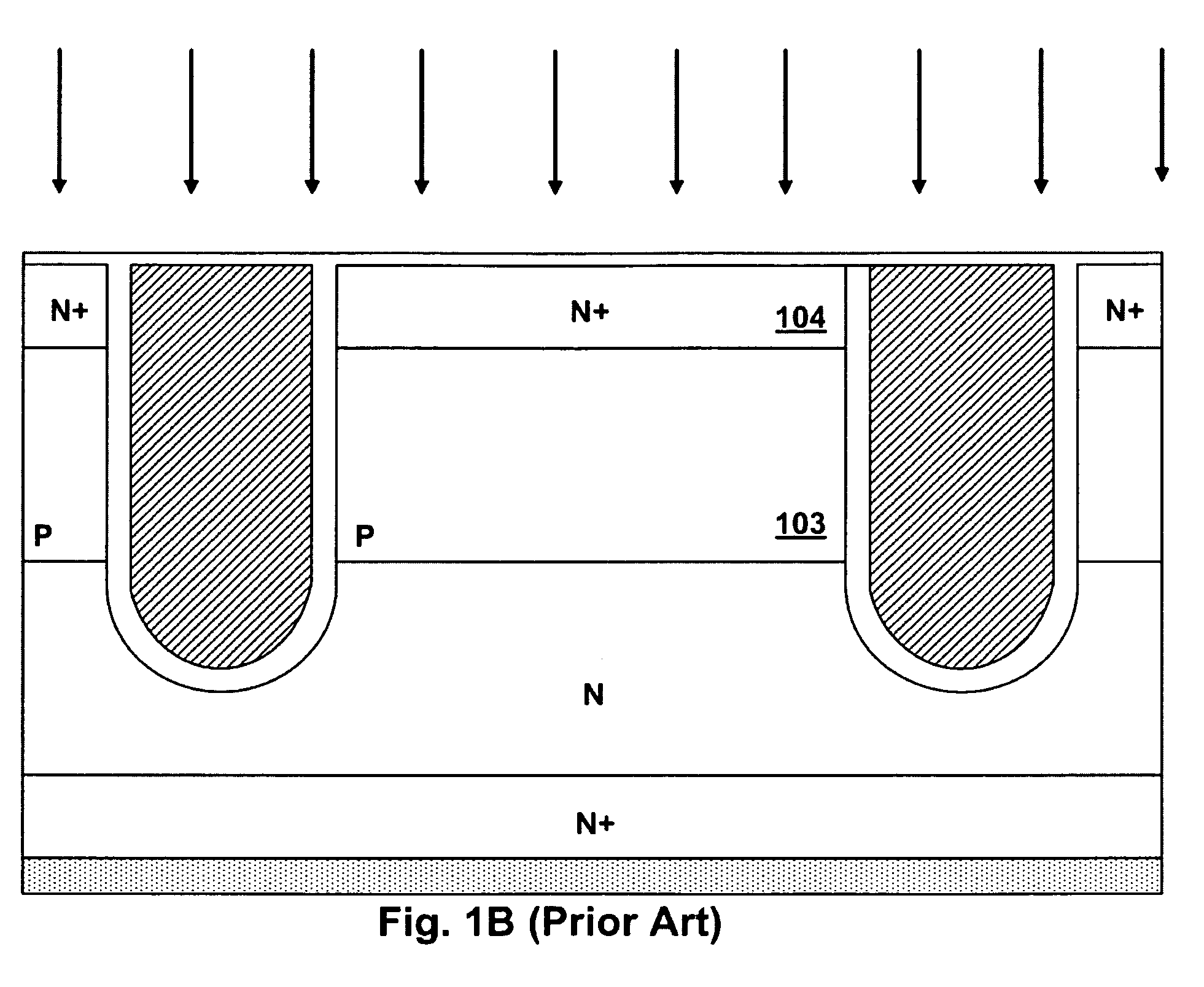

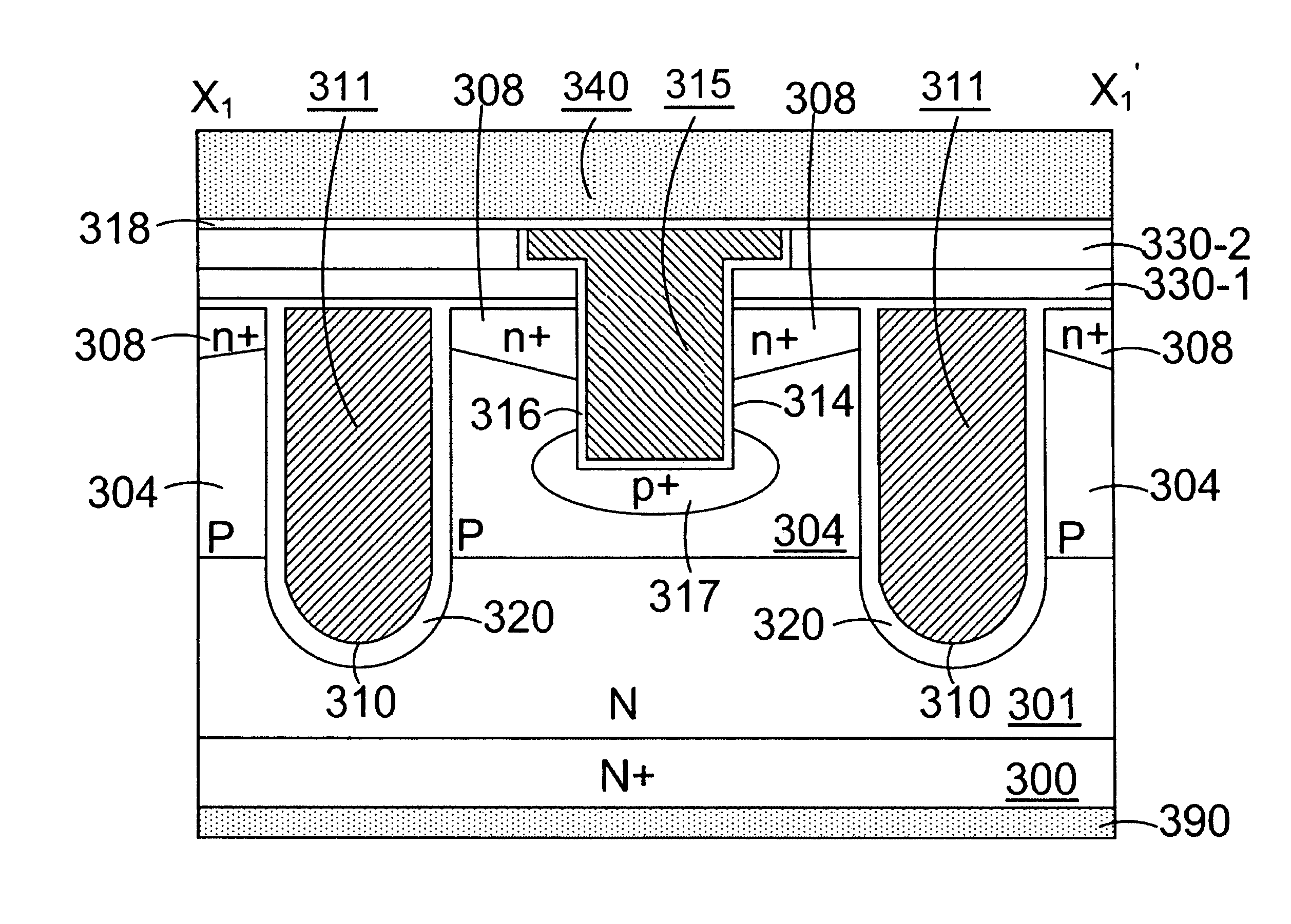

Trench MOSFET structure having improved avalanche capability using three masks process

ActiveUS7816720B1Improve contact effectReduce manufacturing costTransistorSolid-state devicesTrench mosfetBody contact

A trench MOSFET structure having improved avalanche capability is disclosed, wherein the source region is formed by performing source Ion Implantation through contact open region of a thick contact interlayer, and further diffused to optimize a trade-off between Rds and the avalanche capability. Thus, only three masks are needed in fabrication process, which are trench mask, contact mask and metal mask. Furthermore, said source region has a doping concentration along channel region lower than along contact trench region, and source junction depth along channel region shallower than along contact trench, and source doping profile along surface of epitaxial layer has Gaussian-distribution from trenched source-body contact to channel region.

Owner:FORCE MOS TECH CO LTD

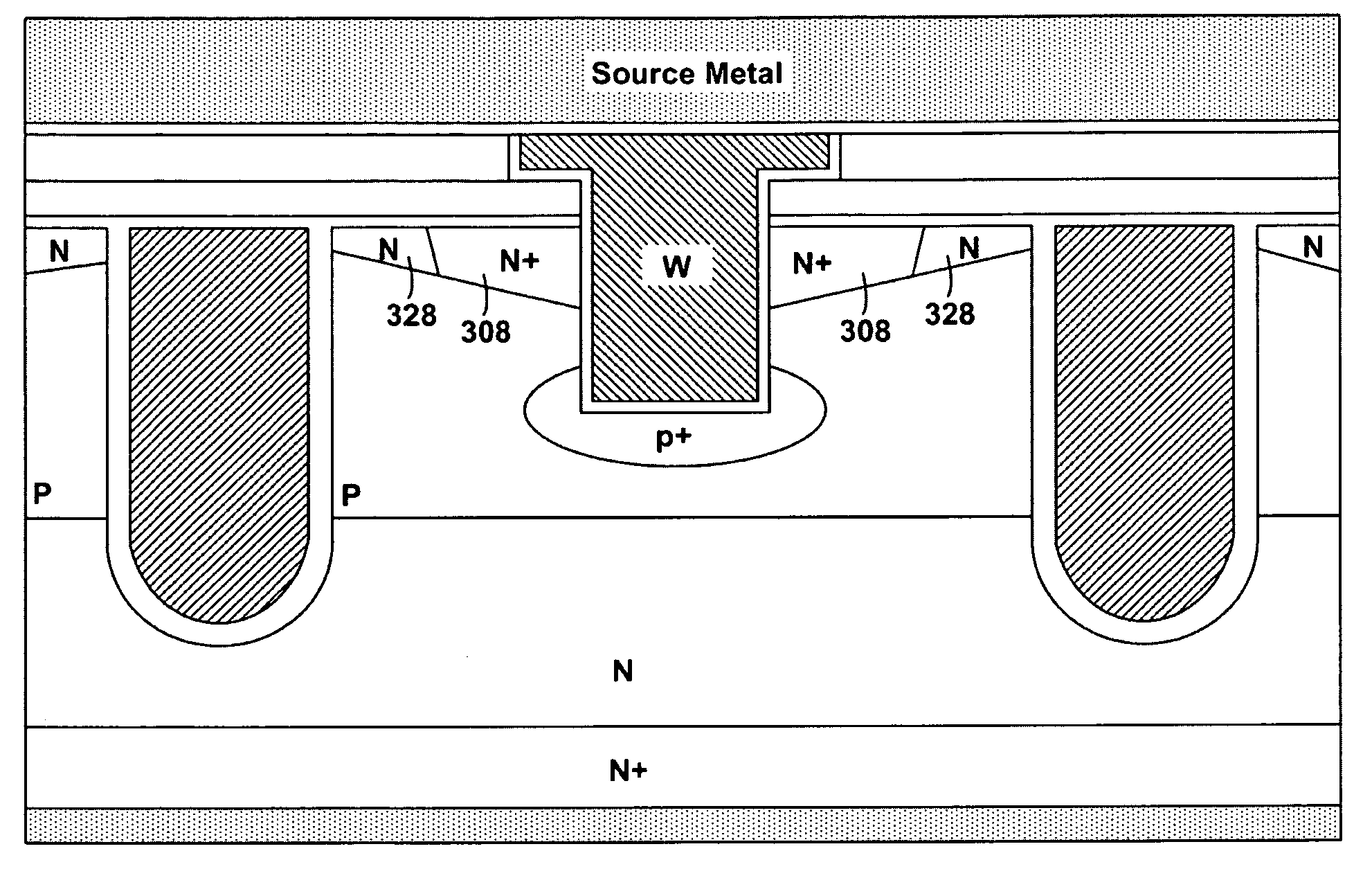

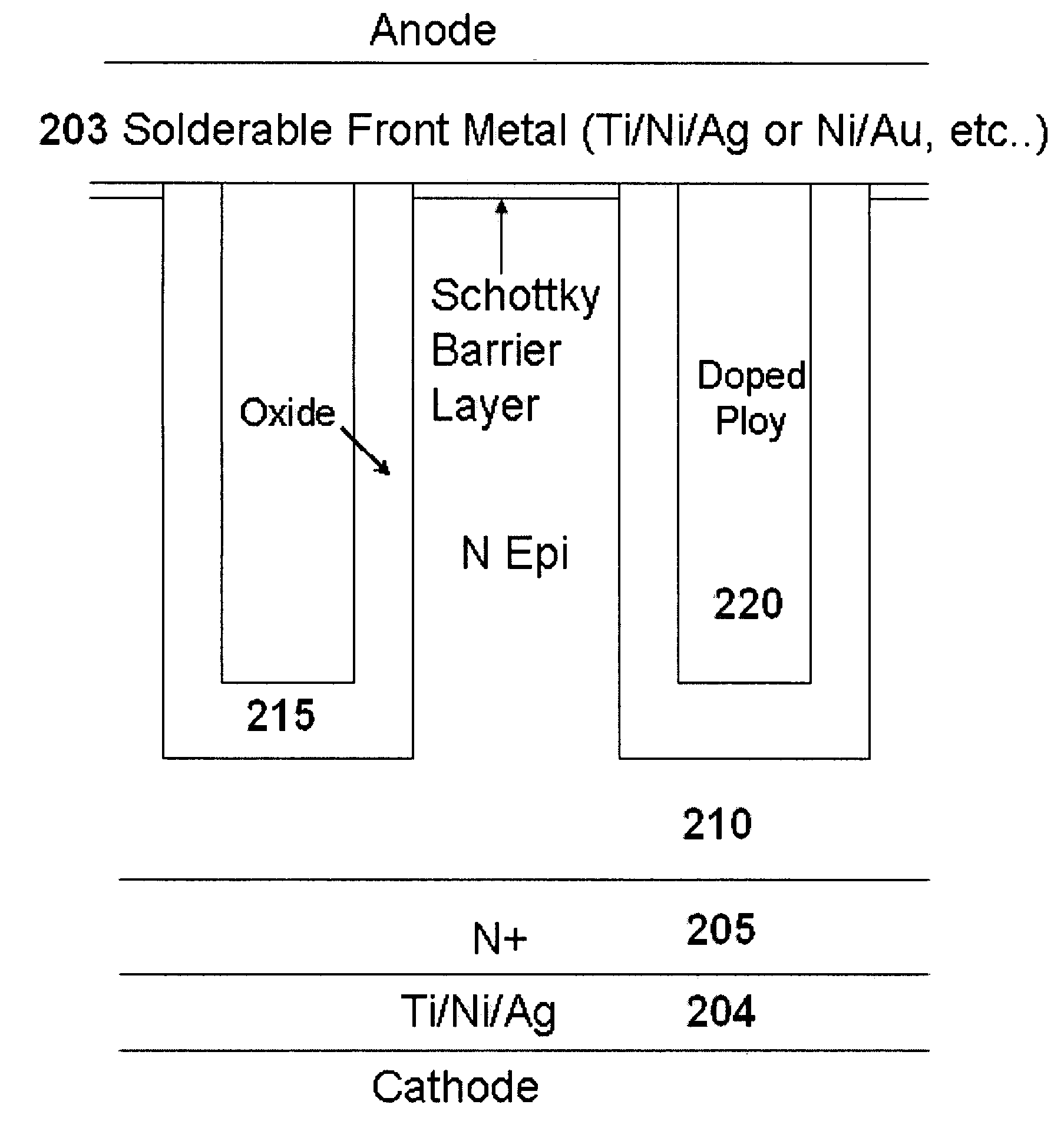

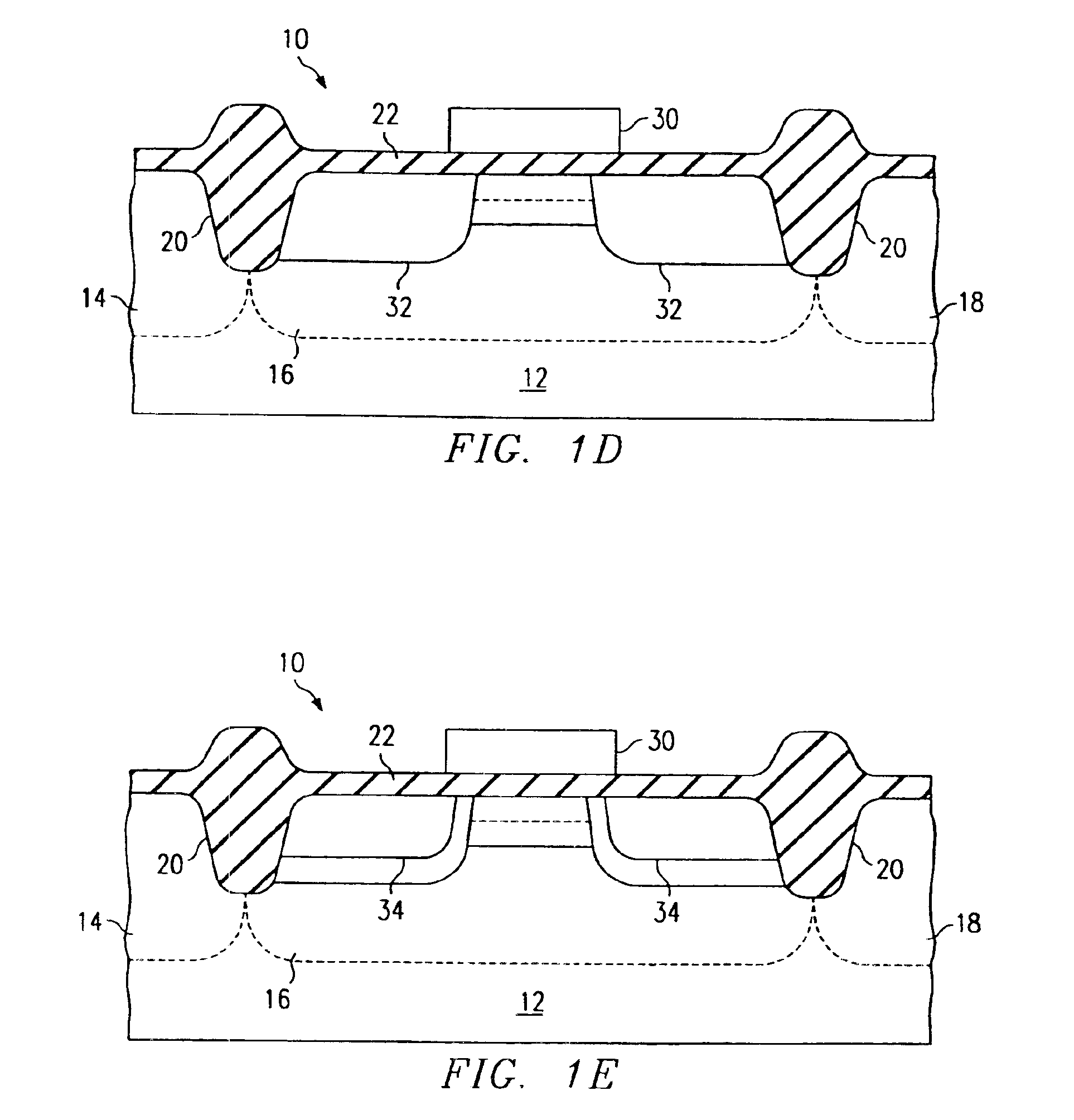

Trench schottky with multiple epi structure

InactiveUS20090309181A1Reduce doping concentrationIncrease the doping concentrationSemiconductor devicesDopantSchottky barrier

A trench Schottky barrier rectifier includes an cathode electrode at a face of a semiconductor substrate and an multiple epitaxial structure in drift region which in combination provide high blocking voltage capability with low reverse-biased leakage current and low forward voltage. The multiple structure of the drift region contains a concentration of first conductivity dopants therein which comprises two or three different uniform value from a Schottky rectifying junction formed between the anode electrode and the drift region. The thickness of the insulating region (e.g., SiO2) in the MOS-filled trenches is greater than 1000 Å to simultaneously inhibit field crowing and increase the breakdown voltage of the device. The multiple epi structure is preferably formed by epitaxial growth from the cathode region and doped in-situ.

Owner:FORCE MOS TECH CO LTD

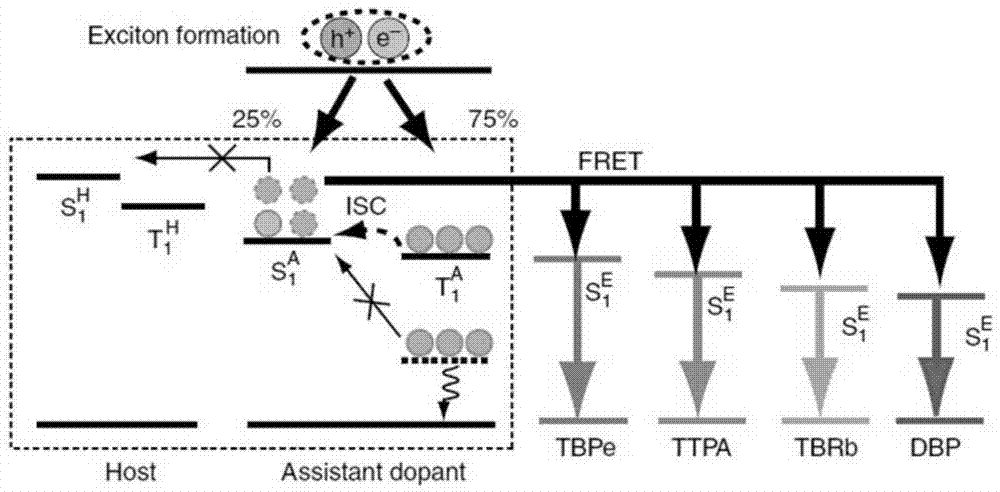

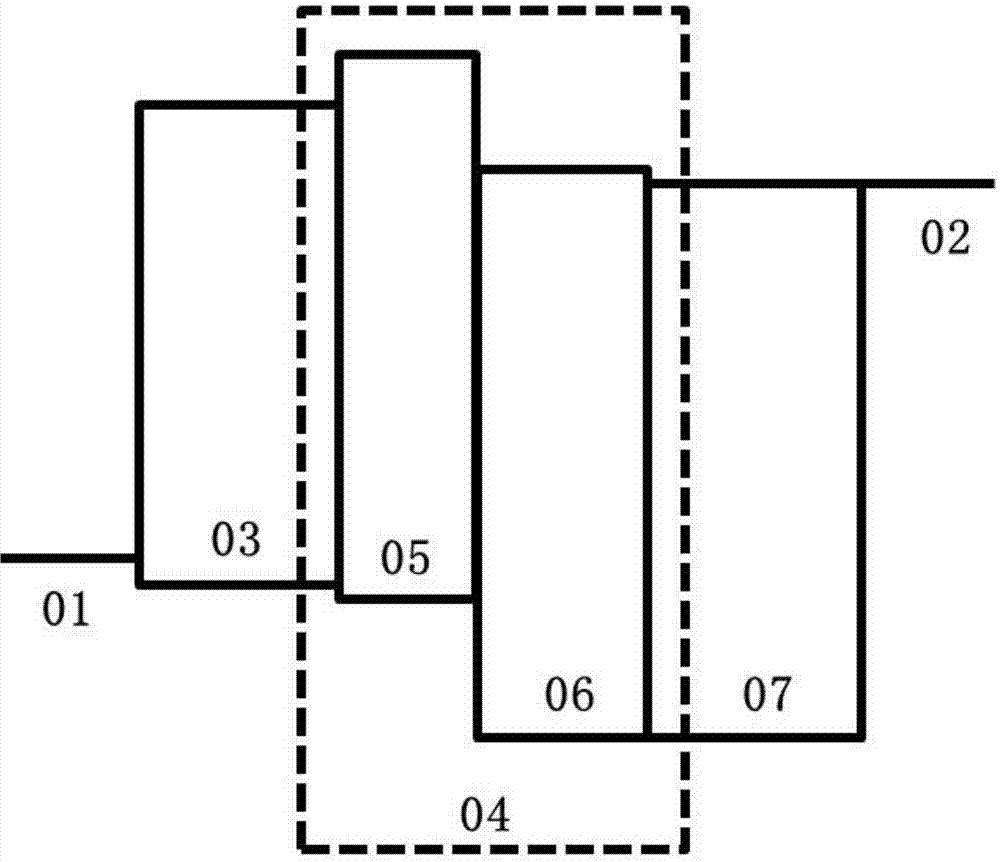

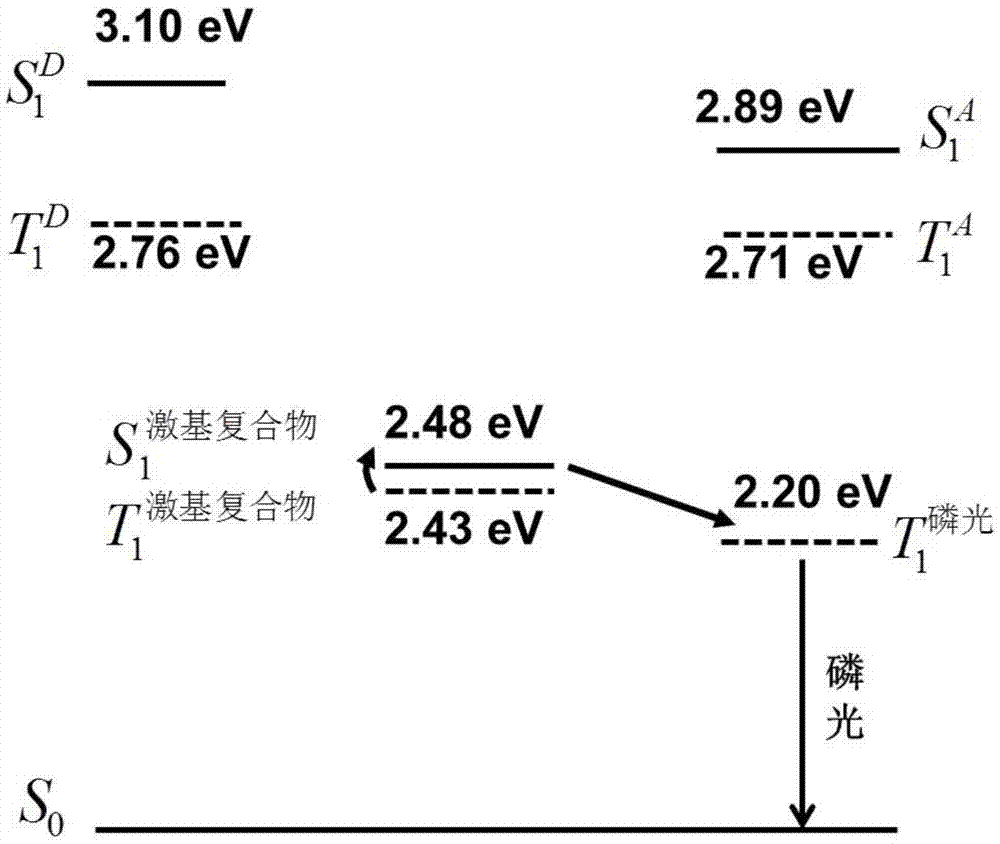

Organic light-emitting device

ActiveCN106920884AIncreased maximum theoretical external quantum efficiencyEasy transferSolid-state devicesSemiconductor/solid-state device manufacturingFluorescenceOrganic light emitting device

The invention relates to an organic light-emitting device. The main body materials of a light-emitting layer comprise materials with hole transfer capability and electron transfer capability; a triplet state T1H of at least one kind of main body material is greater than or equal to a singlet state S1F of a fluorescent dye; a triplet state energy level T1H of a CT excited state of at least one kind material of the main body materials is higher than a singlet state energy level S1H of an n-<pi> excited state, and T1H-S1H is less than or equal to 0.3eV; or the triplet state energy level T1H of the CT excited state of at least one kind of material of the main body materials is higher than a triplet state energy level S1H of the n-<pi> excited state, and T1H-S1H is greater than or equal to 1eV; in addition, the difference value between the second triplet state energy level of the n-<pi> excited state of the main body materials, and the first singlet state energy level of the CT excited state is -0.1eV to 0.1eV; and the triplet states T1 of organic functional layer materials adjacent to the light emitting layer are all higher than the singlet state S1H of the main body materials of the light emitting layer. By adopting a thermal activation delayed florescence material as the main body materials, so that recombination of excitons in the light-emitting region is limited, a phenomenon of efficiency roll-off is effectively suppressed, and the device efficiency can be improved to 13-18%.

Owner:KUNSHAN NEW FLAT PANEL DISPLAY TECH CENT

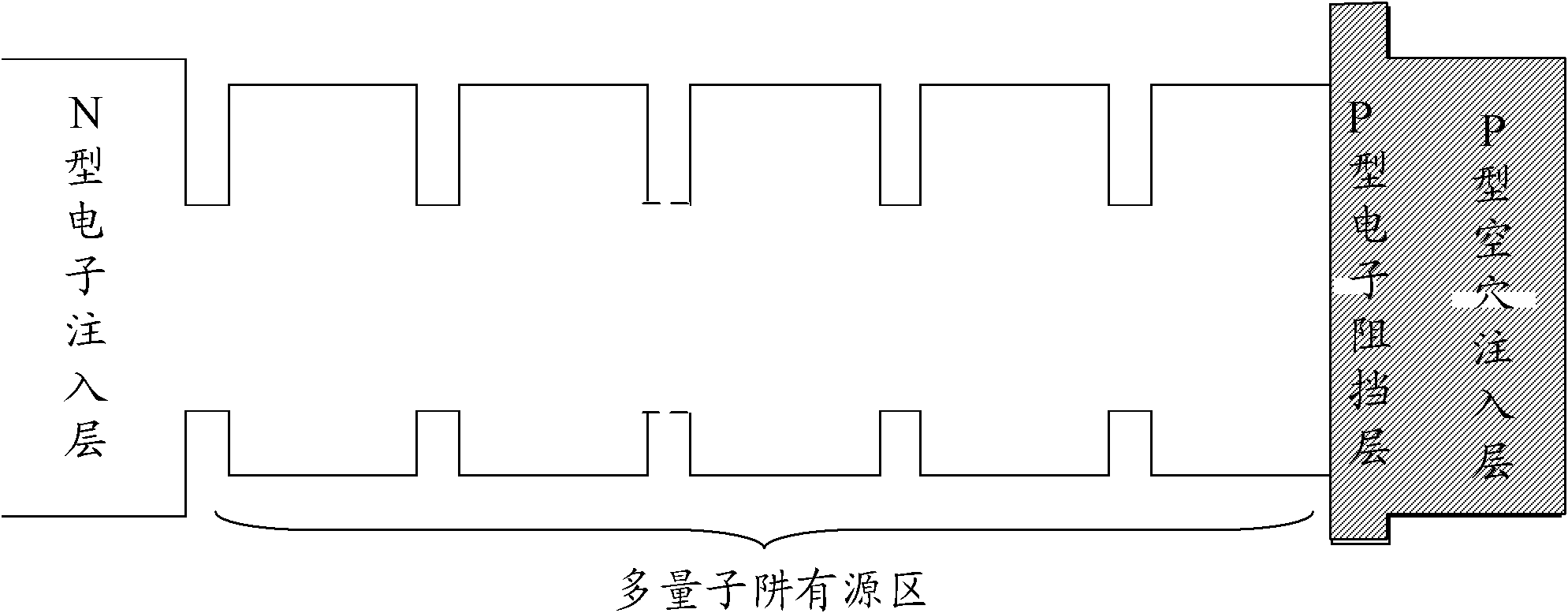

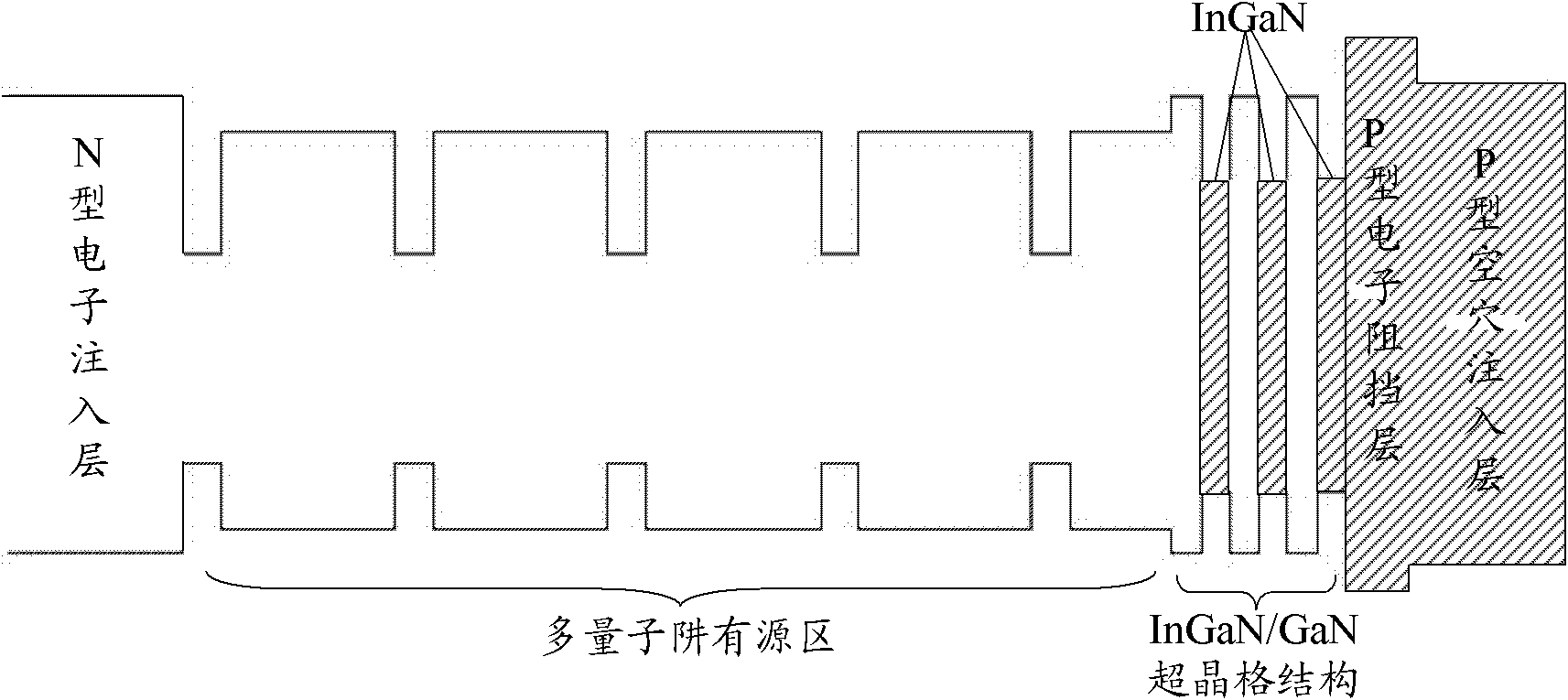

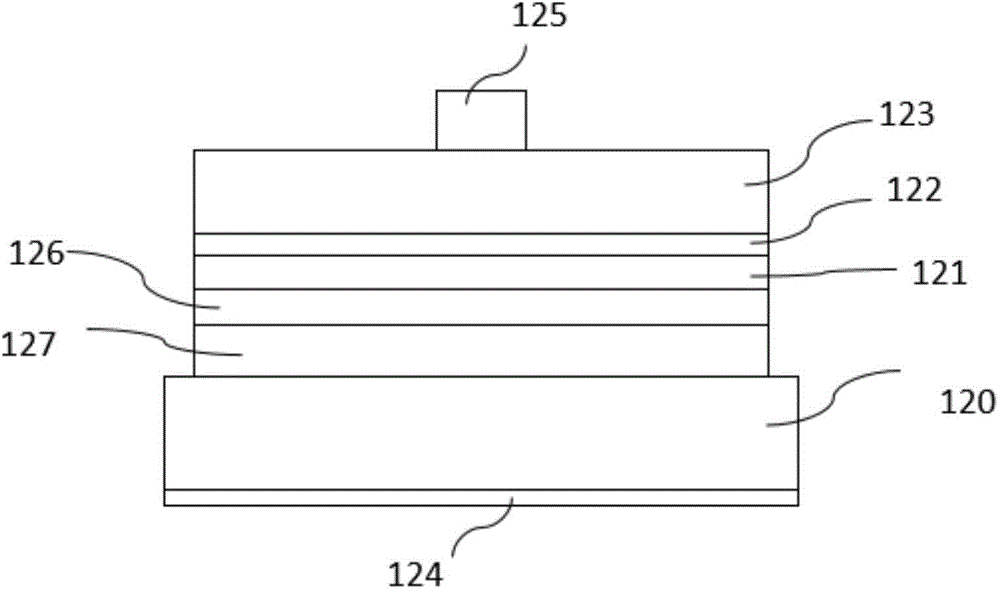

Nitride LED (light-emitting diode) structure and nitride LED structure preparing method

InactiveCN102185057AIncrease hole concentrationImprove internal quantum efficiencySemiconductor devicesPotential wellQuantum efficiency

The invention discloses a nitride LED (light-emitting diode) structure. A P-type doped InGaN / GaN superlattice structure is inserted between a multiple quantum well active layer and an electronic barrier layer so as to improve the hole concentration and reduce the dosage concentration of the P-type hole injection layer; the superlattice structure has polarization effect, thus being capable of improving the doping efficiency and reducing the P-type impurity concentration; and impurity atoms are prevented from being diffused to the potential well, and the inner quantum efficiency and the luminous efficiency of the device can be improved. The invention also discloses a preparation method of the nitride LED structure, through inserting the P-type doped InGaN / GaN superlattice structure between the multiple quantum well active layer and the electronic barrier layer, the hole concentration can be improved, and the dosage concentration of the P-type hole injection layer can be reduced; since the superlattice structure has polarization effect, the doping efficiency can be improved and the P-type impurity concentration can be reduced; and the impurity atoms are prevented from being diffused to the potential well, and the inner quantum efficiency and the luminous efficiency of the device can be improved.

Owner:ENRAYTEK OPTOELECTRONICS

Method for manufacturing insulated gate bipolar transistor (IGBT) device

ActiveCN102420133AEliminate temperature limitationsHigh activation rateSemiconductor/solid-state device manufacturingOhmic contactAlternating current

The invention discloses a method for manufacturing an insulated gate bipolar transistor (IGBT) device. The method sequentially comprises an ion injection step of forming a p type heavily doped collecting region on the back side of a silicon wafer, a partial or whole annealing step and a step of depositing surface metal on the front side of the silicon wafer; and after the p type heavily doped collecting region is formed on the back side of the silicon wafer, a layer of silicon dioxide is deposited on the back side of the p type heavily doped collecting region. The method has the advantages that the temperature limitation of the p type ion annealing on the back side of the silicon wafer is eliminated, and high activity rate is easy to obtain. Simultaneously, the p type impurity distribution in the p type heavily doped collecting region can be optimized. On one hand, the ohmic contact with back metal is easy to form, on the other hand, the emission efficiency of a precision navigation processor (PNP) is favorably controlled, and the alternating current characteristic of the IGBT device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

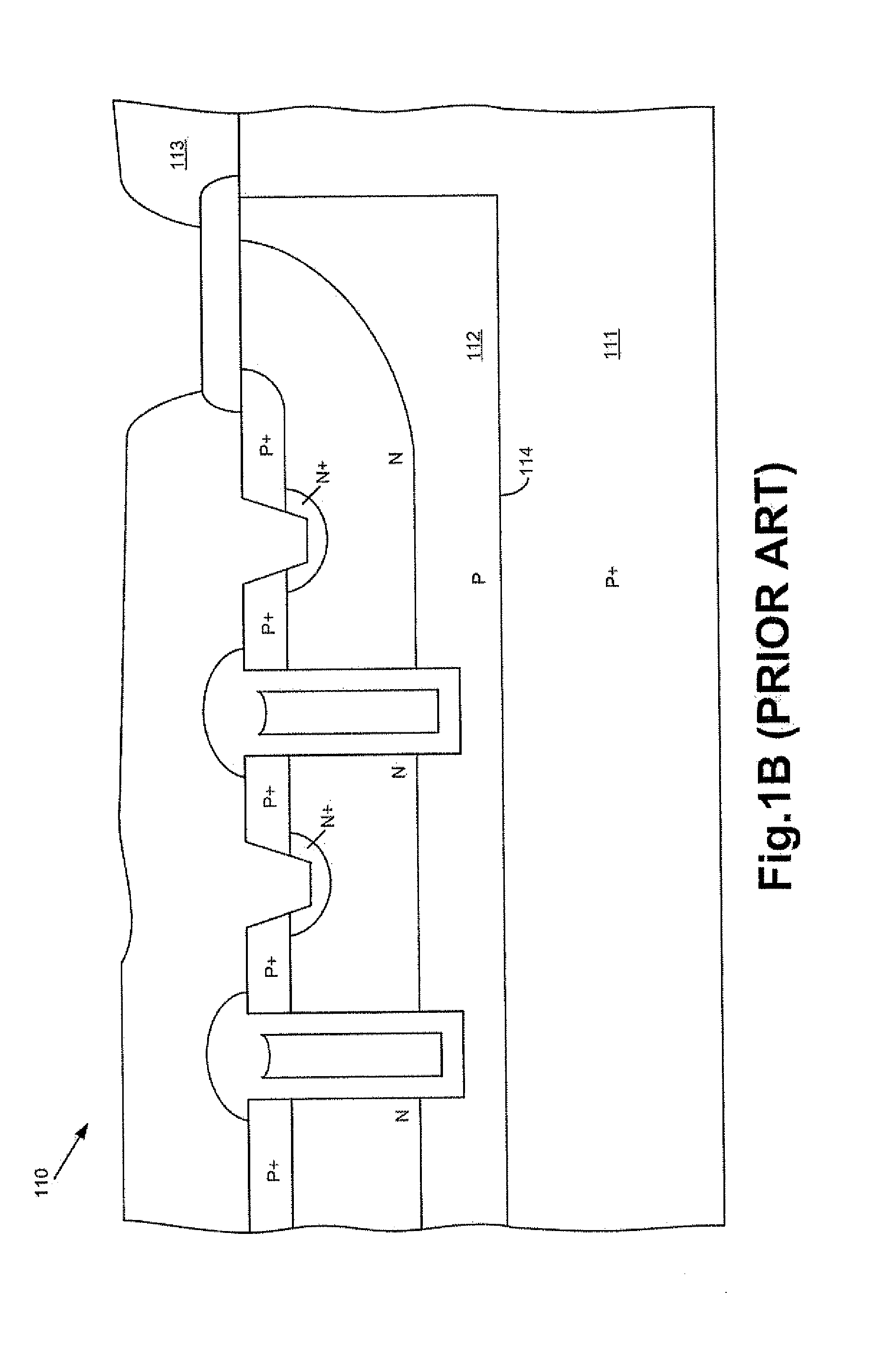

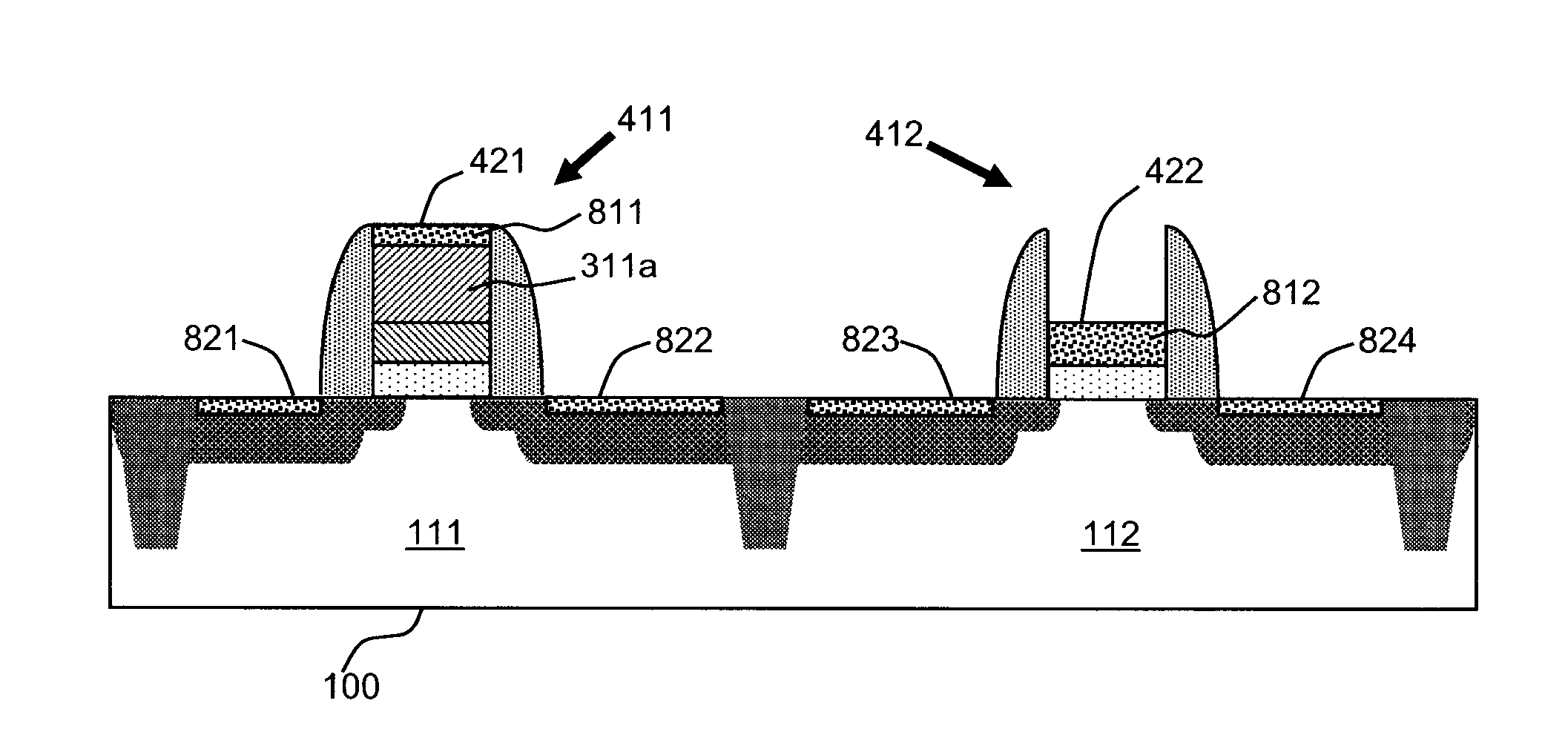

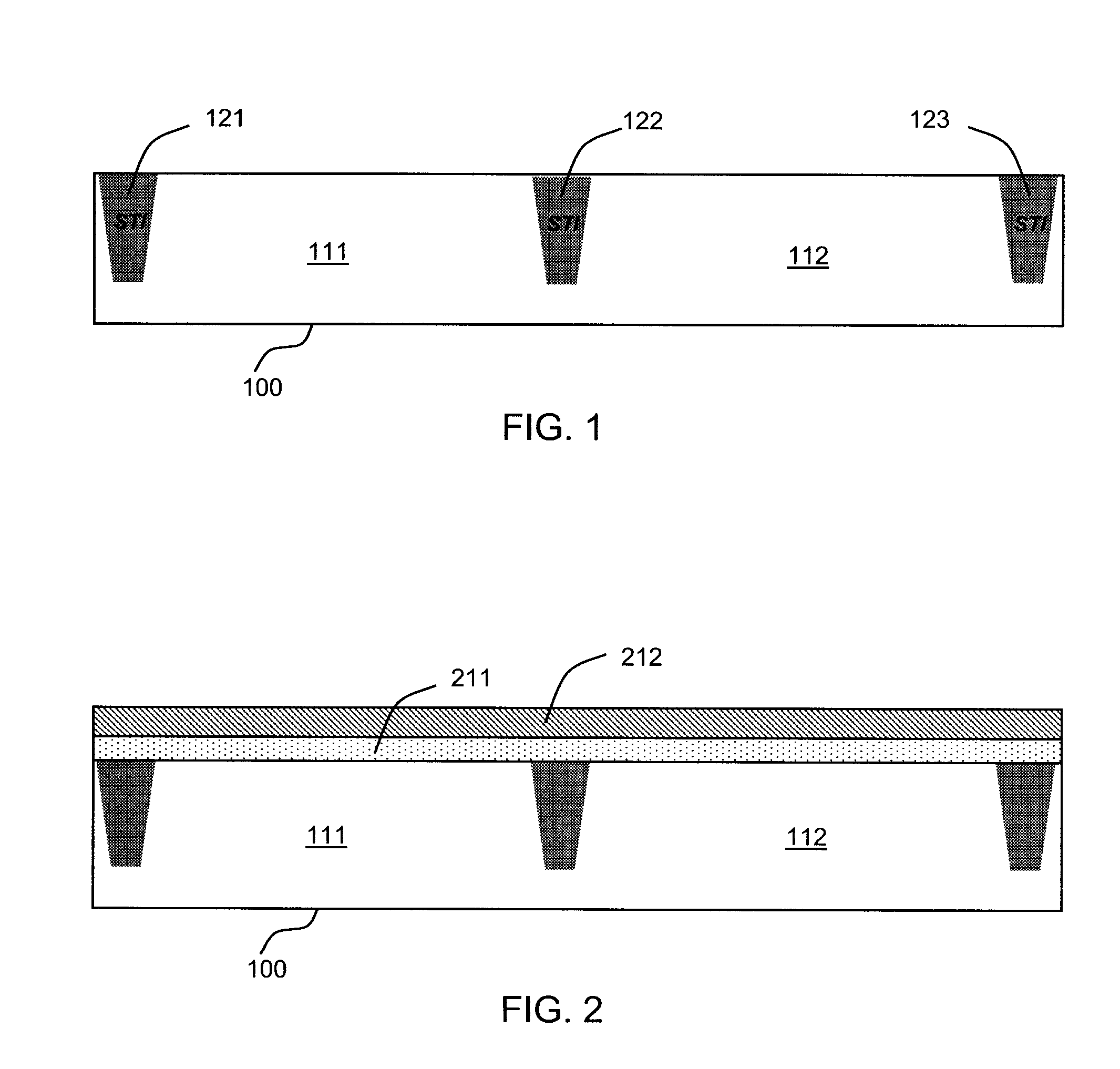

Trench MOSFET structures using three masks process

ActiveUS20110006363A1Reduced footprintSmall sizeTransistorSolid-state devicesTrench mosfetInter layer

A trench MOSFET structure having improved avalanche capability is disclosed, wherein the source region is formed by performing source Ion Implantation through contact open region of a contact interlayer, and further diffused to optimize a trade-off between Rds and the avalanche capability. Thus, only three masks are needed in fabrication process, which are trench mask, contact mask and metal mask. Furthermore, said source region has a doping concentration along channel region lower than along contact trench region, and source junction depth along channel region shallower than along contact trench, and source doping profile along surface of epitaxial layer has Guassian-distribution from trenched source-body contact to channel region.

Owner:FORCE MOS TECH CO LTD

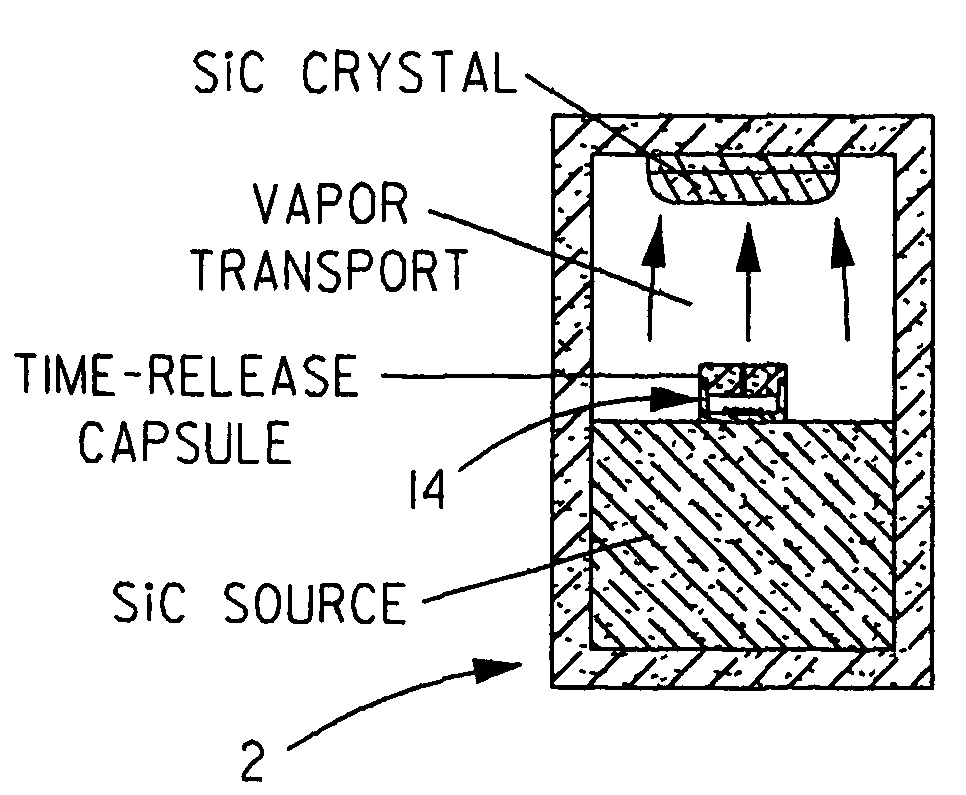

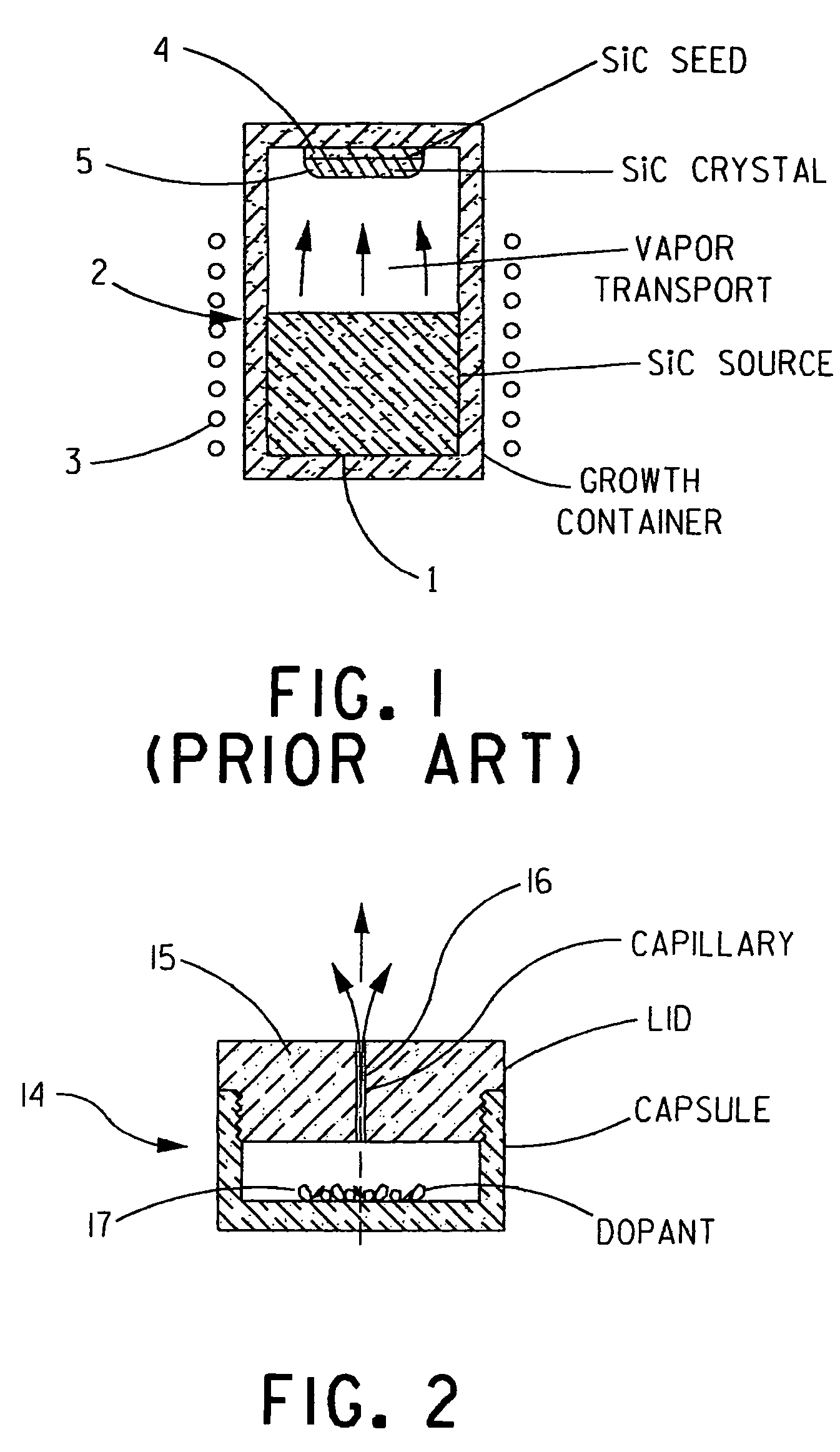

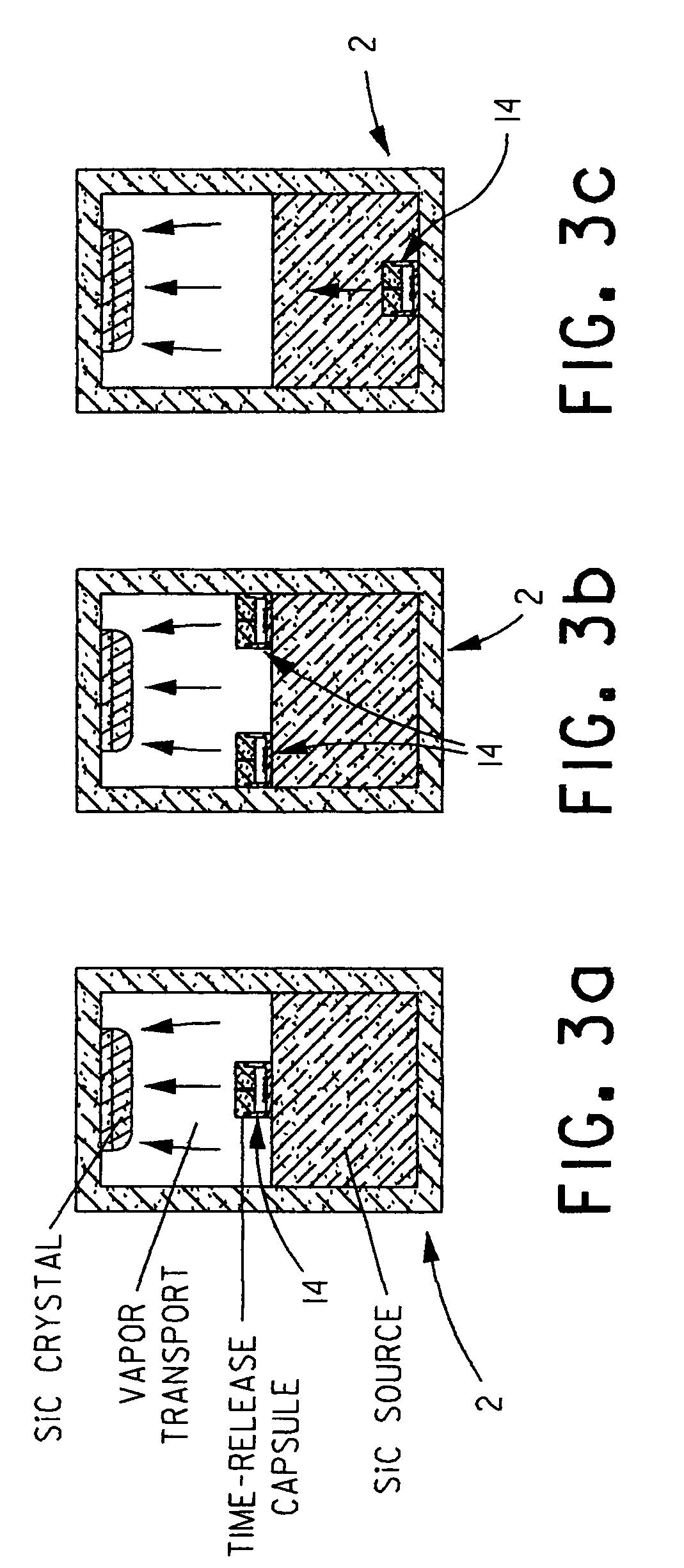

Method of and system for forming SiC crystals having spatially uniform doping impurities

ActiveUS7608524B2Increase the doping concentrationReduce doping concentrationPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantGas phase

In a physical vapor transport method and system, a growth chamber charged with source material and a seed crystal in spaced relation is provided. At least one capsule having at least one capillary extending between an interior thereof and an exterior thereof, wherein the interior of the capsule is charged with a dopant, is also provided. Each capsule is installed in the growth chamber. Through a growth reaction carried out in the growth chamber following installation of each capsule therein, a crystal is formed on the seed crystal using the source material, wherein the formed crystal is doped with the dopant.

Owner:II VI DELAWARE INC

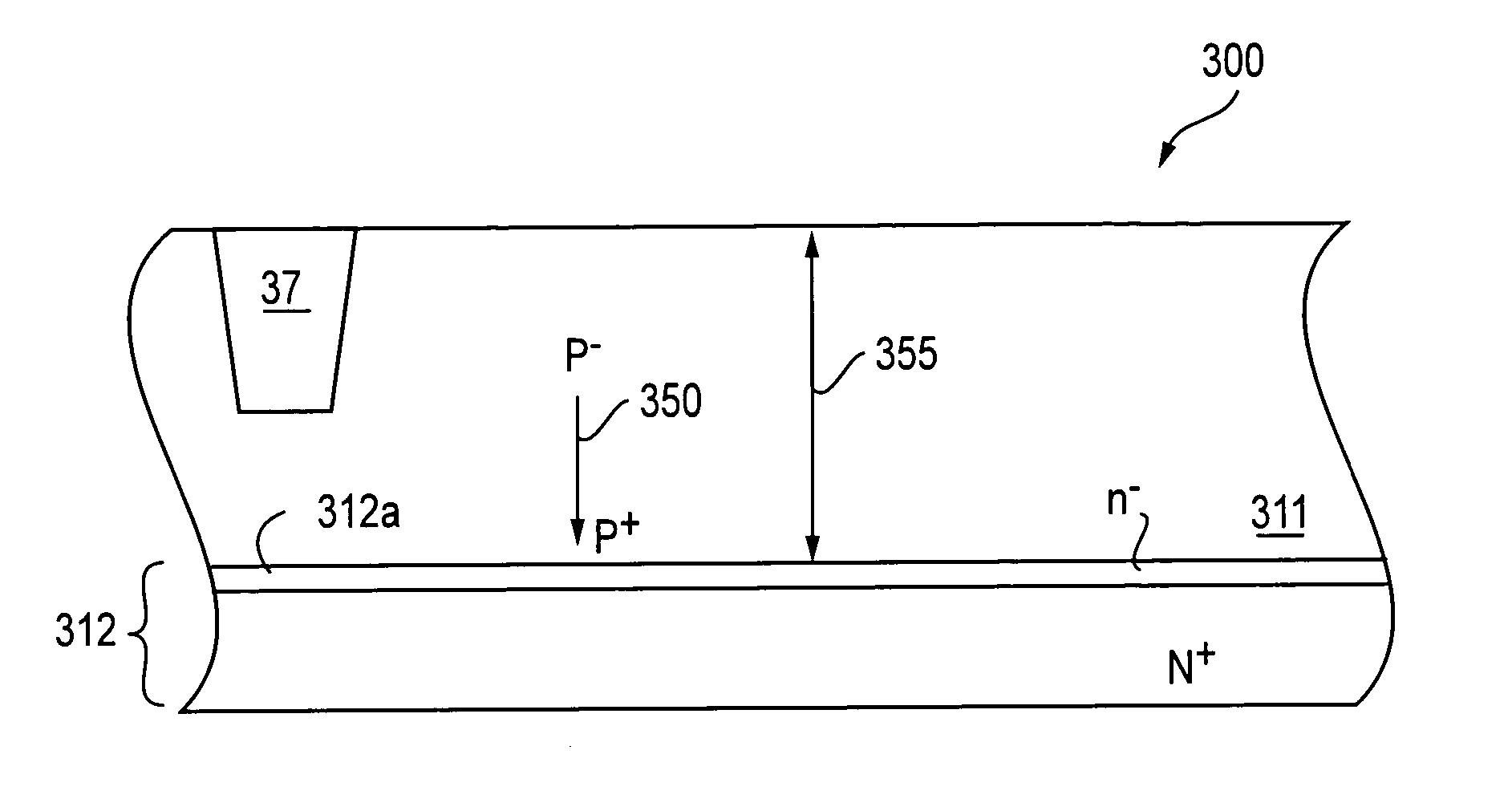

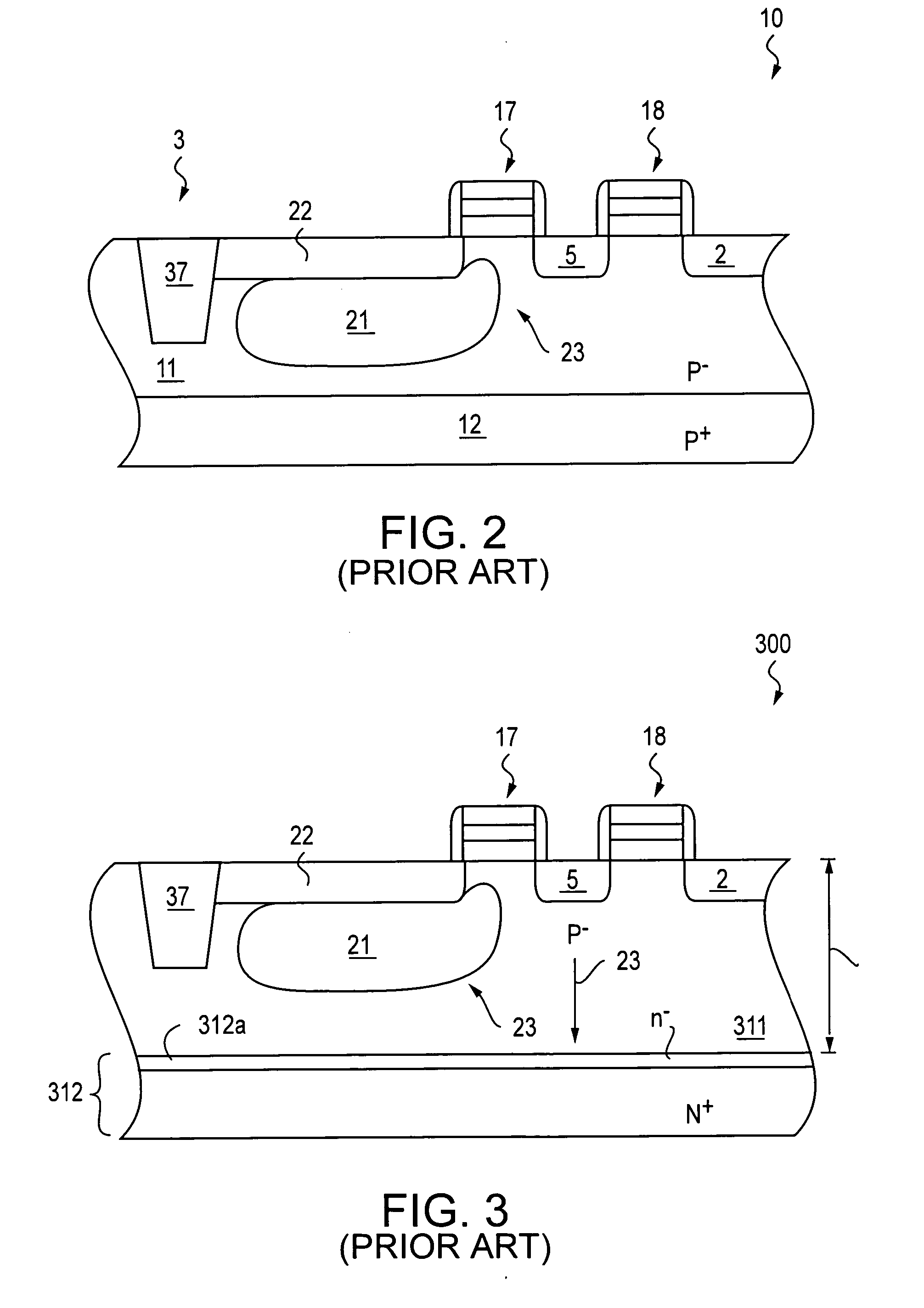

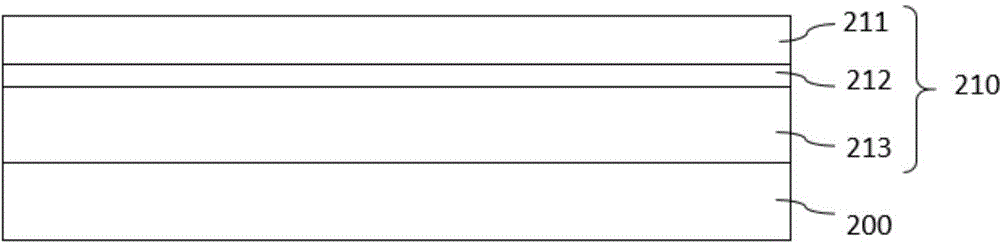

Imager with gradient doped EPI layer

InactiveUS20070045682A1Reduce doping concentrationSolid-state devicesSemiconductor devicesDopantPhoto conversion

A pixel cell including a substrate of a first conductivity type over an epitaxial layer of a second conductivity type. The epitaxial layer has a dopant gradient, wherein the dopant concentration decreases from a surface of the epitaxial layer adjacent the substrate to the surface of the epitaxial layer opposite the substrate. A photo-conversion device is at a surface of the epitaxial layer.

Owner:APTINA IMAGING CORP

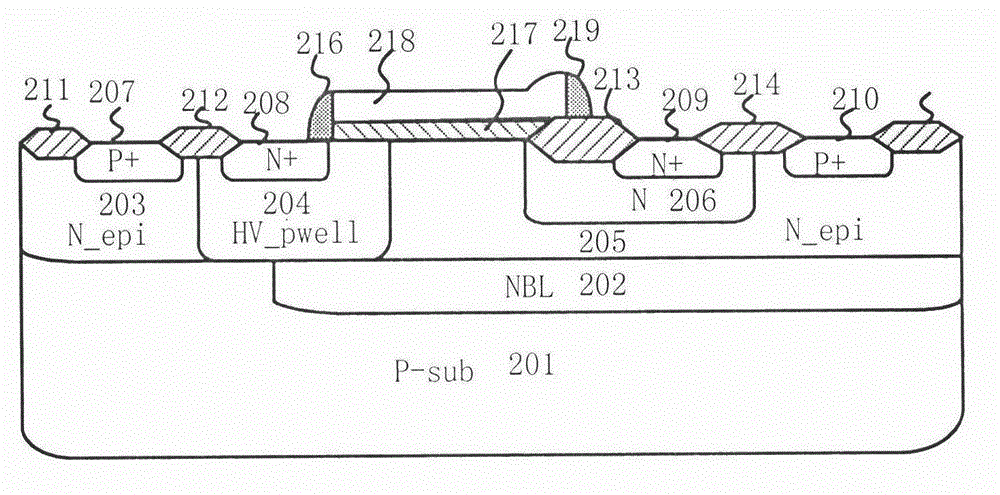

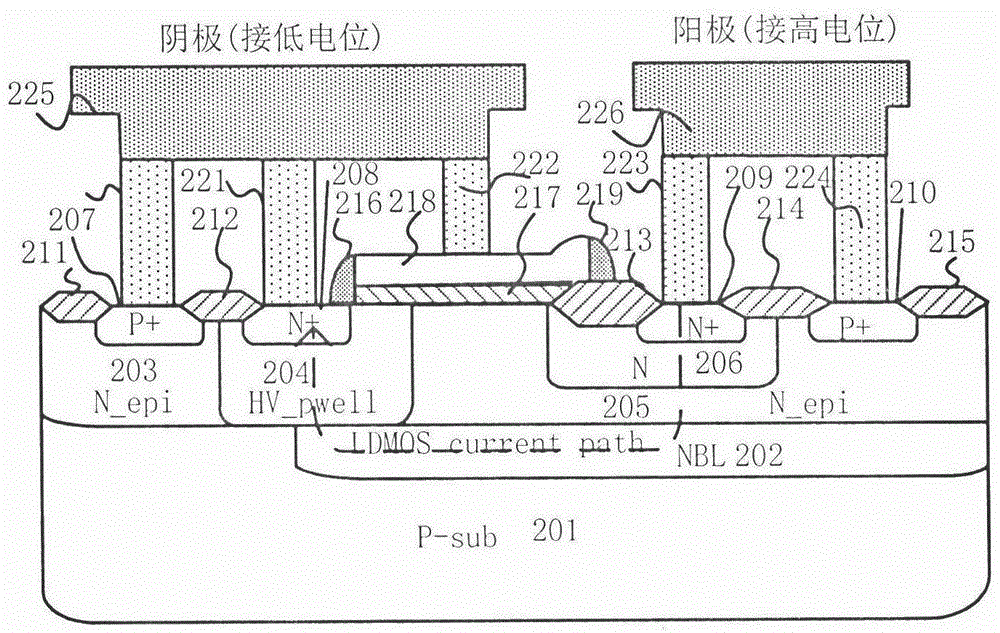

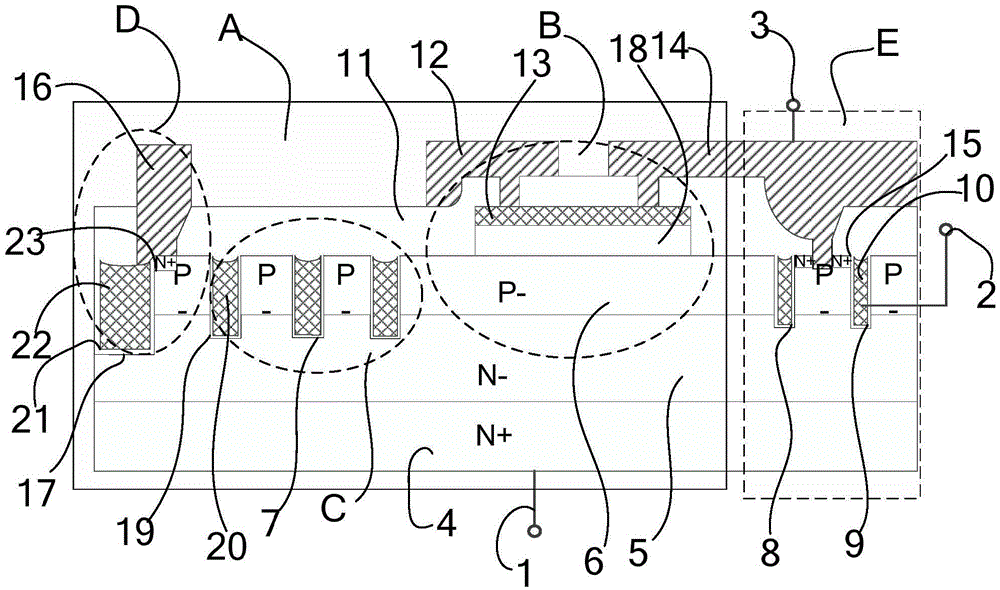

Bidirectional tri-path turn-on high-voltage ESD protective device

ActiveCN102983133ACorrection for weak robustnessCorrection speedSolid-state devicesSemiconductor devicesHigh pressurePolysilicon gate

The invention provides a bidirectional tri-path turn-on high-voltage ESD (Electro-Static Discharge) protective device which can be used in an on-chip IC (Integrated Circuit) high-voltage ESD protective circuit. The bidirectional tri-path turn-on high-voltage ESD protective device comprises a P minus substrate, an N plus buried layer, a left N-type epitaxy, a right N-type epitaxy, a drifting area, a high-voltage P trap, a drain region, a source region, a polysilicon gate, a positive pole contact area and a negative pole contact area, wherein the drifting area, the high-voltage P trap, the drain region, the source region and the polysilicon gate form an NLDMOS (laterally diffused metal oxide semiconductor) structure, and the positive pole contact area, the N plus buried layer, the high-voltage P trap and the source region form a positive SCR (semiconductor control rectifier)structure, so that two high-voltage ESD current discharge paths are formed to improve secondary striking current of the device and reduce the turn-on resistance and trigger voltage; and the negative pole contact area, the left N-type epitaxy, the high-voltage P trap, the N plus buried layer and the drain region form a reverse SCR structure to form a reverse high-voltage ESD current discharge path. The current paths of the two SCR structures are longer, so that the maintaining voltage of the device can be improved, bidirectional discharge of ESD current can be realized, and the device has bidirectional ESD protection function.

Owner:铜陵汇泽科技信息咨询有限公司

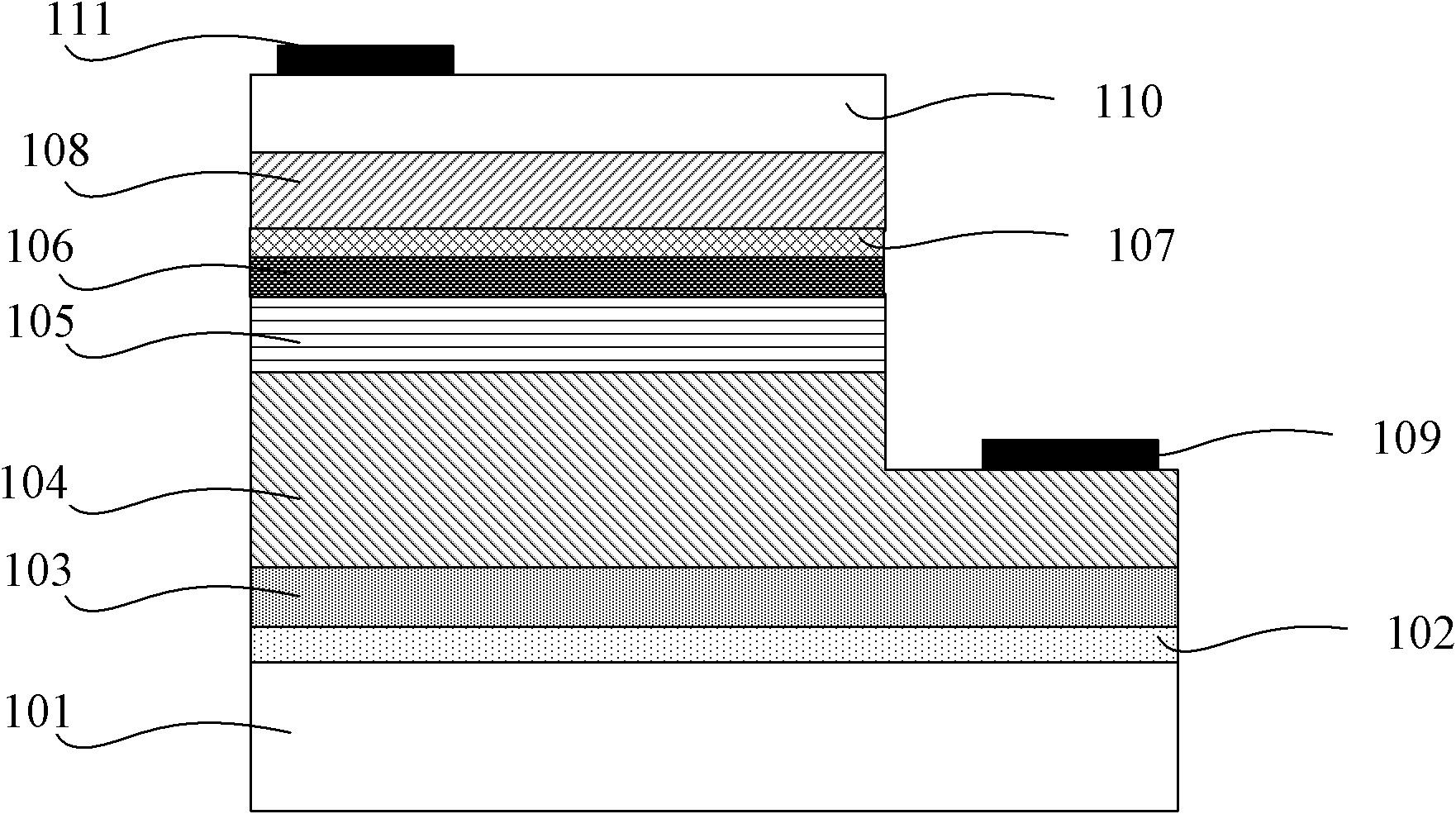

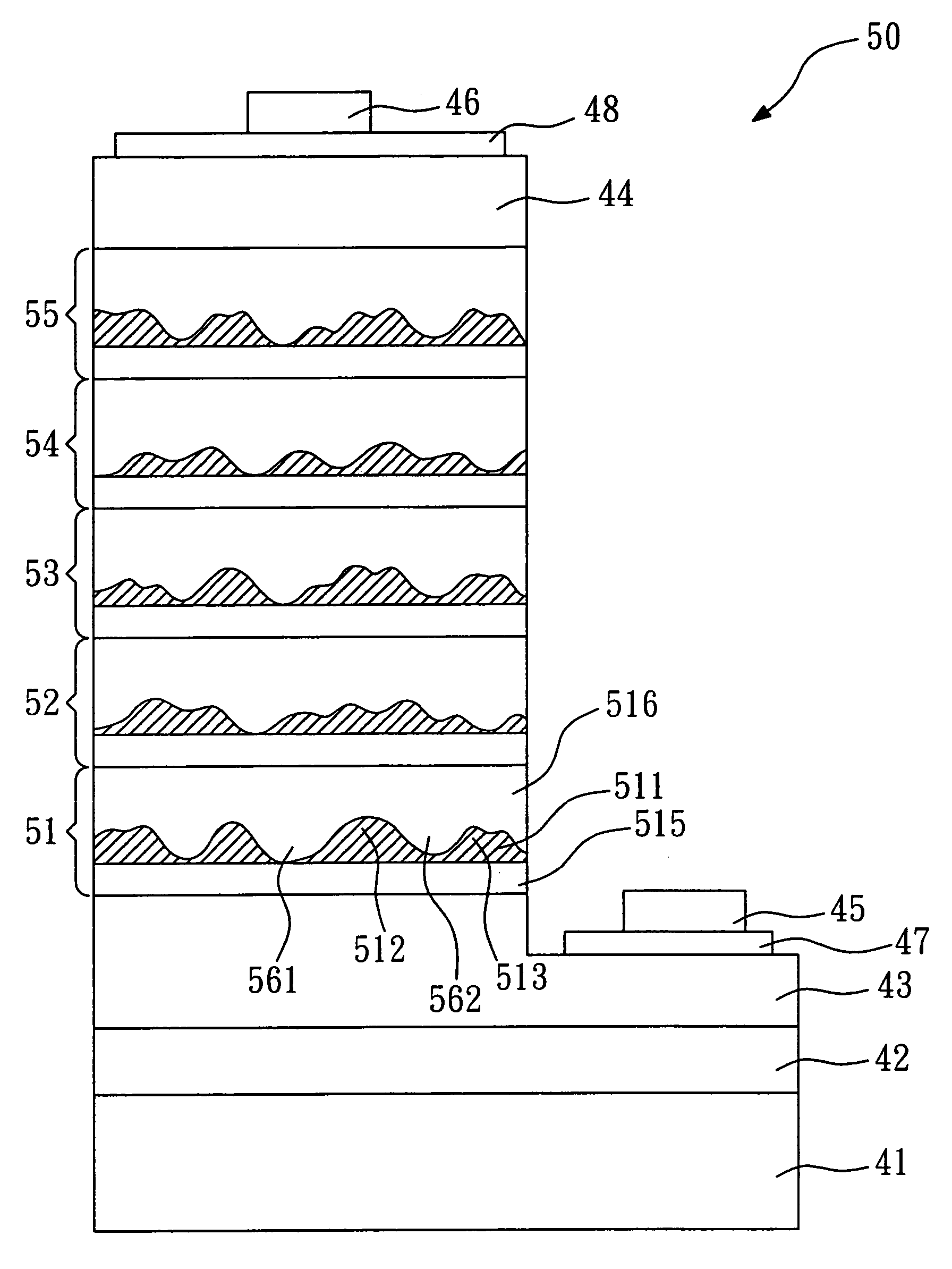

Semiconductor LED chip and manufacturing method thereof

ActiveCN104576872AReduce thicknessReduce doping concentrationSemiconductor devicesSemiconductor chipEngineering

The invention relates to a semiconductor LED (Light-Emitting Diode) chip and a manufacturing method thereof. The semiconductor LED chip comprises a transparent conductive layer, an n-type semiconductor layer, an active layer, a p-type semiconductor layer, a p-type contact layer, a dielectric insulating layer, an n-type contact layer, a bonding metal layer and a substrate, wherein the n-type contact layer reaches the interior of the n-type semiconductor layer or penetrates through the whole n-type semiconductor layer by virtue of through holes penetrating through each layer at the upper part of the n-type contact layer. The manufacturing method for the semiconductor LED chip comprises the following steps of manufacturing an epitaxial wafer, bonding the epitaxial wafer to another conductive or insulating substrate, removing a growing substrate, and manufacturing the transparent conductive layer on the surface of the n-type semiconductor layer. According to the semiconductor LED chip and the manufacturing method thereof, a transparent conductive layer material is adopted as a current expansion layer, so that the thickness or doping concentration of the n-type semiconductor layer is reduced, light is favorably absorbed by an n-type material, and the light extraction efficiency of the LED chip is improved.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

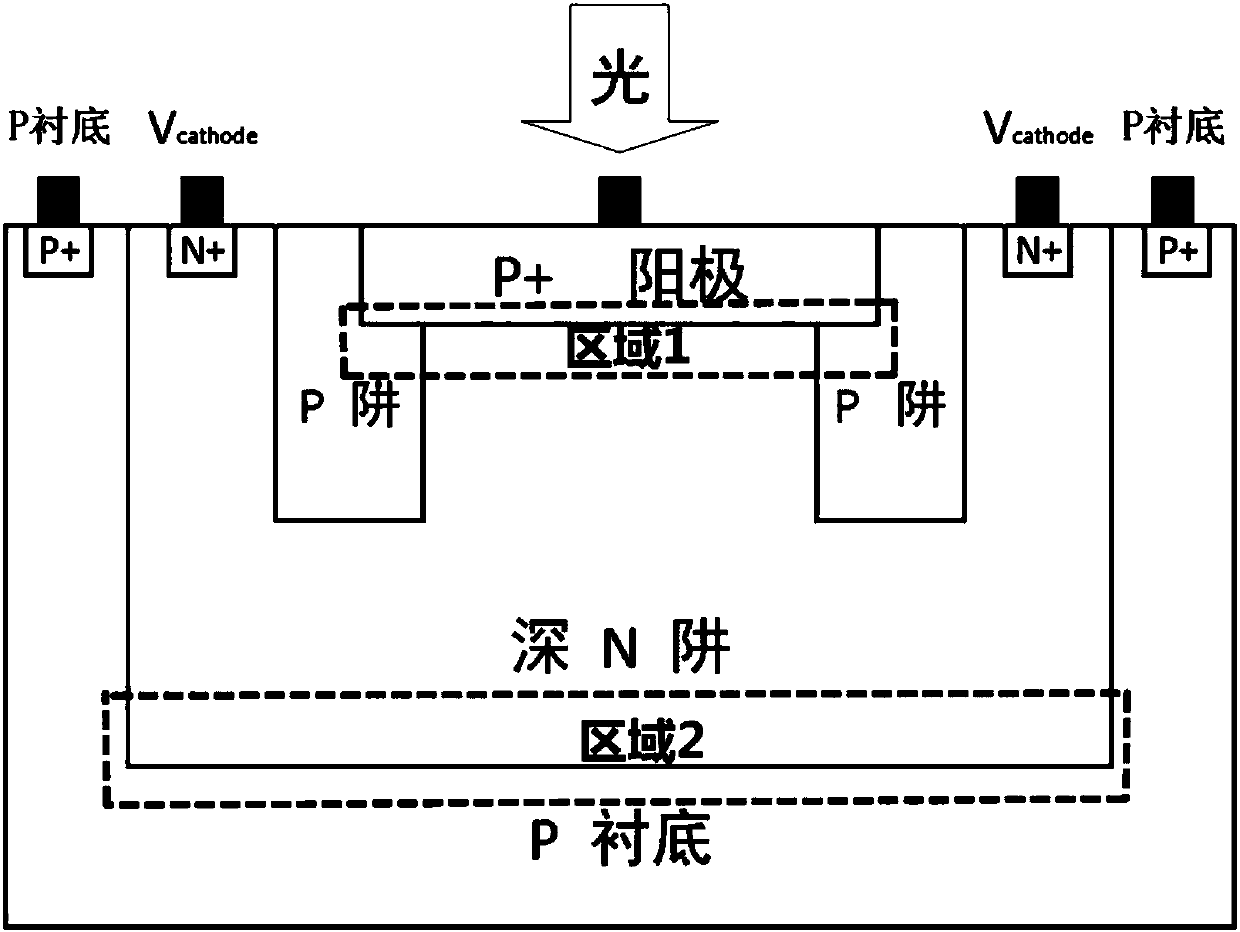

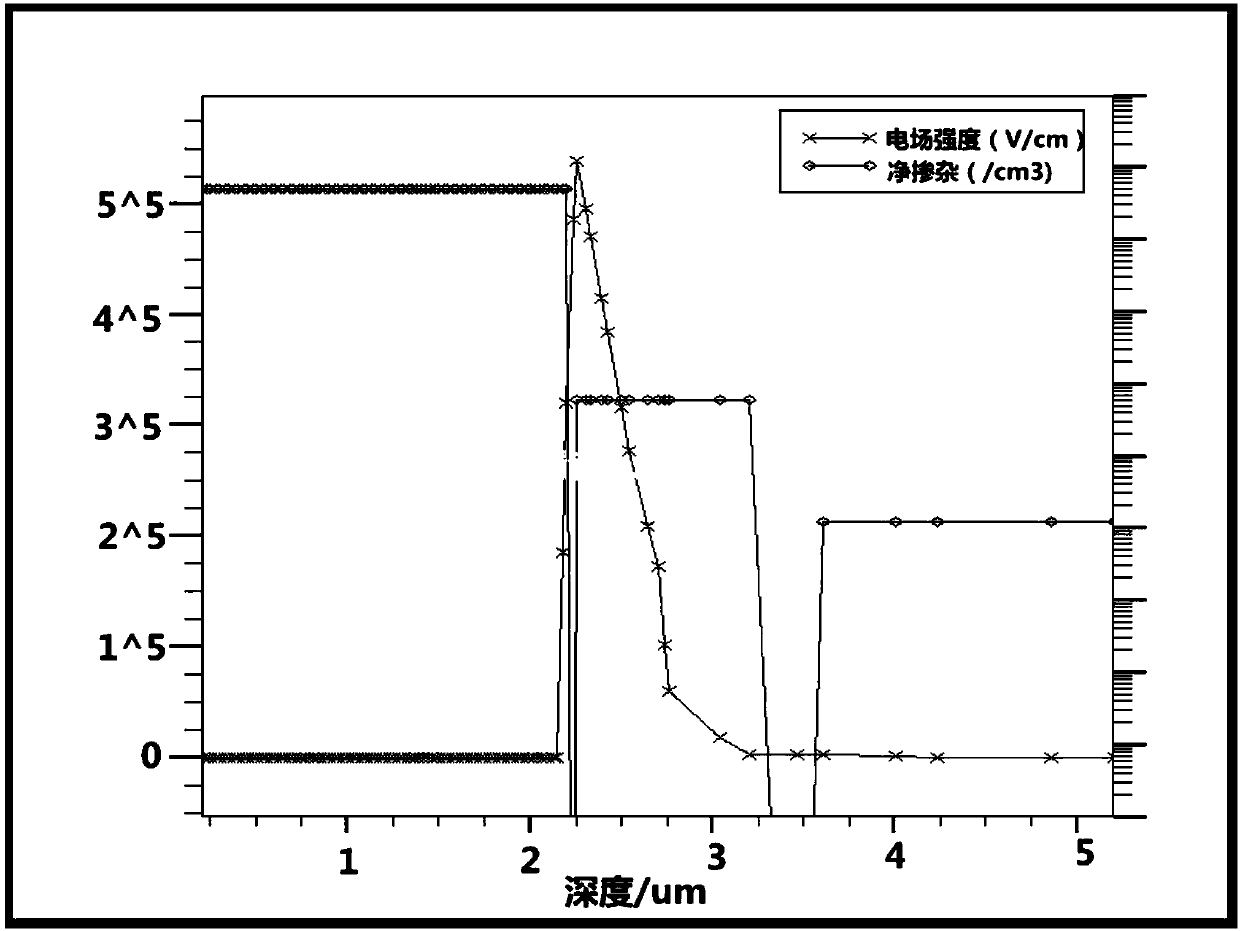

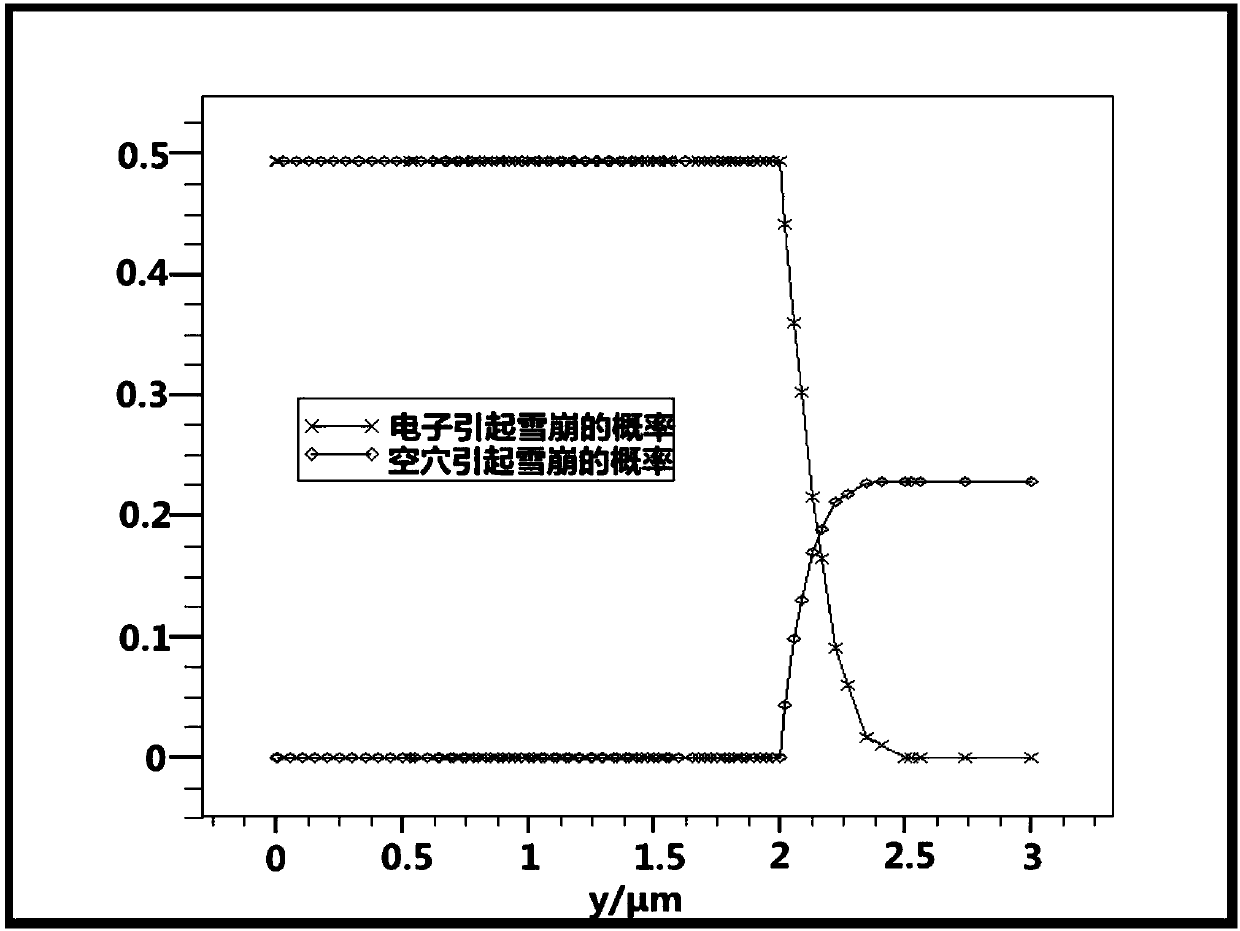

CMOS single-photon avalanche diode specific to long-wave-band weak light

InactiveCN107946389AHigh sensitivityQuick responseFinal product manufactureSemiconductor devicesElectron avalanchePhoton

The invention provides a CMOS single-photon avalanche diode specific to long-wave-band weak light. According to the specific structure, a deep N well is manufactured on a P type substrate; next, a P type heavily doped region is manufactured in the deep N well; a PN junction is formed by a P+ layer and the deep N well to be used as an avalanche multiplication region; the P+ region is surrounded bya lightly doped P well to be used as a protection ring; and after incident light comes to a device, the deep N well region in a medium electric field strength is absorbed, and the generated photon-generated carriers move towards an avalanche multiplication region of a strong electric field region. Electron holes generated by light of relatively long waveband are formed in a relatively deep position of the device, so that the light signals can be detected effectively by the deep N well; by taking the deep N well / P substrate as a shielding diode, diffusion of the substrate photon-generated carriers to the PN junction can be prevented, thereby reducing influence of diffusion of substrate slow photon-generated carriers to the response speed of a photoelectric detector; and the absorption efficiency of the device in a long waveband can be improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

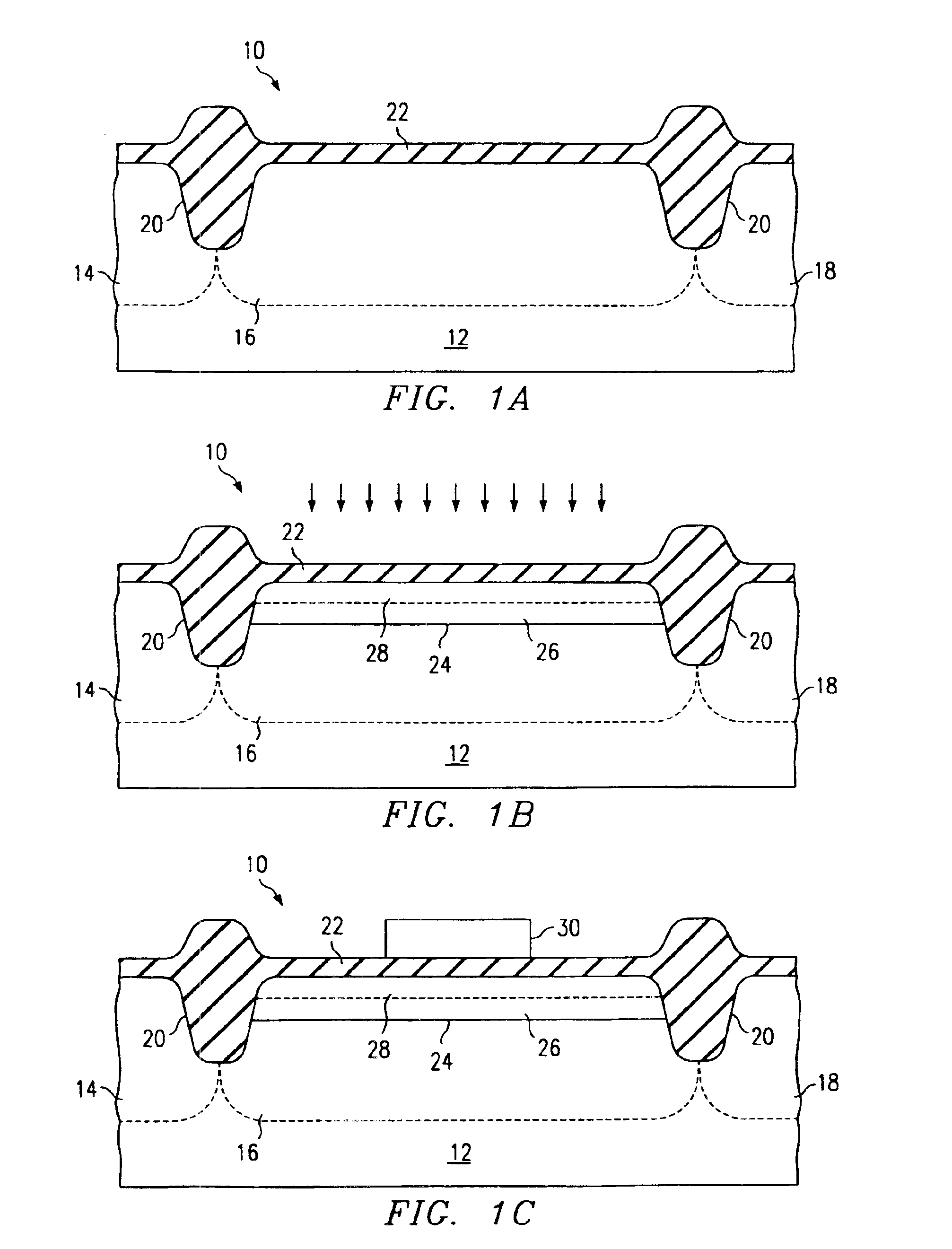

Dual-counterdoped channel field effect transistor and method

InactiveUS6960499B2High carrier mobilityReduce doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesDopantCapacitance

A field effect transistor with a dual-counterdoped channel is disclosed. The transistor features a channel comprising a first doped region (28) and a second doped region (26) underlying the first doped region. A source and drain (32) are formed adjacent to the channel. In one embodiment of the present invention, the first doped region (28) is doped with arsenic, while the second doped region (26) is doped with phosphorus. The high charge-carrier mobility of the subsurface channel layer (28) allowing a lower channel dopant concentration to be used, which in turn allows lower source / drain pocket doping. This reduces the capacitance and response time of the transistor.

Owner:TEXAS INSTR INC

Light-emitting element with porous light-emitting layers

ActiveUS7271417B2Reduce the driving voltageReduce doping concentrationSolid-state devicesSemiconductor/solid-state device manufacturingIndiumCharge carrier

Owner:GENESIS PHOTONICS

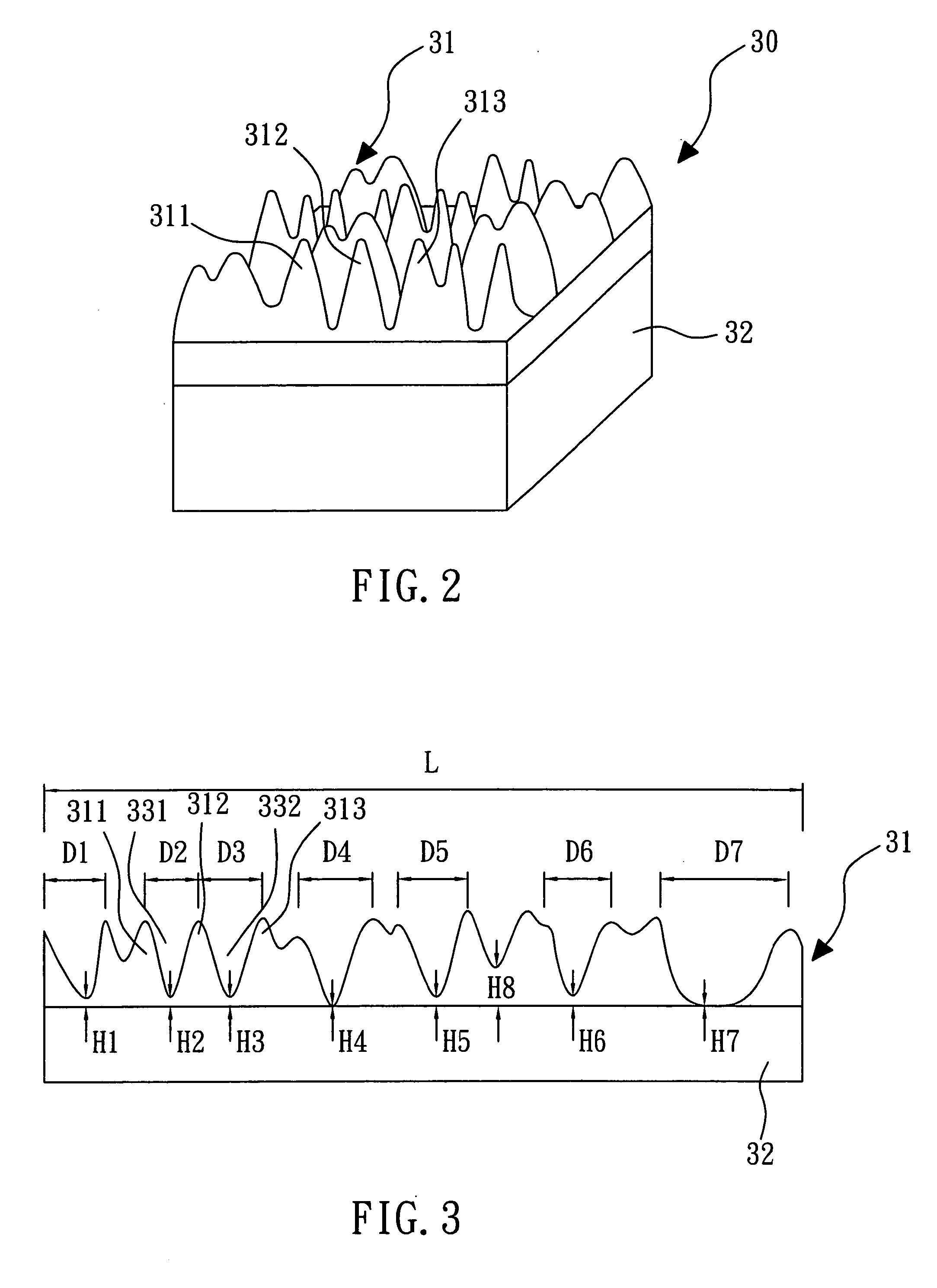

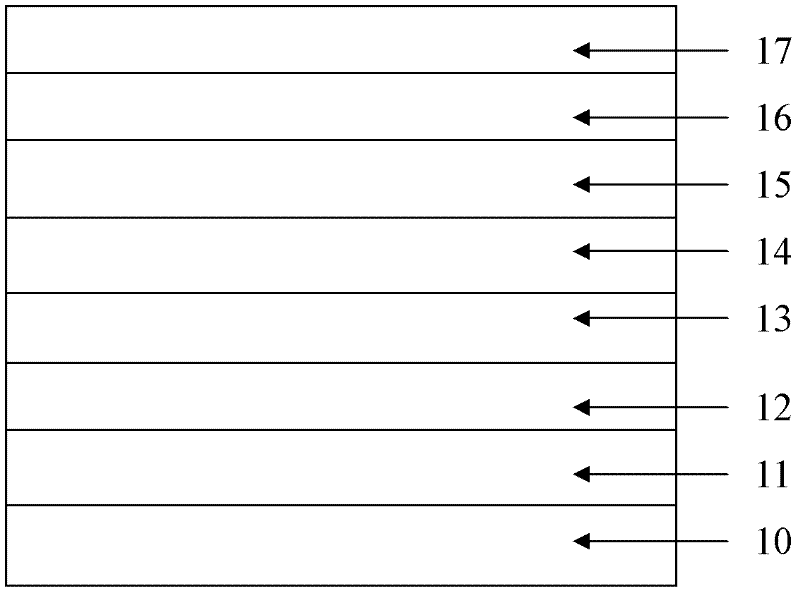

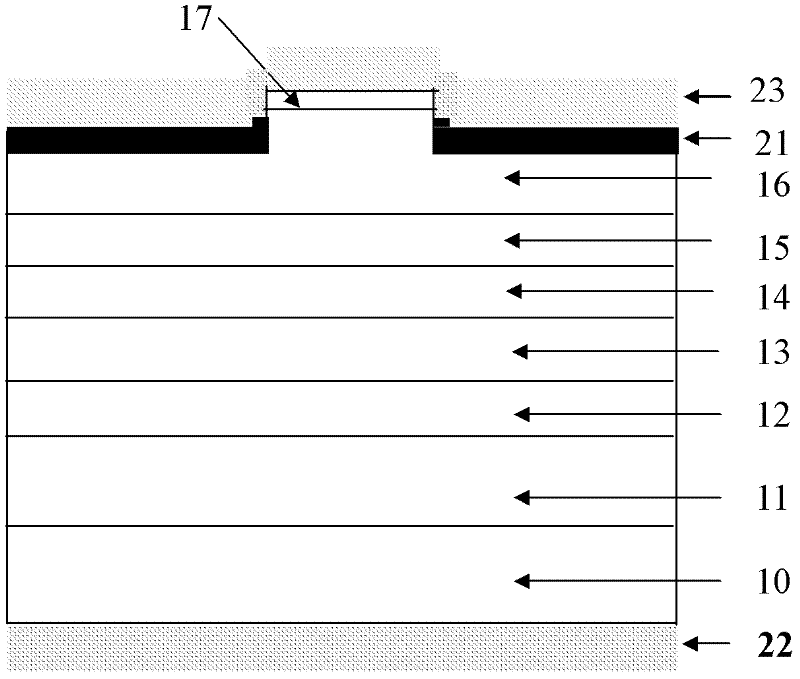

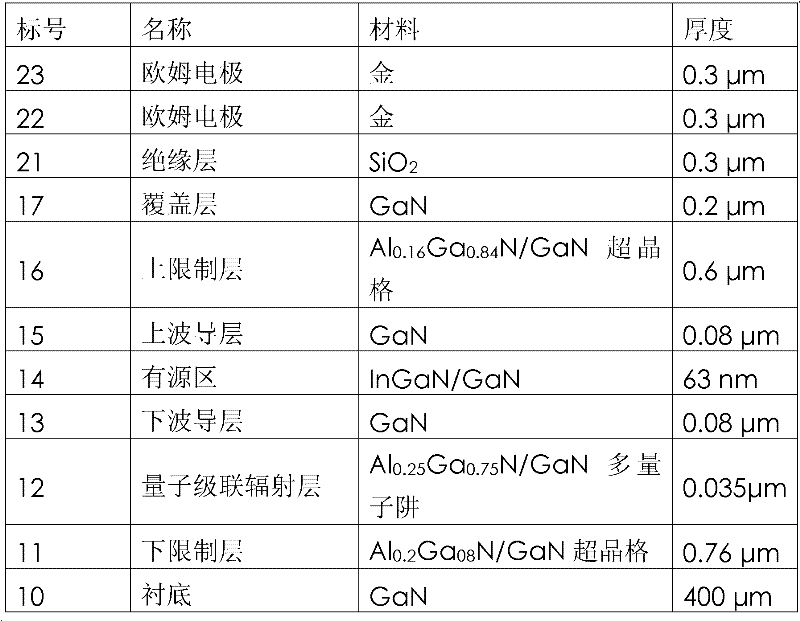

GaN (gallium nitride)-based semiconductor laser and manufacturing method thereof

InactiveCN102227046AReduce leakageIncrease the injection currentLaser detailsSemiconductor lasersIonizationMagnesium

The invention provides a GaN (gallium nitride)-based semiconductor laser and a manufacturing method thereof, belonging to the field of semiconductor lasers. The GaN-based semiconductor laser does not have an electronic barrier layer, thus reducing the working voltage of the laser and prolonging the service life of the laser. For the laser, a quantum cascade radiation layer is arranged between an n-type optical limited layer and an n-type waveguide layer of the laser and utilized to generate infrared radiation when the laser operates, thus realizing ionization of magnesium acceptor impurities in a p-type GaN waveguide layer and a AlGaN optical limited layer, improving carrier concentration in each p-type layer, increasing hole injection current, reducing leakage of electronics from an active area, avoiding introduction of a AlGaN electronic barrier layer and eliminating optical absorption loss caused by the magnesium-doped AlGaN electronic barrier layer, thereby reducing the threshold current of the laser, reducing the working voltage of the laser and prolonging the service life of the laser.

Owner:BEIJING UNIV OF CHEM TECH

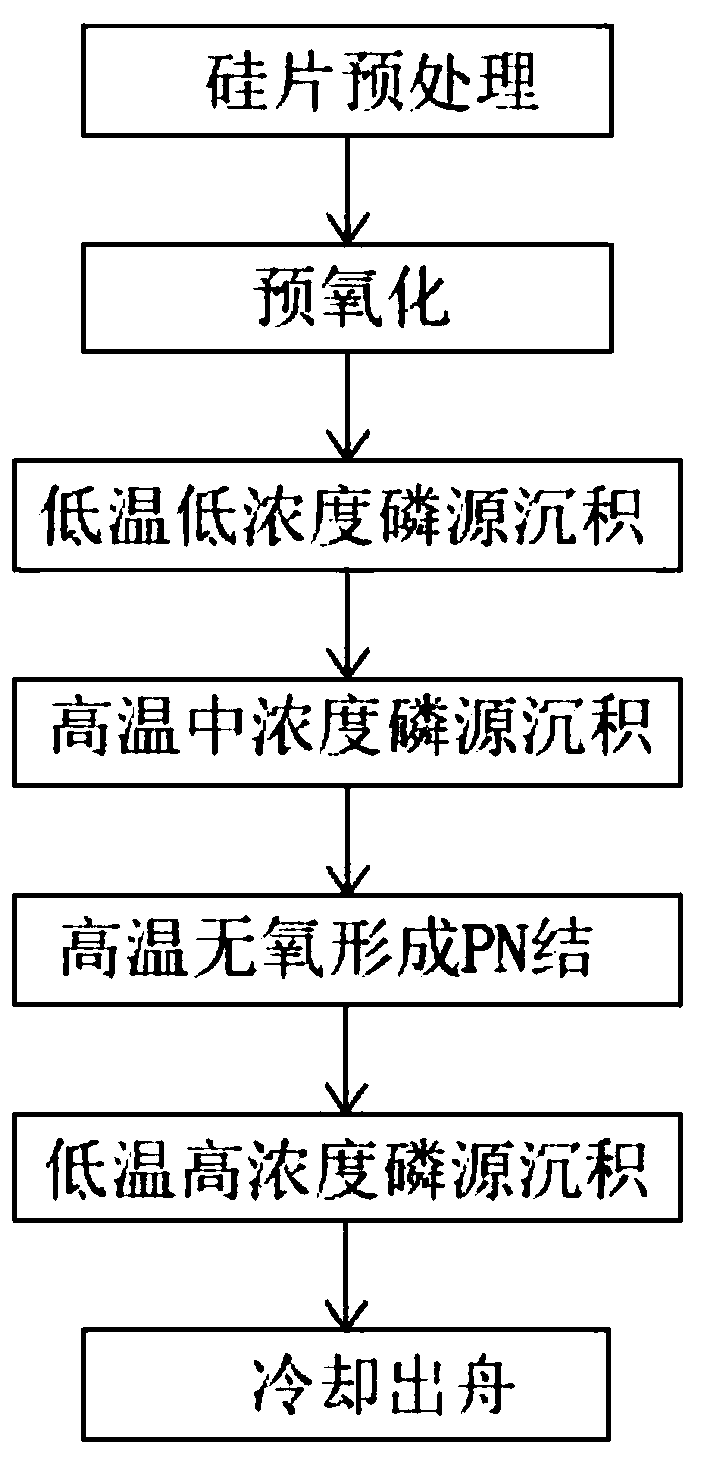

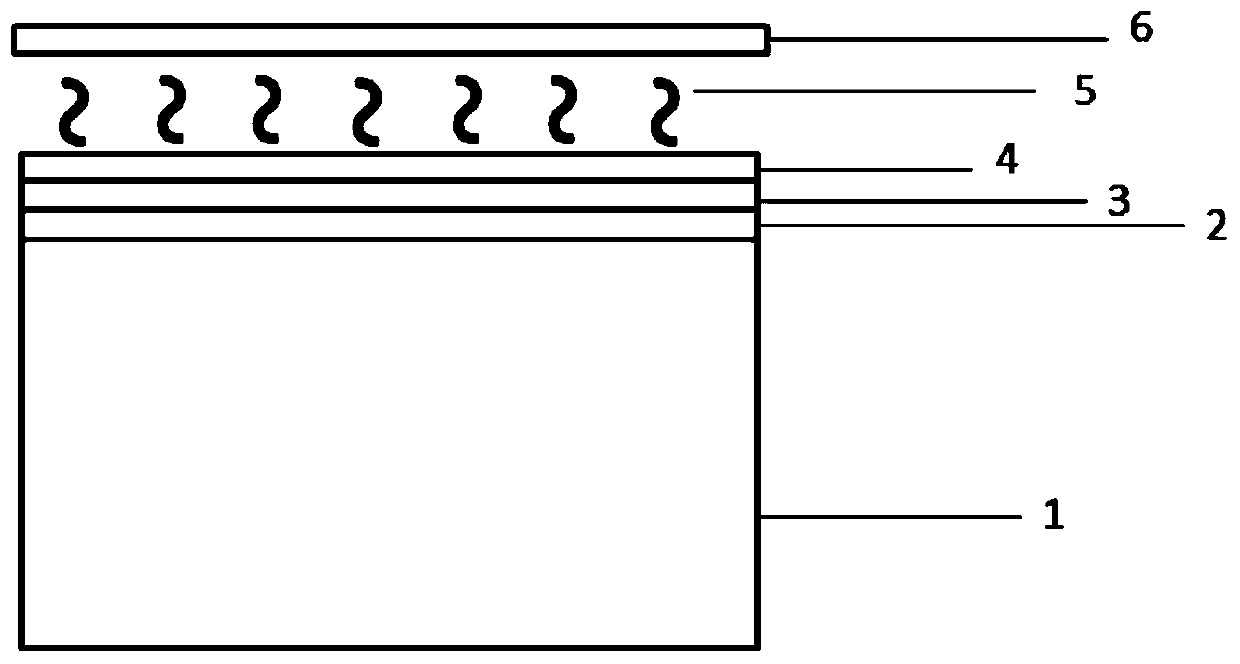

Regional layered deposition diffusion process

ActiveCN110164759AReduce concentrationReduce compoundingFinal product manufactureSemiconductor/solid-state device manufacturingHigh concentrationHigh surface

The invention relates to the technical field of crystalline silicon solar cells, and provides a regional layered deposition diffusion process in order to solve the problems of over-high surface dopingconcentration, weak regional diffusion controllability, poor cell blue light response and short minority carrier lifetime of an existing PERC+LDSE cell sheet. The process comprises the following steps: (1) pretreatment of a silicon wafer; (2) pre-oxidizing; (3) low-temperature low-concentration phosphorus source deposition; (4) high-temperature medium-concentration phosphorus source deposition; (5) forming of a PN junction; (6) depositing of a low-temperature high-concentration phosphorus source; (7) cooling, pushing of a quartz boat, and taking-out of the silicon wafer. Regional layered diffusion control is adopted in the process, so that a uniform phosphorosilicate glass layer is formed on the surface of a silicon wafer, the laser SE heavy doping is facilitated, and the ohmic contact and good contact performance of a battery piece are improved; and the emitter region has low doping concentration and high-quality PN junctions, so that the battery piece has the characteristics of excellent blue light response and long minority carrier lifetime, and finally, the conversion efficiency of the battery piece is improved.

Owner:HENGDIAN GRP DMEGC MAGNETICS CO LTD

Fully silicided gate electrodes and method of making the same

InactiveUS7297618B1Reduce doping concentrationReduce and eliminate gate depletionSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon electrodeField-effect transistor

The present invention relates to a method of selectively fabricating metal gate electrodes in one or more device regions by fully siliciding (FUSI) the gate electrode. The selective formation of FUSI enables metal gate electrodes to be fabricated on devices that are compatible with workfunctions that are different from conventional n+ and p+ doped poly silicon electrodes. Each device region consists of at least one Field Effect Transistor (FET) device which consists of either a polysilicon gate electrode or a fully silicided (FUSI) gate electrode. A gate electrode comprised of silicon and a Ge containing layer is used in combination with a selective removal process of the Ge containing layer. The Ge containing layer is not removed on devices with threshold voltages that are not compatible with the FUSI workfunction. Devices that are compatible with the FUSI workfunction have the Ge containing layer removed prior to the junction silicidation step. The remaining thin silicon layer of the gate electrode becomes fully silicided during the same step as the junction silicidation step.

Owner:GLOBALFOUNDRIES INC

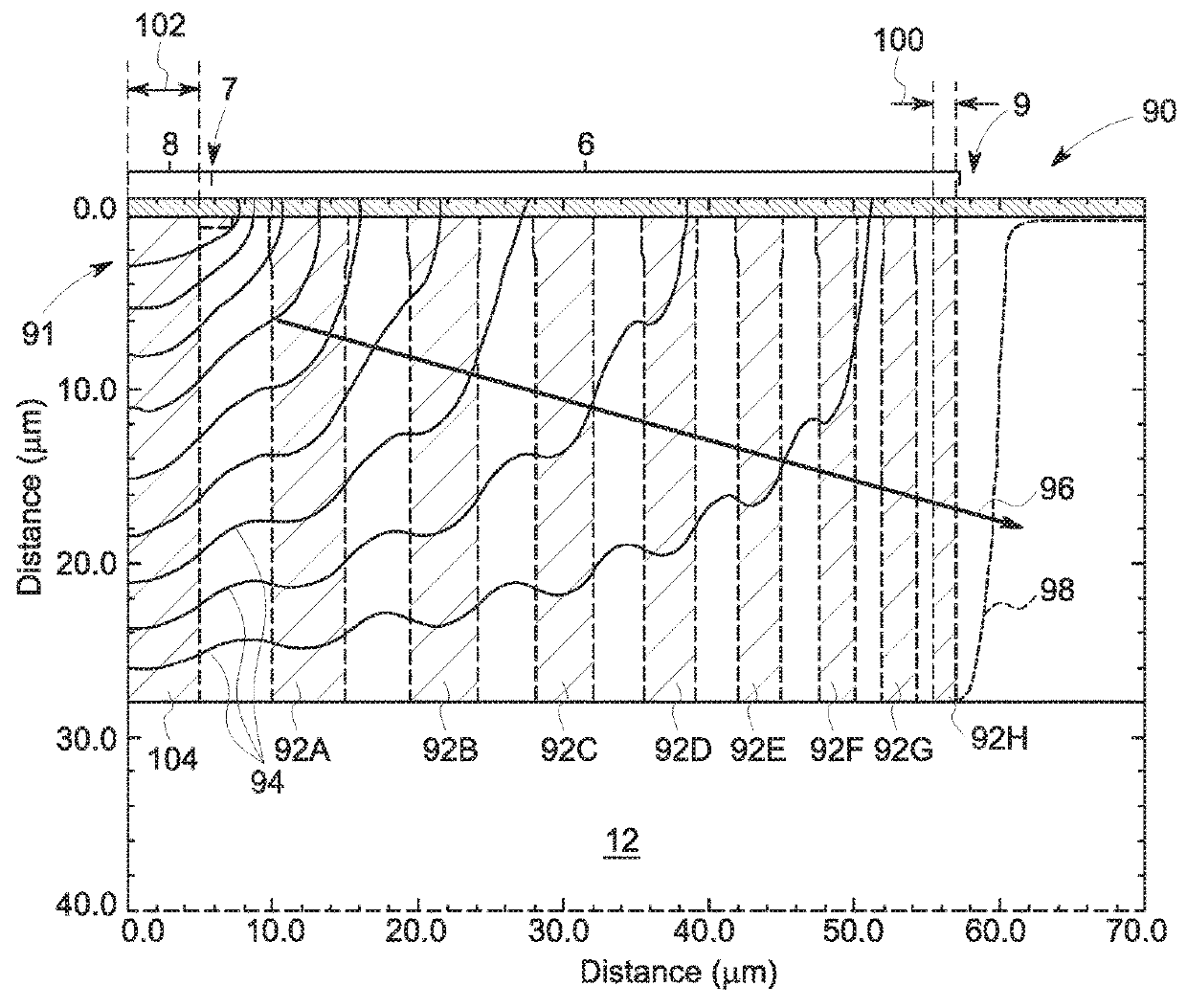

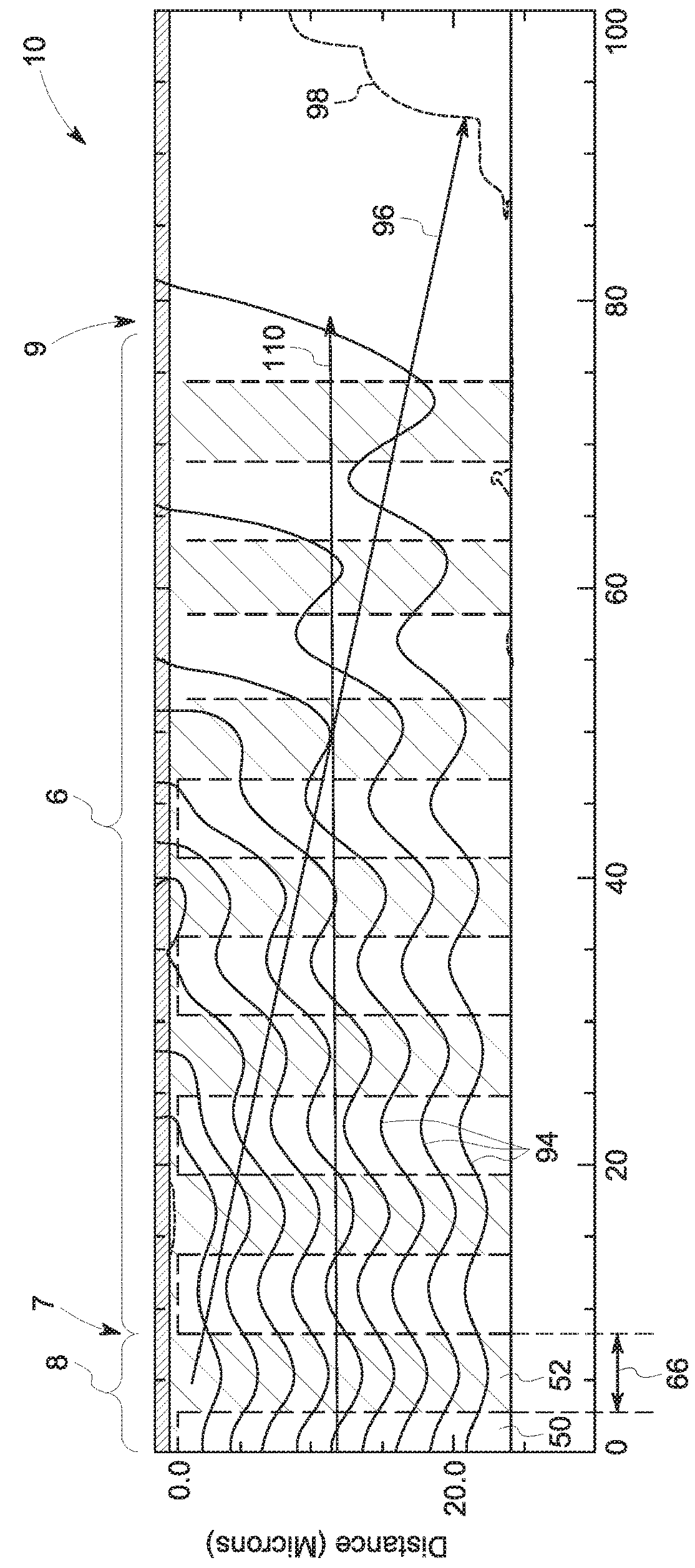

System and method for edge termination of super-junction (SJ) devices

ActiveUS20180166531A1Reduce doping concentrationIncrease the on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSubject matterEngineering

The subject matter disclosed herein relates to super-junction (SJ) power devices and, more specifically, to edge termination techniques for SJ power devices. A semiconductor super-junction (SJ) device includes one or more epitaxial (epi) layers having a termination region disposed adjacent to an active region. The termination region includes a plurality of vertical pillars of a first and a second conductivity-type, wherein, moving outward from the active region, a respective width of each successive vertical pillar is the same or smaller. The termination region also includes a plurality of compensated regions having a low doping concentration disposed directly between a first side of each vertical pillar of the first conductivity-type and a first side of each vertical pillar of the second conductivity-type, wherein, moving outward from the active region, a respective width of each successive compensated region is the same or greater.

Owner:GENERAL ELECTRIC CO

Non polarity A side nitride film growing on the silicon substrate and its making method and use

InactiveCN101009346AEasy to separateIncrease overlapLaser detailsFinal product manufactureSolar batteryLight-emitting diode

The invention relates to a nonpolar (1120)A side nitride film that comprises a silicon underlay, metal layer which grows upon the silicon underlay sequentially, InGaAlN initial growth layer and the first InGaAlN buffer layer, it characterized in that: said silicon underlay is Si underlay which adopts the (100) side, (110) side or offset angle. The nonpolar a side nitride film which grows on the silicon underlay can be used in LBD, laser, solar battery. The component extension configuration is adopted according to different component, for example the LBD and laser, and using the mature silicon craft further to produce relative diprosopia electrode component or peeling off component. Comparing with current technique, the advantages of the invention are: the invention can increase the growth quality of nonpolar GaN base material, and decrease the cost; the craft of current component can be simplified greatly, the cost can be decreased, and increase the elimination efficiency and lightening efficiency greatly.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

Low-voltage MOSFET device with antistatic protection structure and manufacturing method therefor

InactiveCN105470309AIncrease the doping concentrationReduce doping concentrationSemiconductor/solid-state device manufacturingDiodeMOSFETManufacturing cost reduction

The invention relates to a low-voltage MOSFET device with an antistatic protection structure and a manufacturing method therefor. A static protection region comprises a second conductive type well region positioned at the upper part of a first conductive type drift region, and an insulating supporting layer positioned above the second conductive type well region; the second conductive type well region penetrates through a terminal protection region; the insulating supporting layer is positioned on a first main surface of a semiconductor substrate and is in contact with the second conductive type well region; a polycrystalline silicon diode group is arranged on the insulating supporting layer; the polycrystalline silicon diode group comprises a first diode and a second diode; the negative electrode end of the first diode is connected with the negative electrode end of the second diode; the positive electrode end of the first diode is in ohmic contact with the a grid electrode metal on the upward side; and the positive electrode end of the second diode is in ohmic contact with the a source electrode metal on the upward side. The low-voltage MOSFET device is compact in structure, compatible with the existing technological steps, safe, reliable, and capable of improving the voltage resistance of the device with ESD (Electro-static Discharge) protection and reducing manufacturing cost.

Owner:WUXI NCE POWER

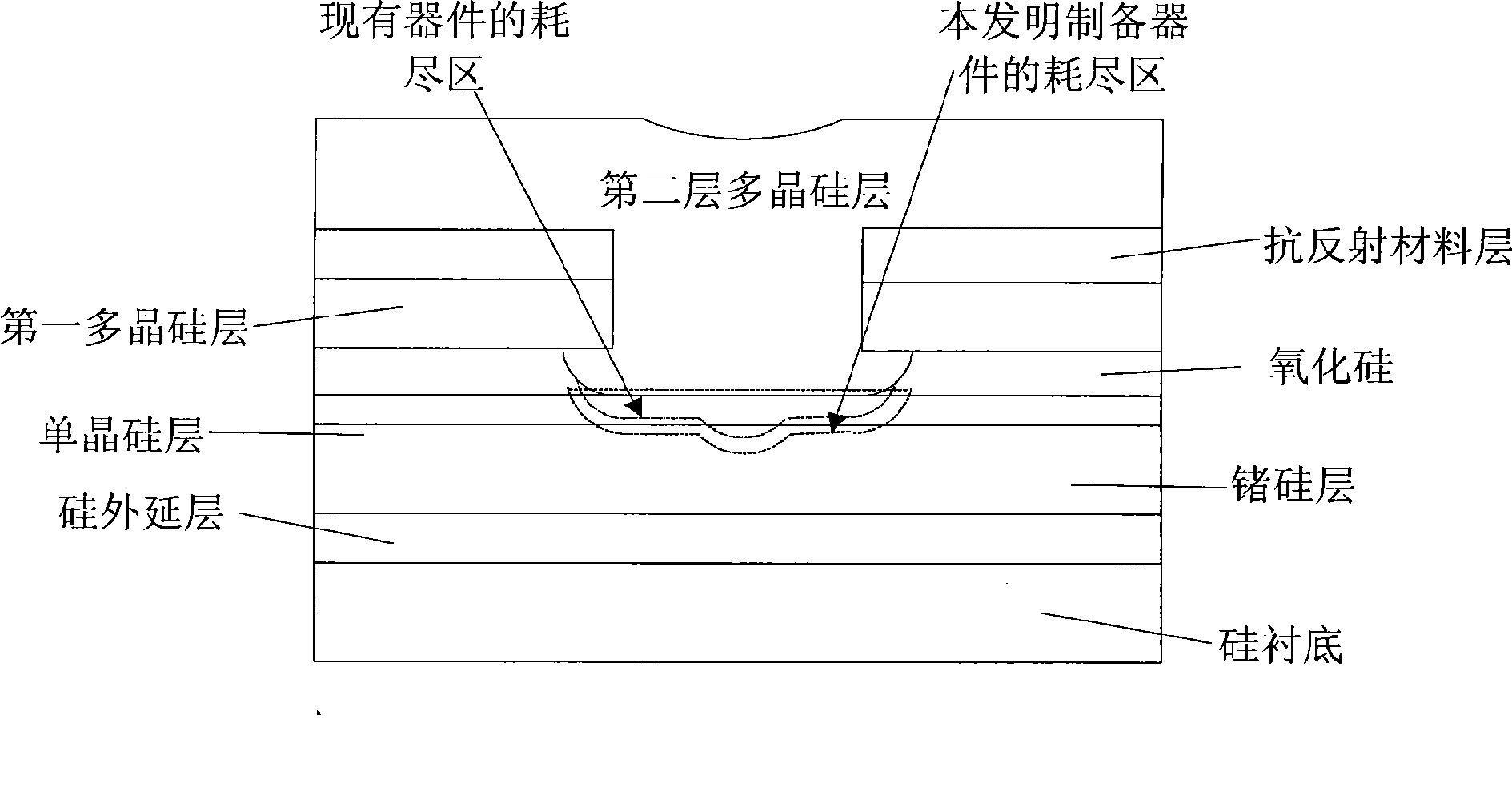

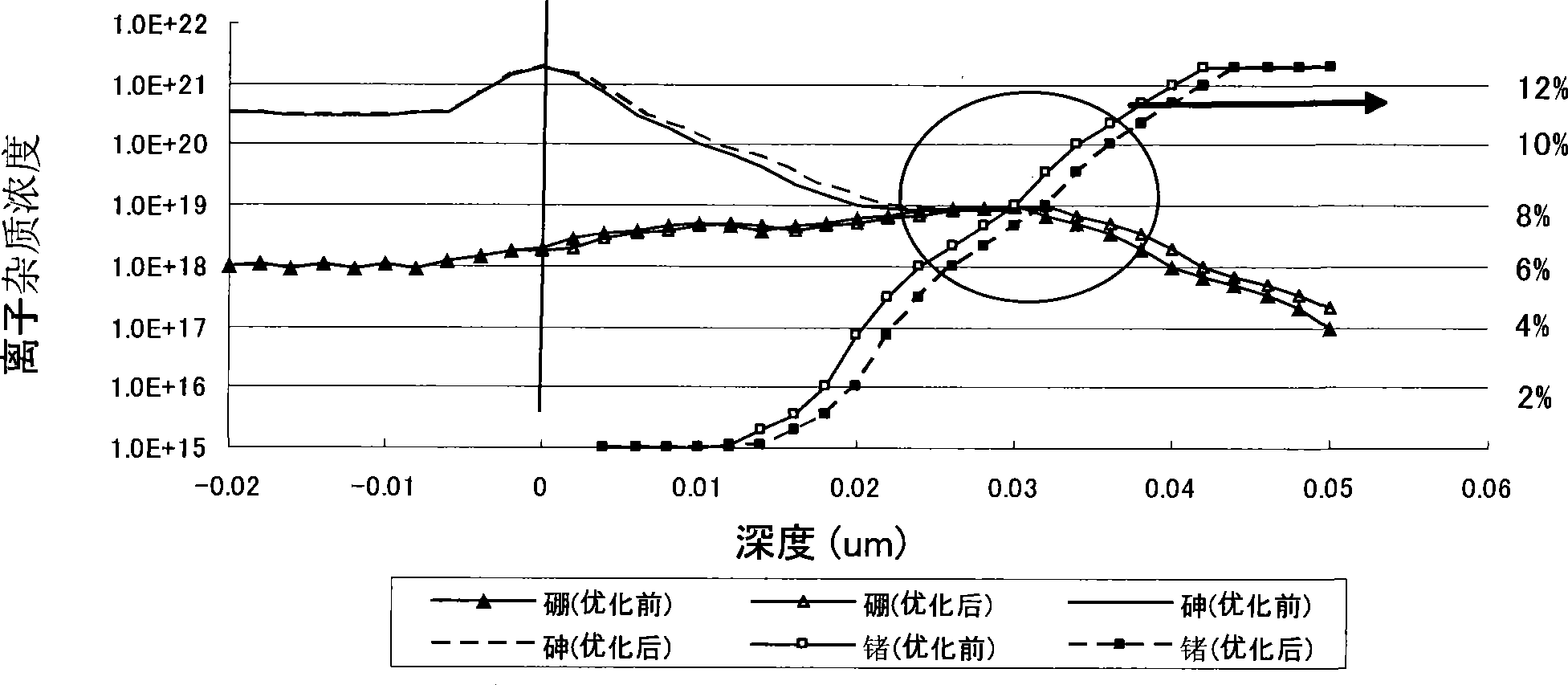

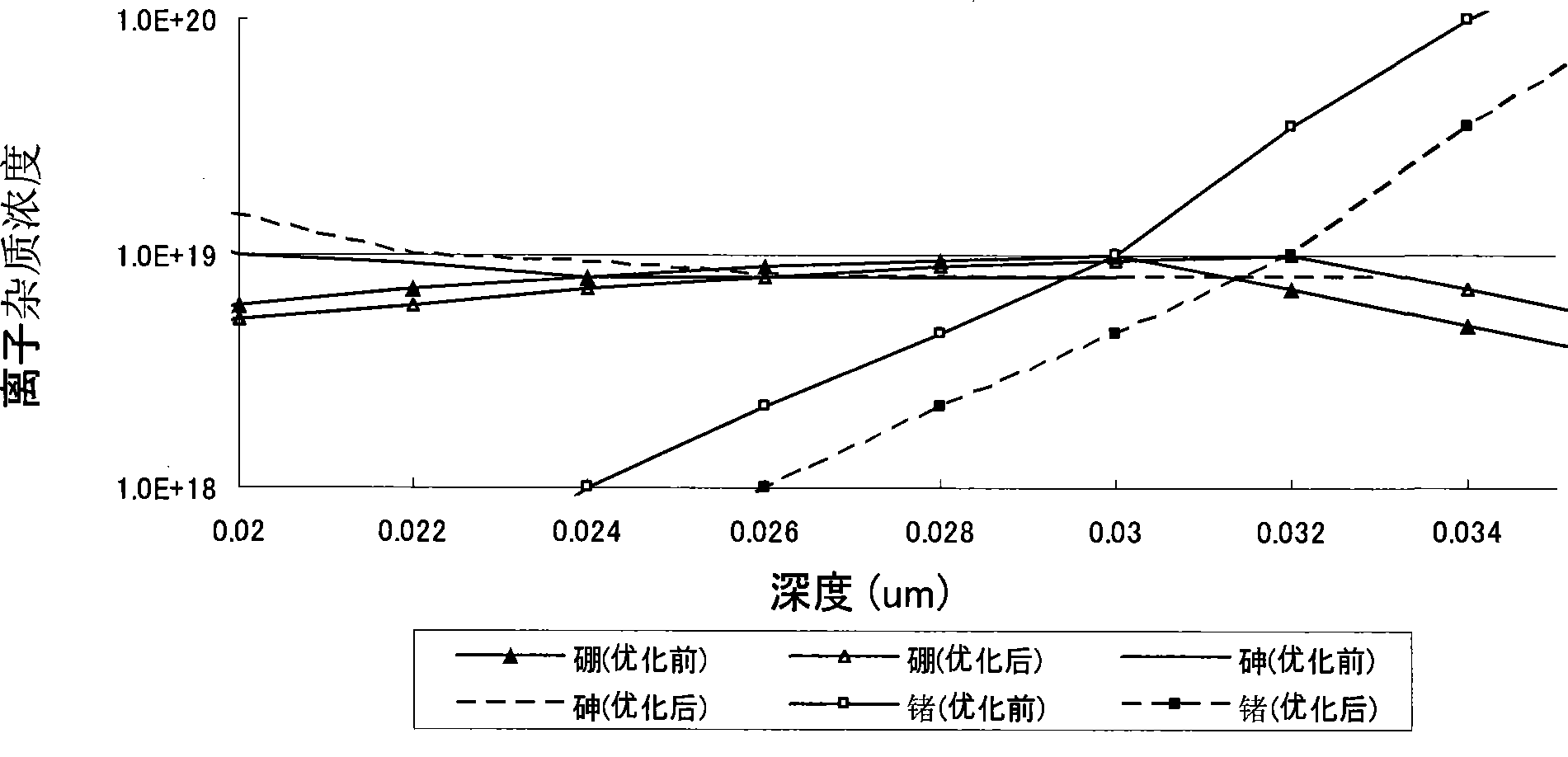

Preparation for SiGe HBT transistor

ActiveCN101459076ARaise the activation temperatureReduce recombination currentSemiconductor/solid-state device manufacturingRecombination currentBiology

The invention discloses a method of producing SiGe HBT transistors, which includes steps of reducing the doping concentration of emitter polysilicon, controlling the undercut dimension of an emitter window, increasing the thickness of an emitter monocystal silicon layer, and increasing the final activation temperature of devices, thereby maintaining bases out of highly defective areas and further greatly reducing the base recombination current.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Manufacturing method of high-square-resistance solar cell

ActiveCN102629643AHigh power outputImprove surface passivation effectFinal product manufactureSemiconductor devicesSolar cellSilicon dioxide

The invention relates to a manufacturing method of a high-square-resistance solar cell. The manufacturing method is characterized by comprising the following steps of: manufacturing an emitter junction on the surface of a silicon wafer through pre-diffusion treatment; removing an edge junction of the silicon wafer by using wet etching or plasma etching equipment; cleaning the silicon wafer by using RCA solution; placing the silicon wafer in a diffusion furnace for treatment to increase the junction depth and forming a silicon dioxide layer on the surface of the silicon wafer; manufacturing a silicon nitride layer on the silicon dioxide layer on the surface of the emitter junction through PECVD (Plasma Enhanced Chemical Vapor Deposition) equipment; and finally, preparing a front face electrode, a back face electrode and a back face electric field by using screen printing equipment, and co-firing the electrodes and the electric field by using a sintering furnace. Thus, the high-square-resistance solar cell is manufactured by promoting an emitter junction process through secondary high temperature, and the doping concentration of the surface of the junction is reduced. Meanwhile, a proper silicon dioxide film is formed on the surface of the silicon wafer, and the film layer and a silicon nitride film which is manufactured subsequently form a stack layer, so that the surface passivation performance of the cell is improved.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

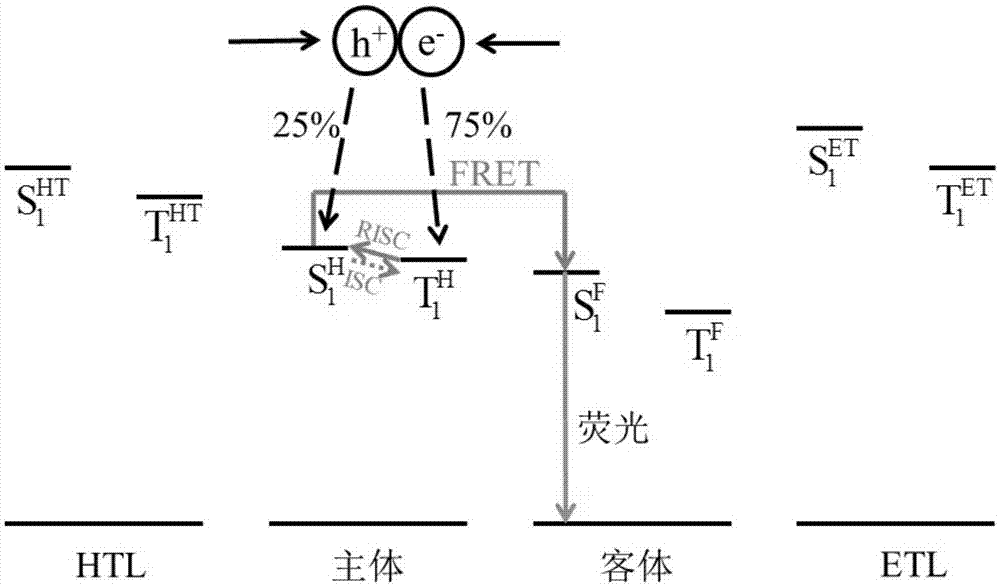

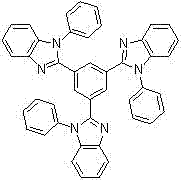

Phosphorescent organic electroluminescent device

ActiveCN106898700AImprove efficiencyImprove stabilityOrganic chemistrySolid-state devicesHole transport layerDye doped

The invention discloses a phosphorescent organic electroluminescent device, and the device comprises a hole transmission layer, a light emitting layer and an electron transmission layer, wherein the hole transmission layer, the light emitting layer and the electron transmission layer are stacked sequentially. The light-emitting layer is of a double-layer structure which consists of a hole transmission material layer and an electron transmission material layer. The hole transmission material layer is disposed between the hole transmission layer and the electron transmission material layer, and the electron transmission material layer is disposed between the hole transmission material layer and the electron transmission layer. A contact interface of the hole transmission material layer and the electron transmission material layer forms a laser-based composite. The hole transmission material layer comprises a main material, and the main material is a material with the capability of hole transmission. The electron transmission material layer comprises a main material and phosphorescent dye doped in the main material, wherein the main material is a material with the capability of electron transmission. The phosphorescent doped density is reduced through the laser-based composite, and the long service life and high efficiency can be maintained.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD +1