Patents

Literature

58 results about "Recombination current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Photovoltaic cells having metal wrap through and improved passivation

InactiveCN101889349ACheap manufacturingFast preparationFinal product manufacturePhotovoltaic energy generationRecombination currentEngineering

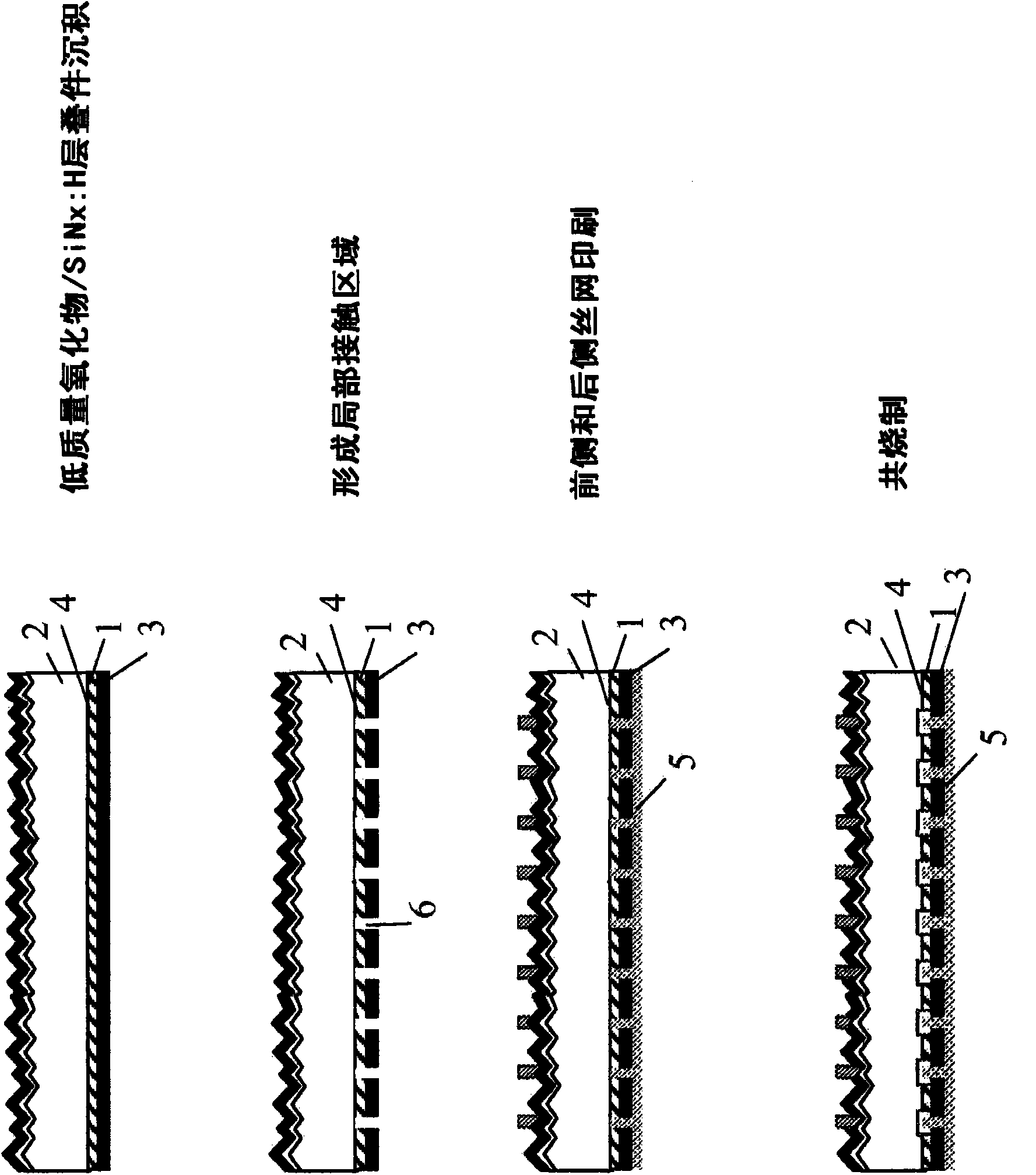

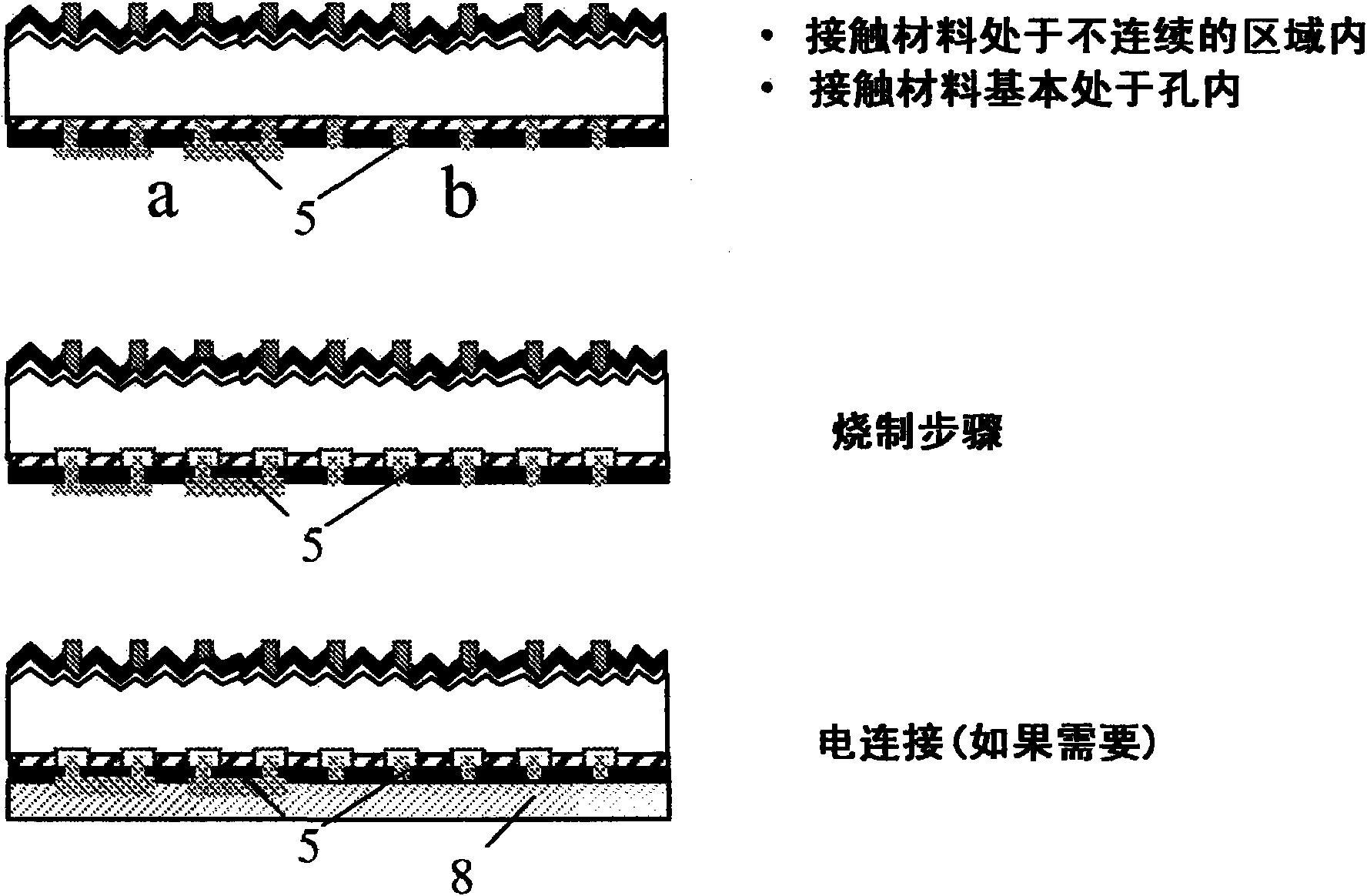

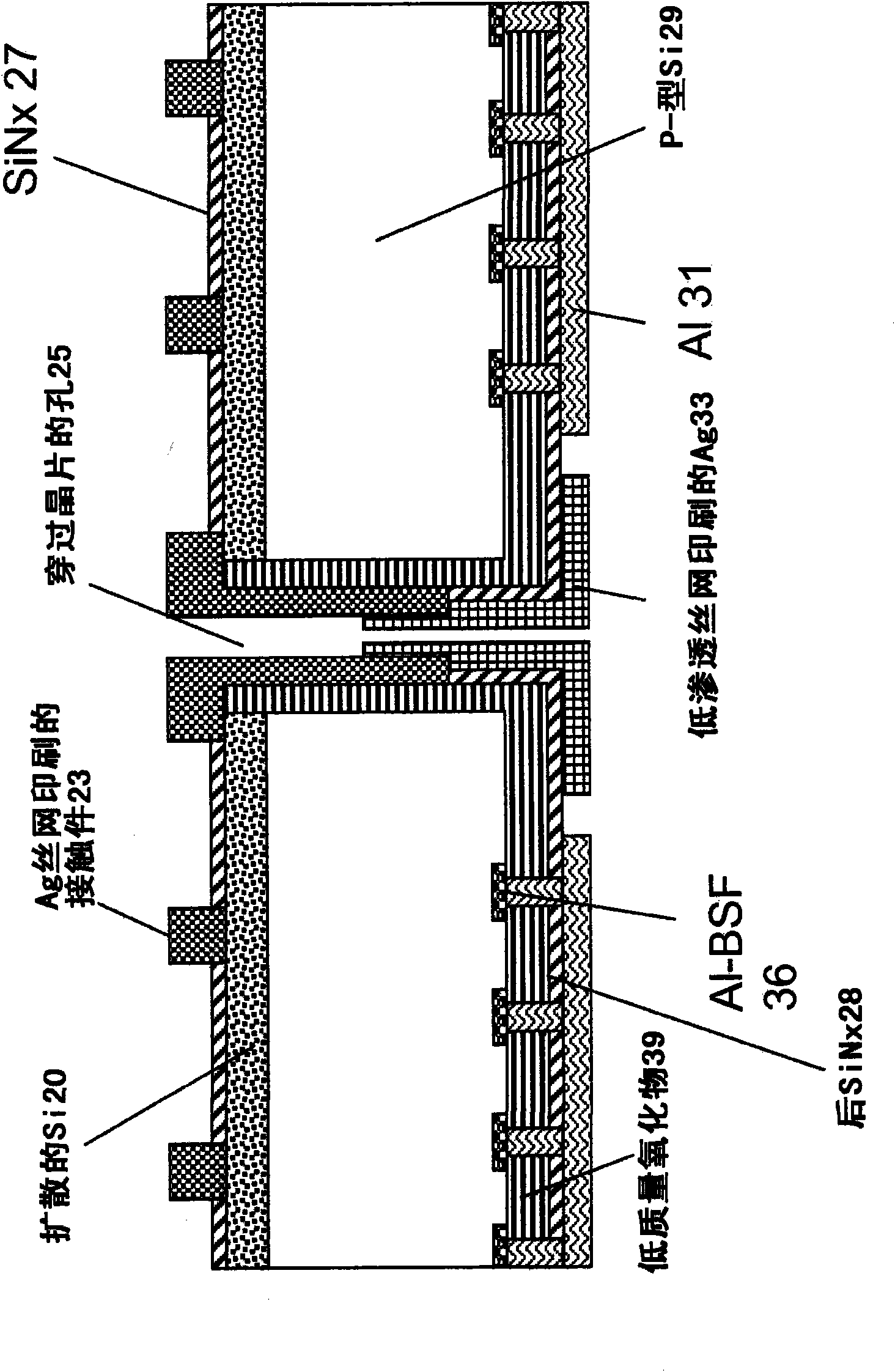

A photovoltaic device in a semiconductor substrate, has a radiation receiving front surface and a rear surface, a first region of one conductivity type (29), and a second region with the opposite conductivity type (20) adjacent to the front surface, and an antireflection layer (27). The rear surface is covered by a dielectric layer (39) covering also an inside surface of the via. The front surface has current collecting conductive contacts (23) and the rear surface has conductive contacts (31) extending through the said dielectric. A conductive path is provided in the via for photogenerated current from the front surface. By having the dielectric all over, no aligning and masking is needed, and the same dielectric serves to insulate, provide thermal protection for the semiconductor, and helps in surface and bulk passivation. It also avoids the need for a junction region near the via, hence reducing unwanted recombination currents.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

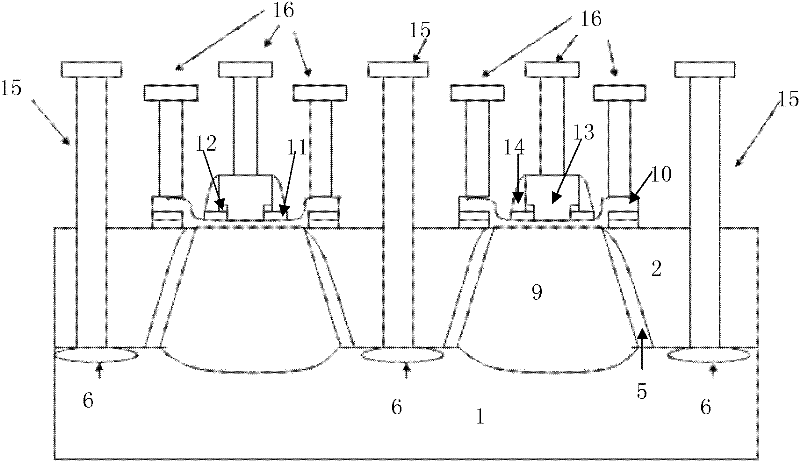

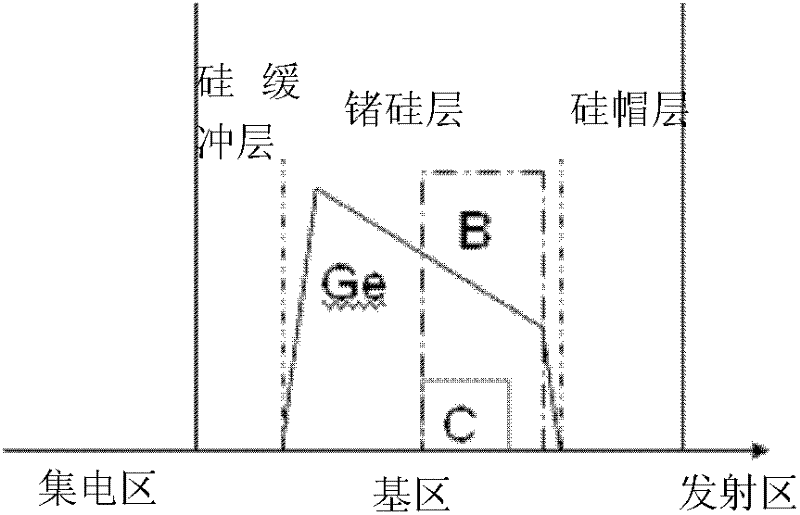

Preparation for SiGe HBT transistor

ActiveCN101459076ARaise the activation temperatureReduce recombination currentSemiconductor/solid-state device manufacturingRecombination currentBiology

The invention discloses a method of producing SiGe HBT transistors, which includes steps of reducing the doping concentration of emitter polysilicon, controlling the undercut dimension of an emitter window, increasing the thickness of an emitter monocystal silicon layer, and increasing the final activation temperature of devices, thereby maintaining bases out of highly defective areas and further greatly reducing the base recombination current.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

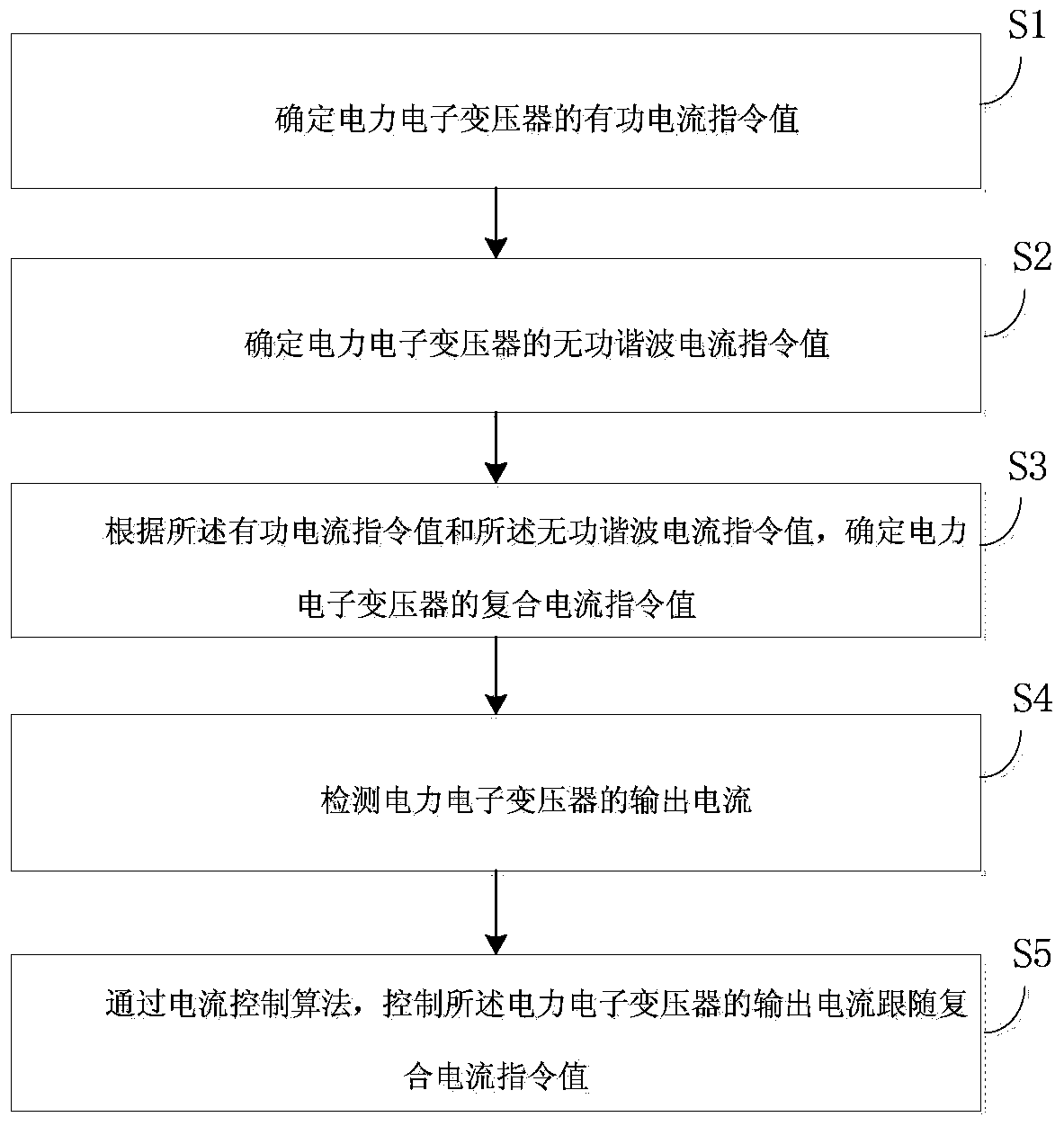

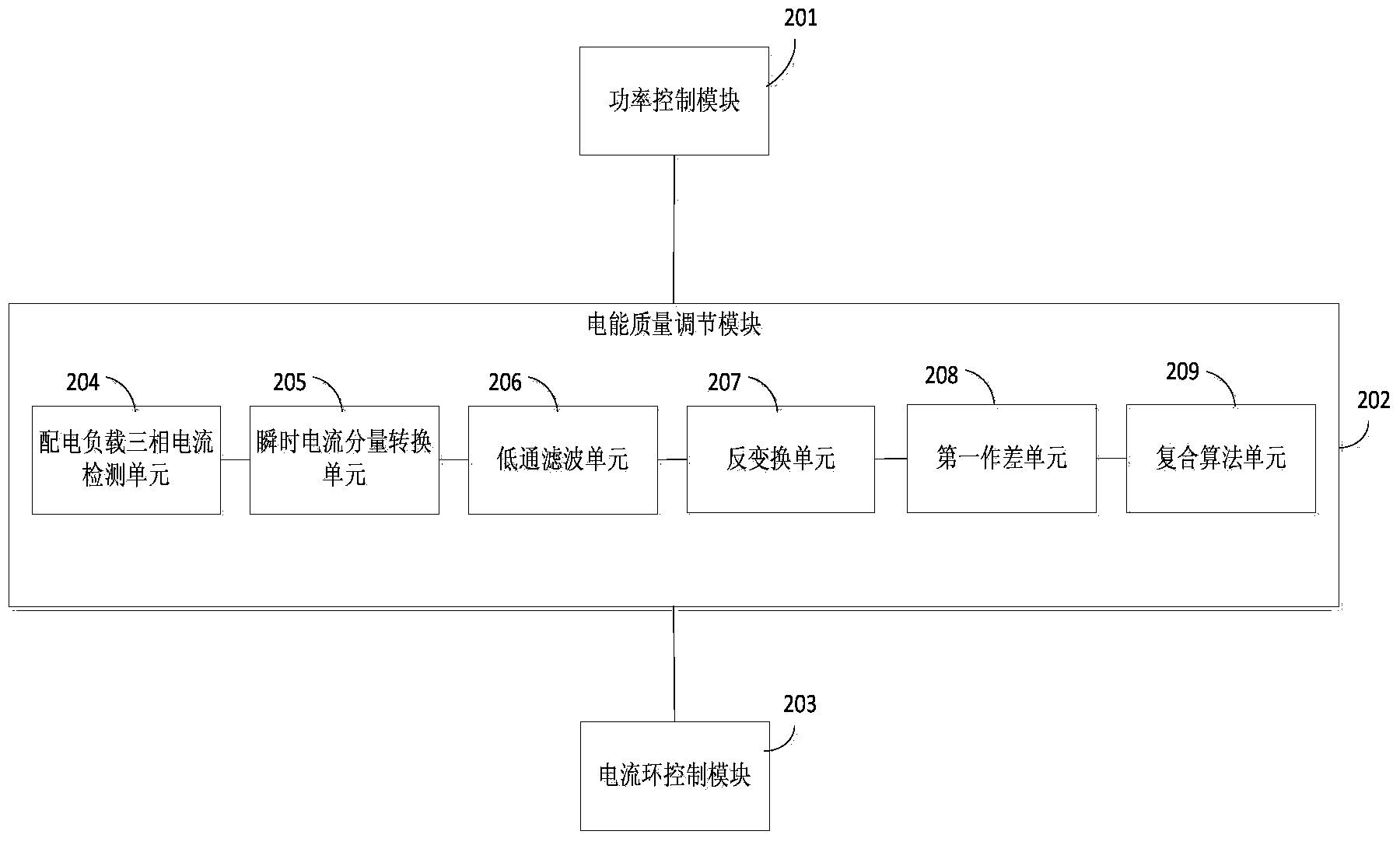

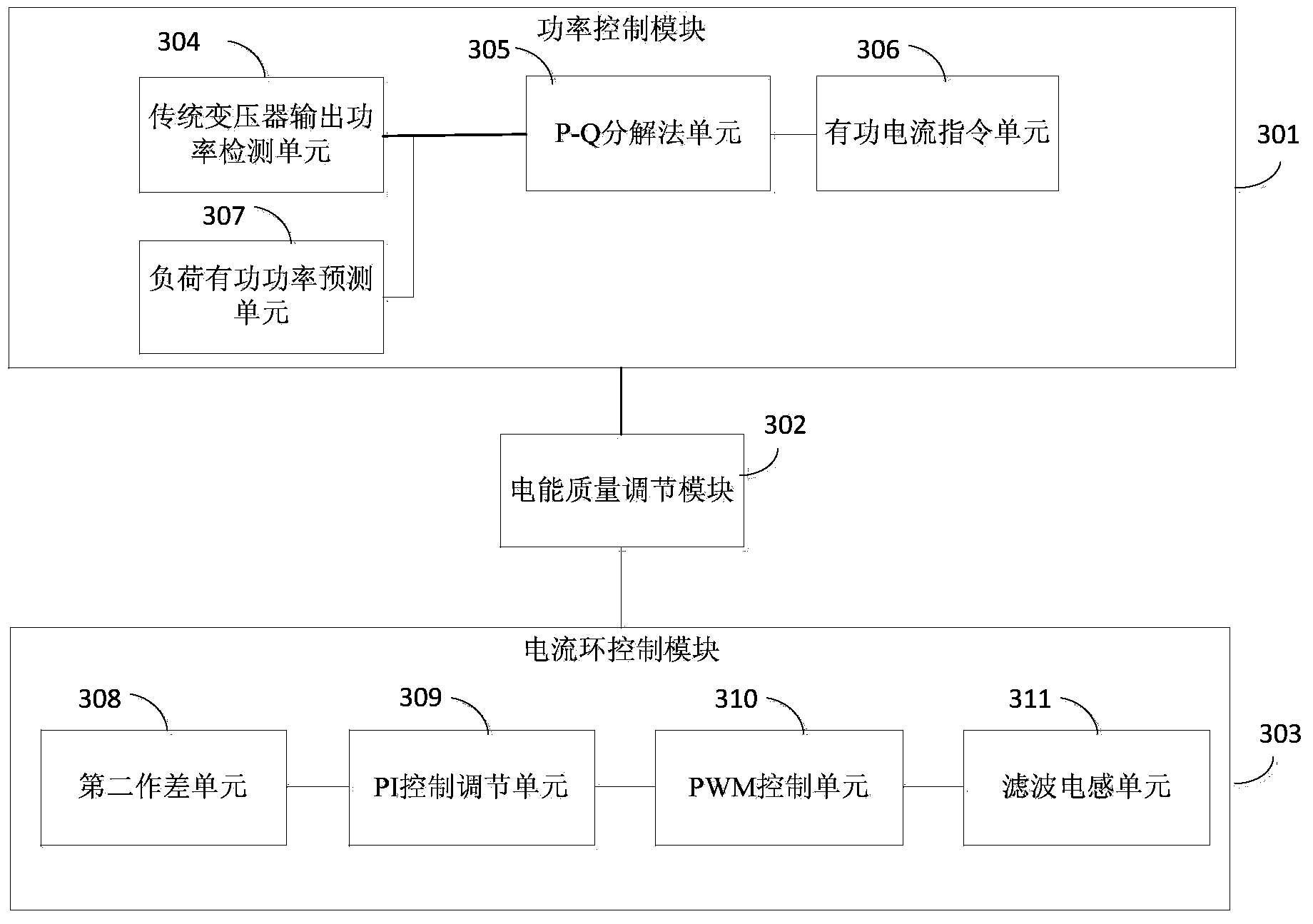

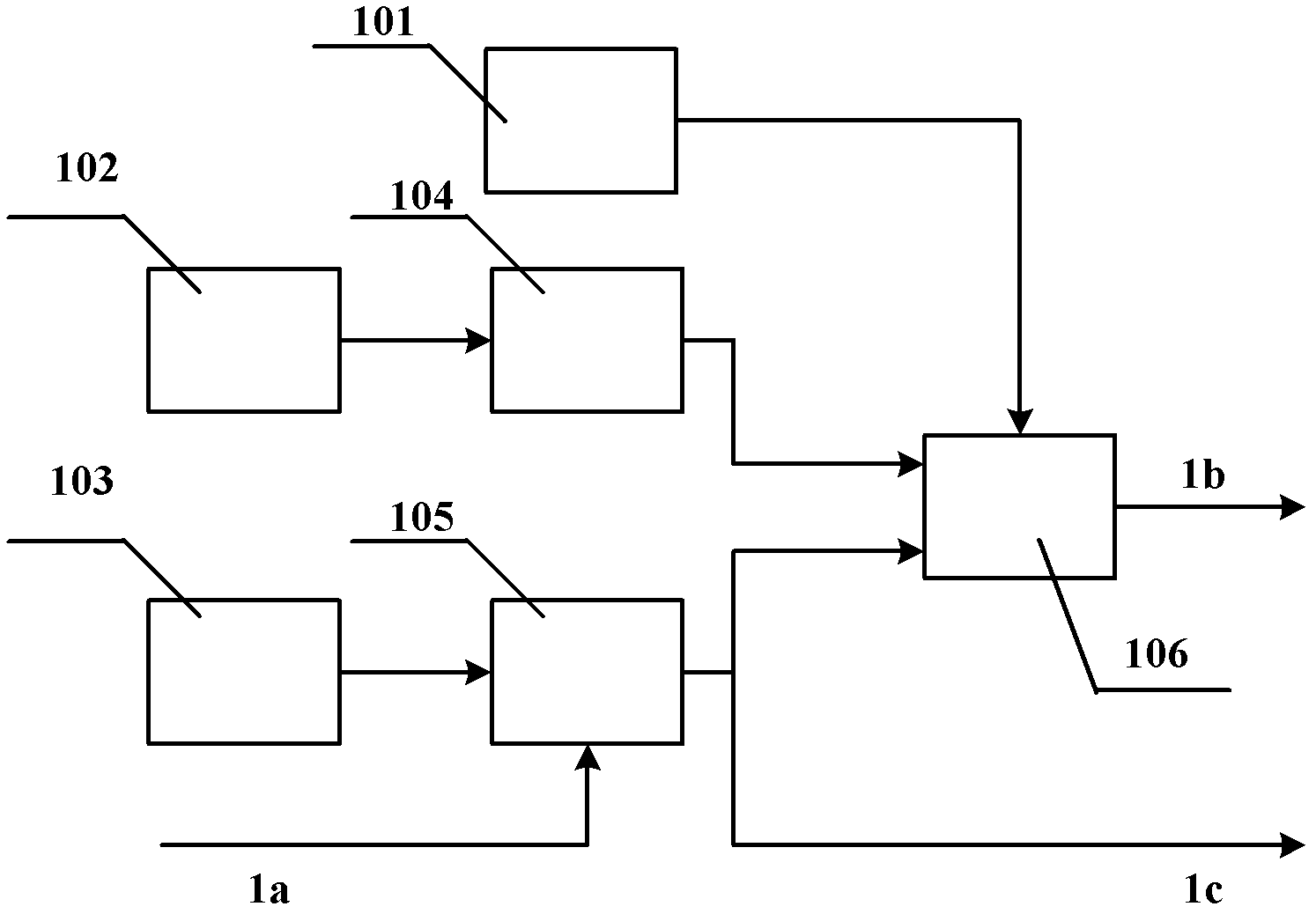

Control method and system for power electronic transformer

ActiveCN103972894AMeet expansion needsLarge capacityReactive power adjustment/elimination/compensationReactive power compensationTransformerDistribution power system

The invention provides a control method and system for a power electronic transformer. The method includes the steps that S1, an active current instruction value of the power electronic transformer is determined, and active power which the power electronic transformer needs to output is controlled; S2, a reactive harmonic current instruction value of the power electronic transformer is determined; S3, according to the active current instruction value and the reactive harmonic current instruction value, a recombination current instruction value of the power electronic transformer is determined; S4, the current of the power electronic transformer is detected; S5, the output current of the power electronic transformer is controlled to follow the recombination current instruction value through a current control algorithm. The power electronic transformer and a traditional transformer operate in a parallel connection mode, while the load active power is provided, the quality of electric energy of a low-voltage grid is adjusted, distribution network contamination is eliminated, and stability and power supply reliability of a power distribution system are improved.

Owner:ELECTRIC POWER RES INST OF GUANGXI POWER GRID CO LTD +1

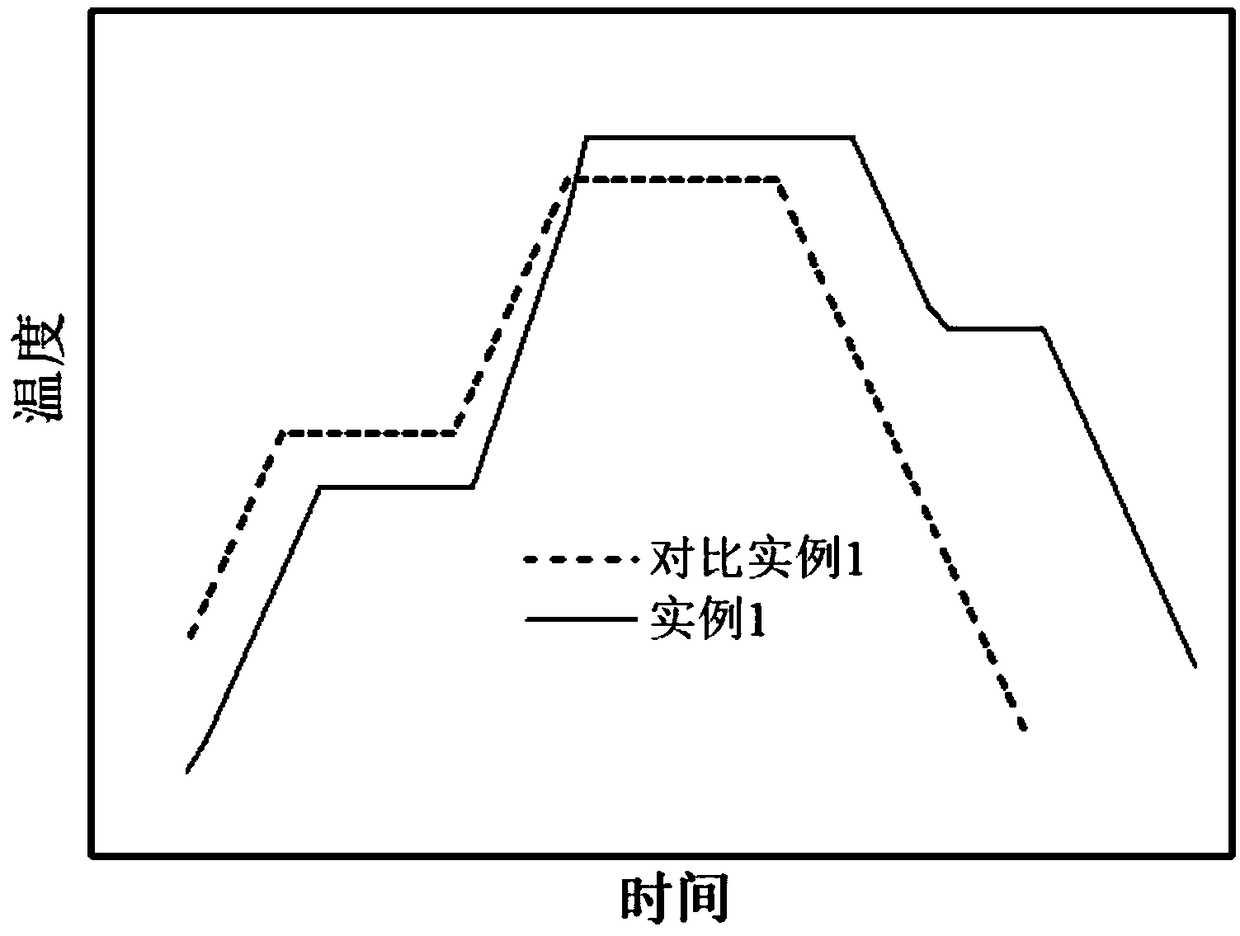

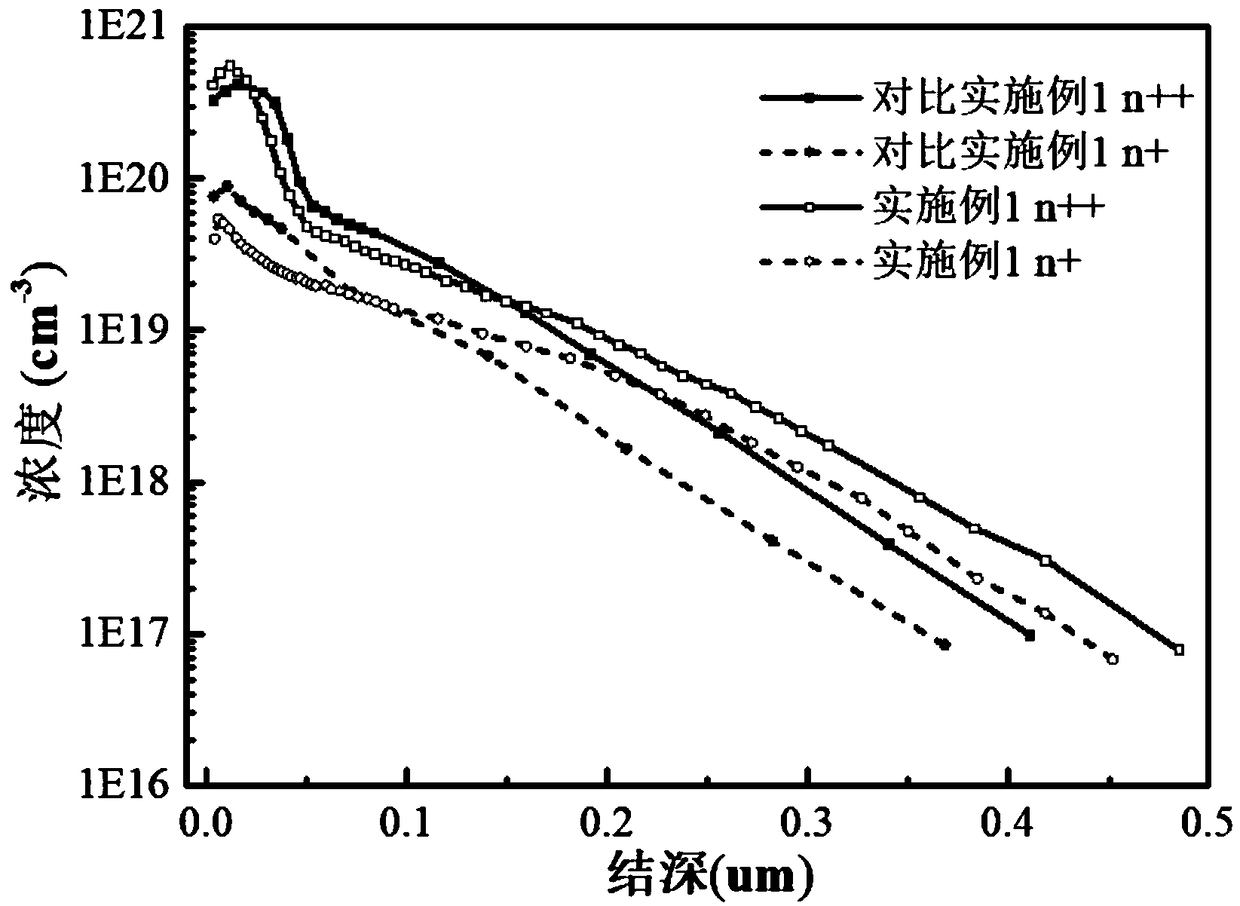

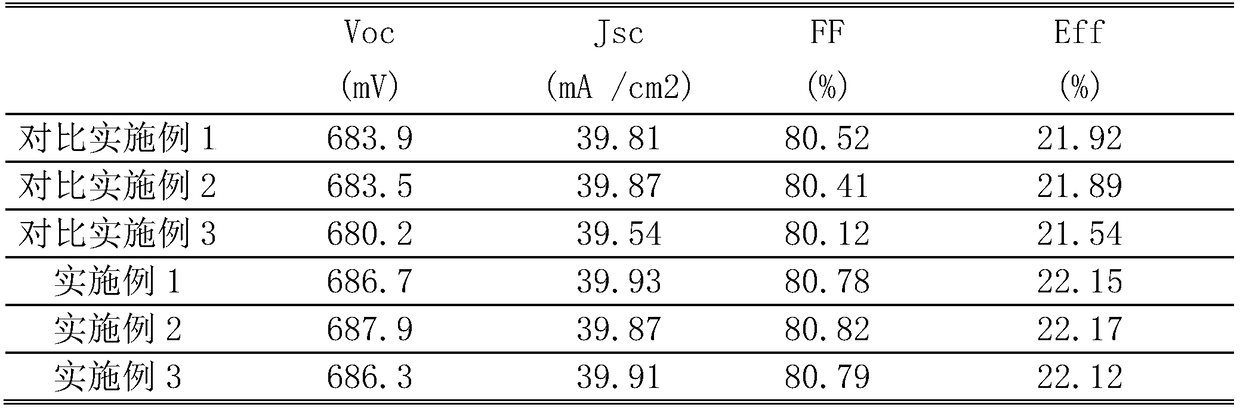

A step-by-step phosphorus doping method for high-efficiency and low-cost crystalline silicon batteries

ActiveCN109166794AIncrease the open circuit voltageReduce concentrationFinal product manufactureSemiconductor/solid-state device manufacturingHigh concentrationHigh surface

The invention belongs to the technical field of solar cell manufacturing, and relates to a step-by-step phosphorus doping method of a high-efficiency and low-cost crystal silicon cell, namely a primary depletion diffusion combined with secondary high-concentration shallow layer diffusion and back etching method. By controlling the flow of oxygen, A low-temperature low-phosphorus source depositionis carry out for that first time on a p-type silicon substrate by nitrogen flow rate and phosphorus oxychloride flow rate, After a long time of high temperature propulsion, the phosphorus in the phosphor-silicate glass is exhausted, and the low surface concentration layer n + is realized. The second time, the phosphor-free glass is deposited on the phosphor-silicate glass, and the high surface concentration layer n + + is pushed to form a very thin high concentration layer, which can be quickly etched off by means of back etching. The method can accurately control the phosphorus doping distribution in different regions independently to ensure that the non-electrode region has low doping concentration and low recombination current so as to ensure higher open-circuit voltage. The electrode region has high doping concentration, which forms good ohmic contact with the metal electrode and ensures that the filling factor is not lost, so as to improve the photoelectric conversion performanceof the battery as a whole.

Owner:CHANGZHOU UNIV +1

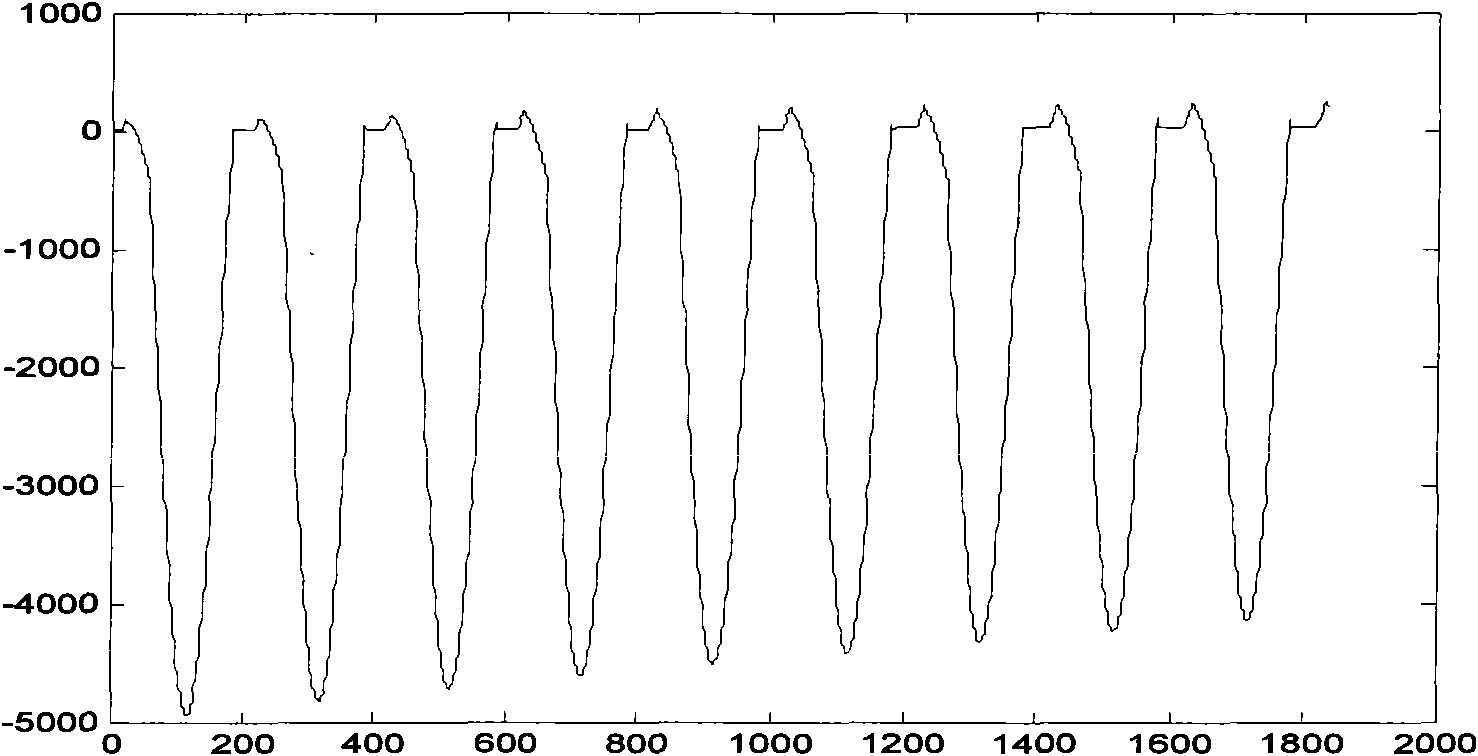

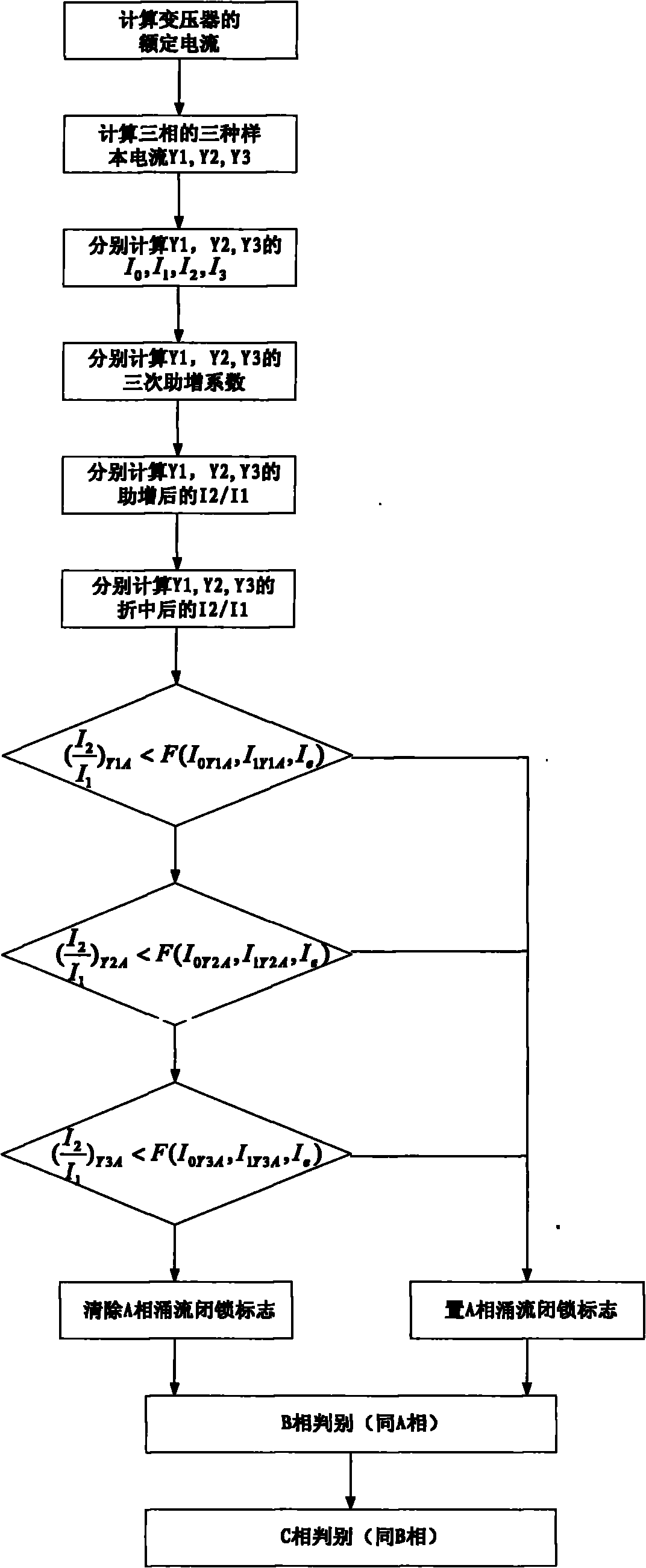

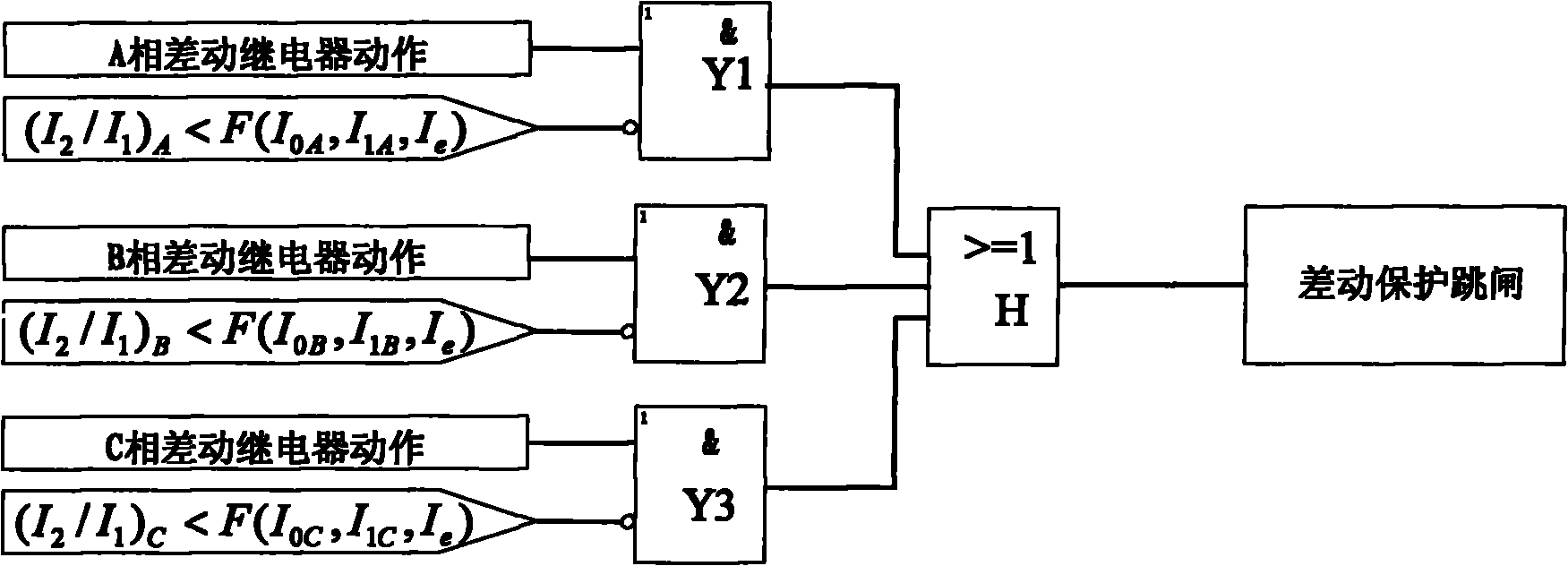

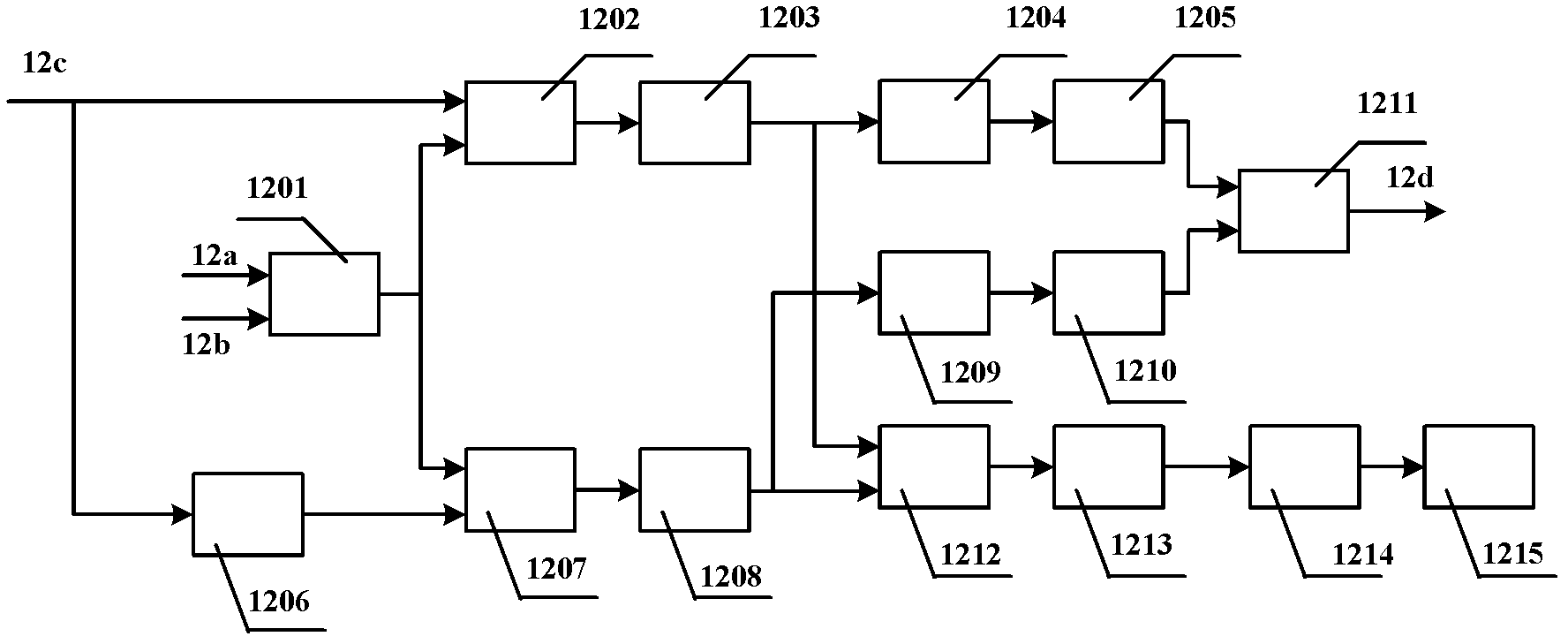

Multi-component recombination current flashy flow judgment method of transformer and block relay

ActiveCN101777753ASolve the problem of slow movement speedReliability is not reducedEmergency protective circuit arrangementsRecombination currentHarmonic

The invention discloses a multi-component recombination current flashy flow block relay for identifying excitation flashy flow of a transformer, aiming at solving the problems of differential protection malfunction caused by excitation flashy flow during air delivery and rapid action of differential protection when a turn-to-turn fault occurs. The invention provides a multi-component recombination current flashy flow block relay which consists of sample current selection of the flashy flow, three-time harmonic infeed scheme, an electric scheme of the current harmonic ratio and self-adaptive flashy flow block criteria, wherein the action logic diagram of the relay is shown in the attached figure. The test result indicates that the relay has good sensitivity, safety and rapidness. The invention also discloses a recombination current flashy flow judgment method.

Owner:CENT CHINA GRID +1

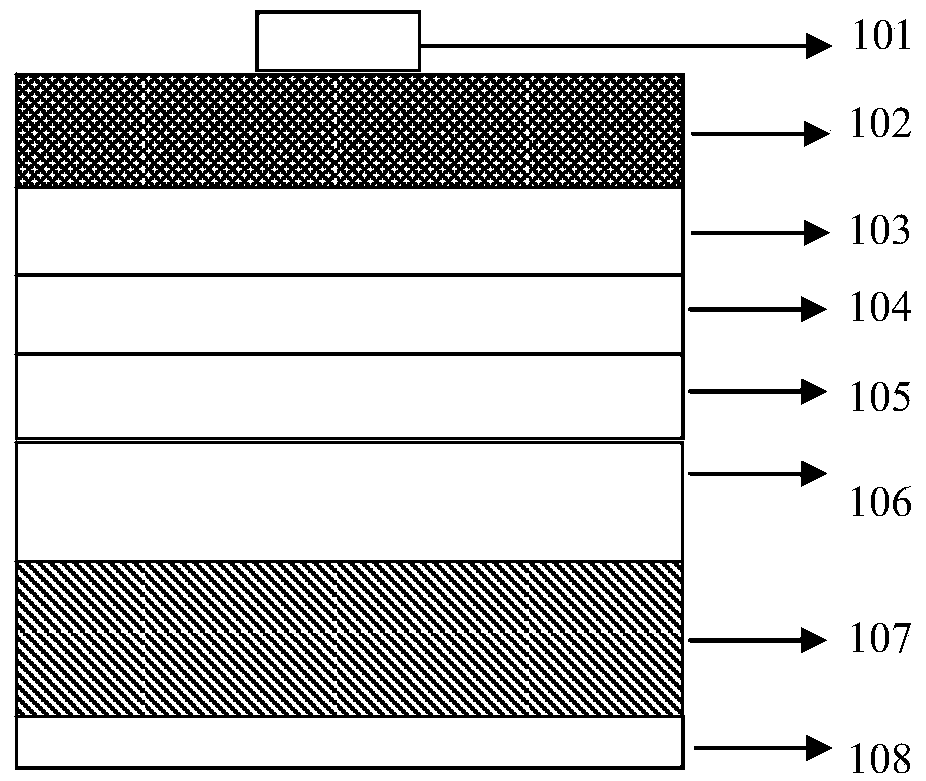

CNT and silver nanometer wire recombination current expanding layer LED and manufacturing method thereof

ActiveCN104009141AImprove efficiencyGuaranteed light transmissionSemiconductor devicesElectricityPower flow

The invention discloses a CNT and silver nanometer wire recombination current expanding layer LED and a manufacturing method thereof. A current expanding layer is composed of a super-aligned CNT and a silver nanometer wire. The CNT and silver nanometer wire recombination current expanding layer LED comprises a substrate, an n-type current limit layer, an active area, a p-type current limit layer and a window layer which are stacked longitudinally in sequence, further comprises a p electrode and an n electrode, and is characterized in that the window layer is paved with the CNT and silver nanometer wire recombination current expanding layer. The LED can enable current to be more evenly diffused to the active area from the electrodes so as to improve the photoelectric conversion efficiency.

Owner:BEIJING UNIV OF TECH

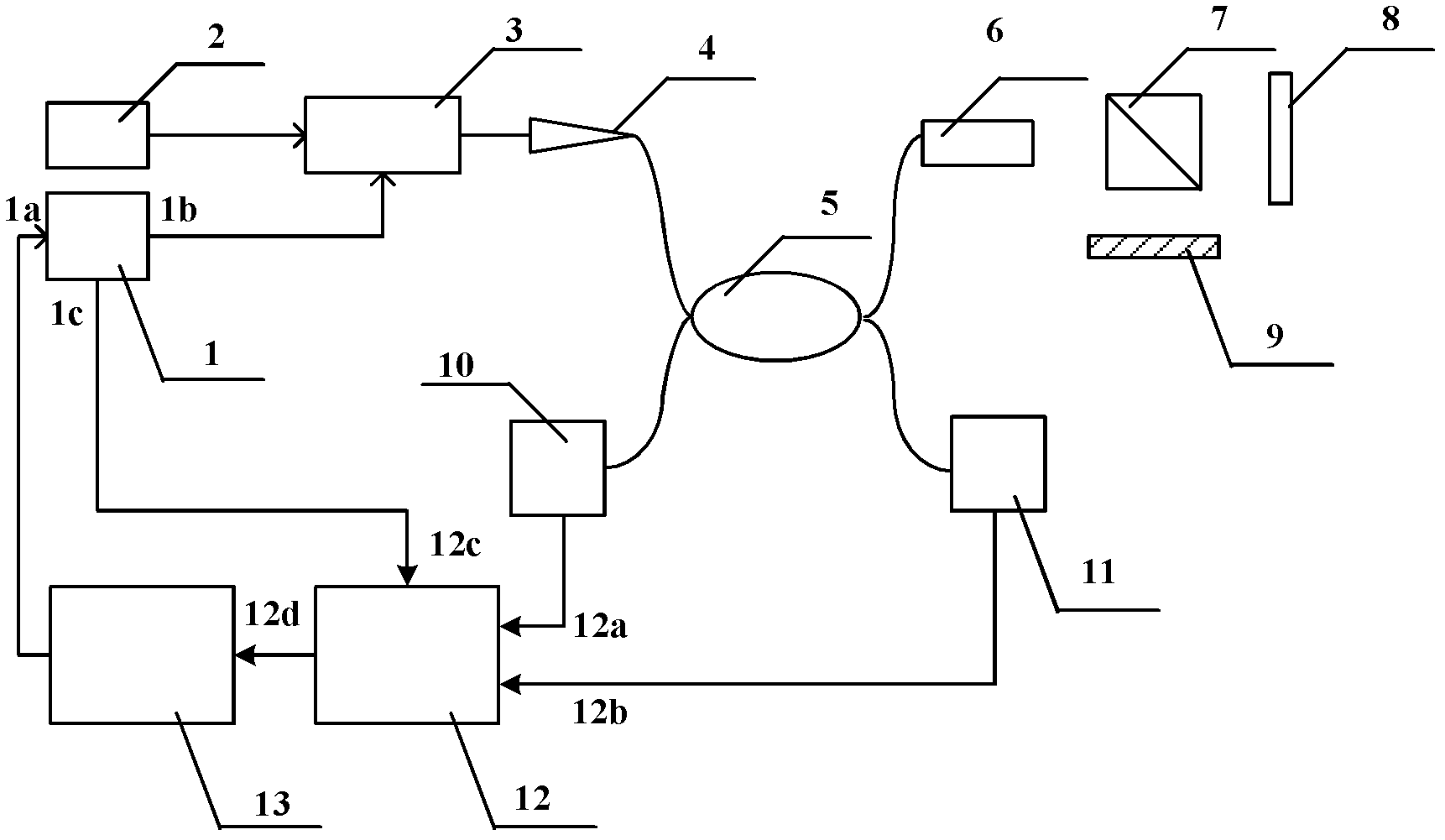

Laser interferometer for recombination current modulation semiconductor

ActiveCN102636109ASimple structureLarge measuring rangeUsing optical meansOptical fiber couplerFeedback control

The invention provides a laser interferometer for a recombination current modulation semiconductor, which is suitable for measuring the distance. The structure of the laser interferometer comprises a light source, an isolator, an optical fiber coupler, a collimator, a photoelectric detector, a beam splitter, a reference mirror, a signal processor and a feedback controller, wherein the light source is provided with a driving power source and a temperature controller; and a driving power supply provides two sinusoidal modulating current with different frequencies to control the light source. The photoelectric detector converts a received interference signal into an electric signal to be input into the signal processor, so that the distance to be measured can be computed. The feedback controller is connected with the photoelectric detector, and the high-frequency modulating depth is locked by the feedback control. Compared with the prior art, the interferometer provided by the invention is simple and compact in structure, so that the double-sinusoidal phase modulation can be realized due to the recombination current; and the work parameter is locked by means of the feedback control, so that the stability of the system can be enhanced, the measurement precision can be improved, and the real-time measurement can be realized.

Owner:杭州光学精密机械研究所

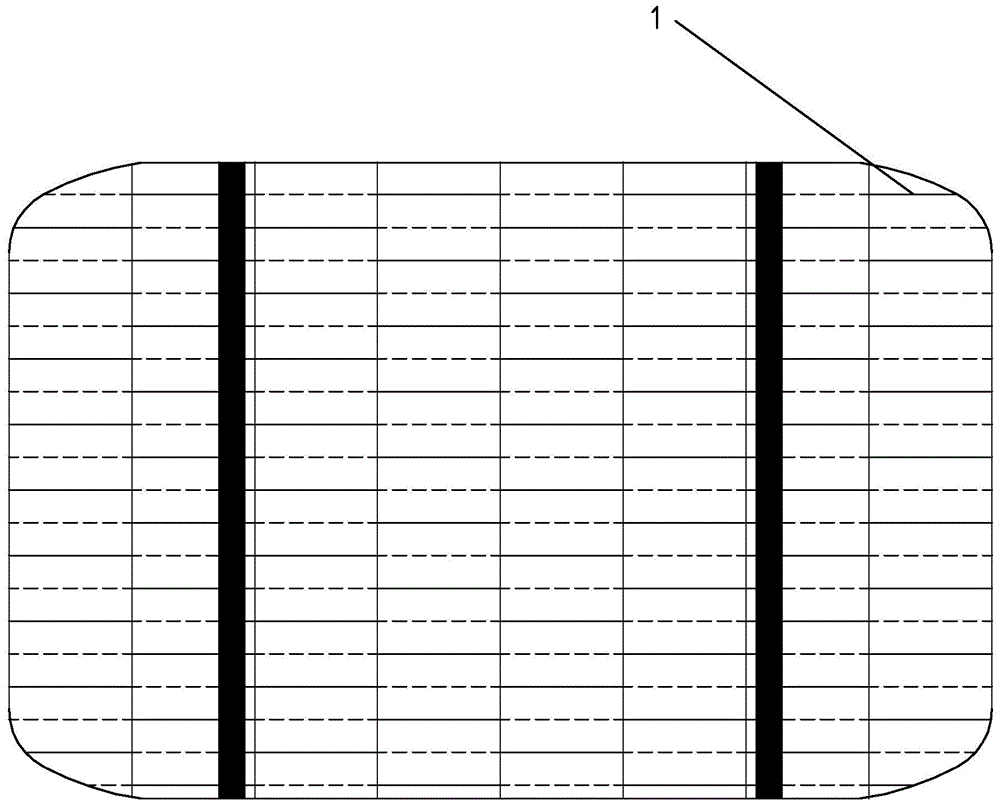

Gate line structure making local contact with obverse surface of solar battery and manufacturing method thereof

ActiveCN104465805AIncrease the open circuit voltageImprove conversion efficiencyFinal product manufacturePhotovoltaic energy generationRecombination currentElectrical battery

The invention discloses a gate line structure making local contact with the obverse surface of a solar battery and a manufacturing method of the gate line structure. The gate line structure making local contact with the obverse surface of the solar battery is provided with a plurality of gate line electrodes. Each gate line electrode is provided with a plurality of local contact metal electrodes and a plurality of non-contact metal electrodes. The local contact metal electrodes are electrically connected with the non-contact metal electrodes. The non-contact metal electrodes are made of non-burnthrough metal electrode paste. The local contact metal electrodes penetrate through a dielectric film of the battery and then make ohmic contact with a silicon substrate. According to the gate line structure, it can be guaranteed that under the condition of avoiding electron transport, the metalized area is effectively reduced, and recombination current of a metalized area is reduced; accordingly, open-circuit voltage of the battery is effectively increased, and the conversion efficiency of the solar battery is improved.

Owner:TRINA SOLAR CO LTD

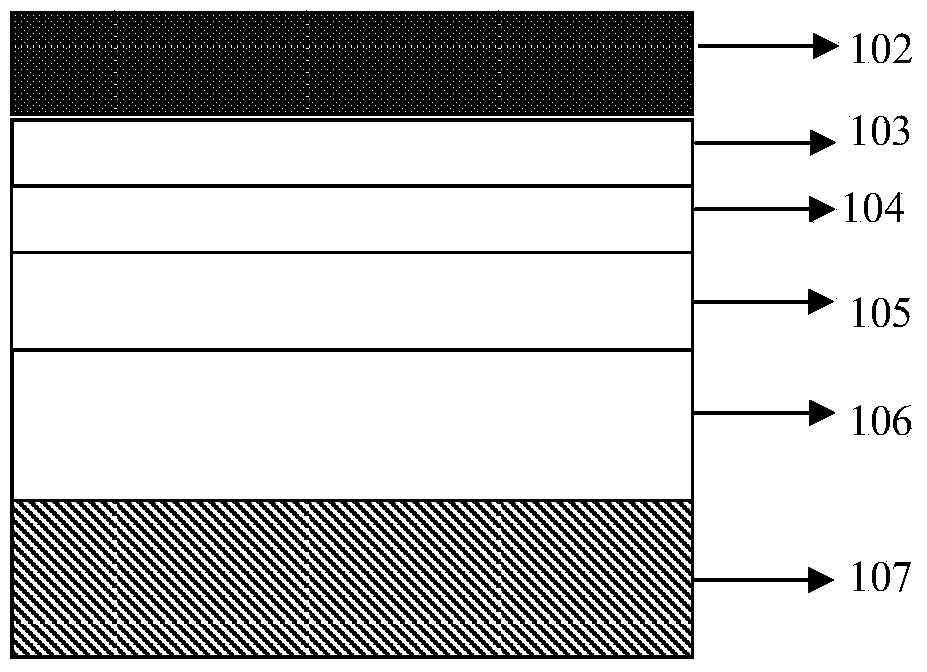

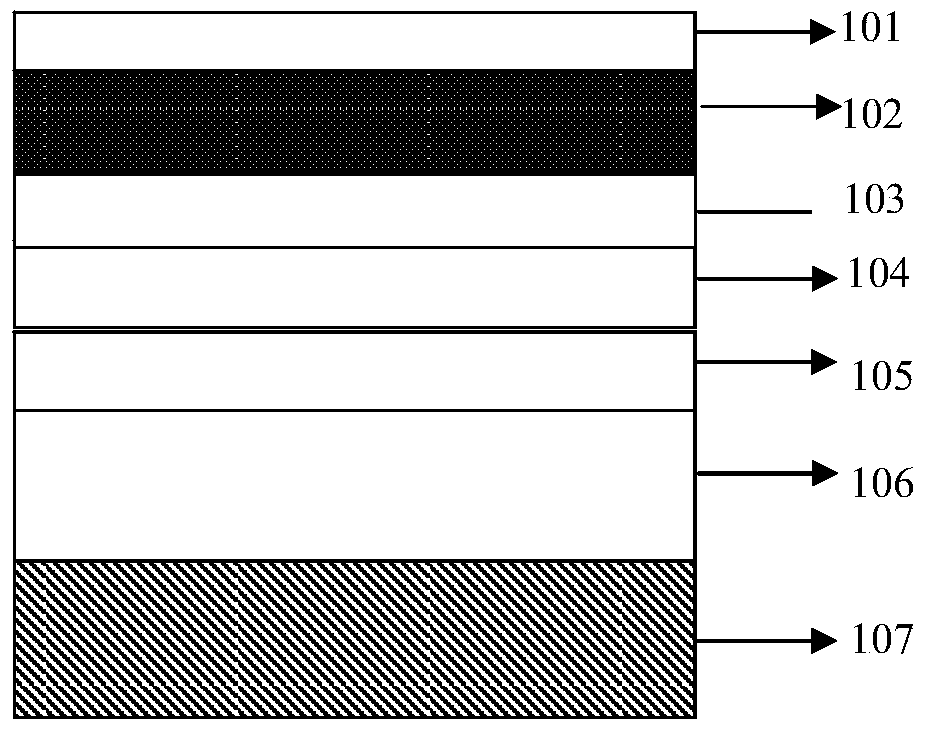

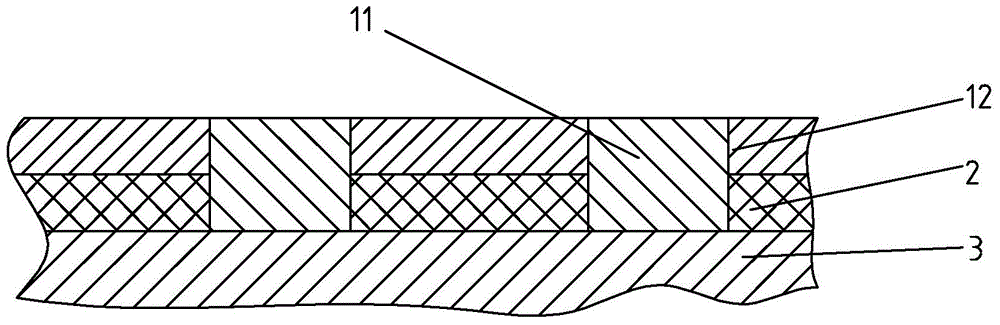

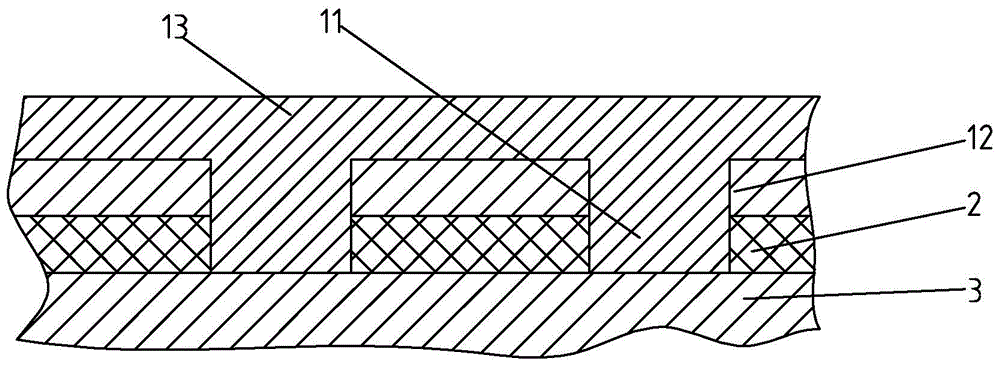

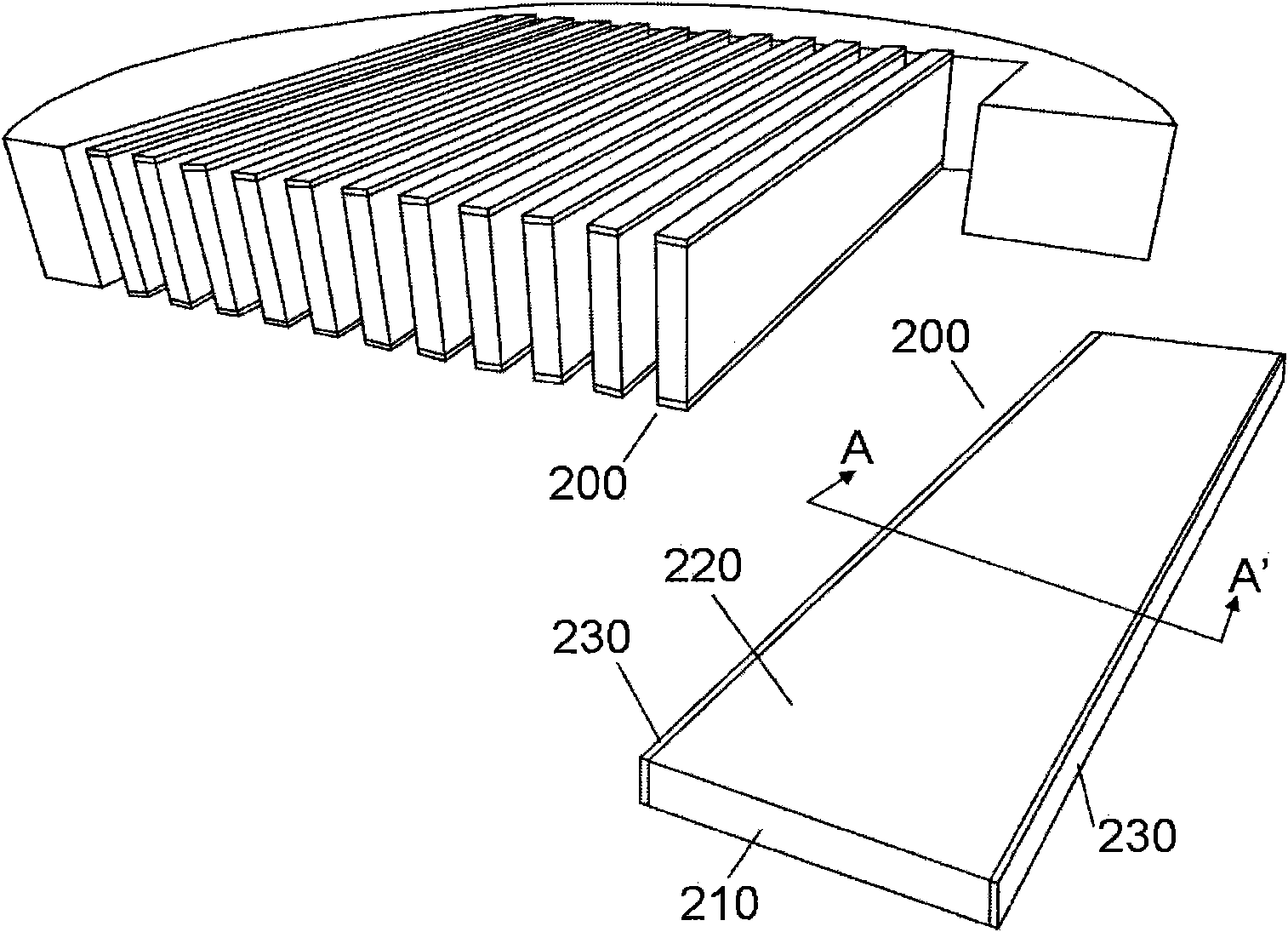

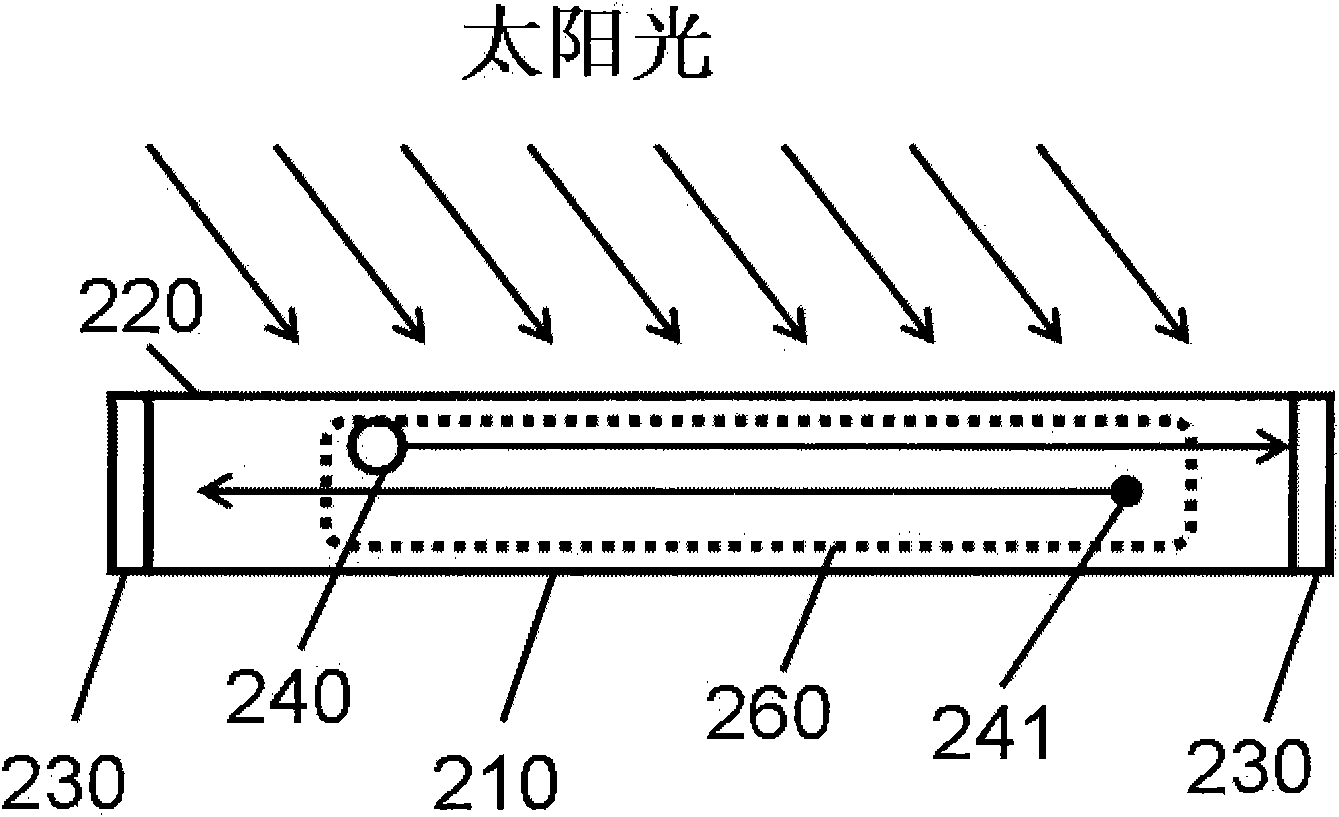

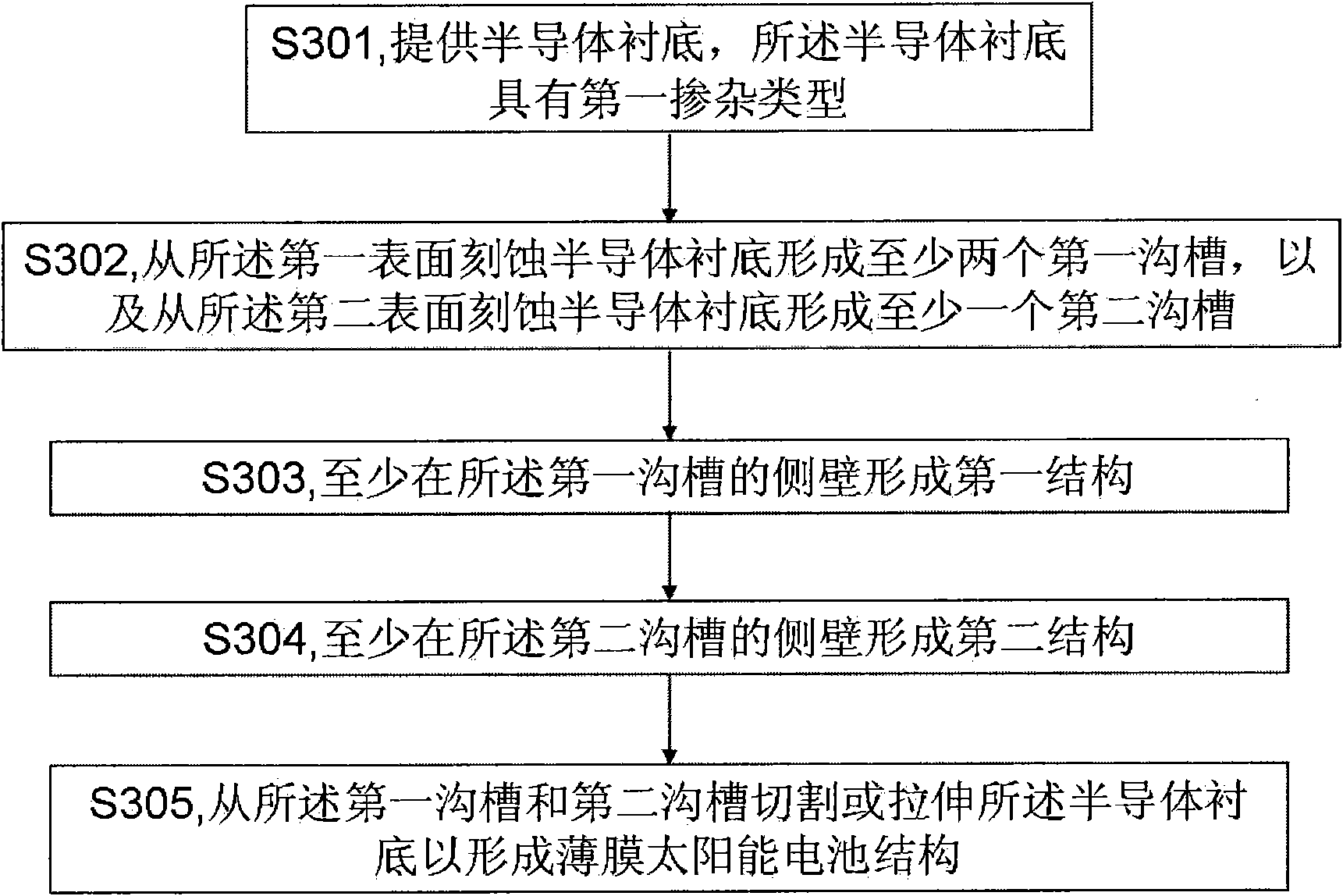

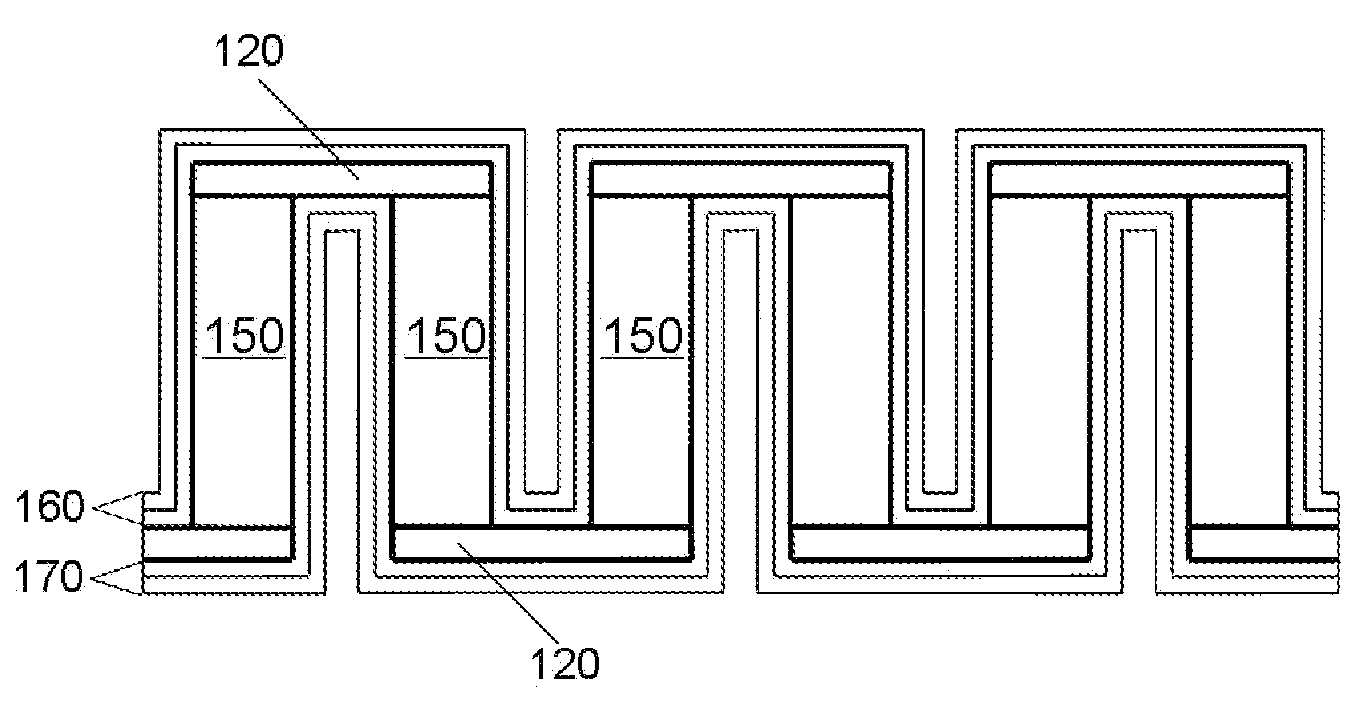

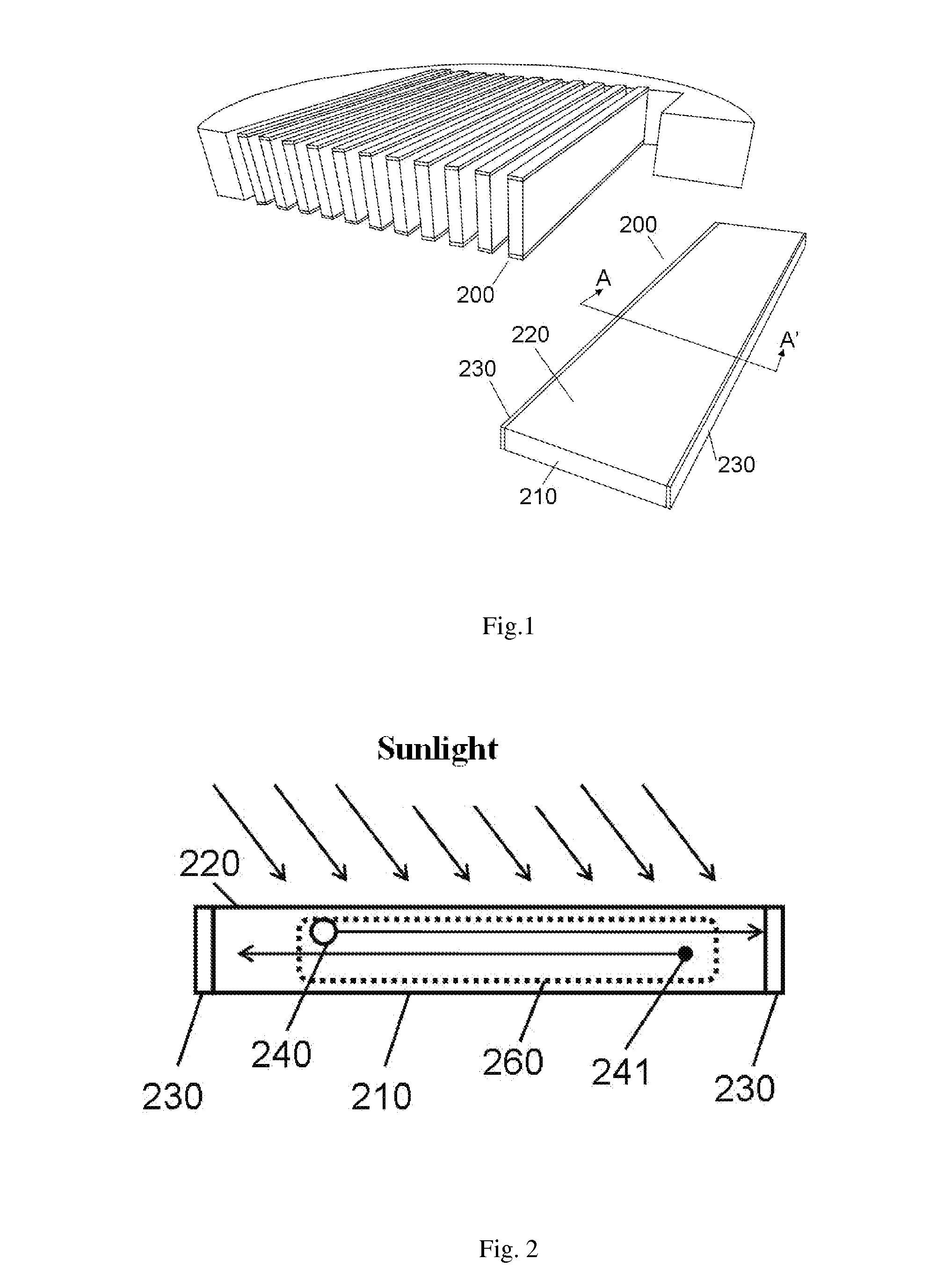

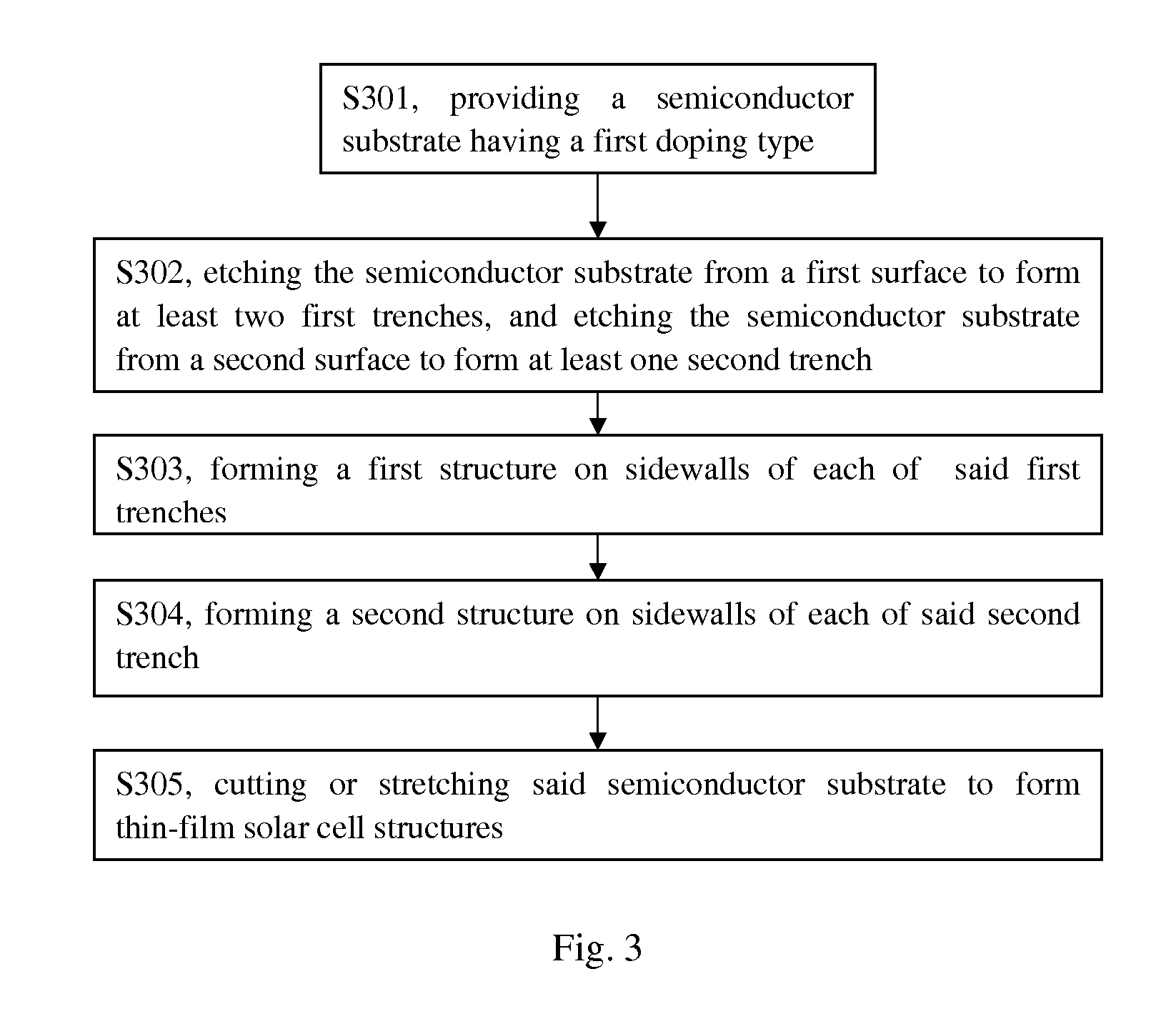

Thin film of solar battery structure, thin film of solar battery array and manufacturing method thereof

ActiveCN102122679AIncrease the effective areaReduce compound distanceFinal product manufactureSemiconductor/solid-state device manufacturingManufacturing cost reductionPower flow

A thin film solar battery structure and a manufacturing method thereof, and a thin film solar battery array are provided. The manufacturing method of the thin film solar battery structure includes: at least two first trenches are formed by etching semiconductor substrate from the first surface; at least one of the second trench is formed by etching the semiconductor substrate from the second surface; each of the second trench is located between two adjacent first trenches; a first structure is formed on the side wall of at least the first trench; a second structure is formed on the side wall of at least the second trench; the semiconductor substrate is cut or drawn from the first trench and the second trench for forming the thin film solar battery structure, the distance of the electrodes can be reduced effectively, the probability recombination of the electron and the hole can be reduced, the bulk recombination current and the surface bulk recombination current can be reduced, the efficiency of the electrical power can be increased, the thin film solar battery structure and the manufacturing method thereof can reduce the semiconductor material and reduce the manufacturing cost.

Owner:江苏盐新汽车产业投资发展集团有限公司

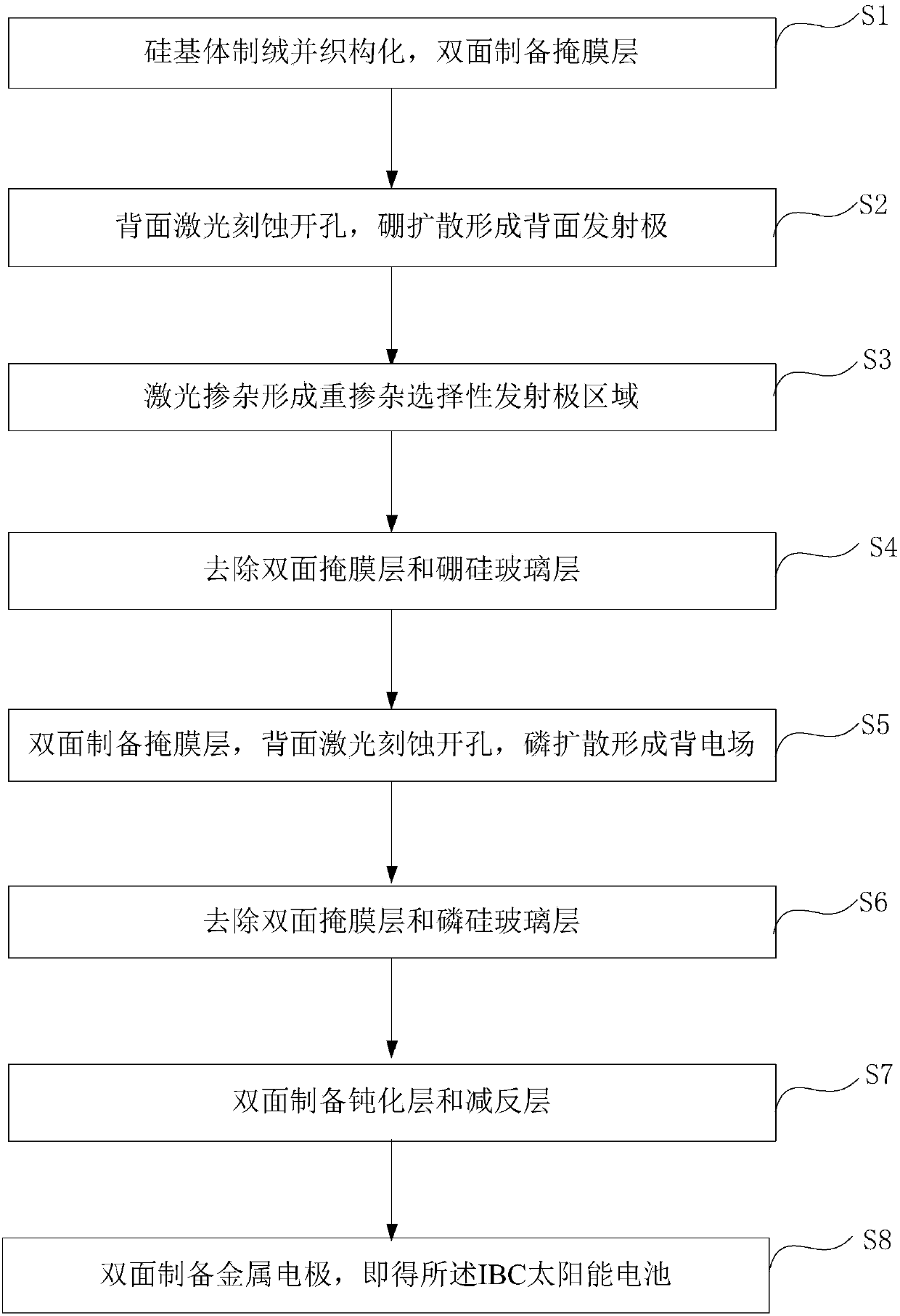

Preparation method of IBC solar cell

InactiveCN107946408ASimple manufacturing processAvoid damageFinal product manufacturePhotovoltaic energy generationLaser etchingRecombination current

The present invention discloses a preparation method of an IBC solar cell. The method comprises the steps of: performing texture surface making and texturing of a silicon substrate, and performing double-sided preparation of a mask layer; performing back surface laser etching opening, and performing boron diffusion to form a back surface emitting electrode; performing laser doping to form a heavydoping selectivity emitting electrode area; removing the double-sided mask layer and a borosilicate glass layer; performing double-sided preparation of a mask layer, performing back surface laser etching opening, and performing phosphorus diffusion to form a back surface field; removing the double-sided mask layer and a phosphorosilicate glass layer; performing double-sided preparation of a passivation layer and an anti-reflection layer; and performing double-sided preparation of a metal electrode, and obtaining an IBC solar cell. The preparation method of an IBC solar cell is simple in preparation process, simplifies the cell preparation process, can avoid damaging of the silicon substrate, can improve the production efficiency and can greatly reduce the recombination current of the emitting electrode.

Owner:ZHEJIANG JINKO SOLAR CO LTD +1

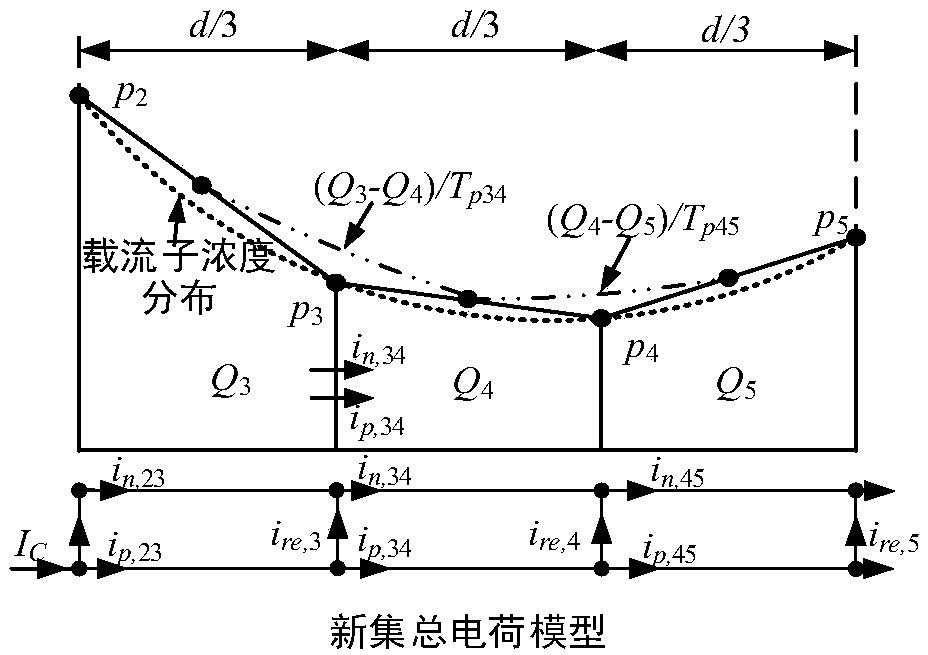

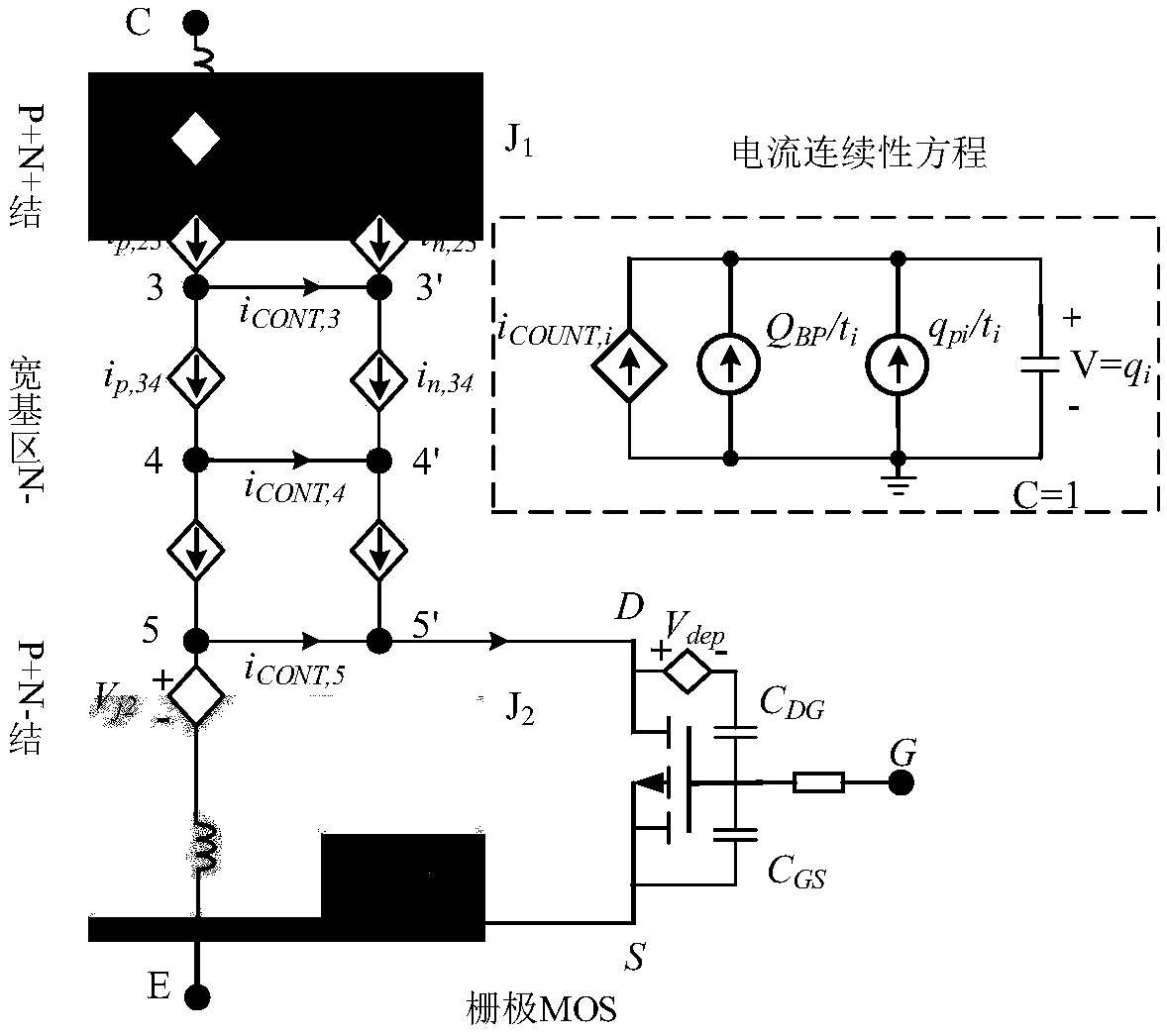

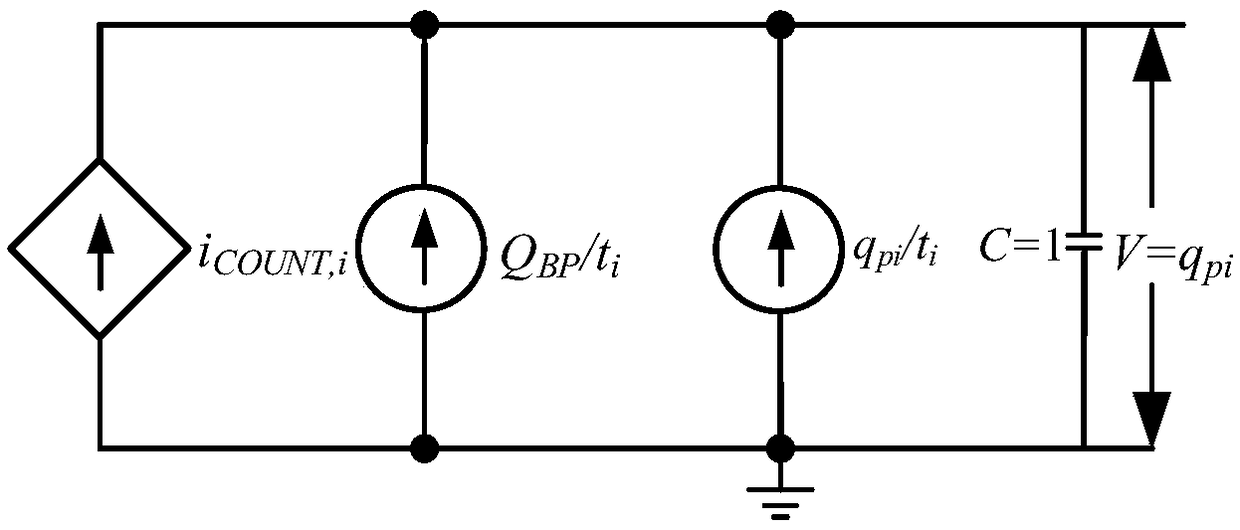

Wide base region lumped electric charge modeling method for large-power bipolar semiconductor device

ActiveCN108763696AImprove simulation accuracyReduce mistakesSpecial data processing applicationsElectron currentRecombination current

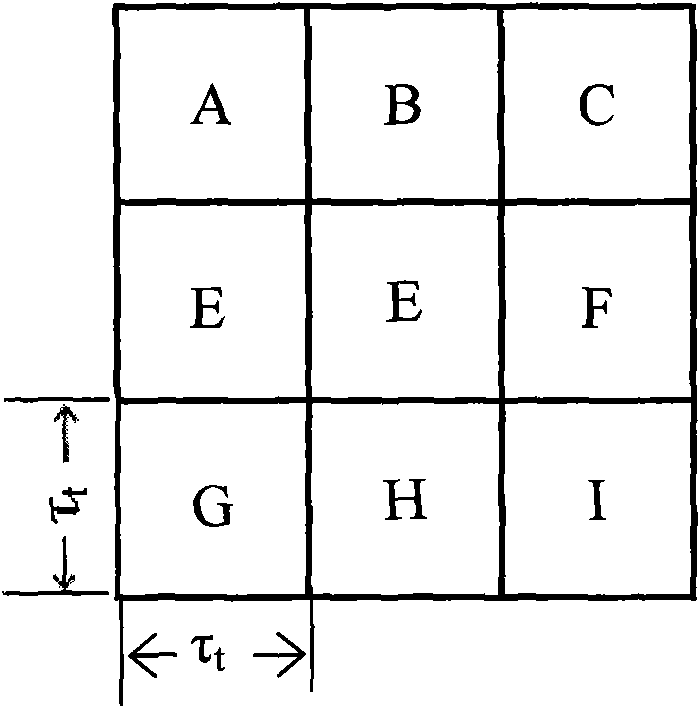

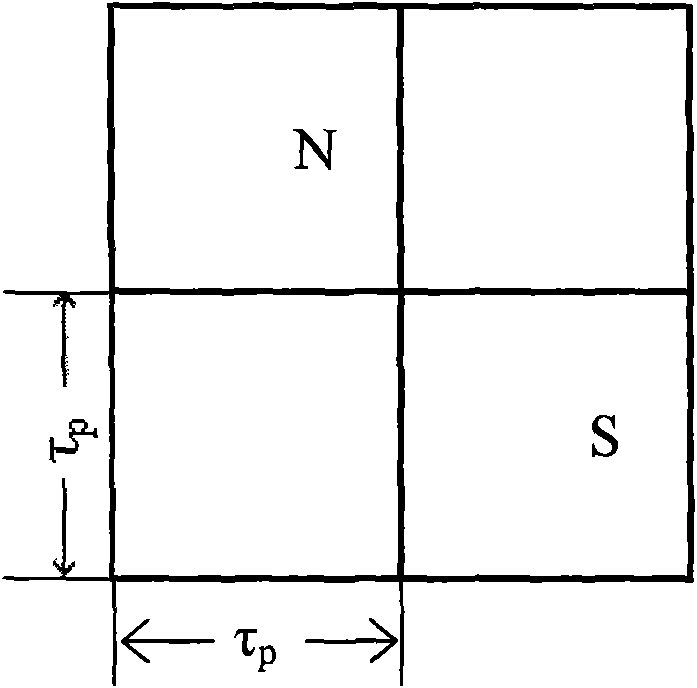

The invention discloses a wide base region lumped electric charge modeling method for a large-power bipolar semiconductor device. A wide base region is divided into n areas with equal width, and n pieces of lumped electric charges are adopted for independently expressing electric charge distribution in the n pieces of areas, wherein n is greater than or equal to 3; according to the electric chargedistribution of the area and an electric charge motion mechanism, drift current and diffusion current are defined; through a current density equation, hole current and electron current between adjacent areas are determined; according to a current continuity equation, recombination current caused by electric charges in each area is determined; and the hole current, the electron current and the recombination current are taken as a basis to establish a wide base region lumped electric charge model. By use of the method, the simulation accuracy of the wide base region lumped electric charge modelis improved, and therefore, the accurate calculation of an electric charge quantity in the wide base region of the large-power bipolar semiconductor device under multiple working conditions is realized.

Owner:NAVAL UNIV OF ENG PLA

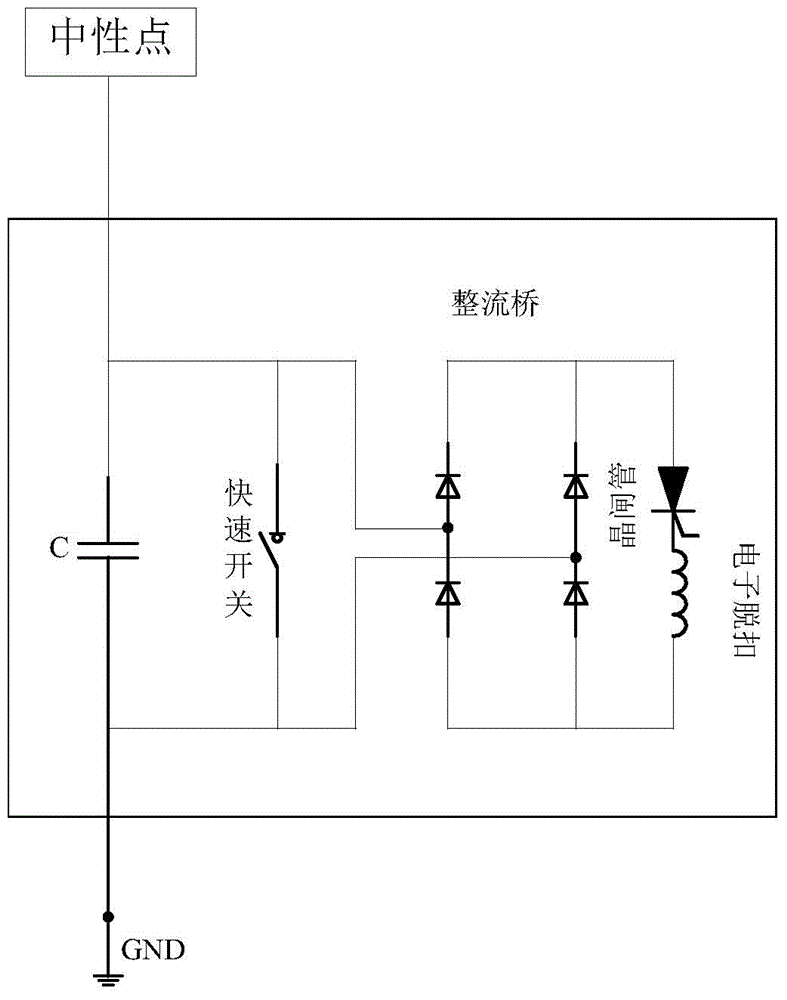

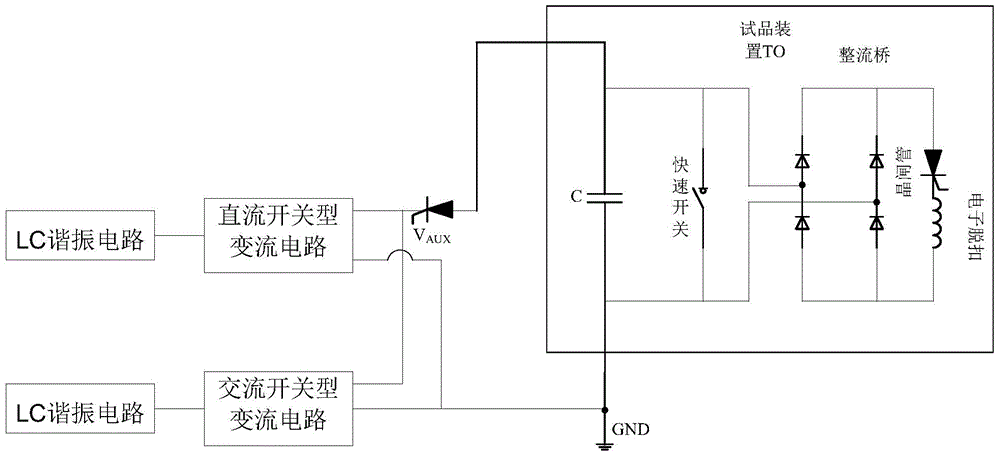

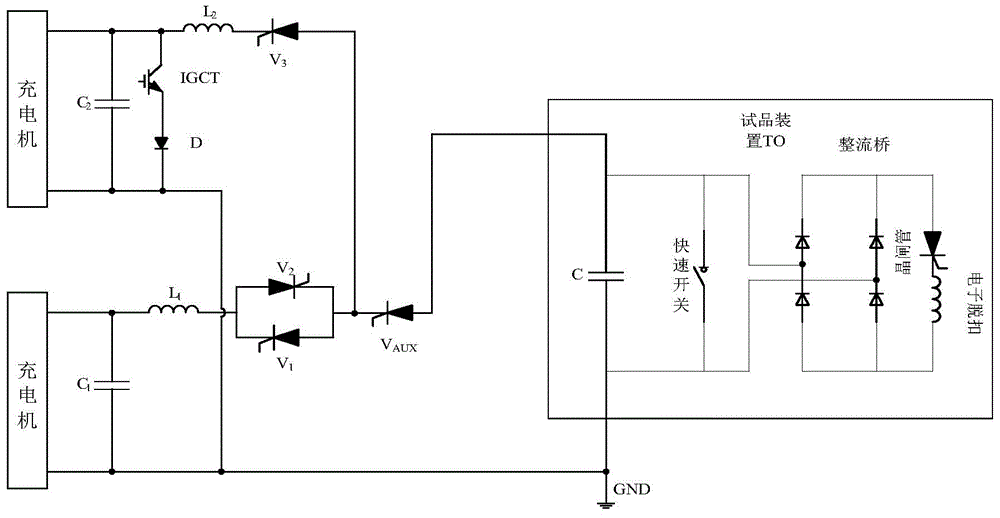

A voltage transformer neutral point direct current suppression apparatus test system

ActiveCN104931840AAchieve currentAchieve stressElectrical testingRecombination currentLc resonant circuit

The invention relates to a voltage transformer neutral point direct current suppression apparatus test system comprising a direct current charging unit, an alternating current charging unit, a trigger valve Vaux, an output terminal and a grounding terminal. One terminal of the alternating current charging unit and one terminal of the direct current charging unit are connected to the output terminal through the trigger valve Vaux. The output terminal is used for connection to a high-voltage terminal test device TO. The other terminal of the alternating current charging unit and the other terminal of the direct current charging unit are connected to the grounding terminal. The grounding terminal is used for grounding after being connected to a grounding terminal of the test device. The direct current charging unit is composed of an LC resonance circuit and a direct current switching mode convertor circuit. The alternating current charging unit is composed of an LC resonance circuit and an alternating current switching mode convertor circuit. A recombination current corresponding to an actual working condition is generated by means of recombining an alternating current with a direct current. The recombination current is then applied to the test device to carry out corresponding examining, so that testing of the current and voltage stress of a voltage transformer neutral point direct current suppression apparatus is realized.

Owner:XJ ELECTRIC +1

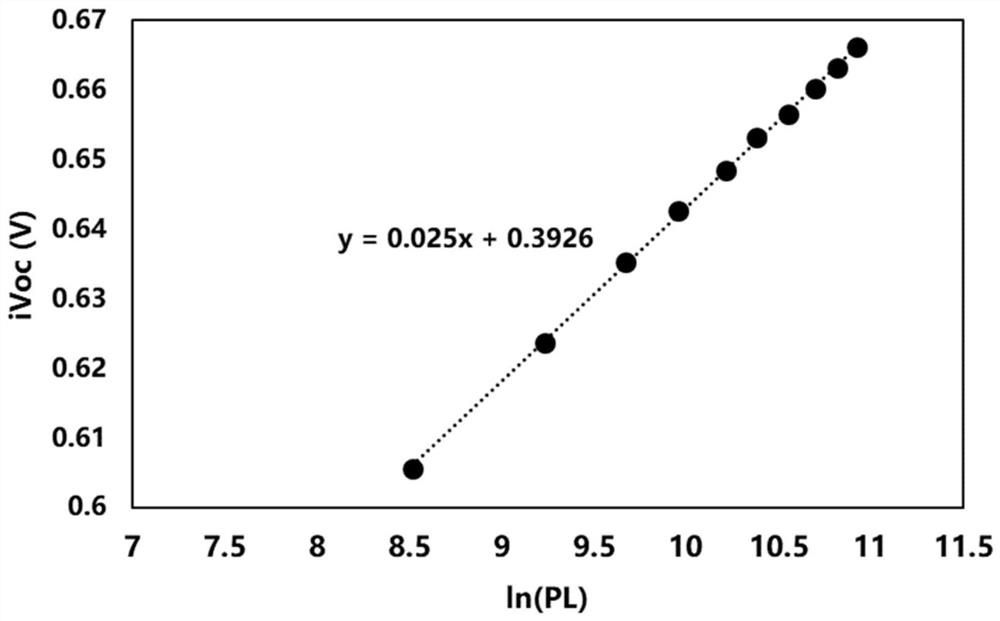

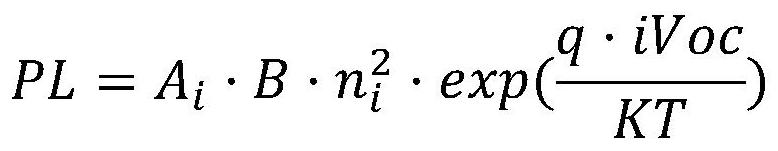

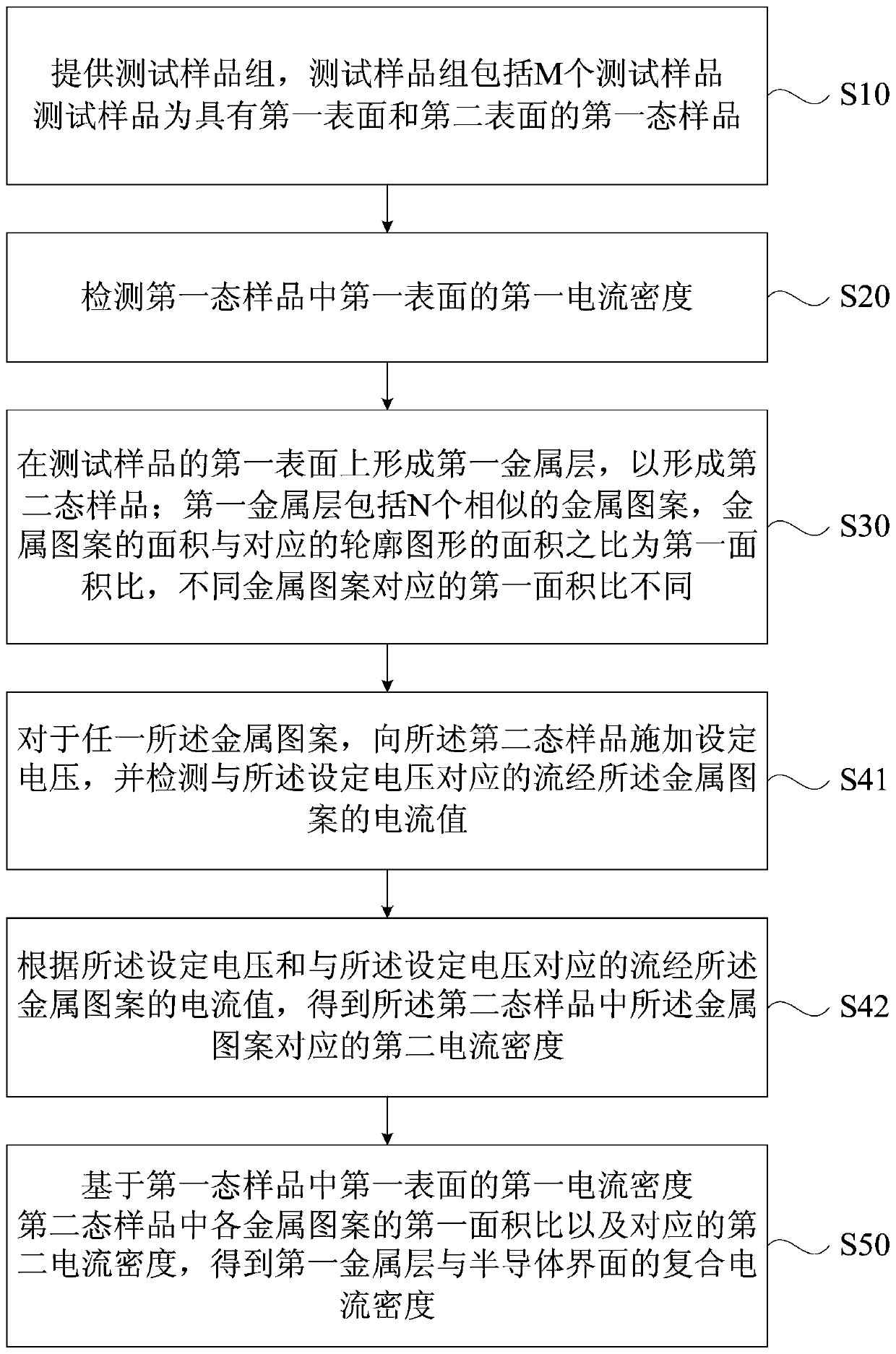

Method for testing density distribution of recombination current on surface of double-sided symmetrical passivated silicon wafer

ActiveCN113075172AHigh resolutionSemiconductor characterisationFluorescence/phosphorescenceLuminous intensityParticle physics

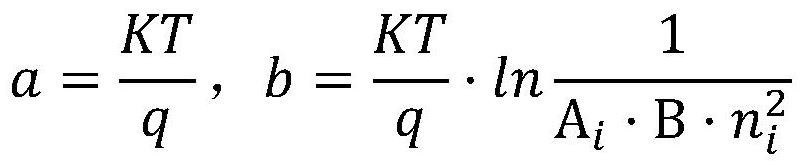

The invention provides a method for testing density distribution of recombination current on the surface of a double-sided symmetrical passivated silicon wafer. The testing method comprises the following steps: preparing a double-sided symmetrical passivated silicon wafer, and testing the thickness and the average reflectivity; under a series of illumination conditions with different intensities, testing excess carrier concentration [delta]n and average luminous intensity PL of a to-be-tested area of a double-sided symmetric passivation silicon wafer, and calculating an iVoC value according to [delta]n; establishing a linear relational expression iVoc=a*ln(PL)+b between the iVoc and the ln (PL); and illuminating the double-sided symmetric passivated silicon wafer, testing the luminous intensity PLij of any region, and calculating the recombination current density distribution J0ij of the surface of the double-sided symmetric passivated silicon wafer according to the relational expression iVOCij =a.ln (PLij)+b and the PLij value. The testing method provided by the invention has the resolution far higher than that of a minority carrier lifetime tester, and can obtain the recombination current density distribution on the whole surface of the double-surface symmetrical passivation silicon wafer.

Owner:CSI CELLS CO LTD +1

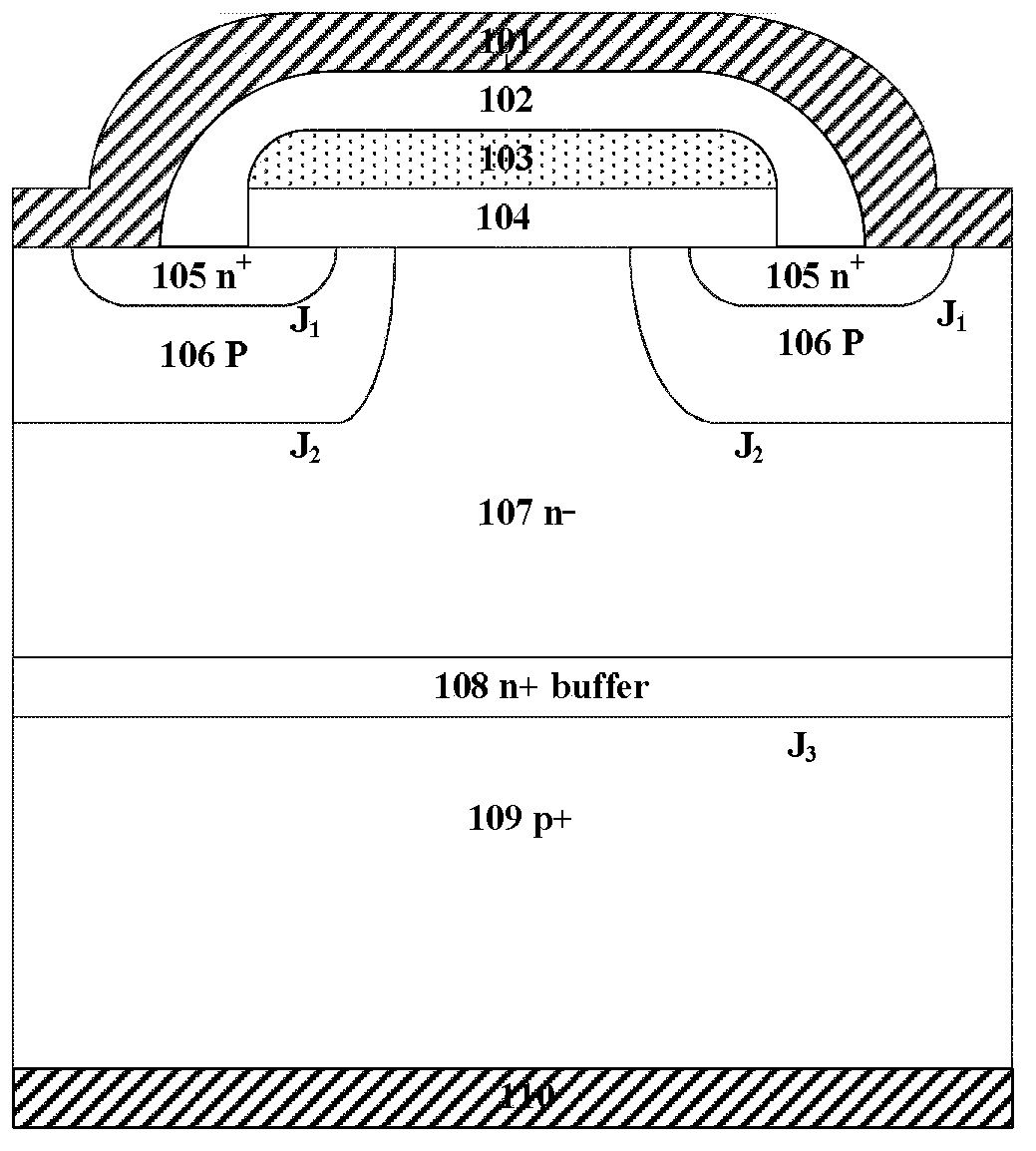

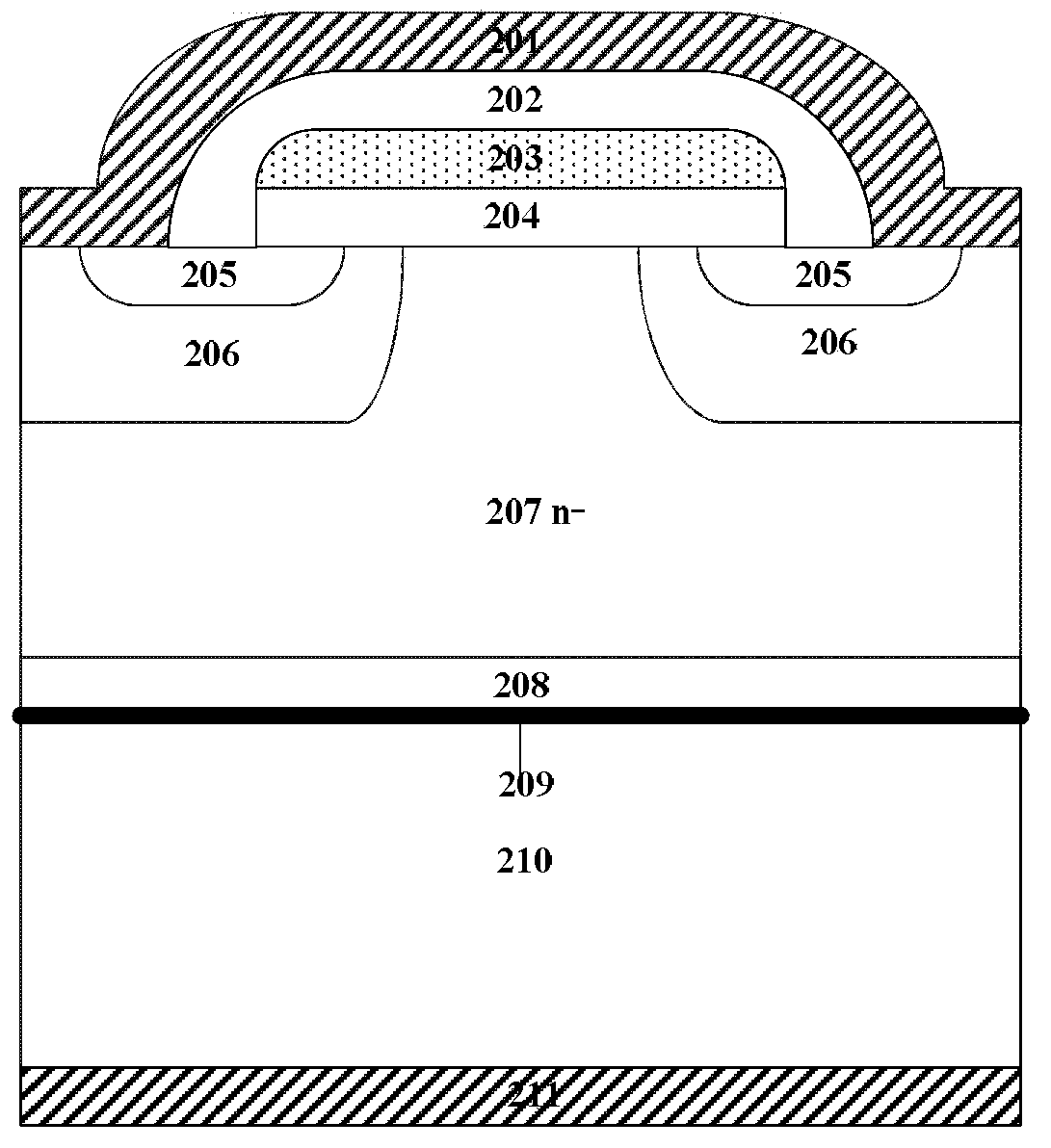

IGBT capable of realizing localized service lifetime controlling and manufacturing method thereof

ActiveCN103633129AShort lifeImprove high temperature characteristicsTransistorSemiconductor/solid-state device manufacturingRecombination currentGate dielectric

The invention brings forward an insulated gate bipolar transistor (IGBT) capable of realizing localized service lifetime controlling and a manufacturing method thereof. The IGBT comprises a current collection region; a buffer layer is formed on the current collection zone; and a drift region is formed on the buffer layer. At least one low-service life high recombination layer is formed between the current collection region and the drift region; and a recombination center is arranged in the low-service life high recombination layer, so that the service life of the carrier is reduced. Besides, well regions are formed in the drift region; emitter regions are formed in the well regions; a gate dielectric layer, a grid electrode and an emitter are successively formed on the drift region; and a collector is formed under the current collection region. According to the invention, because at least one low-service life high recombination layer is formed between the current collection region and the drift region, the low-service life high recombination layer can recombine lots of excess carriers that are generated in a device turn-on state, thereby improving recombination currents and reducing hole injection of the current collection region. Therefore, the turn-off trailing time is shortened; objectives of on-off time reduction and on-off loss reduction can be achieved; and the anti-latch capability of the device is improved.

Owner:BYD SEMICON CO LTD

Composite current driving high pushing force density nine phase plane motor and driver thereof

InactiveCN101394123AReduce volumeReduce weightElectric motor controlPropulsion systemsRange of motionEngineering

A recombination current driving high thrust density nine-phrase planar motor and a driver thereof relate to a recombination current driven high thrust density nine-phrase planar motor and a driver thereof, and belongs to the motor field. Permanent magnets are distributed in a plane matrix type and an armature coil is fixedly arranged on a plane-shaped armature magnet core. The armature coil is divided into nine groups, the coils of each group are connected in series and form nine phrase armature windings, and the nine phrase armature windings are connected in a star-shape manner. When the motor works, all that is required is to connect the nine phrase armature windings to nine driving current signal output ends of the invention, and each driving current is a combined current of an X direction current and a Y direction current. The motor of the invention has the advantages of small size, light weight, simple insulation among winding phrases, large output force in unit volume, quick dynamic response, small positioning force and large rotor motion range. The invention can be applied in the motor which needs two dimensional motions and the controlling field thereof.

Owner:HARBIN INST OF TECH

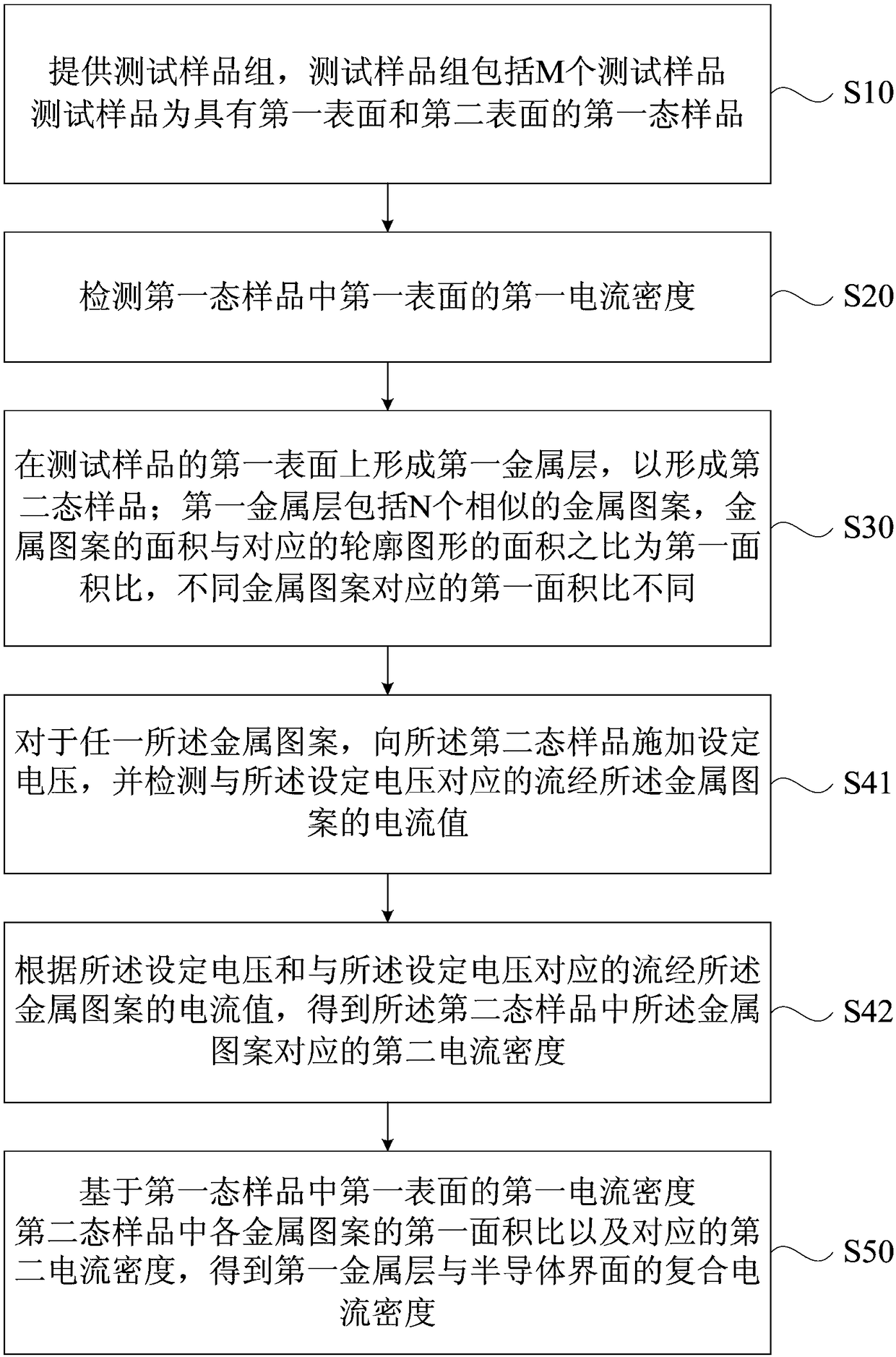

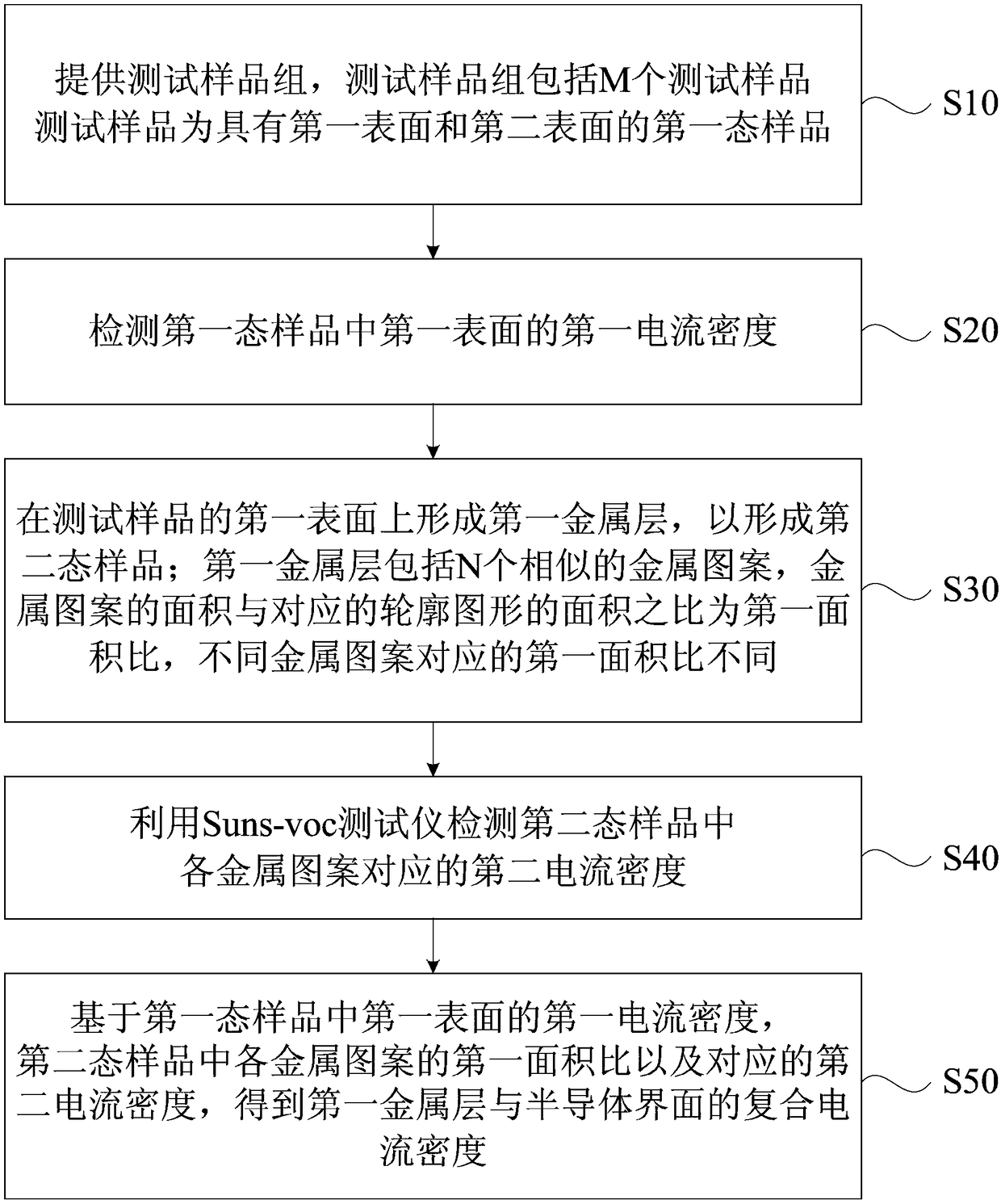

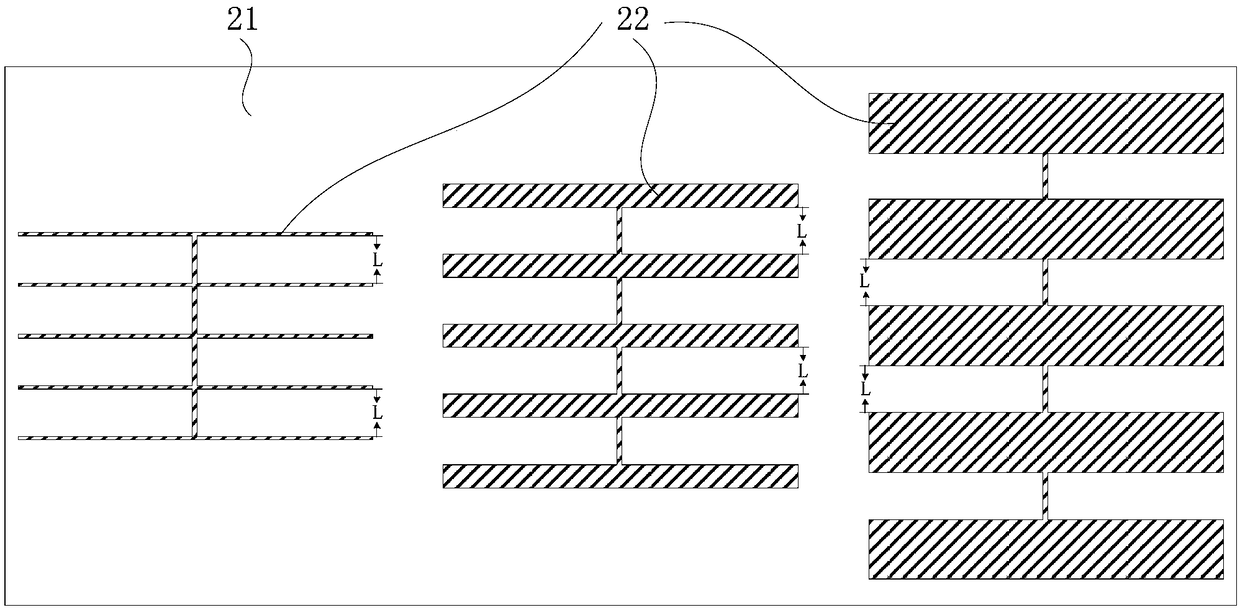

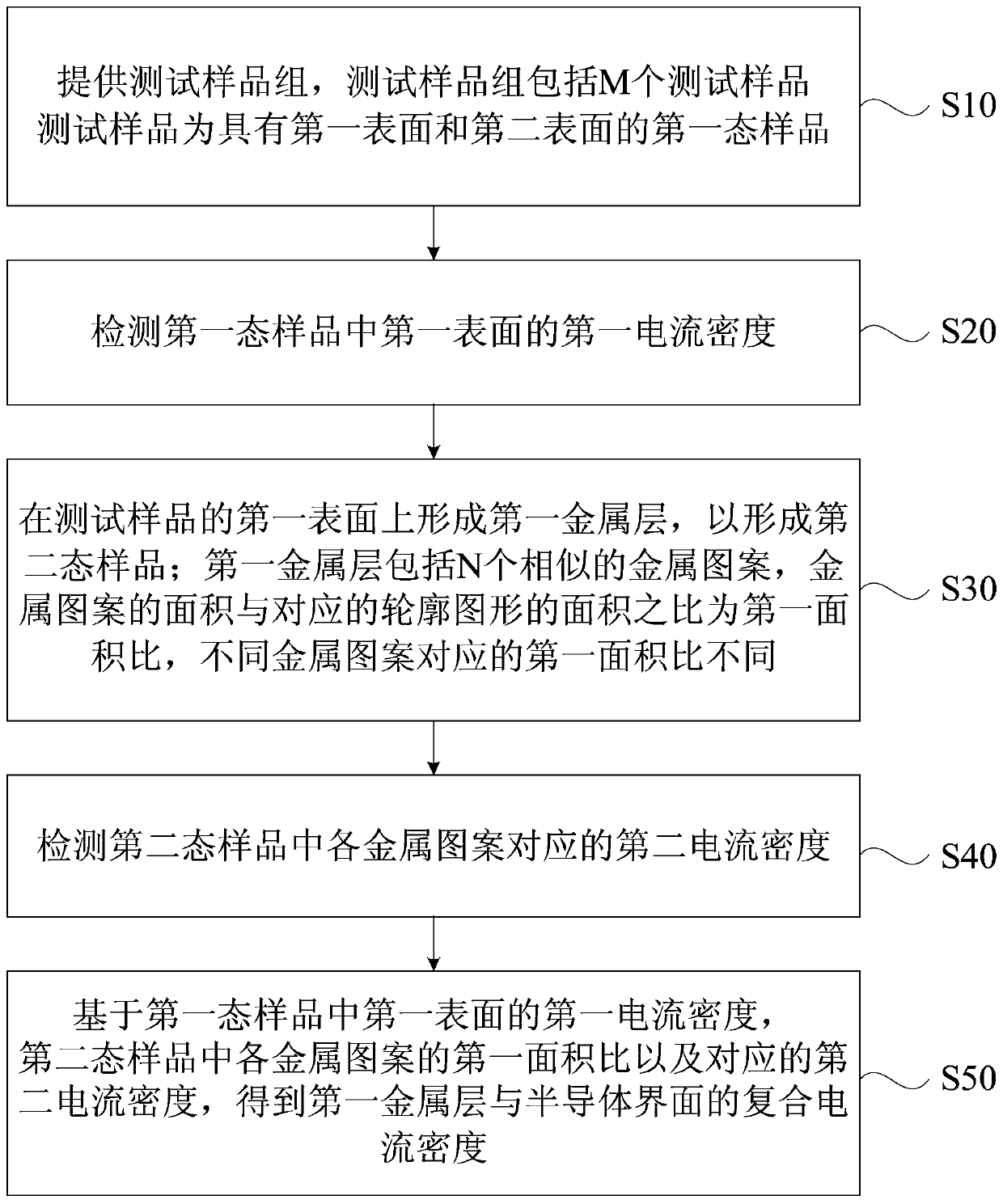

Method and device for testing metal semiconductor interface recombination current density

ActiveCN108196110ASimple processThe test result is accurateCurrent density measurementsRecombination currentArea ratio

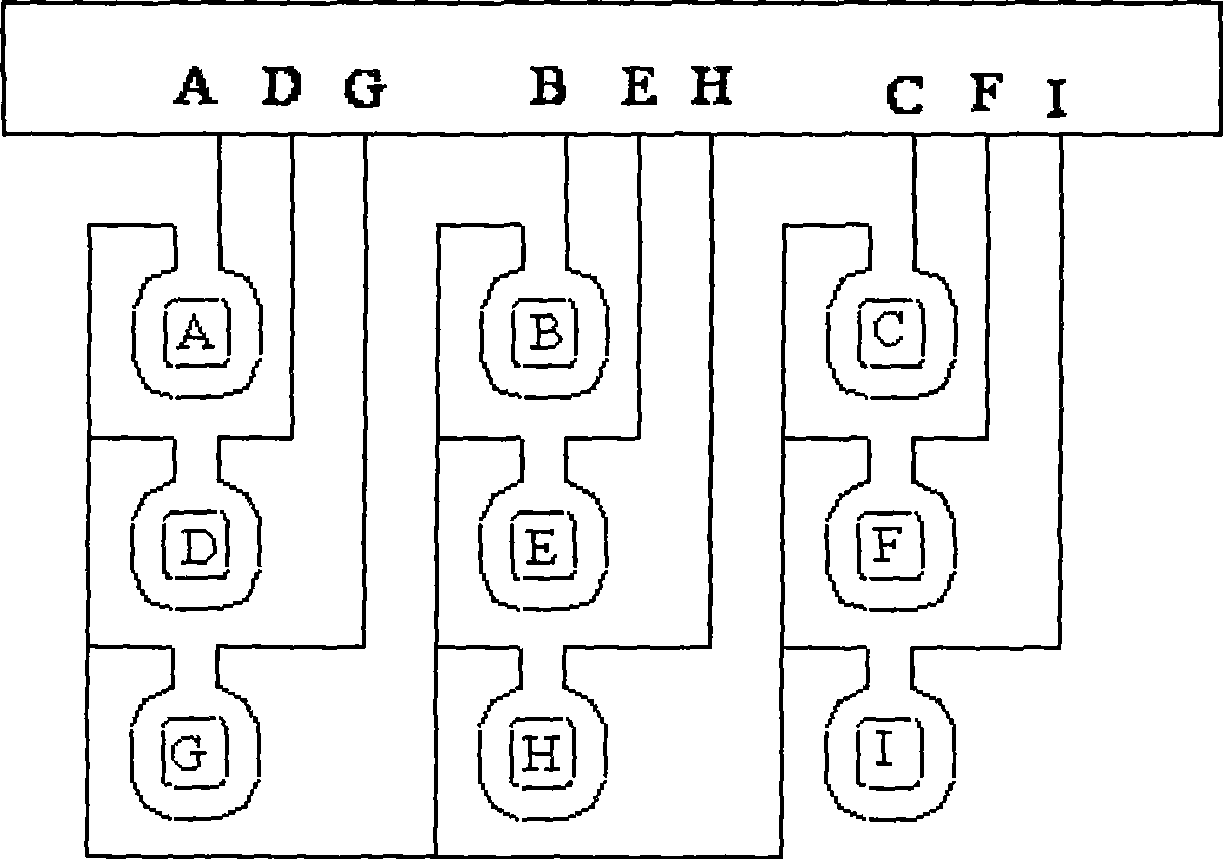

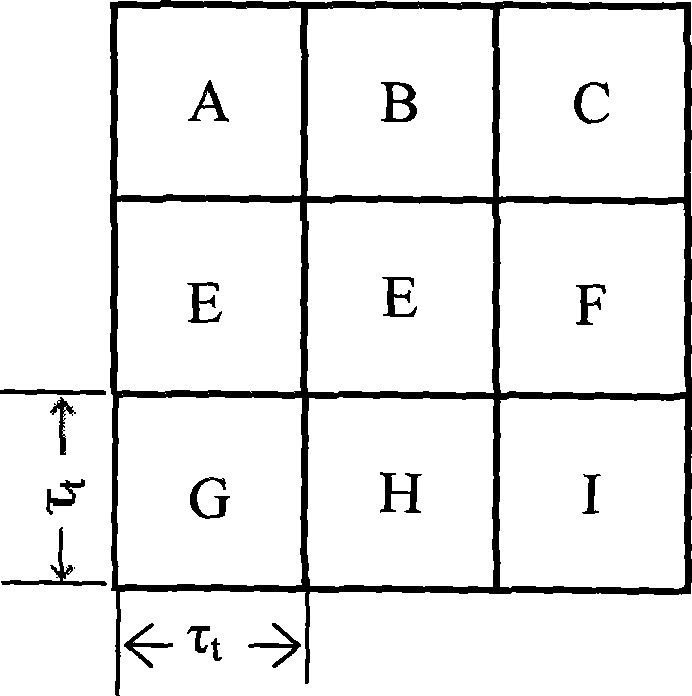

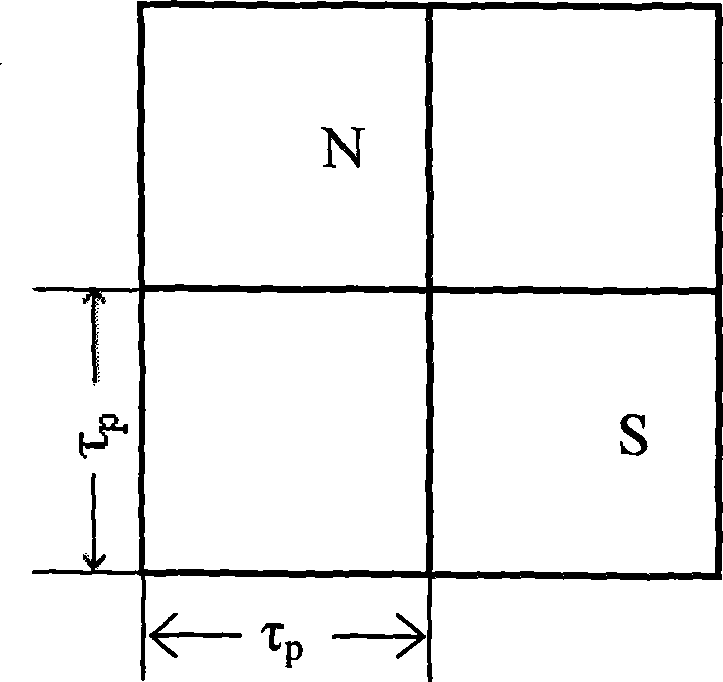

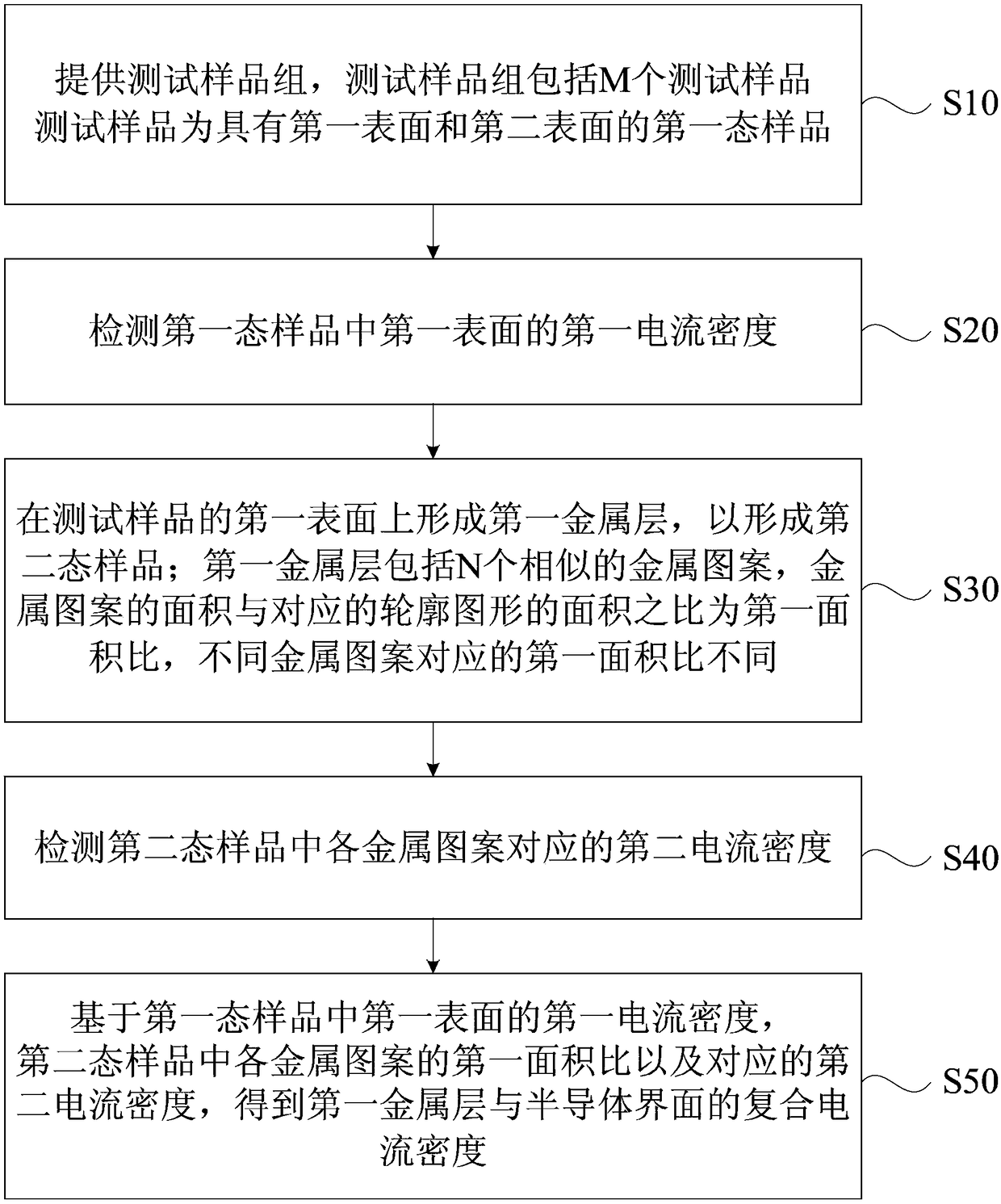

The invention discloses a method and device for testing metal semiconductor interface recombination current density. The method includes: providing a testing sample group, wherein each testing sampleis a first-state sample with a first surface and a second surface; detecting the first current density of the first surface of each first-state sample; forming a first metal layer on each first surface to form a second-state sample; each first metal layer comprises N similar metal patterns, and the first area ratios corresponding to different metal patterns are different; detecting second currentdensity corresponding to each metal pattern in each second-state sample; acquiring the recombination current density of each first metal layer and a semiconductor interface according to the corresponding first current density, the first area ratio of each metal pattern and the corresponding second current density. The method and device has the advantages that the metal semiconductor interface recombination current density can be tested simply and fast, and the testing result is real and accurate.

Owner:CSI SOLAR TECH (JIAXING) CO LTD

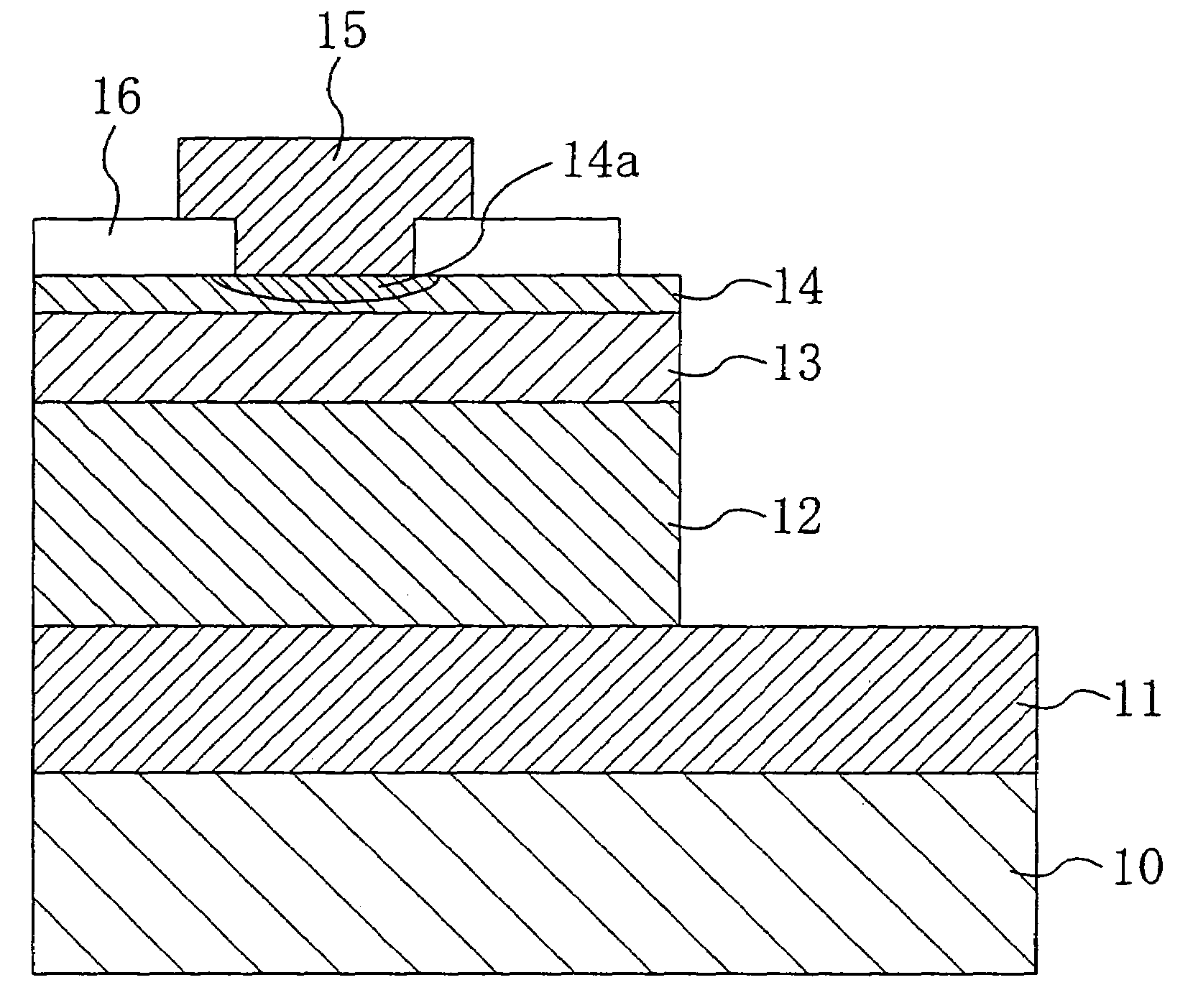

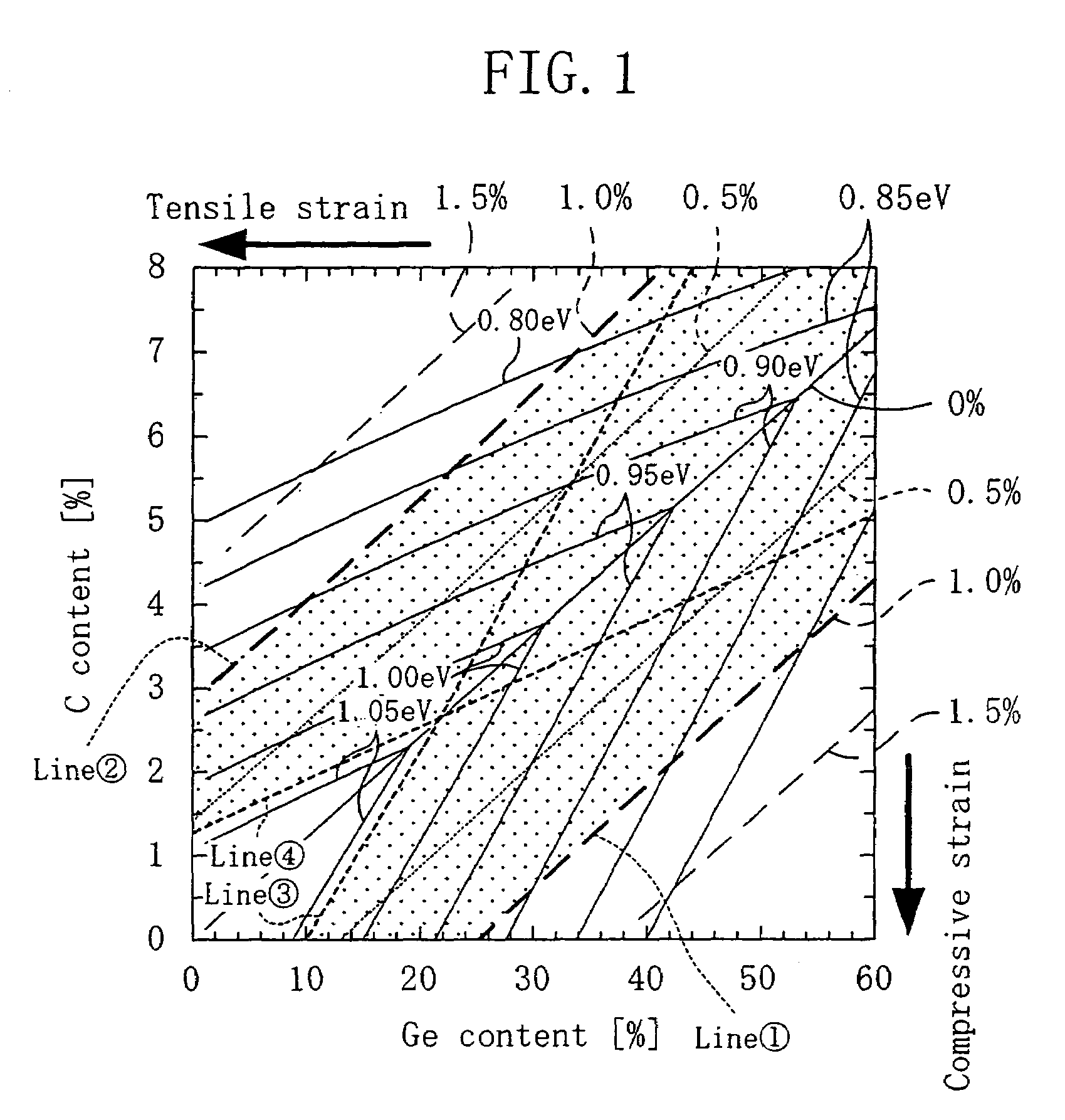

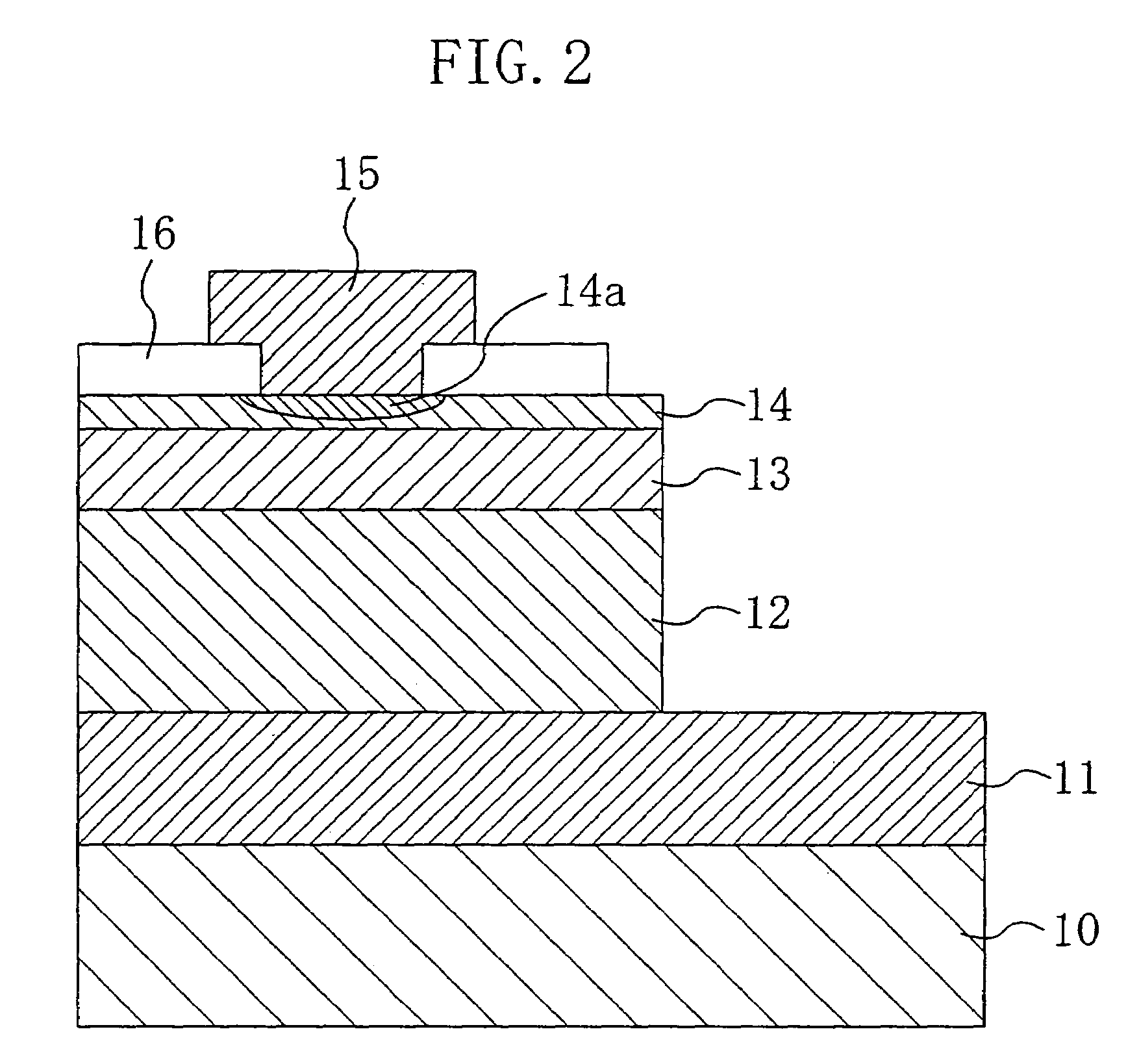

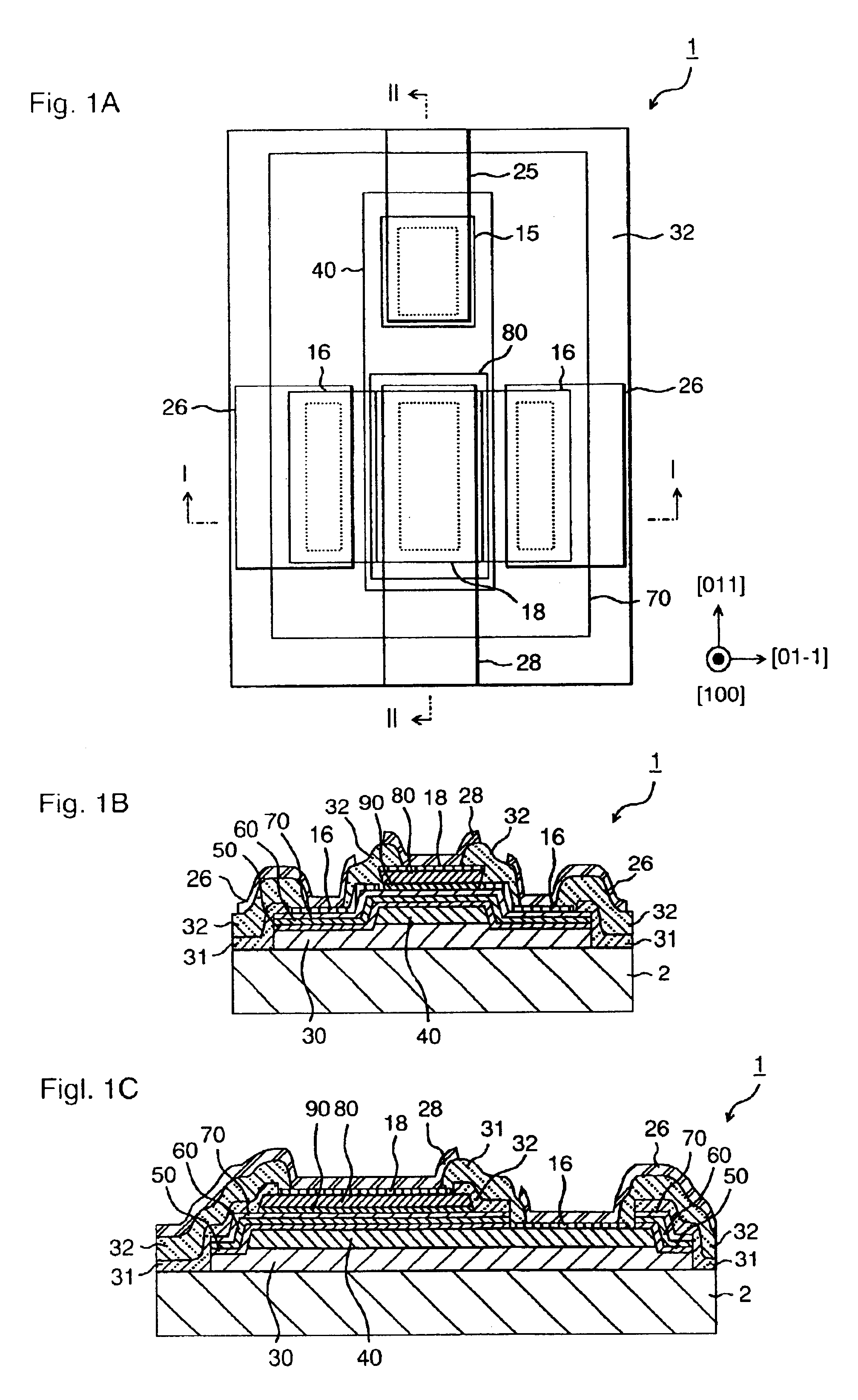

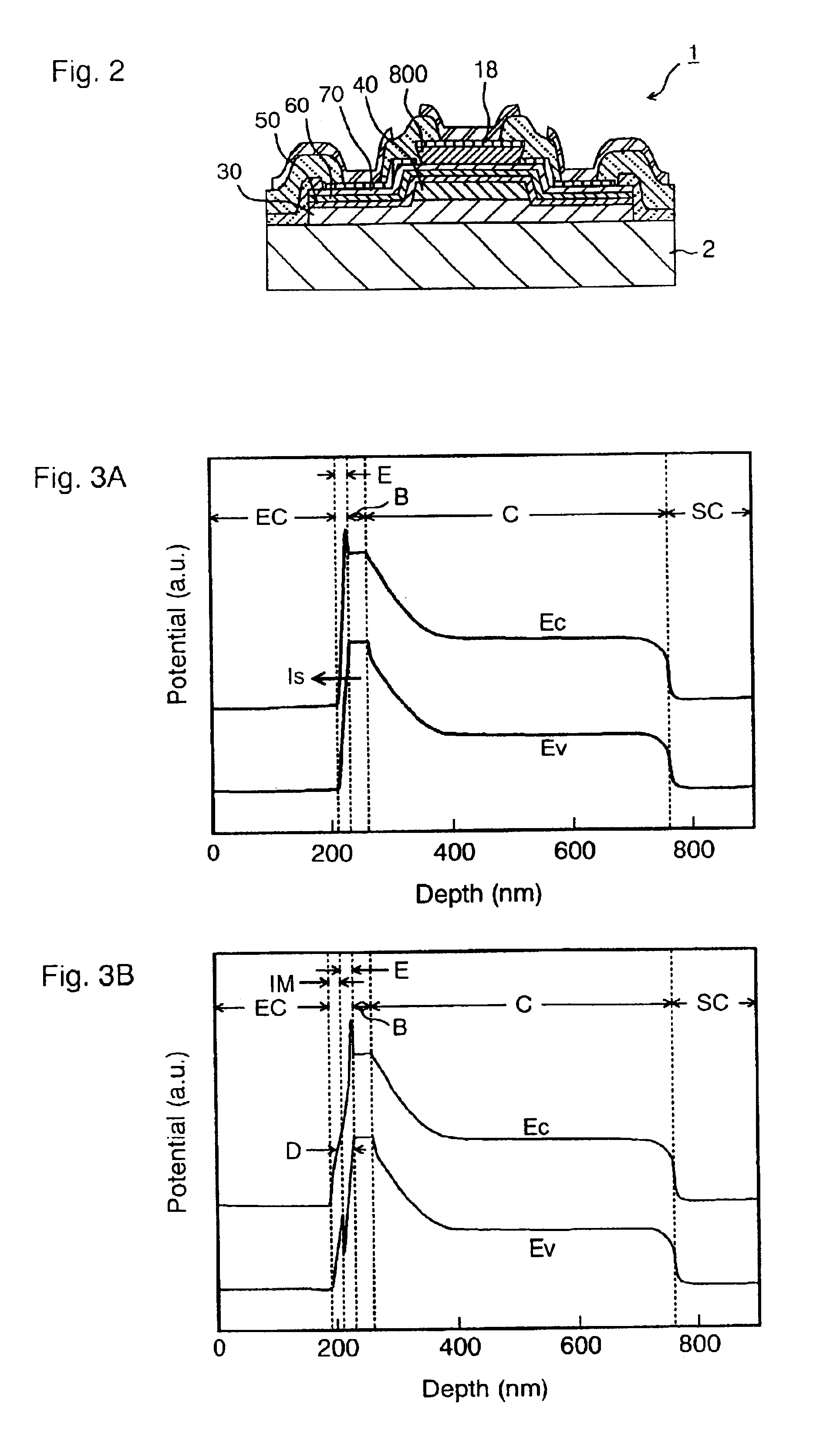

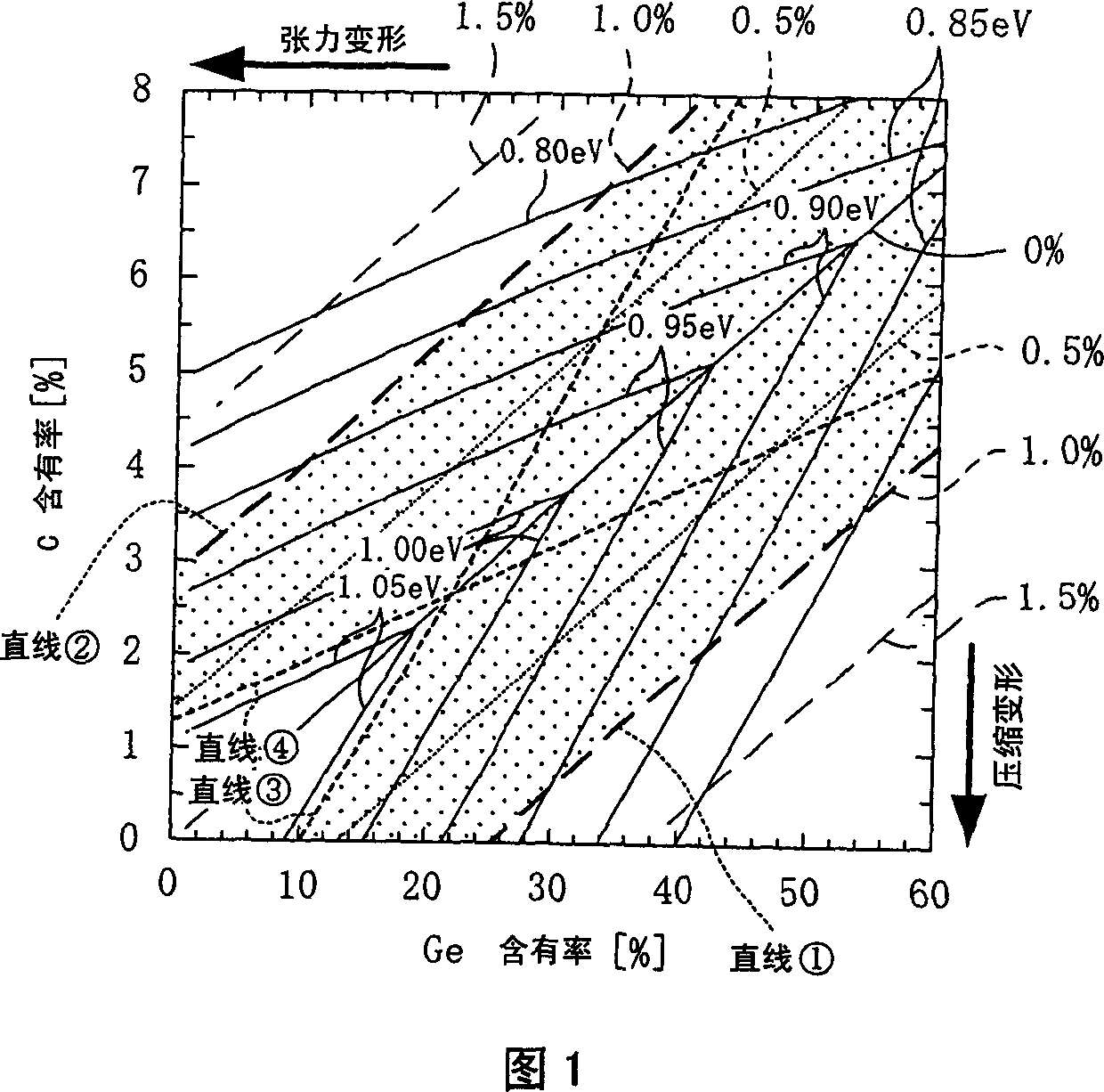

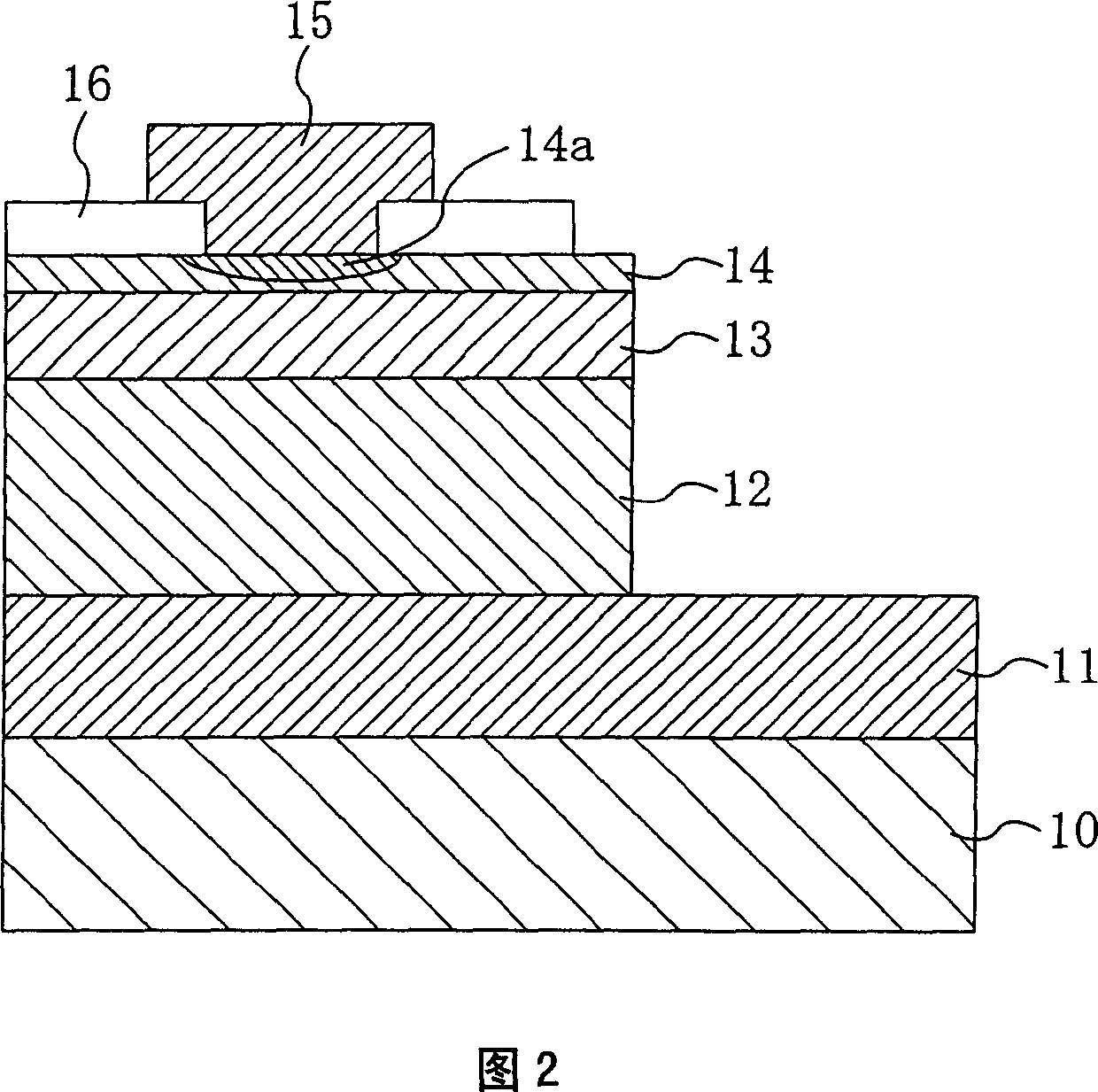

Heterojunction bipolar transistor having reduced driving voltage requirements

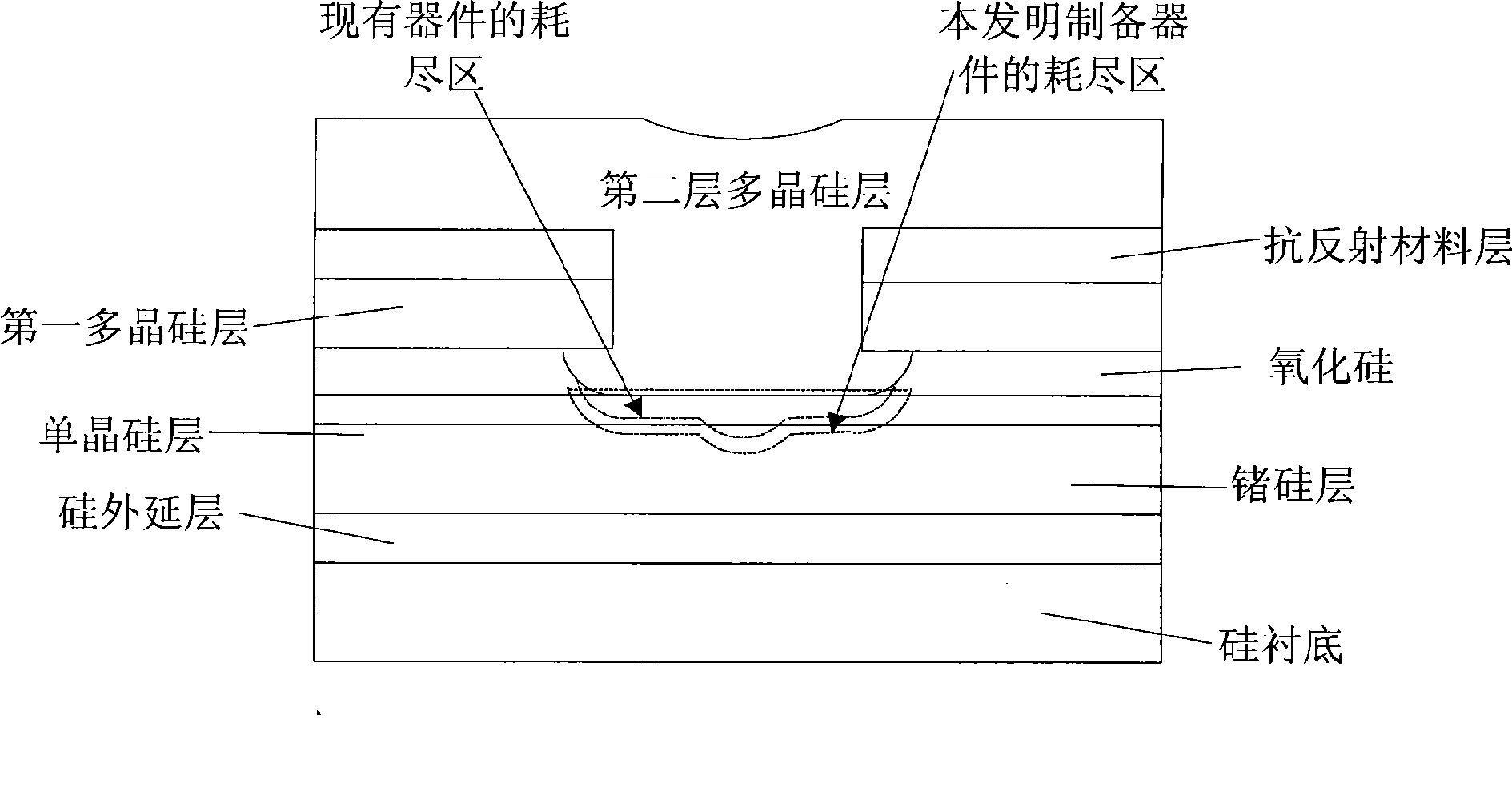

InactiveUS7135721B2Low-voltage drivingTotal current dropSemiconductor/solid-state device manufacturingSemiconductor devicesRecombination currentLow voltage

The bipolar transistor of the present invention includes a Si collector buried layer, a first base region made of a SiGeC layer having a high C content, a second base region made of a SiGeC layer having a low C content or a SiGe layer, and a Si cap layer 14 including an emitter region. The C content is less than 0.8% in at least the emitter-side boundary portion of the second base region. This suppresses formation of recombination centers due to a high C content in a depletion layer at the emitter-base junction, and improves electric characteristics such as the gain thanks to reduction in recombination current, while low-voltage driving is maintained.

Owner:PANNOVA SEMIC

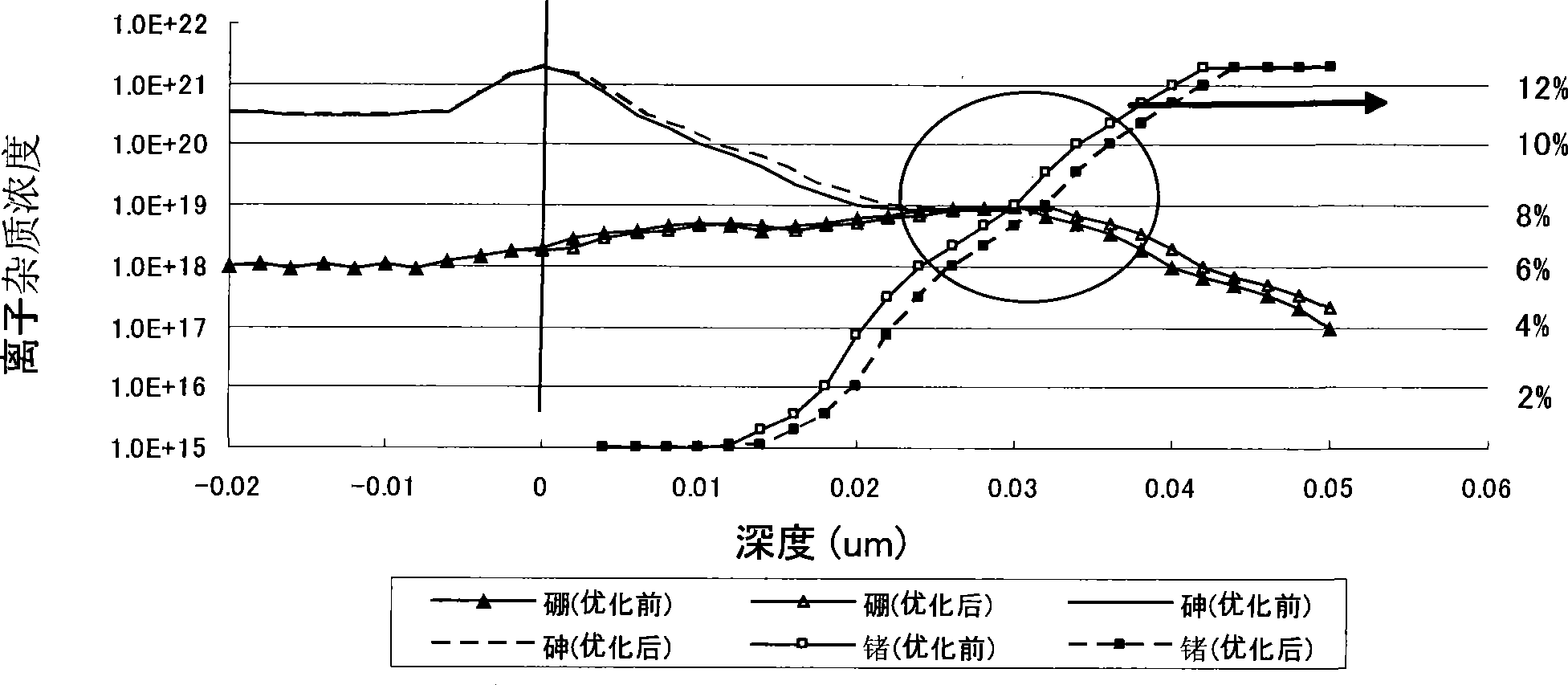

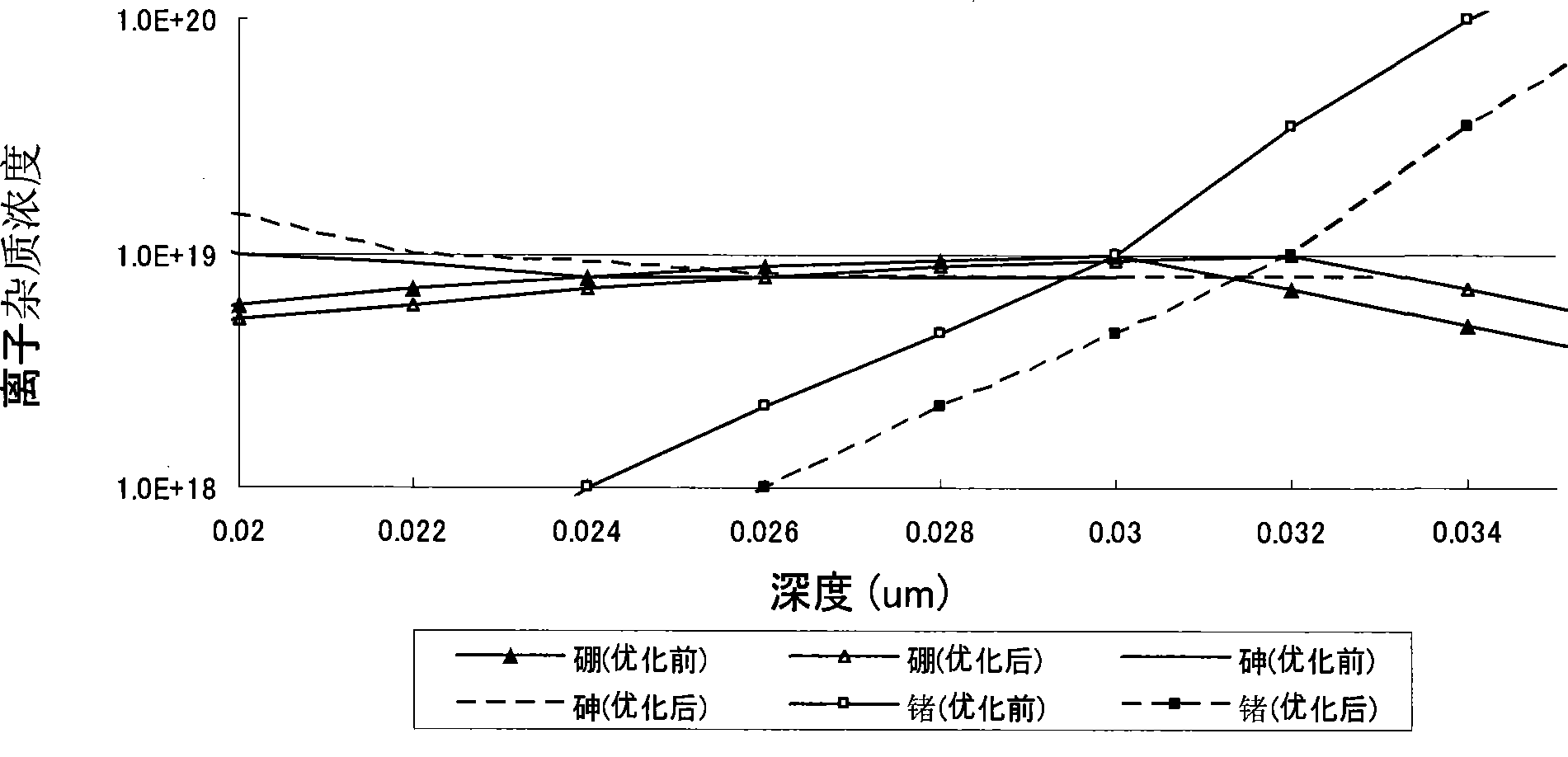

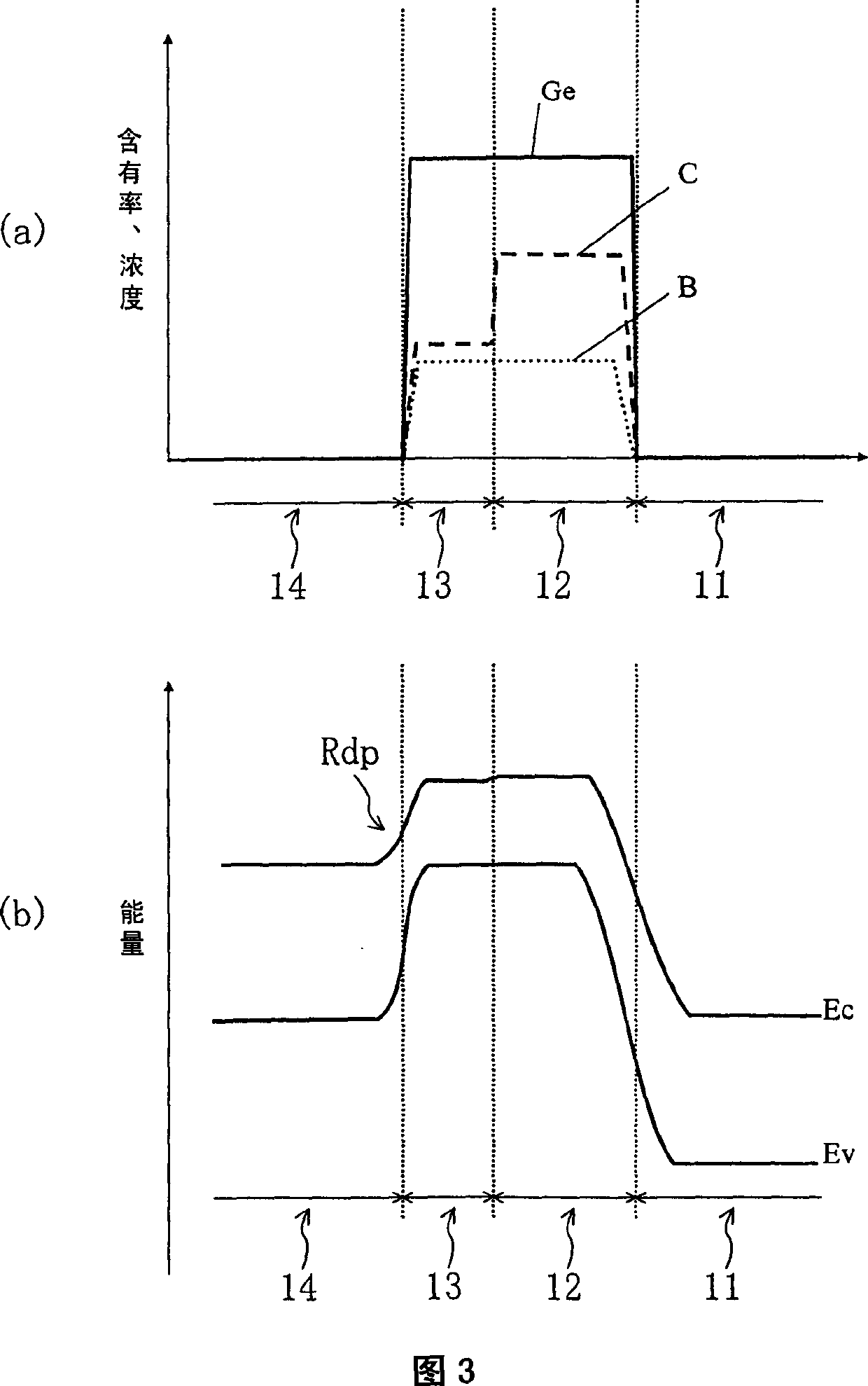

Germanium-silicon heterojunction bipolar transistor and manufacturing method thereof

ActiveCN102420243ASuppress edge effectIncrease current densitySemiconductor/solid-state device manufacturingSemiconductor devicesLinearitySilicon heterojunction

The invention discloses a germanium-silicon heterojunction bipolar transistor. A base region is composed of three layers of structures including a silicon buffering layer, a germanium-silicon layer and a silicon cap layer. An accelerating field of electrons is formed in the base region by the germanium-silicon layer to improve the frequency response of a device. The silicon cap layer can be used for optimizing the position of an emission junction, reducing a recombination current of the base region and improving the linearity and a BVCEO (Breakdown Voltage ceo) of the device. A collector electrode is led out from shallow slot isolation through a fake buried layer and a deep hole contact so that the resistance of the collector electrode can be reduced and the frequency response of the device can be improved. The fake buried layer is doped by arsenic so that the cross diffusion of the fake buried layer can be effectively controlled, the parasitic capacitance is reduced and the frequencyresponse of the device is improved. An emission region is of a narrow emission electrode structure and can be used for inhibiting a current crowding effect and improving a current density in a unit area. One silicon oxidation layer is formed on a contact position between the emission region and the base region so that a barrier height of the emission junction can be improved and the injection frequency of the emission junction is improved. The invention further discloses a manufacturing method of the germanium-silicon heterojunction bipolar transistor.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

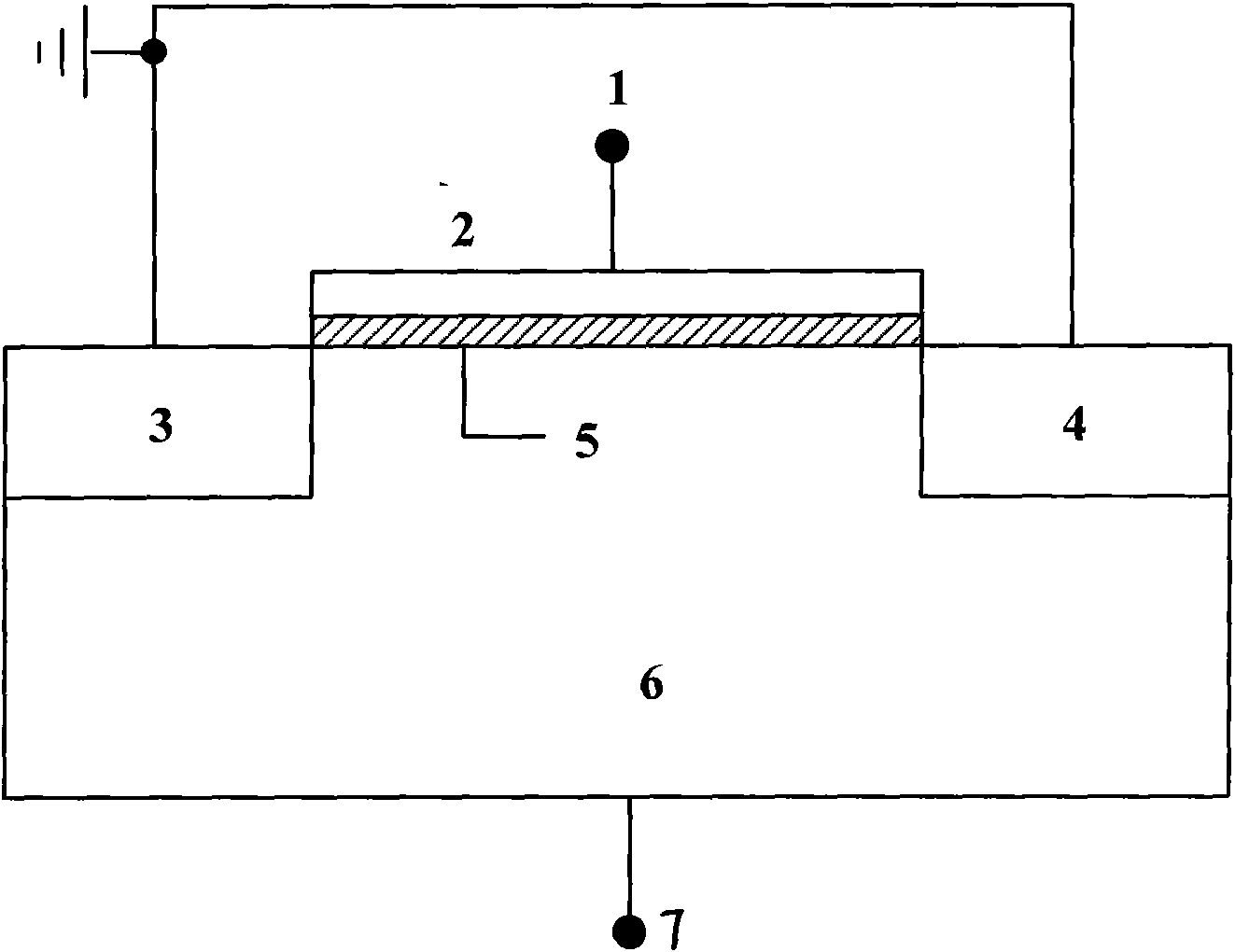

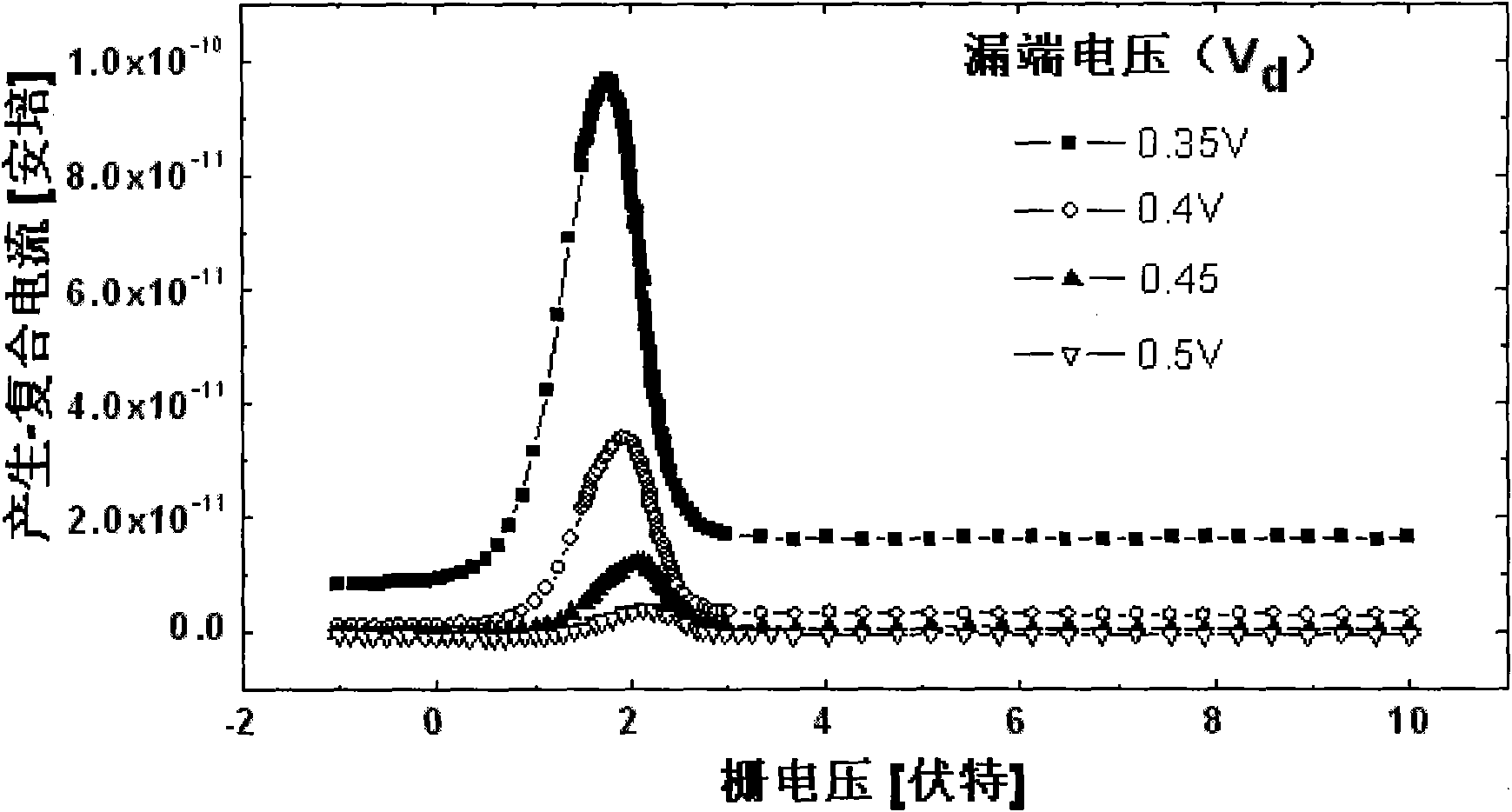

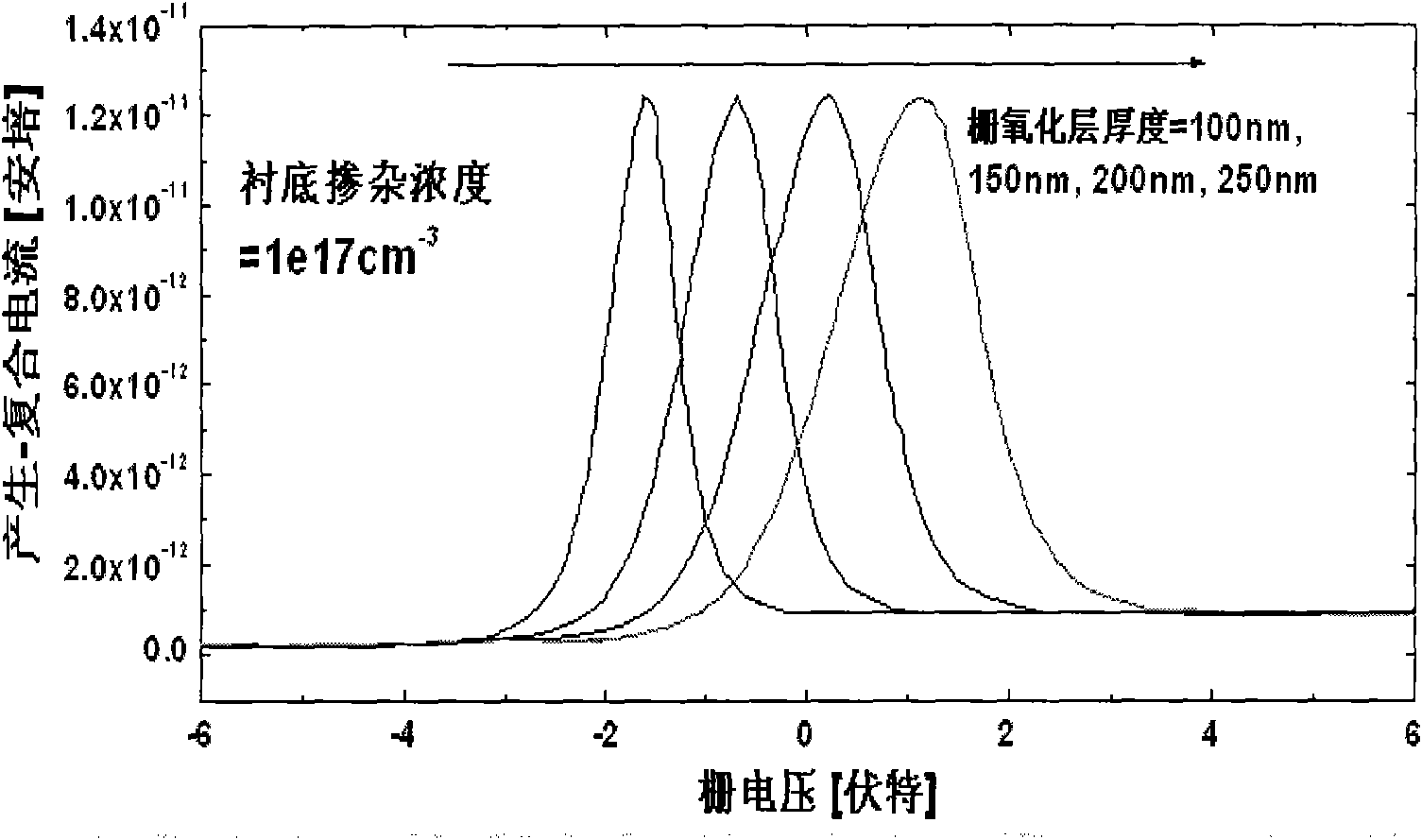

Method for extracting gate-oxide thickness and substrate doping concentration of field effect transistor

InactiveCN102042799ASensitive and accurate extractionImprove accuracyMaterial analysis by electric/magnetic meansElectrical/magnetic thickness measurementsRecombination currentPower flow

The invention provides a method for extracting gate oxide thickness and substrate doping concentration of a field effect transistor, which is characterized by comprising the following steps of: grounding a source electrode and a drain electrode of a device, connecting a substrate with smaller positive bias to enable a drain-body diode to be in positive bias and not conducted, scanning gate voltage from negative voltage to a positive voltage, measuring the relation curve of a generation-recombination current of the substrate and the gate voltage, and accurately extracting the gate oxide thickness and the substrate doping concentration of the field effect transistor by utilizing the position shift of the generation-recombination current peak of the positively-biased diode. In the method, a required measuring structure is simple and has high sensitivity and can be used for accurately reflecting the dependence of the gate oxide thickness on the substrate doping concentration.

Owner:PEKING UNIV

Method for testing recombination current of metal semiconductor interface

ActiveCN108120869ASimple processTest results are simple and fastCurrent density measurementsRecombination currentTest sample

The invention discloses a method for testing the recombination current of a metal semiconductor interface. The method for testing the recombination current of the metal semiconductor interface comprises the following steps: providing a test sample set, wherein test samples are first samples provided with first surfaces and second surfaces; detecting the first current density of the first surfacesin the first samples; forming first metal layers on the first surfaces so as to form second samples, wherein each first metal layer comprises N similar metal patterns, and first area ratios corresponding to different metal patterns are different; using a Suns-Voc tester to detect second current density corresponding to each metal pattern in the second samples; and based on the first current density, the first area ratio of each metal pattern and the corresponding second current density, obtaining the recombination current density of the first metal layer and the semiconductor interface. According to the scheme provided by the invention, the recombination current density testing for the metal semiconductor interface is realized simply and quickly, and the effect that the test result is trueand accurate is achieved.

Owner:CSI SOLAR TECH (JIAXING) CO LTD

A method and device for testing recombination current density at a metal-semiconductor interface

ActiveCN108196110BSimple processThe test result is accurateCurrent density measurementsRecombination currentParticle physics

The invention discloses a method and device for testing metal semiconductor interface recombination current density. The method includes: providing a testing sample group, wherein each testing sampleis a first-state sample with a first surface and a second surface; detecting the first current density of the first surface of each first-state sample; forming a first metal layer on each first surface to form a second-state sample; each first metal layer comprises N similar metal patterns, and the first area ratios corresponding to different metal patterns are different; detecting second currentdensity corresponding to each metal pattern in each second-state sample; acquiring the recombination current density of each first metal layer and a semiconductor interface according to the corresponding first current density, the first area ratio of each metal pattern and the corresponding second current density. The method and device has the advantages that the metal semiconductor interface recombination current density can be tested simply and fast, and the testing result is real and accurate.

Owner:CSI SOLAR TECH (JIAXING) CO LTD

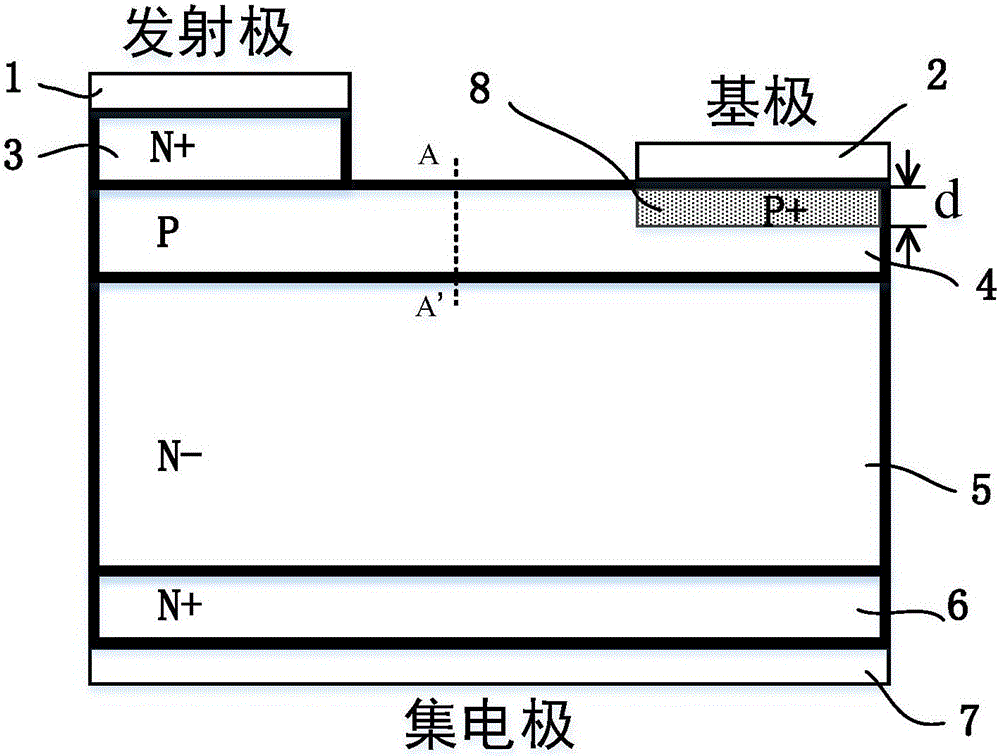

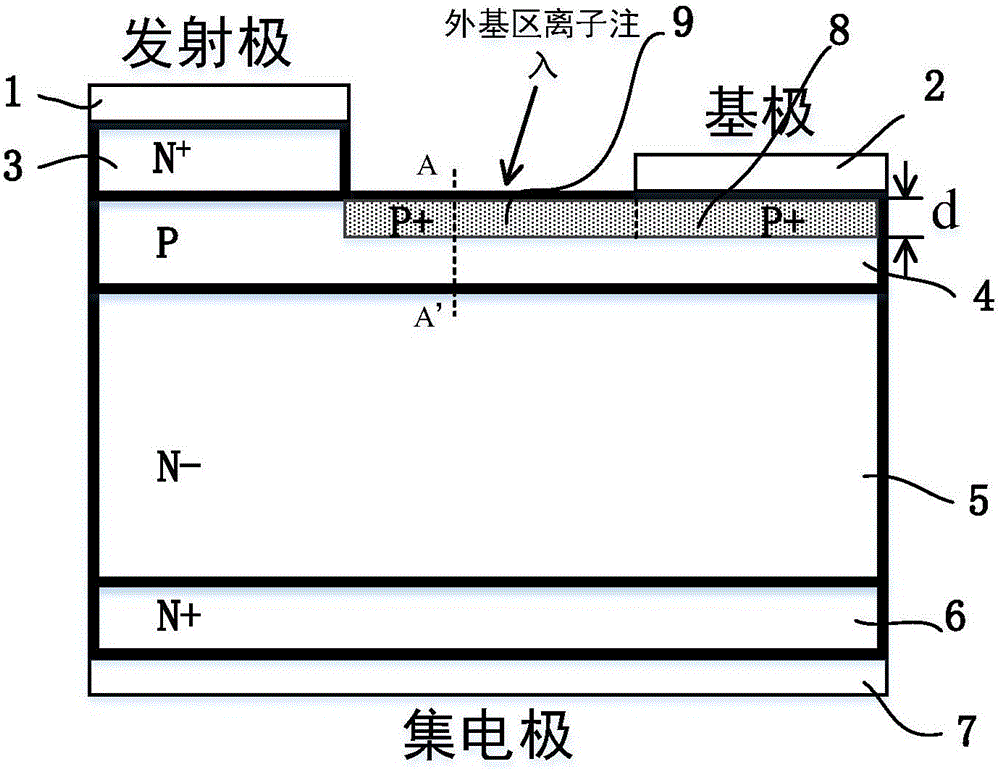

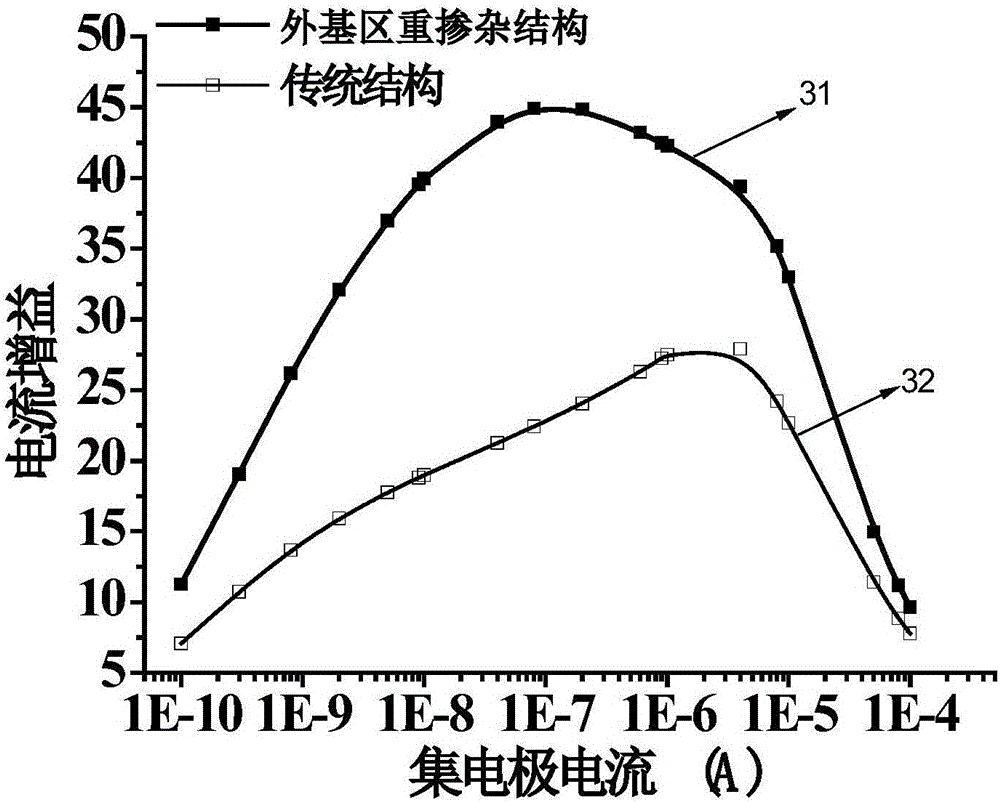

Silicon carbide BJT (bipolar junction transistor)

InactiveCN105870176AReduce electron concentrationReduce recombination currentTransistorRecombination currentOhmic contact

The invention belongs to the technical field of high-power semi-conductors and particularly relates to a silicon carbide BJT (bipolar junction transistor). A second P+ layer 9 is arranged at an outer base region between the edge of an emitter electrode 1 of the BJT and a base electrode ohmic contact of the BJT, is a P-type heavily-doped layer and can be formed with an ion injection process; a P-type base region 4 is a P-type lightly-doped layer, accordingly, an electric field pointing to the heavily-doped layer from the lightly-doped layer is formed between the second P+ layer 9 and the P-type base region 4, the electric filed can prevent minority carriers (electrons) in the base region from diffusing towards the surface of the outer base region, the concentration of the electrons on the surface of the outer base region is reduced, the recombination rate of electrons and holes is reduced, recombination current caused by the interface state is reduced, and the current gain of the device is increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

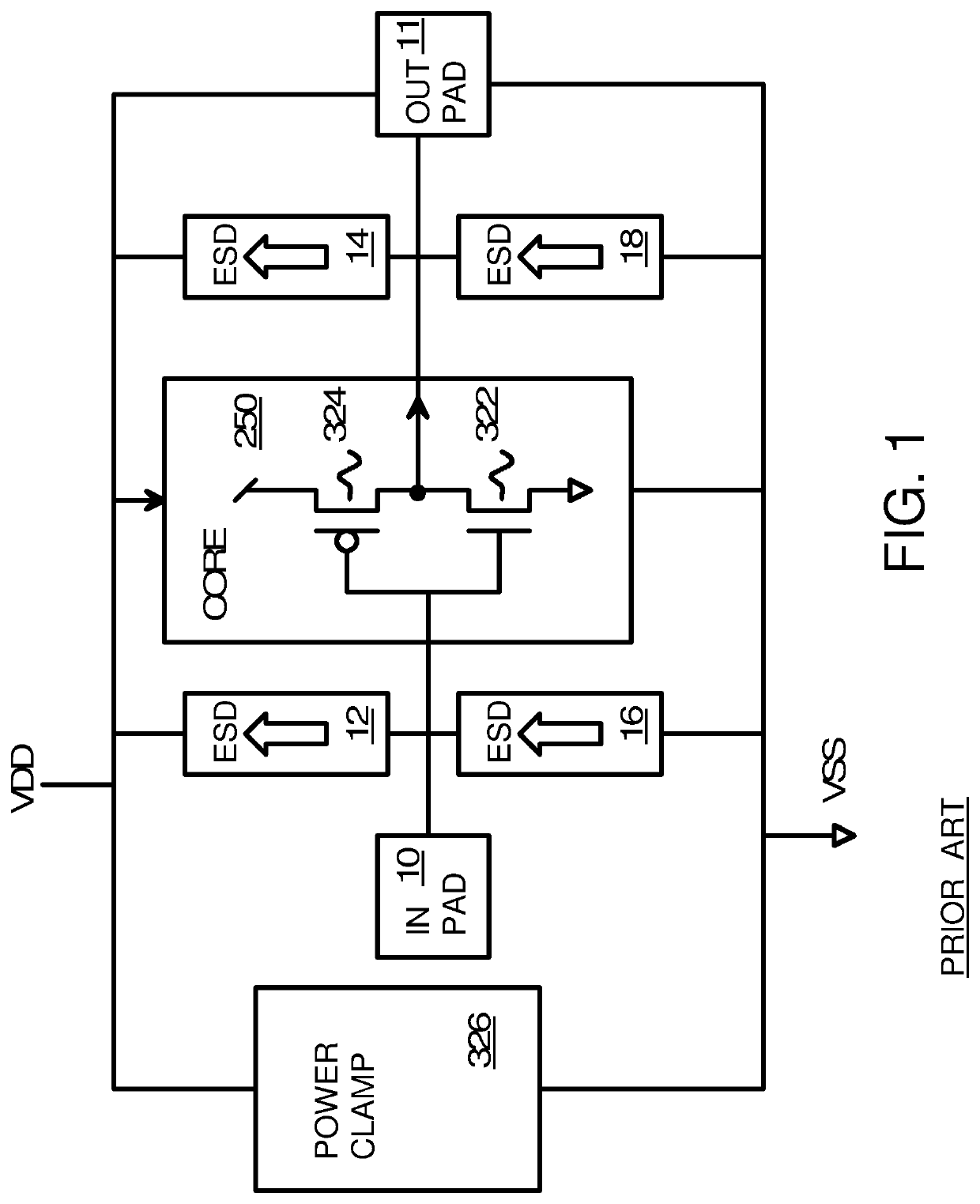

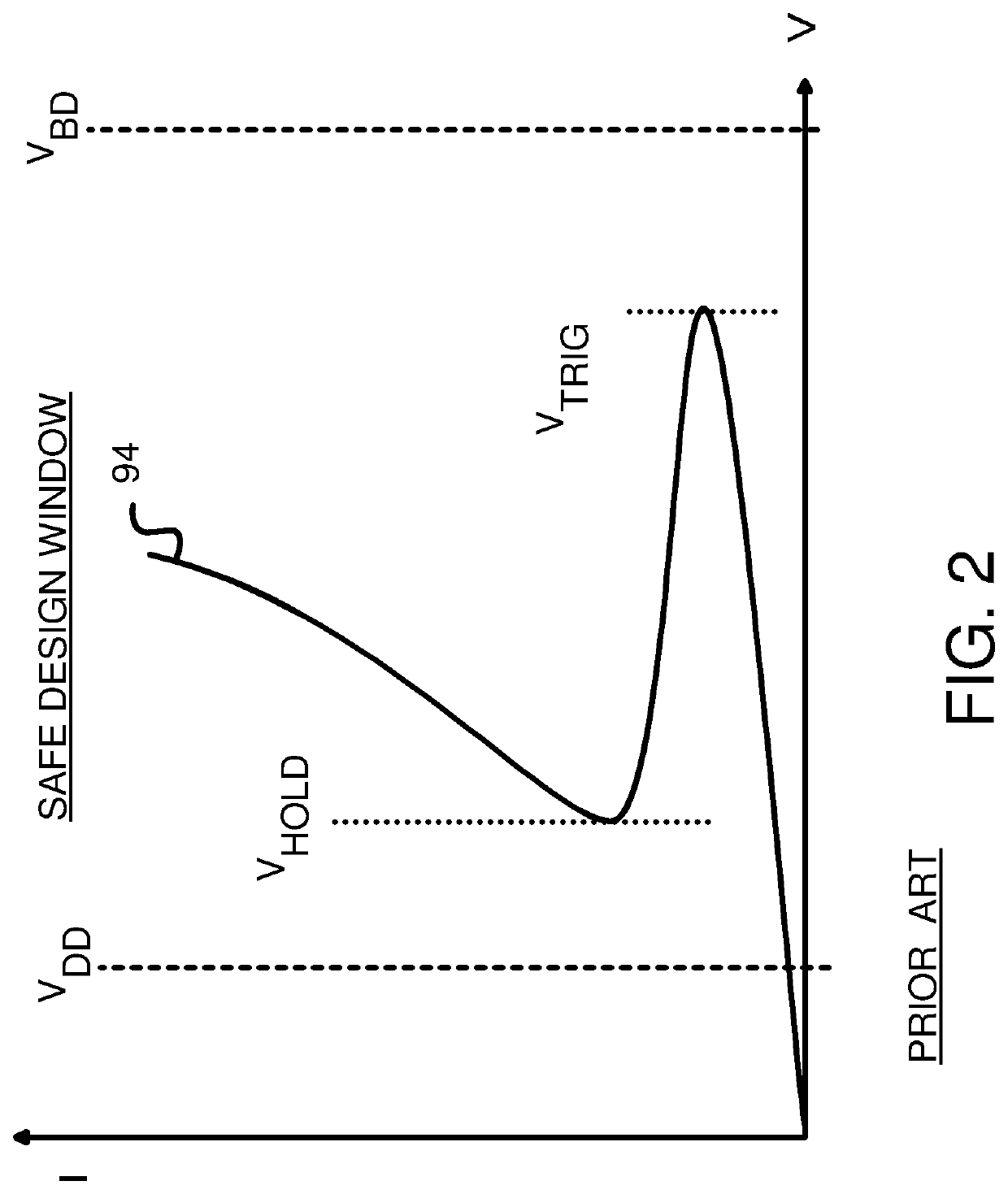

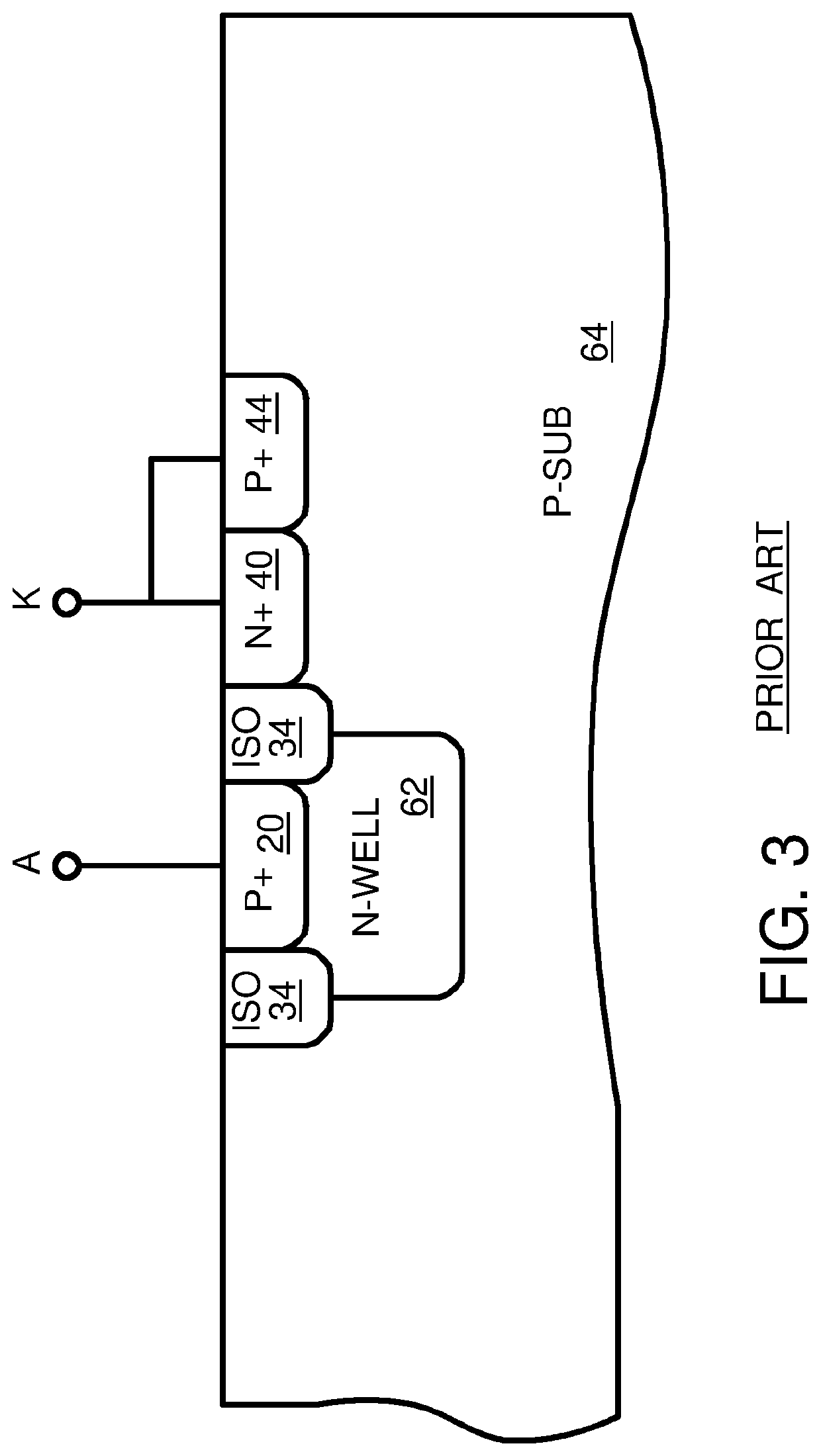

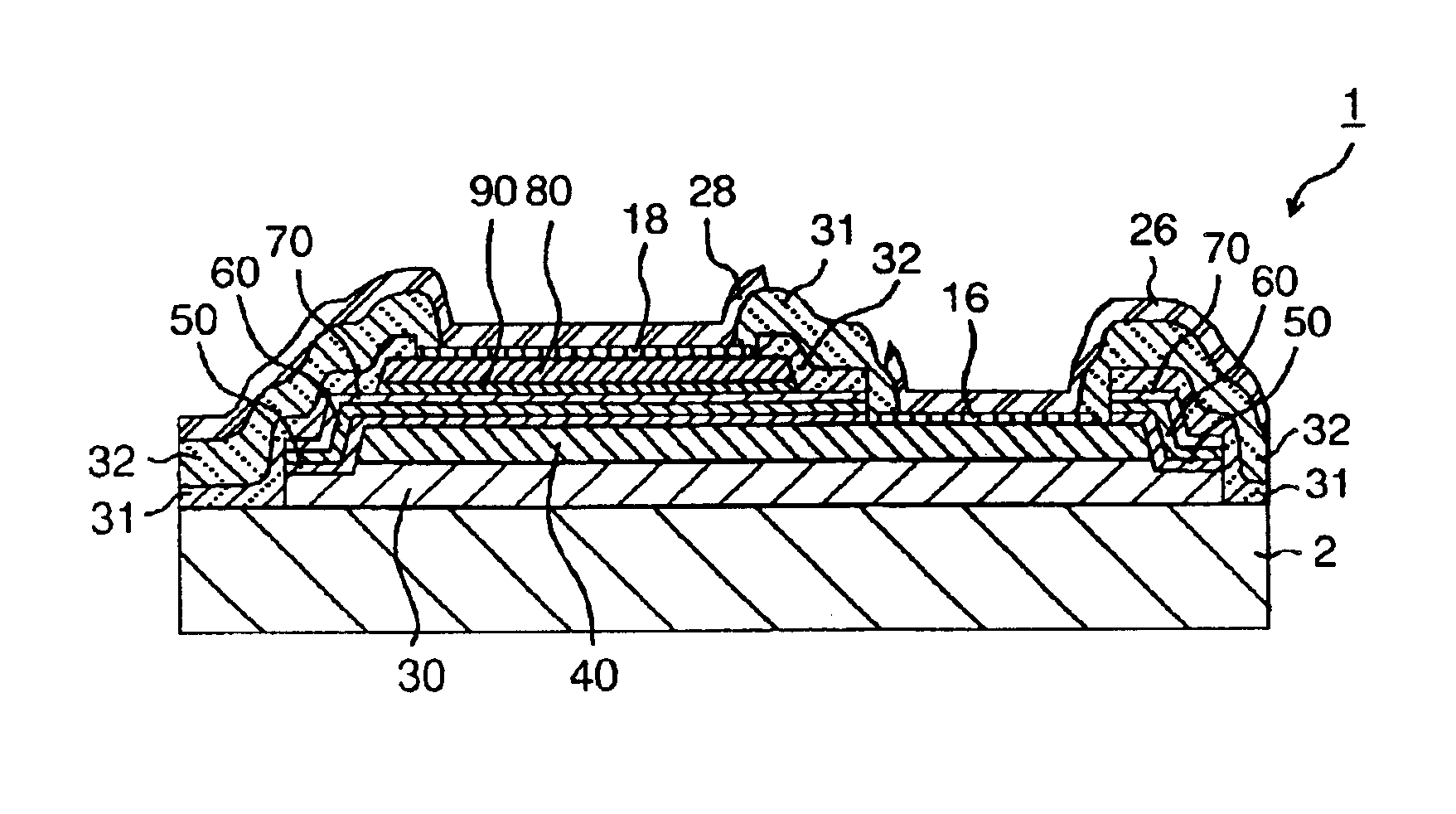

Low capacitance and high-holding-voltage transient-voltage-suppressor (TVS) device for electro-static-discharge (ESD) protection

A well-less Transient Voltage Suppressor (TVS) Silicon-Controlled Rectifier (SCR) has a P+ anode region that is not in an N-well. The P+ anode region 20 is surrounded by N+ isolation regions near the surface, and a deep N+ region underneath that is formed in a p-substrate. A N+ cathode region is formed in the p-substrate. The deep N+ region has a doping of 5×1018 to 5×1019 / cm3, compared to a doping of 1×1016 / cm3 for a typical N-well, or a doping of 1×1013 to 1×1015 / cm3 for the p-substrate. The high doping in the deep N+ region causes a recombination current that can shunt half of the anode current. Since the deep N+ region is much shallower than an N-well, the sidewall capacitance is greatly reduced, allowing for higher speed applications.

Owner:HONG KONG APPLIED SCI & TECH RES INST

Recombination current driven nine-phase plane motor, linear-rotating motor and driver thereof

InactiveCN101599677AReduce volumeReduce weightPropulsion systemsRecombination currentElectric machine

The invention relates to a recombination current driven nine-phase plane motor, a linear-rotating motor and a driver thereof, which belong to the field of motors and motor control. The invention solves the problems that the prior plane motor and the linear-rotating motor have complex structures, low system efficiency, difficult control and the like. The armature coils of the plane motor and the linear-rotating motor are divided into nine groups, each group of the coils are connected in series to form nine phase armature windings which are in star connections, permanent magnets of the motors have array structures, the opposite angles of permanent magnet units are adjacent to each other, parallel with each other, and vertical but not adjacent to each other, and the permanent magnets at the same line or row have same polarities while the permanent magnets at adjacent lines or rows have opposite polarities. The plane motor and the linear-rotating motor have the advantages of small volume, simple insulation between winding phases, large thrust output of unit volume, quick dynamic response, small positioning force and large active cell motion range. The recombination current driven nine-phase plane motor, the linear-rotating motor and the driver are applicable to driving plane two-dimensional movements and linear-rotating two-dimensional movements, and are particularly applicable in the field of precise driving.

Owner:HARBIN INST OF TECH

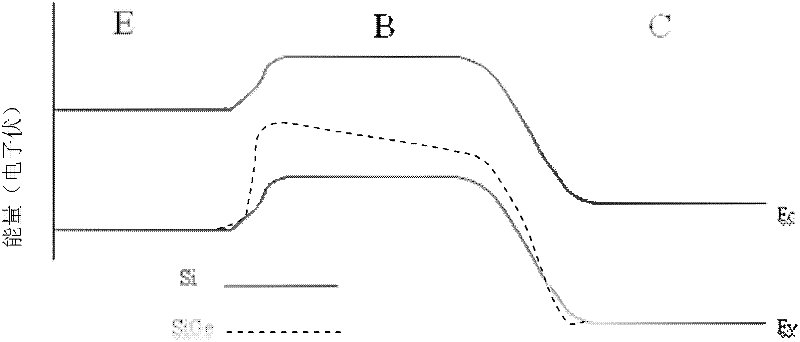

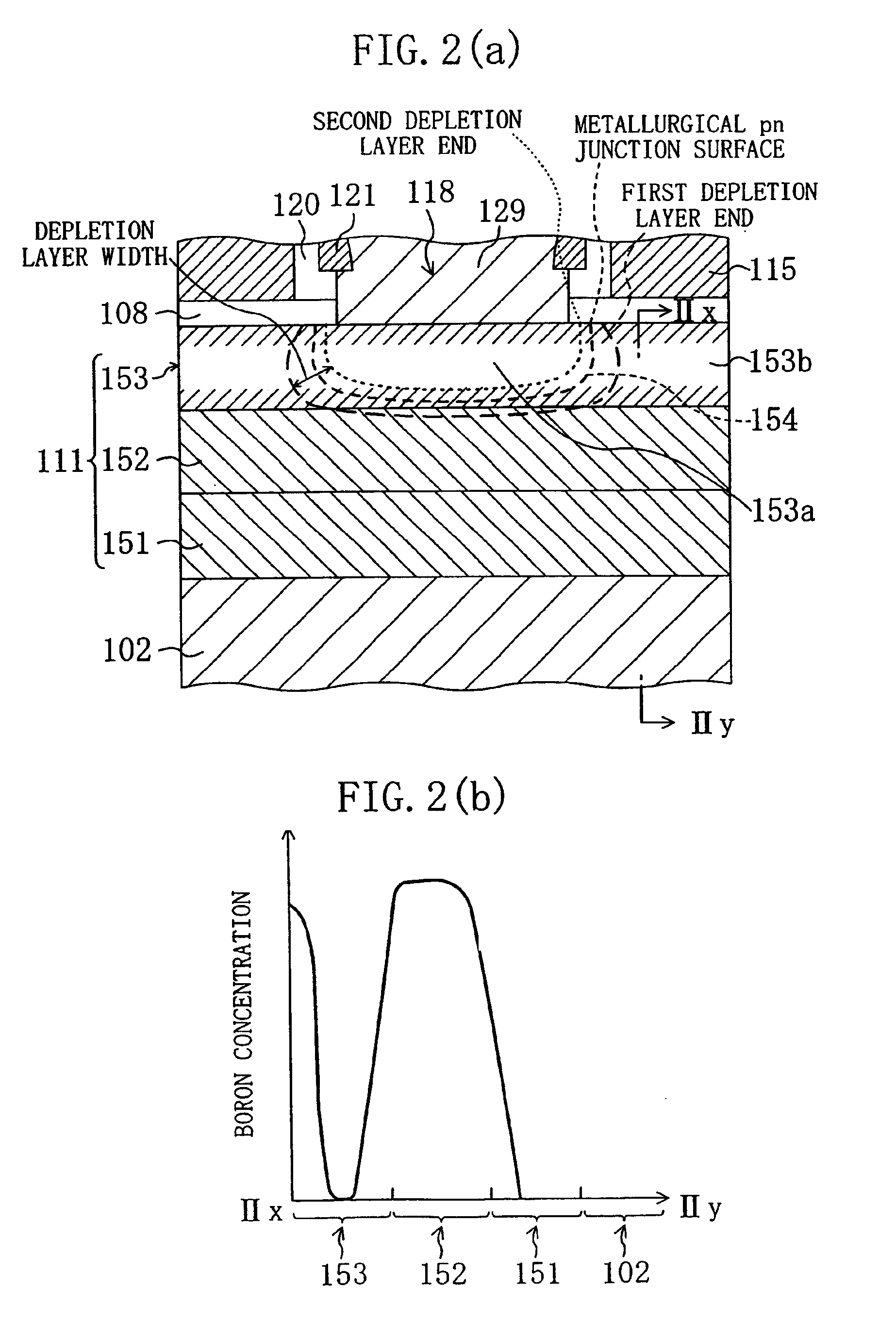

Bipolar transistor and fabrication method thereof

InactiveUS6939772B2Narrow widthReduce in quantityTransistorSemiconductor/solid-state device manufacturingIn situ dopingRecombination current

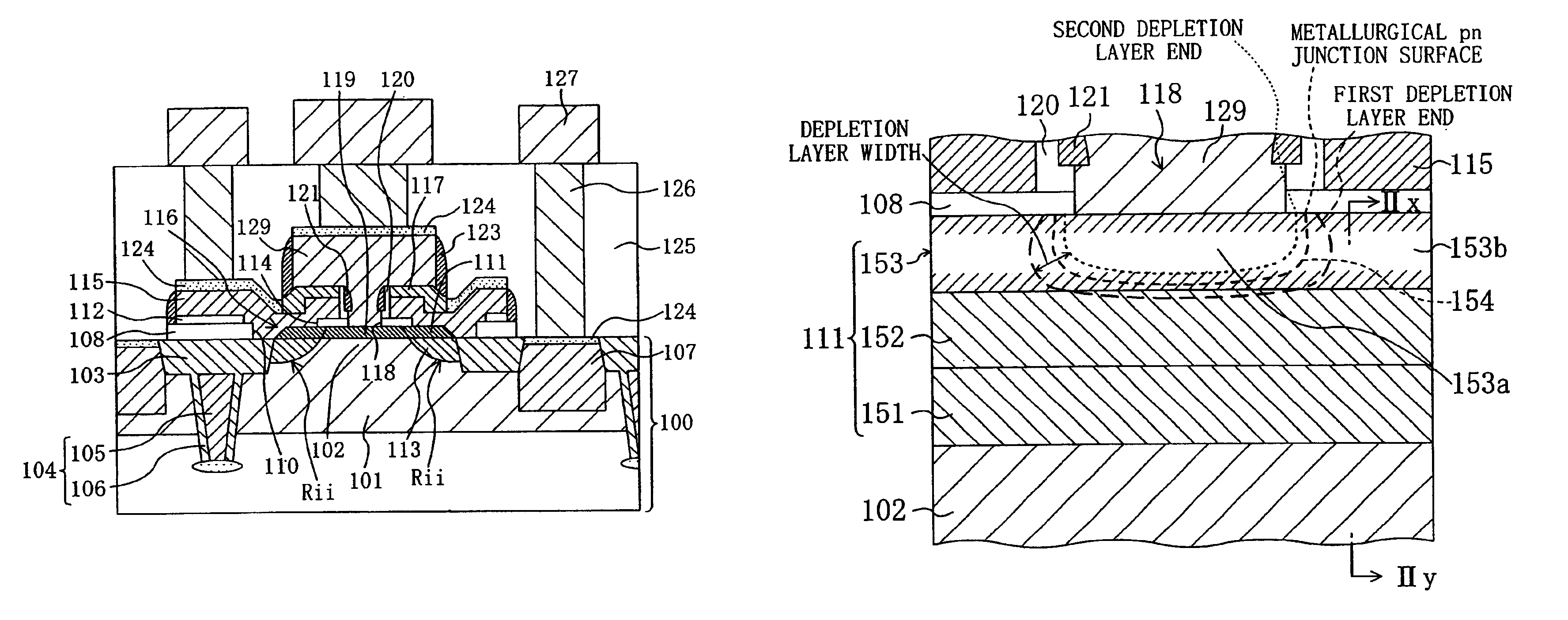

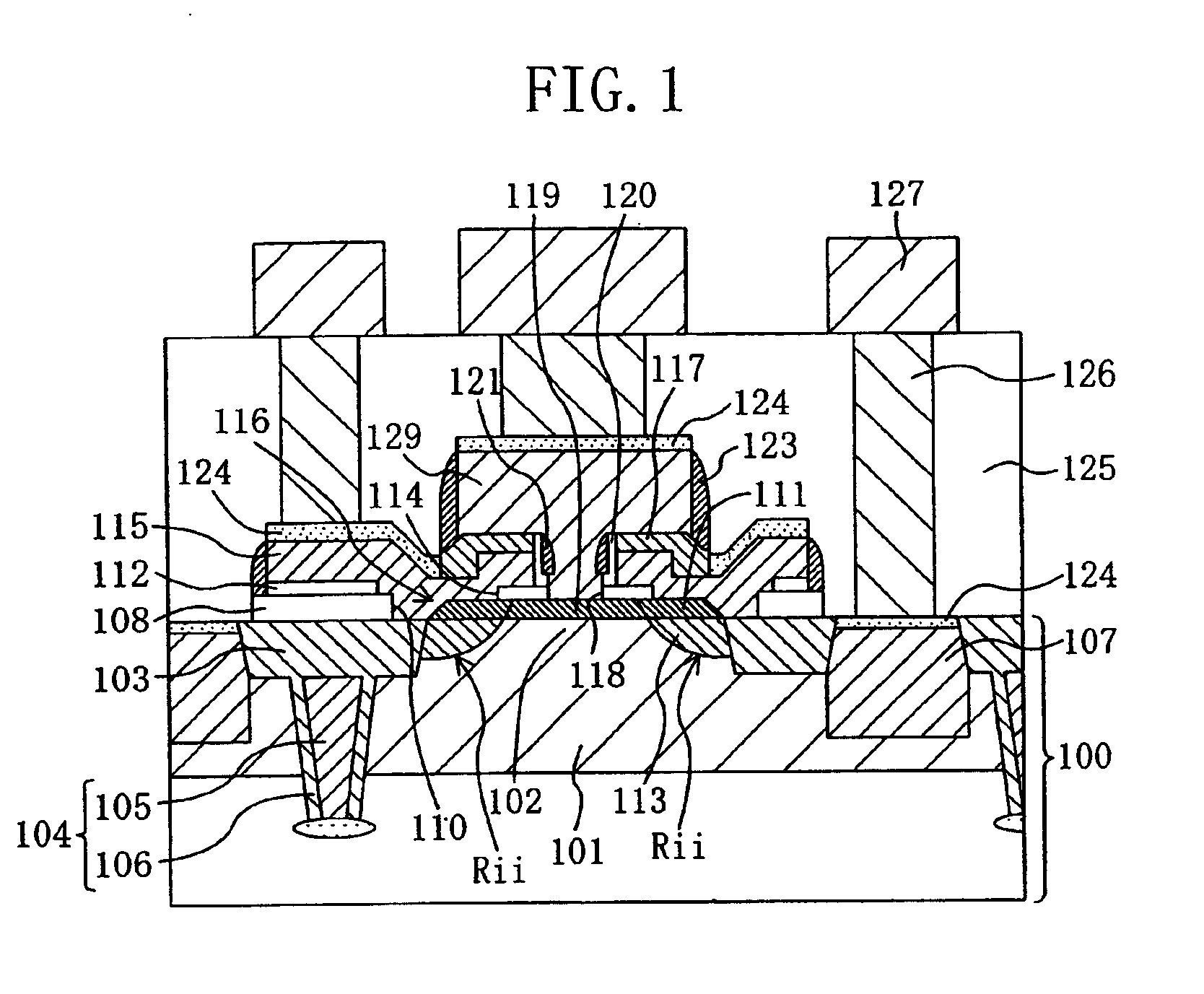

A SiGe spacer layer 151, a graded SiGe base layer 152 including boron, and an Si-cap layer 153 are sequentially grown through epitaxial growth over a collector layer 102 on an Si substrate. A second deposited oxide film 112 having a base opening portion 118 and a P+ polysilicon layer 115 that will be made into an emitter connecting electrode filling the base opening portion are formed on the Si-cap layer 153, and an emitter diffusion layer 153a is formed by diffusing phosphorus into the Si-cap layer 153. When the Si-cap layer 153 is grown, by allowing the Si-cap layer 153 to include boron only at the upper part thereof by in-situ doping, the width of a depletion layer 154 is narrowed and a recombination current is reduced, thereby making it possible to improve the linearity of the current characteristics.

Owner:PANASONIC CORP

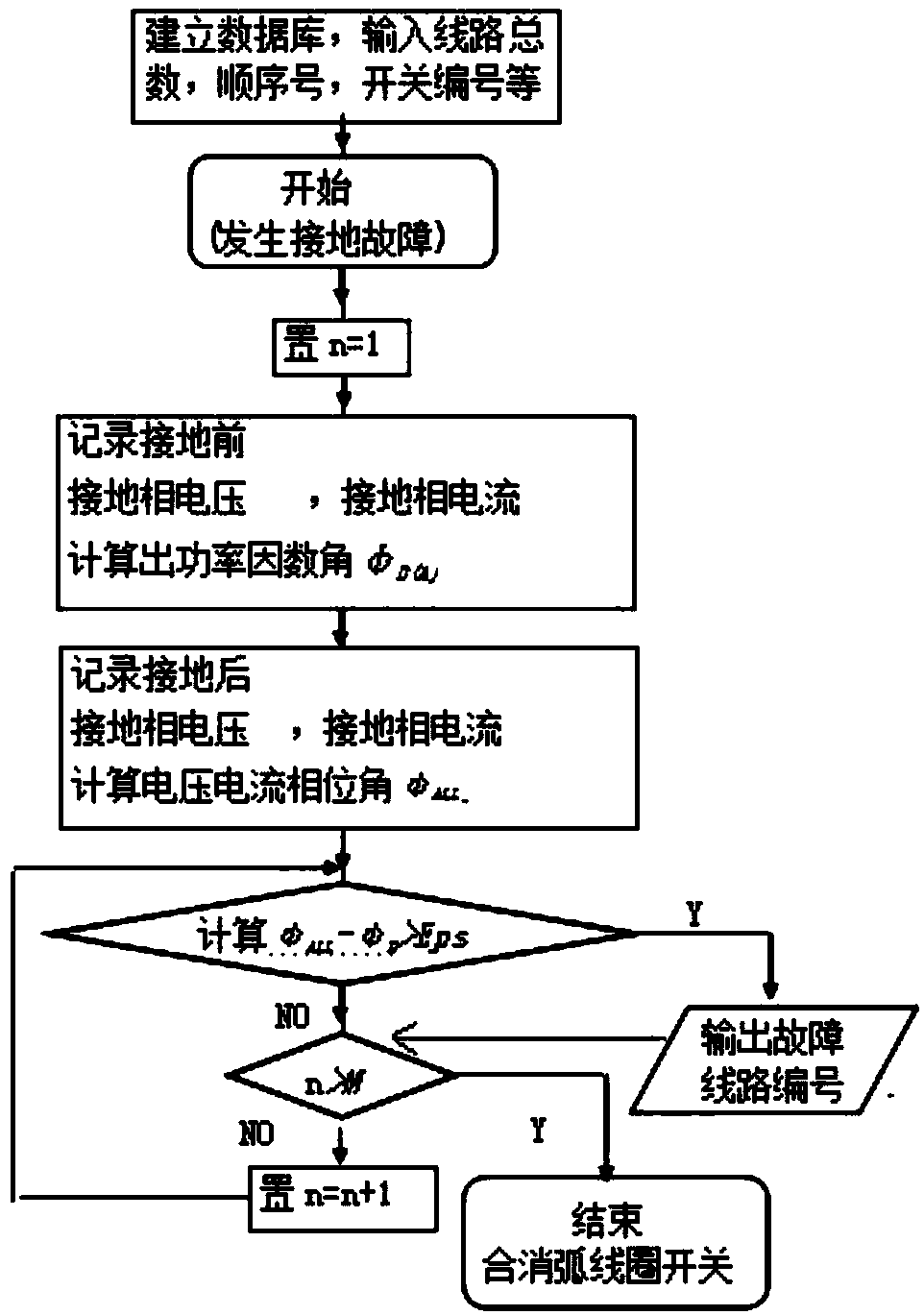

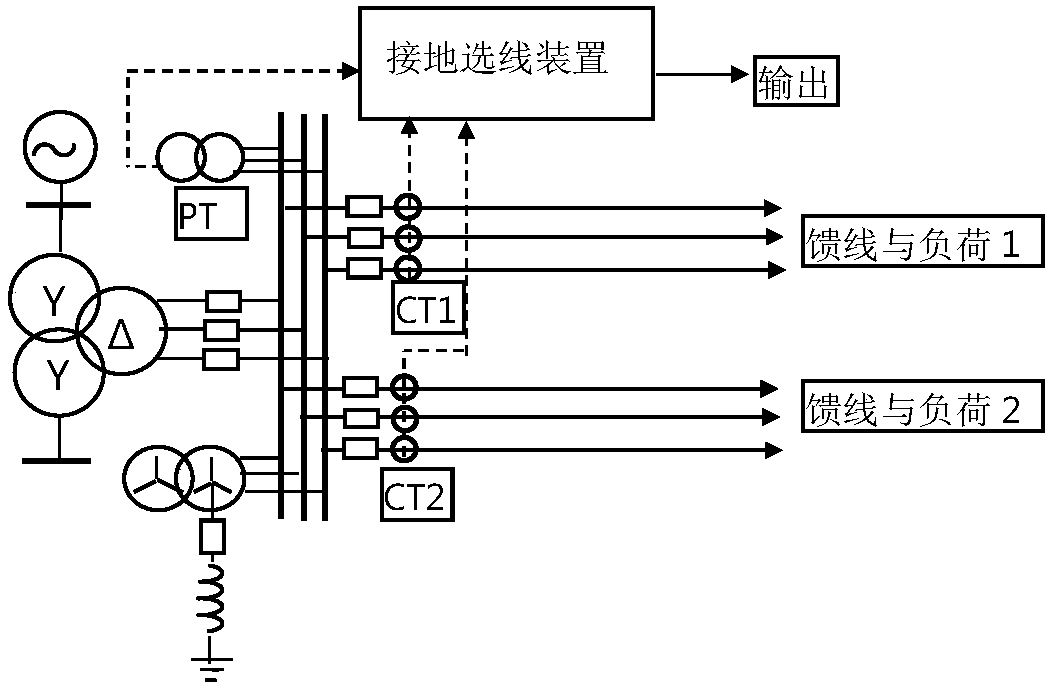

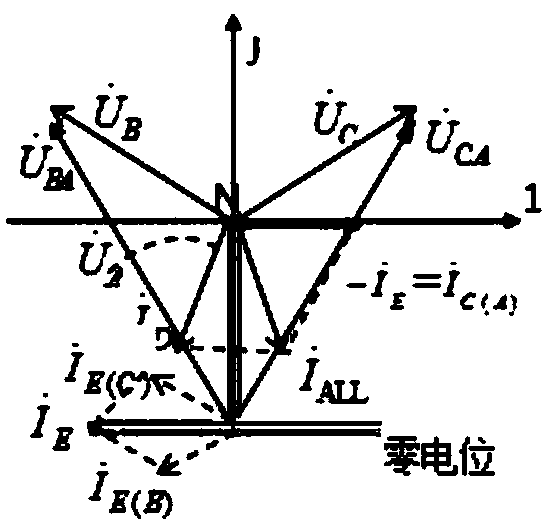

Distribution network grounding line selection method employing recombination current phase detection

ActiveCN107064717AImprove accuracyThe method steps are simpleElectrical testingRecombination currentPower factor

The invention relates to a distribution network grounding line selection method employing recombination current phase detection. The distribution network grounding line selection method can determine whether a circuit is connected to the ground through determining whther Phi ALL(A)-PhiD(A)>Eps is established in a first circuit of a grounding fault phase through recording bus three-phase voltage and waveforms of outgoing line three-phase current, wherein the Phi ALL (A) is a phase angle of voltage and current after the grounding fault, Phi D (A) is a power factor angle before the grounding fault ), and Eps is a smallest phase angle difference between the recombination current and load current, if established, determining the circuit is the grounding fault circuit and outputting the name of a faulty line. The distribution network grounding line selection method is simple in process and reliable in action. The fault line selection does not need flinging and cutting outlet switches, and uninterrupted electric line selection can be performed. The distribution network grounding line selection method can fully use the grounding recombination current phase but the obvious surge in an amplitude to correctively determine the faulty line, which greatly improves the working accuracy.

Owner:INTEGRATED ELECTRONICS SYST LAB

Hetero-bipolar transistor

InactiveUS6876012B2Increase current gainSuppress such carrier recombinationSemiconductor/solid-state device manufacturingSemiconductor devicesValence bandRecombination current

The present invention provides a Hetero-Bipolar Transistor that suppresses a recombination current between electrons in the conduction band of an emitter and holes in the valence band of a base, which results on an enhancement of the current gain of the transistor. The HBT according to the present invention comprises a semi-insulating semiconductor substrate and a series of semiconductor layers on the substrate. The semiconductor layers are a buffer layer, a sub-collector layer a collector layer, a base layer, an emitter layer, an emitter contact layer, and an intermediate layer between the emitter layer and the emitter contact layer. The emitter layer has a carrier concentation of 1.0×1019 cm−3.

Owner:SUMITOMO ELECTRIC IND LTD

Thin Film of Solar Battery Structure, Thin Film of Solar Array and Manufacturing Method Thereof

InactiveUS20120037211A1Reduce power generation efficiencyReduce distancePV power plantsSemiconductor/solid-state device manufacturingRecombination currentSemiconductor materials

The present invention proposes a thin-film solar cell structure, a method for manufacturing the same and a thin-film solar cell array. The method for manufacturing thin-film solar cell structures comprises: forming at least two first trenches through a first surface into said semiconductor substrate, forming at least one second trench through a second surface into said semiconductor substrate, said second trench located between two neighboring said first trenches; forming a first structure on sidewalls of each of said first trenches; to forming a second structure on sidewalls of each of said second trench; and cutting or stretching said semiconductor substrate to form thin-film solar cell structures. The distance between the electrodes can be effectively shortened through the present invention such that the recombination rate between the electrons and the holes can be reduced and the bulk recombination current and the surface recombination current can be reduced to achieve the objective of improving power generation efficiency. The thin-film solar cell structure and the method for manufacturing the same proposed in the present invention can also save semiconductor material and reduce production cost.

Owner:SUNOVEL SUZHOU TECH

Heterojunction field effect transistor

InactiveCN1344033ARecombination current decreasesImprove high frequency characteristicsTransistorRecombination currentLow voltage

A hetero bipolar transistor is provided to have characteristics such as high current amplification factor or the like by suppressing the recombination current of the emitter and base while lowering the drive voltage. An Si-collector buried layer(11), the first base region(12) mode of the SiGeC layer having a high C content, the second base region(13) made of the SiGeC layer or an SiGe layer having a low C content, and an Si-cap layer(14) having an emitter region(14a), are laminated on an Si substrate(10). The C content of at least an emitter region side end of the second base region is less than 0.8%. Thus, in a depletion layer of an emitter-base junction, formation of the recombination center of the C is suppressed. An improvement in electrical characteristic such as a current amplification factor or the like due to a reduction in the recombination current is realized while maintaining low voltage drive properties.

Owner:PANASONIC CORP

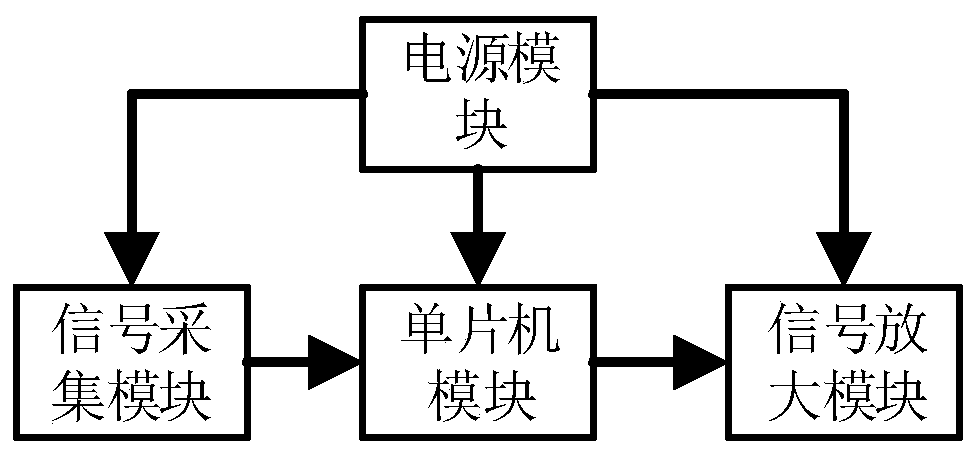

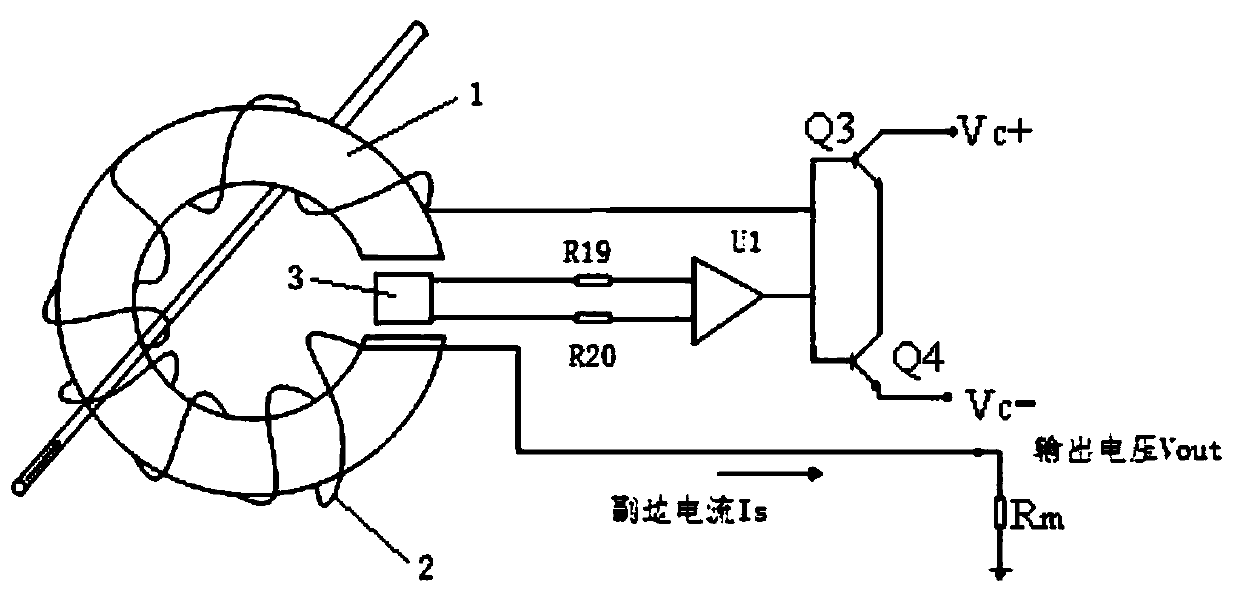

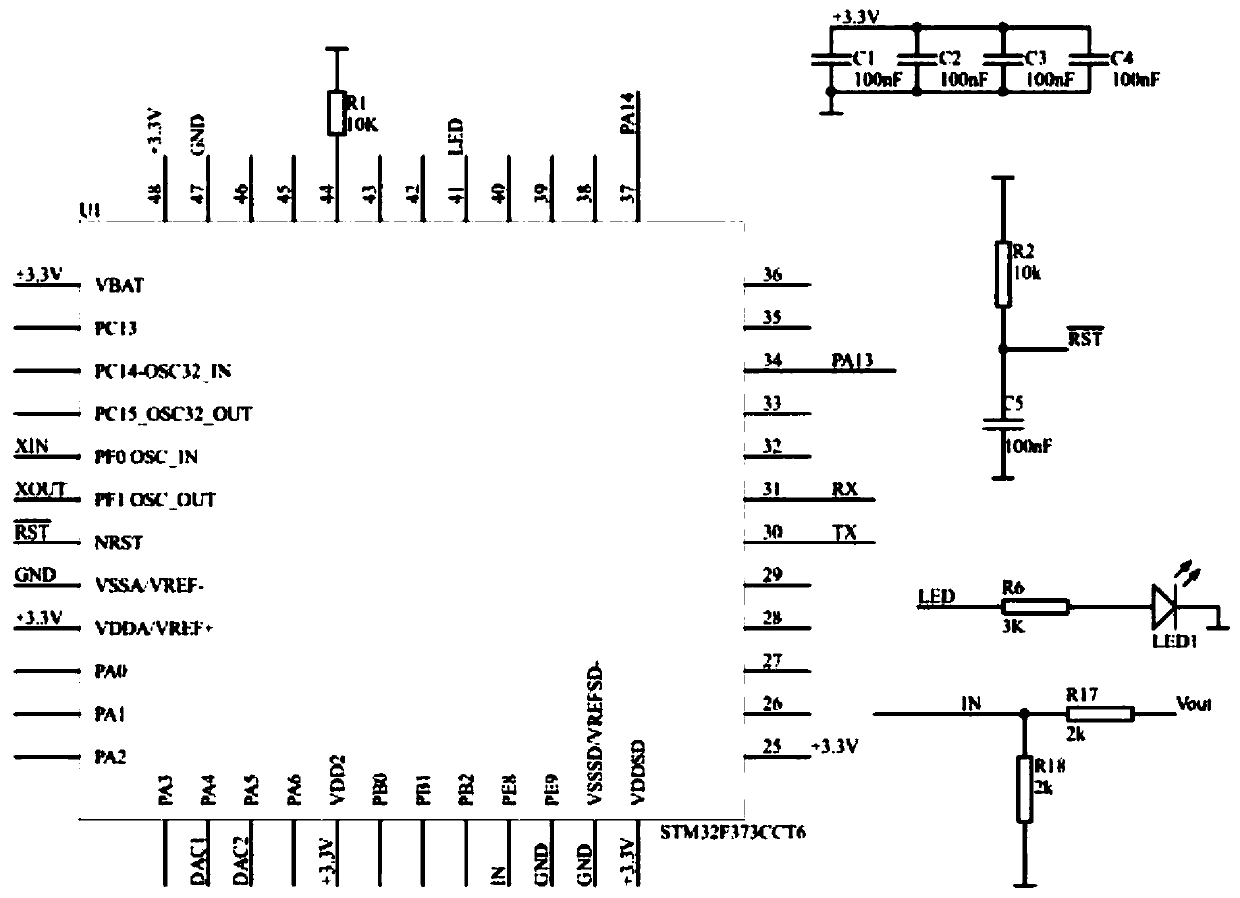

Recombination current frequency sensor

InactiveCN110542788AHigh precisionImprove IP protection levelFrequency measurement arrangementMeasurement using digital techniquesMicrocontrollerClosed loop

The invention relates to a recombination current frequency sensor. The frequency sensor comprises a single chip microcomputer module for performing fast Fourier transform computation on an electric signal detected by the sensor to obtain a current value and a frequency value, and converting the electric signal into an analog signal through the internal DAC to output to a signal amplification module; a signal collection module for conditioning and amplifying a signal of a Hall element; a signal amplifying module for performing signal amplification output on the DAC analog quantity output by thesingle chip microcomputer module; and a power supply module for providing a power supply source for the single chip microcomputer, and converting the input power supply voltage into the power supplyvoltage required by the single chip microcomputer module. The Hall element collection waveform is computed by adopting the fast Fourier transform, and the current and the frequency thereof can be computed and measured at the same time; by adopting a closed-loop effect of the Hall effect, the sensor has the features of being high in precision and good in follow-up characteristics. By adopting the internal potting sealing treatment, the sensor has the feature of being high in IP protection level and good in insulation characteristic.

Owner:WUHAN UNIV OF TECH