Patents

Literature

361results about "Semiconductor characterisation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

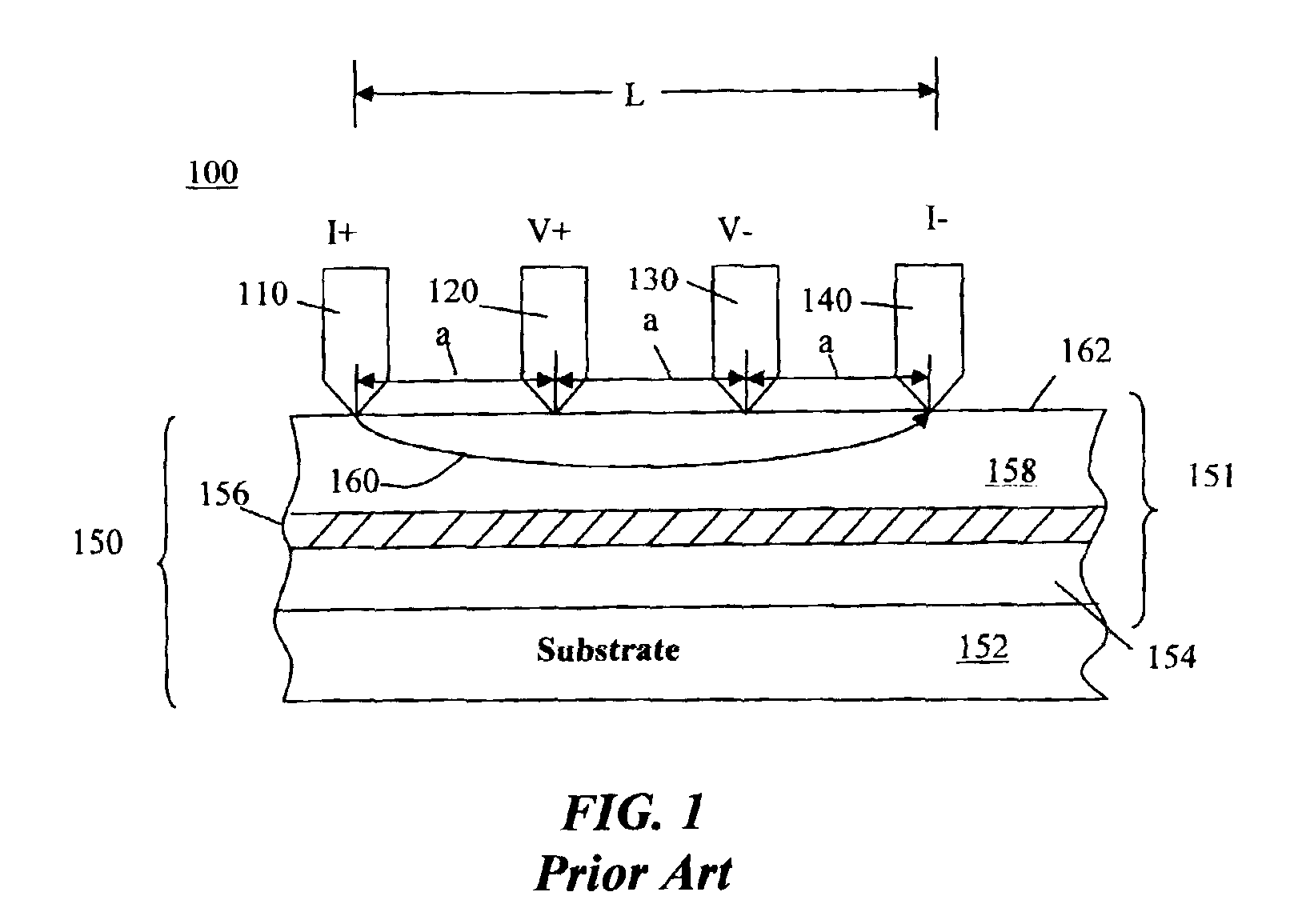

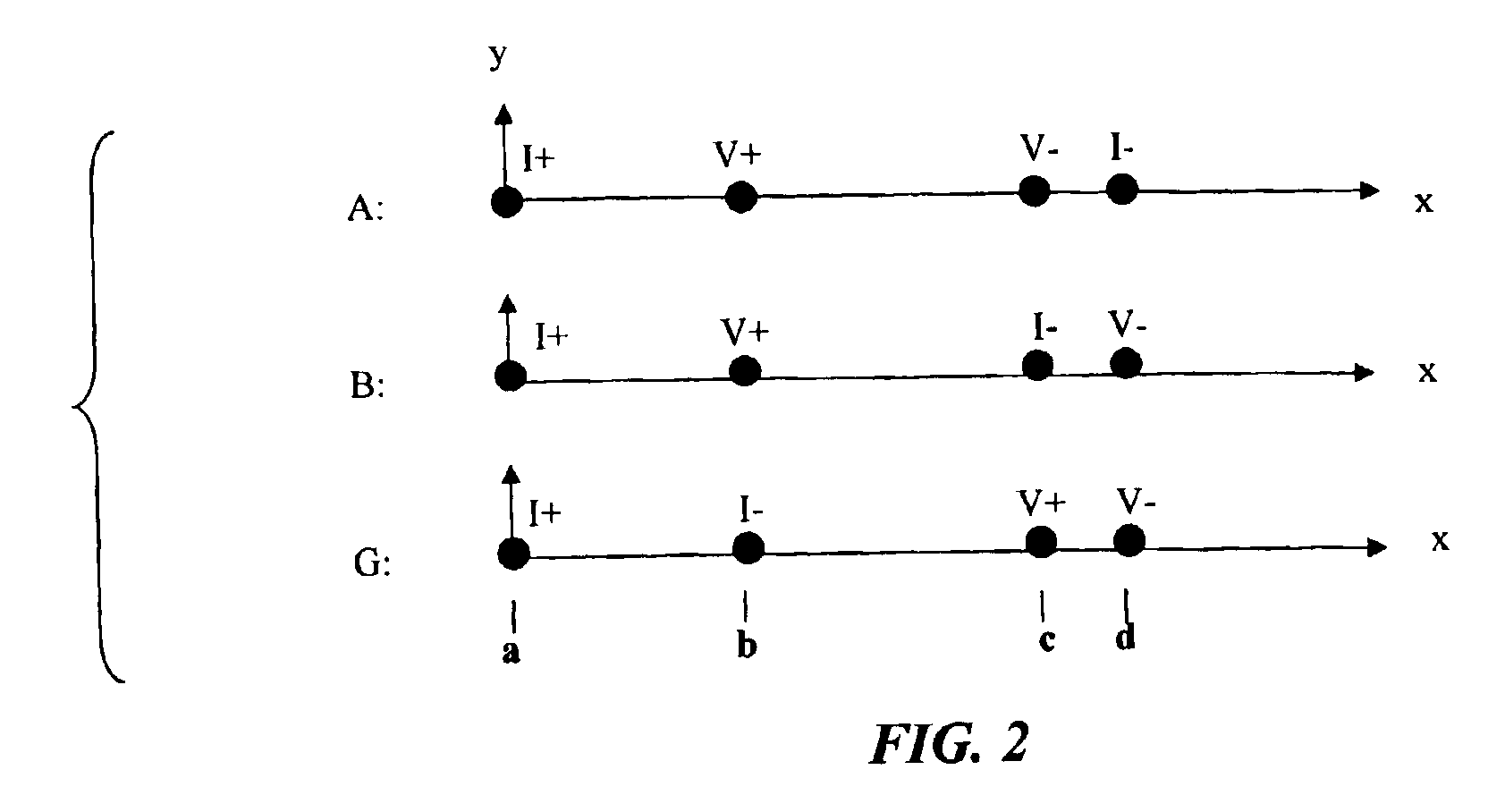

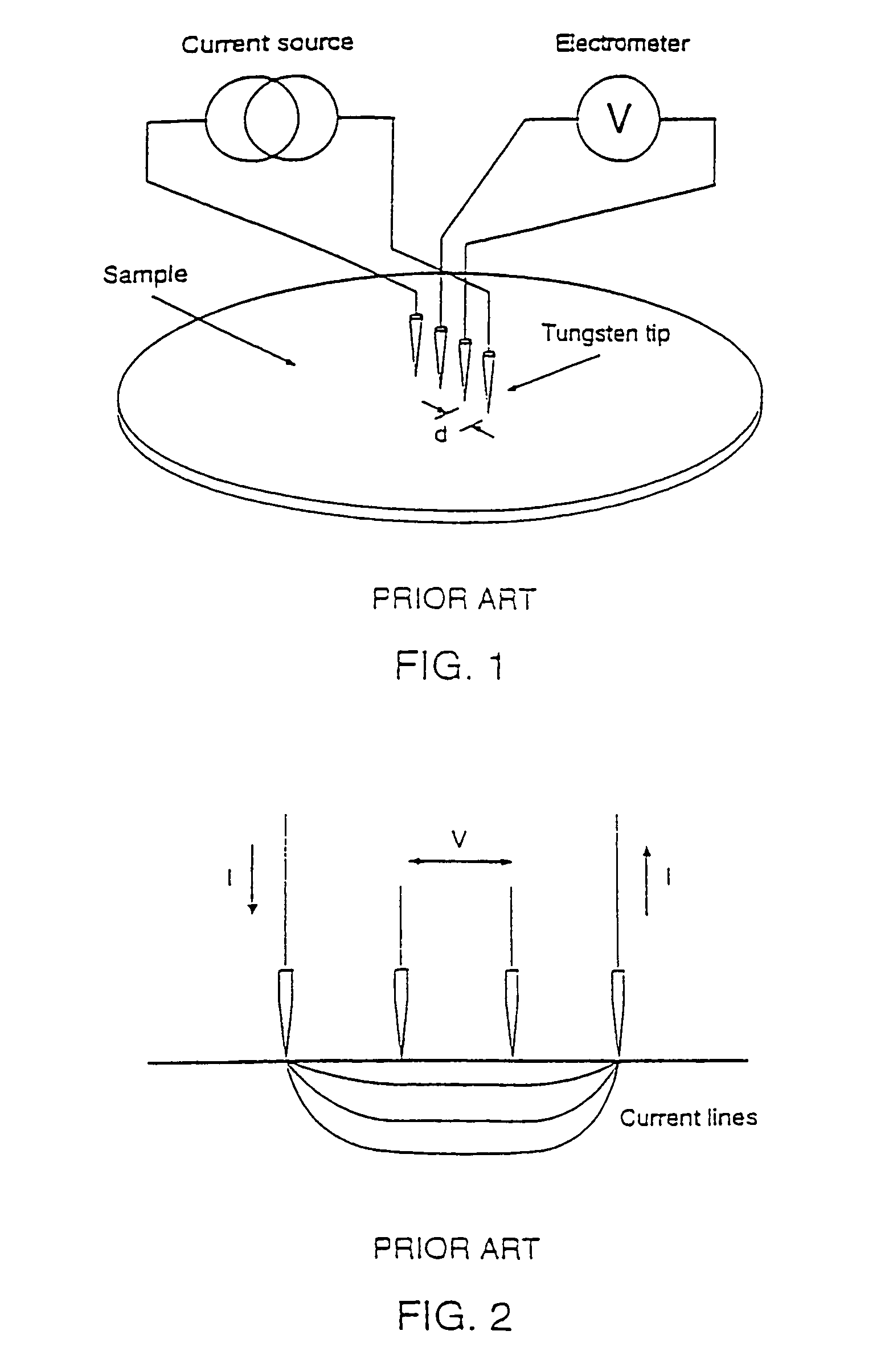

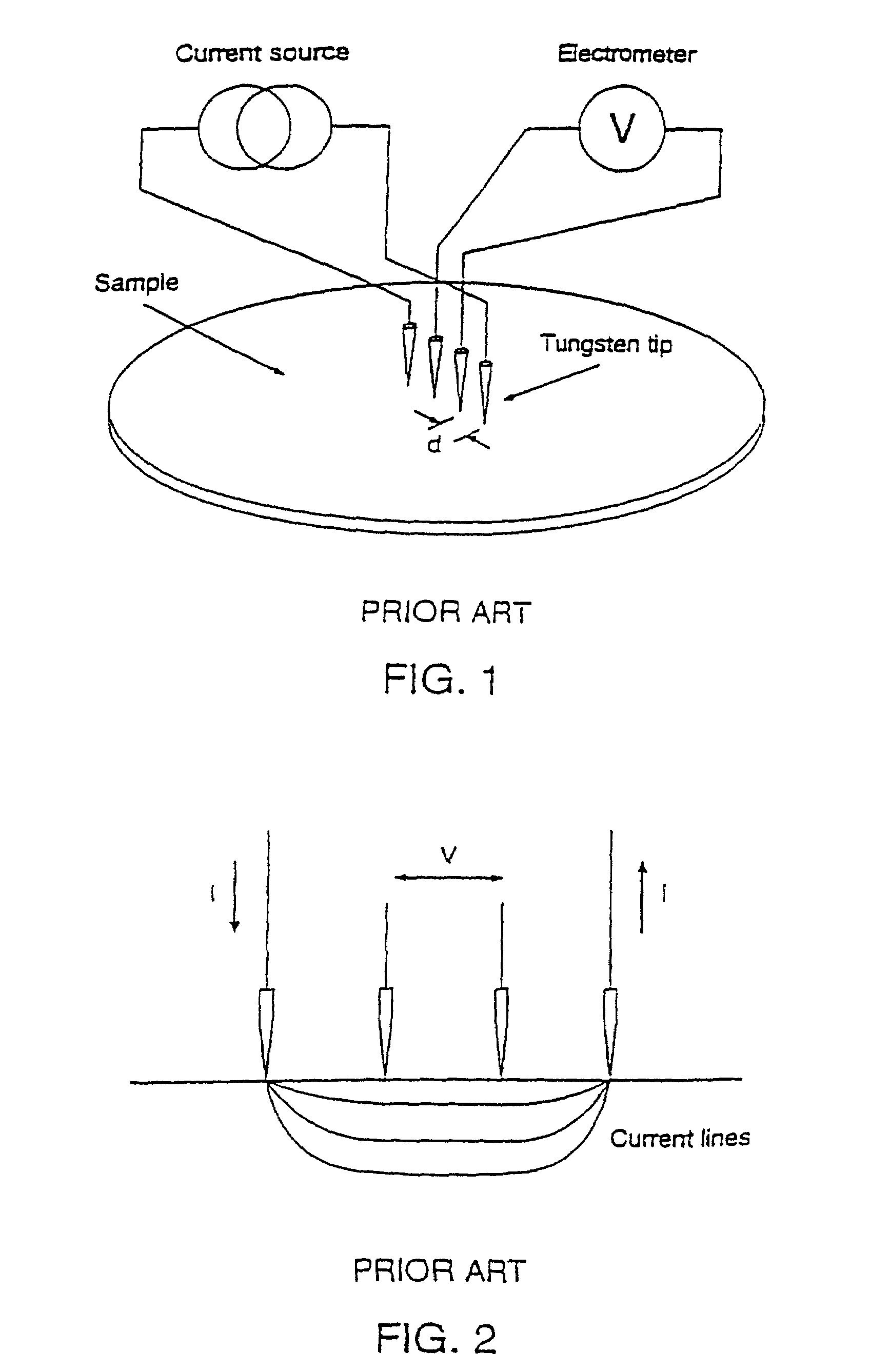

Reduction of positional errors in a four point probe resistance measurement

ActiveUS6943571B2Reduce measurement errorResistance/reactance/impedenceSemiconductor characterisationObservational errorElectrical resistance and conductance

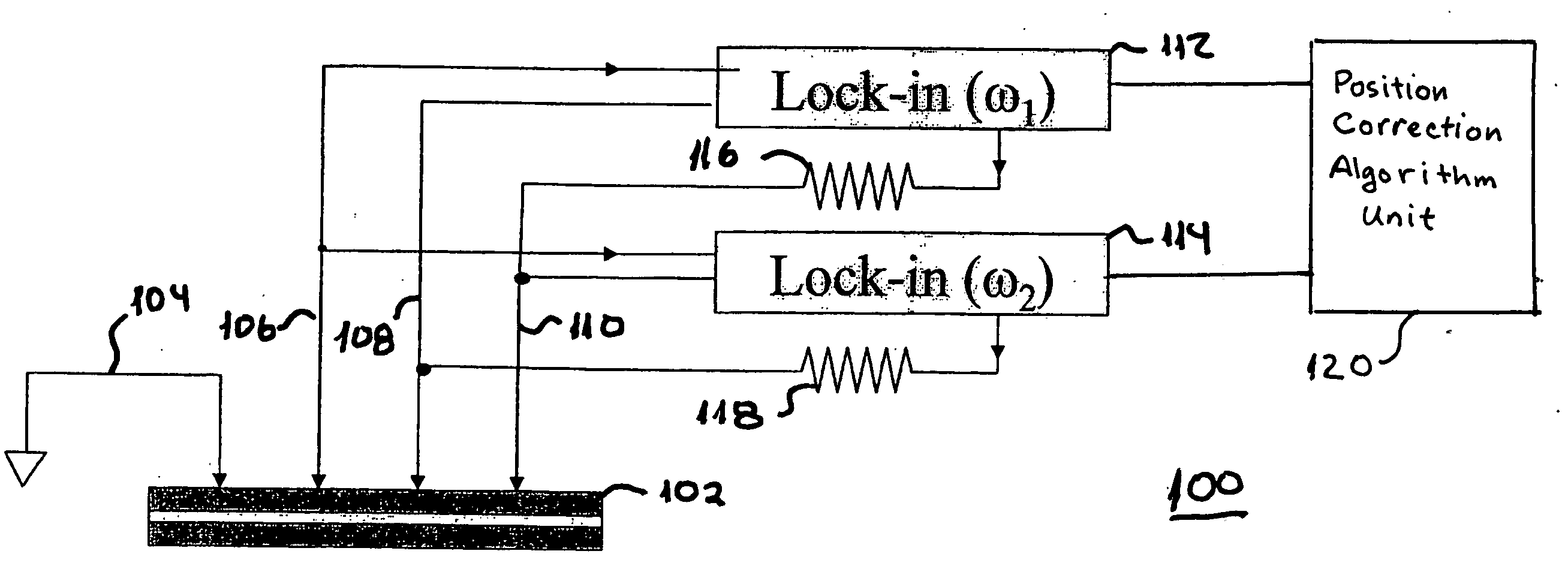

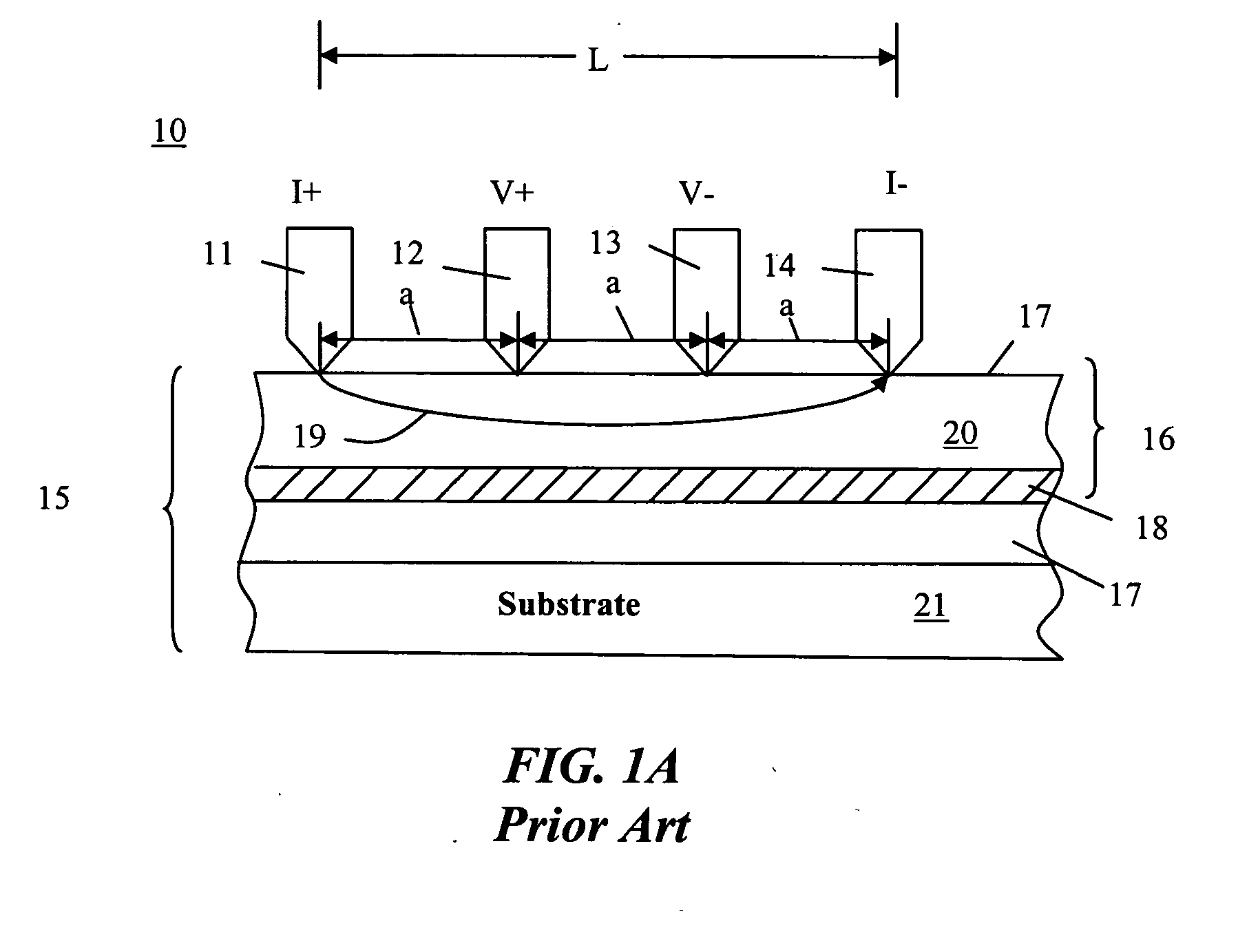

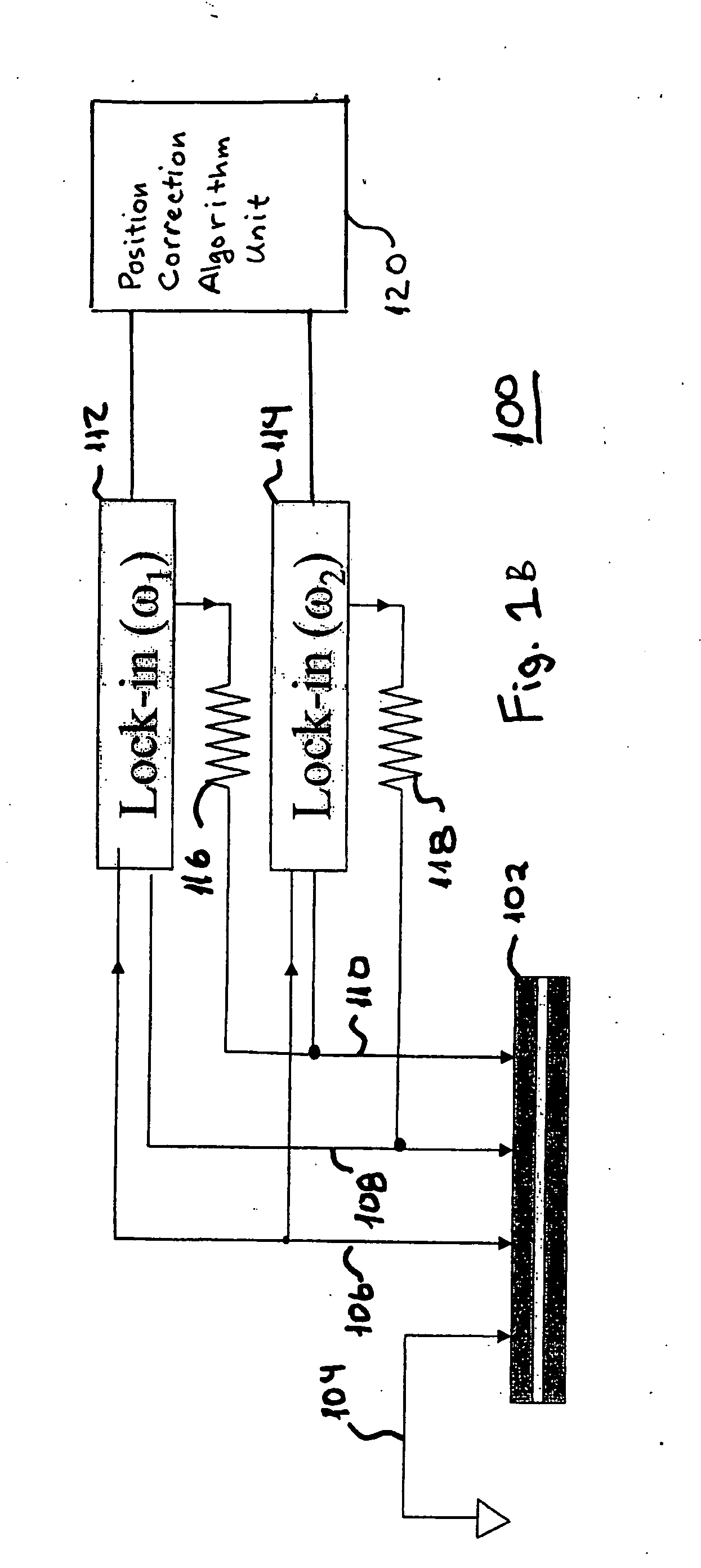

A system and method for measuring a resistance or a resistance per square, Rsq, of a material having a surface using a multi-point probe including four or more collinear contact points placed in the interior of the sample, the method including: making a first measurement using a first set of probe electrodes for inducing a current and a second set of probe electrodes for measuring the voltage difference when the current is induced; making a second measurement using a set of probe electrodes different from the first set for inducing a current and a set of probe electrodes different from the second set for measuring the voltage difference when the current is induced; and using a known relationship among the currents induced, the voltages measured, the nominal probe positions and the resistance per square to determine the resistance per square such that measurement errors resulting from positioning of the probes are reduced.

Owner:IBM CORP

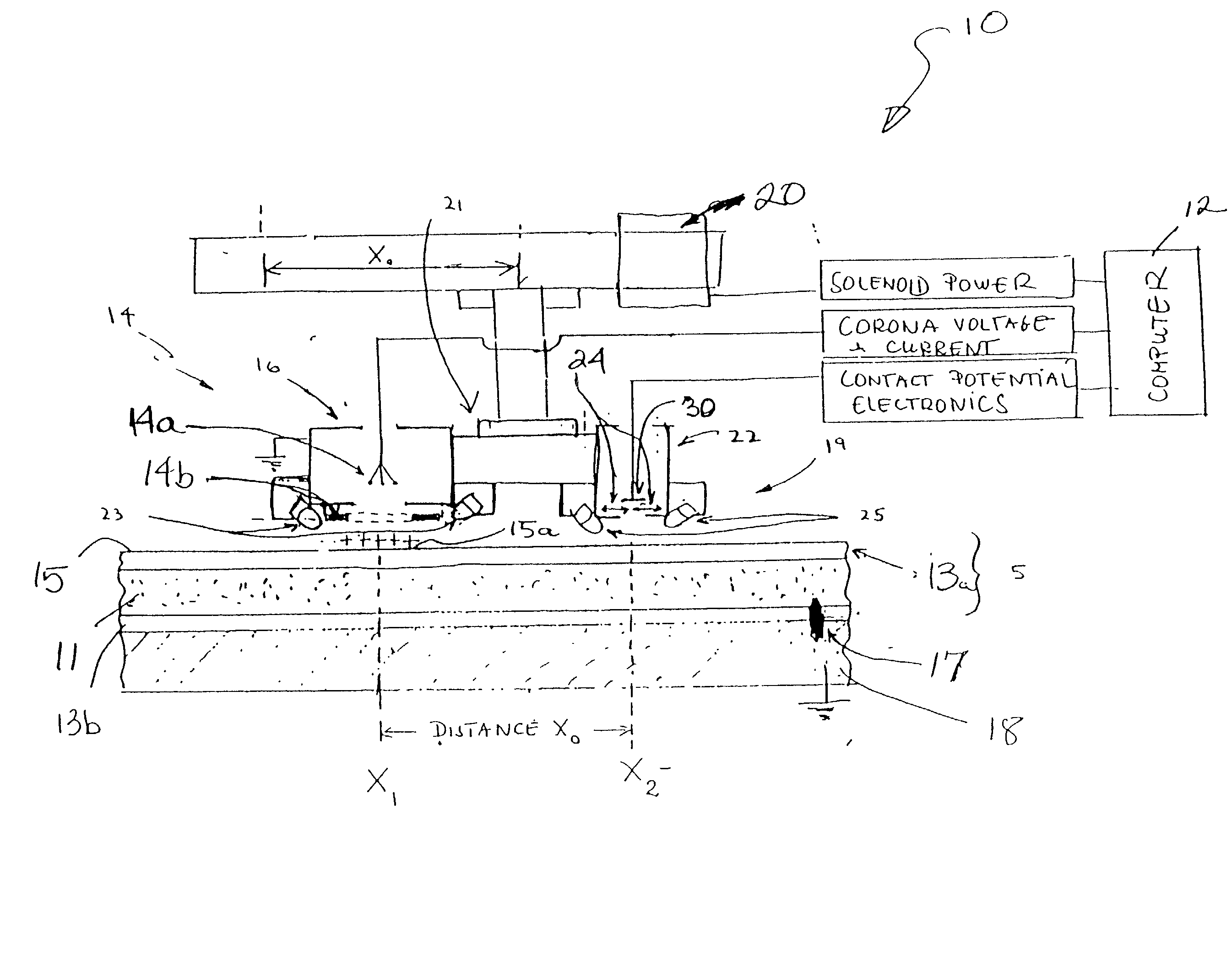

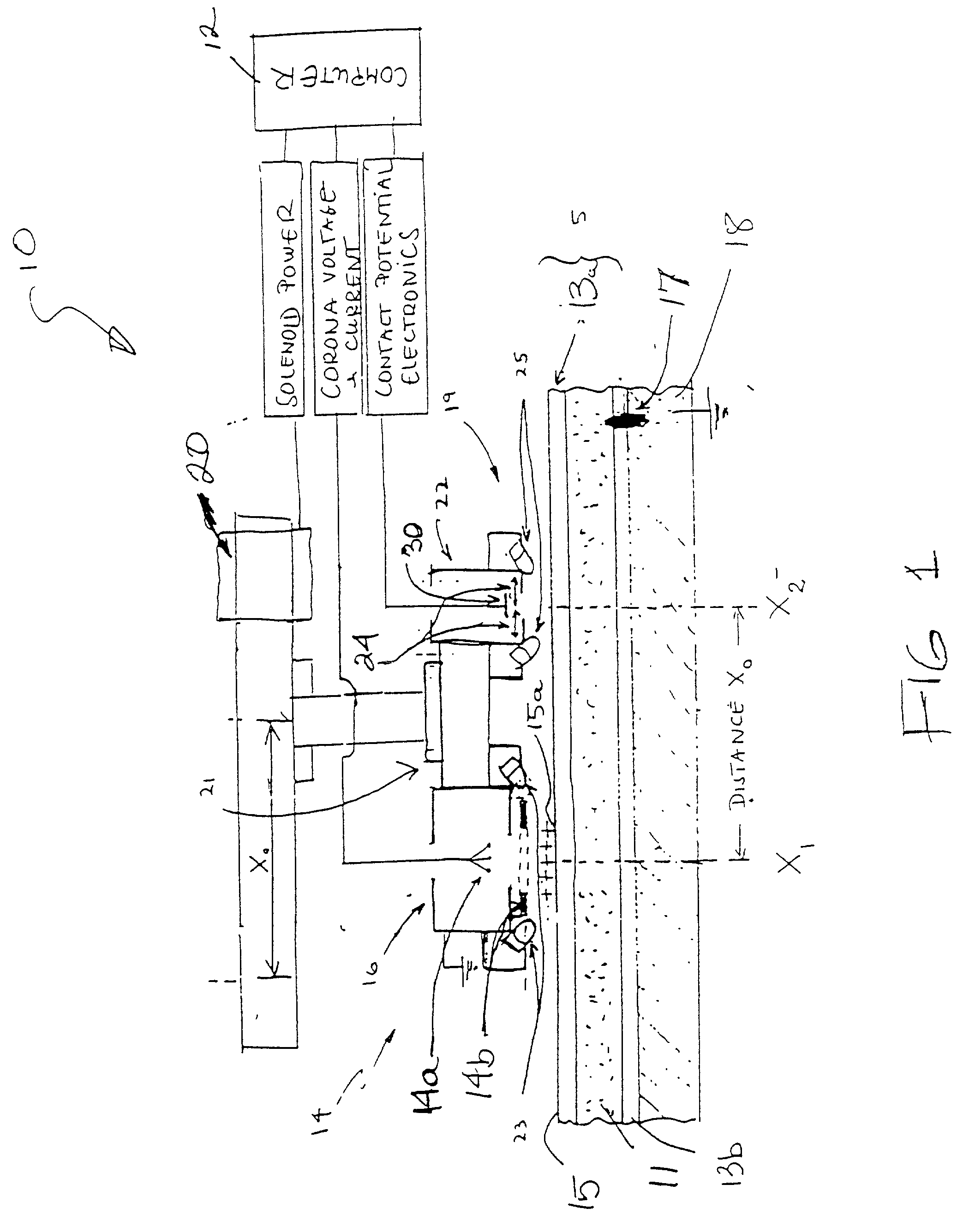

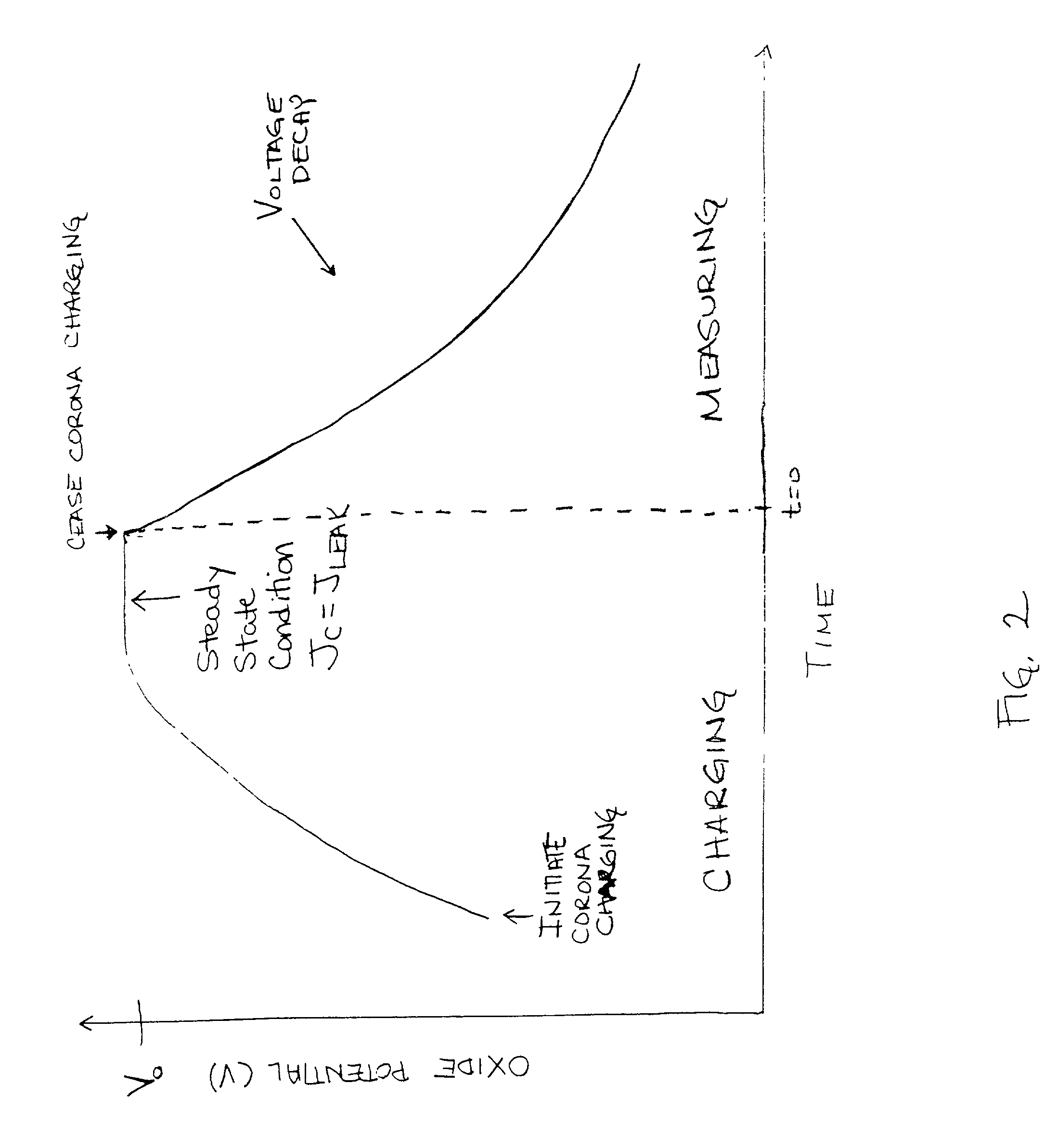

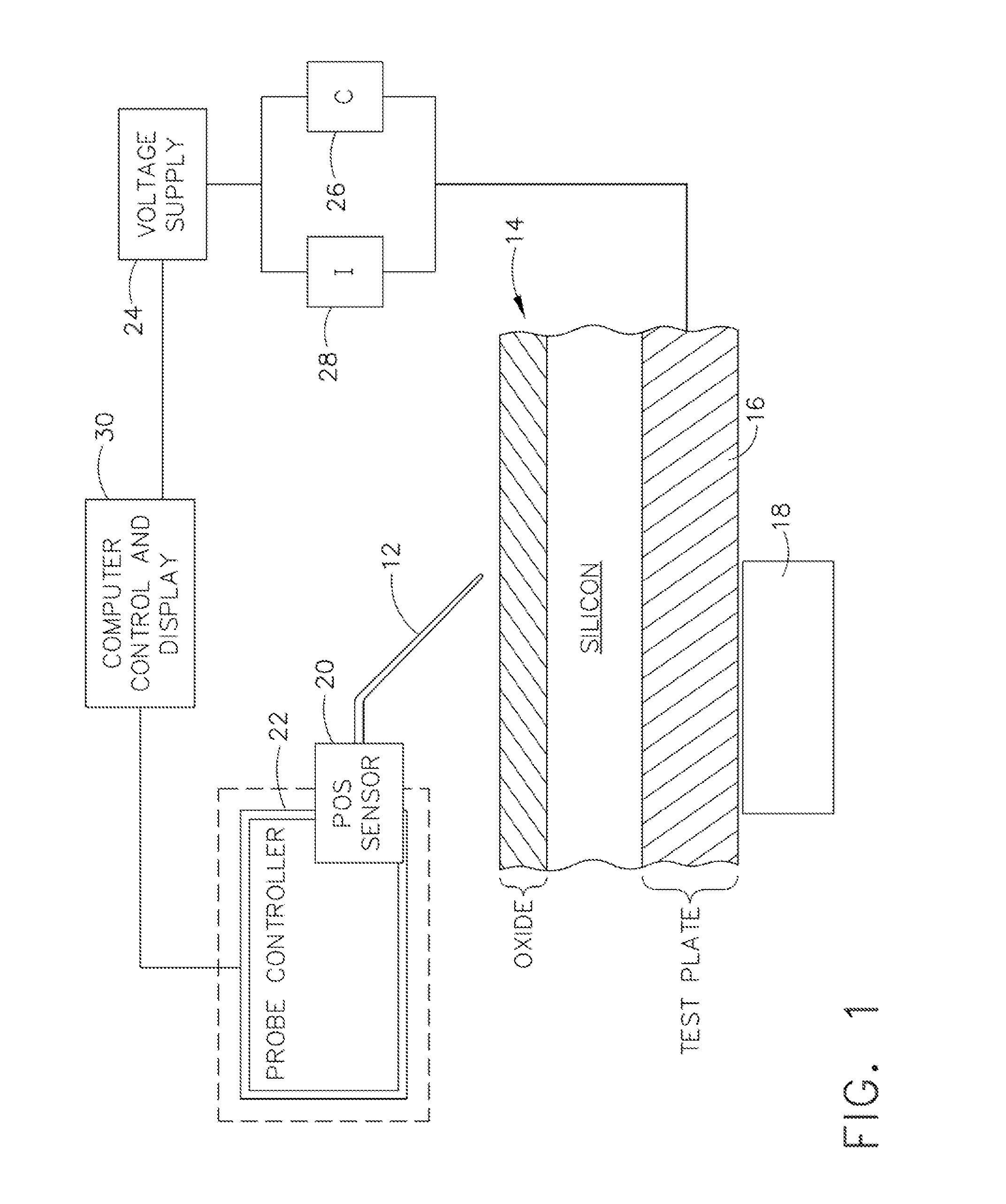

Steady state method for measuring the thickness and the capacitance of ultra thin dielectric in the presence of substantial leakage current

InactiveUS20020125900A1Effective and accurate measurementMaterial analysis by electric/magnetic meansUsing electrical meansEquivalent oxide thicknessCapacitance

A method is described for measuring the capacitance and the equivalent oxide thickness of an ultra thin dielectric layer on a silicon substrate in which the dielectric layer is uniform or patterned. The surface of a dielectric layer is electrically charged by a flux on ions from a corona discharge source until a steady state is reached when the corona flux is balanced by the leakage current across a dielectric. The flux is abruptly terminated and the surface potential of a dielectric is measured versus time. The steady state value of the surface potential is obtained by extrapolation of the potential decay curve to the initial moment of ceasing the corona flux. The thickness of a dielectric layer is determined by using the steady state potential or by using the value of the surface potential after a predetermined time.

Owner:SEMICON DIAGNOSTICS

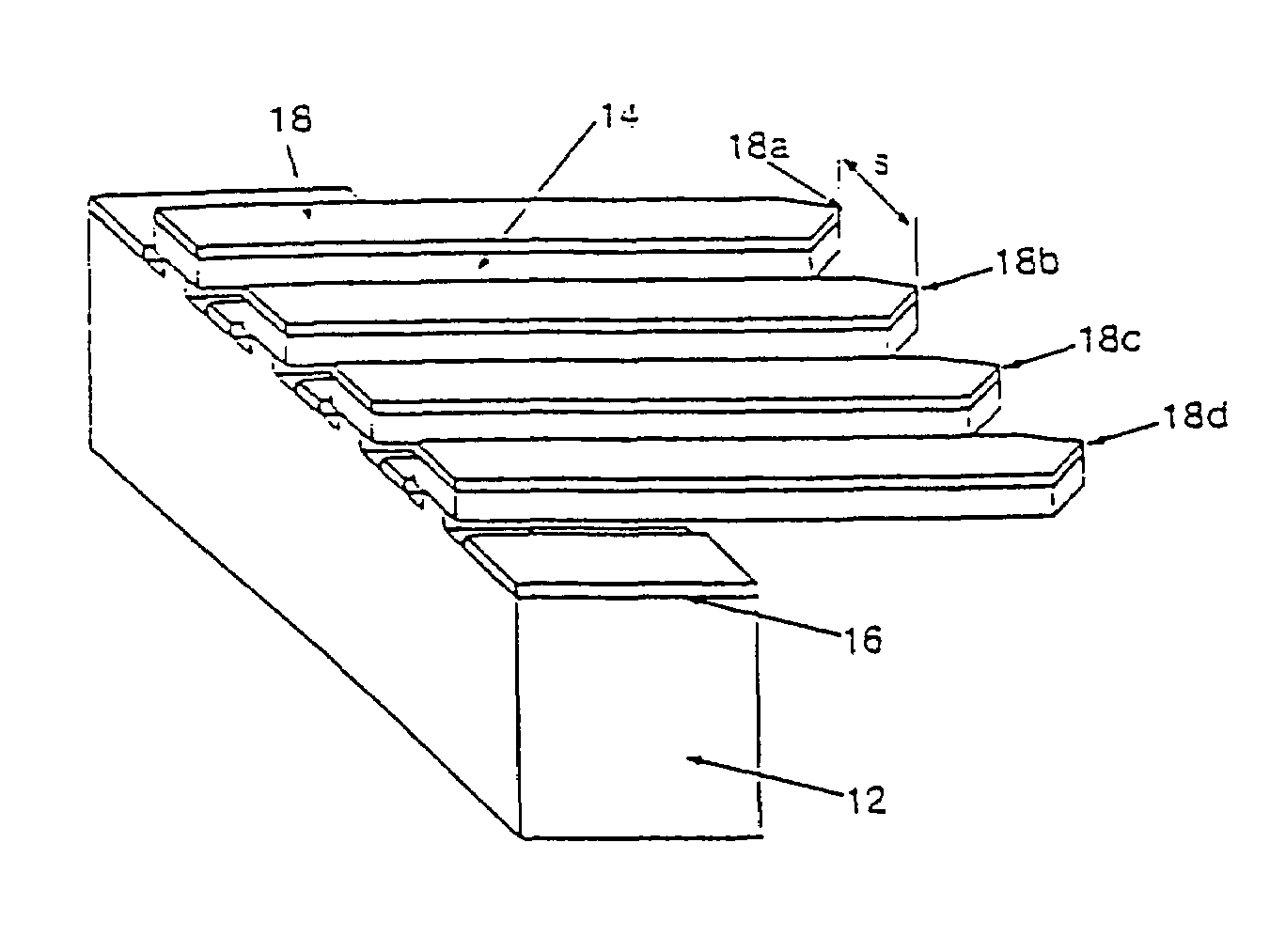

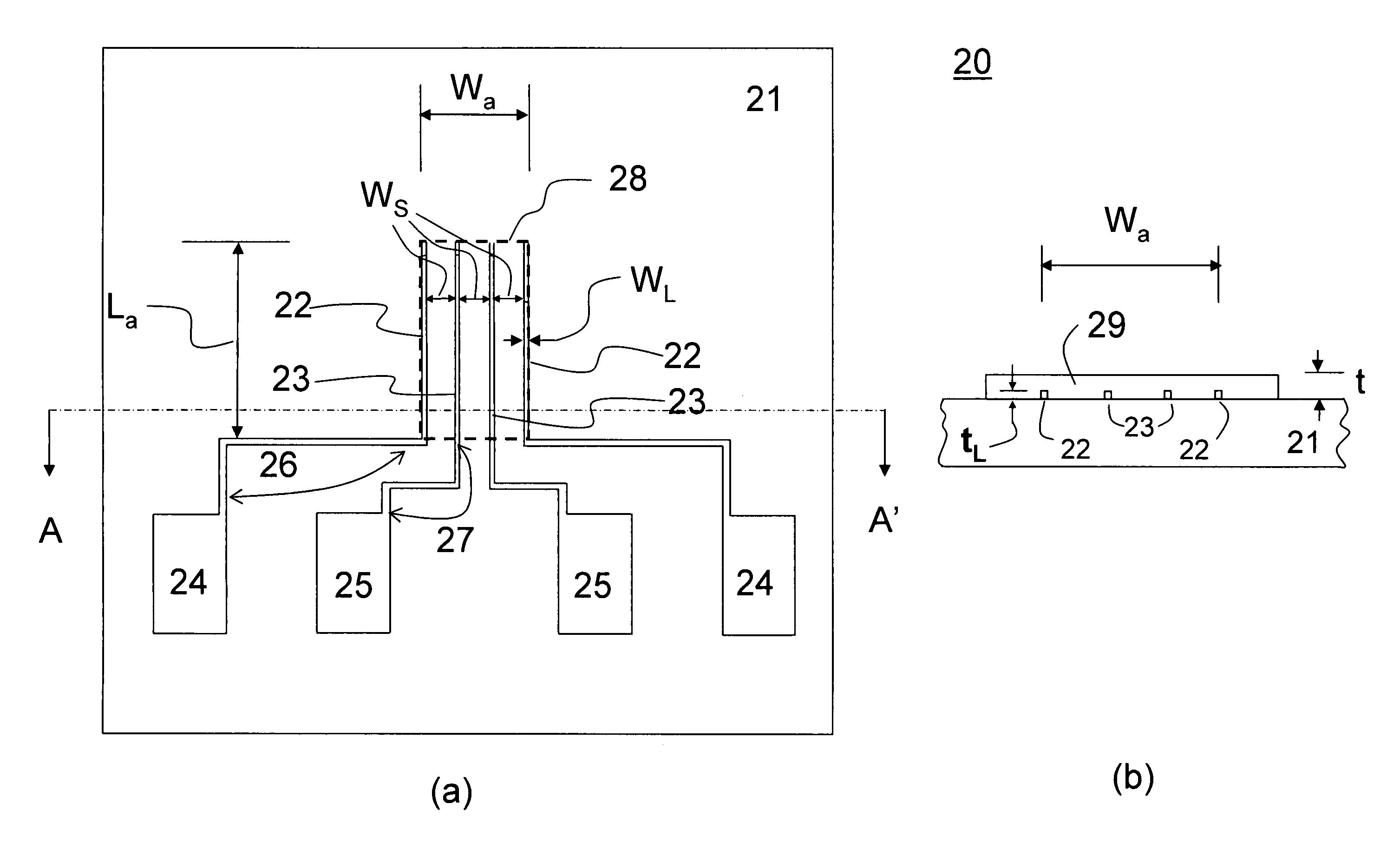

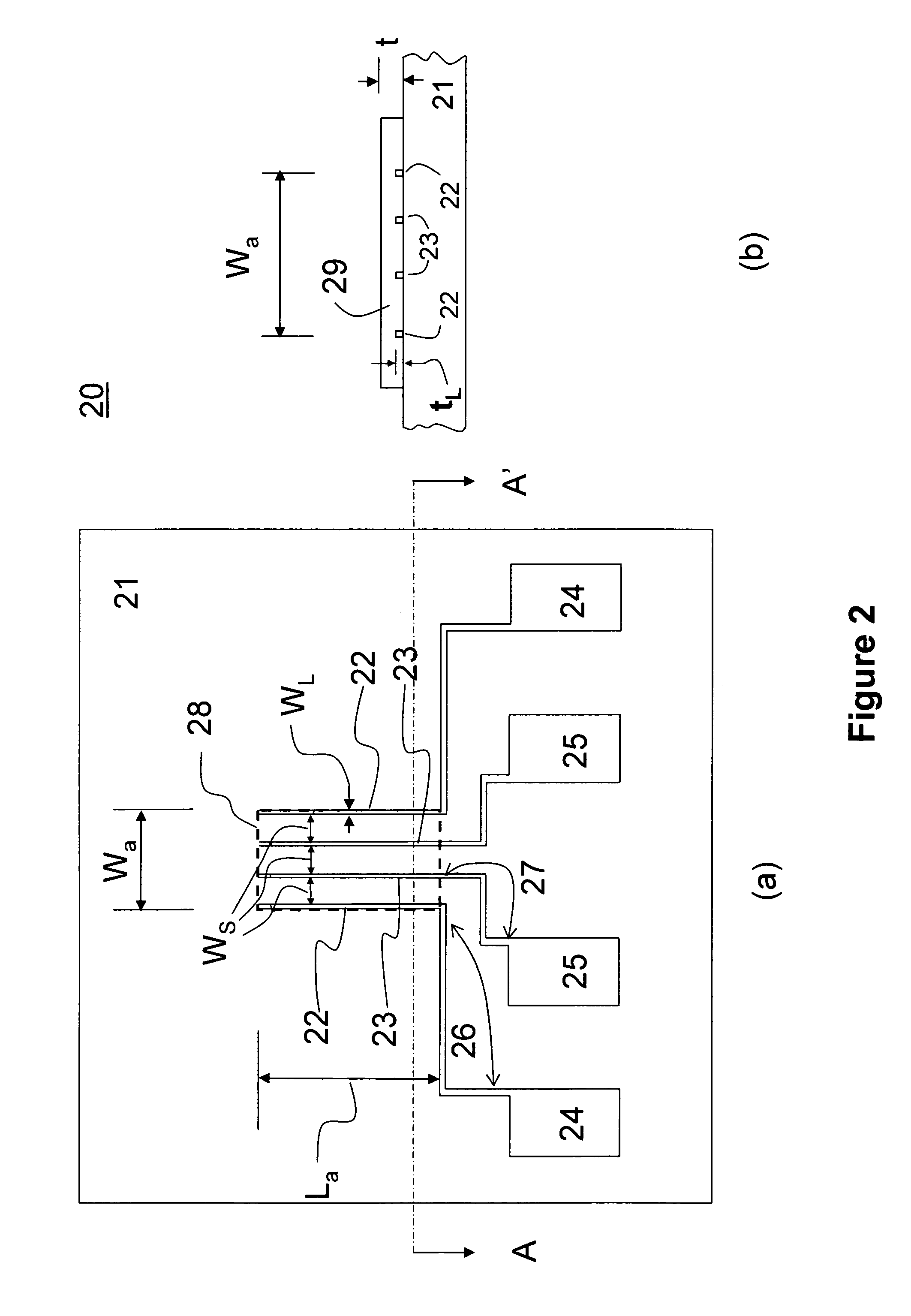

Multi-point probe

InactiveUS7323890B2Semiconductor/solid-state device testing/measurementElectronic circuit testingElectricityElectrical resistance and conductance

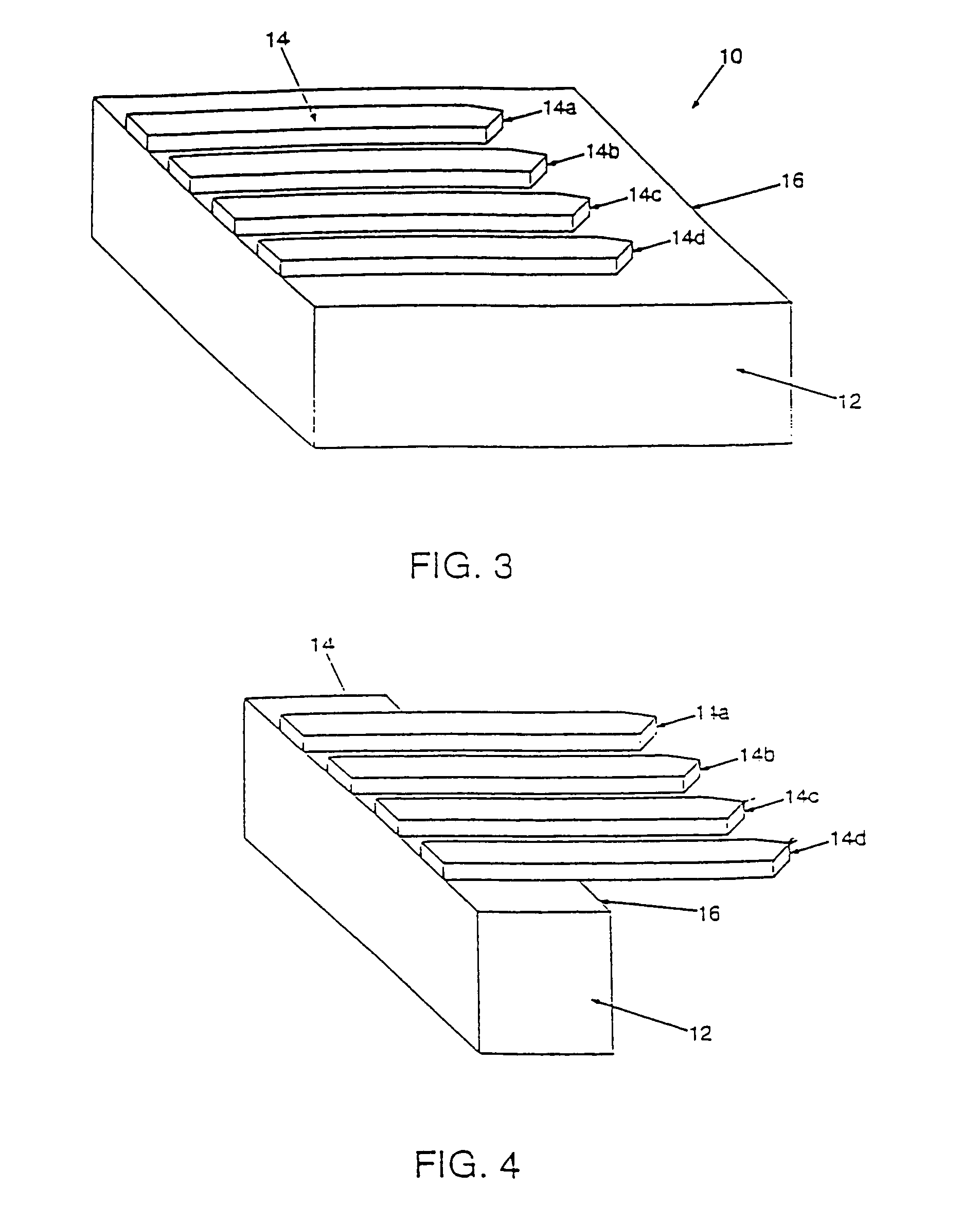

A multi-point electrical probe for testing location-specific electrical properties on circuit boards. Four generally parallel, electrically conducting probe arms are produced preferably by wafer-based techniques, although any even number of probe arms between two and 64 may be used. The precision of wafer-based manufacturing techniques permits miniaturization beyond that which is conventionally obtained by assembling discrete components. The probe arms are generally flexible, and may be shaped suitably to accommodate a particular circuit geometry. The probe and / or the sample under test may be precisely located by suitable translation and / or rotation stages, which may optionally be placed under computer control. A suitable wiring diagram is provided, and preferable manufacturing techniques are discussed. In addition, the conducting probe arms benefit from active guarding, which reduces leakage resistance and increases the measuring accuracy of the probe, by the inclusion of electrically-isolated conducting regions located between the probe arms.

Owner:CAPRES

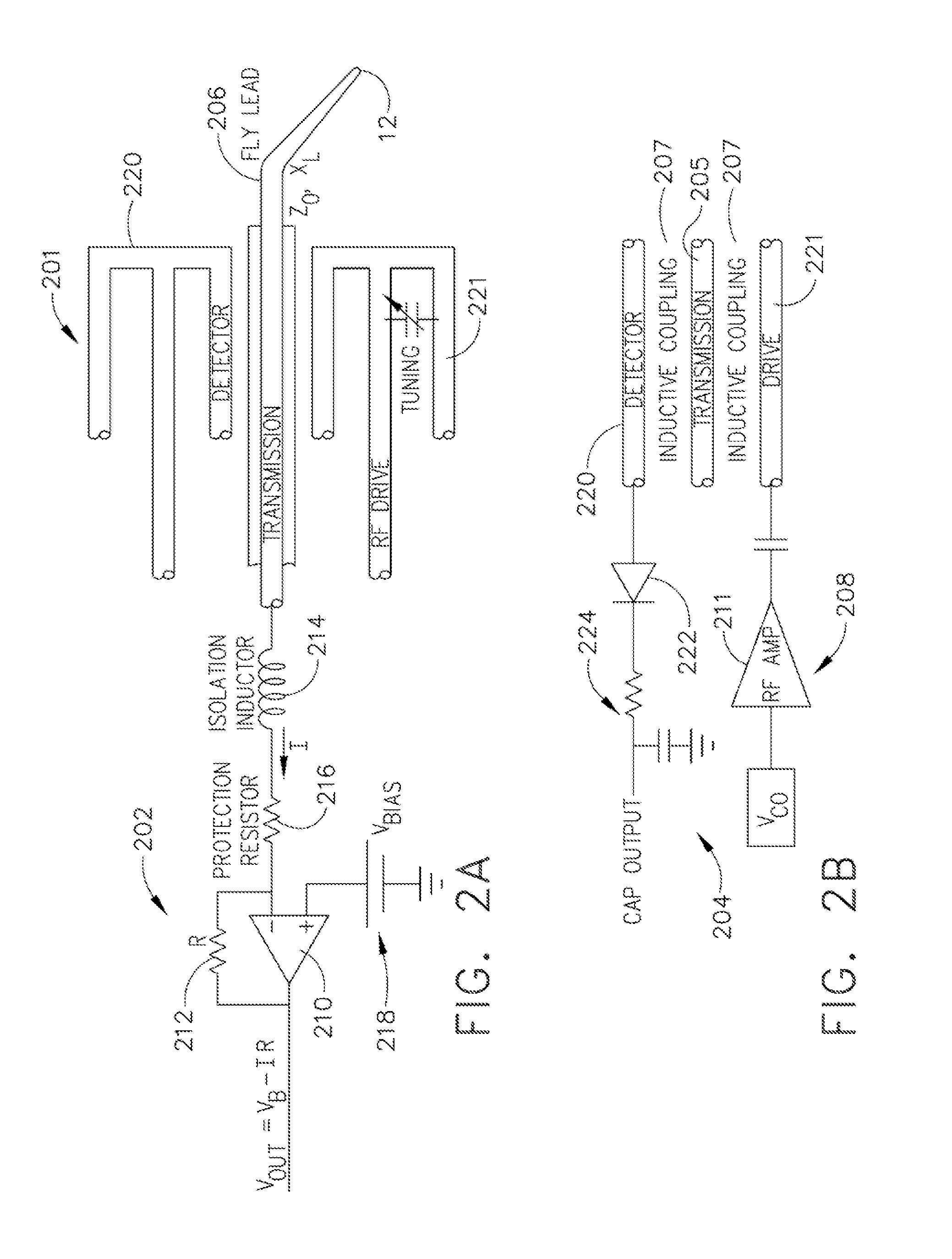

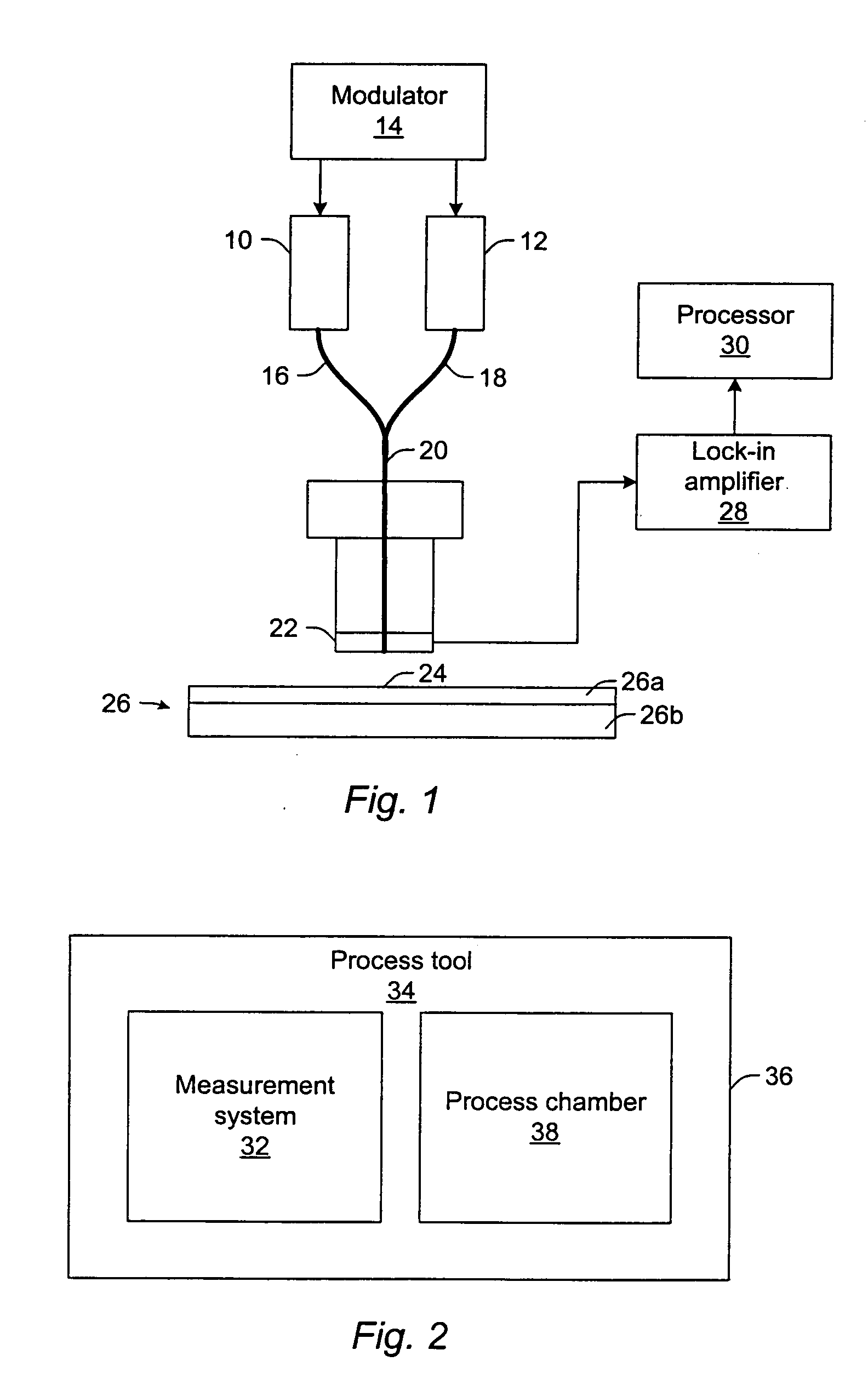

High frequency measurement for current-in-plane-tunneling

InactiveUS20050151552A1Resistance/reactance/impedenceSemiconductor characterisationIn planeImproved method

An improved method and apparatus for determining a property based upon at least two measurements uses simultaneous probe signals having two different frequencies. The probe signals are produced simultaneously such that the position of the probes is identical when the probe signals are produced. The responses to the two probe signals have frequencies that correspond to the probe signals. The individual responses are isolated from each other based upon their differing frequencies by frequency lock-in circuits. By performing the measurements simultaneously, positional errors that are introduced due to small changes that occur in the position of the probes if the measurements are taken sequentially are eliminated.

Owner:IBM CORP

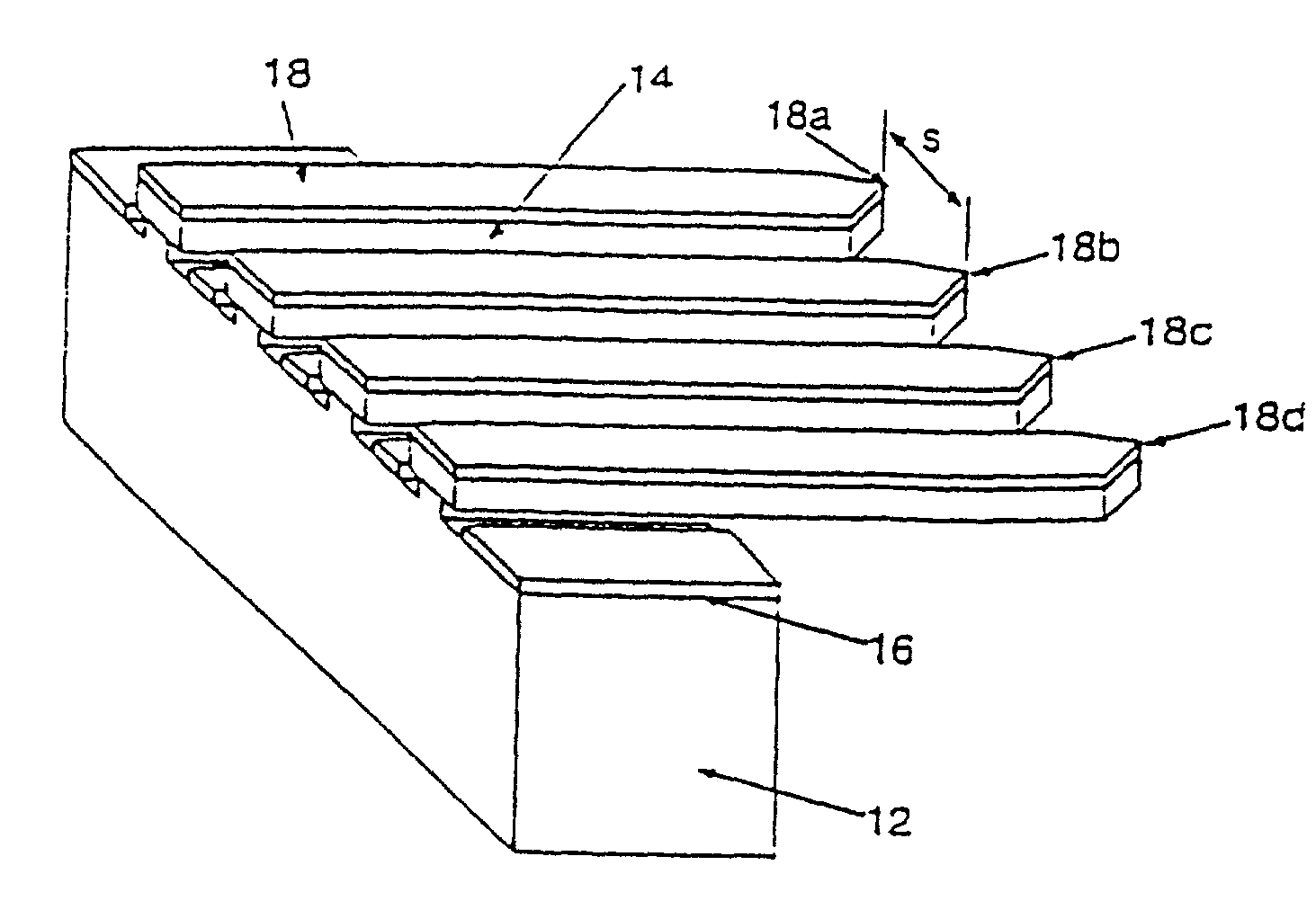

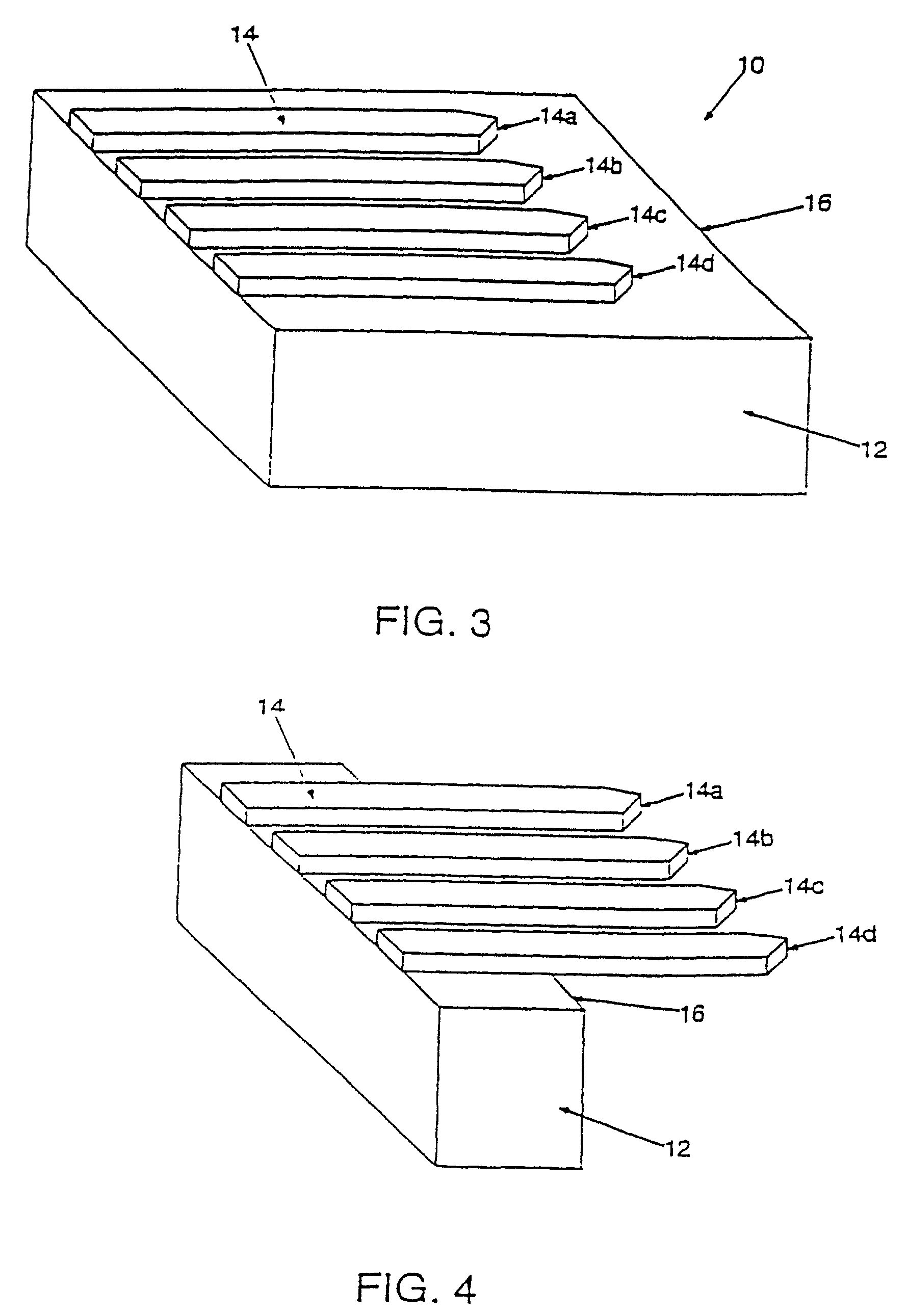

Four-terminal methods for resistivity measurement of semiconducting materials

InactiveUS7030633B1Accurately measure resistivityReduce contact resistanceSemiconductor/solid-state device testing/measurementMaterial analysis by electric/magnetic meansSemiconductor materialsOrganic semiconductor

This invention provides an innovative multi-line structure and an effective four-terminal method for the resistivity measurement of semiconductor materials. The multi-line structure and the four-terminal method not only allow one to perform resistivity measurement on any inorganic and organic semiconductor thin film conveniently, rapidly and accurately but also offer the means to study resistivity uniformity across the semiconductor thin film.

Owner:XIAO STEVEN SHUYONG

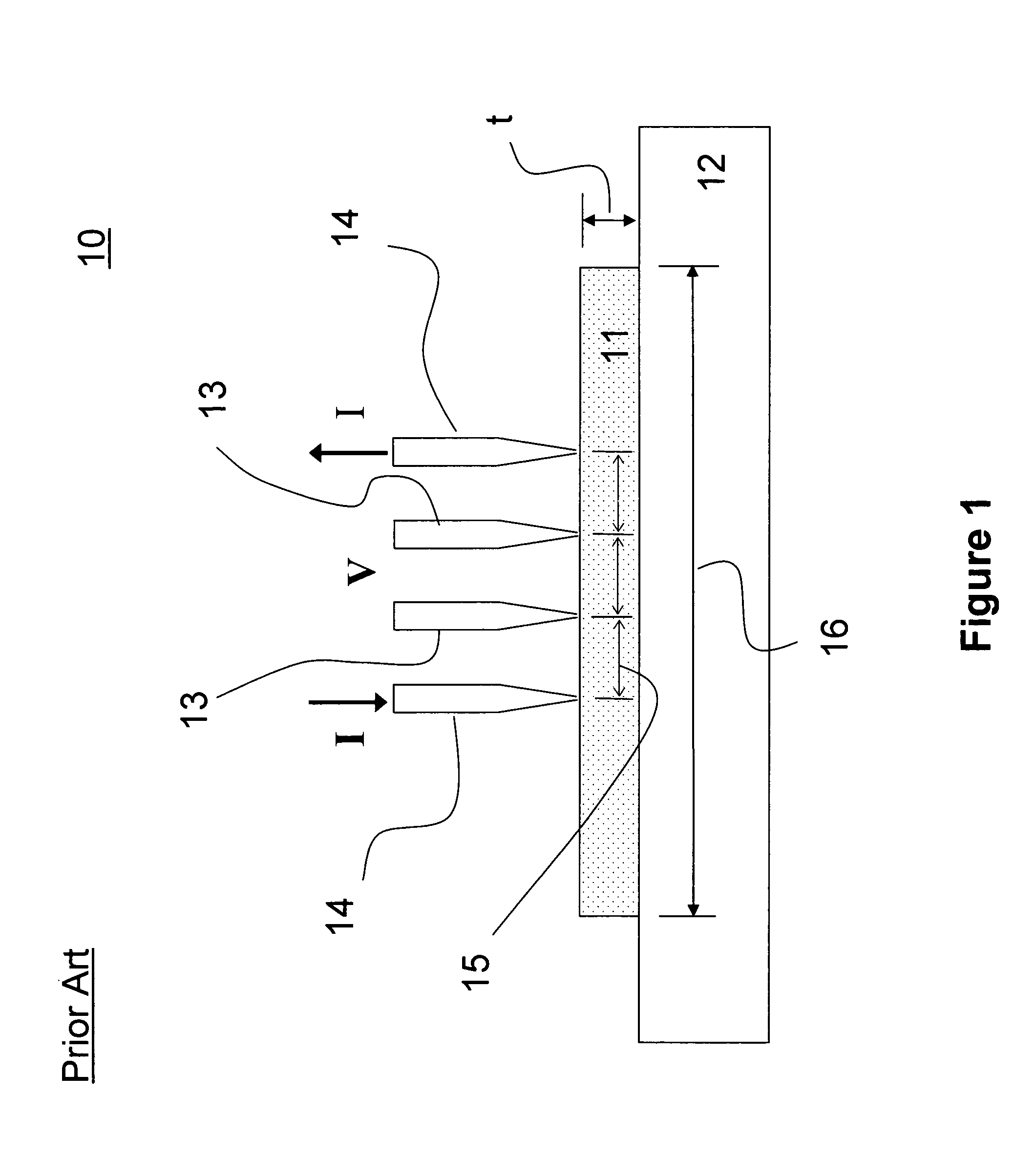

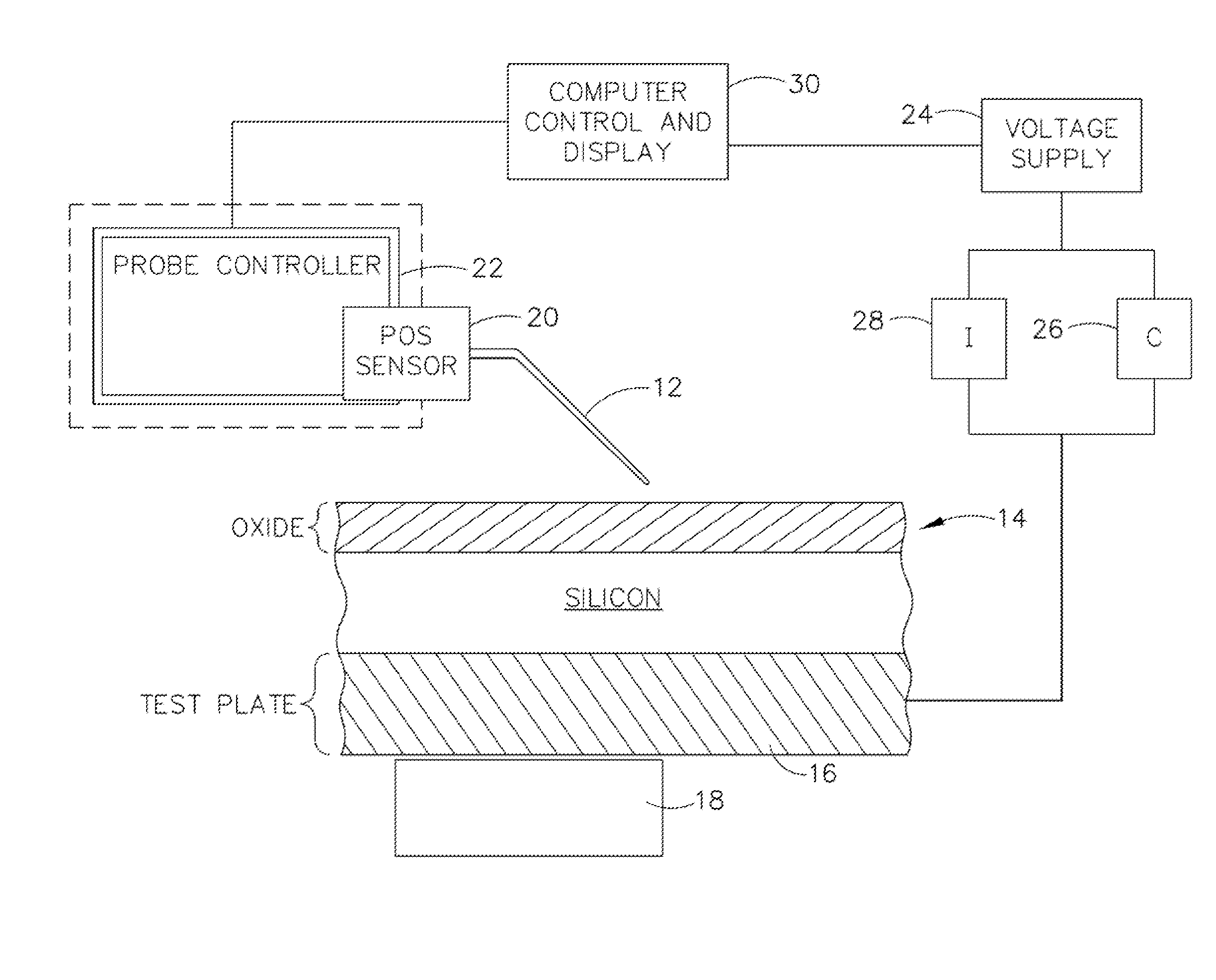

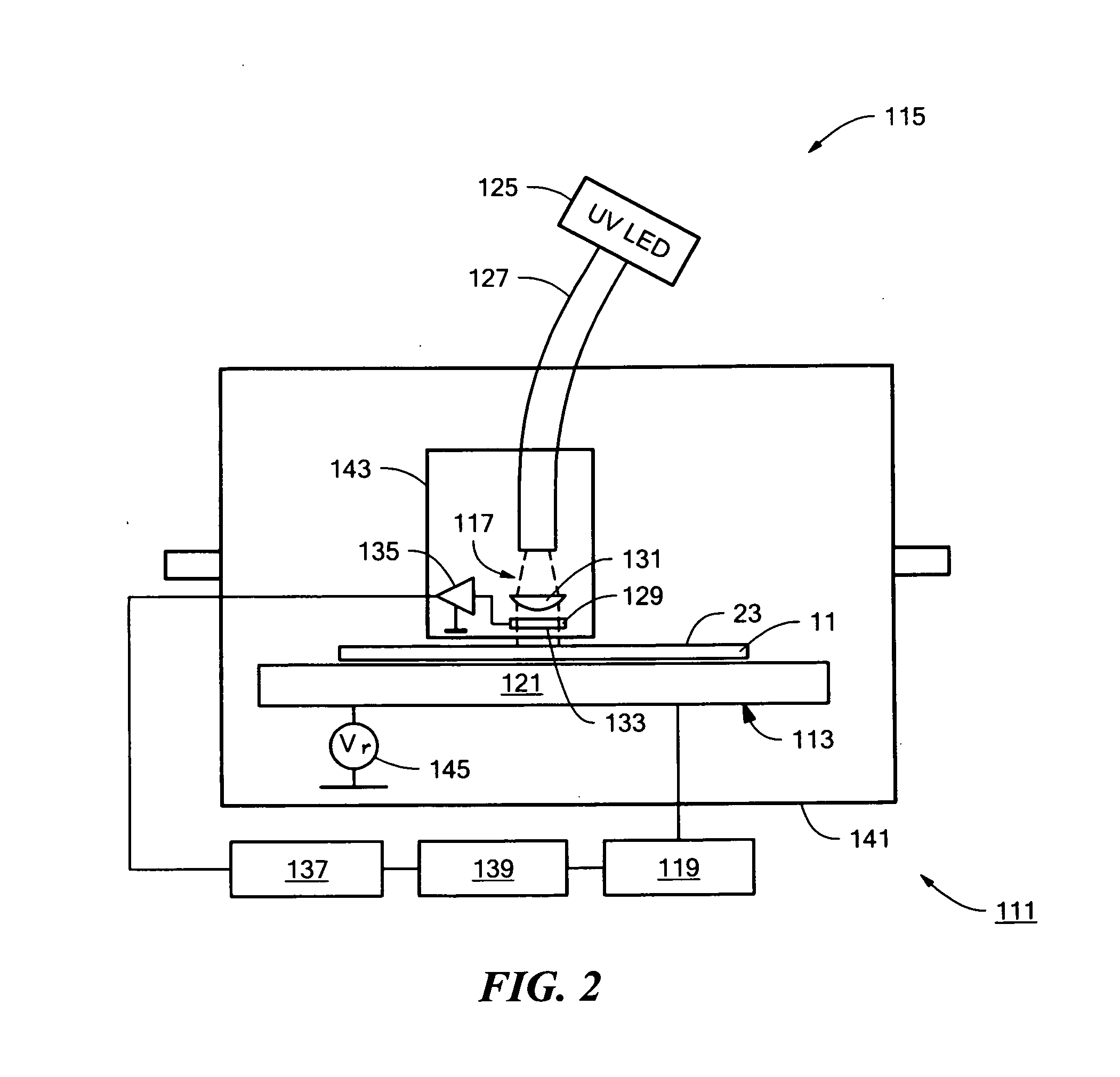

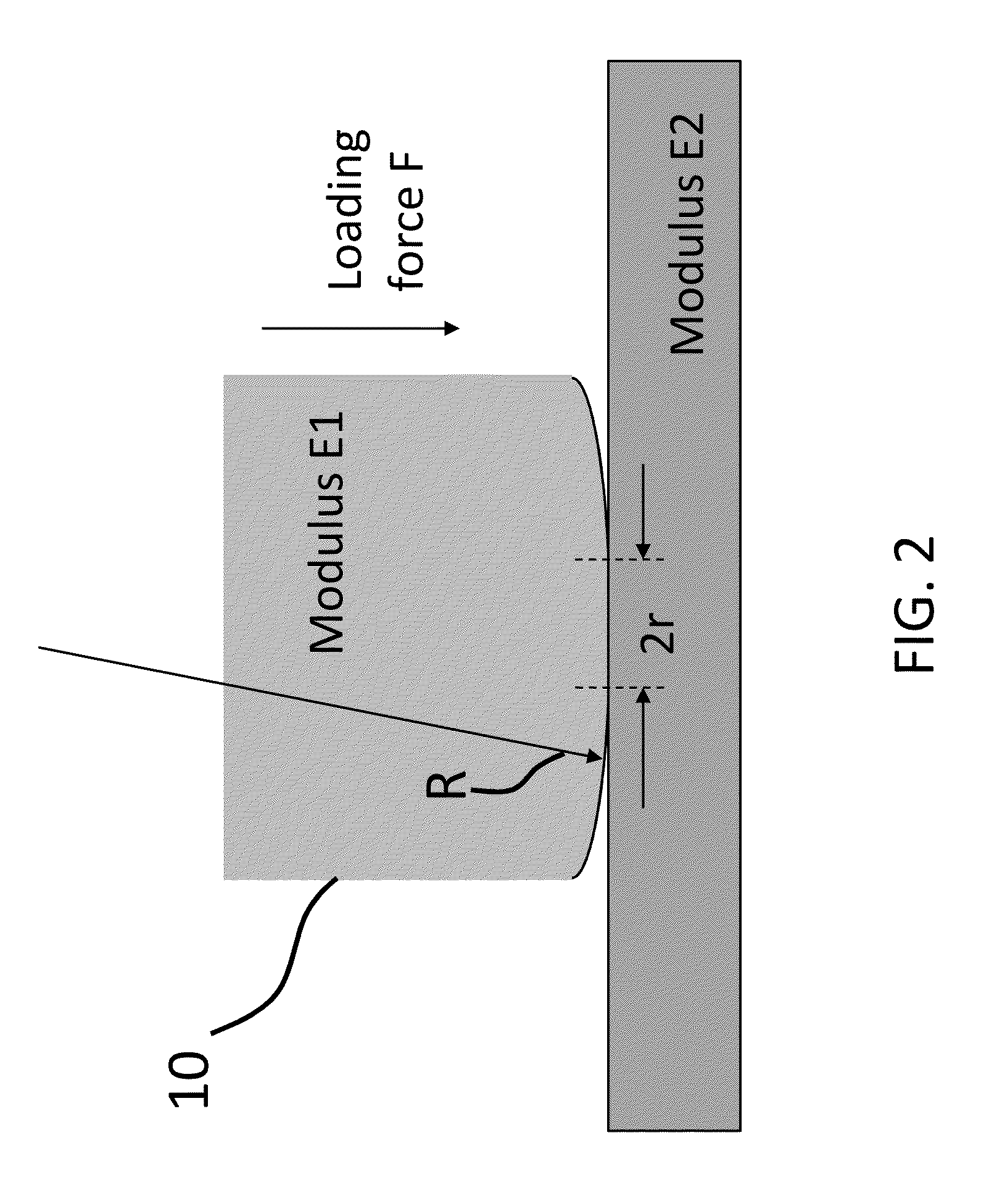

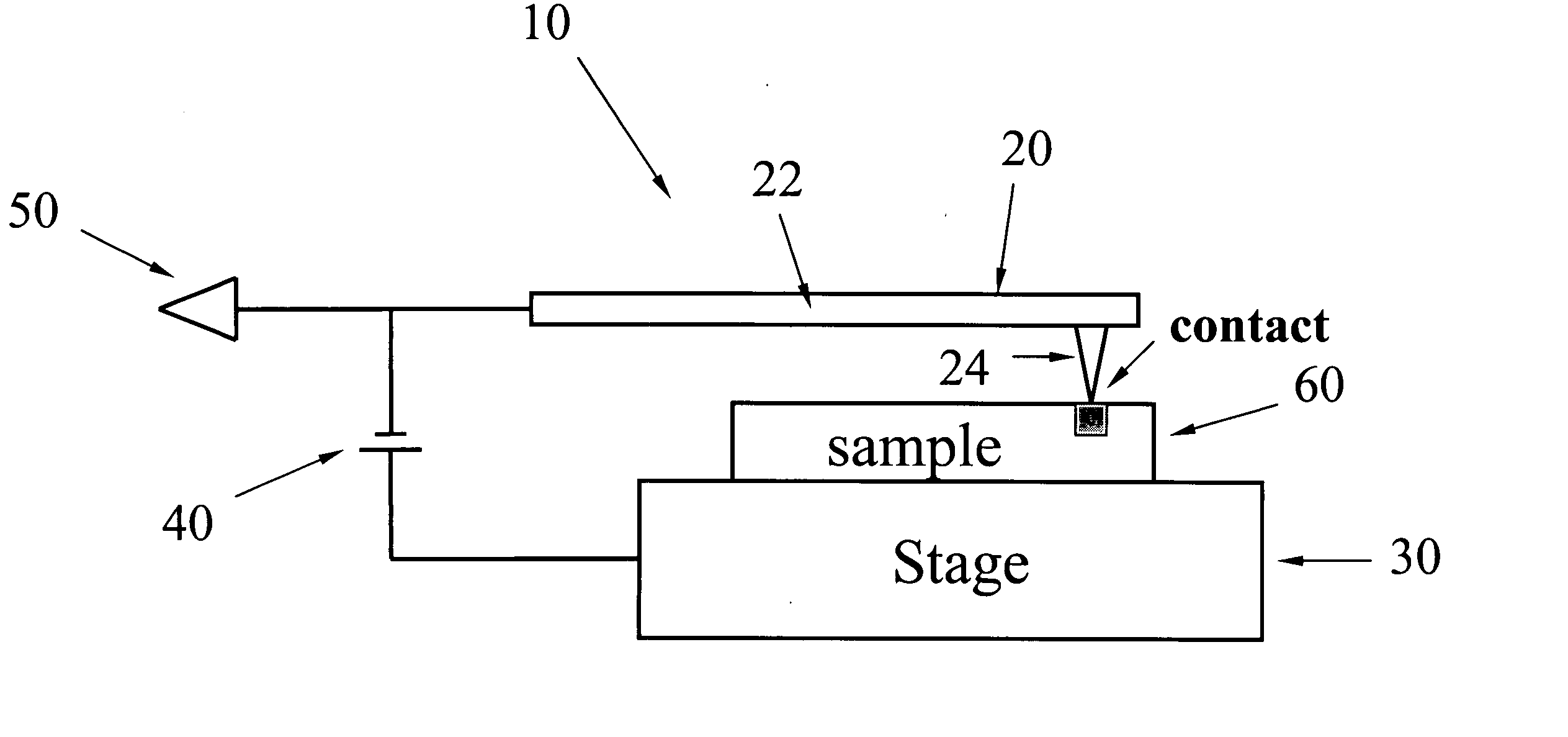

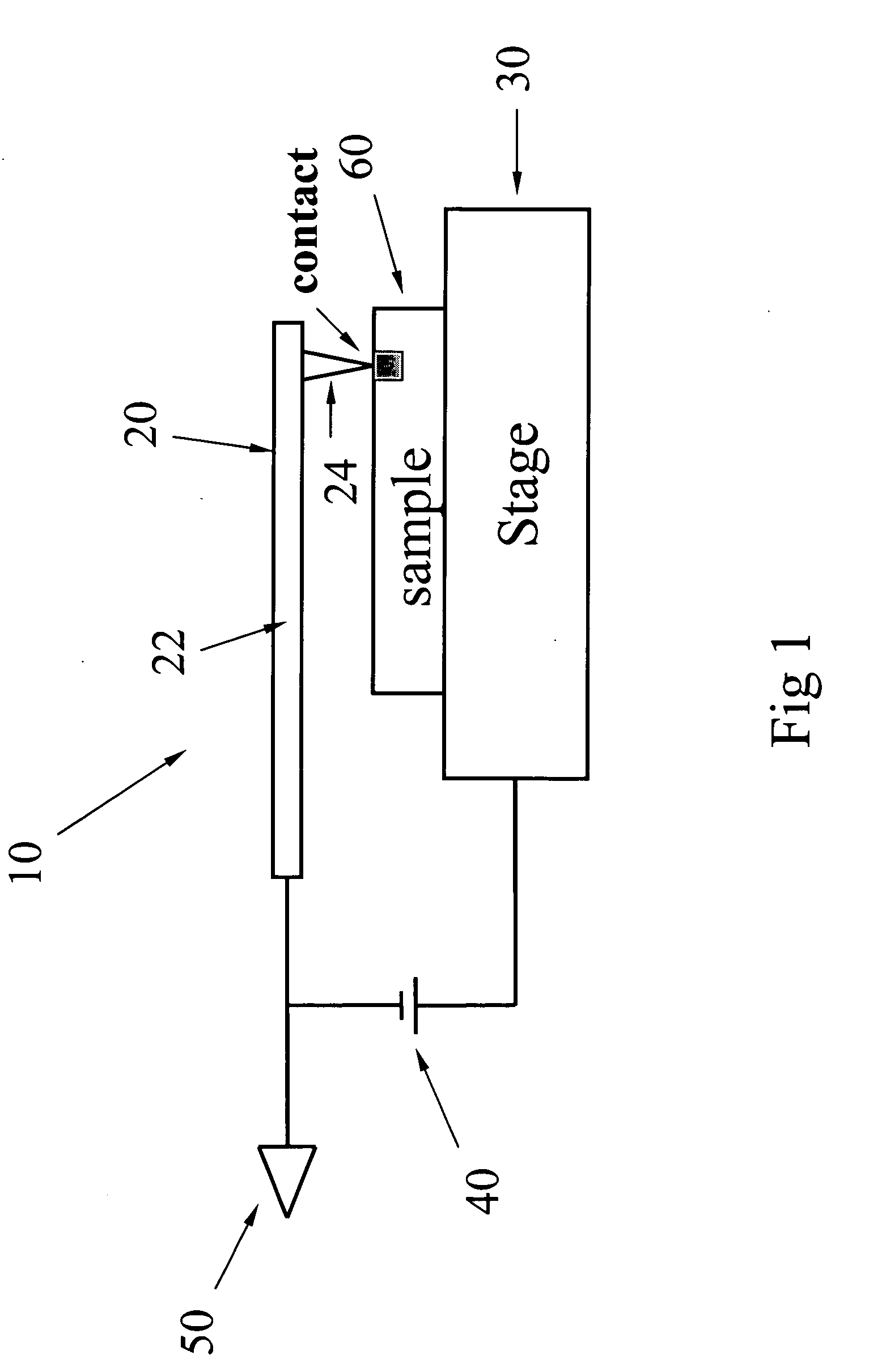

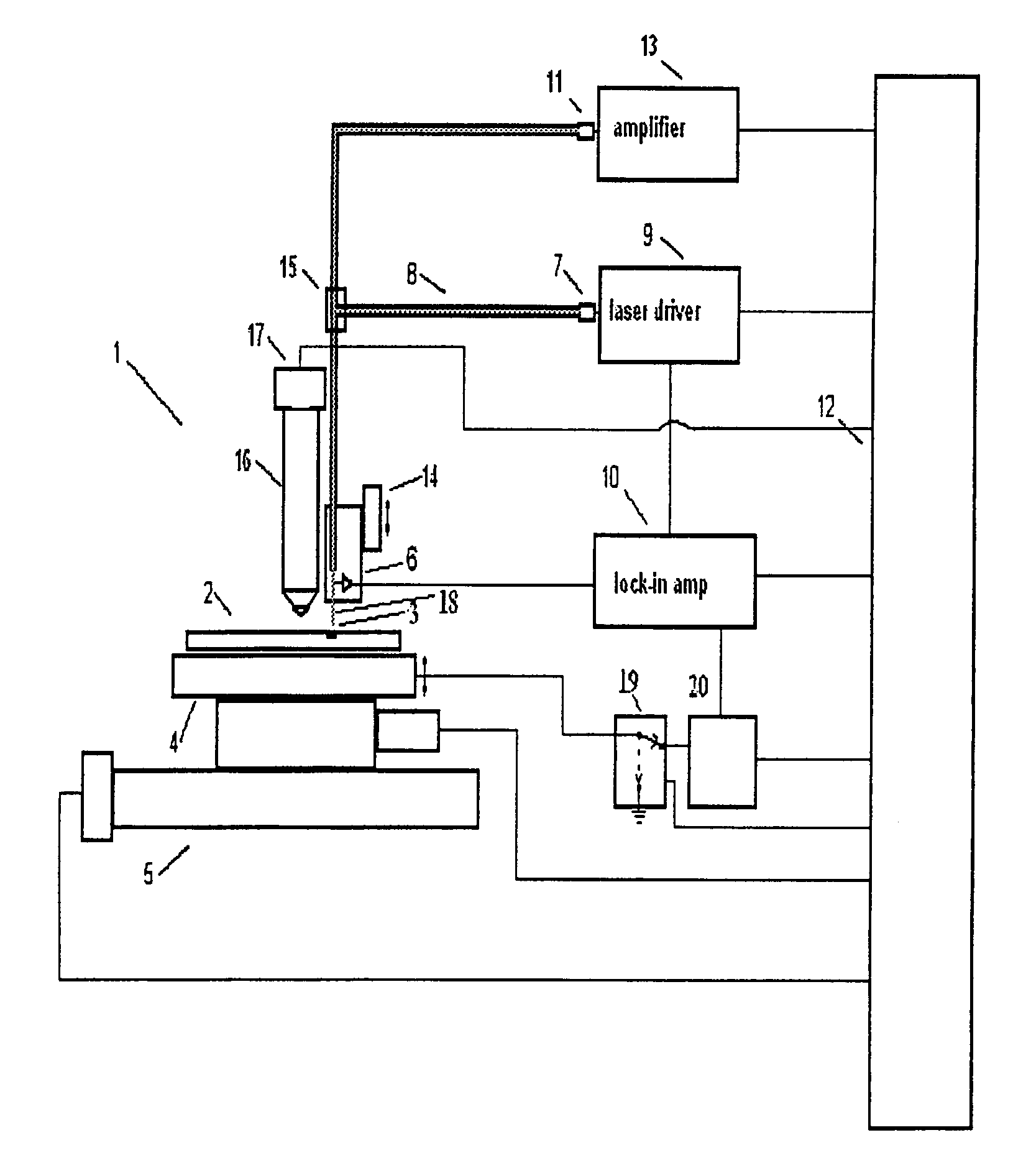

Apparatus and method for combined micro-scale and nano-scale c-v, q-v, and i-v testing of semiconductor materials

InactiveUS20100148813A1Small capacitance variationReduced measurement areaCapacitance measurementsSemiconductor characterisationSemiconductor materialsFowler nordheim

Current Voltage and Capacitance Voltage (IV and CV) measurements are critical in measurement of properties of electronic materials especially semiconductors. A semiconductor testing device to accomplish IV and CV measurement supports a semiconductor wafer and provides a probe for contacting a surface on the wafer under control of an atomic Force Microscope or similar probing device for positioning the probe to a desired measurement point on the wafer surface. Detection of contact by the probe on the surface is accomplished and test voltage is supplied to the semiconductor wafer. A first circuit for measuring capacitance sensed by the probe based on the test voltage and a complimentary circuit for measuring Fowler Nordheim current sensed by the probe based on the test voltage are employed with the probe allowing the calculation of characteristics of the semiconductor wafer based on the measured capacitance and Fowler Nordheim current.

Owner:MULTIPROBE

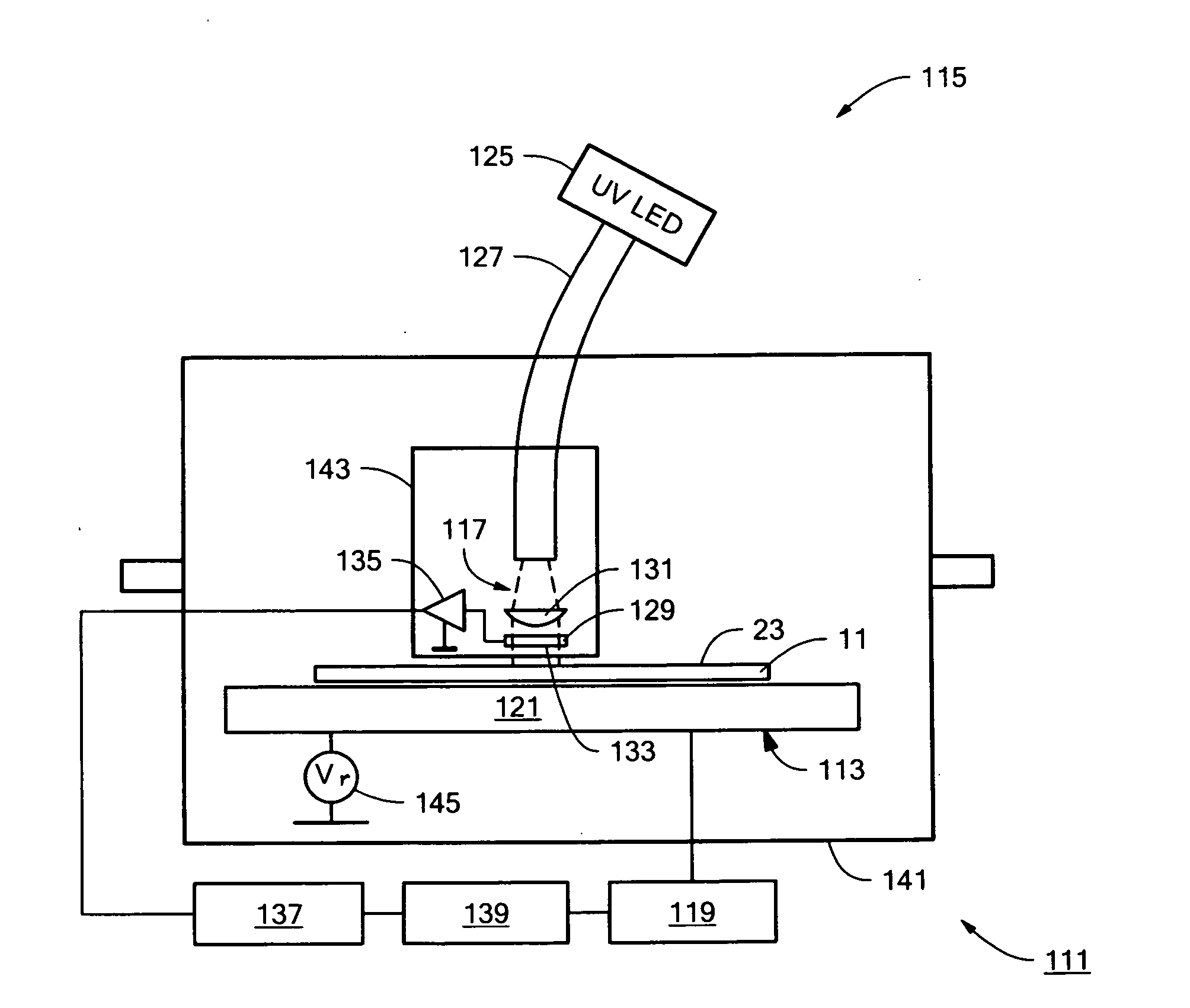

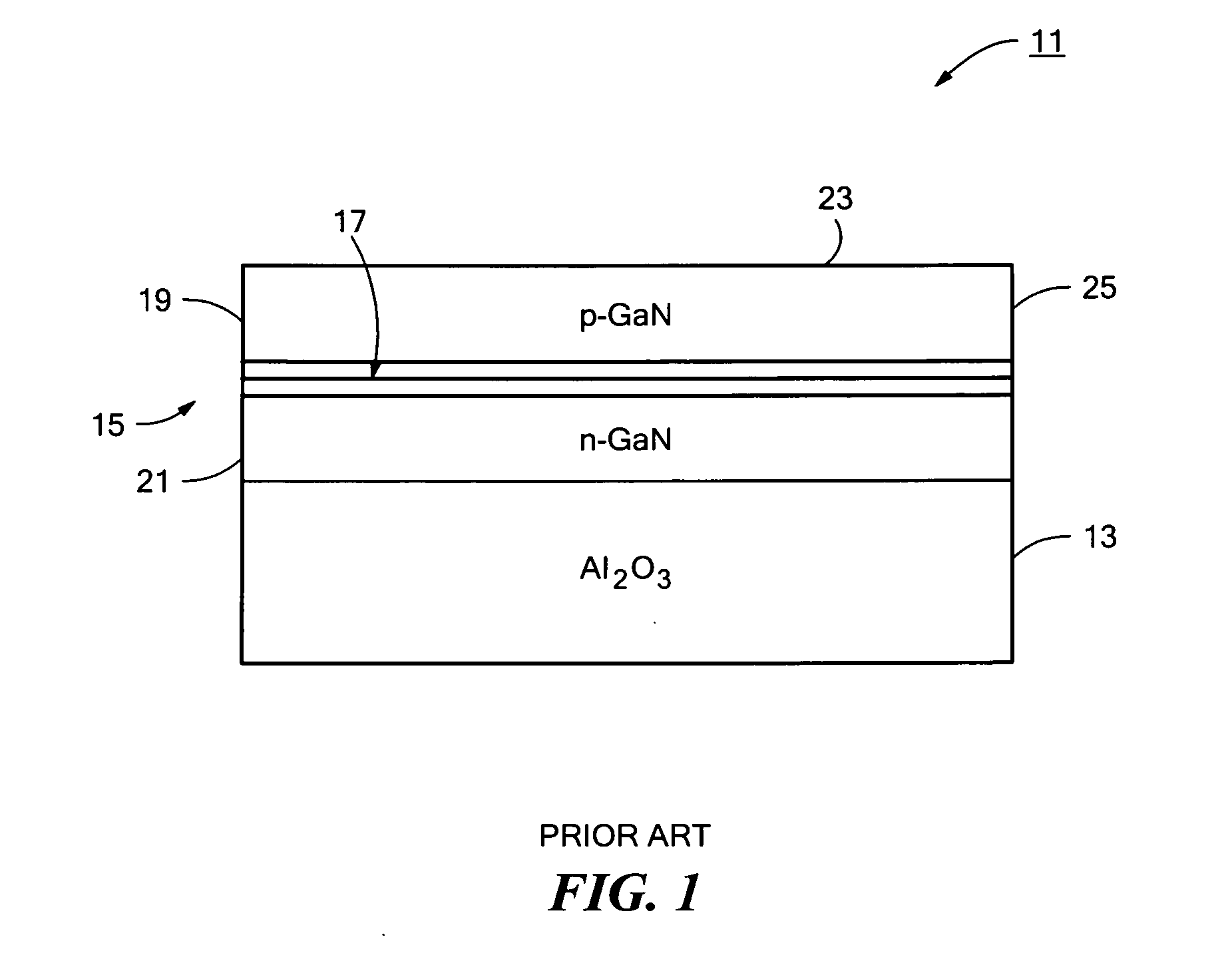

System and method for characterizing the electrical properties of a semiconductor sample

InactiveUS20110301892A1Resistance/reactance/impedenceVoltage-current phase angleCharge carrierLight beam

A system for characterizing the electrical properties of semiconductor wafers with high surface state densities, such as GaN wafers, includes a support subsystem for supporting the semiconductor sample, at least one light source for illuminating a spot on the sample, and a detection subsystem for measuring the photovoltage signal produced from illumination of the sample. In use, the system utilizes in-line, non-contact photovoltage techniques that exploits the presence of the high surface state density and the known components of its associated electrostatic barrier as part of its novel characterization process. Specifically, the system illuminates the sample with one or more light beams that vary in photon energy and duration in order to excite charge carriers in specific layers of the sample while either preserving or collapsing the electrostatic barrier. In this manner, the system is able to electrically characterize individual or combined layers of the sample as well as embedded junctions.

Owner:KAMIENIECKI EMIL

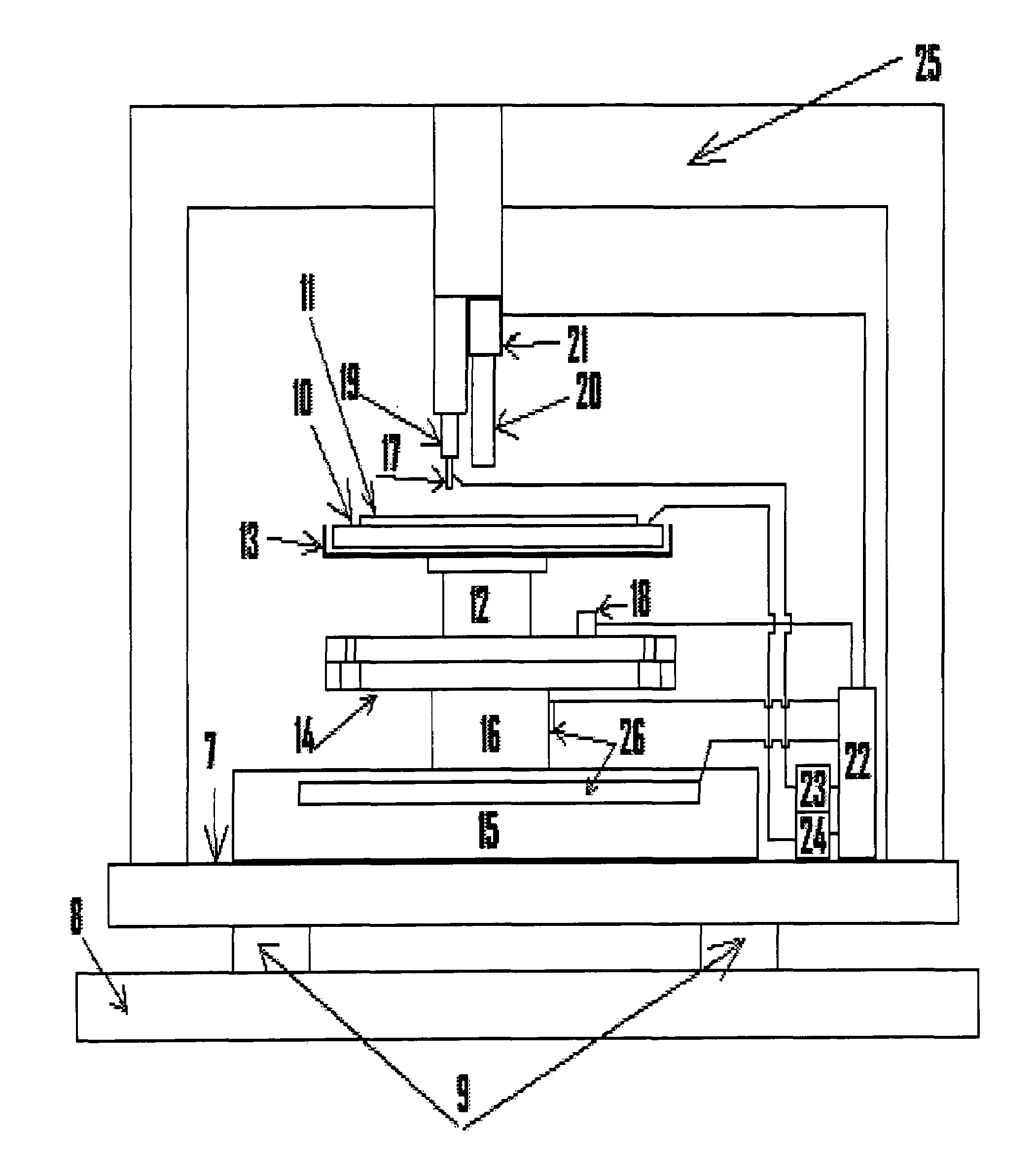

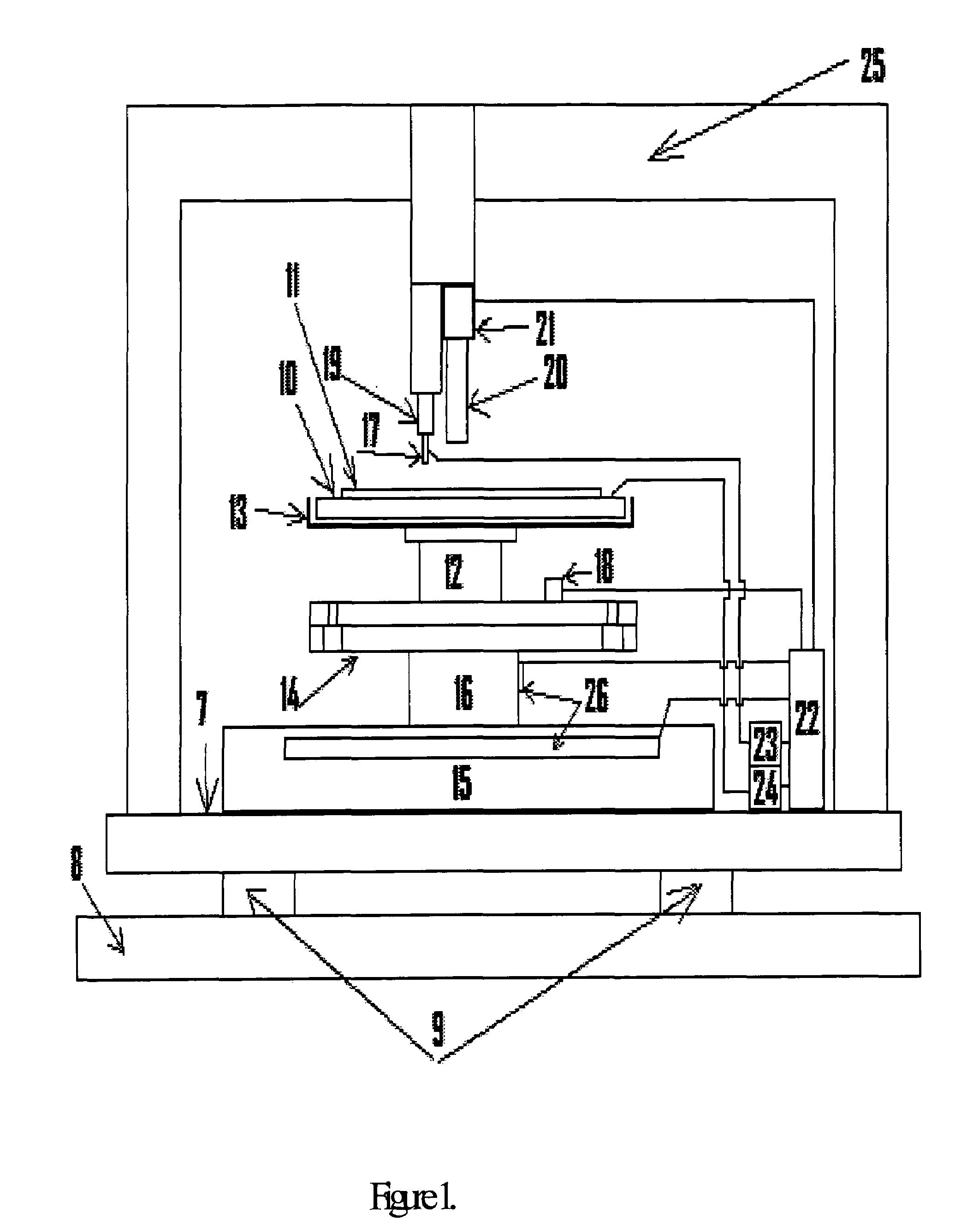

Nano-drive for high resolution positioning and for positioning of a multi-point probe

InactiveUS7304486B2Electronic circuit testingResistance/reactance/impedenceElectron beam depositionEngineering

The multi-point probe comprises a supporting body defining a first surface, a first multitude of conductive probe arms each of the probe arms defining a proximal end and a distal end being positioned in co-planar relationship with the first surface of the supporting body. The probe arms are connected to the supporting body at the proximal ends thereof and have the distal ends freely extending from the supporting body, giving individually flexible motion to the first multitude of probe arms. The probe arms originate from a process of producing the probe arms on a wafer body in facial contact with the wafer body and removal of a part of the wafer body providing the supporting body and providing the probe arms freely extending therefrom. The multi-point probe further comprises a third multitude of tip elements extending from the distal end of the first multitude of probe arms. The tip elements originate from a process of metallization of electron beam depositions on the probe arms at the distal ends thereof.

Owner:CAPRES

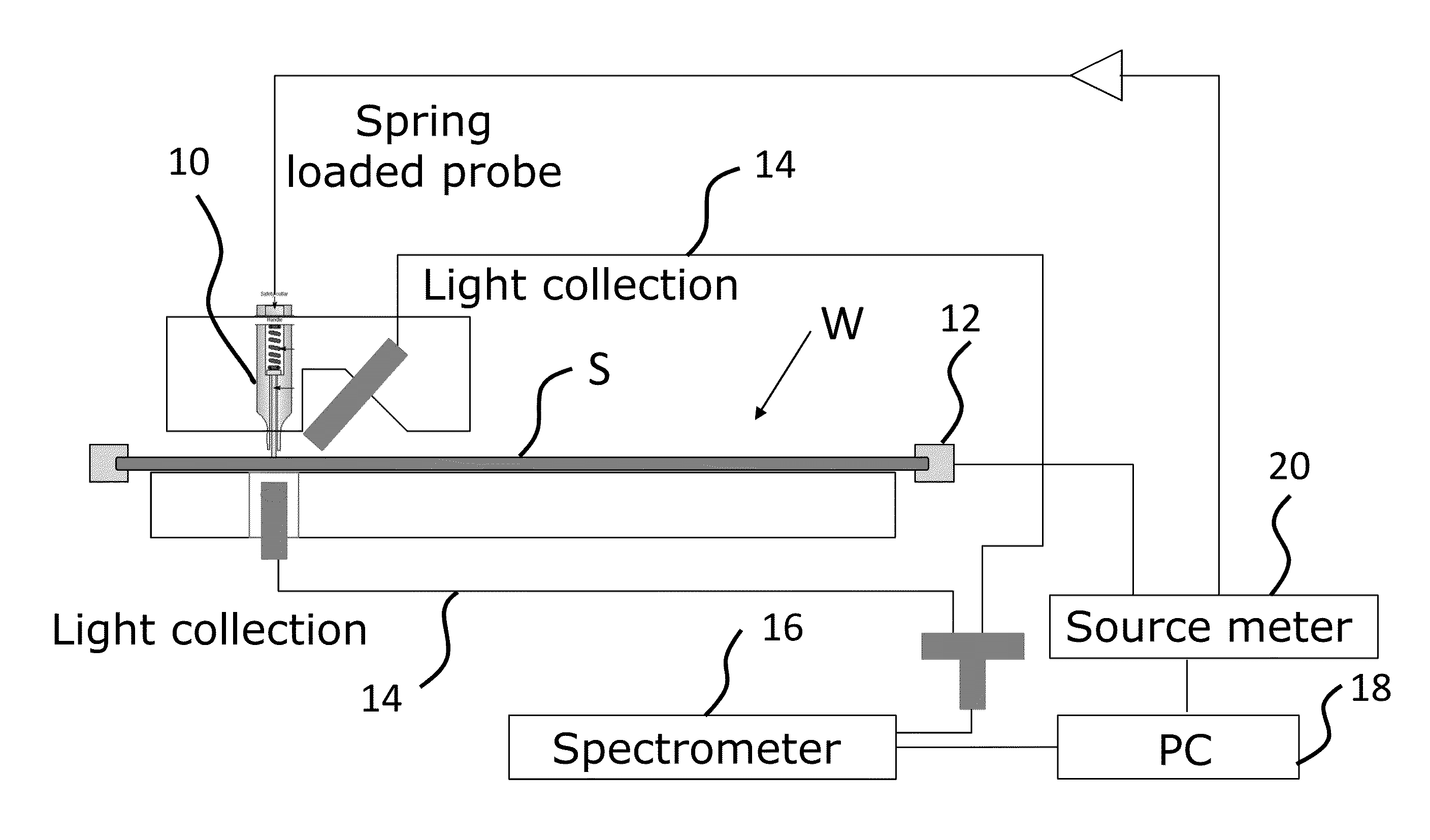

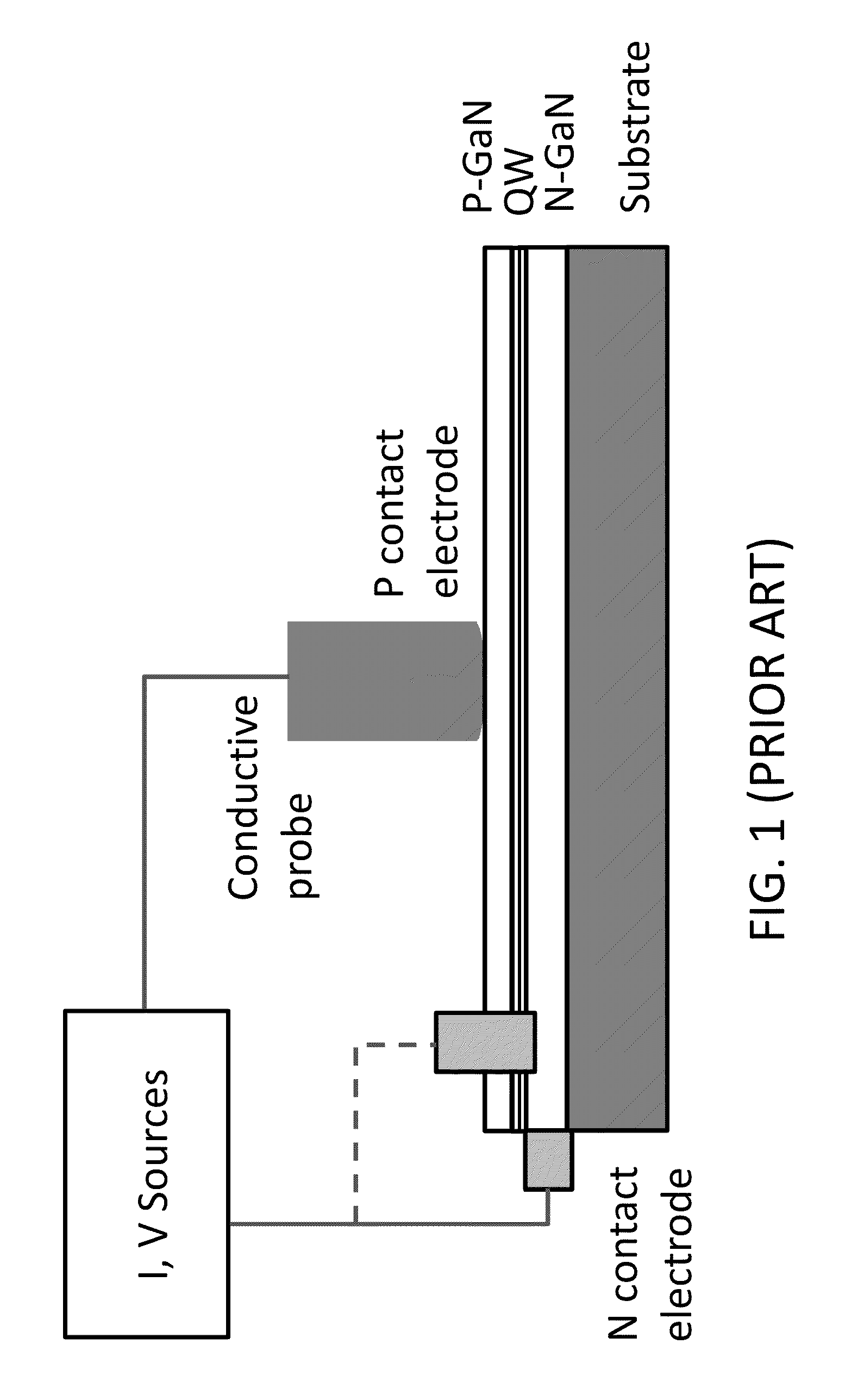

Testing of electroluminescent semiconductor wafers

ActiveUS20130043875A1Reduce memory effectMinimize temperature gradientElongate light sourcesLighting heating/cooling arrangementsEngineeringSet point

Forward voltage drift in a probe system for the characterization of a light-emitting wafer is virtually eliminated by directing compressed air to the probe so as to ensure that the exact same temperature conditions exist during repeated measurements of the wafer. In one embodiment of the invention, an air flow at room temperature is used, either continuously or intermittently. In another embodiment, the temperature of the probe is controlled by flowing a liquid or a gas through micro-channels built into the probe. In yet another embodiment, the probe is connected to a solid-state Peltier cell that is computer-controlled to maintain the probe's temperature at a predetermined set-point. A temperature-controlled chamber or a thermal reservoir enclosing the probe could be used as well. The results obtained showed remarkable repeatability.

Owner:BRUKER NANO INC

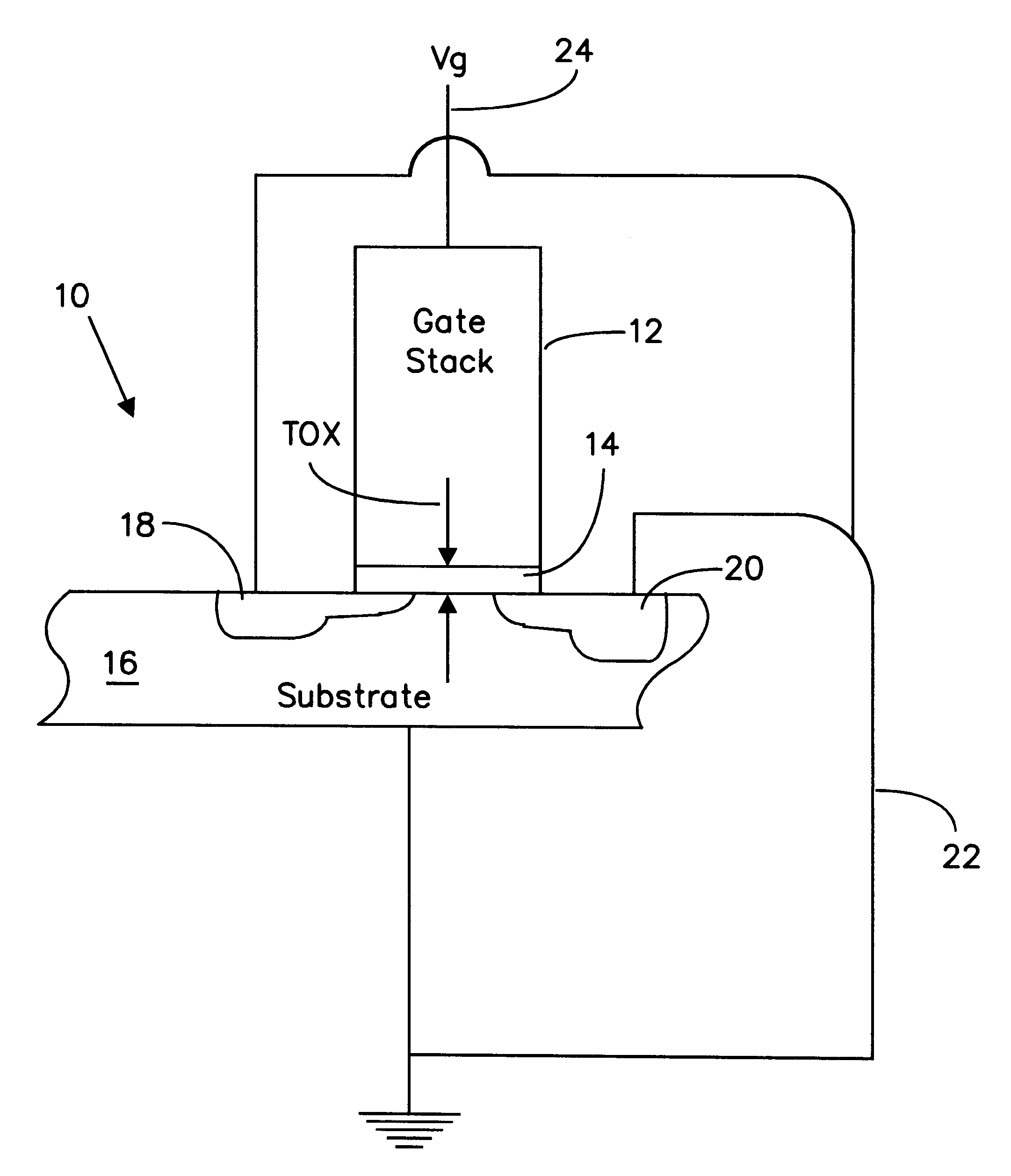

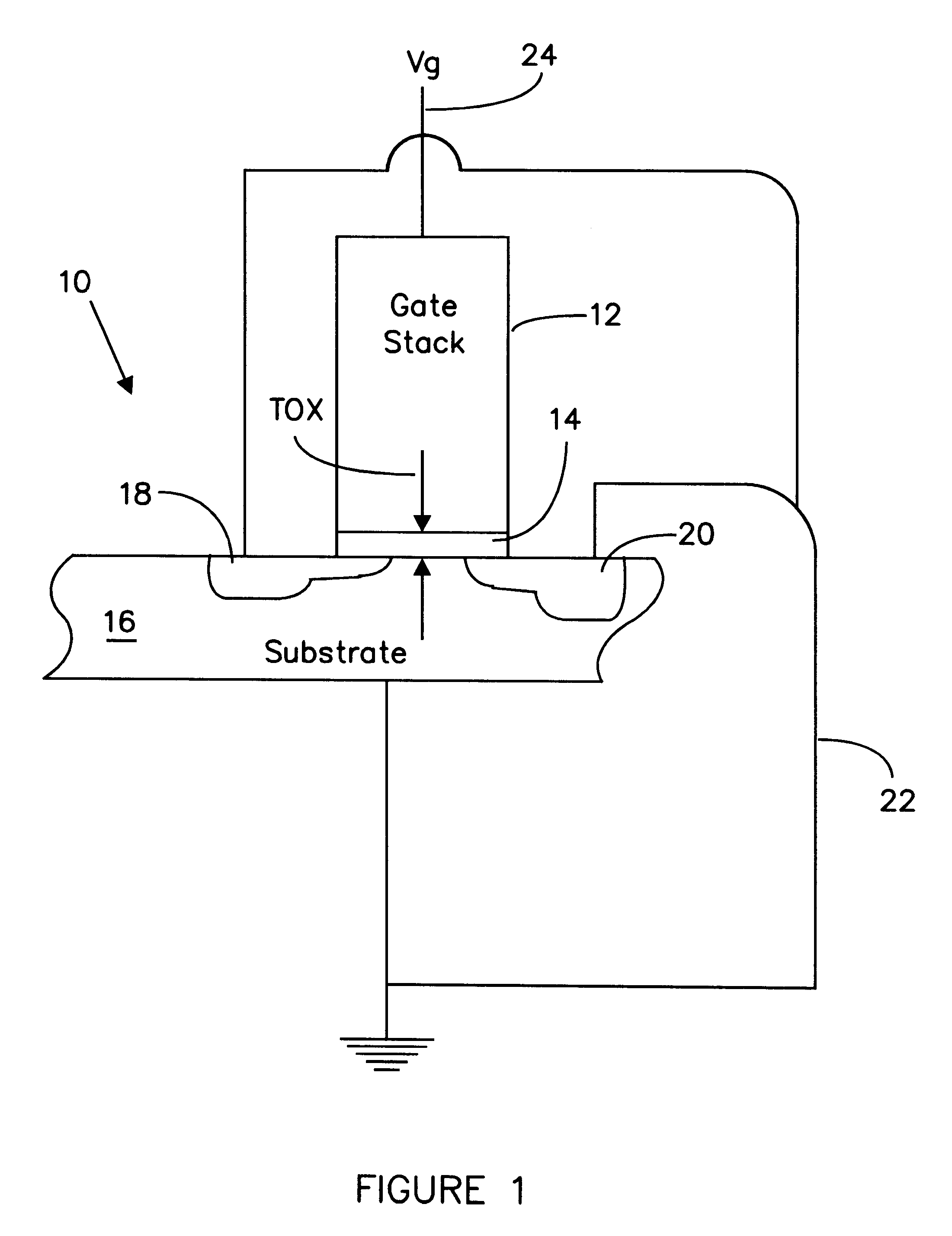

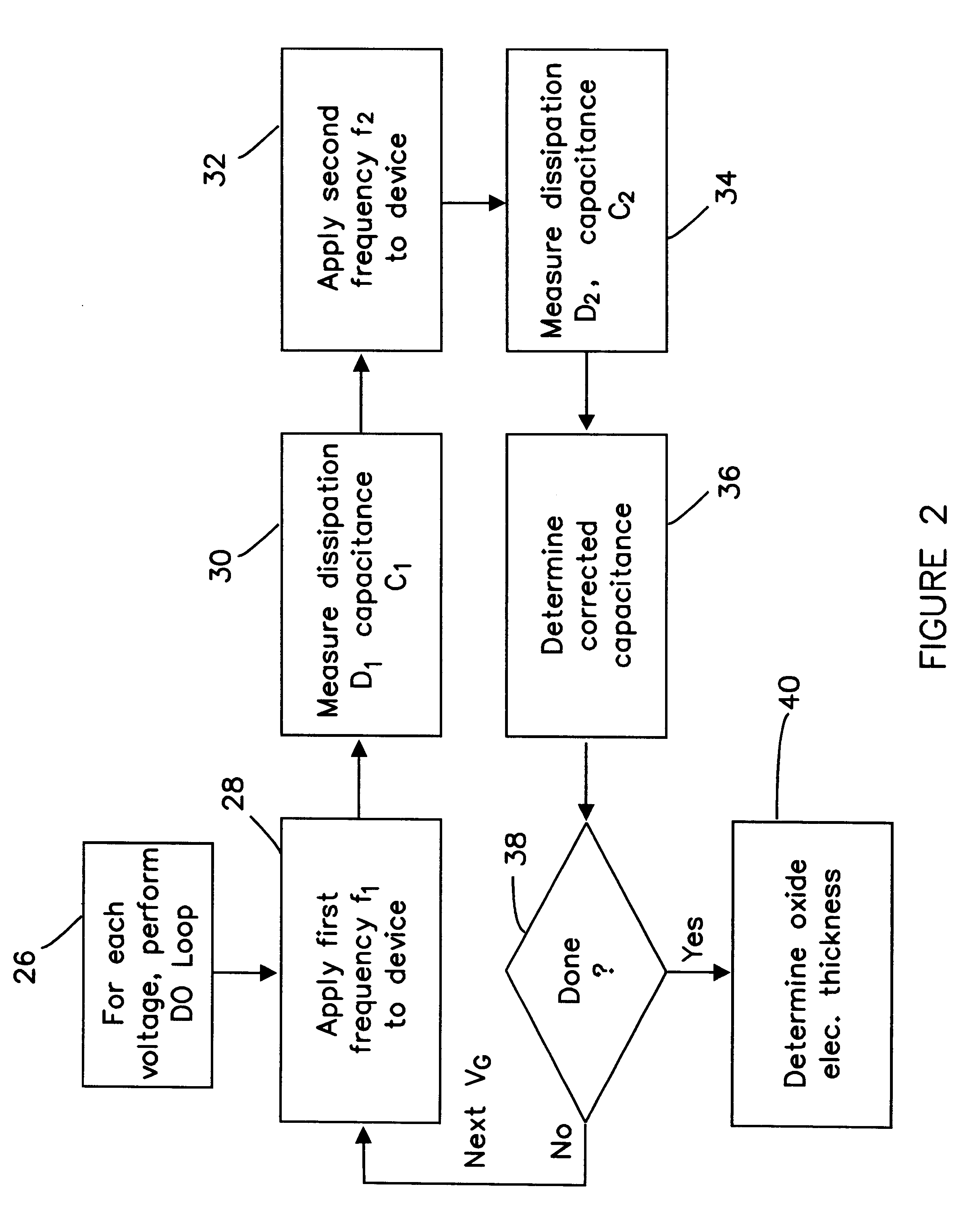

Method for determining transistor gate oxide thickness

InactiveUS6456105B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingMOSFETElectricity

A method for determining the electrical thickness of a very thin gate oxide layer of a MOSFET that is subject to relatively high leakage current owing to its thinness includes measuring first and second frequency-dependent capacitances C.sub.1, C.sub.2 and then using the capacitances to render a corrected capacitance. The electrical thickness is then determined using not the measured capacitances, but rather the corrected capacitance, to render a comparatively more accurate value of gate oxide electrical thickness T.sub.ox.

Owner:ADVANCED MICRO DEVICES INC

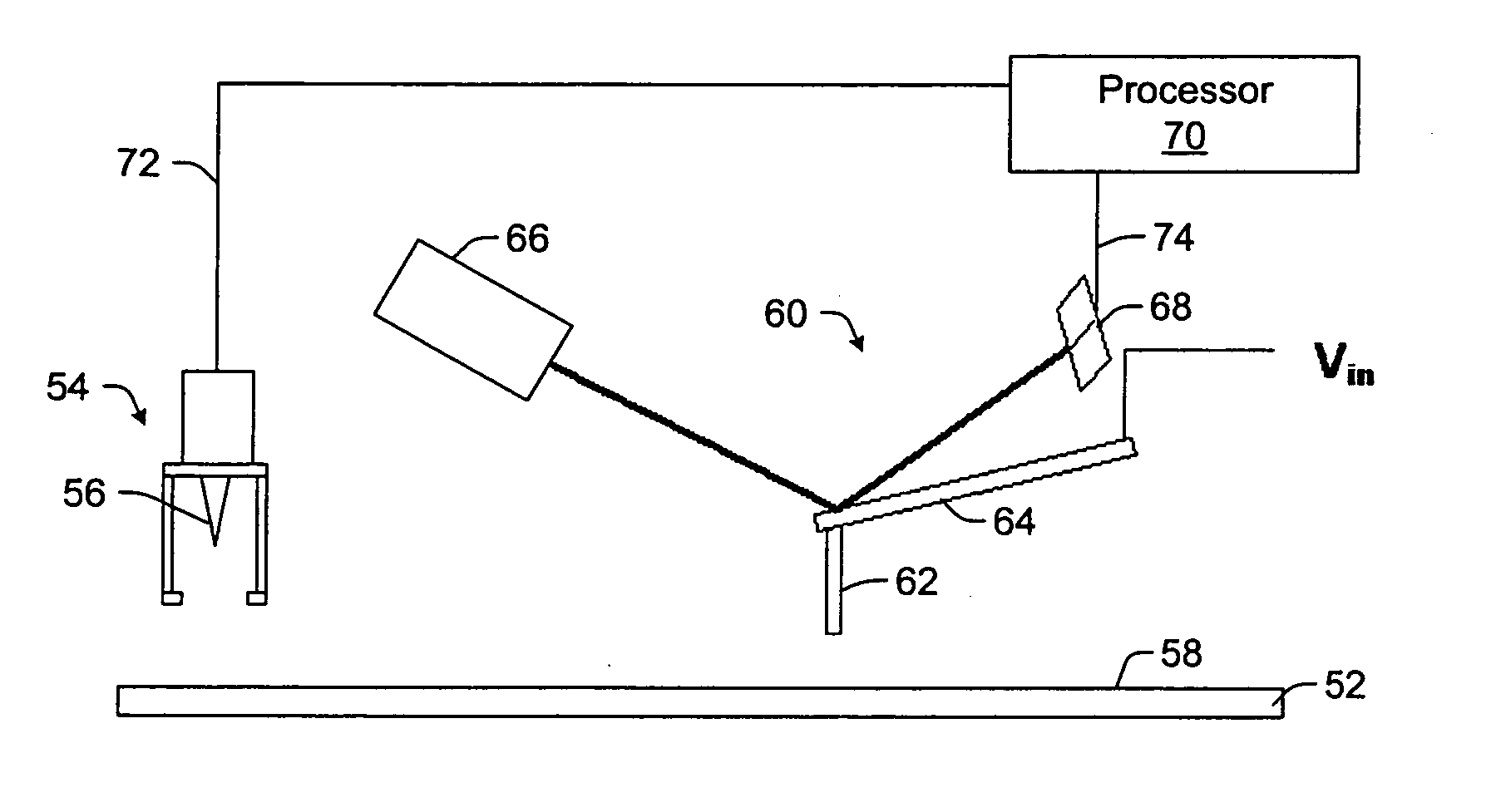

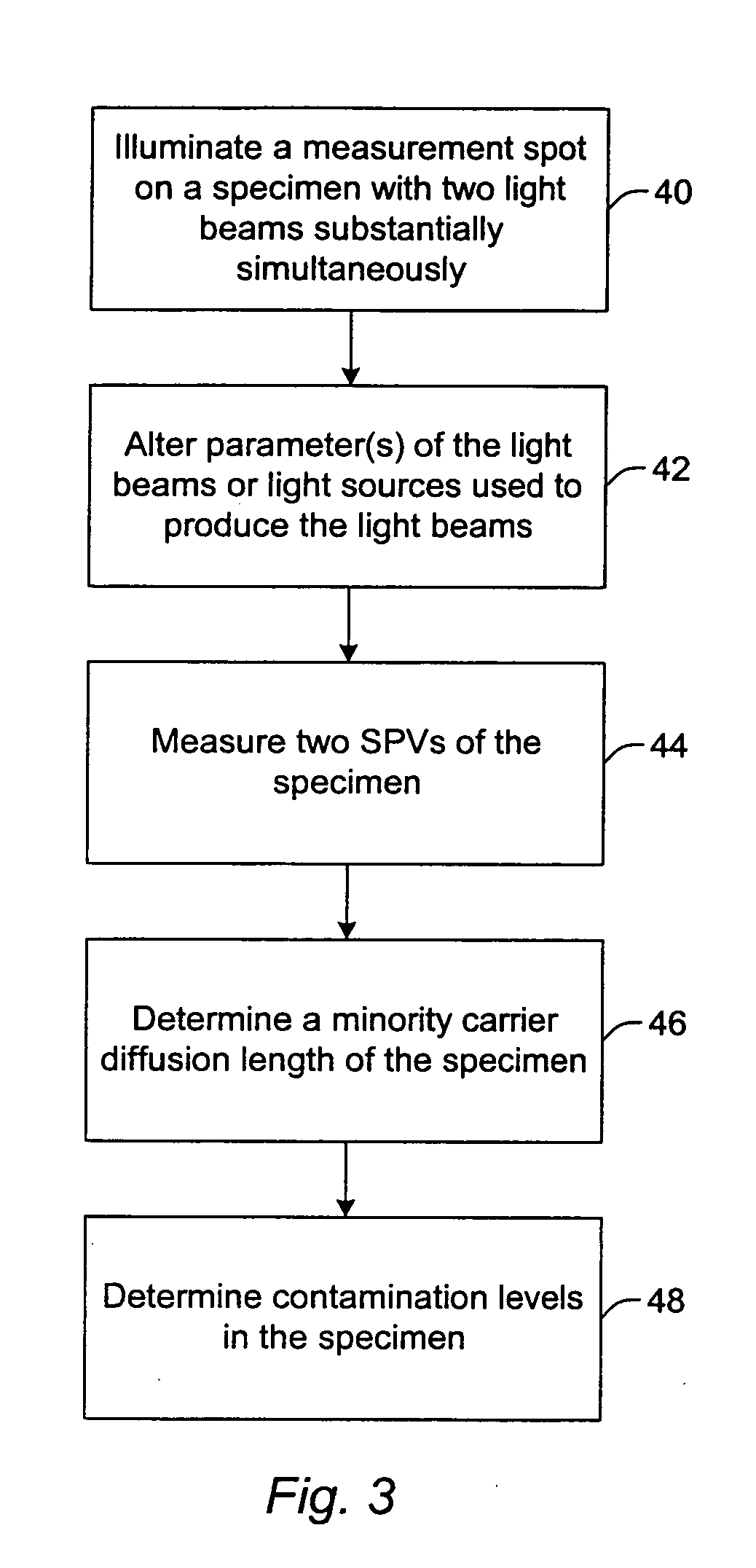

Methods and systems for determining one or more properties of a specimen

ActiveUS20050206402A1Semiconductor/solid-state device testing/measurementSemiconductor characterisationDiffusionLength wave

Various methods and systems for determining one or more properties of a specimen are provided. One system for determining a property of a specimen is configured to illuminate a specimen with different wavelengths of light substantially simultaneously. The different wavelengths of light are modulated at substantially the same frequency. The system is also configured to perform at least two measurements on the specimen. A minority carrier diffusion length of the specimen may be determined from the measurements and absorption coefficients of the specimen at the different wavelengths. Another system for detecting defects on a specimen is configured to deposit a charge at multiple locations on an upper surface of the specimen. This system is also configured to measure a vibration of a probe at the multiple locations. Defects may be detected on the specimen using a two-dimensional map of the specimen generated from the measured surface voltages.

Owner:KLA TENCOR TECH CORP

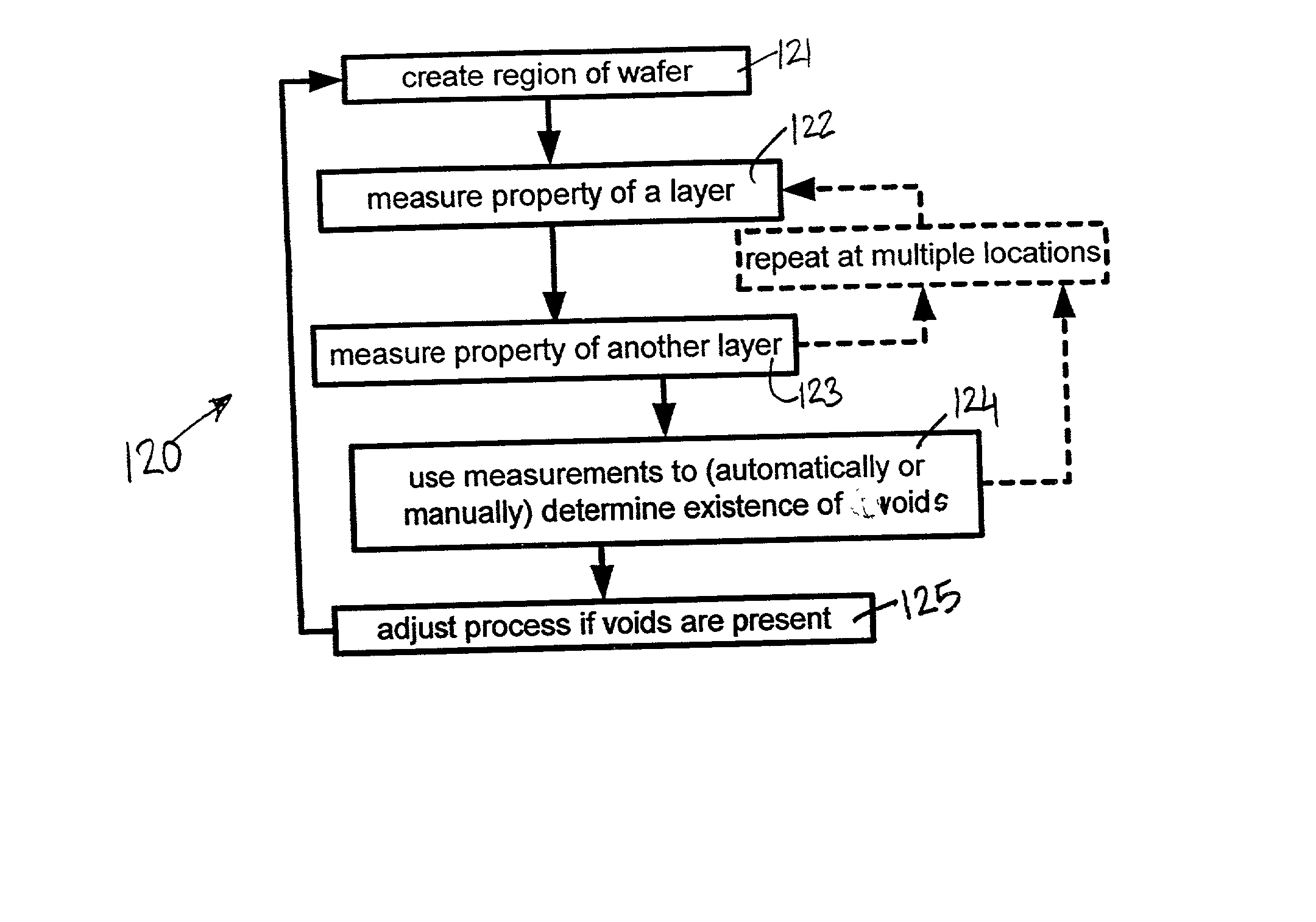

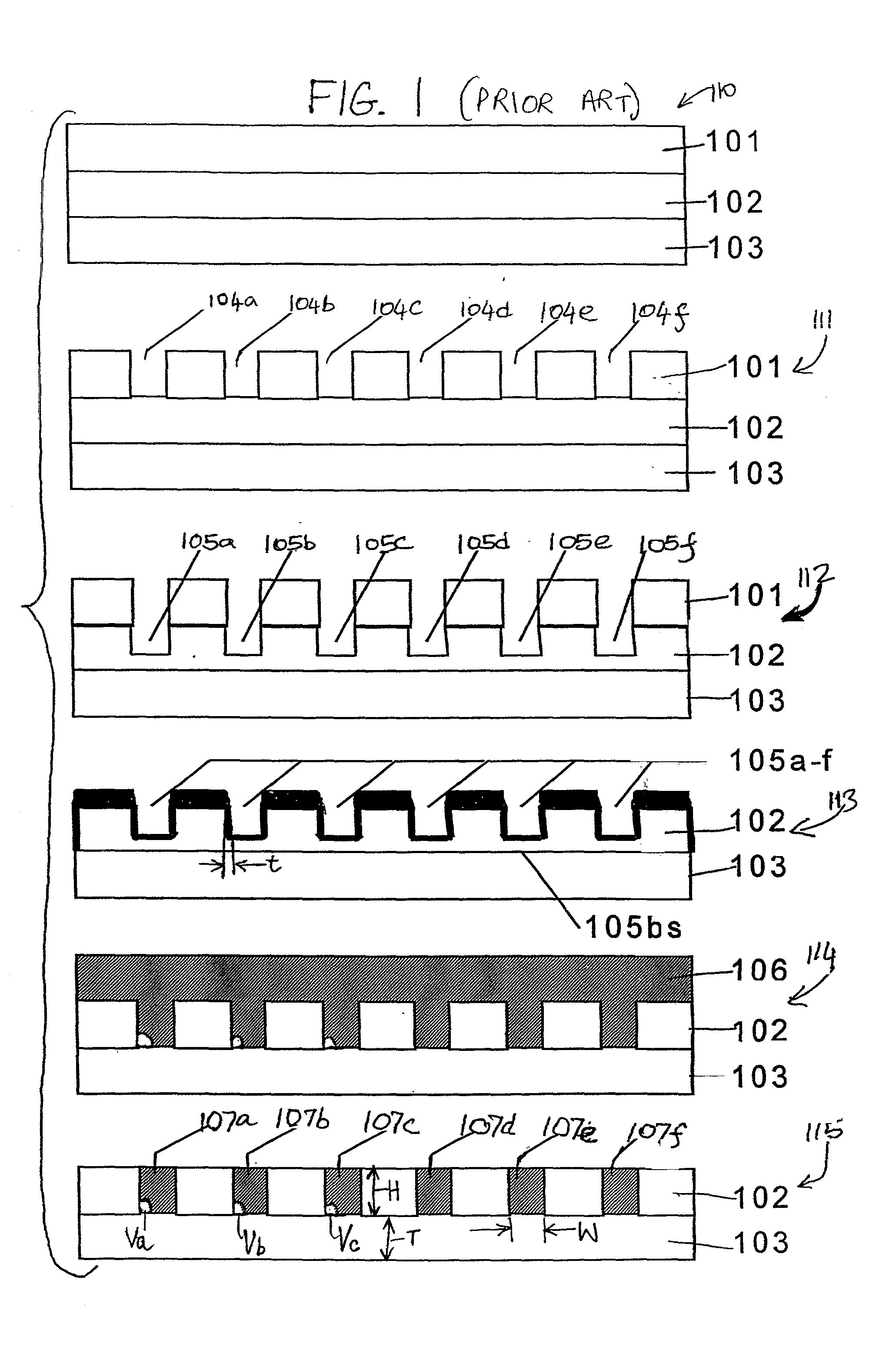

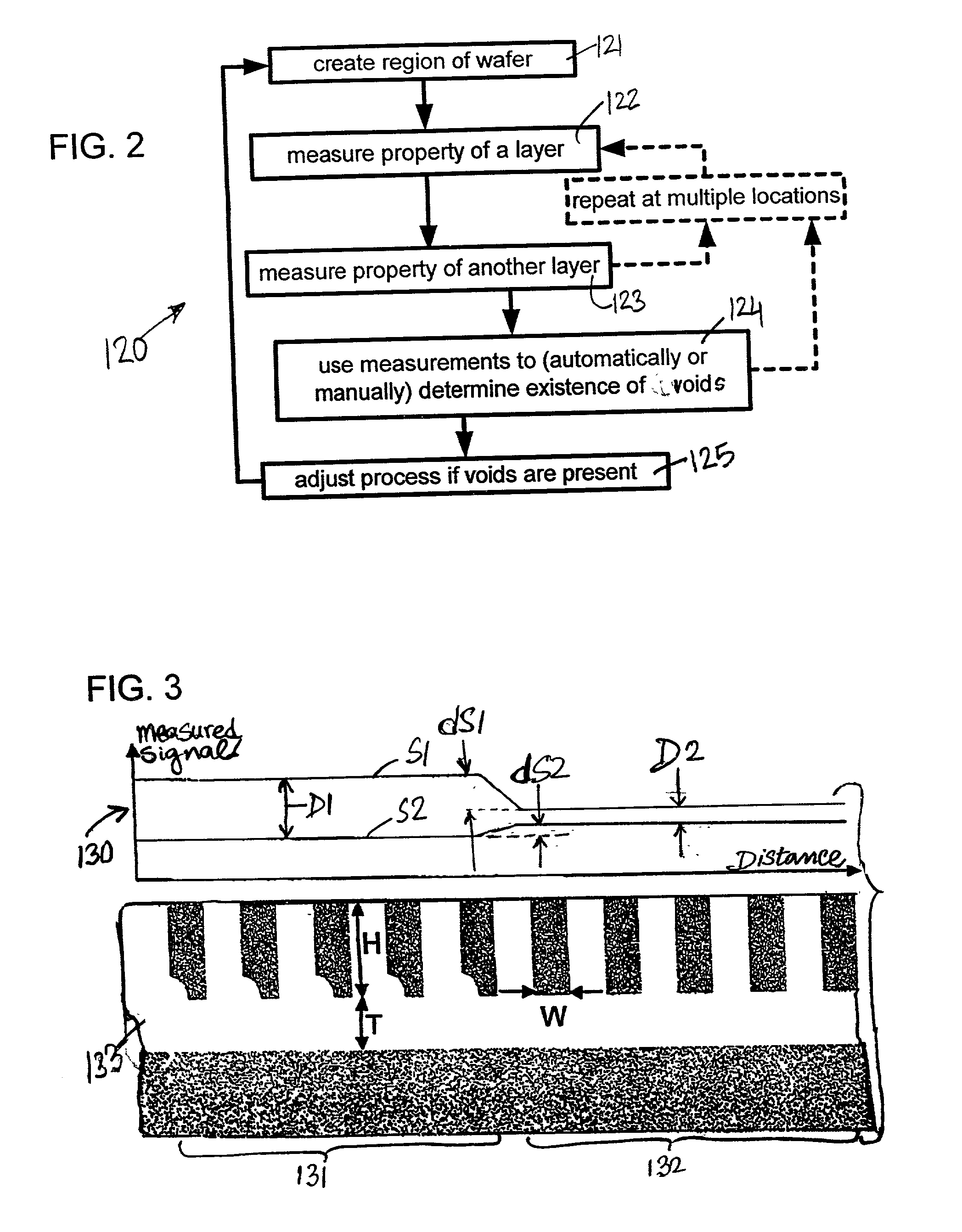

Evaluating a multi-layered structure for voids

InactiveUS20020125905A1Reduce and eliminate voidSemiconductor/solid-state device testing/measurementElectric discharge tubesEngineeringSilicon

A method and apparatus measure properties of two layers of a damascene structure (e.g. a silicon wafer during fabrication), and use the two measurements to identify a location as having voids. The two measurements may be used in any manner, e.g. compared to one another, and voids are deemed to be present when the two measurements diverge from each other. In response to the detection of voids, a process parameter used in fabrication of the damascene structure may be changed, to reduce or eliminate voids in to-be-formed structures.

Owner:APPLIED MATERIALS INC

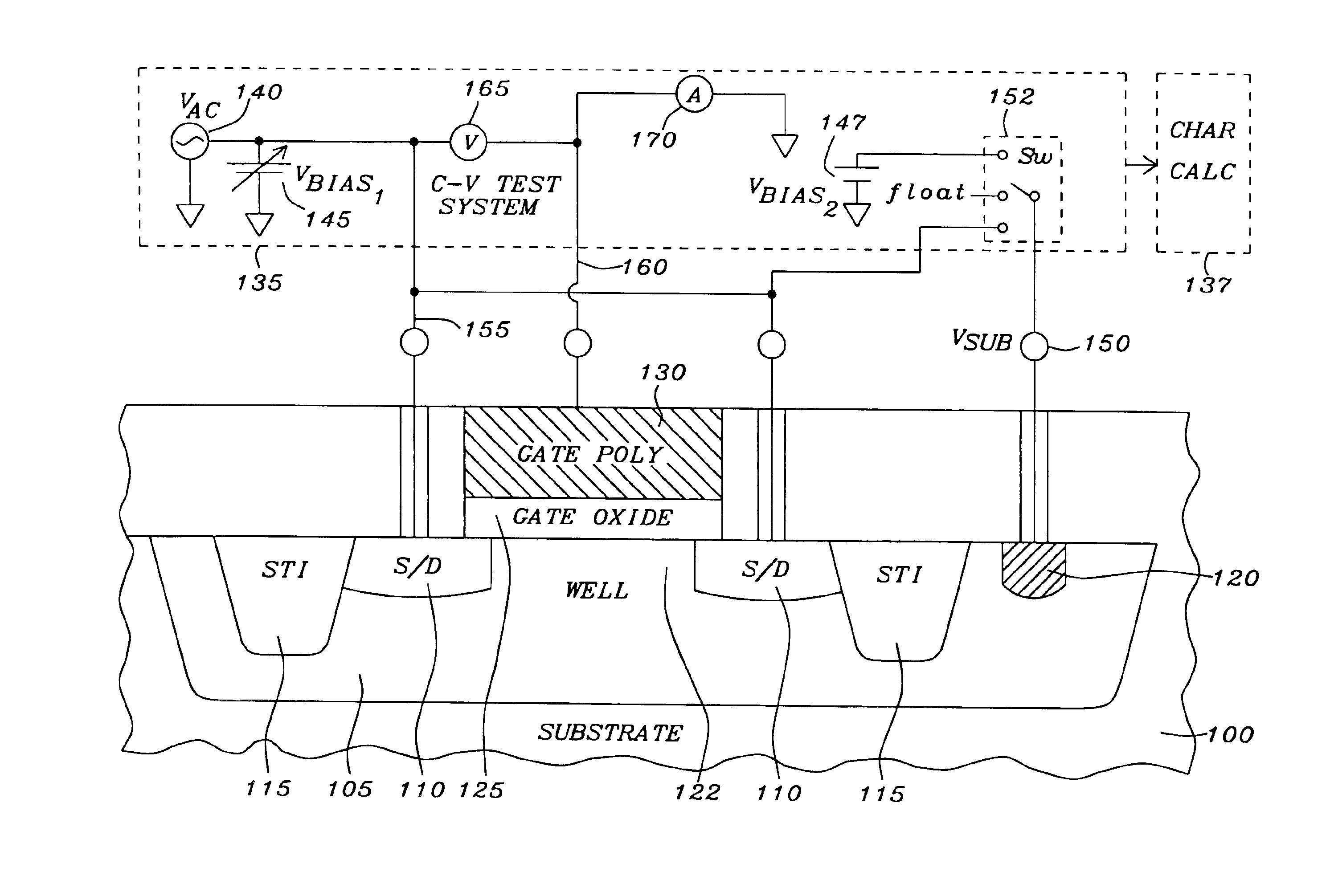

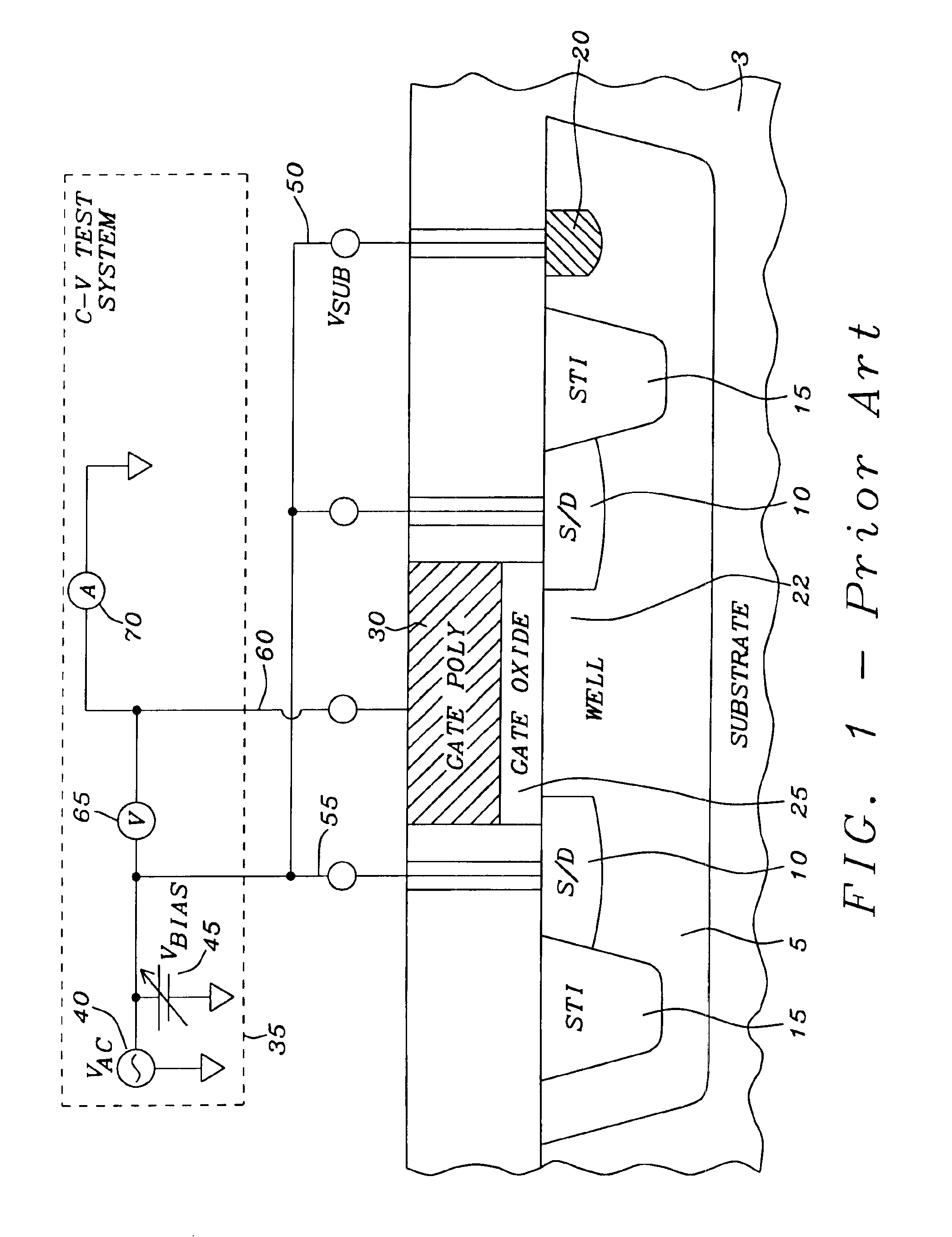

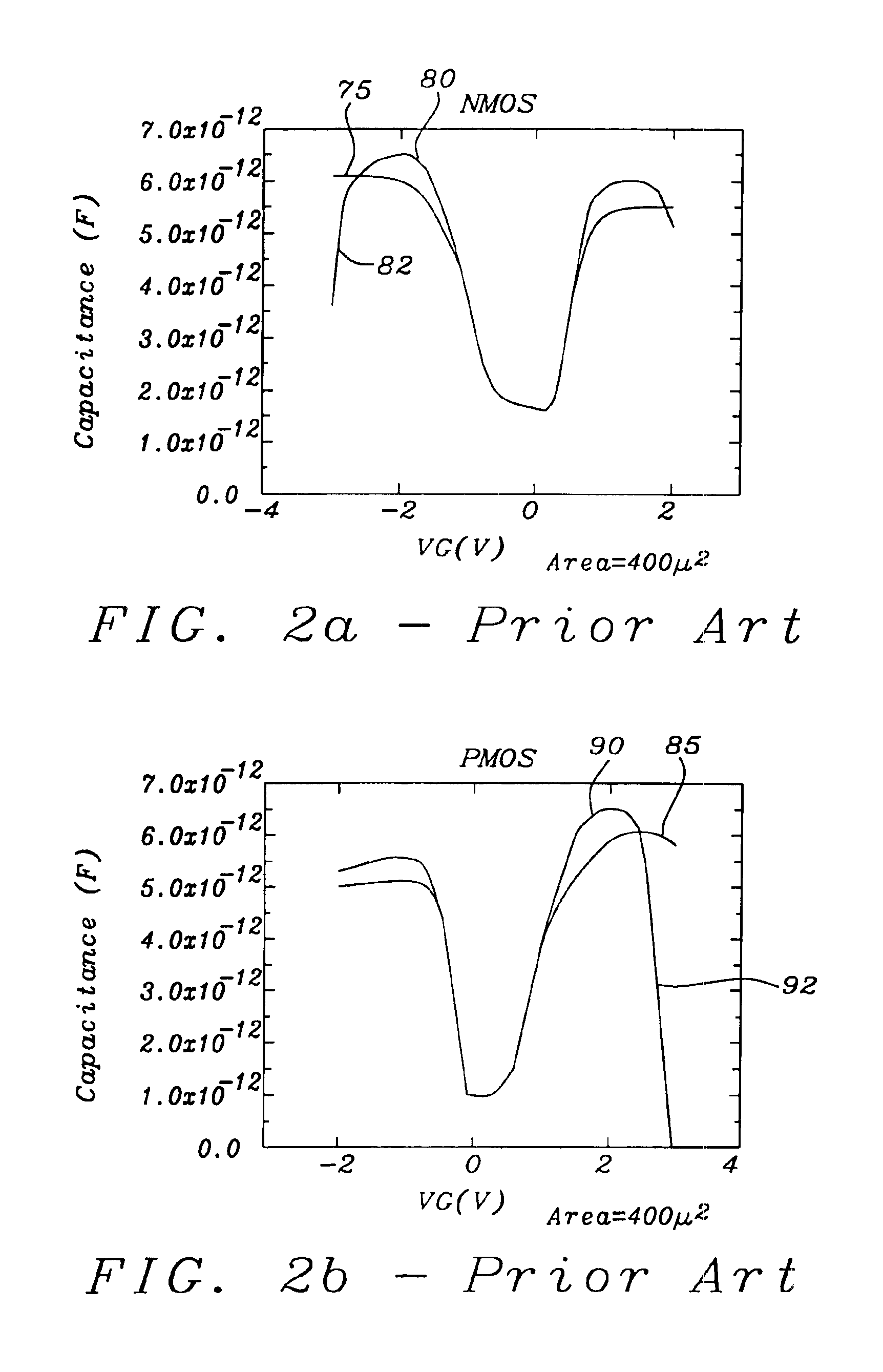

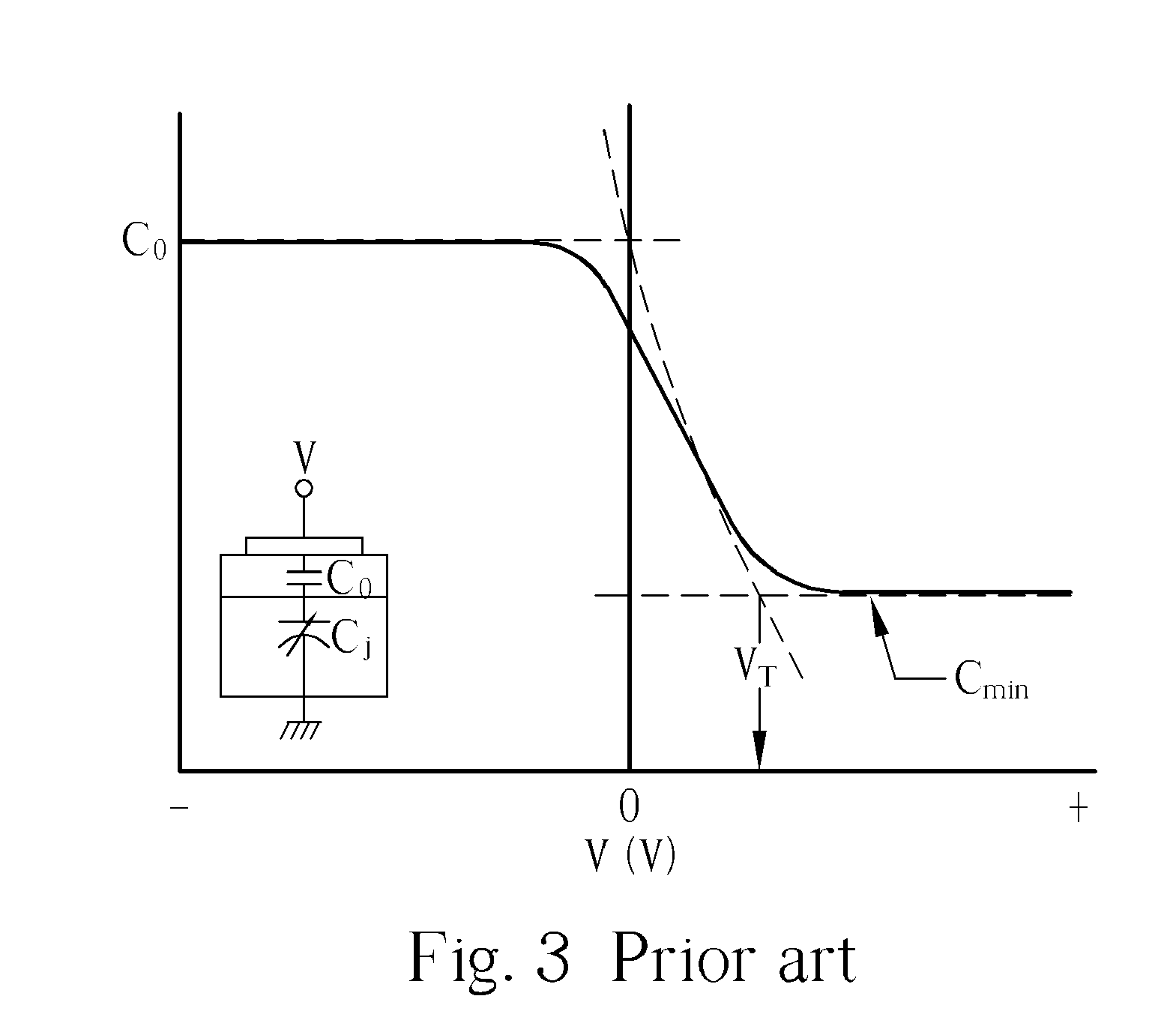

Method for measuring capacitance-voltage curves for transistors

InactiveUS6885214B1Semiconductor characterisationContactless circuit testingMeasurement testLayer thickness

An apparatus for characterizing capacitance and thickness of an insulating layer constructed between a conductive gate and a substrate has at least one test structure formed at a surface of a substrate. Each test structure has a bulk region formed of a semiconductor within the surface. Further the test structure has at least one source region and one drain region within the bulk region. A thin insulating layer is placed above the each source region, each drain region, and the bulk region. A conductive gate is placed above the thin insulating layer. A capacitance-voltage measuring device measures a capacitance value of the test structure, while forcing the bulk region between the source region and the drain region to be floating. An insulating layer thickness calculator determines the thickness of the insulating layer from the capacitance.

Owner:TAIWAN SEMICON MFG CO LTD

Method for monitoring quality of an insulation layer

InactiveUS20050040840A1Quick monitoringEasy to produceTesting dielectric strengthSemiconductor/solid-state device testing/measurementInsulation layerEngineering

The present invention utilizes wafer acceptance testing equipment to fast monitor the quality of an insulation layer. A plurality of swing time-dependent DC ramping voltages are applied to one of the electrode plates in a capacitor and each corresponding leakage current is measured to calculate each corresponding β value. Then, a ratio of each β value is calculated and a β− voltage curve is plotted to actually simulate the device failure.

Owner:UNITED MICROELECTRONICS CORP

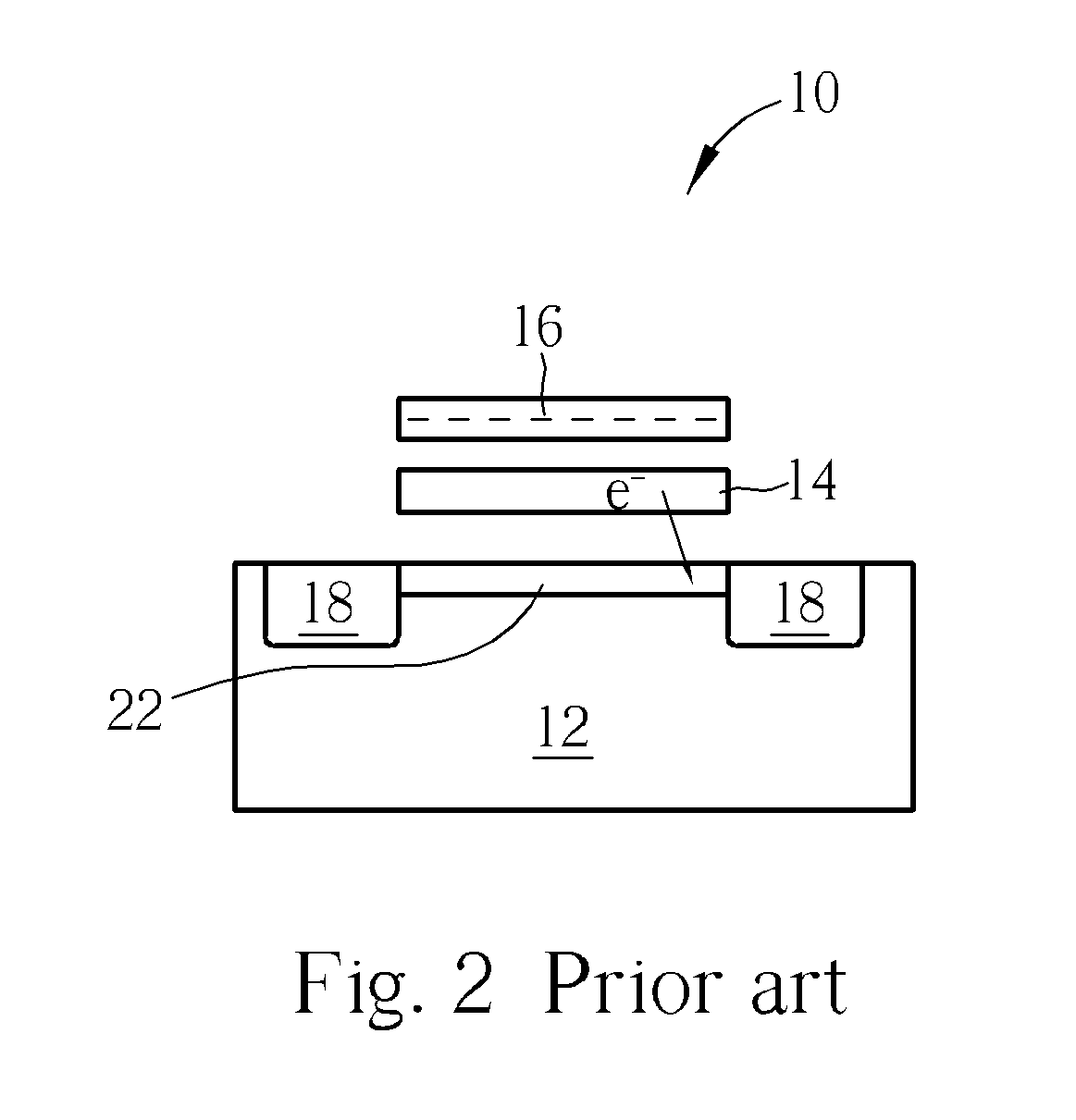

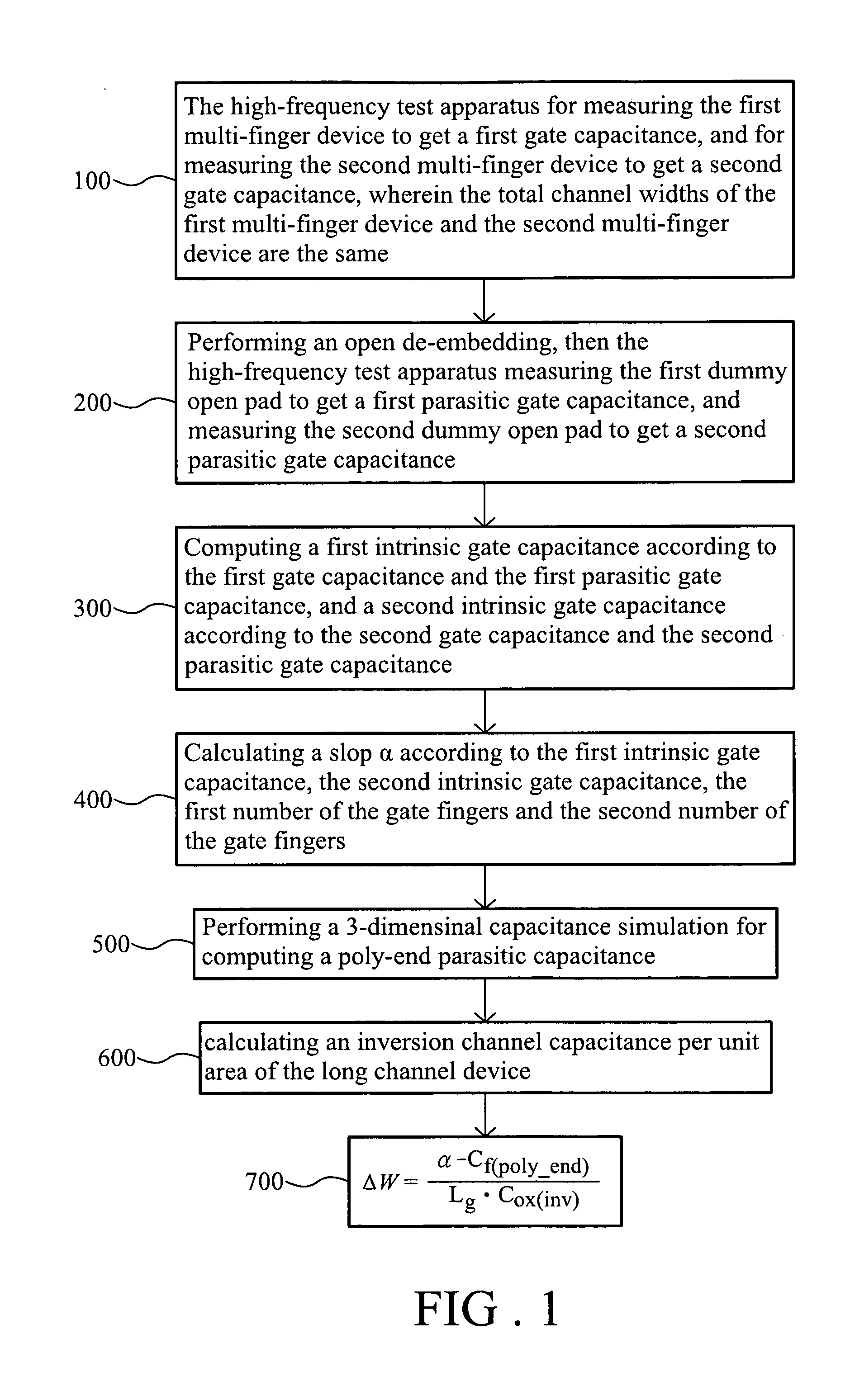

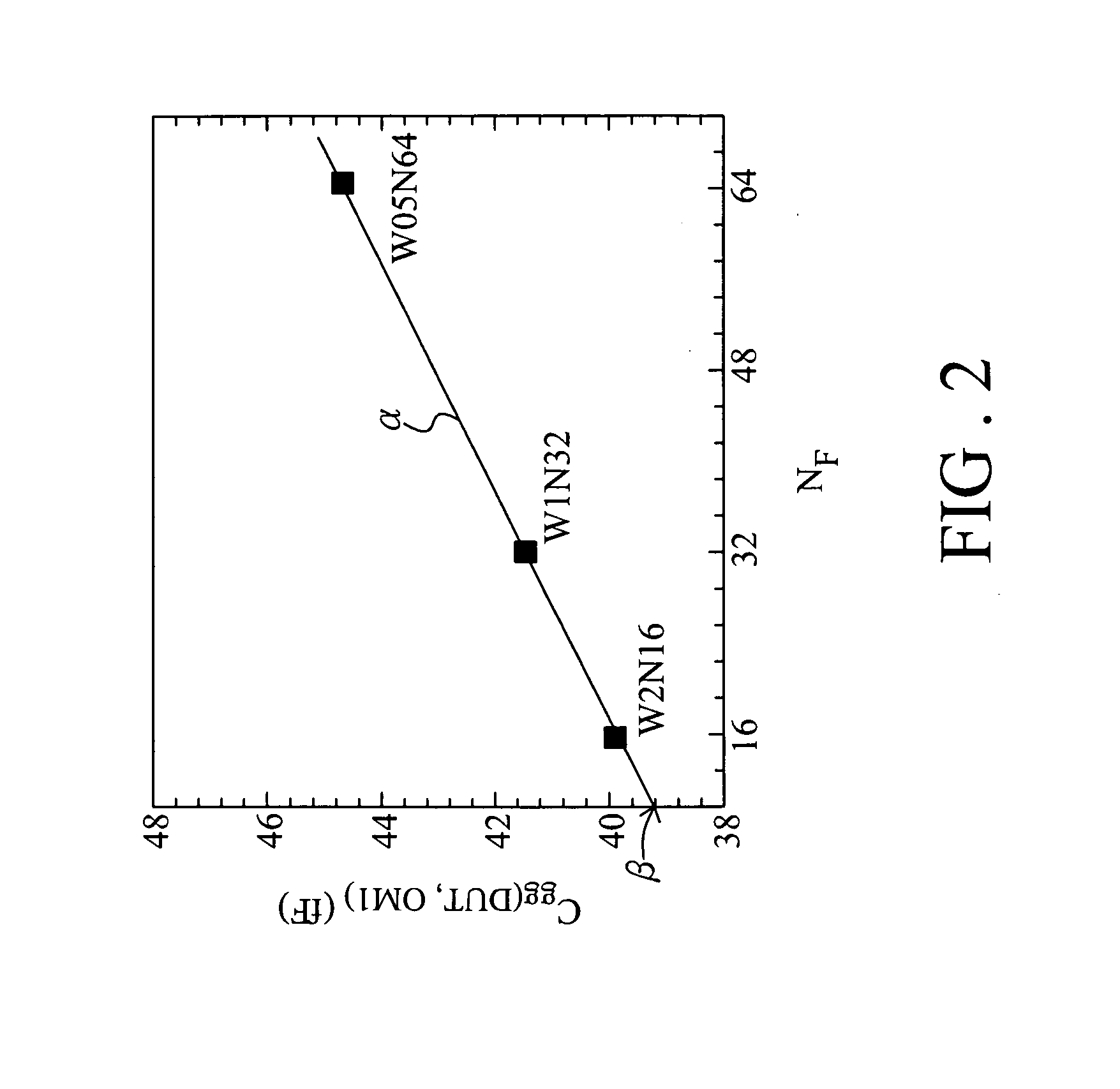

Parameter extraction method for semiconductor device

ActiveUS20120197593A1Simple and precise parameter extractionSemiconductor/solid-state device testing/measurementSolid-state devicesPower semiconductor deviceIntrinsics

A parameter extraction method for semiconductor devices includes: providing a first multi-finger device and a second multi-finger device, wherein the gate-finger numbers between the first and second multi-finger devices are different; performing an open de-embedding, then the high-frequency test apparatus measuring a first intrinsic gate capacitance of the first multi-finger device and a second intrinsic gate capacitance of the second multi-finger device; calculating a slope according to the first and second intrinsic gate capacitances, and the first and second gate-finger numbers; performing a 3D capacitance simulation for computing the poly finger-end fringing capacitances; utilizing a long channel device for measuring the gate capacitance and extracting the intrinsic gate capacitance, then calculating an inversion channel capacitance per unit area; and computing a delta channel width of the semiconductor device, according to the slope, the poly finger-end fringing capacitance, and the inversion channel capacitance per unit area.

Owner:NAT CHIAO TUNG UNIV

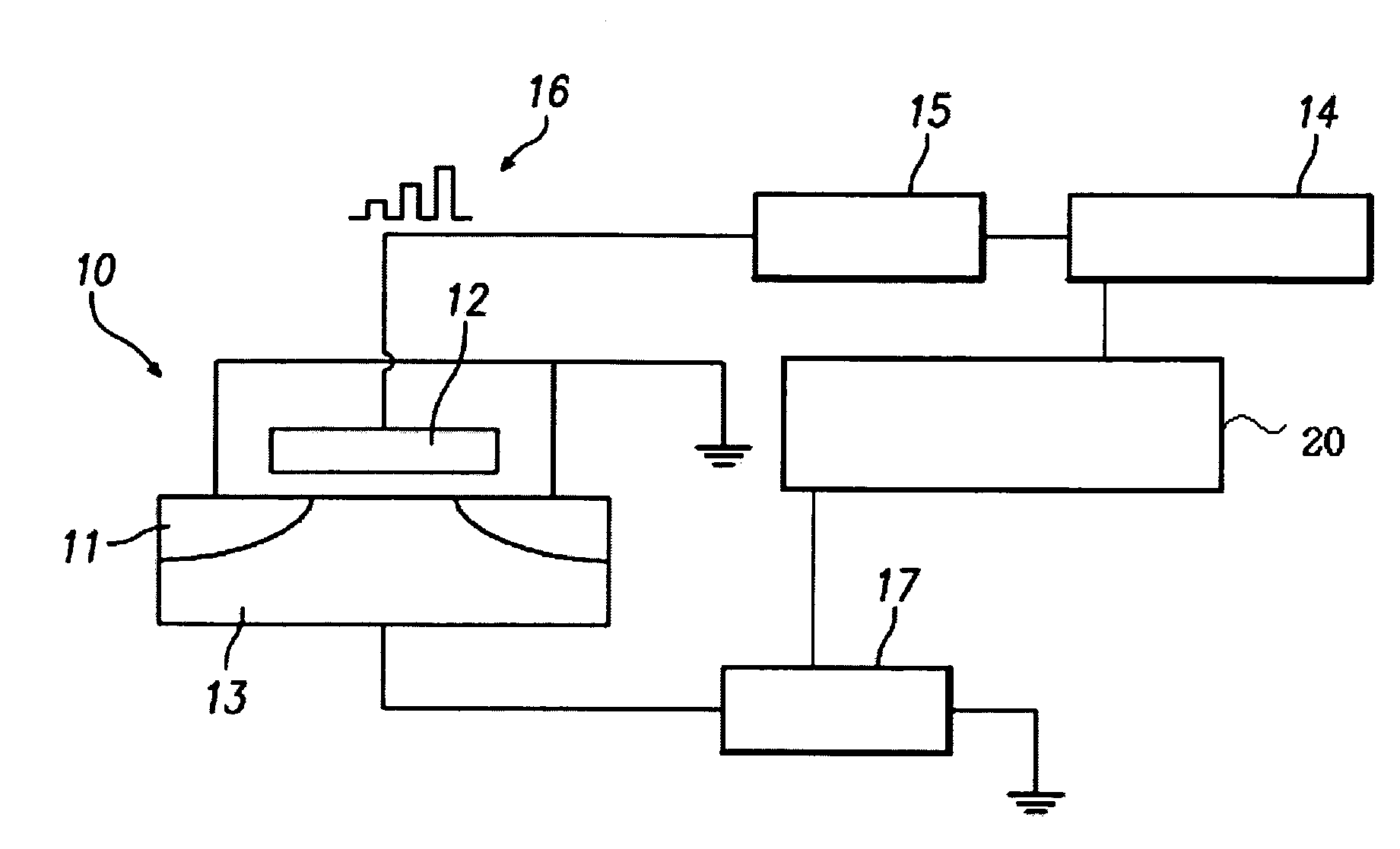

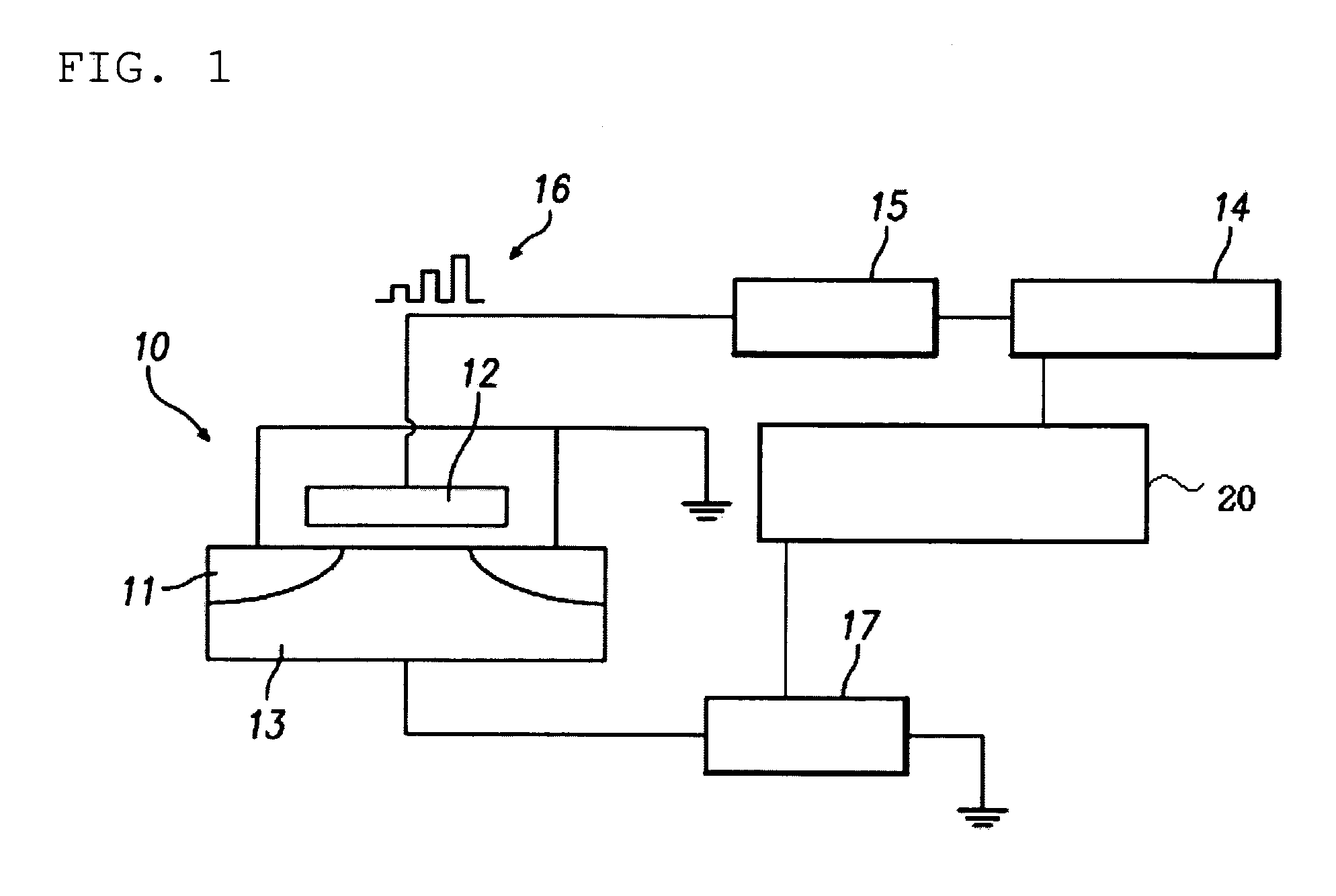

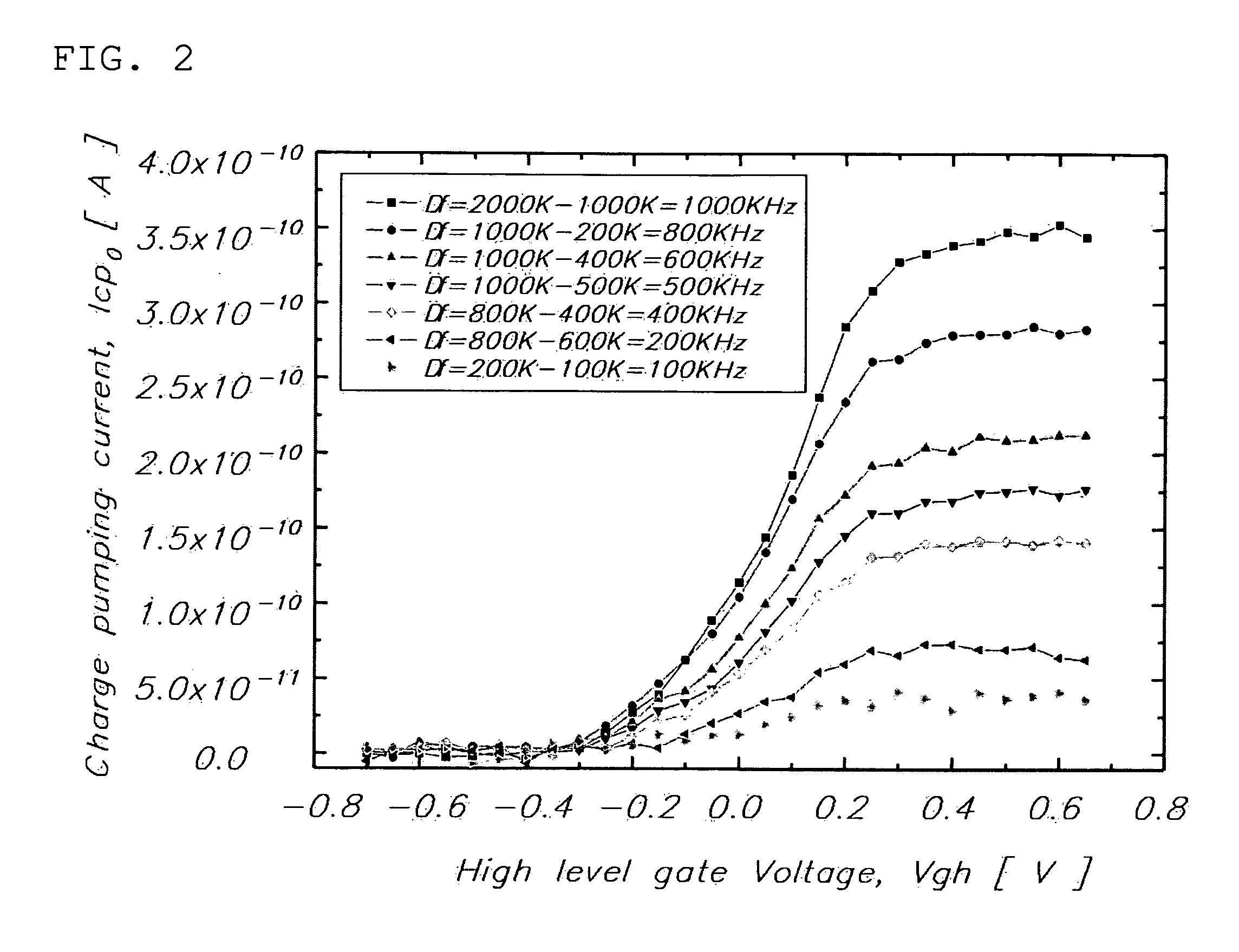

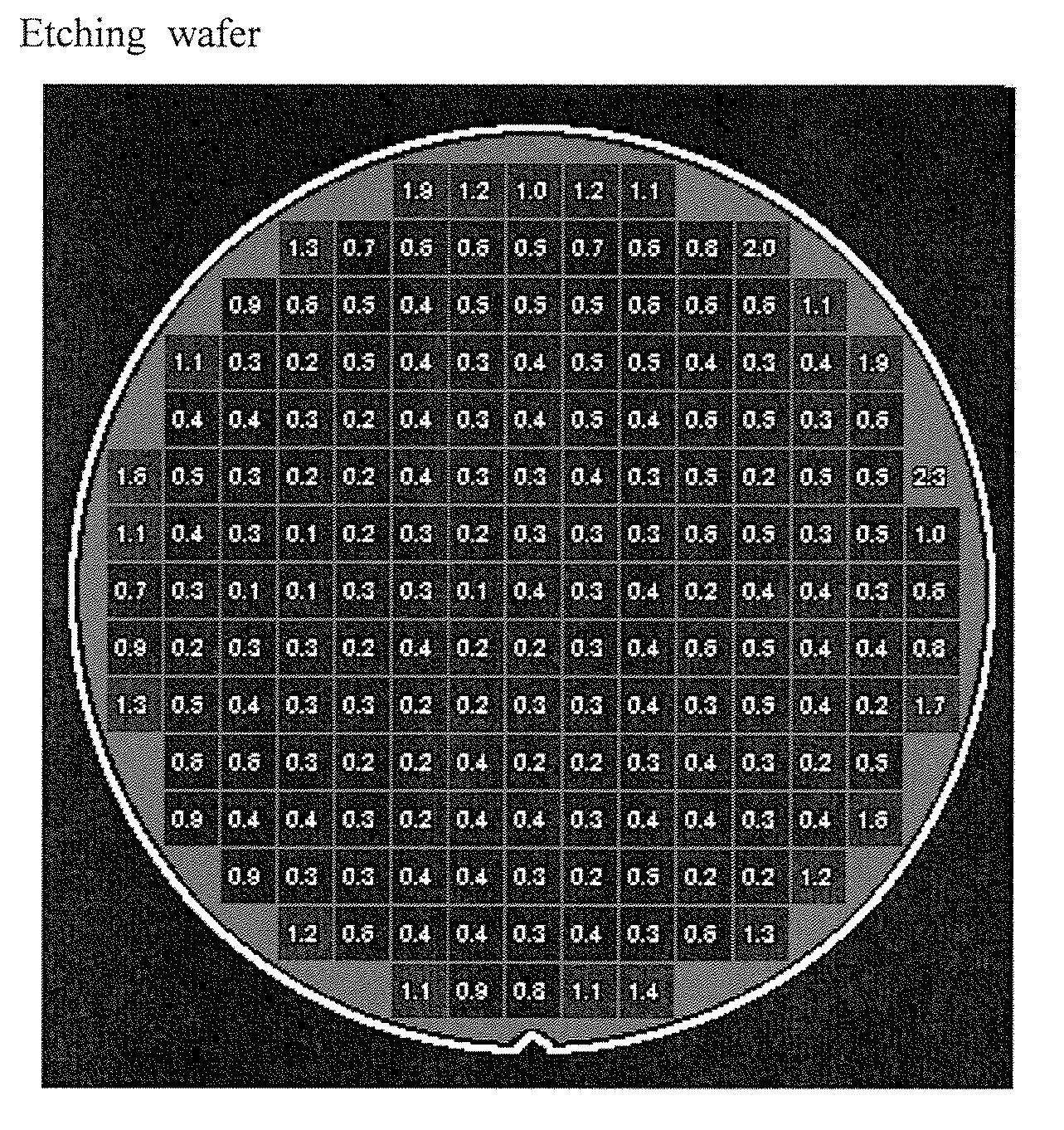

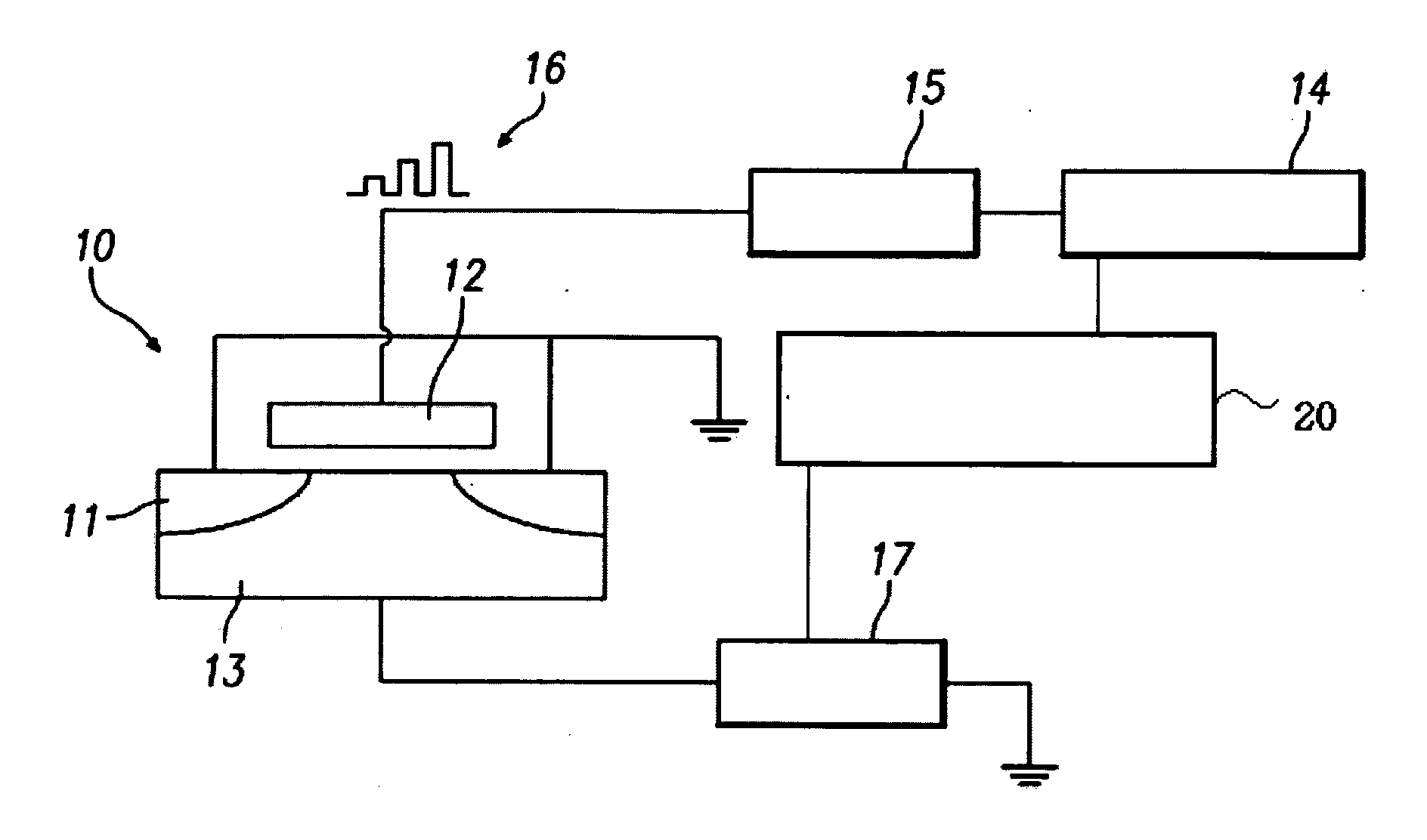

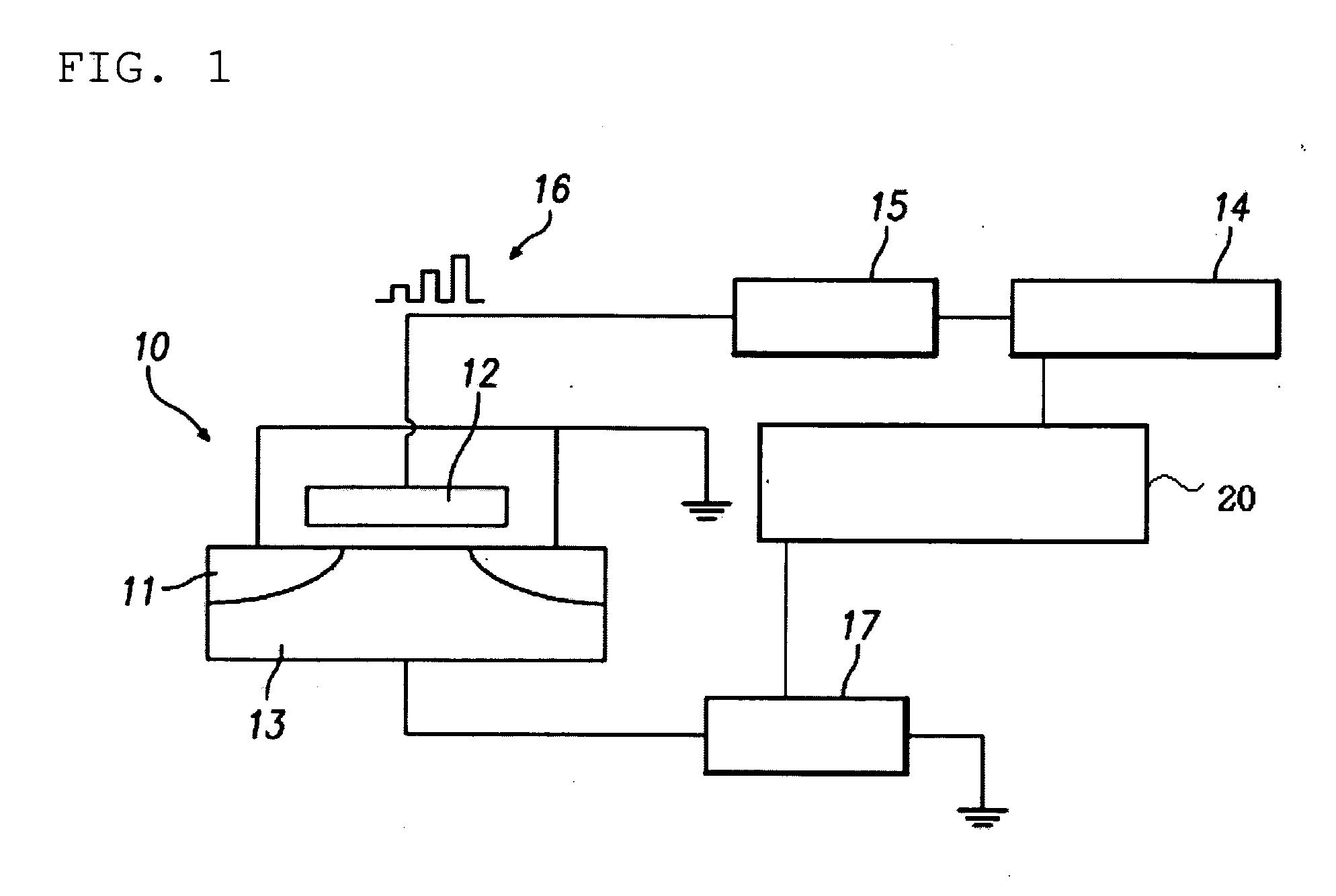

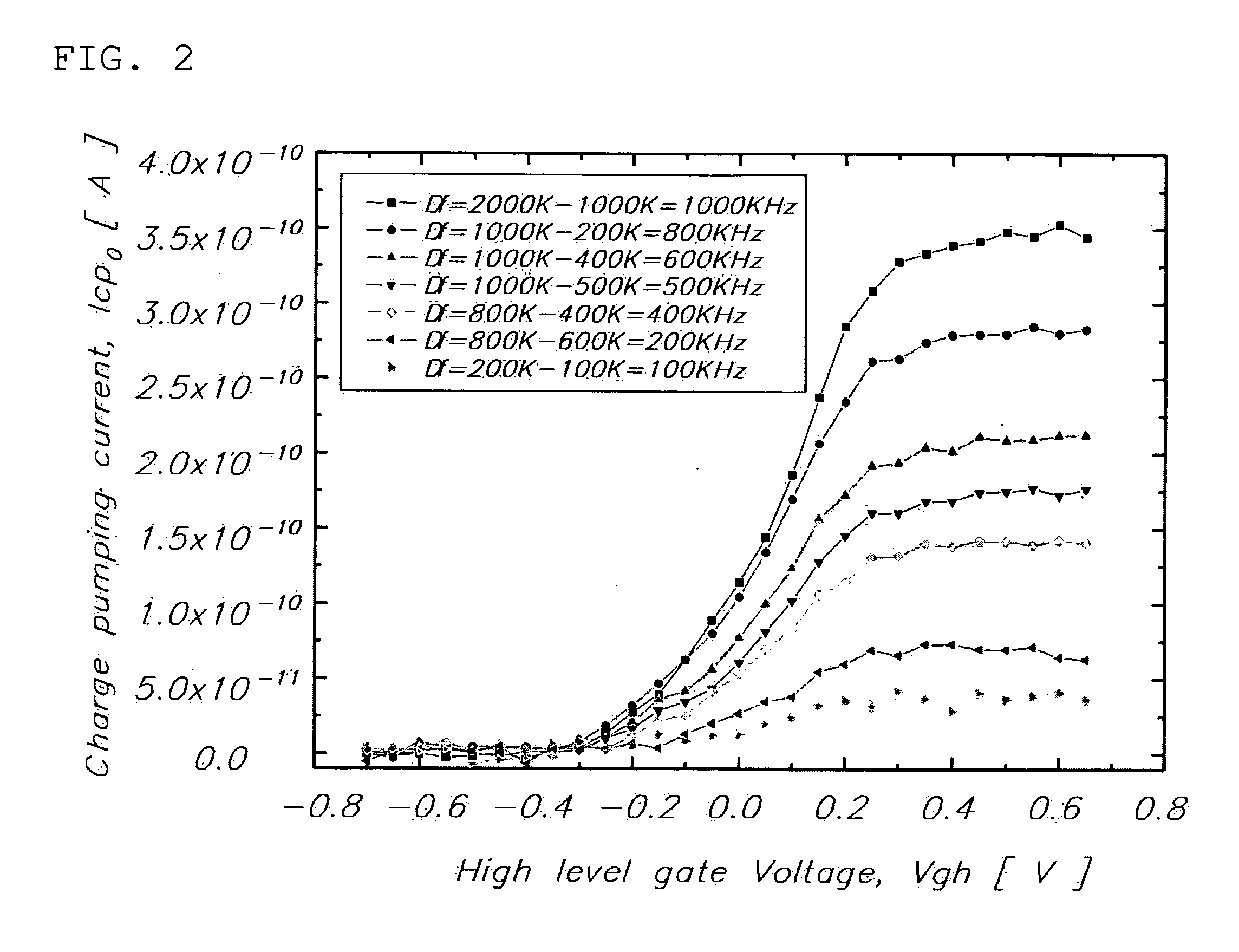

Method and device of measuring interface trap density in semiconductor device

InactiveUS7592828B2Accurately measure and calculateSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceSemiconductorElectrical current

A method is provided for measuring interface trap density in a semiconductor device. In the method, measurement parameters are input to a host computer. A pulse condition is set at a pulse generator using the measurement parameters. A pulse of a predetermined frequency generated by the pulse generator is applied to a gate of a transistor, and a charge pumping current is measured from a bulk of the transistor. A charge pumping current measurement may be repeated for a plurality of frequencies while changing the frequency until a set frequency is reached. A pure charge pumping current is calculated for each frequency where a gate tunneling leakage current is removed from the charge pumping current measured for each frequency. Interface trap density is calculated from the calculated pure charge pumping current for each frequency.

Owner:DONGBU ELECTRONICS CO LTD

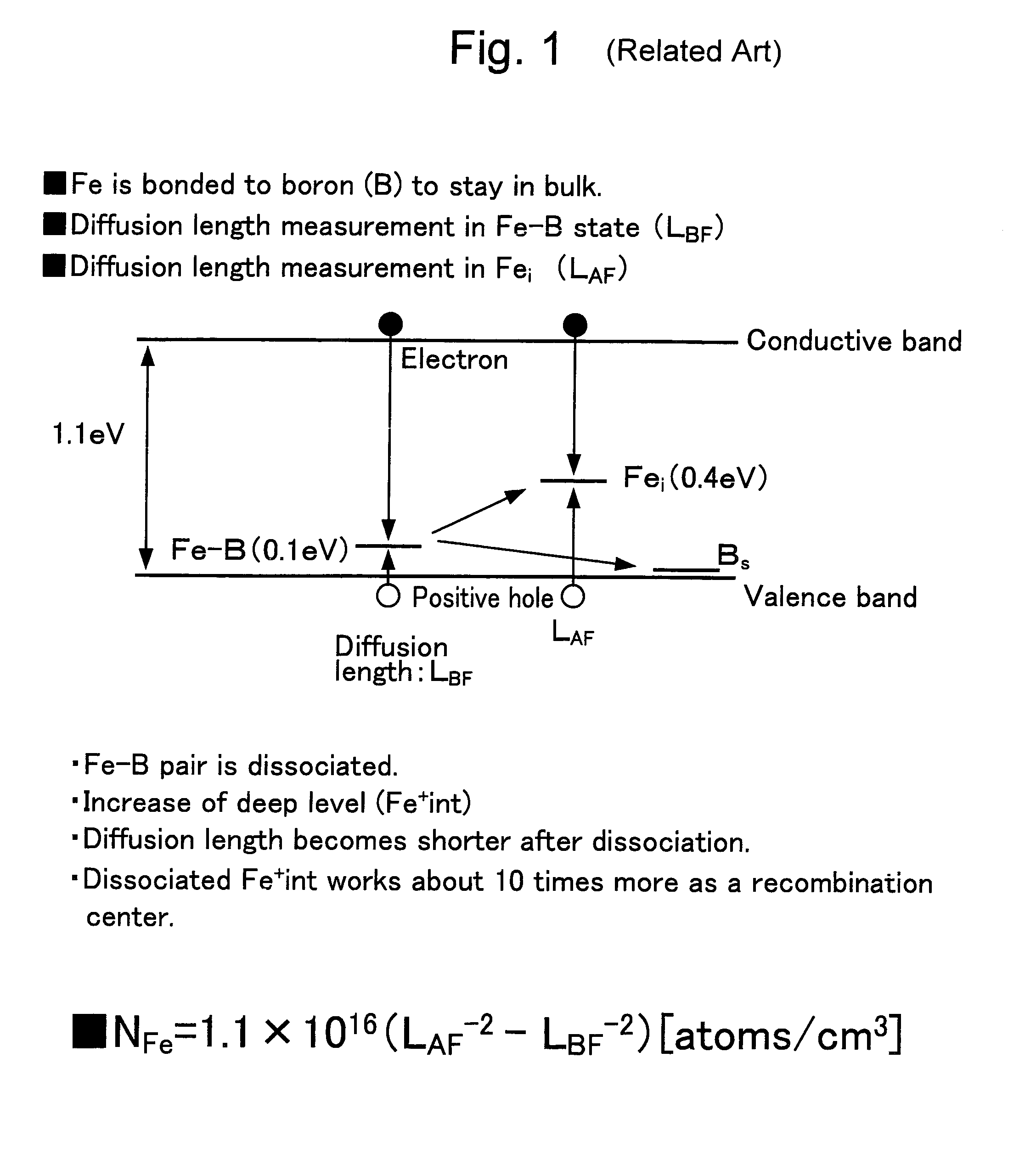

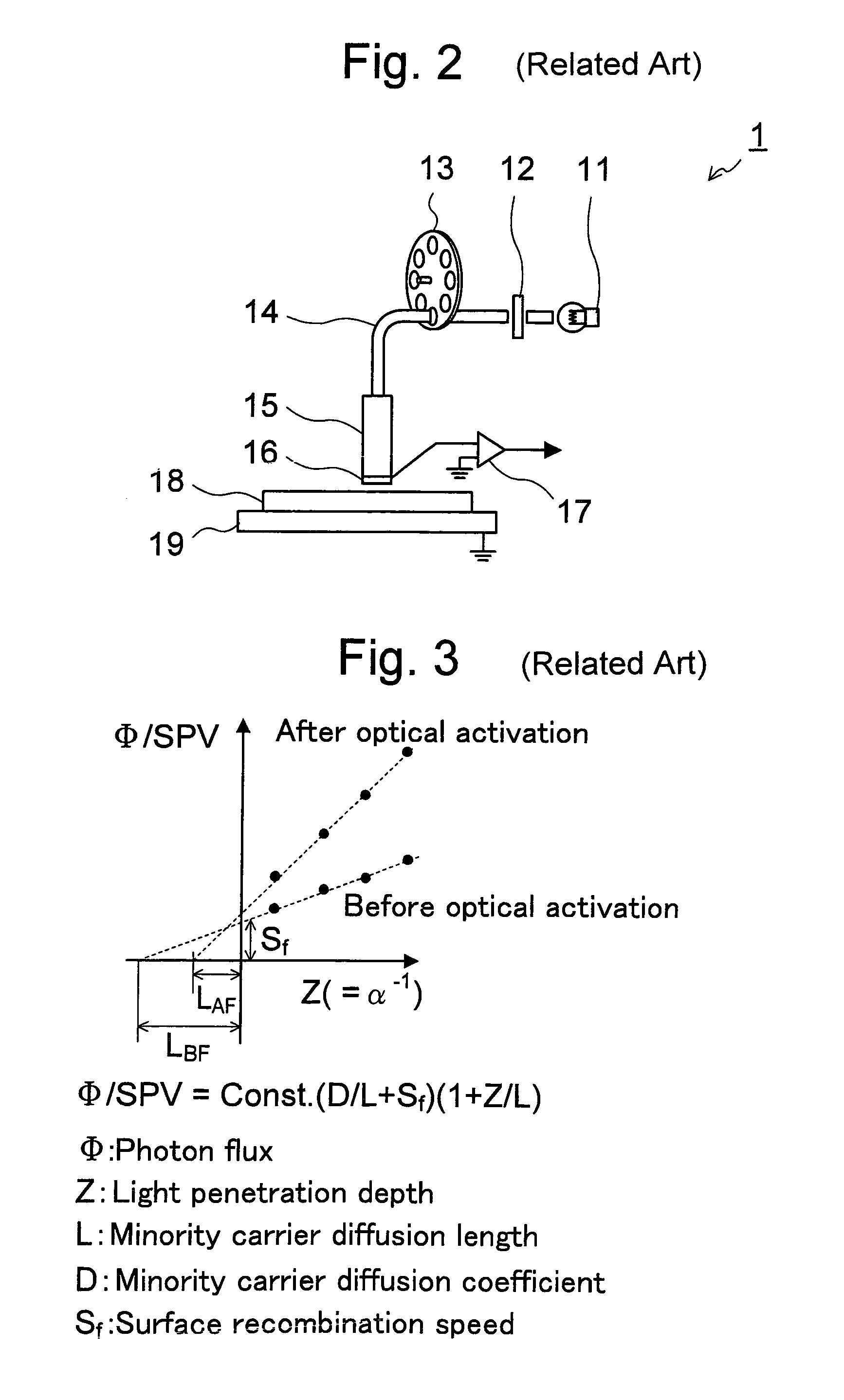

Method of measuring minority carrier diffusion length and method of manufacturing silicon wafer

ActiveUS20070287205A1Rapid and highly reliable measurementImprove reliabilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingDiffusionUltraviolet radiation

A method of measuring a diffusion length of a minority carrier in a silicon wafer by a surface photovoltage method including irradiating the surface-treated silicon wafer with ultraviolet radiation in an oxygen-containing atmosphere, and measuring a diffusion length of a minority carrier in a silicon wafer by a surface photovoltage method.

Owner:SUMCO CORP

Test structure for measuring electrical and dimensional characteristics

ActiveUS7355201B2Semiconductor/solid-state device testing/measurementElectrical measurement instrument detailsEngineeringElectrical and Electronics engineering

Owner:ADVANCED MICRO DEVICES INC

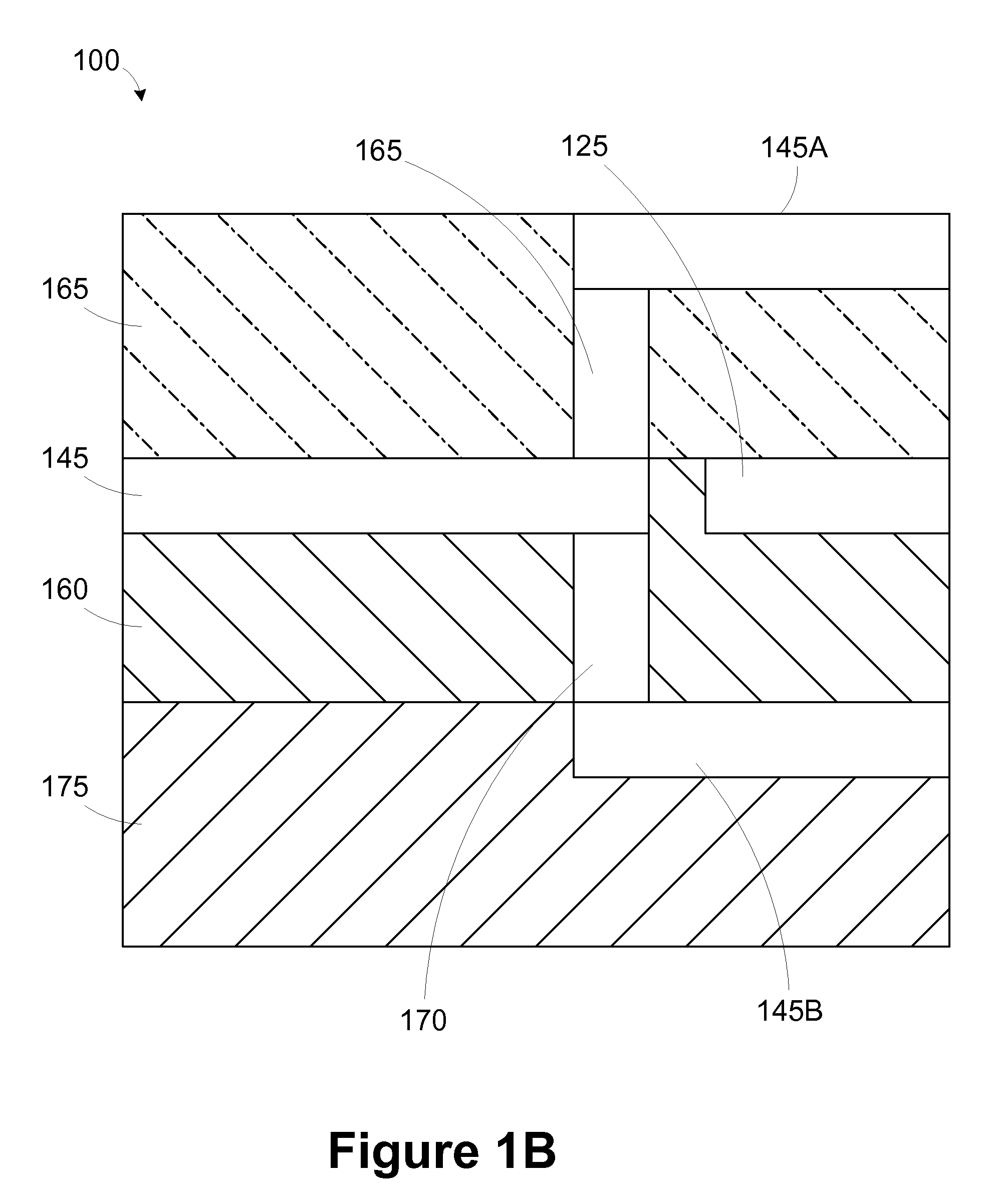

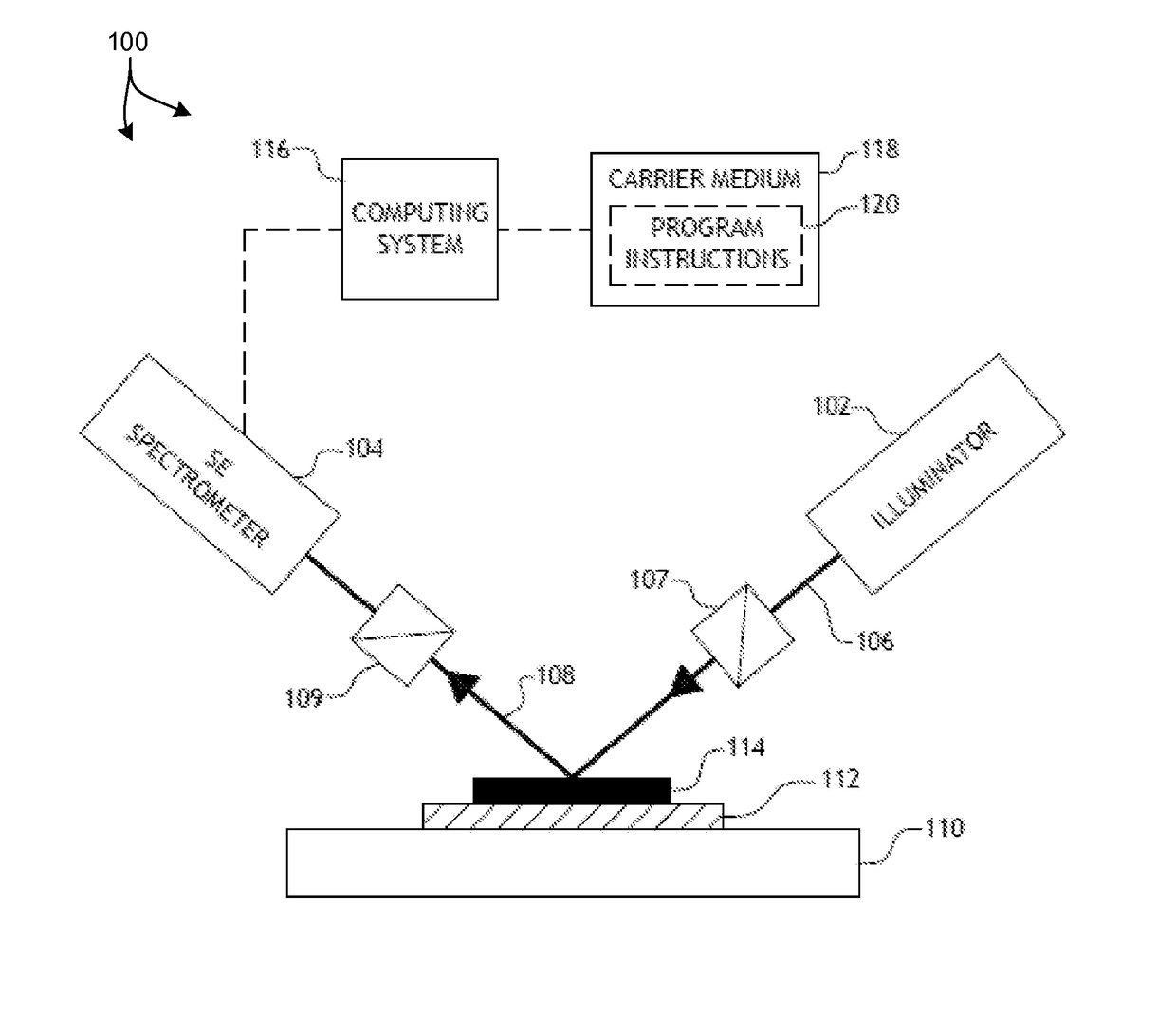

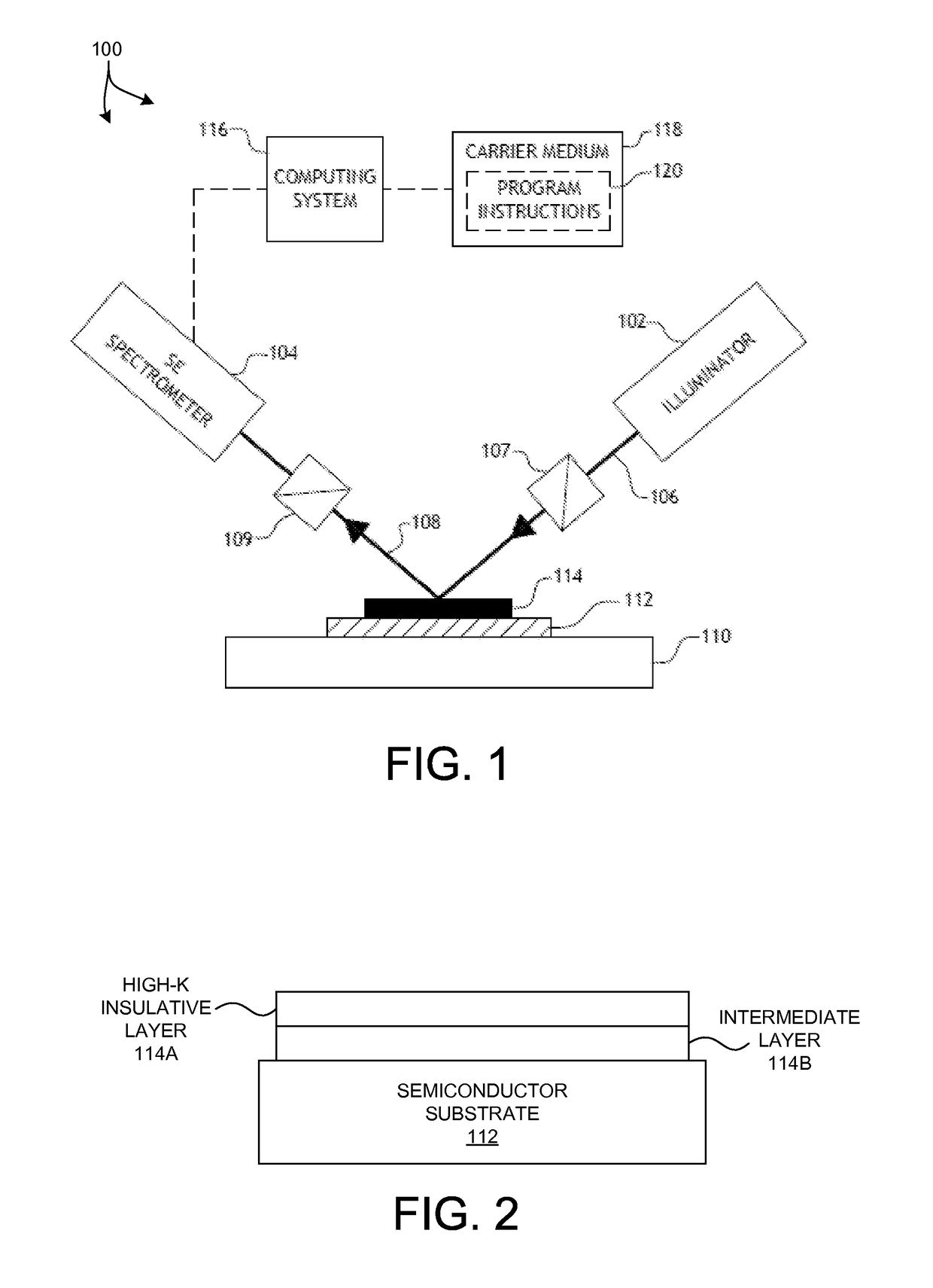

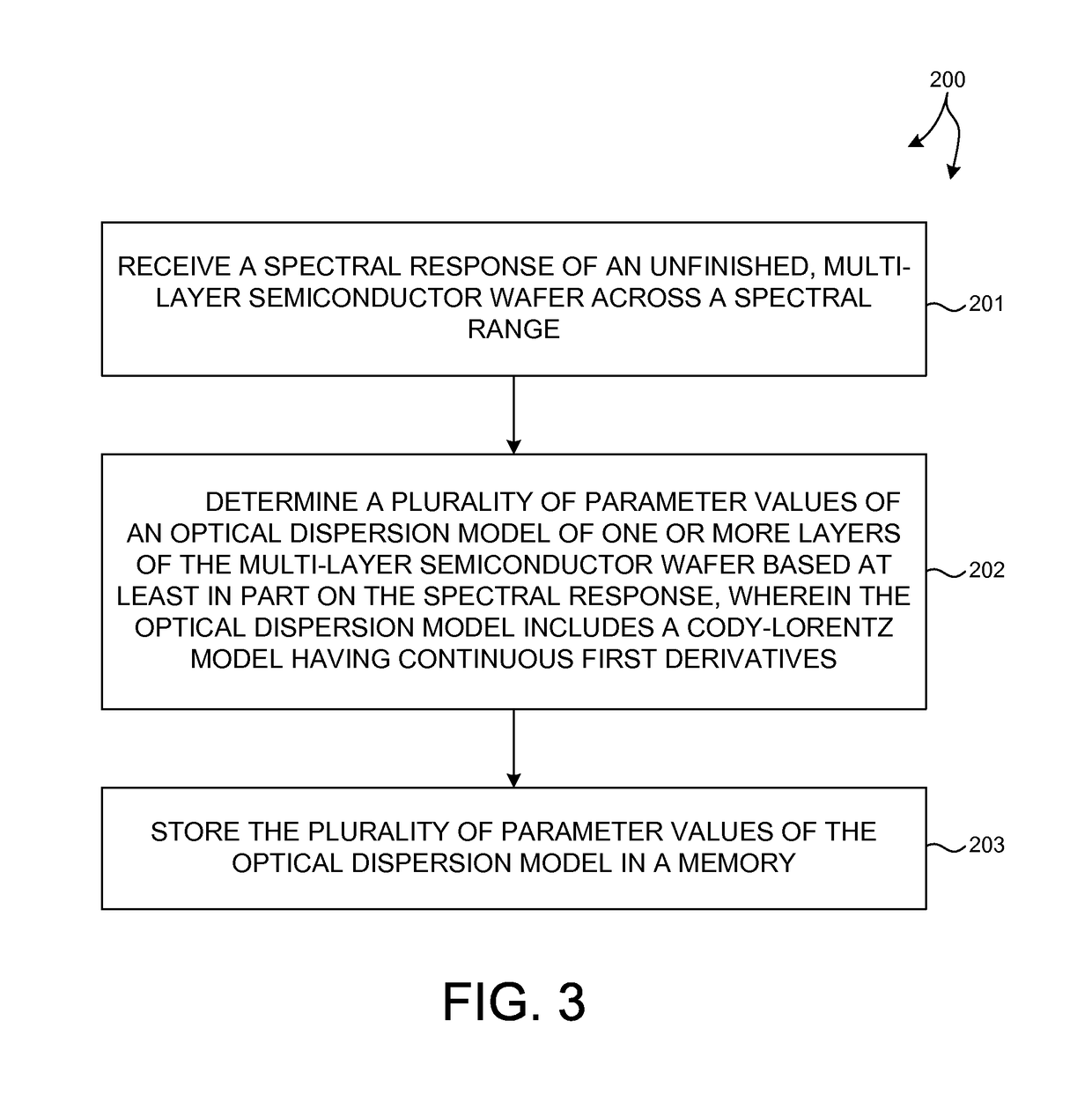

Dispersion model for band gap tracking

ActiveUS9595481B1Accurate representationImprove insightsSemiconductor/solid-state device testing/measurementOptically investigating flaws/contaminationSpectral responseFast measurement

Methods and systems for determining band structure characteristics of high-k dielectric films deposited over a substrate based on spectral response data are presented. High throughput spectrometers are utilized to quickly measure semiconductor wafers early in the manufacturing process. Optical models of semiconductor structures capable of accurate characterization of defects in high-K dielectric layers and embedded nanostructures are presented. In one example, the optical dispersion model includes a continuous Cody-Lorentz model having continuous first derivatives that is sensitive to a band gap of a layer of the unfinished, multi-layer semiconductor wafer. These models quickly and accurately represent experimental results in a physically meaningful manner. The model parameter values can be subsequently used to gain insight and control over a manufacturing process.

Owner:KLA TENCOR TECH CORP

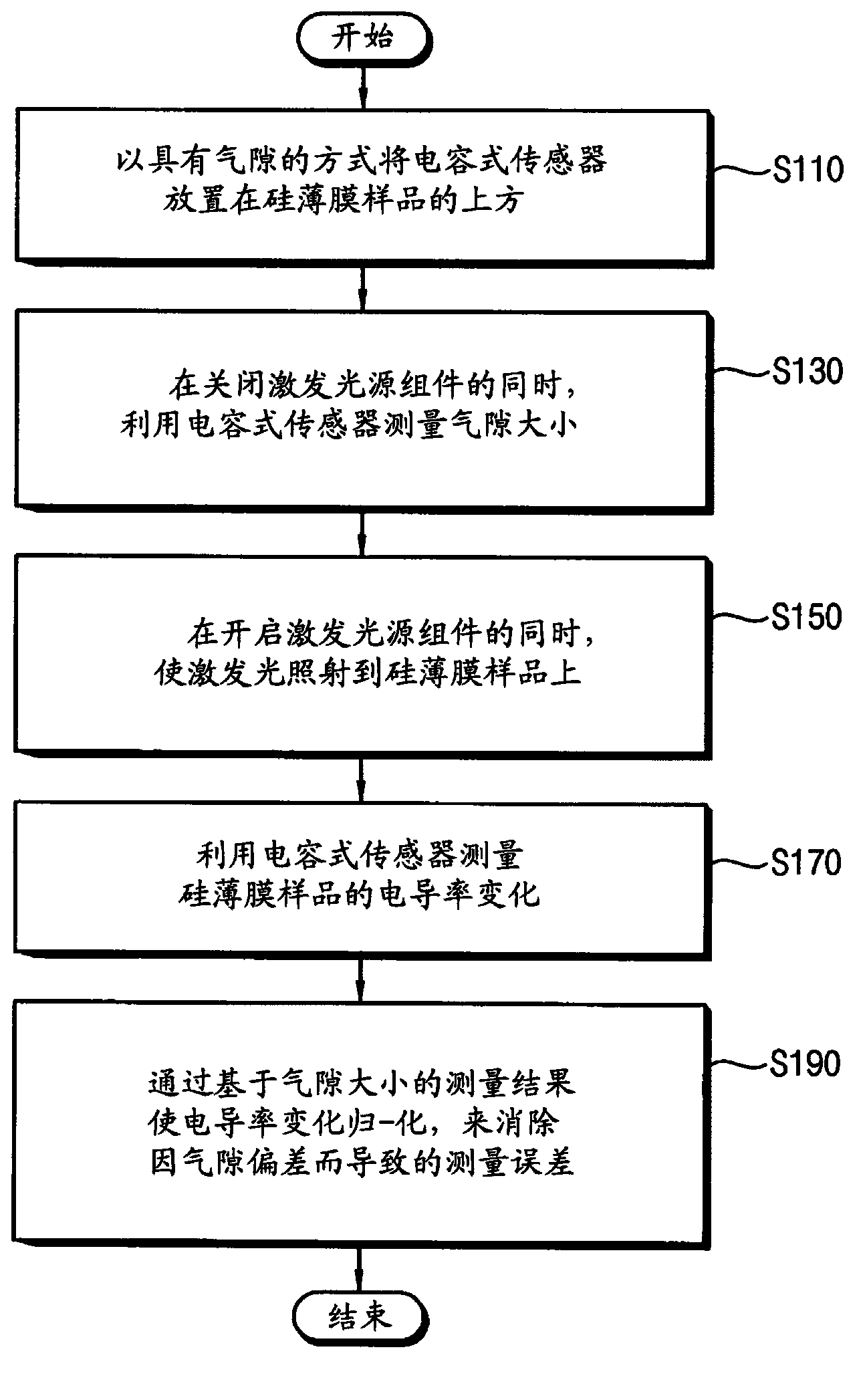

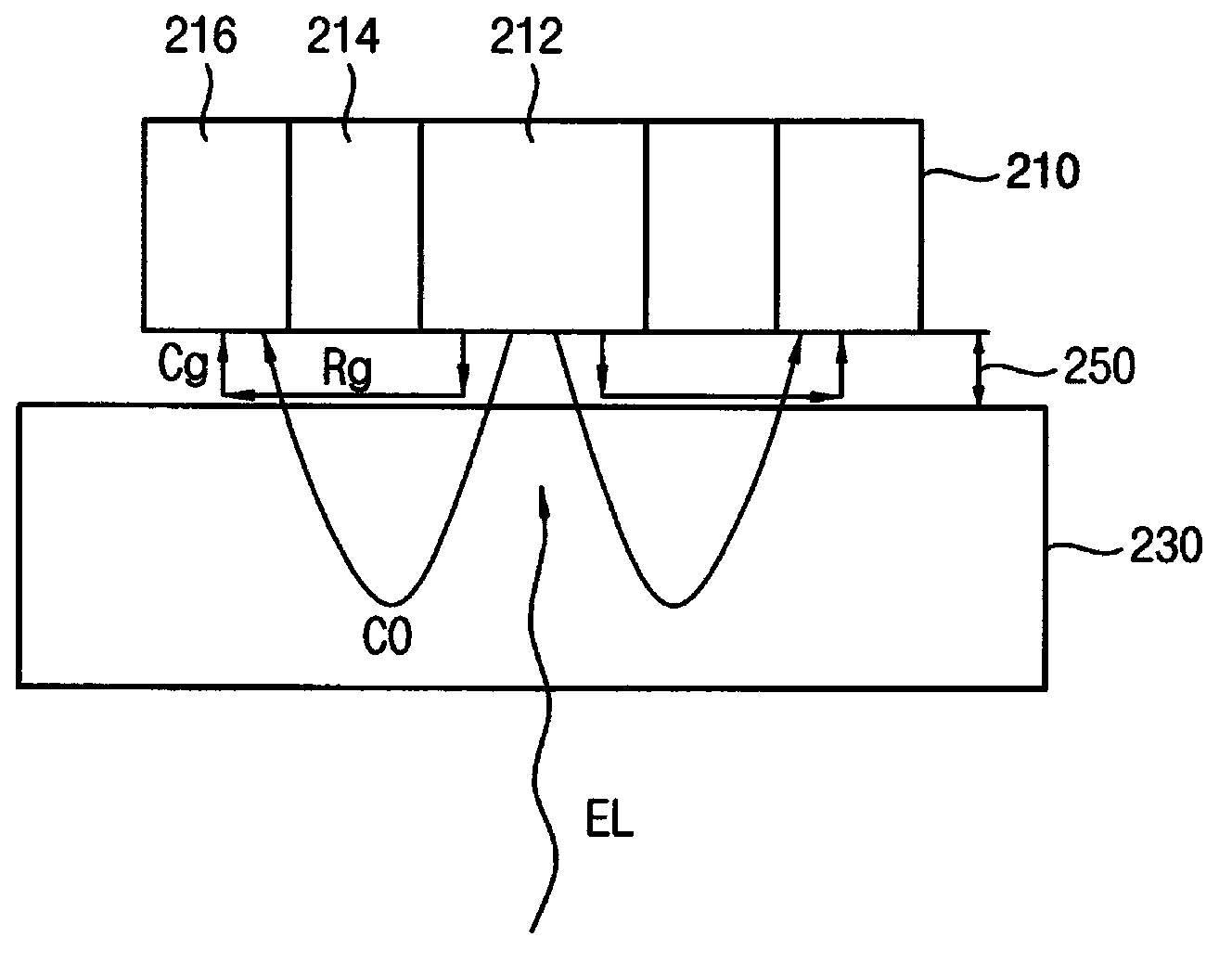

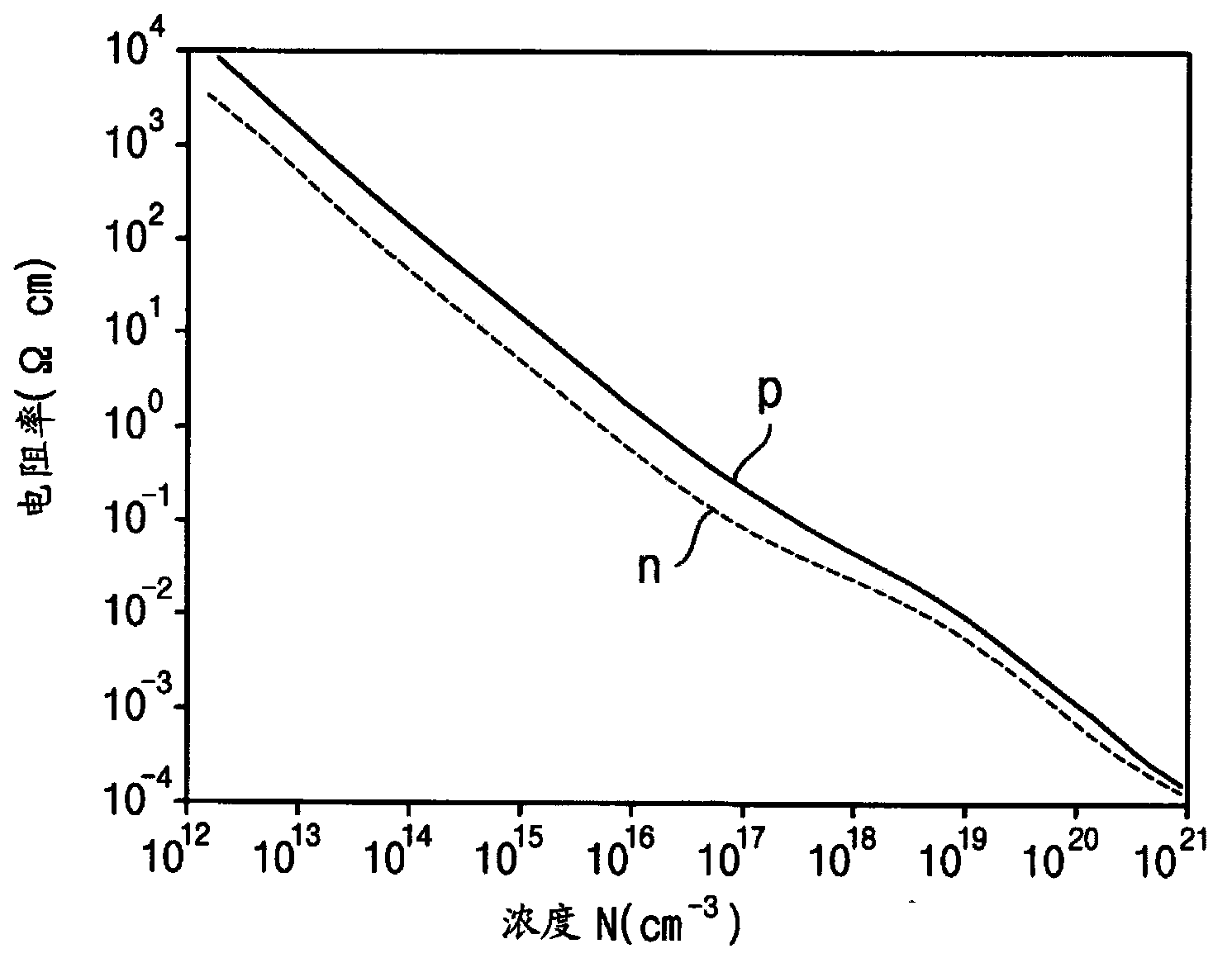

Method of measuring conductivity a silicon thin film, method of detecting defects in a silicon thin film, and silicon thin film defect detection device

ActiveCN103364638AResistance/reactance/impedenceAnalysis by material excitationObservational errorUltraviolet lights

A method of measuring conductivity of a silicon thin film is provided. By the method, a capacitive sensor is positioned over a silicon thin film sample with an air-gap between the sensor and the sample, a size of the air-gap is measured using the capacitive sensor while an excitation light source module is turned off, an excitation light is illuminated on the silicon thin film sample by turning on the excitation light source module, where the excitation light is an ultraviolet light, a conductivity change of the silicon thin film sample is measured using the capacitive sensor, and a measurement error due to a deviation of the air-gap is eliminated by normalizing the conductivity change based on a measurement result of the size of the air-gap.

Owner:SAMSUNG DISPLAY CO LTD

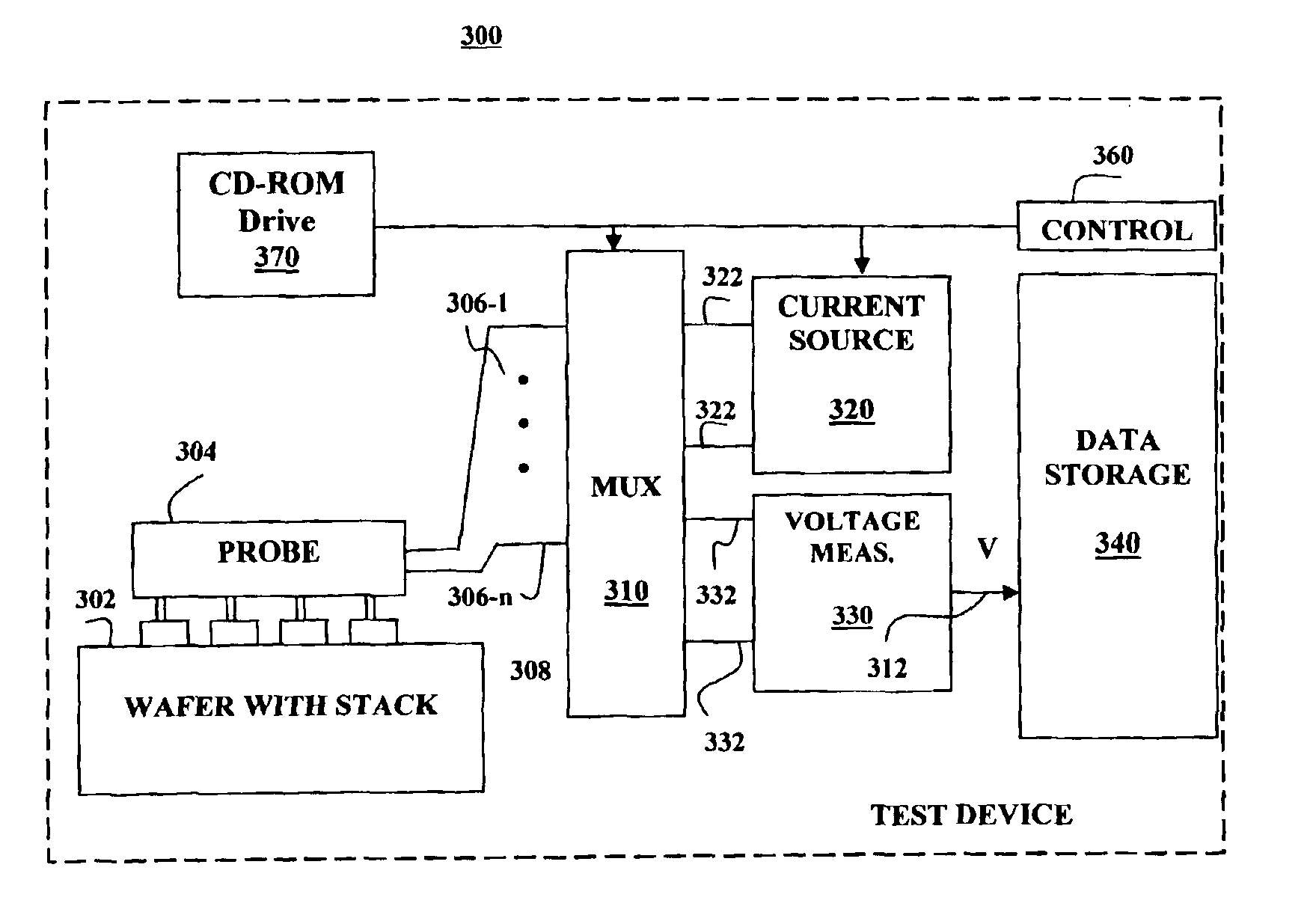

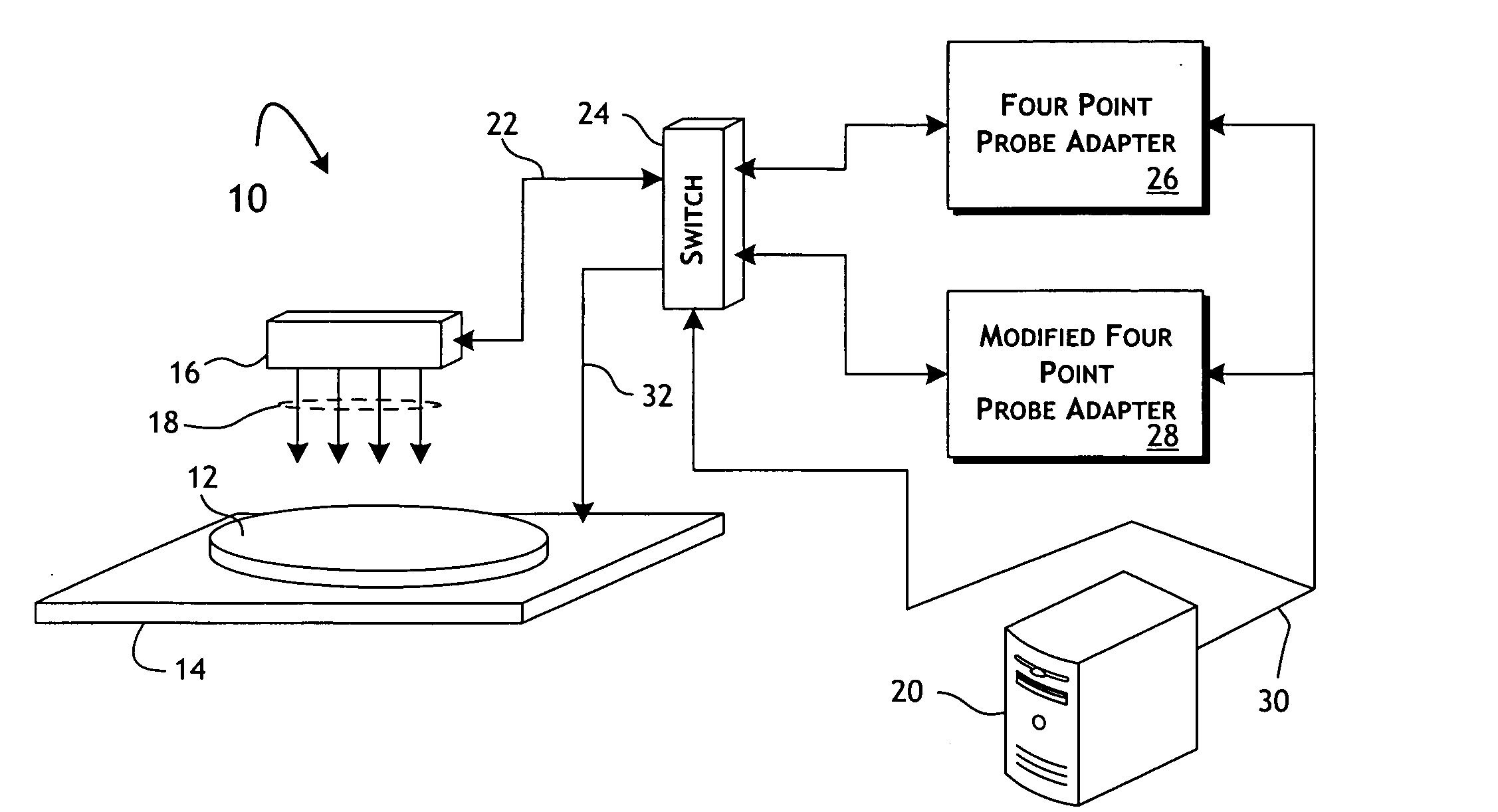

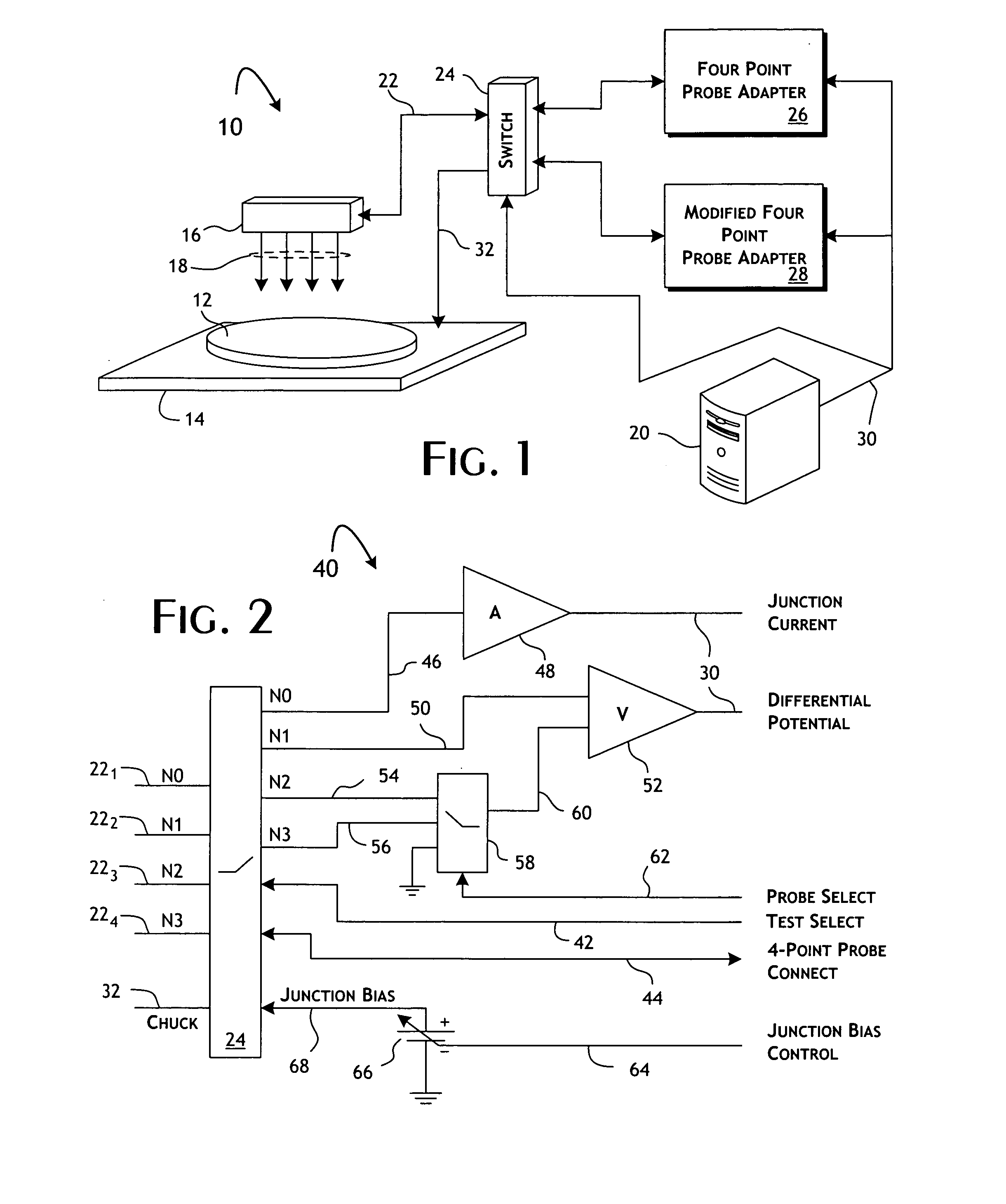

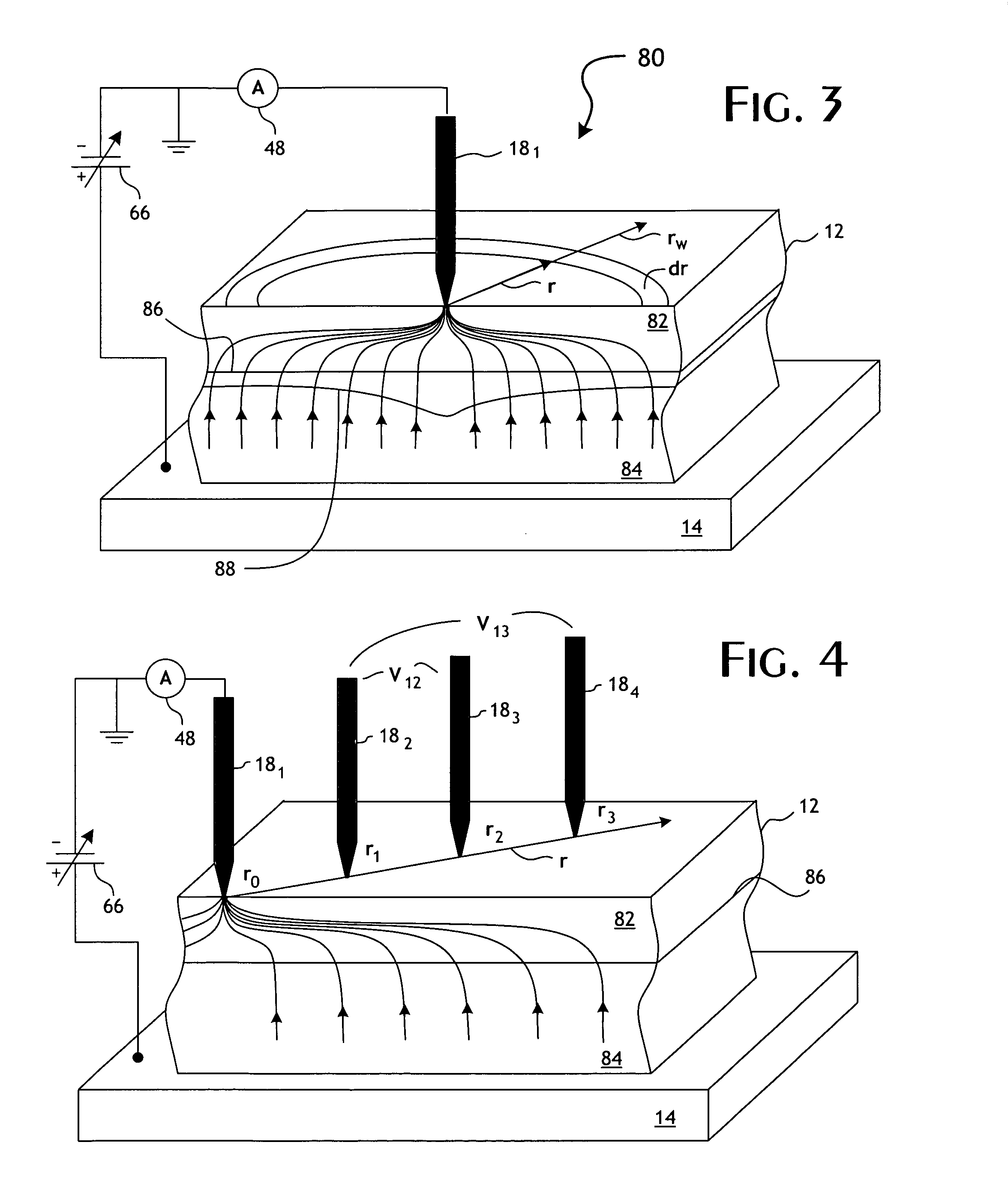

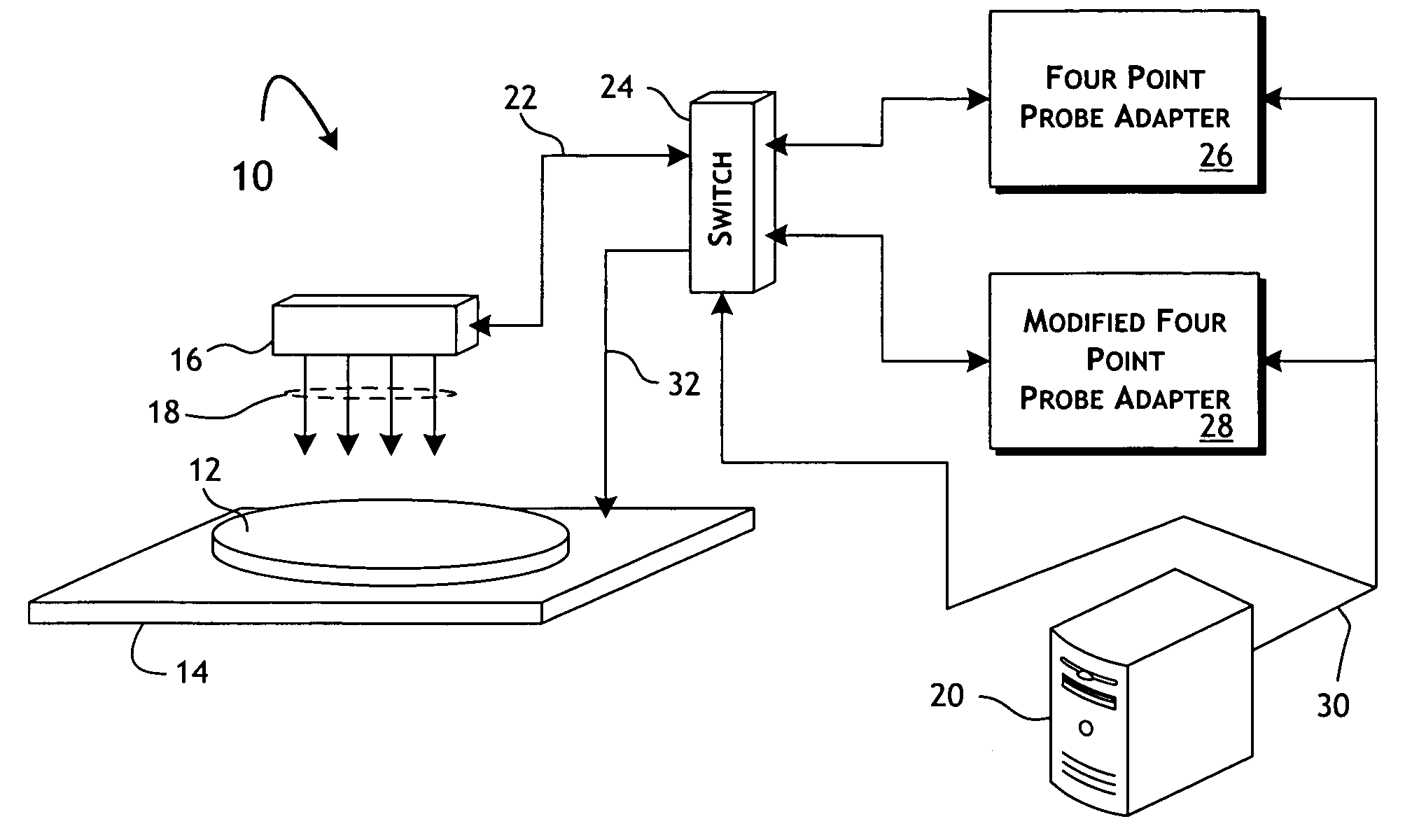

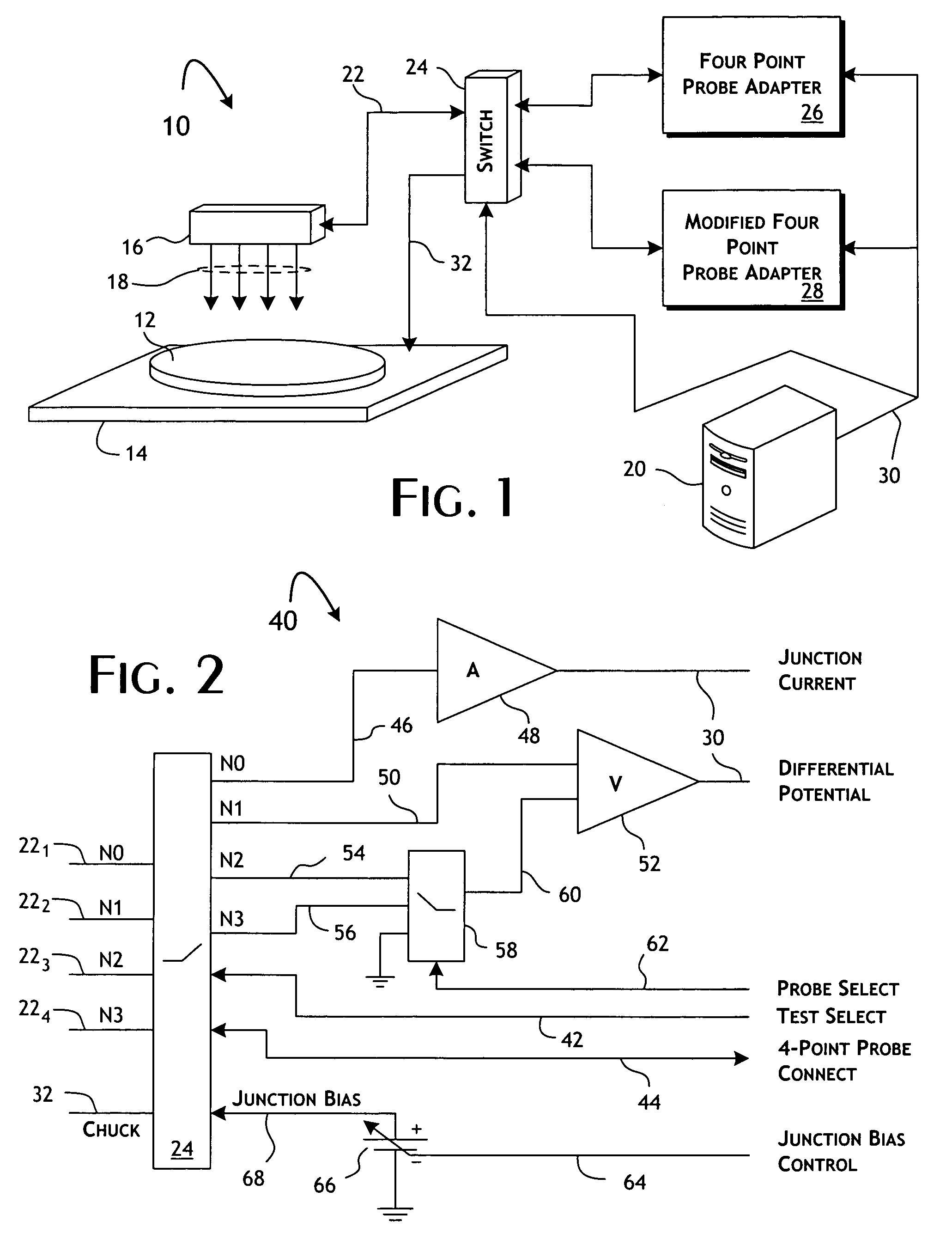

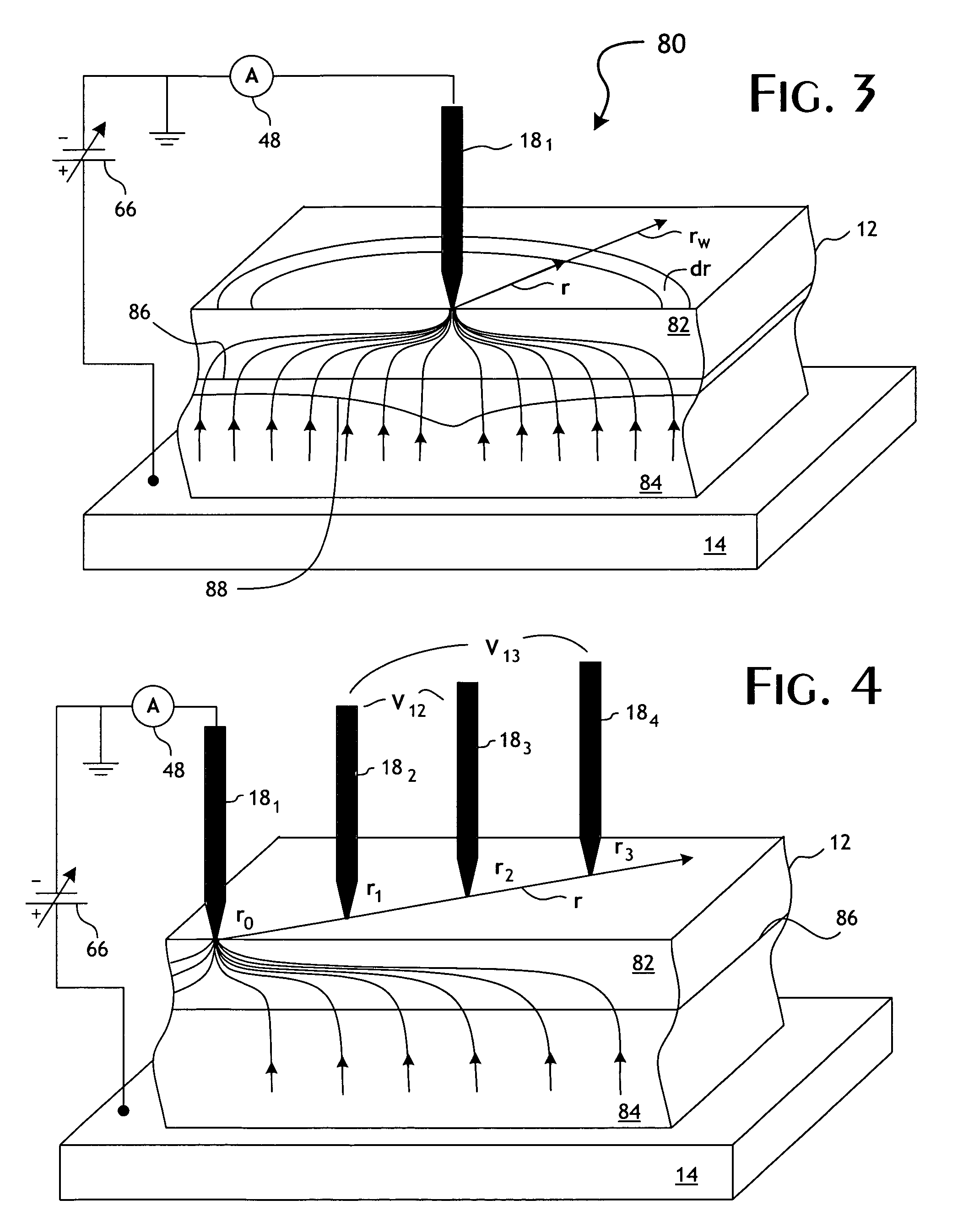

System and methods of measuring semiconductor sheet resistivity and junction leakage current

InactiveUS20080143354A1Improve test accuracyMeasure directlyResistance/reactance/impedenceSemiconductor characterisationElectrical resistance and conductanceCurrent sheet

Sheet resistance, junction leakage and contact conductivity of a semiconductor layer, associated with an ultra-shallow junction layer or metal film are measured by contacting the surface with a plurality of probes. The probes can be used, in conjunction with a four-point probe system, to determine sheet resistivity. Junction leakage through an ultra-shallow junction is determined by establishing a reverse bias across the junction set at a predetermined voltage value, measuring through a first probe a total junction current conduction value, measuring through second, third, and fourth probes a plurality of voltage values. The junction leakage value is then directly computed based on the sheet resistivity value, reverse bias potential, wafer radius, and the measured voltage values. Contact conductivity between a metal film and semiconductor layer can be similarly directly computed.

Owner:FOUR DIMENSIONS

Apparatus for measuring of thin dielectric layer properties on semiconductor wafers with contact self aligning electrodes

InactiveUS7034563B1Stable conditionSemiconductor/solid-state device manufacturingSemiconductor characterisationMetrologyDielectric layer

The invention relates to metrology of thin dielectric layers on semiconductor wafers, interfaces of dielectric layers to the wafer substrates and substrates properties of semiconductor wafers. The invention allows measurement of the metrology data for thin dielectric layers on semiconductor wafers electrically via using contact electrodes that align their contact surface to the wafer surface locally at the measurement sites.

Owner:APPLEJACK 199 +1

Method and device of measuring interface trap density in semiconductor device

InactiveUS20070152673A1Accurate measurementAccurate calculationSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceDevice materialDrain current

A method is provided for measuring interface trap density in a semiconductor device. In the method, measurement parameters are input to a host computer. A pulse condition is set at a pulse generator using the measurement parameters. A pulse of a predetermined frequency generated by the pulse generator is applied to a gate of a transistor, and a charge pumping current is measured from a bulk of the transistor. A charge pumping current measurement may be repeated for a plurality of frequencies while changing the frequency until a set frequency is reached. A pure charge pumping current is calculated for each frequency where a gate tunneling leakage current is removed from the charge pumping current measured for each frequency. Interface trap density is calculated from the calculated pure charge pumping current for each frequency.

Owner:DONGBU ELECTRONICS CO LTD

Device and method for simultaneously measuring Hall coefficient and seebeck coefficient

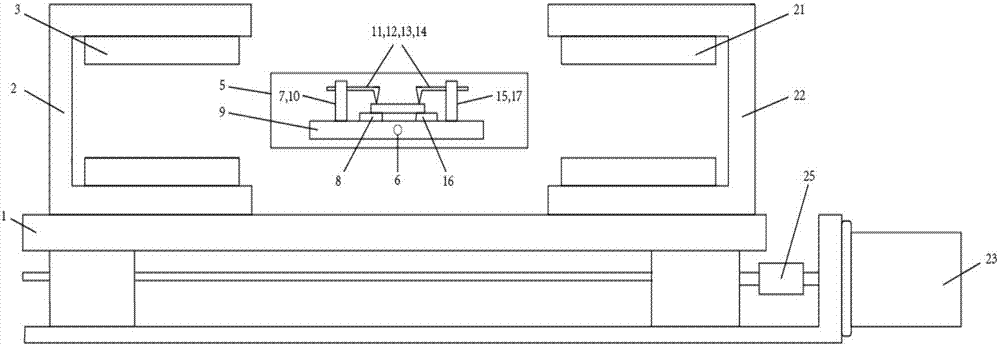

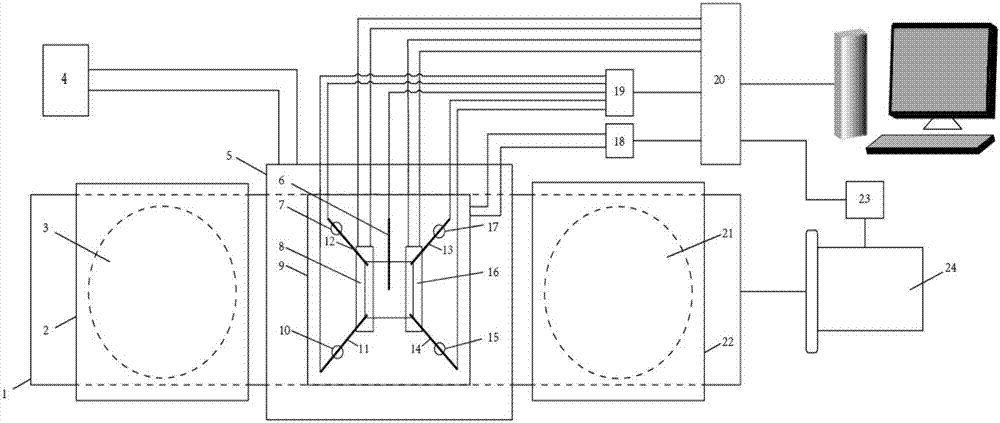

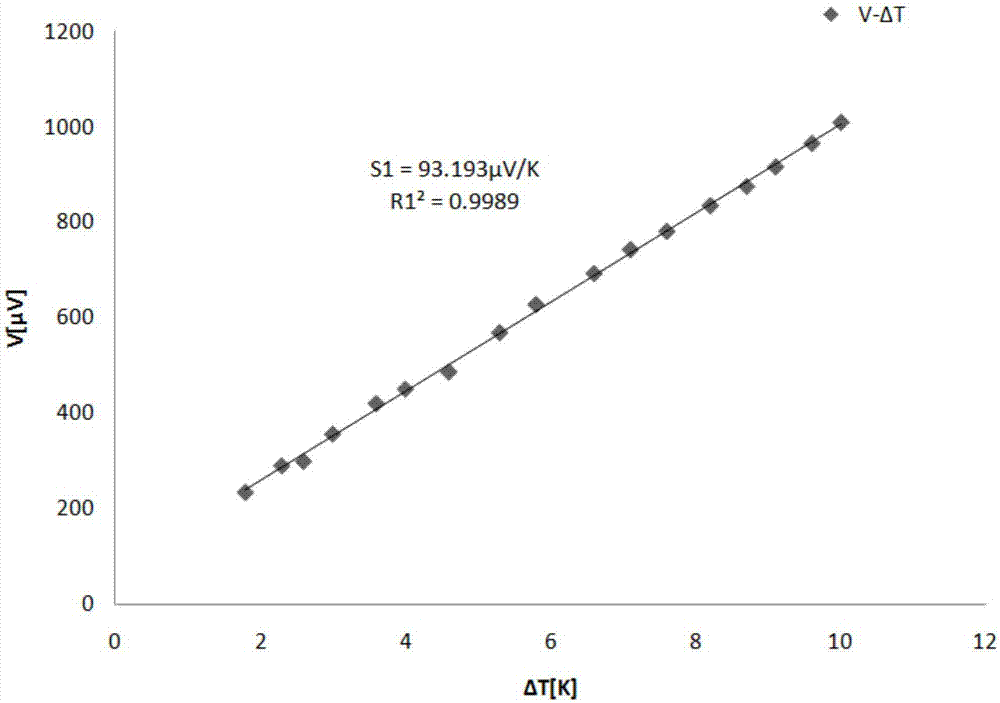

ActiveCN106950484ASolve insulation problemsImplement automated testingMaterial heat developmentSemiconductor characterisationMotor driveSemiconductor materials

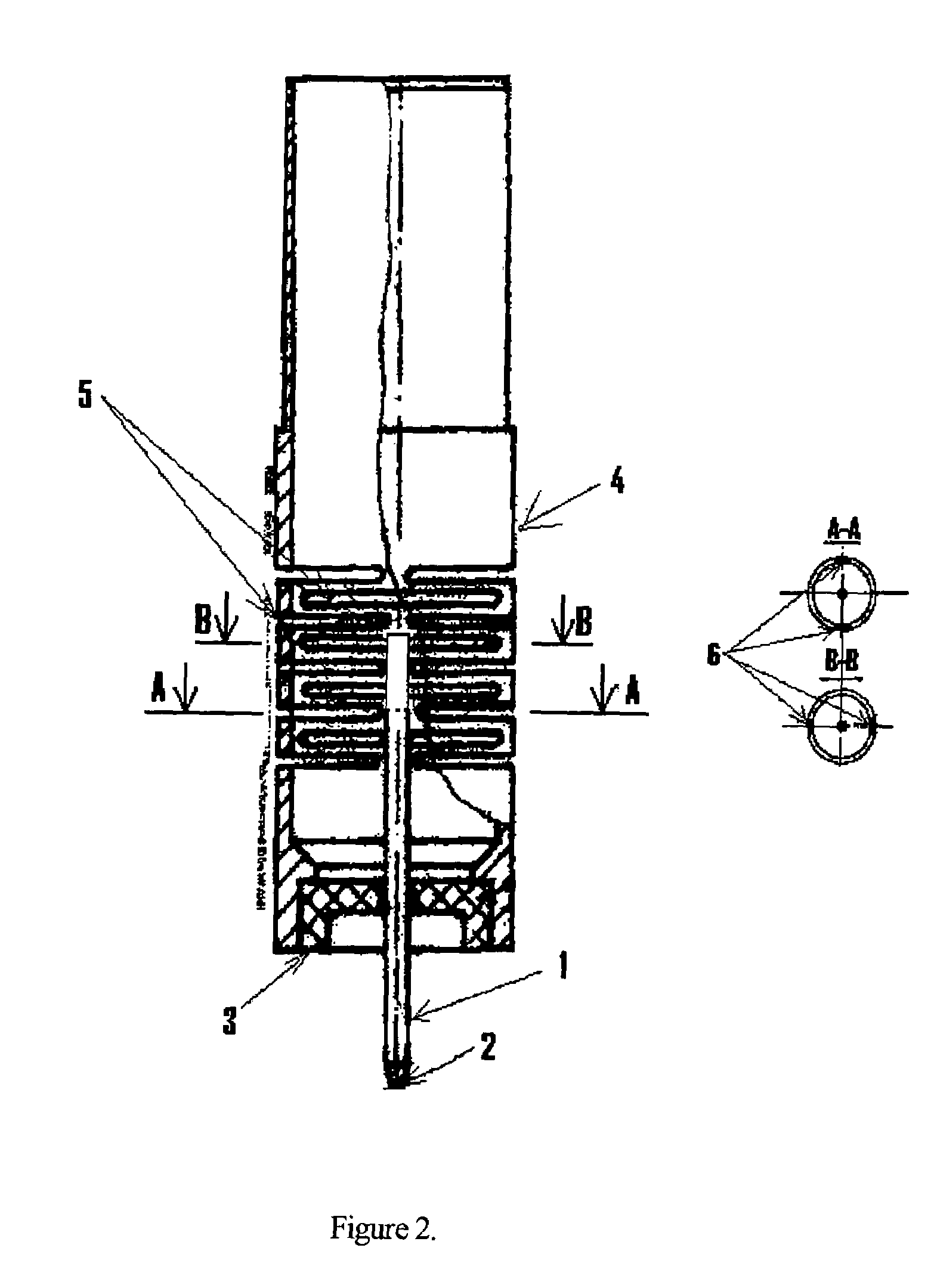

The invention belongs to the technical field of semiconductor material test, and particularly relates to a device and a method for simultaneously measuring a Hall coefficient and a seebeck coefficient. The device comprises a straight running slide rail, a magnet group, a test probe and a main heater. Magnet racks are respectively arranged on two ends of the straight running slide rail. A pair of same magnet groups are arranged on each magnet rack. The main heater is arranged on the straight running slide rail. To-be-tested samples are arranged on two sheets of ceramic sheet auxiliary heaters on the surface of the main heater. Test probes are arranged on the main heater. A motor drives the straight running slide rail to move. The invention also discloses the method for simultaneously measuring a Hall coefficient and a seebeck coefficient by use of the device. According to the invention, a problem of high requirements on shape measurement in measurement of the seebeck coefficient is effectively solved; different sizes and shapes of materials can be measured; measurement of the Hall coefficient and the seebeck coefficient at different temperatures is achieved; automatic operation is achieved; and test precision is high.

Owner:HUAZHONG UNIV OF SCI & TECH

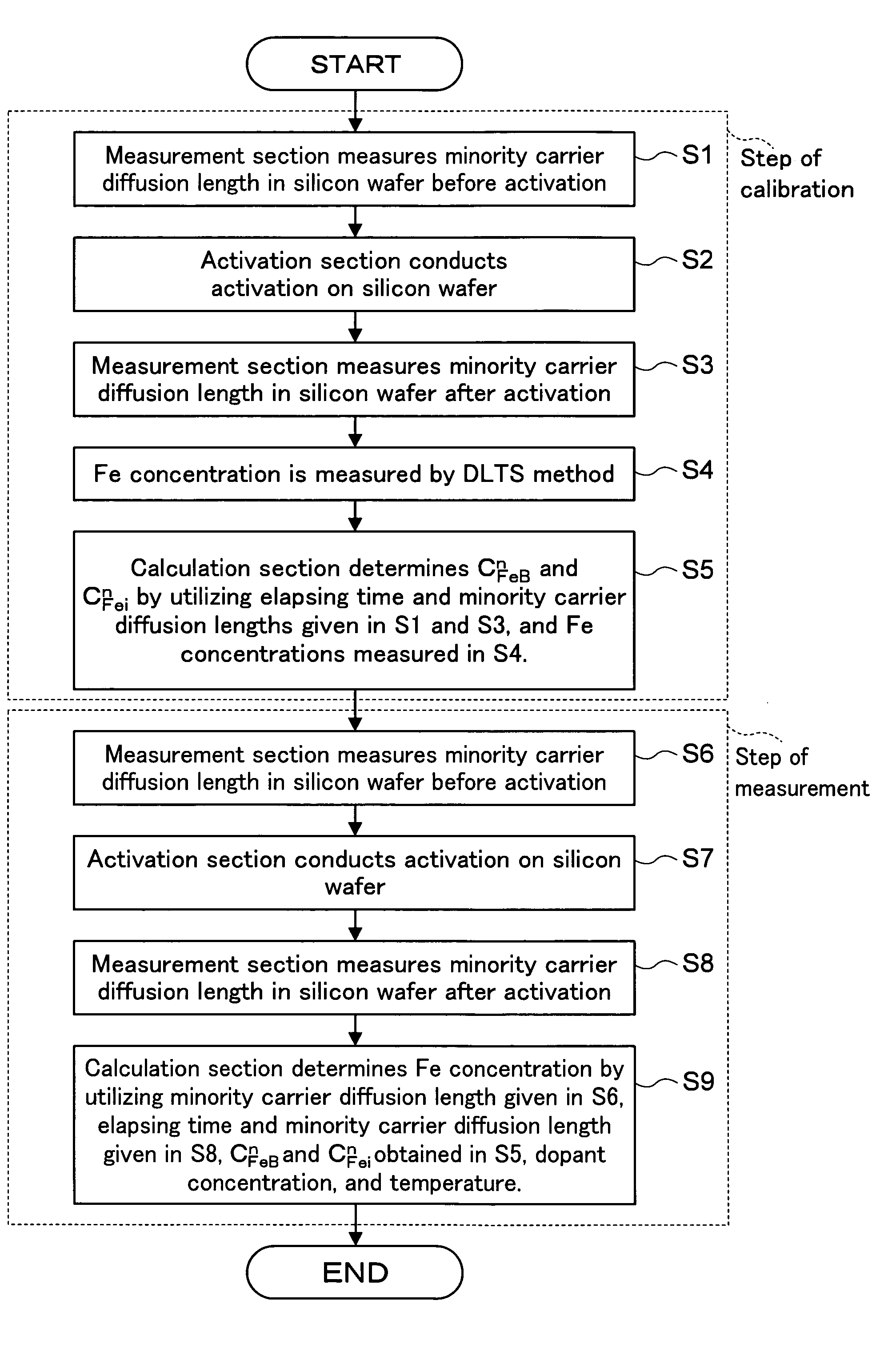

Method for measuring impurity metal concentration

ActiveUS7141992B2Accurate acquisitionAccurate measurementSemiconductor/solid-state device testing/measurementDigital computer detailsDiffusionMetal impurities

There is provided a method for calculating a more accurate metal impurity concentration contained in a silicon wafer by correcting measured values with a calibration based on a dependent relationship of the minority carrier diffusion length with a period of time elapsing from the activation to the actual measurement, an electric resistivity, and a temperature if there is such a relationship, in the measurement of the metal impurity concentration by utilizing the surface photovoltage. In the calibration step, such dependent relationship may be obtained by utilizing the metal impurity concentration measured by methods of different principles and actually measured values are corrected in light of the dependent relationship in the measuring step such that the metal impurity concentration is measured more accurately.

Owner:SUMCO TECHXIV

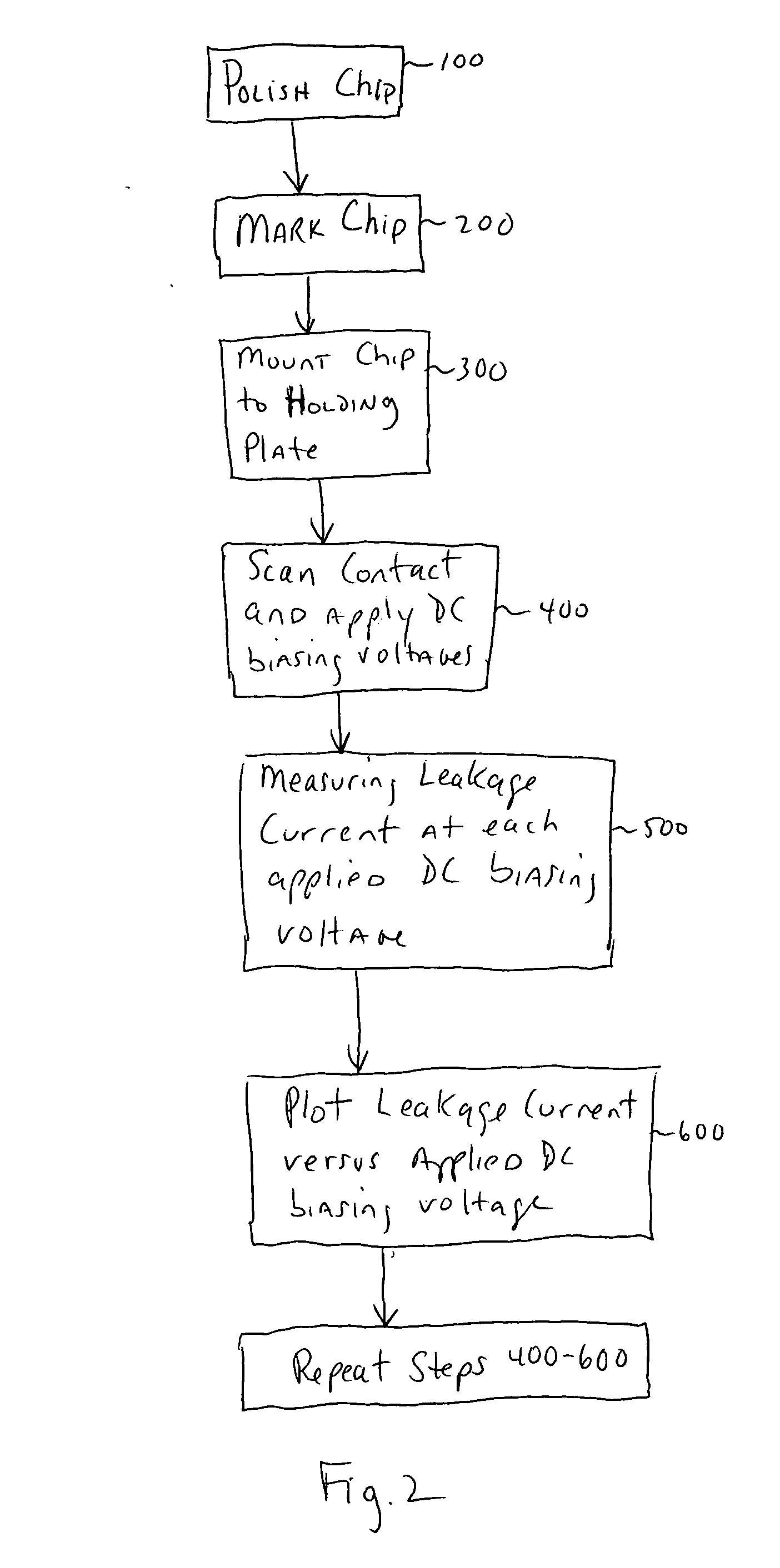

Method using conductive atomic force microscopy to measure contact leakage current

InactiveUS20050127926A1NanotechSemiconductor/solid-state device testing/measurementEngineeringSemiconductor

A method for measuring current leakage of a contact of a semiconductor device formed on or in a substrate, includes scanning the contact with a probe of a conductive atomic force microscope; applying a DC voltage between the substrate and a conductive tip of the probe; and measuring a value of a current passing through the contact to the substrate, in response to the applied DC voltage.

Owner:TAIWAN SEMICON MFG CO LTD

System and methods of measuring semiconductor sheet resistivity and junction leakage current

InactiveUS7714596B2Improve testMeasure directlyResistance/reactance/impedenceSemiconductor characterisationElectrical resistance and conductanceJunction leakage

Sheet resistance, junction leakage and contact conductivity of a semiconductor layer, associated with an ultra-shallow junction layer or metal film are measured by contacting the surface with a plurality of probes. The probes can be used, in conjunction with a four-point probe system, to determine sheet resistivity. Junction leakage through an ultra-shallow junction is determined by establishing a reverse bias across the junction set at a predetermined voltage value, measuring through a first probe a total junction current conduction value, measuring through second, third, and fourth probes a plurality of voltage values. The junction leakage value is then directly computed based on the sheet resistivity value, reverse bias potential, wafer radius, and the measured voltage values. Contact conductivity between a metal film and semiconductor layer can be similarly directly computed.

Owner:FOUR DIMENSIONS

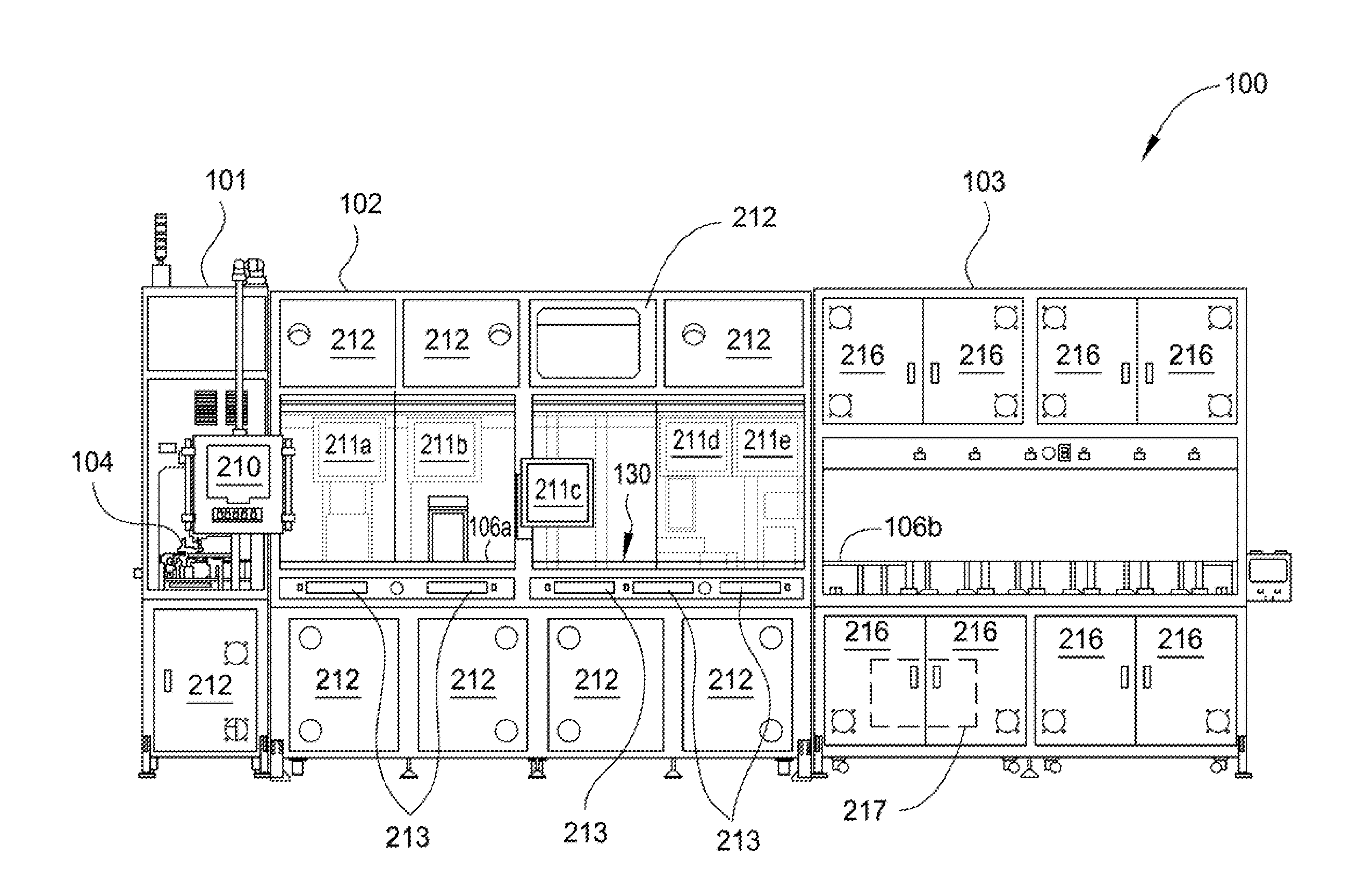

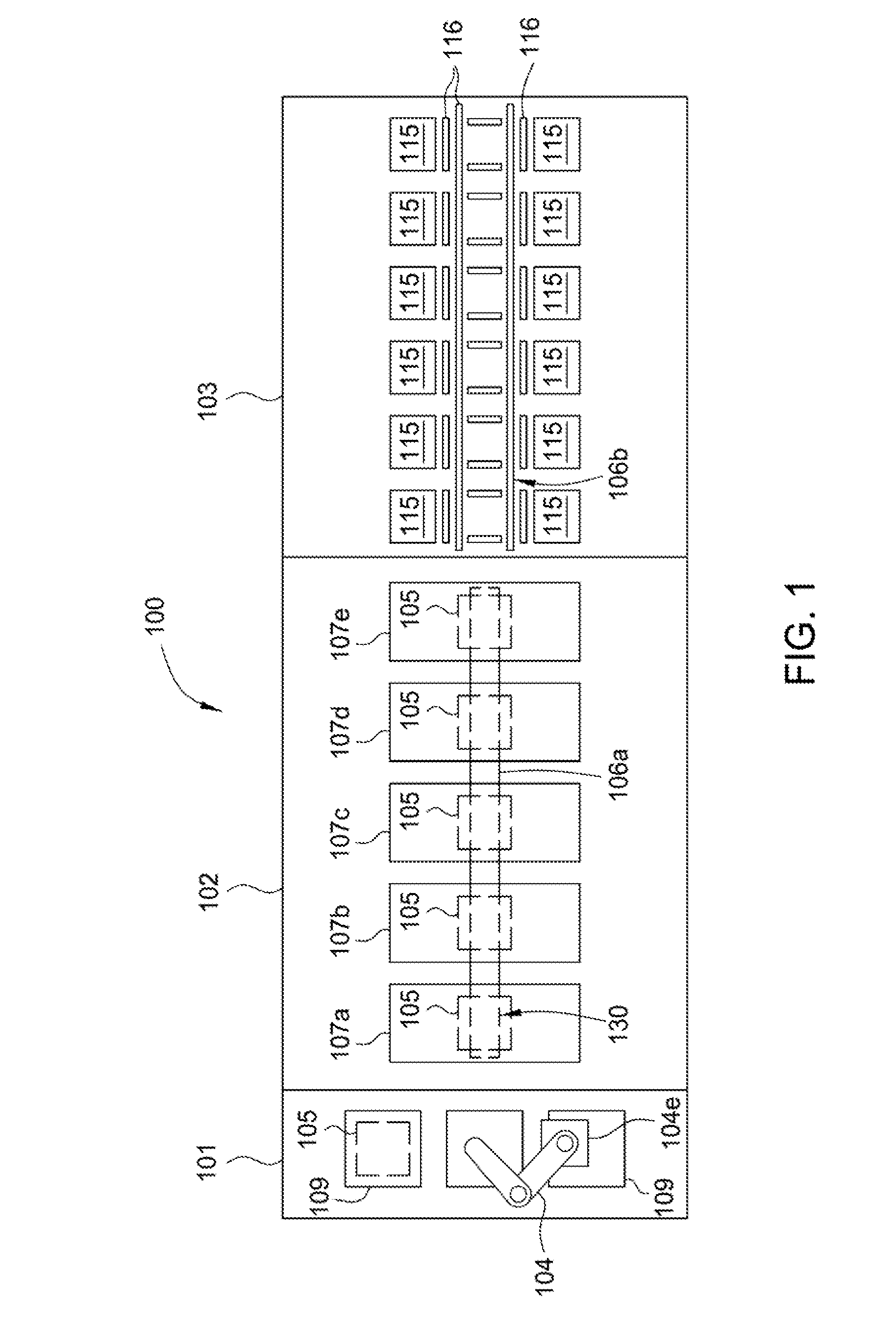

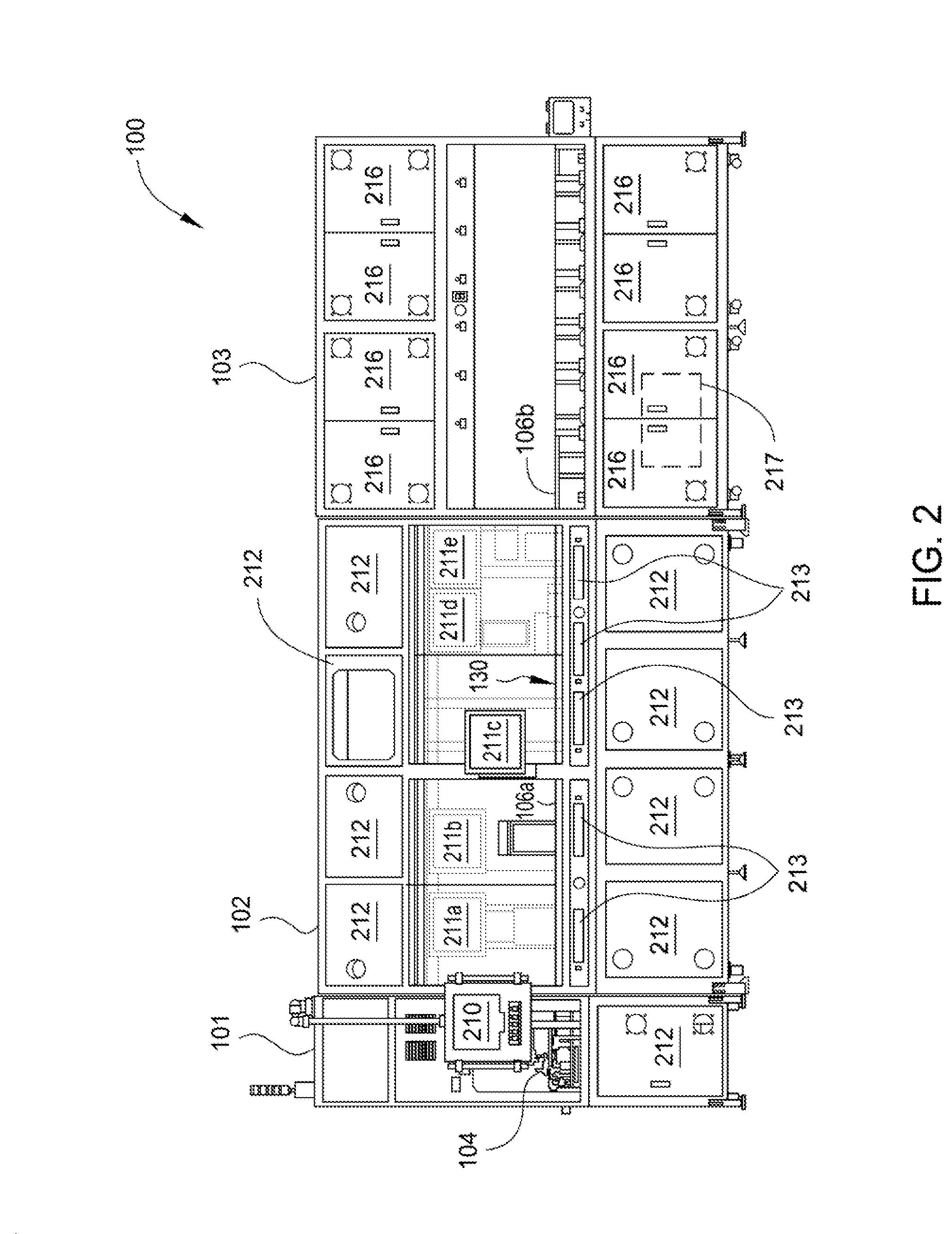

Linear inspection system

ActiveUS20150377796A1Photovoltaic monitoringSemiconductor/solid-state device testing/measurementMetrologyPhotoluminescence

Embodiments of the disclosure generally relate to comprehensive, expandable substrate inspection systems. The inspection systems include multiple metrology units adapted to inspect, detect, or measure one or more characteristics of a substrate, including thickness, resistivity, saw marks, geometry, stains, chips, micro cracks, crystal fraction, and photoluminescence. The inspection systems may be utilized to identify defects on substrates and estimate solar cell efficiency of a solar cell produced with the substrate, prior to processing a substrate into a solar cell. Substrates may be transferred through the inspection system between metrology units on a track or conveyor, and then sorted based upon inspection data.

Owner:APPLIED MATERIALS INC

Non-contact method and apparatus for measurement of leakage current of p-n junctions in IC product wafers

InactiveUS7642772B1Improve accuracy and versatilitySemiconductor characterisationContactless circuit testingCapacitanceFiber

Owner:APPLEJACK 199

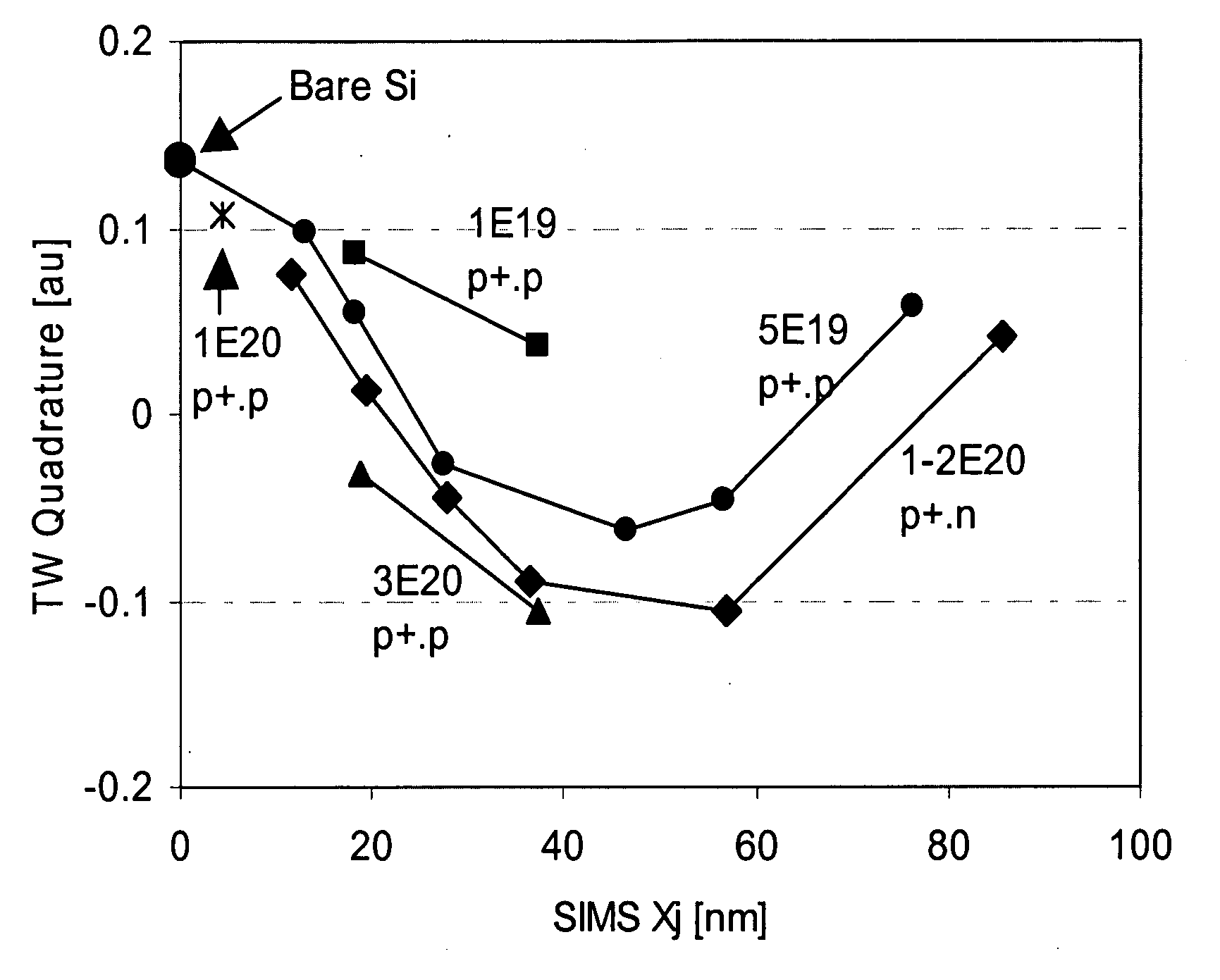

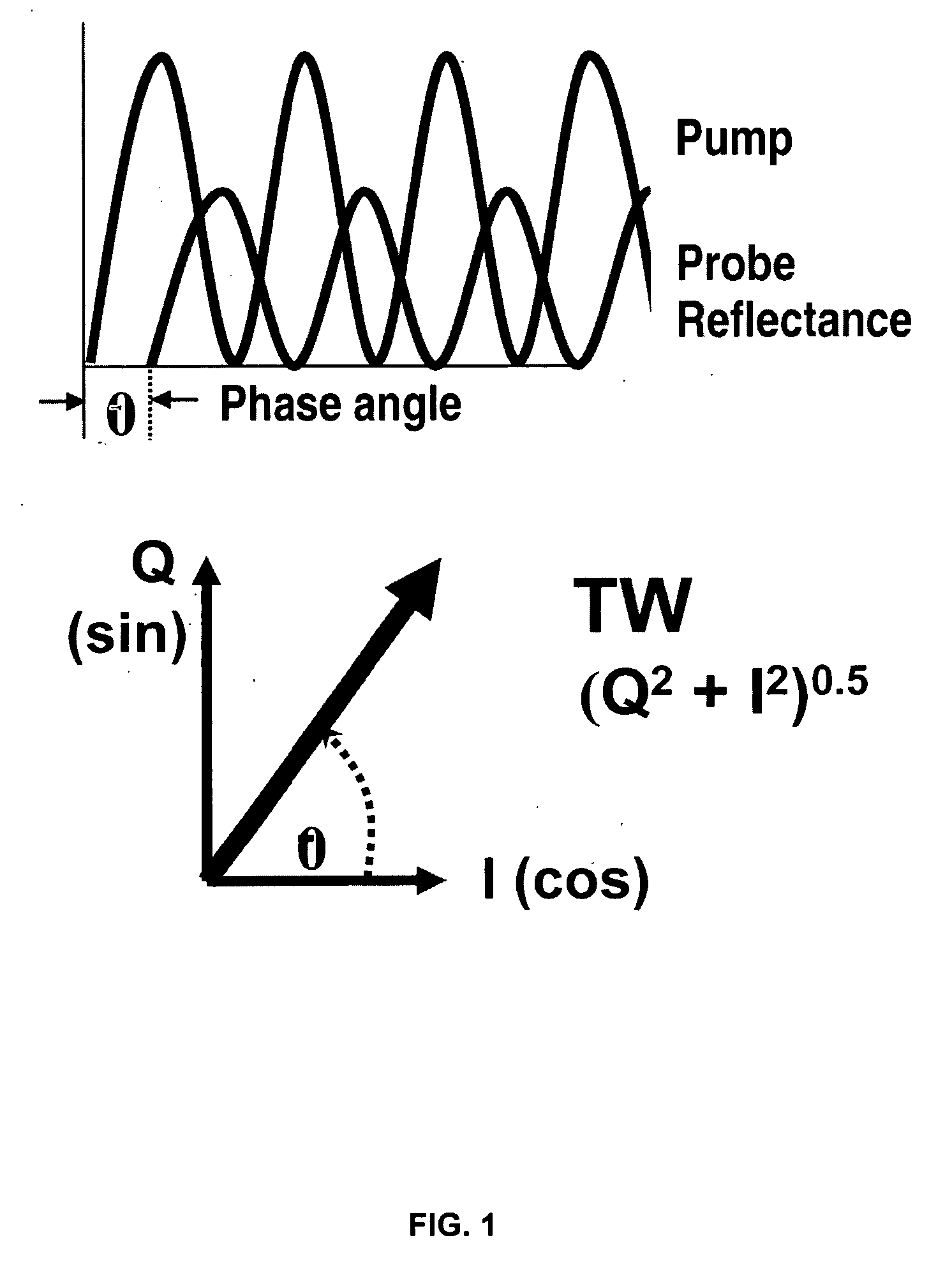

Method for measuring peak carrier concentration in ultra-shallow junctions

InactiveUS20060166385A1Semiconductor/solid-state device testing/measurementElectric discharge tubesPeak valueSynchronous detection

A method is disclosed for determining peak carrier concentration in ultra shallow junctions of semiconductor samples. A region of the surface of the sample is periodically excited. The effects of the excitation are monitored by a probe beam. Synchronous detection produces in-phase (I) and quadrature (Q) signals. These signals are compared to signals obtained from calibration samples to evaluate peak carrier concentration.

Owner:THERMA WAVE INC