Patents

Literature

147 results about "Acceptance testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In engineering and its various subdisciplines, acceptance testing is a test conducted to determine if the requirements of a specification or contract are met. It may involve chemical tests, physical tests, or performance tests.

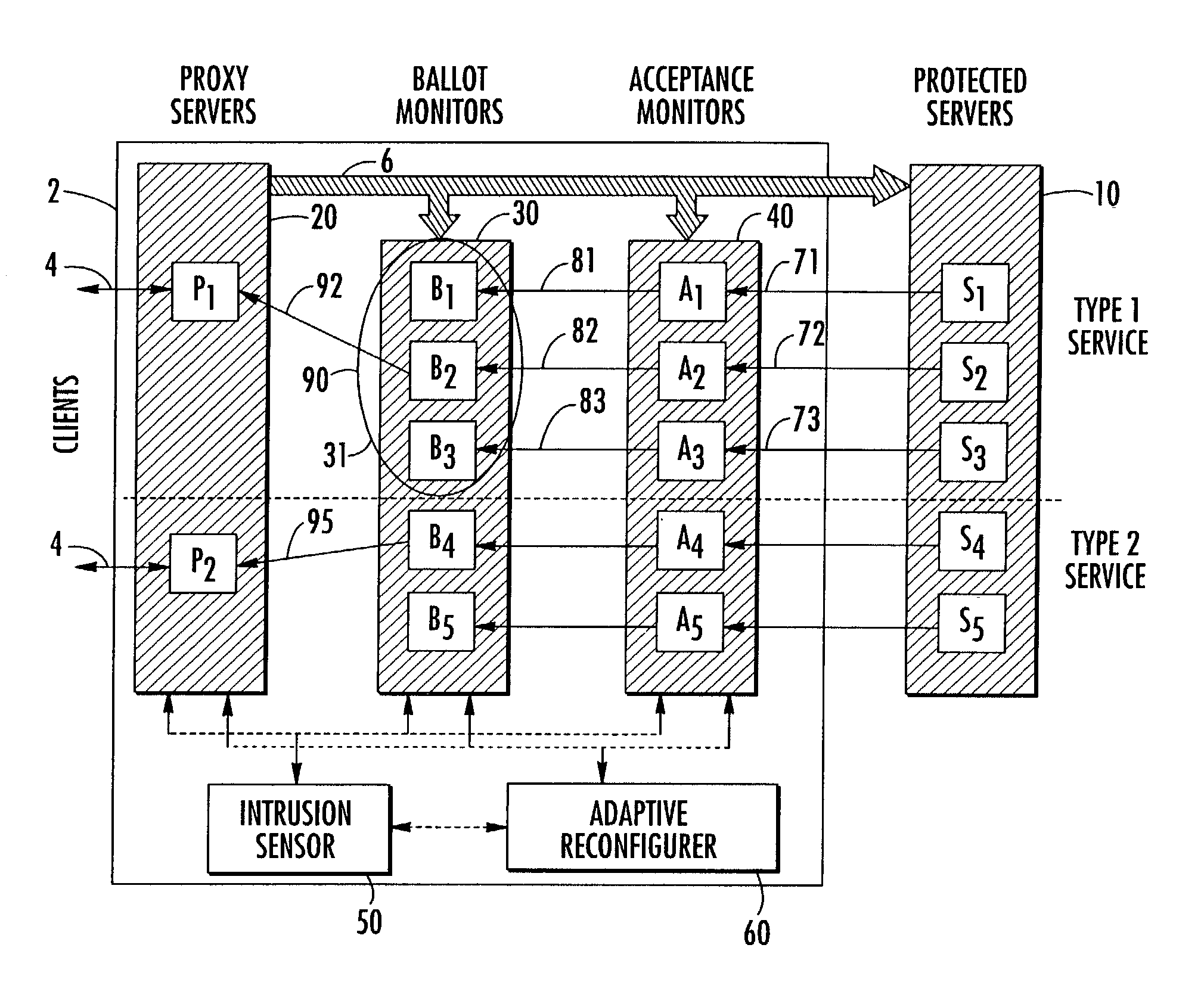

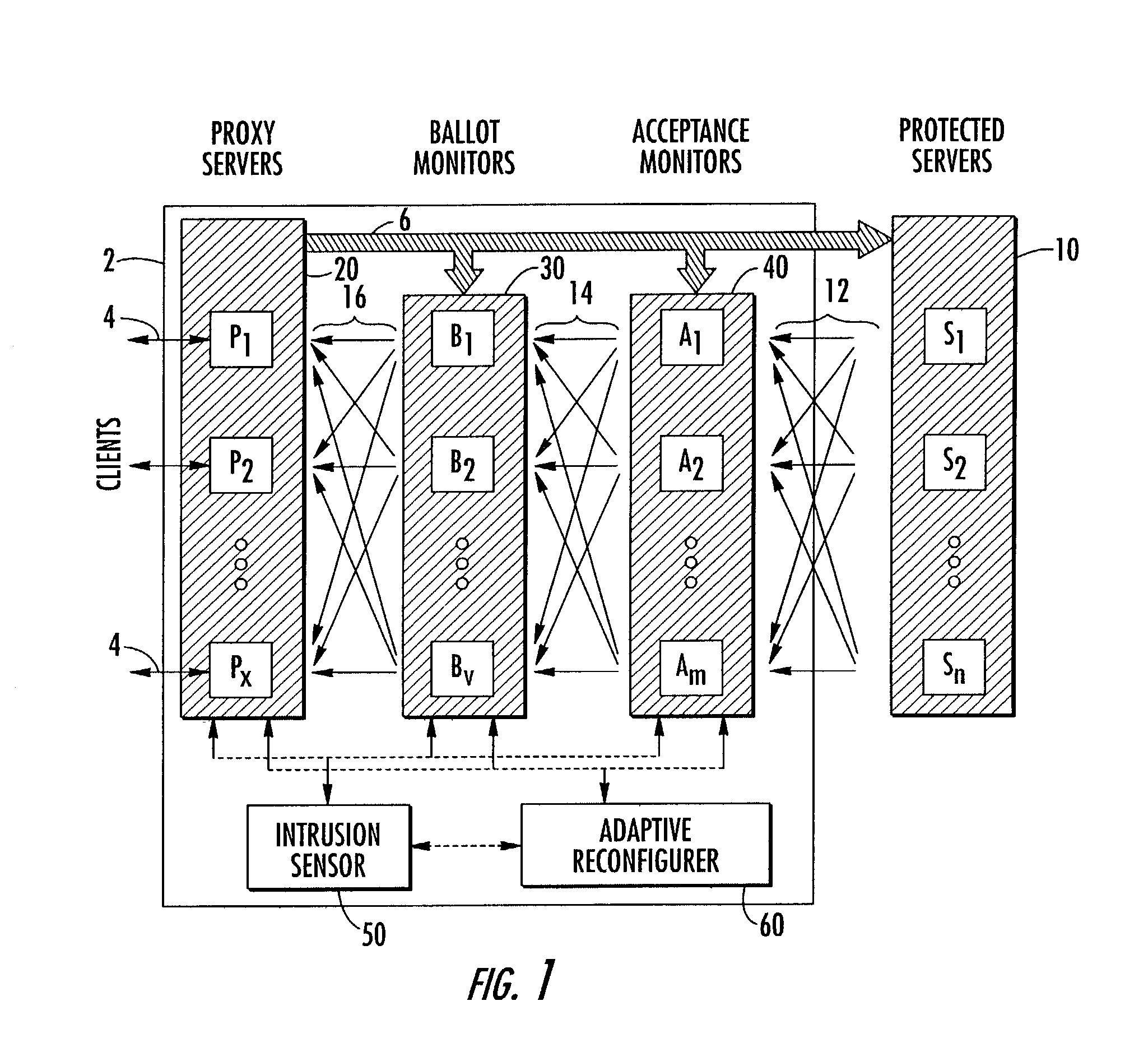

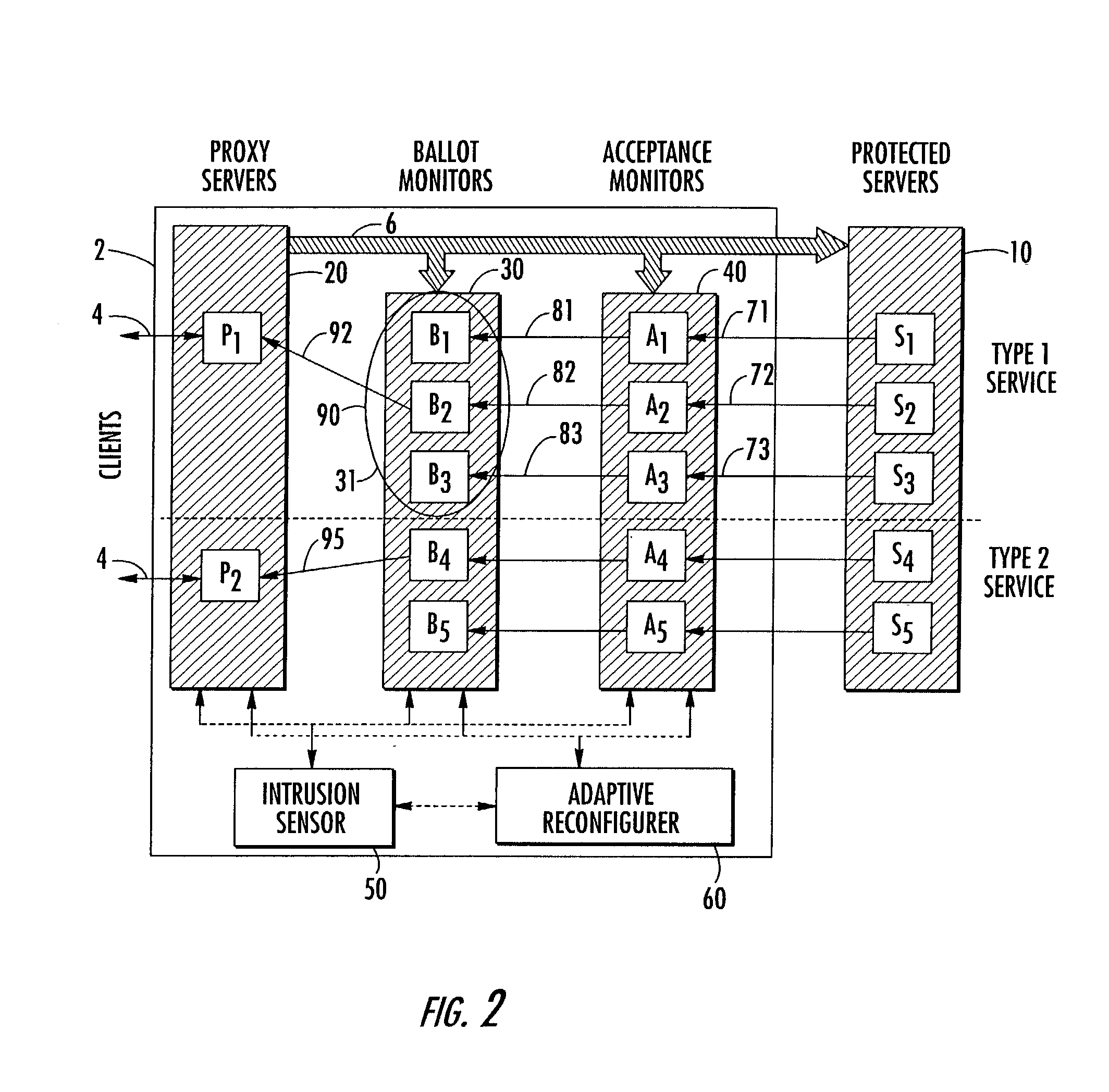

Intrusion tolerant server system

InactiveUS7076801B2Minimize impactDigital data processing detailsMultiple digital computer combinationsIntrusion toleranceClient-side

The invention relates to a reconfigurable scalable intrusion-tolerant network that is interposed between a service requesting client and a protected server to minimize the impact of intrusive events. The apparatus may include a proxy server for receiving the requests from a client and forwarding them to a protected server. Acceptance monitors receive the response from a protected server and apply one or more acceptance tests. A ballot monitor receives the result of the acceptance tests and determines a response to the client. The network may also include an intrusion sensor to detect threats to the network and a reconfigurer to alter the network forwarding scheme. Reconfiguration may include isolating network elements, creating parallel paths, implementing redundant operations, or assessing the validity of responses.

Owner:RES TRIANGLE INST

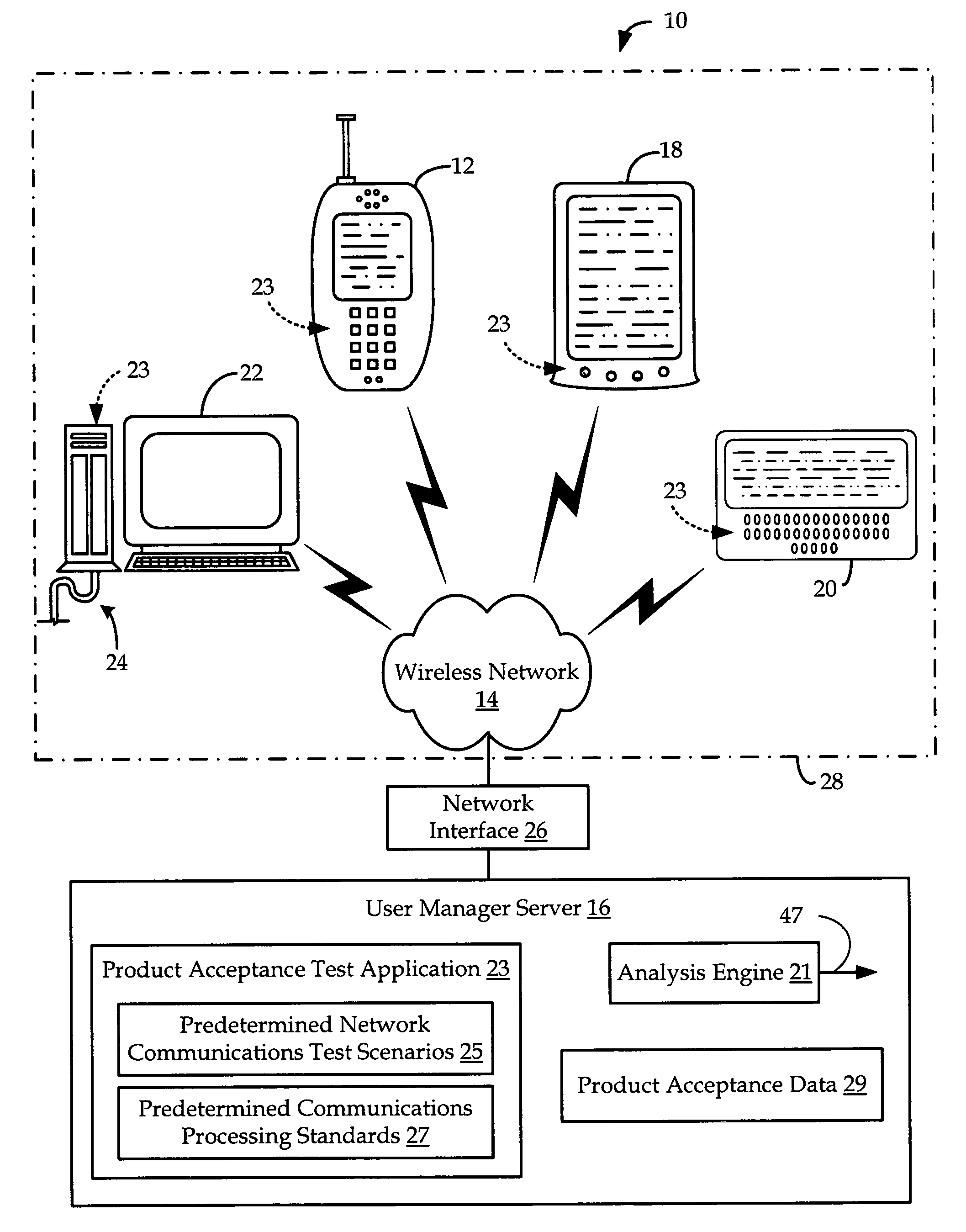

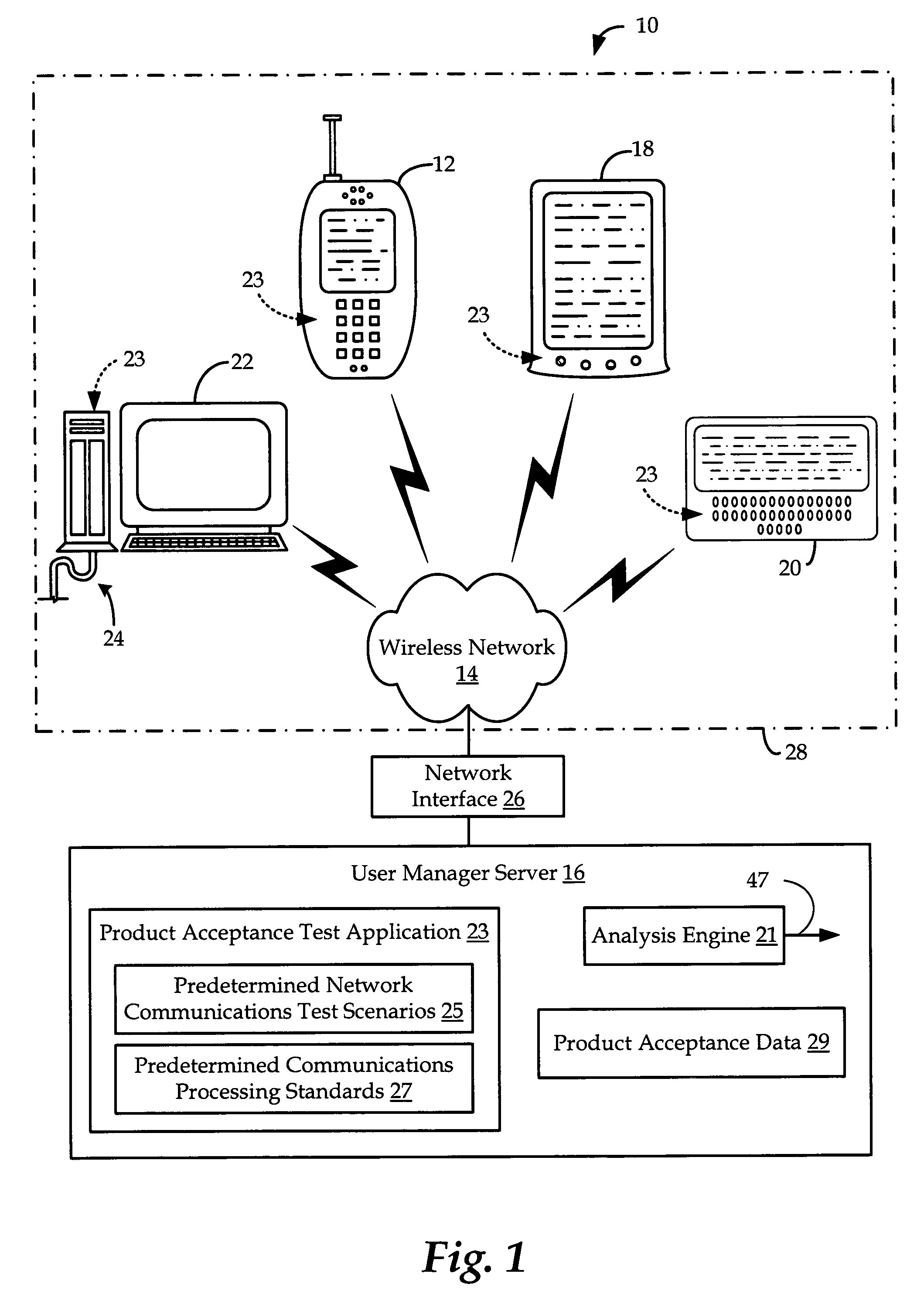

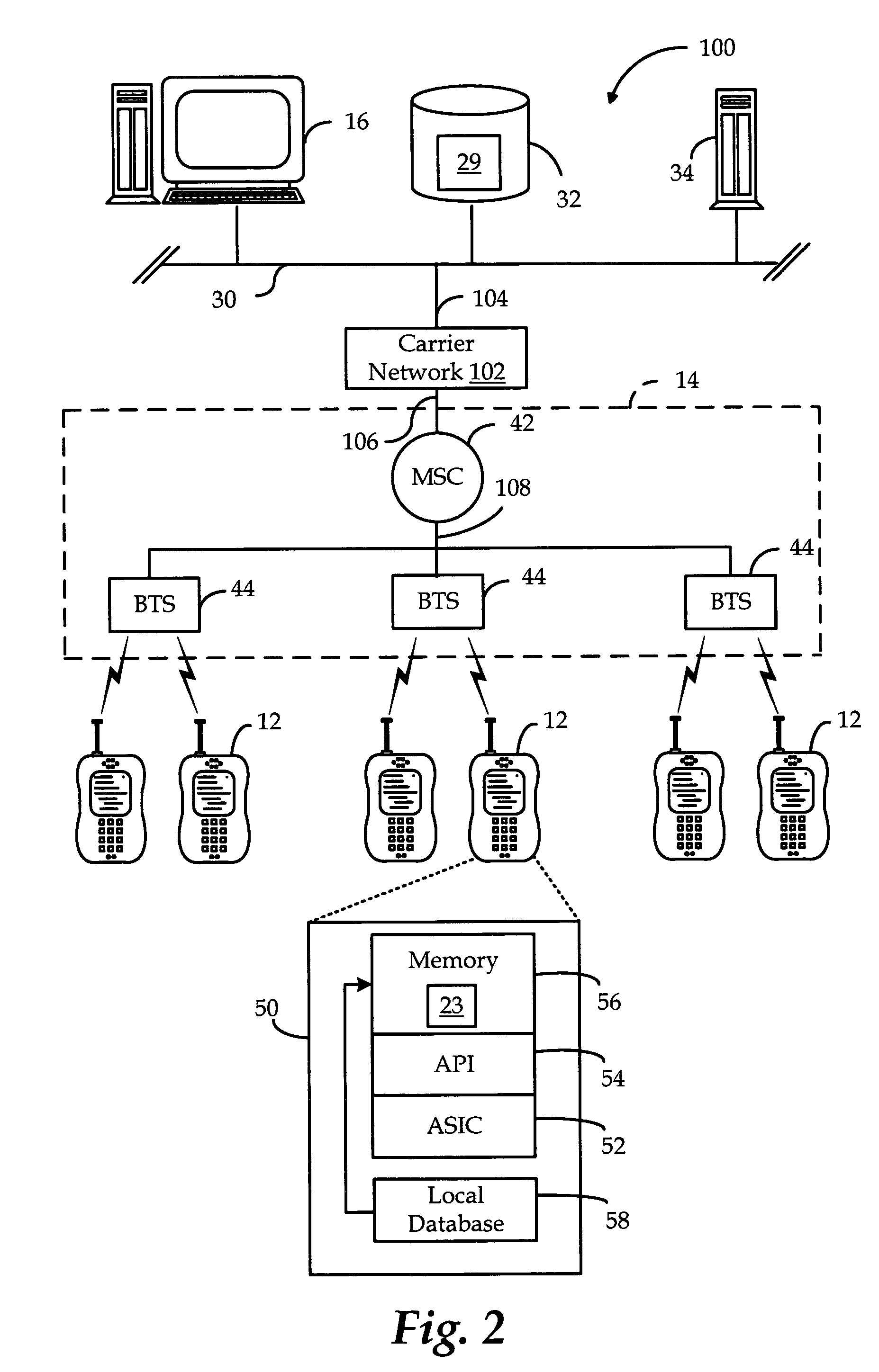

Apparatus and methods for product acceptance testing on a wireless device

InactiveUS20060205398A1Functional testingSoftware testing/debuggingAcceptance testingWireless network

Apparatus, methods, and programs for testing the communications processing ability, and determining product acceptance, of a wireless device. Embodiments include a product acceptance test application disposed on the wireless device and including simulated communications representative of actual communications with a wireless network. A communications processing engine disposed on the wireless device is operable to process the simulated communications, and thereby generates product acceptance data associated with a product acceptance decision.

Owner:QUALCOMM INC

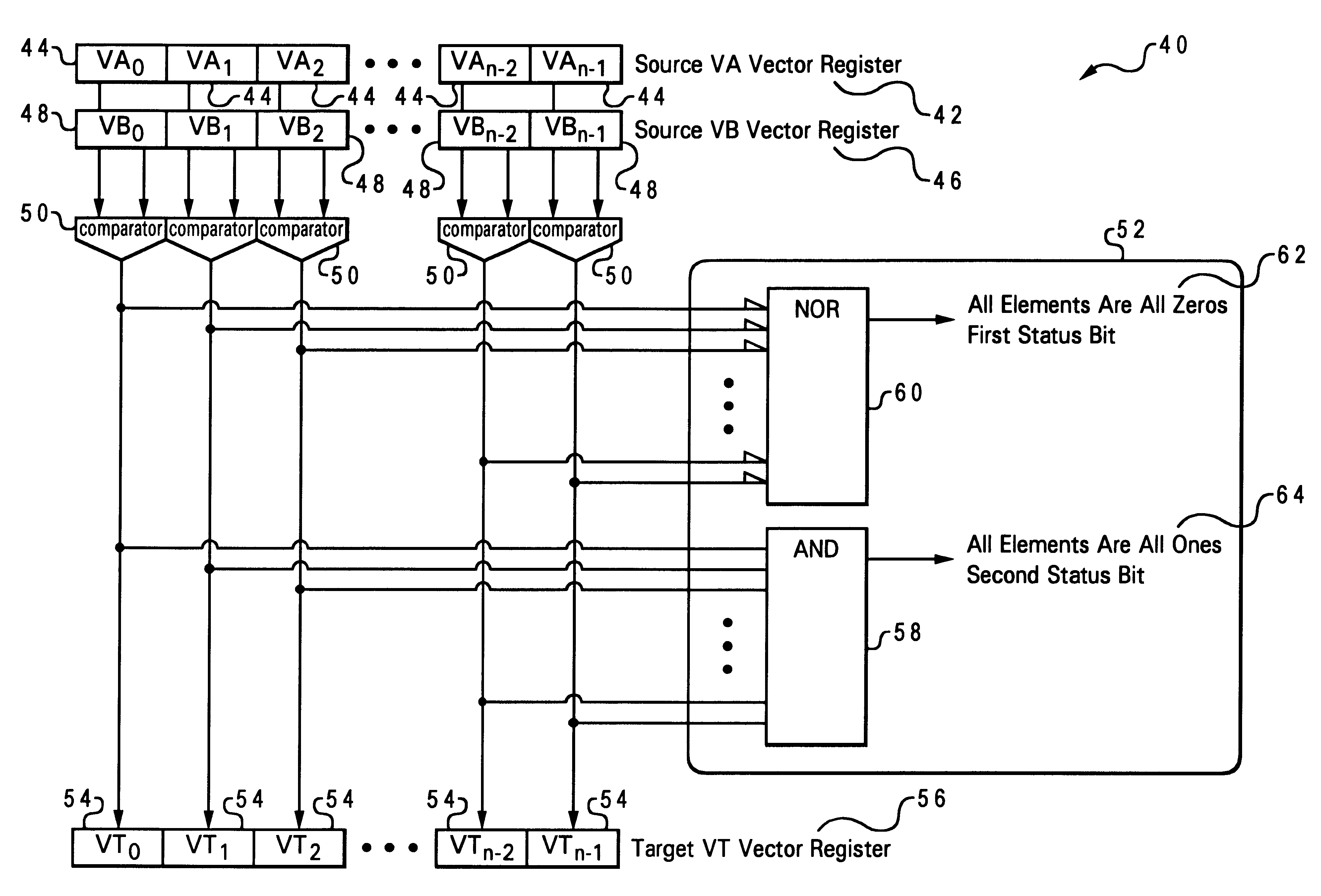

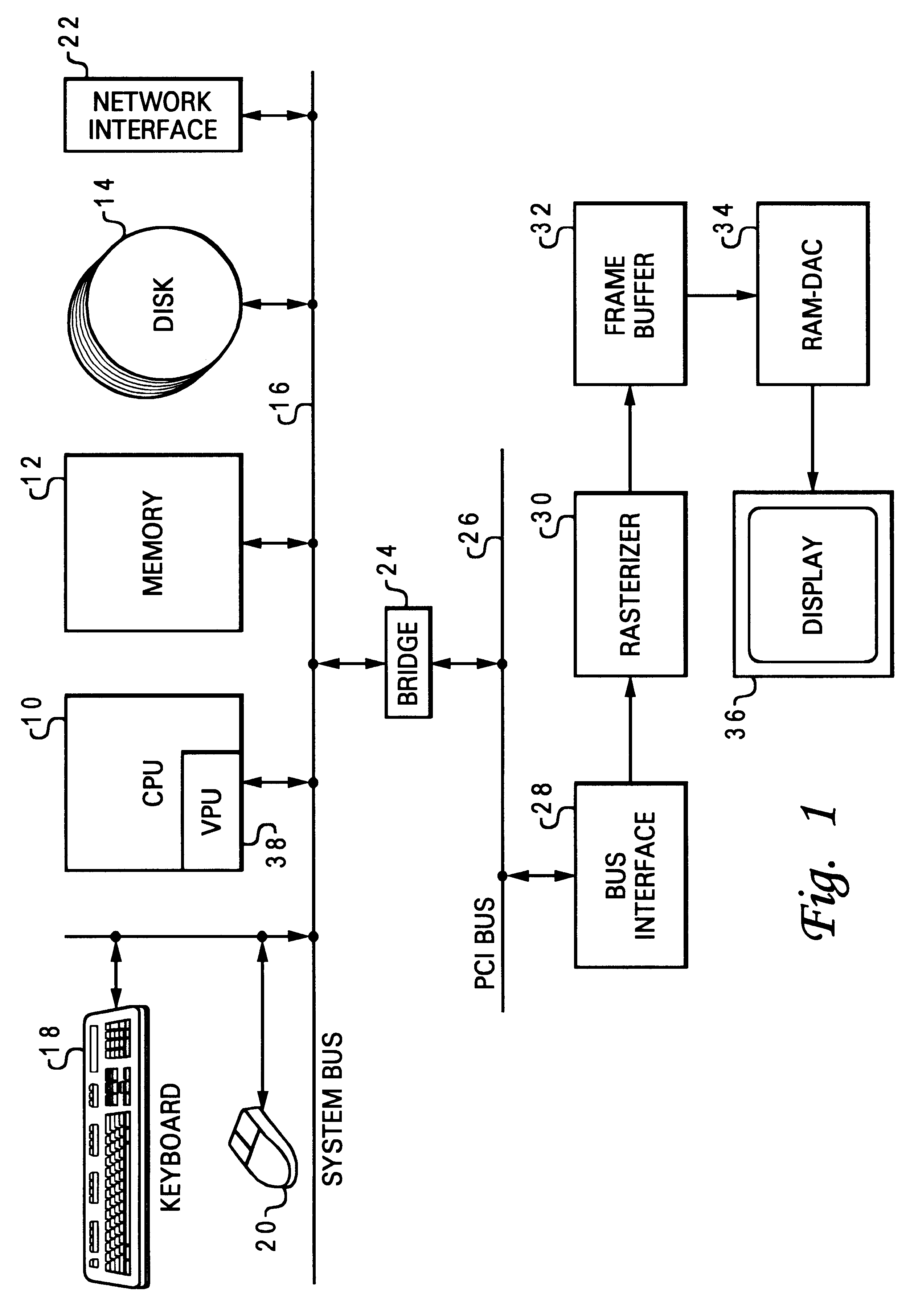

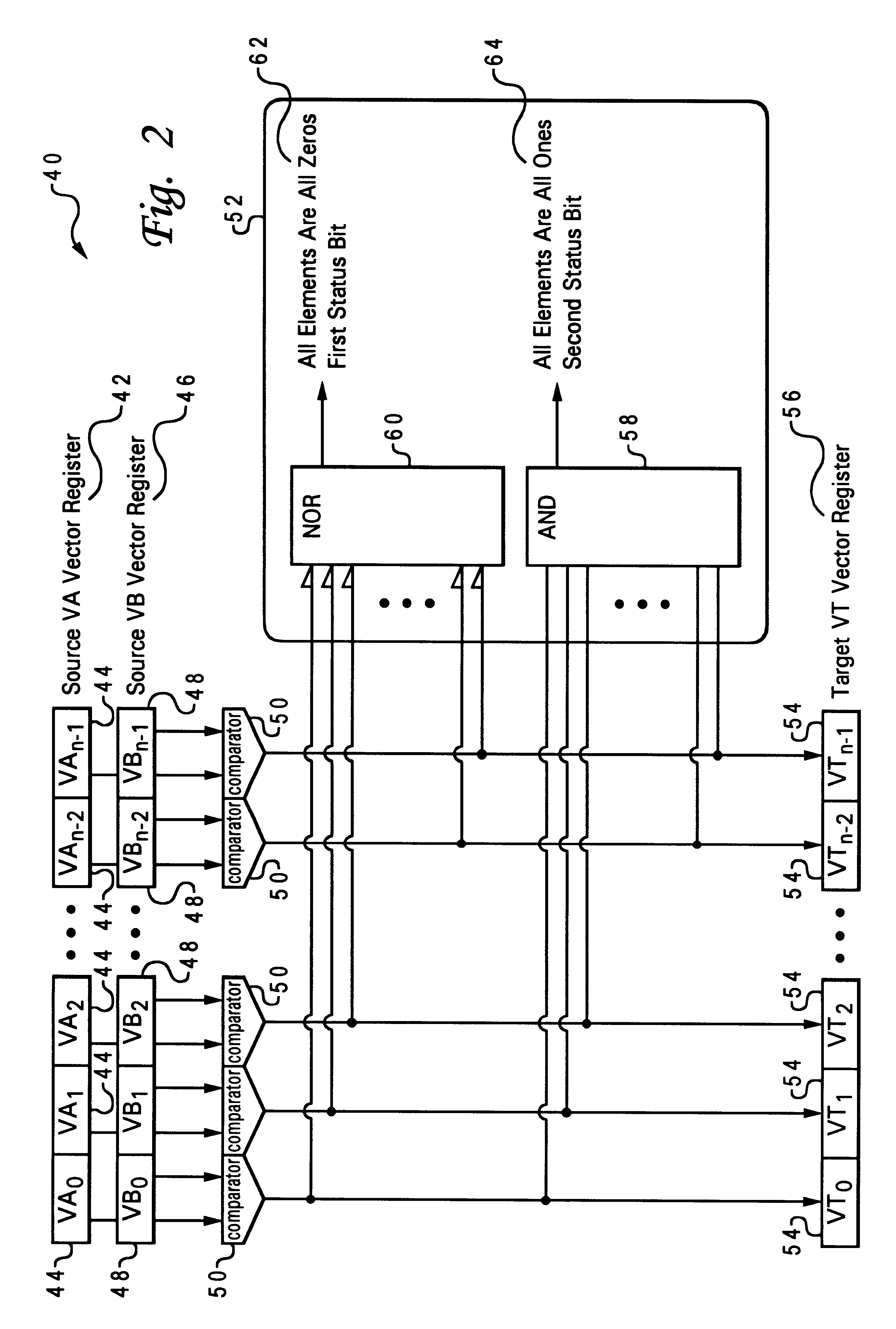

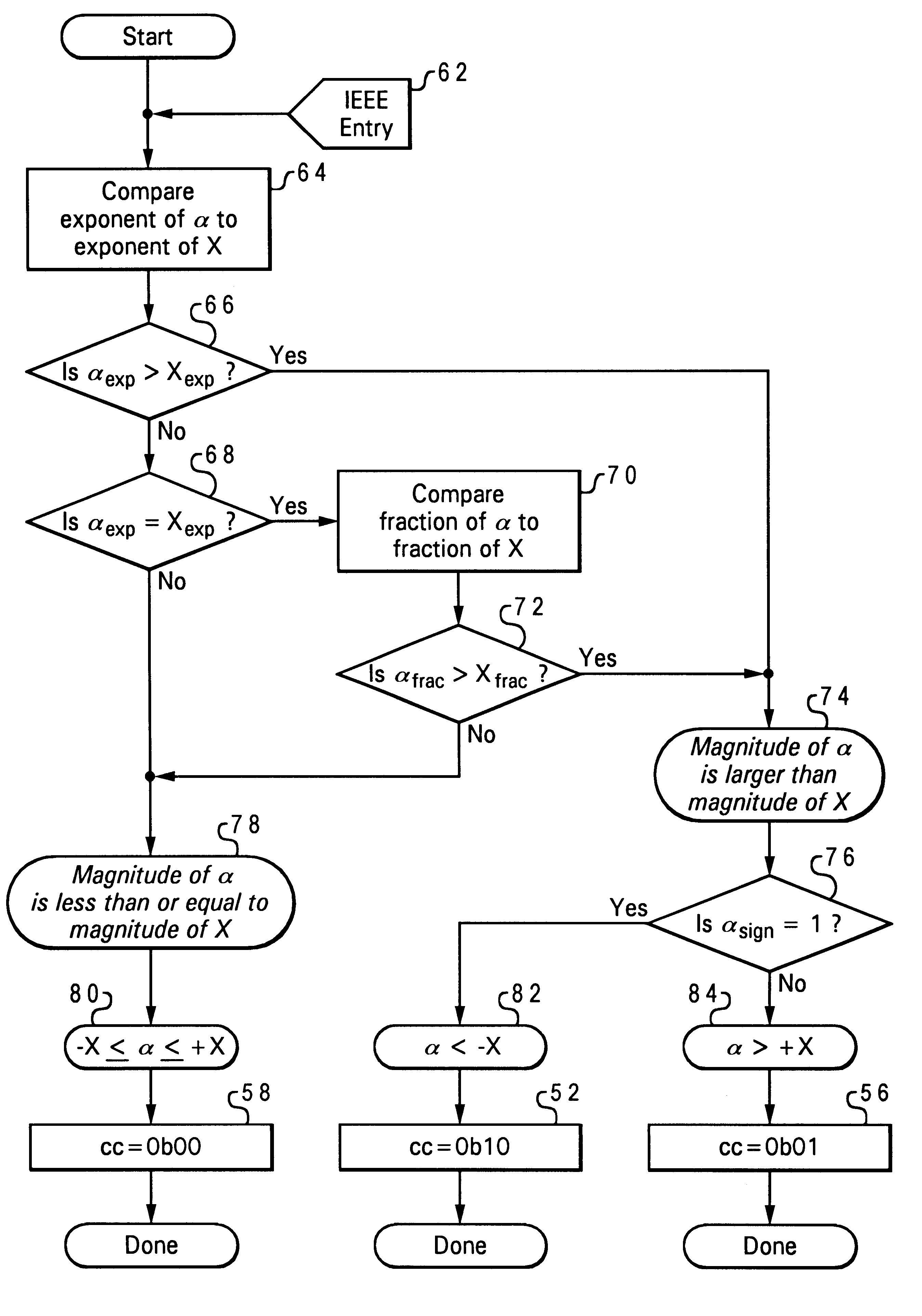

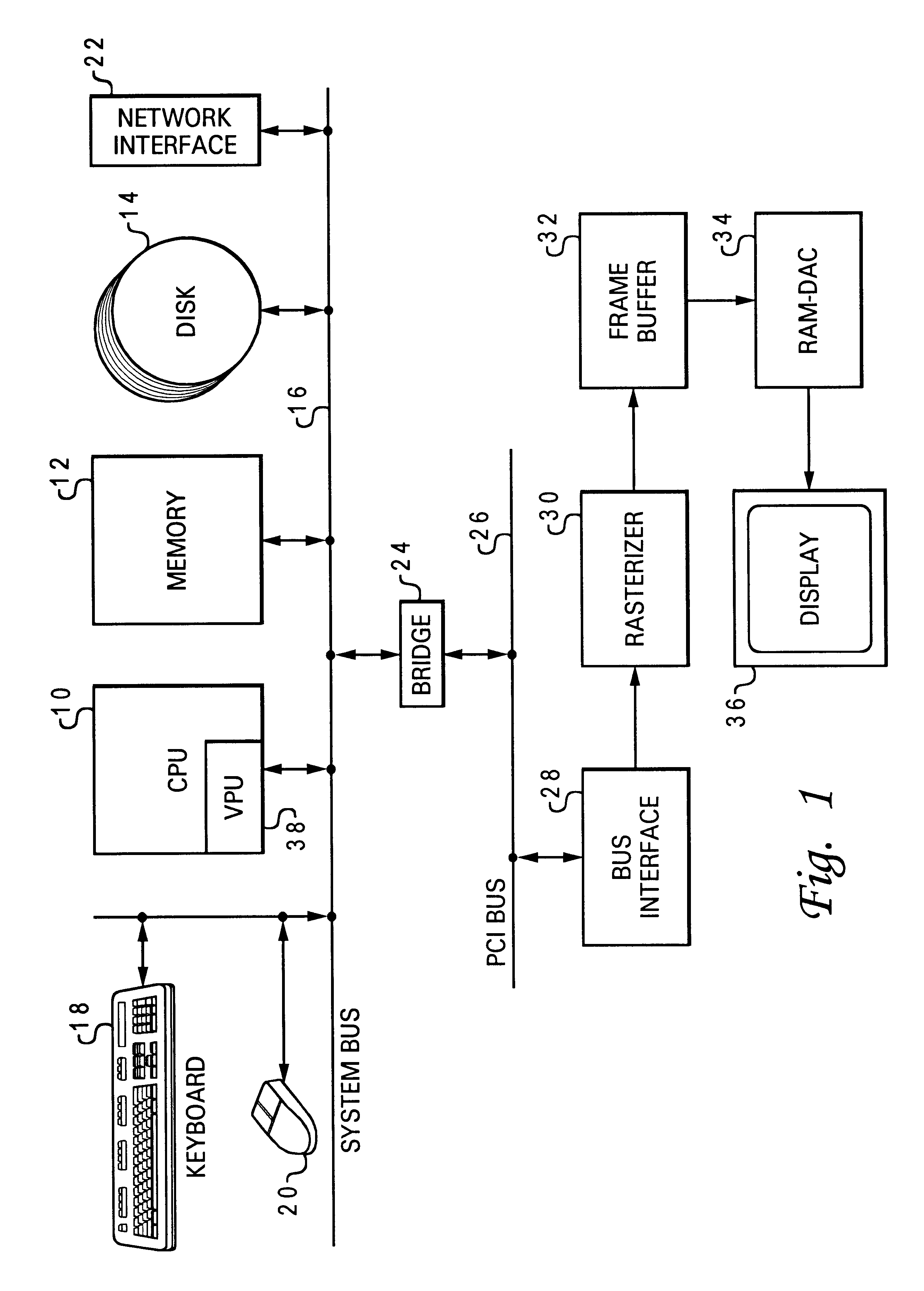

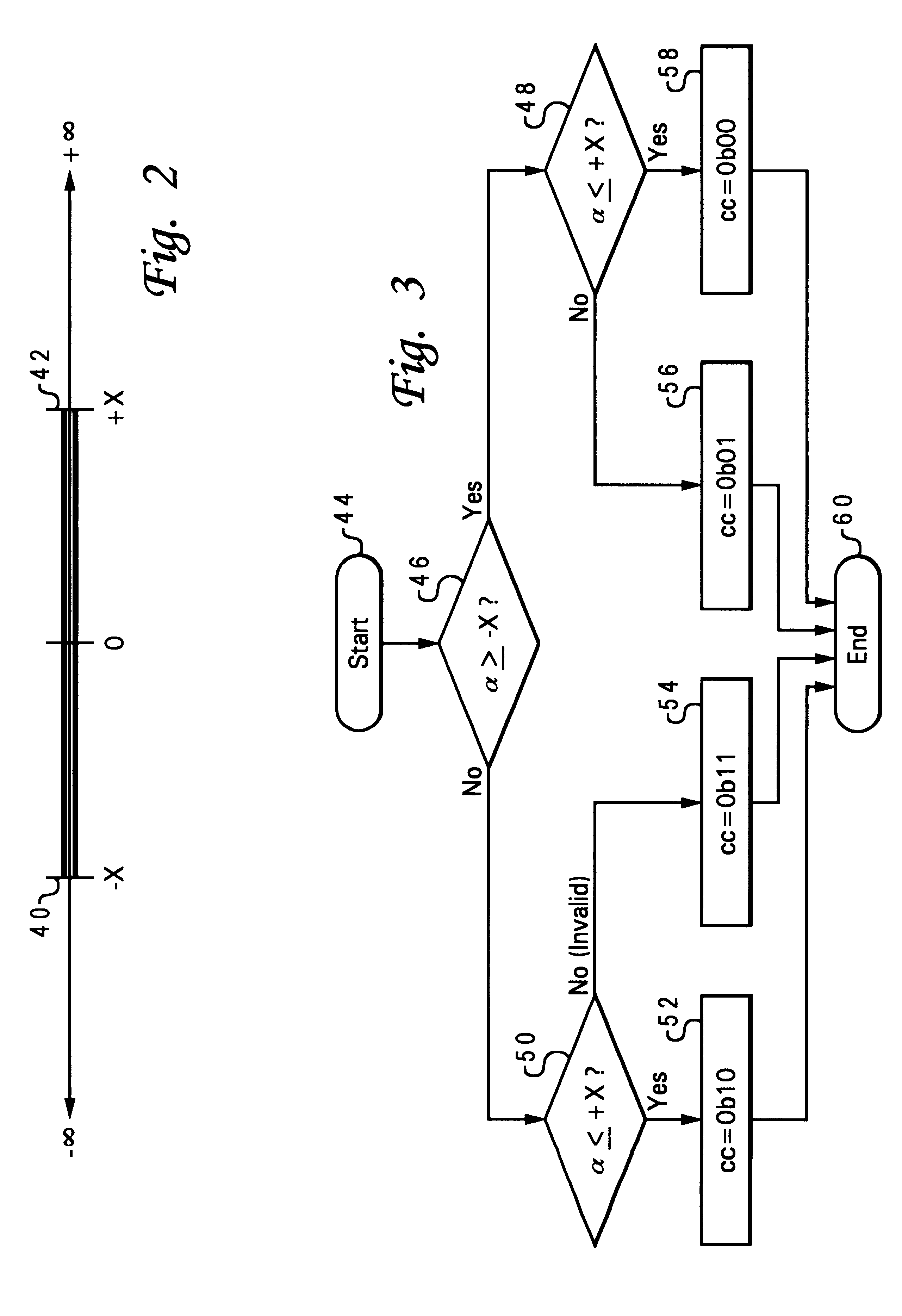

Method and system for a result code for a single-instruction multiple-data predicate compare operation

InactiveUS6282628B1Concurrent instruction executionSpecific program execution arrangementsAcceptance testingStatus register

A method and system is disclosed which summarizes the results of a classical single-instruction multiple-data SIMD predicate comparison operation, signaling whether all comparisons resulted in a false result or true result, and placing that status into a separate status register, such as the Power PC Condition Register. The method and system utilizes first and second status bits to support the signaling whether all element comparisons resulted in true or false. The first status bit is set when all element comparisons resulted in false (i.e. a NOR of all predicate comparison results), and the second status bit is set when all element comparisons resulted in true (i.e. an AND of all predicate comparison results). This capability allows control flow using conditional branching on the event when all comparison results are false or when all comparison results are true. The method and system of the present invention is useful in 3-D graphics such as lighting and trivial acceptance testing where executing down both paths of a branch and then selecting the correct result is not tolerable.

Owner:IBM CORP +2

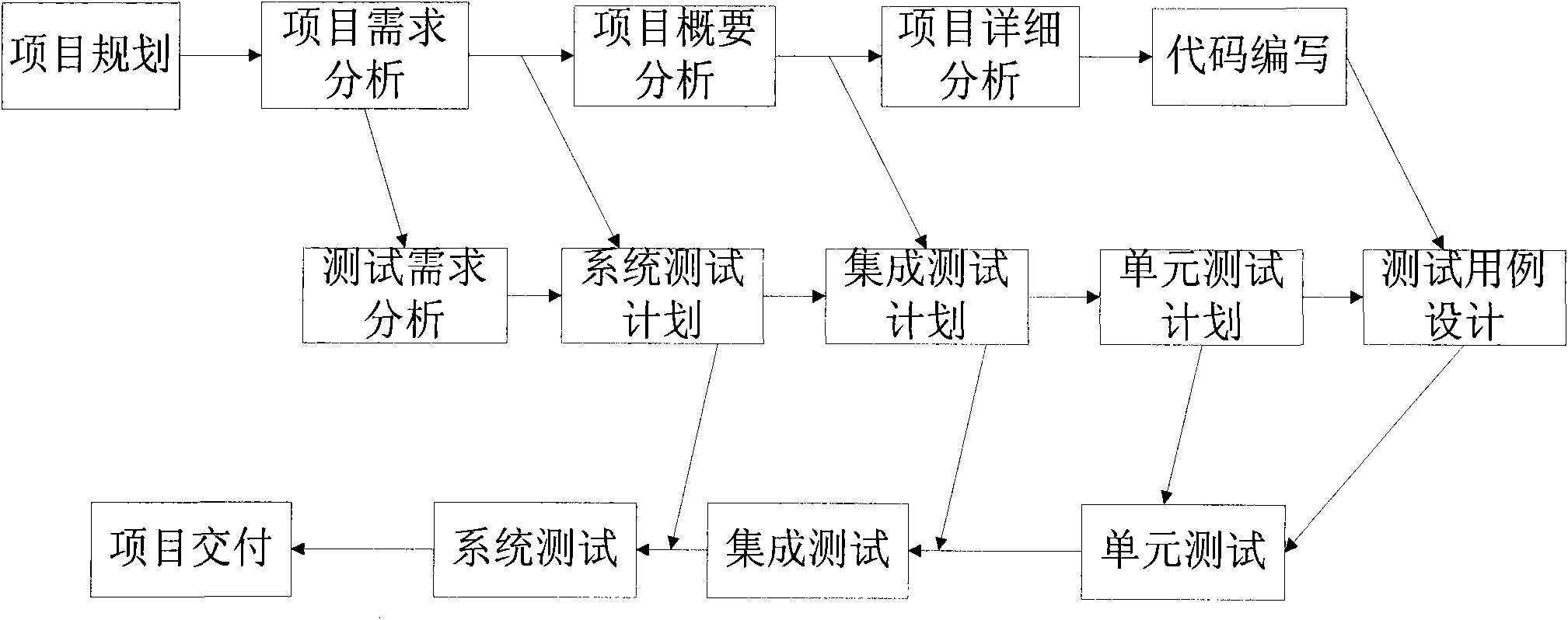

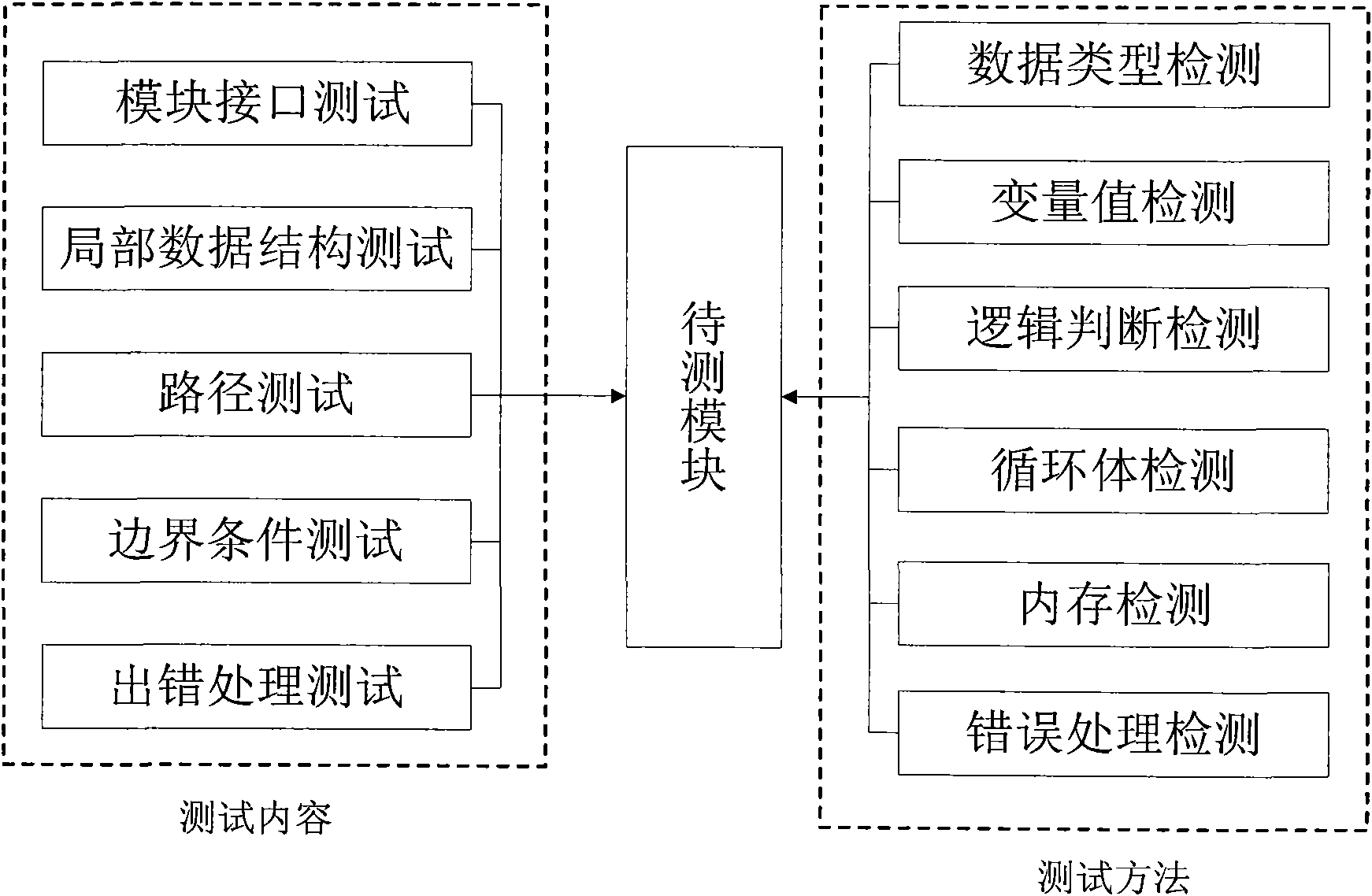

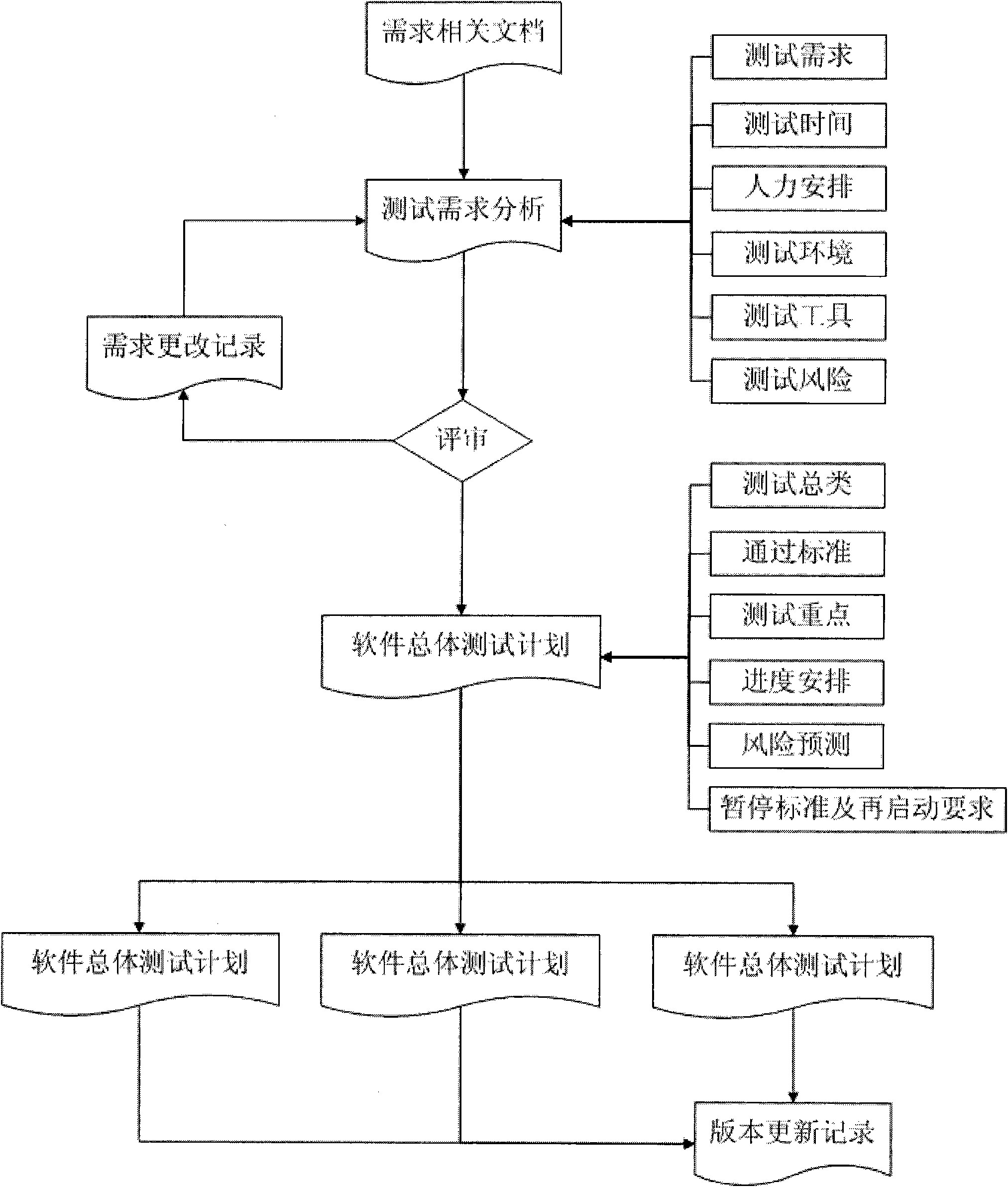

Construction method of airborne computer software testing general system

InactiveCN101847123AShorten test timeImprove normativeSoftware testing/debuggingSoftware systemOnboard computer

The invention relates to a construction method of an airborne computer software testing general system, which comprises five steps: 1, writing a testing plan file and establishing a testing system; 2, carrying out a unit test (static) during code development; 3, carrying out a unit / integration test (dynamic) by an actual operation function module; 4, carrying out a system test after the unit / integration test; and 5, carrying out an acceptance test. The invention provides the airborne computer software testing general system which achieves the testing purpose economically and effectively via establishing a testing system collateral with the code development, and enhances the normalization and reliability of the software system, and the software testing personal can completely and efficiently deploy and execute testing work according to specific needs. The invention has practical value and broad application prospects in the technical field of the airborne computer software test.

Owner:BEIHANG UNIV

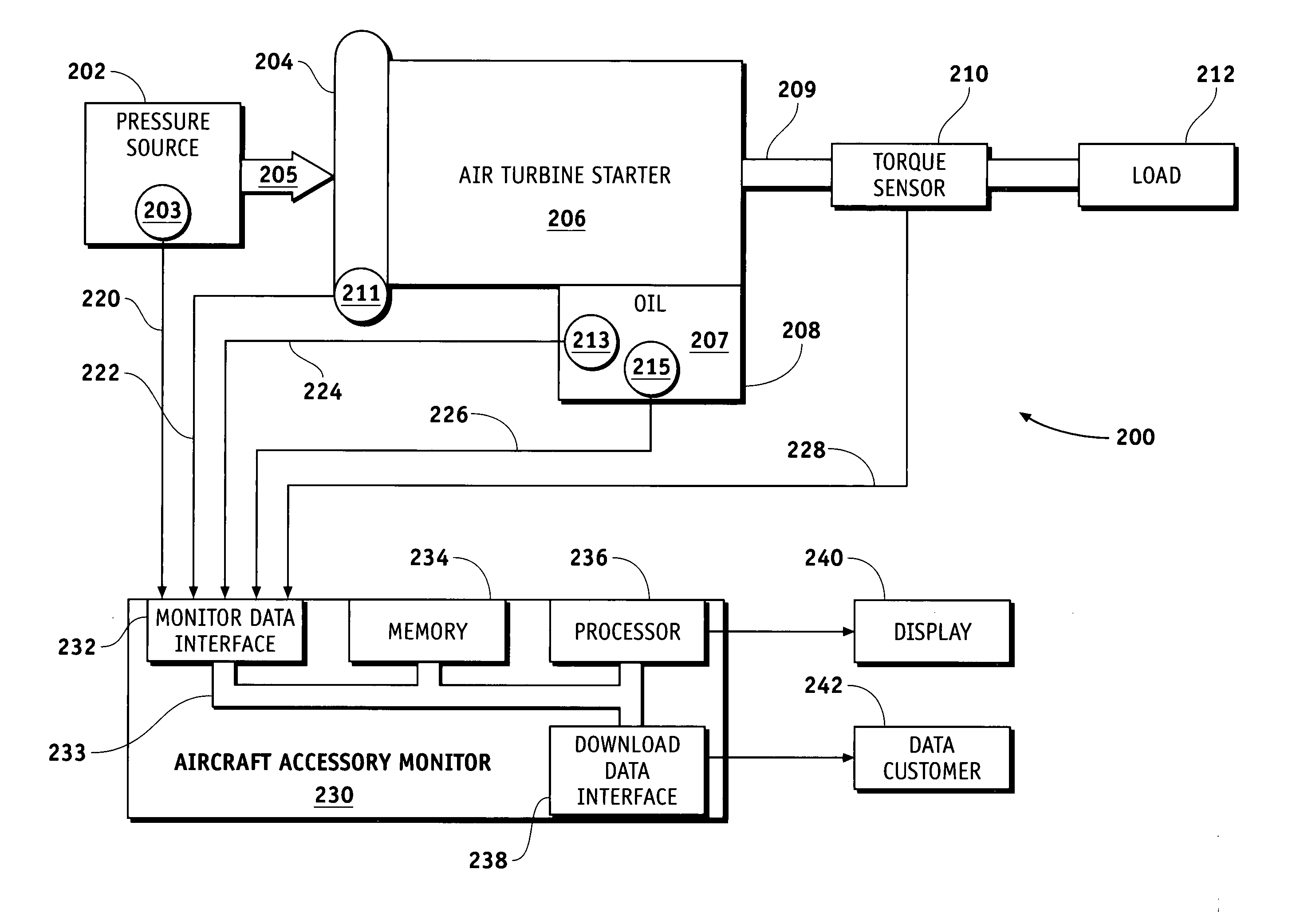

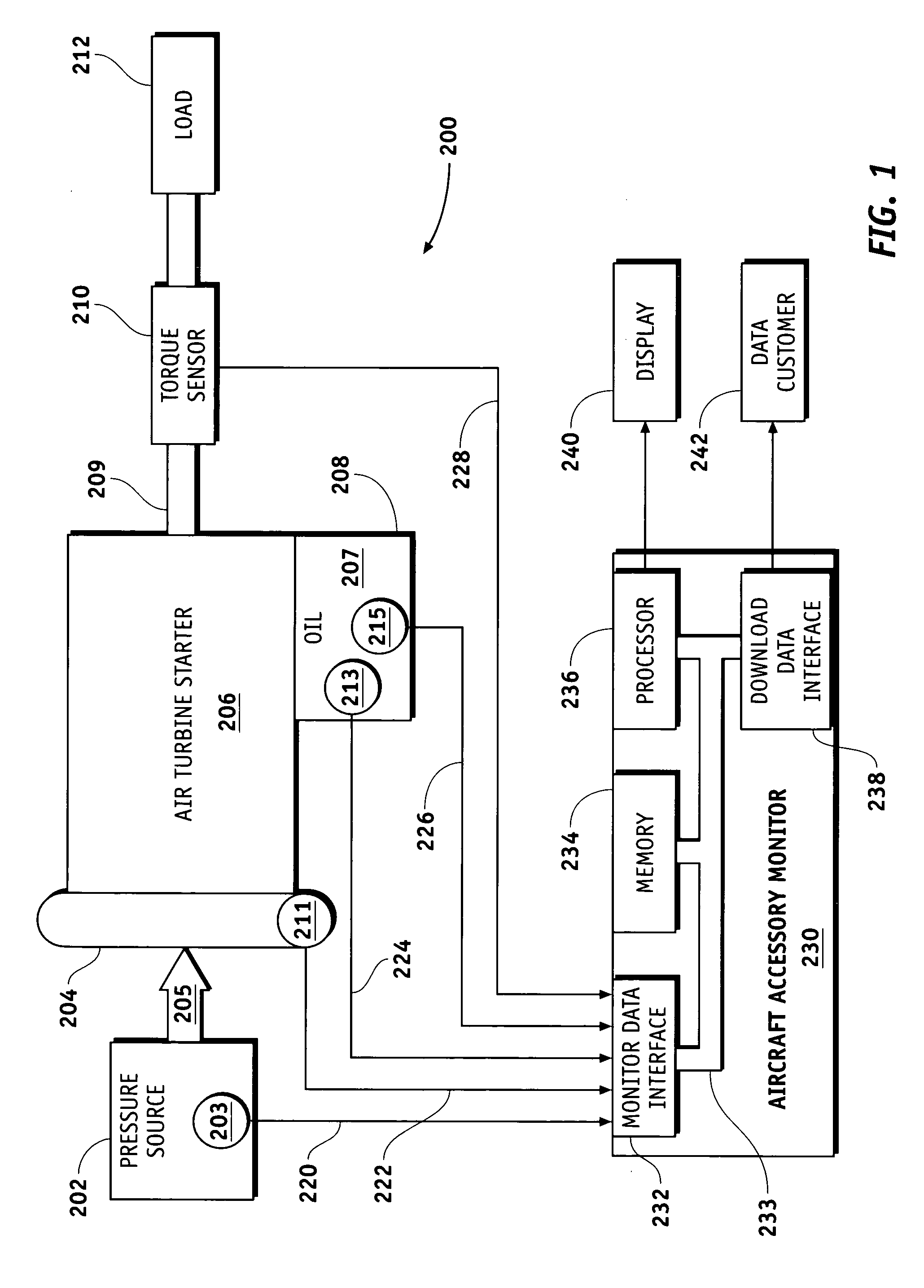

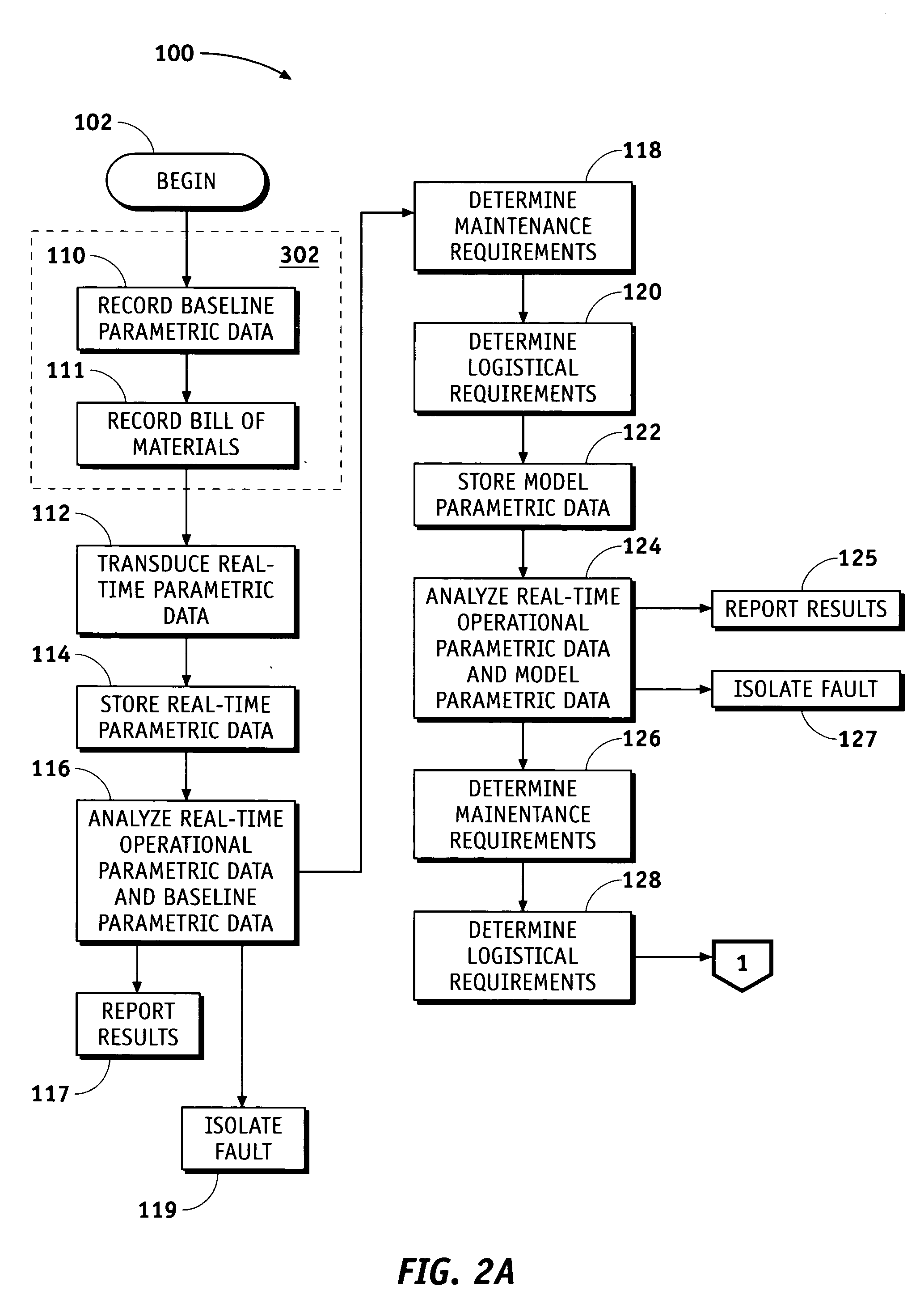

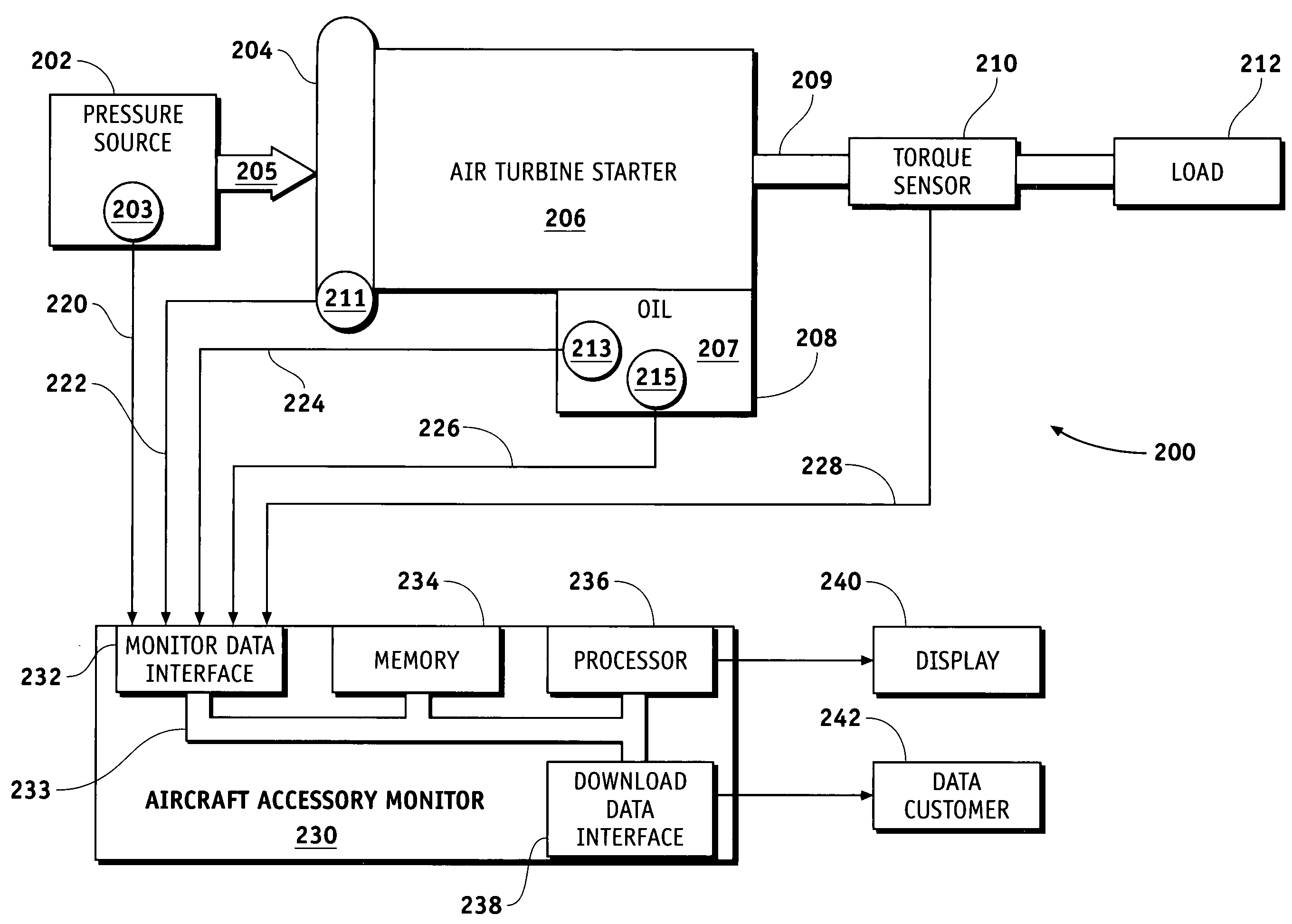

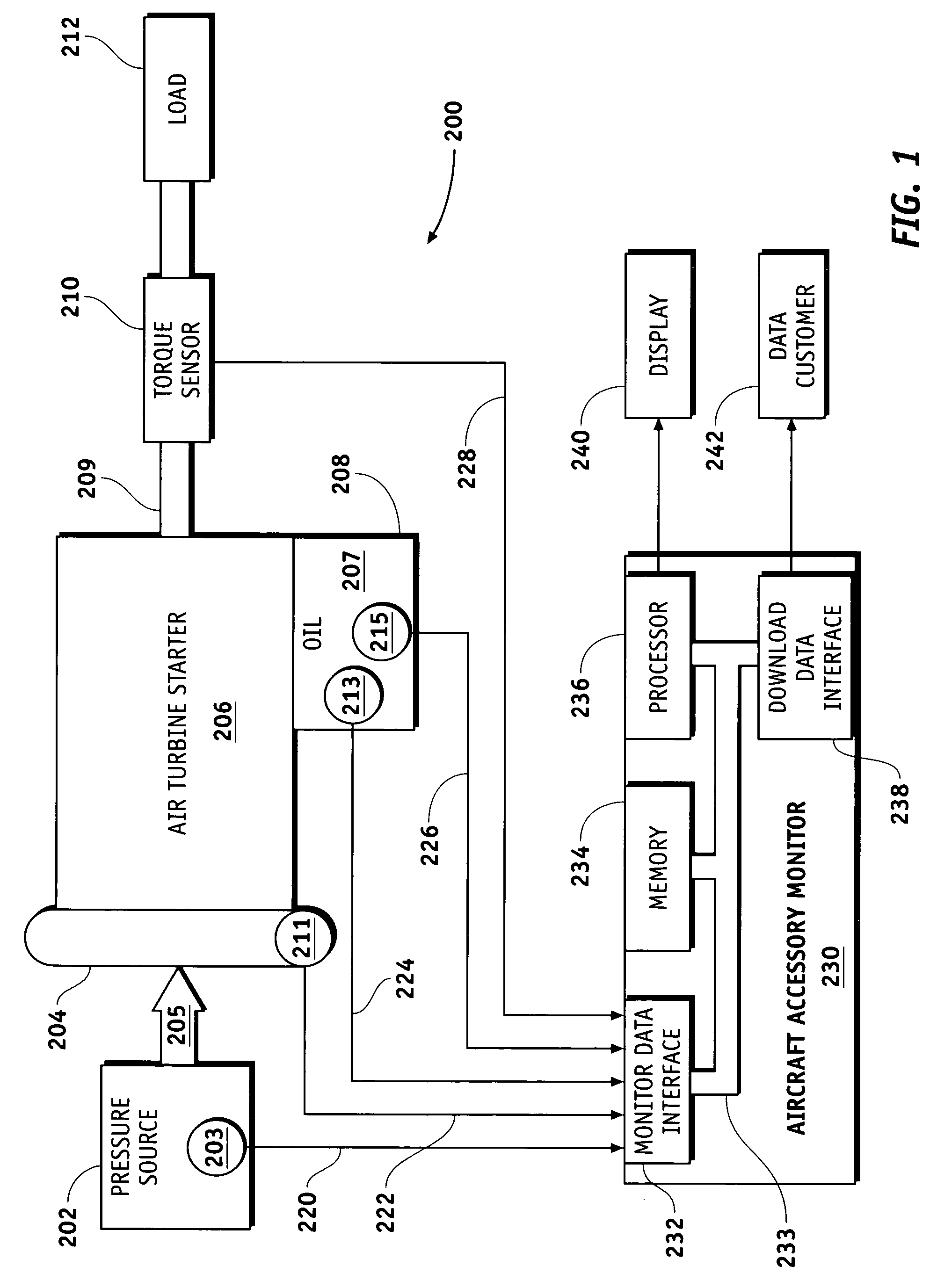

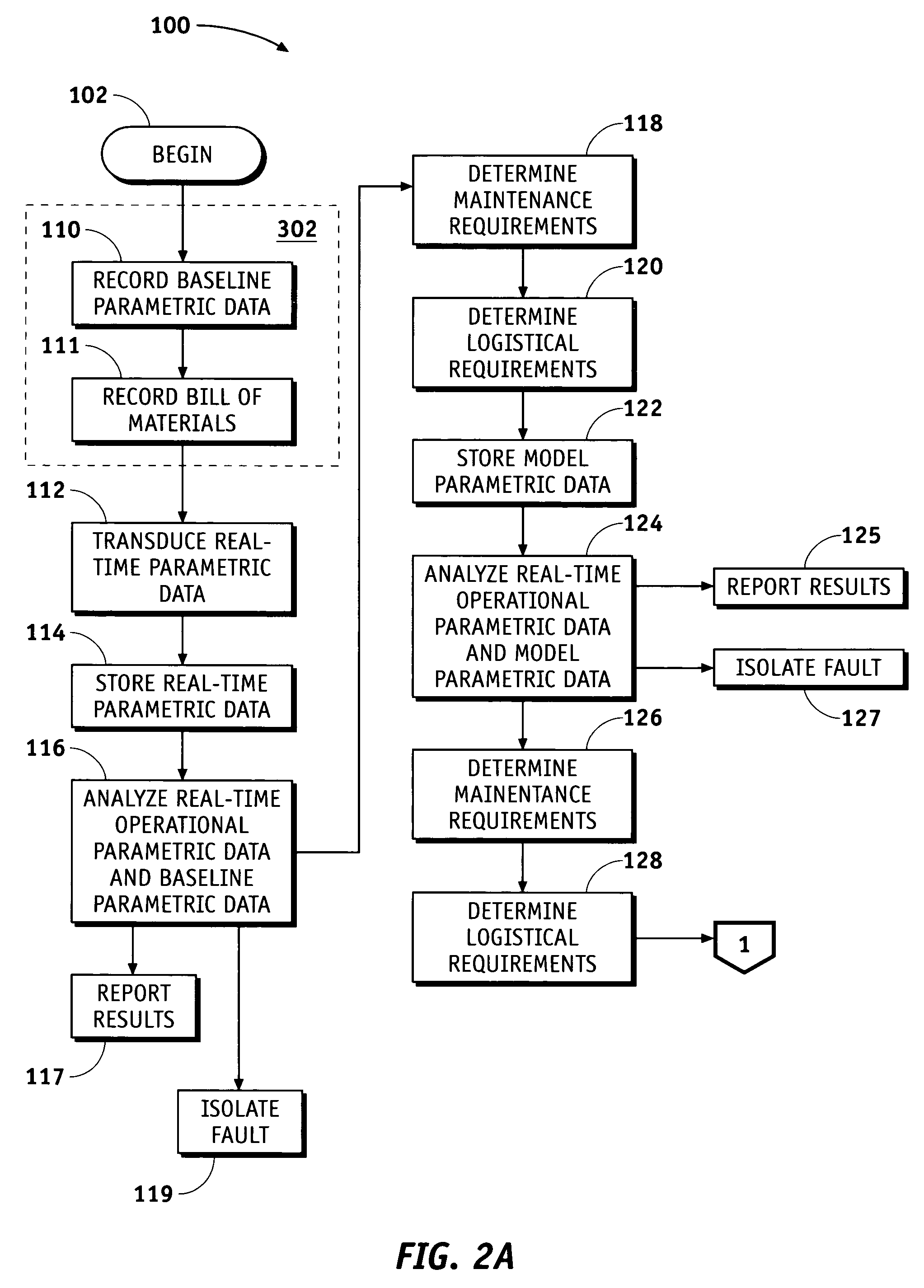

Aircraft accessory monitor

InactiveUS20050075769A1Vehicle testingAnalysing solids using sonic/ultrasonic/infrasonic wavesTransducerTest procedures

Methods and apparatus are provided for monitoring an aircraft accessory. The apparatus comprises a processor associated with said aircraft accessory, a transducer coupled to said processor and operable to produce parametric data relating to said aircraft accessory and a memory coupled to said processor having baseline parametric data residing therein, wherein said baseline parametric data comprises the parametric data obtained during an acceptance test procedure. The method comprises installing a transducer configured to produce parametric data relating to said aircraft accessory, coupling said transducer to a processor associated with said aircraft accessory, coupling said processor to a memory associated with said aircraft accessory, recording baseline parametric data relating to said aircraft accessory in said memory during an acceptance test procedure for said aircraft accessory.

Owner:HONEYWELL INT INC

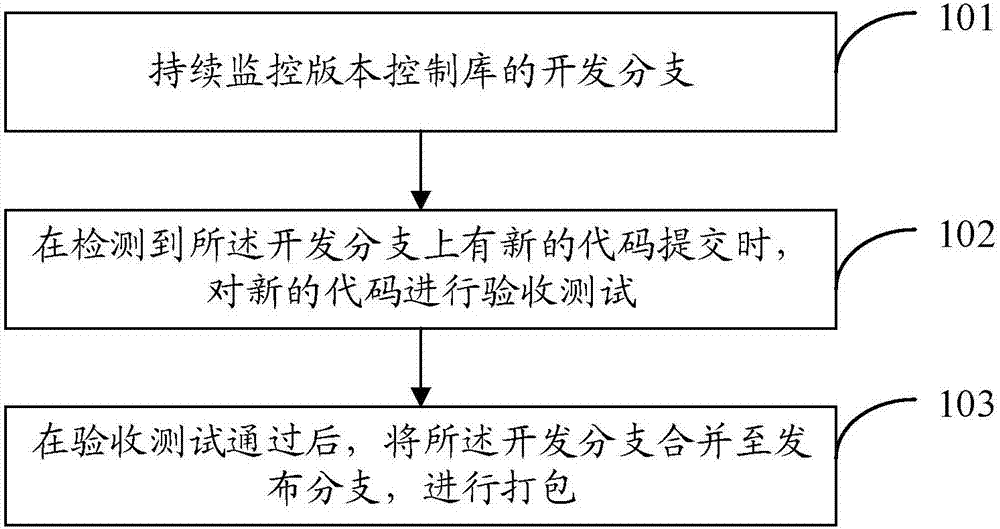

Software continuous integration method and system

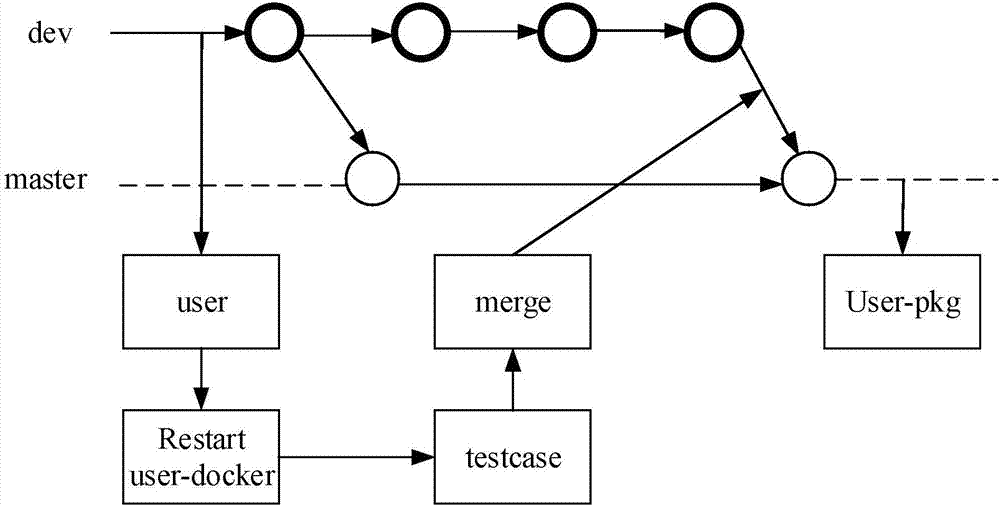

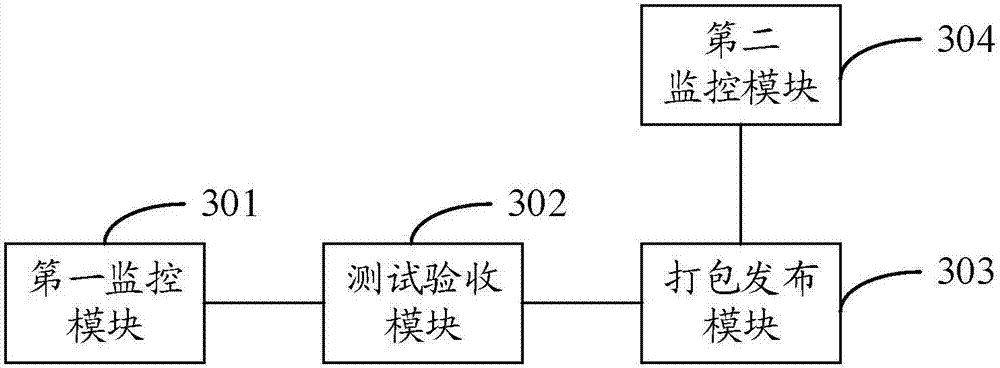

InactiveCN107450933AImprove the efficiency of research and developmentSolve problems that cannot meet the continuous integration needs of existing complex software projectsVersion controlSpecific program execution arrangementsContinuous integrationSoftware development

The invention relates to software development technologies, discloses a software continuous integration method and system and solves the problem that an existing continuous integration system fails to meet continuous integration requirements of existing complex software projects. The method includes: continuously monitoring a development branch of a version control library; when new code submitting on the development branch is detected, subjecting new codes to acceptance test; after the acceptance test is passed, combining the development branch to a release branch, and packing. By the technical scheme, the software continuous integration method and the system are applicable to multi-developer software development continuous integration, and multi-branch based continuous integration management is realized.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

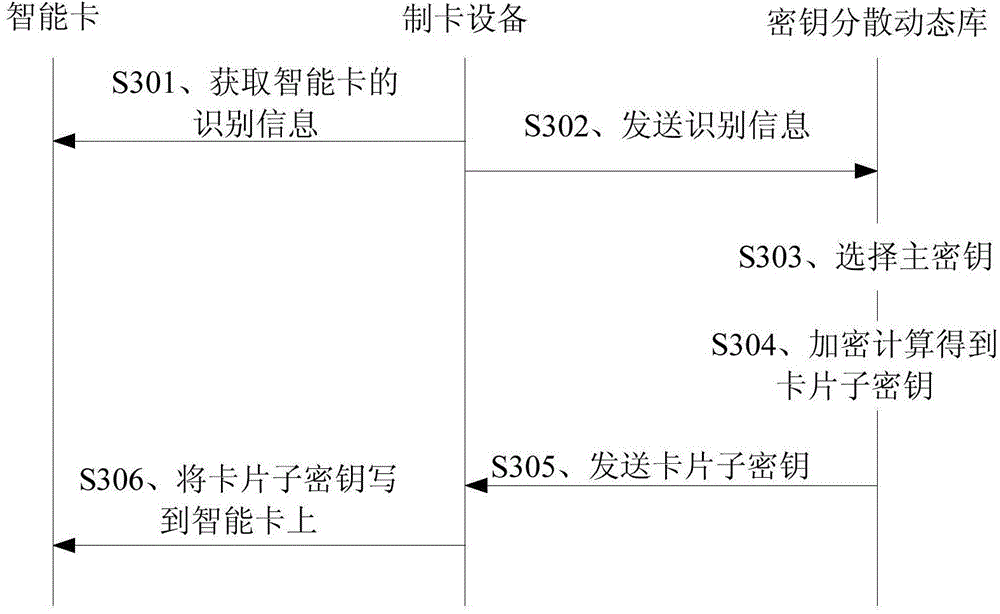

Bidirectional verification method and device of intelligent card and acceptance terminal

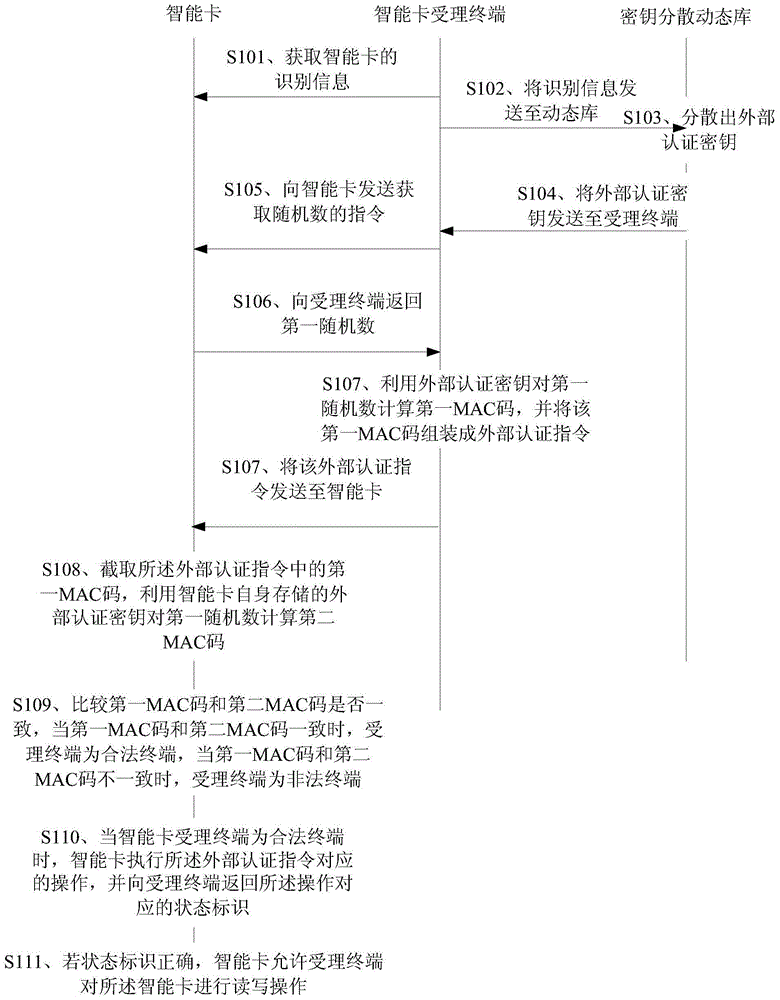

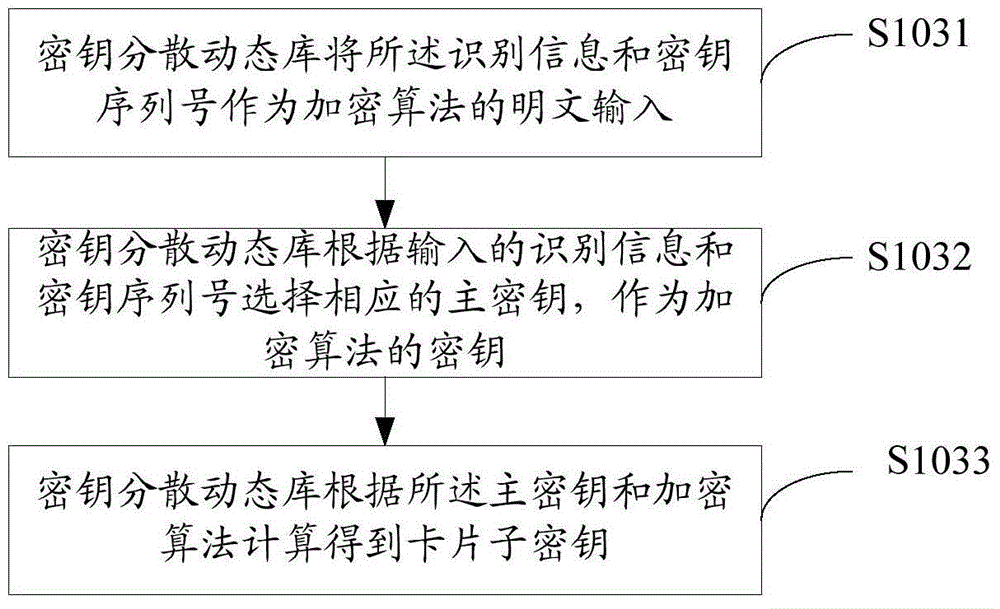

InactiveCN104917614AEnsure safetyLow costKey distribution for secure communicationUser identity/authority verificationValidation methodsSmart card

The invention provides a bidirectional verification method of an intelligent card and an acceptance terminal, and a bidirectional verification device of the intelligent card and the acceptance terminal. The method comprises the following steps: the intelligent card verifies whether the acceptance terminal is legal by utilizing an external authentication secret key, and the acceptance terminal verifies whether the intelligent card is true by utilizing an internal authentication secret key; the external authentication secret key and the internal authentication secret key are dispersed from a main secret key by a secret key dispersion dynamic library according to identification information of the intelligent card and a dispersion algorithm; the secret key dispersion dynamic library is distributed to the acceptance terminal or a server of the acceptance terminal in advance through a network, and the main secret key is stored in the secret key dispersion dynamic library; and the secret key dispersion dynamic library can protect the main secret key form being exposed. The method and the device can guarantee safety of the main secret key and be in favor of reducing hardware cost, and updating management of the main secret key is convenient.

Owner:CHINA CONSTRUCTION BANK

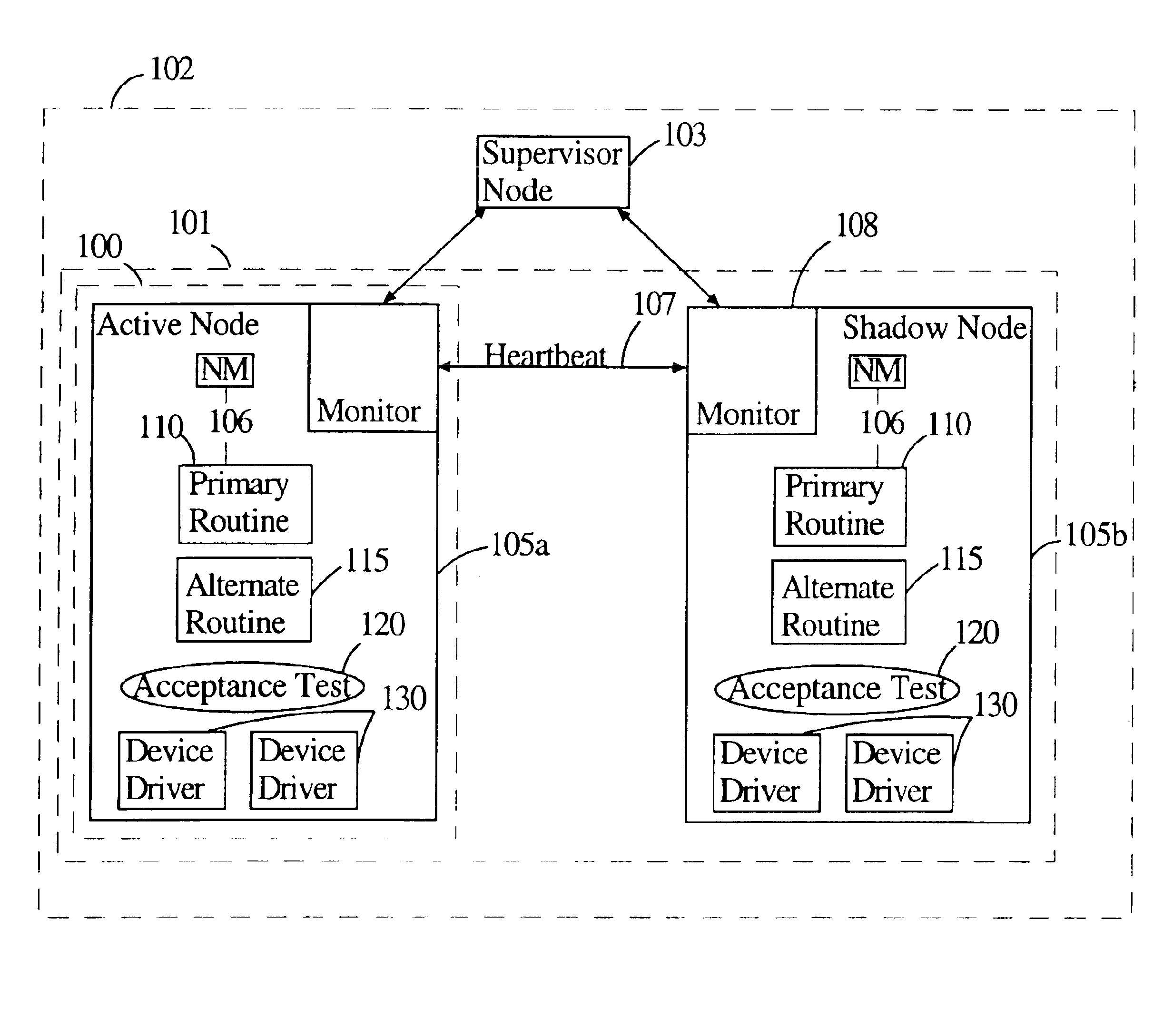

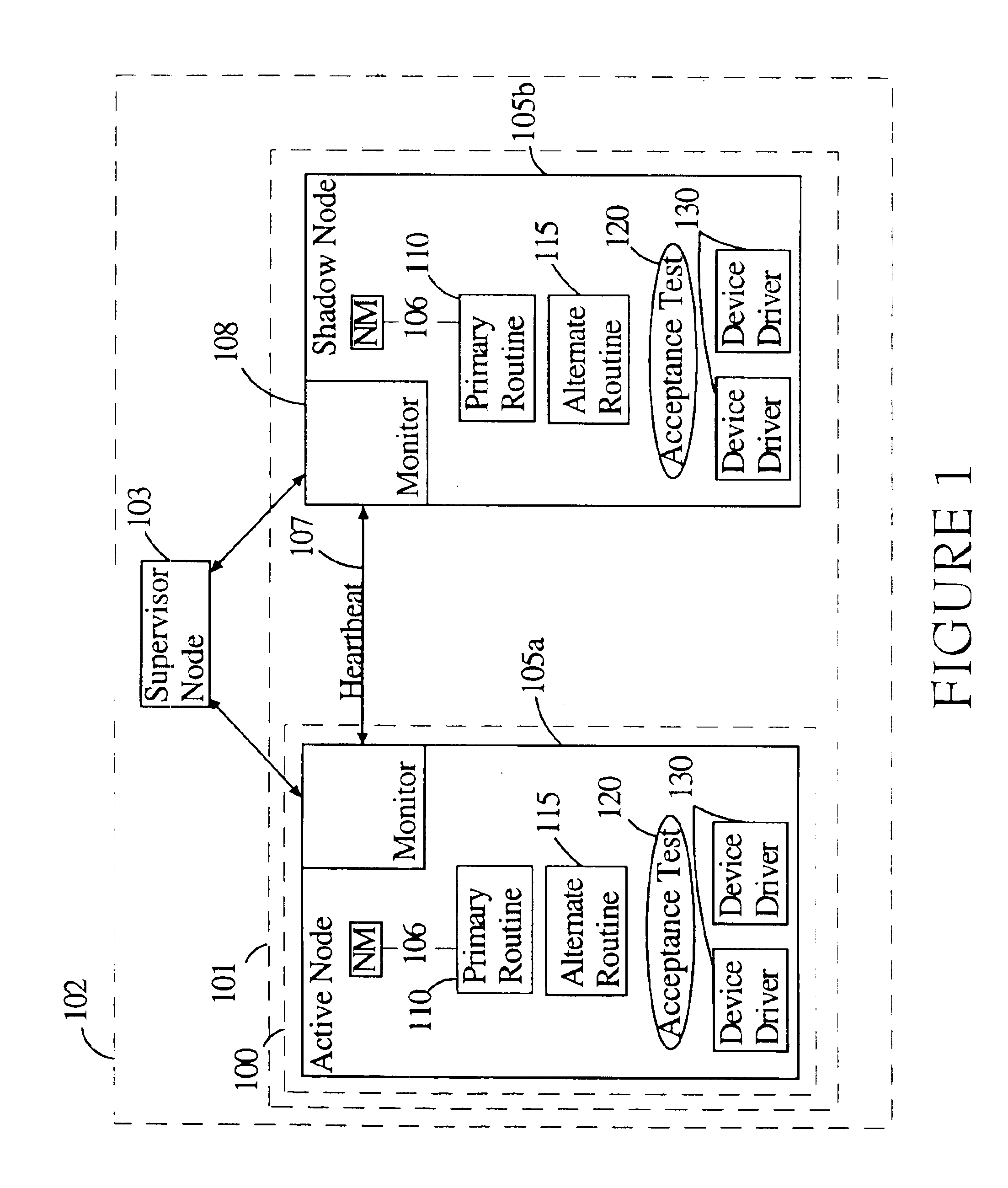

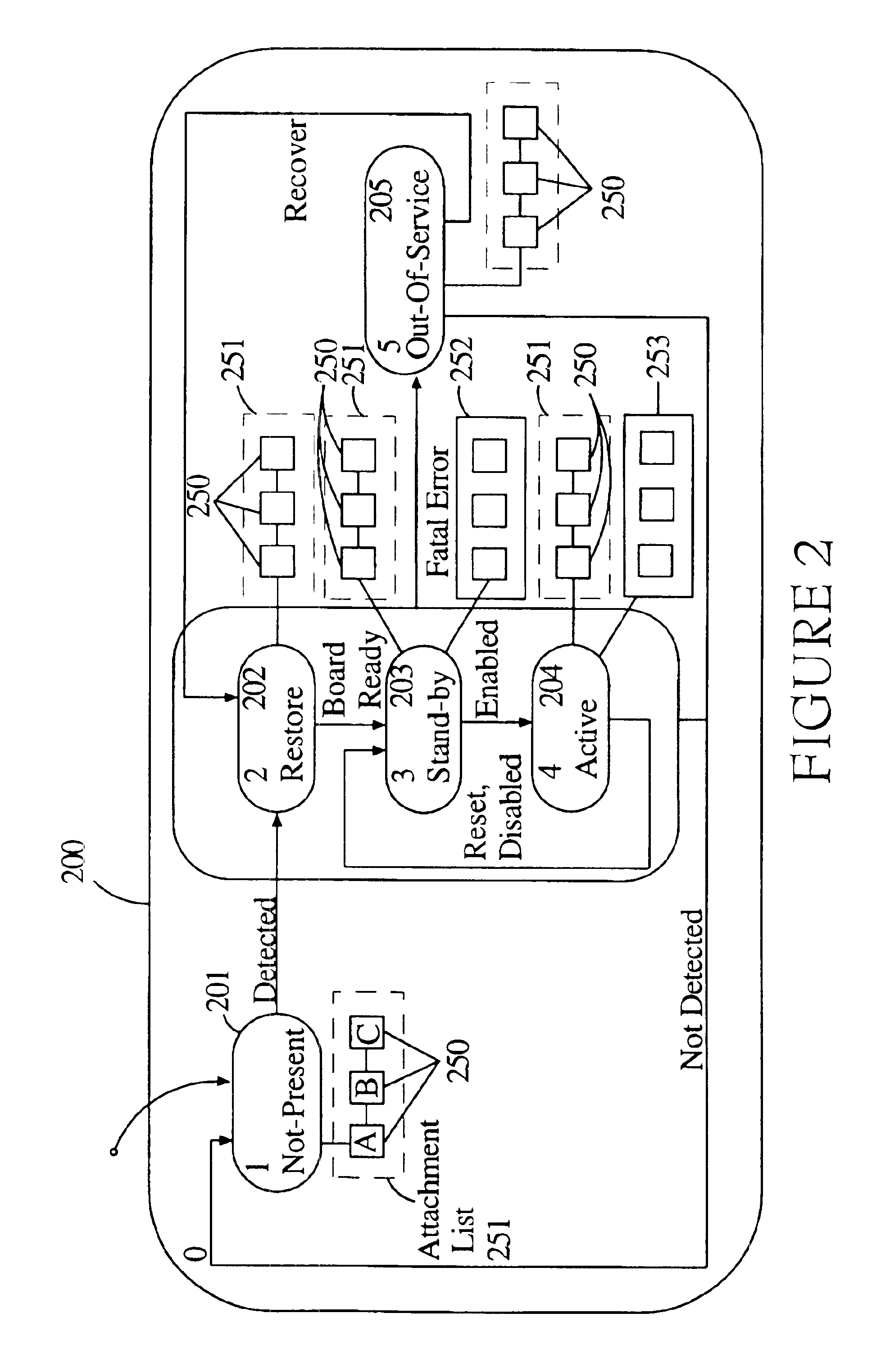

Hybrid agent-oriented object model to provide software fault tolerance between distributed processor nodes

InactiveUS6868067B2Multiplex system selection arrangementsError preventionProcessor nodeFinite-state machine

An apparatus and method for a computer system is used for implementing an extended distributed recovery block fault tolerance scheme. The computer system includes a supervisory node, an active node and a standby node. Each of the nodes has a primary routine, an alternate routine and an acceptance test for testing the output of the routines. Each node also includes a device driver, a monitor and a node manager for determining the operational configuration of the node. The supervisory node coordinates the operation of the active and standby nodes. The primary and alternate routines are implemented with an application task through a plurality of agent objects operating as finite state machines. A reliable data link extends between the monitors of the active and standby nodes.

Owner:NORTH SOUTH HLDG

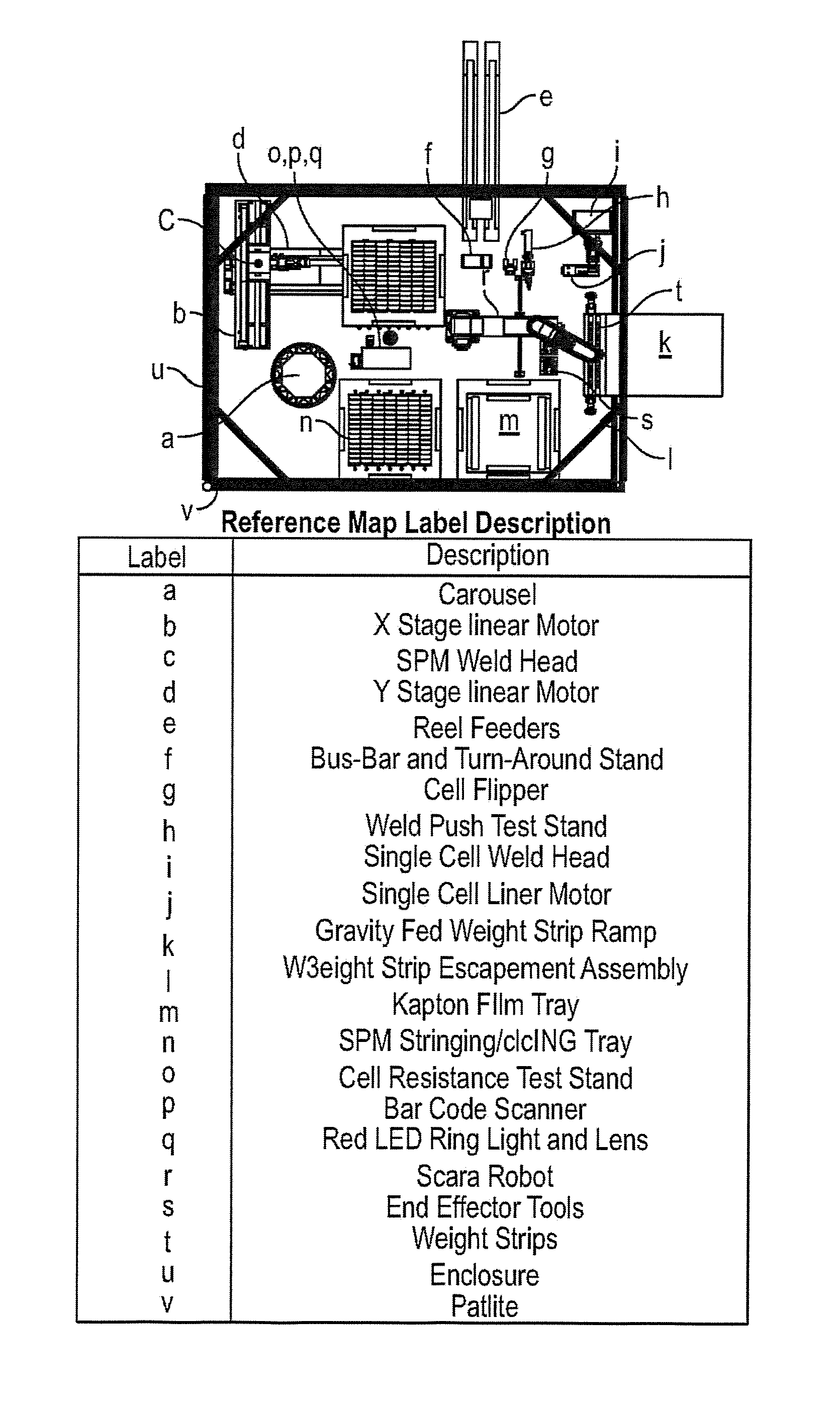

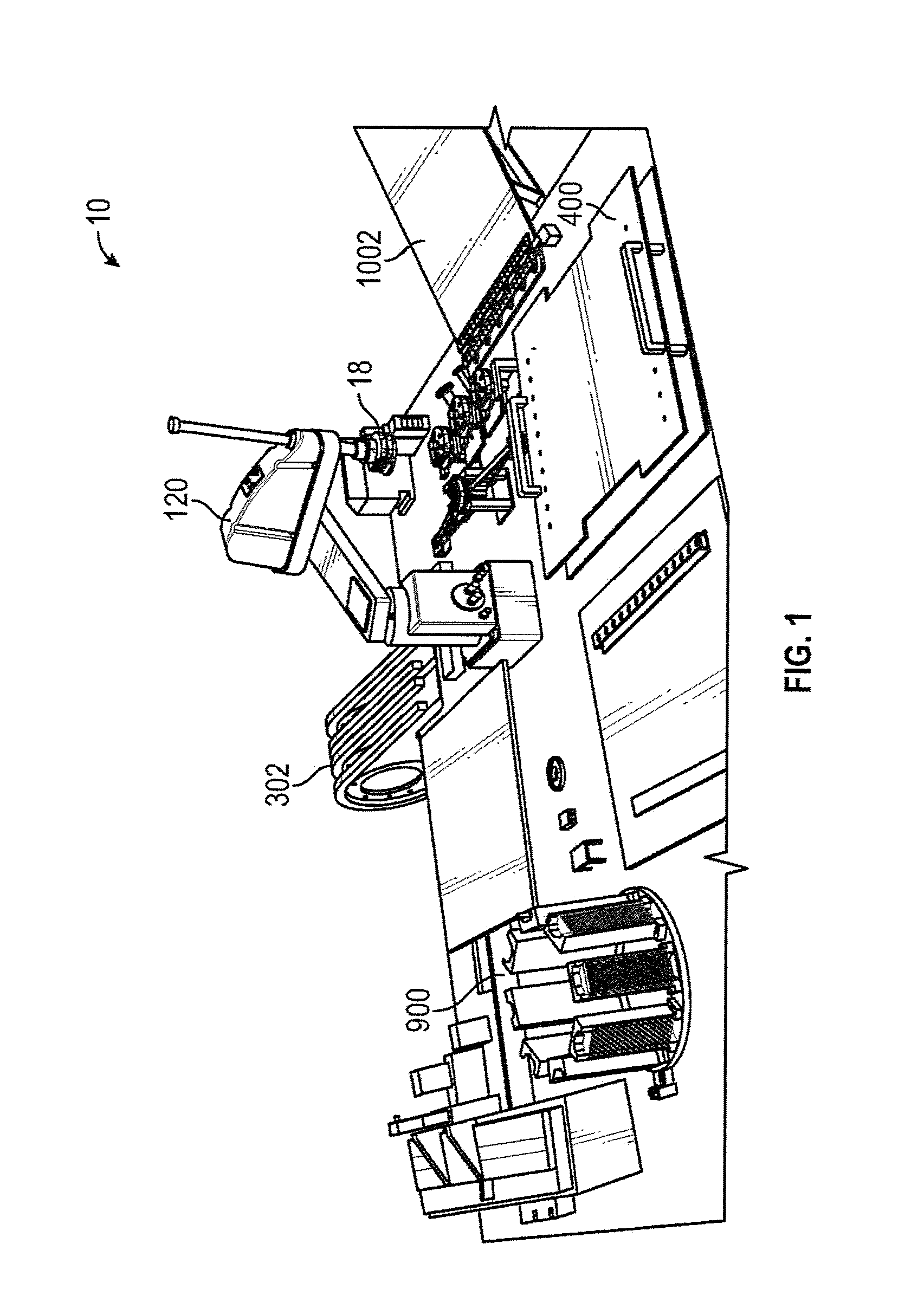

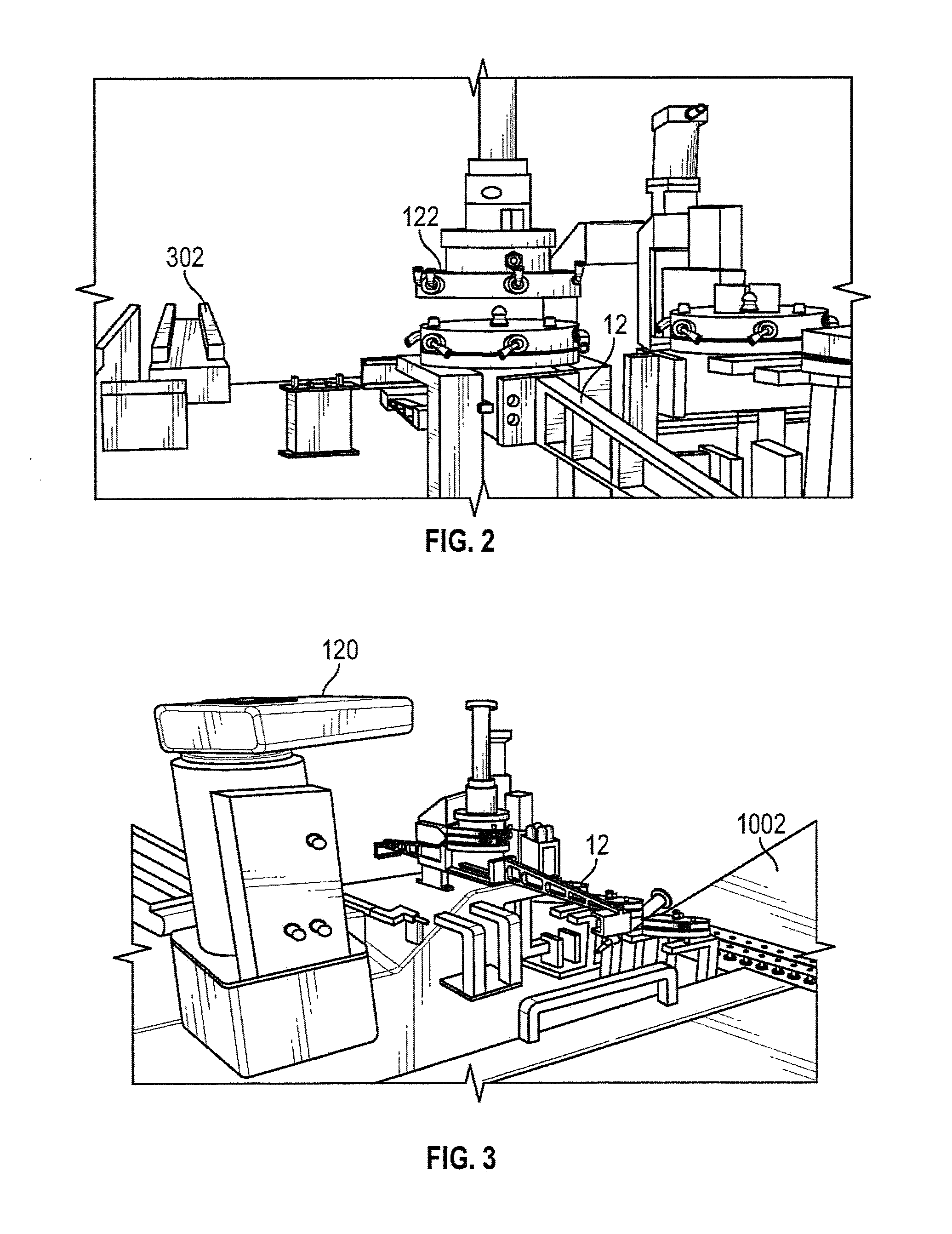

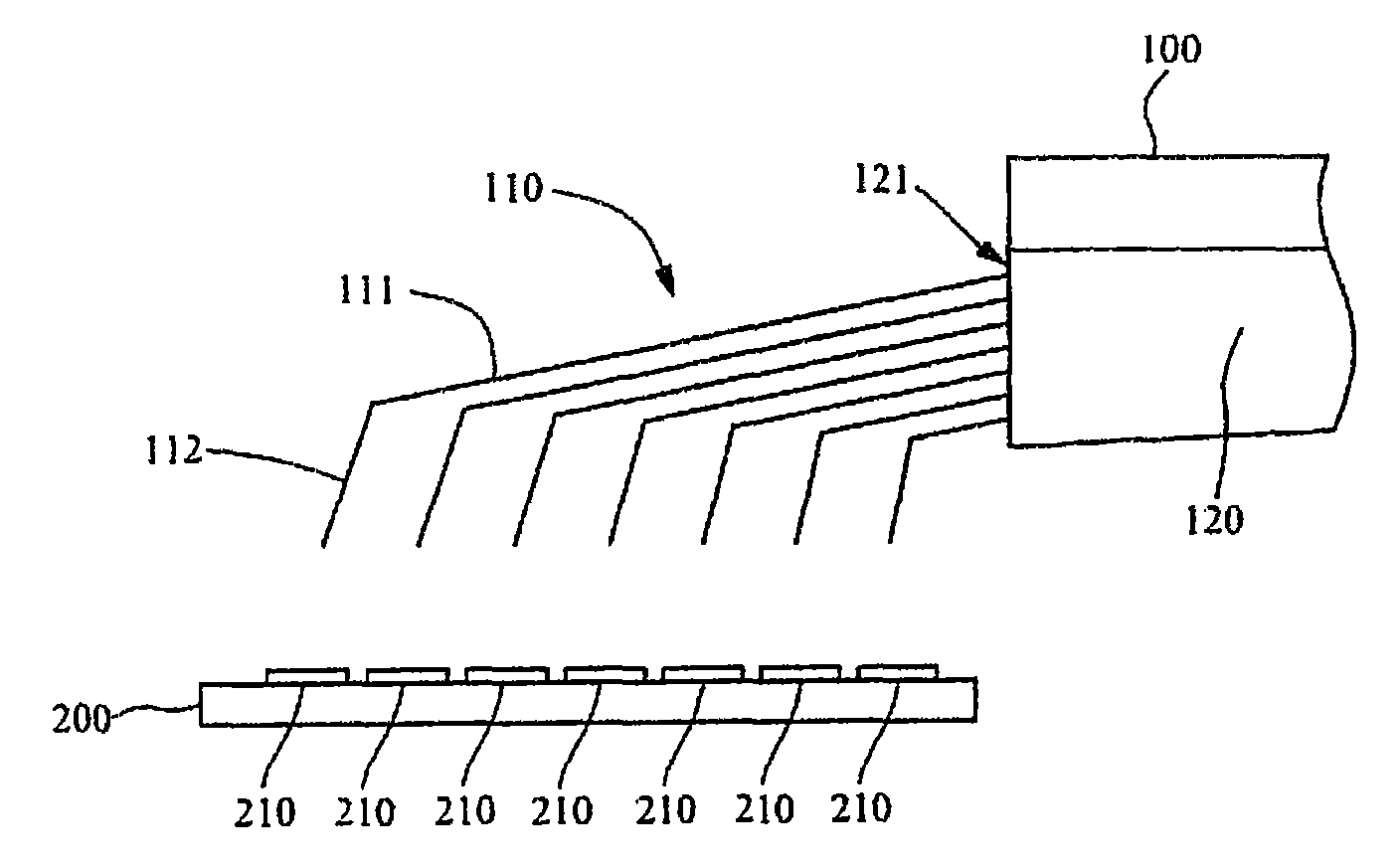

System and method for producing modular photovoltaic panel assemblies for space solar arrays

ActiveUS9444004B1Improve performanceQuality improvementFinal product manufactureWelding/cutting auxillary devicesBusbarEngineering

An automated system provides automated manufacturing of photovoltaic standard power modules for utilization in a space solar array, in both rolled blanket and z-folded configurations. The automated system provides robotically controlled systems for CIC-ing, glassing, stringing, laydown and acceptance testing of interconnected photovoltaic devices. A method of manufacturing the photovoltaic standard power modules includes the steps of robotic positioning of diodes, interconnects and busbars onto a SPM stringing tray followed by the robotic positioning of bare cells into position adjacent to the diodes, interconnects and busbars to form strings. The SPM stringing tray is thereafter robotically positioned adjacent to an integral welder for welding of the front side of the string. Cover glass is thereafter robotically placed over the cells. The string is flipped and the backside of the string is robotically positioned for welding.

Owner:DEPLOYABLE SPACE SYST

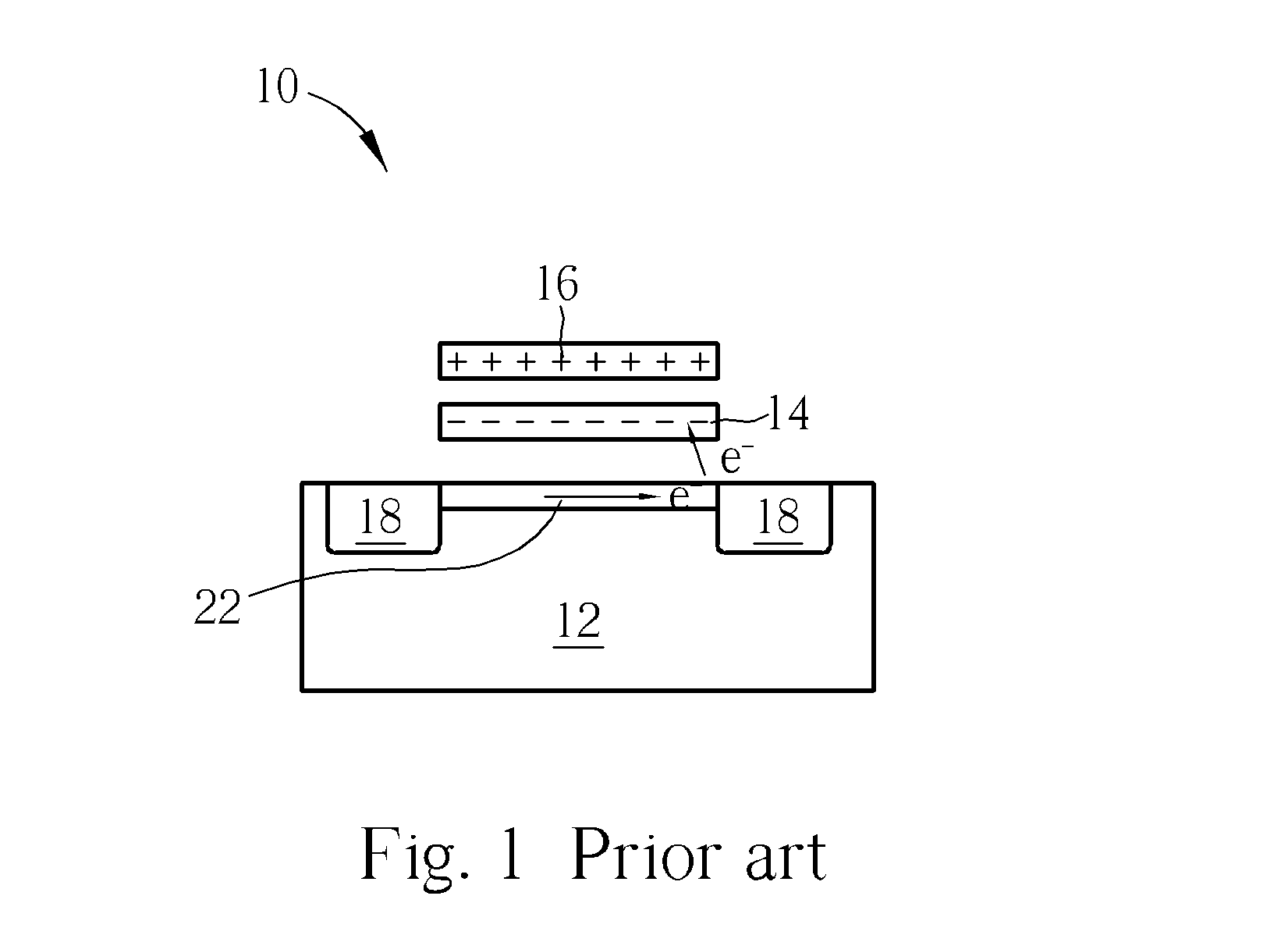

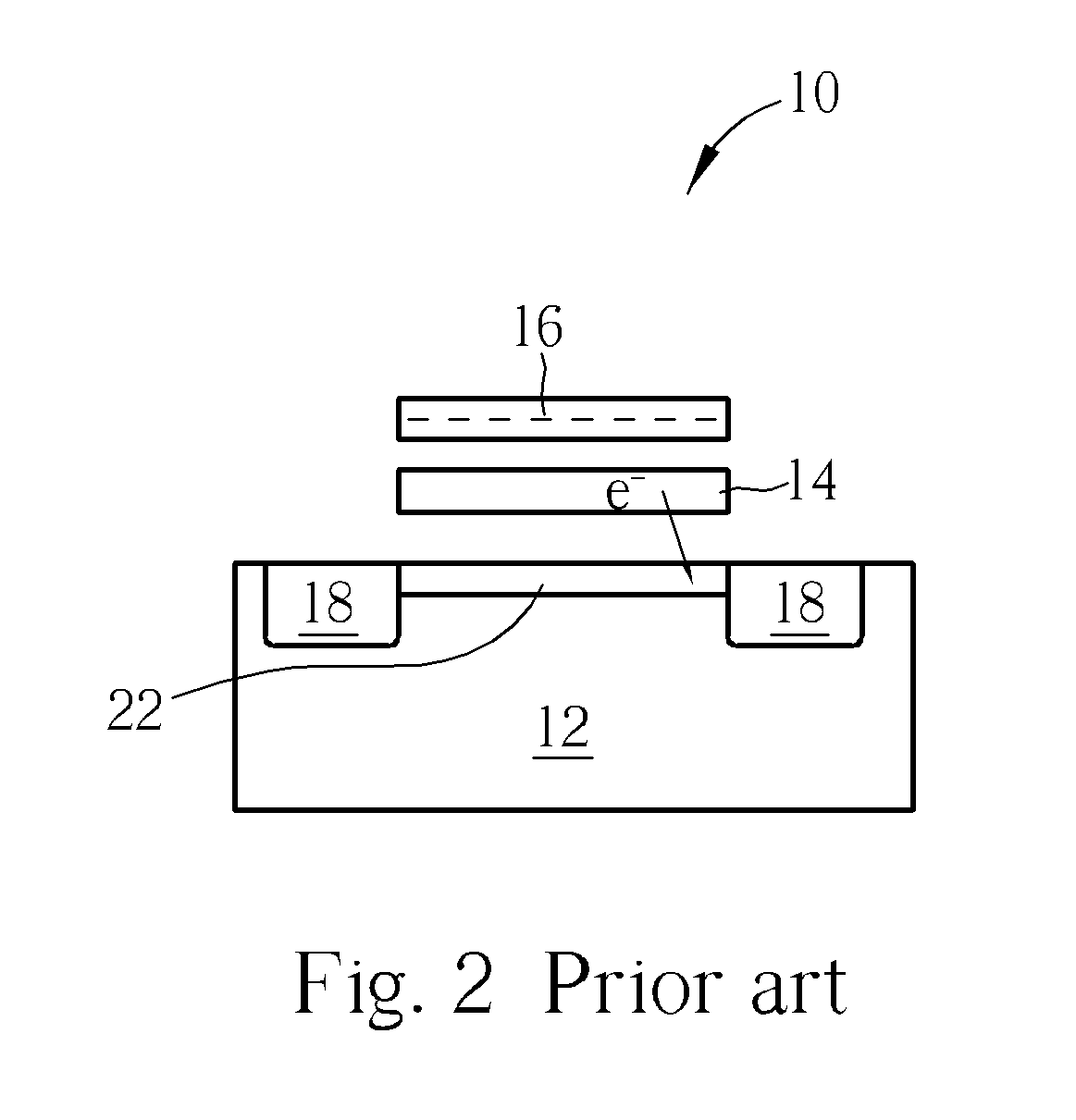

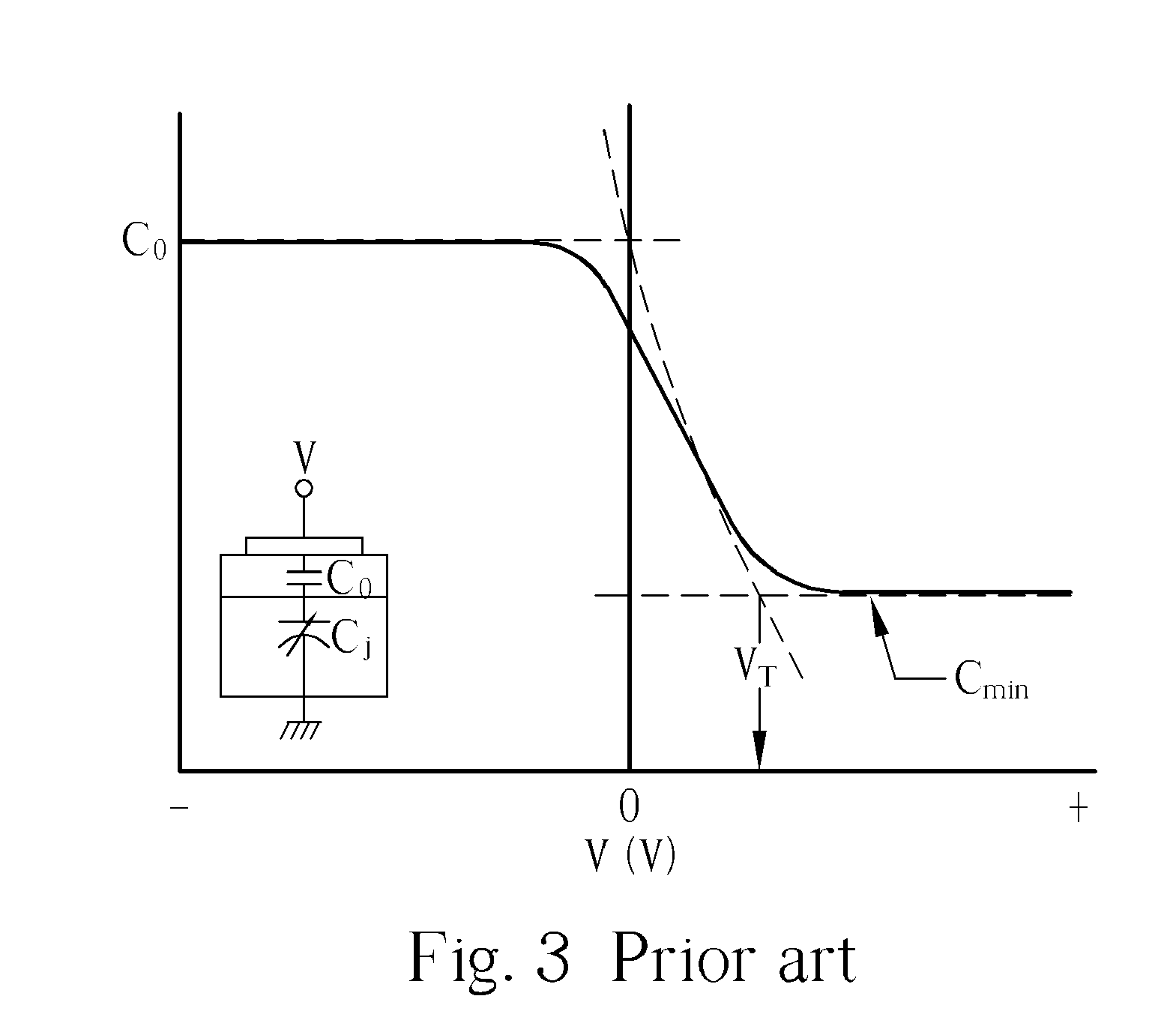

Method for monitoring quality of an insulation layer

InactiveUS20050040840A1Quick monitoringEasy to produceTesting dielectric strengthSemiconductor/solid-state device testing/measurementInsulation layerEngineering

The present invention utilizes wafer acceptance testing equipment to fast monitor the quality of an insulation layer. A plurality of swing time-dependent DC ramping voltages are applied to one of the electrode plates in a capacitor and each corresponding leakage current is measured to calculate each corresponding β value. Then, a ratio of each β value is calculated and a β− voltage curve is plotted to actually simulate the device failure.

Owner:UNITED MICROELECTRONICS CORP

Method and system for bounds comparator

The invention relates to a method of using a "bounds" comparator scheme and to a "bounds" comparator circuit. The method of using this scheme or comparator circuit allows a quick and easy test to characterize, utilizing a single floating-point bounds comparison function, the location of a point with respect to pre-defined end- points. The single floating-point bounds comparison function represents an additional instruction to be incorporated within computer instruction set architectures when performing trivial acceptance testing during the generation of three-dimensional images or graphics.

Owner:NXP USA INC +2

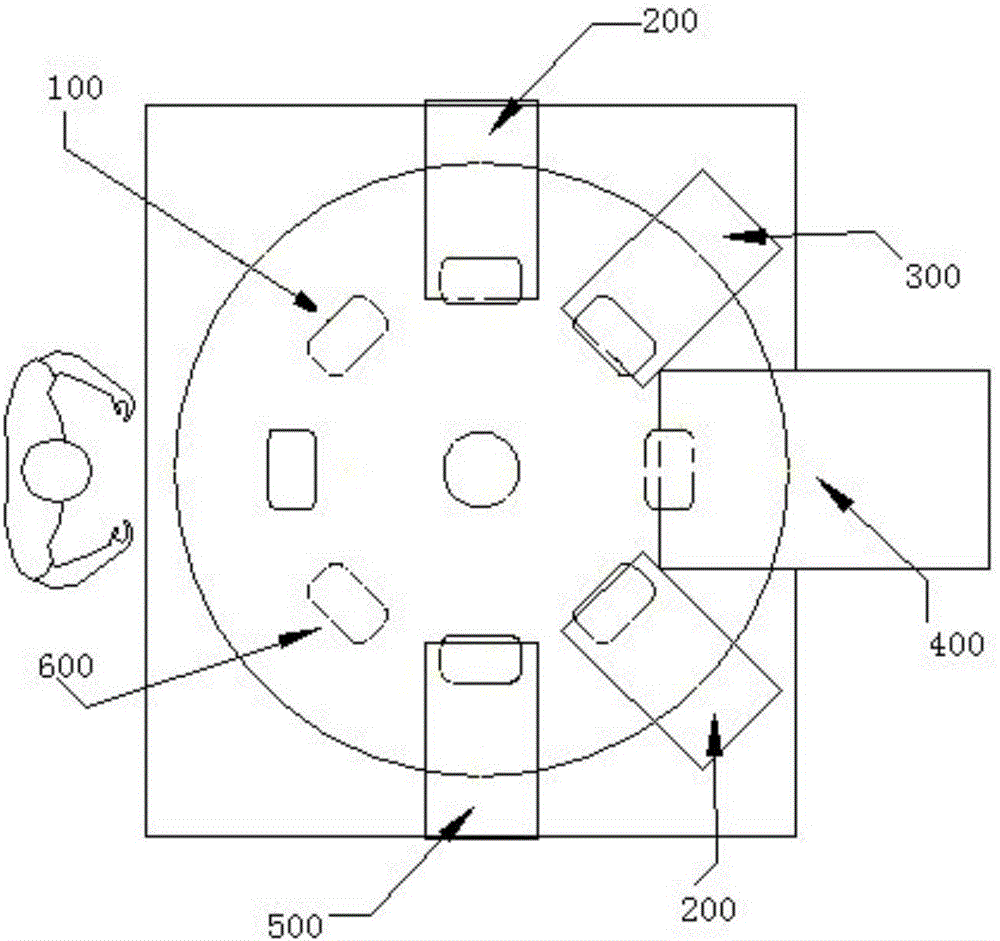

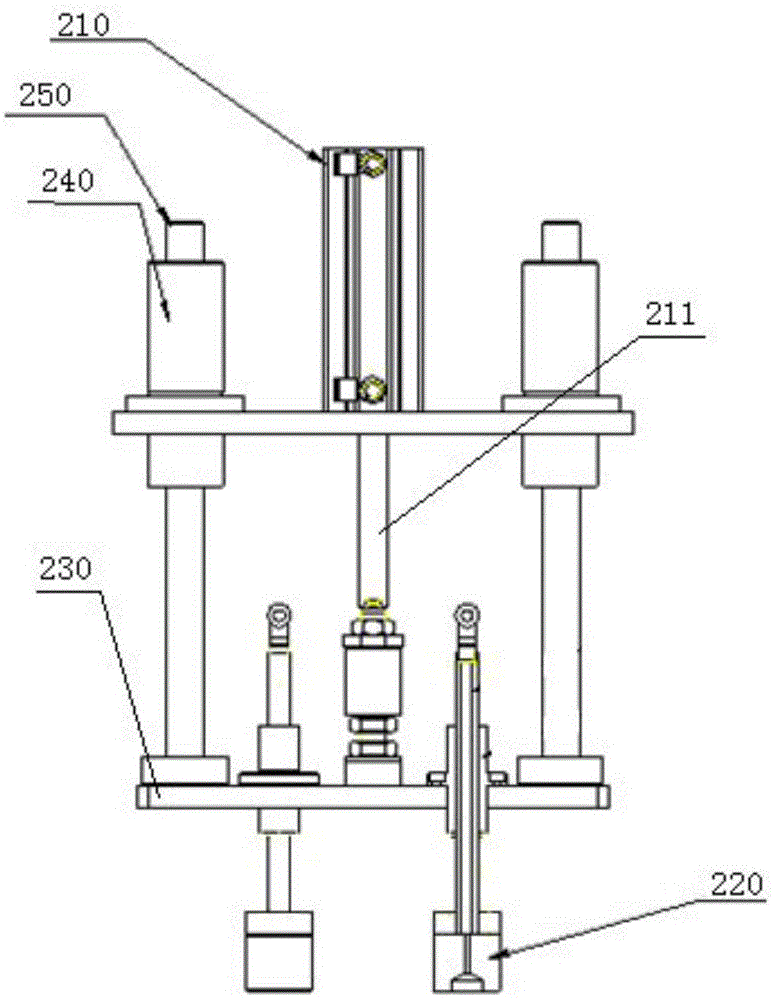

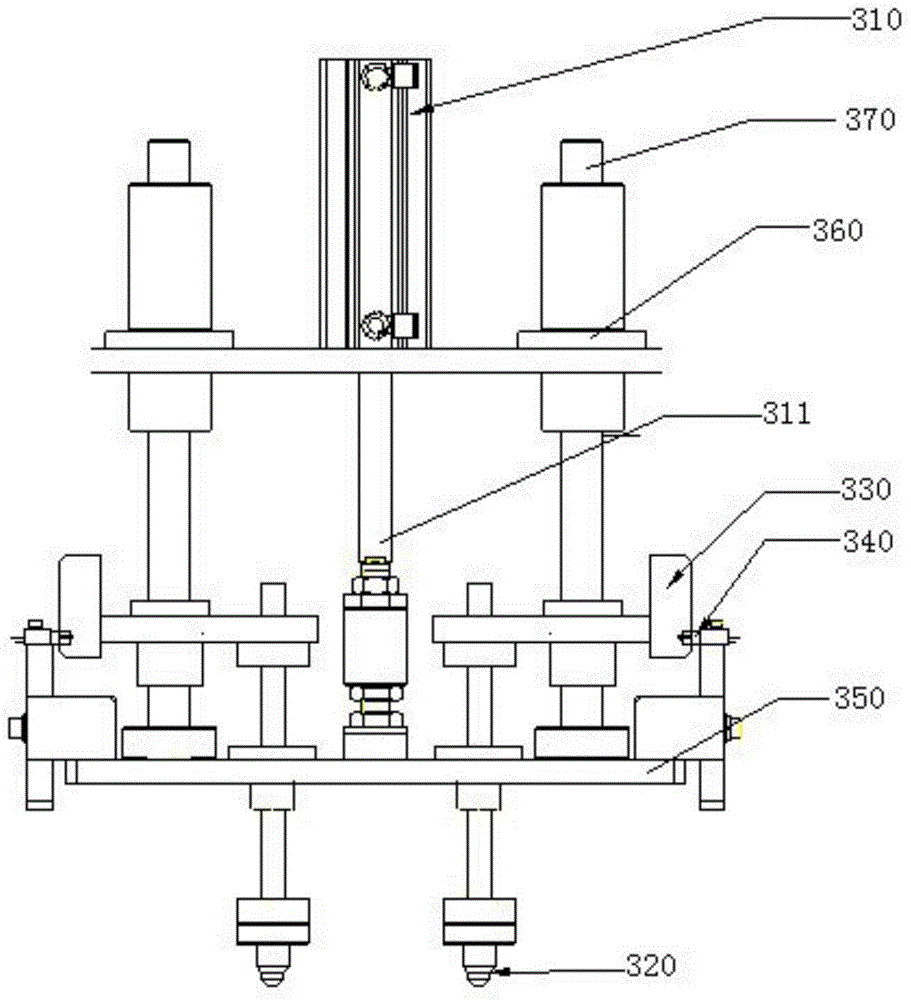

Thread detection device and tapping and detecting production line with thread detection device

InactiveCN104816052AImplement automatic detectionIncrease productivityThread cutting machinesMeasurement/indication equipmentsProduction lineMan-hour

The invention discloses an internal thread detection device and a tapping and detecting production line with the internal thread detection device. According to the invention, the manual internal thread detection standard is imitated, vertical air cylinders and a rotating motor are utilized for driving a go-no go plug gauge to do vertical and rotating motion for detection, and meanwhile three vertical photoelectric sensors and a rotating photoelectric sensor are utilized for sensing the detection progress of the go-no go plug gauge. The tapping and detecting integrated full-automatic production line composed of a rotating indexing disc, first blowing cleaning devices, a height detecting device, a tapping device, a second blowing cleaning device, a thread detecting device, a combination control system and an operation system is adopted, wherein the first blowing cleaning devices, the height detecting device, the tapping device, the second blowing cleaning device and the thread detecting device are sequentially and annularly arranged above the indexing disc according to the operation procedure. Thus, the complete-set production process of incoming machining material detecting, workpiece cleaning, workpiece thread machining, thread forming condition acceptance testing and the like can be completed through one machine and one person; and the aims of greatly improving the production efficiency, reducing the man hour, obtaining multi-ability workers and downsizing the staff to improve the efficiency are achieved.

Owner:江苏晶和自动化工程有限公司

APF (advanced polarizer film) self-adhesive waterproof coiled material construction method

The invention discloses an APF (advanced polarizer film) self-adhesive waterproof coiled material construction method which includes a step of plane construction and a step of facade construction. The step of plane construction includes base layer cleaning, base face line snapping, polymer cement mortar preparing, node processing, reinforcing layer and internal and external corner adding, APF self-adhesive waterproof coiled material layer pre-paving, polymer cement mortar coating and scraping, APF self-adhesive waterproof coiled material layer paving, lapping, rolling, head recovering and organizing for acceptance testing, and the step of facade construction includes facade base layer cleaning, facade base face coiled material positioning and line snapping, base layer treating agent coating and scraping, node processing, APF self-adhesive waterproof coiled material layer paving, lapping, rolling, head recovering and organizing for acceptance testing. The polymer cement mortar is utilized as a bonding layer, so that the bonding layer can be quickly paved on a humid concrete base layer and can also be directly paved on a dry concrete face.

Owner:CHINA CONSTR SENVENTH ENG BUREAU INSTALLATION ENG

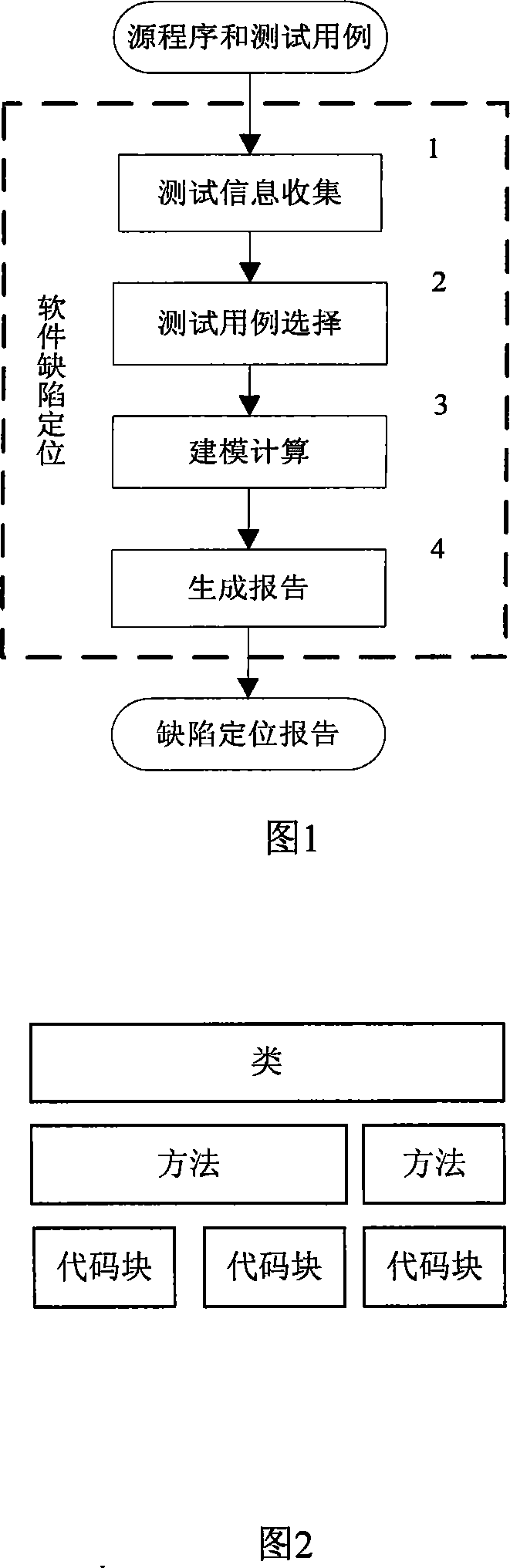

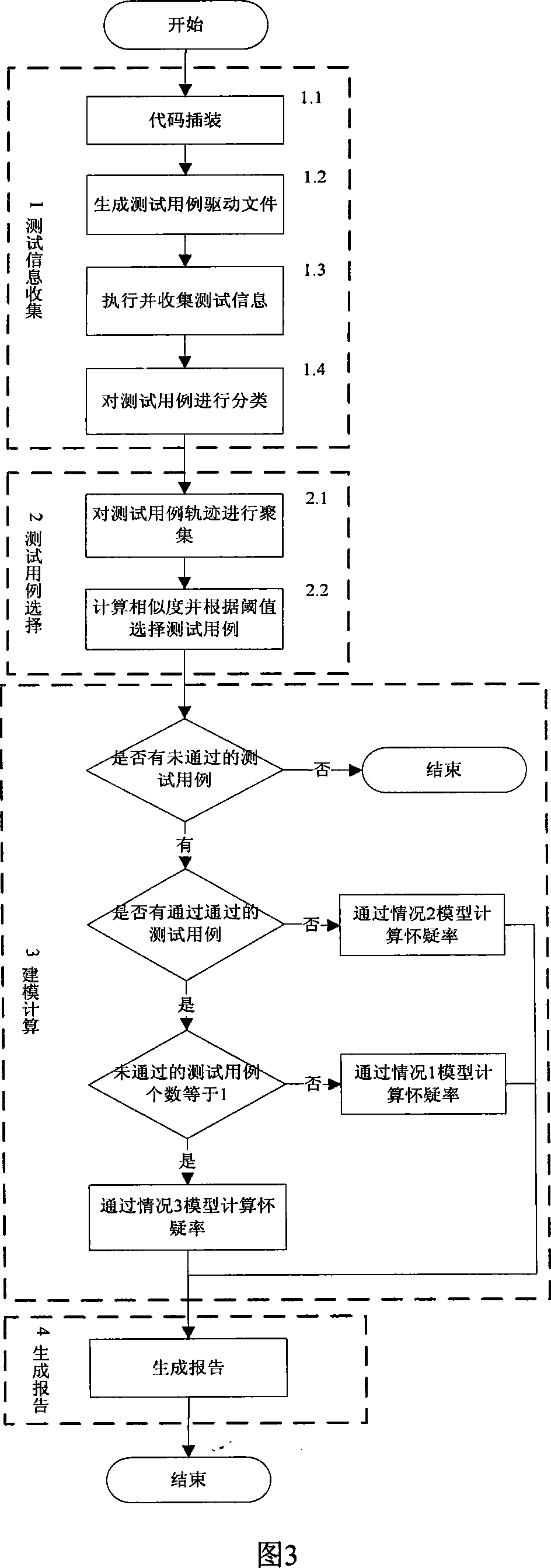

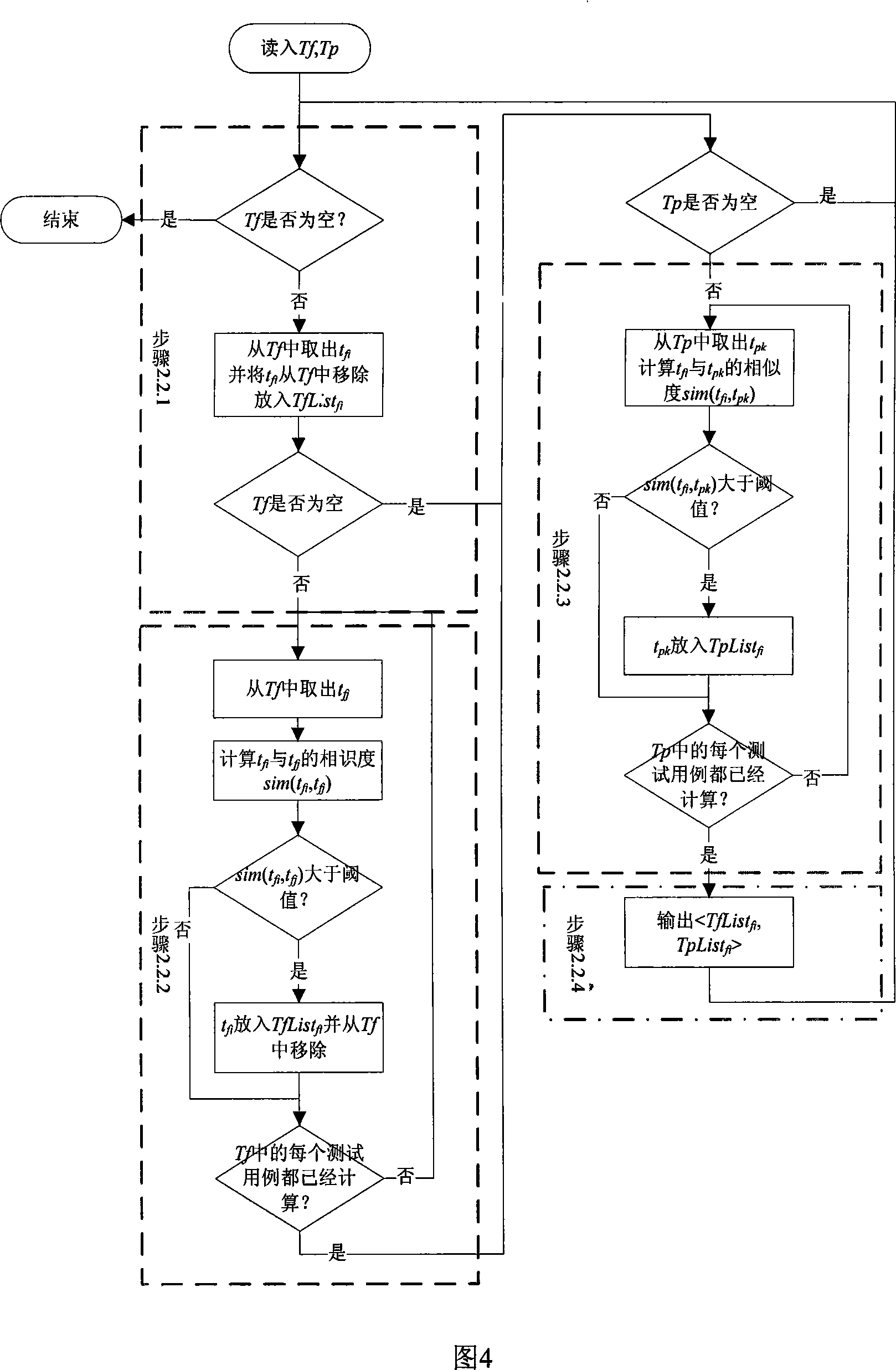

Method for locating software unsoundness base on execution track block semblance

InactiveCN101231614ANarrow searchNarrow down the bug searchSoftware testing/debuggingSoftware systemSystem testing

The invention discloses a software defect locating method which is based on the lump similarity of execution traces, and the method comprises the following steps that: firstly, the executive information of test cases are collected and arranged, and the execution traces are generated; secondly, a test case set which has defects is positioned according to the lump similarity selection of the execution traces; thirdly, the system comparison is carried out to the execution traces of the selected test cases, and the suspecting rate of the operation part is calculated; fourthly, the suspecting rate of the operation part is mapped to the source program to generate a defect locating report. The invention can be widely applied to the automatic test environment of a large-scale software system, and relates to the stage and the work of an integrated test, a system test, an acceptance test, a user problem report analysis, etc.; the existing test data are fully utilized, and the lump similarity of the execution traces is based on to carry out the position to the software defect, thereby effectively reducing the searching range and improving the defect positioning efficiency. The invention can be used in each period and stage of the test, the selected test case set has higher pertinence, the calculation method of the suspecting rate of the operation part is simple and effective, and the expansibility is better.

Owner:NANJING UNIV

Aircraft accessory monitor

InactiveUS7251550B2Vehicle testingAnalysing solids using sonic/ultrasonic/infrasonic wavesTransducerTest procedures

Methods and apparatus are provided for monitoring an aircraft accessory. The apparatus comprises a processor associated with said aircraft accessory, a transducer coupled to said processor and operable to produce parametric data relating to said aircraft accessory and a memory coupled to said processor having baseline parametric data residing therein, wherein said baseline parametric data comprises the parametric data obtained during an acceptance test procedure. The method comprises installing a transducer configured to produce parametric data relating to said aircraft accessory, coupling said transducer to a processor associated with said aircraft accessory, coupling said processor to a memory associated with said aircraft accessory, recording baseline parametric data relating to said aircraft accessory in said memory during an acceptance test procedure for said aircraft accessory.

Owner:HONEYWELL INT INC

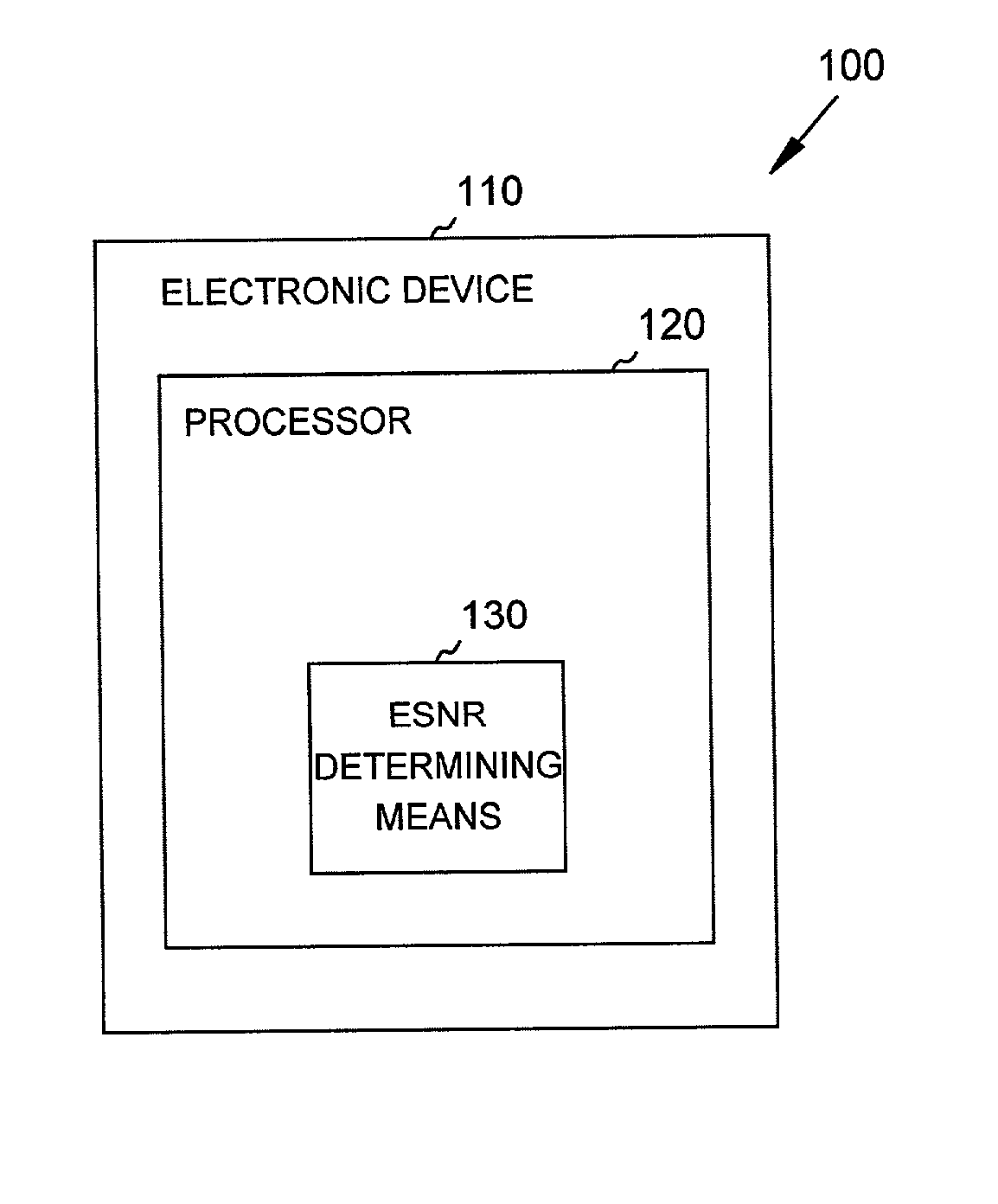

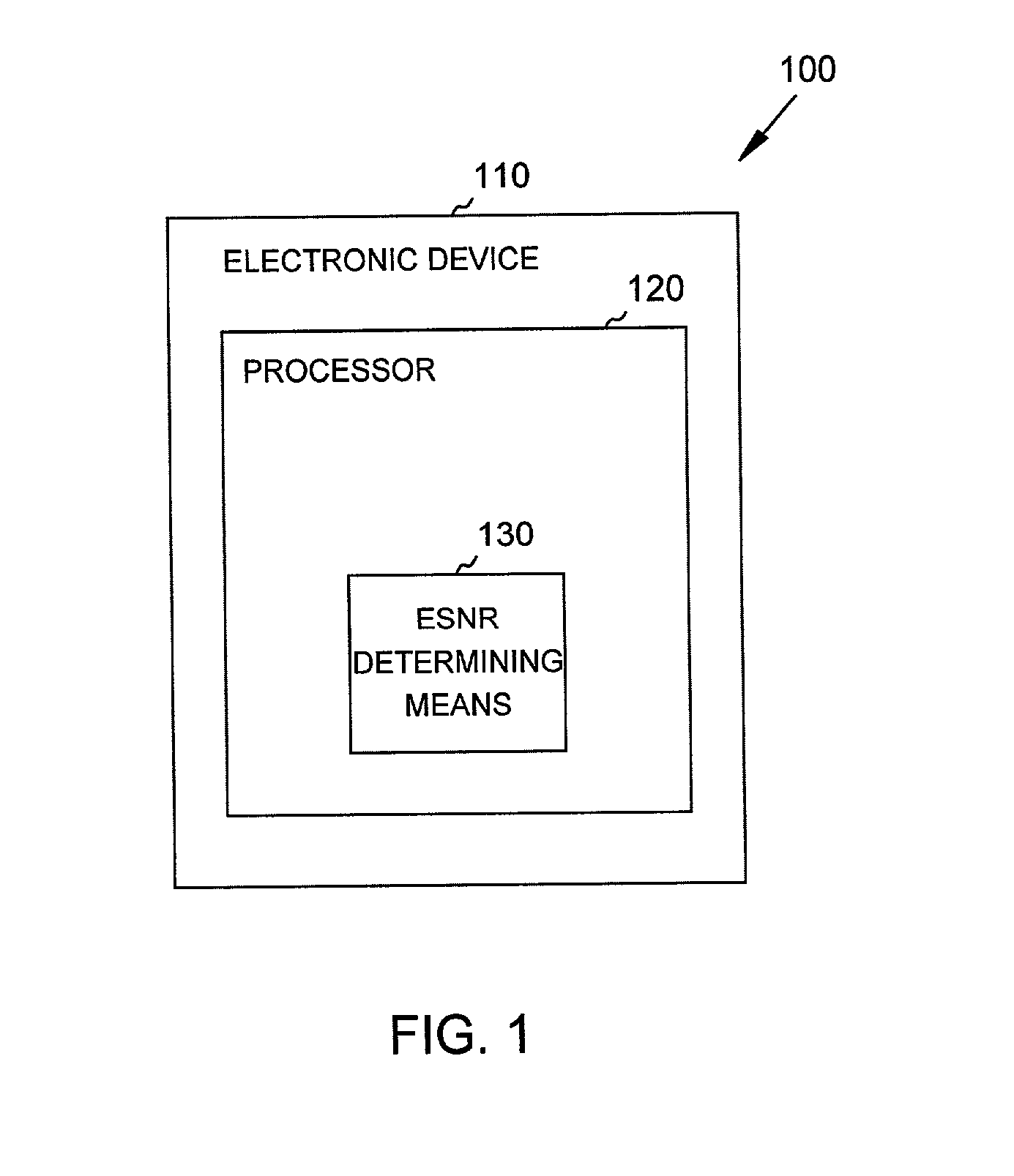

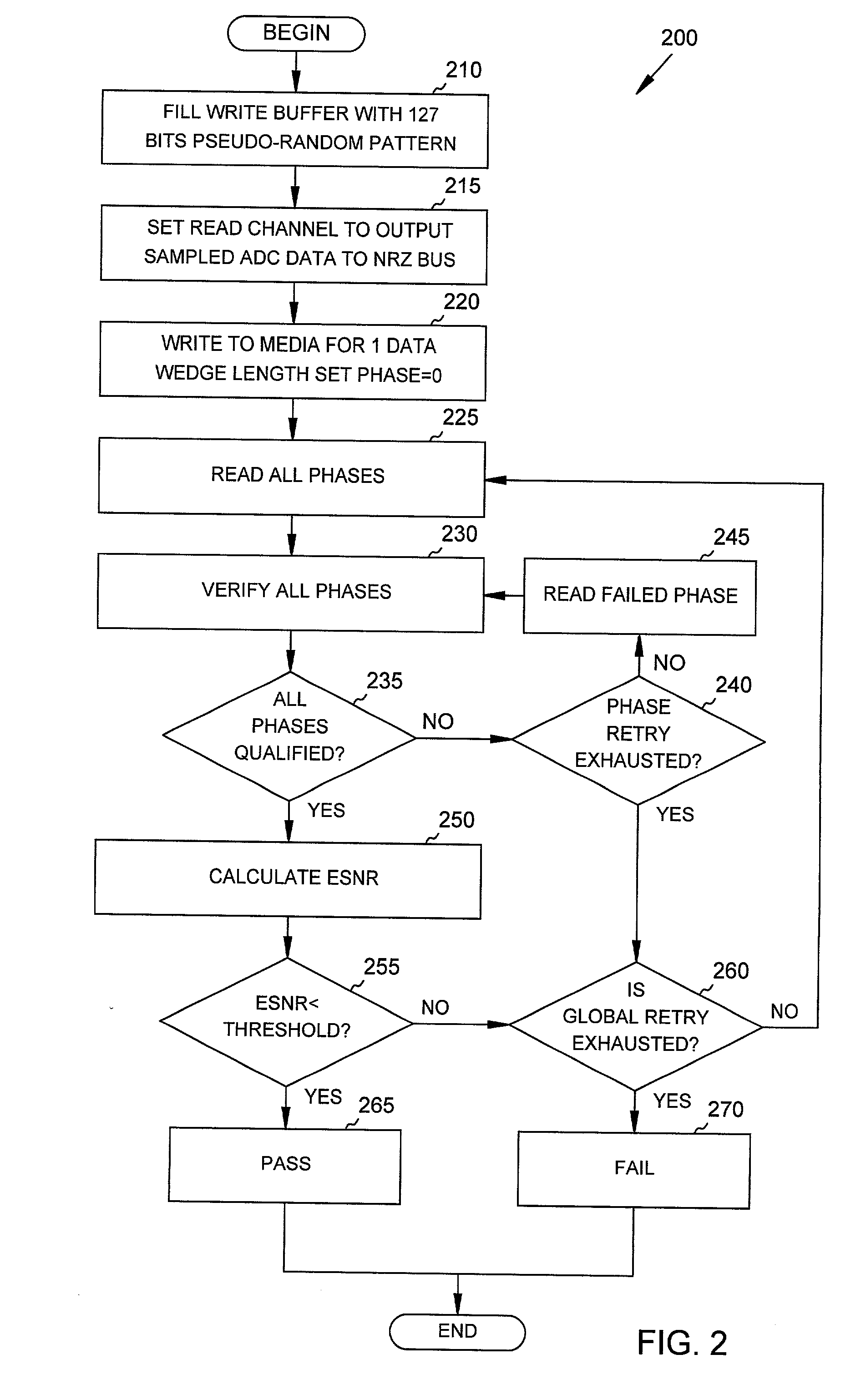

System and method to determine the time domain equalized signal-to-noise ratio of a mass storage device

InactiveUS20020128787A1Accurate measurementLess timeDisc-shaped record carriersError detection/prevention using signal quality detectorTime domainMass storage

Systems and methods are provided through which a time domain equalized signal-to-noise-ratio (ESNR) of an electronic device is determined by executing ESNR determining firmware in the electronic device. The ESNR is used to perform rejection / acceptance testing of the electronic device during manufacturing of the device, and / or to perform read channel tuning and optimization. In one embodiment, determination of the ESNR includes both phase level retry and global level retry.

Owner:SEAGATE TECH LLC

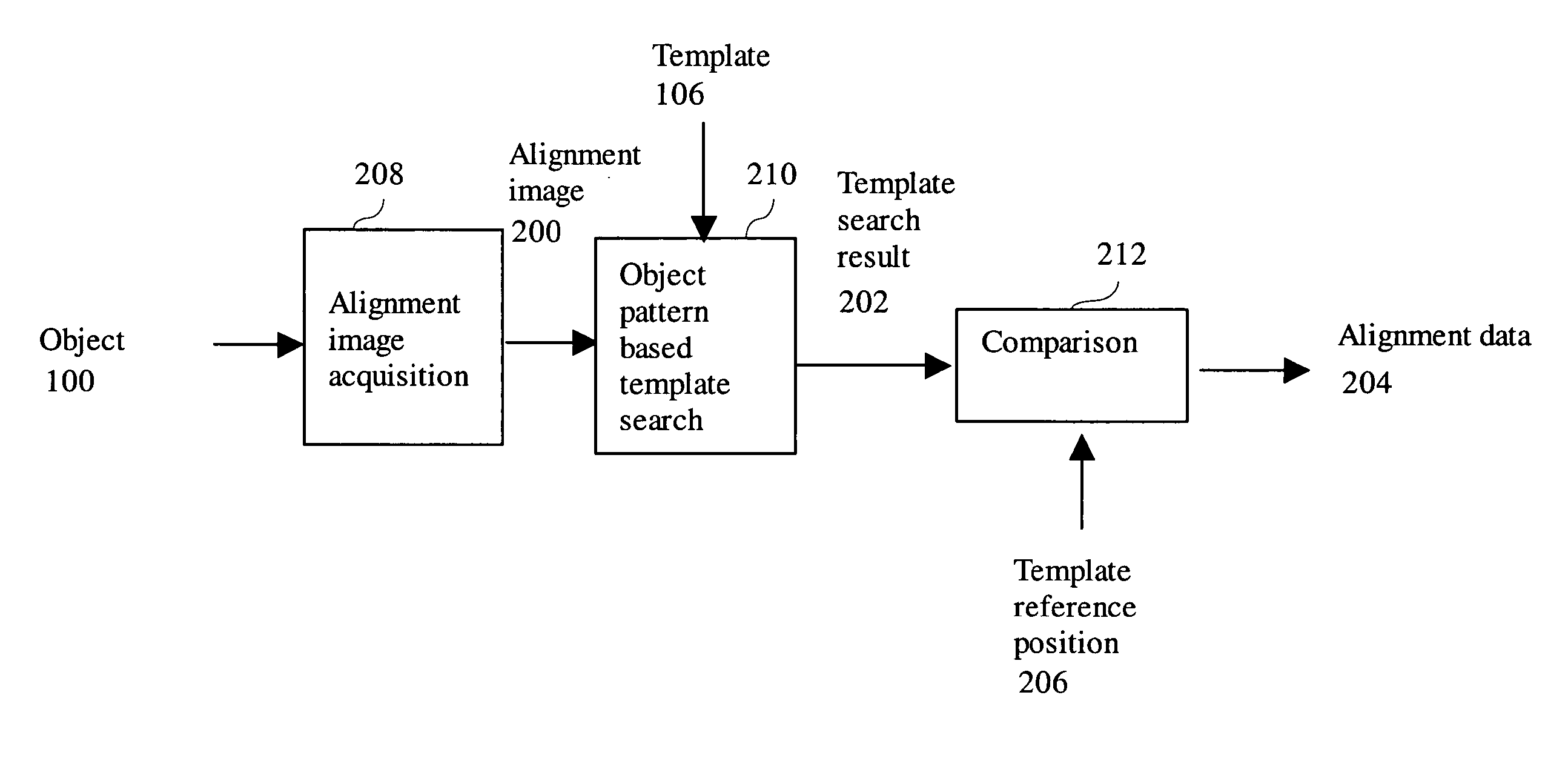

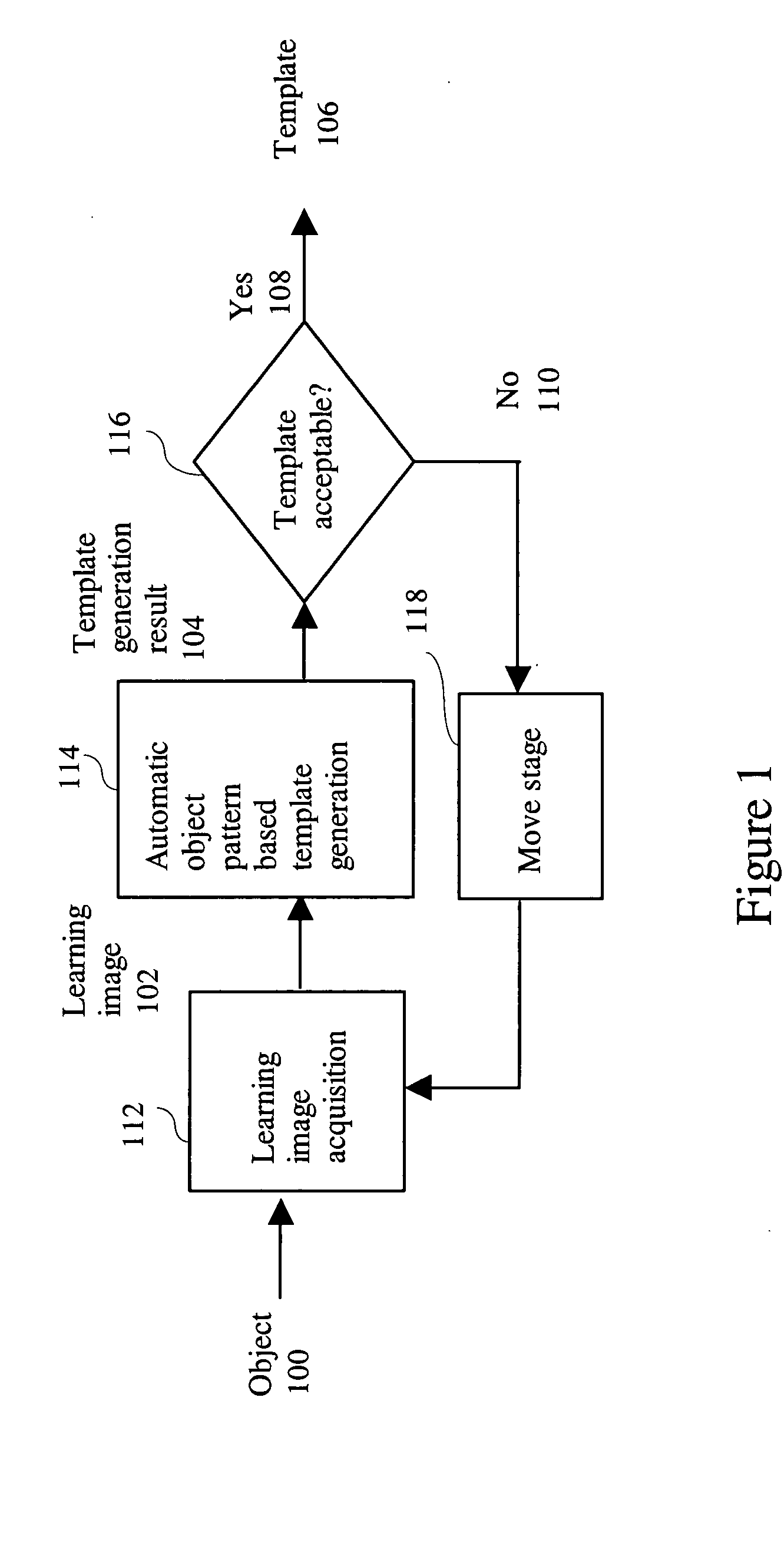

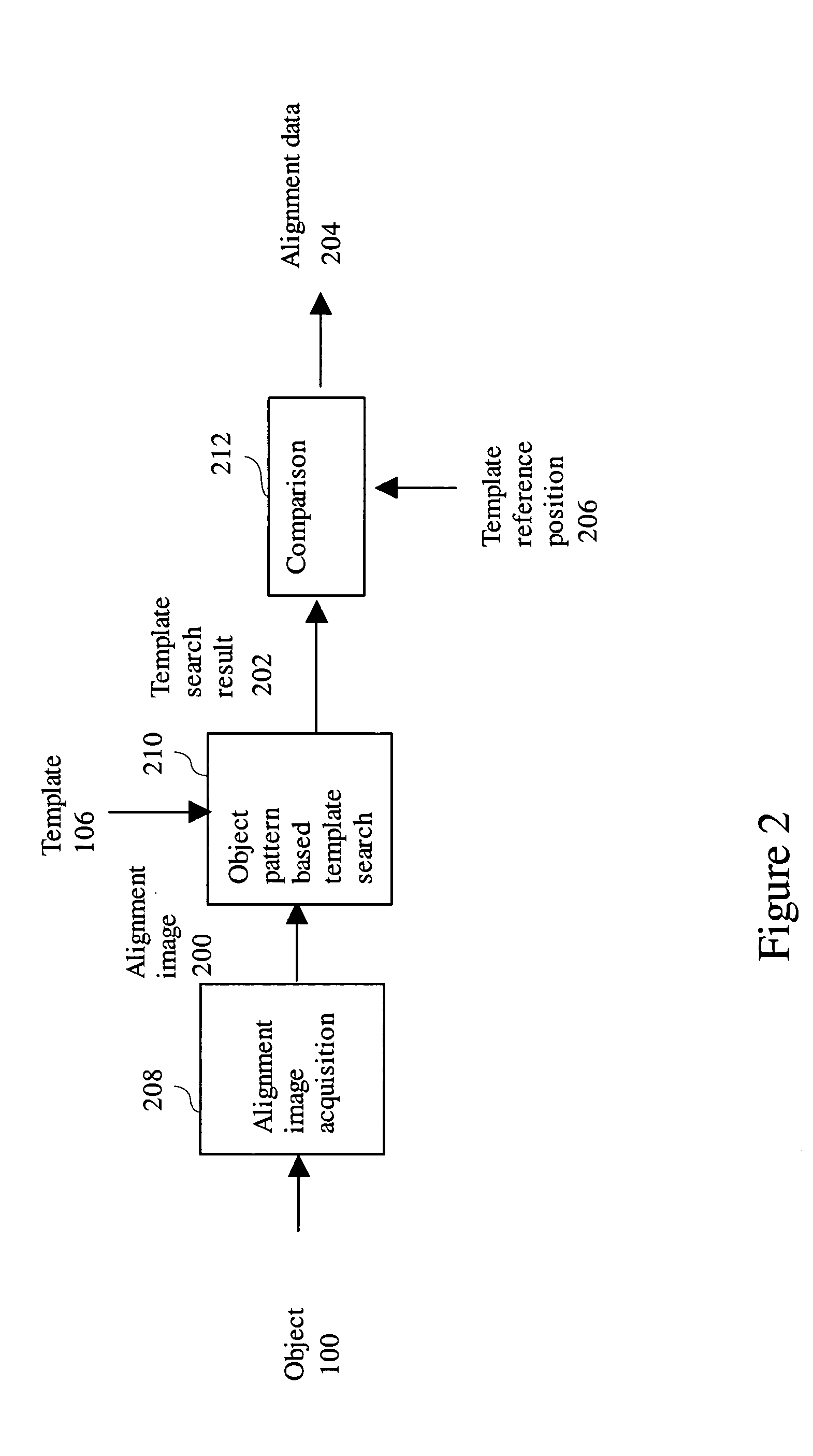

Partition pattern match and integration method for alignment

InactiveUS20060078192A1Improves yield (success rate)Improve accuracyImage enhancementImage analysisTheoretical computer scienceSelf checking

A partition pattern template generation method for alignment receives a learning image and performs partition template generation using the learning image to generate a plurality of partition template result output. A partition template acceptance test is performed using the plurality of partition template results to generate partition templates or failure result. A partition template search method for alignment receives an alignment image and partition templates and performs a plurality of template search steps to generate a plurality of matching scores output. A partition integration method is performed using the plurality of matching scores to generate a partition template search result. A partition integration error self checking method receives a preliminary template search result position and a plurality of the matching scores. A matching score profile comparison is performed using the plurality of the matching scores and the expected matching score profile to generate the template search result.

Owner:NIKON CORP

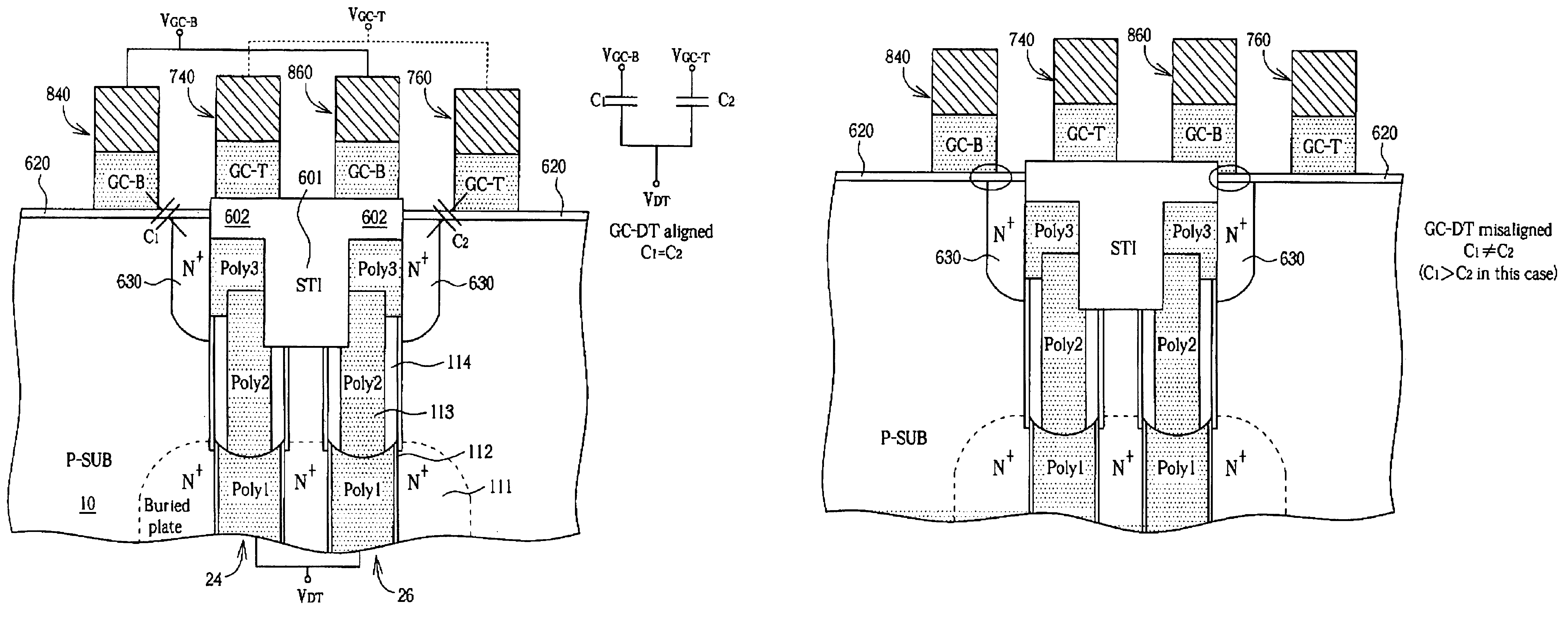

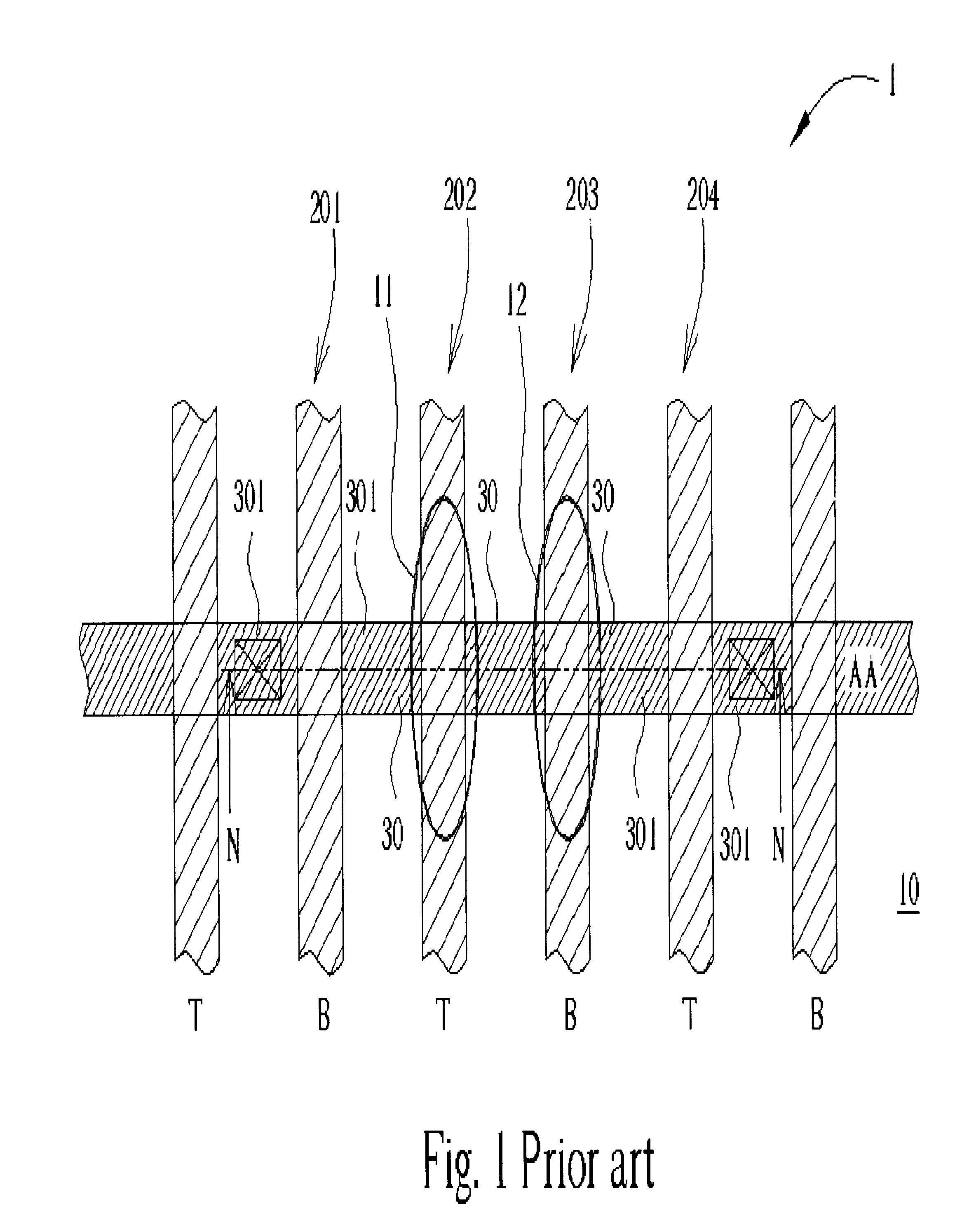

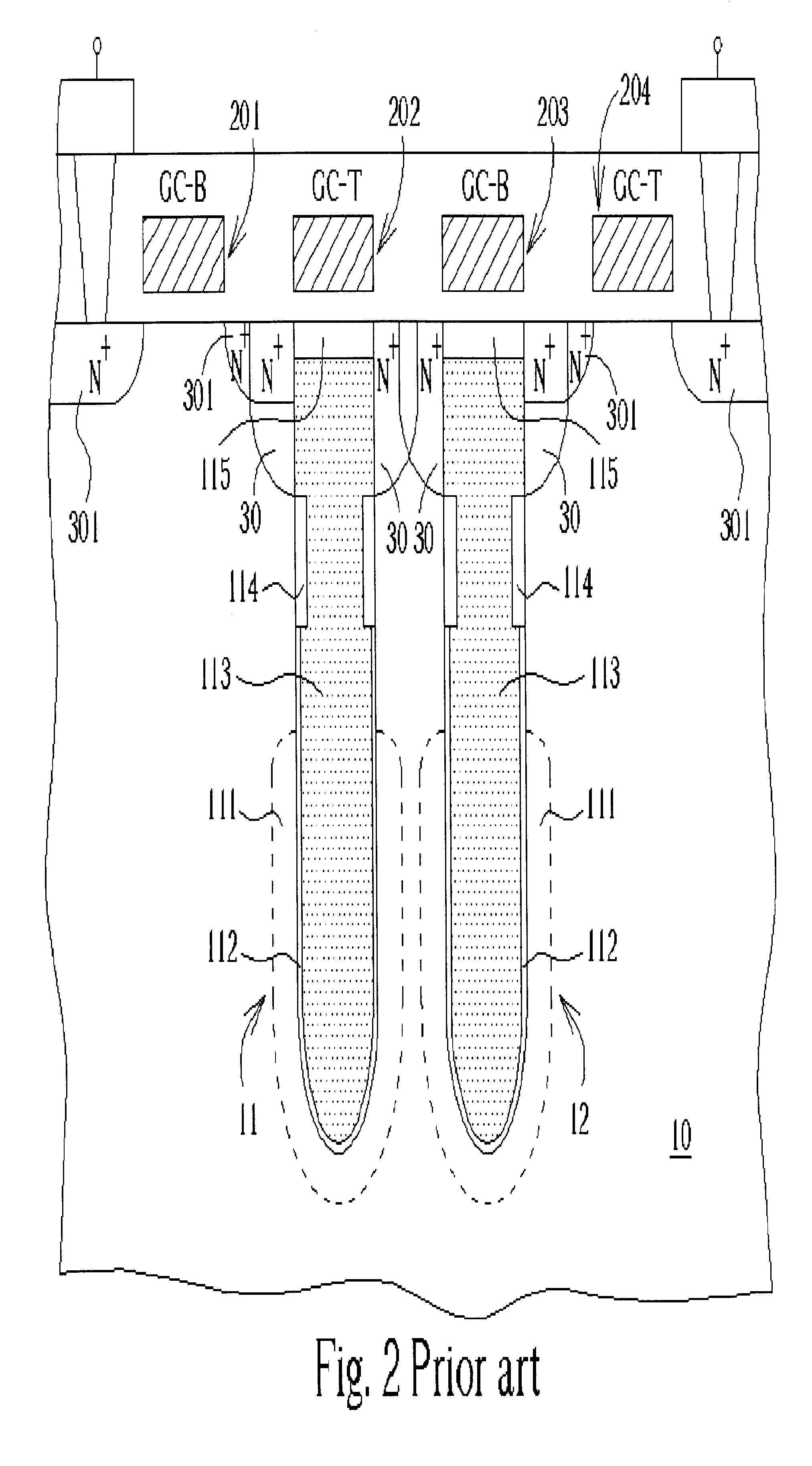

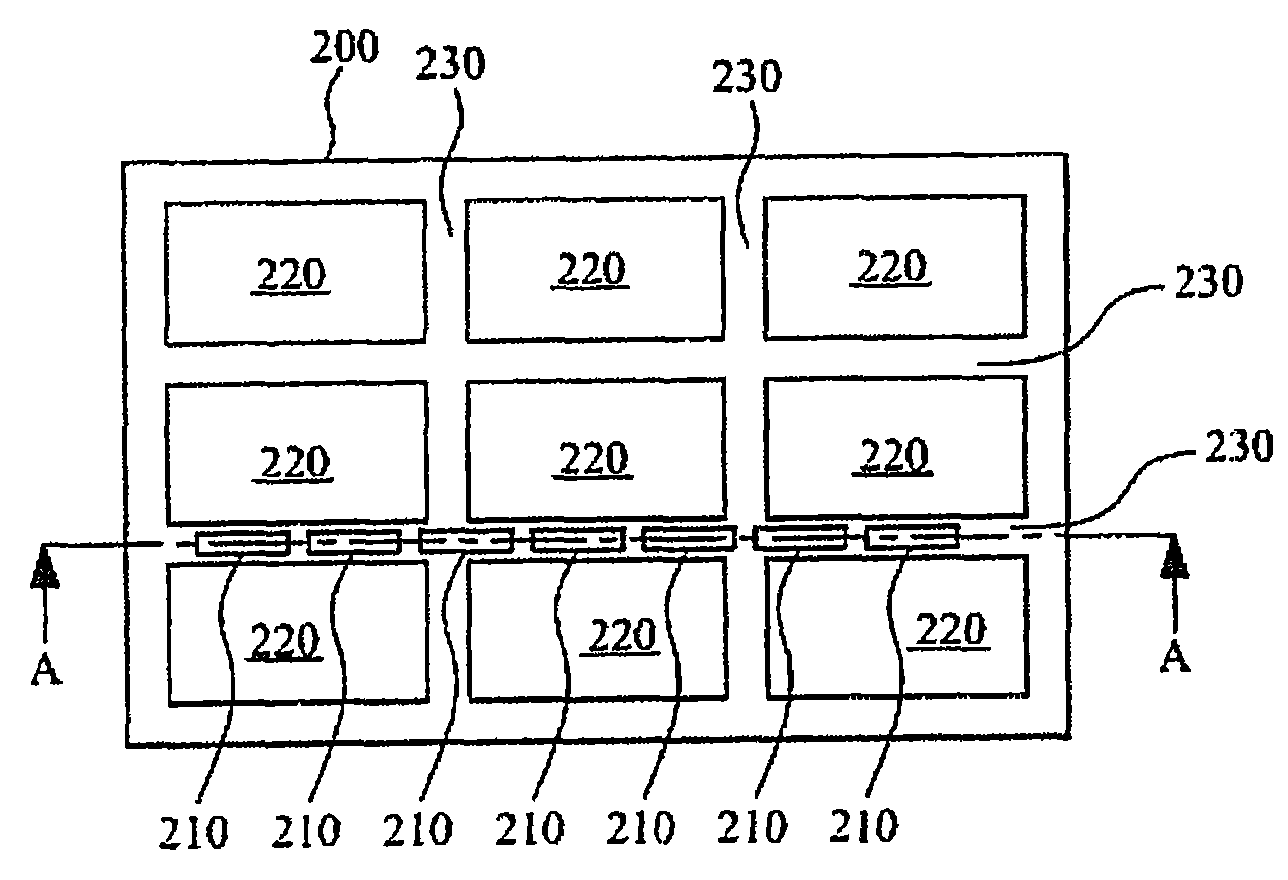

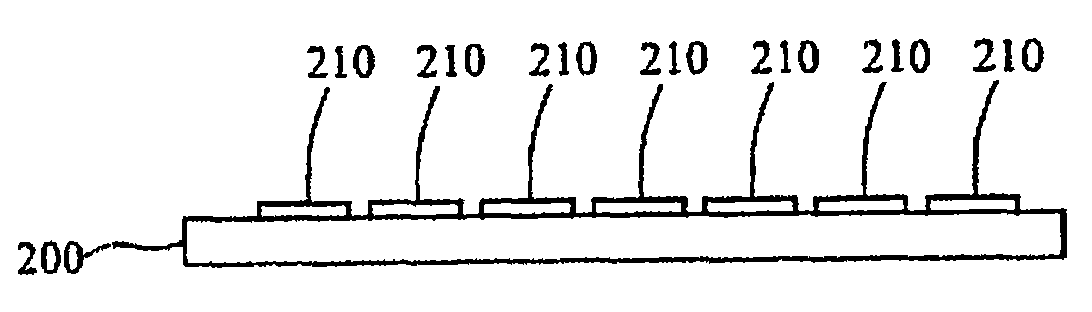

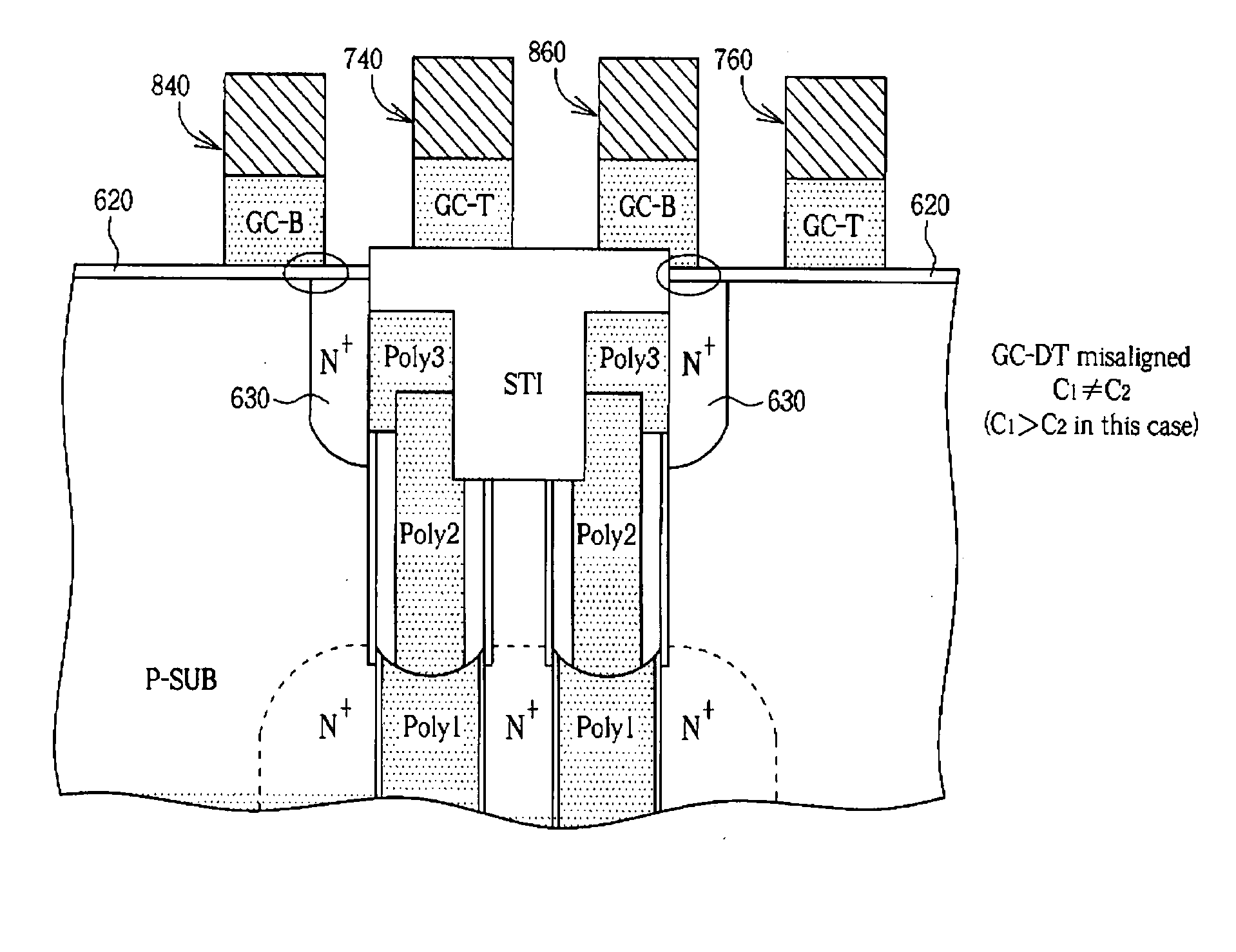

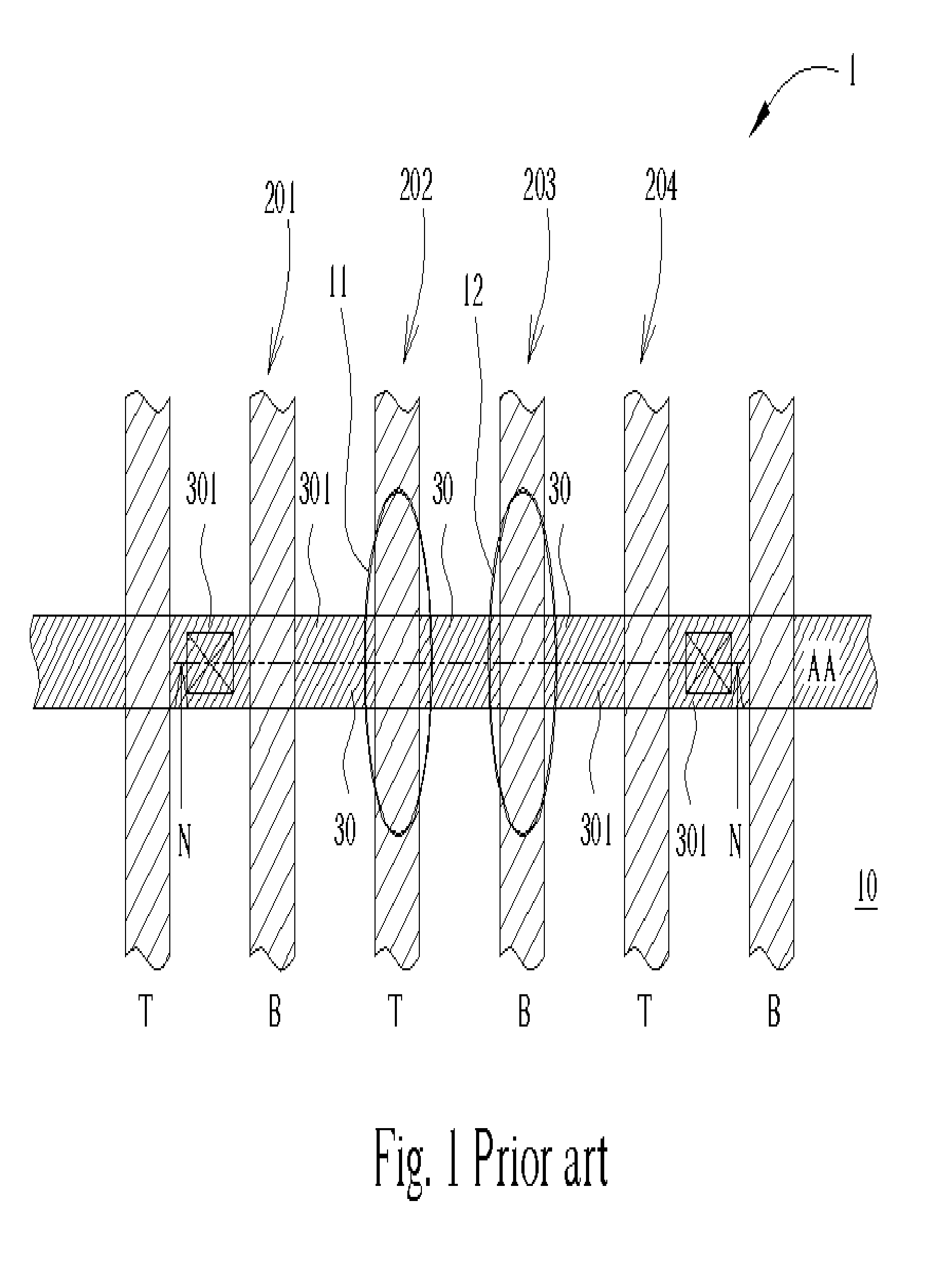

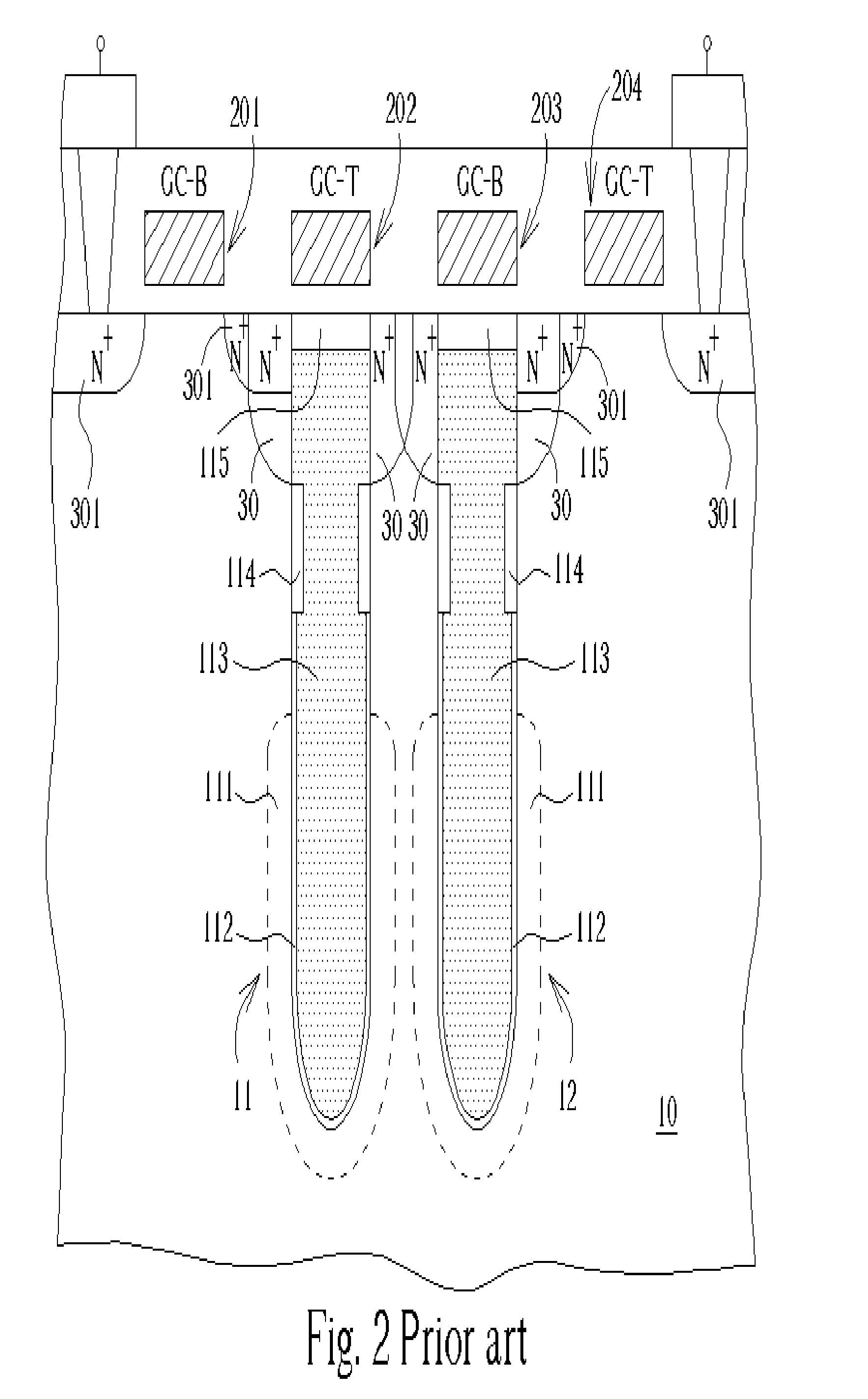

Wafer acceptance testing method and structure of a test key used in the method

ActiveUS6905897B1Accurate monitoringTransistorSemiconductor/solid-state device testing/measurementCapacitanceAcceptance testing

A wafer acceptance testing method for monitoring GC-DT misalignment and a test key structure are disclosed. The test key includes a deep trench capacitor structure biased to a first voltage (VDT). The deep trench capacitor structure includes a buried strap out diffusion region A GC-T electrode layout, which is biased to a second voltage (VGC-T), includes a plurality of columns of GC-T fingers. A GC-B electrode layout, which is biased to a third voltage (VGC-B), includes a plurality of columns of GC-B fingers that interdigitate the GC-T fingers. A first capacitance C1 of a first capacitor contributed by the GC-T fingers and the buried strap out diffusion region is measured. A second capacitance C2 of a second capacitor contributed by the GC-B fingers and the buried strap out diffusion region is measured. The first capacitance C1 and second capacitance C2 are compared, wherein when C1≠C2, GC-DT is misaligned.

Owner:NAN YA TECH

Wafer acceptance testing method, contact mat and probe card

InactiveCN101587165APrevent disengagementReduce widthElectronic circuit testingElectrical measurement instrument detailsProbe cardMechanical engineering

The invention discloses a wafer acceptance testing method, contact mats and a probe card. The wafer acceptance testing method comprises the following steps: firstly, providing a wafer and forming a plurality of devices to be tested and a plurality of scribe lines on the wafer, wherein the devices to be tested are parted by the scribe lines; secondly, arranging at a plurality of strip contact mats linearly in at least one scribe line, wherein the length of the contact mats is greater than the width of the scribe lines and the wide of the contact mats is smaller than the width of the scribe lines; and arranging a plurality of cantilever type probes, arranging the tips of the probes in the same line, and contacting the tips of the probes with the contact mats to test the electrical property of the wafer.

Owner:MPI CORP

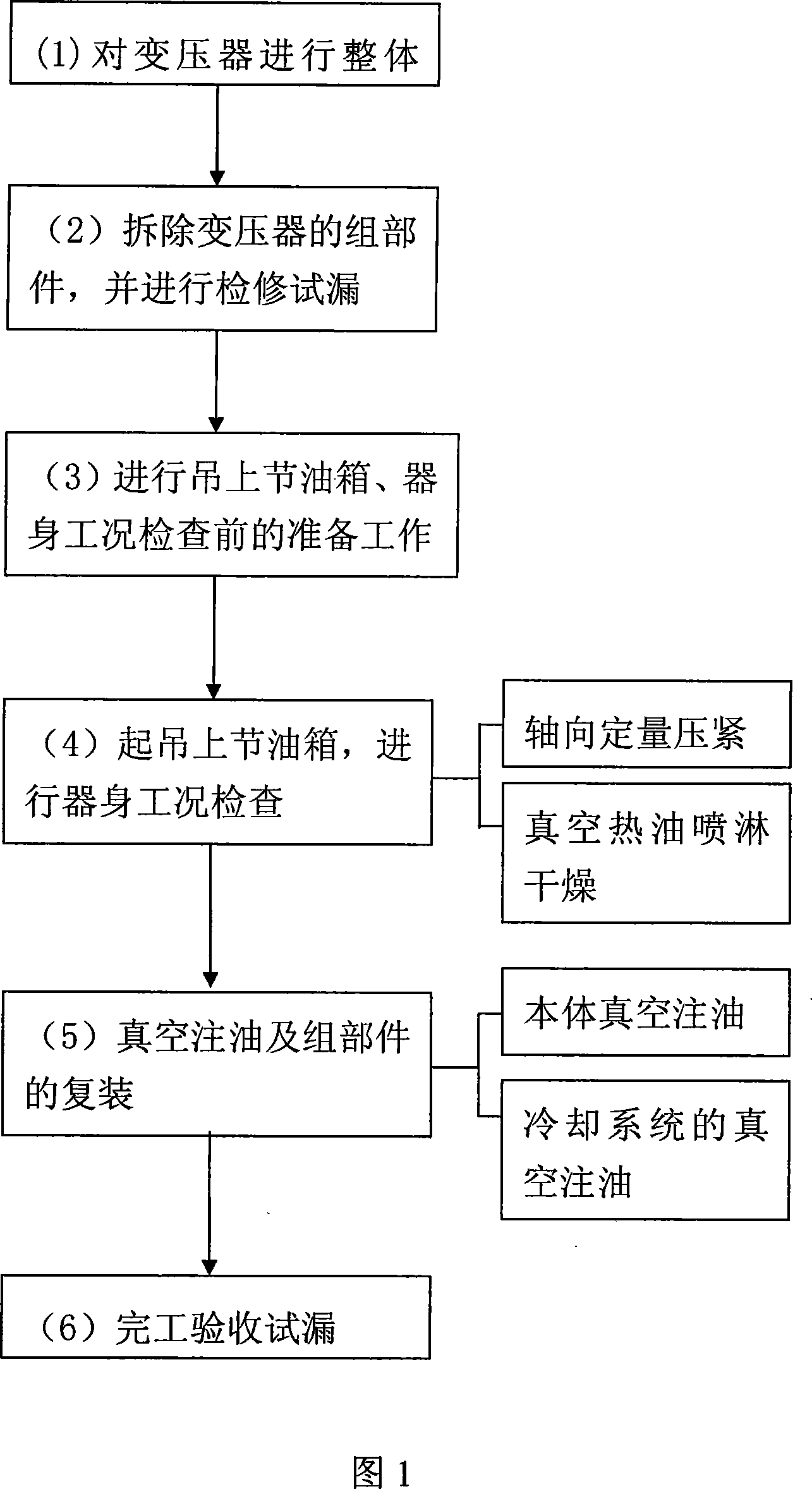

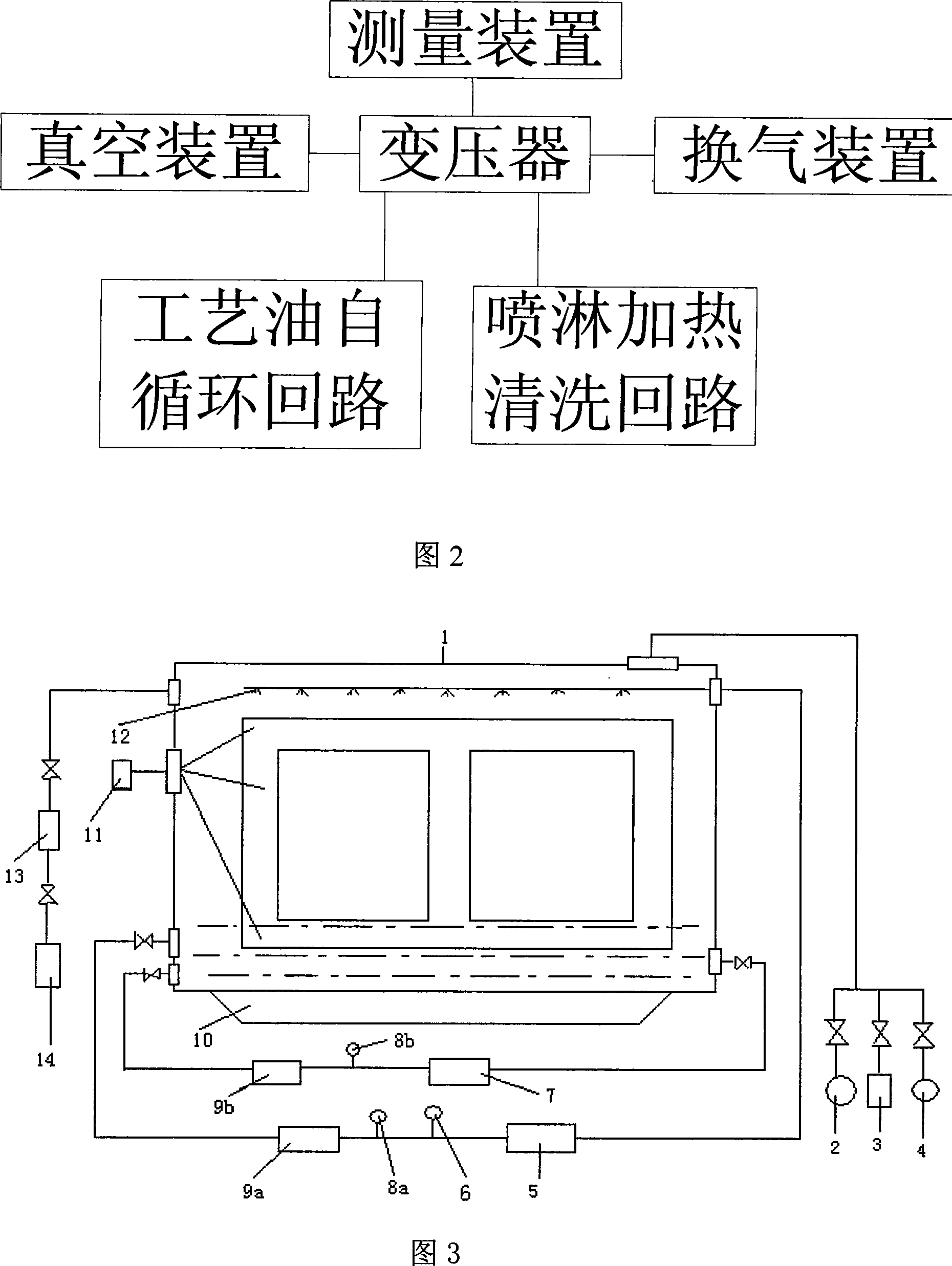

On-site overhaul process of oversize transformer

InactiveCN101226824AGuaranteed reliable performanceNo hydraulic oil leakageInductances/transformers/magnets manufactureTransformerNoise level

A technique for complete overhauling large-size transformer comprises the following steps including (1) conducting whole leak test for the transformer, (2) demounting the assembly and components of the transformer and conducting maintenance, (3) conducting the preparation work before hoisting the upper fuel tank and behavior respecting the machine body, (4) hoisting the upper fuel tank and behavior respecting the machine body, (5) vacuum oiling and replacing the assembly and components, and (6) finishing and acceptance testing. The invention is characterized in that at the same time of conducting step (4), exerting axially quantitative quantification hold-down for the windings and executing vacuum hot oil spraying and drying for the machine body, the vacuum hot oil spraying and drying system comprises a transformer, which is characterized of comprising a spraying, heating and cleaning return circuit, a processing oil self-circulating return circuit, a gas-changing device, measuring device and a vacuum device. The invention has the advantages that (1) the efficiency is high, the hold-down is stable, (2) the process has characteristics of high flow capacity and self-filtering of the processing oil, the flow capacity of the processing oil reaches 70m3 / h and (3) the whole noise level of the transformer is decreased, the ability of resisting short circuit and impact of the transformer is improved.

Owner:TIANJIN SANYUAN POWER TRANSFORMER

Wafer acceptance testing method and structure of a test key used in the method

ActiveUS20050127423A1Accurate monitoringTransistorSemiconductor/solid-state device testing/measurementCapacitanceEngineering

A wafer acceptance testing (WAT) method for monitoring GC-DT misalignment and a test key structure are disclosed. The test key includes a deep trench capacitor structure biased to a first voltage (VDT). The deep trench capacitor structure is formed in a substrate, on which active areas are defined. The deep trench capacitor structure includes a buried strap out diffusion region that is formed within the active area and is electrically connected to the deep trench capacitor structure. The deep trench capacitor structure is isolated by shallow trench isolation (STI). A GC-T electrode layout and a GC-B electrode layout are formed over the substrate. The GC-T electrode layout, which is biased to a second voltage (VGC-T), includes a plurality of columns of GC-T fingers. The GC-B electrode layout, which is biased to a third voltage (VGC-B), includes a plurality of columns of GC-B fingers that interdigitate the plurality of columns of GC-T fingers over the active areas and STI. A first capacitance C1 of a first capacitor contributed by the plurality of columns of GC-T fingers and the buried strap out diffusion region is measured. A second capacitance C2 of a second capacitor contributed by the plurality of columns of GC-B fingers and the buried strap out diffusion region is measured. The first capacitance C1 and second capacitance C2 are compared, wherein when C1≠C2, GC-DT is misaligned.

Owner:NAN YA TECH

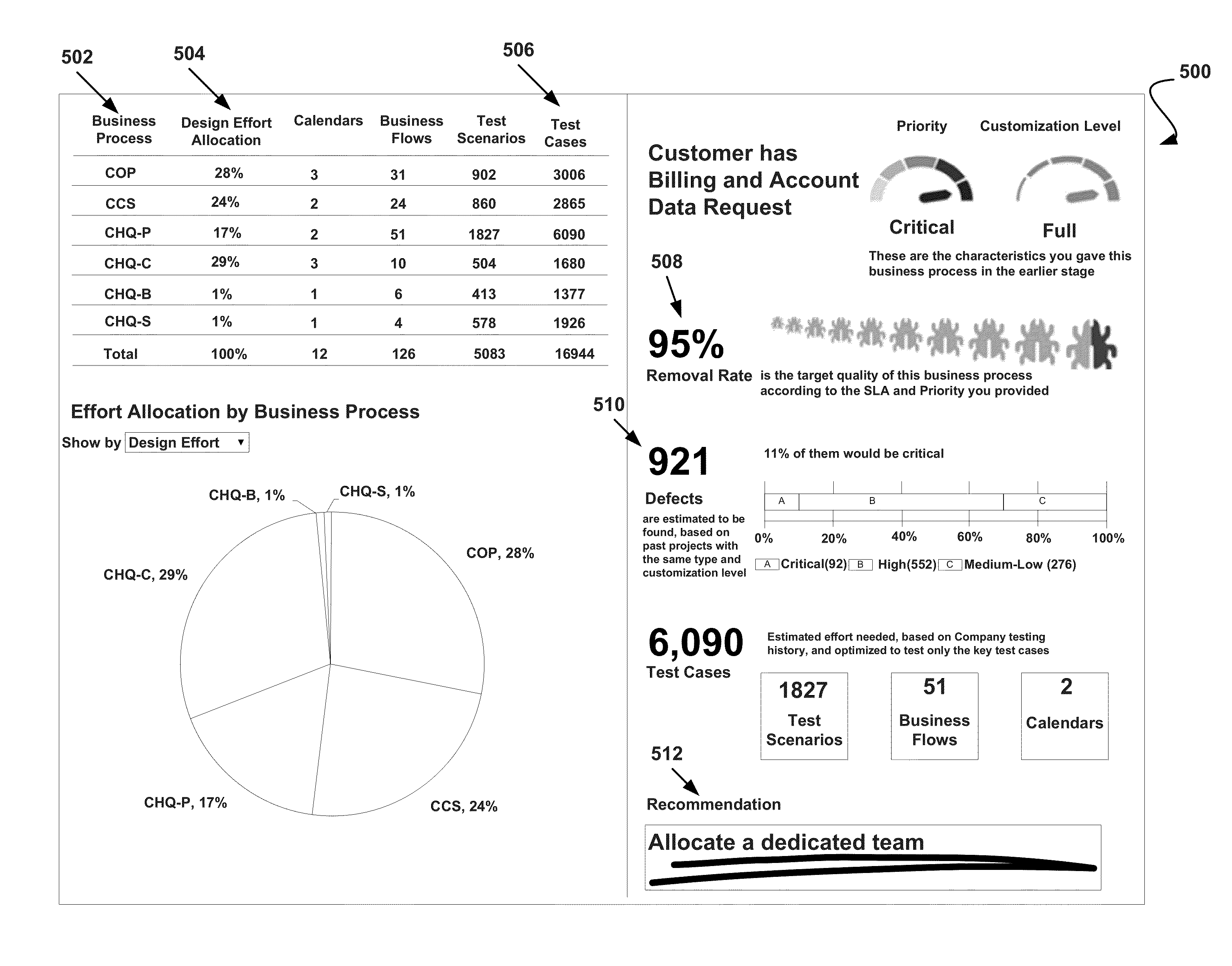

System, method, and computer program for recommending a number of test cases and effort to allocate to one or more business processes associated with a software testing project

ActiveUS9201768B1Software testing/debuggingSpecific program execution arrangementsQuality levelBusiness process

A system, method, and computer program product are provided for recommending a number of test cases and effort to allocate to one or more business processes associated with a software testing project. In use, one or more business processes associated with a software testing project are identified. A business priority and customization level is set for each of the one or more business processes associated with the software testing project Additionally, a number of defects are estimated for each of the one or more business processes associated with the software testing project. Further, a quality level is determined for each of the one or more business processes associated with the User Acceptance Testing software testing project. In addition, a number of test cases to be executed to achieve the quality level is determined for each of the one or more business processes associated with the software testing project, the number of test cases to be executed to achieve the desired quality level being based, at least in part, on the estimated number of defects and the business priority. Furthermore, an effort analysis associated with one or more past software testing projects is identified. Moreover, an estimated effort is determined for each of the one or more business processes associated with the software testing project, the estimated effort being based, at least in part, on the number of test cases to be executed to achieve the quality level, the business priority, and the effort analysis of the one or more past software testing projects. Still yet, the estimated effort is displayed for at least one of the one or more business processes associated with the software testing project utilizing at least one interface.

Owner:AMDOCS SOFTWARE SYST +1

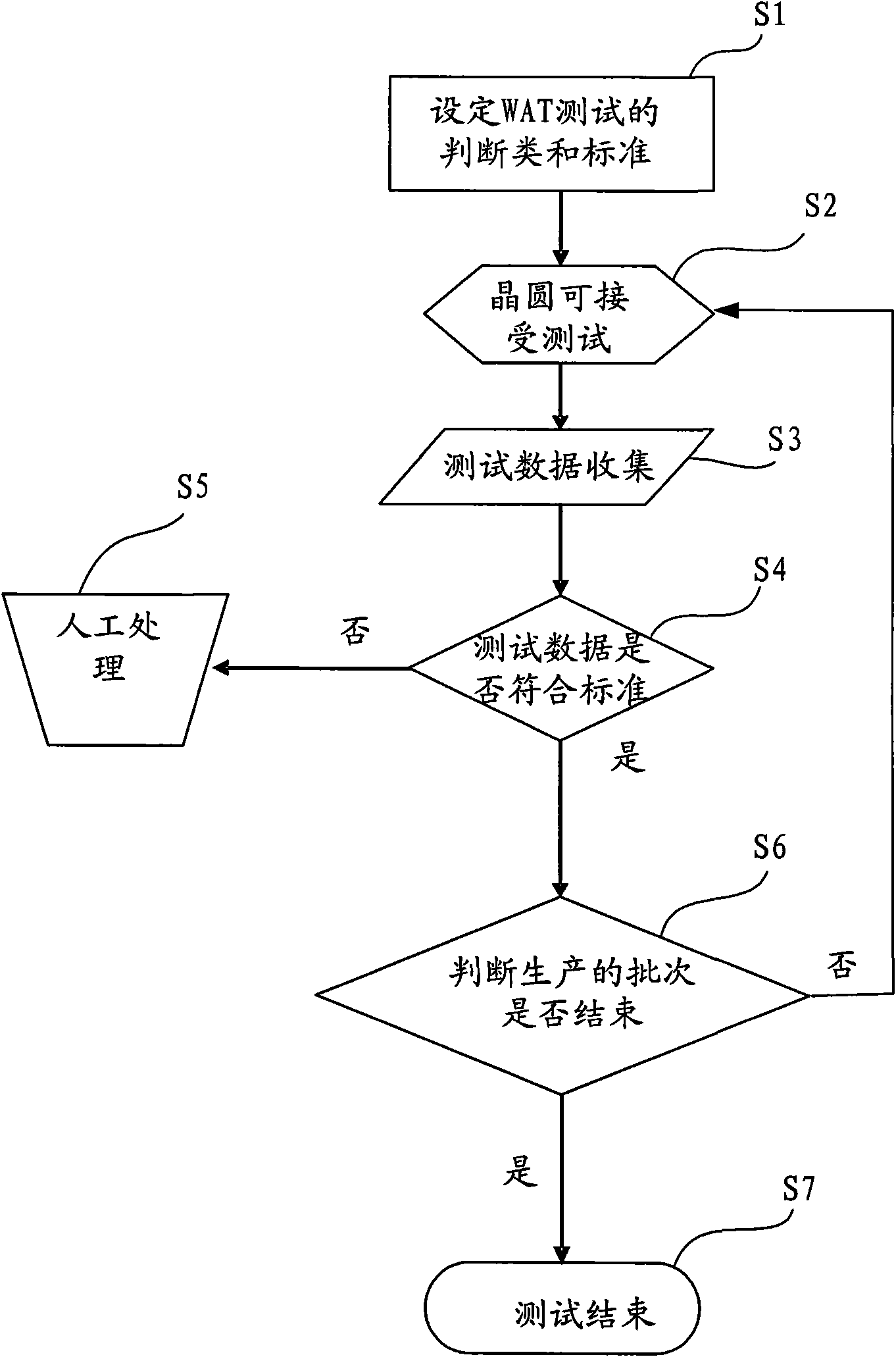

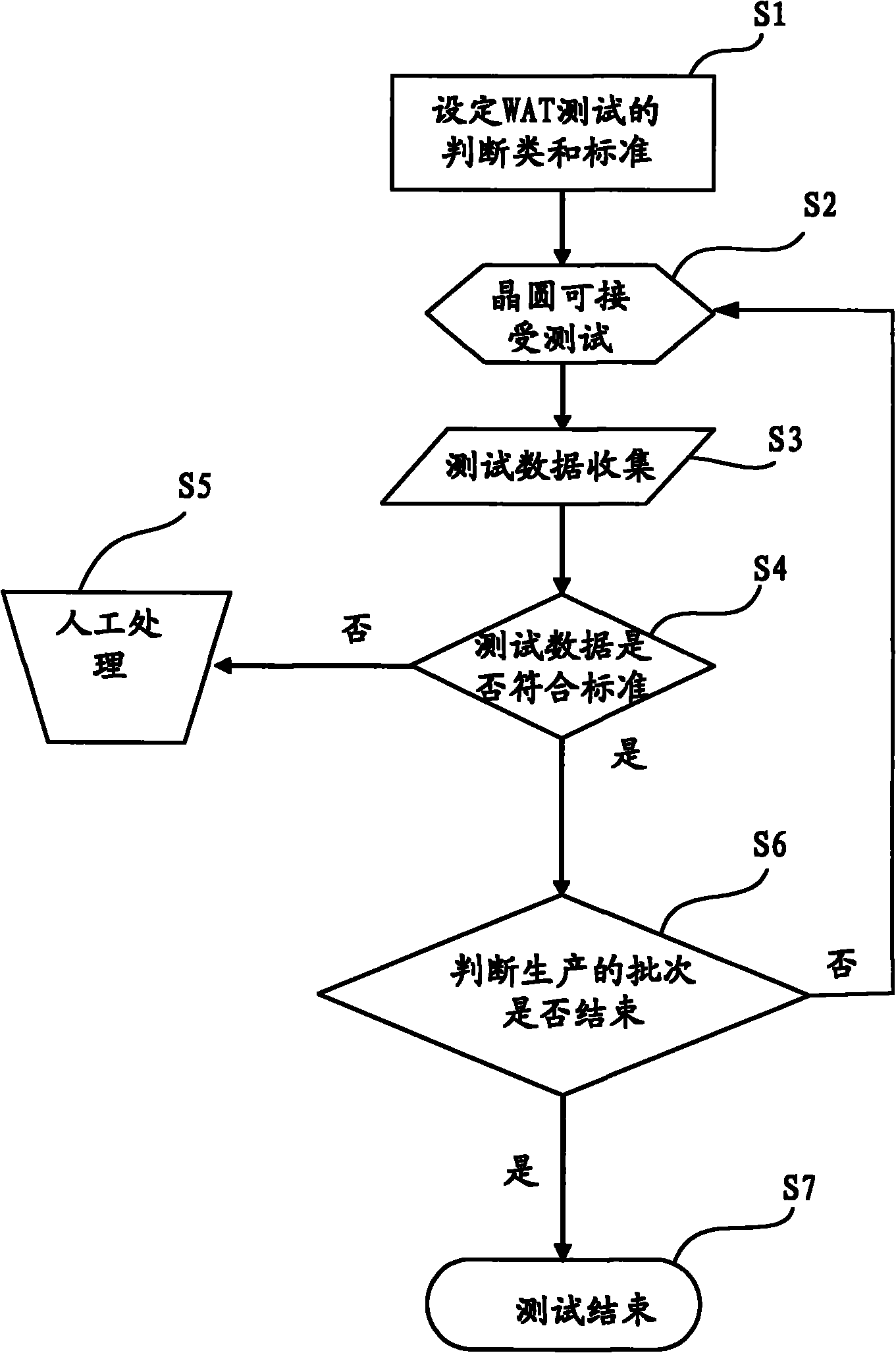

Real-time monitoring method of acceptance test of wafer

InactiveCN101996856AAvoid scratchesReduce lossesSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingProbe cardManual handling

The invention discloses a real-time monitoring method of an acceptance test of a wafer, the wafer is divided into a plurality of points, each point comprises a plurality of test parameters for testing, and part of the parameters are key parameters, and the real-time monitoring method comprises the following steps: setting the type and the judgment standard of the acceptance test of the wafer; carrying out the acceptance test on the wafer; collecting and managing test data obtained by the acceptance test of the wafer; and carrying out judgment according to the type and the judgment standard, monitoring the test data, continuing the test if being judged to be qualified, otherwise, suspending the test and transferring into manual handling. Compared with the prior art, the real-time monitoring method of the acceptance test of the wafer can monitor the data tested by a chip on each wafer, find whether a probe of a probe card is aimed at a probe point on the corresponding chip in time, further avoid the follow-up batch of the chips to be tested from being scratched and reduce the loss.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

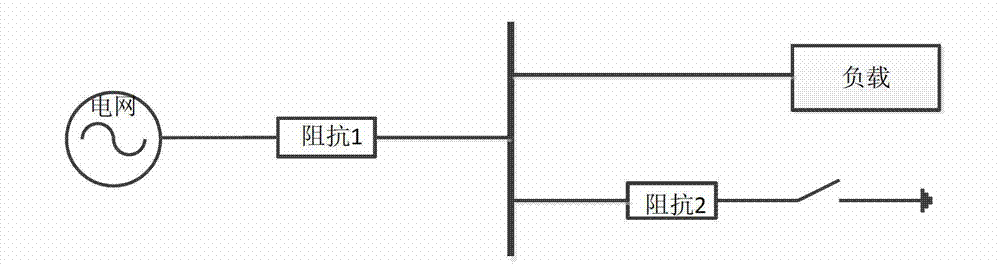

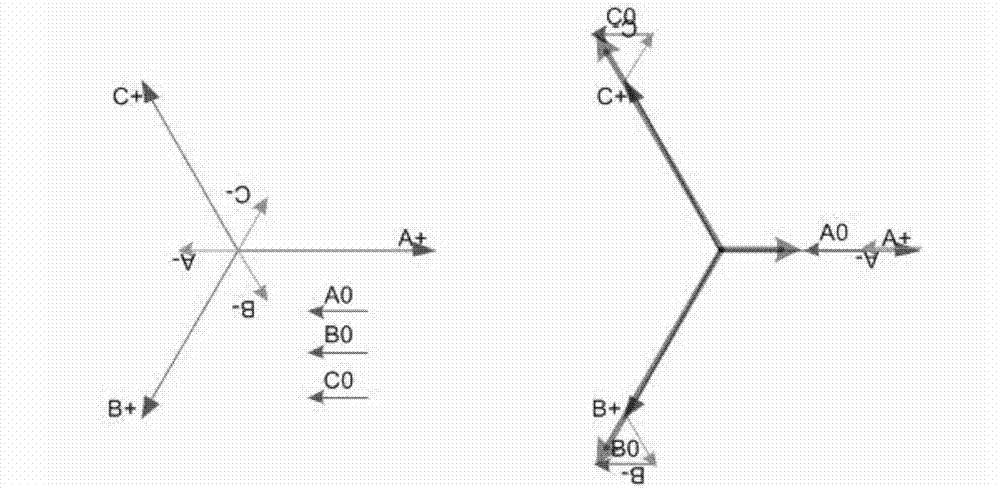

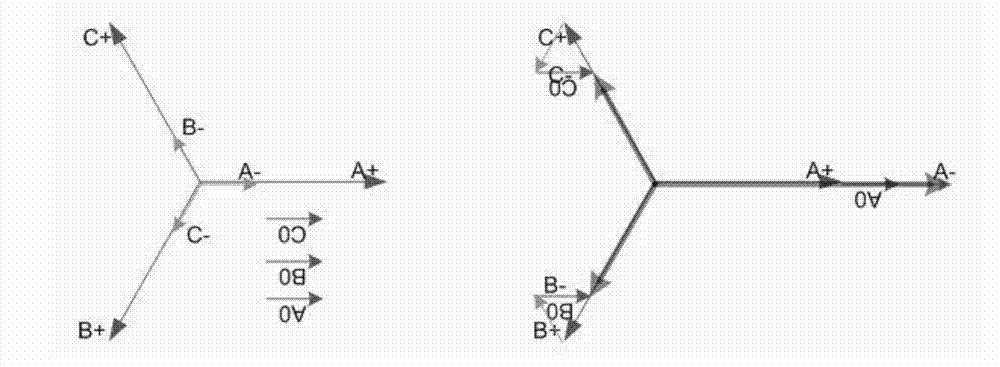

Low voltage generator used for low voltage ride through testing and voltage control method of low voltage generator

ActiveCN103178546ASingle network parallel feeding arrangementsWind energy generationVoltage dropEngineering

The invention relates to a low voltage generator used for low voltage ride through testing and a voltage control method of the low voltage generator. The modulation degree of a d-axis positive sequence and d-axis negative sequence are respectively given, and various voltage drop working conditions such as single-phase unbalance drop, two-phase unbalance drop and three-phase balance drop can be obtained. As the whole device adopts the power electronic converter and applies a full-digital control technology, the low voltage generator has the advantages of simple and flexible control, small device volume, low cost and the like, and can be widely used in on-site grid-connection and acceptance testing of photovoltaic power stations and wind power plants.

Owner:XJ ELECTRIC +2

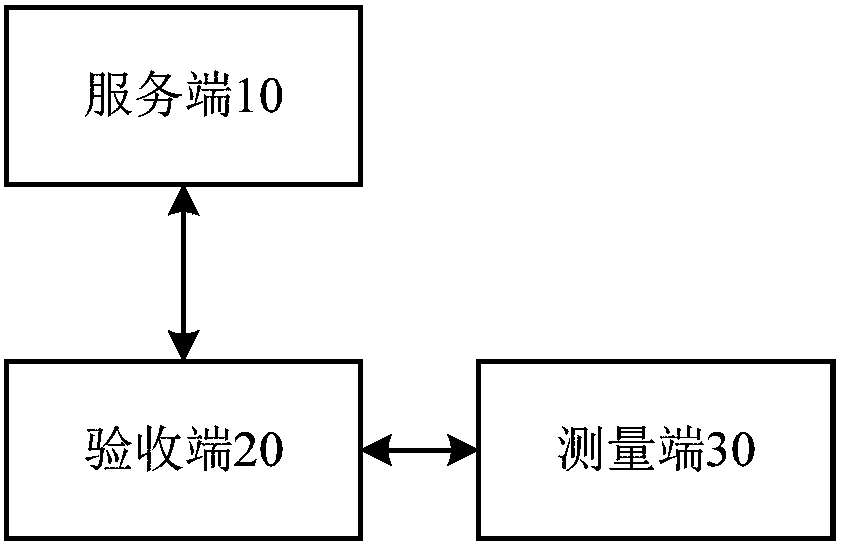

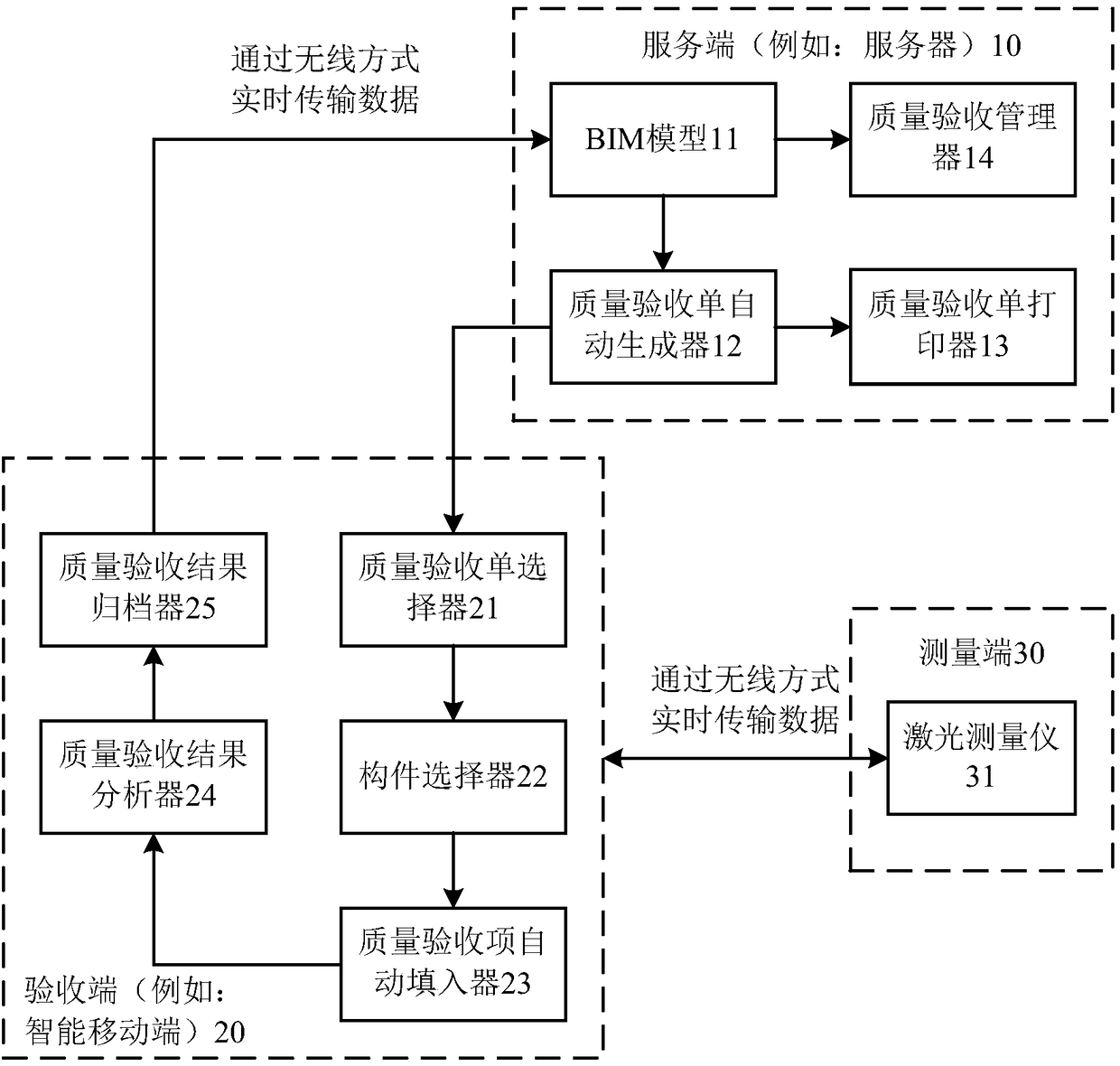

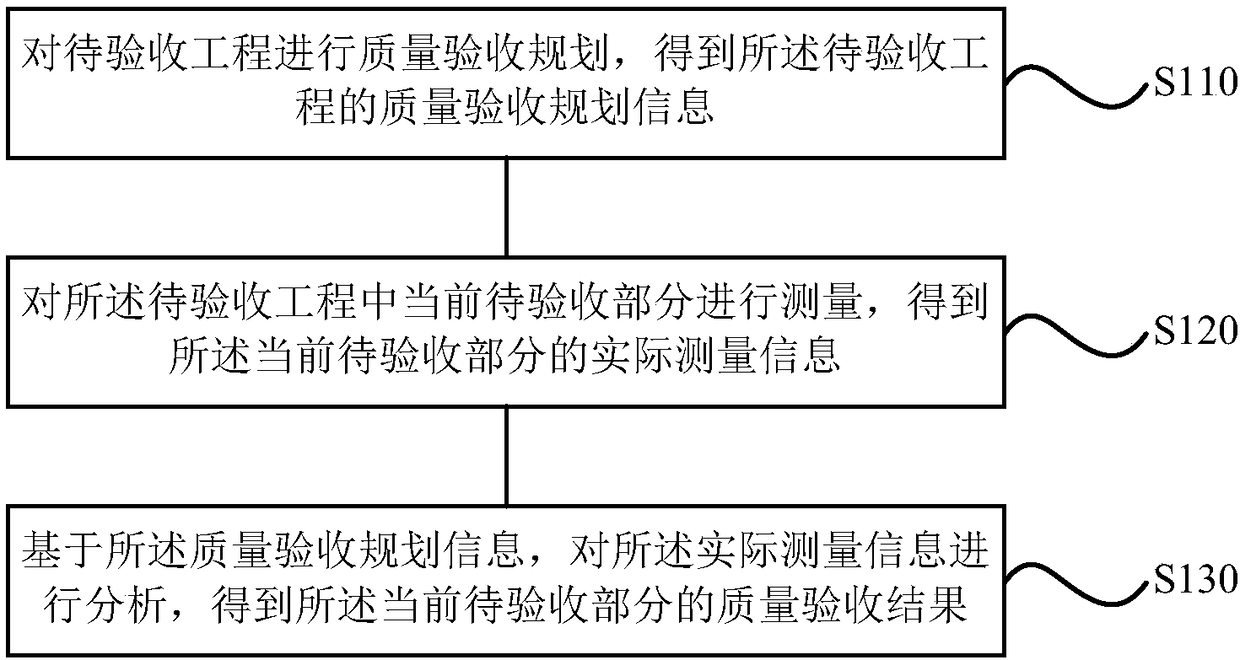

Project quality acceptance device and method

ActiveCN108074032AQuickly generate quality acceptance resultsAchieve the effect of remote supervision quality acceptance workResourcesWork qualityAcceptance testing

The invention discloses a project quality acceptance device and method. The device comprises a service end (10), a measuring end (30) and an acceptance end (20); the service end (10) is used to make aquality acceptance plan for a to-be-accepted project and obtain quality acceptance plan information of the to-be-accepted project; the measuring end (30) is used to measure a part to be accepted at present in the to-be-accepted project and obtain practical measurement information of the part to be accepted at present; and on the basis of the quality acceptance plan information, the acceptance end(20) analyzes the practical measurement information and obtains a quality acceptance result of the part to be accepted at present. Via schemes of the invention, defects including that the working efficiency is low, data is hard to track, and the data accuracy and project quality are hard to ensure in the prior art are overcome, and the working efficiency is high, data can be traced, and the dataaccuracy and project quality can be ensured.

Owner:SHANGHAI NO 4 CONSTR

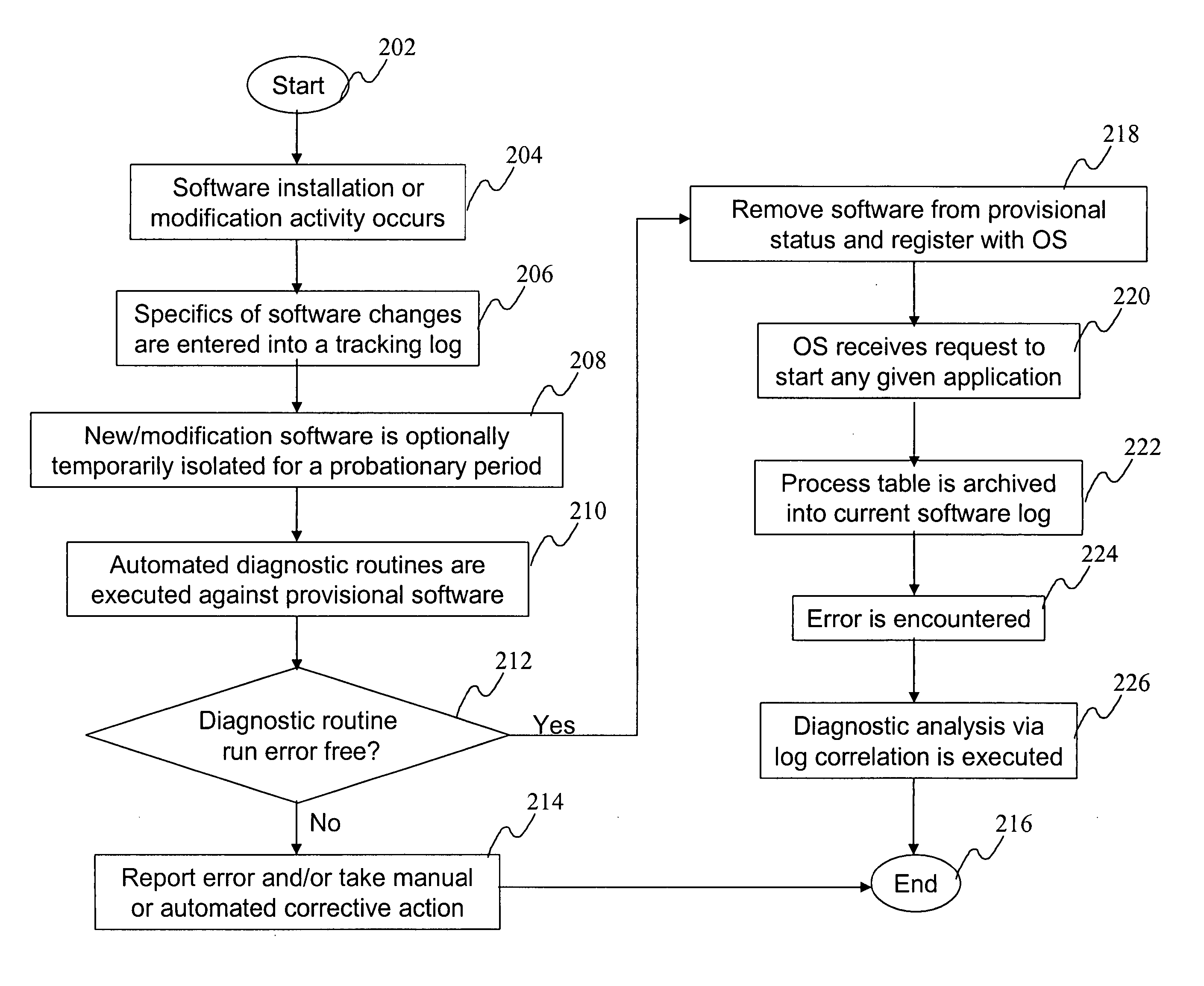

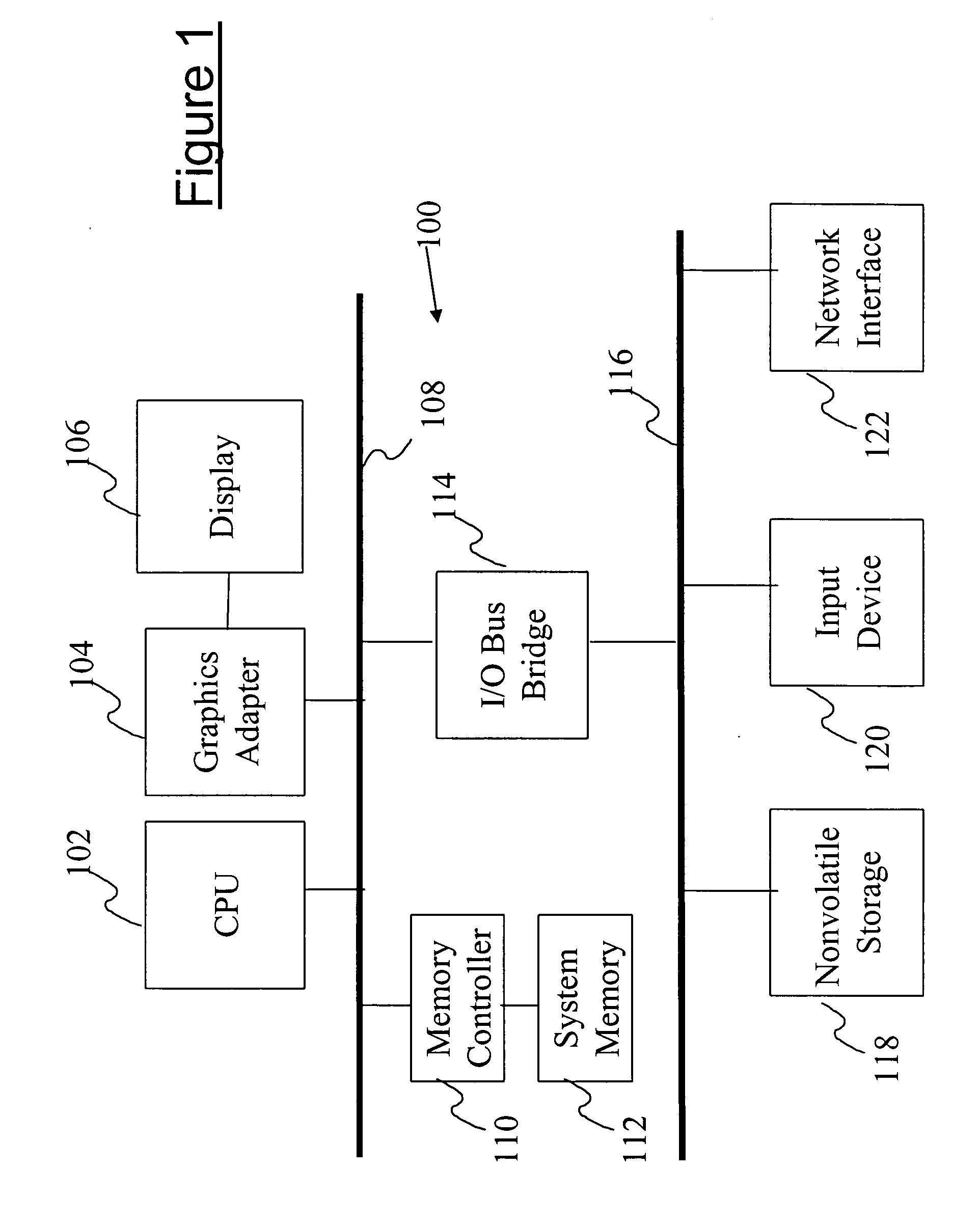

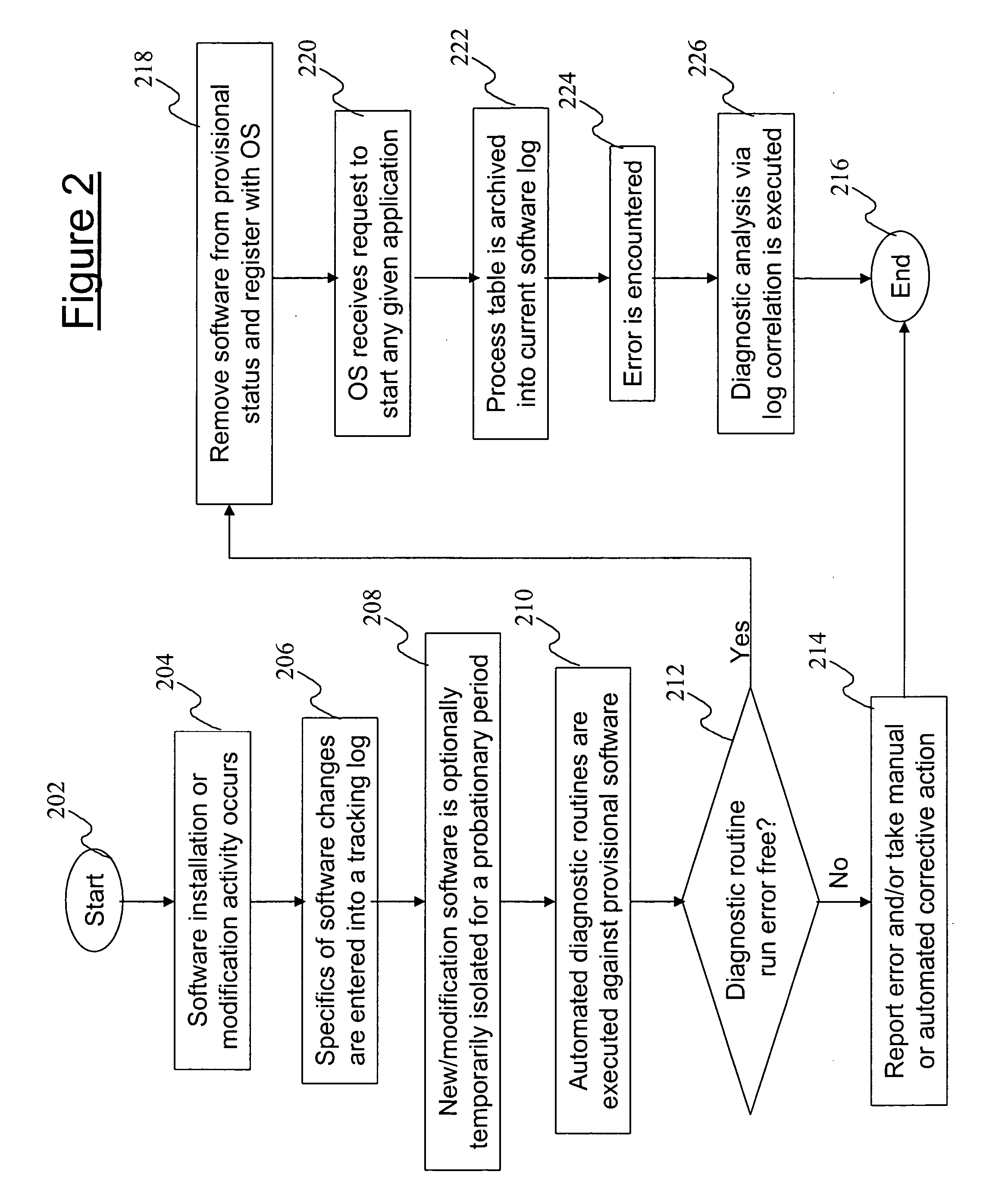

Provisional application management with automated acceptance tests and decision criteria

InactiveUS20060168165A1Error detection/correctionDigital computer detailsComputer compatibilityAcceptance testing

A method and system for testing newly installed or recently upgraded software is presented. All software installation activities are tracked and logged. New and upgrade software is isolated, either physically or logically, and tested using diagnostic software. If the new / upgrade isolated software passes the testing by the diagnostic software, then it is allowed to operate in the presence of other previously installed software. If an error occurs during an execution of the new / upgrade software, either while isolated or in the presence of previously loaded software, a log of other concurrently running software is reviewed to determine a likely software incompatibility with the new / upgrade software.

Owner:IBM CORP

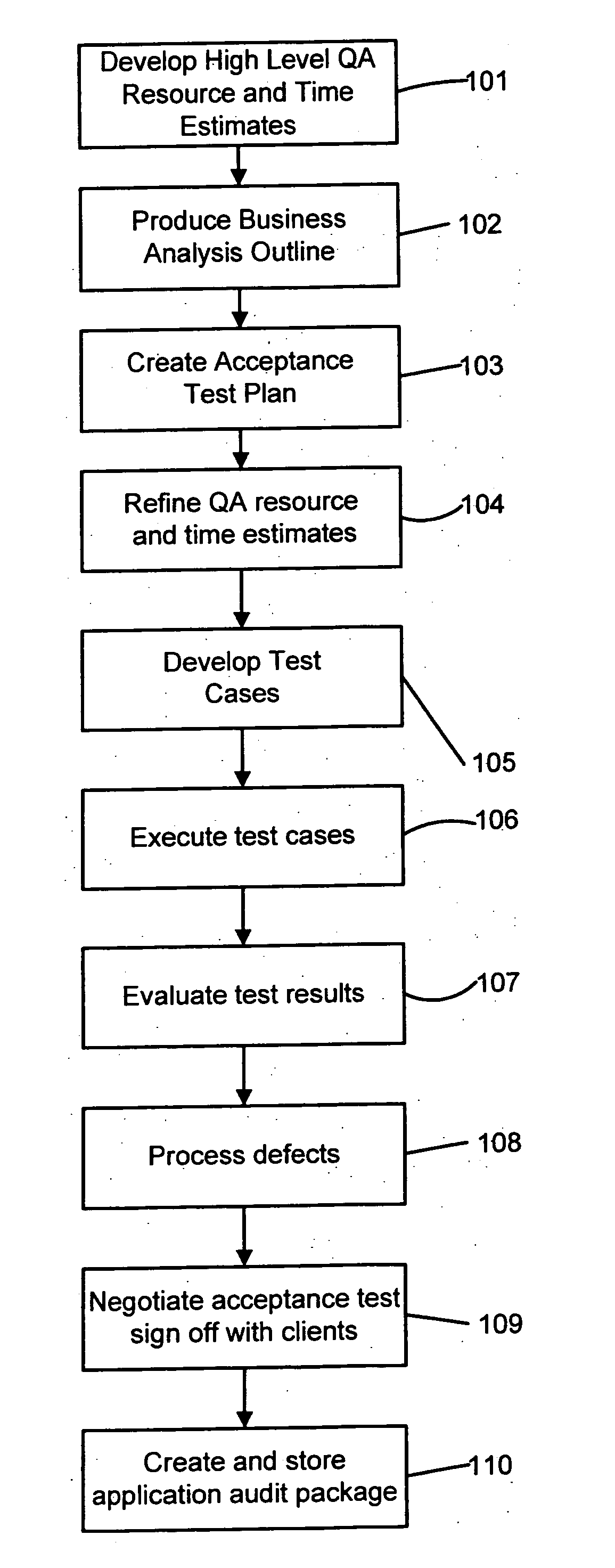

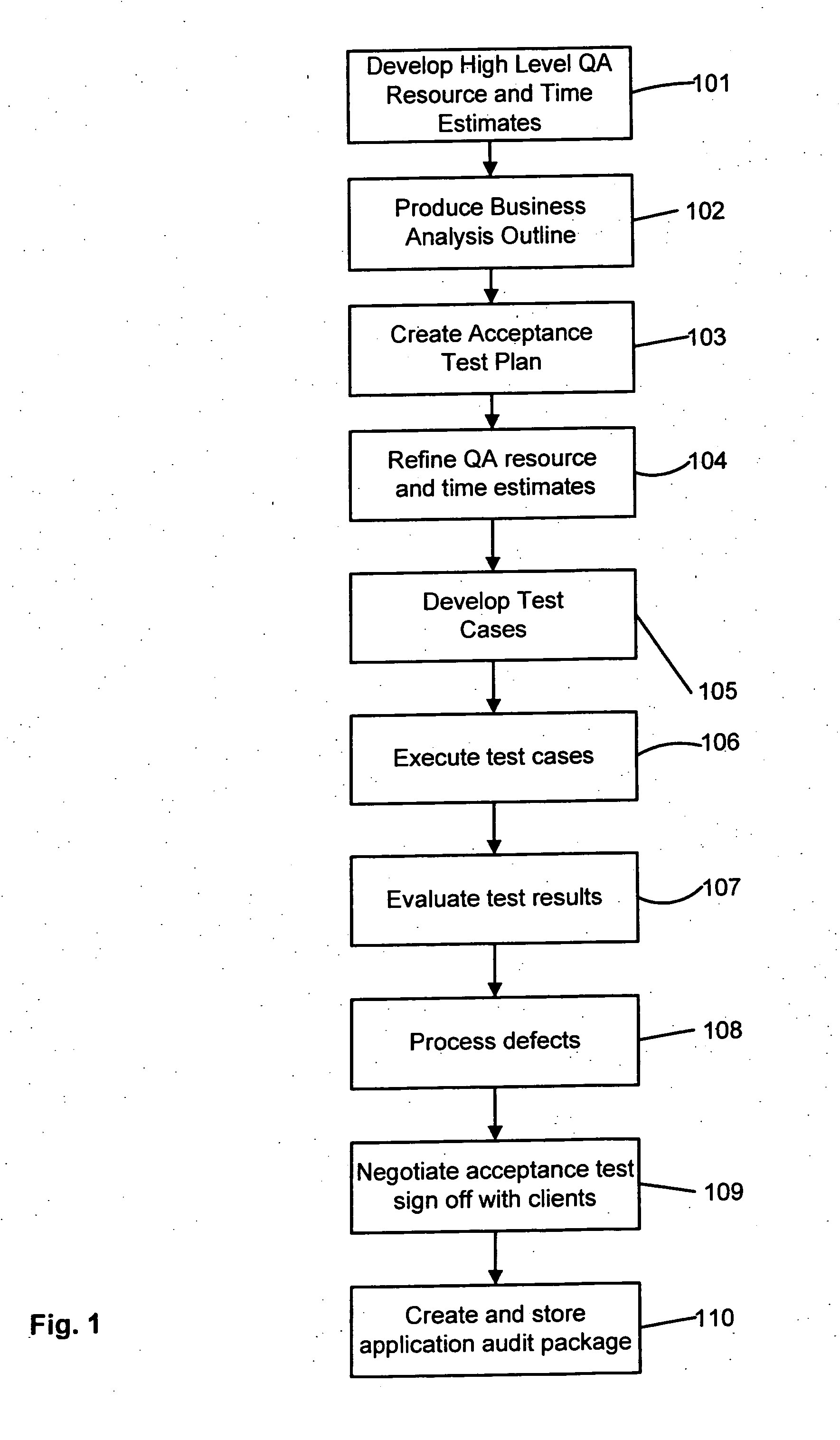

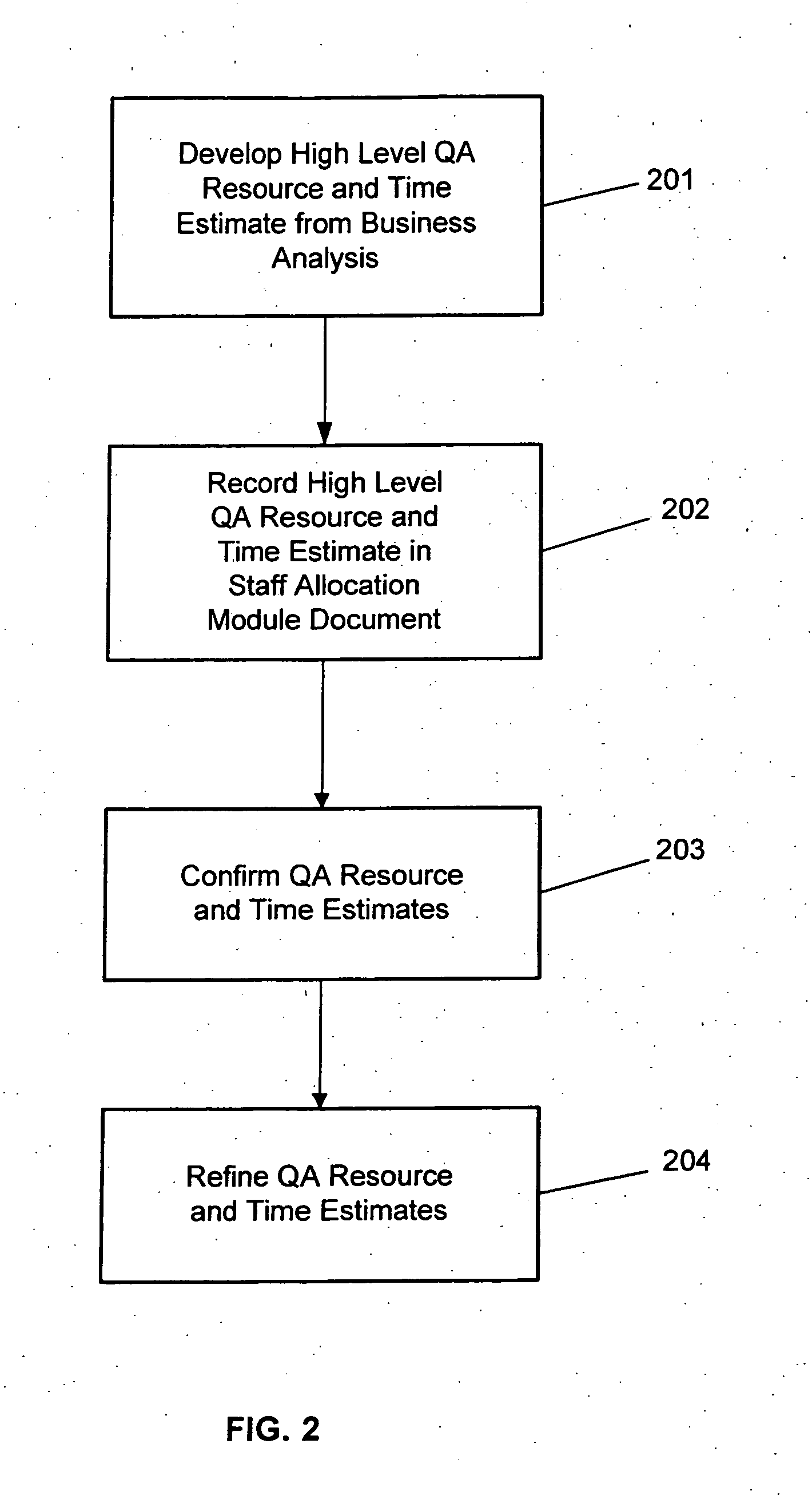

Process and system for quality assurance for software

InactiveUS20050043919A1Digital computer detailsNuclear monitoringQuality assuranceSoftware quality assurance

A process and system for quality assurance. The process includes developing a high level quality assurance resource estimate and a high level quality assurance time estimate; producing a business analysis outline; and creating an acceptance test plan using an acceptance test plan template with the business analysis outline. The process further includes creating a plurality of test cases to be carried out during a test execution phase of the quality assurance process using the acceptance test plan; refining the high level quality assurance resource estimate and the high level quality assurance time estimate based on the acceptance test plan; executing each of the test cases in an acceptance test to produce a set of test results for each of the test cases; and evaluating the test results against the refined high level quality assurance resource estimate and the refined high level quality assurance time estimate. One or more defects tracked during the execution of the test cases are reported and a sign off of the acceptance test is negotiated with a client. An application audit package is created and stored for future reference.

Owner:GE FINANCIAL ASSURANCE HLDG INC A RICHMOND +1

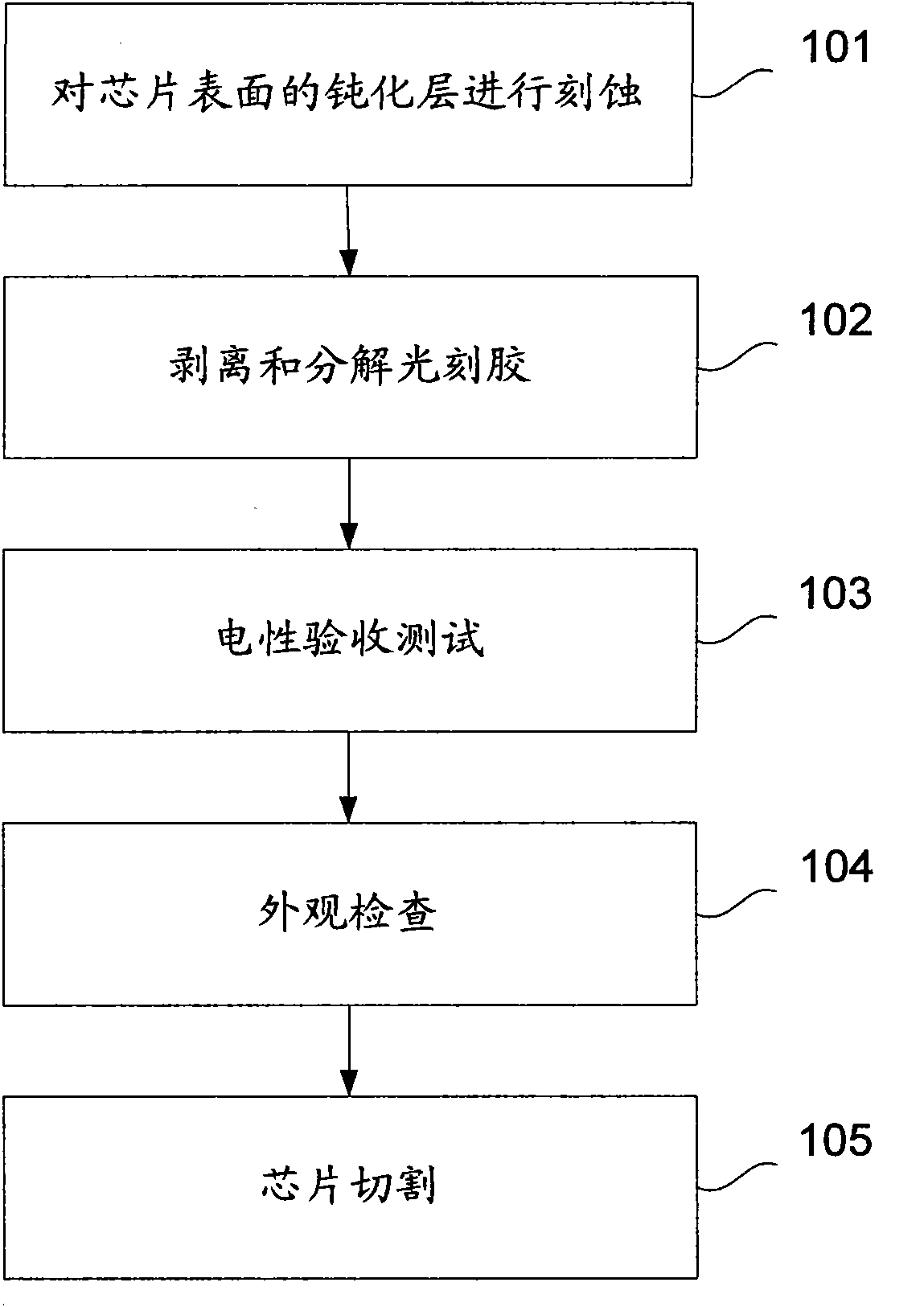

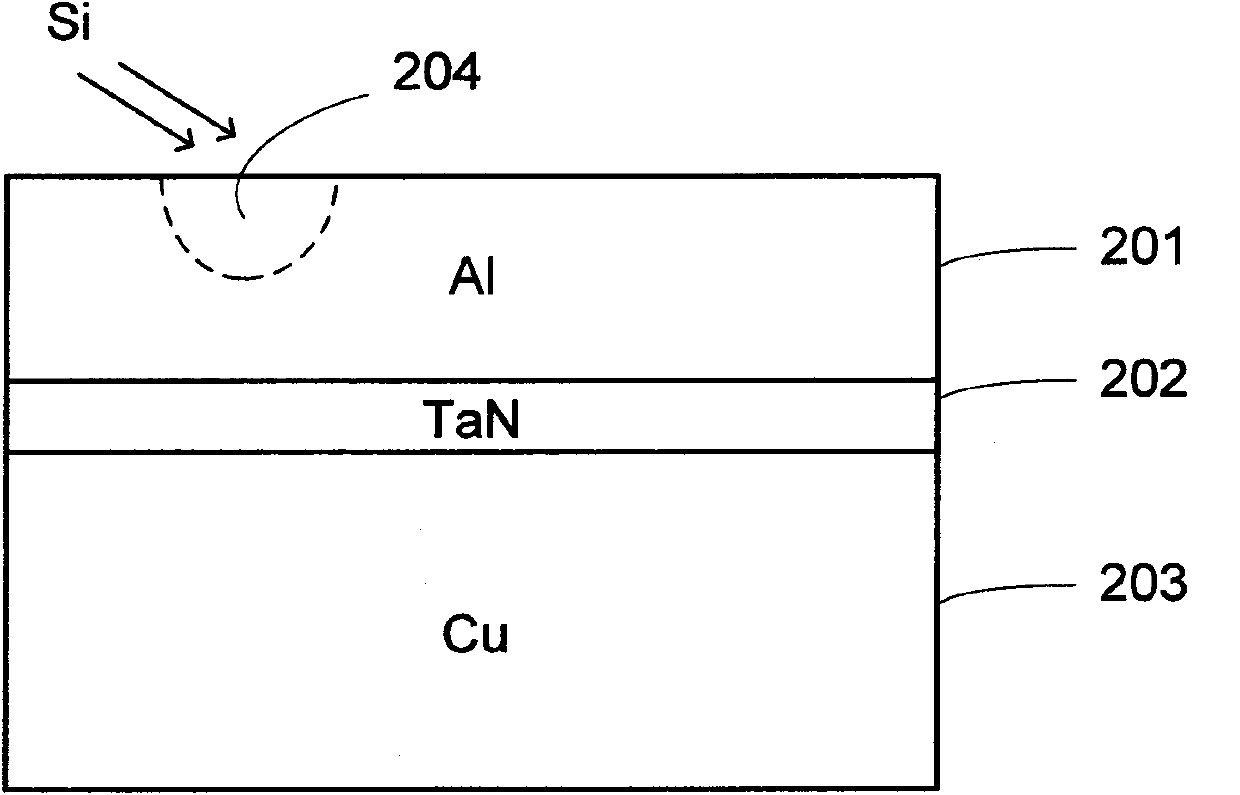

Method for improving chip cutting

ActiveCN102024752AReduce pollutionQuality improvementSolid-state devicesPhotomechanical apparatusPhotoresistSilicon

The invention discloses a method for improving a chip cutting process. The method comprises the following steps of: coating photoresist on a passivation layer on the surface of a chip to be cut; etching the passivation layer on the surface of the chip to expose the surface of a solder pad, and peeling the photoresist; and oxidizing an exposed metal layer to produce a metal oxide layer. The methodalso comprises the steps of: performing an electric acceptance test on the chip; checking the appearance of the chip; and cutting the chip. According to the method of the invention, the cutting of the chip is improved, thus the pollution of silicon dust on the solder pad, especially pollution on a surface Al layer is reduced, and the galvanic effect is inhibited.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

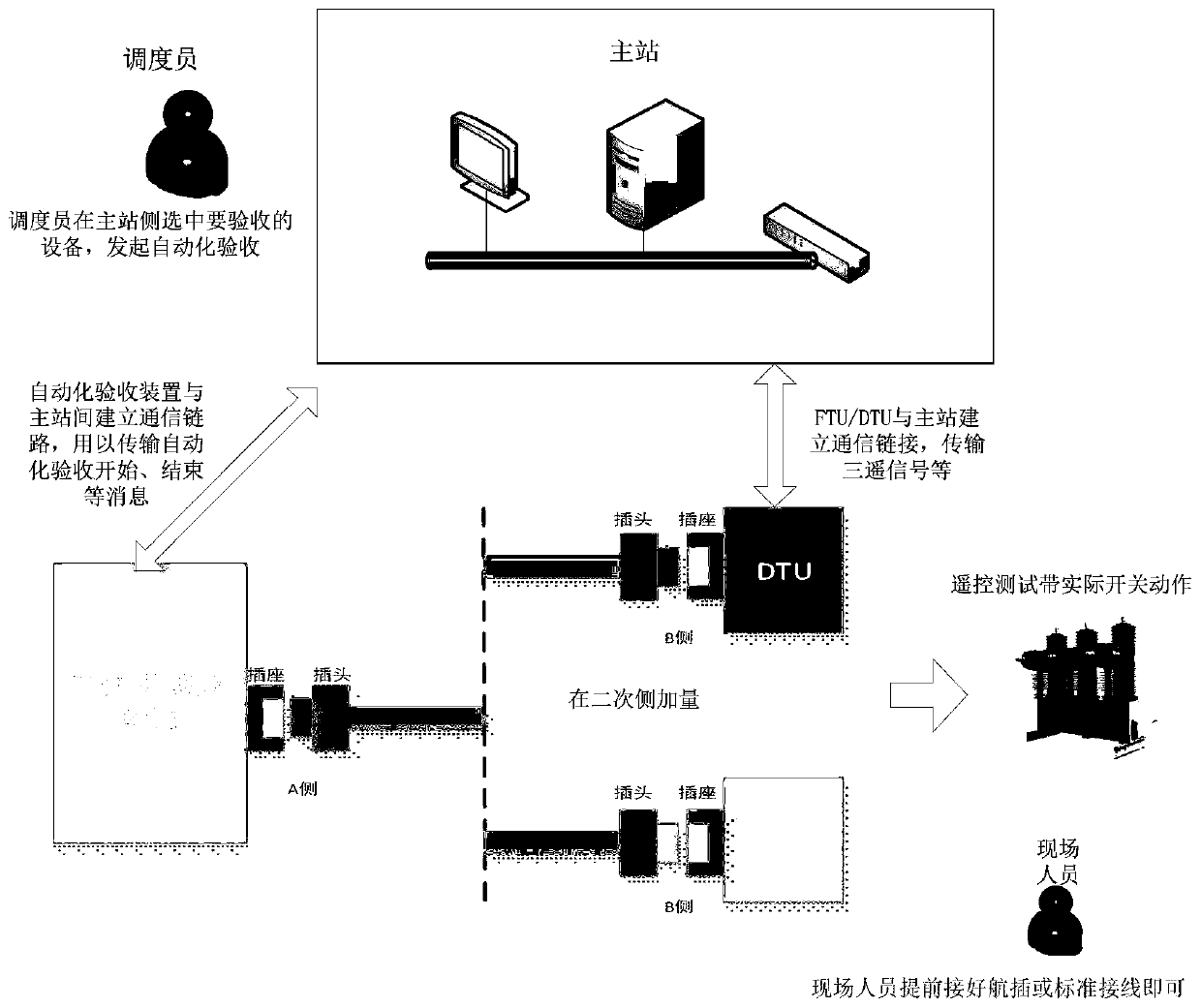

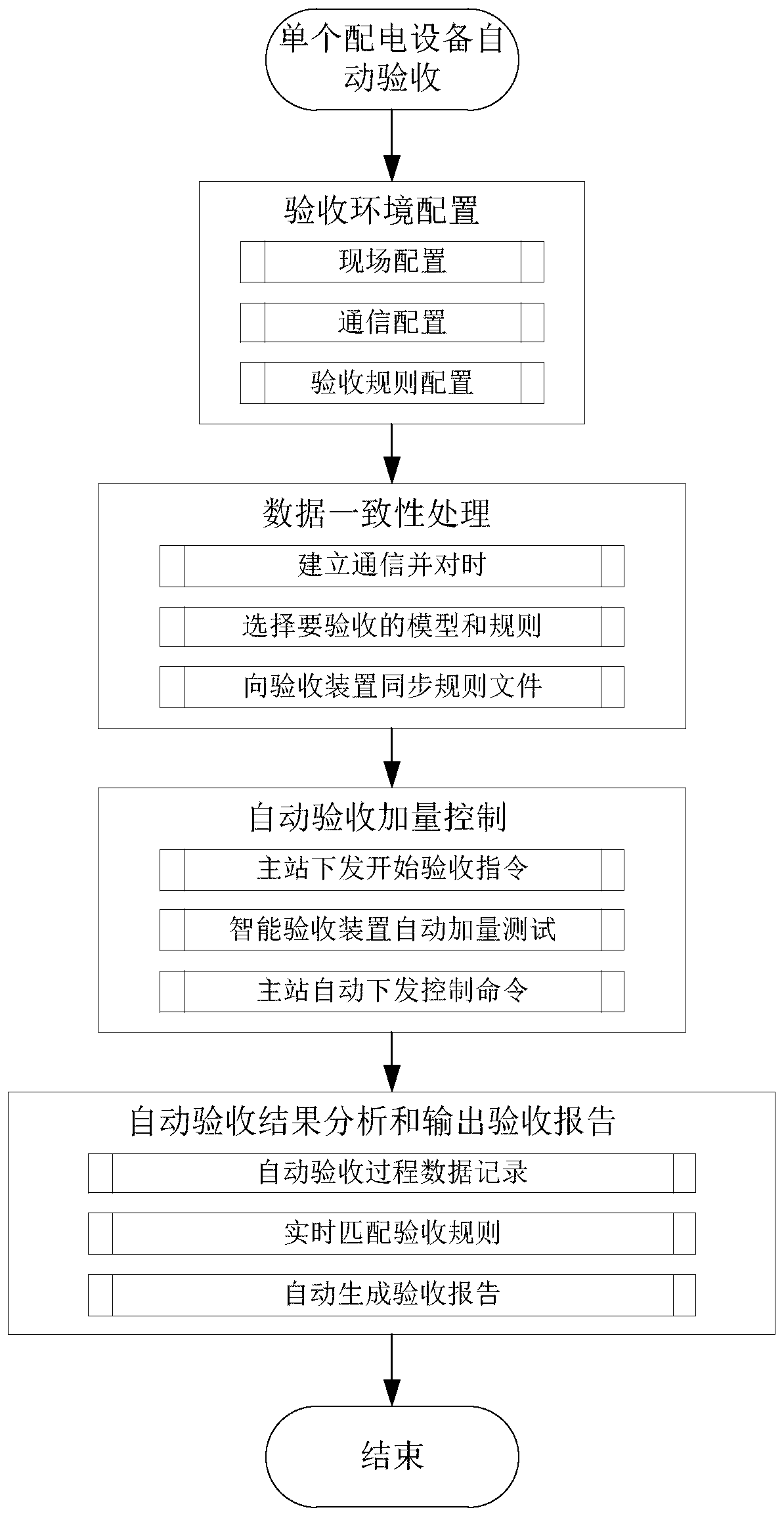

Intelligent acceptance device-based power distribution master station and automatic joint debugging acceptance method of terminal

ActiveCN109873497AReduce dependenceImprove normativeCircuit arrangementsData switching networksMaster stationEngineering

The invention discloses an intelligent acceptance device-based power distribution master station and an automatic joint debugging acceptance method of a terminal. The method comprises the steps of performing site configuration, communication parameter configuration and automatic acceptance planning template configuration; performing uniformization on clock of the power distribution master station,a power distribution terminal and an intelligent acceptance device, a power distribution equipment model and power distribution equipment model; controlling analogue quantity, state quantity and a protection signal which are generated by a power distribution terminal by the power distribution master station, and linking primary equipment; and recording measurement information and warning information which are received during the acceptance process in real time by the power distribution master station, matching with an acceptance rule, finding out an acceptance test item conforming to a condition, and generating an acceptance report. By the method, the labor cost and the communication cost are reduced, the working efficiency and the accuracy are improved, and standard power distribution acceptance operation is achieved.

Owner:STATE GRID JIANGSU ELECTRIC POWER CO LIANYUNGANG POWER SUPPLY CO

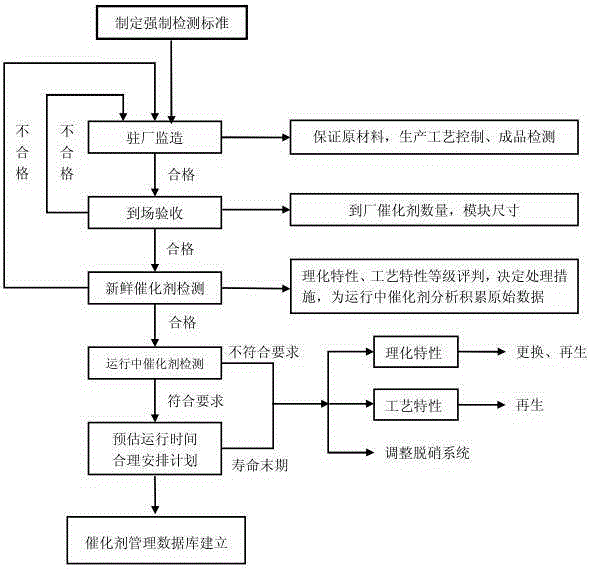

Denitration catalyst life whole-process management method

InactiveCN105214490AEasy to detectImprove efficiencyDispersed particle separationLife managementAcceptance testing

The invention relates to a denitration catalyst life whole-process management method. A denitration catalyst life management method beneficial to stable and efficient running of a denitration system does not exist at present. The method comprises the steps that 1, a catalyst life whole-process management scheme is made; 2, a catalyst manufacturer is determined, and the catalyst production process and product quality are supervised and examined; 3, random sampling performance detection is carried out on qualified catalysts planned to be put into operation; 4, inspection of incoming merchandise, installation and commissioning are carried out on the catalysts which are detected to be qualified before the catalysts are put into operation; 5, performance acceptance testing is carried out on the catalysts which are put into operation for a certain period of time; 6, after quality inspection before acceptance is qualified, catalyst performance detection is carried out at regular intervals, the catalyst commissioning effect is tracked, diagnosis optimization experimentation is carried out, and the catalyst service life is prolonged; 7, a deactivated catalyst is regenerated for use. The denitration catalyst life whole-process management method is beneficial to the sable and efficient running of the denitration system.

Owner:HUADIAN ELECTRIC POWER SCI INST CO LTD