Wafer acceptance testing method and structure of a test key used in the method

a testing key and acceptance technology, applied in semiconductor/solid-state device testing/measurement, semiconductor/solid-state device details, instruments, etc., can solve the problems of difficult for an inspector to judge the gc-dt misalignment merely according, and the prior art gc-dt misalignment evaluation method is not accura

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

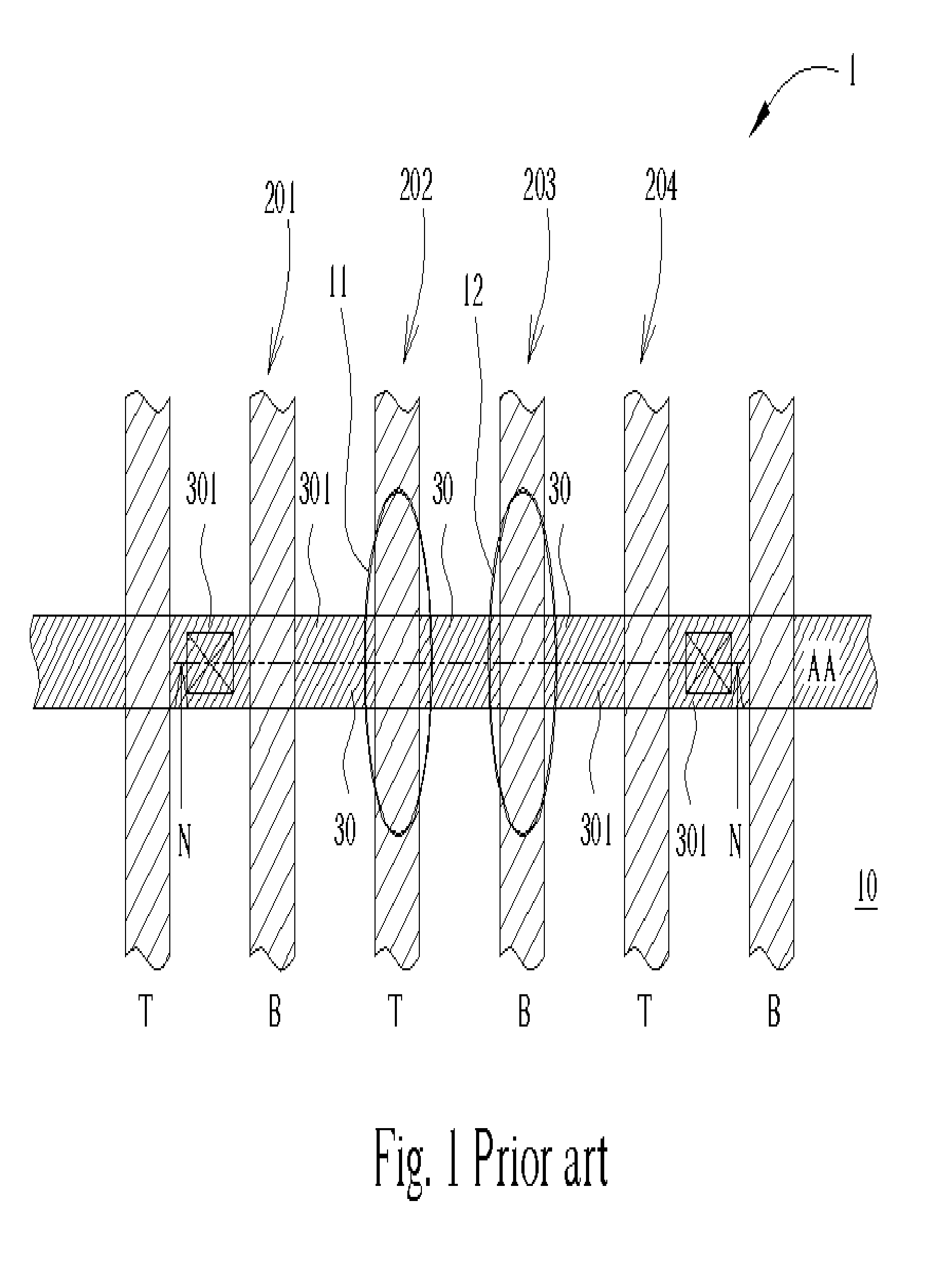

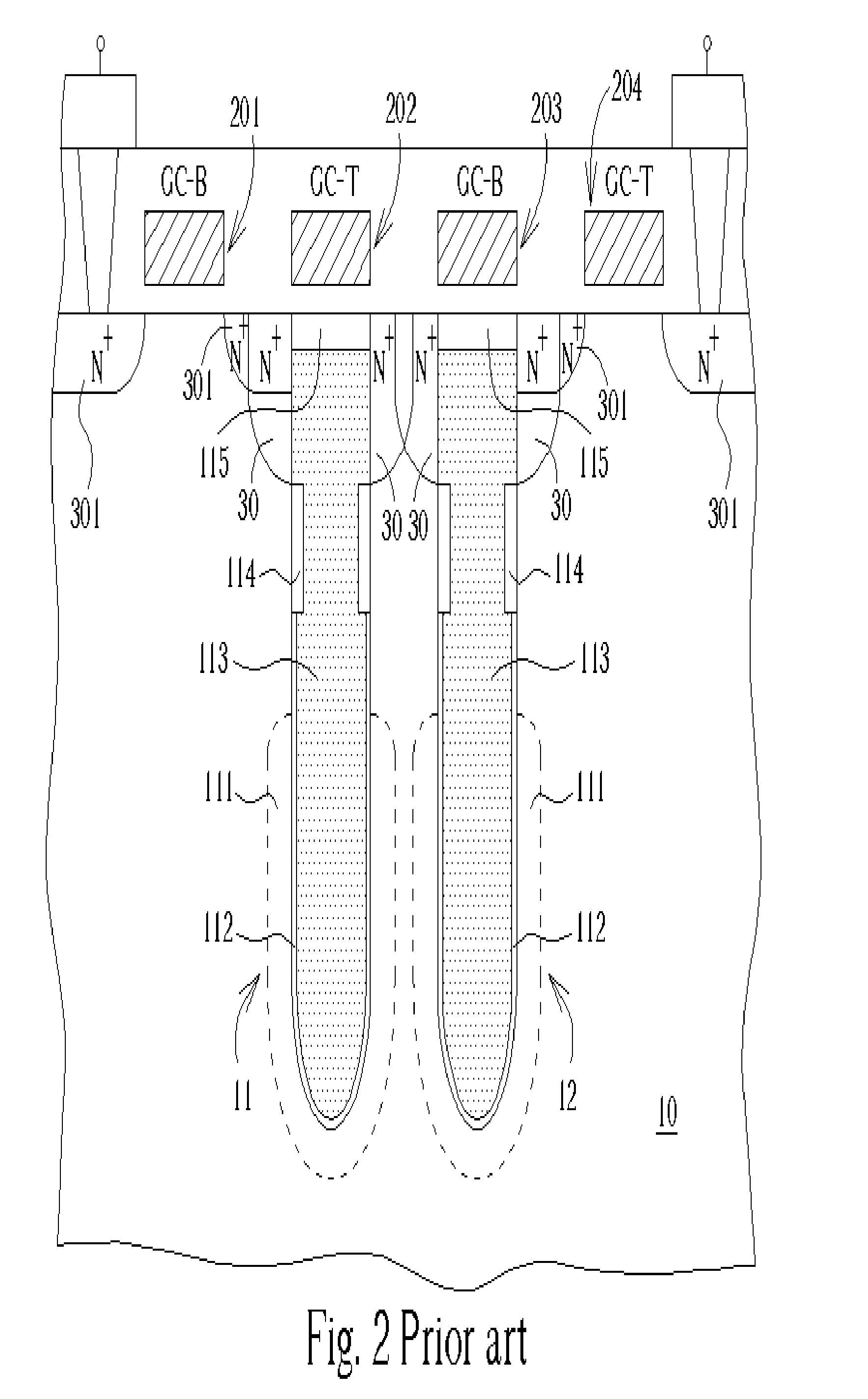

[0015] Please refer to FIG. 3 to FIG. 9. FIG. 3 to FIG. 9 are schematic diagrams illustrating the fabrication processes of making a test key structure for monitoring GC-DT misalignment in accordance with one preferred embodiment of the present invention, wherein FIG. 4 is a cross-sectional view along line A-A of FIG. 3; FIG. 6 is a cross-sectional view along line B-B of FIG. 5; and FIG. 8 is a cross-sectional view along line C-C of FIG. 7. Through FIG. 3 to FIG. 9, similar numerals designate similar devices, regions or elements set forth in FIG. 1 and FIG. 2. The novel wafer acceptance testing (WAT) method using the test key structure of the present invention will also be explained in detail with reference to FIG. 8 and FIG. 9.

[0016] As shown in FIG. 3, a finger-type deep trench layout 20 is fabricated simultaneously with the memory array capacitors (not shown) in a substrate 10 such as a P type silicon substrate. The deep trench layout 20, which is fabricated within a peripheral a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More