Patents

Literature

79 results about "Fringing capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Because of the fringe effect the capacitance of a parallel plate capacitor is more than the capacitance calculated by the formula. Fringe effect occurs when the electric field extends the area of the overlap.

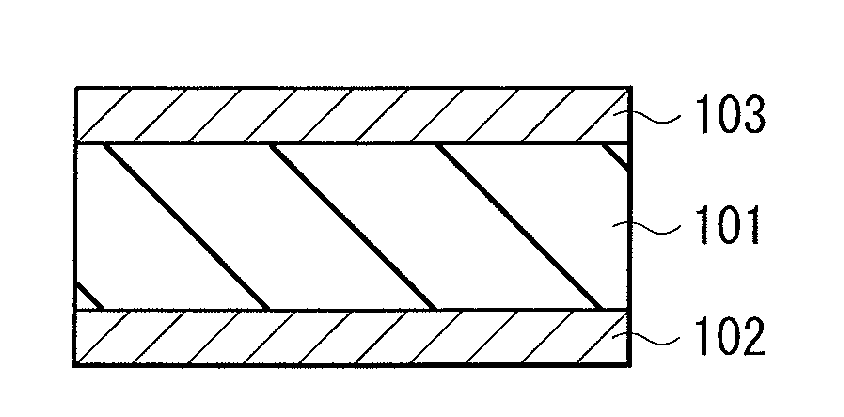

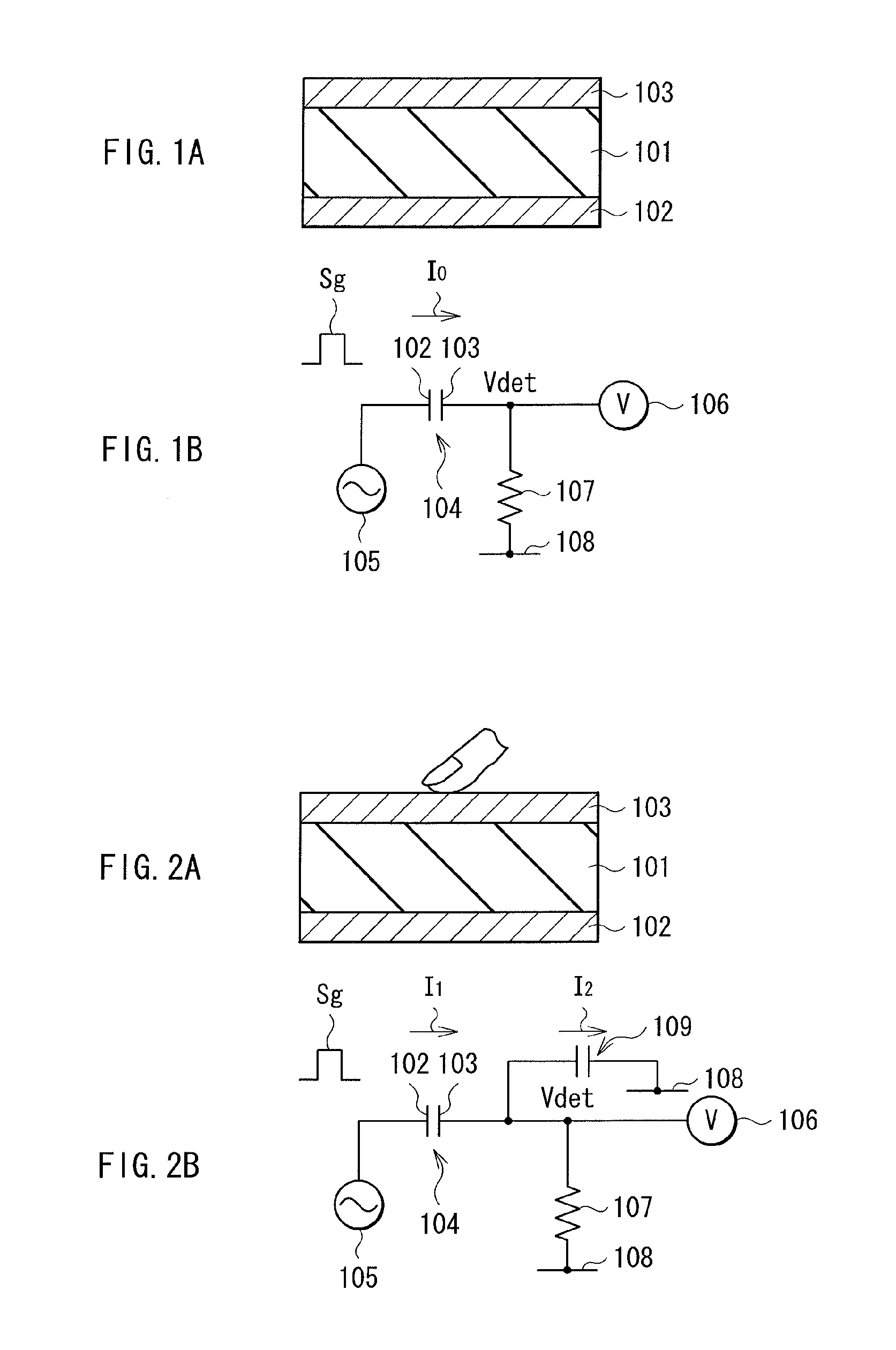

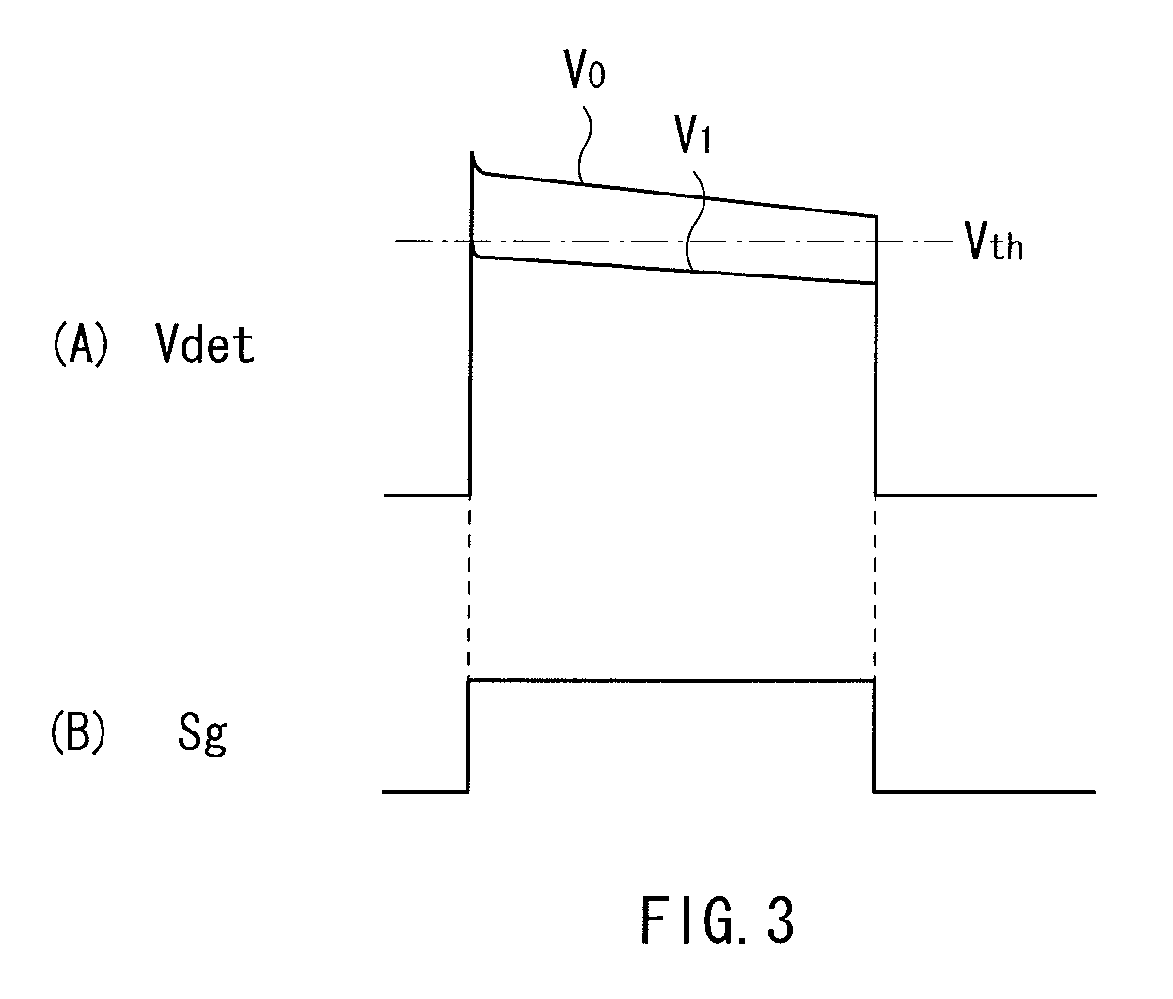

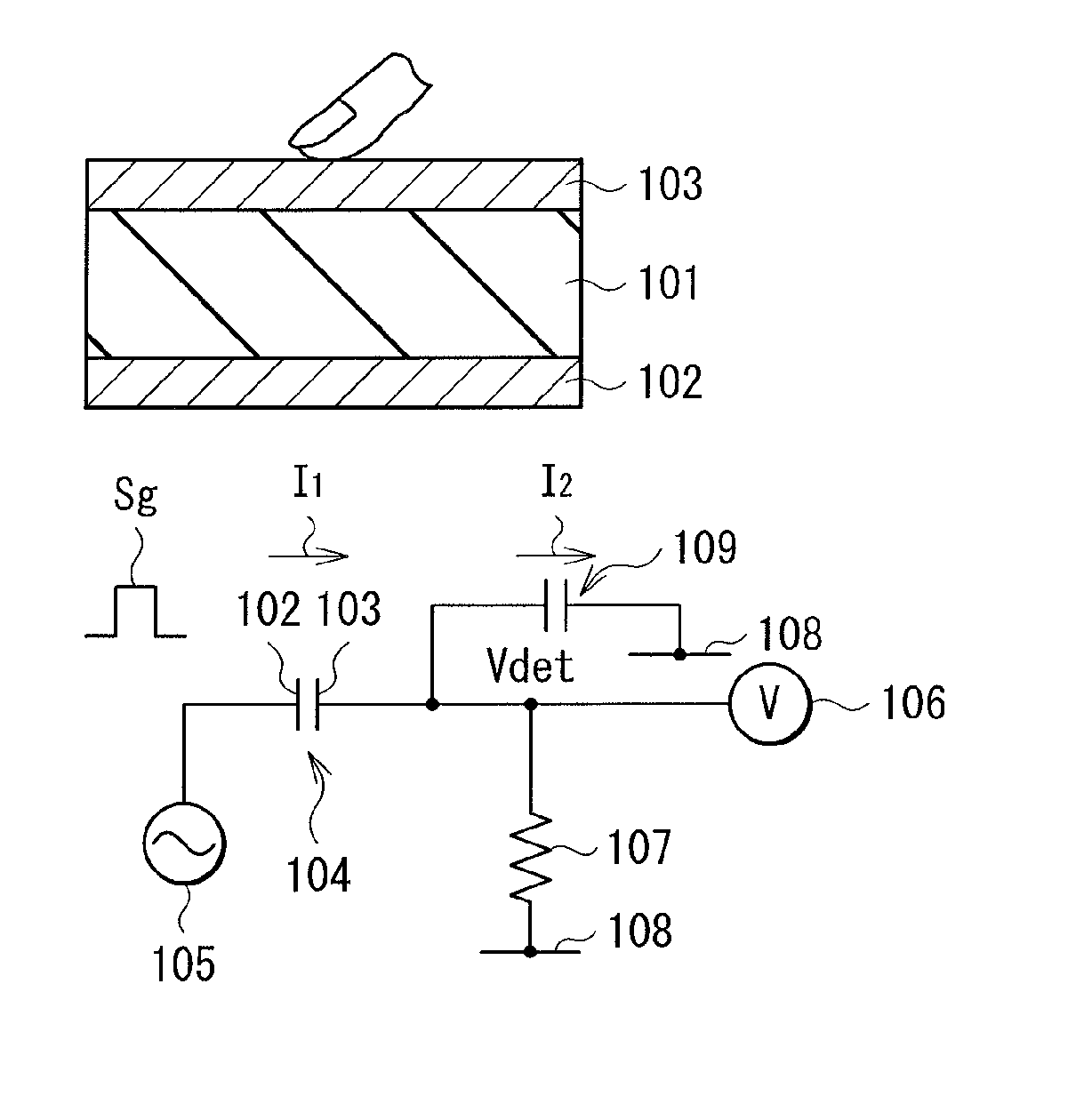

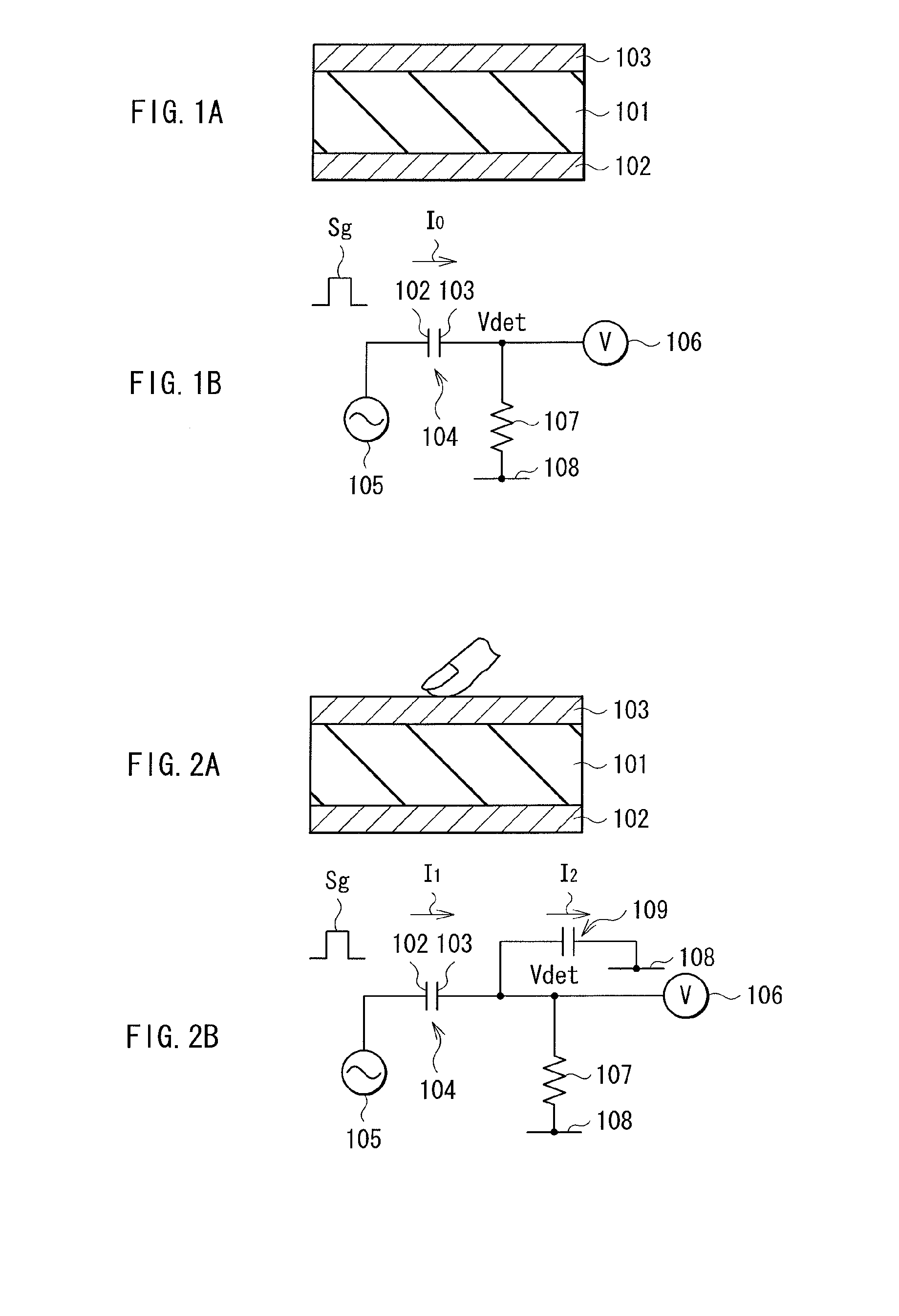

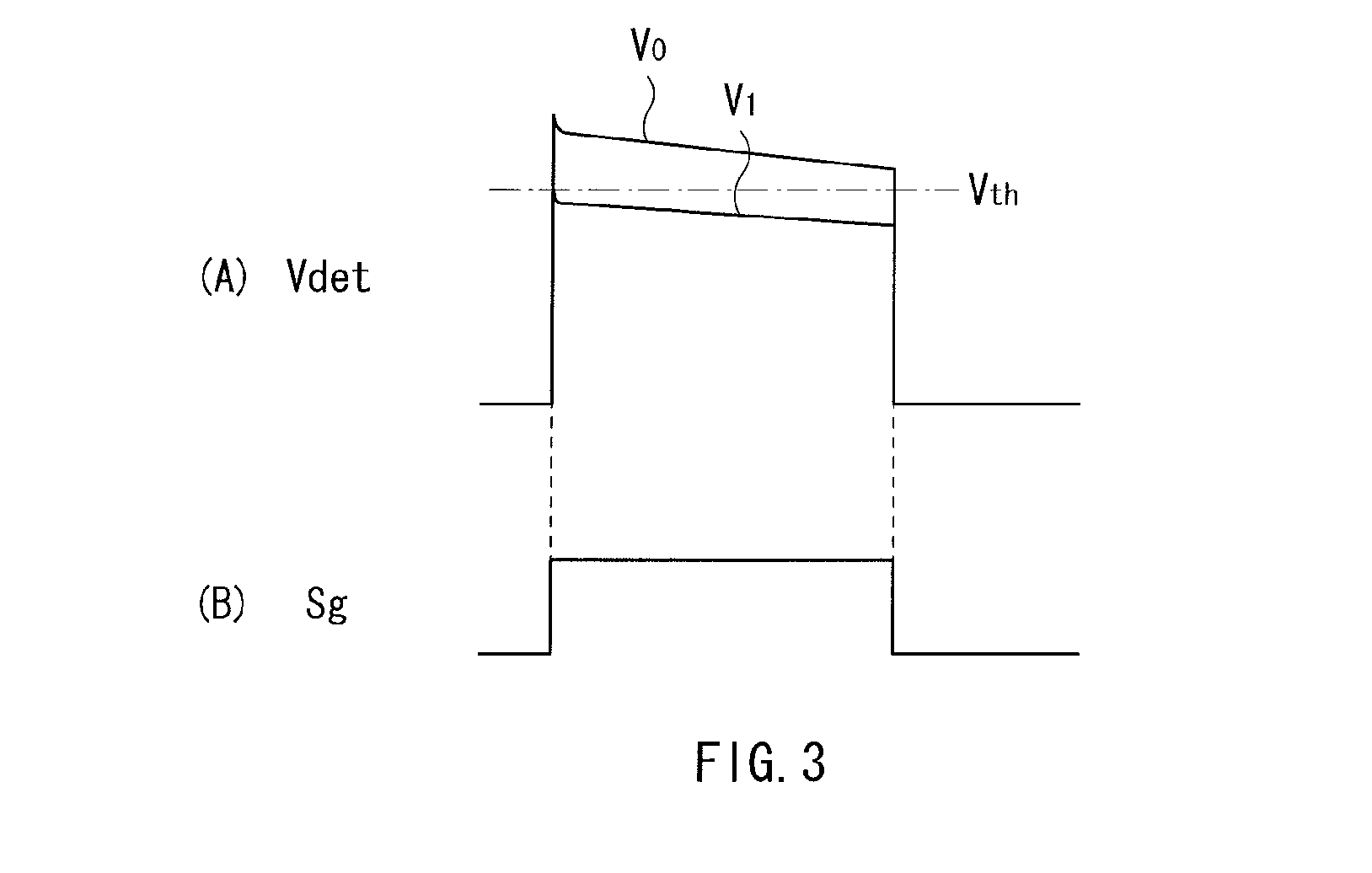

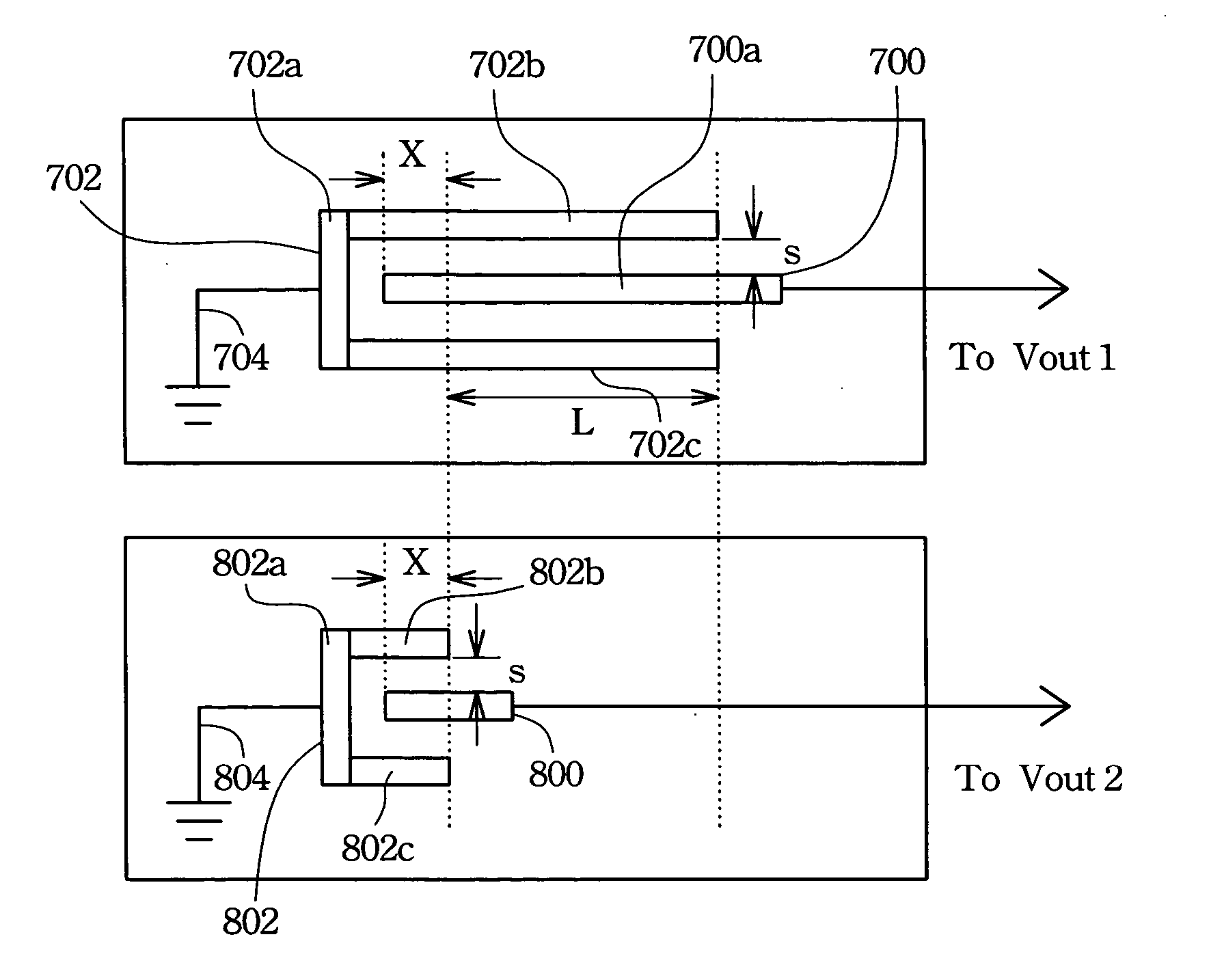

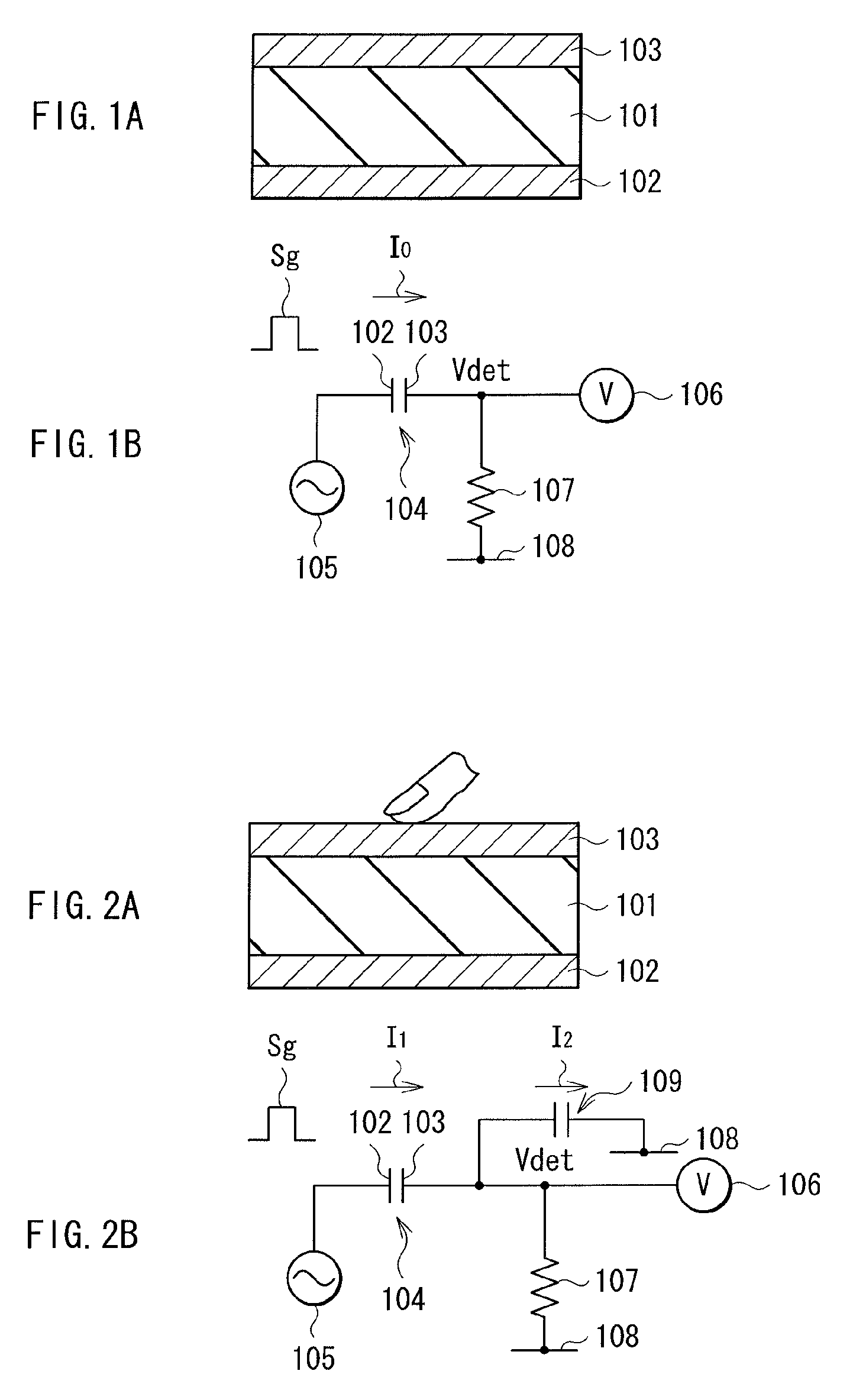

Touch panel, display panel, and display unit

ActiveUS20100309162A1High sensitivityReduce sensitivityStatic indicating devicesAlternating current plasma display panelsEngineeringFringing capacitance

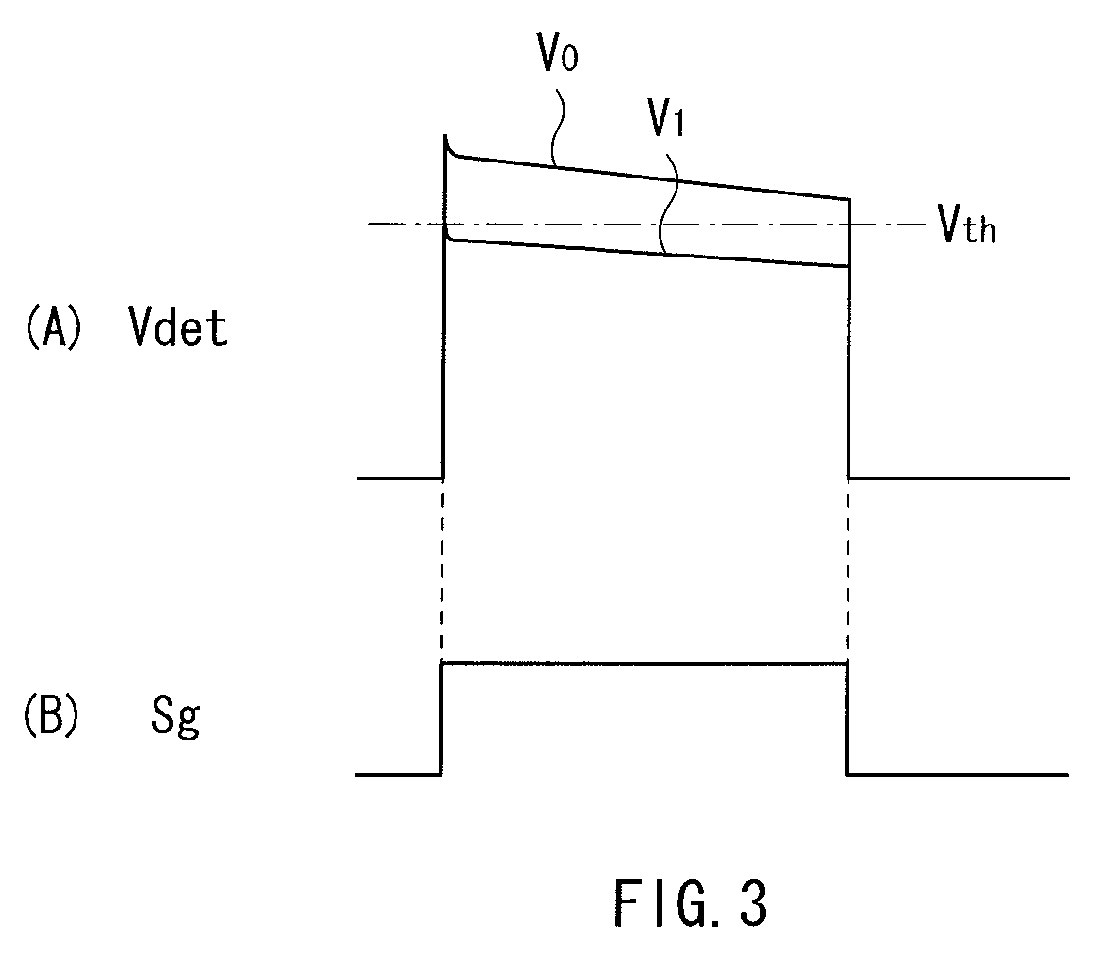

A touch panel, a display panel, and a display unit achieving prevention of erroneous detection caused by external noise, are provided. The touch panel includes: a plurality of detection scan electrodes extending in a first direction; and a plurality of detection electrodes facing the plurality of detection scan electrodes and extending in a second direction which intersects the first direction. A ratio of fringe capacitance to total capacitance between one or more selected detection scan electrodes and a first detection electrode is different from a ratio of fringe capacitance to total capacitance between the one or more selected detection scan electrodes and a second detection electrode. The one or more selected detection scan electrodes are selected, in a desired unit, from the plurality of detection scan electrodes, to be supplied with a selection pulse, and each of the first and the second detection electrodes is selected from the plurality of detection electrodes.

Owner:JAPAN DISPLAY INC

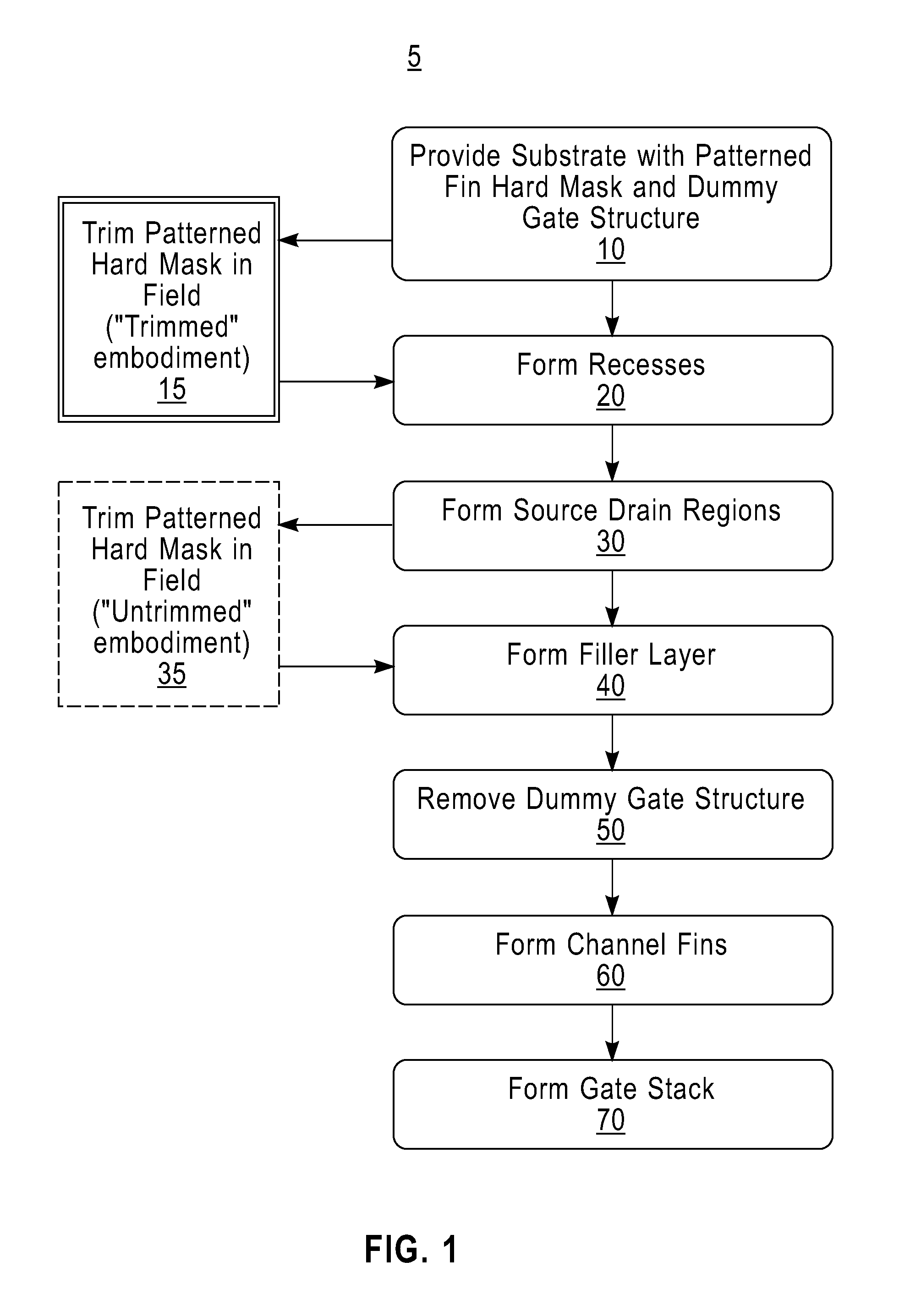

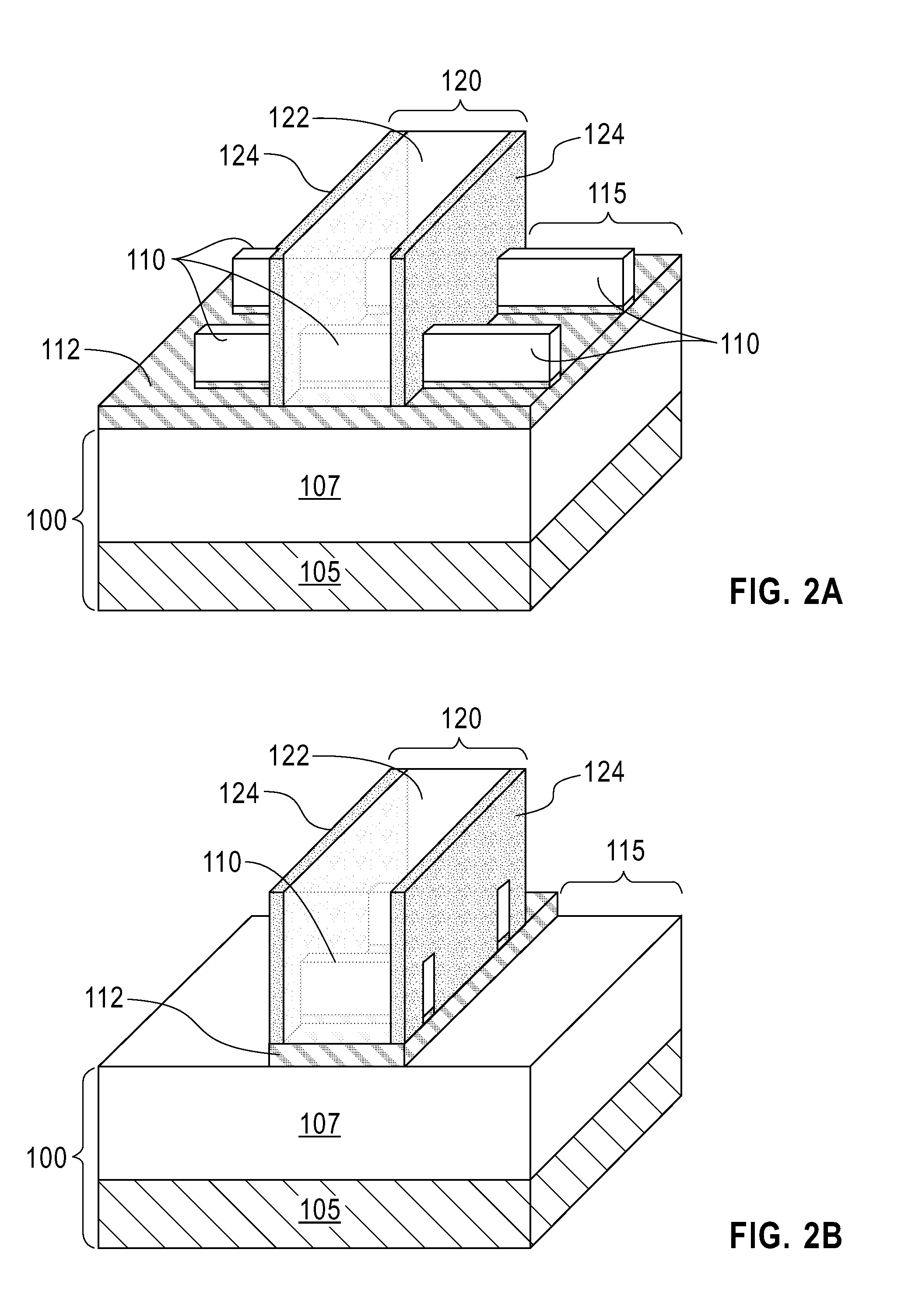

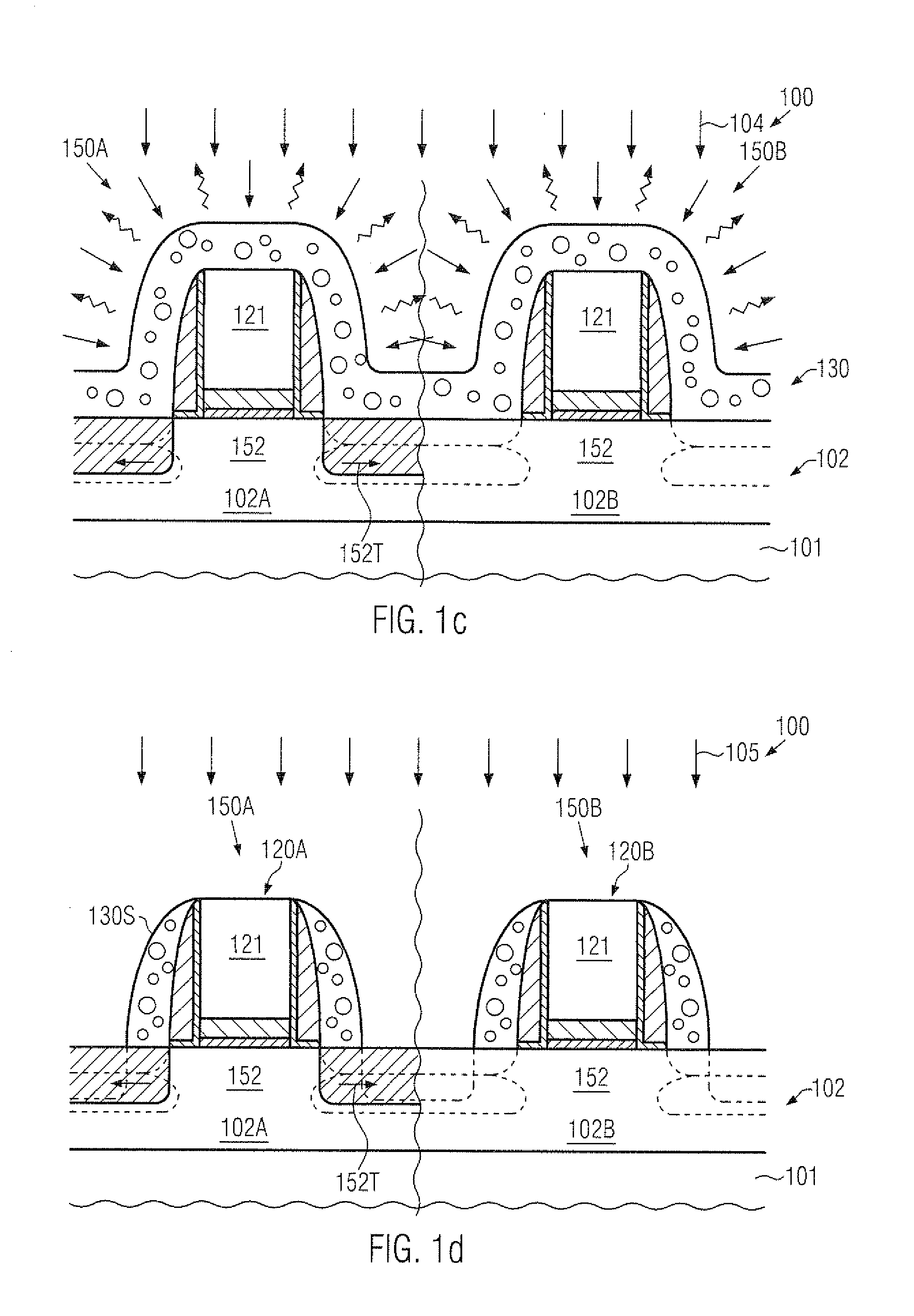

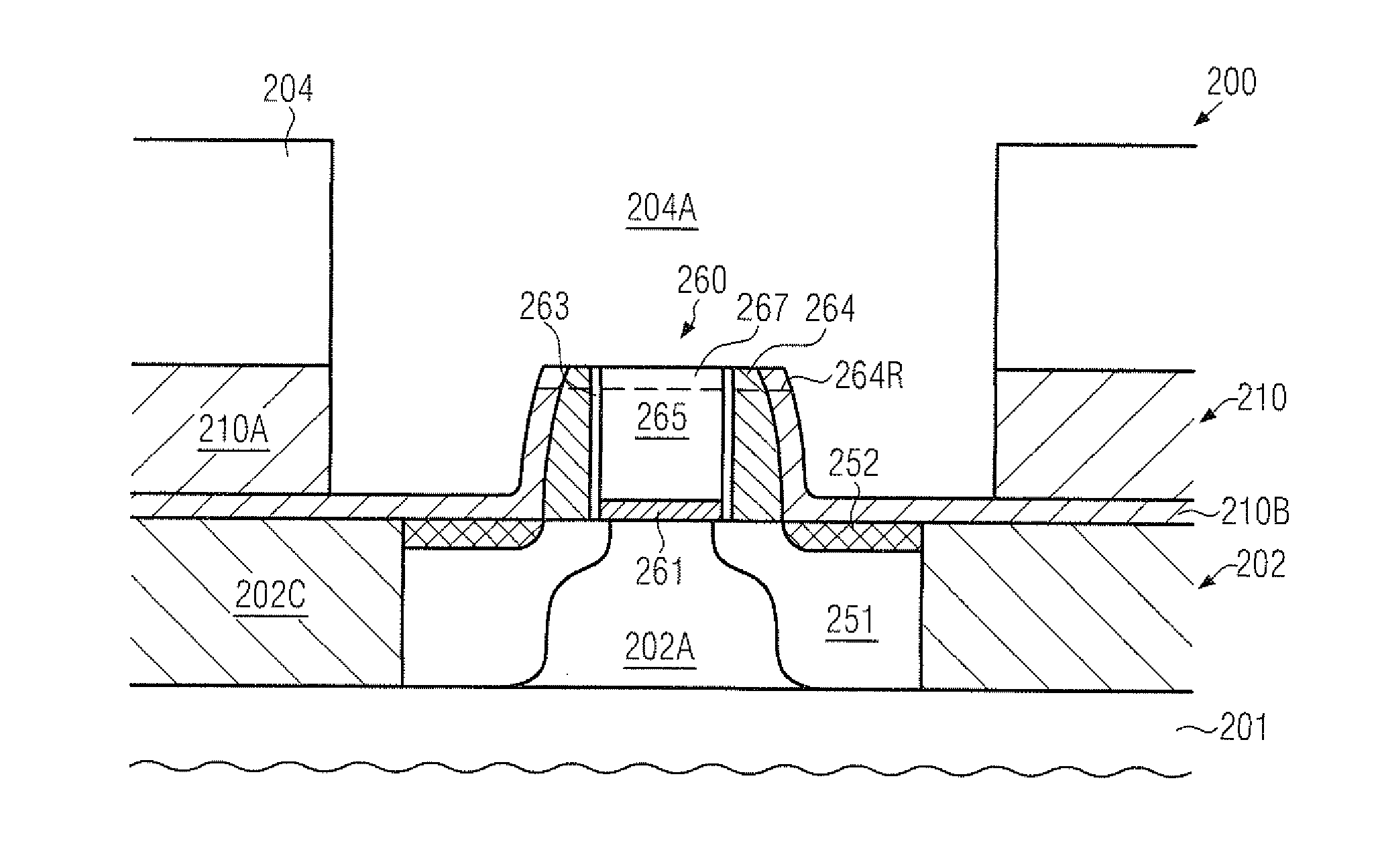

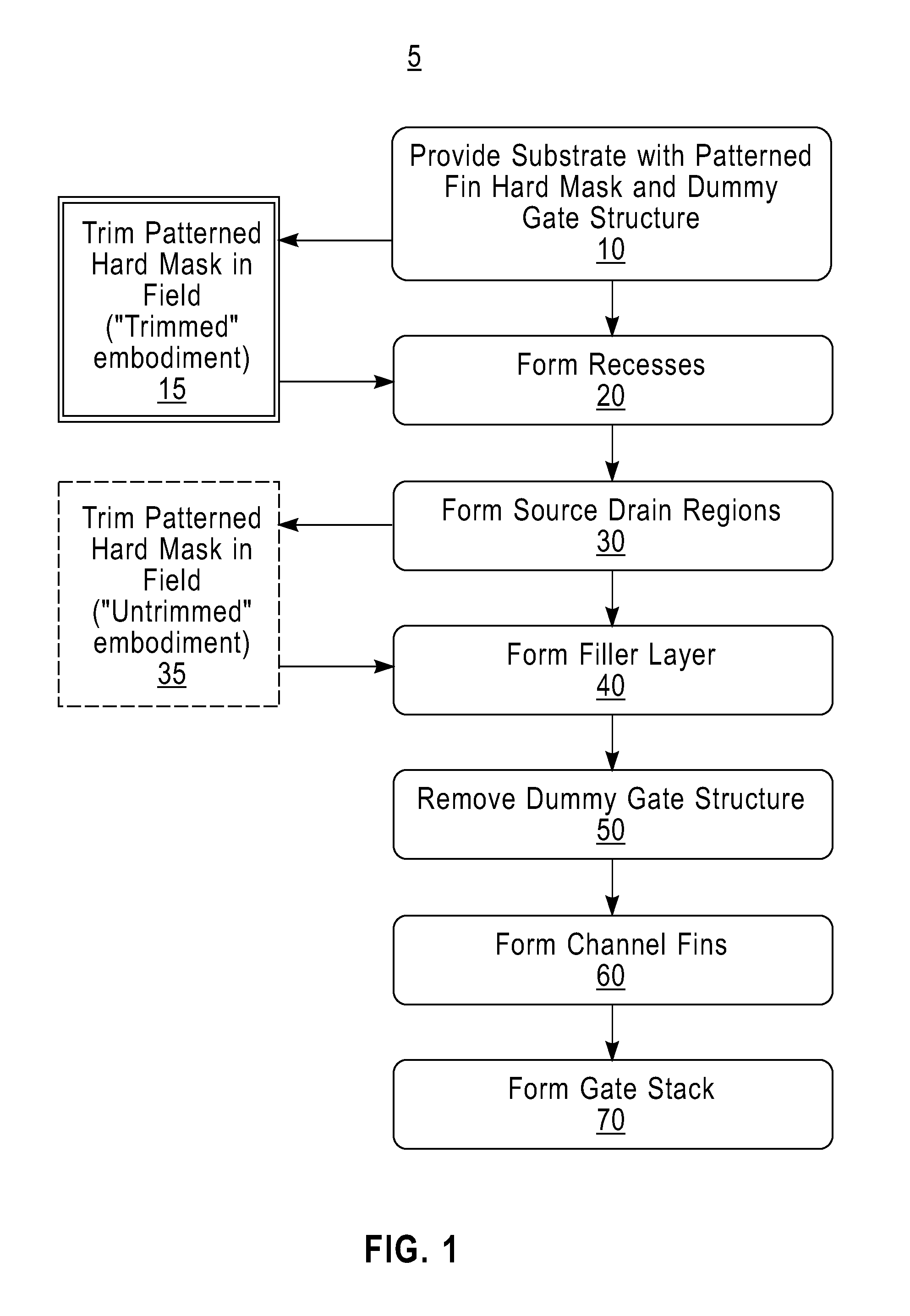

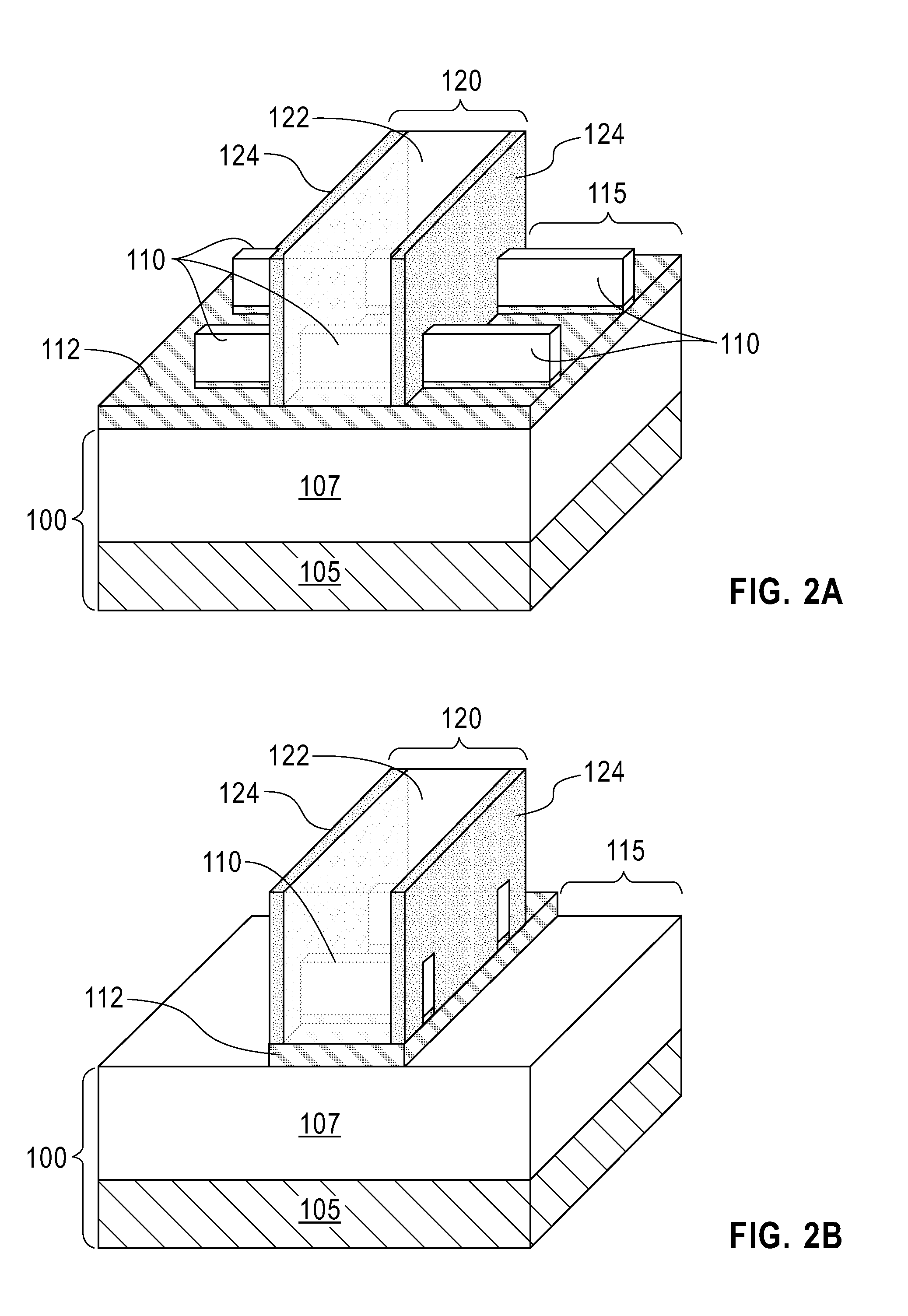

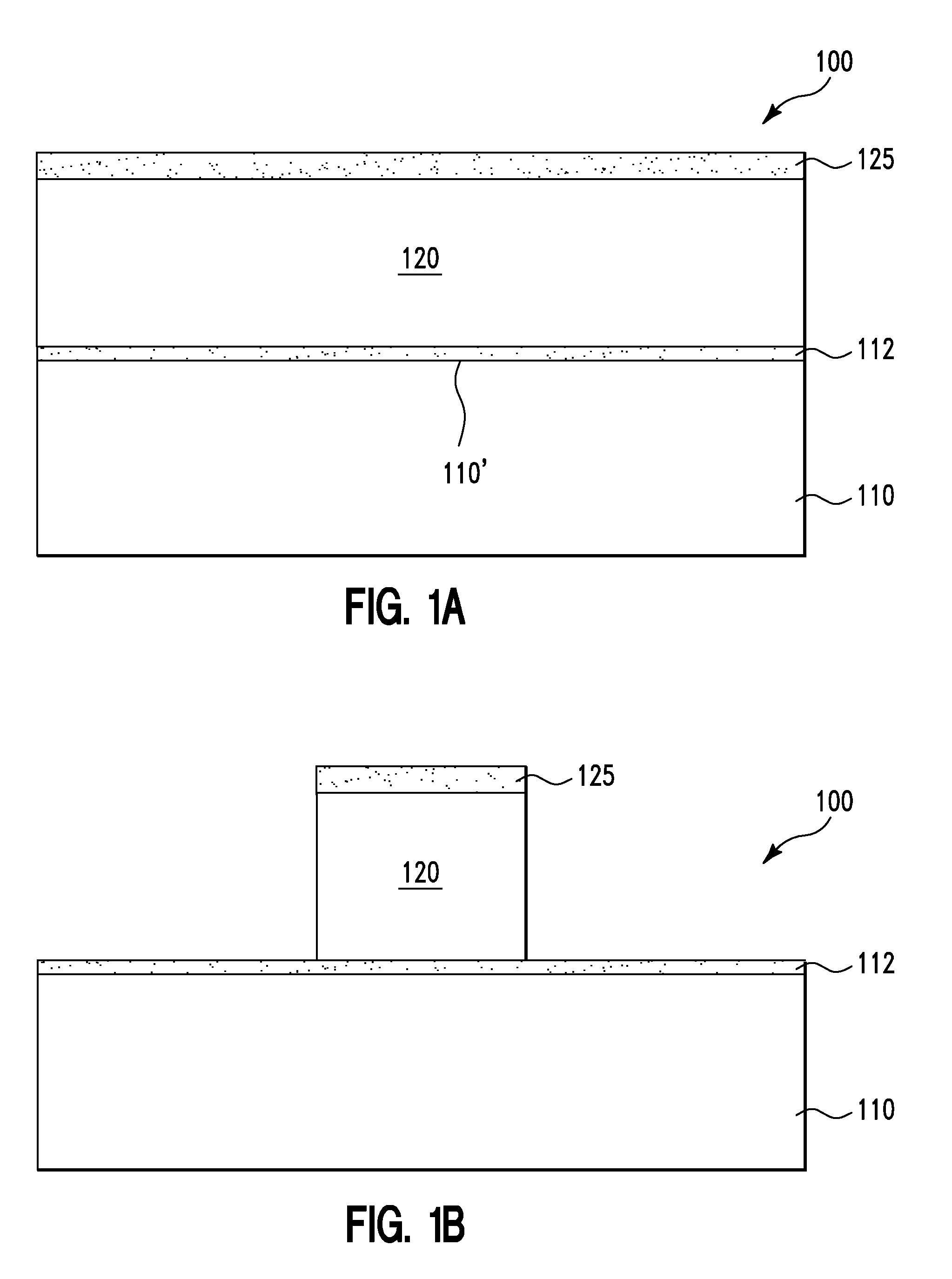

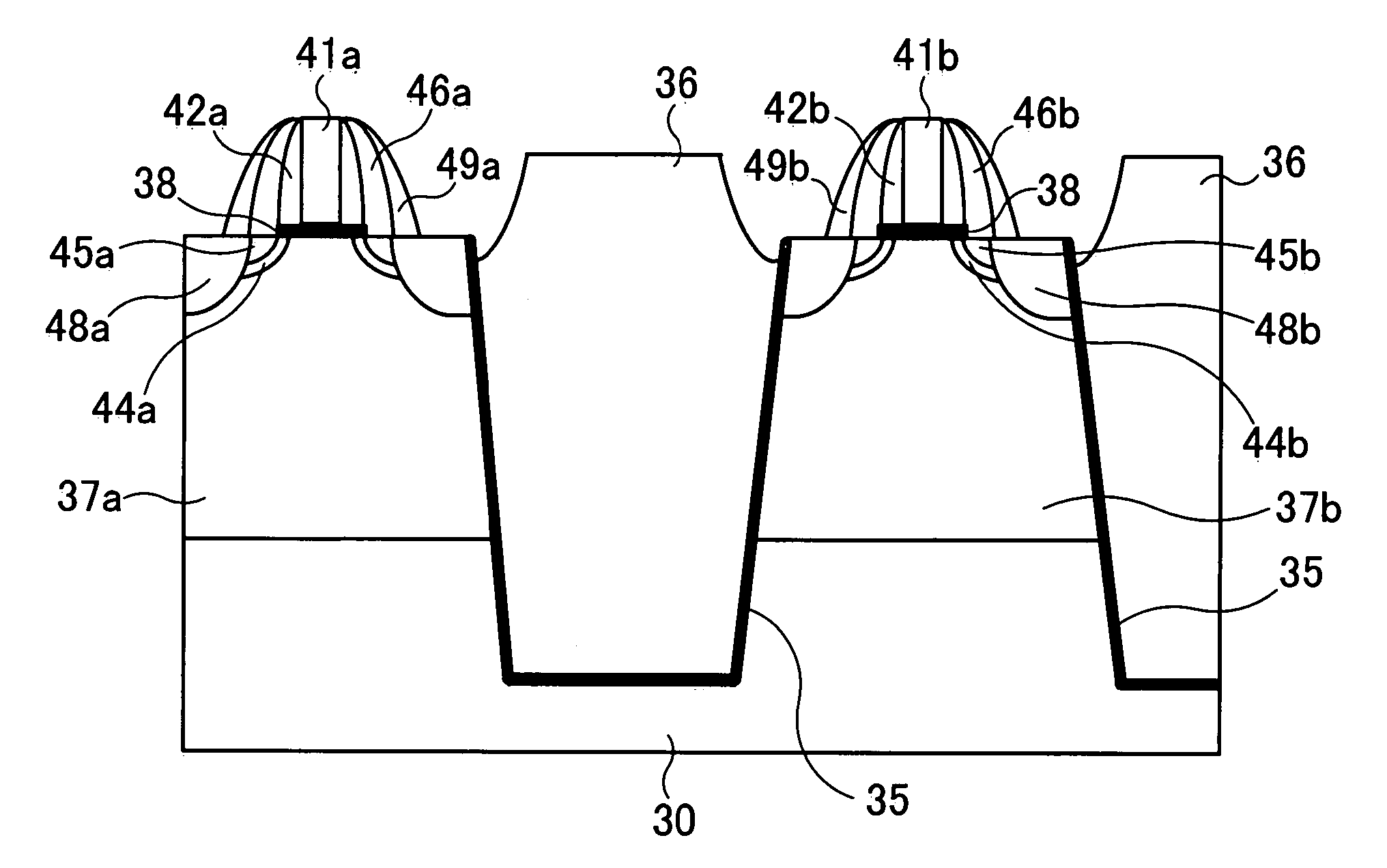

Non-planar mosfet structures with asymmetric recessed source drains and methods for making the same

ActiveUS20130214357A1Reduce fringing capacitanceReduce external resistanceTransistorSolid-state devicesMOSFETEngineering

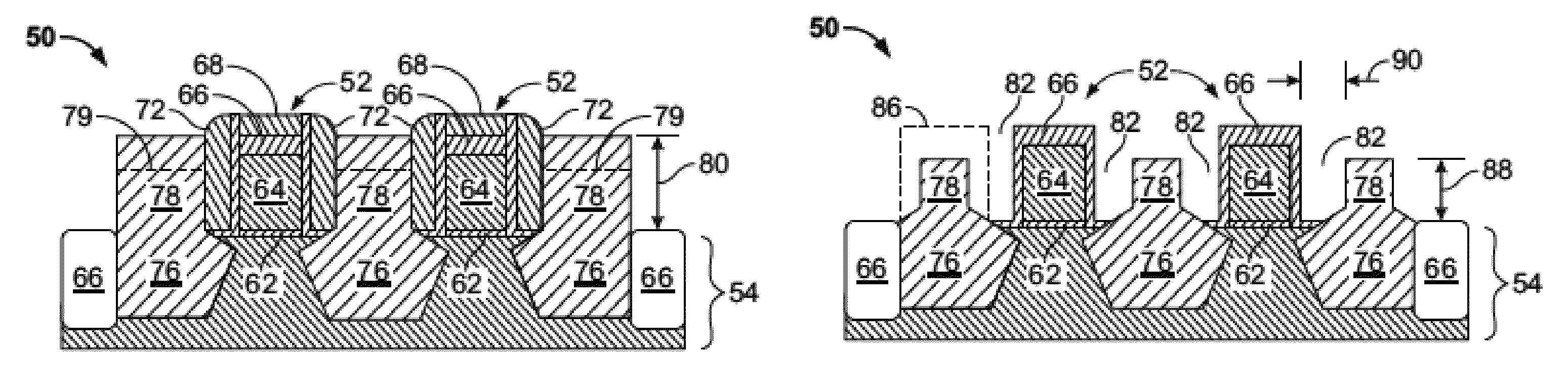

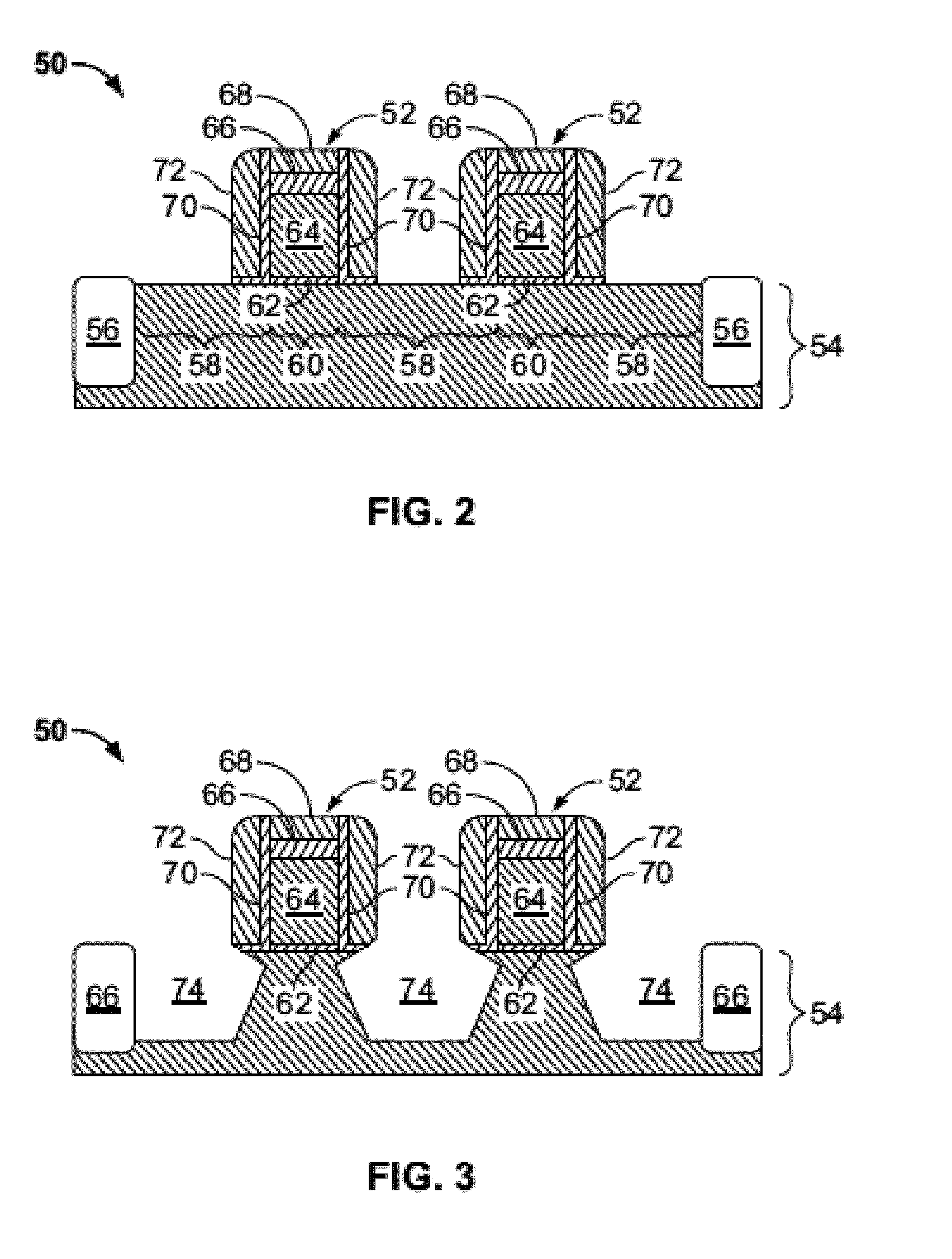

Non-planar Metal Oxide Field Effect Transistors (MOSFETs) and methods for making non-planar MOSFETs with asymmetric, recessed source and drains having improved extrinsic resistance and fringing capacitance. The methods include a fin-last, replacement gate process to form the non-planar MOSFETs and employ a retrograde metal lift-off process to form the asymmetric source / drain recesses. The lift-off process creates one recess which is off-set from a gate structure while a second recess is aligned with the structure. Thus, source / drain asymmetry is achieved by the physical structure of the source / drains, and not merely by ion implantation. The resulting non-planar device has a first channel of a fin contacting a substantially undoped area on the drain side and a doped area on the source side, thus the first channel is asymmetric. A channel on atop surface of a fin is symmetric because it contacts doped areas on both the drain and source sides.

Owner:GLOBALFOUNDRIES US INC

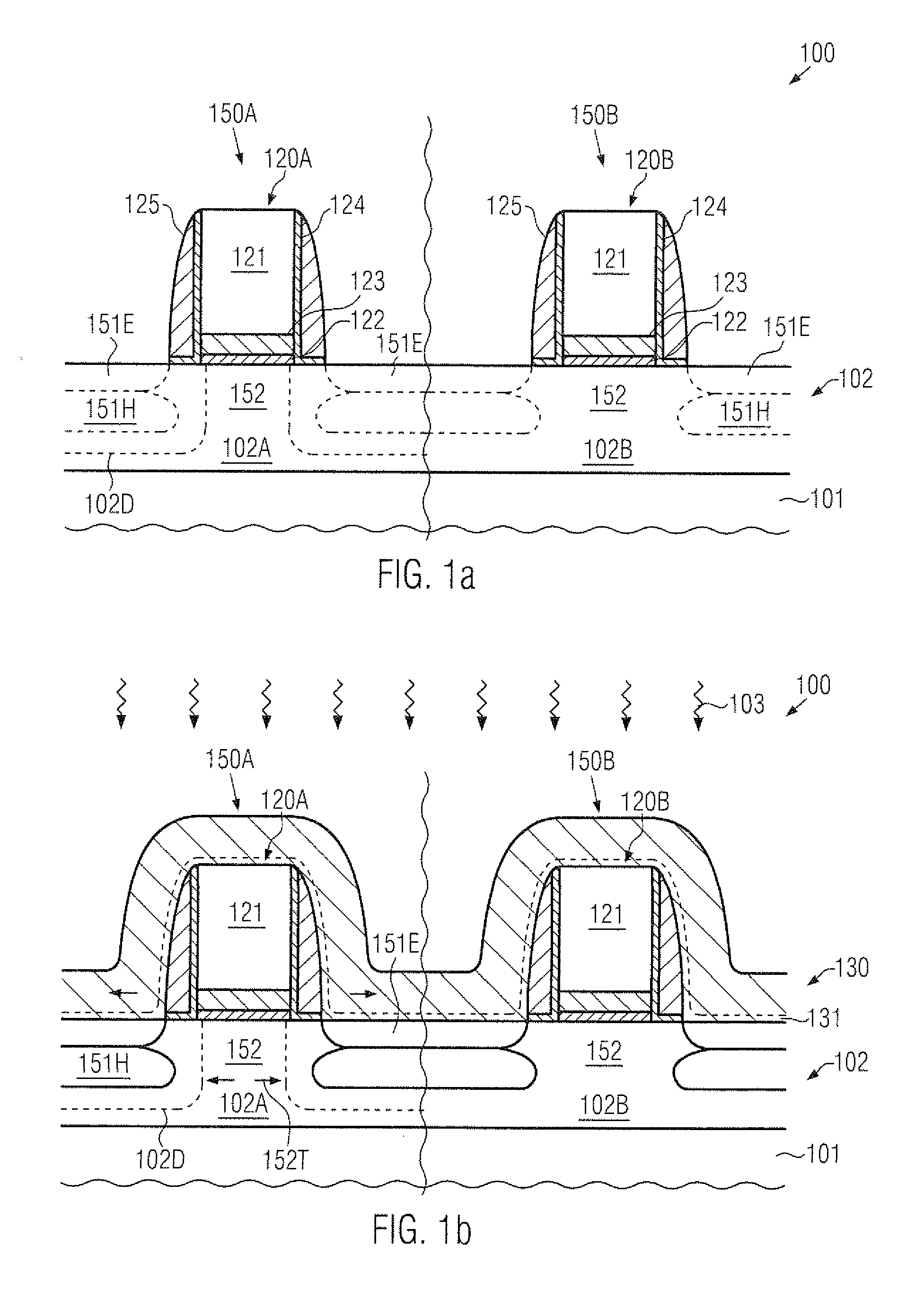

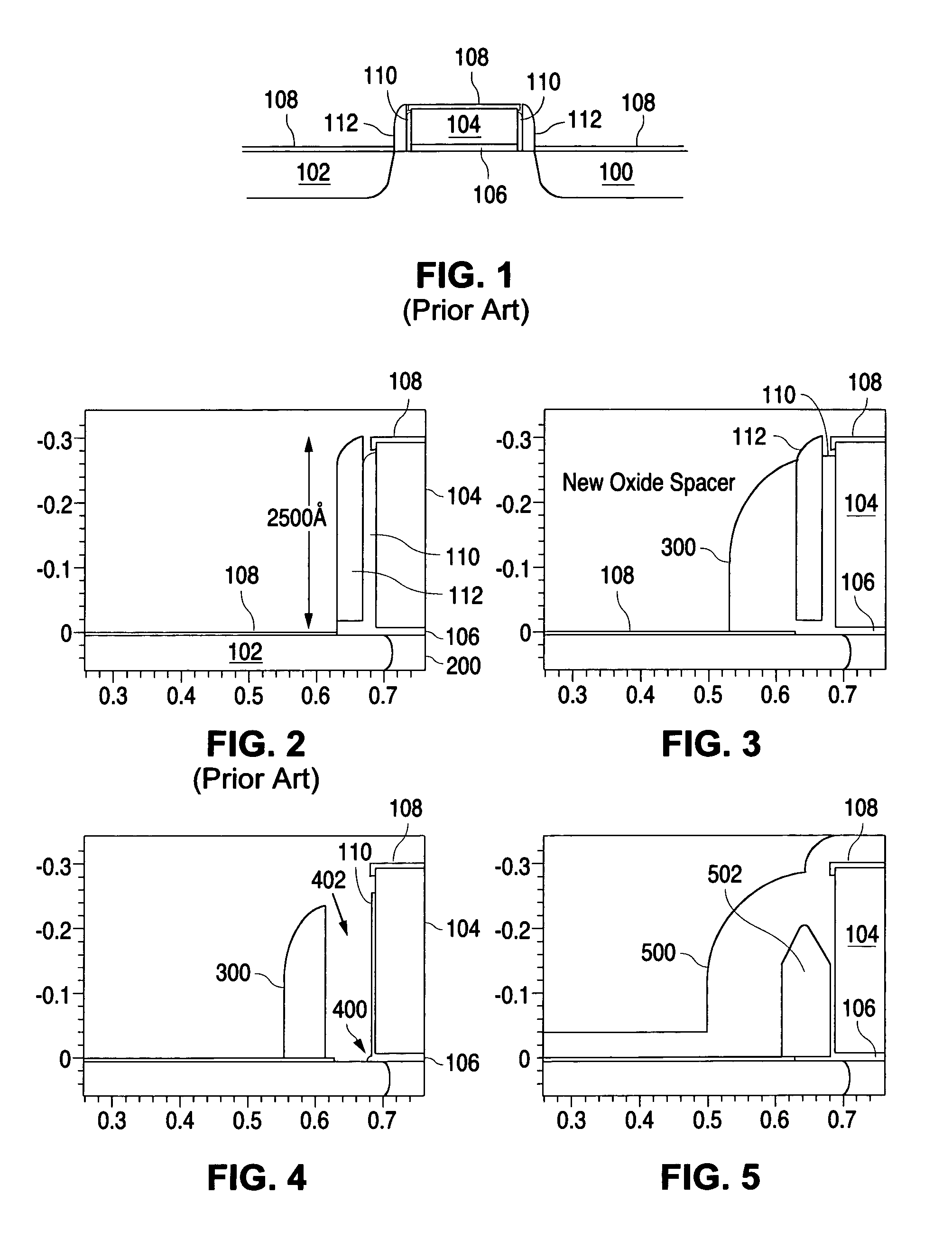

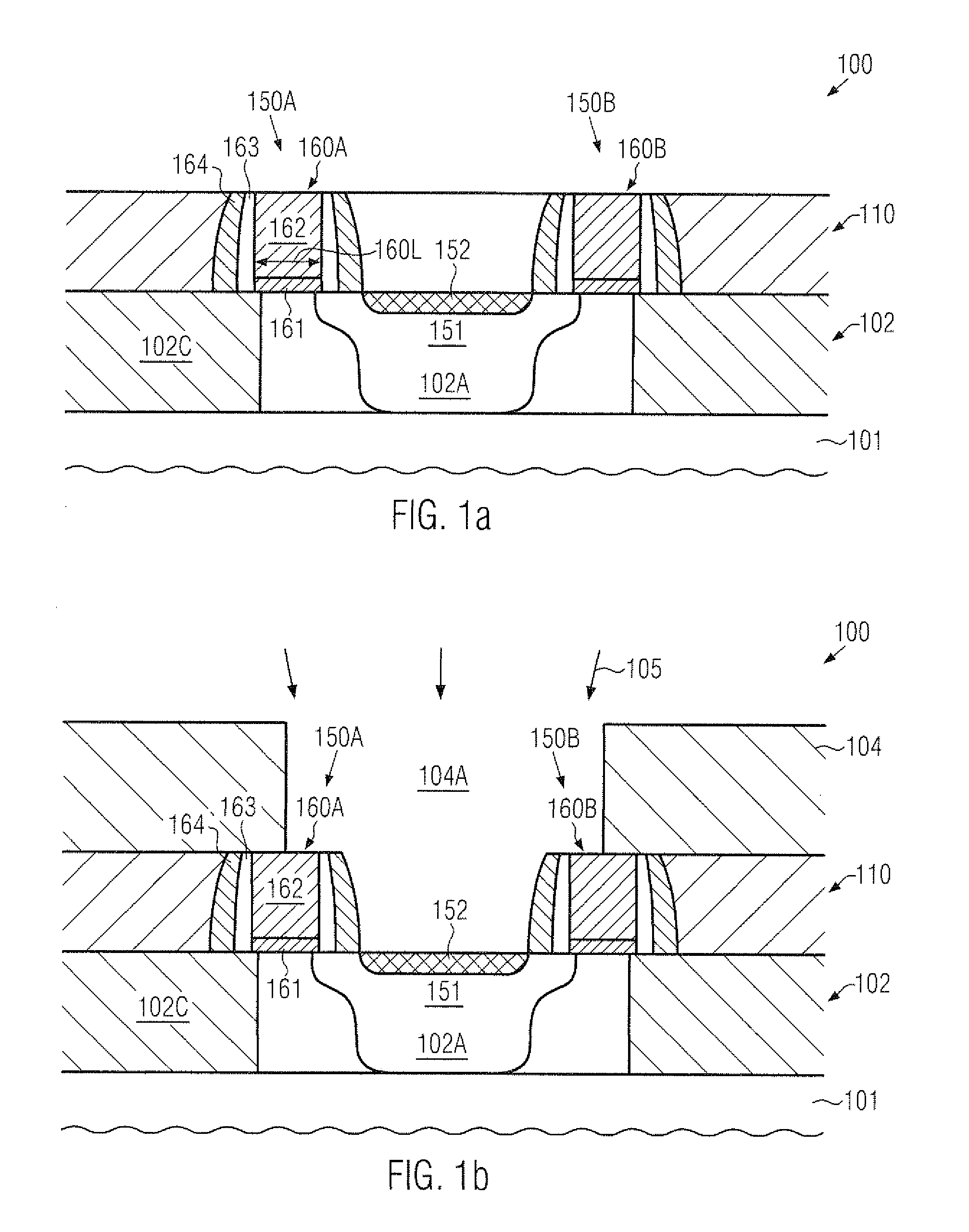

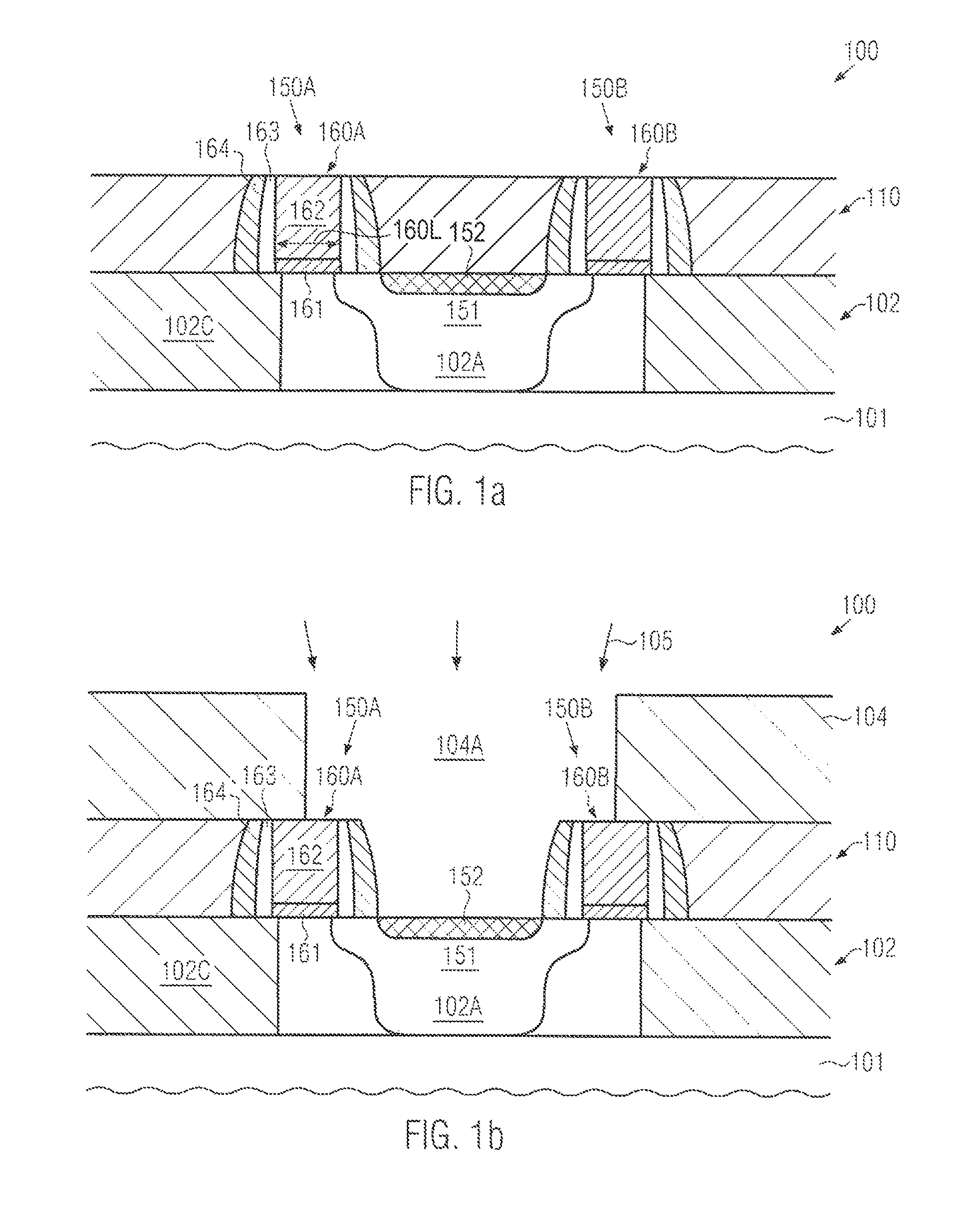

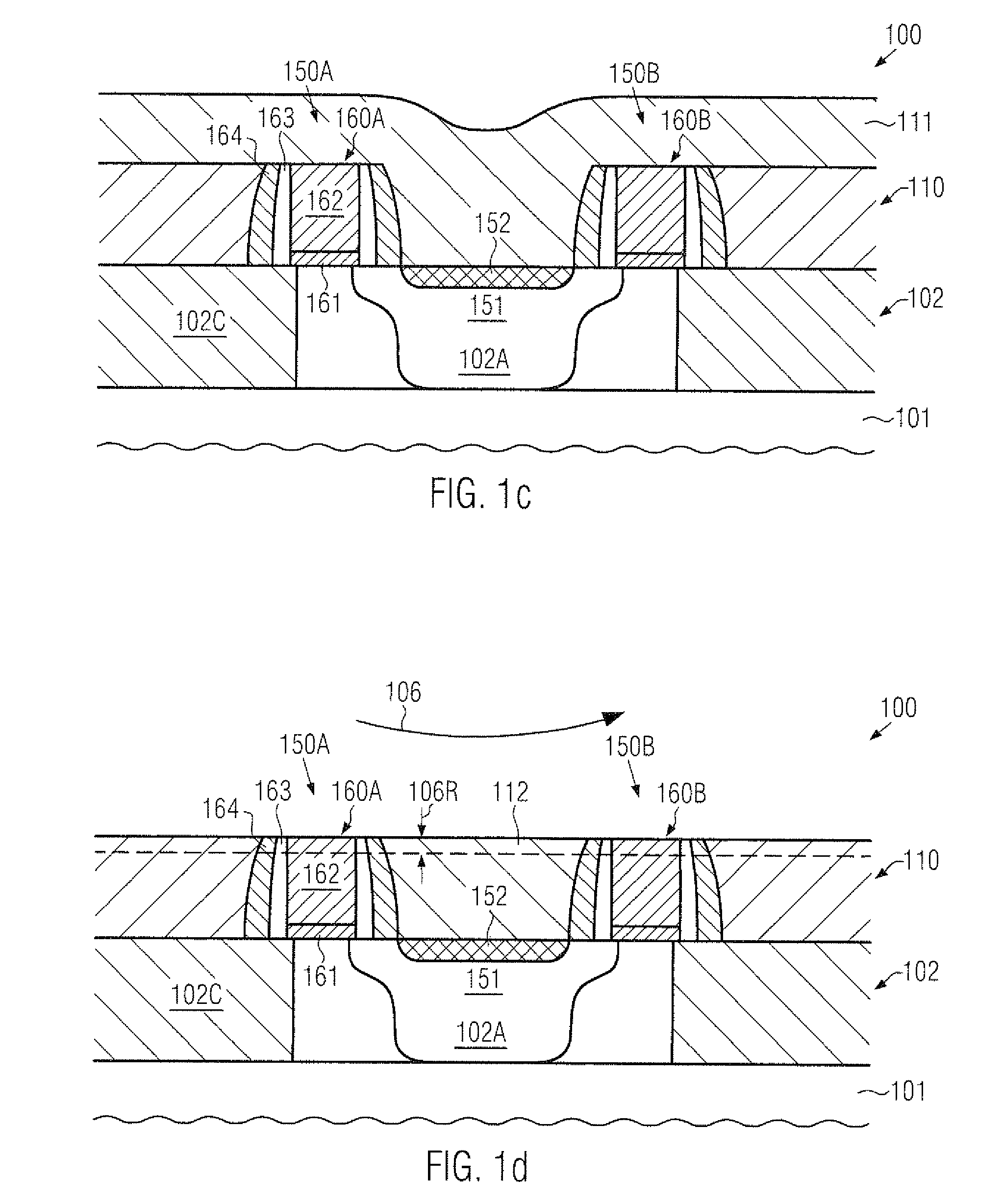

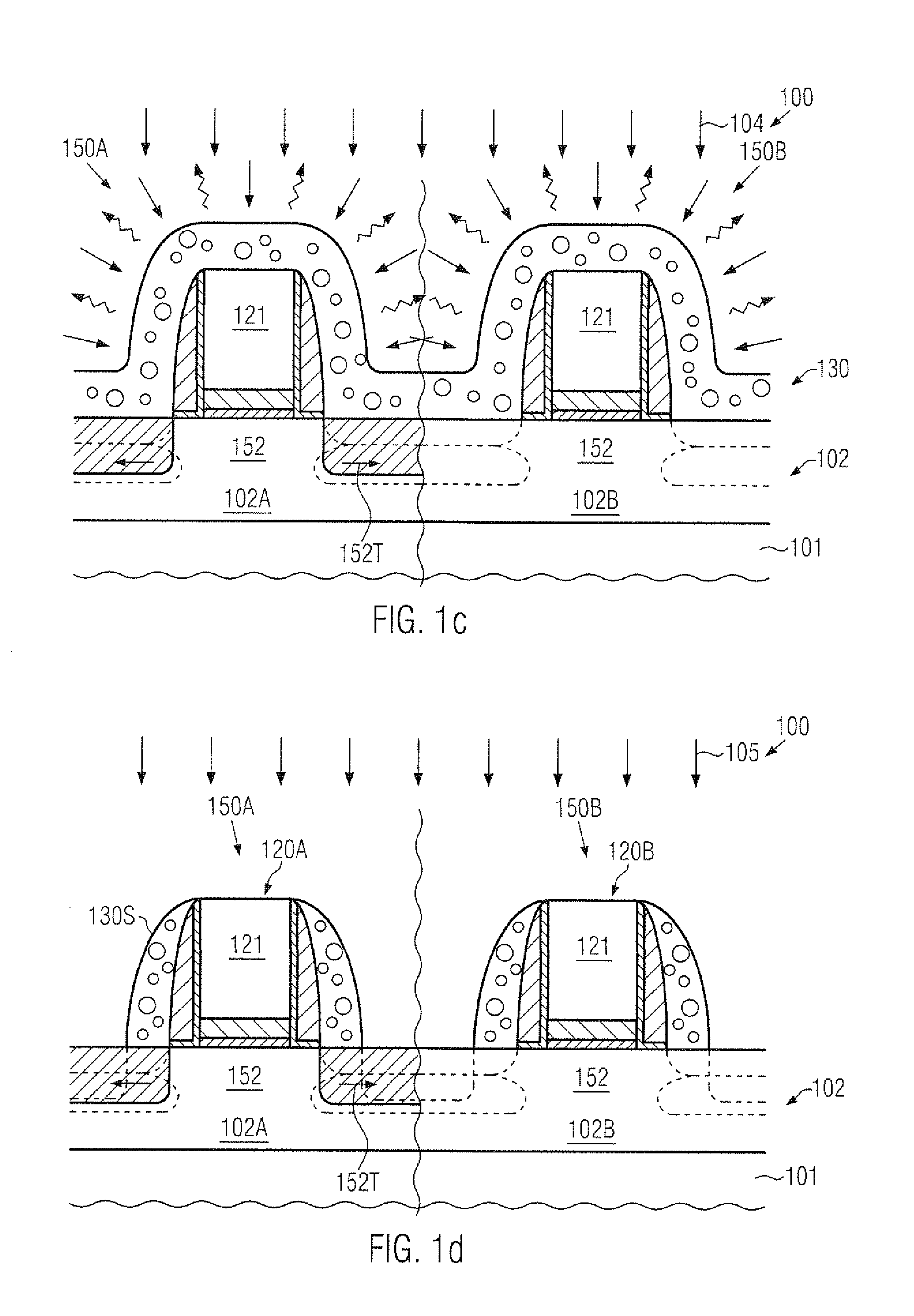

Stress Memorization with Reduced Fringing Capacitance Based on Silicon Nitride in MOS Semiconductor Devices

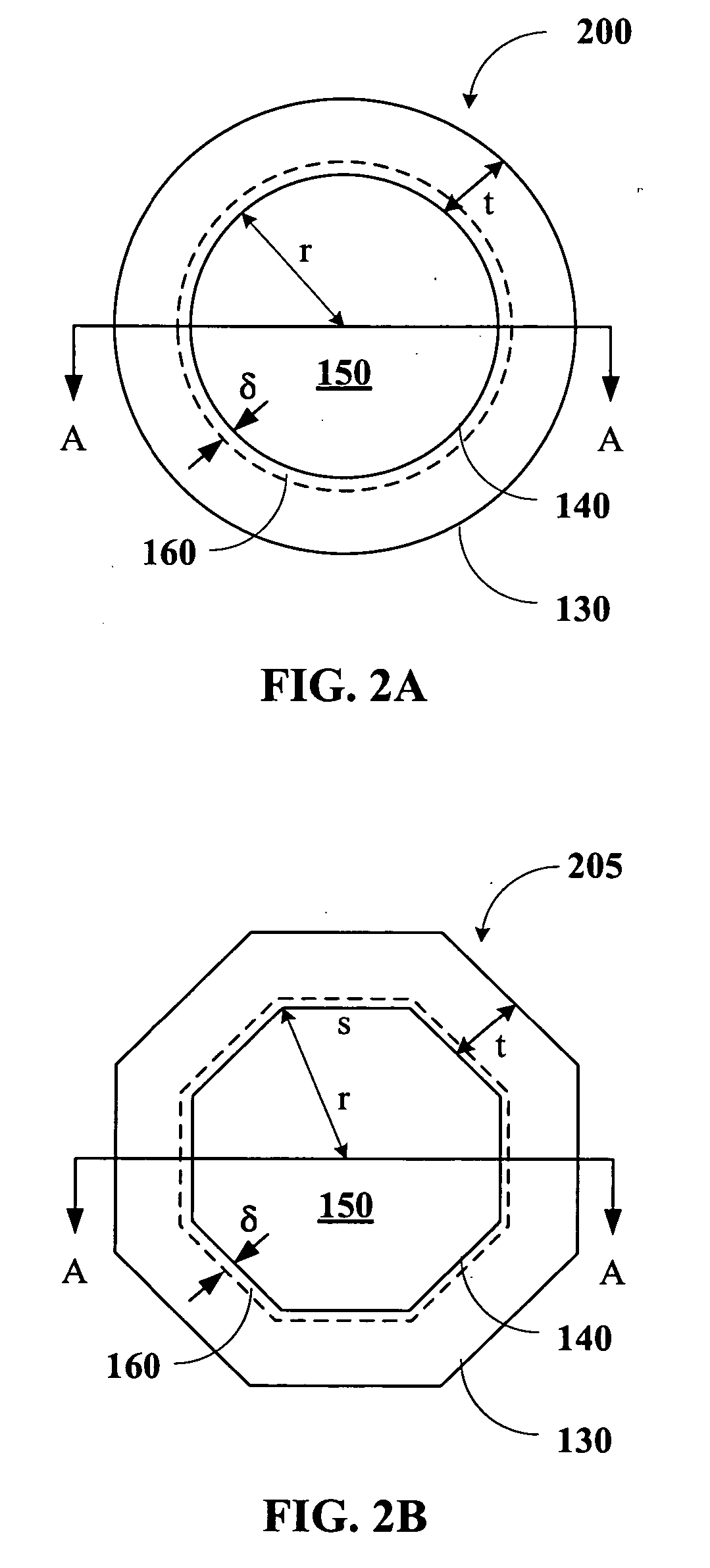

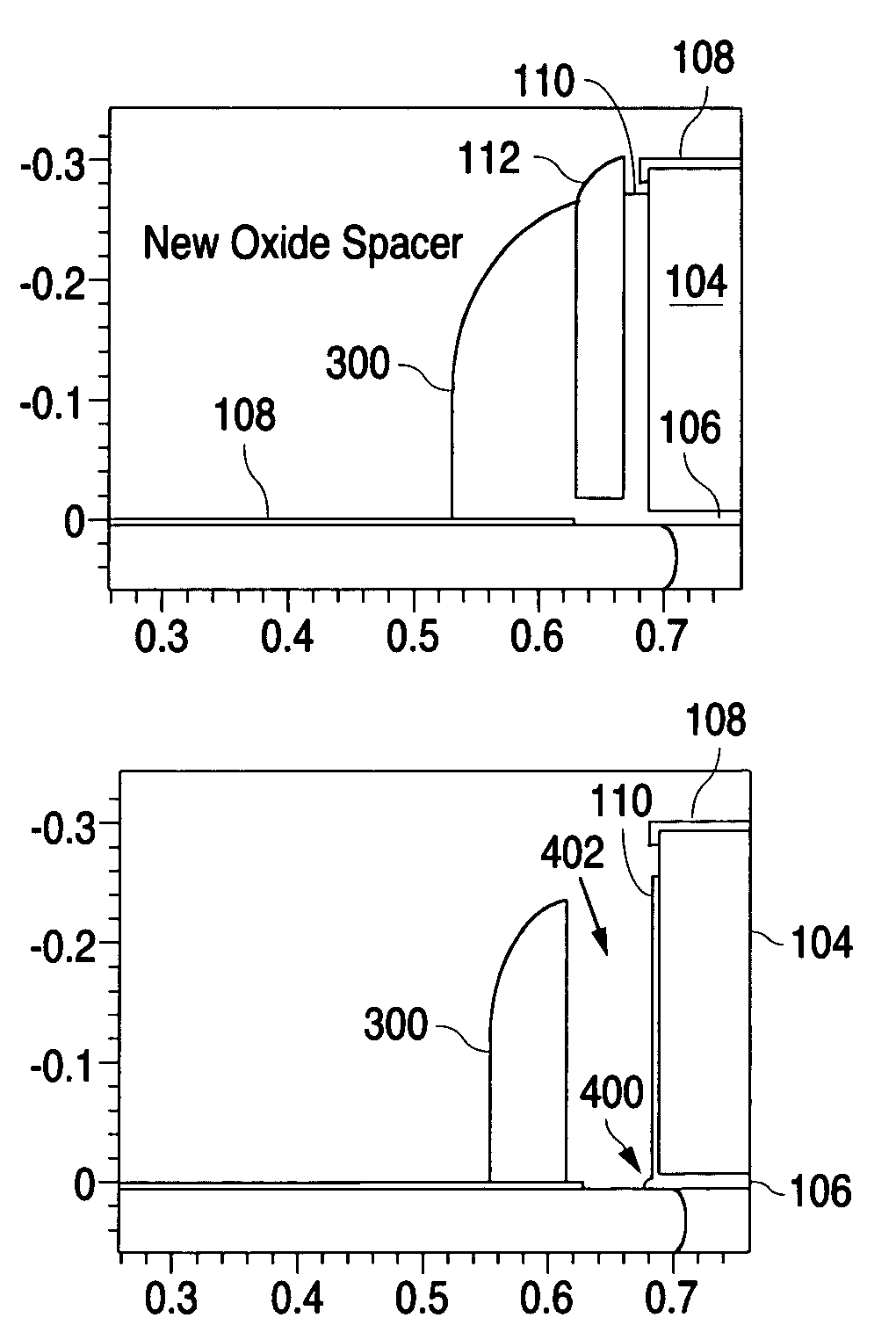

InactiveUS20110269278A1Avoid negative effectsEffective applicationTransistorSemiconductor/solid-state device manufacturingElectricityFringing capacitance

In sophisticated semiconductor devices, stress memorization techniques may be applied on the basis of a silicon nitride material, which may be subsequently modified into a low-k dielectric material in order to obtain low-k spacer elements, thereby enhancing performance of sophisticated semiconductor devices. The modification of the initial silicon nitride-based spacer material may be accomplished on the basis of an oxygen implantation process.

Owner:GLOBALFOUNDRIES INC

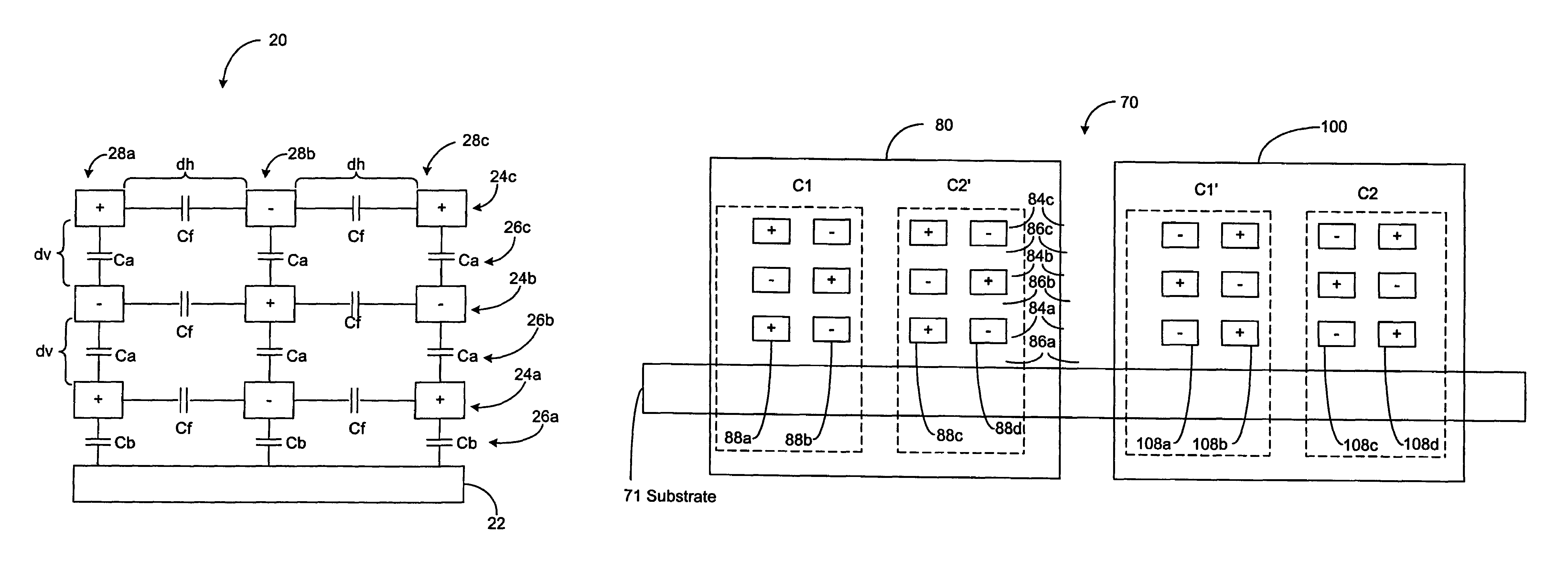

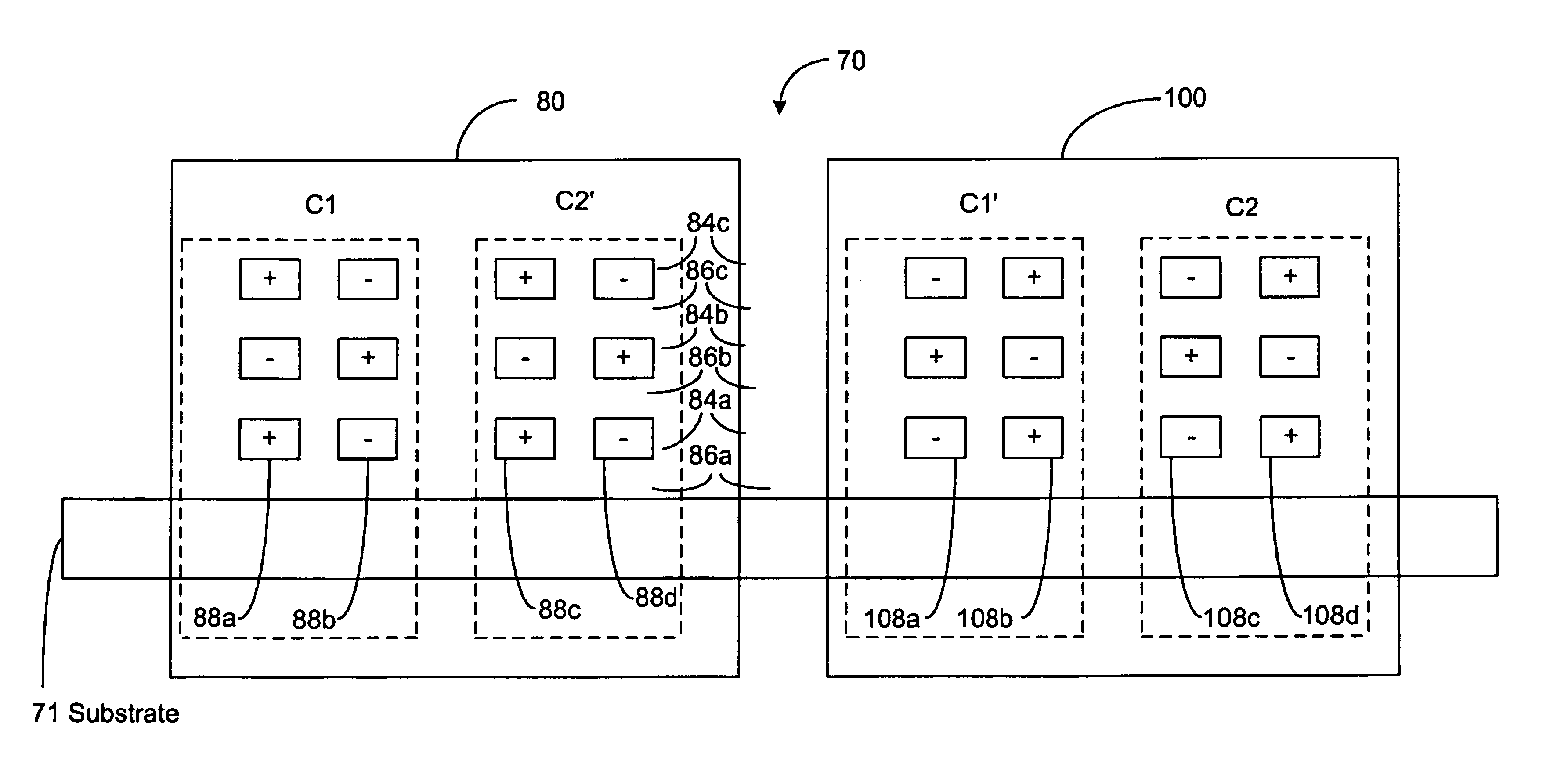

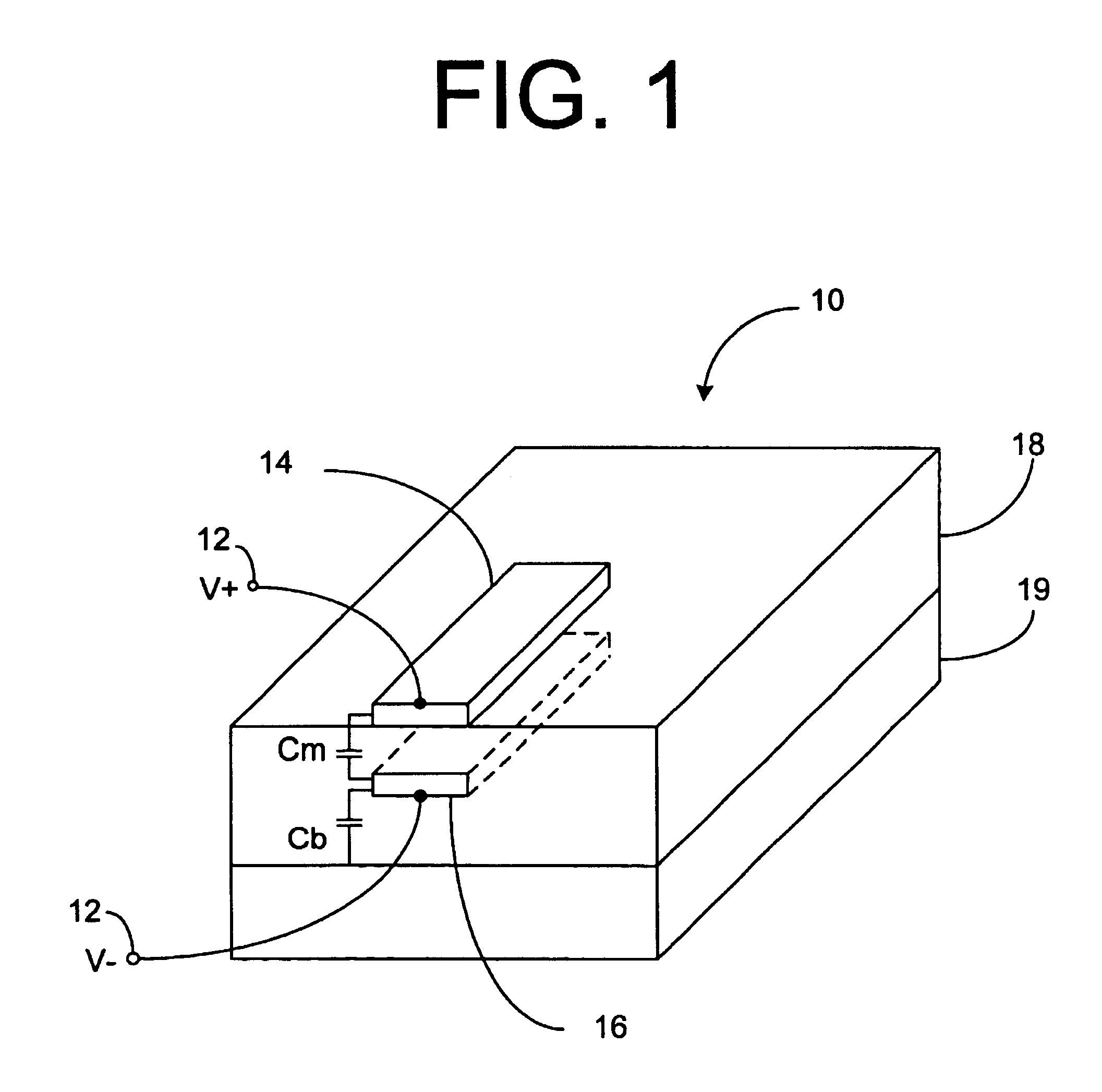

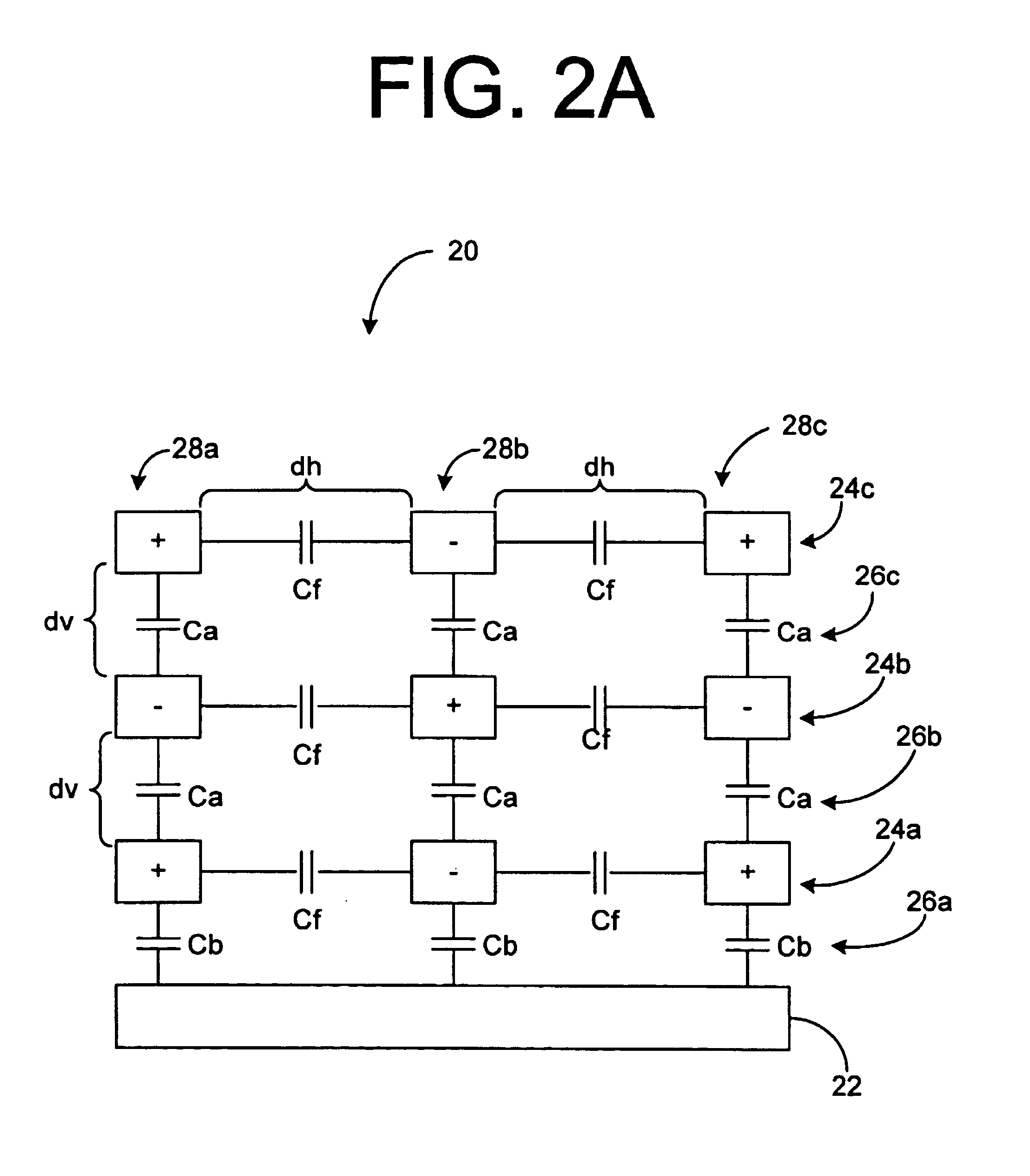

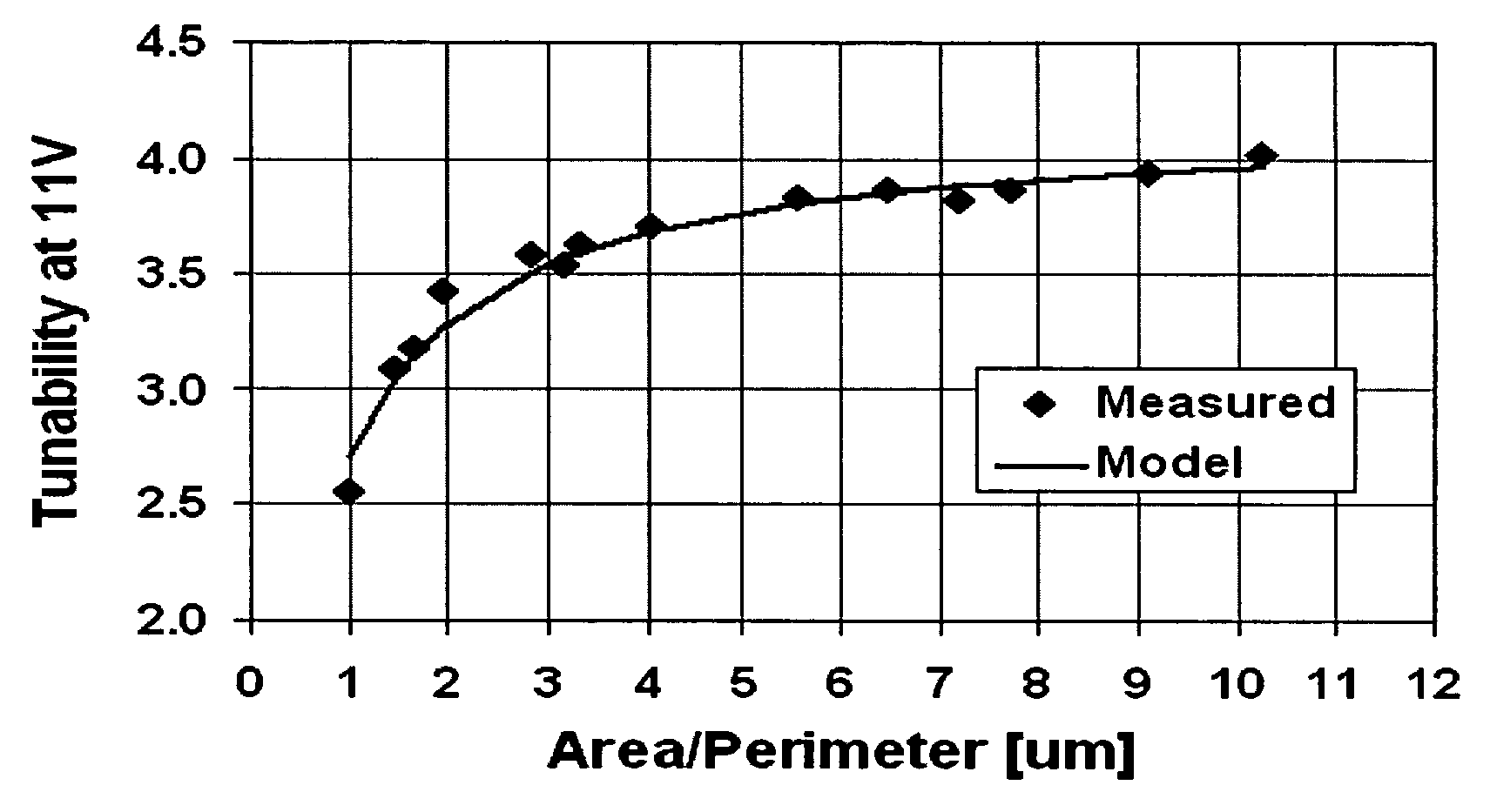

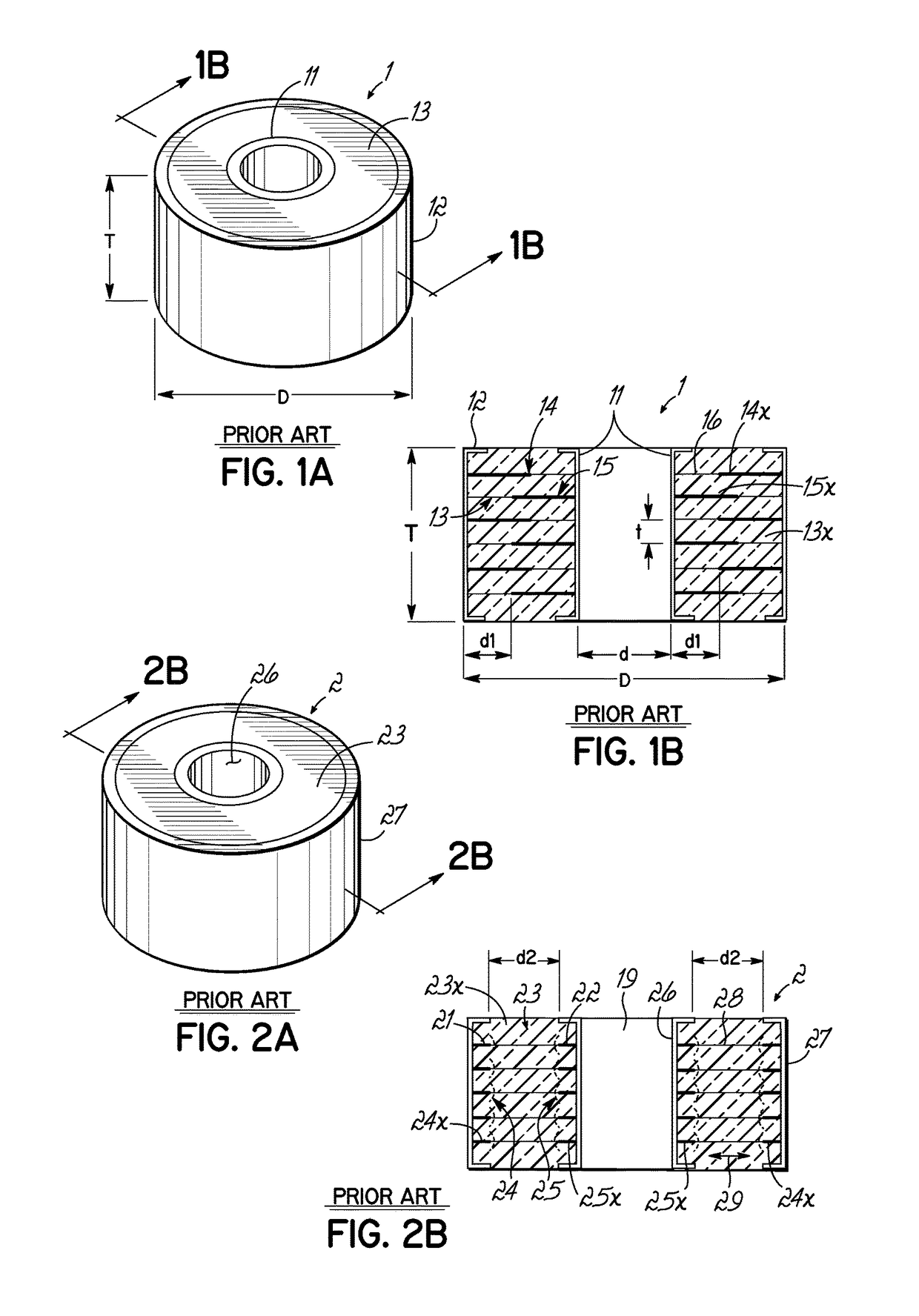

Fringing capacitor structure

InactiveUS6974744B1Multiple fixed capacitorsFixed capacitor electrodesDielectricElectrical conductor

The present invention provides a circuit and method for a fringing capacitor. The fringing capacitor includes at least two conductor layers spaced apart from each other. Each conductor layer includes at least two portions. The portions include odd ones alternating with even ones. Adjacent odd ones and even ones of the portions are spaced apart. The odd ones of the portions on a first one of the conductor layers are configured to substantially overlay the odd ones of the portions on an adjacent one of the conductor layers. The even ones of the portions on the first one of the conductor layers are configured to substantially overlay the even ones of the portions on the adjacent one of the conductor layers. The odd ones of the portions on the first one of the conductor layers are electrically coupled together and to the even ones of the portions on the adjacent one of the conductor layers, thereby defining a first electrode. The even ones of the portions on the first one of the conductor layers are electrically coupled together and to the odd ones of the portions on the adjacent one of the conductor layers, thereby defining a second electrode. A dielectric is interposed between the first and second electrodes. A guardband is spaced from the first and second electrodes.

Owner:MARVELL ASIA PTE LTD

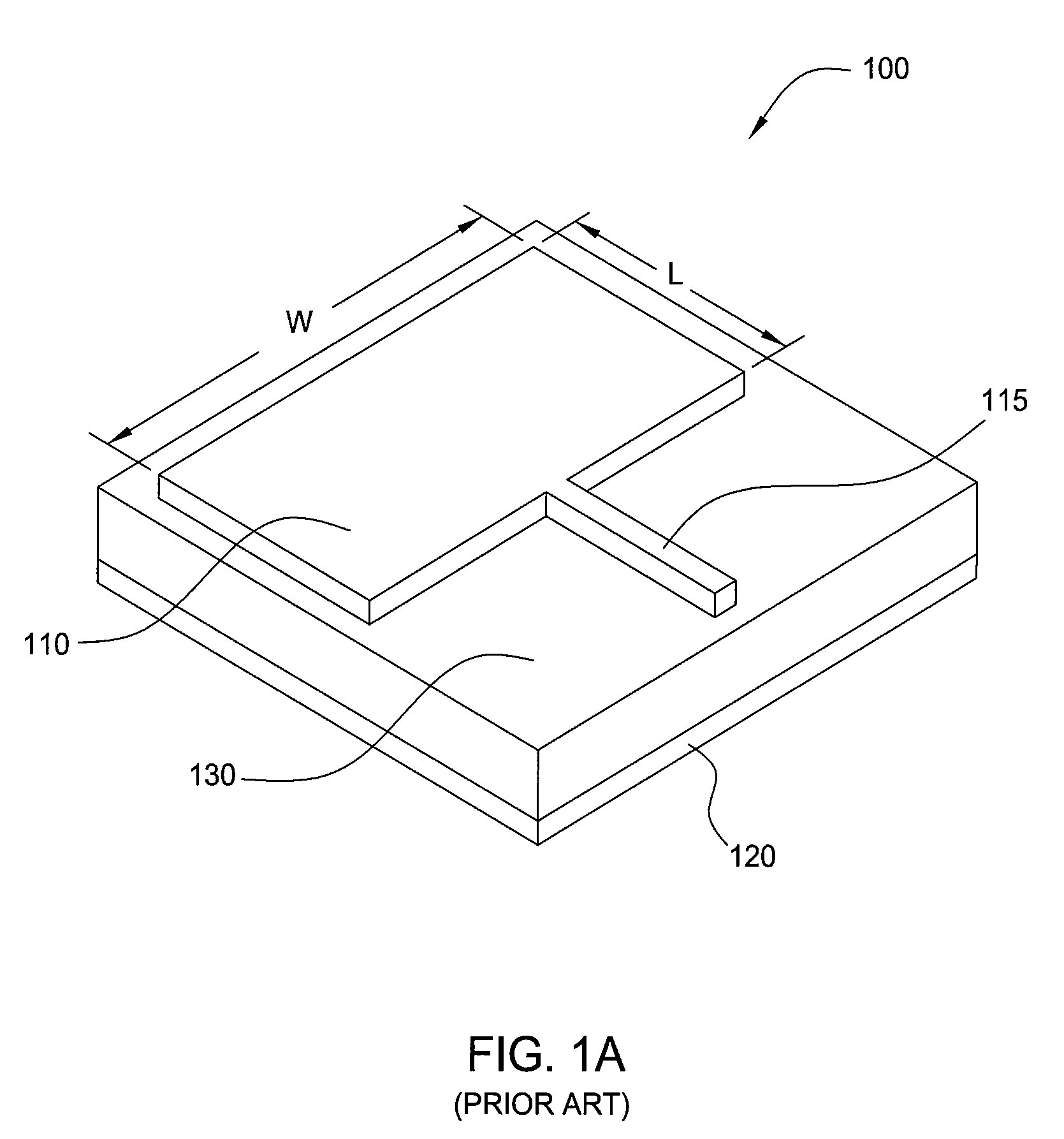

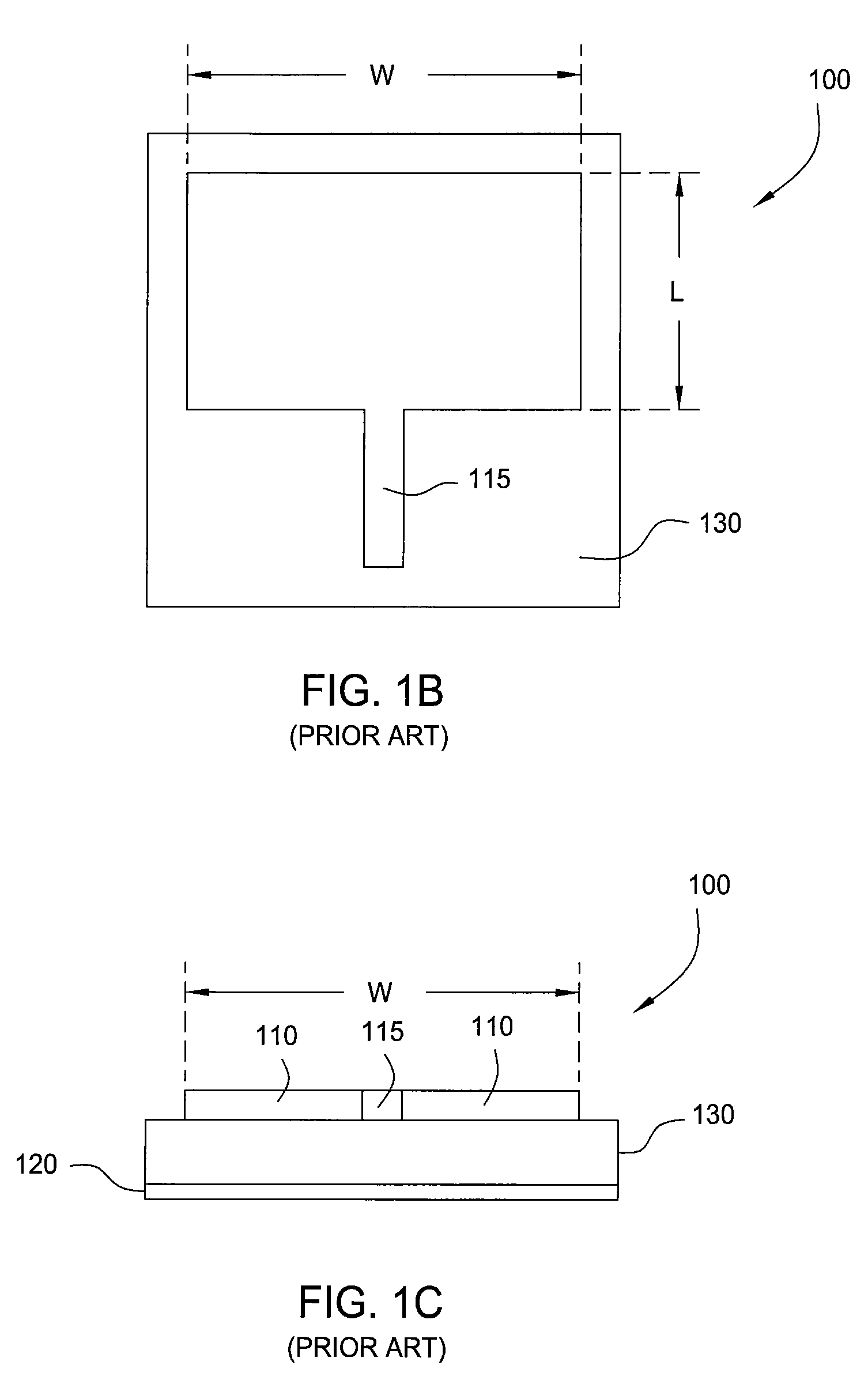

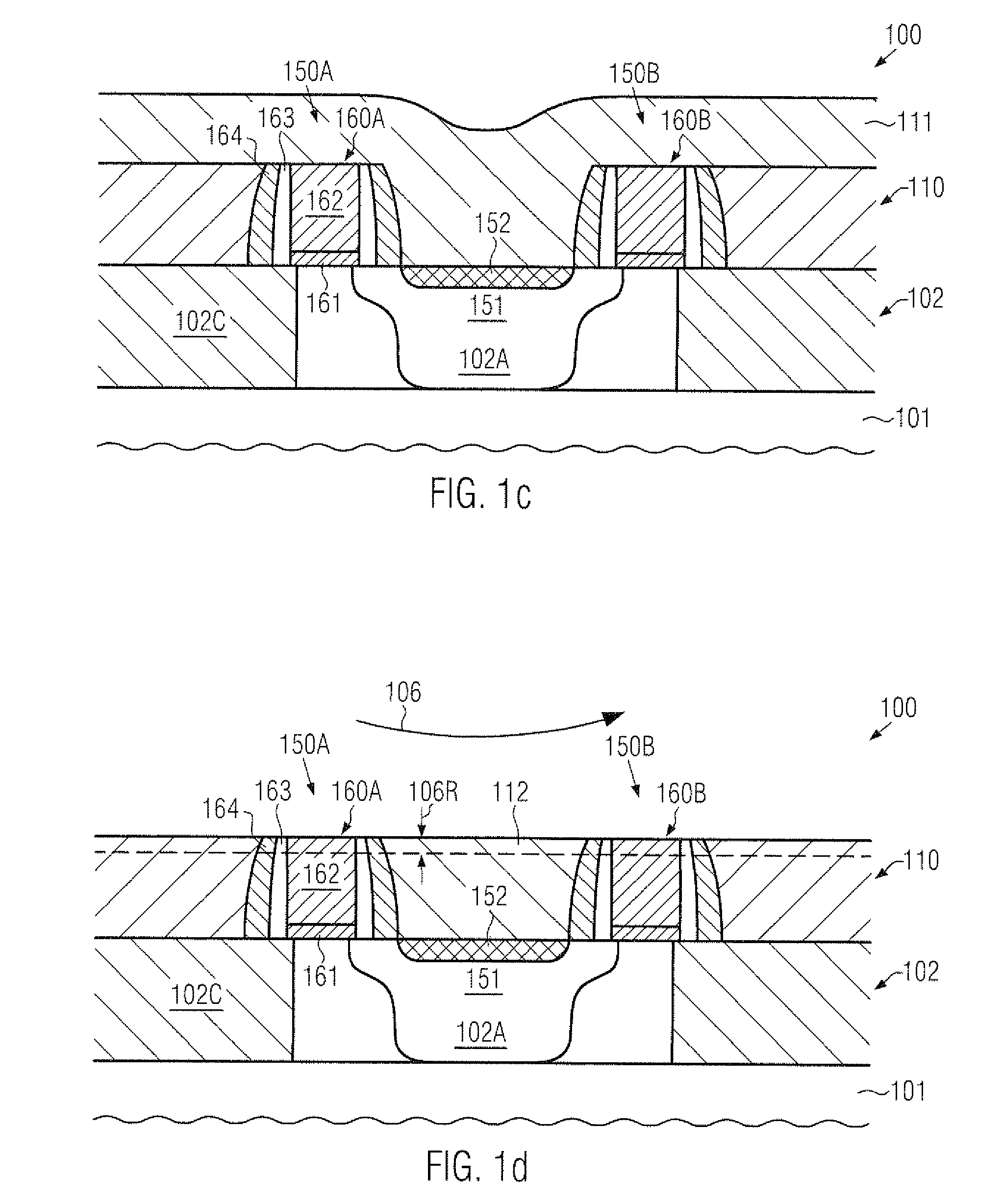

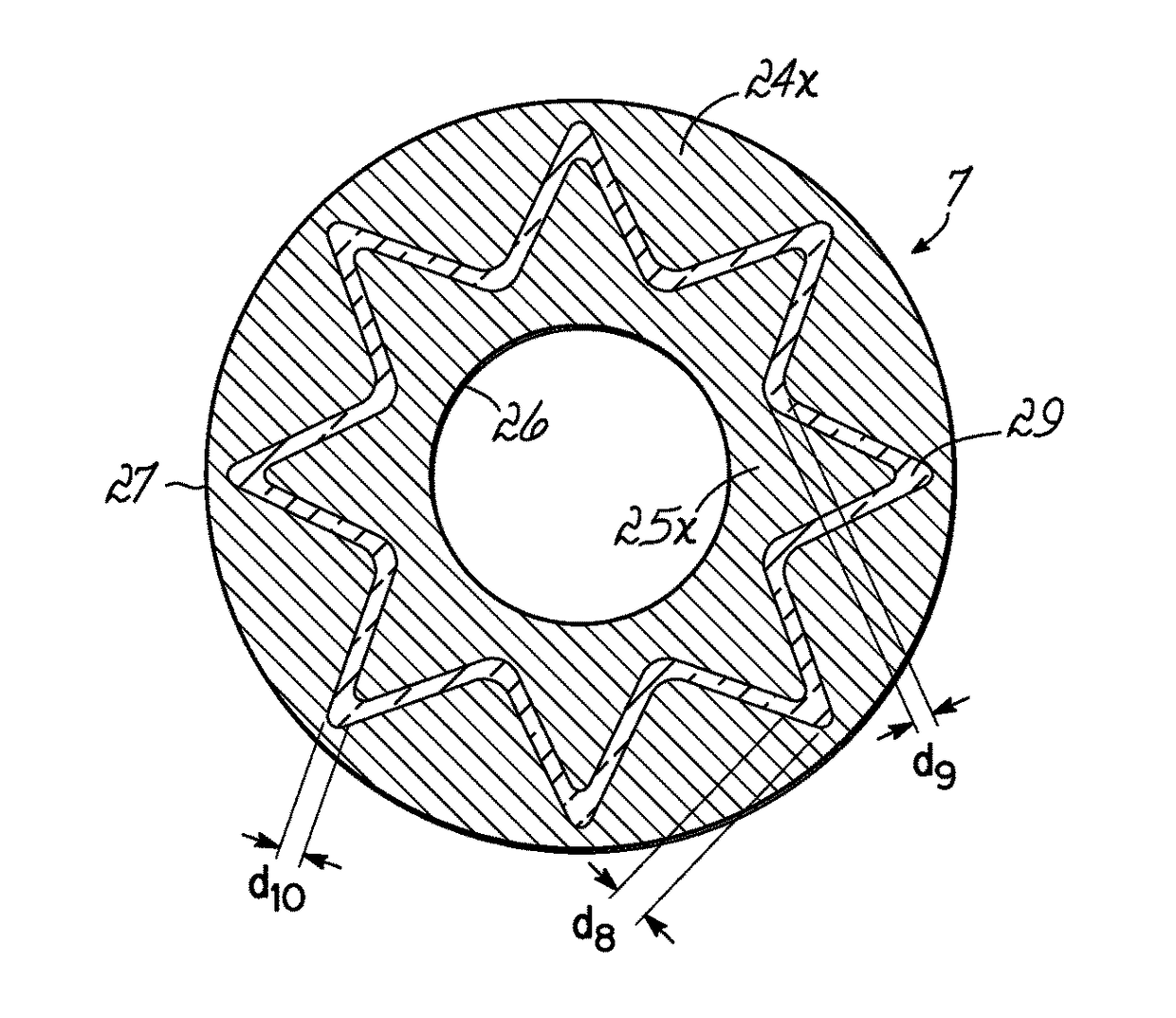

Varactor design using area to perimeter ratio for improved tuning range

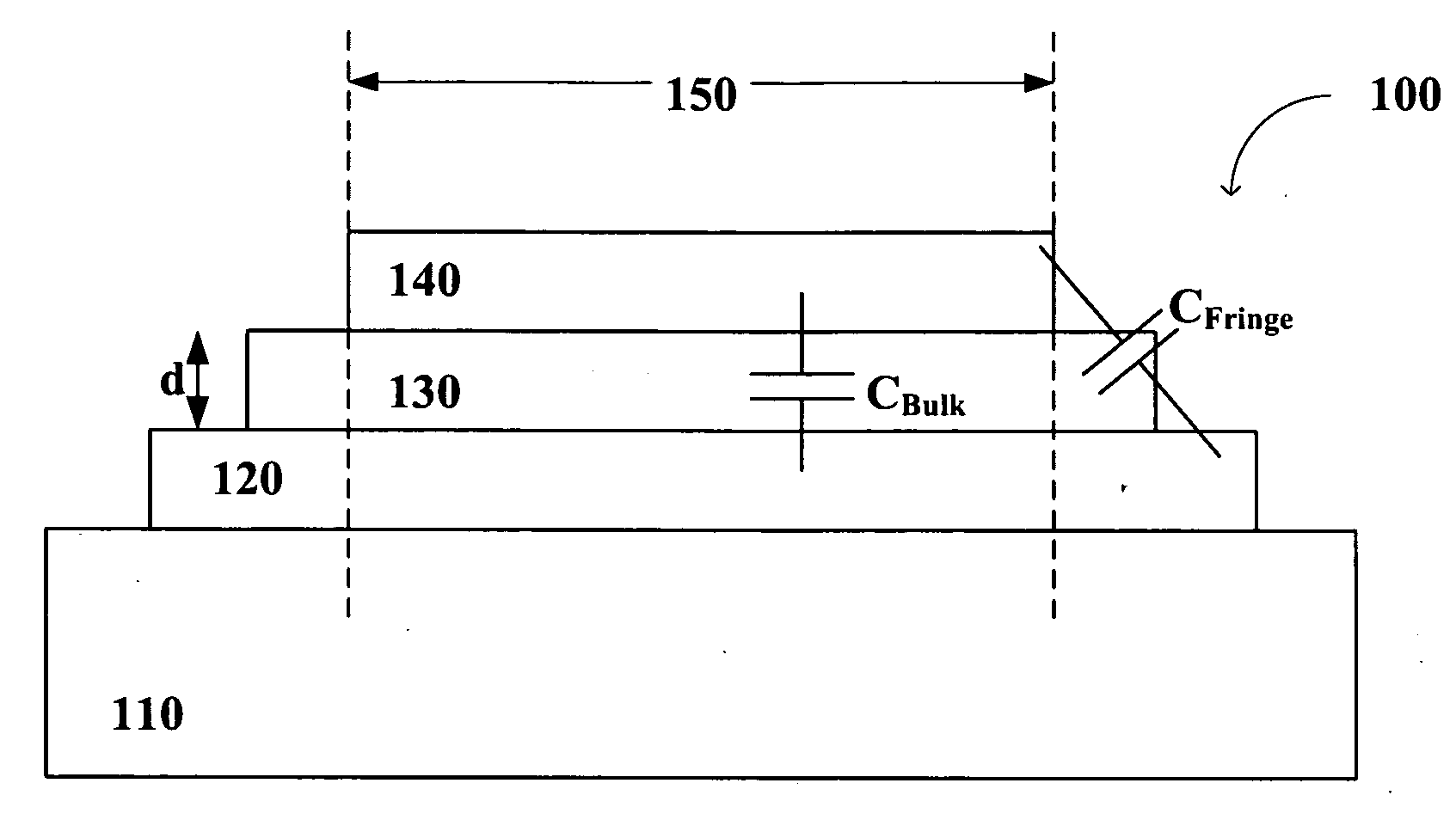

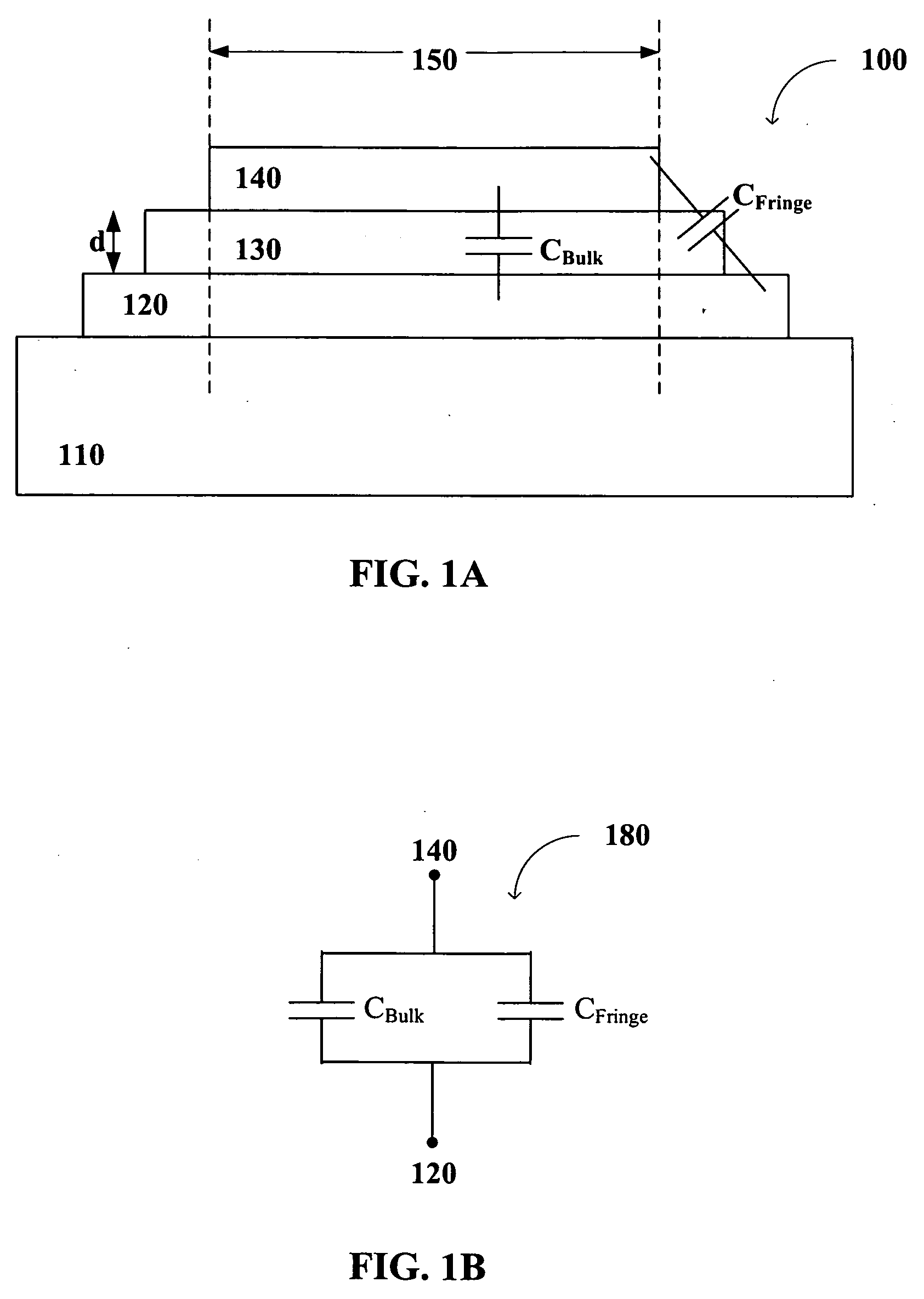

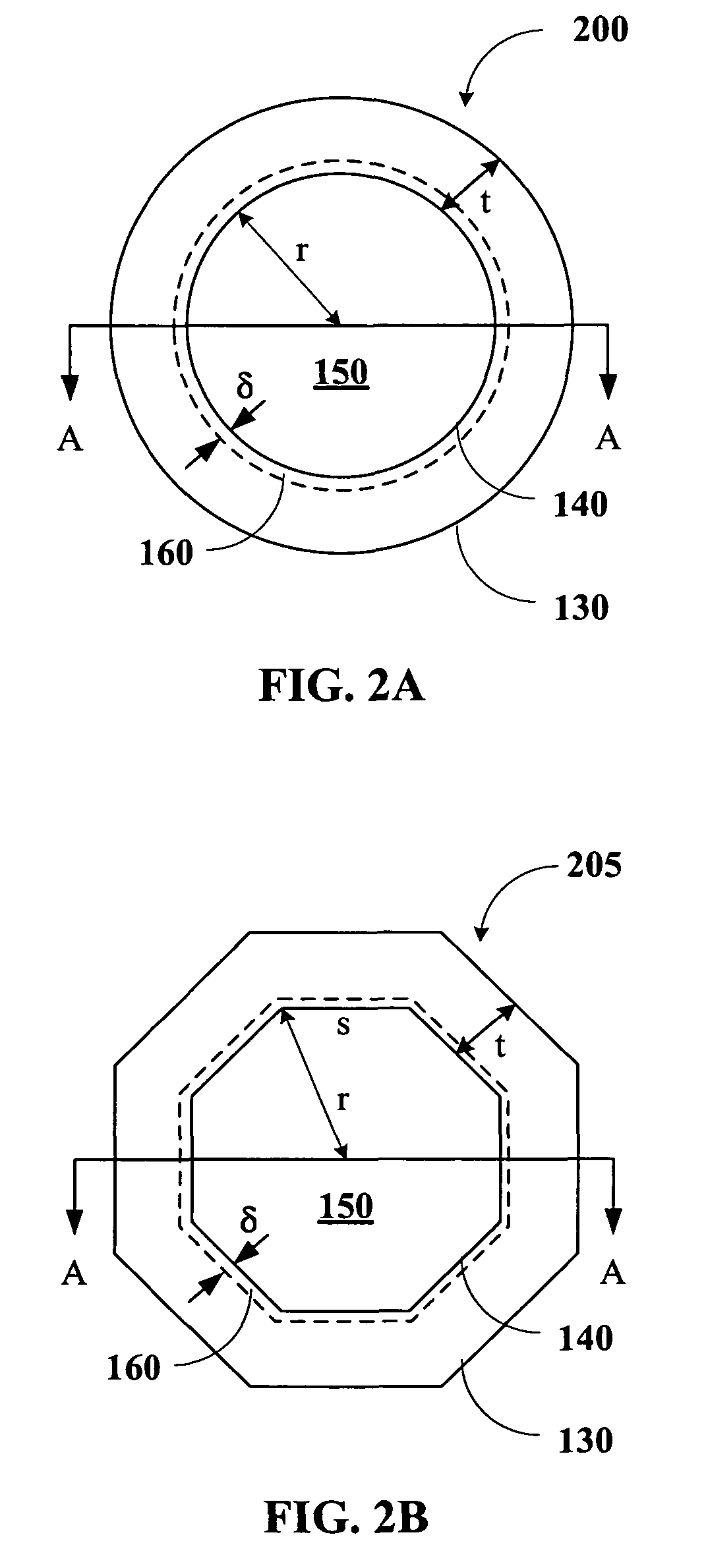

ActiveUS20070069274A1Good tunabilityImproves otherTransistorSolid-state devicesParallel plateEngineering

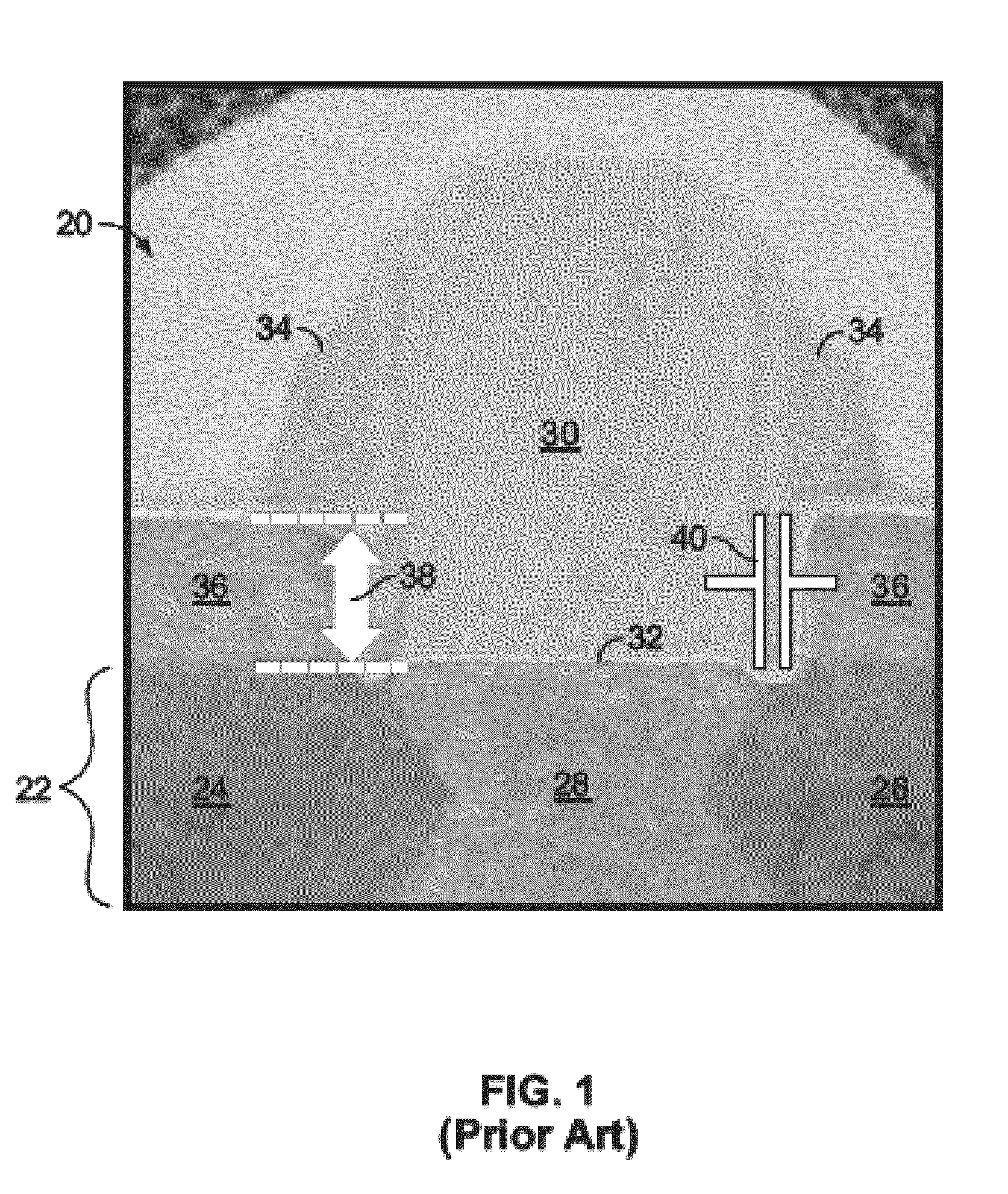

Parallel plate tunable varactors having a bulk capacitance contribution to a total capacitance increased compared to a fringing capacitance contribution are disclosed. The contribution of the bulk capacitance to the total capacitance of an exemplary BST varactor is increased by increasing the area / perimeter ratio of the active region, thereby improving the tunability and other properties of the varactor. In an exemplary embodiment, an active region of the varactor has a lateral shape with a perimeter that is less than a perimeter of an equivalent area square. In various exemplary embodiments, the shape of the active region may be substantially circular or substantially octagonal. Methods for fabricating and designing such varactors are also disclosed.

Owner:QORVO US INC

Method of reducing fringing capacitance in a MOSFET

ActiveUS7132342B1Reduce fringing capacitanceReduce thickness of oxideSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEngineering

In a method of reducing the fringing capacitance of a MOSFET, the nitride spacers on the sides of the MOSFET gate are etched away to form trenches, which are plugged to define air spacers.

Owner:NAT SEMICON CORP

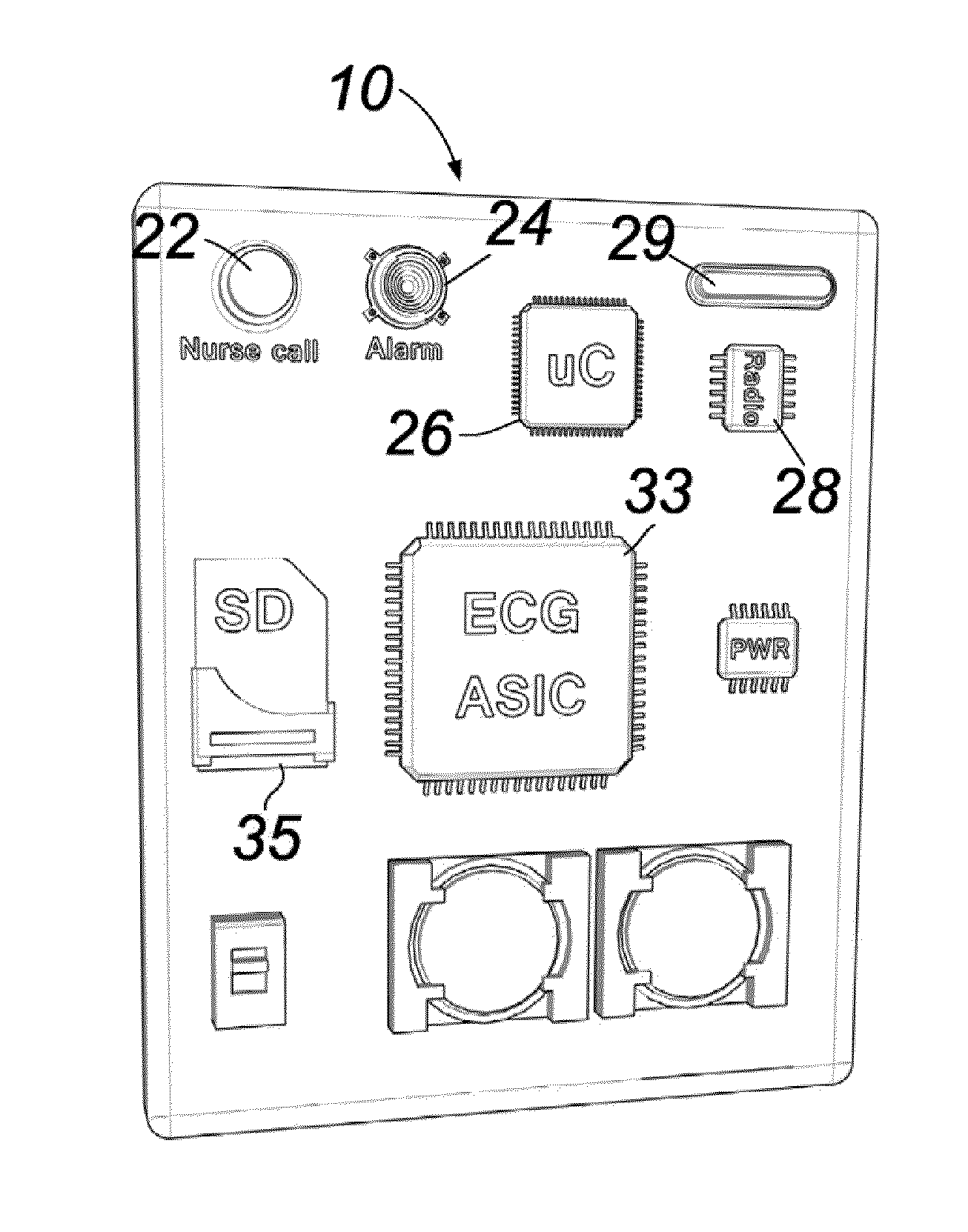

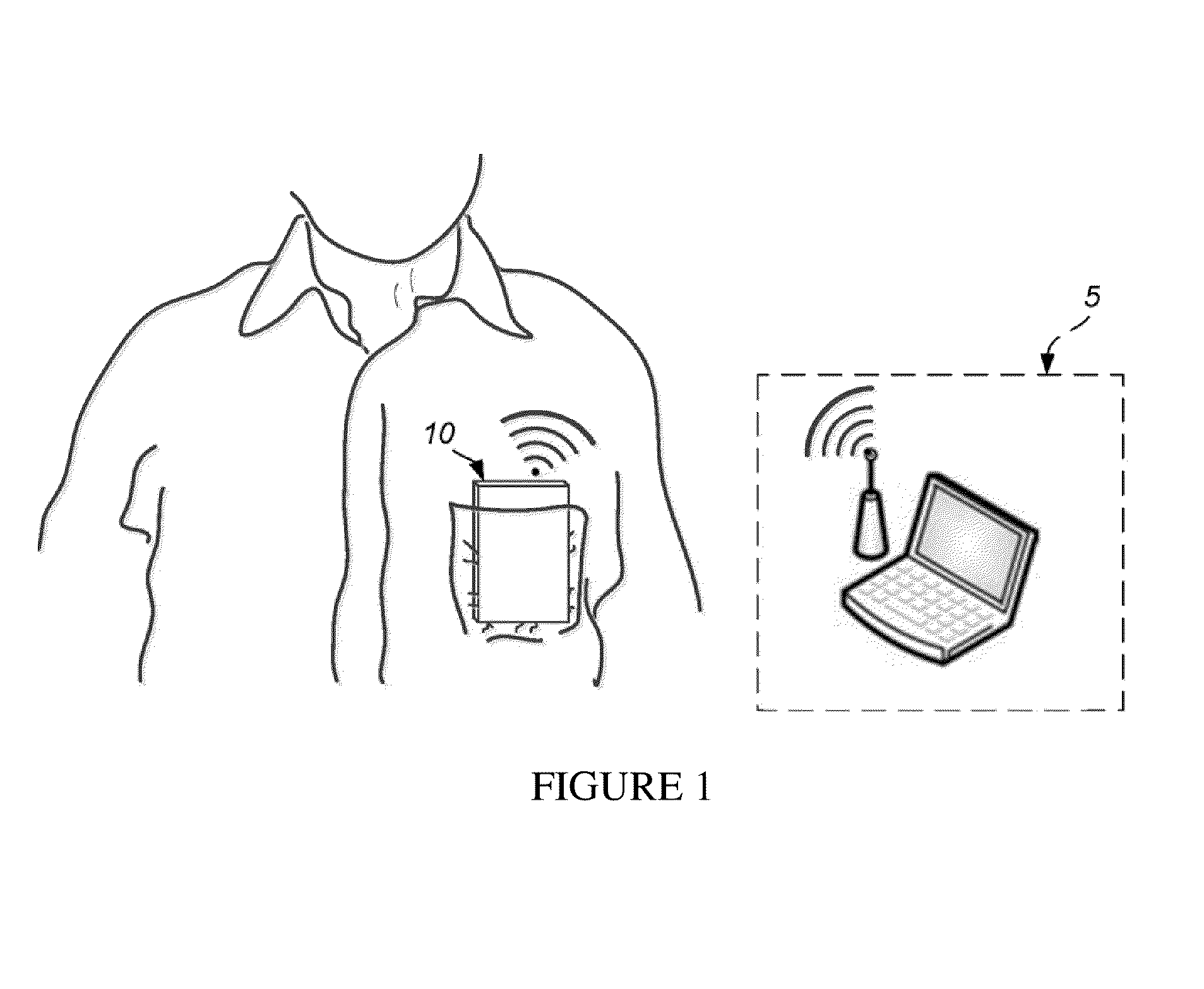

Non-contact electrocardiogram system

ActiveUS20140200469A1Robust and convenientCorrect gain dependenceElectrocardiographySensorsAudio power amplifierEngineering

A non-contact electrocardiogram (ECG) sensor having an ECG electrode and guard electrode coupled to an electronic circuit that actively gain-corrects the electrocardiogram signal based on fringe capacitance signal and filters the gain-corrected signal based on a static charge reference signal. The compensation system first makes a gain correction for the preamplifier to address ECG electrode-to-subject motion and then removes any additive static common mode interference from motion-induced static charge generation.

Owner:UNIVERSITY OF ROCHESTER

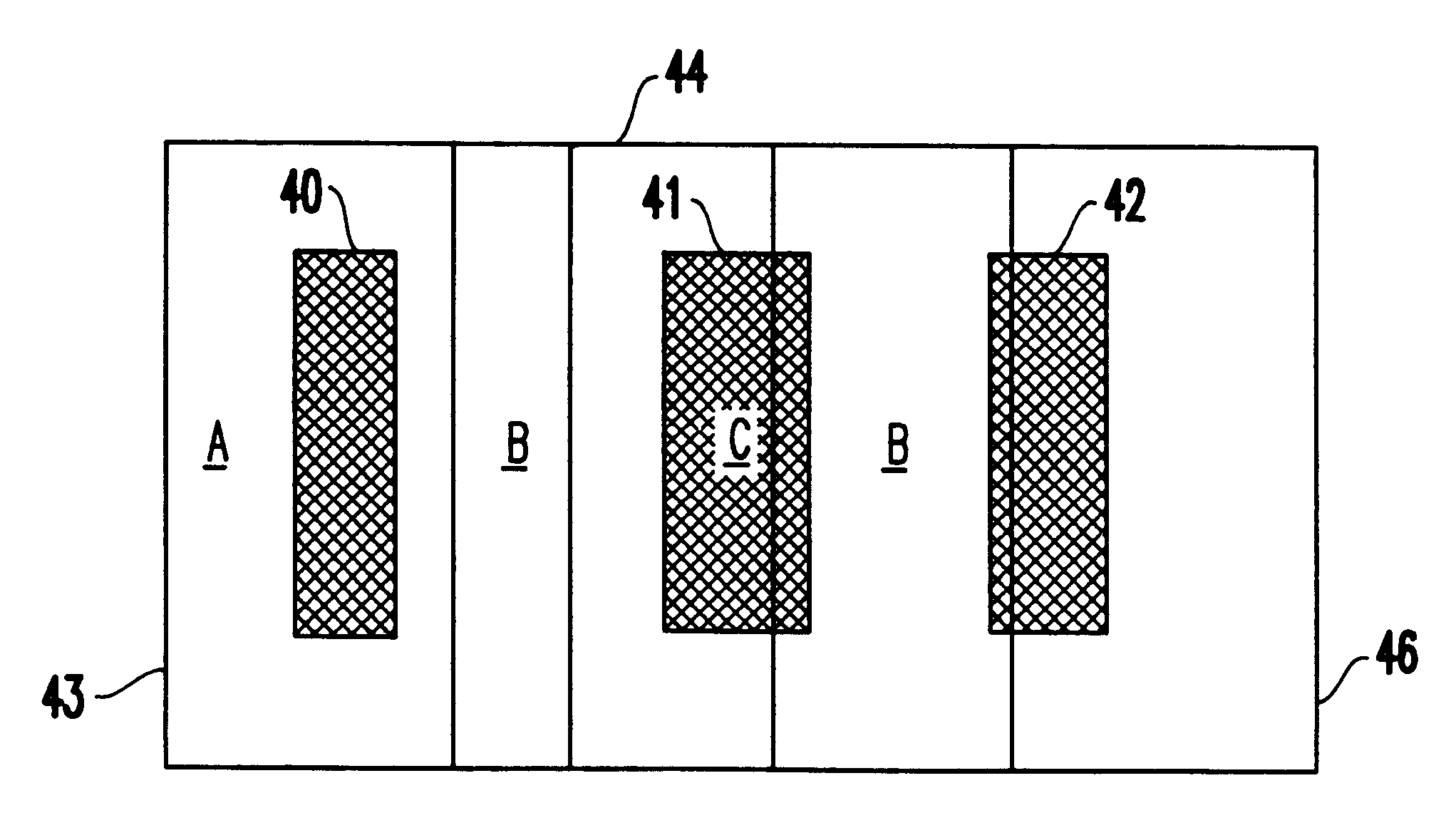

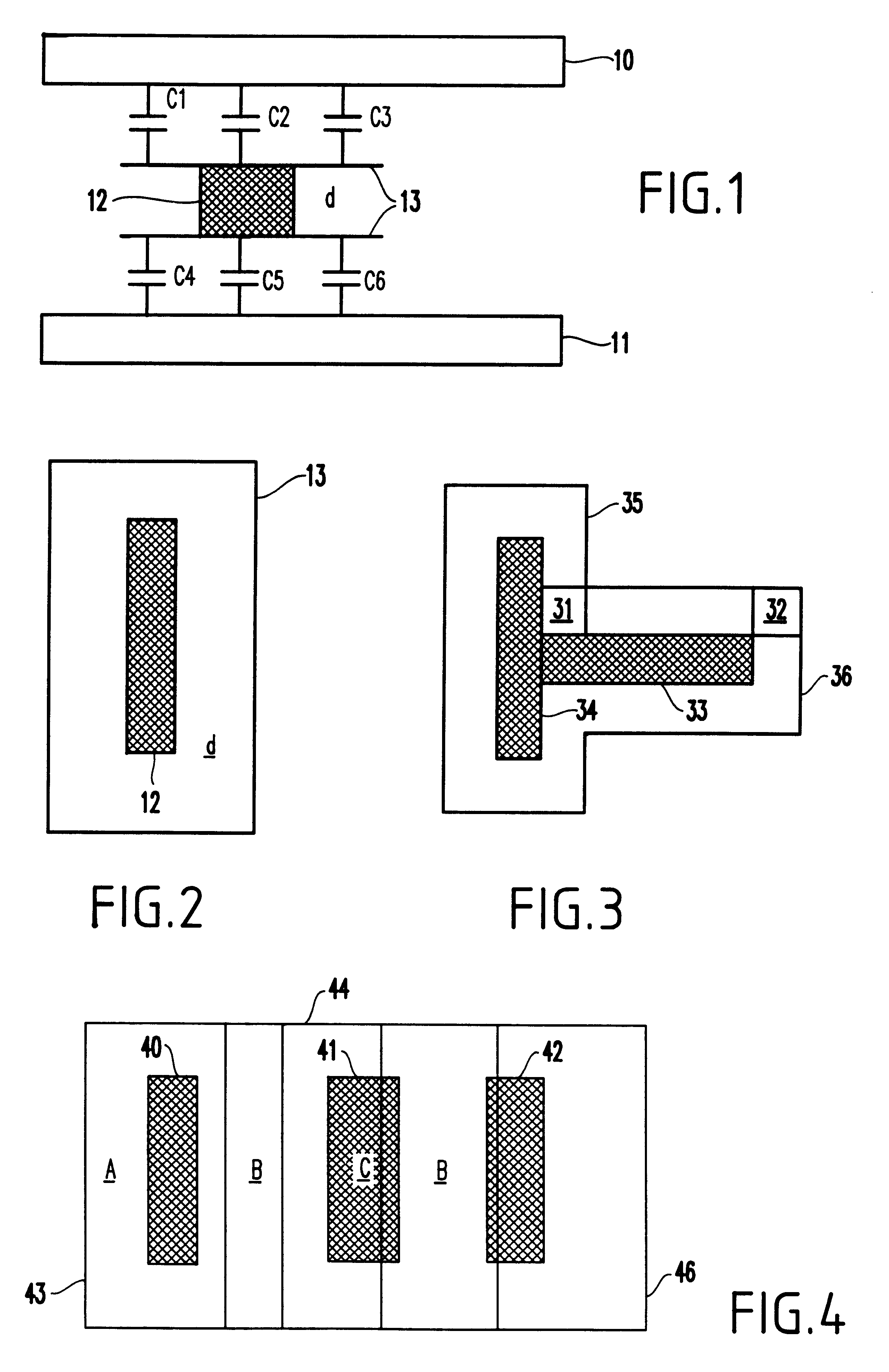

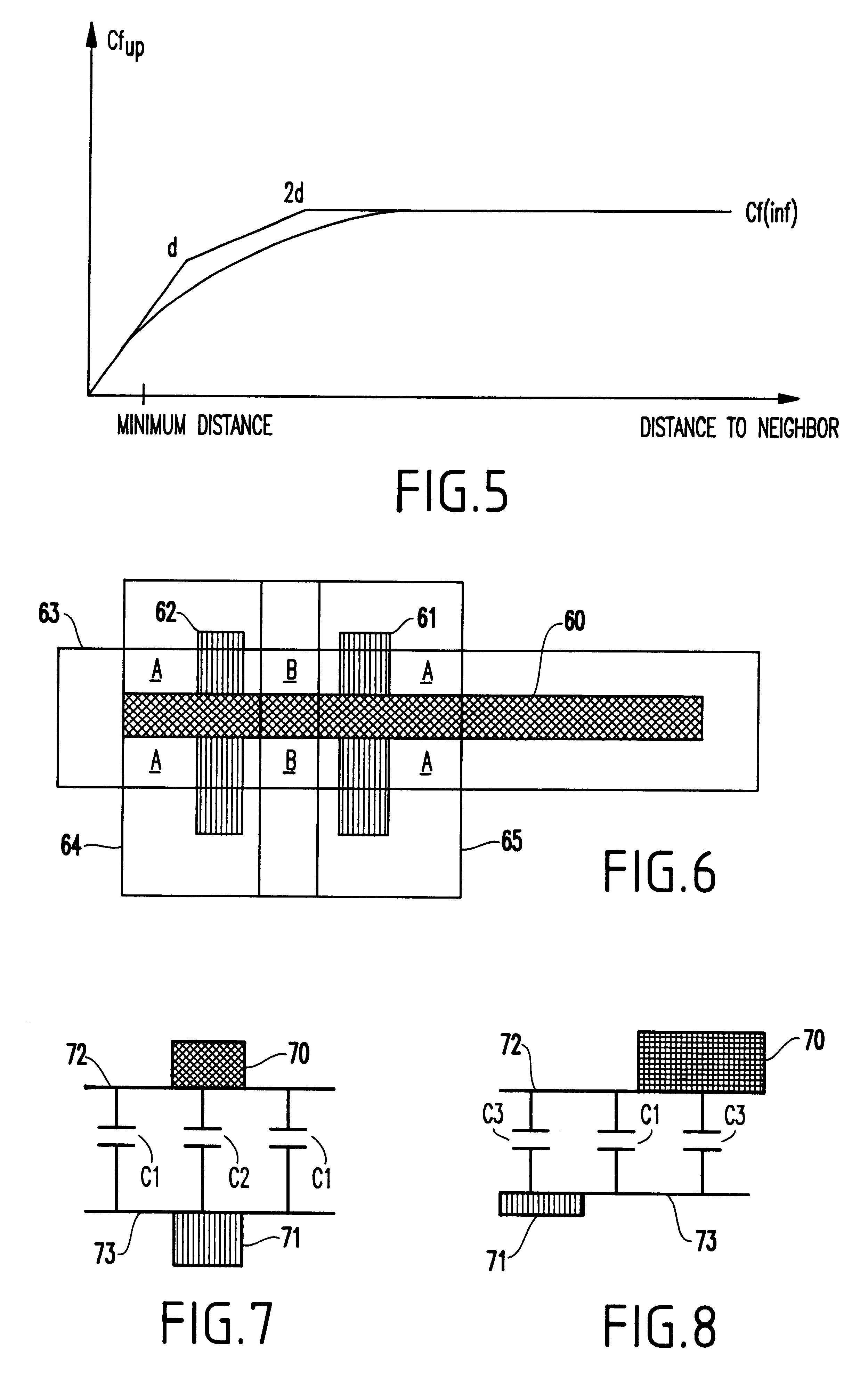

Method of calculating 3-dimensional fringe characteristics using specially formed extension shapes

A structure and method for performing a capacitance extraction on an integrated circuit, includes determining a parallel-plate capacitance between devices on different levels within the integrated circuit, adding extension shapes around each of the devices, reducing an area of overlapping extension shapes, multiplying a remaining area of the extension shapes by a constant to produce a fringe capacitance; and summing the parallel-plate capacitance and the fringe capacitance.

Owner:IBM CORP

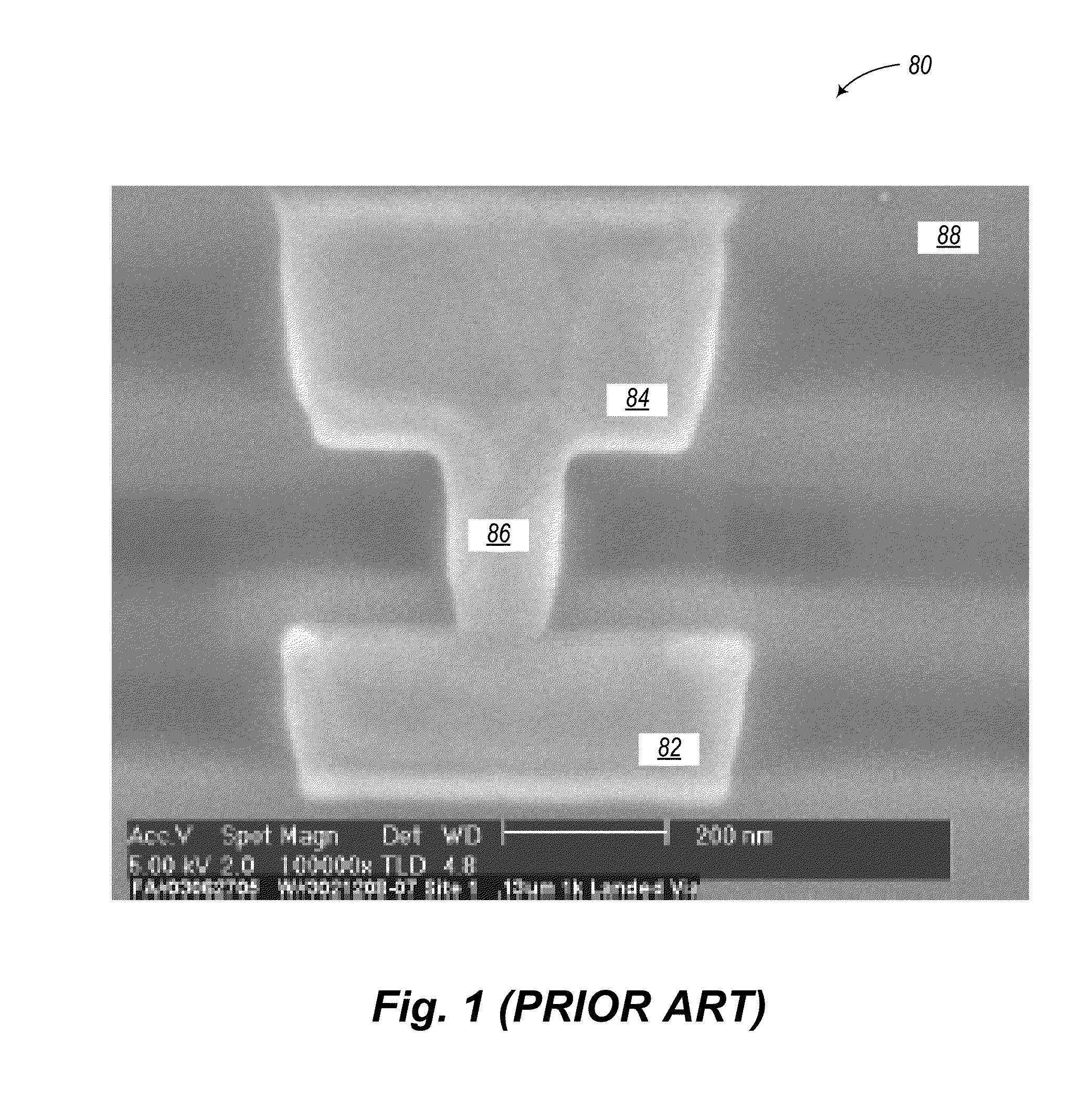

Trench interconnect having reduced fringe capacitance

Ultra-low-k dielectric materials used as inter-layer dielectrics in high-performance integrated circuits are prone to be structurally unstable. The Young's modulus of such materials is decreased, resulting in porosity, poor film strength, cracking, and voids. An alternative dual damascene interconnect structure incorporates deep air gaps into a high modulus dielectric material to maintain structural stability while reducing capacitance between adjacent nanowires. Incorporation of a deep air gap having k=1.0 compensates for the use of a higher modulus film having a dielectric constant greater than the typical ultra-low-k (ULK) dielectric value of about 2.2. The higher modulus film containing the deep air gap is used as an insulator and a means of reducing fringe capacitance between adjacent metal lines. The dielectric layer between two adjacent metal lines thus forms a ULK / high-modulus dielectric bi-layer.

Owner:IBM CORP +1

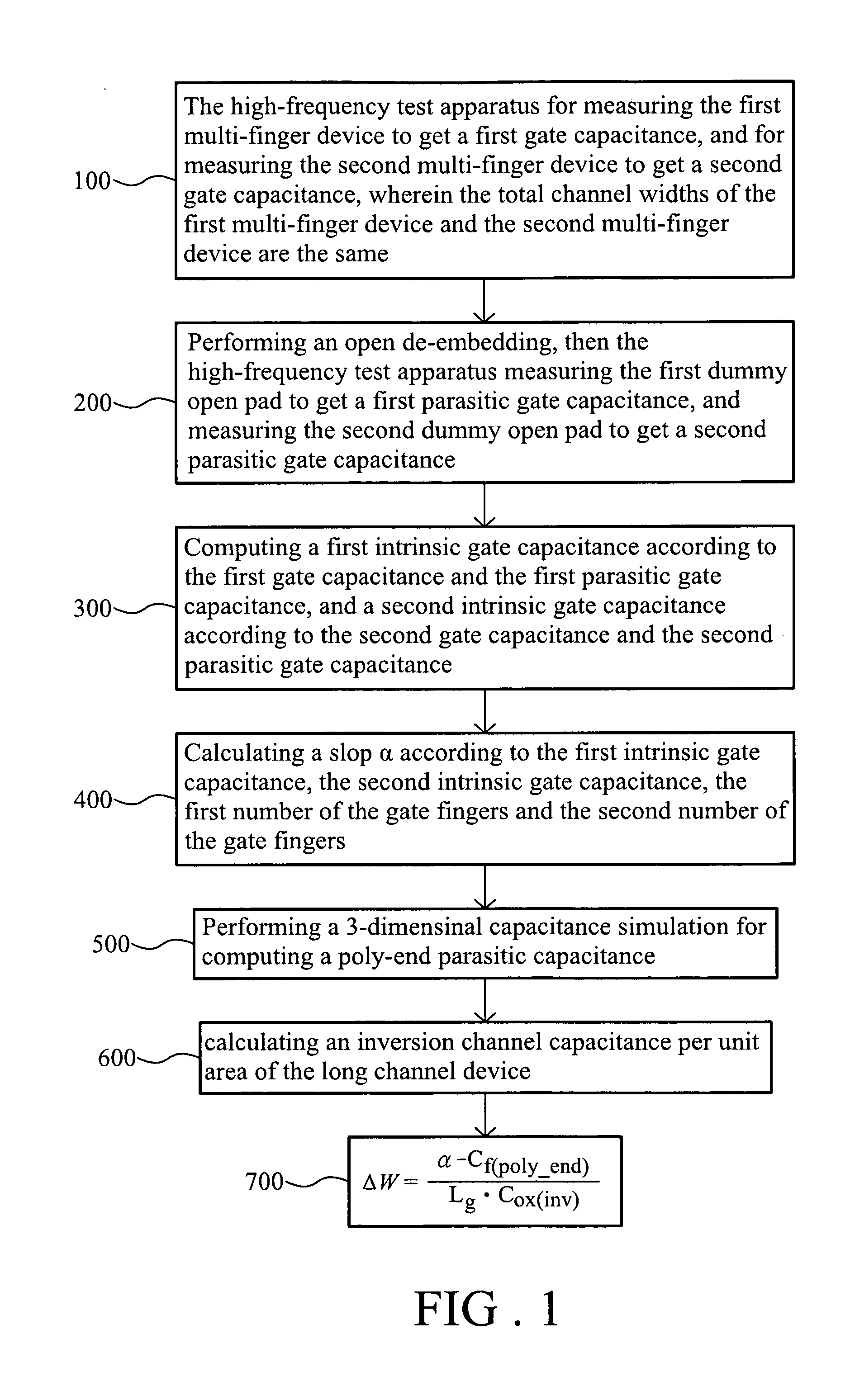

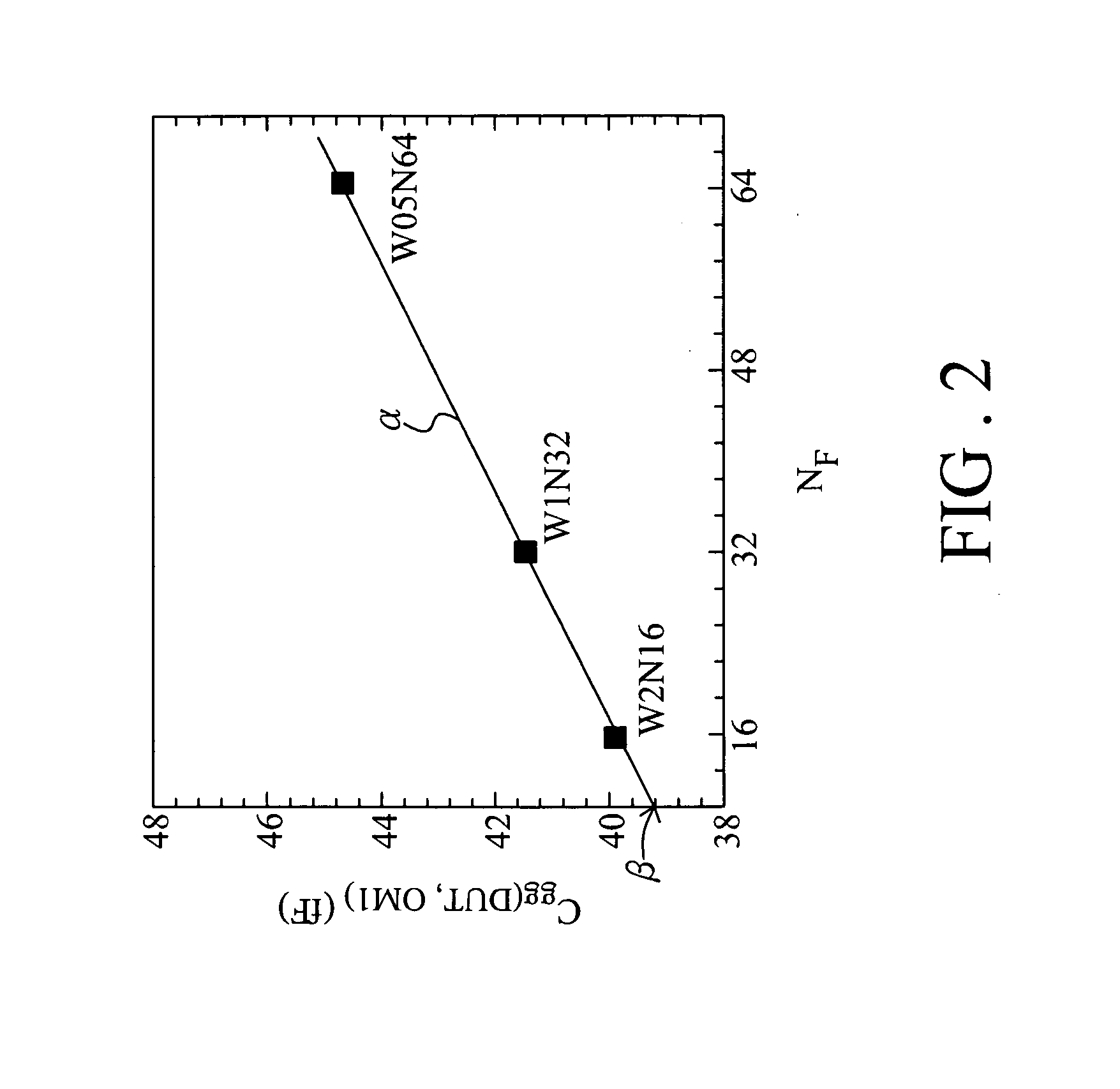

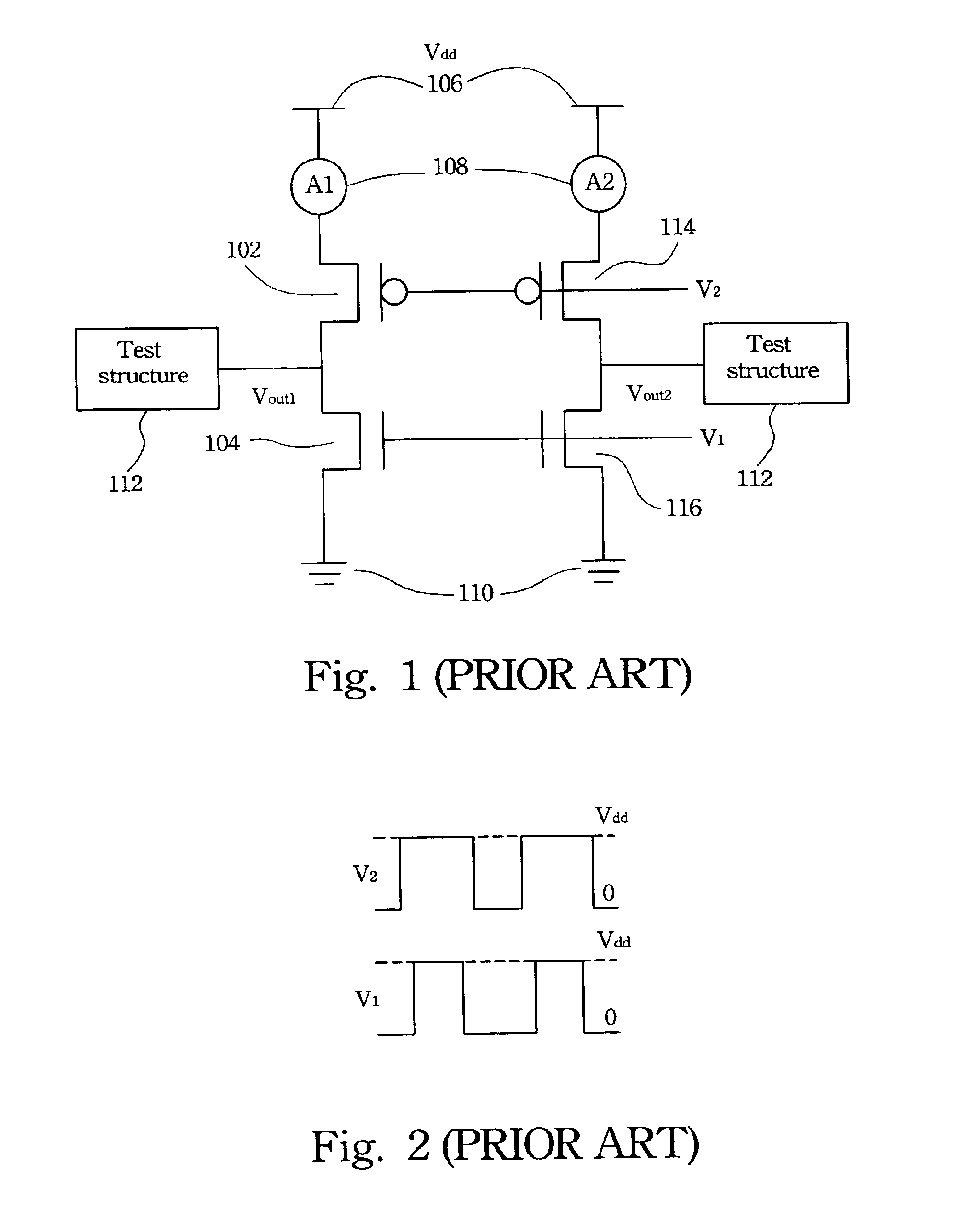

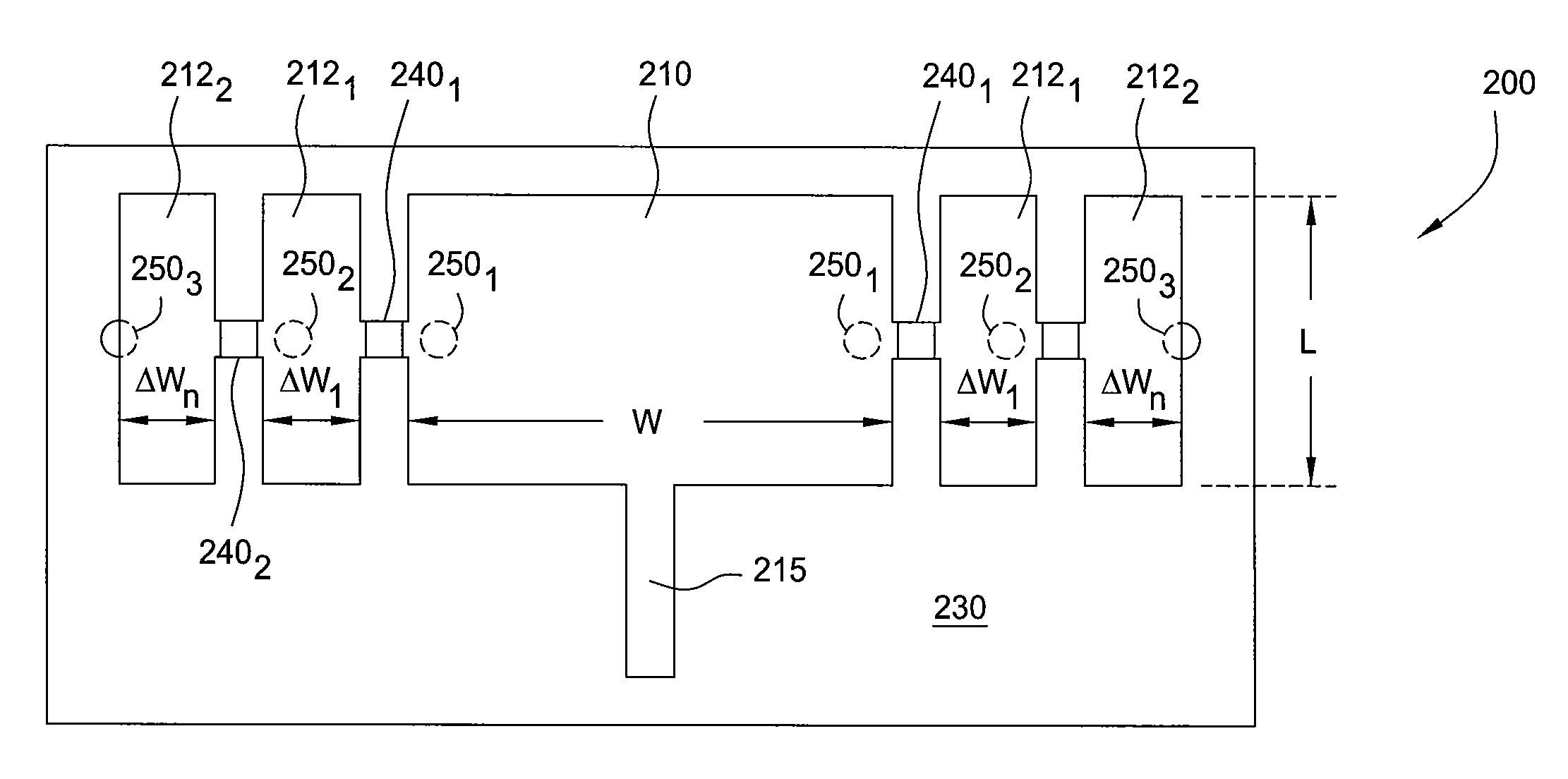

Parameter extraction method for semiconductor device

ActiveUS20120197593A1Simple and precise parameter extractionSemiconductor/solid-state device testing/measurementSolid-state devicesPower semiconductor deviceIntrinsics

A parameter extraction method for semiconductor devices includes: providing a first multi-finger device and a second multi-finger device, wherein the gate-finger numbers between the first and second multi-finger devices are different; performing an open de-embedding, then the high-frequency test apparatus measuring a first intrinsic gate capacitance of the first multi-finger device and a second intrinsic gate capacitance of the second multi-finger device; calculating a slope according to the first and second intrinsic gate capacitances, and the first and second gate-finger numbers; performing a 3D capacitance simulation for computing the poly finger-end fringing capacitances; utilizing a long channel device for measuring the gate capacitance and extracting the intrinsic gate capacitance, then calculating an inversion channel capacitance per unit area; and computing a delta channel width of the semiconductor device, according to the slope, the poly finger-end fringing capacitance, and the inversion channel capacitance per unit area.

Owner:NAT CHIAO TUNG UNIV

Touch panel, display panel, and display unit

ActiveUS20150235607A1Eliminate false detectionsHigh sensitivityStatic indicating devicesAlternating current plasma display panelsEngineeringFringing capacitance

Owner:JAPAN DISPLAY INC

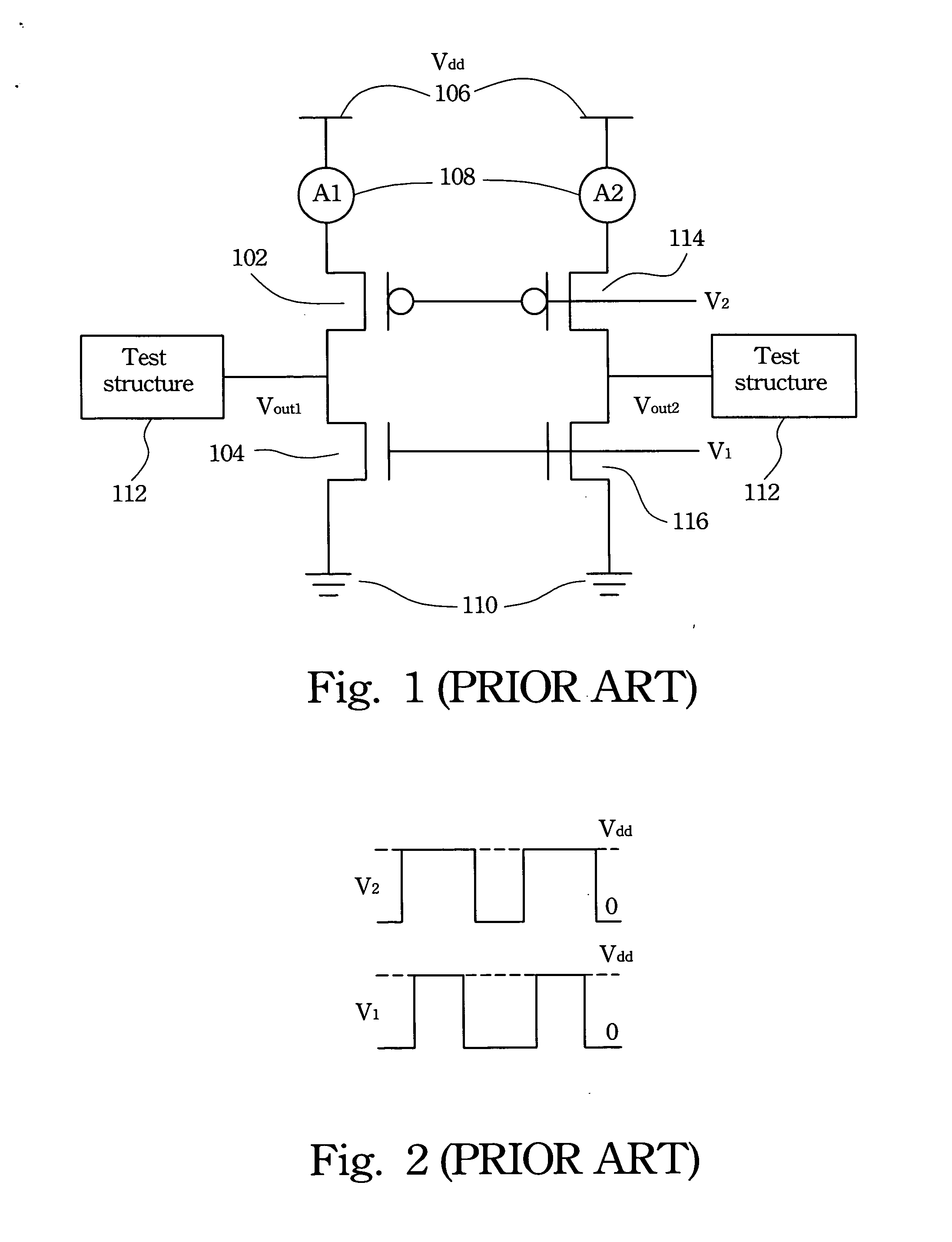

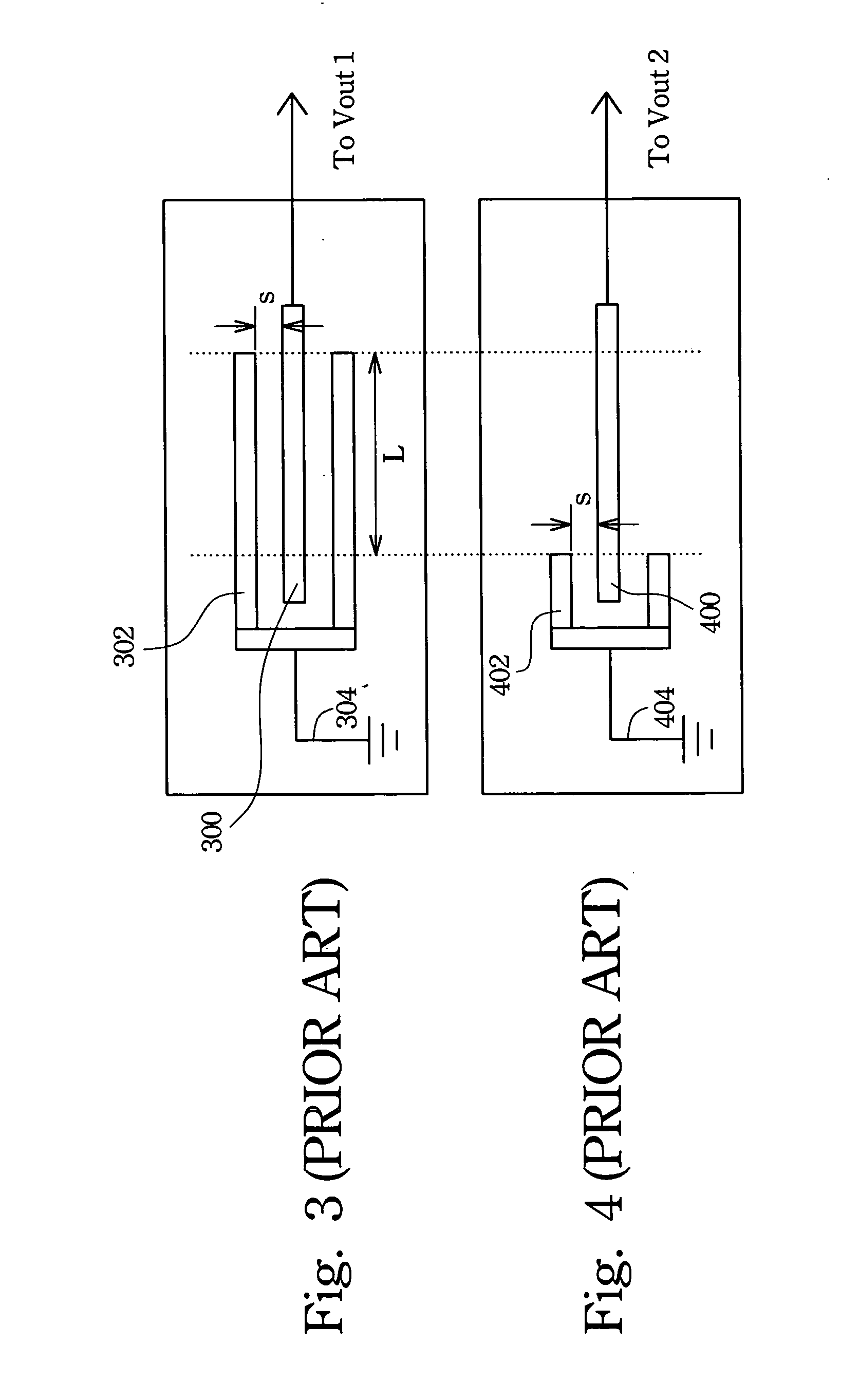

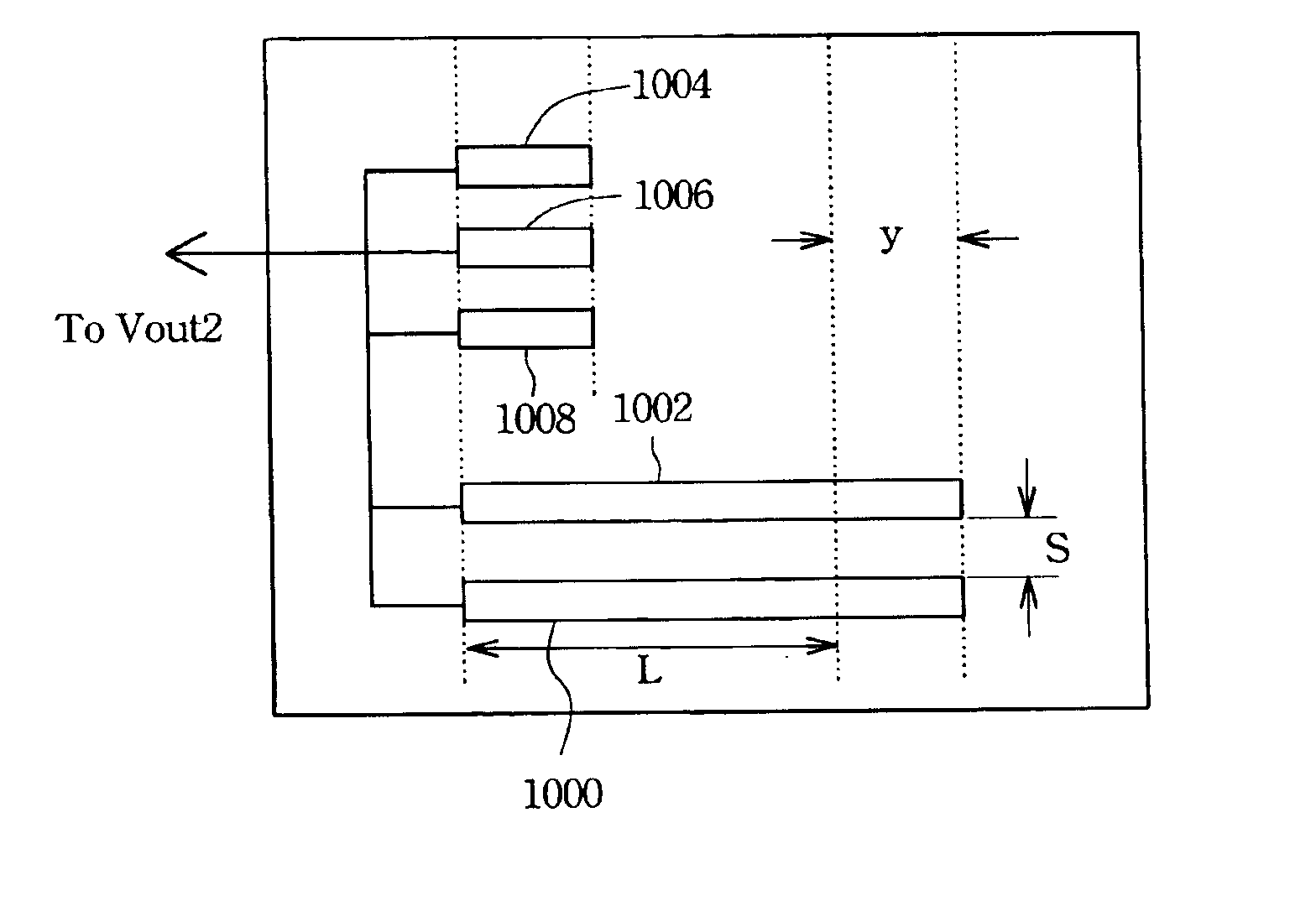

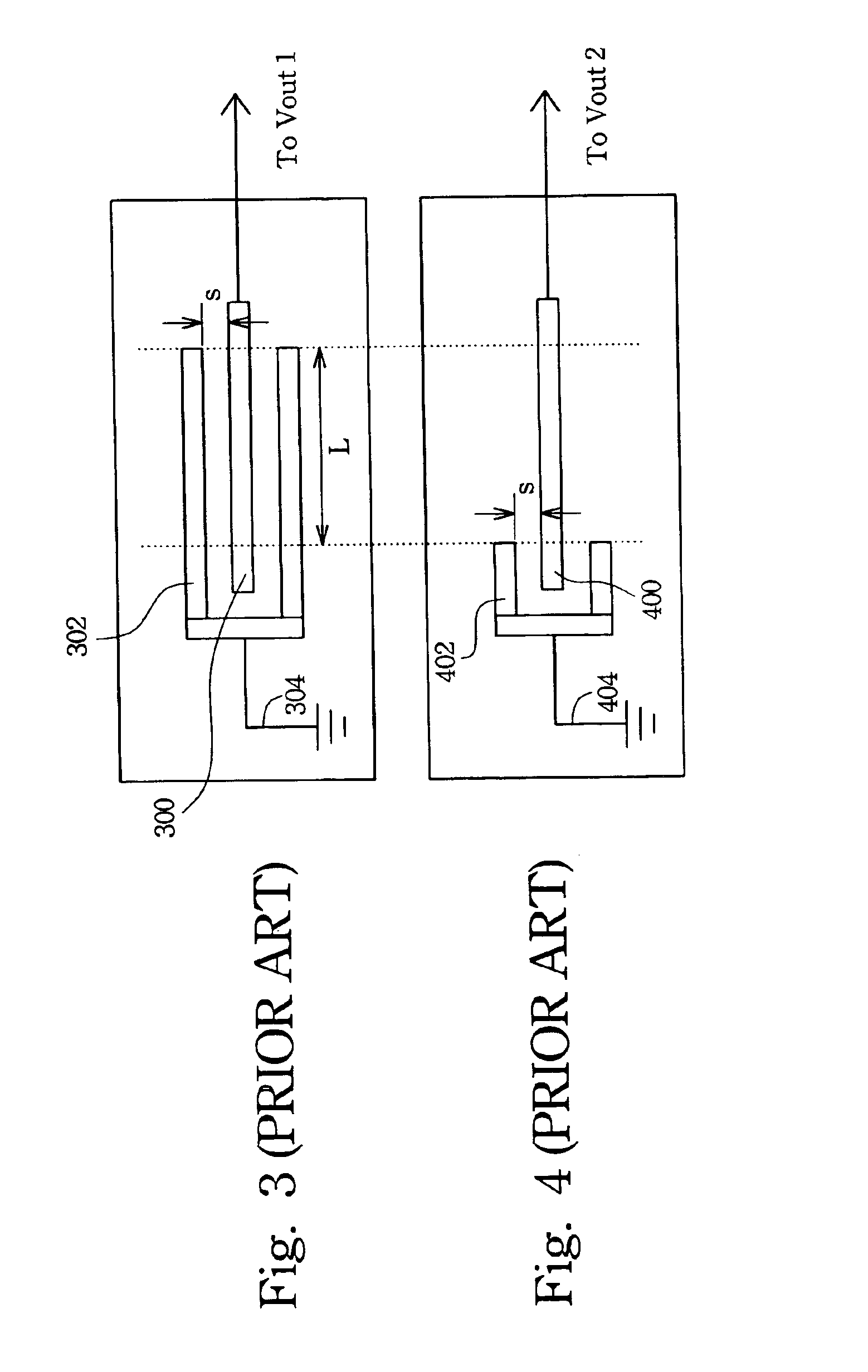

Method and test structures for measuring interconnect coupling capacitance in an IC chip

InactiveUS20050024077A1Accurate measurementImprove accuracyElectronic circuit testingResistance/reactance/impedenceCouplingEngineering

Measurement method and test structures for measuring interconnect coupling capacitance in an IC chip are provided. This method employs CBCM technique. In the first step, two test structures are used to measure a target configuration in order to obtain the total capacitance C of a metal line with respect to ground including line-to-line, fringe and area components(C=2Cc+2Cf+Ca). In the second step, two other test structures are used to measure a dummy configuration in order to obtain the area and fringe capacitance Cdummy of the metal line with respect to ground including fringe and area components (Cdummy=2Cf+Ca). After the two steps, the coupling capacitance Cc between the metal line and another line can be determined according to the formula Cc=(C-Cdummy) / 2.

Owner:WINBOND ELECTRONICS CORP

Method and test structures for measuring interconnect coupling capacitance in an IC chip

InactiveUS6870387B2Accurate measurementImprove accuracyResistance/reactance/impedenceElectronic circuit testingCouplingFringing capacitance

Measurement method and test structures for measuring interconnect coupling capacitance in an IC chip are provided. This method employs CBCM technique. In the first step, two test structures are used to measure a target configuration in order to obtain the total capacitance C of a metal line with respect to ground including line-to-line, fringe and area components (C=2Cc+2Cf+Ca). In the second step, two other test structures are used to measure a dummy configuration in order to obtain the area and fringe capacitance Cdummy of the metal line with respect to ground including fringe and area components (Cdummy=2Cf+Ca). After the two steps, the coupling capacitance Cc between the metal line and another line can be determined according to the formula Cc=(C−Cdummy) / 2.

Owner:WINBOND ELECTRONICS CORP

Method and apparatus for a tunable channelizing patch antenna

ActiveUS7928913B2Simultaneous aerial operationsRadiating elements structural formsEngineeringFringing capacitance

Owner:ALCATEL-LUCENT USA INC

Fringing capacitor structure

InactiveUS6885543B1Fixed capacitor dielectricSemiconductor/solid-state device detailsDielectricElectrical conductor

The present invention provides a circuit and method for a fringing capacitor. The fringing capacitor includes at least two conductor layers spaced apart from each other. Each conductor layer includes at least two portions. The portions include odd ones alternating with even ones. Adjacent odd ones and even ones of the portions are spaced apart. The odd ones of the portions on a first one of the conductor layers are configured to substantially overlay the odd ones of the portions on an adjacent one of the conductor layers. The even ones of the portions on the first one of the conductor layers are configured to substantially overlay the even ones of the portions on the adjacent one of the conductor layers. The odd ones of the portions on the first one of the conductor layers are electrically coupled together and to the even ones of the portions on the adjacent one of the conductor layers, thereby defining a first electrode. The even ones of the portions on the first one of the conductor layers are electrically coupled together and to the odd ones of the portions on the adjacent one of the conductor layers, thereby defining a second electrode. A dielectric is interposed between the first and second electrodes. A guardband is spaced from the first and second electrodes.

Owner:MARVELL INT LTD

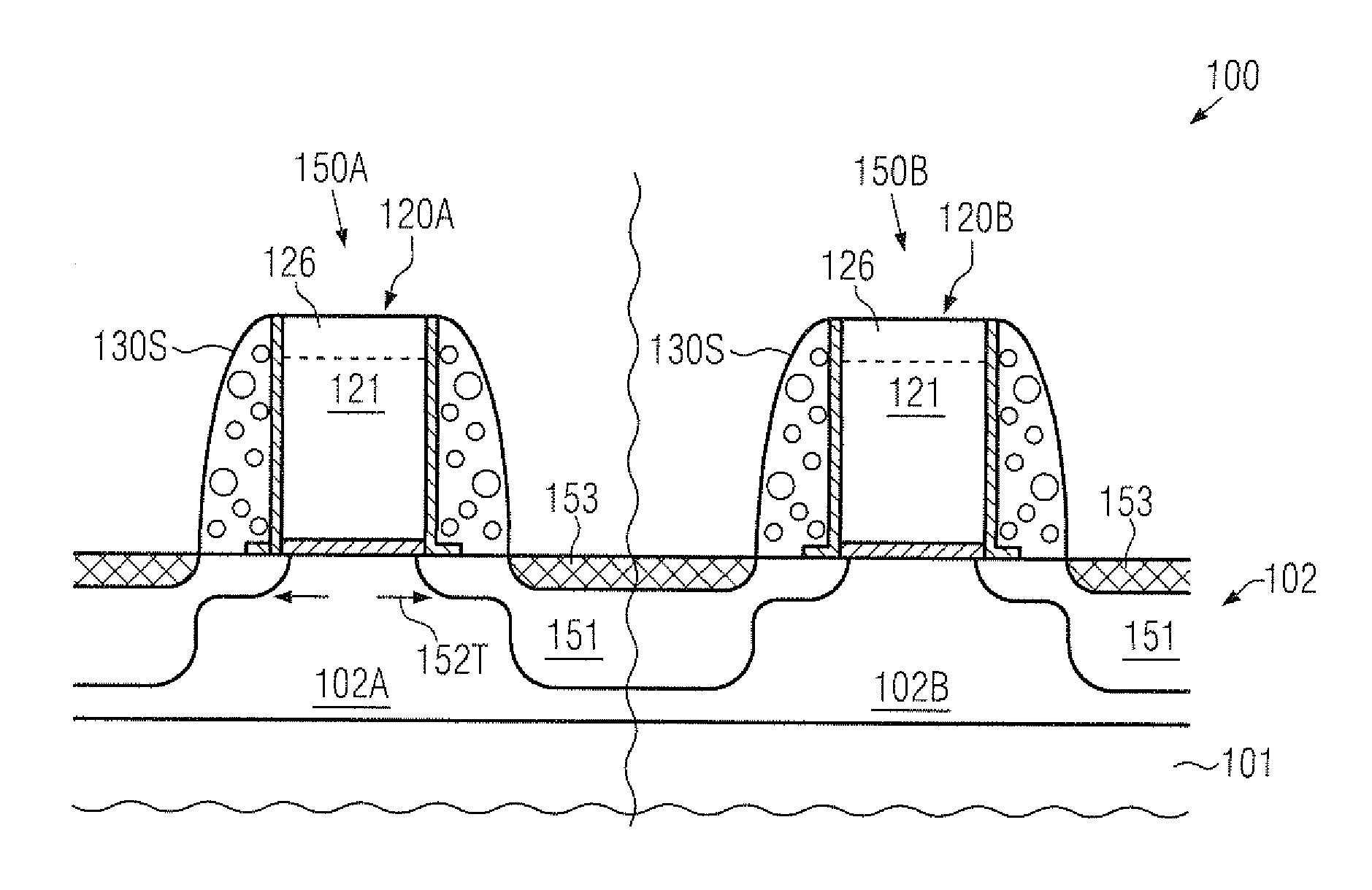

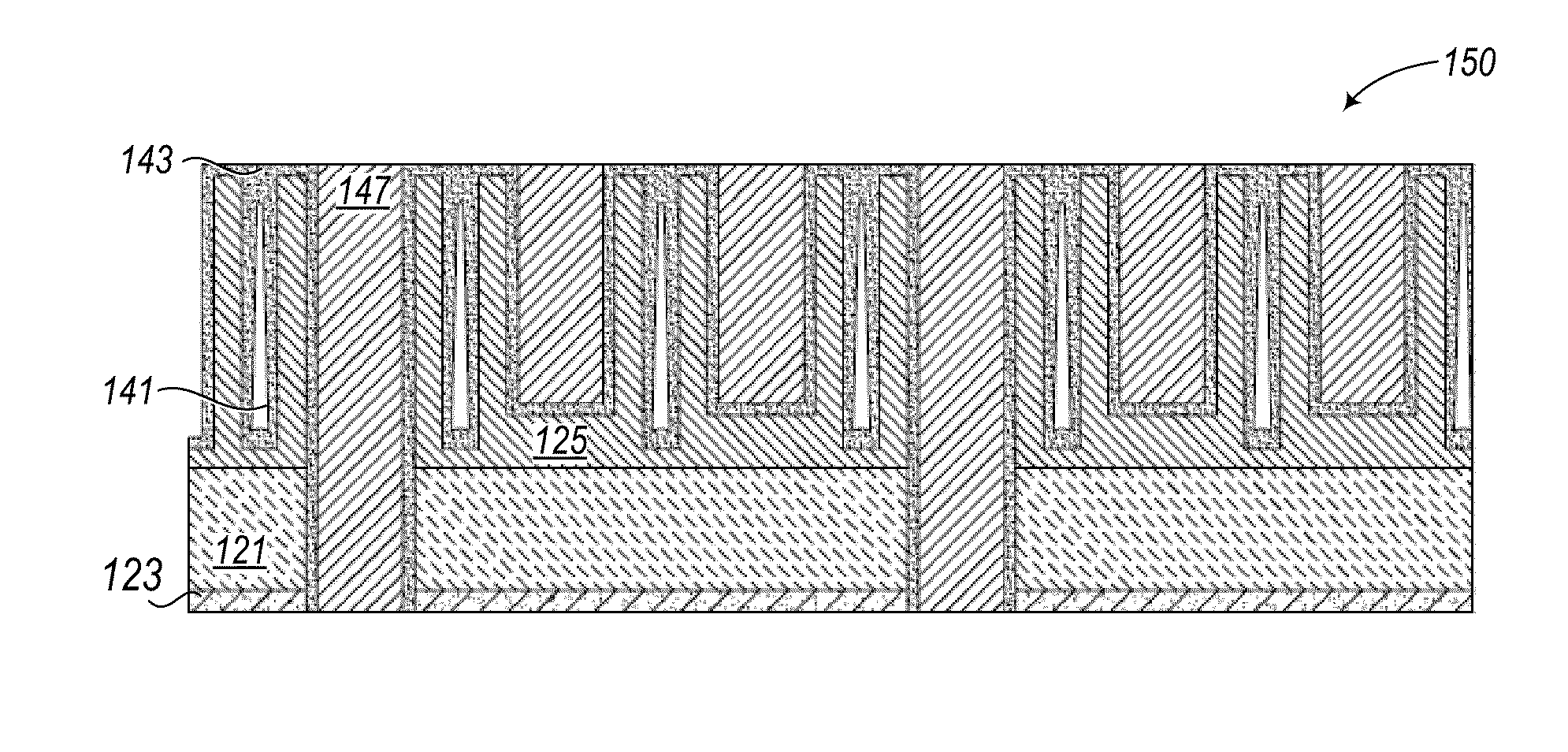

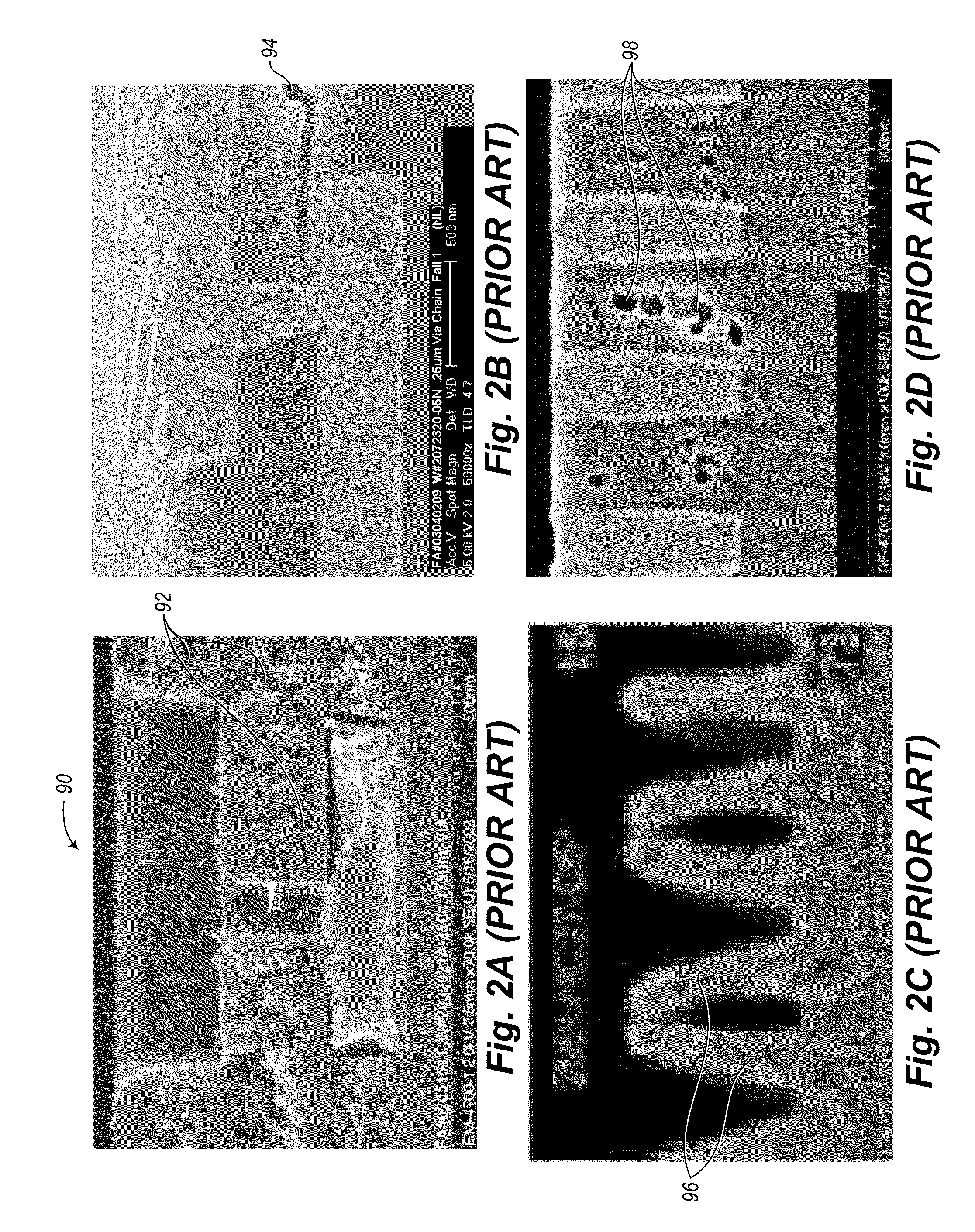

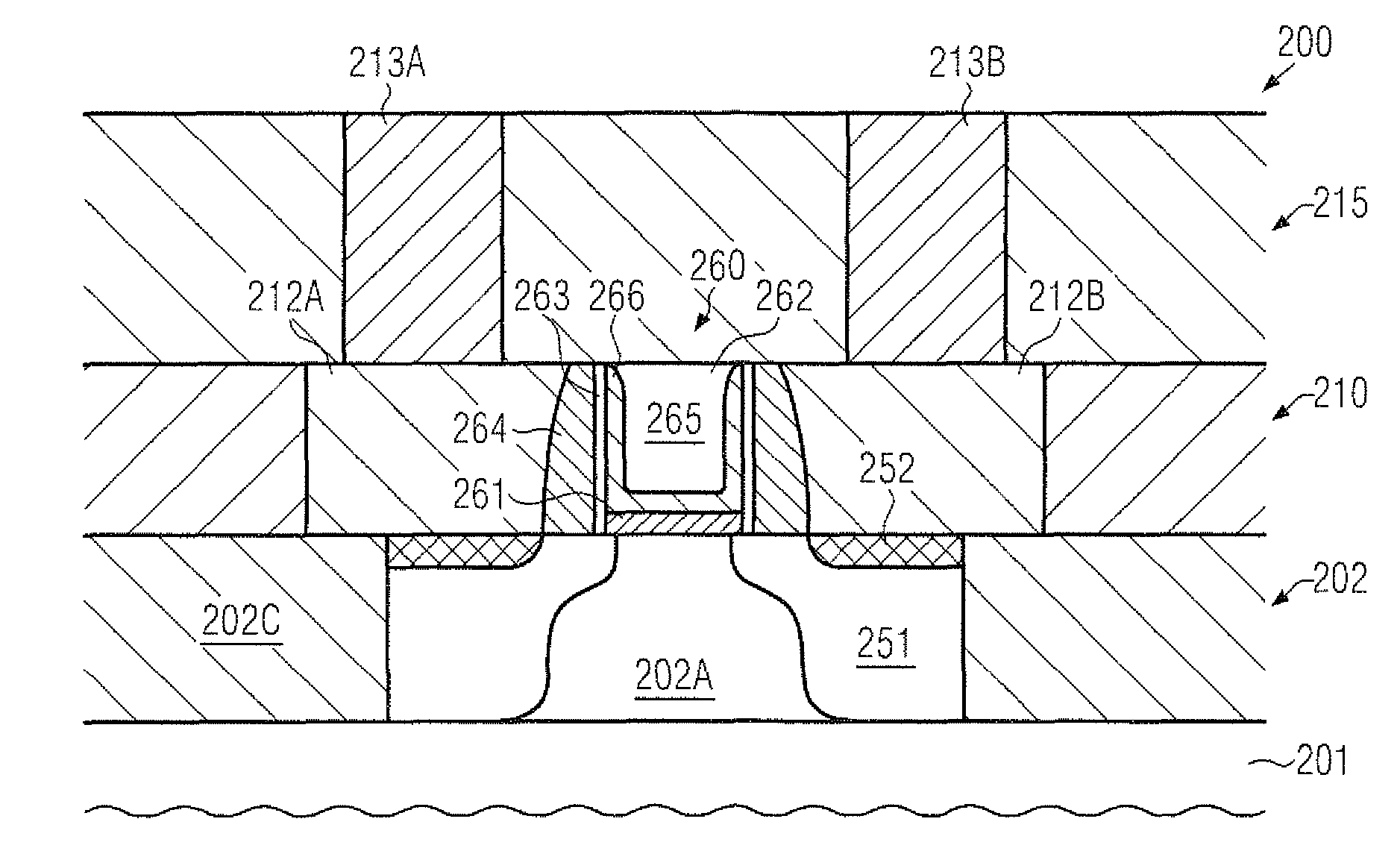

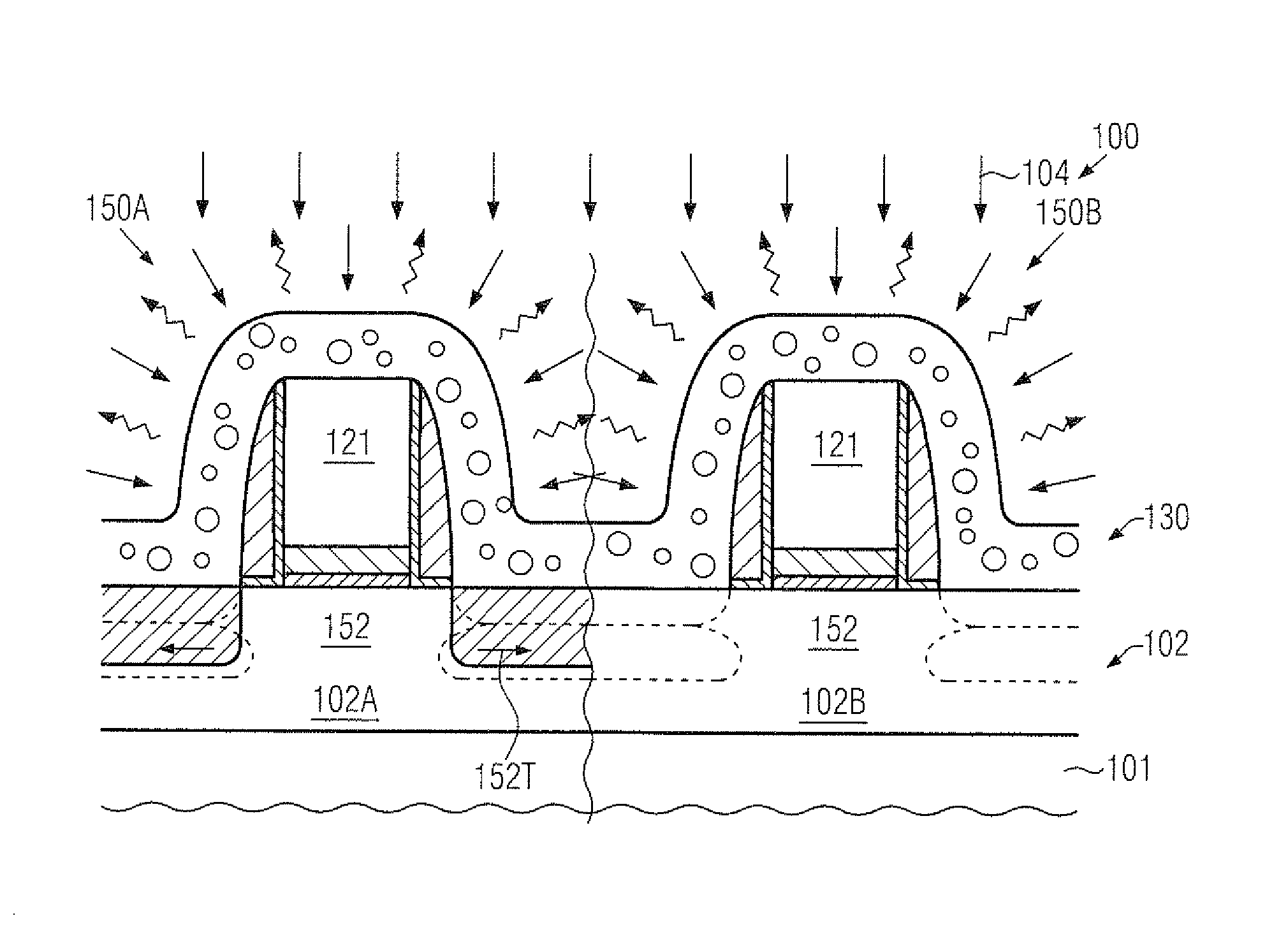

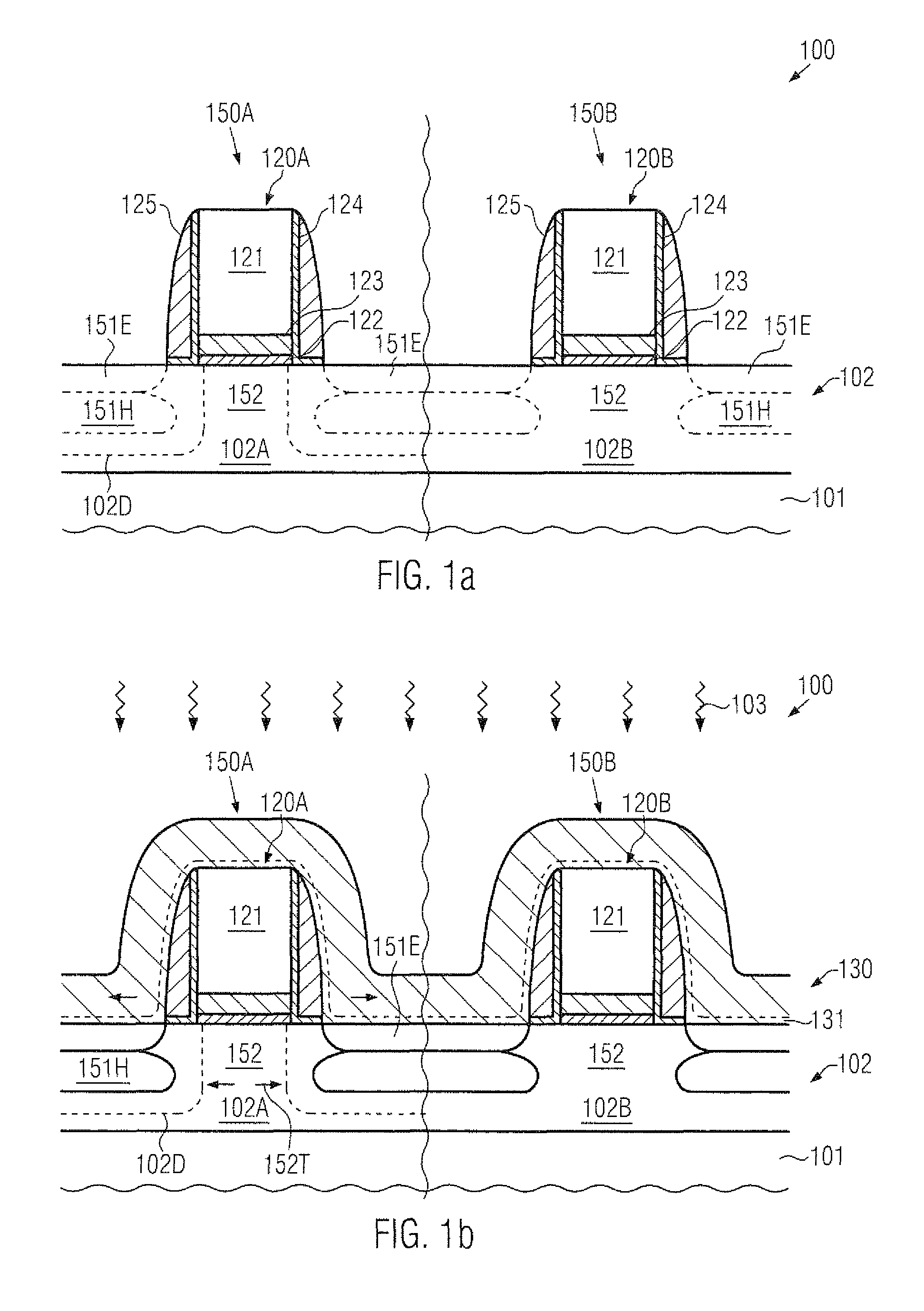

Contact bars with reduced fringing capacitance in a semiconductor device

InactiveUS20110210380A1Increasing overall parasitic fringing capacitanceIncrease overall fringing capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringContact element

In sophisticated semiconductor devices, the contact structure may be formed on the basis of contact bars formed in a lower portion of an interlayer dielectric material, which may then be contacted by contact elements having reduced lateral dimensions so as to preserve a desired low overall fringing capacitance. The concept of contact bars of reduced height level may be efficiently combined with sophisticated replacement gate approaches.

Owner:GLOBALFOUNDRIES INC

Varactor design using area to perimeter ratio for improved tuning range

ActiveUS7728377B2Good tunabilityImproves otherTransistorSolid-state devicesParallel plateEngineering

Parallel plate tunable varactors having a bulk capacitance contribution to a total capacitance increased compared to a fringing capacitance contribution are disclosed. The contribution of the bulk capacitance to the total capacitance of an exemplary BST varactor is increased by increasing the area / perimeter ratio of the active region, thereby improving the tunability and other properties of the varactor. In an exemplary embodiment, an active region of the varactor has a lateral shape with a perimeter that is less than a perimeter of an equivalent area square. In various exemplary embodiments, the shape of the active region may be substantially circular or substantially octagonal. Methods for fabricating and designing such varactors are also disclosed.

Owner:QORVO US INC

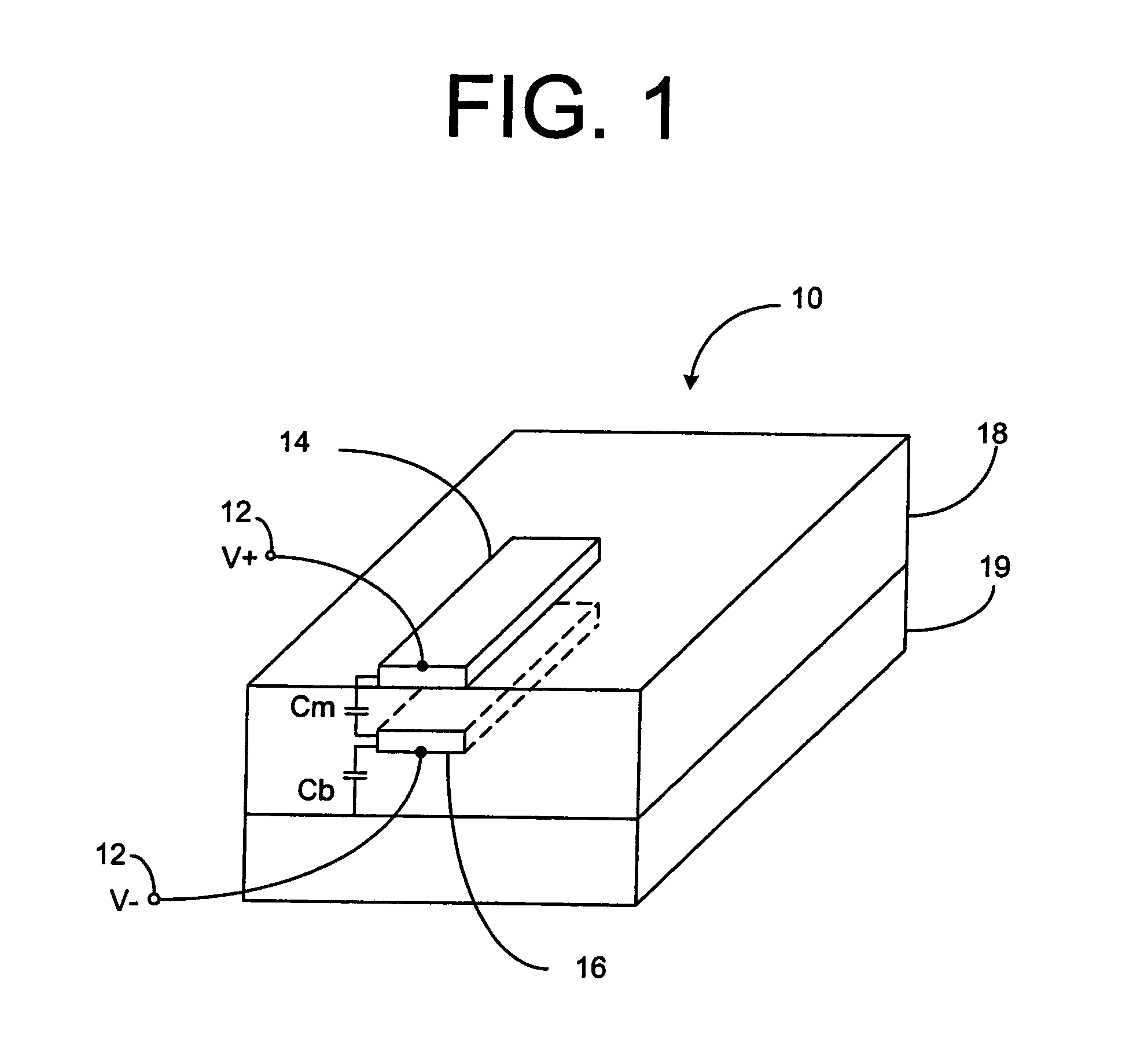

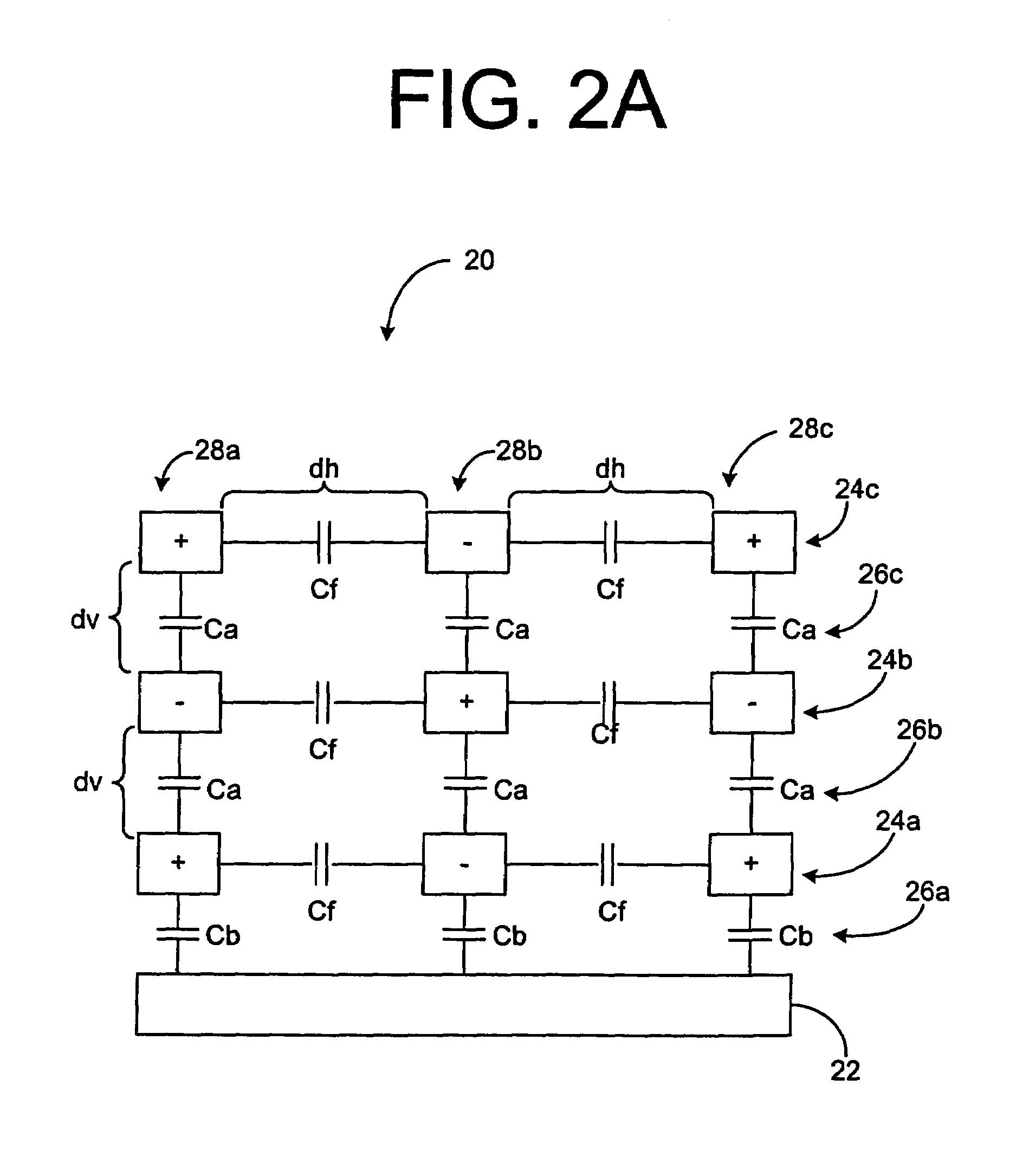

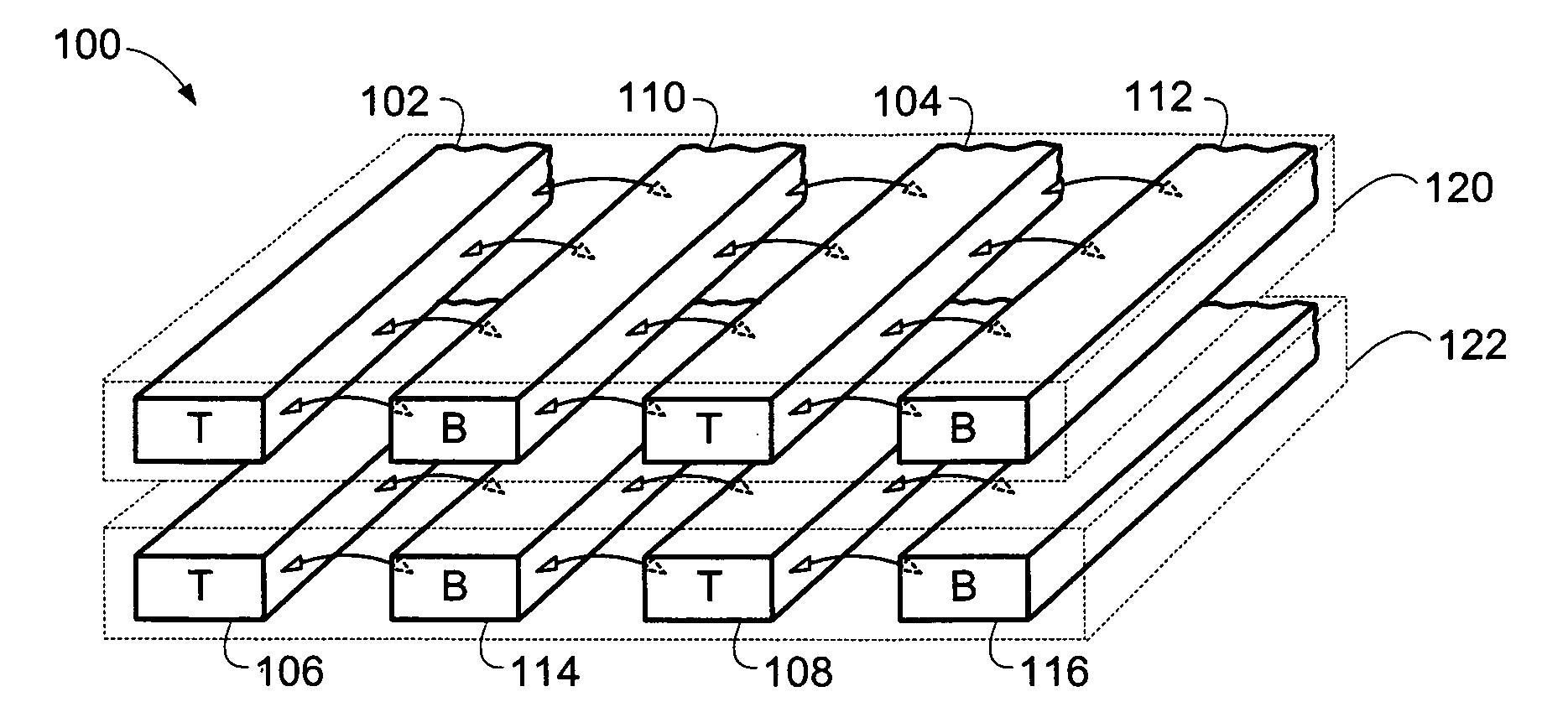

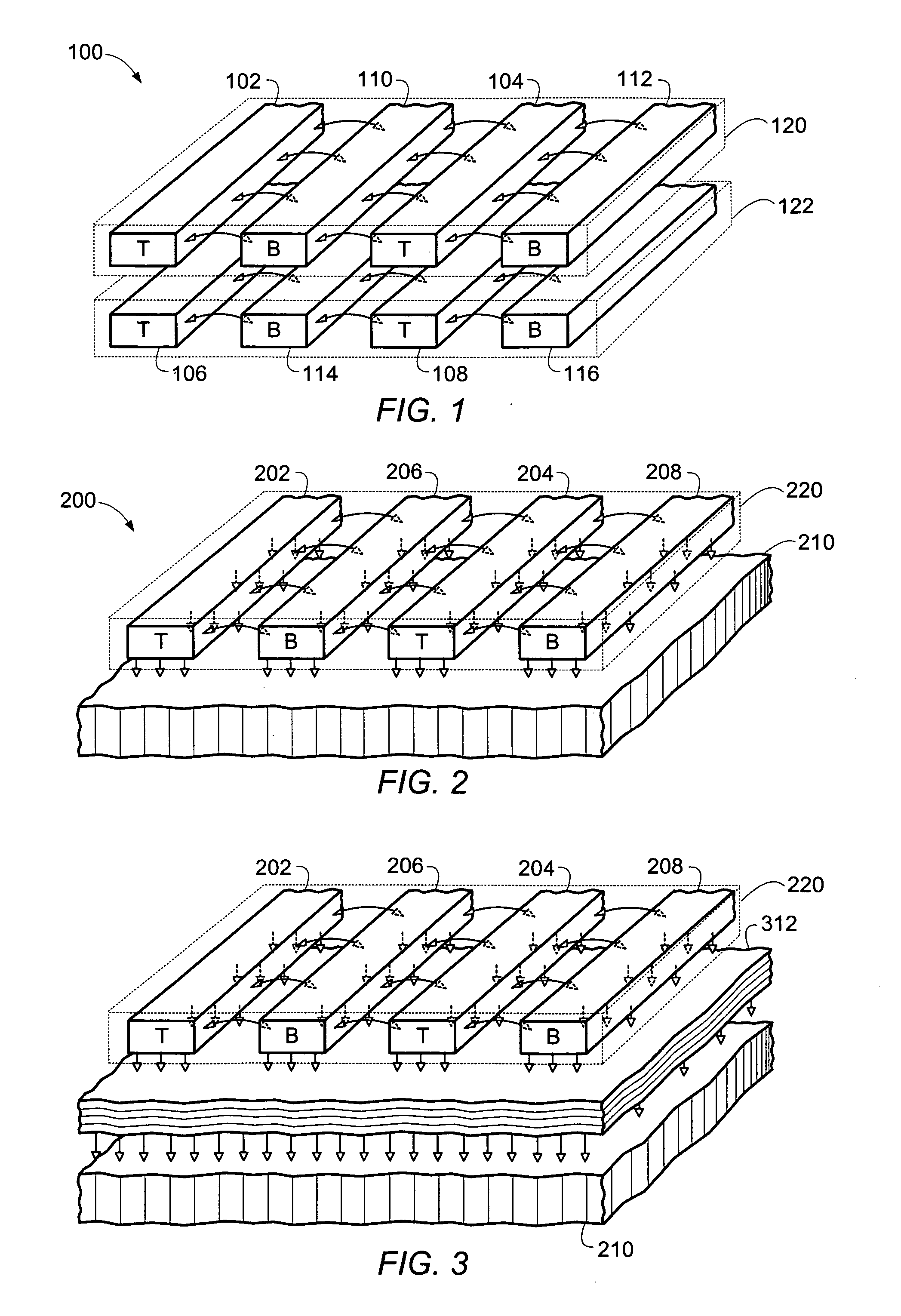

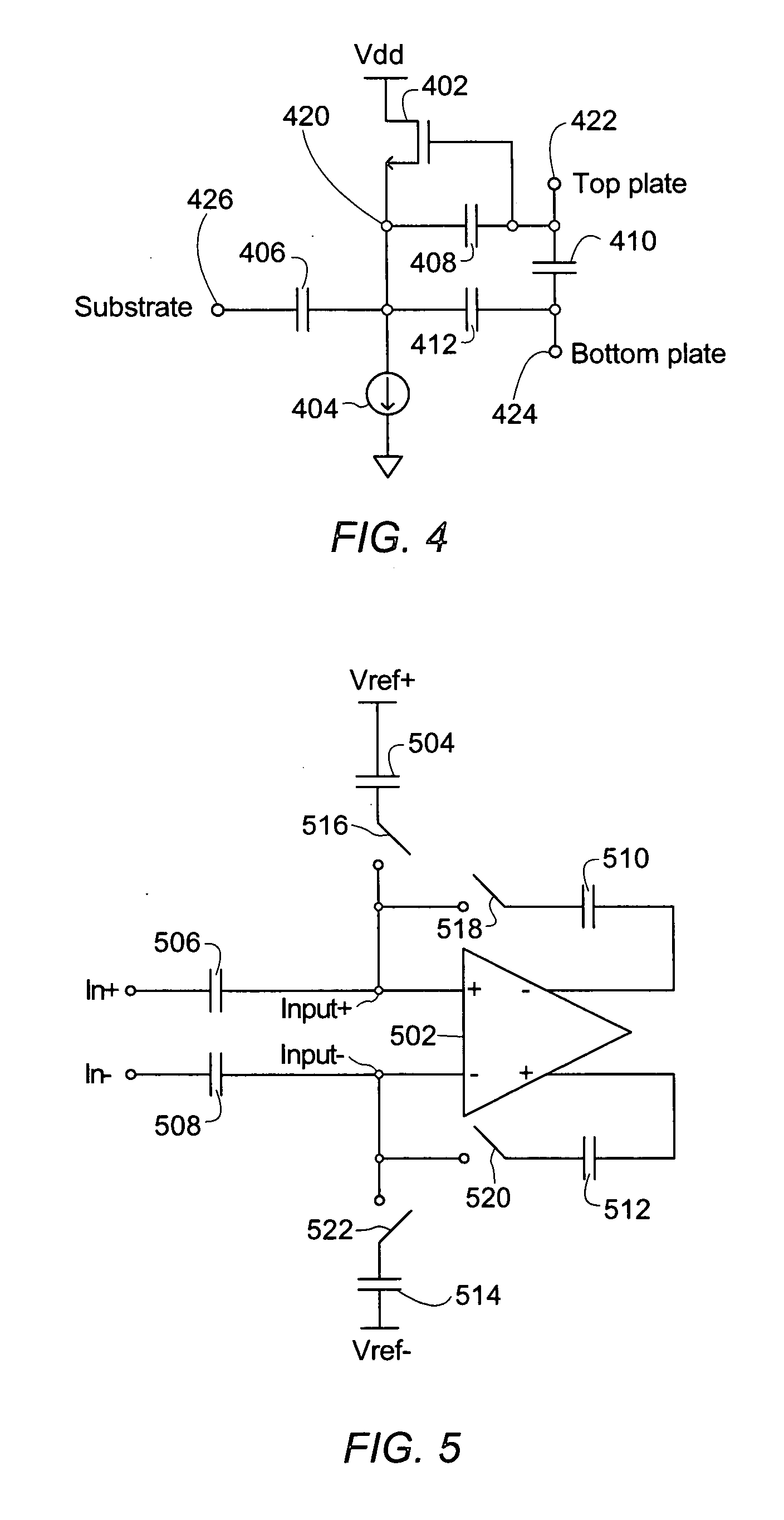

Fringe capacitor using bootstrapped non-metal layer

InactiveUS20070215928A1Maximize fringe-capacitanceMinimize and eliminate any charge transferTransistorSemiconductor/solid-state device detailsAudio power amplifierParallel plate

Capacitors configured in a switched-capacitor circuit on a semiconductor device may comprise very accurately matched, high capacitance density metal-to-metal capacitors, using top-plate-to-bottom-plate fringe-capacitance for obtaining the desired capacitance values. A polysilicon plate may be inserted below the bottom metal layer as a shield, and bootstrapped to the top plate of each capacitor in order to minimize and / or eliminate the parasitic top-plate-to-substrate capacitance. This may free up the bottom metal layer to be used in forming additional fringe-capacitance, thereby increasing capacitance density. By forming each capacitance solely based on fringe-capacitance from the top plate to the bottom plate, no parallel-plate-capacitance is used, which may reduce capacitor mismatch. Parasitic bottom plate capacitance to the substrate may also be eliminated, with only a small capacitance to the bootstrapped polysilicon plate remaining. The capacitors may be bootstrapped by coupling the top plate of each capacitor to a respective one of the differential inputs of an amplifier comprised in the switched-capacitor circuit.

Owner:MICROCHIP TECH INC

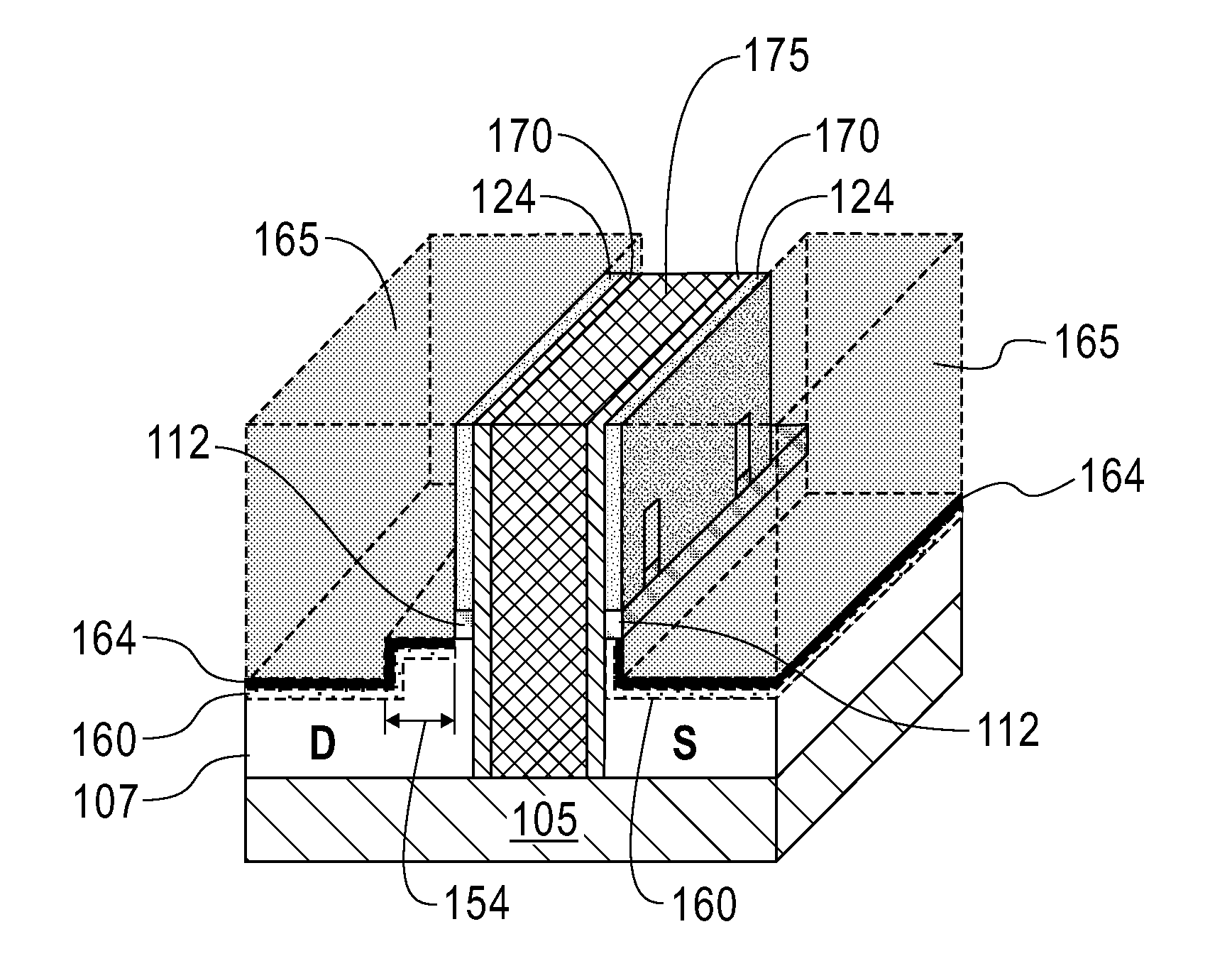

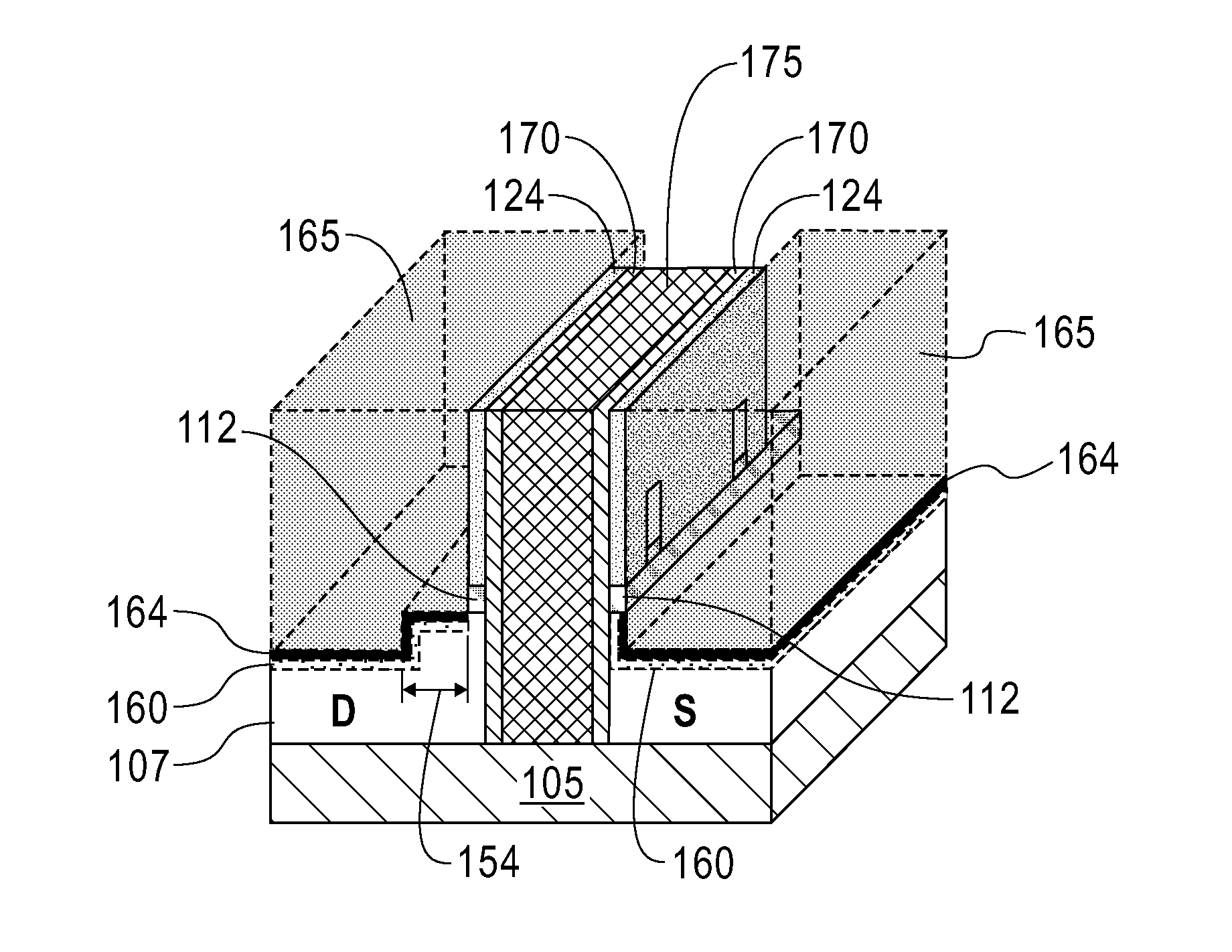

Non-planar MOSFET structures with asymmetric recessed source drains and methods for making the same

ActiveUS8637371B2Solid-state devicesSemiconductor/solid-state device manufacturingMOSFETField-effect transistor

Non-planar Metal Oxide Field Effect Transistors (MOSFETs) and methods for making non-planar MOSFETs with asymmetric, recessed source and drains having improved extrinsic resistance and fringing capacitance. The methods include a fin-last, replacement gate process to form the non-planar MOSFETs and employ a retrograde metal lift-off process to form the asymmetric source / drain recesses. The lift-off process creates one recess which is off-set from a gate structure while a second recess is aligned with the structure. Thus, source / drain asymmetry is achieved by the physical structure of the source / drains, and not merely by ion implantation. The resulting non-planar device has a first channel of a fin contacting a substantially undoped area on the drain side and a doped area on the source side, thus the first channel is asymmetric. A channel on atop surface of a fin is symmetric because it contacts doped areas on both the drain and source sides.

Owner:GLOBALFOUNDRIES US INC

Semiconductor transistors having high-K gate dielectric layers, metal gate electrode regions, and low fringing capacitances

A semiconductor structure and a method for forming the same. The structure includes (i) a semiconductor substrate which includes a channel region, (ii) first and second source / drain regions on the semiconductor substrate, (iii) a gate dielectric region, and (iv) a gate electrode region, (v) a plurality of interconnect layers on the gate electrode region, and (vi) first and second spaces. The gate dielectric region is disposed between and in direct physical contact with the channel region and the gate electrode region. The gate electrode region is disposed between and in direct physical contact with the gate dielectric region and the interconnect layers. The first and second spaces are in direct physical contact with the gate electrode region. The first space is disposed between the first source / drain region and the gate electrode region. The second space is disposed between the second source / drain region and the gate electrode region.

Owner:GLOBALFOUNDRIES INC

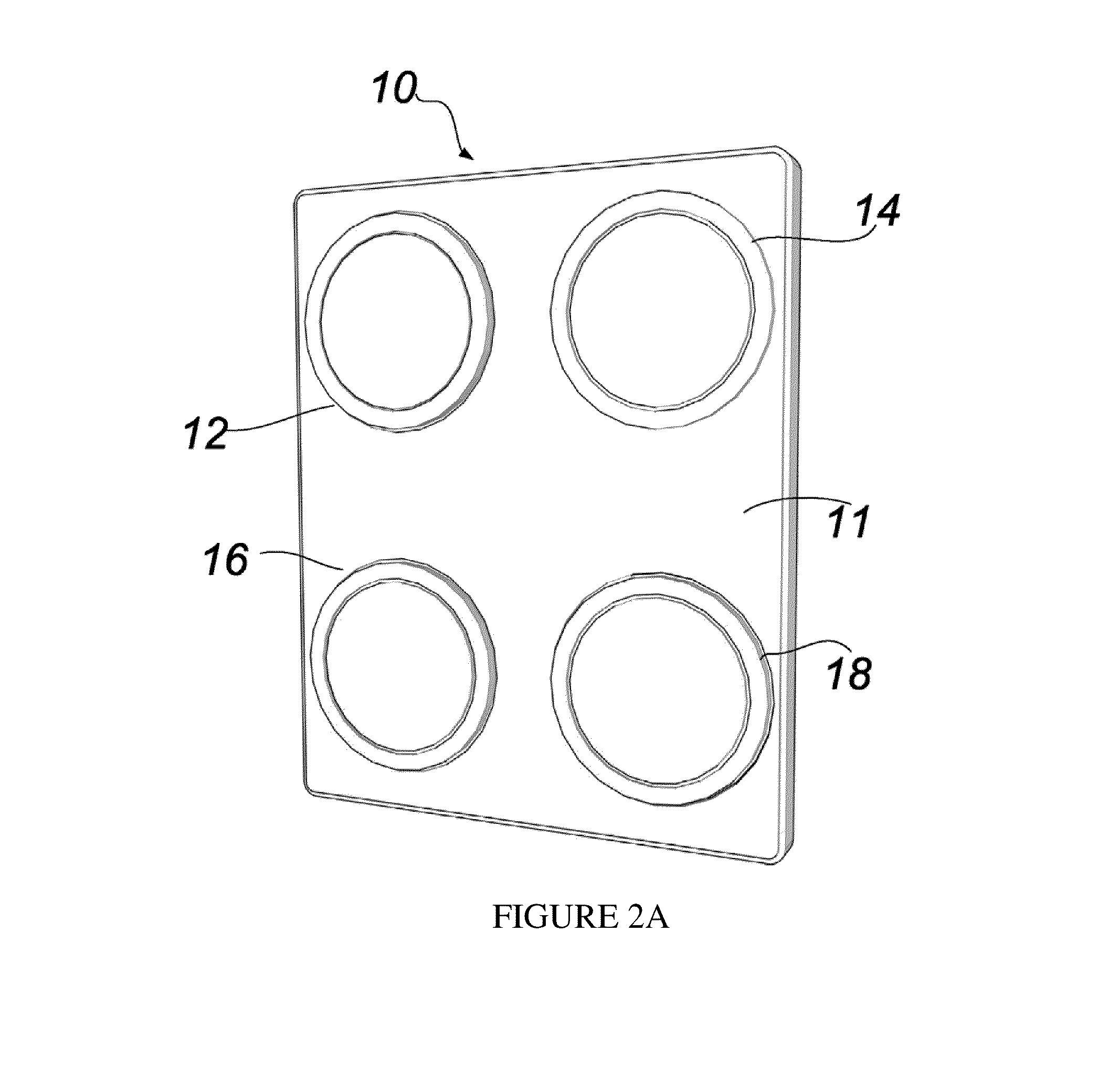

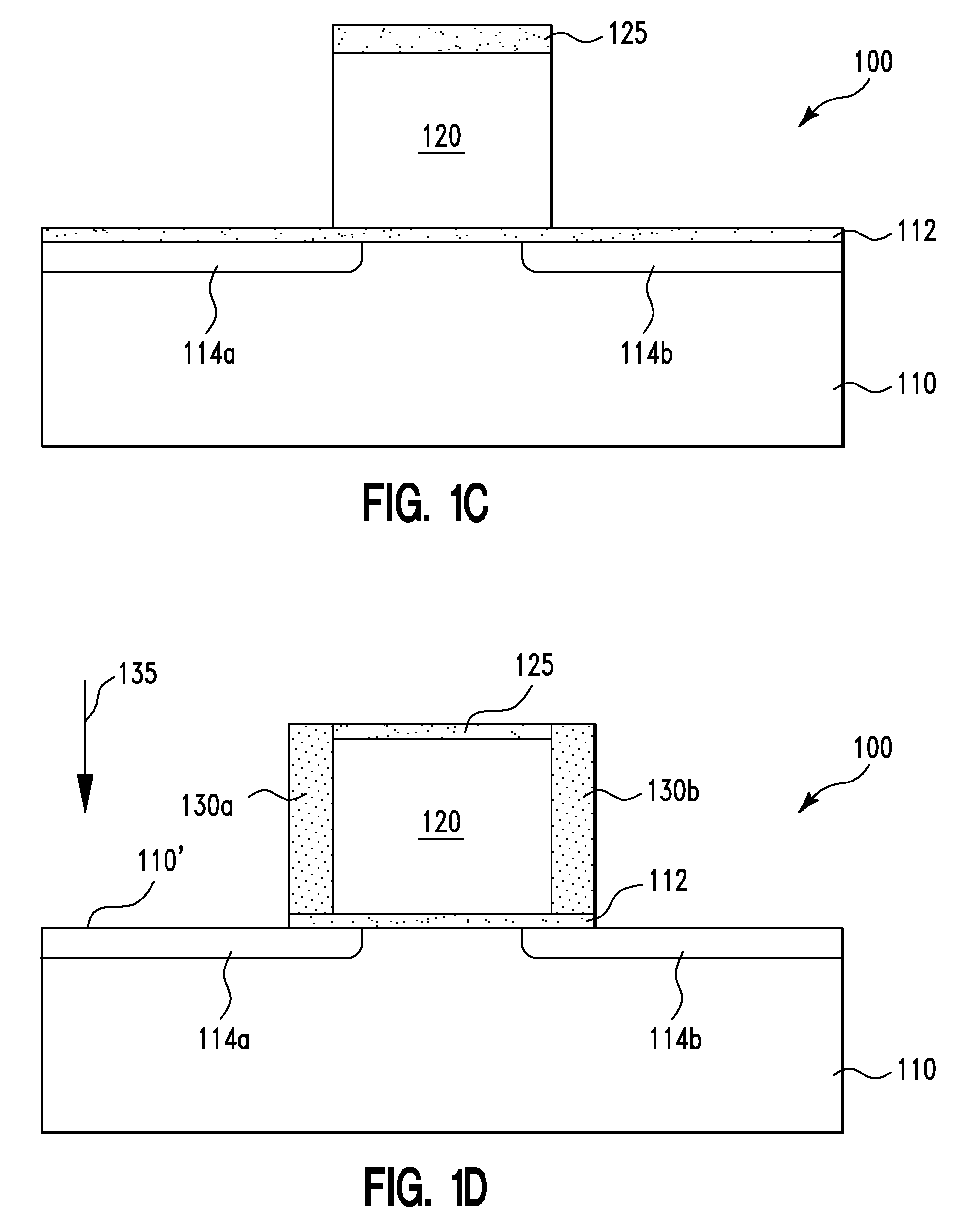

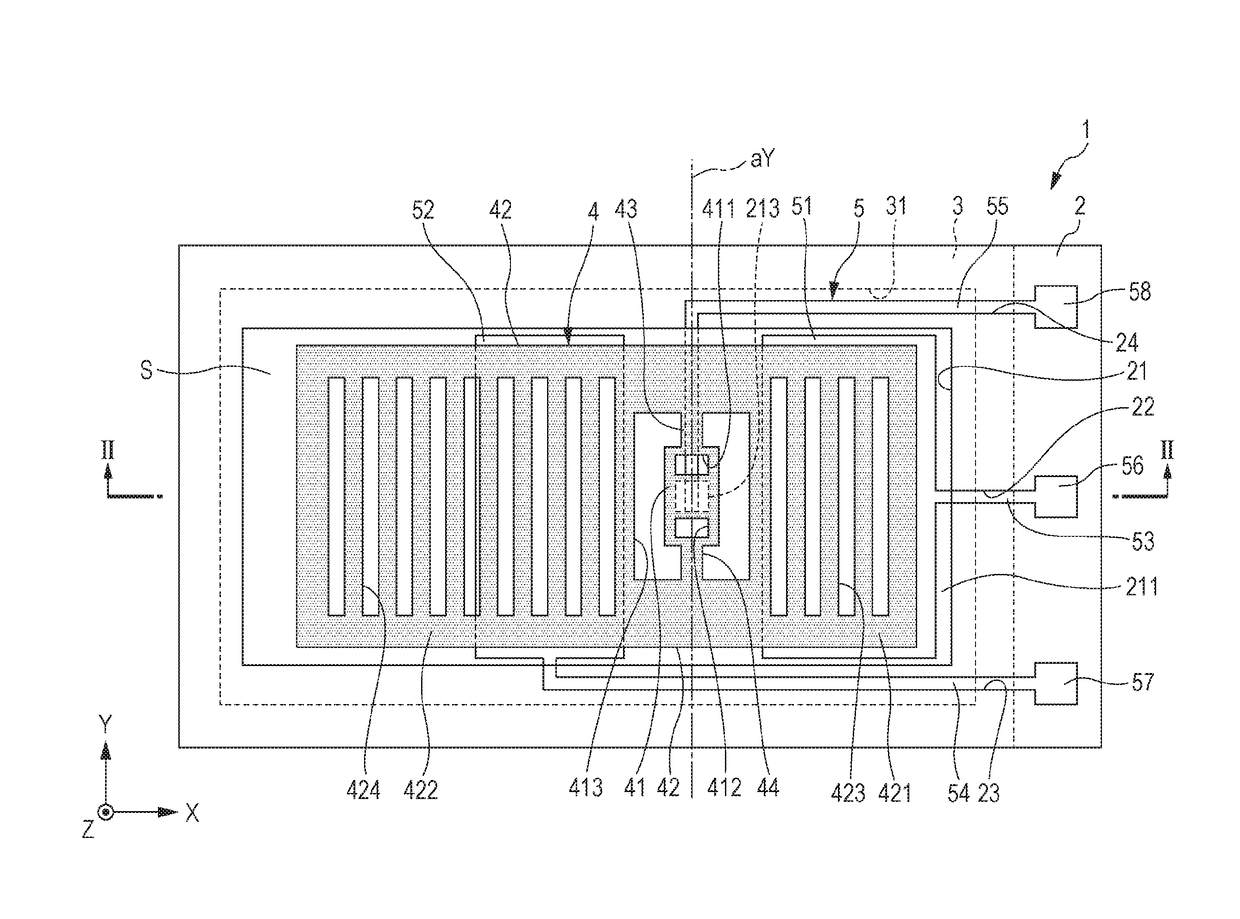

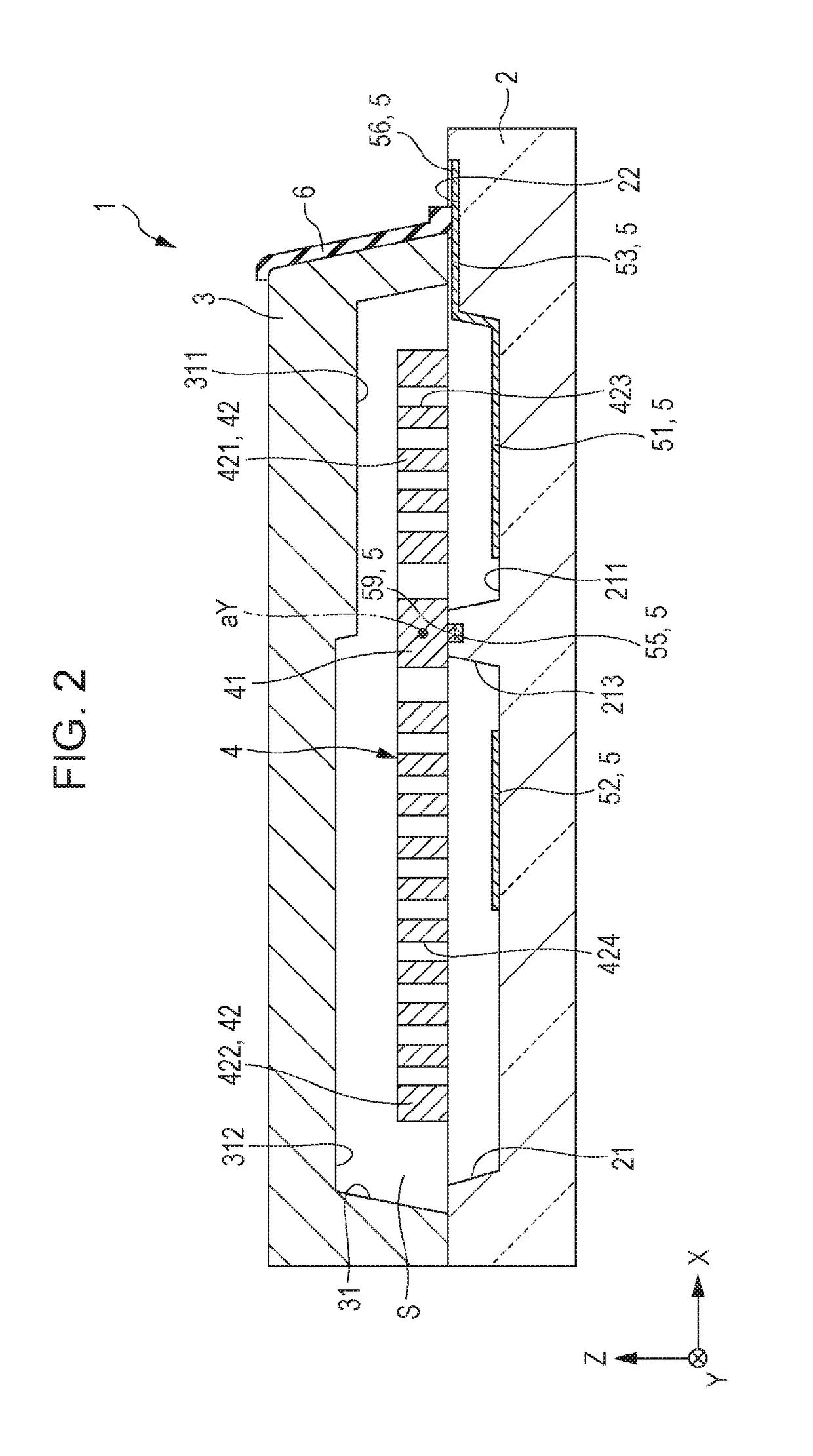

Physical quantity sensor, sensor device, electronic apparatus, and moving object

ActiveUS20170074658A1Improve detection accuracySpeed measurement using gyroscopic effectsAcceleration measurementEngineeringFringing capacitance

A physical quantity sensor includes a base substrate, a movable portion that is oscillatably provided around an axis while facing the base substrate and that is divided into a first movable portion and a second movable portion, a first fixed electrode that is disposed on the base substrate facing the first movable portion, and a second fixed electrode that is disposed on the base substrate facing the second movable portion. The first fixed electrode and the second fixed electrode are configured so as to offset at least a part of a difference between a first fringe capacitance, which is between the first movable portion and the first fixed electrode, and a second fringe capacitance, which is between the second movable portion and the second fixed electrode.

Owner:SEIKO EPSON CORP

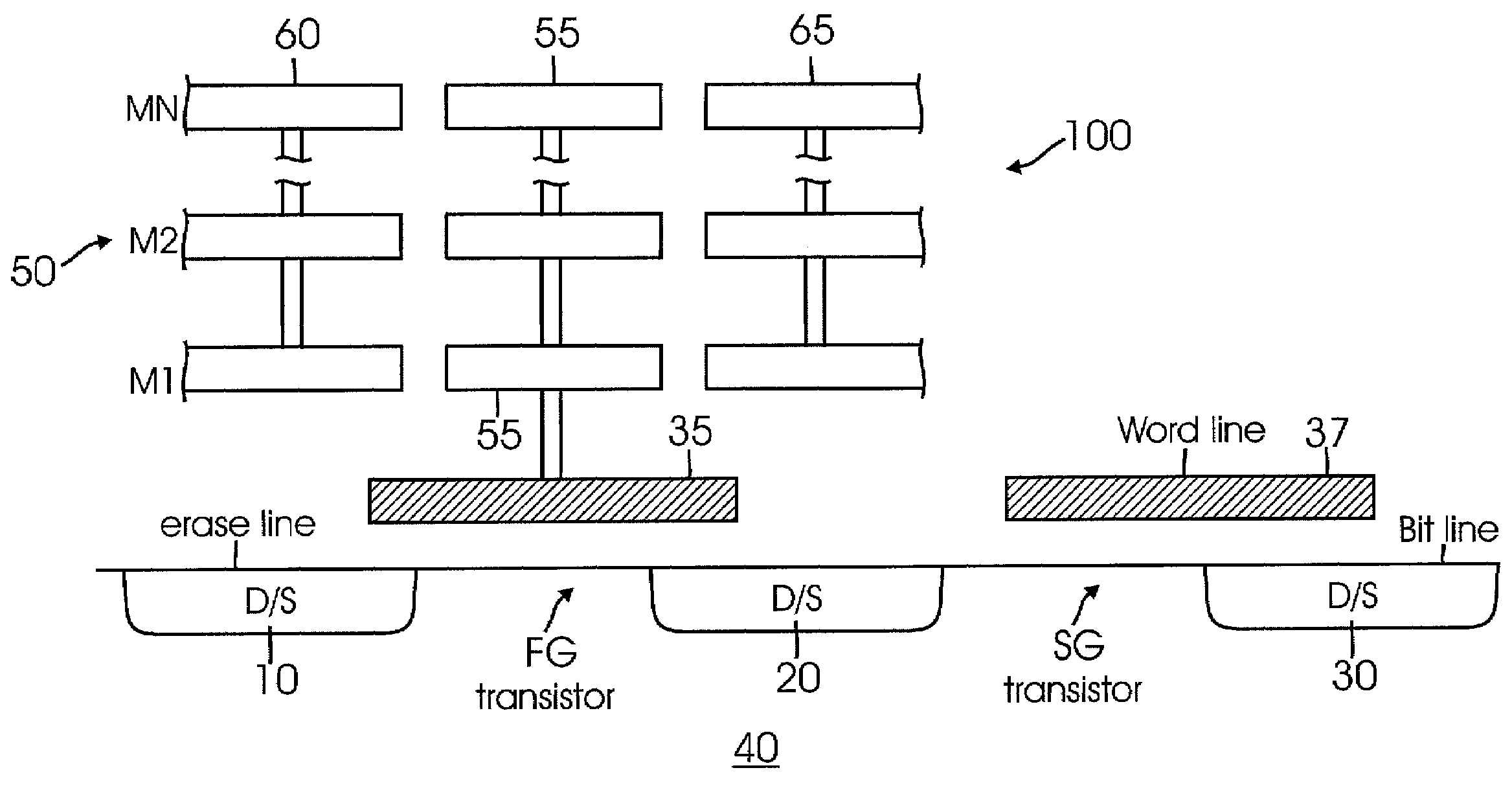

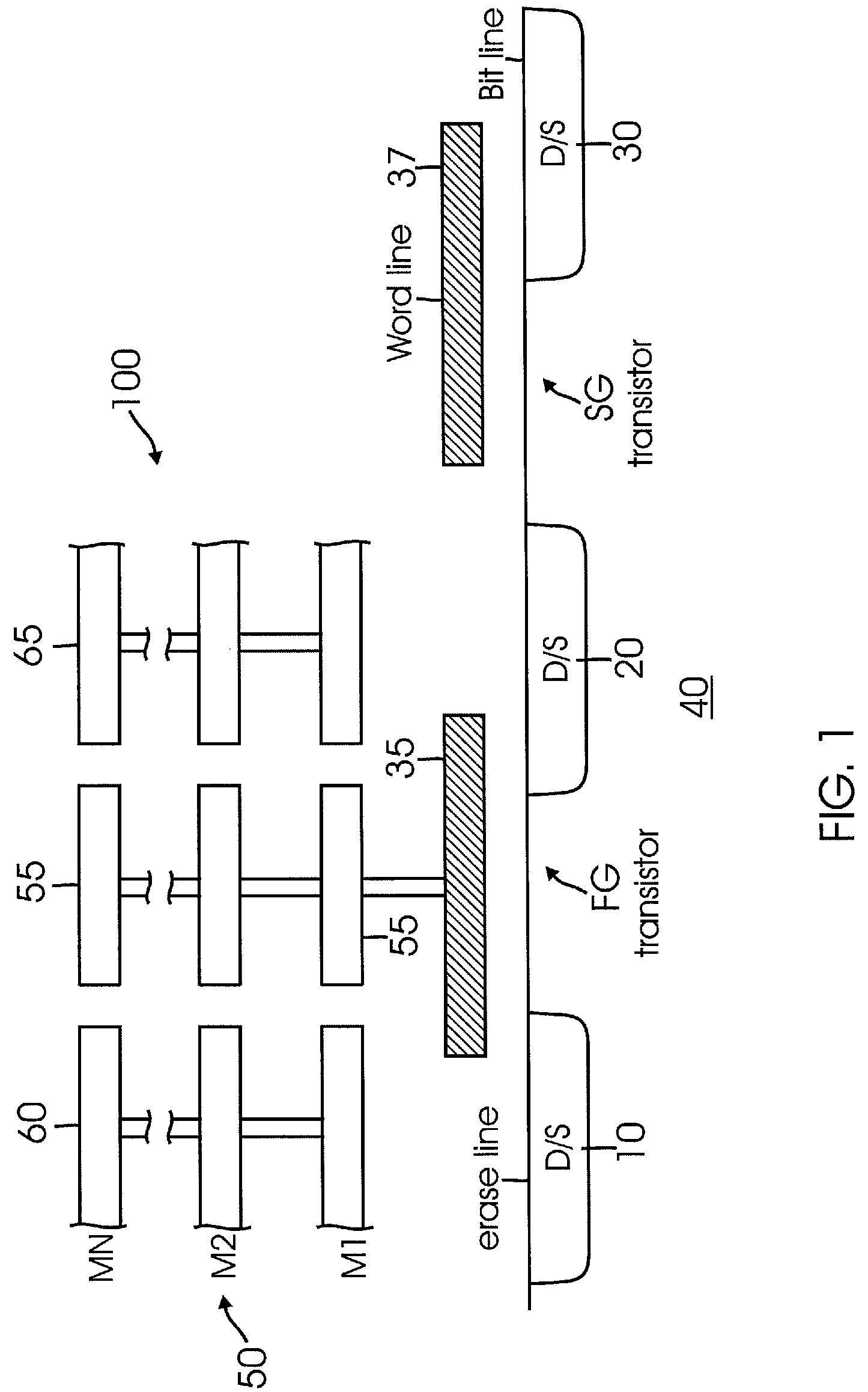

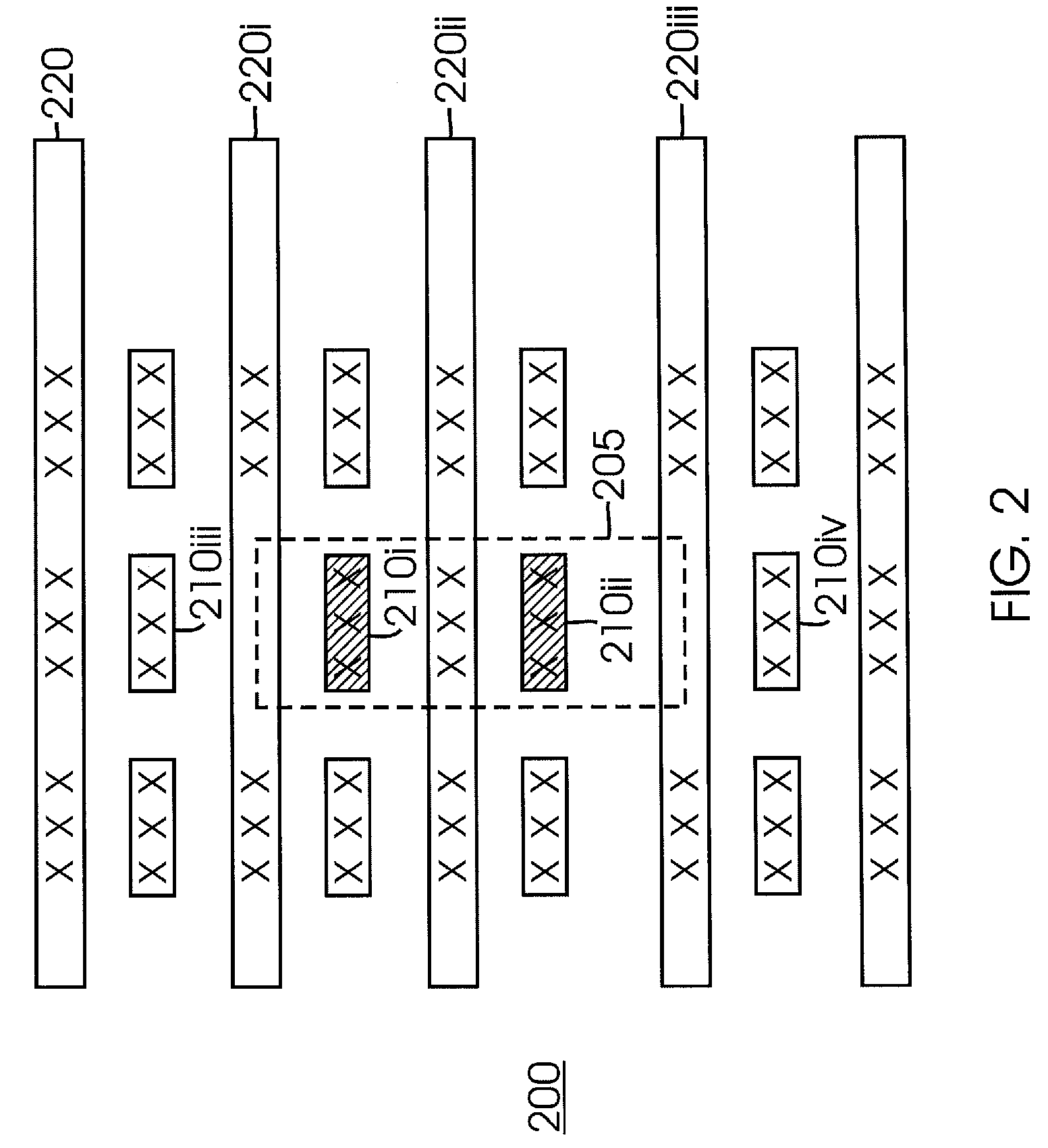

Single-Poly Non-Volatile Memory Cell

A non-volatile memory cell includes a floating gate transistor having a floating gate coupled to a metal layer capacitor defined in one or more metal layers. Within each metal layer, the metal layer capacitor includes a first plate coupled to the floating gate and a second plate separated from the first plate by a fringe capacitance junction.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

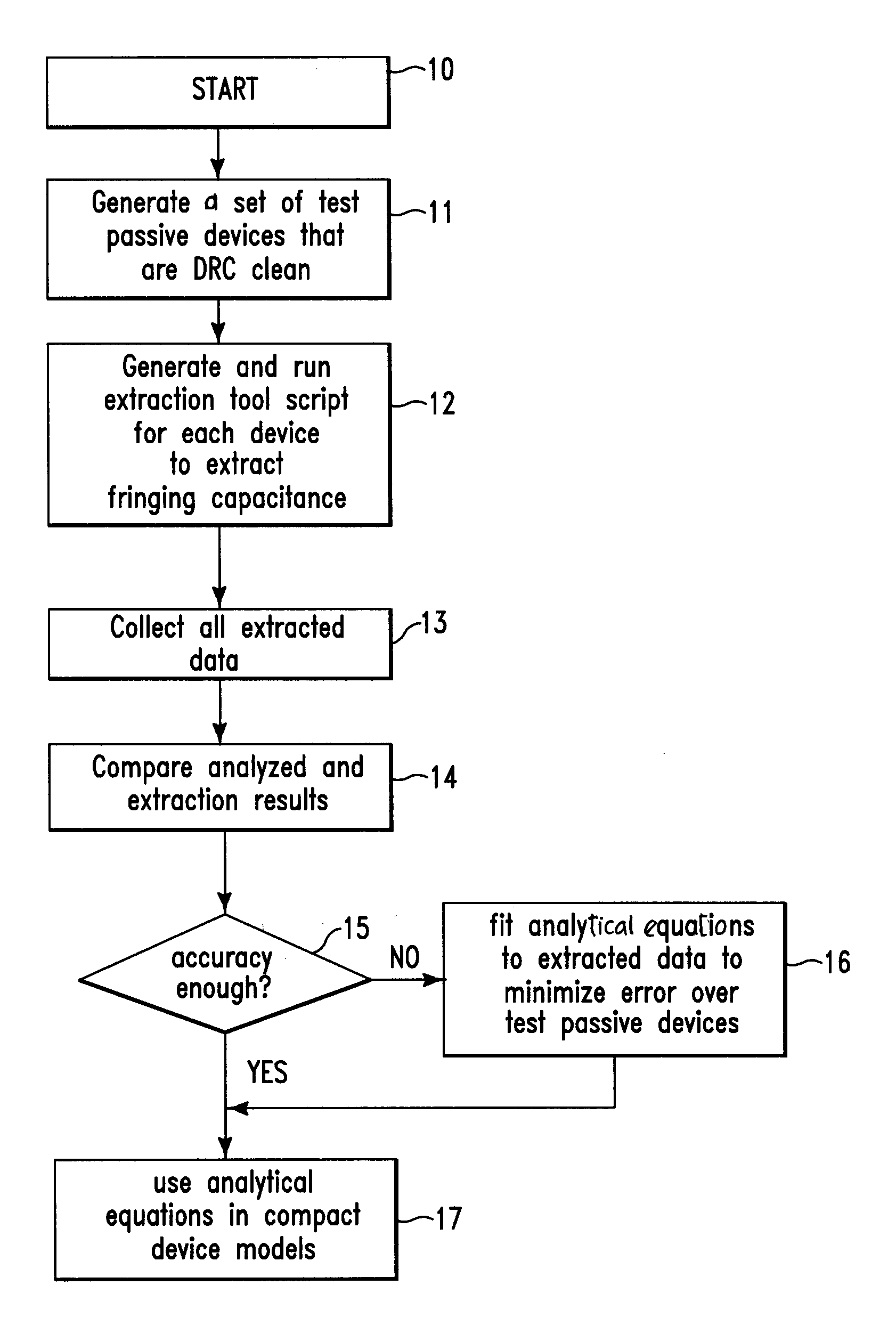

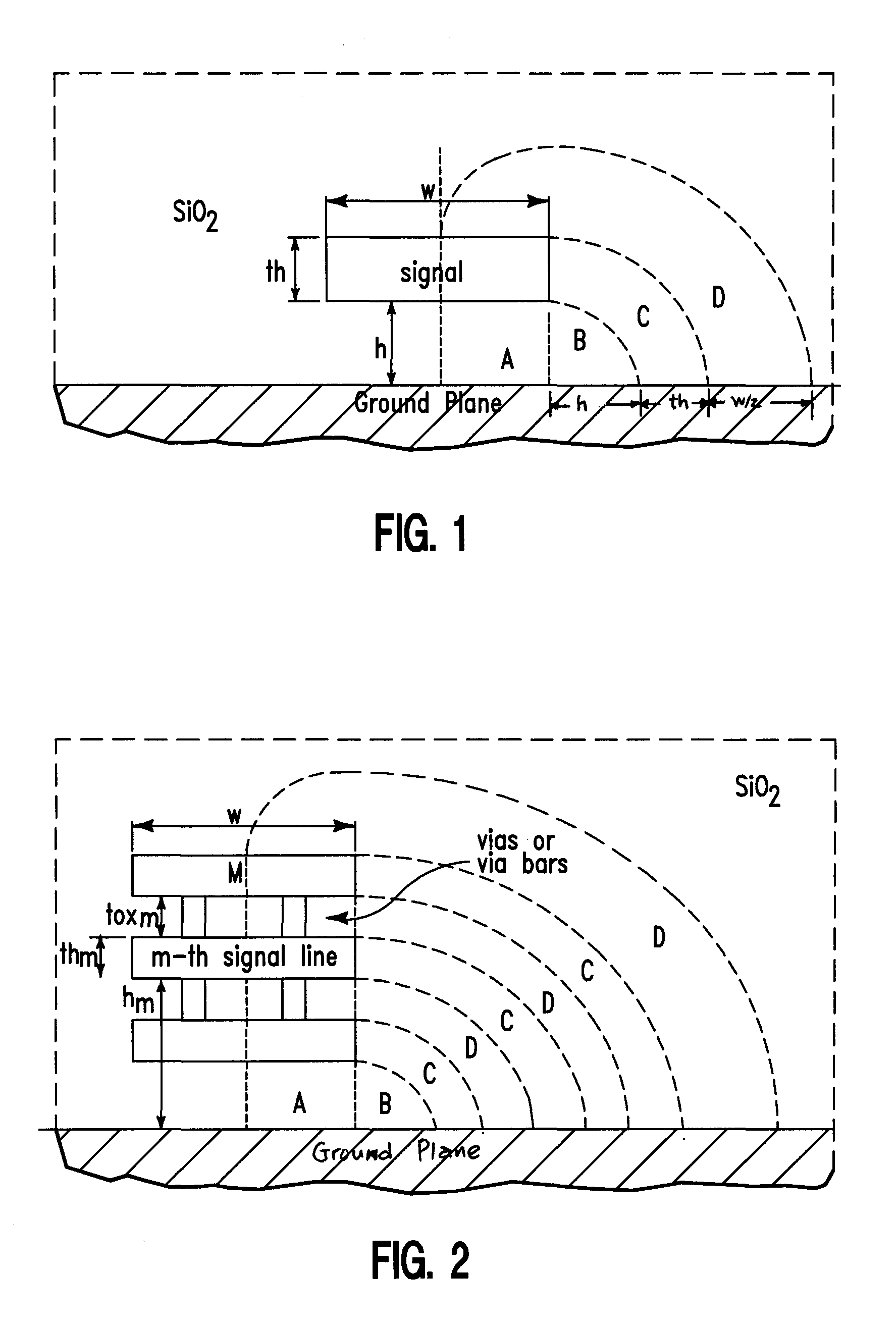

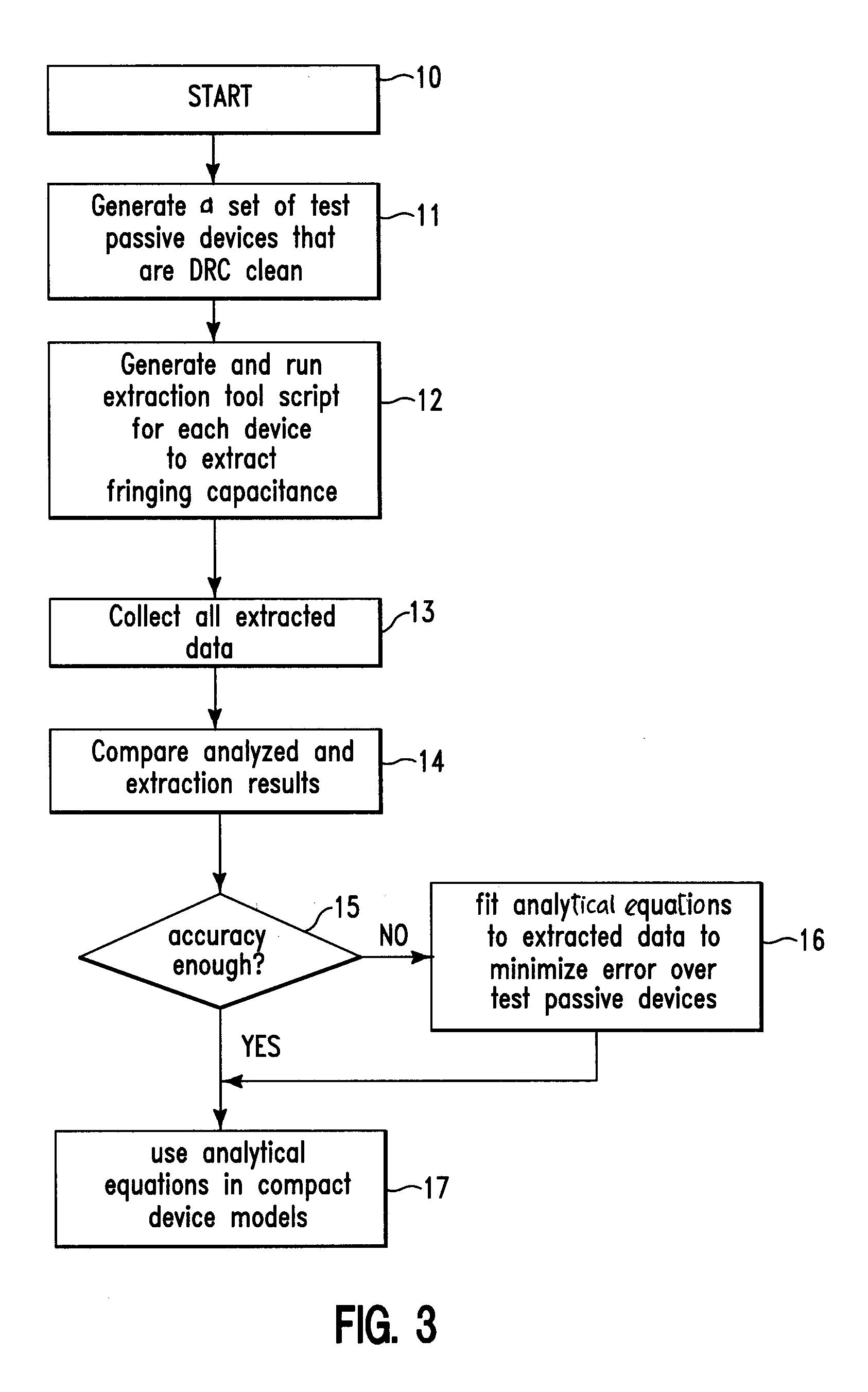

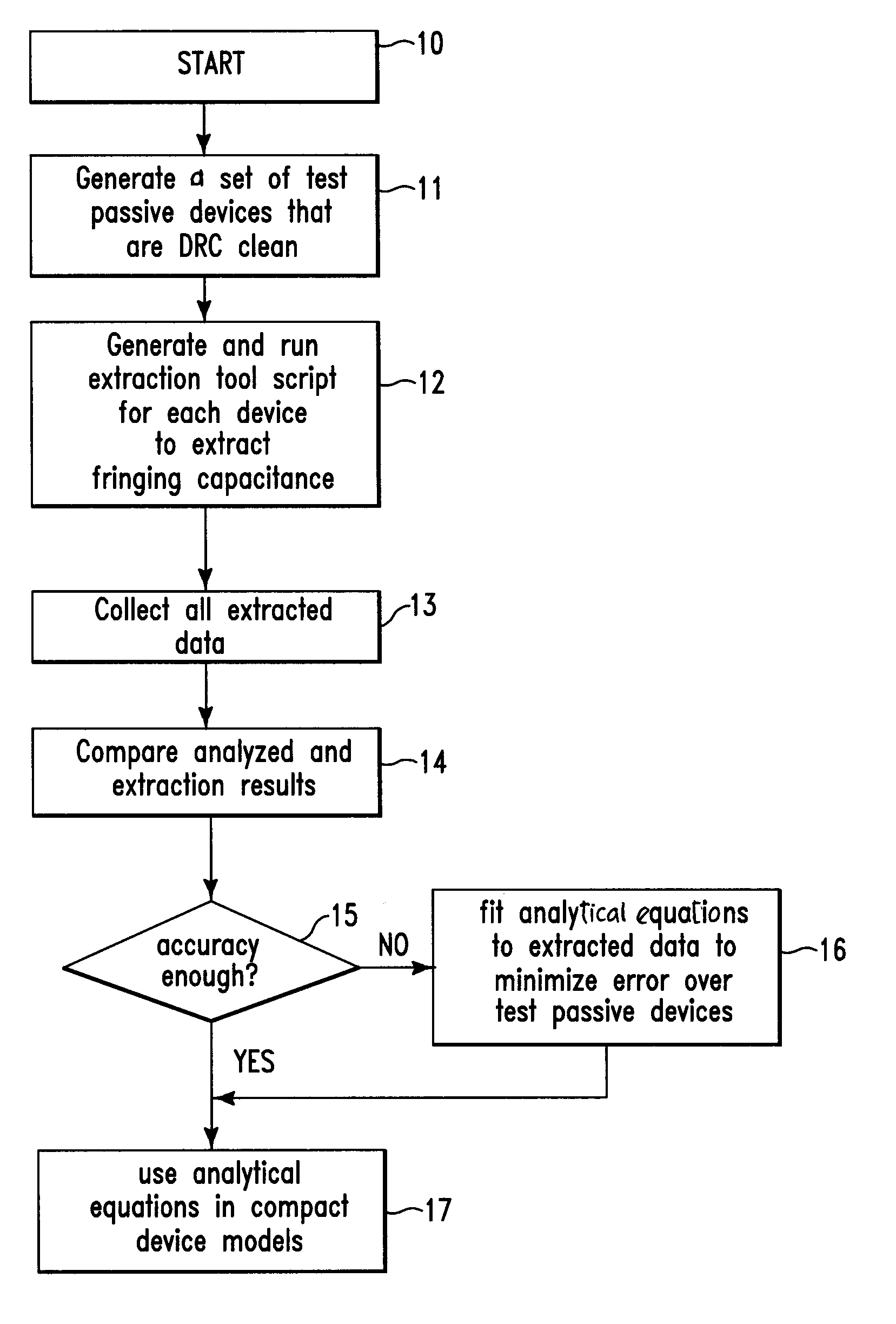

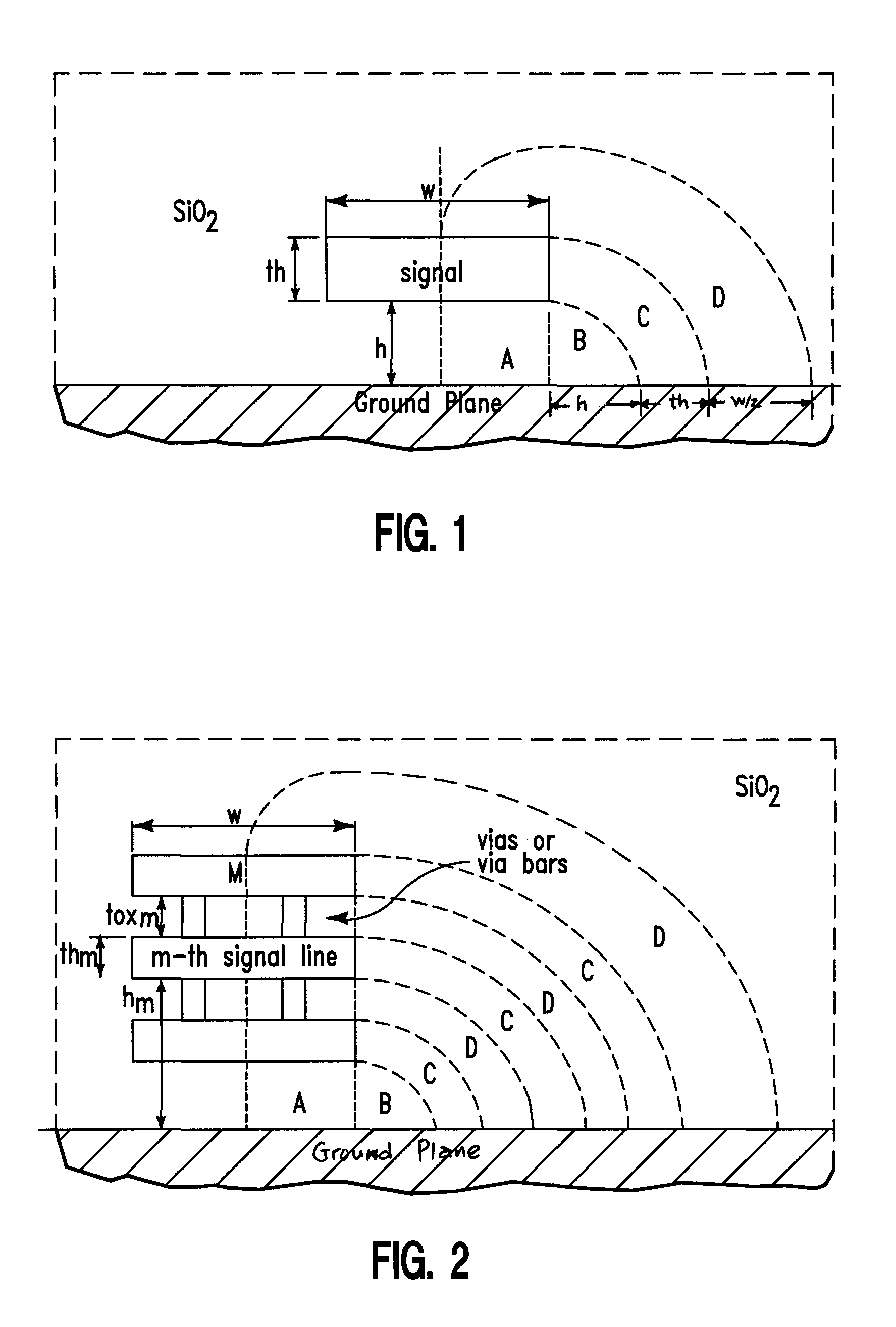

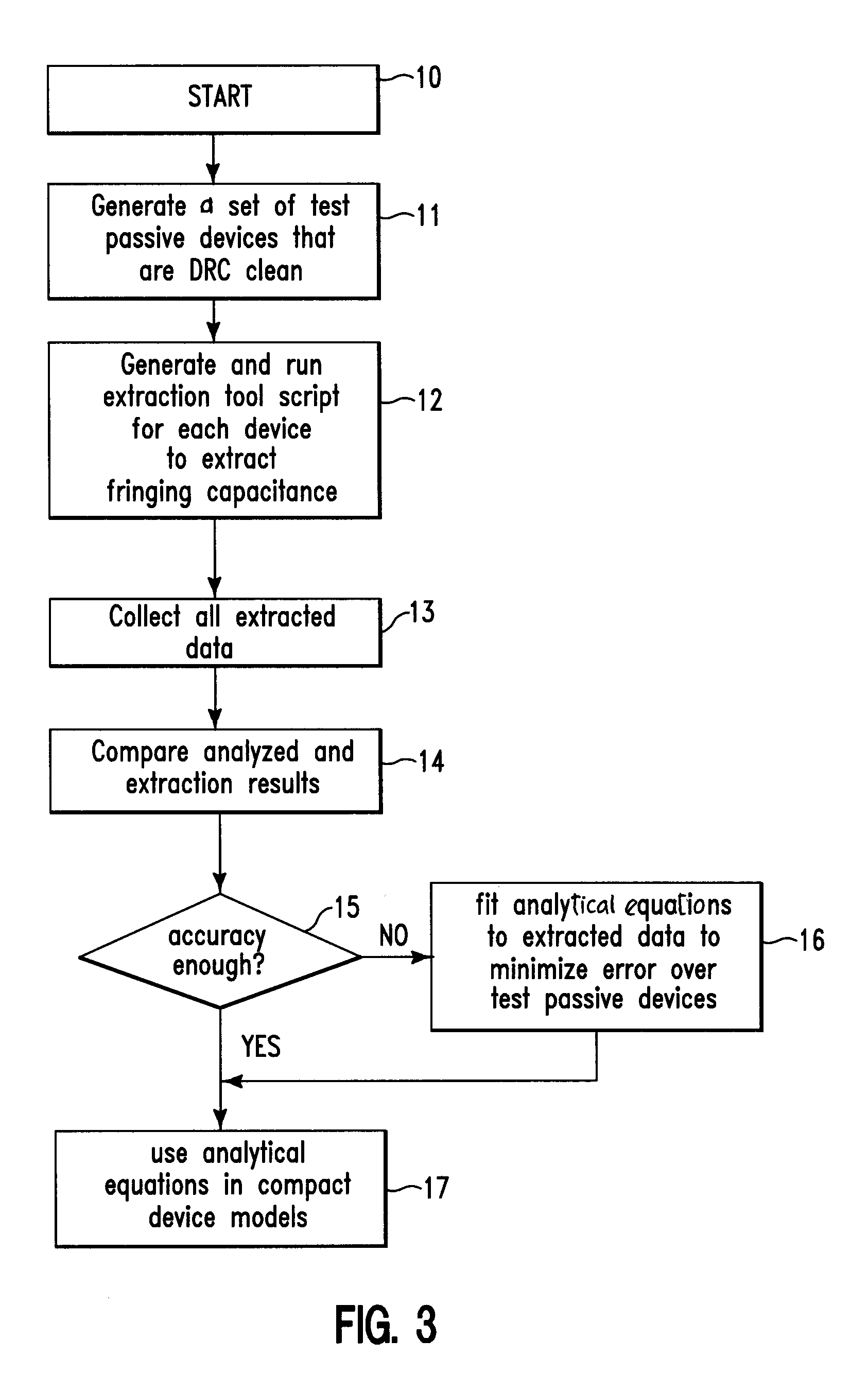

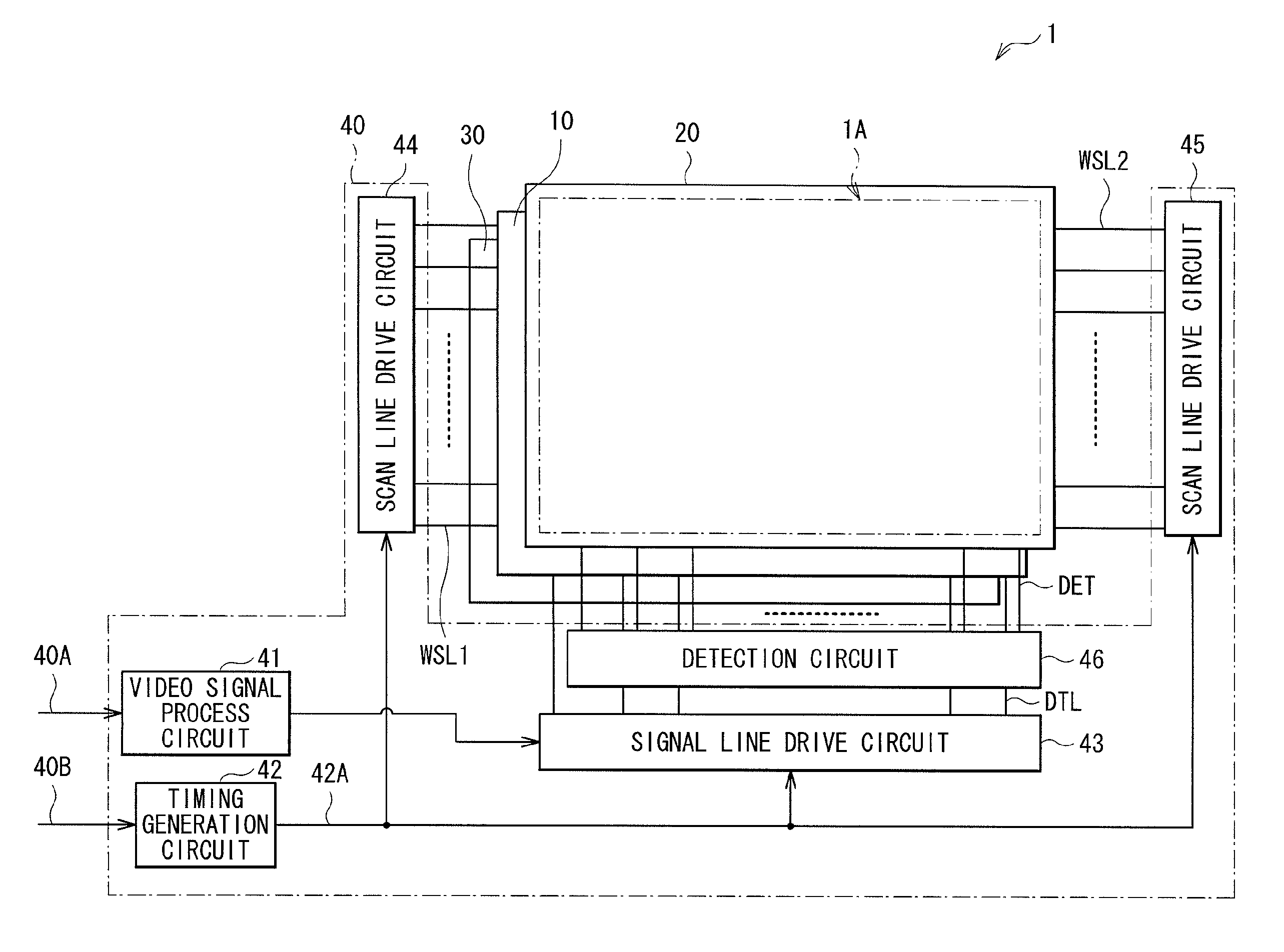

Method for determining fringing capacitances on passive devices within an integrated circuit

InactiveUS20060015276A1Resistance/reactance/impedenceVoltage-current phase angleFringing capacitanceElectric field

A method for determining fringing capacitances on passive devices within an integrated circuit is disclosed. A fringing capacitance region on a passive device is initially divided into a group of fringing electric field areas. A set of fringing capacitance equations is then developed for the fringing electric field areas accordingly. A determination is made as to whether or not an accuracy of the fringing capacitance equations meets a predetermined threshold. If the accuracy of the fringing capacitance equations meets the predetermined threshold, then the fringing capacitance equations are utilized in compact device models to determine fringing capacitance on the passive device. If the accuracy of the fringing capacitance equations does not meet the predetermined threshold, the physically-based fringing capacitance equations are fitted to a set of extracted data to generate a refined set of physically-based fringing capacitance equations, and the refined set of physically-based fringing capacitance equations is utilized in compact device models to determine fringing capacitance on the passive device.

Owner:IBM CORP

Method for determining fringing capacitances on passive devices within an integrated circuit

InactiveUS7103488B2Resistance/reactance/impedenceVoltage-current phase angleEngineeringFringing capacitance

A method for detemiining fringing capacitances on passive devices within an integrated circuit is disclosed. A fringing capacitance region on a passive device is initially divided into a group of fringing electric field areas. A set of fringing capacitance equations is then developed for the fringing electric field areas accordingly. A determination is made as to whether or not an accuracy of the fringing capacitance equations meets a predetermined threshold. If so, then the fringing capacitance equations are utilized in compact device models to determine fringing capacitance on the passive device; otherwise, the physically-based fringing capacitance equations are fitted to a set of extracted data to generate a refined set of physically-based fringing capacitance equations, and the refined set of physically-based fringing capacitance equations is utilized in compact device models to determine fringing capacitance on the passive device.

Owner:IBM CORP

Touch panel, display panel, and display unit

ActiveUS9122357B2Eliminate false detectionsHigh sensitivityStatic indicating devicesAlternating current plasma display panelsEngineeringFringing capacitance

A touch panel, a display panel, and a display unit achieving prevention of erroneous detection caused by external noise, are provided. The touch panel includes: a plurality of detection scan electrodes extending in a first direction; and a plurality of detection electrodes facing the plurality of detection scan electrodes and extending in a second direction which intersects the first direction. A ratio of fringe capacitance to total capacitance between one or more selected detection scan electrodes and a first detection electrode is different from a ratio of fringe capacitance to total capacitance between the one or more selected detection scan electrodes and a second detection electrode. The one or more selected detection scan electrodes are selected, in a desired unit, from the plurality of detection scan electrodes, to be supplied with a selection pulse, and each of the first and the second detection electrodes is selected from the plurality of detection electrodes.

Owner:JAPAN DISPLAY INC

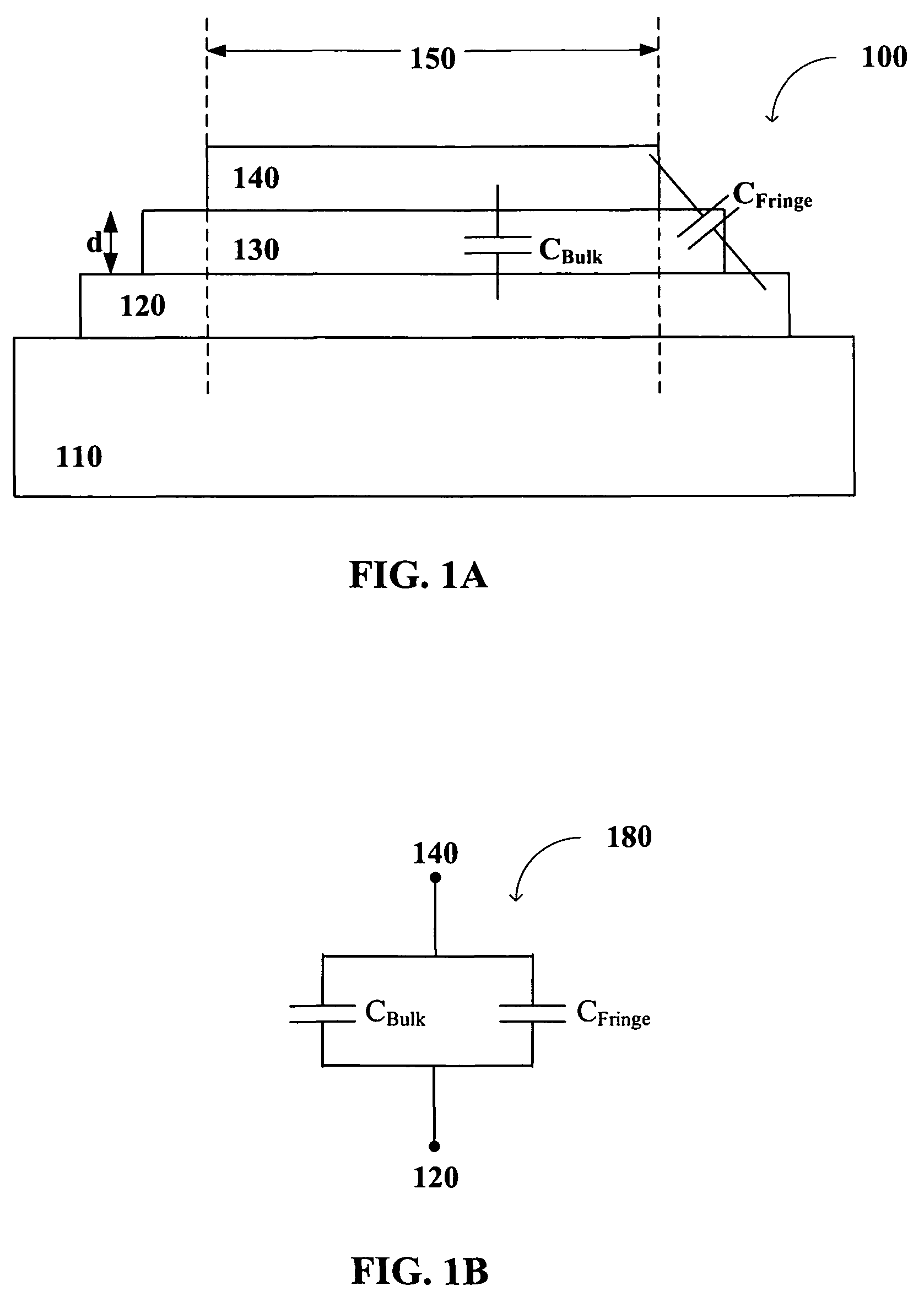

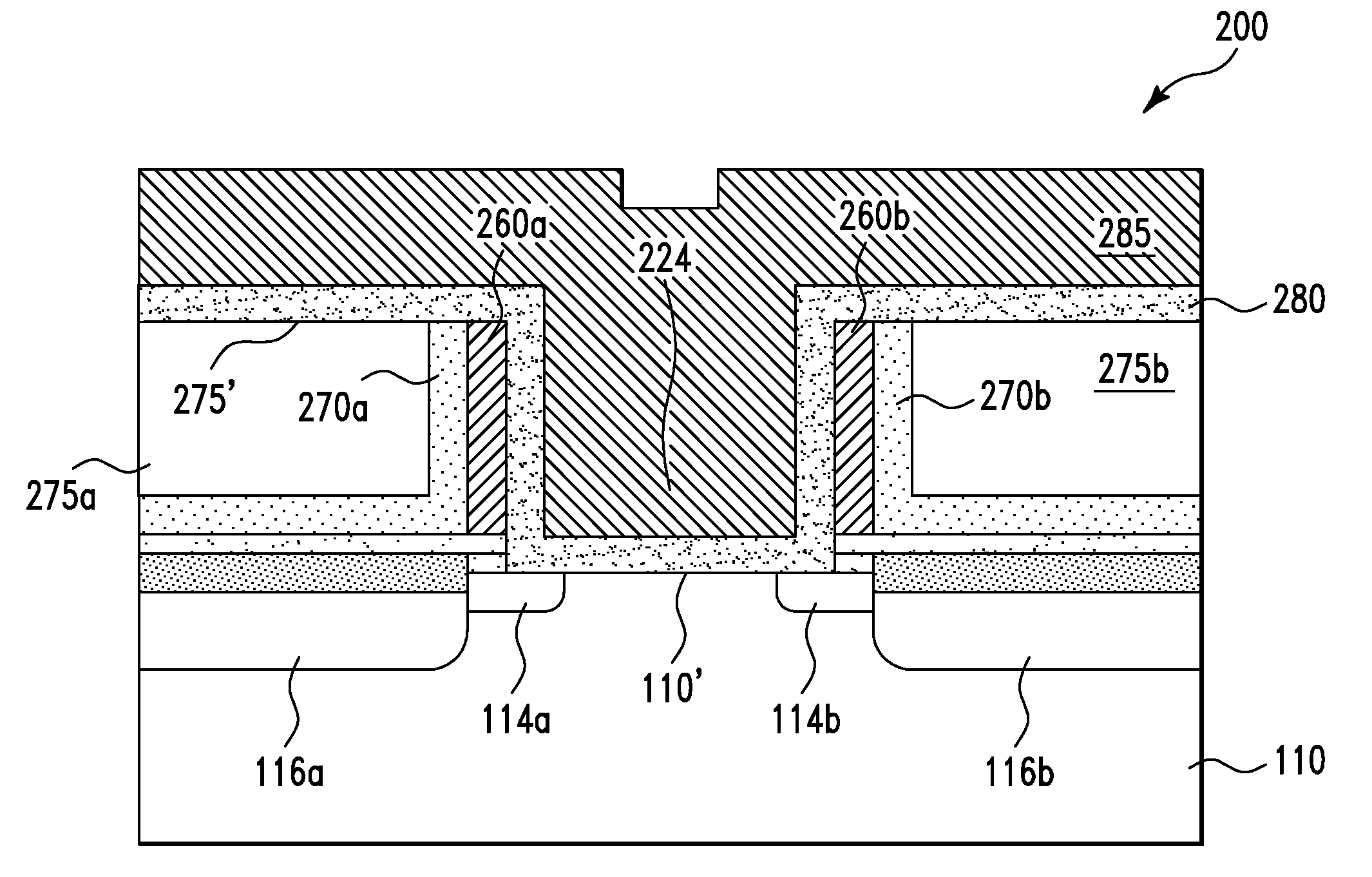

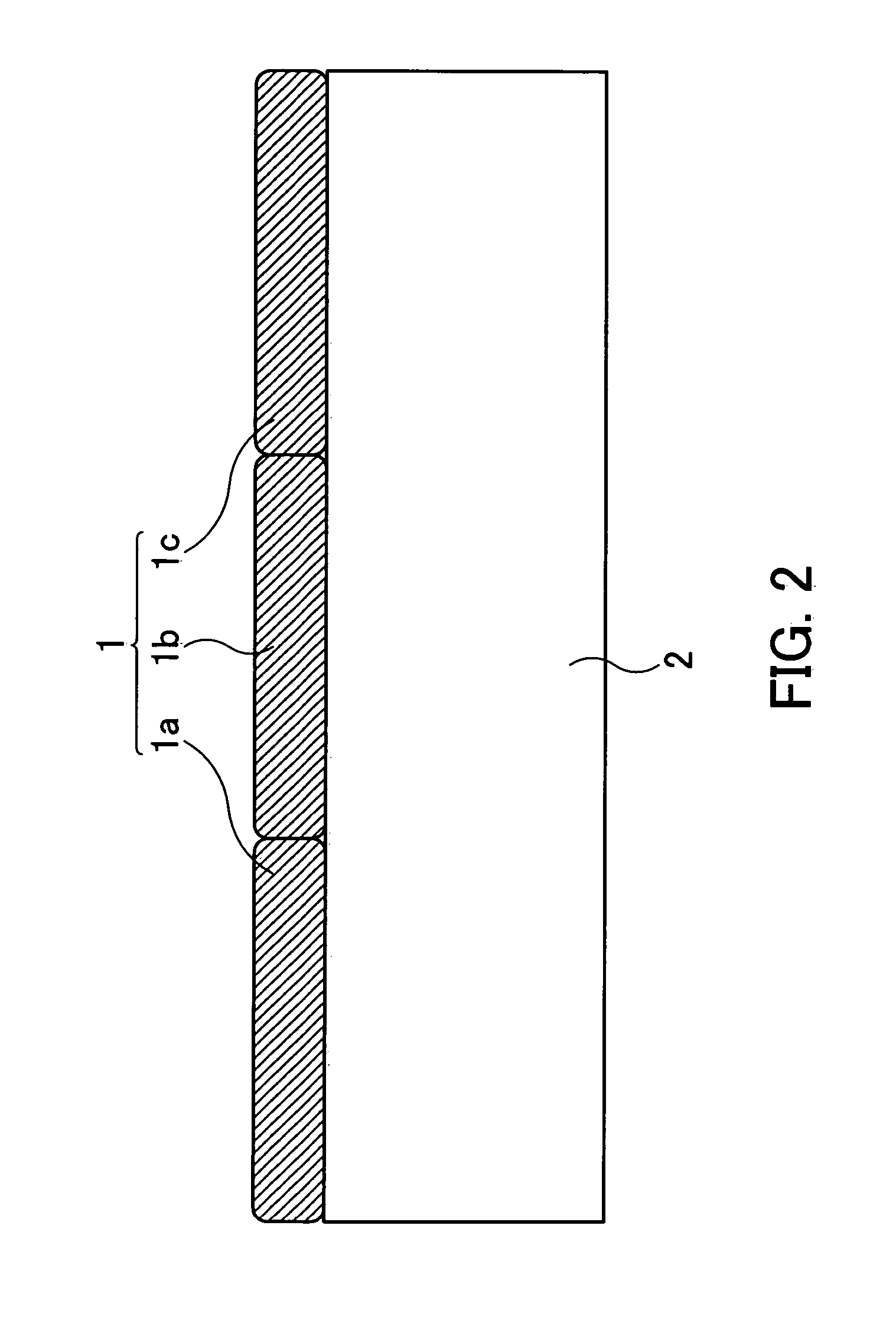

Methods for the fabrication of integrated circuits including back-etching of raised conductive structures

ActiveUS8524566B2Increase widthReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingEtchingEngineering

Embodiments of a method for fabricating an integrated circuit are provided. In one embodiment, the method includes producing a partially-completed semiconductor device including a substrate, source / drain (S / D) regions, a channel region between the S / D regions, and a gate stack over the channel region. At least one raised electrically-conductive structure is formed over at least one of the S / D regions and separated from the gate stack by a lateral gap. The raised electrically-conductive structure is then back-etched to increase the width of the lateral gap and reduce the parasitic fringing capacitance between the raised electrically-conductive structure and the gate stack during operation of the completed semiconductor device.

Owner:GLOBALFOUNDRIES U S INC

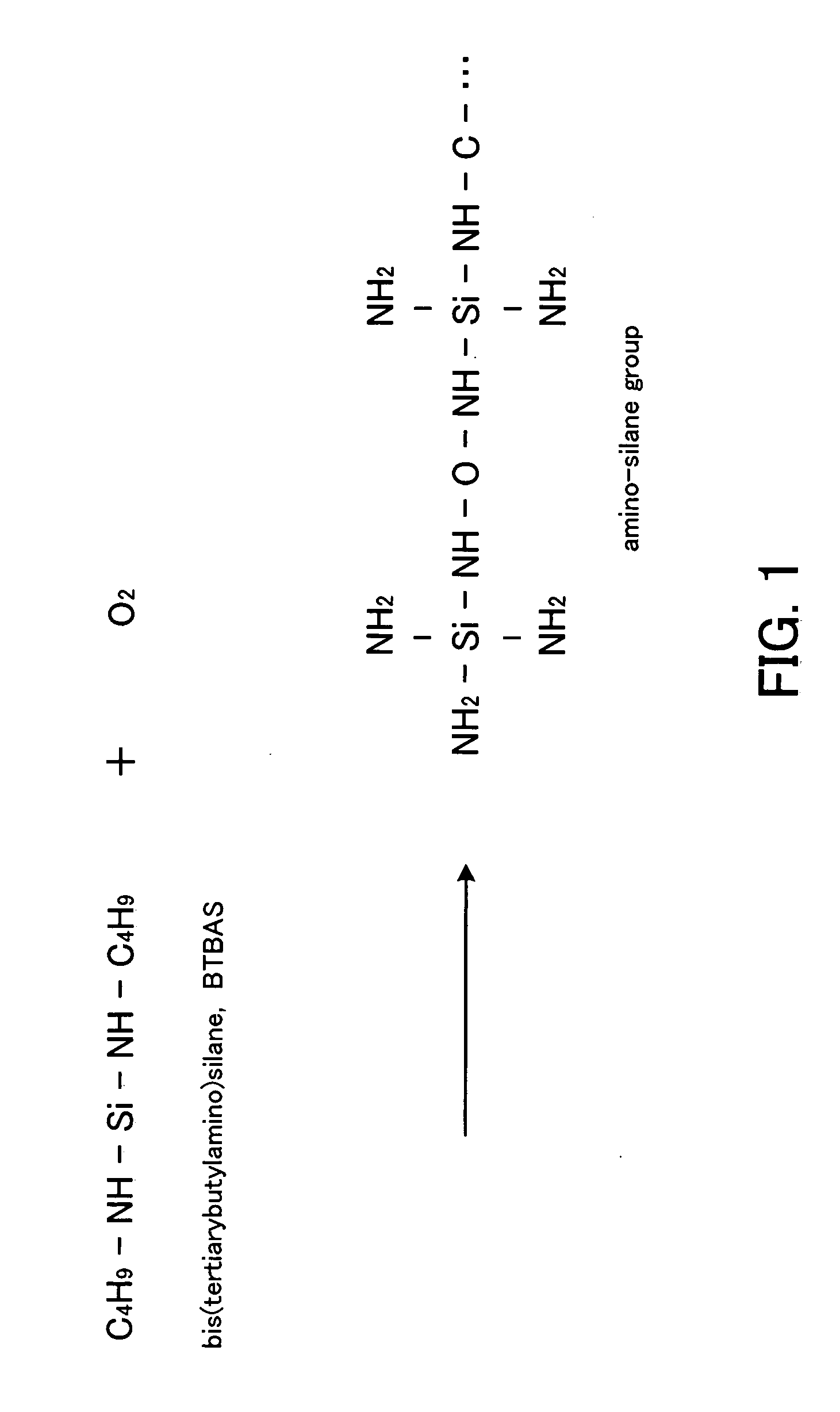

Semiconductor device and method for manufacturing the same

InactiveUS20060121714A1Quality improvementTransistorSemiconductor/solid-state device manufacturingNitrogenOxygen

Disclosed is a method for manufacturing a semiconductor device provided with a sidewall having a high quality and an excellent shape. The sidewall on a gate electrode side wall is formed using a carbon-containing silicon nitride oxide film. The film can be formed by a CVD method using, as starting materials, BTBAS and oxygen where a BTBAS flow rate / oxygen flow rate ratio is appropriately set and a low film formation temperature is set, for example, at about 530° C. When forming the sidewall using this film, improvement in HF resistance and reduction in fringe capacitance can be realized due to contribution of nitrogen atoms and carbon atoms. Further, when forming this film under low temperature conditions, unnecessary diffusion of impurities introduced into a semiconductor substrate can be suppressed. Thus, transistor characteristics are enhanced and stabilized, so that high performance and high quality in the semiconductor device can be realized.

Owner:FUJITSU LTD

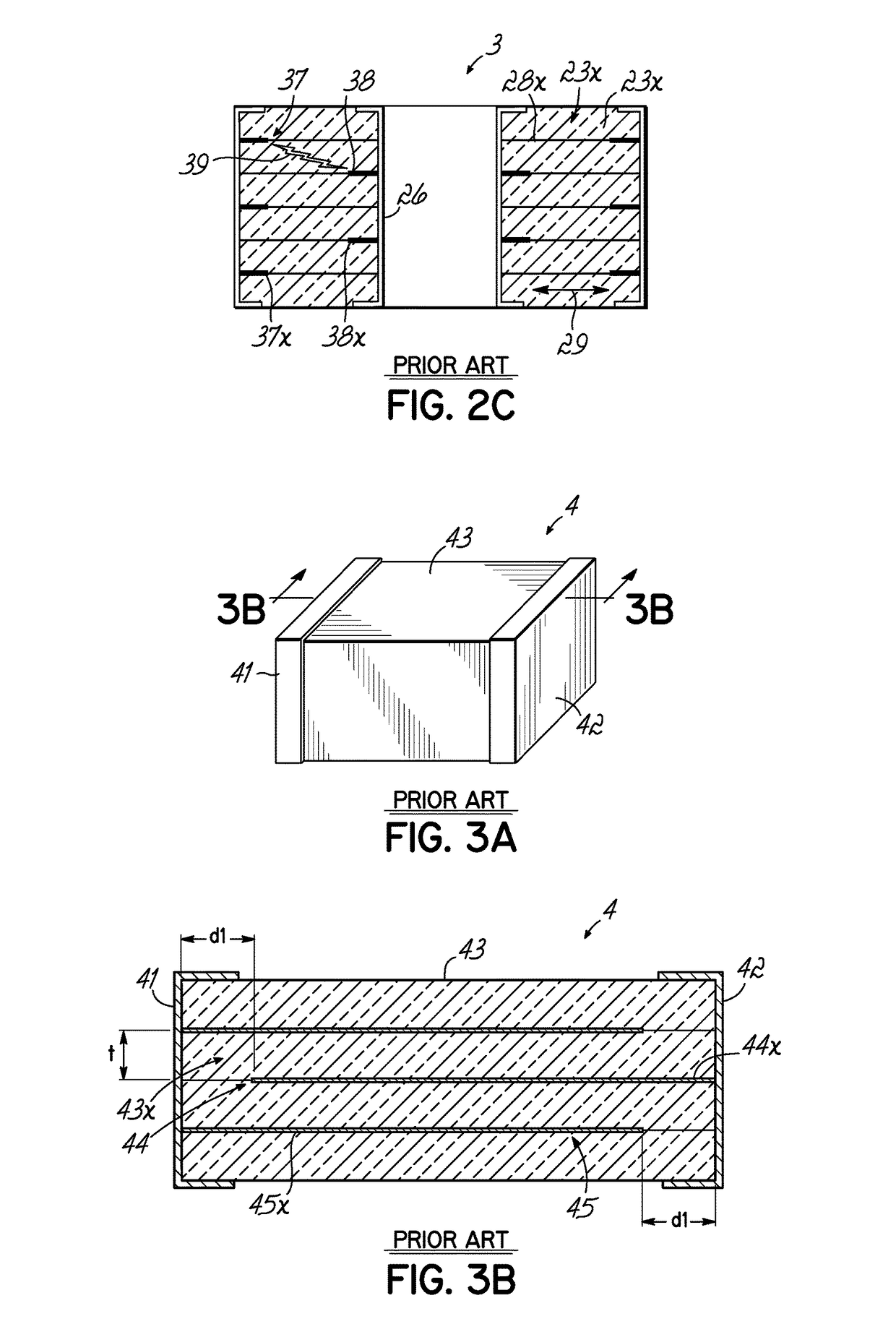

High voltage fringe-effect capacitor

ActiveUS9786437B1Increase capacitanceIncrease valueAnti-noise capacitorsFixed capacitor electrodesPlanar electrodeFringing capacitance

A multilayer chip capacitor includes electrodes comprised of numerous, closely spaced conductive layers interposed within a dielectric laminate. Adjacent conductive layers are essentially non-overlapping, so that fringe capacitance between opposing electrodes provides substantially all of the capacitance. The conductive layers may be shaped to form a non-planer boundary between electrodes. An additional high frequency integrated capacitor is formed from external electrode plates. The non-planar electrode boundary principle is also applied to discoidal capacitors in the form of a non-concentric electrode boundary.

Owner:PRESIDIO COMPONENTS

Contact bars with reduced fringing capacitance in a semiconductor device

InactiveUS9184095B2Increasing overall parasitic fringing capacitanceReduce capacitanceSemiconductor/solid-state device detailsSolid-state devicesFringing capacitanceContact element

In sophisticated semiconductor devices, the contact structure may be formed on the basis of contact bars formed in a lower portion of an interlayer dielectric material, which may then be contacted by contact elements having reduced lateral dimensions so as to preserve a desired low overall fringing capacitance. The concept of contact bars of reduced height level may be efficiently combined with sophisticated replacement gate approaches.

Owner:GLOBALFOUNDRIES INC

Stress memorization with reduced fringing capacitance based on silicon nitride in MOS semiconductor devices

InactiveUS8426266B2Avoid negative effectsReduce the valueTransistorSemiconductor/solid-state device manufacturingElectricityFringing capacitance

In sophisticated semiconductor devices, stress memorization techniques may be applied on the basis of a silicon nitride material, which may be subsequently modified into a low-k dielectric material in order to obtain low-k spacer elements, thereby enhancing performance of sophisticated semiconductor devices. The modification of the initial silicon nitride-based spacer material may be accomplished on the basis of an oxygen implantation process.

Owner:GLOBALFOUNDRIES INC