Patents

Literature

34results about How to "Reduce recombination current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for preparing N-type crystalline silicon solar cell with aluminum-based local emitters on back side

InactiveCN101853897AAvoid damageAvoid Edge Leakage SituationsFinal product manufactureSemiconductor devicesP–n junctionMaterials science

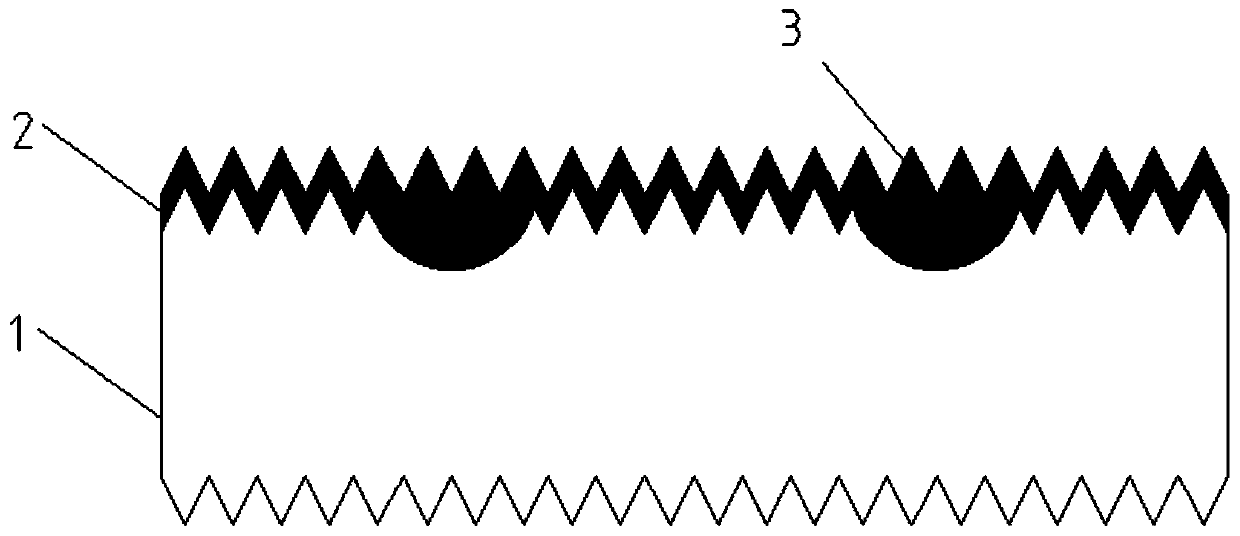

The invention provides a method for preparing an N-type crystalline silicon solar cell with aluminum-based local emitters on the back side. The method comprises the following steps: firstly, selecting N-type silicon wafers to carry out the surface-textured etching process; further forming a front surface field through phosphorous diffusion; depositing a passivating film on the front surface after the phosphorosilicate glass is formed during the removal of diffused phosphorous; carrying out the back-side chemical polishing process on the silicon wafers to remove the N+ layer formed on the back side during the phosphorous diffusion; then, sequentially printing an aluminum layer or a silver-aluminum layer through the passivating film deposited on the back side, local holes or grooves on the back side and screens on the back side; then, printing silver paste on the front surface; and finally, carrying out the one-step sintering process to form a local P+ layer on the back side and allowing the P+ layer to coming into ohmic contact with the electrodes on the front and back surfaces. By using the N-type substrate, forming local aluminum-based P-N junctions on the back side and further using the back-side chemical polishing process to remove the edge junctions, the invention can substitute for the conventional stacking-type plasma etching process, simplify the technological procedures and further bring a series of performance improvement to cells.

Owner:JA YANGZHOU SOLAR PHOTOVOLTAIC ENG

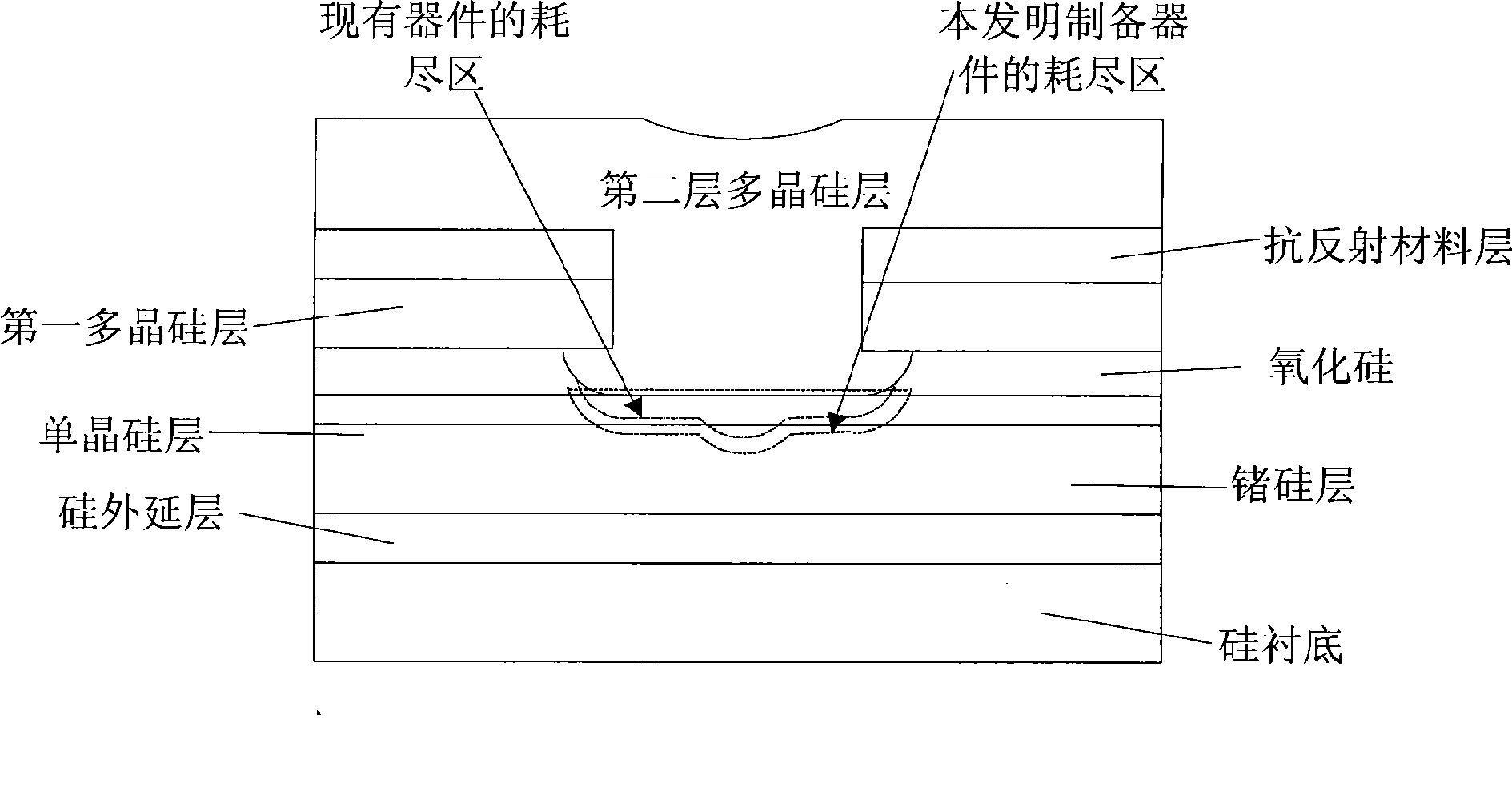

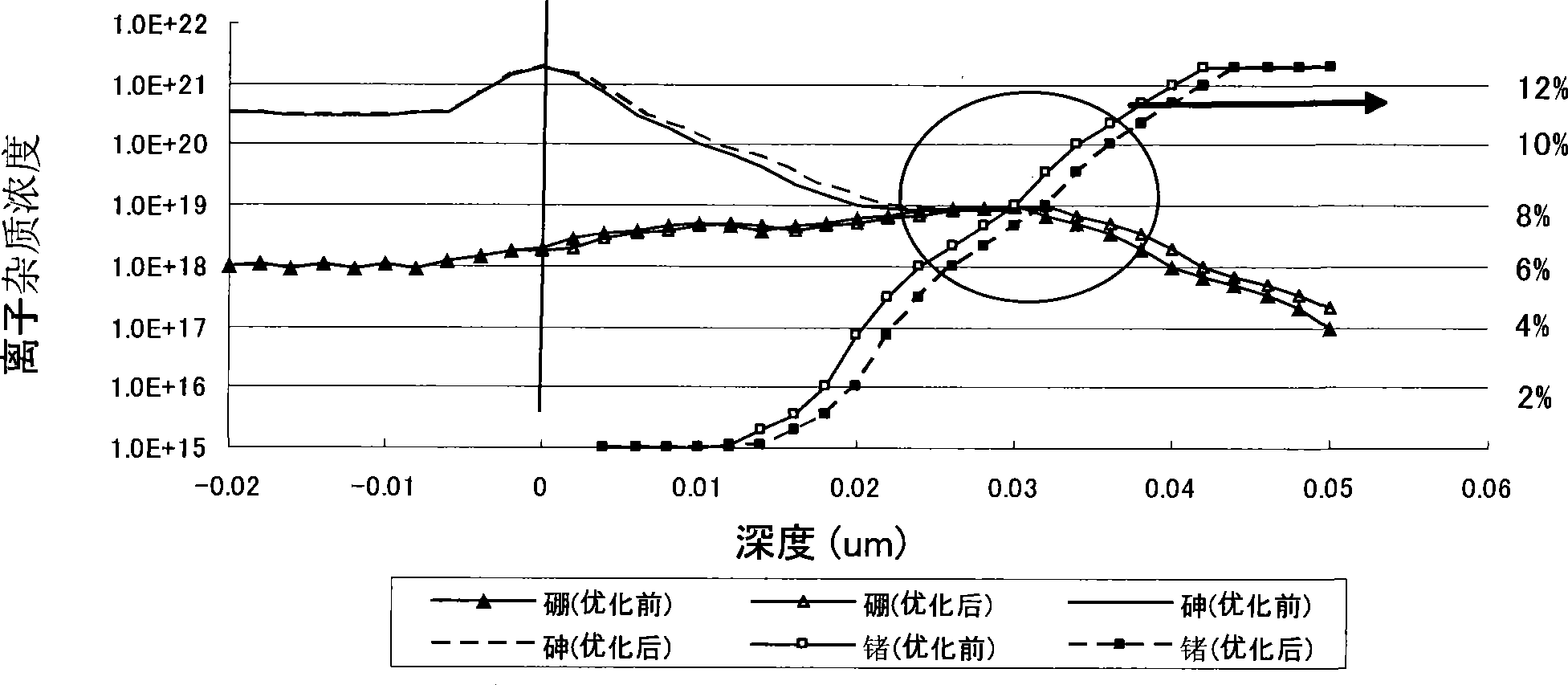

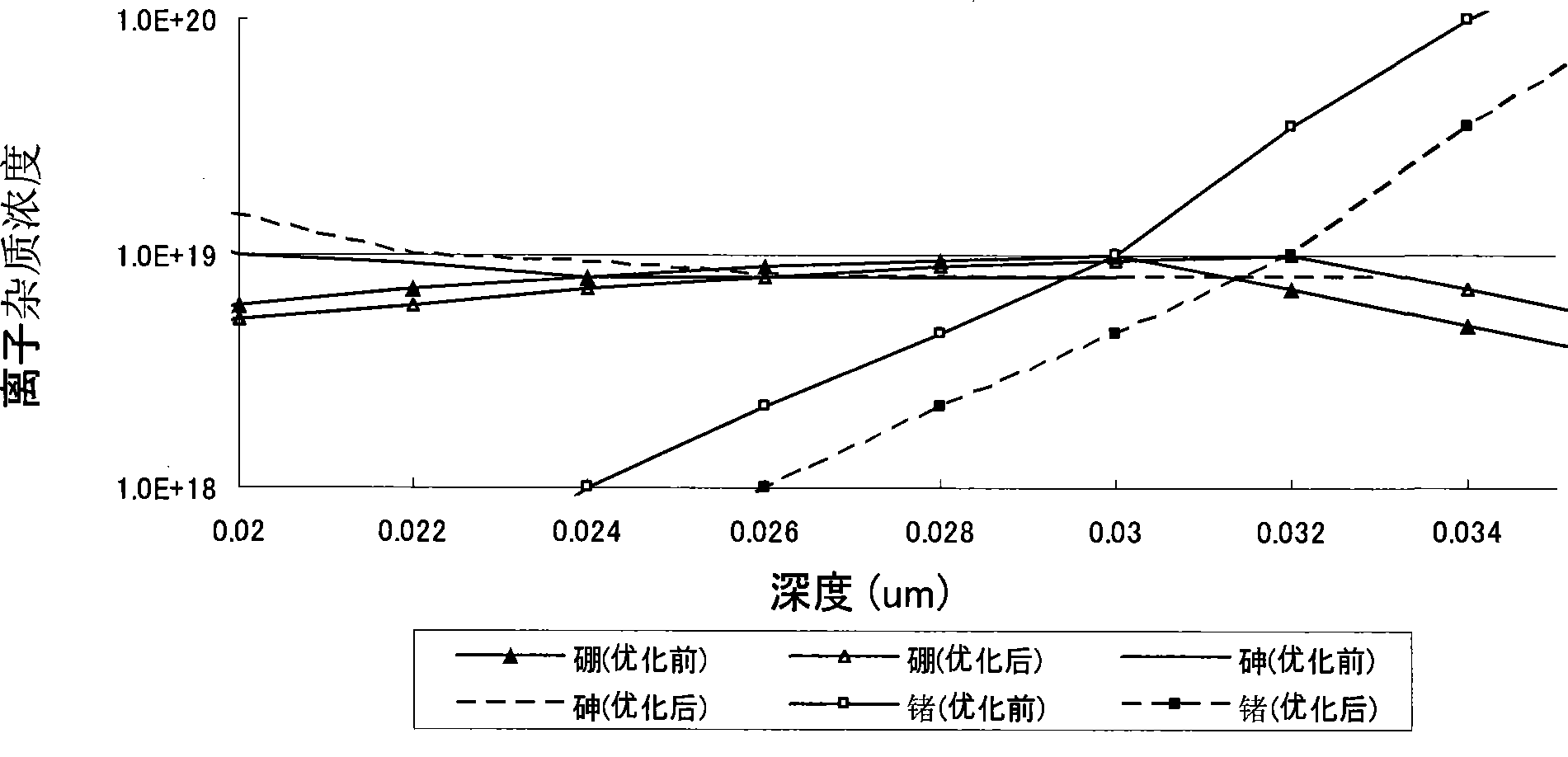

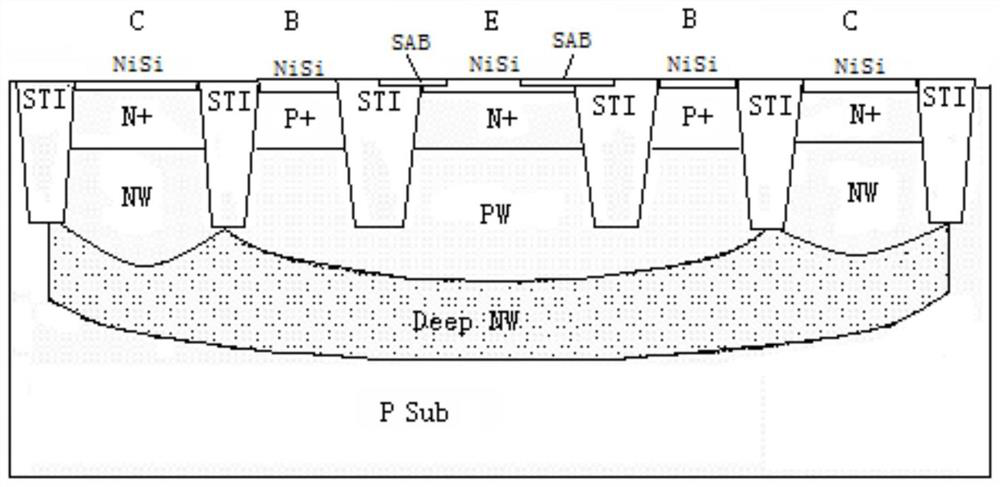

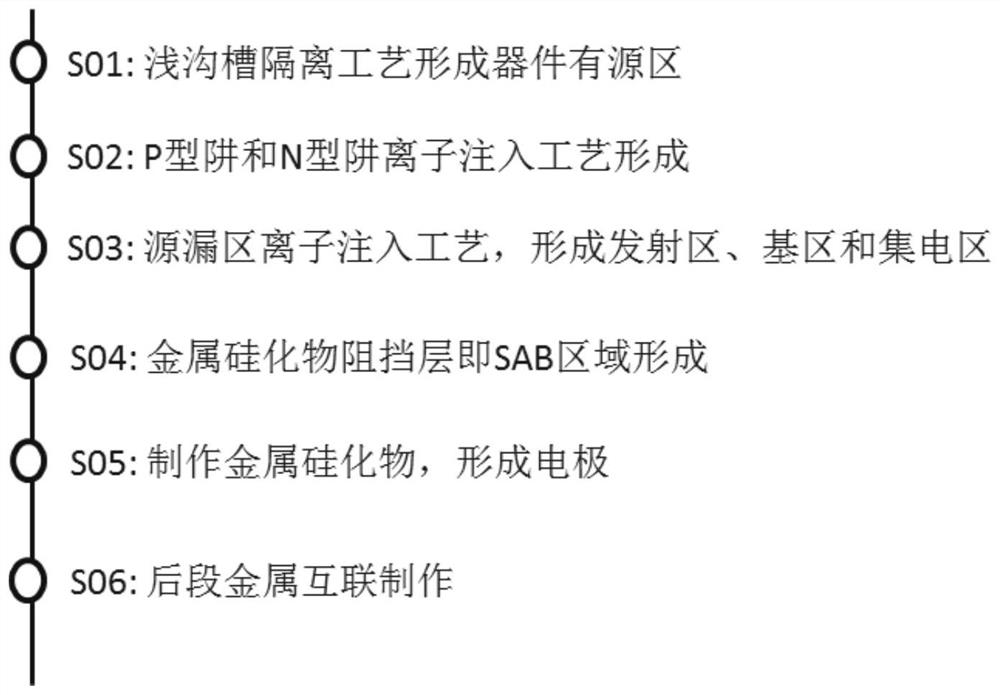

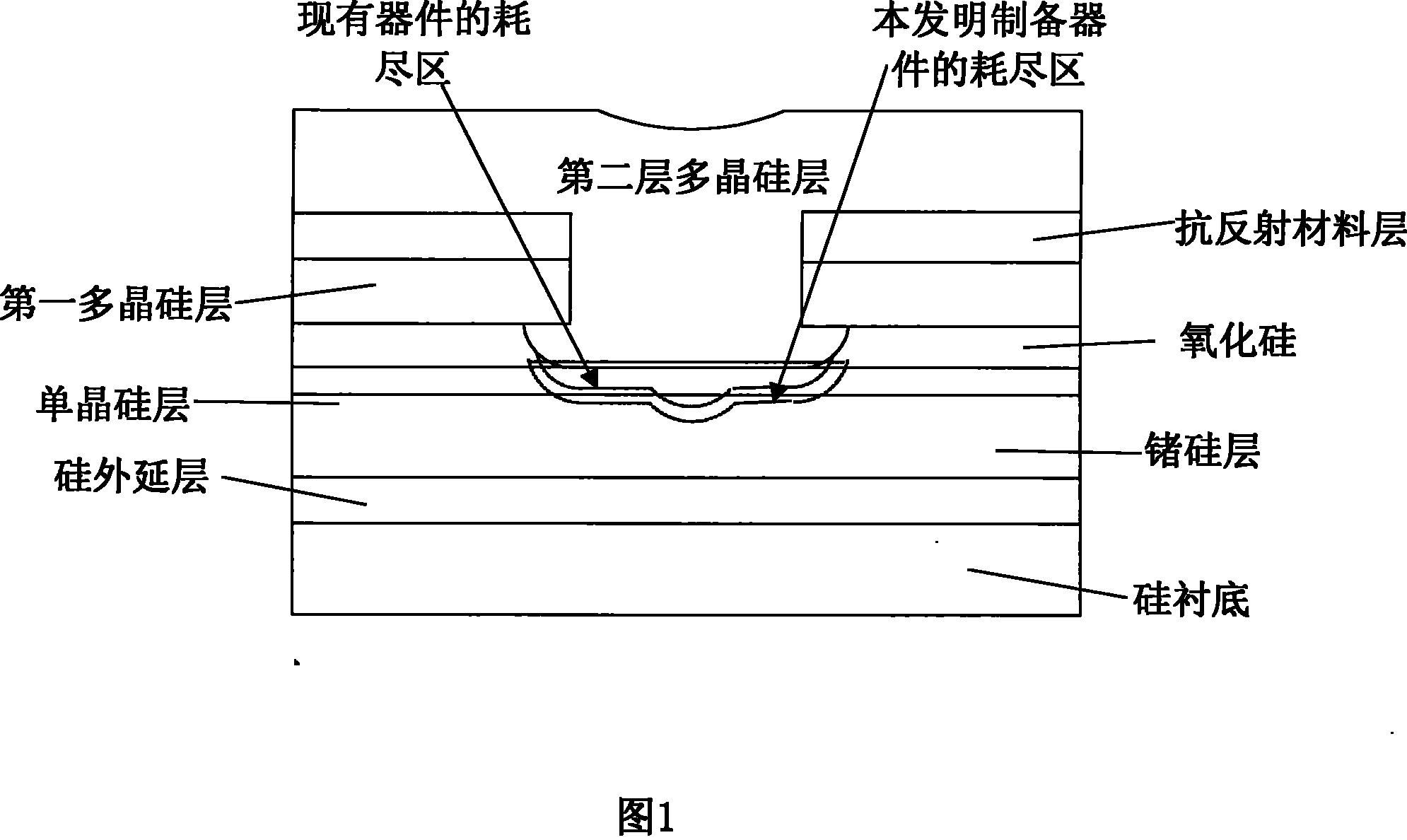

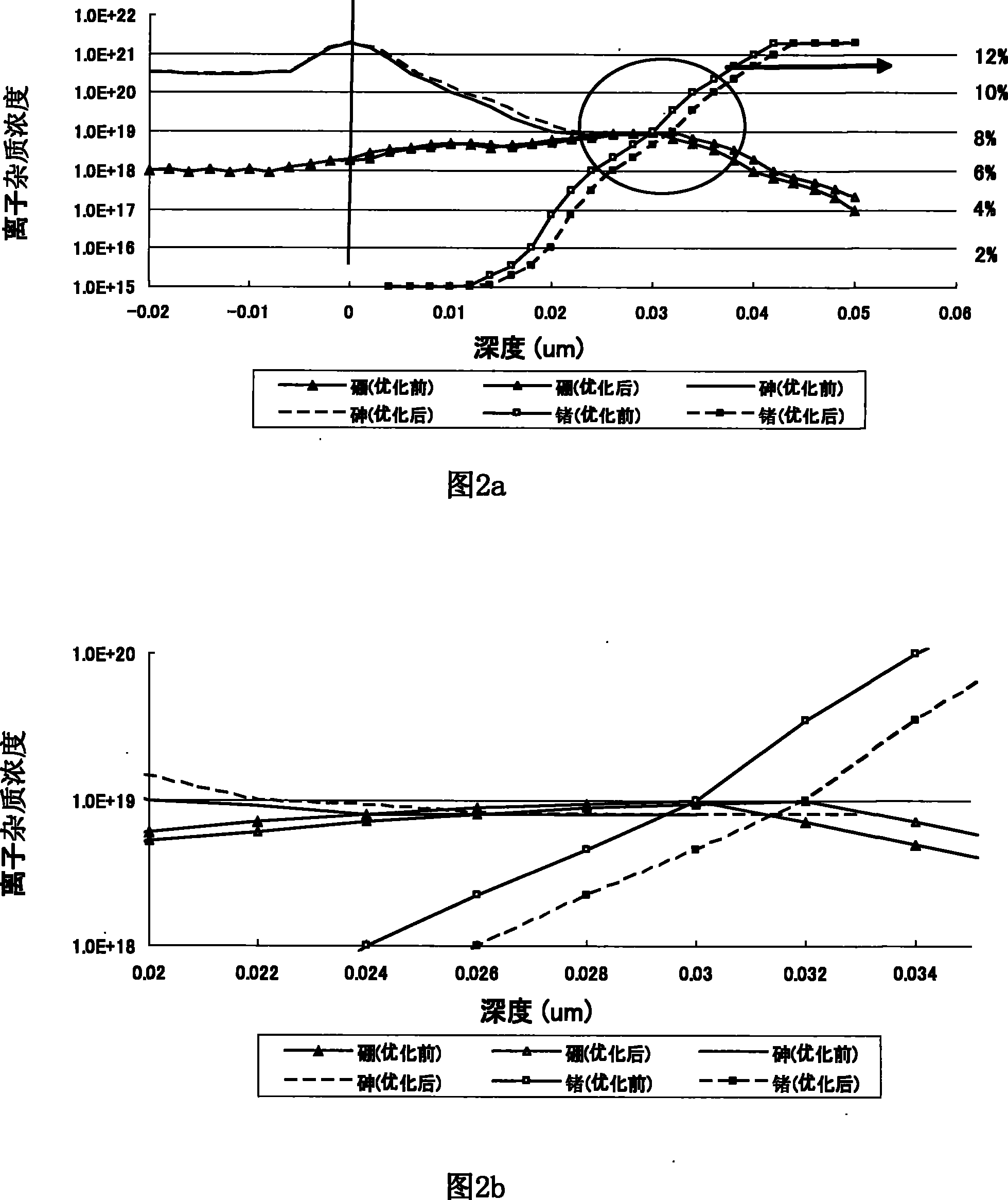

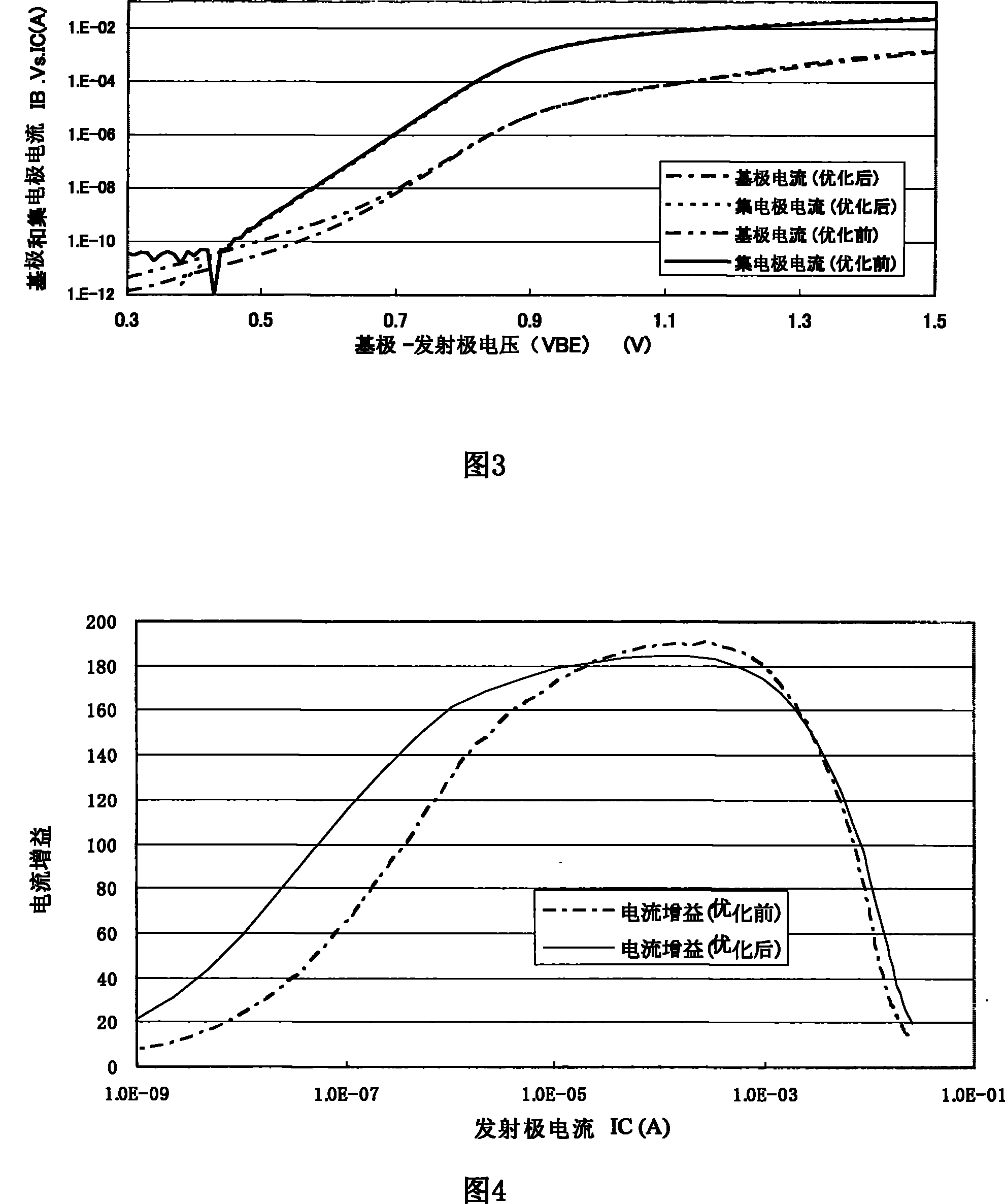

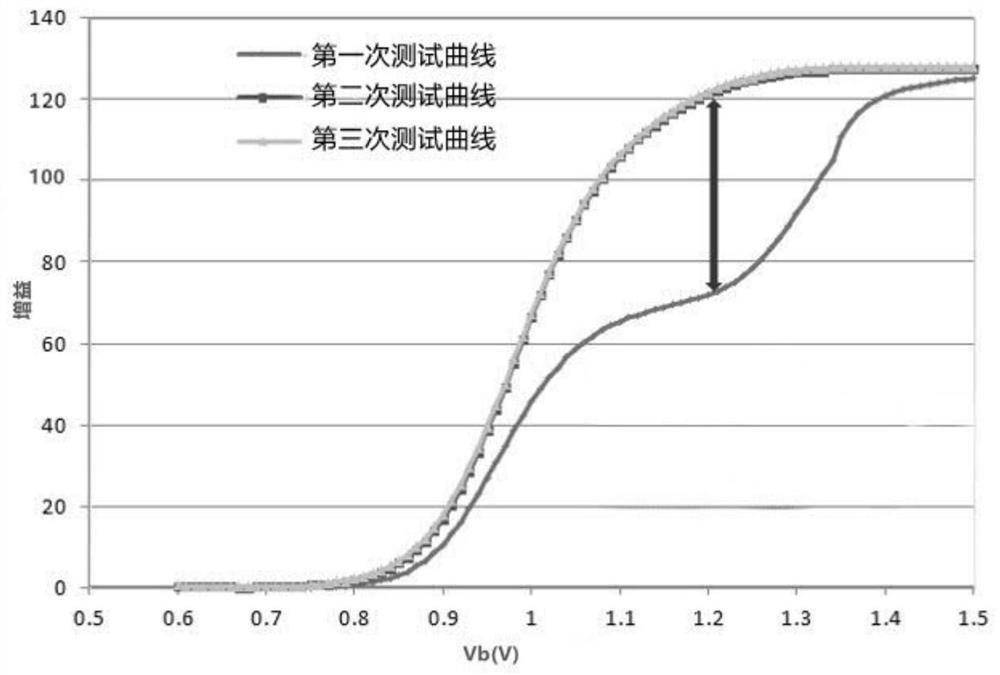

Preparation for SiGe HBT transistor

ActiveCN101459076ARaise the activation temperatureReduce recombination currentSemiconductor/solid-state device manufacturingRecombination currentBiology

The invention discloses a method of producing SiGe HBT transistors, which includes steps of reducing the doping concentration of emitter polysilicon, controlling the undercut dimension of an emitter window, increasing the thickness of an emitter monocystal silicon layer, and increasing the final activation temperature of devices, thereby maintaining bases out of highly defective areas and further greatly reducing the base recombination current.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

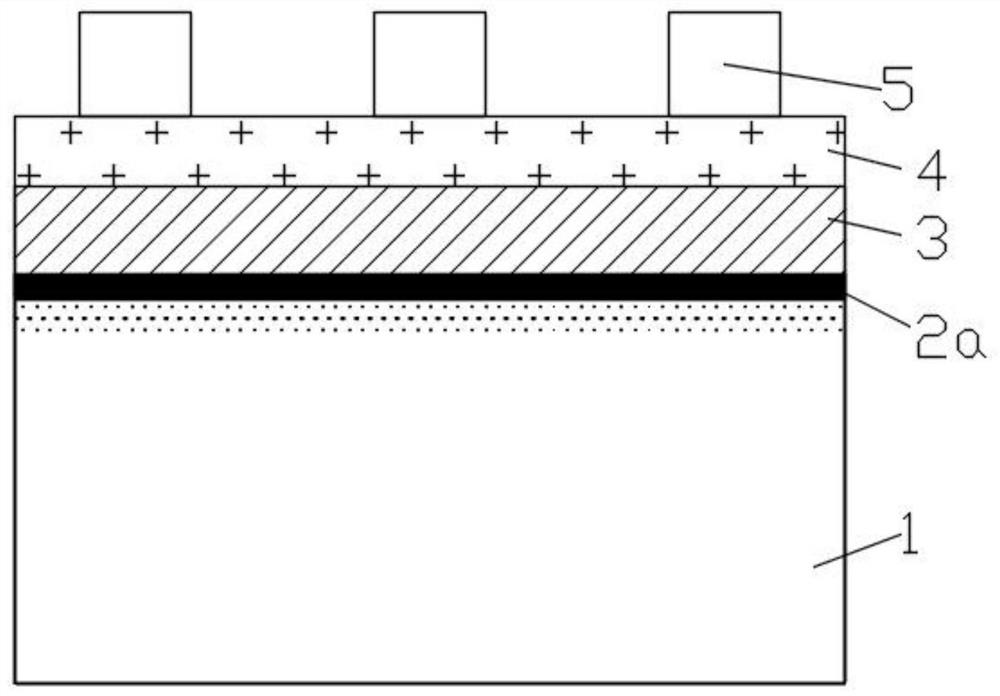

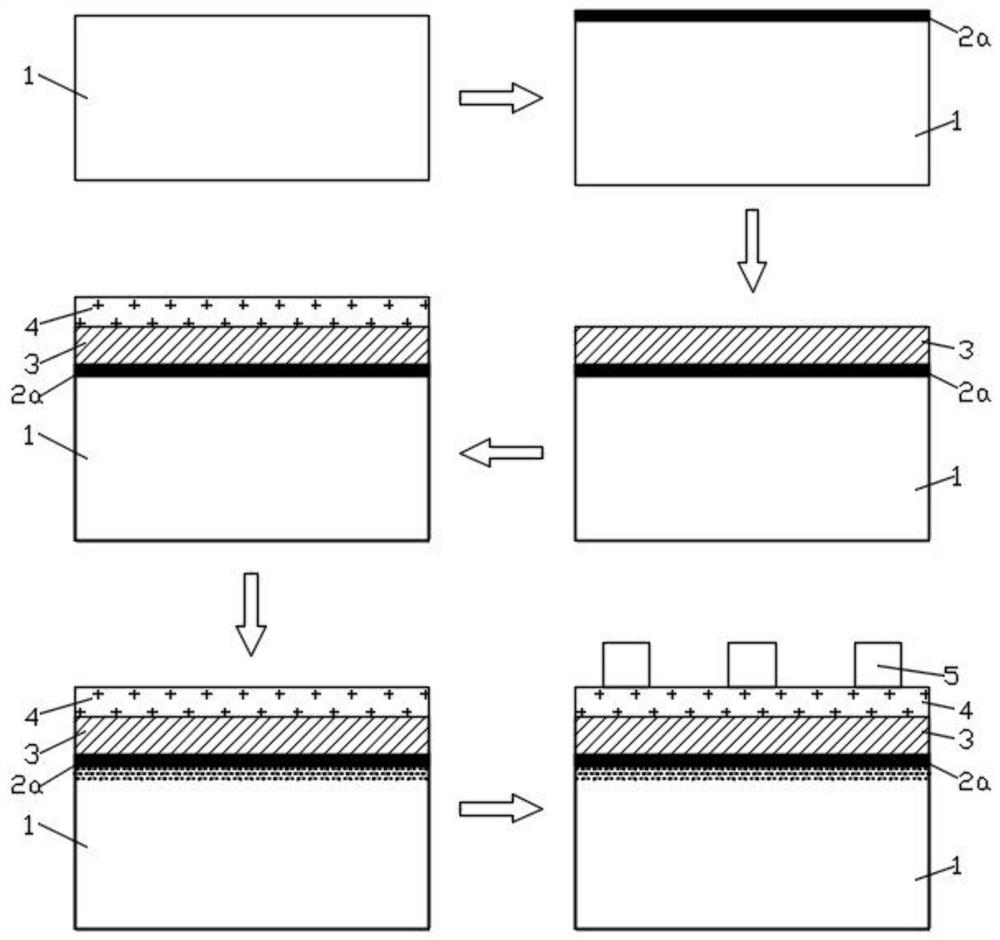

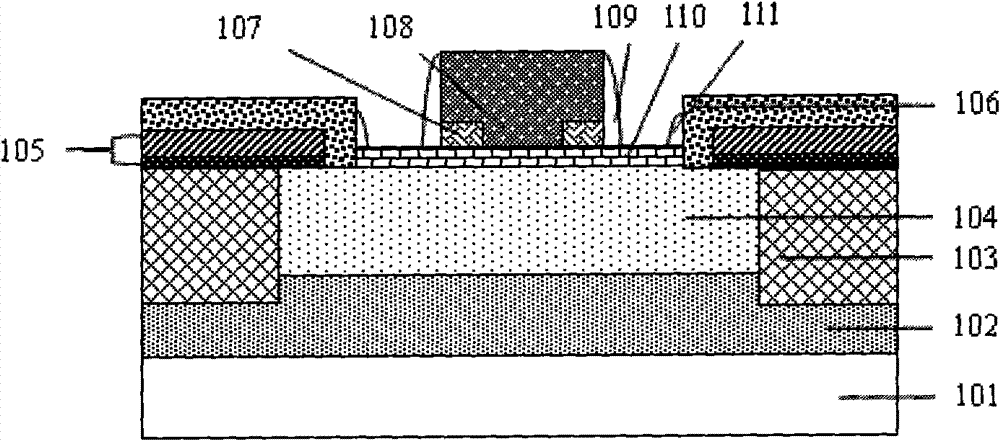

Passivation contact solar cell with selective emitter structure and preparation method of passivation contact solar cell

InactiveCN111162145AImprove efficiencyEasy to prepareFinal product manufacturePhotovoltaic energy generationEngineeringSolar battery

The invention relates to a passivation contact solar cell with a selective emitter structure and a preparation method of the passivation contact solar cell. The method comprises the following steps: (1) preparing texturing surfaces on two surfaces of an N-type crystalline silicon substrate; (2) performing boron diffusion treatment on the texturing surface of the front surface of the substrate to form a lightly doped region layer; (3) performing local boron ion implantation on the lightly doped region layer by using a mask, and annealing to form a local heavily doped region; (4) preparing a tunneling oxide layer on the texturing surface of the back surface of the substrate, and preparing a phosphorus-doped polycrystalline silicon layer on the tunneling oxide layer; (5) preparing a silicon nitride antireflection layer on the phosphorus-doped polycrystalline silicon layer; preparing an aluminum oxide passivation layer on the lightly doped region layer on the front surface of the substrate, and preparing a silicon nitride antireflection layer on the aluminum oxide passivation layer; and (6) carrying out silk-screen printing of metallized slurry on the two surfaces of the substrate, andsintering. According to the invention, the composite current on the surface of the emitter can be remarkably reduced, so that the efficiency of the N-type passivation contact battery can be improvedby more than 0.2%.

Owner:TAIZHOU ZHONGLAI PHOTOELECTRIC TECH CO LTD

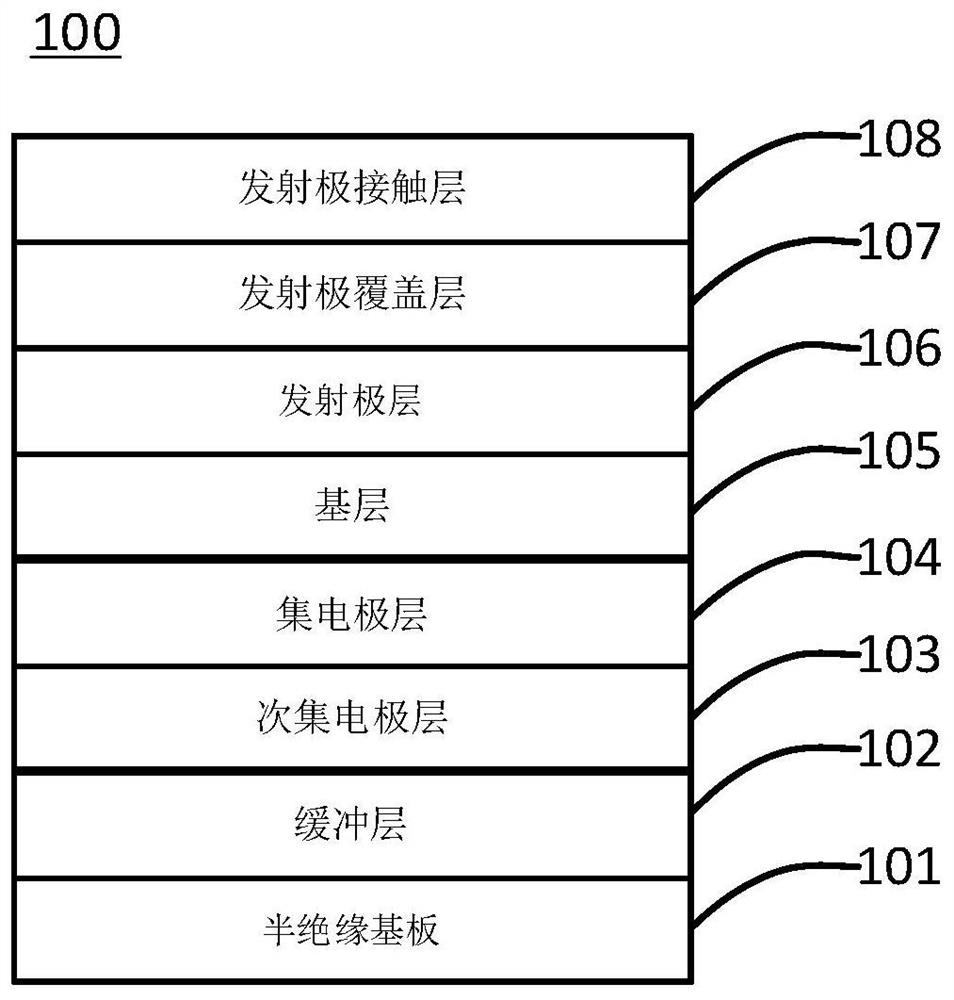

Heterojunction bipolar transistor and manufacturing method thereof

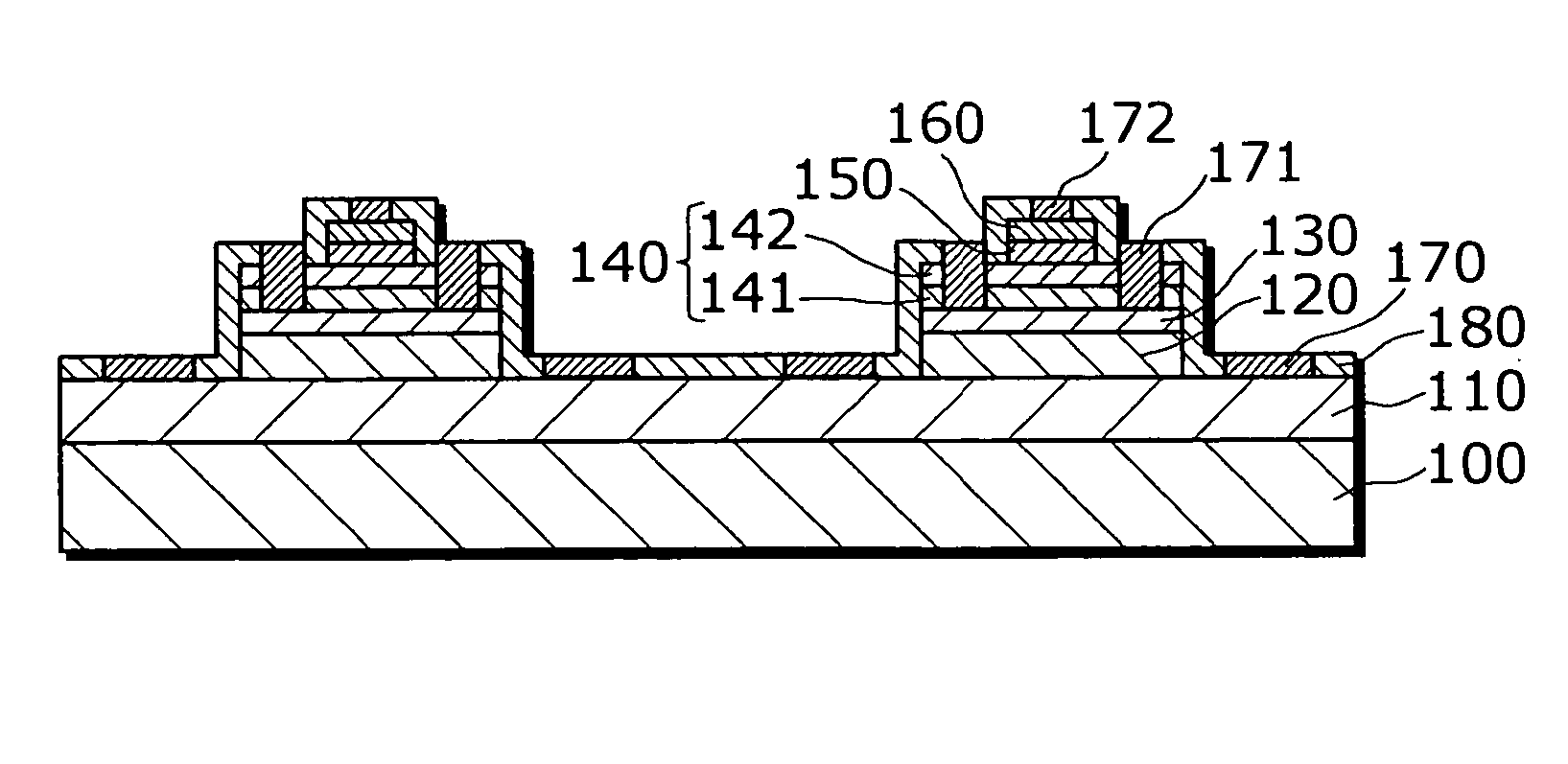

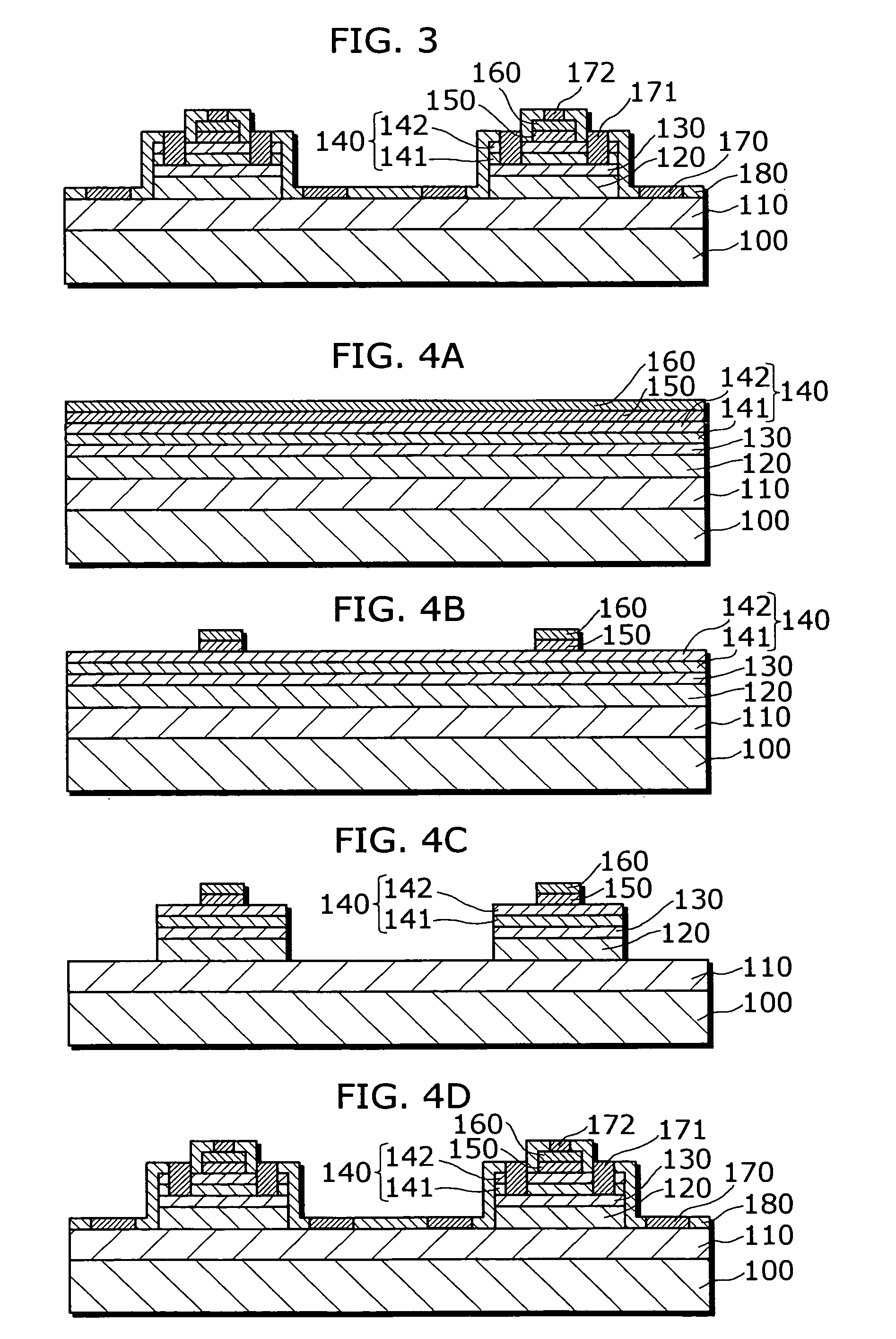

InactiveUS20050199909A1Reduce recombination currentImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunction bipolar transistorEngineering

The present invention aims at providing a heterojunction bipolar transistor having improved breakdown voltage on operation for high power output, and includes: a GaAs semiconductor substrate 100; an n+-type GaAs sub-collector layer 110; an n-type GaAs collector layer 120; a p-type GaAs base layer 130; an emitter layer 140; an n-type GaAs emitter cap layer 150; and an n-type InGaAs emitter contact layer 160. The emitter layer 140 has a multilayer structure including an n-type or non-doped first emitter layer 141 and an n-type second emitter layer 142 which are laminated in sequence. The first emitter layer 141 is made of a semiconductor material including Al, while the second emitter layer 142 is made of InxGa1-xP (0<x<1).

Owner:COLLABO INNOVATIONS INC

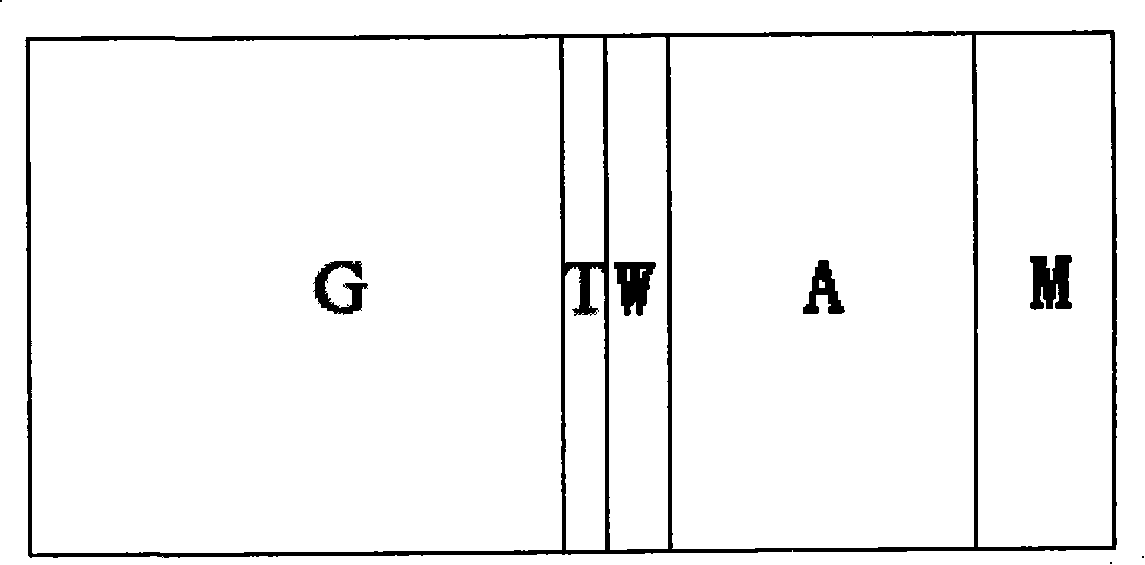

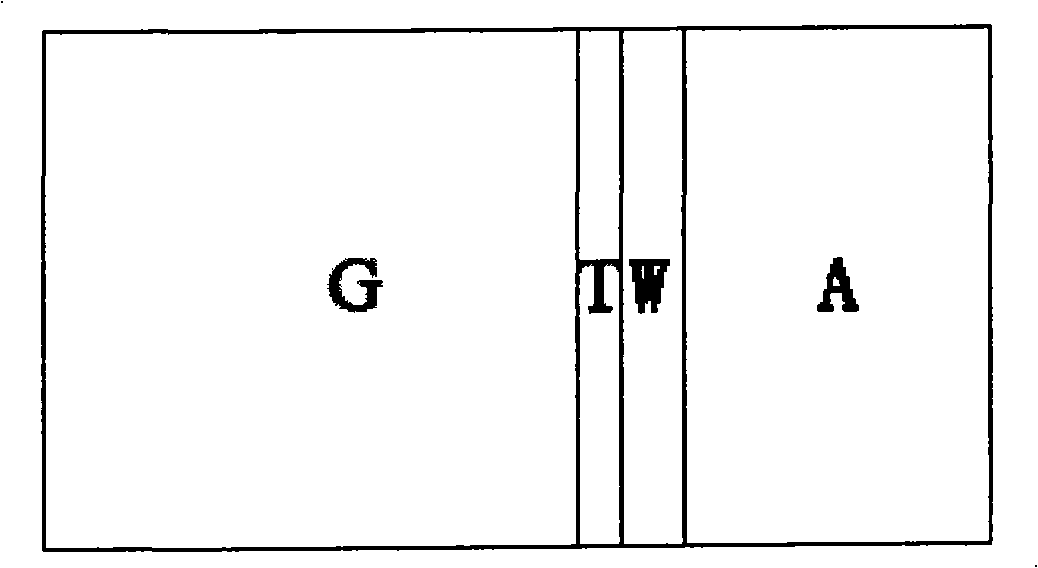

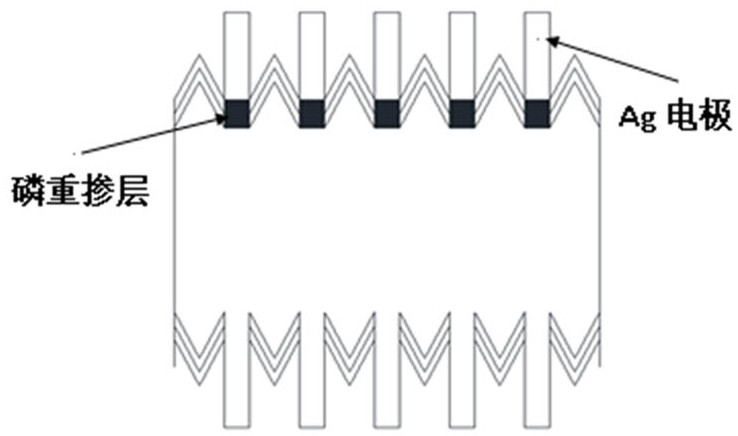

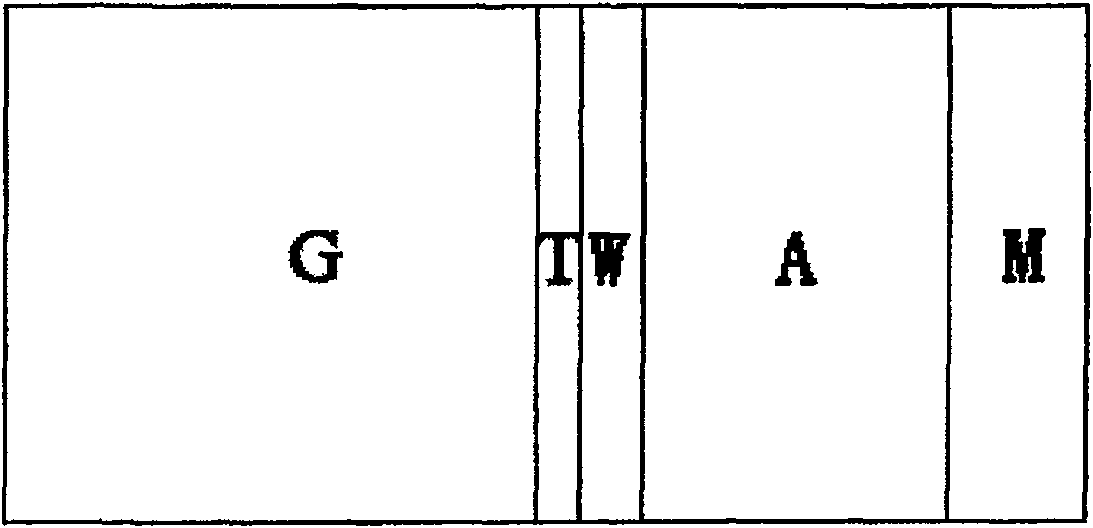

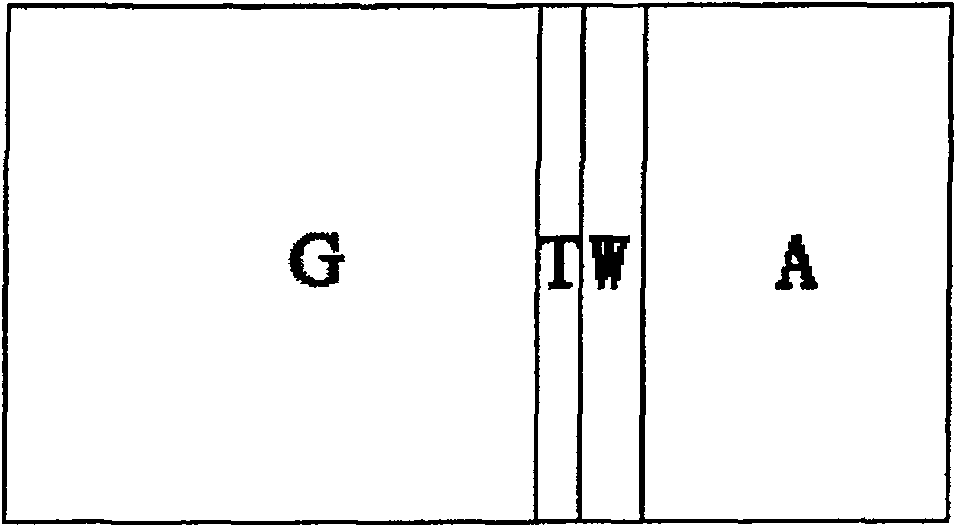

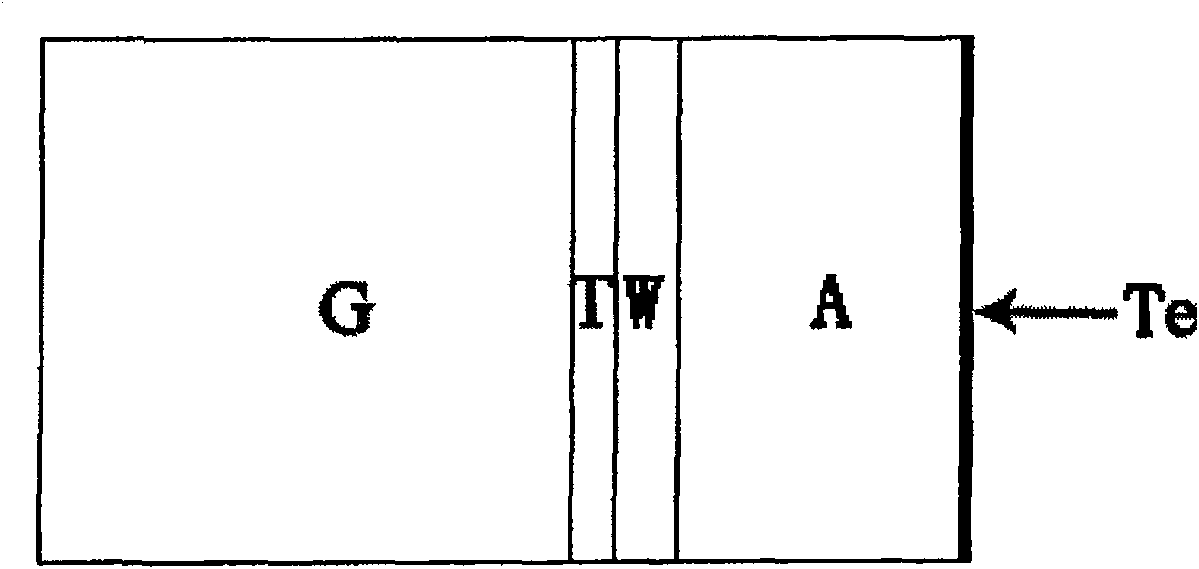

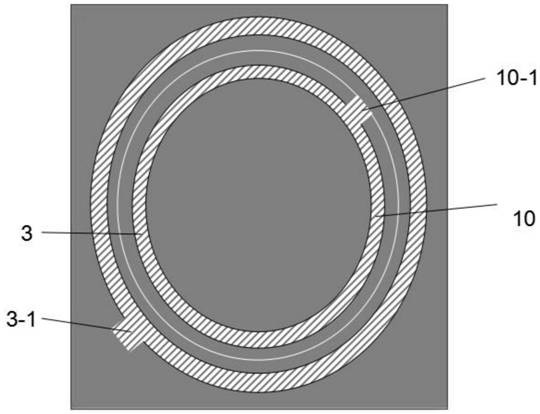

Gate line structure making local contact with obverse surface of solar battery and manufacturing method thereof

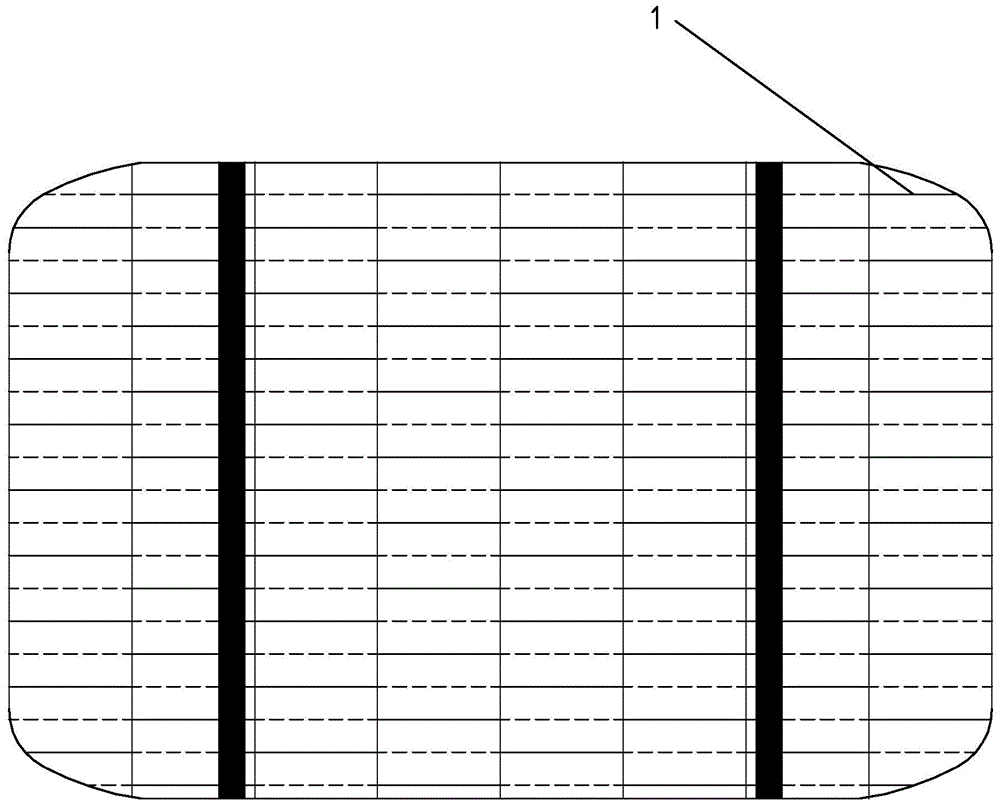

ActiveCN104465805AIncrease the open circuit voltageImprove conversion efficiencyFinal product manufacturePhotovoltaic energy generationRecombination currentElectrical battery

The invention discloses a gate line structure making local contact with the obverse surface of a solar battery and a manufacturing method of the gate line structure. The gate line structure making local contact with the obverse surface of the solar battery is provided with a plurality of gate line electrodes. Each gate line electrode is provided with a plurality of local contact metal electrodes and a plurality of non-contact metal electrodes. The local contact metal electrodes are electrically connected with the non-contact metal electrodes. The non-contact metal electrodes are made of non-burnthrough metal electrode paste. The local contact metal electrodes penetrate through a dielectric film of the battery and then make ohmic contact with a silicon substrate. According to the gate line structure, it can be guaranteed that under the condition of avoiding electron transport, the metalized area is effectively reduced, and recombination current of a metalized area is reduced; accordingly, open-circuit voltage of the battery is effectively increased, and the conversion efficiency of the solar battery is improved.

Owner:TRINA SOLAR CO LTD

Surface corrosion of CdTe film and CdTe solar cell preparing by the process

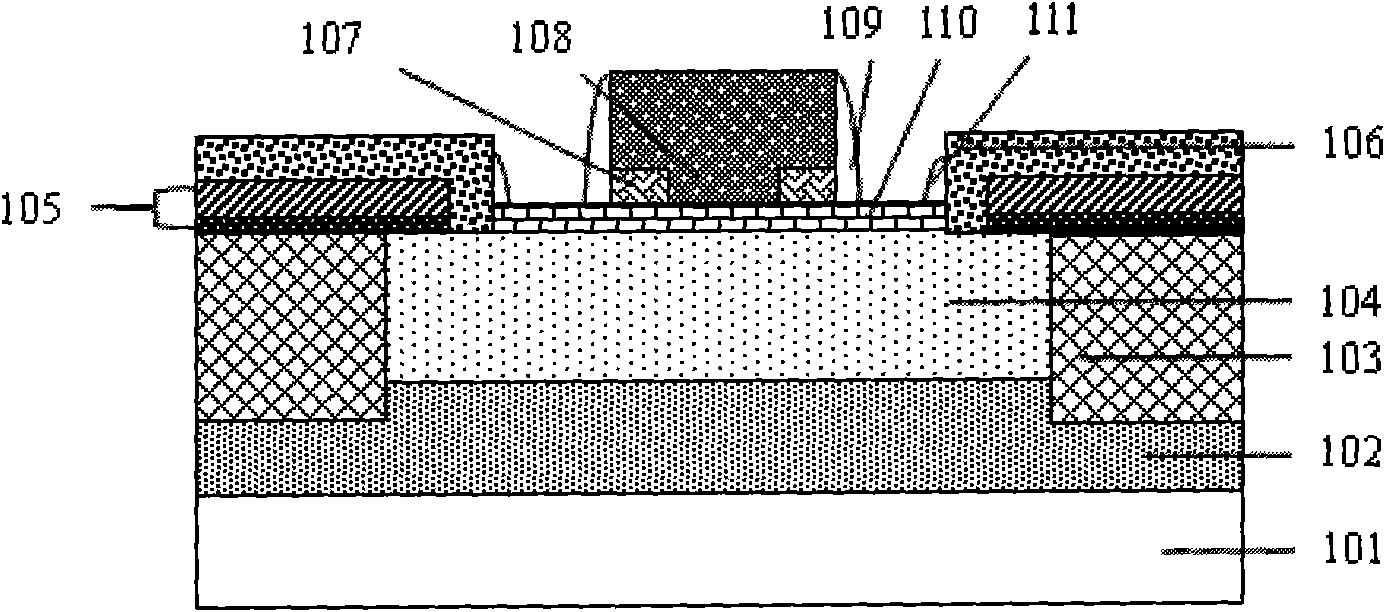

InactiveCN101335310AImprove performanceLower barrier heightFinal product manufactureSemiconductor/solid-state device manufacturingSchottky barrierTe element

The invention relates to a method for surface corrosion of a CdTe film and preparation of a CdTe solar cell by adopting the method, pertaining to the processing field of semiconductor devices. An mixed liquid of nitric acid, glacial acetic acid, NaAc and deionized water is served as corrosive liquid, wherein, the NaAc is served as a buffering agent to keep the pH value of the intermixture unchanged and lead the reaction to be more stable; CdTe and the nitric acid react to generate a layer rich in tellurium; after washing and blow-drying, a back contact layer containing Cu or without Cu is sedimented; finally, a back electrode is sedimented for preparing the CdTe solar cell. Sedimentation of back contact material can increase carrier concentration near a pn junction, reduce the height of Schottky potential barrier and avoid direct sedimentation of Cu from forming a comparatively complex CuxTe structure. By adopting the method for corrosion and the preparation of the CdTe solar cell, the performance of the solar cell can be obviously improved and the stability and the repeatability of the device can be ensured.

Owner:SICHUAN UNIV

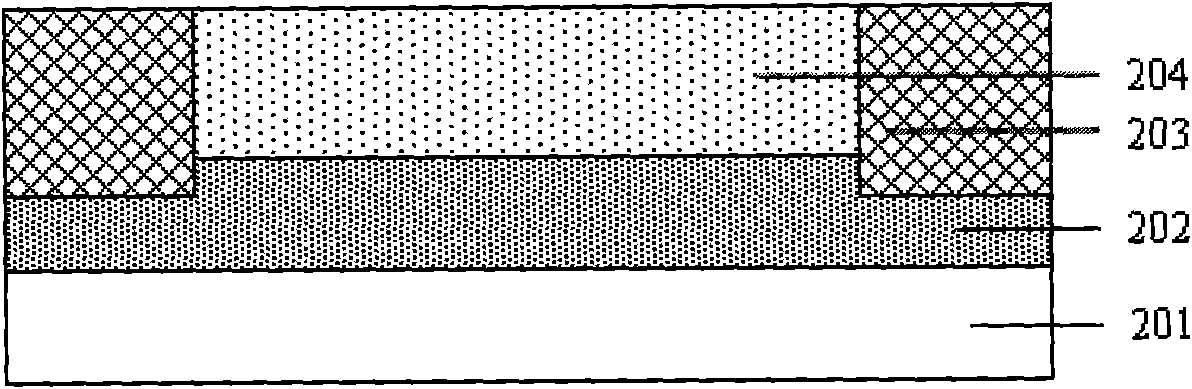

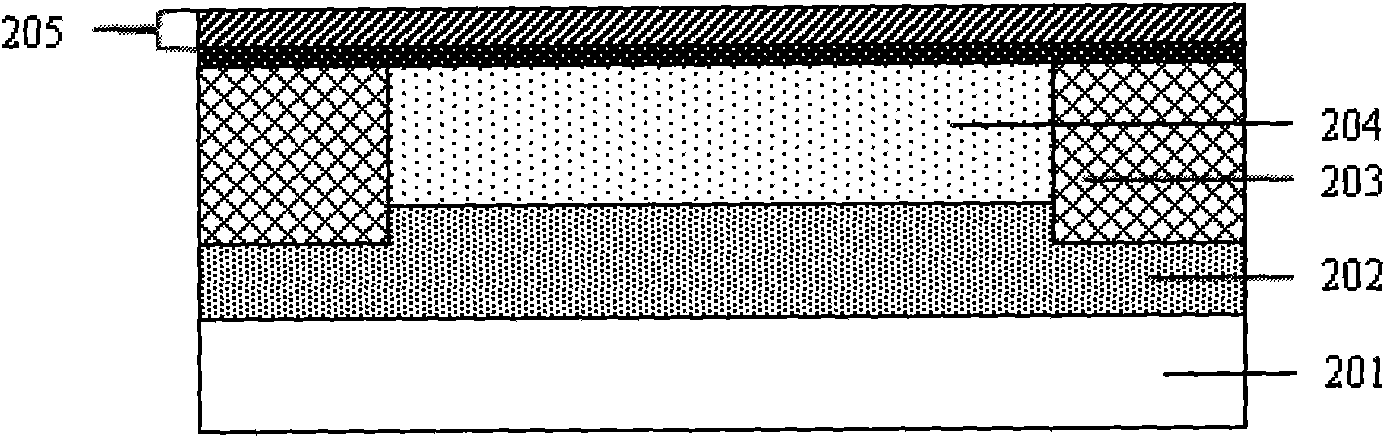

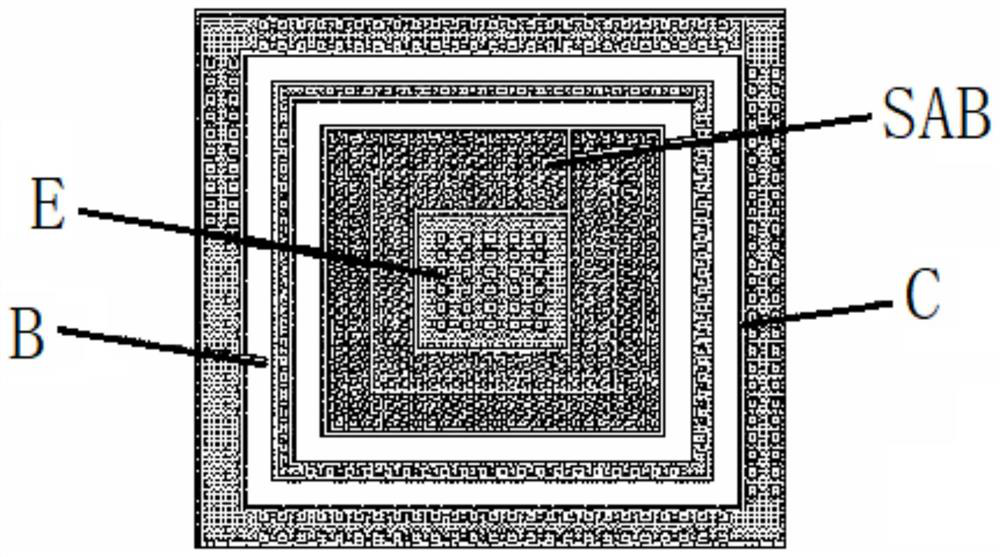

Method for implementing base region window of silicon germanium heterojunction transistor

ActiveCN102097315AReduce defectsImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionMetal silicide

The invention discloses a method for implementing a base region window of a silicon germanium heterojunction transistor, which comprises the following steps of: depositing a composite dielectric film on a silicon chip with an embedded layer, a collector region and a substrate isolation region on a silicon substrate; performing dry etching on the composite dielectric film, defining the base regionwindow, and etching an oxide film stopped on the composite dielectric film; after the base region window is opened and before the oxide film of the composite dielectric film is removed, depositing a dielectric film layer, and forming a D-shaped side wall at the interface step of the base region window by using the dielectric film layer; and meanwhile, performing wet removal on the residual oxide film in the base region window by using the protection of the D-shaped side wall, and epitaxially growing an SiGe base region. The interface step of the base region window is changed slowly because ofthe formation of the D-shaped side wall, and the slowly changed step formed by the D-shaped side wall is continuously reserved after SiGe extension and has no insulator residue in the subsequent emitter polycrystalline silicon side wall process, so that continuous metal silicide is formed, the resistance of an outer base region is reduced, and the performance of the device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

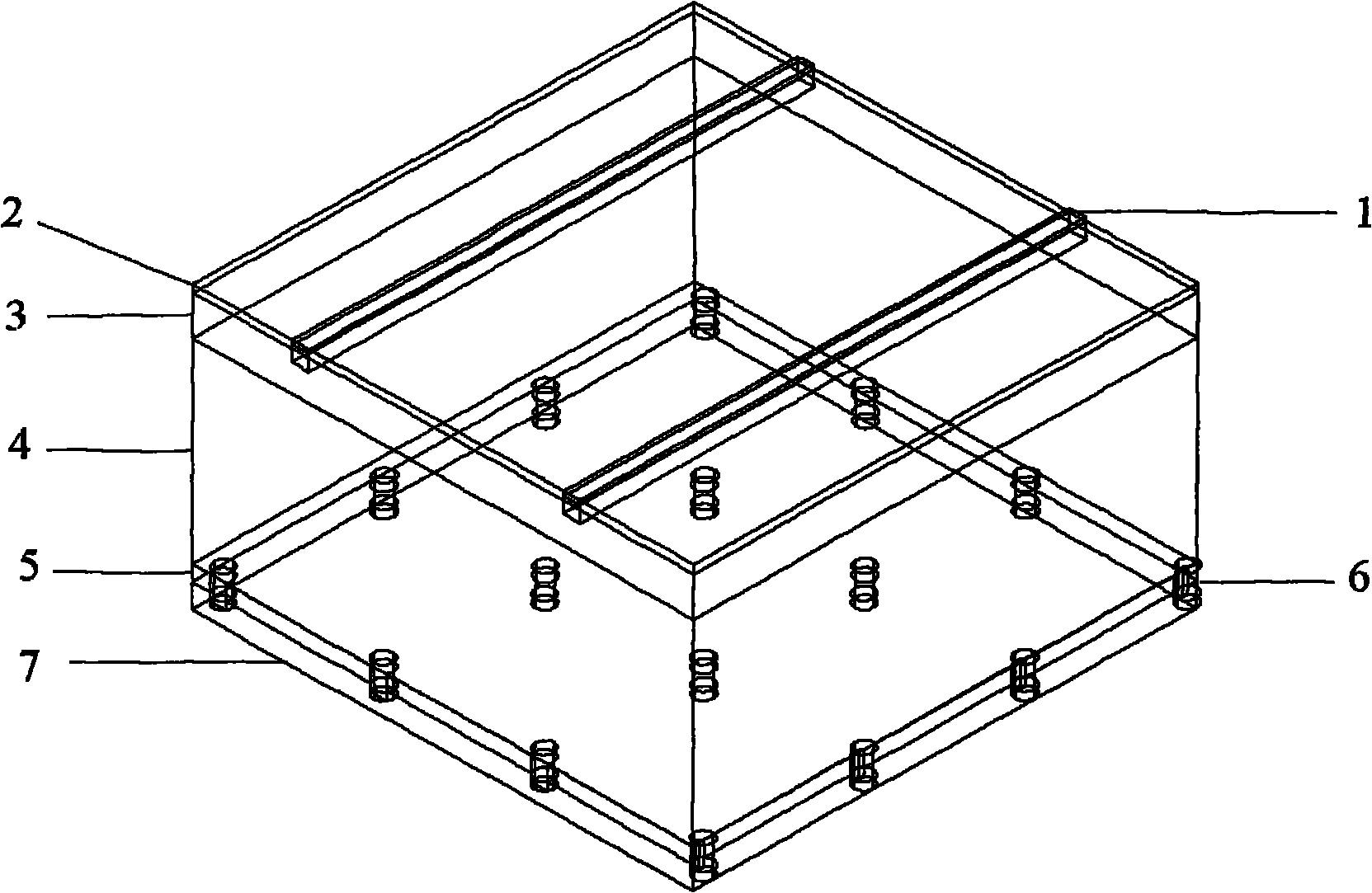

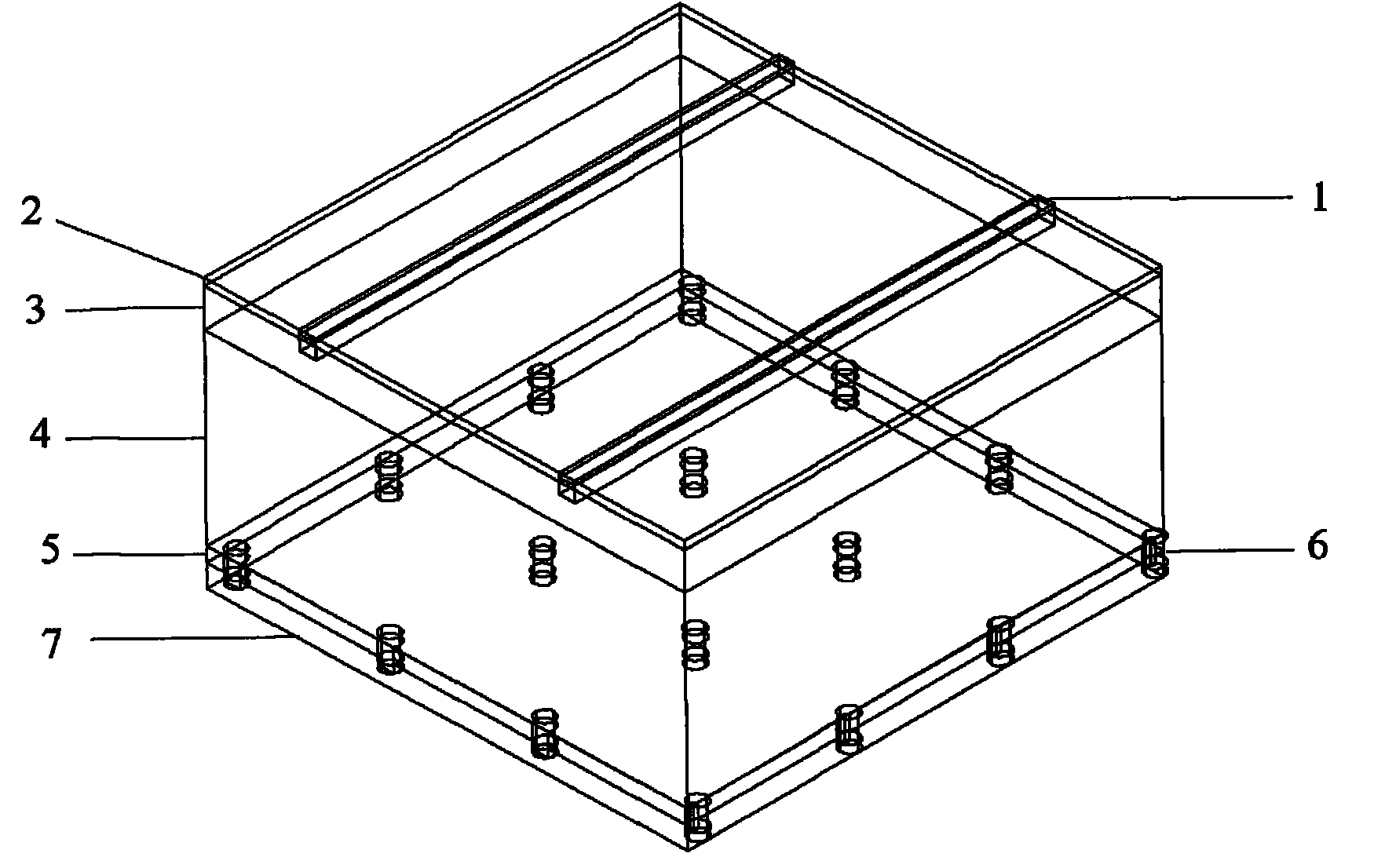

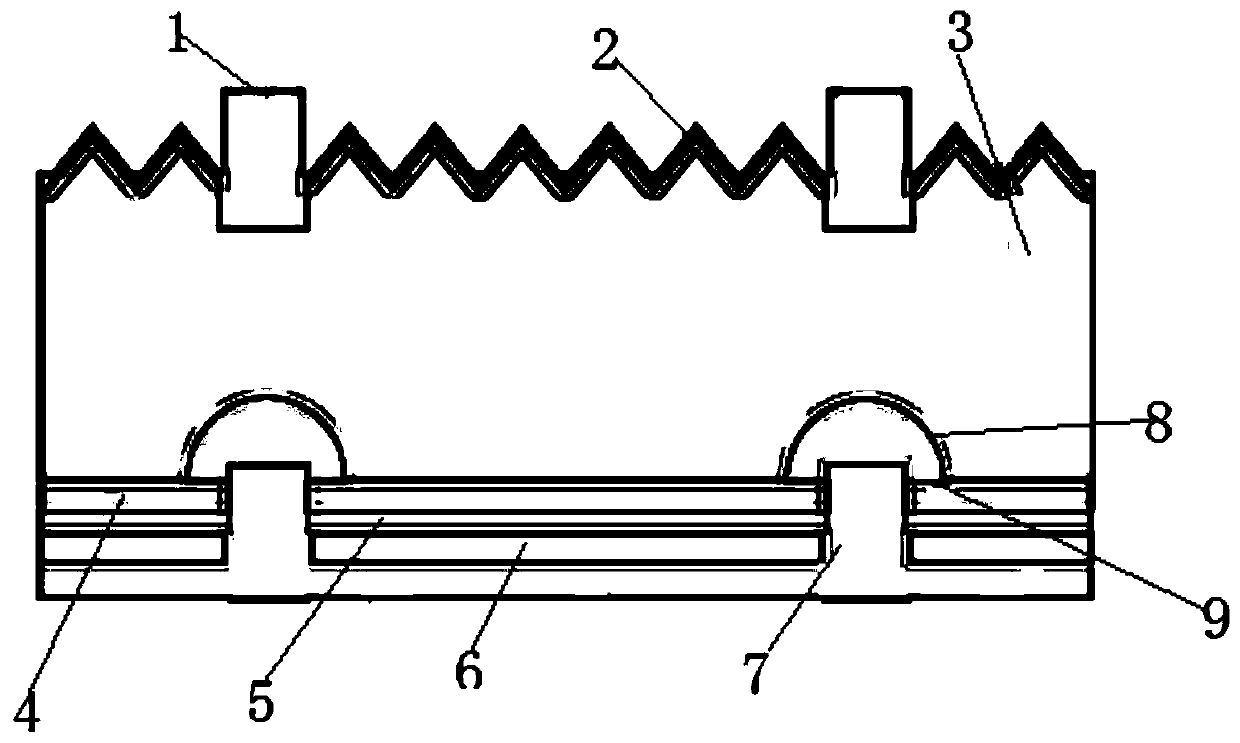

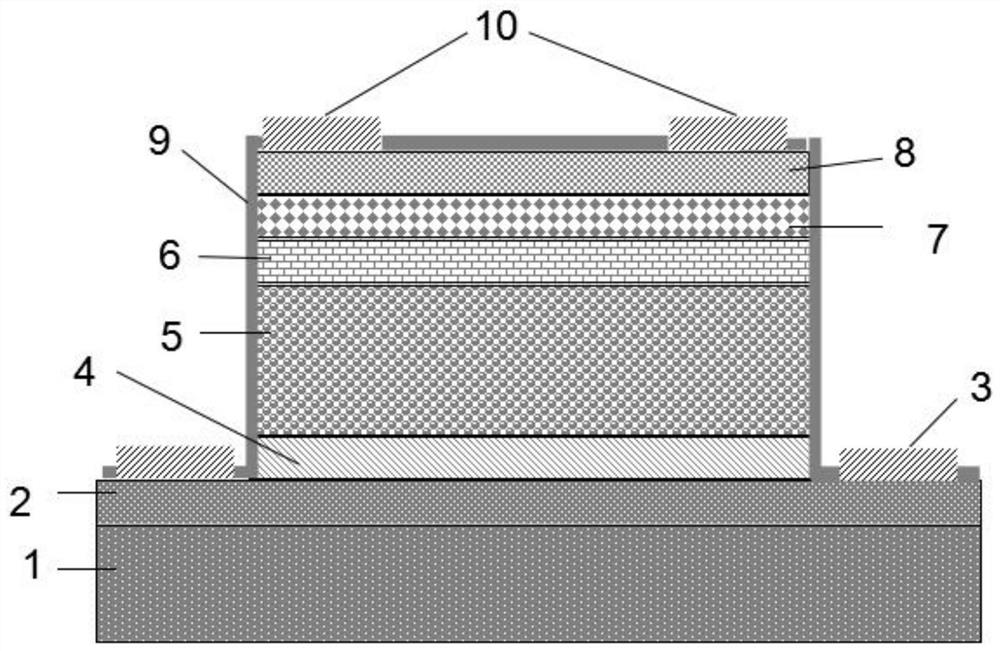

MWT (Metal Wrap Through) solar battery and manufacturing method thereof

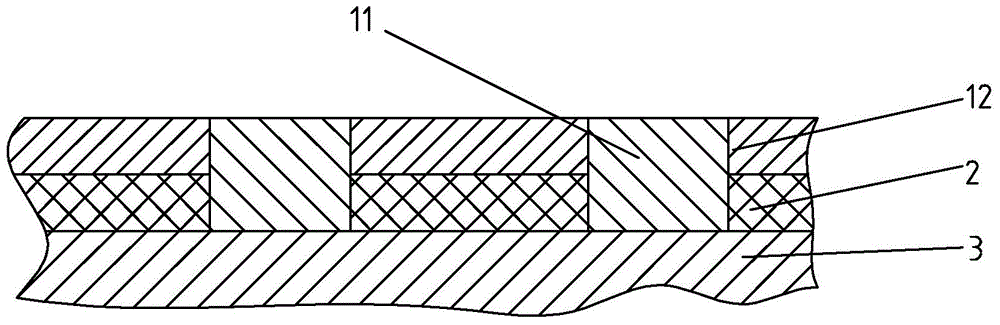

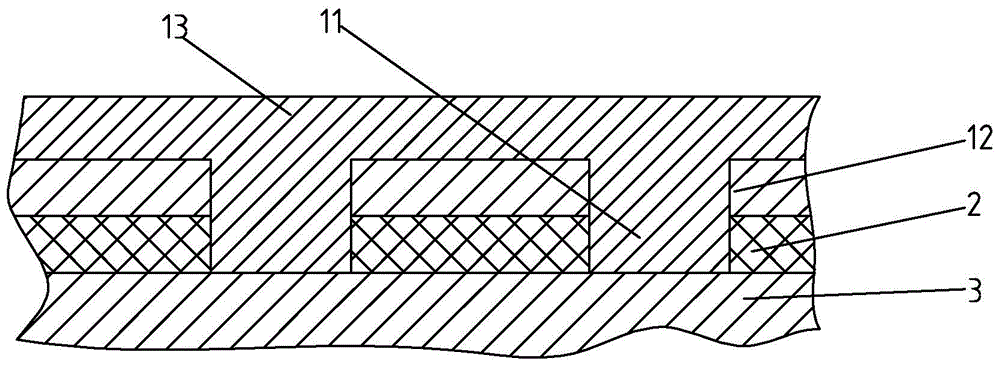

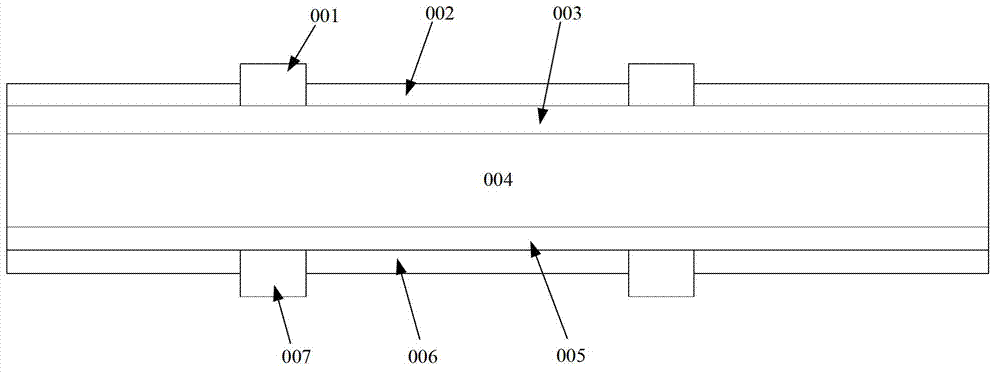

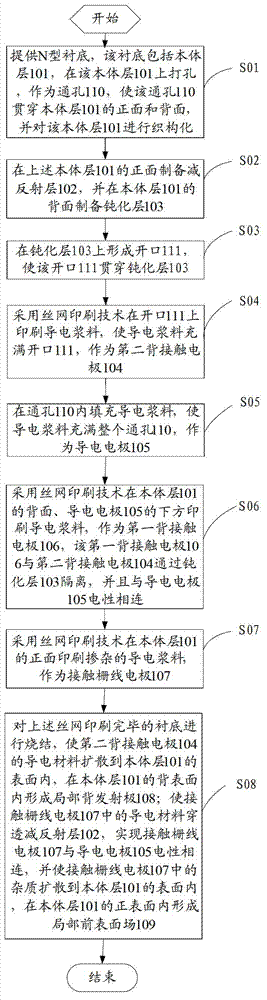

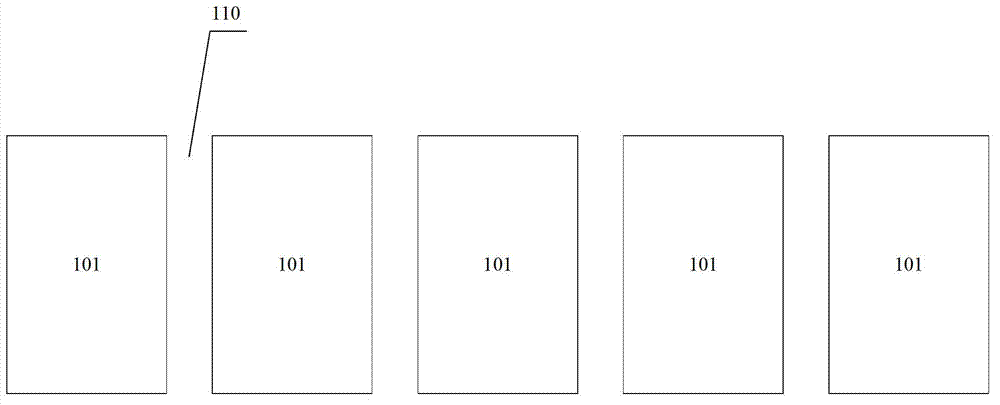

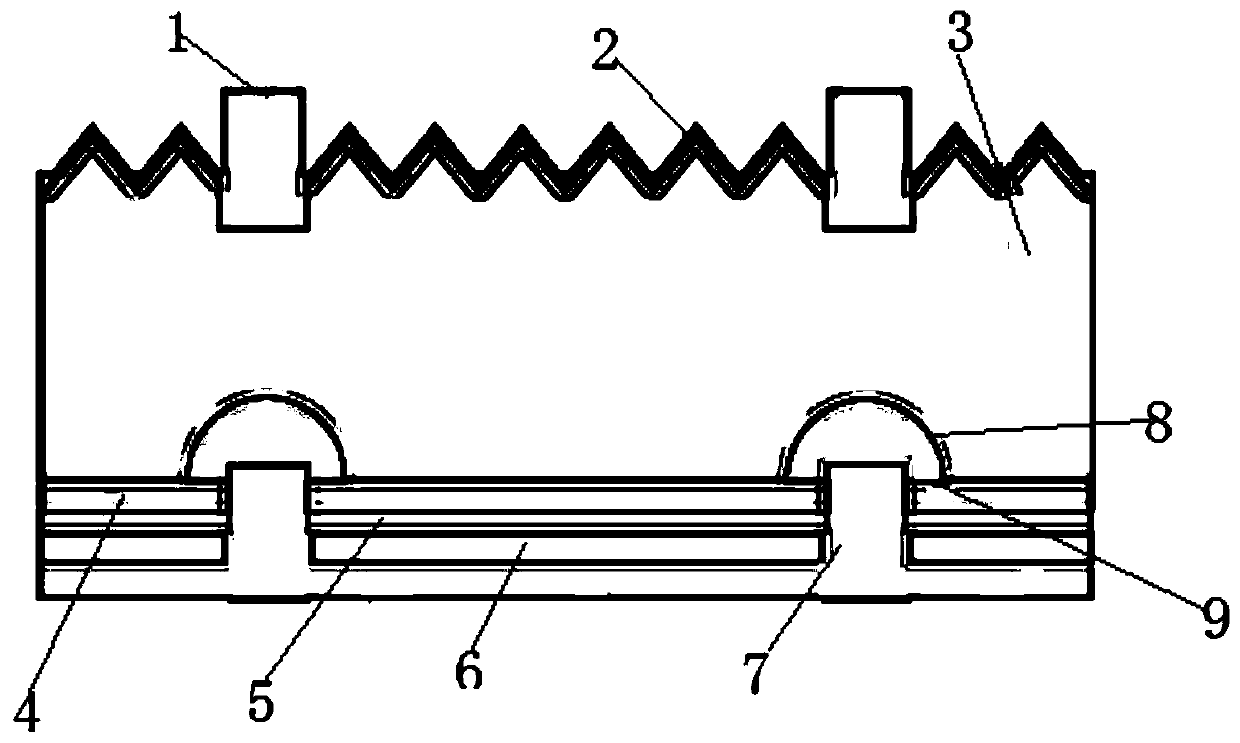

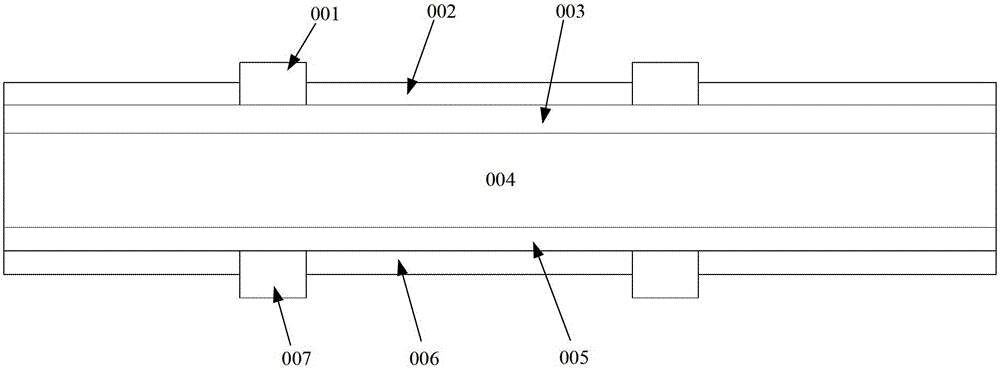

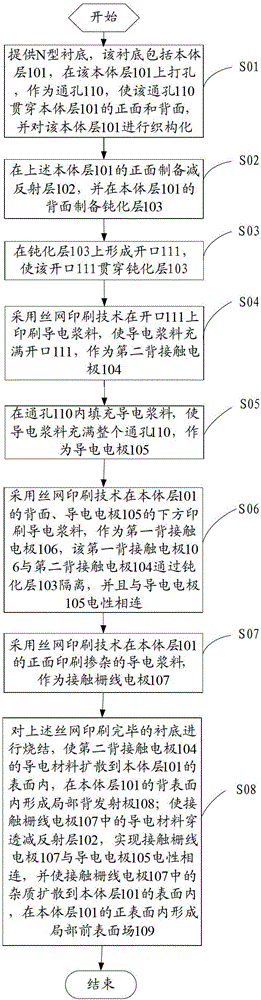

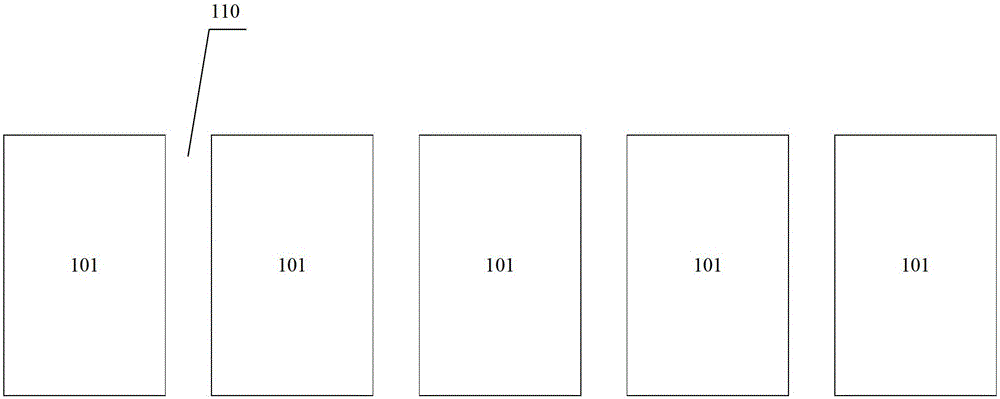

ActiveCN102969399AReduce recombination currentImprove photoelectric conversion efficiencyFinal product manufactureSemiconductor devicesCorrosionEngineering

The invention provides a manufacturing method of a MWT (Metal Wrap Through) solar battery. The method comprises the steps of: providing a substrate which comprises a body layer, a reflection-reducing layer and a passivation layer, wherein a plurality of through holes and openings are arranged on the substrate; forming conductive electrodes in the through holes and forming a first back contact electrode on the back of the substrate; forming second back contact electrodes in the openings; forming a touch grid line electrode on the front face of the substrate; sintering the substrate so that the touch grid line electrode is electrically connected with the conductive electrode; and forming a local front surface field in the front surface of the body layer; and forming a local back emitting electrode in the back surface of the substrate. The MWT solar battery manufactured by the method is small in composite current, large in light receiving area and high in photoelectric conversion efficiency, and the problem that the battery is bended is reduced. In addition, according to the manufacturing method provided by the invention, steps such as diffusive knot manufacture, edge corrosion, glass layer removal and secondary clean in conventional process are avoided, so that the manufacturing process flow is simplified and the production cost is reduced.

Owner:上饶捷泰新能源科技有限公司

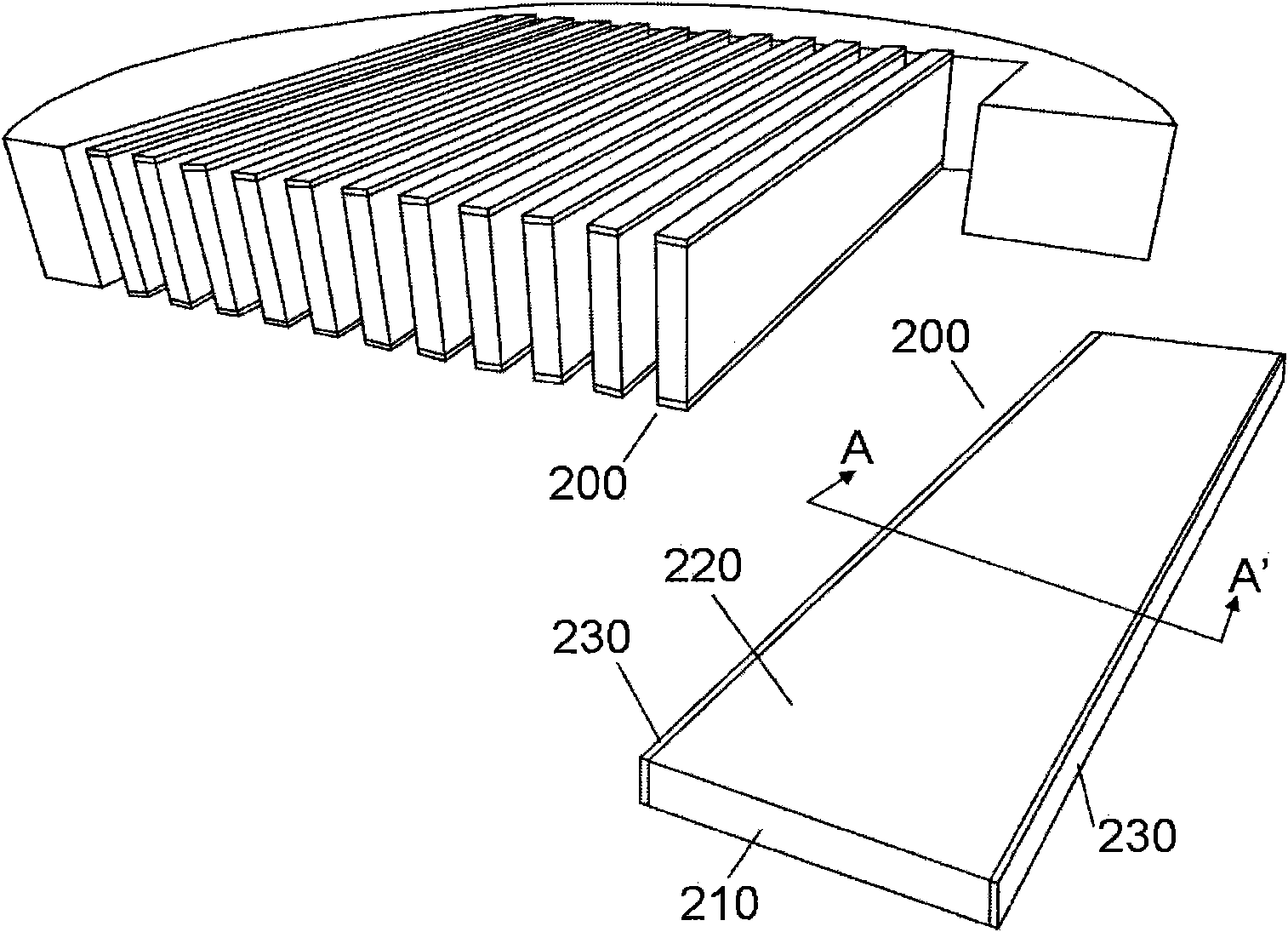

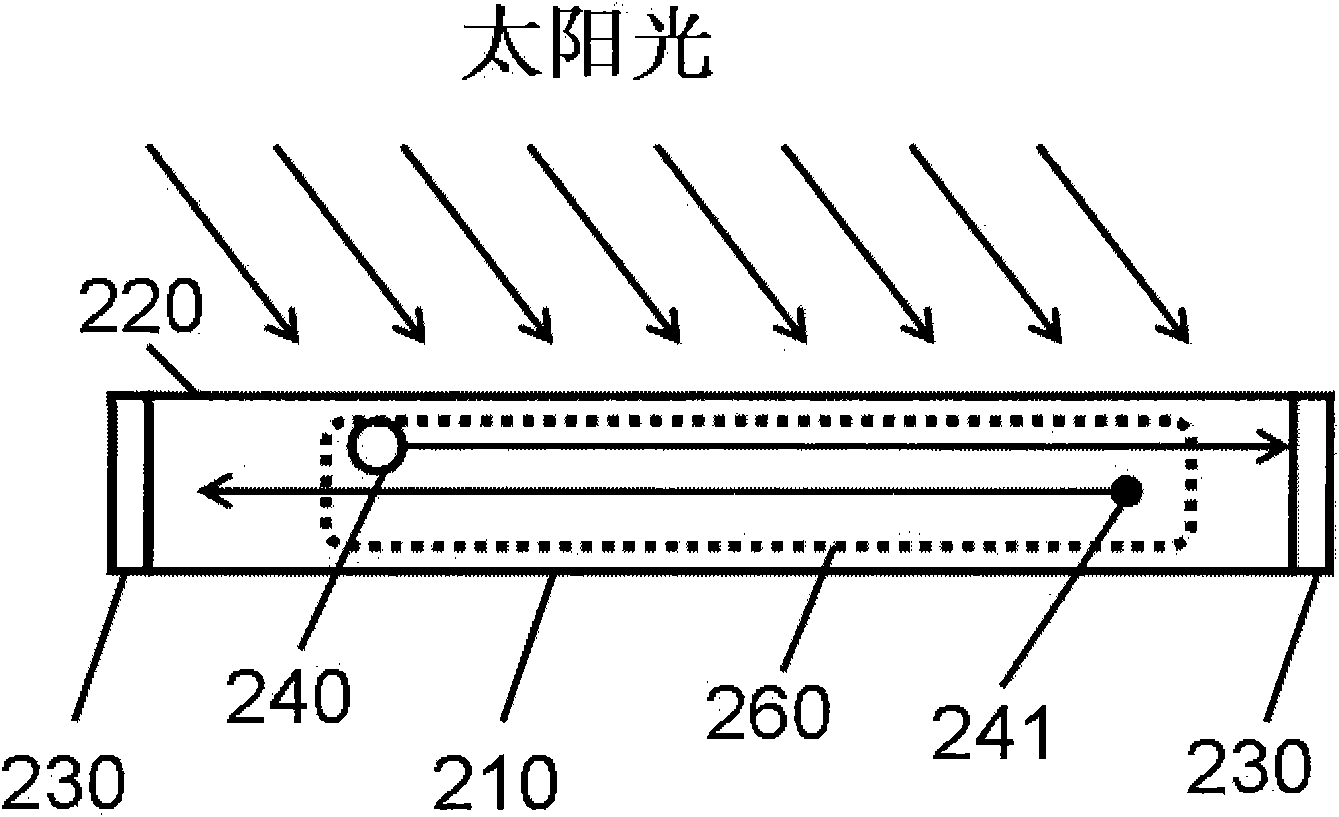

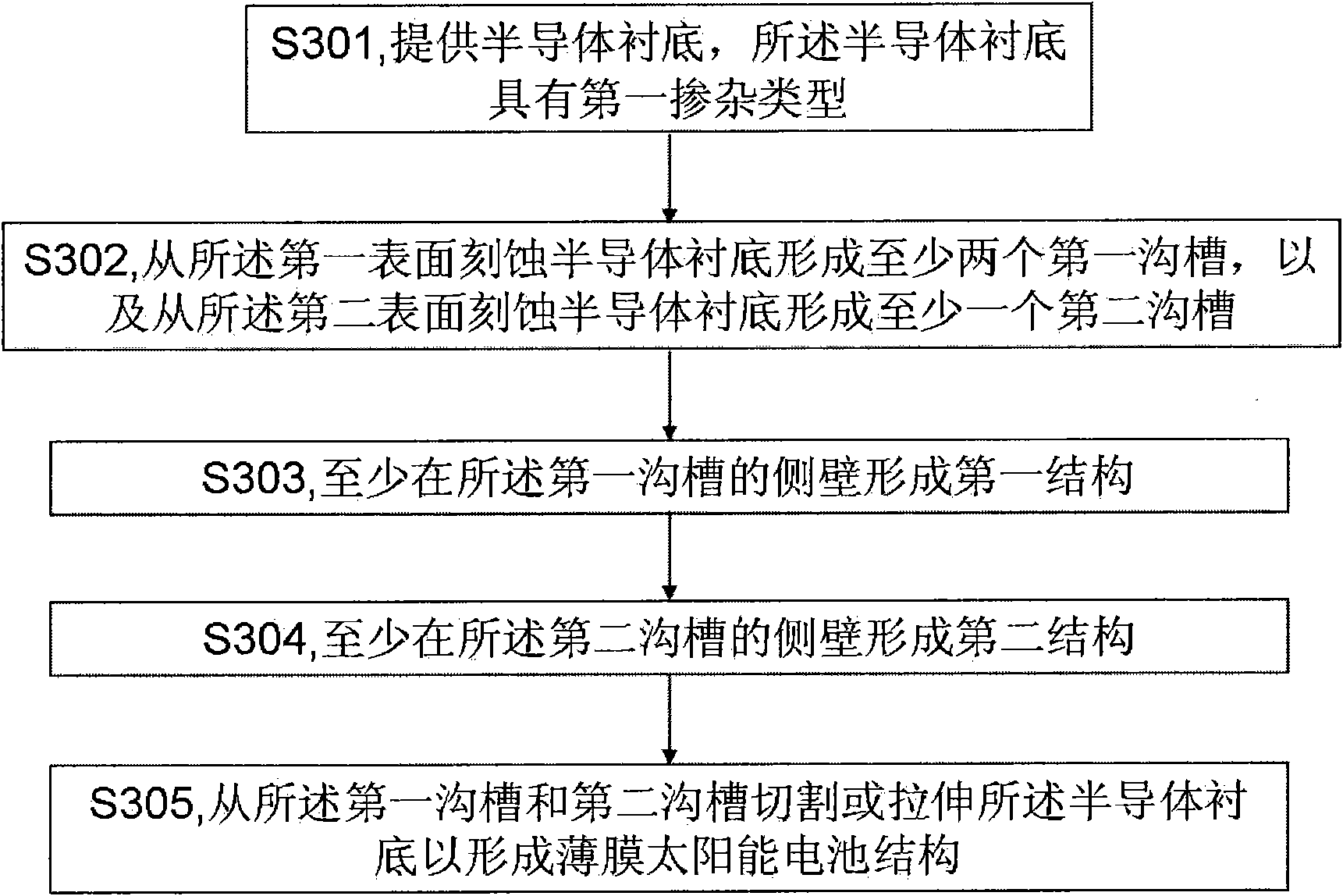

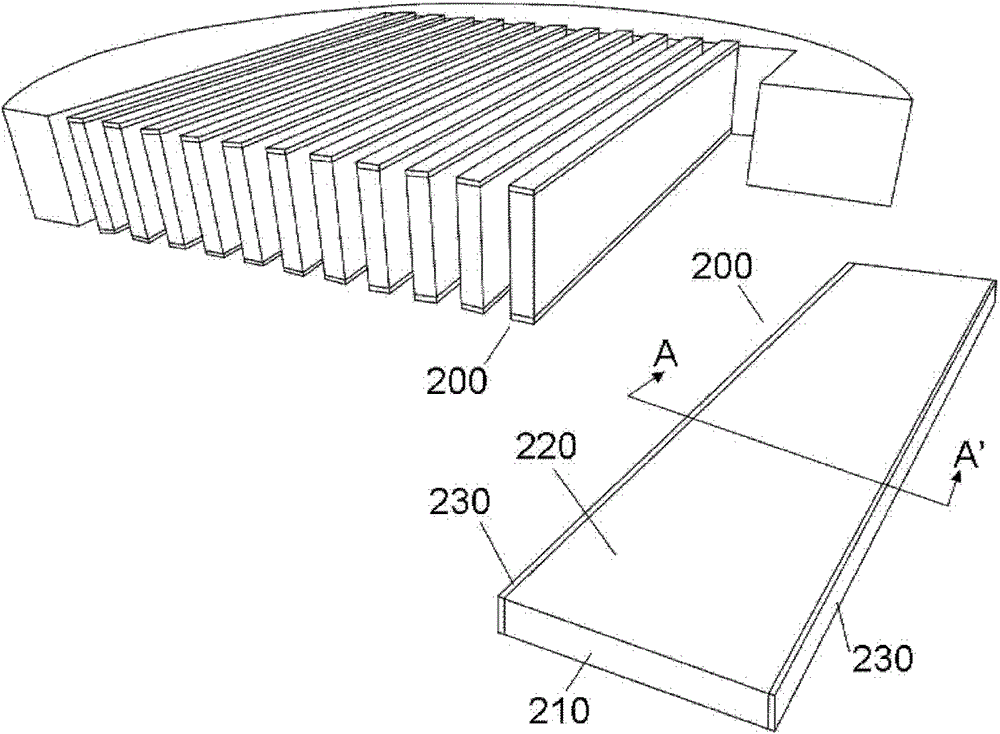

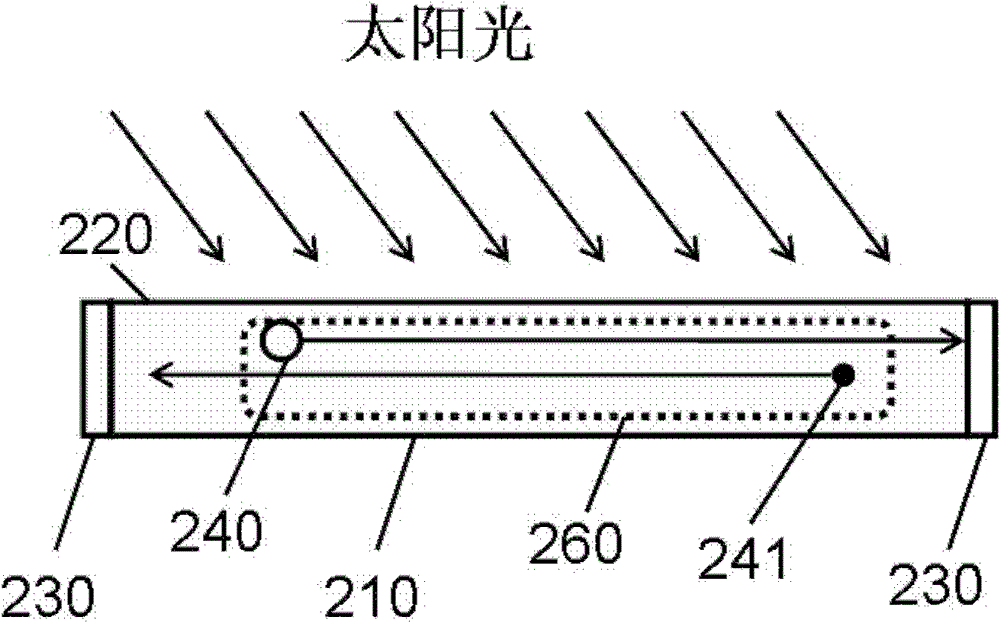

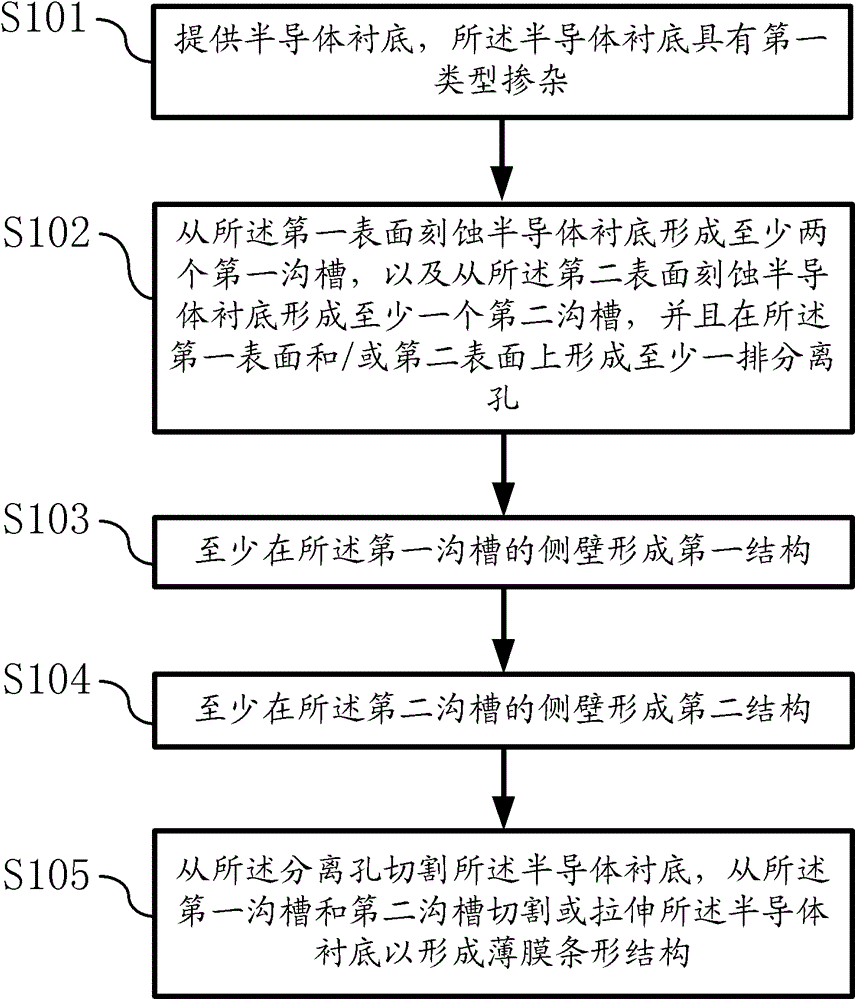

Thin film of solar battery structure, thin film of solar battery array and manufacturing method thereof

ActiveCN102122679AIncrease the effective areaReduce compound distanceFinal product manufactureSemiconductor/solid-state device manufacturingManufacturing cost reductionPower flow

A thin film solar battery structure and a manufacturing method thereof, and a thin film solar battery array are provided. The manufacturing method of the thin film solar battery structure includes: at least two first trenches are formed by etching semiconductor substrate from the first surface; at least one of the second trench is formed by etching the semiconductor substrate from the second surface; each of the second trench is located between two adjacent first trenches; a first structure is formed on the side wall of at least the first trench; a second structure is formed on the side wall of at least the second trench; the semiconductor substrate is cut or drawn from the first trench and the second trench for forming the thin film solar battery structure, the distance of the electrodes can be reduced effectively, the probability recombination of the electron and the hole can be reduced, the bulk recombination current and the surface bulk recombination current can be reduced, the efficiency of the electrical power can be increased, the thin film solar battery structure and the manufacturing method thereof can reduce the semiconductor material and reduce the manufacturing cost.

Owner:江苏盐新汽车产业投资发展集团有限公司

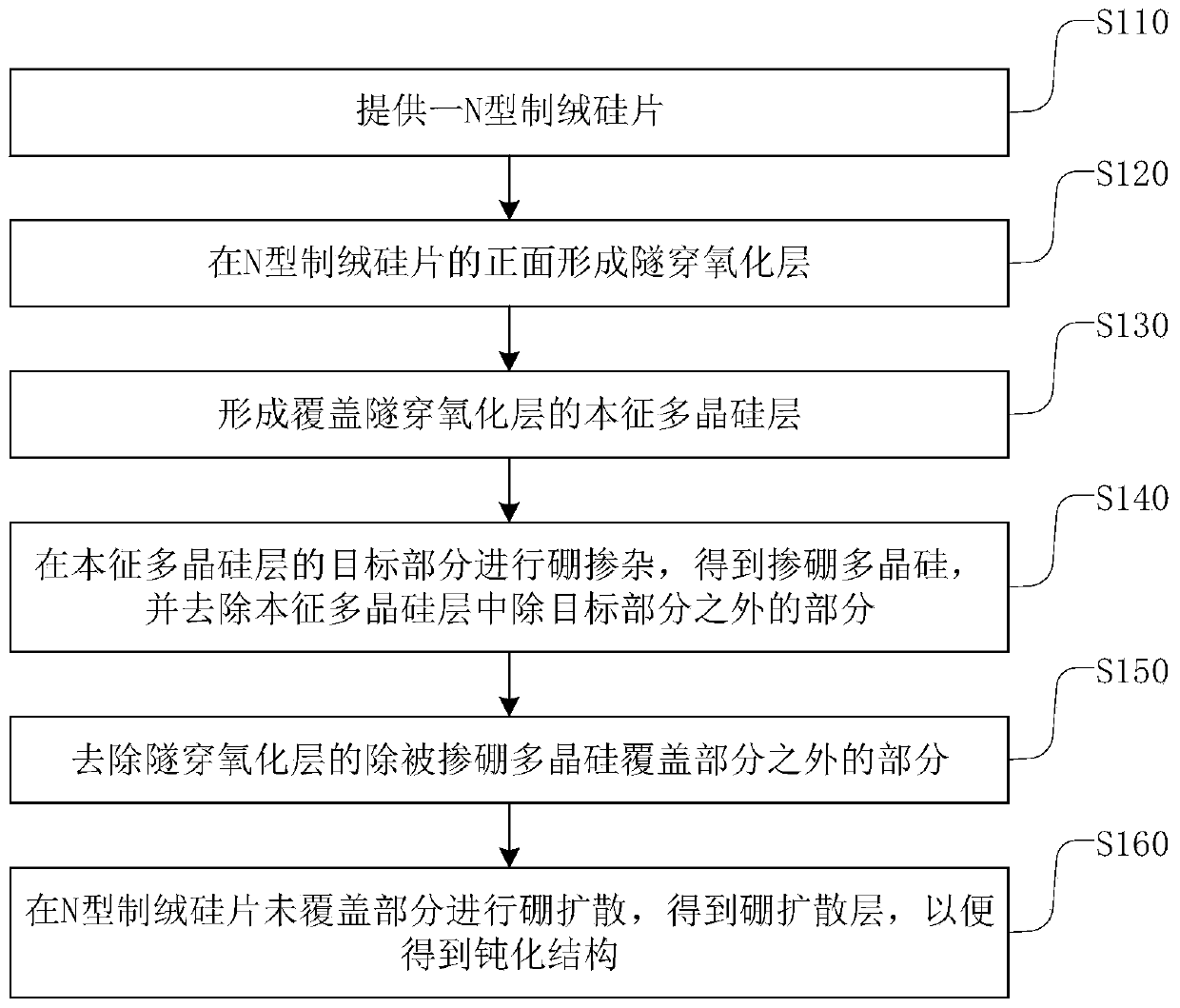

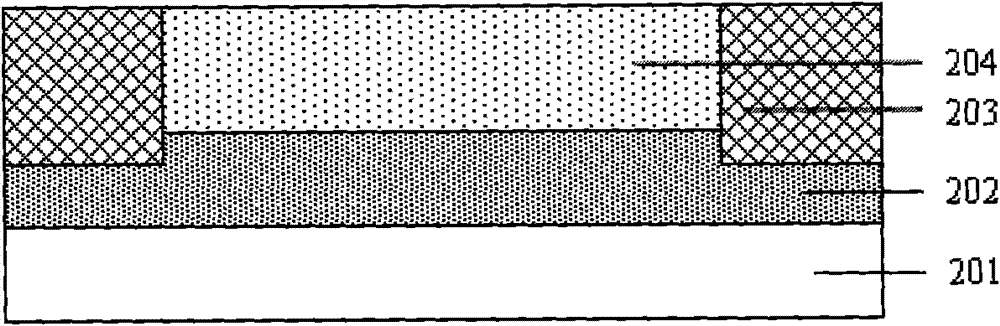

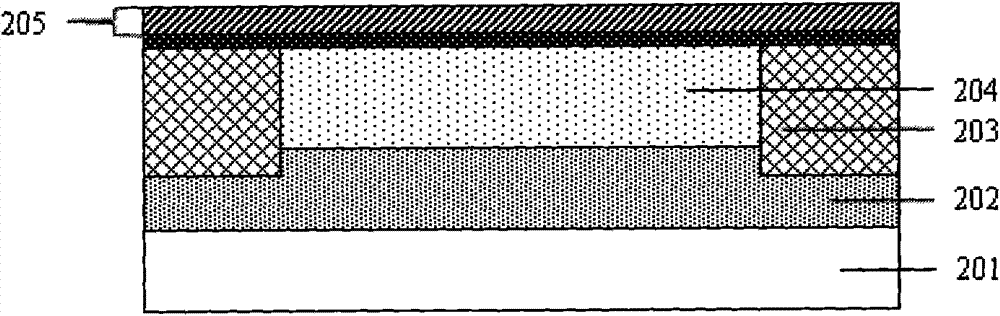

Manufacturing method of passivation structure, passivation structure and photovoltaic cell

InactiveCN110634996AReduce recombination currentIncrease the open circuit voltageFinal product manufacturePhotovoltaic energy generationSolar cellBoron doping

The invention discloses a manufacturing method of a passivation structure. The manufacturing method comprises the following steps: providing an N-type texturing silicon wafer; forming a tunneling oxide layer on the front side of the N-type texturing silicon wafer; forming an intrinsic polysilicon layer covering the tunneling oxide layer; performing boron doping on the target part of the intrinsicpolysilicon layer to obtain boron-doped polysilicon and removing the part of the intrinsic polysilicon layer apart from the target part; removing the part of the tunneling oxide layer apart from the part covered by the boron-doped polysilicon; and performing boron diffusion on the uncovered part of the N-type texturing silicon wafer so as to obtain a boron diffusion layer and obtain the passivation structure. The conversion efficiency of the photovoltaic cell can be improved. Meanwhile, the invention also provides the passivation structure applied to the TopCon solar cell and the photovoltaiccell, all of which have the above beneficial effects.

Owner:ZHEJIANG JINKO SOLAR CO LTD +1

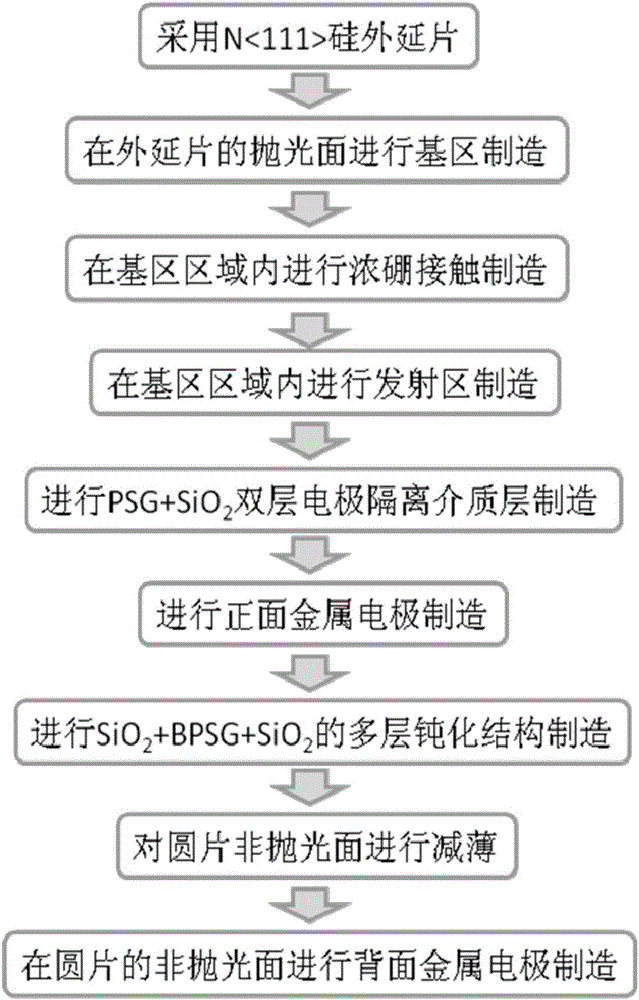

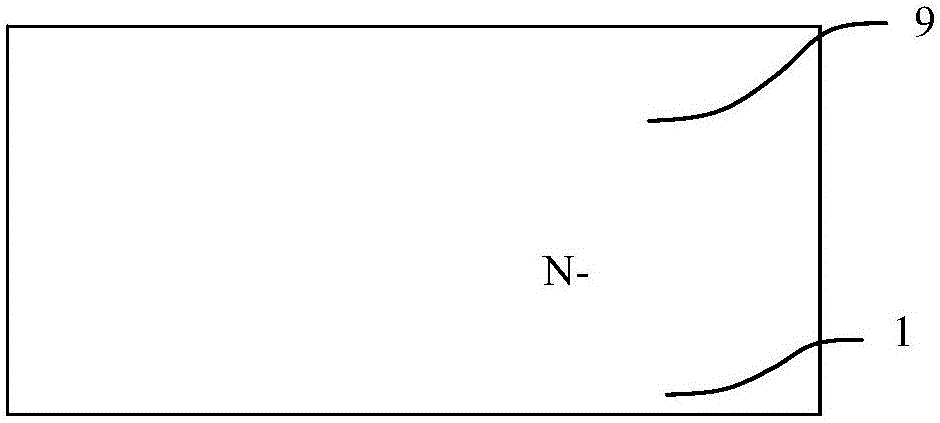

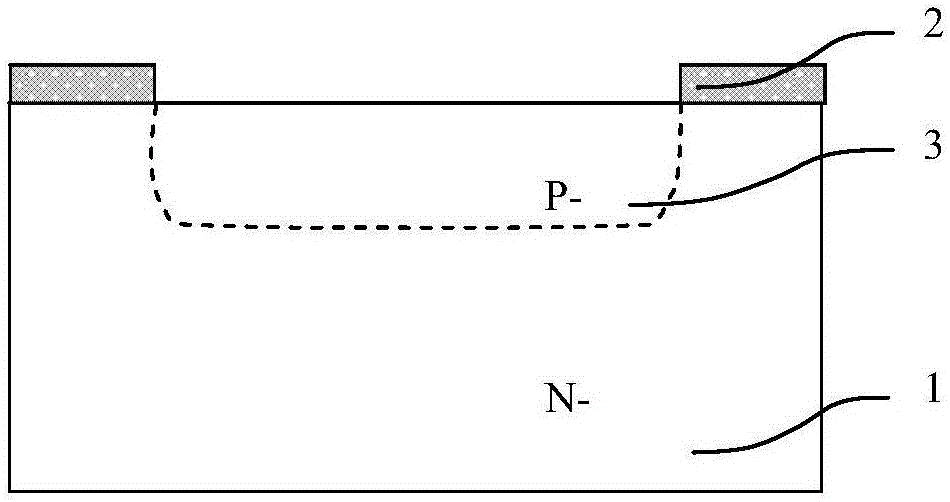

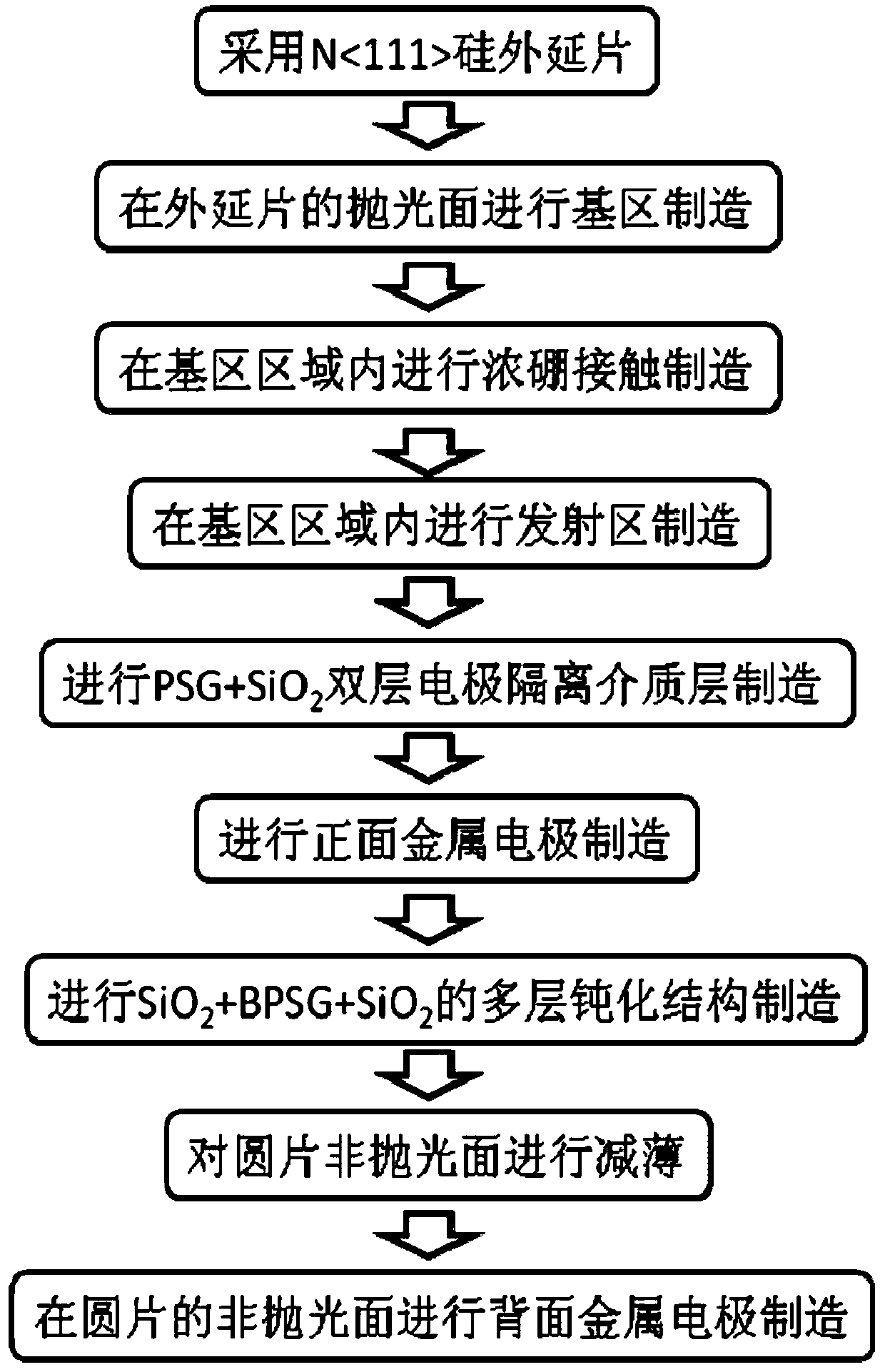

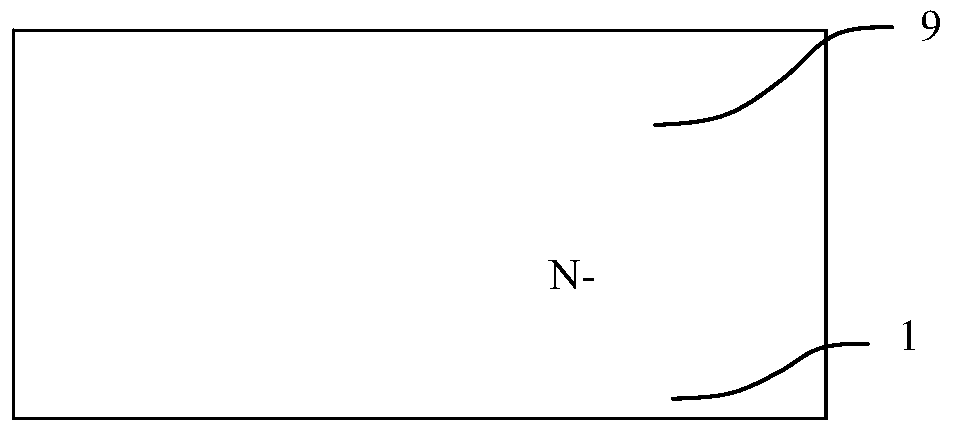

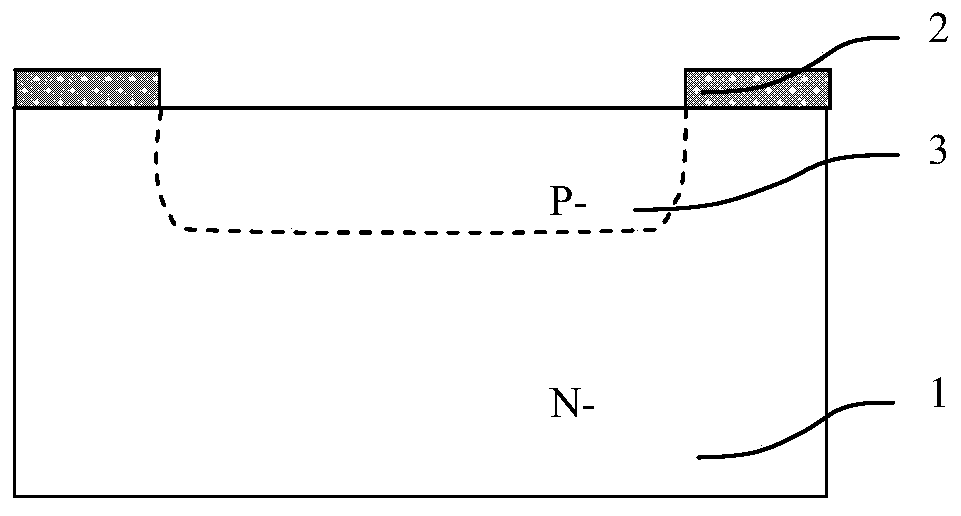

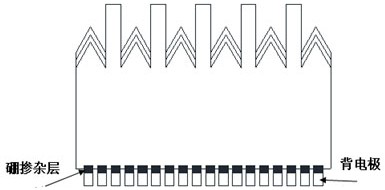

Manufacture method for twin pole device resisting low dosage rate irradiation

ActiveCN106653601AReduce performanceImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesBiochemical engineeringIrradiation

The invention discloses a manufacture method for a twin pole device resisting low dosage rate irradiation. According to the invention, a multi-layer passivation structure employing PSG (Phosphorosilicate Glass) + SiO2 double-layer electrode isolation medium and SiO2+BPSG (Boron Phosphorosilicate Glass)+SiO2. By adopting the above structure, total number of defects in the electrode isolation medium layer is reduced substantially on one hand. On the other hand, through adsorption of positive charges of the PSG and the BPSG, accumulation of the positive changes generated in the irradiation environment on the surface of Si-SiO2 is prevented and further the low dosage rate irradiation resistance of the twin-pole device is improved. The manufacture method provided by the invention is simple in technical procedure and is compatible to Si manufacture technique that is widely applied currently, and can be used for manufacturing the twin pole device having low dosage rate irradiation resistance.

Owner:BEIJING MXTRONICS CORP +1

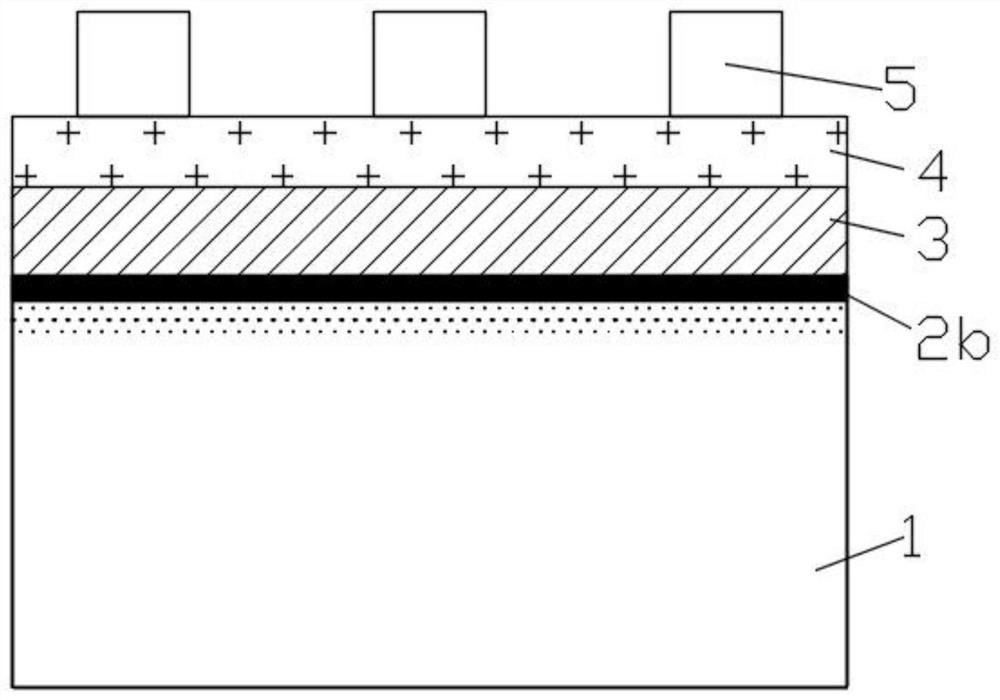

Solar cell with back local area doped heavily, and preparation method thereof

InactiveCN110233189AReduce recombination currentReduce contact resistanceFinal product manufacturePhotovoltaic energy generationDielectricSlurry

The invention discloses a solar cell with a back local area doped heavily. The solar cell comprises a silicon base layer; a metallization area is arranged on the back surface of the silicon base layer; and a local heavily doped area is arranged in the metallization area. The invention provides the solar cell with the back local area doped heavily and a preparation method thereof. The invention discloses a technical method adopting two-time laser treatment. The first-time laser treatment aims to ablate a back passivation dielectric film of the metallization area to expose the silicon surface ofa bottom layer, and then the second-time laser treatment is carried out after doped slurry is printed in open film areas; the second-time laser treatment aims to push doping elements in the doped slurry into a silicon wafer, and then local area heavy doping is formed in the metallization area on the back surface of the solar cell; and then, a metallization process is carried out to complete the preparation of the solar cell with the back local area doped heavily. Therefore, the composite current of the metallization area on the back surface of the solar cell is reduced, and the contact resistance is reduced.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

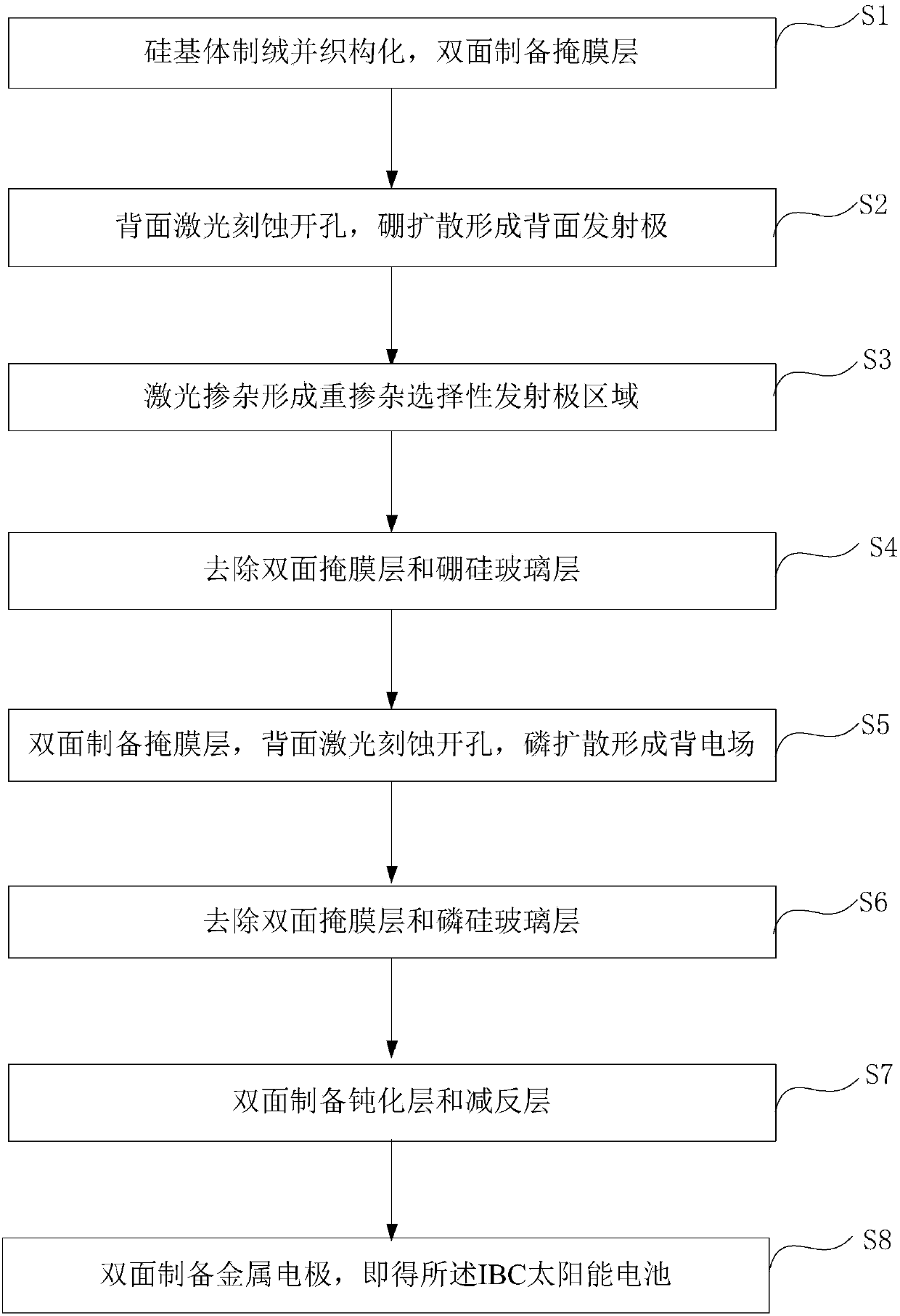

Preparation method of IBC solar cell

InactiveCN107946408ASimple manufacturing processAvoid damageFinal product manufacturePhotovoltaic energy generationLaser etchingRecombination current

The present invention discloses a preparation method of an IBC solar cell. The method comprises the steps of: performing texture surface making and texturing of a silicon substrate, and performing double-sided preparation of a mask layer; performing back surface laser etching opening, and performing boron diffusion to form a back surface emitting electrode; performing laser doping to form a heavydoping selectivity emitting electrode area; removing the double-sided mask layer and a borosilicate glass layer; performing double-sided preparation of a mask layer, performing back surface laser etching opening, and performing phosphorus diffusion to form a back surface field; removing the double-sided mask layer and a phosphorosilicate glass layer; performing double-sided preparation of a passivation layer and an anti-reflection layer; and performing double-sided preparation of a metal electrode, and obtaining an IBC solar cell. The preparation method of an IBC solar cell is simple in preparation process, simplifies the cell preparation process, can avoid damaging of the silicon substrate, can improve the production efficiency and can greatly reduce the recombination current of the emitting electrode.

Owner:ZHEJIANG JINKO SOLAR CO LTD +1

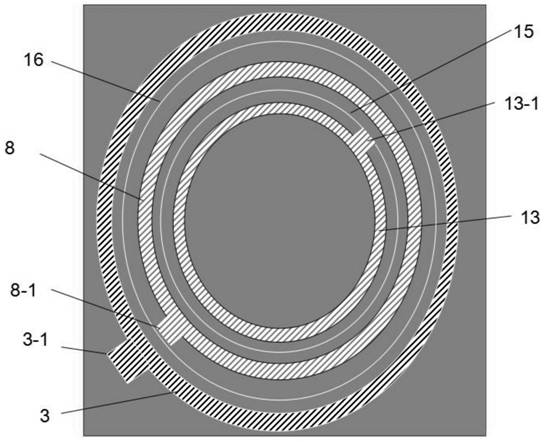

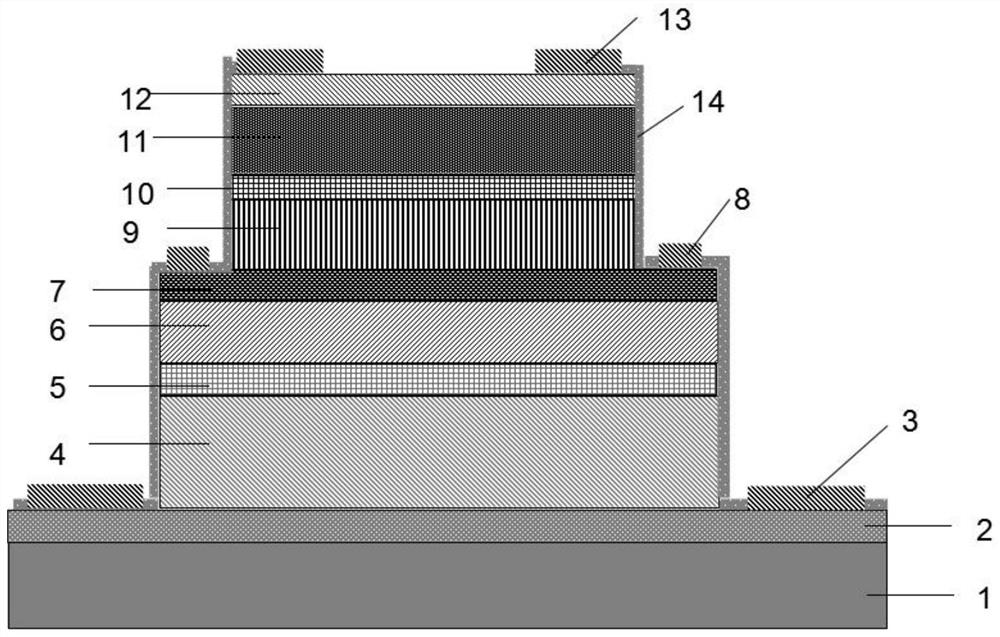

Monolithic integrated nBnBn four-waveband detector

The invention belongs to the technical field of semiconductor photoelectric detectors, and particularly relates to a monolithic integrated nBnBn four-waveband detector, which adopts a longitudinal integrated structure. The monolithic integrated nBnBn four-waveband detector comprises a GaSb substrate, an n-type short-wave channel ohmic contact layer, a first metal electrode layer, a short-wave channel absorption layer, a first barrier layer, a medium-wave channel absorption layer, an n-type medium-wave channel contact layer, a common electrode layer, a long-wave channel absorption layer, a second barrier layer, an ultra-long-wave channel absorption layer, an n-type ultra-long-wave channel contact layer, a second metal electrode layer and a passivation layer. The detector with four wave bands in the detector has an integrated structure from bottom to top, has a four-absorption-layer structure, can respectively detect the four wave bands through voltage control, has the advantages of highresponsivity, low dark current and the like, reduces the false alarm rate, reduces the size of a device, and reduces the complexity of a preparation process and a detection system.

Owner:TIANJIN JINHANG INST OF TECH PHYSICS

Locally doped solar cell and preparation method thereof

InactiveCN110212058AReduce recombination currentRealize large-scale mass productionFinal product manufacturePhotovoltaic energy generationSlurrySolar cell

The invention discloses a preparation method of a locally doped solar cell. The preparation method comprises the steps of 1) prearranging and drying doping slurry: prearranging the doping slurry in aposition where a film is to be opened, contacting the doping slurry with a silicon base layer, and carrying out drying; 2) depositing a dielectric passivation film layer on the back surface of the silicon base layer; 3) carrying out laser ablation: carrying out ablation on the dielectric passivation film layer in a metallization region on the back surface of the silicon base layer by laser in a position as same as that of prearranging the doping slurry in the step 1); and 4) carrying out metallization: preparing a metal electrode through a metallization process. The invention provides the locally doped solar cell and the preparation method thereof. Before the dielectric passivation film layer is deposited on the back surface, the doping slurry is prearranged in the metallization region onthe back surface; and when the laser ablation is carried out on the dielectric passivation film layer, the prearranged doping slurry is pushed into the silicon base layer by utilizing energy of the laser, so that the heavy doping and depth of the metallization region are realized, and the composite current of the metallization region on the back surface of the silicon base layer is reduced; and the large-scale production is realized.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

MWT solar cell and method of making the same

ActiveCN102969399BReduce recombination currentImprove photoelectric conversion efficiencyRenewable energy productsSemiconductor devicesElectrical batterySolar battery

The invention provides a manufacturing method of a MWT (Metal Wrap Through) solar battery. The method comprises the steps of: providing a substrate which comprises a body layer, a reflection-reducing layer and a passivation layer, wherein a plurality of through holes and openings are arranged on the substrate; forming conductive electrodes in the through holes and forming a first back contact electrode on the back of the substrate; forming second back contact electrodes in the openings; forming a touch grid line electrode on the front face of the substrate; sintering the substrate so that the touch grid line electrode is electrically connected with the conductive electrode; and forming a local front surface field in the front surface of the body layer; and forming a local back emitting electrode in the back surface of the substrate. The MWT solar battery manufactured by the method is small in composite current, large in light receiving area and high in photoelectric conversion efficiency, and the problem that the battery is bended is reduced. In addition, according to the manufacturing method provided by the invention, steps such as diffusive knot manufacture, edge corrosion, glass layer removal and secondary clean in conventional process are avoided, so that the manufacturing process flow is simplified and the production cost is reduced.

Owner:淮安捷泰新能源科技有限公司

Polycrystalline silicon thin film containing silicon-oxygen nanocrystalline layer and preparation method and application of polycrystalline silicon thin film

ActiveCN113314630APrevent corrosion rateReduce spreadFinal product manufacturePhotovoltaic energy generationSilicon oxygenThin membrane

The invention discloses a polycrystalline silicon thin film containing a silicon-oxygen nanocrystalline layer, which comprises a tunneling layer positioned on the back surface of a substrate, a doped polycrystalline silicon layer positioned on the back surface of the tunneling layer, a sintered electrode positioned on the back surface of the doped polycrystalline silicon layer, and a first silicon-oxygen nanocrystalline layer positioned between the doped polycrystalline silicon layer and the sintered electrode. According to the polycrystalline silicon thin film containing the silicon-oxygen nanocrystalline layer, the doped silicon-oxygen nanocrystalline layer is added to serve as a barrier layer for diffusion of electrode metal, the polycrystalline silicon layer is prevented from being burnt through in the sintering process of metal slurry to make direct contact with crystalline silicon, and diffusion of the electrode metal to a substrate is blocked; the invention further provides a preparation method and application of the polycrystalline silicon thin film containing the silicon-oxygen nanocrystalline layer, an annealing crystallization process in preparation of a tunneling layer and a doped polycrystalline silicon layer and a high-temperature sintering process in preparation of a sintered electrode are combined into a whole, and the cost is reduced; and the polycrystalline silicon thin film containing the silicon-oxygen nanocrystalline layer is applied to a solar cell, and the cell efficiency is improved.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

Novel p-type crystalline silicon cell emitter contact passivation preparation process

InactiveCN112071958AReduce contact resistanceImprove conversion efficiencyFinal product manufacturePhotovoltaic energy generationScreen printingCrystalline silicon

The invention relates to the field of solar cell production, in particular to a novel p-type crystalline silicon cell emitter contact passivation preparation process which is carried out according tothe processes of cleaning texturing, diffusion junction making, PSG removal and back etching, high-temperature oxidation, front anti-reflection film removal, back passivation and anti-reflection filmremoval, front laser grooving, emitter heavy doping, PSG removal, back laser grooving and silk-screen printing. In the emitter heavy doping process, a thermal diffusion mode is adopted, 300 sccm of N2, 500-1,000 sccm of N2POCl3 and 400-900 sccm of O2 are introduced, the temperature is increased from 780 DEG C to 820 DEG C at a uniform speed, the time is 100-200 s, the temperature is maintained at820 DEG C, 13 slm of N2 is introduced, and the time is 1-2 min. By passivating the emitter, the composite current in the metallization area is reduced, and the conversion efficiency of the cell is improved by 0.3-0.5%.

Owner:SHANXI LUAN PHOTOVOLTAICS TECH

A bipolar device manufacturing method resistant to low dose rate radiation

ActiveCN106653601BReduce performanceImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesLow dose rate irradiationBiochemical engineering

The invention discloses a manufacture method for a twin pole device resisting low dosage rate irradiation. According to the invention, a multi-layer passivation structure employing PSG (Phosphorosilicate Glass) + SiO2 double-layer electrode isolation medium and SiO2+BPSG (Boron Phosphorosilicate Glass)+SiO2. By adopting the above structure, total number of defects in the electrode isolation medium layer is reduced substantially on one hand. On the other hand, through adsorption of positive charges of the PSG and the BPSG, accumulation of the positive changes generated in the irradiation environment on the surface of Si-SiO2 is prevented and further the low dosage rate irradiation resistance of the twin-pole device is improved. The manufacture method provided by the invention is simple in technical procedure and is compatible to Si manufacture technique that is widely applied currently, and can be used for manufacturing the twin pole device having low dosage rate irradiation resistance.

Owner:BEIJING MXTRONICS CORP +1

Novel P-type crystalline silicon cell back contact passivation preparation process

InactiveCN112071959AReduce contact resistanceReduce recombination currentFinal product manufacturePhotovoltaic energy generationSolar batteryNitrogen gas

The invention relates to the field of solar cell production. A novel P-type crystalline silicon cell back contact passivation preparation process comprises the steps: after laser grooving is conductedon the back face, in the process of preparing a boron heavily-doped layer through a back electrode and preparing the boron heavily-doped layer through the back electrode in a thermal diffusion mode,introducing N2 at the flow of 10 slm, increasing the temperature to 900 DEG C, and waiting for 5 min; carrying BBr3 in nitrogen under the condition that the flow of the nitrogen is kept unchanged, enabling the flow of the BBr3 to be 200-400 sccm, introducing 150-300 sccm of O2 while introducing the BBr3, and carrying out constant-rate variable-temperature deposition for 5-10min at the temperatureof 900-960 DEG C; after the temperature rises to 960 DEG C, introducing 610 slm of N2 and 46 slm of O2, and performing high-temperature propelling, wherein the time is 35 min; and finally, introducing10 slm of N2, performing cooling and withdrawing the boat at the temperature of 960-840 DEG C.

Owner:SHANXI LUAN PHOTOVOLTAICS TECH

Thin film strip structure, solar cell and manufacturing method of thin film strip structure

ActiveCN102832116BIncrease the effective areaReduce compound distanceFinal product manufactureSemiconductor/solid-state device manufacturingManufacturing cost reductionSemiconductor materials

Owner:盐城新汇村镇建设发展有限公司

Corrosion method of CdTe film solar cell

InactiveCN100555679CImprove performanceLower barrier heightFinal product manufactureSemiconductor/solid-state device manufacturingSchottky barrierContact layer

The invention relates to a method for surface corrosion of a CdTe film and preparation of a CdTe solar cell by adopting the method, pertaining to the processing field of semiconductor devices. An mixed liquid of nitric acid, glacial acetic acid, NaAc and deionized water is served as corrosive liquid, wherein, the NaAc is served as a buffering agent to keep the pH value of the intermixture unchanged and lead the reaction to be more stable; CdTe and the nitric acid react to generate a layer rich in tellurium; after washing and blow-drying, a back contact layer containing Cu or without Cu is sedimented; finally, a back electrode is sedimented for preparing the CdTe solar cell. Sedimentation of back contact material can increase carrier concentration near a pn junction, reduce the height of Schottky potential barrier and avoid direct sedimentation of Cu from forming a comparatively complex CuxTe structure. By adopting the method for corrosion and the preparation of the CdTe solar cell, the performance of the solar cell can be obviously improved and the stability and the repeatability of the device can be ensured.

Owner:SICHUAN UNIV

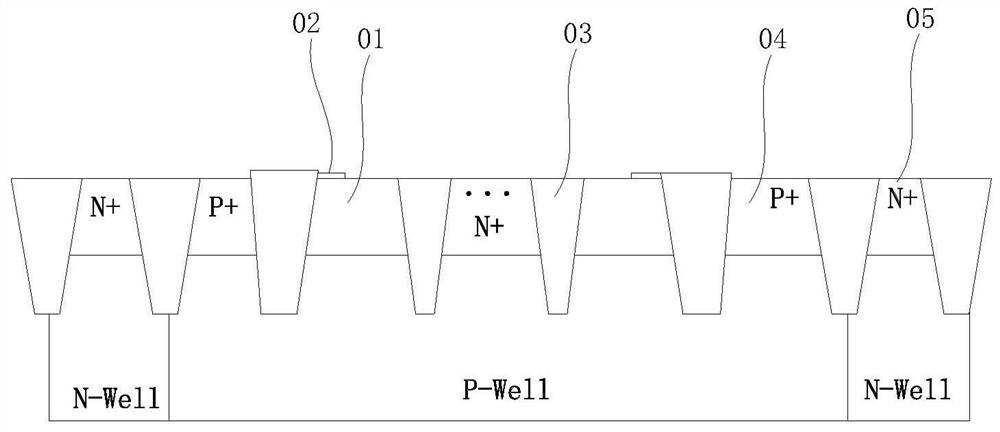

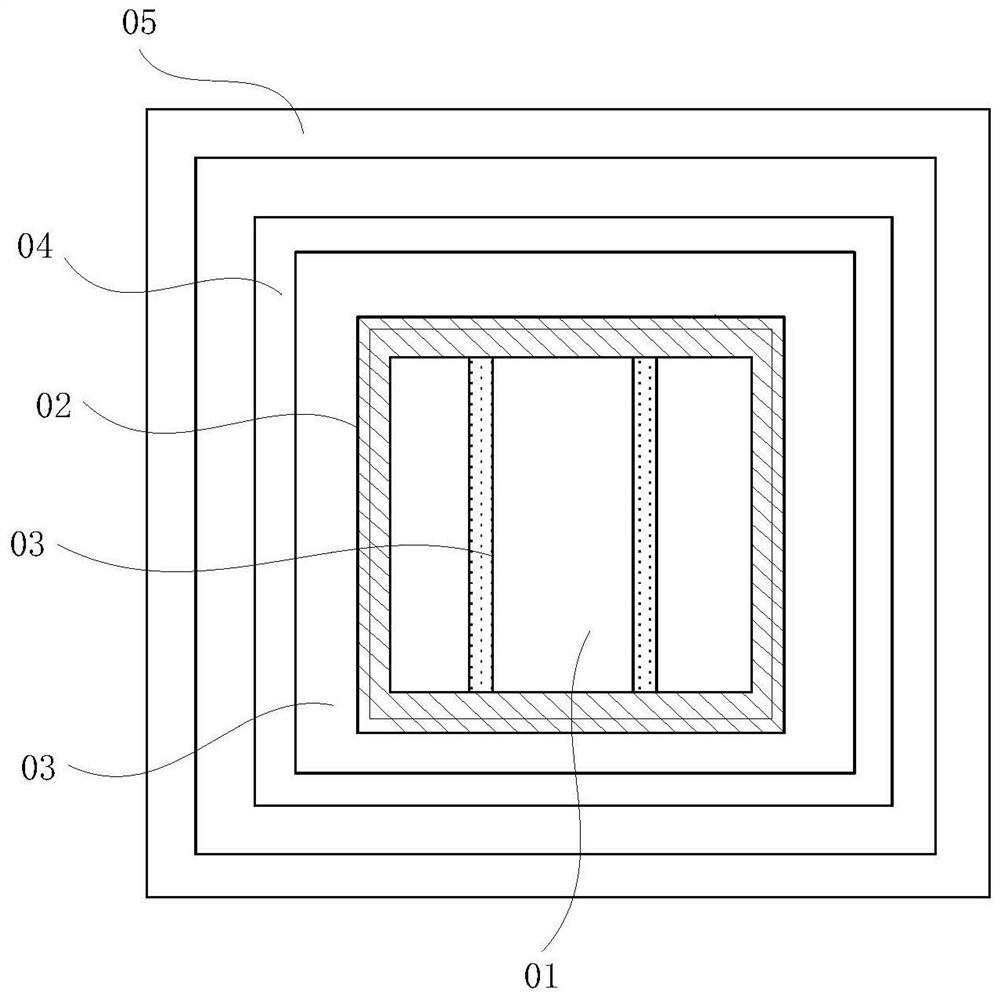

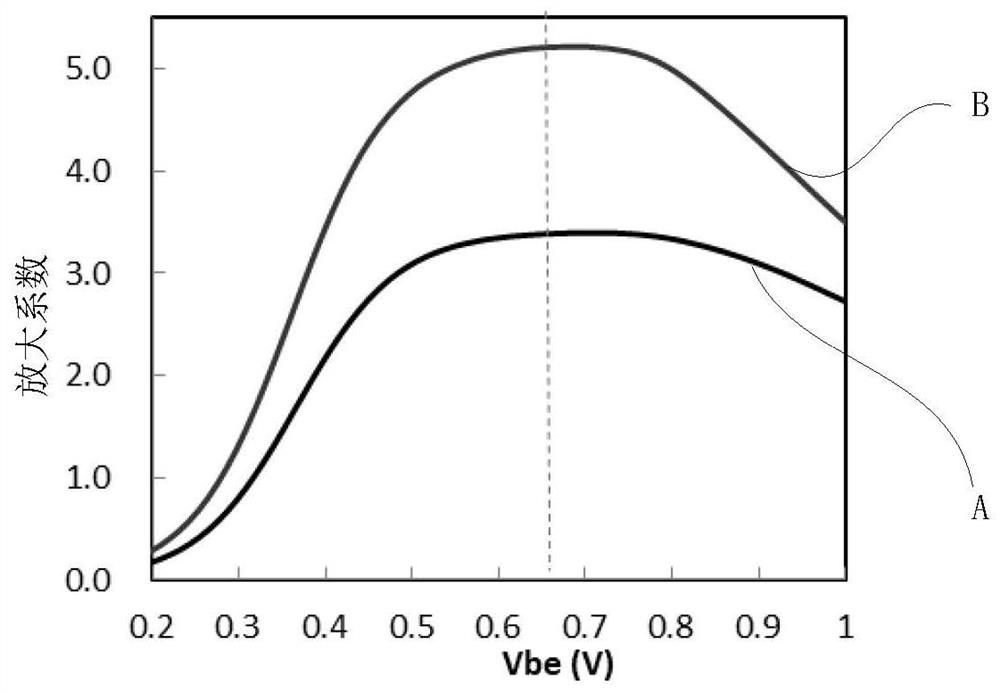

cmos integrated process bjt structure and its manufacturing method

ActiveCN109545849BIncrease current gainCurb churnSemiconductor/solid-state device manufacturingChemical vapor deposition coatingCMOSMetal silicide

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Preparation for SiGe HBT transistor

ActiveCN101459076BRaise the activation temperatureReduce recombination currentSemiconductor/solid-state device manufacturingRecombination currentBiology

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

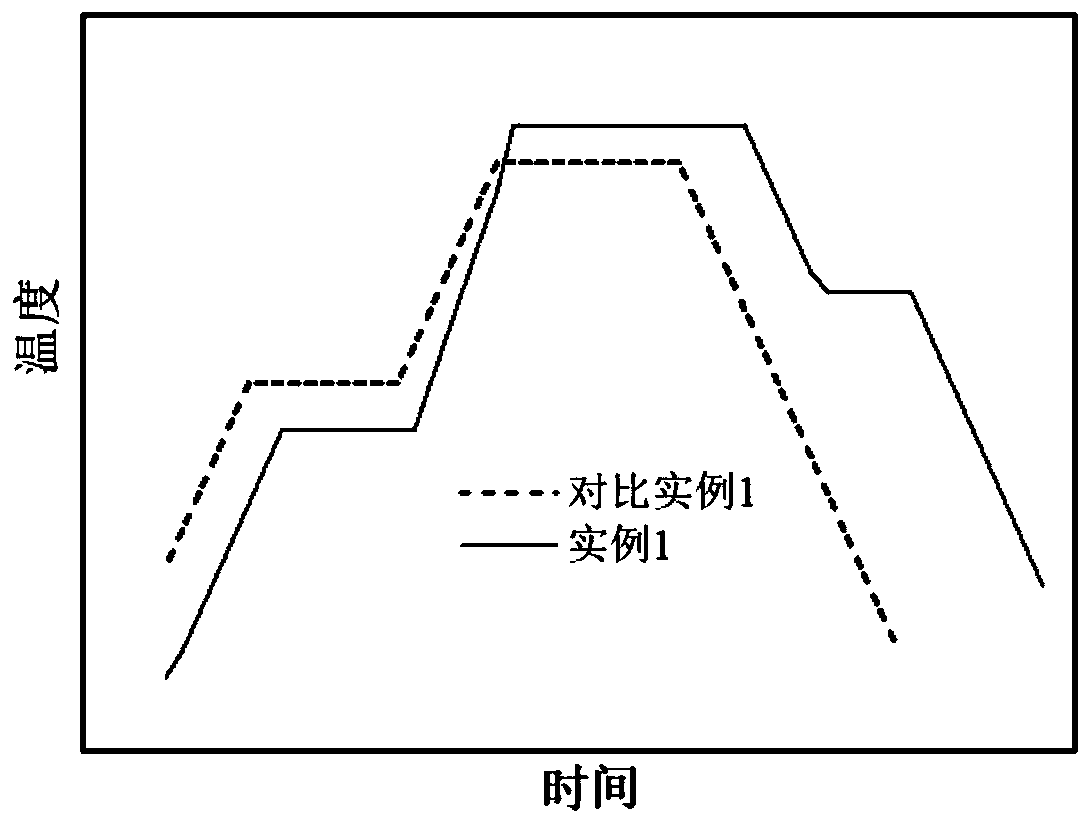

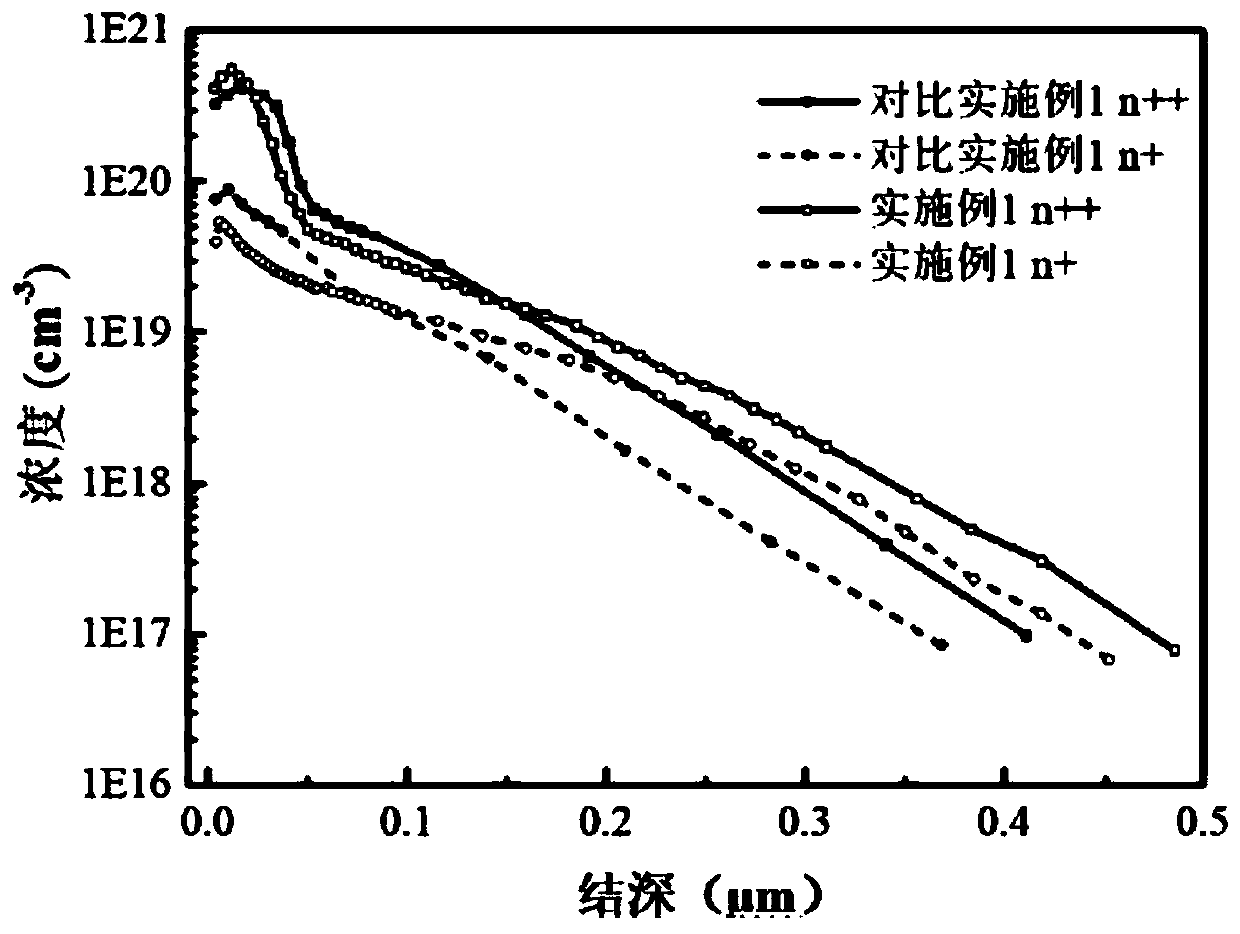

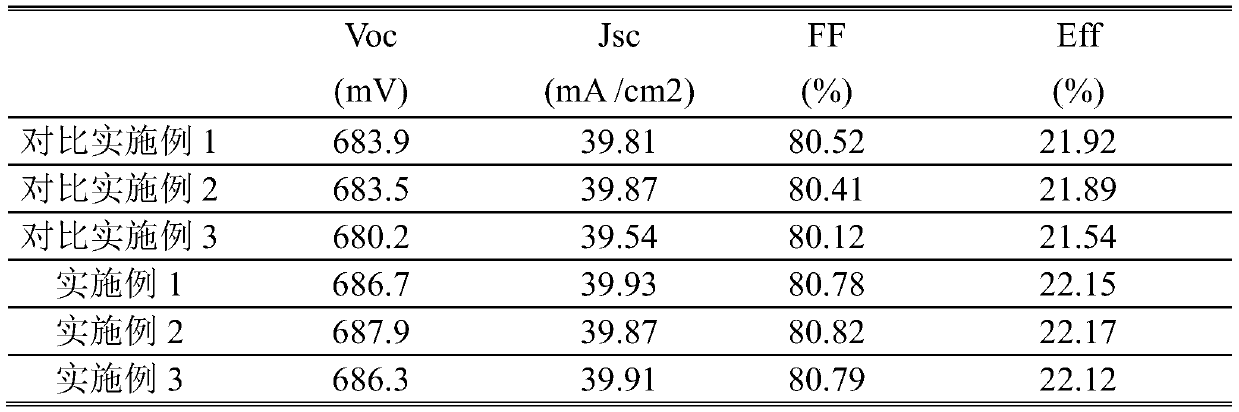

A step-by-step phosphorus doping method for crystalline silicon cells

ActiveCN109166794BIncrease the open circuit voltageReduce concentrationFinal product manufactureSemiconductor/solid-state device manufacturingHigh concentrationHigh surface

The invention belongs to the technical field of solar cell manufacturing, and relates to a step-by-step phosphorus doping method of a high-efficiency and low-cost crystal silicon cell, namely a primary depletion diffusion combined with secondary high-concentration shallow layer diffusion and back etching method. By controlling the flow of oxygen, A low-temperature low-phosphorus source depositionis carry out for that first time on a p-type silicon substrate by nitrogen flow rate and phosphorus oxychloride flow rate, After a long time of high temperature propulsion, the phosphorus in the phosphor-silicate glass is exhausted, and the low surface concentration layer n + is realized. The second time, the phosphor-free glass is deposited on the phosphor-silicate glass, and the high surface concentration layer n + + is pushed to form a very thin high concentration layer, which can be quickly etched off by means of back etching. The method can accurately control the phosphorus doping distribution in different regions independently to ensure that the non-electrode region has low doping concentration and low recombination current so as to ensure higher open-circuit voltage. The electrode region has high doping concentration, which forms good ohmic contact with the metal electrode and ensures that the filling factor is not lost, so as to improve the photoelectric conversion performanceof the battery as a whole.

Owner:CHANGZHOU UNIV +1

Method for implementing base region window of silicon germanium heterojunction transistor

ActiveCN102097315BReduce defectsImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionMetal silicide

The invention discloses a method for implementing a base region window of a silicon germanium heterojunction transistor, which comprises the following steps of: depositing a composite dielectric film on a silicon chip with an embedded layer, a collector region and a substrate isolation region on a silicon substrate; performing dry etching on the composite dielectric film, defining the base region window, and etching an oxide film stopped on the composite dielectric film; after the base region window is opened and before the oxide film of the composite dielectric film is removed, depositing a dielectric film layer, and forming a D-shaped side wall at the interface step of the base region window by using the dielectric film layer; and meanwhile, performing wet removal on the residual oxide film in the base region window by using the protection of the D-shaped side wall, and epitaxially growing an SiGe base region. The interface step of the base region window is changed slowly because of the formation of the D-shaped side wall, and the slowly changed step formed by the D-shaped side wall is continuously reserved after SiGe extension and has no insulator residue in the subsequent emitter polycrystalline silicon side wall process, so that continuous metal silicide is formed, the resistance of an outer base region is reduced, and the performance of the device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A Visible-Ultraviolet Dual Color Detector

ActiveCN112490305BReduce dark currentImprove monolithic integrationSemiconductor devicesMetallic electrodePhotodetector

The invention belongs to the technical field of semiconductor photodetectors, and specifically relates to a visible-ultraviolet dual-color detector. The visible-ultraviolet dual-color detector adopts a vertically integrated structure, including an nGaN substrate, an n-type GaN contact layer, a lower metal electrode, and an AlGaN Matching layer, AlGaN ultraviolet absorbing layer, two-dimensional boron nitride thin film barrier layer, topological insulator visible light absorbing layer, n-type topological insulator thin film contact layer, upper metal electrode and passivation layer. The detectors of the two bands in the detector have a bottom-up integrated structure, which can realize visible and ultraviolet dual-color detection by controlling the bias voltage, reduce the false alarm rate, reduce the size of the device, and reduce the cost of the preparation process and detection system. Complexity.

Owner:TIANJIN JINHANG INST OF TECH PHYSICS

BJT device structure and manufacturing method thereof

PendingCN113725291AIncrease the magnification factorReduce recombination currentSemiconductor/solid-state device manufacturingSemiconductor devicesRecombination currentEngineering

Owner:SHANGHAI HUALI INTEGRATED CIRCUIT CORP

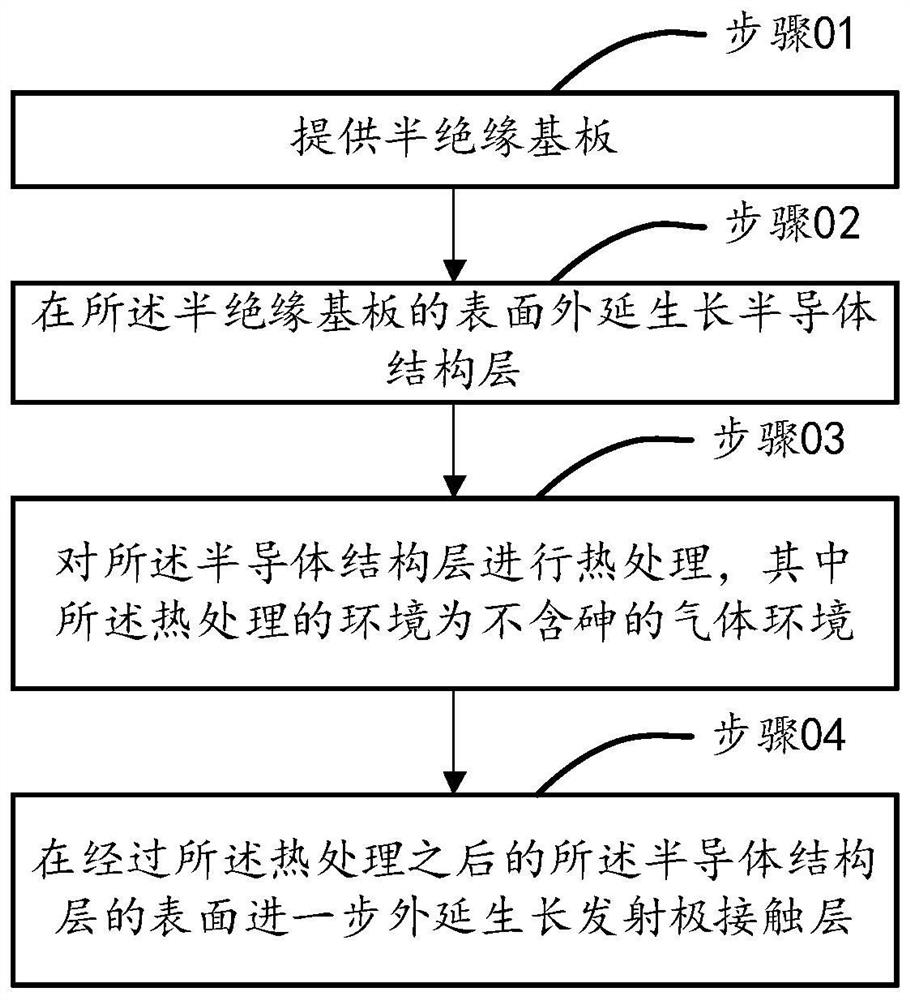

Heterojunction bipolar transistor and epitaxial growth method thereof

PendingCN113851372AImprove transient effectsLittle variation in current gainSemiconductor/solid-state device manufacturingSemiconductor devicesRecombination currentPhysical chemistry

The invention provides a heterojunction bipolar transistor and an epitaxial growth method thereof. In the epitaxial growth method of the heterojunction bipolar transistor, heat treatment is carried out before epitaxial growth of an emitter contact layer. The heat treatment environment is an arsenic-free gas environment. And before the heat treatment process is carried out, the closing of each pipeline valve in the organic metal vapor deposition reaction furnace into which the arsenic-containing gas compound is introduced is controlled. According to the epitaxial growth method of the heterojunction bipolar transistor, the transient effect in the heterojunction bipolar transistor can be improved, the hydrogen ion concentration in the base layer is reduced, the crystallinity of the base layer material is improved, the recombination current in the base layer is reduced, and the current gain variation degree of the heterojunction bipolar transistor is less than 5%.

Owner:深圳市中科光芯半导体科技有限公司

Cadmium telluride diaphragm solar battery corrosive fluid and its corrosive method

InactiveCN100479198CReduce compoundingReduce widthFinal product manufactureSemiconductor devicesAlloyTe element

This is an erode liquid for cadmium telluride film solar battery and its erosion method. A zinc salt soluble in water or methanol is added into traditional HNO3-H3PO4-H2O or Br2-methanol solution with the concentration of ionic Zn between 0.01mol / L - 2mol / L. By applying zinc into the erode liquid, ionic Zn disperses into tellurium rich layer and heavy mixes in P type to form Te, Cd, Zn alloy film of electron reflection layer, and decrease the combination of electrons with cavities, so to effectively decrease surface current.

Owner:HUNAN NORMAL UNIVERSITY