Patents

Literature

118results about How to "Increase current gain" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

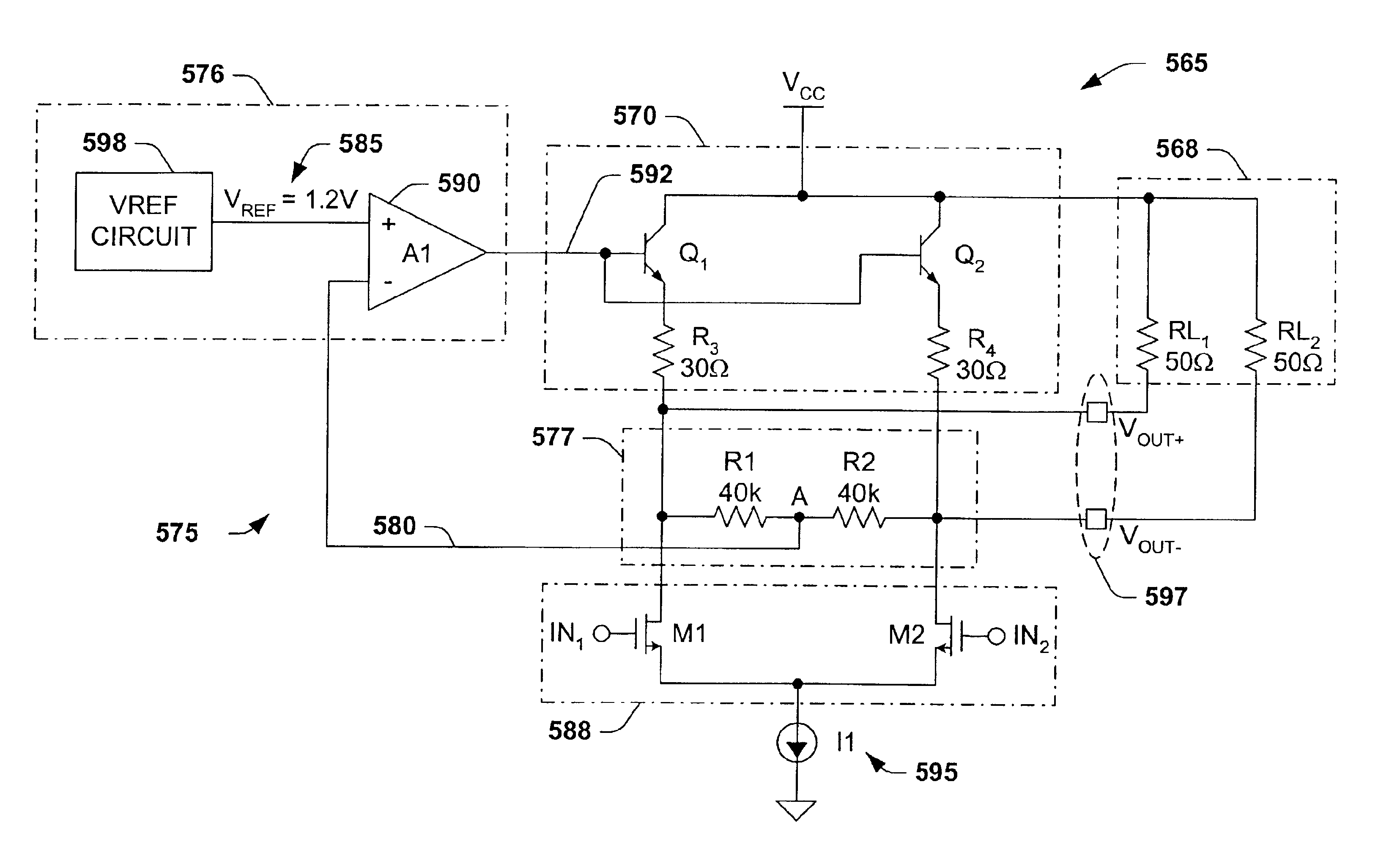

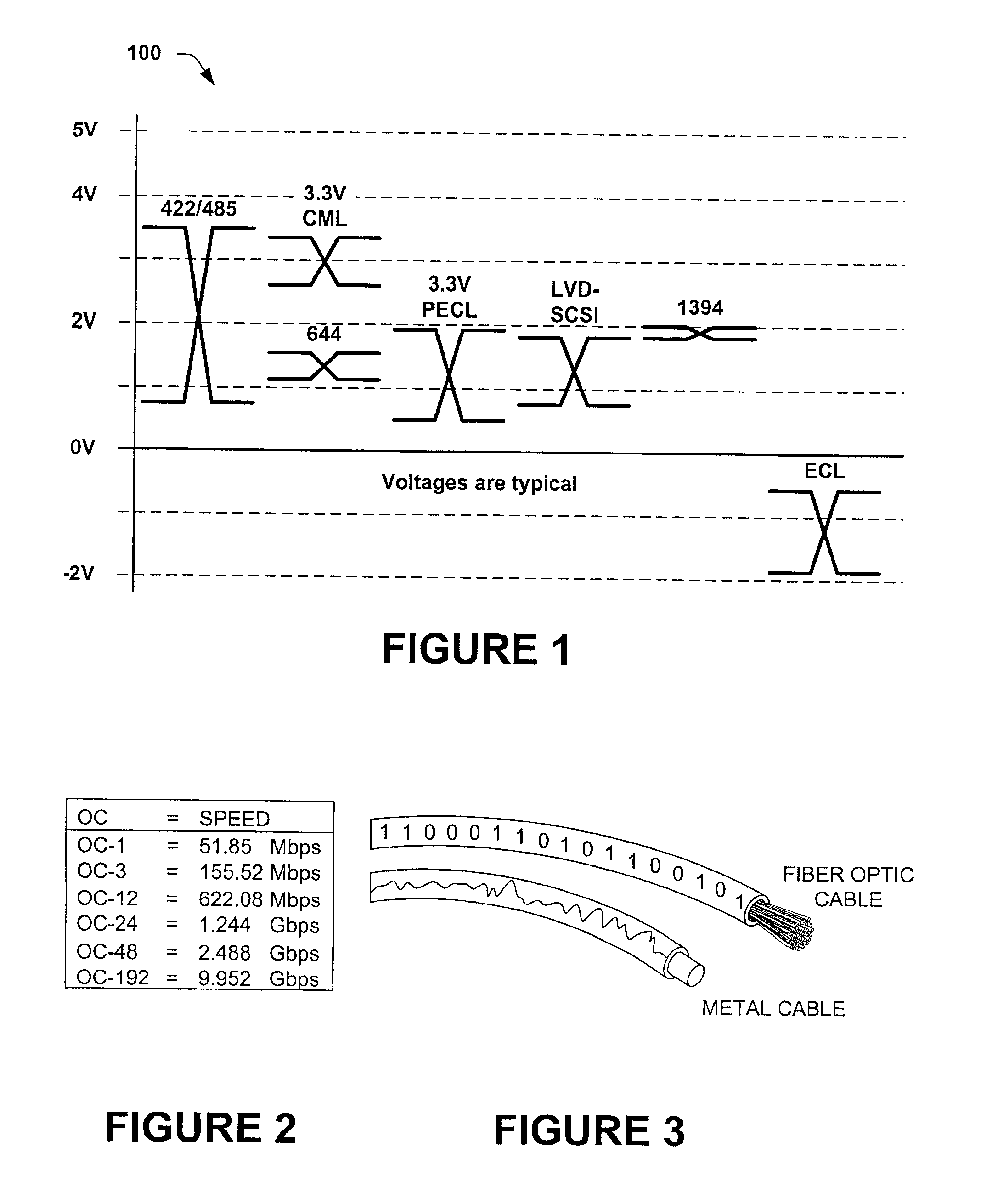

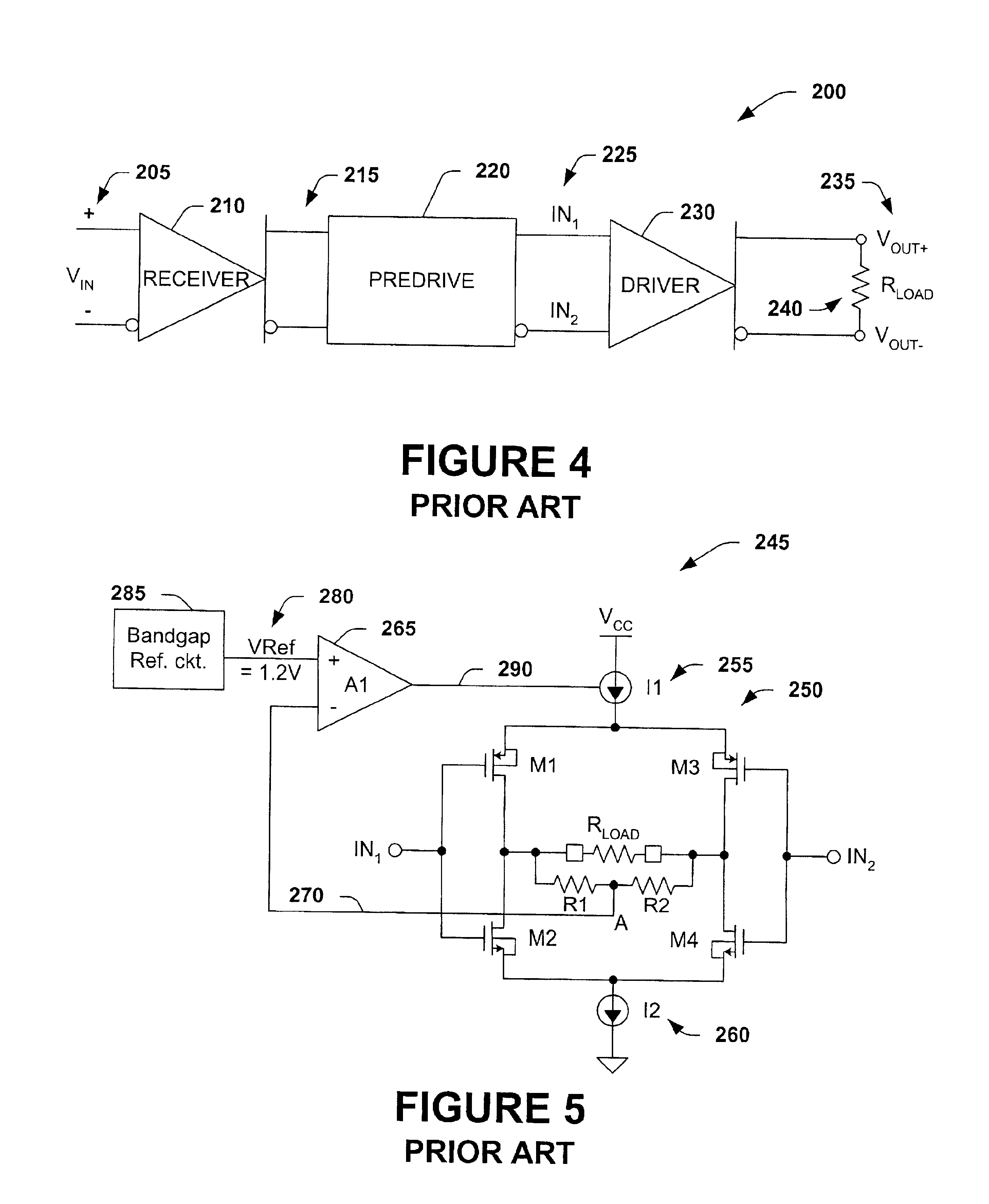

Interchangeable CML/LVDS data transmission circuit

InactiveUS6847232B2Easy to operateReduce input voltageLogic circuits coupling/interface using field-effect transistorsAmplifier with semiconductor-devices/discharge-tubesDriver circuitTransceiver

A system and method is described for a driver circuit used for high speed data transmission in LVDS and CML transceiver device applications. The transceivers are intended to receive a low voltage differential input signal and interchangeably drive a standard LVDS load with a TIA / EIA-644 compliant LVDS signal, and a standard CML load with a standard CML compatible signal. The driver circuit operates at speeds up to 1.36 Gbps, making it compatible with the OC-24 signaling rate for optical transmission. To accomplish this, the driver uses a mixed combination of voltage and current mode drive sections in the output circuit when coupled to LVDS loads, and when the driver is coupled to CML loads, operates purely in a current mode using only the current mode drive section. MOS transistors and a current source are used in the current mode switch portion to switch the drive with a constant current at the high speeds, and NPN transistors in the voltage mode output portion provide variable impedance for the output circuit. A common mode compensation circuit using a feedback voltage from the load generates a compensation signal for variable impedance control of the NPN transistors to yield a regulated voltage for the common mode dc voltage.

Owner:TEXAS INSTR INC

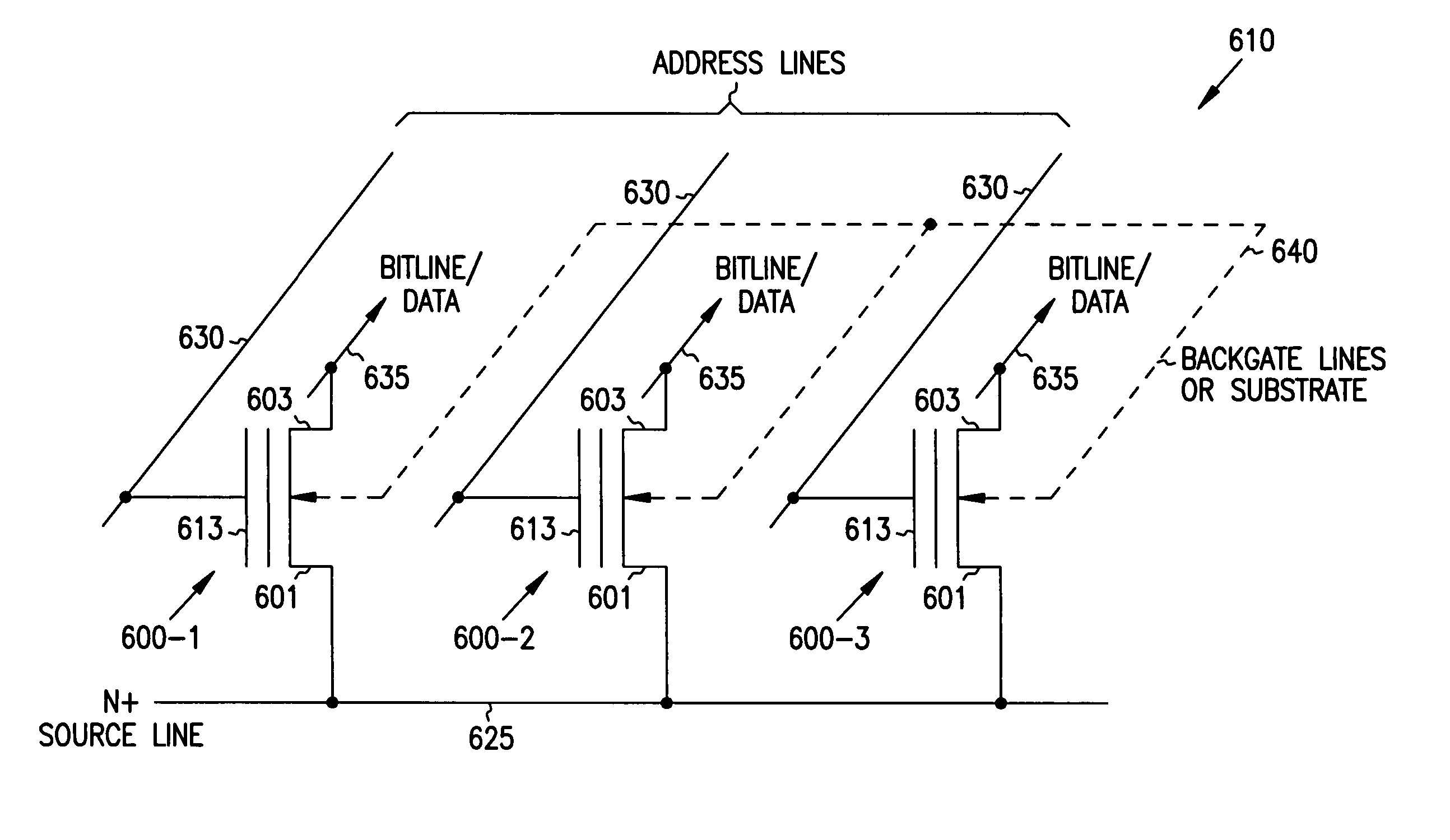

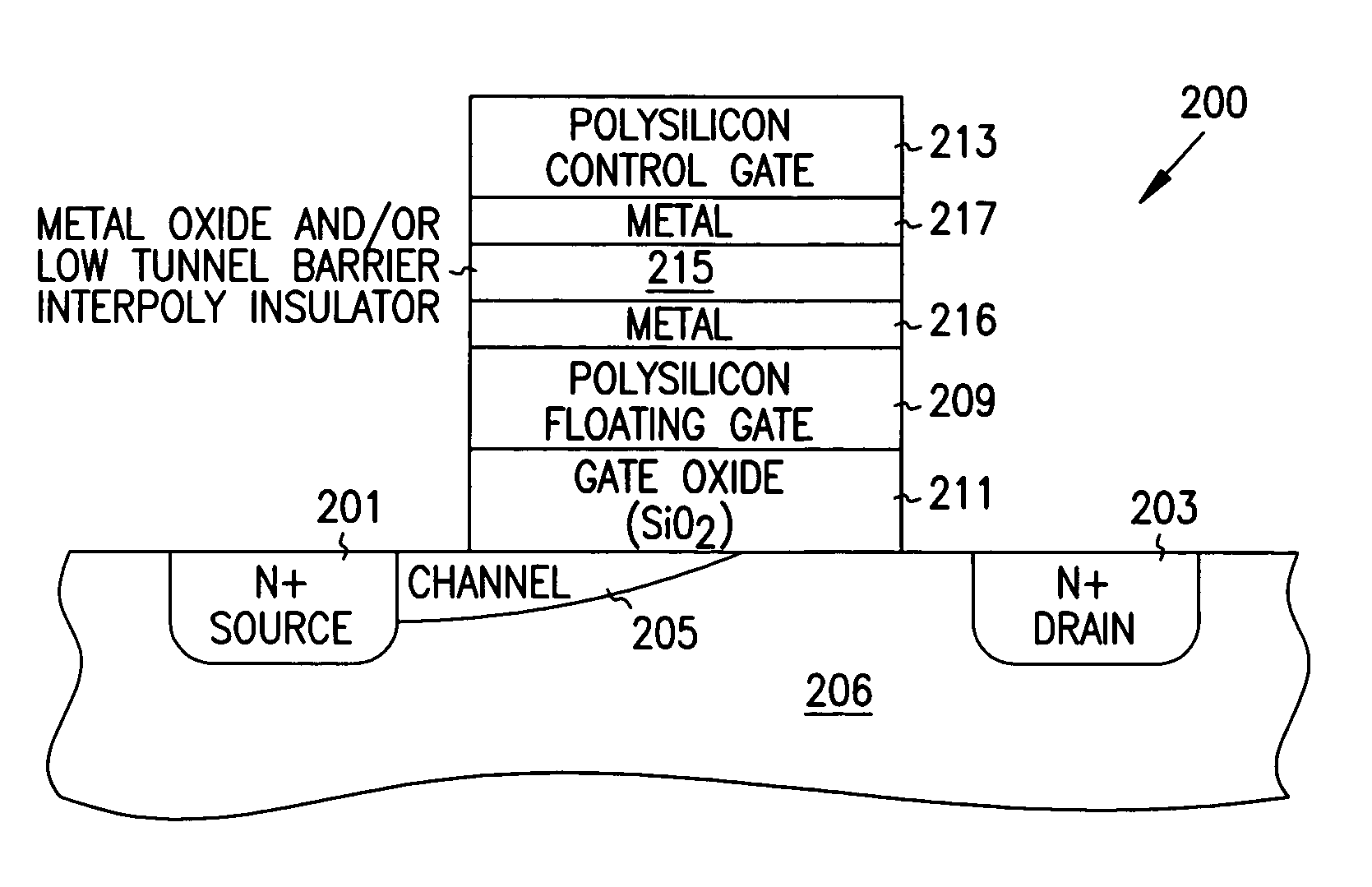

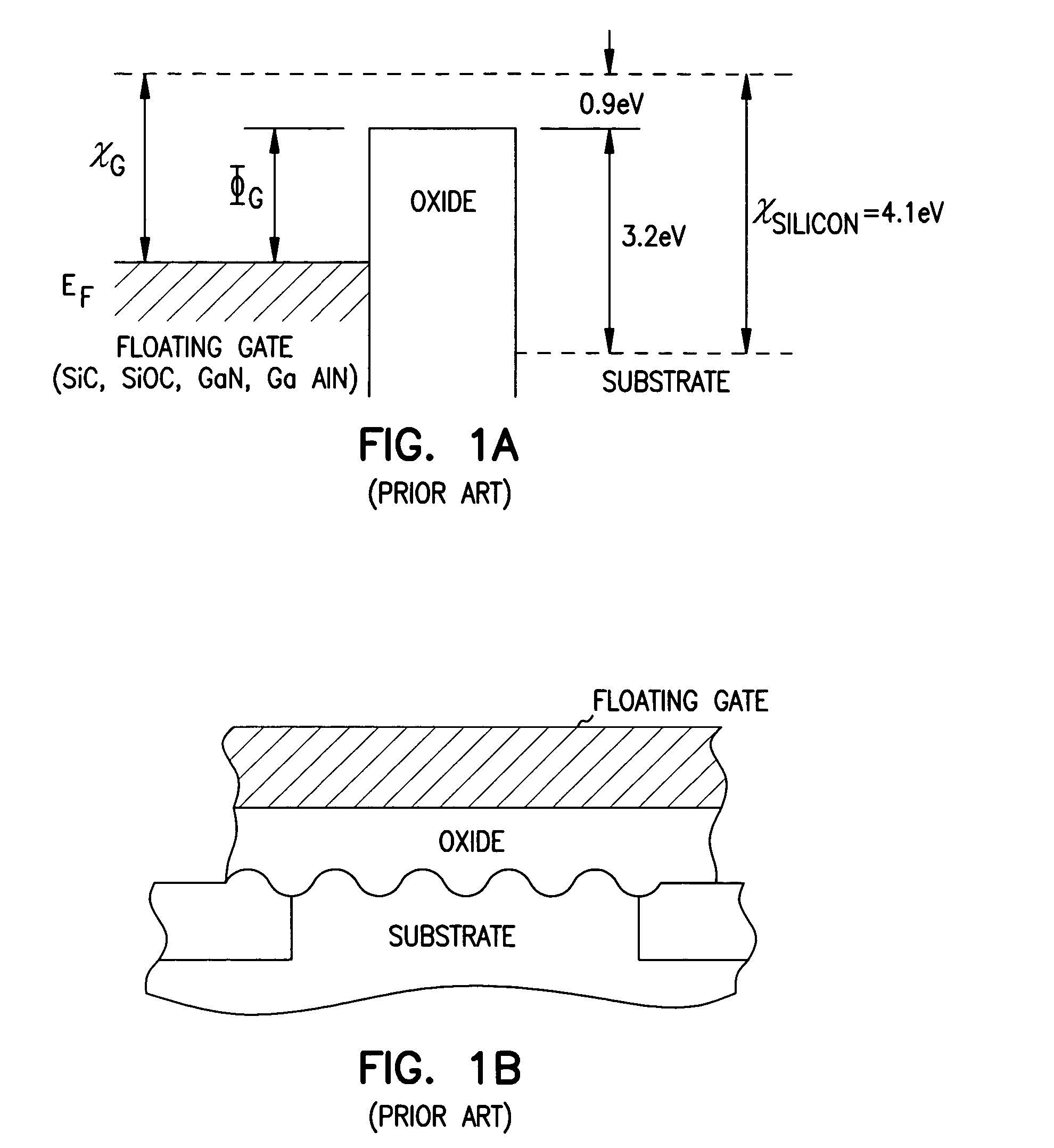

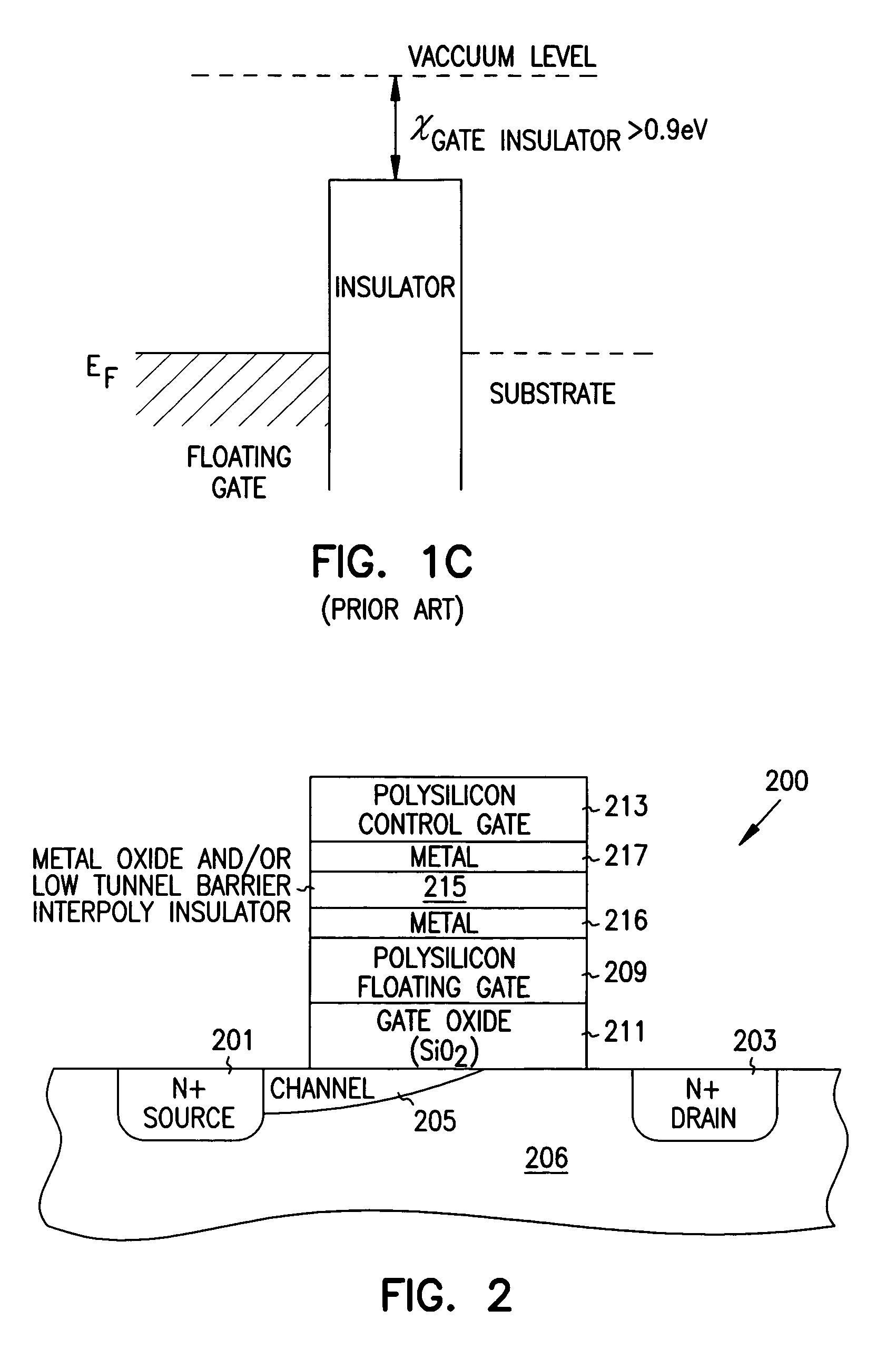

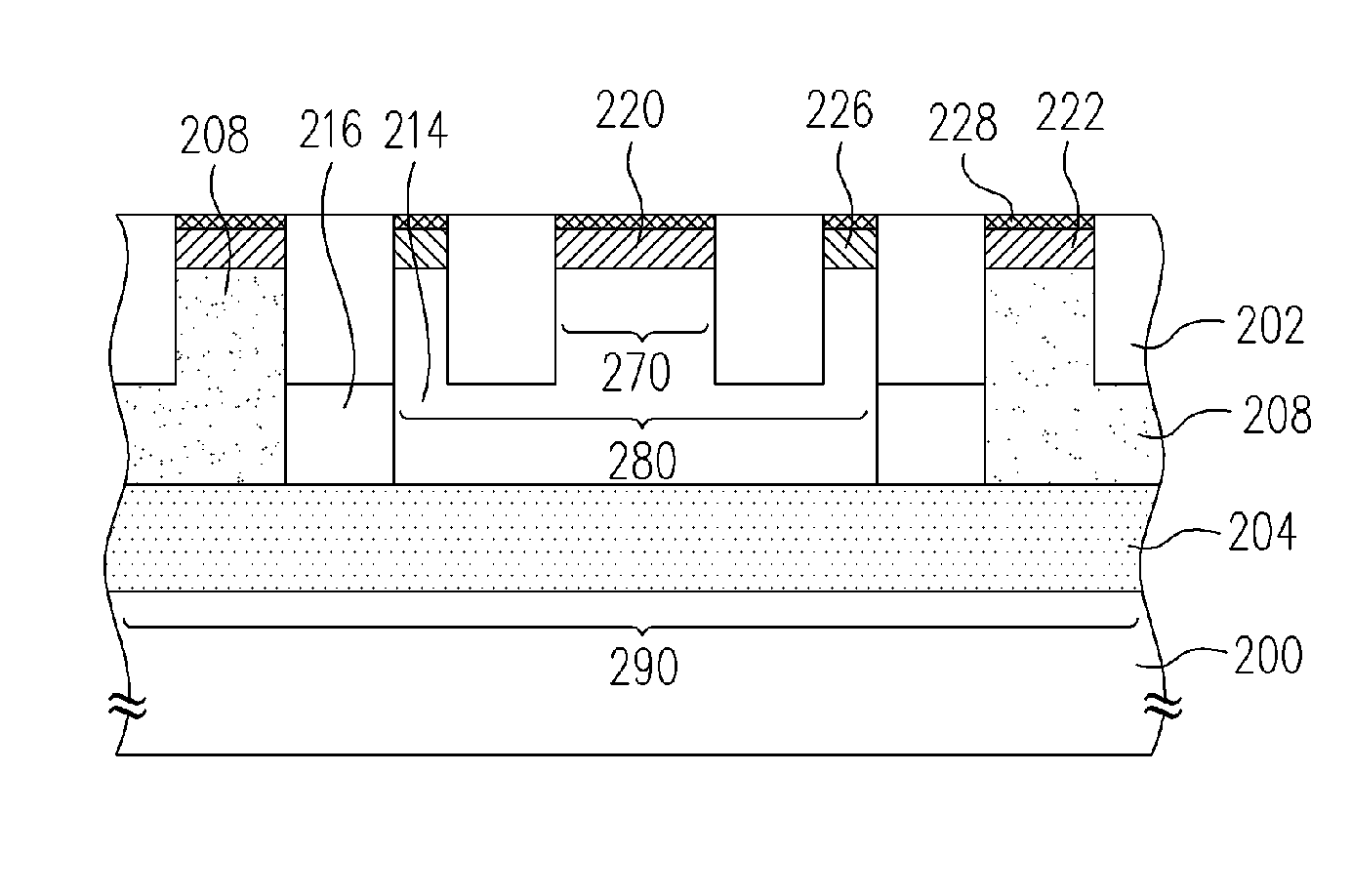

Integrated circuit memory device and method

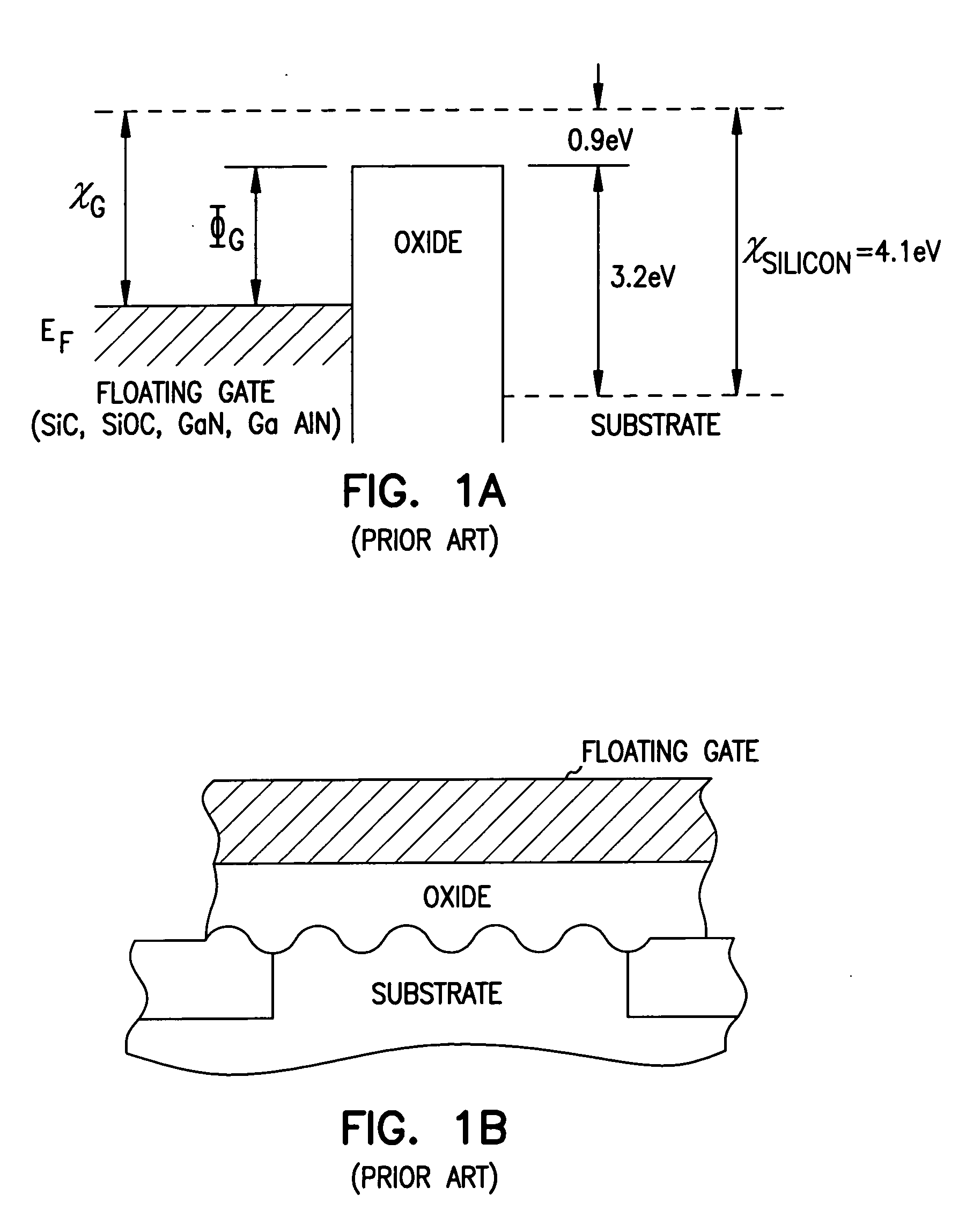

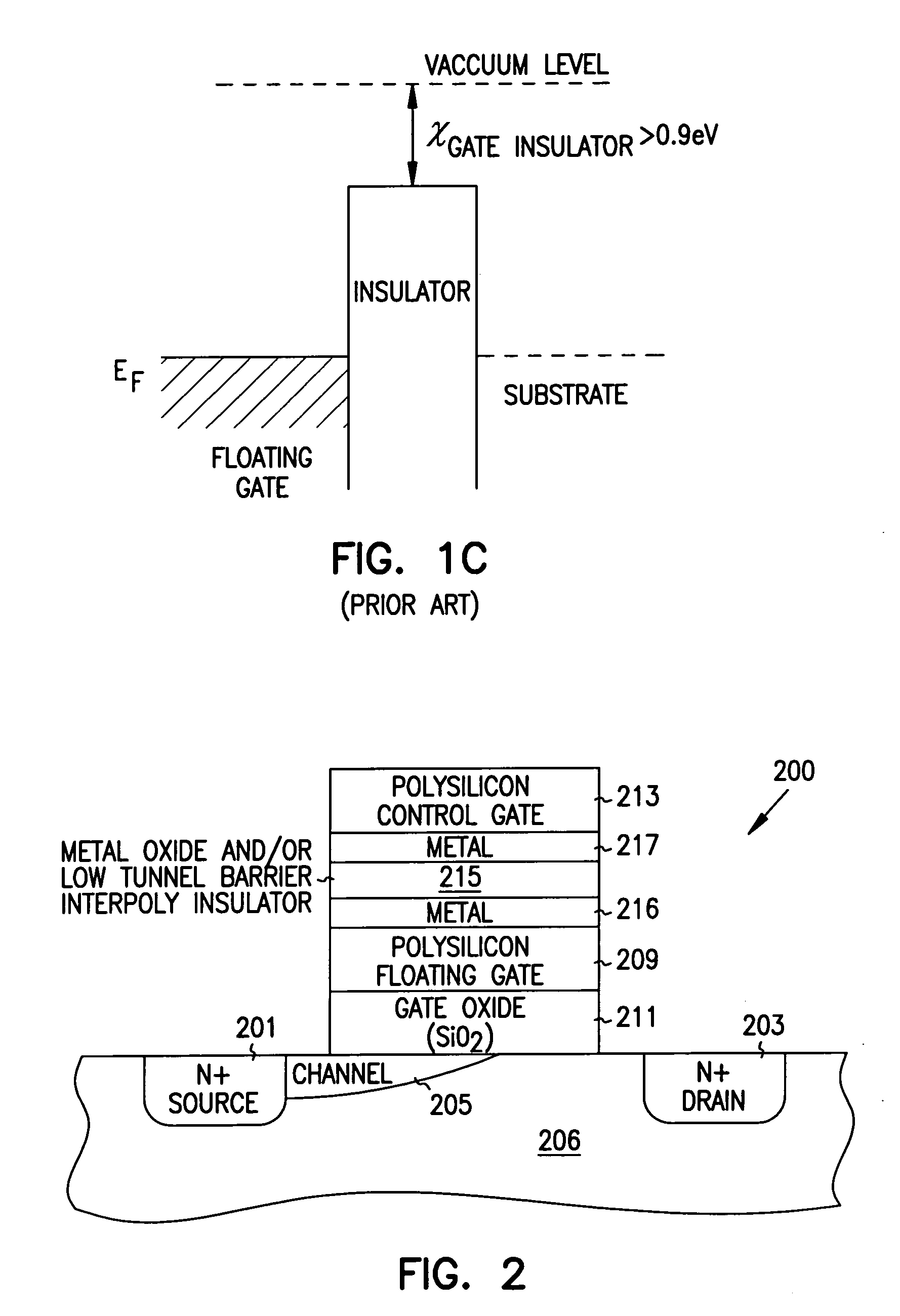

InactiveUS20060002192A1Increase current gainEasy programmingSolid-state devicesRead-only memoriesEngineeringGate oxide

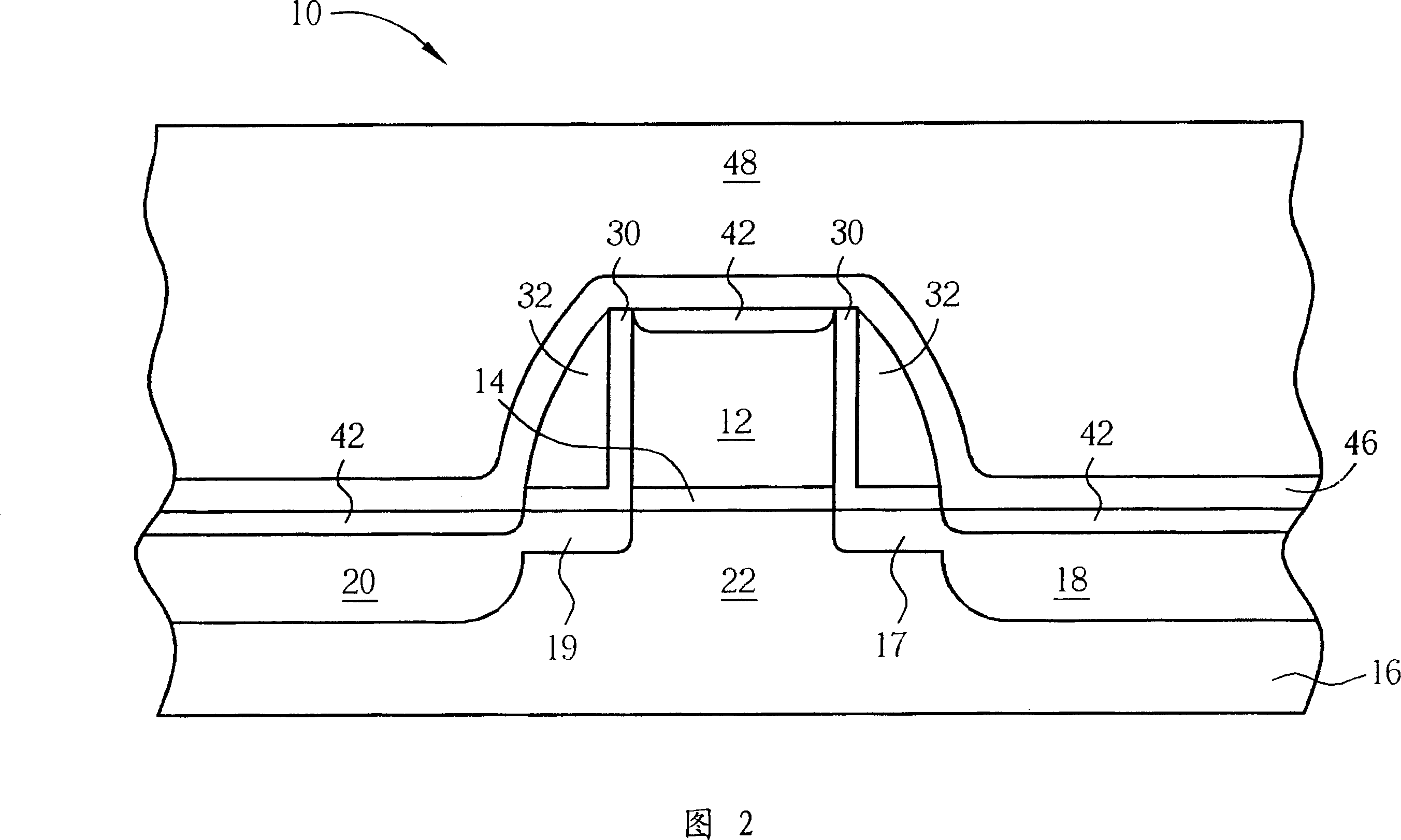

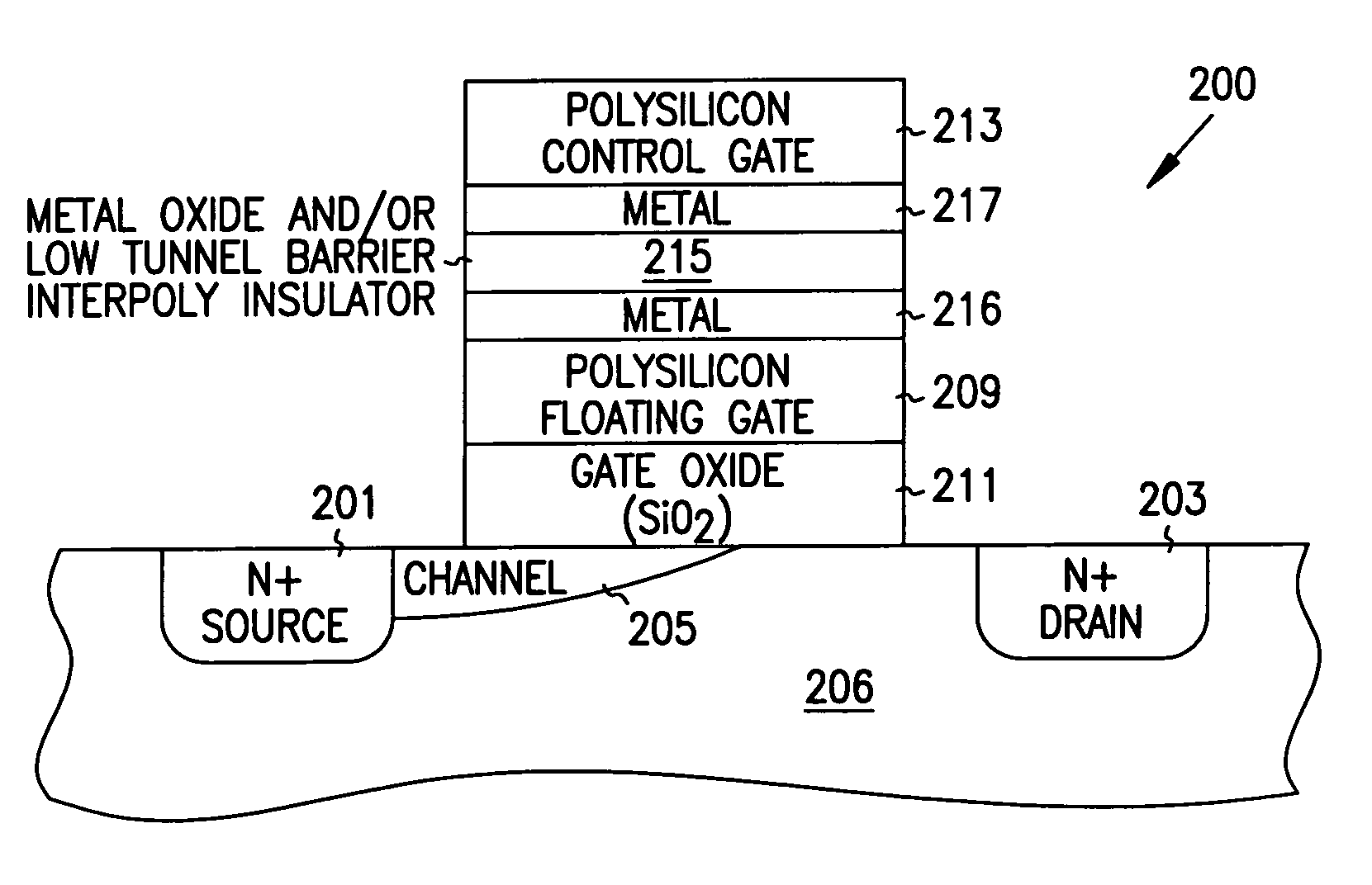

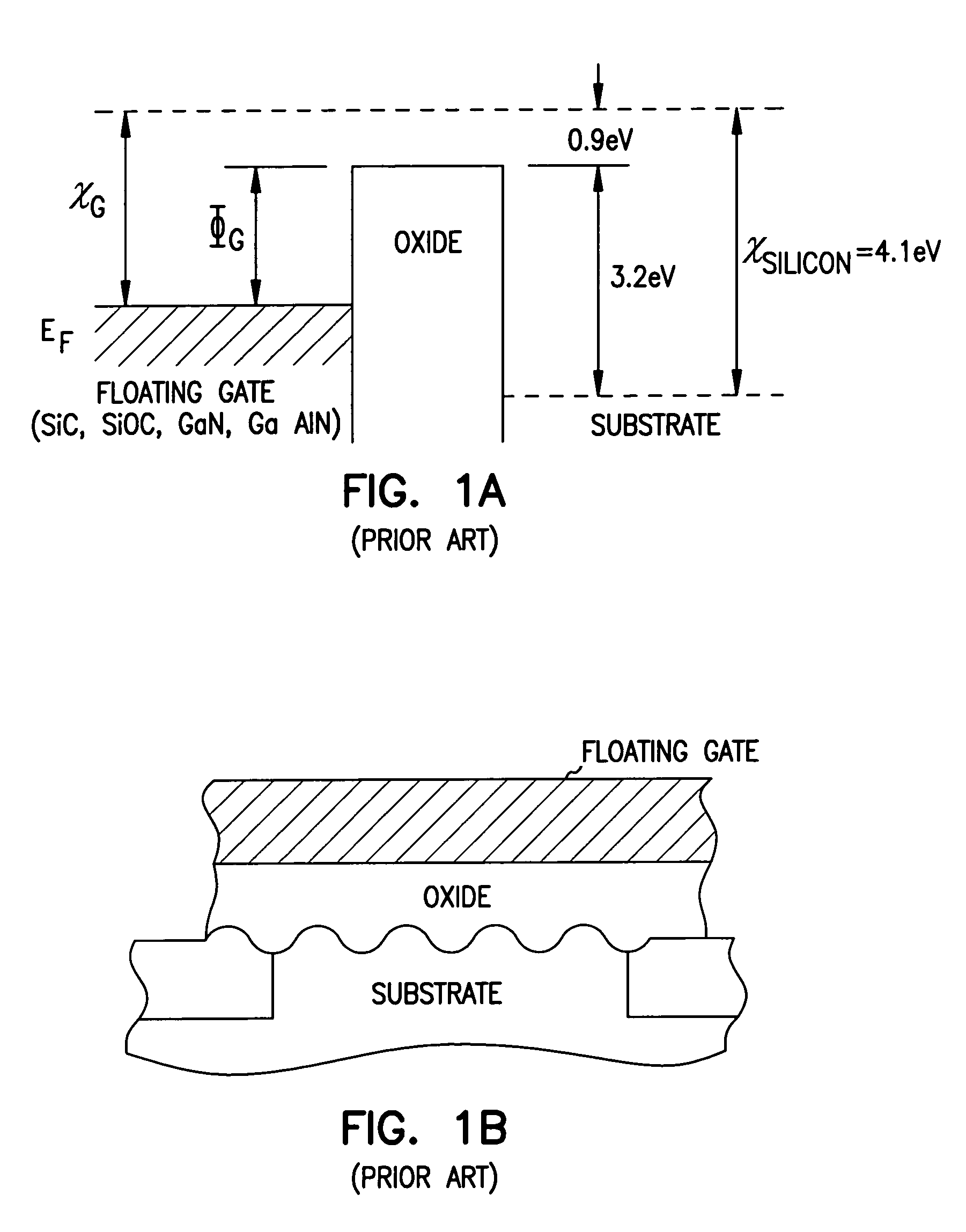

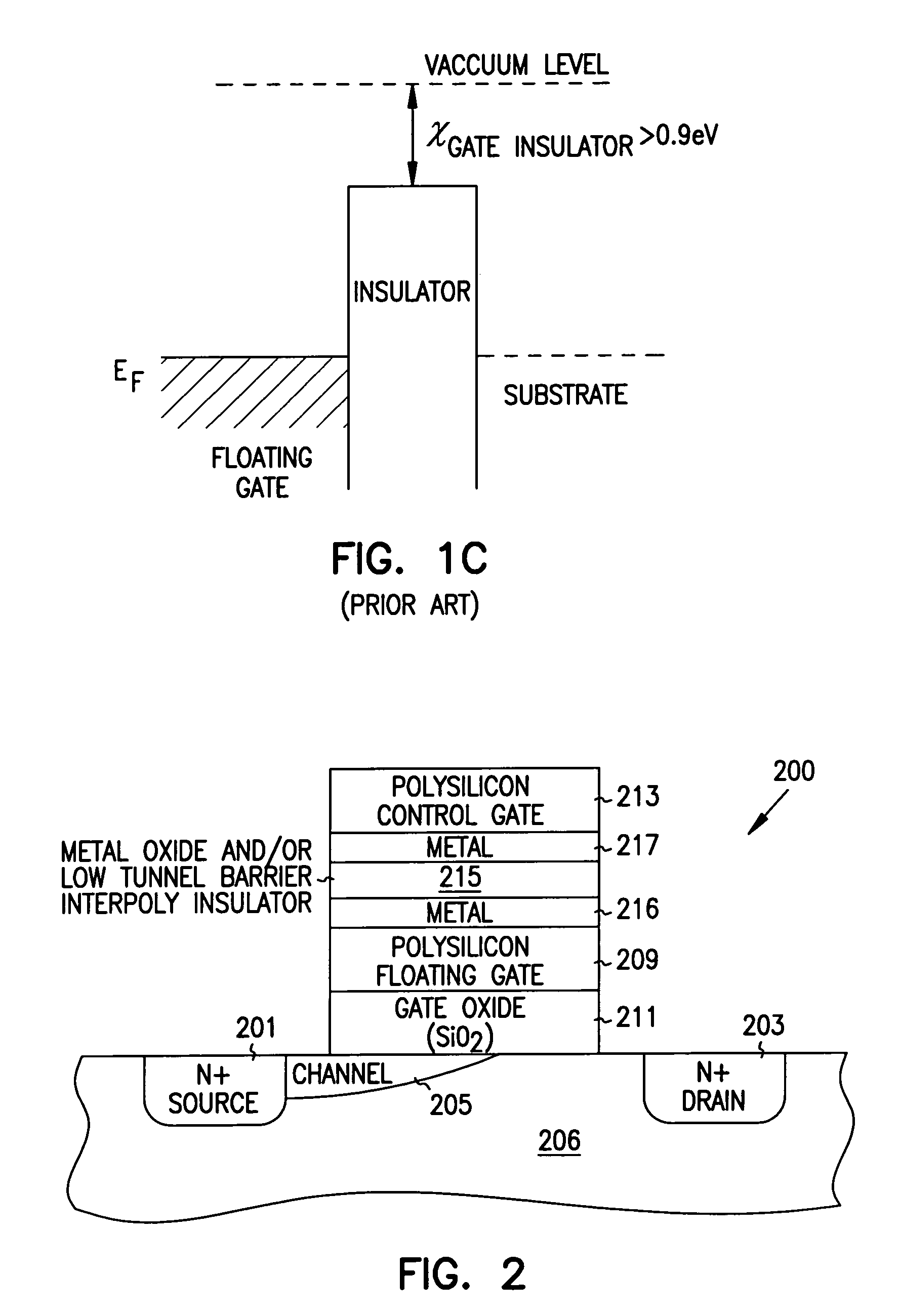

Structures and methods for DEAPROM memory with low tunnel barrier intergate insulators are provided. The DEAPROM memory includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposes the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator having a tunnel barrier of less than 1.5 eV. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of NiO, Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, Y2O3, Gd2O3, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

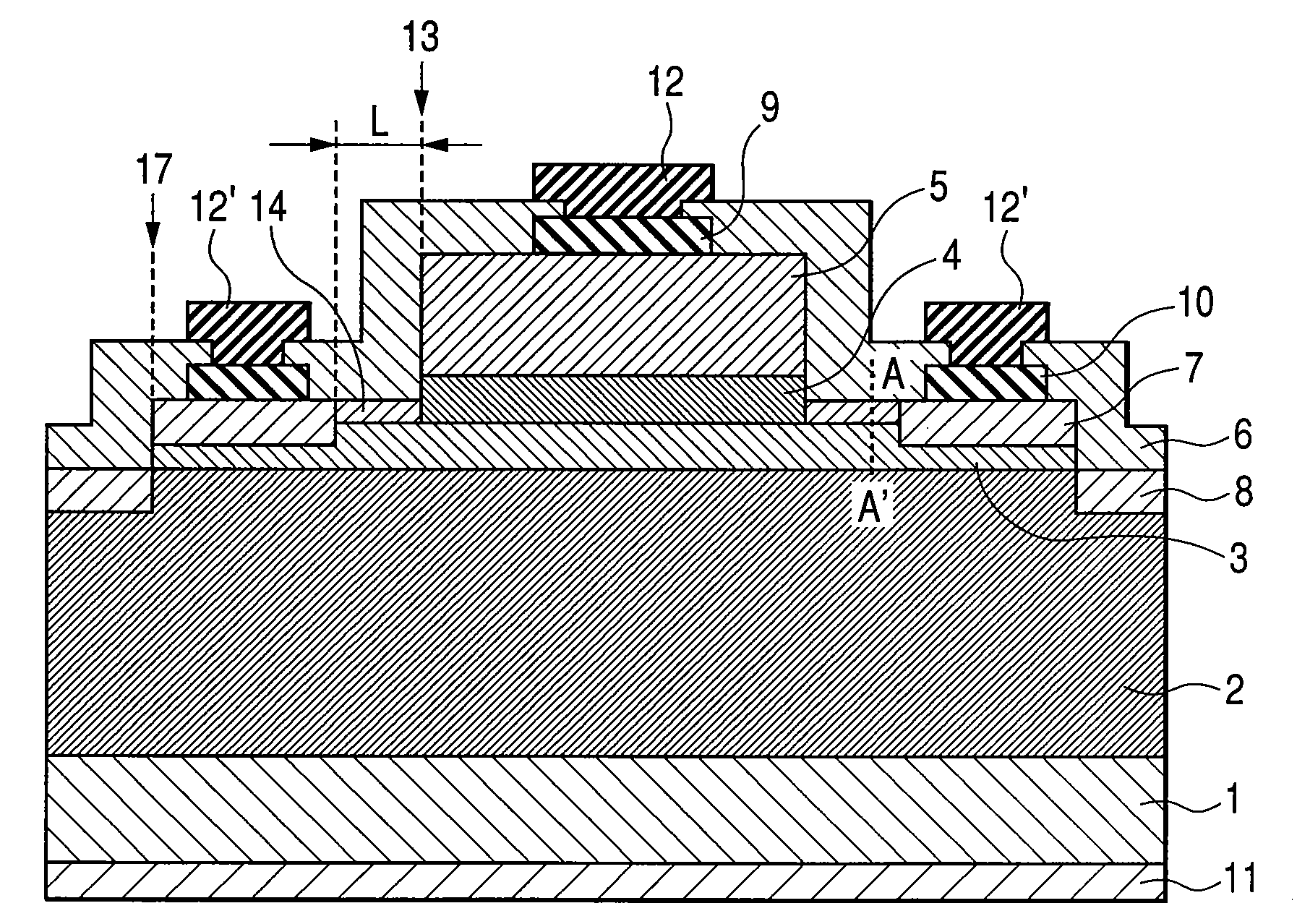

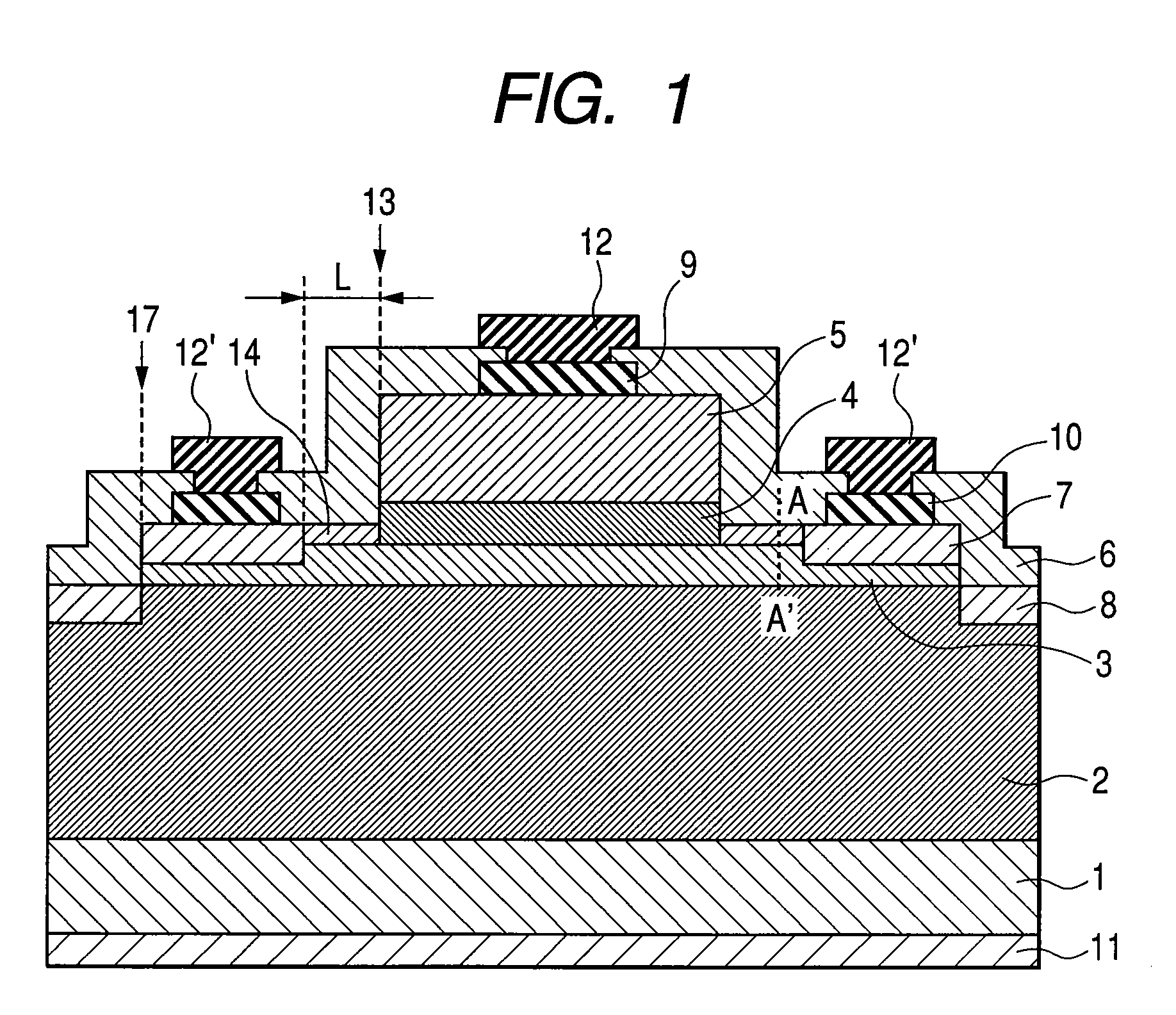

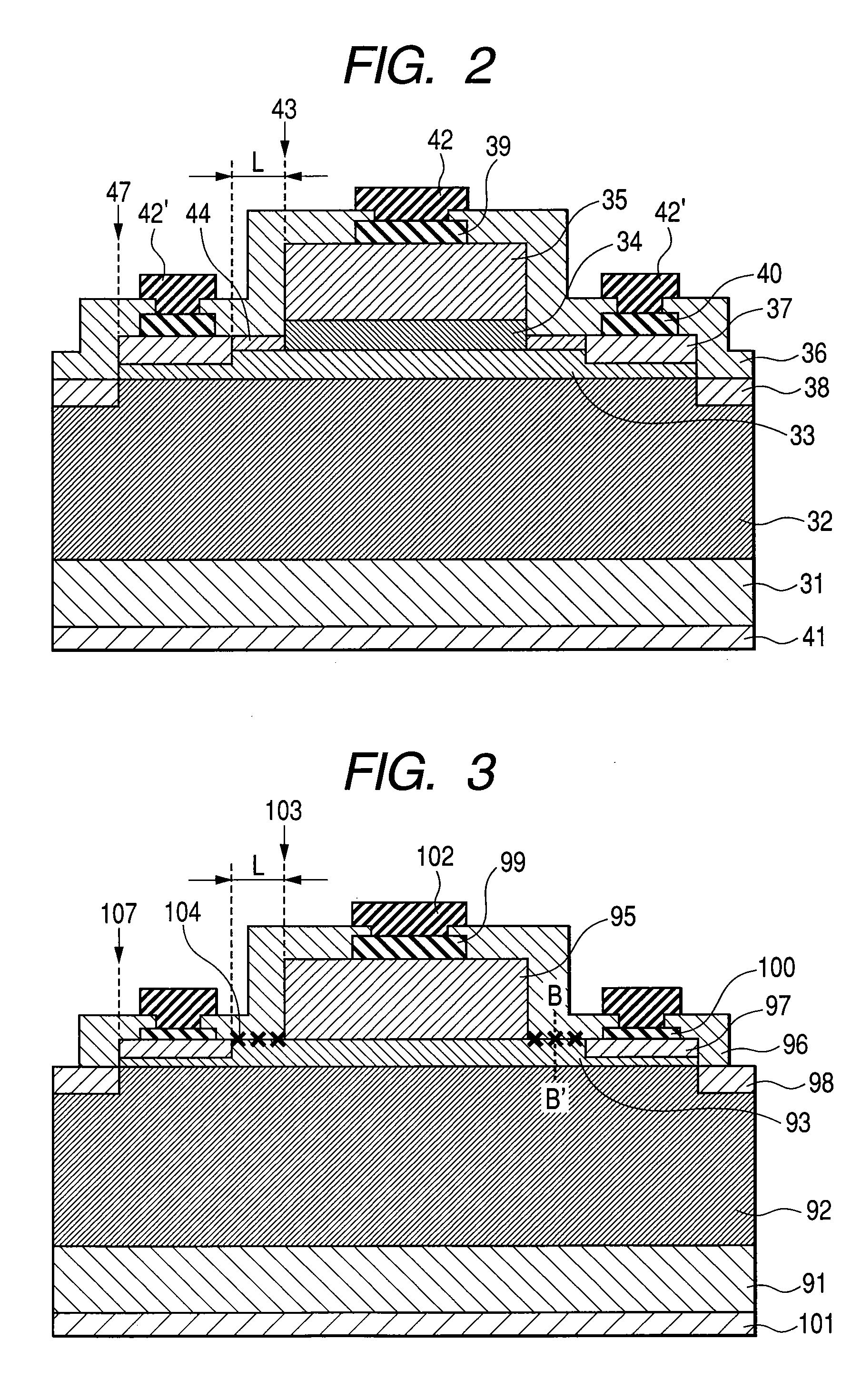

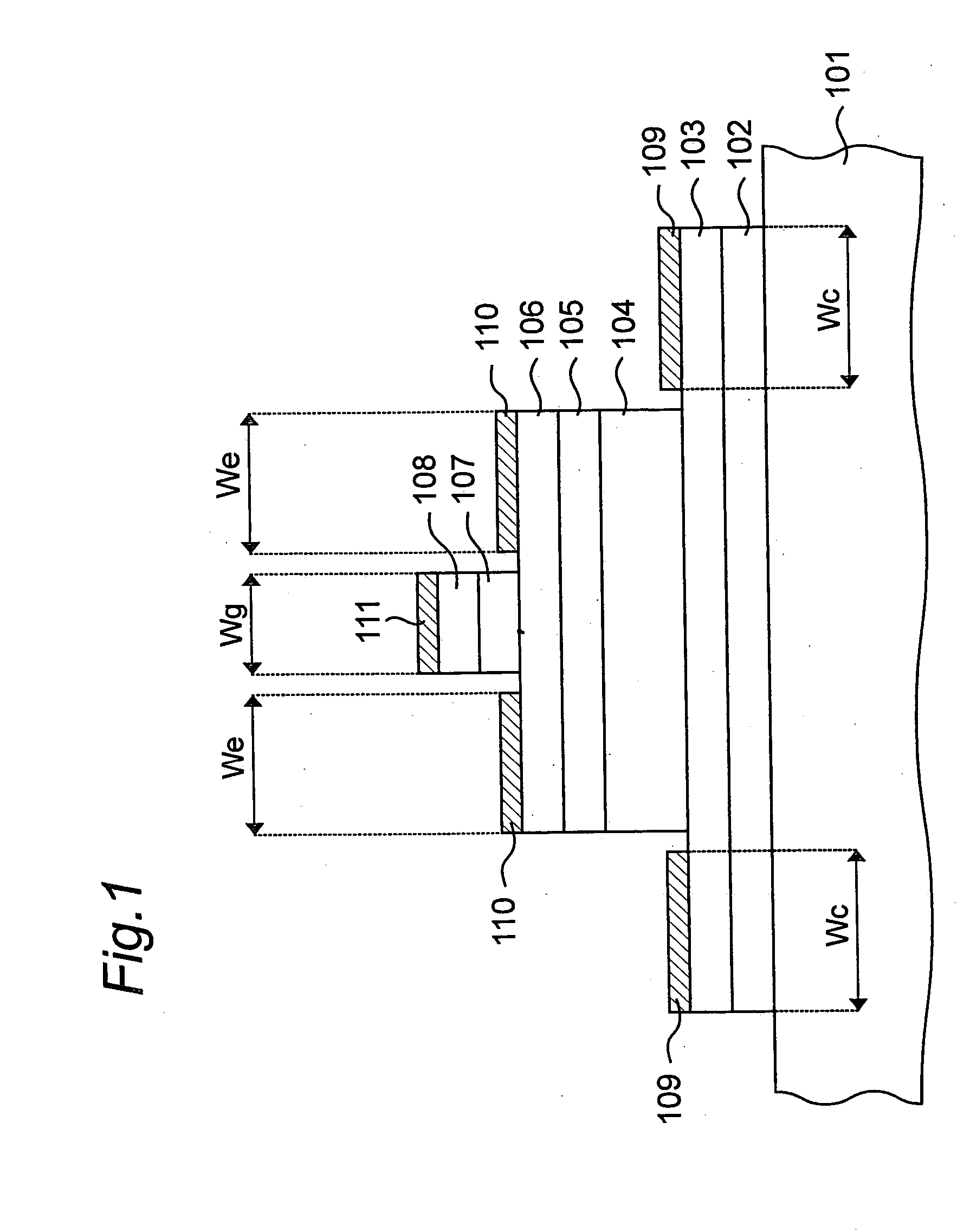

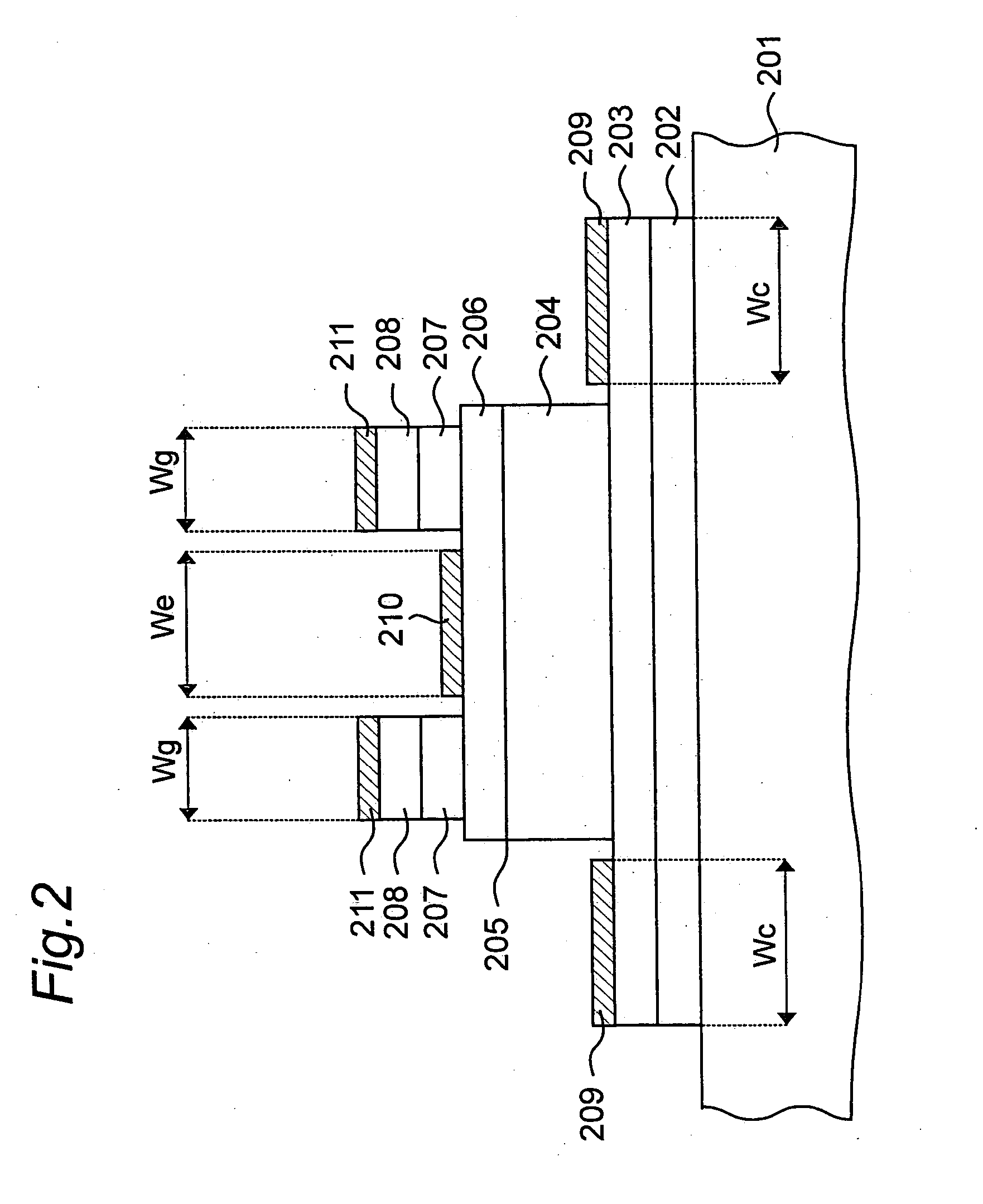

Bipolar device and fabrication method thereof

In a mesa type bipolar transistor or a thyristor, since carriers injected from an emitter layer or an anode layer to a base layer or a gate layer diffuse laterally and are recombined, reduction in the size and improvement for the switching frequency is difficult.In the invention, the emitter layer or the anode layer is formed of two high-doped and low-doped layers, a semiconductor region for suppressing recombination comprising an identical semiconductor having an impurity density identical with that of the low-doped layer is present being in contact with a base layer or a gate layer and a surface passivation layer, and the width of the semiconductor region for suppressing recombination is defined equal with or longer than the diffusion length of the carrier. This provides an effect of attaining reduction in the size of the bipolar transistor or improvement of the switching frequency of the thyristor without deteriorating the performance. Further, this has an effect of greatly improving the current gain by successively stacking above the high-doped emitter layer of the bipolar transistor, a hole barrier layer, a conduction band discontinuity relaxed layer and an emitter contact layer.

Owner:HITACHI LTD

Integrated circuit memory device and method

InactiveUS7027328B2Increase current gainEasy programmingTransistorSolid-state devicesEngineeringGate oxide

Structures and methods for DEAPROM memory with low tunnel barrier intergate insulators are provided. The DEAPROM memory includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposes the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator having a tunnel barrier of less than 1.5 eV. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of NiO, Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, Y2O3, Gd2O3, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Lateral bipolar junction transistor and method for manufacturing the same

ActiveCN101814433AHigh frequencyIncrease current gainTransistorSemiconductor/solid-state device manufacturingEngineeringThreshold voltage

The invention relates to a lateral bipolar junction transistor and a method for manufacturing the same. The lateral bipolar junction transistor includes an emitter region; a base region surrounding the emitter region; a gate disposed at least over a portion of the base region; and a collector region surrounding the base region; wherein the portion of the base region under the gate does not under go a threshold voltage implant process.

Owner:MEDIATEK INC

Semiconductor transistor element and its production

ActiveCN101030541AIncrease current gainEasy to operateTransistorSemiconductor/solid-state device manufacturingField-effect transistorSemiconductor

The invention is concerned with the method of making metal oxide semiconductor (MOS)transistor element, the characteristic is: the back-etching step that uses the silicon nitride covering layer with different stress and the superfluity shallow gully insulating layer, the field effect transistor element of N or P metal oxide semiconductor can with higher current gain, improves the operating efficiency of the semiconductor transistor element.

Owner:UNITED MICROELECTRONICS CORP

Integrated circuit memory device and method

InactiveUS7136302B2Increase current gainEasy programmingTransistorSolid-state devicesEngineeringGate oxide

Structures and methods for DEAPROM memory with low tunnel barrier intergate insulators are provided. The DEAPROM memory includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposes the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator having a tunnel barrier of less than 1.5 eV. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of NiO, Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, Y2O3, Gd2O3, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Bipolar junction transistor

InactiveCN101425536AImprove transportation capacityIncrease common emitter current gainTransistorDc dc converterSemiconductor

A bipolar junction transistor relates to the technical field of a semiconductor power device. The transistor comprises an underlay, a collecting region, an emitting region, a base region, an emitting electrode, a base electrode and a collecting electrode. The transistor is characterized in that a floating buried layer is arranged inside the base region; and the materials of the floating buried layer are different from that of the base region. The invention has the advantages of both good direct current characteristic and breakdown characteristic, namely both high current gain and higher breakdown voltage, and can be widely applied to the field of high-power converters (such as DC-DC converter and inverter).

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Solar real-time tracking system

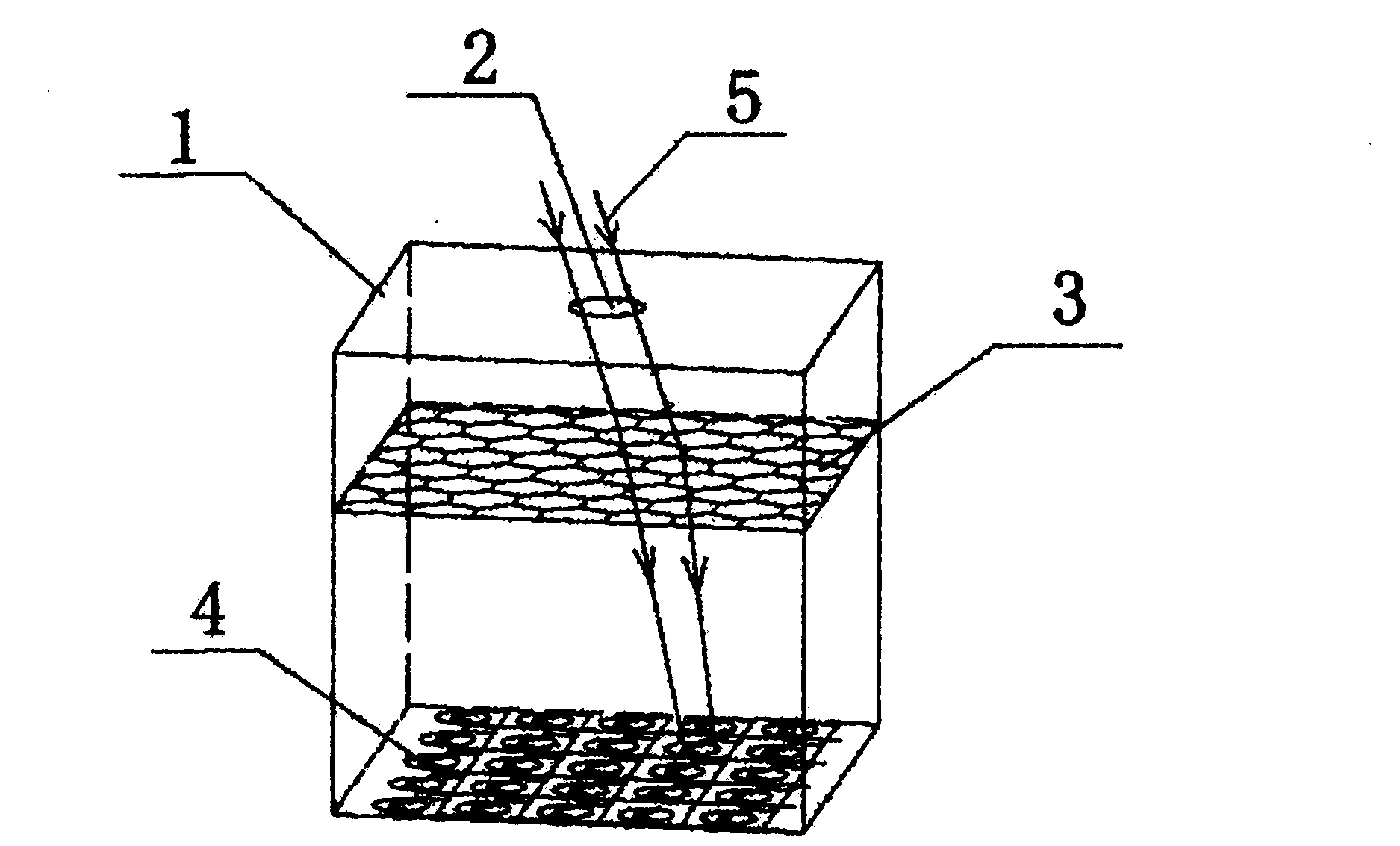

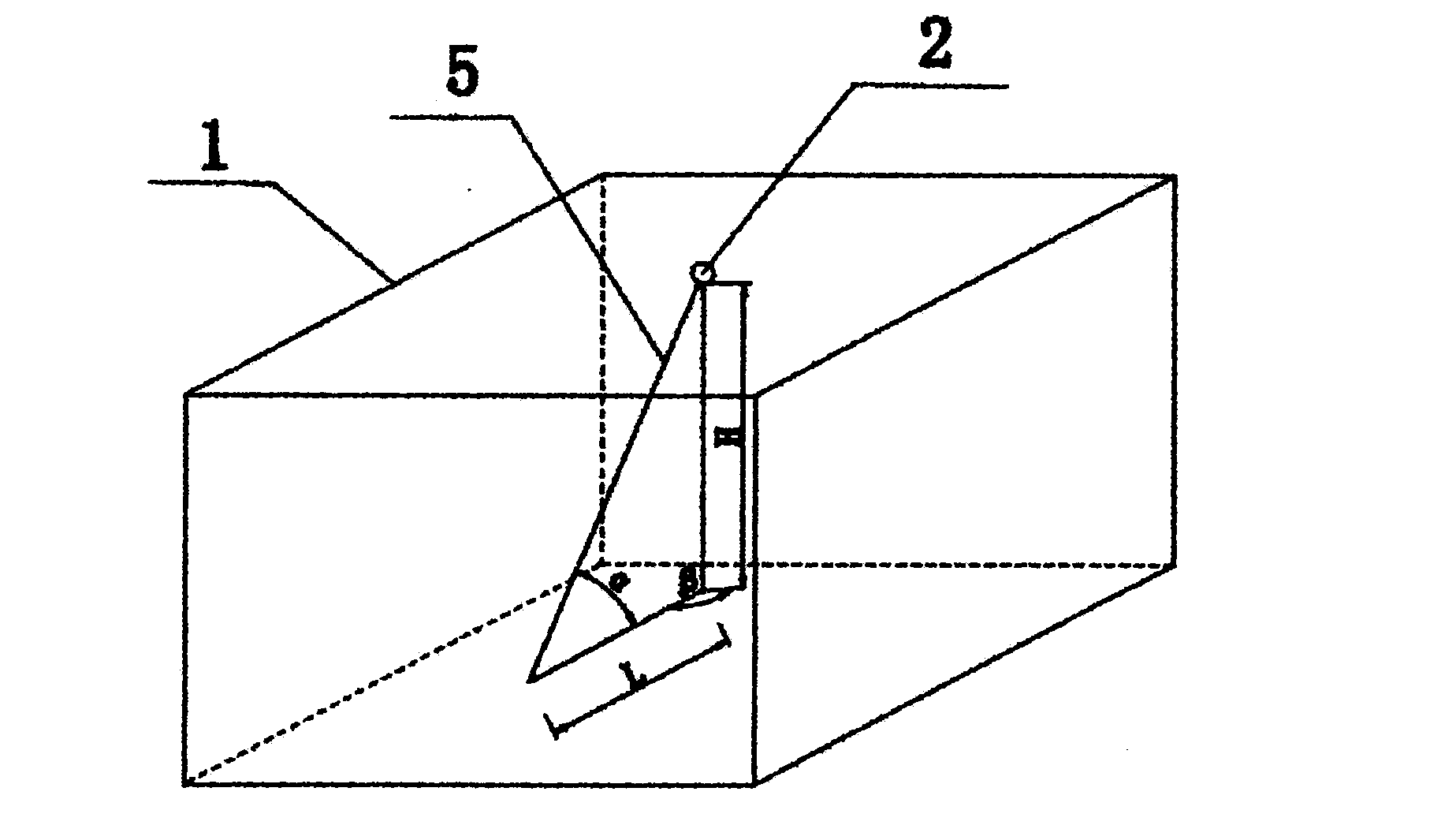

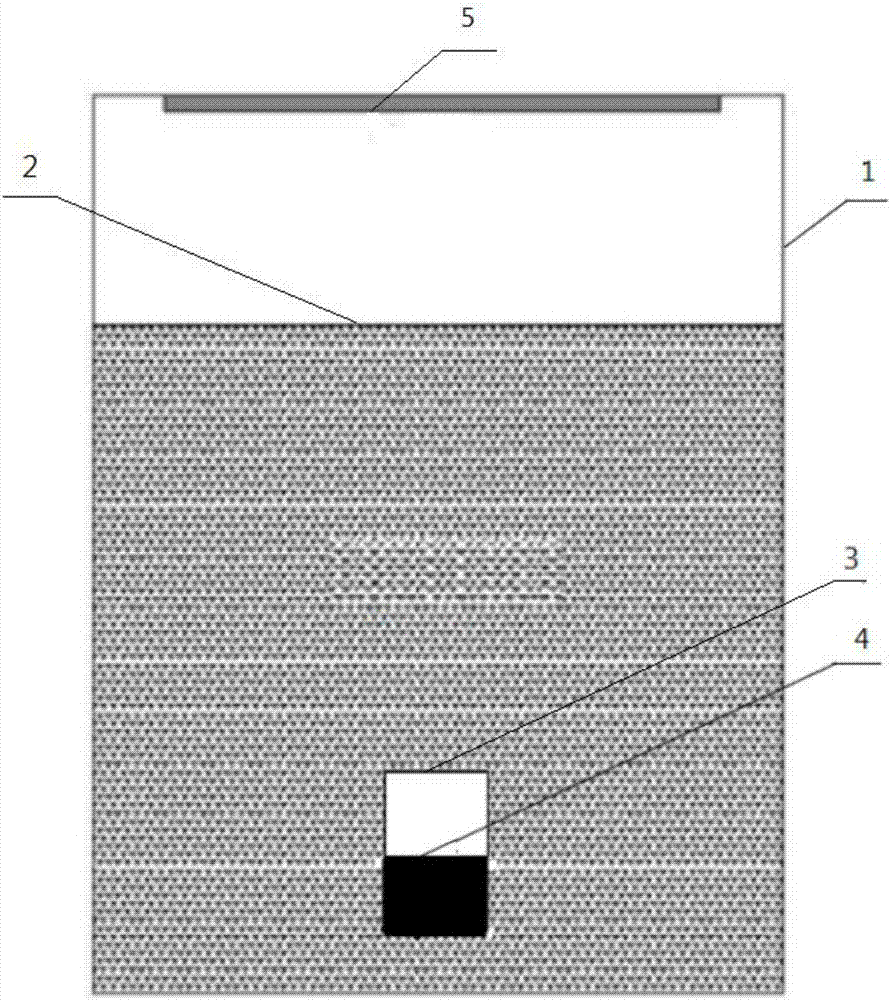

InactiveCN103425137AAvoid enteringImprove detection accuracyPhotovoltaic supportsSolar heating energyMicrocontrollerOptoelectronics

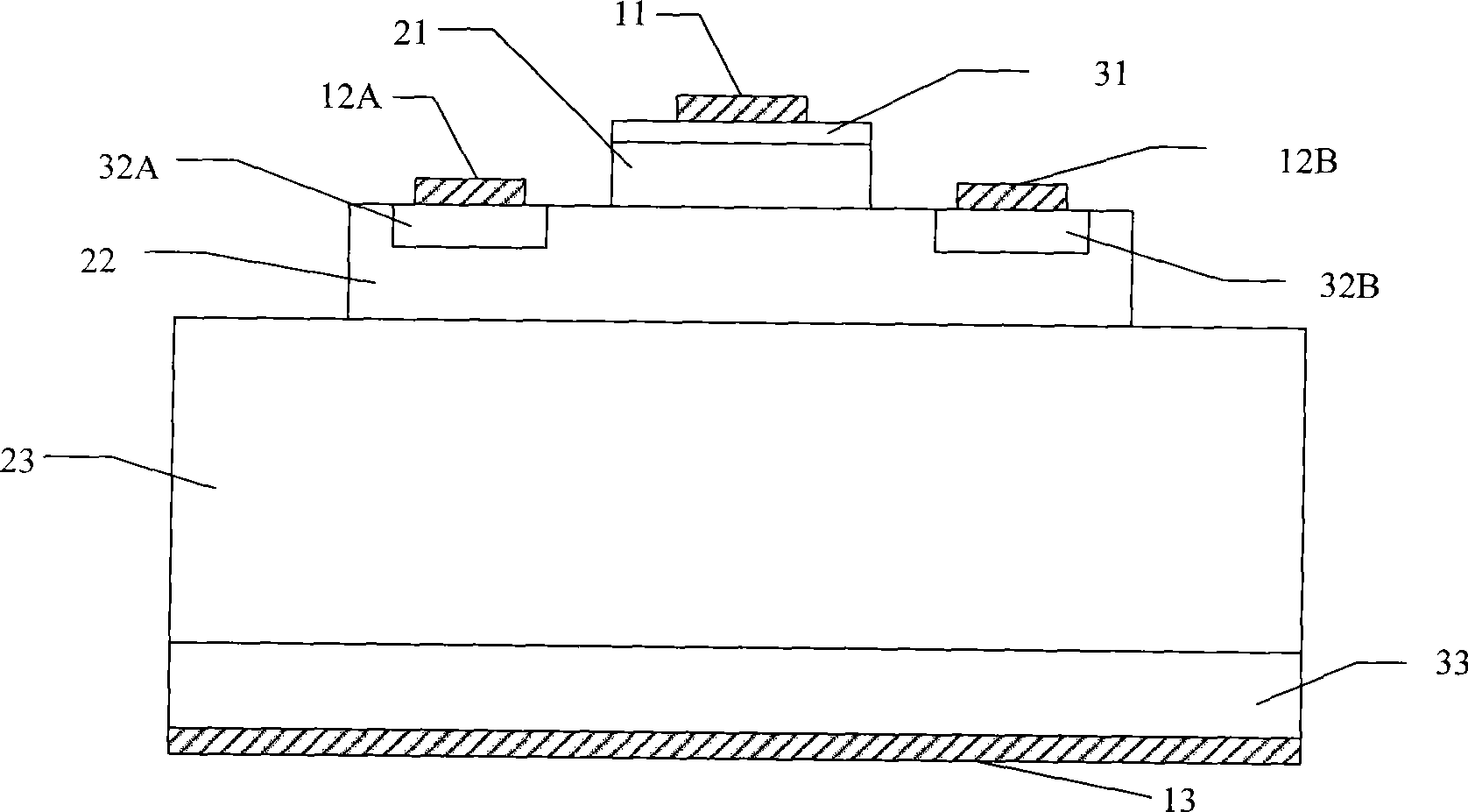

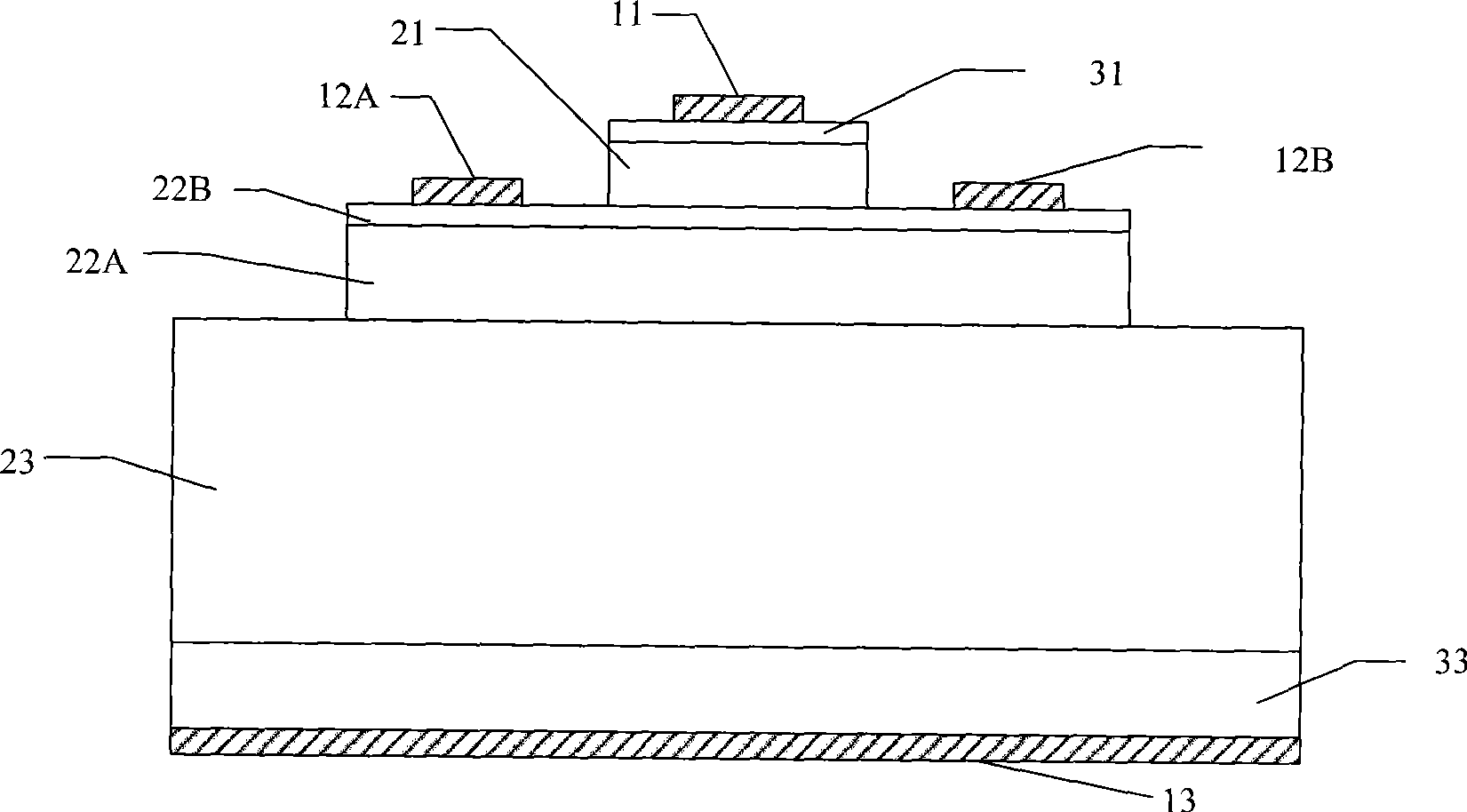

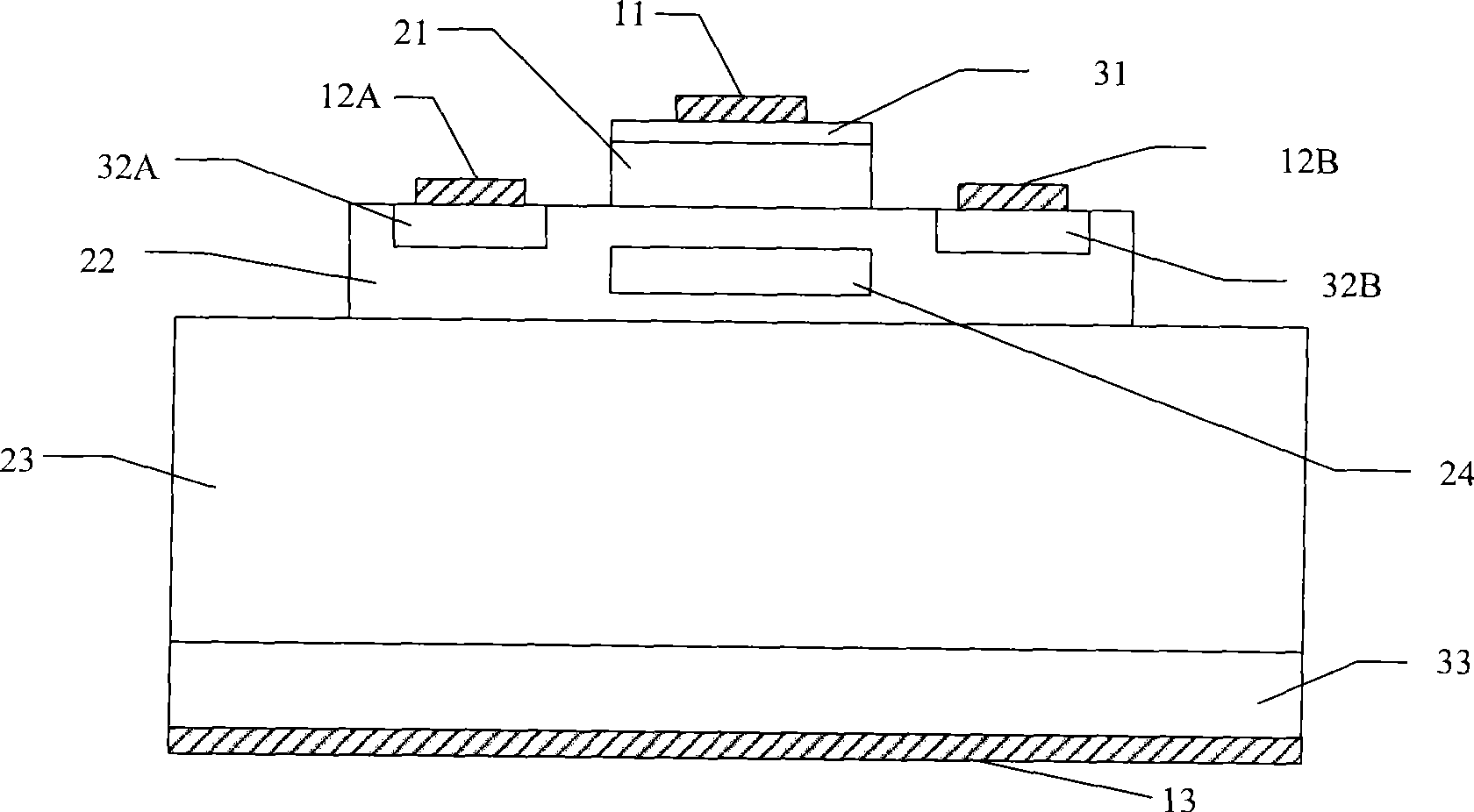

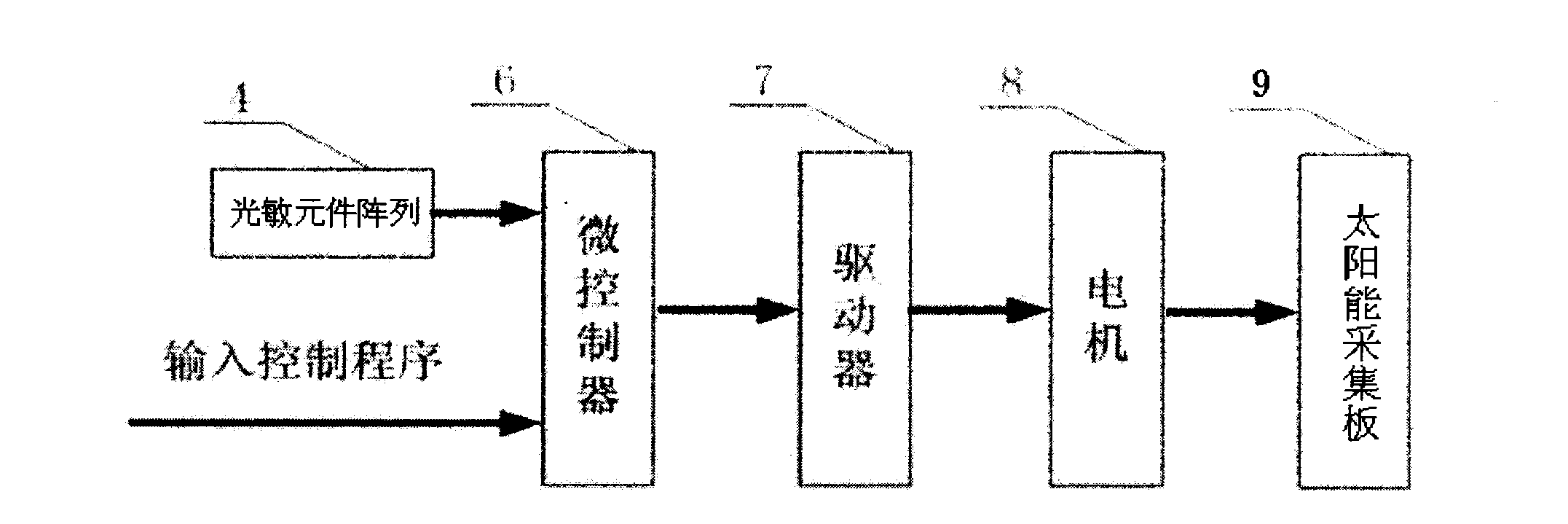

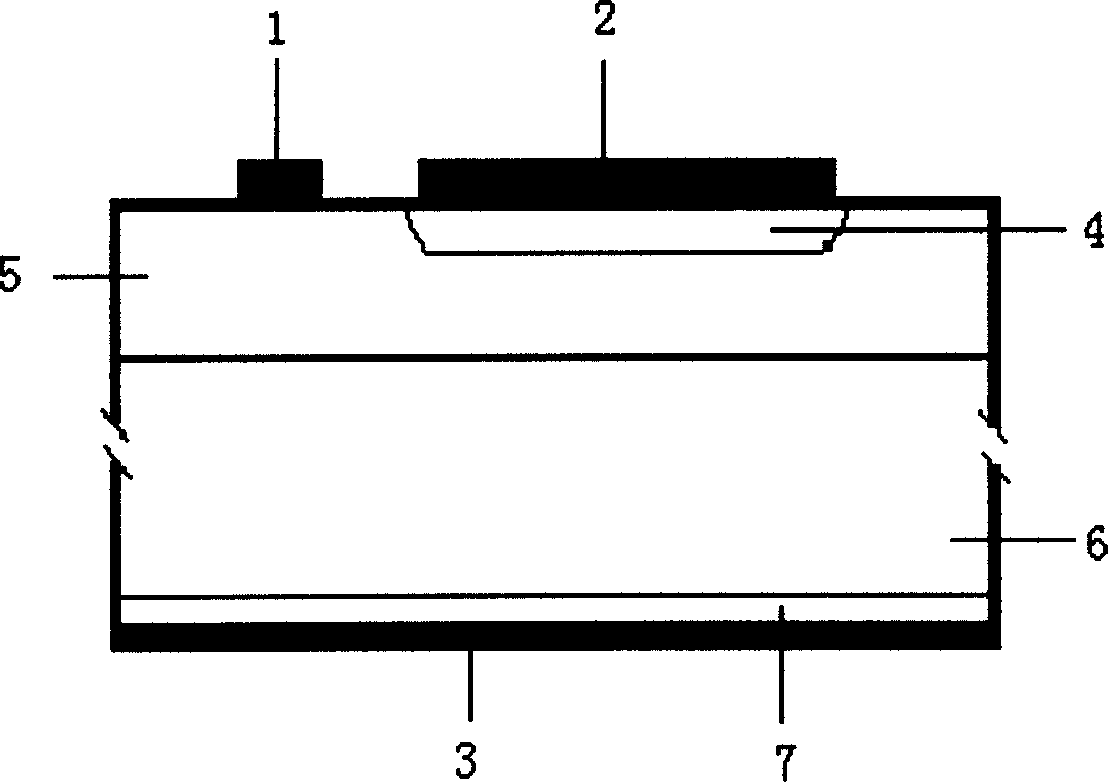

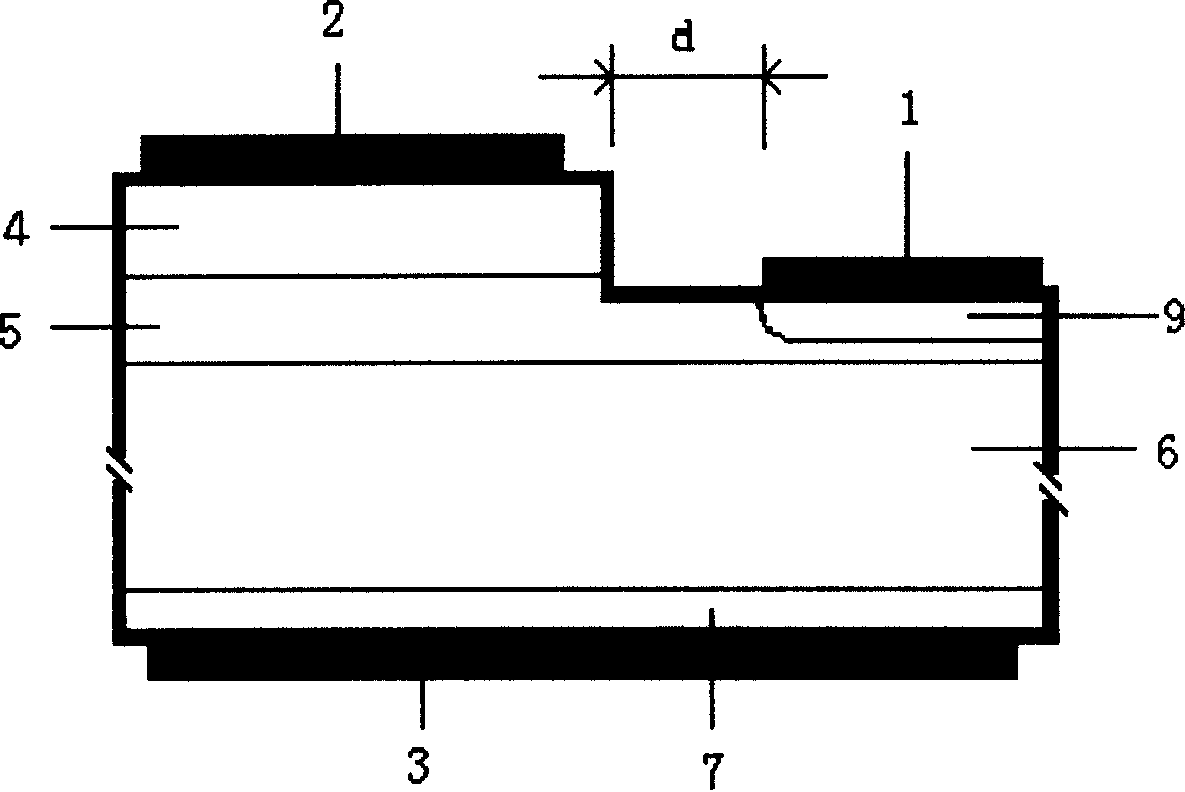

A real-time solar energy tracking system comprises a light resistant box (1), the top surface of the light resistant box (1) being provided thereon with a loophole (2), the interior of the light resistant box (1) being provided with a planar convex lens array (3) which is arranged in a manner of being parallel to the bottom surface of the light resistant box, and the bottom of the light resistant box (1) being provided with a photosensitive element array (4); a microcontroller (6) which is connected to the photosensitive element array (4), and used for obtaining a solar azimuth signal from the photosensitive element array (4) and calculating a solar azimuth; a driver (7) which is connected to the microcontroller (6) through a data line, and used for receiving an instruction from the microcontroller (6); a motor (8) which is connected to the driver (7) through a conductor, and driven by the driver (7); and a solar collection plate (9) which is mechanically connected to the motor (8), and used for adjusting the direction to collect solar energy under the drive of the motor (8). The real-time solar energy tracking system is applied to a solar power generation system, and has a high detection accuracy, a high automation and intelligentizion degree, a good adaptive capability to the environment, high system reliability, low costs and a simple structure.

Owner:SHANGHAI ZHIJING BIOLOGICAL TECH

Method for growth of germanium nitrogen codoped silicon carbide single crystal material

ActiveCN106968018AAchieve dopingRealize germanium nitrogen co-dopingPolycrystalline material growthFrom condensed vaporsHigh concentrationOptoelectronics

The invention relates to a method for growth of a germanium nitrogen codoped silicon carbide single crystal material. A PVT method is adopted according to the method; in the germanium-doped silicon carbide single crystal growth process, nitrogen at a certain proportion is led into a growth atmosphere, argon is led in to serve as a carrier gas with the pressure controlled to be 700-850 mbar, argon flow is 15-30 sccm, and the nitrogen flow is 0.5-2 sccm; and the germanium nitrogen codoped silicon carbide single crystal is obtained. On the one hand, high-concentration germanium element doping is implemented, and on the other hand, by adjusting specific doping concentration of germanium and nitrogen, the goal of increasing silicon carbide crystal lattice fitness degree, reducing crystal stress and improving crystal quality is achieved. Application of the silicon carbide crystal material to visible light and infrared light wave bands is expanded.

Owner:SHANDONG UNIV

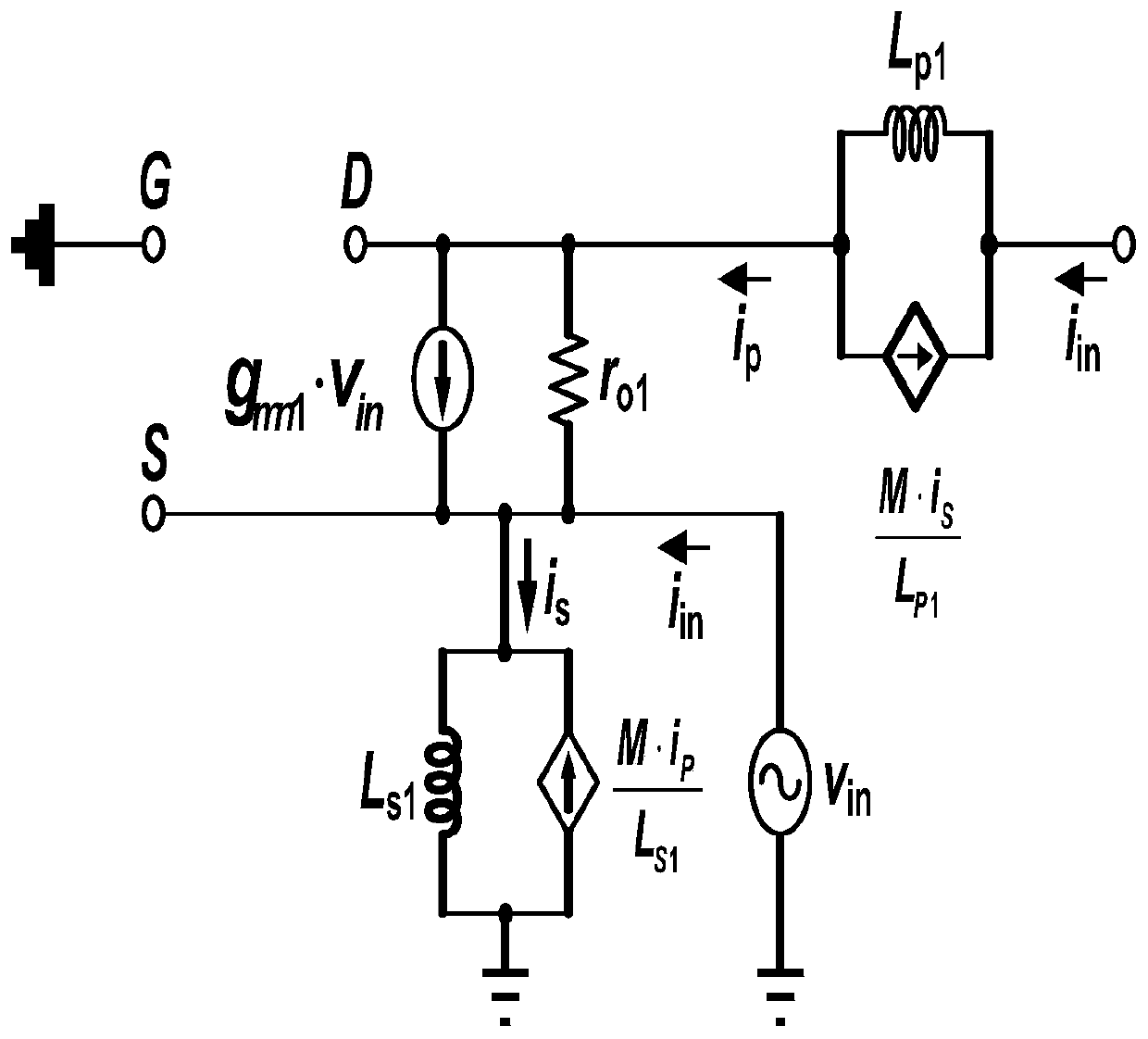

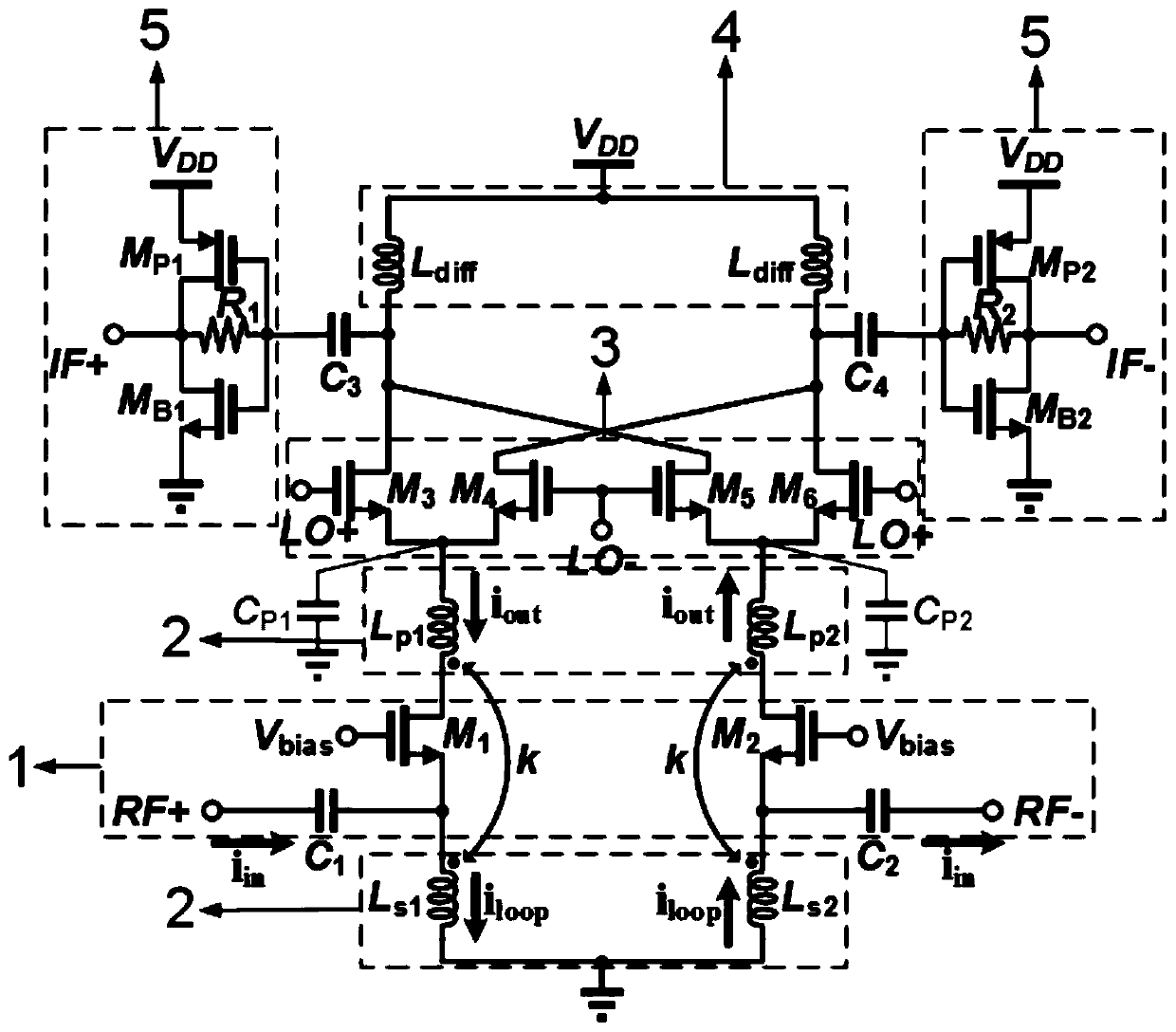

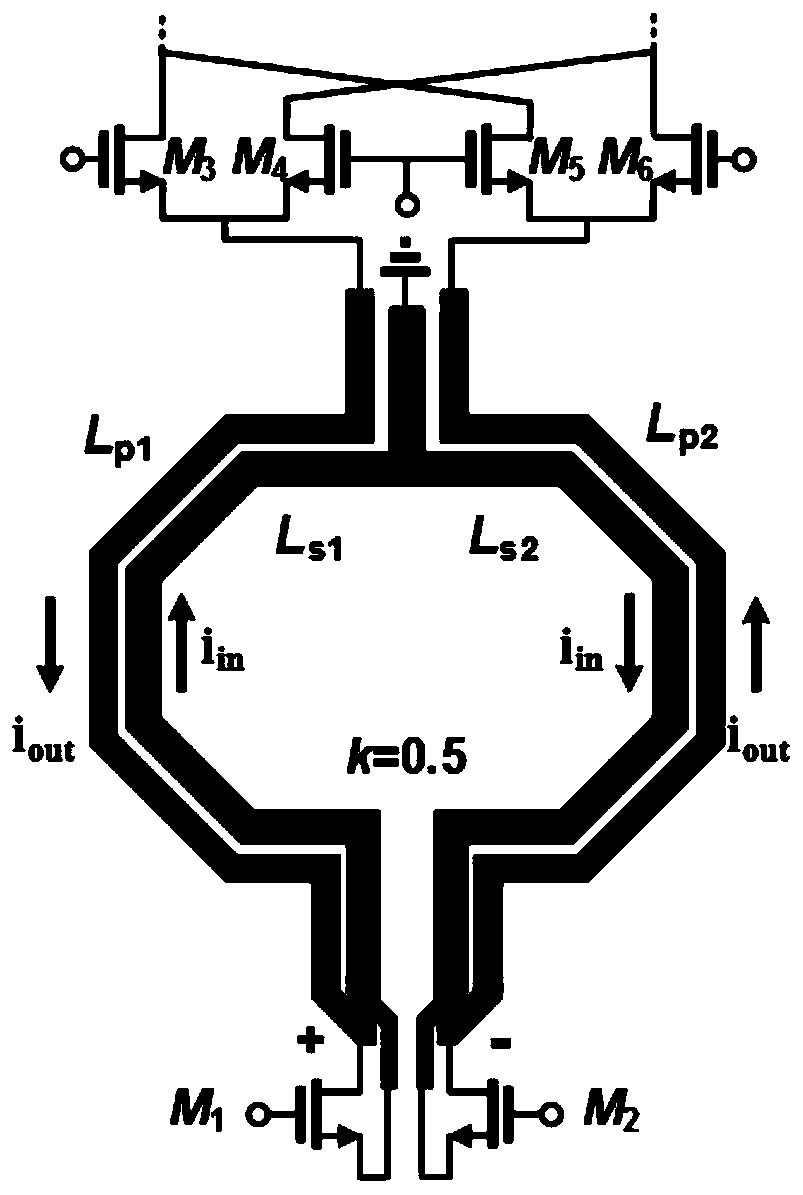

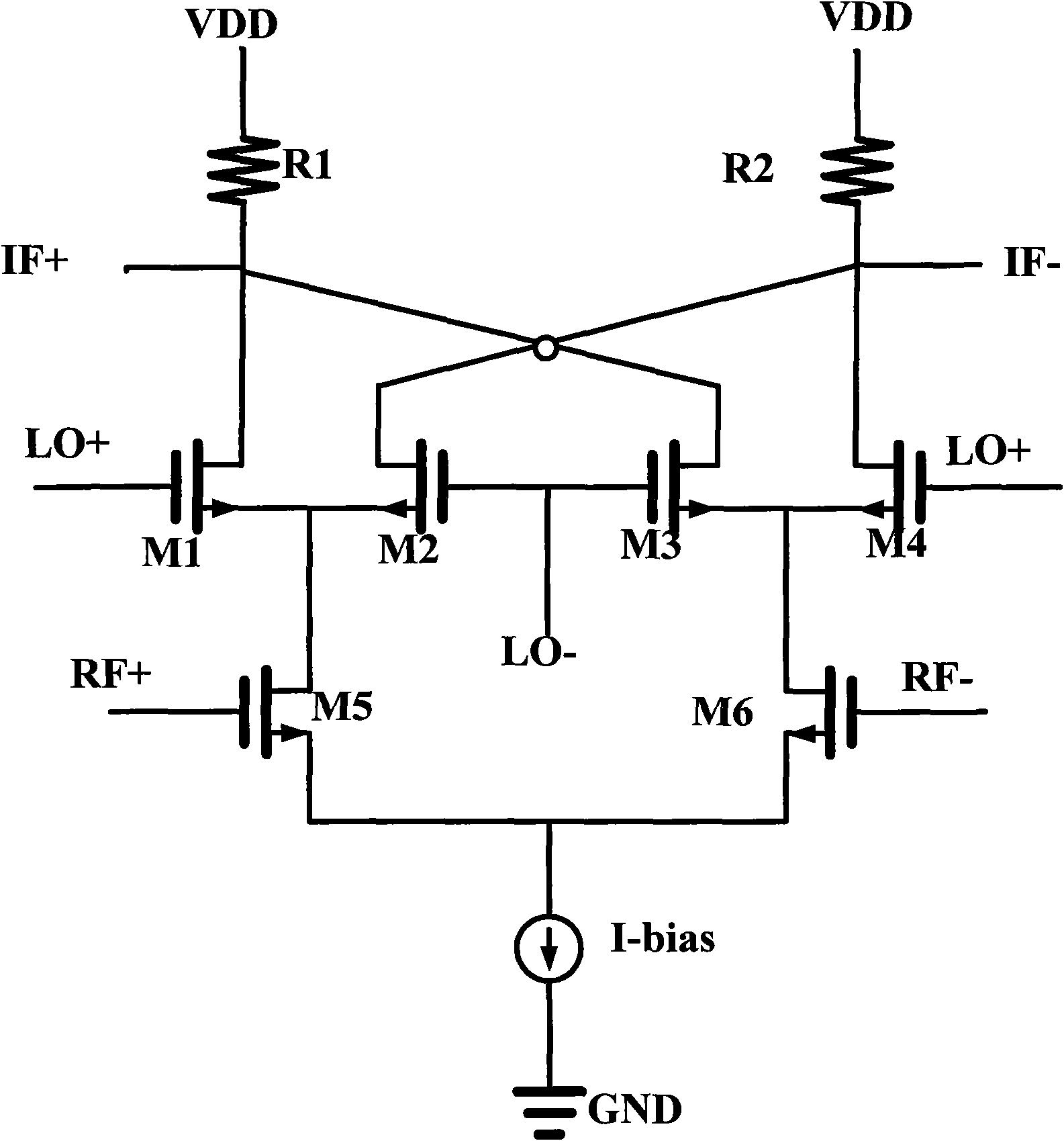

High-isolation broadband millimeter wave mixer applied to 5G communication

InactiveCN110535441APrevent leakageHigh Q valueMulti-frequency-changing modulation transferenceTransformerHigh isolation

The invention belongs to the technical field of wireless communication, and relates to a mixer, in particular to a high-isolation broadband millimeter wave mixer applied to 5G communication, which comprises a transconductance stage unit 1, an electromagnetic coupling unit 2, a switch stage unit 3, a load stage unit 4 and a buffer stage unit 5. According to the electromagnetic coupling type common-gate structure mixer based on the CMOS technology, the common-gate input transconductance stage is adopted, system-level design is facilitated, and broadband matching can be achieved without an extramatching network; the transformer network and the standard inductor LP introduced in the middle can counteract the interstage parasitic capacitance, so that the noise is reduced, the gain is improved,the differential inductor LS can be matched with and form feedback requirements, and the gain is further improved; and meanwhile, the circuit structure is symmetrical, so that the circuit structure can be well symmetrical when an actual layout is implemented, thereby being beneficial to the isolation of the mixer.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

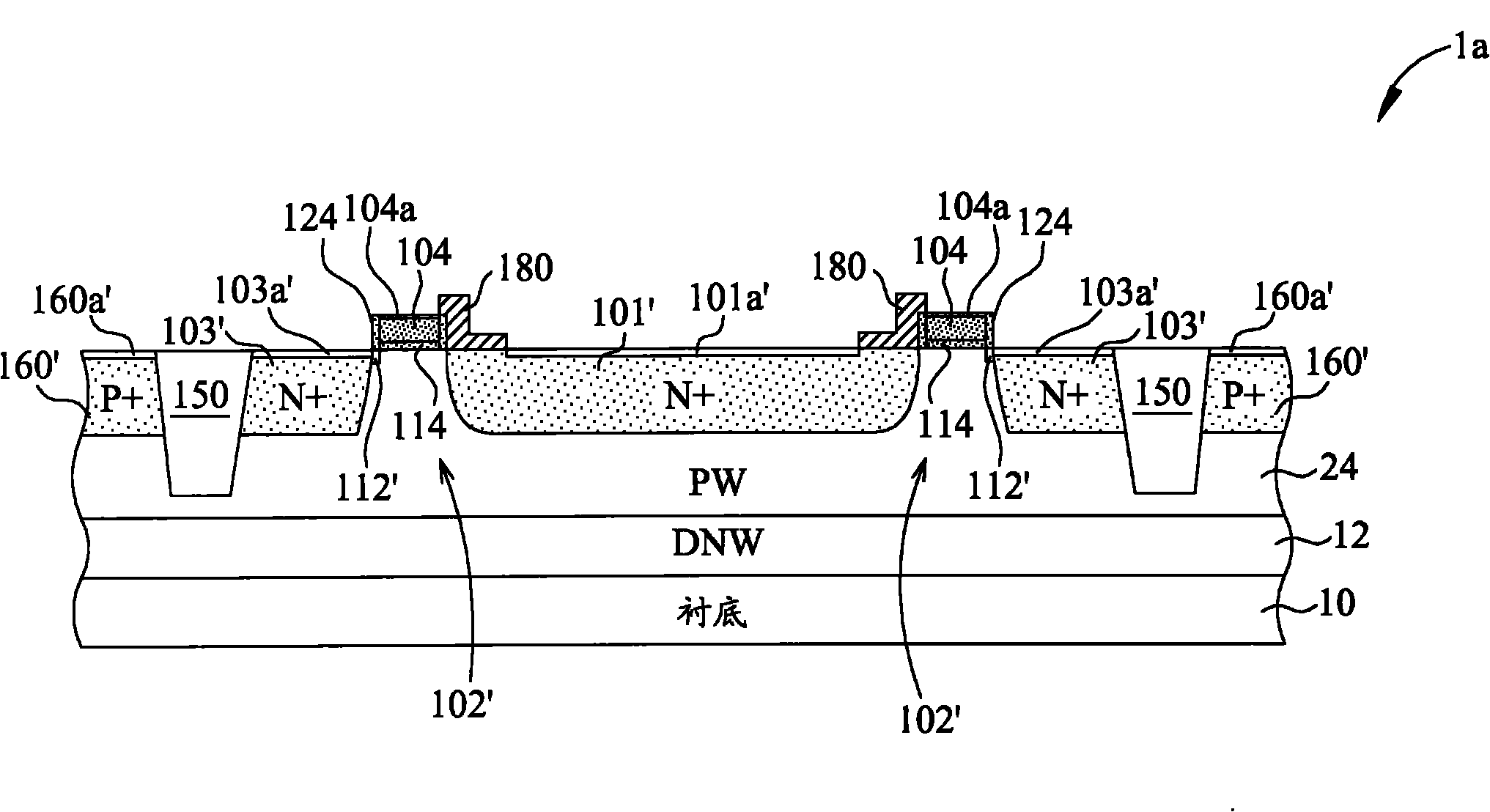

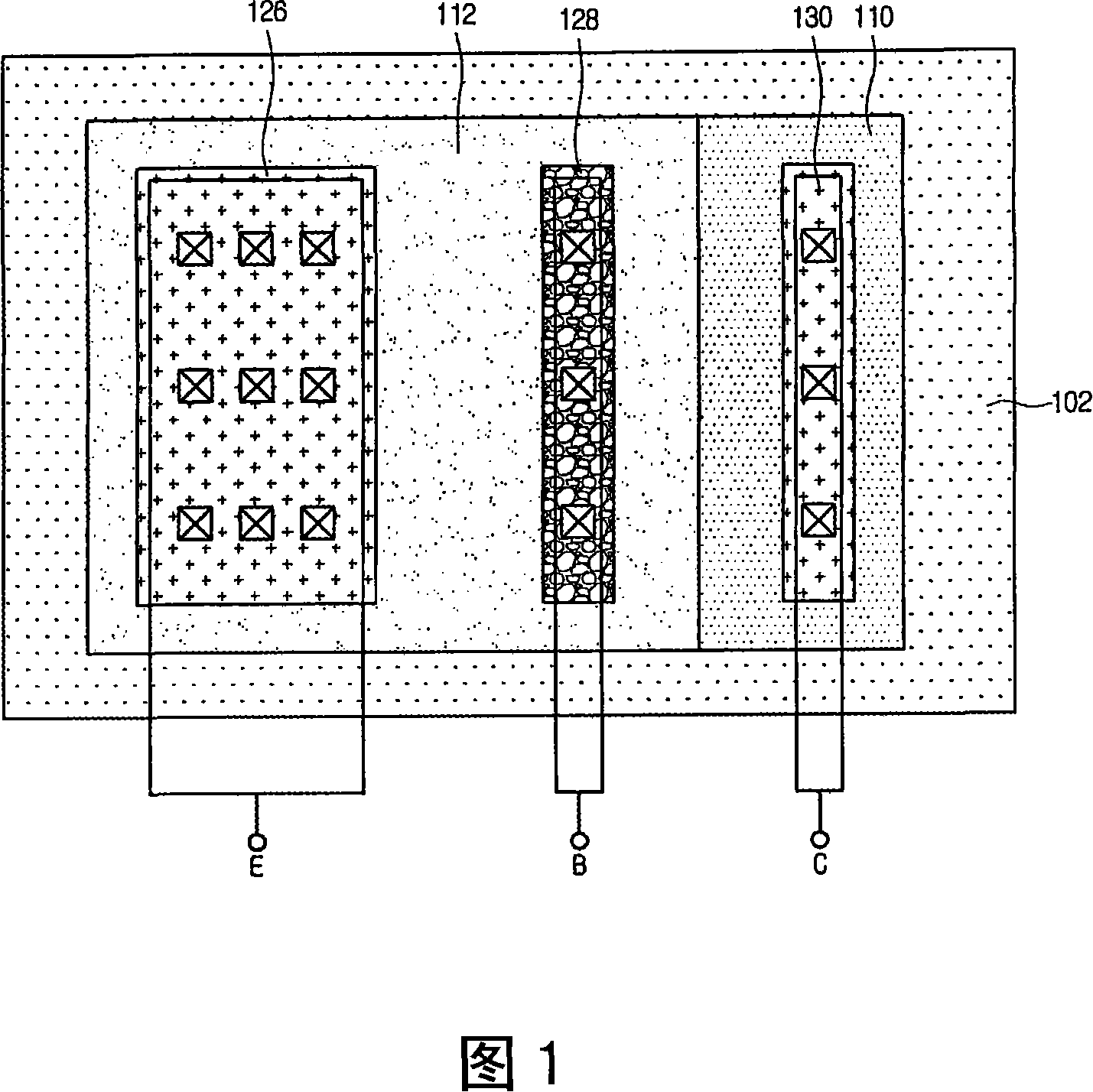

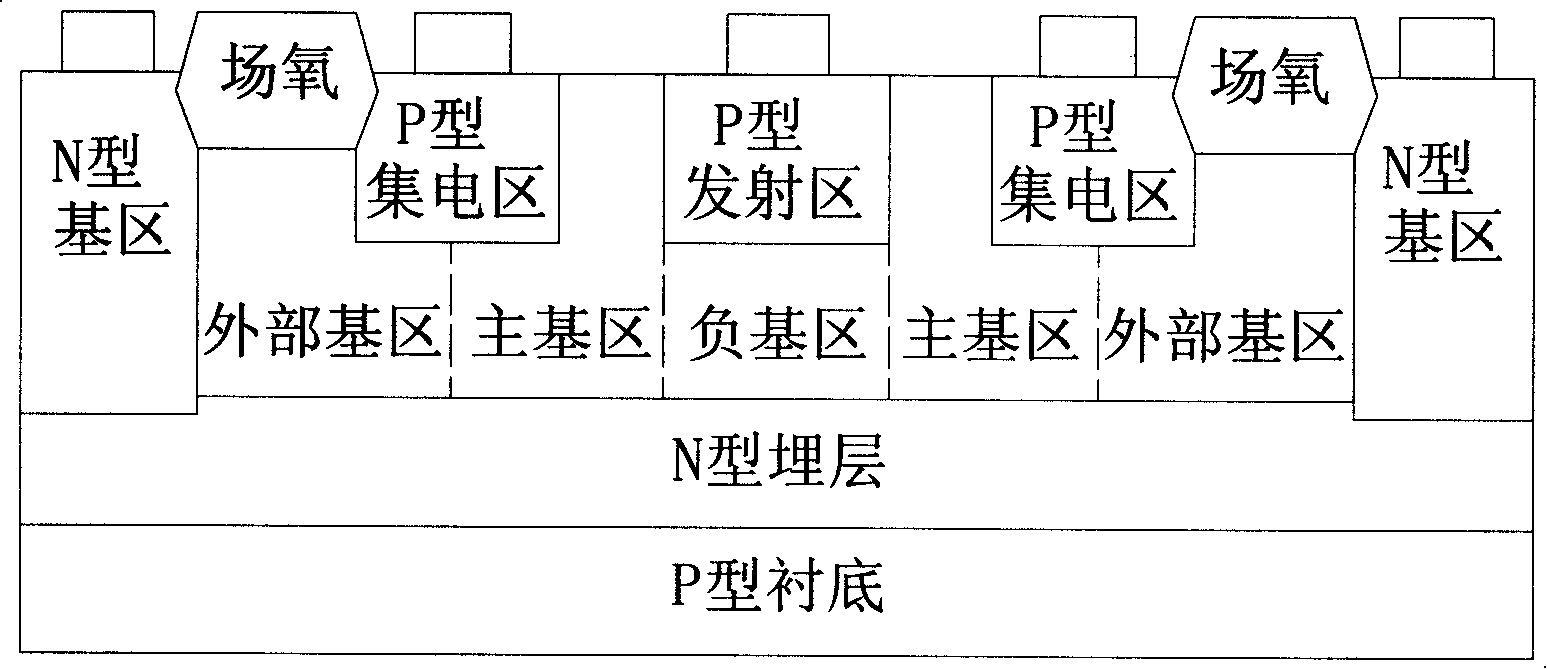

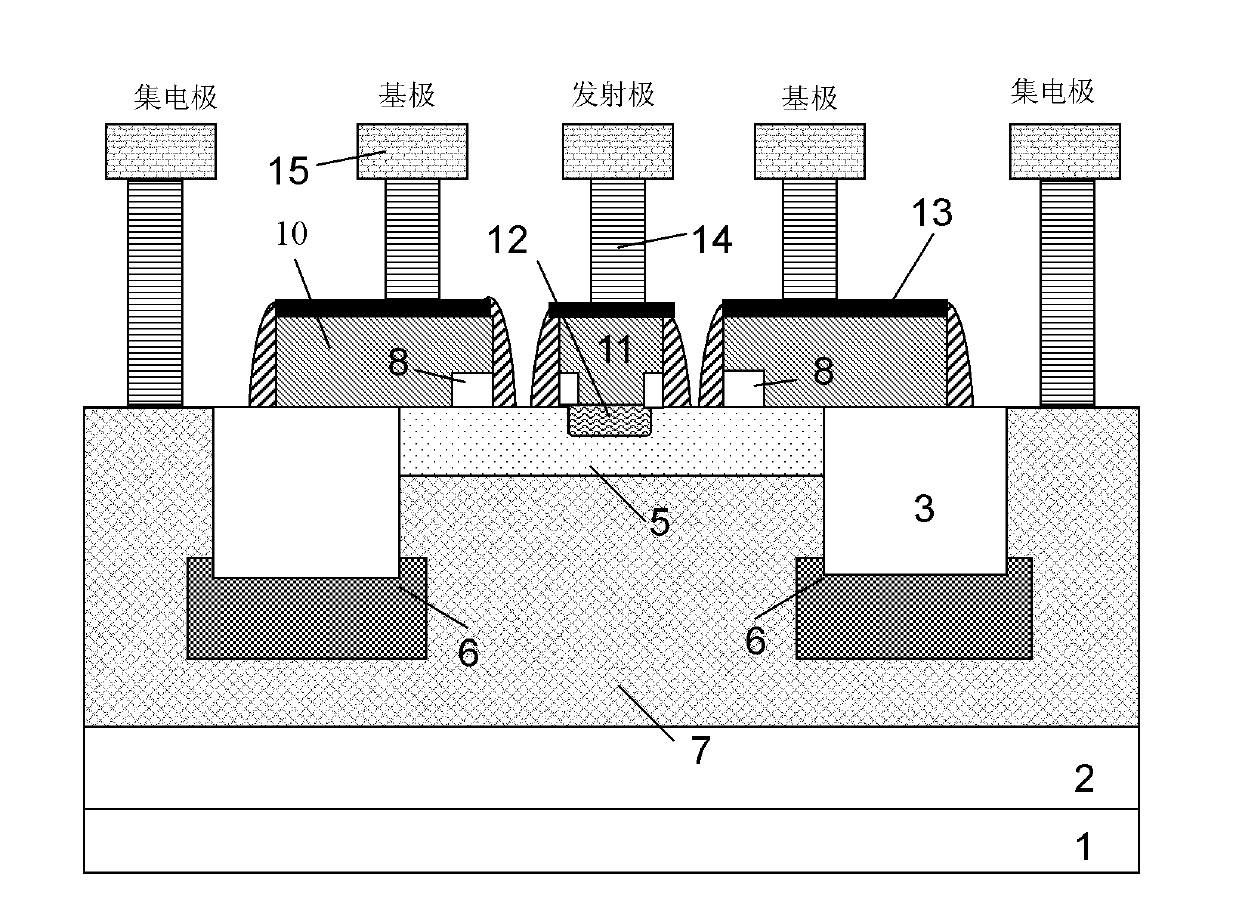

Vertical parasitic PNP device in BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor) process and preparation method thereof

ActiveCN102487077ALarge current amplification factorImprove frequency characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesProcess conditionsBicmos circuits

The invention discloses a vertical parasitic PNP device in a BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor) process. The vertical parasitic PNP device comprises a collector region, a base region, an emitter region, a P type buried layer and N type polycrystalline silicon, wherein the buried layer is formed at a shallow trench filed oxide bottom surrounding the collector region and is in contact with the collector region through a deep hole formed at the top of the buried layer to lead out a collector electrode; the N type polycrystalline silicon is formed at the upper part of the base region and is used for leading out a base electrode; and the emitter region is composed of a P type shallow junction formed in the base region and P type polycrystalline silicon arranged above the base region. The invention also discloses a preparation method of the vertical parasitic PNP device in the BiCMOS process. The device disclosed by the invention can serve as an output device in a high-speed high-gain BiCMOS circuit, and therefore another device choice is provided for the circuit. According to the invention, the area of the device can be reduced effectively, the resistance of the collector electrode of a PNP transistor can be lowered, the frequency performance of the device can be improved and the gain of the device can be enhanced. No extra process condition is required in the preparation method disclosed by the invention, thereby reducing the production cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

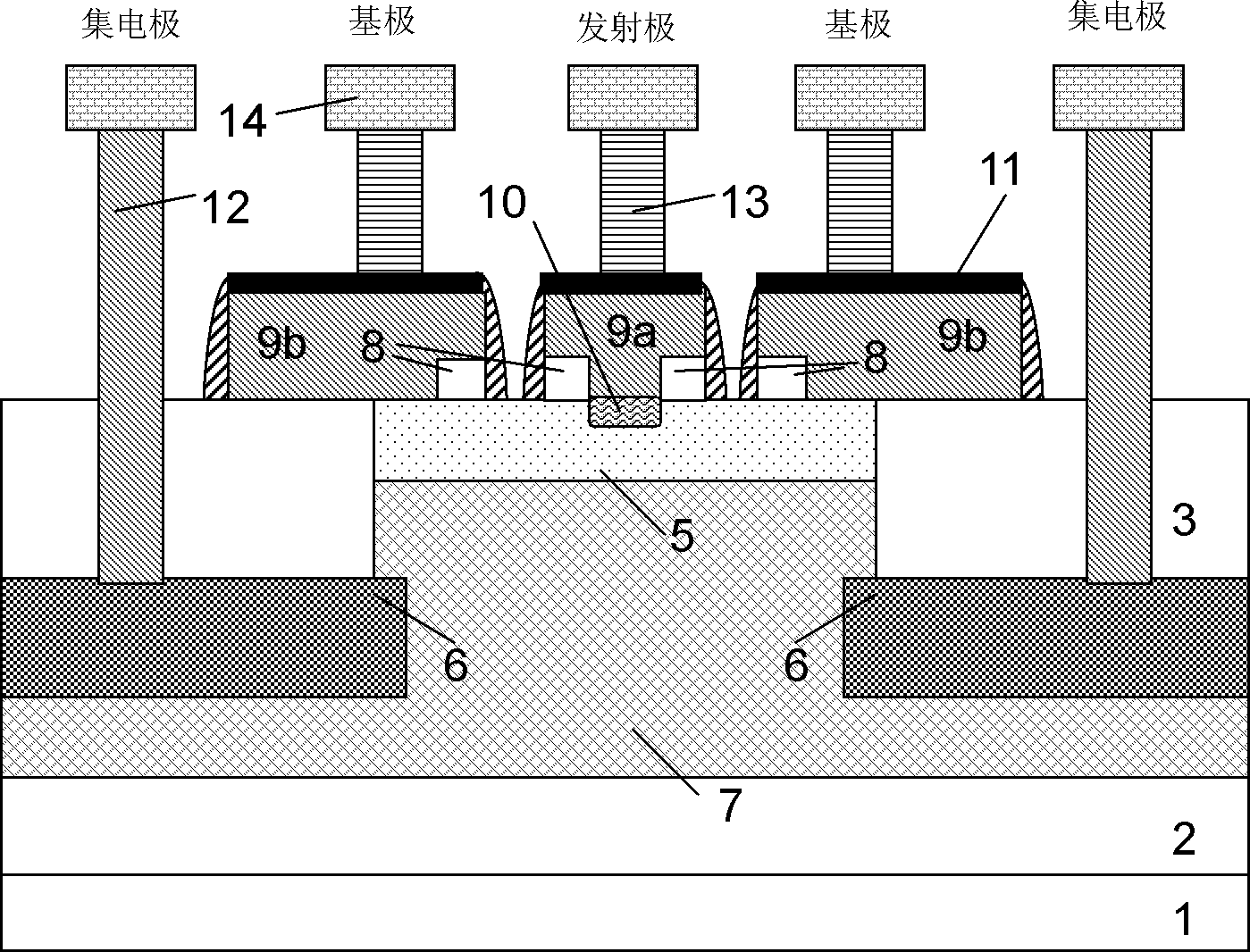

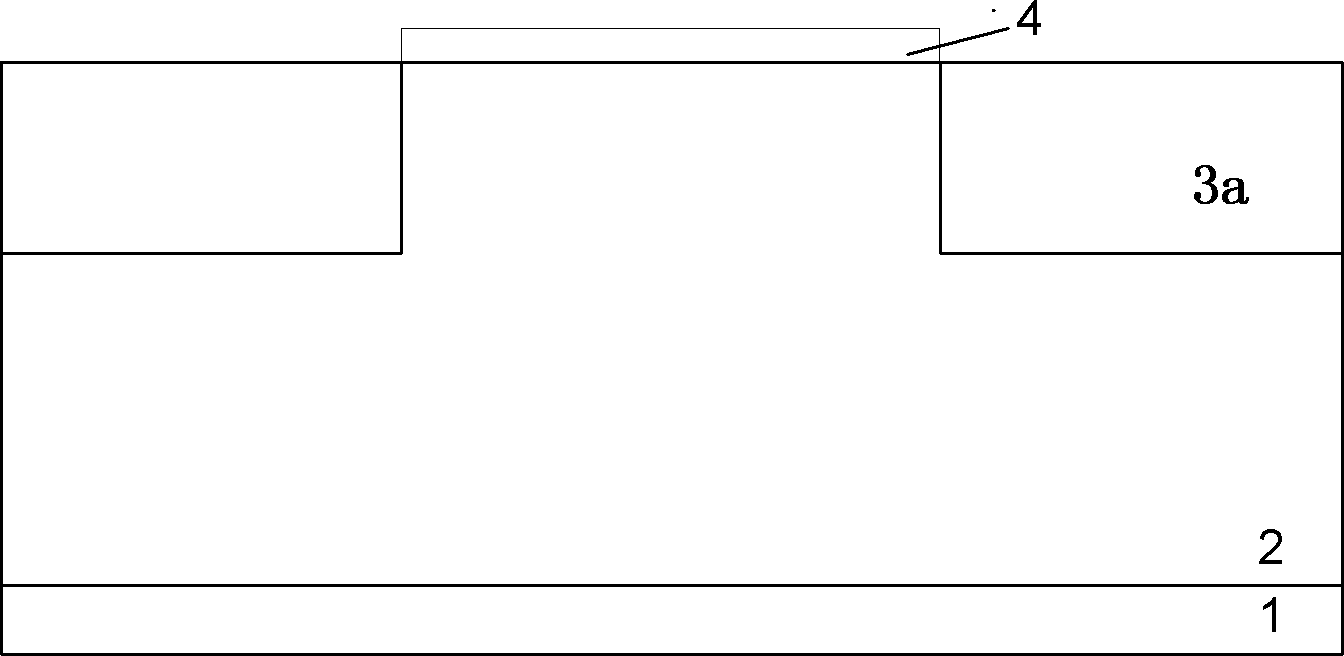

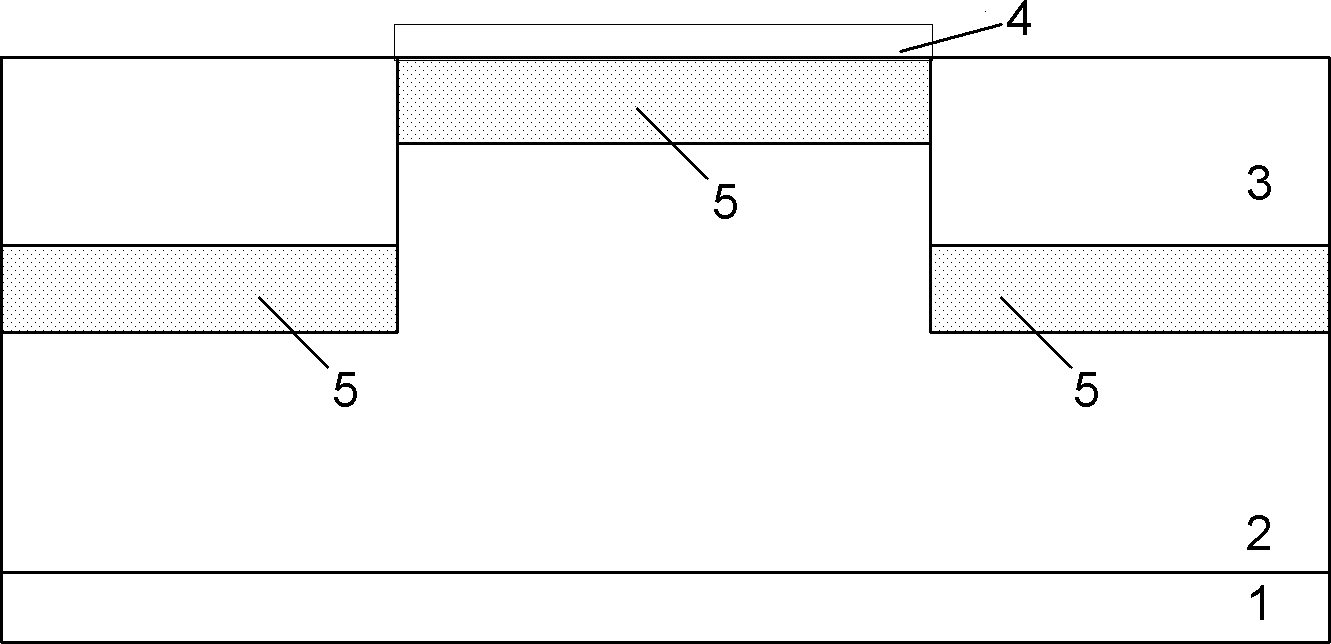

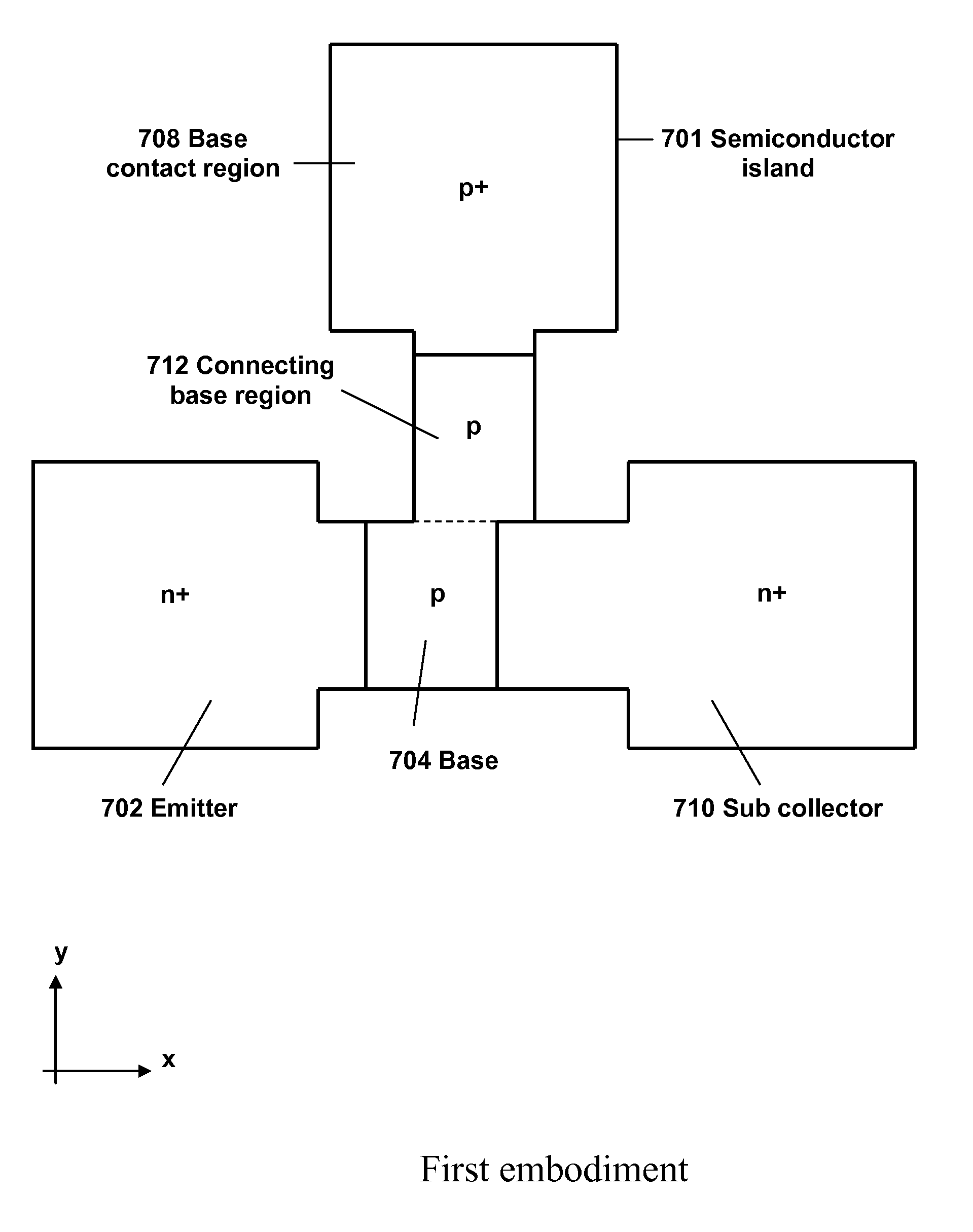

Bipolar junction transistor

InactiveUS20120061802A1Total current dropIncrease current gainTransistorSemiconductorBipolar junction transistor

A bipolar junction transistor includes a semiconductor island on an insulating substrate; an emitter and at least one of a collector and sub collector within the semiconductor island, the emitter and the at least one of the collector and the sub collector being of a first conductivity type; a base within the semiconductor island separating the emitter and the at least one of the collector and the sub collector, the base being of a second conductivity type; a base contact region within the semiconductor island, the base contact region being of the second conductivity type; and a connecting base region adjacent the base within the semiconductor island and connecting the base to the base contact region while not directly contacting the emitter, the connecting base region being of the second conductivity type with a doping concentration less than a doping concentration of the base contact region.

Owner:SHARP KK

Power bipolar transistor with base local heavy saturation

This invention relates to a bipolar transistor with base partially heave doping horsepower, characterized by partially heave doping on the base 5 of the present power bipolar transistor to form heave base 9, the doping type of heave base 9 is the same with the base 5( P type or N type), and its density is larger than that of base 5, the heave base 9 is located in the base 5 under the base electrode 1, and close contacting with the base electrode 1. Compared with the nominal power bipolar transistor, the invention can largely improve the current gain of the device.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

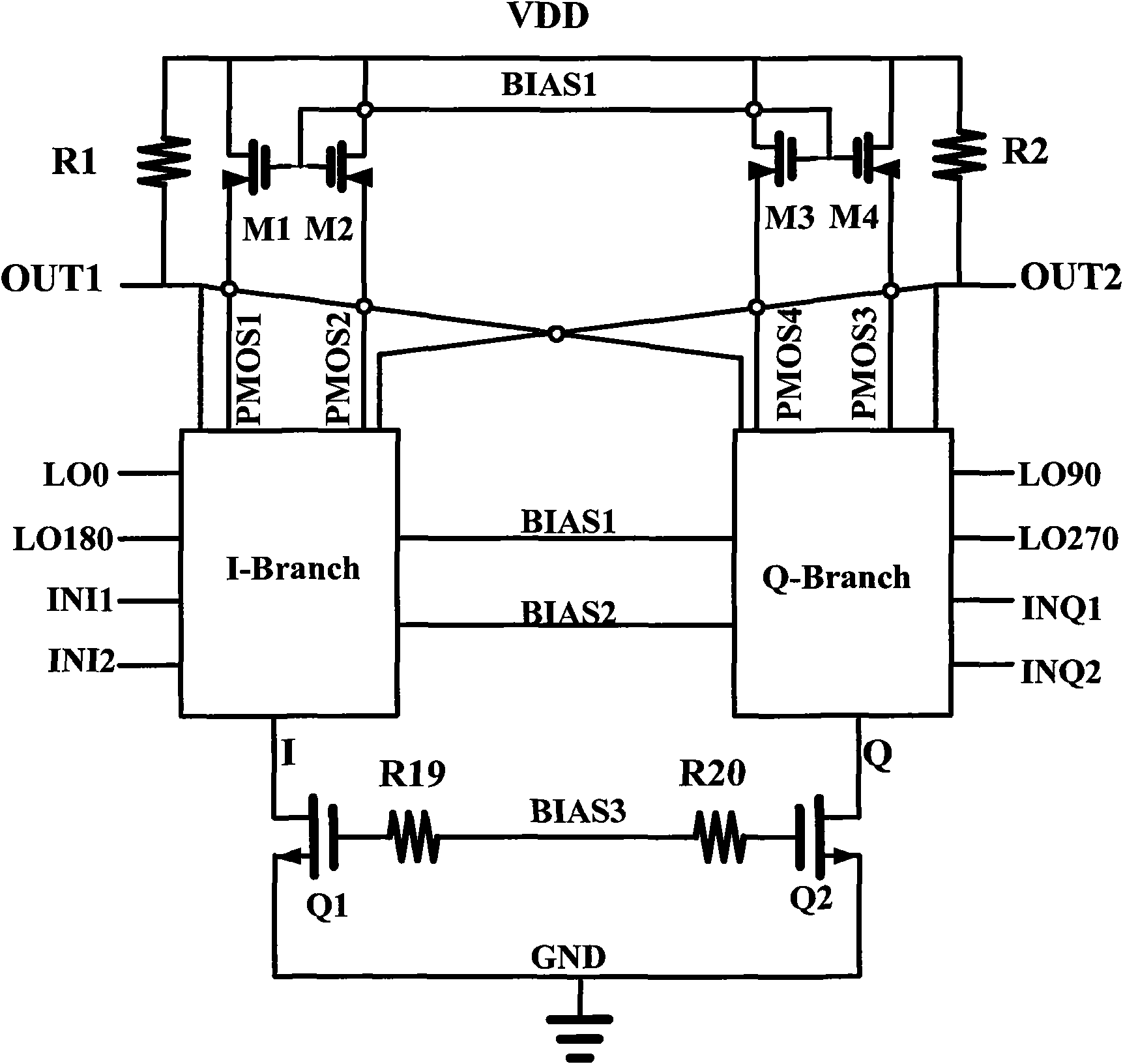

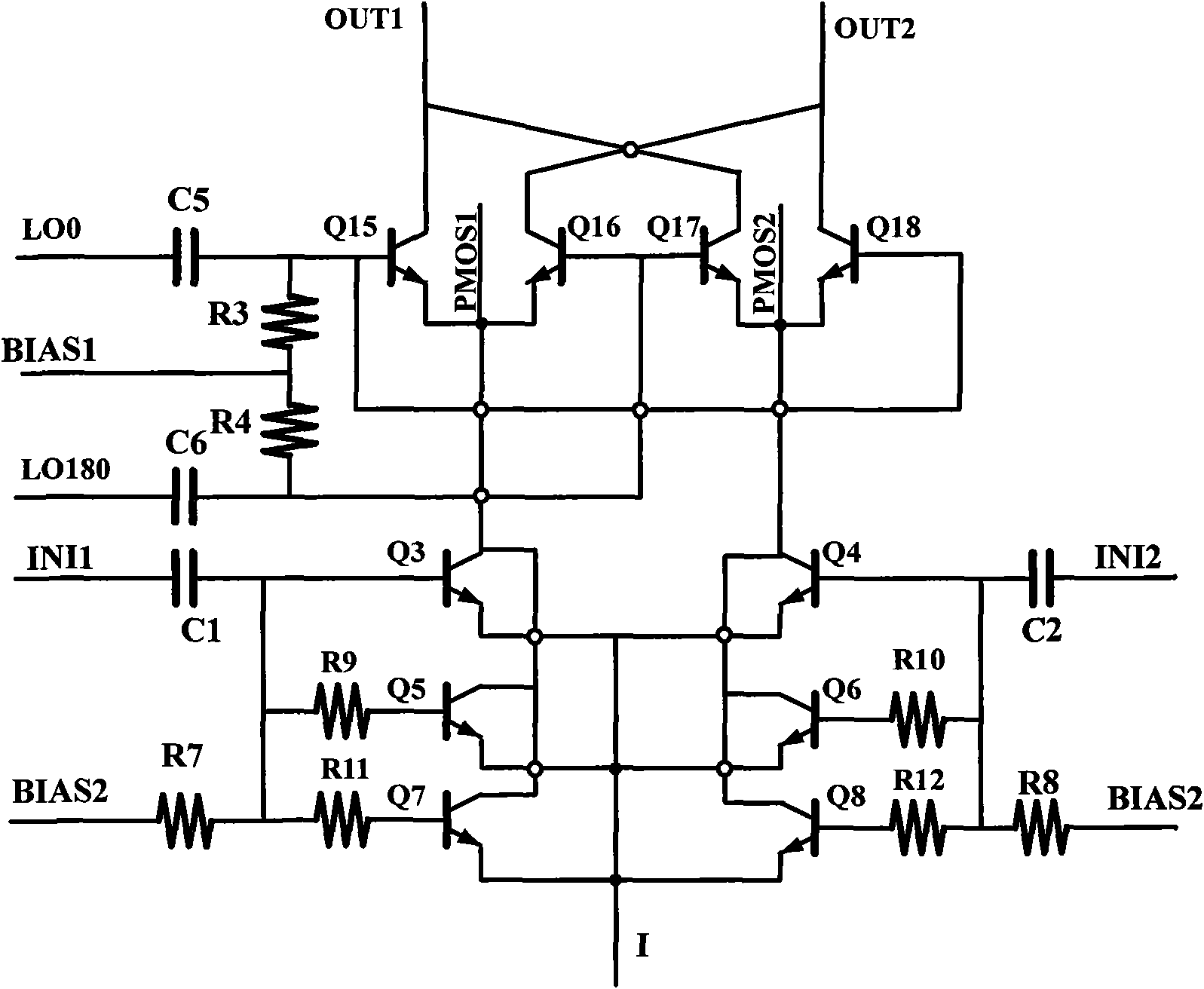

Improved double Gilbert structure radio-frequency orthogonal upper frequency mixer

InactiveCN101964631AIncrease current gainLower noise figureModulation transference by semiconductor devices with minimum 2 electrodesOxide semiconductorCode division multiple access

The invention discloses an improved double Gilbert structure radio-frequency orthogonal upper frequency mixer. The frequency mixer comprises a transconductance level circuit, a switching level circuit and a tail current source circuit. Silicon germanium double pole-complementary metal oxide semiconductor process technology is adopted in the integral circuit; and the frequency mixer combines the advantages of a bipolar device and a complementary metal oxide semiconductor, and can improve the conversion gain at the same time of effectively reducing circuit noise. The transconductance level circuit has a parallel-connection structure of three pairs of transconductances, and improves the linearity of the frequency mixer at the same time of increasing the transconductance parameter of the transconductance level. The switching level circuit works in an ideal switching state according to the simulation result. A current injection mode is also adopted in the circuit, and partial current is extracted at the emitter of the switching level so that the current of the switching level is low enough and the hot noise and the flicker noise of the circuit are effectively reduced. According to the design, the frequency mixer works at 1.95GHz and can be applied in personal communication service and wideband code division multiple access communication systems.

Owner:EAST CHINA NORMAL UNIVERSITY

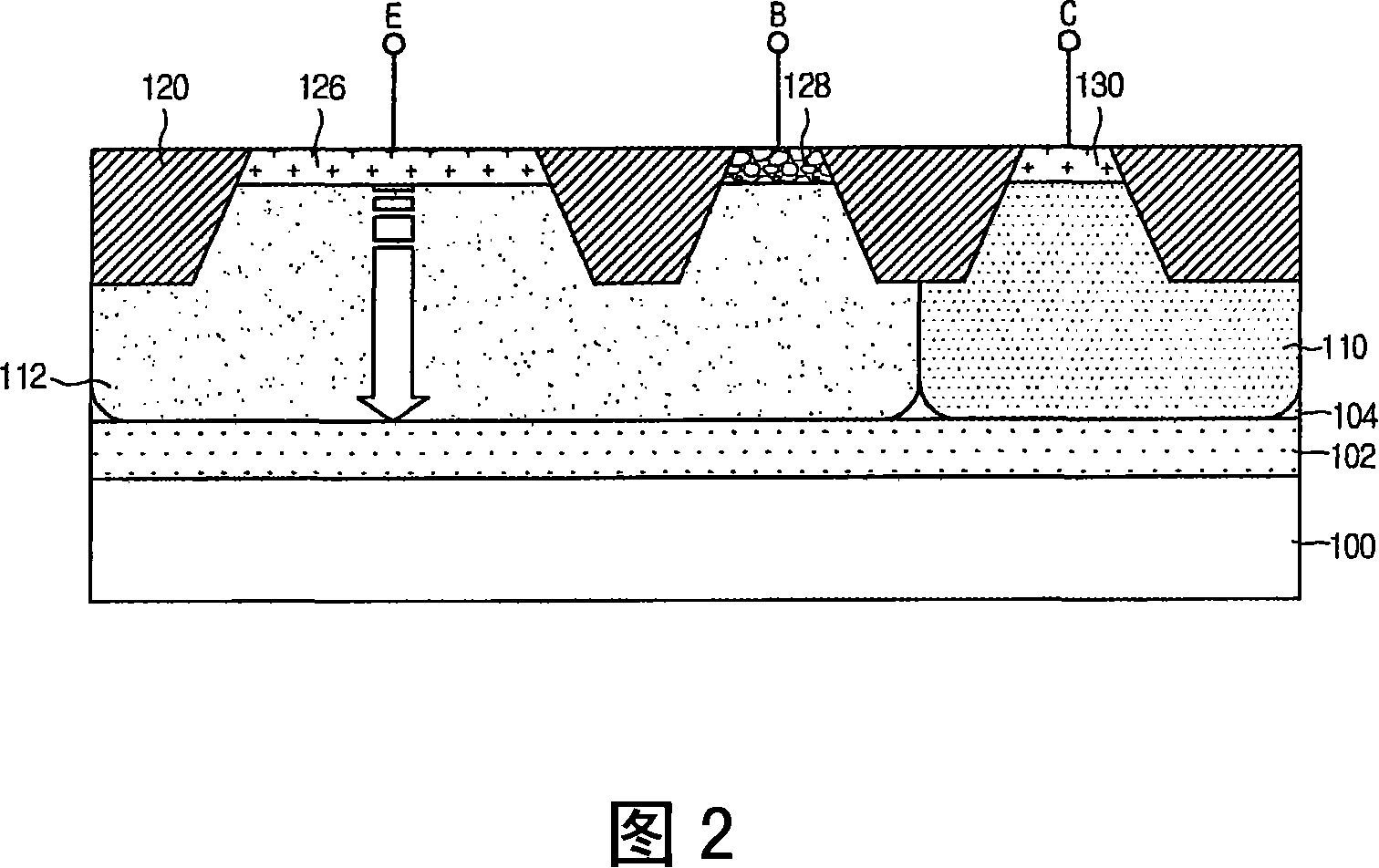

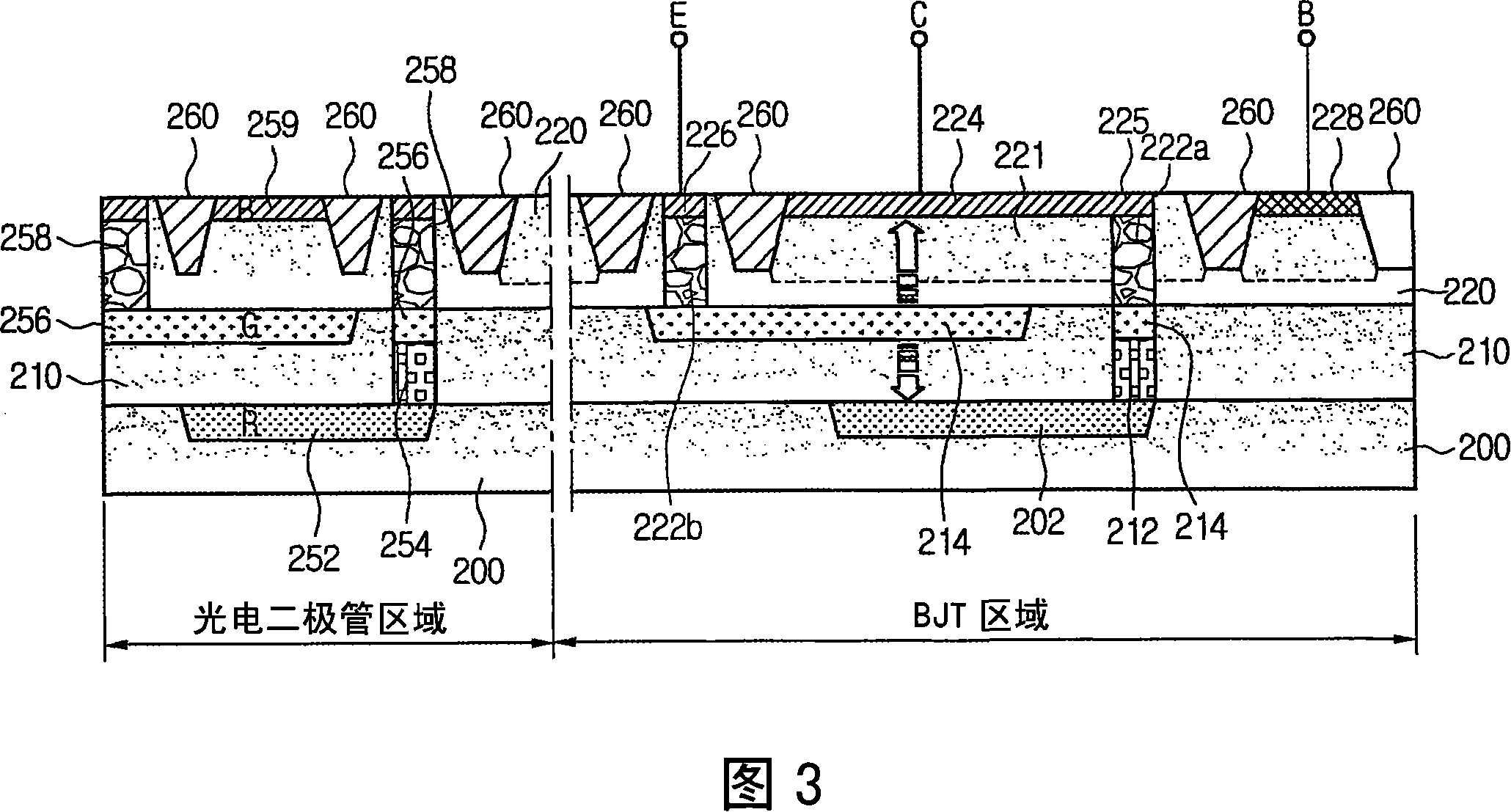

Vertical BJT, manufacturing method thereof

InactiveCN101132021AIncrease current gainBig-amplitudeTransistorSemiconductor/solid-state device manufacturingEngineeringPhotodiode

A vertical BJT with maximum current gain in the photodiode region and its manufacturing method, the vertical BJT includes first and second collector regions located in different epitaxial layers; an emitter region inserted in the first and second collector regions Between; a base region formed on the first collector region and the emitter region, and the second collector region and the emitter region. According to an embodiment, since a BJT may be formed together with a photodiode, and a collector current flows up and down based on a double base structure, the magnitude of current may be increased.

Owner:DONGBU HITEK CO LTD

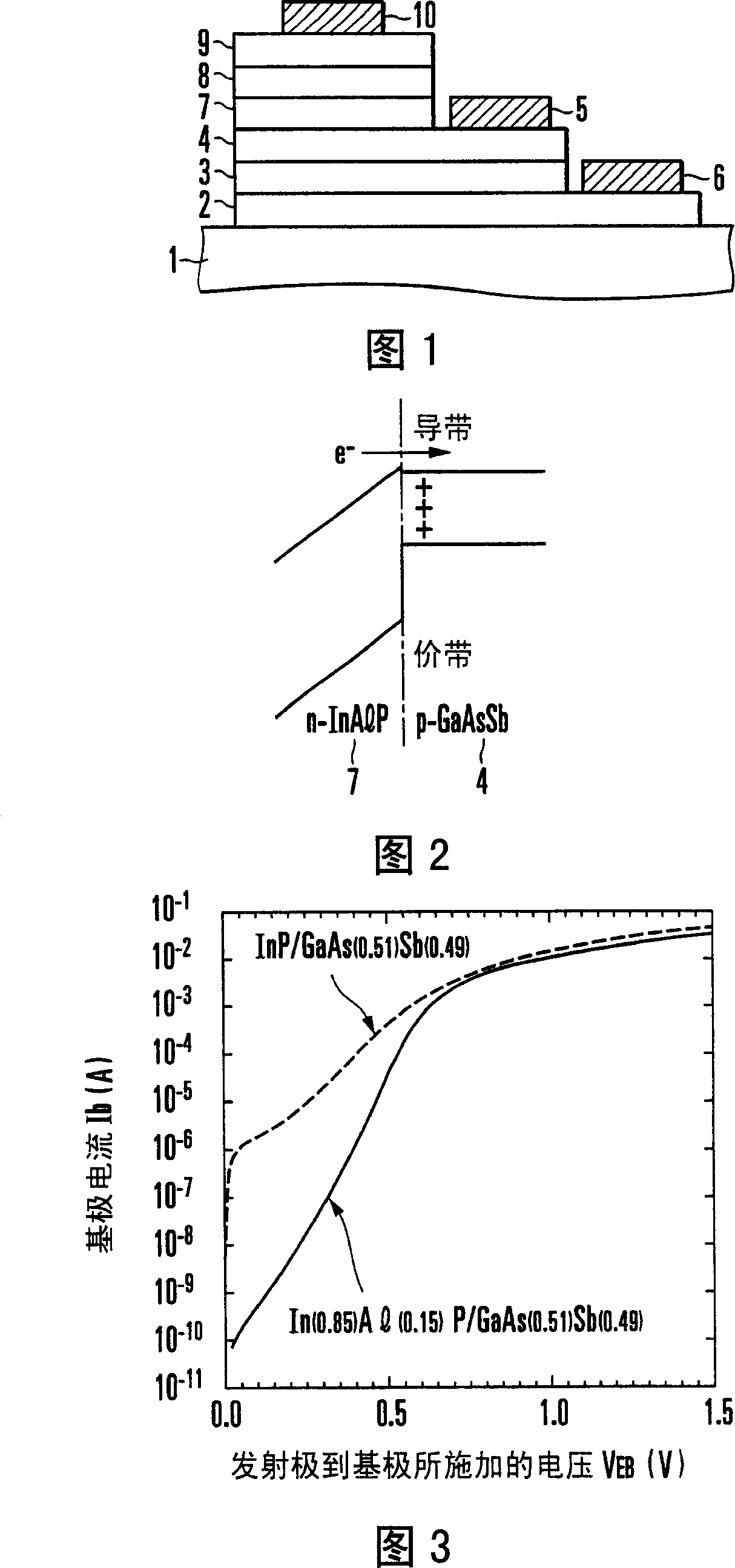

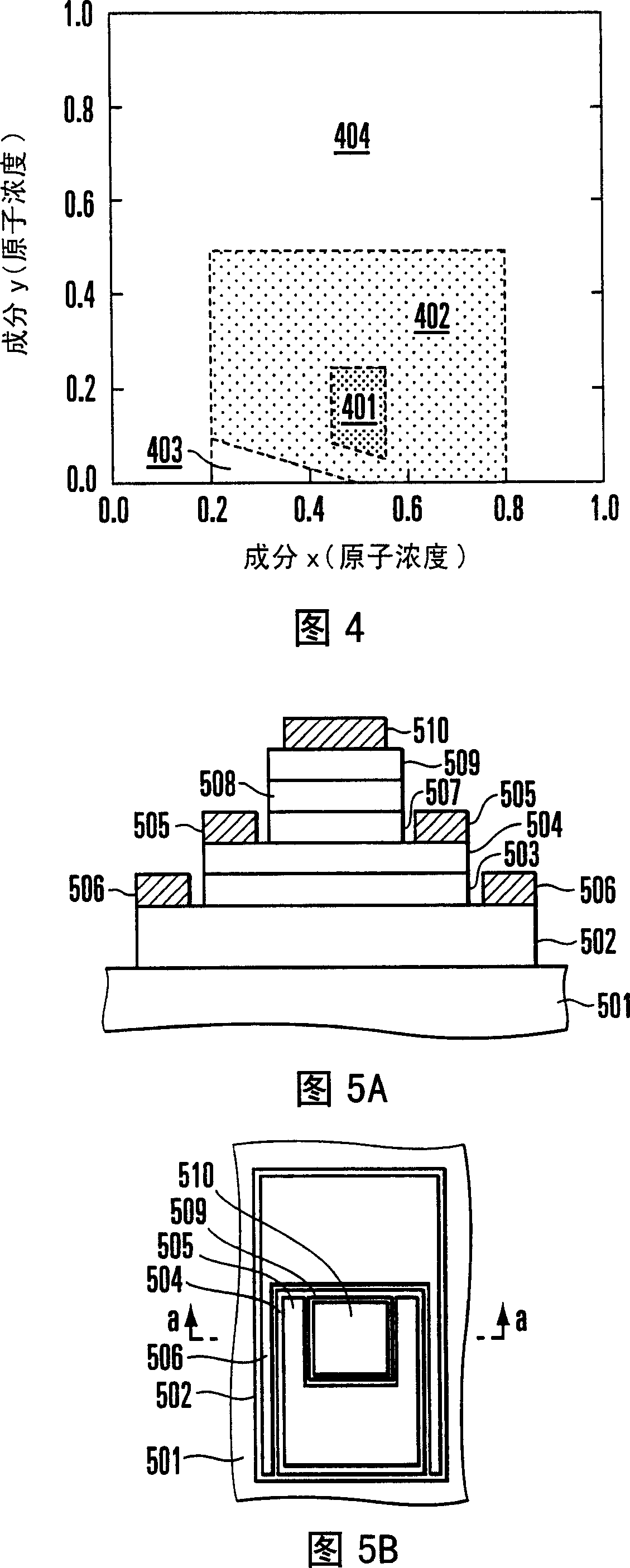

Heterojunction bipolar transistor

InactiveCN1965398AIncrease potential energyReduce capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesContact layerSilicon

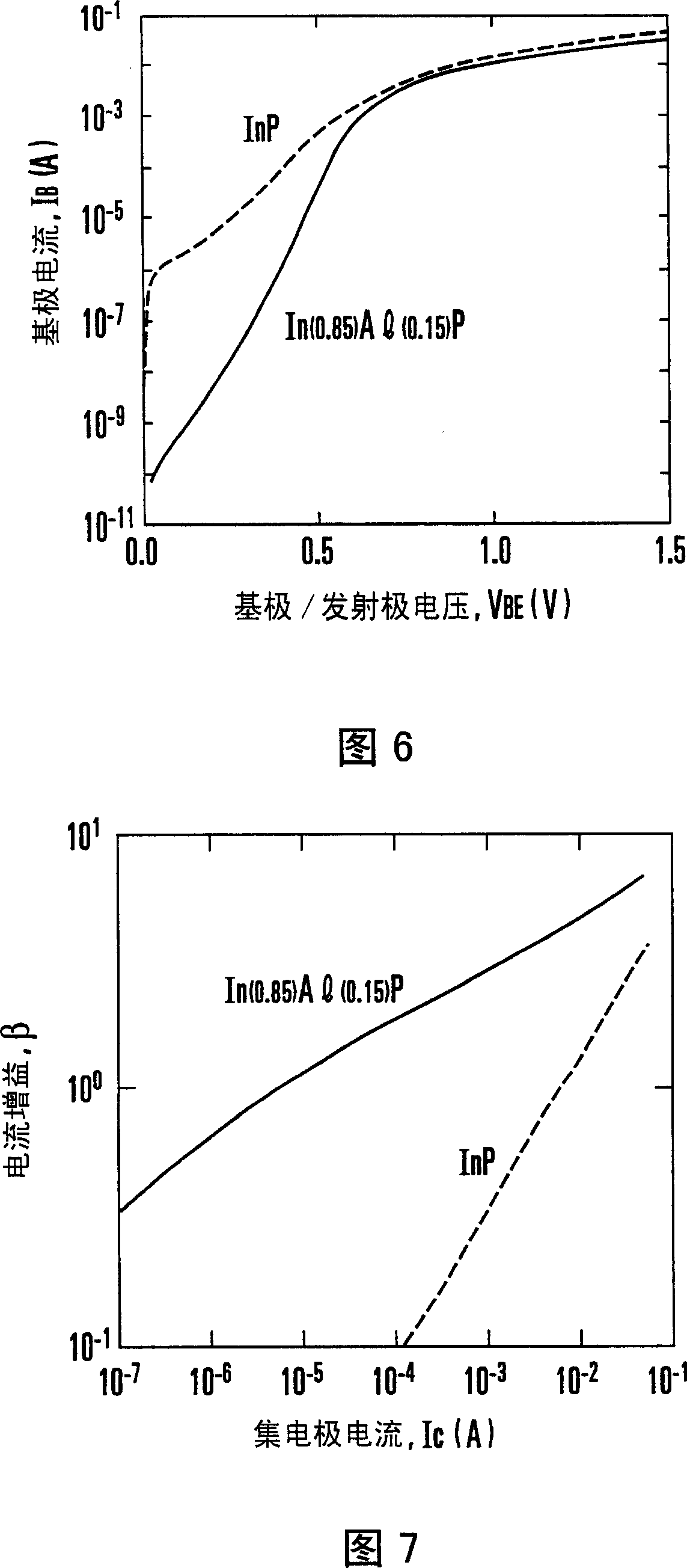

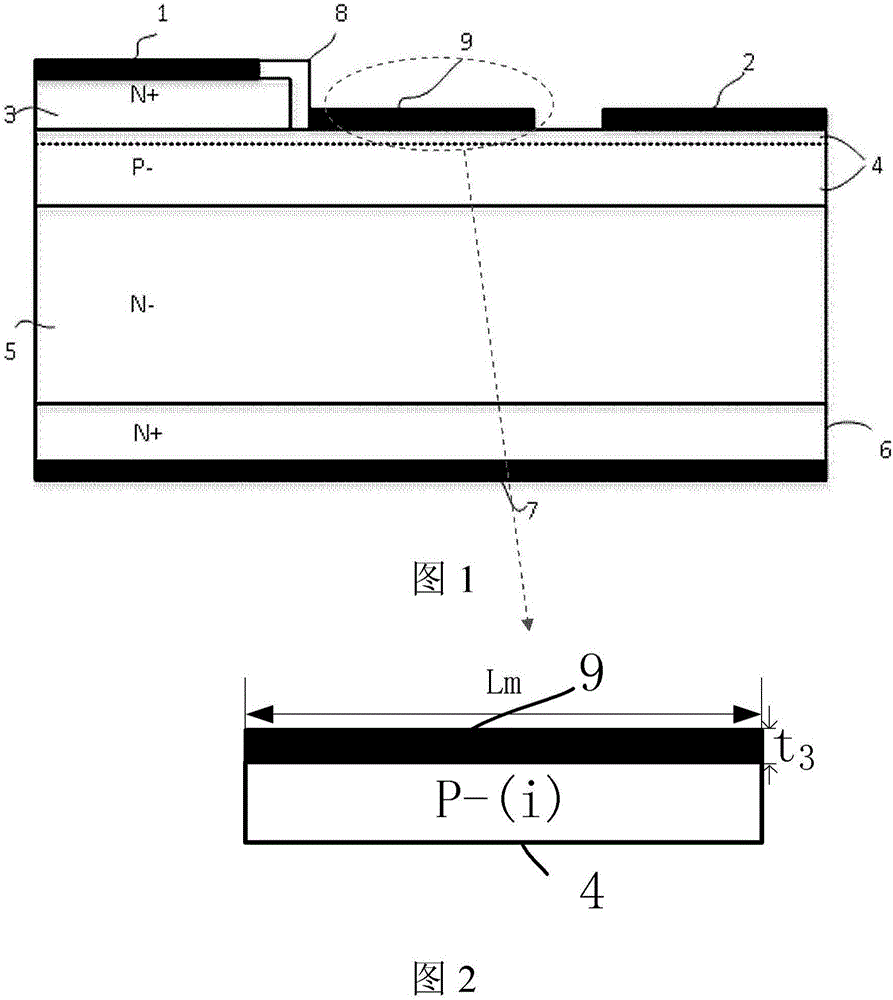

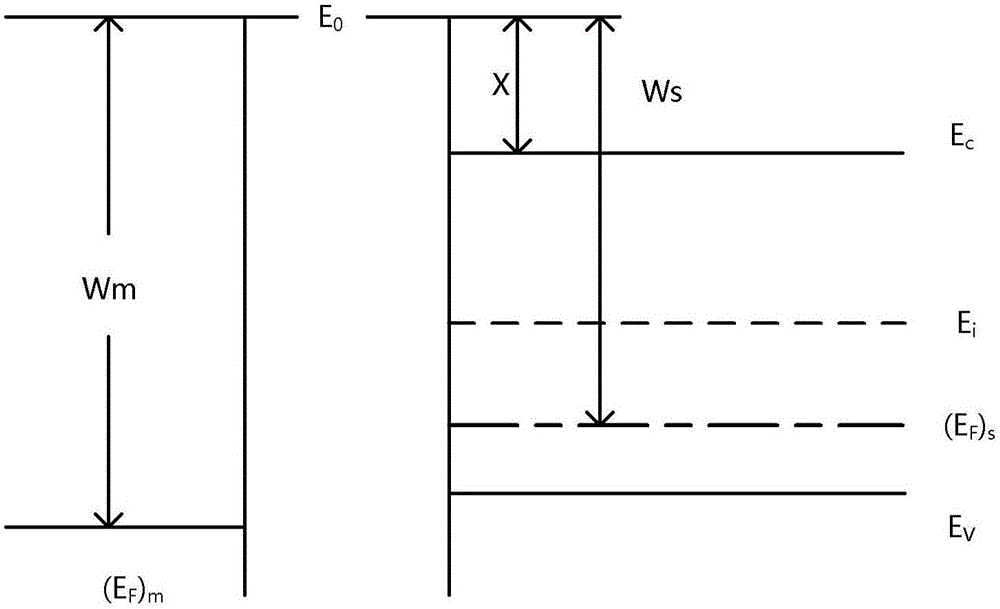

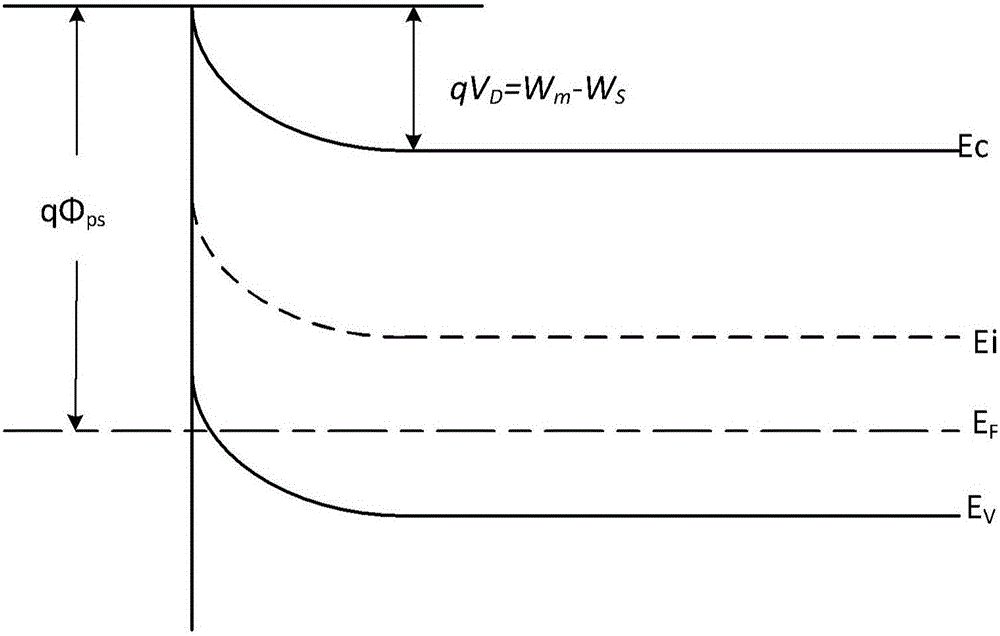

An n-type InP sub collector layer 2 heavily doped with silicon (Si), an InP collector layer 3, a p-type GaAs(0.51)Sb(0.49) base layer 4 heavily doped with carbon (C), an n-type In(1-y)Al(y)P emitter layer 7 doped with Si, an n-type InP cap layer 8 heavily doped with Si, and an n-type In(0.53)Ga(0.47). As contact layer 9 heavily doped with Si are stacked on a substrate 1.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

Silicon carbide bipolar junction transistor

The invention provides a silicon carbide bipolar junction transistor. The transistor is provided with a Schottky contact structure on an outer base area surface between a countertop edge of an emitter (1) and ohmic contact of a base (2), so as to form a Schottky barrier on the outer base area surface. The Schottky contact structure comprises a base area and a metal layer located on the base area. The silicon carbide bipolar junction transistor provided by the invention can prevent electrons from moving toward the surface through the Schottky contact structure, restrain the surface recombination and improve the current gain of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

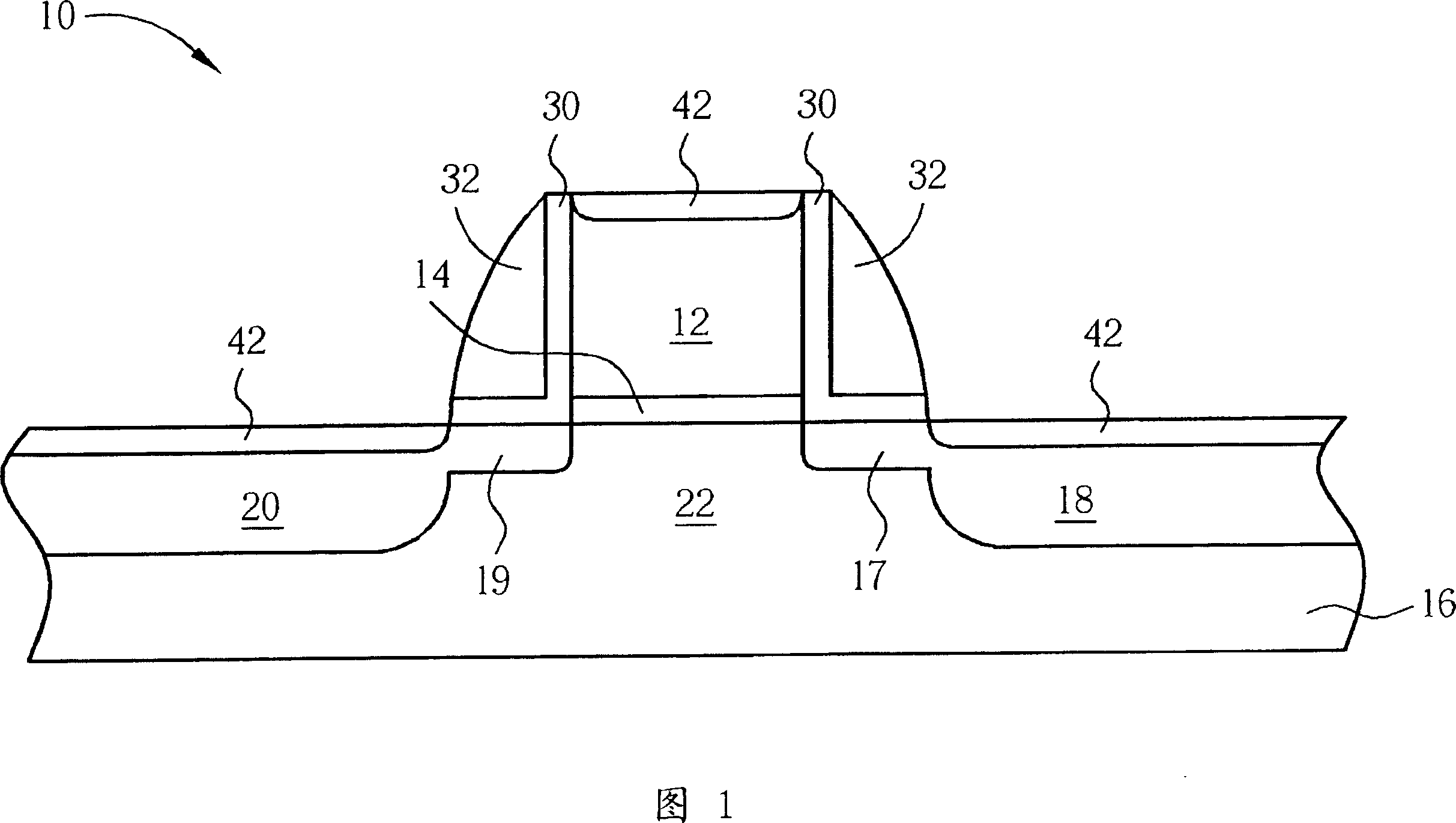

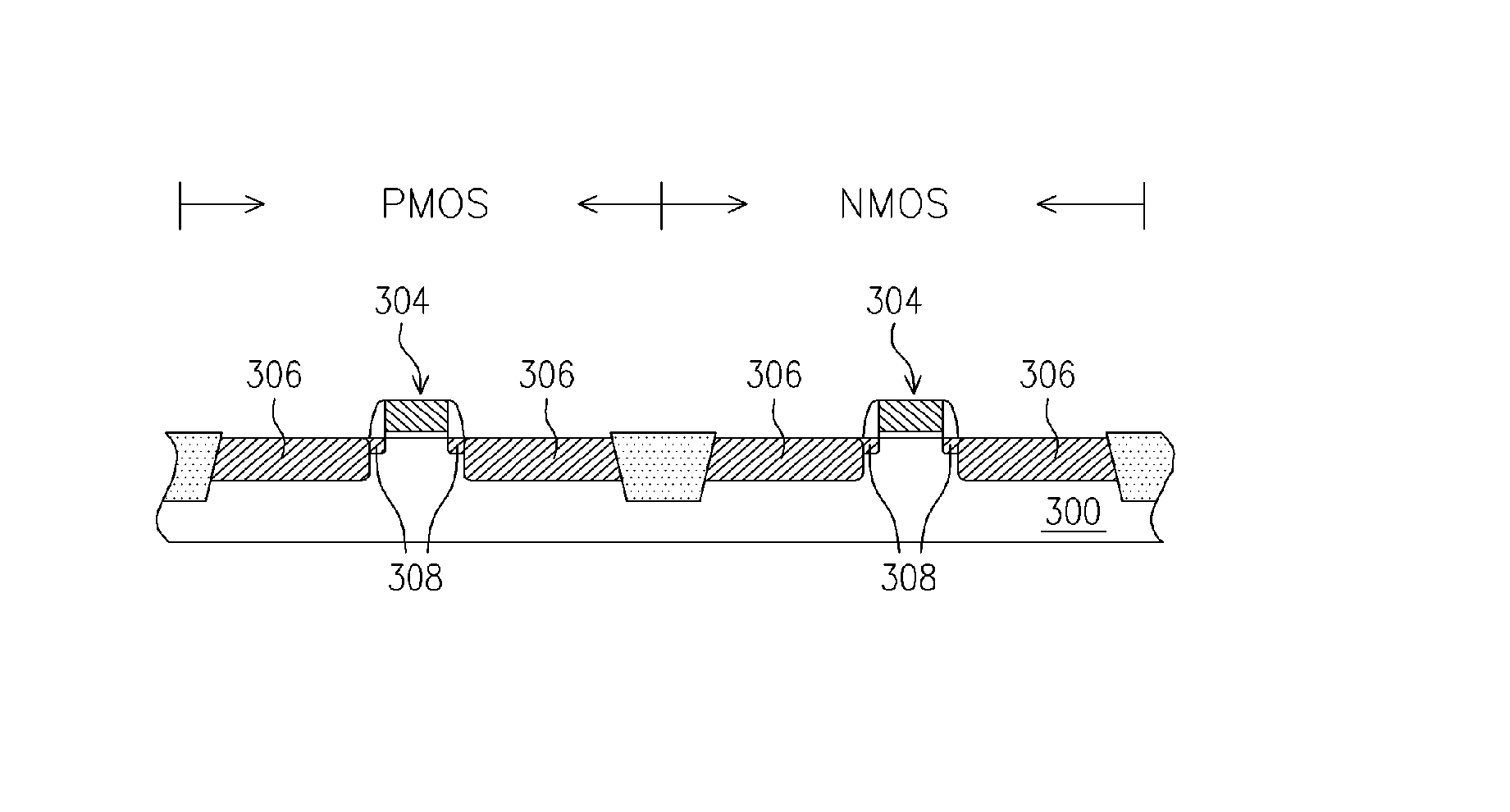

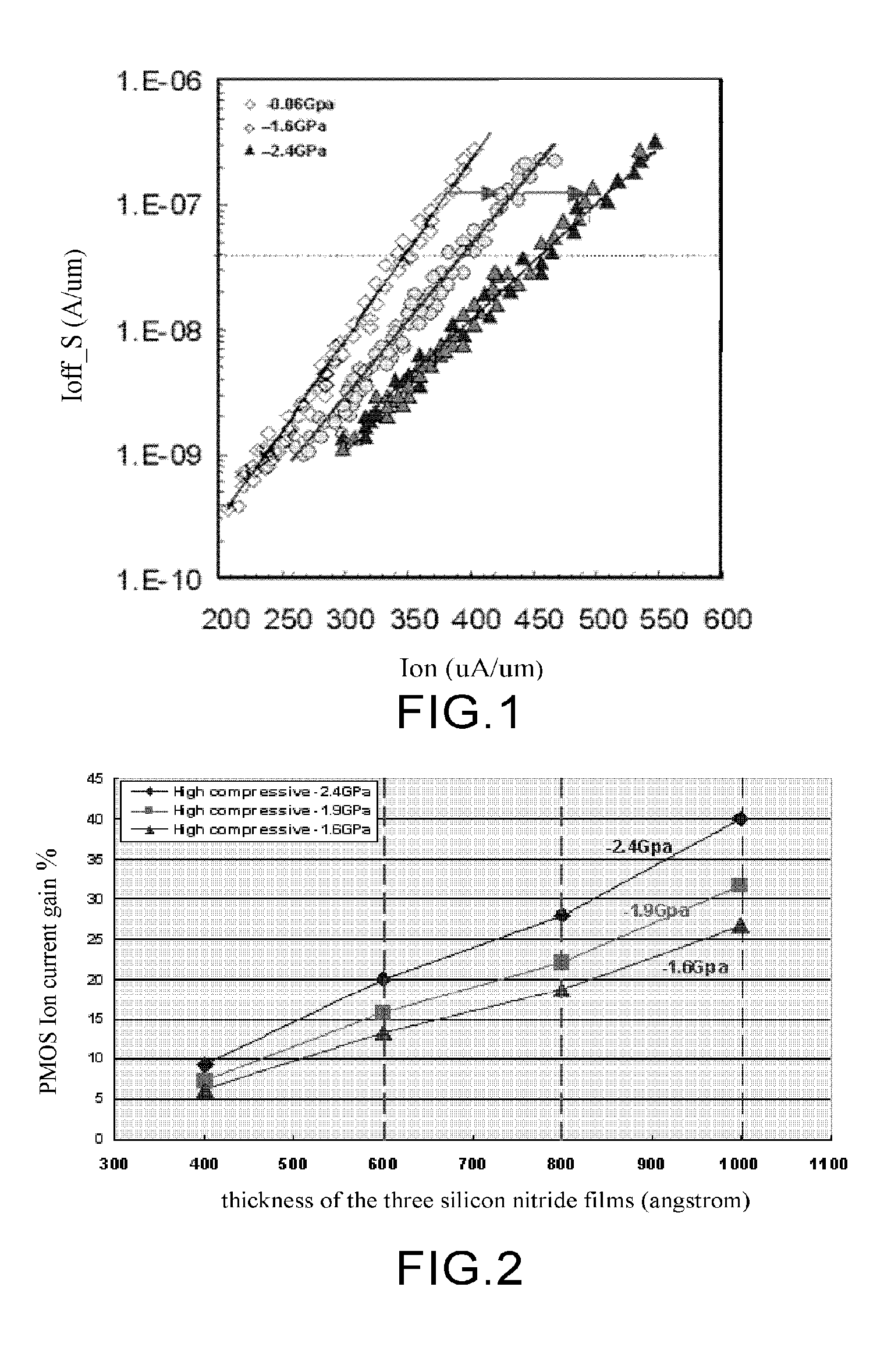

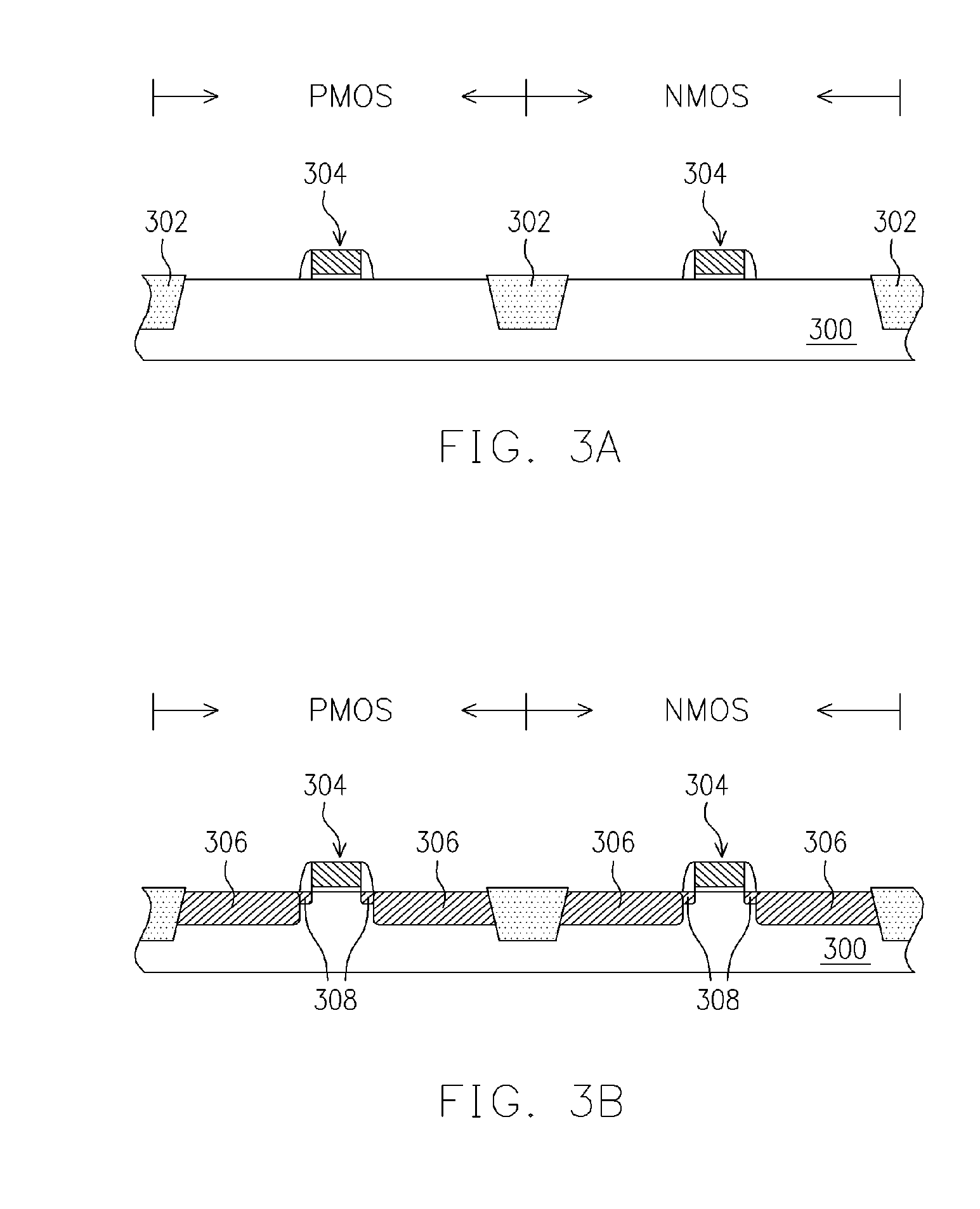

Method of forming compressive nitride film and method of manufacturing metal oxide semiconductor

ActiveUS20070243686A1Increasing PMOS drive current gainIncrease pressureSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentChemical vapor deposition

A method of forming compressive nitride film is provided. The method includes performing a chemical vapor deposition (CVD) process to form a nitride film on a substrate, and the method is characterized by adding a certain gas, selected from among Ar, N2, Kr, Xe, and mixtures thereof. Due to the addition of the foregoing certain gas, it can reduce the compressive stress, thereby increasing PMOS drive current gain.

Owner:UNITED MICROELECTRONICS CORP

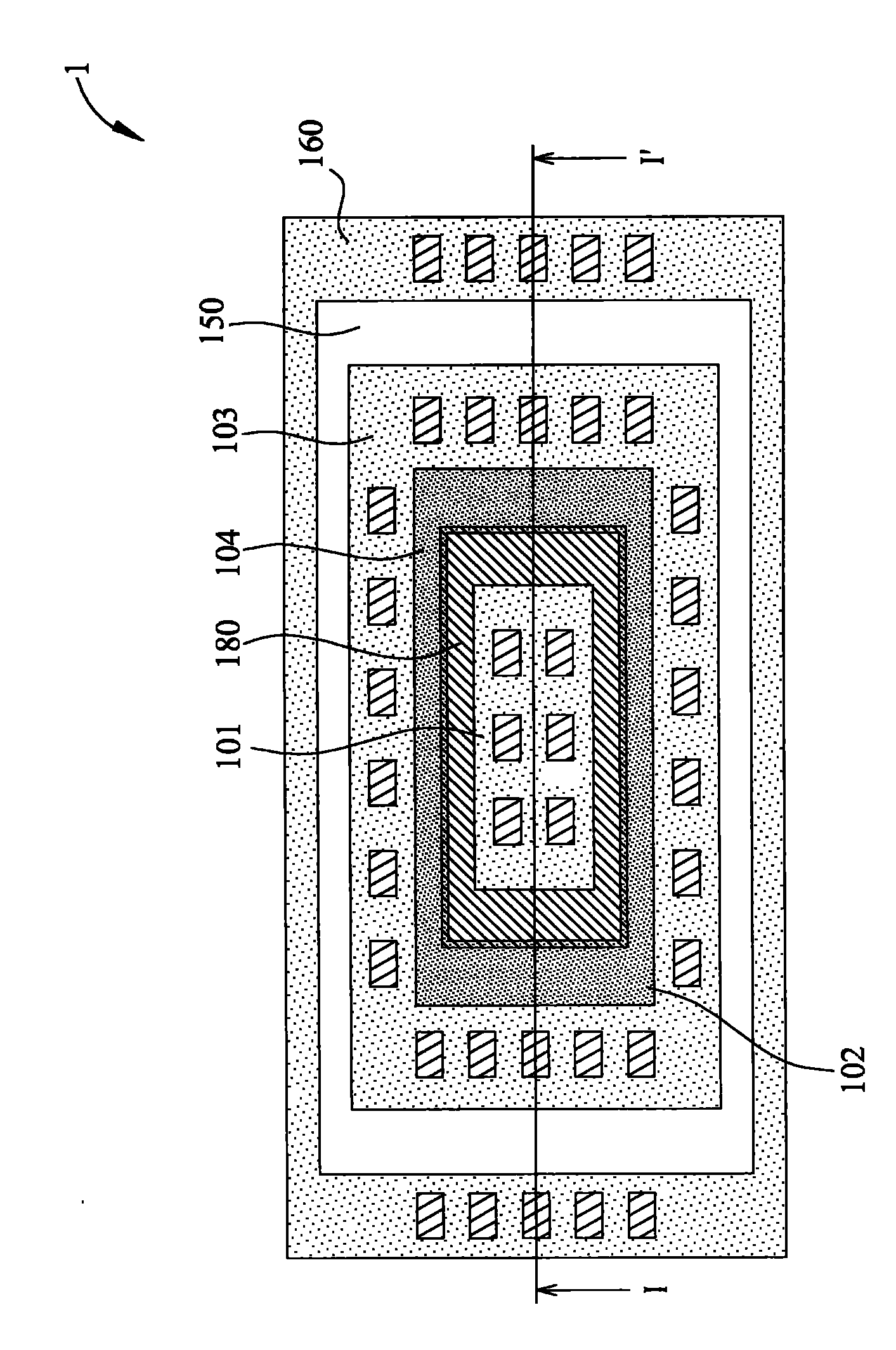

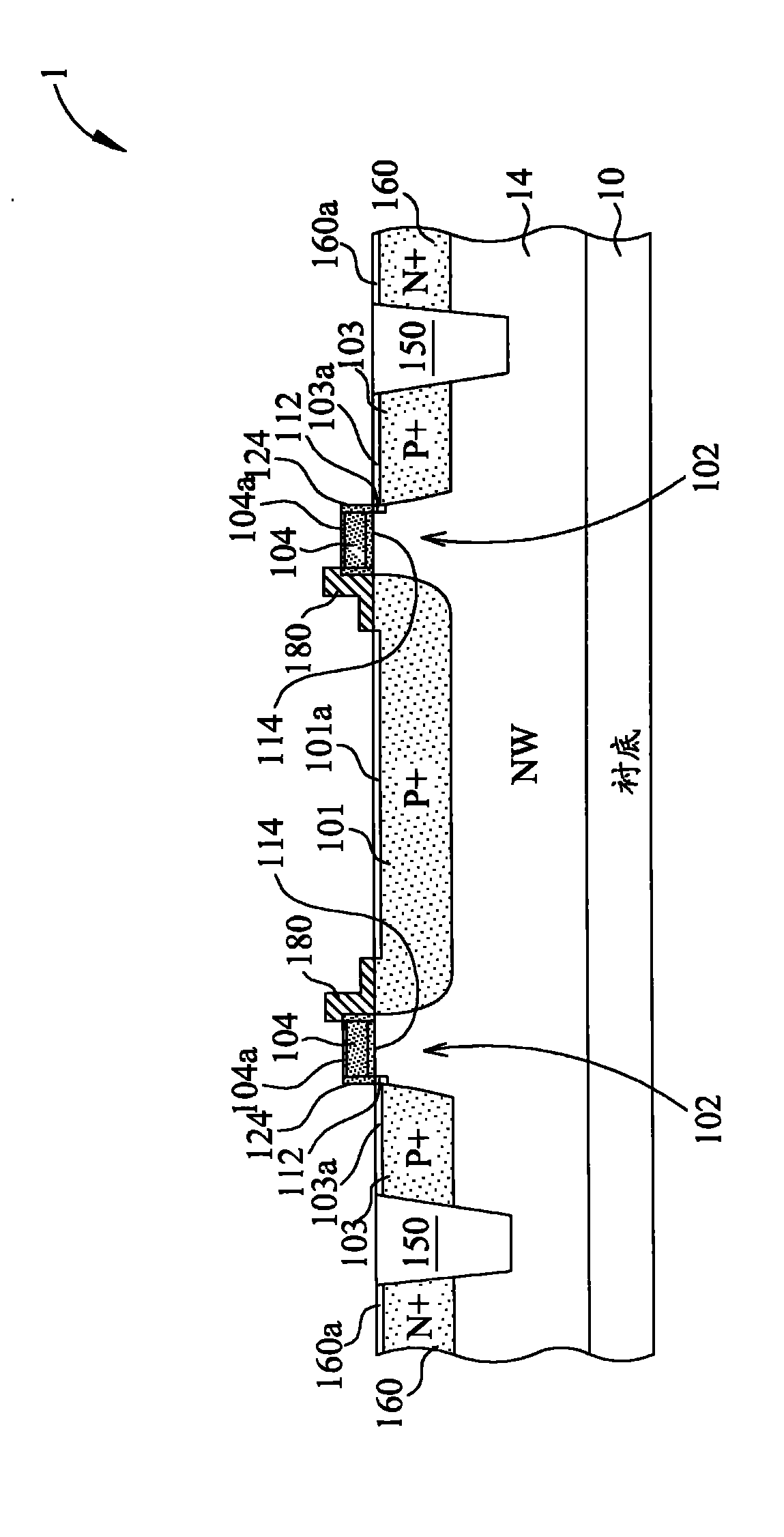

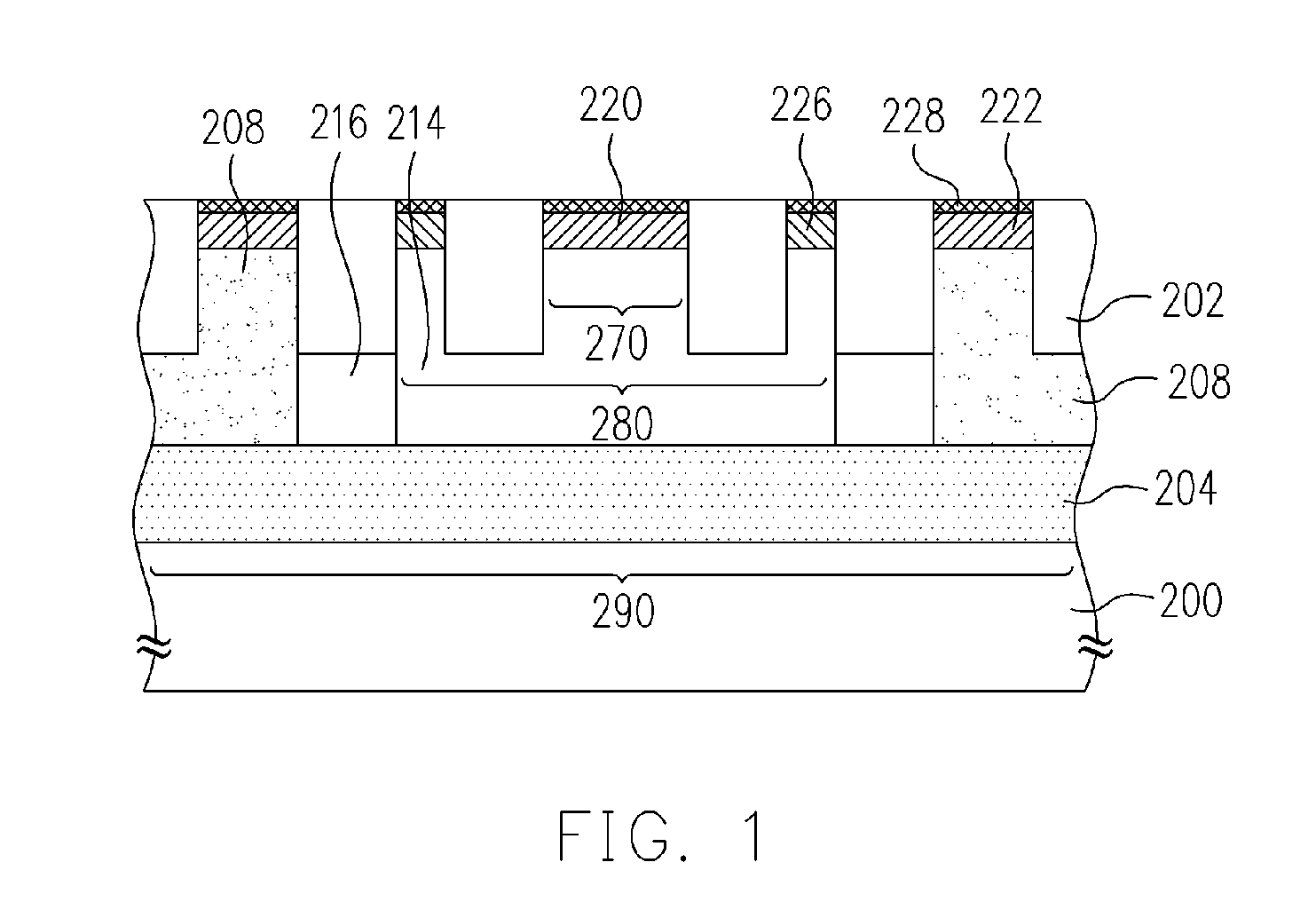

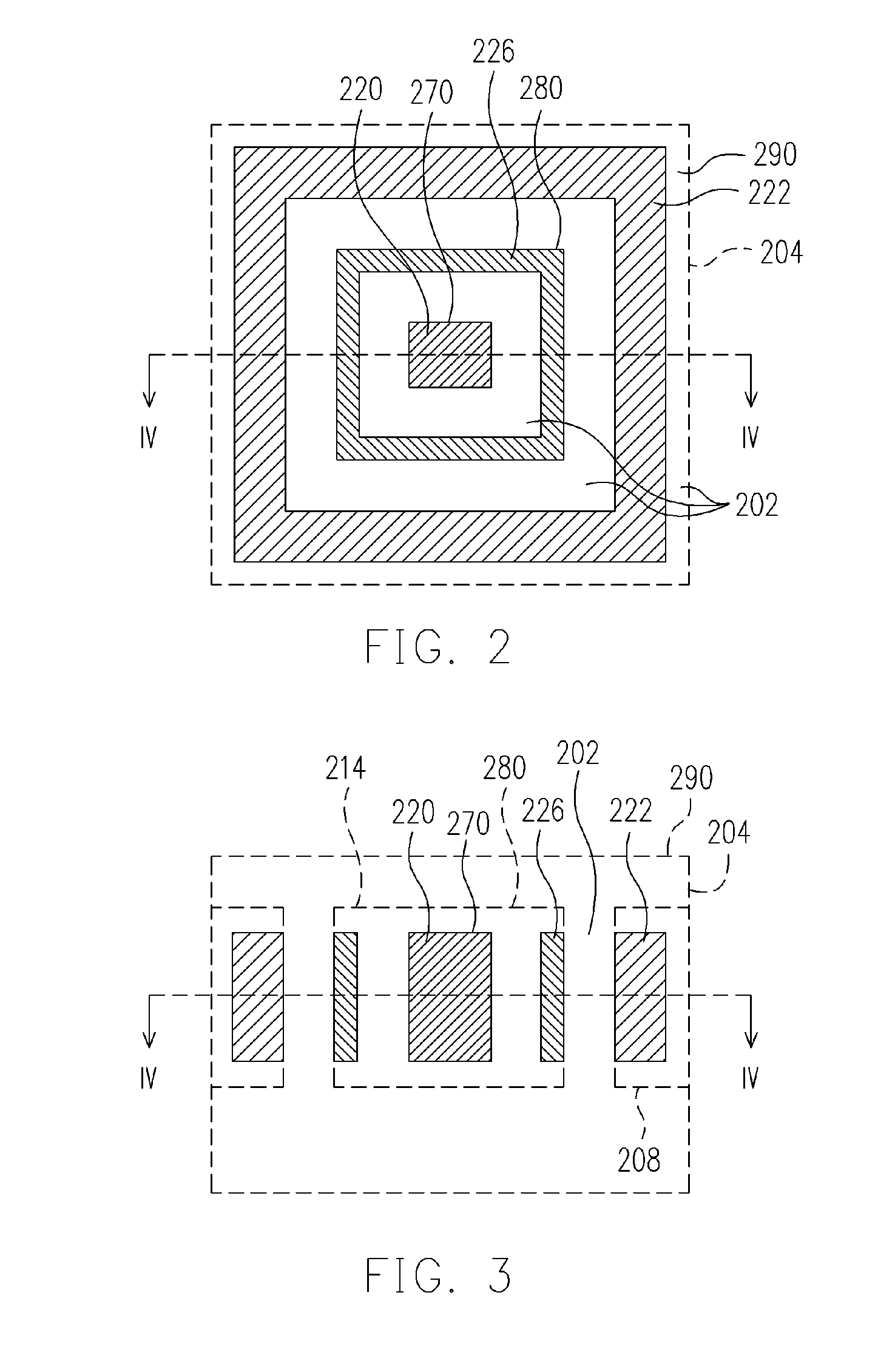

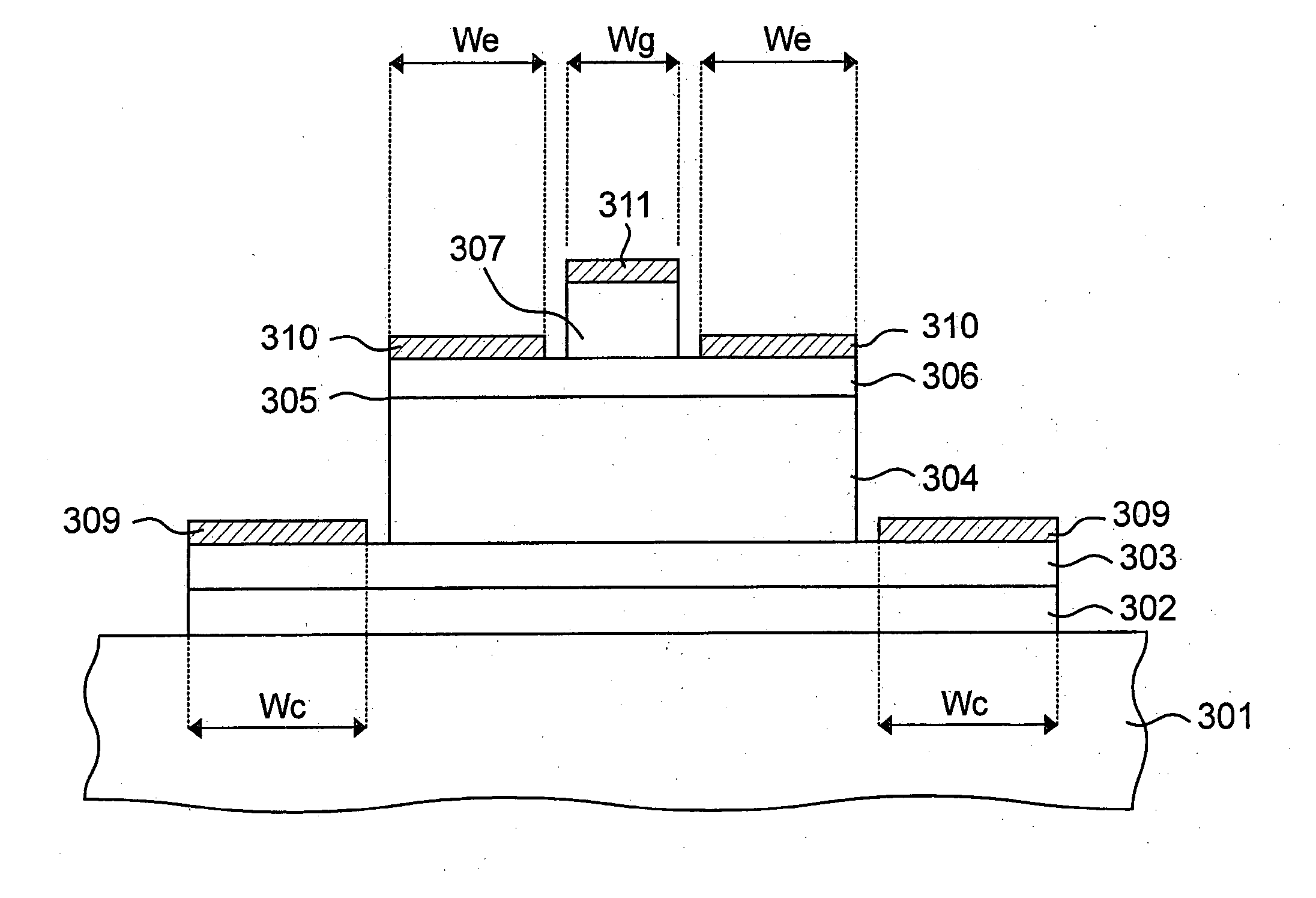

Bipolar junction transistor and method of fabricating the same

ActiveUS20070034900A1Reduce reverse junction leakage currentIncrease current gainSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringTransistor

A bipolar junction transistor is provided. A p-type well region surrounds an n-type emitter and connects with the bottom of the emitter to serve as a base. A p-type base pick-up region connects with the base and surrounds the emitter. An n-type deep well, connected to the bottom of the base and the bottom of the n-type well, is used as a collector. The n-type well surrounds the base and connects with the n-type deep well. An n-type collector pick-up region connects with the n-type well and surrounds the base. An isolation structure is disposed between the emitter and the base and between a portion of the base and a portion of the n-type well. A buffer region is disposed under a portion of the isolation structure. Furthermore, the buffer region together with a portion of the isolation structure isolates the p-type base from the n-type well.

Owner:UNITED MICROELECTRONICS CORP

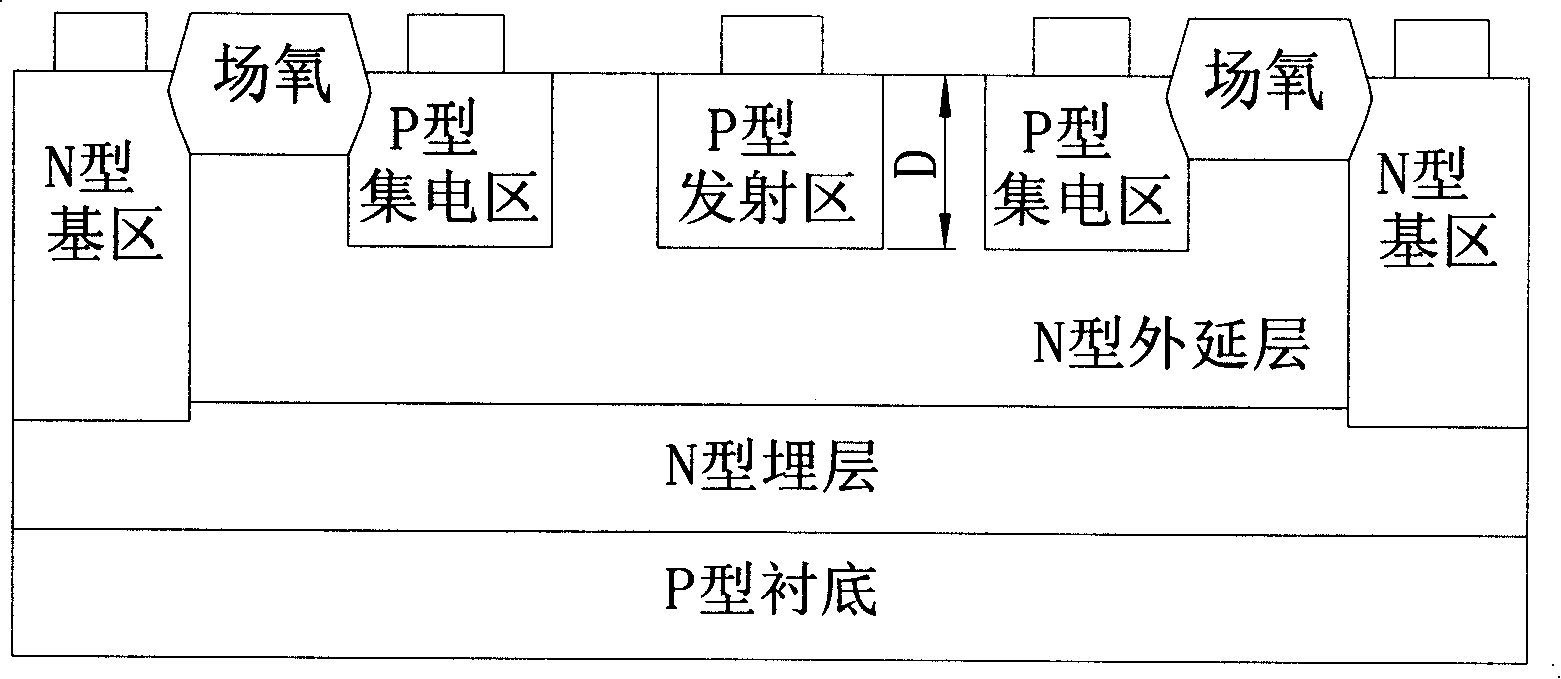

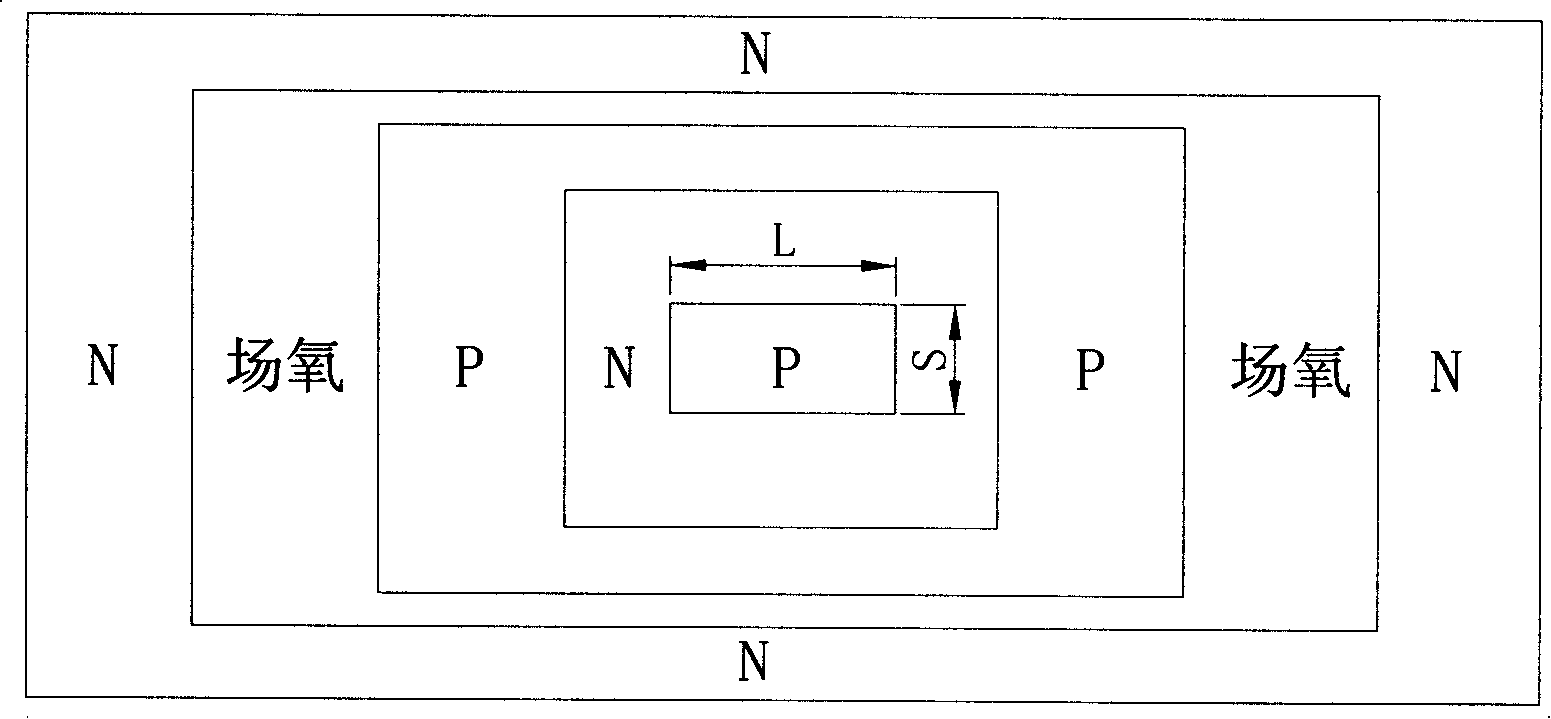

Horizontal PNP type audion and its making method

ActiveCN101170128ALaunch changeIncrease current gainSemiconductor/solid-state device manufacturingSemiconductor devicesOxygen ionsOptoelectronics

The invention discloses a transverse PNP type triode and a manufacturing method thereof. A silicon dioxide buried layer is arranged between a P type emitter region and an N type buried layer. The manufacturing method includes injecting oxygen ions partially in an N type epitaxial layer after the completion of the N type epitaxial layer growth; the position of injecting oxygen ions is between the N type buried layer and the P type emitter region to be formed and the injected oxygen ions can facilitate to form the silicon dioxide buried layer partially between the N type buried layer and the P type emitter layer in subsequent heating course. The transverse PNP type triode manufactured according to the method provided by the invention can improve the collection efficiency of collecting electrodes and the current gain of the triode.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

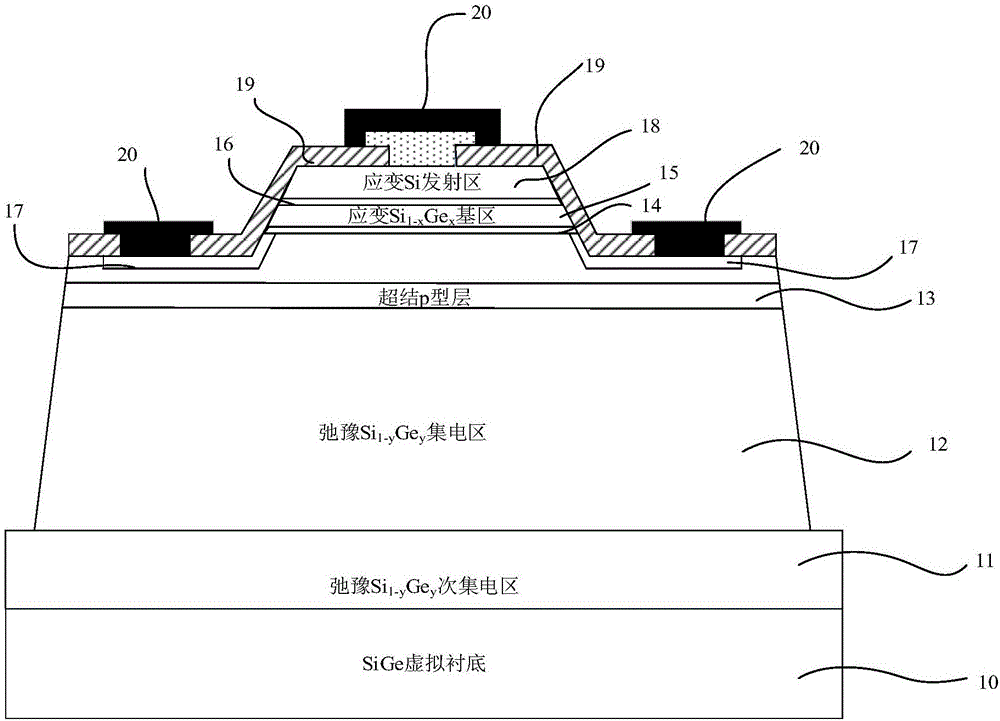

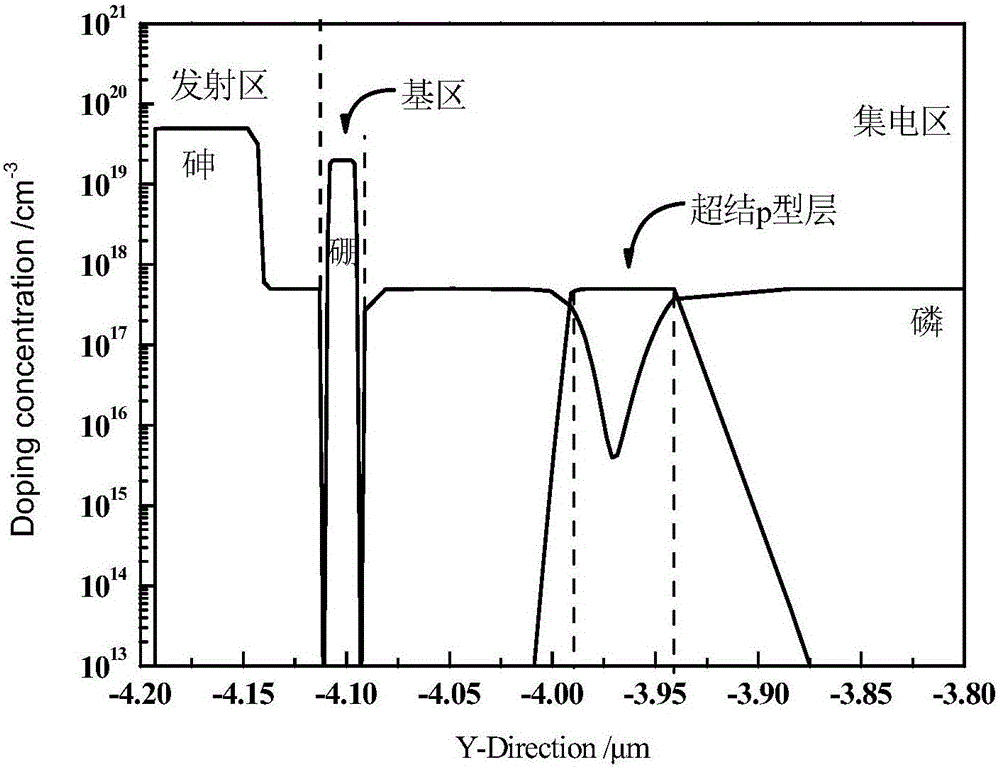

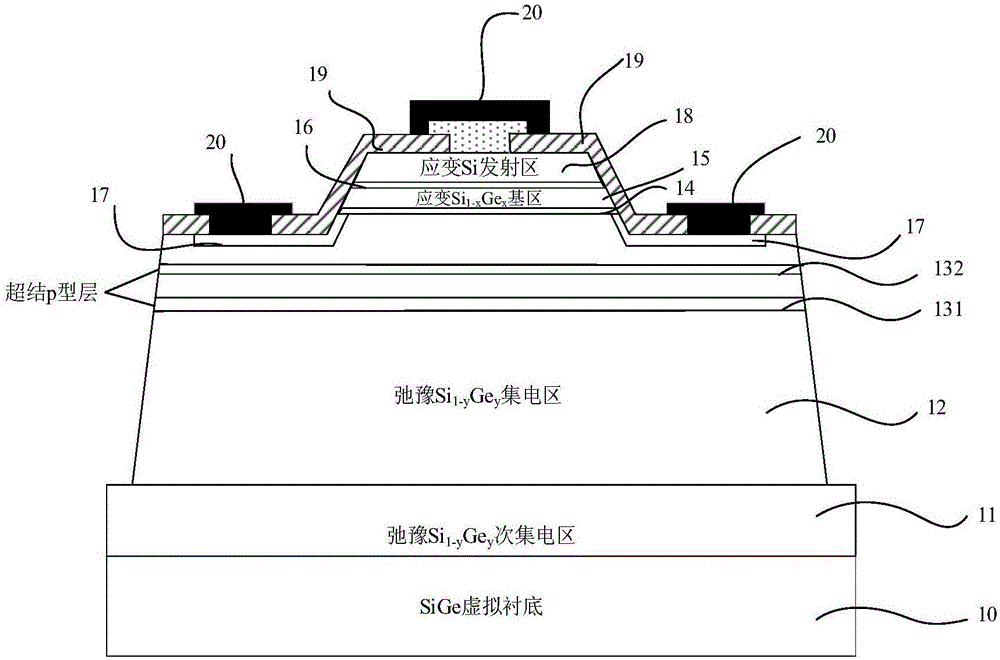

High-thermostability super-junction stress Si/SiGe heterojunction bipolar transistor

ActiveCN106169498AImprove thermal stabilityIncreased sensitivitySemiconductor devicesElectronic temperatureWorking temperature

The invention discloses a super-junction stress Si / SiGe heterojunction bipolar transistor with a high thermostability. A SiGe virtual substrate structure is adopted by the transistor; and a Si<1-y>Ge<y> secondary collector region, a relaxation Si<1-y>Ge<y> collector region, a stress Si<1-x>Ge<x> base region and a stress Si emitter region are respectively and epitaxially grown on the SiGe virtual substrate structure. According to the transistor, by introducing a super-junction p-type layer parallel to the stress Si<1-x>Ge<x> base region to the relaxation Si<1-y>Ge<y> collector region, the purposes of improving the electric field distribution in a collector junction space-charge region, reducing the peak electronic temperature, inhibiting the impact ionization and improving a device breakdown voltage are achieved; and meanwhile, with the introduction of the super-junction p-type layer, the doping concentration and the phonon scattering rate of the relaxation Si<1-y>Ge<y> collector region are effectively reduced, and the thermal conductivity of the relaxation Si<1-y>Ge<y> collector region is improved; the transistor has the characteristics of large current gain and high breakdown voltage; the internal temperature distribution is significantly reduced, the characteristic frequency and the temperature sensibility are improved, and the high-thermostability work can be realized in a relatively wide working temperature range.

Owner:BEIJING UNIV OF TECH

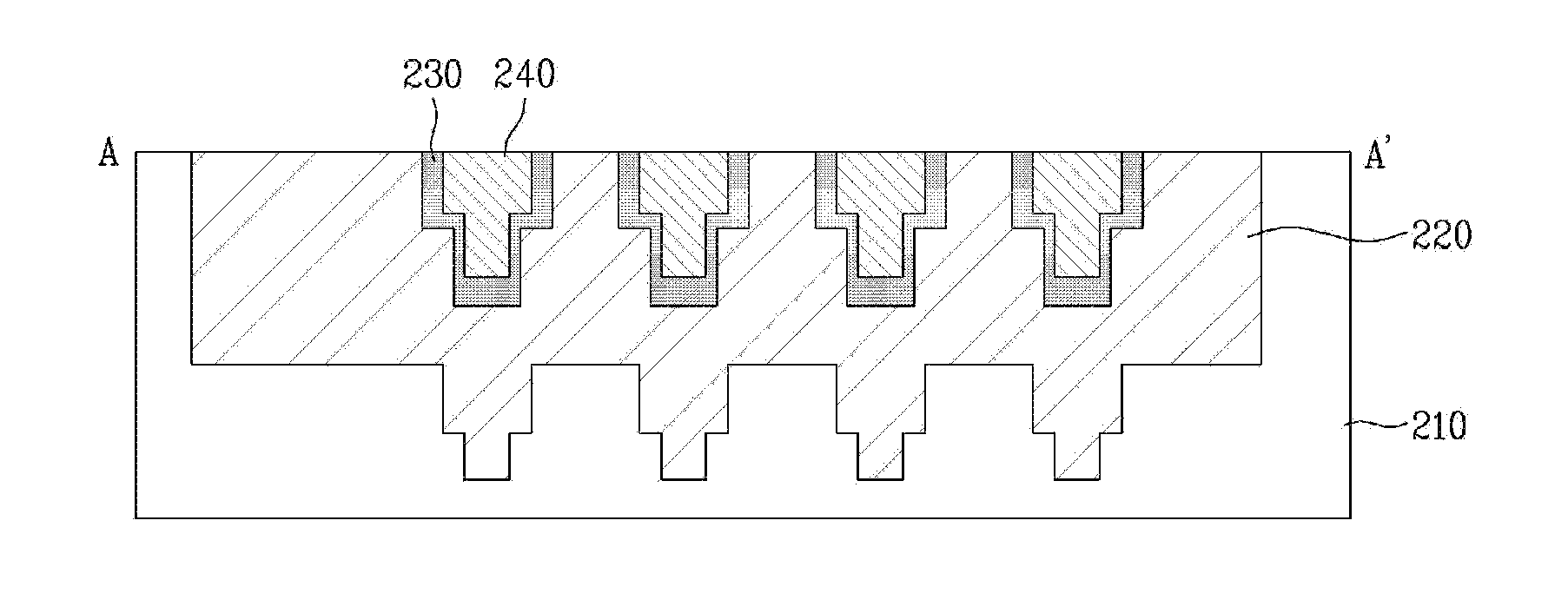

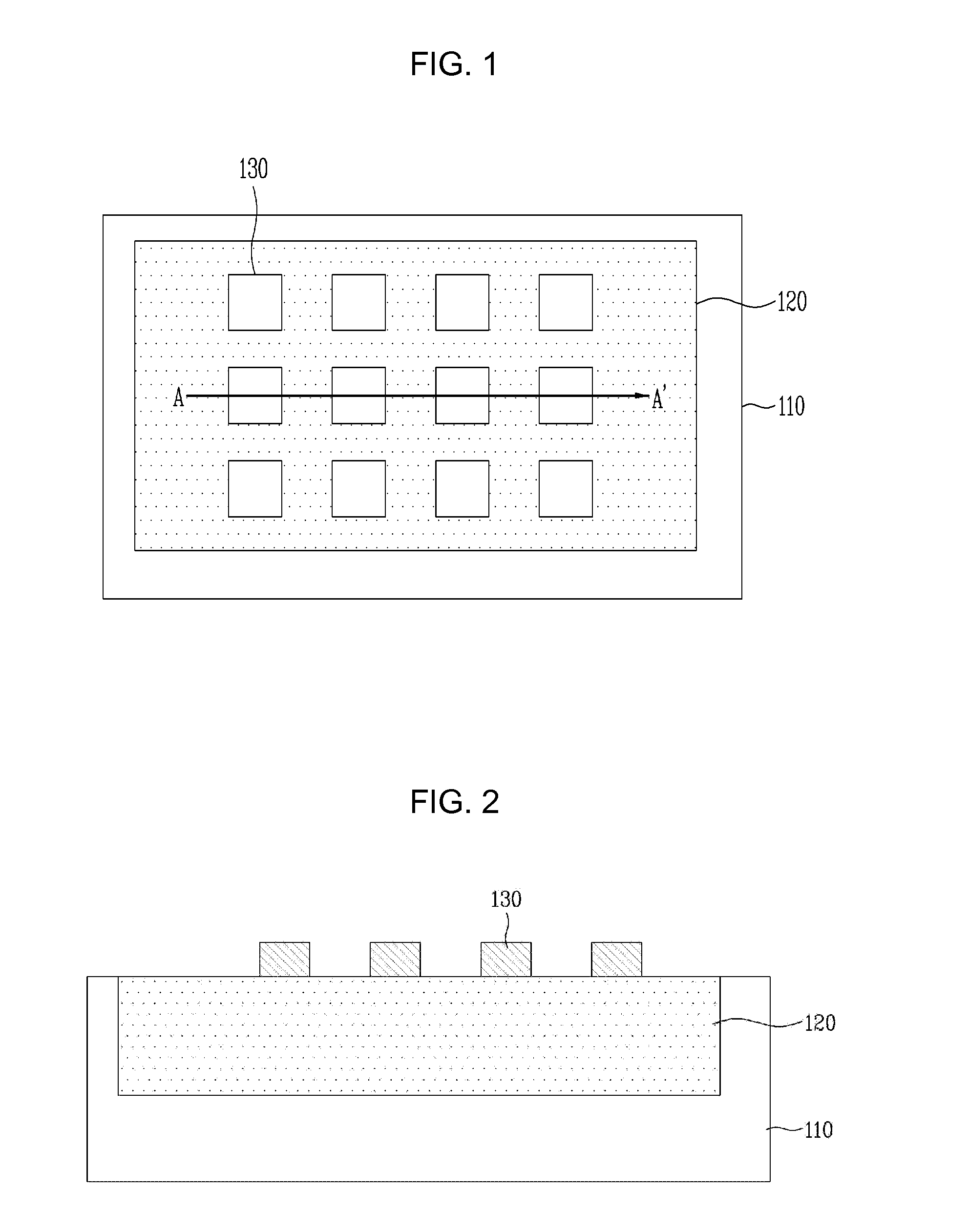

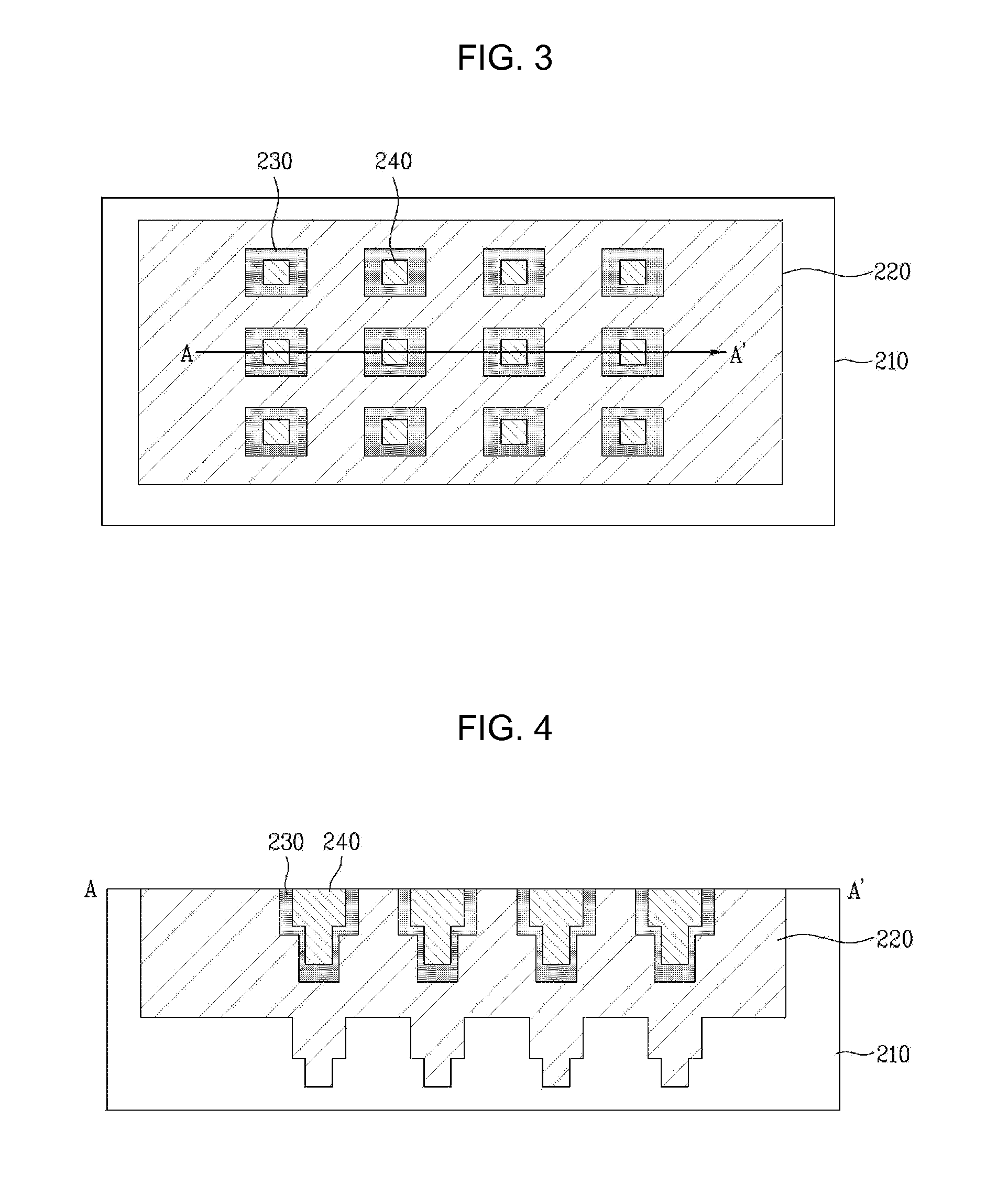

Bipolar Junction Transistor and Method of Manufacturing the Same

InactiveUS20100163872A1Contact areaIncrease currentTransistorSemiconductor/solid-state device manufacturingEngineeringImpurity

A bipolar junction transistor and a method of manufacturing a bipolar junction transistor are disclosed. An exemplary bipolar junction transistor includes a second conductivity type base region in a first conductivity type substrate, step-shaped recesses in the base region, a polysilicon layer doped with a first conductivity type impurity in the step-shaped recesses, and a step-shaped emitter region between the polysilicon layer and the base region.

Owner:DONGBU HITEK CO LTD

Bipolar transistor

InactiveUS20050116319A1Increase current gainReduce power consumptionTransistorSolid-state devicesSemiconductorHigh current gain

A bipolar transistor of the present invention comprises a collector layer made of an n-type semiconductor and an emitter layer made of an n-type semiconductor provided on this collector layer. A gate layer for injecting p-type carriers (holes) into the emitter layer is provided on the emitter layer. A p-type carrier retaining layer is formed between the collector layer and the emitter layer. The p-type carrier retaining layer temporarily retains the p-type carriers that are injected from the gate layer into the emitter layer and diffused in the emitter layer and reach the p-type carrier retaining layer. The bipolar transistor has a structure whose performance is not influenced by sheet resistance of the base layer, and is able to exhibit a high current gain even in a high-frequency region.

Owner:SHARP KK

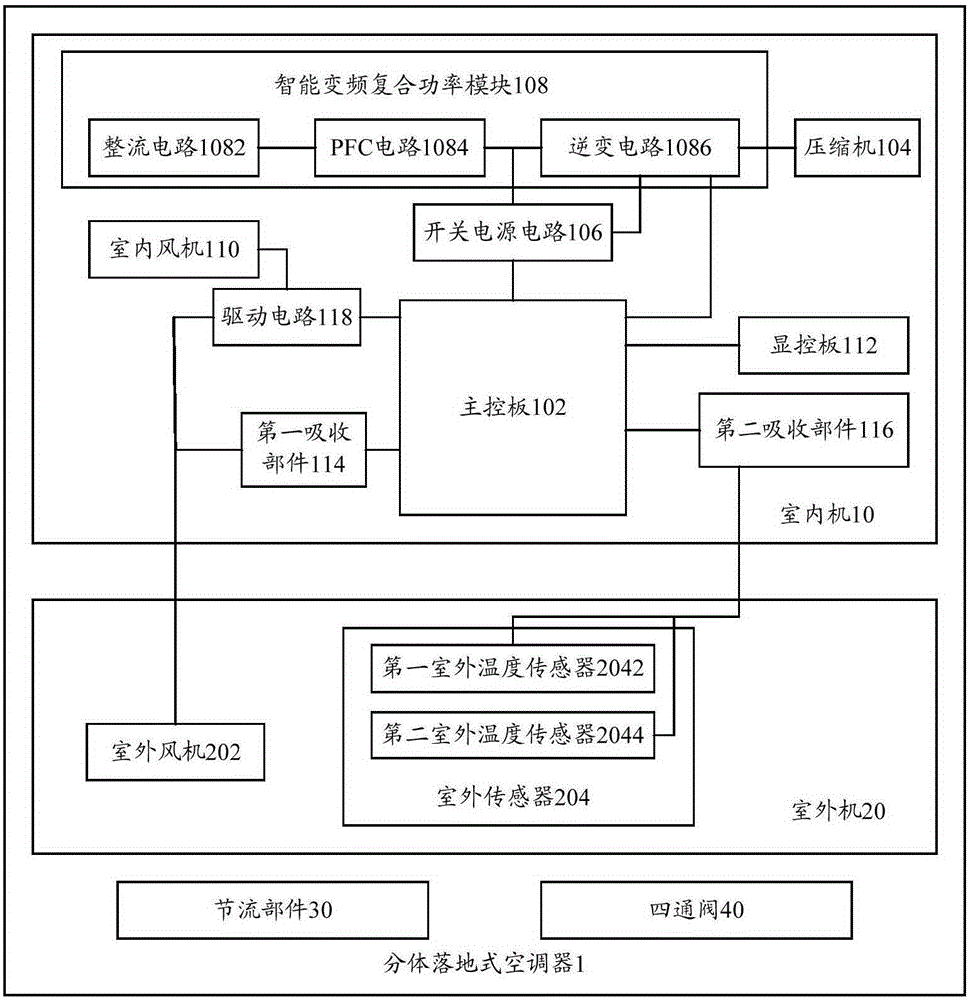

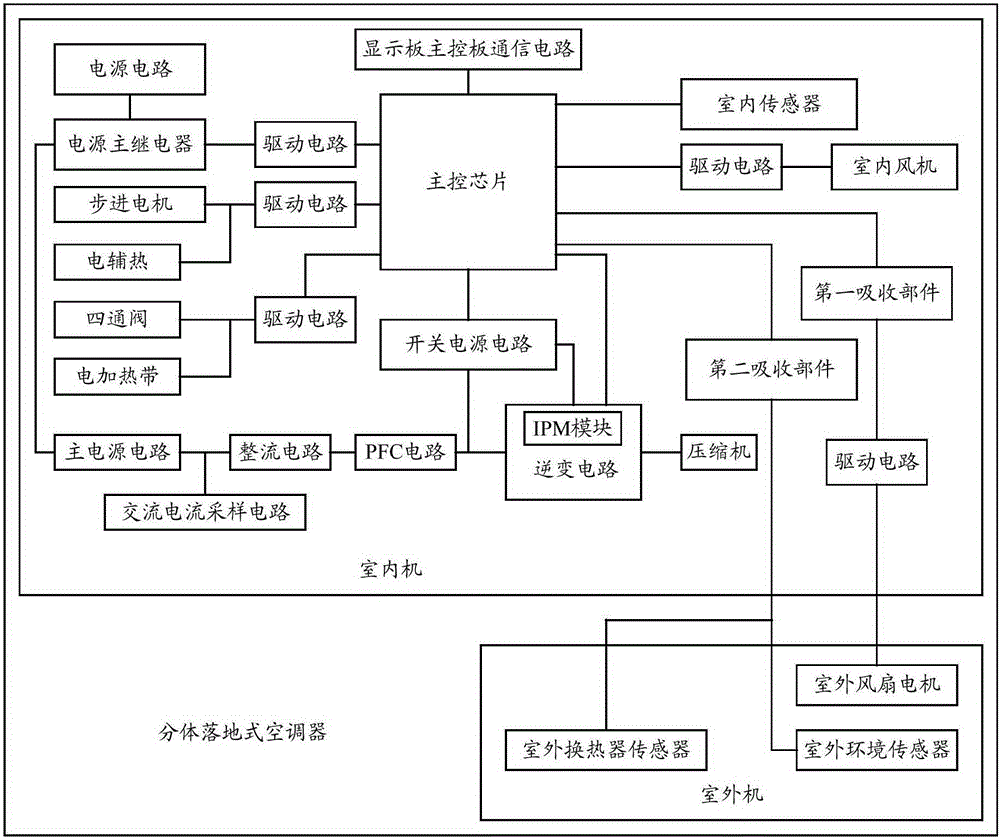

Floor-type split air conditioner

InactiveCN105180278AAvoid damageExtended service lifeSpace heating and ventilation safety systemsLighting and heating apparatusOvervoltageEngineering

The invention provides a floor-type split air conditioner. The floor-type split air conditioner comprises an indoor machine provided with an indoor heat exchanger and a compressor, an outdoor machine provided with an outdoor heat exchanger, an outdoor fan and an outdoor sensor, and a main control board which is used for controlling the compressor, the outdoor fan and the outdoor sensor to work and arranged in the indoor machine, wherein a throttling component is arranged in the indoor machine or the outdoor machine; the indoor heat exchanger, the throttling component, the outdoor heat exchanger and the compressor sequentially communicate circularly, so that a refrigerant loop is formed; the outdoor fan is connected to a fan wire leading port of the main control board; the outdoor sensor is connected to a temperature sampling port of the main control board; a first absorption component is arranged at the fan wire leading port, and a second absorption component is arranged at the temperature sampling port, so that the floor-type split air conditioner is protected. Through the technical scheme adopted by the floor-type split air conditioner disclosed by the invention, dangers caused by overcurrent or overvoltage in electronic control can be effectively avoided, the service life of the floor-type split air conditioner is prolonged, and the applicability and the safety of the floor-type split air conditioner are improved; besides, the production cost of the floor-type split air conditioner is reduced, and the production efficiency of the floor-type split air conditioner is improved.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD +1

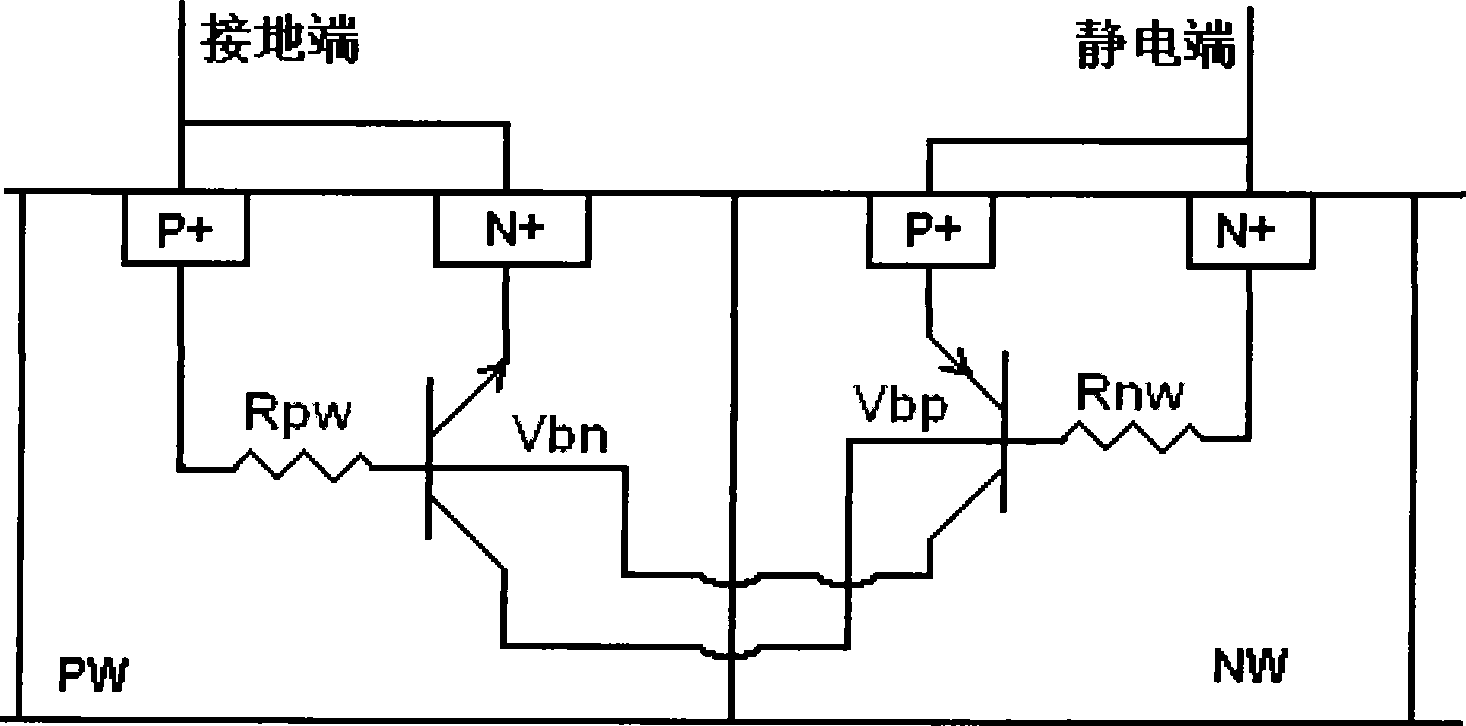

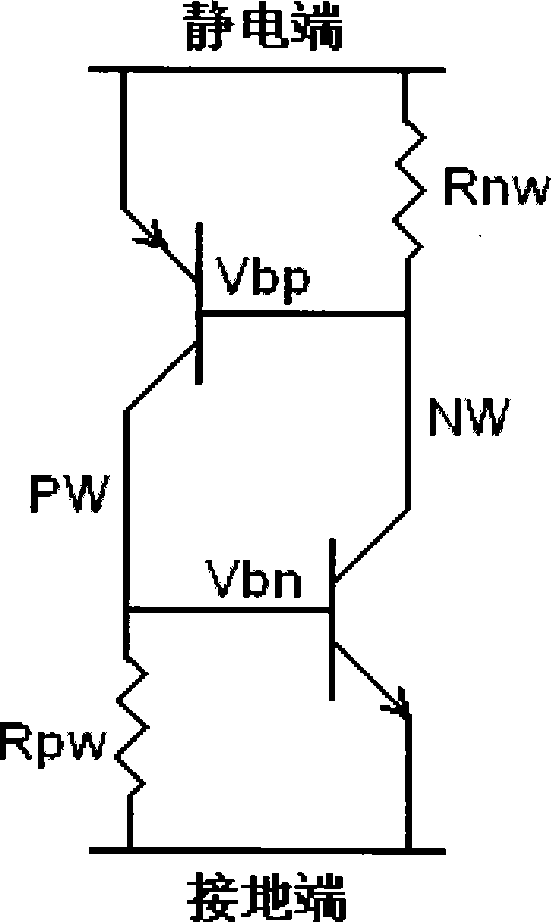

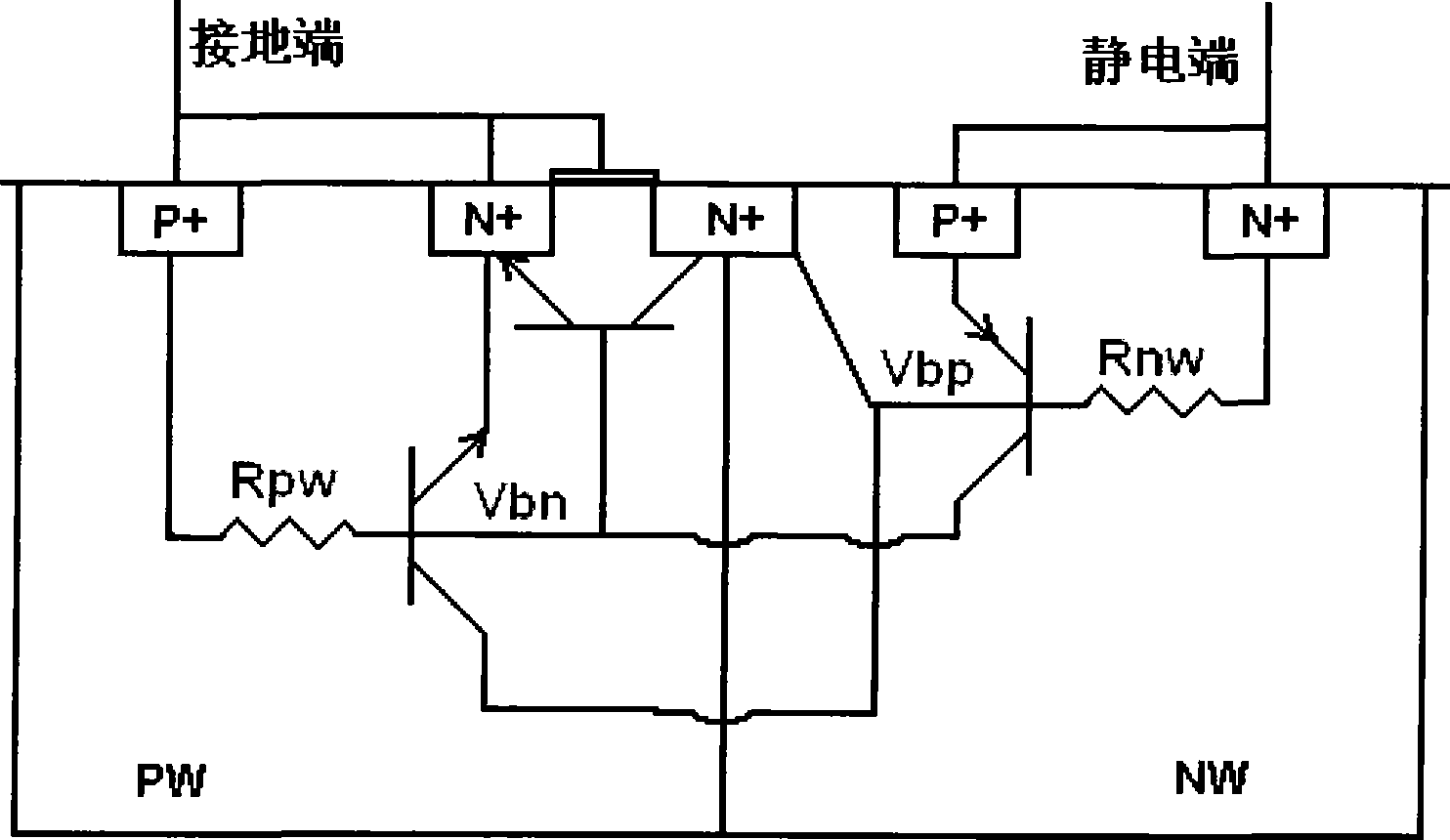

Electrostatic protection structure for low trigger voltage thyristor

ActiveCN101442047ASimple designIncrease current gainSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical connection

The invention discloses a low-trigger voltage thyristor static protective structure, which comprises an NMOS transistor and an SCR structure, wherein the NMOS transistor is formed in PW; an NPN transistor formed by N+ / PW / N+ parasitized by the NMOS transistor and an NPN transistor formed by parasitic N+ / PW / NW have the same emitter terminal and base terminal; the SCR structure consists of a parasitic PNP transistor formed by N+ / PW / NW and a parasitic NPN transistor formed by N+ / PW / NW; a drain electrode of the NMOS transistor is in electrical connection with the static terminal through an NW resistor Rnw1; and trigger of the SCR structure is controlled by the NMOS transistor and the NW resistor Rnw1. The low-trigger voltage thyristor static protective structure can effectively reduce trigger voltage during SCR static protection, and can adjust the trigger voltage according to requirement so as to greatly facilitate static protection design, and can adjust current gain of the SCR structure according to requirement, thereby improving the static protecting capability of the structure.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

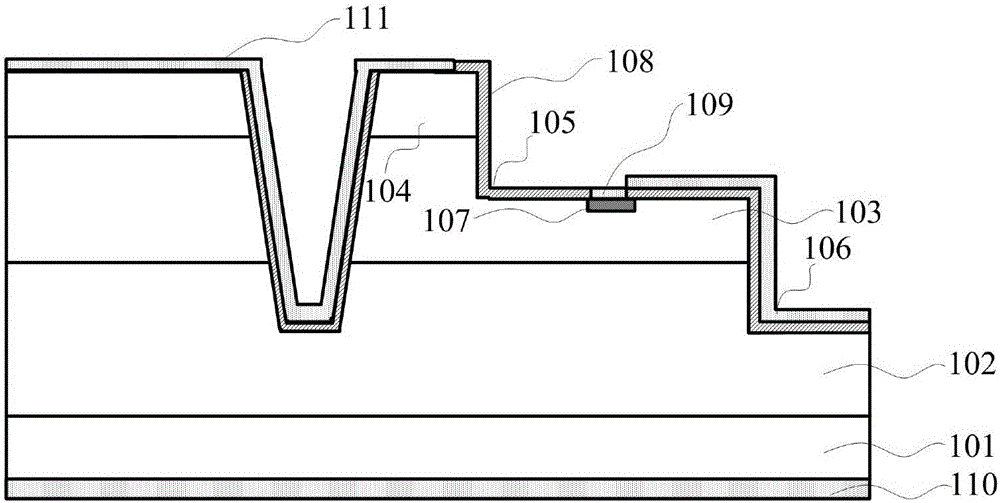

Vertical parasitic PNP (plug-and-play) triode in BiCMOS (bipolar complementary metal oxide semiconductor) process and manufacturing method

ActiveCN102569371ALarge current amplification factorImprove frequency characteristicsTransistorSemiconductor/solid-state device manufacturingOutput deviceEngineering

The invention discloses a vertical parasitic PNP (plug-and-play) triode in a BiCMOS (bipolar complementary metal oxide semiconductor) process, a collector region is formed in a first active area; a pseudo buried layer is formed at the bottom of a shallow groove field oxide, transversely extends, enters into the first active area and is in contact with the collector region; the connection between the collector region and the adjacent active area is realized through the pseudo buried layer, and a collector is led out by forming metal contact at the top of the adjacent active area. N type polysilicon is formed at the upper part of a base region and a base is led out. An emitter region comprises a P type ion-implanted layer and a P type polysilicon formed above the base region. The invention further discloses a manufacturing method of the vertical parasitic PNP triode in the BiCMOS process. The vertical parasitic PNP triode disclosed by the invention can be used as an output device in a high-speed and high-gain BiCMOS circuit, one more device choice is provided for a circuit, the resistance of the collector of the PNP triode can be reduced, the frequency performance of the device can be improved, a polysilicon emitter can improve the gain of the device, and the production cost can also be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

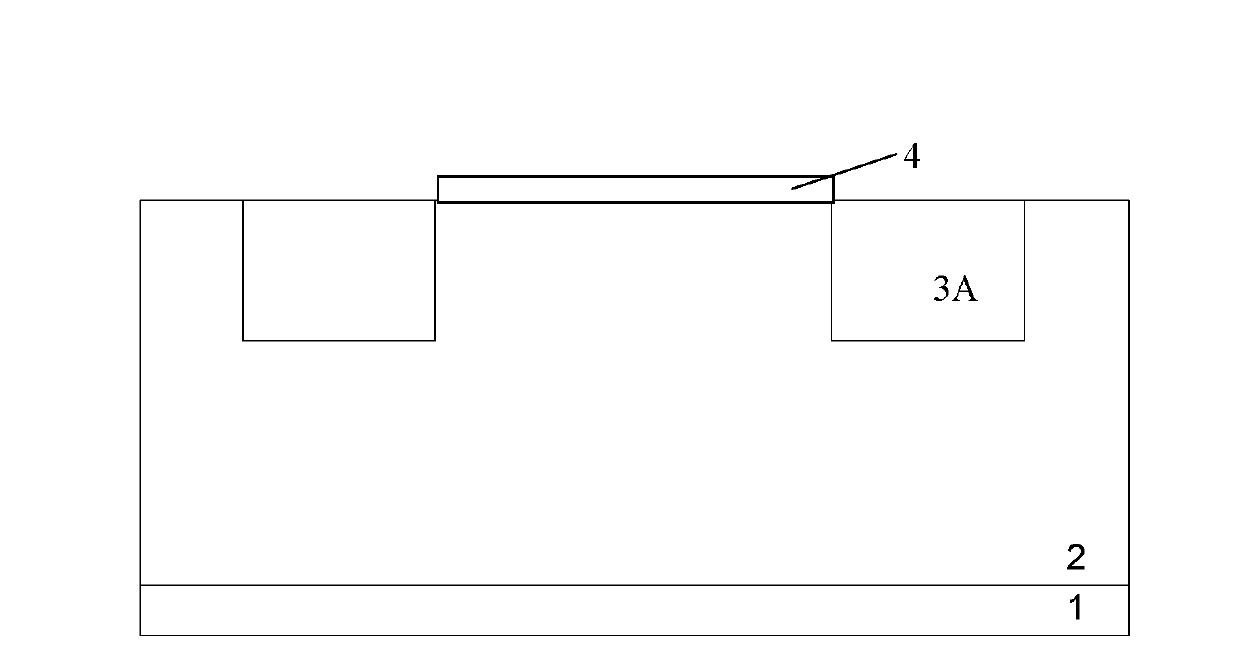

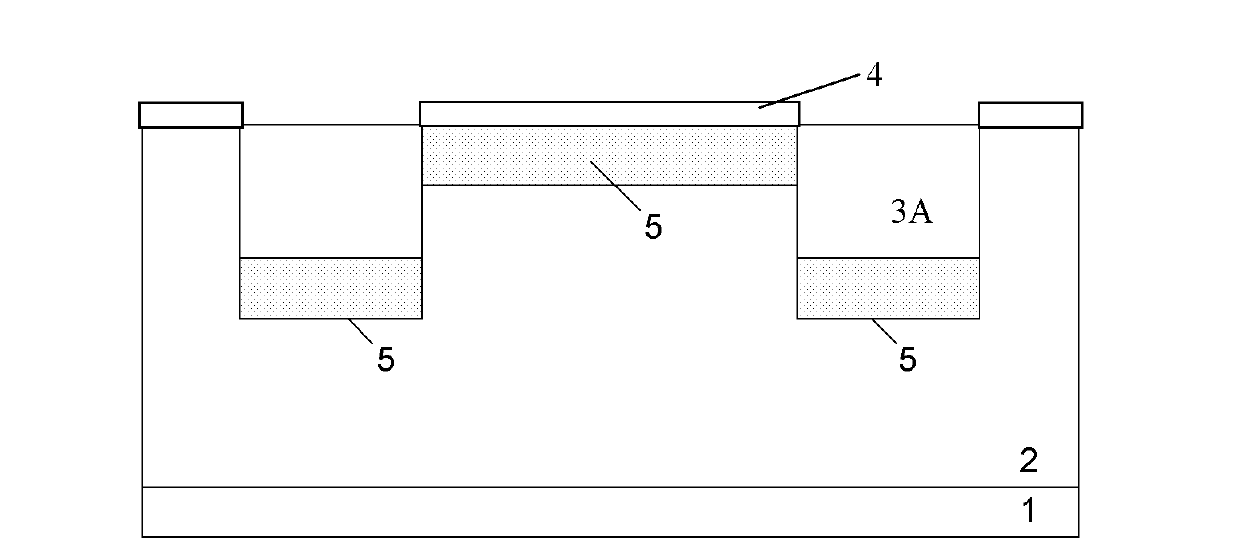

Silicon carbide bipolar transistor based on active region trench structure and manufacturing method thereof

ActiveCN106684132AImprove efficiencyIncrease current gainSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic bipolar transistorSilicon

The invention discloses a silicon carbide bipolar transistor based on an active region trench structure. The invention belongs to the technical field of microelectronics. The mentioned transistor can solve the problem that a thin substrate structure of the existing silicon bipolar transistor may lead to low breakdown voltage. The transistor comprises N+ launching area that is provided on the surface of the base, a device groove that is in the form of incline groove, a launching zone platform with vertical groove type and a device isolation zone. Base P + an injection zone is placed on lower surface of the launching zone platform and in the base and the device groove is provided in the N+ the launching area and extended to the upper part of a N- collector area while the device isolation zone is provided in the base and extended to the upper part of the N- collector zone.

Owner:XIDIAN UNIV

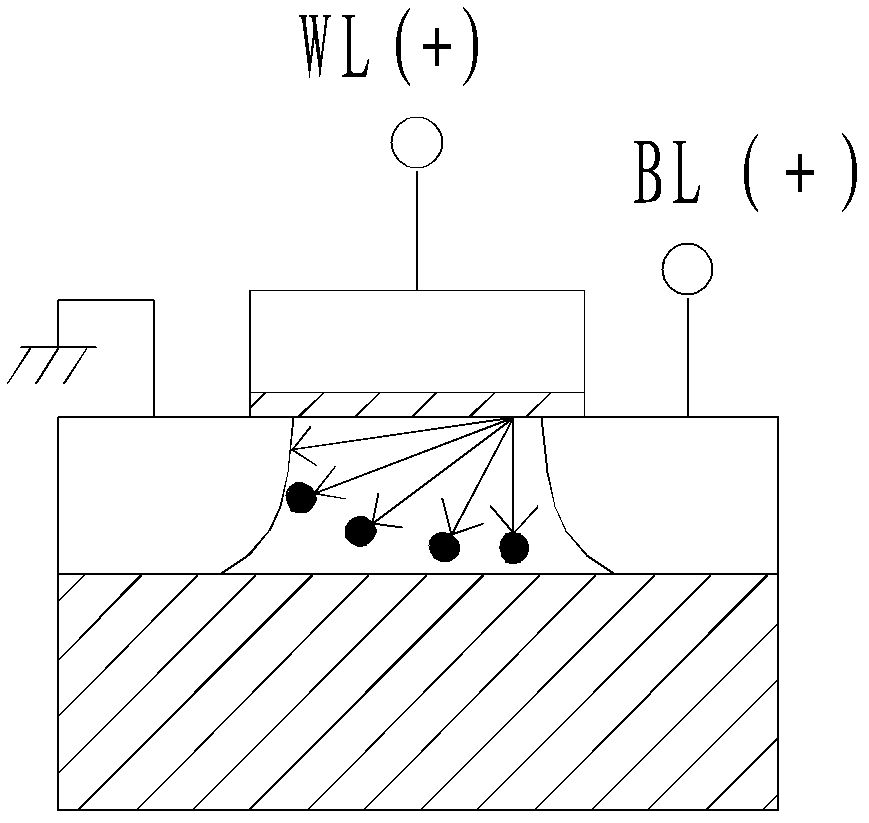

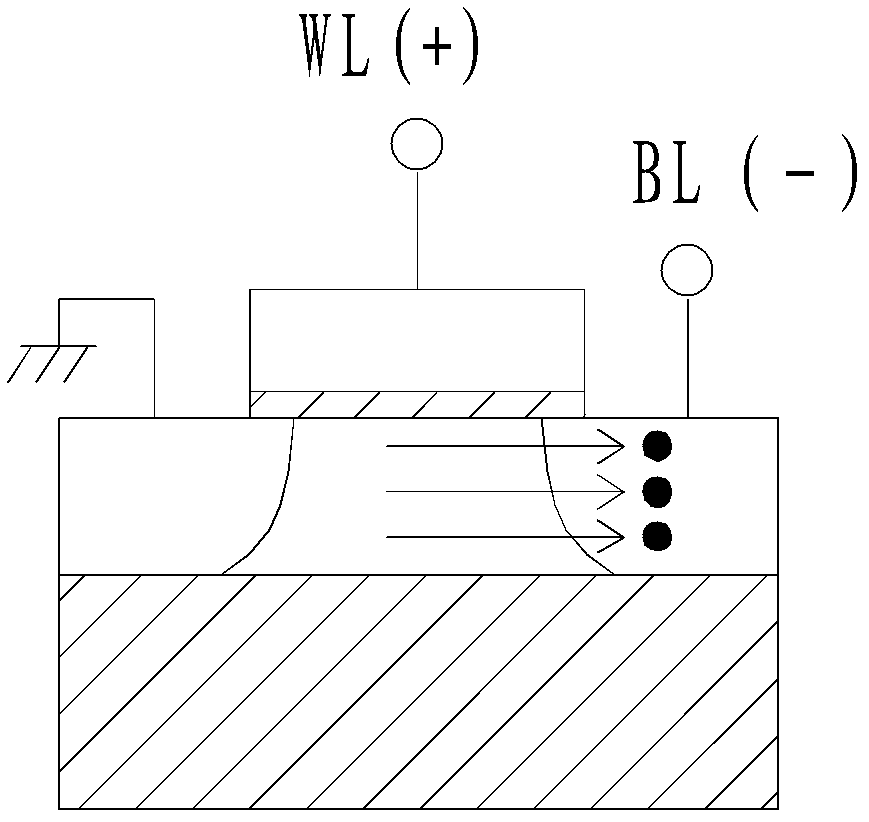

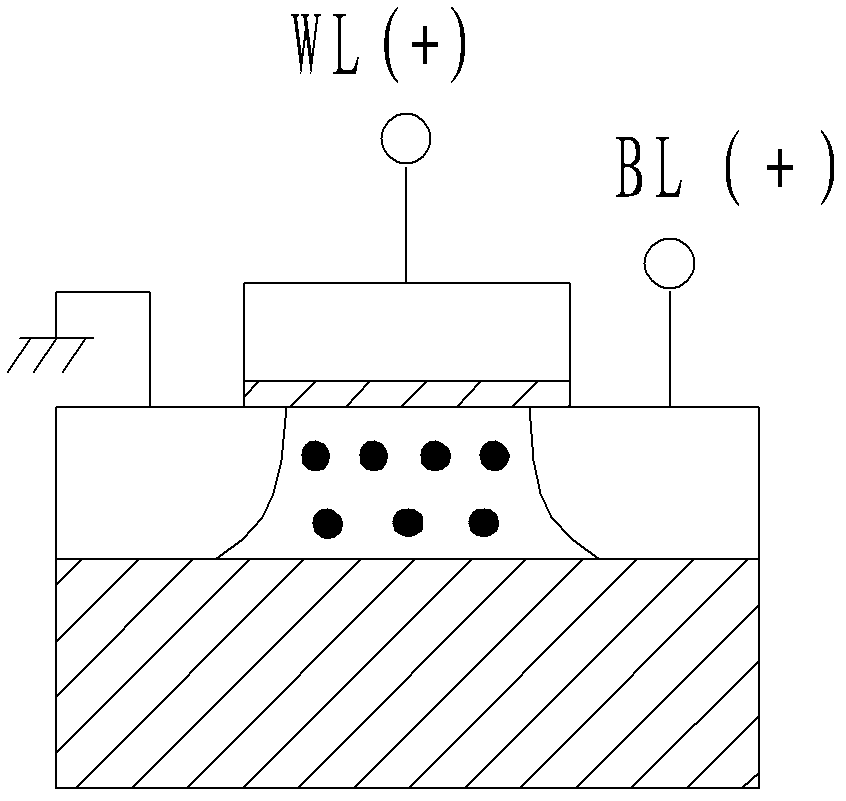

One-transistor dynamic random access memory (DRAM) unit based on silicon-germanium silicon heterojunction, and method for preparing one-transistor DRAM unit

InactiveCN102437127AIncreased impact ionization effectIncrease spawn rateTransistorSemiconductor/solid-state device manufacturingHeterojunctionSilicon heterojunction

The invention discloses a one-transistor dynamic random access memory (DRAM) unit based on a silicon-germanium silicon heterojunction and a method for preparing the one-transistor DRAM unit. The method for preparing the single-transistor DRAM unit comprises the following steps of: forming a SiGe epitaxial layer in the top layer of a silicon wafer on an insulator; performing a surface dry oxidization process on the SiGe epitaxial layer so as to form a first conductive type SiGe body region, wherein the dry oxidization process is not stopped until a valence band position of the first conductive type SiGe body region is higher than that of the material of the top layer of the silicon wafer on the insulator according to a mole ratio of the germanium content in the first conductive type SiGe body region; and forming an N-channel metal oxide semiconductor (NMOS) transistor comprising the heterojunction based on silicon-germanium silicon in the silicon wafer on the insulator, wherein the NMOS transistor is a single transistor. The 1T-DRAM unit can effectively reduce the working voltage and increase the balance of output current between readings '0' and '1', namely the signal margin is increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Laser diode control device with good stability

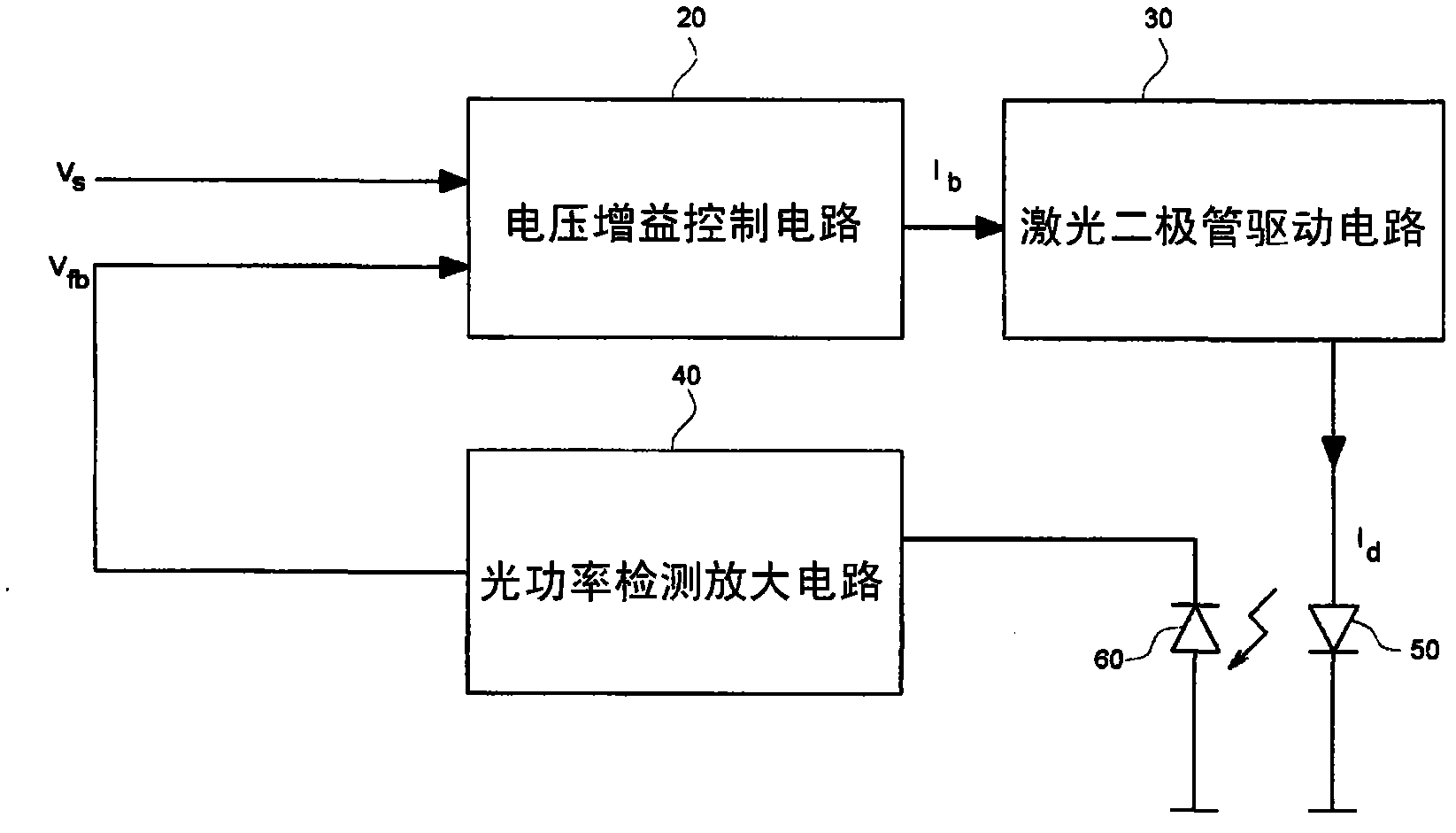

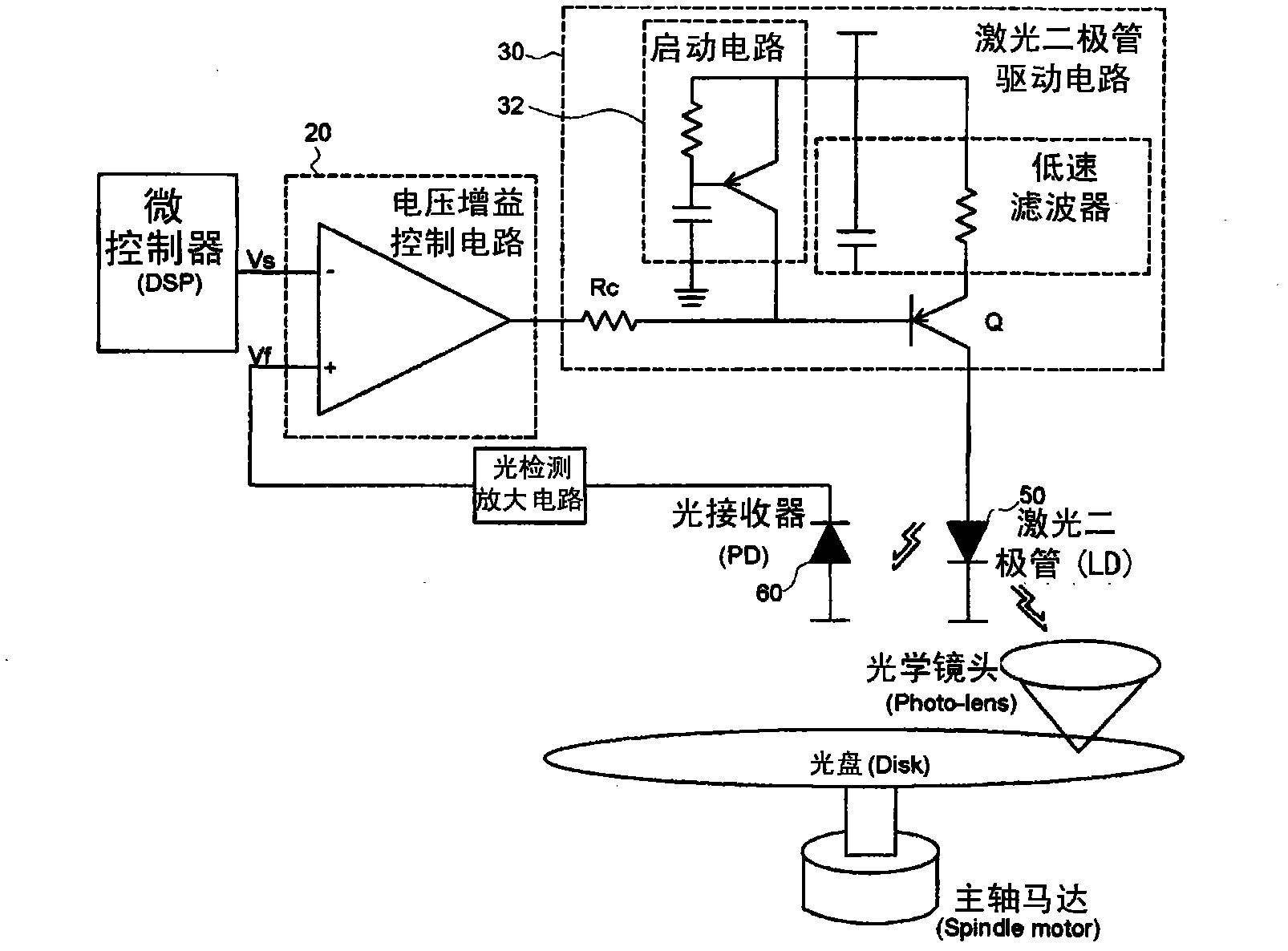

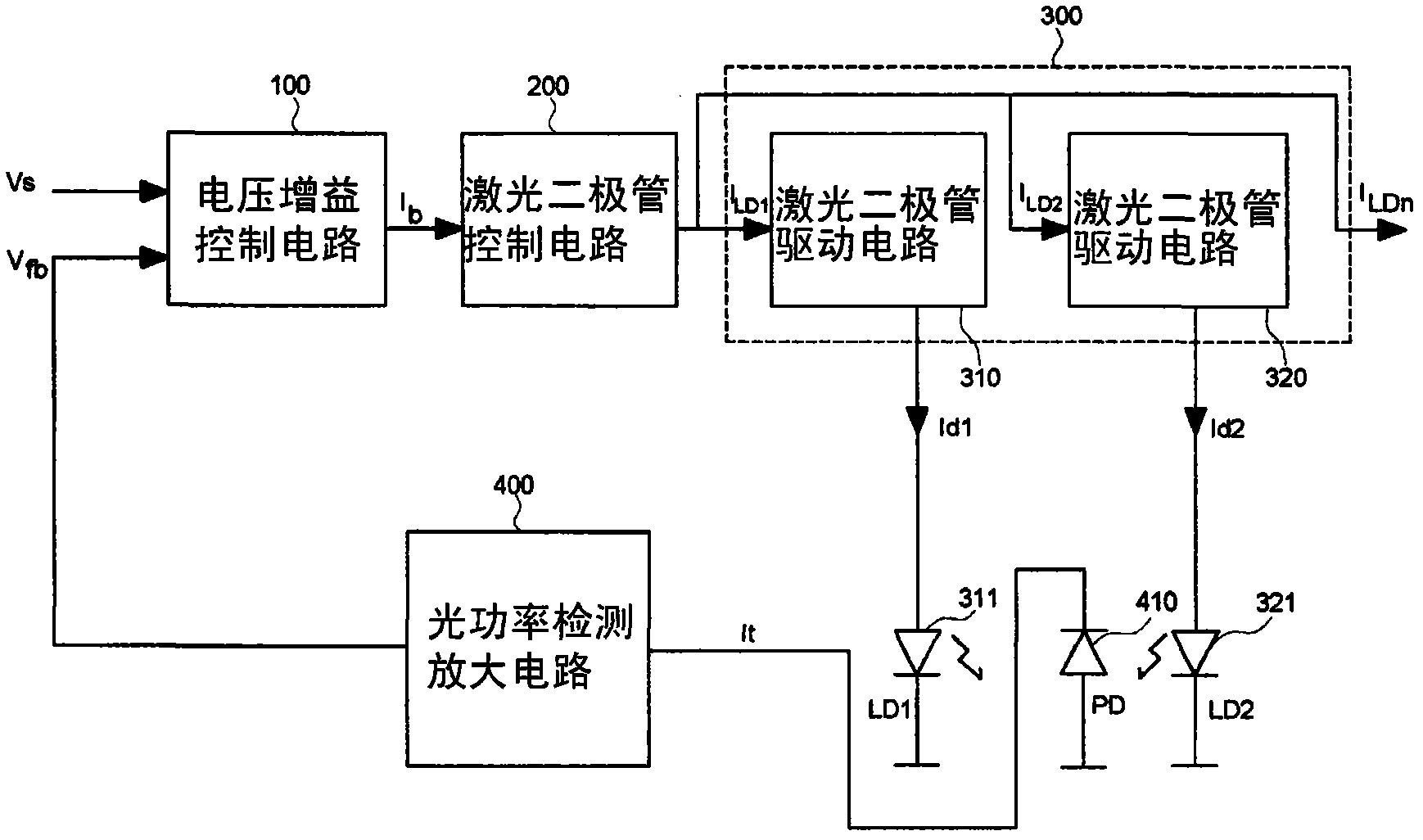

InactiveCN102855889AIncrease current gainExtend your lifeOptical beam sourcesOptical recording/reproducing/erasing methodsCapacitanceReference current

The invention provides a laser diode control device capable of sharing an automatic power control circuit. The laser diode control device comprises a voltage gain control circuit, a laser diode control circuit, and a light power detecting amplification circuit. The laser diode control device is characterized in that the laser diode control circuit comprises a voltage detecting circuit and a soft starting circuit, wherein one input end of the voltage detecting circuit is connected with detection bias voltage, and another input end of the voltage detecting circuit is connected with reference voltage and supplies output voltage; the soft starting circuit is formed by a plurality of transistor current mirror circuits; the load ends of the transistor current mirror circuits are connected with a plurality of laser diode driving circuits, and the reference current ends of the current mirror circuits are connected with one end of a resistor; the other end of the resistor is connected with the emitter end of a transistor; and the base end of the crystal tube is connected with a capacitor and the output voltage.

Owner:AMTEK SEMICON