Heterojunction bipolar transistor

A technology of bipolar transistors and heterostructures, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem of not reducing ΔEc well, deteriorating base layer and base/collector cross section Crystal quality, difficulty in obtaining satisfactory InAlAs/GaAsSb interface, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] Embodiments of the present invention will be described below with reference to the drawings.

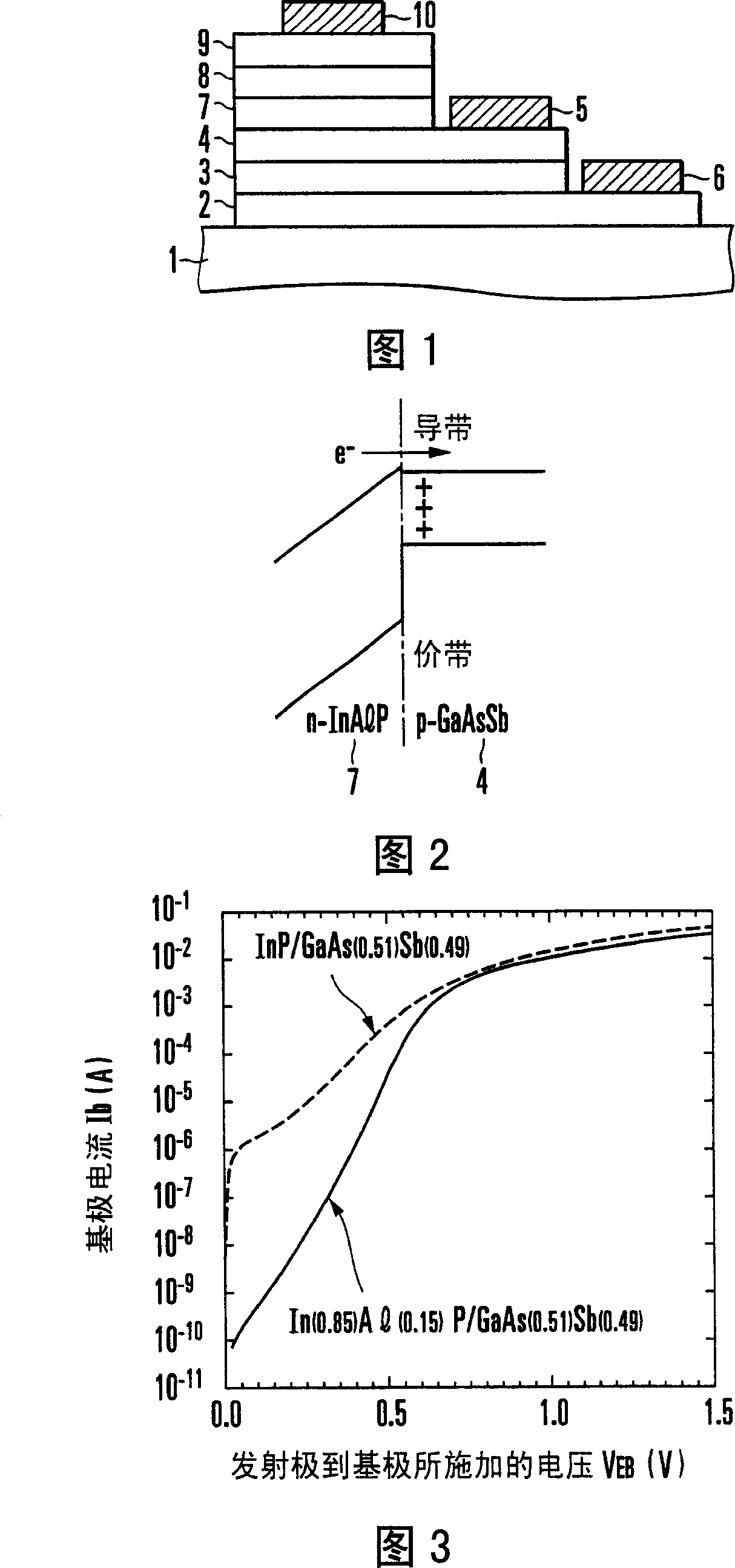

[0037] FIG. 1 is a schematic cross-sectional view showing an example of the arrangement of a heterostructure bipolar transistor according to an embodiment of the present invention. In this heterostructure bipolar transistor shown in Fig. 1, the n-type InP sub-collector layer 2 heavily doped with silicon (Si), the InP collector layer 3, and the n-type InP sub-collector layer 3 heavily doped with carbon (C) p-type GaAs (0.51) Sb (0.49) Base layer 4, n-type In doped with Si (1-y) Al (y) P emitter layer 7, n-type InP capping layer 8 heavily doped with Si, and n-type In heavily doped with Si (0.53) Ga (0.47) As contact layer 9 is stacked on InP substrate 1 which has increased resistance due to doping with iron (Fe) as an impurity and has a (100) main surface.

[0038] In addition, an ohmic-contact collector electrode 6 is formed on a region of the sub-collector layer 2 where ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More