Patents

Literature

31 results about "Bicmos circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

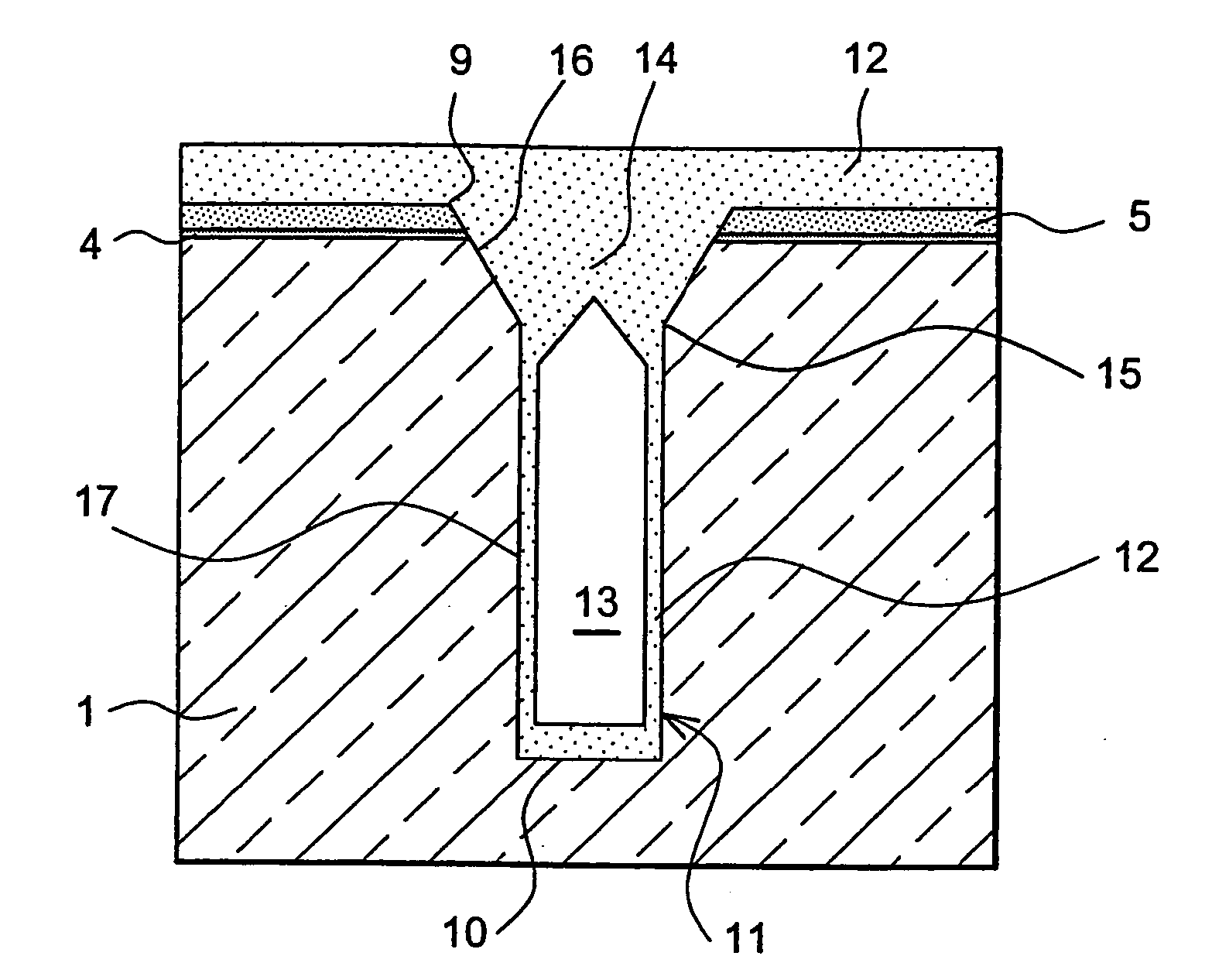

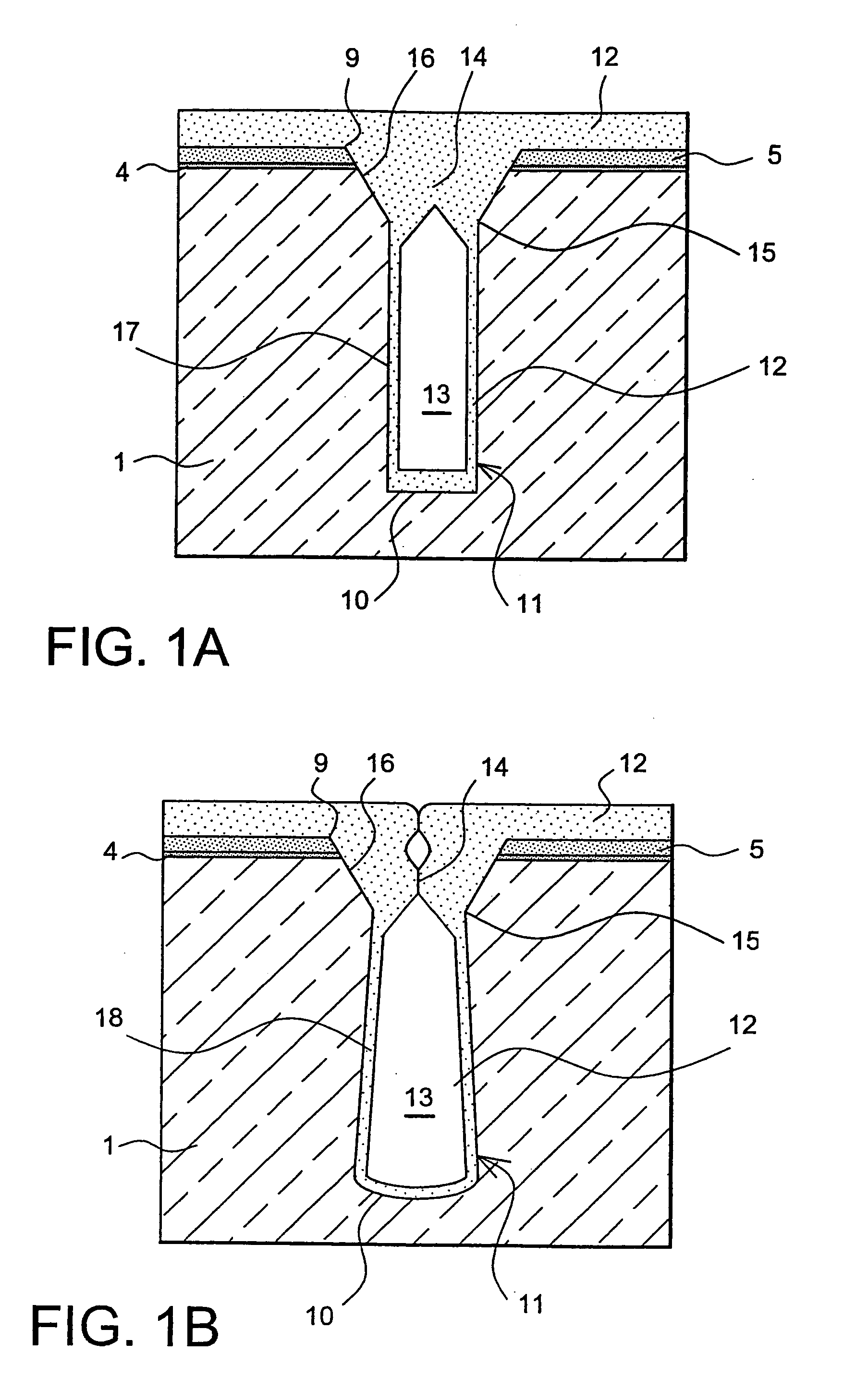

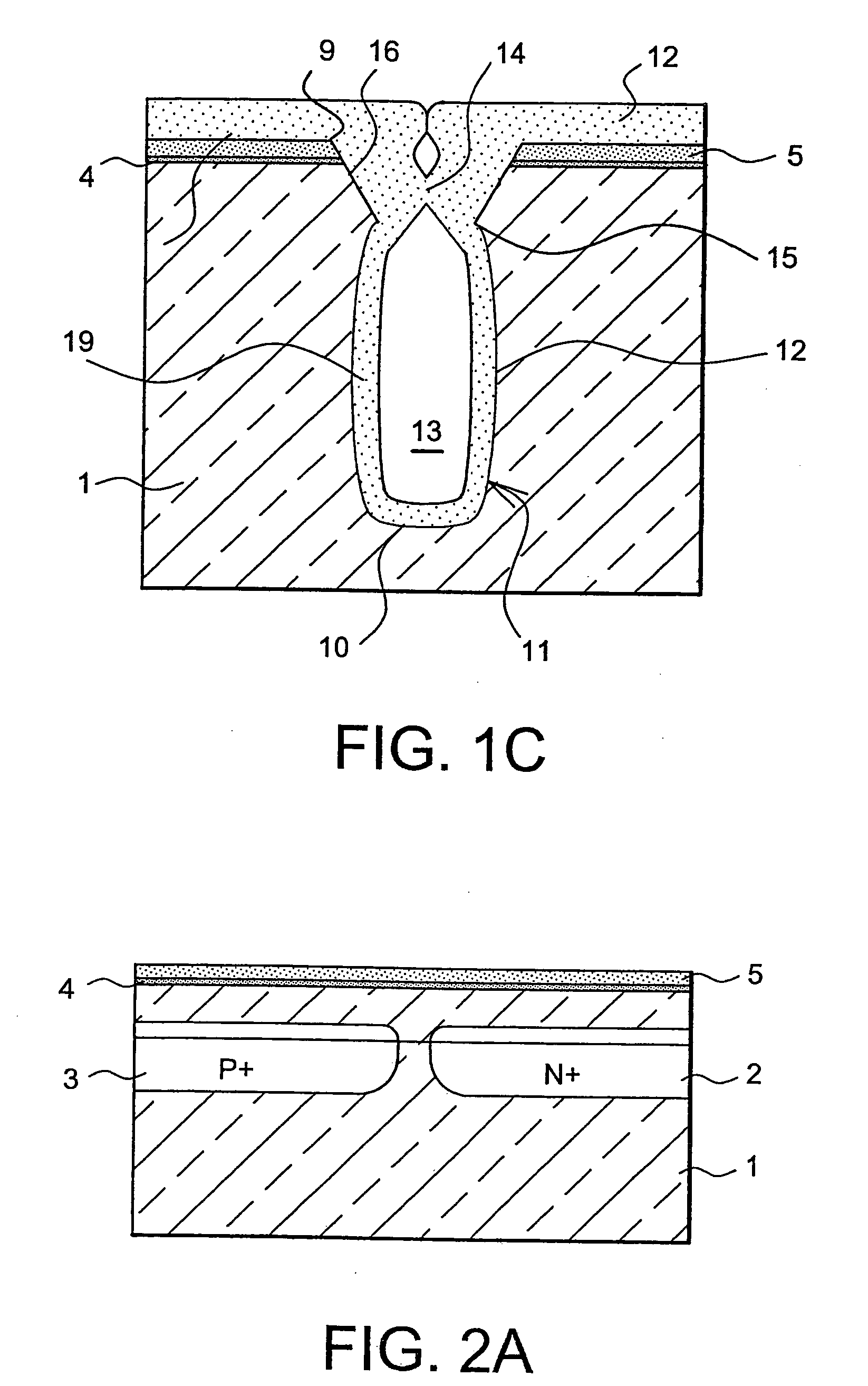

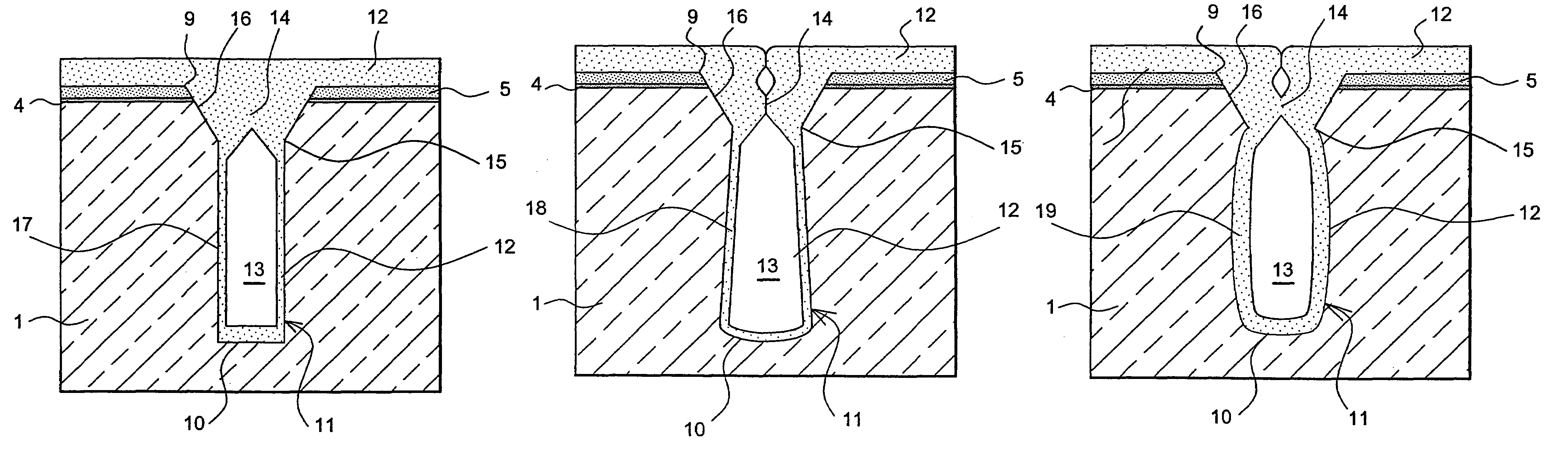

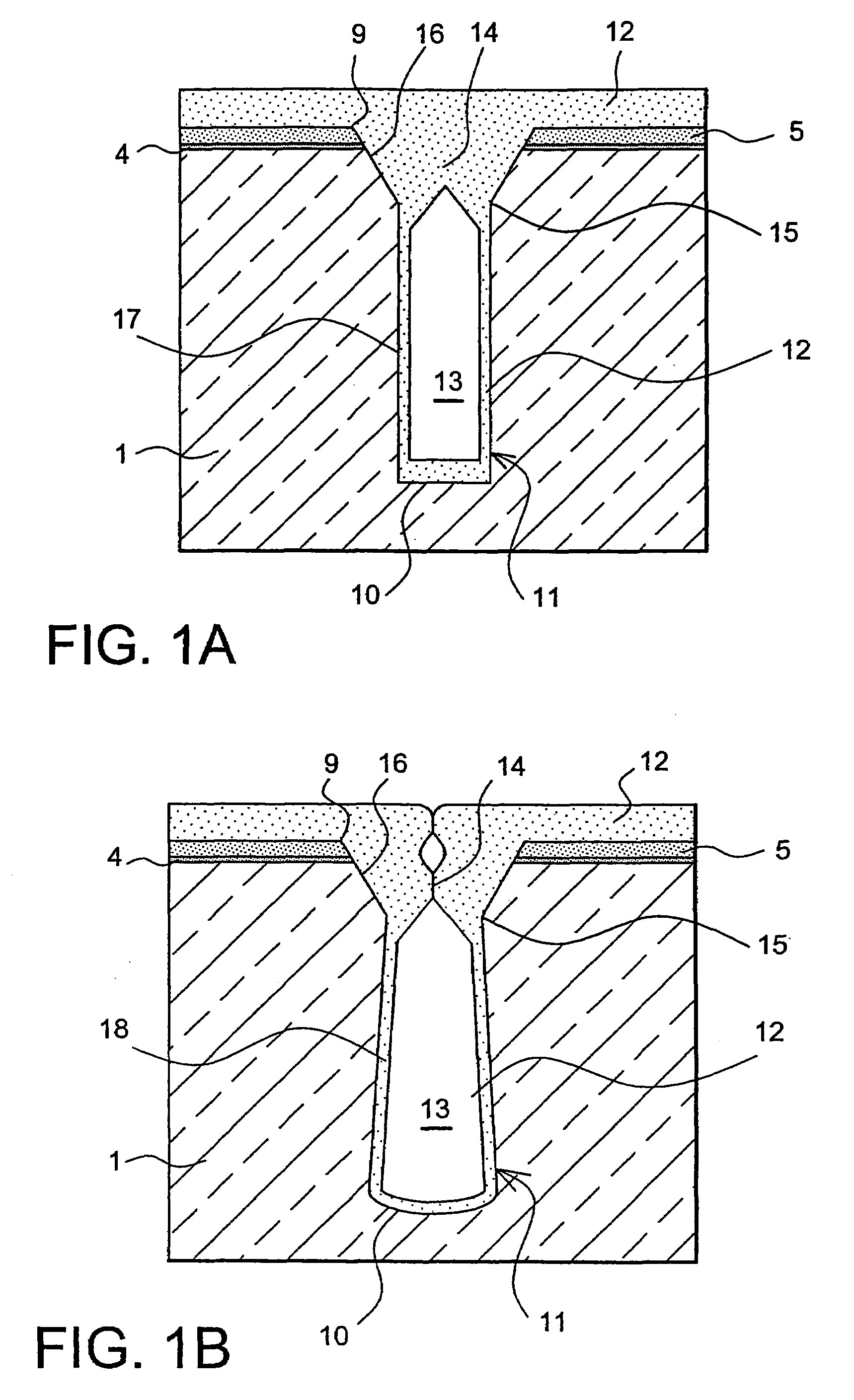

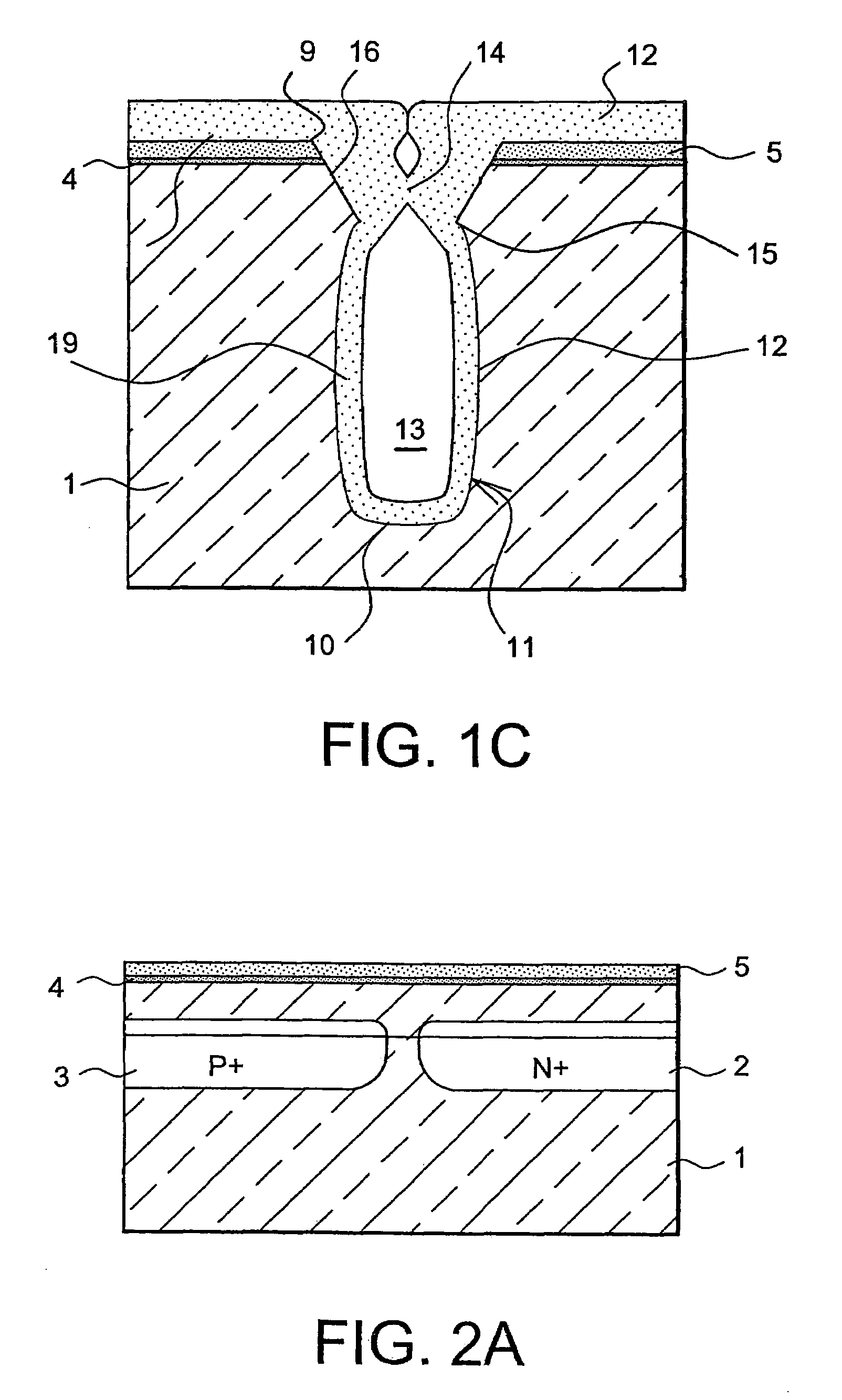

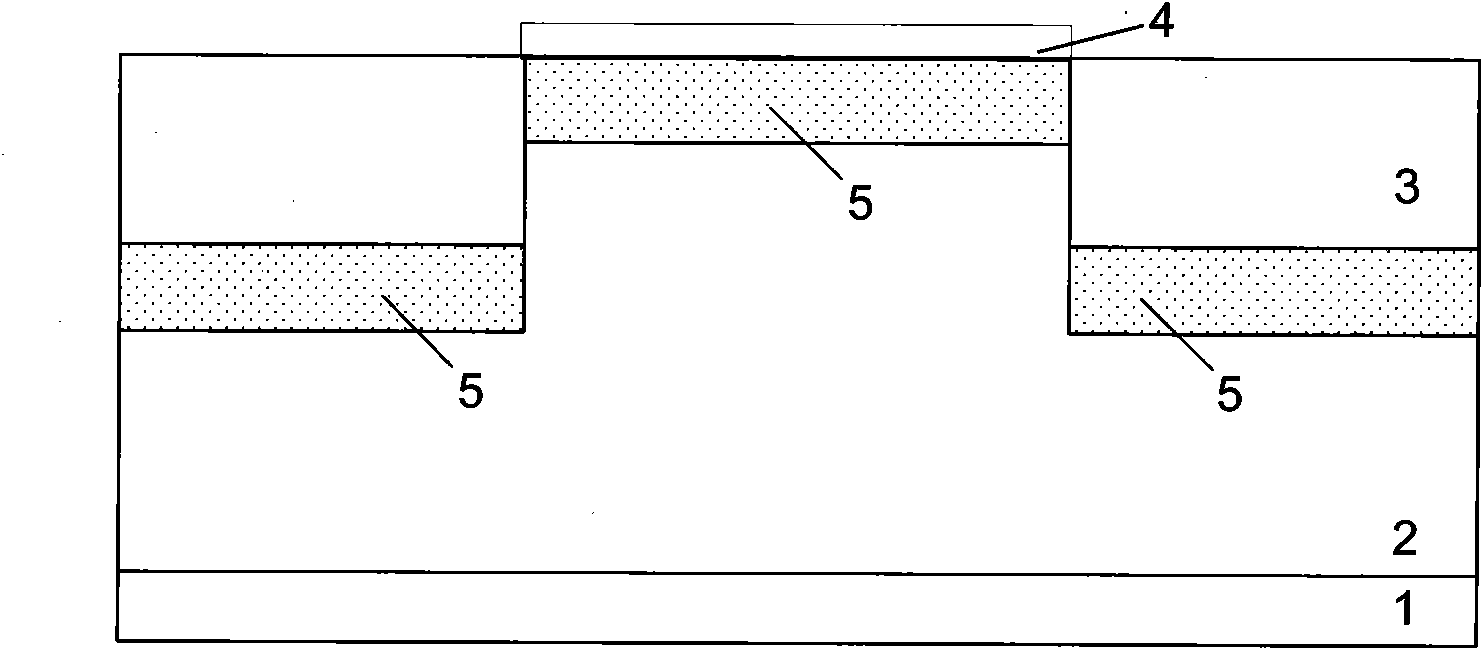

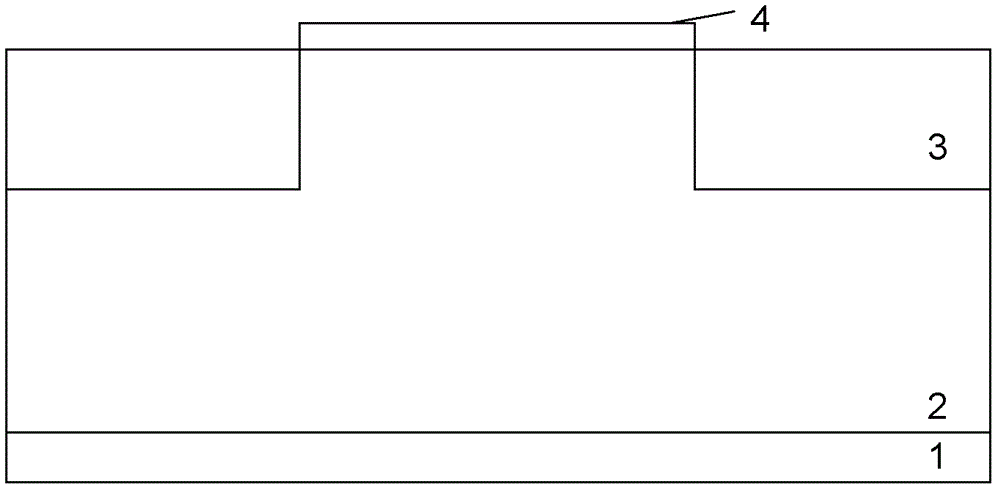

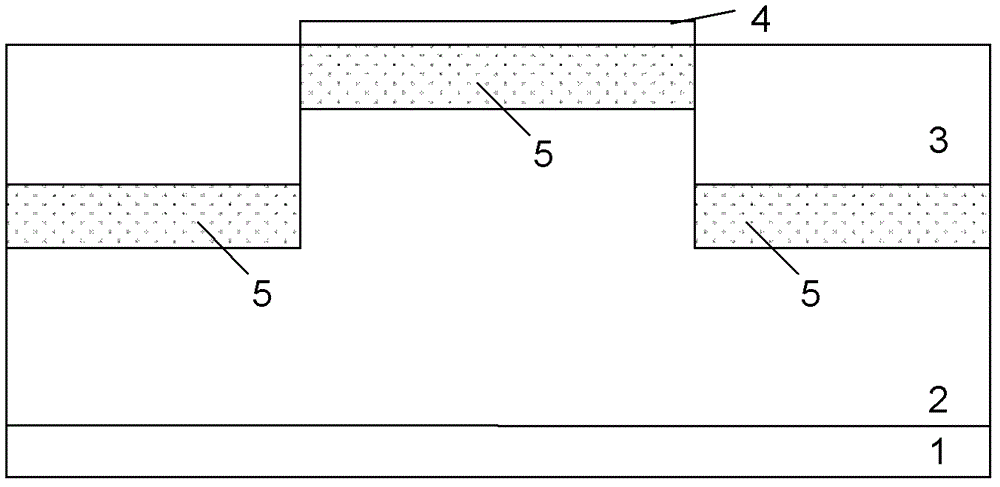

Deep insulating trench and method for production thereof

InactiveUS20040147093A1Semiconductor/solid-state device manufacturingSemiconductor devicesBungBicmos circuits

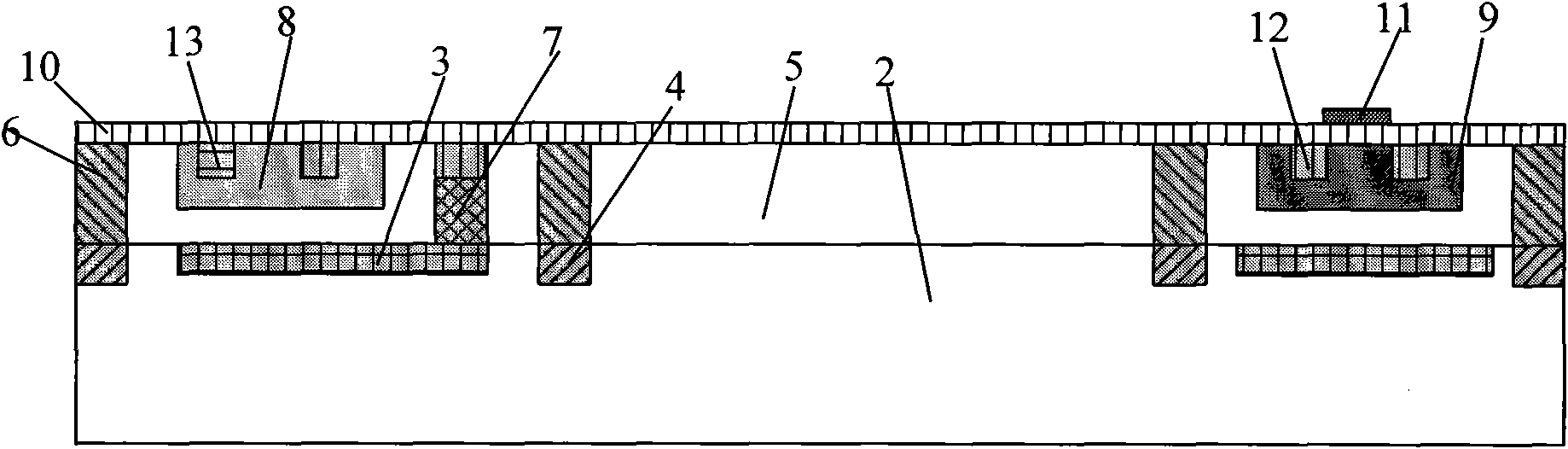

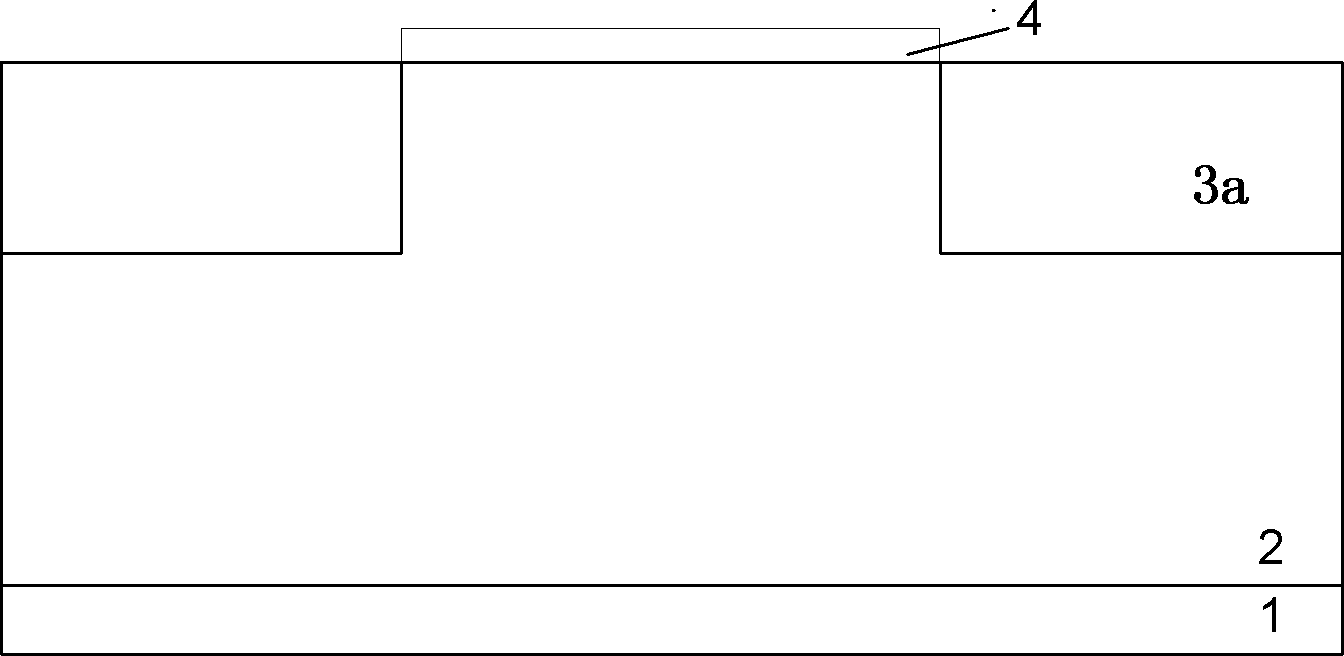

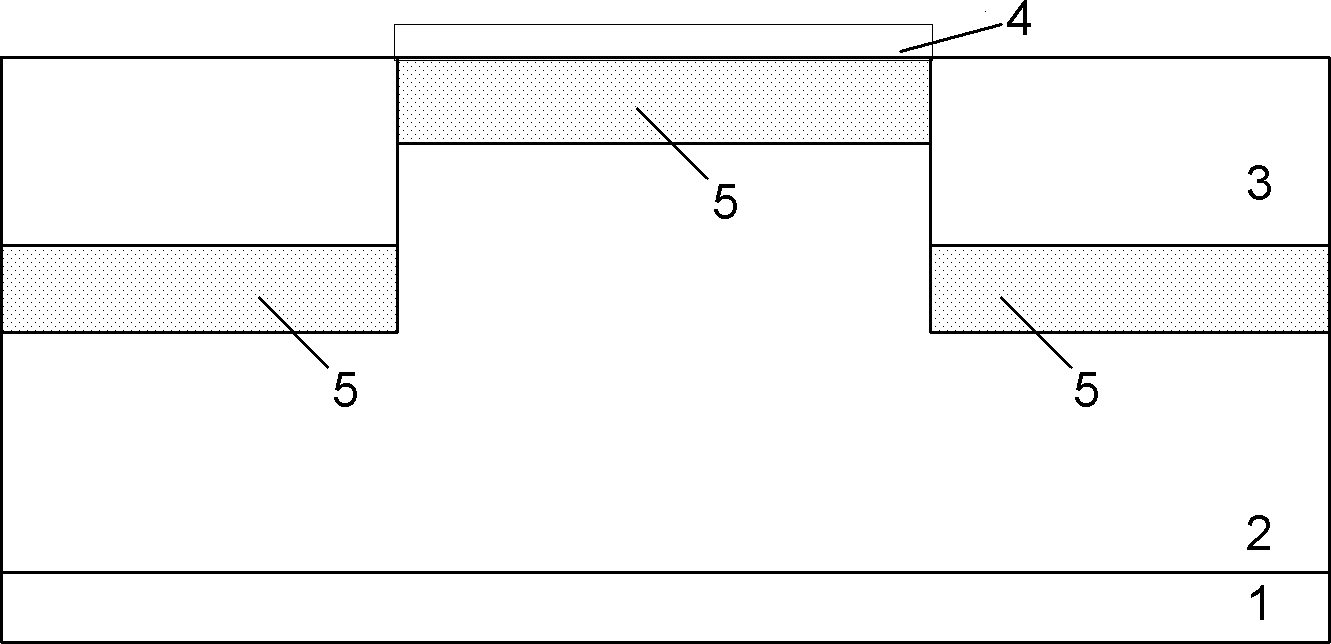

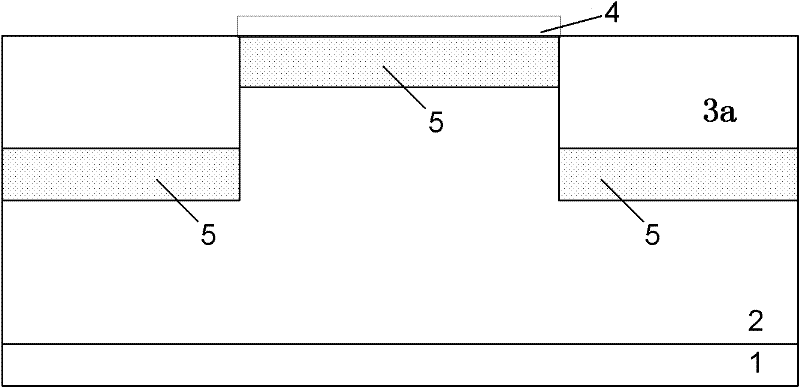

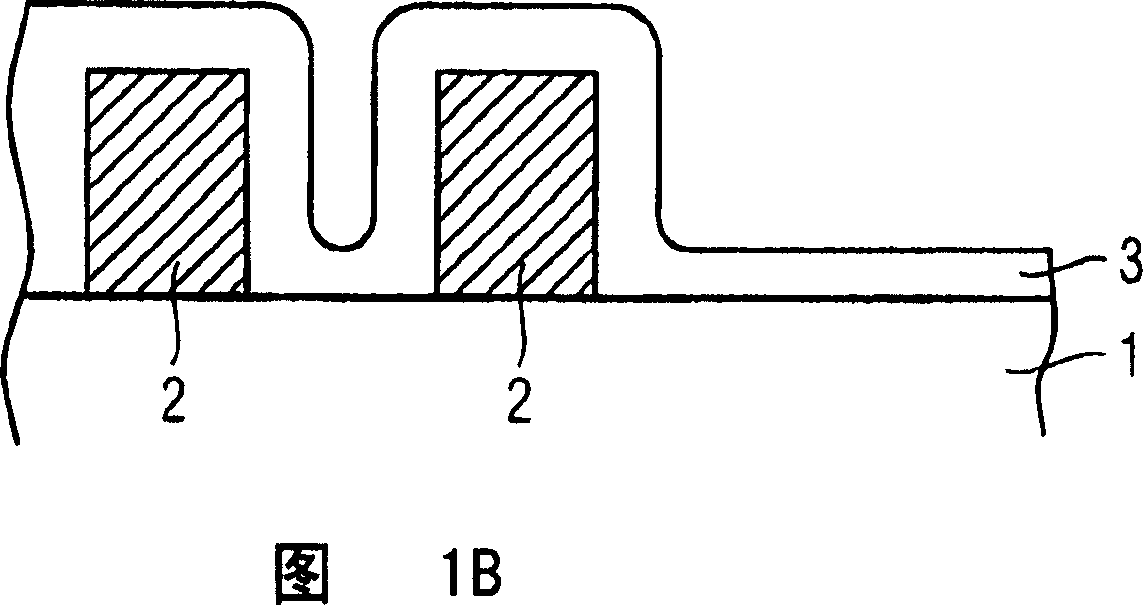

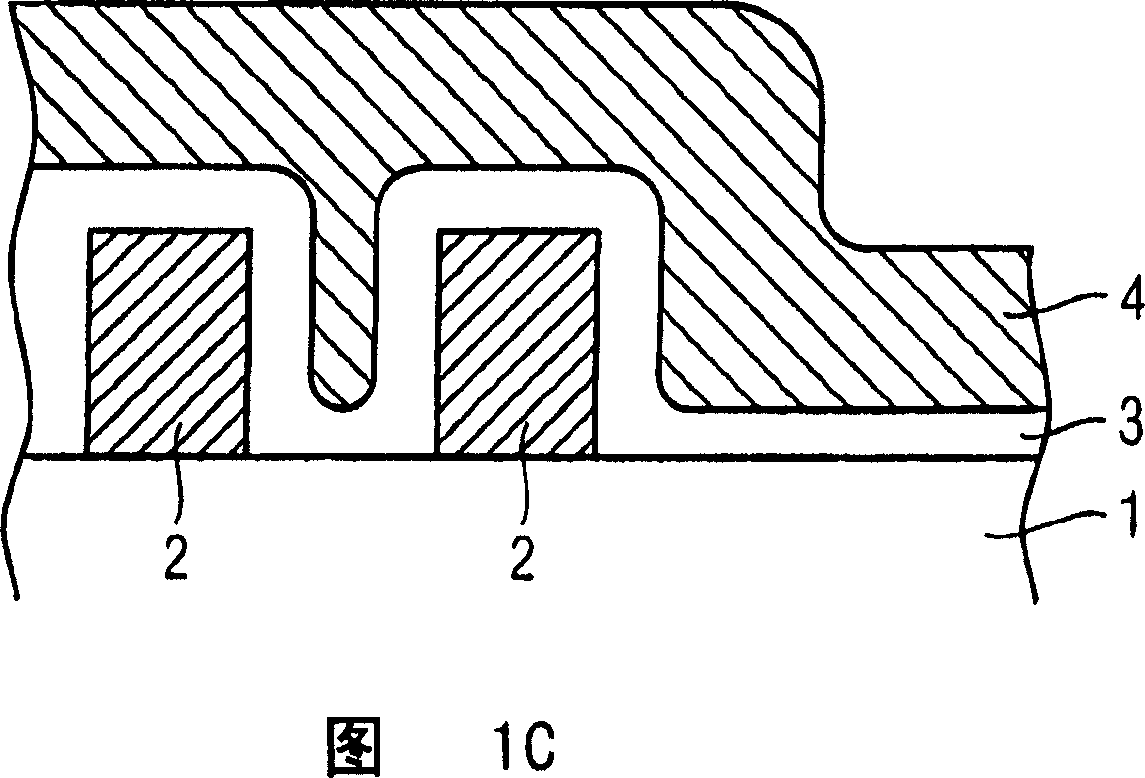

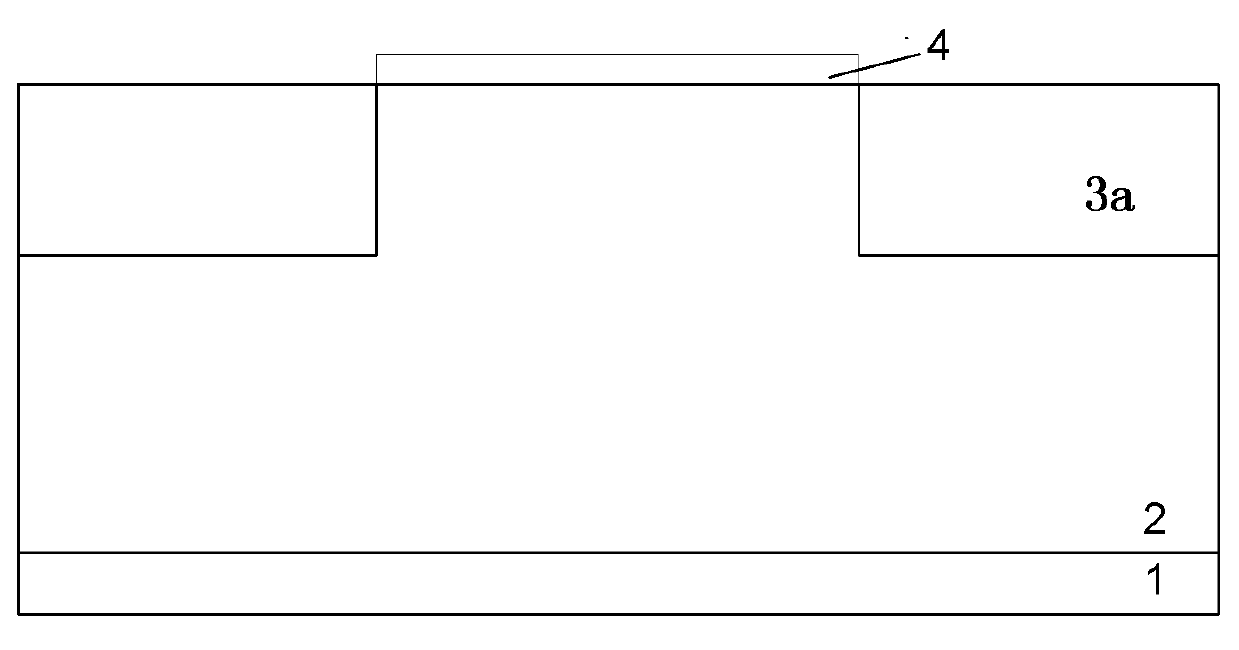

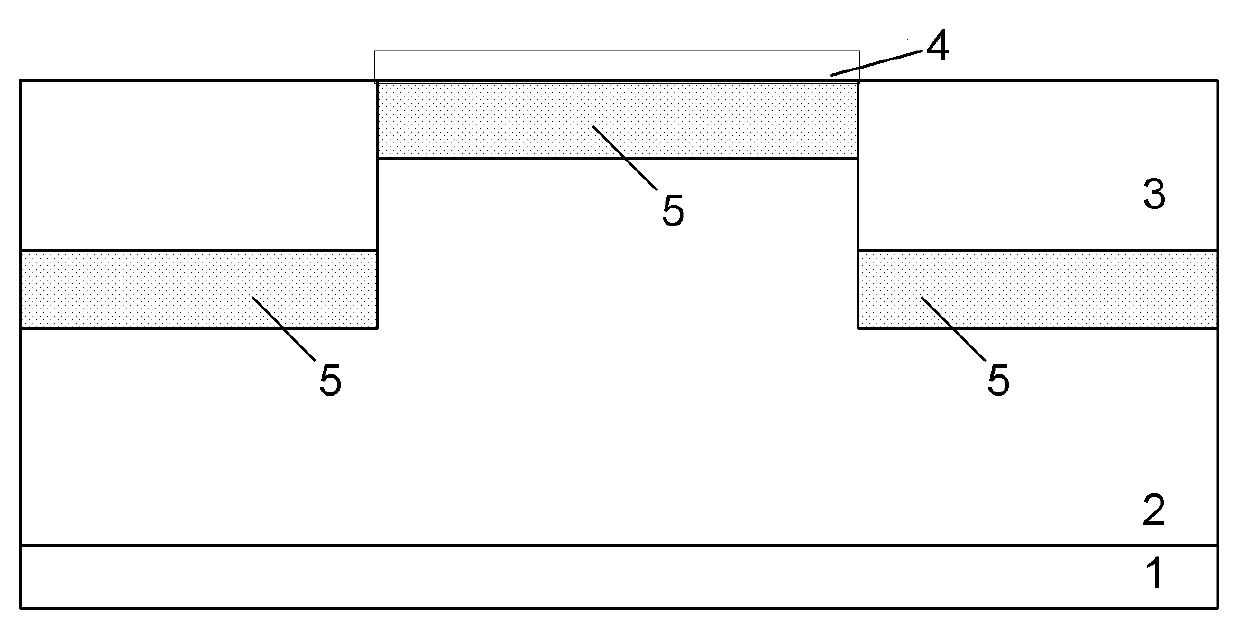

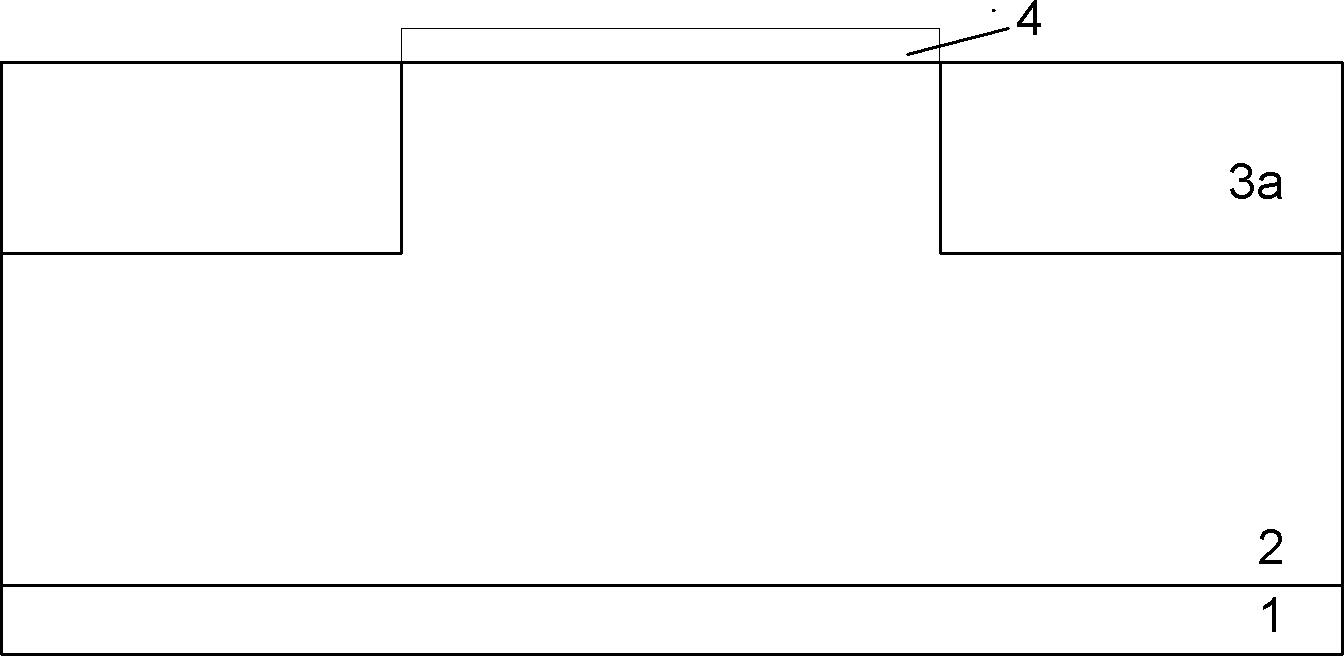

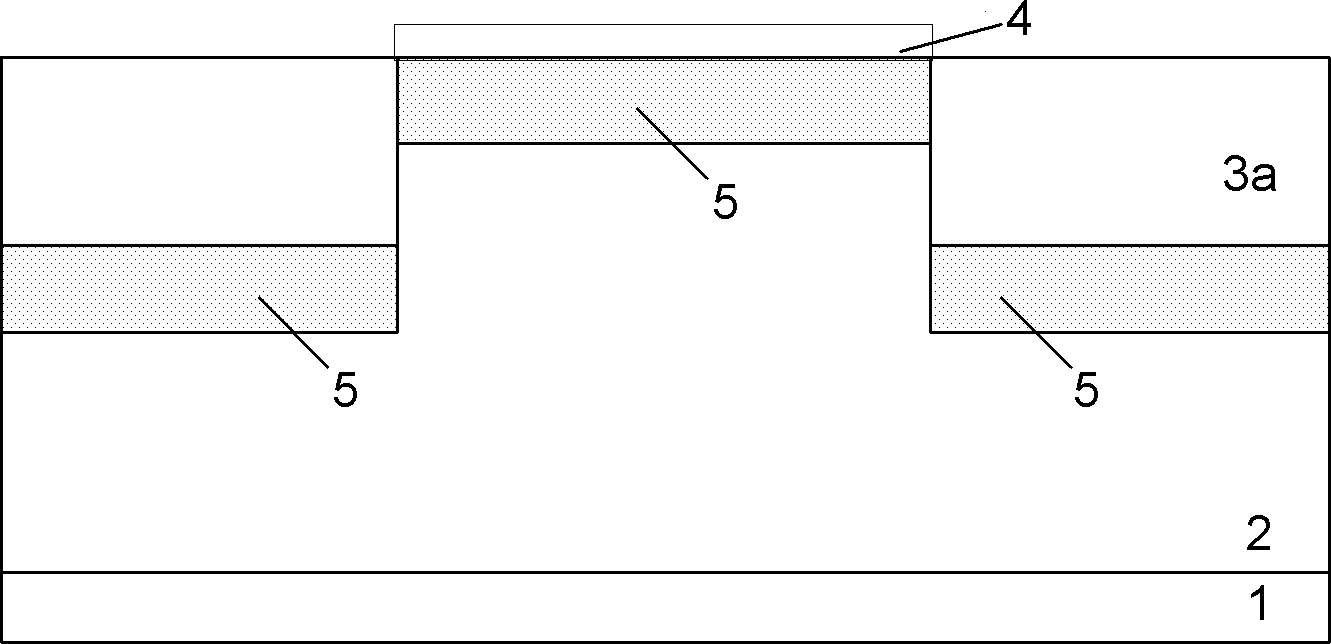

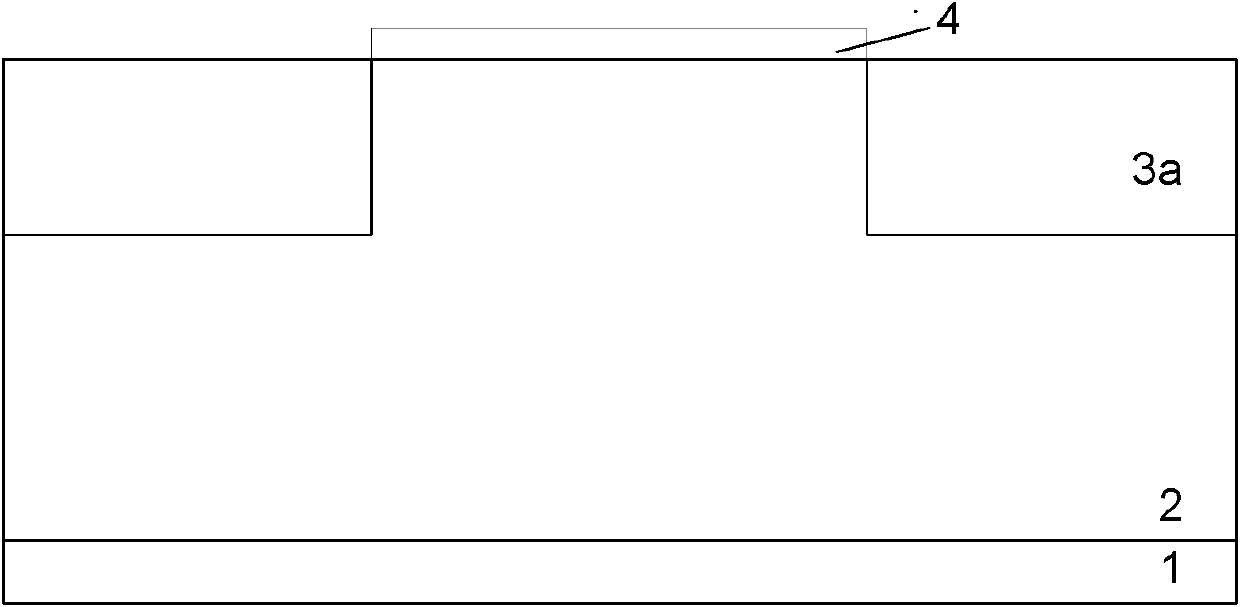

Deep isolation trenches having sides and a bottom are formed in a semiconductor substrate. The sides and the bottom are coated with an electrically insulating material that delimits an empty cavity, and forms a plug to close the cavity. The sides of the trench are configured with a neck that determines the depth of the plug, and a first portion that tapers outwards from the neck as the distance from the bottom increases. Deep isolation trenches may be applied, in particular, to bipole and BiCMOS circuits.

Owner:STMICROELECTRONICS SRL +1

Deep insulating trench

InactiveUS7038289B2Without introducing any risk of dislocation of the substrateMinimize capacitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorBicmos circuits

Deep isolation trenches having sides and a bottom are formed in a semiconductor substrate. The sides and the bottom are coated with an electrically insulating material that delimits an empty cavity, and forms a plug to close the cavity. The sides of the trench are configured with a neck that determines the depth of the plug, and a first portion that tapers outwards from the neck as the distance from the bottom increases. Deep isolation trenches may be applied, in particular, to bipole and BiCMOS circuits.

Owner:STMICROELECTRONICS SRL +1

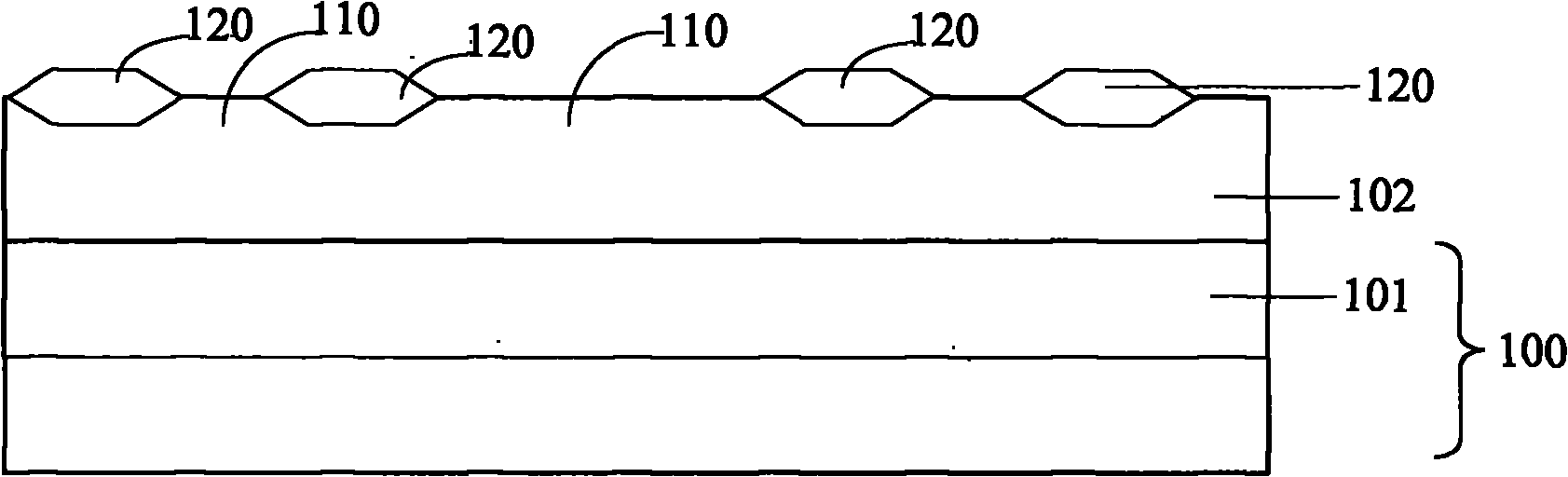

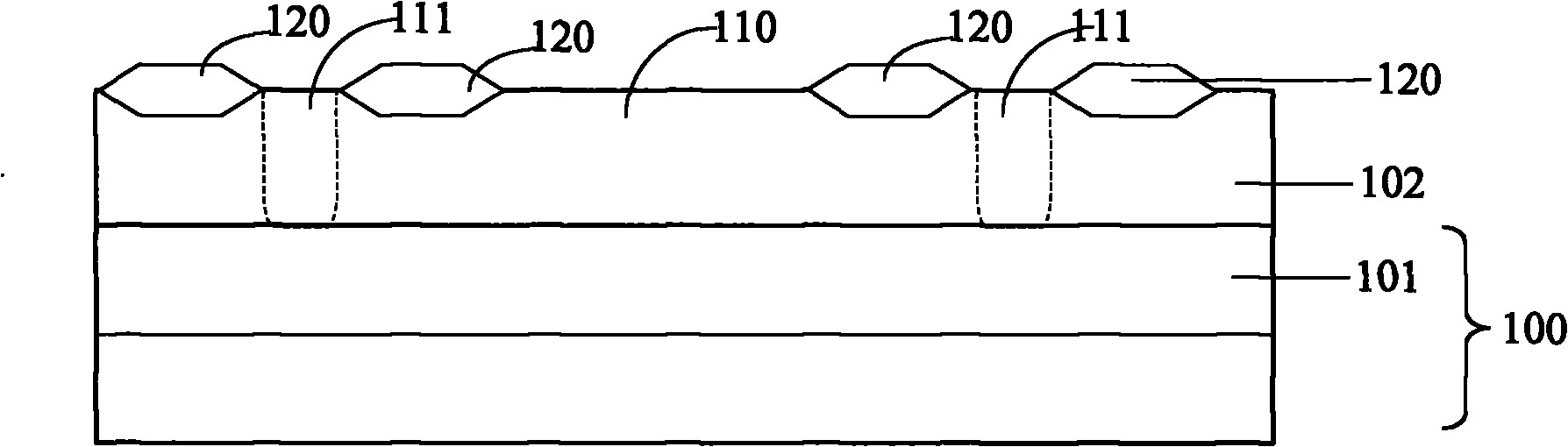

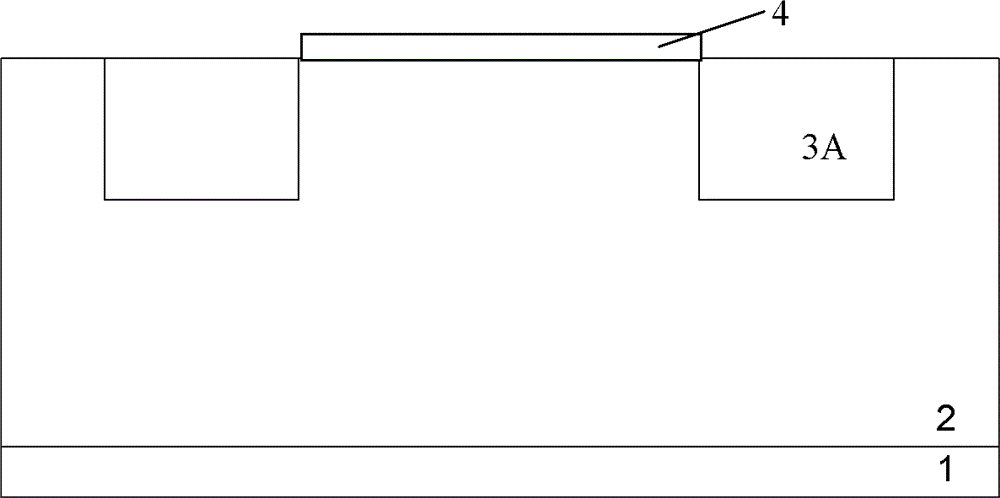

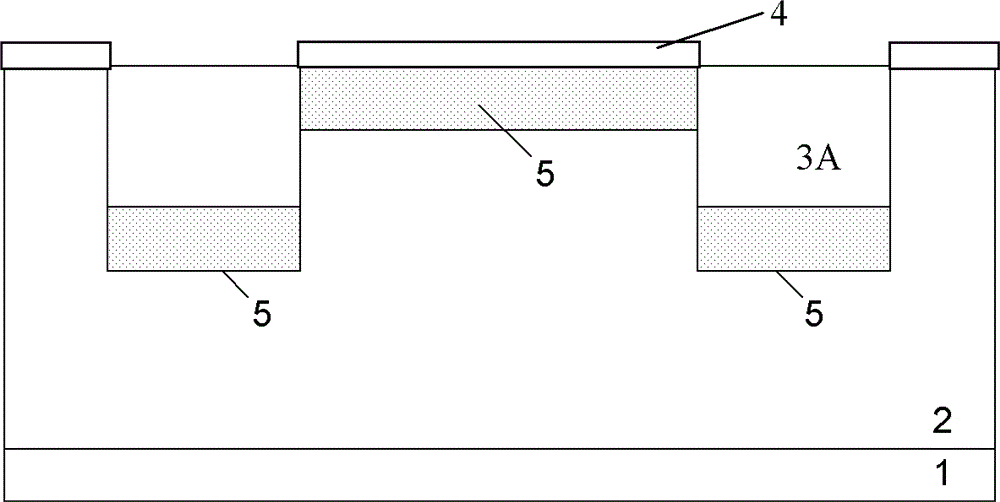

Method for manufacturing monolithic polysilicon cantilever structure

InactiveCN102086019ASolve stickingAchieve monolithic integrationDecorative surface effectsChemical vapor deposition coatingGyroscopeSignal processing circuits

The invention relates to a method for manufacturing a monolithic polysilicon cantilever structure. In the invention, a processing step of the polysilicon cantilever structure is inserted in a conventional BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) technical process, the deposition and the annealing of polysilicon are finished and an MEMS (Micro-Electro-Mechanical Systems) high-temperature process is prevented from influencing on the metalation process before the metalation process. In the release process of the polysilicon cantilever structure, a special etching solution is adopted, and a negative photoresist is used as a post of the polysilicon cantilever structure so as to effectively avoid the problem of substrate adhesion in the cantilever structure release process by using a wet method. The method provided by the invention solves the technical problems of compatibility between a manufacture process of the polysilicon cantilever structure and a processing process of a BiCMOS circuit, realizes the monolithic integration of the polysilicon cantilever structure and a BiCMOS signal processing circuit, and can be widely applied to the monolithic integration manufacture field of MEMS sensors, such as capacitive accelerometers, gyroscopes, and the like.

Owner:NO 24 RES INST OF CETC

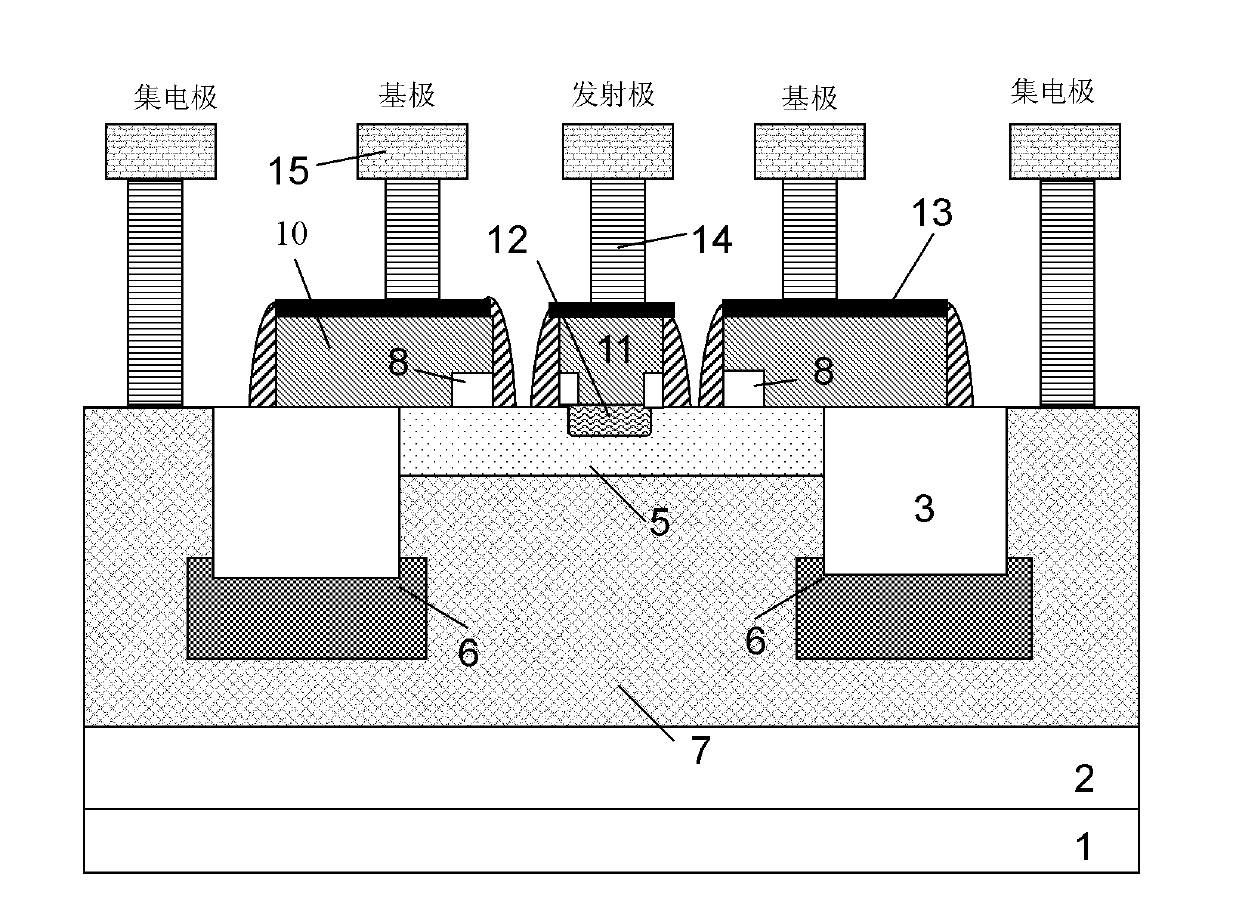

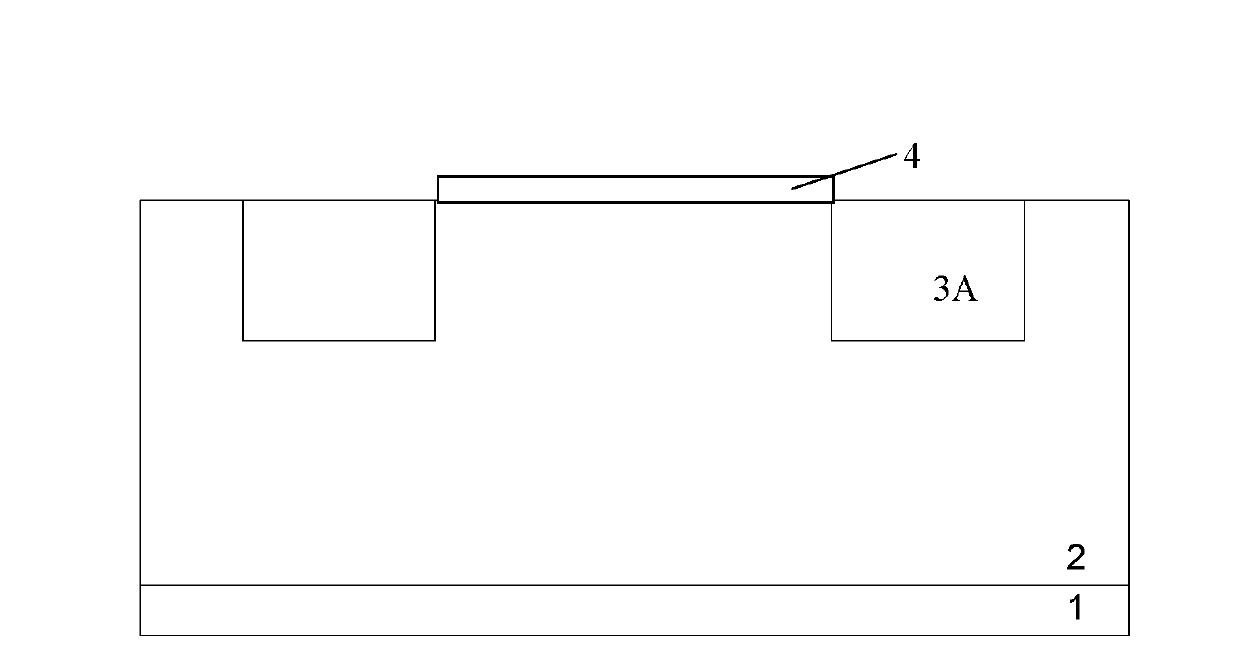

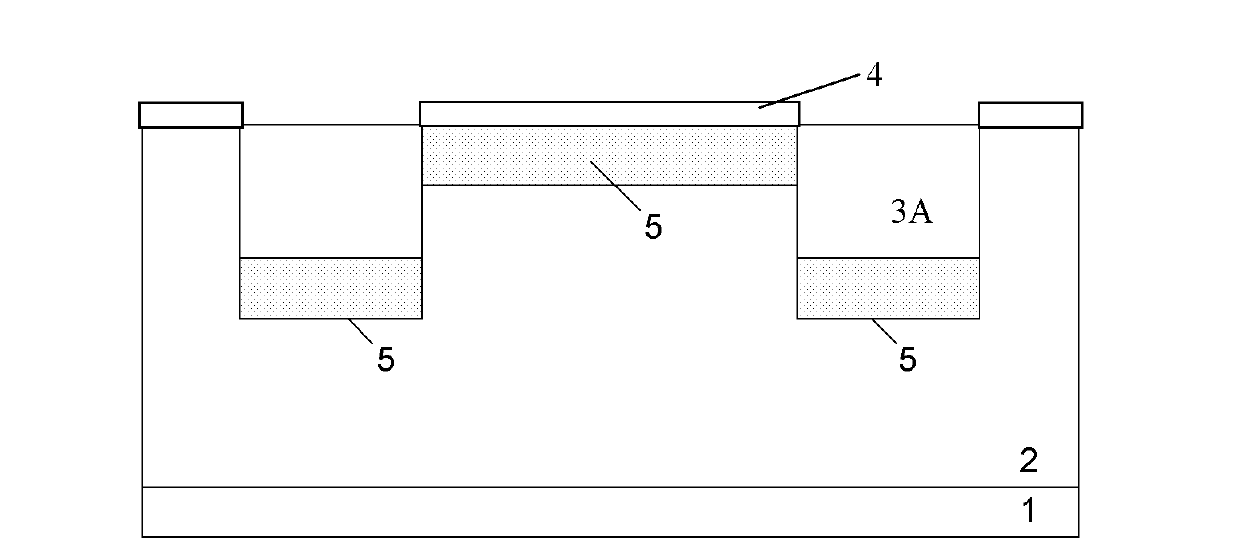

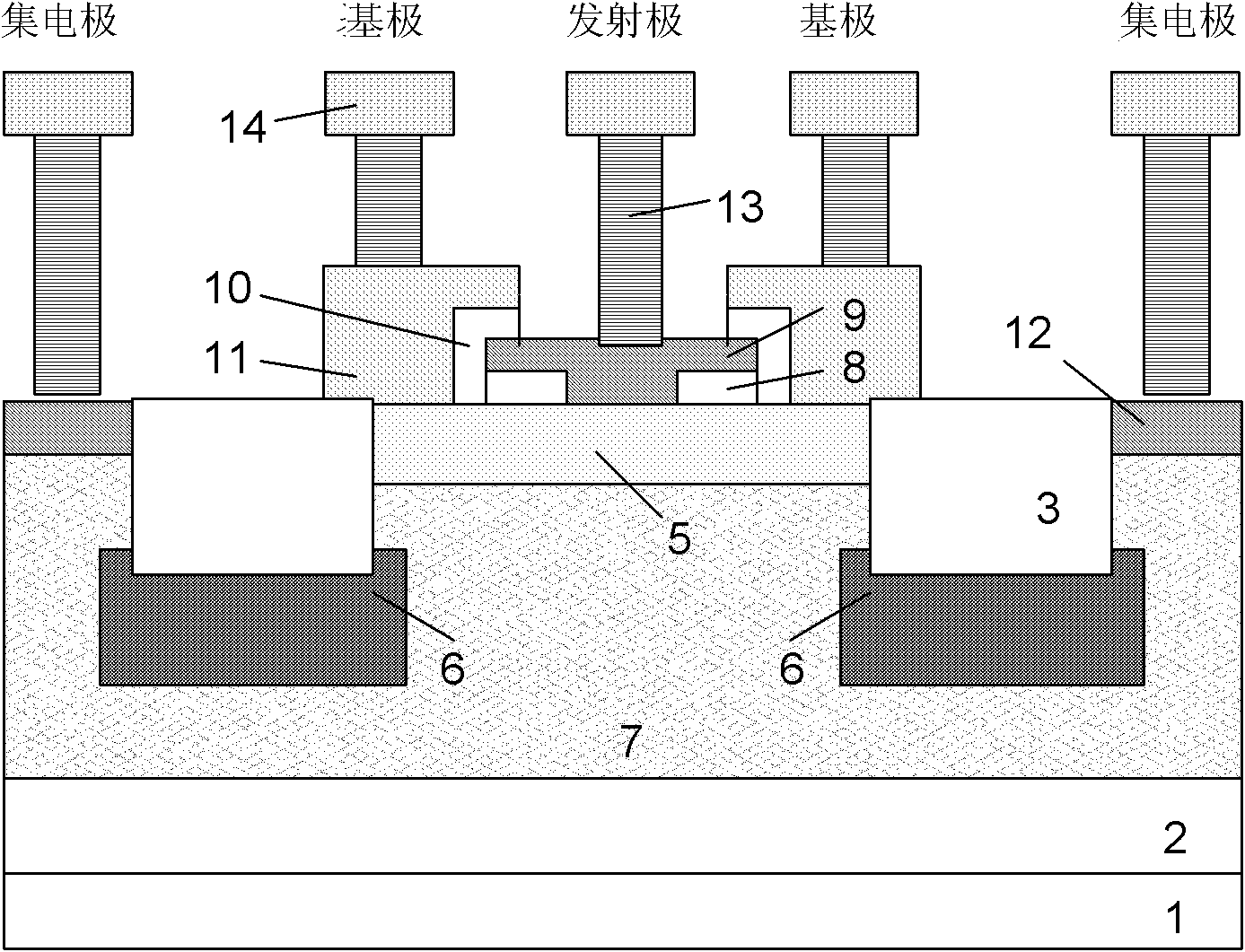

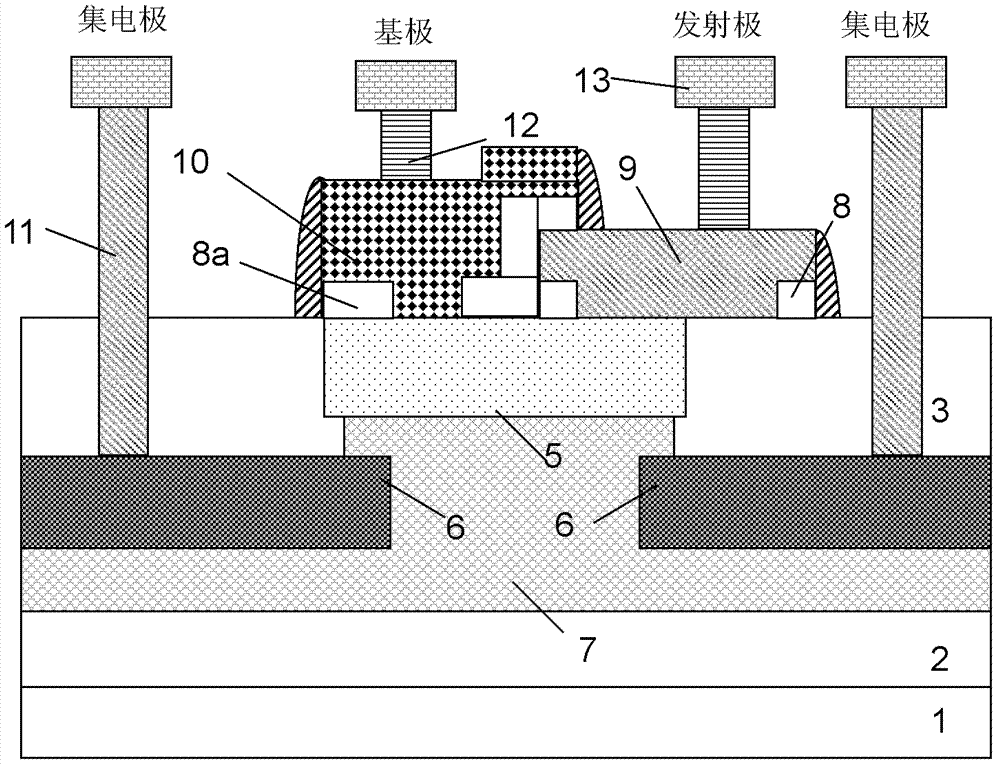

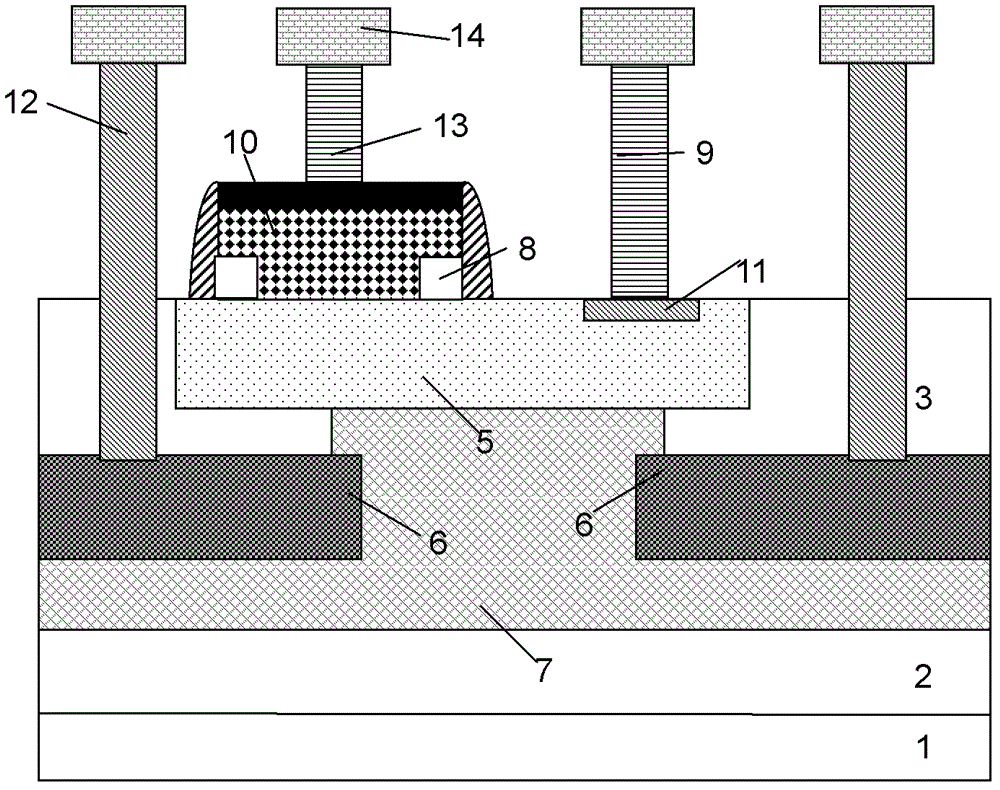

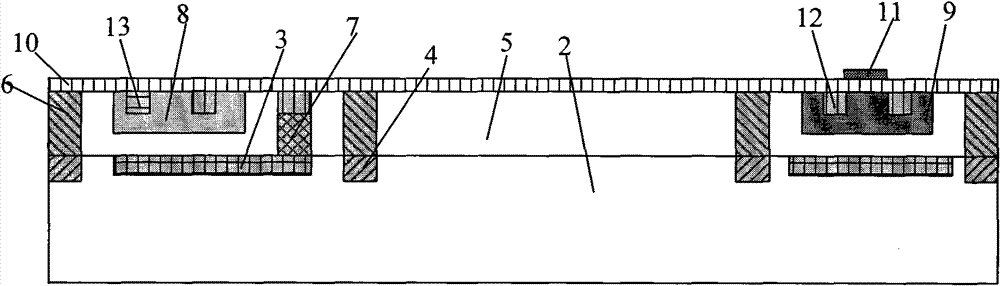

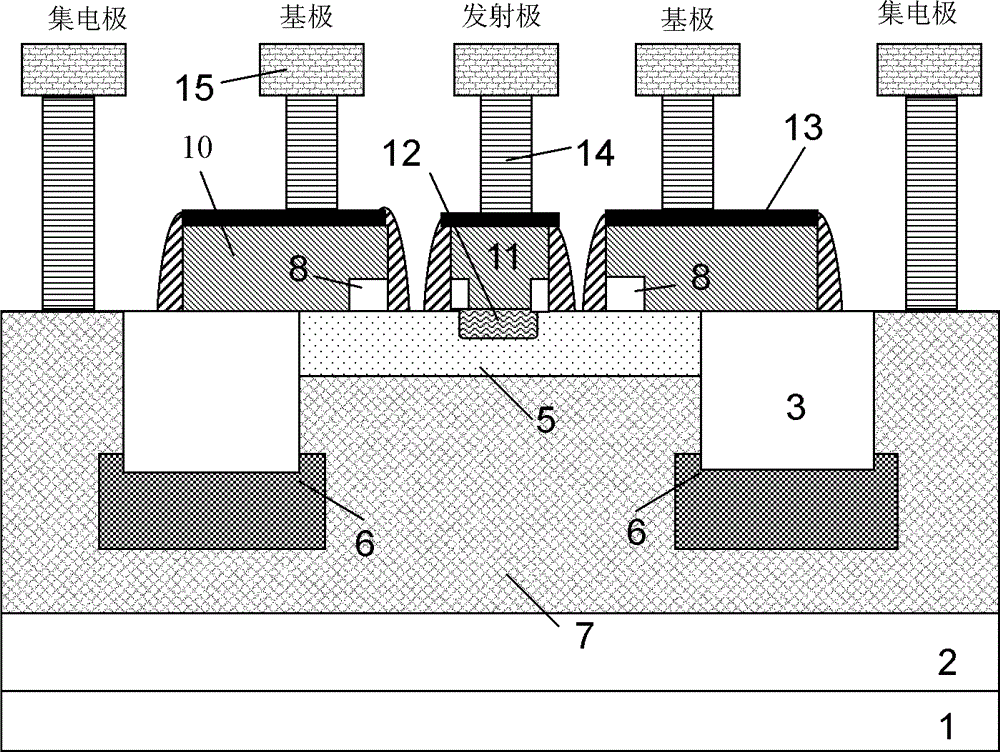

Vertical parasitic PNP device in BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor) process and preparation method thereof

ActiveCN102487077ALarge current amplification factorImprove frequency characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesProcess conditionsBicmos circuits

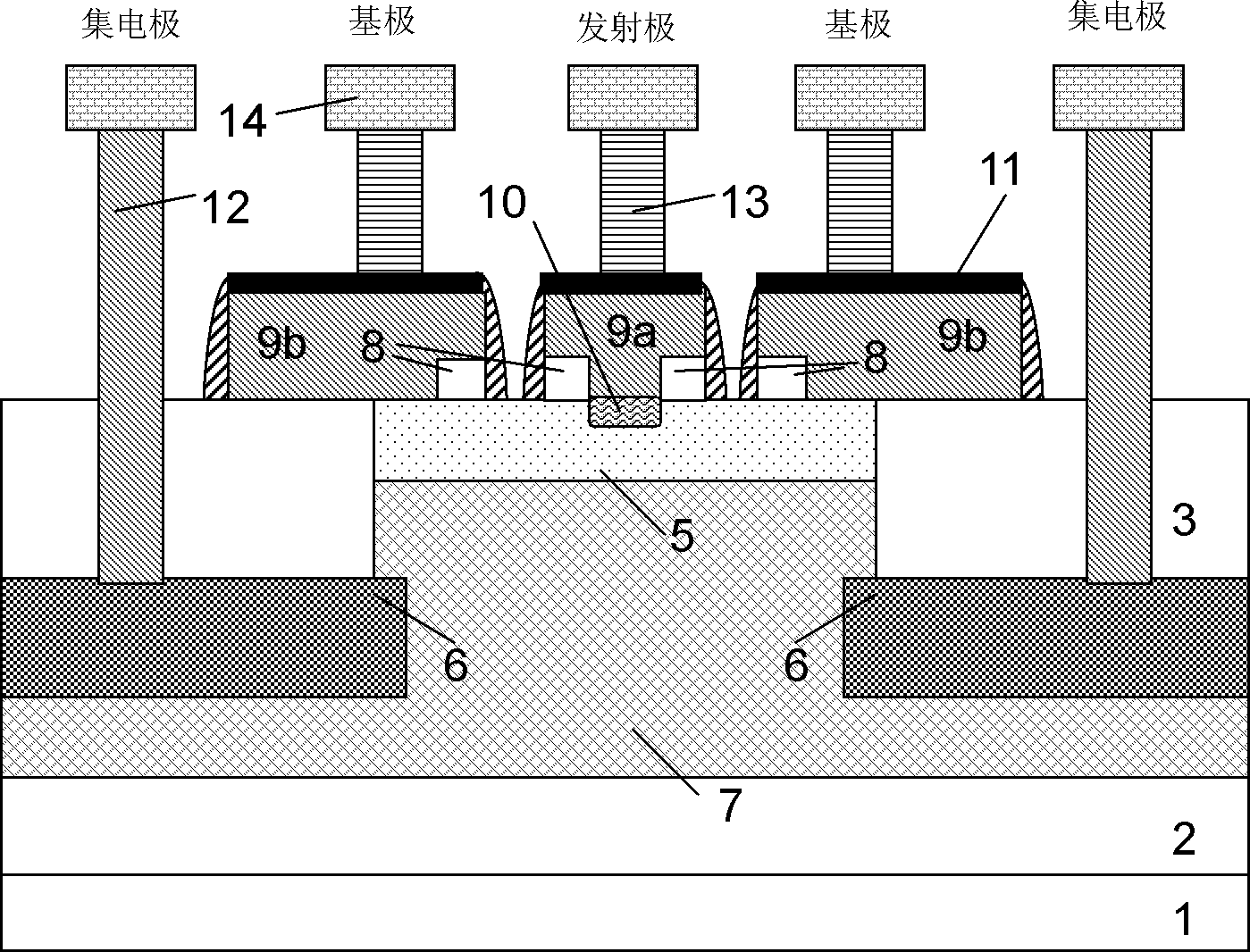

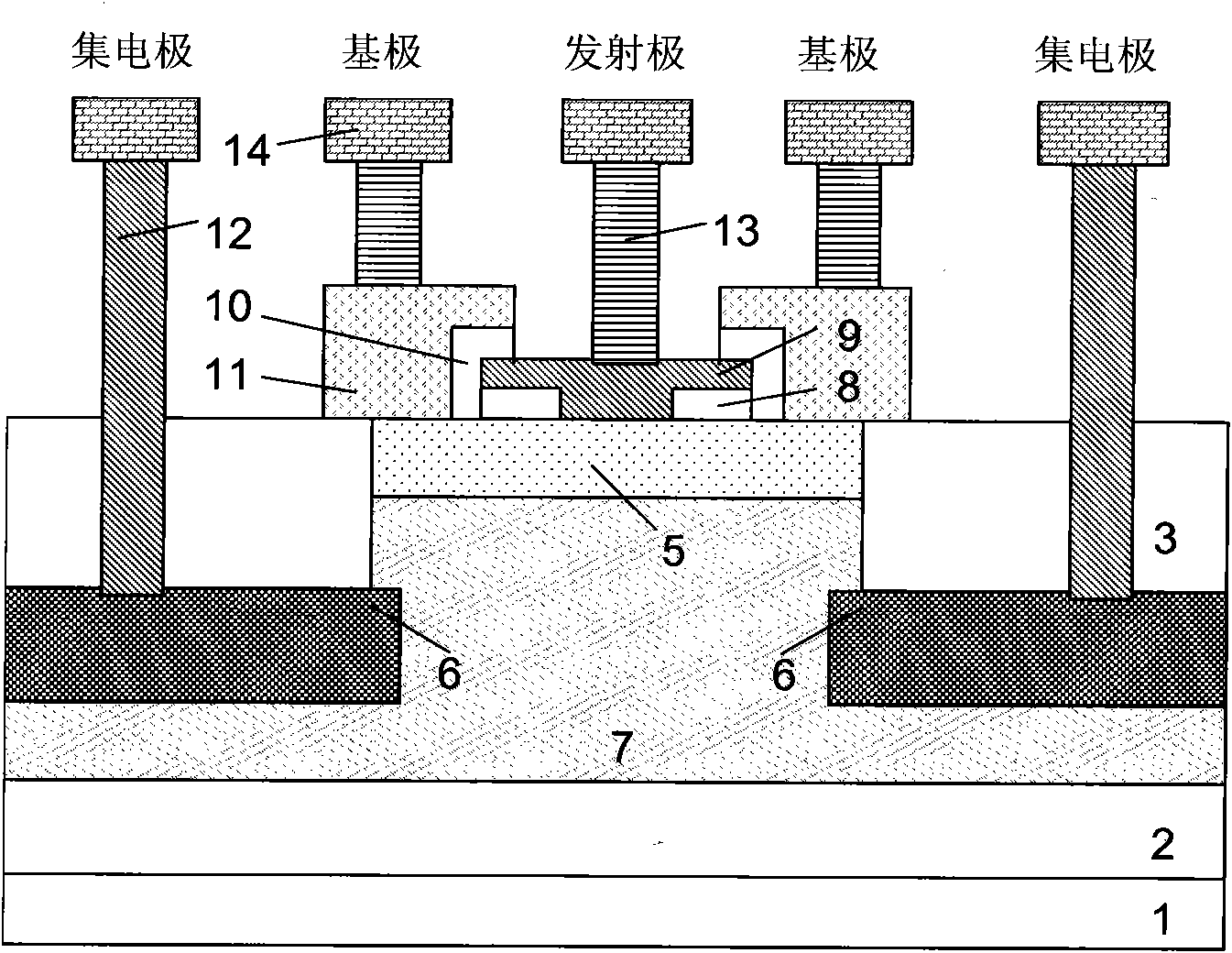

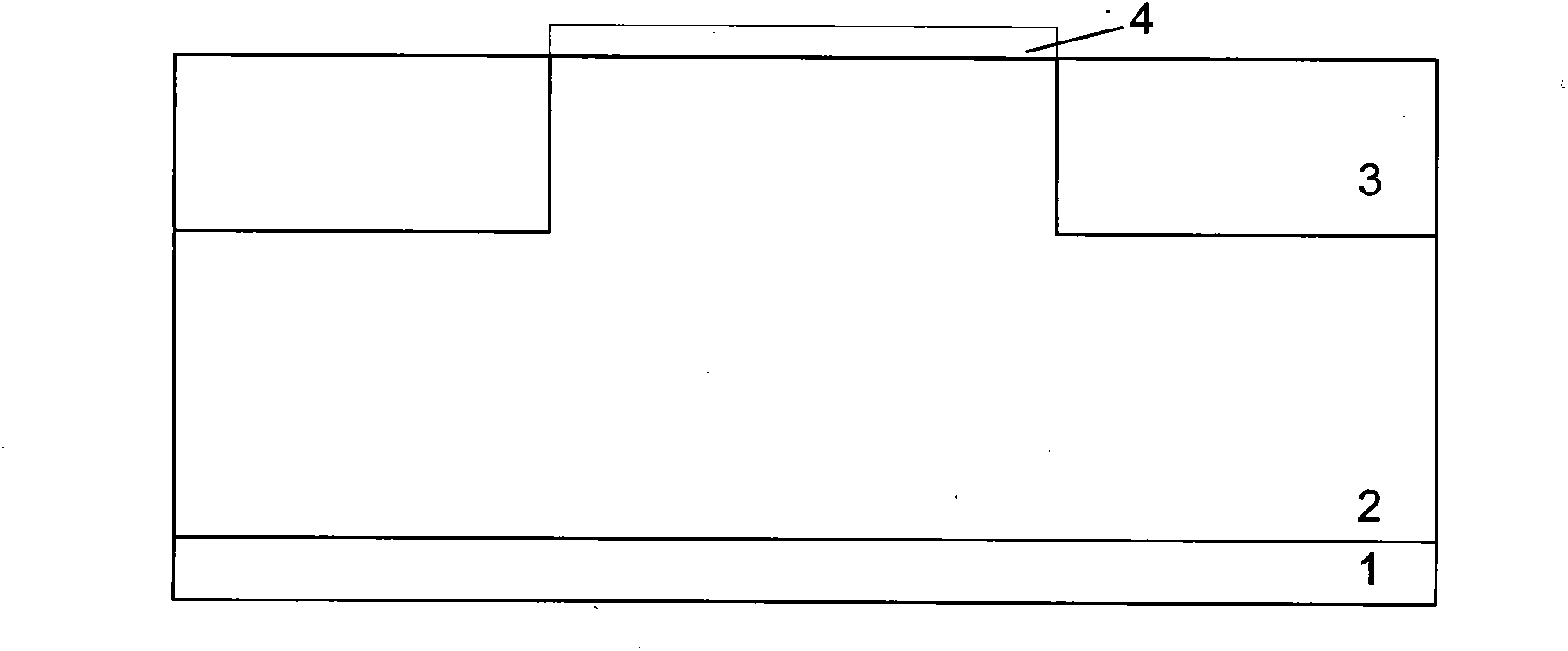

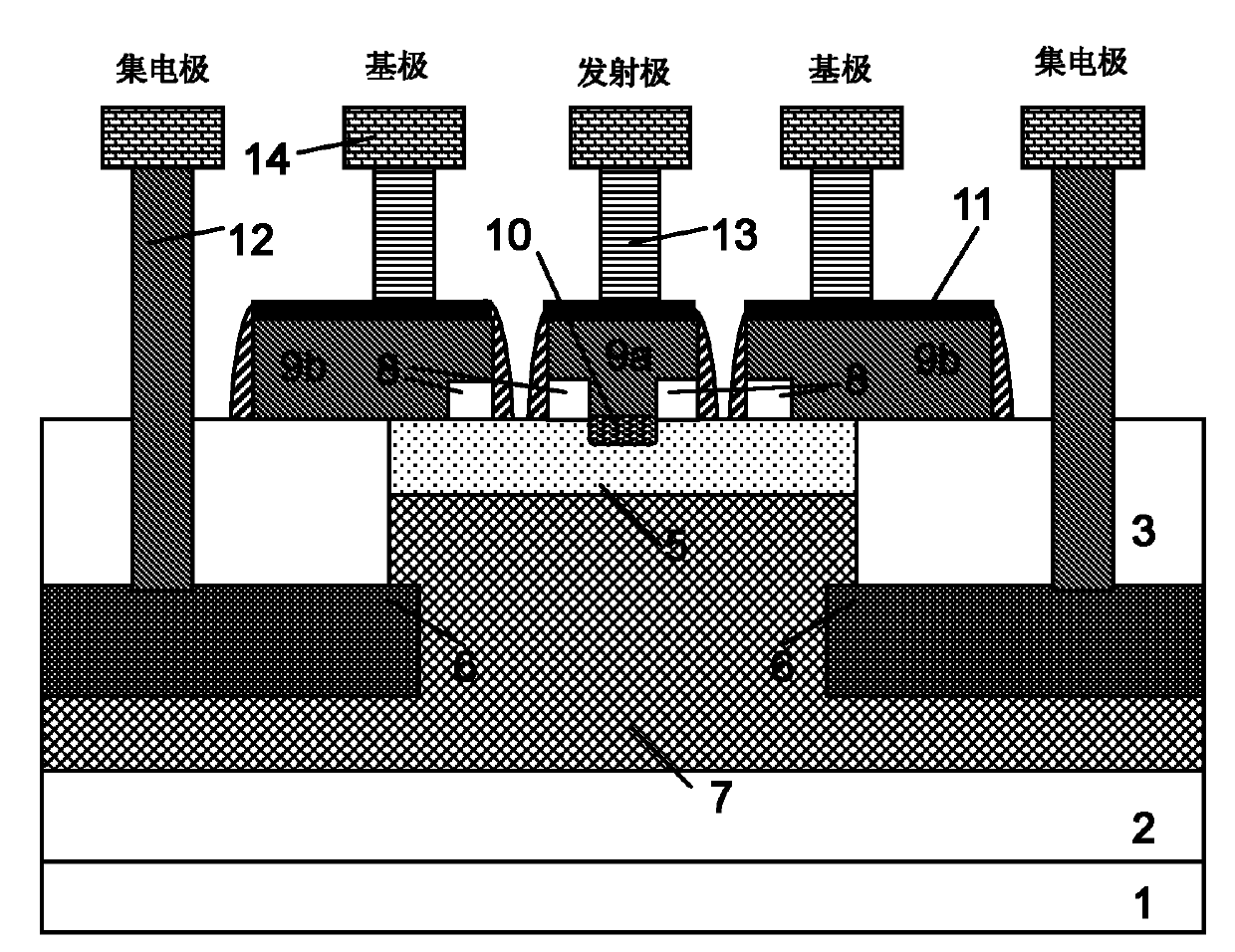

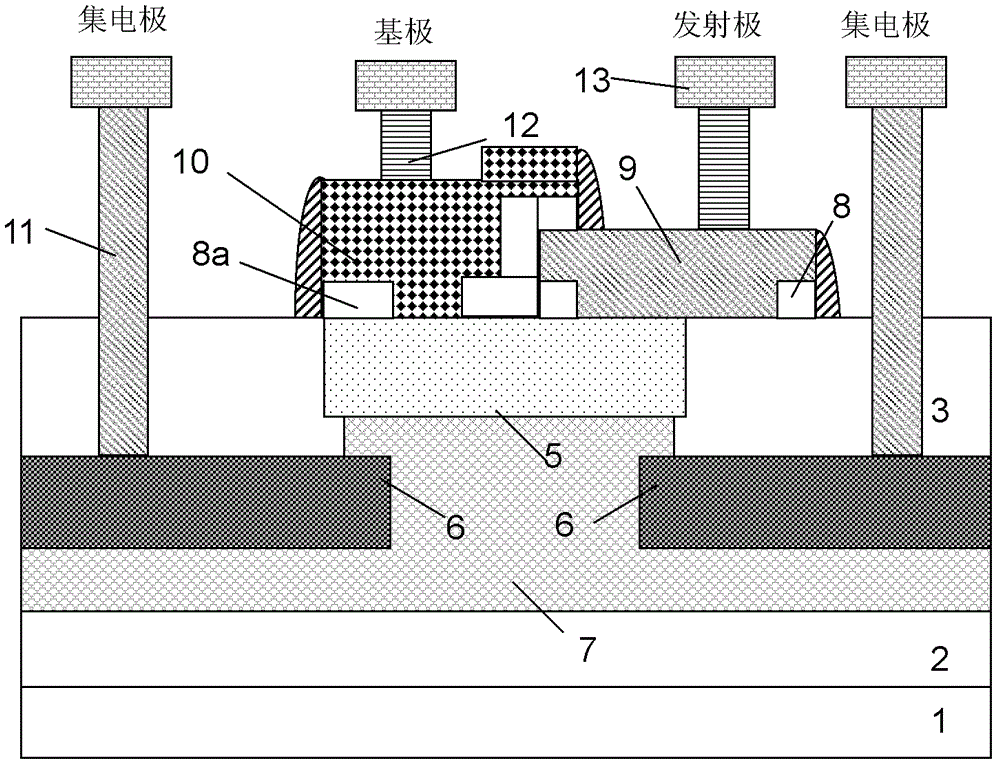

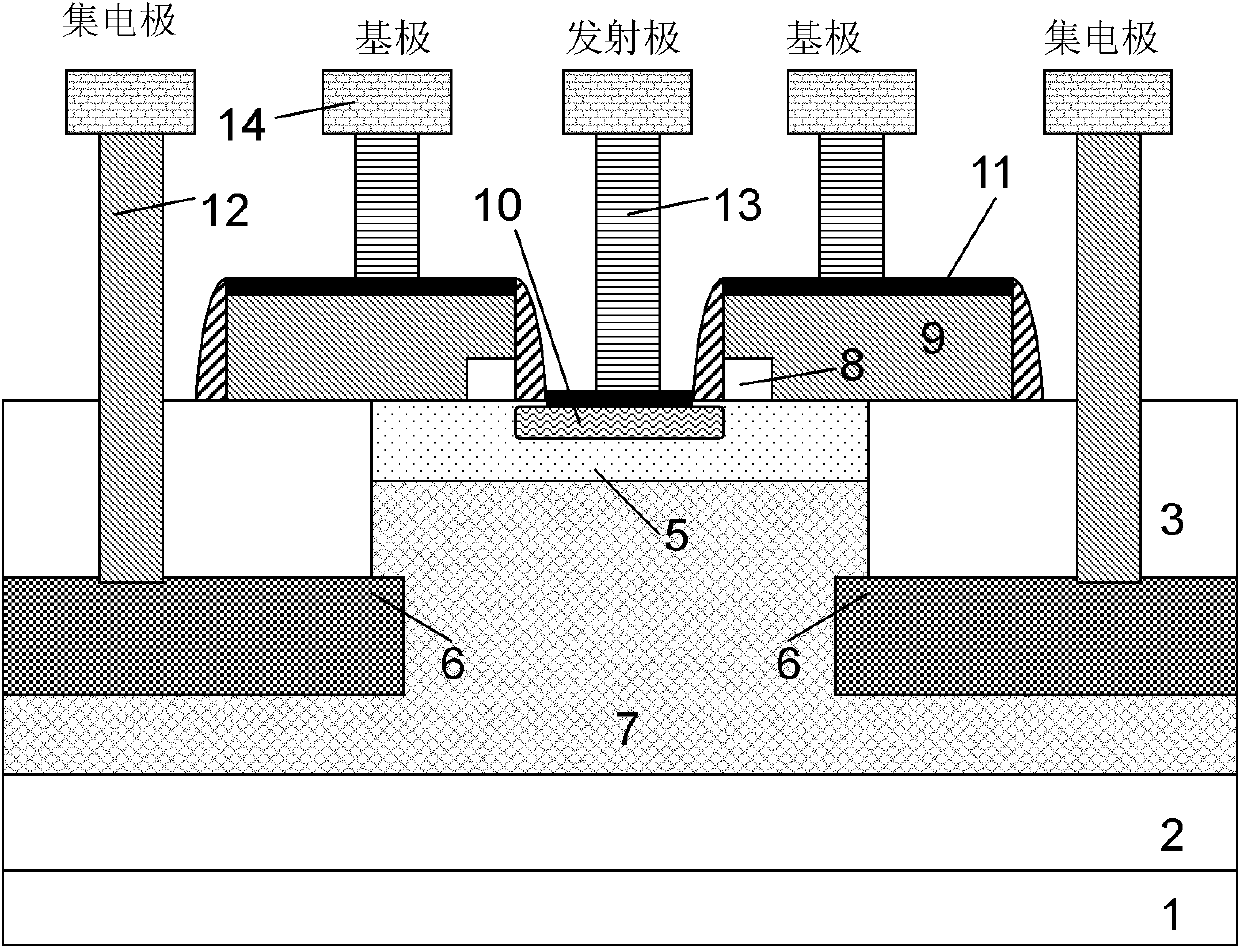

The invention discloses a vertical parasitic PNP device in a BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor) process. The vertical parasitic PNP device comprises a collector region, a base region, an emitter region, a P type buried layer and N type polycrystalline silicon, wherein the buried layer is formed at a shallow trench filed oxide bottom surrounding the collector region and is in contact with the collector region through a deep hole formed at the top of the buried layer to lead out a collector electrode; the N type polycrystalline silicon is formed at the upper part of the base region and is used for leading out a base electrode; and the emitter region is composed of a P type shallow junction formed in the base region and P type polycrystalline silicon arranged above the base region. The invention also discloses a preparation method of the vertical parasitic PNP device in the BiCMOS process. The device disclosed by the invention can serve as an output device in a high-speed high-gain BiCMOS circuit, and therefore another device choice is provided for the circuit. According to the invention, the area of the device can be reduced effectively, the resistance of the collector electrode of a PNP transistor can be lowered, the frequency performance of the device can be improved and the gain of the device can be enhanced. No extra process condition is required in the preparation method disclosed by the invention, thereby reducing the production cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Vertical parasitic PNP (plug-and-play) triode in BiCMOS (bipolar complementary metal oxide semiconductor) process and manufacturing method

ActiveCN102569371ALarge current amplification factorImprove frequency characteristicsTransistorSemiconductor/solid-state device manufacturingOutput deviceEngineering

The invention discloses a vertical parasitic PNP (plug-and-play) triode in a BiCMOS (bipolar complementary metal oxide semiconductor) process, a collector region is formed in a first active area; a pseudo buried layer is formed at the bottom of a shallow groove field oxide, transversely extends, enters into the first active area and is in contact with the collector region; the connection between the collector region and the adjacent active area is realized through the pseudo buried layer, and a collector is led out by forming metal contact at the top of the adjacent active area. N type polysilicon is formed at the upper part of a base region and a base is led out. An emitter region comprises a P type ion-implanted layer and a P type polysilicon formed above the base region. The invention further discloses a manufacturing method of the vertical parasitic PNP triode in the BiCMOS process. The vertical parasitic PNP triode disclosed by the invention can be used as an output device in a high-speed and high-gain BiCMOS circuit, one more device choice is provided for a circuit, the resistance of the collector of the PNP triode can be reduced, the frequency performance of the device can be improved, a polysilicon emitter can improve the gain of the device, and the production cost can also be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

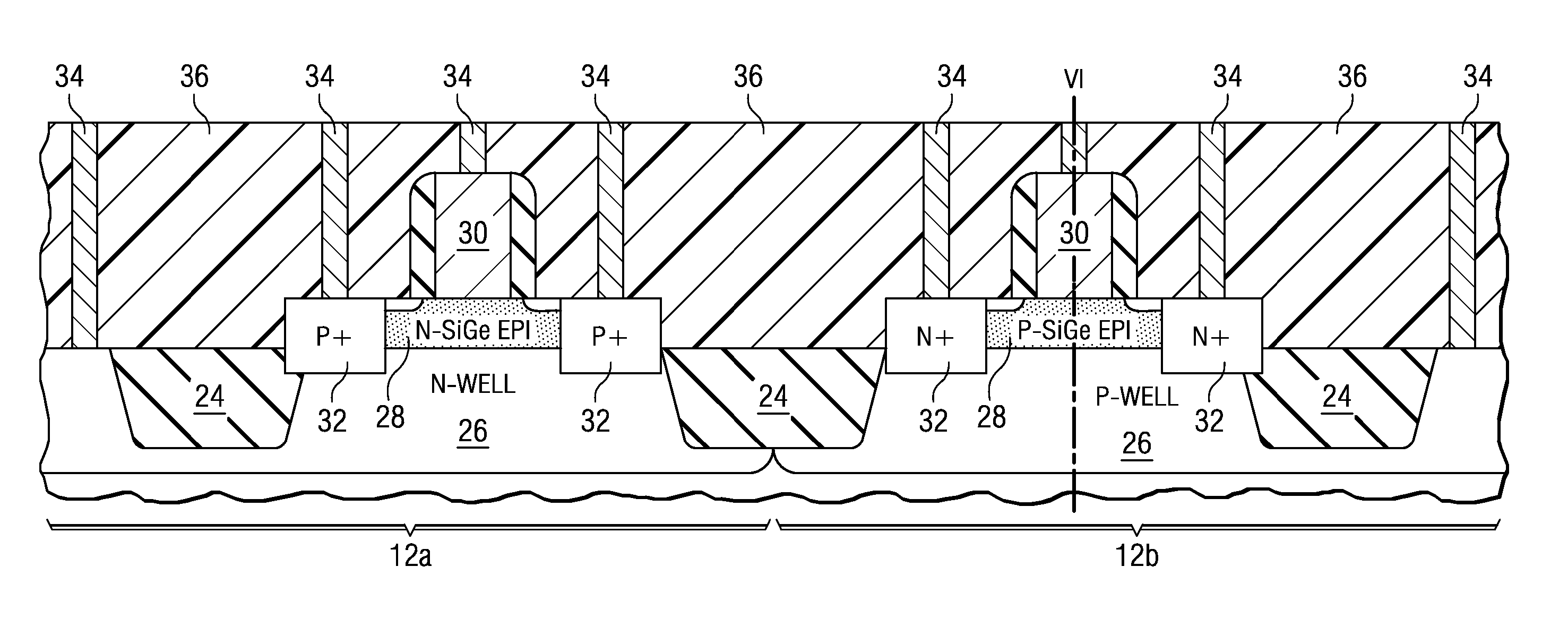

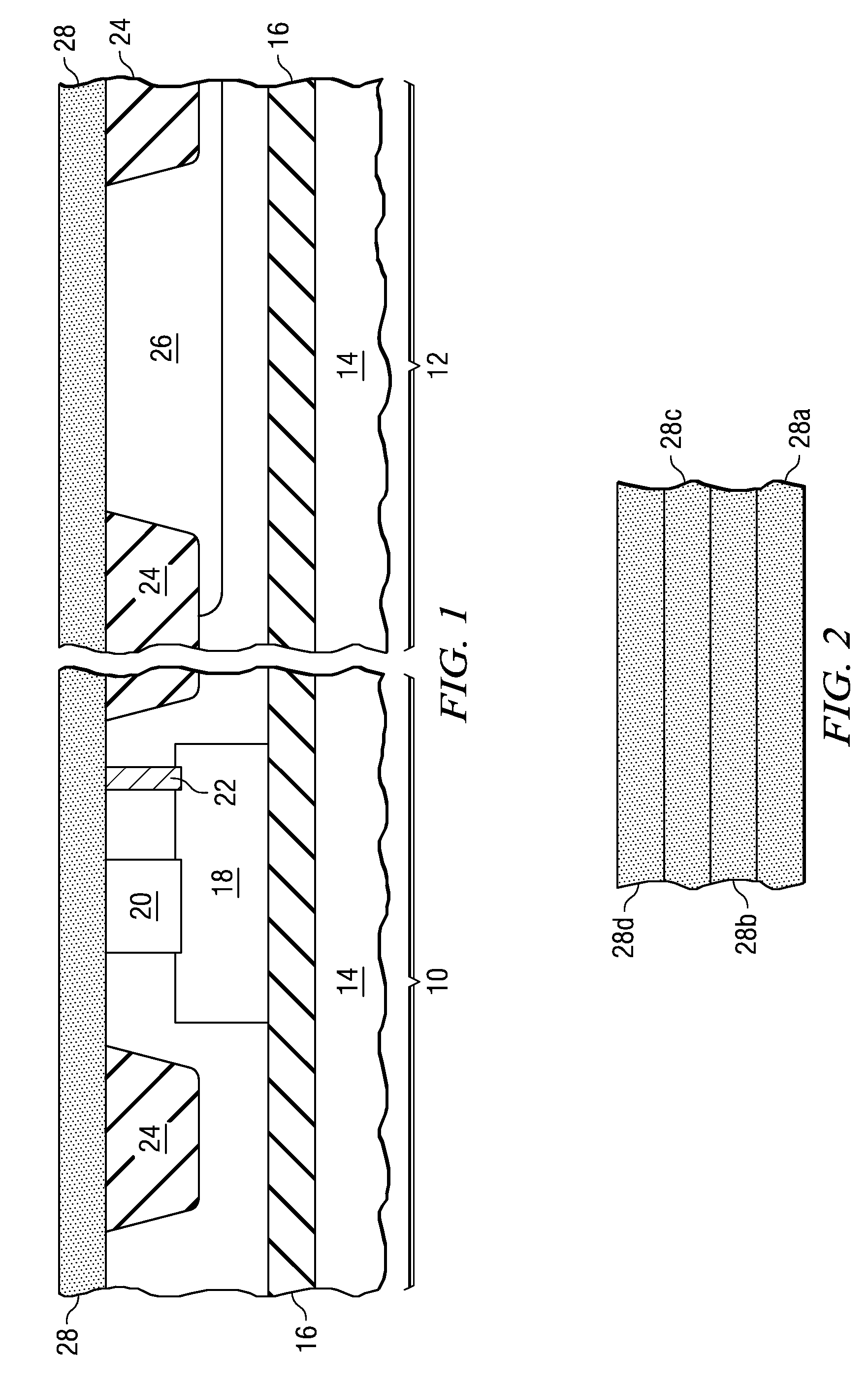

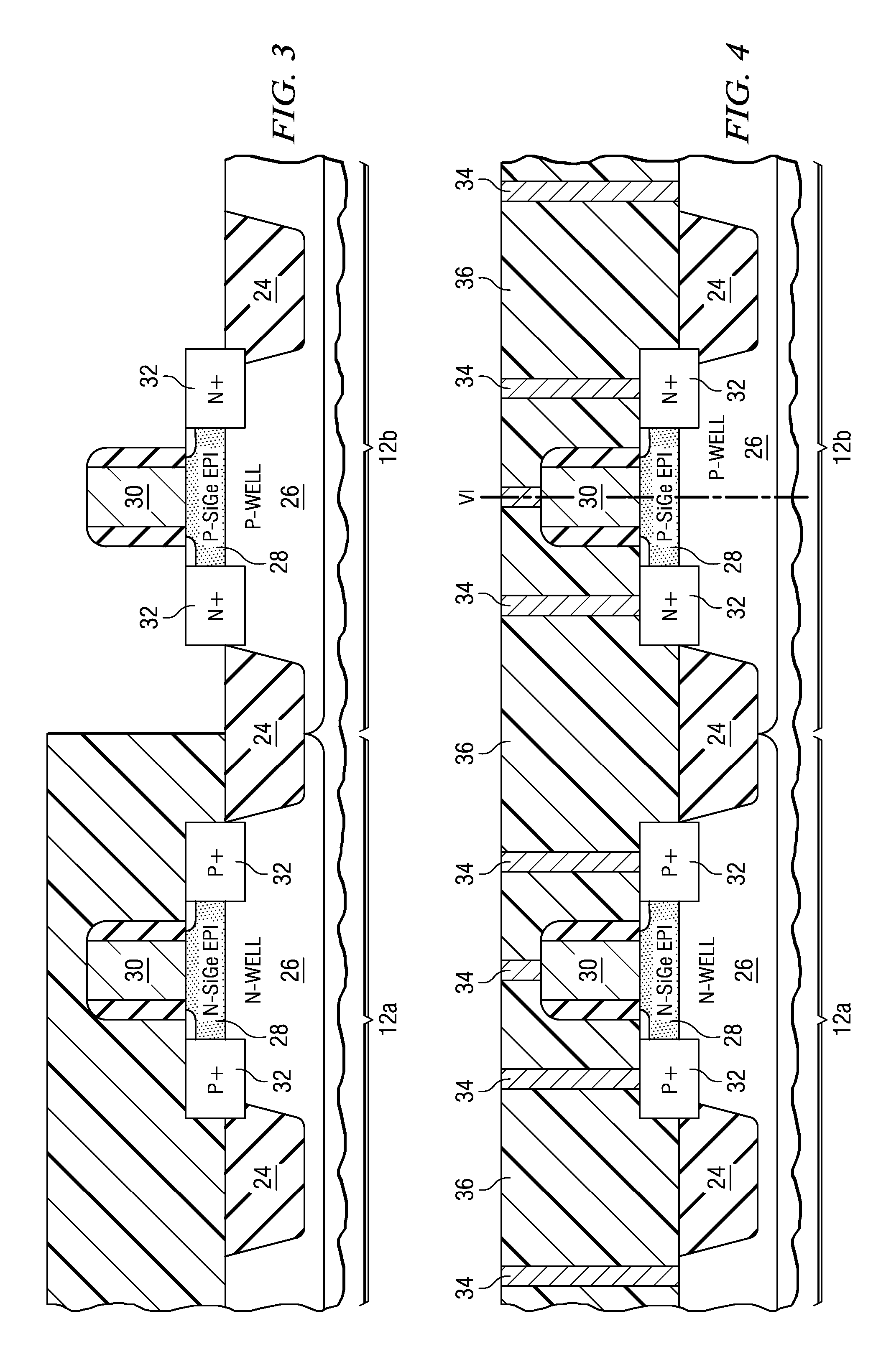

Integrated SiGe NMOS and PMOS transistors

A method of fabricating an integrated BiCMOS circuit is provided, the circuit including bipolar transistors 10 and CMOS transistors 12 on a substrate. The method comprises the step of forming an epitaxial layer 28 to form a channel region of a MOS transistor and a base region of a bipolar transistor. Growing of the epitaxial layer includes growing a first sublayer of silicon 28a, a first sublayer of silicon-germanium 28b onto the first sublayer of silicon, a second sublayer of silicon 28c onto the first sublayer of silicon-germanium, and a second sublayer of silicon-germanium 28d onto the second sublayer of silicon. Furthermore, an integrated BiCMOS circuit is provided, which includes an epitaxial layer 28 as described above.

Owner:TEXAS INSTR INC

Vertical parasitic type precision navigation processor (PNP) device in bipolar complementary metal oxide semiconductor (BiCMOS) technology and manufacture method thereof

ActiveCN102386218ALarge current amplification factorImprove frequency characteristicsTransistorSemiconductor/solid-state device manufacturingOutput deviceOxygen

The invention discloses a vertical parasitic type precision navigation processor (PNP) device in a bipolar complementary metal oxide semiconductor (BiCMOS) technology, which comprises a collector region, a base region, an emitter region, a counterfeit burying layer and a N-type polycrystalline silicon. The counterfeit burying layer is arranged at the bottom of shallow groove field oxygen at two sides of the collector region and transversely extends into an active area so as to be contacted with the collector region, and a collector electrode is led out due to the deep hole contact formed in the shallow groove field oxygen at the top of the counterfeit burying layer. The N-type polycrystalline silicon is formed at the upper part of the base region to be contacted with the base region, and a base electrode is lead out due to the metal contact on the N-type polycrystalline silicon. The invention further discloses a manufacture method of the vertical parasitic type PNP device in the BiCMOS technology. The device disclosed by the intention can be taken as an output device in a high-speed and high-grain BiCMOS circuit, so that one more device selection can be provided to a circuit, the area of the device can be effectively reduced, the electric resistance of the collector electrode of the PNP pipe can be reduced, and the performance of the device can be improved. The production costcan be reduced without needing an extra technical condition.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

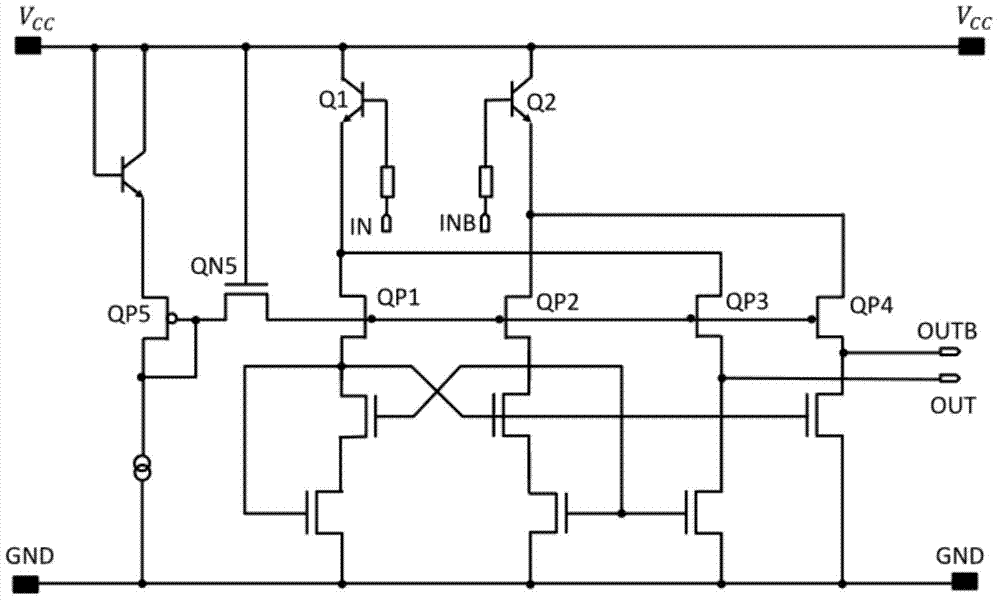

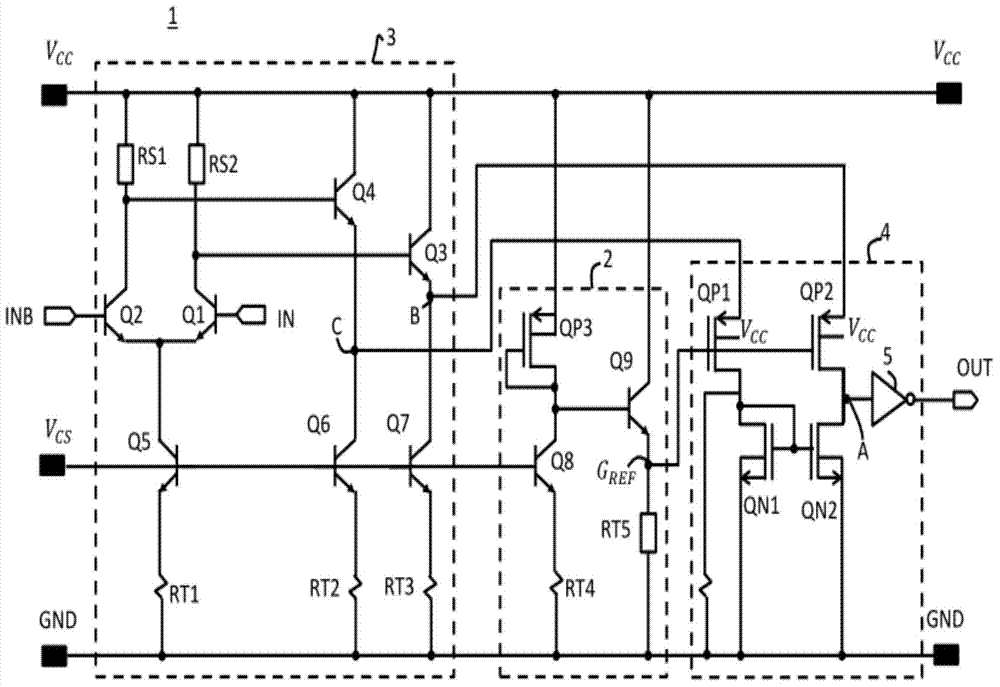

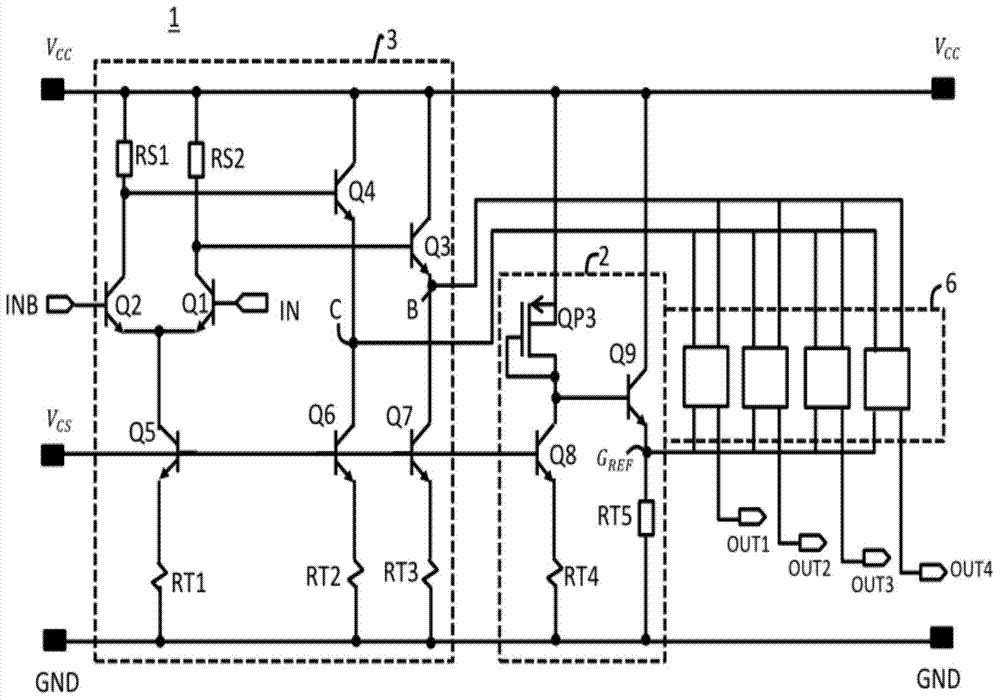

BICMOS circuit converting ECL logic level into MOS logic level

InactiveCN103618539AQuick conversionConversion impactLogic circuits coupling/interface using field-effect transistorsCMOSEngineering

The invention discloses a BICMOS circuit converting an ECL logic level into an MOS logic level. The conversion circuit is used for converting the range of a first logic level into the range of a second logic level, just like the commonly-revolved phenomenon that the ECL stage is converted into the CMOS stage.

Owner:SUZHOU BATELAB MICROELECTRONICS

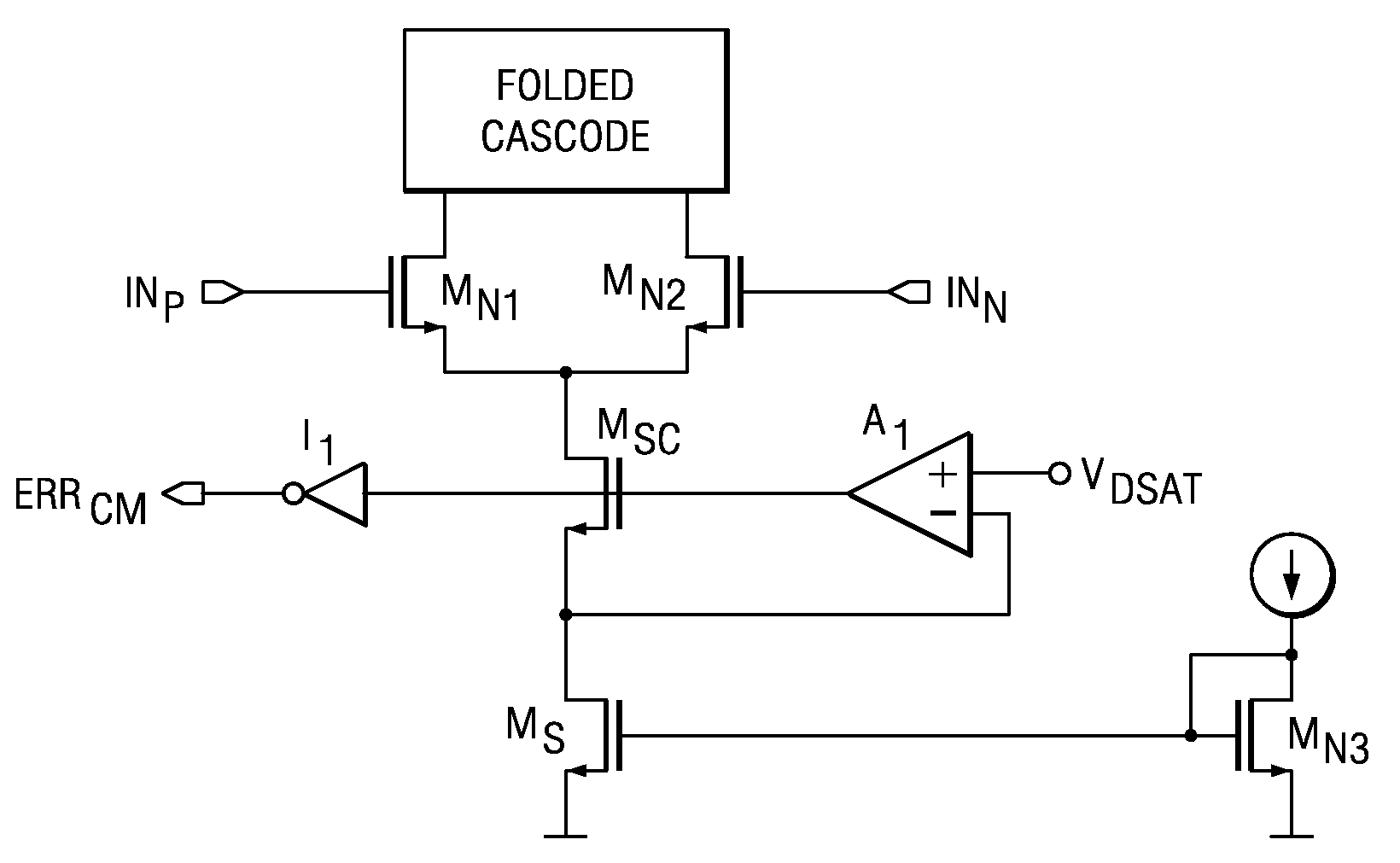

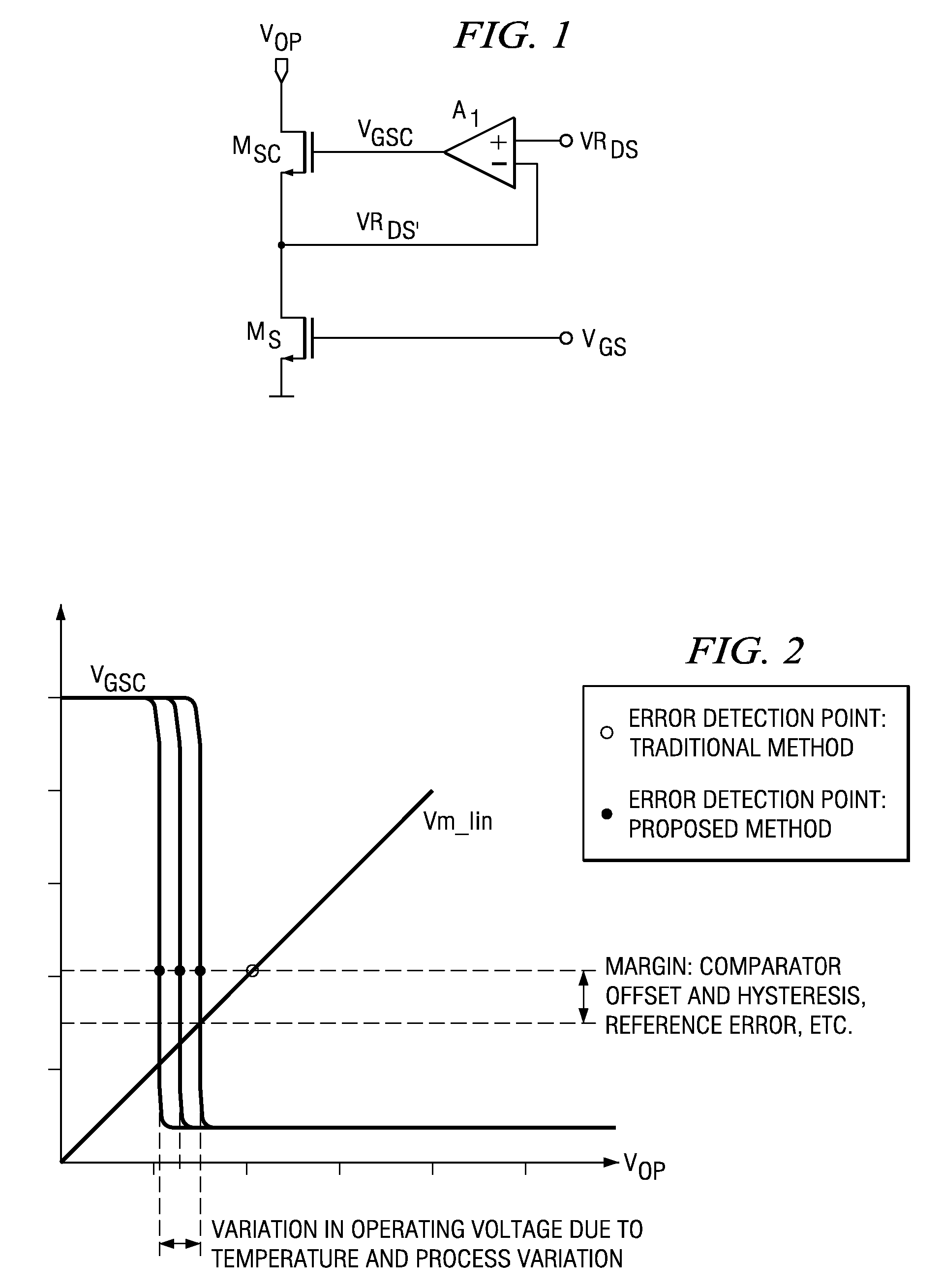

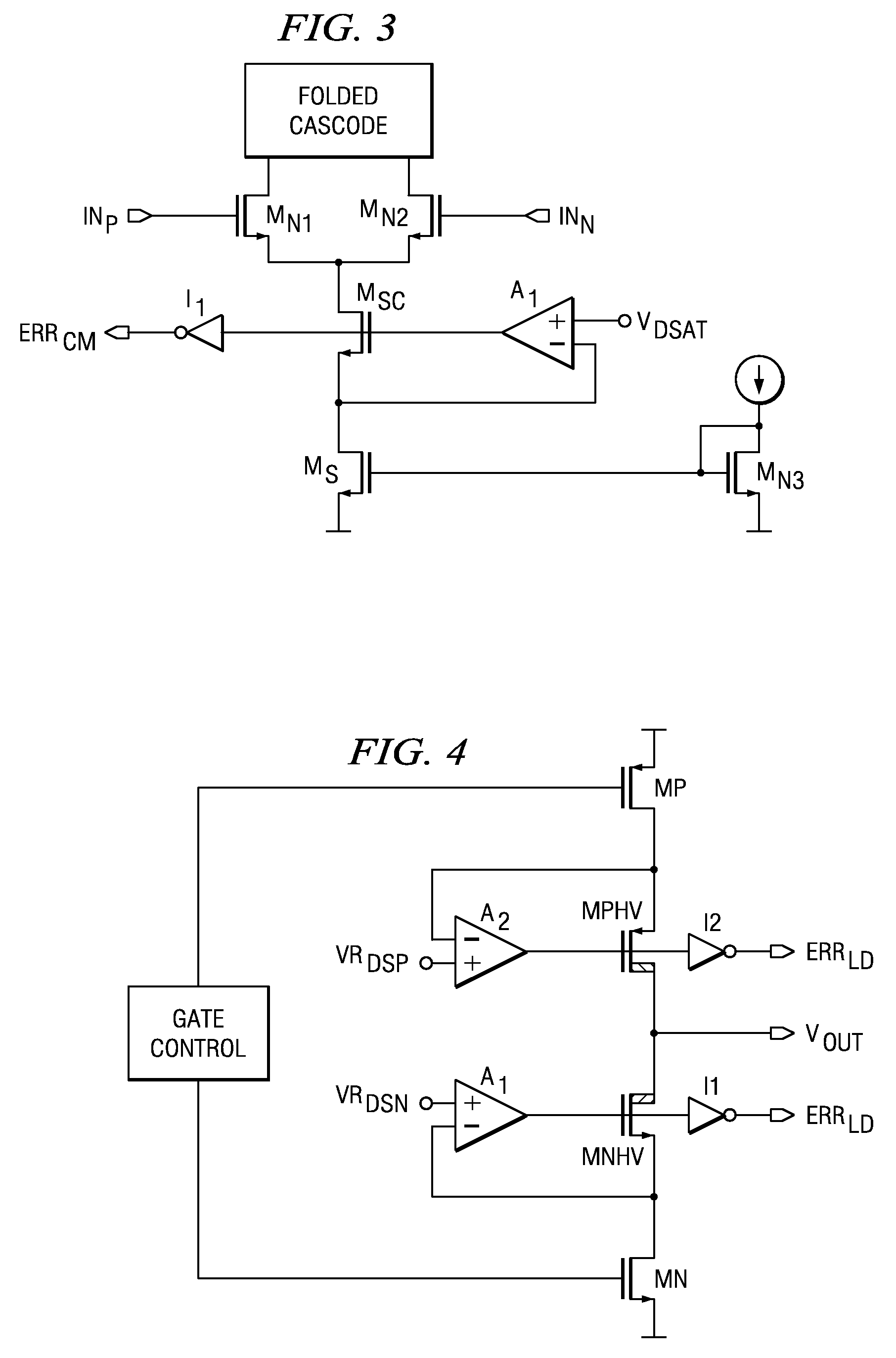

Detecting amplifier out-of-range conditions

ActiveUS7427898B2Accurately detect occurrenceIncrease rangeAmplifier combinationsAmplifiers with semiconductor devices onlyCMOSAudio power amplifier

Out-of-range conditions are detected in amplifier CMOS or BiCMOS circuitry that includes a control transistor (MS) connected in series with a cascode transistor (MSC), and a differential amplifier (A1) with an inverting input connected to the node between the control transistor and the cascode transistor, a non-inverting input connected to a reference voltage source (VRDS) and an output connected to the gate of the cascode transistor (MSC). The voltage at the output of the differential amplifier (A1) is monitored, and an error condition is determined when the voltage exceeds or drops below a predetermined threshold value. The invention considerably widens the useful operating range, without requiring sophisticated or complex detection circuitry.

Owner:TEXAS INSTR INC

Vertical parasitic PNP device in BiCMOS (bipolar complementary metal oxide semiconductor) process and manufacturing method

ActiveCN102403343BLarge current amplification factorImprove frequency characteristicsTransistorSemiconductor/solid-state device manufacturingBicmos circuitsBicmos process

The invention discloses a vertical parasitic PNP device in the BiCMOS (bipolar complementary metal oxide semiconductor) process, which comprises a collector region, a base region, an emitter region, a buried layer and N-shaped polycrystalline silicon. The collector region is formed in a first active region, the buried layer is formed at the bottom of shallow trench field oxides on two sides of the collector region and transversely extends to enter the first active region and contact with the collector region, the collector region is connected with an adjacent second active region and an adjacent third active region through the buried layer, and collectors are led out by metallic contacts formed at the tops of the second active region and the third active region. The N-shaped polycrystalline silicon is formed on the upper portion of the base region and contacts with the base region, and bases are led out by metallic contacts formed on the N-shaped polycrystalline silicon. The inventionfurther discloses a manufacturing method for the vertical parasitic PNP device in the BiCMOS process. The vertical parasitic PNP device can be used as an output device in a high-speed and high-gain BiCMOS circuit so as to provide one more choice for the circuit, and the resistance of the collectors can be decreased and the performance of the devices is improved without increasing the area of the device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

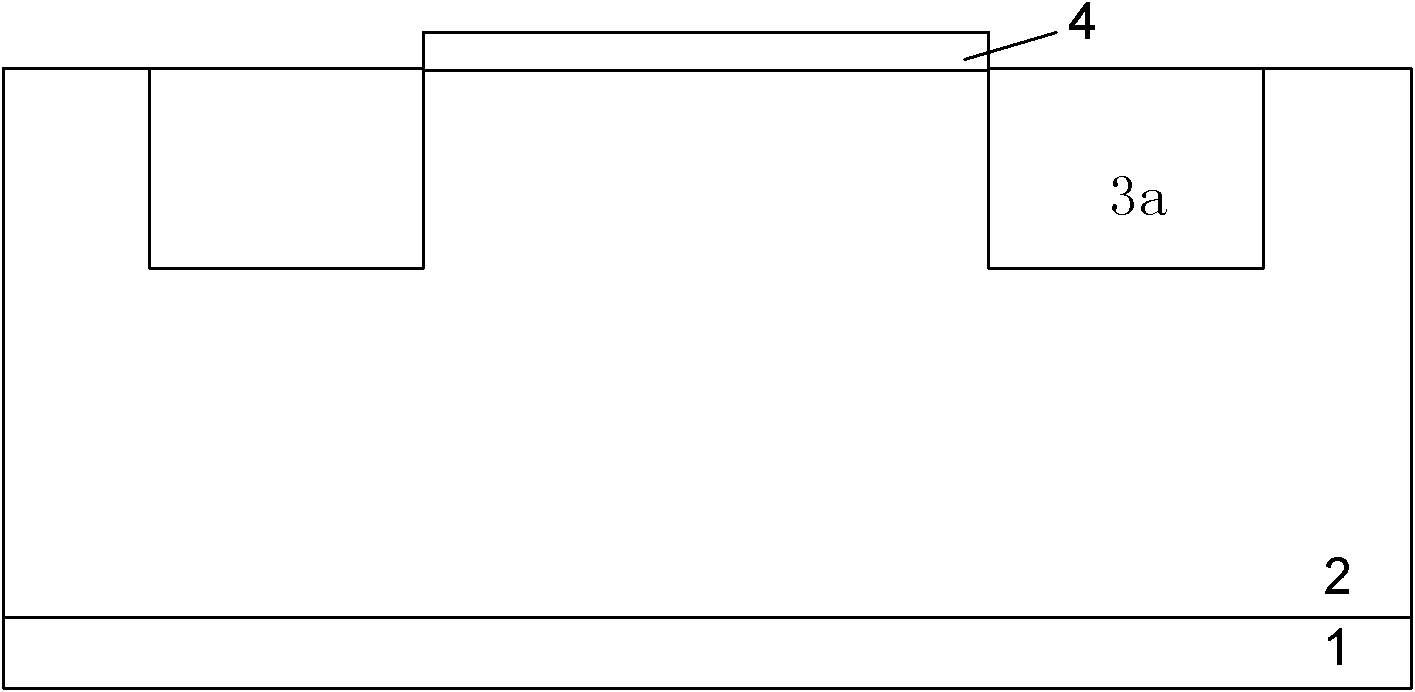

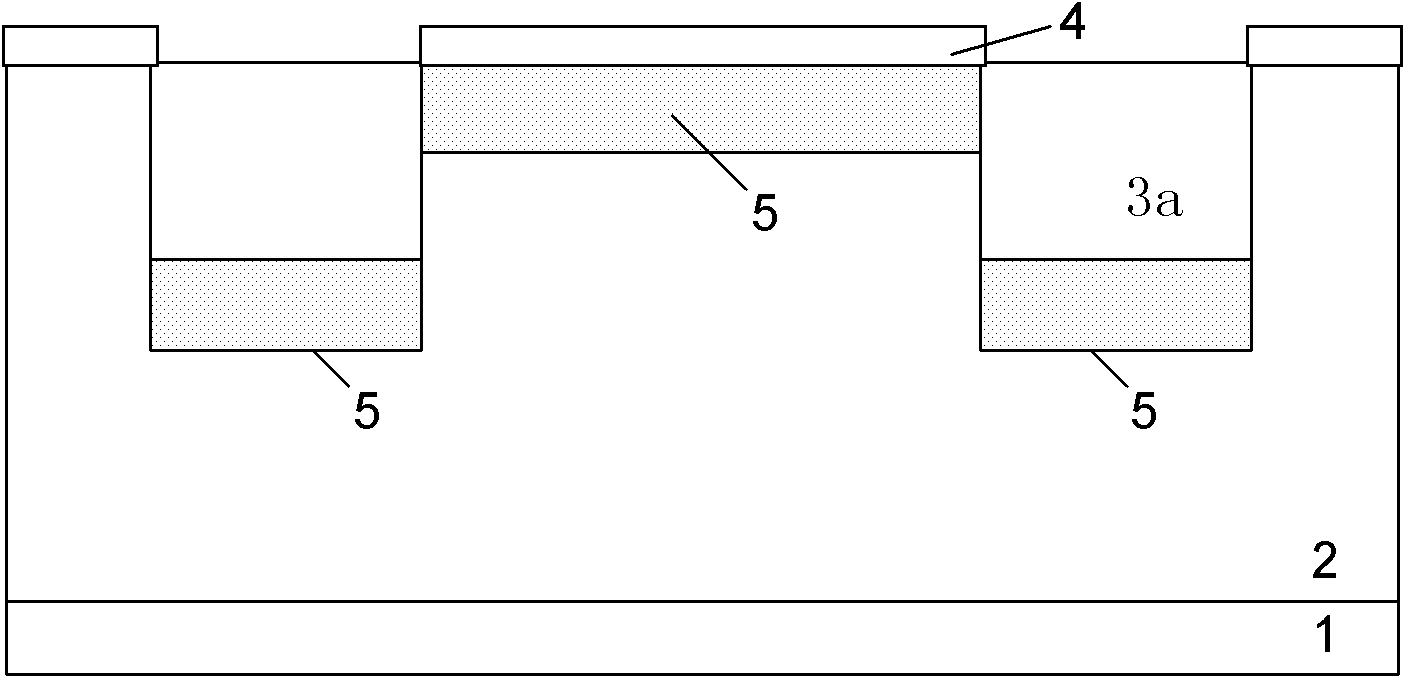

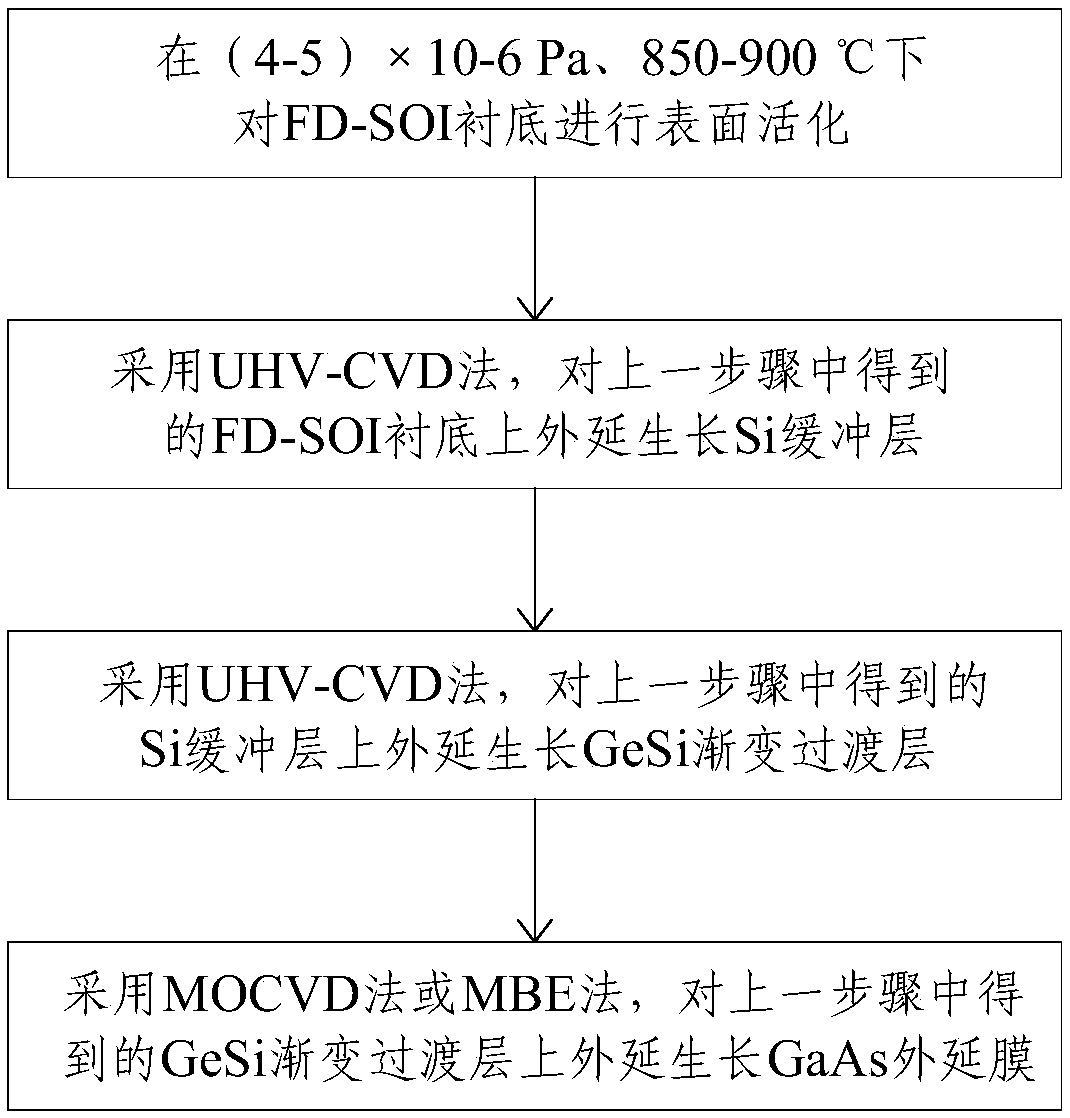

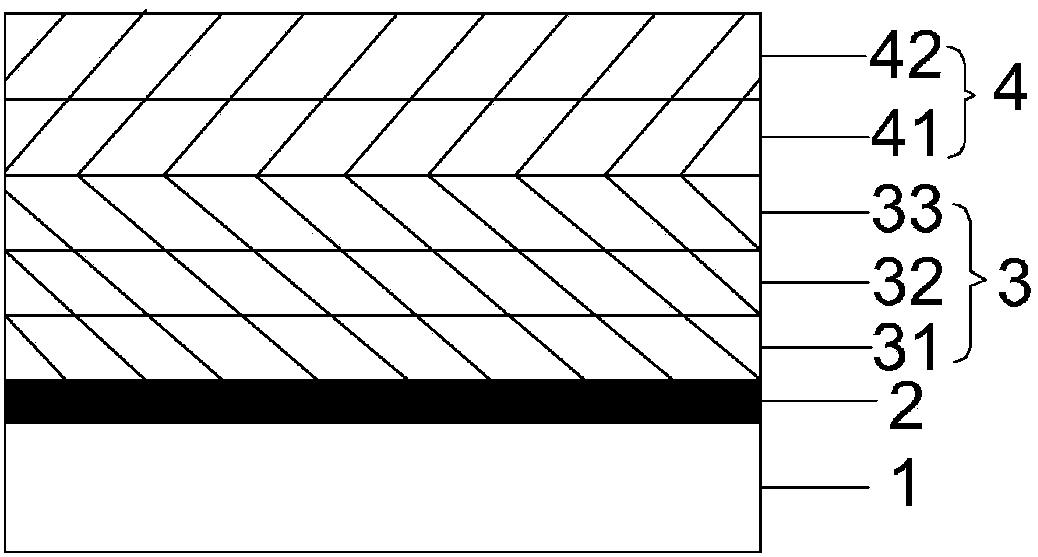

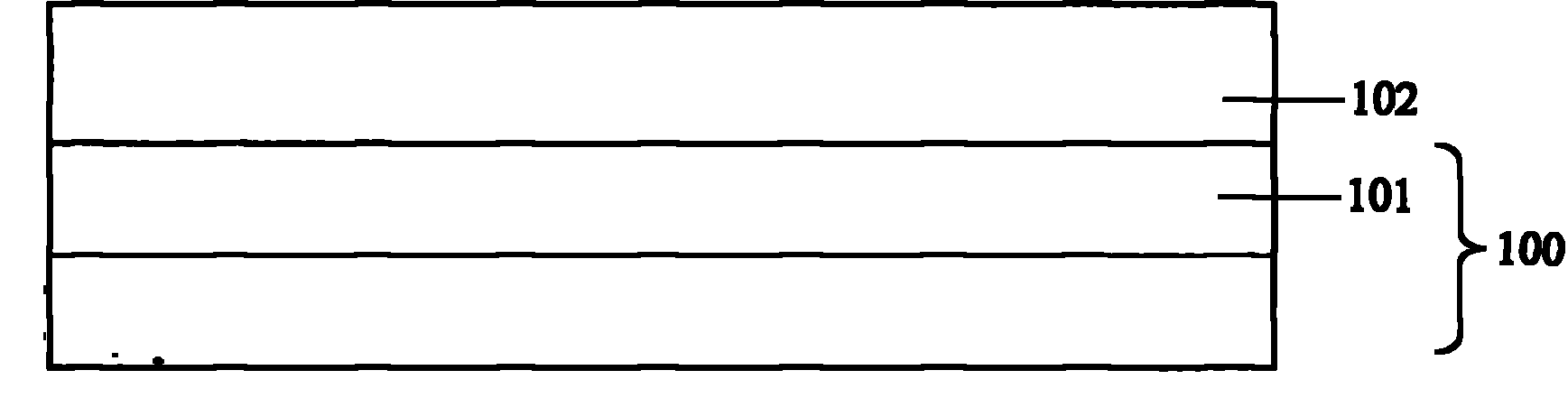

GaAs epitaxial film based on SOI substrate, preparation method and application

InactiveCN108565209AQuality improvementReduce dislocation densitySolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceHeterojunction

The invention discloses a GaAs epitaxial film based on an SOI substrate and a preparation method and application. The GaAs epitaxial film includes an FD-SOI substrate, a Si buffer layer, a GeSi gradedtransition layer, and a GaAs epitaxial film arranged in this order from bottom to top; The preparation method includes a substrate selection and pretreatment, a Si buffer layer growth, a GeSi gradient transition layer growth, and a GaAs epitaxial film growth; the method can be widely used in the preparation of CMOS circuits and devices, HEMT RF devices, bipolar circuits and devices, BiCMOS circuits and heterojunction devices. The lattice constant and the thermal expansion coefficient of the GeSi graded transition layer material are close to the GaAs epitaxial film, and are used as a transition layer. The method combines the high frequency, low power consumption and high output power characteristics of GaAs materials with the junction capacitance, low leakage current and low power consumption of SOI materials with important theoretical and practical significance.

Owner:BEIJING UNIV OF TECH

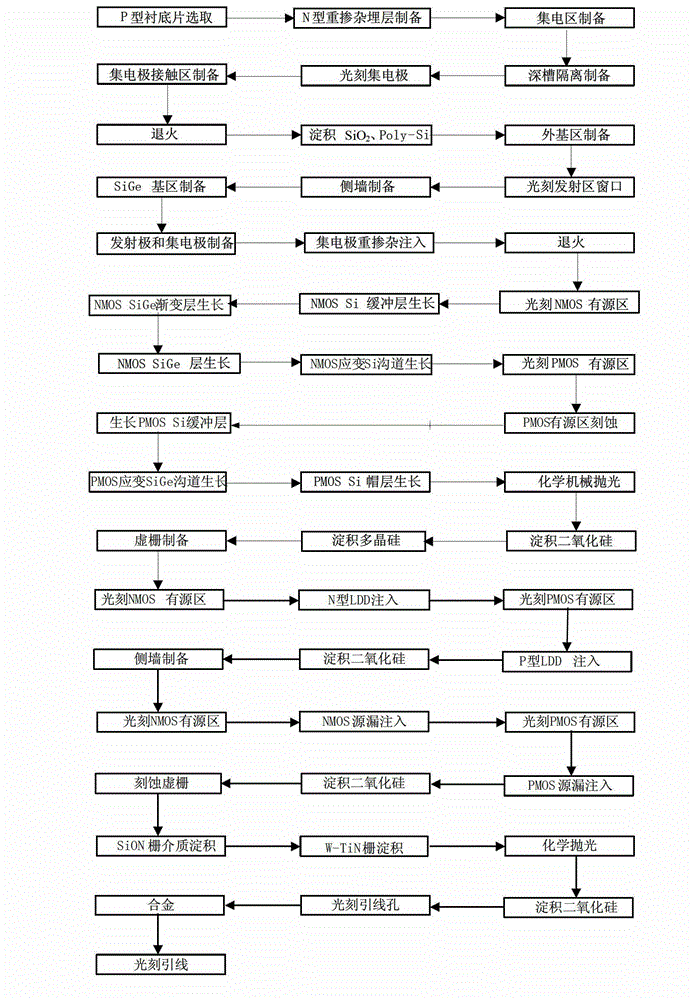

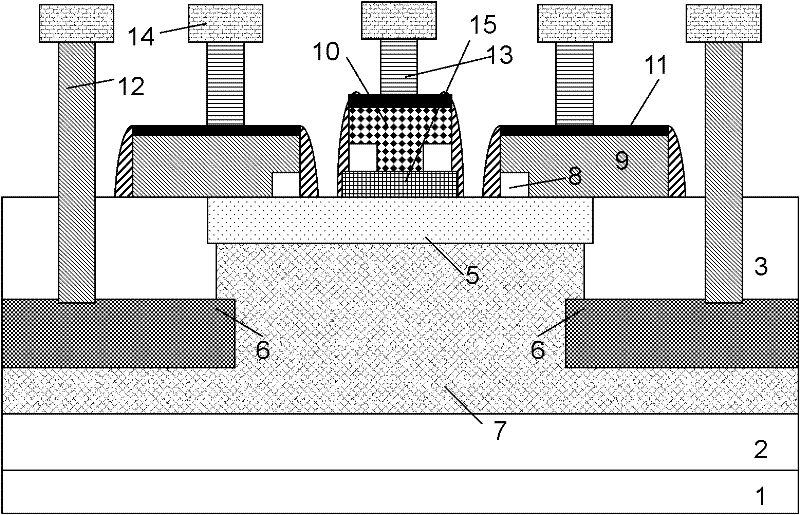

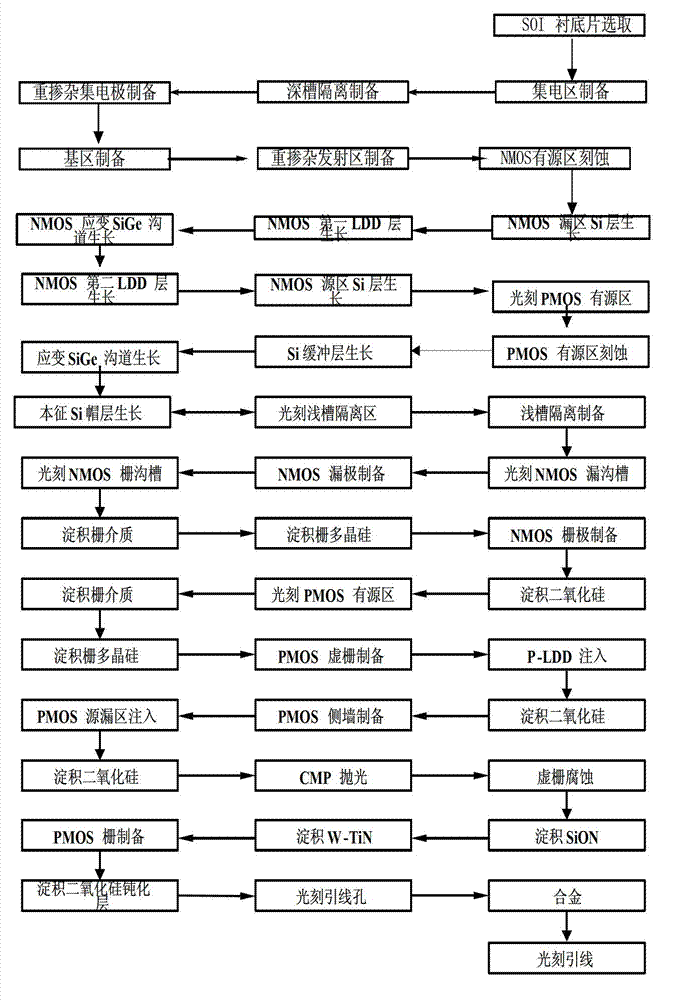

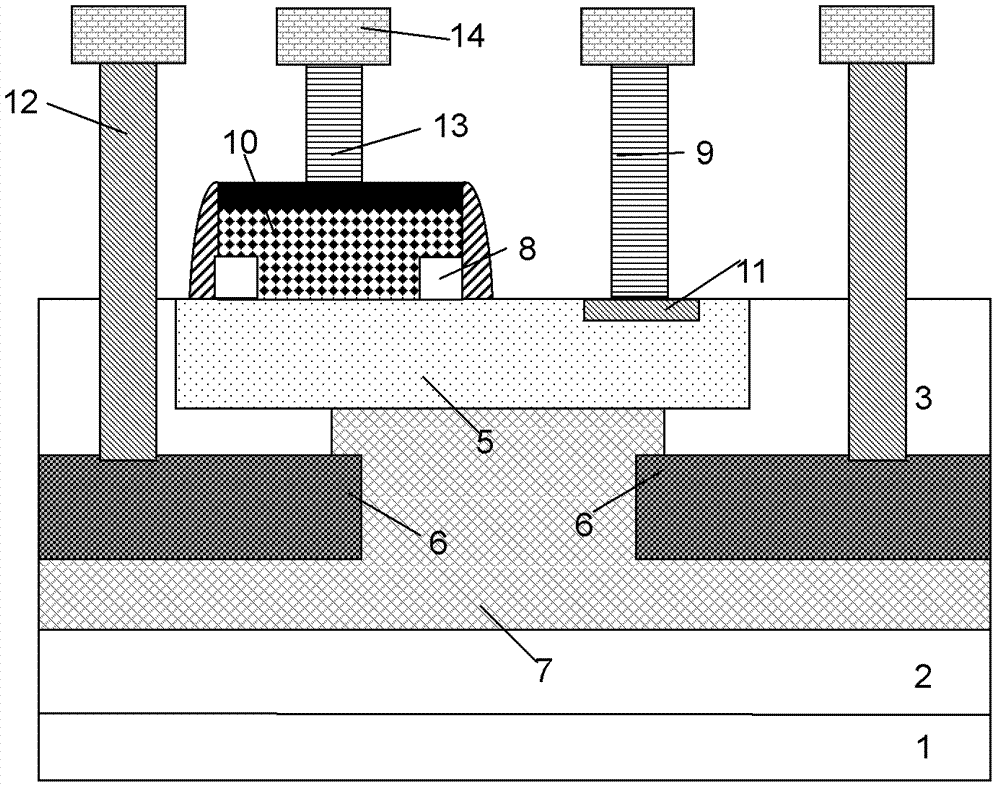

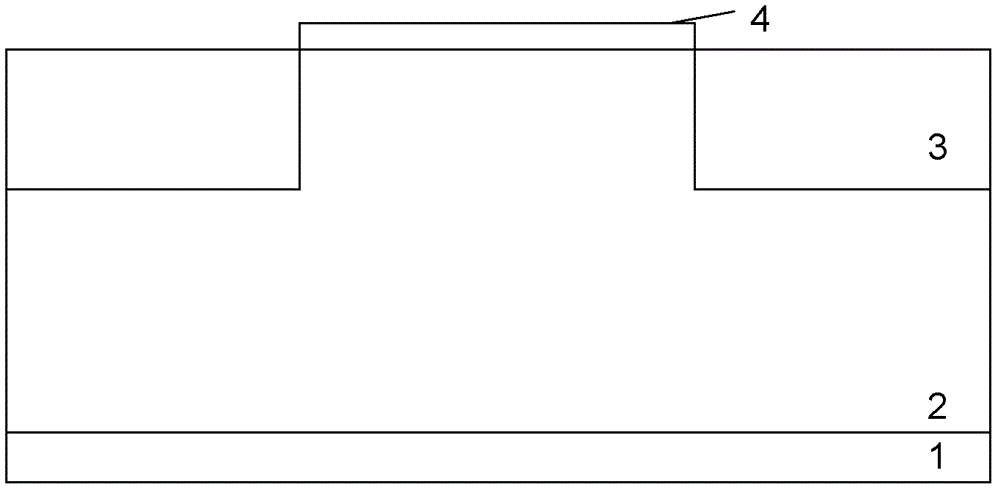

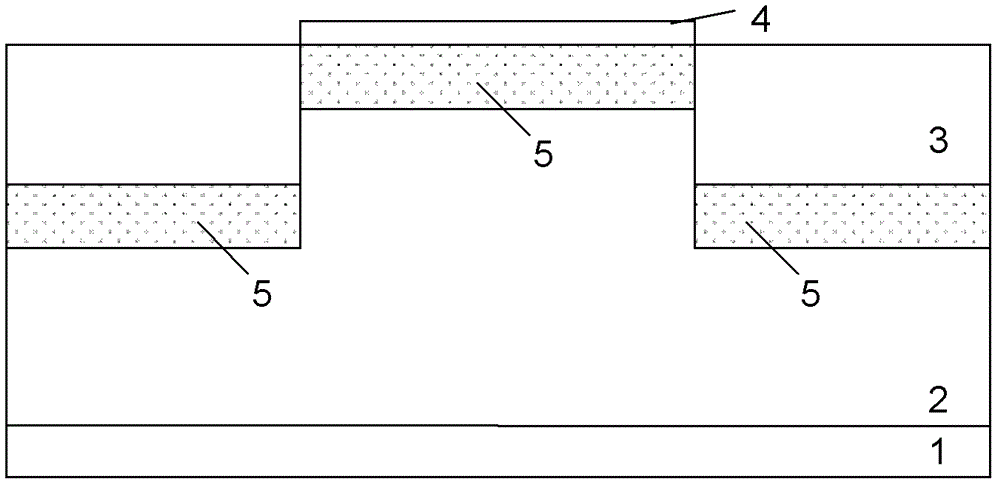

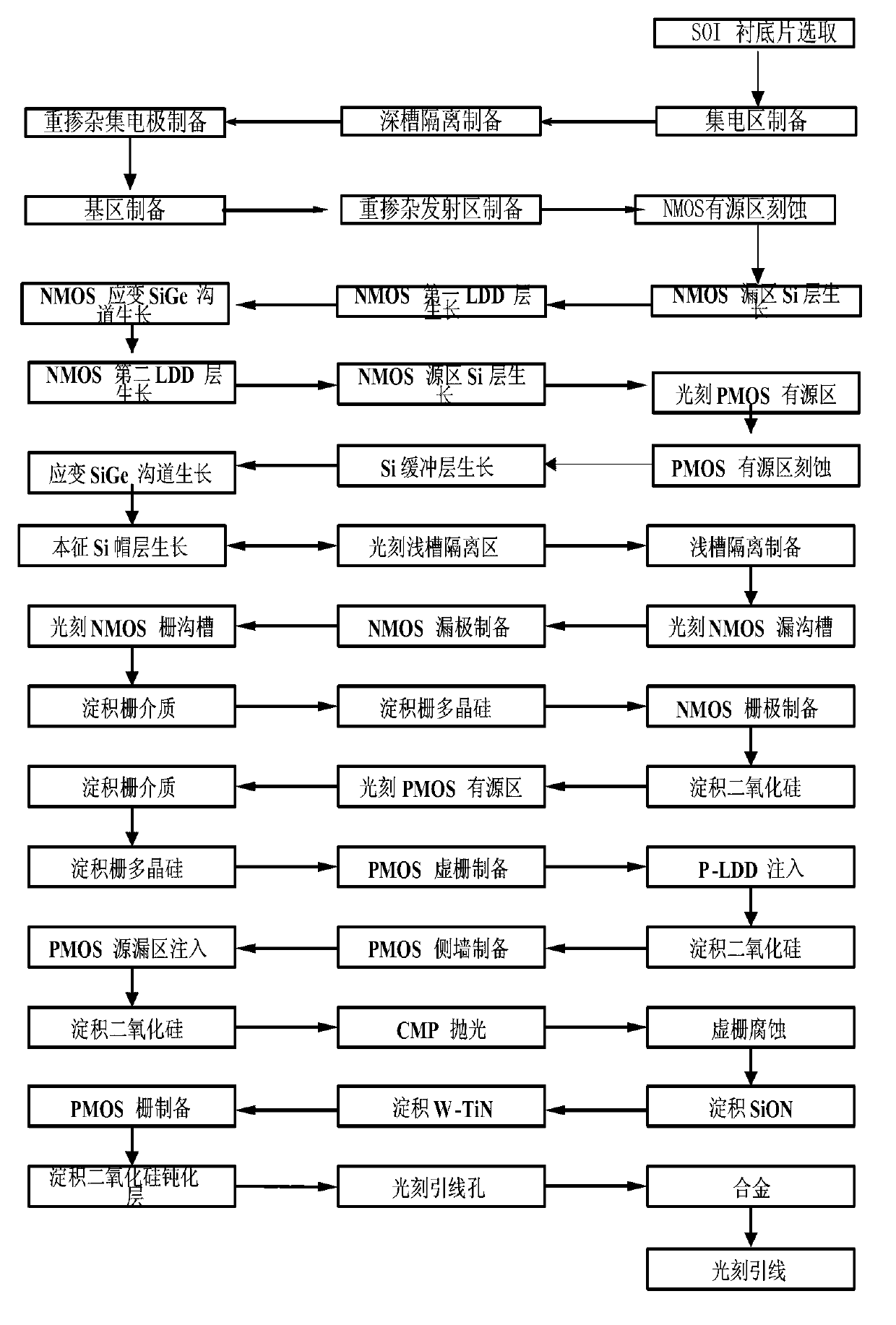

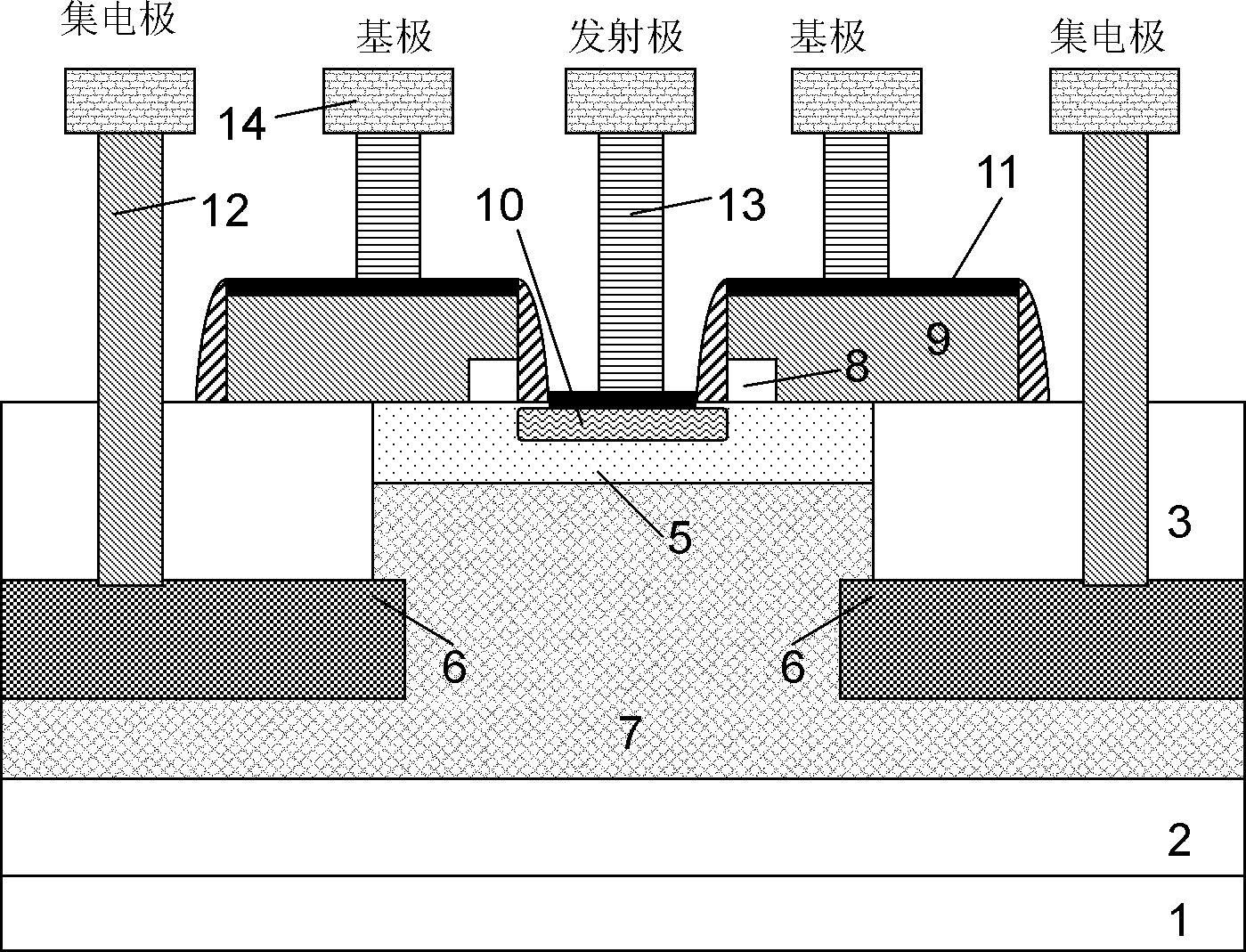

Tri-strain tri-polycrystal-plane BiCMOS (Bipolar complementary metal oxide semiconductor) integrated device and preparation method thereof

InactiveCN102867824AImprove electrical performanceHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingElectrode ContactComposite grid

The invention discloses a tri-strain tri-polycrystal-plane BiCMOS (Bipolar complementary metal oxide semiconductor) integrated device and a preparation method thereof. The method comprises the following steps: preparing an embedded layer on a substrate plate, growing N-type Si epitaxy, preparing a deep channel isolator, preparing a collecting electrode contact area, preparing a base area and a transmission area, and forming a SiGe HBT (Heterojunction bipolar transistor) device; etching deep channels in the active areas of an NMOS (N-channel metal oxide semiconductor) device and a PMOS (P-channel metal oxide semiconductor) device, selectively epitaxially growing the following layers in the channel: a P-type Si layer, a P-type SiGe gradient layer, a P-type SiGe layer, a P-type strain Si layer as the active area of the NMOS device, an N-type Si layer, an N-type strain SiGe layer, and an N-type Si cap layer as the active area of the PMOS device; preparing a virtual grid, performing MOS (Metal oxide semiconductor) device light doped source / drain (LDD) injection, preparing a spacer, and self-aligning to form an MOS device source / drain; and etching the virtual grid, and sedimentating an SiON grid dielectric layer and a W-TiN composite grid to form a CMOS structure, and finally forming a BiCMOS circuit. According to the method, a tensile strain Si with high electron mobility and a compressive strain SiGe with high hole mobility are fully utilized as the conductive channels of the NMOS device and the PMOS device respectively, thus the performances of a BiCMOS integrated circuit are effectively improved.

Owner:XIDIAN UNIV

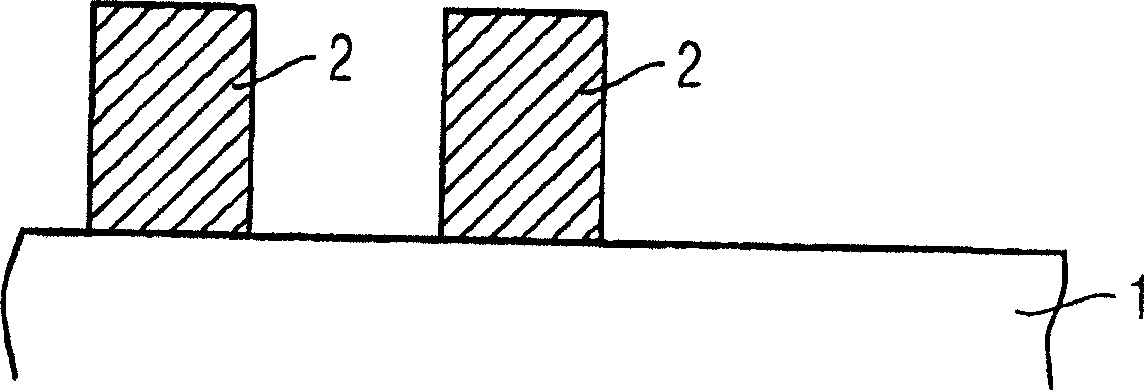

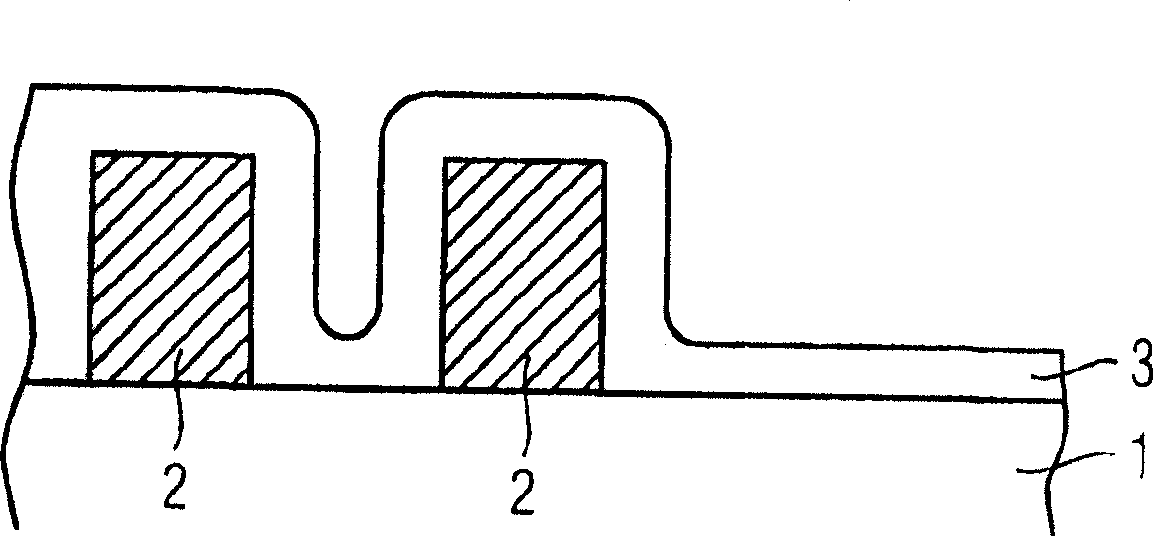

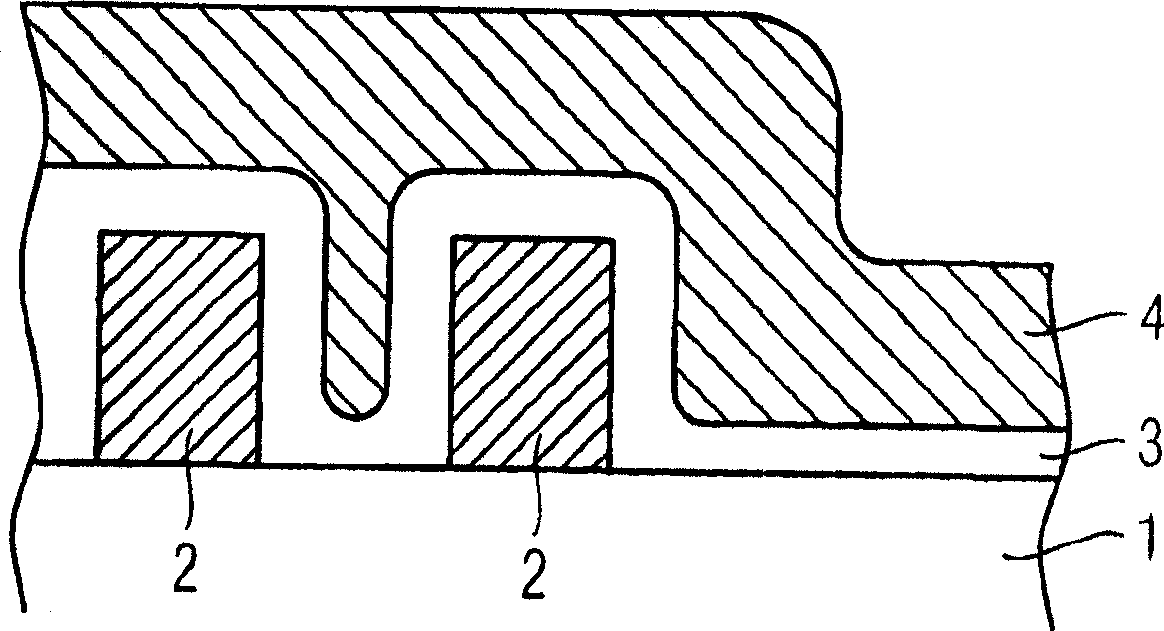

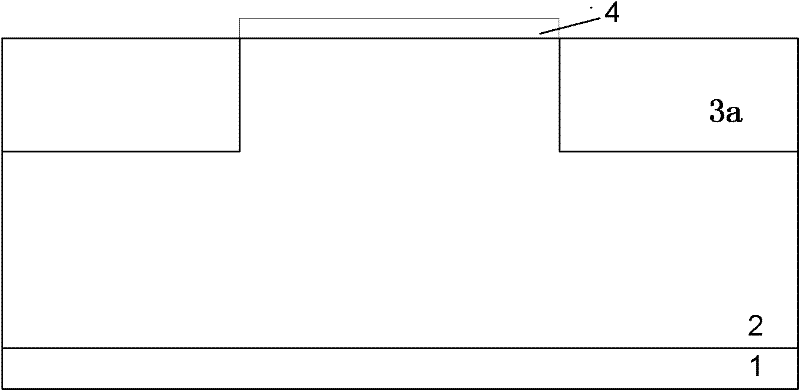

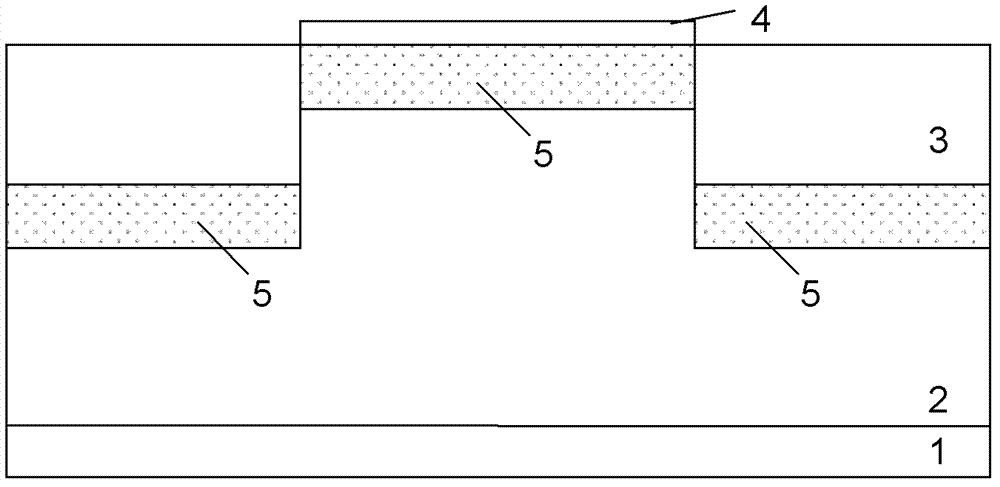

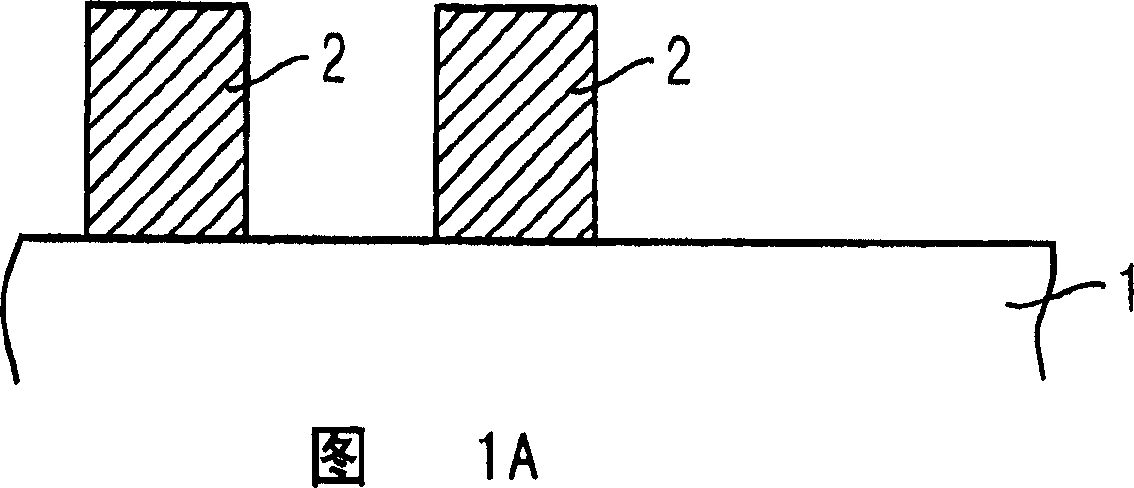

Method for producing a planar spacer, an associated bipolar transistor and an associated BiCMOS circuit arrangement

InactiveCN100524700CExcellent electrical propertiesEasy to implementSemiconductor/solid-state device manufacturingSemiconductor devicesHemt circuitsEngineering

Method for producing a planar spacer, an associated bipolar transistor and an associated BiCMOS circuit arrangement. The invention relates to a method for production of a planar spacer, of an associated bipolar transistor and of an associated BiCMOS circuit arrangement, in which first and second spacer layers are formed after the formation of a sacrificial mask on a mount substrate. A first anisotropic etching process of the second spacer layer is carried out to produce auxiliary spacers. A second anisotropic etching step is then carried out, in order to produce the planar spacers, using the auxiliary spacers as an etch mask.

Owner:INFINEON TECH AG

Vertical parasitic type precision navigation processor (PNP) device and manufacturing method thereof in bipolar complementary metal-oxide-semiconductor transistor (BiCMOS) technology

ActiveCN103066057BLarge current amplification factorImprove frequency characteristicsSemiconductor/solid-state device detailsSolid-state devicesEngineeringOutput device

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

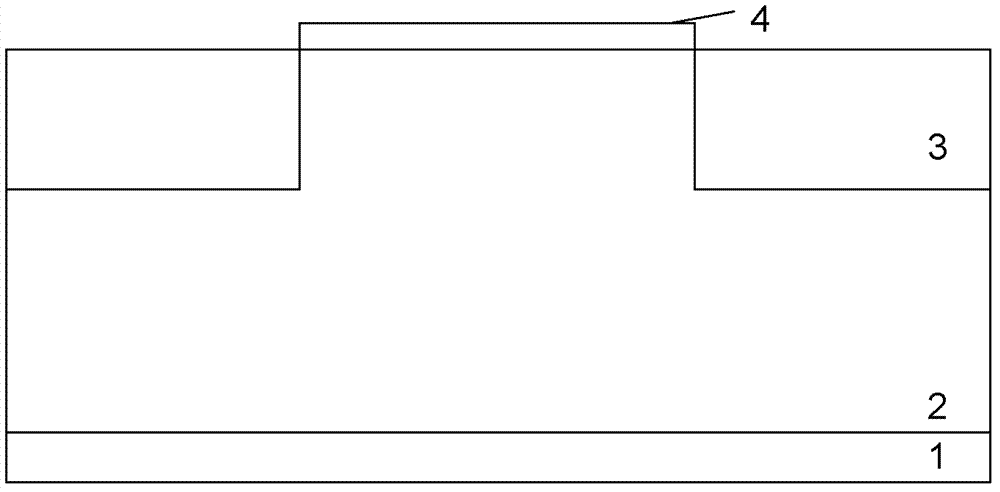

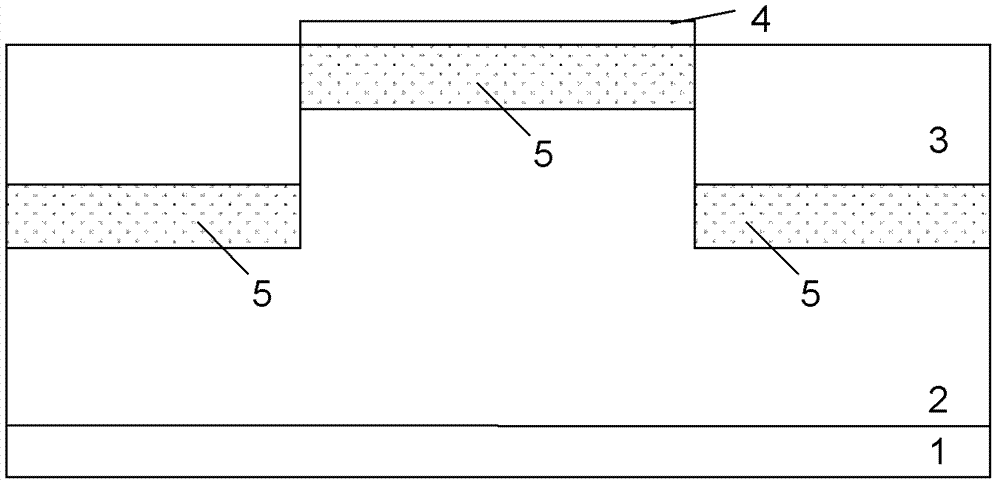

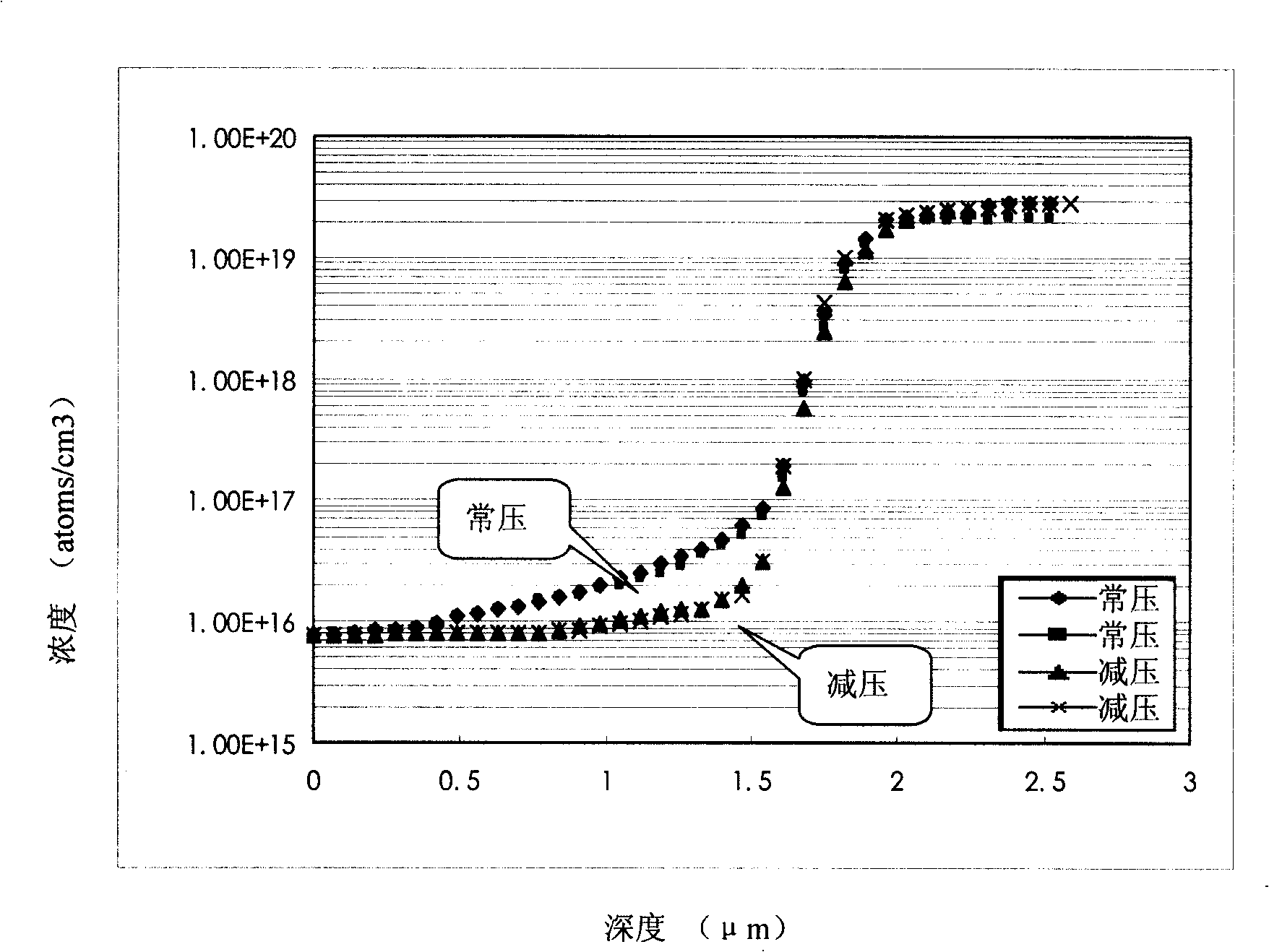

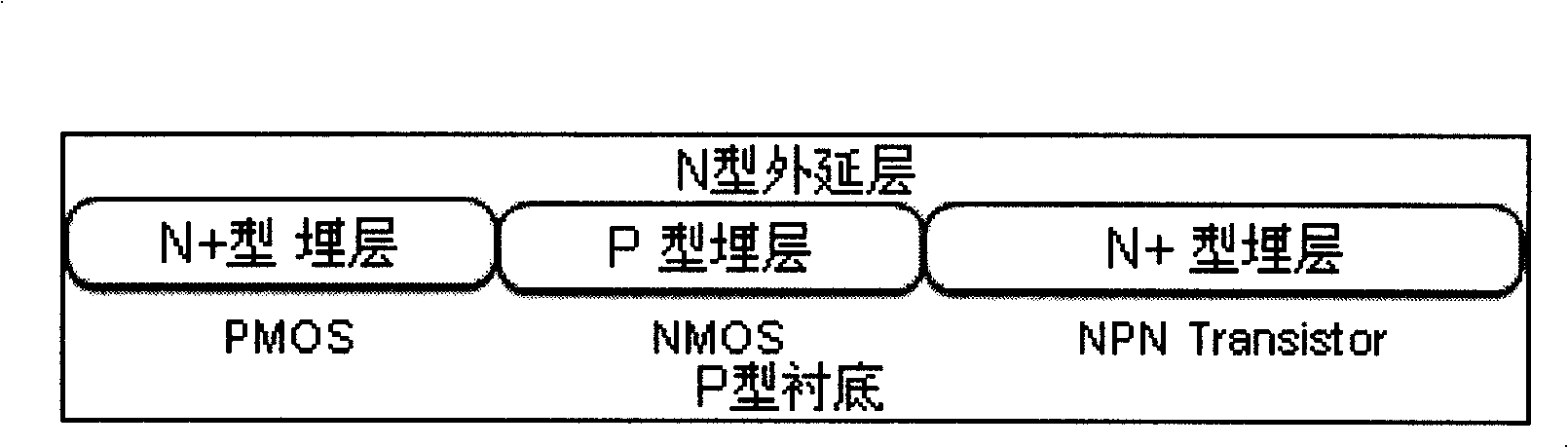

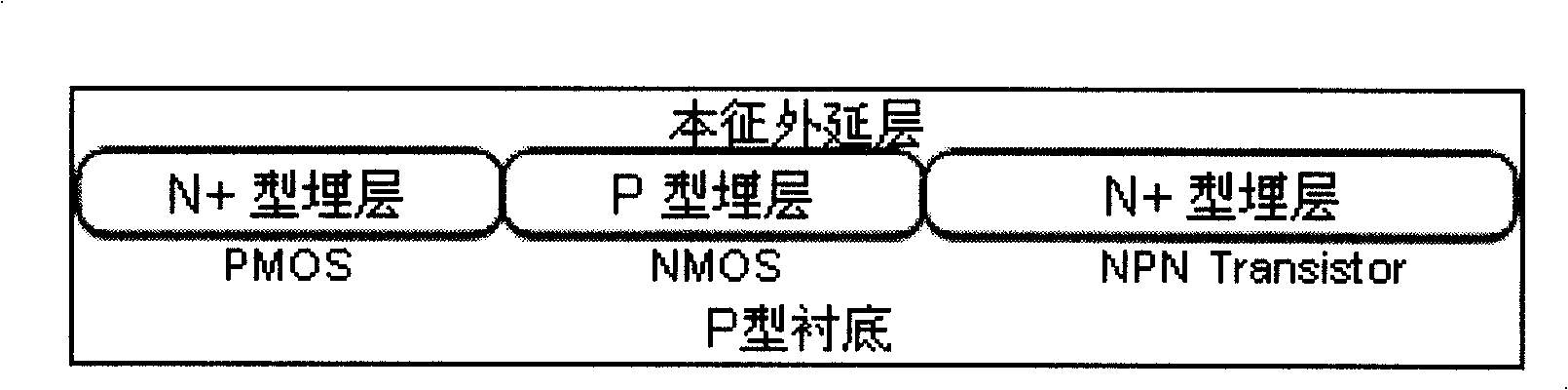

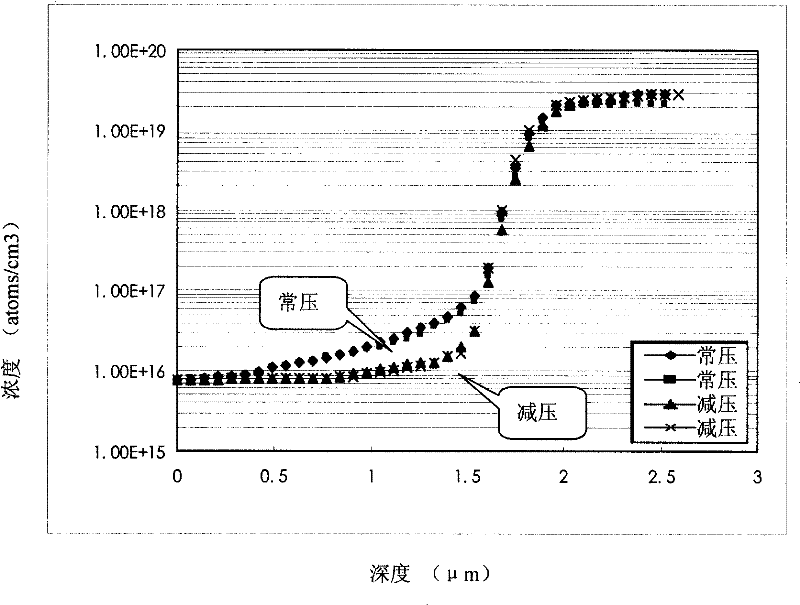

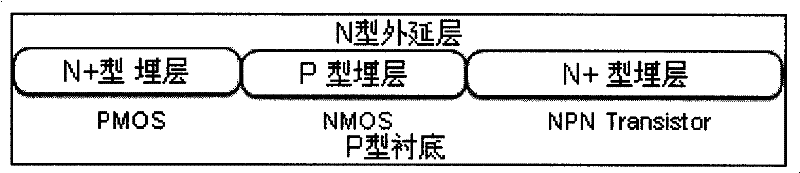

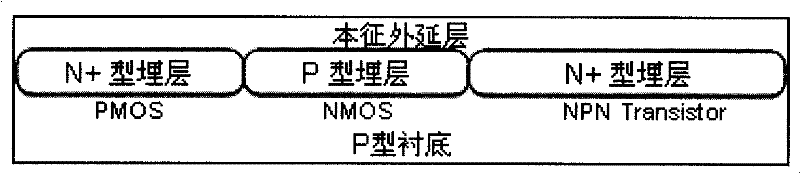

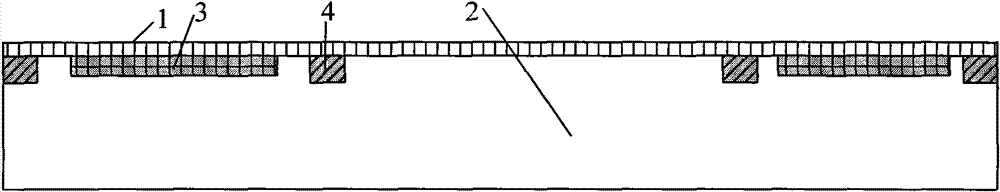

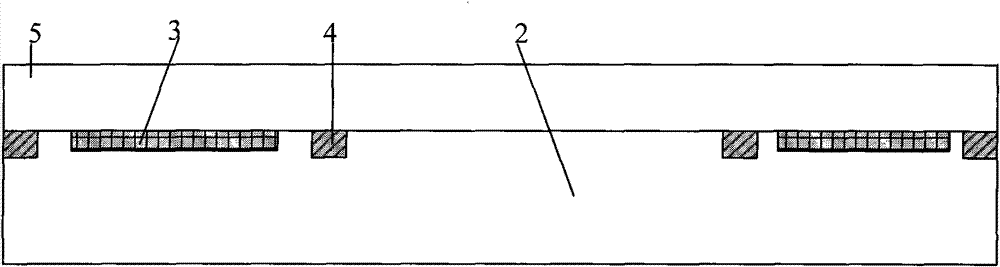

BICMOS circuit buried layer epitaxial method by cylinder epitaxial furnace

ActiveCN101335236AIncrease production capacitySemiconductor/solid-state device manufacturingEngineeringBicmos circuits

The invention relates to a preparation method which utilizes a cylinder epitaxial furnace to carry out buried layer epitaxy for preparing BICMOS circuits and belongs to the field of microelectronic technology, in particular to a new technology using the cylinder epitaxial furnace for preparing BICMOS raw materials, namely, a new preparation method thereof. Compared with the general preparation method by utilizing a single-wafer furnace, the novel preparation method not only can meet high requirements of preparation of the BICMOS circuits but also has the advantages of high yield and low cost, etc.

Owner:SHANGHAI SIMGUI TECH

Vertically parasitic PNP device in germanium-silicon HBT (heterojunction bipolar transistor) process and fabrication method thereof

ActiveCN102412274ALarge current amplification factorImprove featuresTransistorSemiconductor/solid-state device manufacturingEngineeringOutput device

The invention discloses a vertically parasitic PNP device in a germanium-silicon HBT process. The vertically parasitic PNP device comprises a collector region, a base region, an emitter region, a P-type pseudo-buried layer and N-type polysilicon, wherein, the pseudo-buried layer is formed at the bottom of a shallow trench field oxide around the collector region and is in contact with the collector region, and a collector is led through a deep hole contact formed at the top of the pseudo-buried layer; the N-type polysilicon is formed at the upper part of the base region, and is used for leading out a base; and the emitter region consists of a P-type germanium-silicon epitaxial layer and P-type polysilicon which are formed on the base region. The invention also discloses a fabrication method of the vertically parasitic PNP device in the germanium-silicon HBT process. The vertically parasitic PNP device can be used as an output device in a high-speed and high-gain BiCMOS (bipolar complementary metal oxide semiconductor) circuit, thereby providing another device option for the circuit. The vertically parasitic PNP device has the beneficial effects that the area of the device is effectively decreased, the collector resistance of a PNP transistor is reduced, and the frequency performance of the device is enhanced. By adopting the fabrication method, additional process conditions are not required, thereby reducing the production cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

BICMOS circuit buried layer epitaxial method by cylinder epitaxial furnace

ActiveCN101335236BIncrease production capacitySemiconductor/solid-state device manufacturingEngineeringBicmos circuits

The invention relates to a preparation method which utilizes a cylinder epitaxial furnace to carry out buried layer epitaxy for preparing BICMOS circuits and belongs to the field of microelectronic technology, in particular to a new technology using the cylinder epitaxial furnace for preparing BICMOS raw materials, namely, a new preparation method thereof. Compared with the general preparation method by utilizing a single-wafer furnace, the novel preparation method not only can meet high requirements of preparation of the BICMOS circuits but also has the advantages of high yield and low cost,etc.

Owner:SHANGHAI SIMGUI TECH

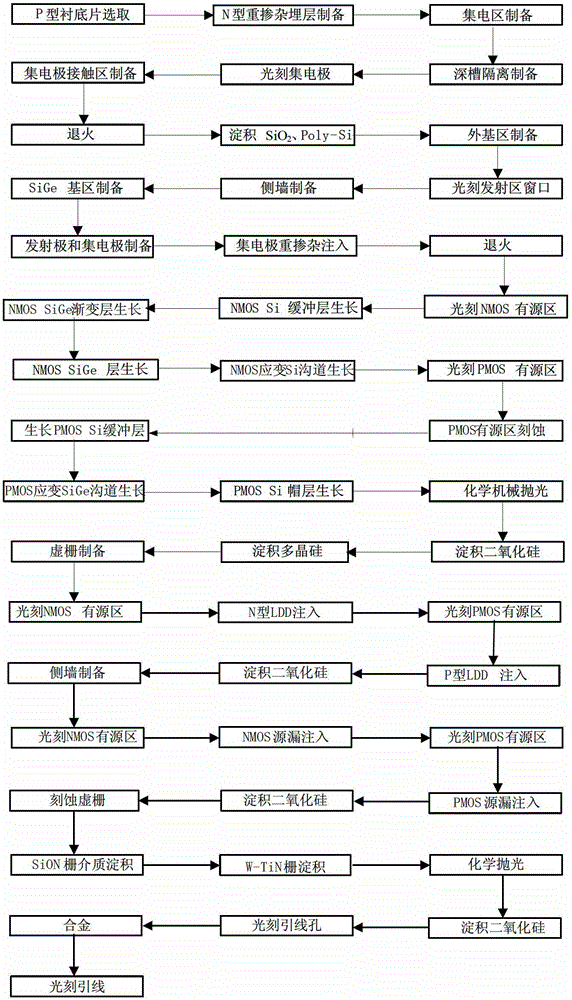

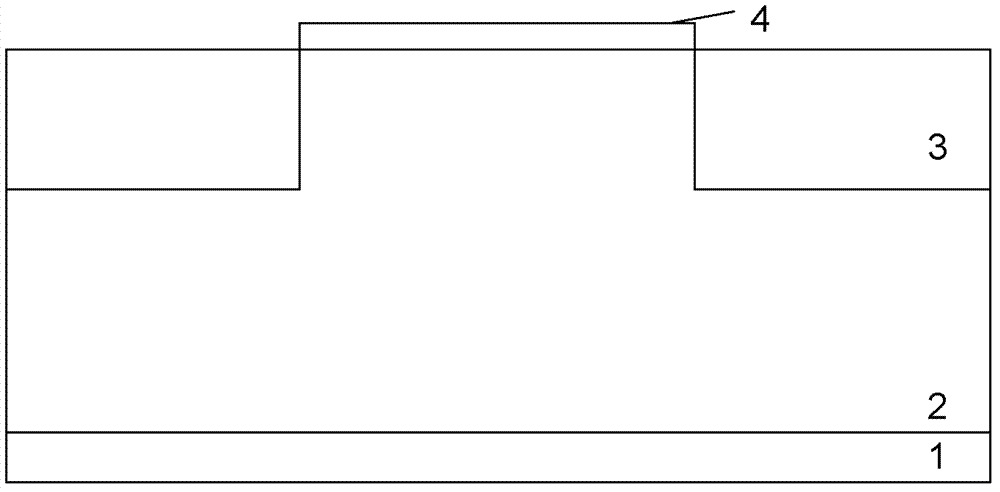

SOI (Silicon On Insulator)-BJT (Bipolar Junction Transistor) Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device with strain SiGe clip-shaped channel and preparation method thereof

InactiveCN102723339BHigh hole mobilityHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingP channelTin

The invention discloses a preparation method of an SOI (Silicon On Insulator)-BJT (Bipolar Junction Transistor) Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device with a strain SiGe clip-shaped channel and a circuit. The preparation process is as follows: preparing a buried layer on an SOI (Silicon On Insulator) substrate sheet, growing an N type Si epitaxy, preparing a deep-trench isolator, and manufacturing a conventional Si bipolar transistor in the bipolar device region; respectively and continuously growing an N type Si epitaxial layer, an N type strain SiGe layer and the like on the active regions of a substrate NMOS (N-Channel Metal Oxide Semiconductor) device and a substrate PMOS (P-Channel Metal Oxide Semiconductor) device at 600 DEG C-780 DEG C, and respectively preparing a drain electrode, a grid electrode and a source region on the active region of the NMOS device to prepare the NMOS device; depositing SiO2 and Poly-Si on the active region of the PMOS device to prepare a virtual grid electrode, depositing a medium layer to form a grid wall, injecting to form the source electrode and the drain electrode of the PMOS device; etching a virtual grid, depositing SiON and W-TiN to be respectively taken as a grid medium and a composite metal grid to prepare the PMOS device, and thus forming a Bi CMOS circuit. According to the preparation method, the characteristic that the electronic mobility of strain SiGe material in the vertical direction and the hole mobility of the strain SiGe material in the horizontal direction are higher than those of relaxation Si is utilized, and the SOI-BJT Bi CMOS integrated device with the strain SiGe clip-shaped channel and the circuit, which are enhanced in strength, are manufactured by a low-temperature process.

Owner:XIDIAN UNIV

Tri-strain tri-polycrystal-plane BiCMOS (Bipolar complementary metal oxide semiconductor) integrated device and preparation method thereof

InactiveCN102867824BImprove electrical performanceHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingElectrode ContactComposite grid

The invention discloses a tri-strain tri-polycrystal-plane BiCMOS (Bipolar complementary metal oxide semiconductor) integrated device and a preparation method thereof. The method comprises the following steps: preparing an embedded layer on a substrate plate, growing N-type Si epitaxy, preparing a deep channel isolator, preparing a collecting electrode contact area, preparing a base area and a transmission area, and forming a SiGe HBT (Heterojunction bipolar transistor) device; etching deep channels in the active areas of an NMOS (N-channel metal oxide semiconductor) device and a PMOS (P-channel metal oxide semiconductor) device, selectively epitaxially growing the following layers in the channel: a P-type Si layer, a P-type SiGe gradient layer, a P-type SiGe layer, a P-type strain Si layer as the active area of the NMOS device, an N-type Si layer, an N-type strain SiGe layer, and an N-type Si cap layer as the active area of the PMOS device; preparing a virtual grid, performing MOS (Metal oxide semiconductor) device light doped source / drain (LDD) injection, preparing a spacer, and self-aligning to form an MOS device source / drain; and etching the virtual grid, and sedimentating an SiON grid dielectric layer and a W-TiN composite grid to form a CMOS structure, and finally forming a BiCMOS circuit. According to the method, a tensile strain Si with high electron mobility and a compressive strain SiGe with high hole mobility are fully utilized as the conductive channels of the NMOS device and the PMOS device respectively, thus the performances of a BiCMOS integrated circuit are effectively improved.

Owner:XIDIAN UNIV

Vertical parasitic type precision navigation processor (PNP) device and manufacturing method thereof in bipolar complementary metal-oxide-semiconductor transistor (BiCMOS) technology

ActiveCN103066056BLarge current amplification factorImprove frequency characteristicsSemiconductor/solid-state device detailsSolid-state devicesOutput deviceBicmos technology

The invention discloses a vertical parasitic type precision navigation processor (PNP) device in bipolar complementary metal-oxide-semiconductor transistor (BiCMOS) technology. The vertical parasitic type PNP device in the BiCMOS technology comprises a collector region, a base region, an emitter region and an artifact buried layer. The artifact buried layer is formed on the bottom of shallow groove field oxide on two sides of the collector region, expands horizontally into an active region and contacts with the collector region. A collector is led out by contacting with a deep hole which is formed in the shallow groove field oxide on the top of the artifact buried layer. The emitter region is constituted of P type polycrystalline silicon which is formed on the upper portion of the base region, and the emitter region is placed on one side which deviates from the active region. Metallic contact in the base region is placed on the other side of the active region. The invention further discloses a manufacturing method of the vertical parasitic type PNP device in the BiCMOS technology. The vertical parasitic type PNP device in the BiCMOS technology can be used as an output device in a high speed and high gain (HG) BiCMOS circuit, and thus one more device option is supplied to circuits, the area of the device can be effectively reduced, the collector resistance of a PNP tube is decreased, and the performance of the device is improved. By means of the manufacturing method of the vertical parasitic type PNP device in the BiCMOS technology, extra technological conditions are of no need, and production cost can be lowered.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method for forming semiconductor structure

InactiveCN102054784AImprove leakageAvoid influenceSemiconductor/solid-state device manufacturingSemiconductor structureGate oxide

The invention relates to a method for forming semiconductor structure. The method comprises the following steps: providing a substrate, injecting ions into the substrate so as to form an n buried layer area, forming an n type epitaxial layer on the n buried layer area; forming a plurality of active areas and isolation areas in the n type epitaxial layer, forming an NSINK area on the active area in the n type epitaxial layer, communicating the NSINK area with the n buried layer area; forming a thickened gate-oxide layer on the surface of the epitaxial layer; injecting ions into the surface of the epitaxial layer covered by the gate-oxide layer; forming a gate polycrystalline layer covered by the gate-oxide layer on the surface of the epitaxial layer; injecting ions into the gate polycrystalline layer, forming a side wall on the side walls of the gate-oxide layer and the gate polycrystalline layer, forming an N well in the NSINK area, and injecting ions into the active area so as to form a P well. The invention can reduce the static leaked current of BiCMOS (Bipolar complementary metal oxide semiconductor) circuit.

Owner:CSMC TECH FAB1 +1

Vertical parasitic type precision navigation processor (PNP) device and manufacturing method thereof in bipolar complementary metal-oxide-semiconductor transistor (BiCMOS) technology

ActiveCN103066056ALarge current amplification factorImprove frequency characteristicsSemiconductor/solid-state device detailsSolid-state devicesEngineeringOutput device

The invention discloses a vertical parasitic type precision navigation processor (PNP) device in bipolar complementary metal-oxide-semiconductor transistor (BiCMOS) technology. The vertical parasitic type PNP device in the BiCMOS technology comprises a collector region, a base region, an emitter region and an artifact buried layer. The artifact buried layer is formed on the bottom of shallow groove field oxide on two sides of the collector region, expands horizontally into an active region and contacts with the collector region. A collector is led out by contacting with a deep hole which is formed in the shallow groove field oxide on the top of the artifact buried layer. The emitter region is constituted of P type polycrystalline silicon which is formed on the upper portion of the base region, and the emitter region is placed on one side which deviates from the active region. Metallic contact in the base region is placed on the other side of the active region. The invention further discloses a manufacturing method of the vertical parasitic type PNP device in the BiCMOS technology. The vertical parasitic type PNP device in the BiCMOS technology can be used as an output device in a high speed and high gain (HG) BiCMOS circuit, and thus one more device option is supplied to circuits, the area of the device can be effectively reduced, the collector resistance of a PNP tube is decreased, and the performance of the device is improved. By means of the manufacturing method of the vertical parasitic type PNP device in the BiCMOS technology, extra technological conditions are of no need, and production cost can be lowered.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

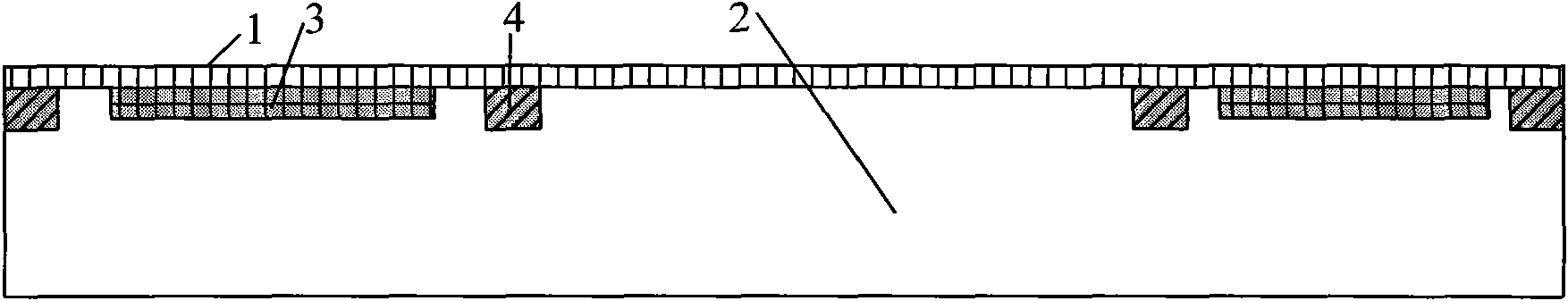

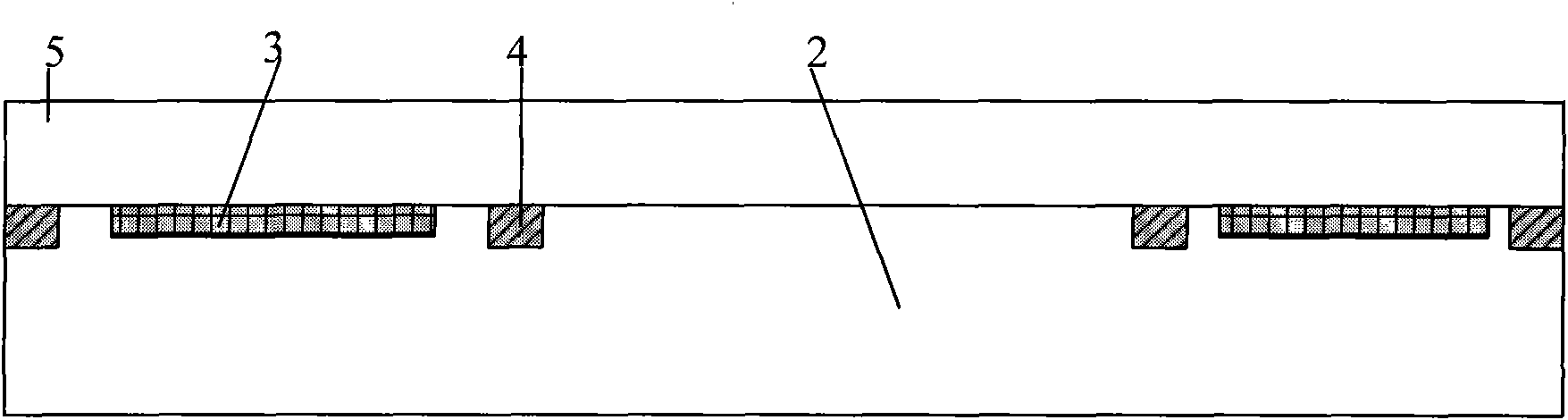

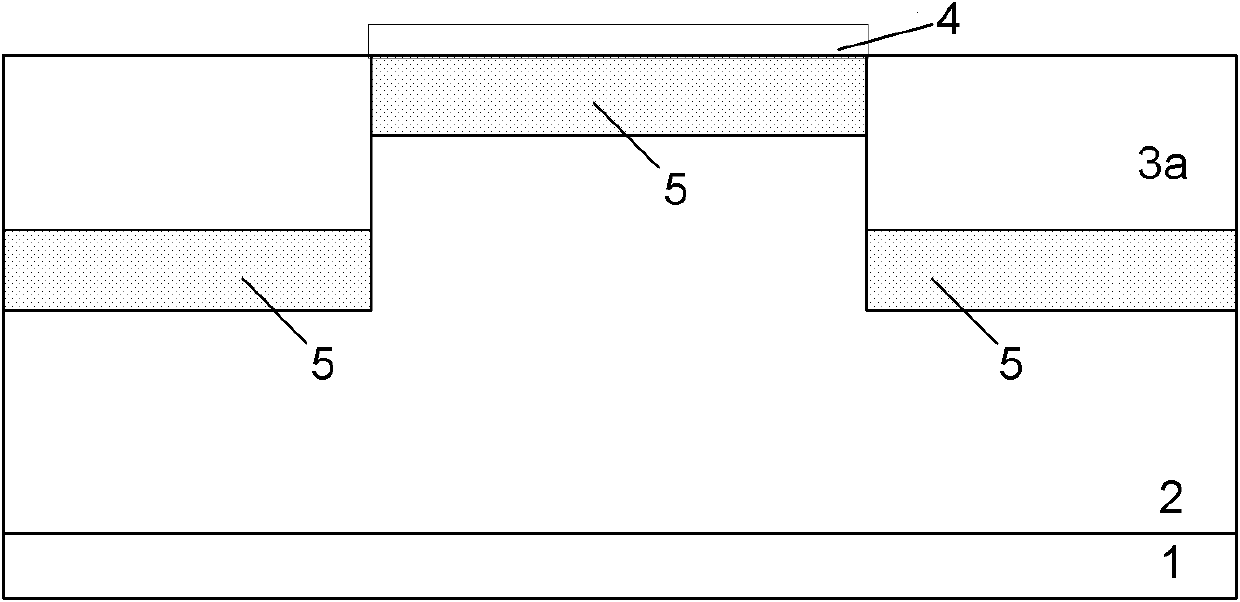

Method for producing a planar spacer, an associated bipolar transistor and an associated BiCMOS circuit arrangement

InactiveCN1977374AExcellent electrical propertiesEasy to implementSemiconductor/solid-state device manufacturingSemiconductor devicesAnisotropic etchingBicmos circuits

The invention relates to a method for producing a planar spacer, an associated bipolar transistor and an associated biCMOS circuit arrangement, wherein the first and second spacer layers (3, 4) are formed on a substrate (1) after a sacrifice mask (2) is formed and first and second spacer layers (3, 4) are embodied. In order to produce auxiliary spacers (4S) on the second spacer layer (4), a first anisotropic etching process is carried out. Afterwards, a second anisotropic etching process is carried out by means of the auxiliary spacers (4S) for producing a planar spacer (PS), thereby making it possible to freely select the height of the thus produced planar spacer (PS), wherein the planarity thereof very much simplifies the continuation of the process. The inventive method makes it possible to produce components exhibiting improved electric properties.

Owner:INFINEON TECH AG

Method for manufacturing monolithic polysilicon cantilever structure

InactiveCN102086019BSolve stickingAchieve monolithic integrationDecorative surface effectsSemiconductor/solid-state device manufacturingSignal processing circuitsGyroscope

The invention relates to a method for manufacturing a monolithic polysilicon cantilever structure. In the invention, a processing step of the polysilicon cantilever structure is inserted in a conventional BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) technical process, the deposition and the annealing of polysilicon are finished and an MEMS (Micro-Electro-Mechanical Systems) high-temperature process is prevented from influencing on the metalation process before the metalation process. In the release process of the polysilicon cantilever structure, a special etching solution is adopted, and a negative photoresist is used as a post of the polysilicon cantilever structure so as to effectively avoid the problem of substrate adhesion in the cantilever structure release process by using a wet method. The method provided by the invention solves the technical problems of compatibility between a manufacture process of the polysilicon cantilever structure and a processing process of a BiCMOS circuit, realizes the monolithic integration of the polysilicon cantilever structure and a BiCMOS signal processing circuit, and can be widely applied to the monolithic integration manufacture field of MEMS sensors, such as capacitive accelerometers, gyroscopes, and the like.

Owner:NO 24 RES INST OF CETC

Vertical parasitic PNP (plug-and-play) triode in BiCMOS (bipolar complementary metal oxide semiconductor) process and manufacturing method

ActiveCN102569371BLarge current amplification factorImprove frequency characteristicsTransistorSemiconductor/solid-state device manufacturingEngineeringBicmos circuits

The invention discloses a vertical parasitic PNP (plug-and-play) triode in a BiCMOS (bipolar complementary metal oxide semiconductor) process, a collector region is formed in a first active area; a pseudo buried layer is formed at the bottom of a shallow groove field oxide, transversely extends, enters into the first active area and is in contact with the collector region; the connection between the collector region and the adjacent active area is realized through the pseudo buried layer, and a collector is led out by forming metal contact at the top of the adjacent active area. N type polysilicon is formed at the upper part of a base region and a base is led out. An emitter region comprises a P type ion-implanted layer and a P type polysilicon formed above the base region. The invention further discloses a manufacturing method of the vertical parasitic PNP triode in the BiCMOS process. The vertical parasitic PNP triode disclosed by the invention can be used as an output device in a high-speed and high-gain BiCMOS circuit, one more device choice is provided for a circuit, the resistance of the collector of the PNP triode can be reduced, the frequency performance of the device can be improved, a polysilicon emitter can improve the gain of the device, and the production cost can also be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Vertical parasitic PNP device in BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor) process and preparation method thereof

ActiveCN102487077BLarge current amplification factorImprove frequency characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesOutput deviceOxygen

The invention discloses a vertical parasitic PNP device in a BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor) process. The vertical parasitic PNP device comprises a collector region, a base region, an emitter region, a P type buried layer and N type polycrystalline silicon, wherein the buried layer is formed at a shallow trench filed oxide bottom surrounding the collector region and is in contact with the collector region through a deep hole formed at the top of the buried layer to lead out a collector electrode; the N type polycrystalline silicon is formed at the upper part of the base region and is used for leading out a base electrode; and the emitter region is composed of a P type shallow junction formed in the base region and P type polycrystalline silicon arranged above the base region. The invention also discloses a preparation method of the vertical parasitic PNP device in the BiCMOS process. The device disclosed by the invention can serve as an output device in a high-speed high-gain BiCMOS circuit, and therefore another device choice is provided for the circuit. According to the invention, the area of the device can be reduced effectively, the resistance of the collector electrode of a PNP transistor can be lowered, the frequency performance of the device can be improved and the gain of the device can be enhanced. No extra process condition is required in the preparation method disclosed by the invention, thereby reducing the production cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Vertical parasitic type precision navigation processor (PNP) device and manufacturing method thereof in bipolar complementary metal-oxide-semiconductor transistor (BiCMOS) technology

ActiveCN103066057ALarge current amplification factorImprove frequency characteristicsSemiconductor/solid-state device detailsSolid-state devicesOutput deviceP type silicon

The invention discloses a vertical parasitic type precision navigation processor (PNP) device in bipolar complementary metal-oxide-semiconductor transistor (BiCMOS) technology. The vertical parasitic type PNP device in the BiCMOS technology comprises a collector region, a base region, an emitter region and an artifact buried layer. The artifact buried layer is formed on the bottom of shallow groove field oxide on two sides of the collector region, expands horizontally into an active region and contacts with the collector region. A collector is led out by contacting with a deep hole which is formed in the shallow groove field oxide on the top of the artifact buried layer. The emitter region is constituted of a P type silicon epitaxy epitaxial layer which is formed on the upper portion of the base region, and the emitter region is placed on one side which deviates from the center of the active region. N type polycrystalline silicon which is placed on the other side of the active region is arranged at a leading-out end of the base region. The invention further discloses a manufacturing method of the vertical parasitic type PNP device in the BiCMOS technology. The vertical parasitic type PNP device in the BiCMOS technology can be used as an output device in a high speed and high gain (HG) BiCMOS circuit, and thus one more device option is supplied to circuits, the area of the device can be effectively reduced, the collector resistance of a PNP tube is decreased, and the performance of the device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

SOI (Silicon On Insulator)-BJT (Bipolar Junction Transistor) Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device with strain SiGe clip-shaped channel and preparation method thereof

InactiveCN102723339AAchieve anisotropyImprove mobilitySolid-state devicesSemiconductor/solid-state device manufacturingP channelTin

The invention discloses a preparation method of an SOI (Silicon On Insulator)-BJT (Bipolar Junction Transistor) Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device with a strain SiGe clip-shaped channel and a circuit. The preparation process is as follows: preparing a buried layer on an SOI (Silicon On Insulator) substrate sheet, growing an N type Si epitaxy, preparing a deep-trench isolator, and manufacturing a conventional Si bipolar transistor in the bipolar device region; respectively and continuously growing an N type Si epitaxial layer, an N type strain SiGe layer and the like on the active regions of a substrate NMOS (N-Channel Metal Oxide Semiconductor) device and a substrate PMOS (P-Channel Metal Oxide Semiconductor) device at 600 DEG C-780 DEG C, and respectively preparing a drain electrode, a grid electrode and a source region on the active region of the NMOS device to prepare the NMOS device; depositing SiO2 and Poly-Si on the active region of the PMOS device to prepare a virtual grid electrode, depositing a medium layer to form a grid wall, injecting to form the source electrode and the drain electrode of the PMOS device; etching a virtual grid, depositing SiON and W-TiN to be respectively taken as a grid medium and a composite metal grid to prepare the PMOS device, and thus forming a Bi CMOS circuit. According to the preparation method, the characteristic that the electronic mobility of strain SiGe material in the vertical direction and the hole mobility of the strain SiGe material in the horizontal direction are higher than those of relaxation Si is utilized, and the SOI-BJT Bi CMOS integrated device with the strain SiGe clip-shaped channel and the circuit, which are enhanced in strength, are manufactured by a low-temperature process.

Owner:XIDIAN UNIV

Vertical parasitic PNP device in BiCMOS technology and manufacturing method

ActiveCN102569370BImprove frequency characteristicsReduce areaTransistorSemiconductor/solid-state device manufacturingOutput deviceEngineering

The invention discloses a vertical parasitic PNP device in the BiCMOS technology, which includes a current collection region, a base region, an emitter region, a pseudo buried layer and an N-type polycrystalline silicon, wherein the pseudo buried layer is formed at shallow slot field oxide bottoms on the two sides of the current collection region, transversely extends to an active region, is contacted with the current collection region, and forms deep hole contact in the shallow slot field oxide at the top of the pseudo buried layer to lead out collector electrodes; the emitter region is formed in a P-type ion injection region at the upper part of the base region; and the N-type polycrystalline silicon is formed at the upper part of the base region, is contacted with the base region, and leads out base electrodes through metal contacts connected with the N-type polycrystalline silicon. The invention further discloses a manufacturing method for the vertical parasitic PNP device in the BiCMOS technology. The device provided by the invention can be used as an output device in a high-speed and high-gain BiCMOS circuit, can effectively reduce the area as well as the resistance of the collector electrodes of a PNP tube, and improve the performance. The method provided by the invention needs no additional technology condition, and can reduce the manufacturing cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Vertical parasitic PNP device in BiCMOS technology and manufacturing method

ActiveCN102569370AImprove frequency characteristicsReduce areaTransistorSemiconductor/solid-state device manufacturingEngineeringOutput device

The invention discloses a vertical parasitic PNP device in the BiCMOS technology, which includes a current collection region, a base region, an emitter region, a pseudo buried layer and an N-type polycrystalline silicon, wherein the pseudo buried layer is formed at shallow slot field oxide bottoms on the two sides of the current collection region, transversely extends to an active region, is contacted with the current collection region, and forms deep hole contact in the shallow slot field oxide at the top of the pseudo buried layer to lead out collector electrodes; the emitter region is formed in a P-type ion injection region at the upper part of the base region; and the N-type polycrystalline silicon is formed at the upper part of the base region, is contacted with the base region, and leads out base electrodes through metal contacts connected with the N-type polycrystalline silicon. The invention further discloses a manufacturing method for the vertical parasitic PNP device in the BiCMOS technology. The device provided by the invention can be used as an output device in a high-speed and high-gain BiCMOS circuit, can effectively reduce the area as well as the resistance of the collector electrodes of a PNP tube, and improve the performance. The method provided by the invention needs no additional technology condition, and can reduce the manufacturing cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP