Method for forming semiconductor structure

A semiconductor and graphics technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as large leakage current, high power consumption, and large leakage, so as to save manufacturing costs, do not change the chip area, and save costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

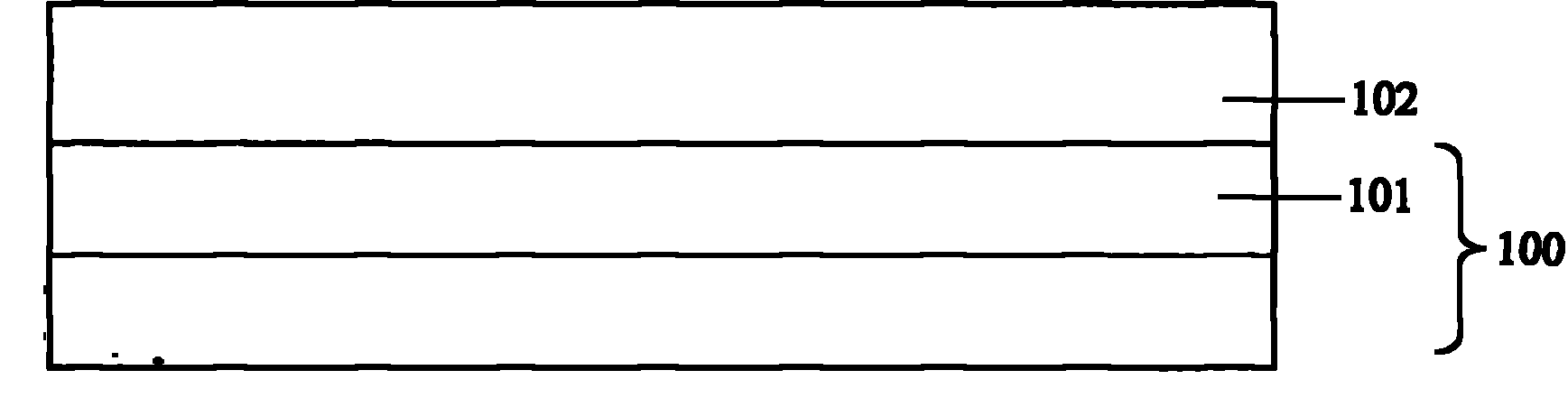

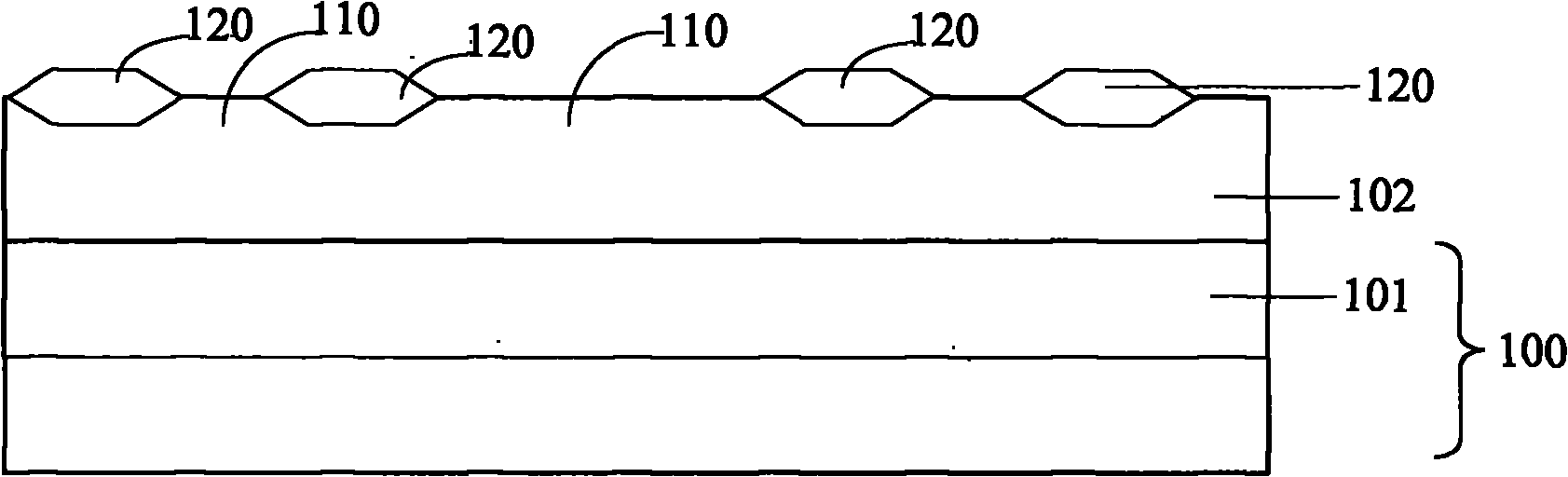

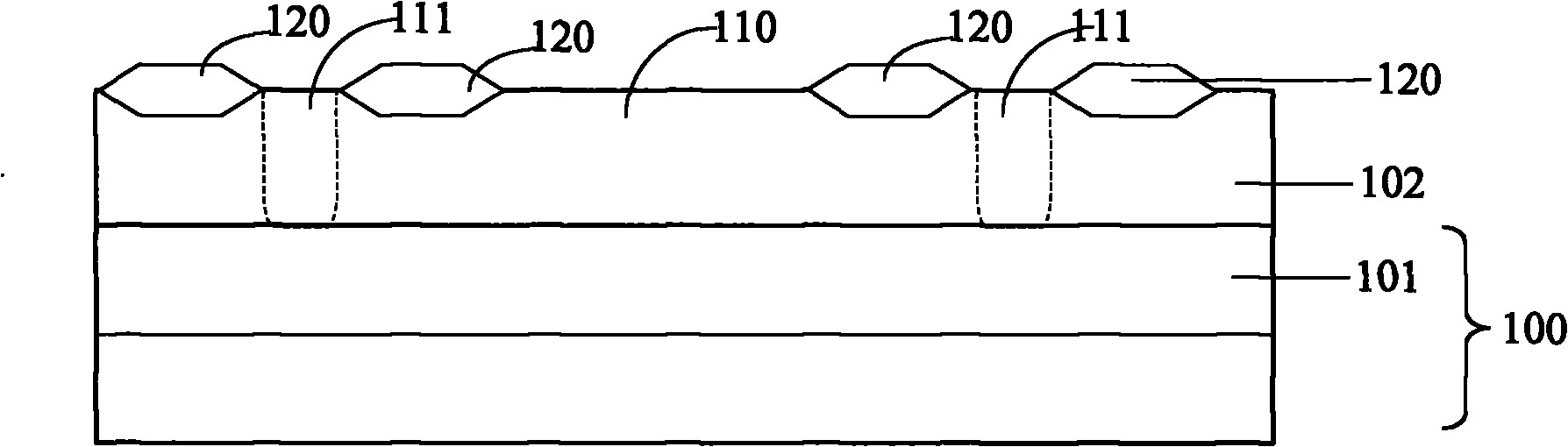

[0016] It can be seen from the background technology that the leakage current of the lateral PNP structure in the existing BiCMOS is relatively large, especially at the process node of 0.5um, the leakage current of the existing PNP structure can reach dozens of nanoamps when the applied voltage is 5V, resulting in the static state of the entire BiCMOS circuit. The leakage current is large, the power consumption is high, and even the entire BiCMOS circuit cannot work normally in severe cases. Usually, the resistivity of the epitaxial layer is adjusted in the process of forming BiCMOS, specifically by adjusting the doping that is generally implanted on the epitaxial layer. Concentration to improve the phenomenon of relatively large leakage in the lateral PNP structure. Another improvement method is to adjust the concentration of the base region of the lateral PNP structure by adding a photolithography process and an implantation process. In addition, the existing process will also...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More