Method for producing a planar spacer, an associated bipolar transistor and an associated BiCMOS circuit arrangement

A bipolar transistor and spacer technology, applied in circuits, semiconductor/solid-state device manufacturing, electrical components, etc., to achieve cost-effective, improved electrical characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The following diagrammatic description illustrates the concept of producing a planar spacer according to the present invention, especially when a planar spacer is used in bipolar transistors and related BiCMOS circuit devices.

[0024] In particular, the sacrificial mask is used as implant hardmask and foundation, so that planar spacers can be formed in a self-adjusting manner to connect multiple regions with one region as close as possible, which will be later Explain, for example, the intrinsic base of a single-multiple bipolar transistor.

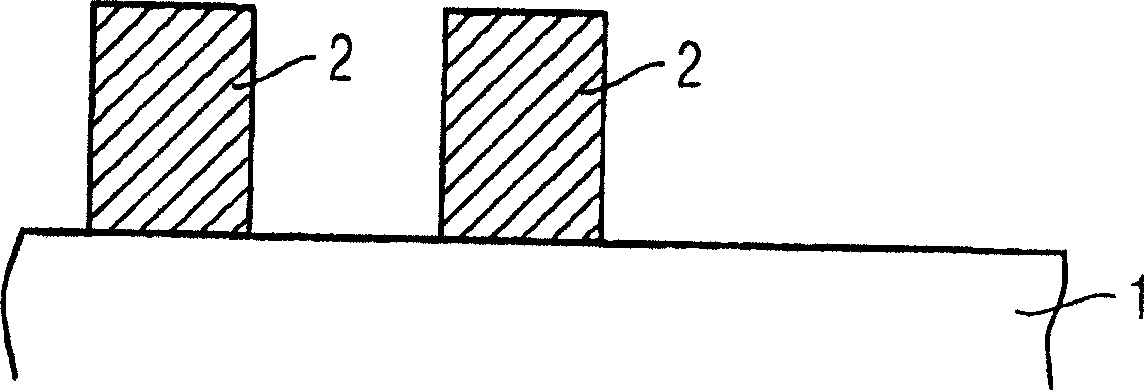

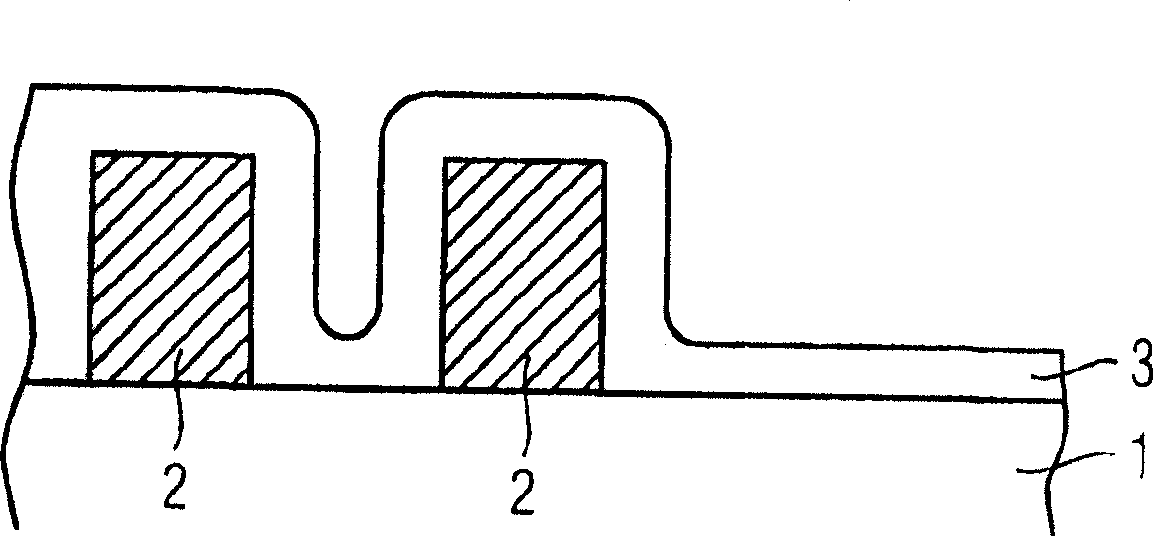

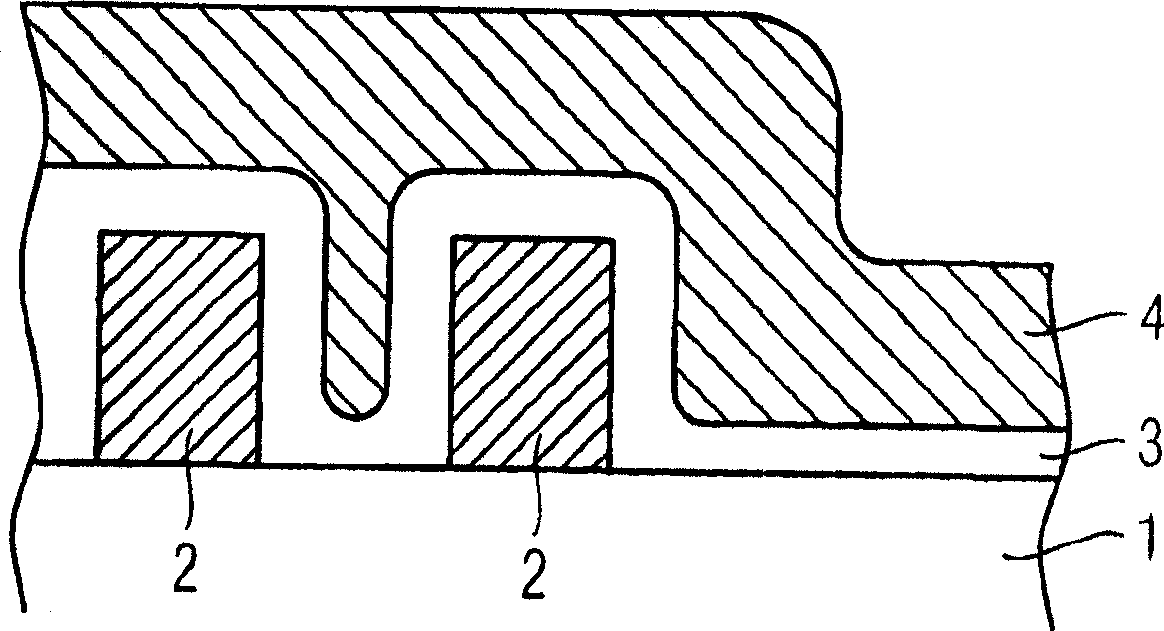

[0025] First, the method of producing a planar spacer according to the present invention, especially the method of producing a planar outer spacer, will be referred to Figure 1A-1F Be explained. Hereinafter, the term "planar outer spacer" means a substantially flat planar spacer formed on the sidewall of the mask pillar.

[0026] Such as Figure 1A As shown, first a sacrificial mask 2 is formed on the mounting substrate 1, for ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More