Method for producing a planar spacer, an associated bipolar transistor and an associated BiCMOS circuit arrangement

A technology of bipolar transistors and spacers, applied in circuits, semiconductor/solid-state device manufacturing, electrical components, etc., to achieve cost-effective and improved electrical characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

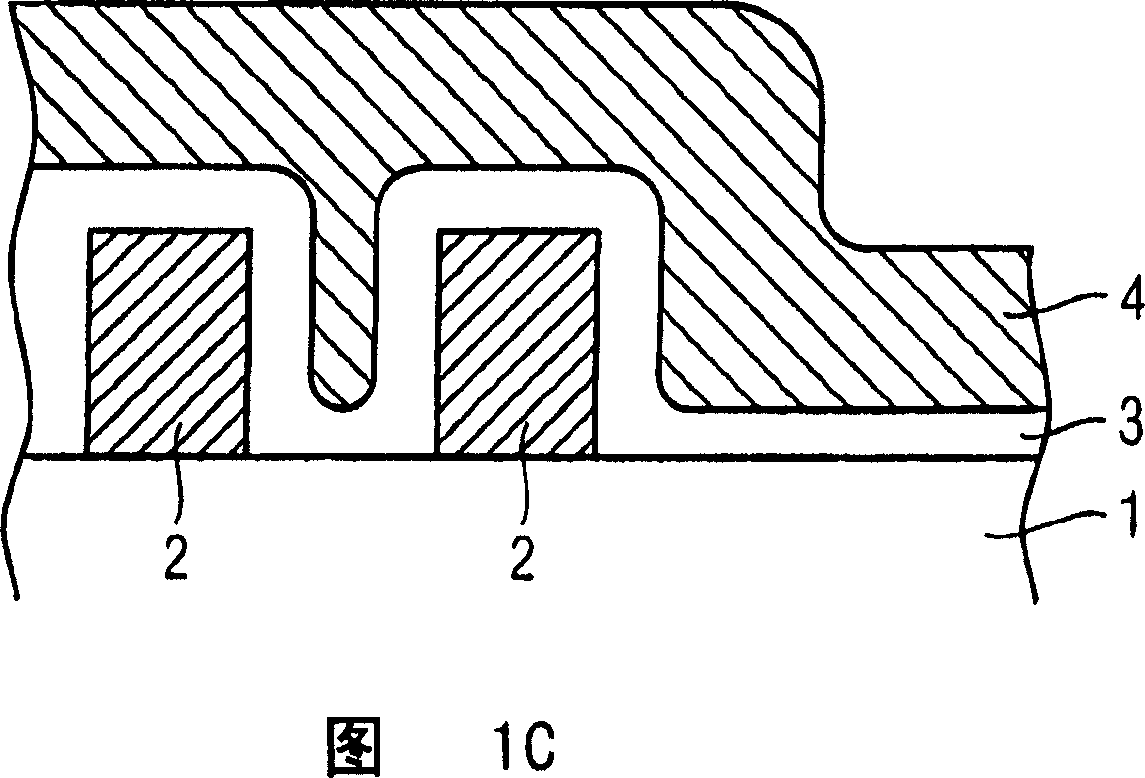

[0023] The following diagrammatic description illustrates the concept of producing a planar spacer according to the present invention, especially when a planar spacer is used in bipolar transistors and related BiCMOS circuit devices.

[0024] In particular, the sacrificial mask is used as implant hardmask and foundation, so that planar spacers can be formed in a self-adjusting manner to connect multiple regions with one region as close as possible, which will be later Explain, for example, the intrinsic base of a single-multiple bipolar transistor.

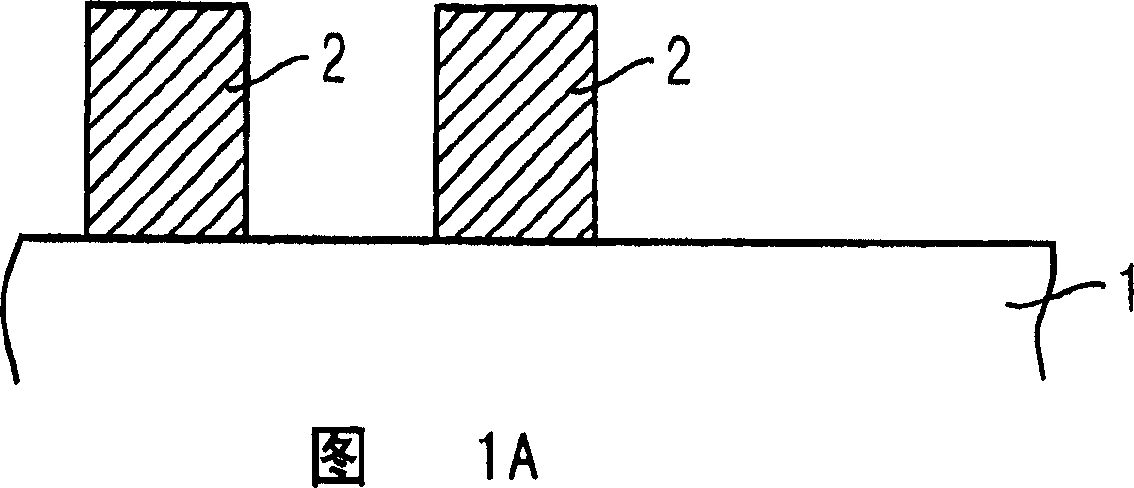

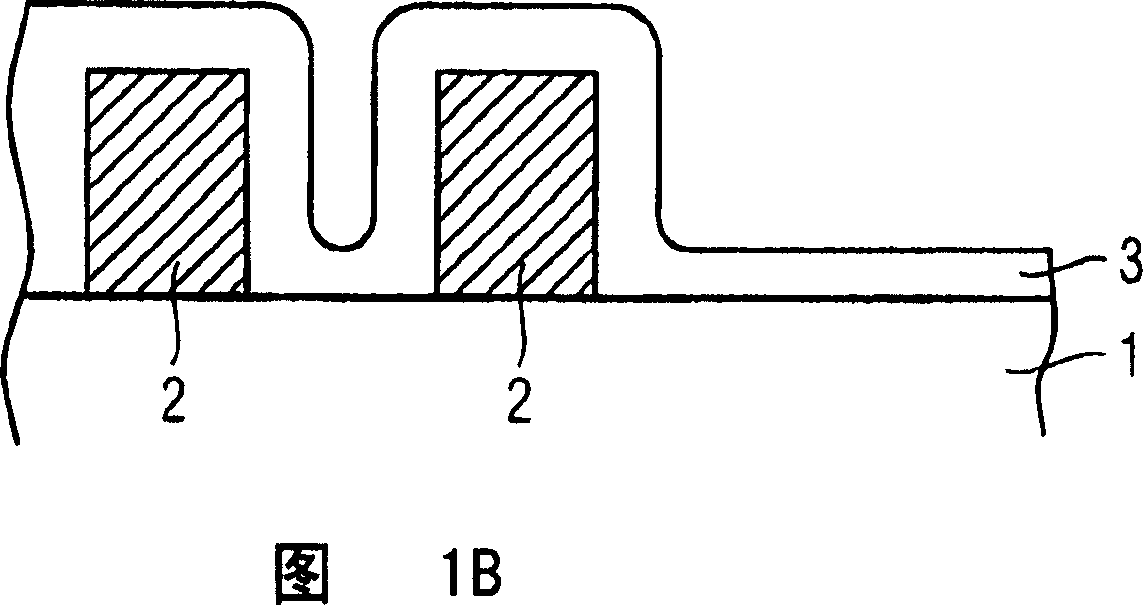

[0025] First, a method of producing a planar spacer, particularly a method of producing a planar outer spacer according to the present invention will be described with reference to FIGS. 1A to 1F. Hereinafter, the term "planar outer spacer" means a substantially flat planar spacer formed on the sidewall of the mask pillar.

[0026] As shown in Figure 1A, firstly a sacrificial mask 2 is formed on the mounting substrate 1, such as ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More