Tri-strain tri-polycrystal-plane BiCMOS (Bipolar complementary metal oxide semiconductor) integrated device and preparation method thereof

An integrated device and three-strain technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as incompatibility, complicated preparation process, and poor heat dissipation performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

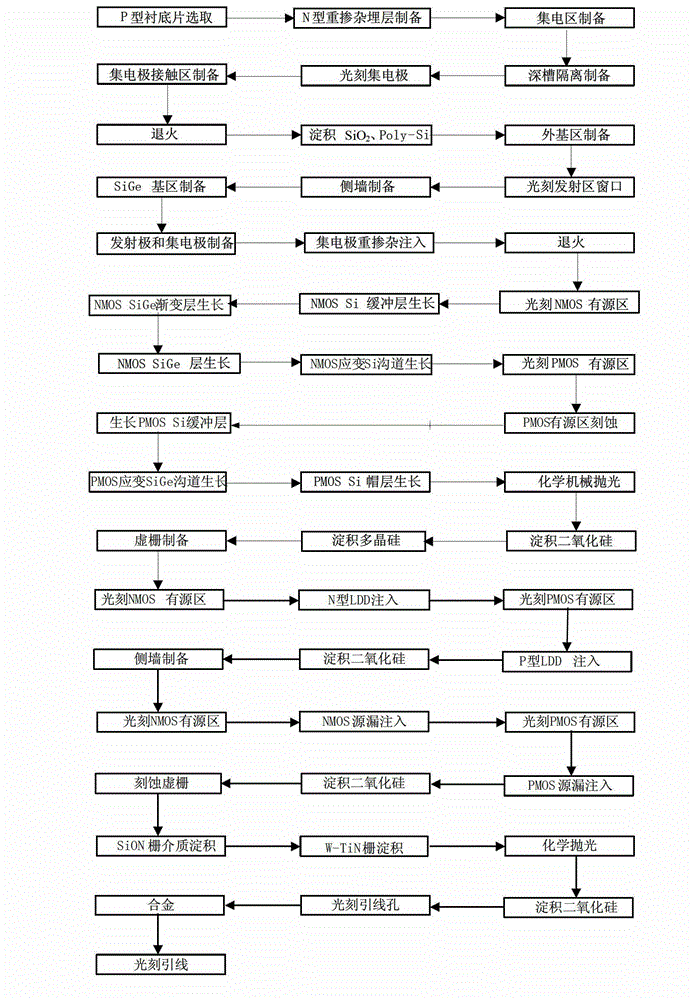

Image

Examples

Embodiment 1

[0124] Embodiment 1: Preparation of a three-strain, three-polycrystalline planar BiCMOS integrated device and circuit with a 45nm conductive channel, the specific steps are as follows:

[0125] Step 1, epitaxial growth.

[0126] (1a) Choose the doping concentration as 5×10 14 cm -3 P-type Si wafer as the substrate;

[0127] (1b) Thermally oxidize a layer of SiO with a thickness of 300nm on the surface of the substrate 2 Floor;

[0128] (1c) Photoetching the buried region, implanting N-type impurities in the buried region, and annealing at 800°C for 90 min to activate the impurities to form an N-type heavily doped buried region.

[0129] Step 2. Preparation of isolation area.

[0130] (2a) Remove the excess oxide layer on the surface, and epitaxially grow a layer with a doping concentration of 1×10 16 cm -3 The Si layer with a thickness of 2μm serves as a collector area;

[0131] (2b) Thermally oxidize a layer of SiO with a thickness of 300nm on the surface of the substrate 2 Floor;

[0132...

Embodiment 2

[0193] Embodiment 2: Preparation of a three-strain, three-polycrystalline planar BiCMOS integrated device and circuit with a conductive channel of 30 nm, the specific steps are as follows:

[0194] Step 1, epitaxial growth.

[0195] (1a) Choose the doping concentration as 1×10 15 cm -3 P-type Si wafer as the substrate;

[0196] (1b) Thermally oxidize a layer of SiO with a thickness of 400nm on the surface of the substrate 2 Floor;

[0197] (1c) Photoetching the buried region, implanting N-type impurities in the buried region, and annealing at 900°C for 60 minutes to activate the impurities to form an N-type heavily doped buried region.

[0198] Step 2. Preparation of isolation area.

[0199] (2a) Remove the excess oxide layer on the surface, and epitaxially grow a layer with a doping concentration of 5×10 16 cm -3 The Si layer with a thickness of 2.5μm is used as a collector area;

[0200] (2b) Thermally oxidize a layer of SiO with a thickness of 400nm on the surface of the substrate 2 Fl...

Embodiment 3

[0262] Embodiment 3: Preparation of a three-strain, three-polycrystalline planar BiCMOS integrated device and circuit with a 22nm conduction channel, the specific steps are as follows:

[0263] Step 1, epitaxial growth.

[0264] (1a) Choose the doping concentration as 5×10 15 cm -3 P-type Si wafer as the substrate;

[0265] (1b) Thermal oxidation of a layer of SiO with a thickness of 500nm on the surface of the substrate 2 Floor;

[0266] (1c) Photoetching the buried region, implanting N-type impurities in the buried region, and annealing at 950°C for 30 minutes to activate the impurities to form an N-type heavily doped buried region.

[0267] Step 2. Preparation of isolation area.

[0268] (2a) Remove the excess oxide layer on the surface, and epitaxially grow a layer with a doping concentration of 1×10 17 cm -3 The Si layer with a thickness of 3μm is used as a collector area;

[0269] (2b) Thermally oxidize a layer of SiO with a thickness of 500nm on the surface of the substrate 2 Floor...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More