Patents

Literature

184 results about "Bicmos process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

BiCMOS process is essentially a combination of Bipolar transistor and CMOS transistors, it offers many technical advantages and some semiconductor foundries still provide access to BiCMOS technology. Besides having BiCMOS wafer production as an ongoing business they also have a clear roadmap to develop more advanced nodes...

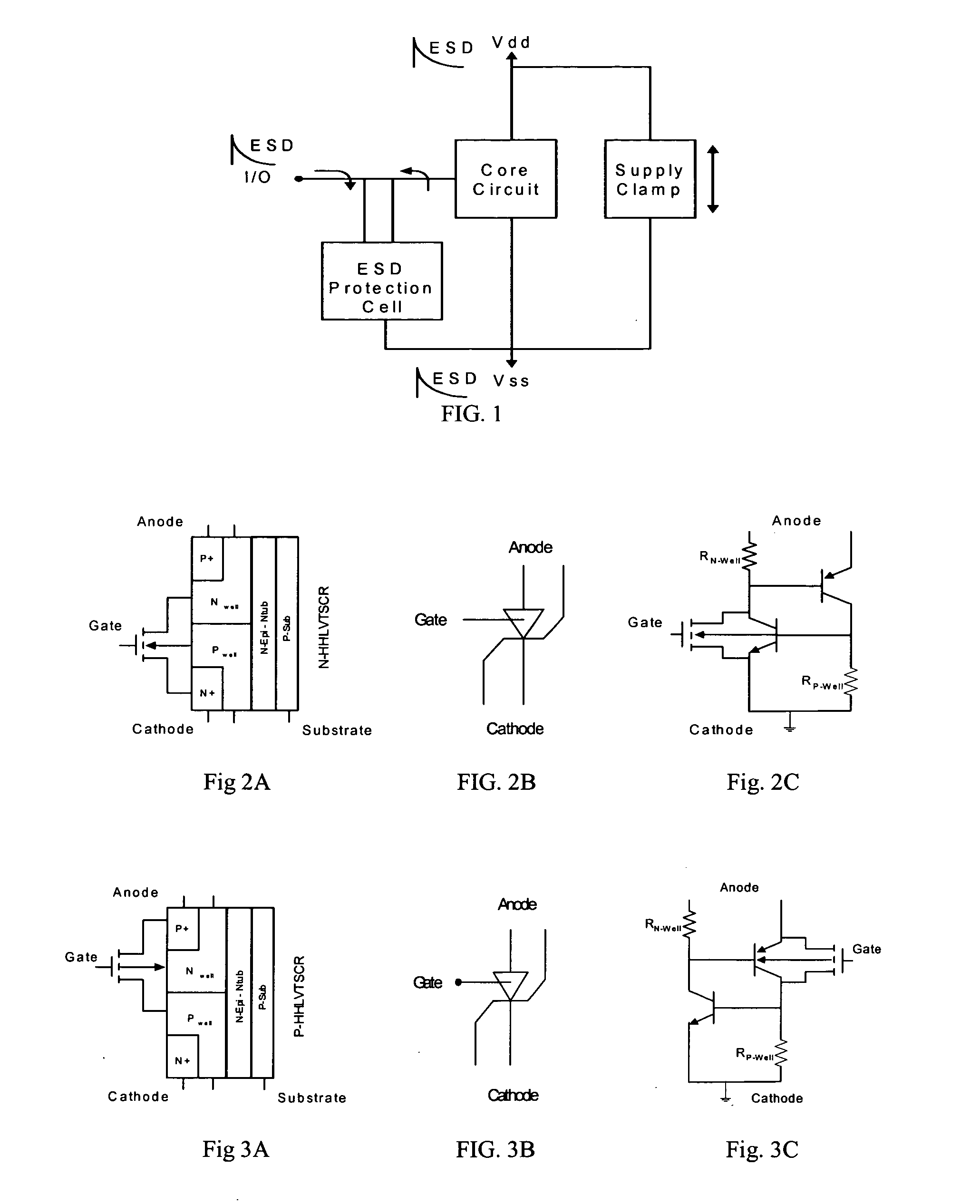

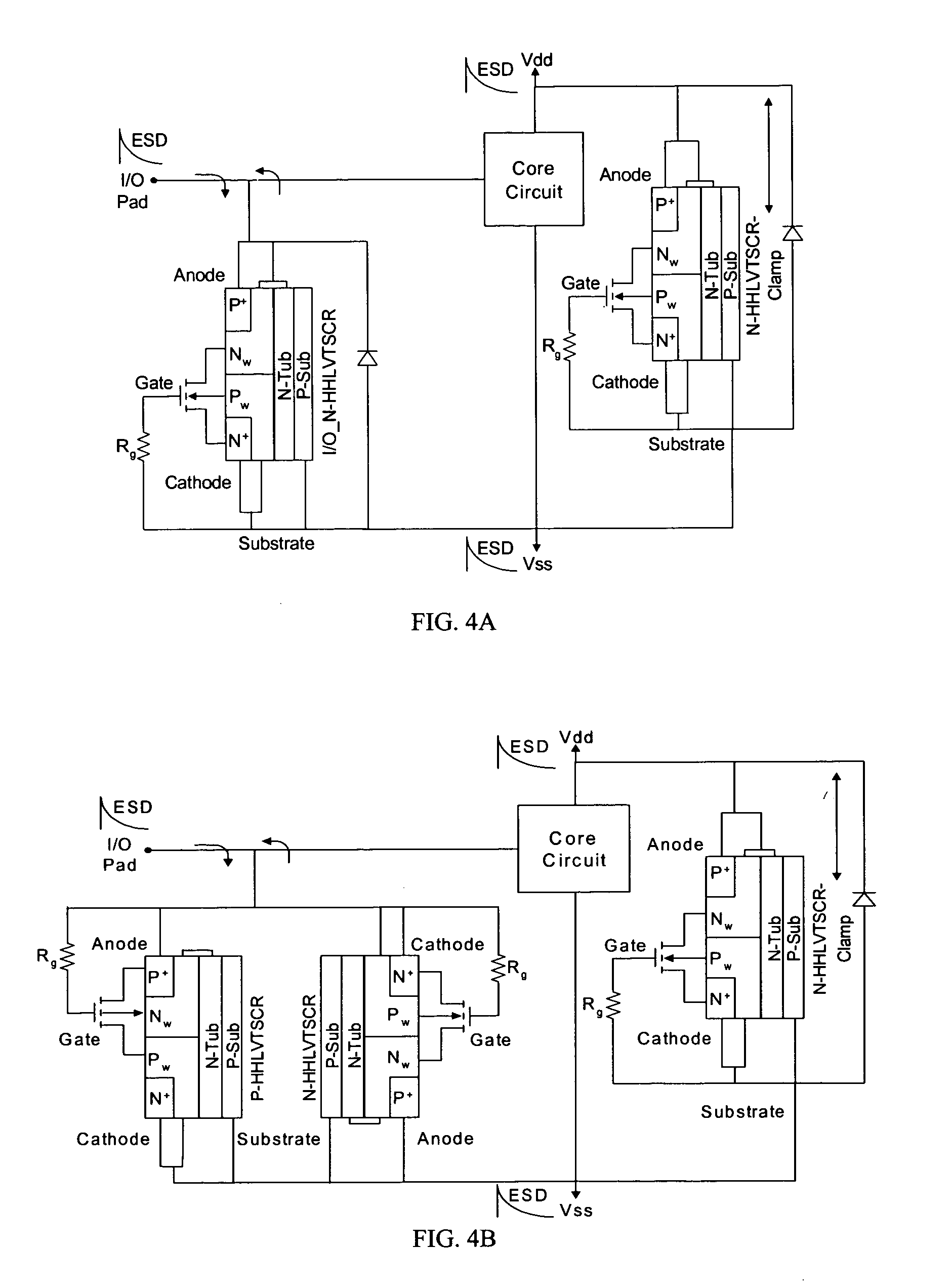

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

InactiveUS20070007545A1Impaired immunityHigh protection levelTransistorThyristorNon symmetricTransmission-line pulse

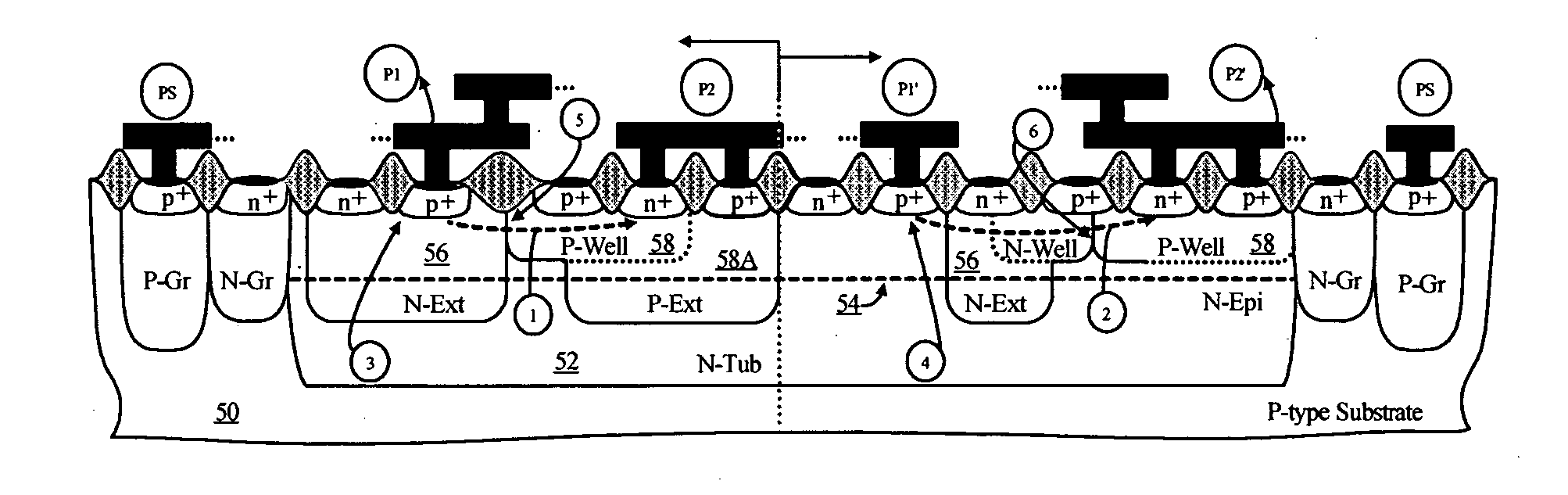

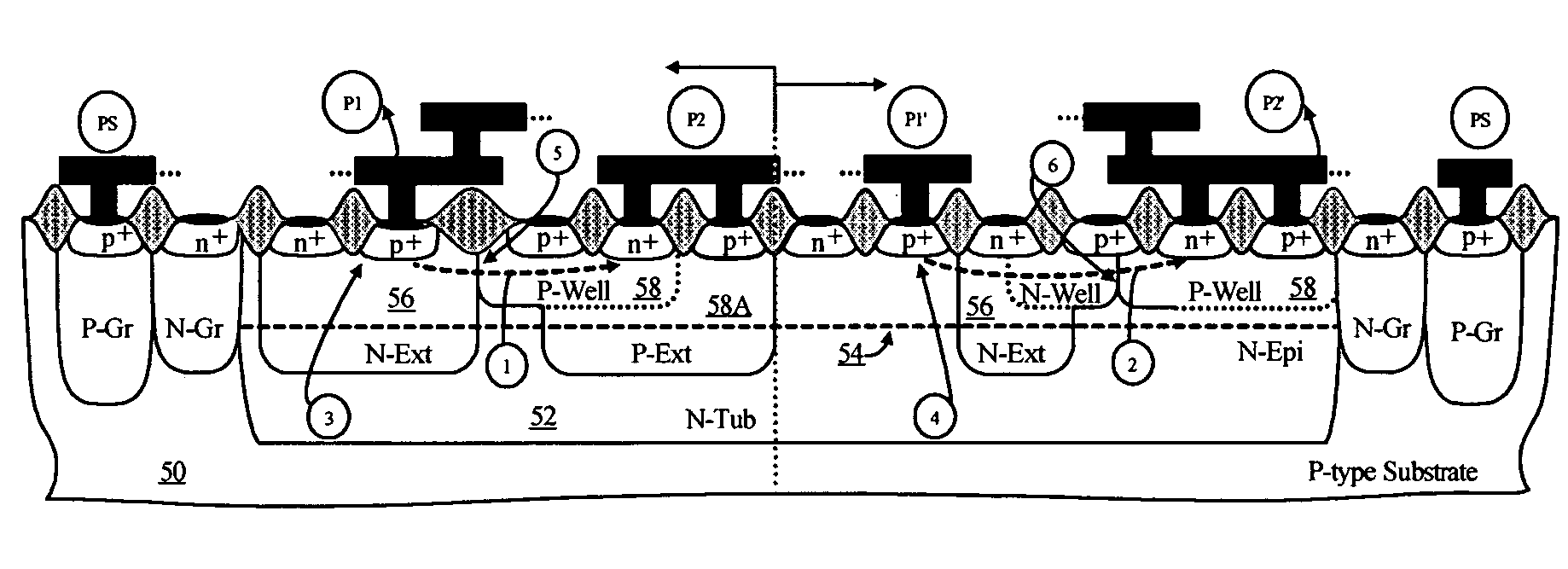

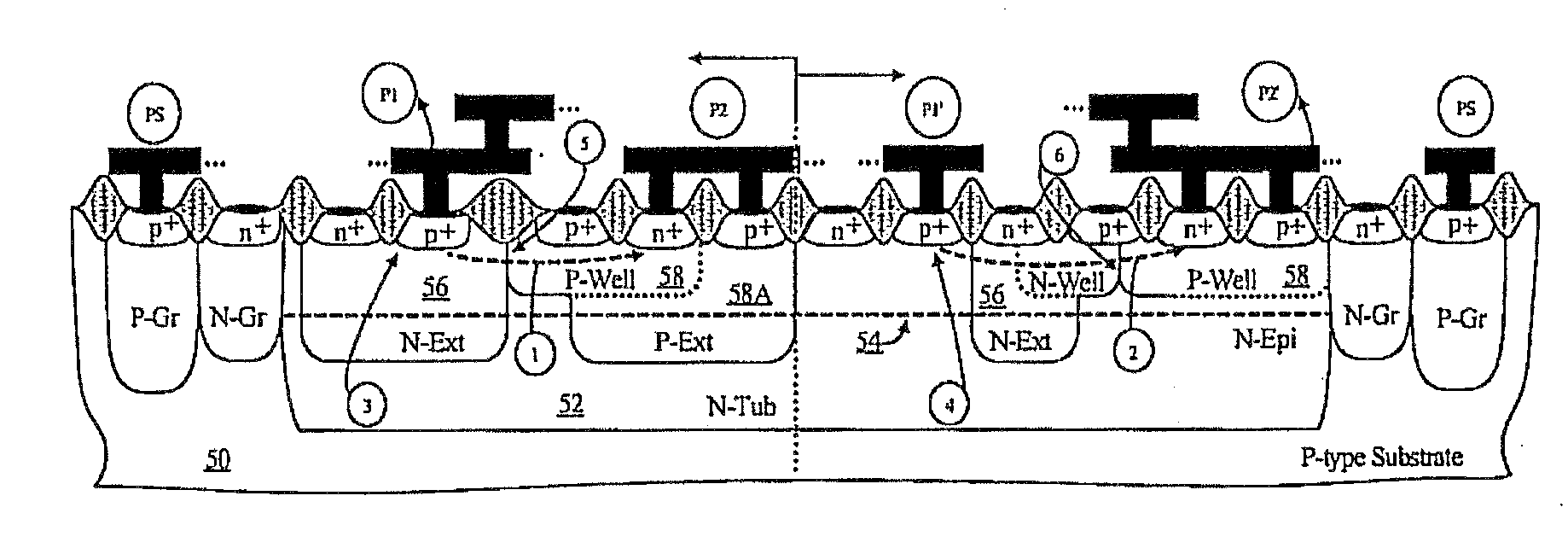

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

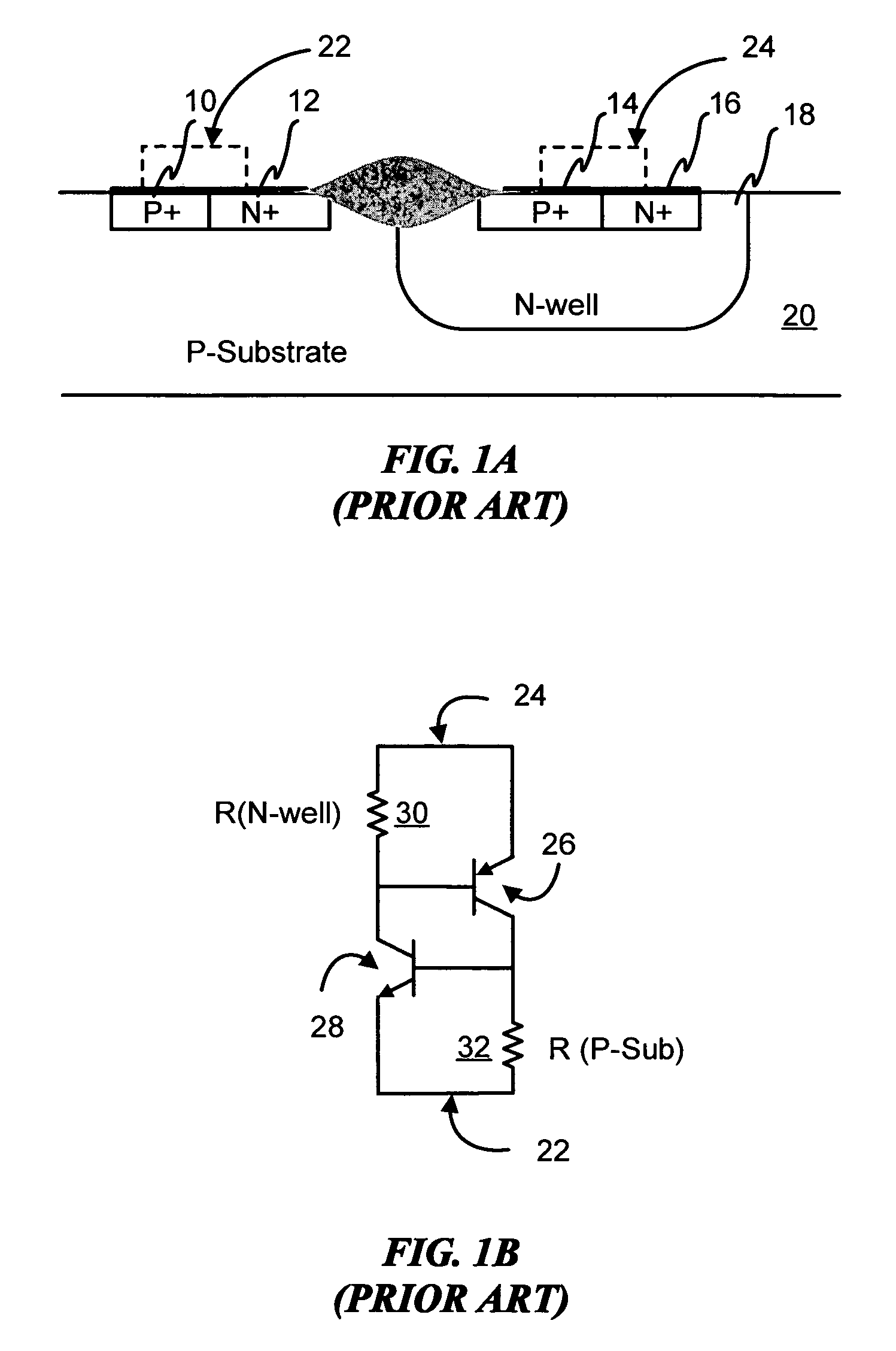

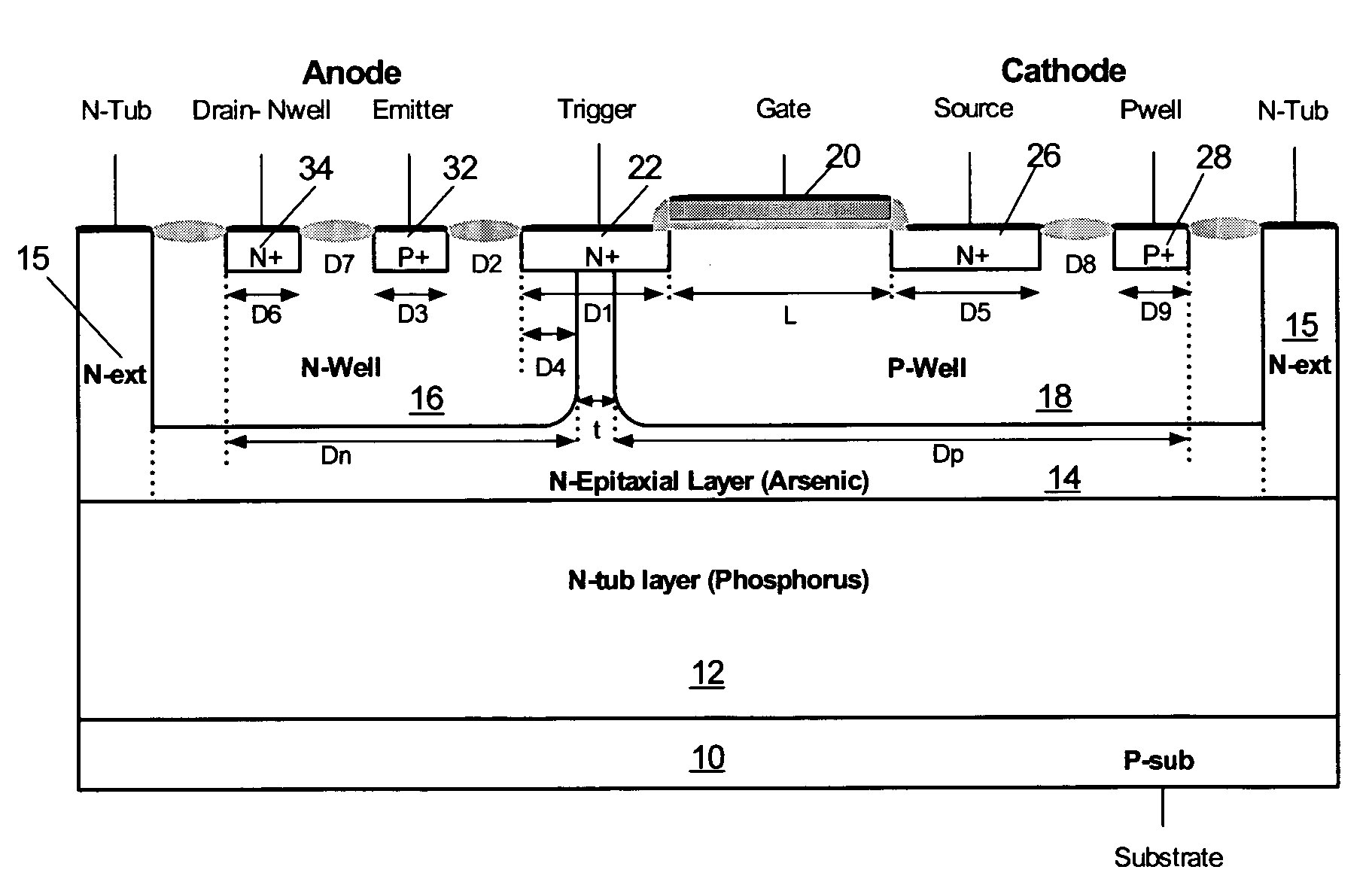

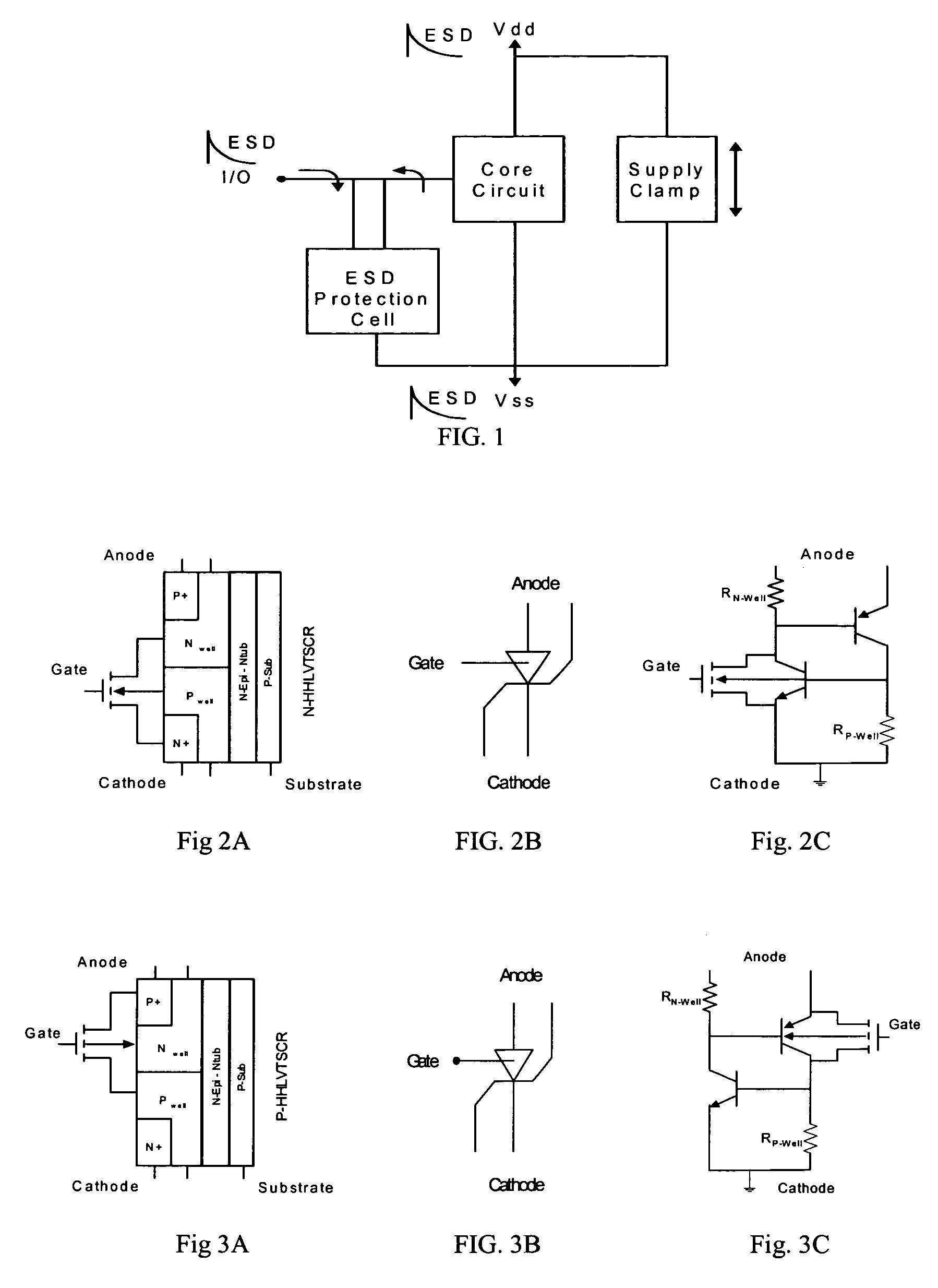

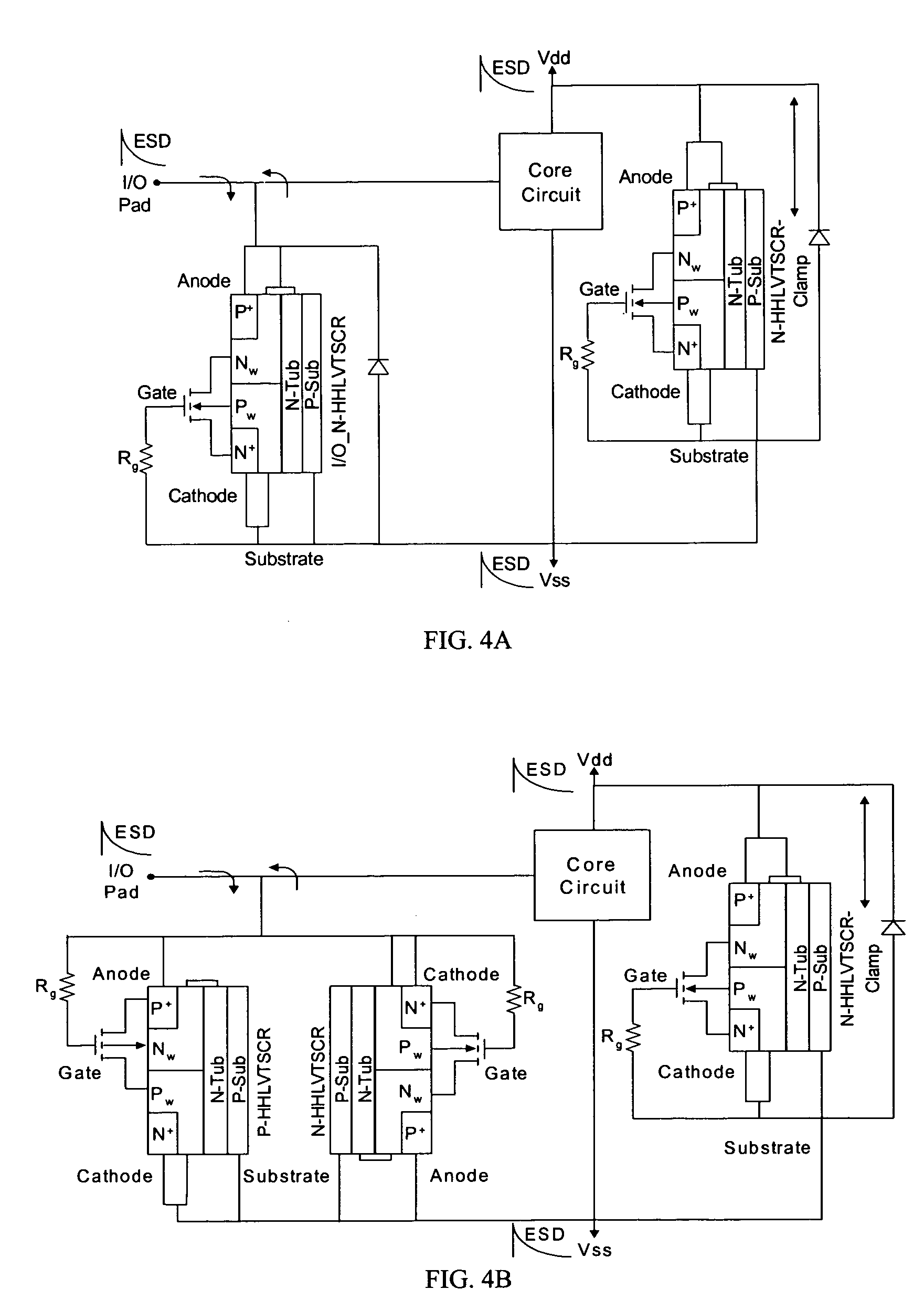

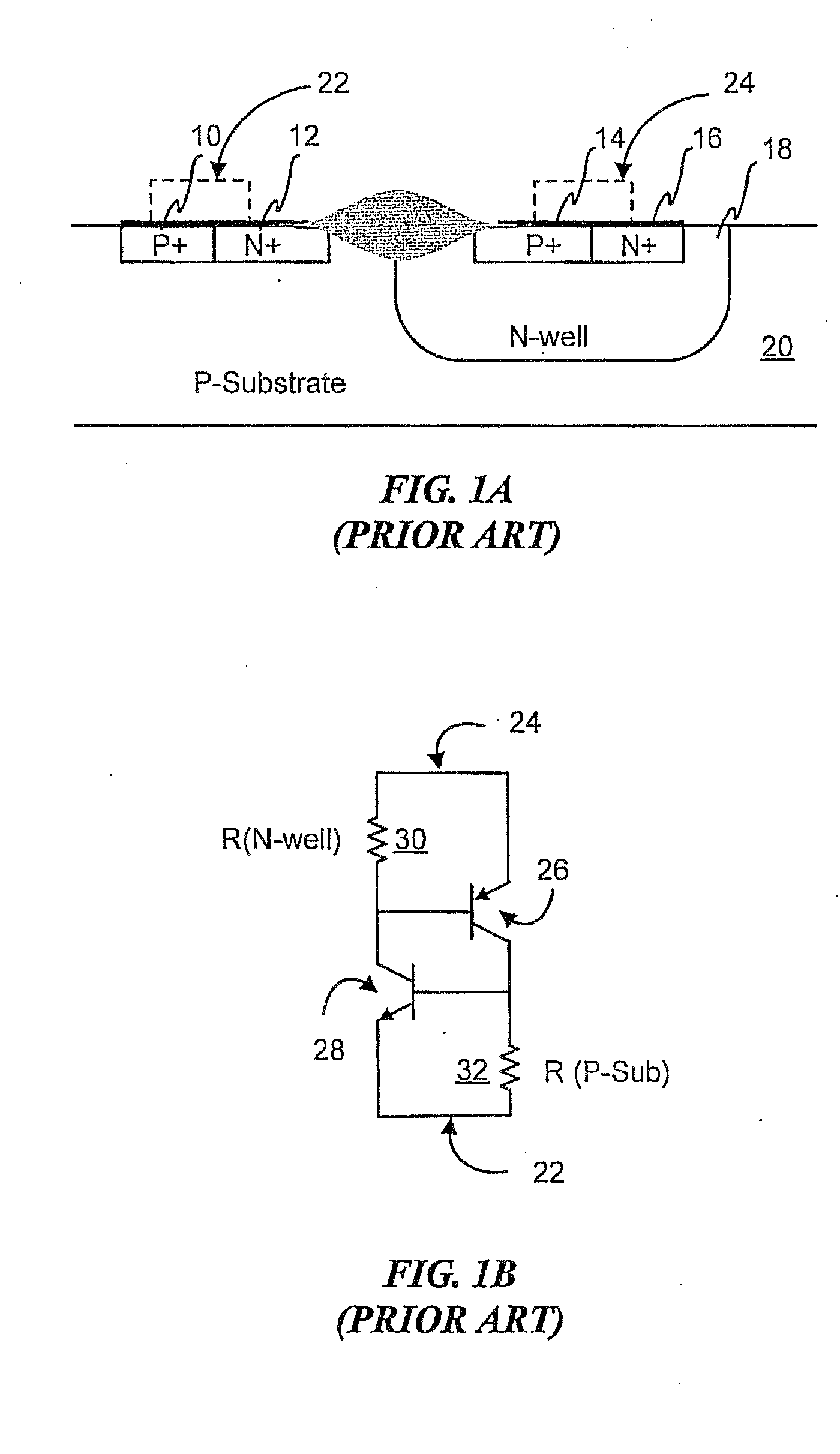

On-chip structure for electrostatic discharge (ESD) protection

InactiveUS20050151160A1Efficient and reliableRobust and ESD protectionTransistorSemiconductor/solid-state device detailsCMOSLow voltage

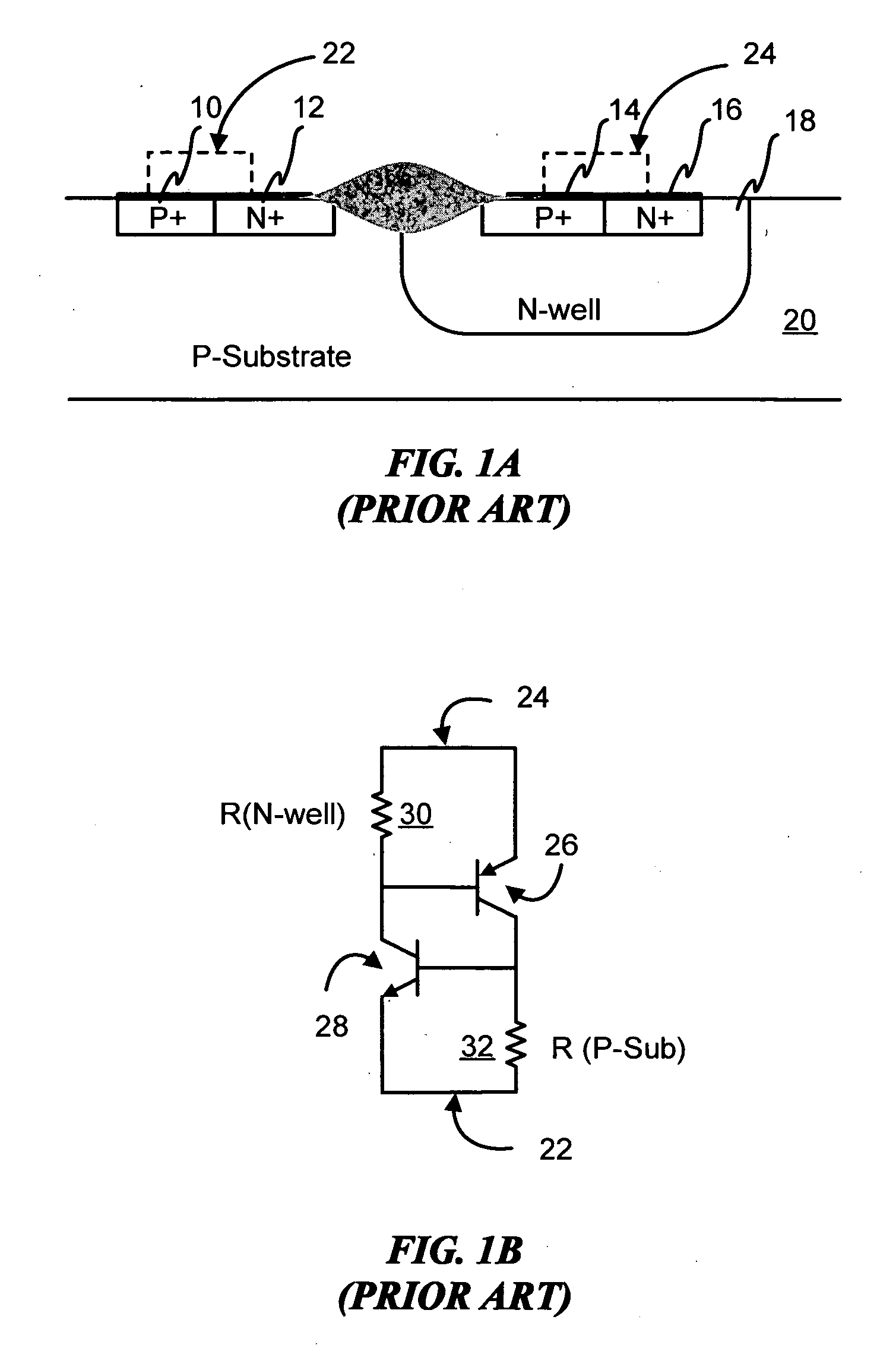

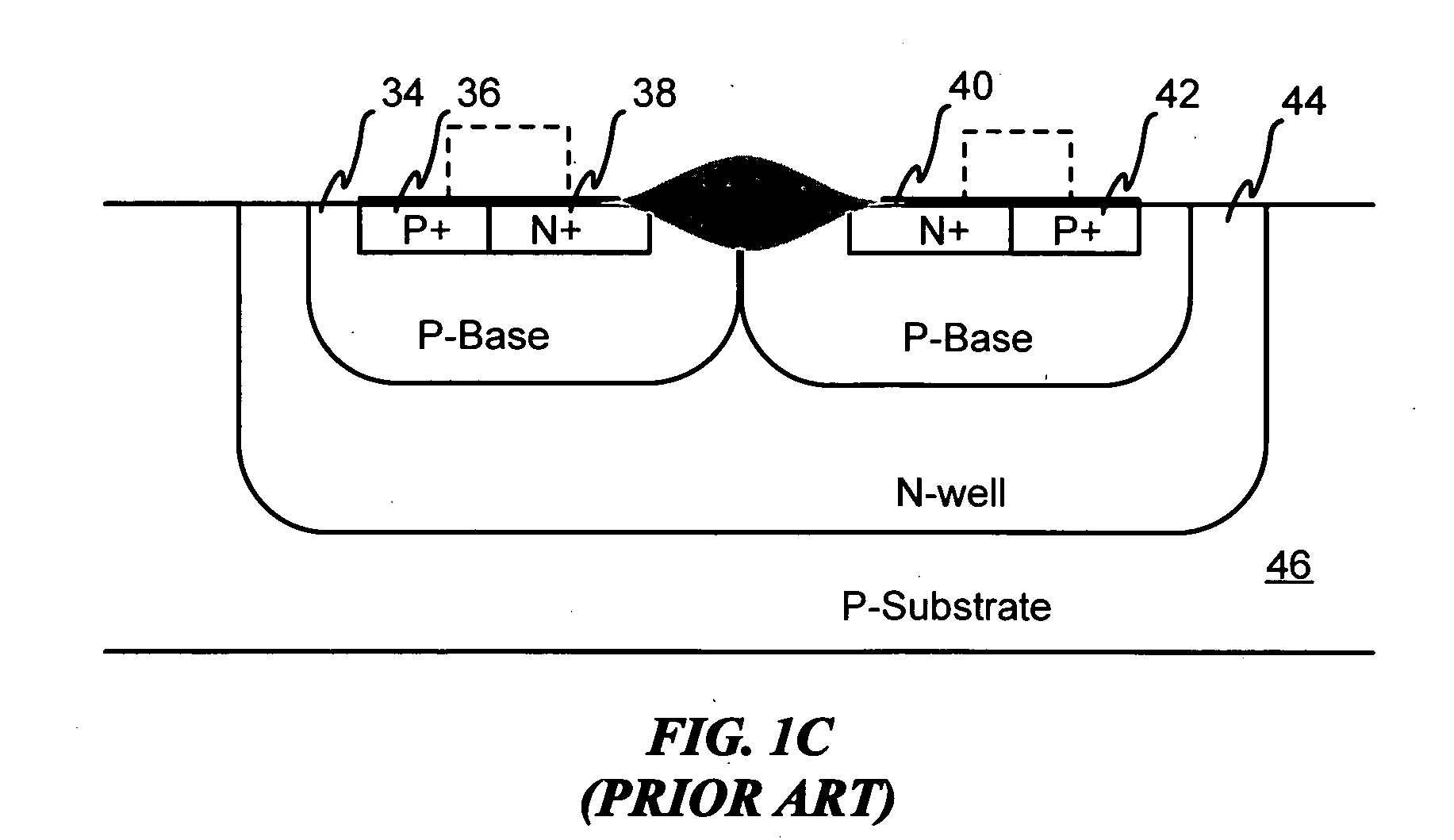

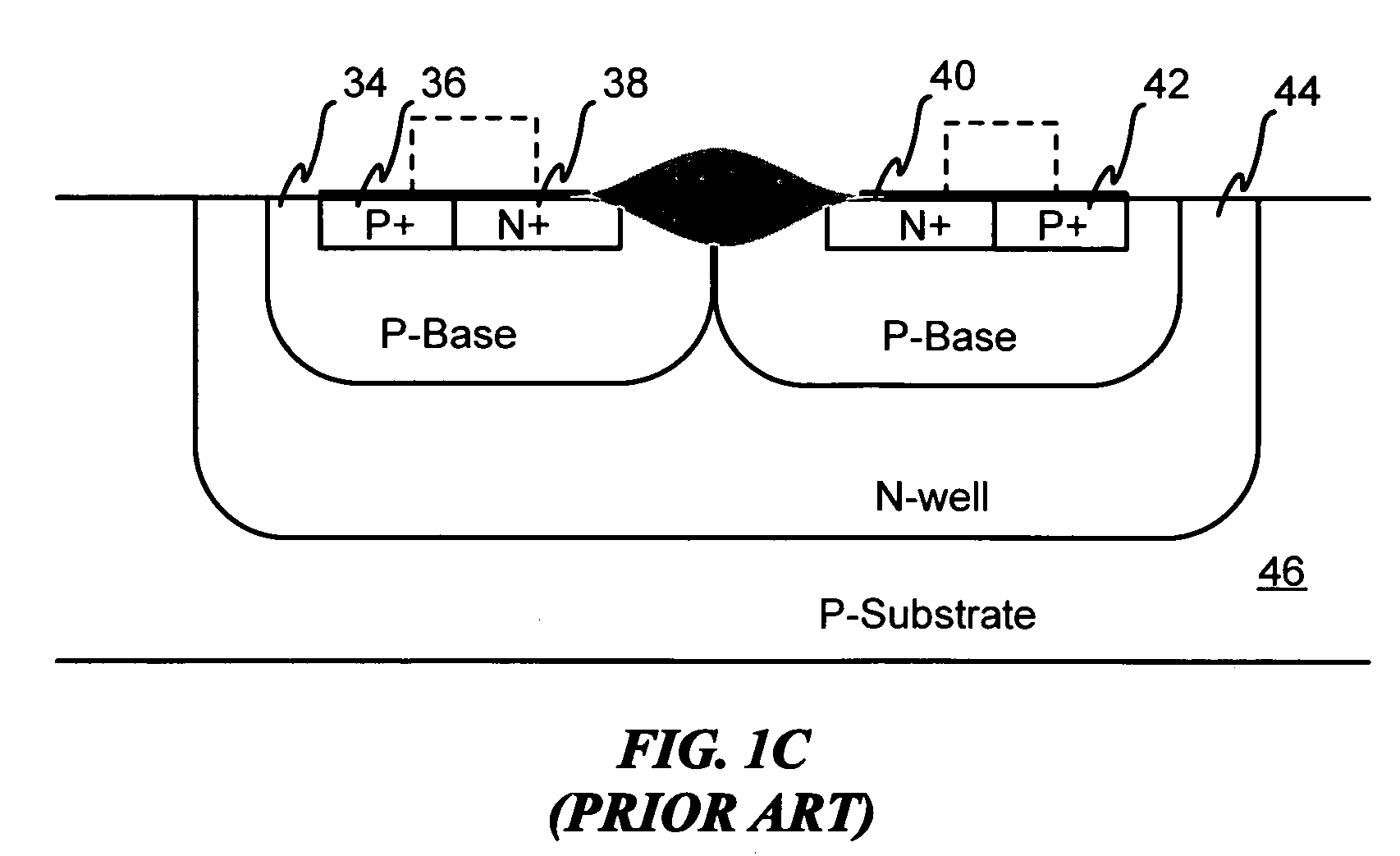

A complementary SCR-based structure enables a tunable holding voltage for robust and versatile ESD protection. The structure are n-channel high-holding-voltage low-voltage-trigger silicon controller rectifier (N-HHLVTSCR) device and p-channel high-holding-voltage low-voltage-trigger silicon controller rectifier (P-HHLVTSCR) device. The regions of the N-HHLVTSCR and P-HHLVTSCR devices are formed during normal processing steps in a CMOS or BICMOS process. The spacing and dimensions of the doped regions of N-HHLVTSCR and P-HHLVTSCR devices are used to produce the desired characteristics. The tunable HHLVTSCRs makes possible the use of this protection circuit in a broad range of ESD applications including protecting integrated circuits where the I / O signal swing can be either within the range of the bias of the internal circuit or below / above the range of the bias of the internal circuit.

Owner:INTERSIL INC

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

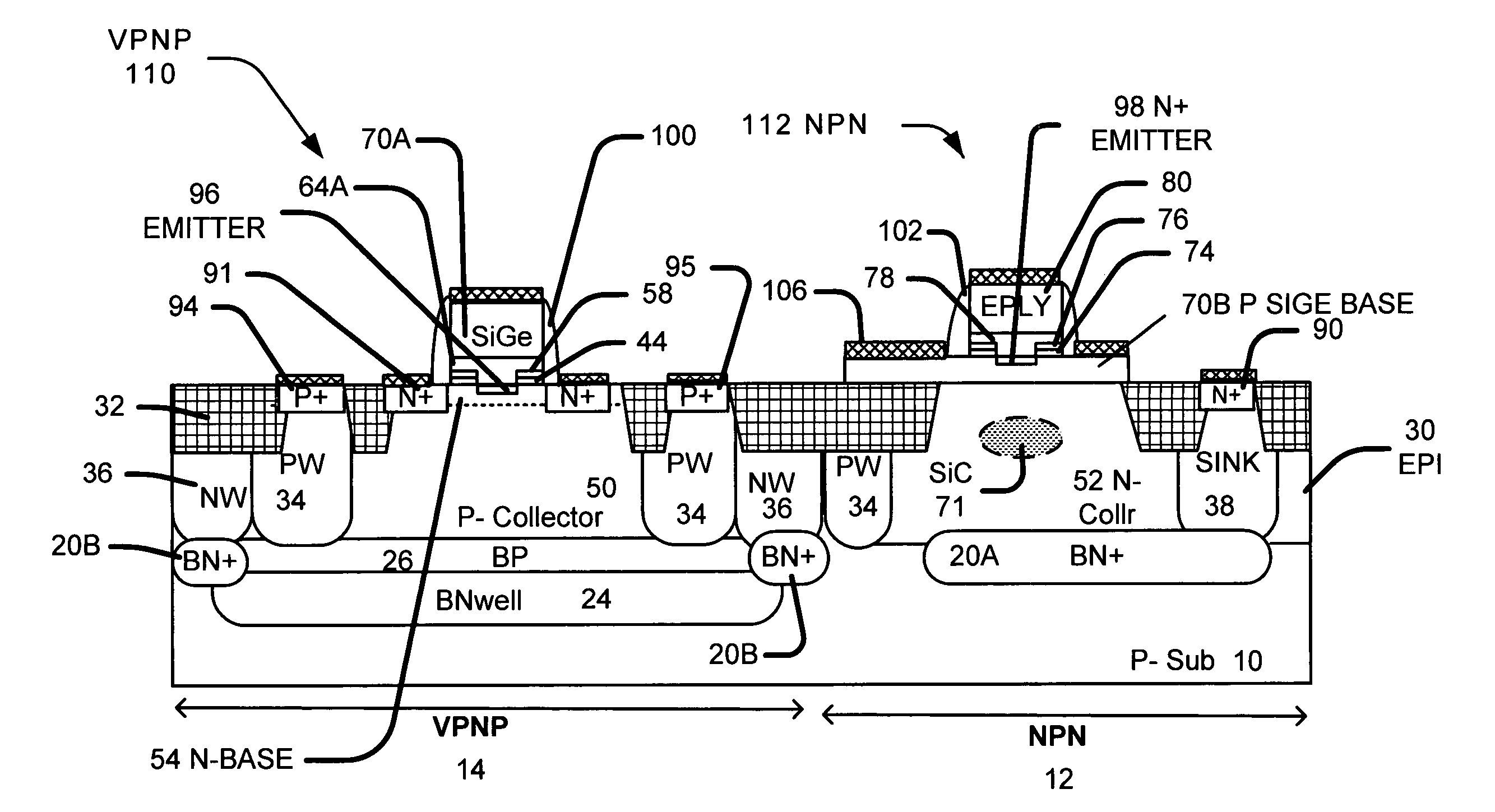

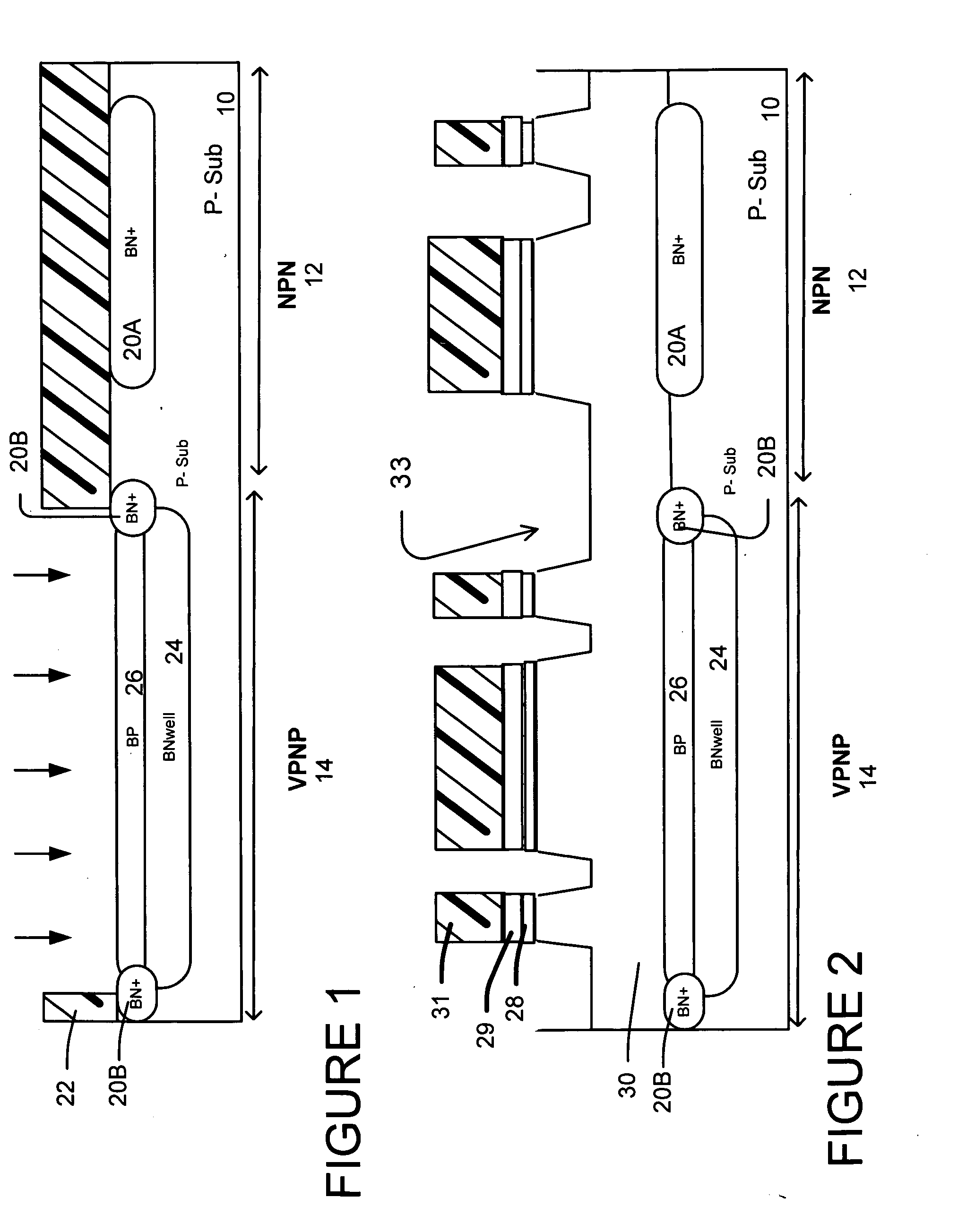

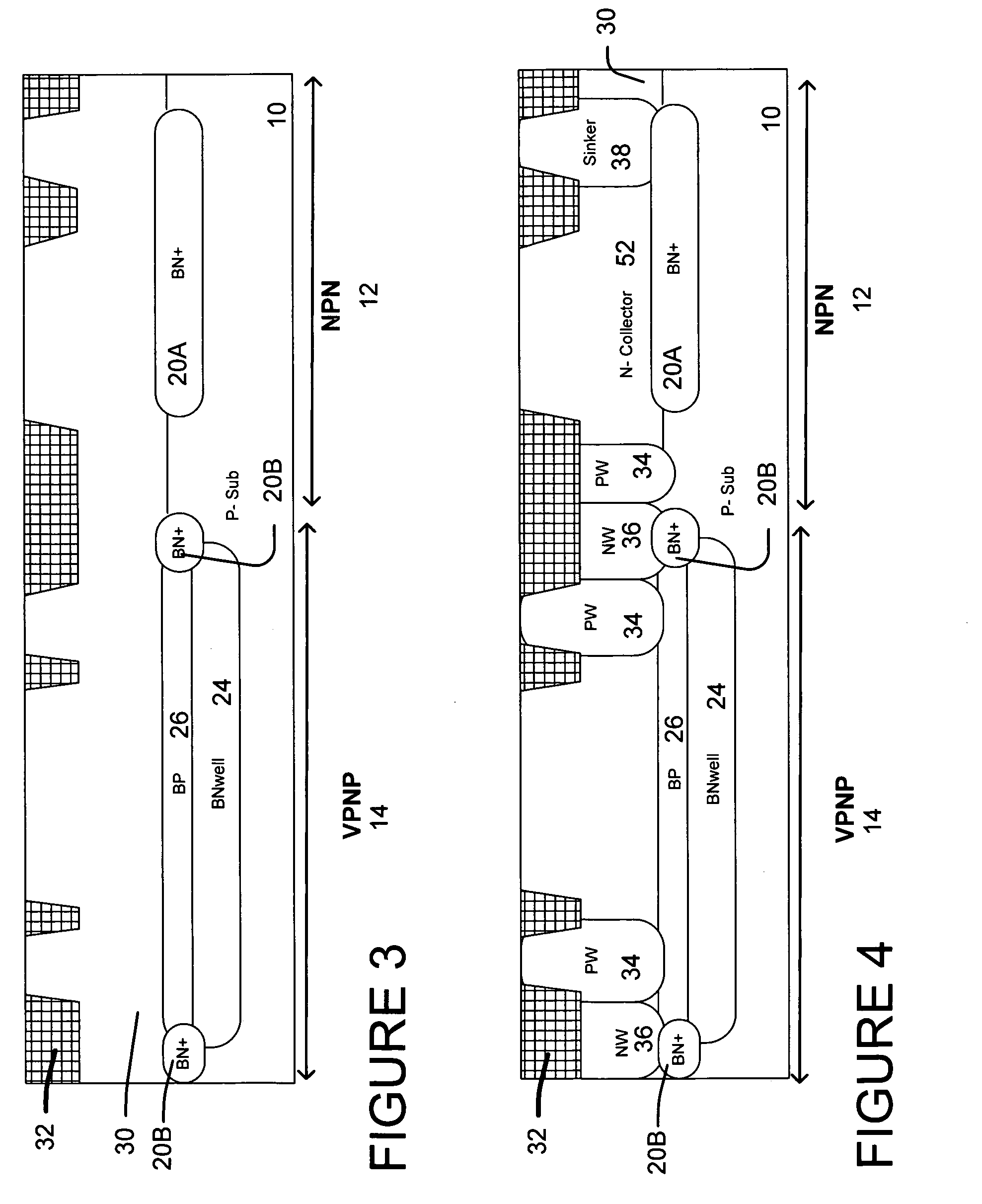

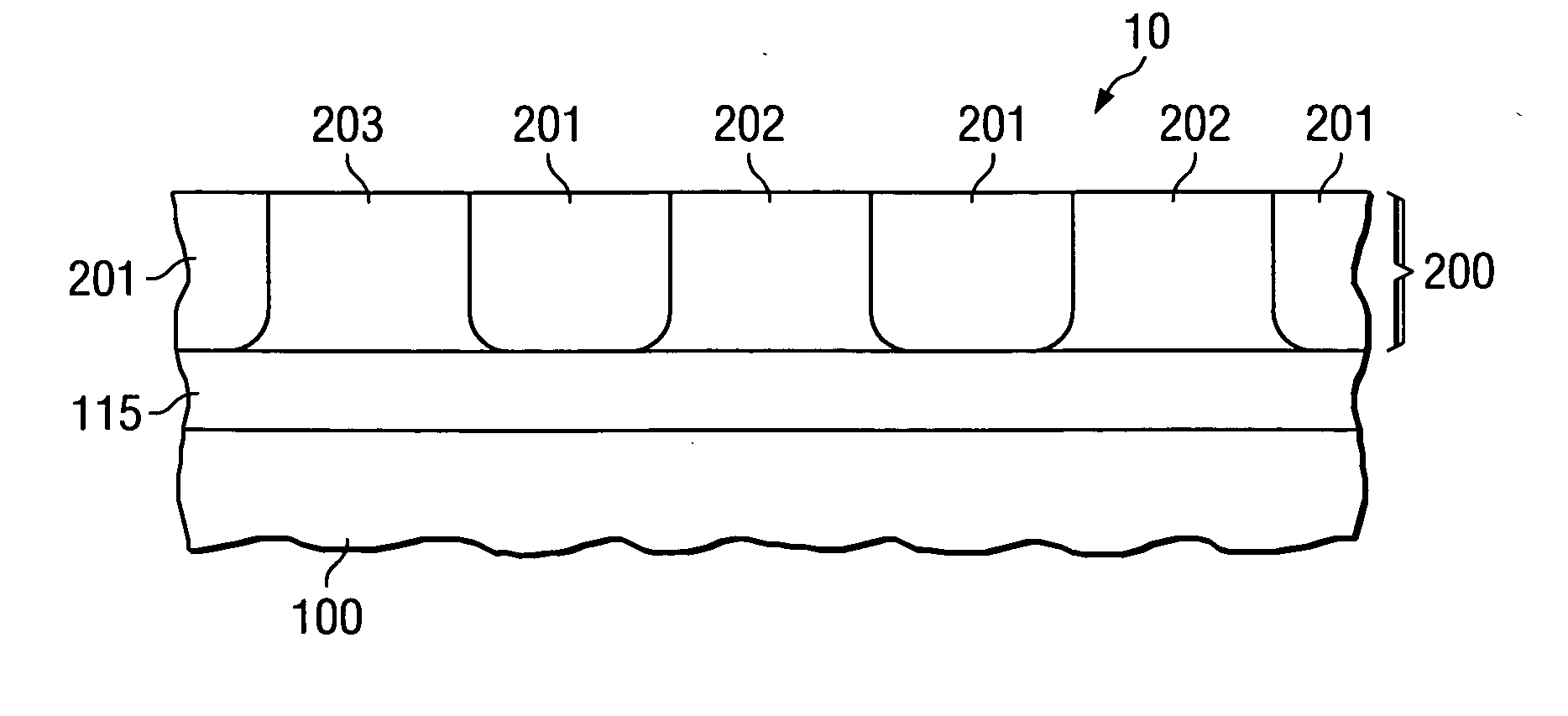

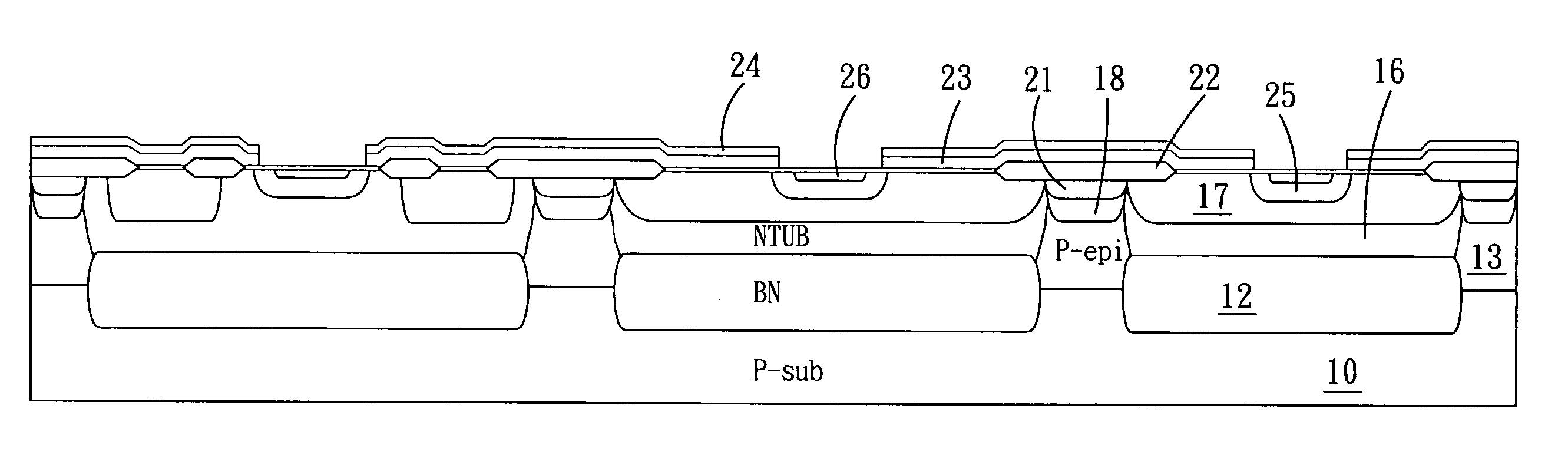

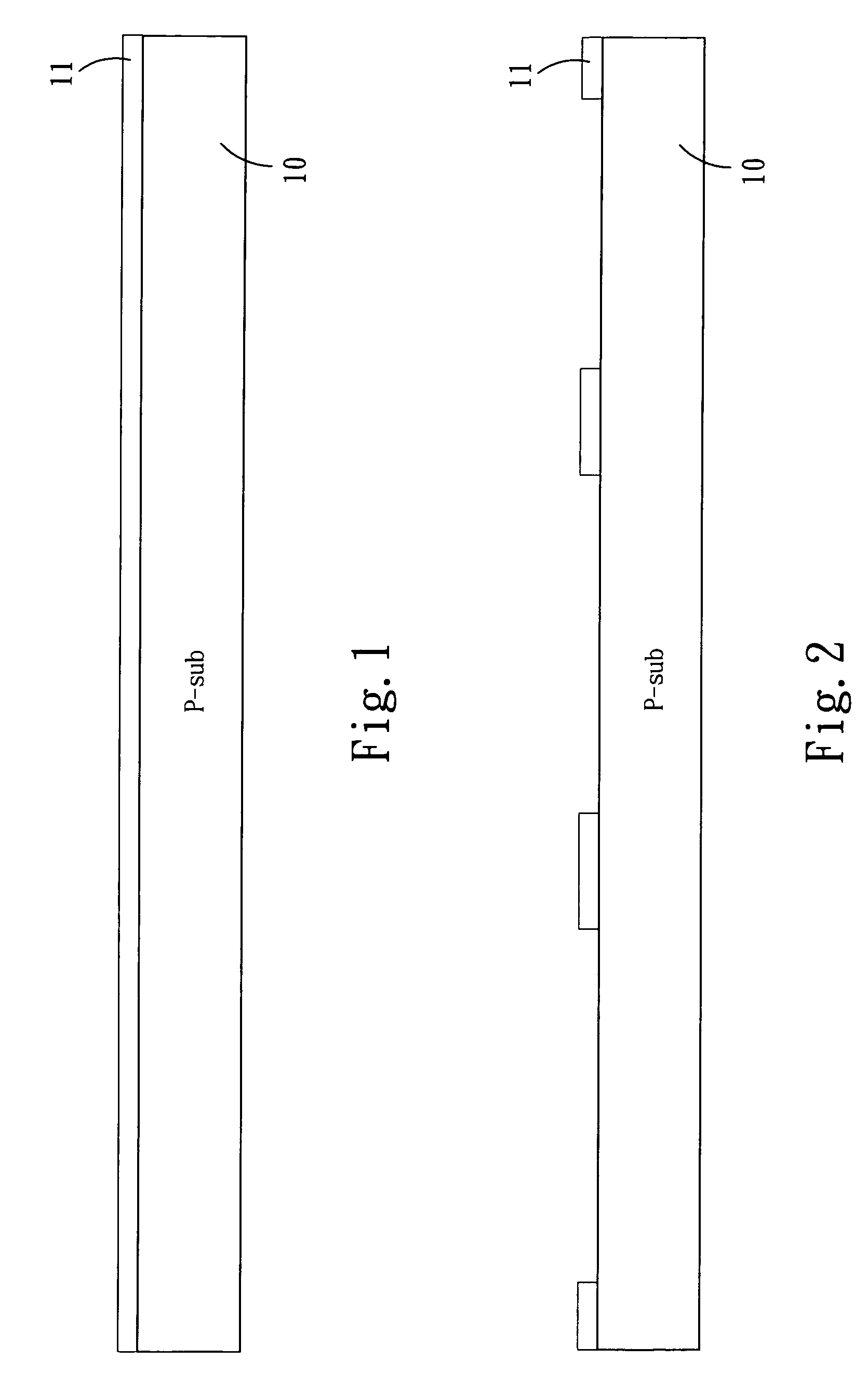

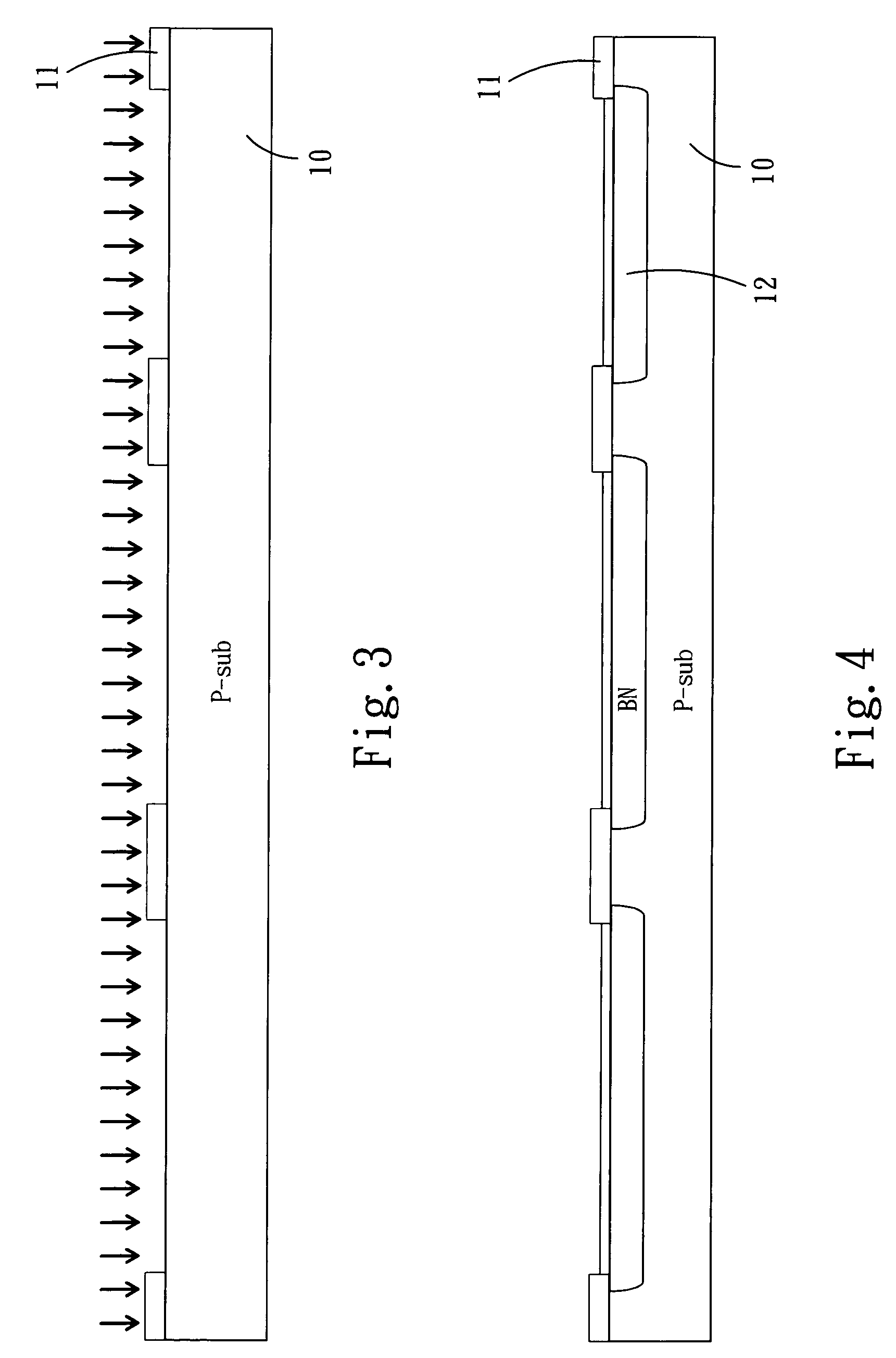

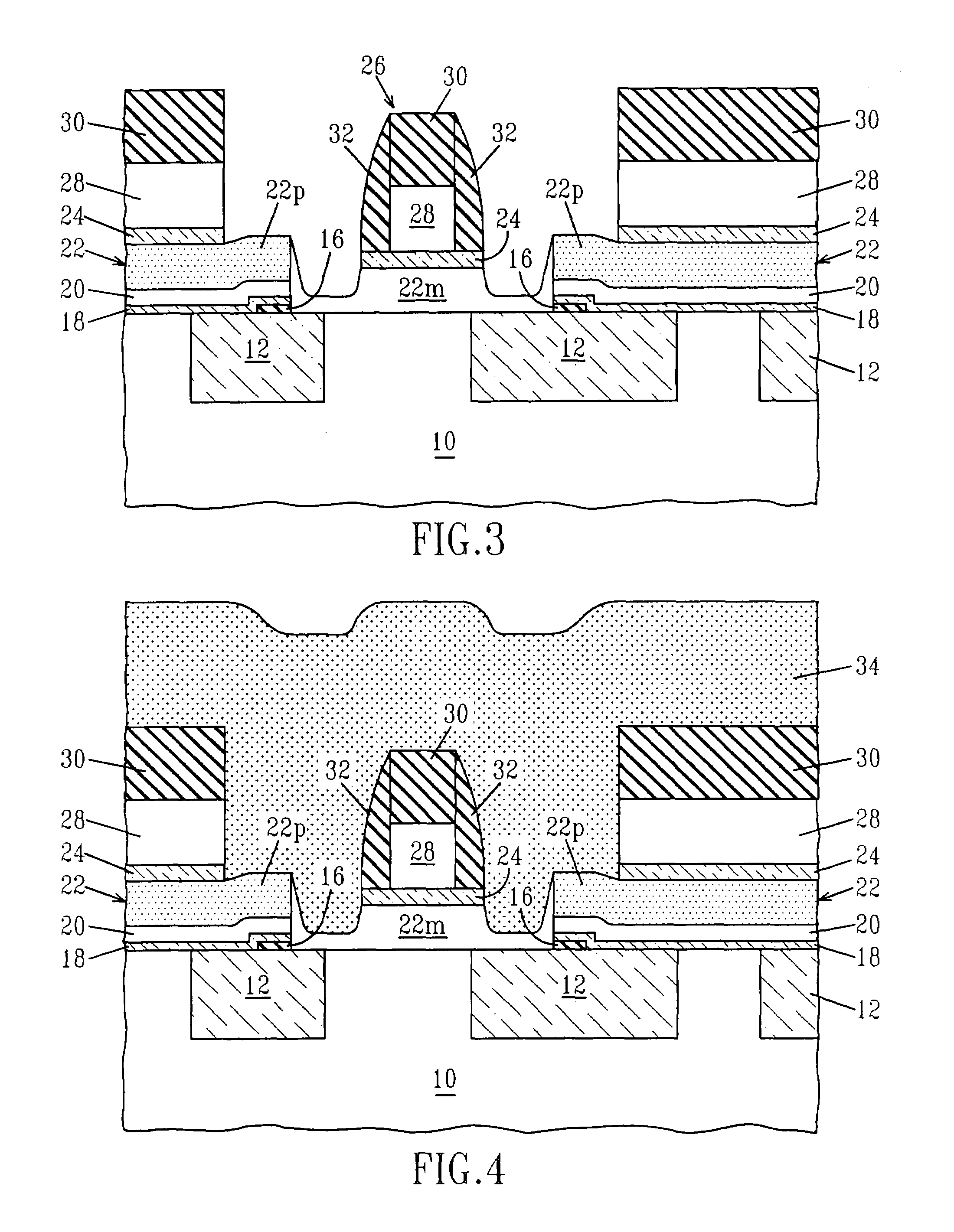

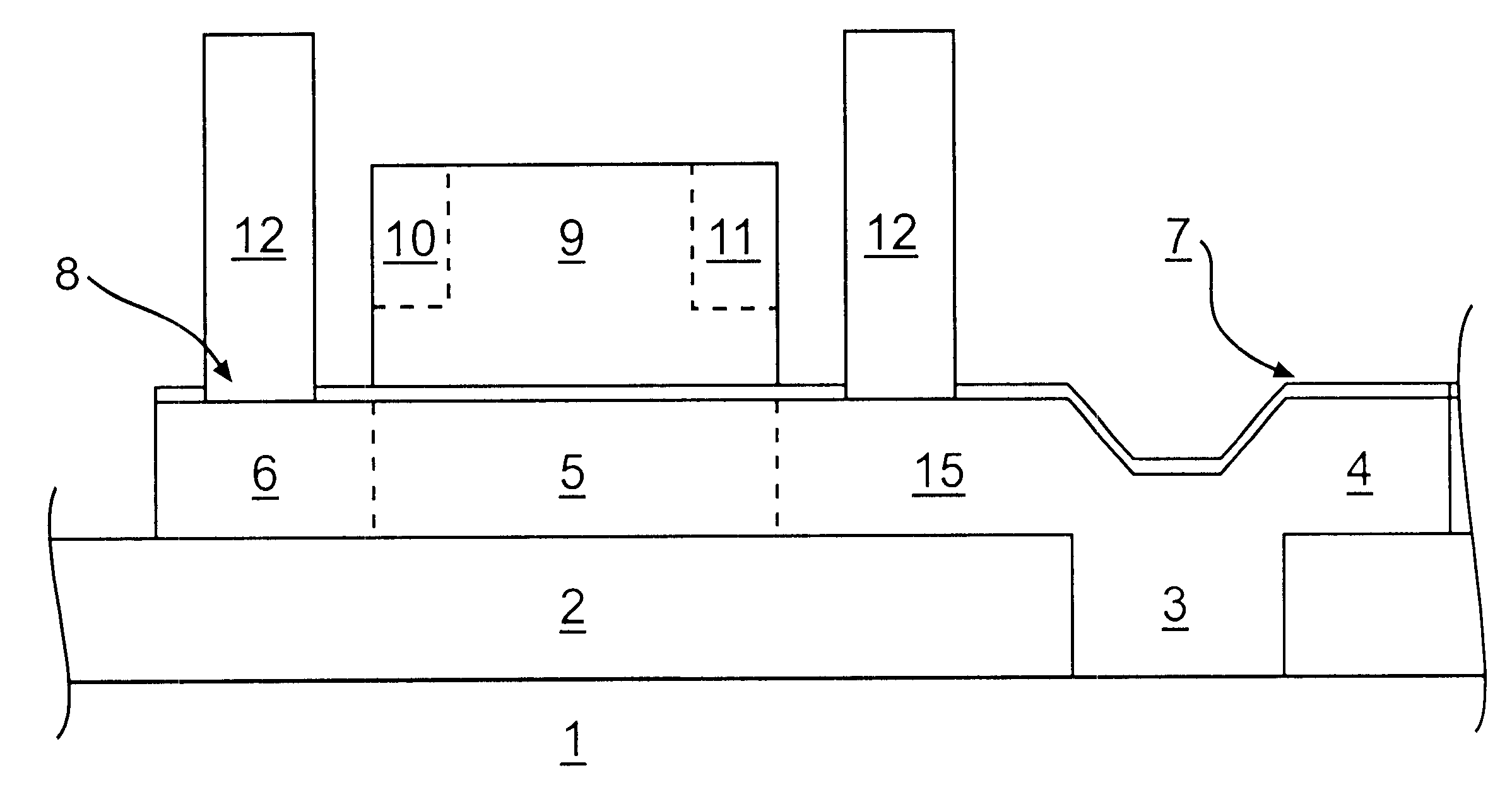

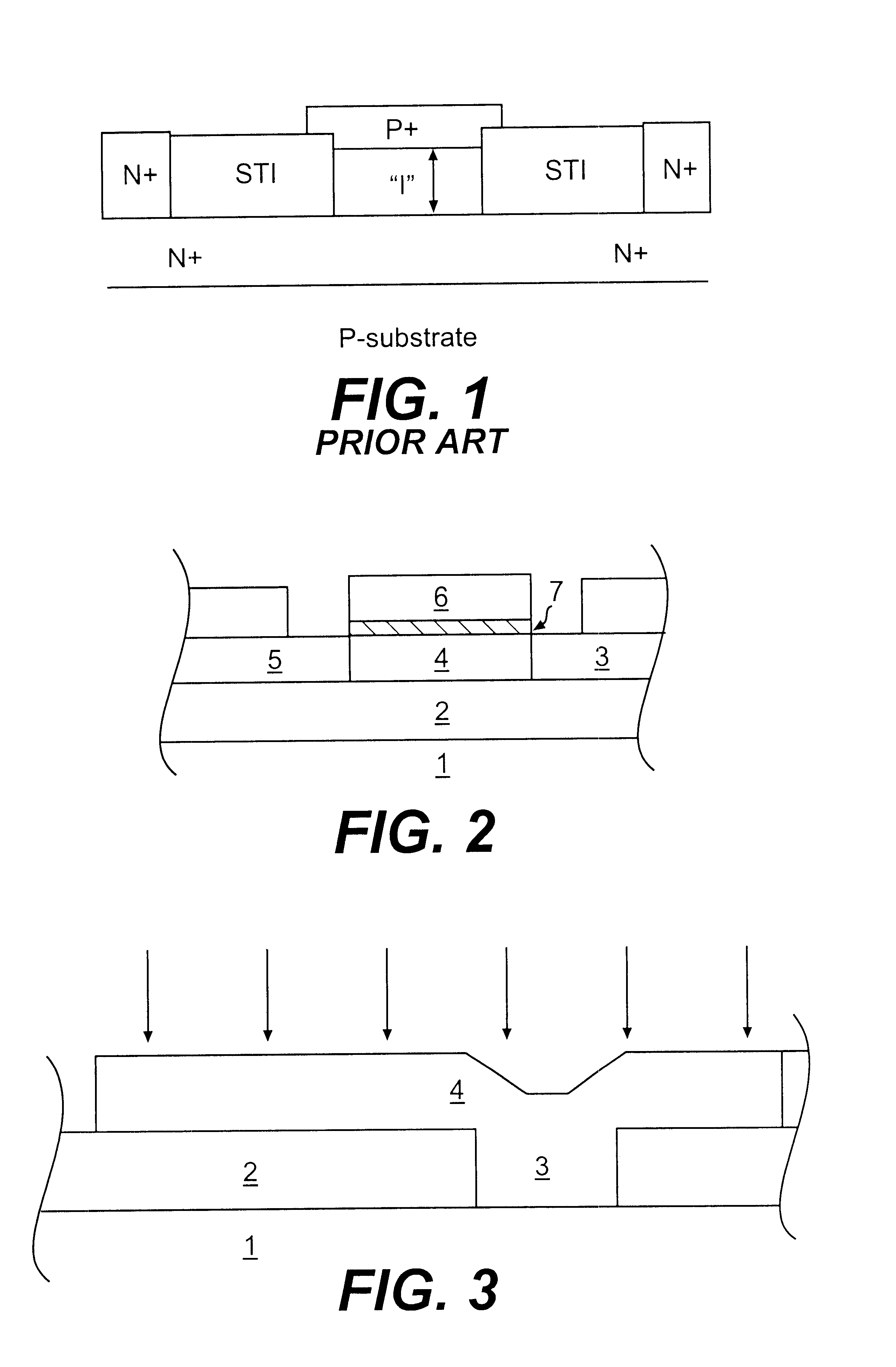

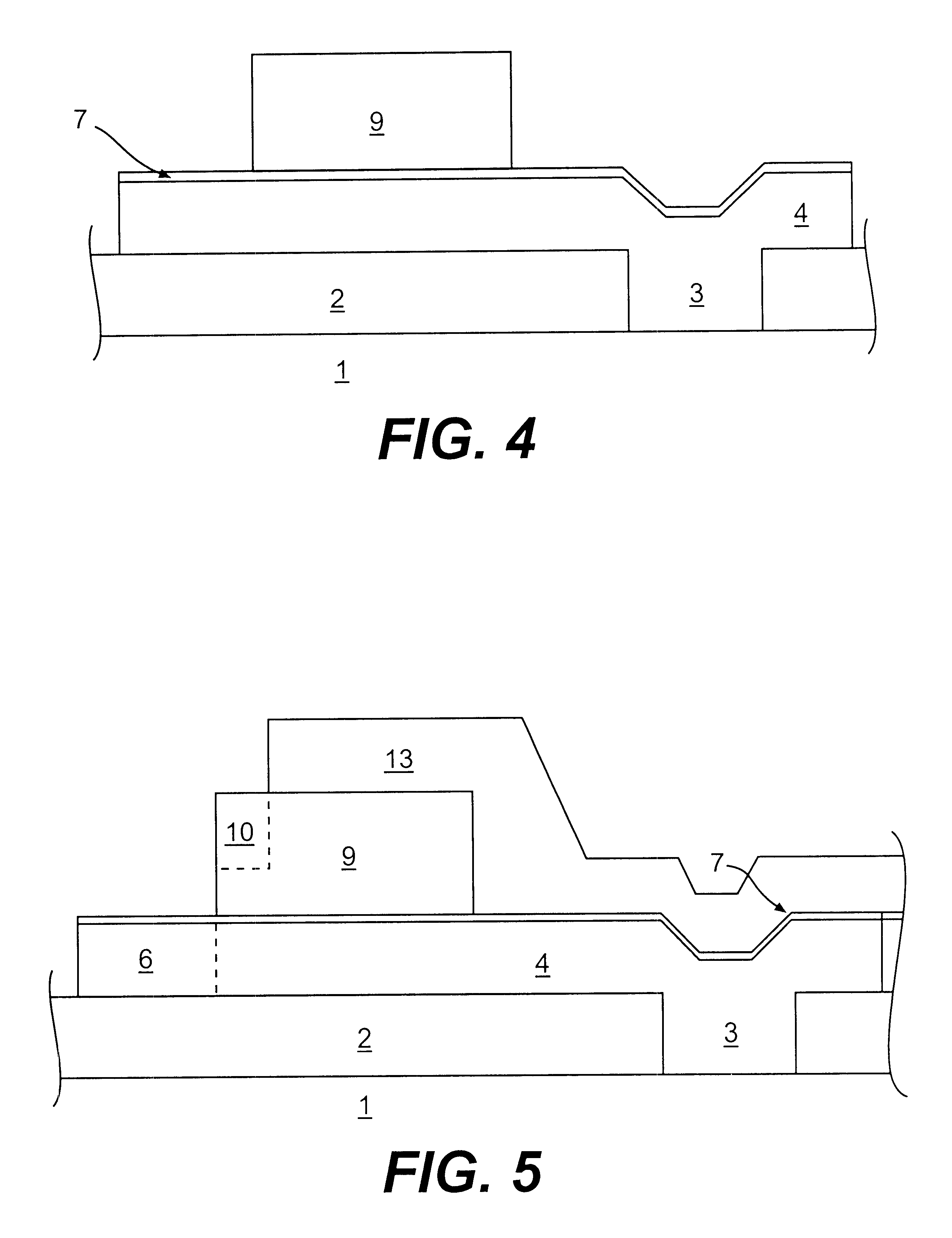

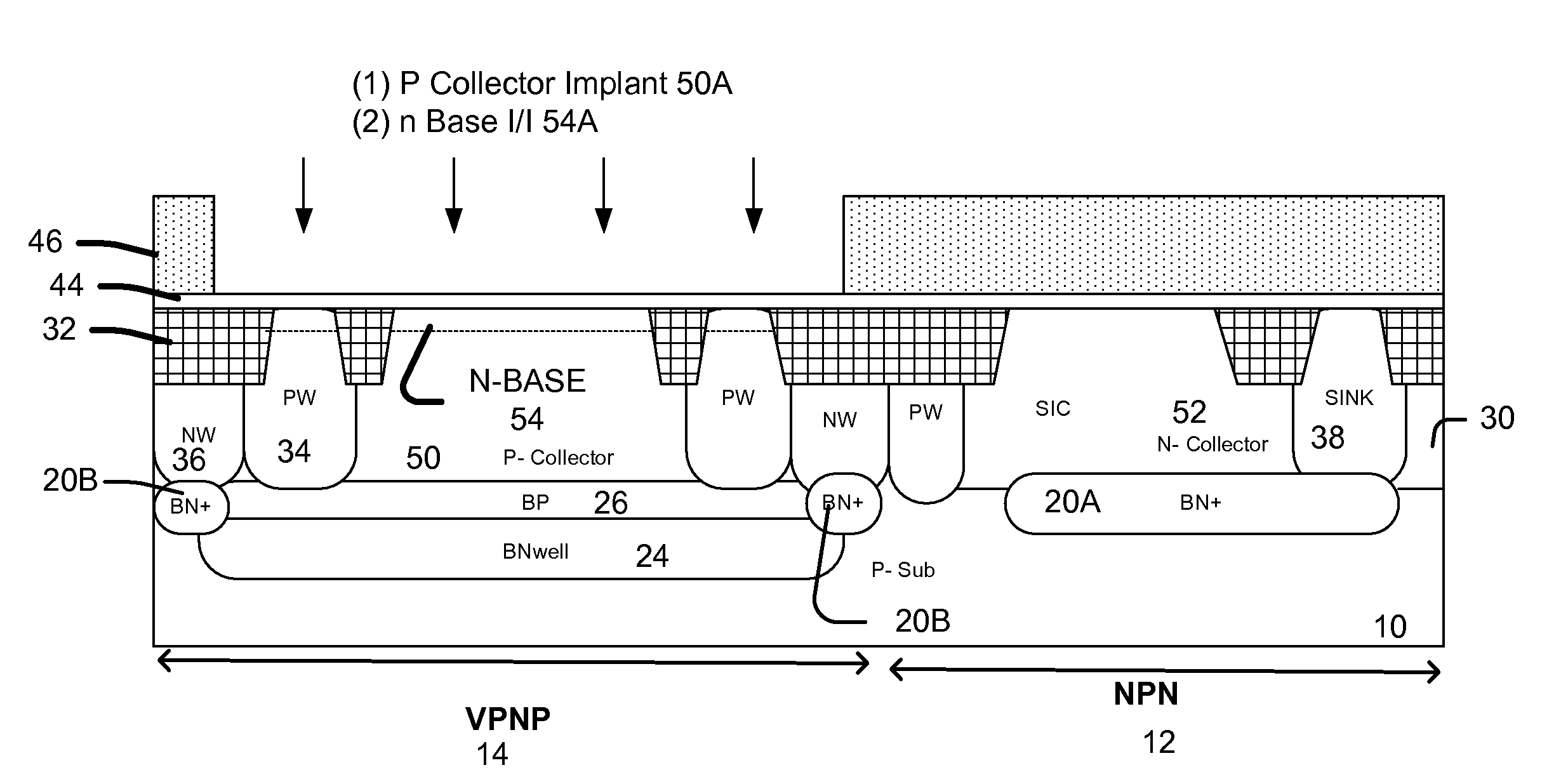

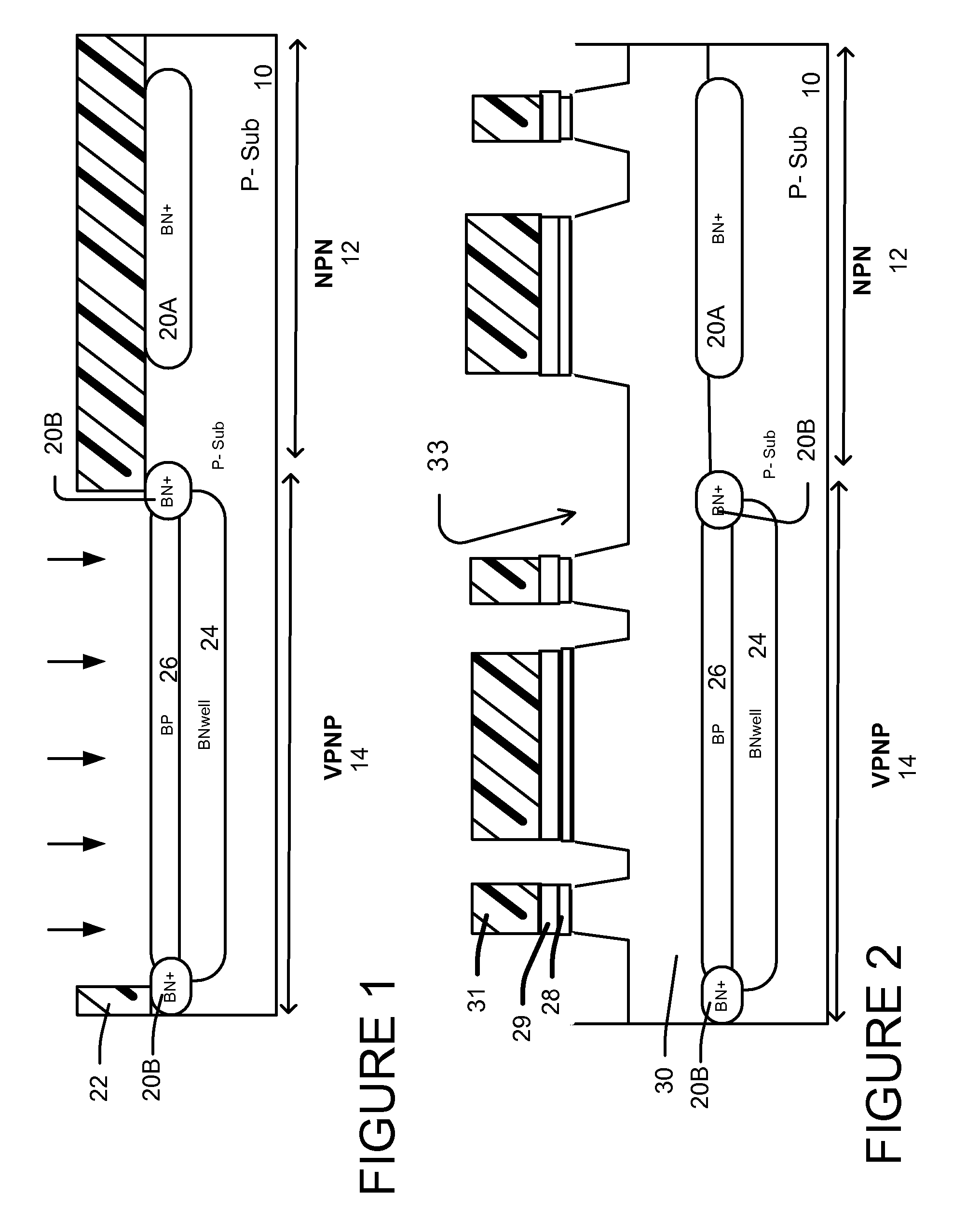

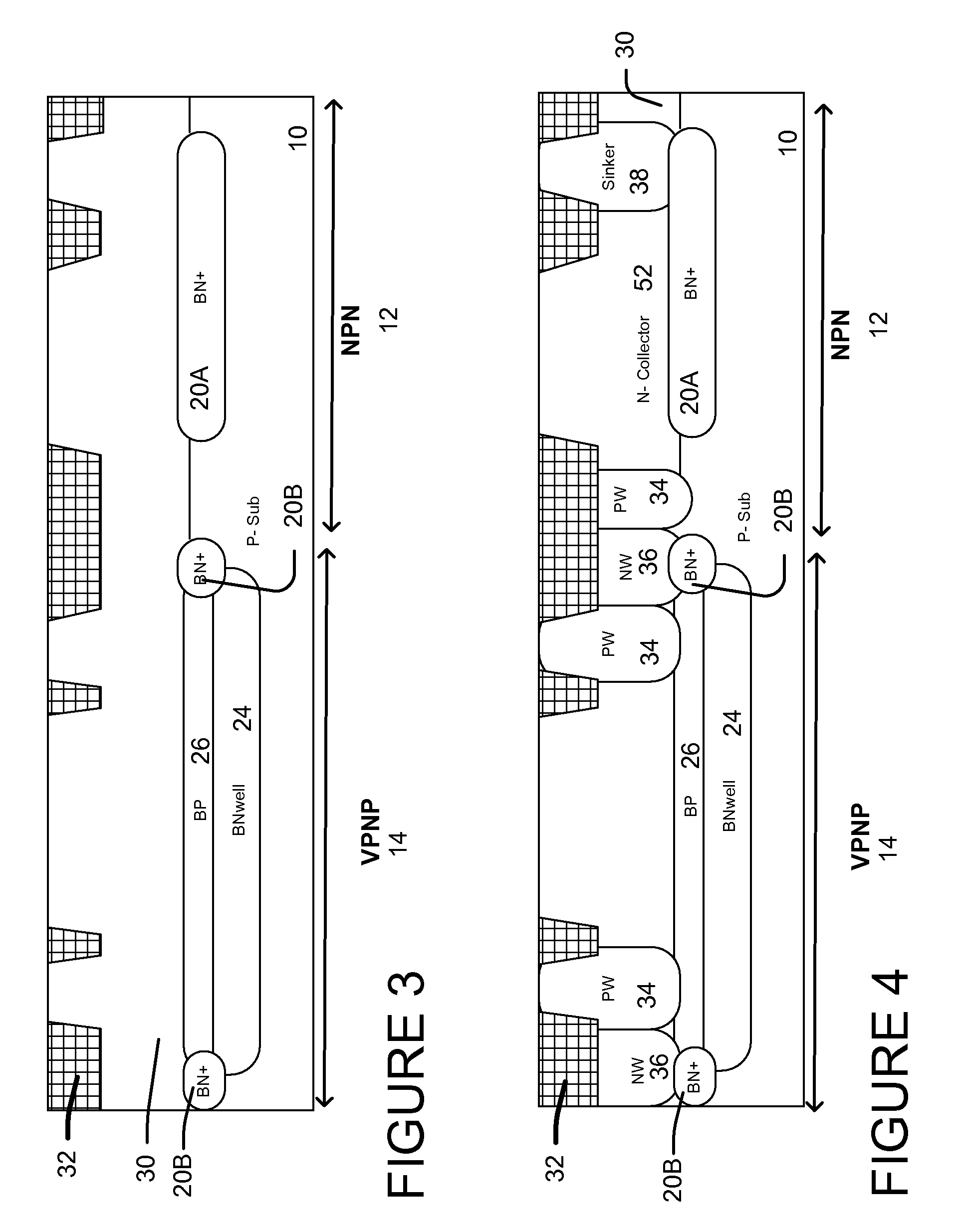

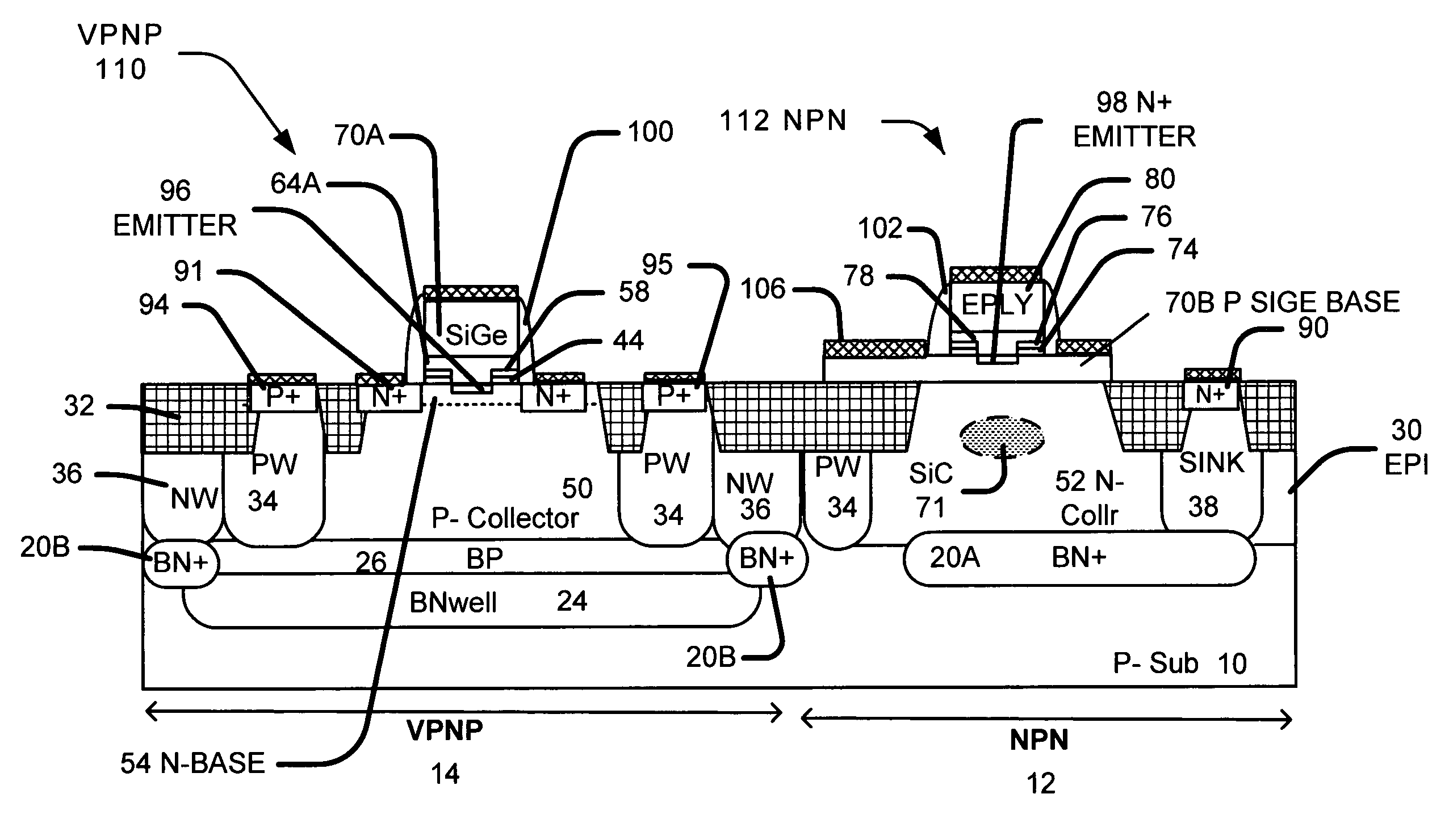

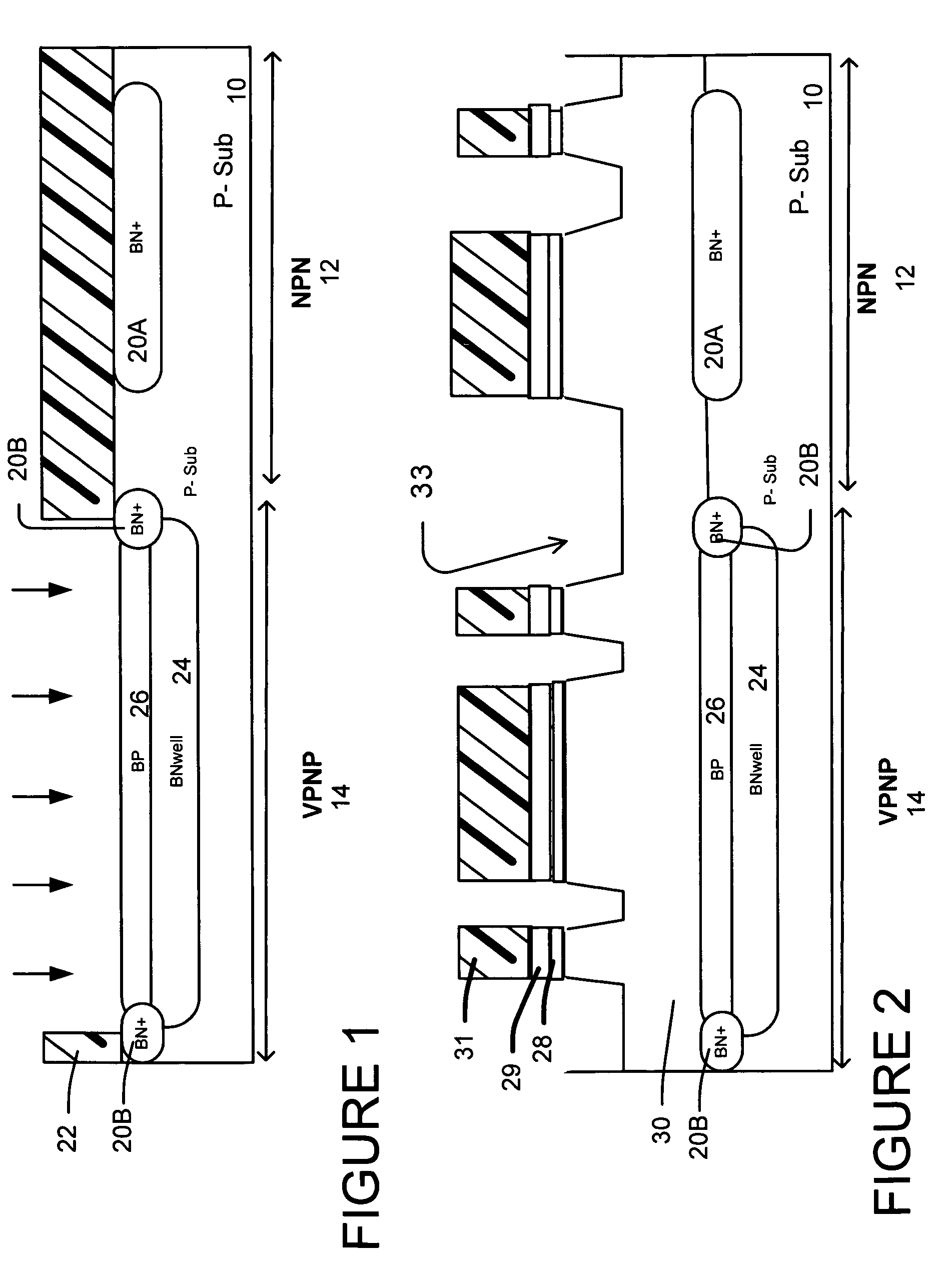

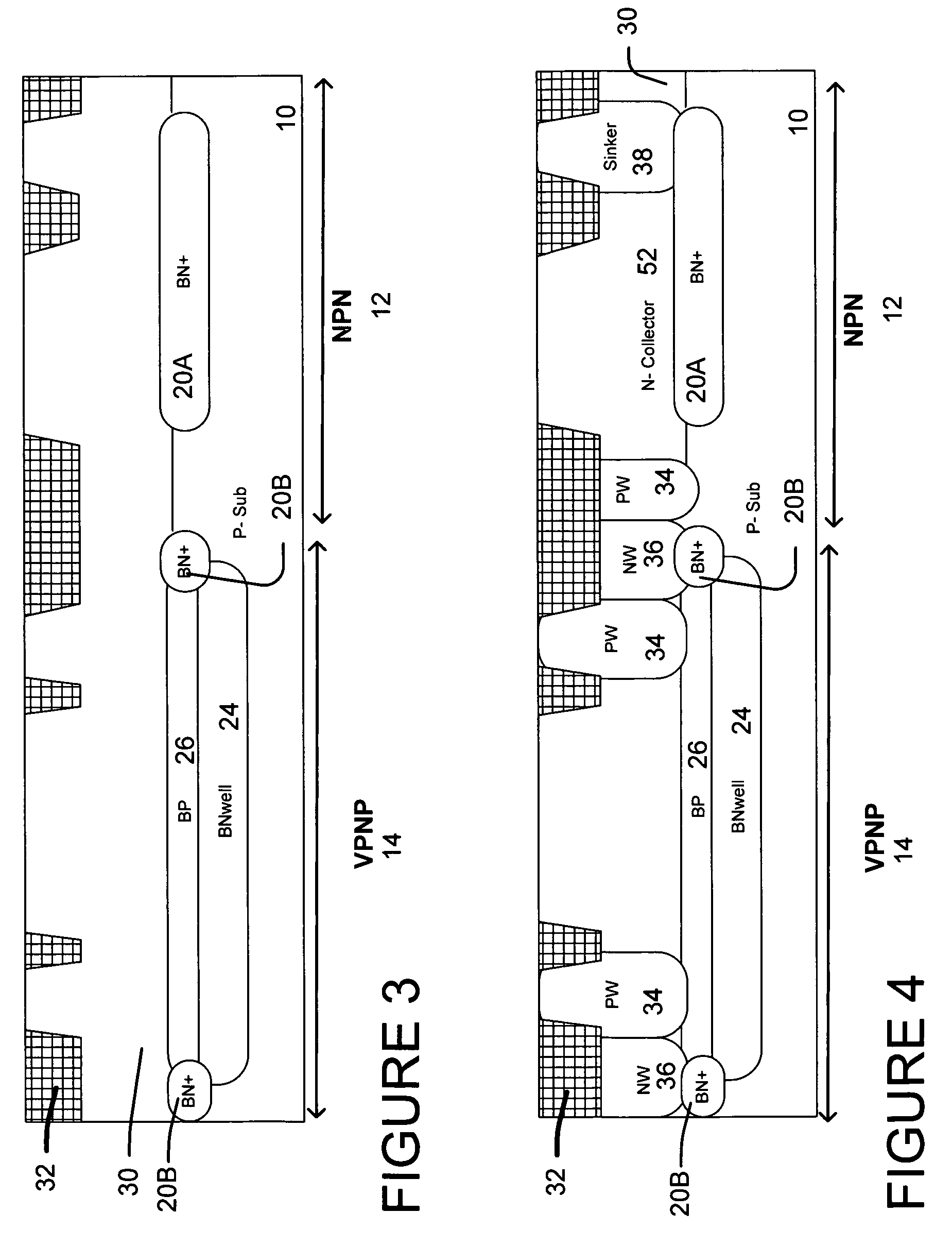

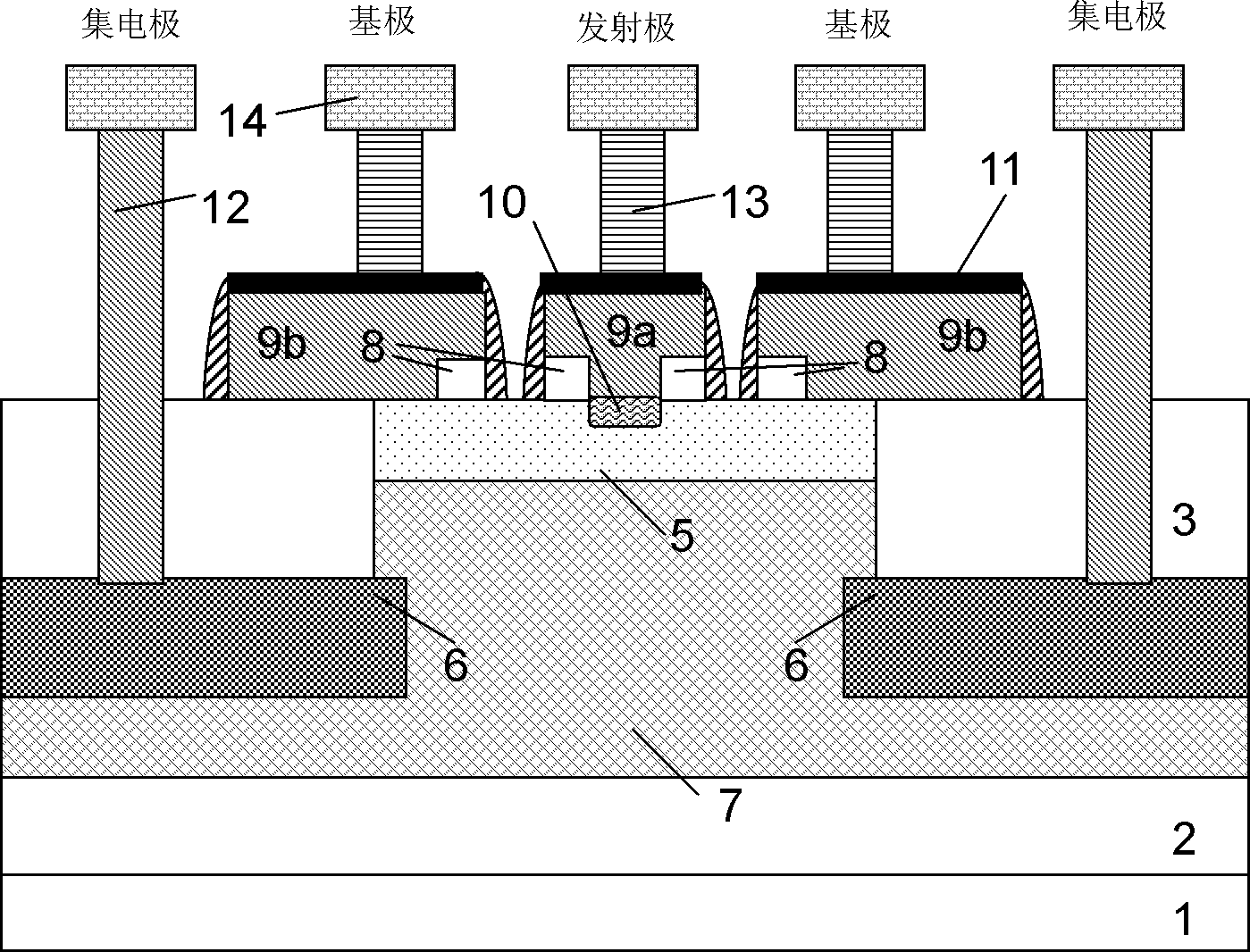

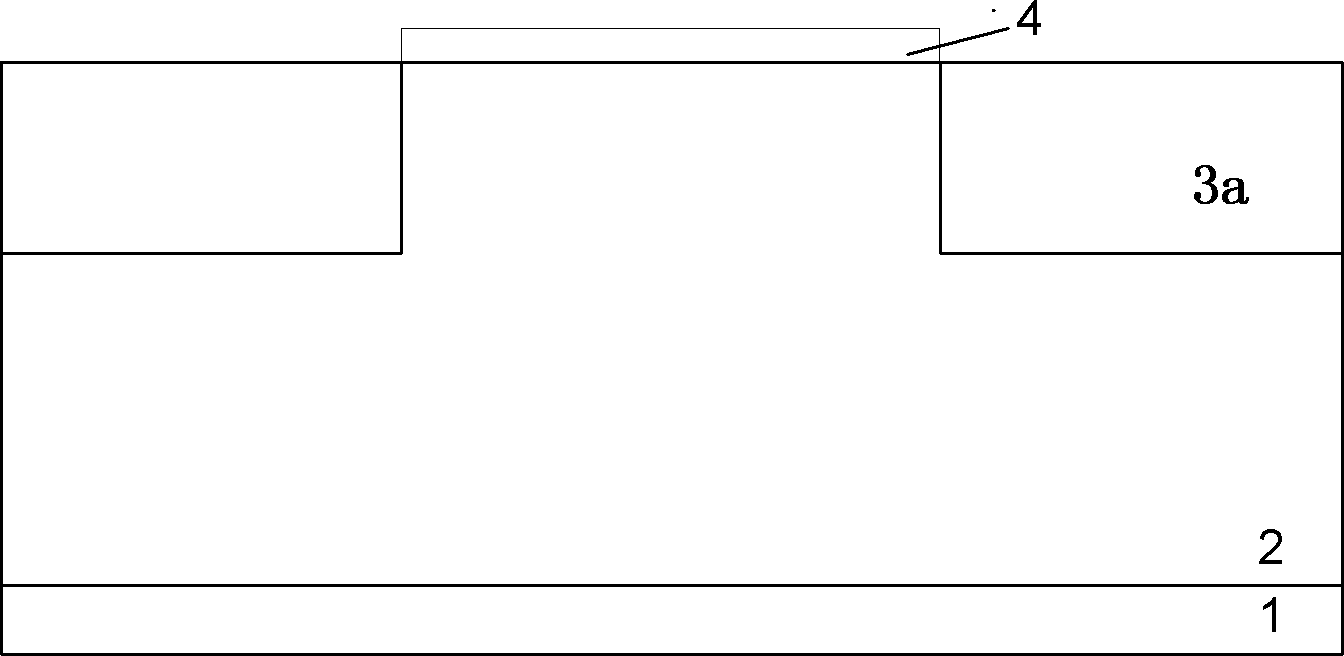

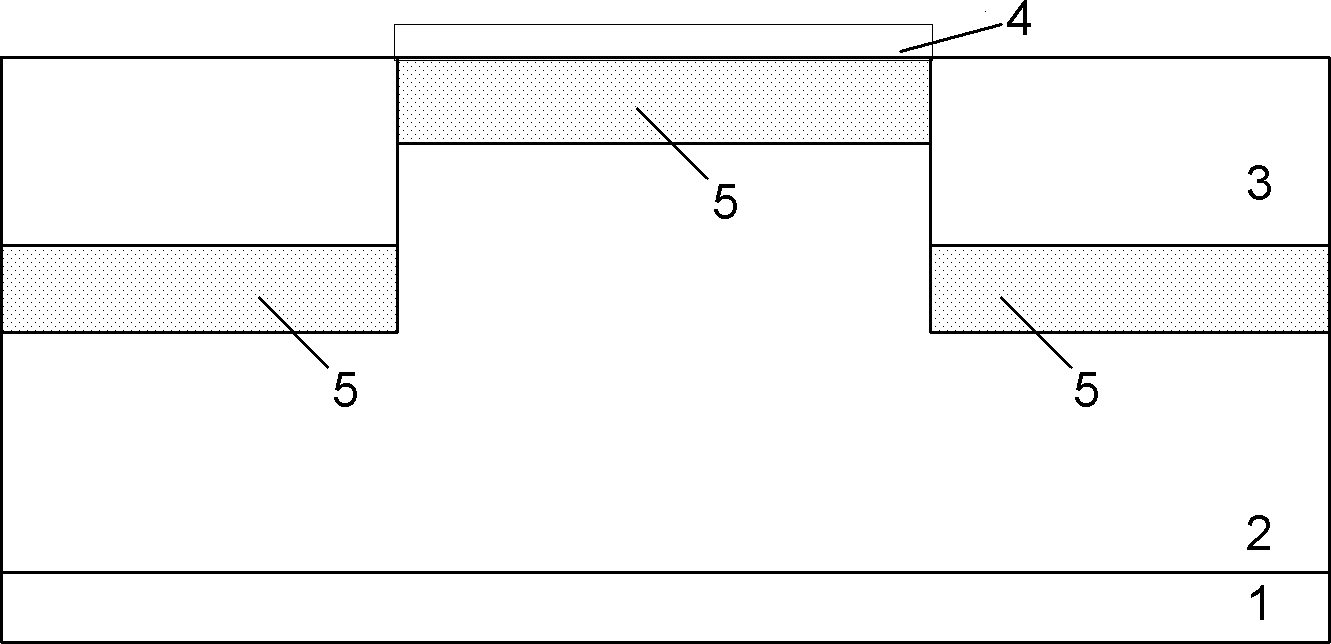

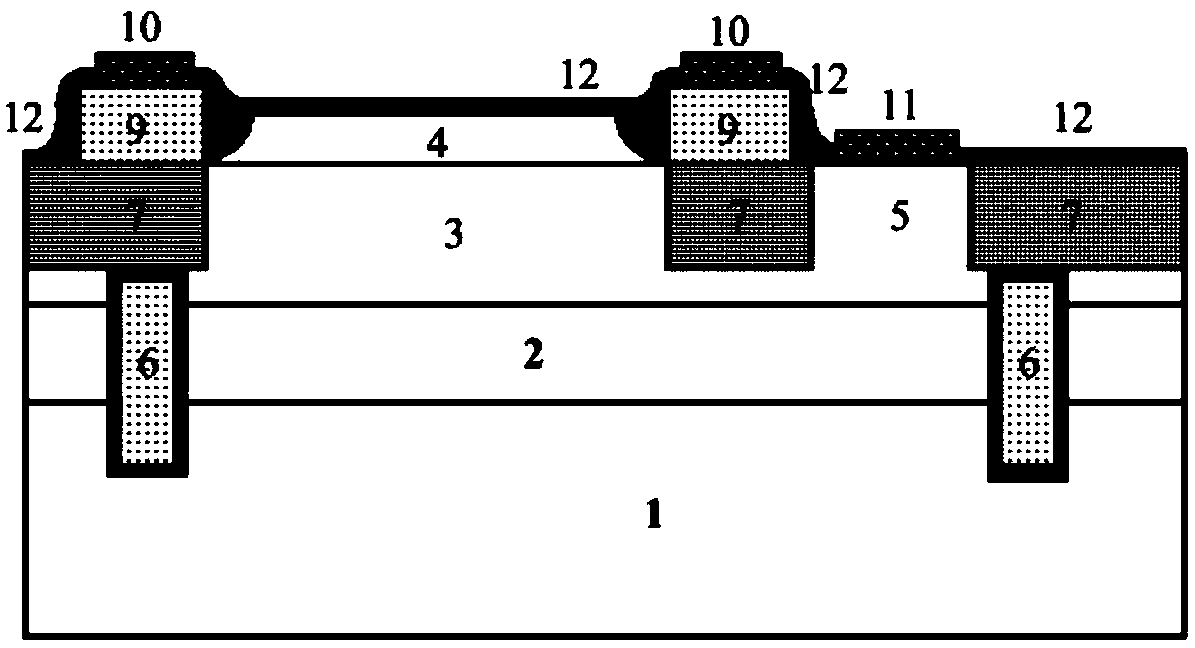

Self-aligned vertical PNP transistor for high performance SiGe CBiCMOS process

A structure and a process for a self-aligned vertical PNP transistor for high performance SiGe CBiCMOS process. Embodiments include SiGe CBiCMOS with high-performance SiGe NPN transistors and PNP transistors. As the PNP transistors and NPN transistors contained different types of impurity profile, they need separate lithography and doping step for each transistor. The process is easy to integrate with existing CMOS process to save manufacturing time and cost. As plug-in module, fully integration with SiGe BiCMOS processes. High doping Polysilicon Emitter can increase hole injection efficiency from emitter to base, reduce emitter resistor, and form very shallow EB junction. Self-aligned N+ base implant can reduce base resistor and parasitical EB capacitor. Very low collector resistor benefits from BP layer. PNP transistor can be Isolated from other CMOS and NPN devices by BNwell, Nwell and BN+ junction.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

On-chip structure for electrostatic discharge (ESD) protection

InactiveUS7202114B2Robust and ESD protectionEfficient and reliableTransistorThyristorCMOSLow voltage

A complementary SCR-based structure enables a tunable holding voltage for robust and versatile ESD protection. The structure are n-channel high-holding-voltage low-voltage-trigger silicon controller rectifier (N-HHLVTSCR) device and p-channel high-holding-voltage low-voltage-trigger silicon controller rectifier (P-HHLVTSCR) device. The regions of the N-HHLVTSCR and P-HHLVTSCR devices are formed during normal processing steps in a CMOS or BICMOS process. The spacing and dimensions of the doped regions of N-HHLVTSCR and P-HHLVTSCR devices are used to produce the desired characteristics. The tunable HHLVTSCRs makes possible the use of this protection circuit in a broad range of ESD applications including protecting integrated circuits where the I / O signal swing can be either within the range of the bias of the internal circuit or below / above the range of the bias of the internal circuit.

Owner:INTERSIL INC

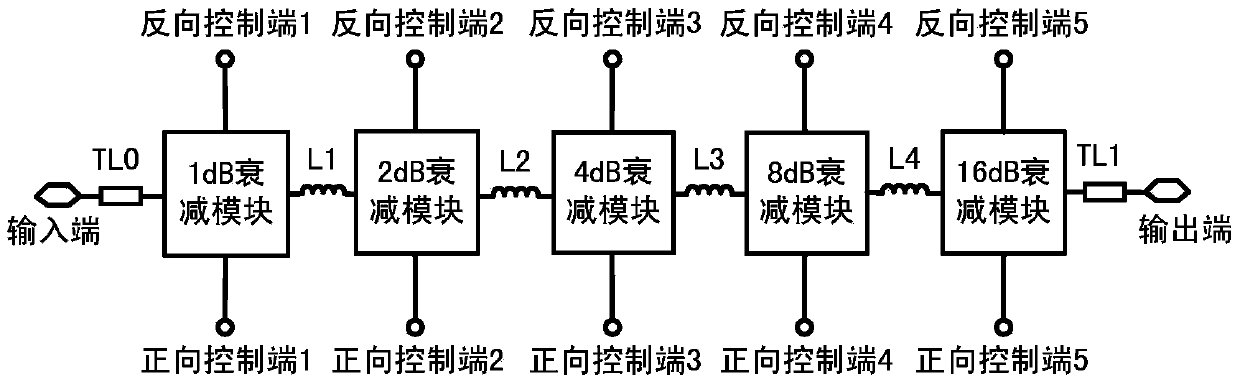

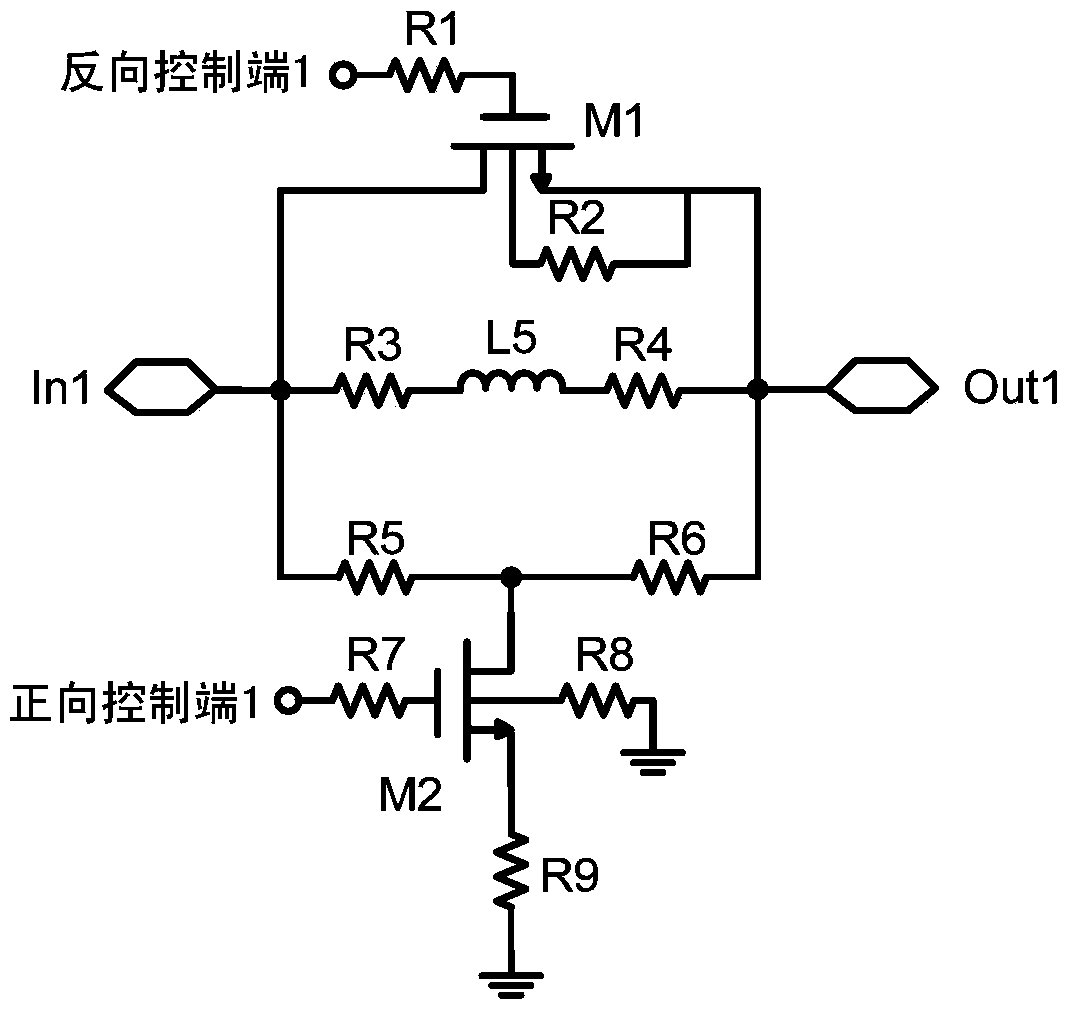

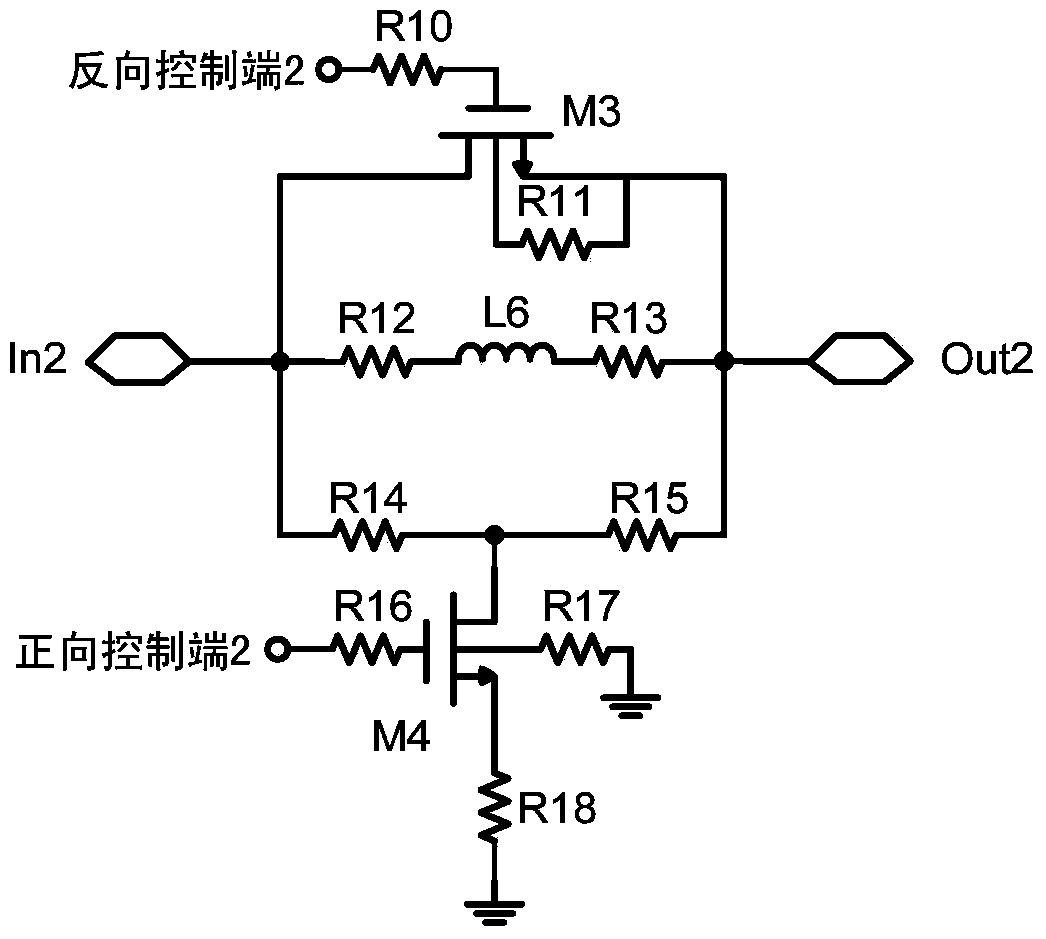

Silicone substrate high-linearity low-phase-shift ultra-broad-band digital attenuator

ActiveCN103427781AOvercoming lossTo overcome the large additional phase shiftMultiple-port networksEngineeringField-effect transistor

The invention discloses a silicone substrate high-linearity low-phase-shift ultra-broad-band digital attenuator which comprises a 1dB attenuating module, a 2dB attenuating module, a 4dB attenuating module, a 8dB attenuating module and a 16dB attenuating module. Two NMOS field effect transistors which are of a channel parallel-connection resistor structure and of a solid suspension structure and manufactured through SiGe BiCMOS technology are adopted to be used as control switches, five sets of complementary digital signals are used for controlling the five attenuating modules independently to work, a low-pass network is used for conducting phase compensation, inductance is used for matching between the adjacent attenuating modules, matching between the input end of the1dB attenuating module and 50 omega input impedance and matching between the output end of the 16dB attenuating module and 50 omega output impedance are realized through transmission wires, the working frequency range is 1-25GHz, and low-differential-loss low-phase-shift attenuation of signal amplitudes under 32 states can be realized with the 1dB length stepping in the attenuating range of 0-31dB. The silicone substrate high-linearity low-phase-shift ultra-broad-band digital attenuator has the advantages of being low in differential loss, low in accessory phase shift, high in linearity, low in production cost and low in chip area, and can be used for large-amplitude signal processing and single chip integration.

Owner:XIDIAN UNIV

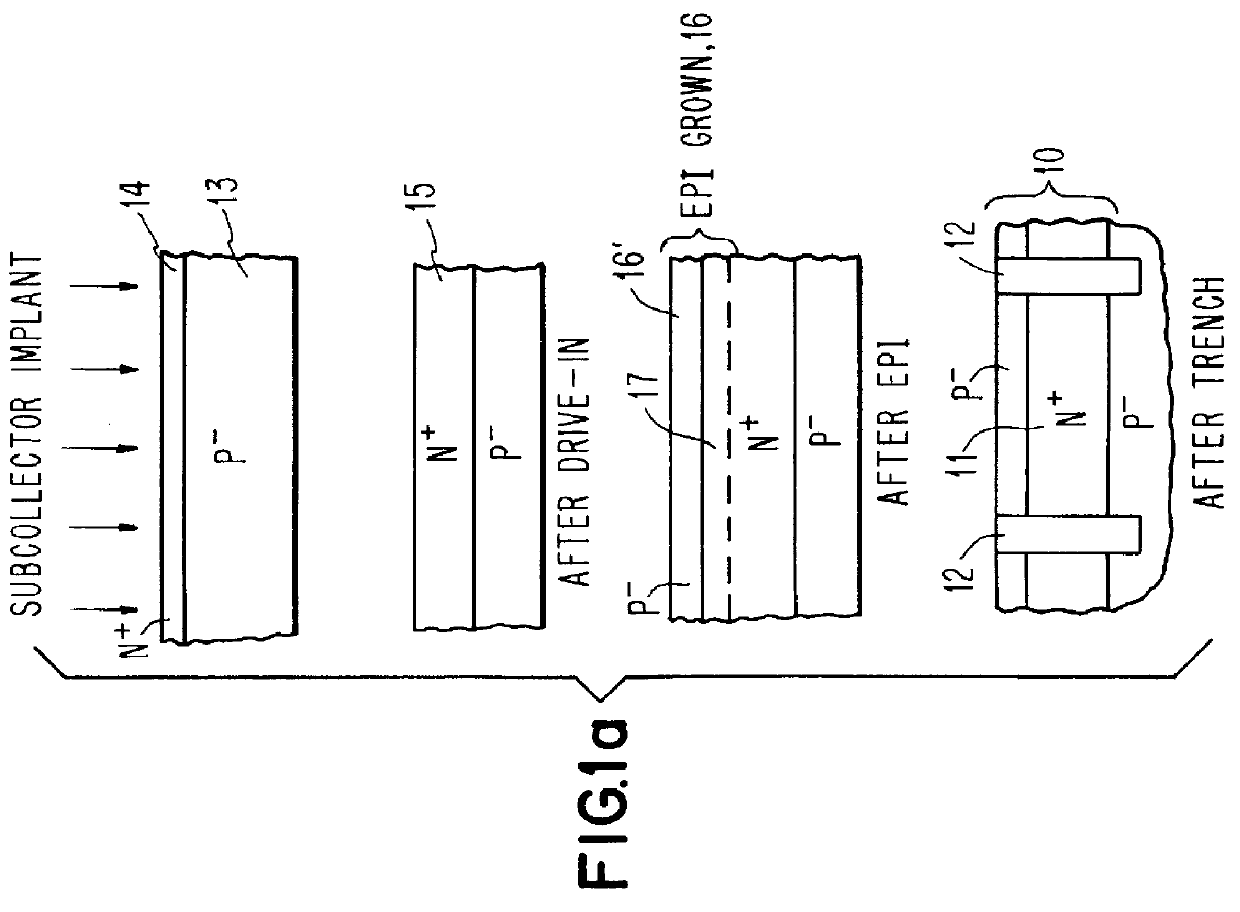

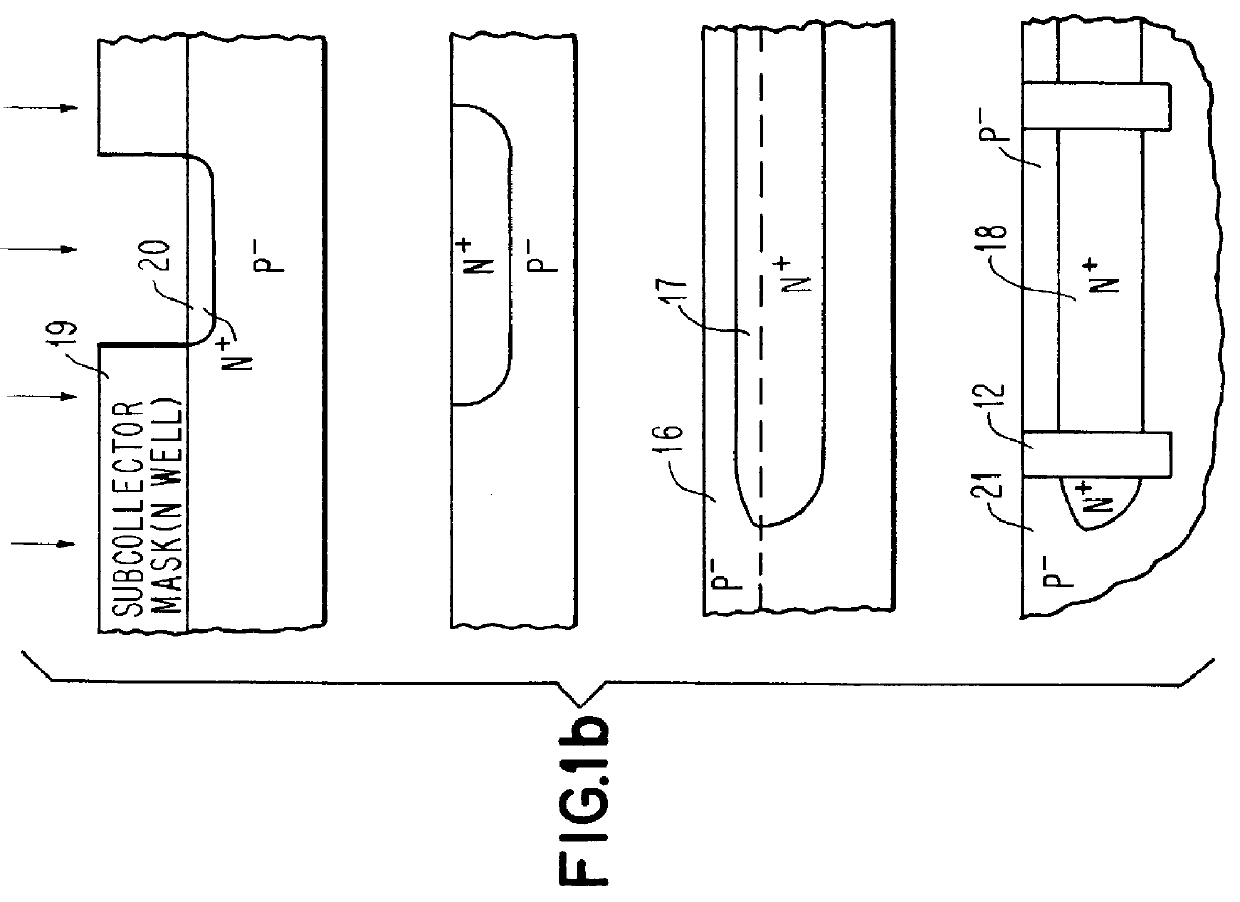

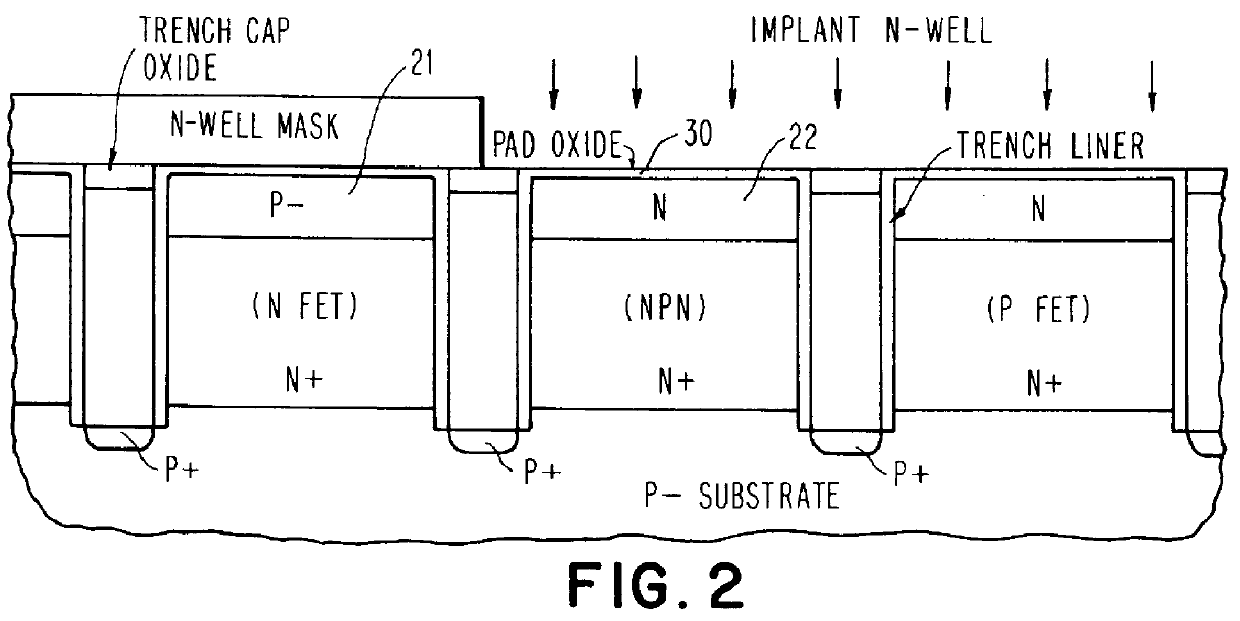

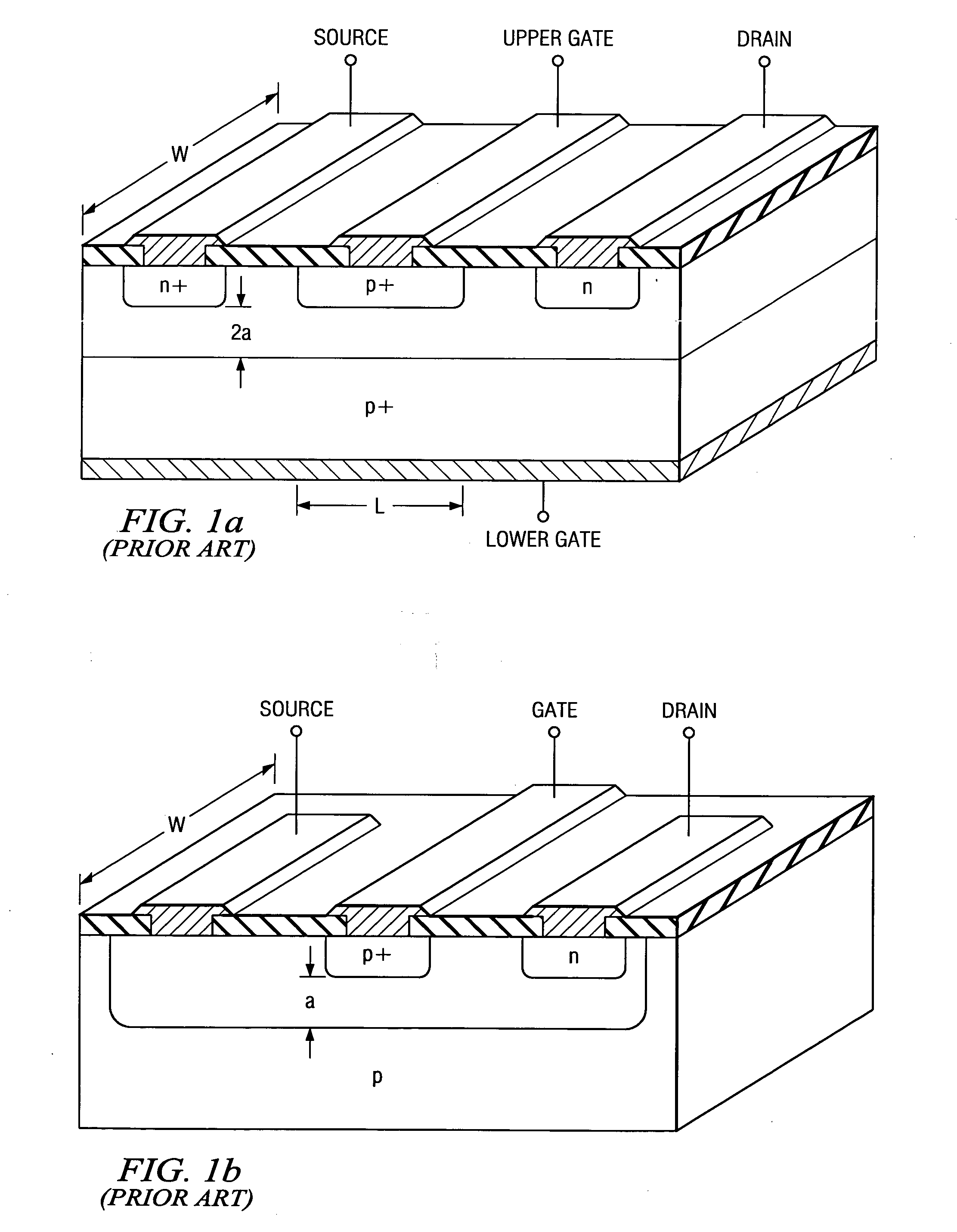

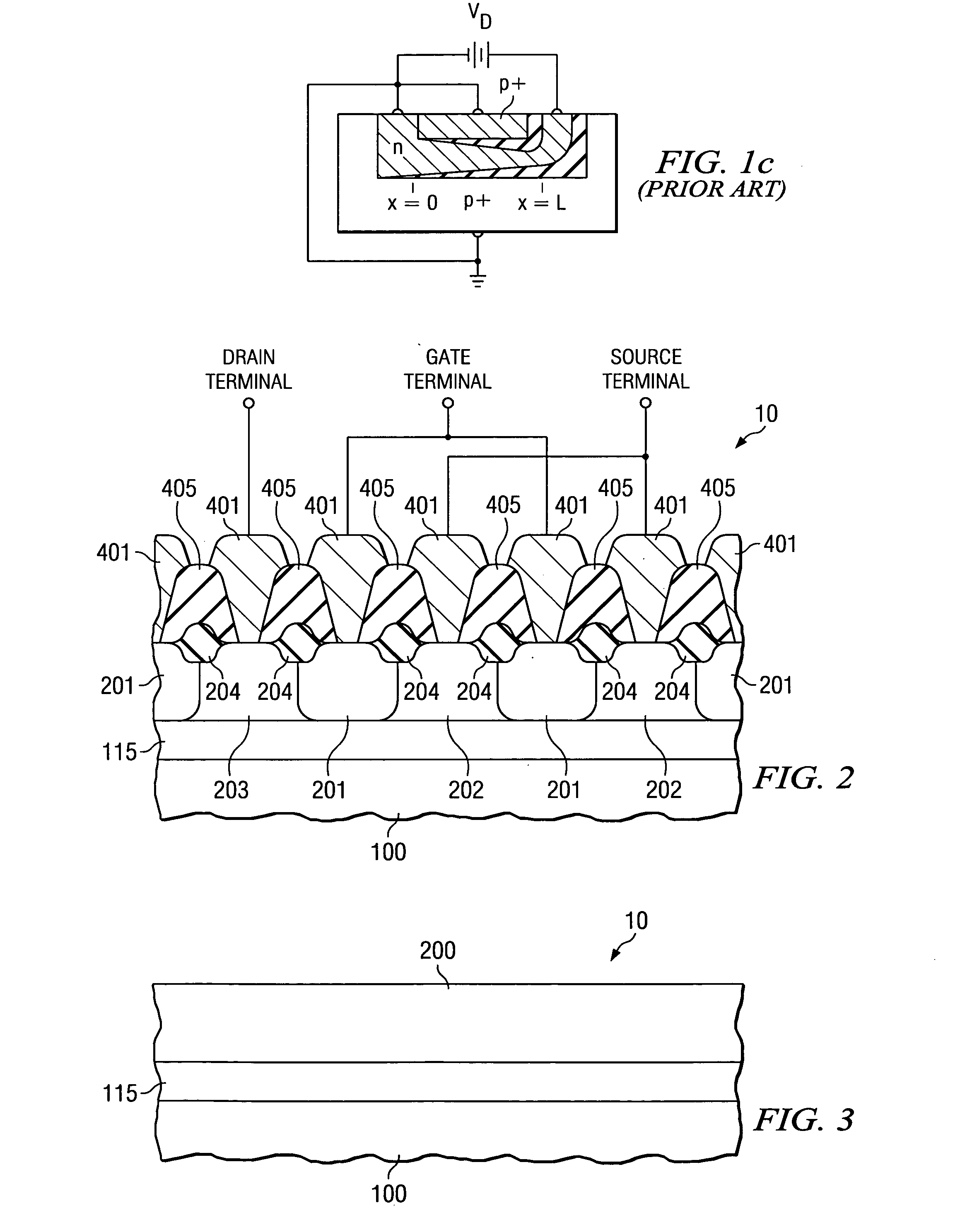

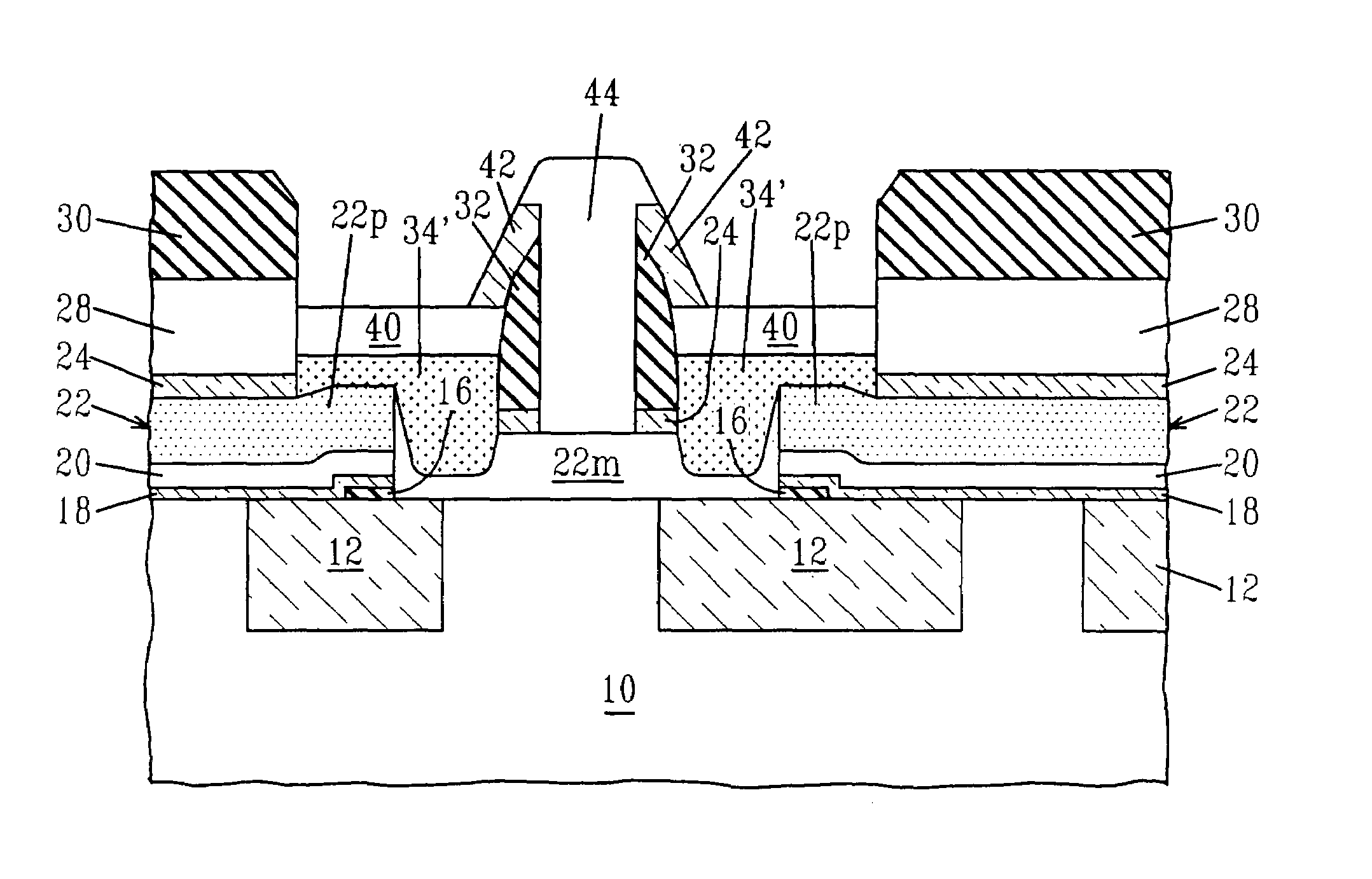

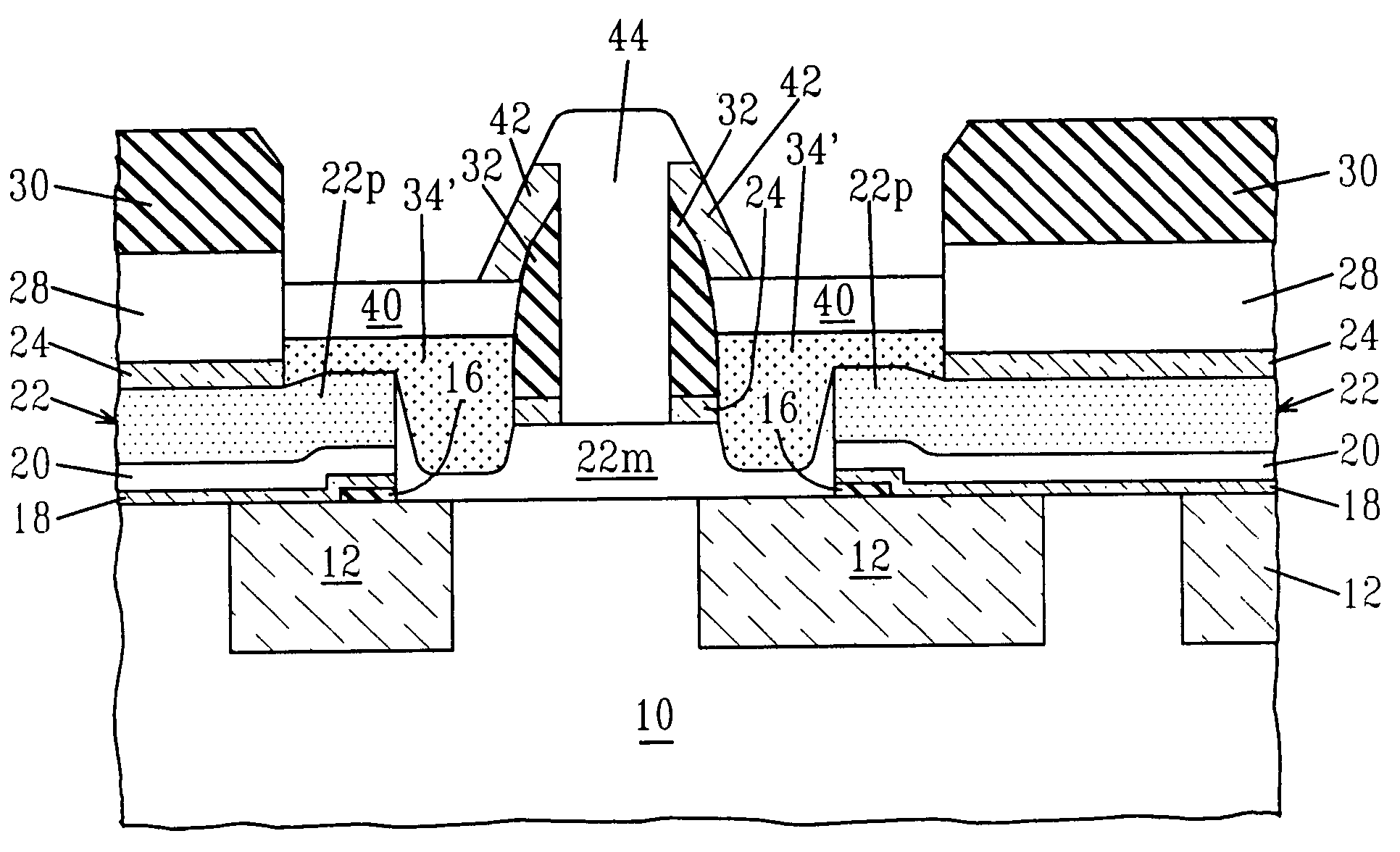

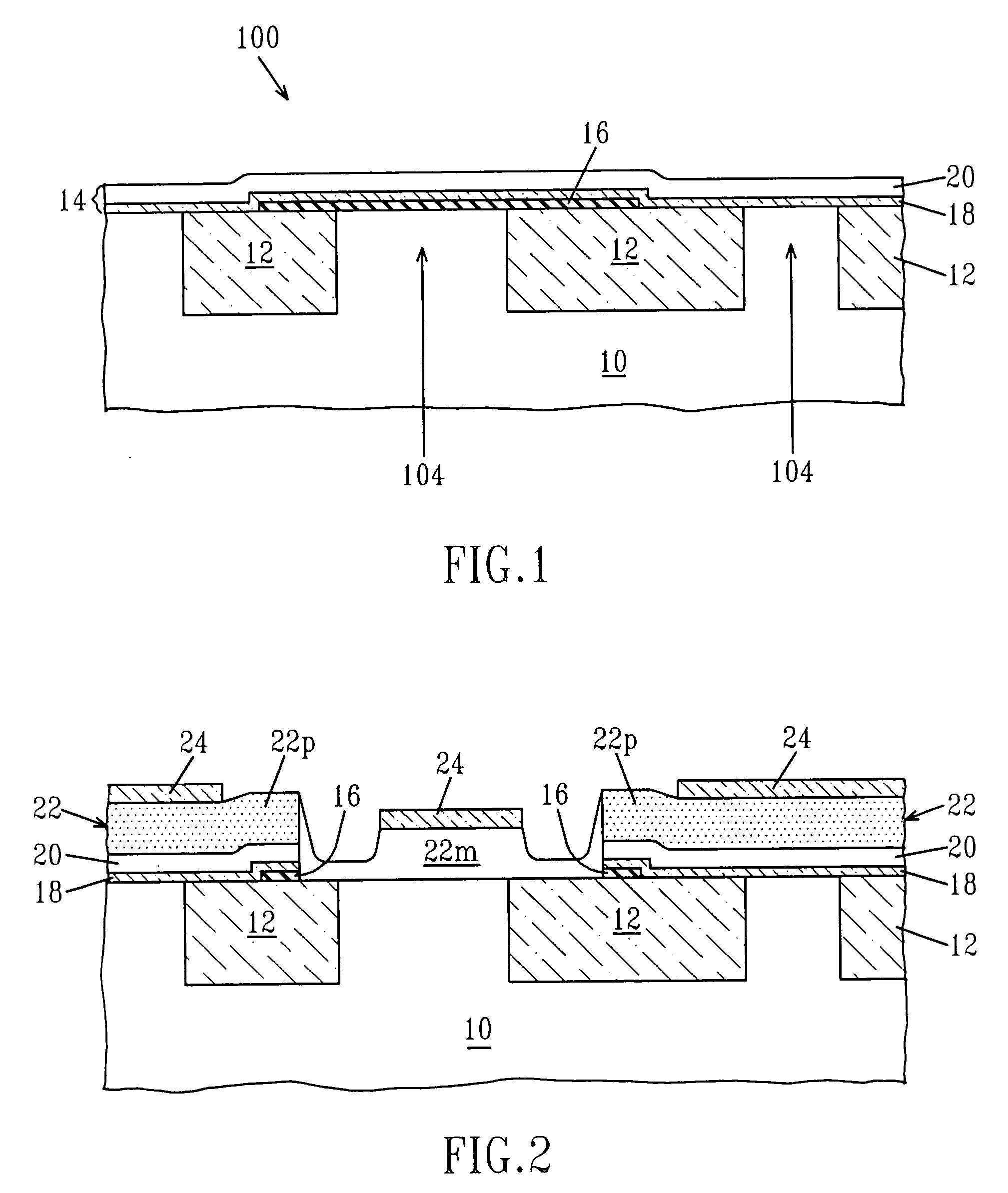

High performance/high density BICMOS process

InactiveUS6071767AReliably carry-outImprove production yieldSolid-state devicesSemiconductor/solid-state device manufacturingDevice typeHigh density

An integrated circuit using high-performance bipolar and CMOS transistor elements on a single chip is fabricated by a simplified process requiring minimal, if any, changes in the process used for forming either type of device in accordance with a variety of possible device designs. The method according to the invention makes maximal use of self-aligned and self-masking processes to reduce the number of processing steps. The number of processing steps is further reduced by performing some steps concurrently on different device types. Further, the masking steps which are employed are reasonably misregistration tolerant, resulting in high manufacturing yield for the process. Consequently, the process according to the invention substantially eliminates the existence of trade-offs between element performance, integration density and process complexity and cost when plural technologies are integrated on the same chip.

Owner:IBM CORP

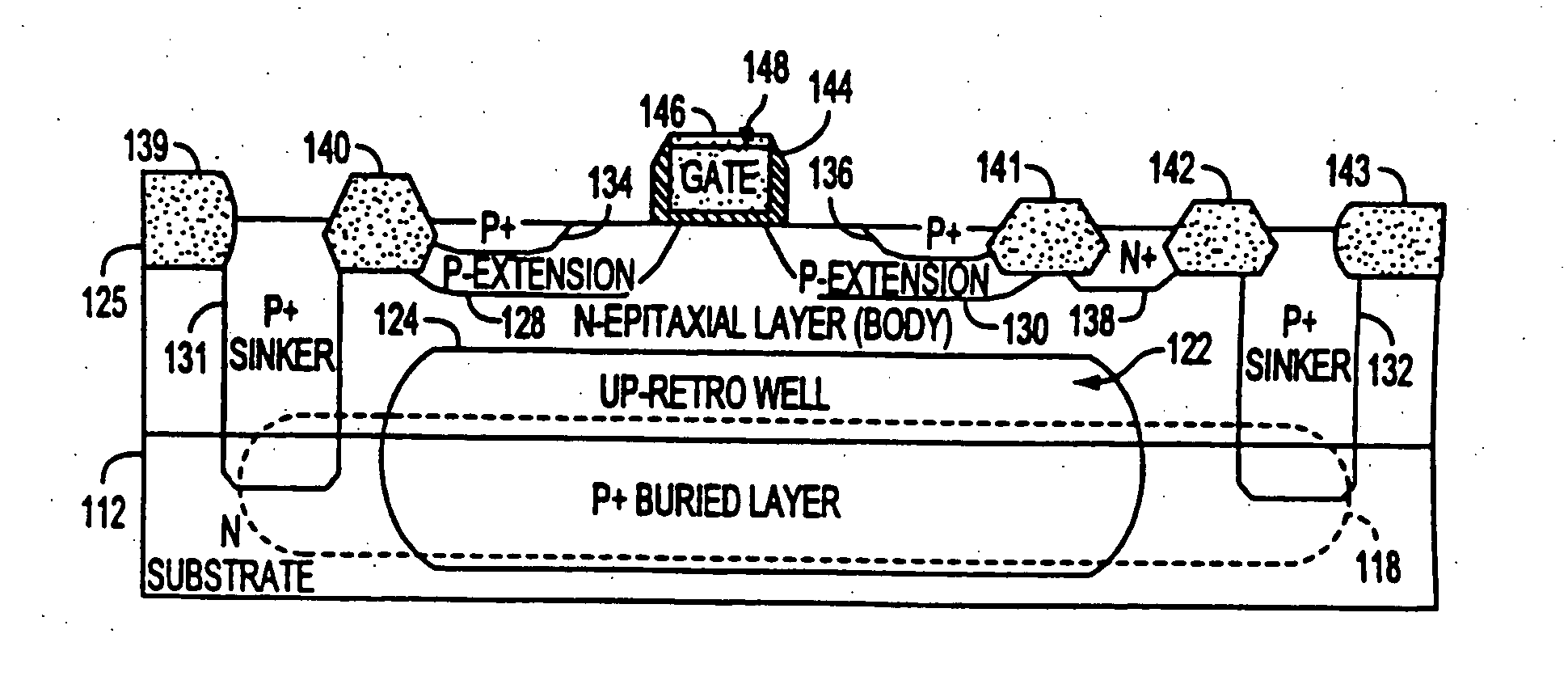

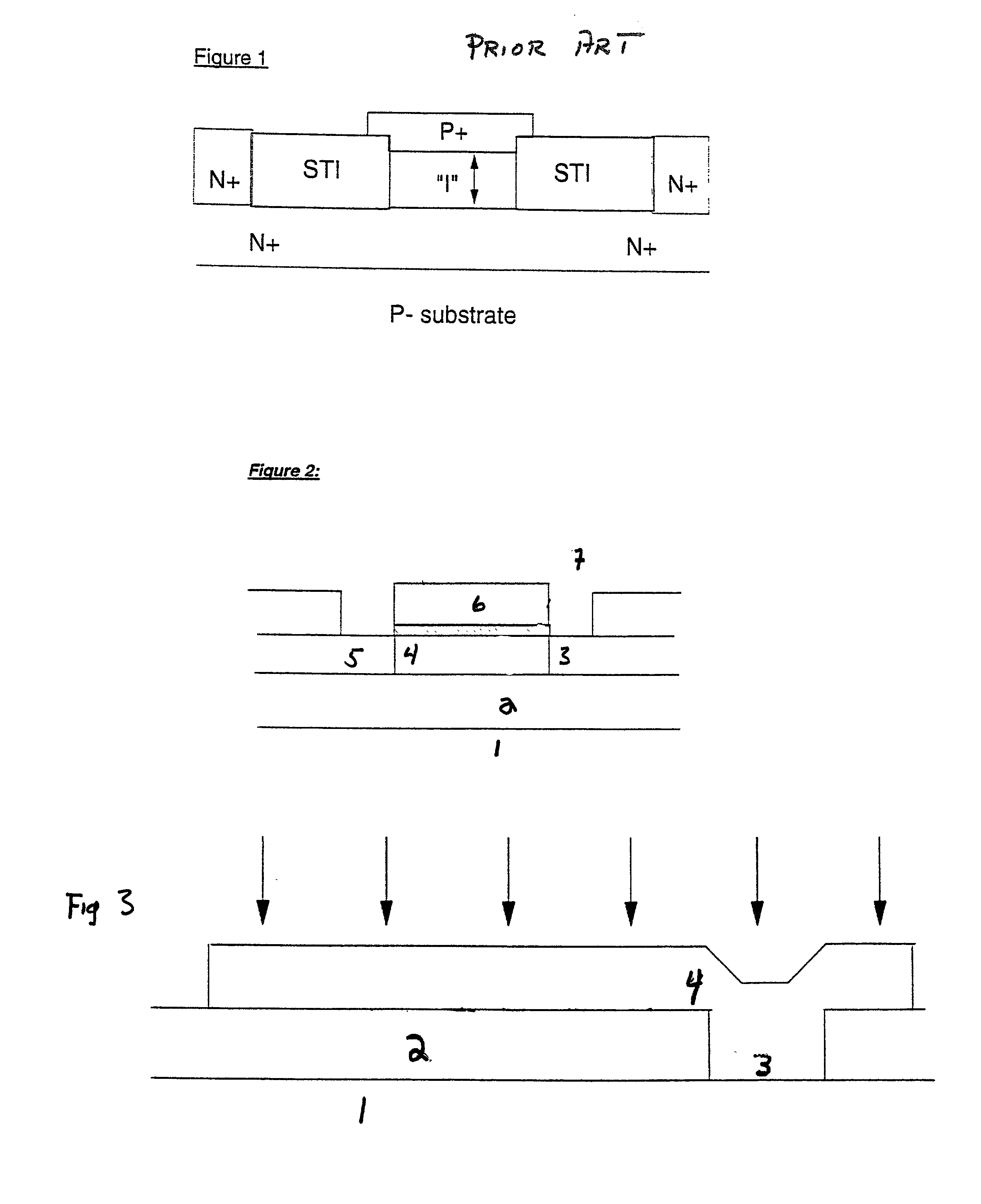

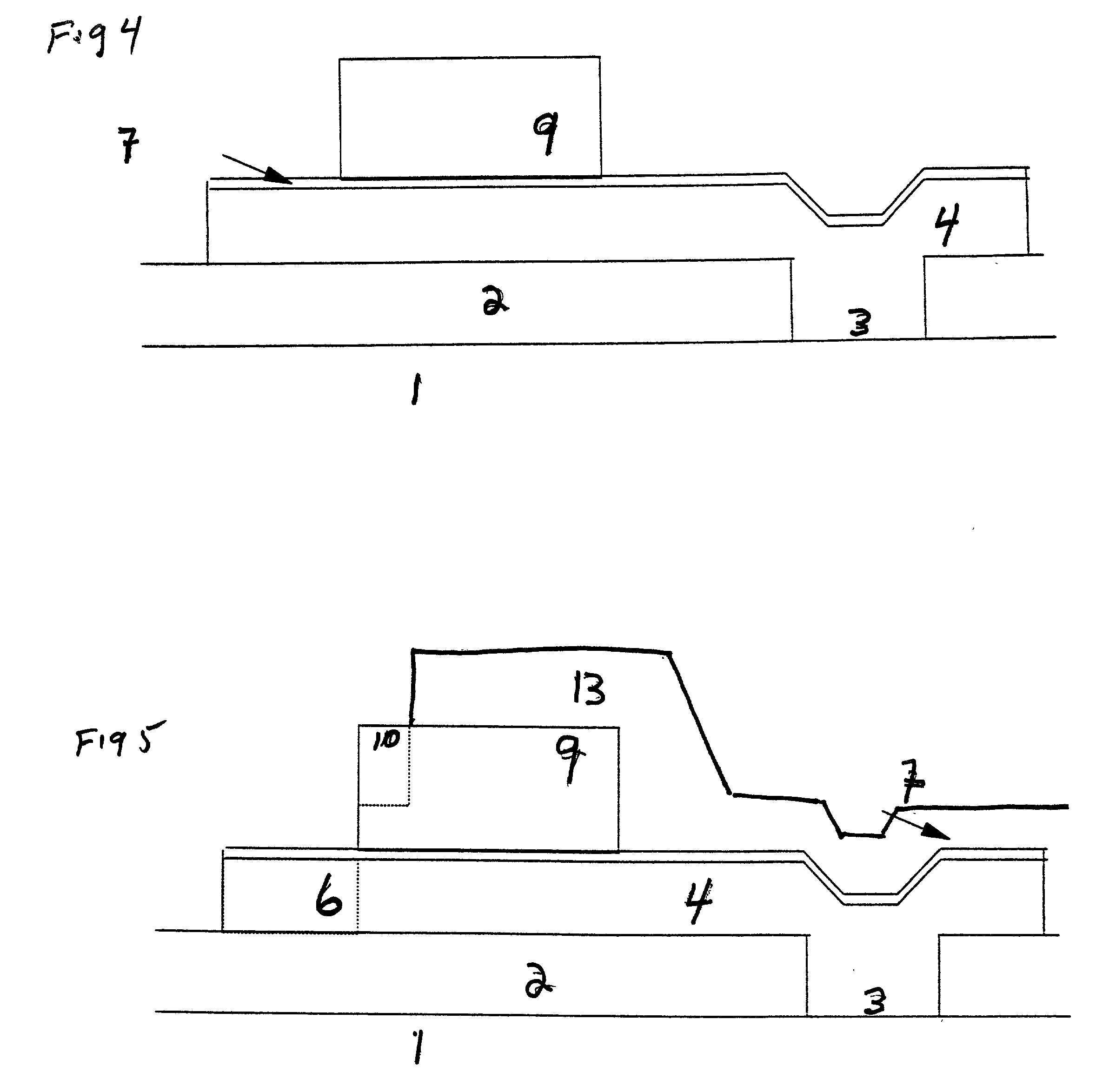

High voltage MOS transistor with up-retro well

InactiveUS20060071269A1Thin layerHigh voltageTransistorSemiconductor/solid-state device detailsDopantCMOS

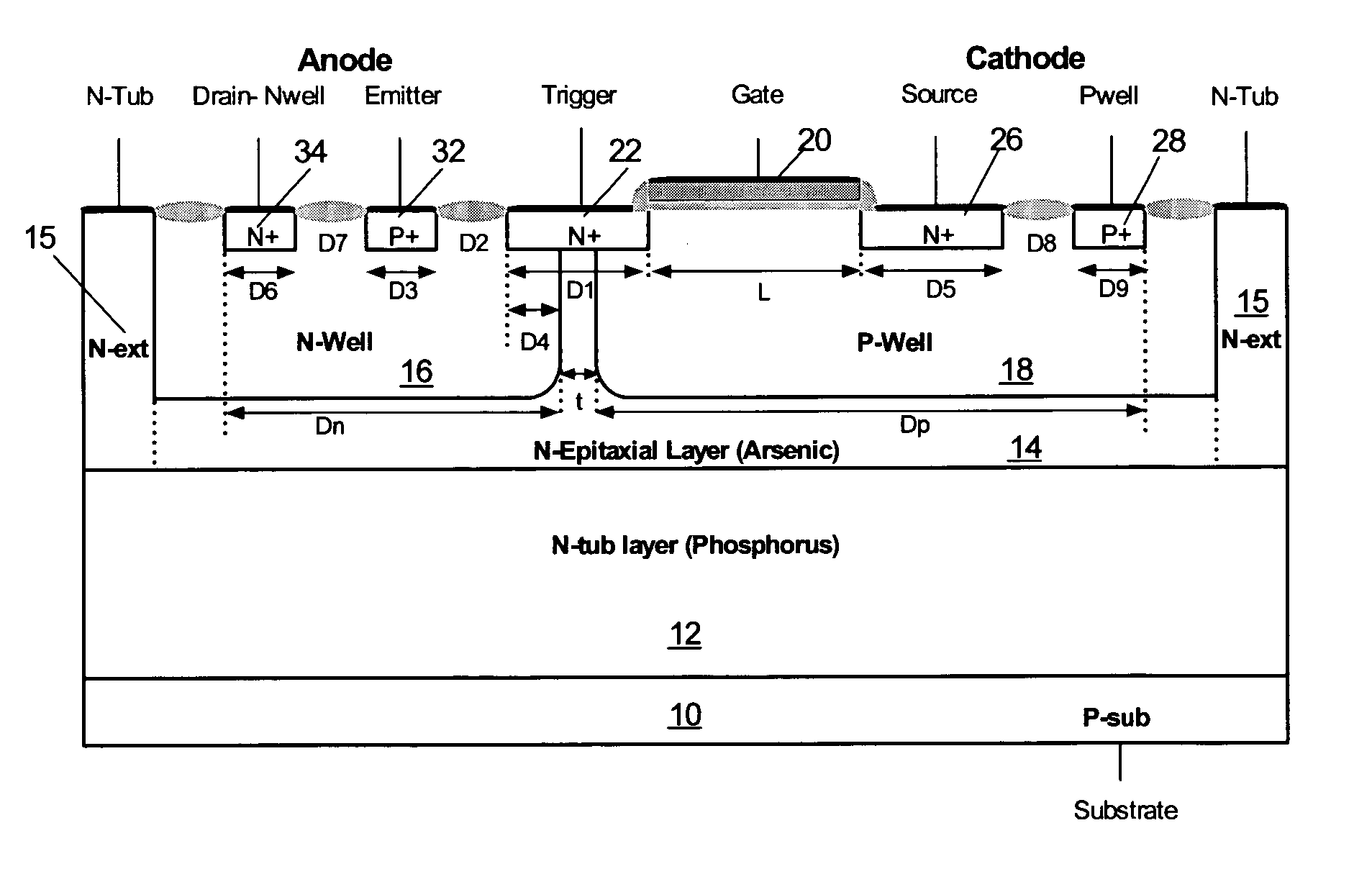

A high voltage MOS transistor is provided that is compatible with low-voltage, sub-micron CMOS and BiCMOS processes. The high voltage transistor of the present invention has dopants that are implanted into the substrate prior to formation of the epitaxial layer. The implanted dopants diffuse into the epitaxial layer from the substrate during the formation of the epitaxial layer and subsequent heating steps. The implanted dopants increase the doping concentration in a lower portion of the epitaxial layer. The implanted dopants may diffuse father into the epitaxial layer than dopants in the buried layer forming an up-retro well that prevents vertical punch-through at high operating voltages for thin epitaxial layers. In addition, the doping concentration below the gate may be light so that the threshold voltage of the transistor is low. Also, the high voltage transistor of the present invention may be isolated from the substrate and the buried layer, and have symmetrical source and drain regions so that it can be used as a pass transistor.

Owner:ANALOG DEVICES INT UNLTD

Low noise vertical variable gate control voltage JFET device in a BiCMOS process and methods to build this device

We disclose the structure of a JFET device, the method of making the device and the operation of the device. The device is built near the top of a substrate. It has a buried layer that is electrically communicable to a drain terminal. It has a channel region over the buried layer contacting gate regions that connect to a gate terminal. The channel region, of which the length spans the distance between the buried layer and a source region, is connected to a source terminal. The device current flows in the channel substantially perpendicularly to the top surface of the substrate.

Owner:TEXAS INSTR INC

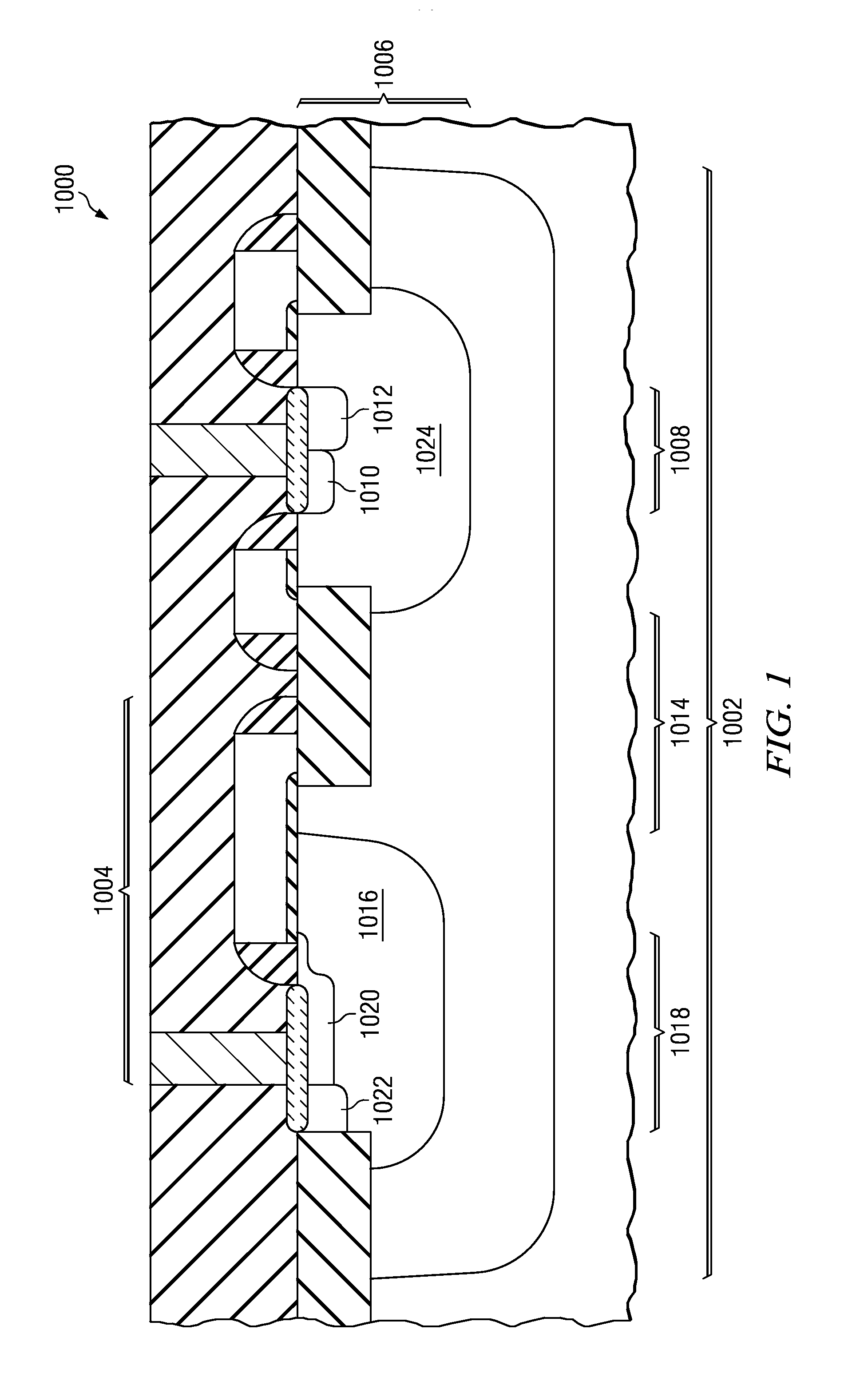

Method to fabricate high-performance NPN transistors in a BiCMOS process

InactiveUS6906401B2Simple and reliable processImprove reliabilityTransistorSolid-state devicesLithographic artistEngineering

A method of forming a quasi-self-aligned heterojunction bipolar transistor (HBT) that exhibits high-performance is provided. The method includes the use of a patterned emitter landing pad stack which serves to improve the alignment for the emitter-opening lithography and as an etch stop layer for the emitter opening etch. The present invention also provides an HBT that includes a raised extrinsic base having monocrystalline regions located beneath the emitter landing pad stack.

Owner:GLOBALFOUNDRIES US INC

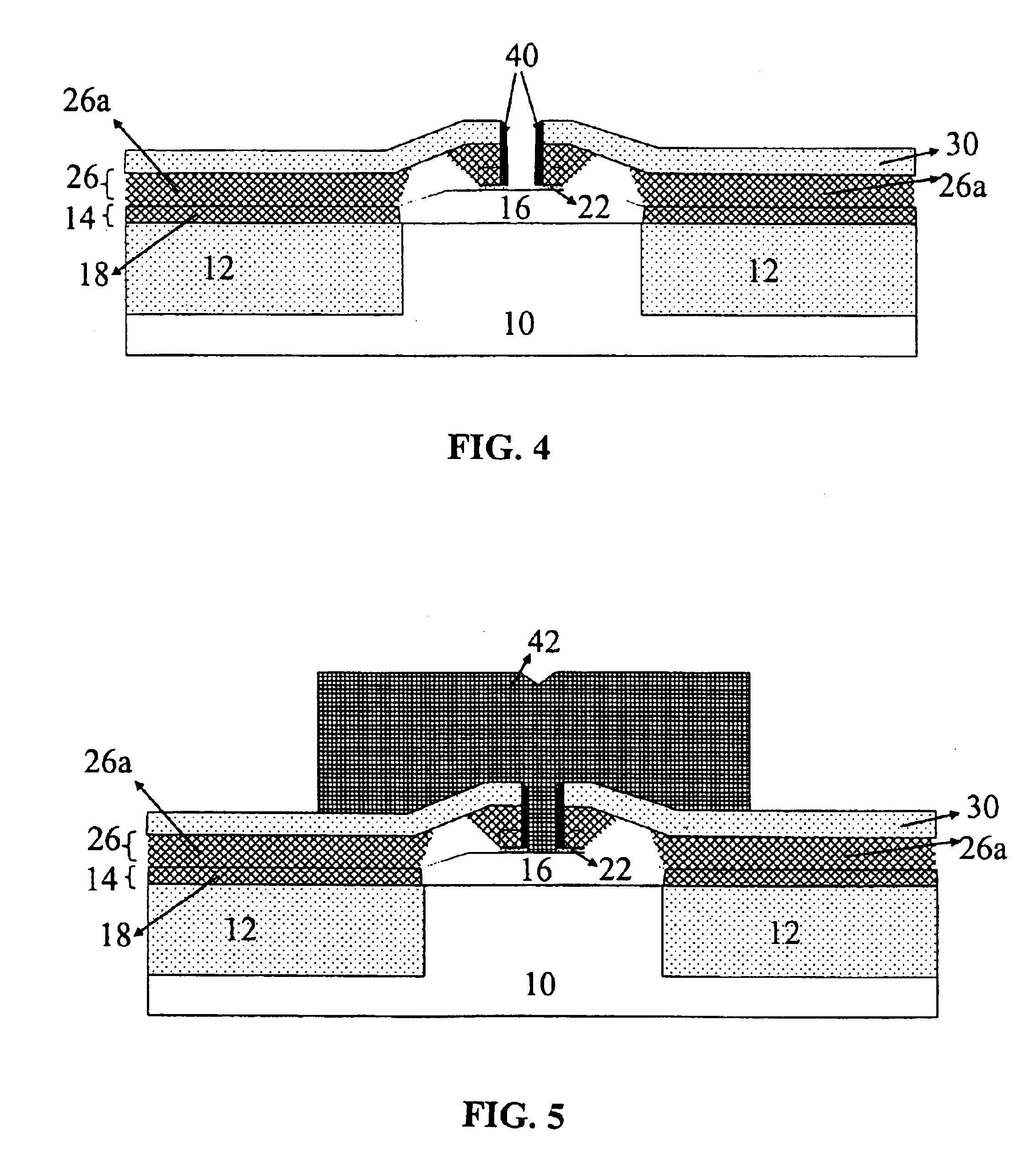

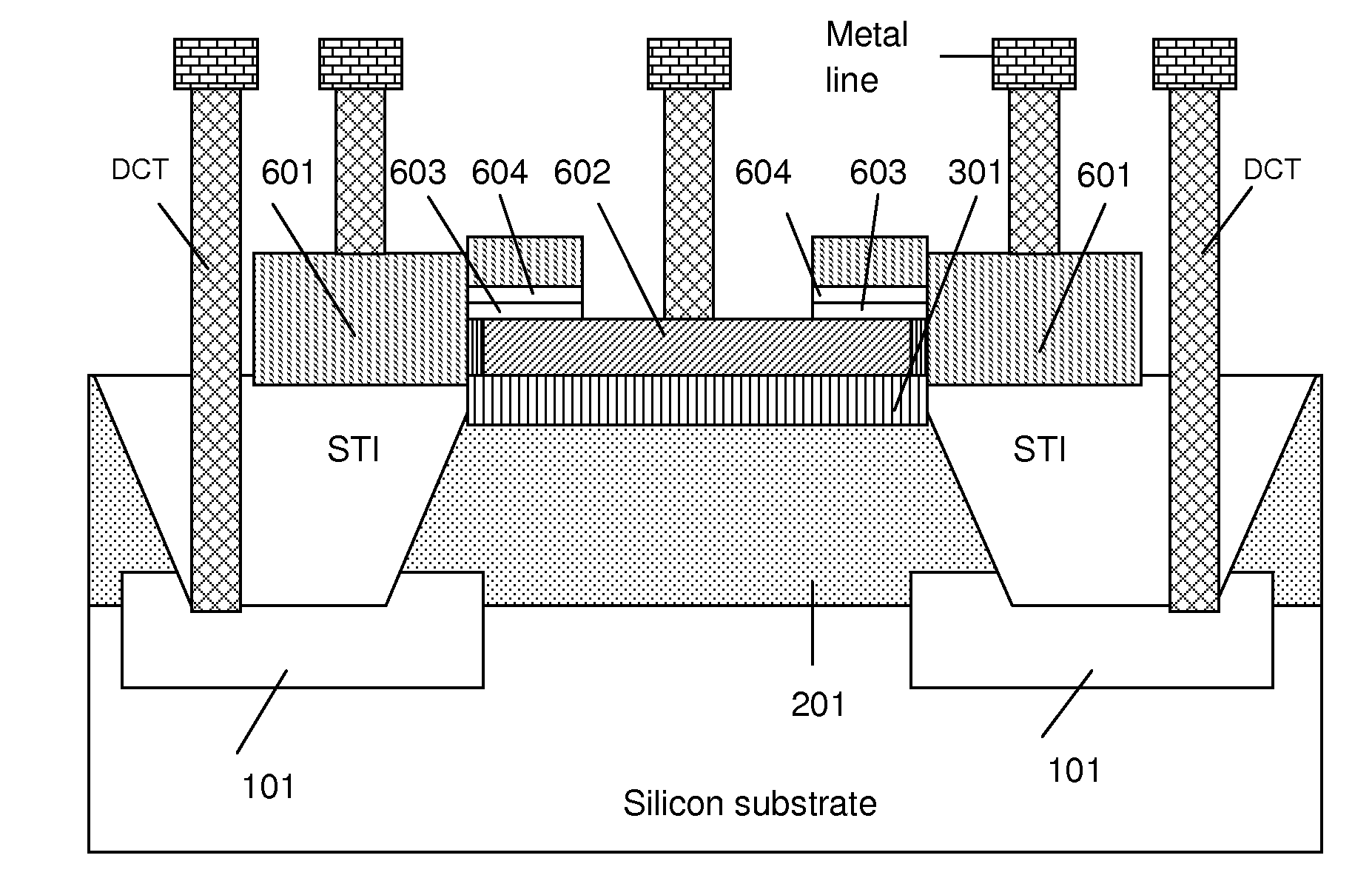

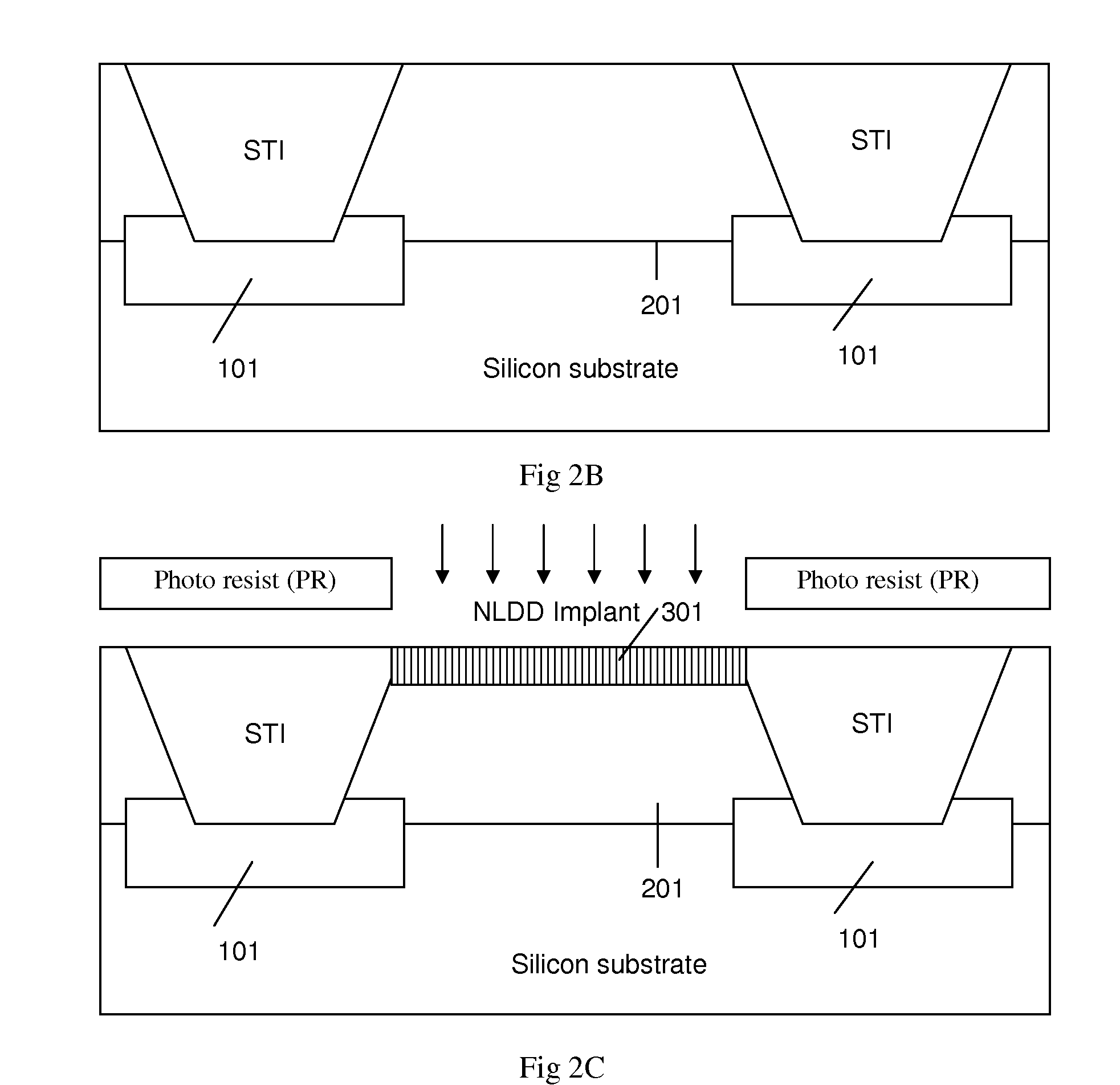

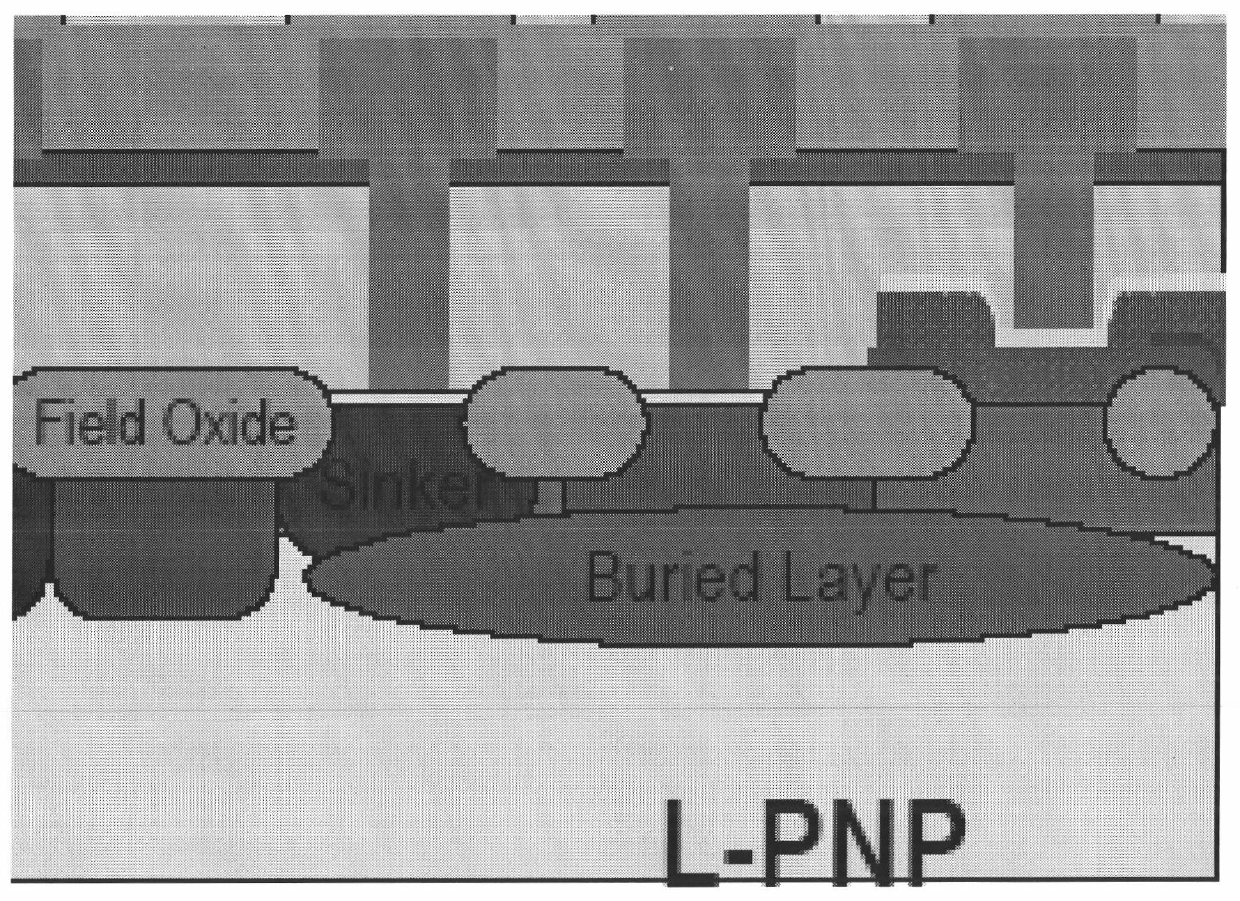

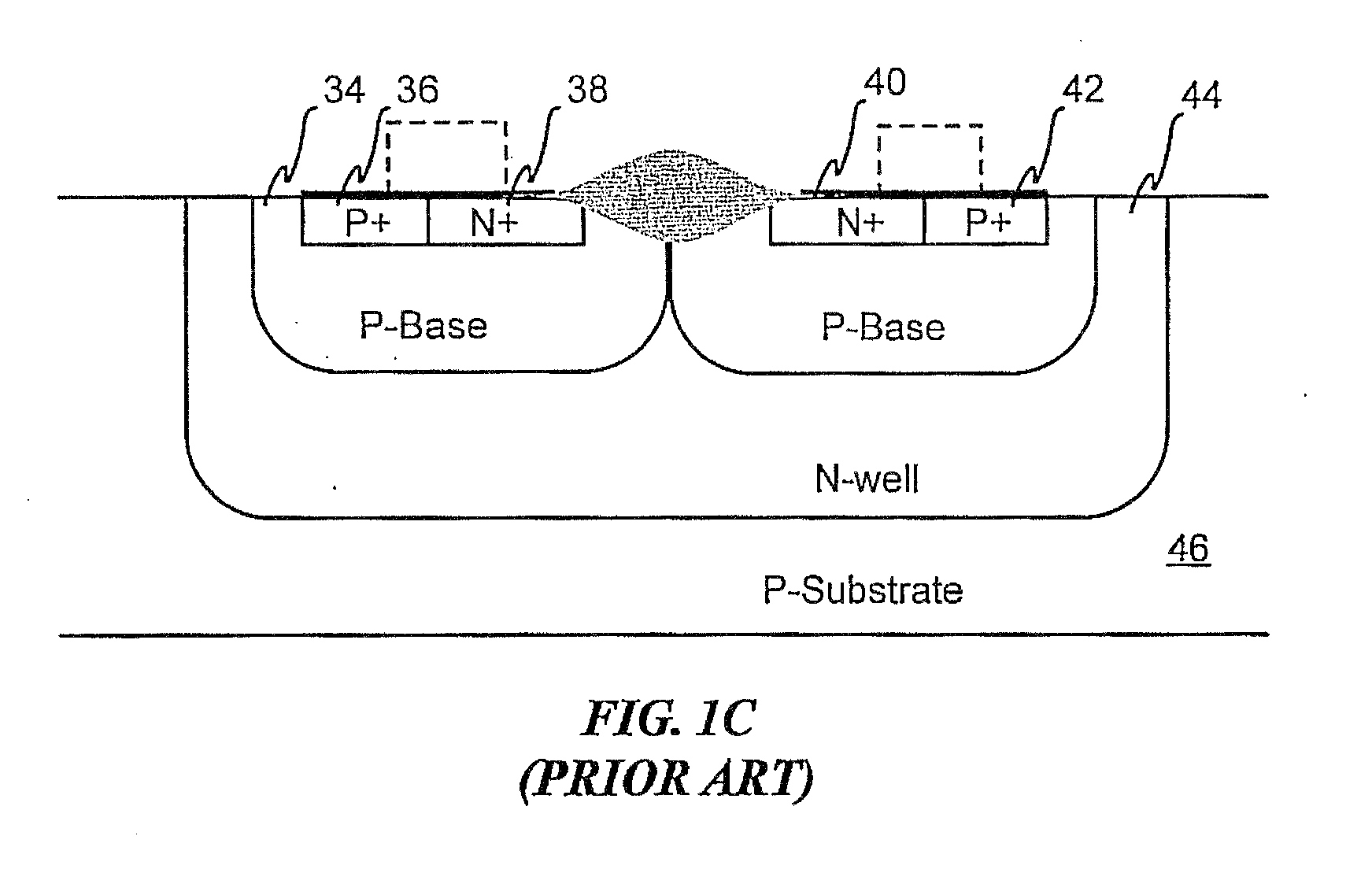

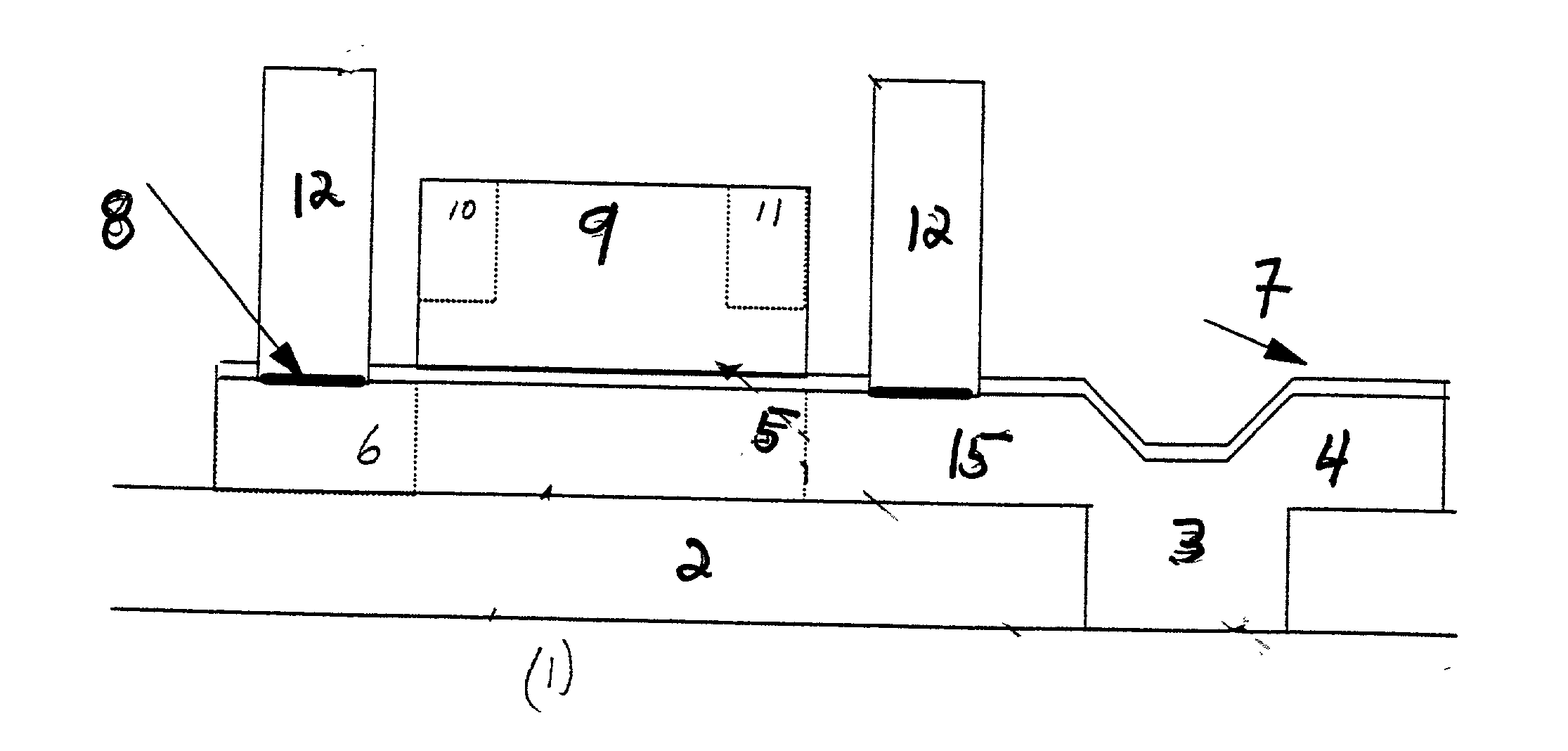

Parasitic Vertical PNP Bipolar Transistor in BICMOS Process

ActiveUS20110156202A1Small device sizeLower resistanceTransistorSolid-state devicesImpurity ionsIon implantation

A parasitic vertical PNP device in one type of BiCMOS process with shallow trench isolation (STI) comprises a collector formed by a p type impurity ion implantation layer inside active area, the bottom of collector connects to a p type buried layer, the p type pseudo buried layer is formed in bottom of shallow trench at both sides of collector active region through ion implantation, deep contacts through field oxide to connect pseudo buried layers and to pick up the collector; a base, formed by n type impurity ion implantation layer which sits on top of above stated collector; an emitter, a p type epitaxy layer lies above base and is connected out directly by a metal contact. Part of the p type epitaxy layer is converted into n type, which serves as connection path of base. Present invented PNP can be used as output device of BiCMOS high frequency circuit. It has a small device area and conduction resistance.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

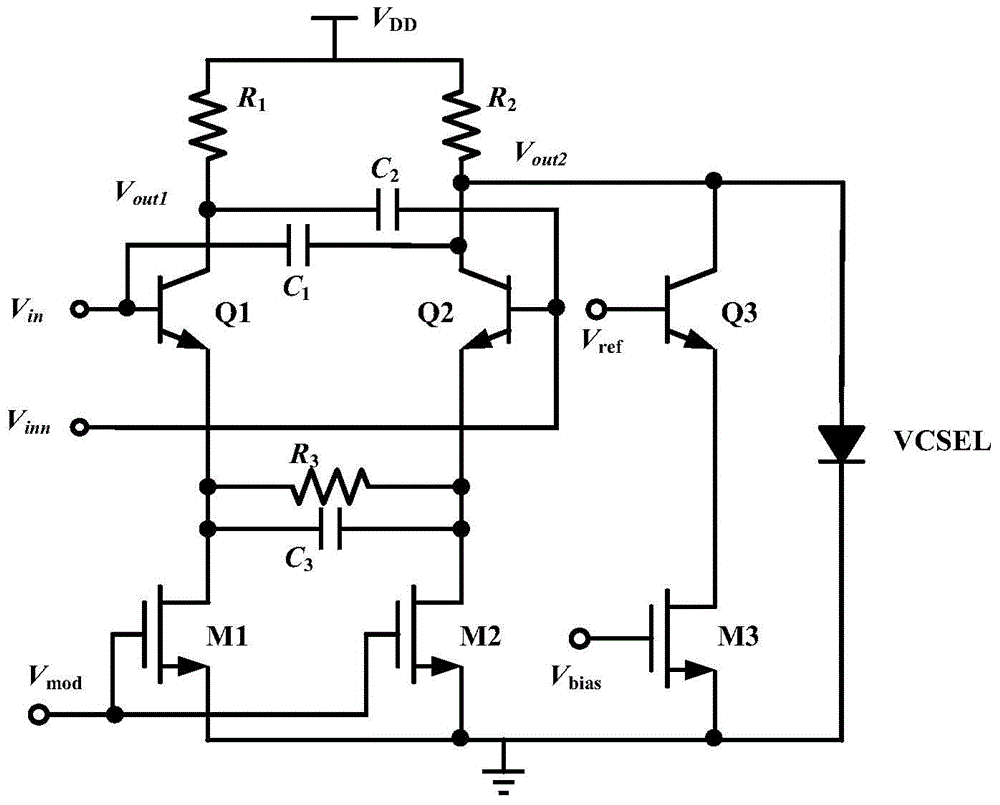

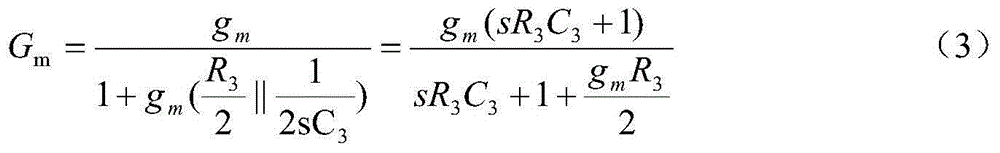

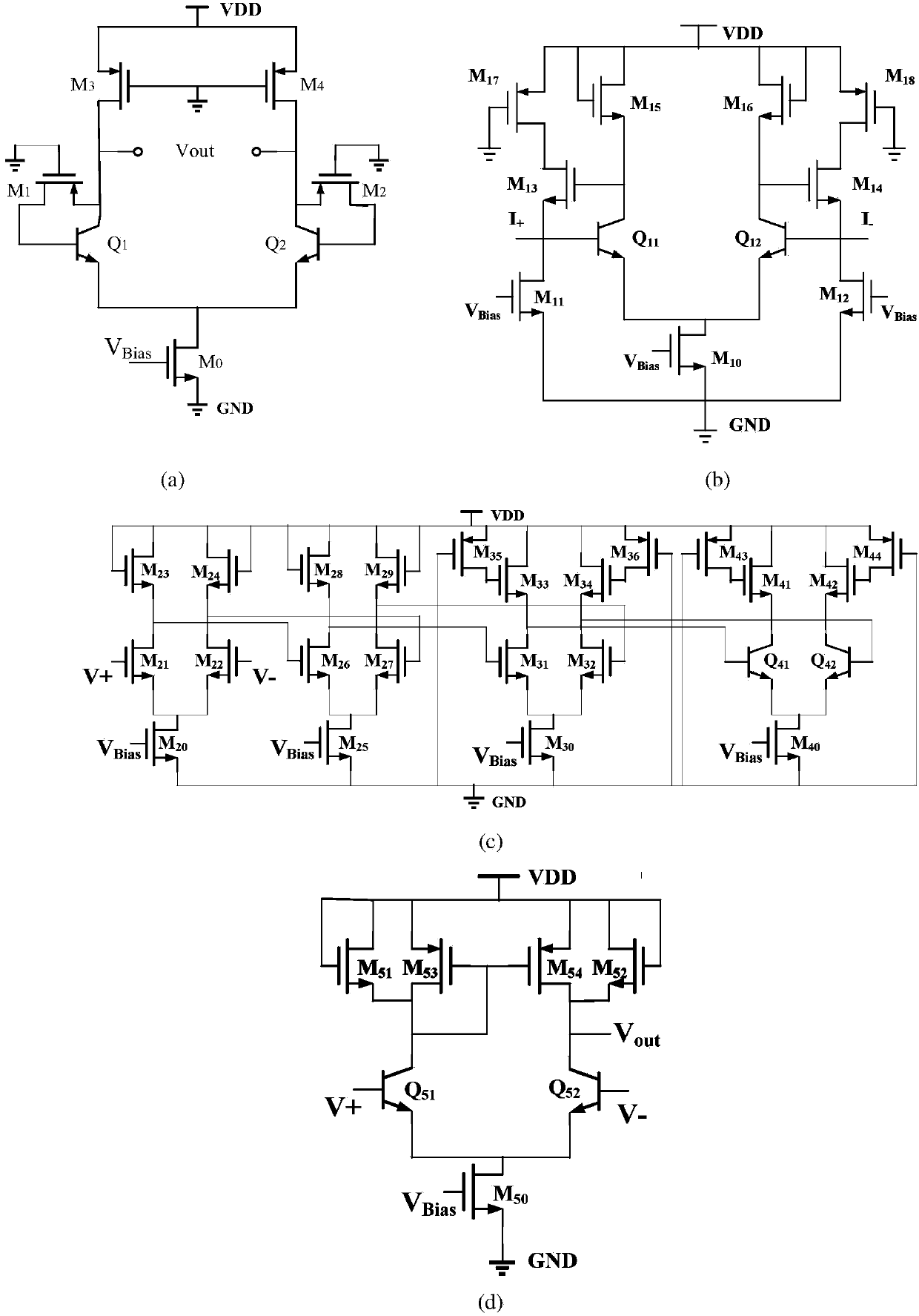

Ultra high speed laser driver circuit with bandwidth compensation and driver chip

ActiveCN104617483AMinimize the effect of parasitic capacitanceHigh bandwidthLaser detailsSemiconductor lasersEngineeringFeedback circuits

The invention discloses an ultra high speed laser driver circuit with bandwidth compensation and a diver chip; the feedback circuit composed of two cross coupling capacitors and the capacitor and the resistor connected in a parallel mode is used for executing the laser driver bandwidth compensation. For two cross coupling capacitors, the stray capacitance between the base and the collector can be eliminated; for the feedback mode of one capacitor and one resistor, one zero point is generated for compensating the pole for realizing the bandwidth compensation; and the modulating current directly flows to the laser diode through the load resistor, so that the laser diode can obtain larger modulating current. The laser driver circuit and the driver chip having pre-emphasis function are simple in structure, high in bandwidth, large in modulating current and low in power consumption; the chip adopts the resistor and capacitor for expanding the bandwidth, the occupied area is small and the chip cost is reduced; the work speed is 40Gb / s through the 0.13 mum BiCMOS process certification and the output modulating current is greater than 10 mA.

Owner:SOUTHEAST UNIV

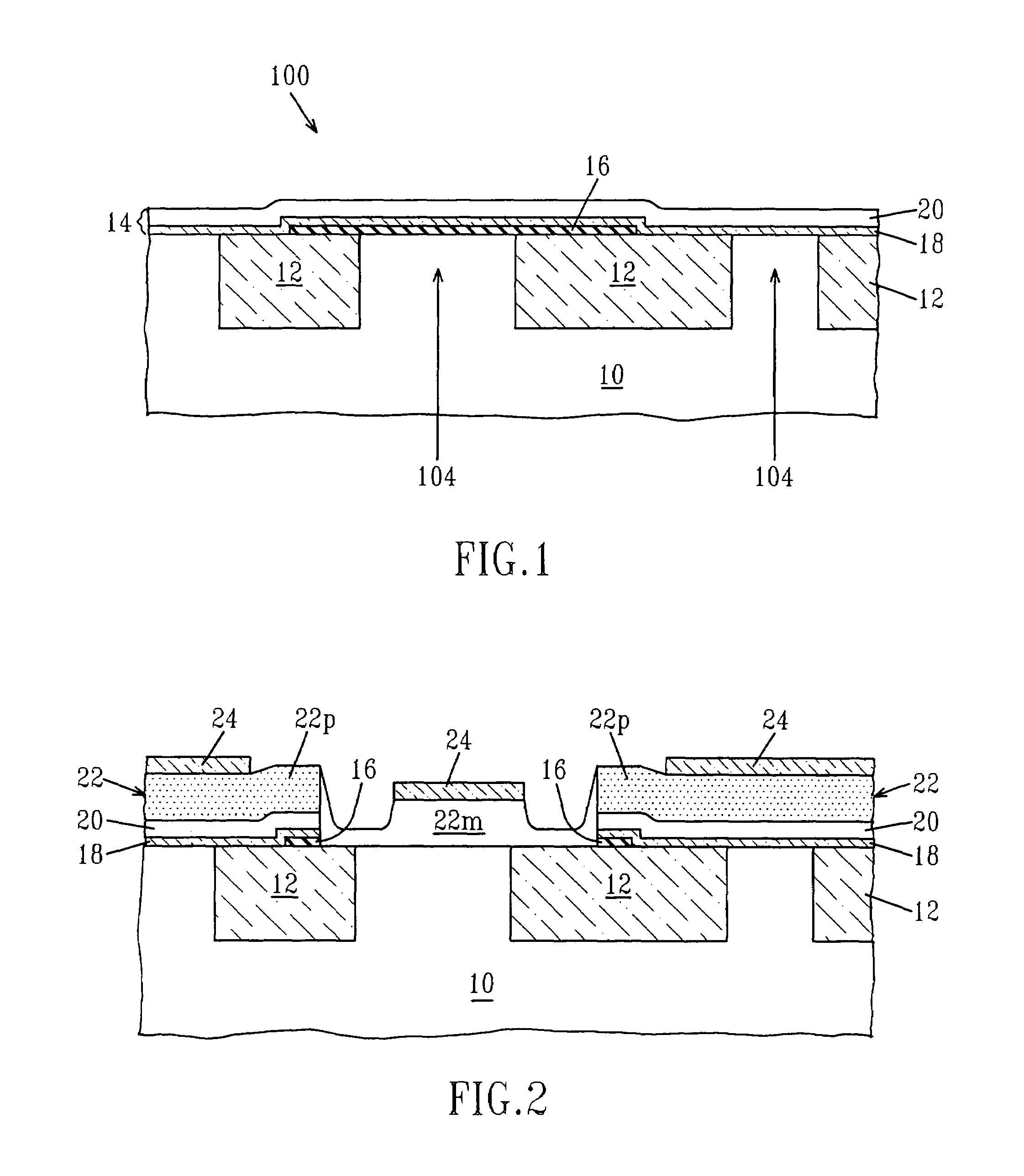

Method for integrating DMOS into sub-micron CMOS process

ActiveUS7544558B2Easy to addTransistorSemiconductor/solid-state device manufacturingContinuous useDevice form

This invention is forming the DMOS channel after CMOS active layer before gate poly layer to make the modular DMOS process step easily adding into the sub-micron CMOS or BiCMOS process. And DMOS source is formed by implant which is separated by a spacer self-aligned to the window for DMOS body. By this method, the performance of CMOS and bipolar devices formed original CMOS or BiCMOS process keeps no change. The product design kit, such as standard cell library of CMOS and BiCMOS, can be used continuously with no change.

Owner:BCD SHANGHAI MICRO ELECTRONICS CO LTD

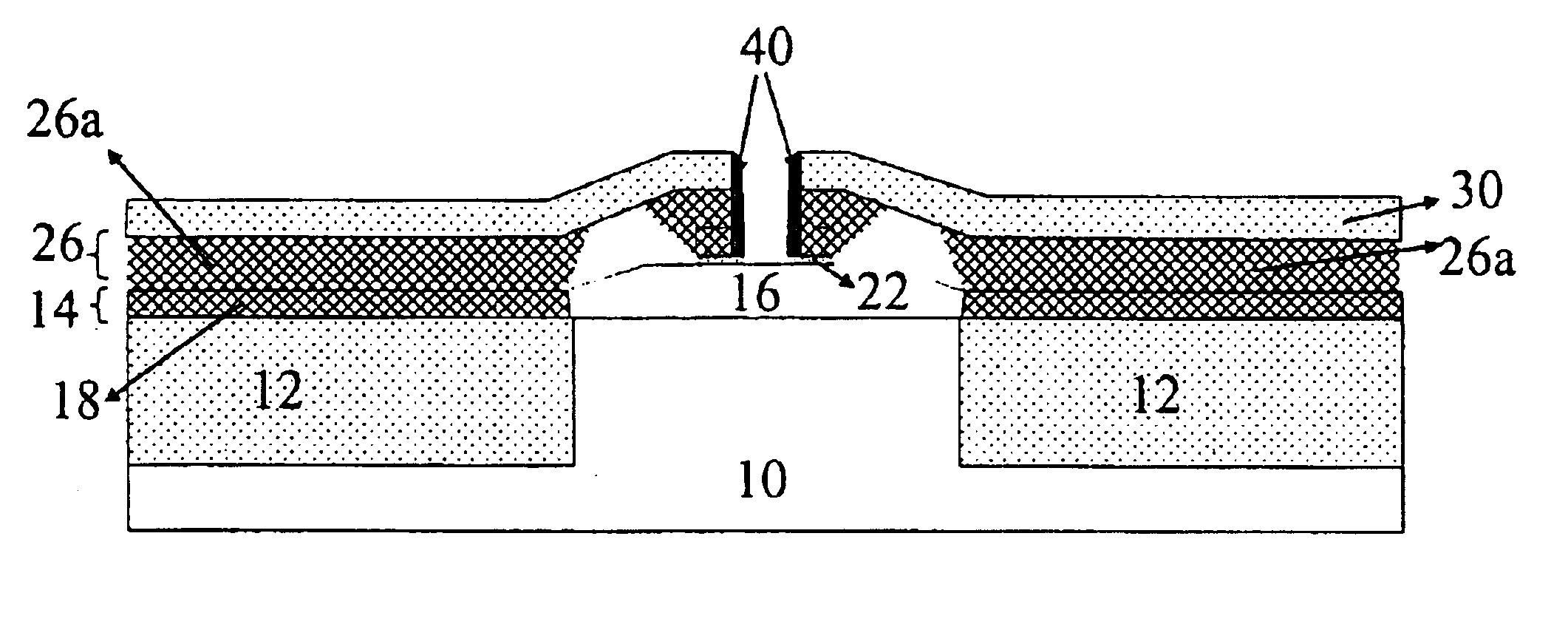

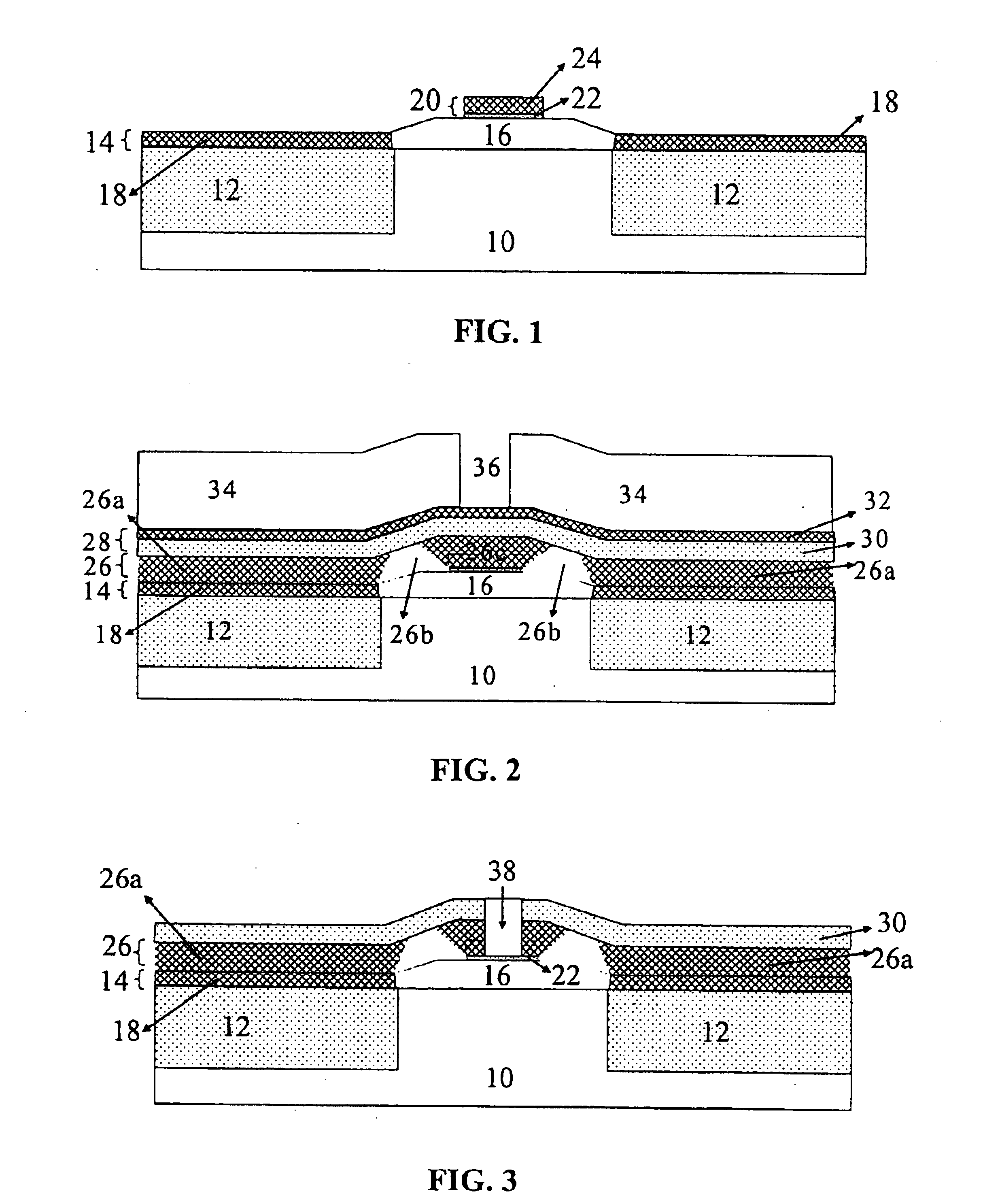

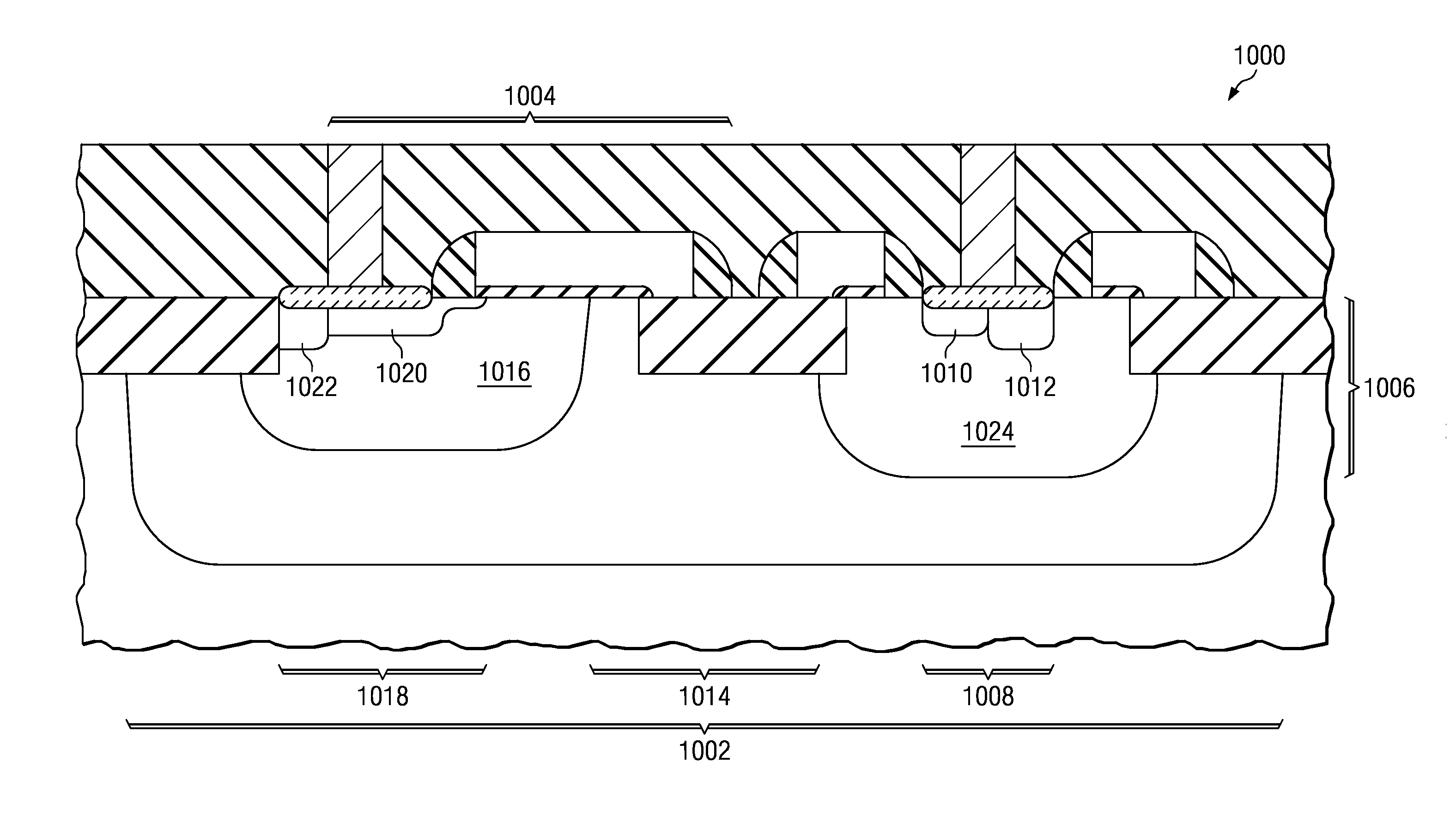

Method of base formation in a BiCMOS process

Methods for fabricating a heterojunction bipolar transistor having a raised extrinsic base is provided in which the base resistance is reduced by forming a silicide atop the raised extrinsic base that extends to the emitter region in a self-aligned manner. The silicide formation is incorporated into a BiCMOS process flow after the raised extrinsic base has been formed. The present invention also provides a heterojunction bipolar transistor having a raised extrinsic base and a silicide located atop the raised extrinsic base. The silicide atop the raised extrinsic base extends to the emitter in a self-aligned manner. The emitter is separated from the silicide by a spacer.

Owner:INT BUSINESS MASCH CORP

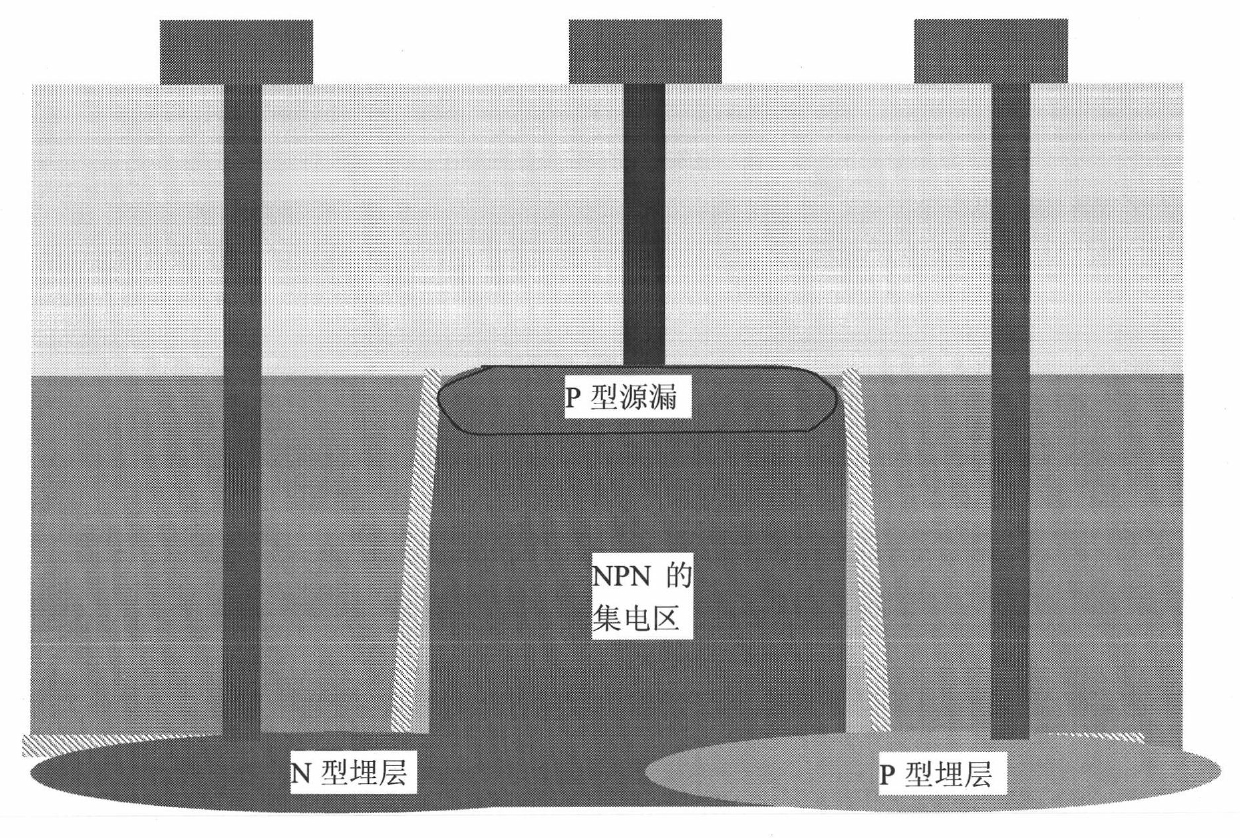

PNP bipolar transistor in SiGe BiCMOS technology

ActiveCN102088029AReduce areaIncreased current amplification factorSemiconductor/solid-state device manufacturingSemiconductor devicesBicmos technologyIon implantation

The present invention discloses a PNP bipolar transistor in a SiGe BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) technology, an active region of the bipolar transistor is isolated by making use of shallow groove field oxide layers and comprises a collector region, a base region and an emitter region, wherein the collector region is formed by a P-type buried layer located at the bottom of the shallow groove, and led out by making a deep trap contact on the field oxide layers; the base region is formed by N-type ion implantation in the active region, peripheral sides of the base region are the shallow groove field oxide layers, width of the base region is equal to depth of the shallow groove, and the bottom of the base region is connected with the collector region; an N-type buried layer is formed at the bottom of the shallow groove located at the opposite side of the collector region, the base region is connected with the N-type buried layer and led out by making the deep trap contact on the field oxide layer on the N-type buried layer; and the emitter region is formed by a P-type ion implantation layer formed above the base region or by further providing a P-type polycrystalline silicon. The PNP bipolar transistor in the present invention can reduce area of the PNP transistor and raise current amplification factor of the PNP transistor.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Lateral polysilicon pin diode and method for so fabricating

InactiveUS6426547B1Increase storage areaReduce parasitic capacitancePhotovoltaic energy generationSemiconductor devicesEngineeringBicmos process

Owner:GLOBALFOUNDRIES INC

SELF-ALIGNED VERTICAL PNP TRANSISTOR FOR HIGH PERFORMANCE SiGe CBiCMOS PROCESS

A structure and a process for a self-aligned vertical PNP transistor for high performance SiGe CBiCMOS process. Embodiments include SiGe CBiCMOS with high-performance SiGe NPN transistors and PNP transistors. As the PNP transistors and NPN transistors contained different types of impurity profile, they need separate lithography and doping step for each transistor. The process is easy to integrate with existing CMOS process to save manufacturing time and cost. As plug-in module, fully integration with SiGe BiCMOS processes. High doping Polysilicon Emitter can increase hole injection efficiency from emitter to base, reduce emitter resistor, and form very shallow EB junction. Self-aligned N+ base implant can reduce base resistor and parasitical EB capacitor. Very low collector resistor benefits from BP layer. PNP transistor can be Isolated from other CMOS and NPN devices by BNwell, Nwell and BN+ junction.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Self-aligned vertical PNP transistor for high performance SiGe CBiCMOS process

A structure and a process for a self-aligned vertical PNP transistor for high performance SiGe CBiCMOS process. Embodiments include SiGe CBiCMOS with high-performance SiGe NPN transistors and PNP transistors. As the PNP transistors and NPN transistors contained different types of impurity profile, they need separate lithography and doping step for each transistor. The process is easy to integrate with existing CMOS process to save manufacturing time and cost. As plug-in module, fully integration with SiGe BiCMOS processes. High doping Polysilicon Emitter can increase hole injection efficiency from emitter to base, reduce emitter resistor, and form very shallow EB junction. Self-aligned N+ base implant can reduce base resistor and parasitical EB capacitor. Very low collector resistor benefits from BP layer. PNP transistor can be Isolated from other CMOS and NPN devices by BNwell, Nwell and BN+ junction.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Method of base formation in a bicmos process

Methods for fabricating a heterojunction bipolar transistor having a raised extrinsic base is provided in which the base resistance is reduced by forming a silicide atop the raised extrinsic base that extends to the emitter region in a self-aligned manner. The silicide formation is incorporated into a BiCMOS process flow after the raised extrinsic base has been formed. The present invention also provides a heterojunction bipolar transistor having a raised extrinsic base and a silicide located atop the raised extrinsic base. The silicide atop the raised extrinsic base extends to the emitter in a self-aligned manner. The emitter is separated from the silicide by a spacer.

Owner:IBM CORP

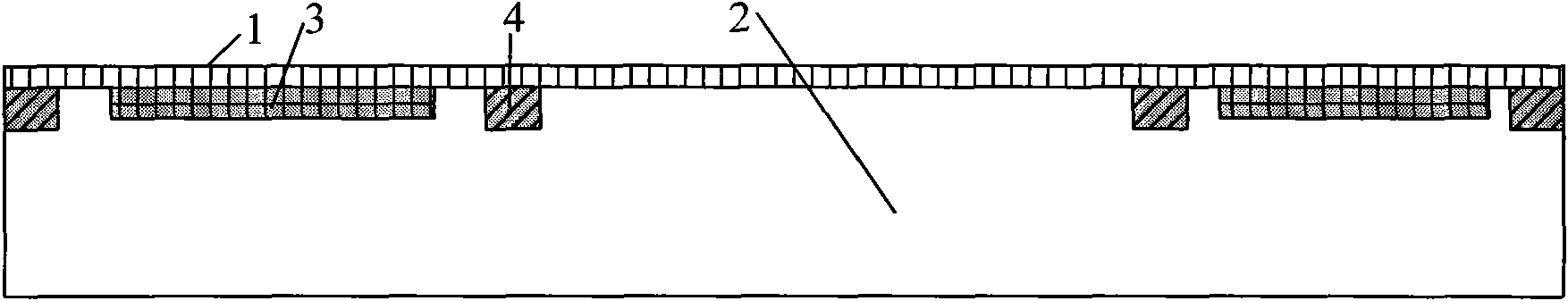

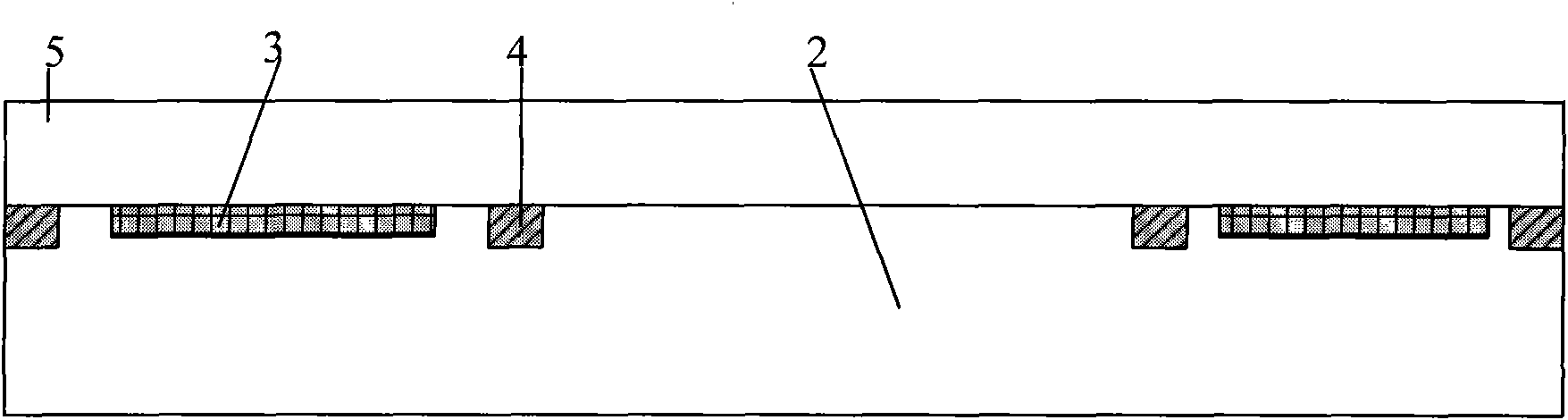

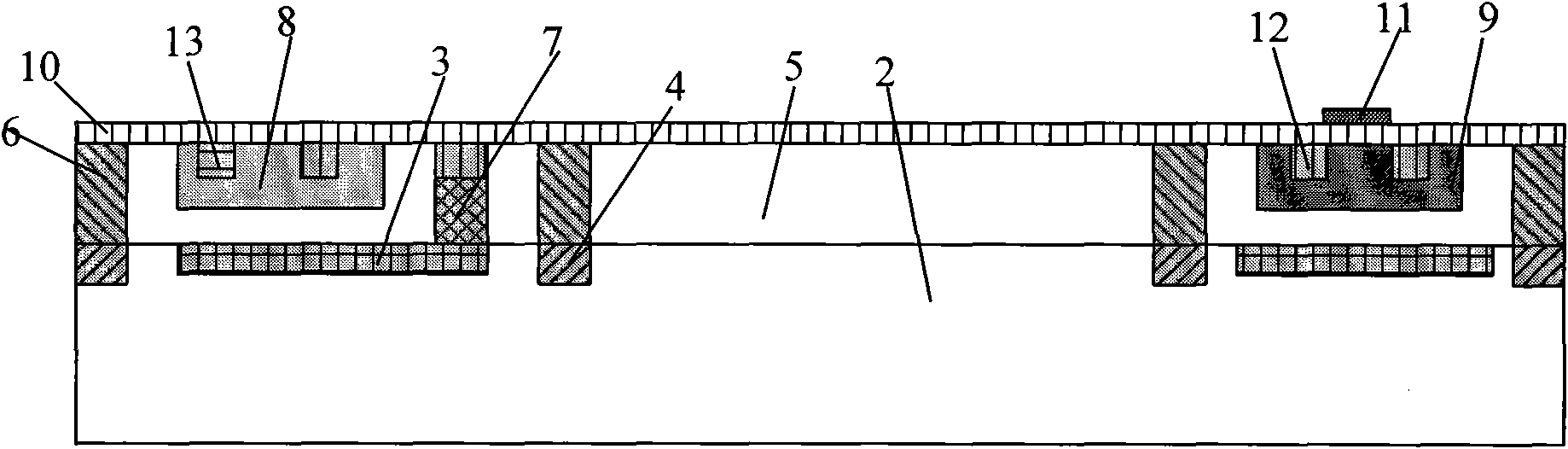

Method for manufacturing monolithic polysilicon cantilever structure

InactiveCN102086019ASolve stickingAchieve monolithic integrationDecorative surface effectsChemical vapor deposition coatingGyroscopeSignal processing circuits

The invention relates to a method for manufacturing a monolithic polysilicon cantilever structure. In the invention, a processing step of the polysilicon cantilever structure is inserted in a conventional BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) technical process, the deposition and the annealing of polysilicon are finished and an MEMS (Micro-Electro-Mechanical Systems) high-temperature process is prevented from influencing on the metalation process before the metalation process. In the release process of the polysilicon cantilever structure, a special etching solution is adopted, and a negative photoresist is used as a post of the polysilicon cantilever structure so as to effectively avoid the problem of substrate adhesion in the cantilever structure release process by using a wet method. The method provided by the invention solves the technical problems of compatibility between a manufacture process of the polysilicon cantilever structure and a processing process of a BiCMOS circuit, realizes the monolithic integration of the polysilicon cantilever structure and a BiCMOS signal processing circuit, and can be widely applied to the monolithic integration manufacture field of MEMS sensors, such as capacitive accelerometers, gyroscopes, and the like.

Owner:NO 24 RES INST OF CETC

Devices with adjustable dual-polarity trigger - and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal cmos/bicmos integrated

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1—N2—P2—N1 / / N1—P3—N3—P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2_standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC

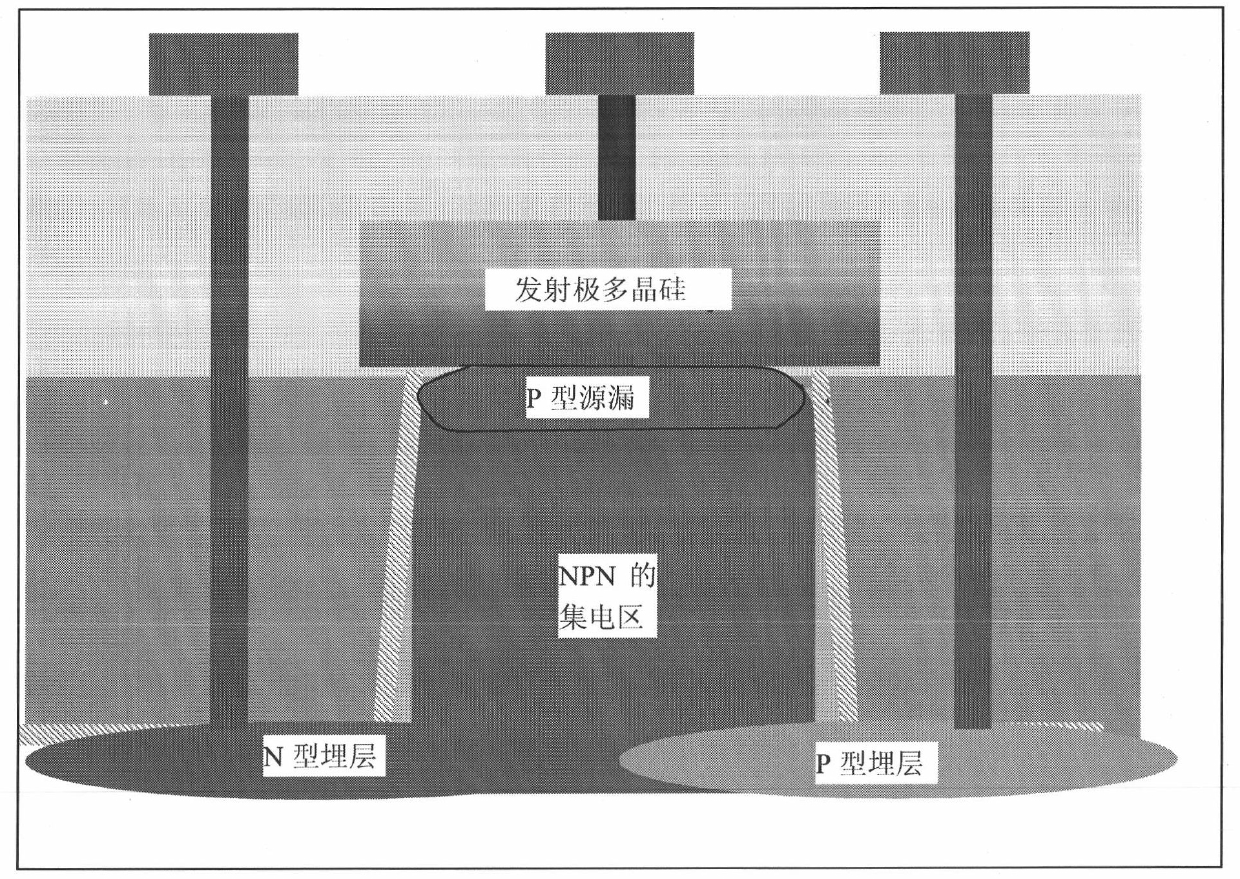

Vertical parasitic PNP device in BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor) process and preparation method thereof

ActiveCN102487077ALarge current amplification factorImprove frequency characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesProcess conditionsBicmos circuits

The invention discloses a vertical parasitic PNP device in a BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor) process. The vertical parasitic PNP device comprises a collector region, a base region, an emitter region, a P type buried layer and N type polycrystalline silicon, wherein the buried layer is formed at a shallow trench filed oxide bottom surrounding the collector region and is in contact with the collector region through a deep hole formed at the top of the buried layer to lead out a collector electrode; the N type polycrystalline silicon is formed at the upper part of the base region and is used for leading out a base electrode; and the emitter region is composed of a P type shallow junction formed in the base region and P type polycrystalline silicon arranged above the base region. The invention also discloses a preparation method of the vertical parasitic PNP device in the BiCMOS process. The device disclosed by the invention can serve as an output device in a high-speed high-gain BiCMOS circuit, and therefore another device choice is provided for the circuit. According to the invention, the area of the device can be reduced effectively, the resistance of the collector electrode of a PNP transistor can be lowered, the frequency performance of the device can be improved and the gain of the device can be enhanced. No extra process condition is required in the preparation method disclosed by the invention, thereby reducing the production cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

HIGH VOLTAGE SCRMOS IN BiCMOS PROCESS TECHNOLOGIES

ActiveUS20110180870A1Reduce negative resistance behaviorTransistorThyristorHigh pressureBicmos process

An integrated circuit having an SCRMOS transistor with a RESURF region around the drain region and SCR terminal. The RESURF region is the same conductivity type as the drift region and is more heavily doped than the drift region. An SCRMOS transistor with a RESURF region around the drain region and SCR terminal. A process of forming an integrated circuit having an SCRMOS transistor with a RESURF region around the drain region and SCR terminal.

Owner:TEXAS INSTR INC

Lateral polysilicon pin diode and method for so fabricating

InactiveUS20020070388A1Extending charge storage areaIncrease storage areaSolid-state devicesPhotovoltaic energy generationEngineeringBicmos process

Owner:GLOBALFOUNDRIES INC

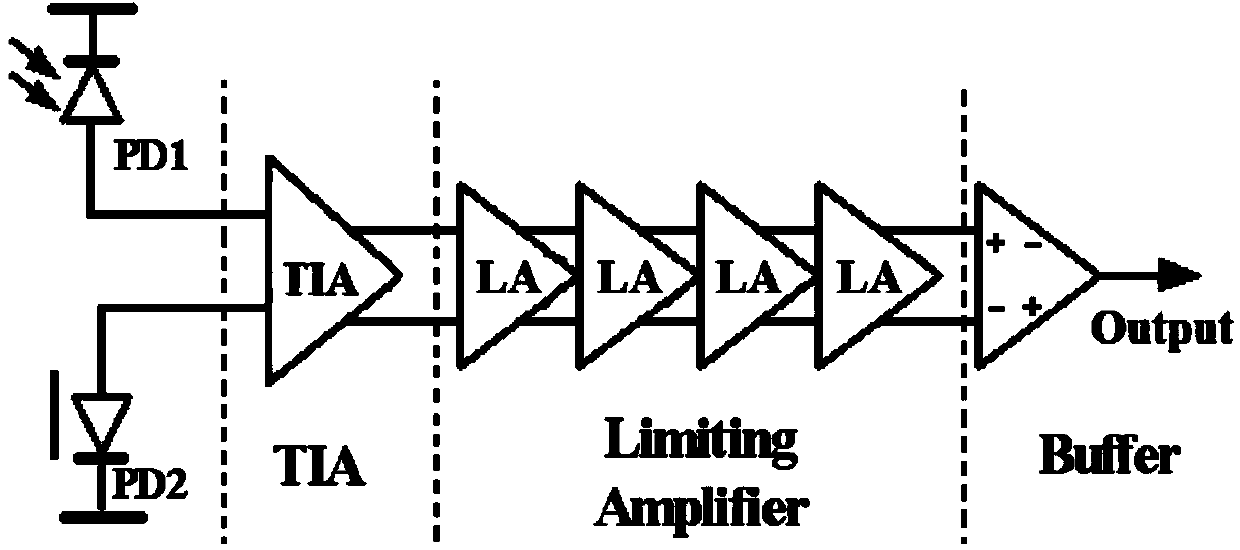

Standard SiGe bipolar complementary metal-oxide-semiconductor transistor (BiCMOS) process-based optoelectronic integrated receiver

InactiveCN103701533AImprove responsivenessHigh absorption coefficientElectromagnetic receiversRadiation controlled devicesPhotovoltaic detectorsAudio power amplifier

The invention belongs to the fields of optical fiber communication systems and optical interconnection, and aims to achieve the advantages of small size, low cost, high reliability, rich functions and the like of monolithic integration. The invention provides a photoelectric detector compatible with a standard SiGe bipolar complementary metal-oxide-semiconductor transistor (BiCMOS) process, and a high-speed and high-sensitivity monolithic integrated optical receiver integrated with the detector. To meet the technical requirements, the standard SiGe BiCMOS process-based optoelectronic integrated receiver comprises two photoelectric detectors with completely symmetrical structures, a trans-impedence amplifier with a full differential structure, a group of sequentially cascaded full differential limiting amplifier and an output buffer stage which is used for converting differential voltage signals output by the limiting amplifier into single-end output voltage signals and providing driving force. The optoelectronic integrated receiver is mainly applied to design and manufacture of the optical fiber communication systems.

Owner:TIANJIN UNIV

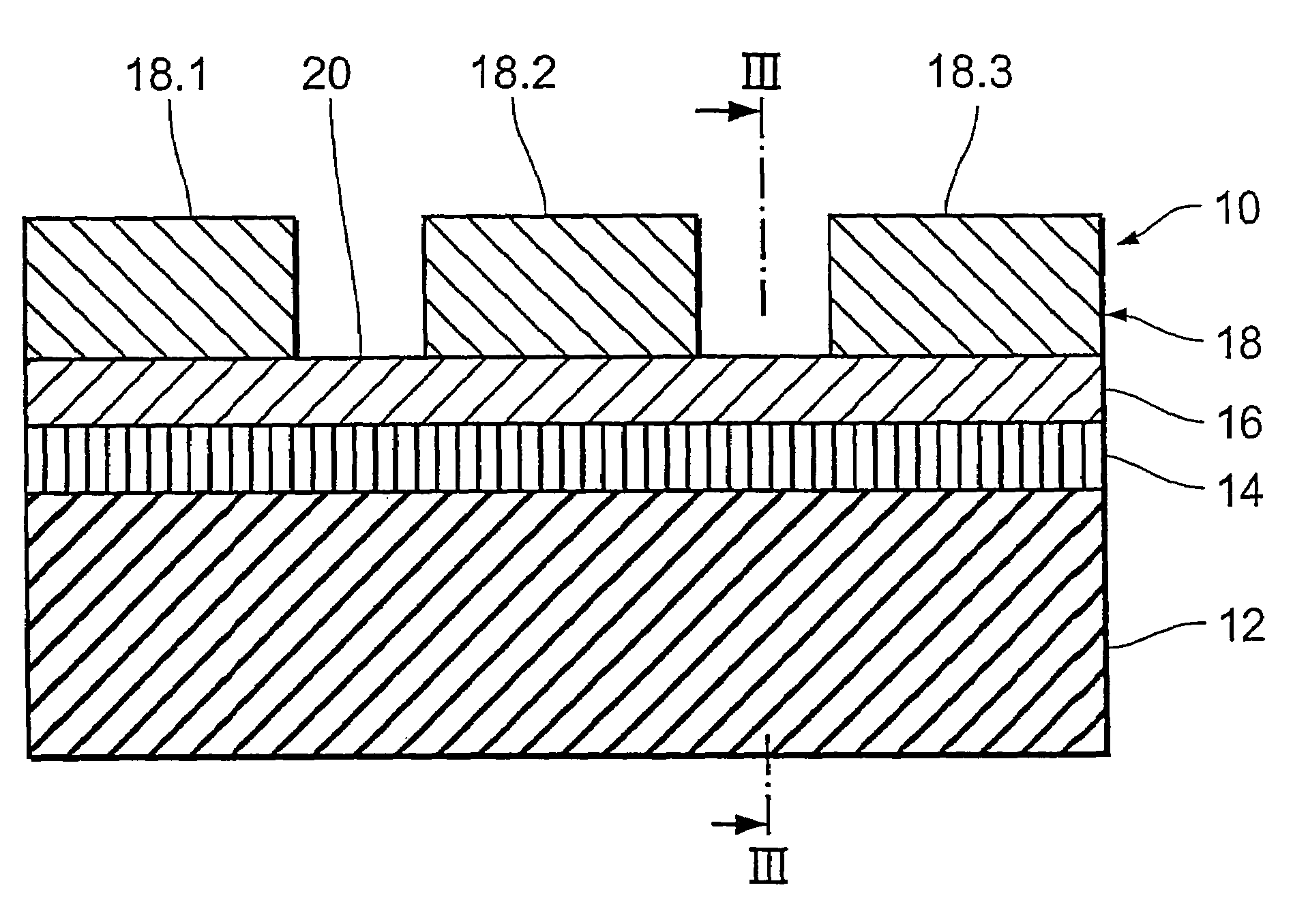

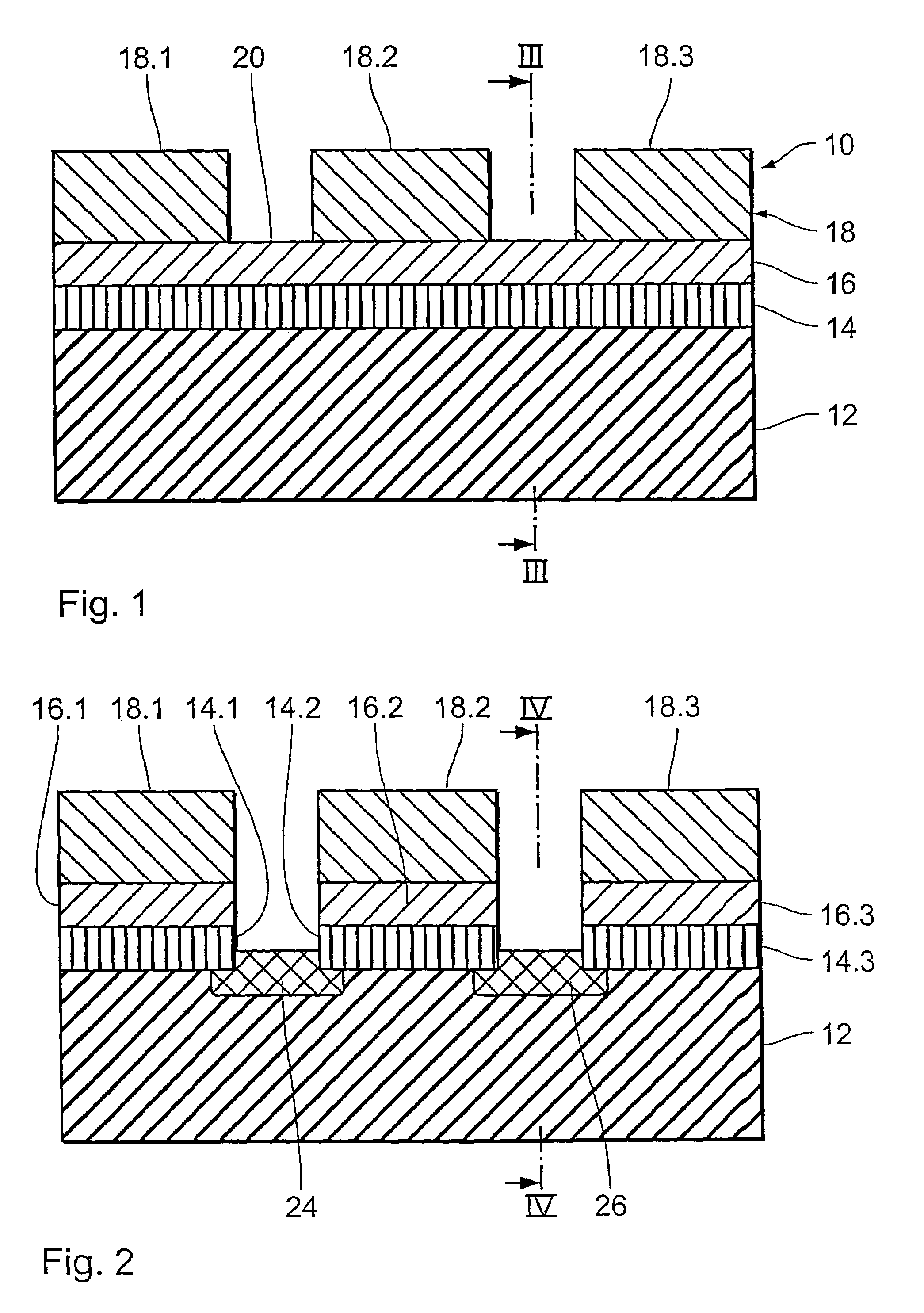

Transistor, method for producing an integrated circuit and a method of producing a metal silicide layer

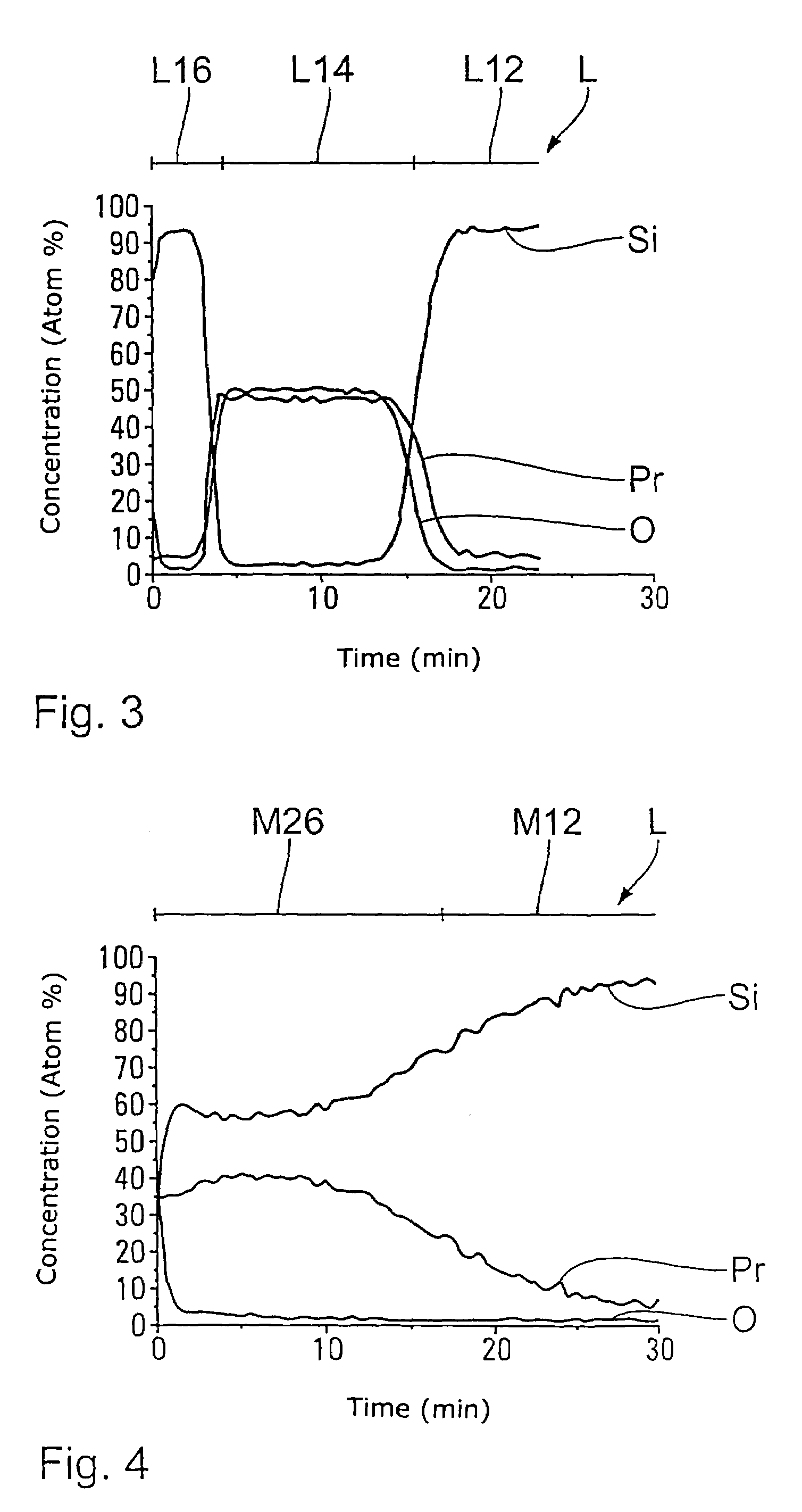

InactiveUS7196382B2Highly integratedSimple methodSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideOxygen

The invention relates to a method for the selective silicidation of contact areas that allow the production of highly integrated circuits, preferably in a SMOS or BiCMOS process. To this end, a metal oxide layer (14) that contains for example praseodymium oxide is deposited onto a prepared wafer (12). A silicon layer (16) and on top of said silicon layer a cover layer (18) is deposited onto the metal oxide layer (14), said cover layer being laterally structured. In a subsequent tempering step in an oxygen-free, reducing gas atmosphere the silicon layer (16) and the metal oxide layer (14) are converted to a metal silicide layer in lateral sections (20, 22) in which the cover layer (18) was previously removed.

Owner:IHP GMBH INNOVATIONS FOR HIGH PERFORMANCE MICROELECTRONICS LEIBNIZ INST FUR INNOVATIVE

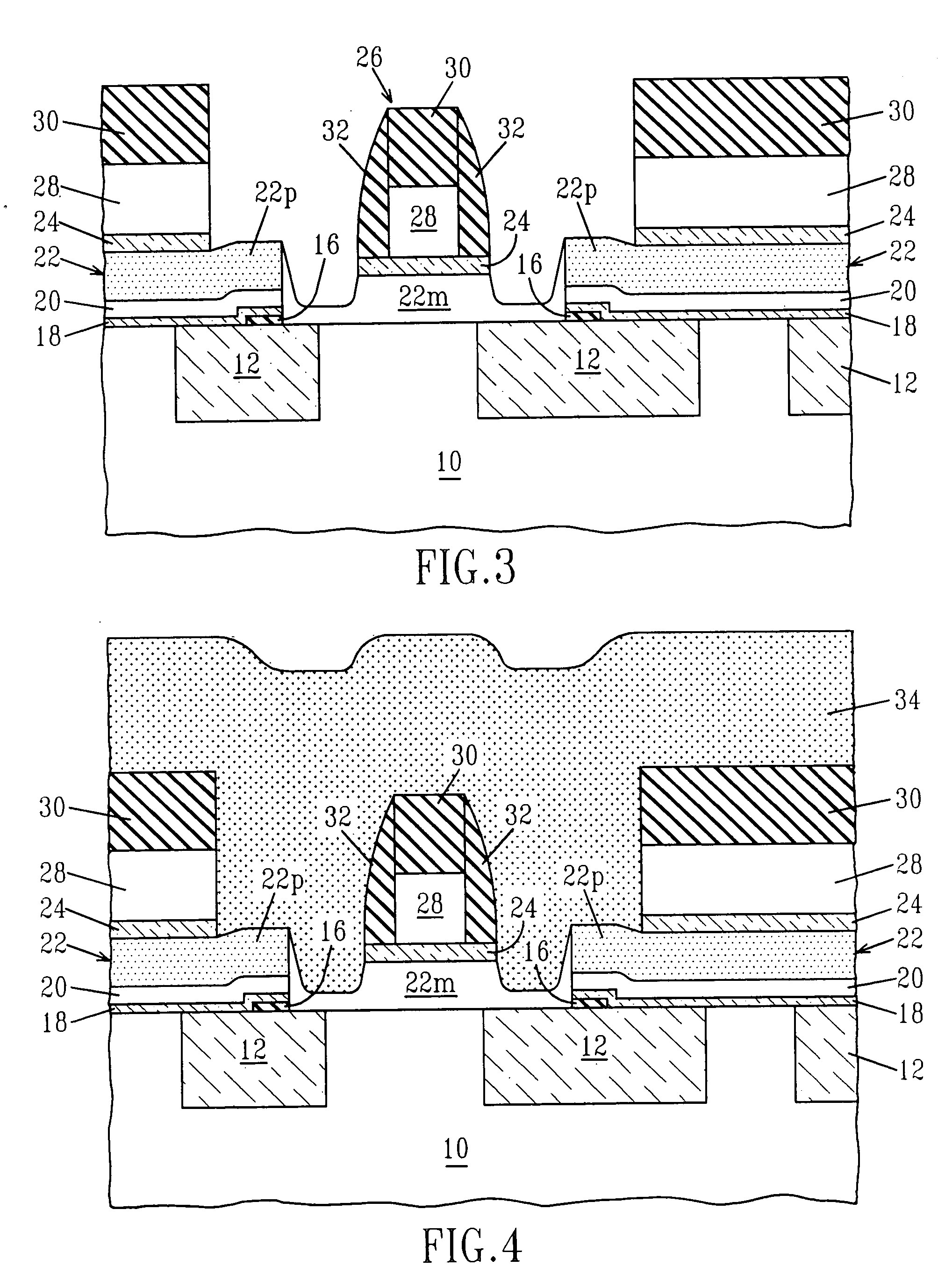

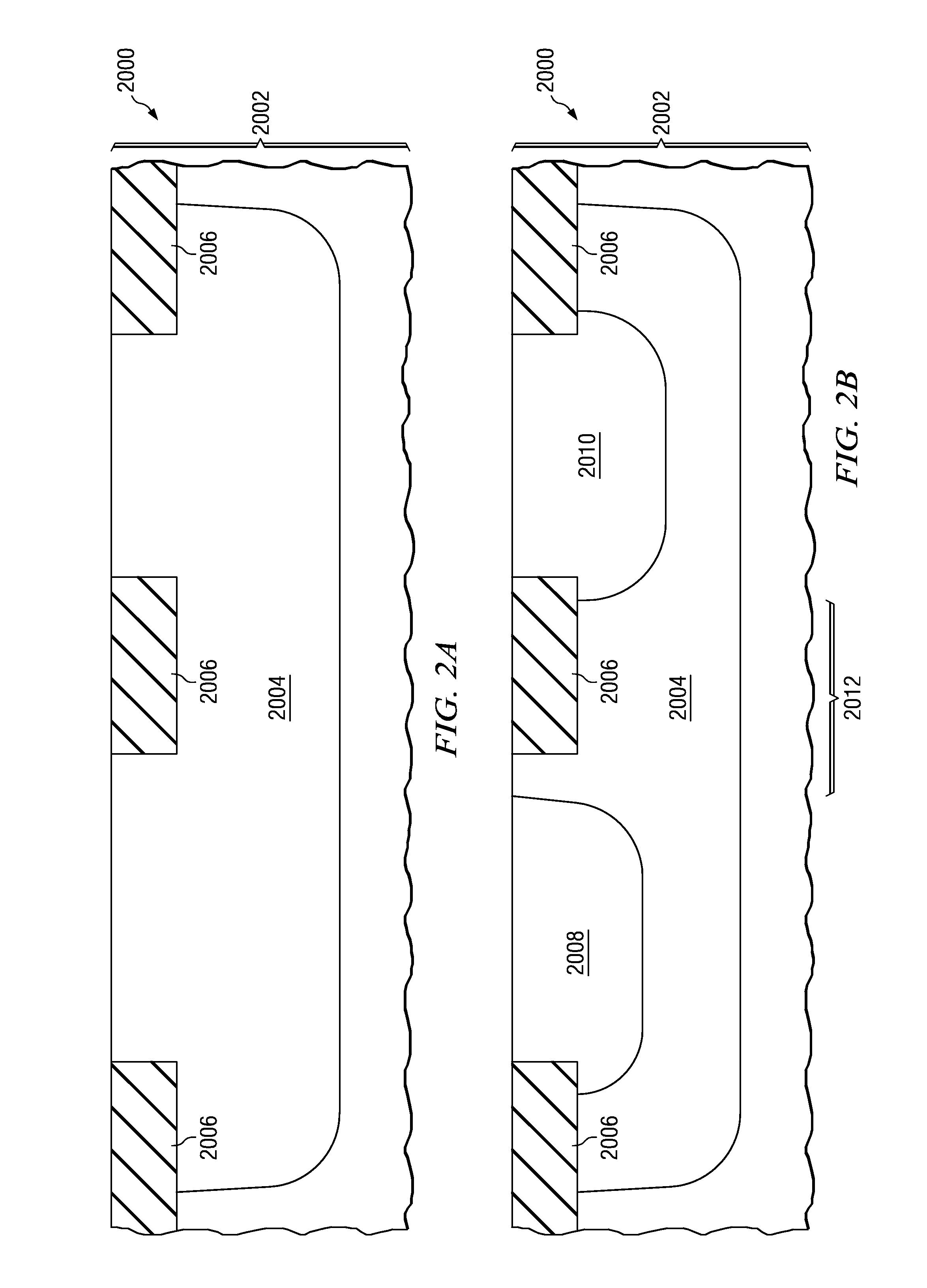

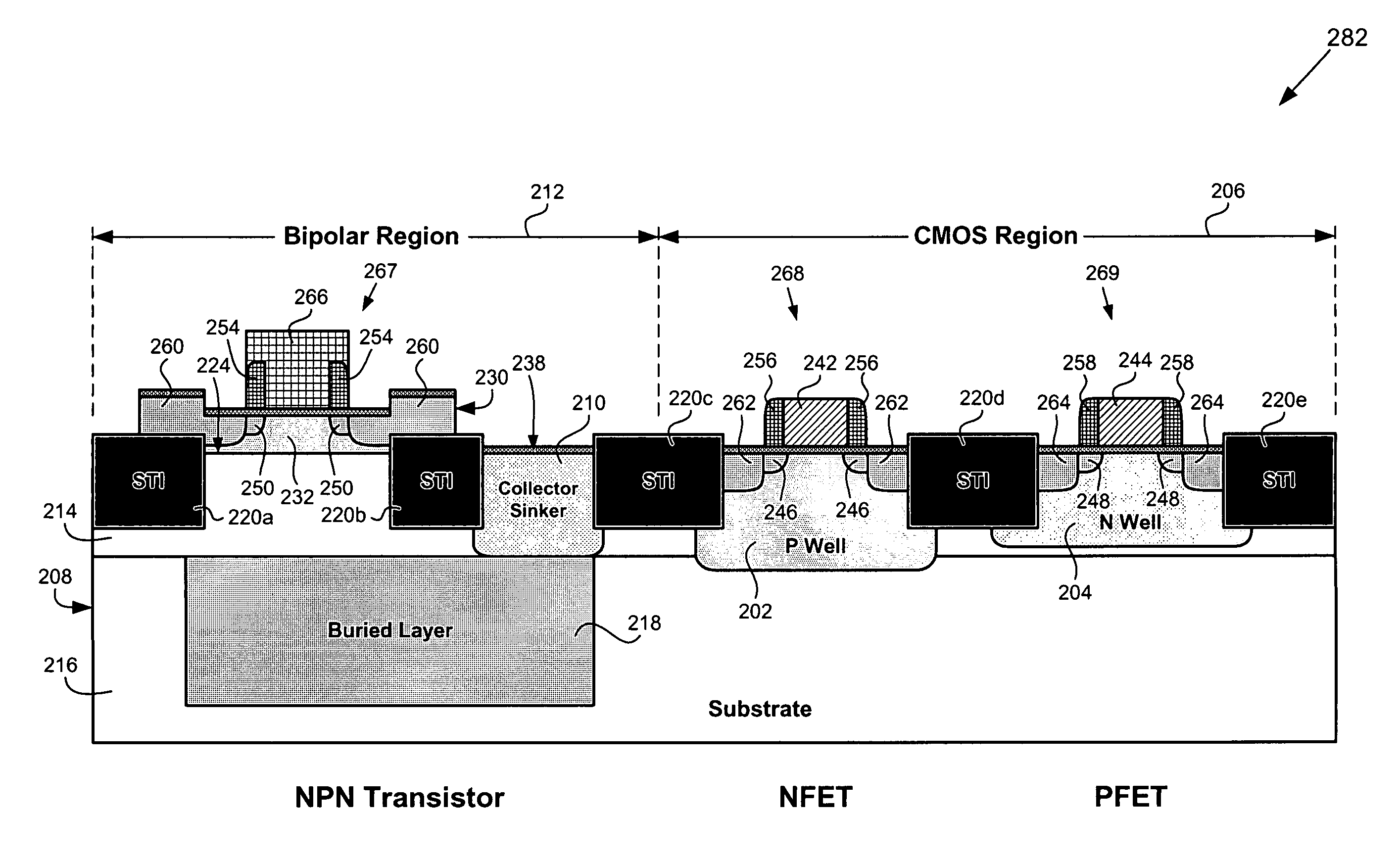

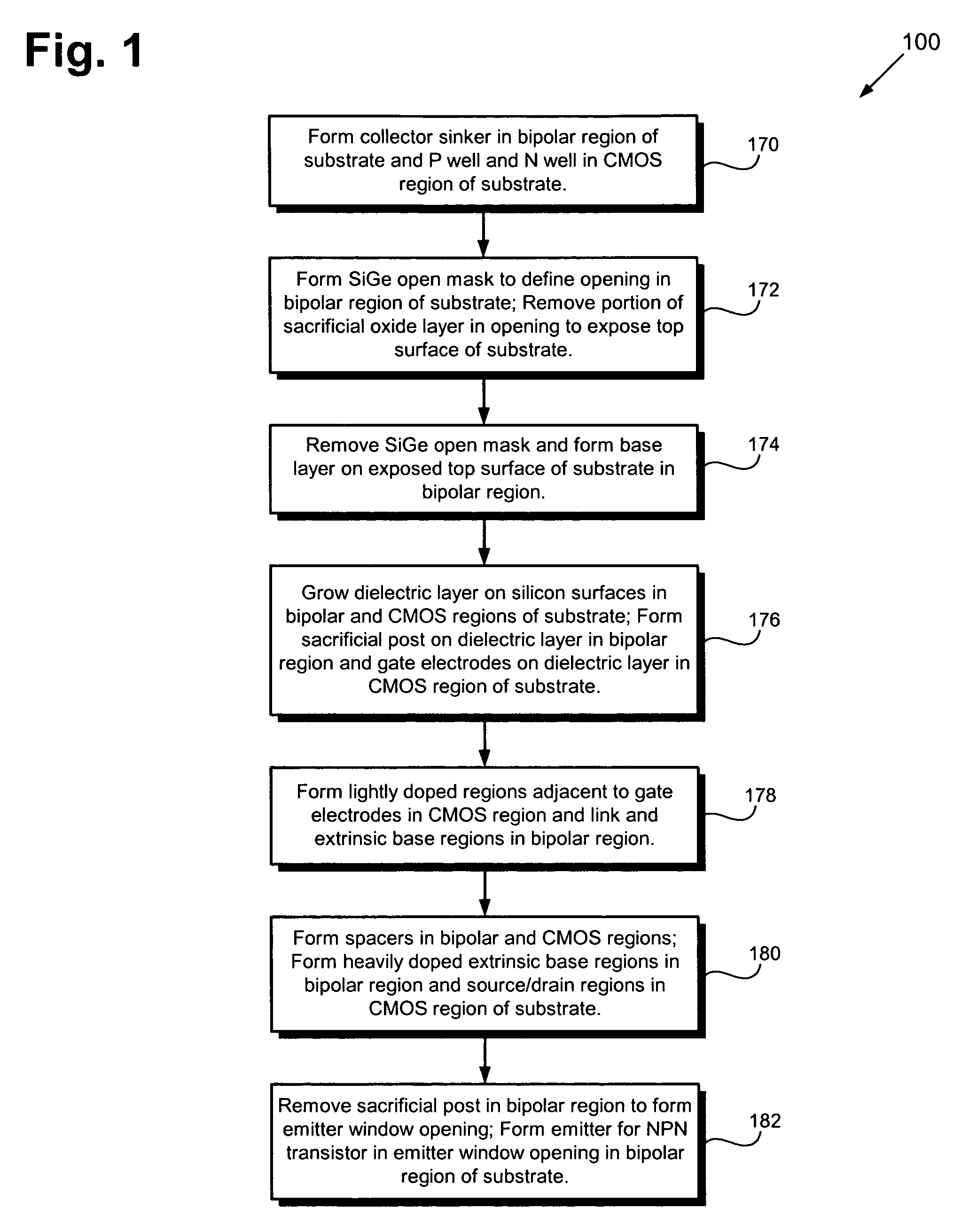

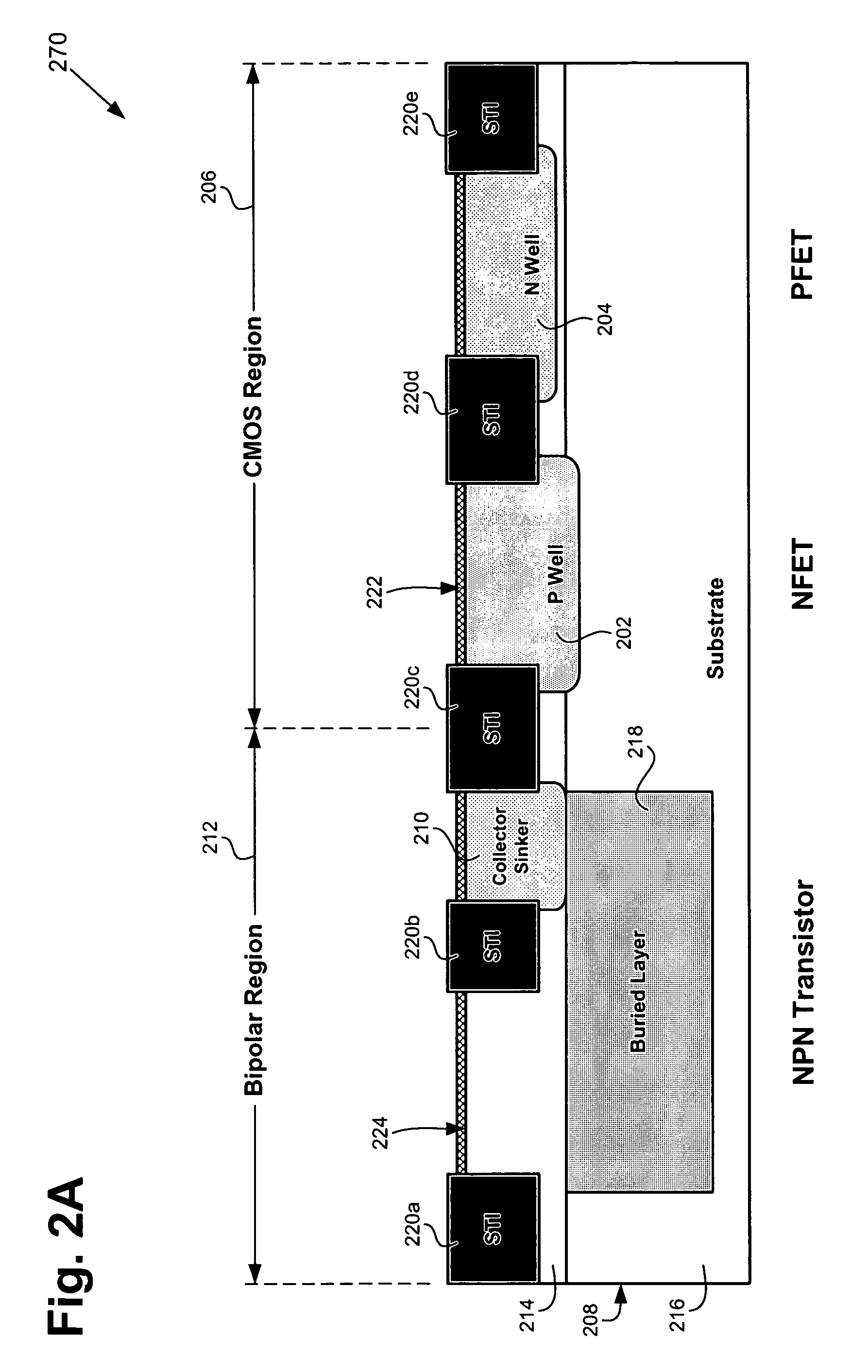

Method for effective BiCMOS process integration

According to an exemplary embodiment, a method for integrating bipolar and CMOS devices on a substrate, where the substrate includes bipolar and CMOS regions and has a sacrificial oxide layer situated thereon, includes removing a portion of the sacrificial oxide layer in the bipolar region of the substrate to expose a top surface of the substrate. The method includes forming a base layer on the top surface of the substrate in the bipolar region. The base layer forms a bipolar transistor base. The method further includes forming a sacrificial post on the base layer in the bipolar region and at least one gate electrode in the CMOS region of the substrate. A common mask is used to form the sacrificial post and the at least one gate electrode. The method further includes forming LDD regions adjacent to the at least one gate electrode in the CMOS region.

Owner:NEWPORT FAB

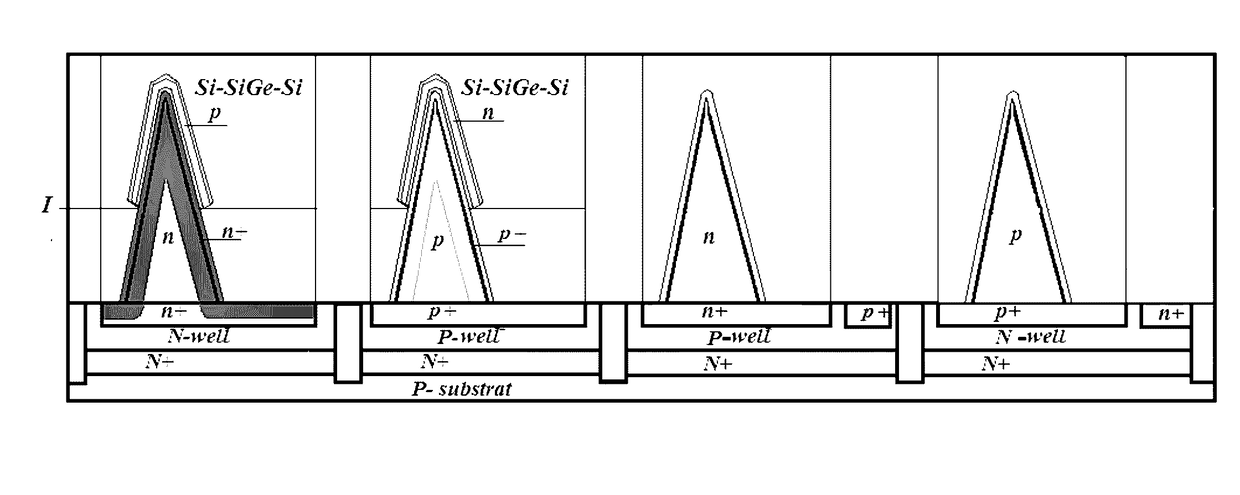

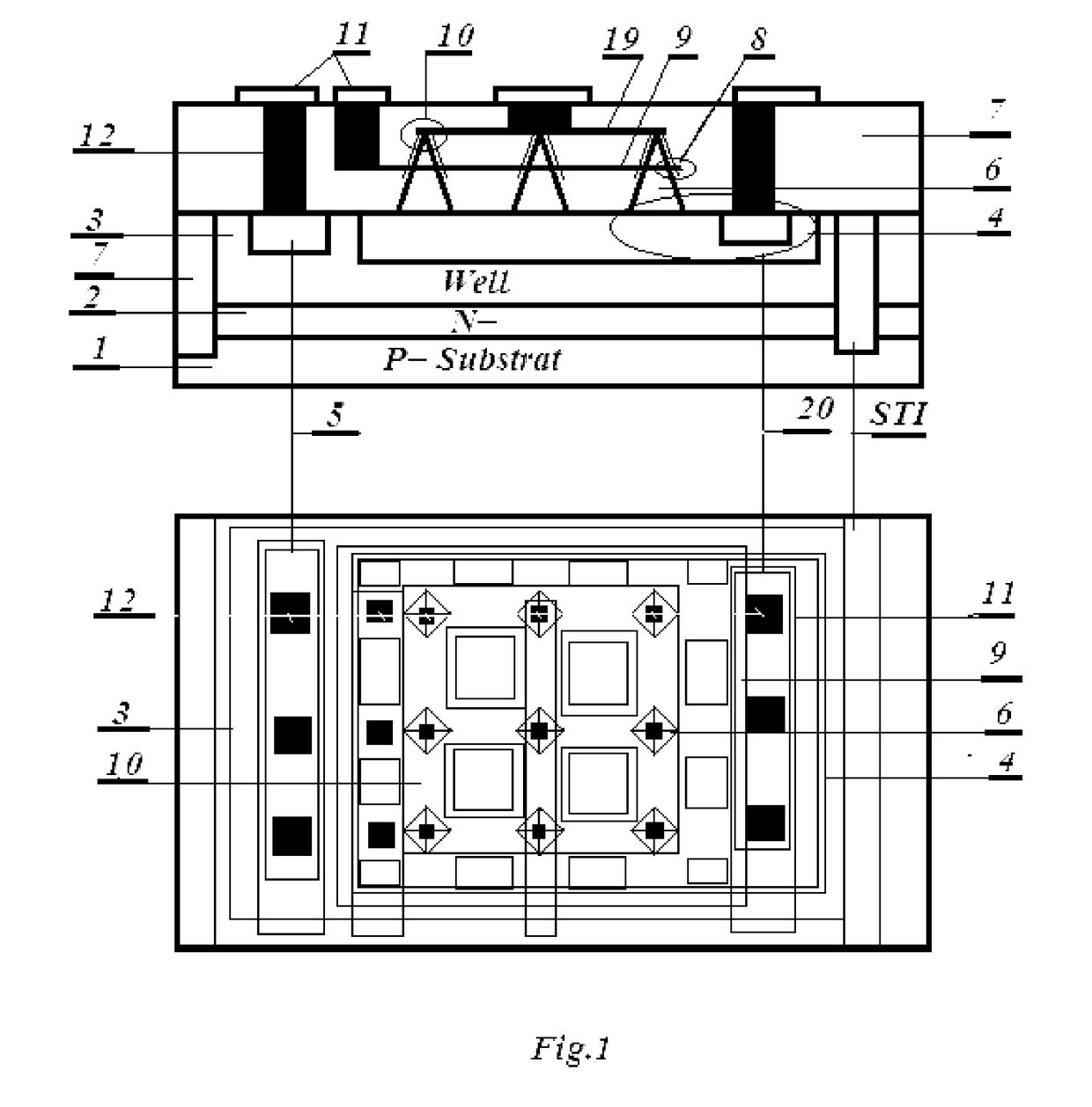

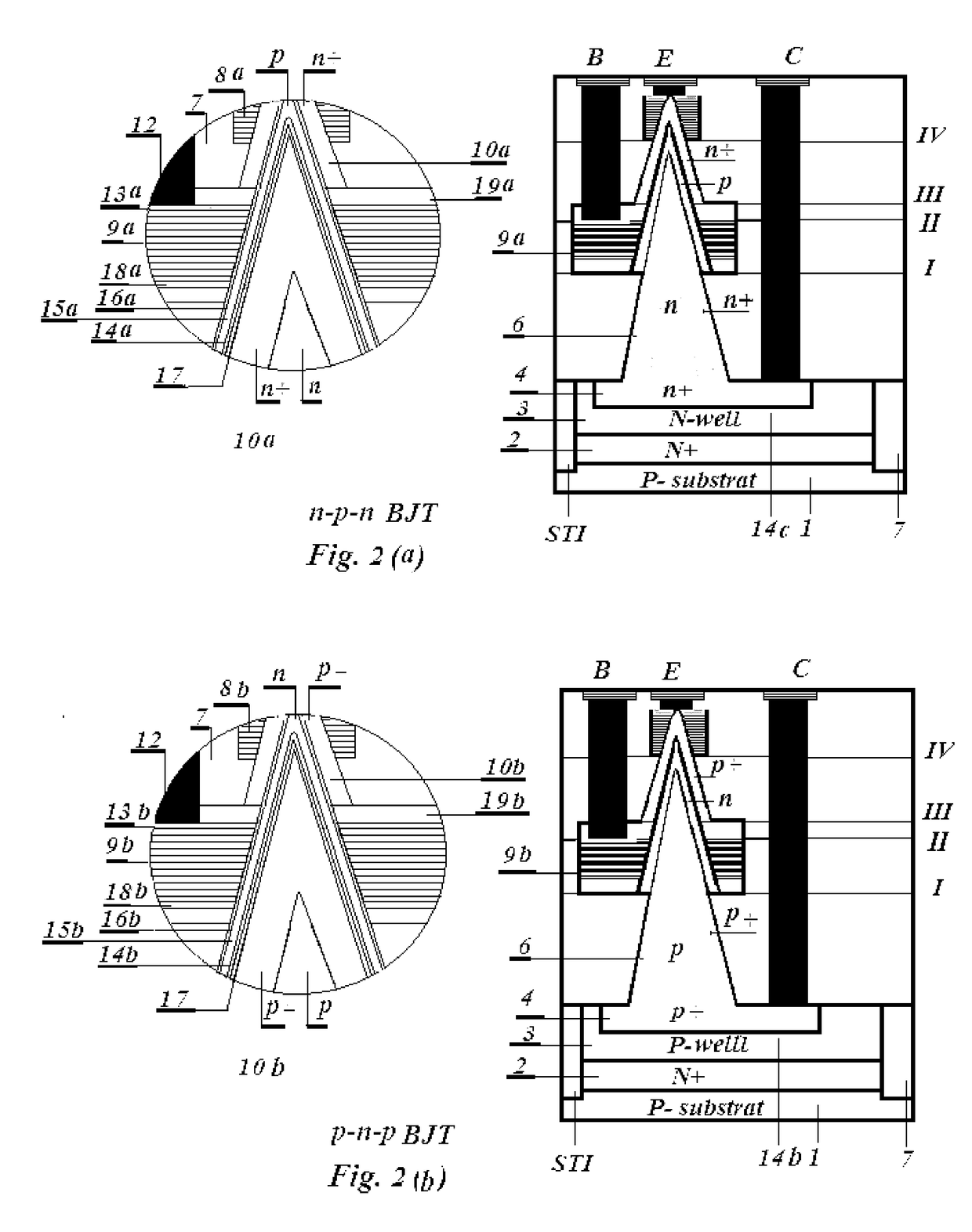

Integrated vertical sharp transistor and fabrication method thereof

The present invention relates to vertical integrated, quantized FET with sharp drain and BJT with sharp emitter implemented in one nano-BiCMOS process, using multiple identical single crystalline semiconductor pyramids, placed in-situ directly on the surface of diffusion regions. The devices' gate and base structures are formed at a level of 35-45 nm below the top of the pyramids. The bottom region of the pyramids contains the collector / source structures, while the top region of the pyramids contains the emitter / drain structures. The base structure for BJT is formed by selective epitaxial growth of Si—SixGe1-x—Si with opposite conductivity type as COR, and interconnected by a horizontal polysilicon grid. The self-aligned gate structure for FET is formed by high dopant implantation of impurity with the same type of conductivity as COR through horizontal gate bridge, which represent a grid of horizontal stacked layers Si3N4 —high-k insulator—polysilicon—high-k insulator—Si3N4.

Owner:LESENCO DUMITRU NICOLAE

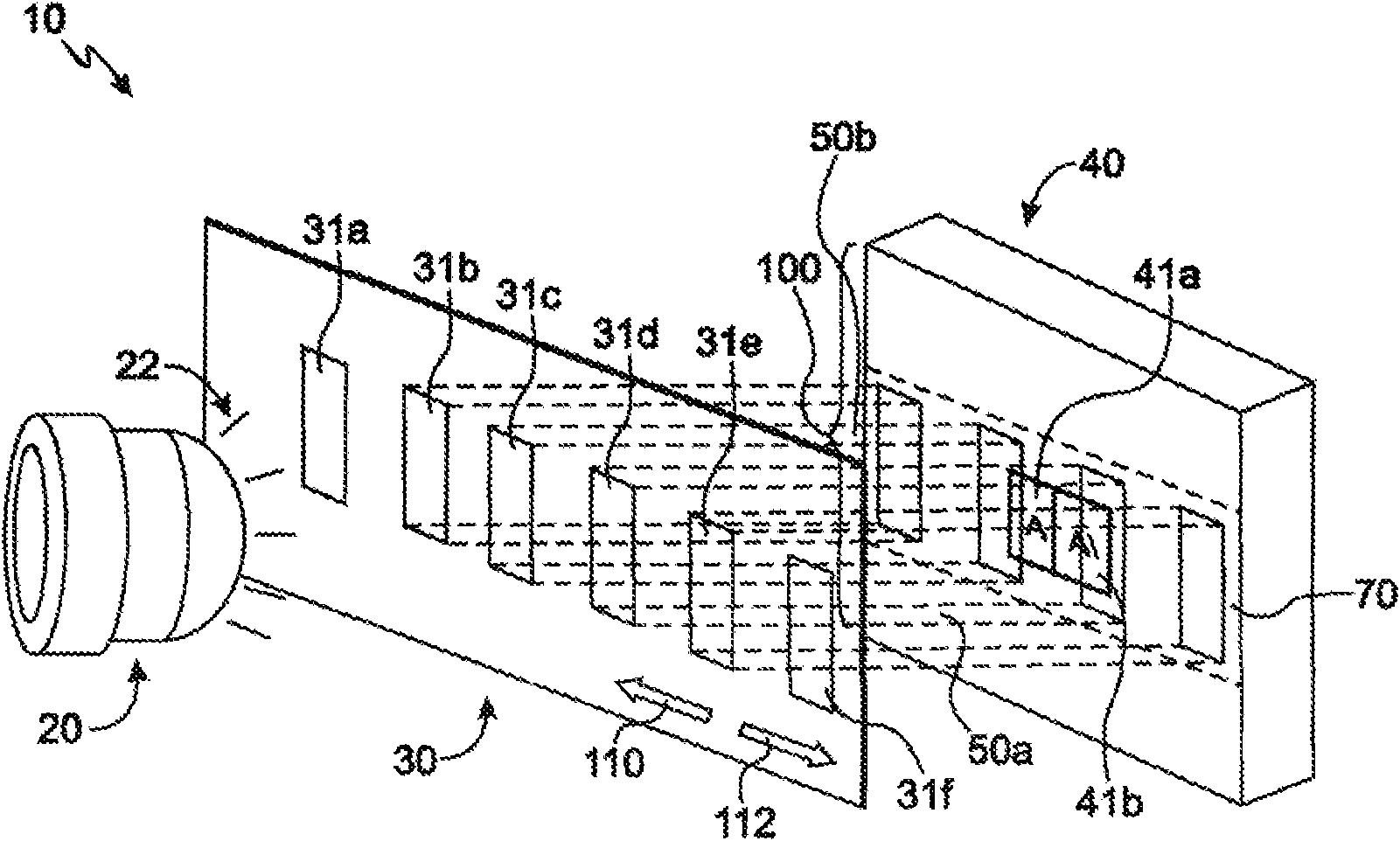

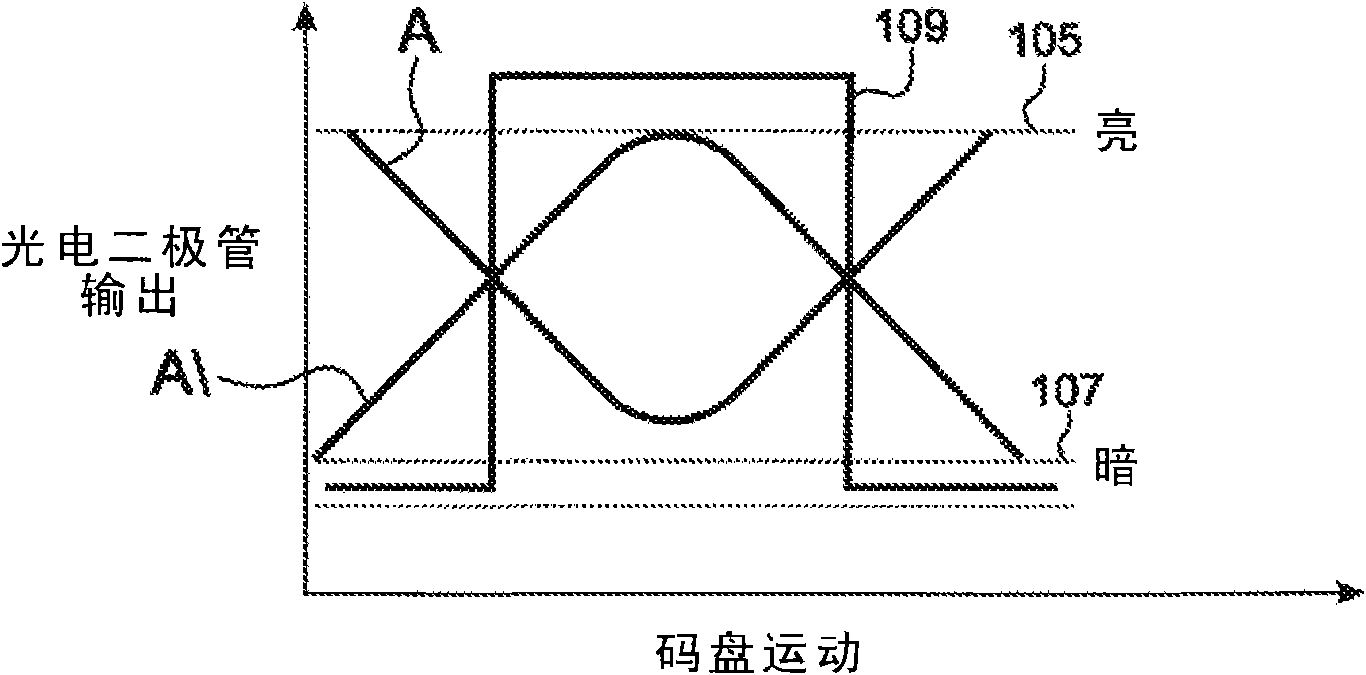

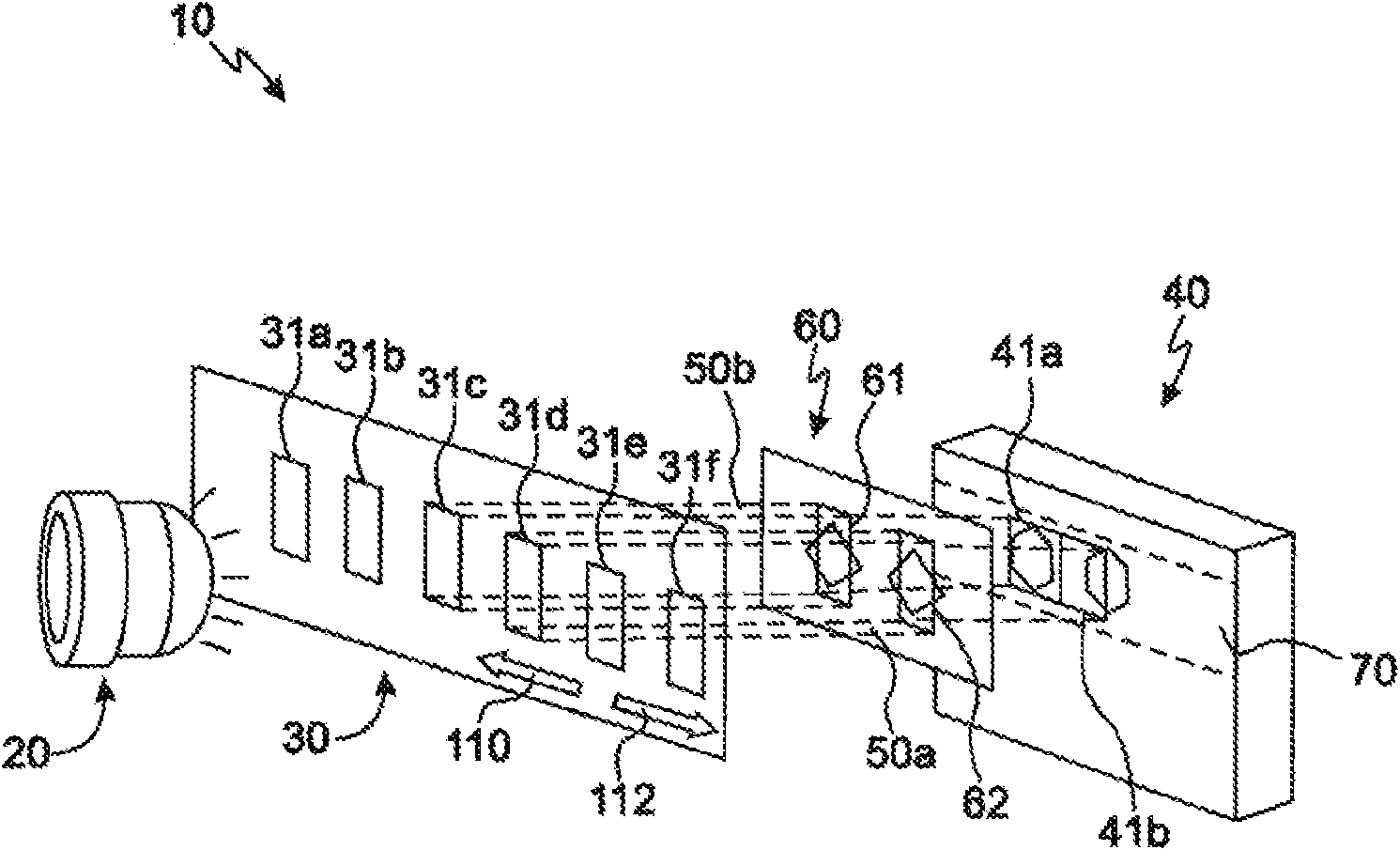

High resolution optical encoder systems, devices and methods

The invention provide high resolution optical encoder systems, devices and methods. Disclosed are various embodiments of front-end analog circuitry for use in conjunction with optical encoders. Highly accurate analog output signals are provided by front-end analog circuitry in incremental or absolute motion encoders to interpolation circuitry, which is capable of providing high interpolation factor output signals having high timing accuracy. The disclosed interpolation circuits may be implemented using CMOS or BiCMOS processes without undue effort.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

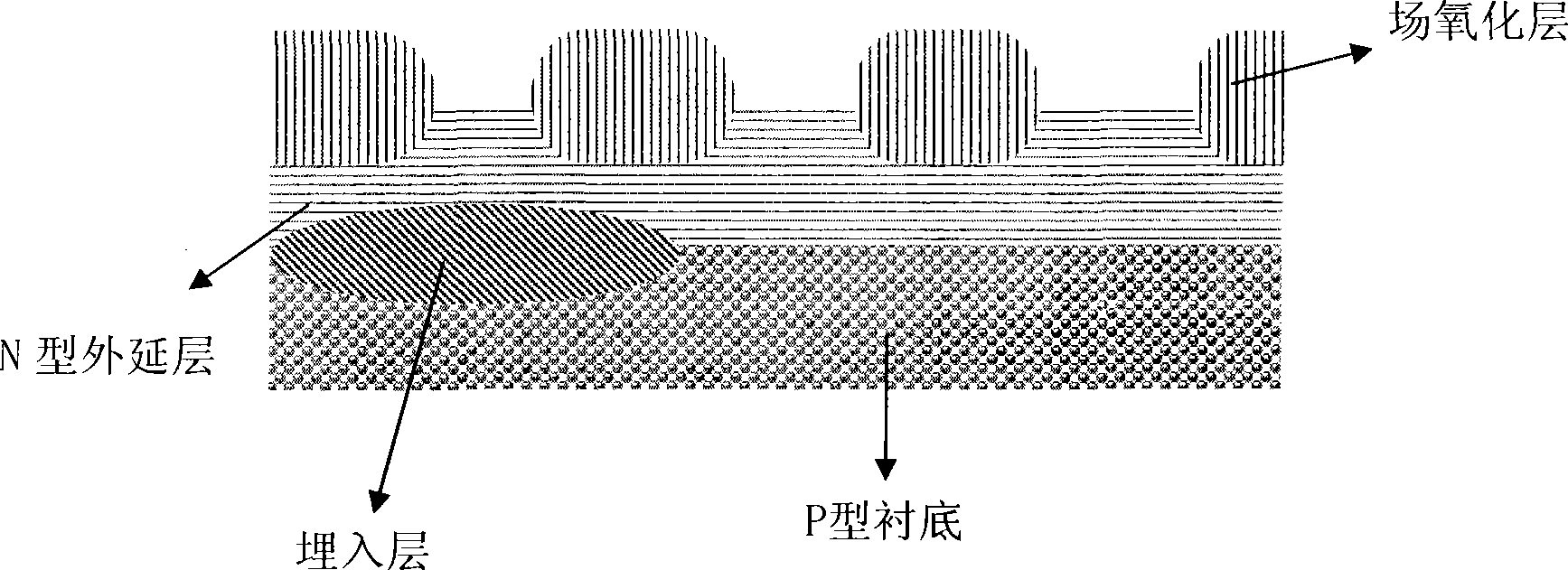

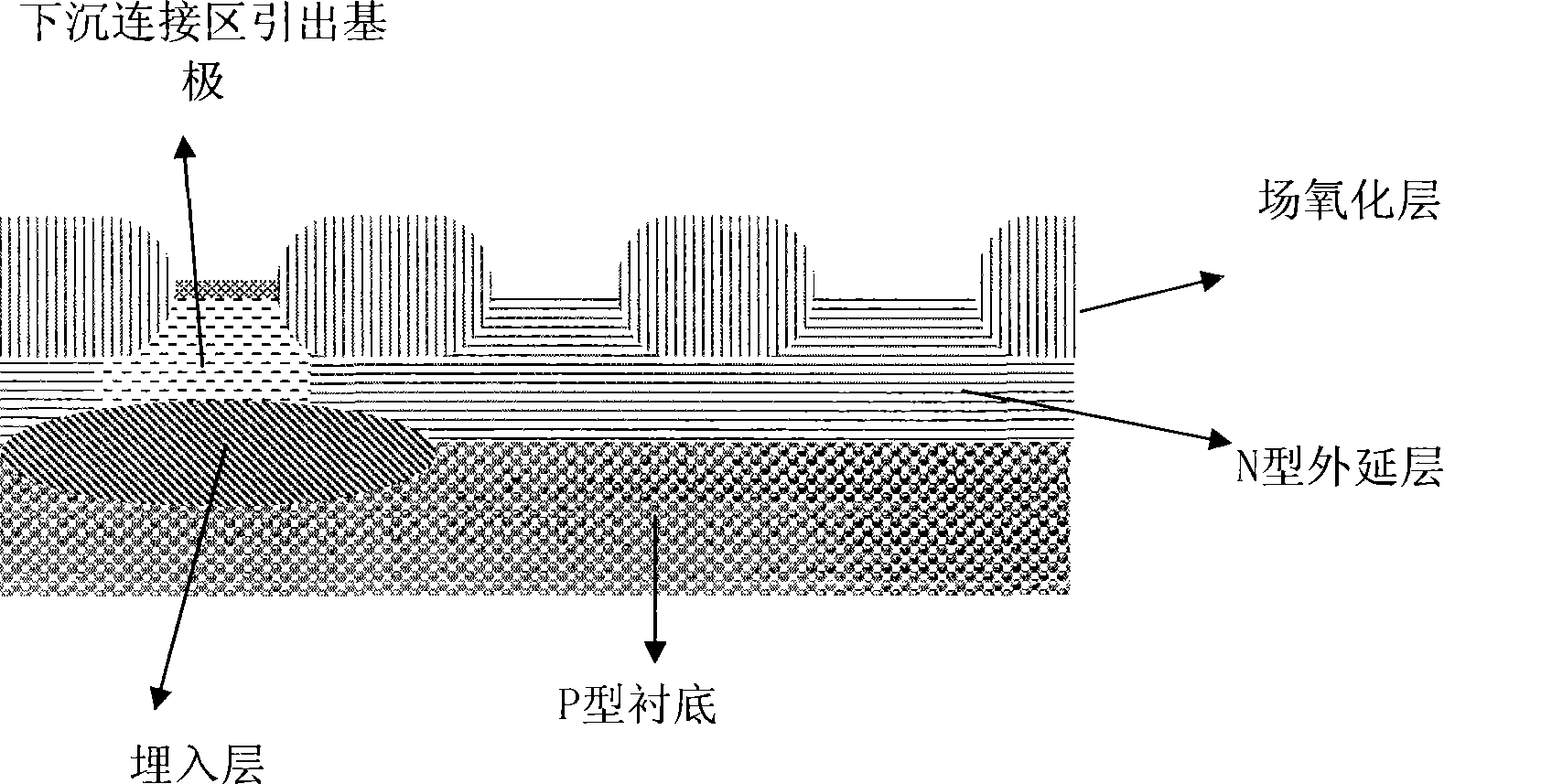

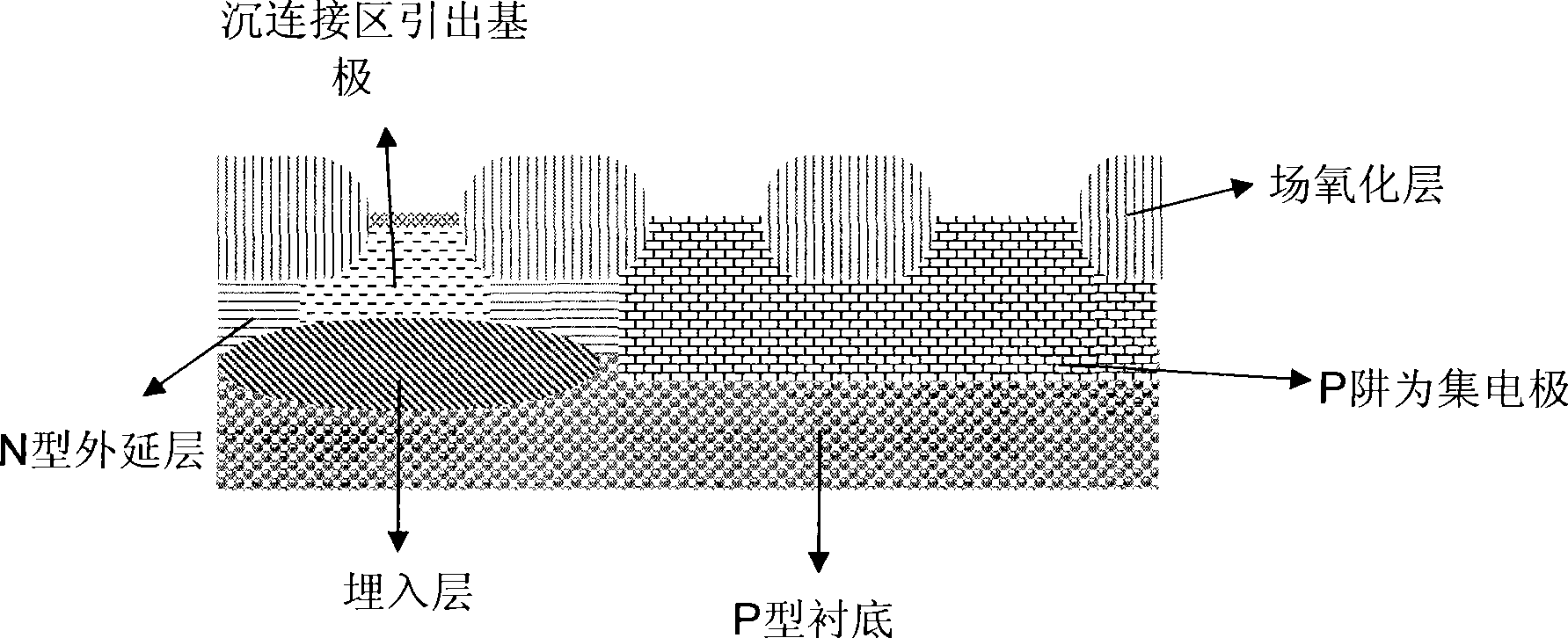

Parasitic vertical PNP and manufacturing process thereof in BiCMOS process

InactiveCN101459130AEliminate bad effectsIncrease the magnification factorTransistorSemiconductor/solid-state device manufacturingCMOSBoron

The invention discloses a preparing method of a parasitic vertical PNP in the BiCMOS process, which comprises steps of 1, ion implantation of a buried layer, N type epitaxial growth and formation of an active region, 2, ion implantation of a subsided connection layer, 3, P-well isolating ion implantation of a CMOS, 4, N-well ion implantation of the CMOS, 5, forming a layer of oxide thin film through the oxidizing annealing treatment, growing base polysilicon and implanting boron as a P-type emitter, and finally etching away the base polysilicon in the non-vertical PNP region. The invention further discloses a parasitic vertical PNP in the BiCMOS process, which utilizes the P-well isolating ion implantation to form a collector electrode, uses the N-well reverse-punch ion implantation to form a base electrode, and utilizes base polysilicon implanted with boron as an emitter. By adjusting the ion implantation conditions of the N-well and the P-well, the invention can prepare parasitic vertical PNP triodes without adding a photomask or other cost, thereby increasing amplifying coefficient and cutoff frequency.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS