Patents

Literature

142 results about "Ballast resistor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

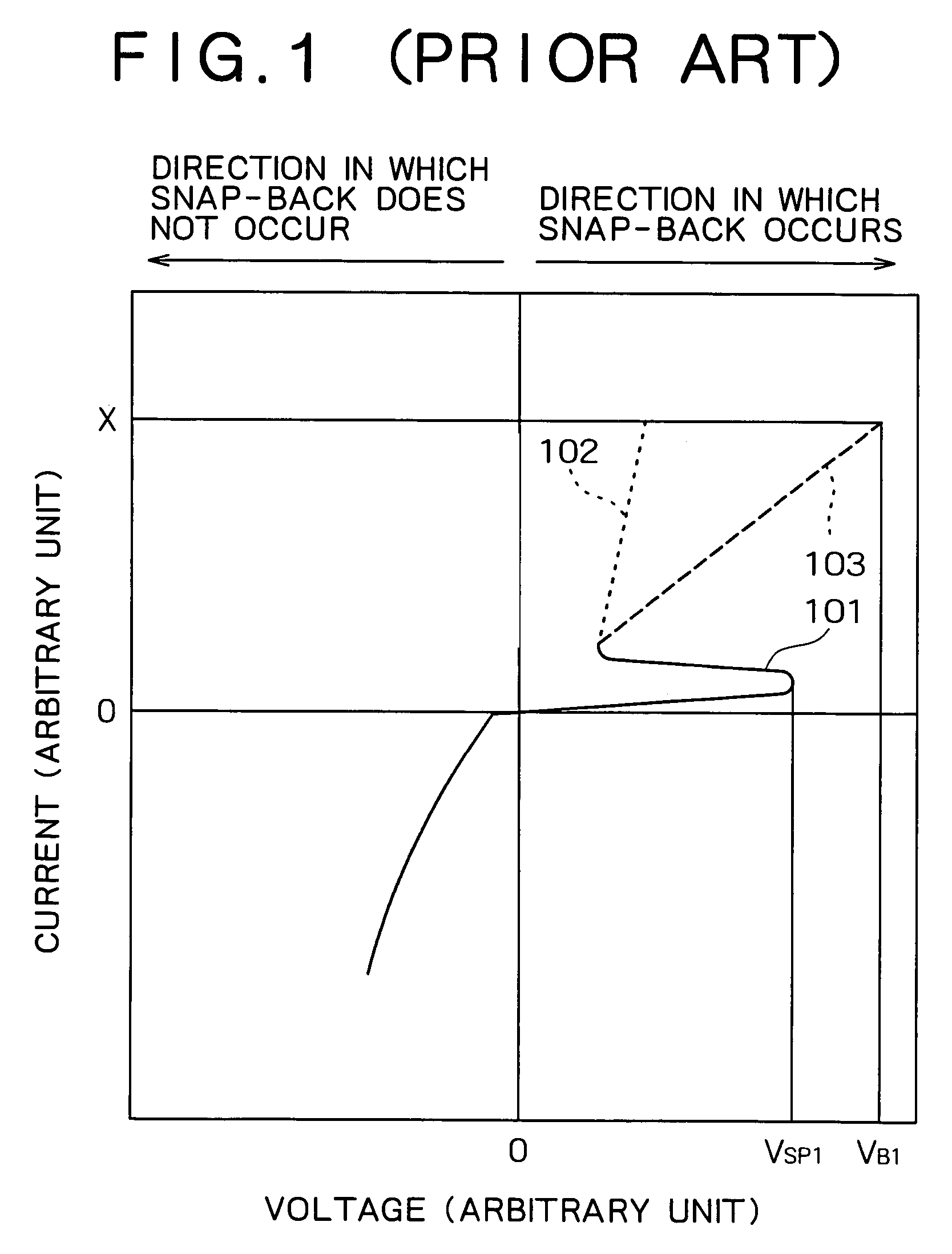

InactiveUS20070007545A1Impaired immunityHigh protection levelTransistorThyristorNon symmetricTransmission-line pulse

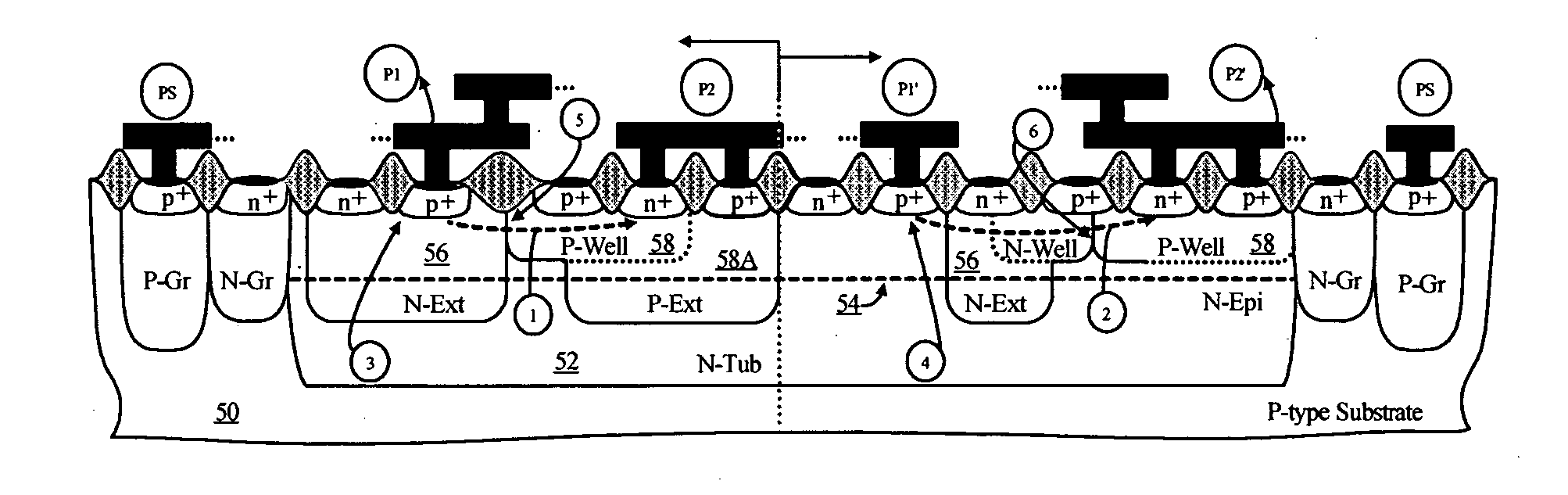

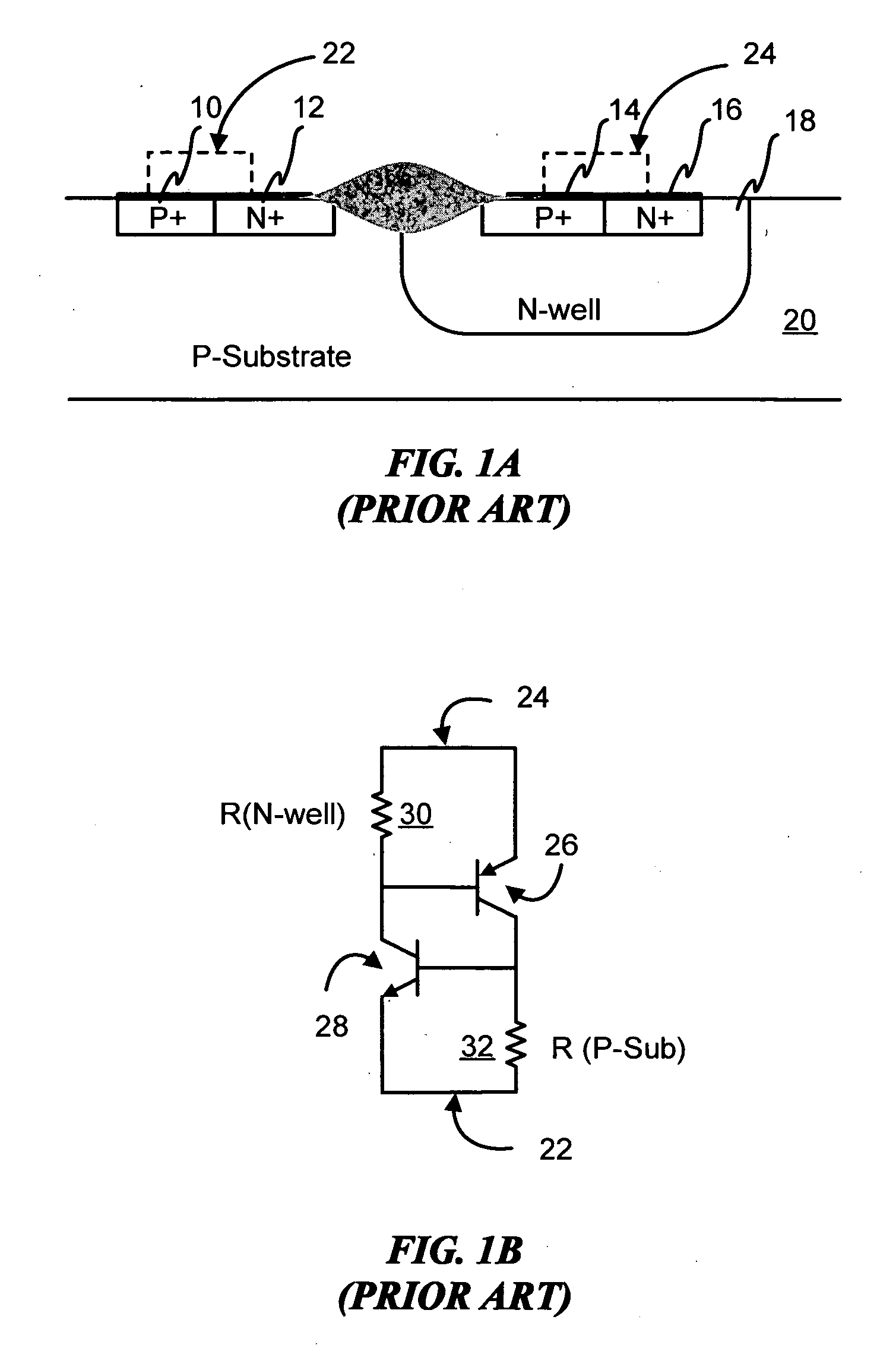

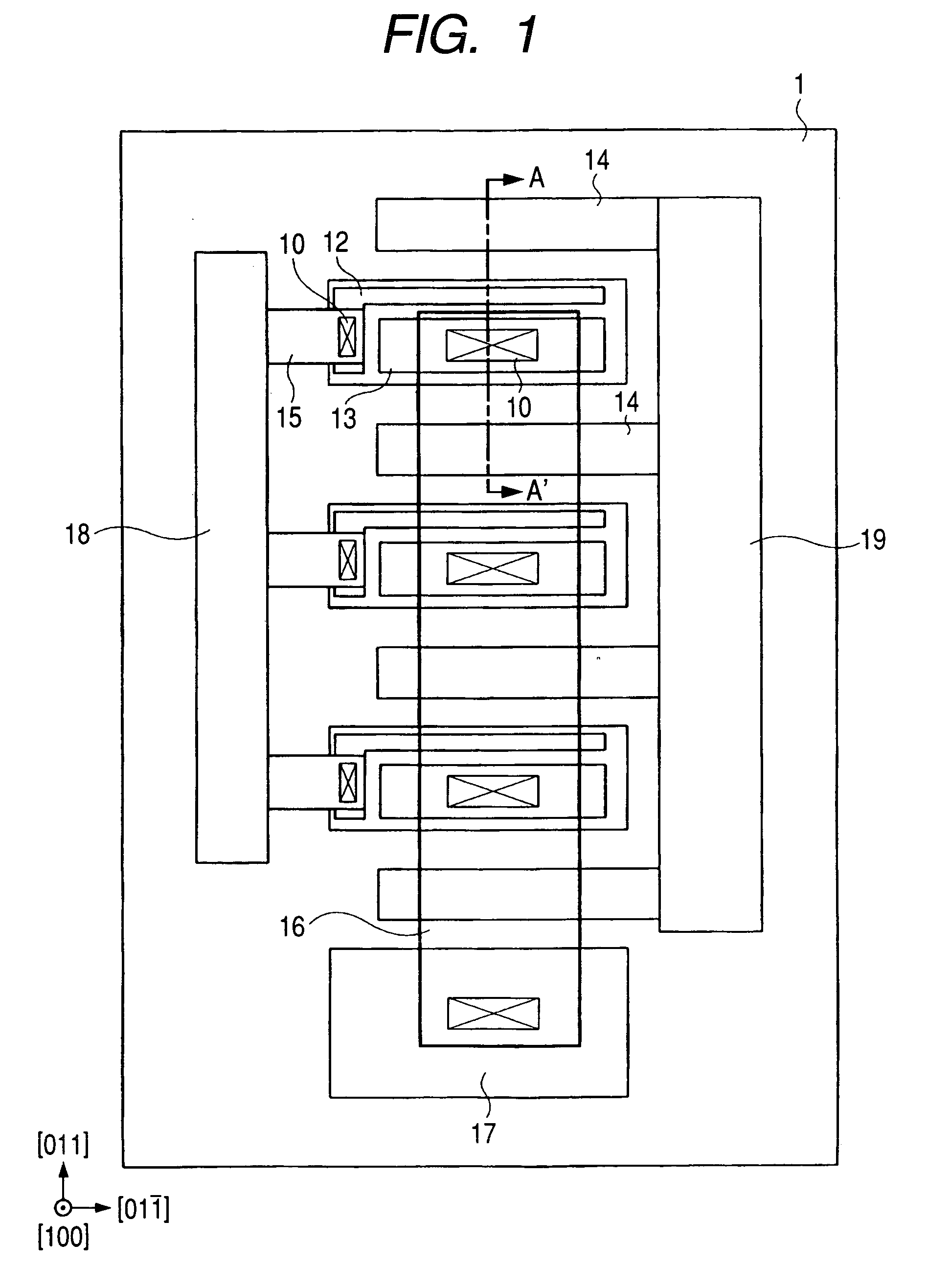

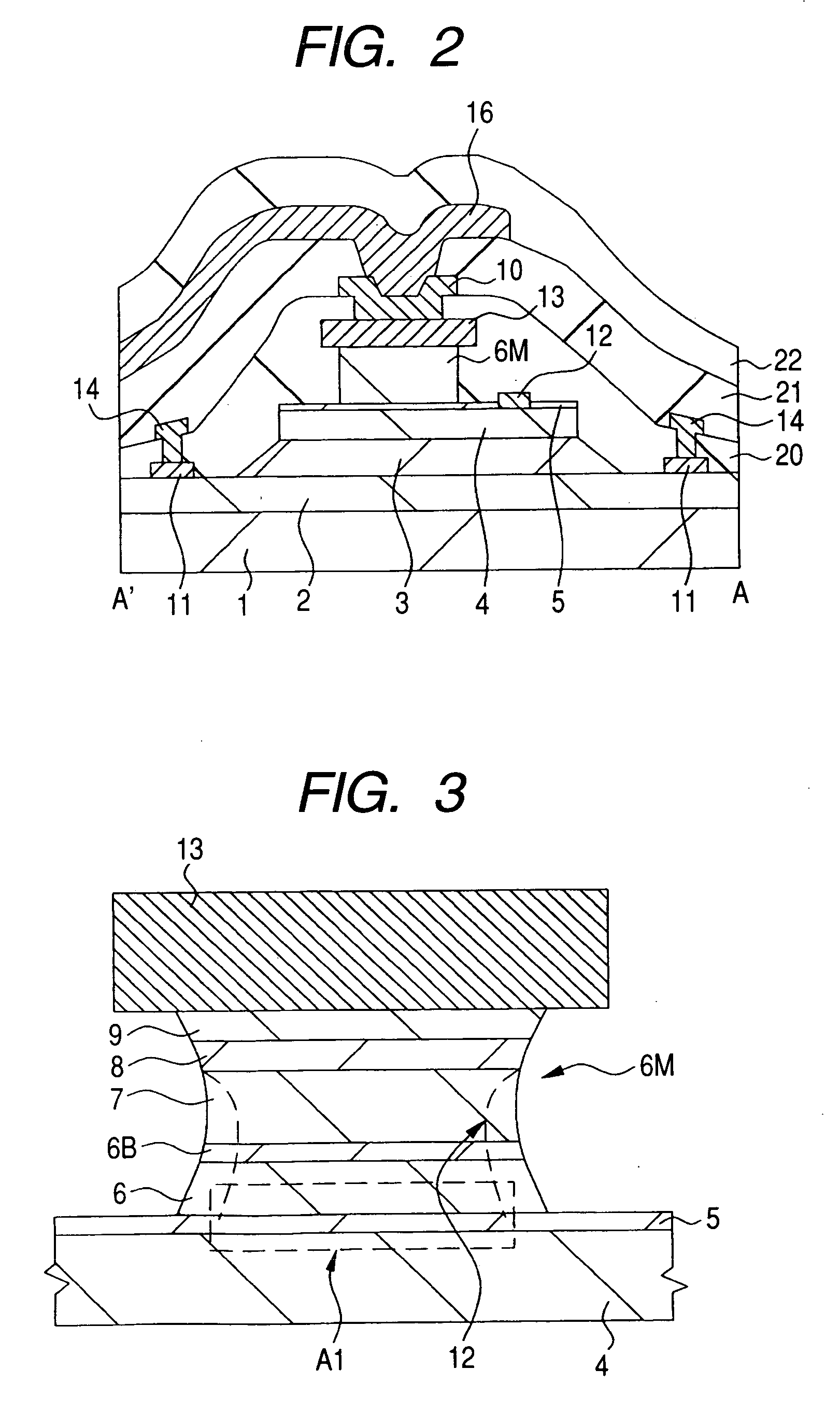

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

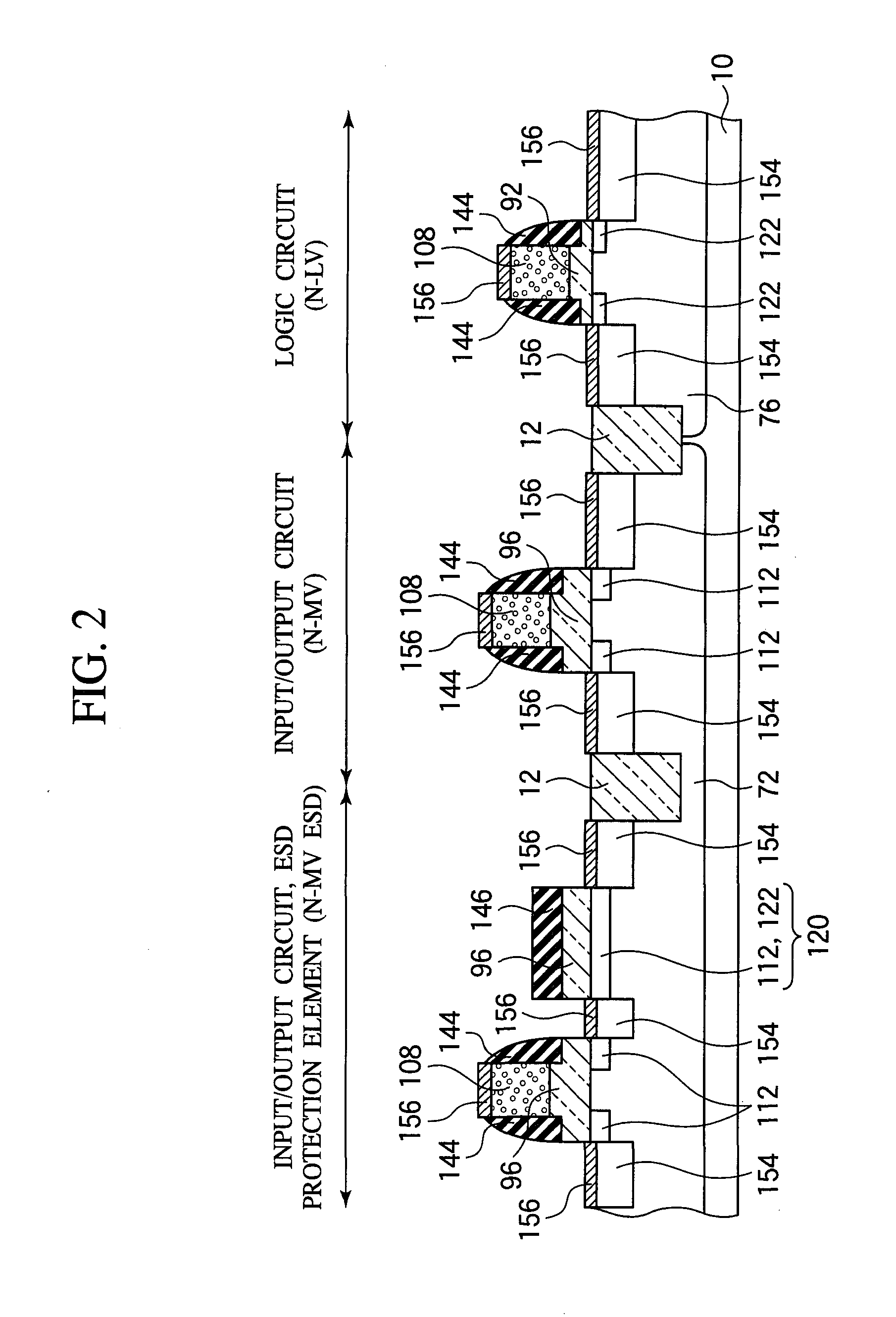

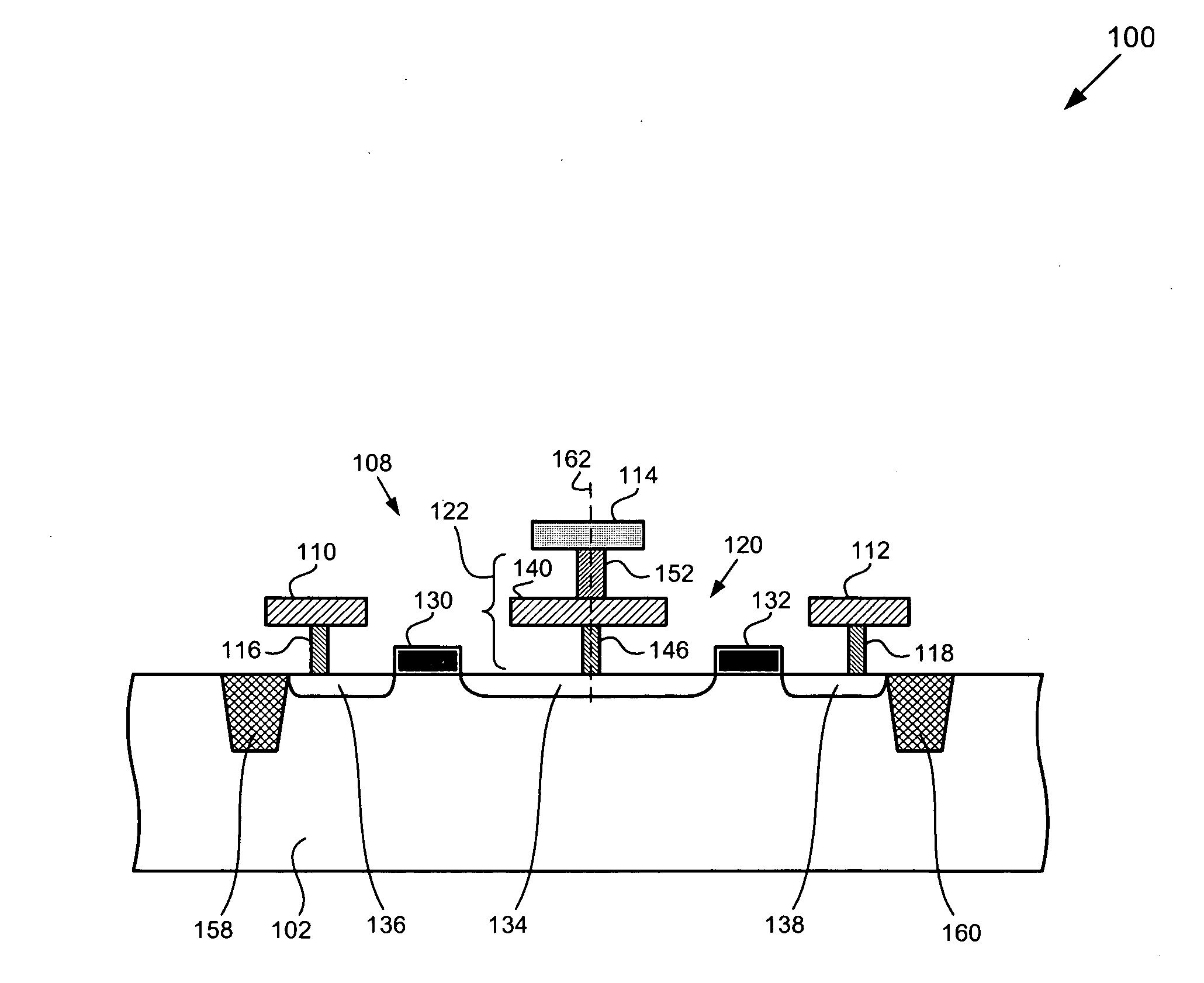

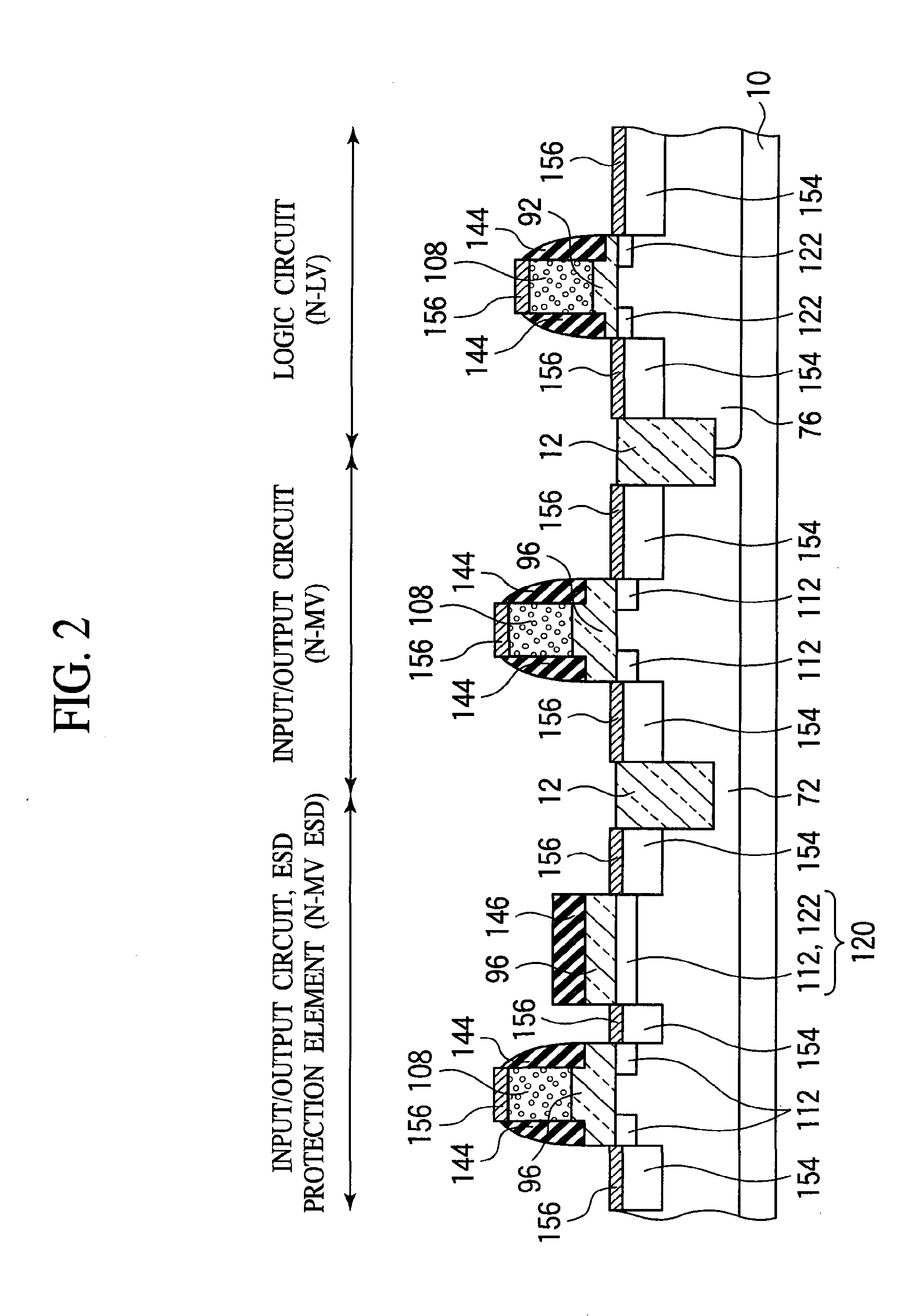

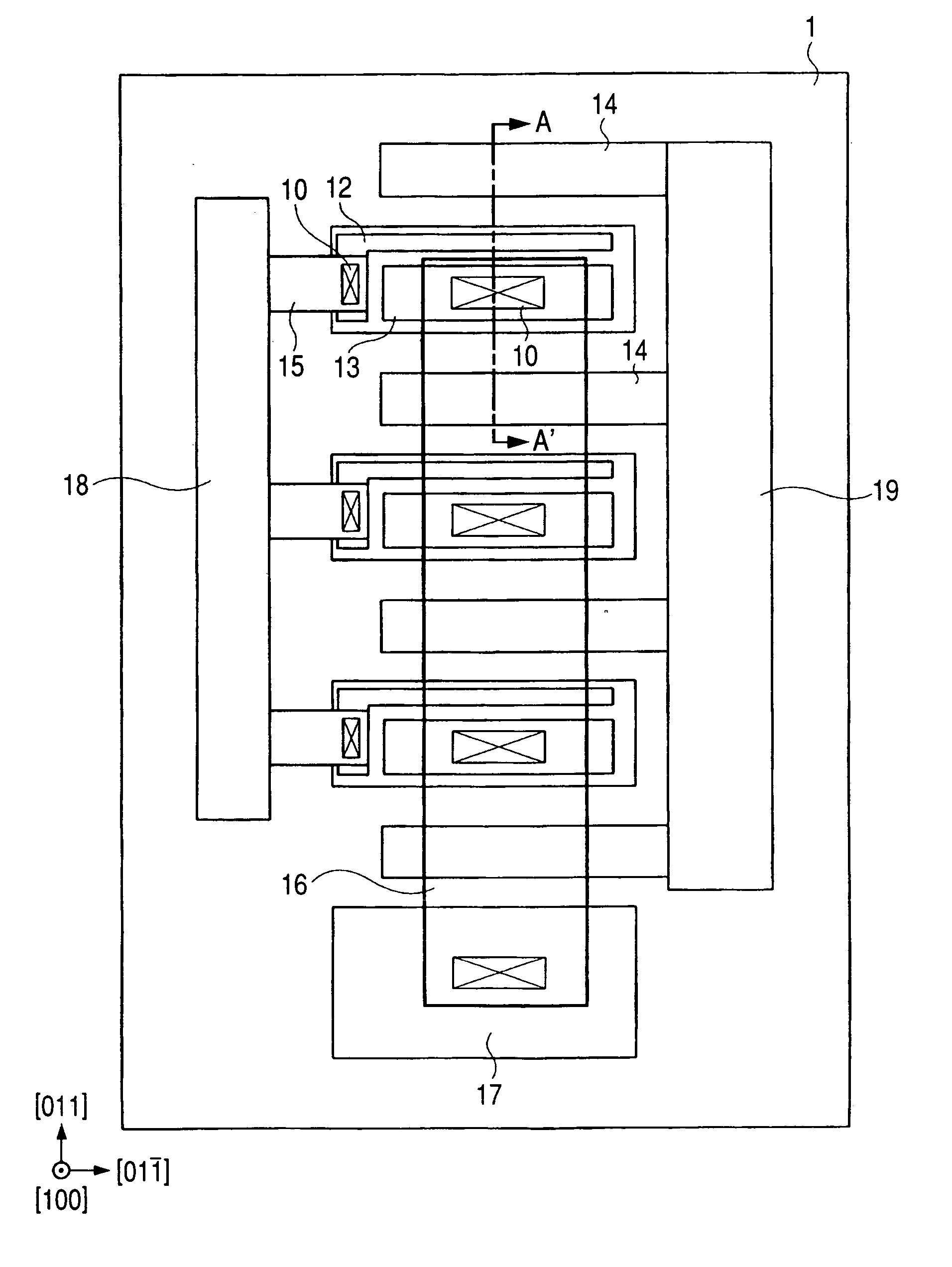

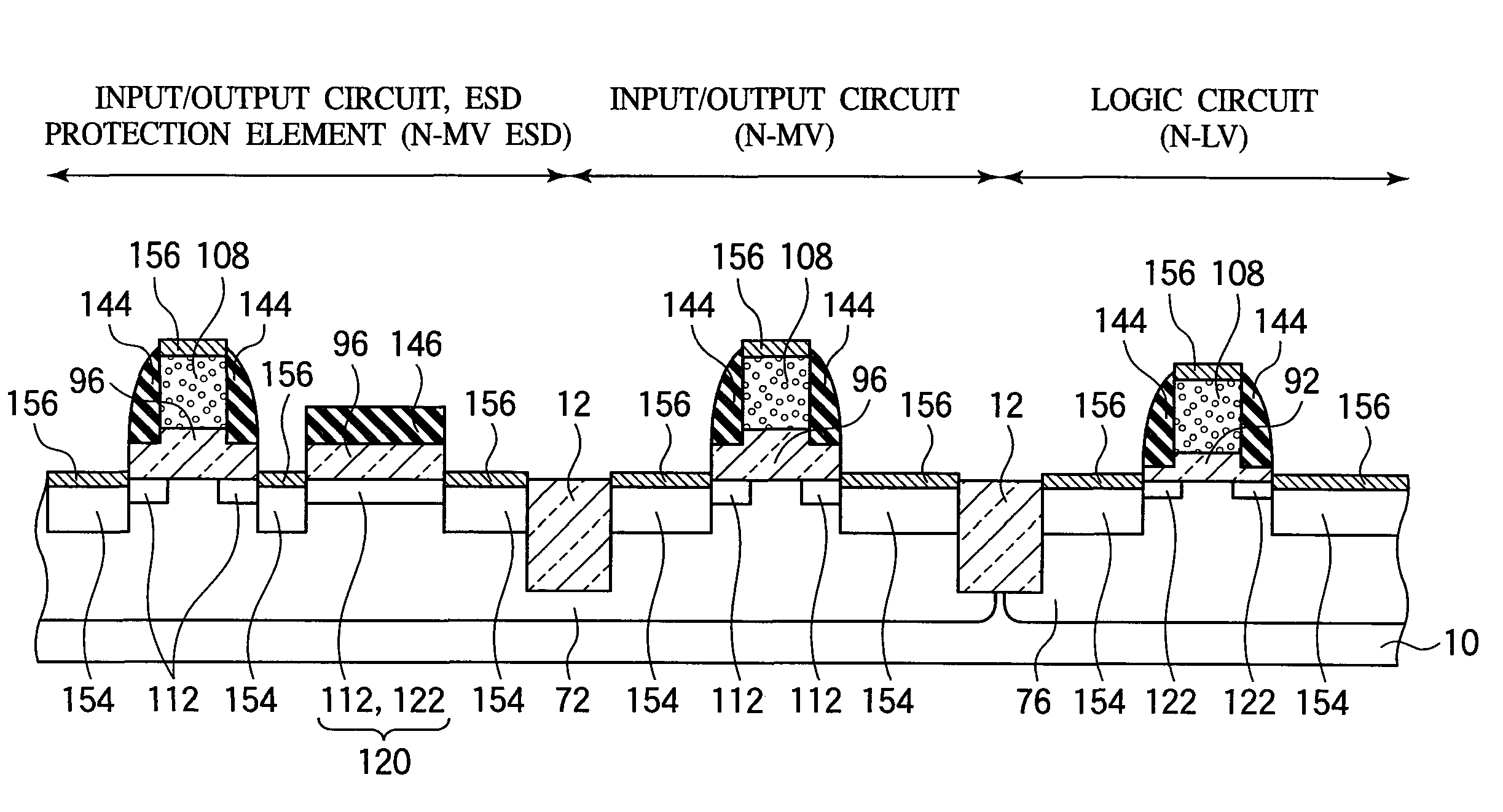

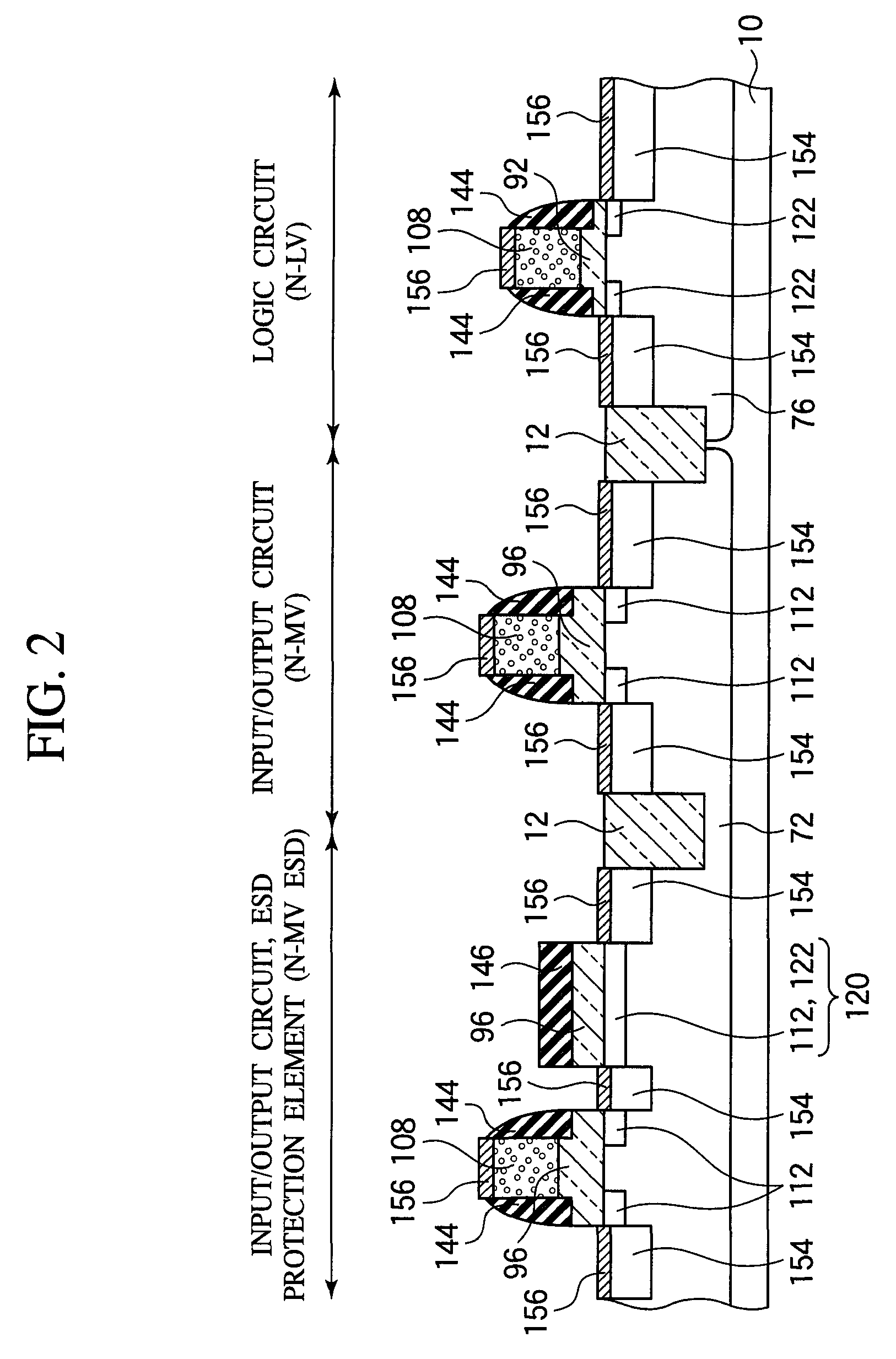

Semiconductor device and method of manufacturing the same

ActiveUS20080067599A1Suppress fluctuationsTransistorSemiconductor/solid-state device detailsSalicideBallast resistor

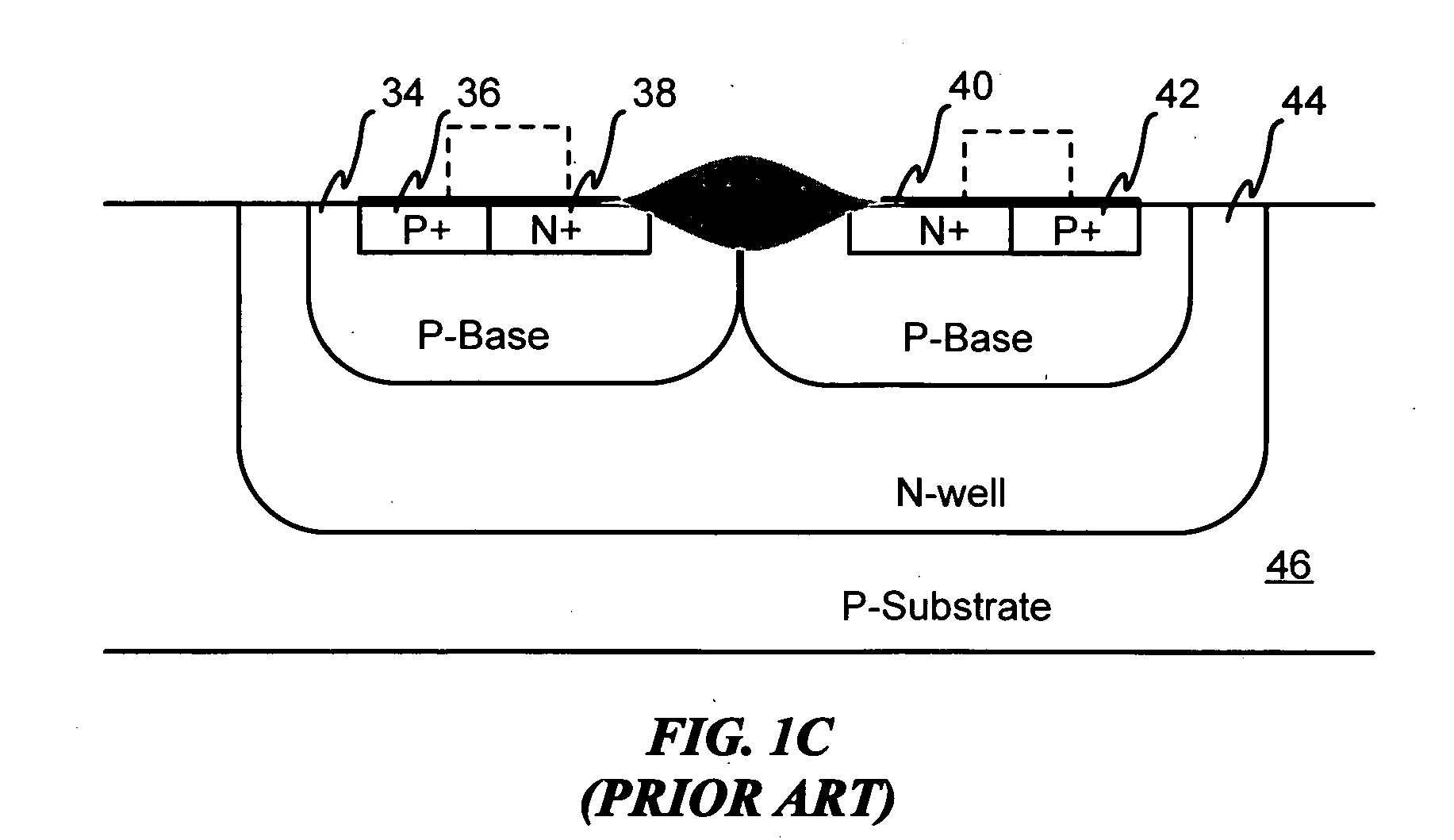

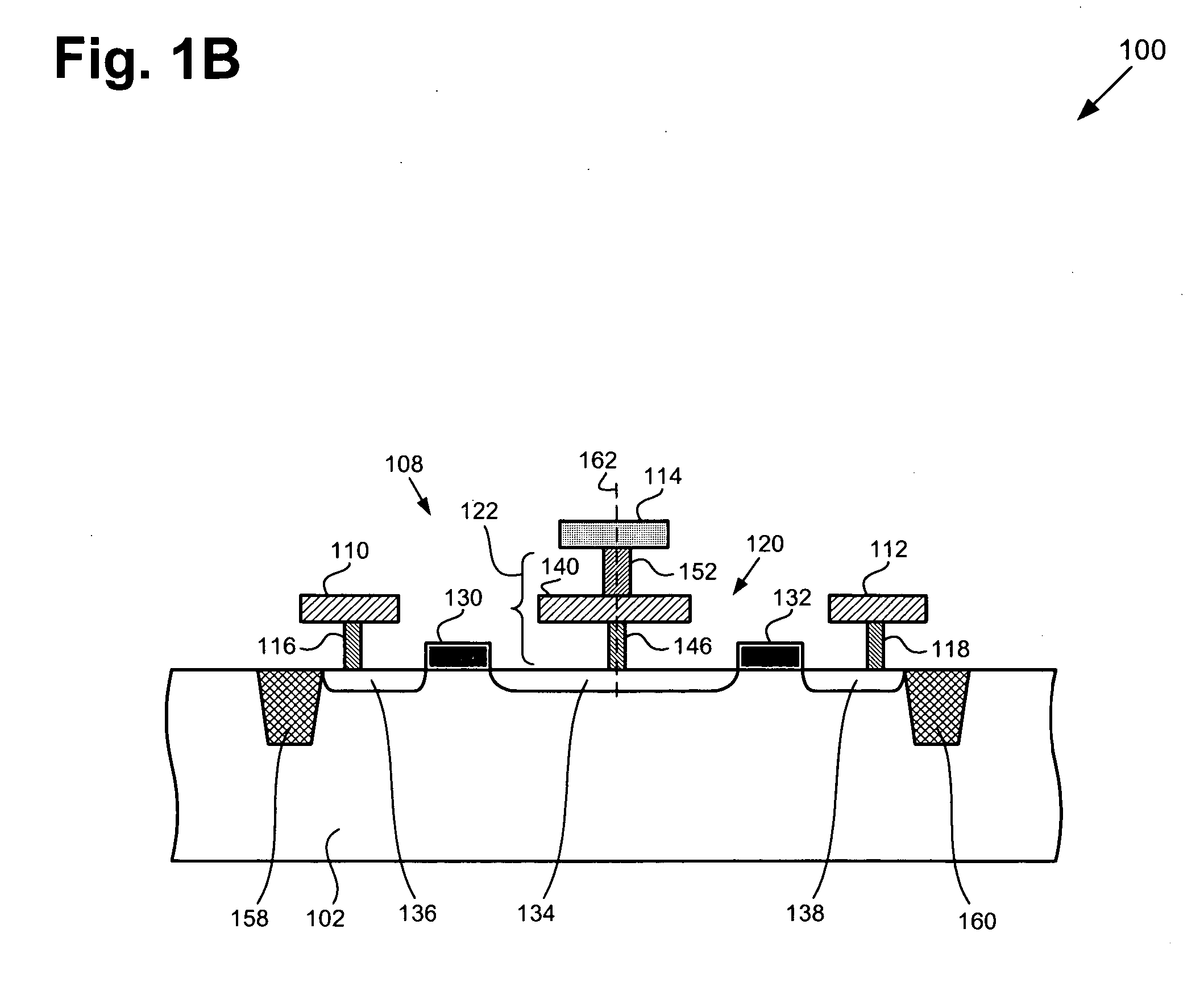

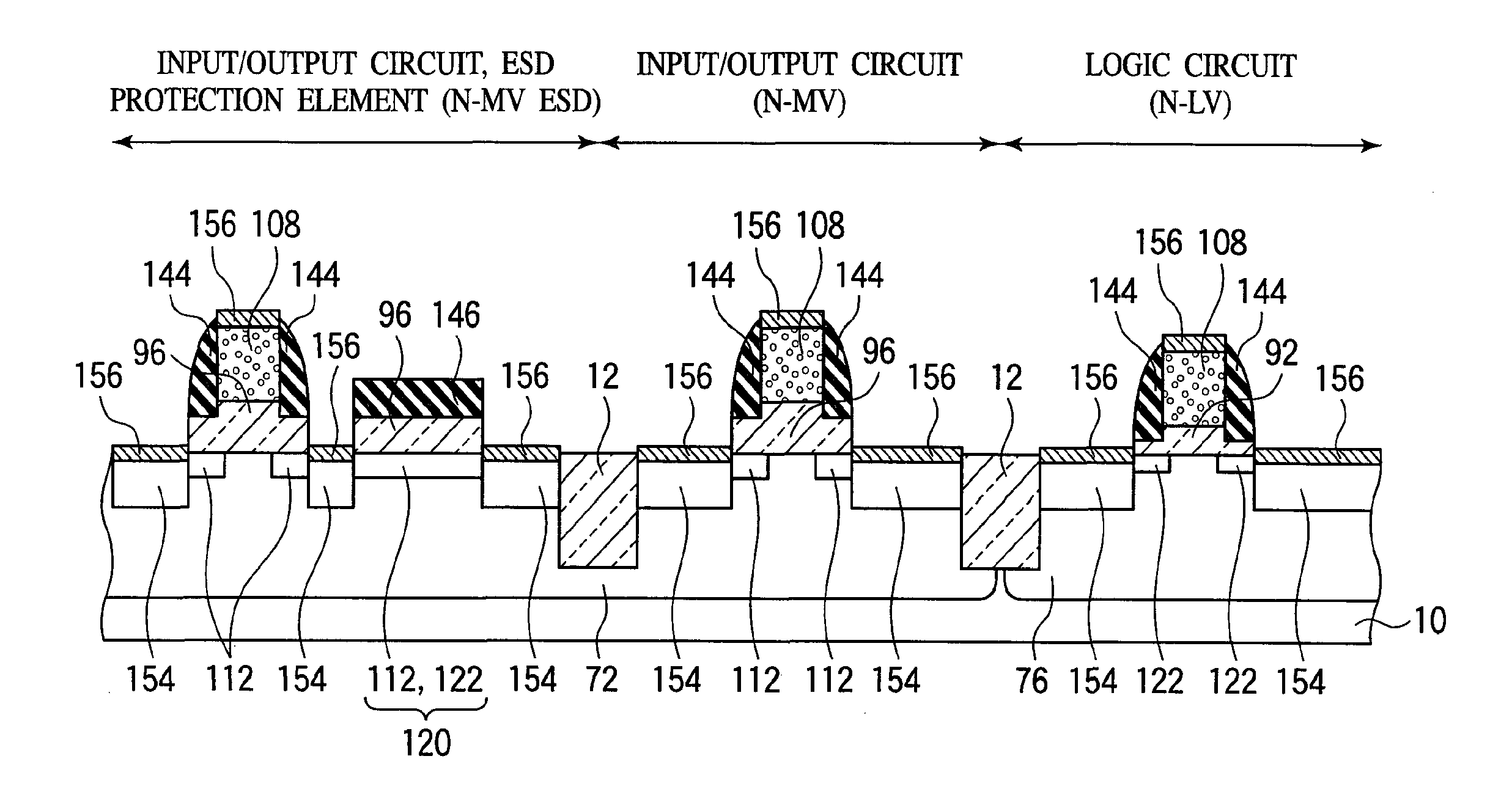

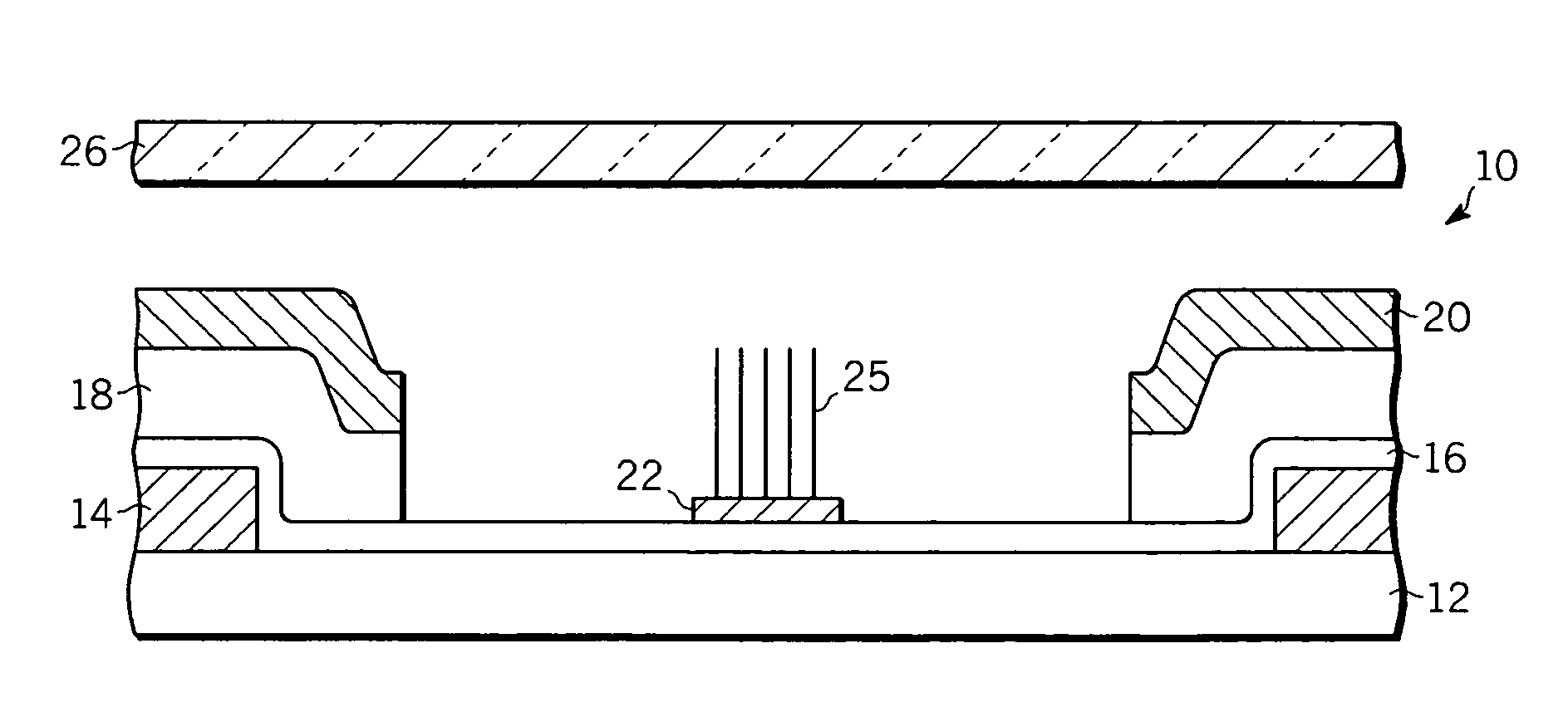

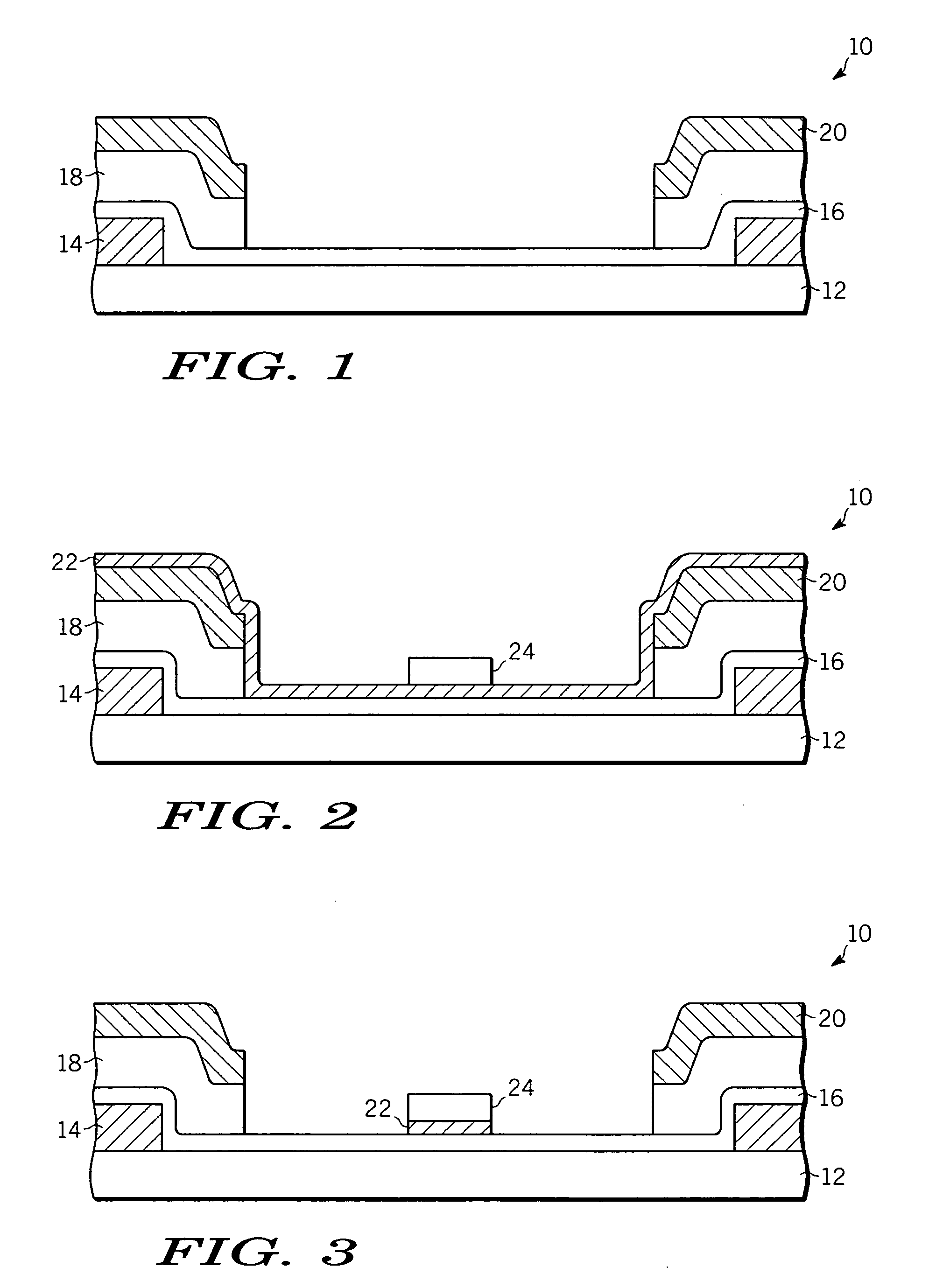

The semiconductor device includes a first MIS transistor including a gate insulating film 92, a gate electrode 108 formed on the gate insulating film 92 and source / drain regions 154, a second MIS transistor including a gate insulating film 96 thicker than the gate insulating film 92, a gate electrode 108 formed on the gate insulating film 96, source / drain regions 154 and a ballast resistor 120 connected to one of the source / drain regions 154, a salicide block insulating film 146 formed on the ballast resistor 120 with an insulating film 92 thinner than the gate insulating film 96 interposed therebetween, and a silicide film 156 formed on the source / drain regions 154.

Owner:SOCIONEXT INC

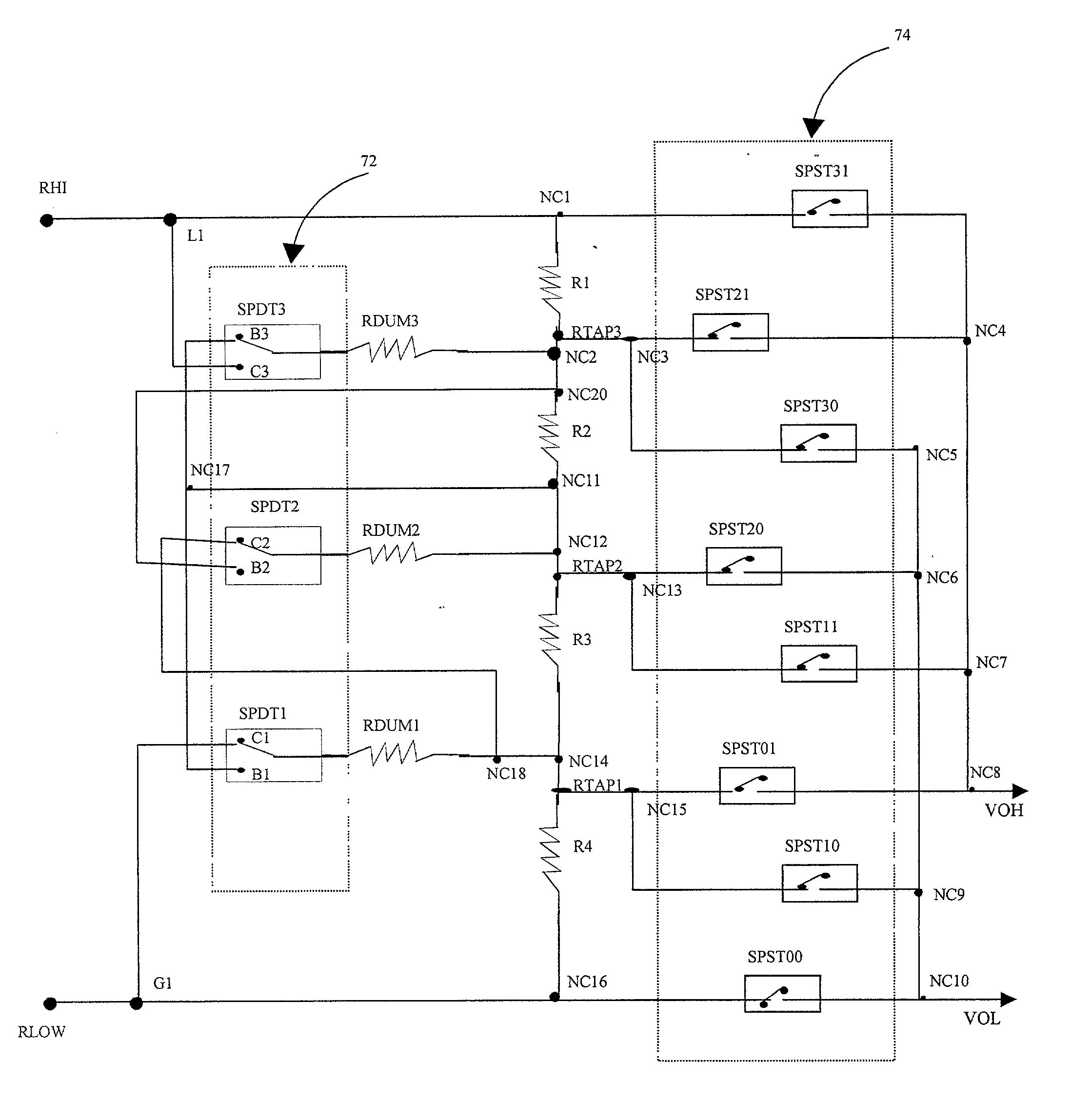

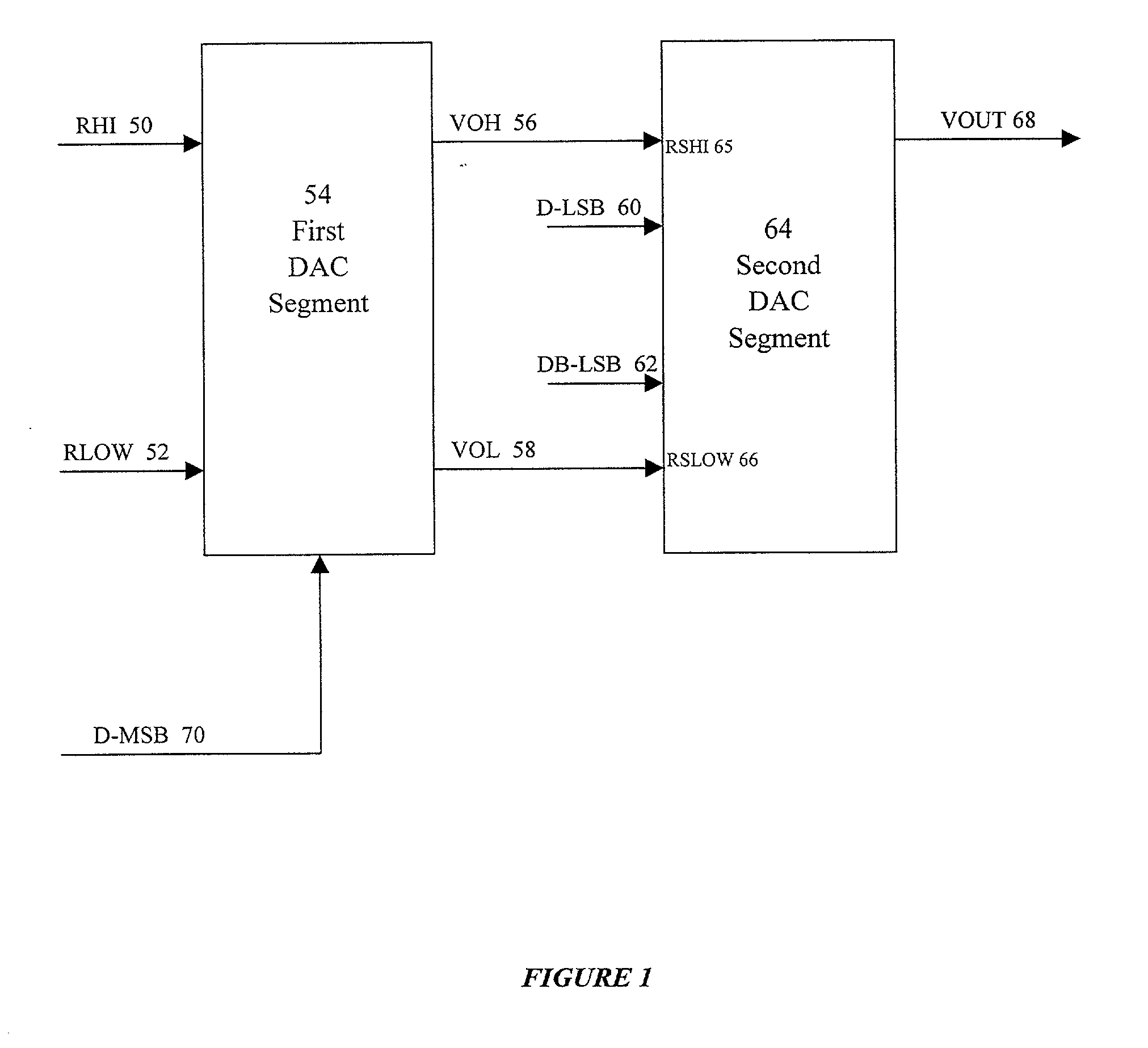

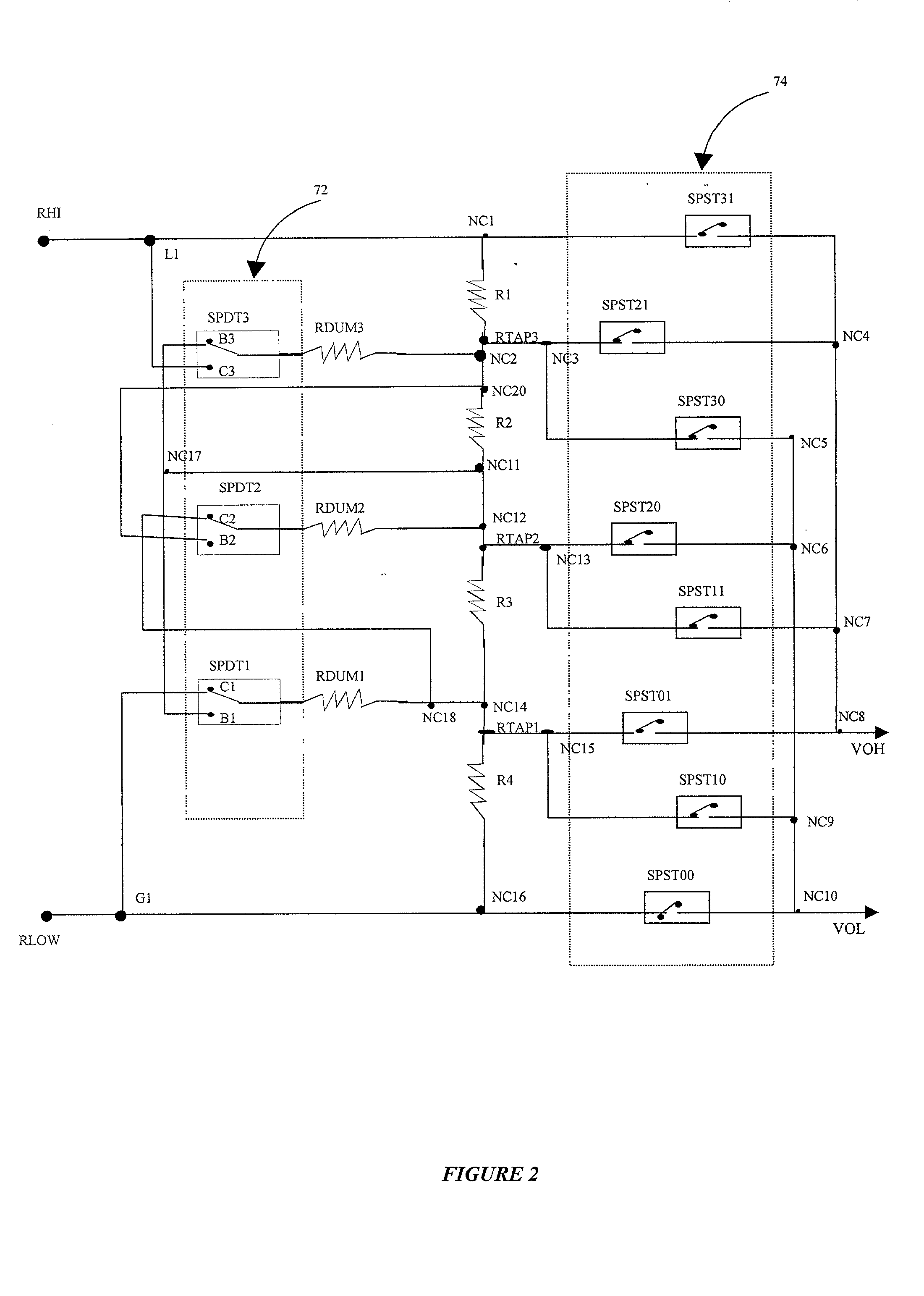

Apparatus and method for digital to analog conversion

InactiveUS20020121995A1Reduce in quantityImproved performance characteristicsElectric signal transmission systemsDigital-analogue convertorsBallast resistorLeast significant bit

The invention includes a segmented digital-to-analog converter (DAC) processing an N-bit input digital signal. A first segment converter processes the most significant bits and subsequent segment converters process the least significant bits of the N-bit input digital signal. The first segment converter includes ballast resistors that nullify the effect of any imbalance of the resistance of the first segment DAC versus the sum of the resistances in the remaining segment DACs. The first segment may be a 2, 4, 6, 8 or higher bit DAC while the second or subsequent segments may similarly be 2, 4, 6, 8, or higher bit DACs.

Owner:QUALCOMM INC

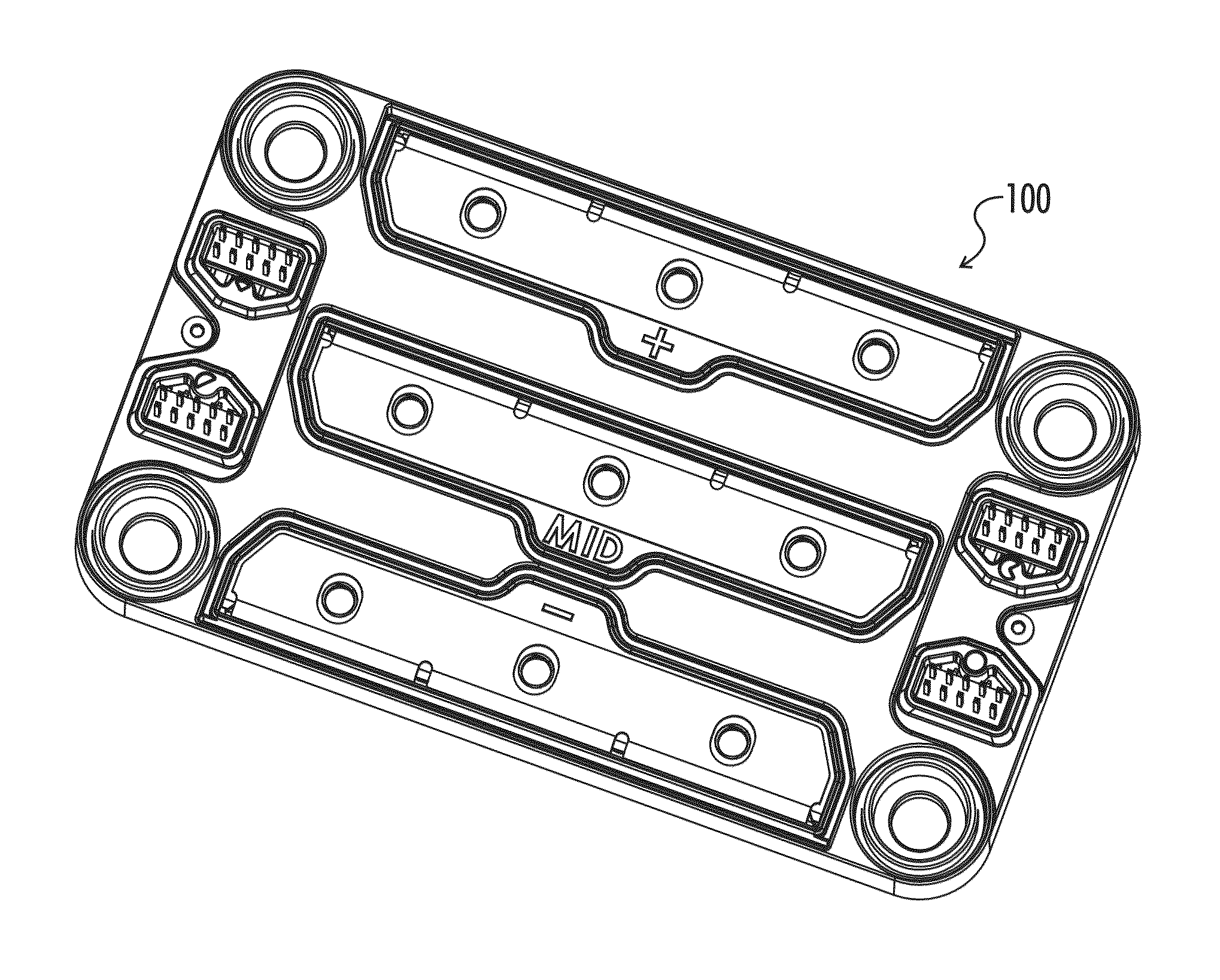

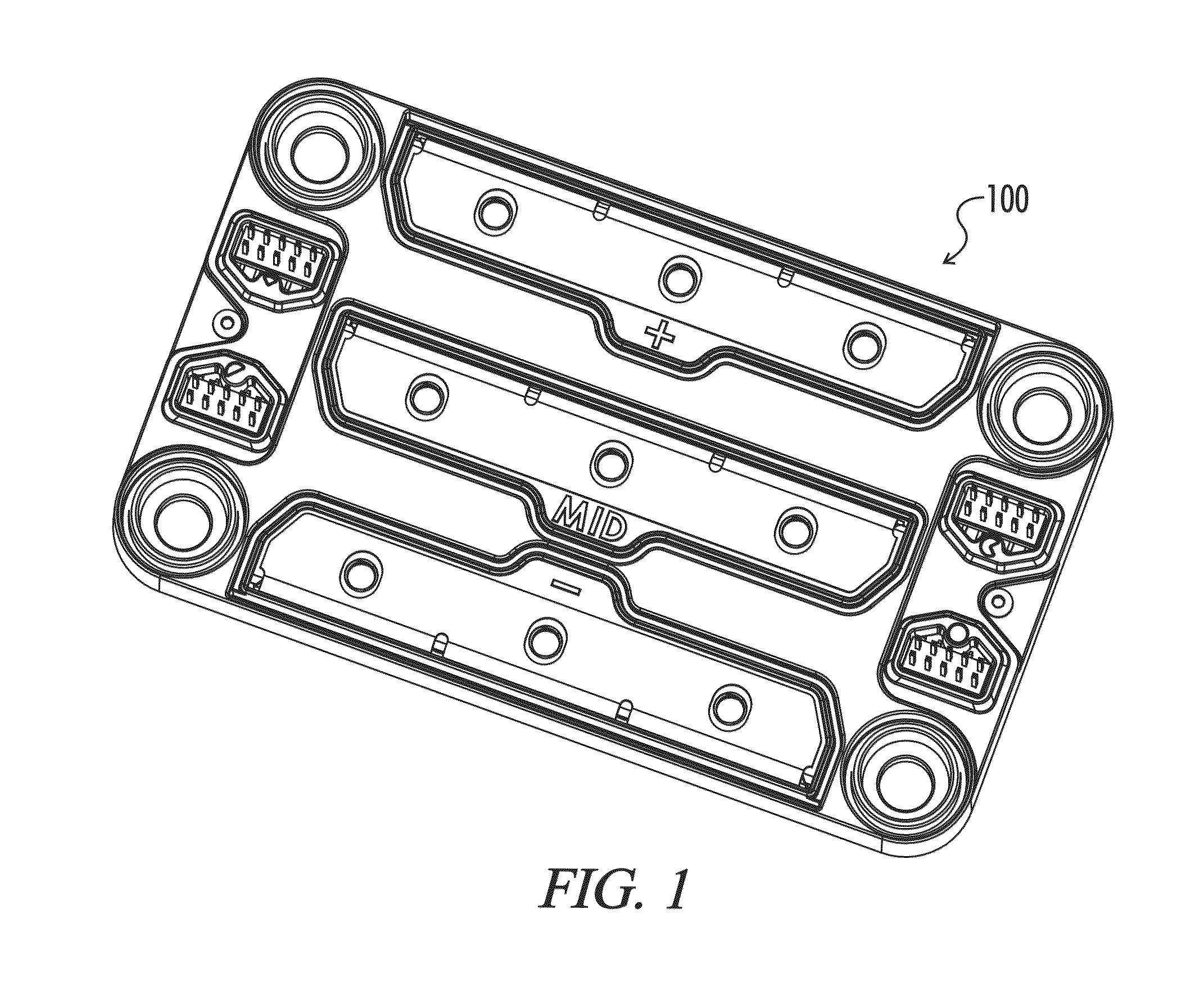

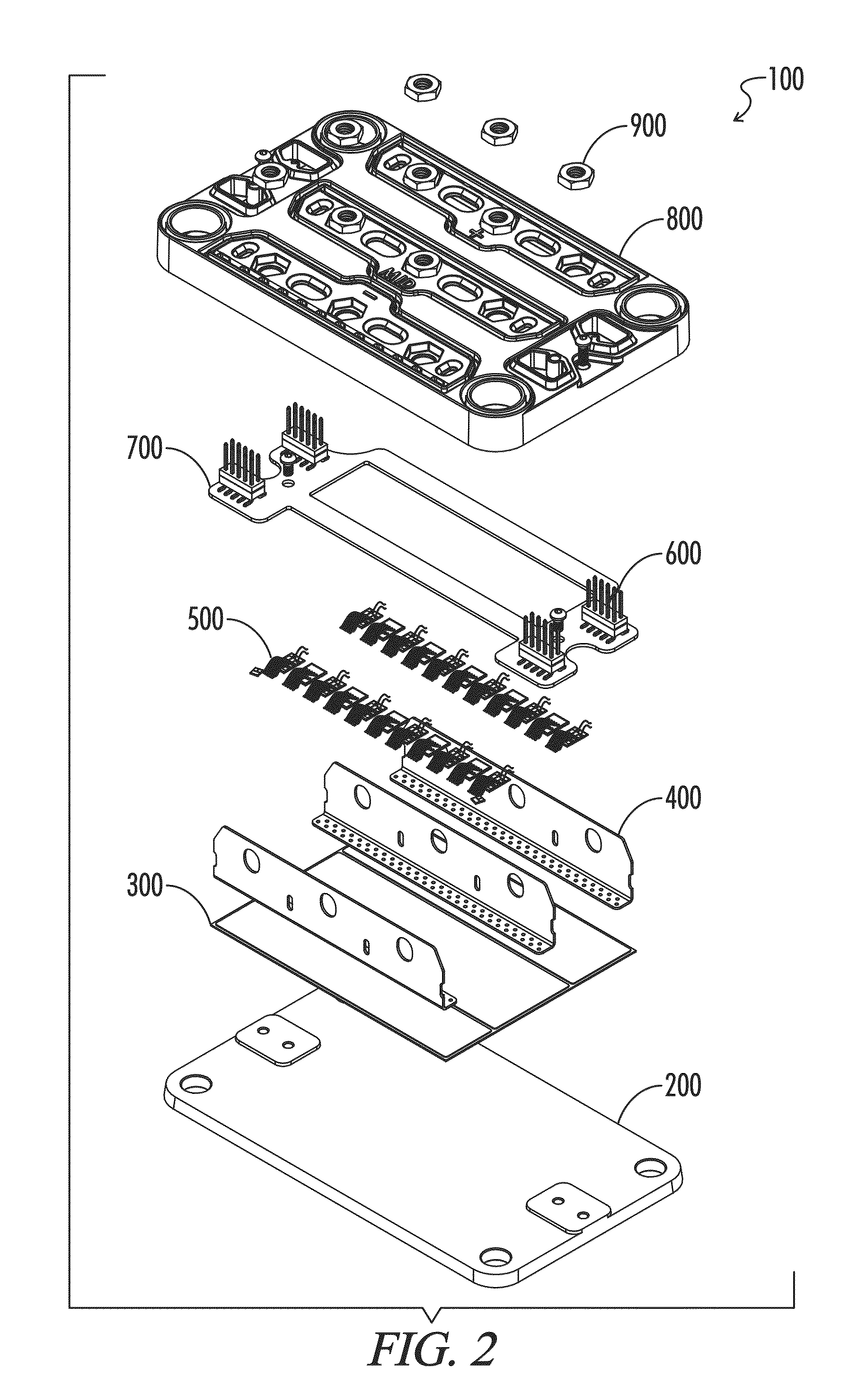

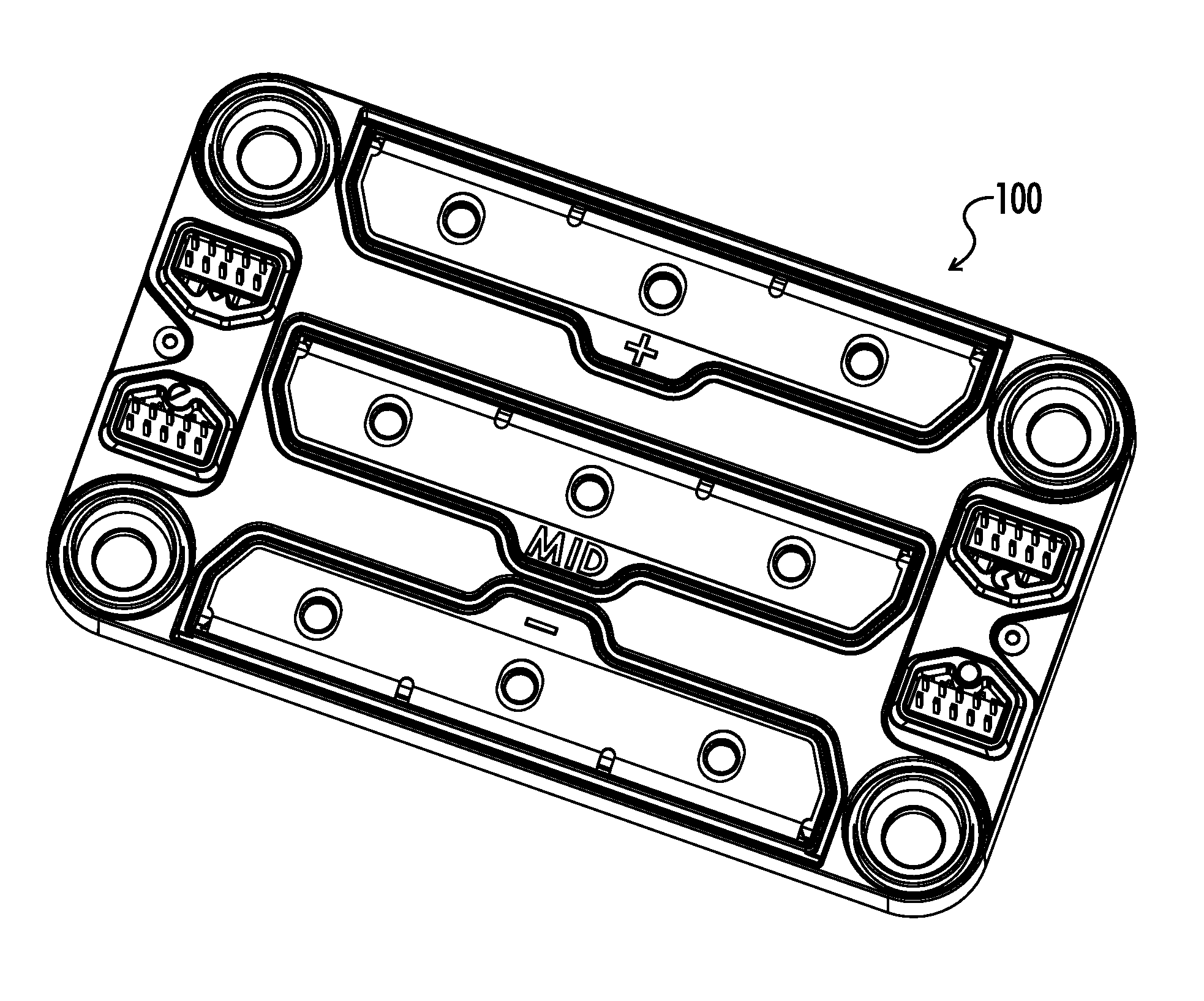

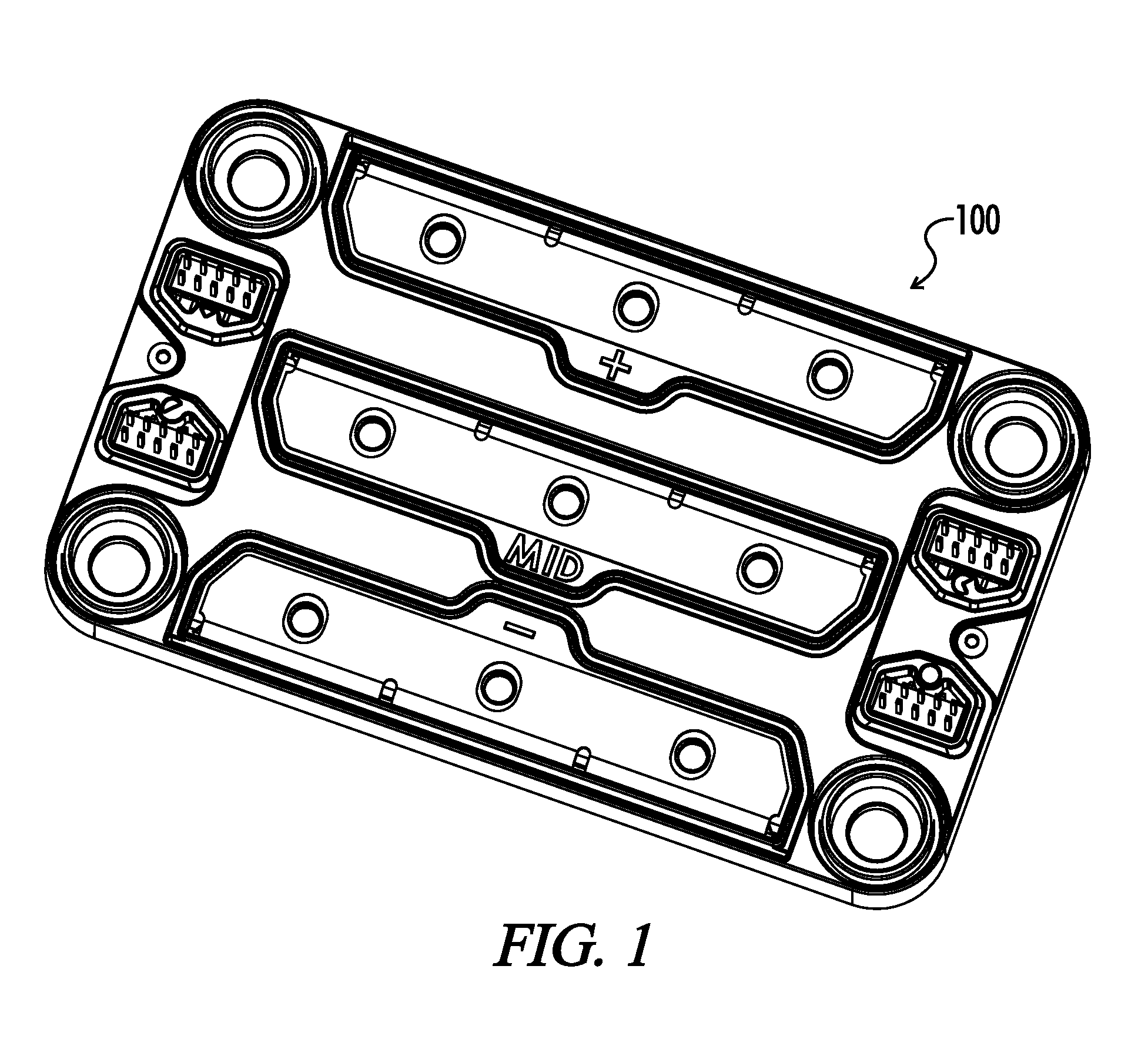

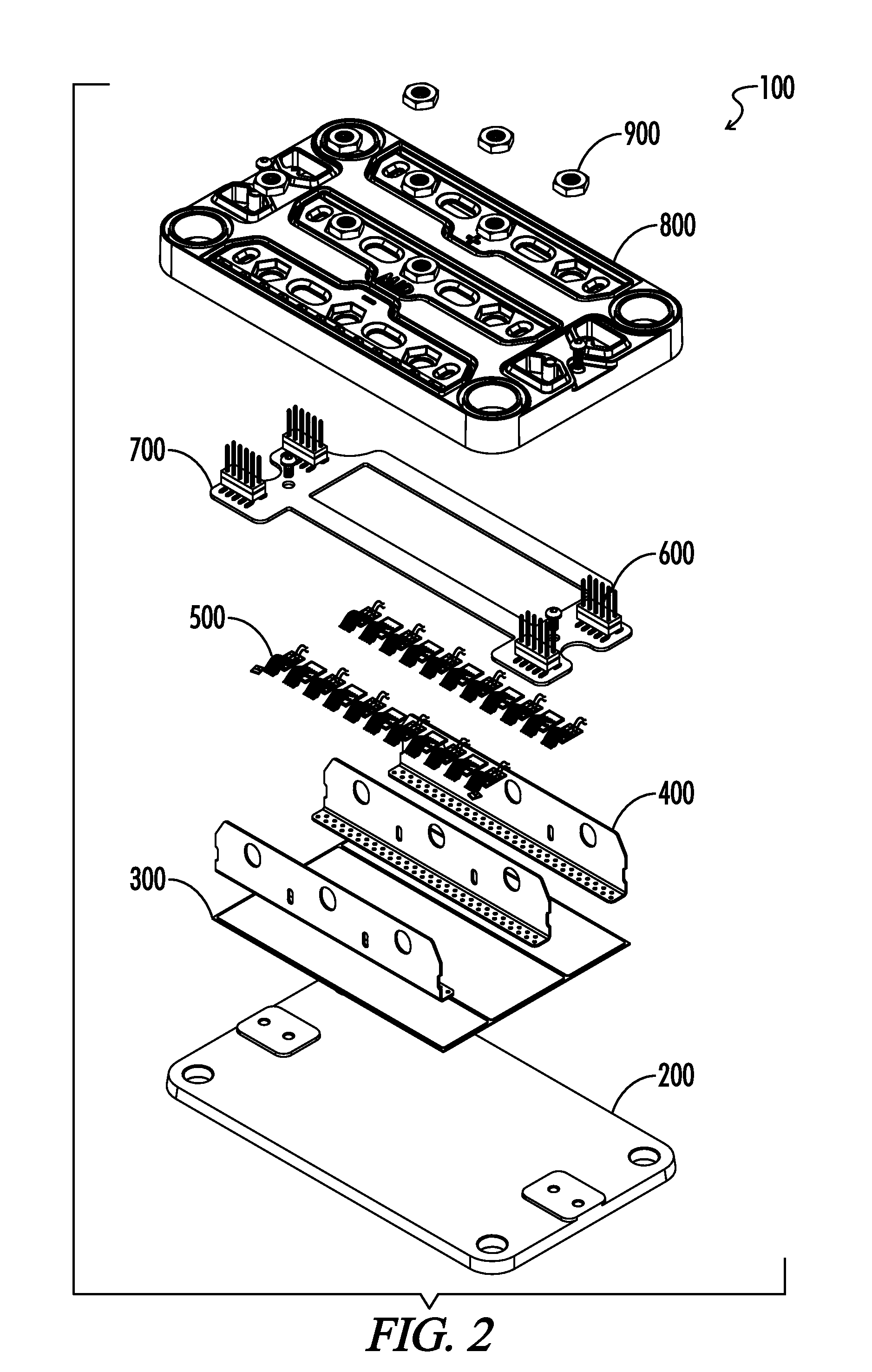

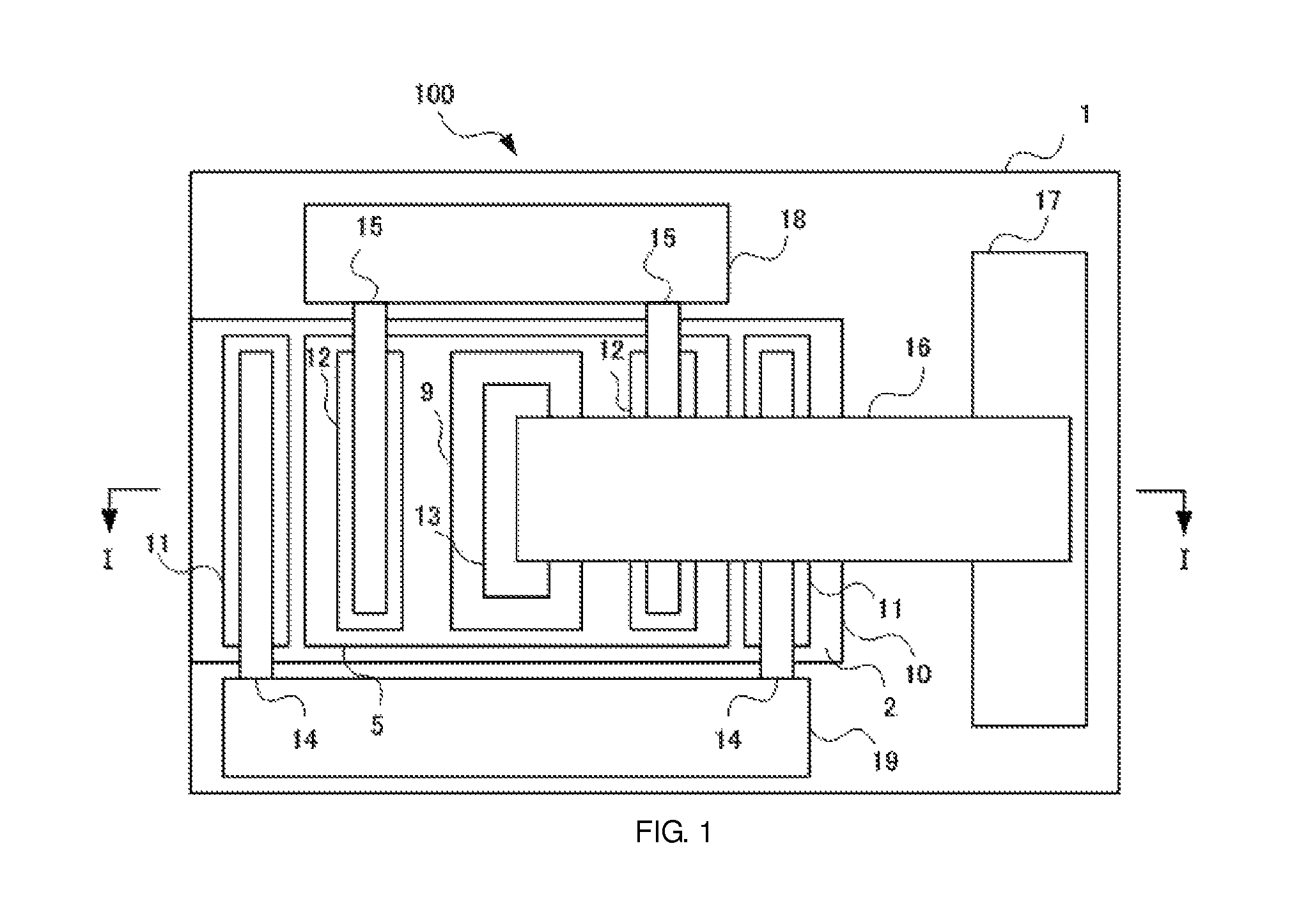

Low profile, highly configurable, current sharing paralleled wide band gap power device power module

ActiveUS9426883B2Closed casingsSemiconductor/solid-state device detailsElectrical conductorFull bridge

Owner:WOLFSPEED INC

Ballast resistors for transistor devices

InactiveUS7087973B2High voltageIncrease voltage marginTransistorSemiconductor/solid-state device detailsLDMOSBallast resistor

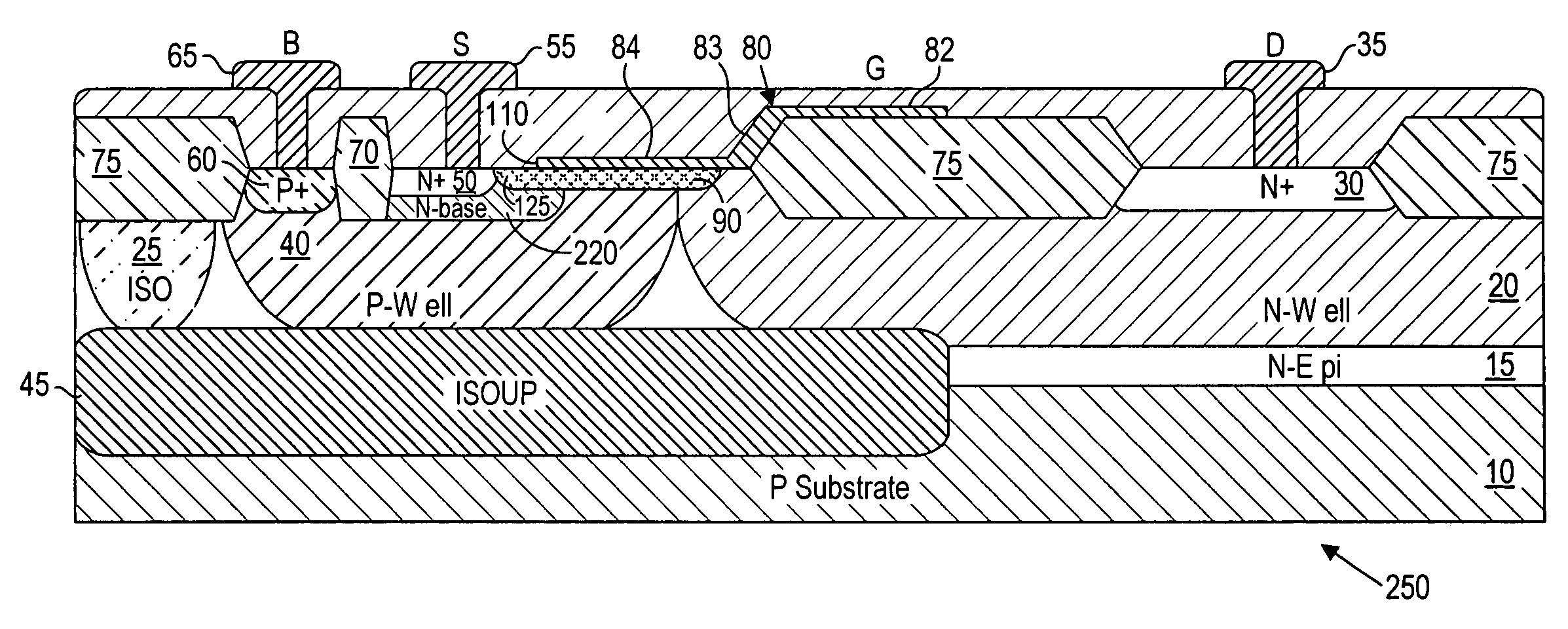

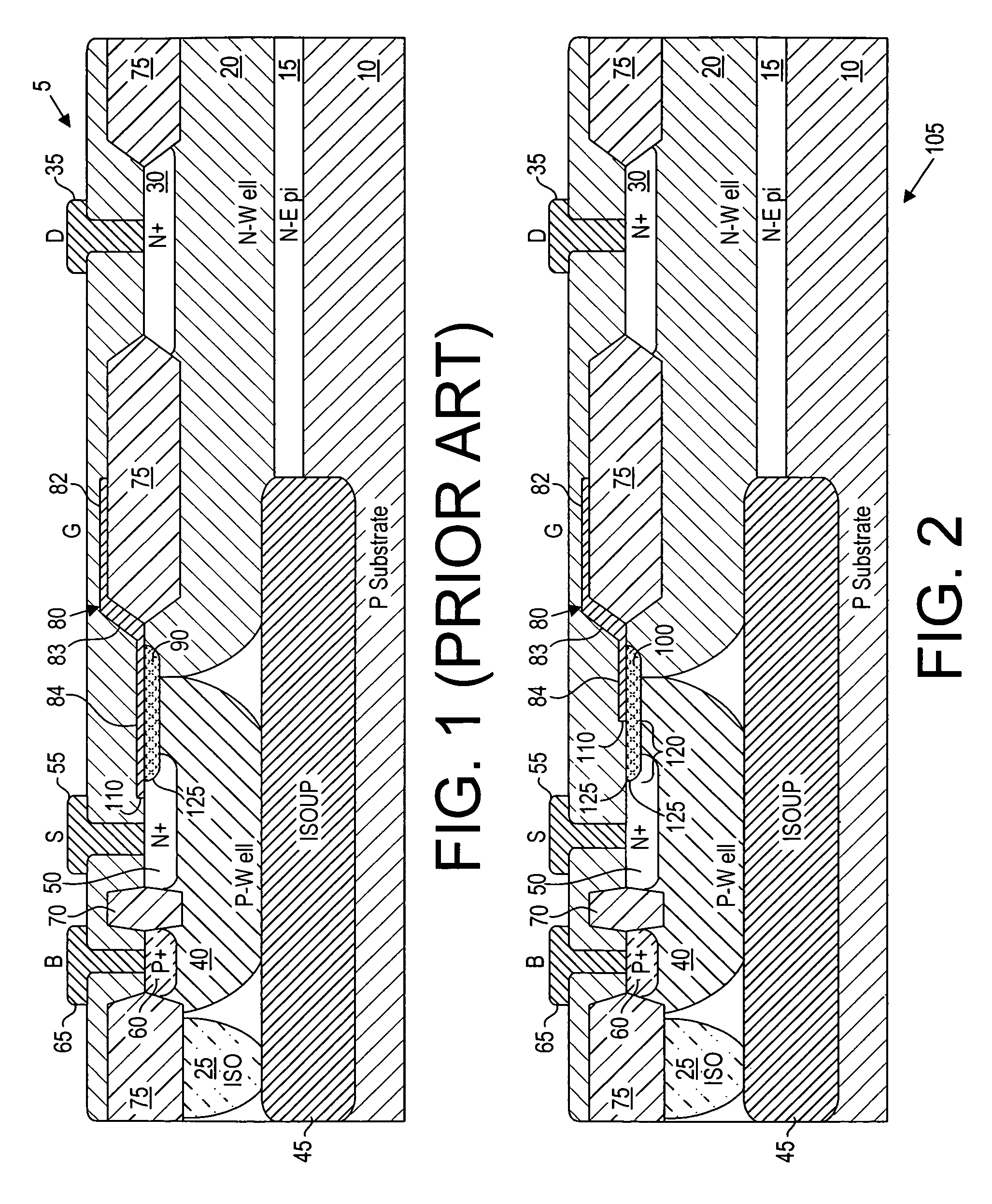

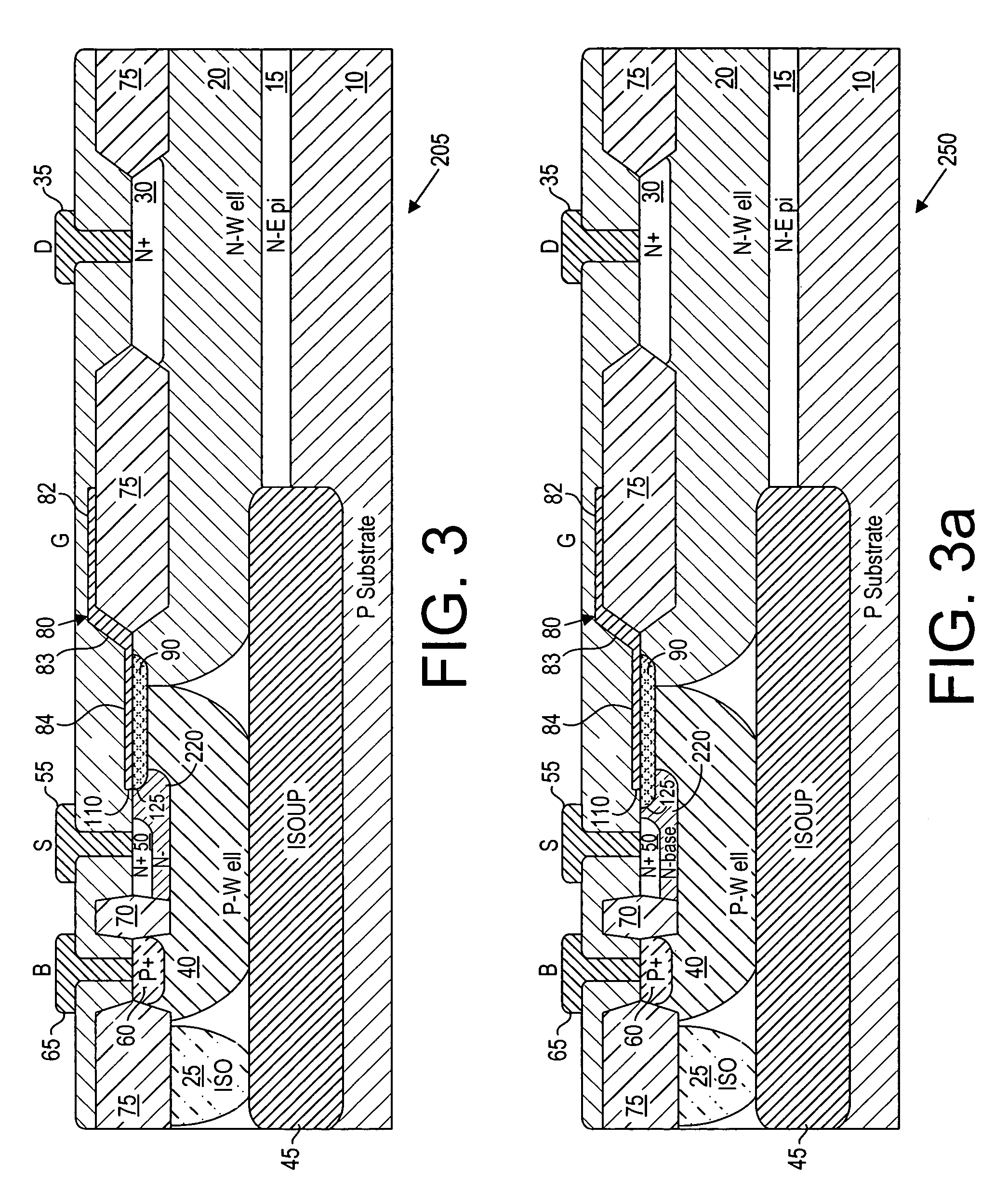

A transistor is formed with a source ballast resistor that regulates channel current. In an LDMOS transistor embodiment, the source ballast resistance may be formed using a high sheet resistance diffusion self aligned to the polysilicon gate, and / or by extending a depletion implant from under the polysilicon gate toward the source region. The teachings herein may be used to form effective ballast resistors for source and / or drain regions, and may be used in many types of transistors, including lateral and vertical transistors operating in a depletion or an enhancement mode, and BJT devices.

Owner:MICREL

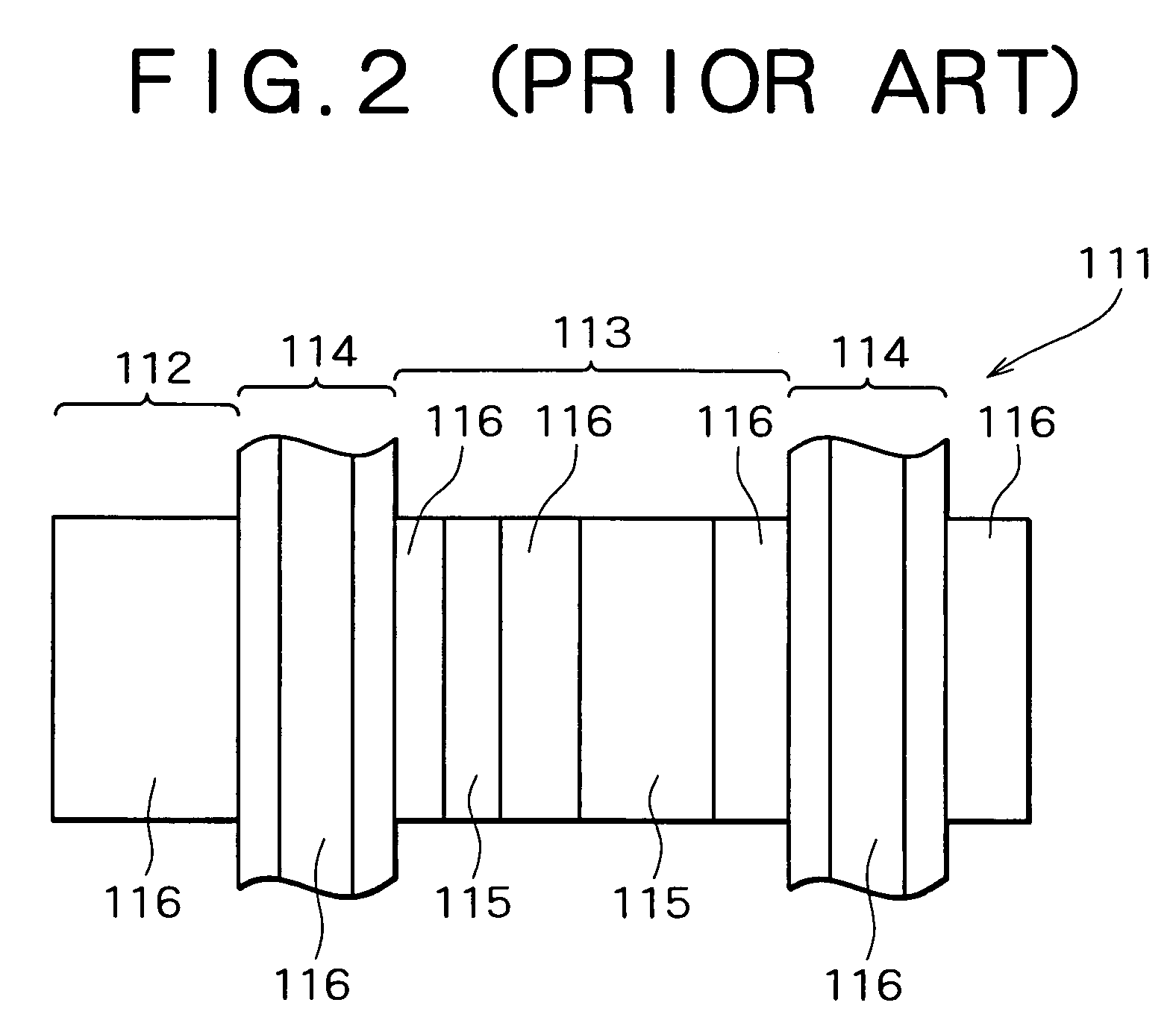

Semiconductor device having an electrostatic discharge protecting element

ActiveUS7183612B2Sufficient protection performanceLarge lengthTransistorSolid-state devicesBallast resistorEngineering

In an ESD protecting element, a plurality of source regions and a plurality of ballast resistor regions are formed. A drain region is formed at a region which is in contact with a channel region in the ballast resistor region, and an n+ type diffusion region is formed at a region isolated from the drain region via an STI region. A third contact is provided on the drain region, first and second contacts are formed on the n+ type diffusion region, and the first contact is connected to a pad. The second contact is coupled to the third contact by a metal wire. The first and second contacts are laid out along the widthwise direction of a gate.

Owner:RENESAS ELECTRONICS CORP

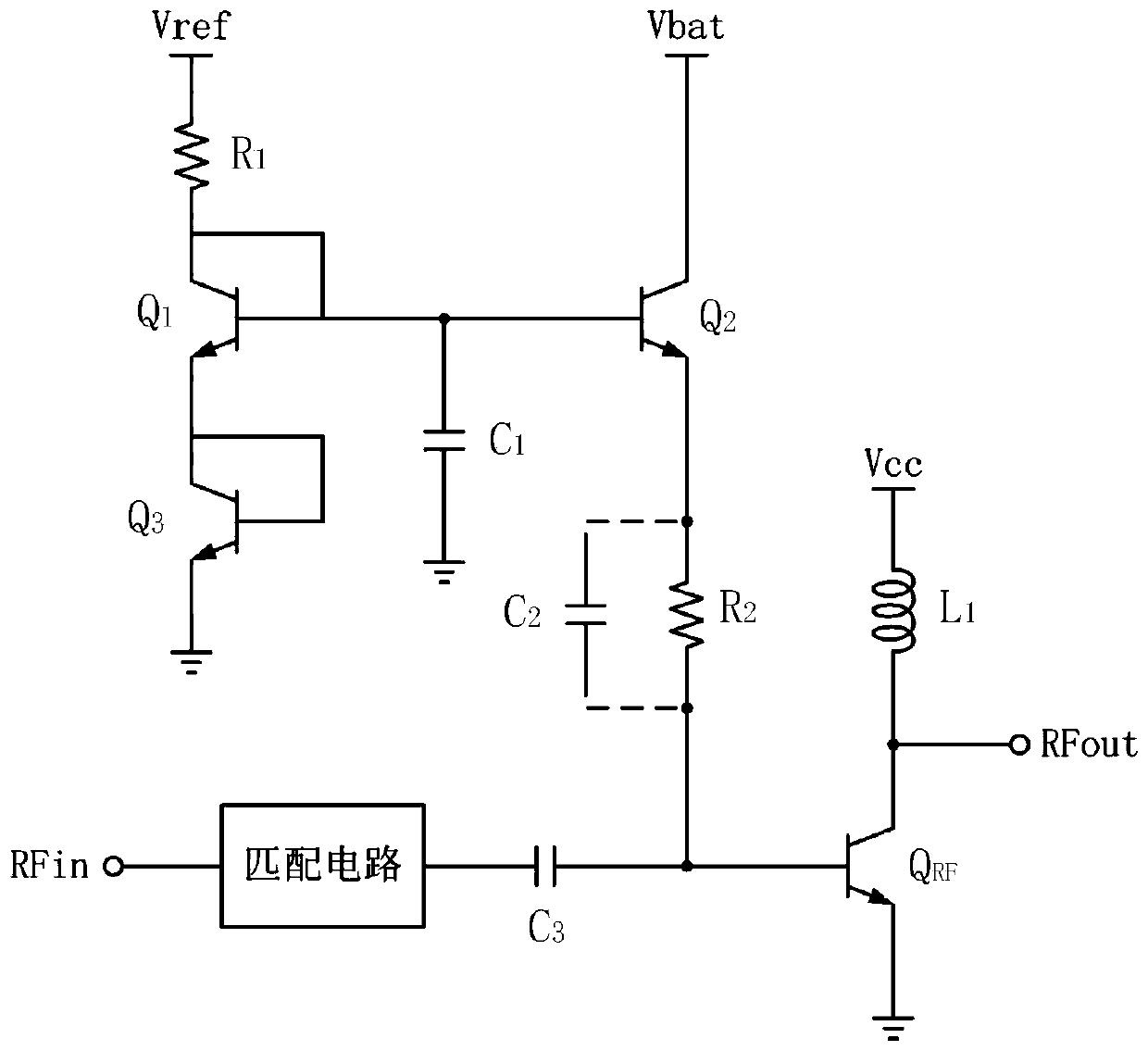

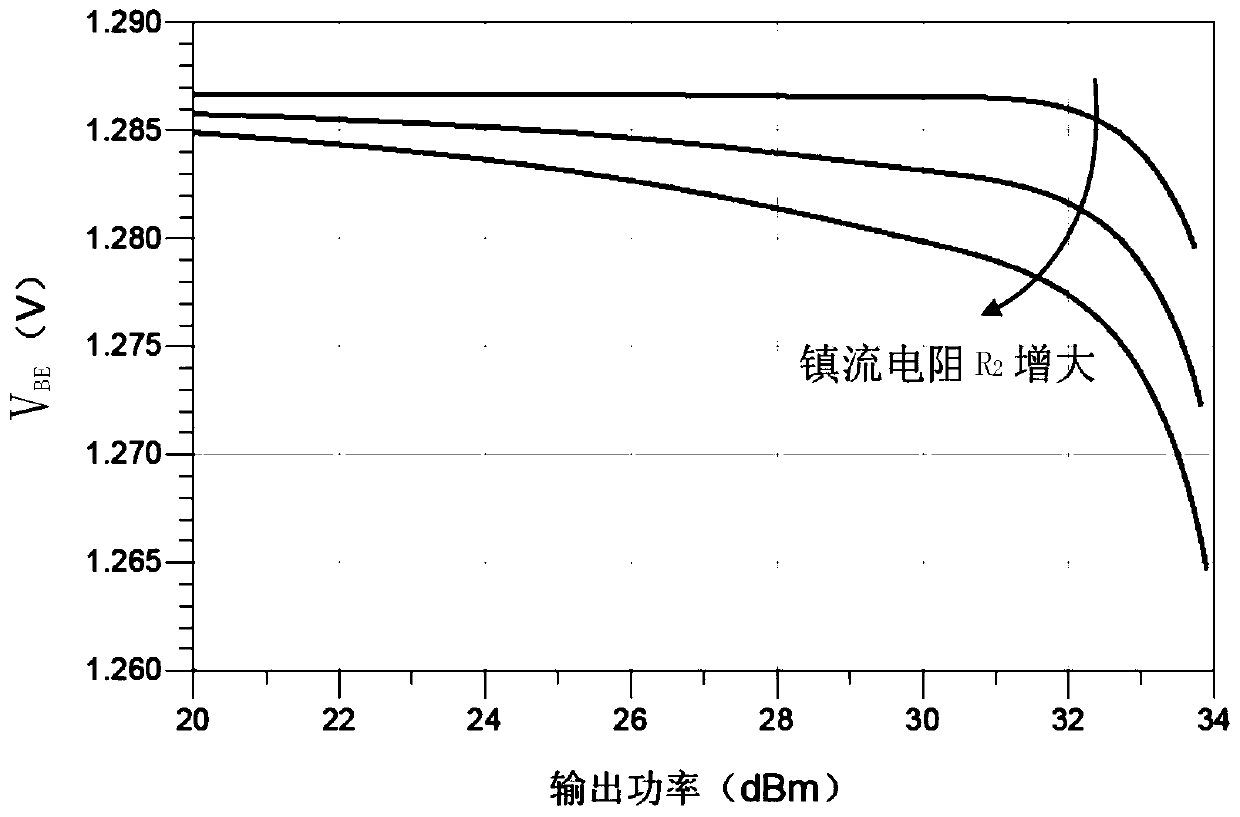

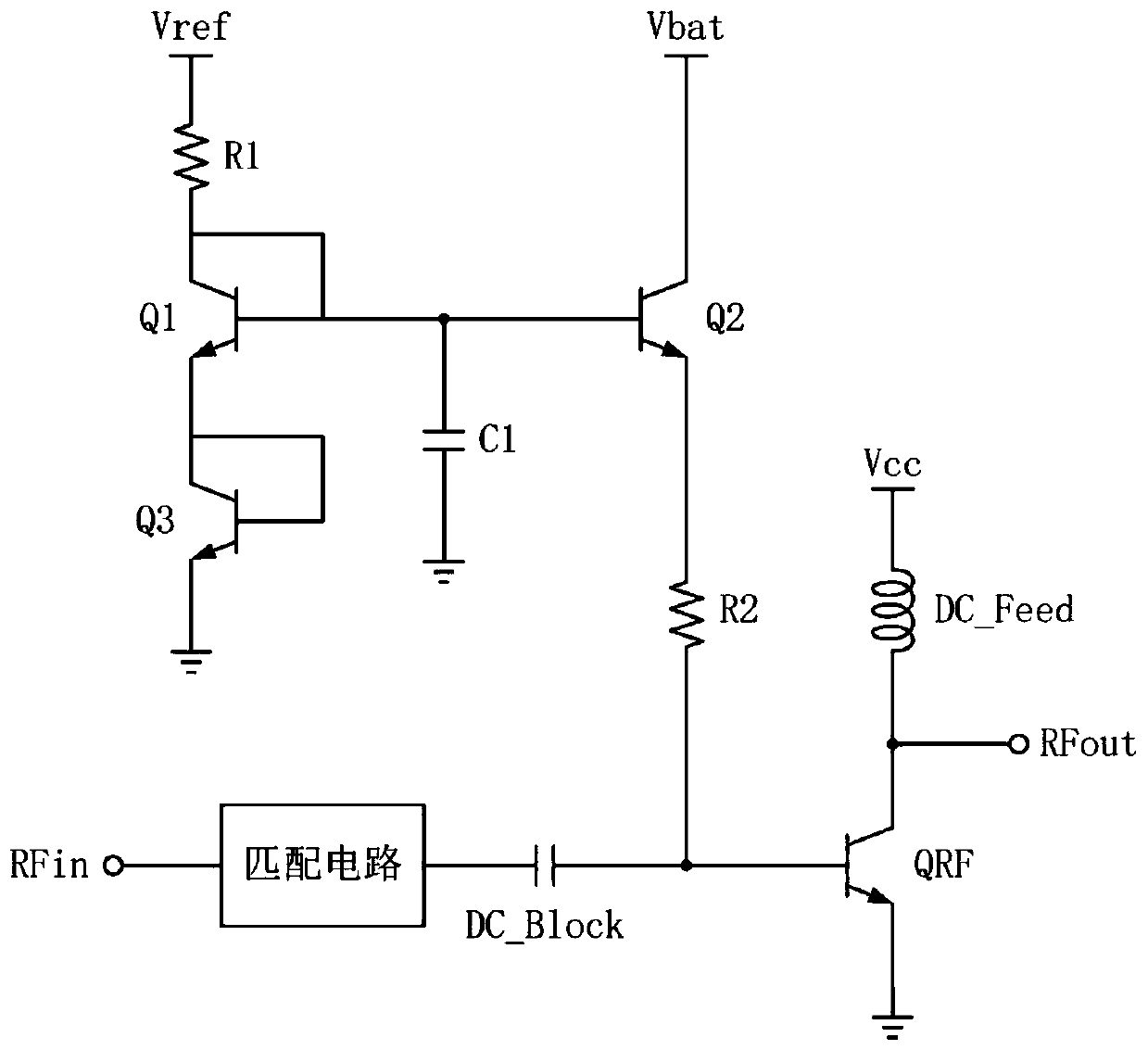

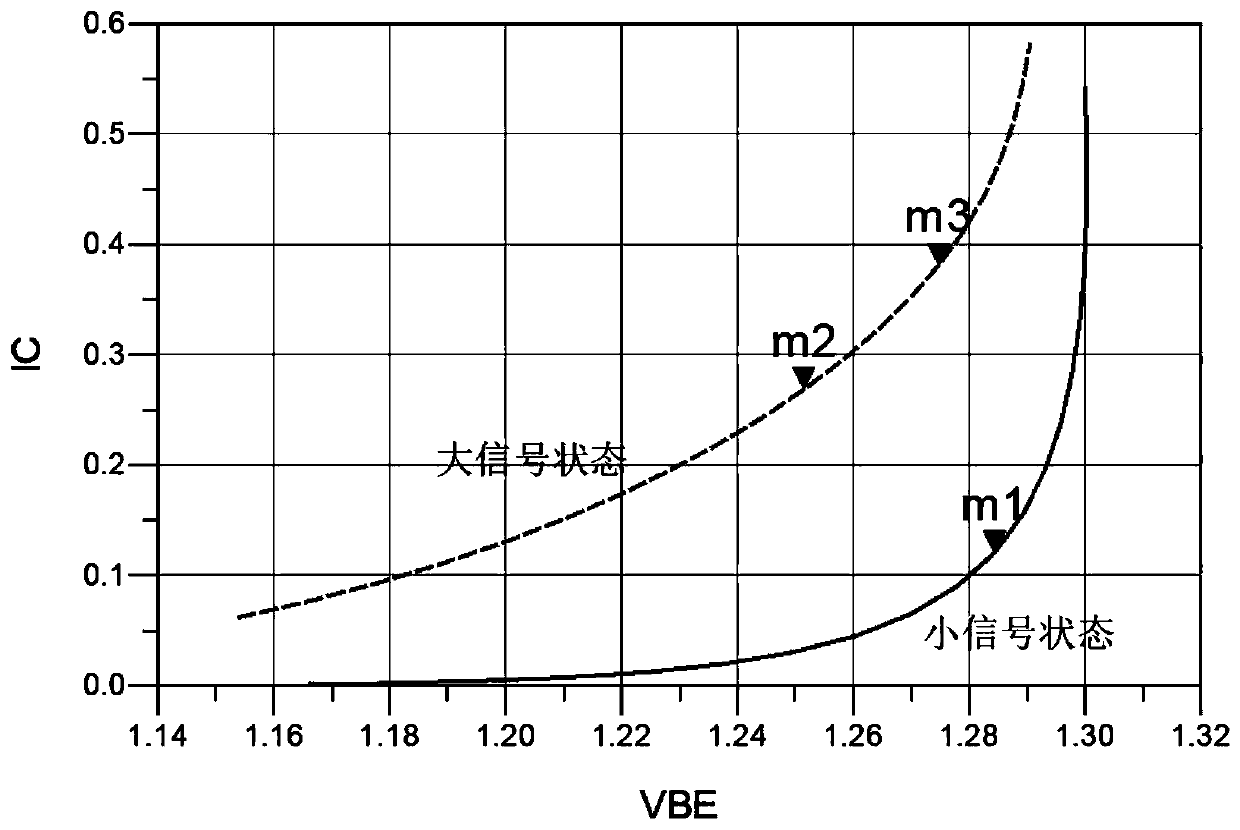

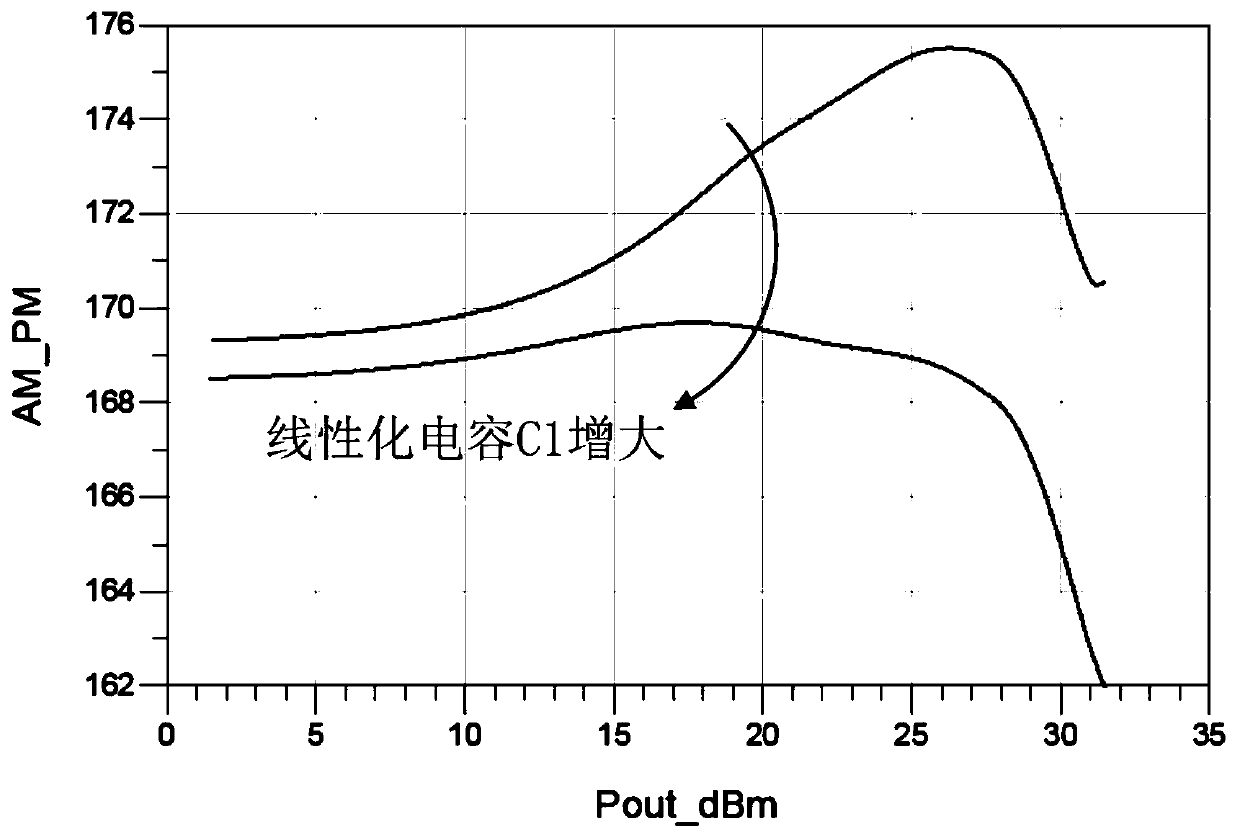

Biasing circuit for power amplifier and power amplifier

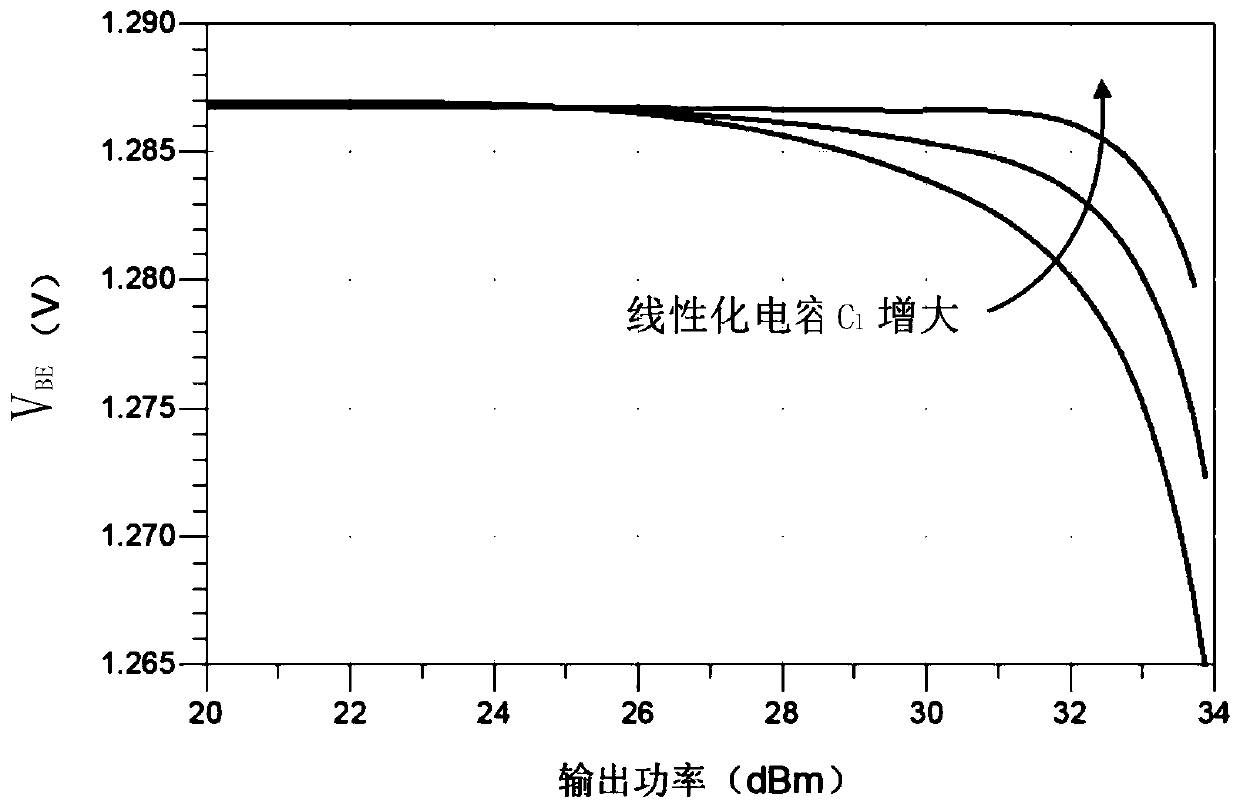

PendingCN110120788ALarge resistanceImprove linearityAmplifier modifications to reduce non-linear distortionHigh frequency amplifiersCompensation effectFeedback circuits

The invention discloses a biasing circuit for a power amplifier. within order to solve the problem that contradiction among the temperature compensation effect, the linearization effect and the signalintegrity in the bias circuit in the prior art, a current negative feedback circuit is composed of a ballast resistor, a first transistor, a second resistor, a third resistor, a current mirror and asecond transistor, compensation is carried out in a manner of reducing current flowing through a ballast resistor, and a self-adaptive temperature negative feedback effect is achieved; therefore, whenthe resistance value of the ballast resistor is increased to enhance the temperature compensation effect, the linearity of the radio frequency power tube is not influenced, the contradiction betweenthe temperature compensation and the linear compensation is eliminated, the contradiction between the linear compensation and the signal integrity is further avoided, and the power amplifier realizesthe double improvement of the thermal stability and the linearity. The invention also discloses a power amplifier which has the above beneficial effects.

Owner:GUANGDONG UNIV OF TECH

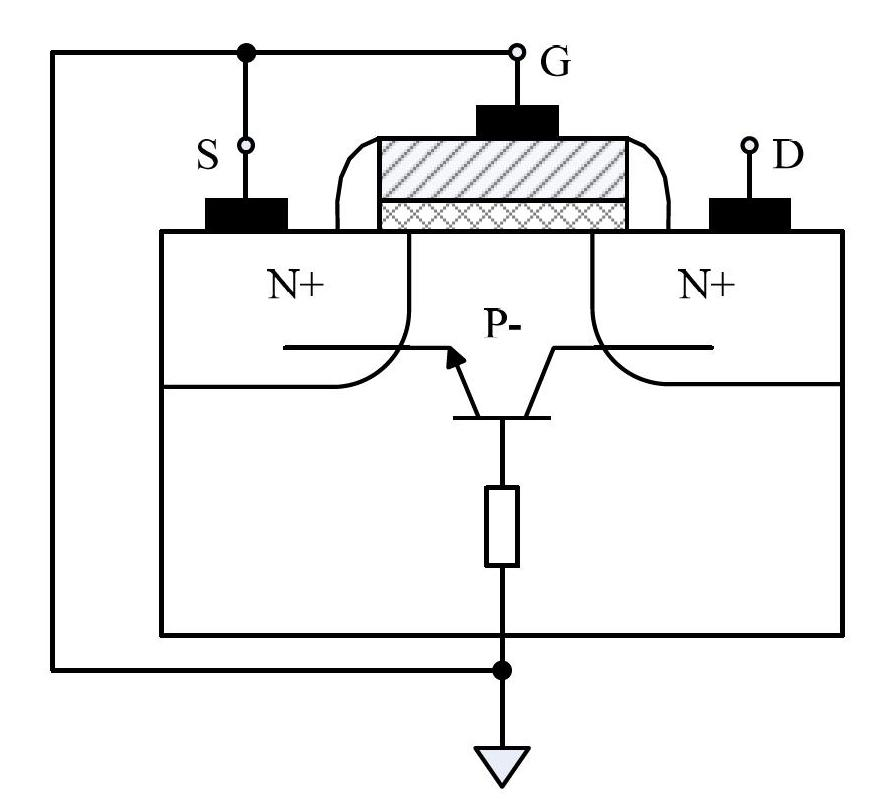

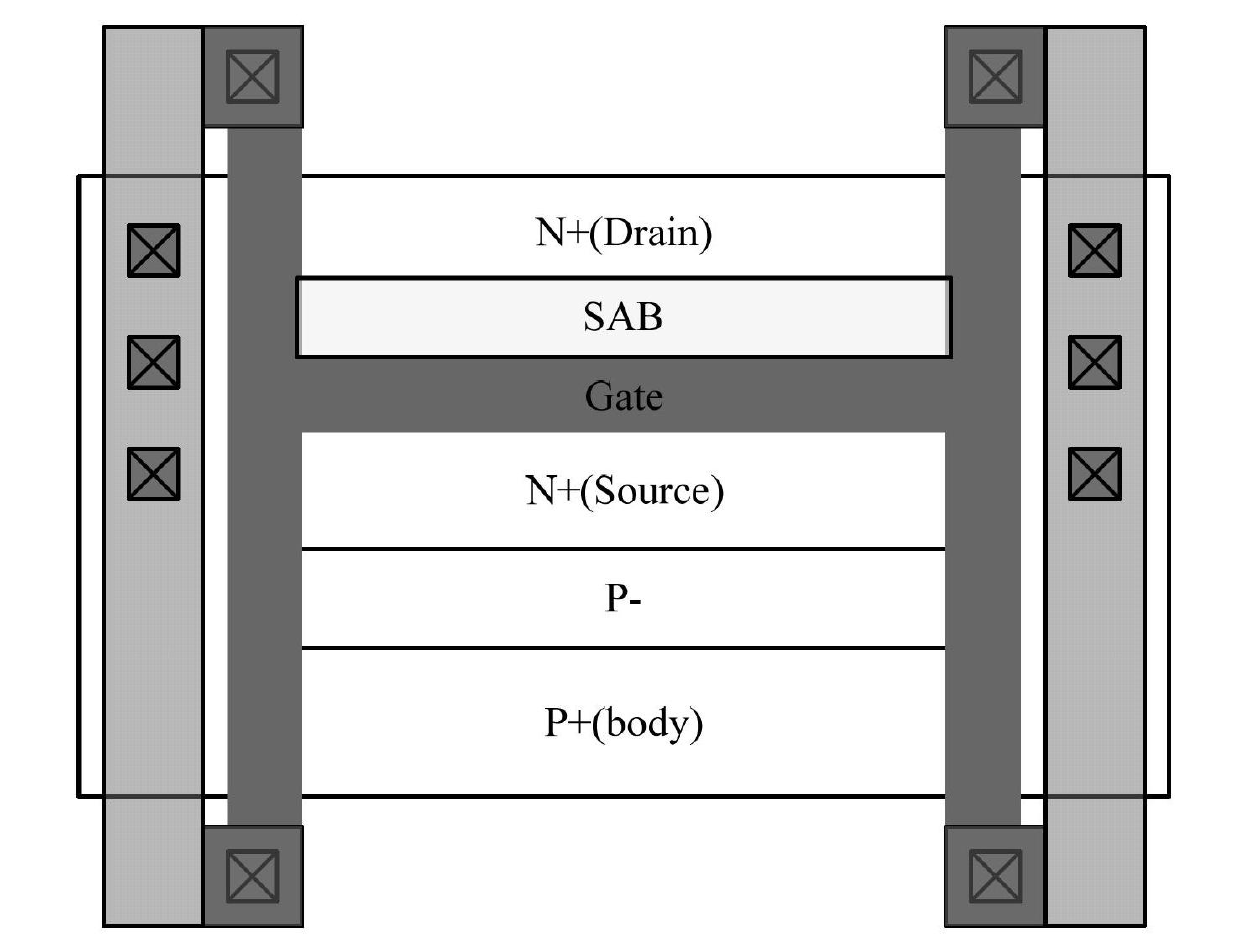

PD SOI (partially-depleted silicon on insulator) technology-based body grid coupling ESD (electro-static discharge) protection structure

ActiveCN102655149AReduce areaReduce or even eliminate leakage problemsSolid-state devicesSemiconductor devicesParasitic capacitorCapacitance

The invention discloses a PD SOI (partially-depleted silicon on insulator) technology-based body grid coupling NMOS ESD (n-channel metal oxide semiconductor electro-static discharge) protection structure, wherein a grid electrode in the structure adopts an H-shaped structure, the inner side and the outer side of an edge grid of an H-shaped grid adopt two body region P+ implantation, a drain region adopts N+ deep implantation, a silicon film on an SOI substrate is punched through, a source region adopts N+ shallow implantation, and some silicon film on the SOI substrate adopts the implantation, so that the body region P+ implantation is carried out at the outer side of the source region, and body region contact is led out, and some drain region baffles the silicide by an SAB (salicide block) layer, so that a ballast resistor can be formed. When the protection structure is used, the drain region is connected with a PAD, the body region at the outer side of the edge grid of the H-shaped grid is connected with the grid electrode, and the source region and the body region at the inner side of the H-shaped grid are grounded. According to the protection structure, the body region at the outer side of the edge grid of the H-shaped grid is connected with the grid electrode, so that a coupling circuit can be formed by sufficiently using a parasitic capacitor of a drain body and a parasitic resistor of a body region under the source region, and the grid electrode is coupled with a certain voltage, so that the starting voltage of the ESD protection structure can be reduced, the even conduction of the plurality of structures can be guaranteed, and the ESD protection capability can be improved.

Owner:西安西岳电子技术有限公司

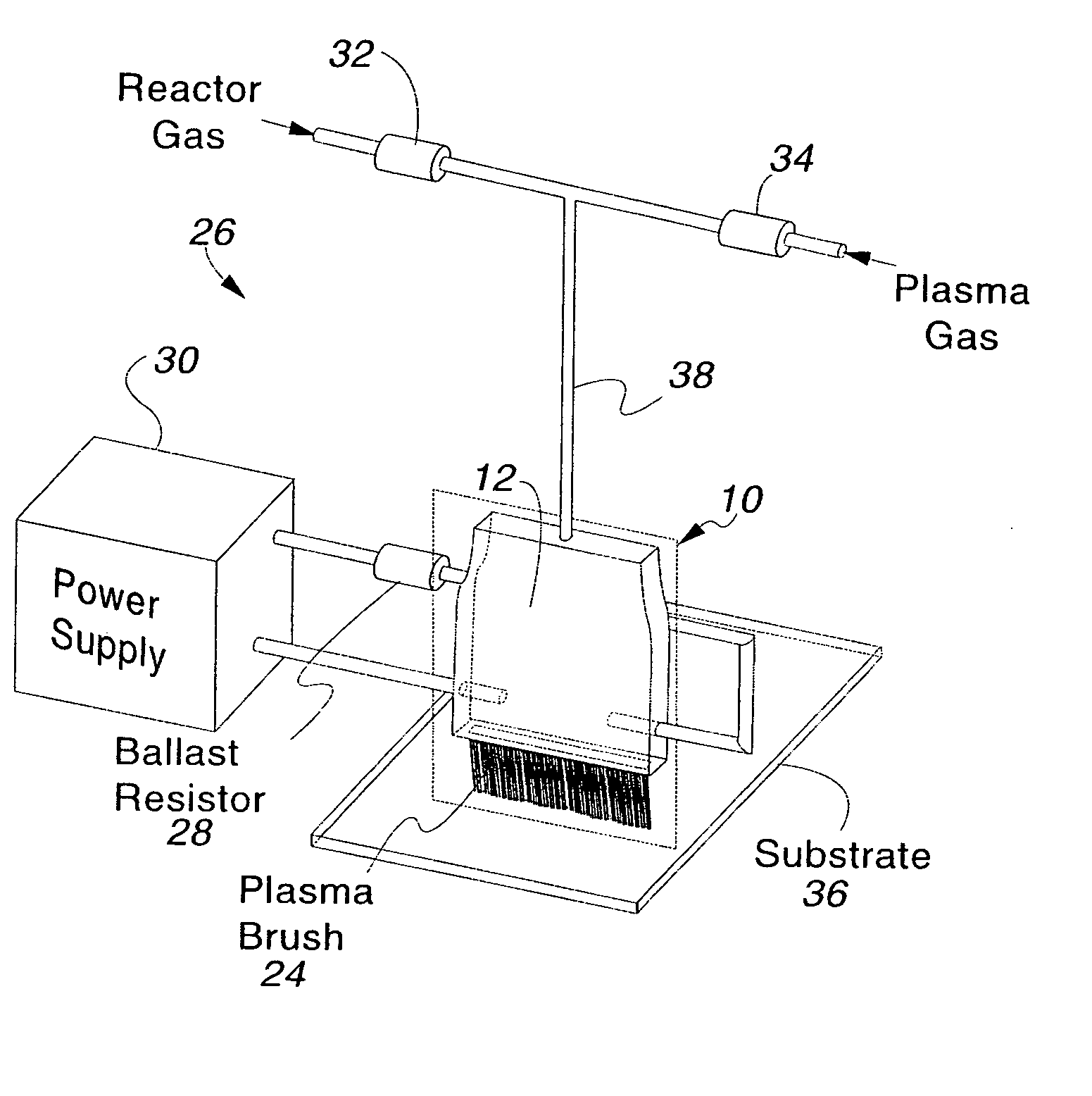

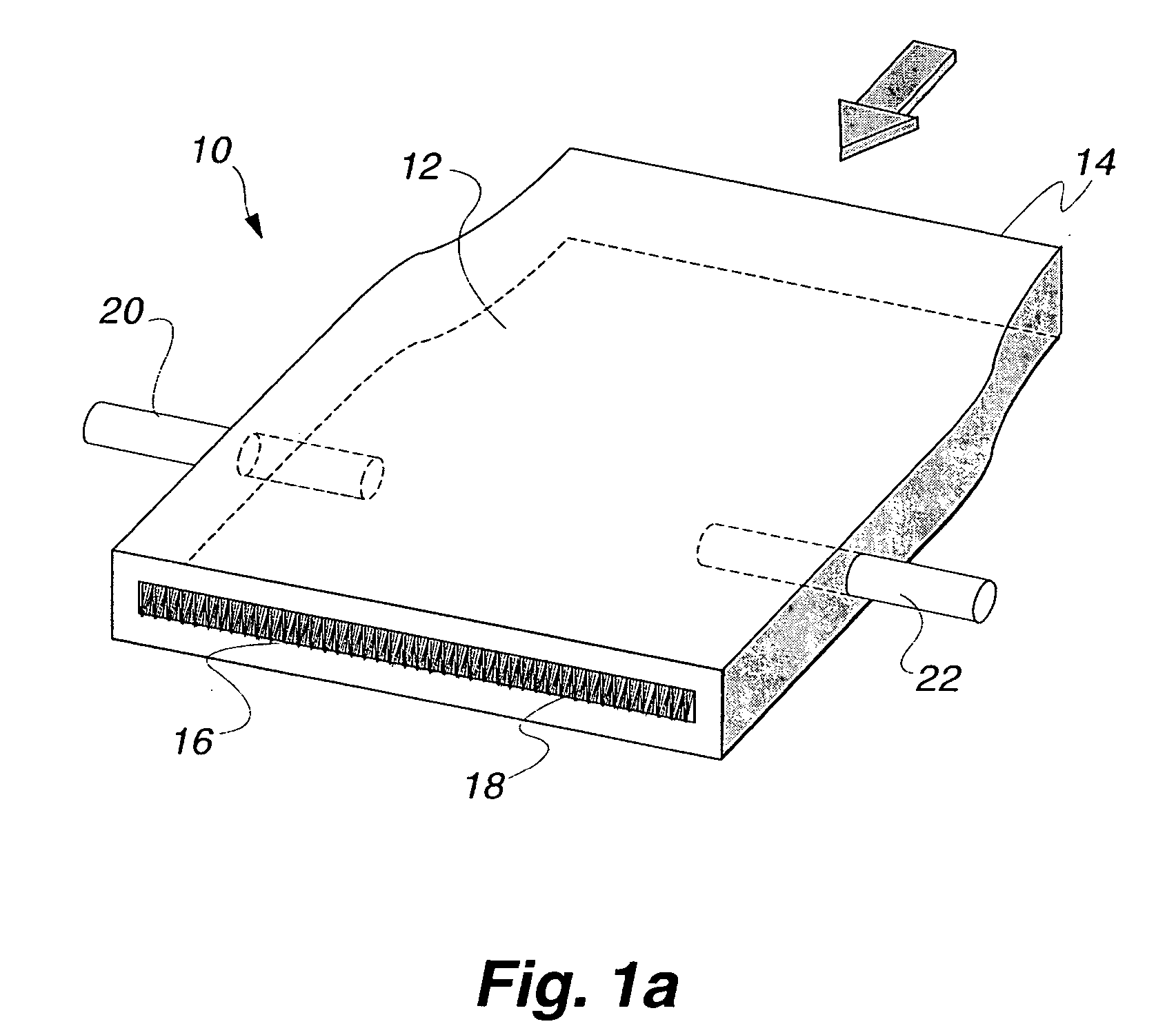

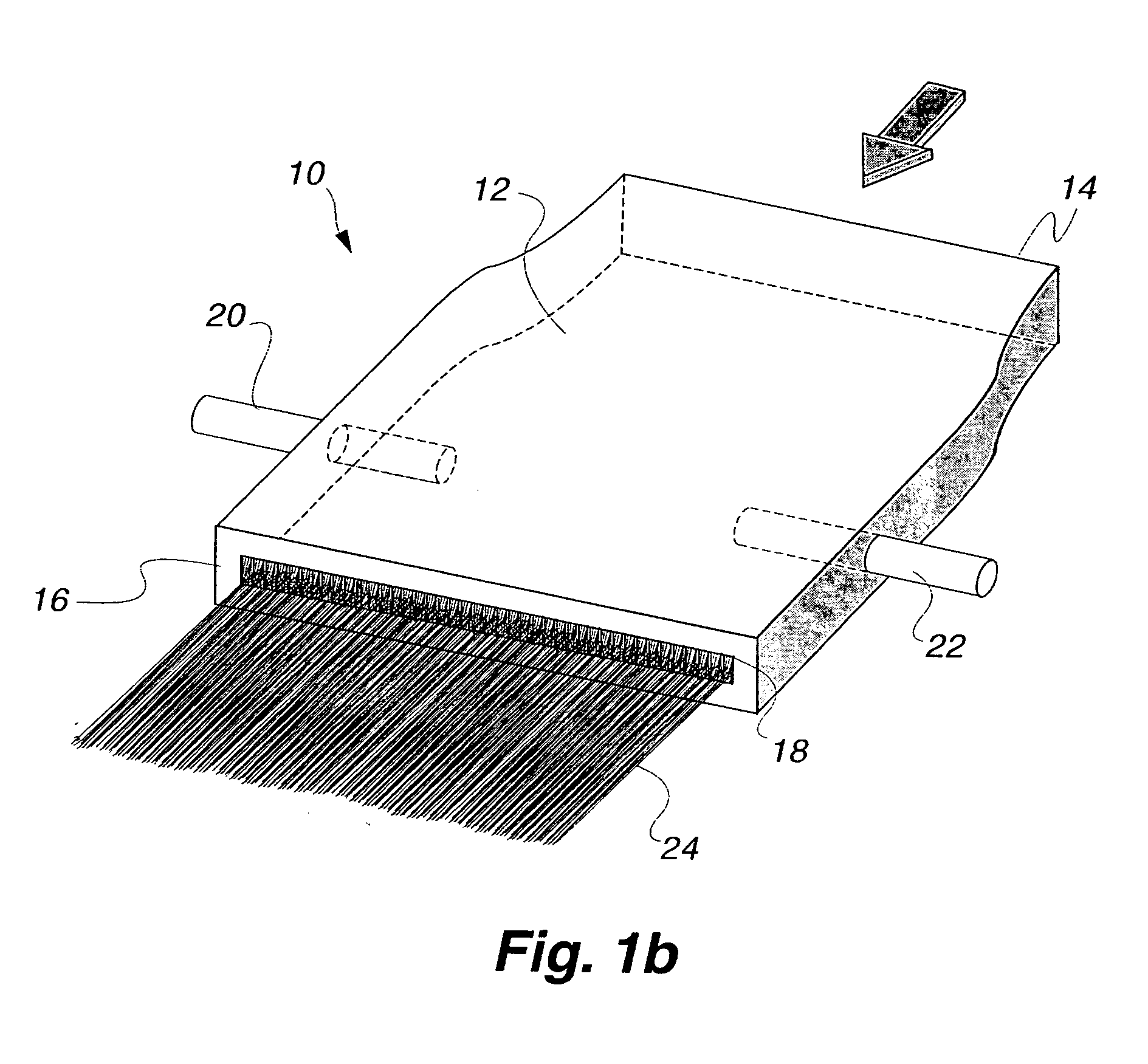

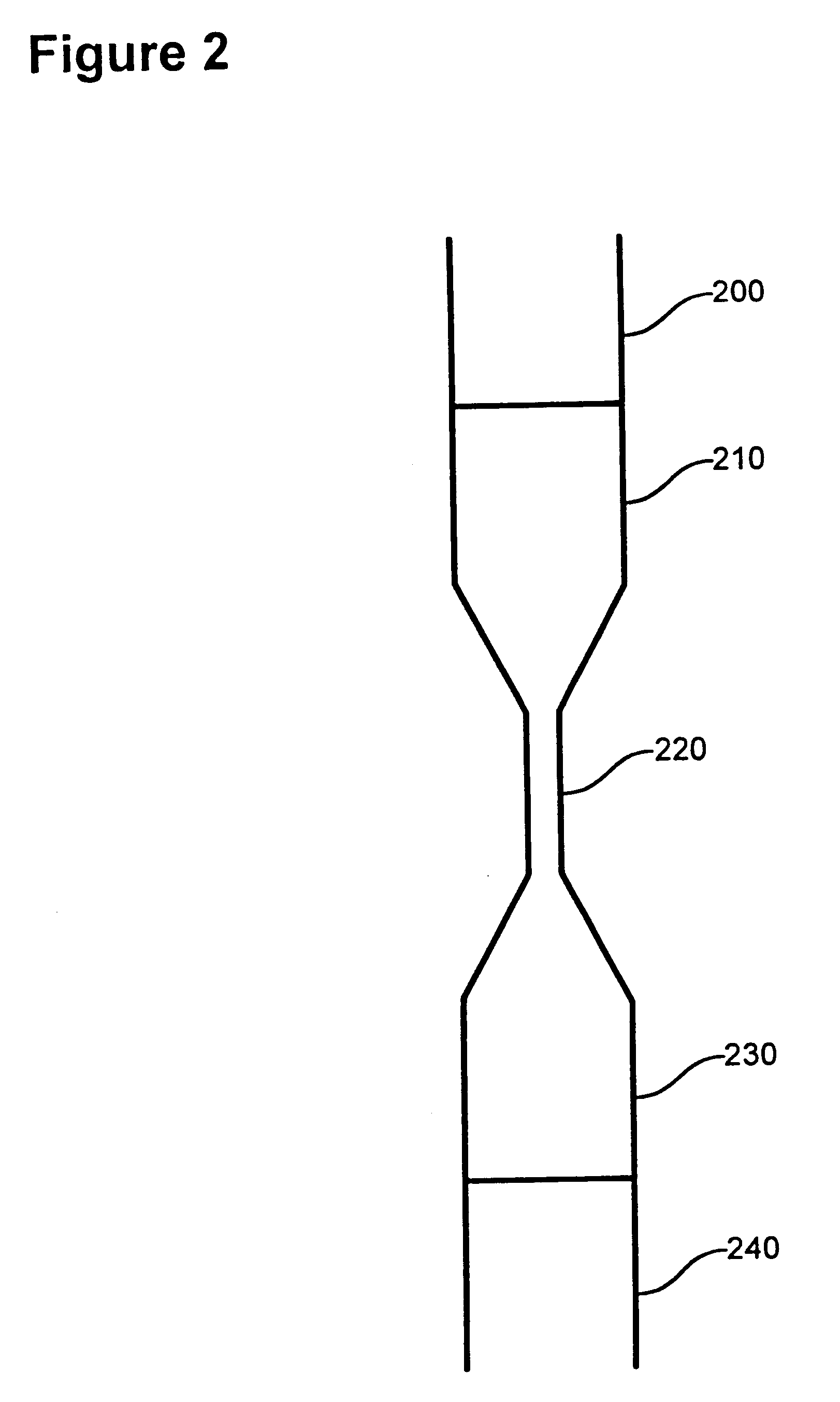

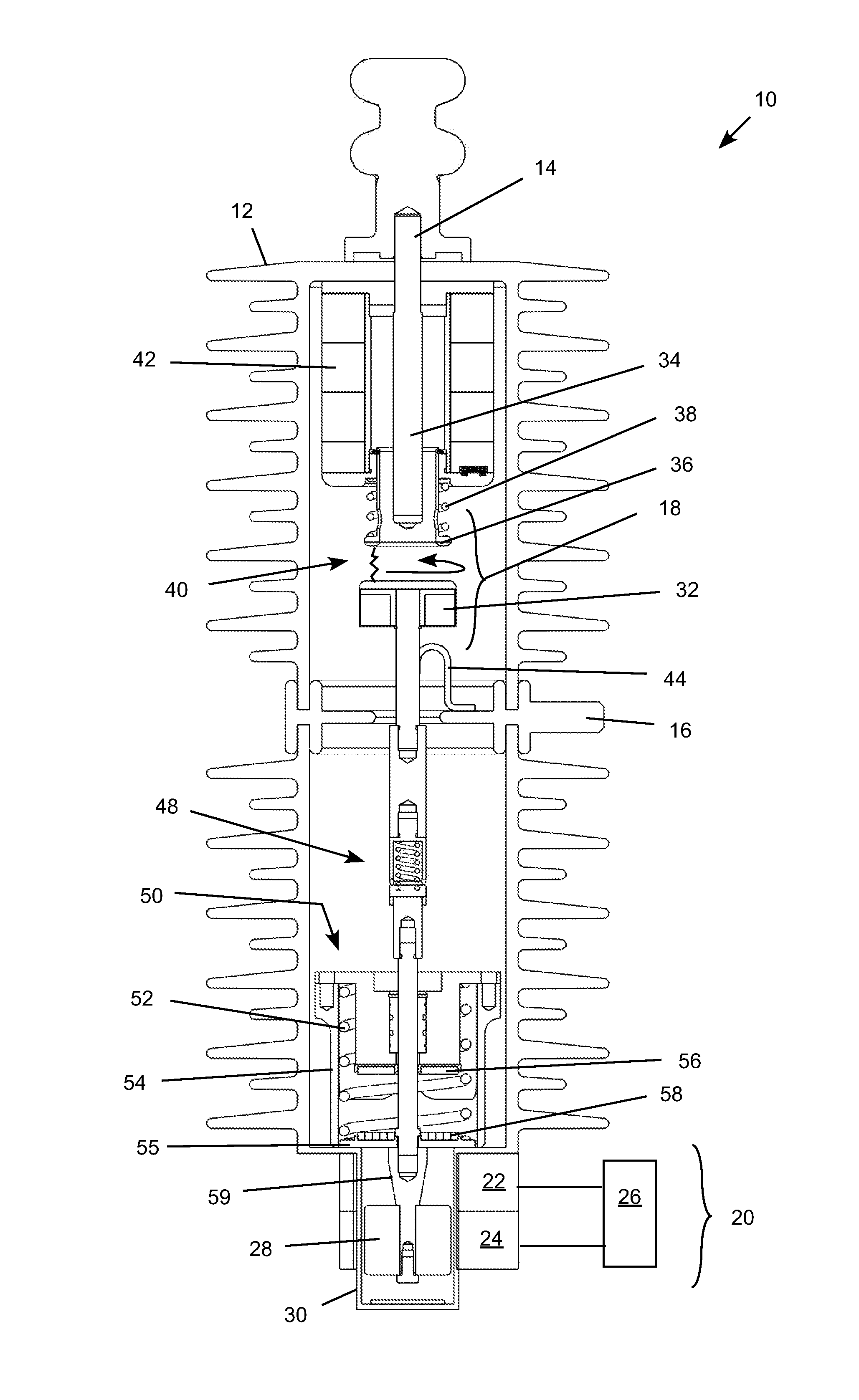

Plasma brush apparatus and method

InactiveUS20070116891A1Pretreated surfacesChemical vapor deposition coatingPlasma jetPlasma deposition

An apparatus with a narrow slit chamber generates plasma having non-equilibrium characteristics and a brush-like shape at a temperature near room temperature and at a pressure of about one atmosphere. Plasma gas enters the narrow slit chamber. An external power source provides power to electrodes near the exit that excite the plasma gas and produce a plasma jet having a brush-like shape that exits the chamber. The apparatus operates with low power consumption, and the temperature of the plasma is low. Glow-to-arc transitions are prevented using a ballast resistor and appropriate plasma gases with the narrow slit chamber design. The brush-like shaped plasma extends beyond the exit of the chamber, and possesses the reactive features of low-pressure or non-equilibrium plasmas. The plasma brush apparatus can be used for plasma treatment, plasma cleaning, plasma deposition, plasma sterilization, and plasma decontamination of chemical and biological warfare agents.

Owner:LOS ALAMOS NATIONAL SECURITY

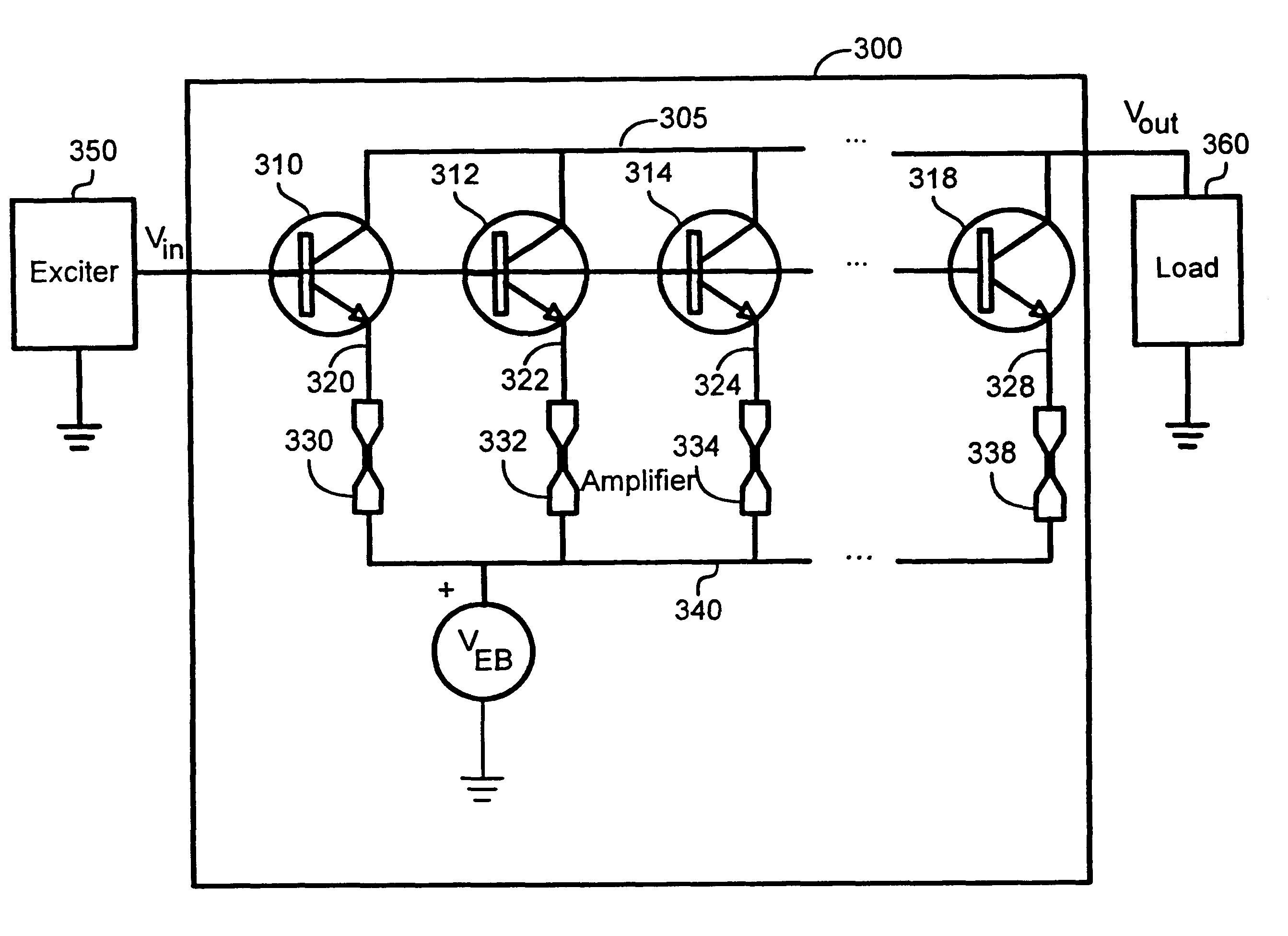

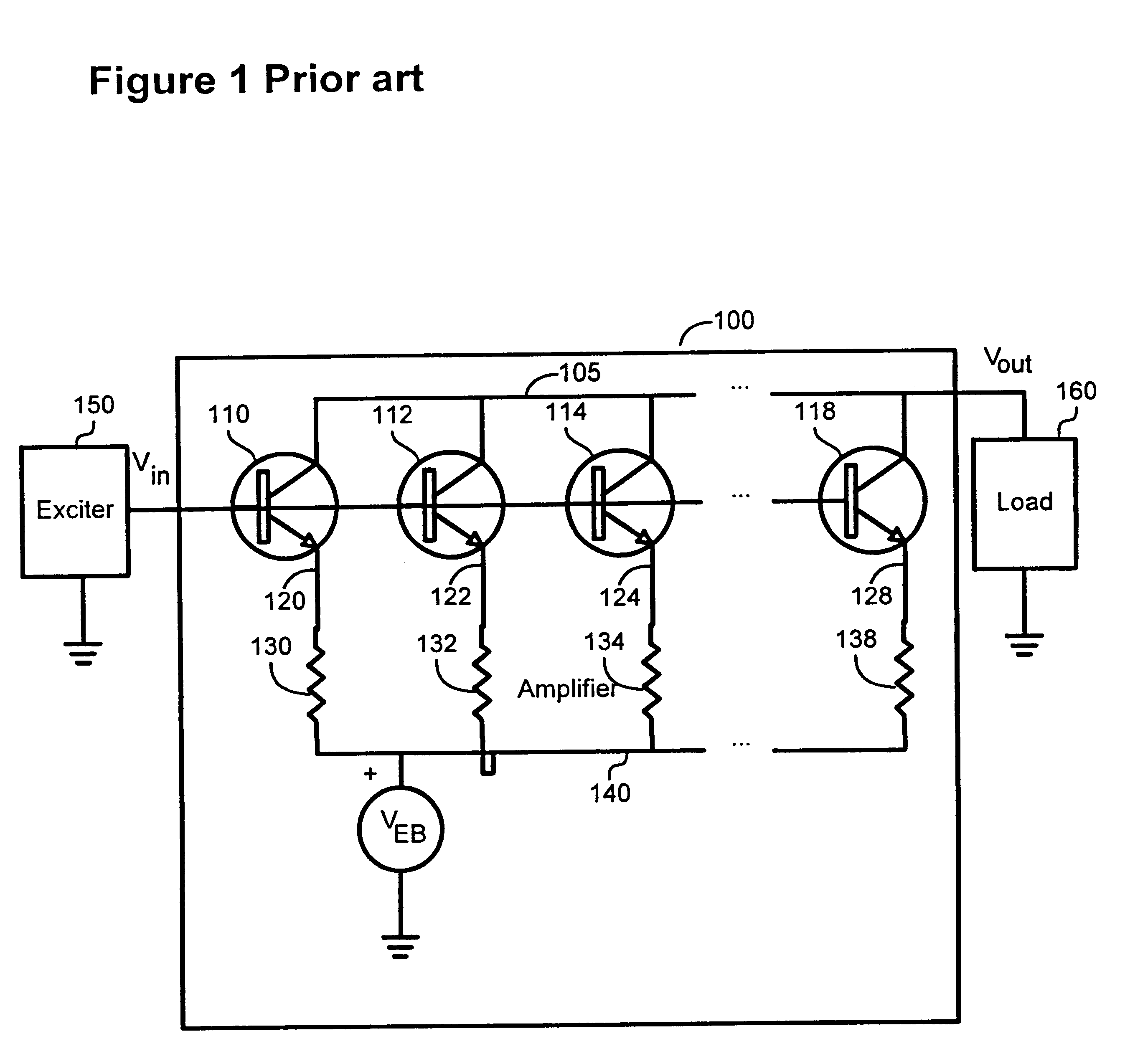

Protection scheme for multi-transistor amplifiers

InactiveUS6225867B1Simple power deviceLess prone to damageAmplifier modifications to reduce temperature/voltage variationGain controlBallast resistorAmplifier

The present invention deals with the problems related to thermal runaway and over-voltage breakdown in integrated circuits using a series of power transistors interconnected in a parallel circuit arrangement. The general technique described consists of a protection scheme that involves the application of a fusible material to form ballast resistor components. These components are connected in series with each of the transistors in the integrated circuits. The main advantages are significant area and cost savings in the manufacturing of the integrated circuits as well as an increase in their yield, thereby reducing costly field maintenance and equipment returns.

Owner:RPX CLEARINGHOUSE

Low profile, highly configurable, current sharing paralleled wide band gap power device power module

ActiveUS20150216067A1Shorten the counting processReduce system costSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorFull bridge

A power module with multiple equalized parallel power paths supporting multiple parallel bare die power devices constructed with low inductance equalized current paths for even current sharing and clean switching events. Wide low profile power contacts provide low inductance, short current paths, and large conductor cross section area provides for massive current carrying. An internal gate & source kelvin interconnection substrate is provided with individual ballast resistors and simple bolted construction. Gate drive connectors are provided on either left or right size of the module. The module is configurable as half bridge, full bridge, common source, and common drain topologies.

Owner:WOLFSPEED INC

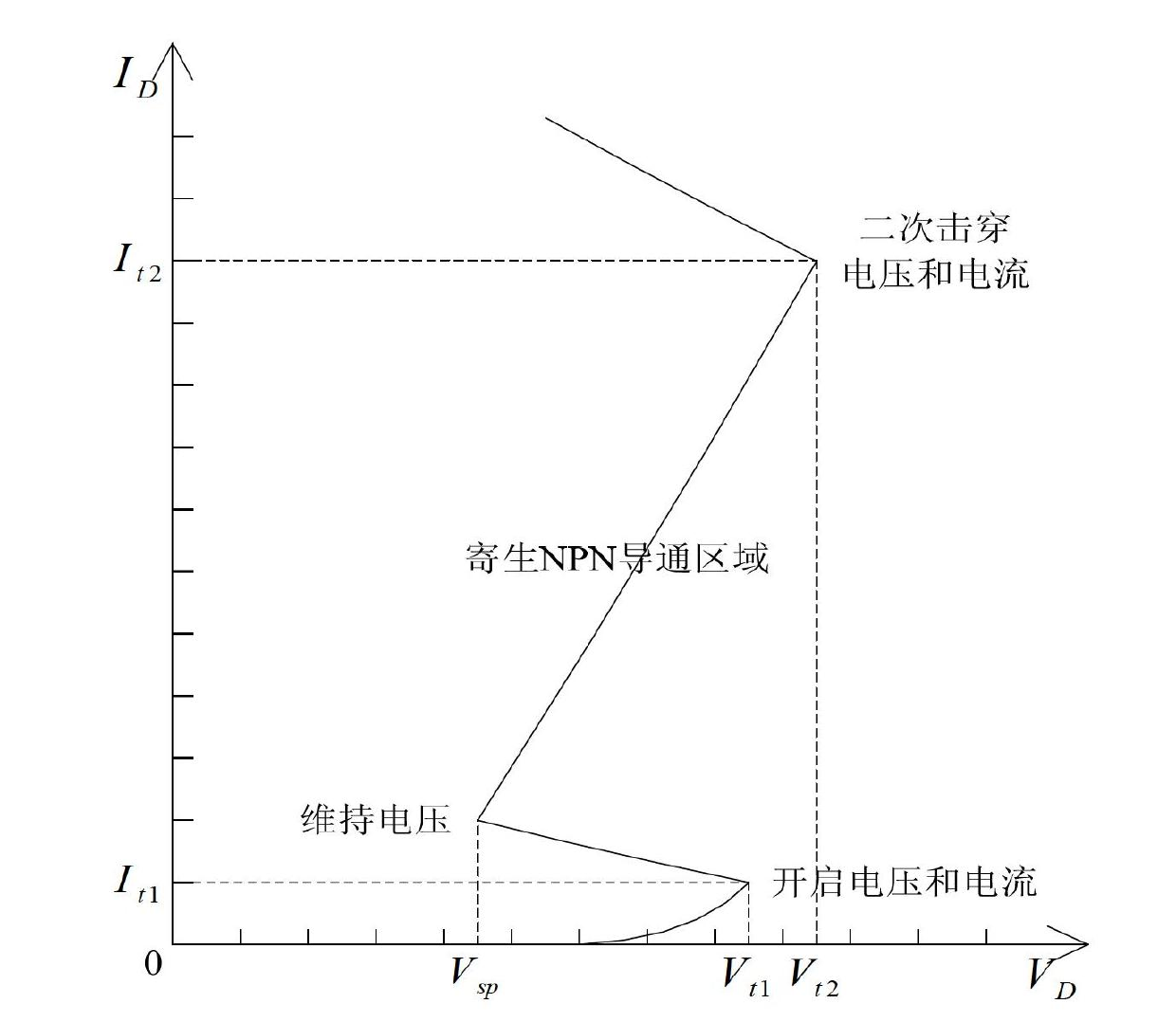

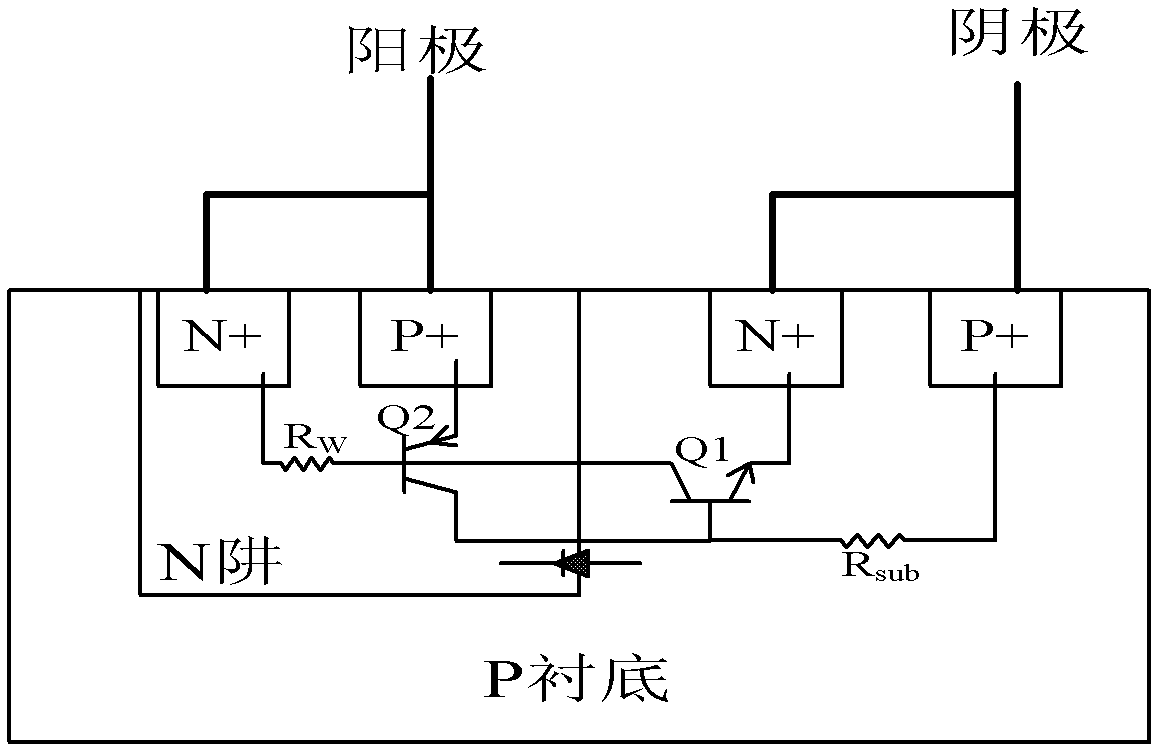

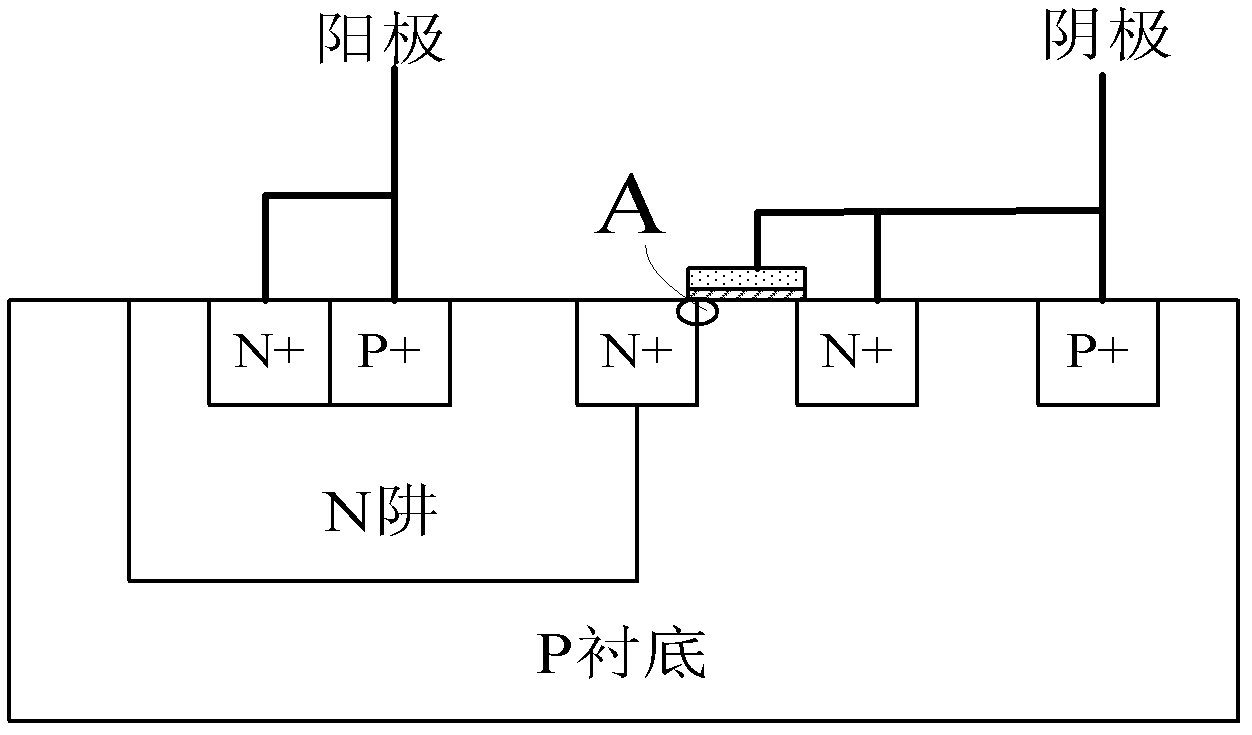

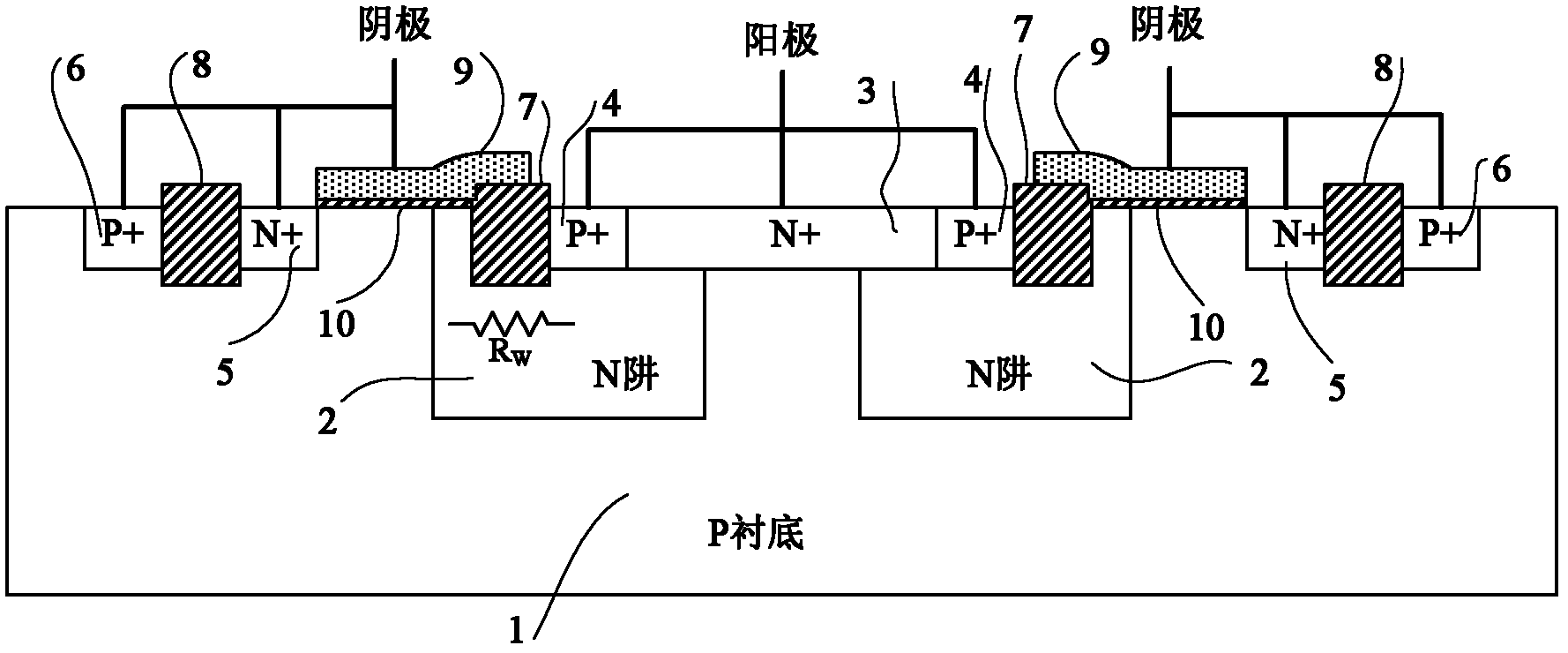

ESD (Electro-Static discharge) protection device with low trigger voltage and high balllast resistance for SCR (Silicon Controlled Rectifier)

The invention discloses an ESD (Electro-Static discharge) protection device with low trigger voltage and high balllast resistance for an SCR (Silicon Controlled Rectifier), belonging to the technical field of electronics. By making use of the triggering of a heavily doped region and a substrate region in the vertical direction, the ESD protection device successfully transfers the avalanche breakdown from the surface of the device to the interior of the device, and with the addition of an STI (shallow trench isolation) region, the adverse effect of the silidide process is eliminated and the ballast resistance of the ESD protection device is effective improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

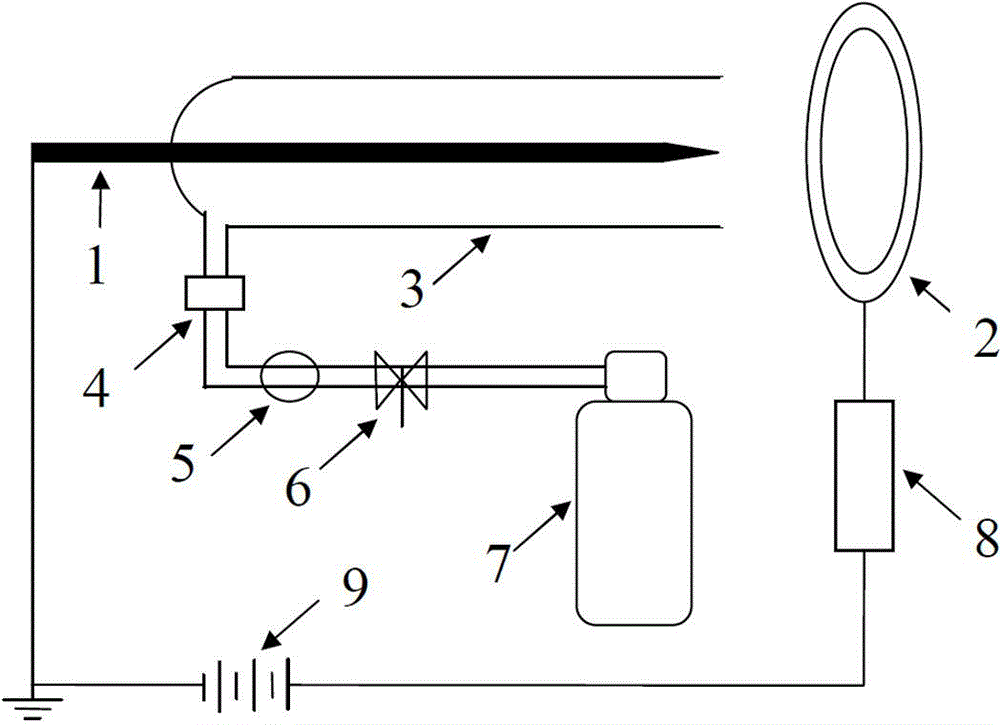

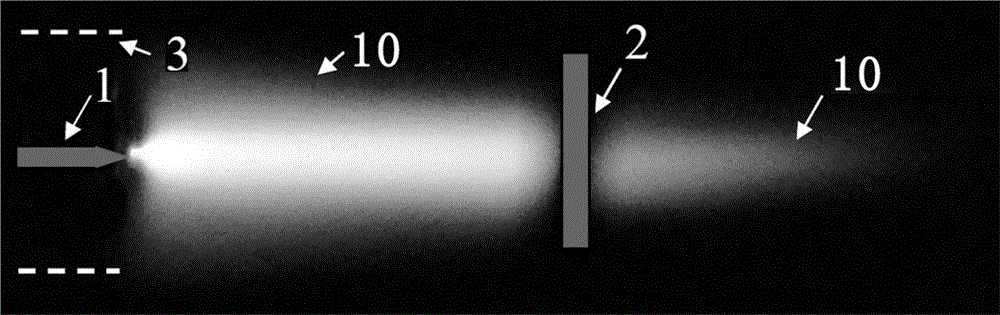

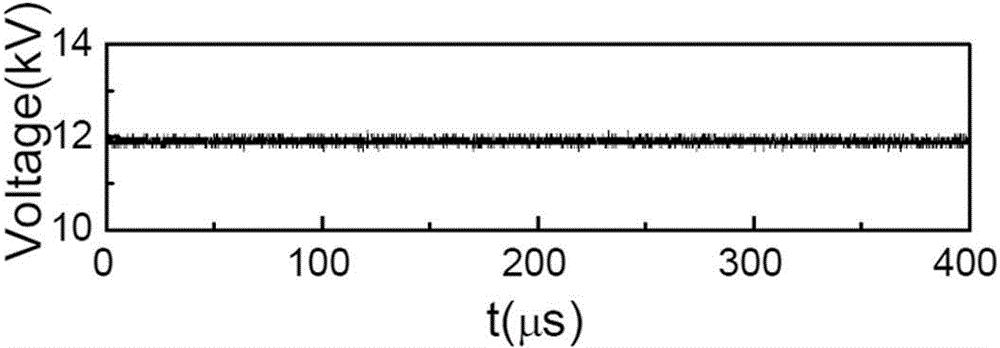

Device and method for producing continuous low-temperature large-section atmospheric pressure plasma plumes

The invention provides a device and a method for producing continuous low-temperature large-section atmospheric pressure plasma plumes. The device comprises a spray gun mechanism, a gas supply mechanism and a power supply mechanism, wherein the spray gun mechanism comprises a metallic cathode, a hollow closed anode and a U-shaped medium pipe; the metallic cathode extends into a central axis in the U-shaped medium pipe, and the free end is flush with the opening end of the U-shaped medium pipe; the hollow closed anode is oppositely arranged with the metallic cathode, and the central axes of the hollow closed anode and the metallic cathode are overlapped; the gas supply mechanism is used for feeding discharge gas to the U-shaped medium pipe; the power supply mechanism comprises a high-voltage direct-current power supply and a ballast resistor; the positive high voltage output end of the high-voltage direct-current power supply is electrically connected with the hollow closed anode through the ballast resistor. The device provided by the invention is a plasma spray gun device which is excited by atmospheric pressure direct current, simple in structure and low in price; the plasma plumes generated by the device have the advantages of constant time, large cross sectional area, low gas temperature during the discharge process, and high chemical reaction efficiency.

Owner:HEBEI UNIVERSITY

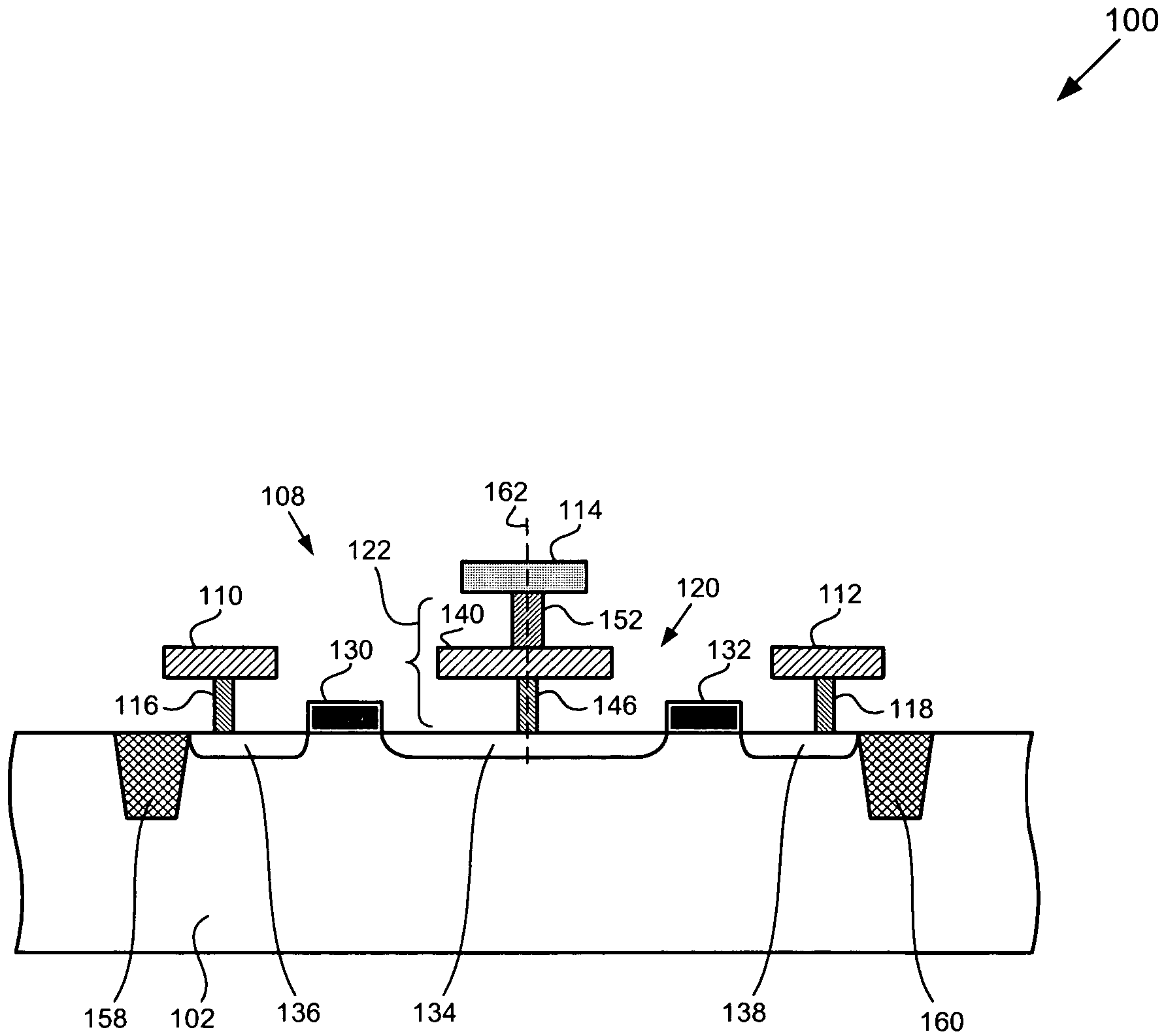

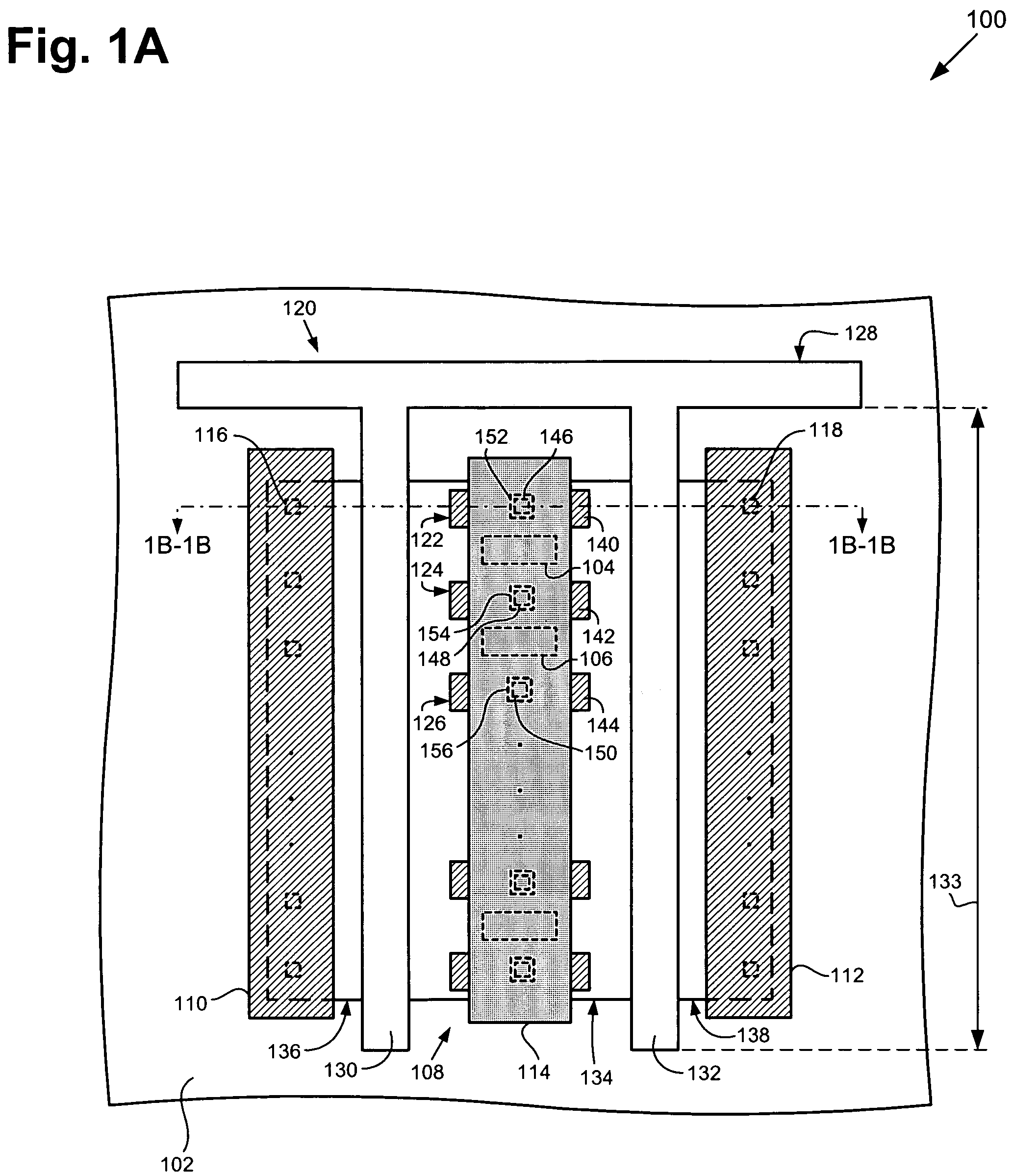

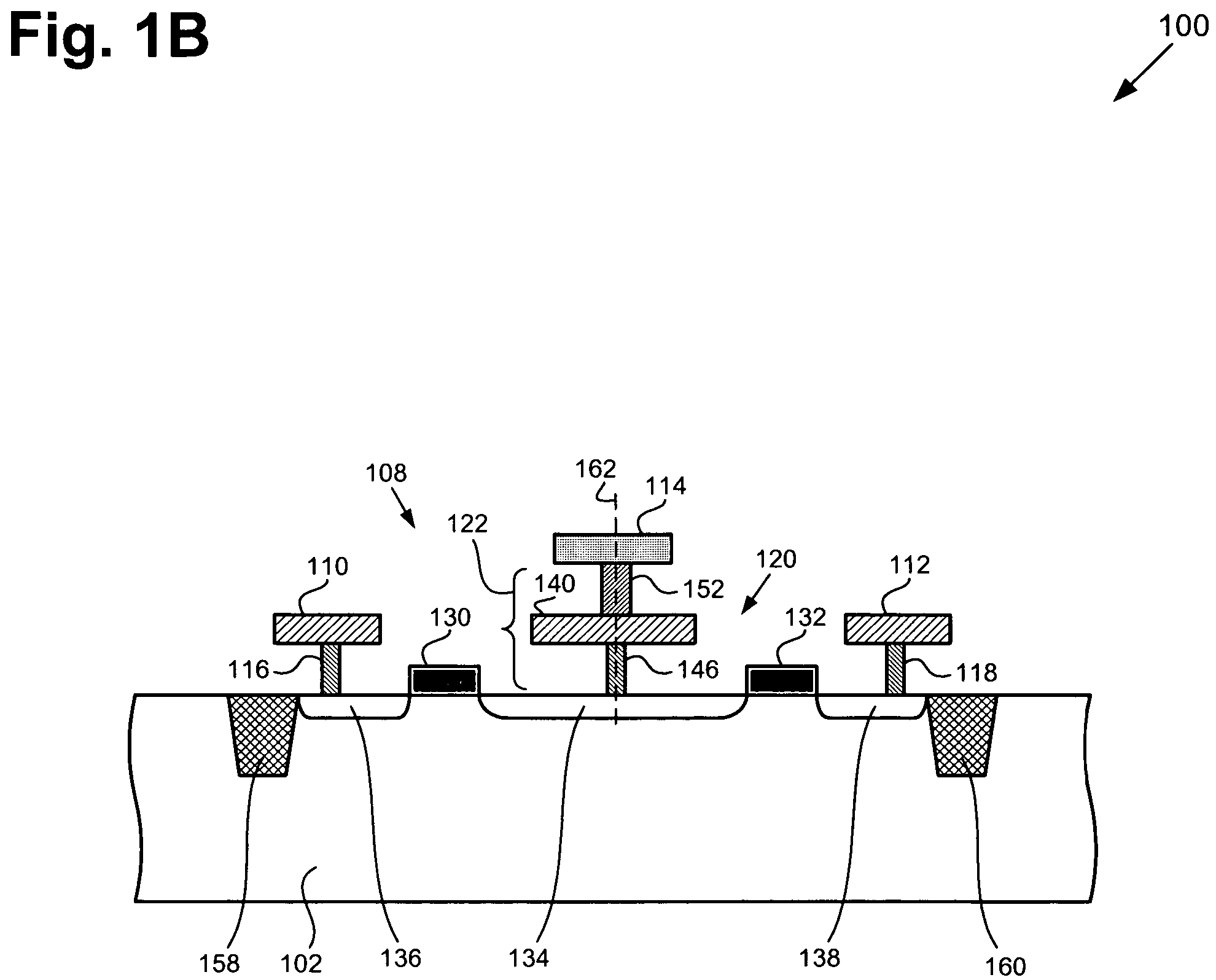

ESD protection structure using contact-via chains as ballast resistors

ActiveUS20070034960A1Increased ESD current distribution uniformityIncrease layout areaTransistorSemiconductor/solid-state device detailsBallast resistorCurrent distribution

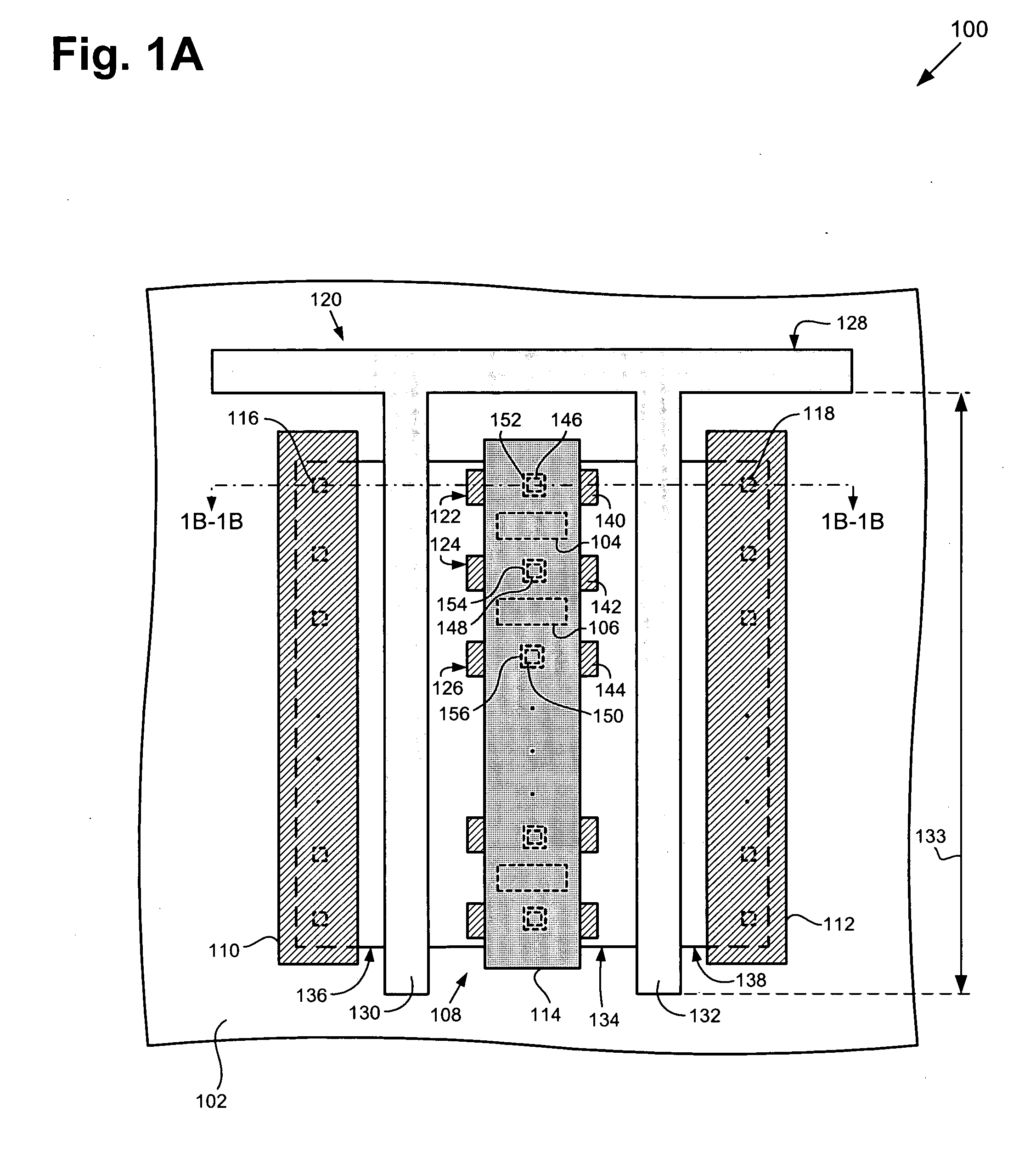

According to an exemplary embodiment, an ESD protection structure situated in a semiconductor die includes a FET including a gate and first and second active regions, where the gate includes at least one gate finger, and where the at least one gate finger is situated between the first and second active regions. The ESD protection structure further includes at least one contact-via chain connected to the first active region, where the at least one contact-via chain includes a contact connected to a via. The at least one contact-via chain forms a ballast resistor for increased ESD current distribution uniformity. The contact is connected to the via by a first metal segment situated in a first interconnect metal layer of a die. The at least one contact-via chain is connected between the first active region and a second metal segment situated in a second interconnect metal layer of the die.

Owner:SKYWORKS SOLUTIONS INC

Semiconductor device and method of manufacturing the same

ActiveUS20110073950A1Suppress fluctuationsTransistorSemiconductor/solid-state device detailsBallast resistorSalicide

The semiconductor device includes a first MIS transistor including a gate insulating film 92, a gate electrode 108 formed on the gate insulating film 92 and source / drain regions 154, a second MIS transistor including a gate insulating film 96 thicker than the gate insulating film 92, a gate electrode 108 formed on the gate insulating film 96, source / drain regions 154 and a ballast resistor 120 connected to one of the source / drain regions 154, a salicide block insulating film 146 formed on the ballast resistor 120 with an insulating film 92 thinner than the gate insulating film 96 interposed therebetween, and a silicide film 156 formed on the source / drain regions 154.

Owner:SOCIONEXT INC

ESD protection structure using contact-via chains as ballast resistors

ActiveUS7397089B2Increase layout areaWithout degrading high-frequency performanceTransistorSemiconductor/solid-state device detailsBallast resistorCurrent distribution

According to an exemplary embodiment, an ESD protection structure situated in a semiconductor die includes a FET including a gate and first and second active regions, where the gate includes at least one gate finger, and where the at least one gate finger is situated between the first and second active regions. The ESD protection structure further includes at least one contact-via chain connected to the first active region, where the at least one contact-via chain includes a contact connected to a via. The at least one contact-via chain forms a ballast resistor for increased ESD current distribution uniformity. The contact is connected to the via by a first metal segment situated in a first interconnect metal layer of a die. The at least one contact-via chain is connected between the first active region and a second metal segment situated in a second interconnect metal layer of the die.

Owner:SKYWORKS SOLUTIONS INC

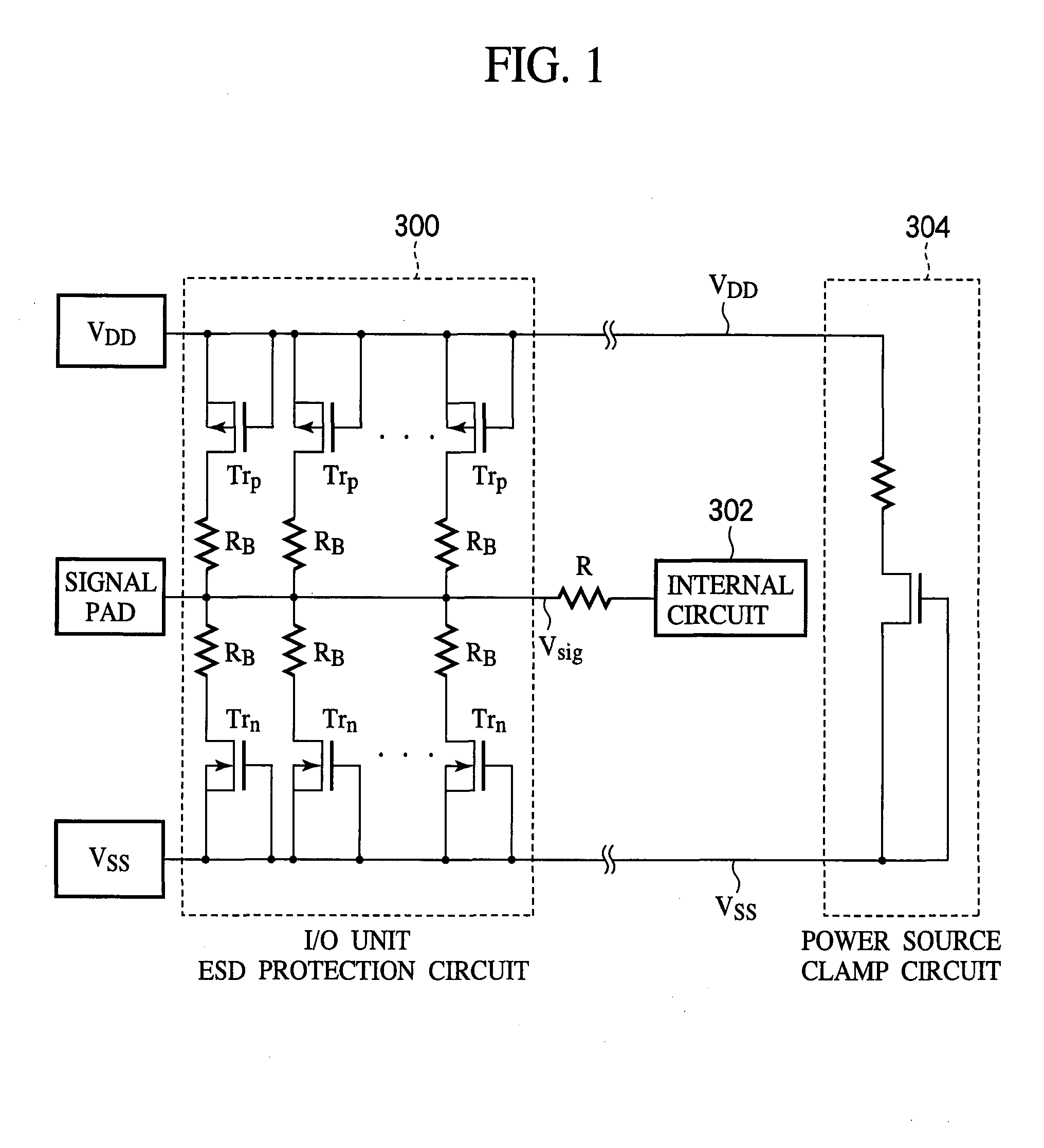

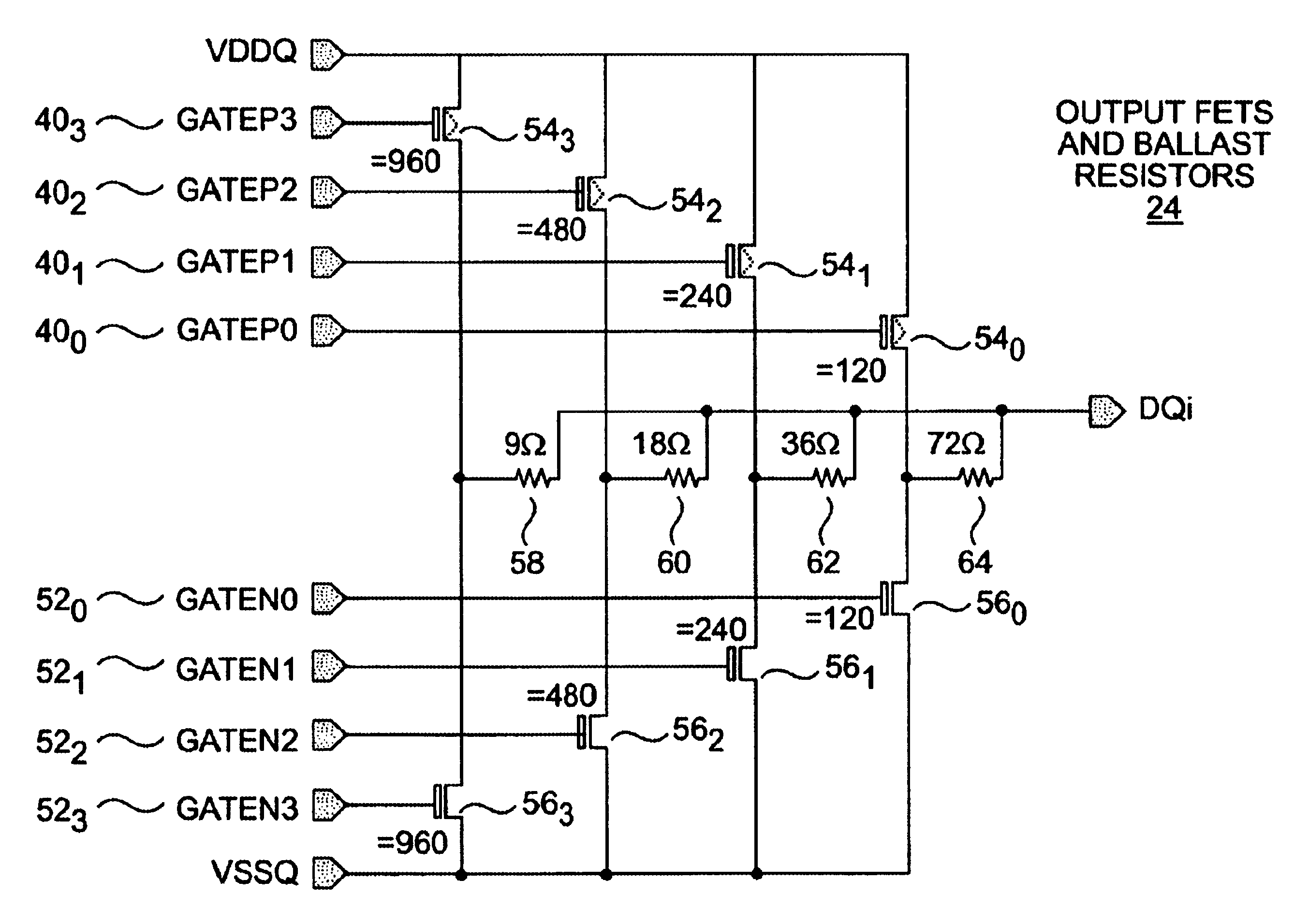

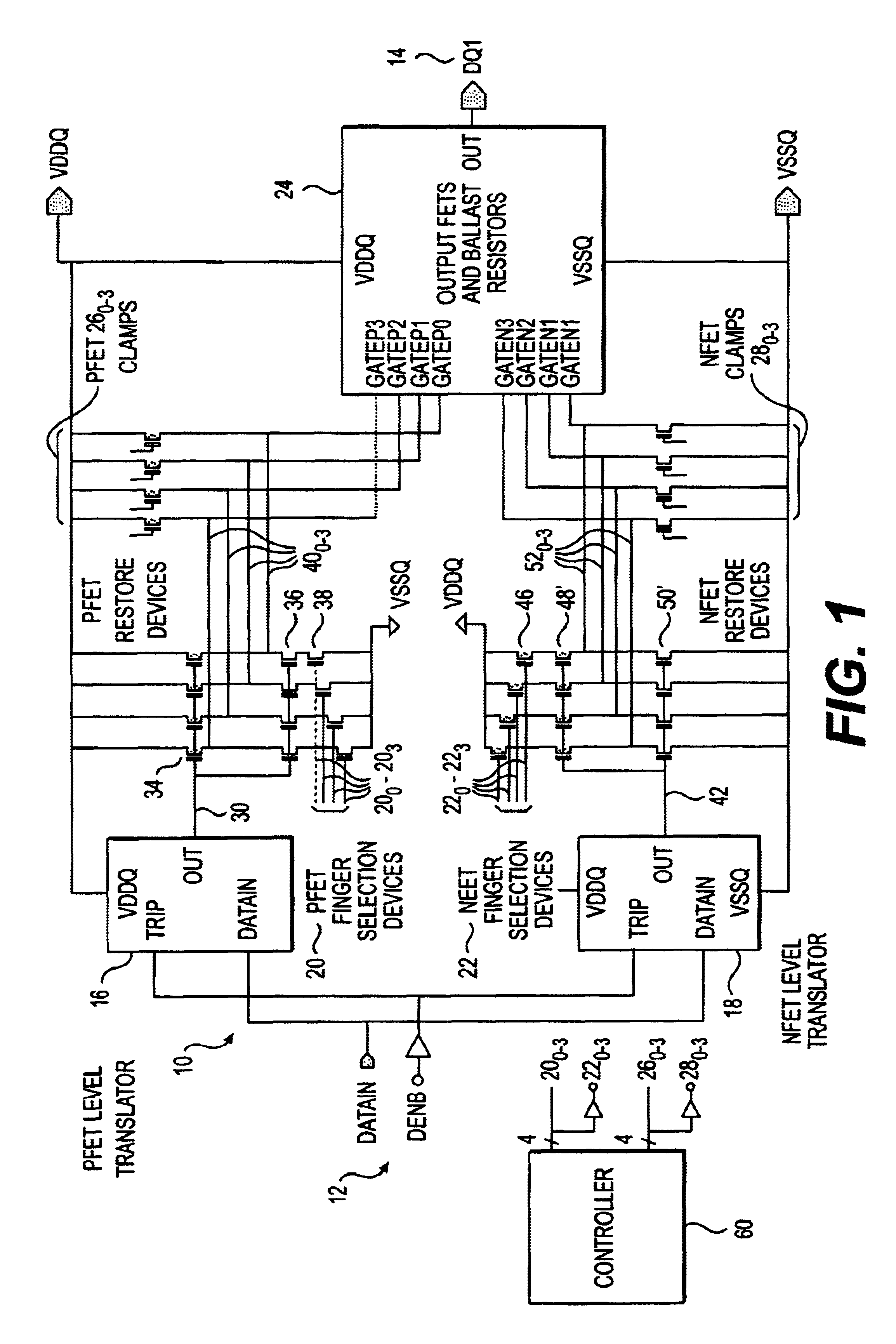

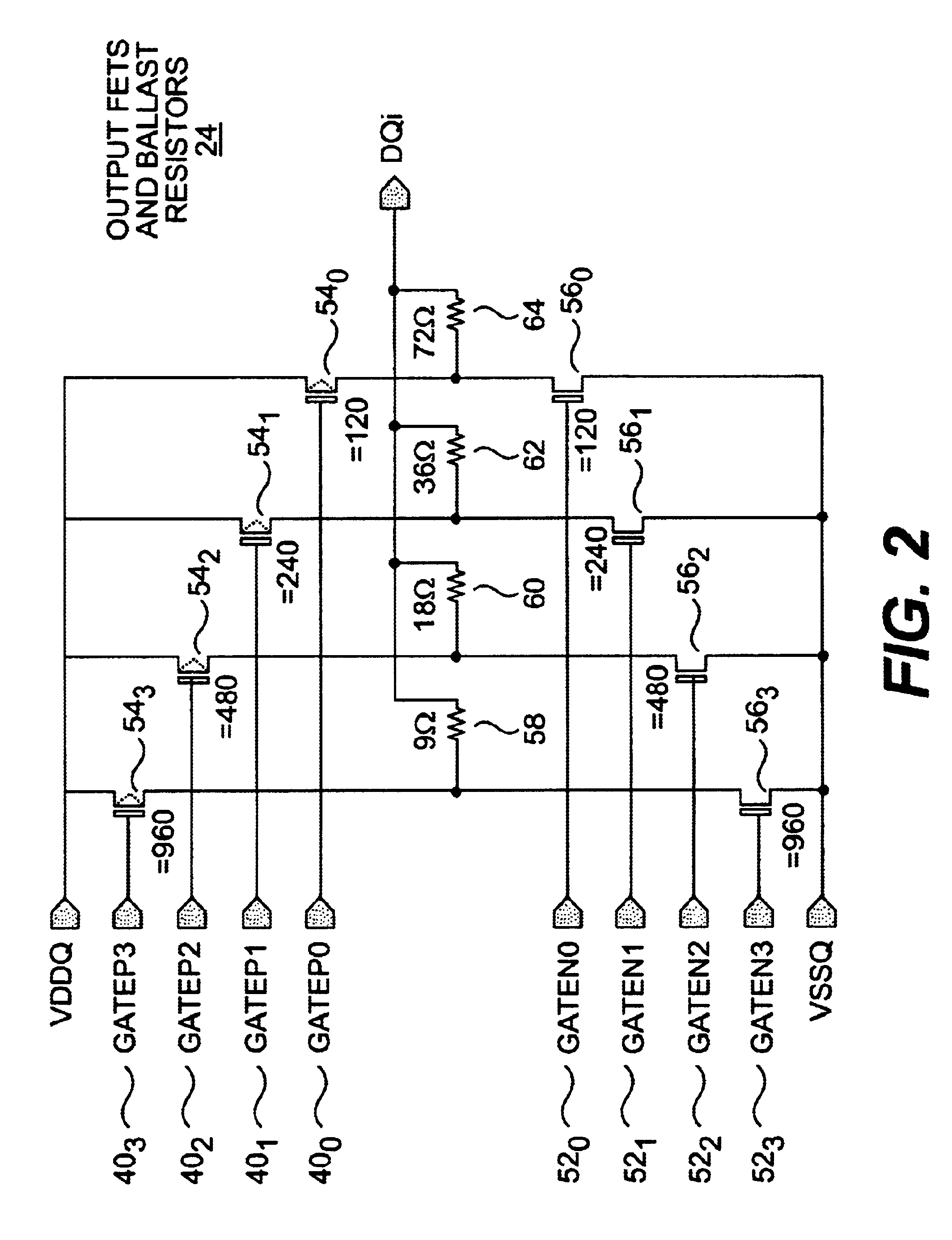

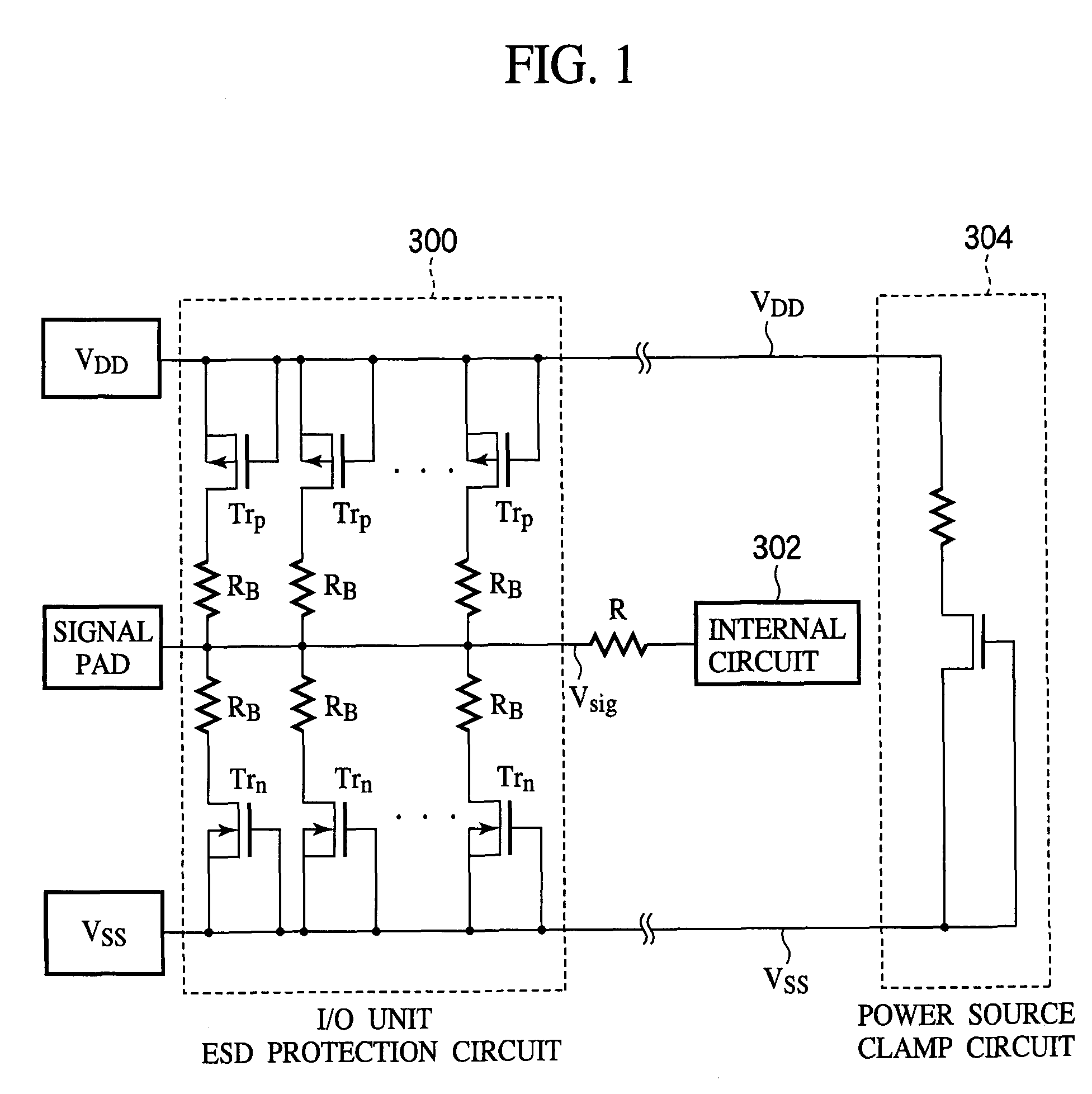

Multiple finger off chip driver (OCD) with single level translator

InactiveUS6667633B2Input/output impedence modificationReliability increasing modificationsBallast resistorSingle level

Owner:INT BUSINESS MASCH CORP +1

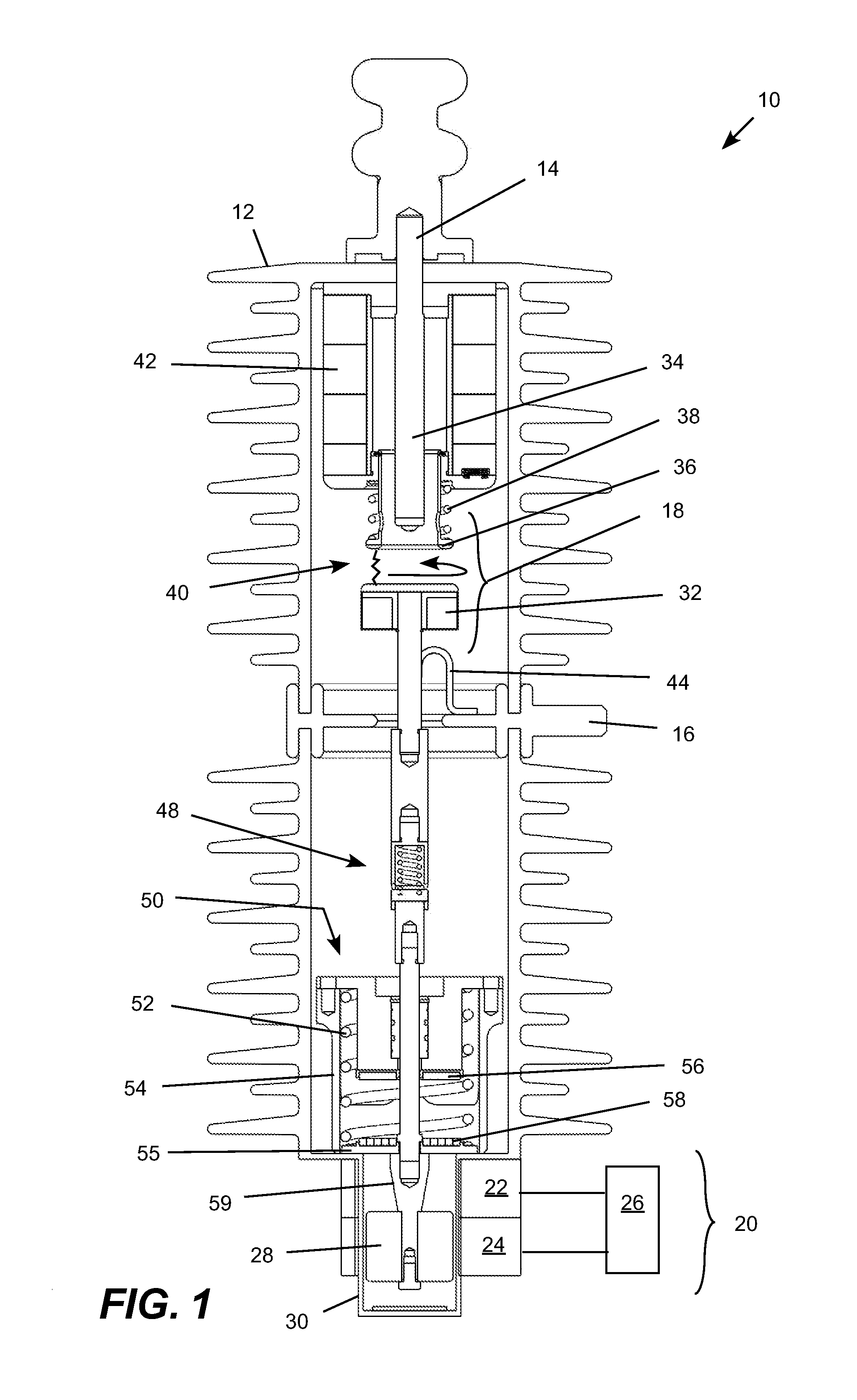

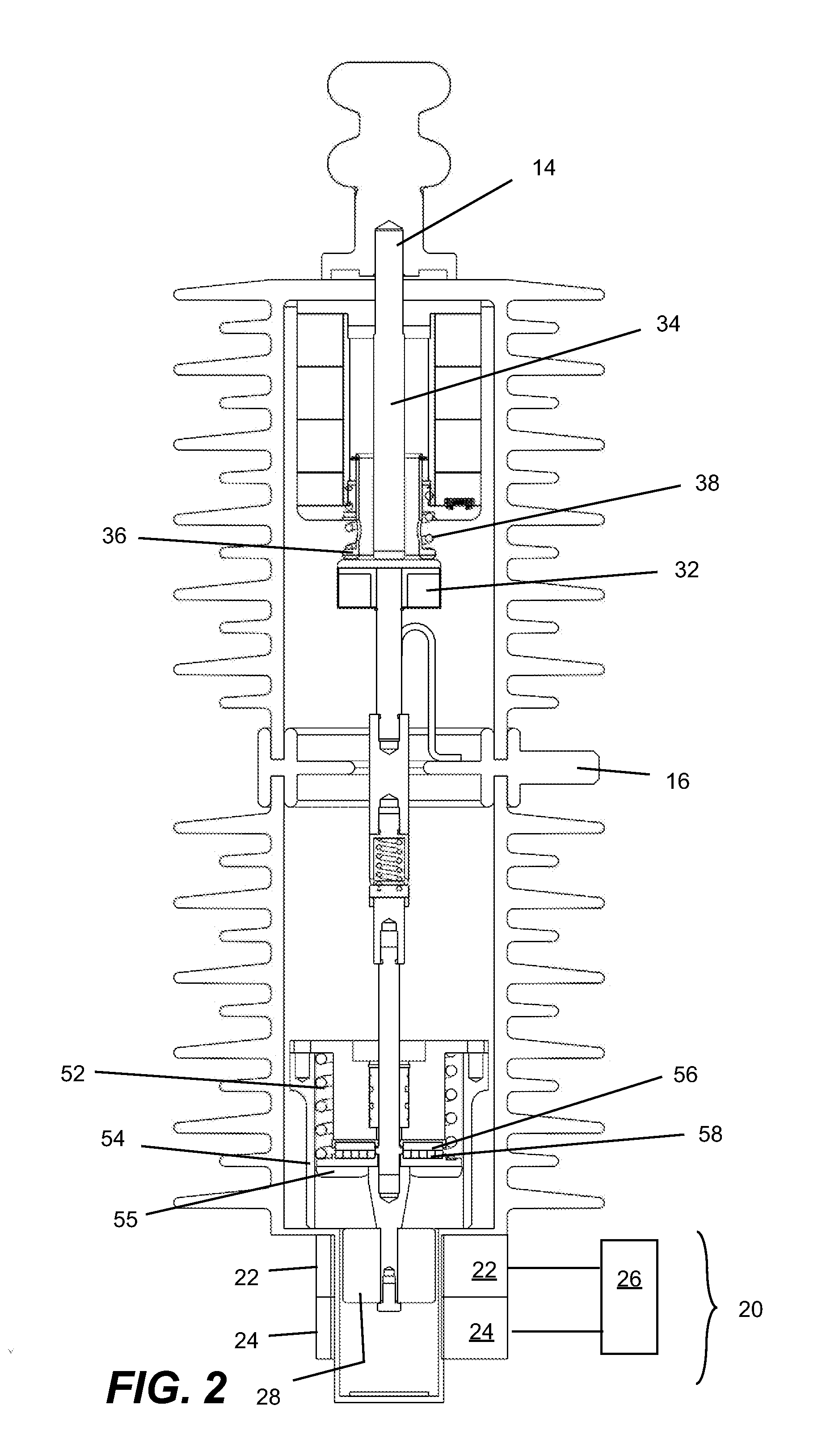

Sealed solenoid magnetically operated high voltage electric power switch

InactiveUS20140158665A1Nuclear energy generationElectromagnetic relaysBallast resistorElectrical ballast

A sealed solenoid, magnetically operated electric power switch is suitable for use as capacitor, line and load switch operating at transmission and distribution voltages that includes no seals through the sealed container housing the contactor portion of the switch. The sealed solenoid switch includes a magnetically operated drive system with an actuator that magnetically couples across the container wall to avoid the use of a moving or sliding seal as part of the drive system. The sealed solenoid switch may also include a ballast resistor and resistor contact located inside the sealed container to avoid another seal as part of the ballast system. A magnetic latch holds the switch in a closed position, and a spring holds the switch in the closed position, to avoid the need for an energizing current to maintain the switch in either position.

Owner:SOUTHERN STATES

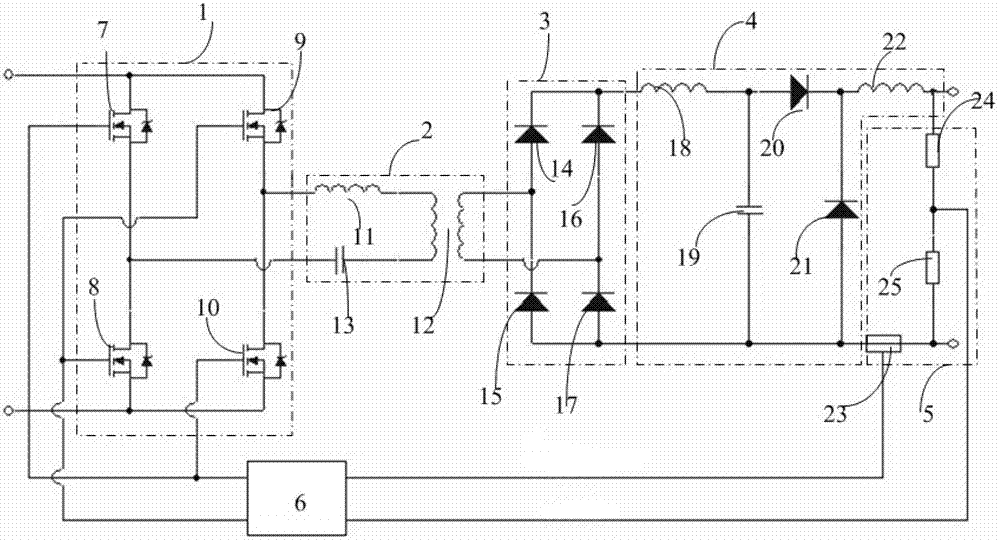

Constant current source for high voltage magnetic switch resetting

A constant current source for high voltage magnetic switch resetting belongs to the technical field of power and resolves the problem that the existing constant current source lacks a high voltage isolation circuit. The constant current source is used for high voltage pulse occasions. The constant current source comprises a full bridge inverter, a resonant circuit, a rectifying bridge, a high frequency filter circuit, a feedback circuit and a control circuit. The constant current source utilizes a metal oxide semiconductor (MOS) field effect tube which works in zero current state to enable input energy to be transmitted to a series resonant circuit in lossless mode, and is capable of adjusting size of output current by adjusting period of the MOS field effect tube to output characteristics with the constant current source without providing an extra steady resistor at the output end. The constant current source adopts a high frequency filter circuit, a filter capacitor, an isolation diode and a catching diode, stops effect of high voltage pulse coupled in a resetting circuit of a pulse power supply magnetic switch or a transformer and ensures safety.

Owner:HUAZHONG UNIV OF SCI & TECH

Semiconductor device, manufacturing method of the same and electronic device

InactiveUS20060138459A1Improved electrostatic breakdown voltageAvoid consumptionSemiconductor devicesHigh concentrationBallast resistor

Provided is a semiconductor device equipped with HBTs capable of satisfying both thermal stability and reliability and having improved electrostatic breakdown voltage. The HBT according to the present invention is obtained by successively forming, over the main surface of a substrate made of a compound semiconductor, a sub-collector layer, a collector layer, a base layer, an emitter layer, a collector electrode electrically connected to the collector layer, a base electrode electrically connected to the base layer, an emitter mesa layer formed over the emitter layer and electrically connected to the emitter layer, and an emitter electrode electrically connected to the emitter mesa layer. The emitter mesa layer has a semiconductor layer made of an n type GaAs layer, a high concentration semiconductor layer made of an n+ type GaAs layer over the semiconductor layer and a ballast resistor layer made of an n type InGaAs layer over the high concentration semiconductor layer.

Owner:RENESAS TECH CORP

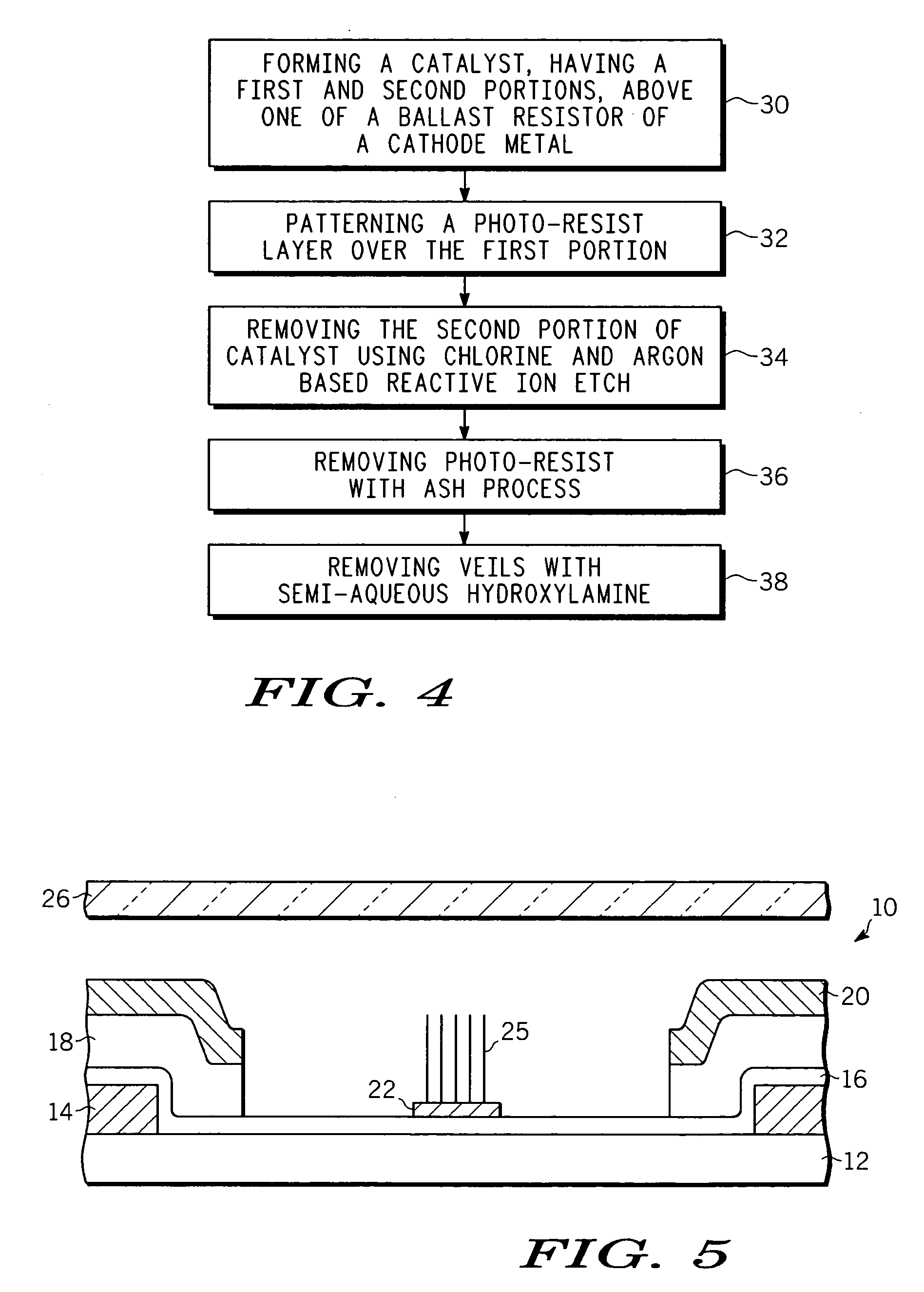

Plasma etch process for defining catalyst pads on nanoemissive displays

A process for forming a catalyst layer for carbon nanotube growth comprising forming a catalyst layer having a first and second portion over one of a cathode metal layer or a ballast resistor layer; patterning a photoresist over the first portion; etching the second portion with a chlorine / argon plasma; removing the photoresist with an ash process; and removing the veils and preparing the surface for carbon nanotube growth with a semi-aqueous hydroxylamine solution.

Owner:MOTOROLA SOLUTIONS INC

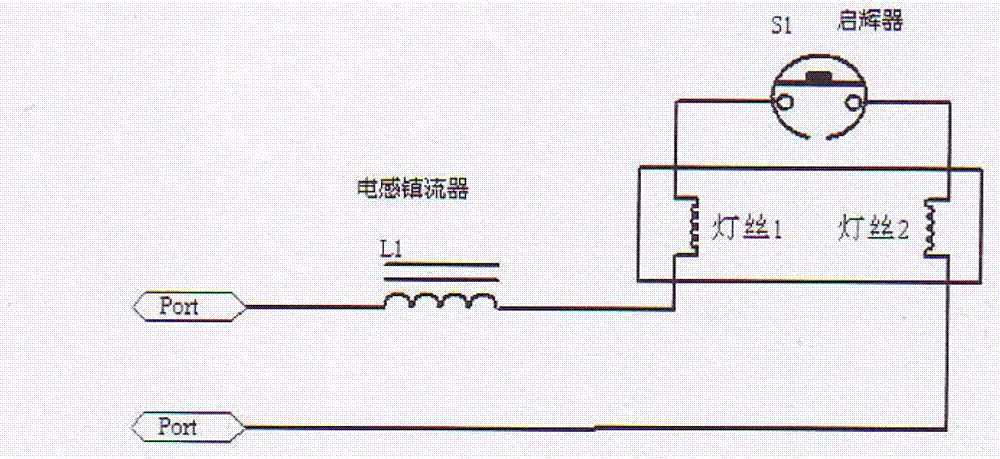

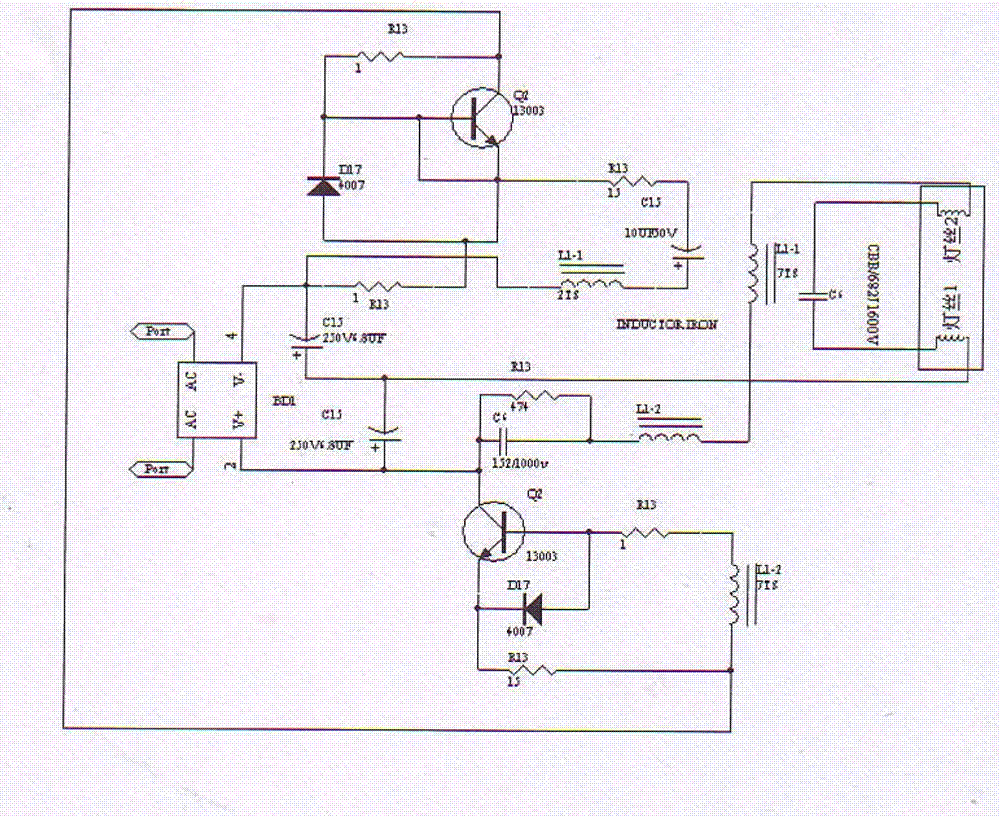

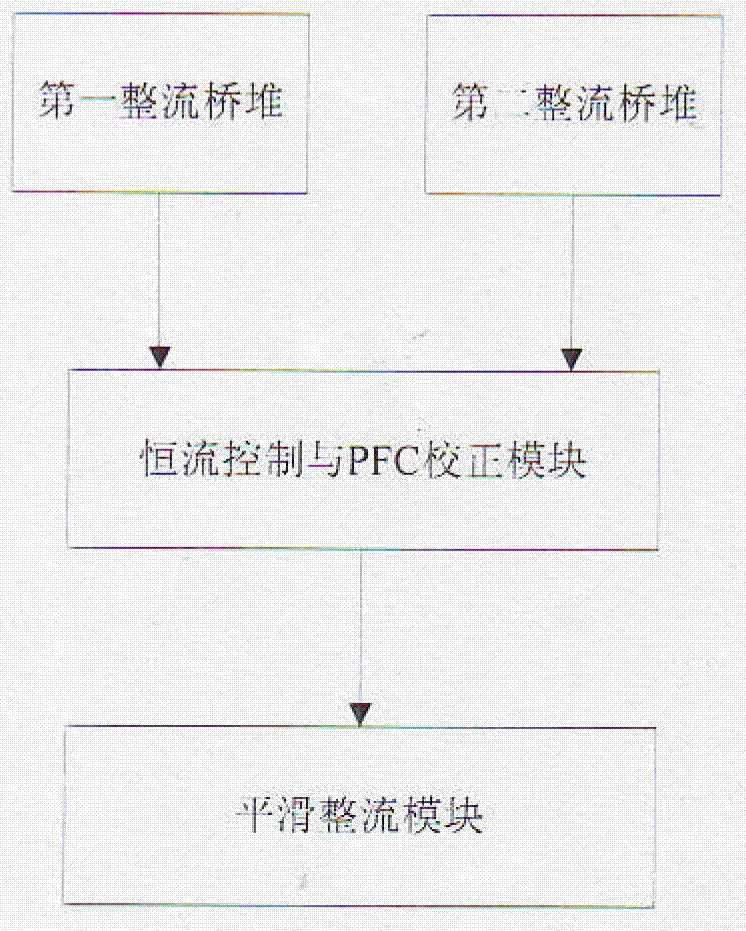

Light-emitted diode (LED) daylight lamp power source compatible with fluorescent lamp system

InactiveCN103037582APopular and convenientEasy to useElectric light circuit arrangementBallast resistorEngineering

The invention provides a light-emitted diode (LED) daylight lamp power source compatible with a fluorescent lamp system. The LED daylight lamp power source compatible with the fluorescent lamp system comprises a first bridge rectifier, a second bridge rectifier, a constant-current control and positive feedback circuit (PFC) correcting module and a smooth rectifier module. The first bridge rectifier and the second bridge rectifier are respectively connected with the constant-current control and PFC correcting module which is connected with the smooth rectifier module. The first bridge rectifier and the second bridge rectifier are used for converting an input alternating current into a direct current and sending the direct current to the constant-current control and PFC correcting module. The constant-current control and PFC correcting module is used for adjusting the direct current and sending the direct current to the smooth rectifier module which is used for smoothing and rectifying the direct current and outputting the direct current. According to the technical scheme of the LED daylight lamp power source compatible with the fluorescent lamp system, no matter which kind of ballast resistors is arranged inside a traditional daylight lamp support, the daylight lamp support is not needed to be changed. After the LED source is installed, the LED daylight lamp can be used, and therefore a first condition is conveniently provided for popularization and using of the LED daylight lamp.

Owner:LINKUN DONGGUAN SEMICON LIGHTING

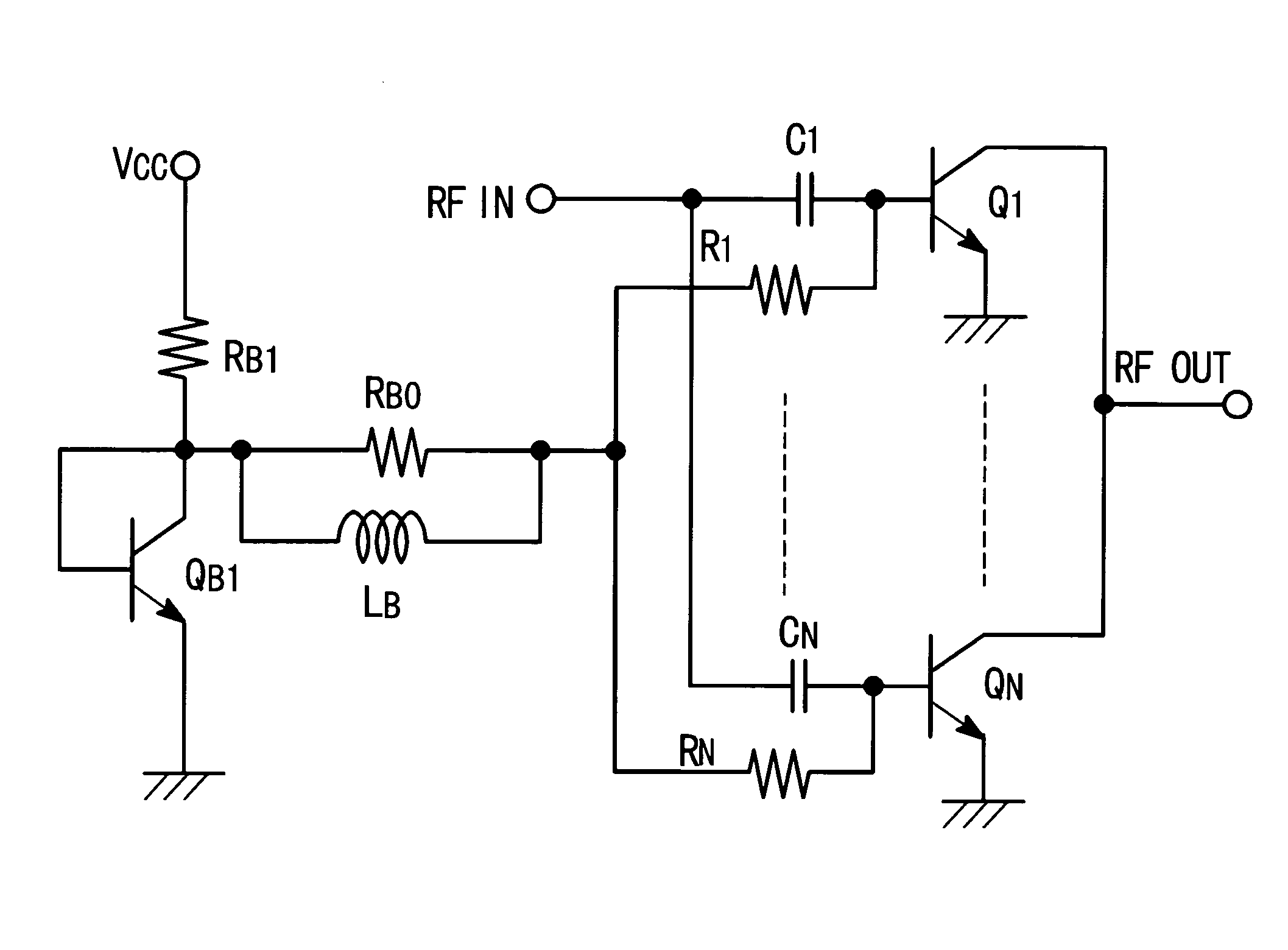

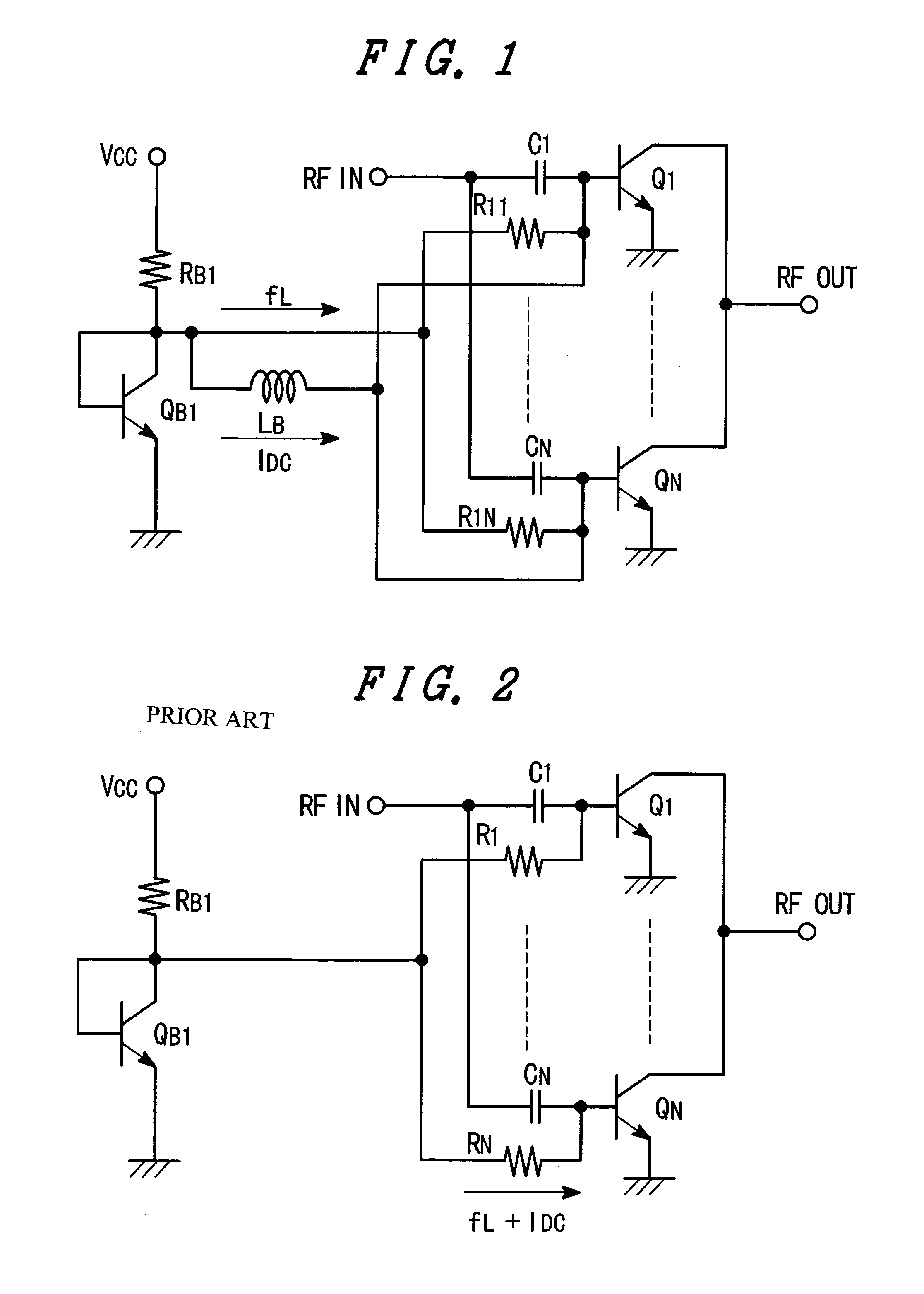

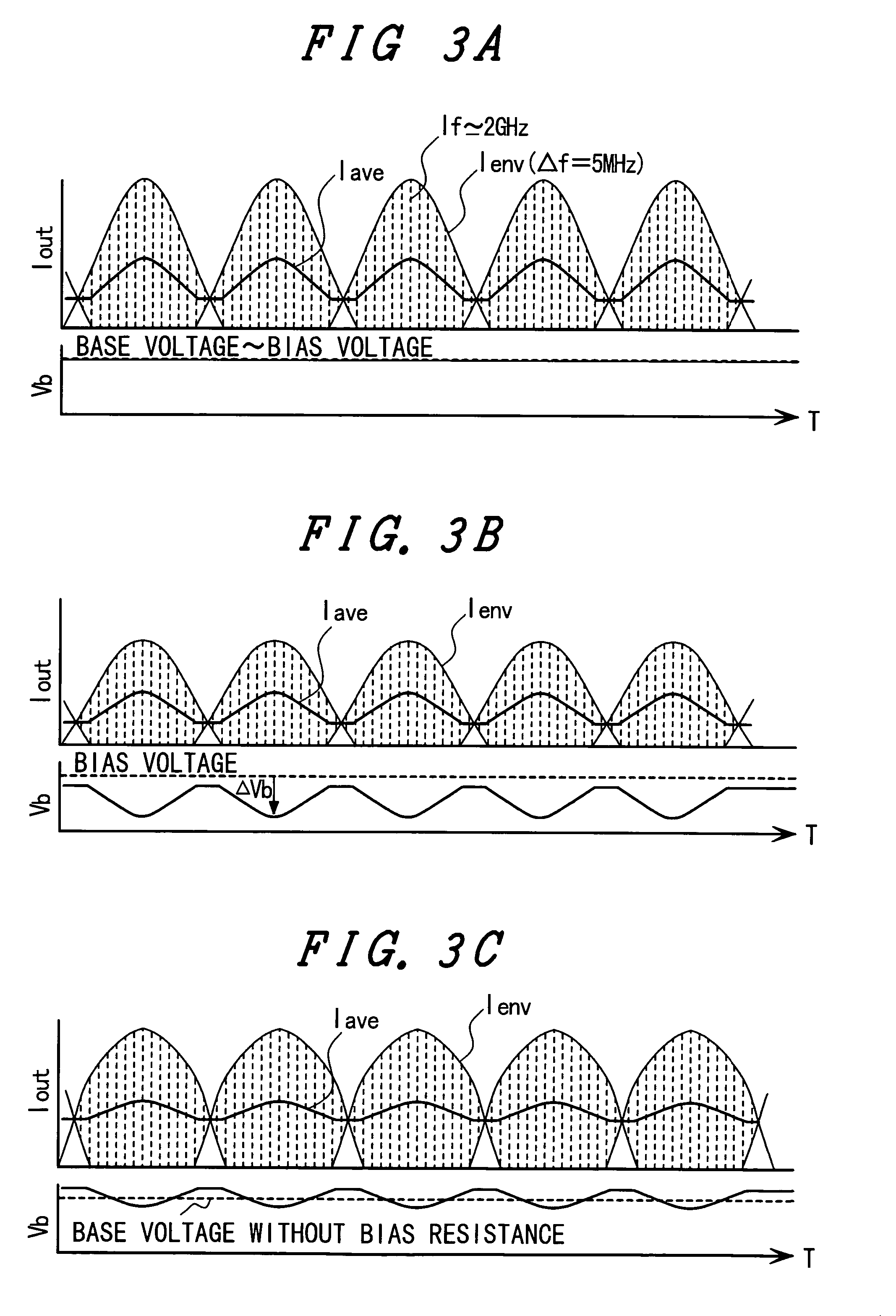

Radio frequency power amplifier and communication system

InactiveUS7098740B2Improve efficiencySuppression of distortionAmplifier modifications to reduce non-linear distortionAmplifier modifications to reduce temperature/voltage variationBallast resistorCommunications system

There is provided not only a radio frequency power amplifier using an SiGe HBT subject to a little amplification distortion, but also a communication system using the same. A conventional radio frequency power amplifier provides base bias paths of transistors Q1 through QN (SiGe HBT) with bias resistors R11 through R1N having resistance values three to five times higher than those of a ballast resistor attached to each transistor's base. A coil LB is provided in parallel with the bias resistor as a means for compensating a voltage drop due to direct current component IDC flowing through the bias resistor. Addition of the bias resistor suppresses non-linearity of low-frequency variations in an output current. Addition of the coil compensates for voltage drop. Accordingly, the maximum linear output power can be improved. As a result, it is possible to provide the power amplifier subject to a little amplification distortion within a wide output range.

Owner:RENESAS TECH CORP

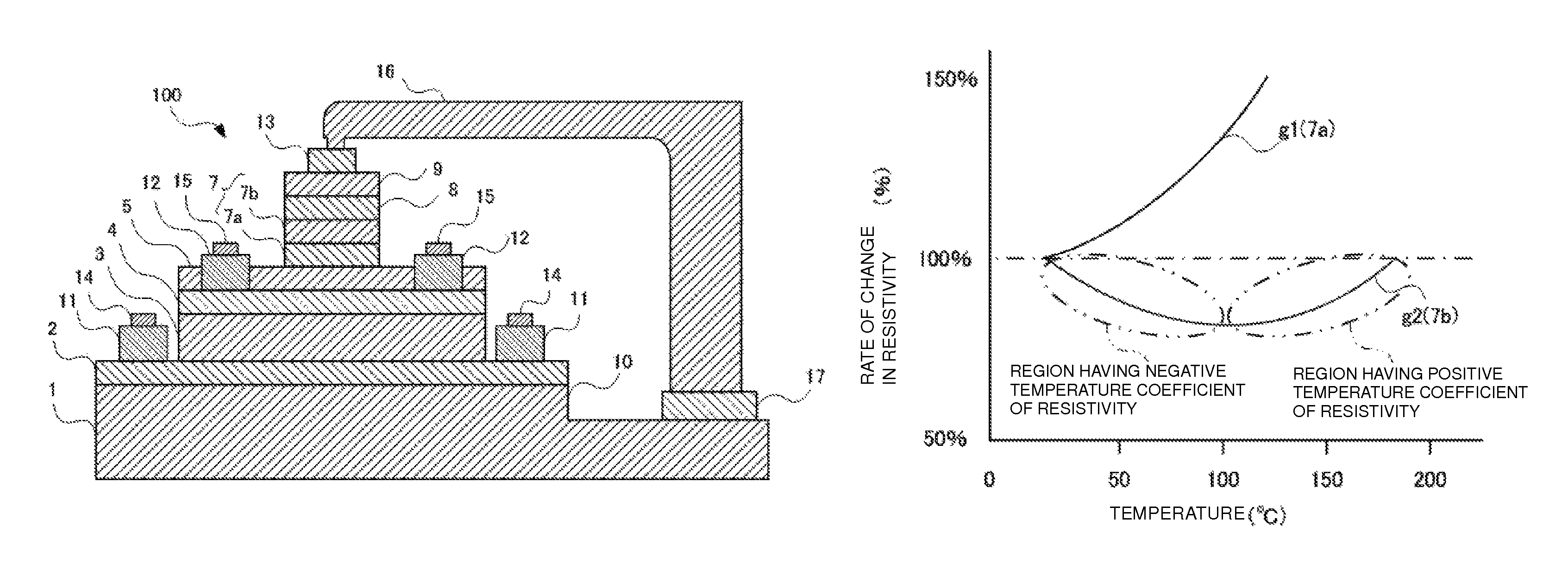

Heterojunction bipolar transistor, power amplifier including the same, and method for fabricating heterojunction bipolar transistor

ActiveUS9130004B2Prevents both thermal runaway and the deterioration of power amplifier characteristicsIncrease powerTransistorSolid-state devicesElectrical resistance and conductanceBallast resistor

A heterojunction bipolar transistor includes a ballast resistor layer of which resistance increases with an increase in temperature. The ballast resistor layer includes a first ballast resistor sub-layer having a positive temperature coefficient of resistivity in a first temperature range and a second temperature range and a second ballast resistor sub-layer having a negative temperature coefficient of resistivity in the first temperature range and a positive temperature coefficient of resistivity in the second temperature range.

Owner:MURATA MFG CO LTD

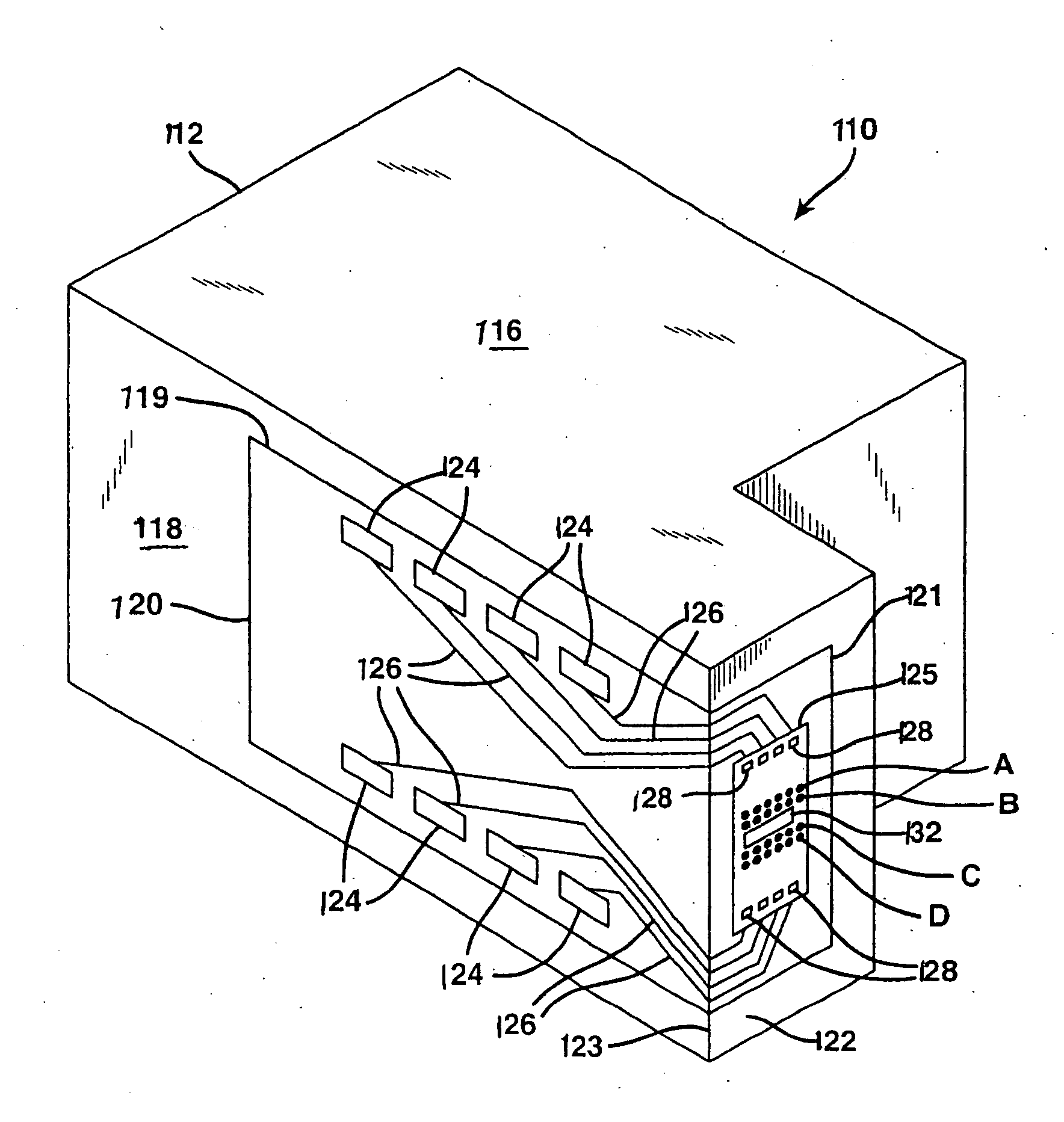

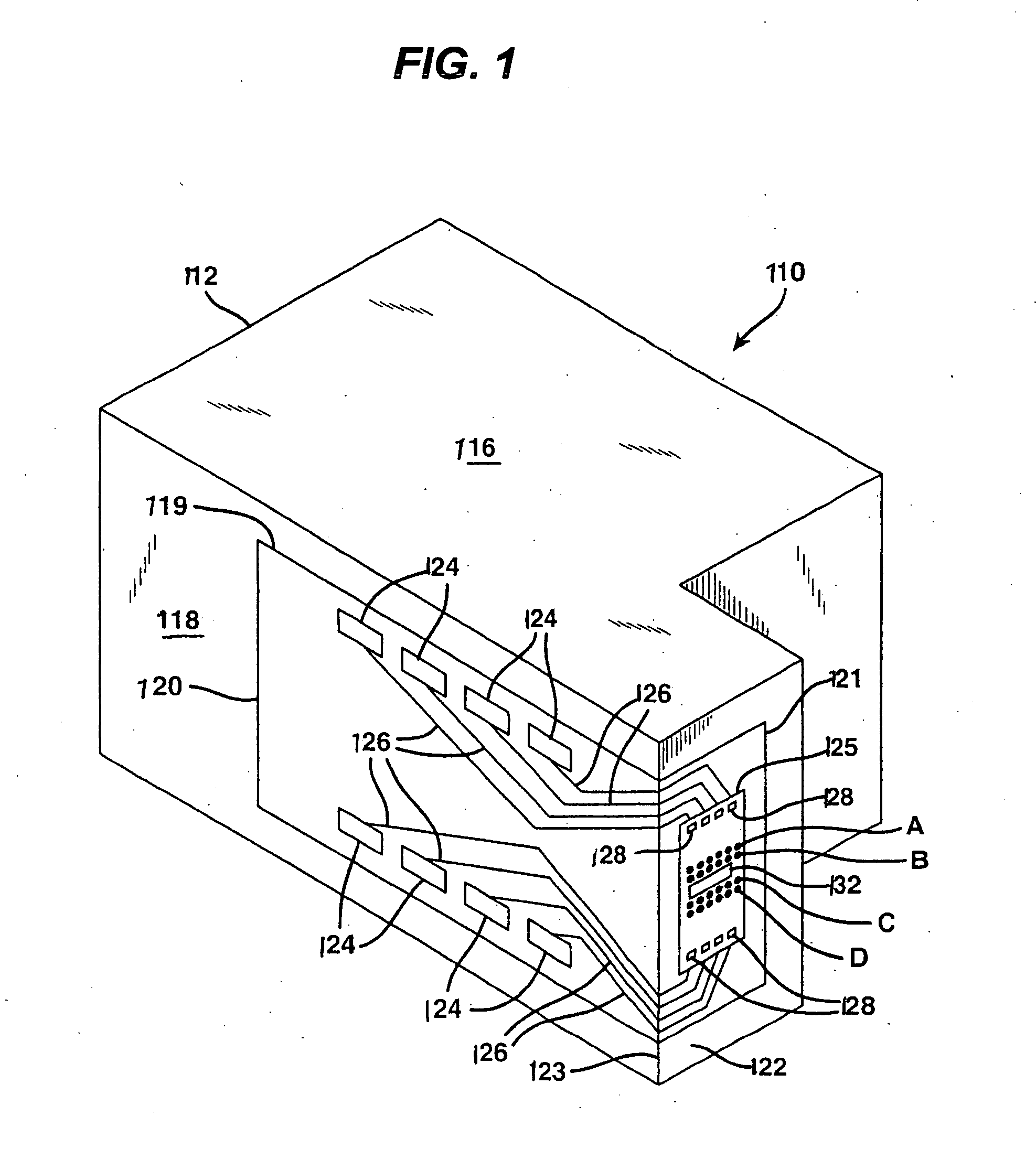

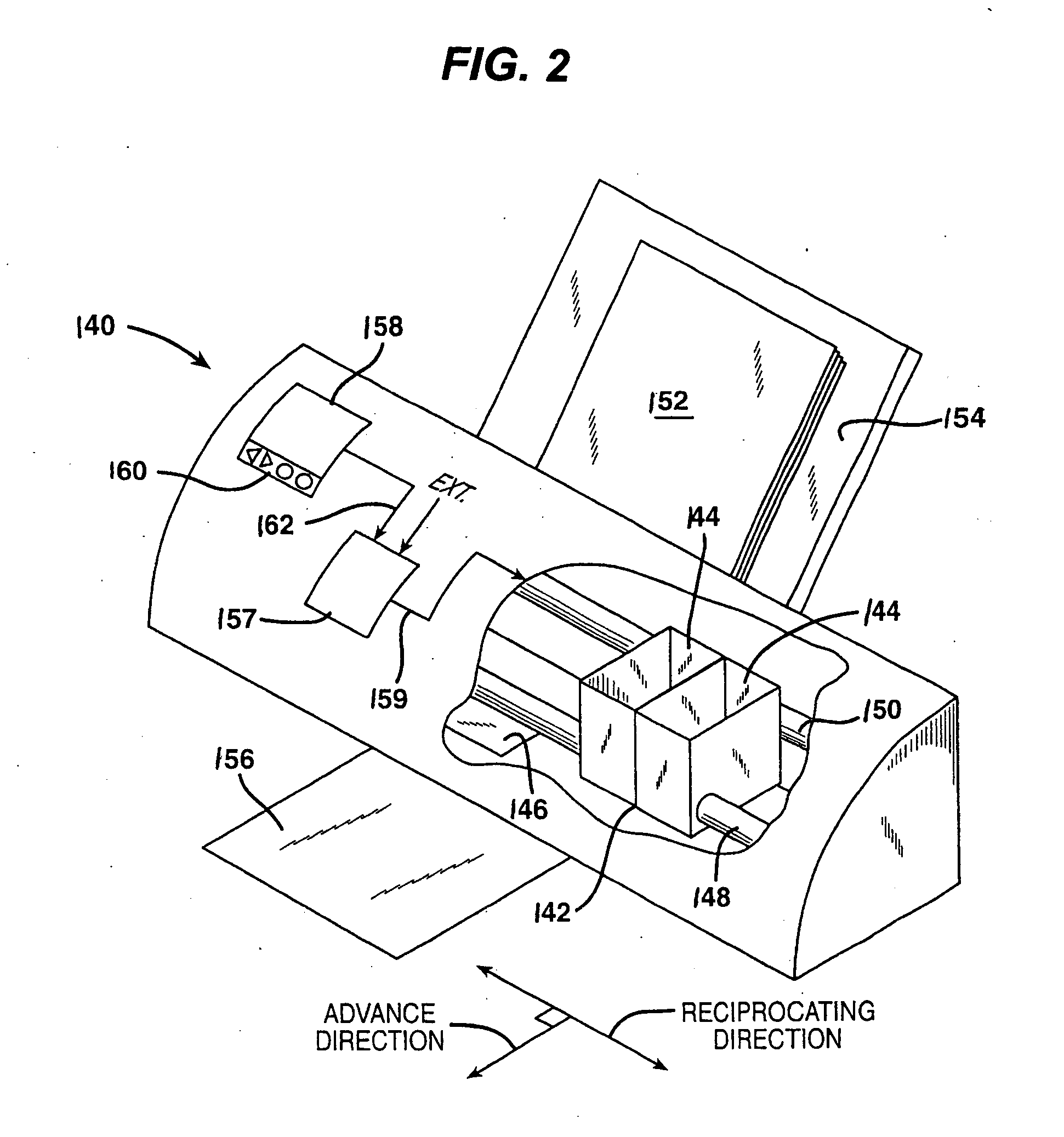

Actuator chip for inkjet printhead with electrostatic discharge protection

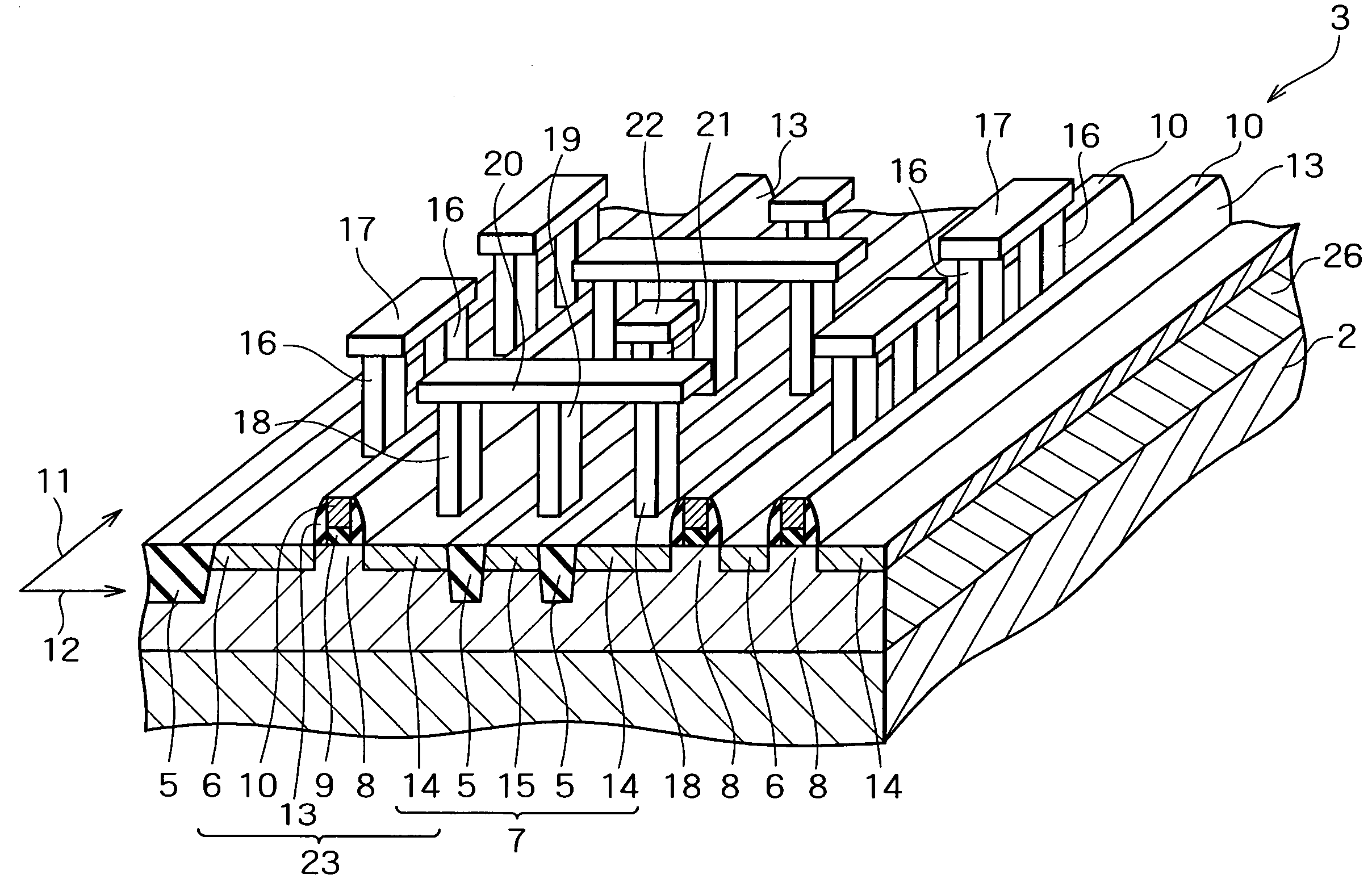

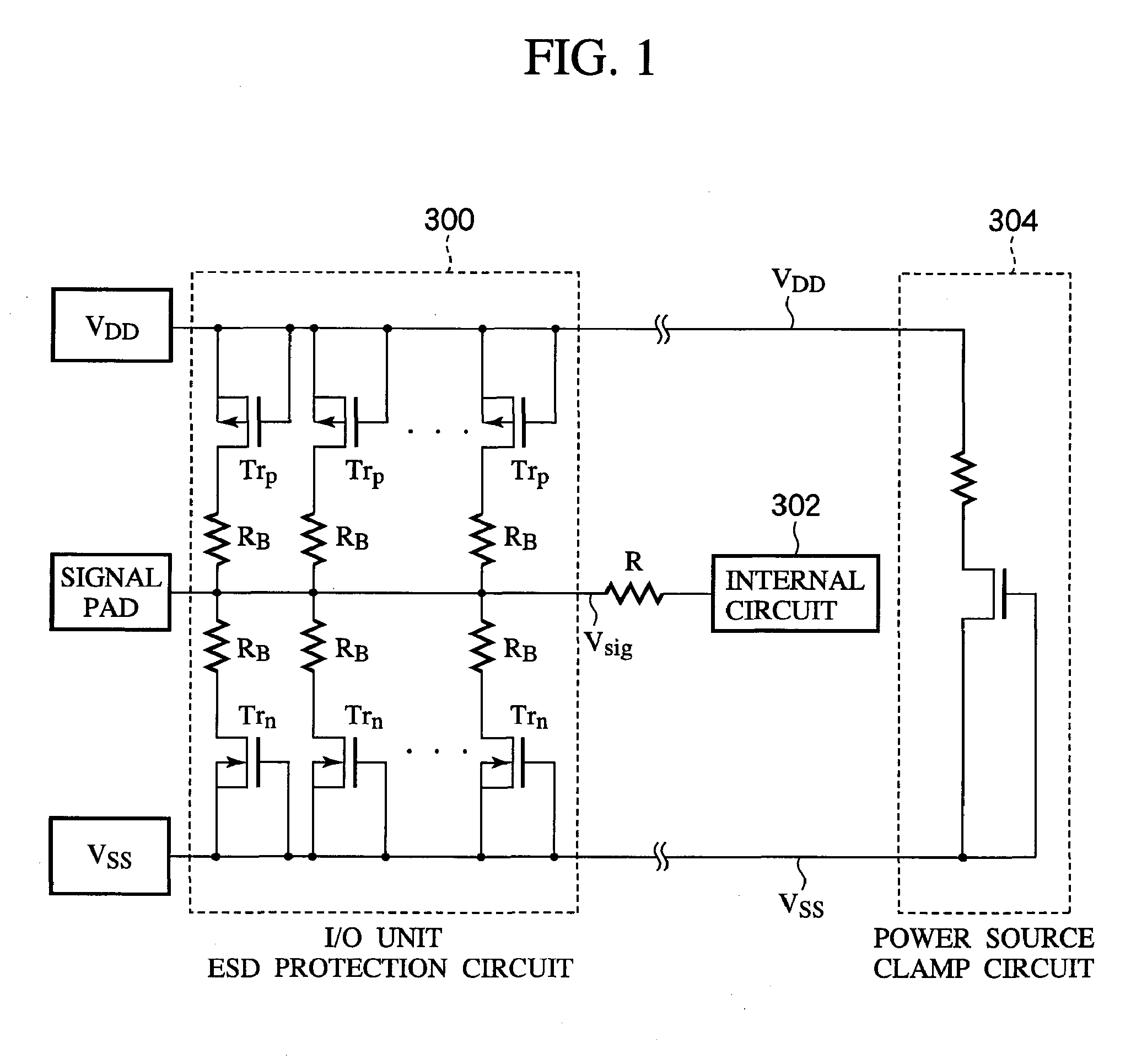

InactiveUS20070188540A1Discharge safetyEnsure safe distributionSemiconductor/solid-state device manufacturingPrintingBallast resistorCavitation

An inkjet printhead chip includes electrostatic discharge (ESD) circuits to protect the chip during ESD events, such as one especially to prevent a thin dielectric layer on a substrate from breakdown. In one embodiment, the chip includes an ESD circuit essentially dedicated per each actuator. In another, ESD circuits alternate connection between power and ground. In still another, actuators are approximately equidistantly spaced with respect to respective ESD circuits. Exemplary ESD circuits include a ballast resistor in series with a diode. In turn, diodes are either forward biased toward power or away from ground. In a thermal inkjet embodiment, a cavitation layer above a resistor and dielectric layer have pluralities of fingers connecting the cavitation layer to a metal buss. The metal buss attaches to the ballast resistors. Protection typically embodies the safe distribution of ESD current to ground during both chip manufacture and user printhead installation. Inkjet printheads and printers are also disclosed.

Owner:FUNAI ELECTRIC CO LTD

Radio frequency linear power amplifier circuit

ActiveCN110677132AImprove efficiencyShorten the timeAmplifier modifications to reduce non-linear distortionPower amplifiersBallast resistorCapacitance

The invention provides a radio frequency linear power amplifier circuit which comprises a radio frequency drive tube (Q1) and a radio frequency power amplifier tube (Q2). The base electrode of the radio frequency drive tube (Q1) is connected with the input end (RF IN) of the amplifier circuit, the collector electrode of the radio frequency drive tube (Q1) is connected with the base electrode of the radio frequency power amplifier tube (Q2), and the collector electrode of the radio frequency power amplifier tube (Q2) is connected with the output end (RF out) of the amplifier circuit; a pre-distortion circuit and a bias circuit (1) are connected in parallel between the base electrode of the radio frequency drive tube (Q1) and the input end (IN) of the amplifier circuit, and a ballast resistor (R10) is connected in series between the base electrode of the radio frequency drive tube (Q1) and the input end (IN) of the amplifier circuit, and the ballast resistor (R10) is connected in parallel with a capacitor (C10); a bias circuit (2) is connected in parallel between the base electrode of the radio frequency power amplifier tube (Q2) and the radio frequency drive tube (Q1), and a ballastresistor (R20) is connected in series between the base electrode of the radio frequency power amplifier tube (Q2) and the radio frequency drive tube (Q1), and the ballast resistor (R20) is connectedin parallel with a capacitor (C20); the radio frequency linear power amplifier not only can improve the design efficiency of the power amplifier, but also can realize good linearity.

Owner:广州穗源微电子科技有限公司

Semiconductor device and method of manufacturing the same

ActiveUS7888740B2Suppress fluctuationsTransistorSemiconductor/solid-state device detailsBallast resistorDevice material

The semiconductor device includes a first MIS transistor including a gate insulating film 92, a gate electrode 108 formed on the gate insulating film 92 and source / drain regions 154, a second MIS transistor including a gate insulating film 96 thicker than the gate insulating film 92, a gate electrode 108 formed on the gate insulating film 96, source / drain regions 154 and a ballast resistor 120 connected to one of the source / drain regions 154, a salicide block insulating film 146 formed on the ballast resistor 120 with an insulating film 92 thinner than the gate insulating film 96 interposed therebetween, and a silicide film 156 formed on the source / drain regions 154.

Owner:SOCIONEXT INC

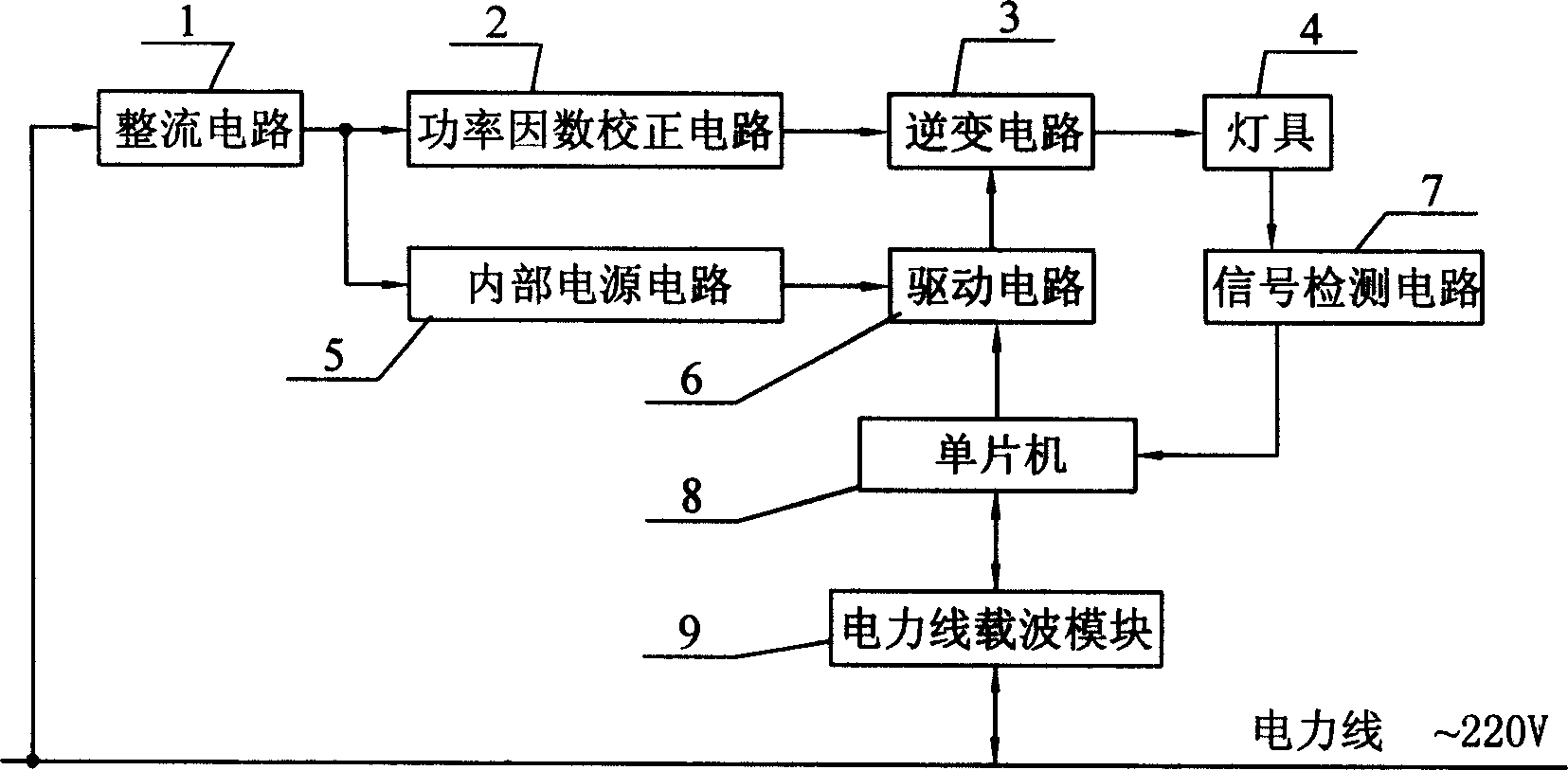

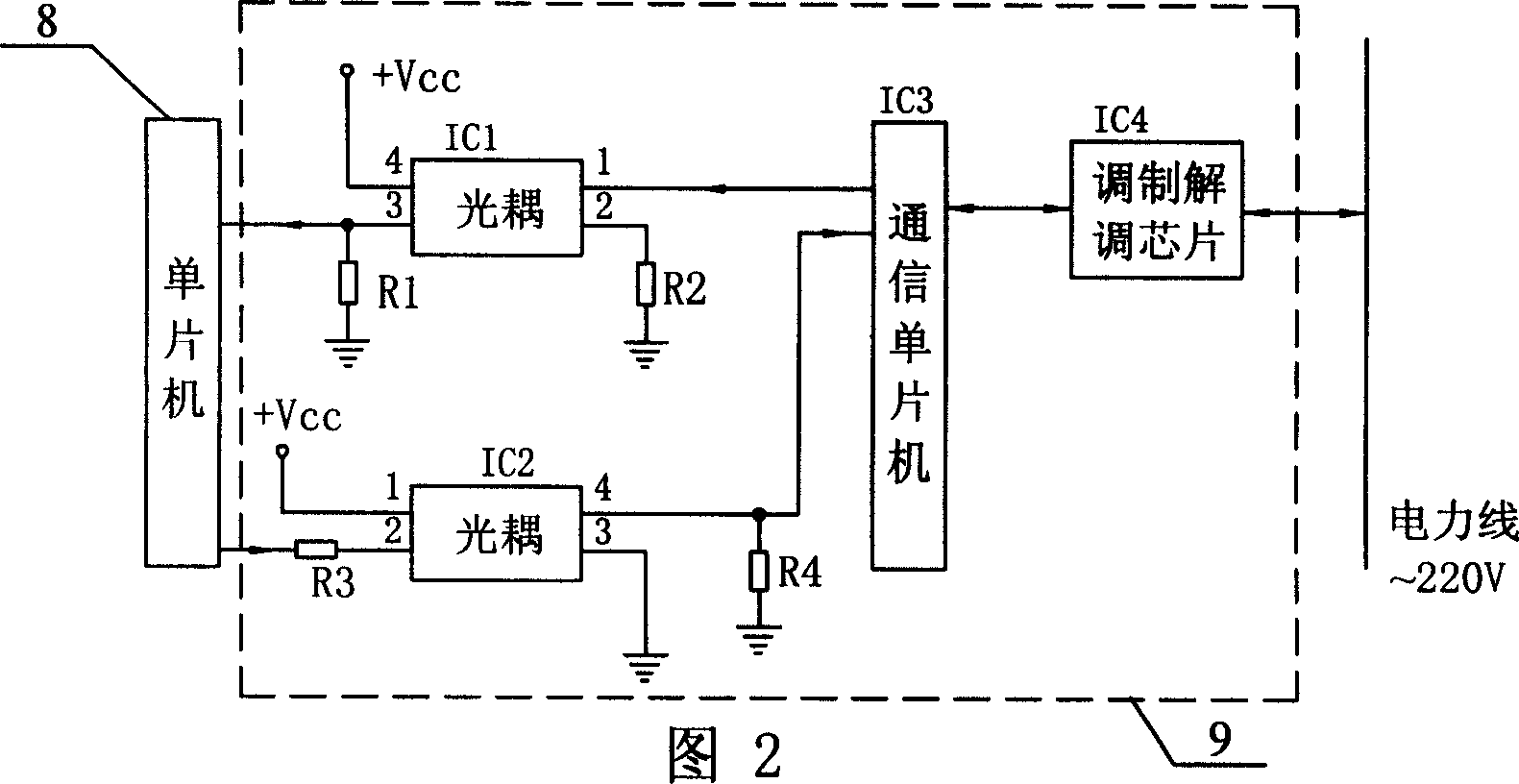

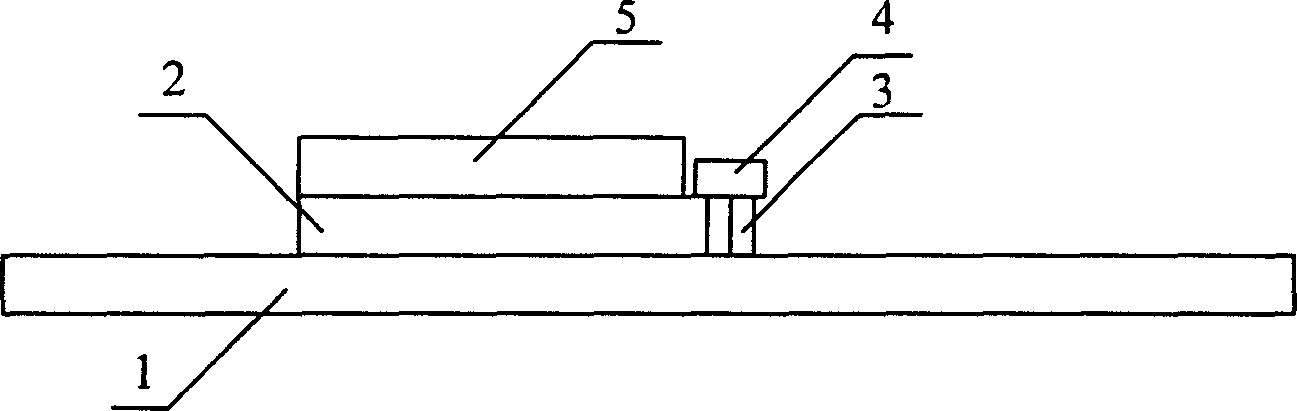

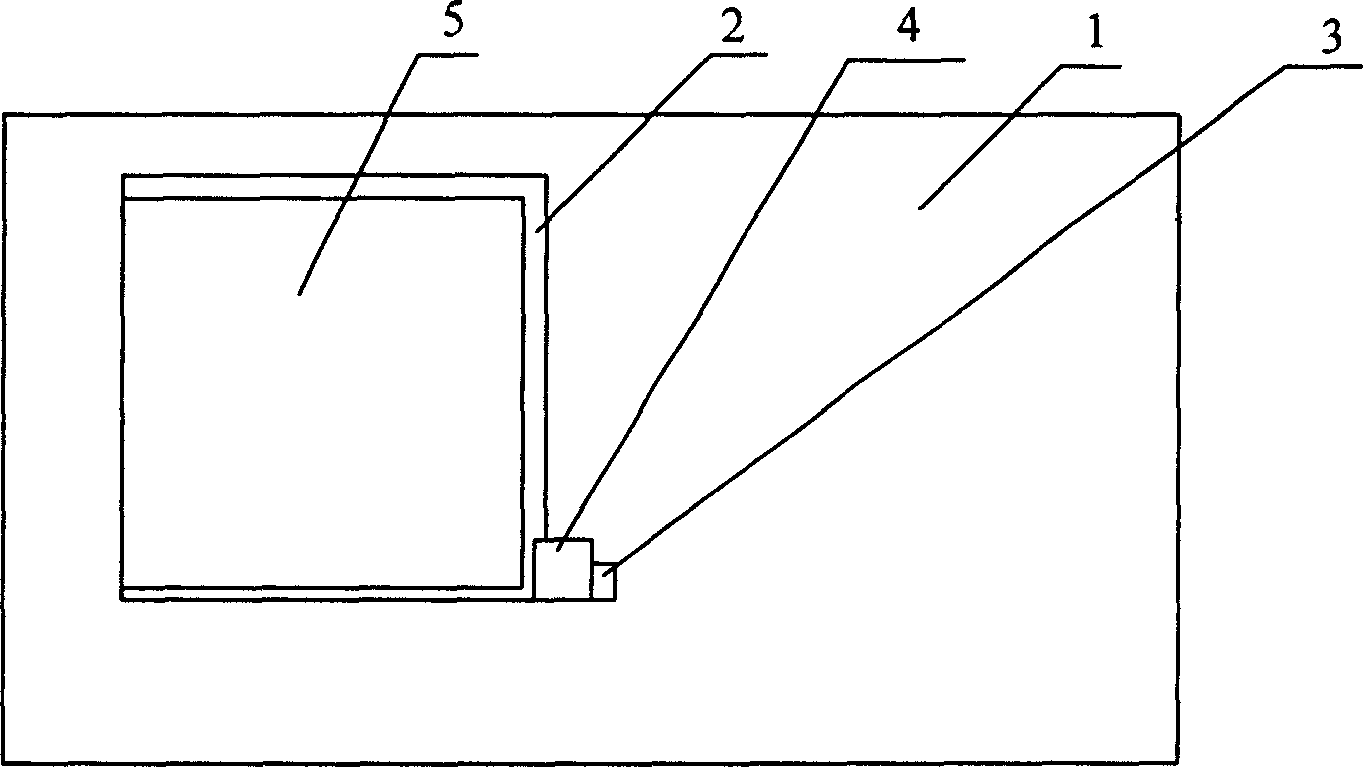

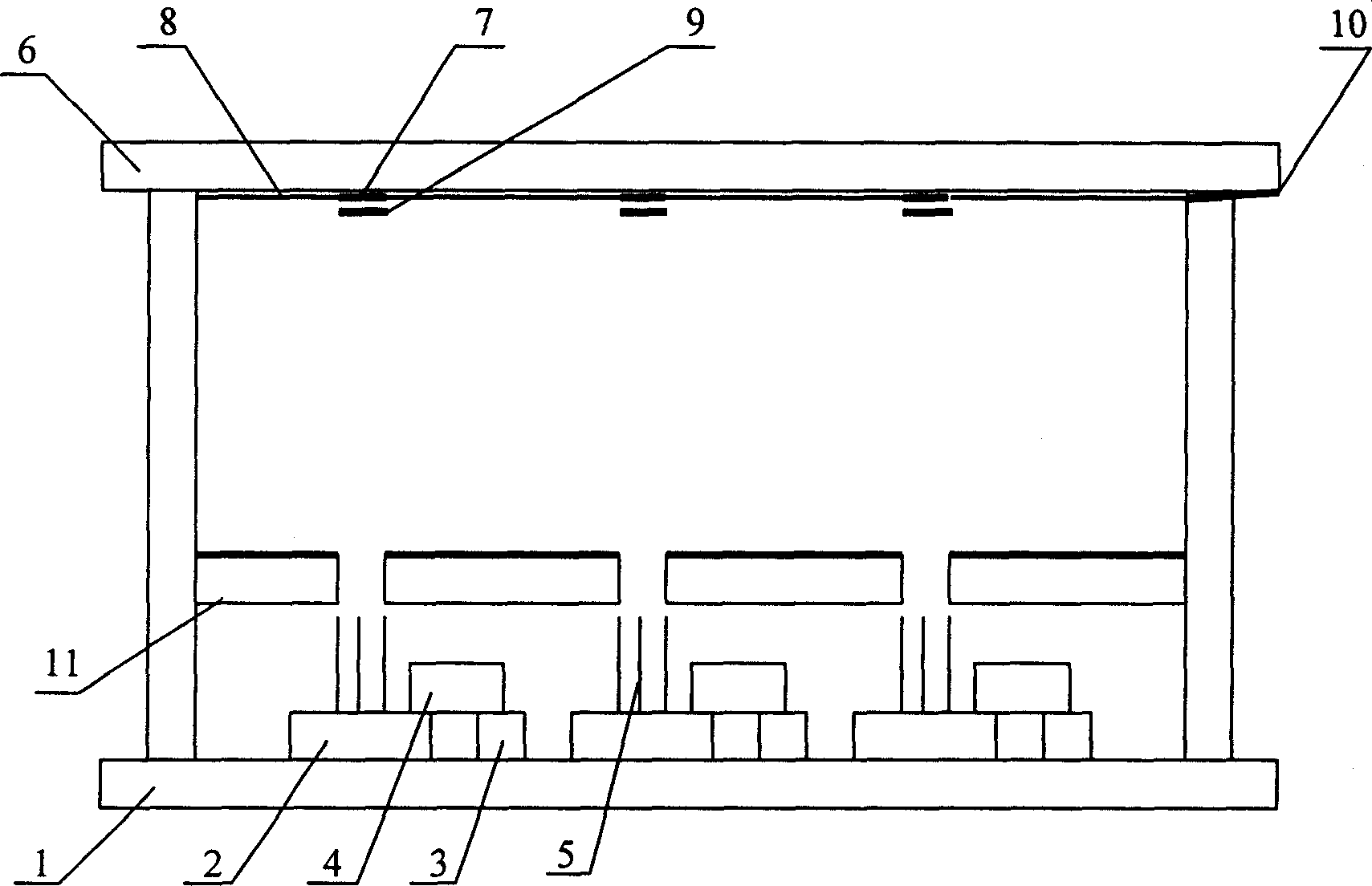

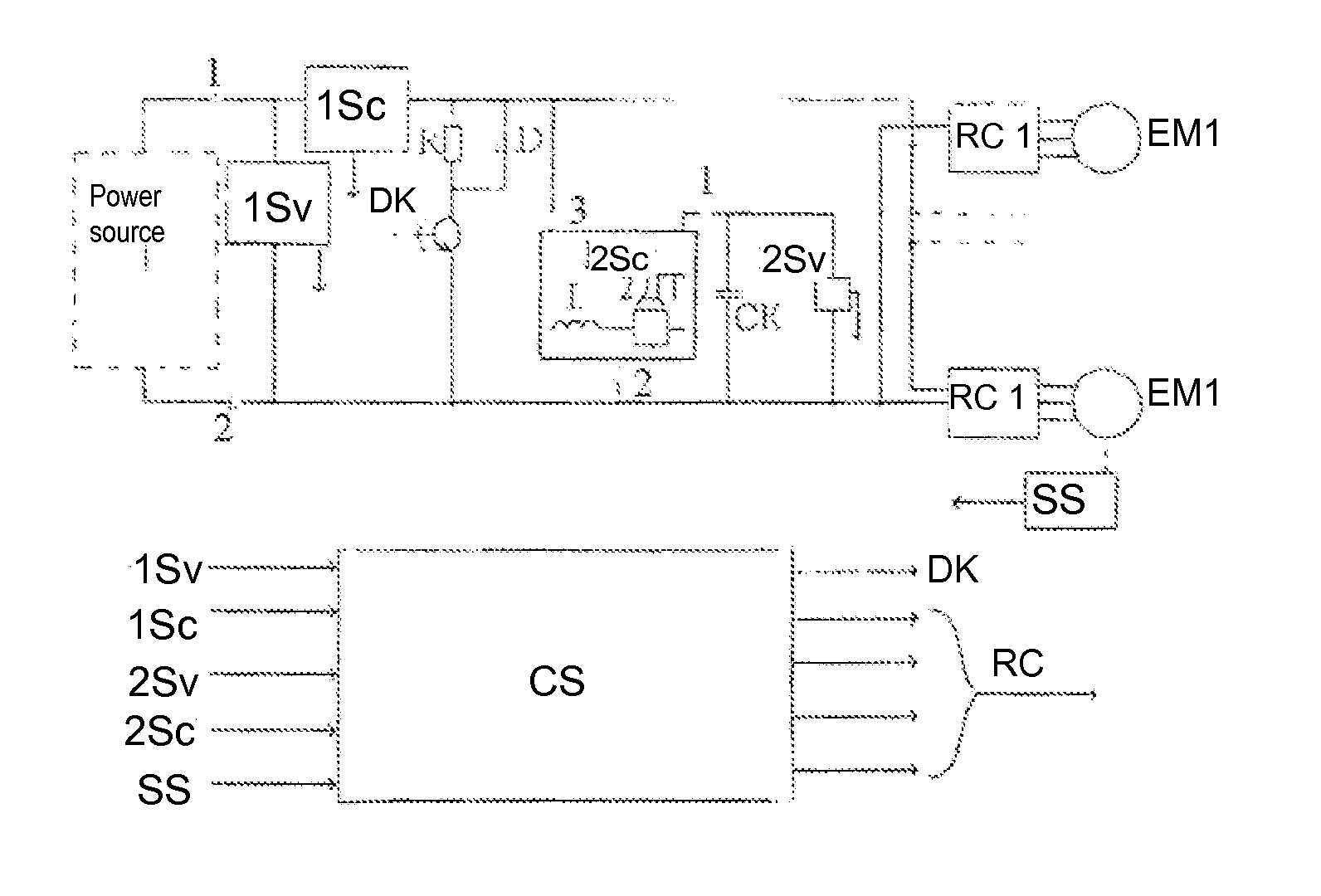

Special electronic ballast resistor in gas discharging light long-range controlling system

ActiveCN1585587AWith remote monitoring functionReal-time monitoring of working statusElectrical apparatusElectric lighting sourcesDriver circuitBallast resistor

The invention is electron ballast used in remote control system of gas discharging light. The 220v AC power is connected with the input end of rectifying circuit. The output end of rectifying circuit is separately connected with PFC circuit and input end of internal power circuit. Input end of inverter circuit is connected with input end of inverter circuit. The inverter circuit is connected with input end of the light. State sensing terminal of the light is connected with input end of signal sensing circuit. The output end of internal power circuit is connected with driving circuit. The output end of driving circuit is connected with inverter circuit. The output end of control signal of singlechip is connected with driving circuit. The input end of singlechip is connected with output end of signal sensing circuit. The data end of singlechip is connected with data end of power line carrier module. The communication end of power line carrier module is connected with 220v power line.

Owner:日照大象房屋建设有限公司

Three-pole carbon nano tube field emission flat display with ballast resistor structure and fabrication process thereof

InactiveCN1622272AHigh success rate of preparationSimple manufacturing processImage/pattern display tubesCold cathode manufactureBallast resistorPhosphor

The present invention relates to field emission display with carbon nanotube cathode, and is especially field emission plate display with ballast resistor structure and its manufacture. The field emission plate display includes sealed vacuum cavity comprising cathode panel, anode panel and glass frame, conductive In-Sn oxide film layer and phosphor layer on the anode panel, control grid, conductive cathode carbon nanotube layer on the cathode panel, ballast resistor layer and carbon nanotube cathode. The ballast resistor structure includes ballast resistors for the carbon nanotube cathode under each pixel to regulate the electron emitting capacity of the carbon nanotube, to raise the electron emitting homogeneity and stability of the whole cathode, to strengthen the adhesion carbon nanotube and cathode panel and to improve the quality of the displayed image. The present invention has the advantages of simple structure, low cost, etc.

Owner:ZHONGYUAN ENGINEERING COLLEGE

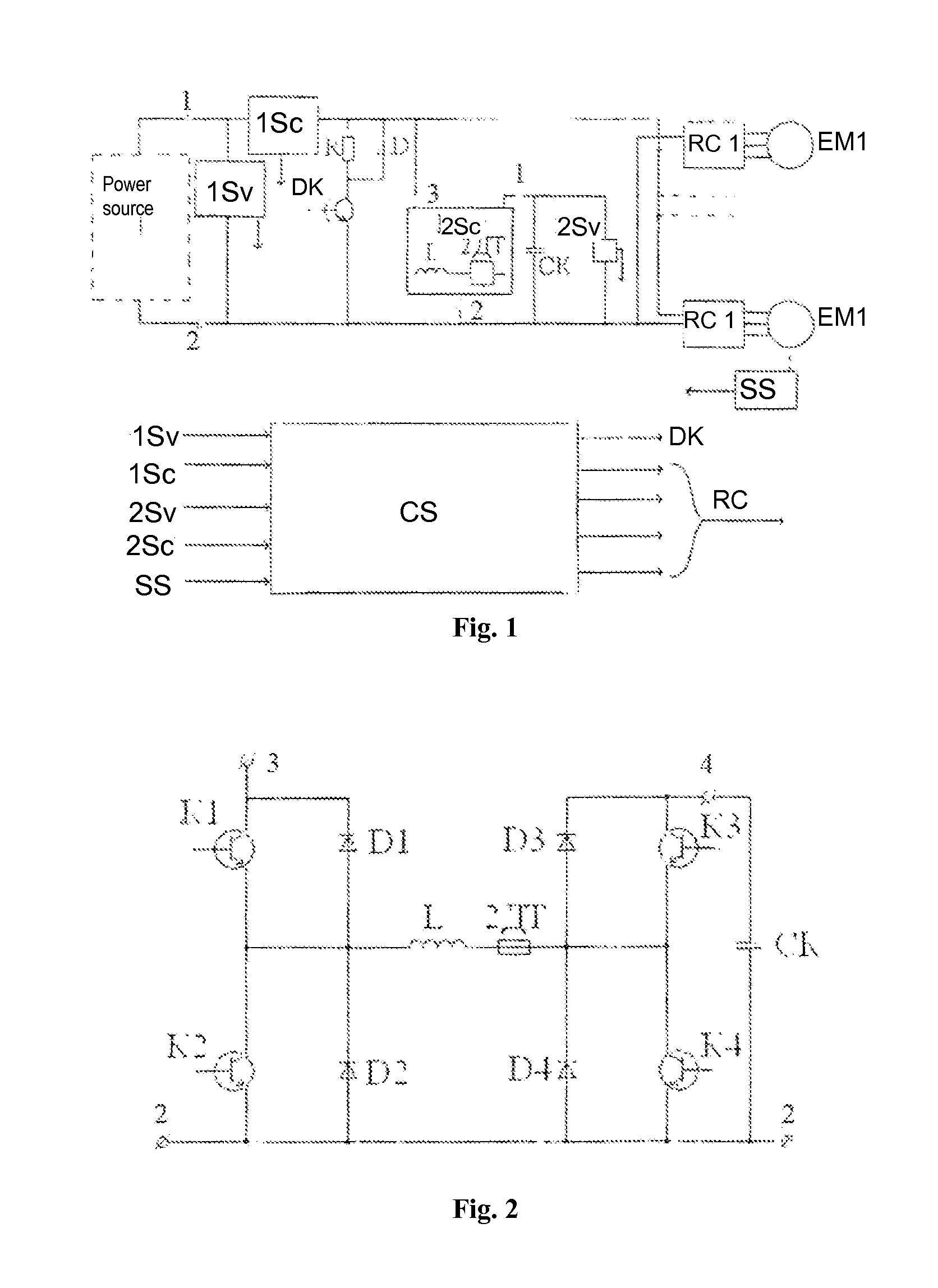

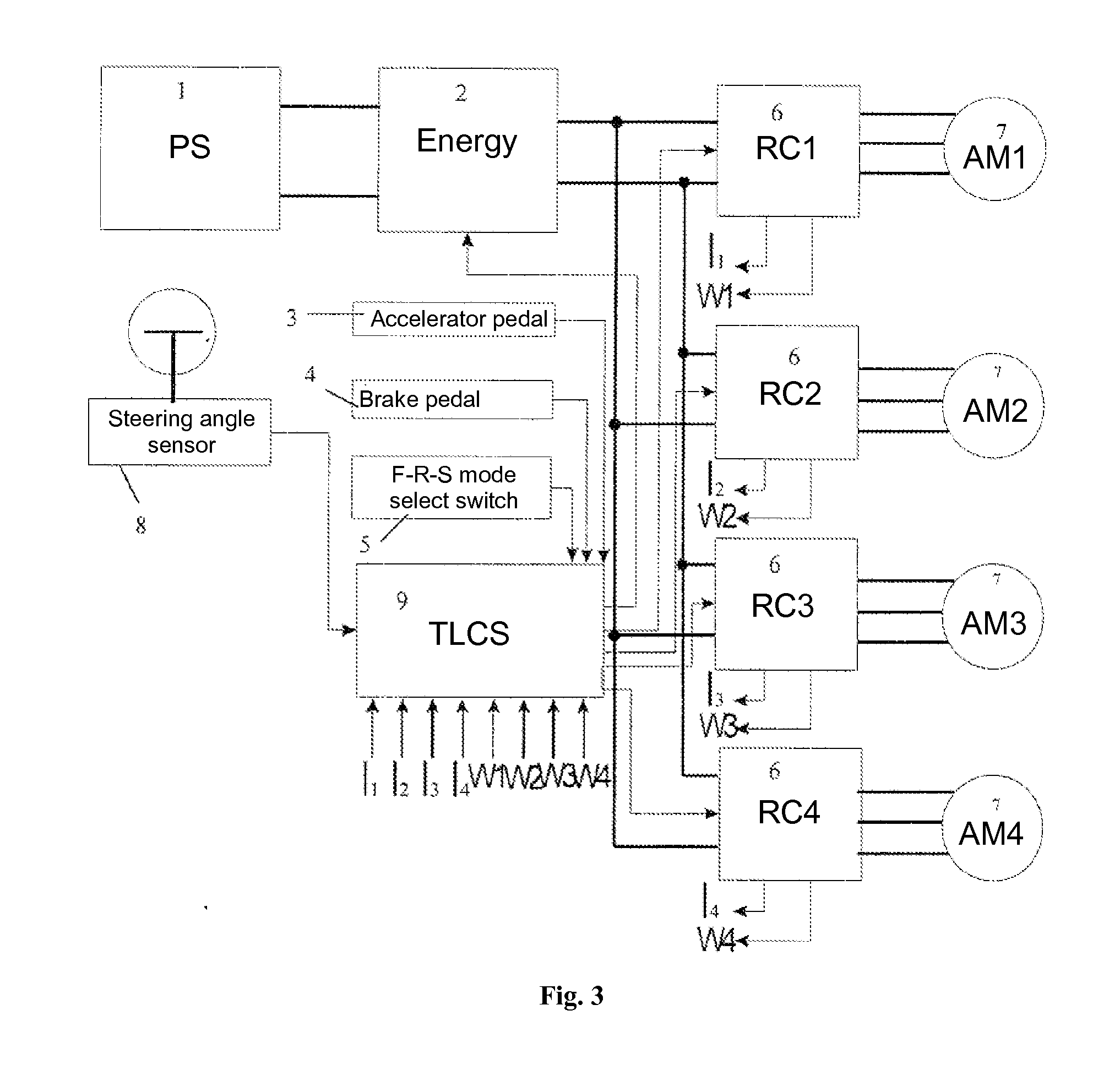

Electric vehicle

InactiveUS20130221745A1Improve energy efficiencyImprovement of EV performance characteristicPropulsion by batteries/cellsVehicular energy storageTransformerEngineering

An electric vehicle is proposed which comprises a reversible power supply (or which is coupled with a reversible power supply), one or more electric motors that are connected to wheels via a mechanical transmission (or without such transmission), one or several reversible converters, which make it possible to control the speed and / or torque of the aforesaid electric motors in all four quadrants of electromechanical characteristic, a high capacity capacitor (supercapacitor) and a ballast resistor.The vehicle is provided with a reversible dc step-up / step-down transformer, two current sensors, two voltage sensors, a vehicle speed sensor, a speed sensor for one of the electric motors and a control system, wherein one or several reversible converters are connected directly to the terminals of the reversible power supply. The supercapacitor is connected to the terminals via the reversible transformer. The ballast resistor, parallel-connected to a bypass diode, is connected in series with a discharge key to the same terminals. One sensor indicates the current value and direction of the reversible power supply, the second sensor takes measurements of coil (inductance choke) current being a component of the transformer. One voltage sensor measures the voltage at the capacitor terminals. The outputs of the aforesaid sensors, together with the output of the speed sensor, are connected to the inputs of the control system, the outputs of which are connected to the control inputs of the transformer and a discharge key. The technical result is a reduction in energy loss as a result of the increased use of recovered energy.

Owner:OBSCHESTVO S OGRANICHENNOY OTVETSTVENNOSTYU TOVARISCHESTVO ENERGETICHESKIKH I ELEKTROMOBILNIKH PROEKTOV