PD SOI (partially-depleted silicon on insulator) technology-based body grid coupling ESD (electro-static discharge) protection structure

A protection structure and body gate technology, applied in the field of electrostatic discharge (ESD) protection circuits and semiconductor integrated circuits, can solve problems such as uneven conduction of multi-finger parallel GGNMOS, eliminate the problem of back channel leakage, strong anti-irradiation effect of ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Below in conjunction with accompanying drawing, the present invention is described in further detail:

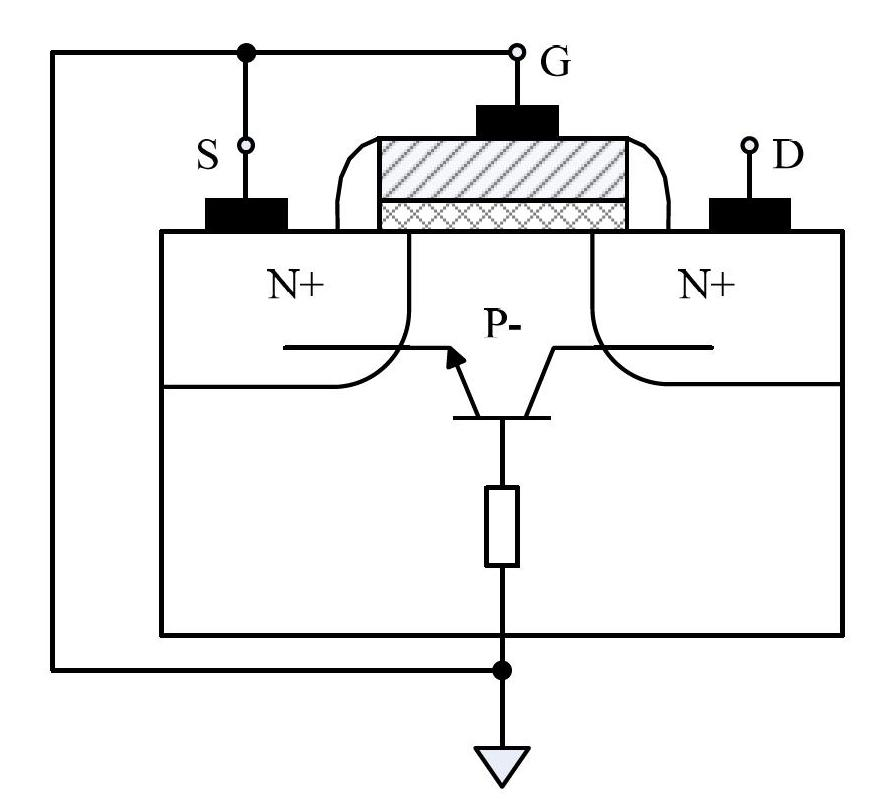

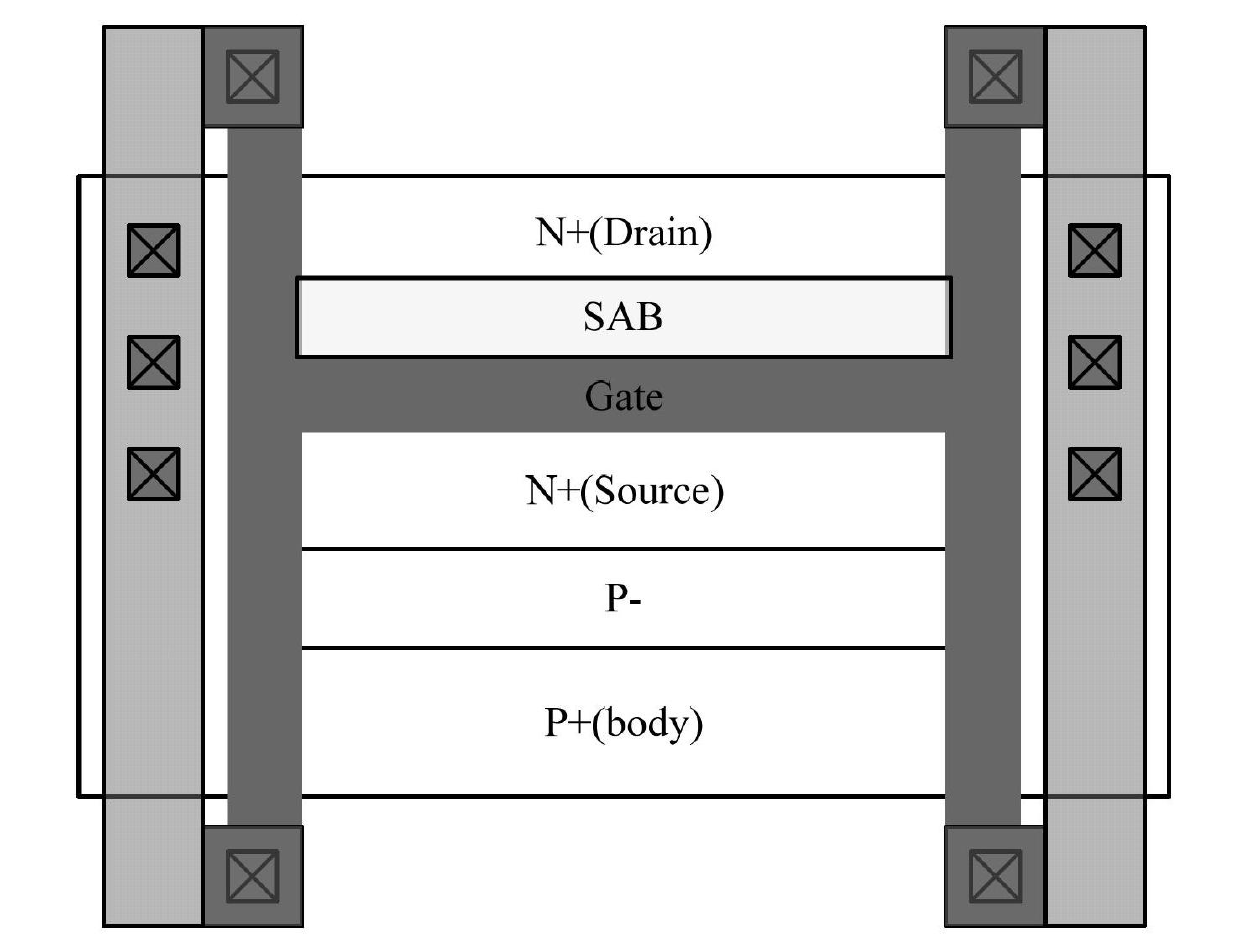

[0022] Such as image 3 , Figure 4 and Figure 5 As shown, a body-gate coupled NMOS ESD protection structure is proposed. In this structure, the gate adopts an H gate structure, and a body implant is performed on the outside and inside of the side gate of the H gate, and the body implant outside the side gate of the H gate is connected to the H gate. Make connections and ground. The source region and the drain region adopt an asymmetric structure of shallow source and deep drain, and the drain region uses the SAB layer to block the silicide to form a ballast resistance, which is conducive to the uniform conduction of multiple parallel tubes. A top view of the structure is image 3 As shown, the cross-sectional view along the source-drain direction is shown in Figure 4 shown.

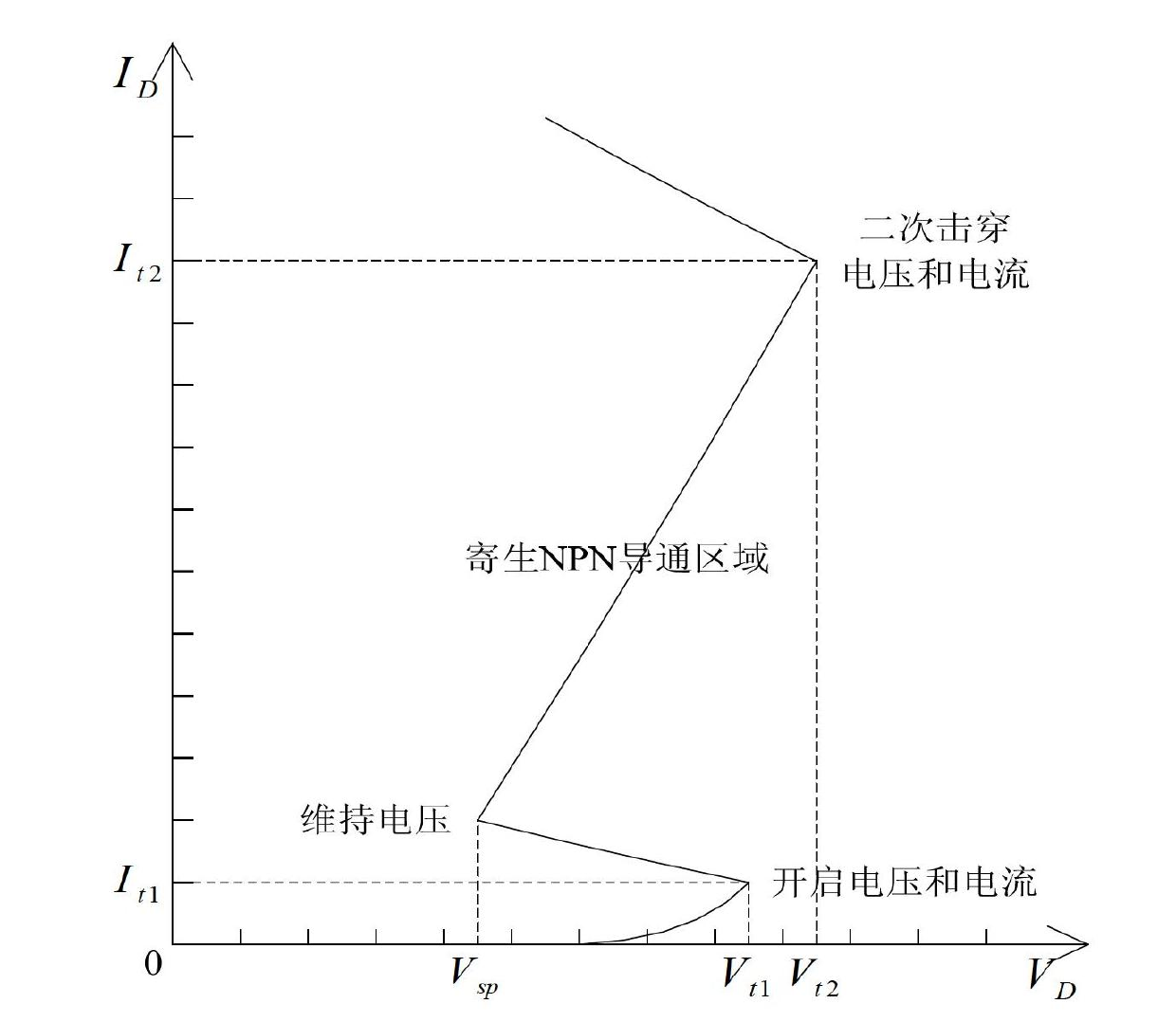

[0023] The equivalent circuit of the body-gate coupled NMOS ESD protection structur...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More