Patents

Literature

37results about How to "Increase voltage margin" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

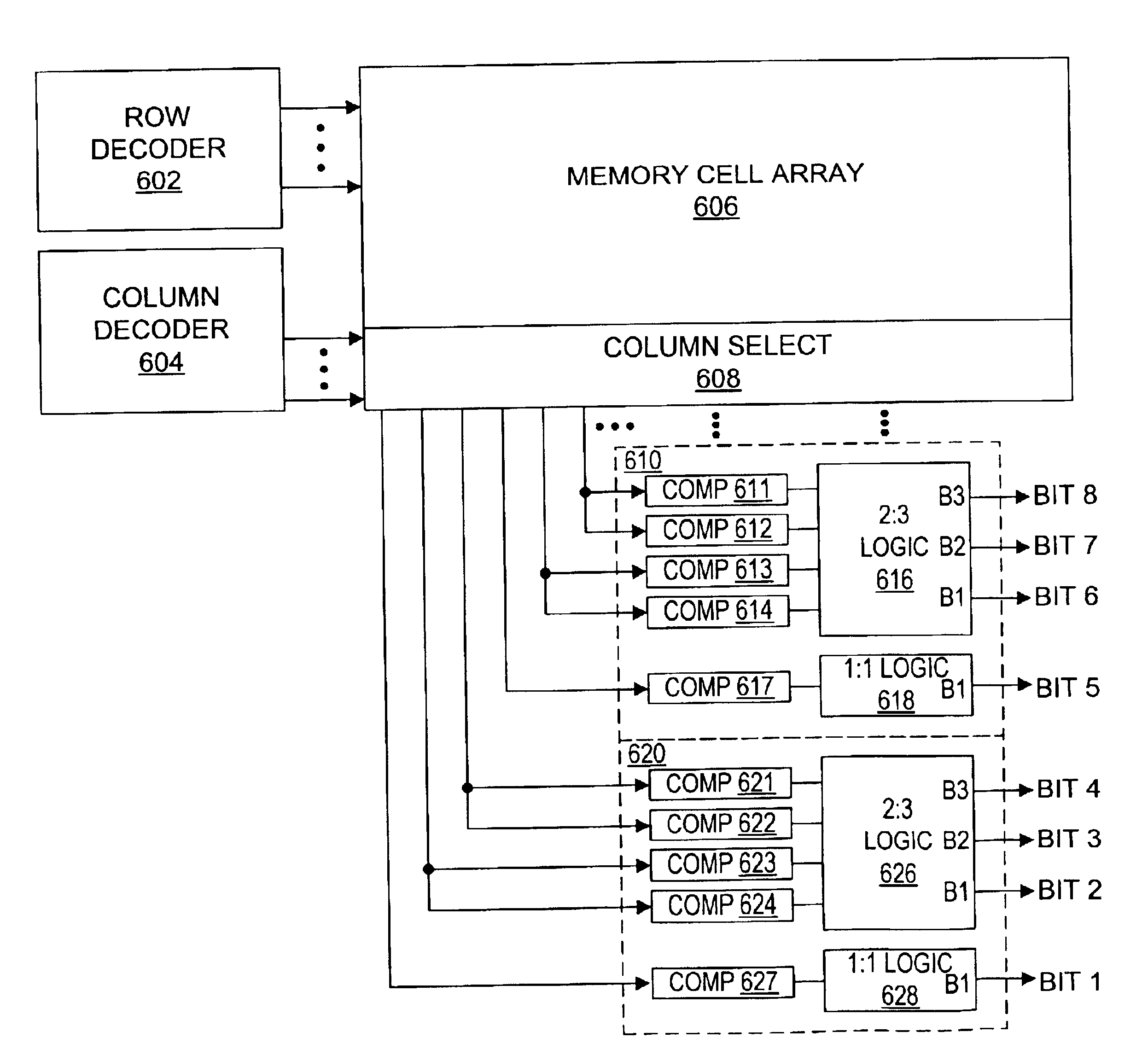

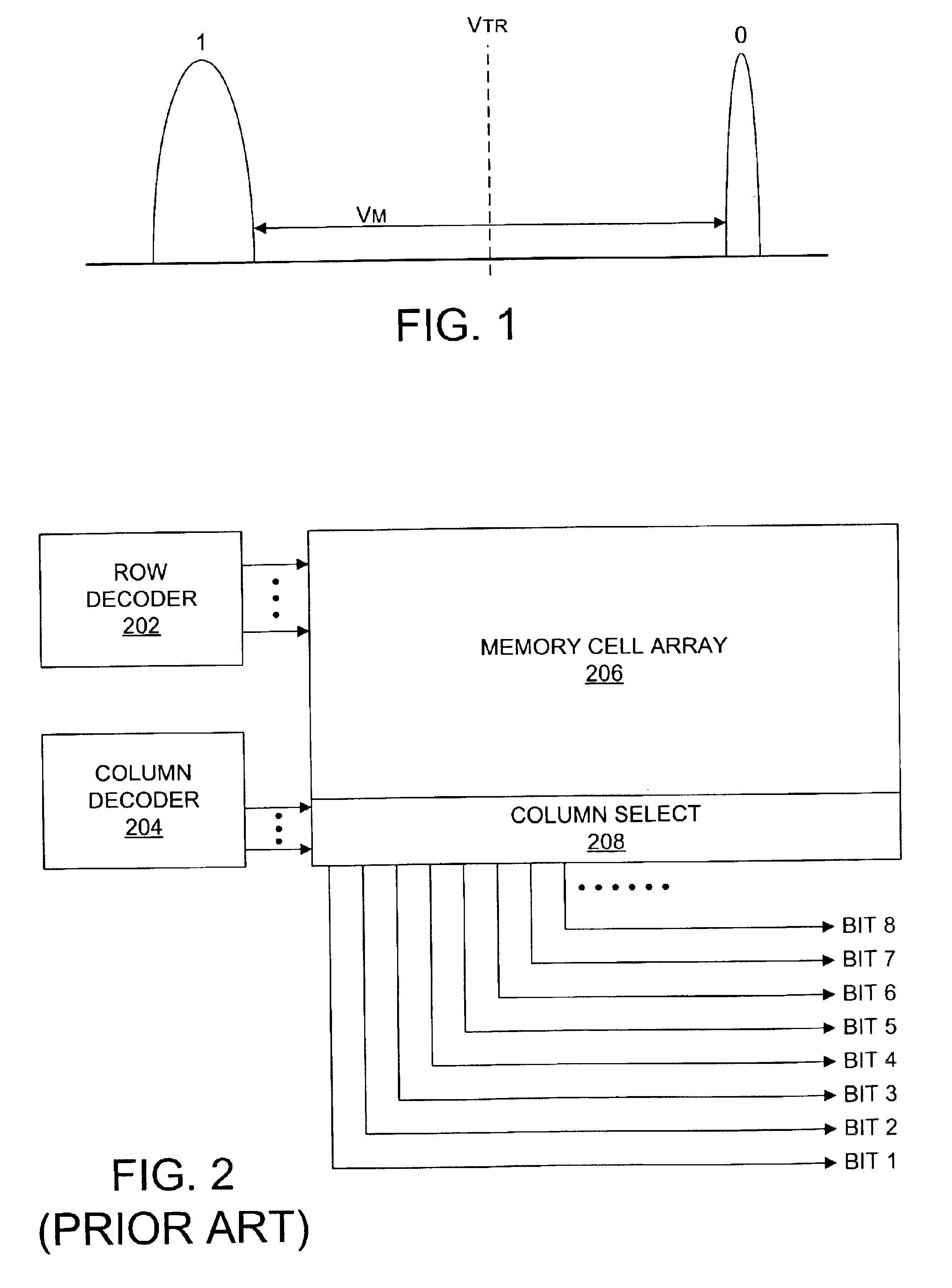

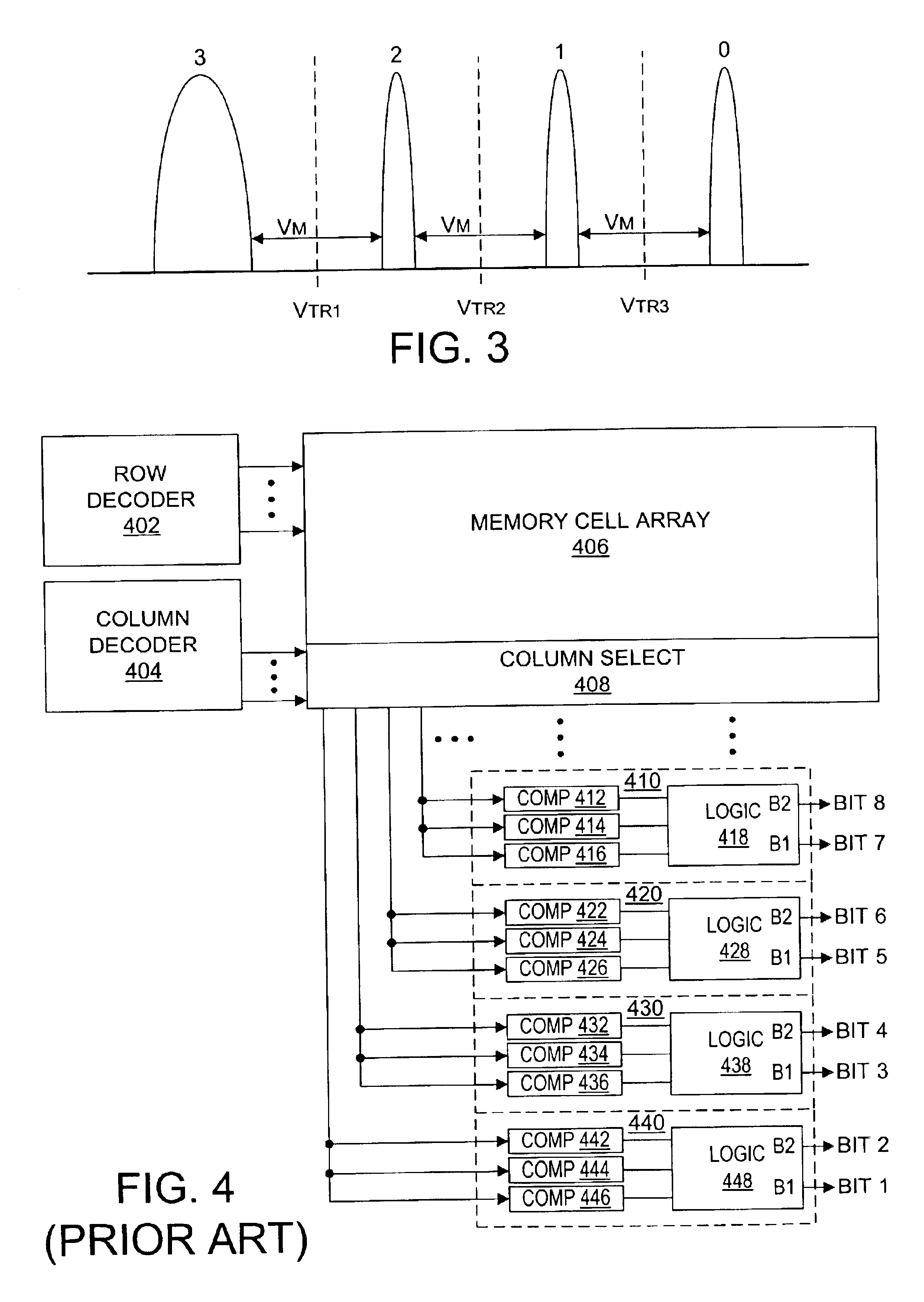

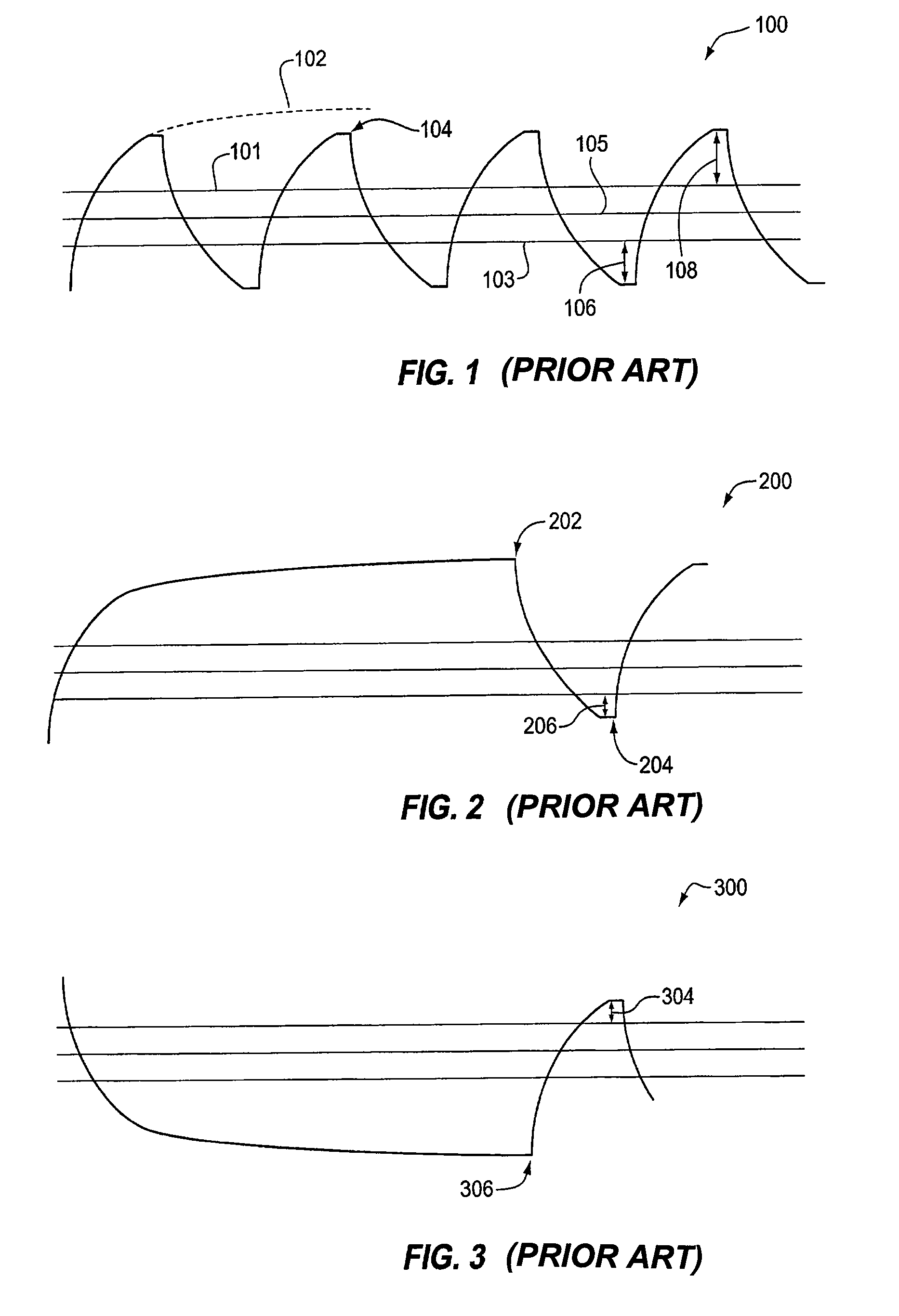

Nonvolatile semiconductor memory having three-level memory cells and program and read mapping circuits therefor

InactiveUS6847550B2Improve reliabilityHigh voltageRead-only memoriesDigital storageThree levelNon symmetric

A memory uses multiple threshold levels in a memory cell that are not a power of two, and further uses a cell mapping technique wherein the read mapping is only a partial function The domain of read states for a single three-level memory cell, for example, has three states, but only two of them can be uniquely mapped to a bit. The domain of read states for two three-level memory cell, for example, has nine states, but only eight of them can be uniquely mapped to three bits. Although the read mapping is only partial, the voltage margin for the three-level memory cells is larger that the voltage margin available in the commonly used four-level memory cells. This increased voltage margin facilitates memory cell threshold voltage sensing, thereby increasing the reliability of the memory. Memory reliability may be further improved by increasing the voltage margin between the memory cell 0 state and the 1 state relative to the voltage margin between the 1 state and the 2 state, which more effectively accommodates charge loss from the 0 state through electron leakage. Asymmetrical read and program mapping may also be used to improve read reliability in the presence of ground noise or VCC noise.

Owner:WINBOND ELECTRONICS CORP

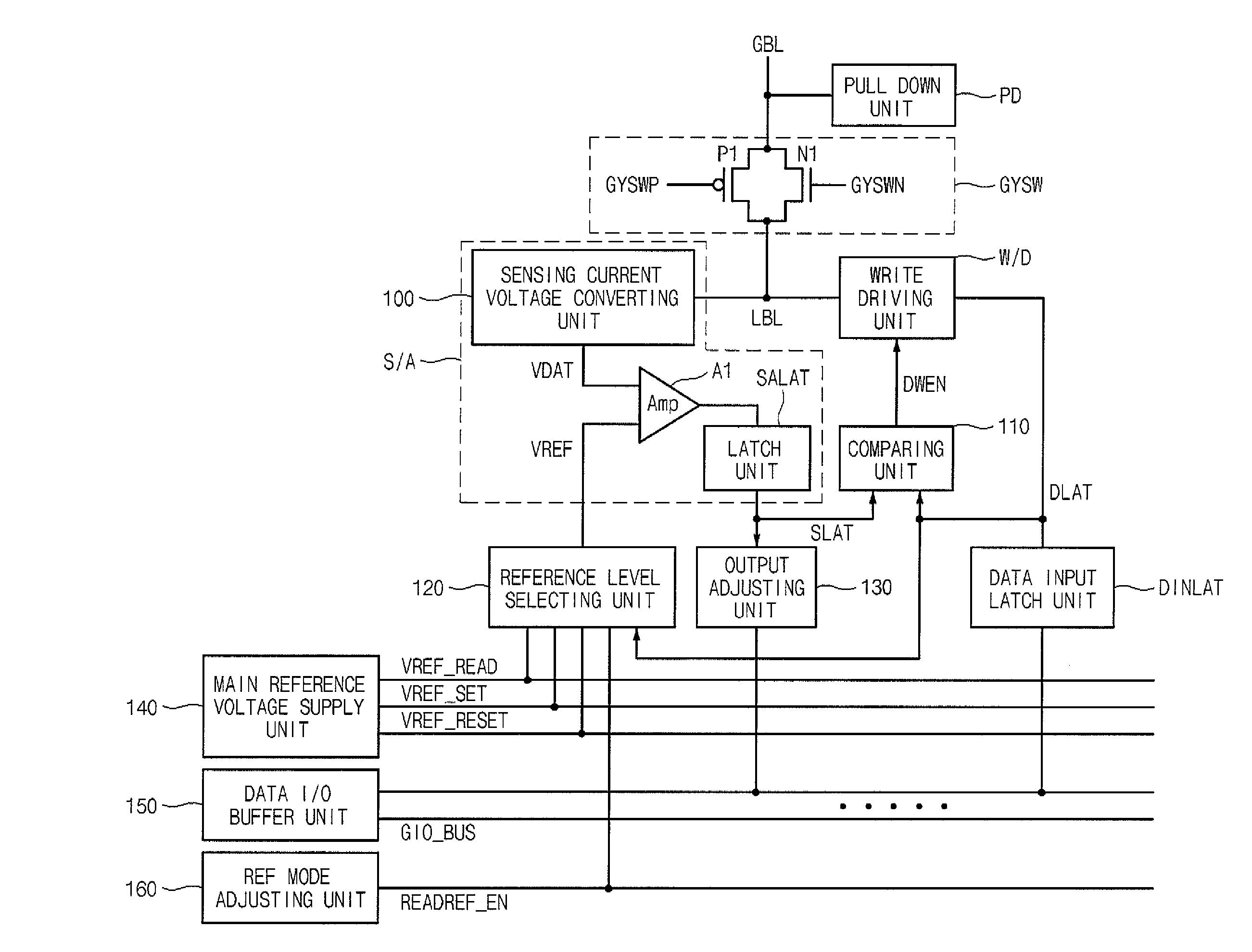

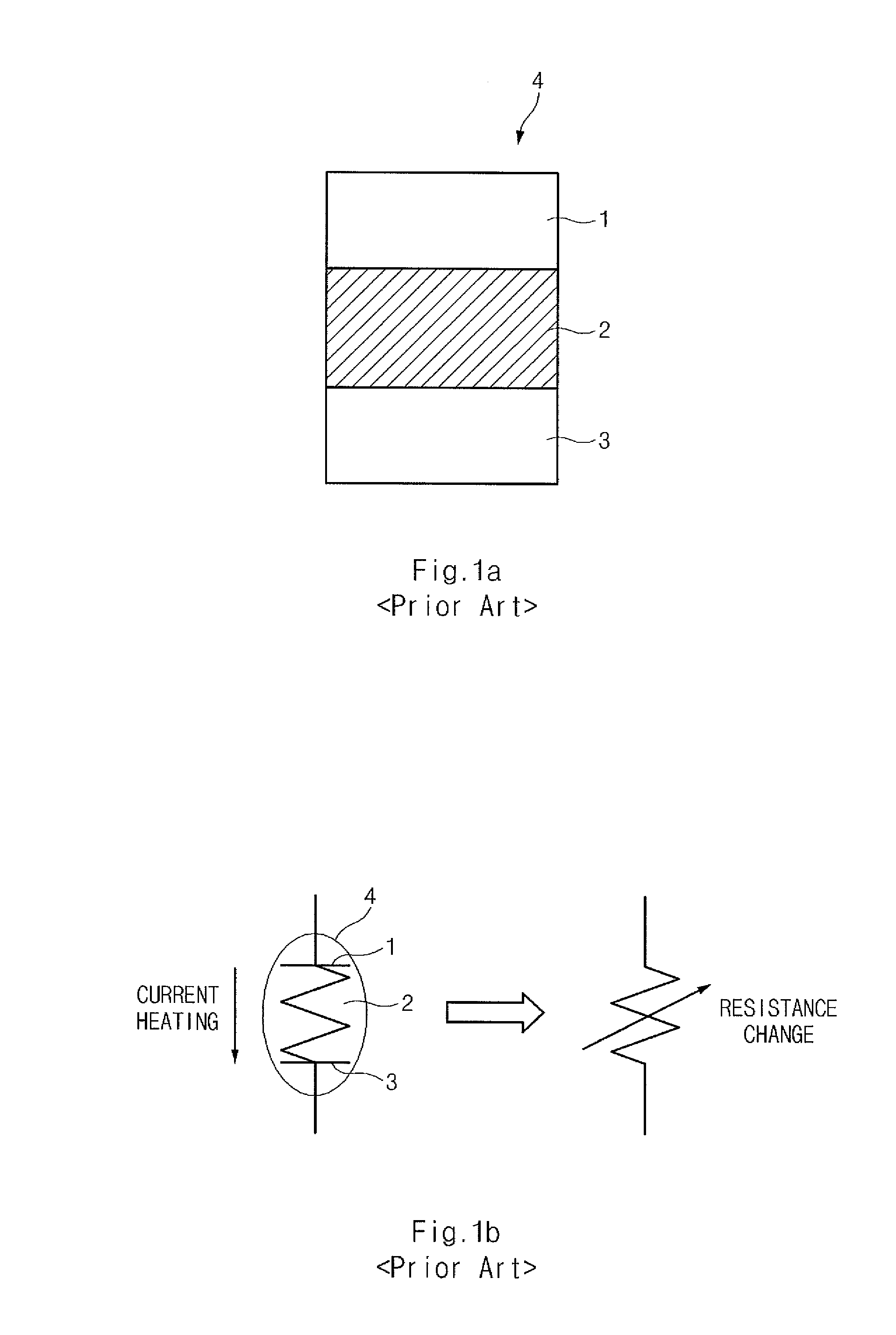

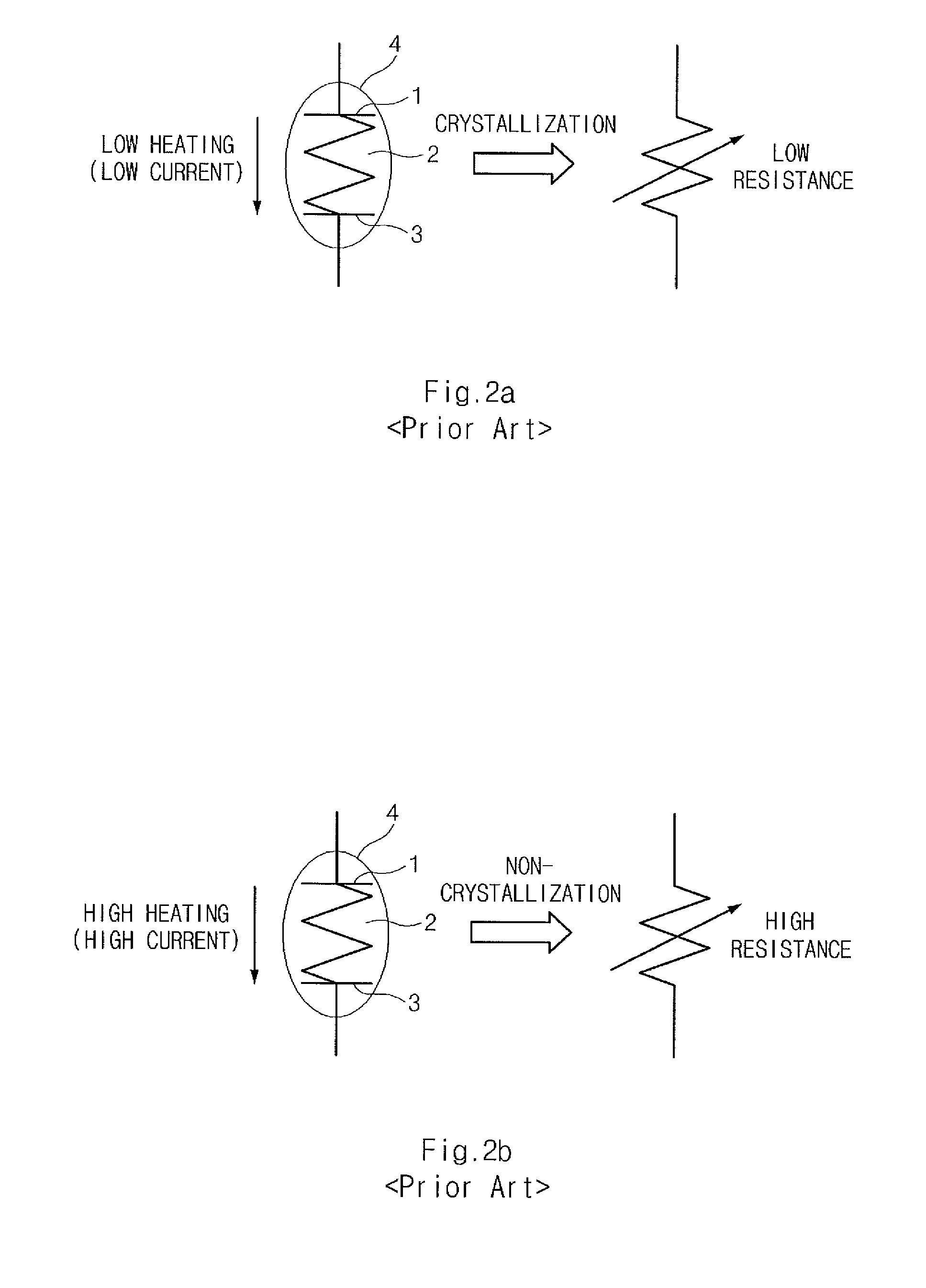

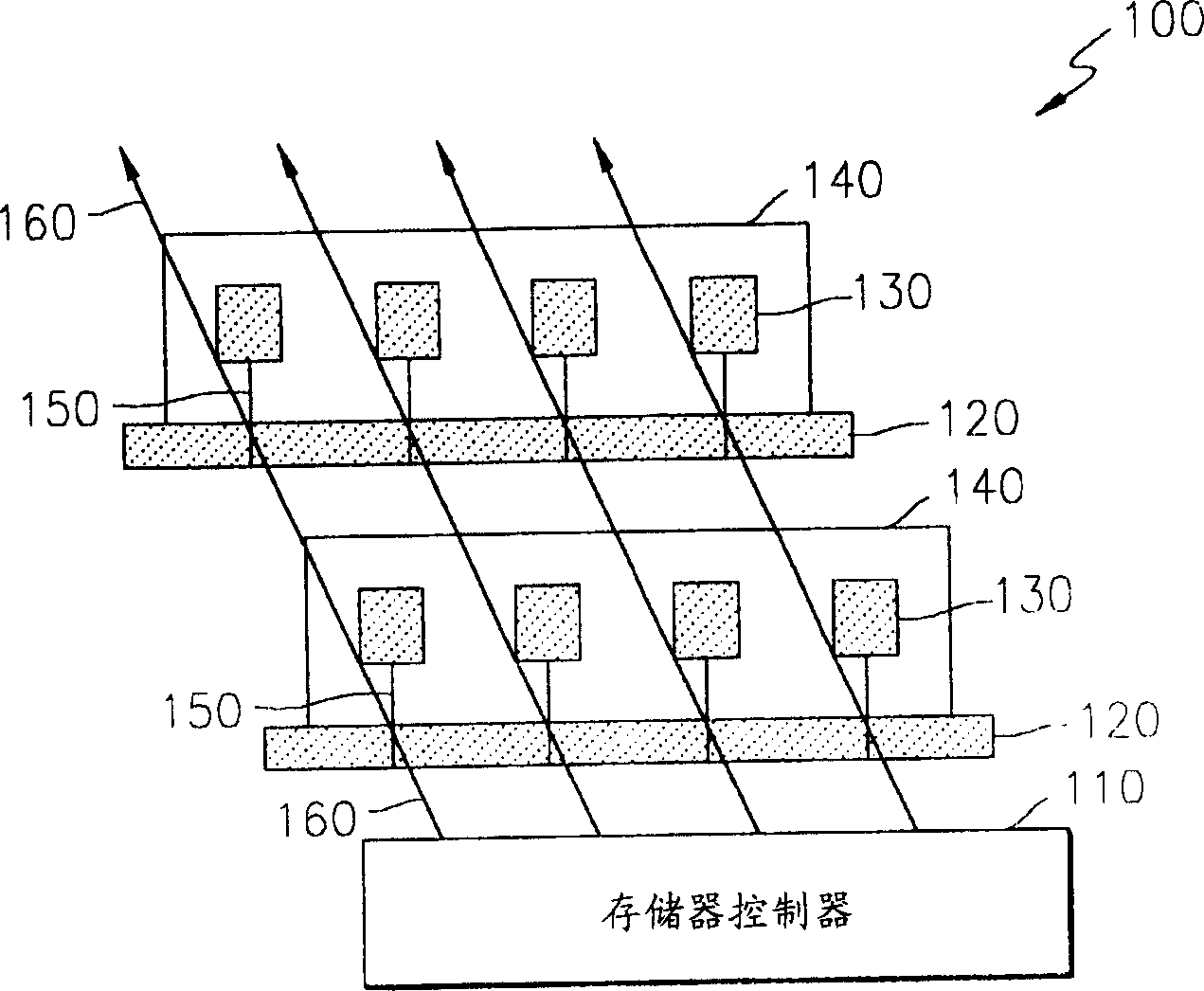

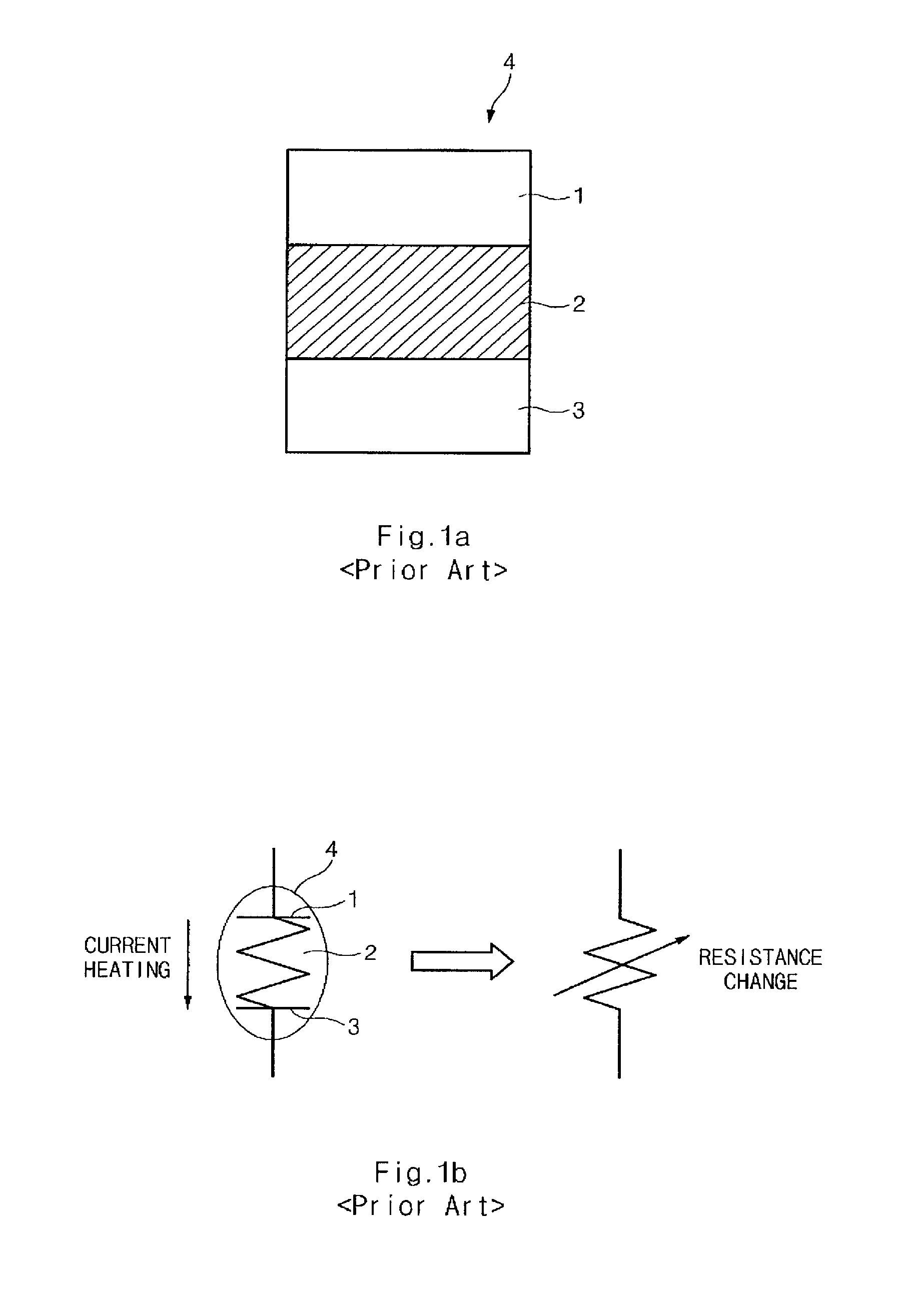

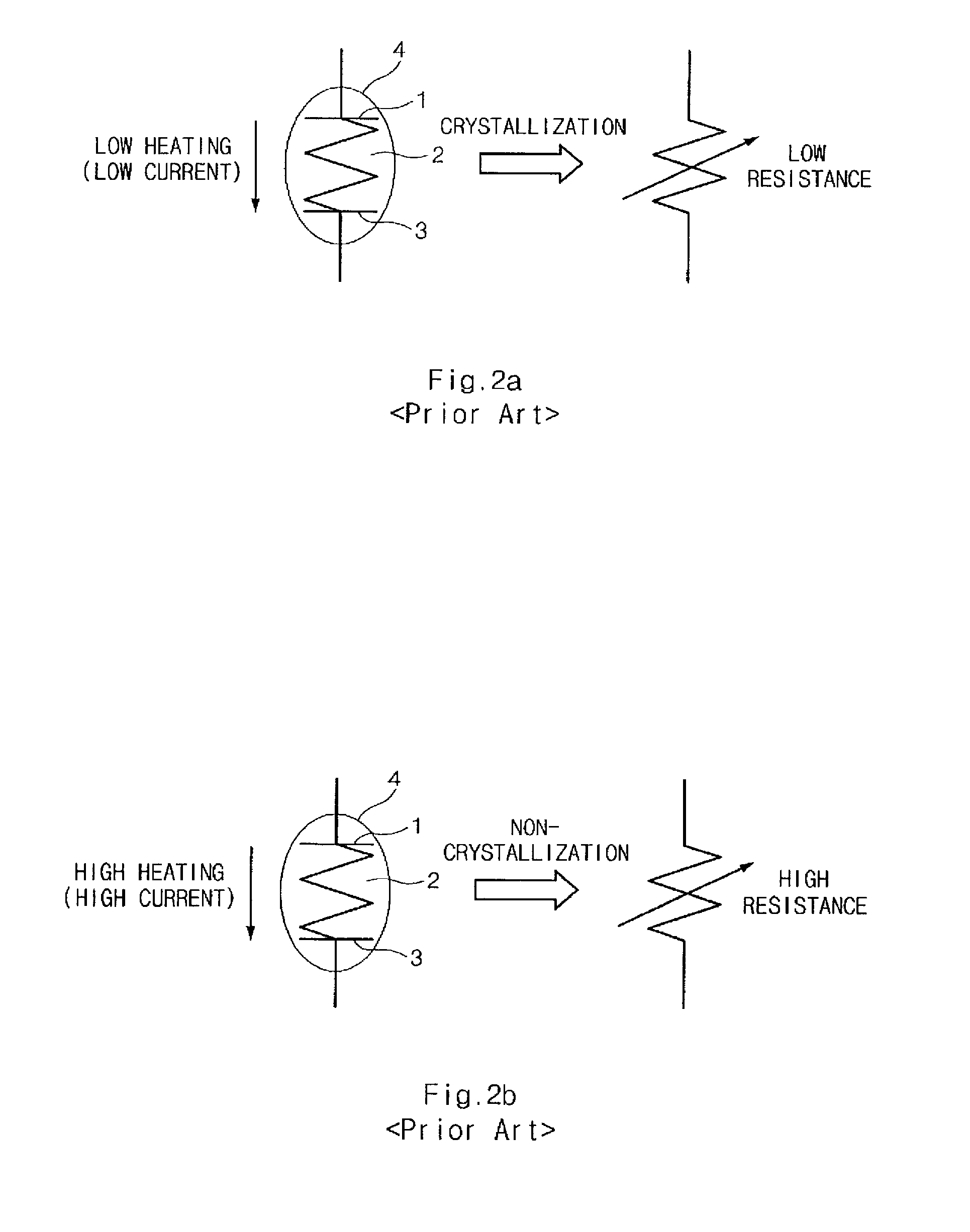

Phase change memory device with improved performance that minimizes cell degradation

InactiveUS20090097336A1Improve stabilityImprove reliabilityDigital storagePhase-change memoryAudio power amplifier

A phase change memory device having an improved performance that minimizes cell degradation is presented. The phase change memory device includes: a cell array, a sense amplifier, a write driving unit, and a reference level selecting unit. The cell array has a phase change resistor is configured to read / write data. The sense amplifier is configured to compare a reference voltage with a sensing voltage received from the cell array. The write driving unit is configured to supply a driving voltage corresponding to write data to the cell array. The reference level selecting unit is configured to select a read reference voltage in a read mode so as to output the reference voltage, and to select a reference voltage corresponding to input data in a write verifying mode so as to output the reference voltage.

Owner:SK HYNIX INC

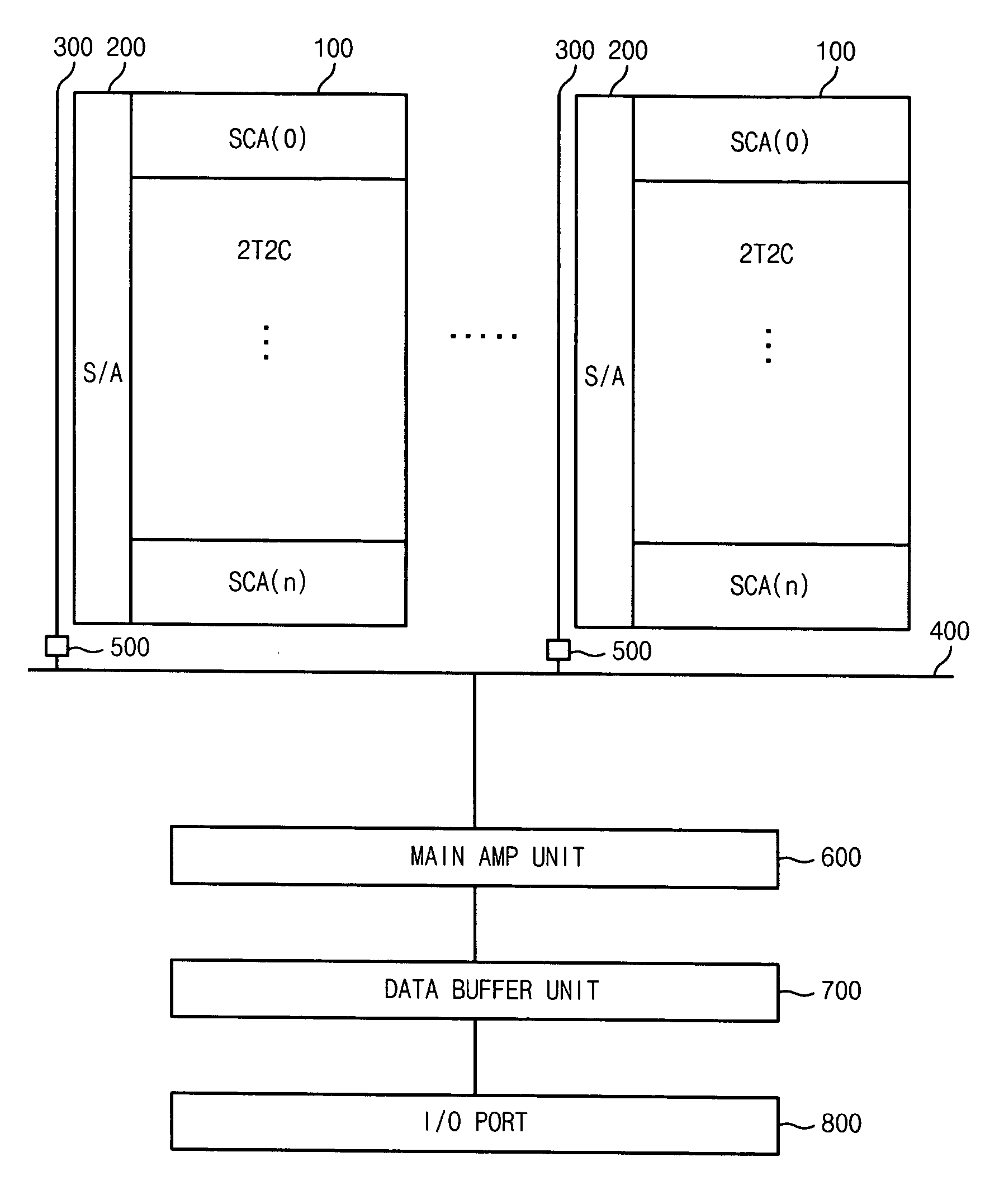

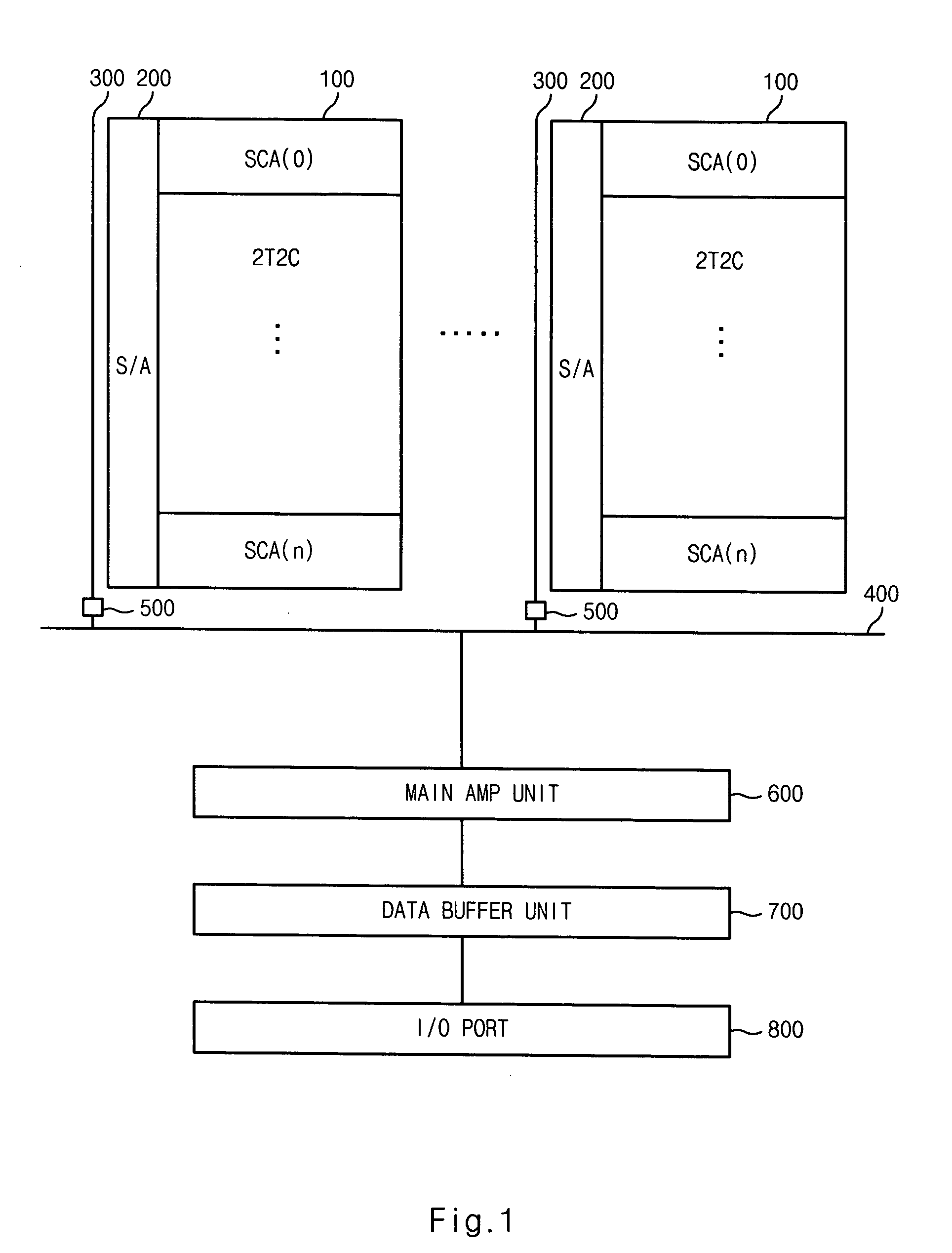

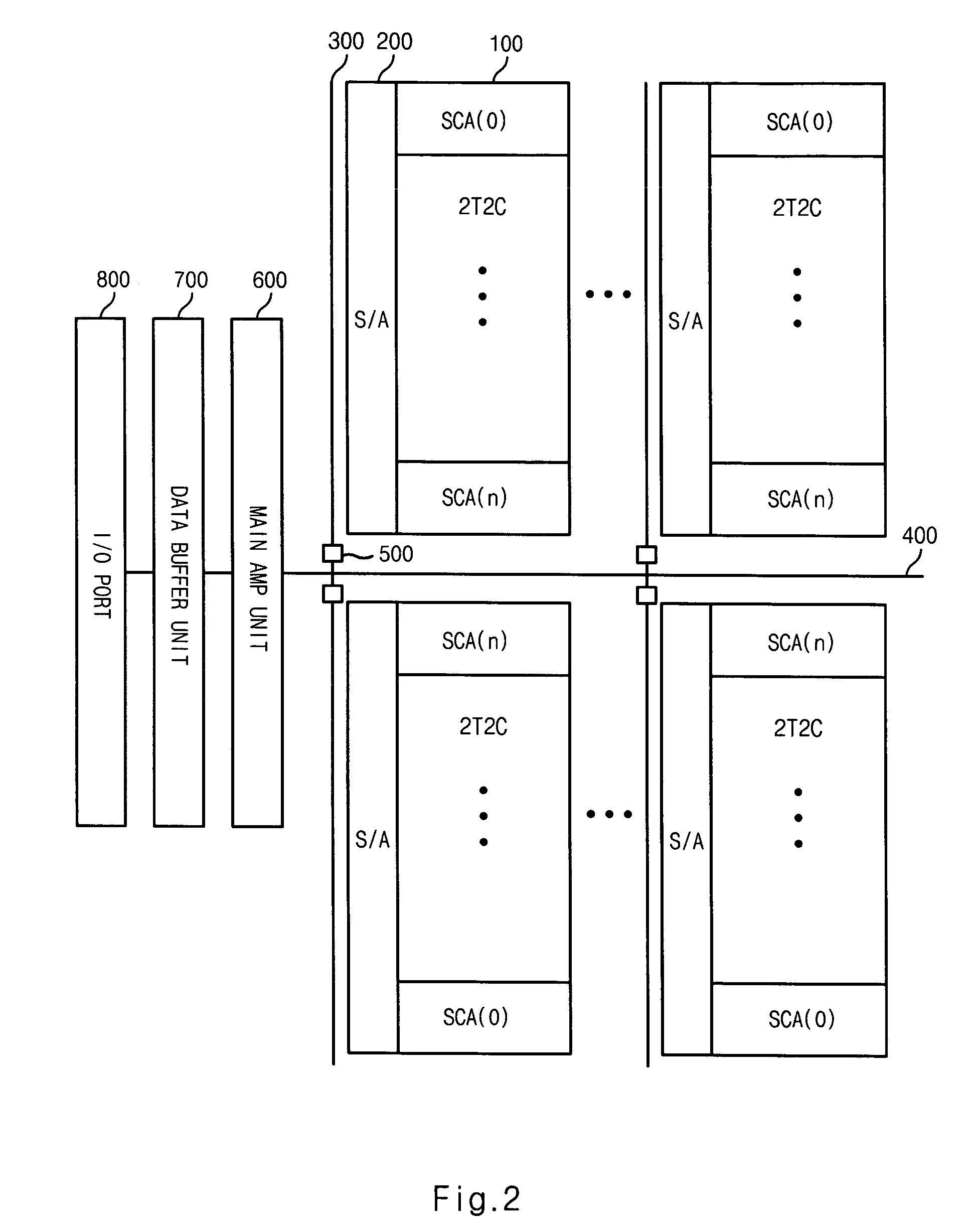

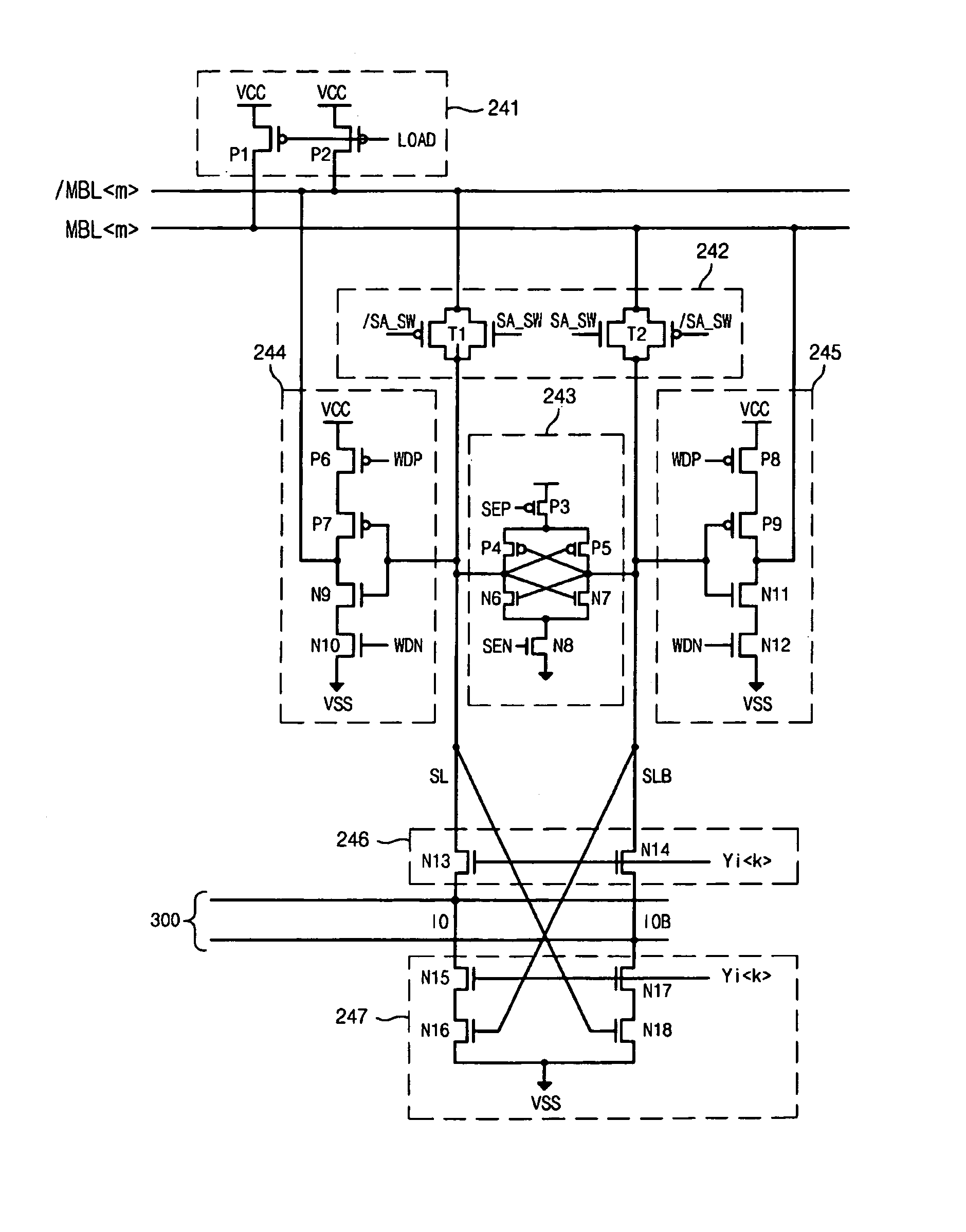

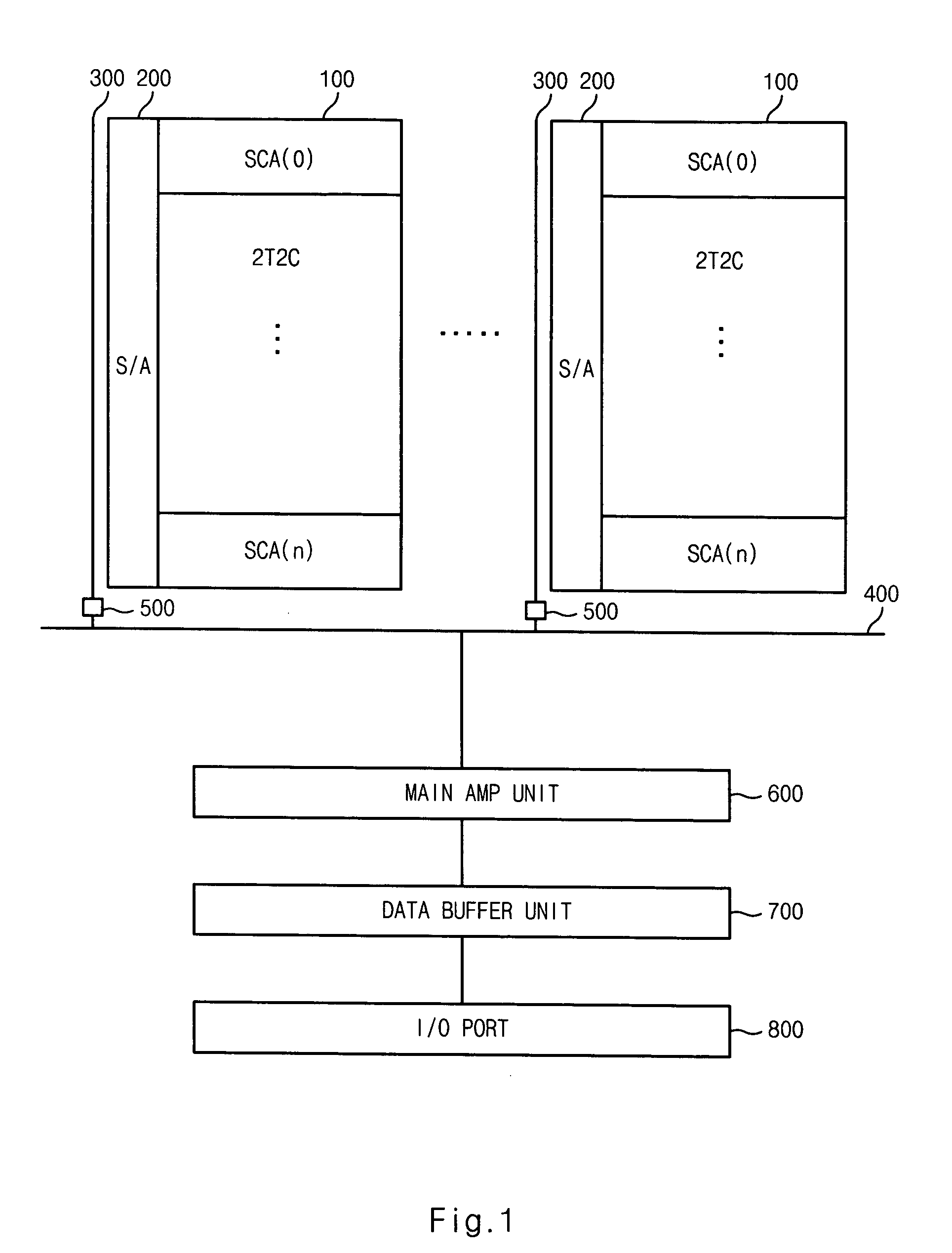

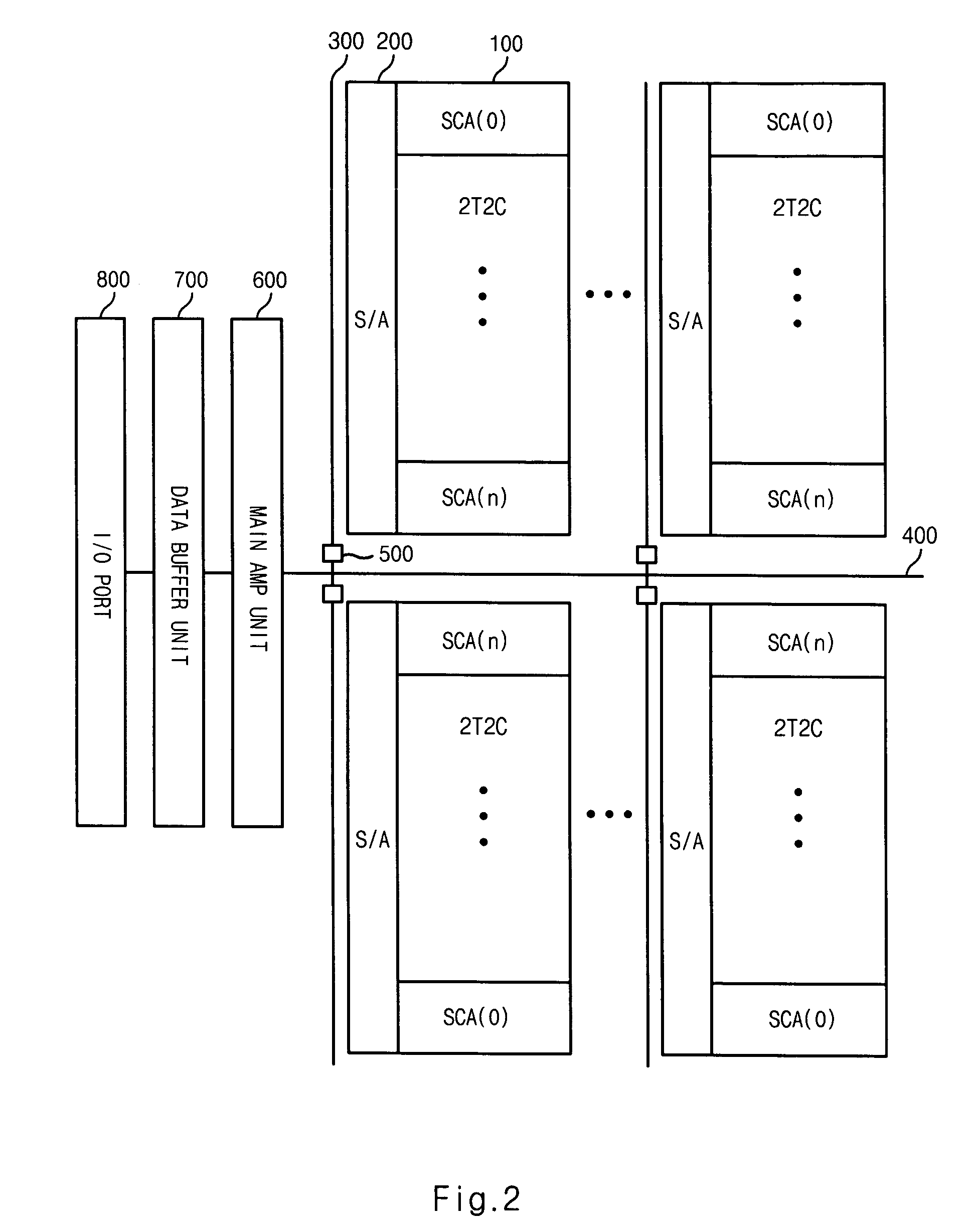

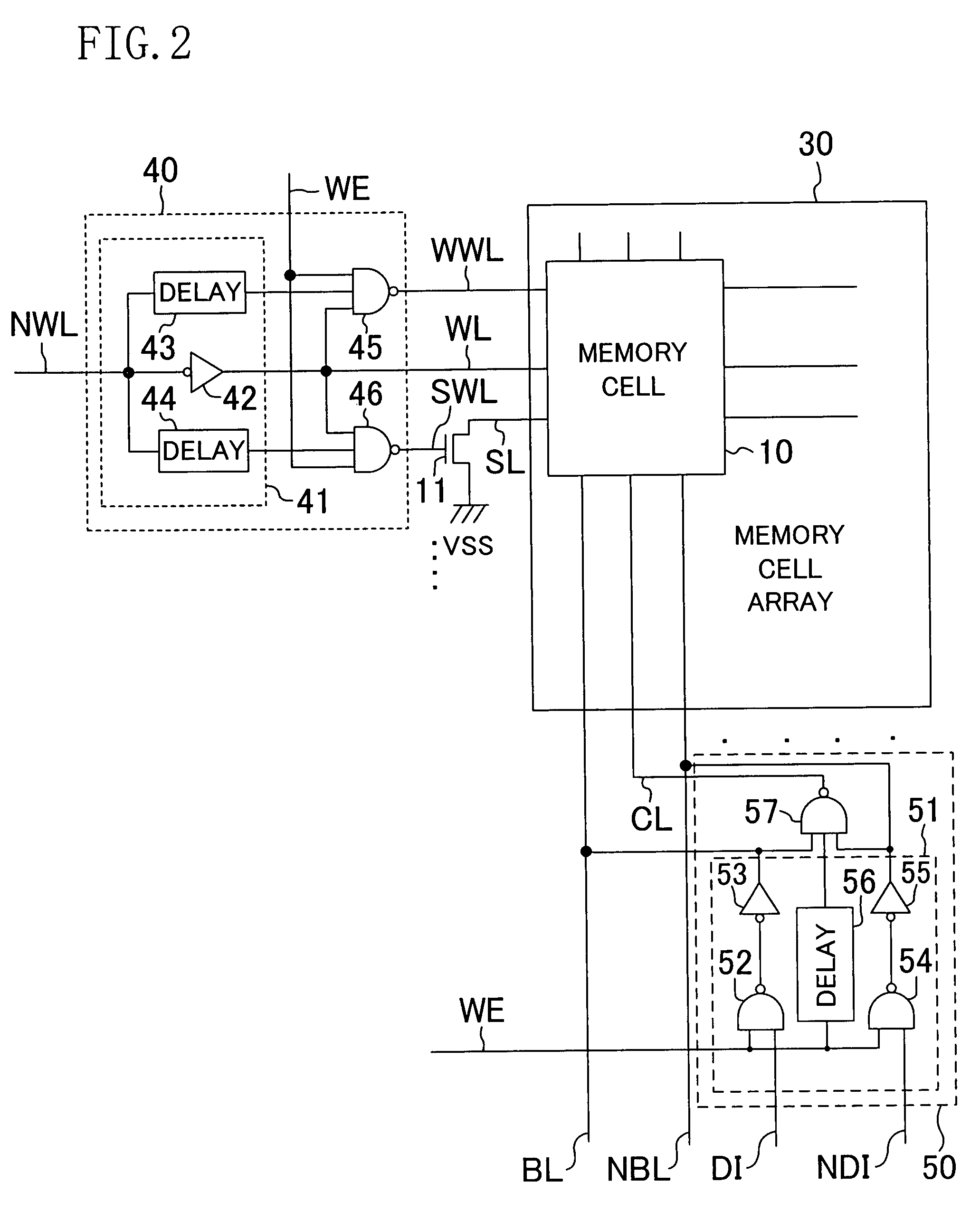

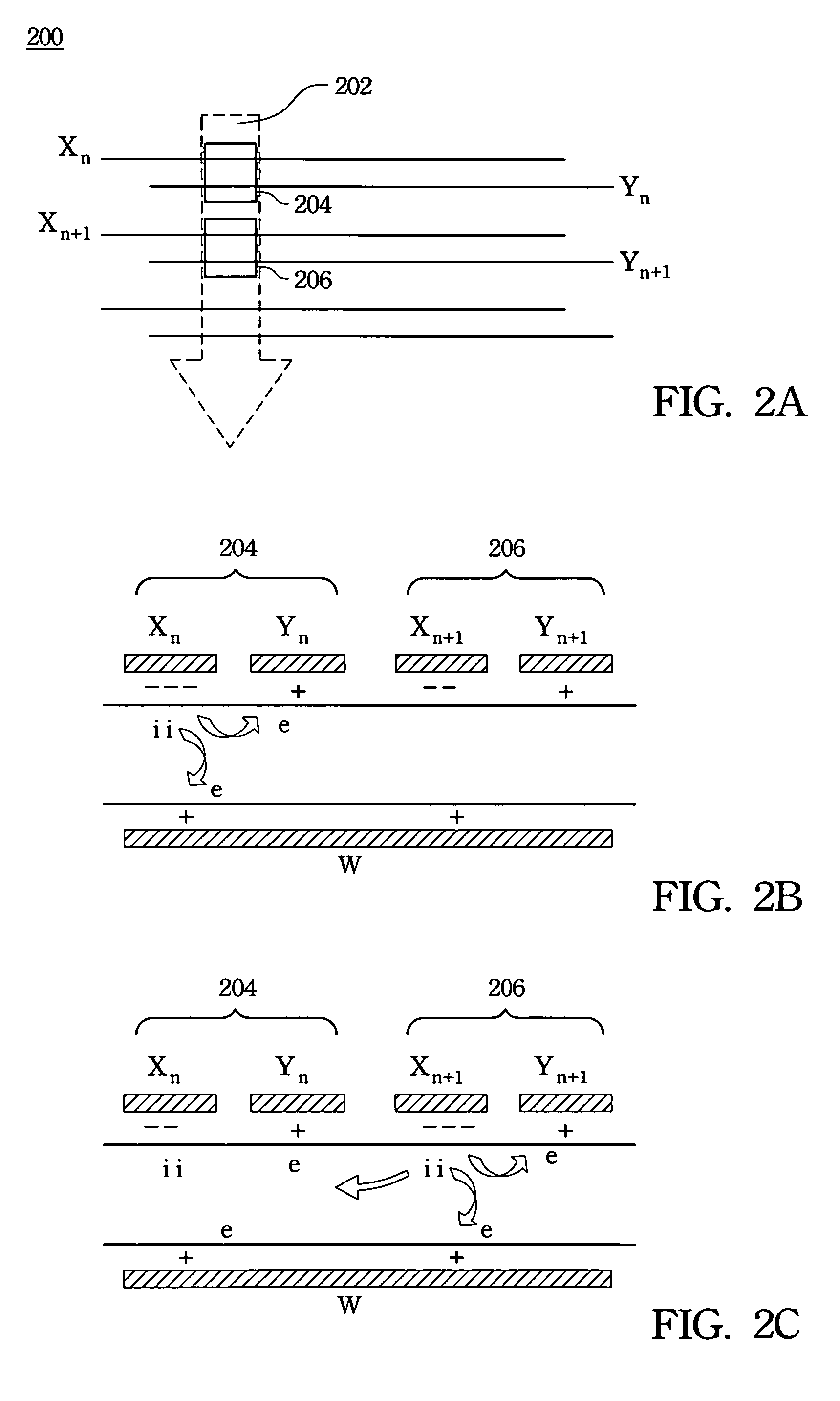

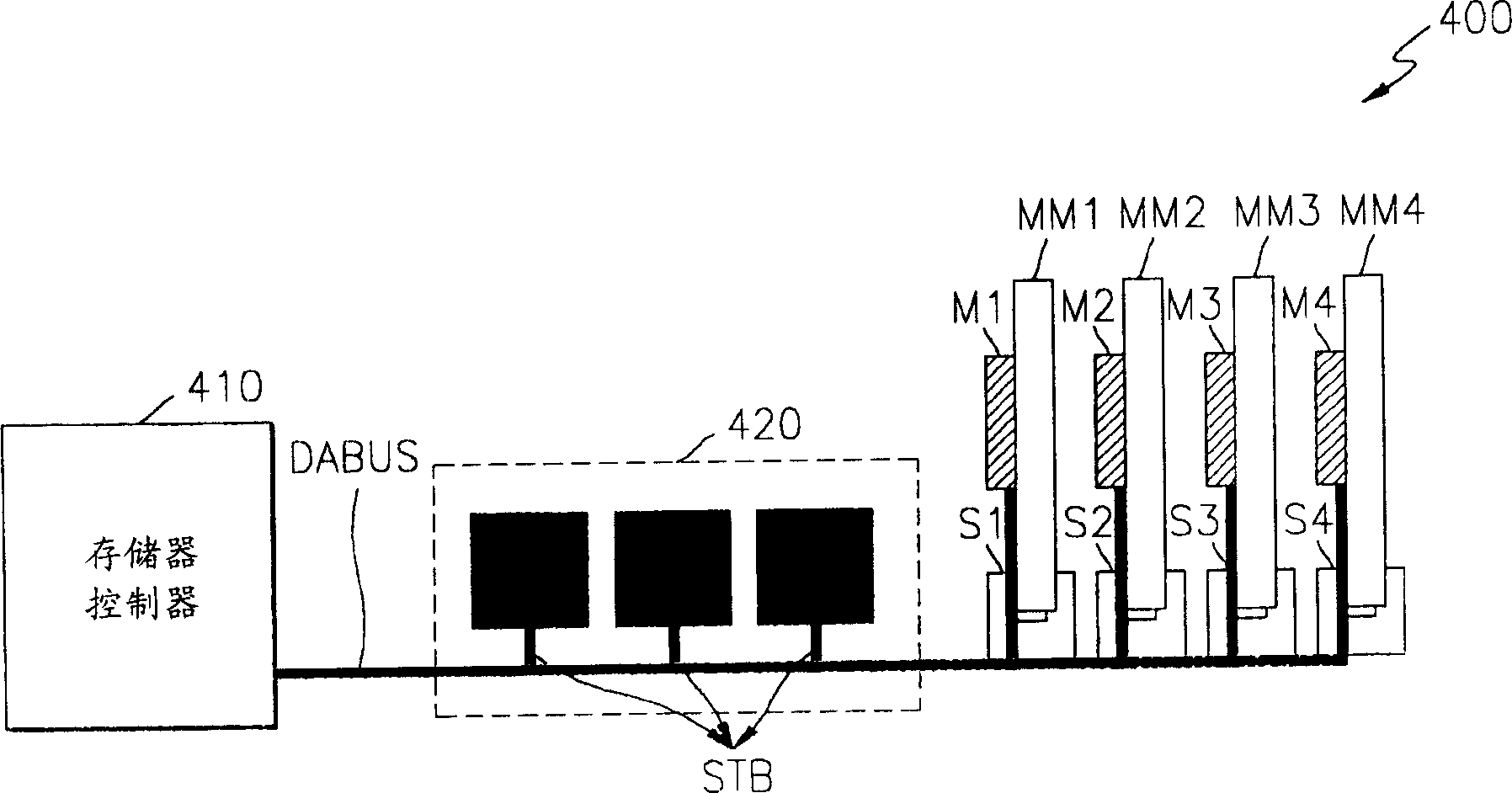

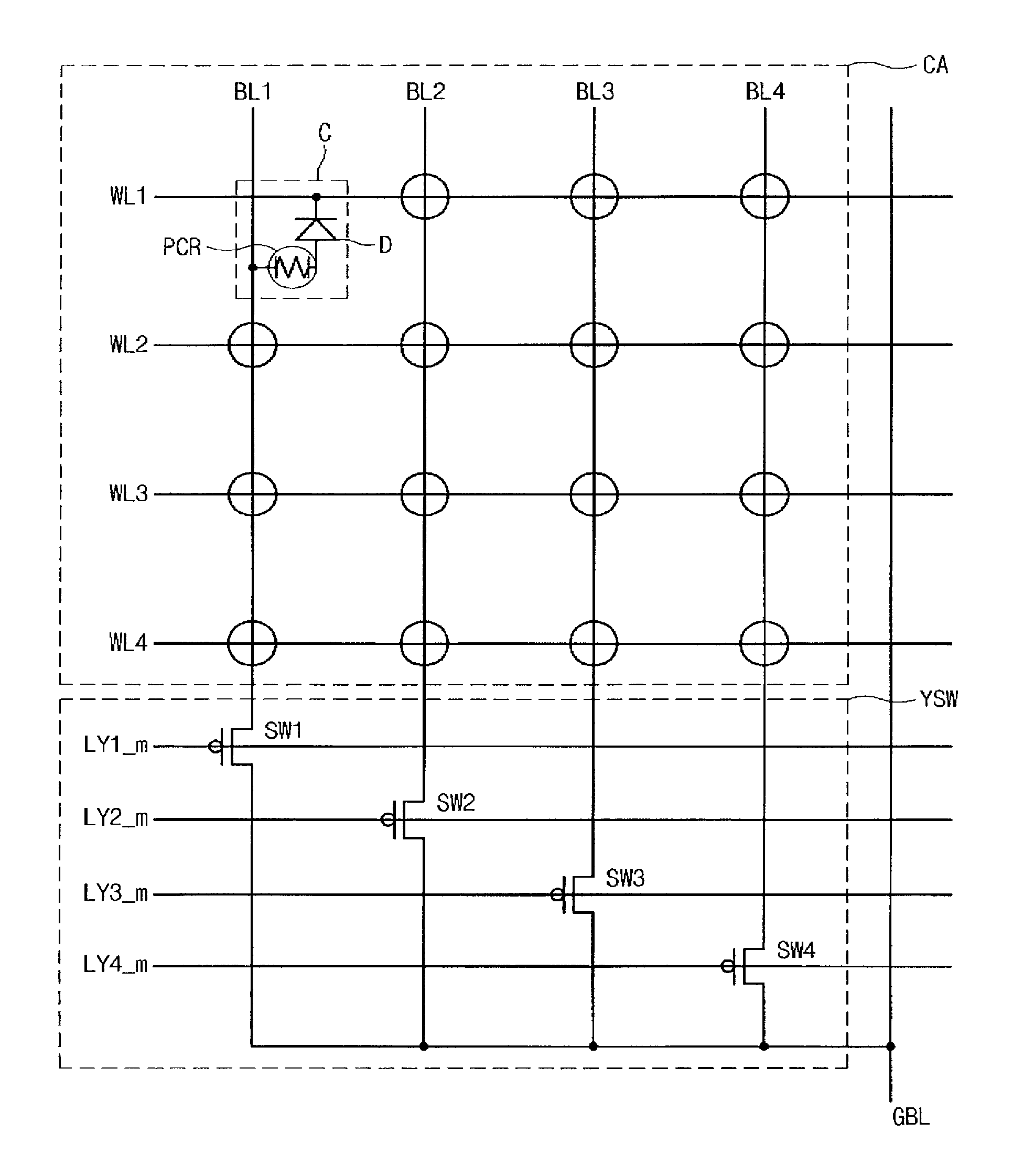

FeRAM for high speed sensing

ActiveUS20050141258A1Increase speedIncrease voltage marginDigital storageBit lineAudio power amplifier

A non-volatile ferroelectric memory device senses a cell data at high speed. Preferably, the non-volatile ferroelectric memory device includes a plurality of cell array blocks, a plurality of sense amplifier units, a plurality of sense amplifier units, a plurality of local data buses, a global data bus, and a plurality of data bus switch arrays. Each of the plurality of cell array blocks has a hierarchical bit line architecture including sub bit lines and a main bit line group corresponding to a plurality of unit cells for storing differential data. The plurality of sense amplifier units, corresponding one-by-one to the cell array blocks, sense and amplify the differential data induced on the main bit line group during a sensing operation. The plurality of local data buses, corresponding one-by-one to the sense amplifier units, transfer the differential data outputted from the sense amplifier units and differential data to be transferred to the sense amplifier units. The global data bus, shared by a plurality of the local data buses, transfers the differential data. The plurality of data bus switch arrays selectively couple the local data buses to the global data bus.

Owner:SK HYNIX INC

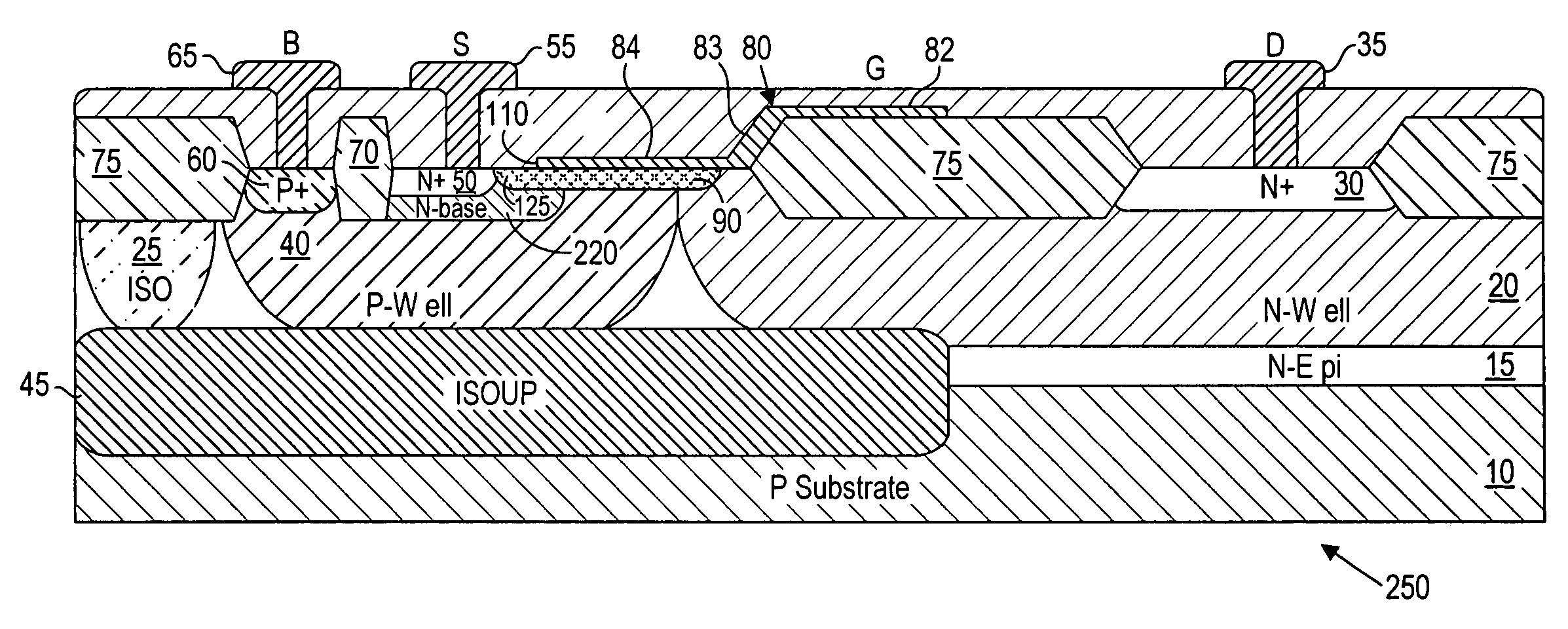

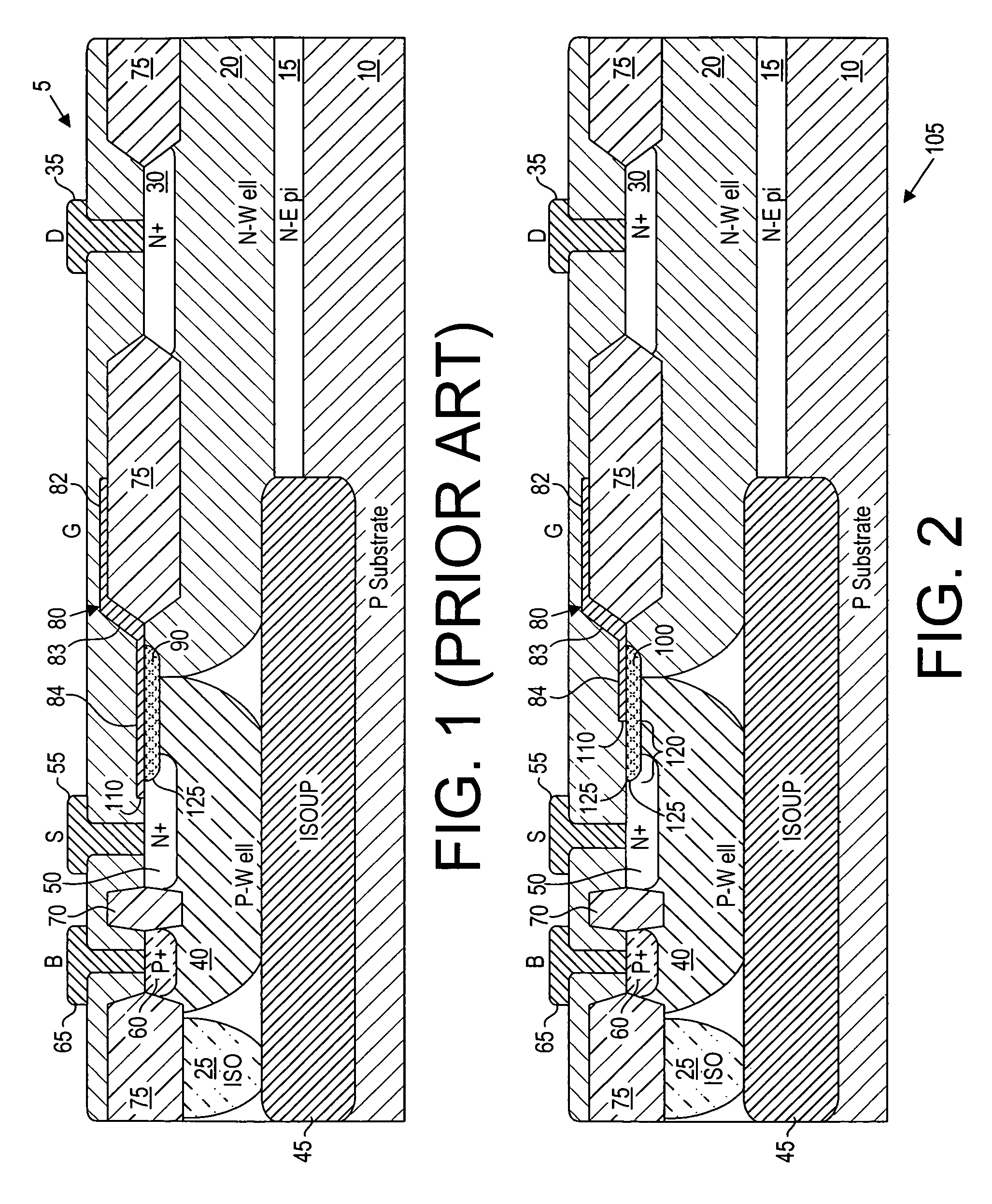

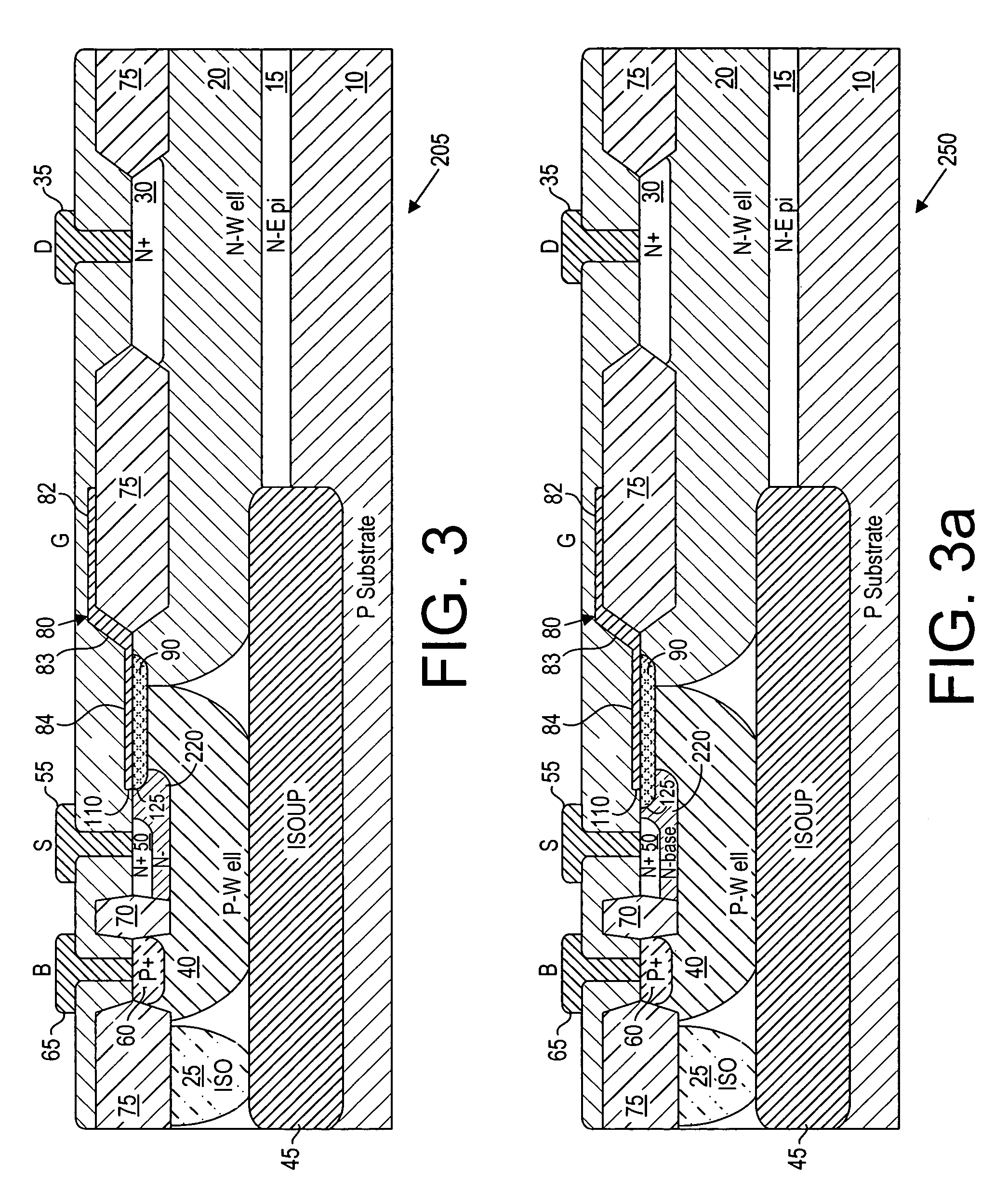

Ballast resistors for transistor devices

InactiveUS7087973B2High voltageIncrease voltage marginTransistorSemiconductor/solid-state device detailsLDMOSBallast resistor

A transistor is formed with a source ballast resistor that regulates channel current. In an LDMOS transistor embodiment, the source ballast resistance may be formed using a high sheet resistance diffusion self aligned to the polysilicon gate, and / or by extending a depletion implant from under the polysilicon gate toward the source region. The teachings herein may be used to form effective ballast resistors for source and / or drain regions, and may be used in many types of transistors, including lateral and vertical transistors operating in a depletion or an enhancement mode, and BJT devices.

Owner:MICREL

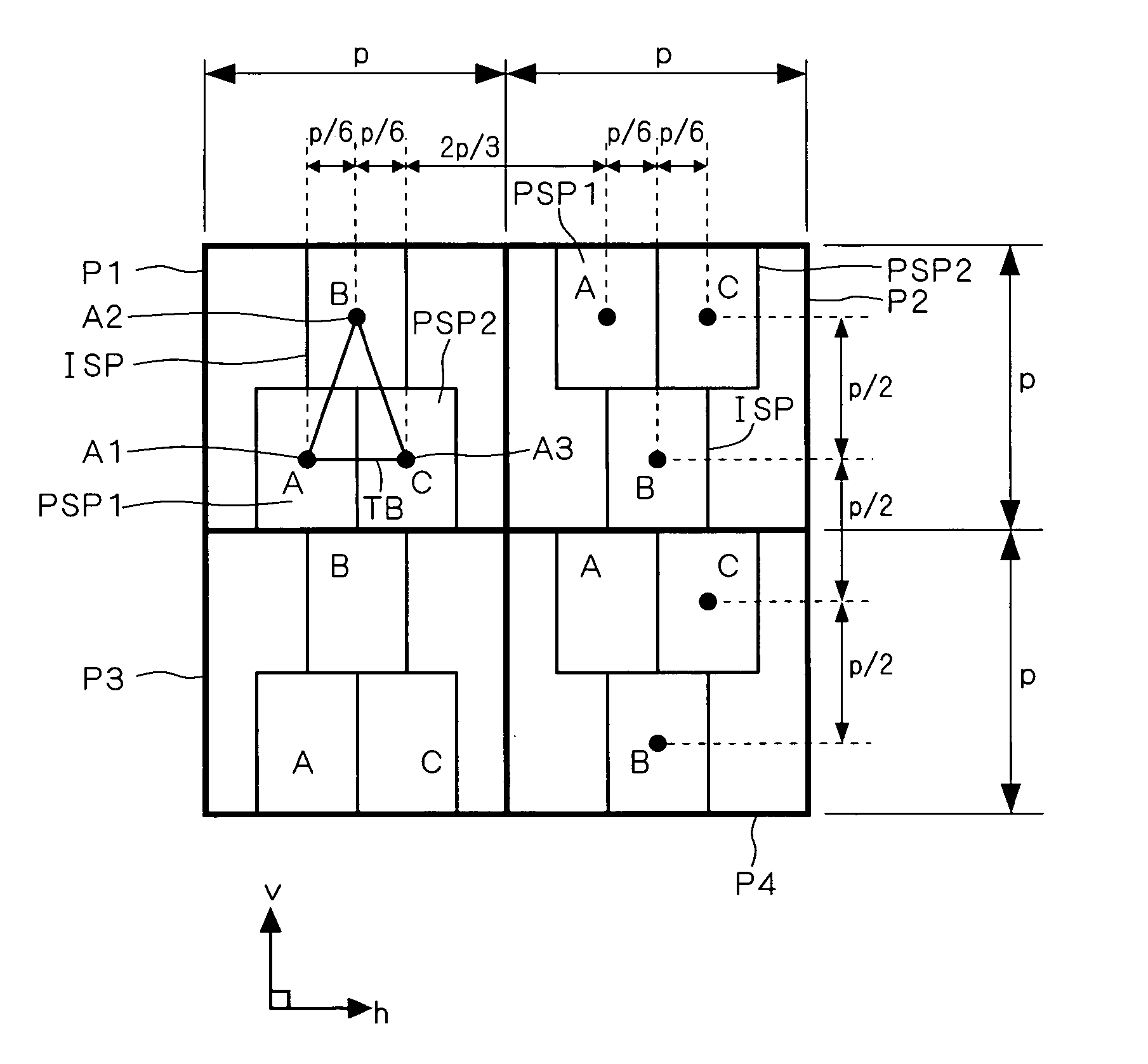

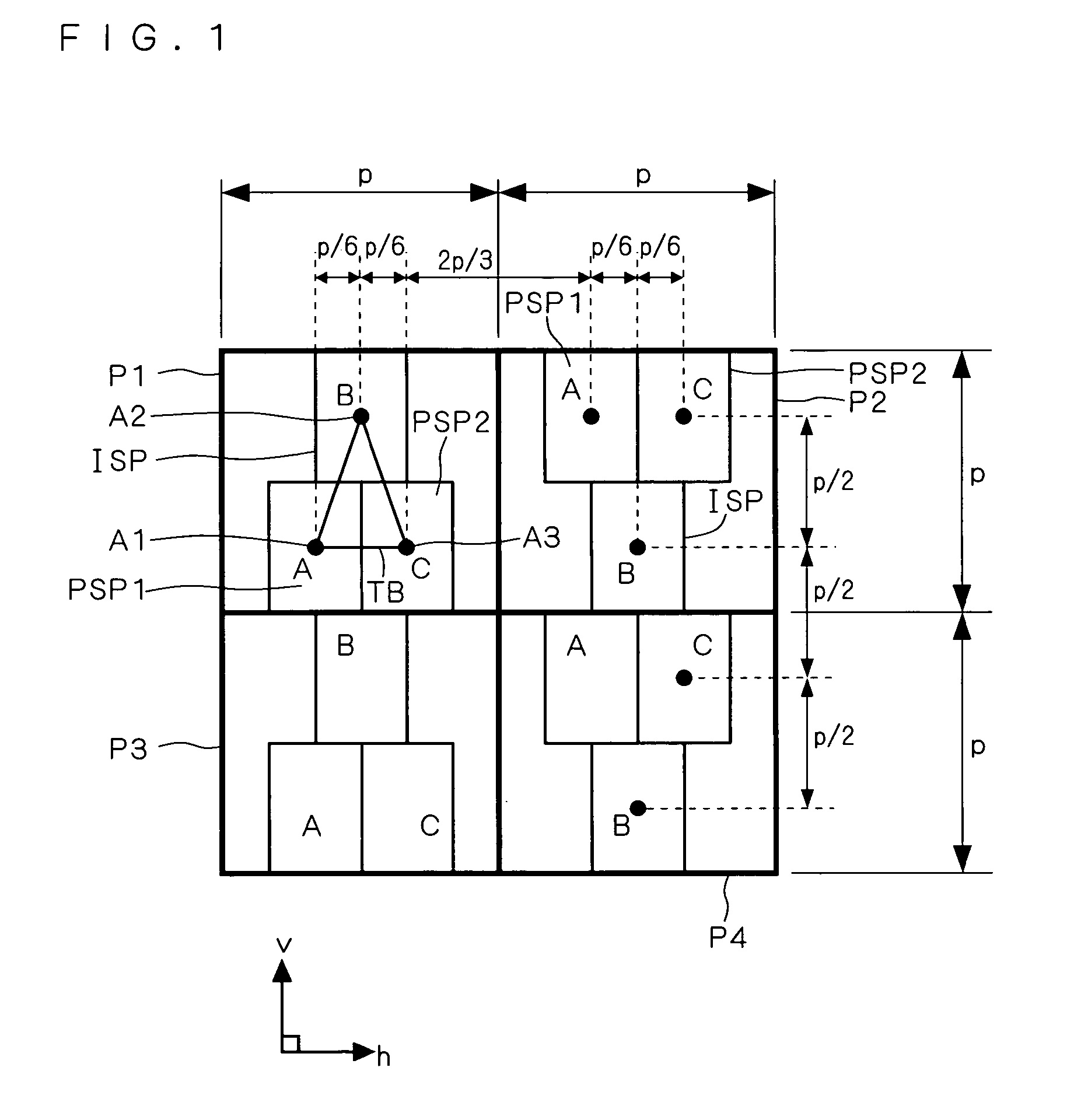

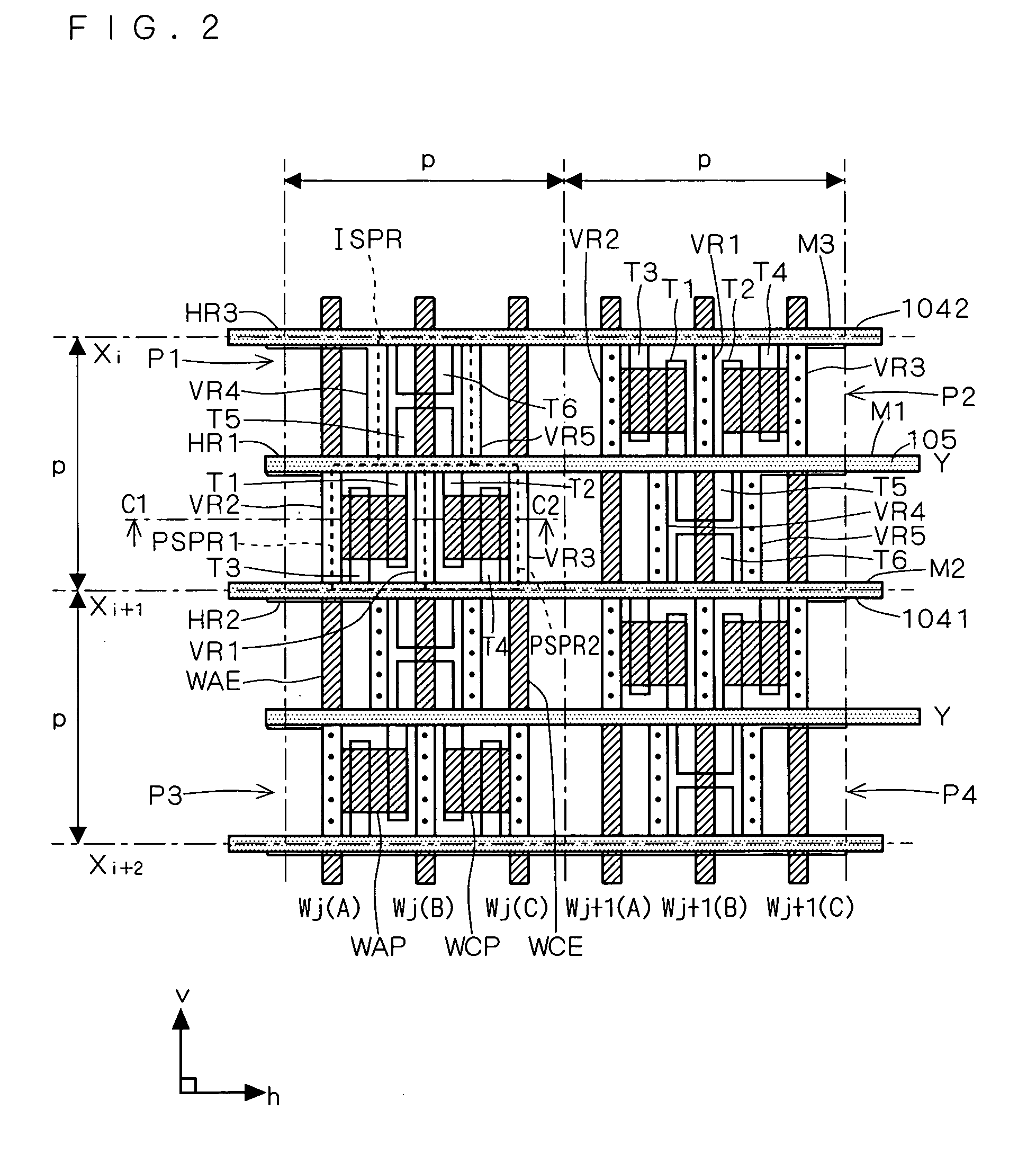

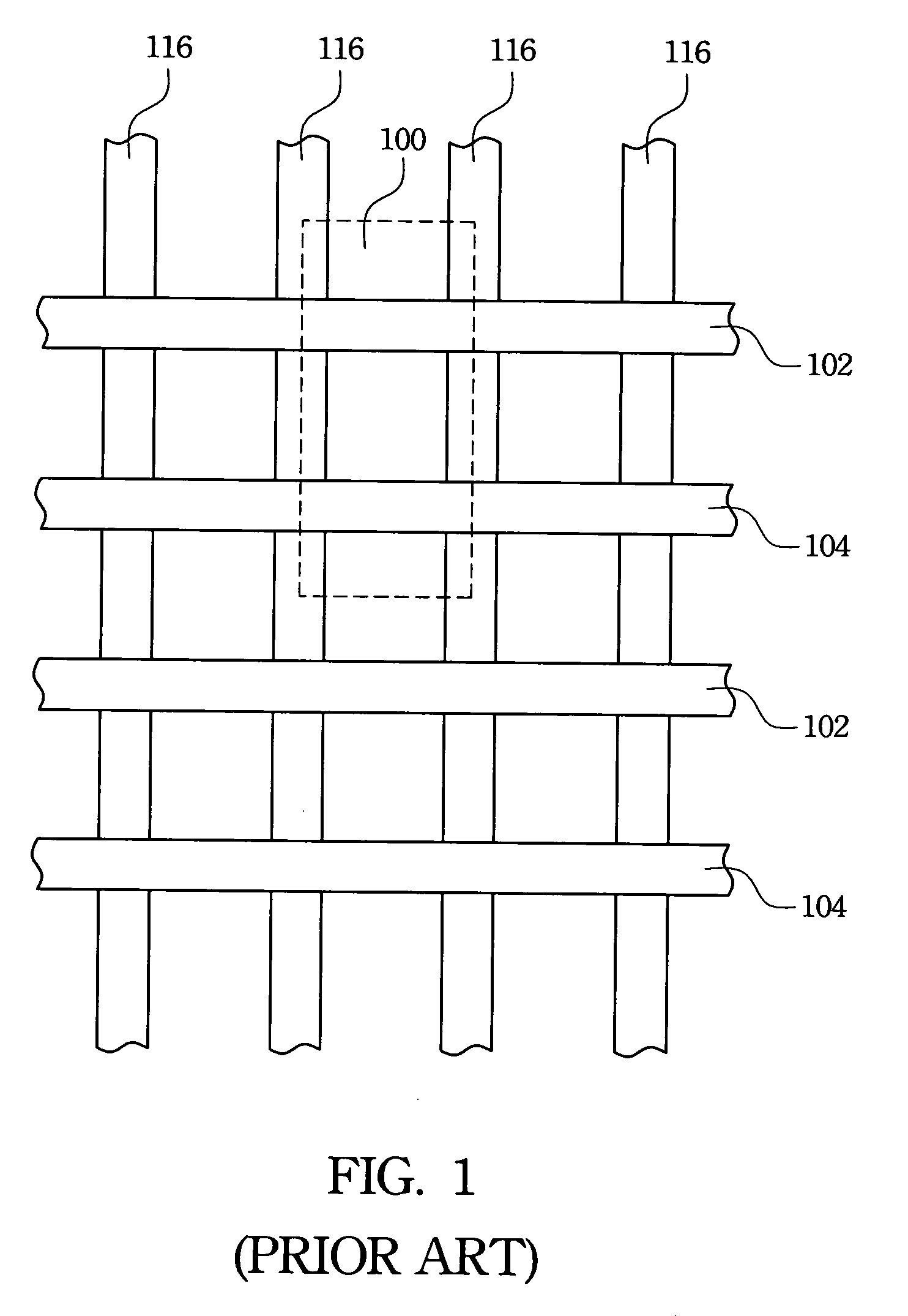

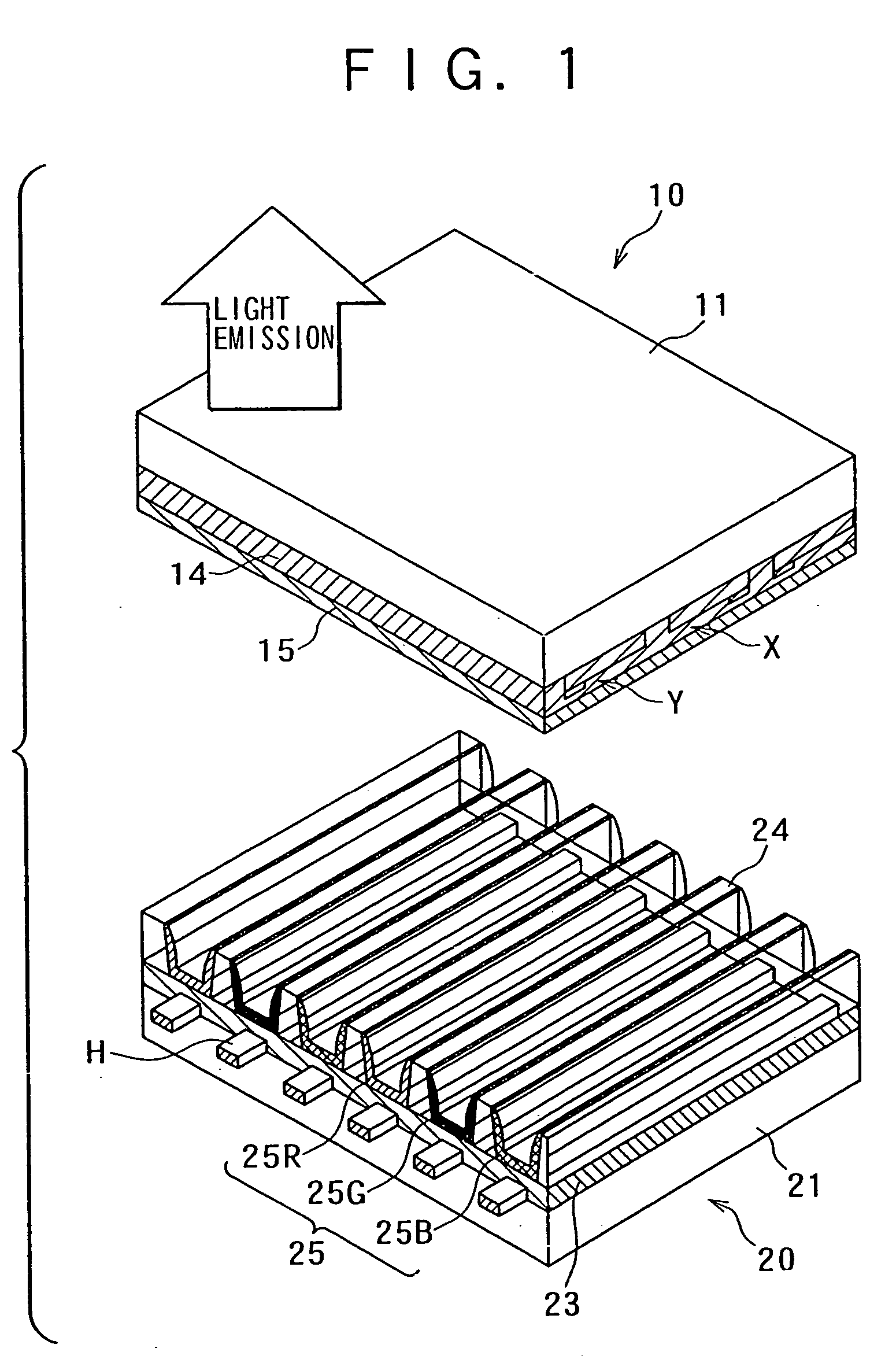

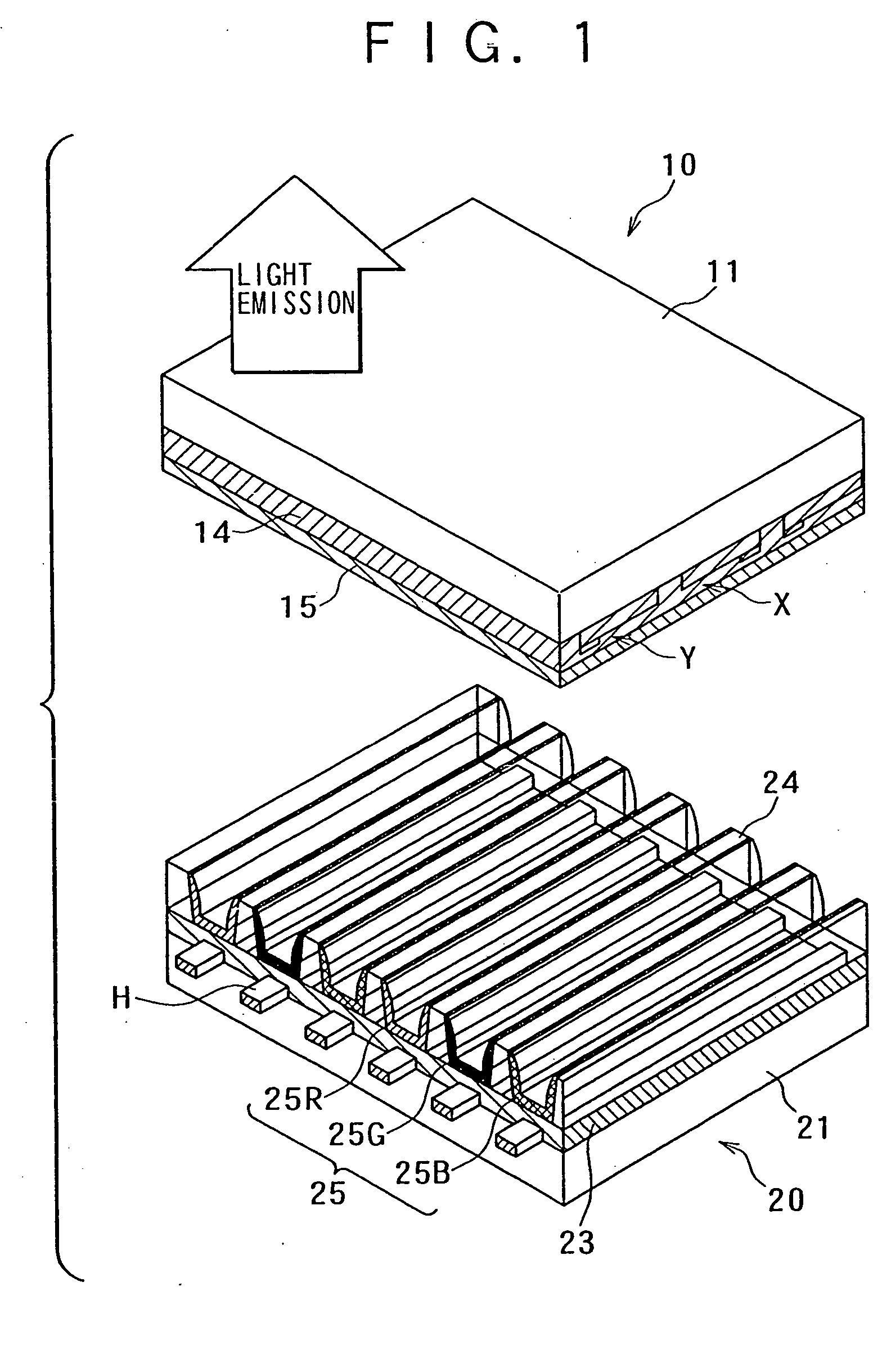

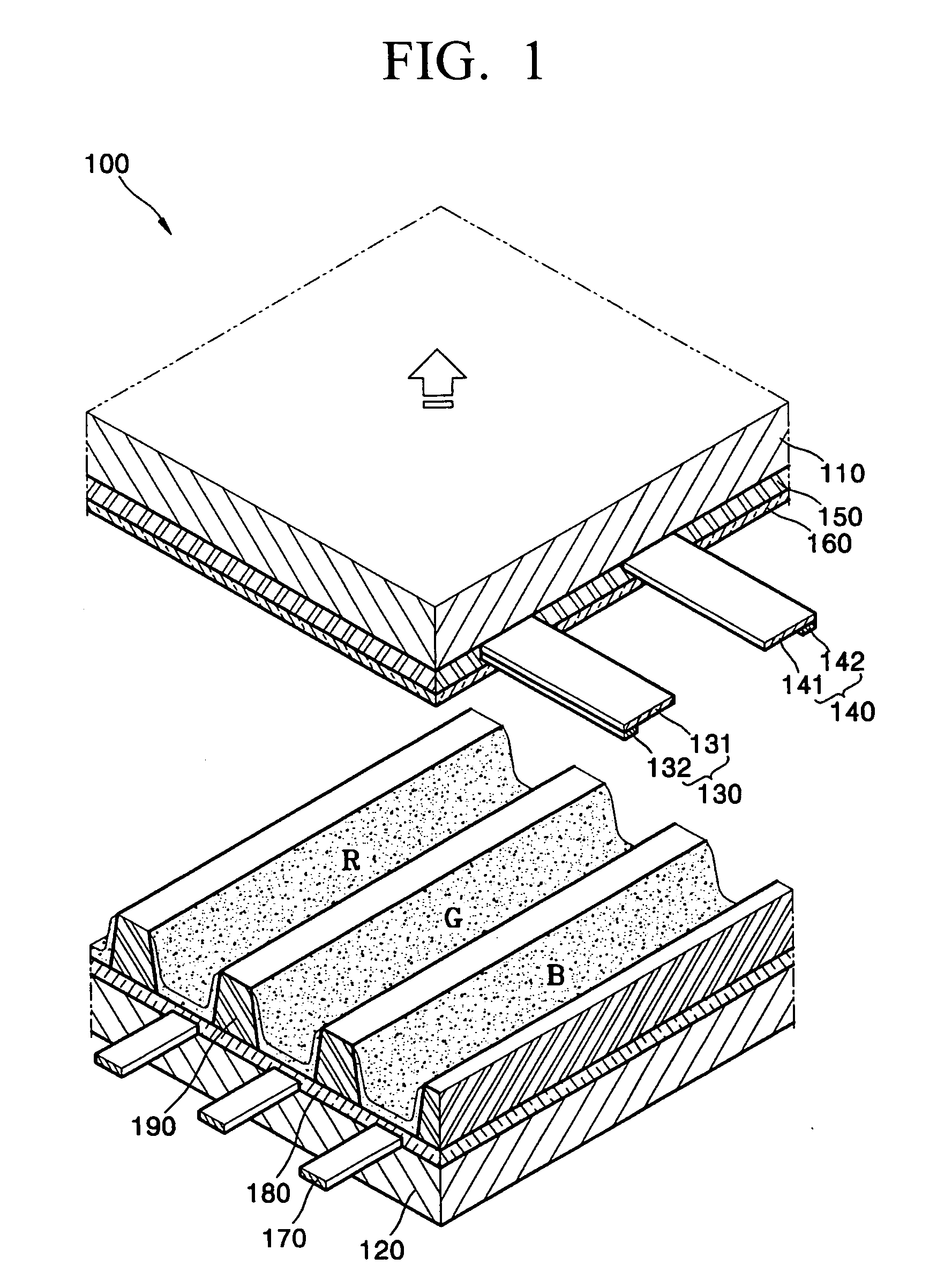

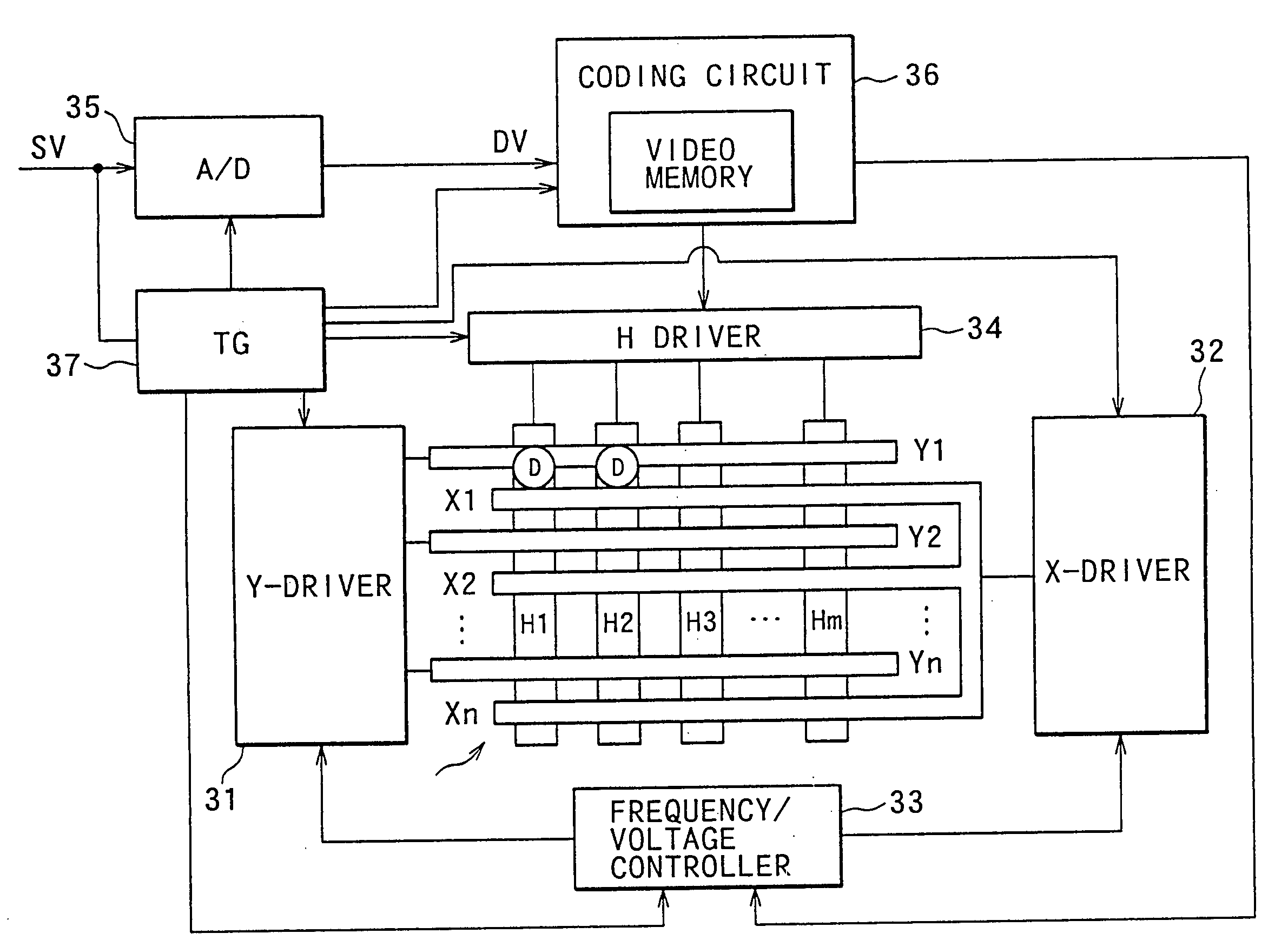

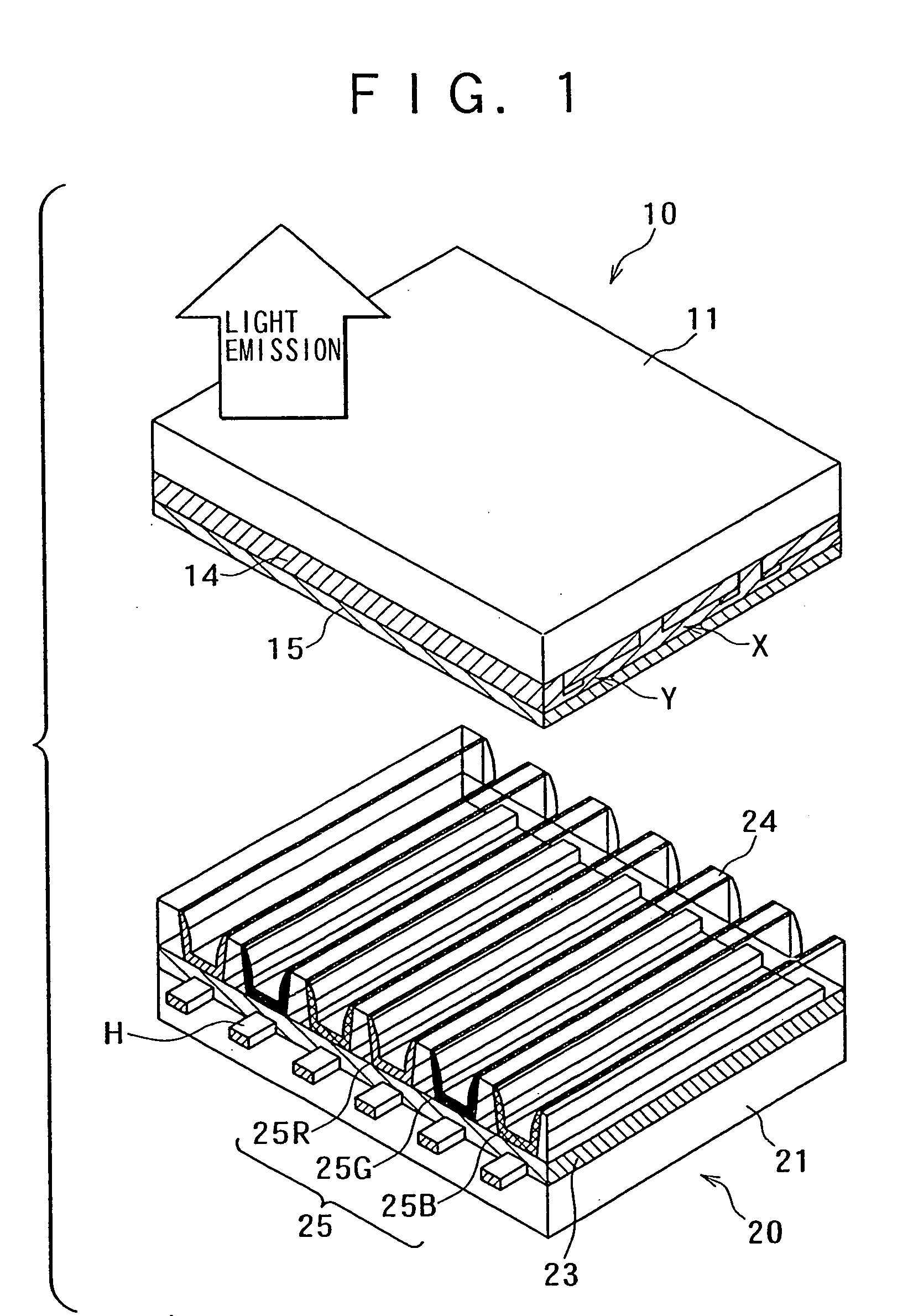

Surface discharge type plasma display panel having an isosceles delta array type pixel

InactiveUS7088314B2Suppress generationIncrease voltage marginAddress electrodesSustain/scan electrodesDisplay deviceOptoelectronics

The present invention relates to an AC drive surface discharge type plasma display panel having an isosceles delta array type pixel. The background art has a problem of being apt to cause a wrong writing discharge and having a narrow writing voltage margin. Then, in the present invention, transparent electrodes for X electrode (T3, T4) in first and second pair subpixel regions (PSPR1, PSPR2) of an isosceles delta array type pixel (P1) are provided at portions farther away from a first write electrode (Wj(B)) in an isolated subpixel region (ISPR). Specifically, a central axis of the third transparent electrode (T3) along a vertical direction (v) is positioned closer to an extending portion (WAE) of a second write electrode (Wj(A)) from a vertical direction central axis of the first pair subpixel region (PSPR1). Similarly, a vertical direction central axis of the fourth transparent electrode (T4) is positioned closer to an extending portion (WCE) of a third write electrode (Wj(C)) from a vertical direction central axis of the second pair subpixel region (PSPR2). The present invention is mainly used for a display device such as a plasma television.

Owner:MITSUBISHI ELECTRIC CORP

FeRAM for high speed sensing

ActiveUS7382641B2Increase speedImproving the architecture of a memory deviceDigital storageBit lineAudio power amplifier

Owner:SK HYNIX INC

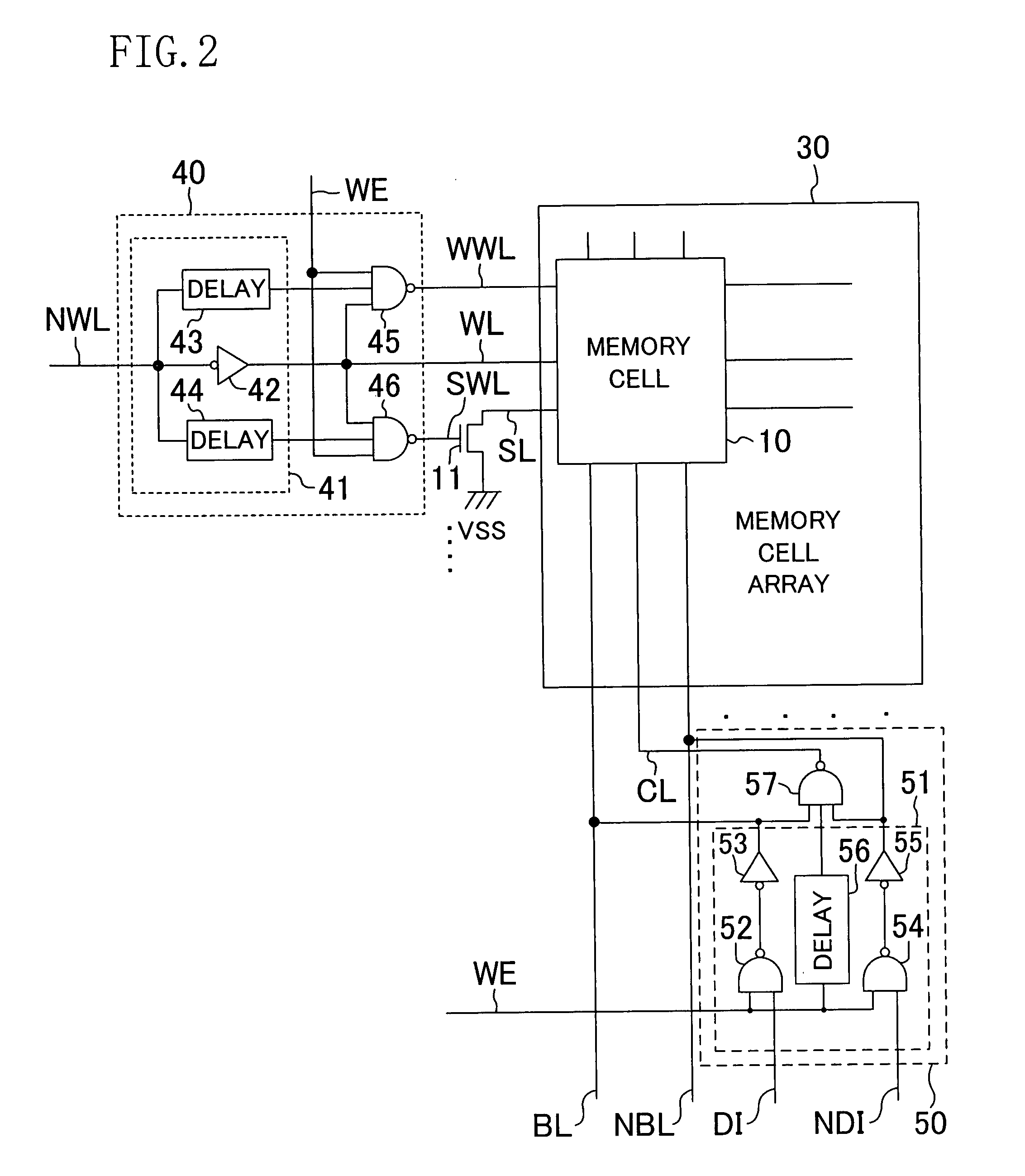

Semiconductor memory device

A storage node voltage control circuit is added to a memory cell including two load transistors, two drive transistors and two access transistors. The storage node voltage control circuit performs control so that in writing data into the memory cell, a voltage at one of the two storage nodes holding a low logic level is raised without changing voltages at respective sources of the load transistors.

Owner:SOCIONEXT INC

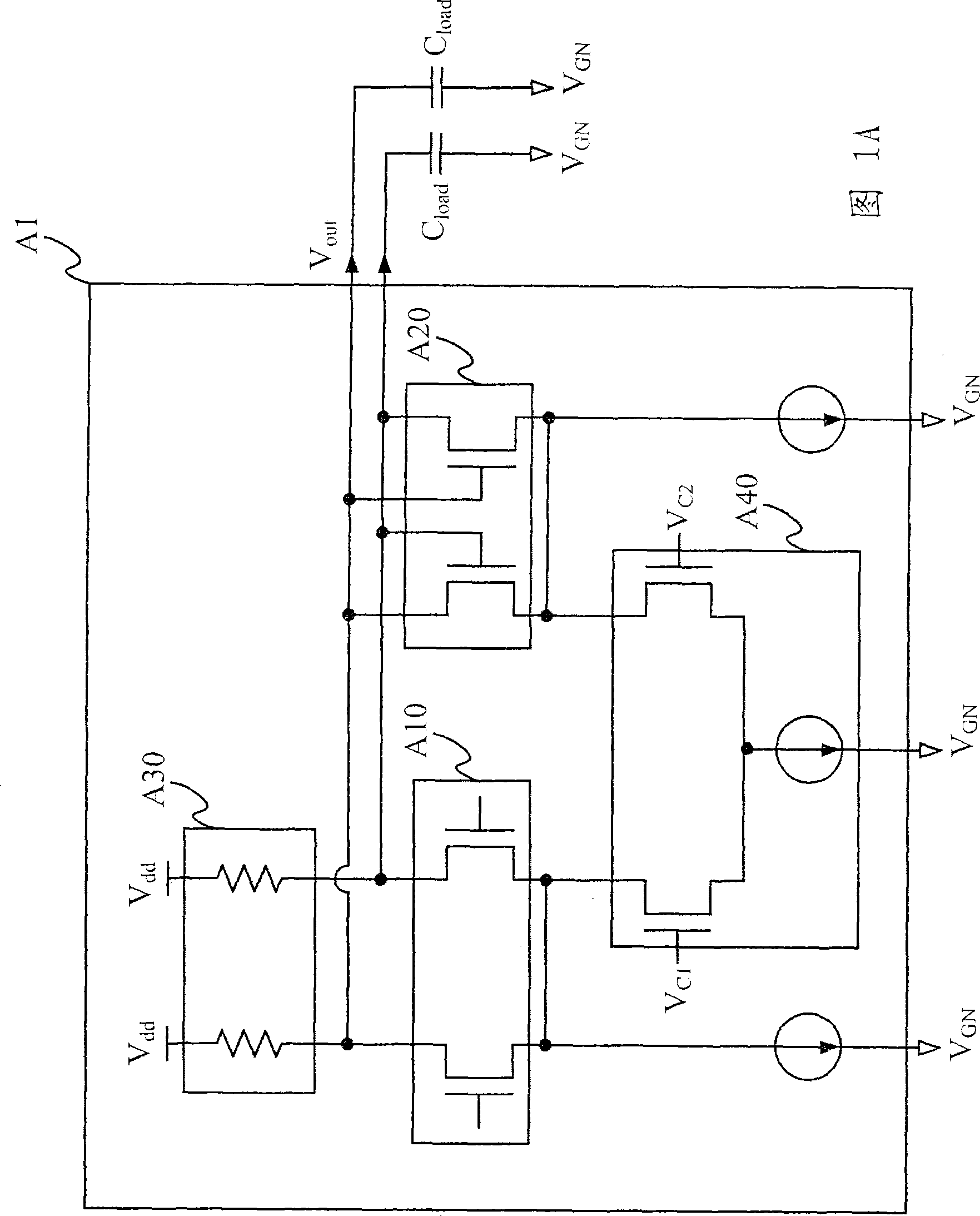

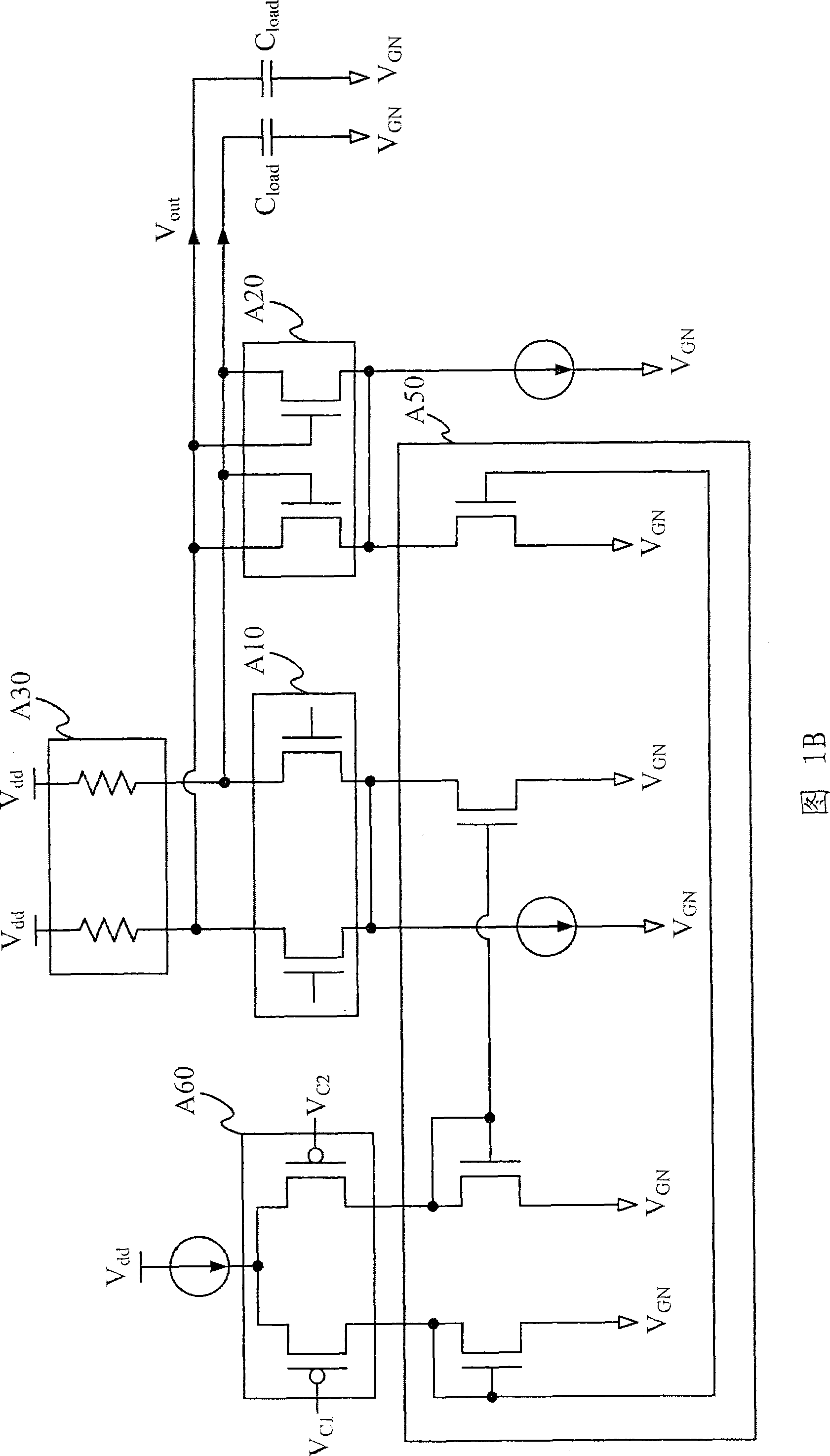

Voltage control oscillating circuit

InactiveCN101442310AAvoid the disadvantages of mismatchingIncrease voltage marginPulse automatic controlElectronic switchingLoad resistanceVoltage control

The invention provides a voltage control oscillating circuit, which comprises an amplifying circuit provided with a first node, an amplifying circuit end current source, of which one end is connected with the first node and the other end is connected with grounding voltage(VGN), a latch circuit provided with a second node, a latch circuit end current source, of which one end is connected with the second node and the other end is connected with the grounding voltage, a load resistance, of which one end is electrically connected with the amplifying circuit and the latch circuit and the other end is electrically connected with power supply voltage(Vdd) and a current modulation circuit comprising a first PMOS switch, a second PMOS switch and a modulation circuit end current source, wherein the first PMOS switch is connected with the first node, the second PMOS switch is connected with the second node, one end of the modulation circuit end current source is connected with the first PMOS switch and the second PMOS switch, and the other end of the modulation circuit end current source is connected with the power supply voltage.

Owner:REALTEK SEMICON CORP

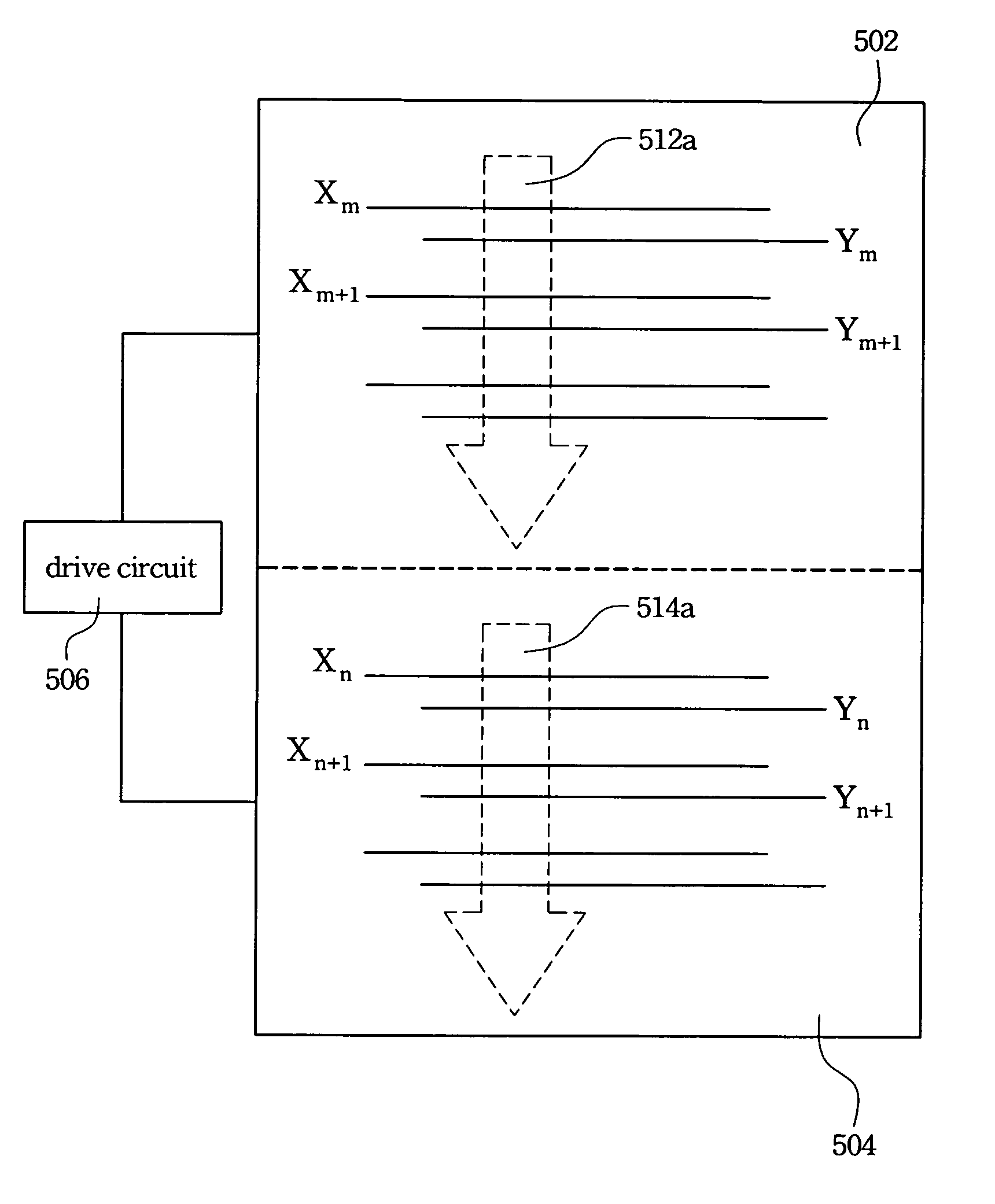

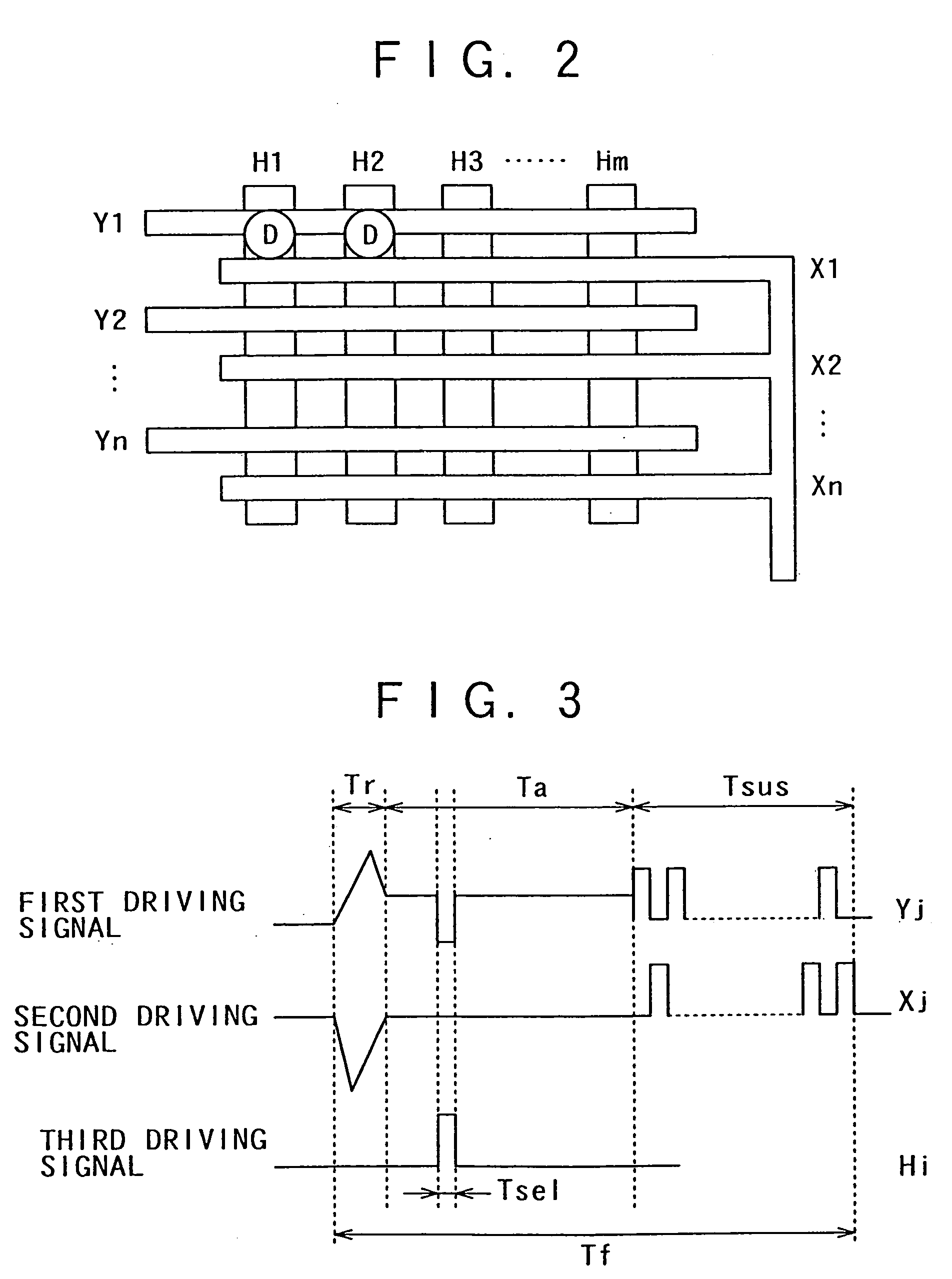

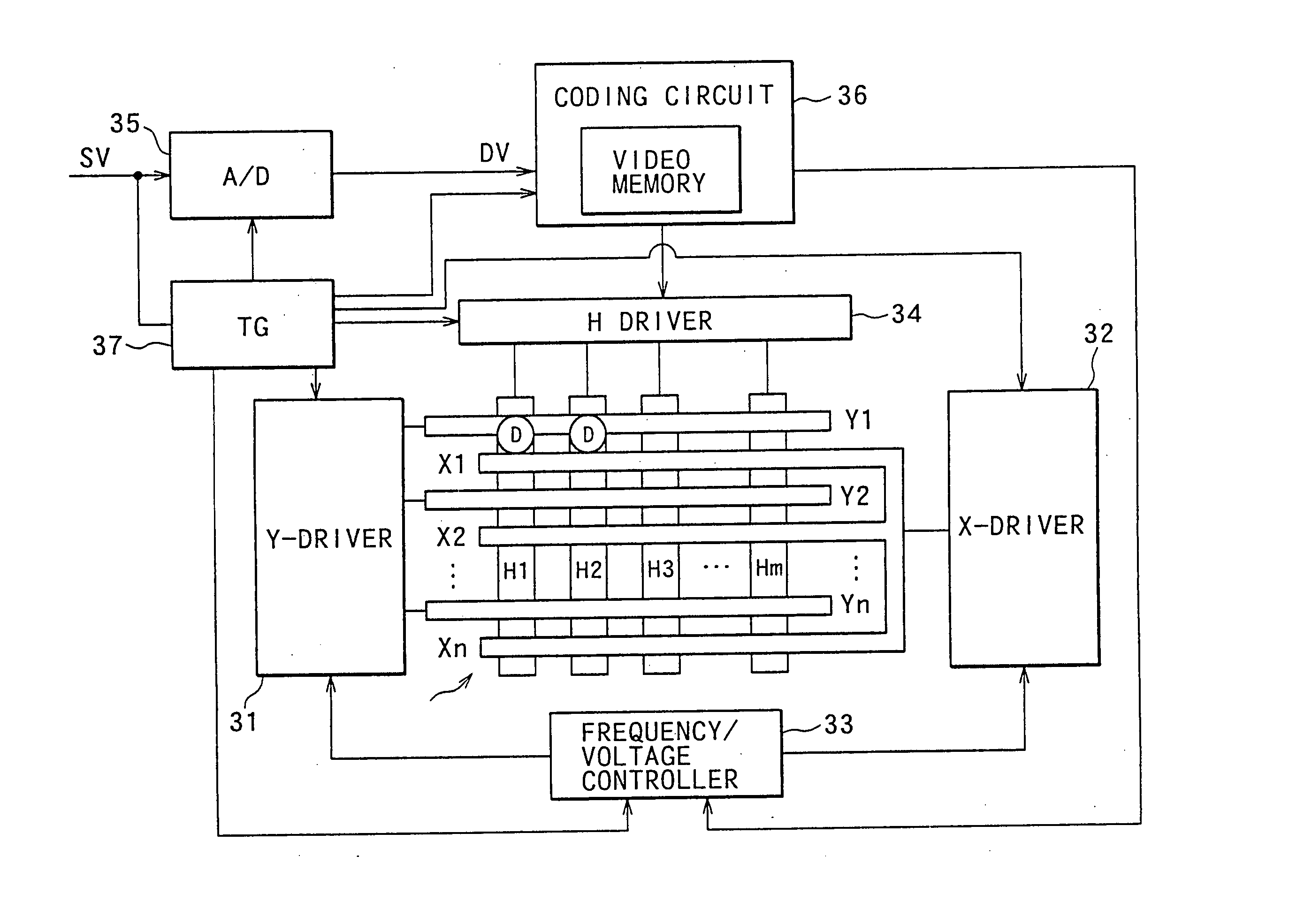

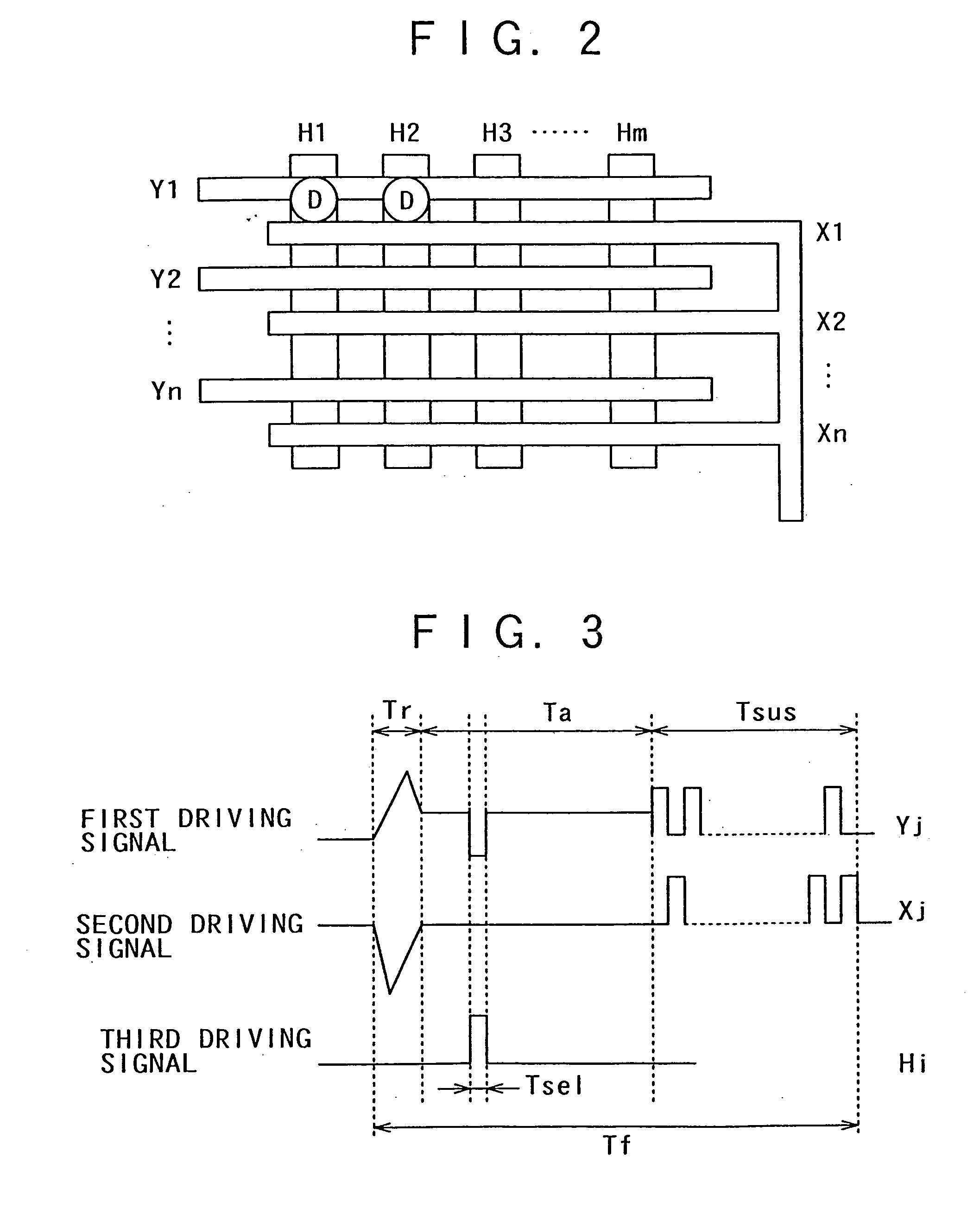

Method for driving plasma display panels

A method for driving plasma display panels (PDPs) includes dividing a plasma display panel having stripe ribs into at least two scanning regions. Each of the scanning regions has a plurality of scan and common electrodes, and these electrodes are arranged in an interlaced fashion according to an electrode arrangement sequence. Then, the emitting cells in each scanning region are addressed, and a scanning direction of each scanning region corresponds to the electrode arrangement sequence of the same scanning region.

Owner:CHUNGHWA PICTURE TUBES LTD

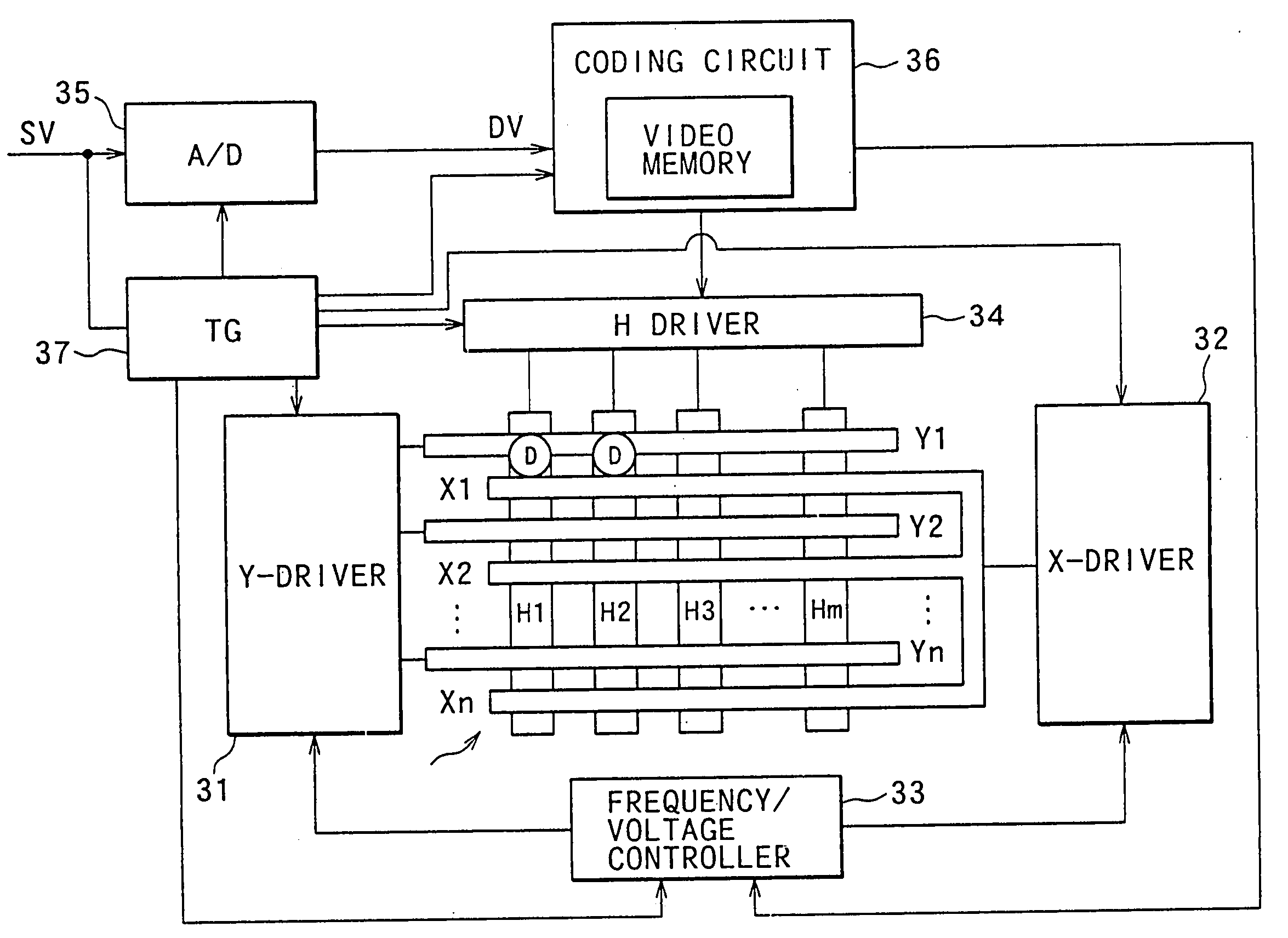

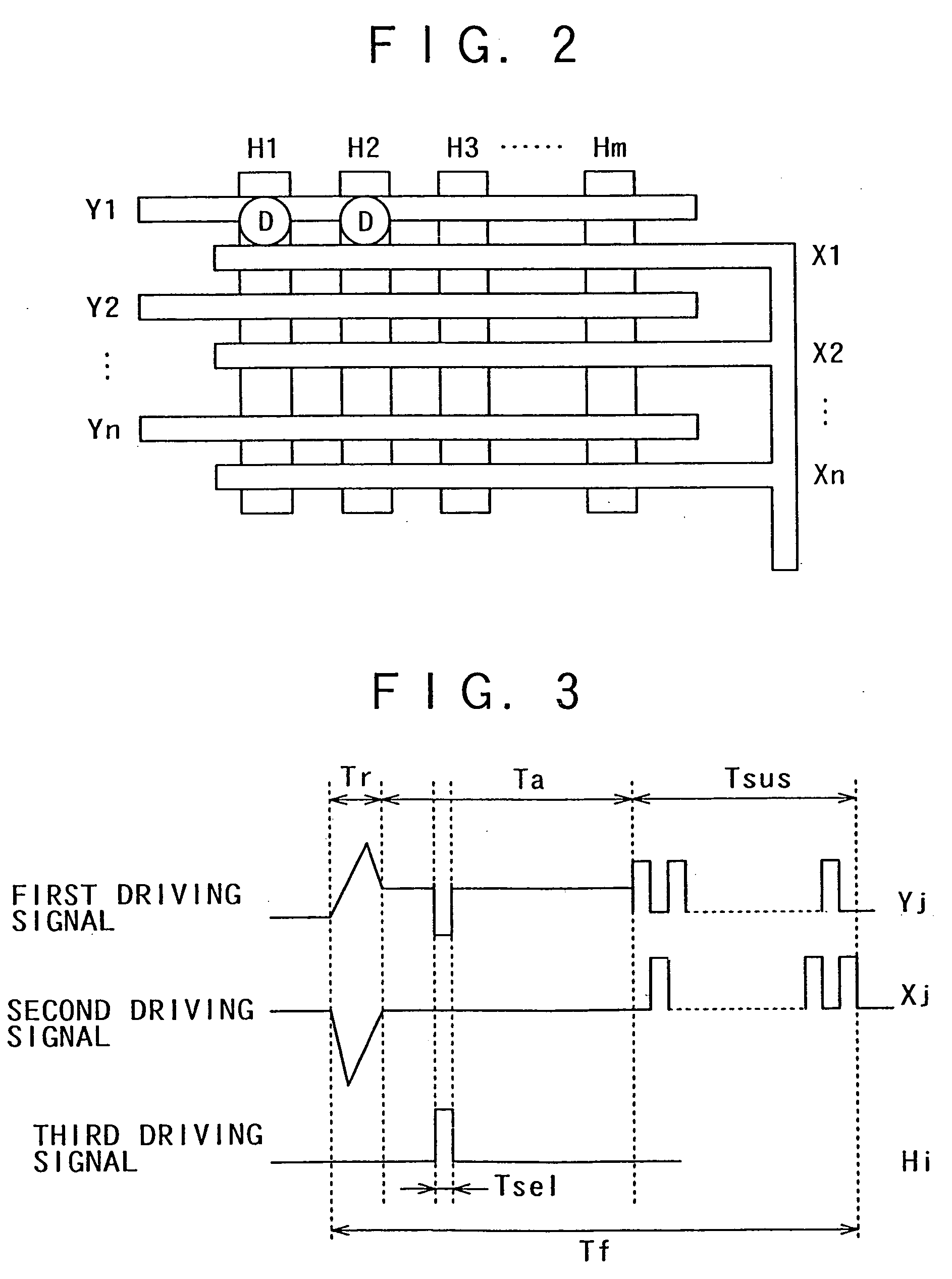

Plasma display apparatus and driving method thereof

InactiveUS20050168413A1Increase brightnessQuality improvementTelevision system detailsStatic indicating devicesEngineeringDouble frequency

According to a plasma display apparatus of the present invention, at least in one sub-field, a driving signal applied to retain data written in each pixel has a frequency applied first and a frequency applied thereafter, the frequencies being different from each other. The first frequency is controlled to be low and the frequency thereafter is controlled to be high, for example (two-frequency driving method). With a first low-frequency pulse, initial discharge in a sustaining period is started stably, and with a high-frequency pulse thereafter, the discharge is sustained. Use of the high-frequency pulse increases the number of light emissions, thus leading to improvement in brightness. Thus, the present invention enables both discharge stabilization and increase in brightness, and can therefore improve picture quality of the plasma display apparatus.

Owner:SONY CORP

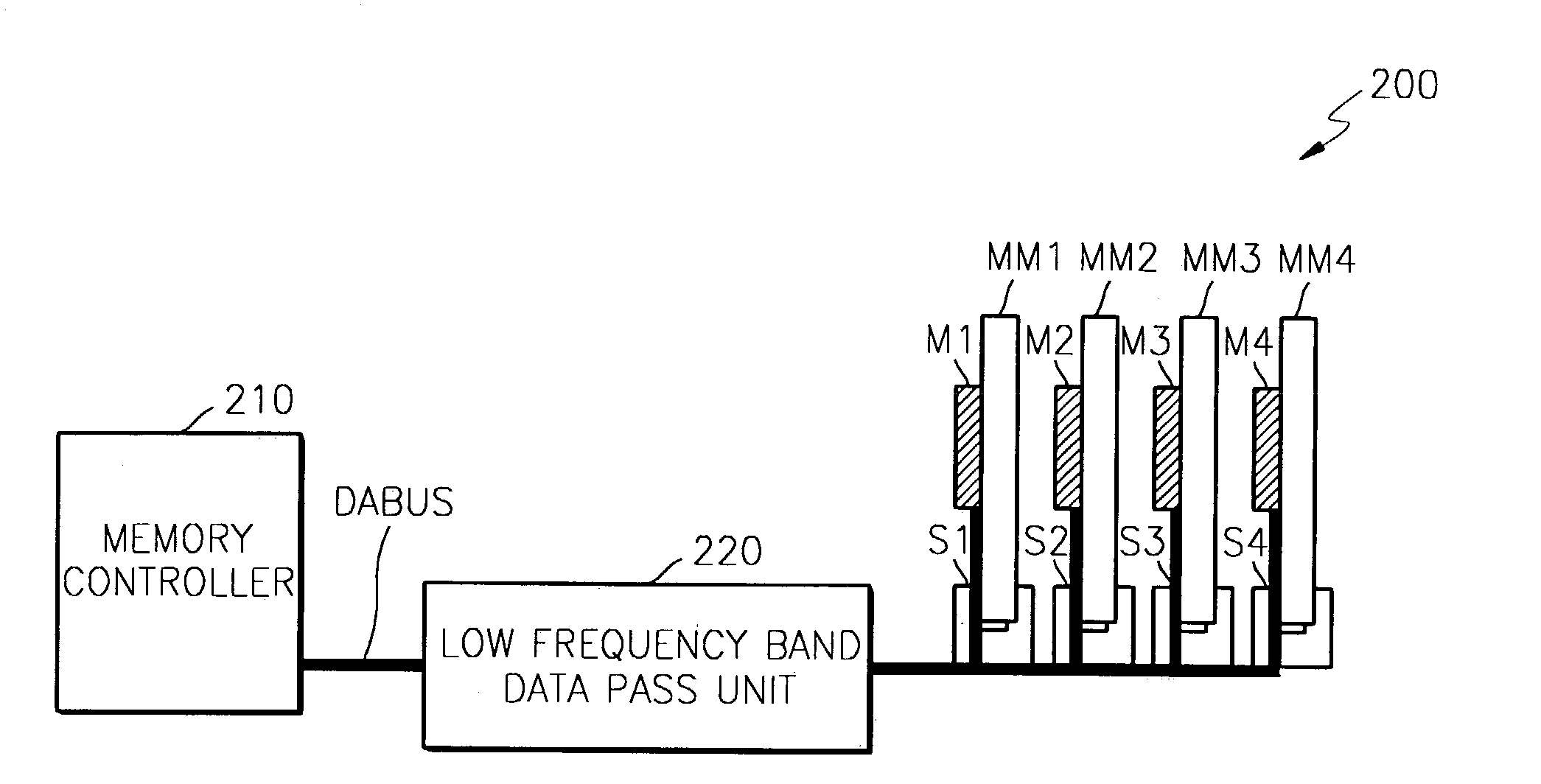

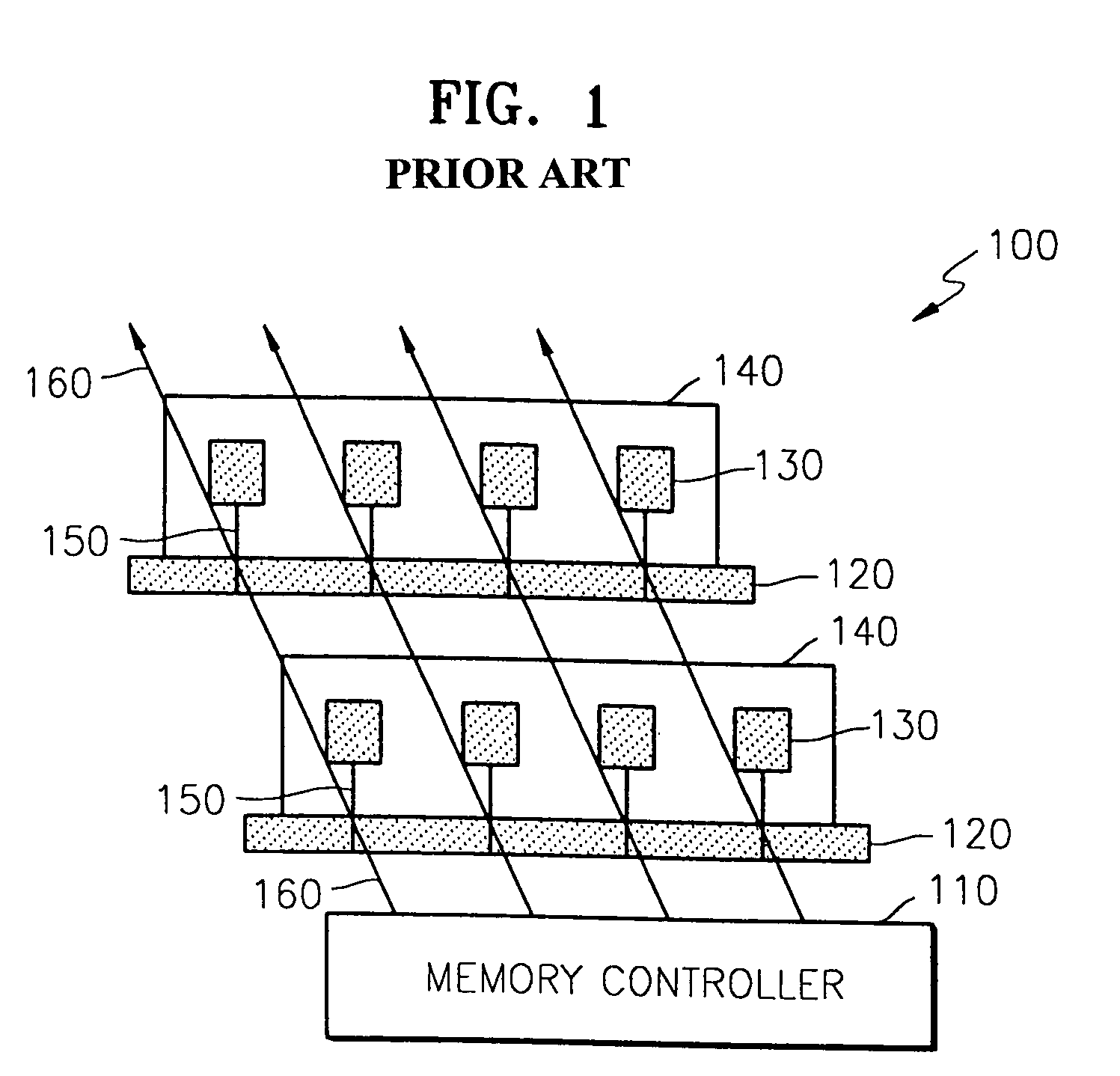

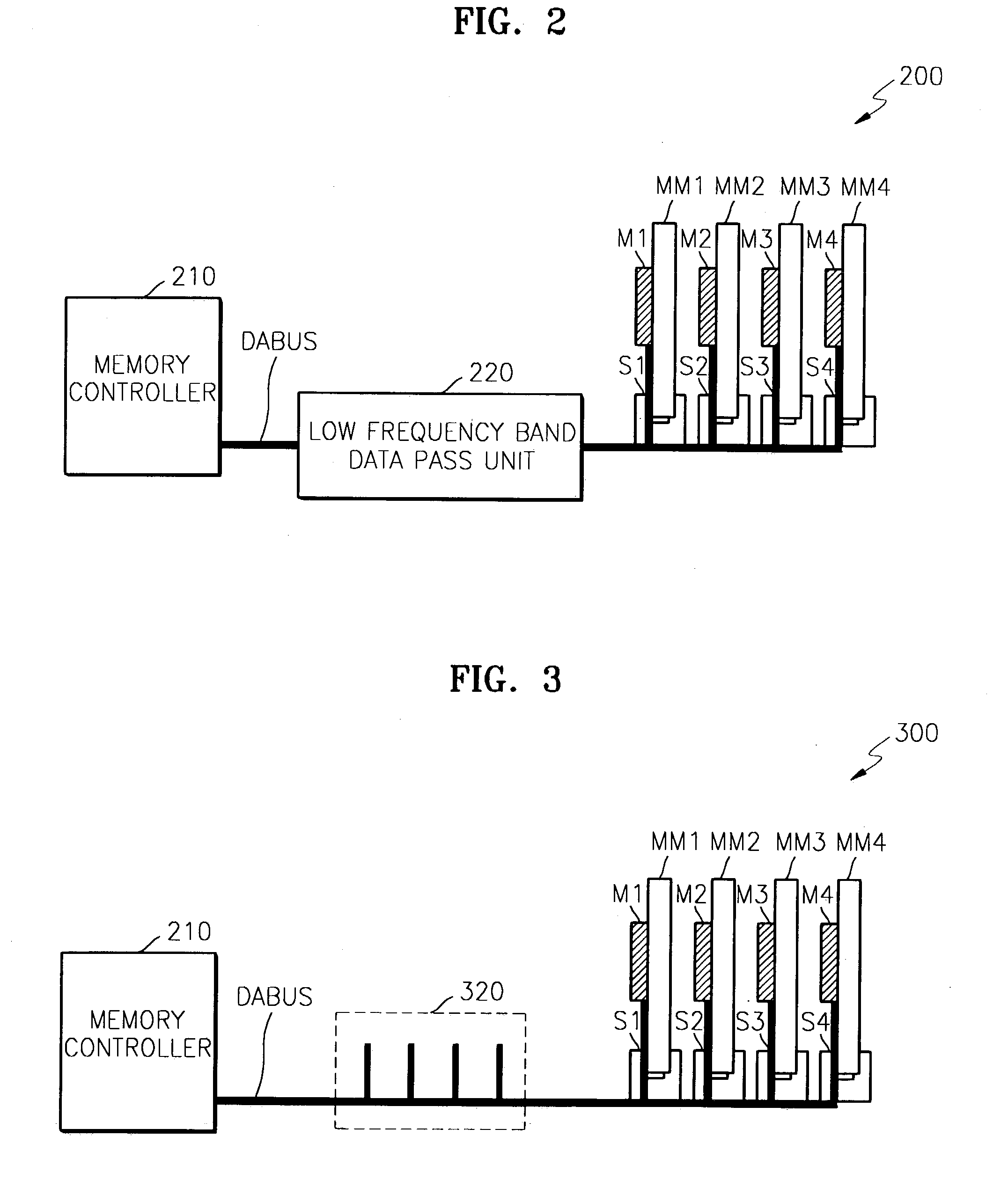

Semiconductor memory device with data bus scheme for reducing high frequency noise

InactiveUS7239216B2Reduce high frequency noiseIncrease voltage marginCross-talk/noise/interference reductionHigh frequency circuit adaptationsLow frequency bandTerm memory

A semiconductor memory device includes memory modules which have memories and a data bus which transfers data to the memory modules, in which the data bus comprises a low frequency band data pass unit which removes the high frequency component of the data and sends the data to the memory modules. The low frequency band data pass unit comprises a plurality of stubs which are connected to the data bus in parallel and are formed as printed circuit board (PCB) patterns. The low frequency band data pass unit comprises a plurality of plates that are connected to the data bus in parallel and are formed as PCB patterns. The low frequency band data pass unit has a shape in which parts having a wide width and parts having a narrow width are alternately connected. Therefore, without adding a separate passive device, the semiconductor memory device reduces the high frequency noise of data transferred through a data bus such that the voltage margin of the data improves, the cost for passive devices such as capacitors, is reduced, and the process for attaching the passive devices is simplified.

Owner:SAMSUNG ELECTRONICS CO LTD

Plasma display apparatus and driving method thereof

InactiveUS20050168411A1Increase brightnessQuality improvementTelevision system detailsStatic indicating devicesEngineeringDouble frequency

Owner:SONY CORP

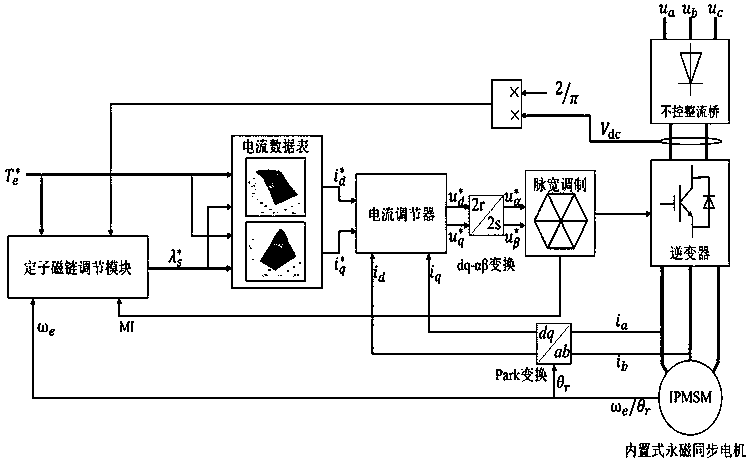

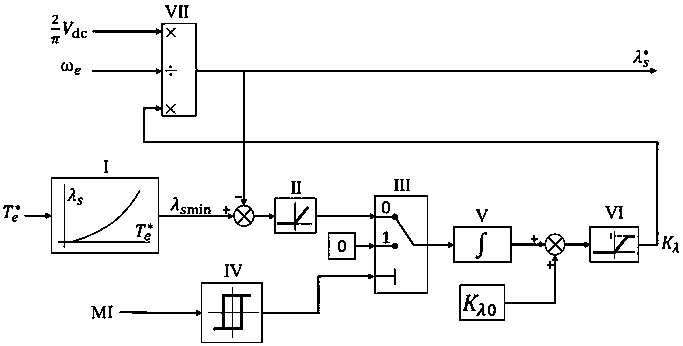

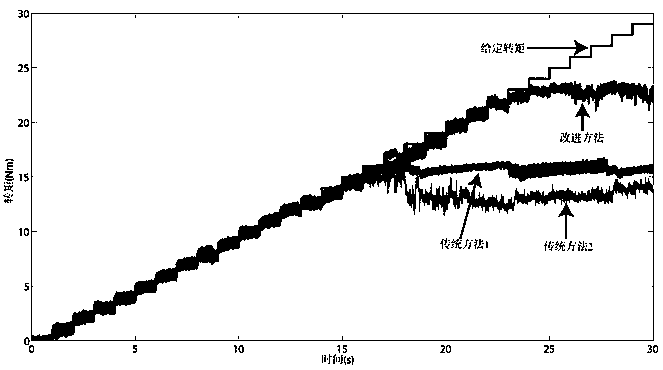

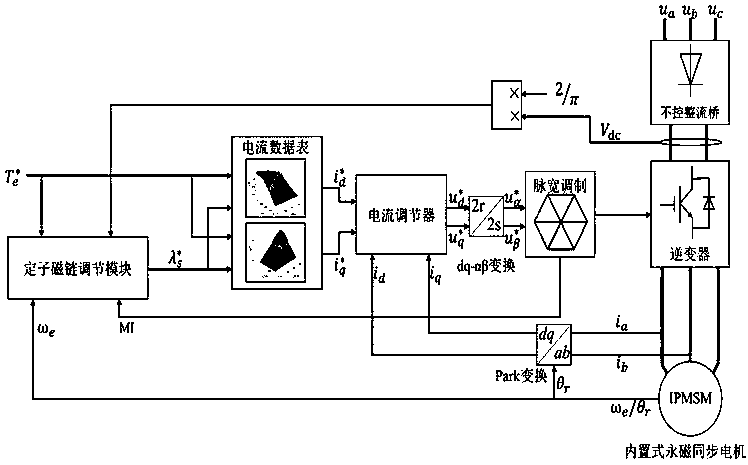

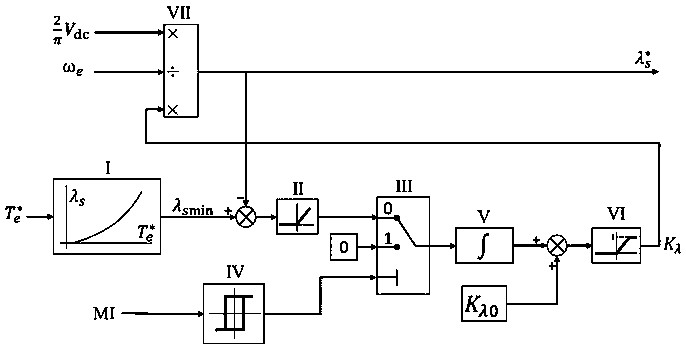

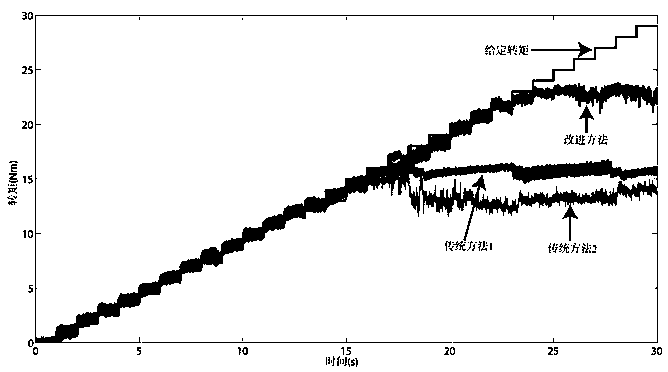

Field weakening control method for built-in permanent magnet synchronous motor based on torque feedforward control technology

ActiveCN107749727AGuaranteed stabilityIncrease voltage marginElectronic commutation motor controlElectric motor controlPhysicsCurrent regulator

The invention discloses a field weakening control method for a built-in permanent magnet synchronous motor based on a torque feedforward control technology, which mainly comprises a stator flux adjustment module, a current data table, a current regulator, a pulse width modulation module, dq-[alpha][beta] transformation, Park transformation, an uncontrolled rectifier bridge and an inverter, and ischaracterized in that the stator flux adjustment module calculates an appropriate stator flux set value to serve as the output according to an input torque set value, DC bus voltage, motor speed and amodulation factor; the stator flux adjustment module comprises seven modules I-VII, wherein the module I is a one-dimensional table and records the corresponding minimum stator flux at different given torques. The field weakening control method realizes the maximization of torque output of the motor in a field weakening area through introducing a proportionality factor into stator flux adjustment, and ensures the stability of the torque at the same time. The factor automatically changes in size according to operating conditions of the current motor, the voltage margin is improved when the speed is high and the torque is low, the torque output capacity is improved when the speed is high and the torque is large, and thus the maximum utilization ratio of the DC bus voltage is achieved.

Owner:ZHEJIANG UNIV

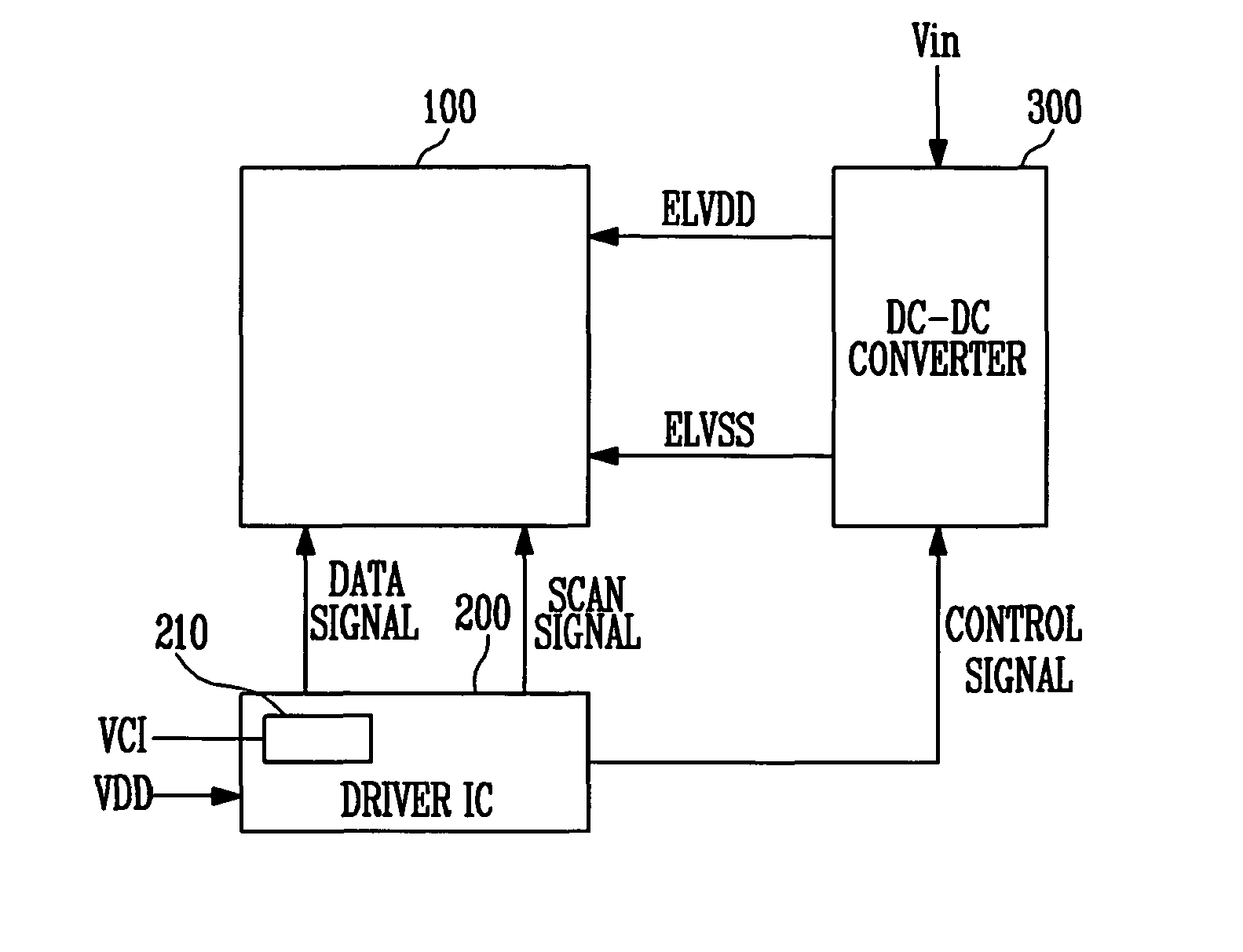

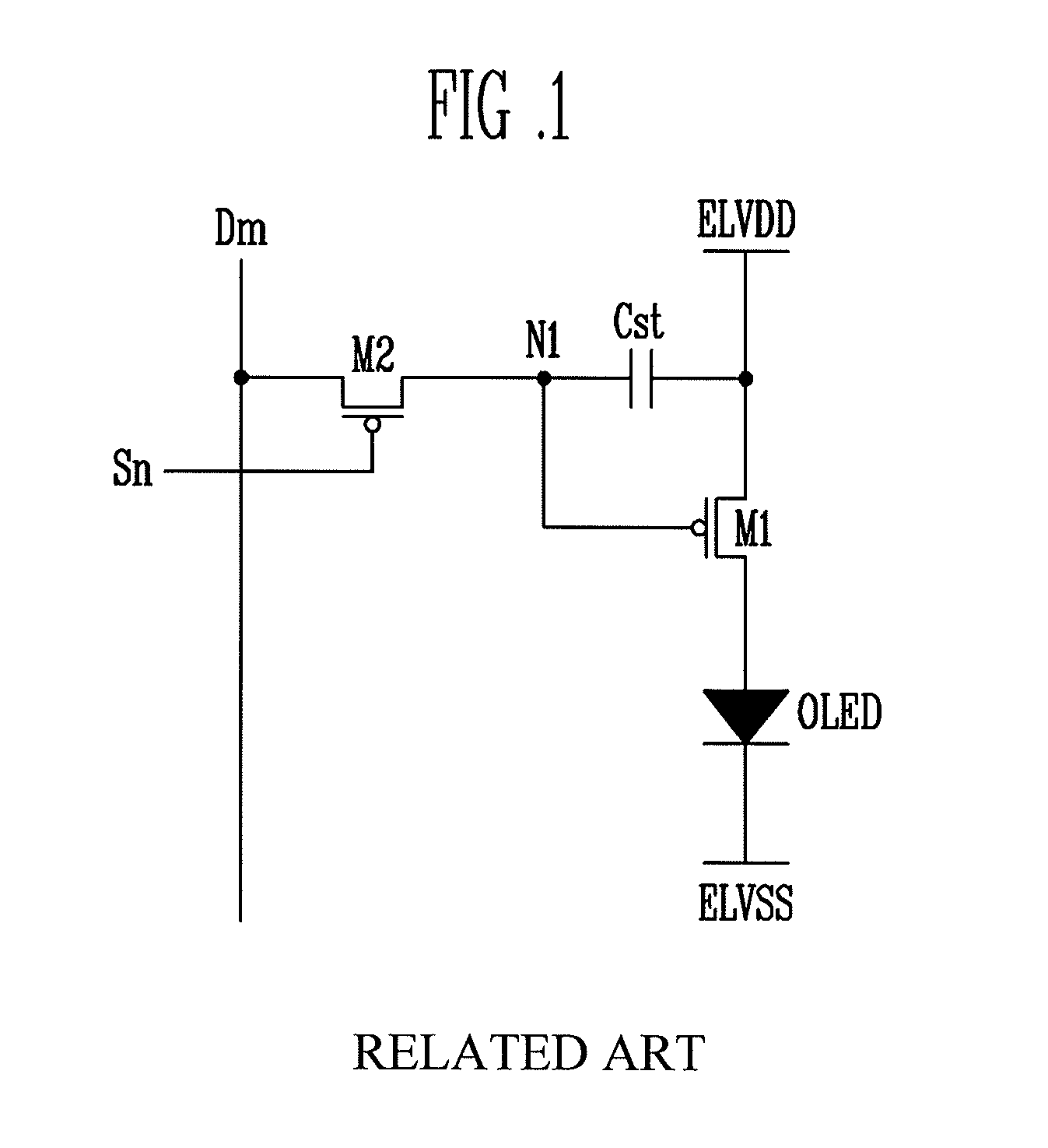

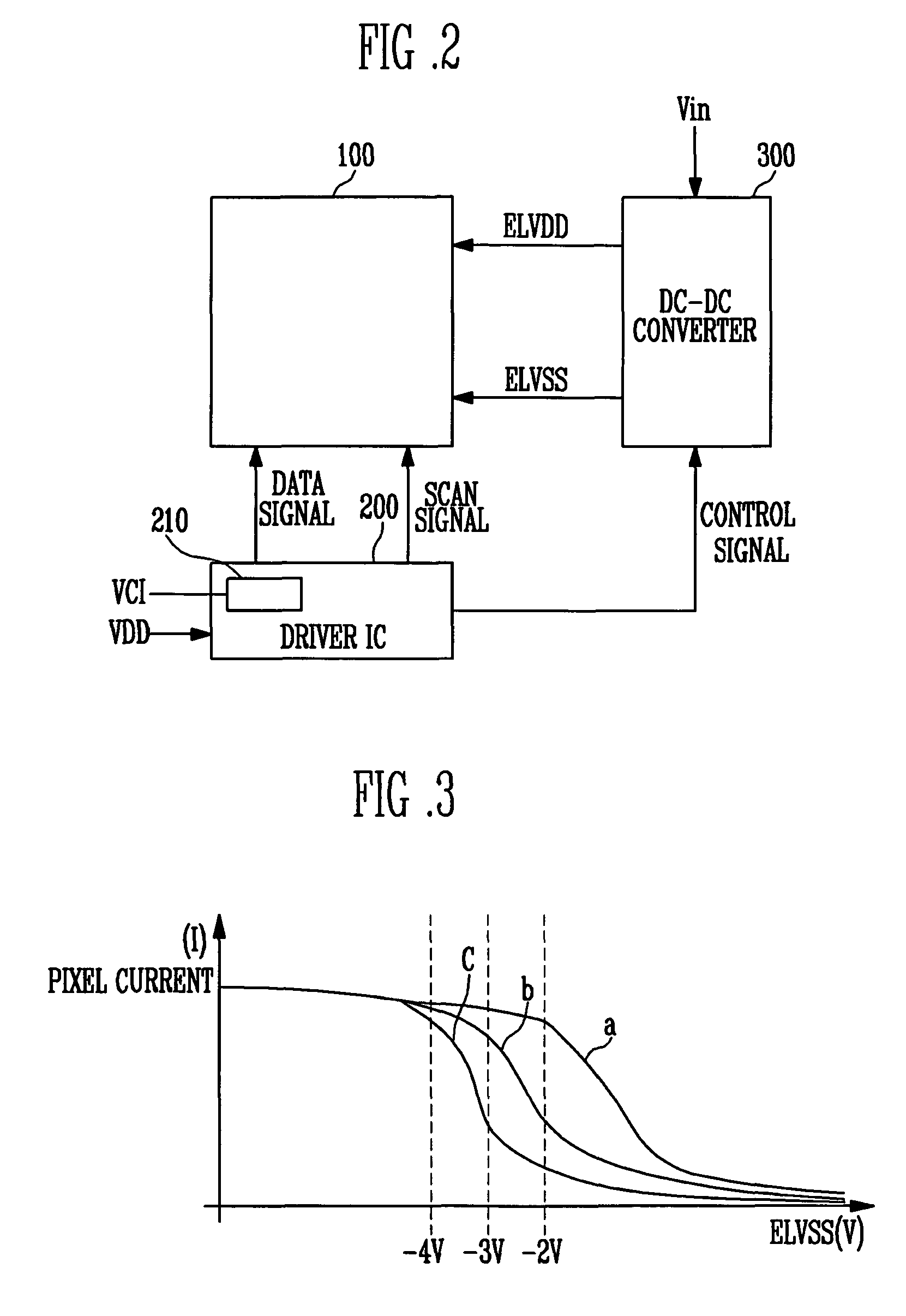

Organic light emitting display and method of driving the same

ActiveUS8593448B2Improve efficiencyIncrease voltage marginCathode-ray tube indicatorsInput/output processes for data processingDc dc converterControl signal

An organic light emitting display, and a method of driving the same, controls the voltage of a second power source in accordance with an ambient temperature. The organic light emitting display includes a driver IC configured to drive a pixel unit and to generate a control signal in accordance with an ambient temperature, and a DC-DC converter configured to generate a first power source and a second power source from an input voltage, to change a voltage of the second power source in accordance with the control signal from the driver IC, and to output the changed voltage of the second power source and the first power source.

Owner:SAMSUNG DISPLAY CO LTD

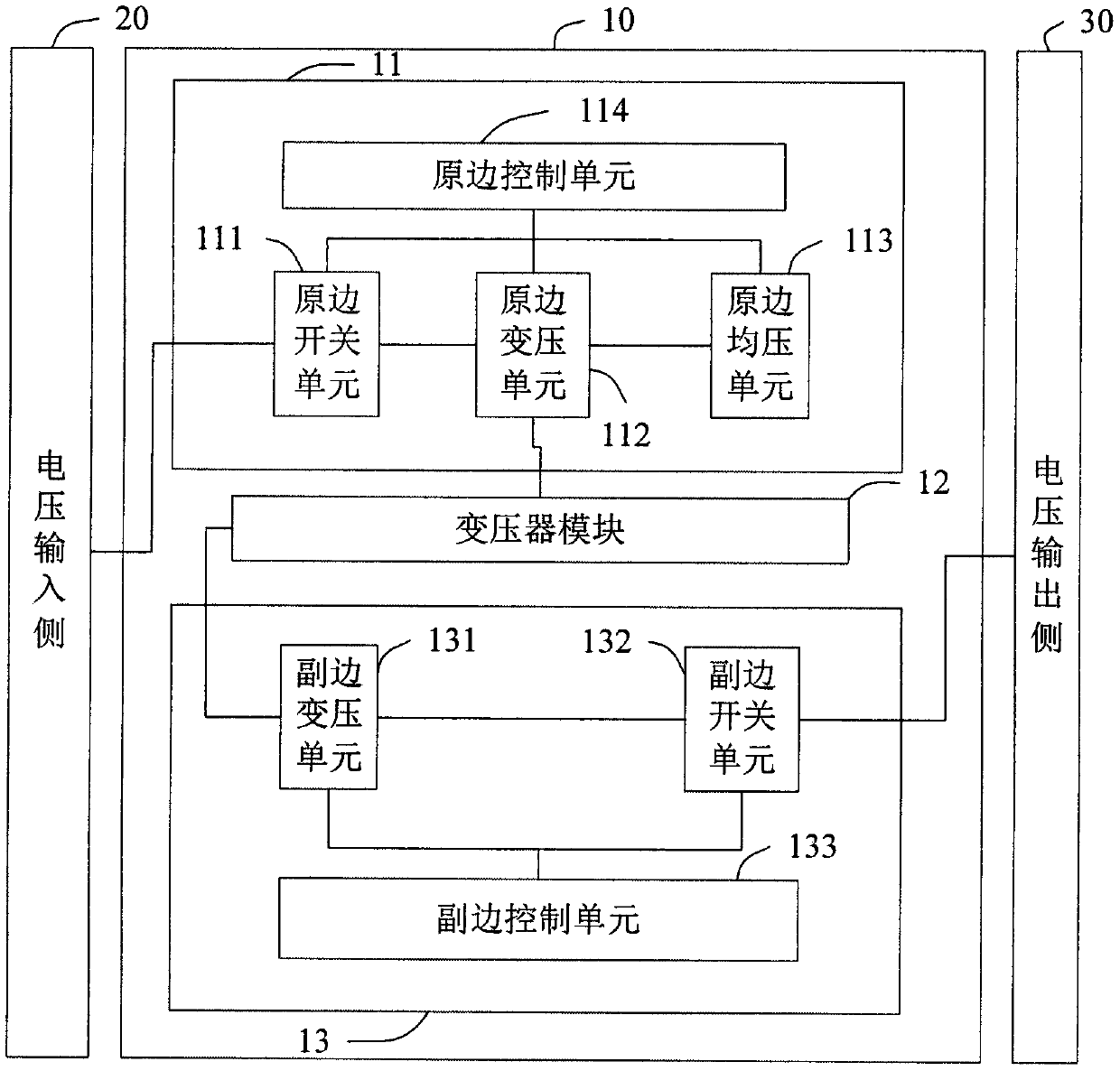

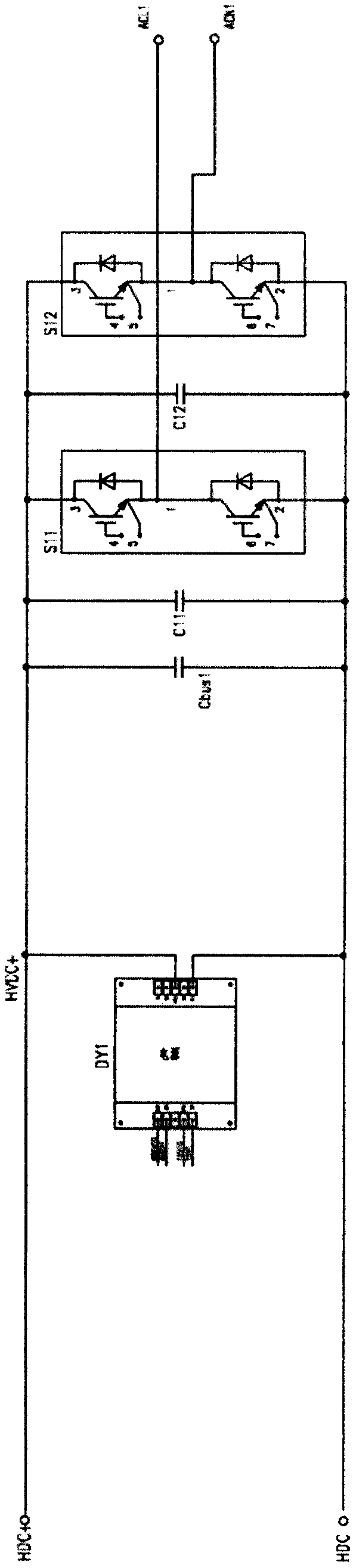

Voltage conversion device

InactiveCN109921642AImprove stabilityImprove securityAc-dc conversionApparatus with intermediate ac conversionEngineeringEqualization

The disclosure relates to a voltage conversion device comprising a primary side module, a transformer module and a secondary side module which are sequentially connected, wherein the primary side module comprises a primary side switching unit, a primary side transformer unit, a primary side voltage equalization resistance unit and a primary side control unit which are sequentially connected and isconfigured to convert the first DC voltage input to the voltage input side into a first AC voltage; the transformer module is connected to the primary side transformer unit for converting the first AC voltage into a second AC voltage; the secondary side module comprises a secondary side transformer unit, a secondary side switching unit and a secondary side control unit which are sequentially connected and is configured to convert the second AC voltage into a second DC voltage and input the second DC voltage to the voltage output side. The device provided by the disclosure realizes DC-to-DC voltage conversion through mutual cooperation between three modules, and has the advantages such as high stability, high safety and high startup success rate.

Owner:BEIJING SIFANG JIBAO AUTOMATION +1

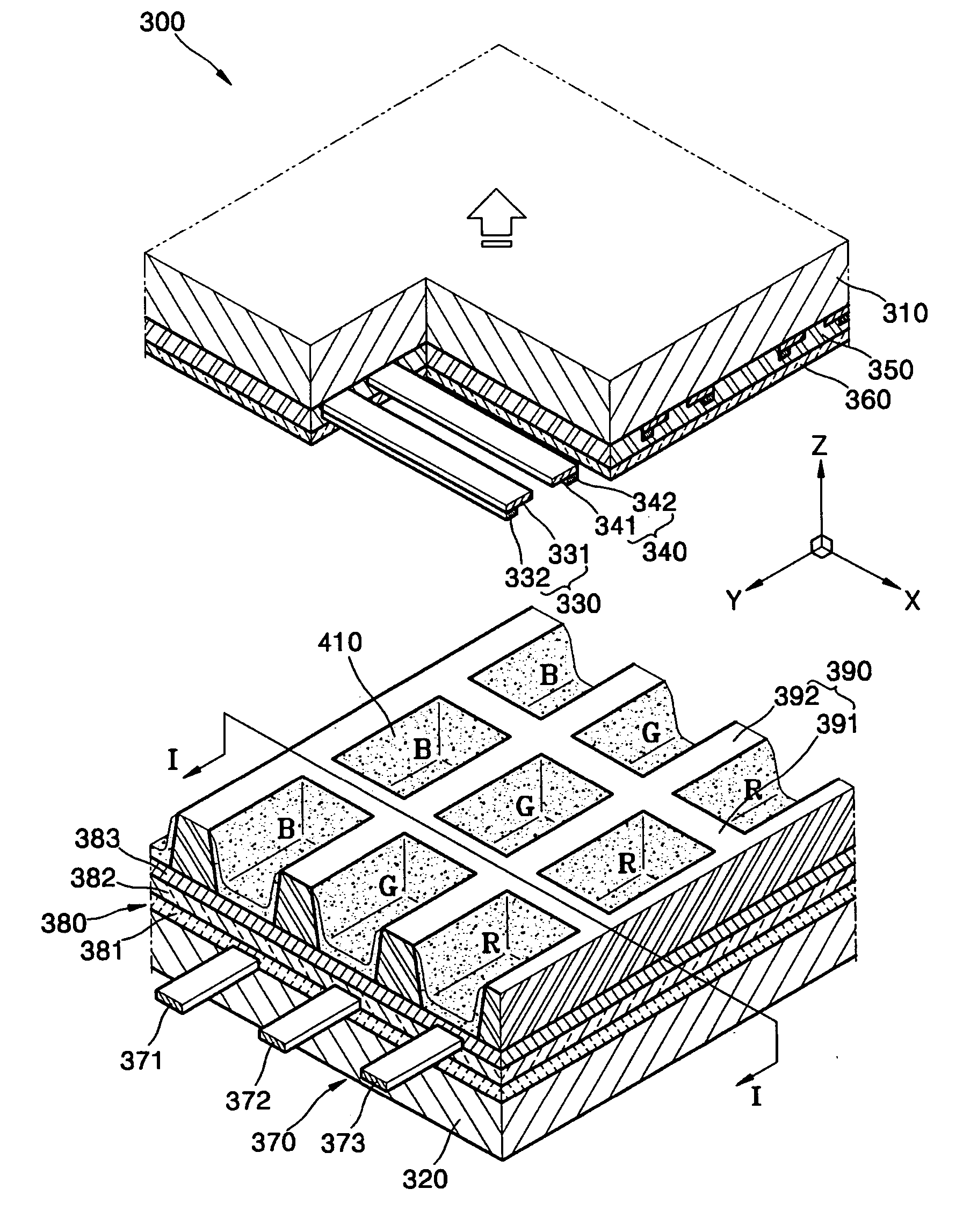

Plasma display panel (PDP) and its method of manufacture

InactiveUS20060082306A1Increase voltage marginReduces a variation among voltage marginsAddress electrodesSustain/scan electrodesPhosphorEngineering

A Plasma Display Panel (PDP) and its method of manufacture includes: a first substrate; a plurality of first discharge electrodes arranged on the first substrate; a second substrate arranged opposite to the first substrate and in parallel therewith; a plurality of second discharge electrodes arranged on the second substrate to cross the first discharge electrodes, the second discharge electrodes being adapted to be addressed with the first discharge electrodes and located on different levels; barrier ribs disposed between the first and second substrates to define discharge cells; and Red (R), Green (G), and Blue (B) phosphor layers coated on lateral sides of the barrier ribs. Address electrodes for discharge cells coated with R, G, and B phosphor layers are positioned on different levels, so that address voltages become more uniform regardless of the color of a phosphor layer.

Owner:SAMSUNG SDI CO LTD

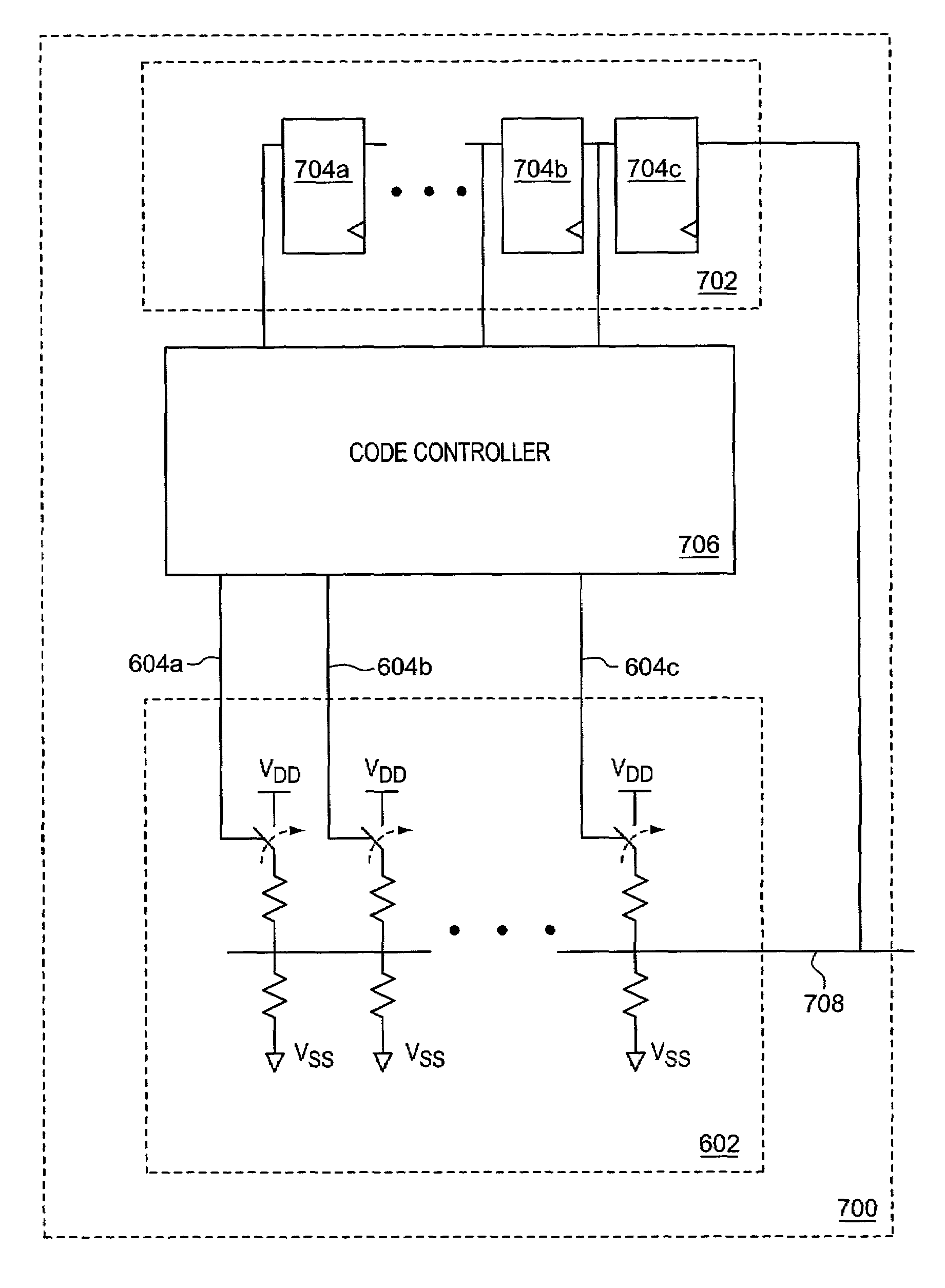

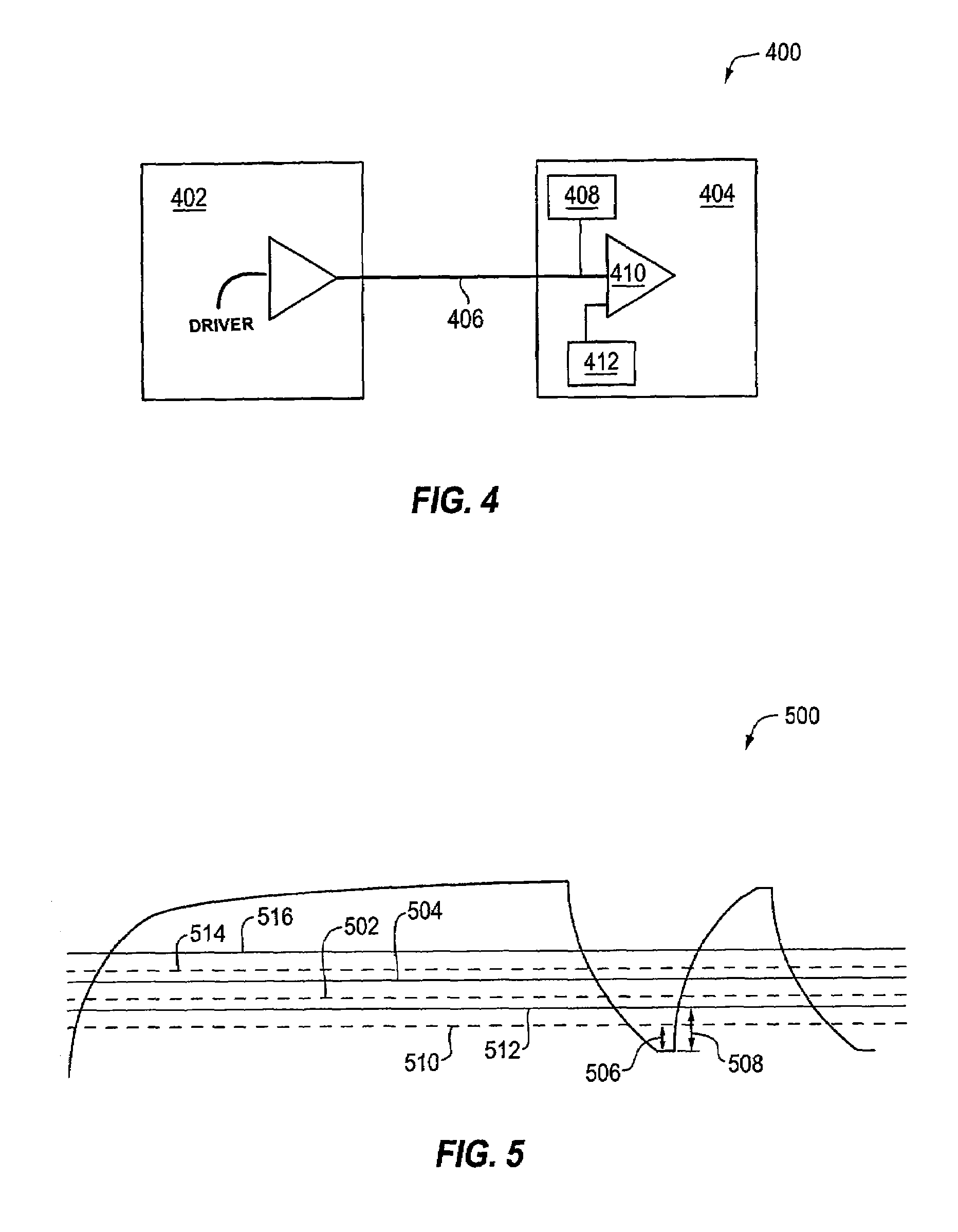

Methods and apparatus for equalization in single-ended chip-to-chip communication

ActiveUS7433396B2Increase voltage marginMultiple-port networksResonant long antennasEngineeringVoltage reference

Disclosed are novel methods and apparatus for efficiently providing equalization in single-ended chip-to-chip communication. In an embodiment, a method of adjusting signal levels to provide improved communication between a sender device and a receiver device is disclosed. The method includes providing a plurality of voltage dividers. The plurality of voltage dividers may be coupled to each other to provide a reference voltage to the receiver device. The method further includes providing a storage device to store previously received data by the receiver device and providing a controller to selectively activate the plurality of voltage dividers.

Owner:ORACLE INT CORP

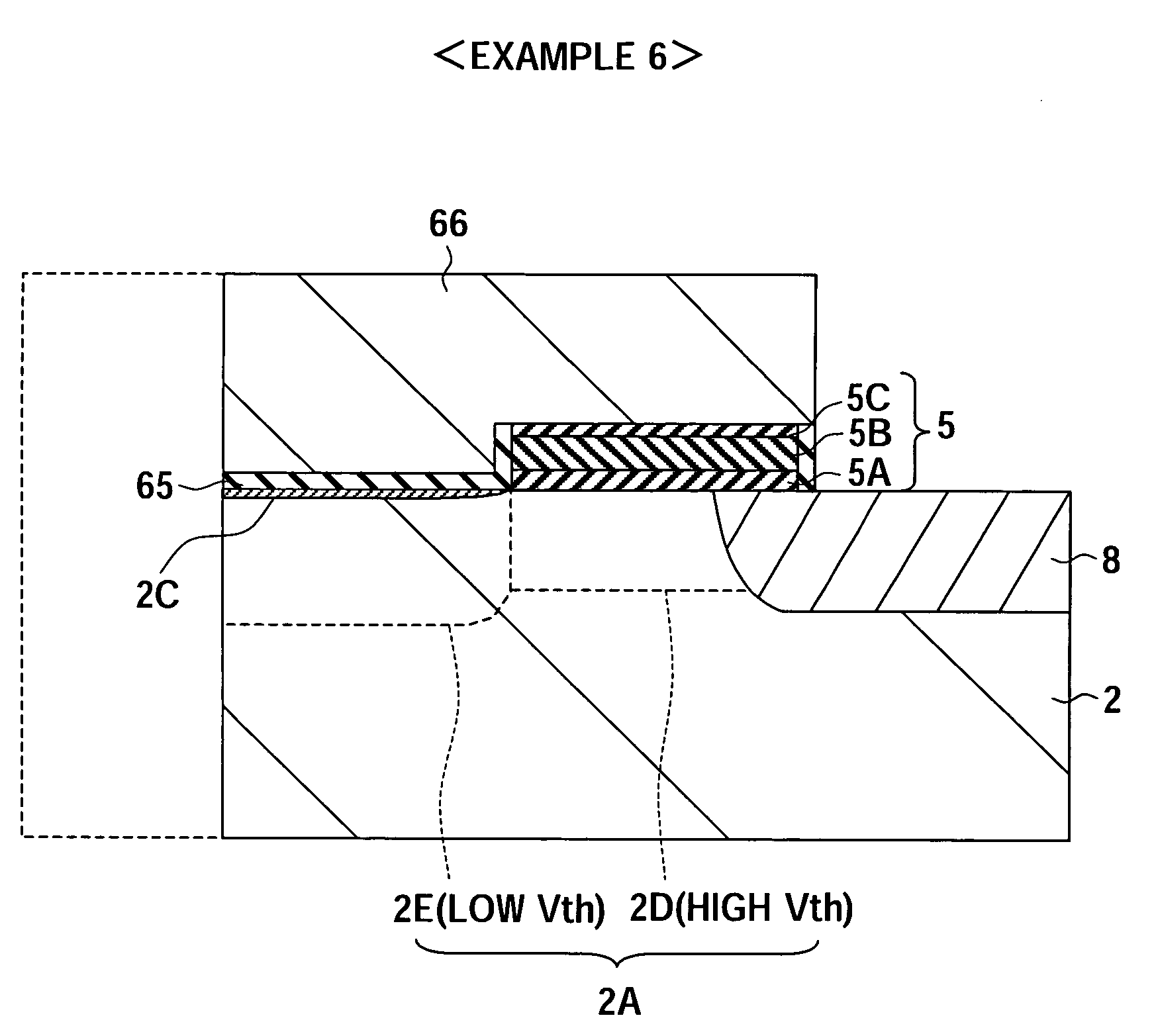

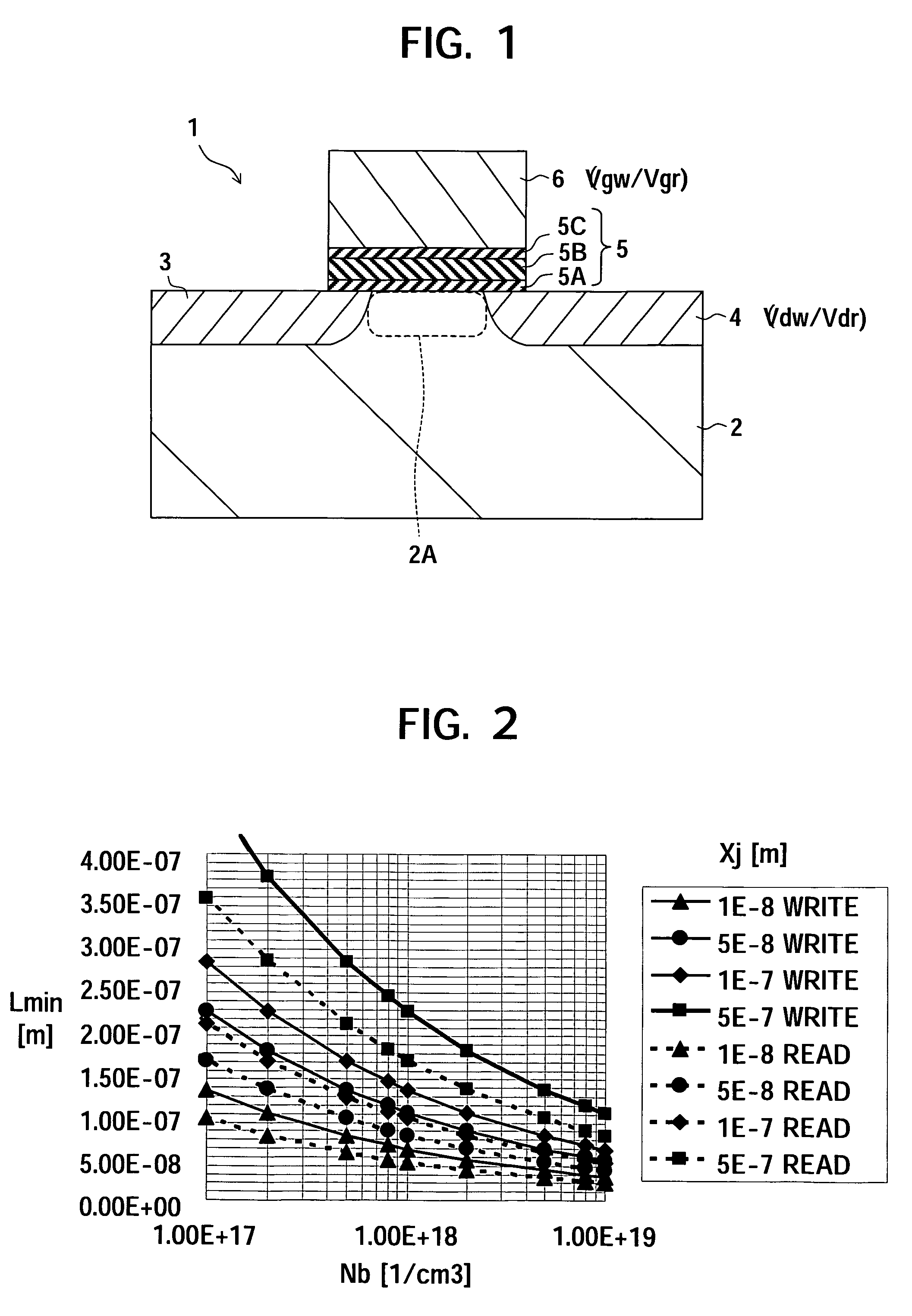

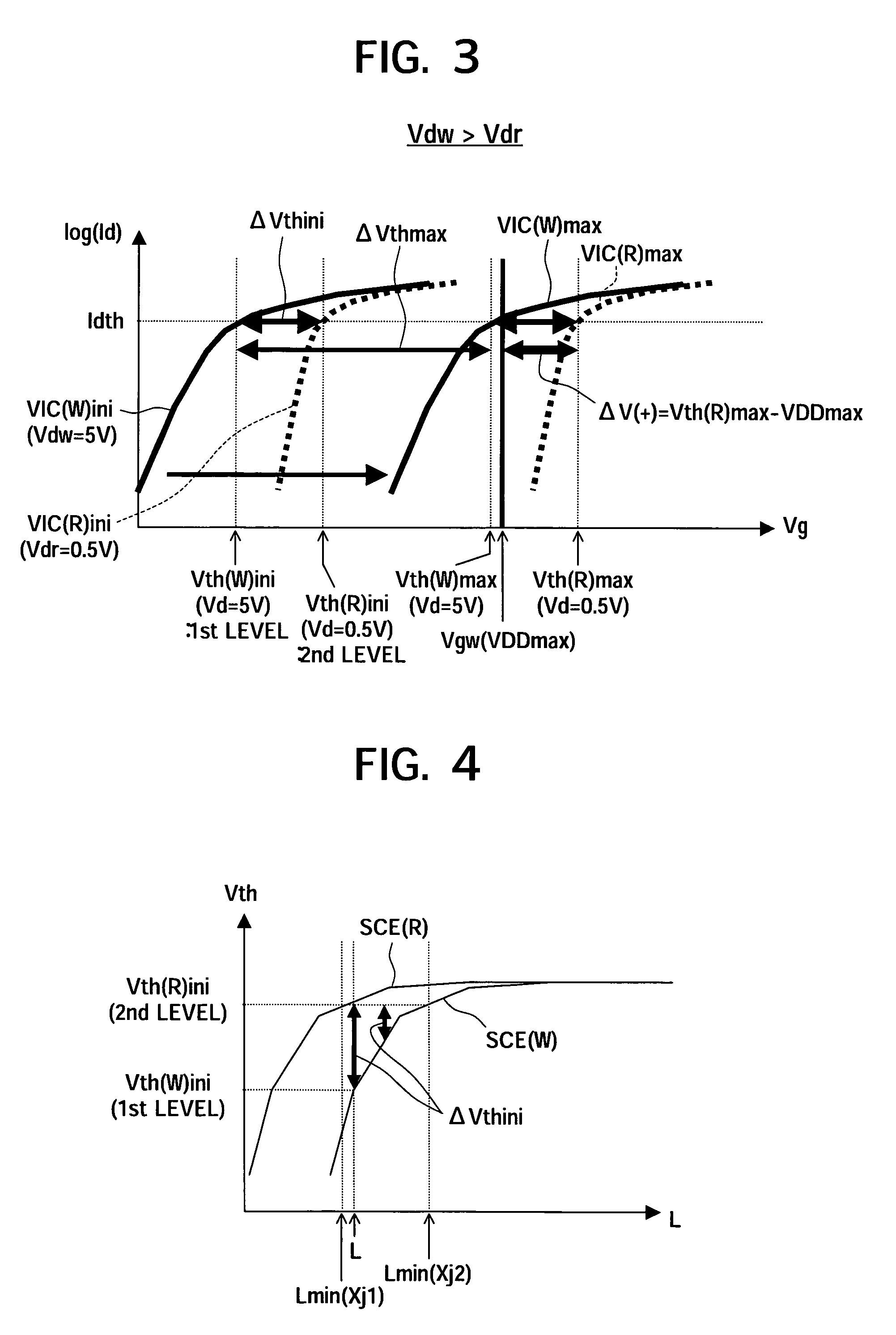

Non-volatile semiconductor memory

InactiveUS7265409B2Increase voltage marginExcellent characteristicsRead-only memoriesSemiconductor/solid-state device manufacturingSemiconductorShort-channel effect

A non-volatile semiconductor memory having a memory transistor including a stacked-layer film formed between a semiconductor substrate and a gate electrode and having a charge storage ability, a first conductivity type region of the semiconductor substrate in which a channel is formed under the control of the gate electrode via the stacked-layer film, and two second conductivity type regions formed at the semiconductor substrate sandwiching the first conductivity type region therebetween, the memory transistor having a channel length L which is between channel lengths L1 and L2. with the channel length L1 being estimated as the boundary of occurrence of a short channel effect at the time of a write operation and the channel length L2 the time of a read operation, with the channel length L1 being different from the channel length L2.

Owner:SONY CORP

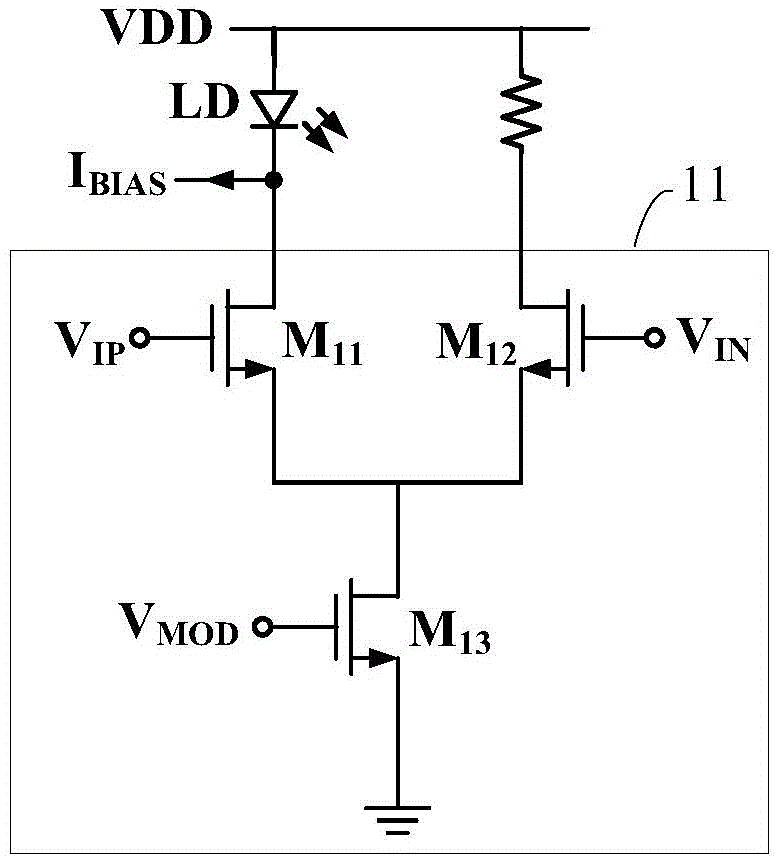

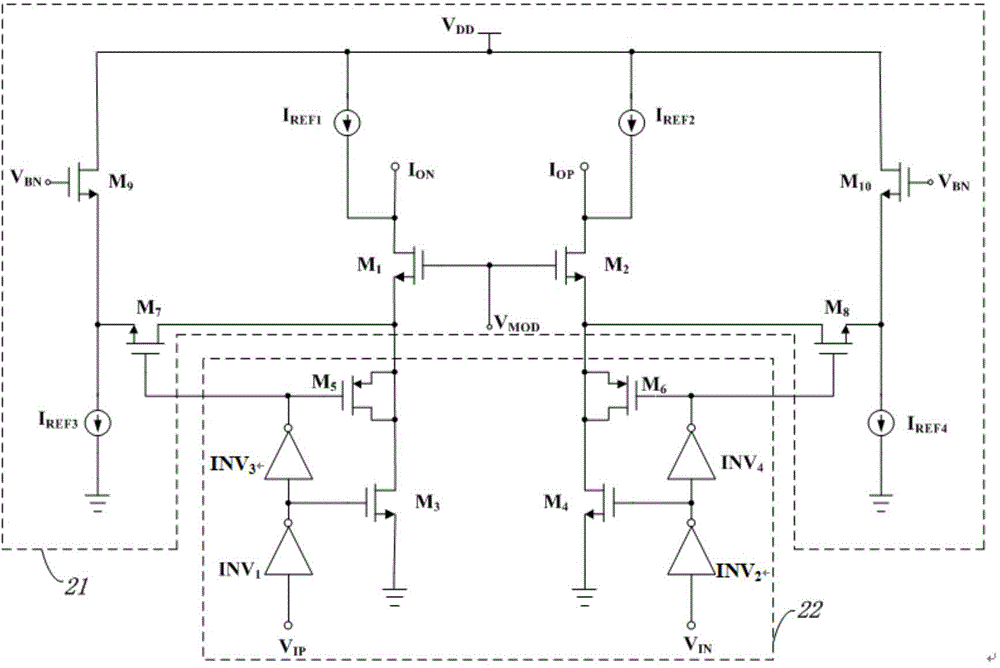

Modulation driving output stage circuit

ActiveCN103957059AReduce the voltage marginQuick switchElectronic switchingElectromagnetic transmissionPower flowReference current

The invention provides a modulation driving output stage circuit. The modulation driving output stage circuit comprises a switch control circuit part and a current generation circuit part. The modulation driving output stage circuit receives a pair of difference input voltages and outputs a pair of difference output currents. The current generation circuit part comprises a first transistor, a second transistor, a first reference current source and a second reference current source. The switch control circuit part comprises a third transistor, a fourth transistor, a first phase inverter and a second inverter. The first difference voltage in the pair of difference input voltages is input into the grid electrode of the third transistor through the first phase inverter, the second difference voltage in the pair of difference input voltages is input into the grid electrode of the fourth transistor through the second phase inverter, the drain electrode of the second transistor outputs the first difference current in the pair of difference output currents, and the drain electrode of the first transistor outputs the second difference current in the pair of difference output currents. The modulation driving output stage circuit can increase the voltage margin of a driver.

Owner:JIAXING HEROIC ELECTRONICS TECH

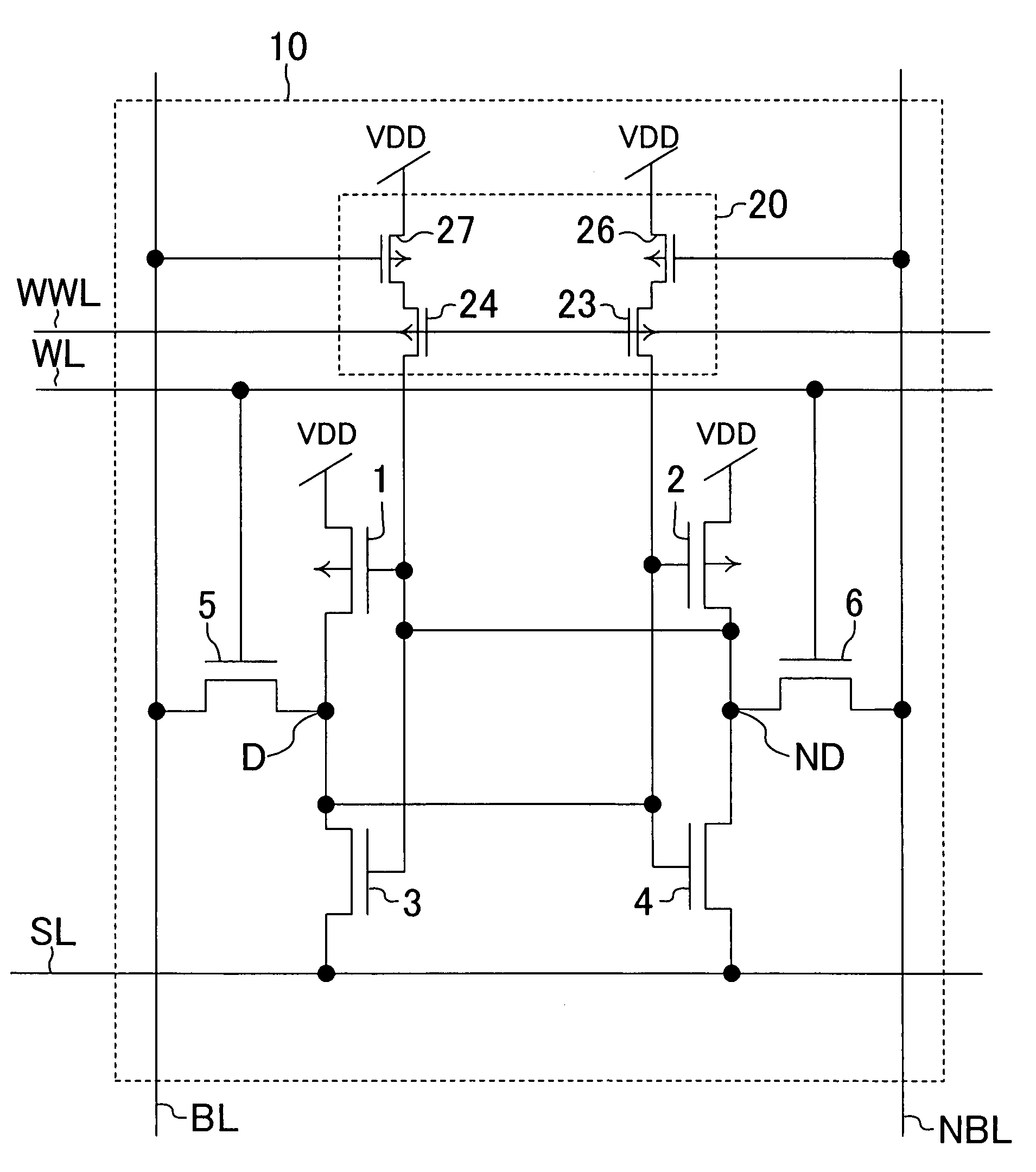

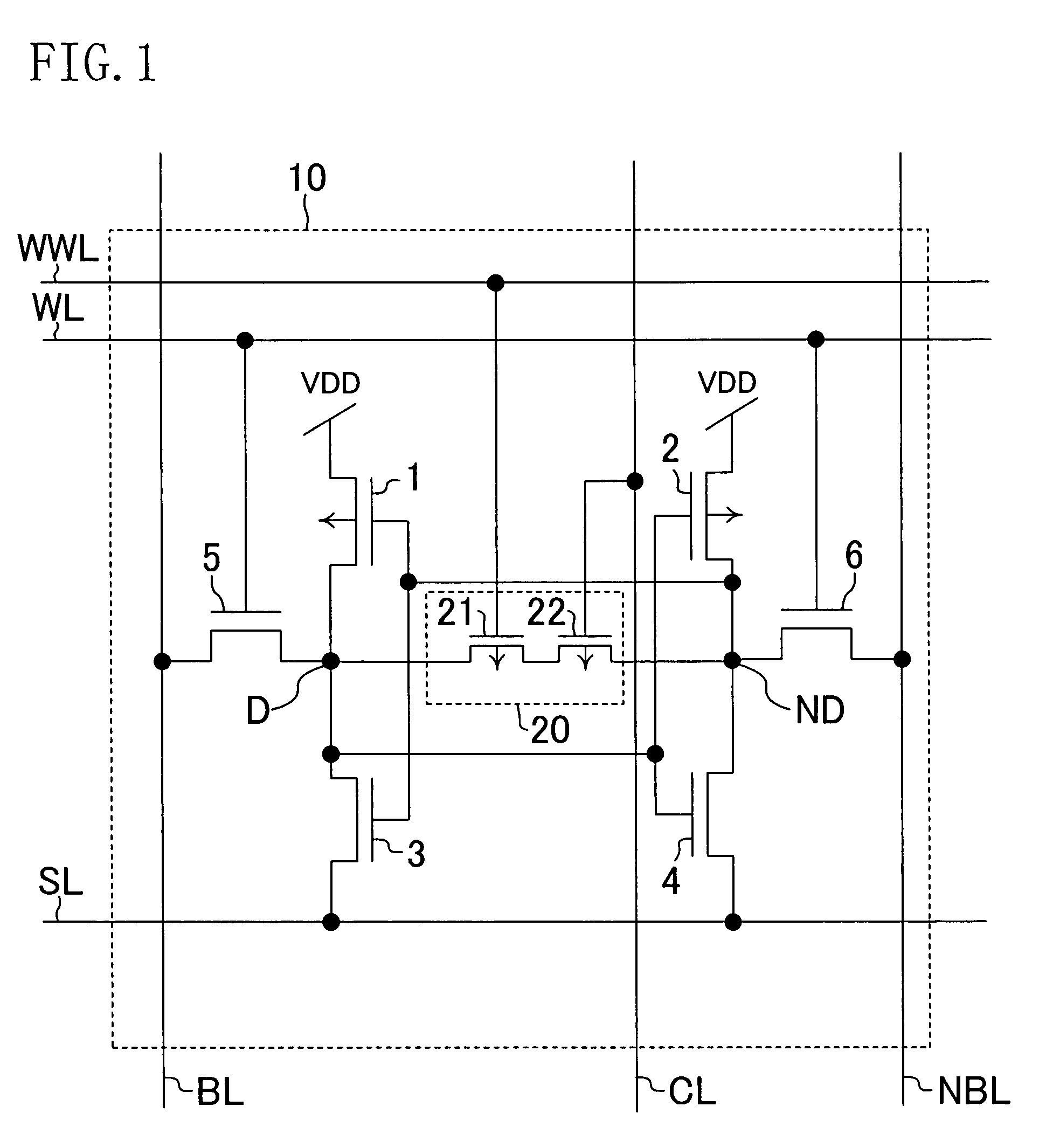

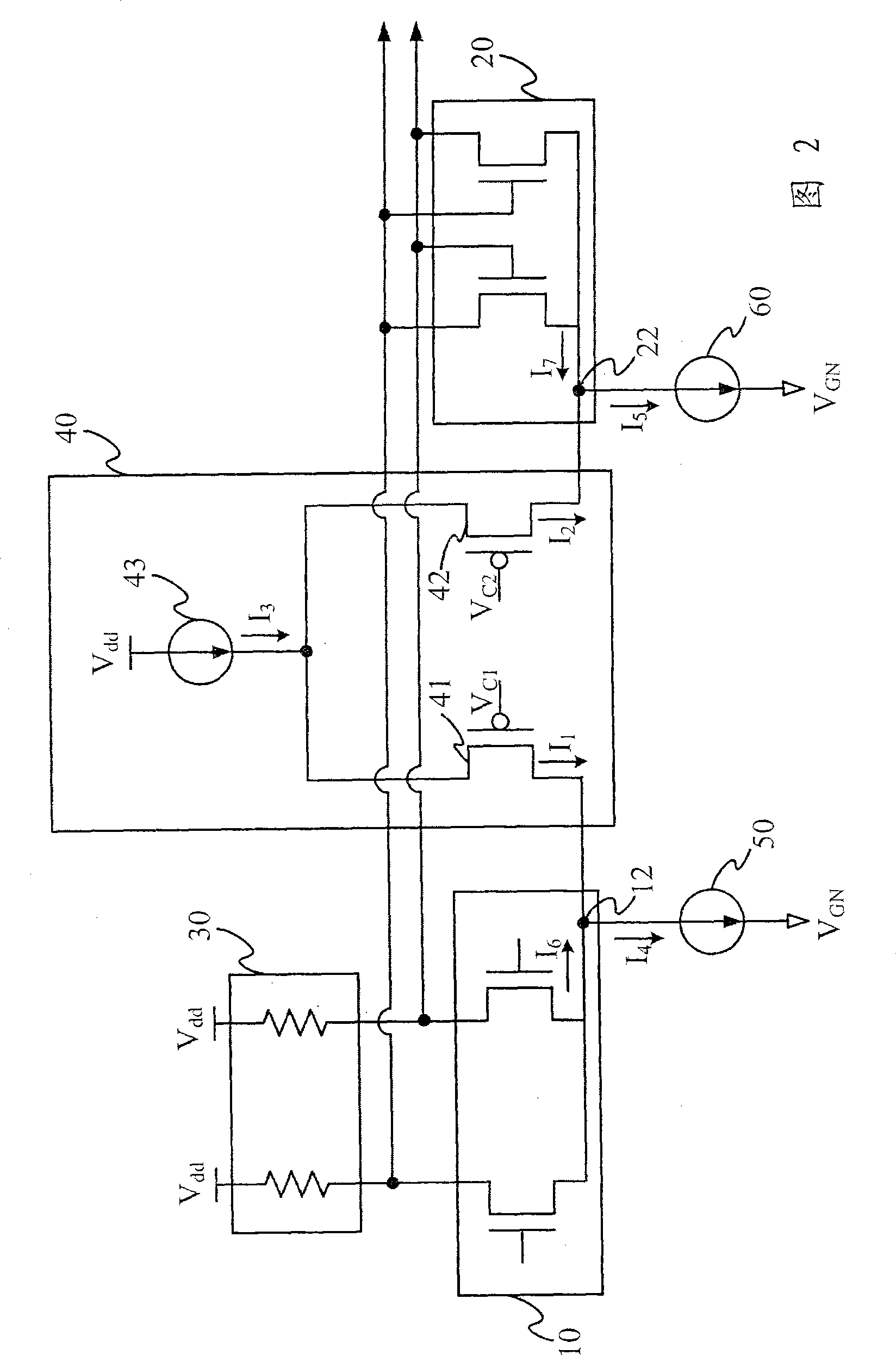

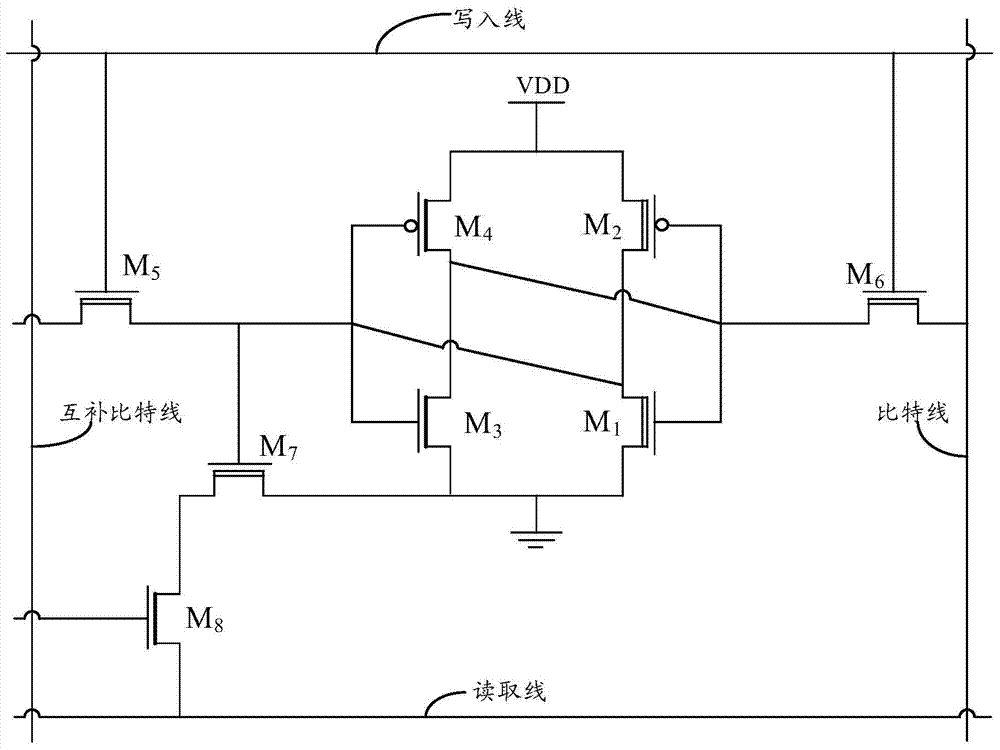

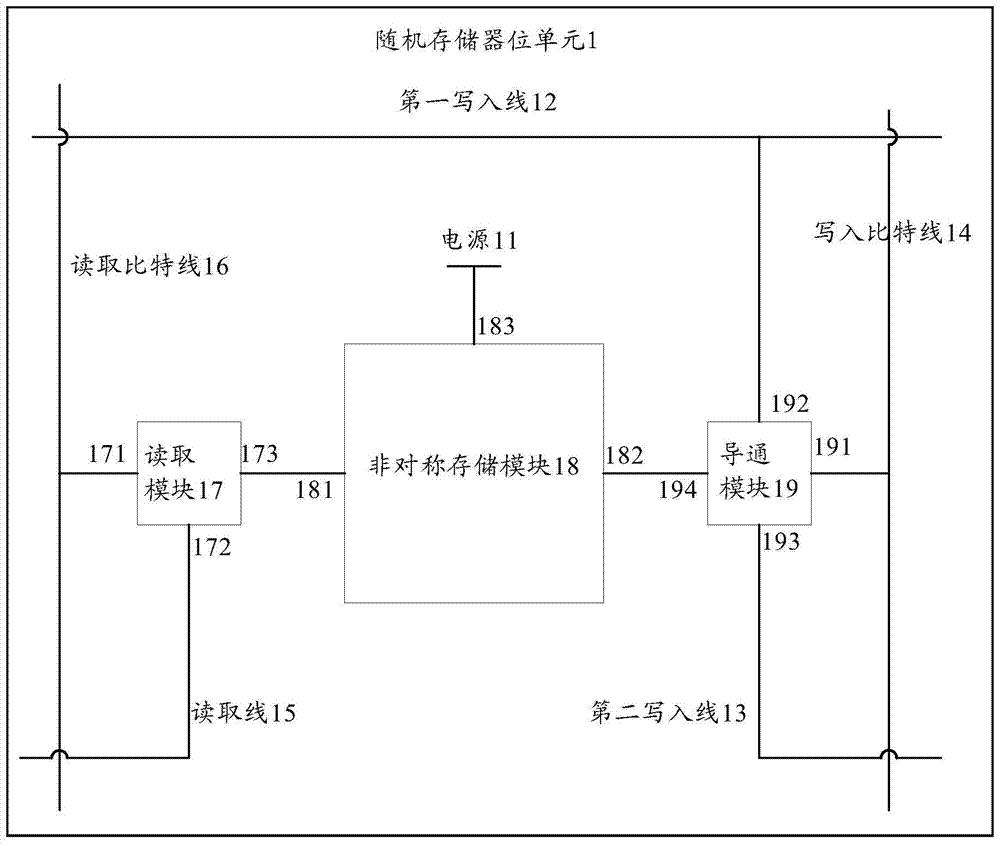

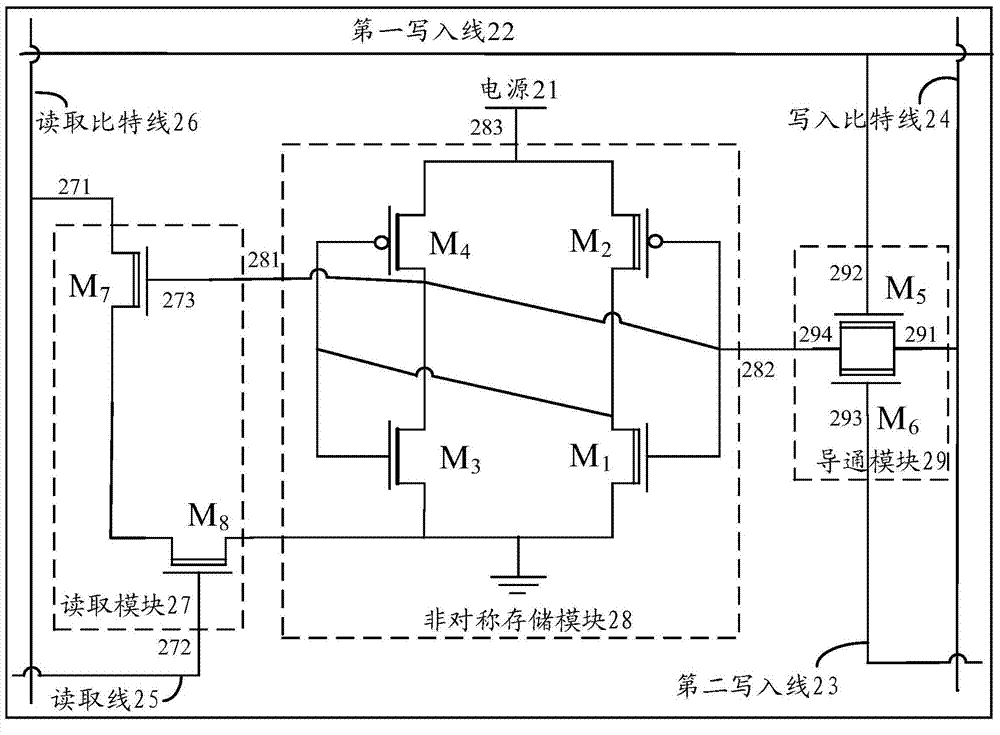

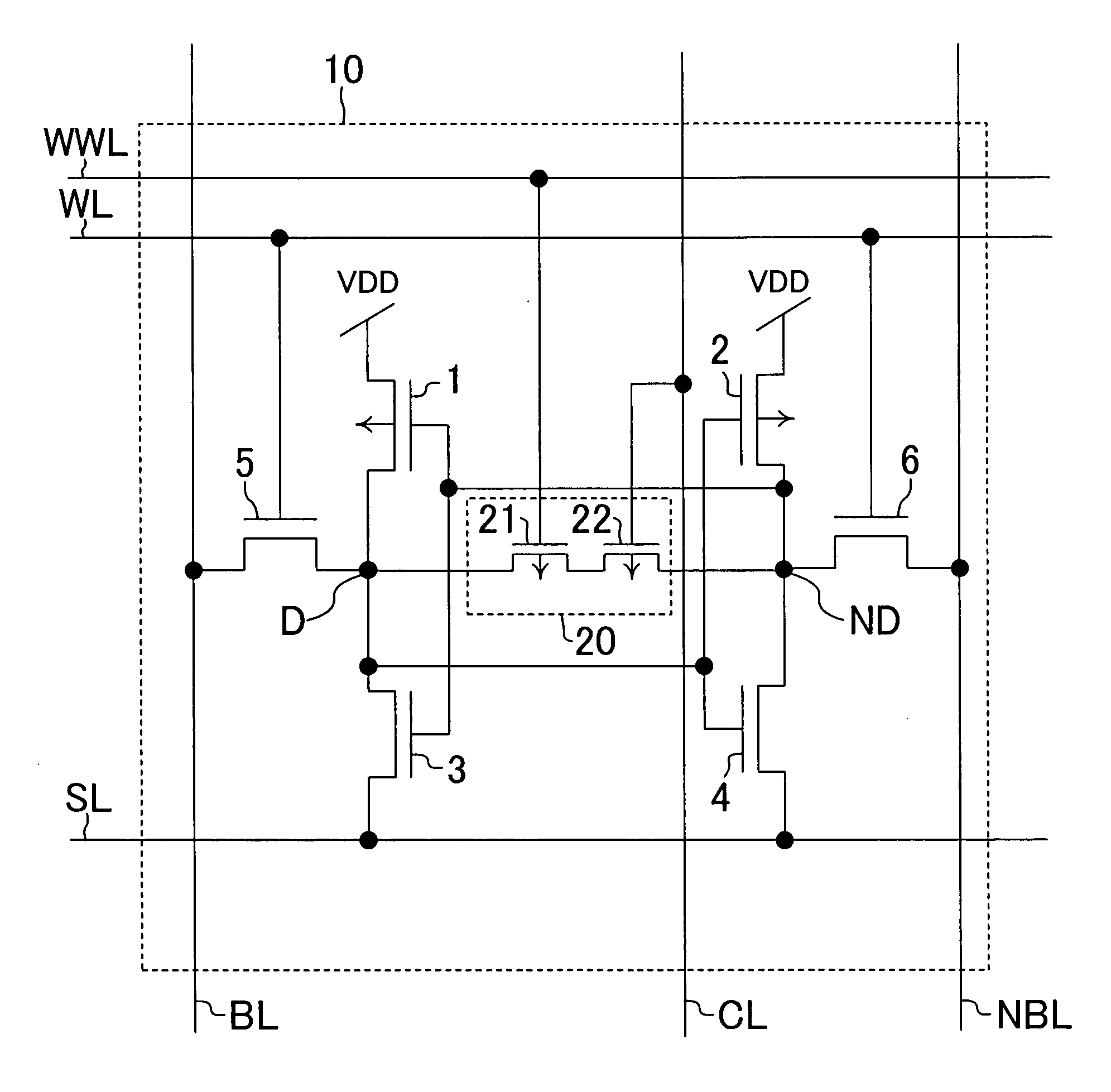

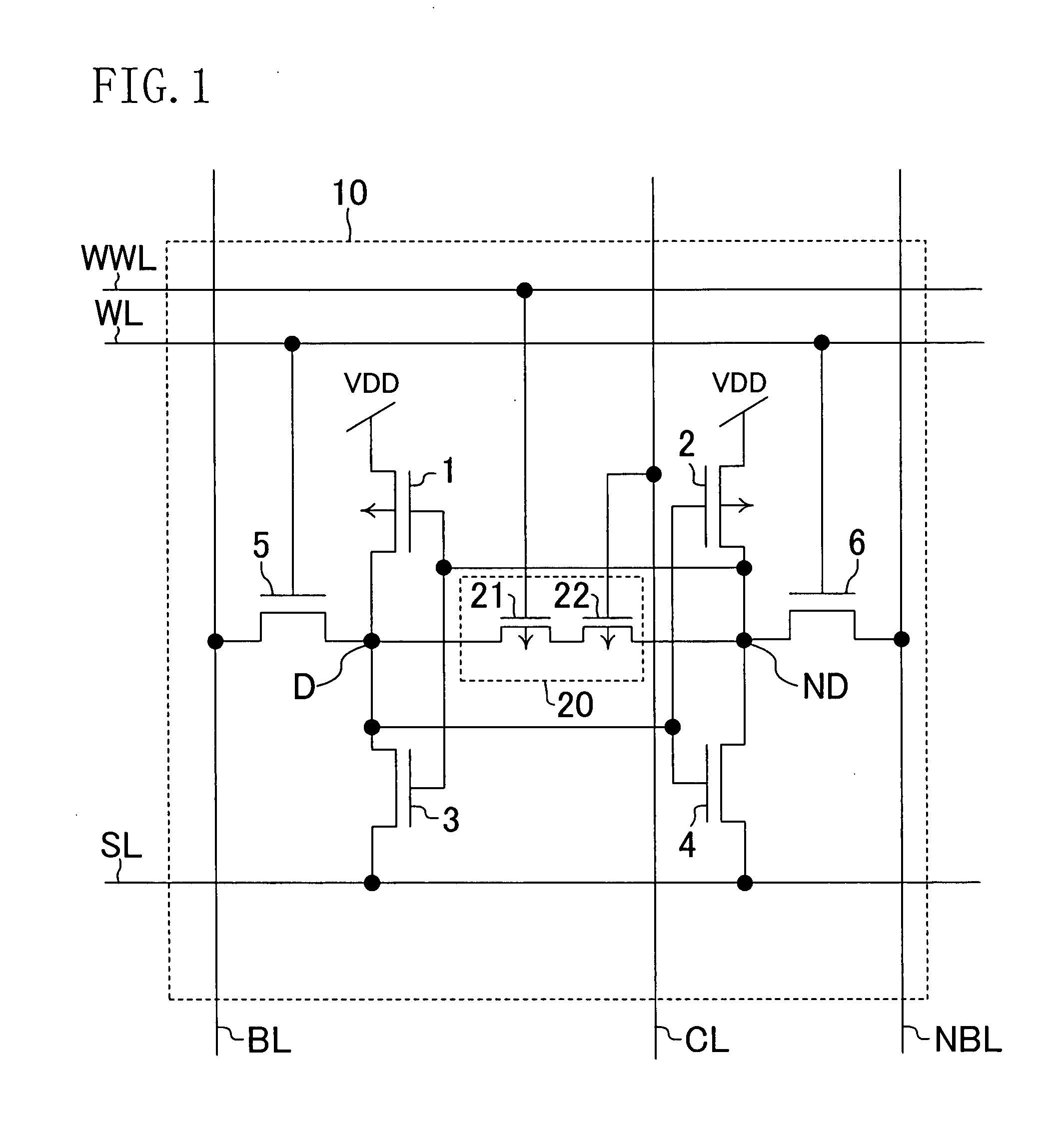

Random access memory bit cell, random access memory and electronic chip

ActiveCN103928051AIncrease voltage marginImprove reliabilityDigital storageStatic random-access memoryRandom access memory

The embodiment of the invention provides a random access memory bit cell, a random access memory and an electronic chip, belonging to the field of storages, and aiming at solving the problems of reliability and power consumption of the memory. The random access memory bit cell comprises at least one power supply, a first write-in wire, a second write-in wire, a write-in bit wire, a reading wire, a reading bit wire, a reading module, an asymmetrical storage module and a conduction module. The random access memory consists of the random access memory bit cells with preset number; the electronic chip comprises the random access memory. The reliability and the power consumption of the random access memory can be optimized.

Owner:HUAWEI TECH CO LTD

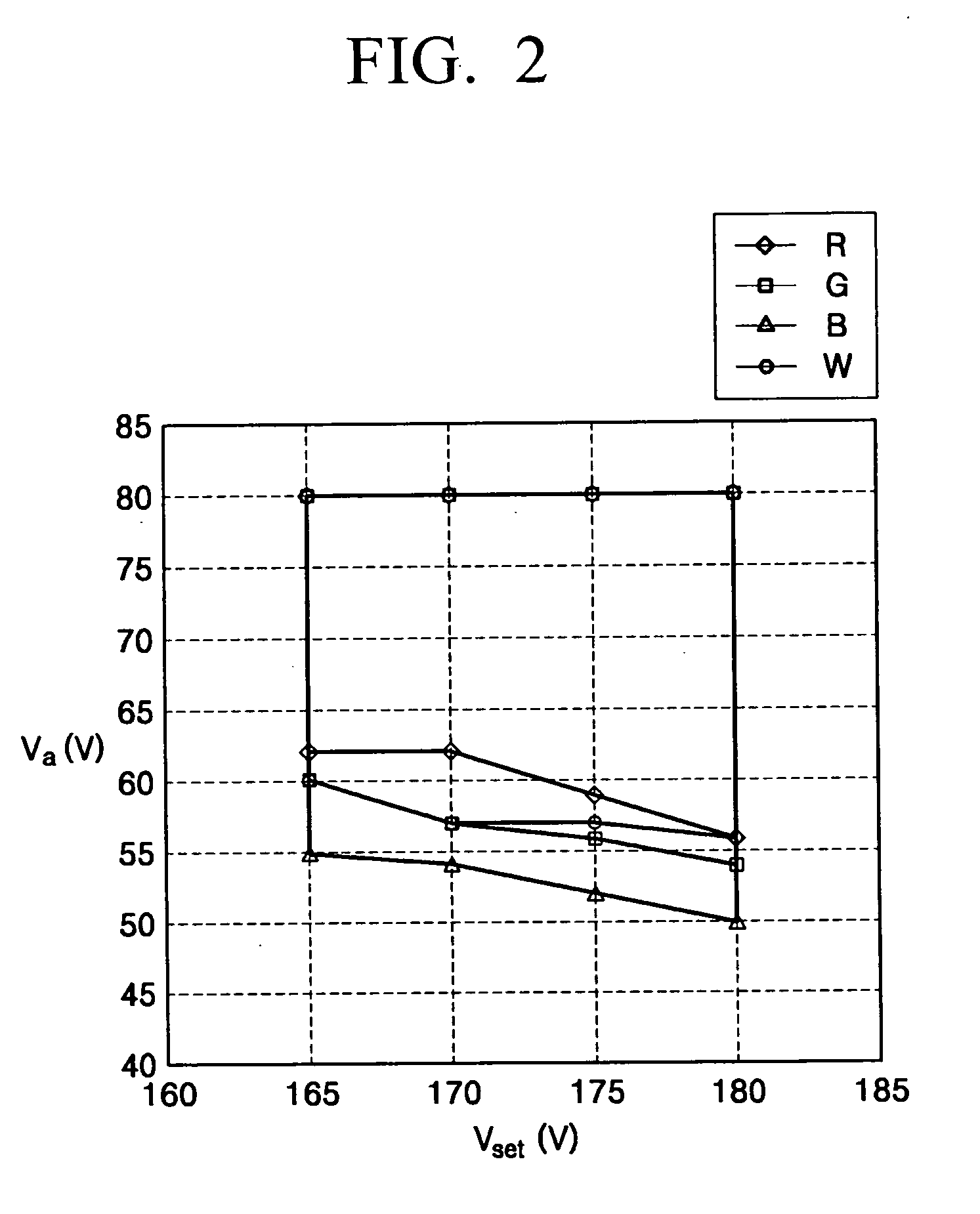

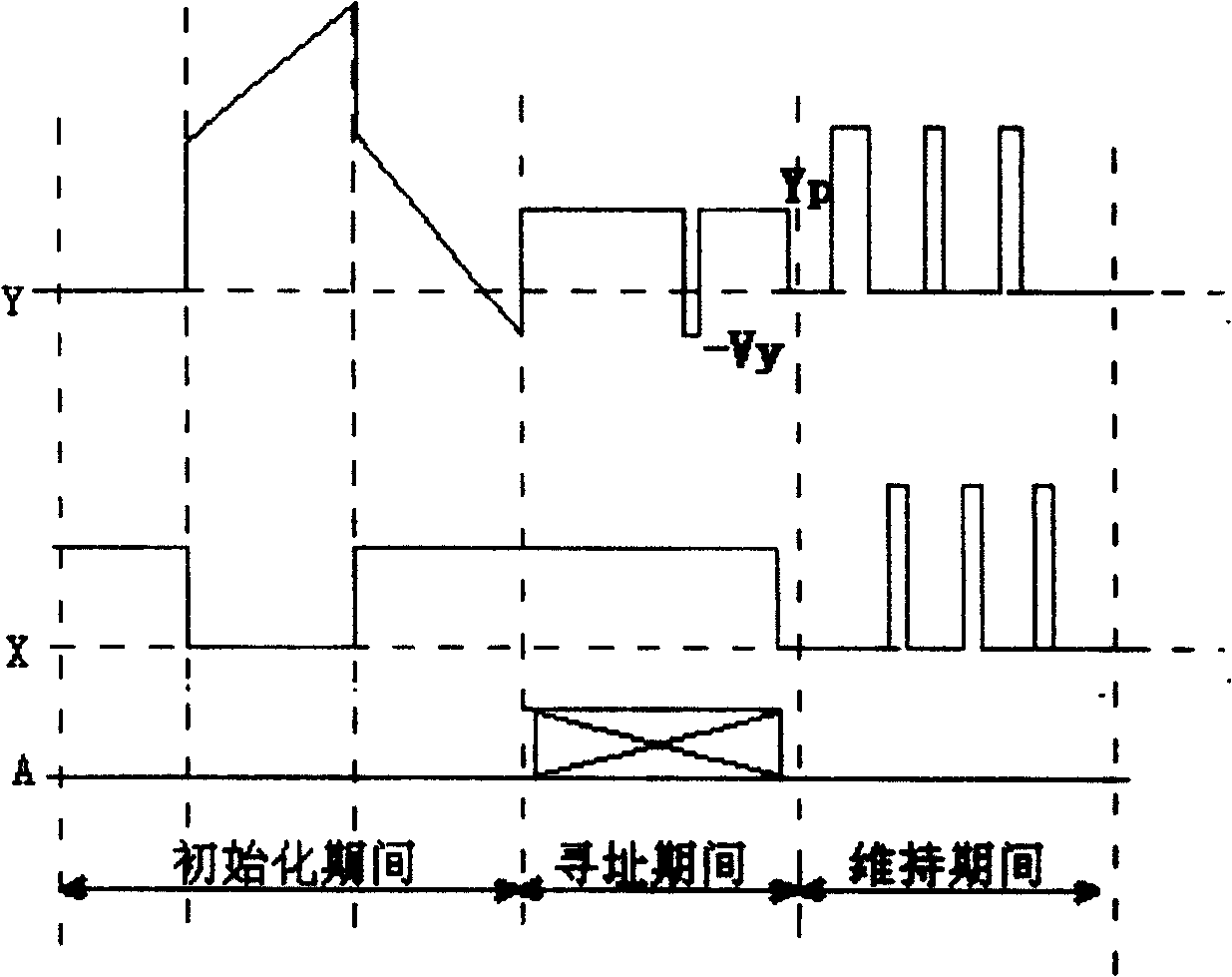

Method for improving scan pulse voltage to reduce power consumption

InactiveCN100447837CIncrease voltage marginImprove picture qualityStatic indicating devicesCold-cathode tubesImaging qualityEngineering

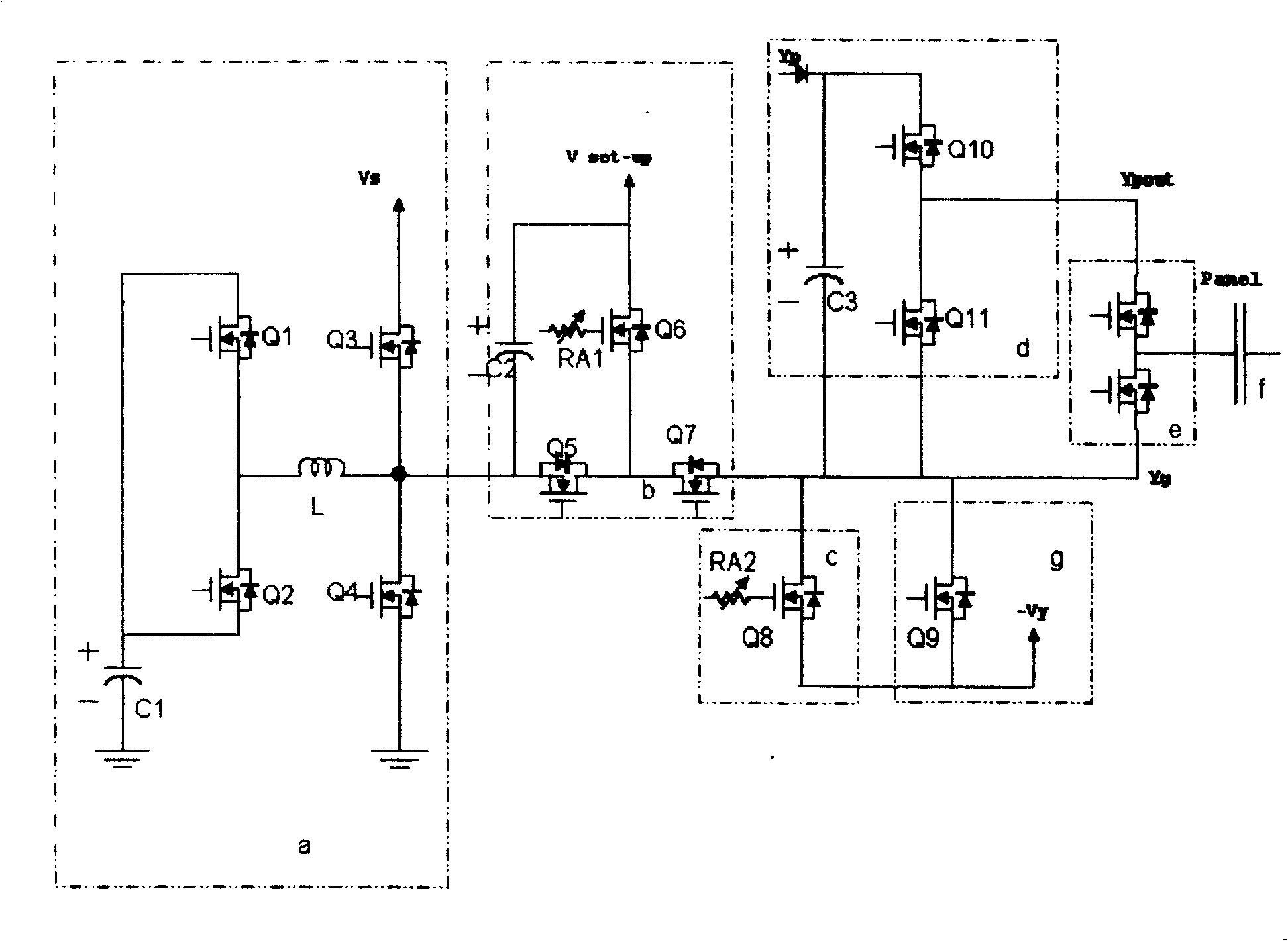

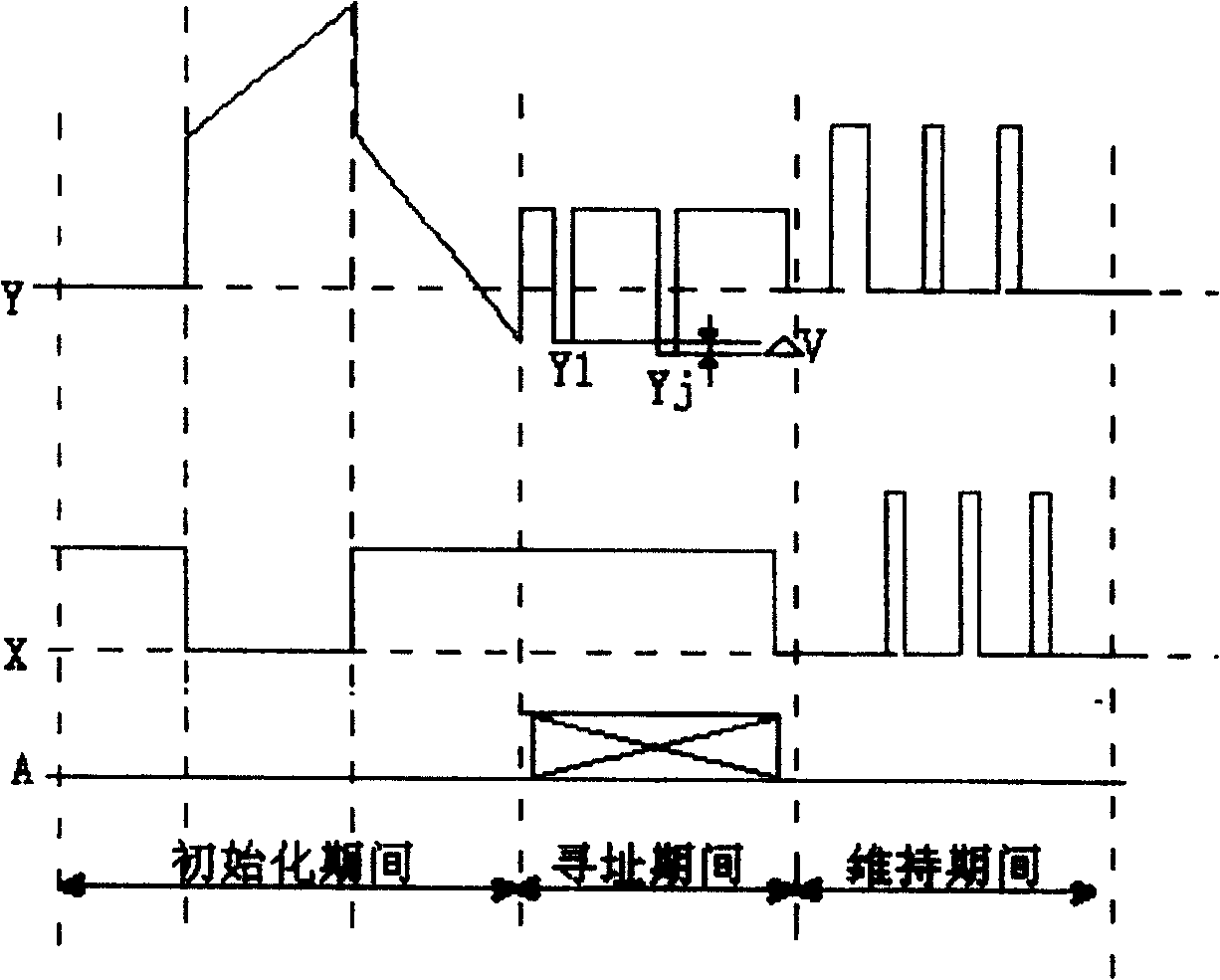

The invention discloses a method for improving the scanning pulse voltage and reducing power consumption. By improving the scanning pulse voltage and adjusting the step voltage of the scanning driving voltage, the purpose of increasing voltage margin and reducing power consumption is finally achieved. Each subfield is divided into an initialization period, an address period, and a sustain period. The formation circuit during the initialization period is composed of the formation circuit b of the rising edge of the ramp and the formation circuit c of the falling edge of the ramp; the formation circuit during the addressing period is composed of a step voltage The formation circuit d of Yp, the formation circuit g of negative pressure-Vy and the scanning chip e are formed; the formation circuit during the maintenance period is composed of the energy recovery circuit a; the invention can increase the voltage margin, reduce power consumption, and improve image quality.

Owner:四川世纪双虹显示器件份有限公司

Semiconductor memory device

InactiveUS20080094879A1Improve featuresIncrease voltage marginDigital storageHemt circuitsEngineering

A storage node voltage control circuit is added to a memory cell including two load transistors, two drive transistors and two access transistors. The storage node voltage control circuit performs control so that in writing data into the memory cell, a voltage at one of the two storage nodes holding a low logic level is raised without changing voltages at respective sources of the load transistors.

Owner:SOCIONEXT INC

Plasma display apparatus and driving method thereof

InactiveUS20050168412A1Increase brightnessQuality improvementTelevision system detailsStatic indicating devicesEngineeringDouble frequency

Owner:SONY CORP

Semiconductor memory device with data bus scheme for reducing high frequency noise

InactiveCN1467850ALow costReduce high frequency noiseSemiconductor/solid-state device detailsCross-talk/noise/interference reductionCapacitanceLow frequency band

A semiconductor memory device includes memory modules which have memories and a data bus which transfers data to the memory modules, in which the data bus comprises a low frequency band data pass unit which removes the high frequency component of the data and sends the data to the memory modules. The low frequency band data pass unit comprises a plurality of stubs which are connected to the data bus in parallel and are formed as printed circuit board (PCB) patterns. The low frequency band data pass unit comprises a plurality of plates that are connected to the data bus in parallel and are formed as PCB patterns. The low frequency band data pass unit has a shape in which parts having a wide width and parts having a narrow width are alternately connected. Therefore, without adding a separate passive device, the semiconductor memory device reduces the high frequency noise of data transferred through a data bus such that the voltage margin of the data improves, the cost for passive devices such as capacitors, is reduced, and the process for attaching the passive devices is simplified.

Owner:SAMSUNG ELECTRONICS CO LTD

Phase change memory device with improved performance that minimizes cell degradation

ActiveUS20110255333A1Improve writing stabilityImprove reliabilityDigital storageAudio power amplifierPhase-change memory

A phase change memory device having an improved performance that minimizes cell degradation is presented. The phase change memory device includes: a cell array, a sense amplifier, a write driving unit, and a reference level selecting unit. The cell array has a phase change resistor is configured to read / write data. The sense amplifier is configured to compare a reference voltage with a sensing voltage received from the cell array. The write driving unit is configured to supply a driving voltage corresponding to write data to the cell array. The reference level selecting unit is configured to select a read reference voltage in a read mode so as to output the reference voltage, and to select a reference voltage corresponding to input data in a write verifying mode so as to output the reference voltage.

Owner:SK HYNIX INC

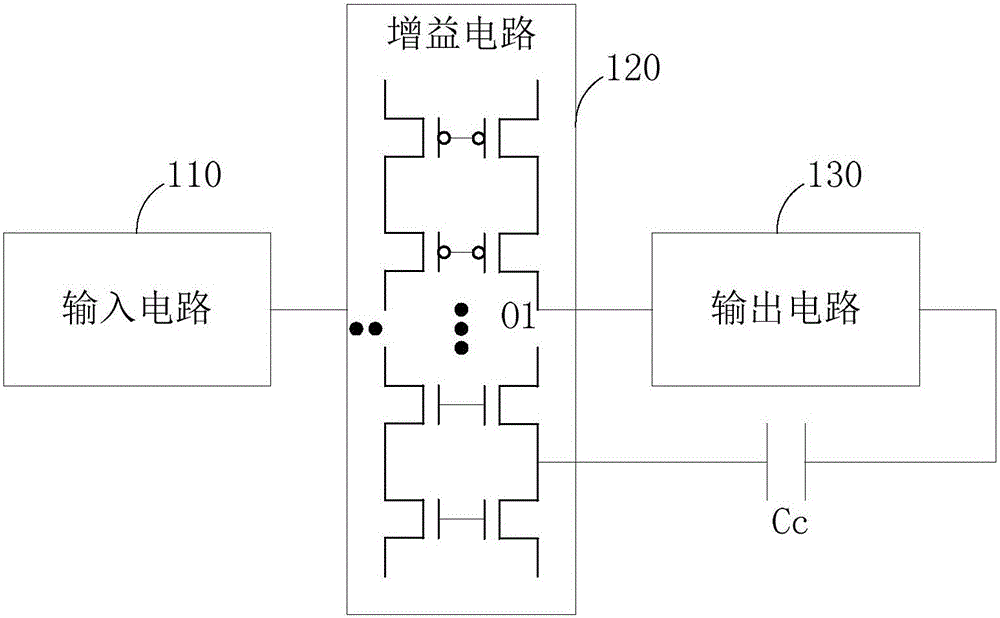

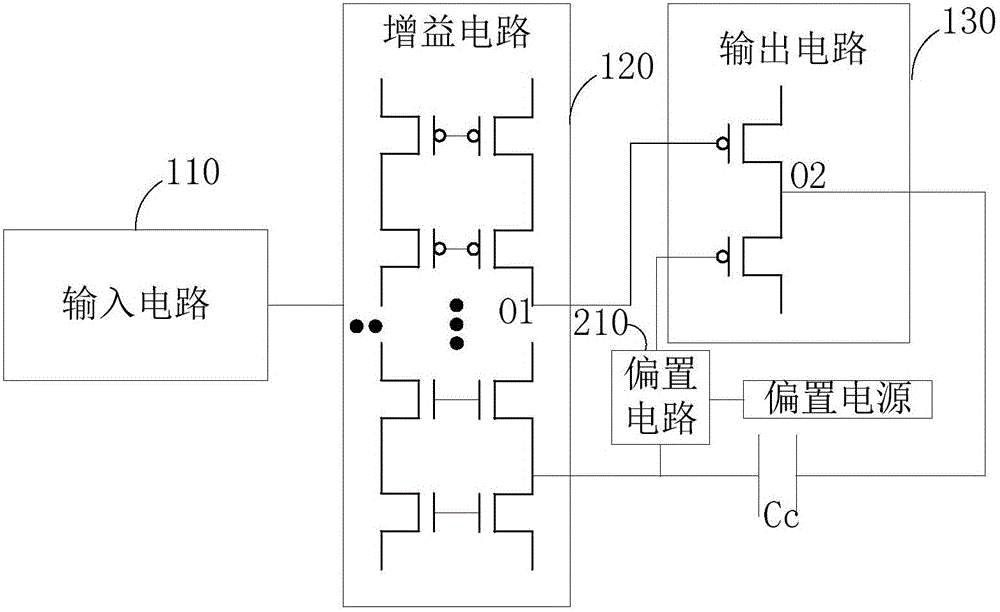

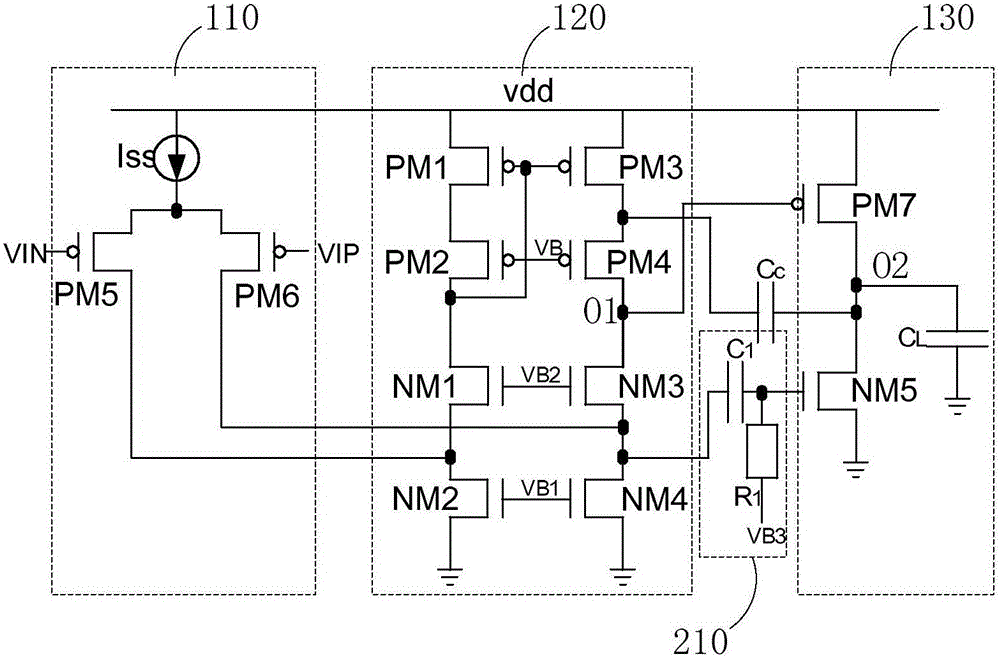

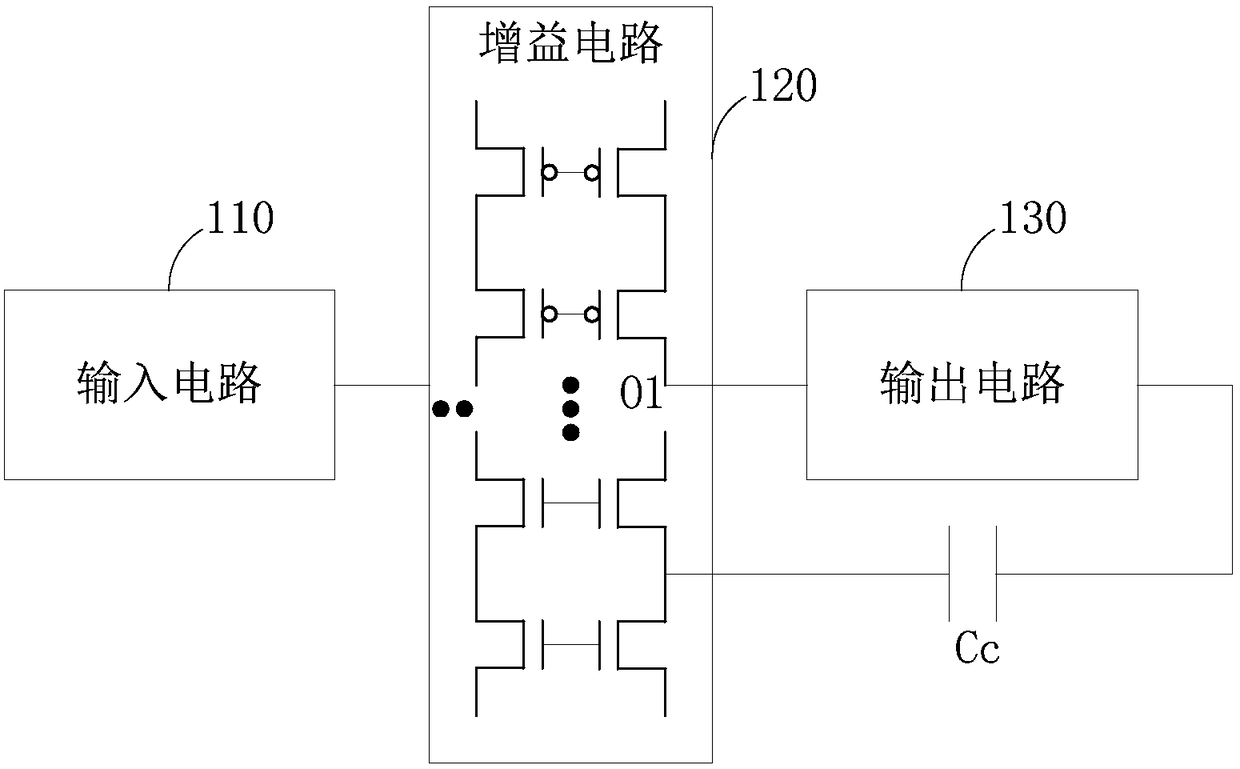

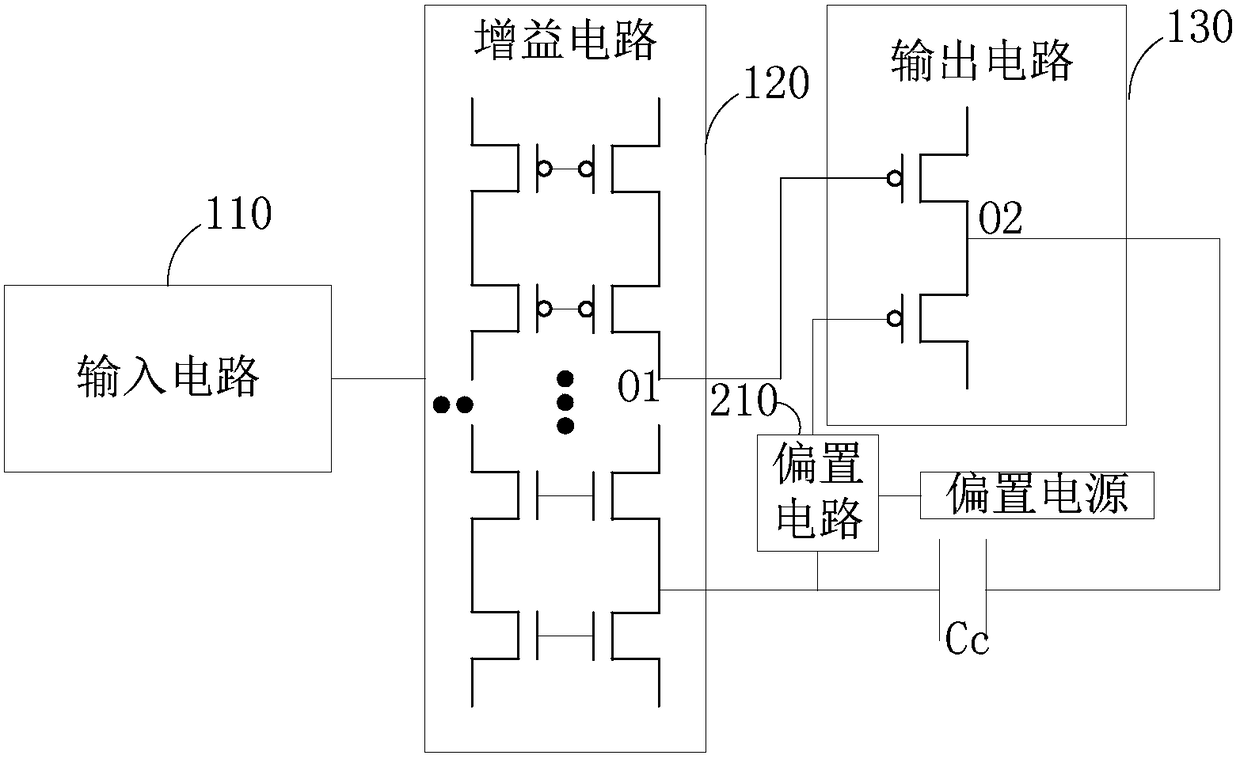

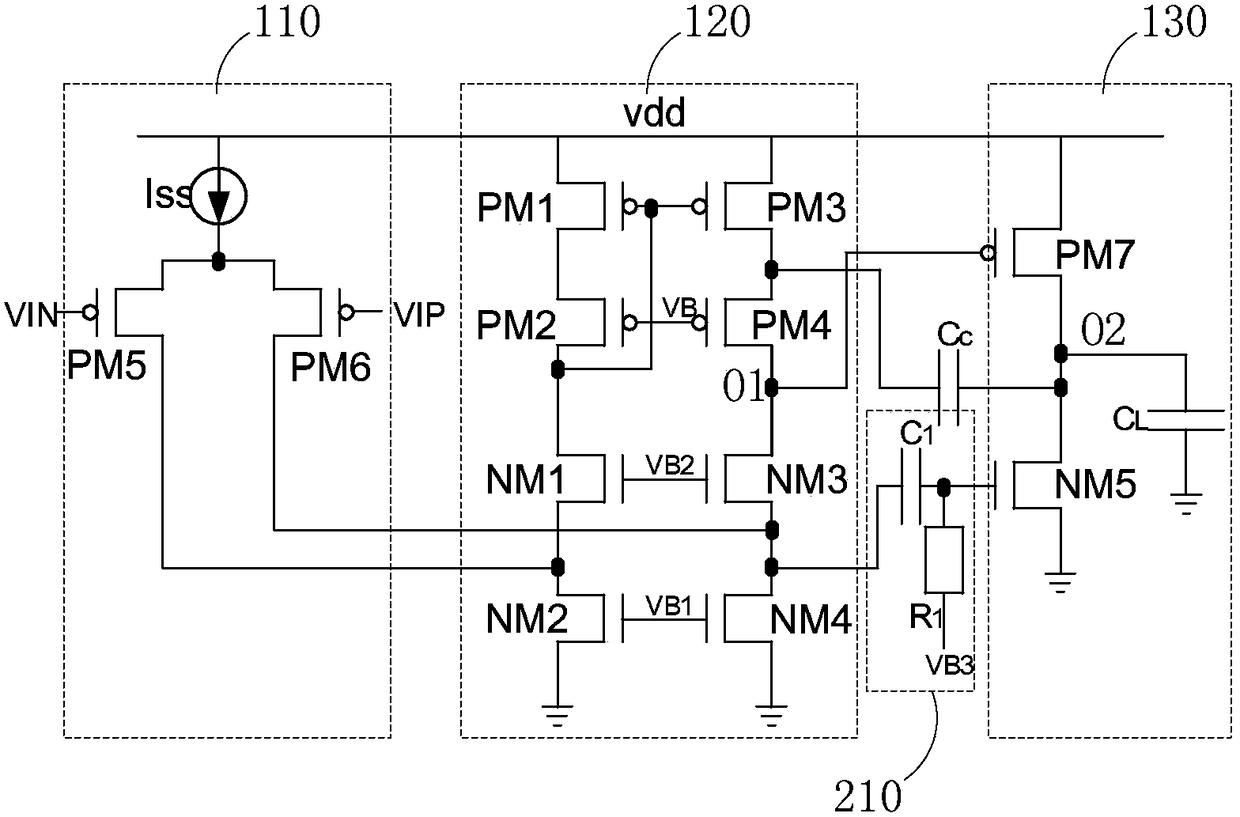

Transconductance amplifier

ActiveCN105915188AIncrease the dominant pole frequencyIncrease the capacitance of the compensation capacitor to reduce the dominant pole frequencyDifferential amplifiersAmplifier modifications to extend bandwidthTransistor arrayCapacitance

The present invention provides a transconductance amplifier comprising an input circuit, a gain circuit and an output circuit which are successively connected. The gain circuit comprises a MOS transistor array composed of a plurality of MOS transistors, grids of the corresponding MOS transistors between every two adjacent columns of the MOS transistor array are connected, the MOS transistors in each column of the MOS transistors are successively connected, and compensation capacitors are arranged between asymmetrical connection points of the MOS transistors in the output column of the MOS transistor array and an output terminal of the output circuit. According to the transconductance amplifier, compared with a traditional frequency compensation technology, dominant pole frequency of the transconductance amplifier can be reduced through increasing capacitance values of the compensation capacitors, right half plane zero frequency of the transconductance amplifier can also be prevented from being reduced, so that a distance between the dominant pole frequency and the right half plane zero frequency of the transconductance amplifier can be increased, the influence of frequency compensation on frequency characteristics of the transconductance amplifier can be reduced, unity-gain bandwidth of the transconductance amplifier can be improved, and the problem that the transconductance amplifier is possibly unstable can be solved.

Owner:NO 24 RES INST OF CETC

Field Weakening Control Method of Built-in Permanent Magnet Synchronous Motor Based on Torque Feedforward Control Technology

ActiveCN107749727BAchieve maximum utilizationGuaranteed stabilityElectronic commutation motor controlElectric motor controlMotor speedPermanent magnet synchronous motor

The invention discloses a field weakening control method for a built-in permanent magnet synchronous motor based on a torque feedforward control technology, which mainly comprises a stator flux adjustment module, a current data table, a current regulator, a pulse width modulation module, dq-[alpha][beta] transformation, Park transformation, an uncontrolled rectifier bridge and an inverter, and ischaracterized in that the stator flux adjustment module calculates an appropriate stator flux set value to serve as the output according to an input torque set value, DC bus voltage, motor speed and amodulation factor; the stator flux adjustment module comprises seven modules I-VII, wherein the module I is a one-dimensional table and records the corresponding minimum stator flux at different given torques. The field weakening control method realizes the maximization of torque output of the motor in a field weakening area through introducing a proportionality factor into stator flux adjustment, and ensures the stability of the torque at the same time. The factor automatically changes in size according to operating conditions of the current motor, the voltage margin is improved when the speed is high and the torque is low, the torque output capacity is improved when the speed is high and the torque is large, and thus the maximum utilization ratio of the DC bus voltage is achieved.

Owner:ZHEJIANG UNIV

transconductance amplifier

ActiveCN105915188BIncrease the dominant pole frequencyIncrease the capacitance of the compensation capacitor to reduce the dominant pole frequencyDifferential amplifiersAmplifier modifications to extend bandwidthTransistor arrayCapacitance

Owner:NO 24 RES INST OF CETC

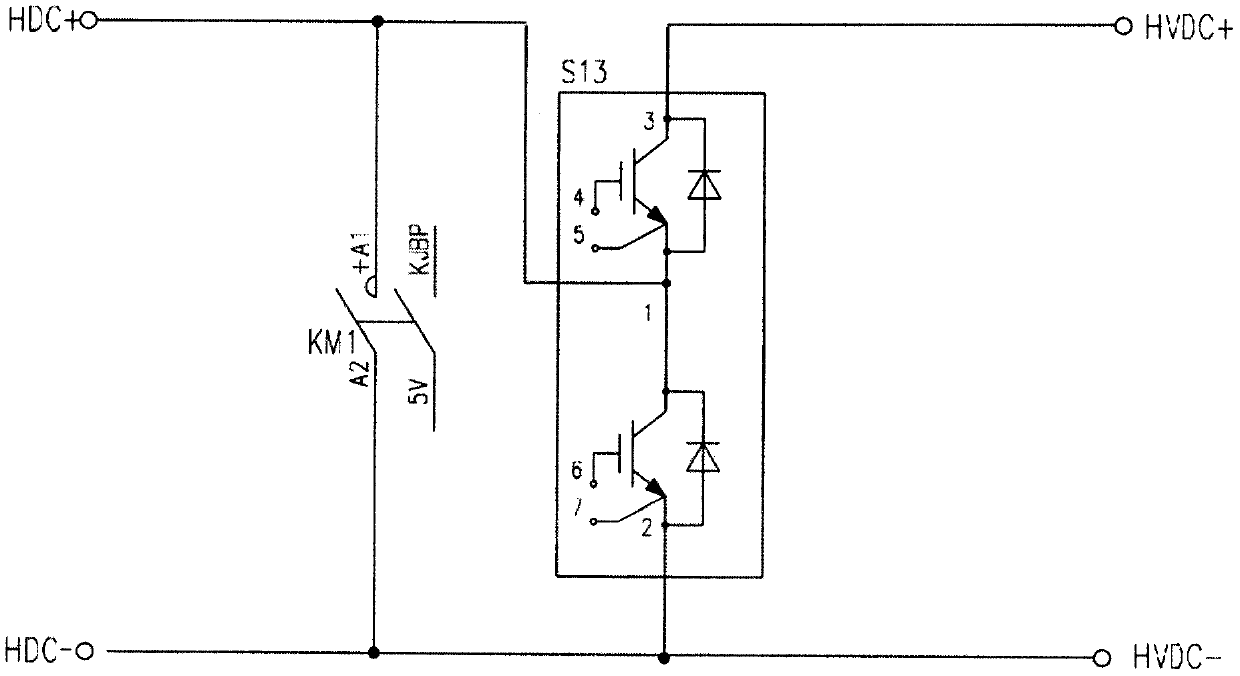

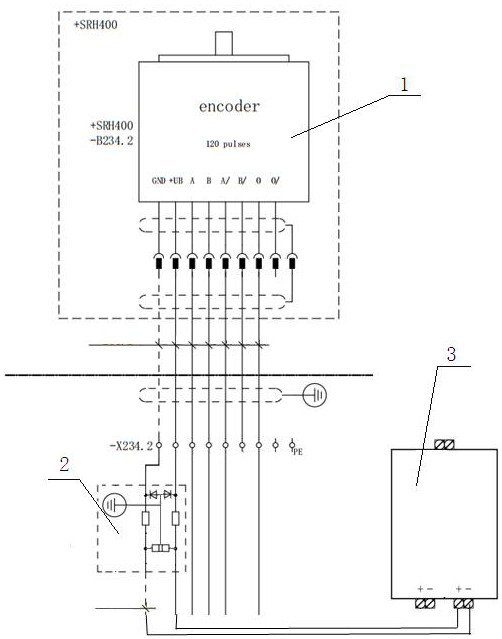

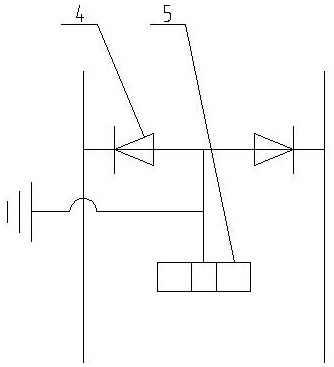

Power supply circuit for slip ring encoder of wind generating set

PendingCN114498593AIncrease voltage marginShort power supply distanceEmergency protective arrangements for limiting excess voltage/currentCapacitanceElectric control

Provided is a wind generating set slip ring encoder power supply circuit. The surge protector is far away from the slip ring encoder, the slip ring is installed in the hub, and a circuit can be connected to a master controller only through a hollow shaft of the gearbox. The device comprises an encoder (1) and a variable-pitch electric control cabinet, a power module (3) is additionally arranged in the variable-pitch electric control cabinet, and the power module is connected with the encoder; a lightning protection circuit (2) for preventing the encoder from being damaged by lightning stroke is connected to a circuit where the power supply module is connected with the encoder; the lightning protection circuit comprises two diodes (4) and a resistance-capacitance protector (5), the two diodes are connected in series and then connected with the resistance-capacitance protector in parallel, and the grounding end of the resistance-capacitance protector is connected with a series circuit formed by the two diodes and then grounded. The invention is used for supplying power to the slip ring encoder of the wind generating set.

Owner:HUANENG NEW ENERGY CO LTD SHANXI BRANCH

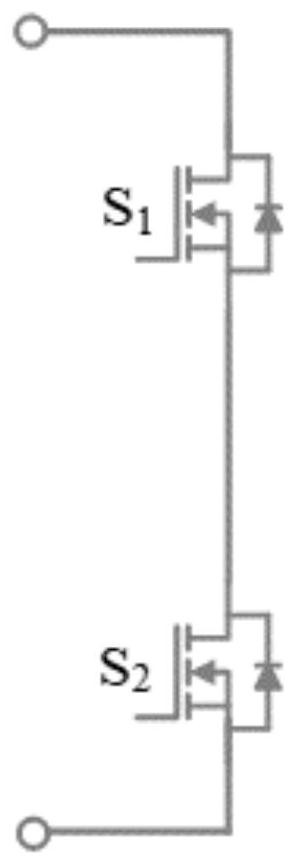

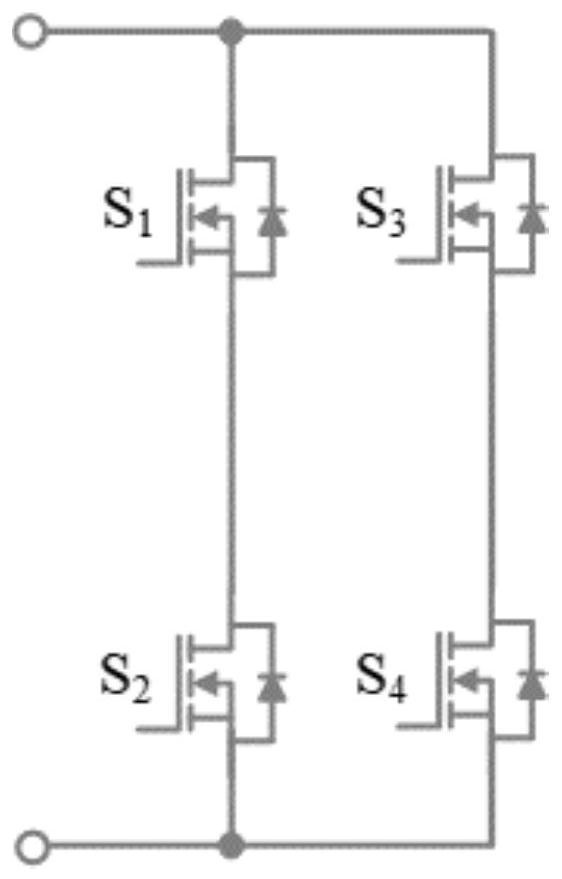

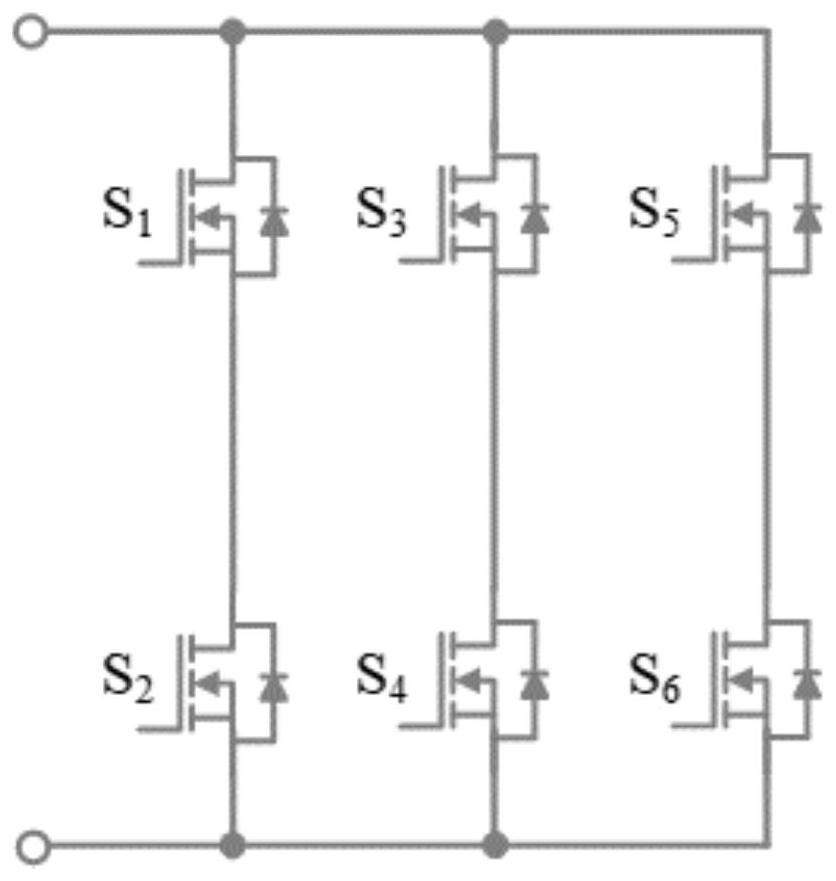

Silicon carbide power semiconductor module device integrated with buffer circuit

PendingCN113556030AReduce switching lossesReduce voltageEfficient power electronics conversionSemiconductor devicesCarbide siliconFull bridge

The invention provides a silicon carbide power semiconductor module device integrated with a buffer circuit. An active buffer circuit is integrated in a single-phase half-bridge, single-phase full-bridge or three-phase bridge type silicon carbide power semiconductor module, so that the switching loss of the silicon carbide power semiconductor module can be reduced, the oscillation and damping loss can be reduced, the voltage peak can be reduced, the silicon carbide power semiconductor module can work at a higher voltage, or a low-voltage-grade chip is selected to reduce the conduction loss, and the efficiency of the silicon carbide power electronic system is improved.

Owner:GUANGHUA LINGANG ENG APPL & TECH R&D (SHANGHAI) CO LTD