Patents

Literature

601results about How to "Minimize degradation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

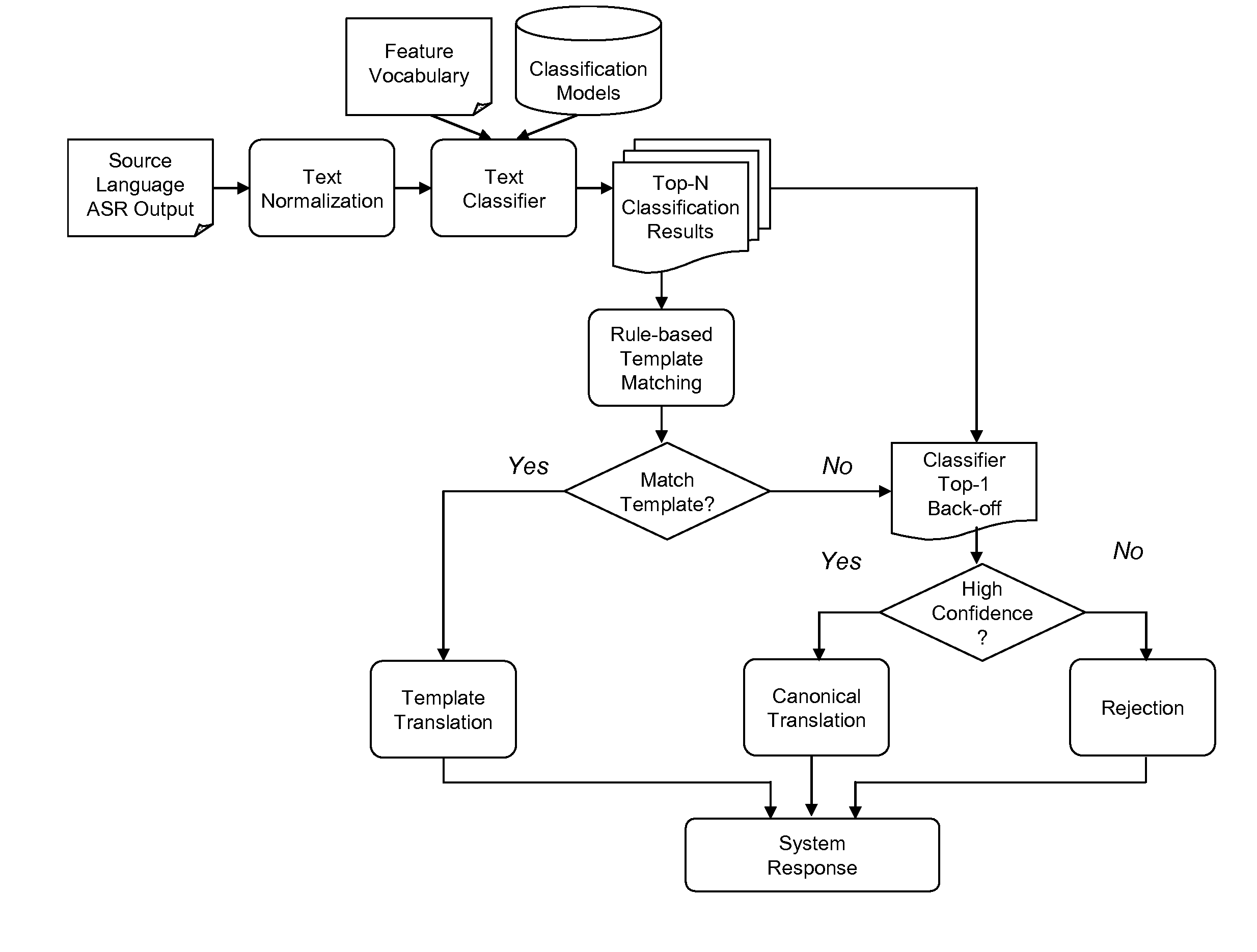

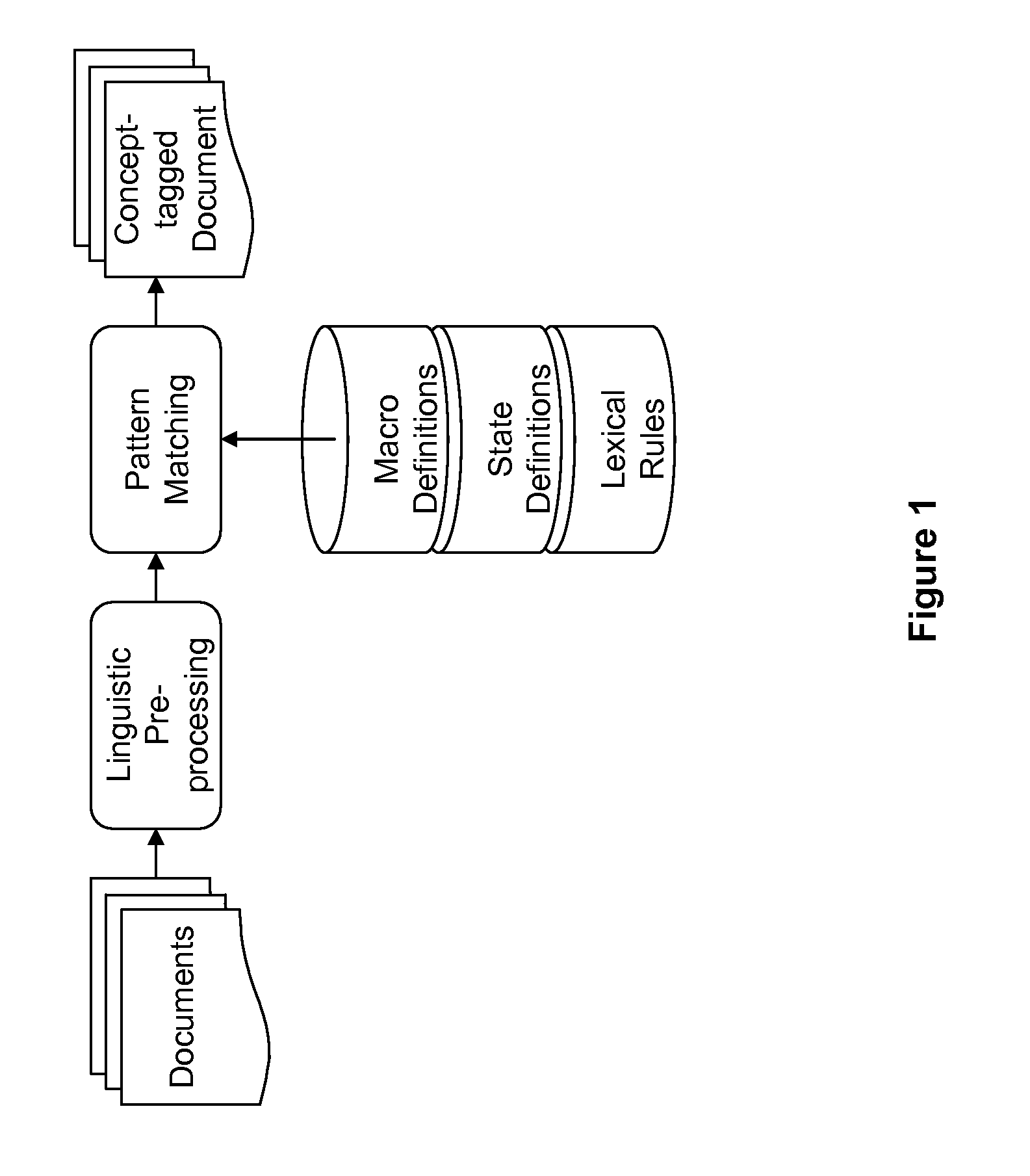

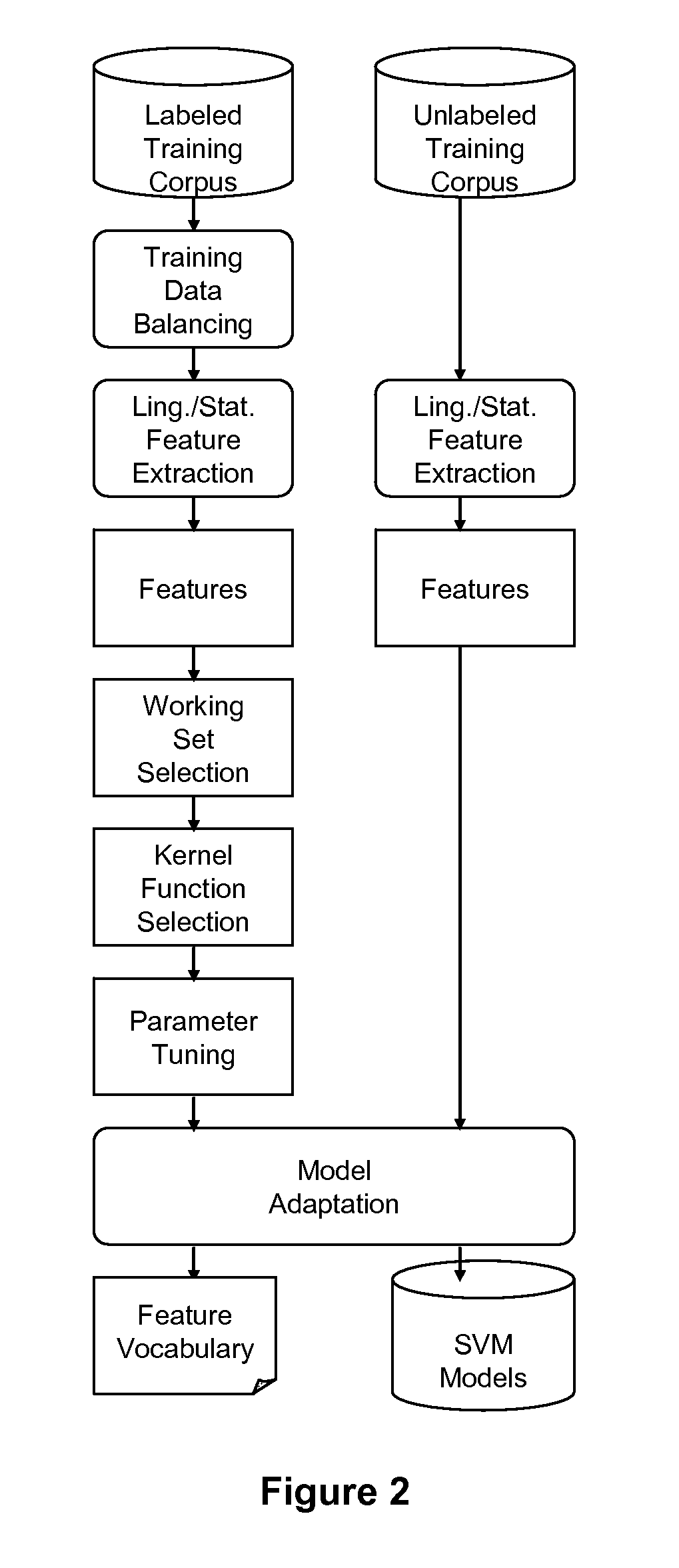

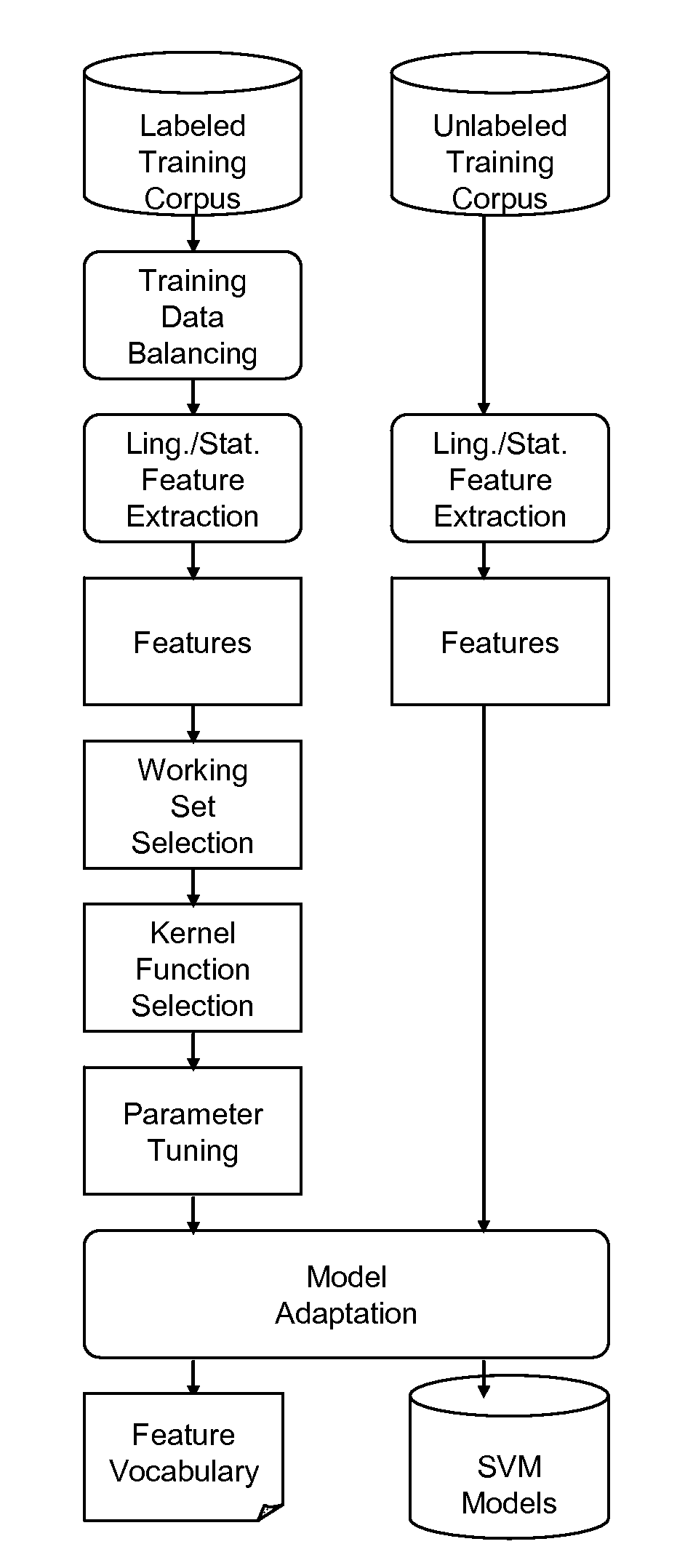

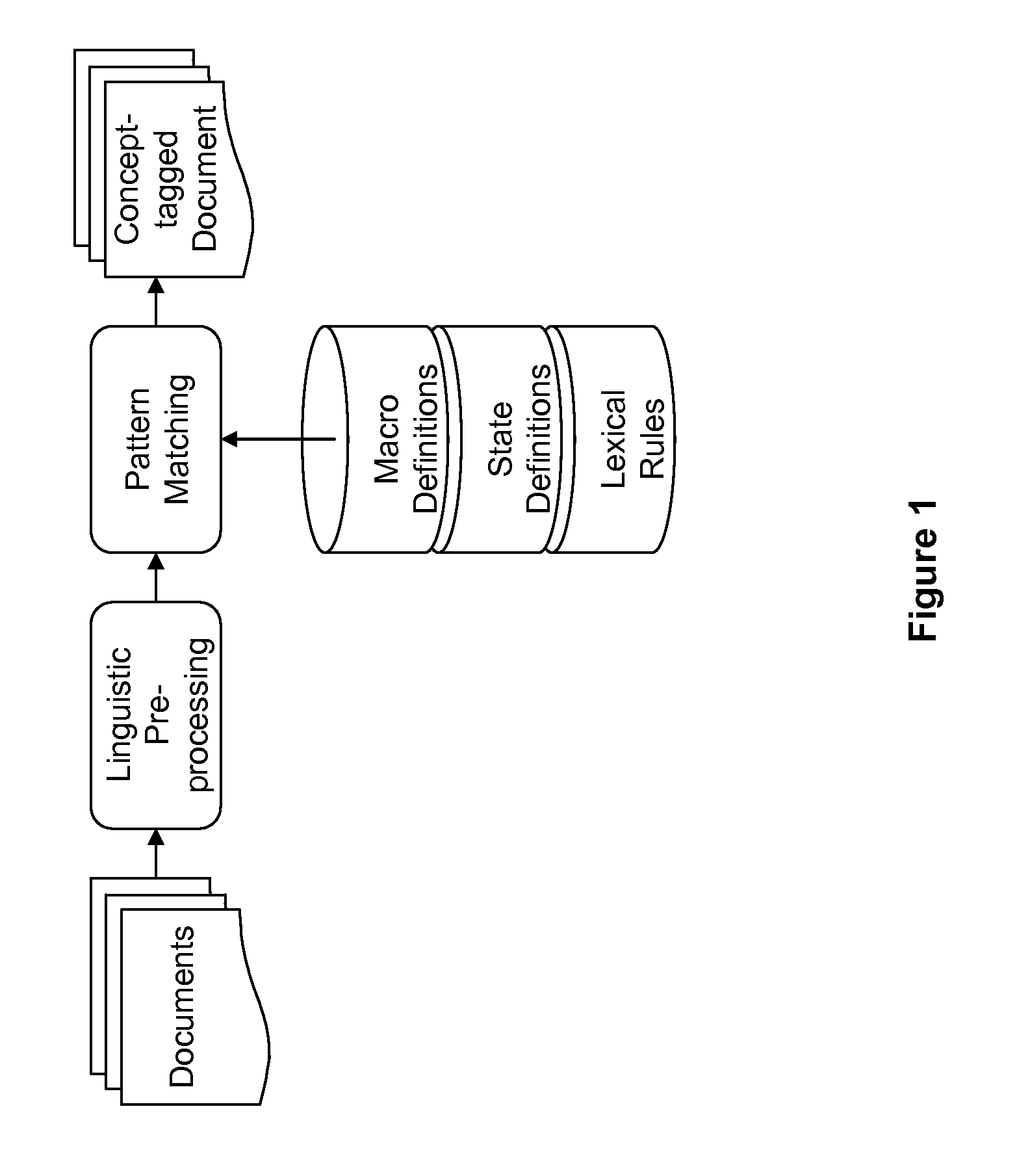

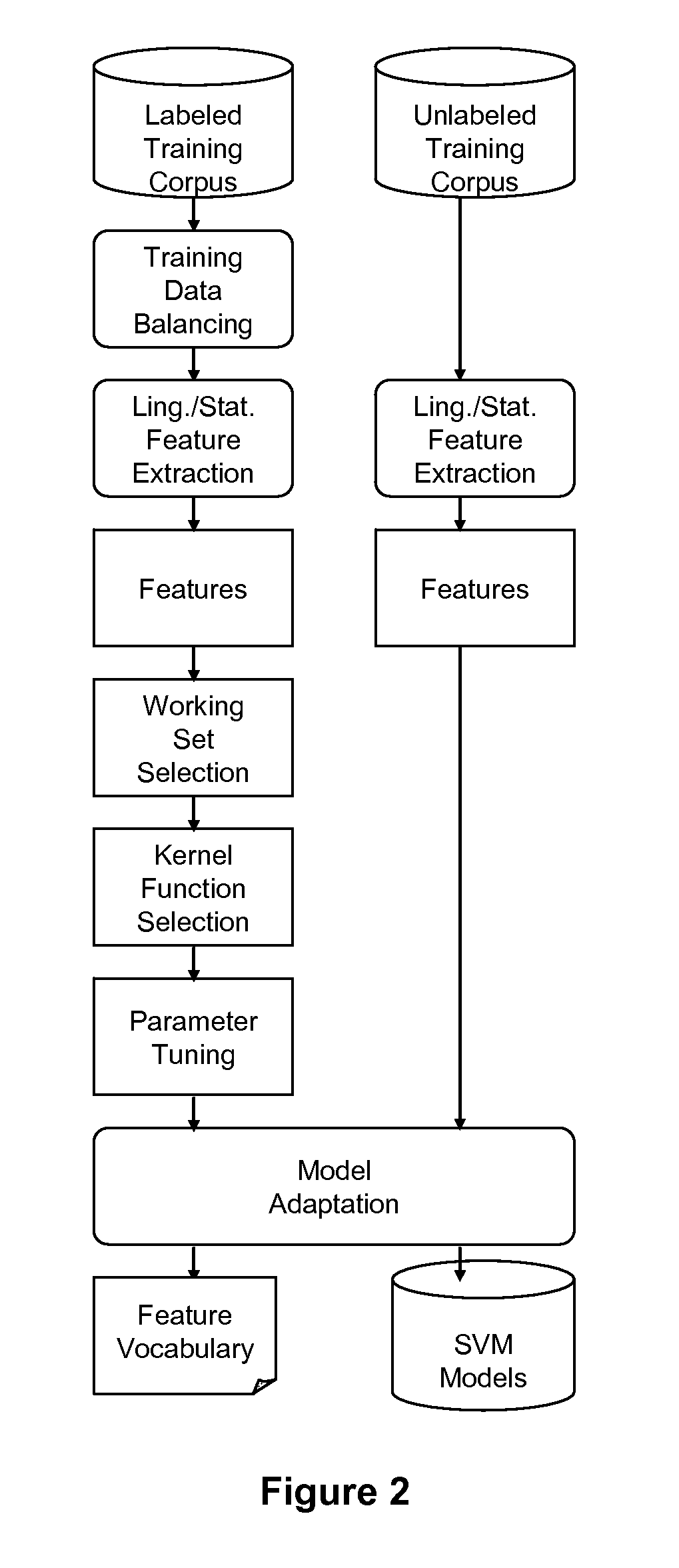

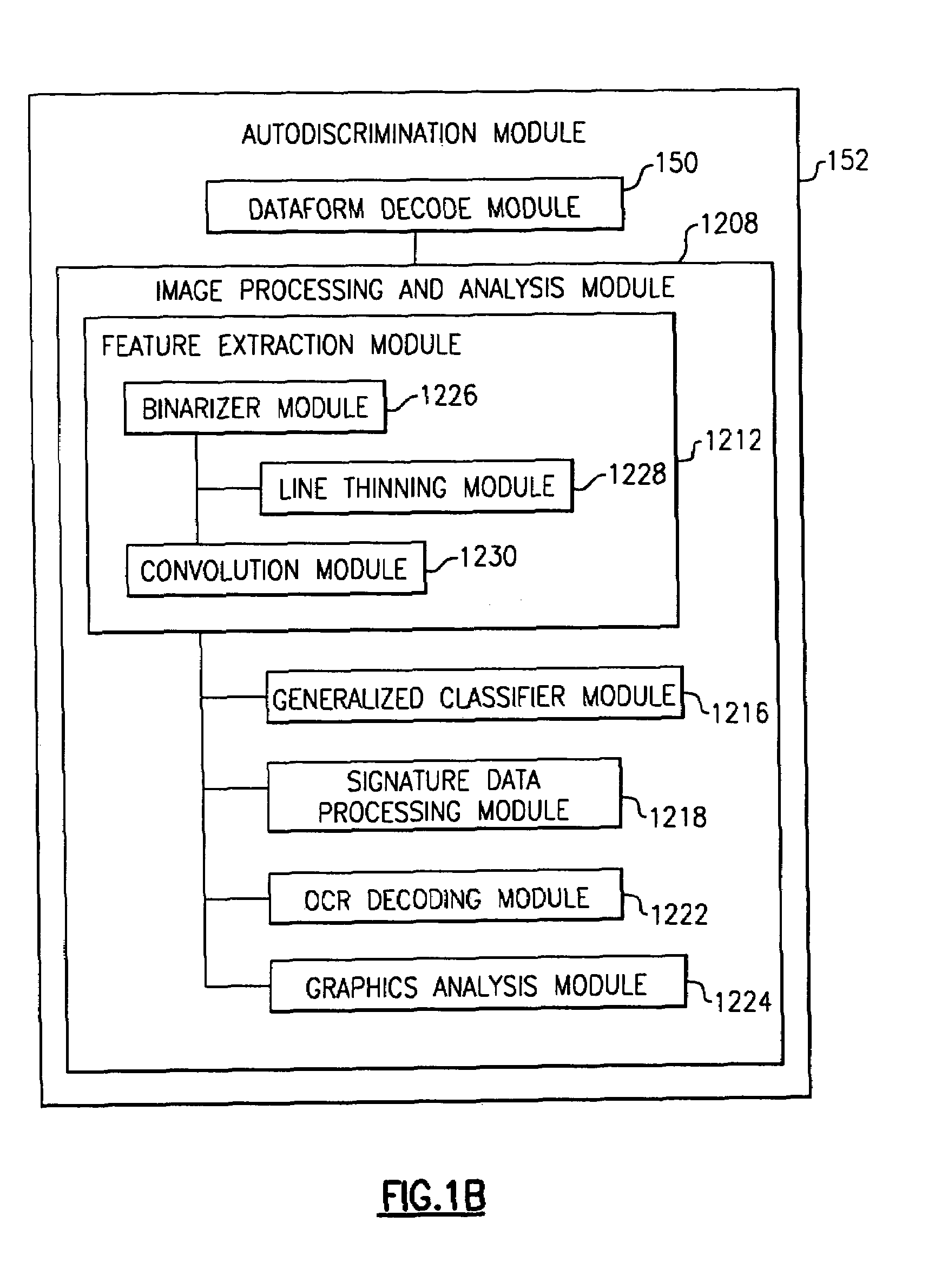

Robust information extraction from utterances

ActiveUS8583416B2Increase cross-entropyHigh precisionSpeech recognitionSpecial data processing applicationsFeature extractionText categorization

The performance of traditional speech recognition systems (as applied to information extraction or translation) decreases significantly with, larger domain size, scarce training data as well as under noisy environmental conditions. This invention mitigates these problems through the introduction of a novel predictive feature extraction method which combines linguistic and statistical information for representation of information embedded in a noisy source language. The predictive features are combined with text classifiers to map the noisy text to one of the semantically or functionally similar groups. The features used by the classifier can be syntactic, semantic, and statistical.

Owner:NANT HLDG IP LLC

Robust Information Extraction from Utterances

ActiveUS20090171662A1Increase cross-entropyImprove precisionSpeech recognitionSpecial data processing applicationsFeature extractionText categorization

The performance of traditional speech recognition systems (as applied to information extraction or translation) decreases significantly with, larger domain size, scarce training data as well as under noisy environmental conditions. This invention mitigates these problems through the introduction of a novel predictive feature extraction method which combines linguistic and statistical information for representation of information embedded in a noisy source language. The predictive features are combined with text classifiers to map the noisy text to one of the semantically or functionally similar groups. The features used by the classifier can be syntactic, semantic, and statistical.

Owner:NANT HLDG IP LLC

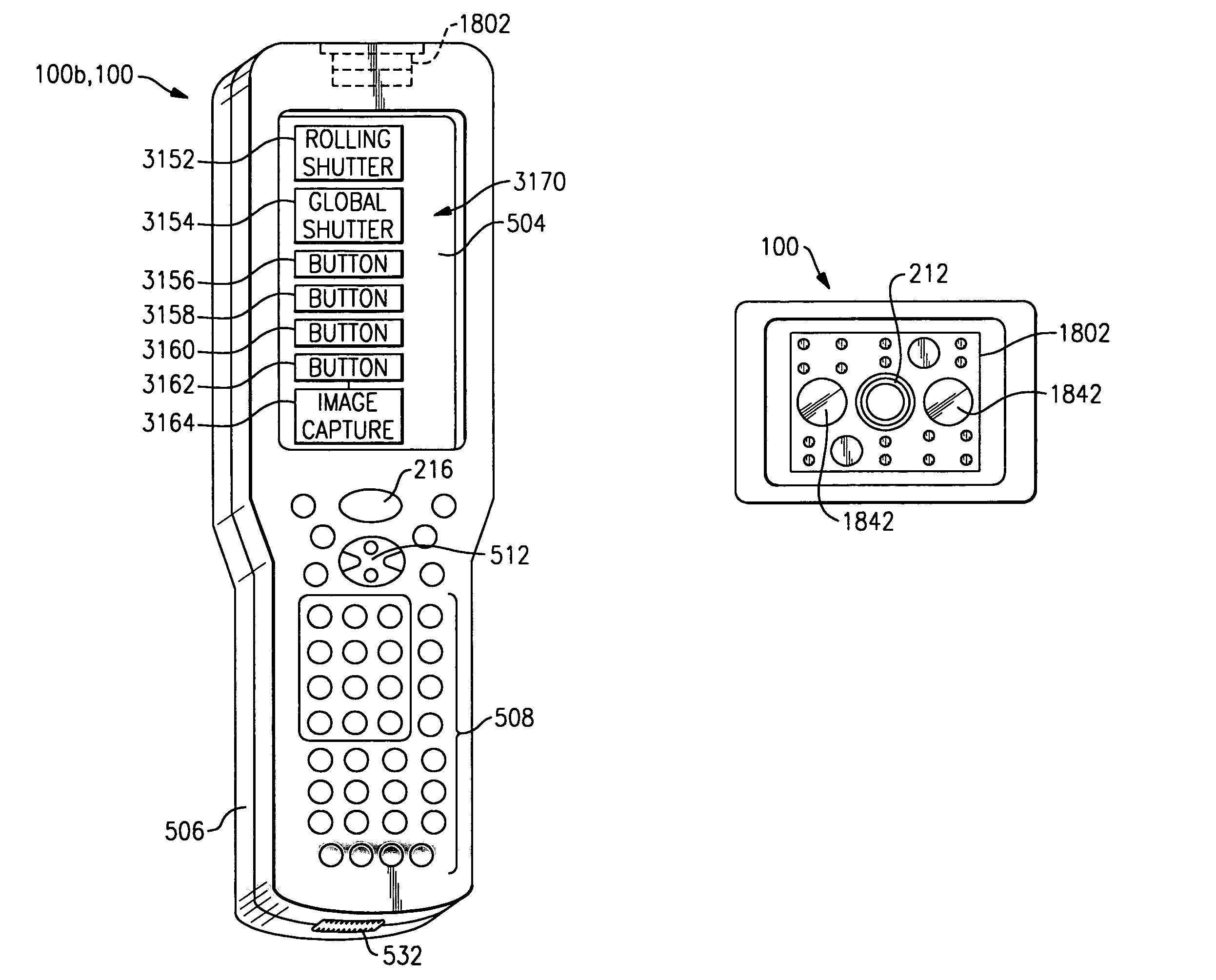

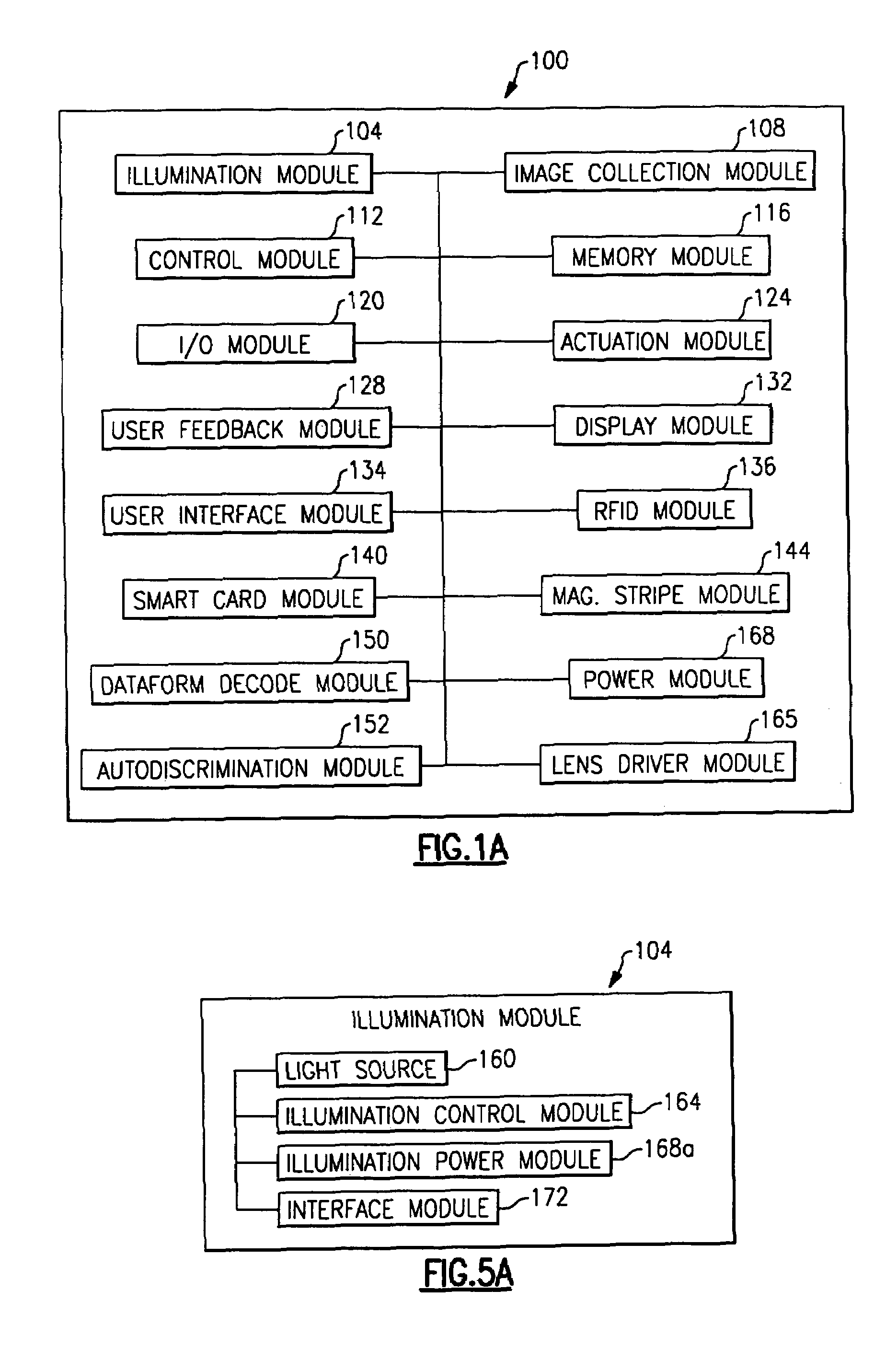

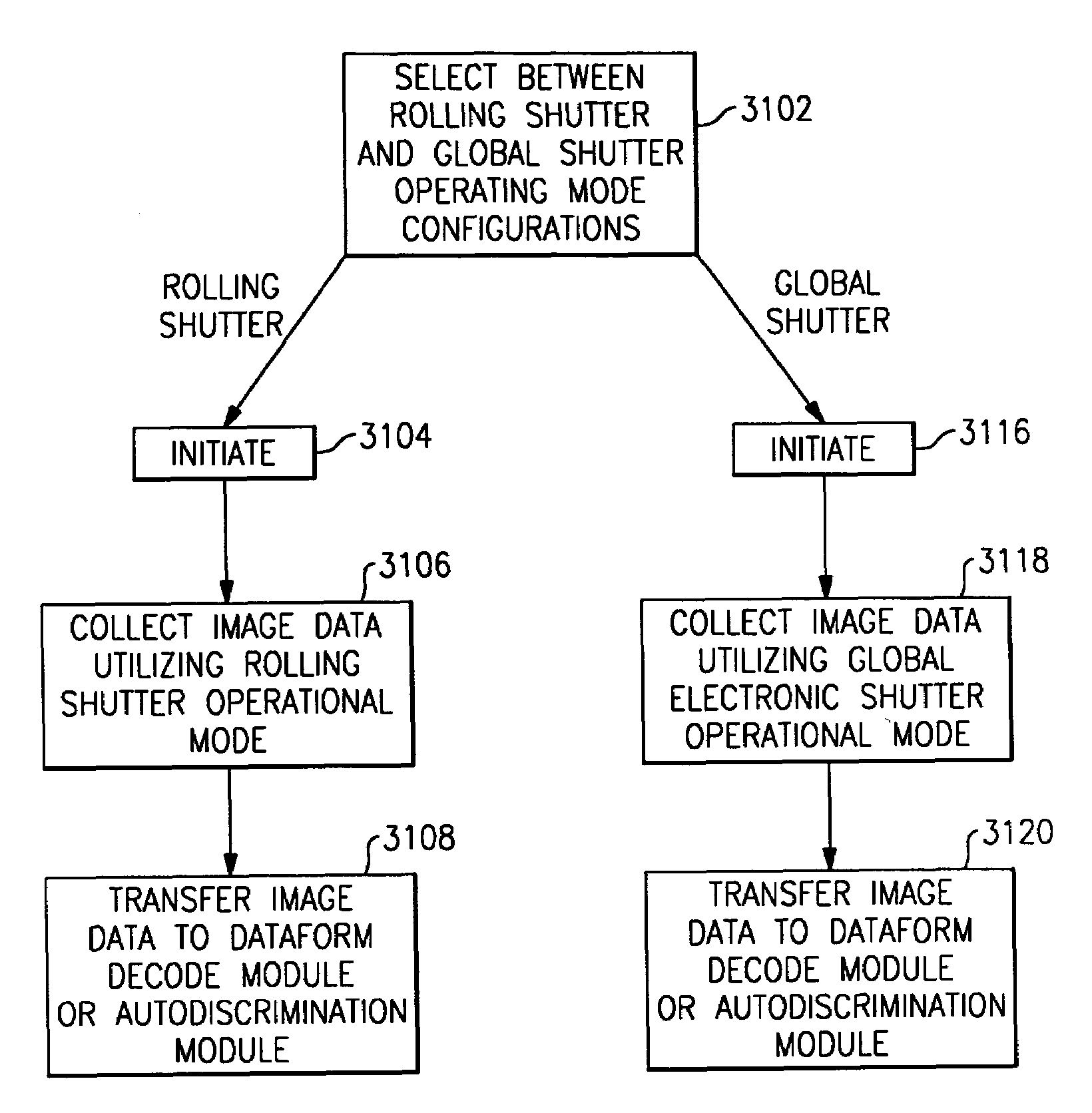

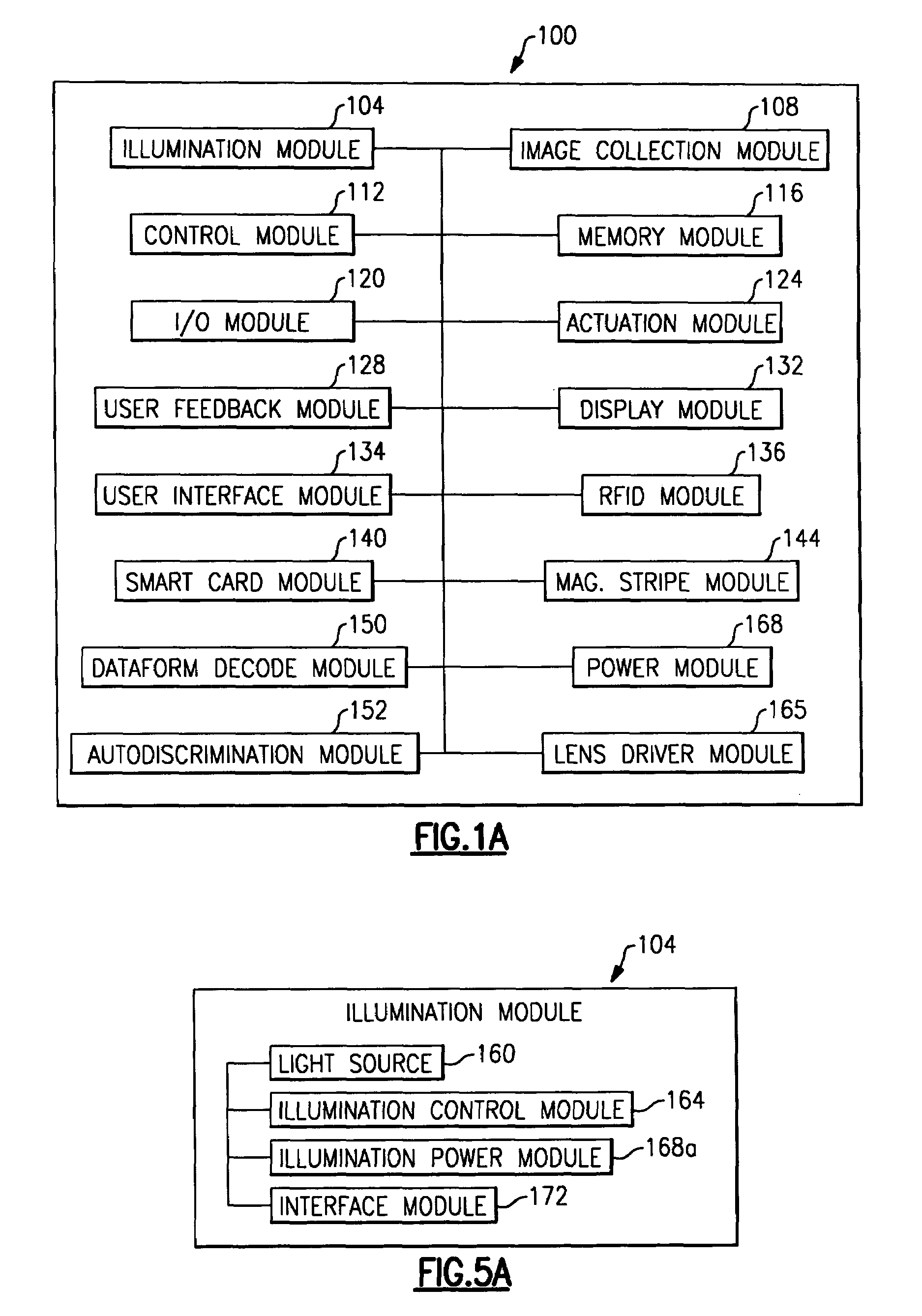

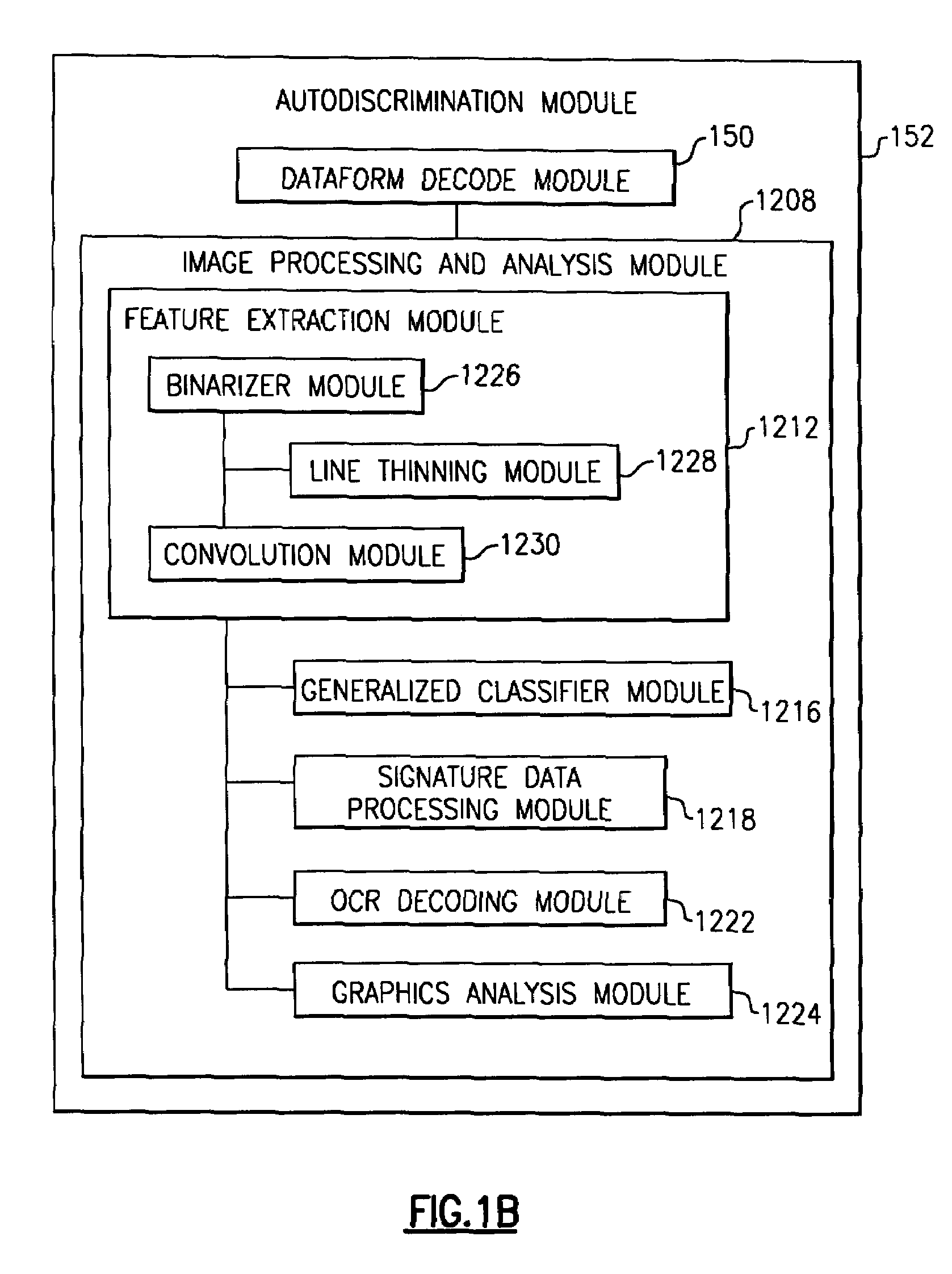

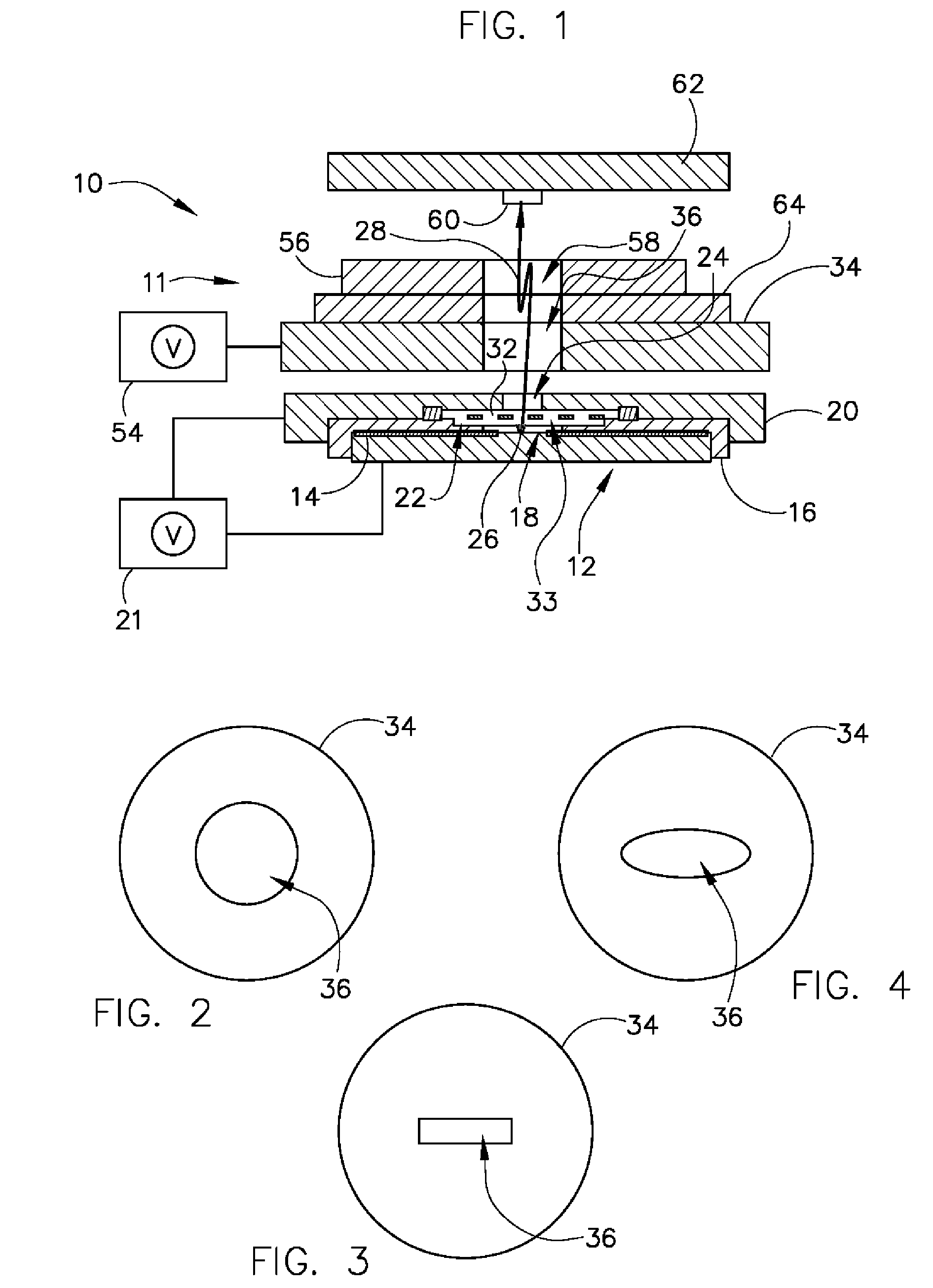

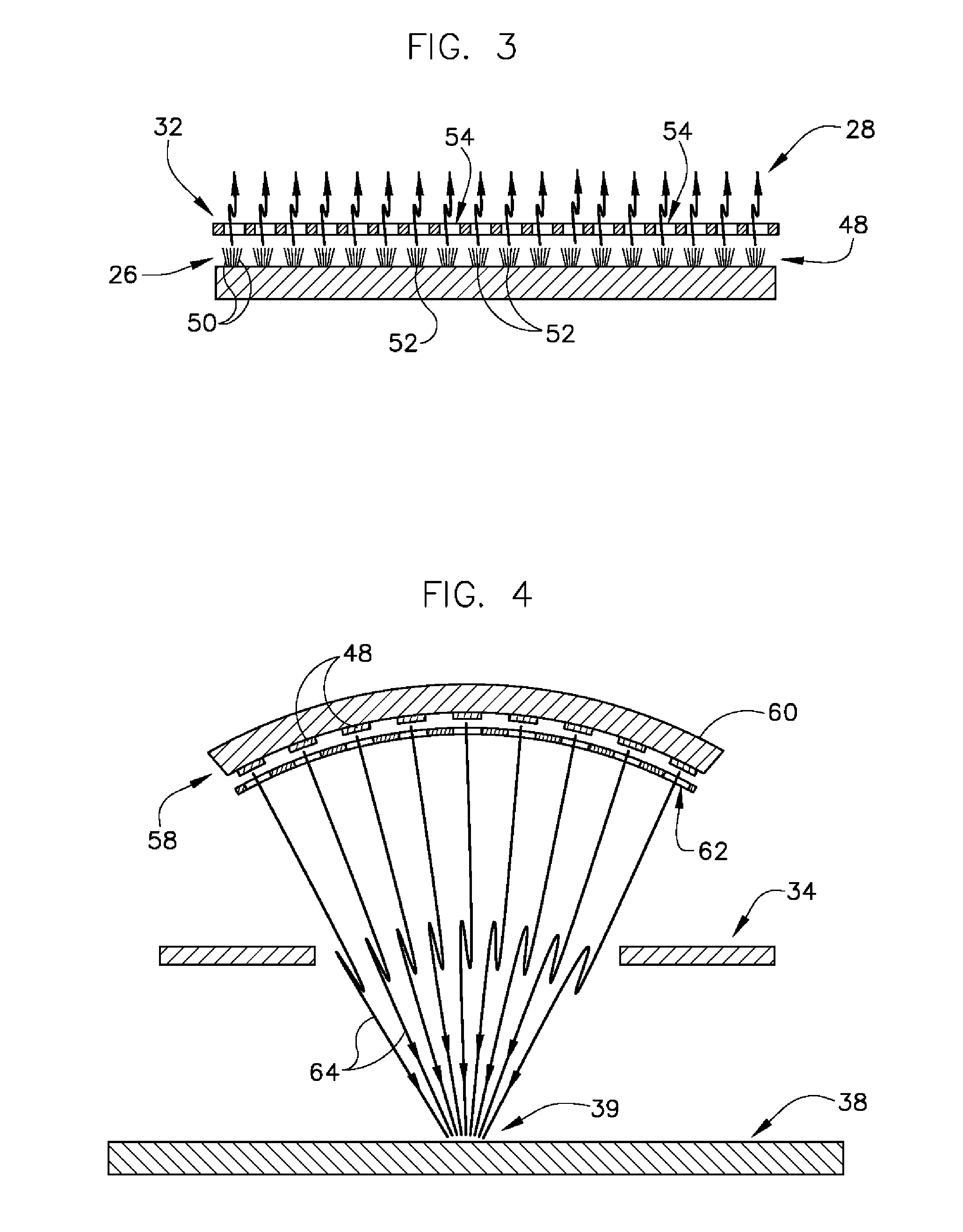

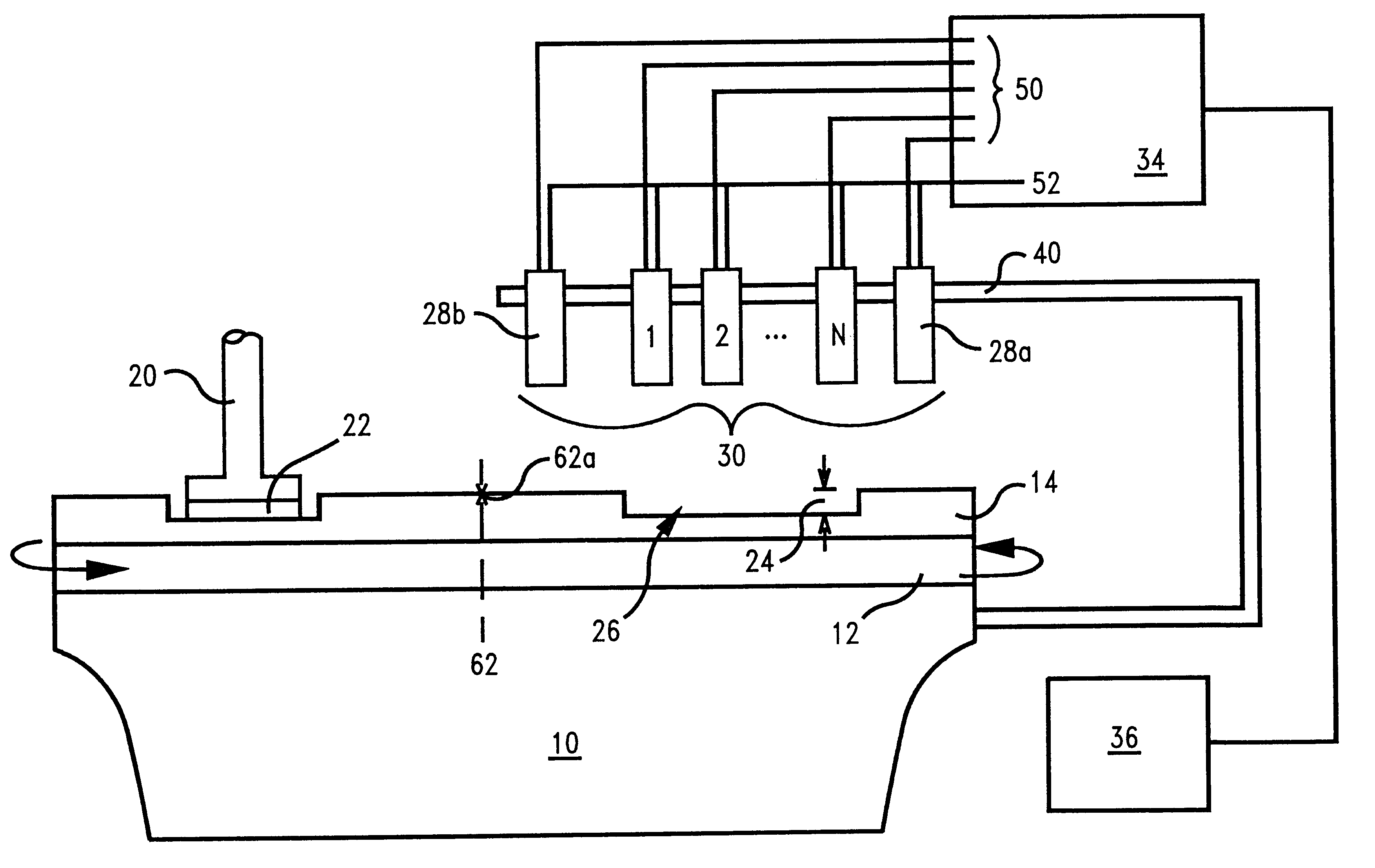

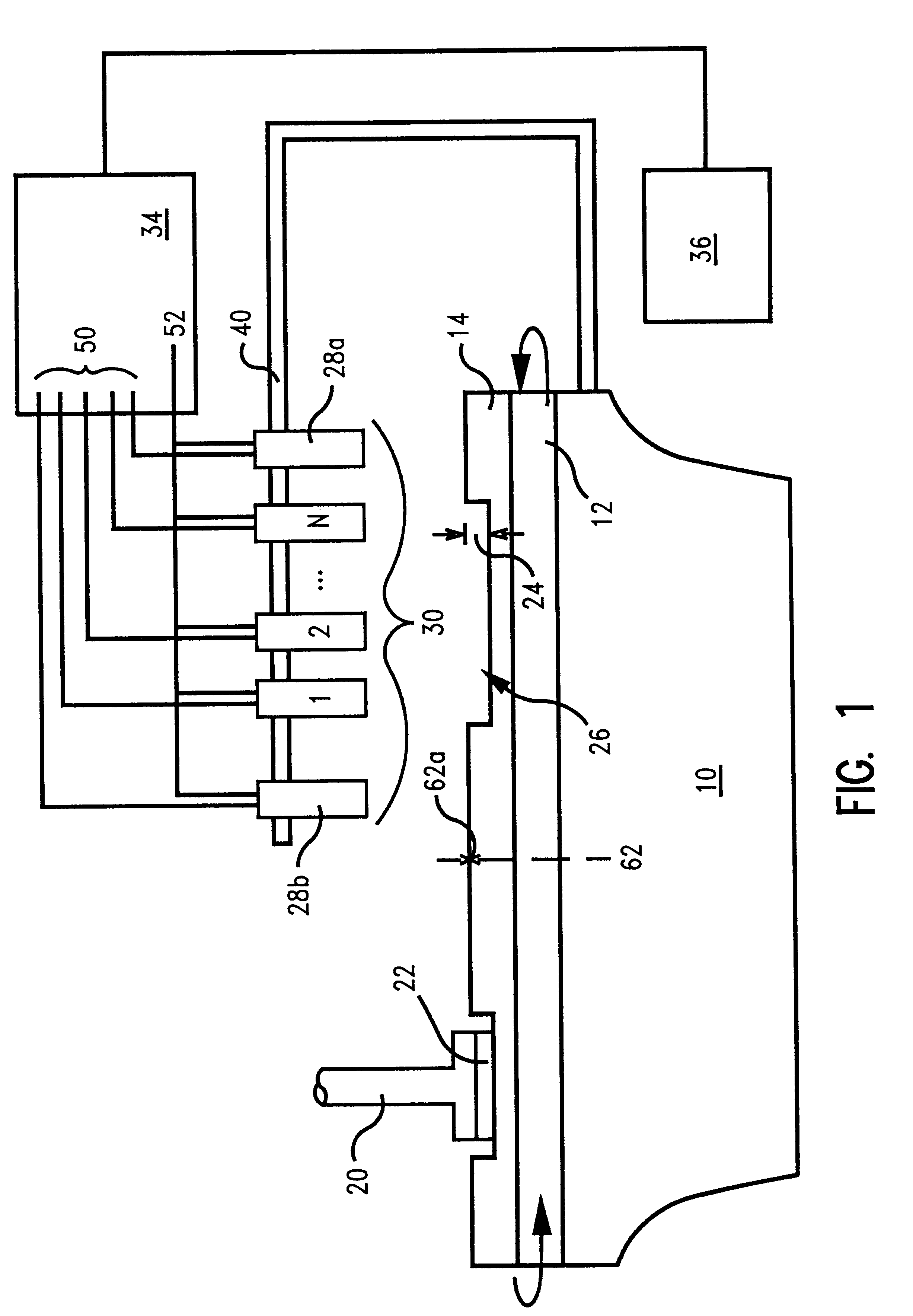

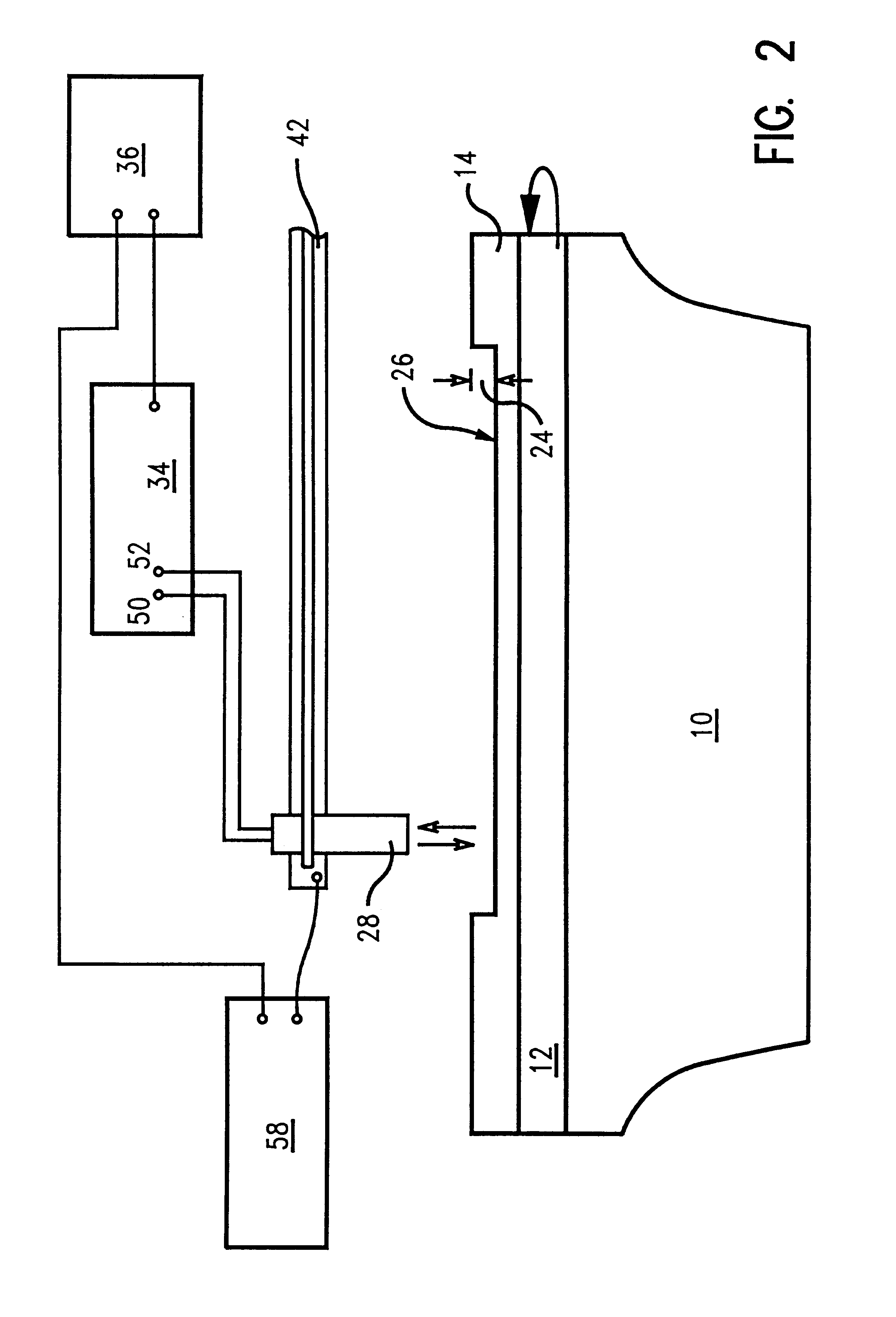

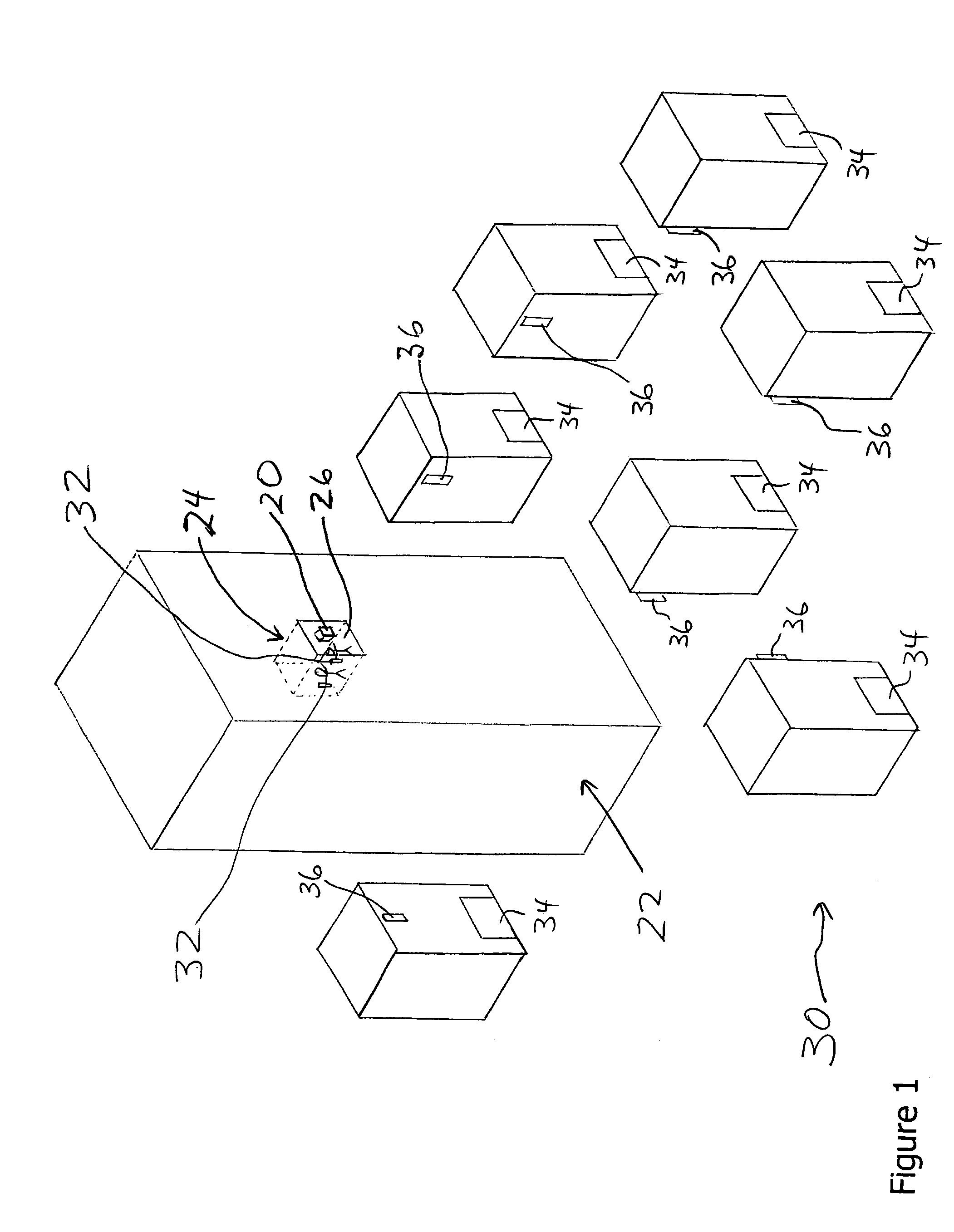

Bar code reading device with global electronic shutter control

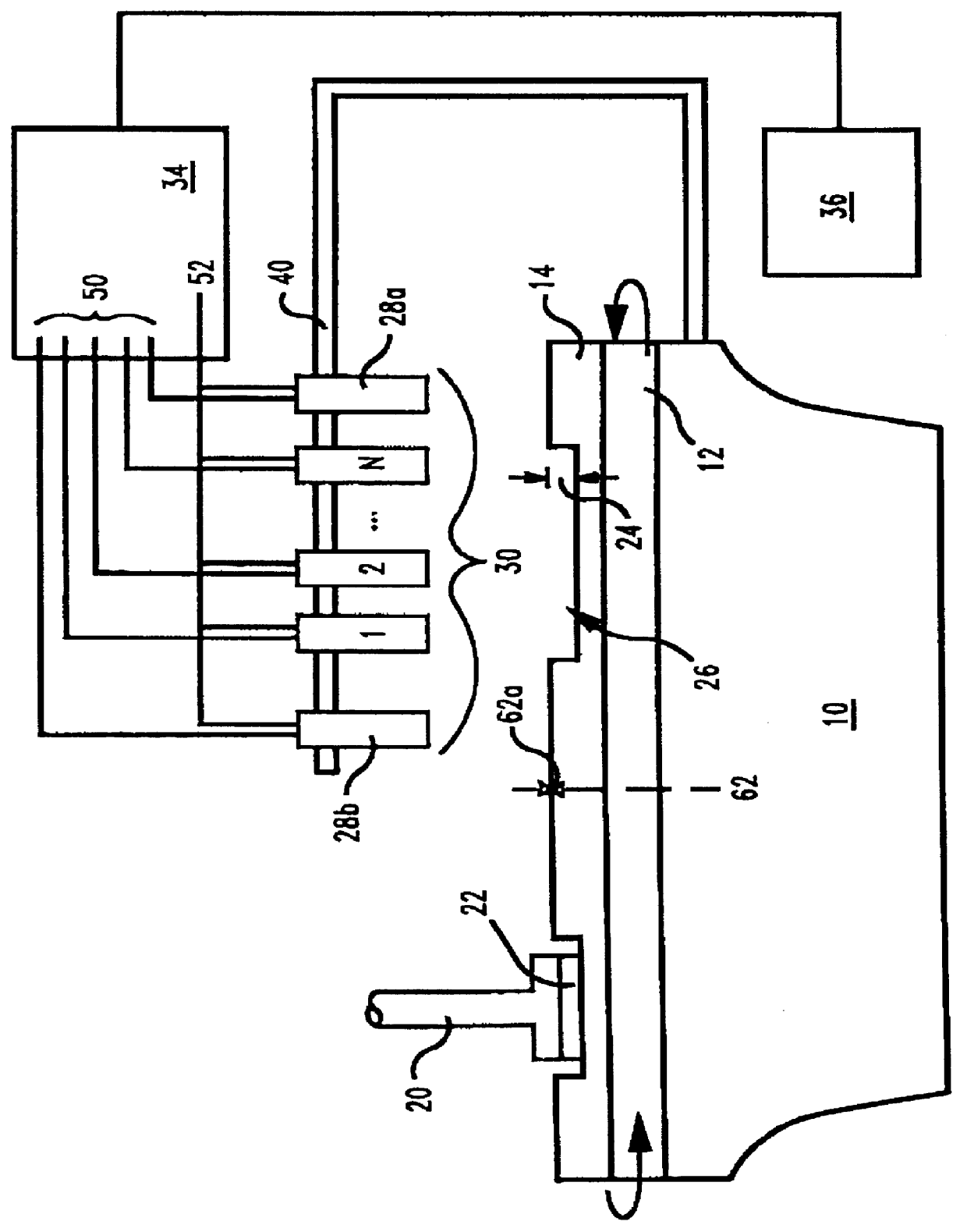

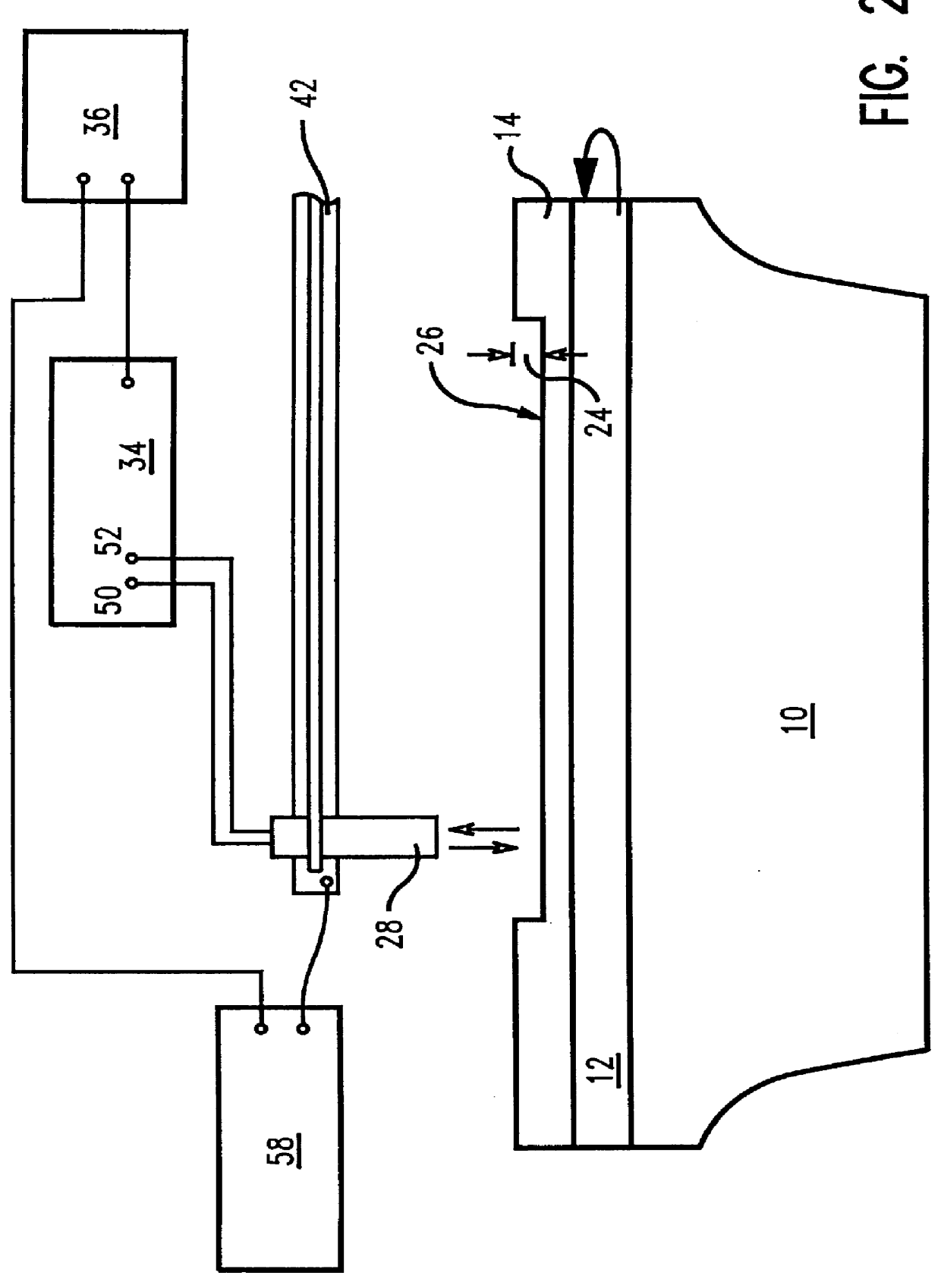

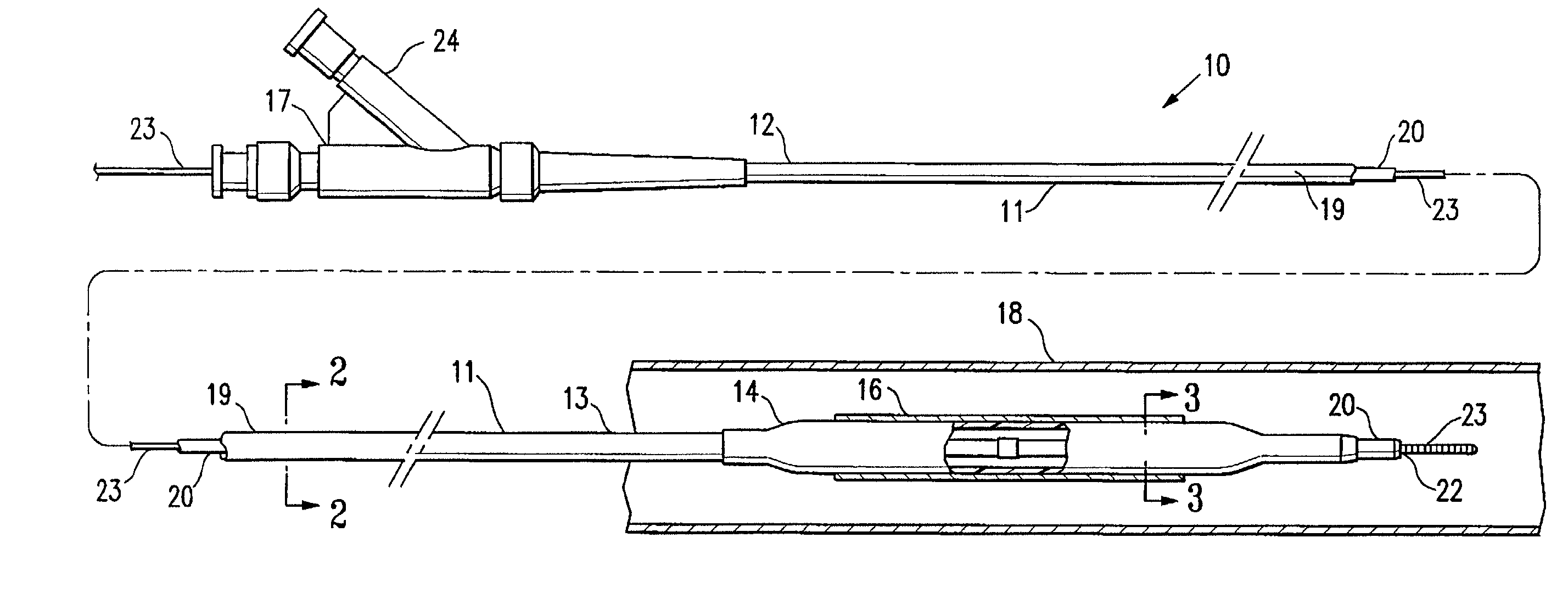

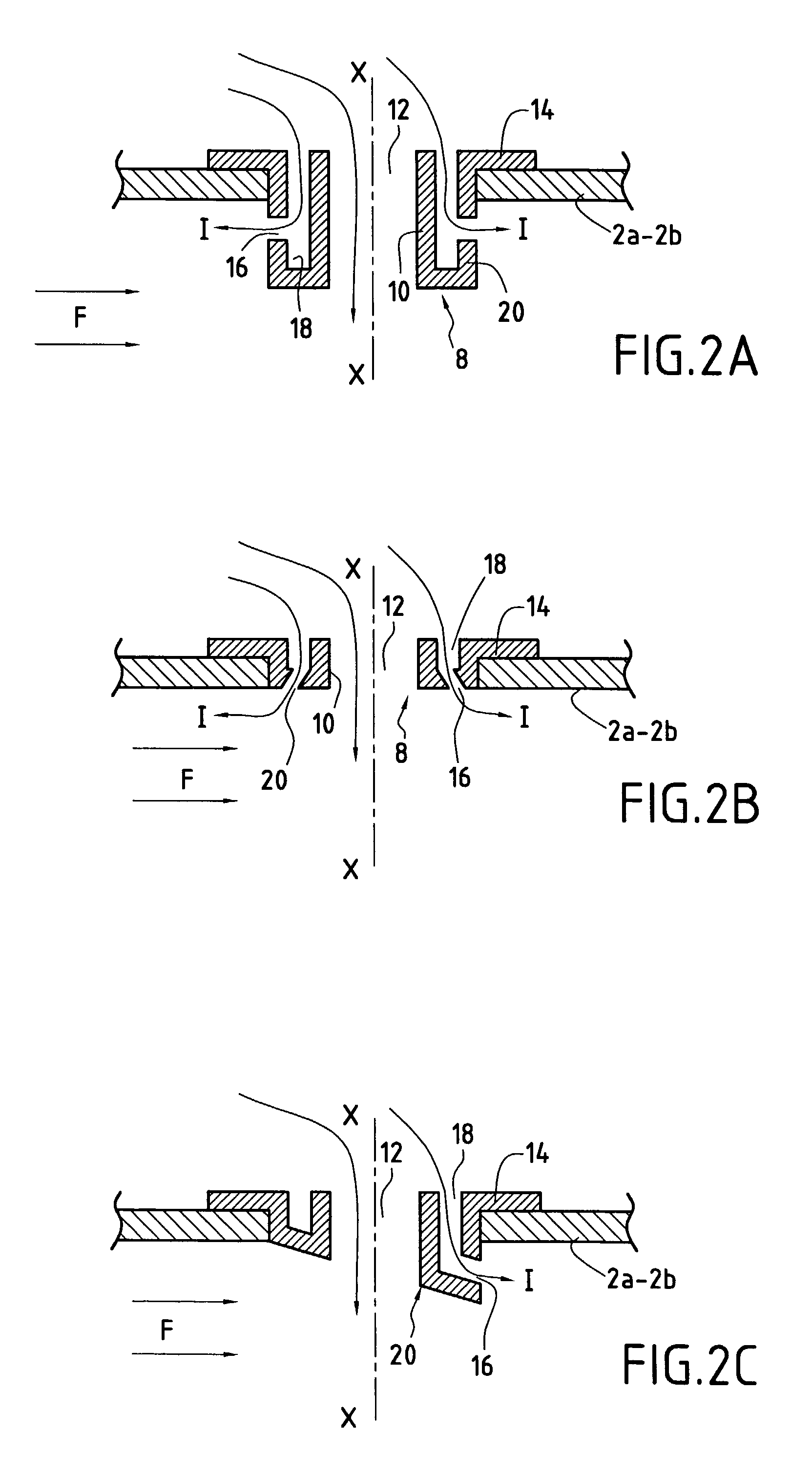

ActiveUS7568628B2Minimize degradationTelevision system detailsTransmission systemsSensor arrayElectronic shutter

The invention features an image reader and a corresponding method for capturing a sharp distortion free image of a target, such as a one or two-dimensional bar code. In one embodiment, the image reader comprises a two-dimensional CMOS based image sensor array, a timing module, an illumination module, and a control module. The time during which the target is illuminated is referred to as the illumination period. The capture of the image by the image sensor array is driven by the timing module that, in one embodiment, is able to simultaneously expose substantially all of the pixels in the array. The time during which the pixels are collectively activated to photo-convert incident light into charge defines the exposure period for the sensor array. In one embodiment, at least a portion of the exposure period occurs during the illumination period.

Owner:HAND HELD PRODS

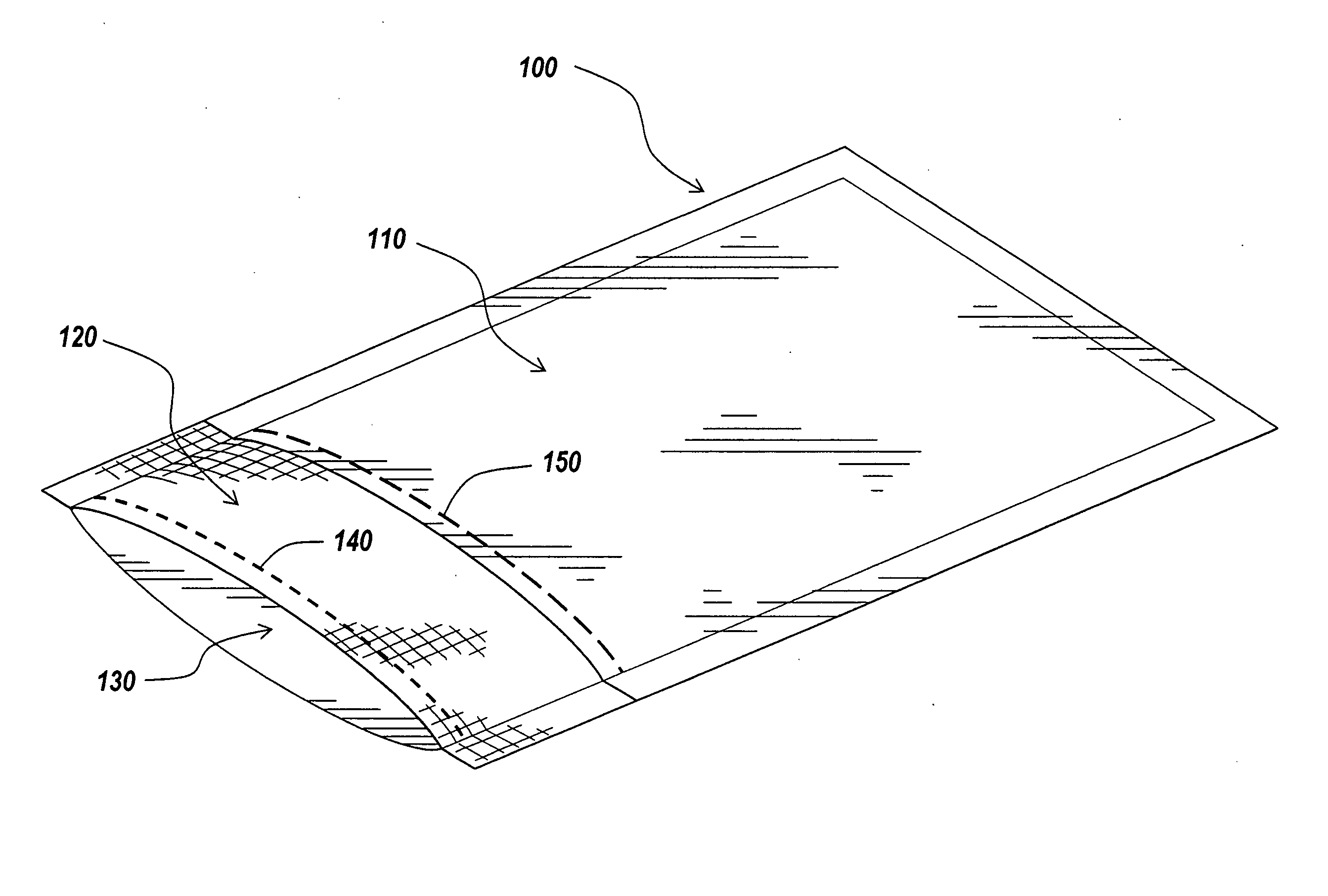

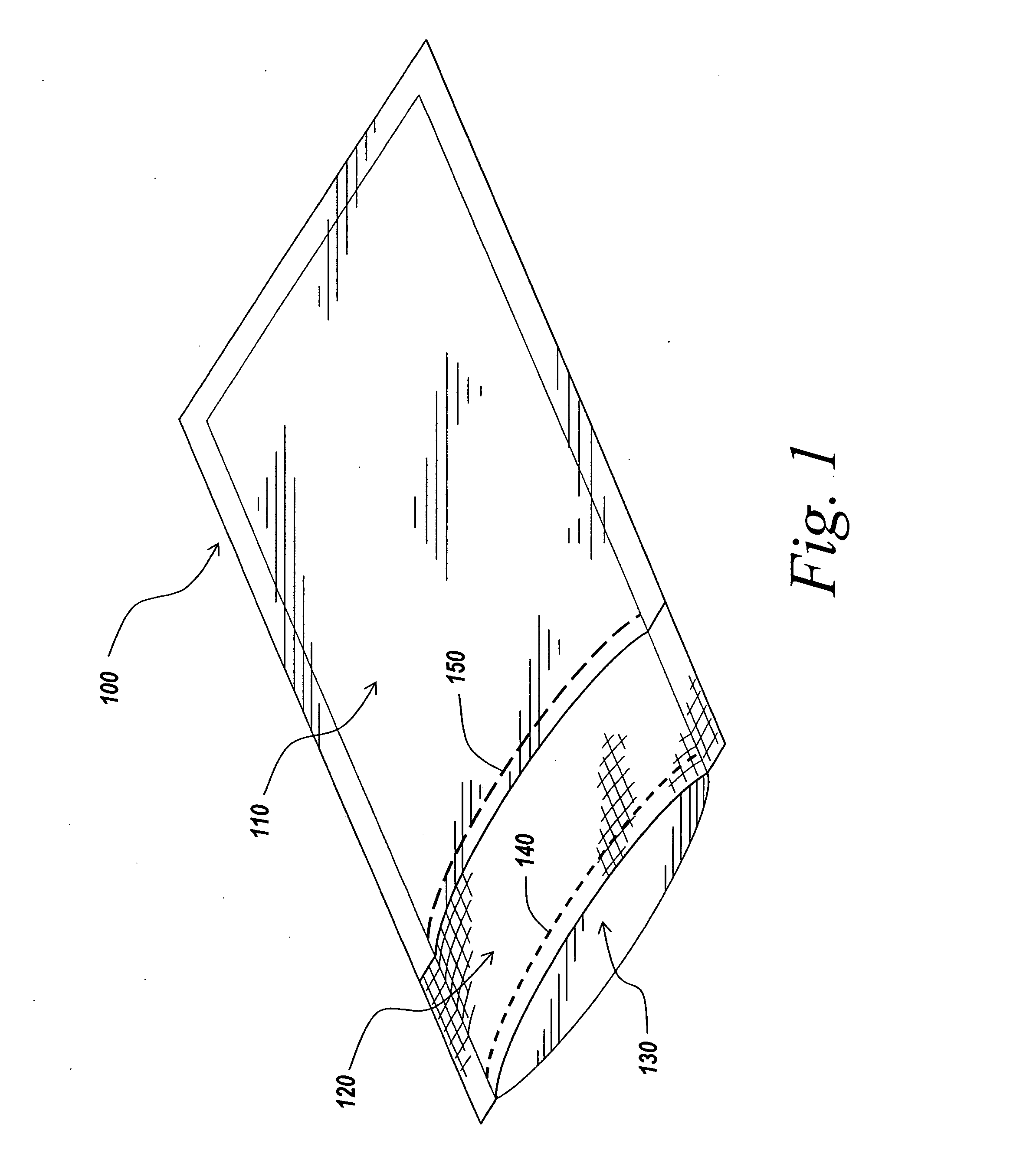

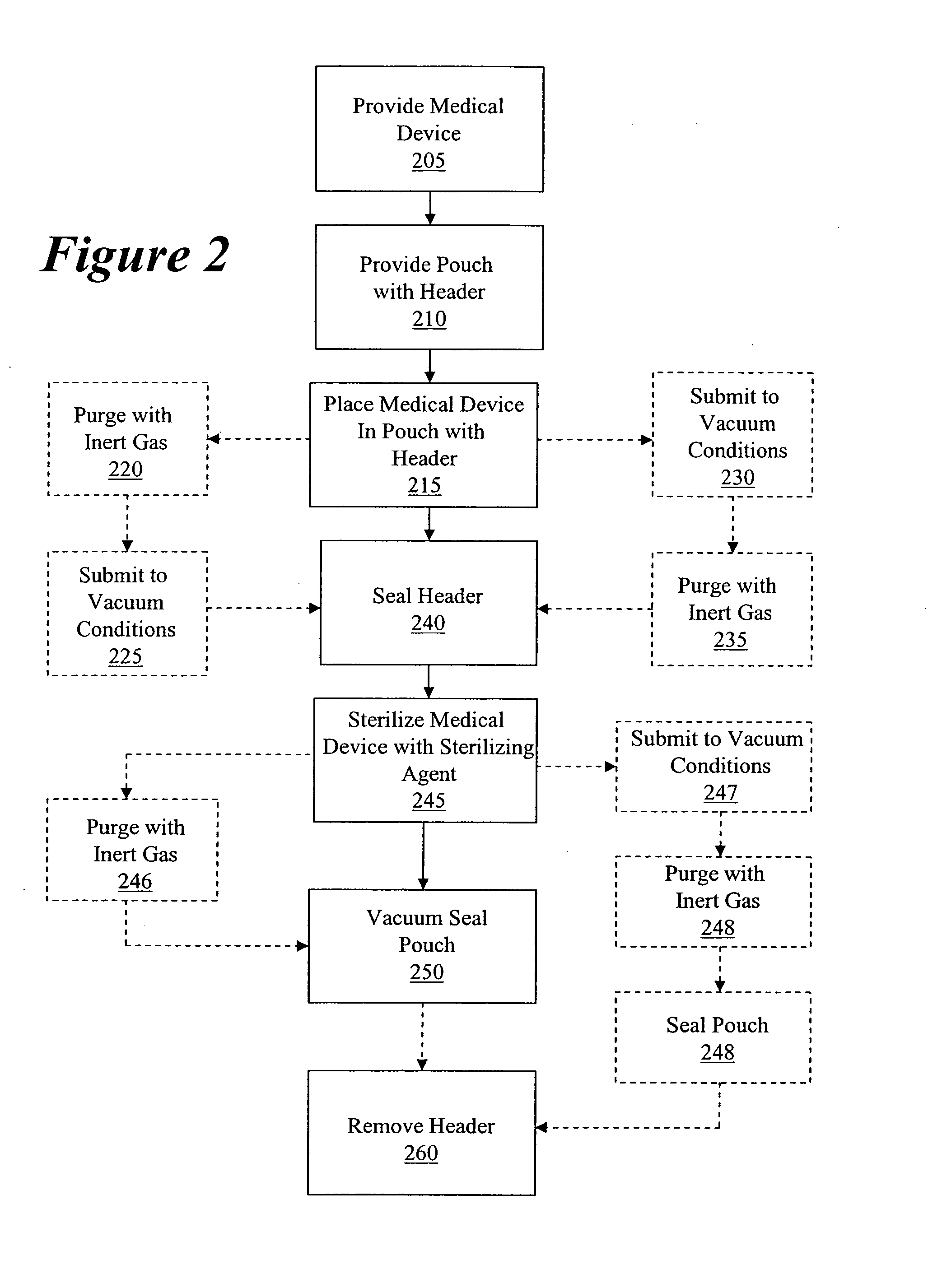

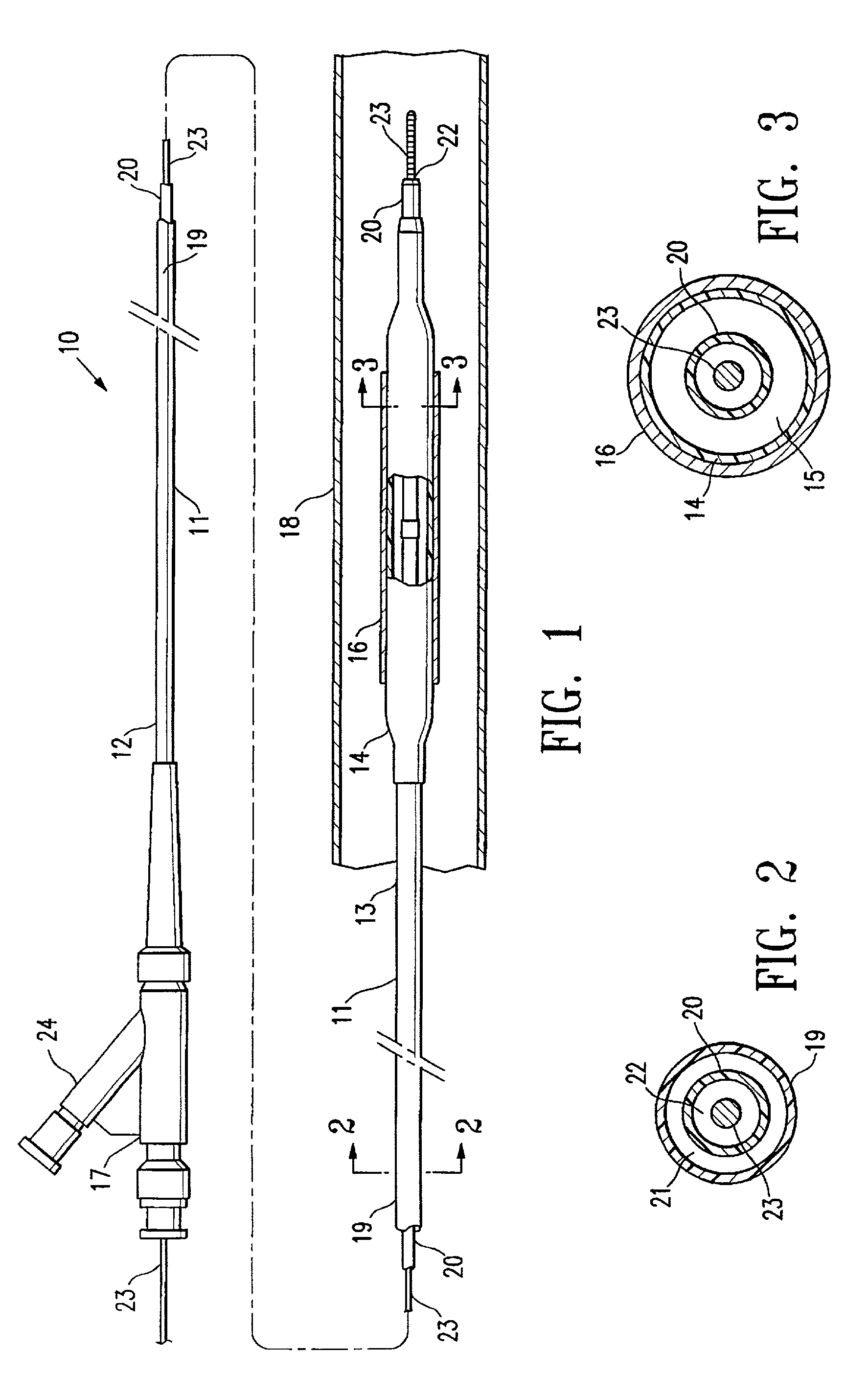

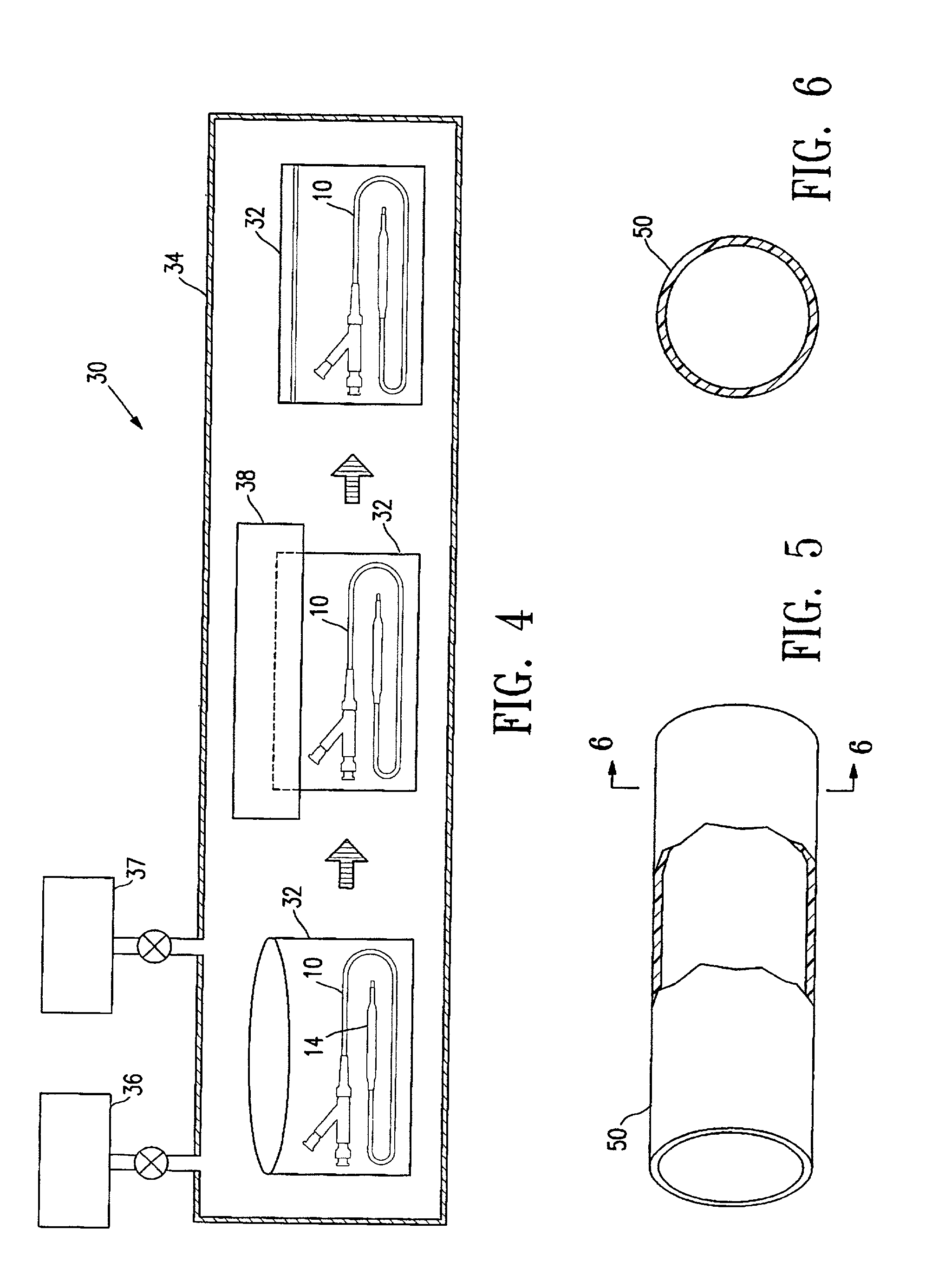

Packaging and sterilization of medical devices

InactiveUS20070084144A1Minimize timeExtended shelf lifeStentsSurgical furnitureCompound (substance)Fish oil

A method for the sterilization and packaging of a chemically sensitive medical device is provided. The chemically sensitive medical device has a coating derived from fish oil, a vitamin E compound or a combination thereof. The packaging pouch for the chemically sensitive medical device comprises a non-permeable chamber and a gas-permeable header. The sterilizing agent is administered to the packaged chemically sensitive medical device at a temperature of between about 20° C. and 40° C.

Owner:ATRIUM MEDICAL

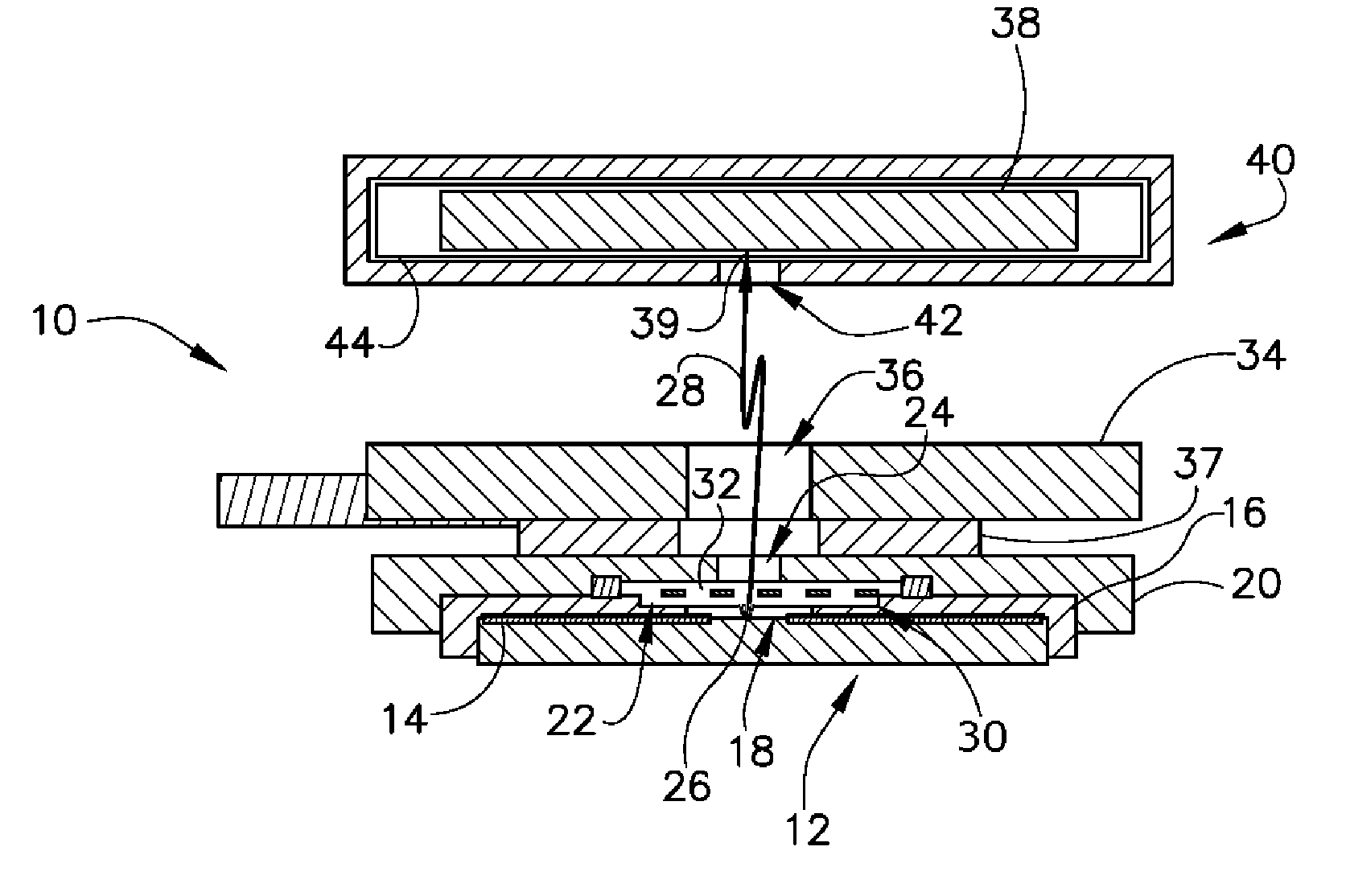

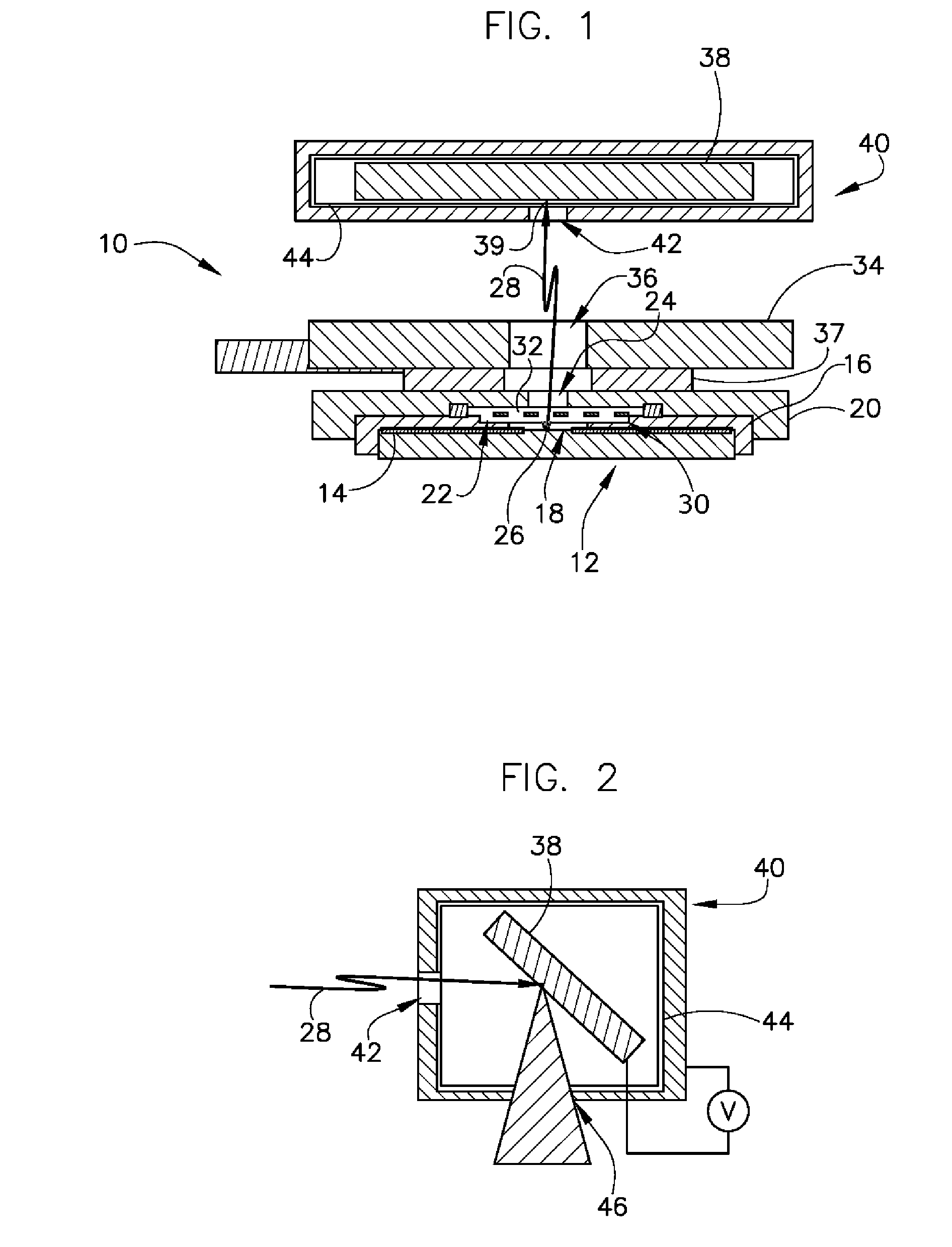

System and method to automatically focus an image reader

ActiveUS7611060B2Minimize degradationProjector focusing arrangementCamera focusing arrangementImaging dataSingle frame

The invention features a system and method to automatically focus an image reader using a single frame of image data. The method comprises exposing sequentially a plurality of rows of pixels in the image sensor. The method further comprising varying in incremental steps the focus of the image reader's optical system from a first setting where a distinct image of objects located at a first distance from the image reader is formed on the image sensor to a second setting where a distinct image of objects located at a second distance from the image reader is formed on the image sensor. As part of the method, the varying of the focus of the optical system occurs during the exposure of the plurality of rows of pixels.

Owner:HAND HELD PRODS

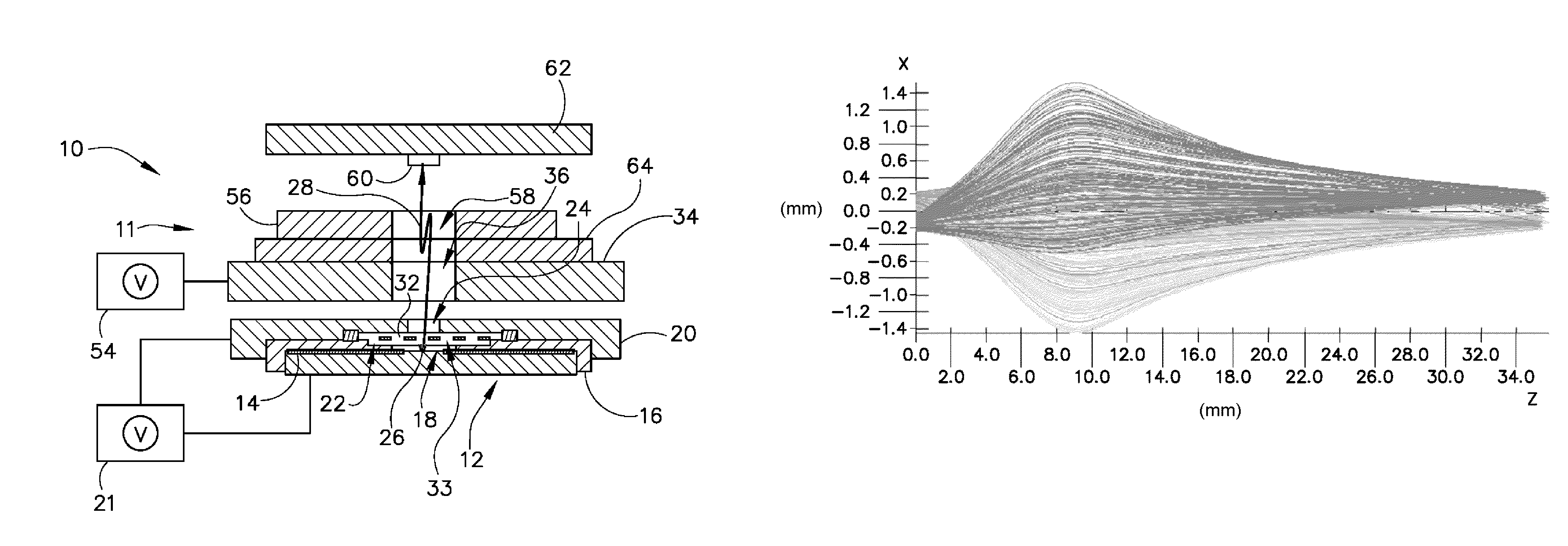

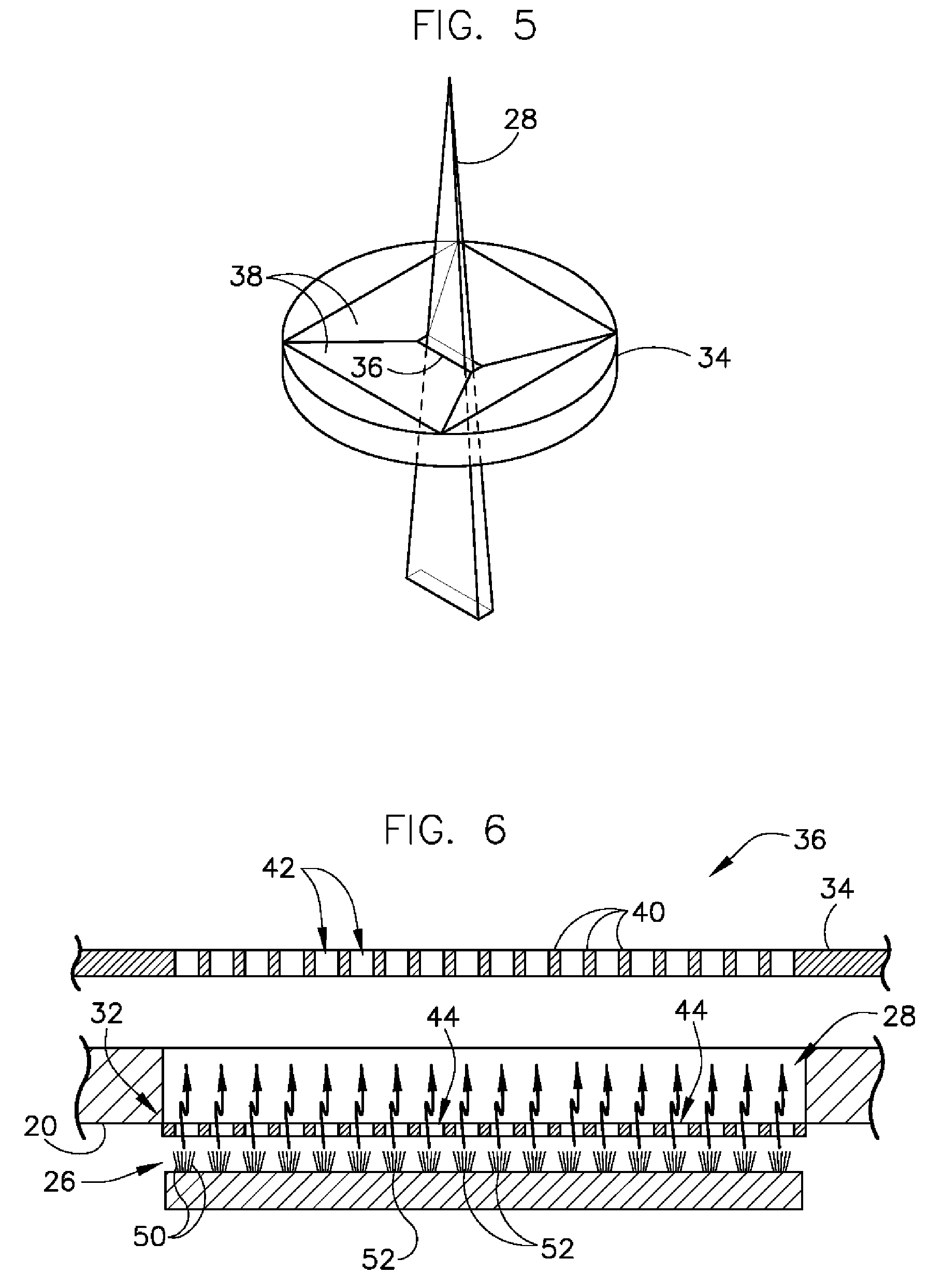

Field emitter based electron source with minimized beam emittance growth

InactiveUS7801277B2Low voltage extractionMinimal emittance growthCathode ray concentrating/focusing/directingElectrode and associated part arrangementsEmissivityElectron source

A system and method for limiting emittance growth in an electron beam is disclosed. The system includes an emitter element configured to generate an electron beam and an extraction electrode positioned adjacent to the emitter element to extract the electron beam out therefrom, the extraction electrode including an opening therethrough. The system also includes a meshed grid disposed in the opening of the extraction electrode to enhance intensity and uniformity of an electric field at a surface of the emitter element and an emittance compensation electrode (ECE) positioned adjacent to the meshed grid on the side of the meshed grid opposite that of the emitter element and configured to control emittance growth of the electron beam.

Owner:GENERAL ELECTRIC CO

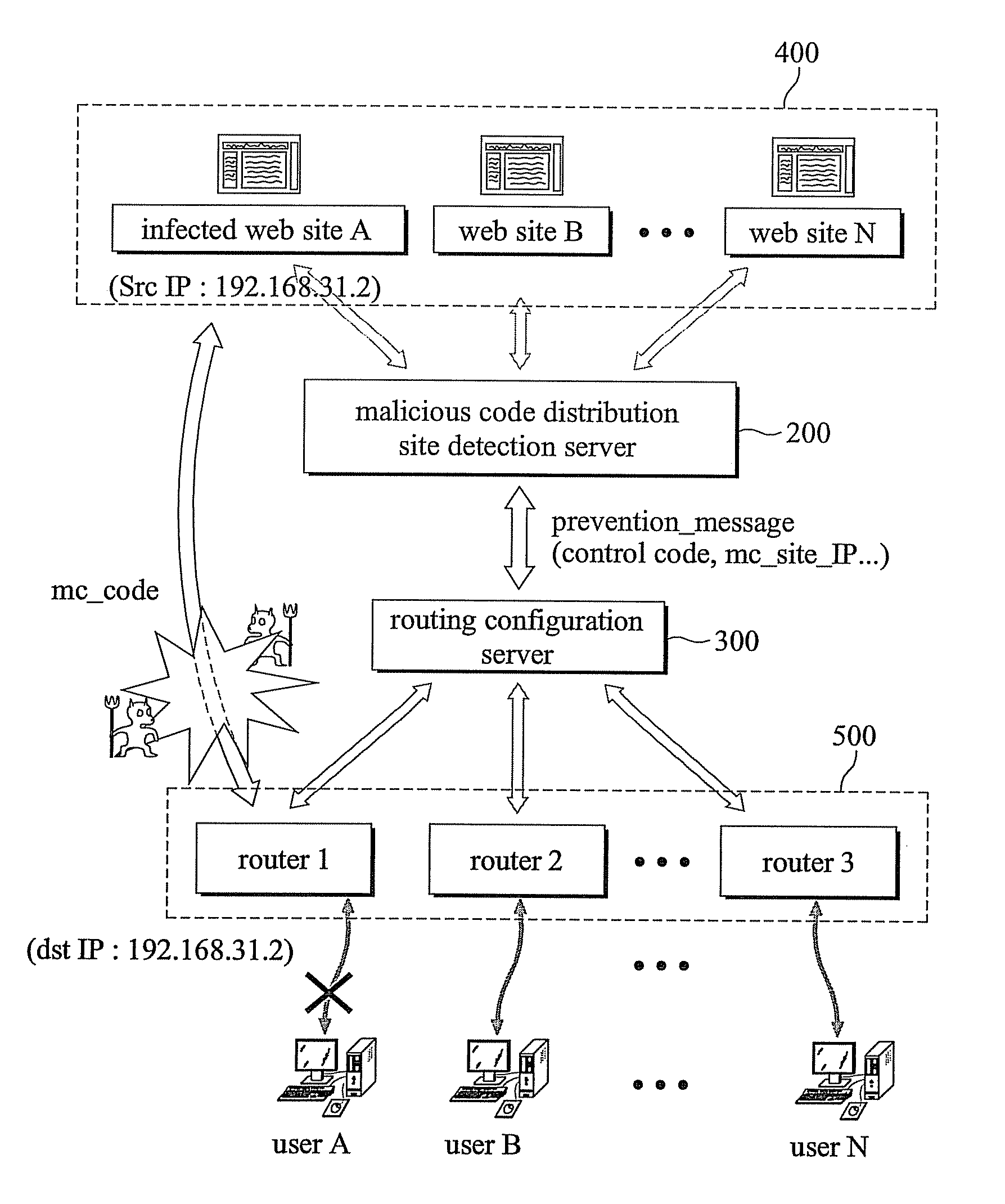

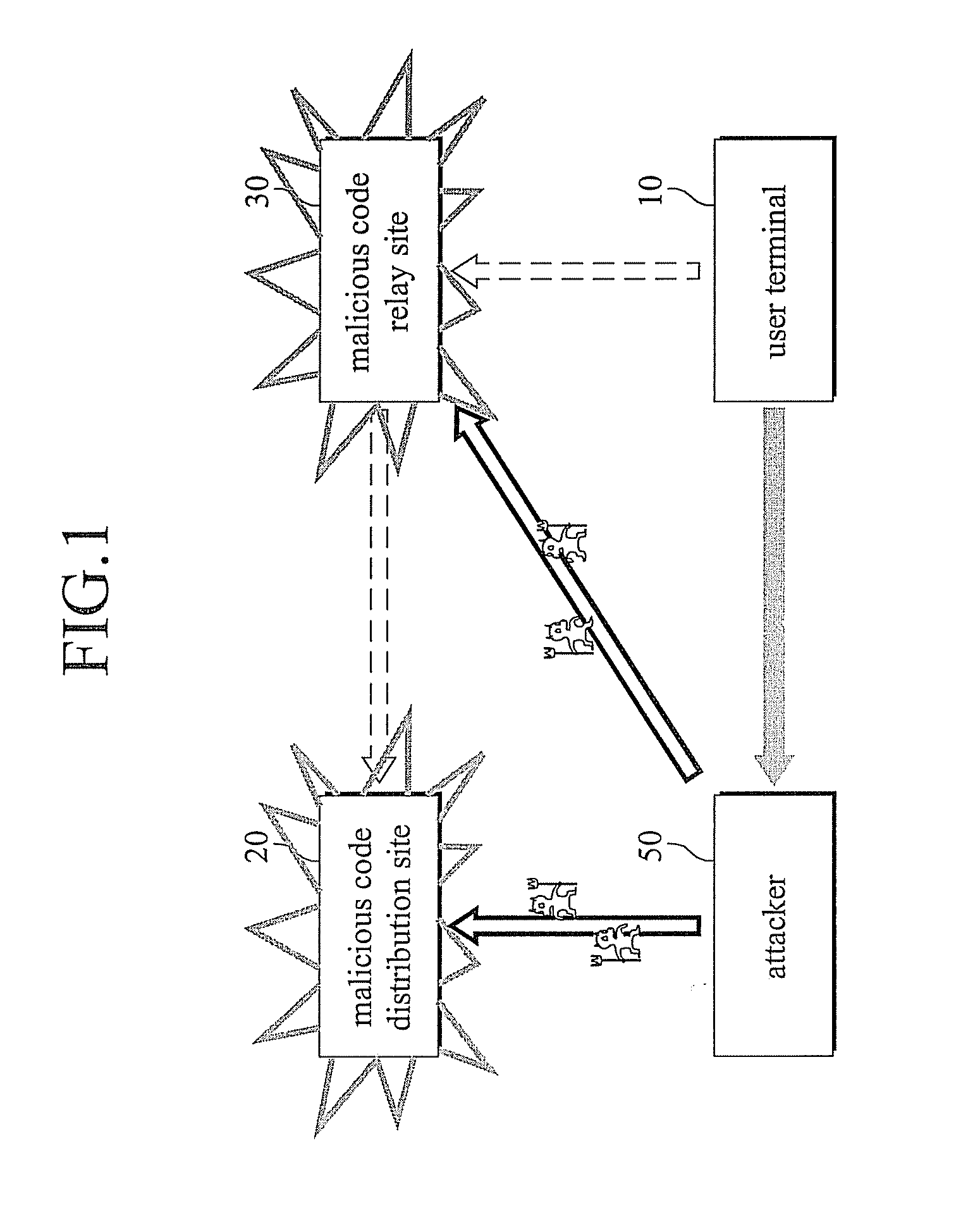

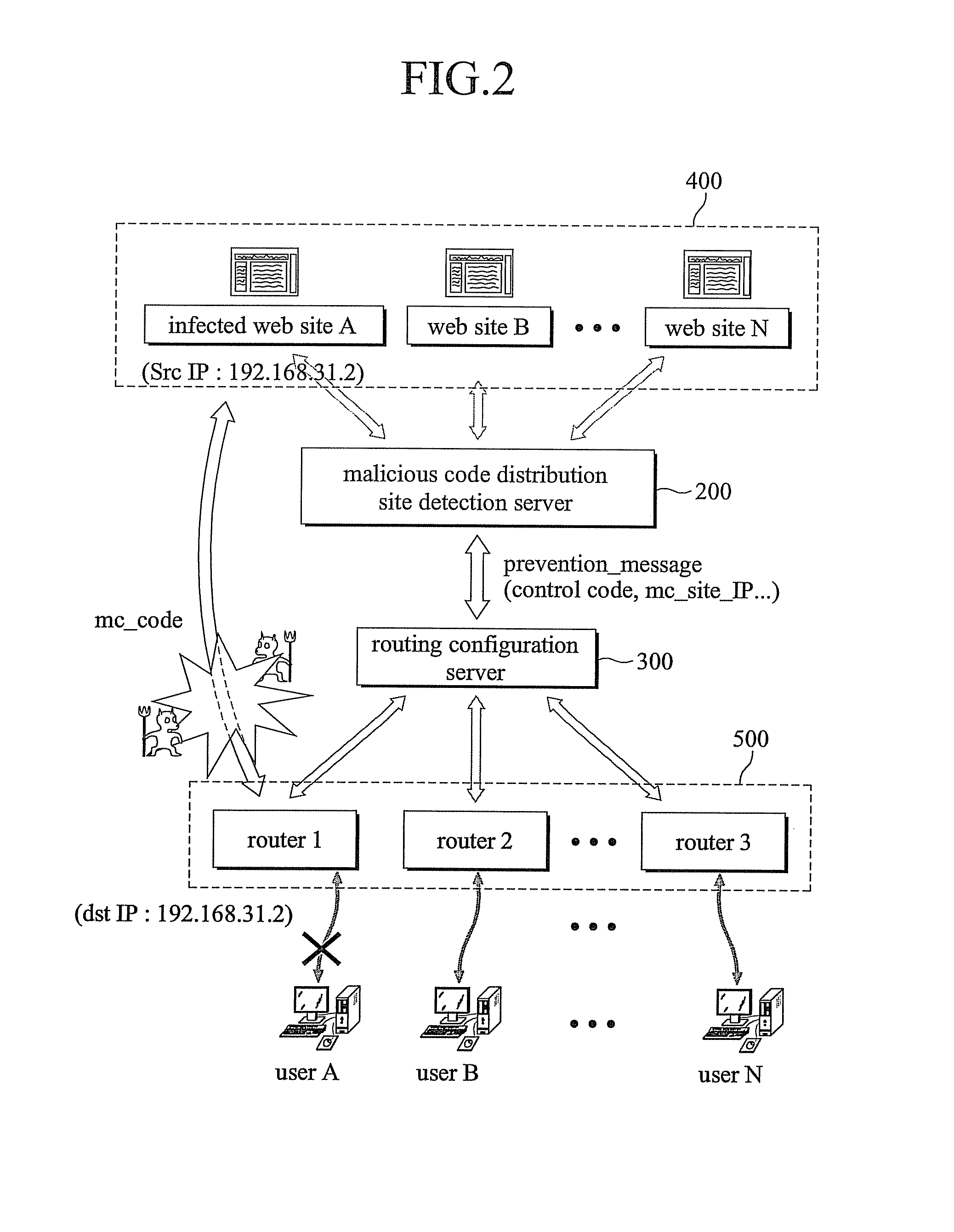

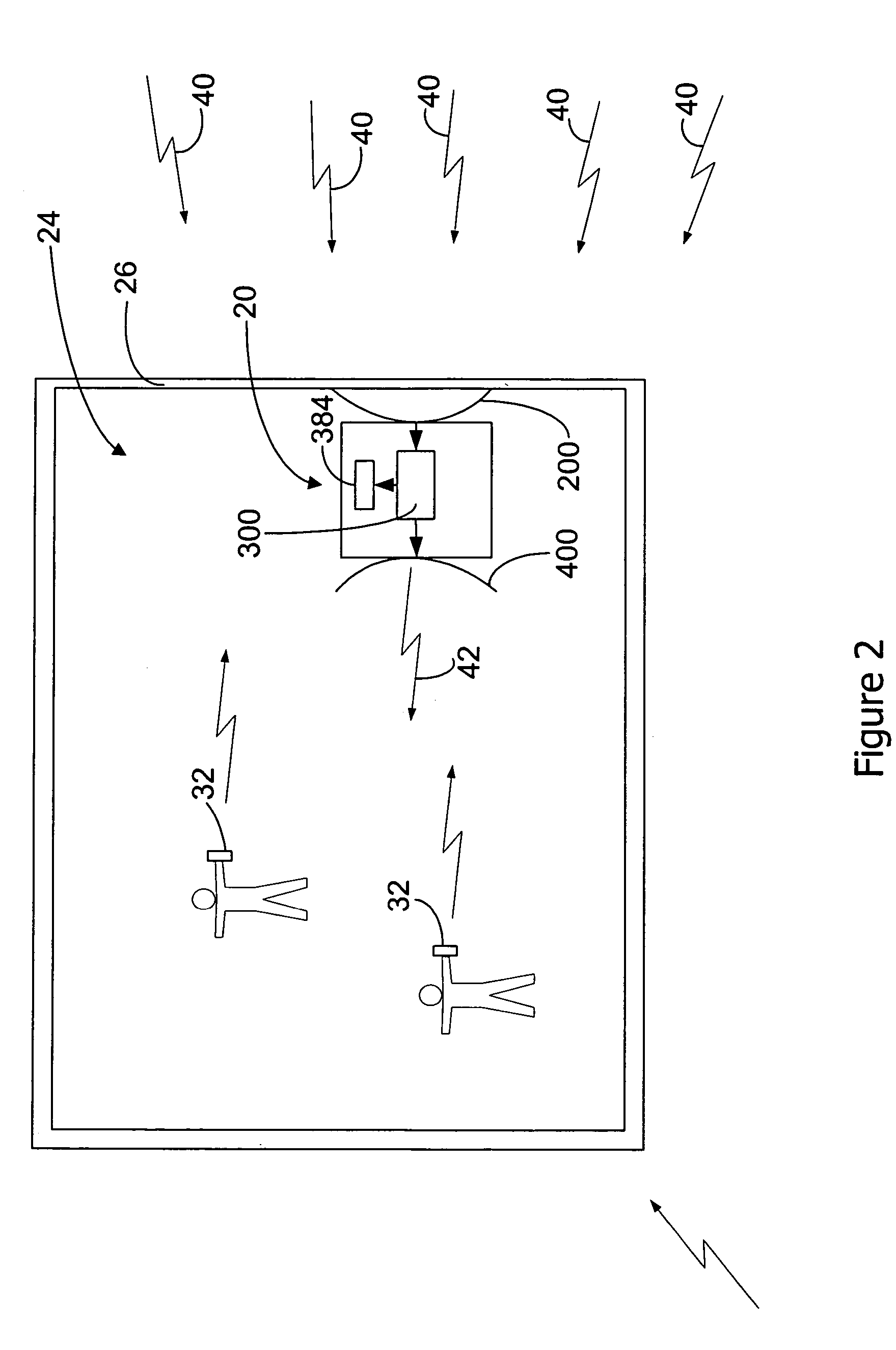

System and method for preventing malicious code spread using web technology

InactiveUS20080127338A1Avoid attackPrevent malicious attacksMemory loss protectionError detection/correctionCode distributionTransmitter

The present invention relates to a system and a method for preventing an attack of a malicious program spread using a web technology comprising a malicious code distribution site detection server comprising a malicious code distribution site detector for detecting a malicious code distribution site, and a prevention message transmitter for transmitting a prevention message to a routing configuration server, wherein the prevention message includes an IP address of the malicious code distribution site detected by the malicious code distribution site detector; a plurality of routers including a virtual IP address; and the routing configuration server for advertising the IP address of the malicious code distribution site such that a routing path of a packet having the IP address of the malicious code distribution site as a target address or an starting address is guided to the virtual IP address according to an reception of the prevention message to block a connection to the malicious code distribution site.

Owner:KOREA INTERNET & SECURITY AGENCY

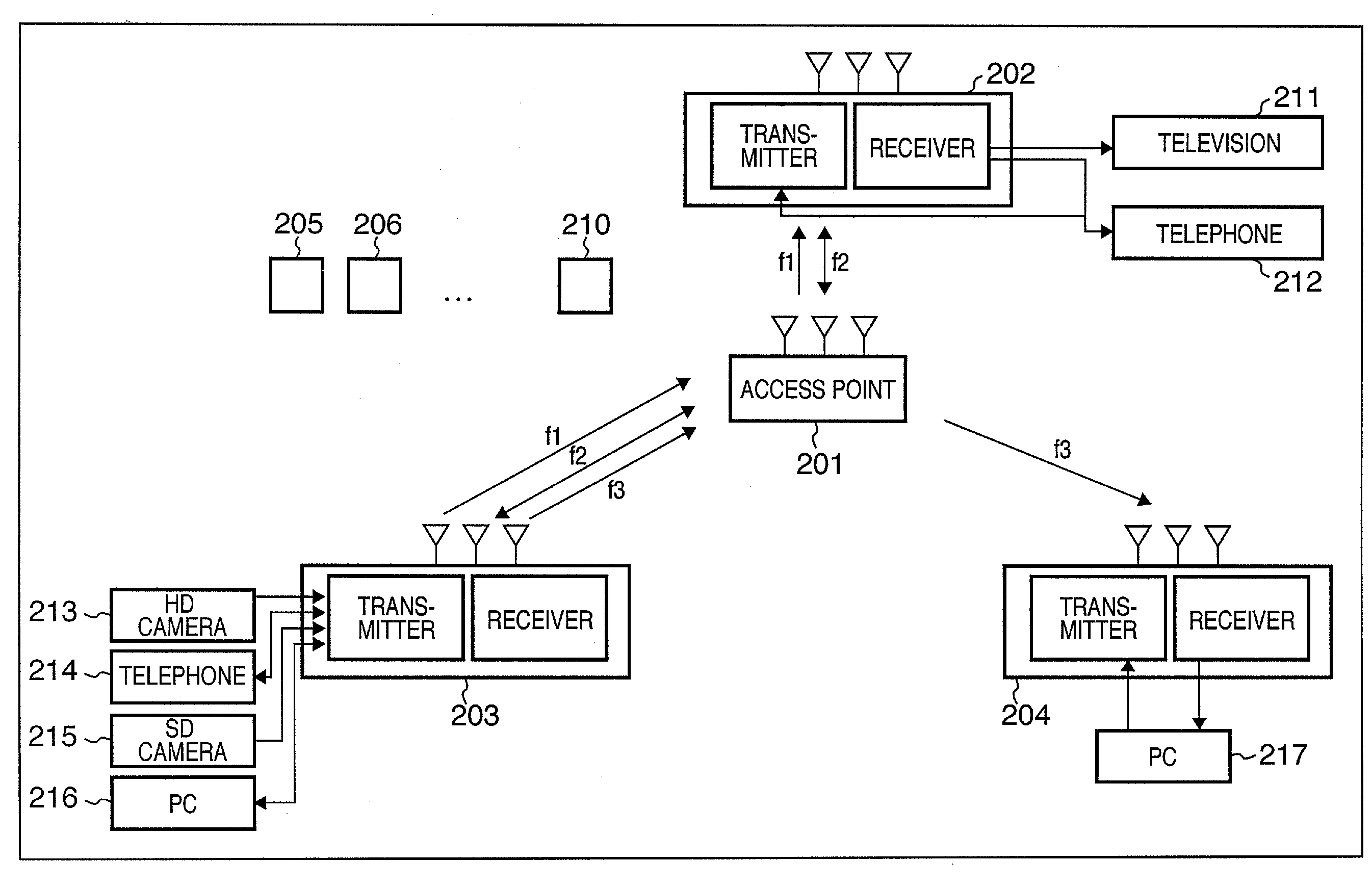

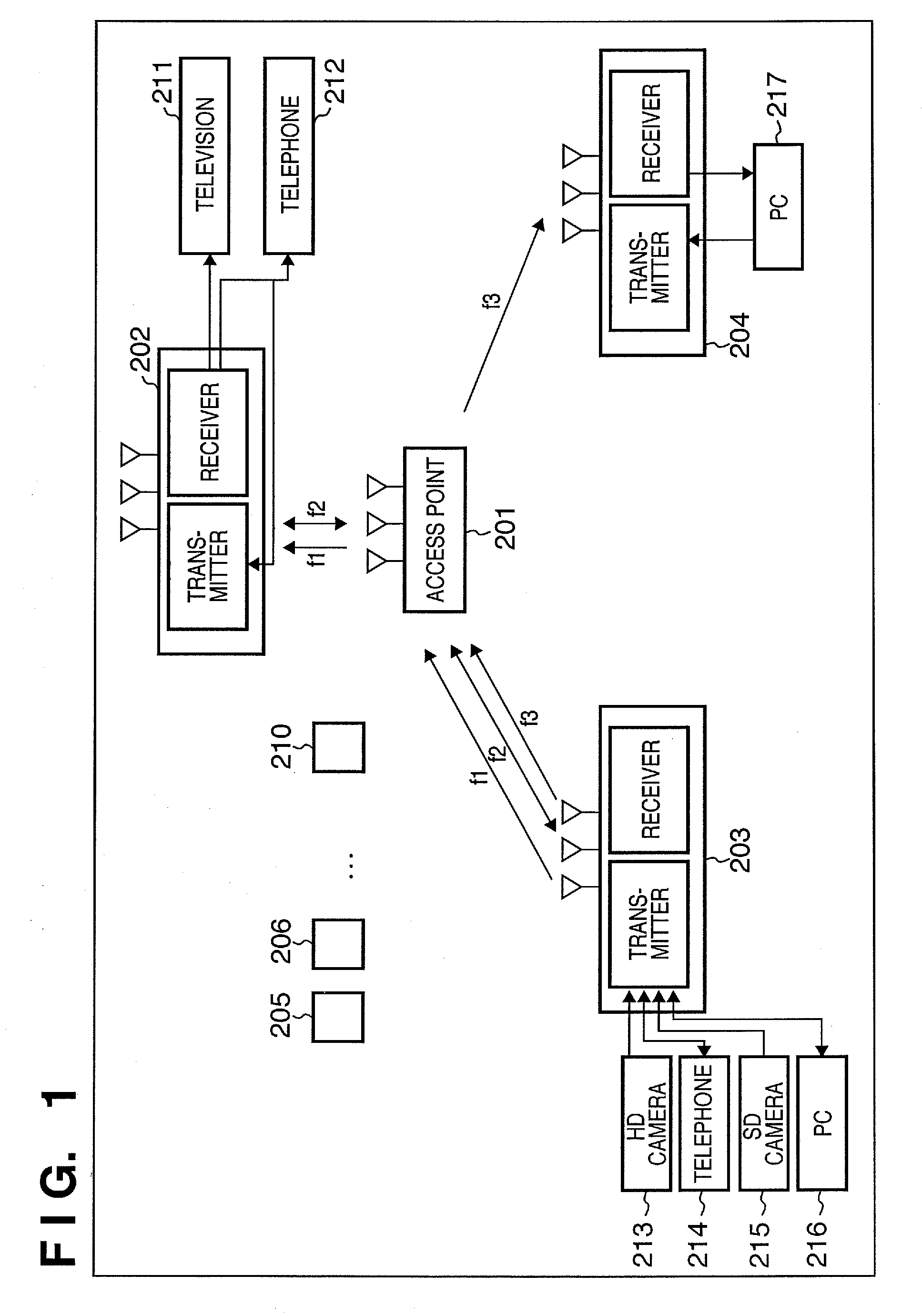

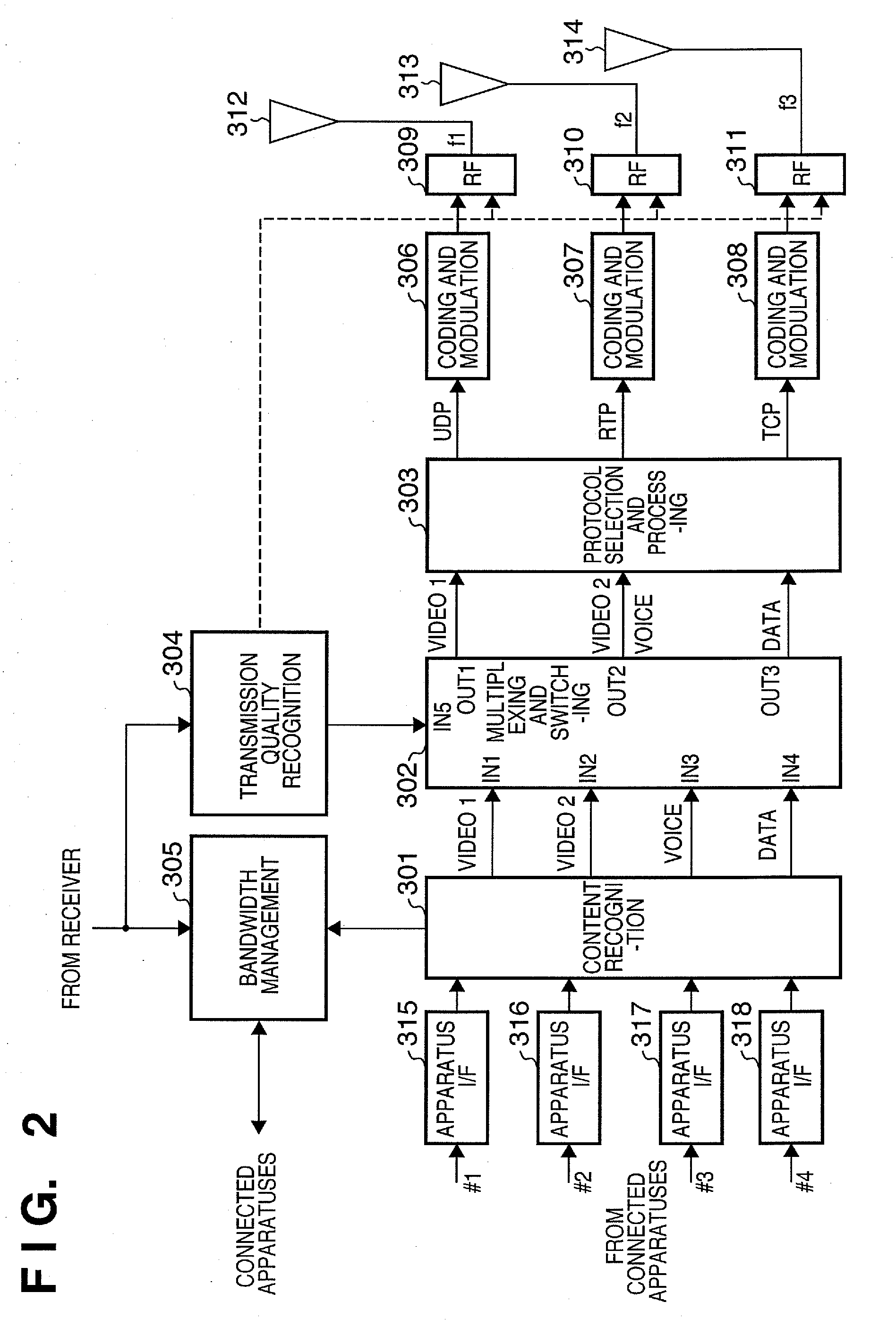

Transmission system and method for assigning transmission channel

InactiveUS20090064250A1Easy to useMinimize degradationNetwork topologiesTime-division multiplexComputer hardwareTransport system

A transmission terminal measures an error rate by periodically transmitting an error rate measuring packet to all transmission channels and all transmission paths. Content to be transmitted is classified, so that a transmission channel of the best transmission quality is assigned to content requiring real-timeness and a wide transmission bandwidth. According to the type of the content, a required communication protocol is selected to perform processing thereof. The transmission bandwidth for the content requiring a wide transmission bandwidth is assigned at a peak rate, while the transmission bandwidth for the content requiring a narrow transmission bandwidth is assigned at an average rate.

Owner:CANON KK

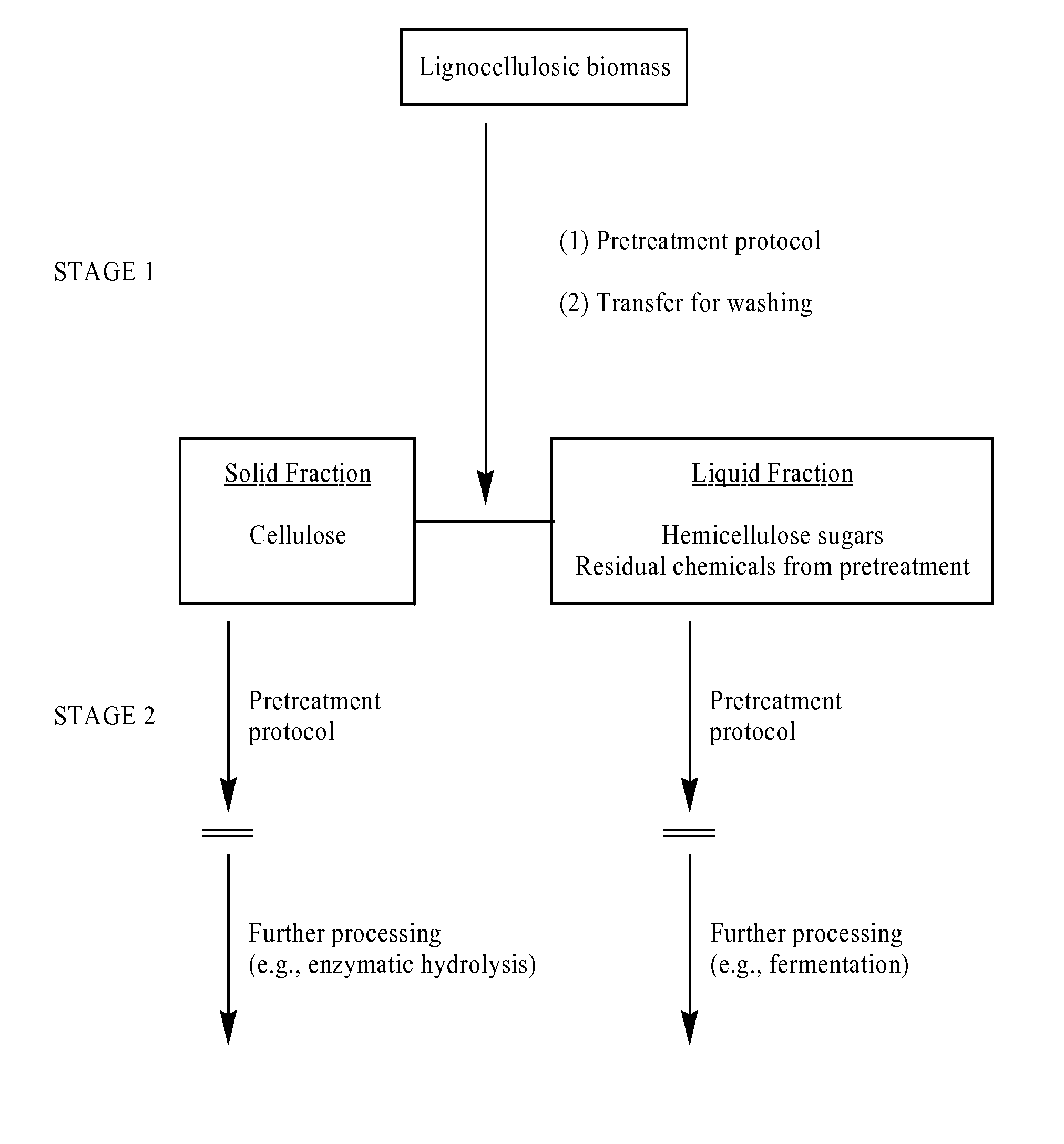

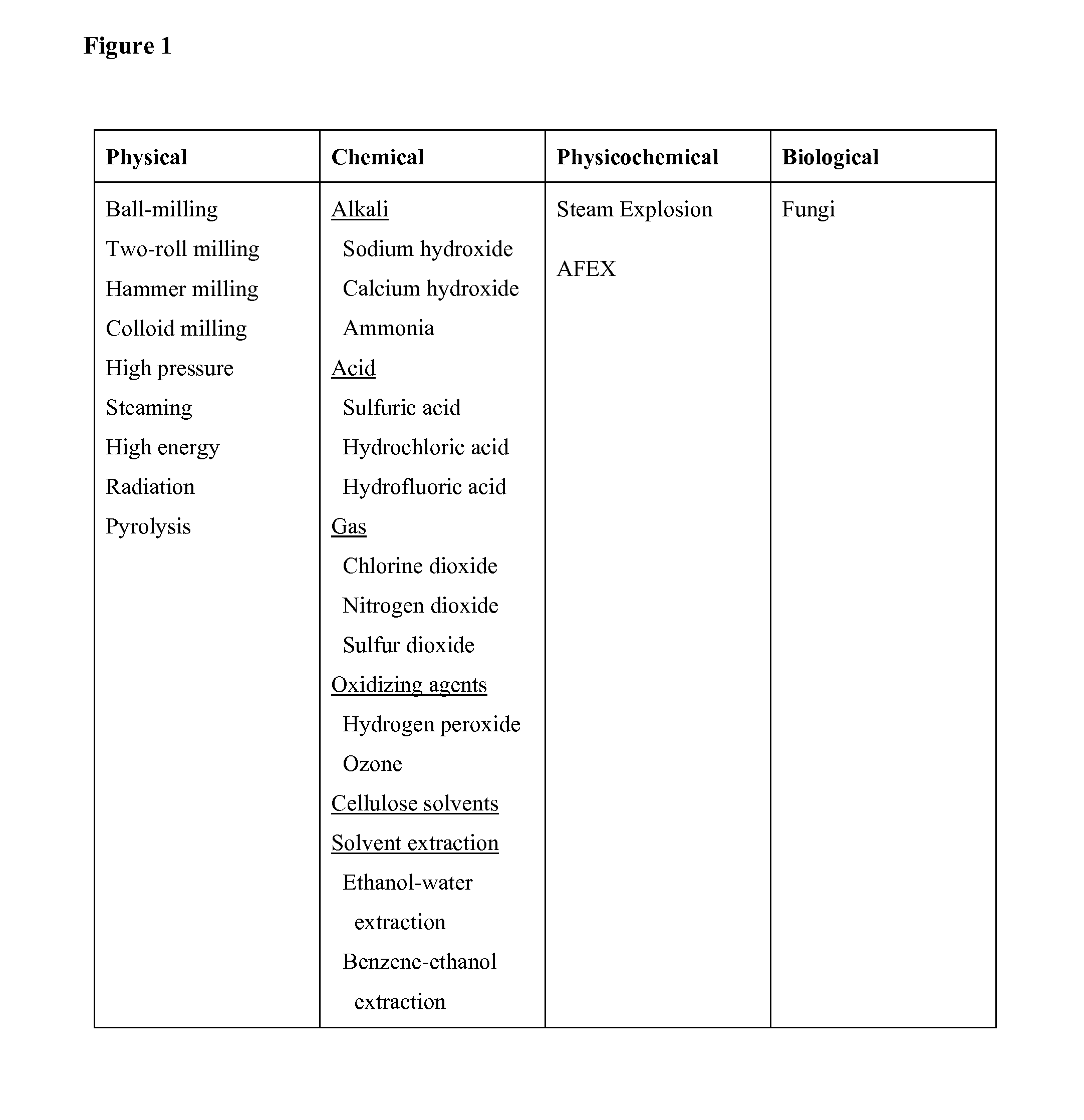

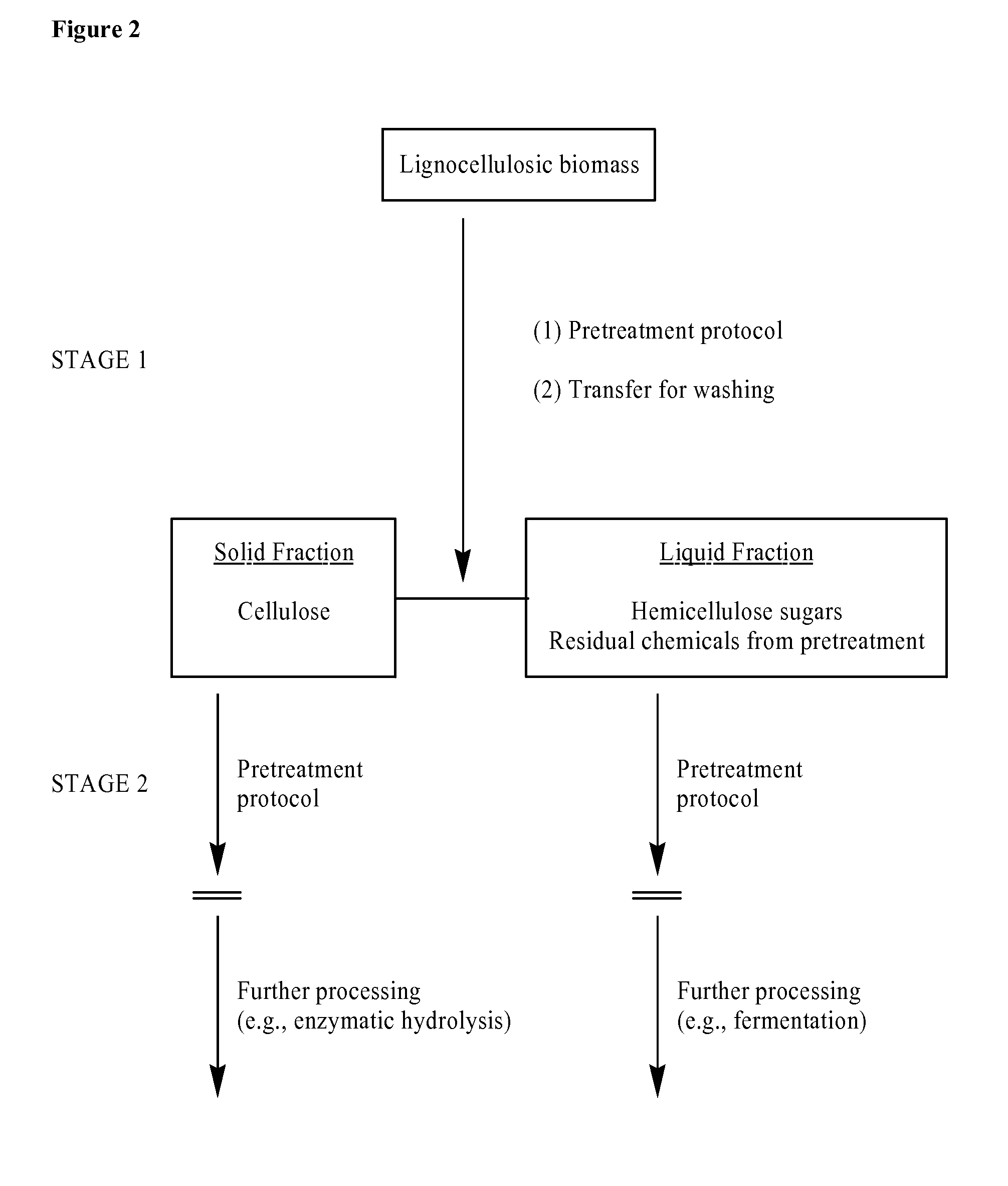

Two-stage method for pretreatment of lignocellulosic biomass

InactiveUS20100279361A1Reduce decreaseMaximize efficiencyOrganic compound preparationFood processingCelluloseFiber

One aspect of the invention relates to a process, comprising treating lignocellulosic biomass according to a first pretreatment protocol, thereby generating a first product mixture; separating the first product mixture into a first plurality of fractions; and treating at least one fraction of said first plurality of fractions according to a second pretreatment protocol, thereby generating a second product mixture. In one embodiment, the lignocellulosic biomass is selected from the group consisting of grass, switch grass, cord grass, rye grass, reed canary grass, miscanthus, sugar-processing residues, sugarcane bagasse, agricultural wastes, rice straw, rice hulls, barley straw, corn cobs, cereal straw, wheat straw, canola straw, oat straw, oat hulls, corn fiber, stover, soybean stover, corn stover, forestry wastes, recycled wood pulp protocol protocol fiber, paper sludge, sawdust, hardwood, softwood, and combinations thereof.

Owner:MASCOMA CORPORATION

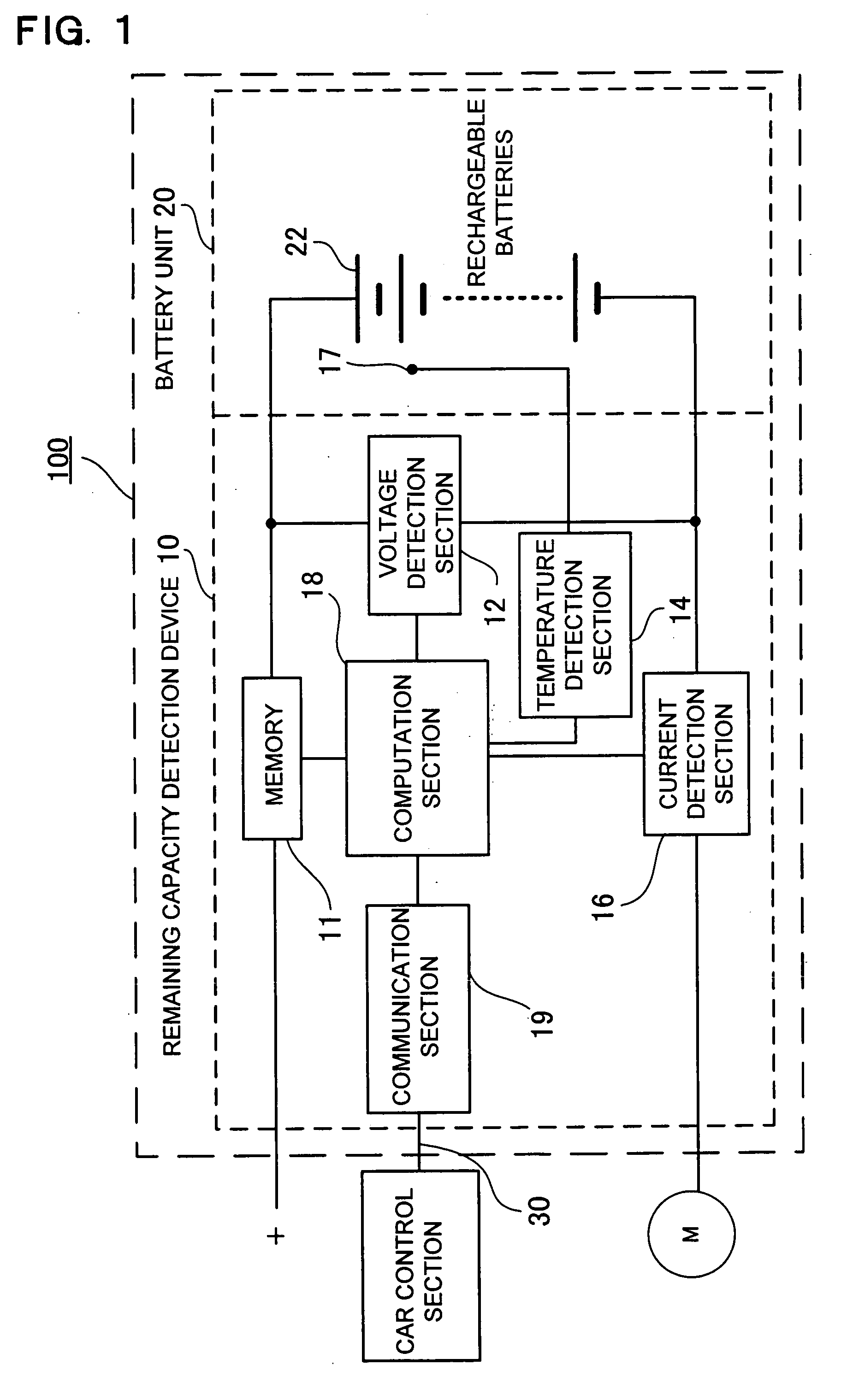

Method of controlling battery current limiting

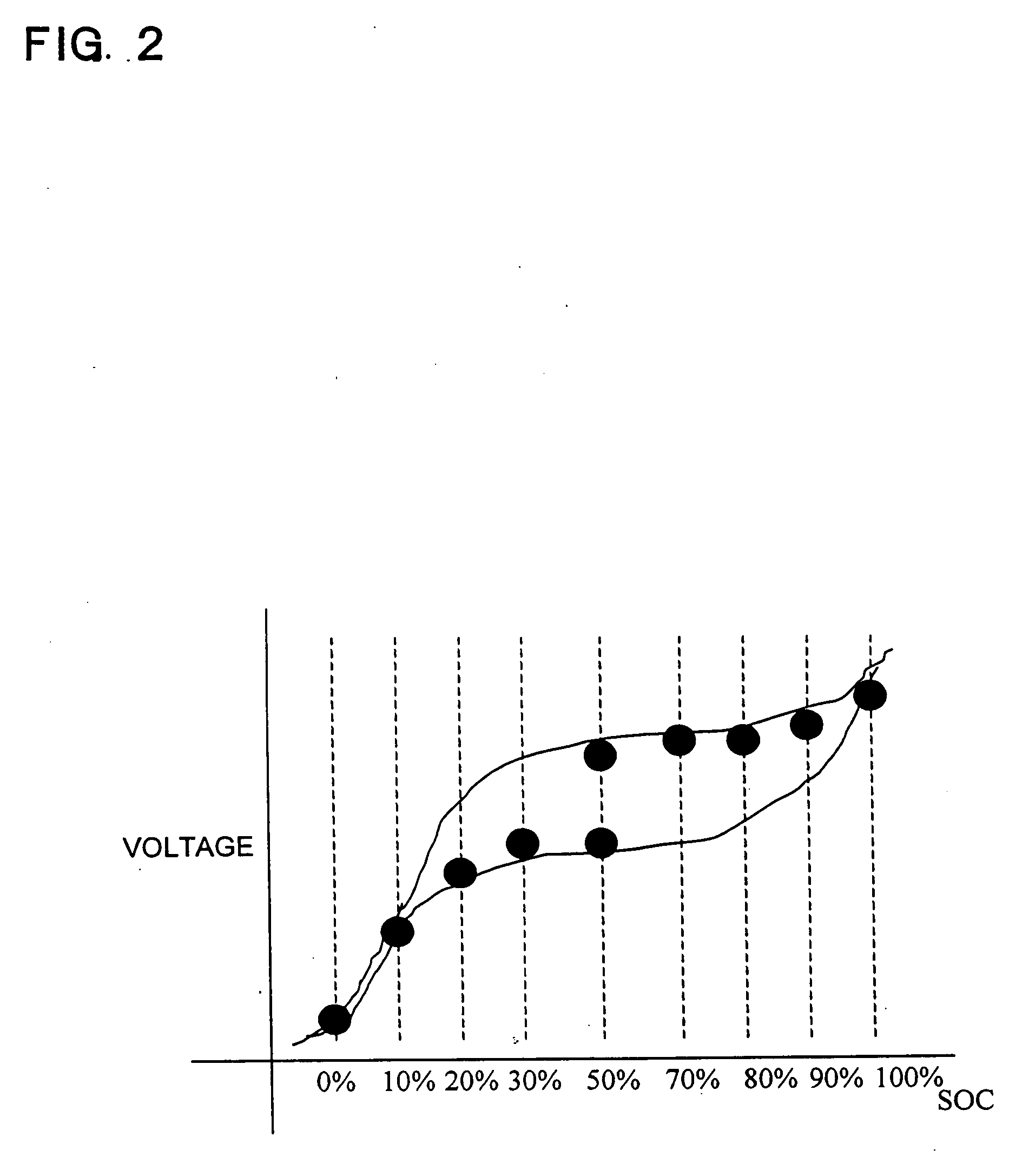

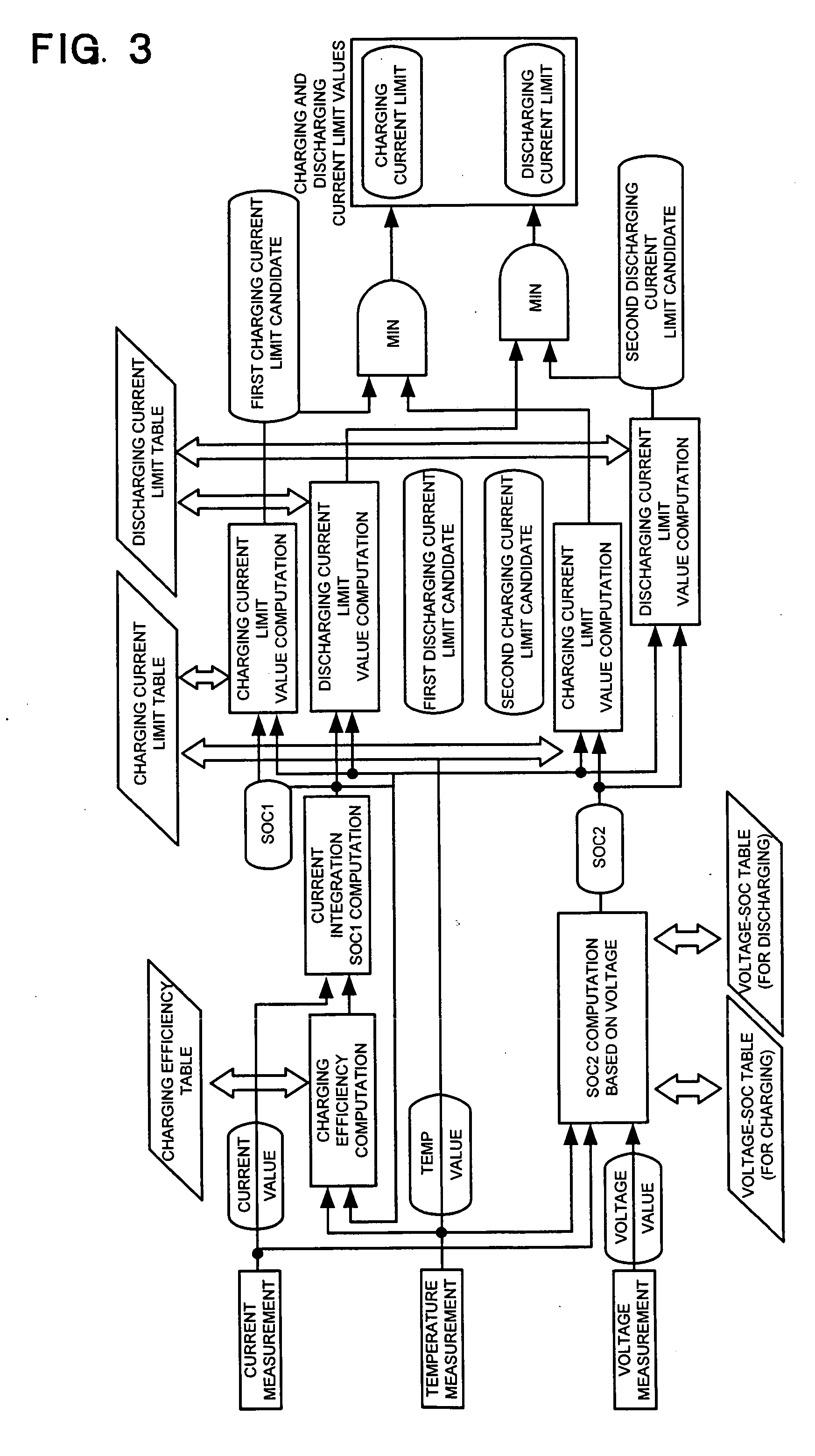

InactiveUS20060152196A1Reduce battery degradationReduce degradationElectric powerBattery overcharge protectionCurrent limitingBattery charge

The method of controlling battery current limiting controls maximum charging and discharging current values according to the state of charge of the battery. The method of controlling current limiting integrates battery charging and discharging current to compute a first state of charge, determines first charging and discharging current limit value candidates from that first state of charge, computes a second state of charge based on battery voltage, and determines second charging and discharging current limit value candidates from that second state of charge. Further, the method takes the smaller of the first and second charging and discharging current limit value candidates as the charging and discharging current limit values for charging and discharging the battery.

Owner:SANYO ELECTRIC CO LTD

Method and apparatus of monitoring polishing pad wear during processing

InactiveUS6045434AMinimize degradationPolishing machinesRevolution surface grinding machinesClosed loopEngineering

A method and apparatus for monitoring polishing pad wear during processing is developed to extend the pad's useful life, and maintain pad uniformity. This is accomplished in the present invention by measuring and monitoring the diminished pad thickness using a non-intrusive measurement system, and creating a closed-loop system for adjusting the chemical-mechanical polishing tool process parameters. The non-intrusive measurement system consists of an interferometer measurement technique utilizing ultrasound or electromagnetic radiation transmitters and receivers aligned to cover any portion of the radial length of a polishing pad surface. The measurement system is sensitive to relative changes in pad thickness for uniformity, and to abrupt changes such as detecting wafer detachment from the CMP wafer carrier.

Owner:IBM CORP

Manufacturing process for the production of peptides grown in insect cell lines

InactiveUS20060246544A1Improve purityHigh concentrationHydrolasesPeptide/protein ingredientsPeptideGlycosyltransferase

The present invention provides a manufacturing method for the production of peptides that are grown in insect cell lines. The peptides are grown in insect cell cultures that are infected with baculovirus particles in a culture supplemented with a lipid mixture. The peptides are then isolated from the insect cell culture using a method that employs a tangential flow filtration cascade. The isolated peptides are glycopeptides having an insect specific glycosylation pattern. The glycopeptides may then be conjugated to a modifying group via linkage through a glycosyl linking group interposed between and covalently attached to the peptide and the modifying group. The conjugates are formed from glycosylated peptides by the action of a glycosyltransferase.

Owner:NOVO NORDISK AS

Method of sterilizing a medical device

InactiveUS7150853B2Inhibit and prevent formationReduce materialStentsBalloon catheterVascular graftBalloon catheter

A method of sterilizing a medical device component, such as a catheter balloon, in which an electron beam (i.e., e-beam) is applied to the component in an evacuated or inert gas-filled container. The method of the invention allows for electron beam sterilization without significant degradation of the component polymeric material. In one embodiment, the device component is configured to be pressurized or expanded during use. The method of the invention provides a component with a rupture pressure that is not significantly decreased due to electron beam sterilization. Another aspect of the invention is a medical device component, e-beam sterilized according to a method of the invention. A variety of medical device components can be sterilized by the method of the invention, and particularly intracorporeal devices for therapeutic or diagnostic purposes, such as balloon catheters, catheter shafts and balloons, stent covers, and vascular grafts.

Owner:ABBOTT CARDIOVASCULAR

Multimeric VLA-4 antagonists comprising polymer moieties

InactiveUS20060013799A1Minimize degradationSenses disorderNervous disorderLymphatic SpreadWhite blood cell

Disclosed are conjugates which bind VLA-4. Certain of these conjugates also inhibit leukocyte adhesion and, in particular, leukocyte adhesion mediated by VLA-4. Such conjugates are useful in the treatment of inflammatory diseases in a mammalian patient, e.g., human, such as asthma, Alzheimer's disease, atherosclerosis, AIDS dementia, diabetes, inflammatory bowel disease, rheumatoid arthritis, tissue transplantation, tumor metastasis and myocardial ischemia. The conjugates can also be administered for the treatment of inflammatory brain diseases such as multiple sclerosis.

Owner:ELAN PHARM INC

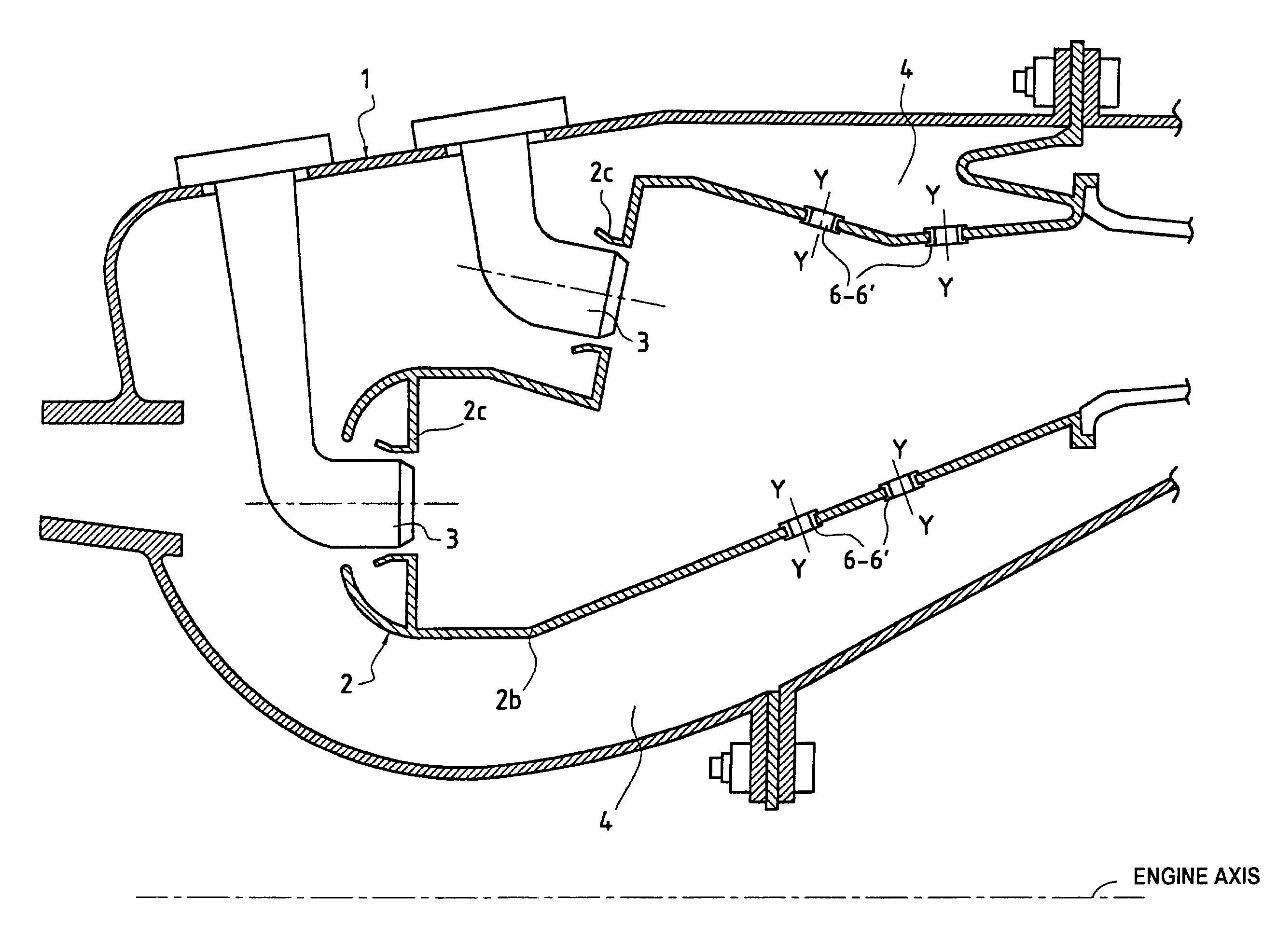

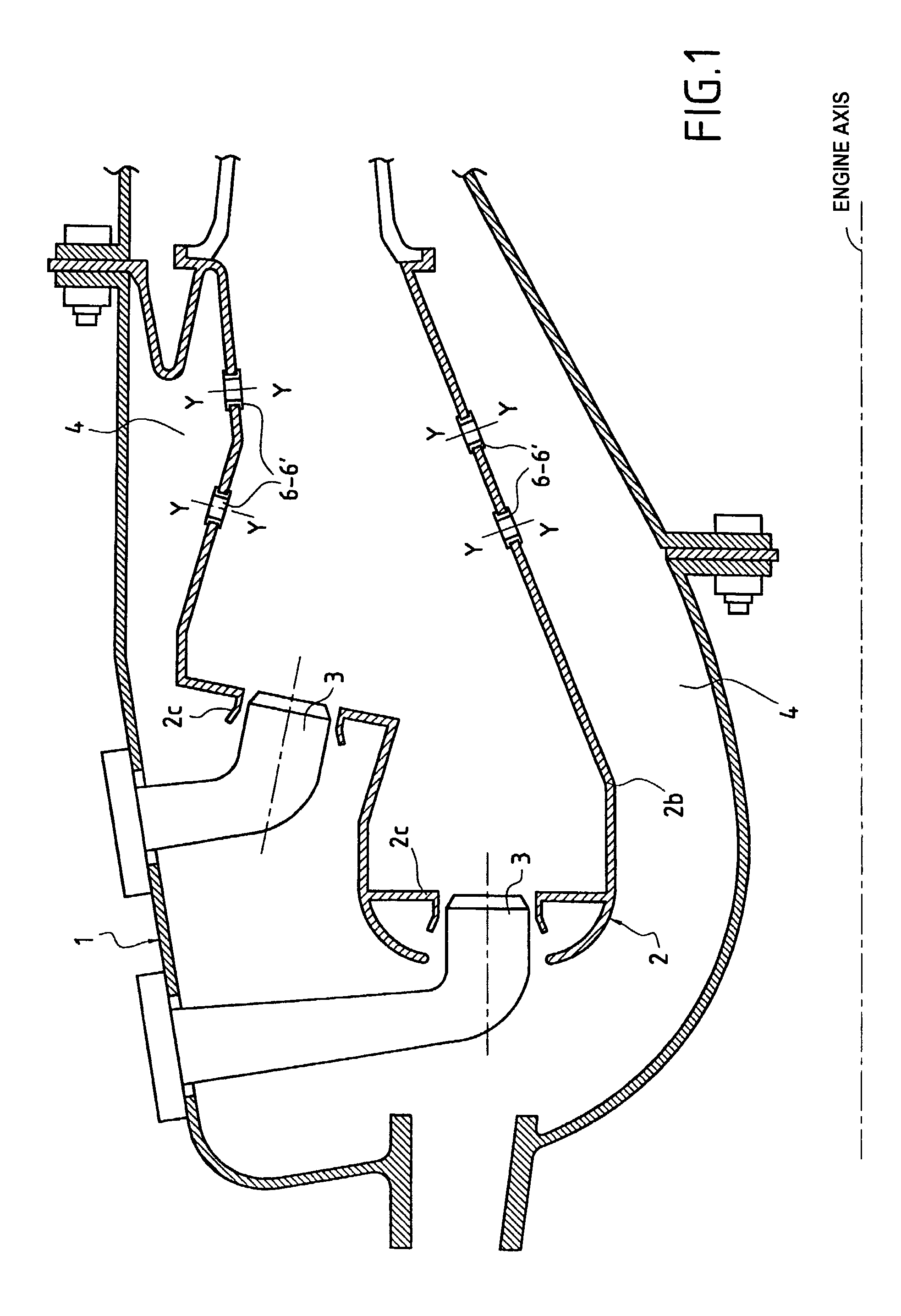

Gas turbine combustion chambers

InactiveUS20020189260A1Improve temperature behaviorMitigate such drawbackContinuous combustion chamberGas turbine plantsCombustion chamberInjection air

A combustion chamber for a gas turbine made up of outer and inner side walls, the combustion chamber being received in a casing so as to define an annular space between the combustion chamber and the casing in which there flows air for combustion, for dilution, and for cooling the combustion chamber, the side walls of the combustion chamber being pierced by a plurality of holes in which bushings of substantially elliptical right section are fixed to define air injection passages for injecting air into the combustion chamber, each bushing having a peripheral wall in which at least one additional orifice is formed opening out into the combustion chamber in the immediate vicinity of the side wall of the combustion chamber in which said bushing is fixed so that the air passing through said orifice flows substantially along said peripheral wall, the peripheral wall of each bushing having at least one groove opening out into the annular space and into which the or each orifice opens out so as to be fed with air and so as to cool the peripheral wall of the bushing.

Owner:SNECMA MOTEURS SA

Spectral gamma ray logging-while-drilling system

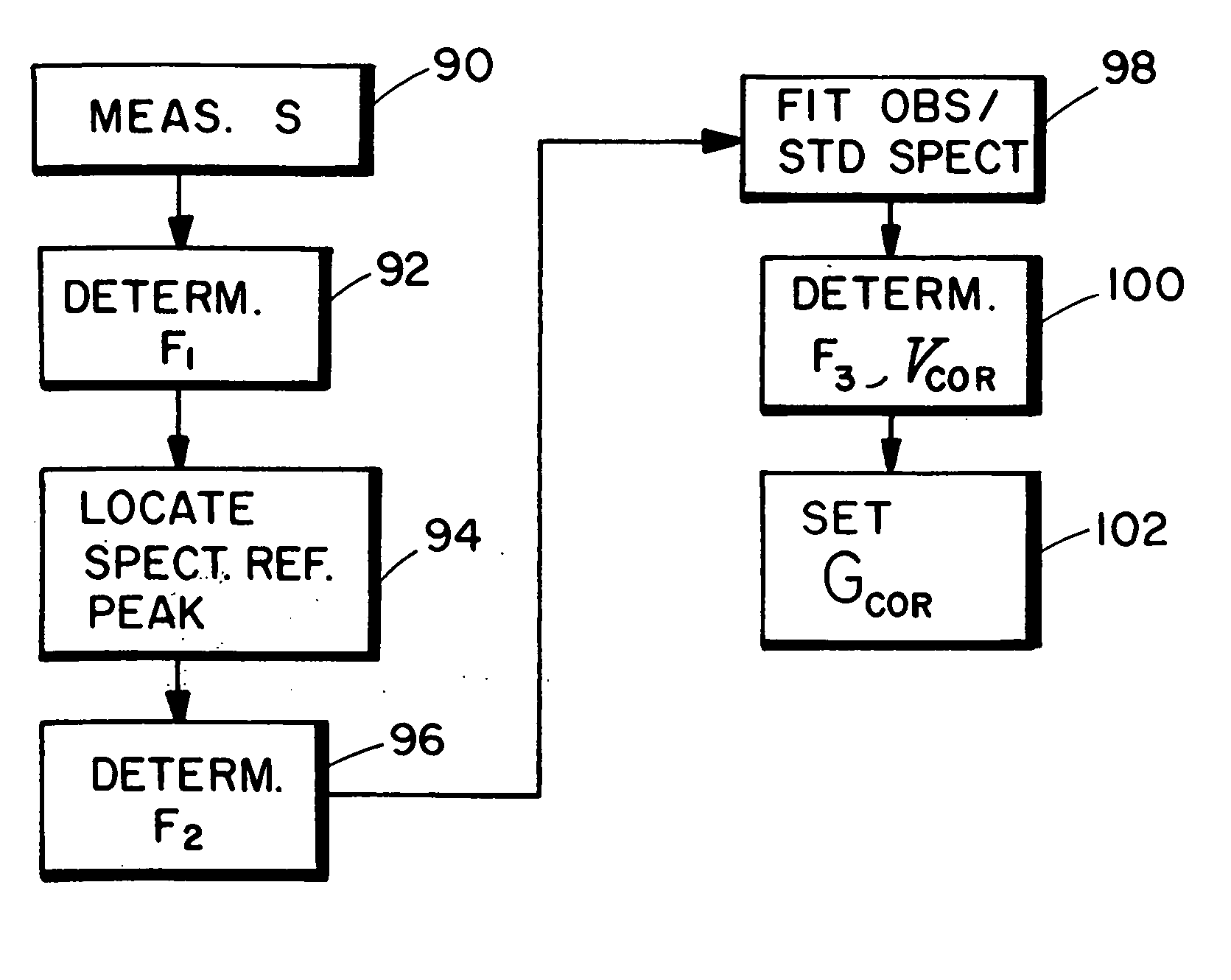

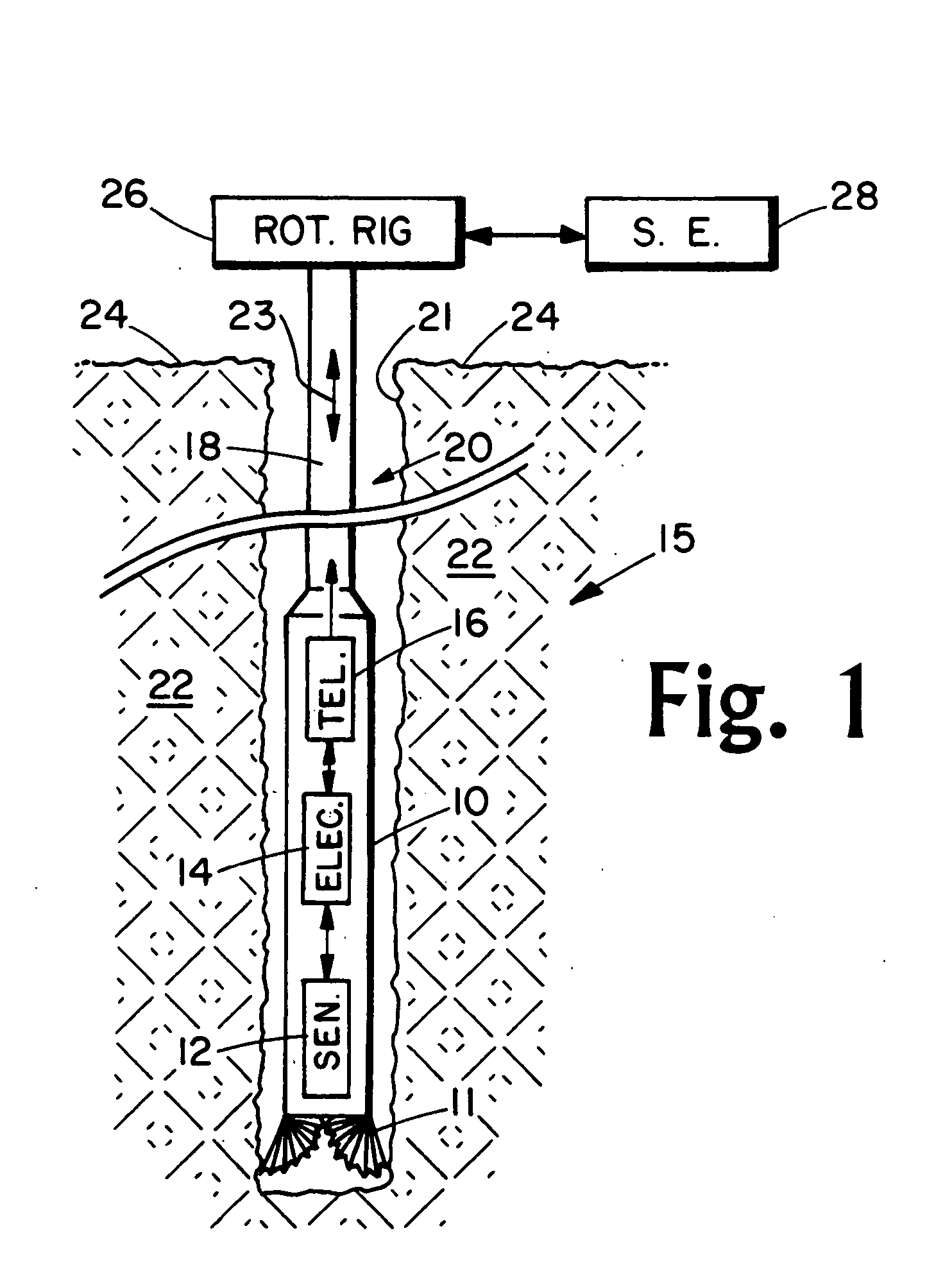

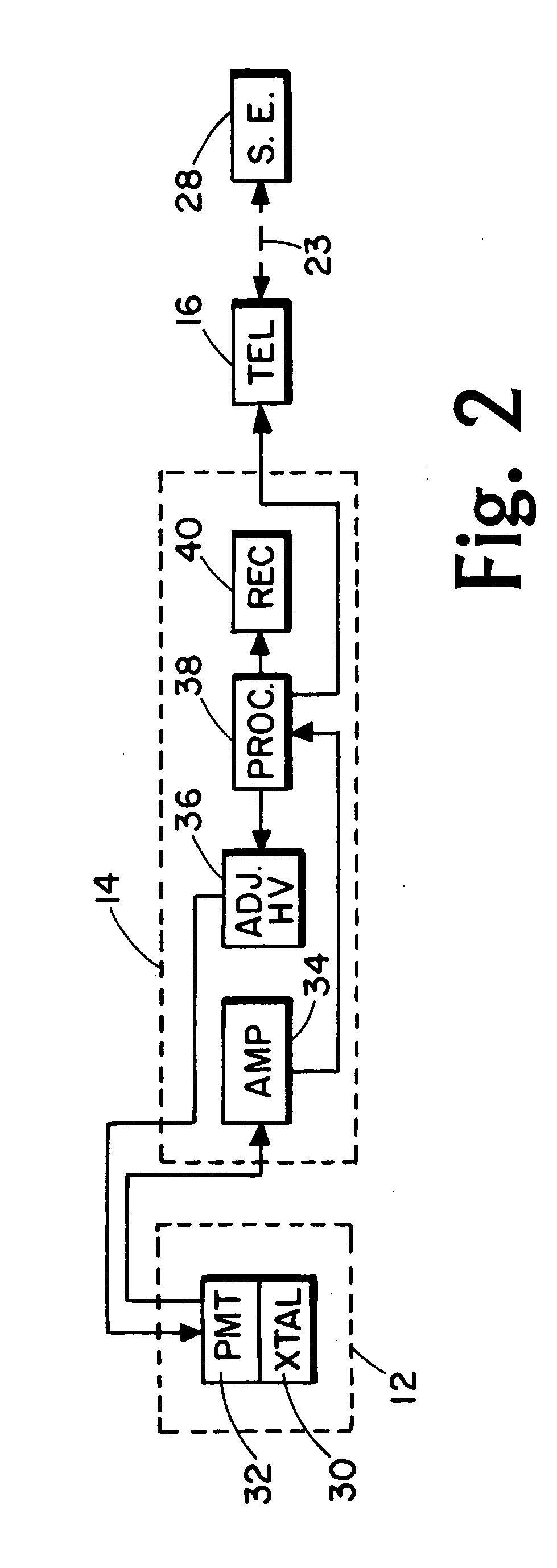

ActiveUS20050199794A1Minimize degradationMaximizing counting rateCalibration apparatusBorehole/well accessoriesPotassiumDrilling system

A method for determining concentrations of naturally occurring radioactive elements in earth formation by analysis of gamma ray energy spectra measured by at least one gamma ray detector while the borehole is being drilled. Gain of the gamma ray detector is controlled automatically through analysis of the spectra. The one or more gamma ray detectors are disposed at the periphery of the downhole instrumentation to maximize sensitivity. Elemental concentrations of naturally occurring radioactive elements such as potassium, uranium and thorium are measured either as a function of depth in the borehole, or as a function of aximuthal sectors around the borehole wall, or as a function of both depth and azimuthal sectors.

Owner:WEATHERFORD CANADA

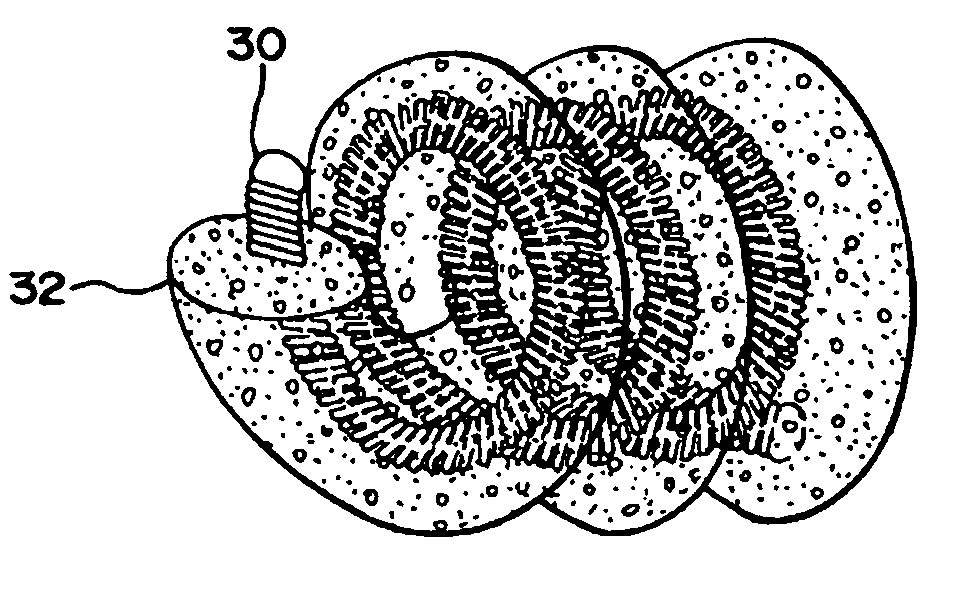

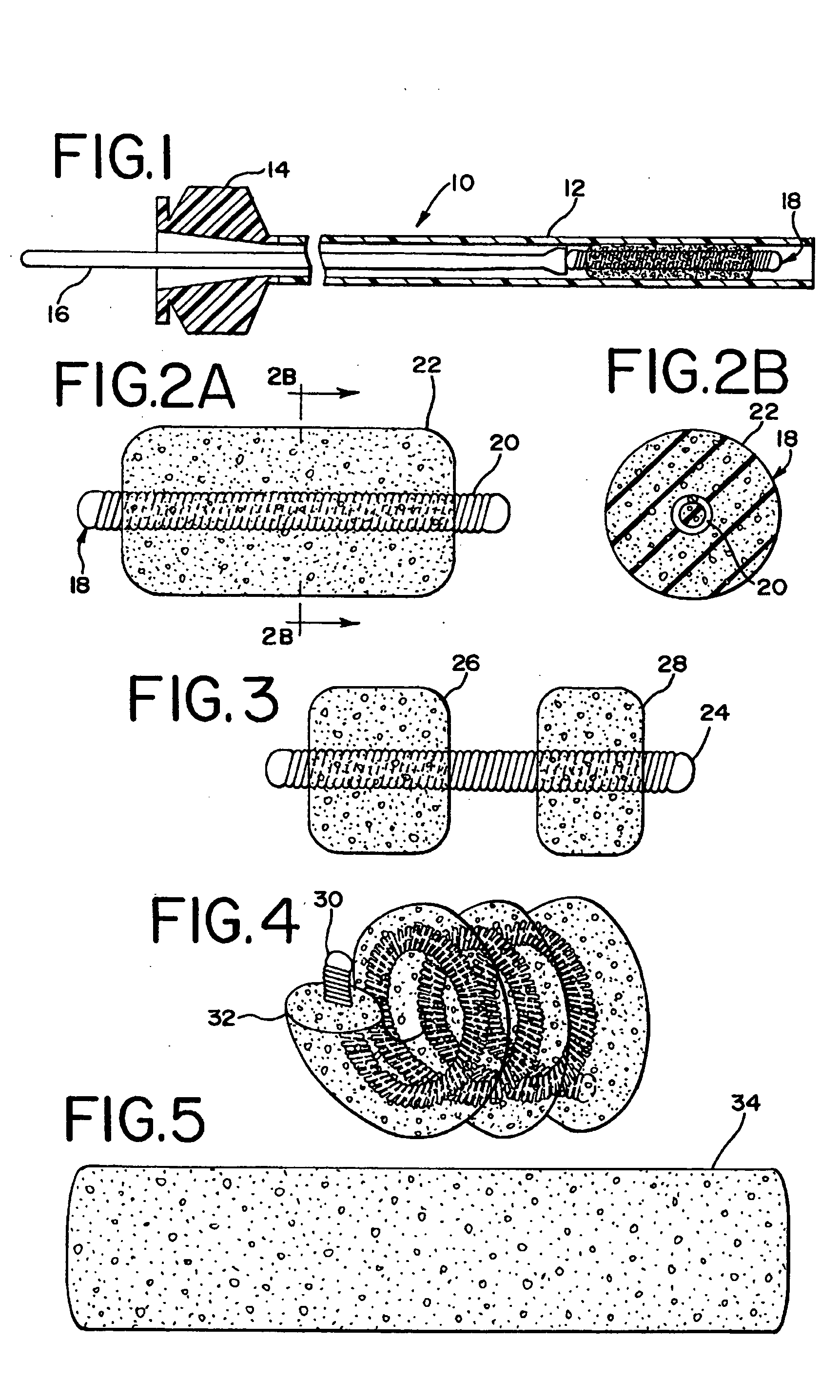

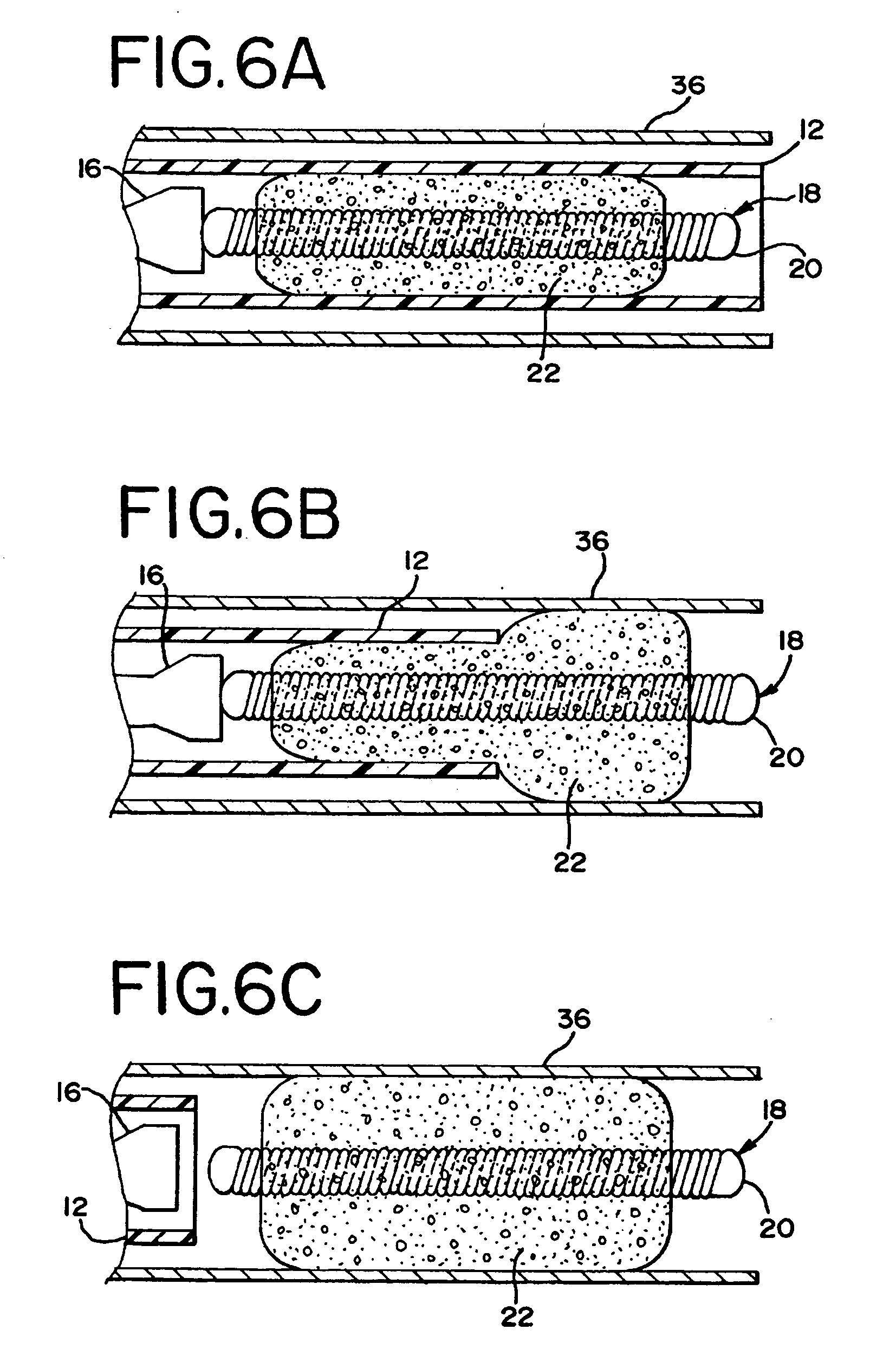

Foam matrix embolization device

InactiveUS20060058834A1Reduce coil stretchingImprove sponge mechanical integrityStentsDilatorsHuman bodyWater insoluble

The present invention relates to a medical device for placement at a predetermined location within a passageway of the human body, and more particularly, relates to a flexible embolization device which may be delivered by a catheter to a pre-selected position within a blood vessel to thereby embolize a blood vessel or a blood vessel defect, such as an aneurysm or fistula. Specifically, the embolization device comprises an elongated coil having a lumen, the coil and lumen being at least partially embedded in an elongated foam member comprising, in some embodiments, a flexible, biodegradable, water insoluble, open, interconnecting-cell foam material having embolic characteristics, and capable of allowing cell proliferation into the open cell foam interior.

Owner:CORDIS CORP

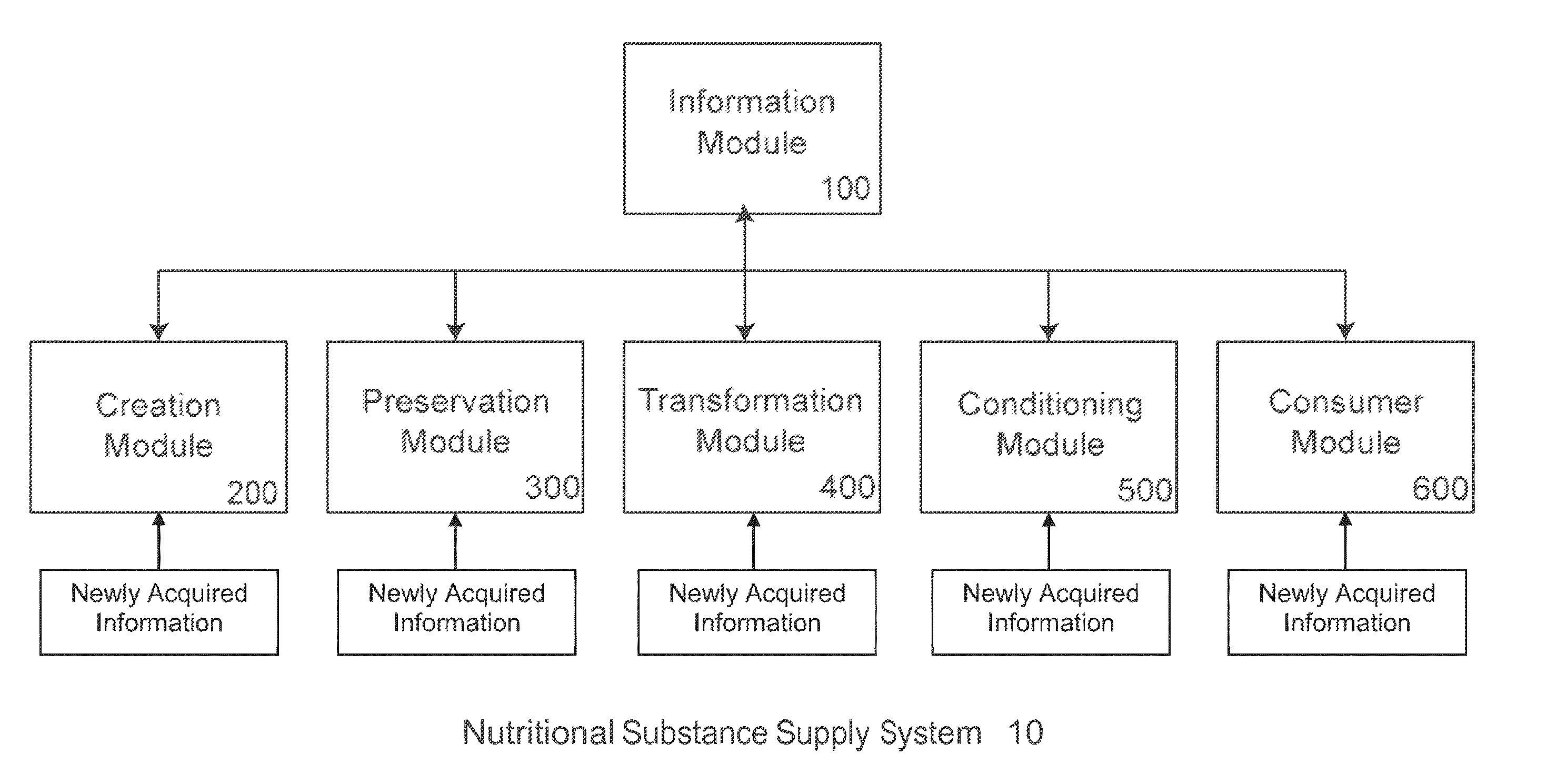

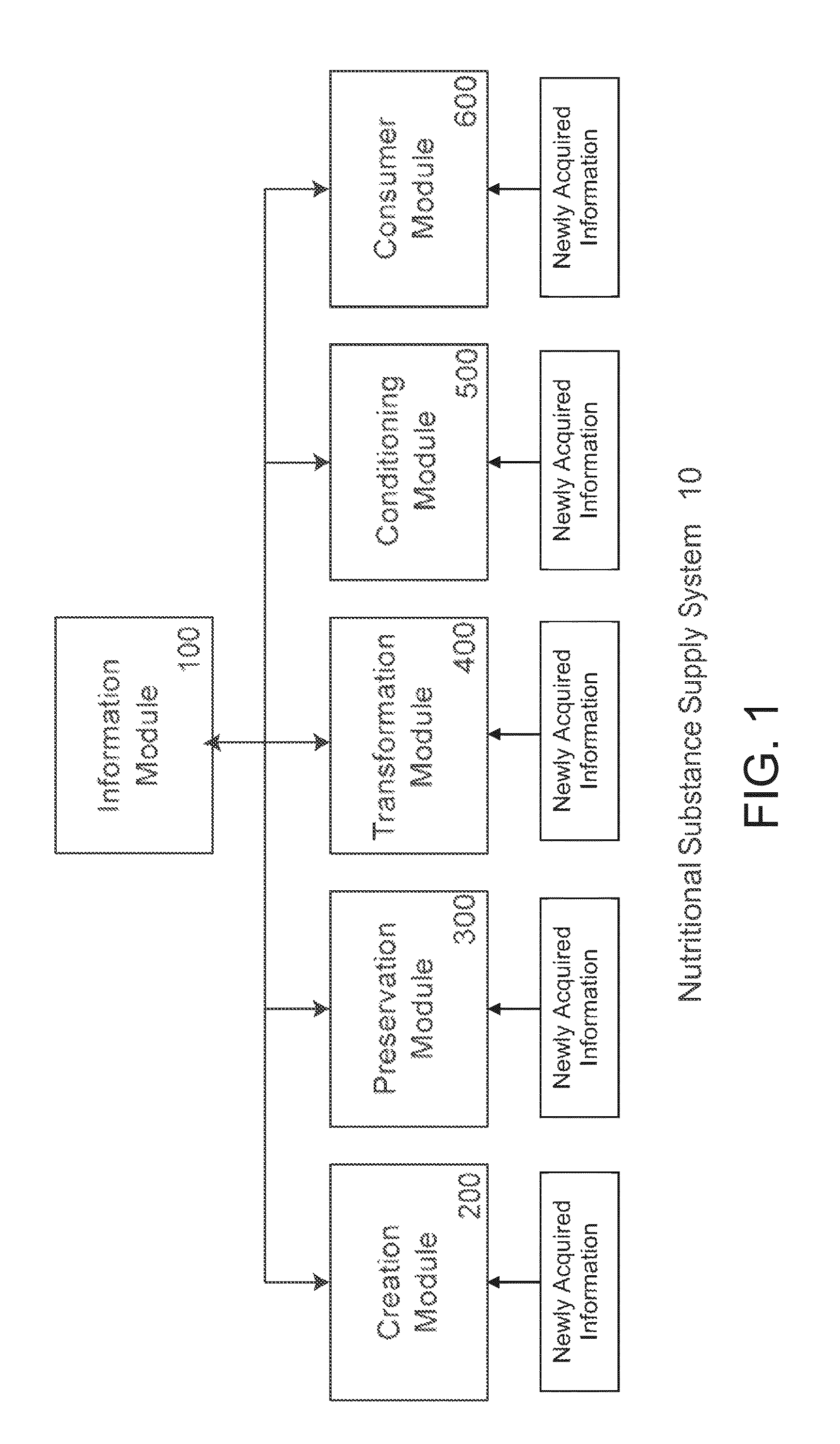

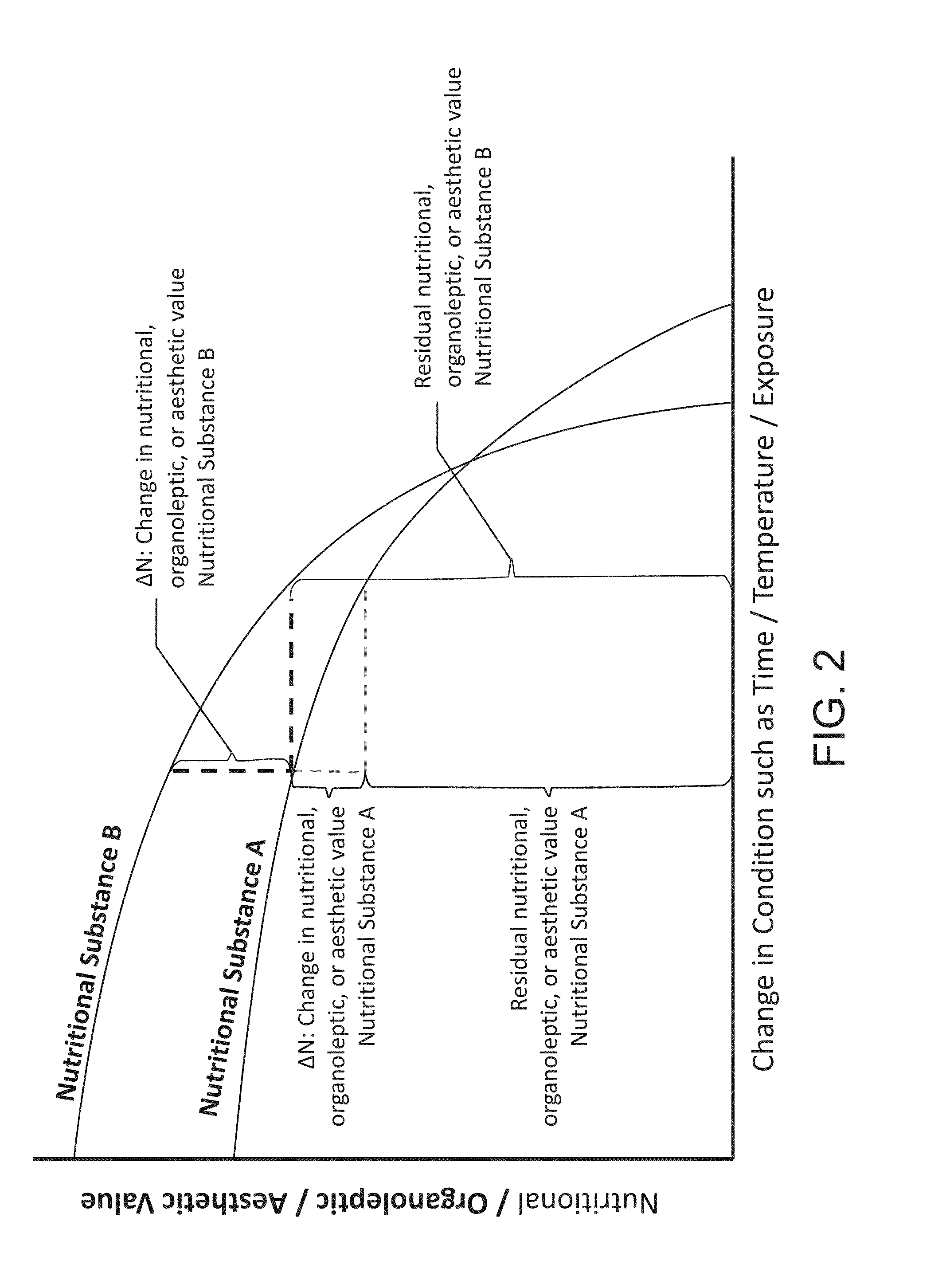

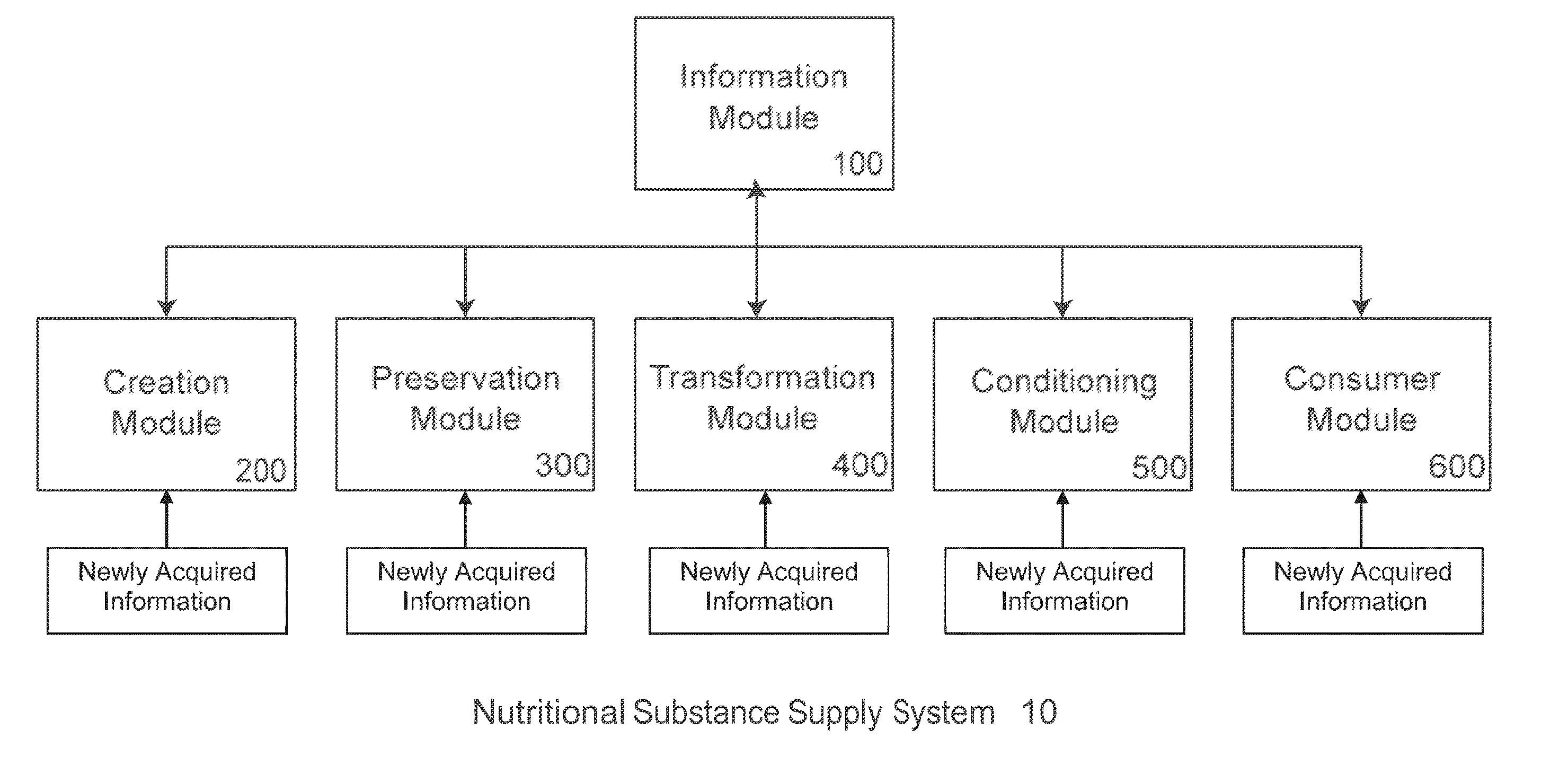

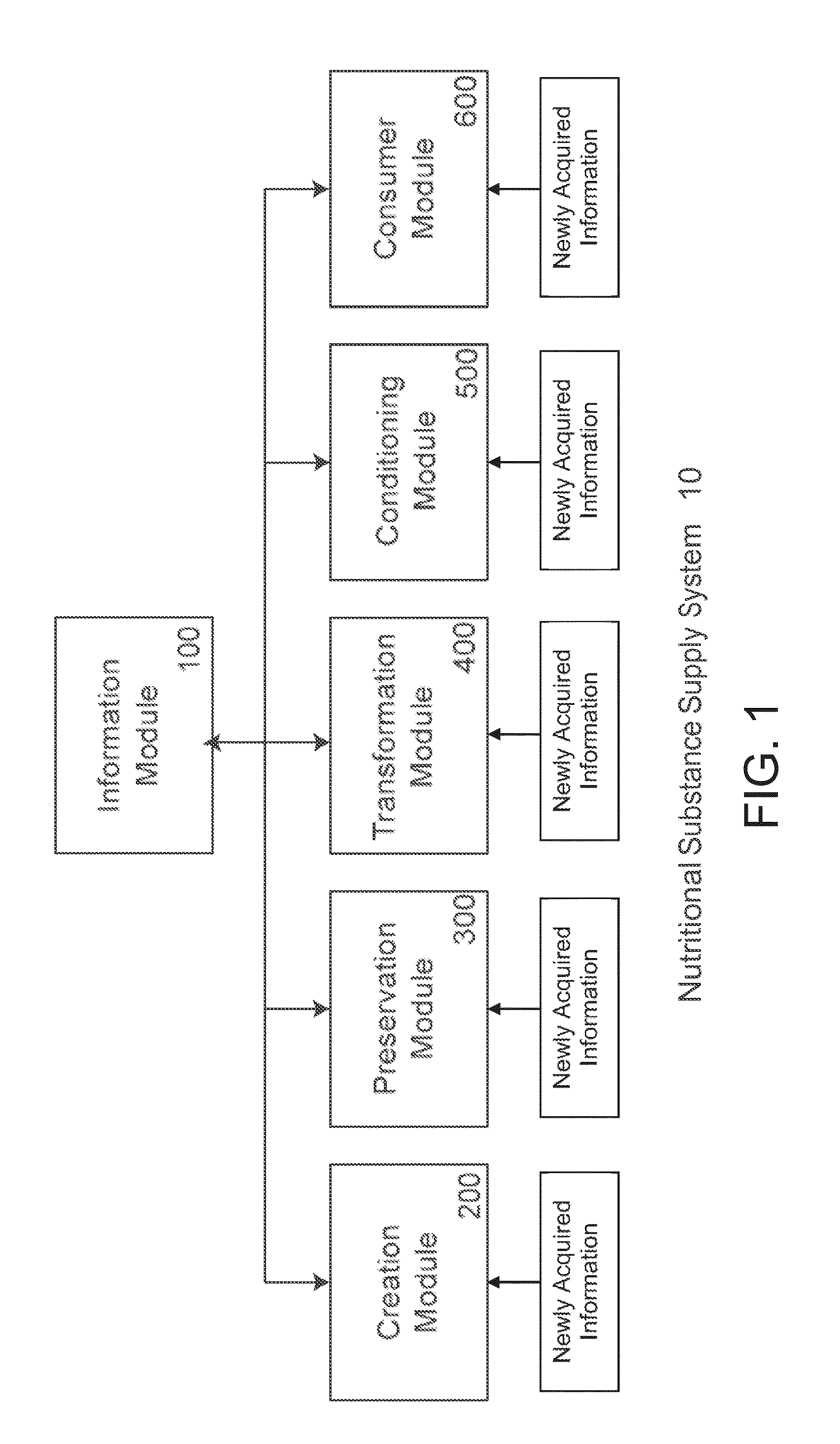

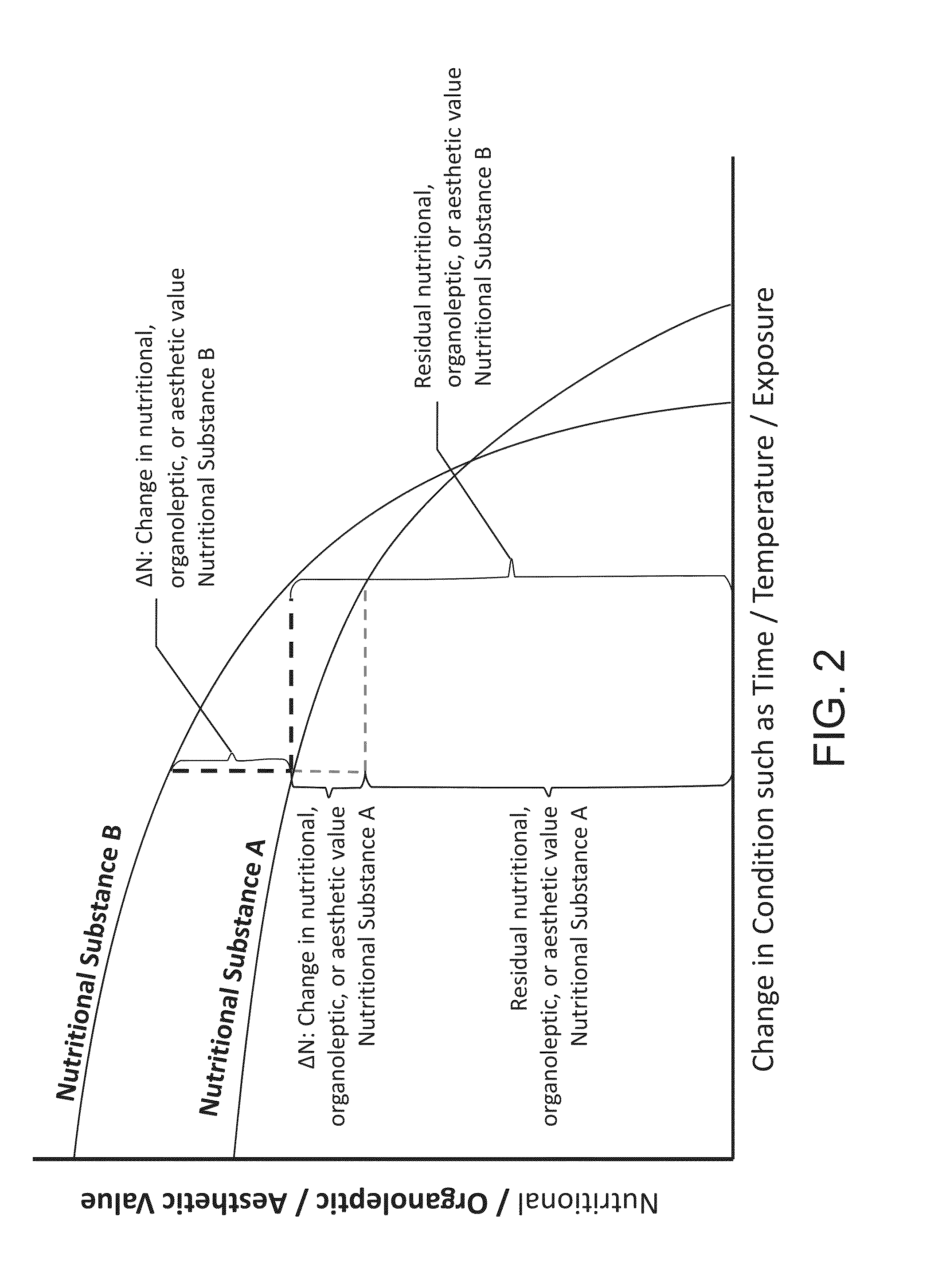

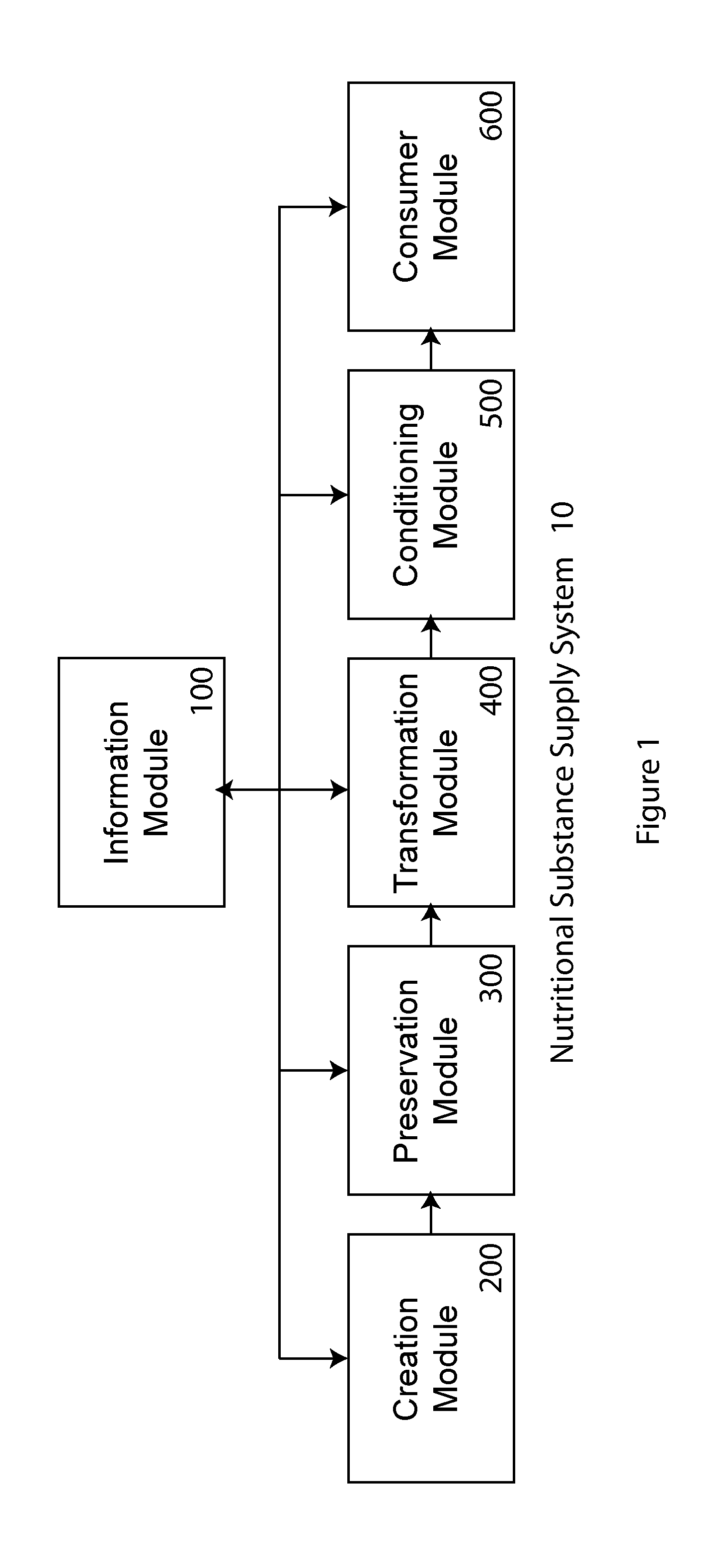

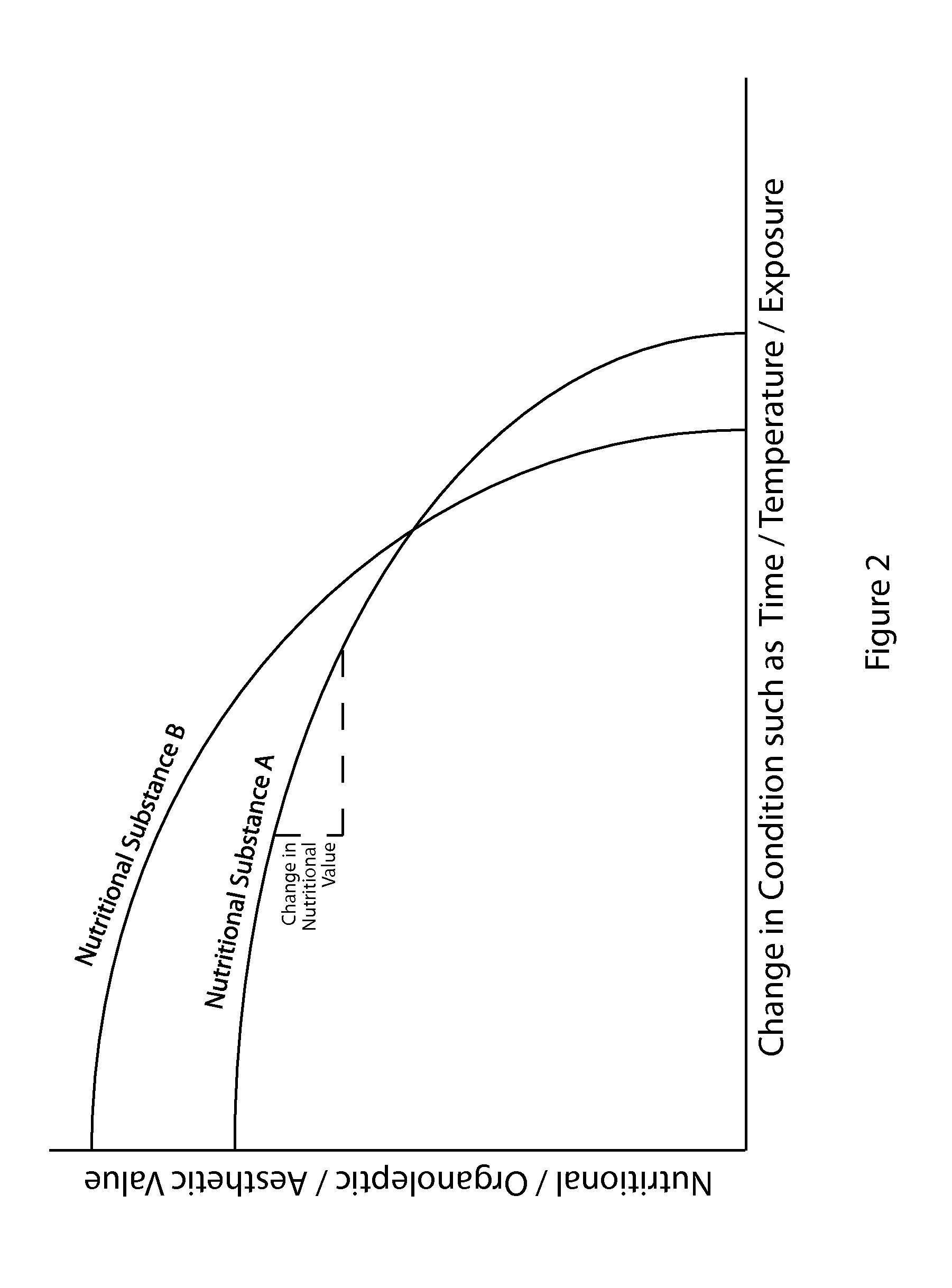

Dynamic recipe control

ActiveUS9528972B2Improve nutritional and organoleptic and aesthetic valueMinimize degradationNutrition controlSteam cooking vesselsComputer scienceRecipe

Nutritional substance systems and methods are disclosed enabling the tracking and communication of changes in nutritional, organoleptic, and aesthetic values of nutritional substances, and further enabling the adaptive storage and adaptive conditioning of nutritional substances.

Owner:ICEBERG LUXEMBOURG S A R L

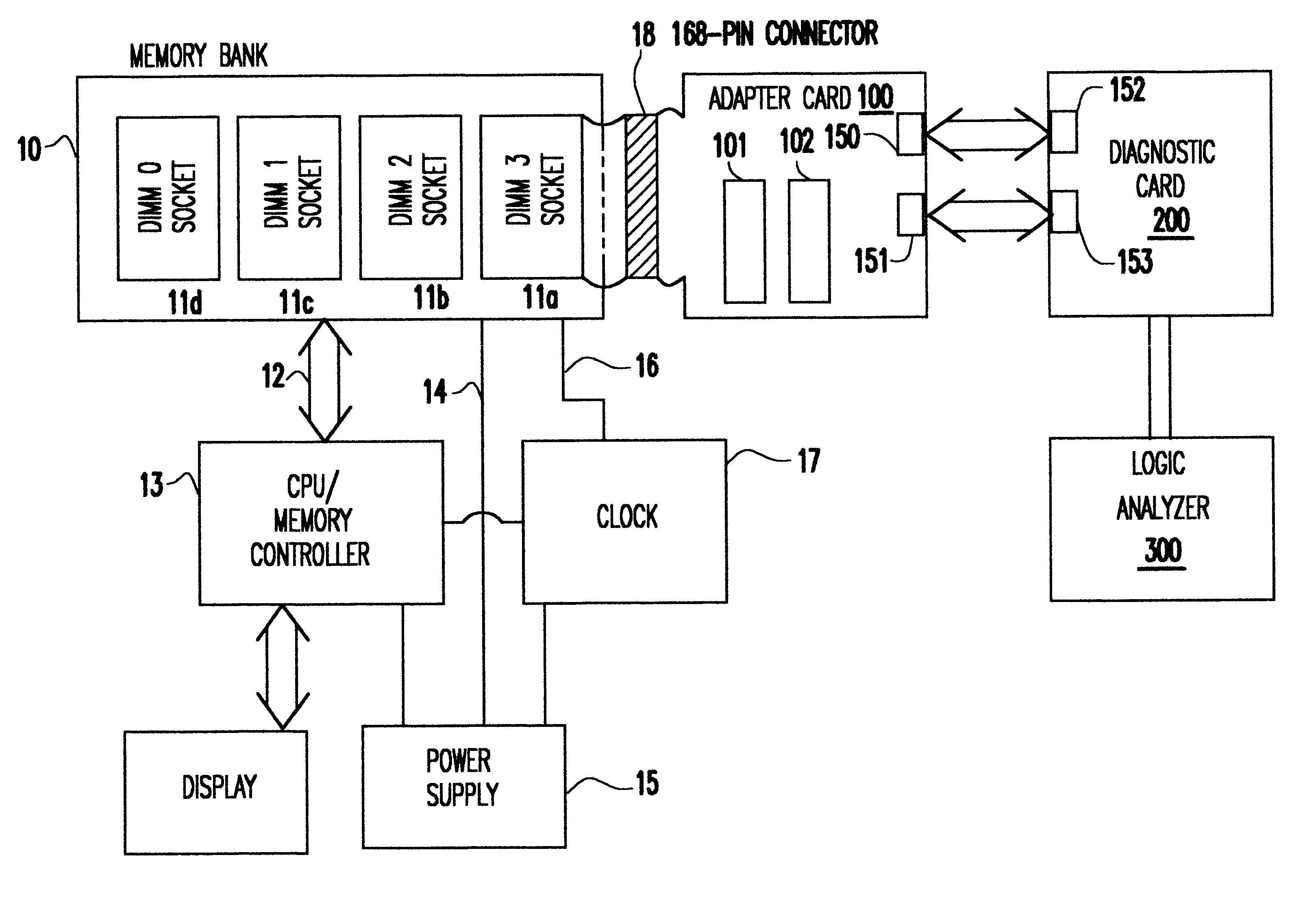

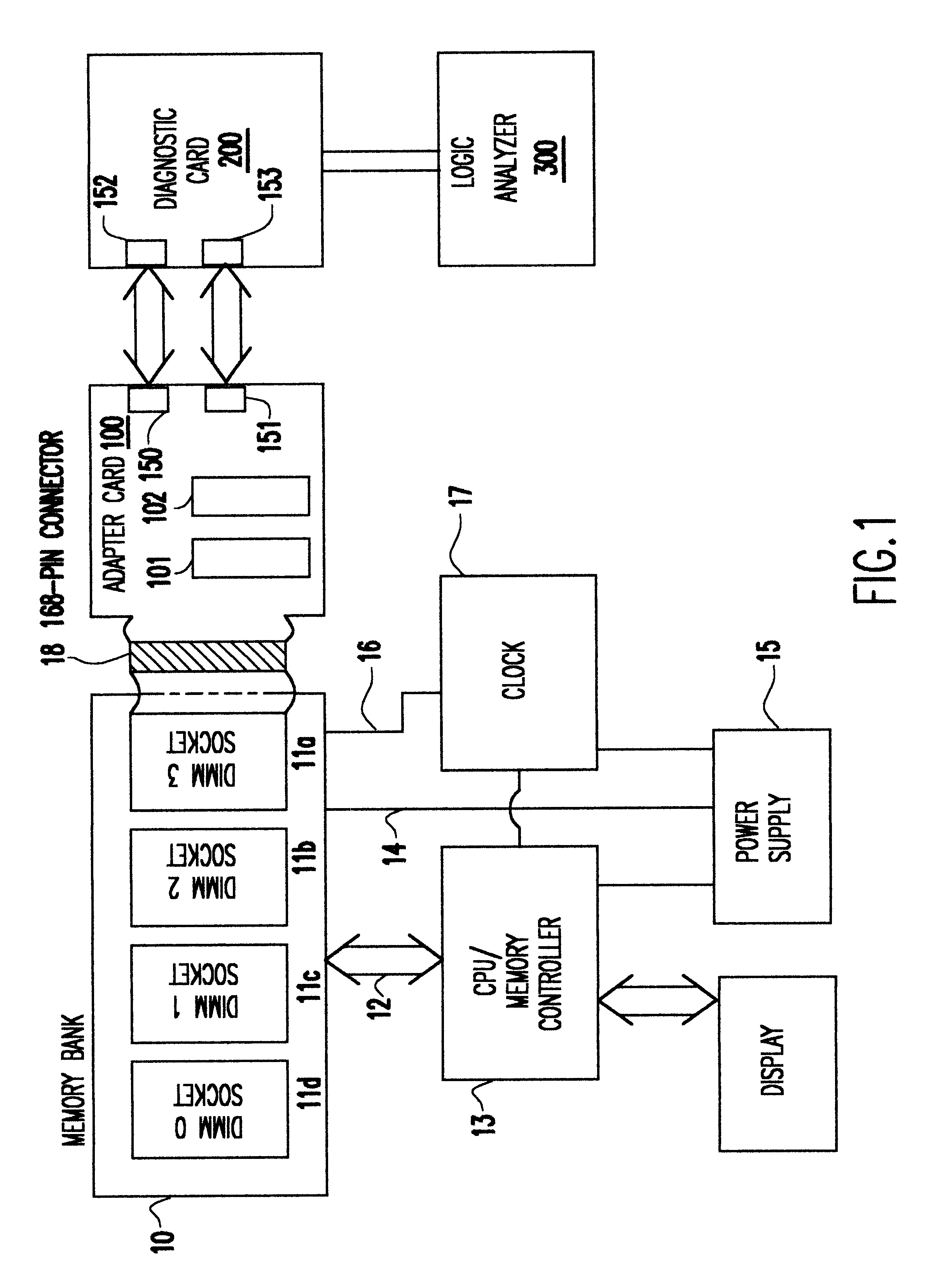

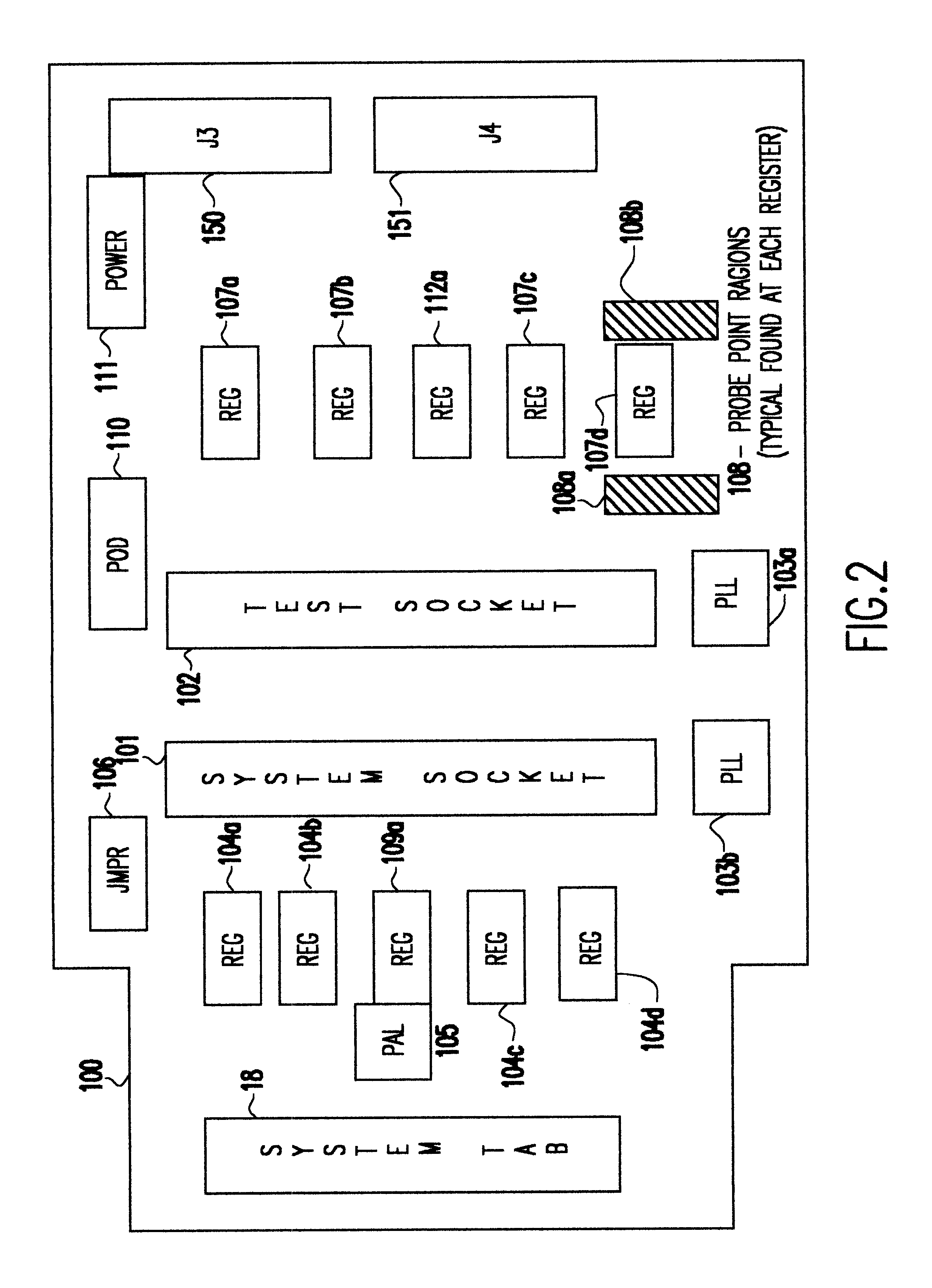

Captured synchronous DRAM fails in a working environment

InactiveUS6467053B1Minimize degradationError detection/correctionComponent plug-in assemblagesLength variationDram memory

A Synchronous DRAM memory test assembly that converts a normal PC or Workstation with a synchronous bus into a memory tester. The test assembly may be split into two segments: a diagnostic card and an adapter card to limit mechanical load on the system socket as well as permit varying form factors. This test assembly architecture supports memory bus speeds of 66 MHz and above, and provides easy access for a logic analyzer. The test assembly supports Registered and Unbuffered Synchronous DRAM products. The test assembly permits good and questionable synchronous modules to be compared using an external logic analyzer. It permits resolution of in-system fails that occur uniquely in system environments and may be otherwise difficult or impossible to replicate. The test assembly re-drives the system clocks with a phase lock loop (PLL) buffer to a memory module socket on the test assembly to permit timing adjustments to minimize the degradation to the system's memory bus timings due to the additional wire length and loading. The test assembly is programmable to adjust to varying bus timings such as: CAS (column address strobe) Latencies and Burst Length variations. It is designed with Field Programmable Gate Arrays (FPGAs) to allow for changes internally without modifying the test assembly.

Owner:GLOBALFOUNDRIES INC

Field emitter based electron source for multiple spot x-ray

ActiveUS20090185660A1Increase intensityImprove uniformityX-ray tube electrodesCathode ray concentrating/focusing/directingElectric fieldX-ray generator

A multiple spot x-ray generator is provided that includes a plurality of electron generators. Each electron generator includes an emitter element to emit an electron beam, a meshed grid adjacent each emitter element to enhance an electric field at a surface of the emitter element, and a focusing element positioned to receive the electron beam from each of the emitter elements and focus the electron beam to form a focal spot on a shielded target anode, the shielded target anode structure producing an array of x-ray focal spots when impinged by electron beams generated by the plurality of electron generators. The plurality of electron generators are arranged to form an electron generator matrix that includes activation connections electrically connected to the plurality of electron generators, wherein each electron generator is connected to a pair of the activation connections to receive an electric potential therefrom.

Owner:GENERAL ELECTRIC CO

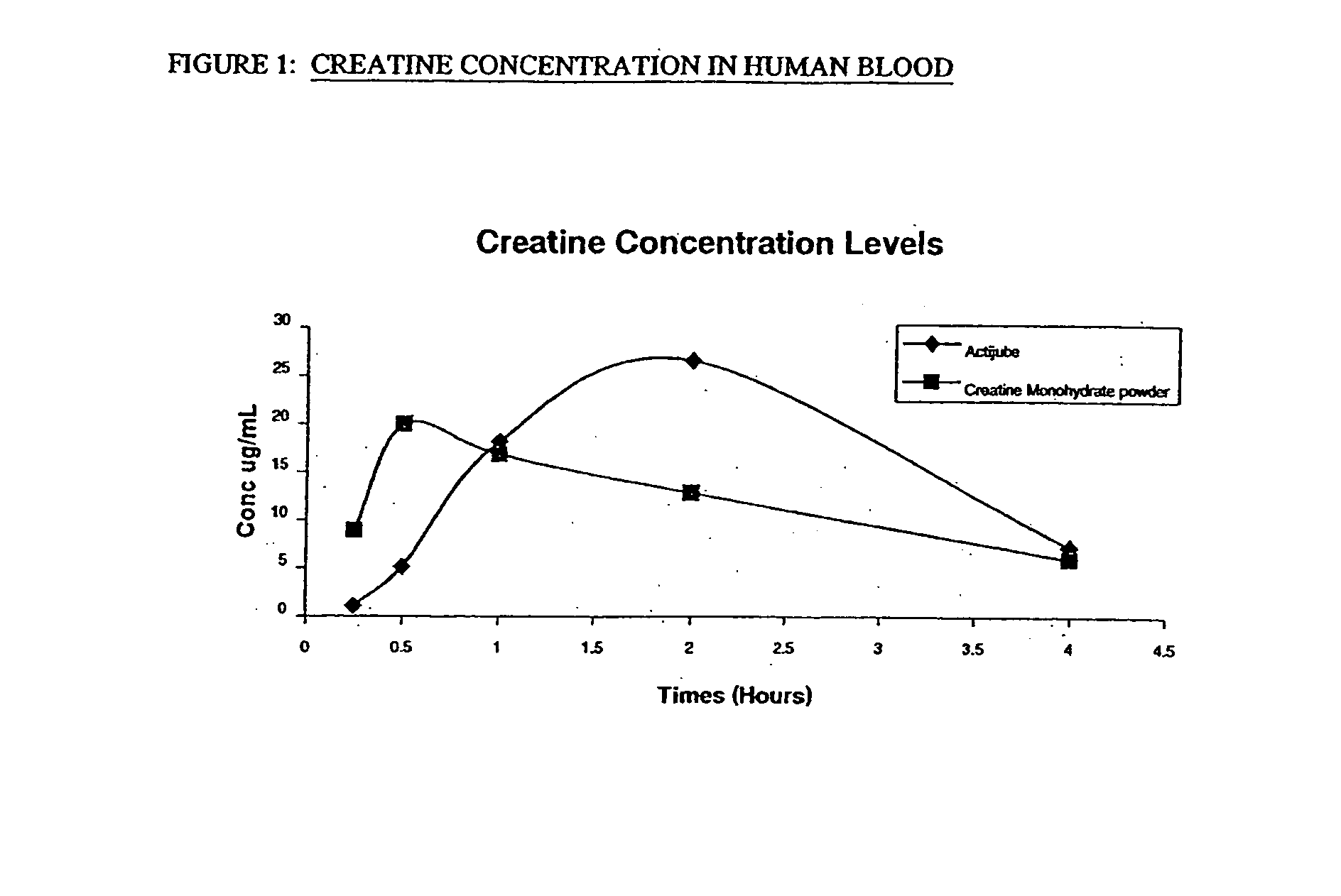

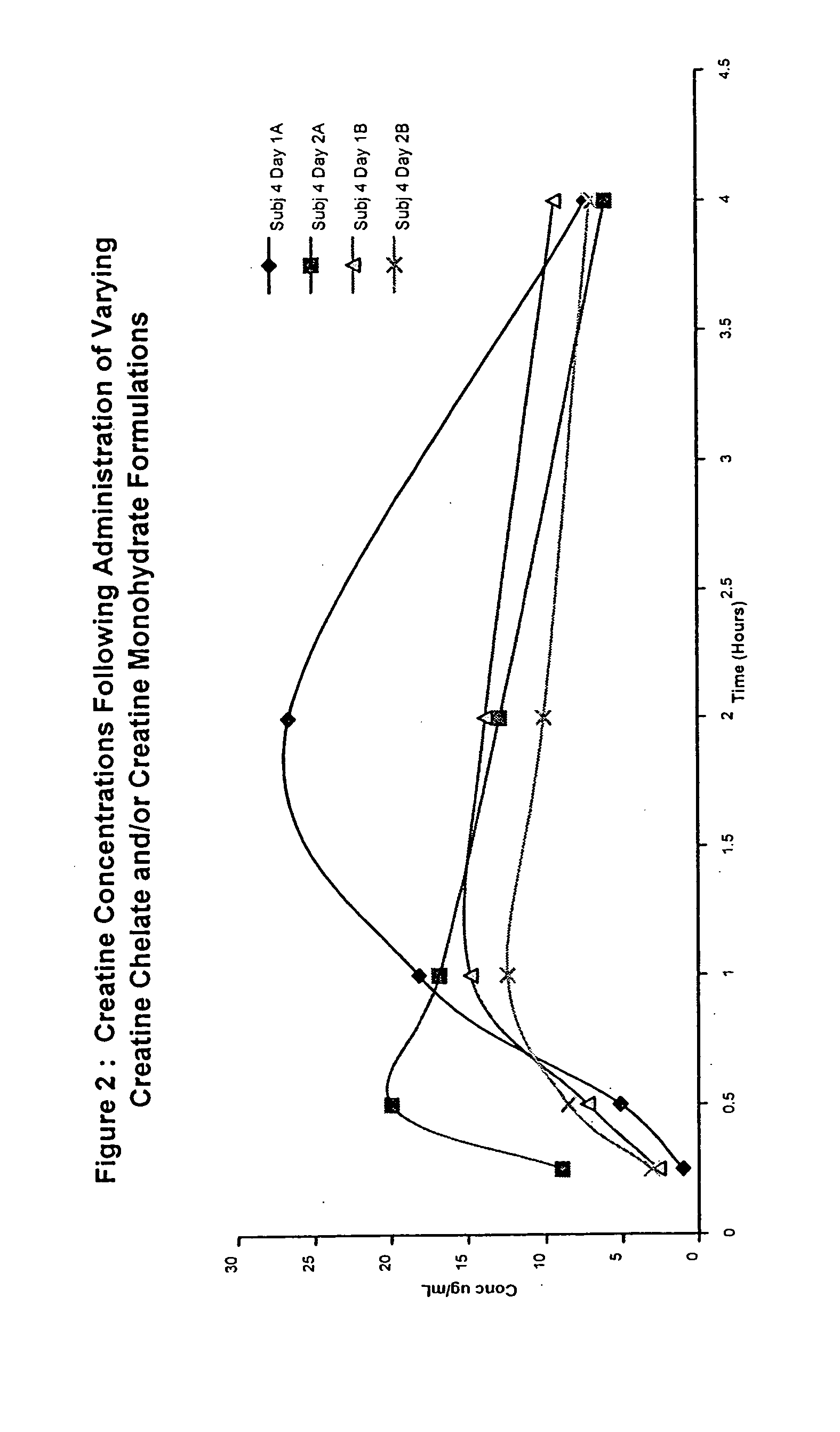

Starch-based delivery system for creatine

InactiveUS20040013732A1Promote absorptionMinimize degradationPowder deliverySugar food ingredientsAdditive ingredientVitamin

The present invention provides an oral delivery system for creatine. The creatine delivery system may additionally contain other bioactive ingredients such as nutraceuticals, botanicals, and vitamins. The delivery system comprises an ingestible matrix within which a creatine formulation and optionally one or more bioactives are substantially uniformly and completely dispersed and in which degradation of the creatine and other bioactives is minimised or eliminated. The invention also provides methods of preparing and using the delivery system.

Owner:2120812 ONTARIO

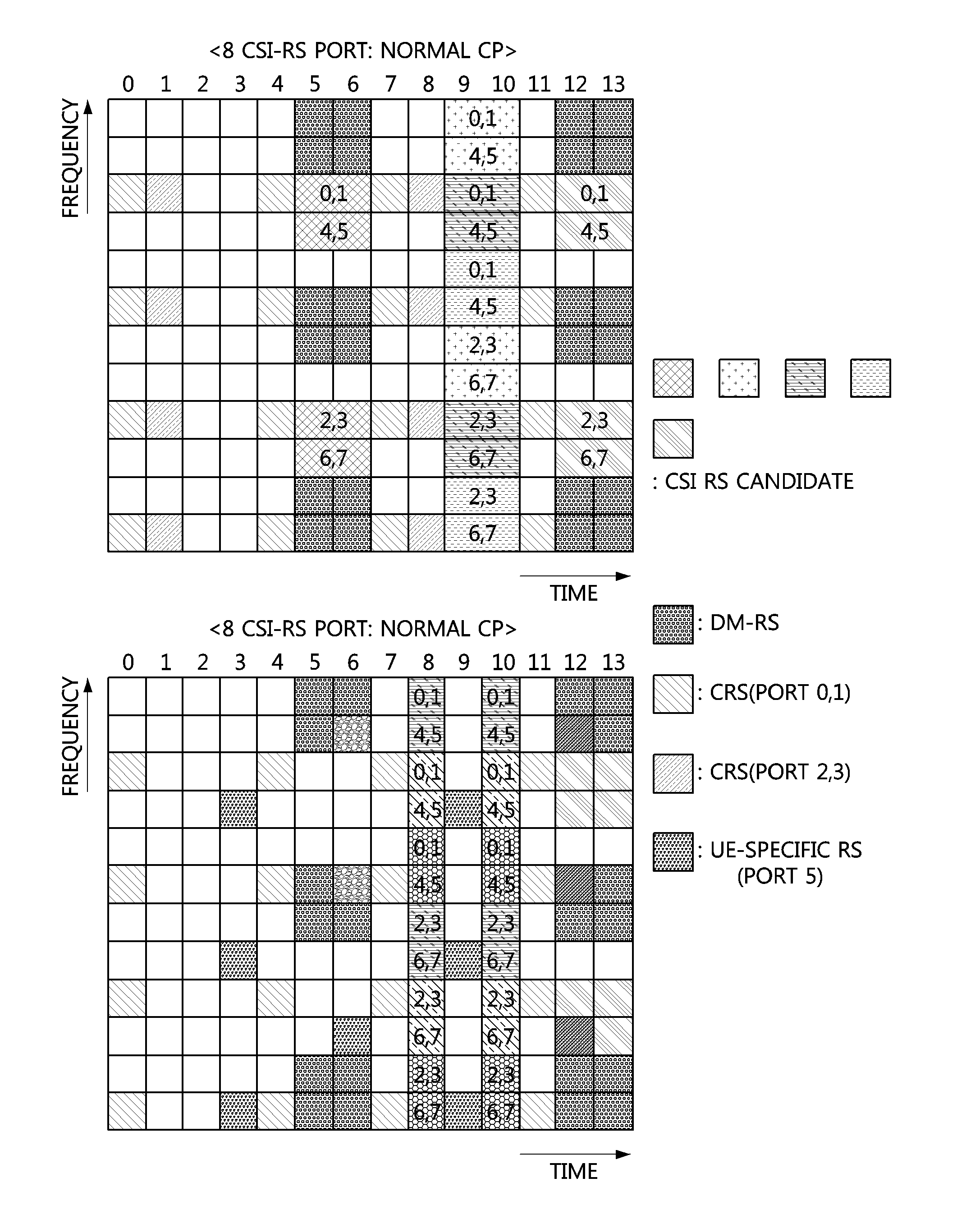

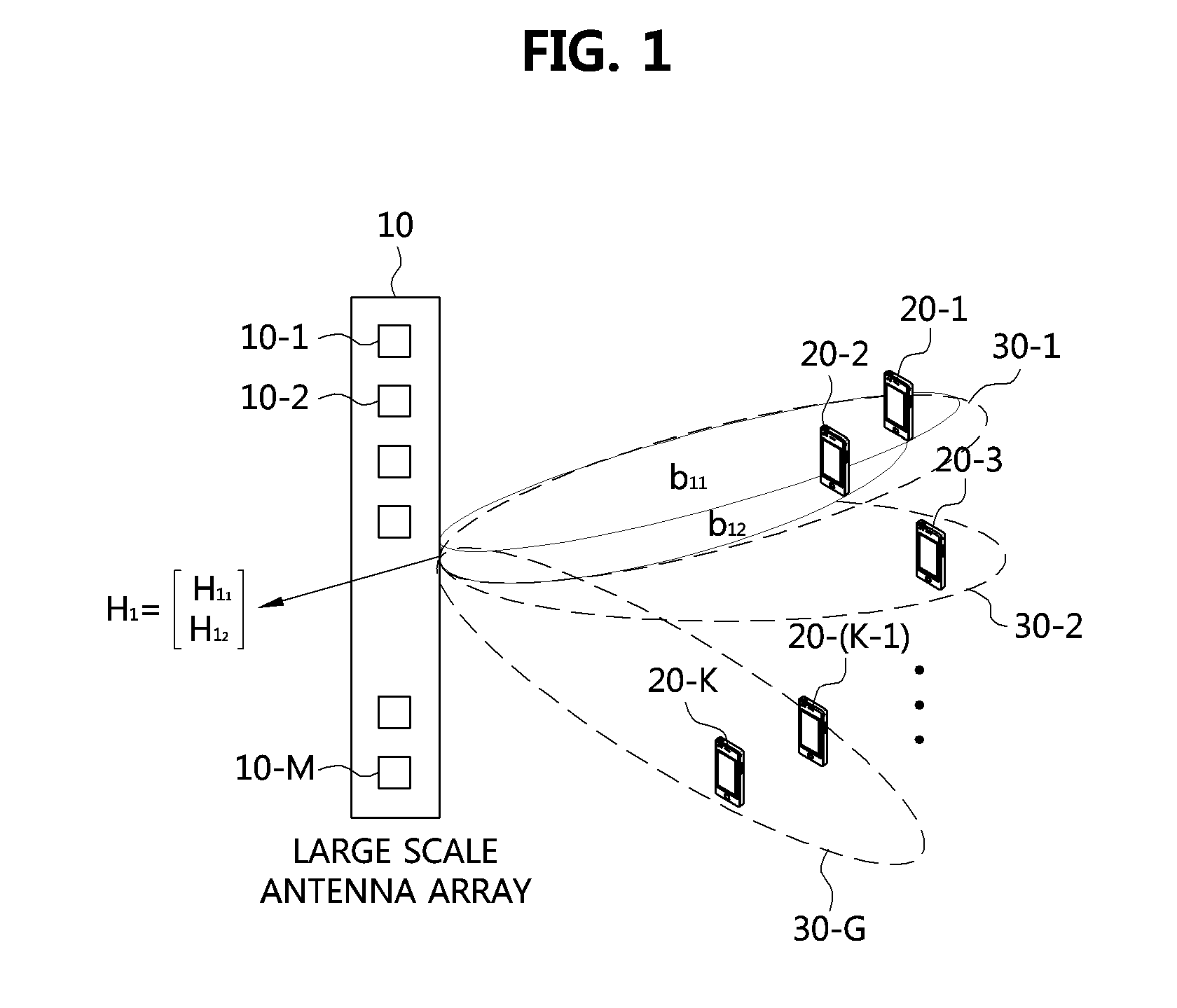

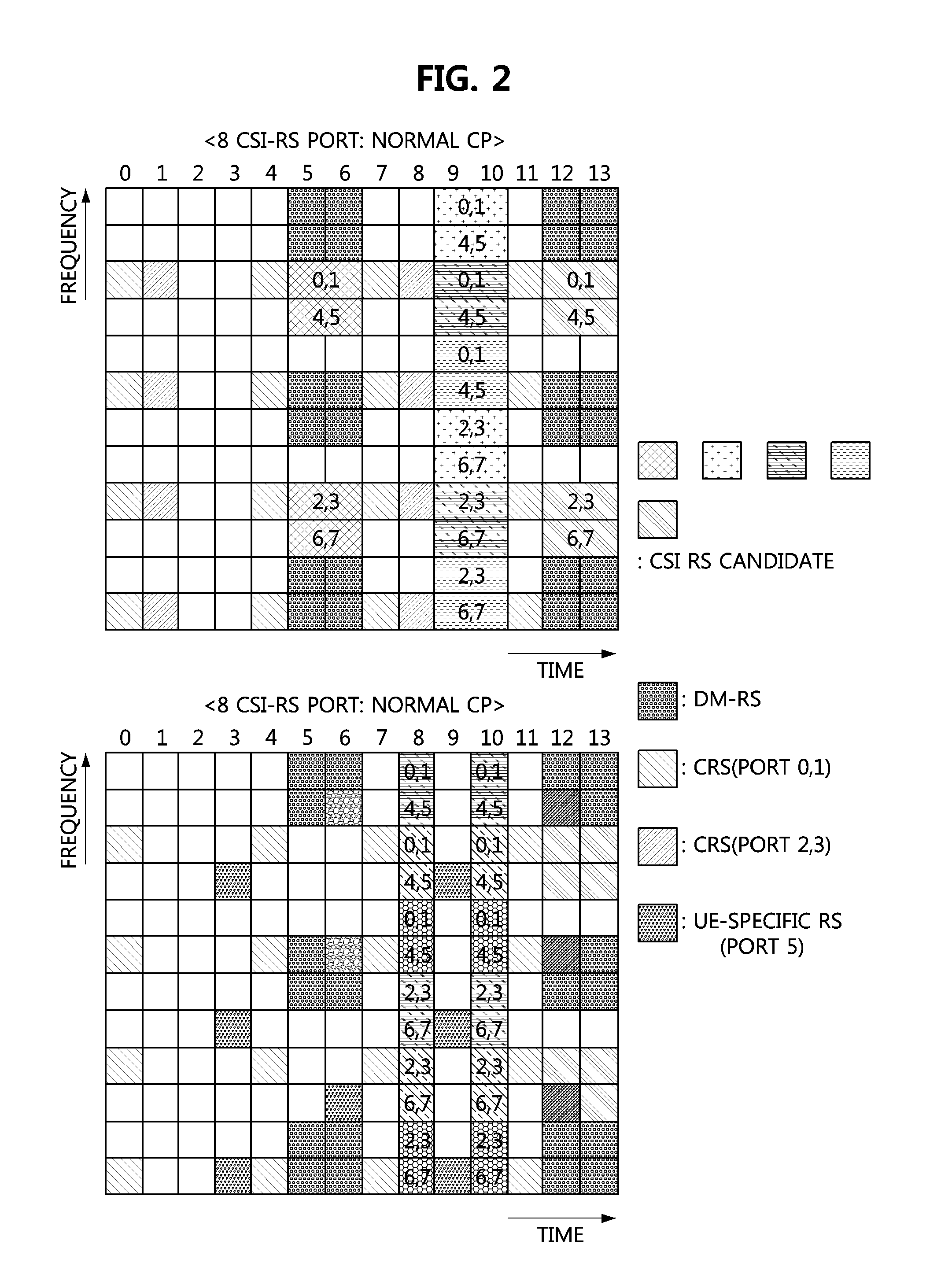

Method for multi-input multi-output communication in large-scale antenna system

InactiveUS20140254517A1Minimize degradationWithout increasing amount of requiredSpatial transmit diversitySignal allocationMulti inputCommunications system

Disclosed is a method for multi-input multi-output transmission of a base station in a wireless communication system. The method includes obtaining channel information of one or more terminals, classifying the one or more terminals into one or more classes and one or more groups dependent on the class based on the channel information, determining a group beamforming matrix for each of the one or more groups, performing group beamforming transmission on terminals belonging to each of the one or more groups based on the group beamforming matrix, obtaining single user-channel quality indicator (SU-CQI) information and interference signal information of each of the terminals belonging to each of the one or more groups, and scheduling the terminals based on the SU-CQI information and the interference signal information.

Owner:ELECTRONICS & TELECOMM RES INST

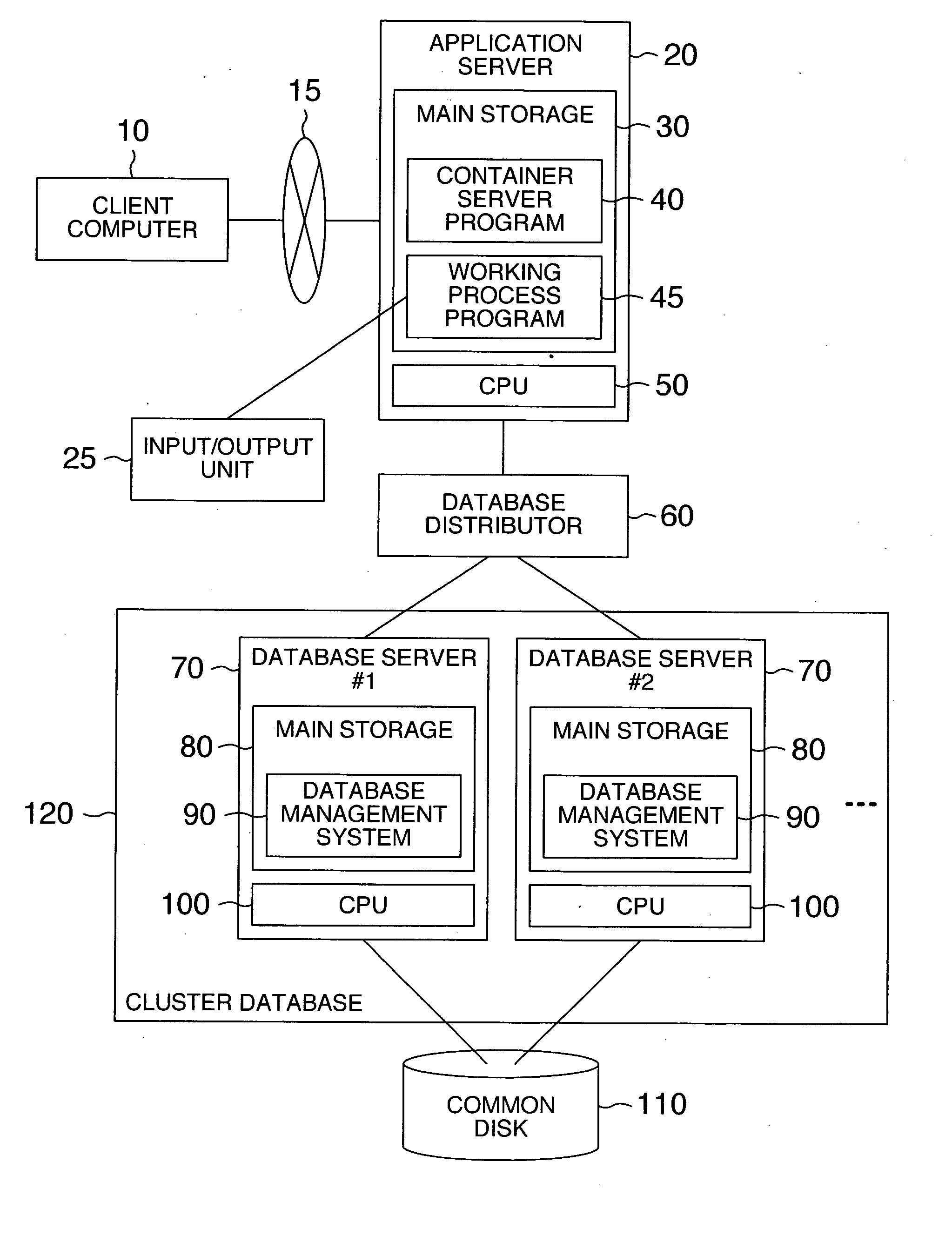

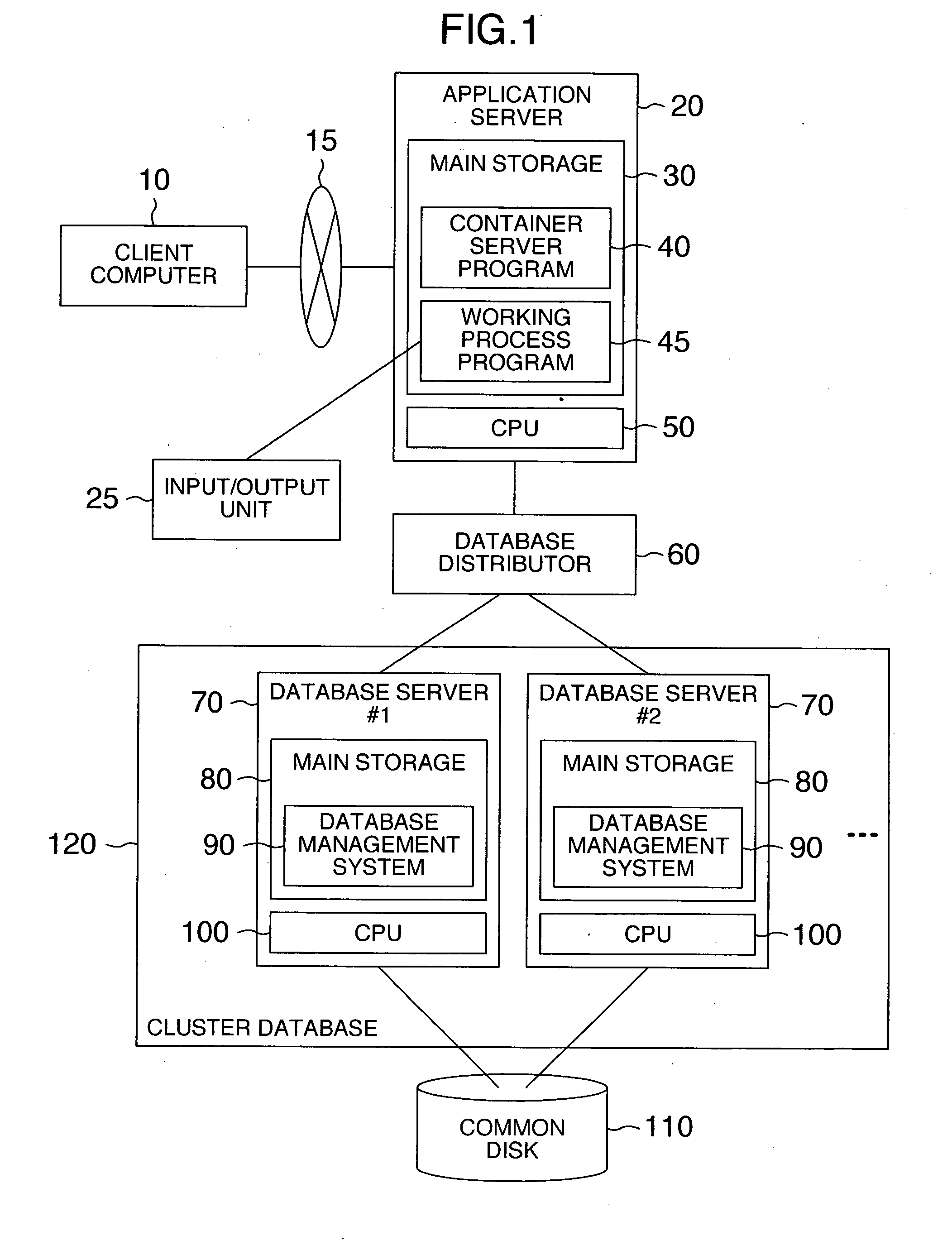

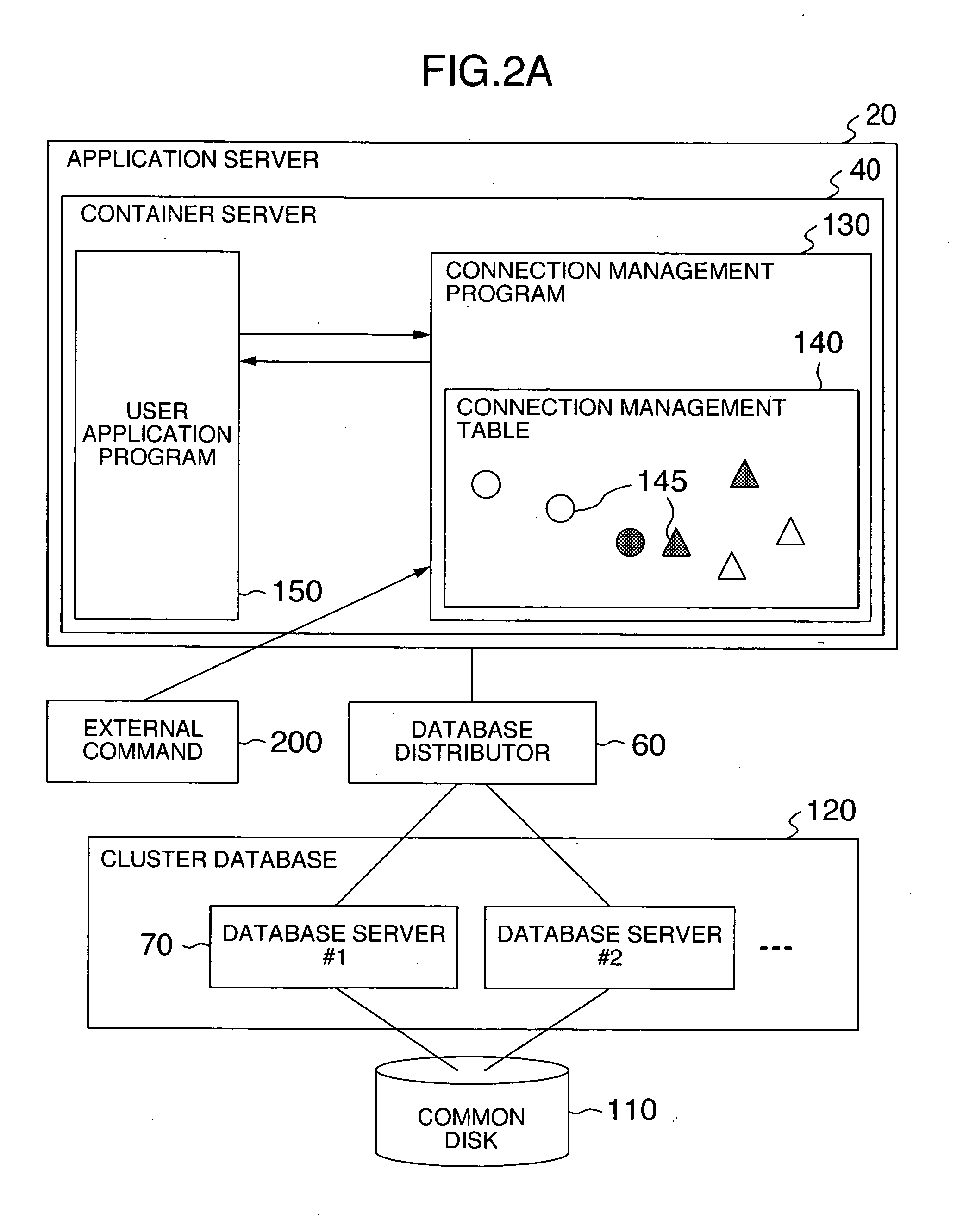

Method and system for data processing with connection pool for the same

InactiveUS20070198684A1Minimize degradationDigital computer detailsTransmissionApplication serverDatabase server

When an application server prepares the connection made to the database server, an identifier for definitely identifying the database server of connection destination is allotted to the connection. When a fault occurs in a database system, the database identifier of the connection is specified and only a connection allotted with the same identifier as the specified identification is discarded from a connection pool. When a request is received from a client computer, a connection is acquired from the connection pool. The acquired connection is decided as to whether to be faulty and if the acquired connection is determined as being faulty, a database server to be coupled to the faulty connection is specified by consulting connection management information. All connections made or coupled to the specified database server are discarded from the connection pool and a new connection is prepared.

Owner:HITACHI LTD

Dynamic recipe control

ActiveUS20150260699A1Minimize degradationImprove nutritional and organoleptic and aesthetic valueDatabase queryingComputer controlComputer science

Nutritional substance systems and methods are disclosed enabling the tracking and communication of changes in nutritional, organoleptic, and aesthetic values of nutritional substances, and further enabling the adaptive storage and adaptive conditioning of nutritional substances.

Owner:ICEBERG LUXEMBOURG S A R L

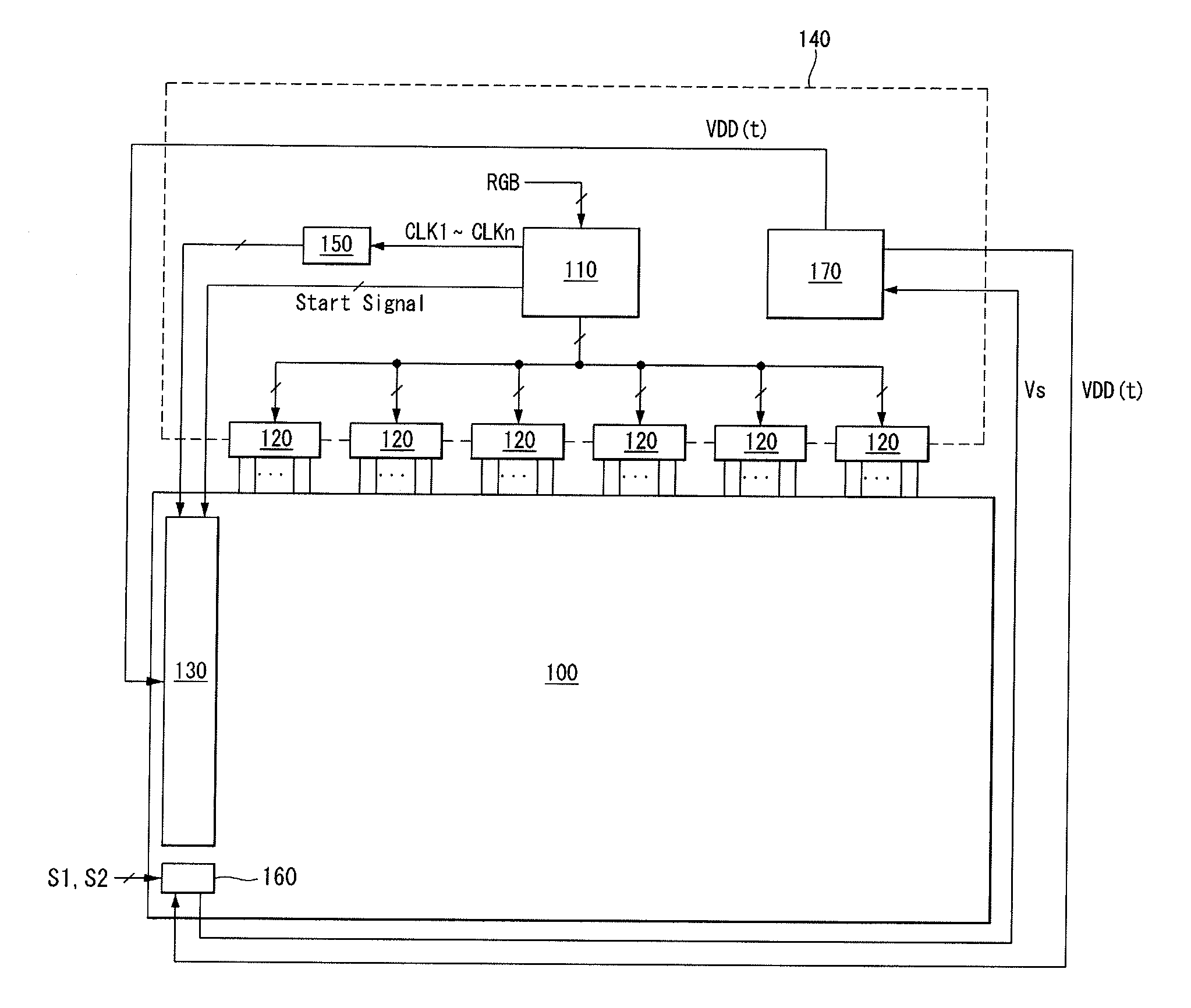

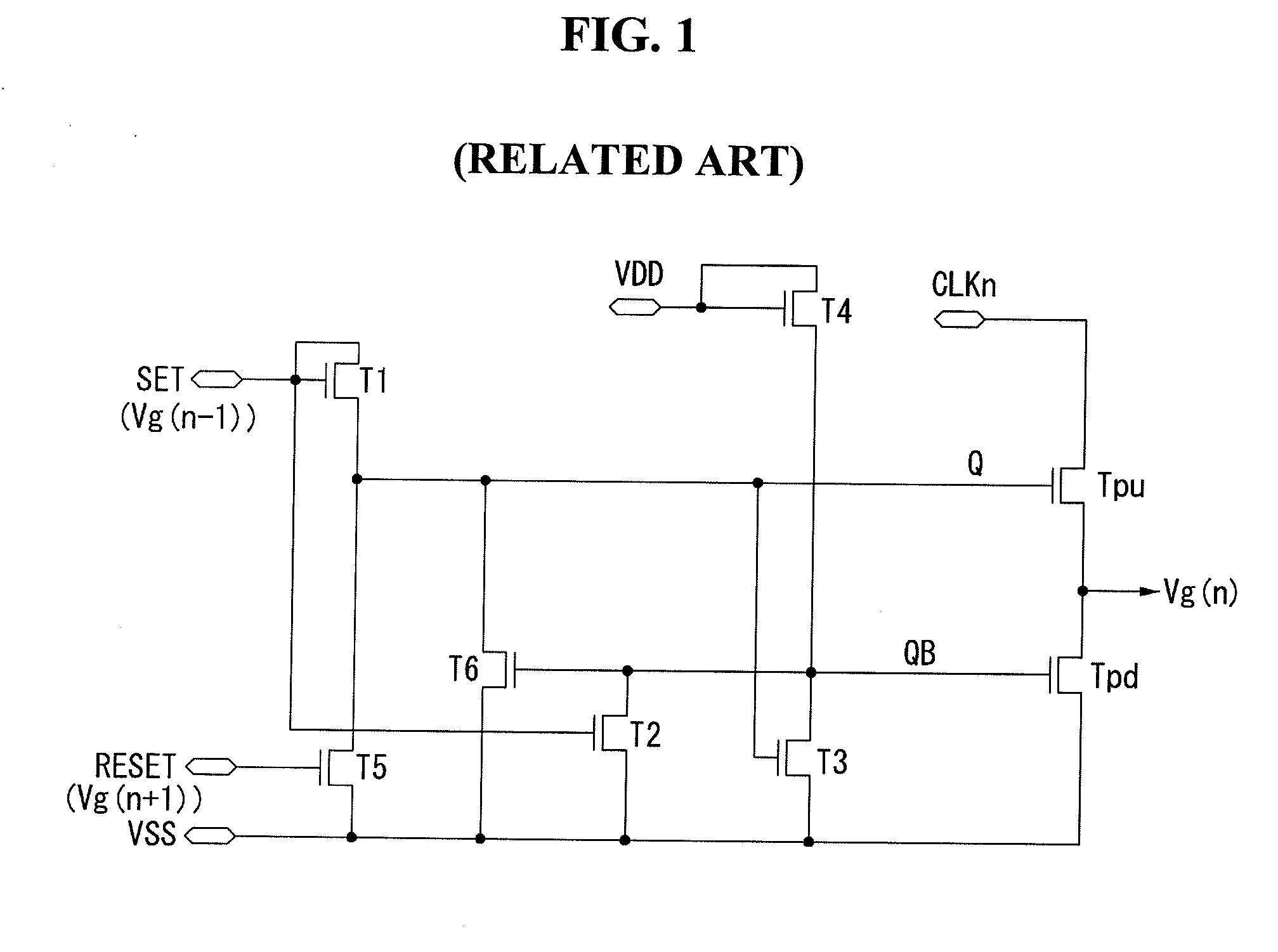

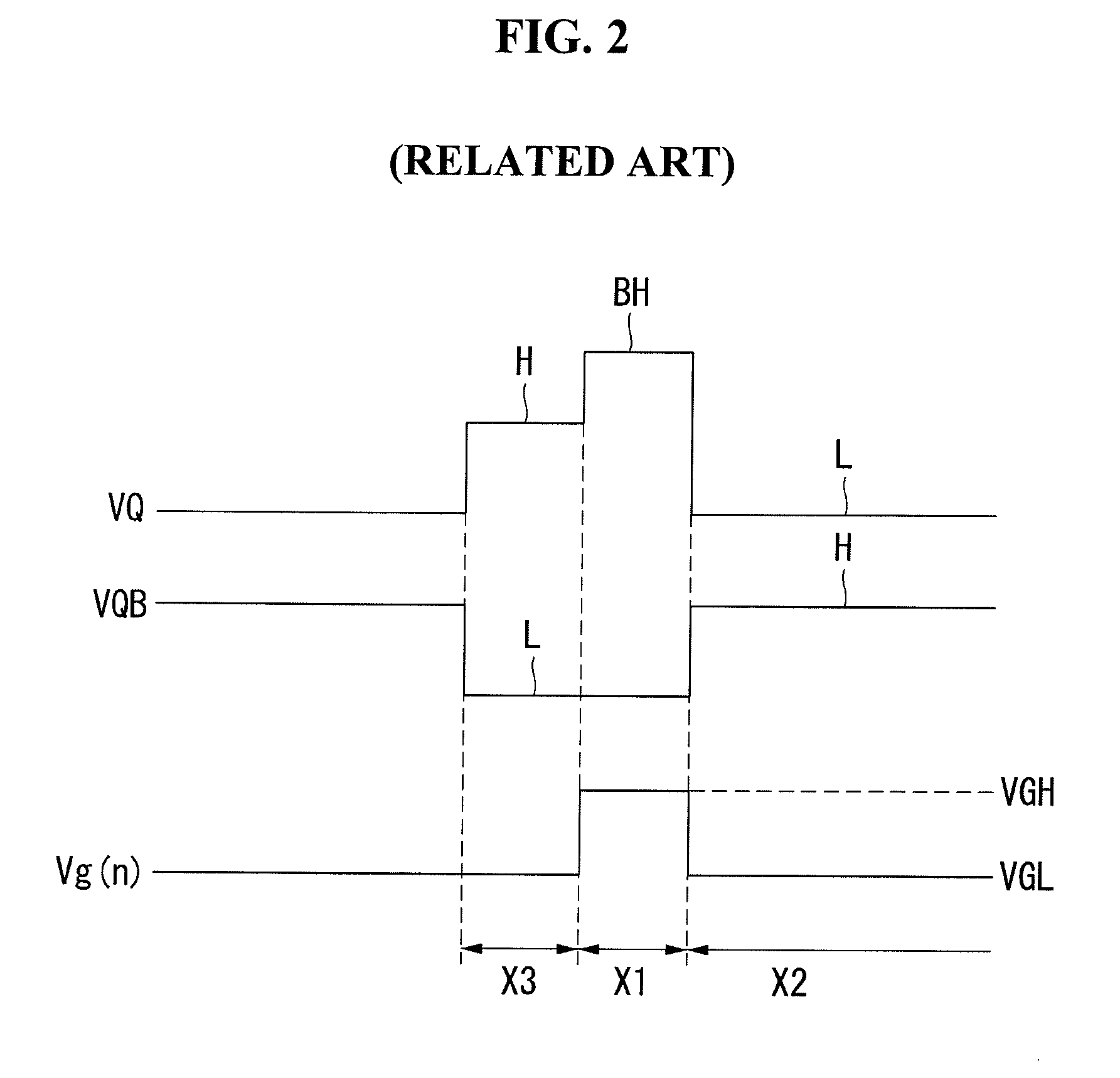

Gate shift register and display device comprising the same

ActiveUS20140085285A1Stable outputMinimizing device degradationCathode-ray tube indicatorsDigital storageShift registerLow voltage

According to an embodiment, a gate shift register includes a plurality of stages cascade-connected to each other. An nth one of the stages includes: a pull-up transistor that outputs any one of gate shift clocks as an nth scan pulse of a gate high voltage in accordance with the potential of a Q node; a pull-down transistor that is connected to the pull-up transistor through an output node, and outputs a low-potential voltage as an nth scan pulse of a gate low voltage in accordance with the potential of a QB node; and a switching circuit that charges and discharges the Q node and the QB node, respectively, or vice versa in response to a set signal and a reset signal, wherein an adaptively adjusted variable high-potential voltage is applied to the QB node to correspond to a shift in the threshold voltage of the pull-down transistor.

Owner:LG DISPLAY CO LTD

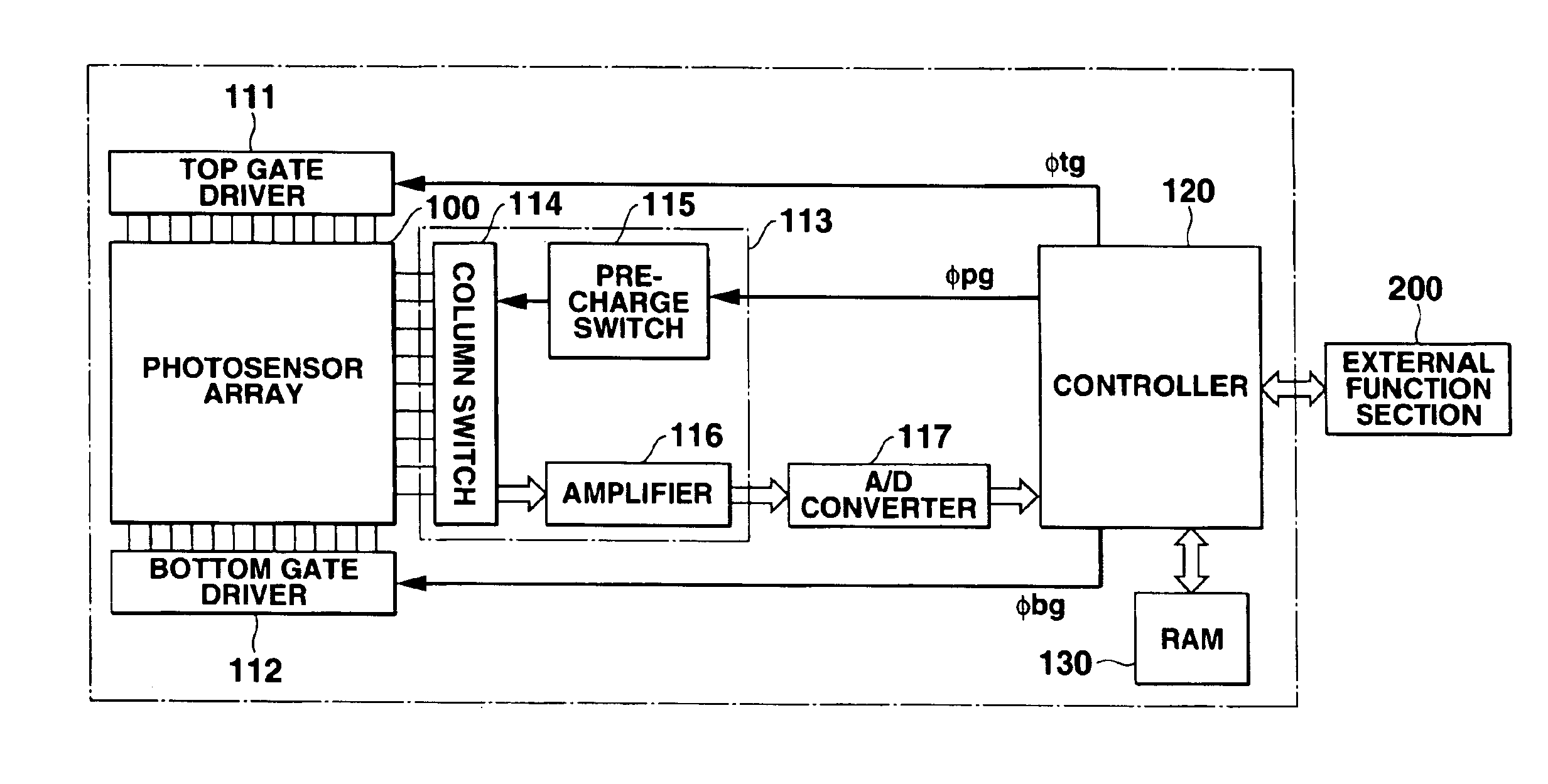

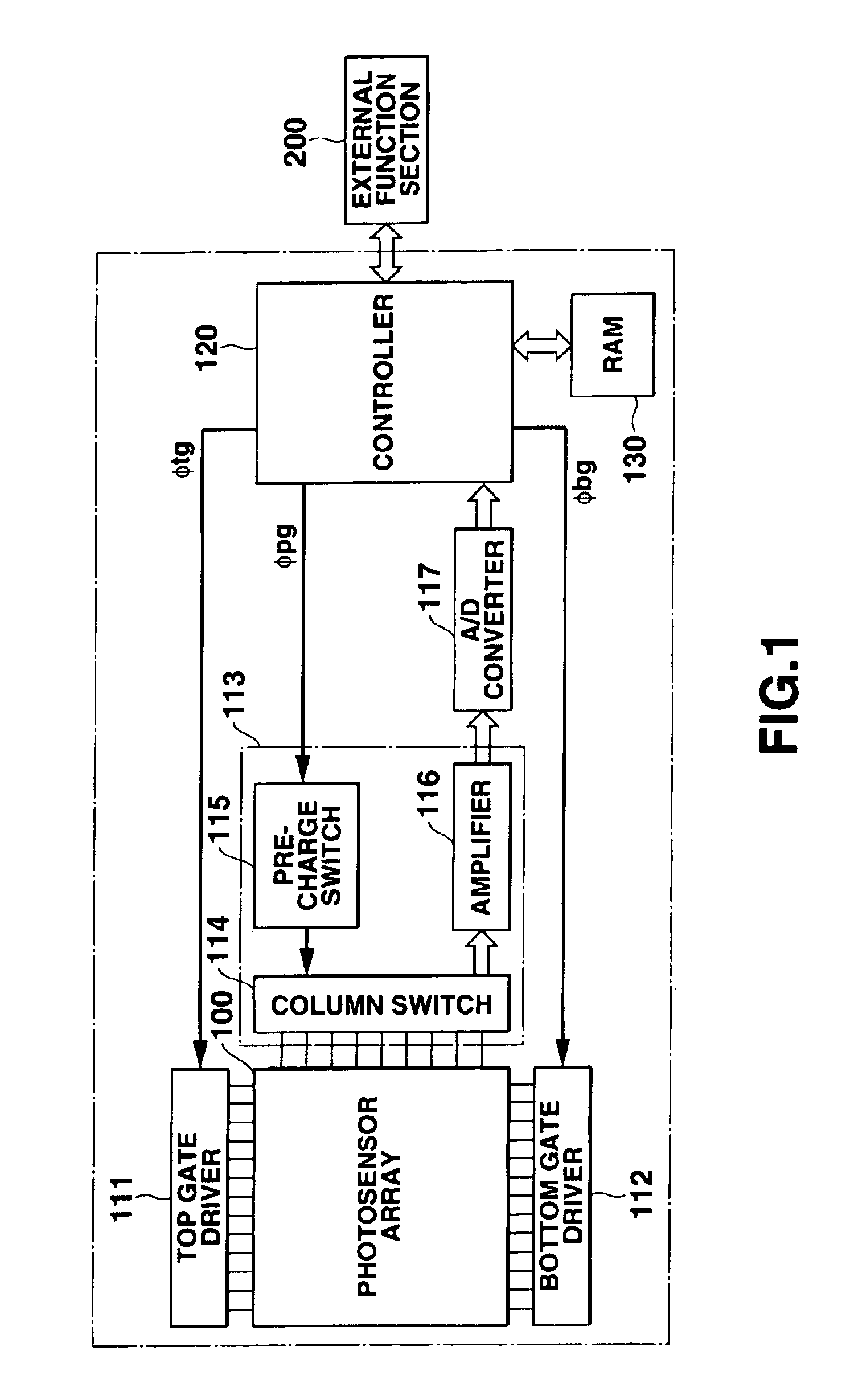

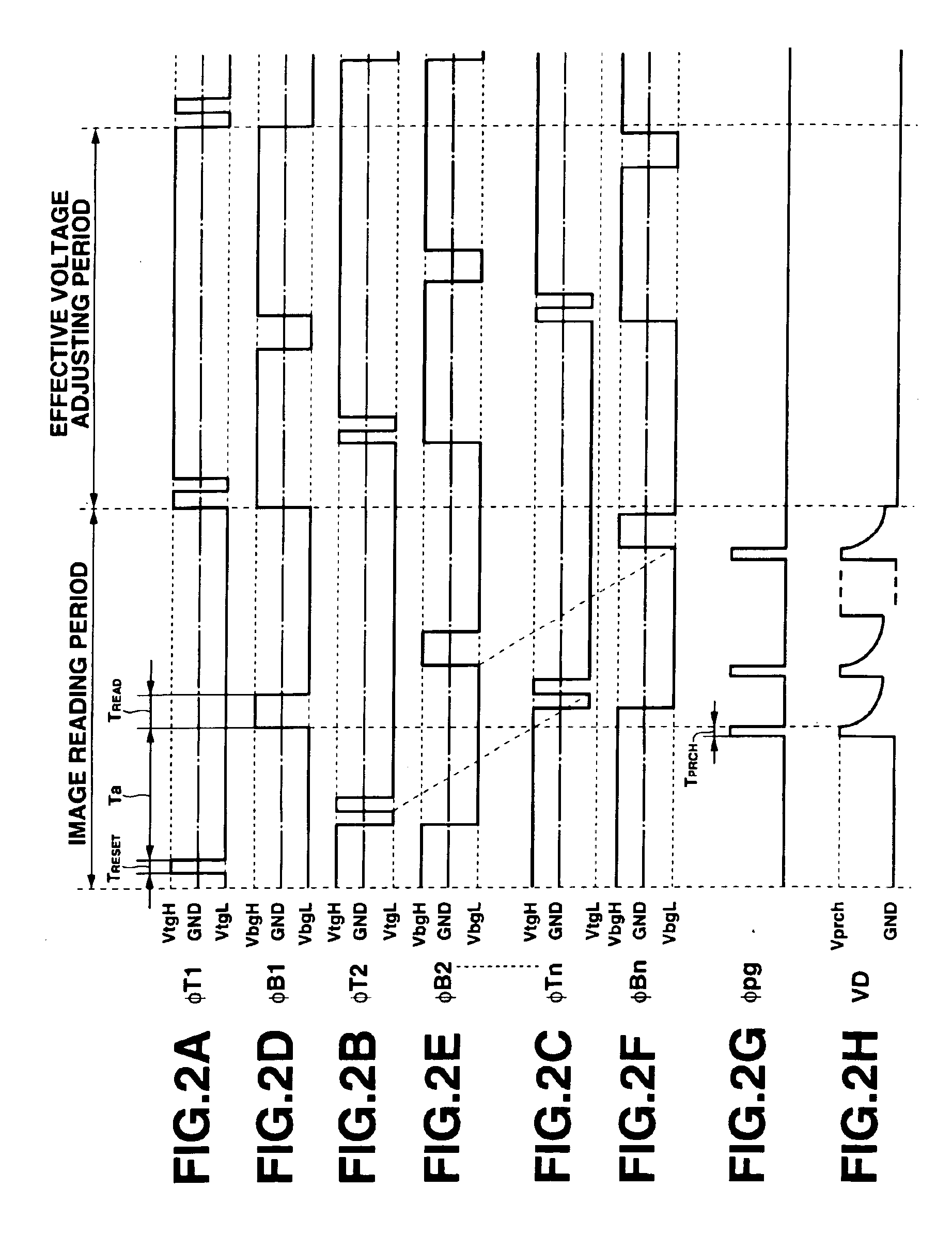

Photosensor system and drive control method thereof

InactiveUS6888571B1Improve reliabilityChange in its sensitivity characteristicTelevision system detailsTelevision system scanning detailsDriver circuitVoltage regulation

A photosensor system including a photosensor array having a plurality of photosensors arranged two-dimensionally comprises a driver circuit and a readout circuit for applying signal voltages to each photosensor, and also a control circuit having a function of controlling the voltages applied to each photosensor and adjusting the sensitivity of each photosensor. During an image reading operation and a reading operation for setting the sensitivity of each photosensor, a correction signal is generated, which has an effective voltage that can adjust an effective voltage, applied to each gate electrode of each photosensor, to 0 V, or to a value that minimizes degradation of the characteristics of each photosensor. This correction signal is applied to each gate electrode.

Owner:CASIO COMPUTER CO LTD

Method and apparatus for monitoring polishing pad wear during processing

InactiveUS6186864B1Minimize degradationPolishing machinesRevolution surface grinding machinesMaterial removalClosed loop

In a chemical-mechanical polishing (CMP) process, semiconductor substrates are rotated against a polishing pad in order to planarize substrate layers. The condition of the polishing pad directly affects the polishing rate of material removal and uniformity of removal from the semiconductor wafer. Conditioning of the polishing pad surface with an abrasive improves polishing uniformity and rates, however, it has the detrimental affect of removing a quantity of pad material. A method and apparatus for monitoring polishing pad wear during processing is developed to extend the pad's useful life, and maintain pad uniformity. This is accomplished in the present invention by measuring and monitoring the diminished pad thickness using a non-intrusive measurement system, and creating a closed-loop system for adjusting the chemical-mechanical polishing tool process parameters. The non-intrusive measurement system consists of an interferometer measurement technique utilizing ultrasound or electromagnetic radiation transmitters and receivers aligned to cover any portion of the radial length of a polishing pad surface. The measurement system is sensitive to relative changes in pad thickness for uniformity, and to abrupt changes such as detecting wafer detachment from the CMP wafer carrier.

Owner:INT BUSINESS MASCH CORP

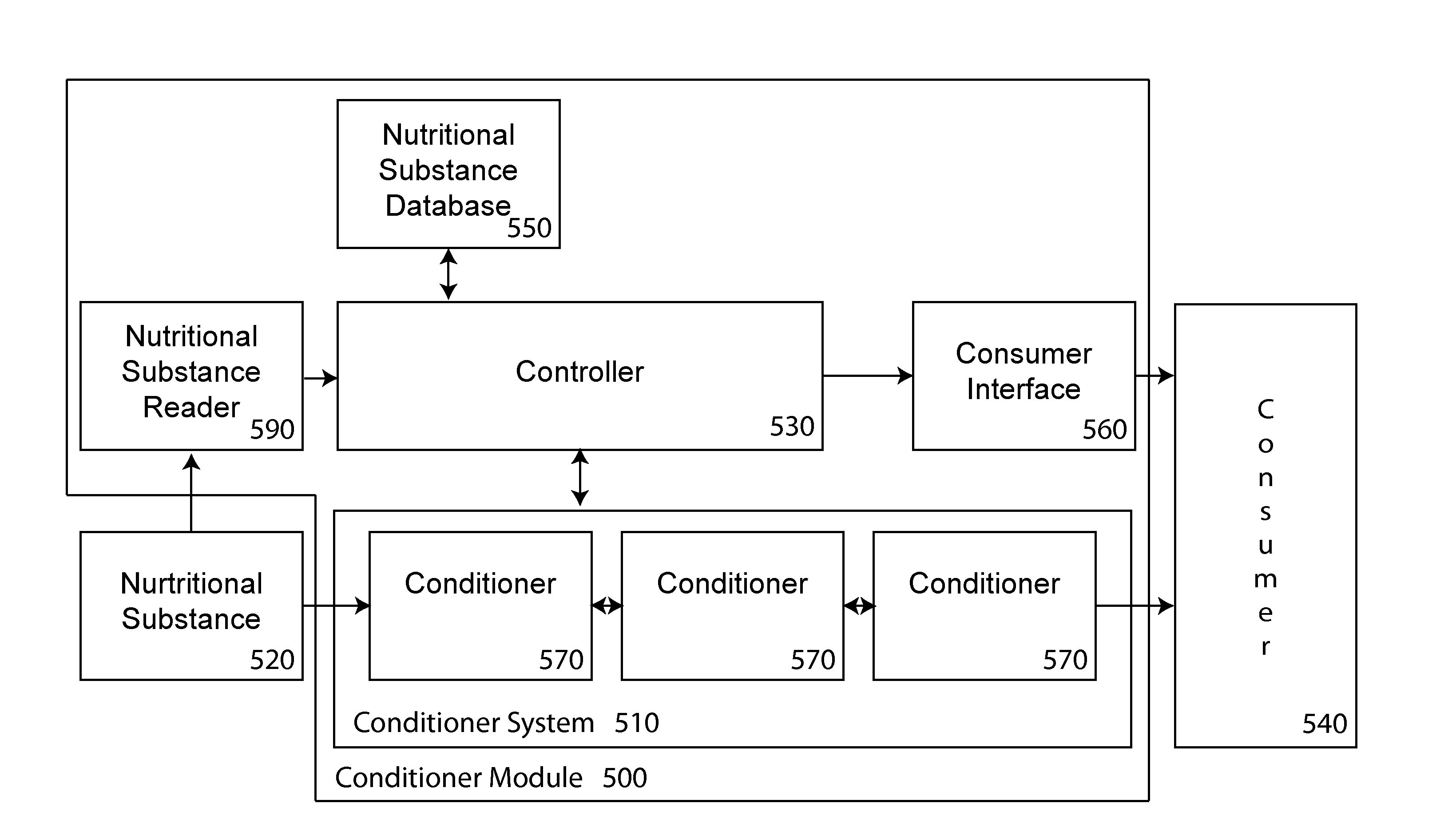

Conditioning system for nutritional substances

ActiveUS20130273217A1Minimize degradationHigh aesthetic valueDigital data processing detailsCocoaNutritional contentBiology

Disclosed herein is a conditioning system for nutritional substances. The conditioning system obtains information regarding the nutritional substance to be conditioned, the desired conditioning, and the desired properties, including nutritional content, of the conditioned nutritional substance, and dynamically controls the conditioning in response to this information optimize the organoleptic properties of the conditioned nutritional substance, while minimizing any detrimental changes to the nutritional content.

Owner:ICEBERG LUXEMBOURG S A R L

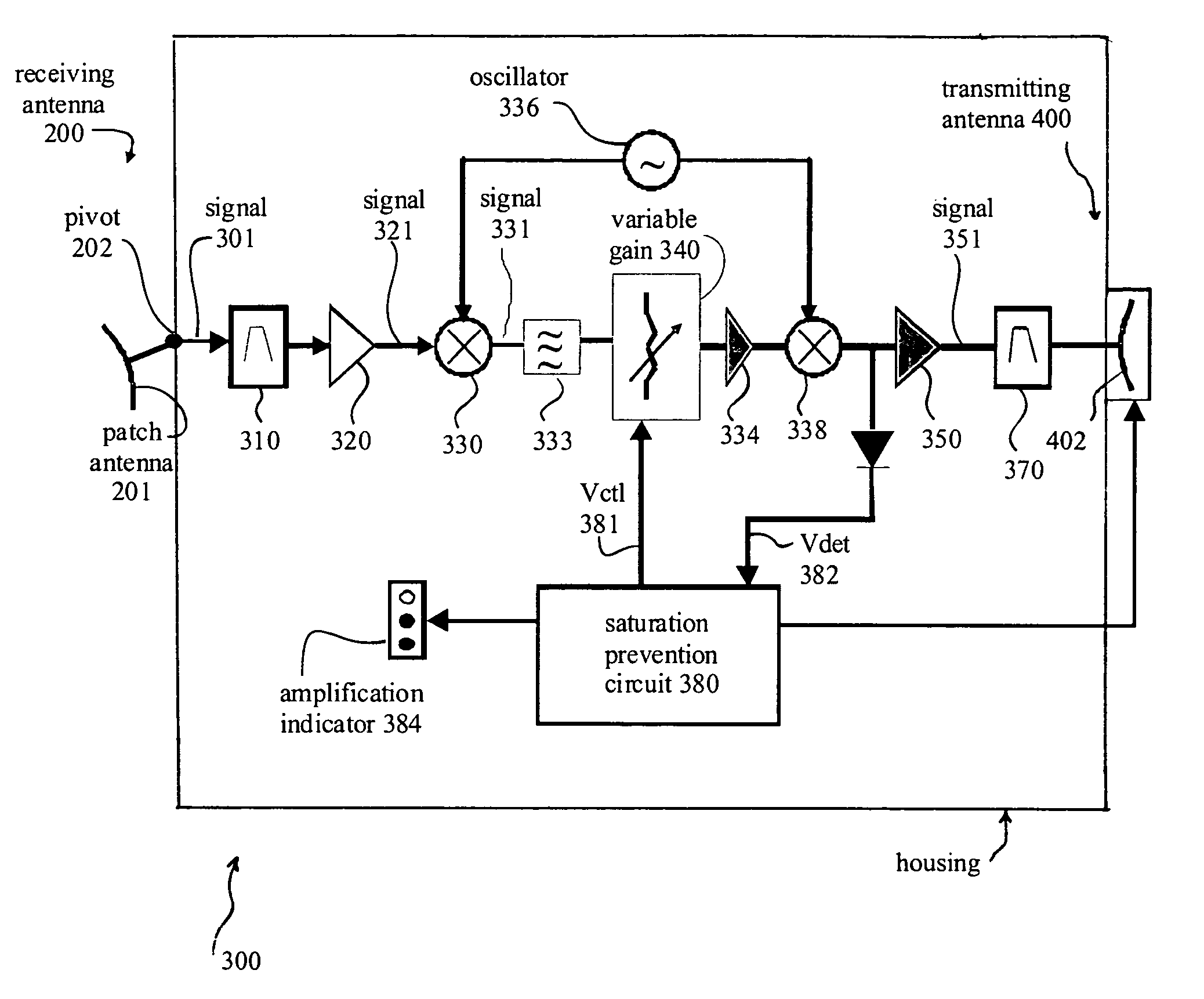

Repeater system for strong signal environments

ActiveUS6993287B2Reduce co-channel interferenceEasy to installActive radio relay systemsRepeater circuitsEngineeringCo-channel interference

A repeater system combines co-located antennas, limited and controlled downlink signal amplification, stability management and an amplification indicator to create a user-installed solution to co-channel interference within cellular systems, in strong signal environments such as elevated locations or high-rise building. The invention may be particularly relevant to cellular systems, such as CDMA, that allow limited imbalance between uplink and downlink path losses, thus enabling the design of an inexpensive downlink repeater which creates moderate signal amplification for selected line-of-sight signals, defeating co-channel interference over a small area. Signal amplification is maintained at a level below the capacity of the system to support imbalance, guaranteeing reliable cellular calls.

Owner:CUFER ASSET LTD LLC

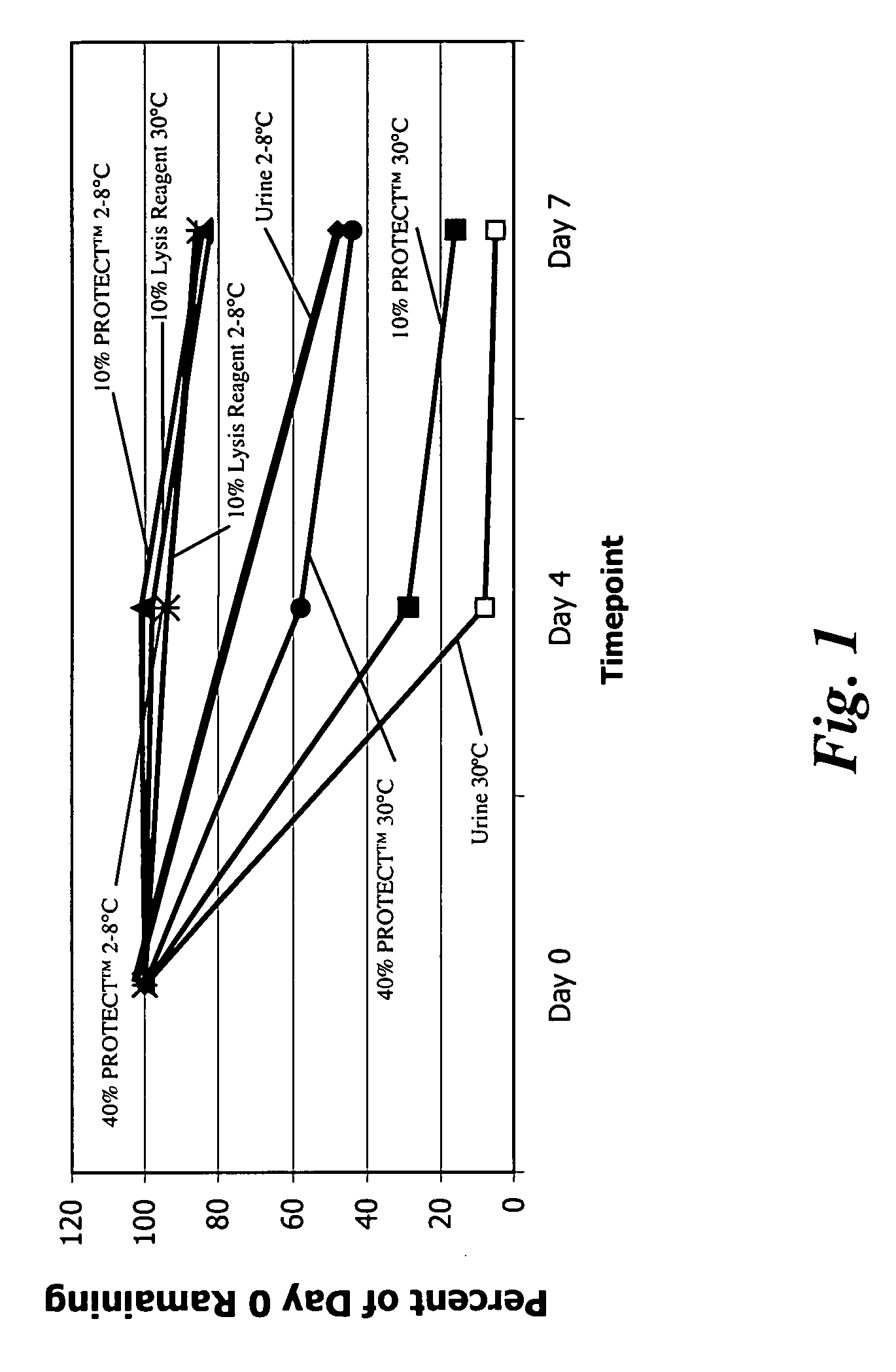

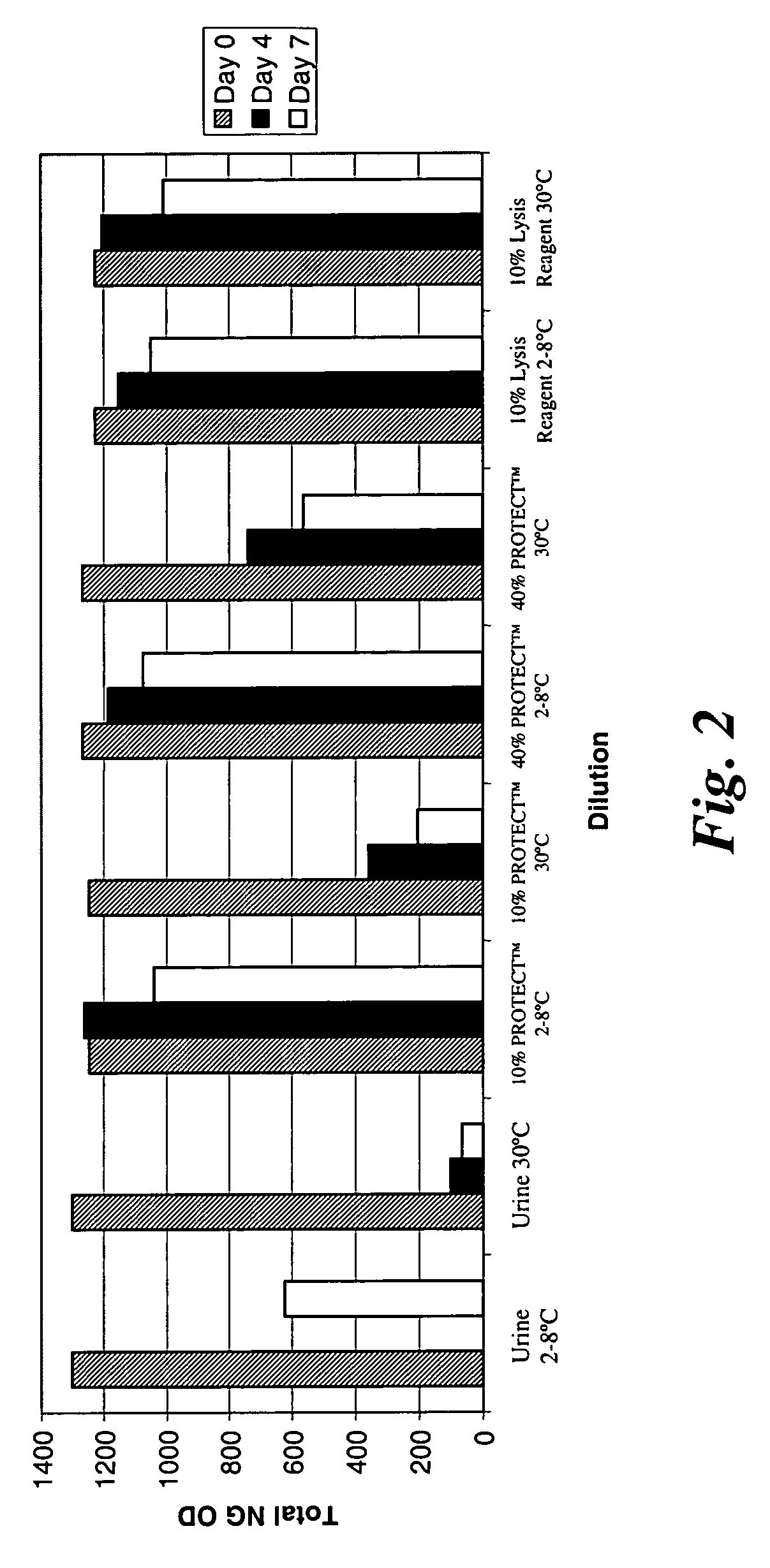

Stabilization of biomolecules in samples

InactiveUS20050227225A1Minimize degradationReduce expensesMicrobiological testing/measurementLavatory sanitoryReagentBiomolecule

This invention generally relates to stabilized non-blood-based samples in which microbial biomolecules in non-blood-based samples are stable at high temperatures. The stabilized non-blood-based samples include effective amounts of stabilization components to stabilize the microbial biomolecules in the samples. Stabilization components are typically effective at low levels in these stabilized non-blood-based samples. This provides the advantage of minimizing reagent expenses related to the stabilized non-blood-based samples of the invention. The invention also provides methods of stabilizing microbial biomolecules in non-blood-based samples and related kits.

Owner:ROCHE MOLECULAR SYST INC