ESD (Electro-Static discharge) protection device with low trigger voltage and high balllast resistance for SCR (Silicon Controlled Rectifier)

A technology with low trigger voltage and device protection, applied in the field of electronics, can solve the problems of ESD performance degradation, uneven current, device overheating and burning, etc., to improve the ESD performance degradation, solve the effect of early device damage and high current discharge capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

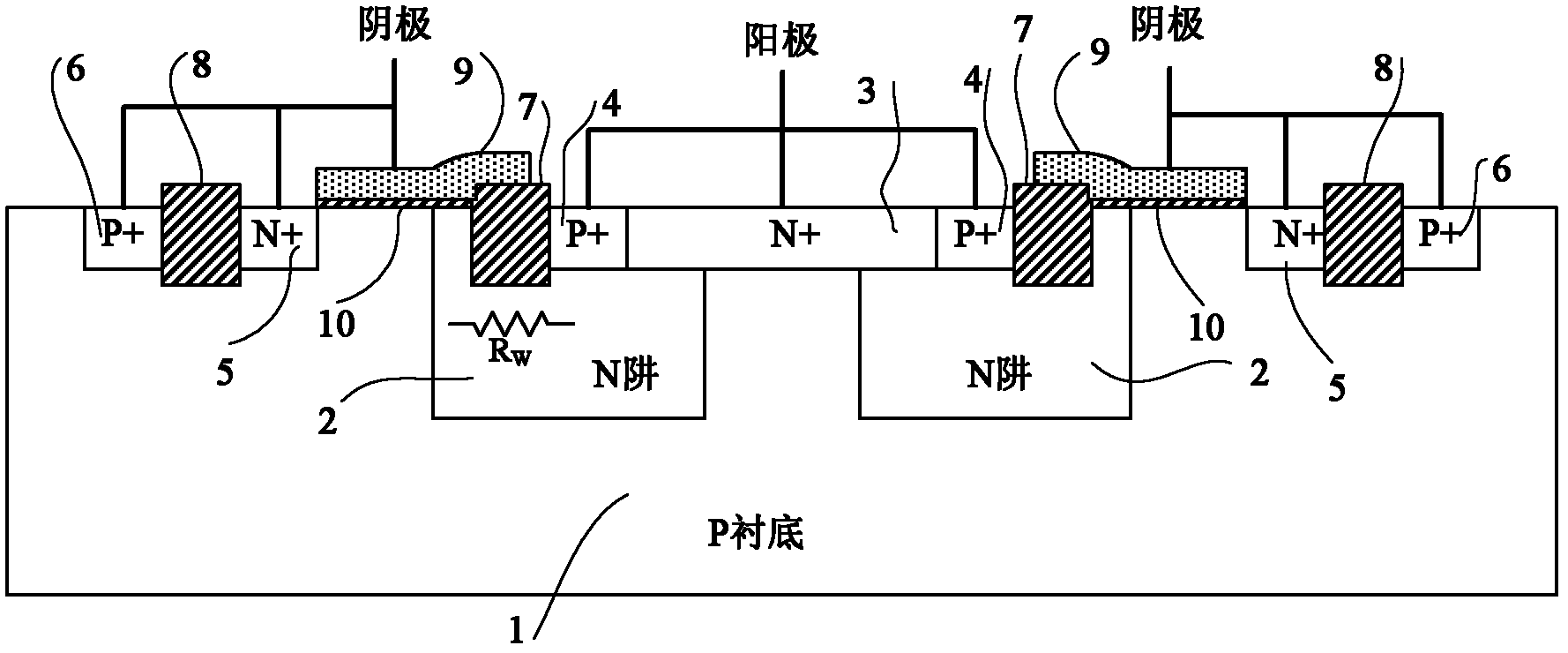

[0033] A SCR ESD protection device with low trigger voltage and high ballast resistance, such as image 3 As shown, it includes: P-type substrate 1, N-type well region 2 located on the P-type substrate, two N+ heavily doped regions 3 and 5, two P+ heavily doped regions 4 and 6, two shallow grooves Isolation regions 7 and 8 (Shallow Trench Isolation, STI for short) and a polysilicon gate region 9 . The N-type well region 2 is located at the top of the P-type substrate 1, the first P+ heavily doped region 4 and the first shallow trench isolation region 7 are located at the top of the N-type well region 2, and the first N+ heavily doped region 3 is connected to the P-type substrate. Type substrate 1 and the top of N-type well region 2 , the first P+ heavily doped region 4 is located between the first shallow trench isolation region 7 and the first N+ heavily doped region 3 . The second N+ heavily doped region 5, the second P+ heavily doped region 6 and the second shallow trench ...

specific Embodiment approach 2

[0034] A SCR ESD protection device with low trigger voltage and high ballast resistance, such as Figure 6 shown in image 3 On the basis of the shown structure, two P-type well regions 11 and 12 are added on the P-type substrate. The N-type well region 2 is sandwiched between two P-type well regions, the first N+ heavily doped region 3 spans the top of the N-type well region 2 and the first P-type well region 11, and the second N+ heavily doped region 5. The second P+ heavily doped region 6 and the second shallow trench isolation region 8 are located at the top of the second P-type well region 12 .

specific Embodiment approach 3

[0035] A SCR ESD protection device with low trigger voltage and high ballast resistance, such as Figure 7 shown in image 3 Based on the structure shown, a PBL buried layer region 15 is added in the P-type substrate 1 under the first N+ heavily doped region 3 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More