Patents

Literature

107results about How to "Lower base resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

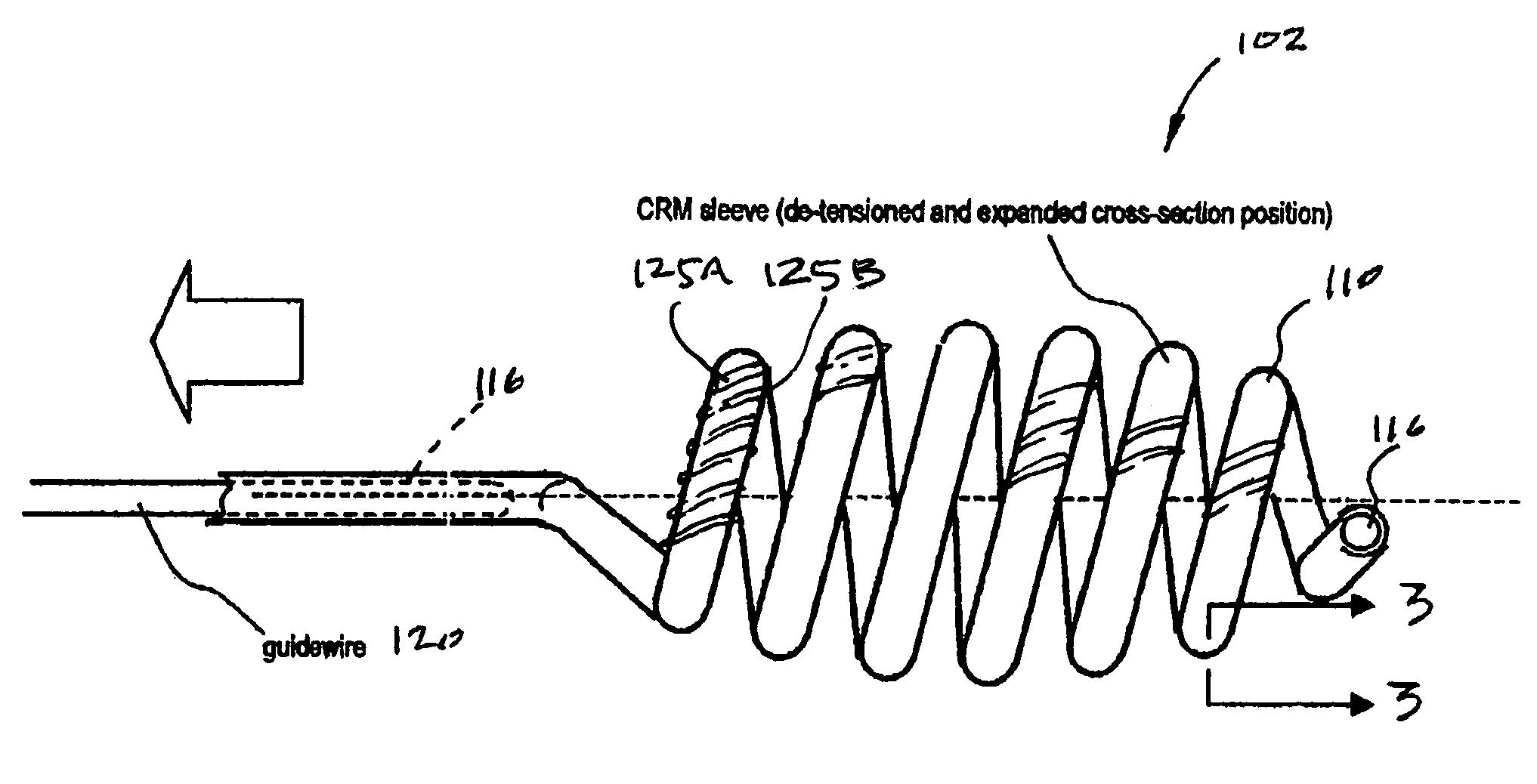

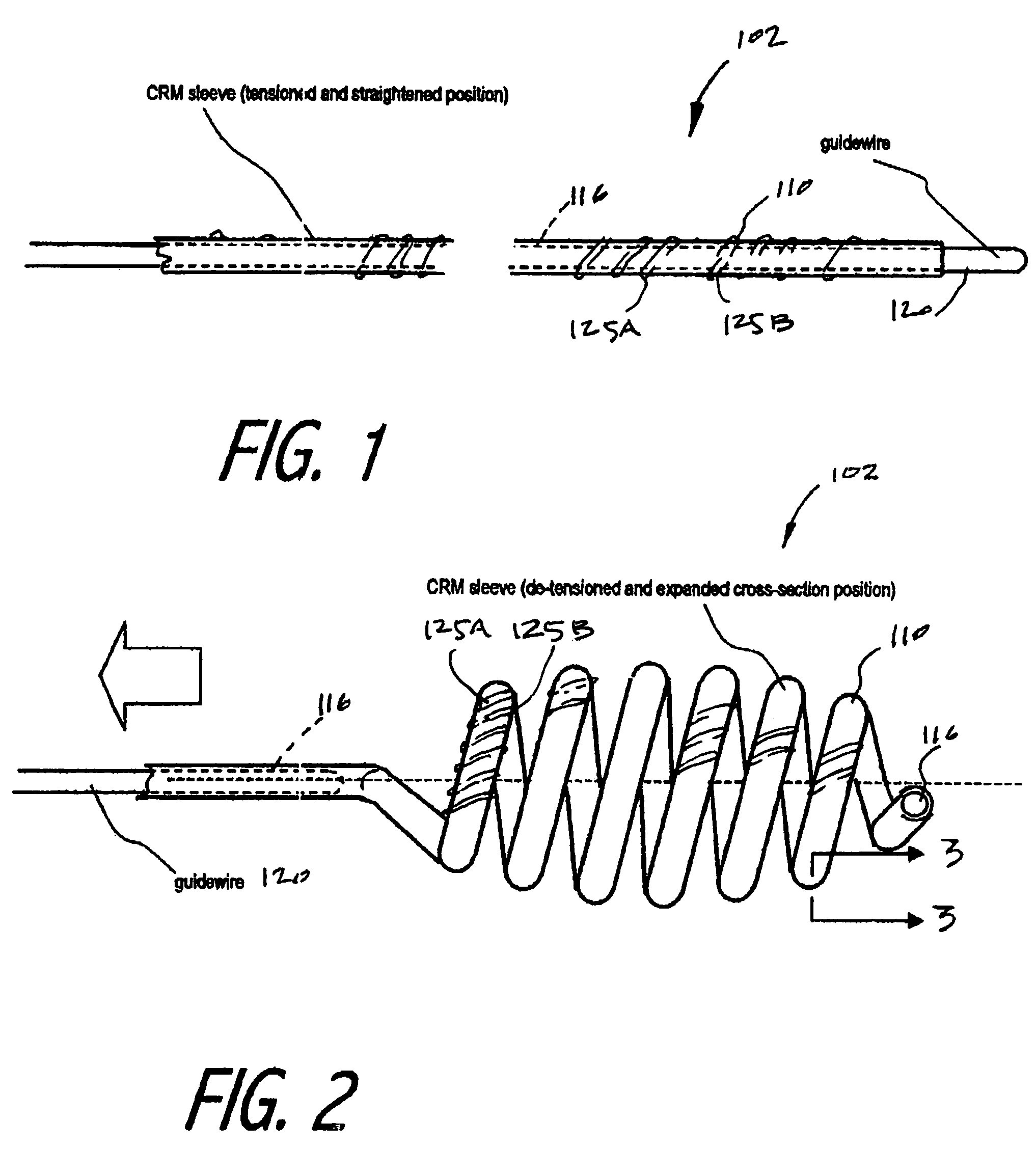

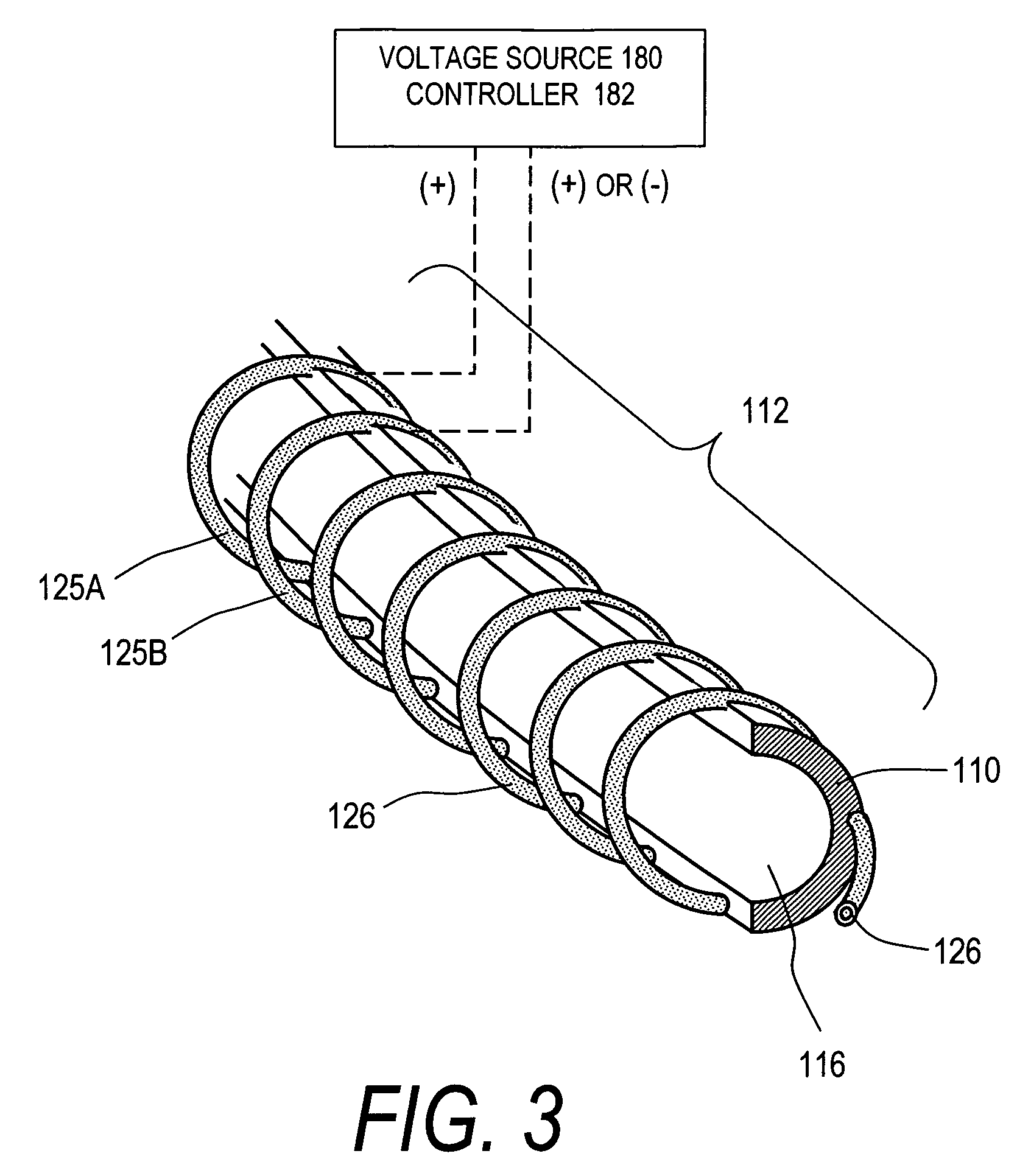

Electrosurgical instrument and method

InactiveUS7517349B2Lower base resistanceRule out the possibilityDiagnosticsSurgical instruments for heatingElectrical resistance and conductanceVaricose veins

Owner:TYCO HEALTHCARE GRP LP

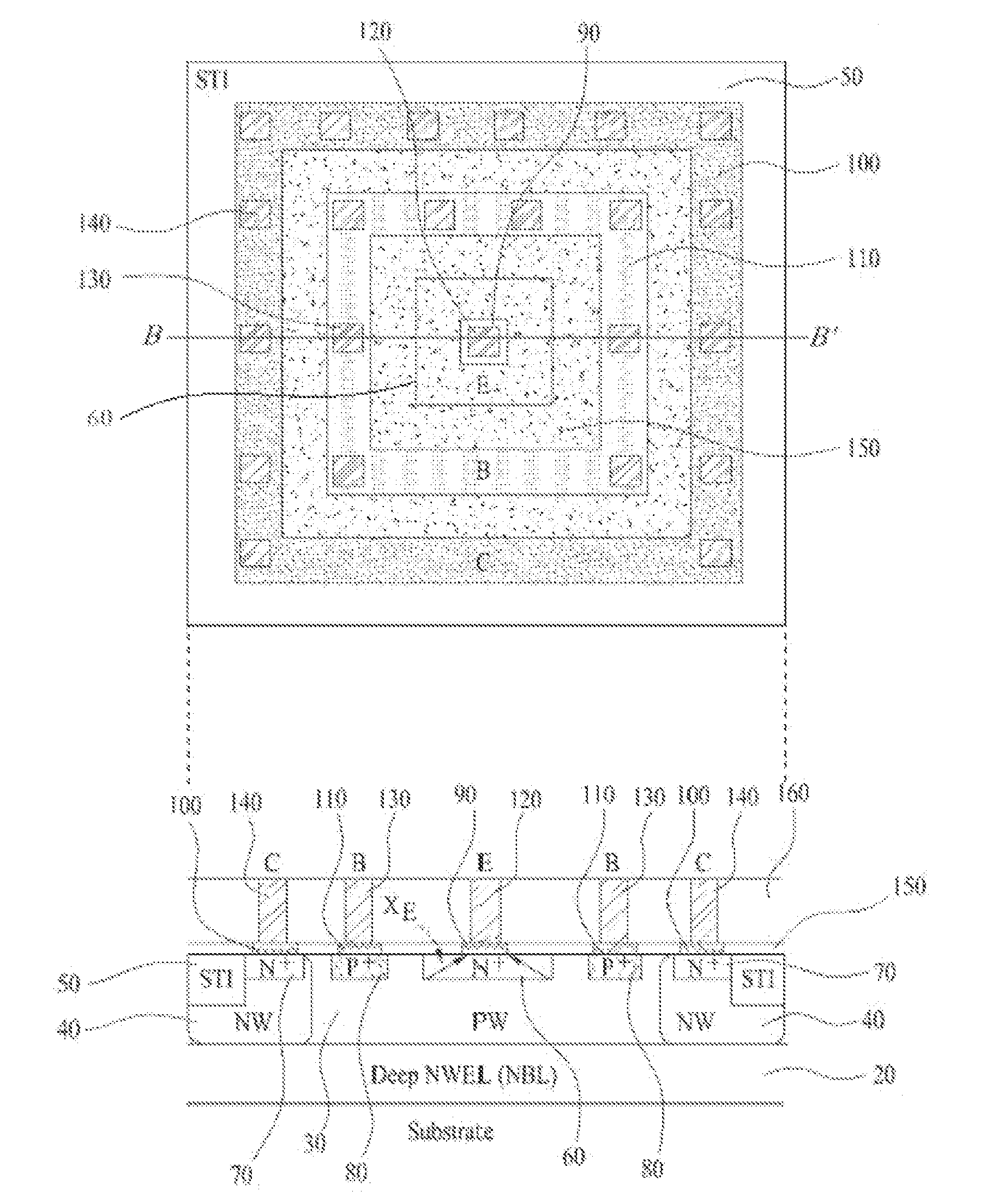

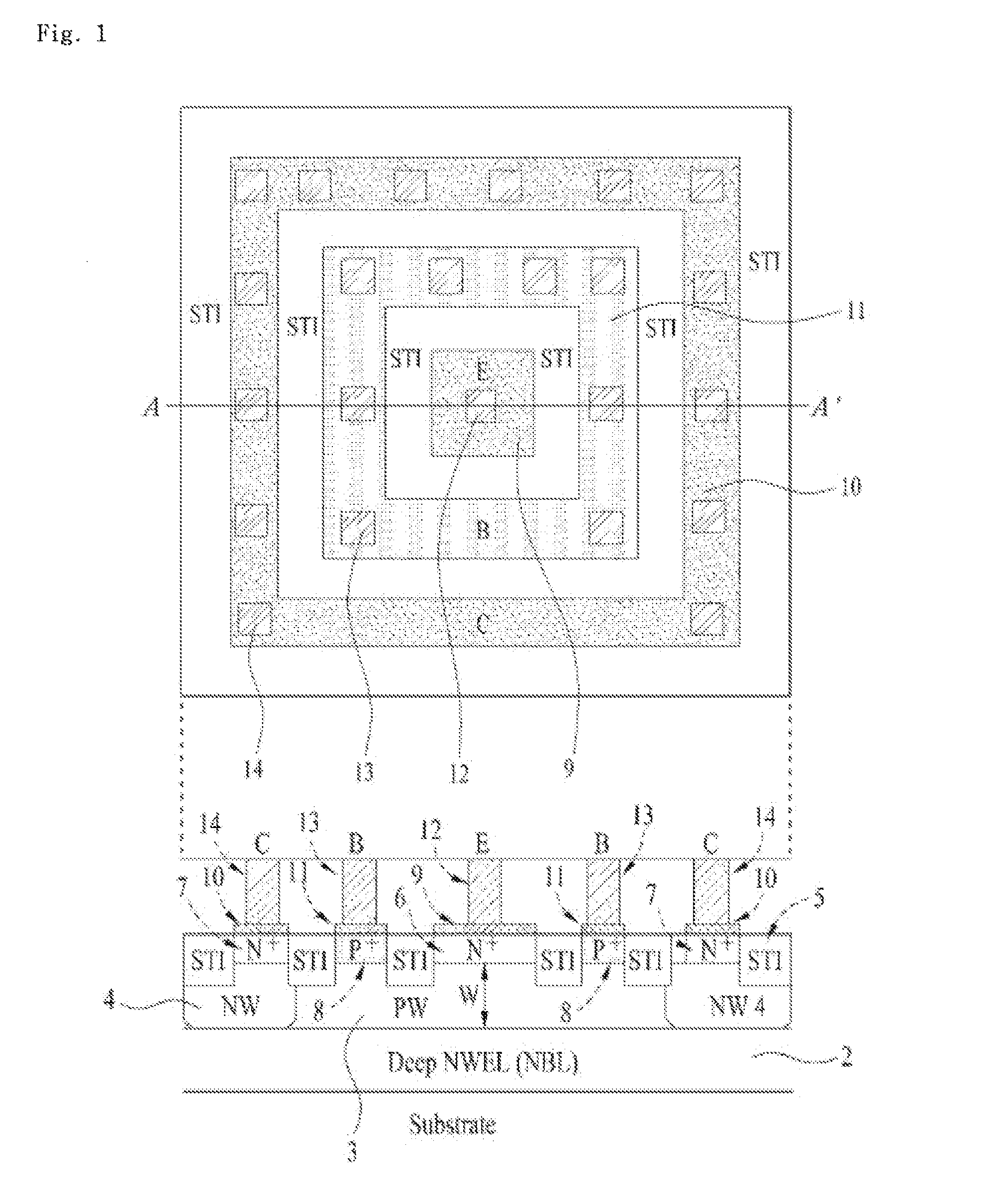

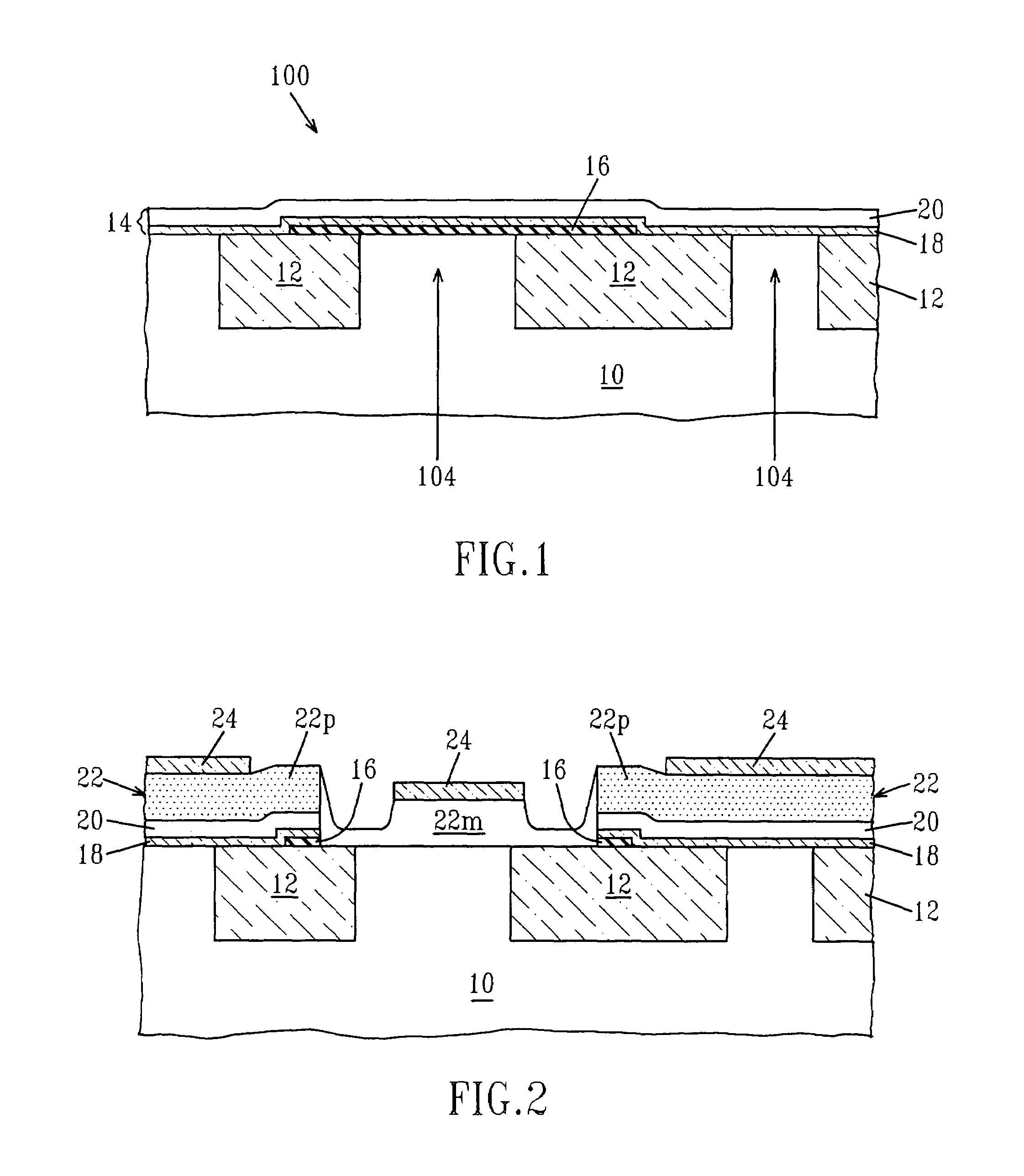

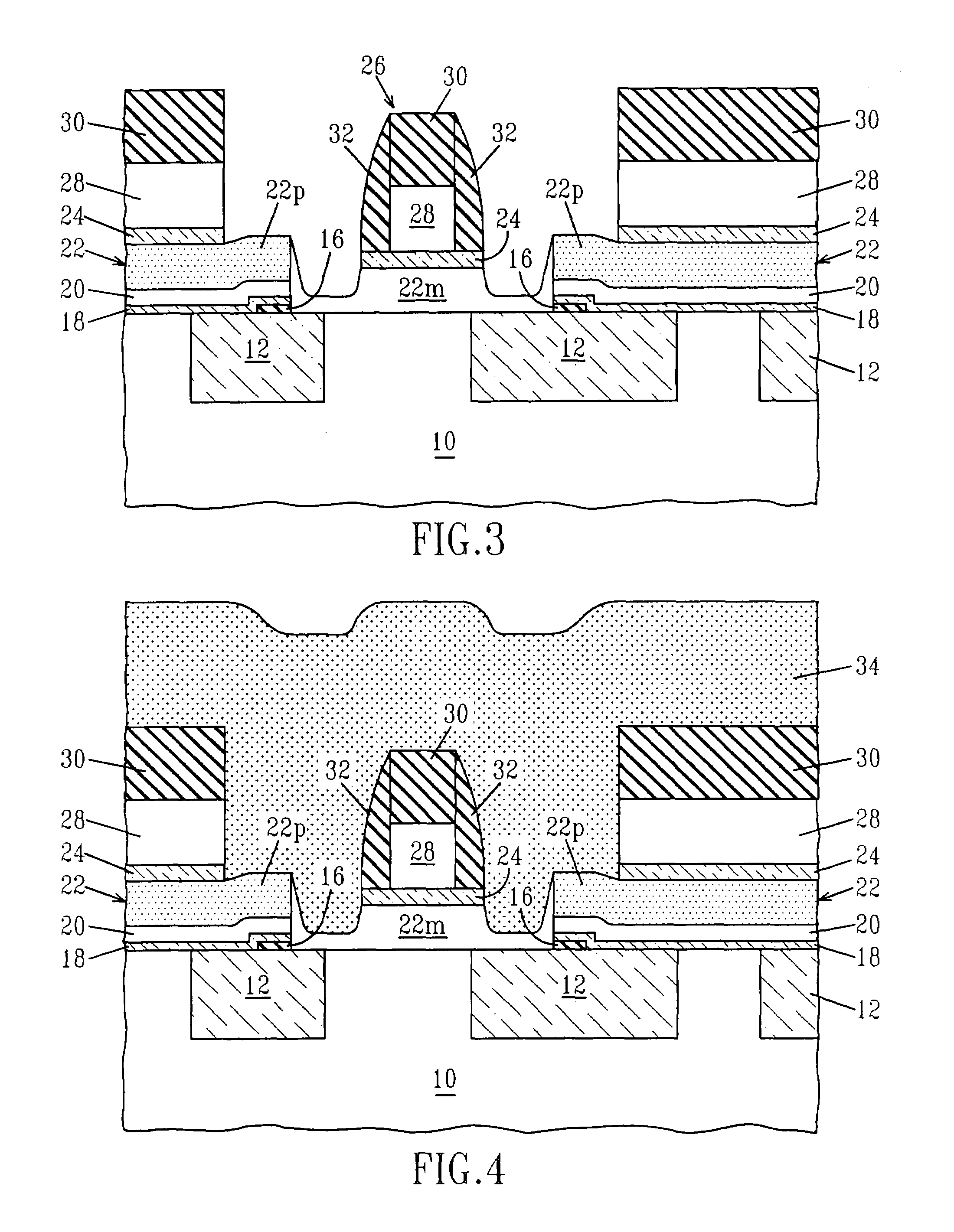

Bipolar Junction Transistor Based on CMOS Technology

InactiveUS20120032303A1Increase currentHigh base resistanceTransistorSemiconductor/solid-state device manufacturingCMOSEngineering

The present invention relates to semiconductor technologies, and more particularly to a bipolar junction transistor (BJT) in a CMOS base technology and methods of forming the same. The BJT includes a semiconductor substrate having an emitter region, a base having a first contact, and a collector having a second contact and a well plug; a first silicide film on the first contact; a second silicide film on the second contact; a first silicide blocking layer on or over the semiconductor substrate between the first and second silicide films, and a second silicide blocking layer on the semiconductor substrate between the first silicide film and the emitter region.

Owner:DONGBU HITEK CO LTD

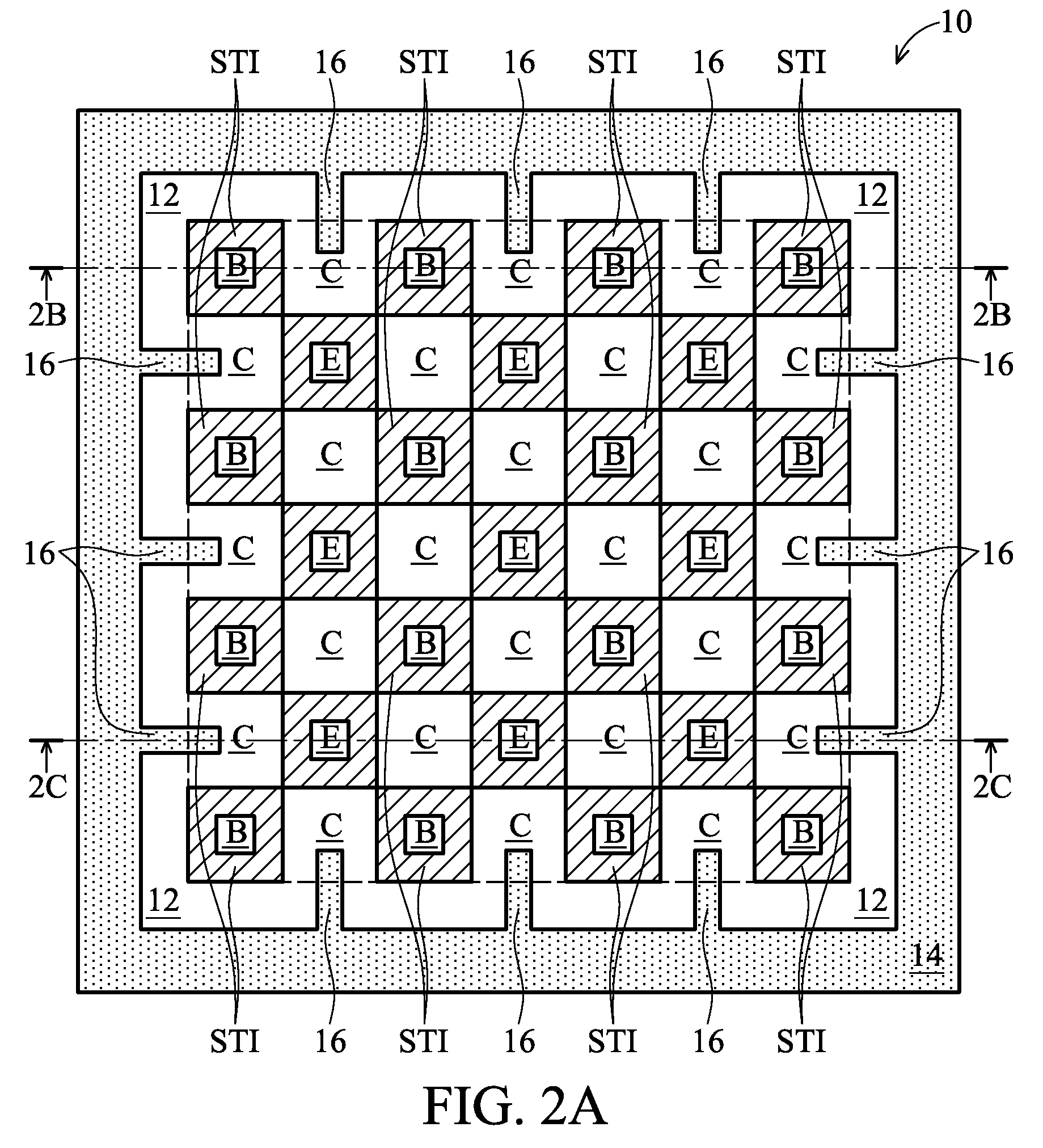

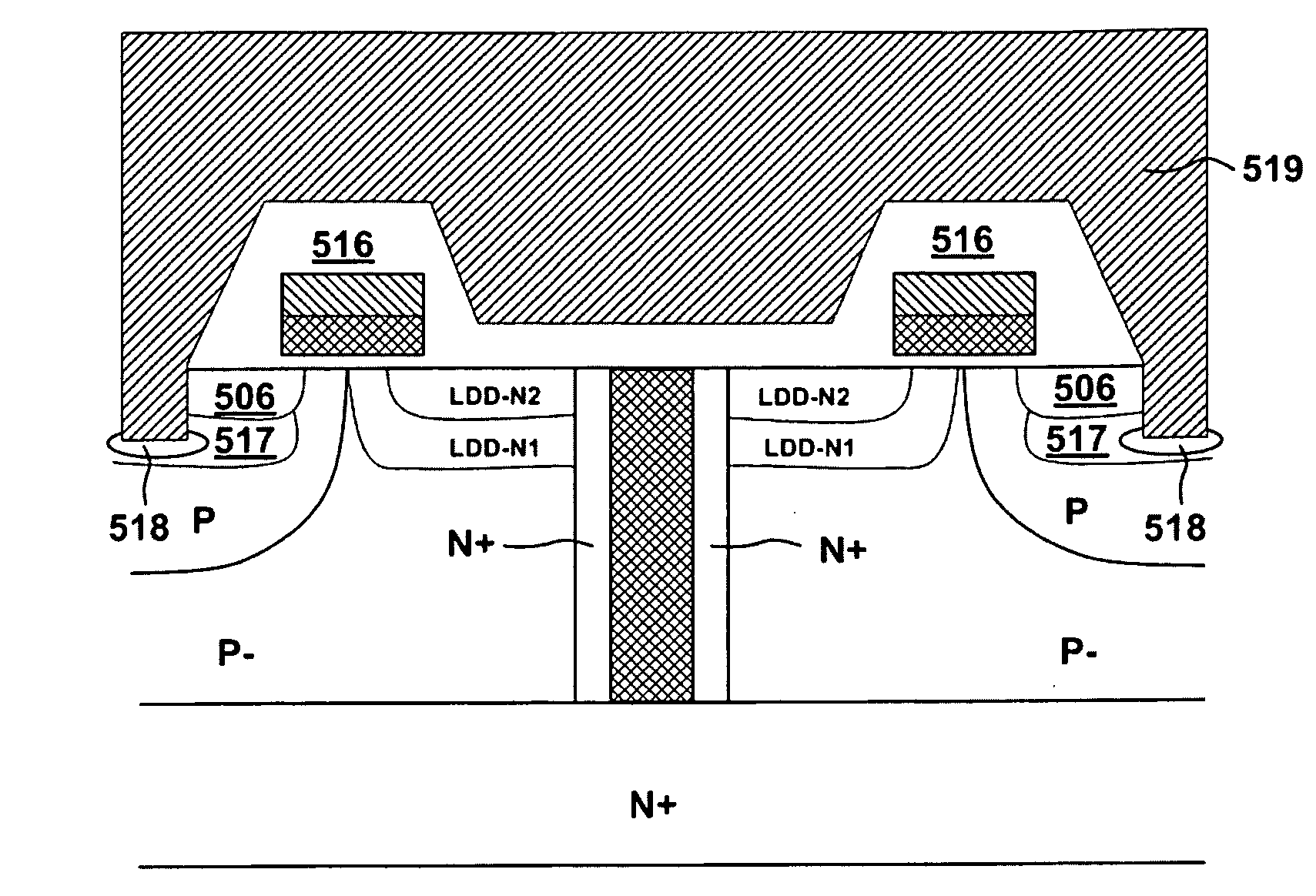

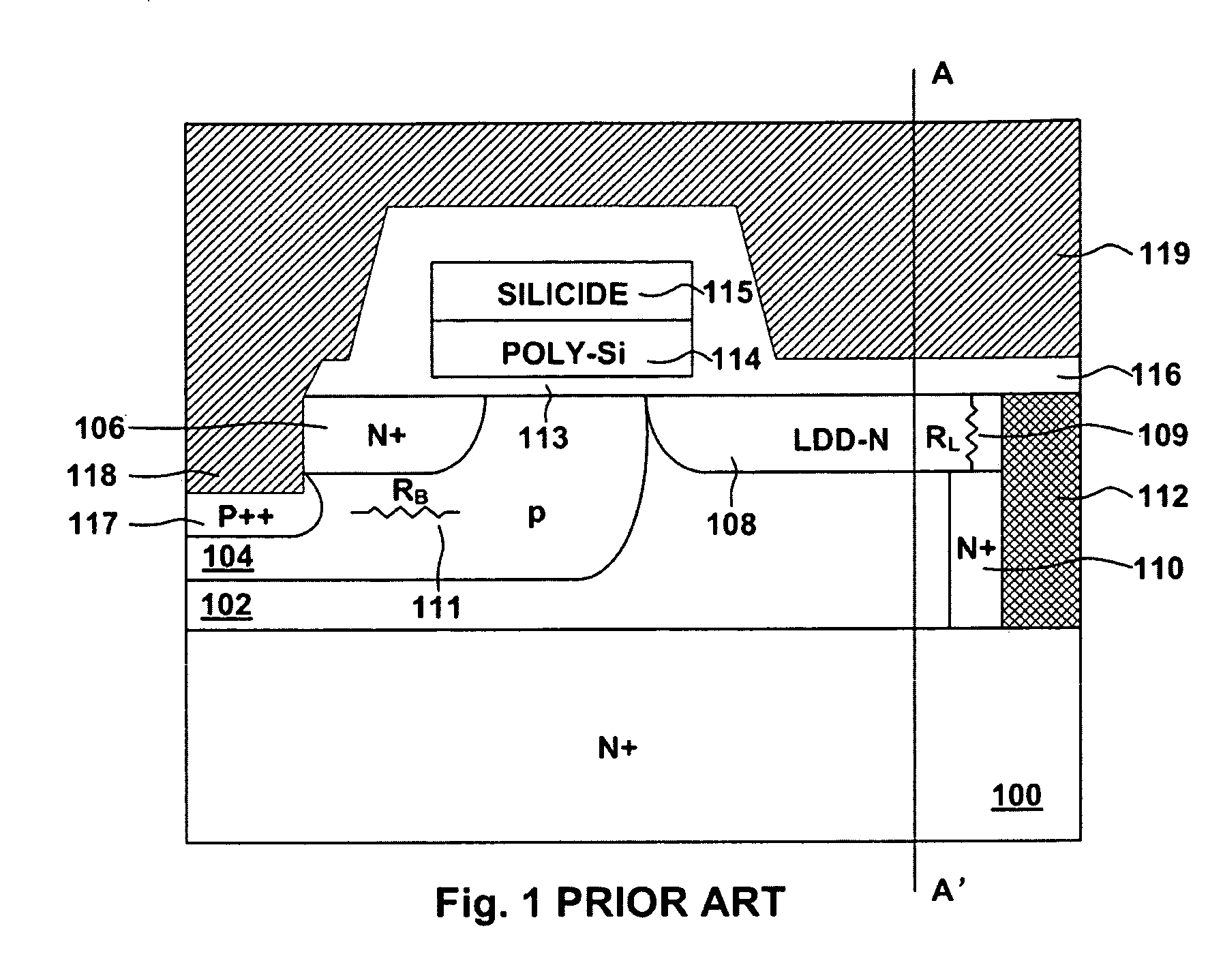

High-voltage BJT formed using CMOS HV processes

An integrated circuit device includes a semiconductor substrate having a top surface; at least one insulation region extending from the top surface into the semiconductor substrate; a plurality of base contacts of a first conductivity type electrically interconnected to each other; and a plurality of emitters and a plurality of collectors of a second conductivity type opposite the first conductivity type. Each of the plurality of emitters, the plurality of collectors, and the plurality of base contacts is laterally spaced apart from each other by the at least one insulation region. The integrated circuit device further includes a buried layer of the second conductivity type in the semiconductor substrate, wherein the buried layer has an upper surface adjoining bottom surfaces of the plurality of collectors.

Owner:TAIWAN SEMICON MFG CO LTD

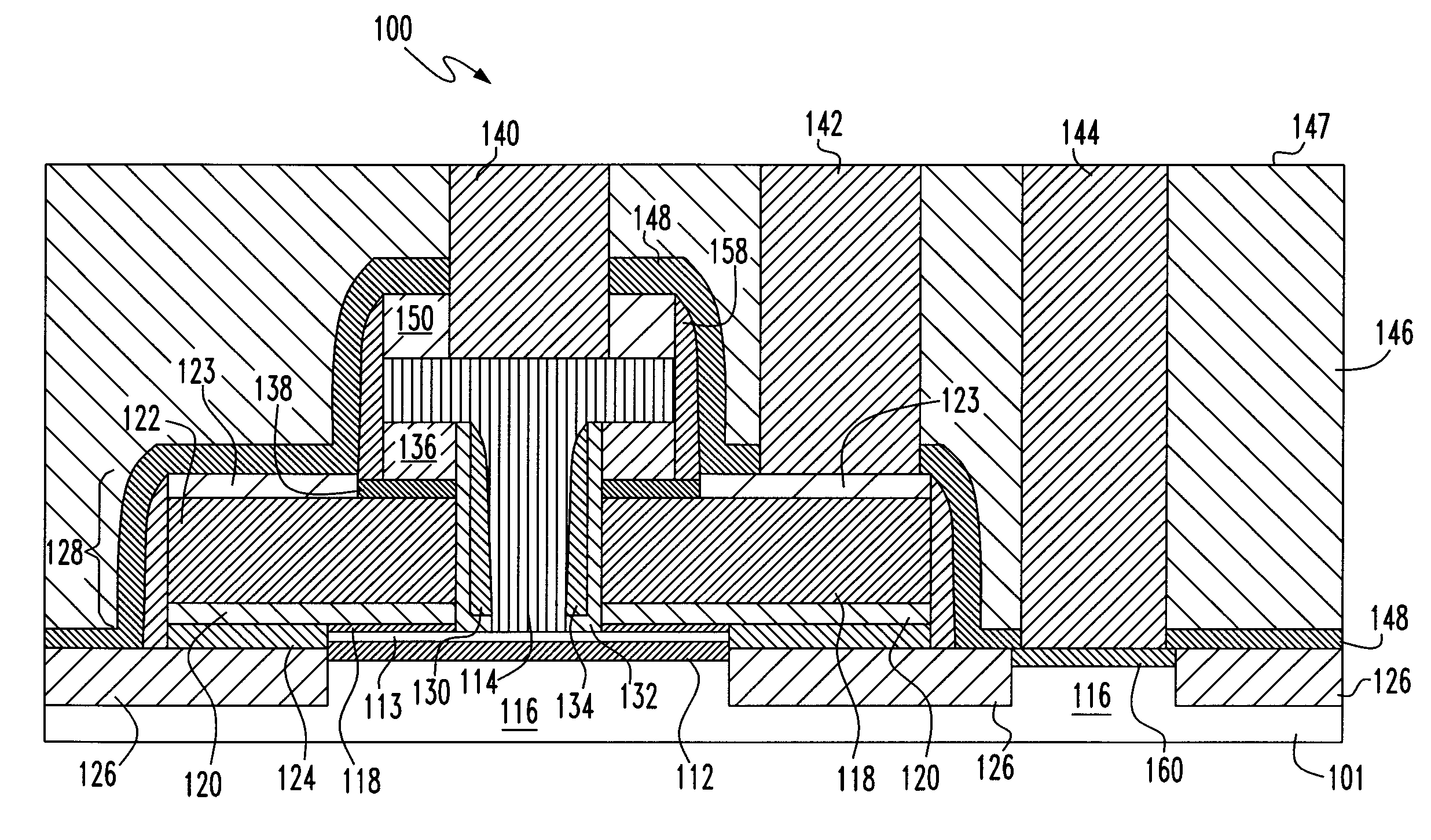

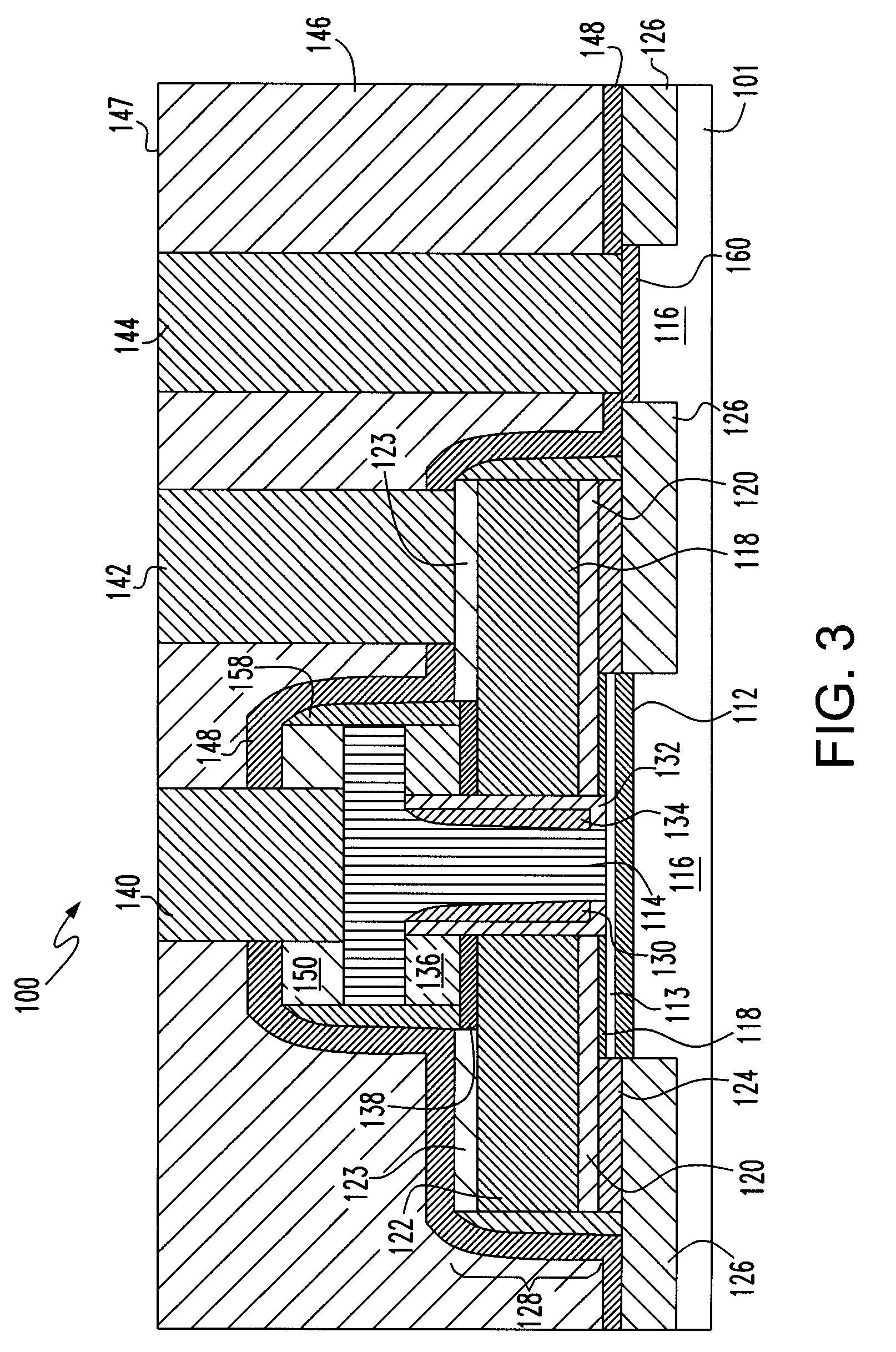

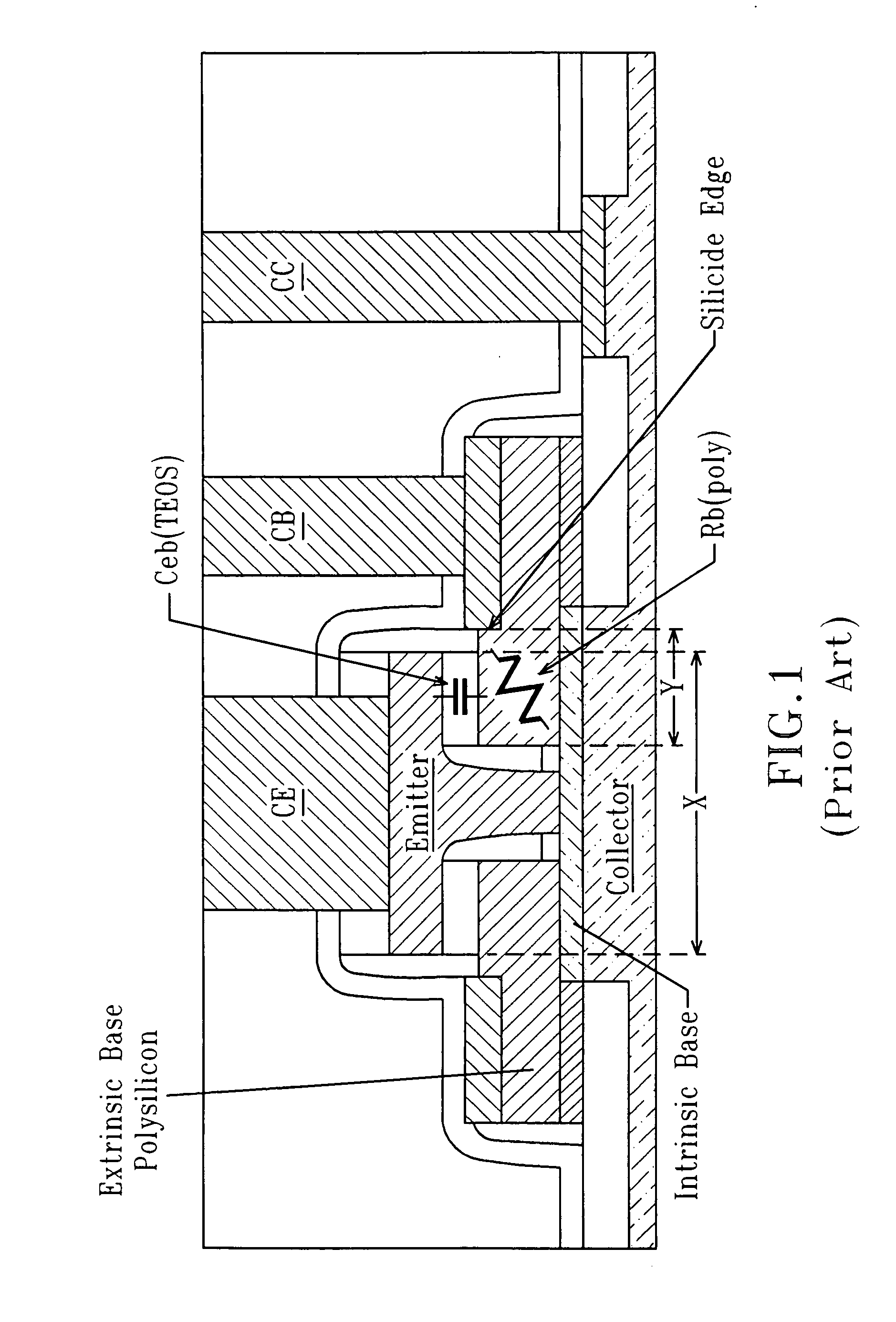

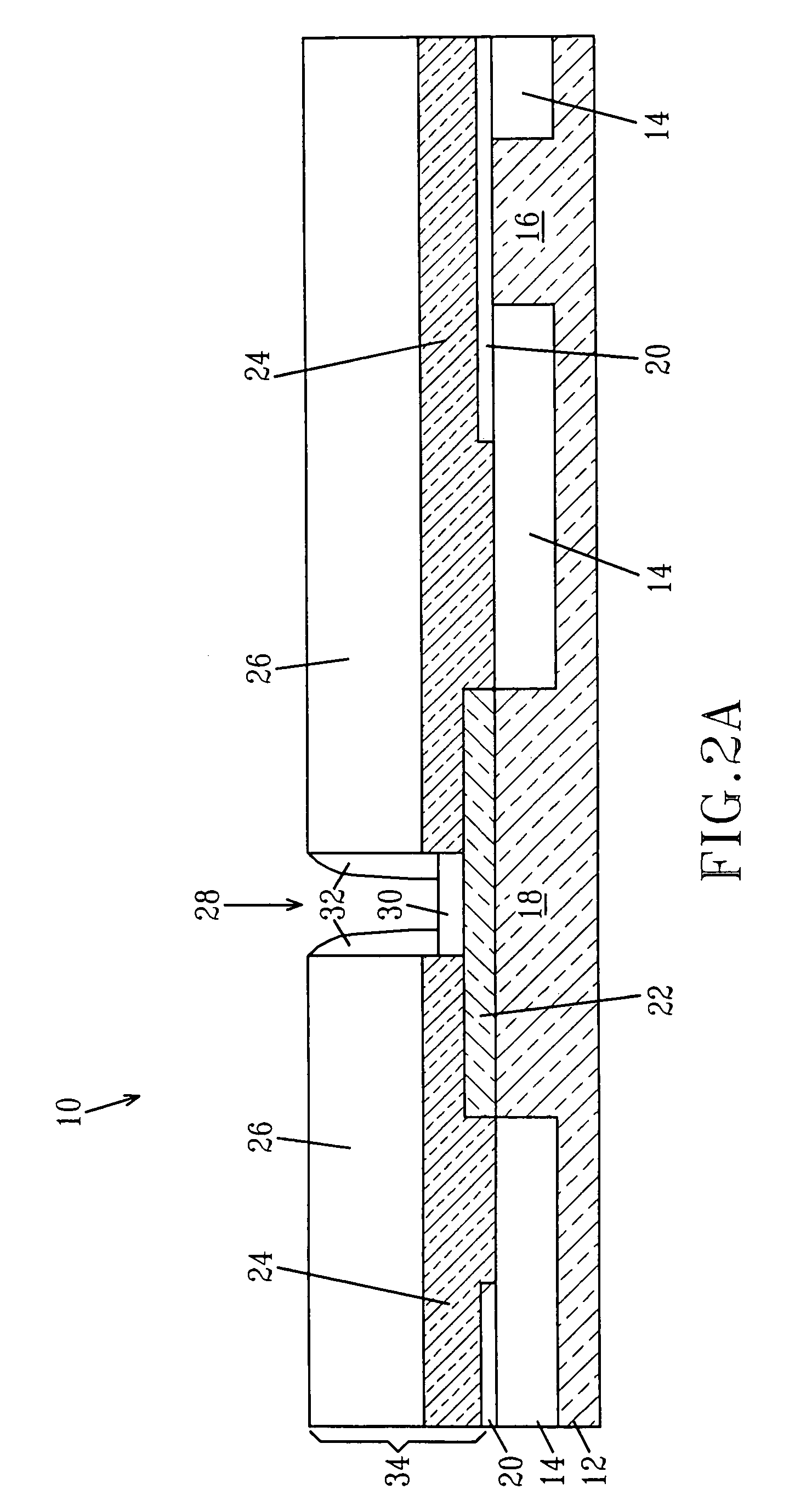

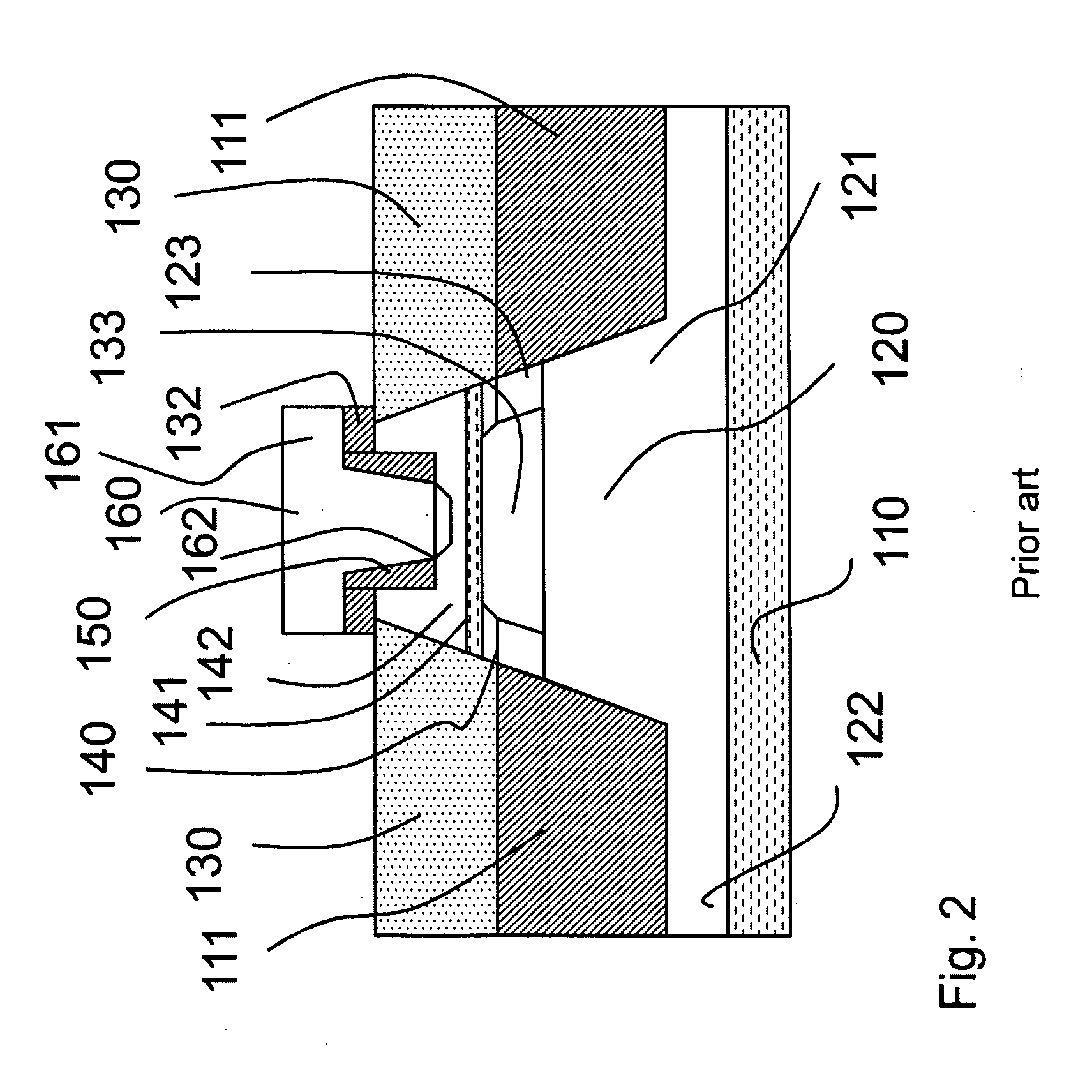

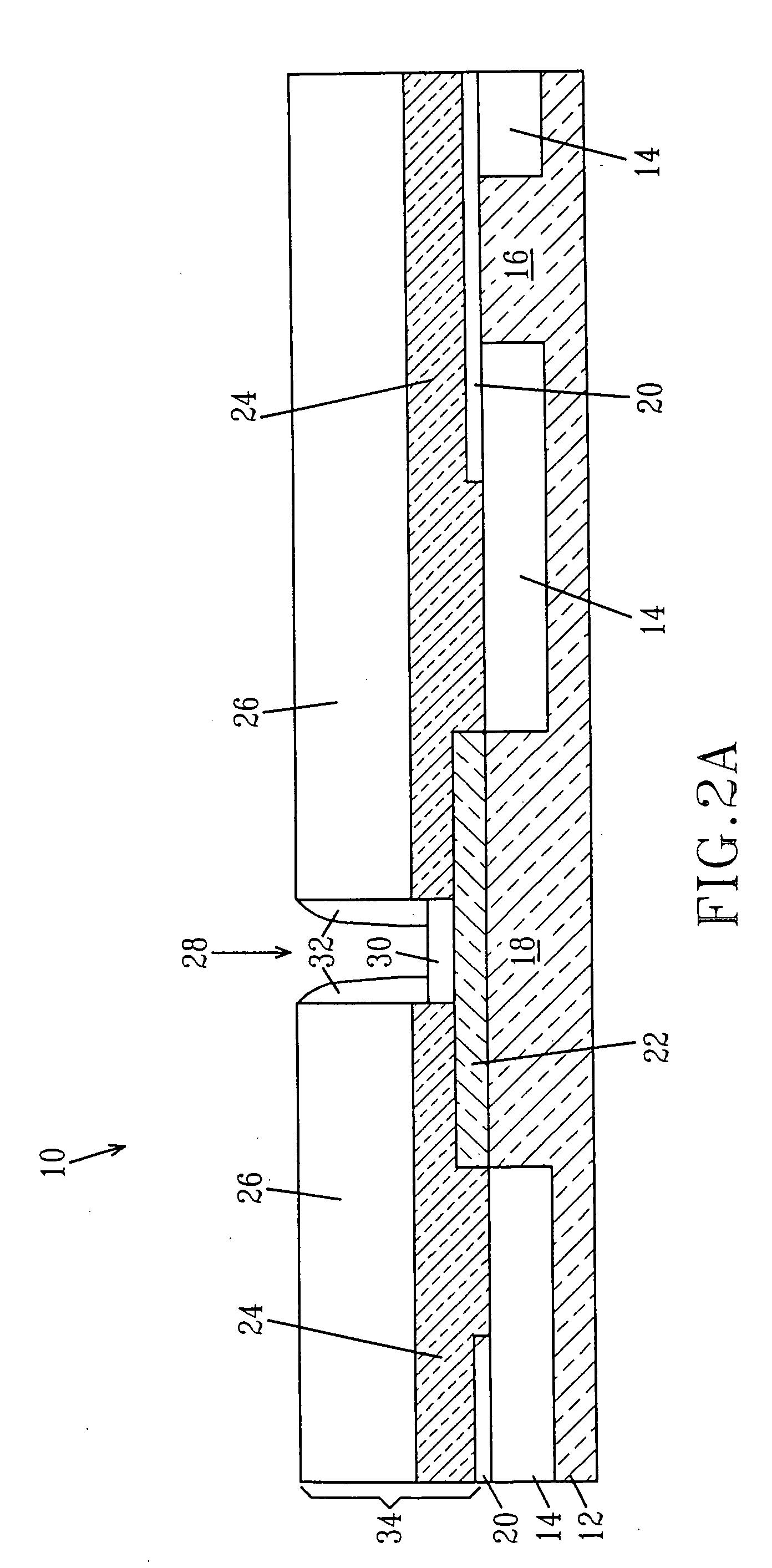

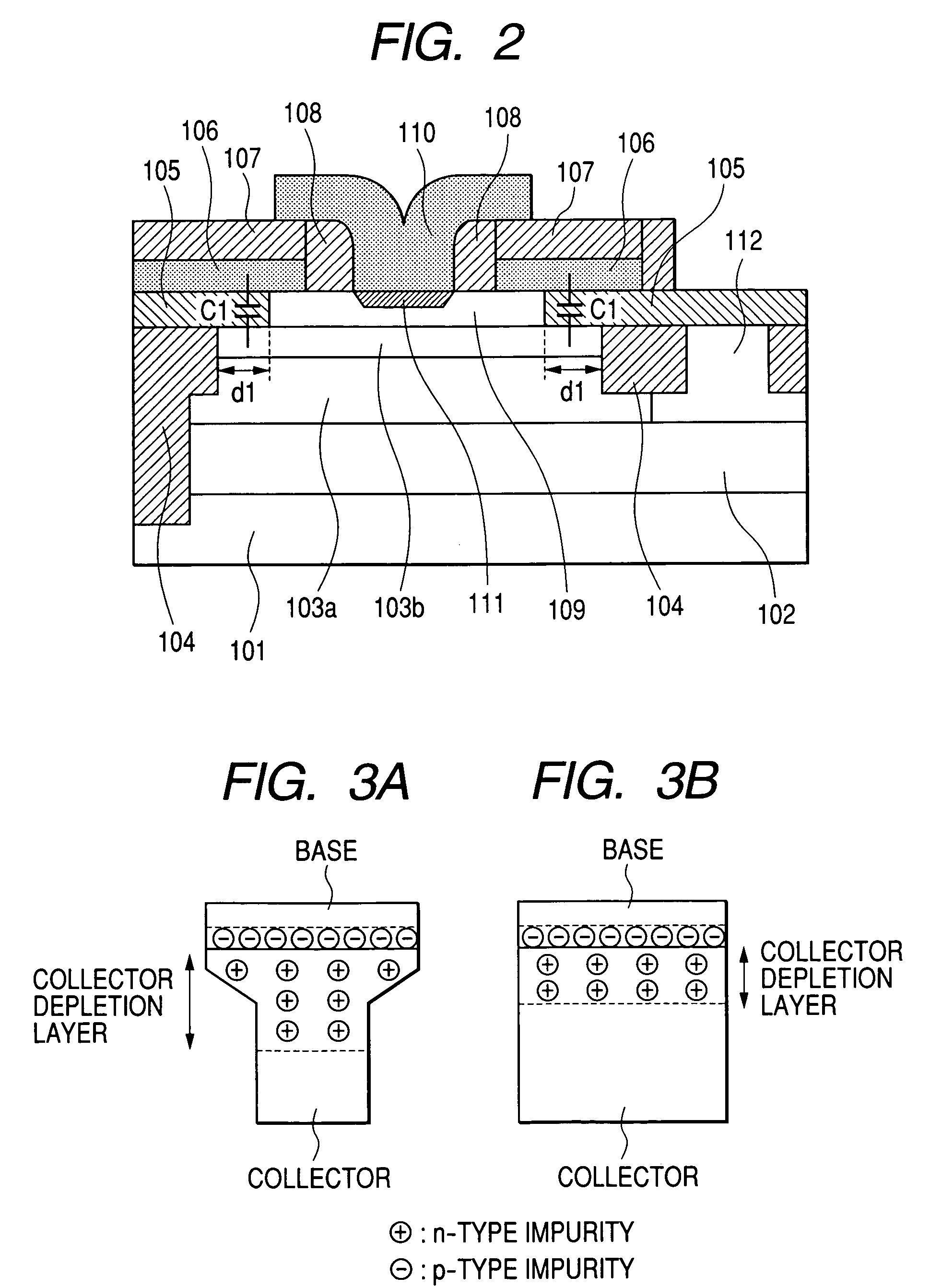

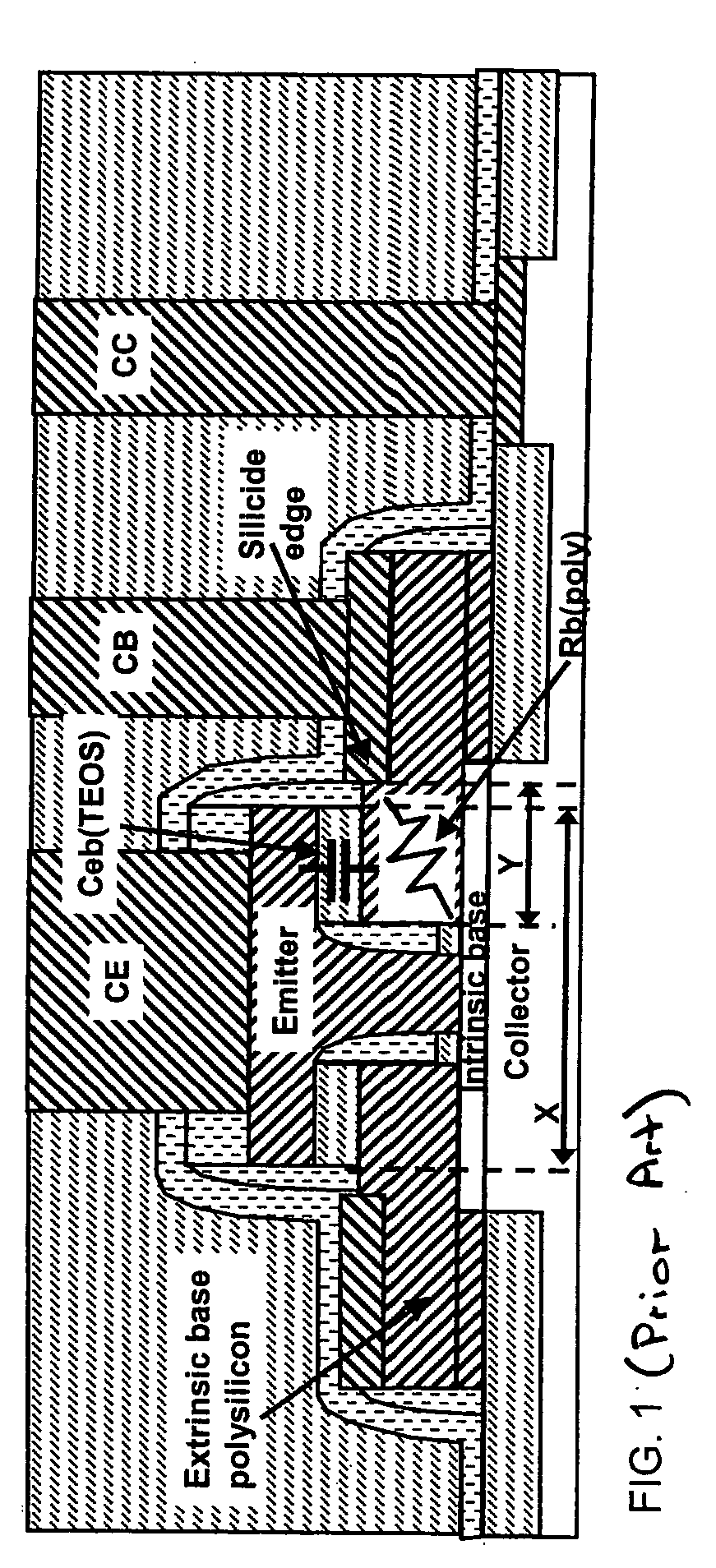

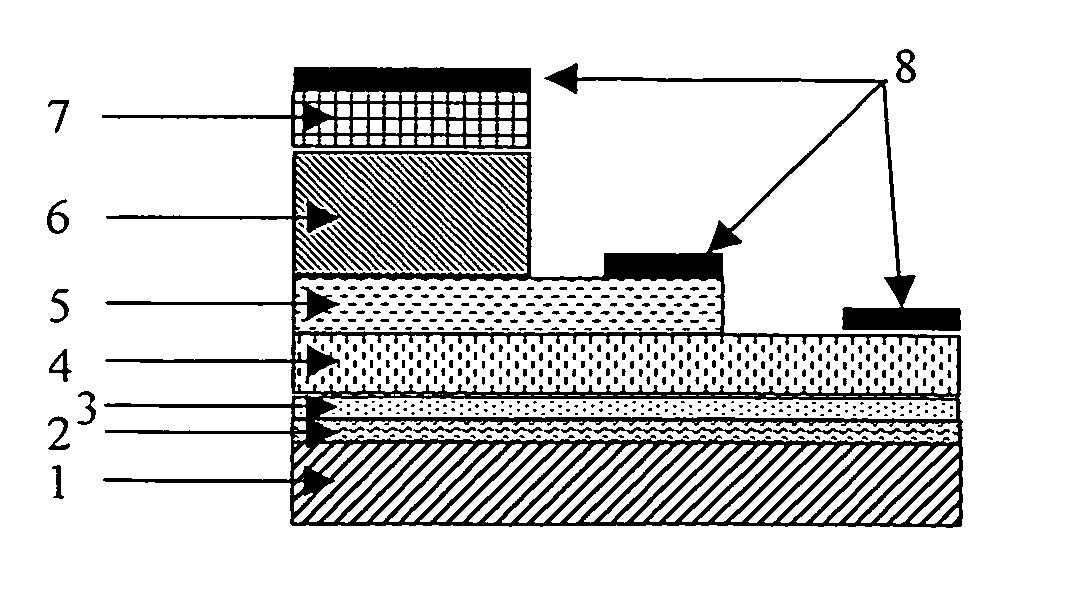

Structure and method for making heterojunction bipolar transistor having self-aligned silicon-germanium raised extrinsic base

InactiveUS6982442B2High selectivityLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor alloys

A heterojunction bipolar transistor (HBT) and method of making an HBT are provided. The HBT includes a collector, and an intrinsic base overlying the collector. The intrinsic base includes a layer of a single-crystal semiconductor alloy. The HBT further includes a raised extrinsic base having a first semiconductive layer overlying the intrinsic base and a second semiconductive layer formed on the first semiconductive layer. An emitter overlies the intrinsic base, and is disposed in an opening of the first and second semiconductive layers, such that the raised extrinsic base is self-aligned to the emitter.

Owner:INT BUSINESS MASCH CORP

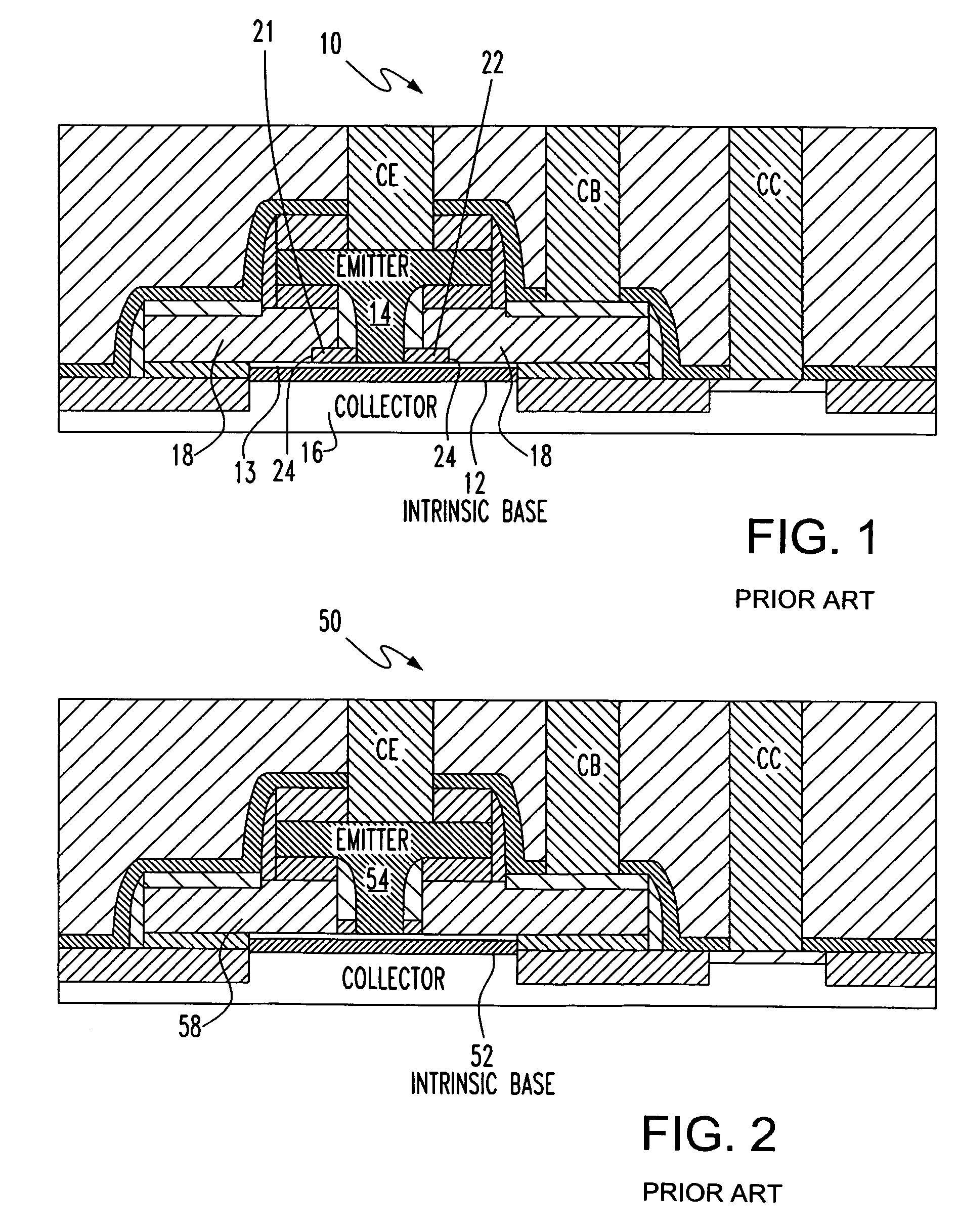

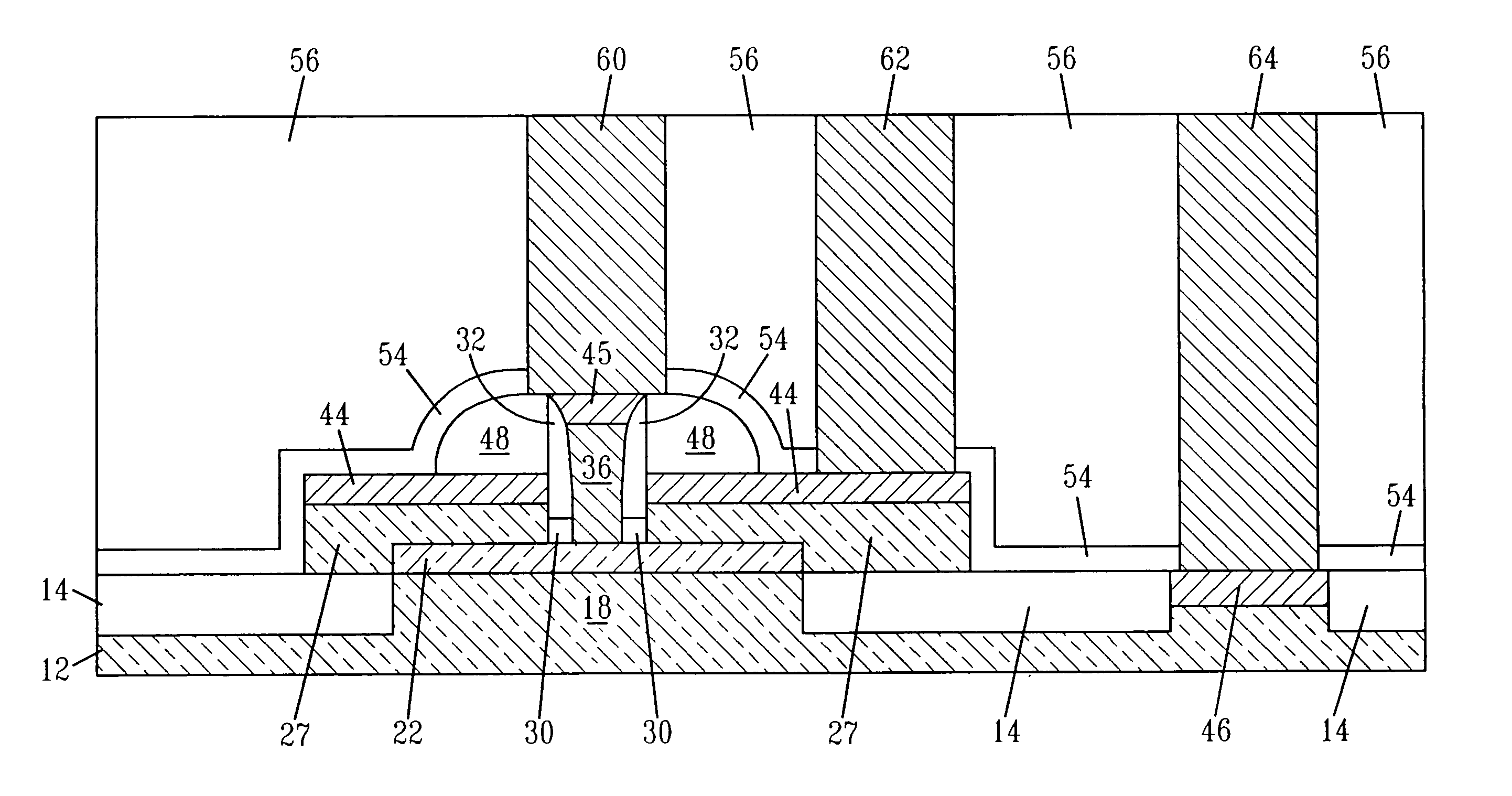

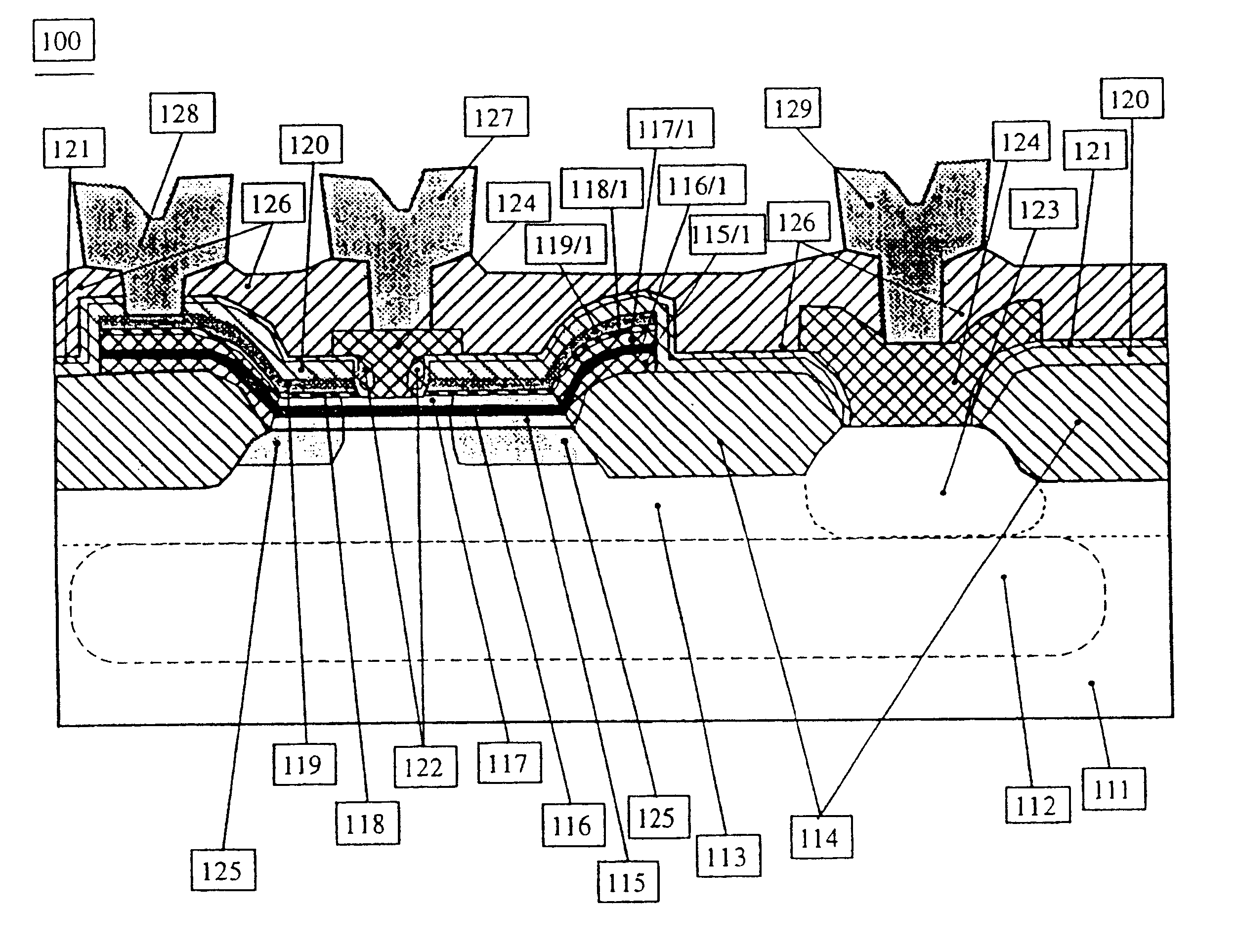

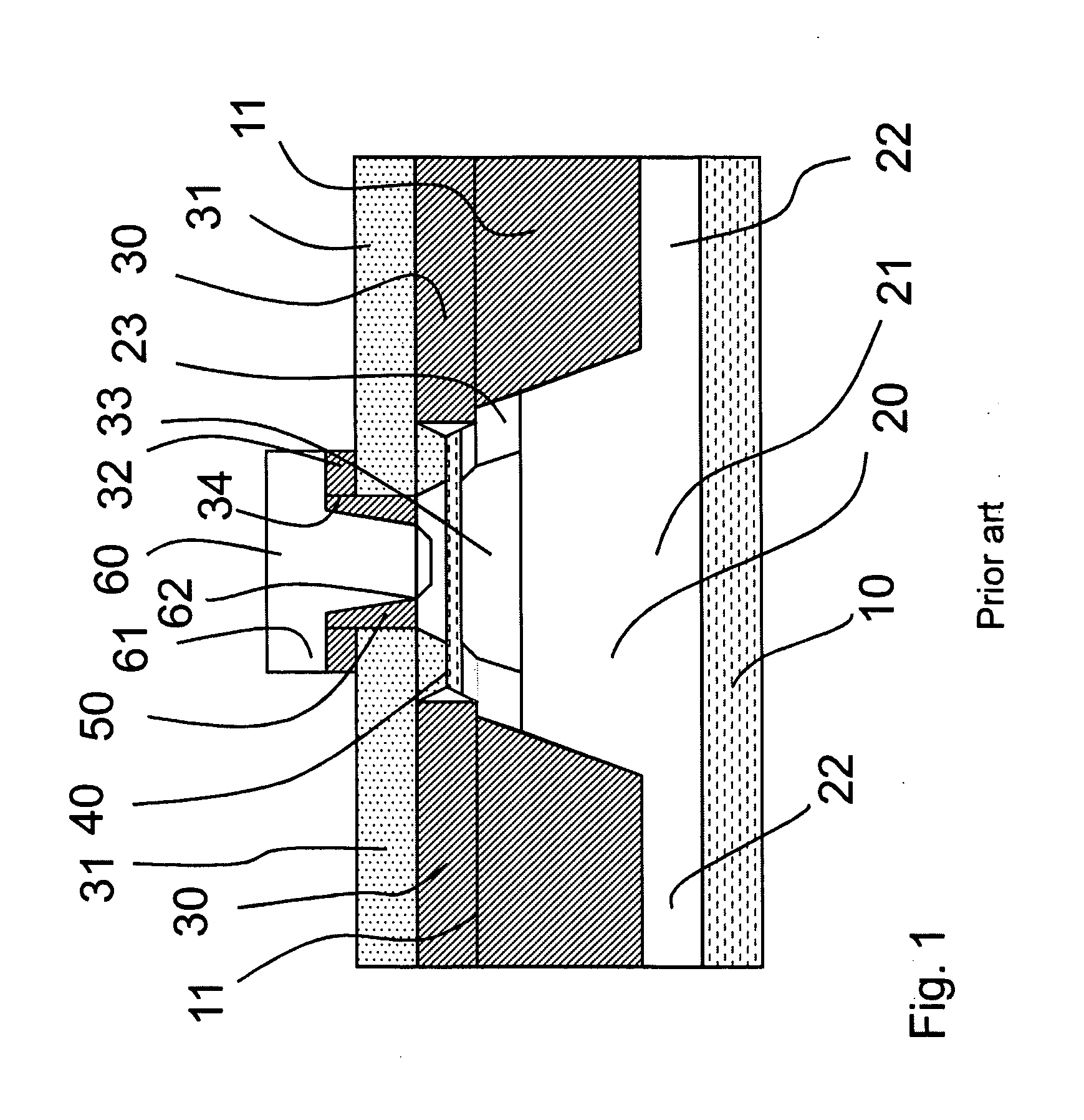

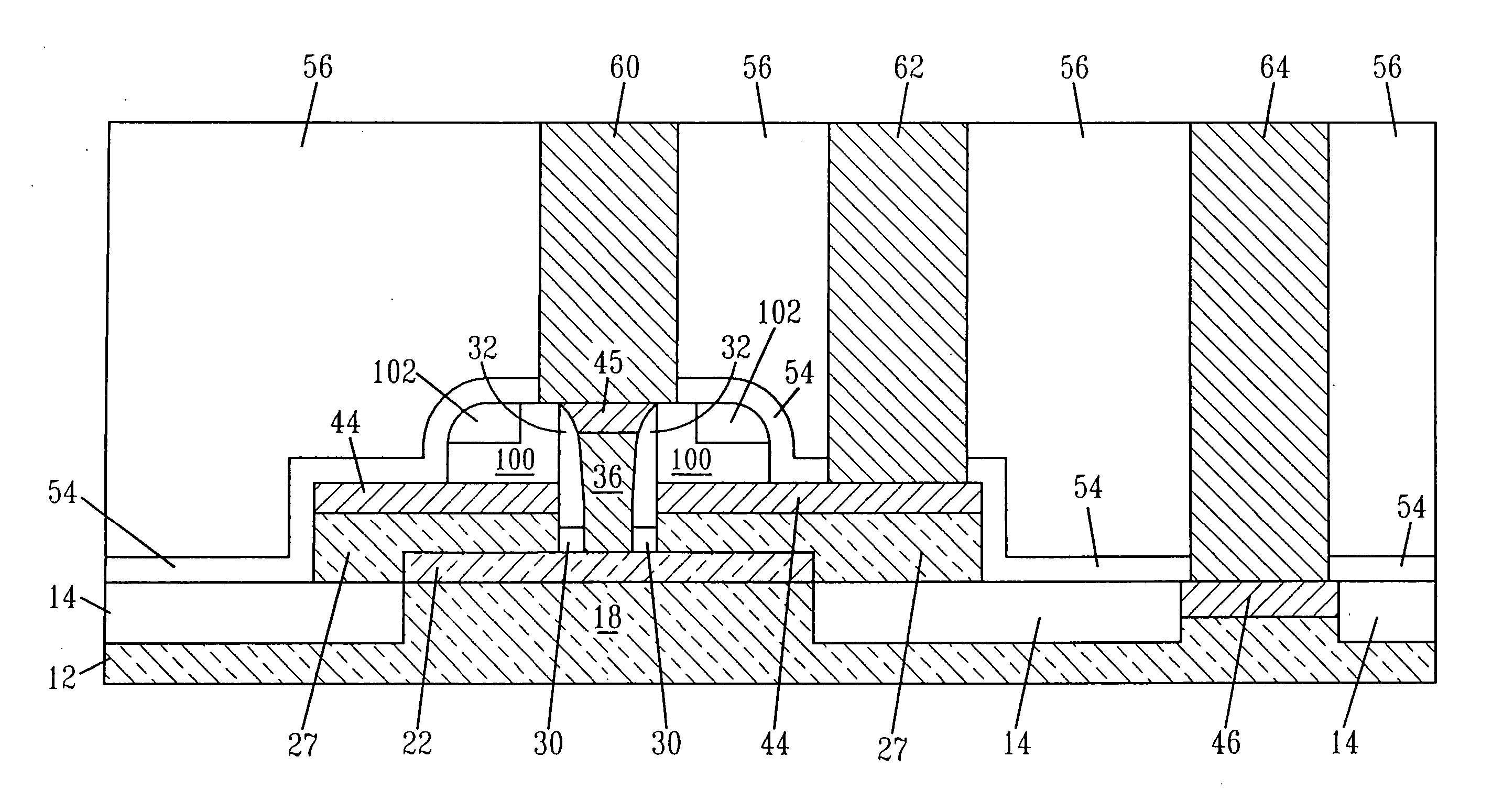

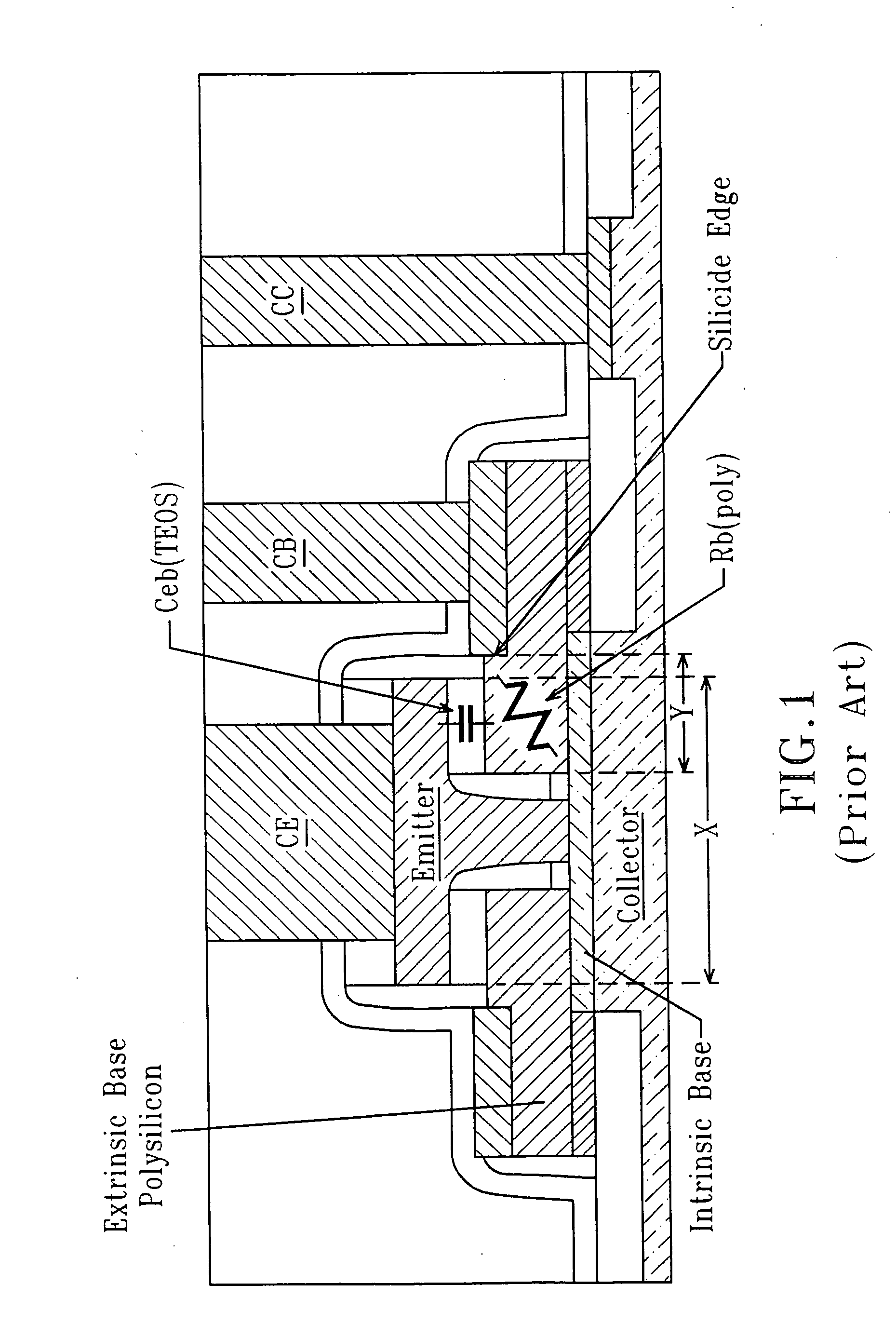

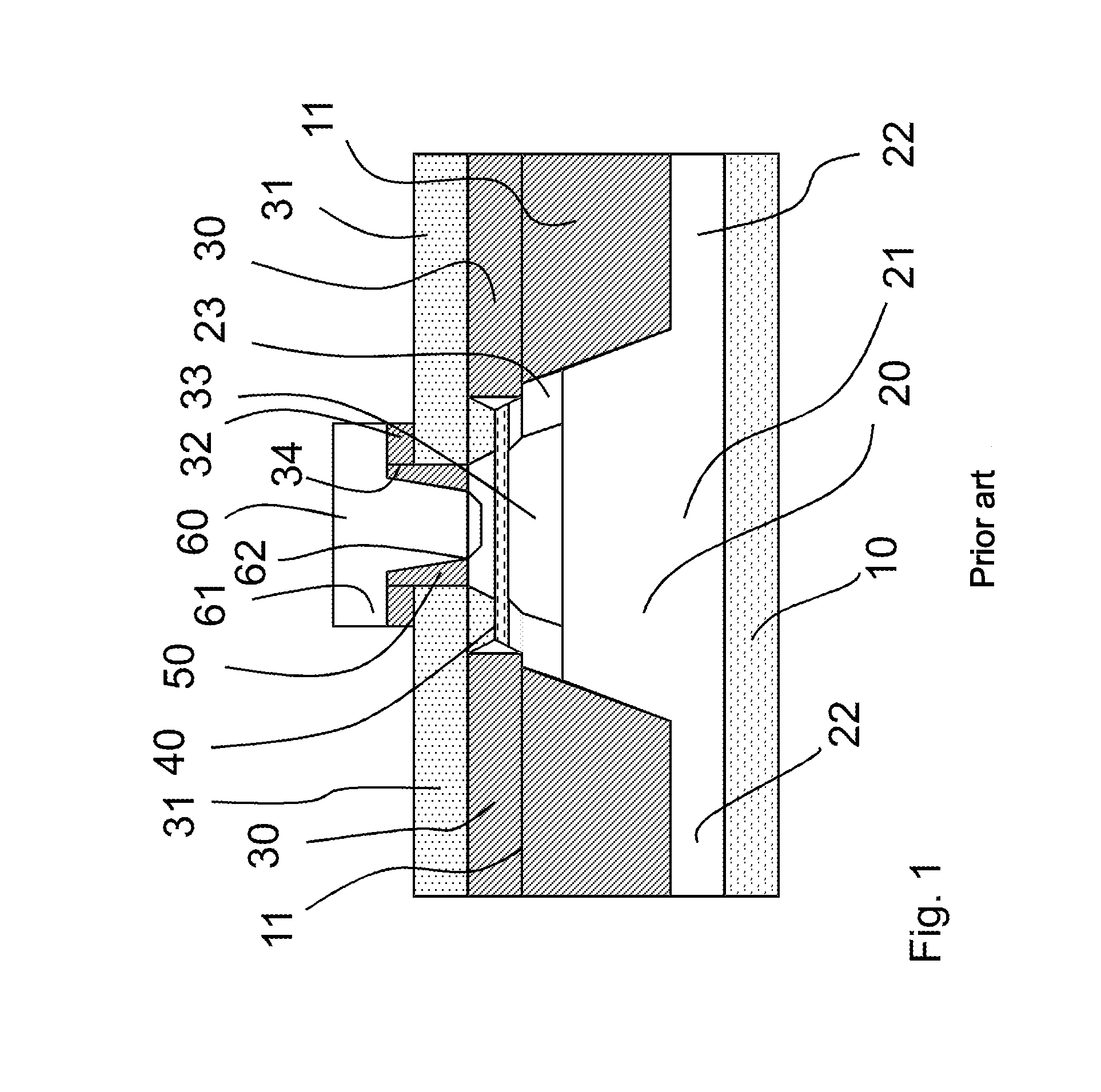

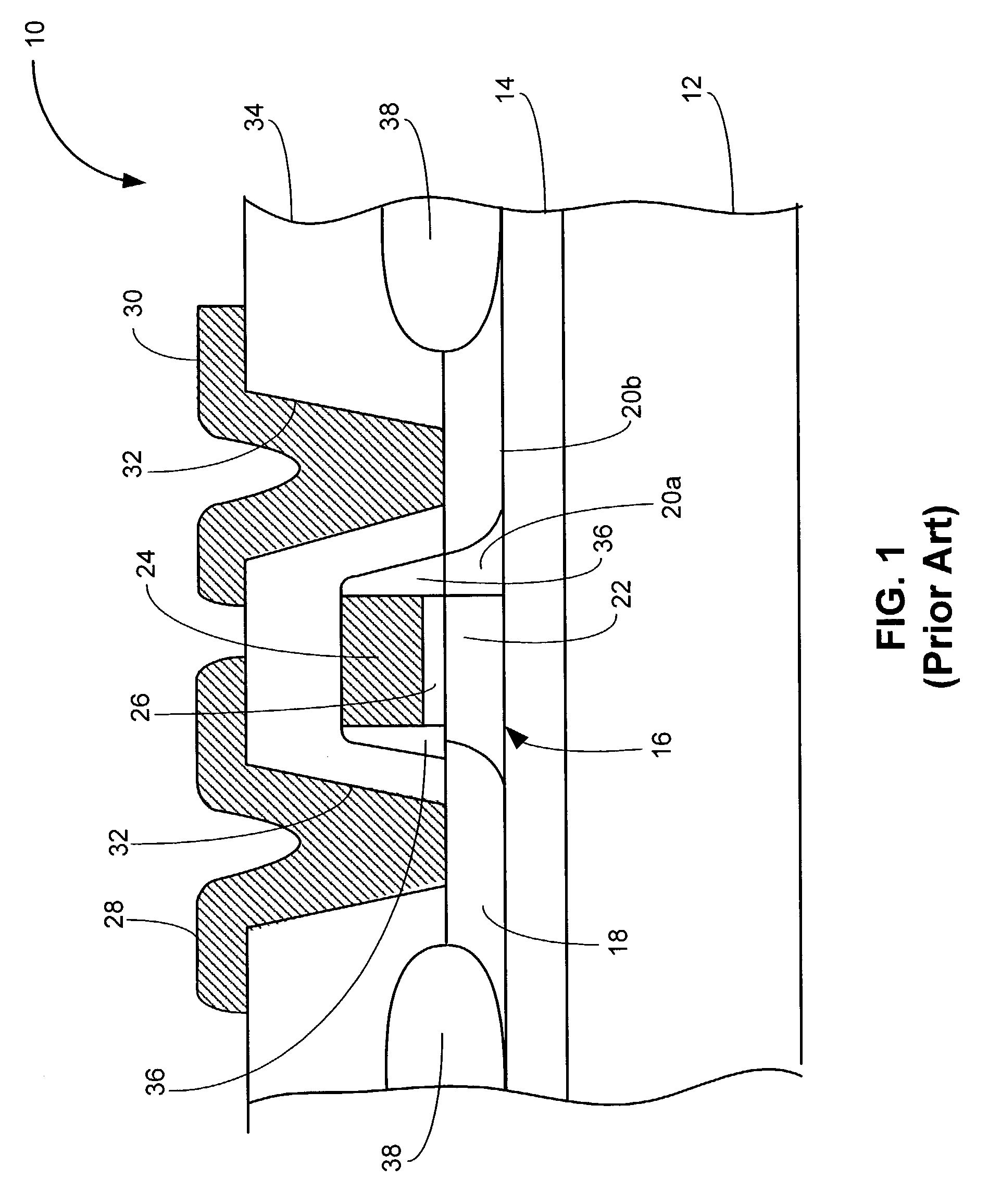

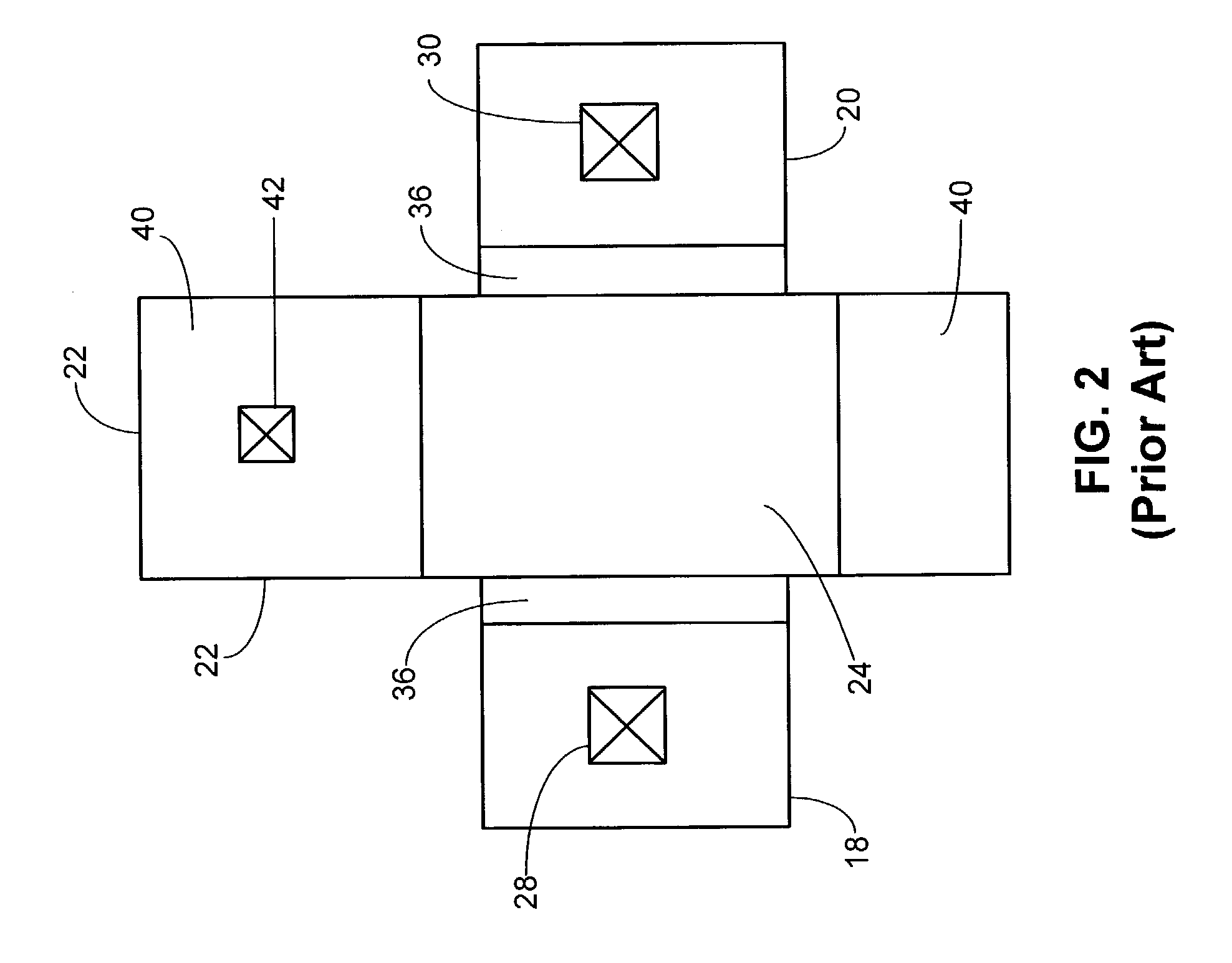

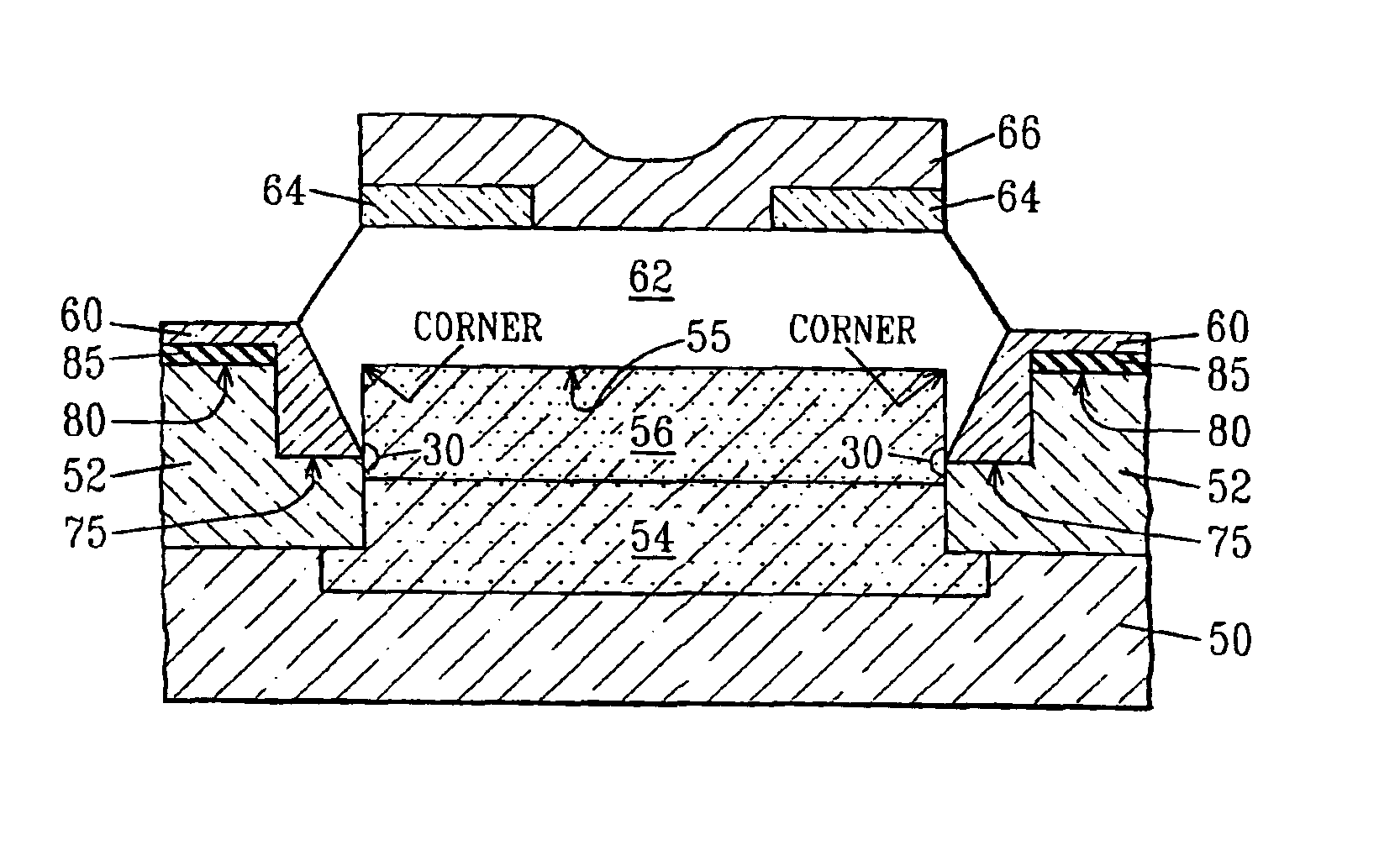

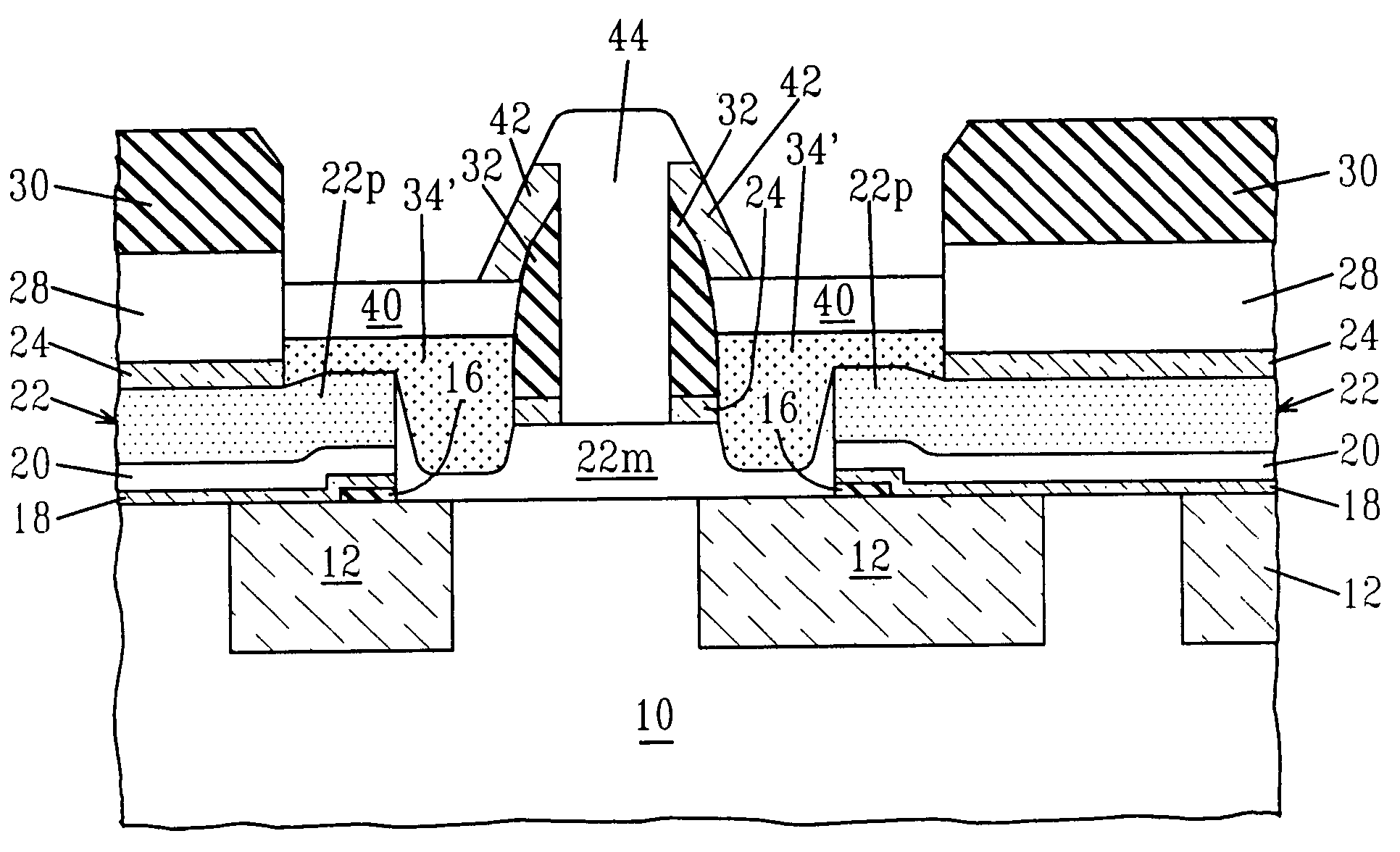

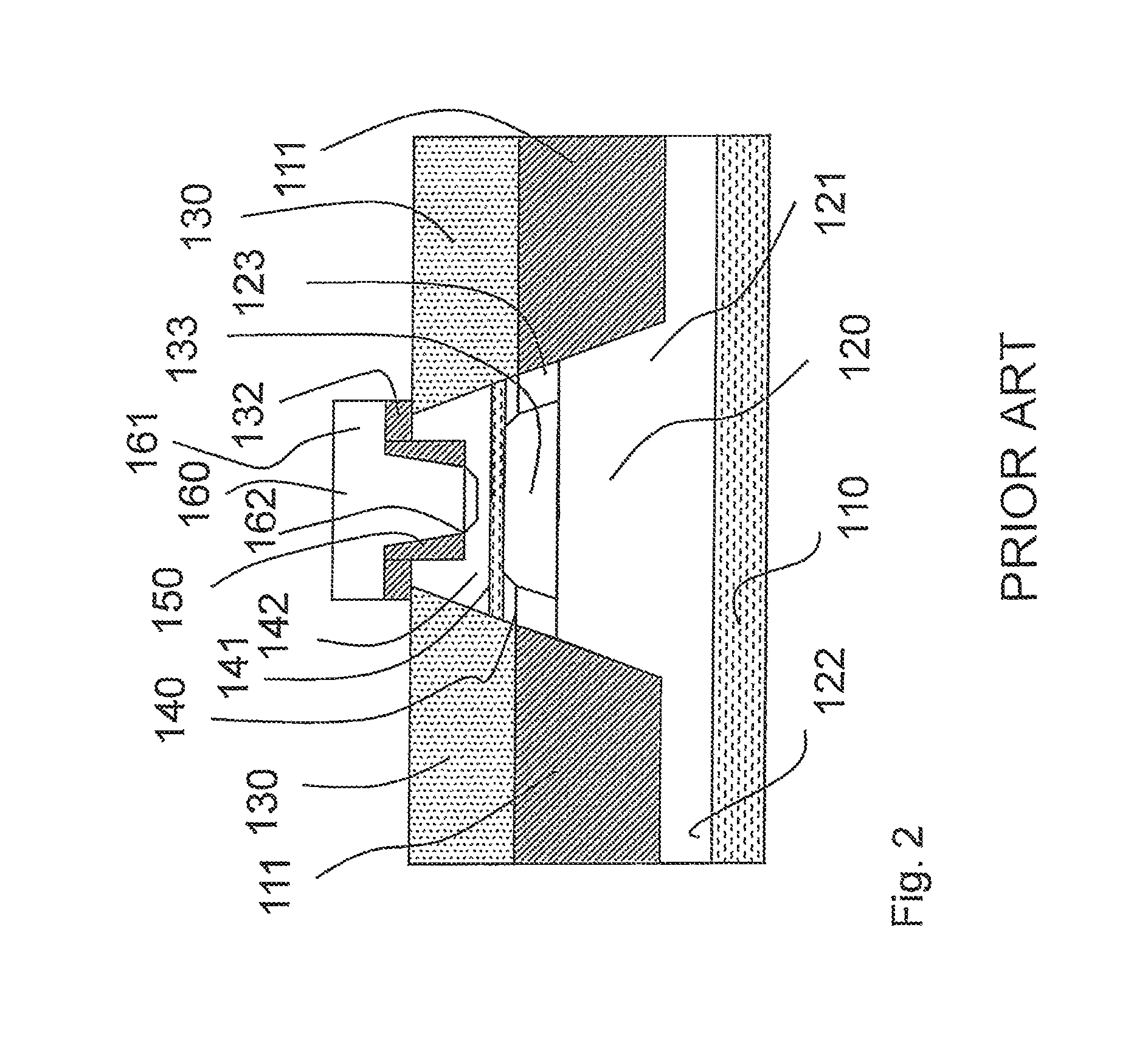

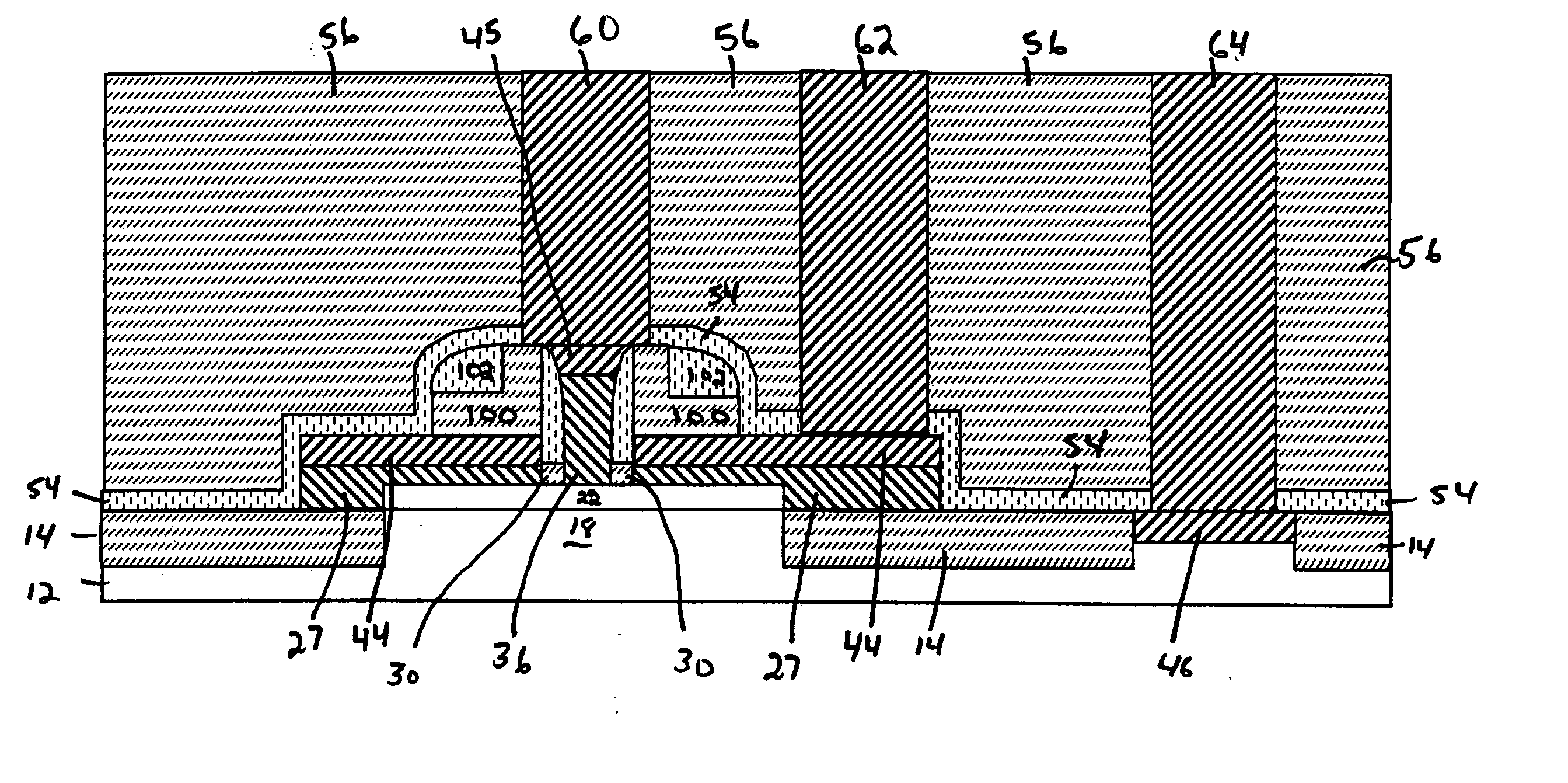

Bipolar transistor having self-aligned silicide and a self-aligned emitter contact border

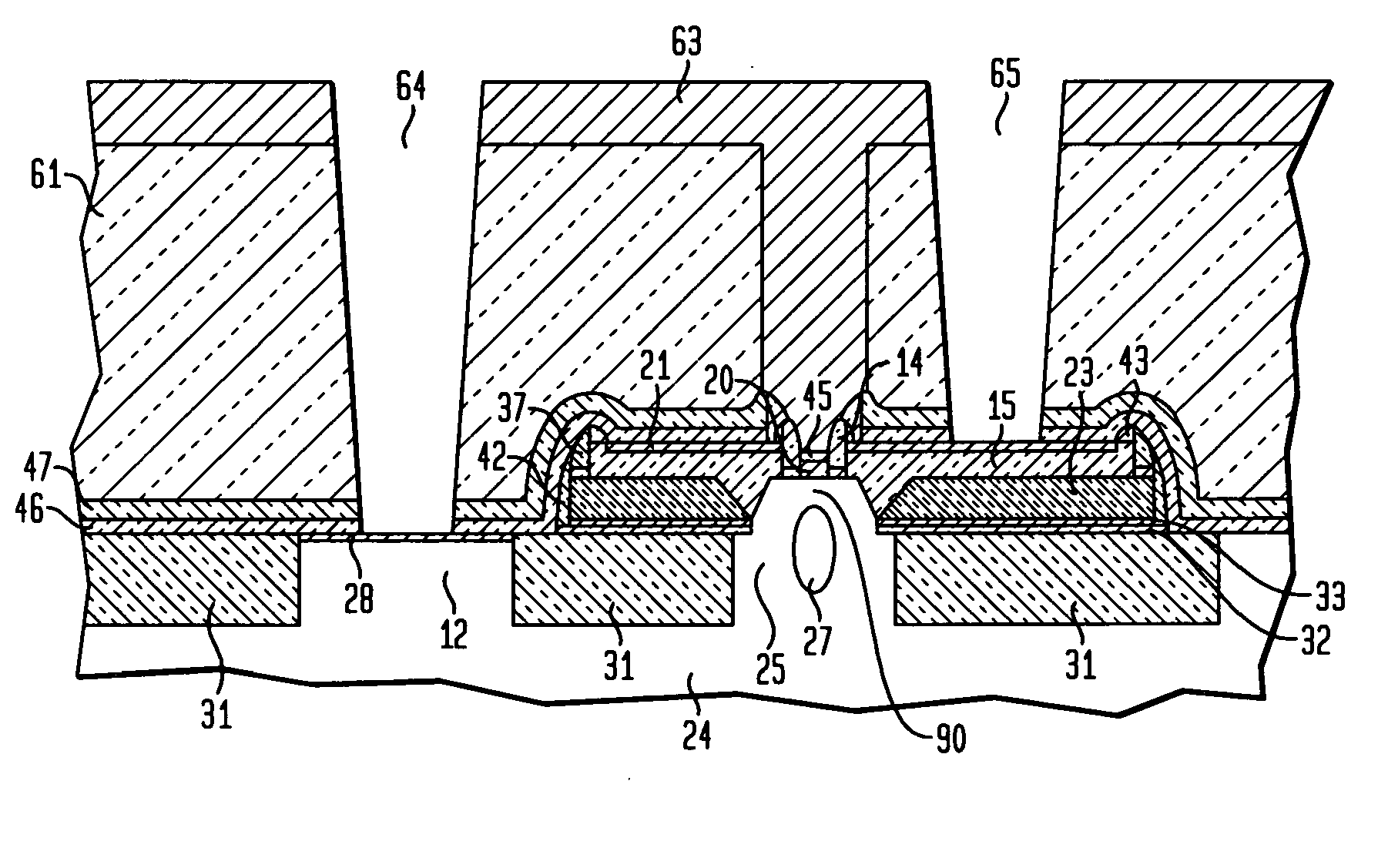

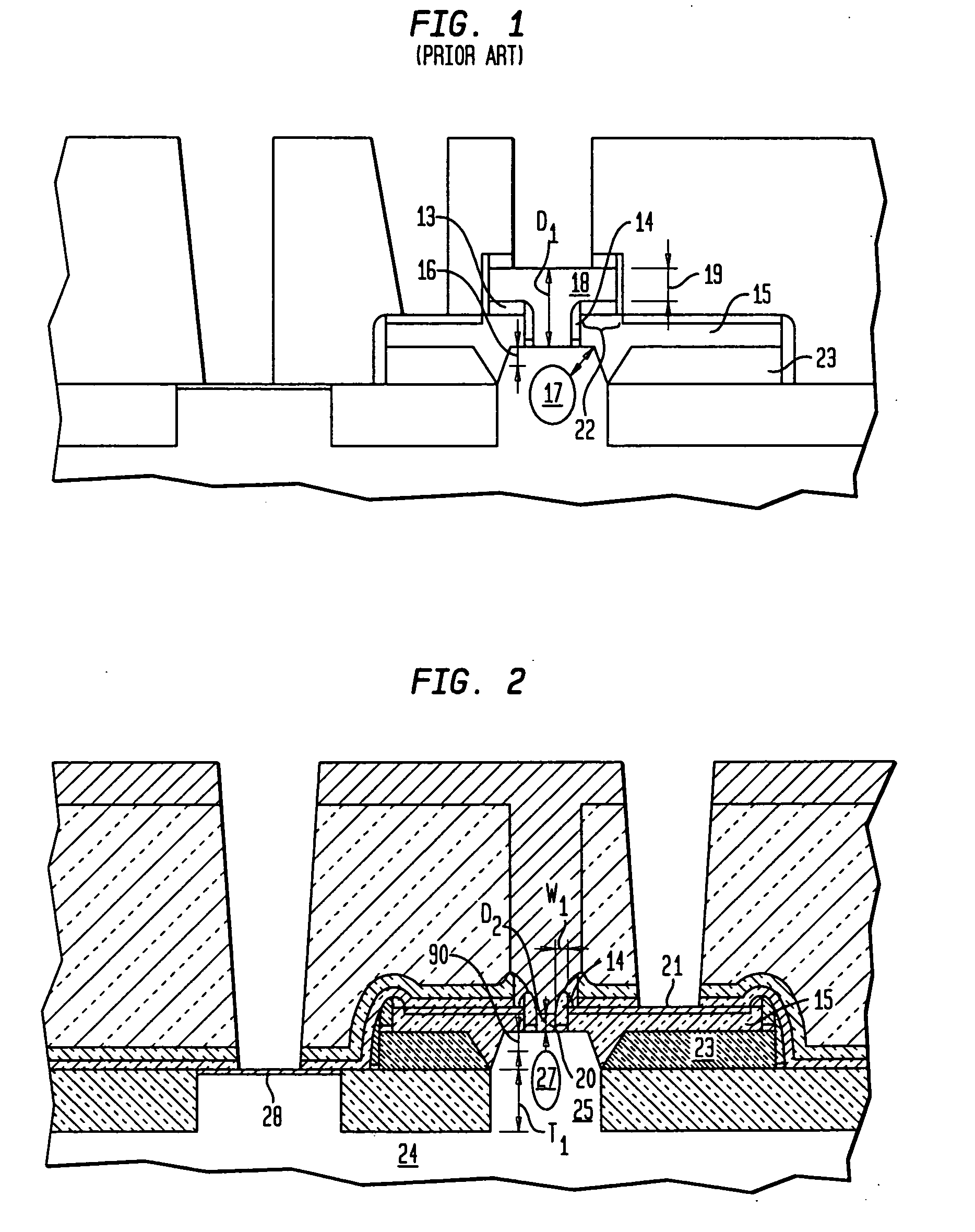

InactiveUS6979884B2Reduce capacitanceReduce resistanceTransistorSemiconductor/solid-state device detailsSalicideEngineering

The present invention provides a bipolar transistor having a raised extrinsic base silicide and an emitter contact border that are self-aligned. The bipolar transistor of the present invention exhibit reduced parasitics as compared with bipolar transistors that do not include a self-aligned silicide and a self-aligned emitter contact border. The present invention also is related to methods of fabricating the inventive bipolar transistor structure. In the methods of the present invention, a block emitter polysilicon region replaces a conventional T-shaped emitter polysilicon.

Owner:INT BUSINESS MASCH CORP

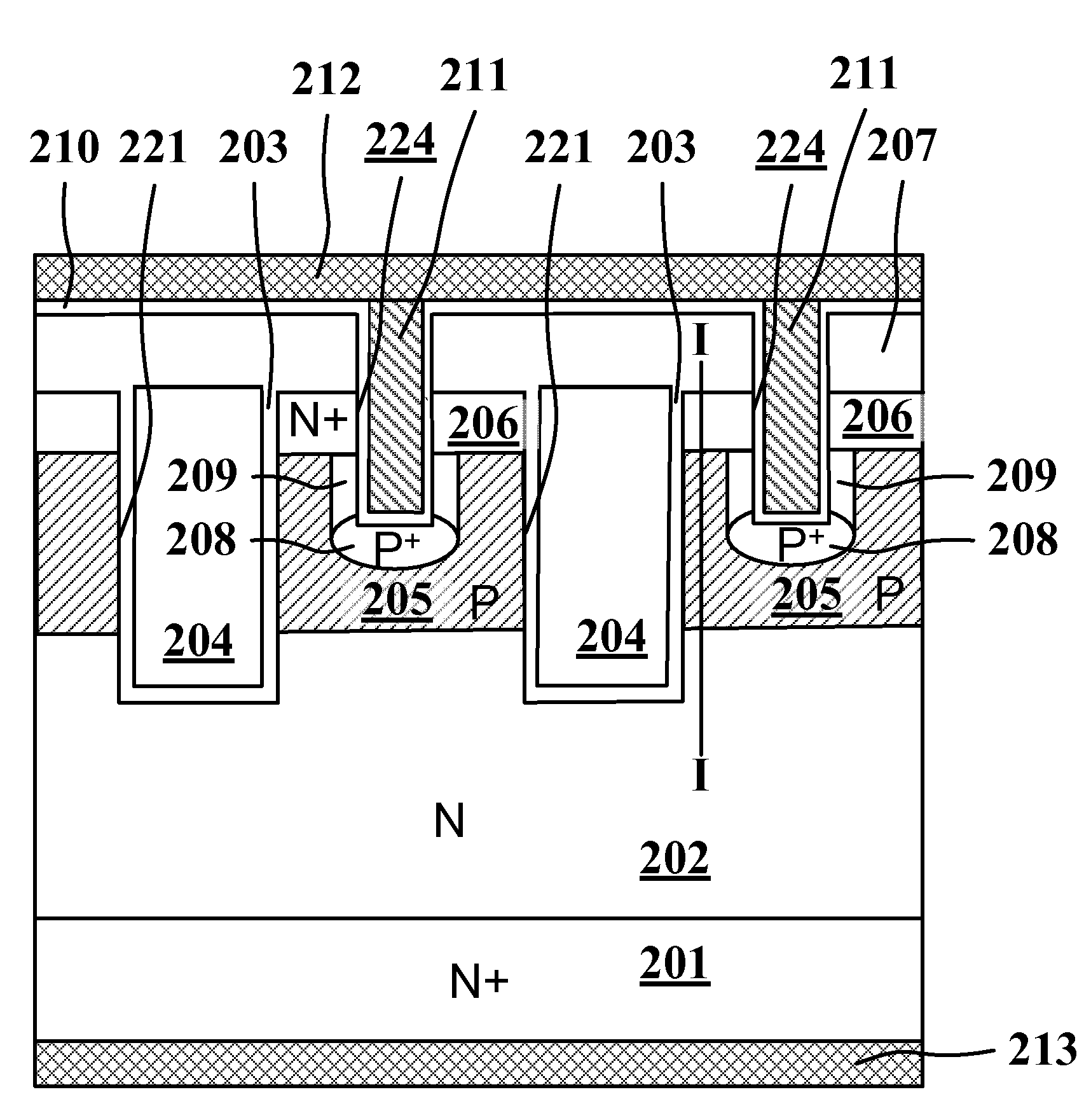

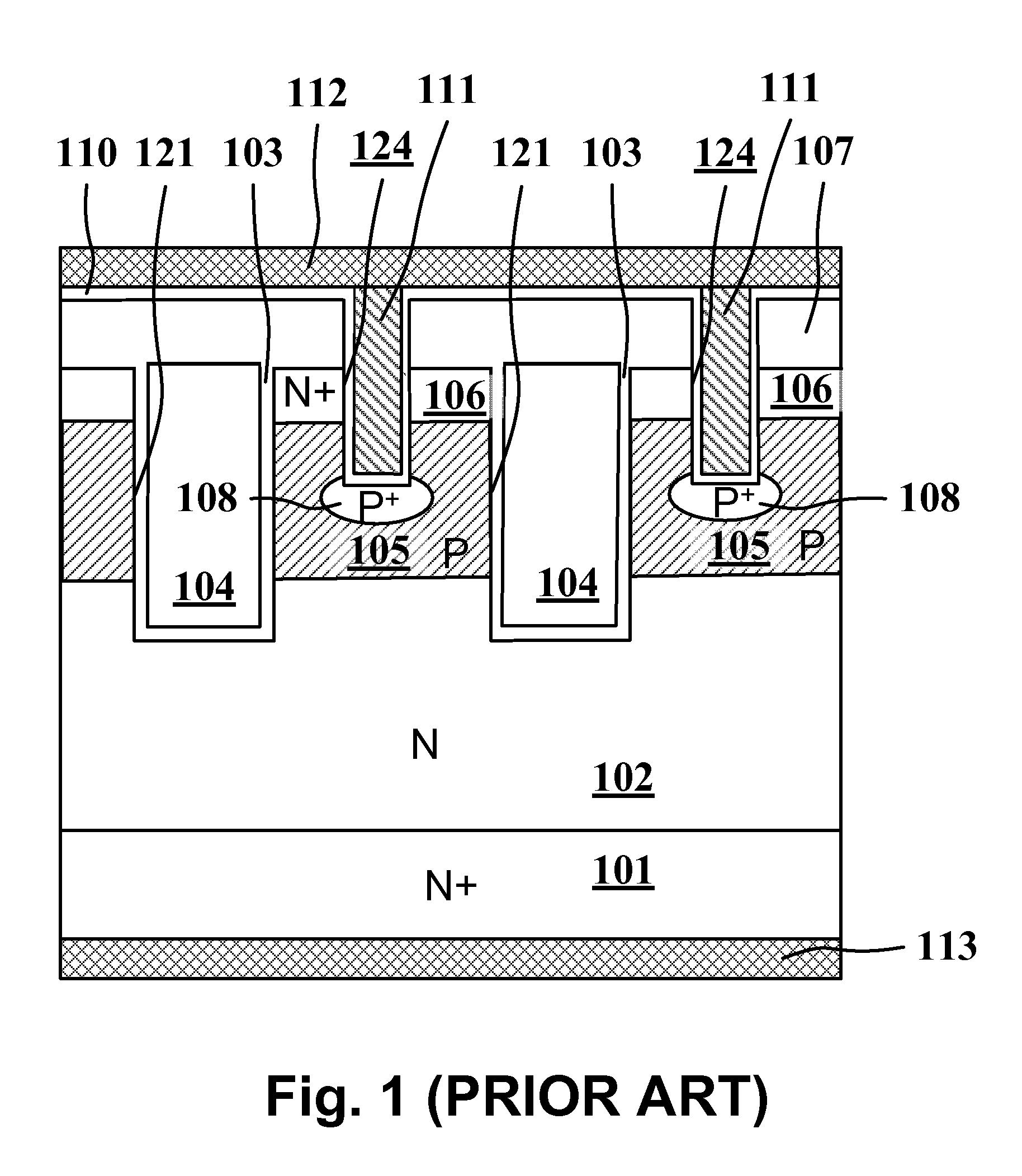

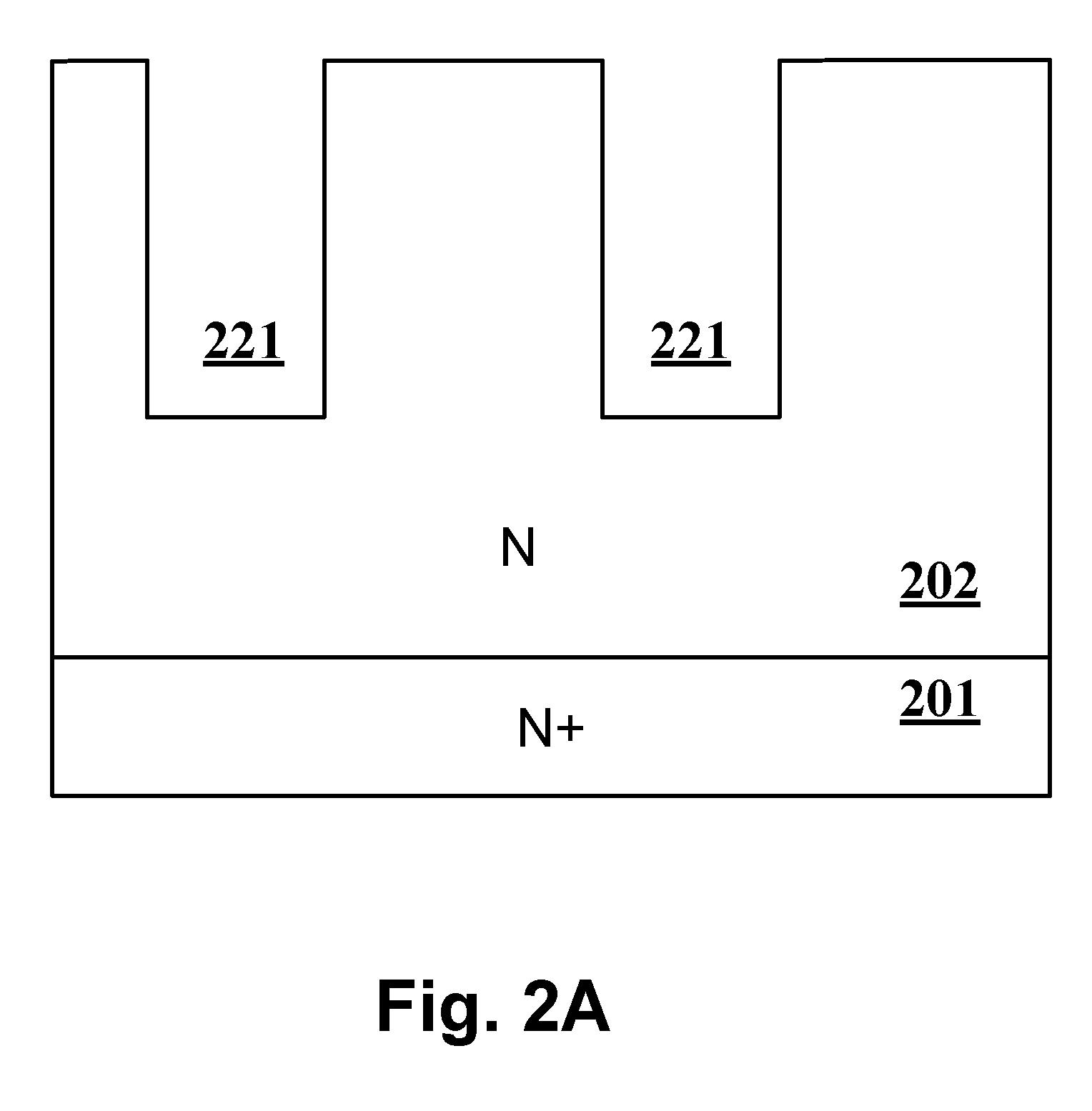

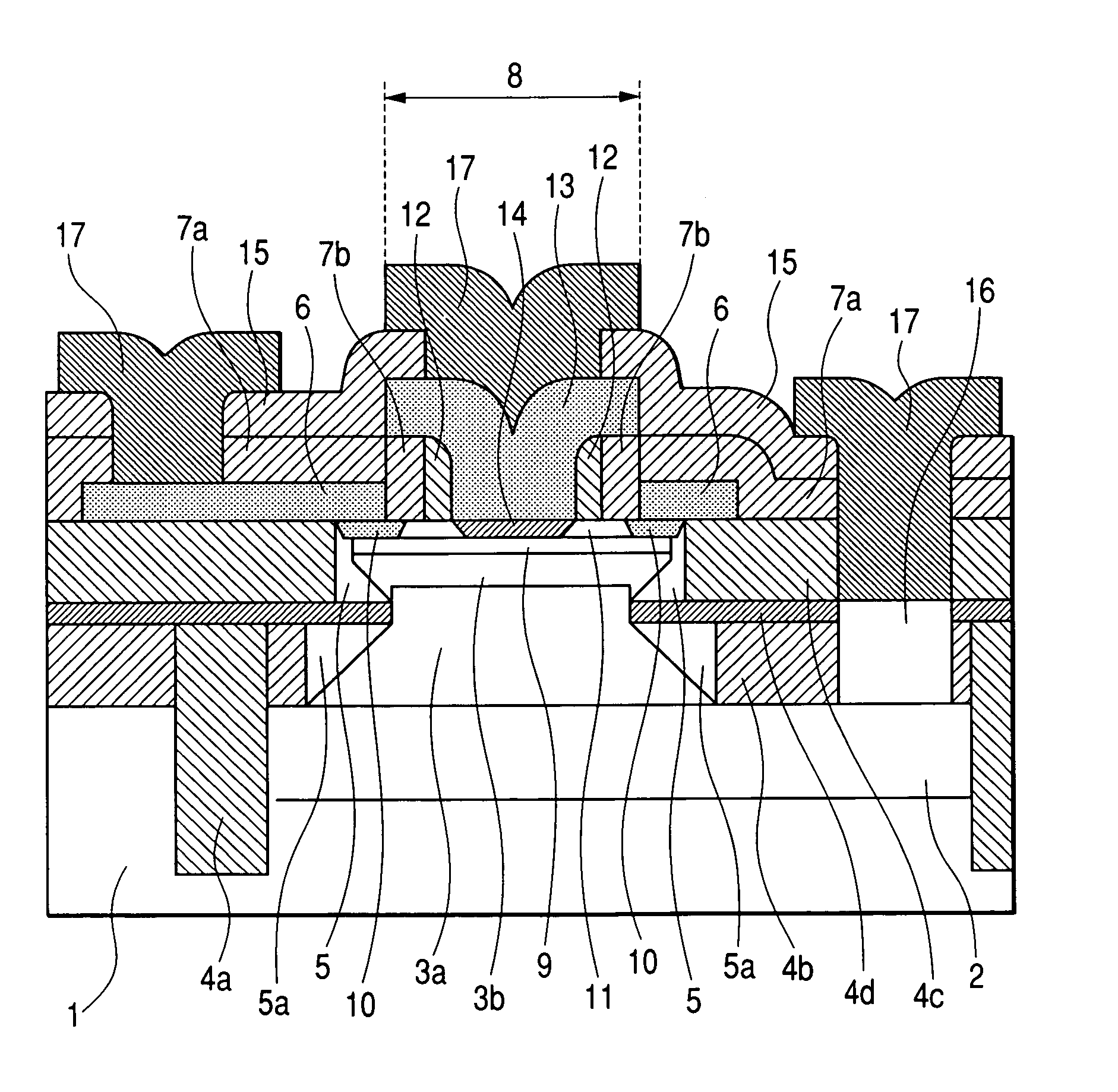

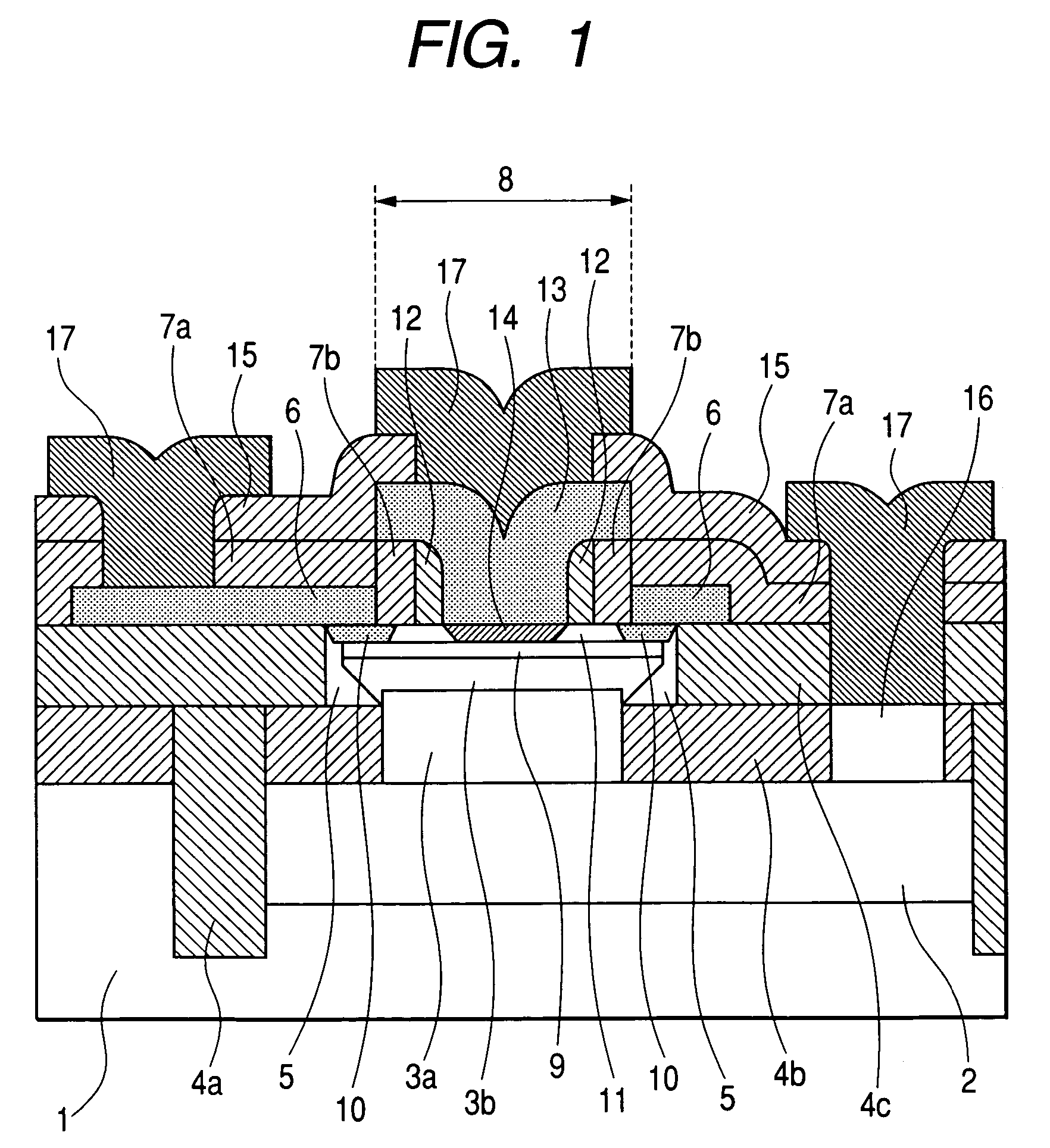

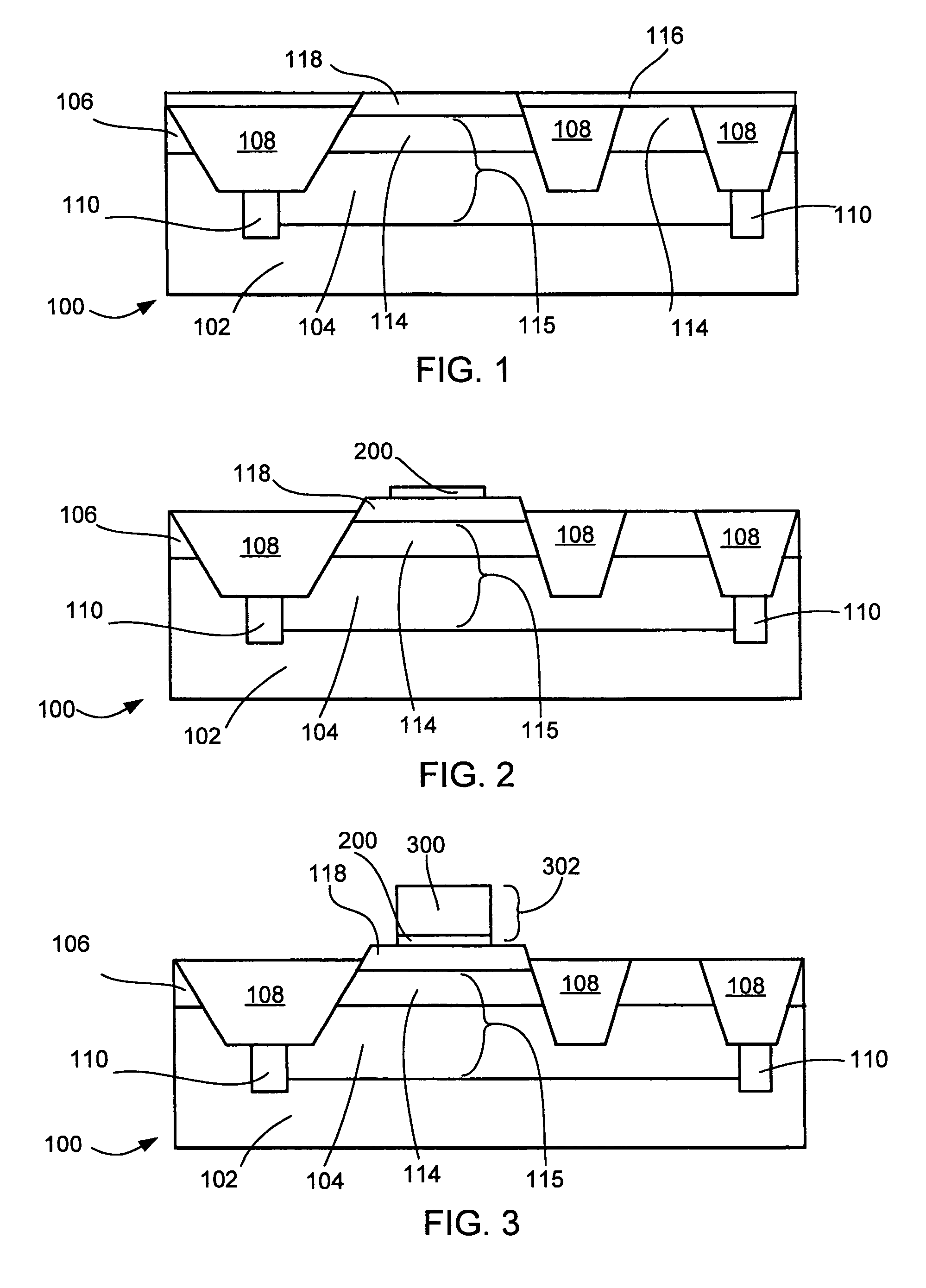

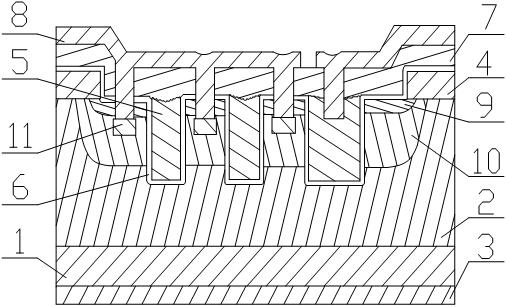

Trenched mosfet with trenched source contact

ActiveUS20090212359A1Base resistanceLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionTrench mosfet

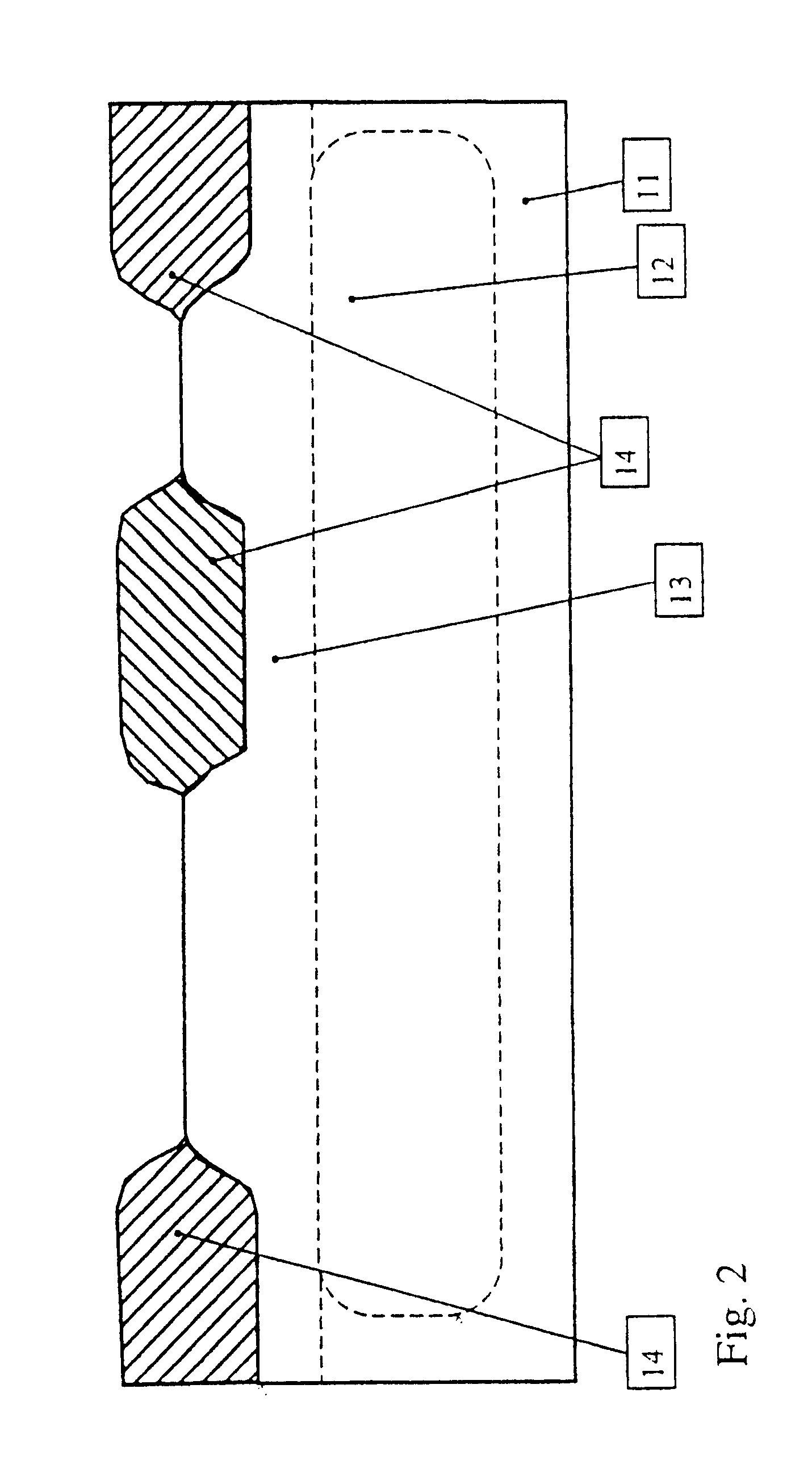

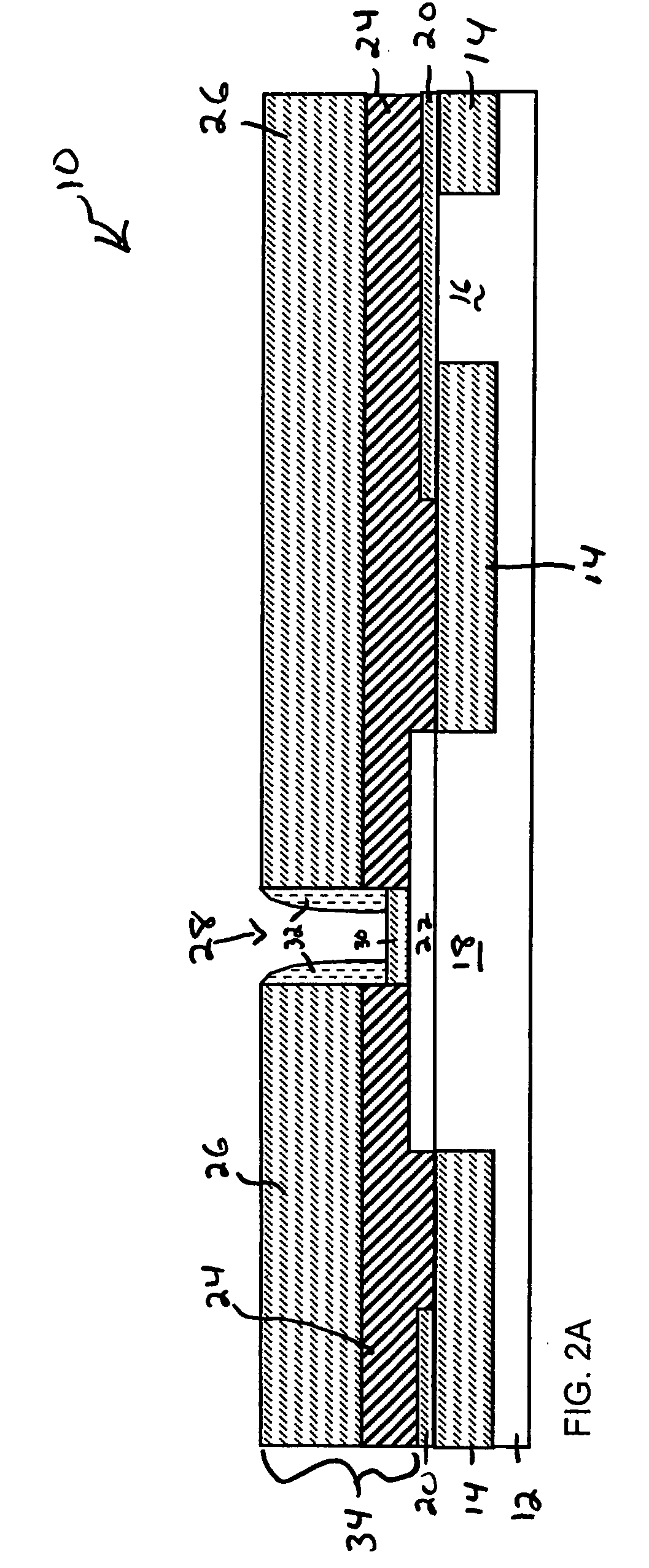

A trenched MOSFET with trenched source contact, comprising: a semiconductor region, further comprising a silicon substrate, a epitaxial layer corresponding to the drain region of the trenched MOSFET, a base layer corresponding to the body region of the trenched MOSFET, and a source layer corresponding to the source region of the trenched MOSFET; an interlayer oxide film formed on the source layer; a front metal layer formed on a upper surface of the semiconductor region; a back metal layer formed on a lower surface of the semiconductor region; a plurality of trenched gates formed to reach the epitaxial layer through the source layer and the base layer, and is covered by the interlayer oxide film; and a plurality of source contact trenches formed to reach the base layer through the interlayer oxide film and the source layer, and is covered by the front metal layer; wherein the silicon substrate, the epitaxial layer, the base layer, and the source layer are stacked in sequence; and each of the source contact trenches has a lateral contact layer at a sidewall thereof.

Owner:FORCE MOS TECH CO LTD

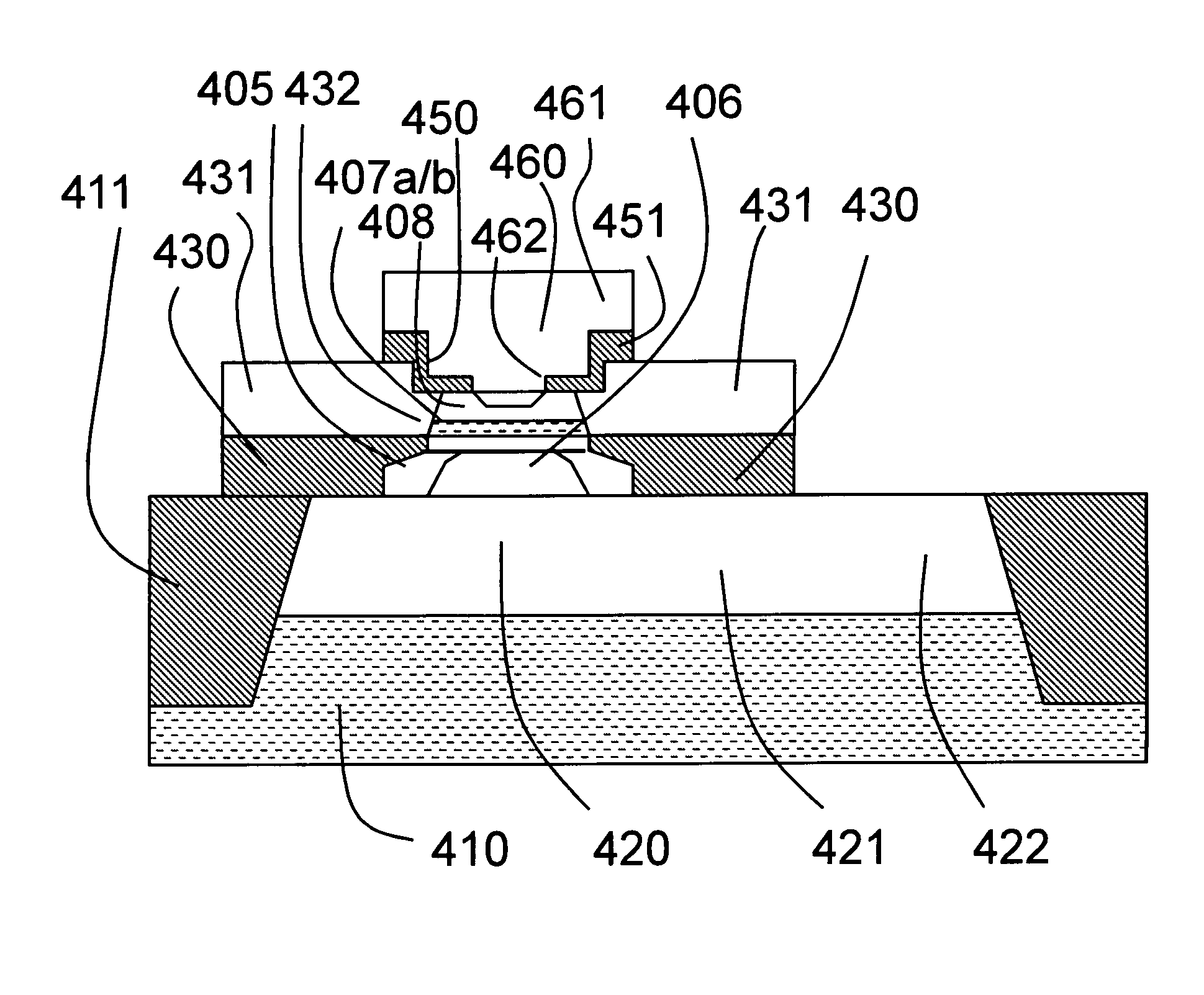

Bipolar transistor and method for producing same

InactiveUS6642553B1Reduced external base resistanceReduce capacitanceTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceSingle process

The invention relates to a bipolar transistor and a method for producing same. The aim of the invention is to provide a bipolar transistor and a method for producing same, which during the use of a single-process poly-silicon technology with differential epitaxis for the production of bases overcomes the disadvantages of conventional systems, so as notably further to improve the high-speed properties of a bipolar transistor, provide the most conductive connections possible between the metal contacts and the active (internal) transistor region as well as a minimized passive transistor surface, while at the same time avoiding greater process complexity and increased contact resistances. To this end a surface relief is produced in the active emitter region by a wet-chemical process. A single-process poly-silicon bipolar transistor having a base produced by epitaxis in accordance with the invention permits a reduction in external base resistance without causing a deterioration in emitter properties. Because the internal and external base regions are deposited continuously no interface problems arise during connection of the base. Base-collector capacity can also be lowered.

Owner:INST FUR HALBLEITERPHYSIK FRFURT ODER

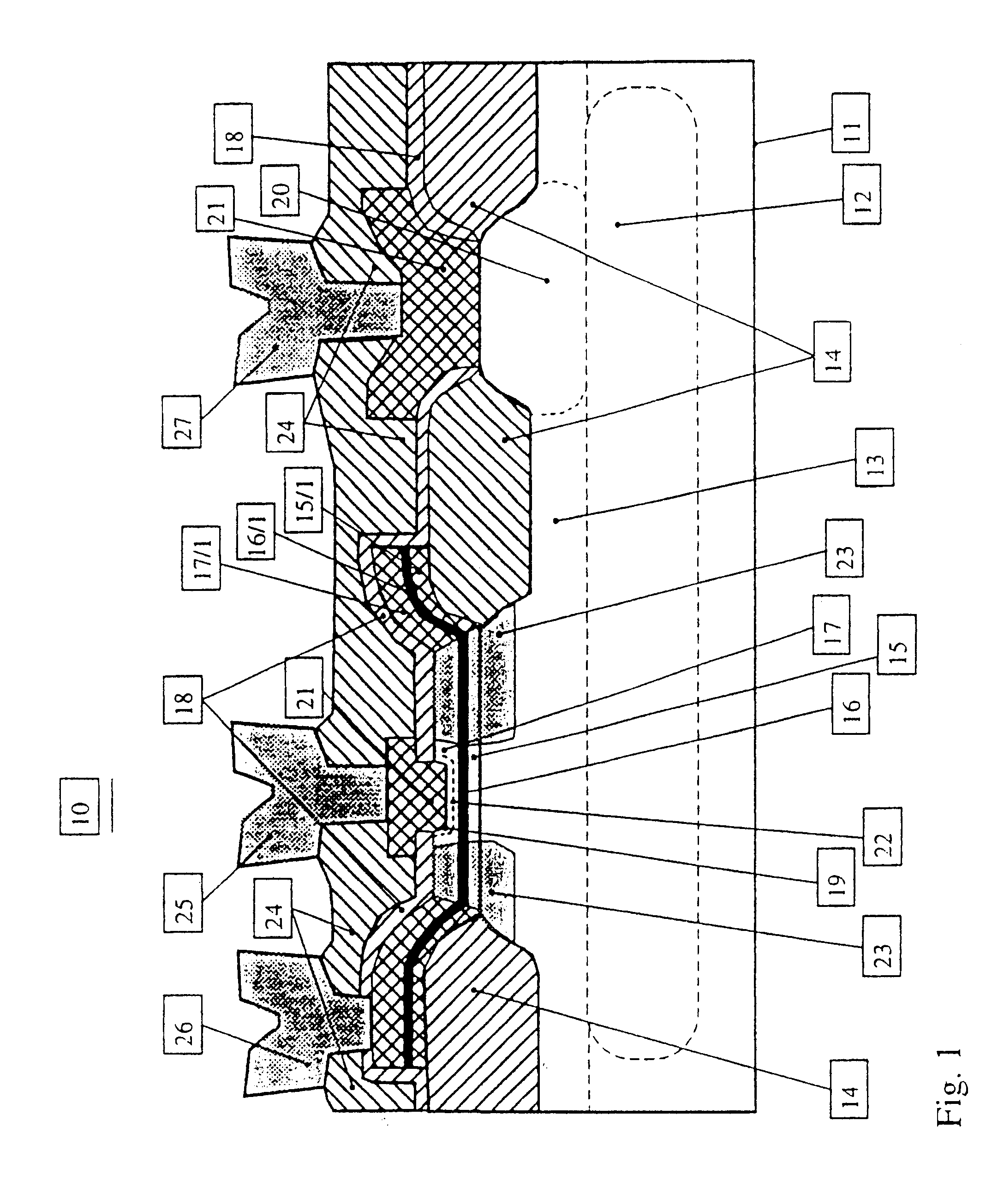

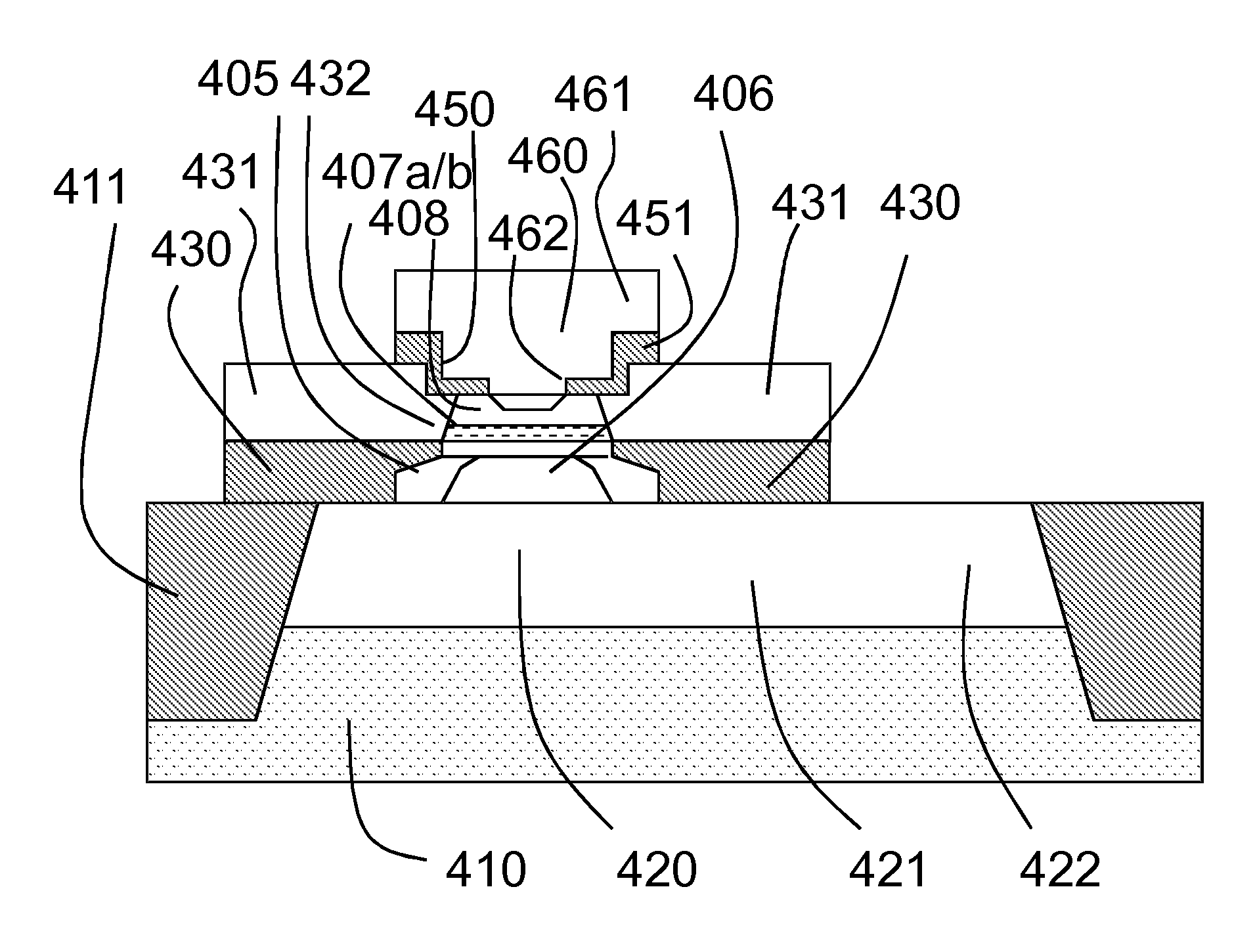

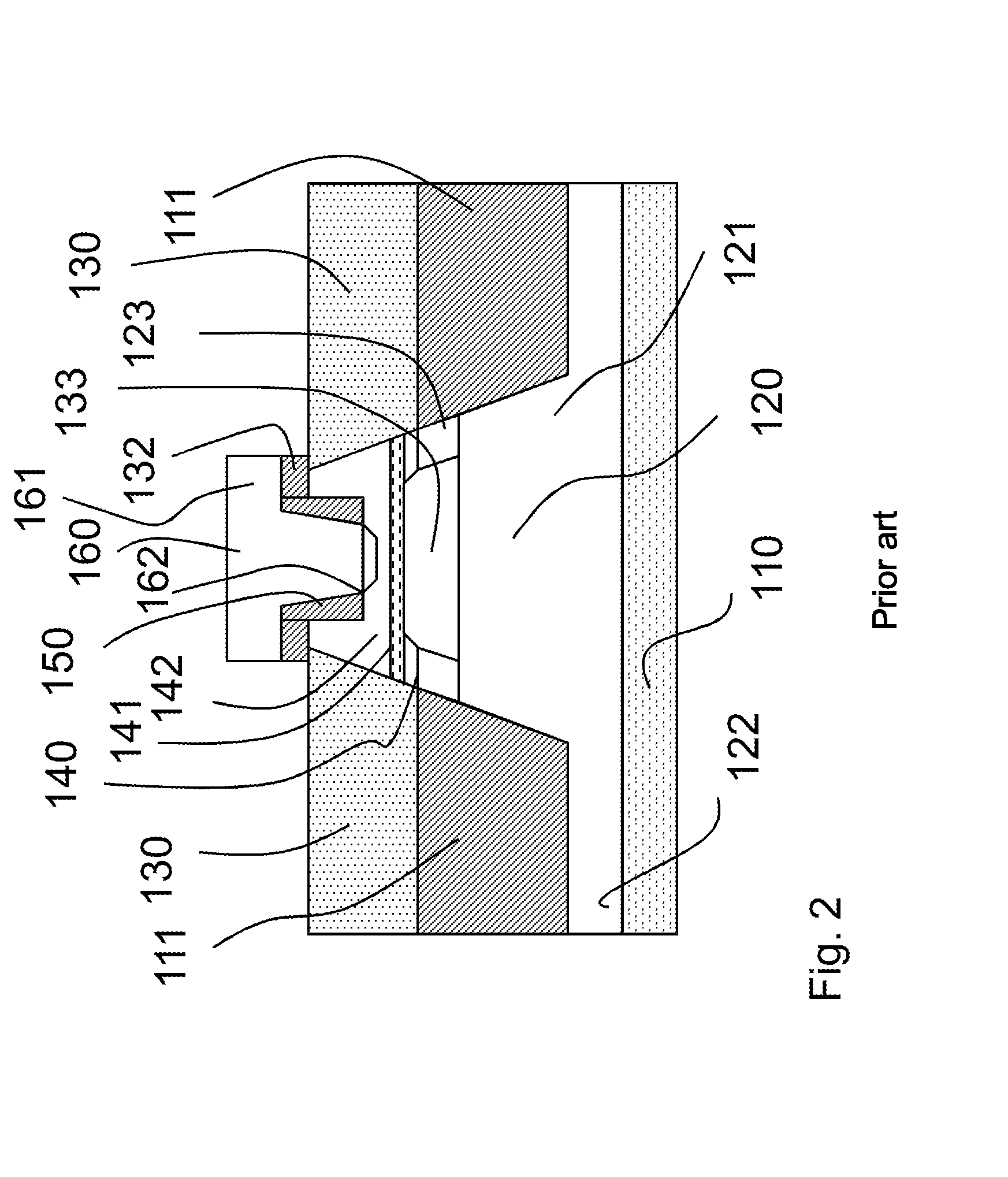

Bipolar transistor having self-adjusted emitter contact

ActiveUS20120001192A1Good high-frequency characteristicReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesChemical compositionSemiconductor materials

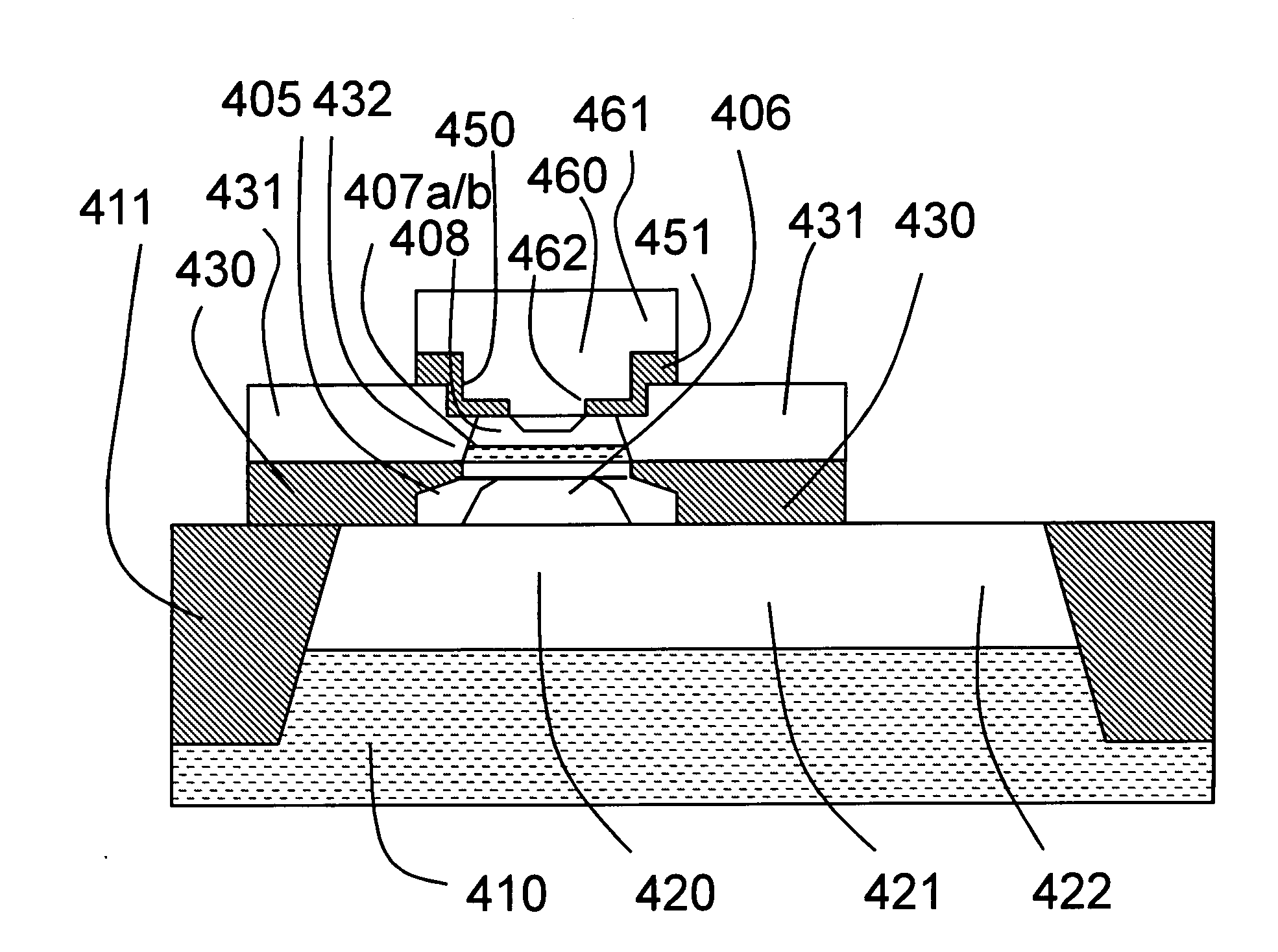

A semiconductor device, comprising a substrate layer made of a semiconductor material of a first conductivity type and having a first insulation region, and a vertical bipolar transistor having a first vertical portion of a collector made of monocrystalline semiconductor material of a second conductivity type and disposed in an opening of the first insulation region, a second insulation region lying partly on the first vertical portion of the collector and partly on the first insulation region and having an opening in the region of the collector, in which opening a second vertical portion of the collector made of monocrystalline material is disposed, said portion including an inner region of the second conductivity type, a base made of monocrystalline semiconductor material of the first conductivity type, a base connection region surrounding the base in the lateral direction, a T-shaped emitter made of semiconductor material of the second conductivity type and overlapping the base connection region, wherein the base connection region, aside from a seeding layer adjacent the substrate or a metallization layer adjacent a base contact, consists of a semiconductor material which differs in its chemical composition from the semiconductor material of the collector, the base and the emitter and in which the majority charge carriers of the first conductivity type have greater mobility compared thereto.

Owner:IHP GMBH INNOVATIONS FOR HIGH PERFORMANCE MICROELECTRONICS LEIBNIZ INST FUR INNOVATIVE

Bipolar transistor having self-aligned silicide and a self-aligned emitter contact border

ActiveUS20050242373A1Reduce capacitanceReduce resistanceSemiconductor/solid-state device detailsSolid-state devicesSalicideEngineering

The present invention provides a bipolar transistor having a raised extrinsic base silicide and an emitter contact border that are self-aligned. The bipolar transistor of the present invention exhibit reduced parasitics as compared with bipolar transistors that do not include a self-aligned silicide and a self-aligned emitter contact border. The present invention also is related to methods of fabricating the inventive bipolar transistor structure. In the methods of the present invention, a block emitter polysilicon region replaces a conventional T-shaped emitter polysilicon.

Owner:IBM CORP

Method for fabricating a bipolar transistor having self-aligned emitter contact

ActiveUS20150140771A1Good high-frequency characteristicReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesChemical compositionSemiconductor materials

A method of producing a semiconductor device, comprising a substrate layer made of a semiconductor material of a first conductivity type and having a first insulation region, and a vertical bipolar transistor having a first vertical portion of a collector made of monocrystalline semiconductor material of a second conductivity type and disposed in an opening of the first insulation region, a second insulation region lying partly on the first vertical portion of the collector and partly on the first insulation region and having an opening in the region of the collector, in which opening a second vertical portion of the collector made of monocrystalline material is disposed, the portion including an inner region of the second conductivity type, a base made of monocrystalline semiconductor material of the first conductivity type, a base connection region surrounding the base in the lateral direction, a T-shaped emitter made of semiconductor material of the second conductivity type and overlapping the base connection region, wherein the base connection region, aside from a seeding layer adjacent the substrate or a metallization layer adjacent a base contact, consists of a semiconductor material which differs in its chemical composition from the semiconductor material of the collector, the base and the emitter and in which the majority charge carriers of the first conductivity type have greater mobility compared thereto.

Owner:IHP GMBH INNOVATIONS FOR HIGH PERFORMANCE MICROELECTRONICS LEIBNIZ INST FUR INNOVATIVE

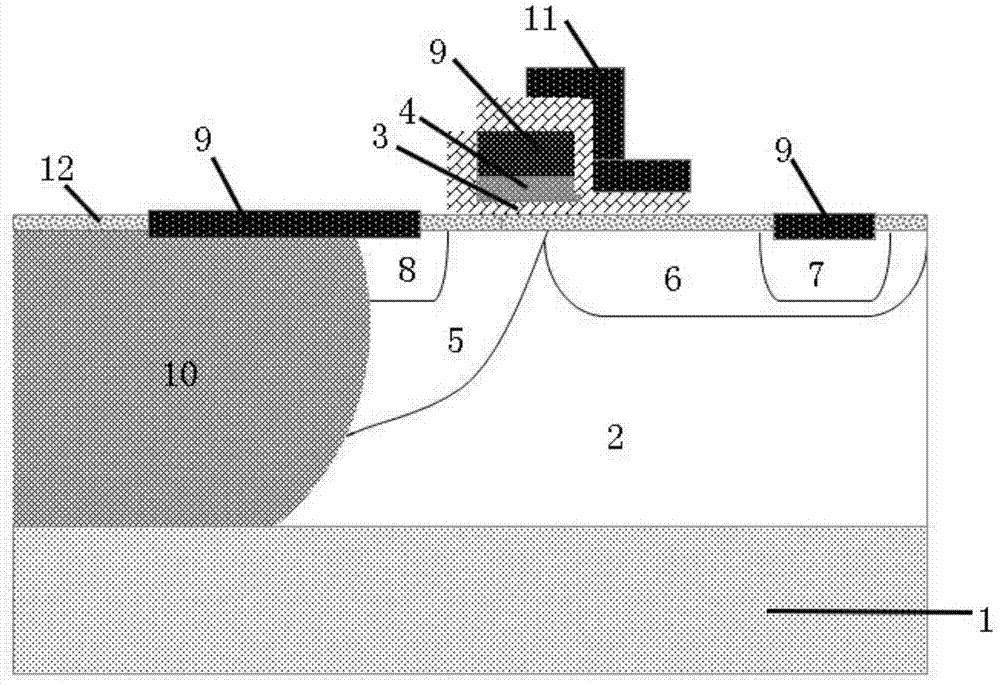

crosswise double diffusion MOFET and manufacturing method thereof

ActiveCN102738215ALower base resistanceImprove stabilityTransistorSemiconductor/solid-state device manufacturingDouble diffusionBody area

The invention provides a crosswise DMOS with cupped source electrode contact and a method for forming the crosswise DMOS. The crosswise DMOS comprises a cupped source electrode contact, wherein the cupped source electrode contact comprises a cupped part which longitudinally extends and penetrates the source area of the crosswise DMOS and contacts the body area,and the cupped part is electrically coupled with the source area and the body area. The crosswise DMOS not only has smaller size, but also is low in production cost.

Owner:CHENGDU MONOLITHIC POWER SYST

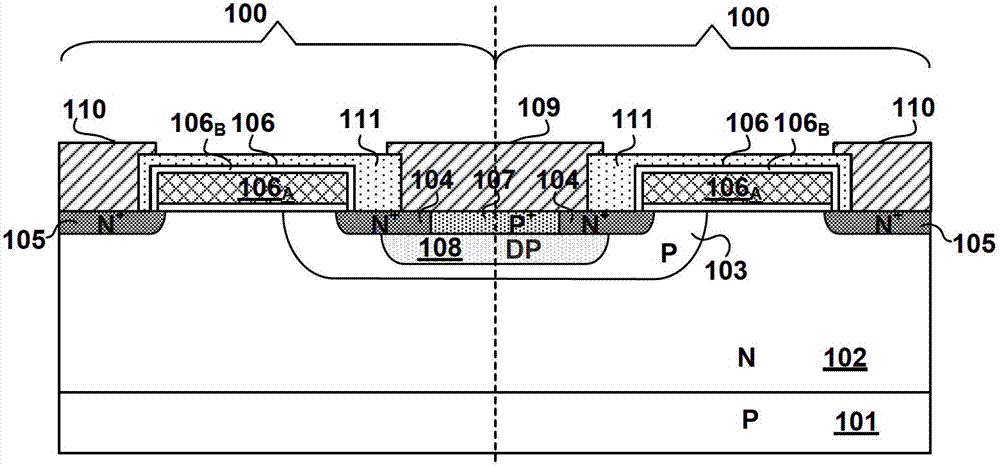

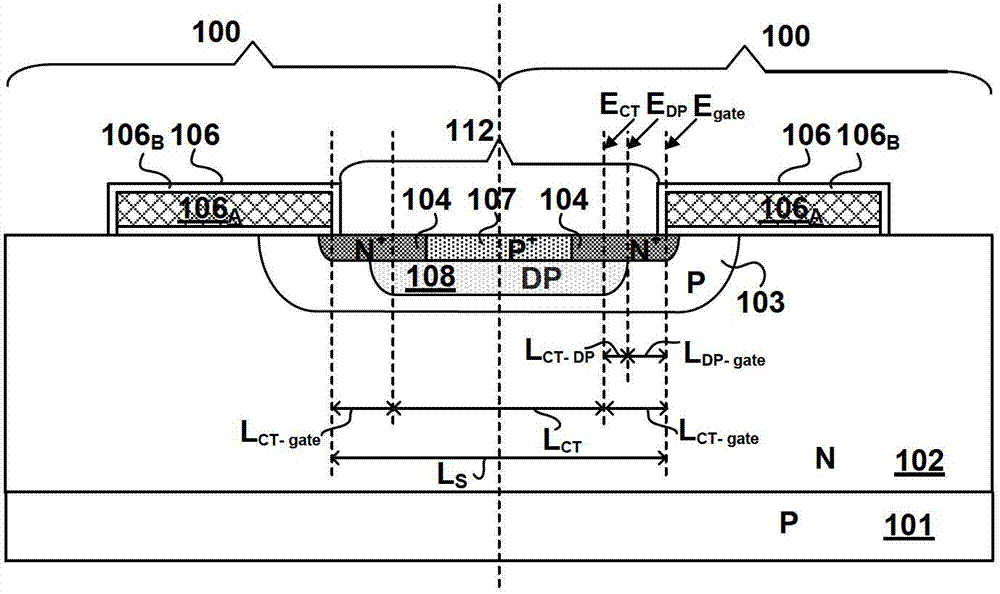

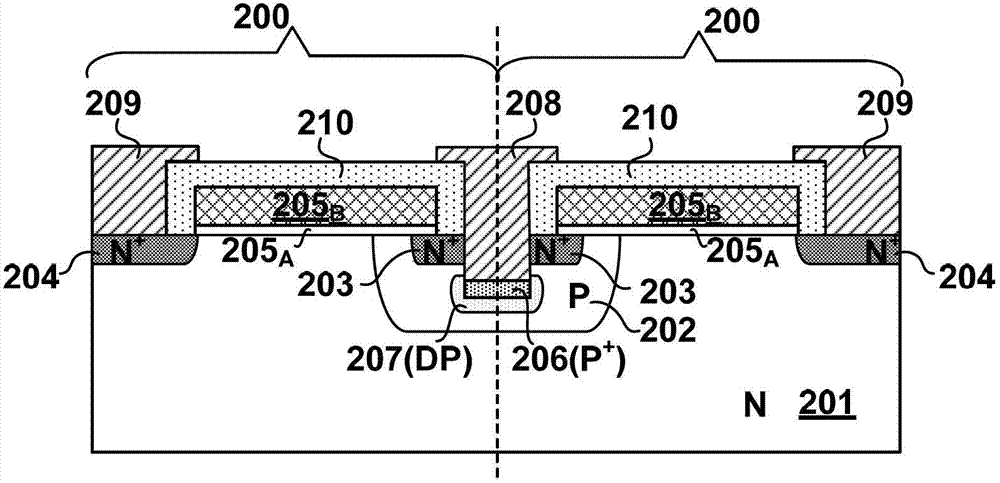

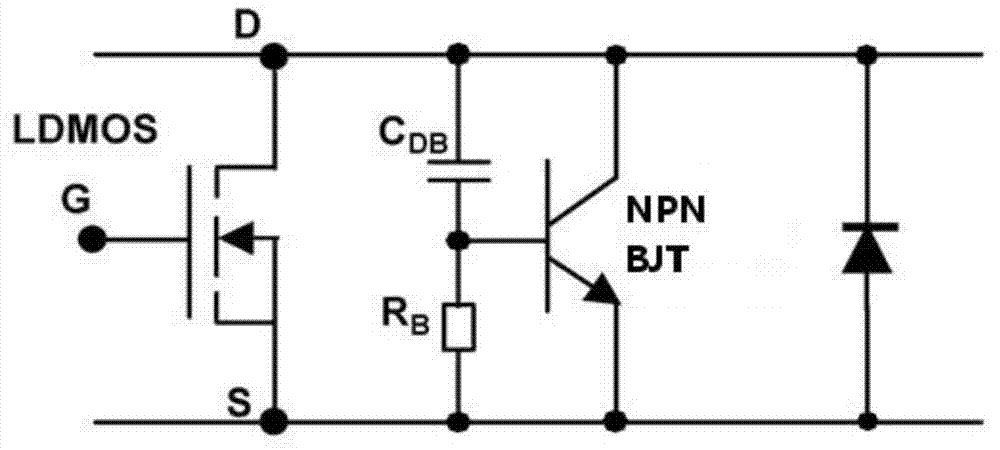

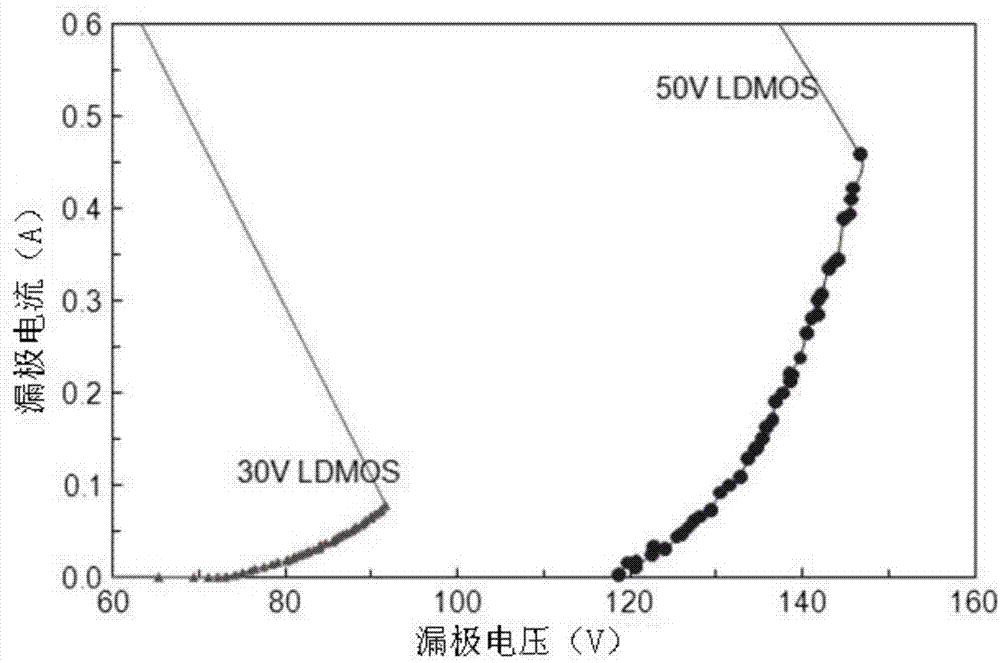

Radio frequency (RF) laterally diffused metal oxide semiconductor (LDMOS) component and manufacture method

ActiveCN103035727AImprove transconductanceLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesRadio frequencyTransconductance

The invention discloses a radio frequency (RF) laterally diffused metal oxide semiconductor (LDMOS) component. A light dope P type buried layer and a middle dope buried layer in the light dope P type buried layer are additionally arranged under a P type channel region. The base electrode resistance of a parasitic non-protein nitrogen (NPN) pipe can be reduced, so that snapback effect is not prone to be generated. A reversed diode formed by a source electrode, the channel and the buried layer can strangulate drain-source voltage of an LDMOS and can sink extra current on a substrate. Thick gate oxide at the drain electrode end can reduce hot carrier effect, and thin gate oxide at the source electrode end can improve transconductance of the component. The invention further discloses a manufacture method of the RF LDMOS component. In process realization, the manufacture method only adds two photoetching steps in an existing process so as to be easy to implement.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Transistor structure with minimized parasitics and method of fabricating the same

InactiveUS20050191911A1Reduce parasitic effectsImprove performanceTransistorThyristorIntrinsicsWindow opening

A transistor having minimized parasitics is provided including an emitter having a recessed extrinsic emitter portion atop an intrinsic emitter portion; a base including an intrinsic base portion in electrical contact with the intrinsic emitter portion and an extrinsic base portion in electrical contact with the intrinsic base portion and electrically isolated from the recessed extrinsic emitter portion by a set of emitter / base spacers; and a collector in electrical contact with the intrinsic base portion. The transistor may further include extrinsic base having top surfaces entirely silicided to the emitter / base spacer. Additionally, the transistor may include a base window opening within the transistor's active area. Methods of forming the above-described transistor are also provided.

Owner:GLOBALFOUNDRIES INC

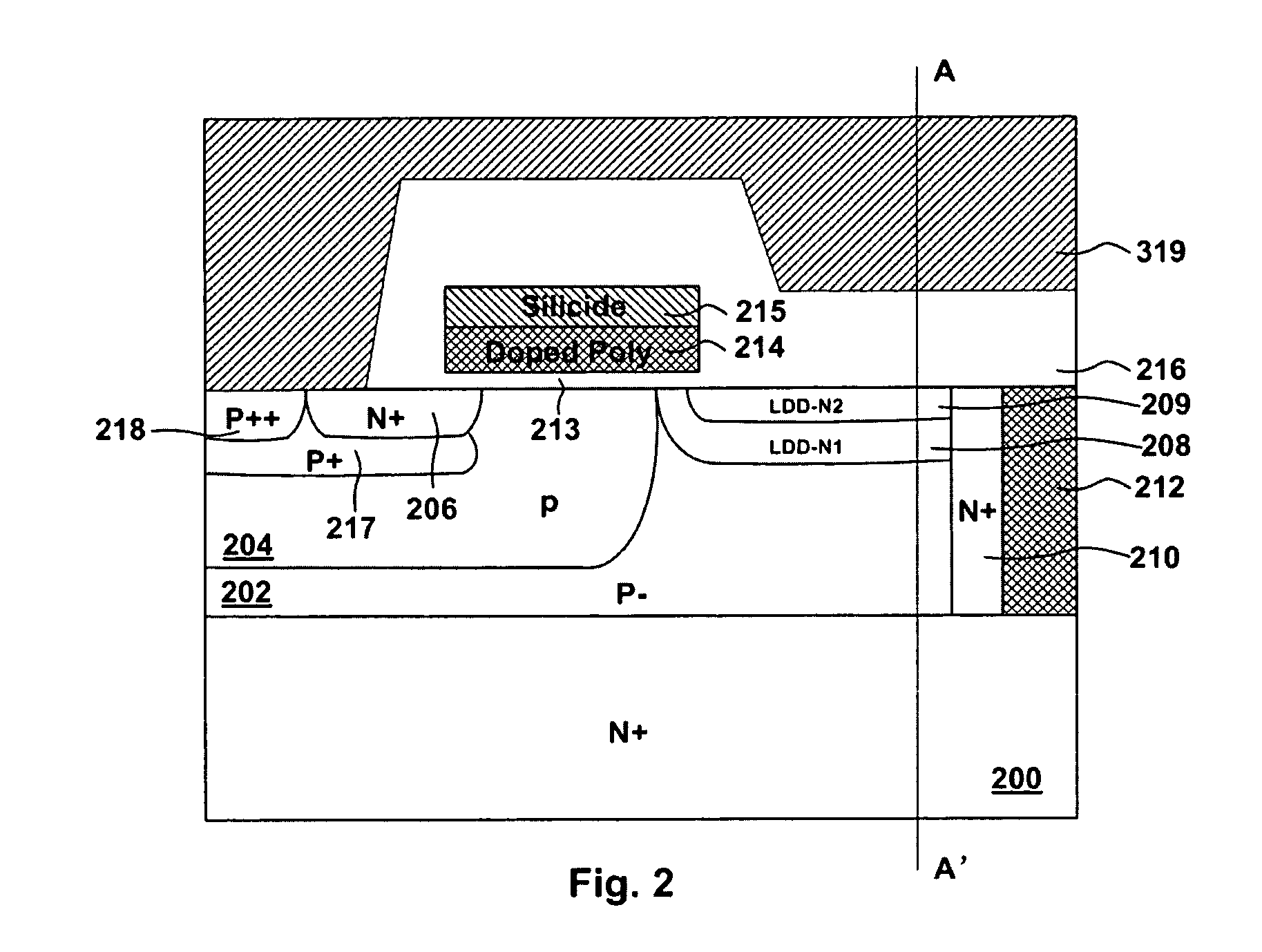

LDMOS with double LDD and trenched drain

InactiveUS20100237411A1Reduce contact resistanceReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSHigh energy

A LDMOS with double LDD and trenched drain is disclosed. According to some preferred embodiment of the present invention, the structure contains a double LDD region, including a high energy implantation to form lightly doped region and a low energy implantation thereon to provide a low resistance path for current flow without degrading breakdown voltage. At the same time, a P+ junction made by source mask is provided underneath source region to avoid latch-up effect from happening.

Owner:FORCE MOS TECH CO LTD

Semiconductor device and manufacturing method for the same

InactiveUS7071500B2Low consumption powerHigh speedSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A bipolar semiconductor device including a collector layer covered at a portion of an outer periphery thereof with an insulating film and having a shape extending in an upper direction and a horizontal direction, with a gap being formed between the collector layer and the insulating film, and further including a base layer and an emitter layer disposed over the collector layer, and a manufacturing method of the semiconductor device. Since the collector layer has a shape extending in a portion thereof in the upward direction and the horizontal direction, an external collector region can be deleted, and both the parasitic capacitance and the collector capacitance in the intrinsic portion attributable to the collector can be decreased and, accordingly, a bipolar transistor capable of high speed operation at a reduced consumption power can be constituted.

Owner:RENESAS ELECTRONICS CORP

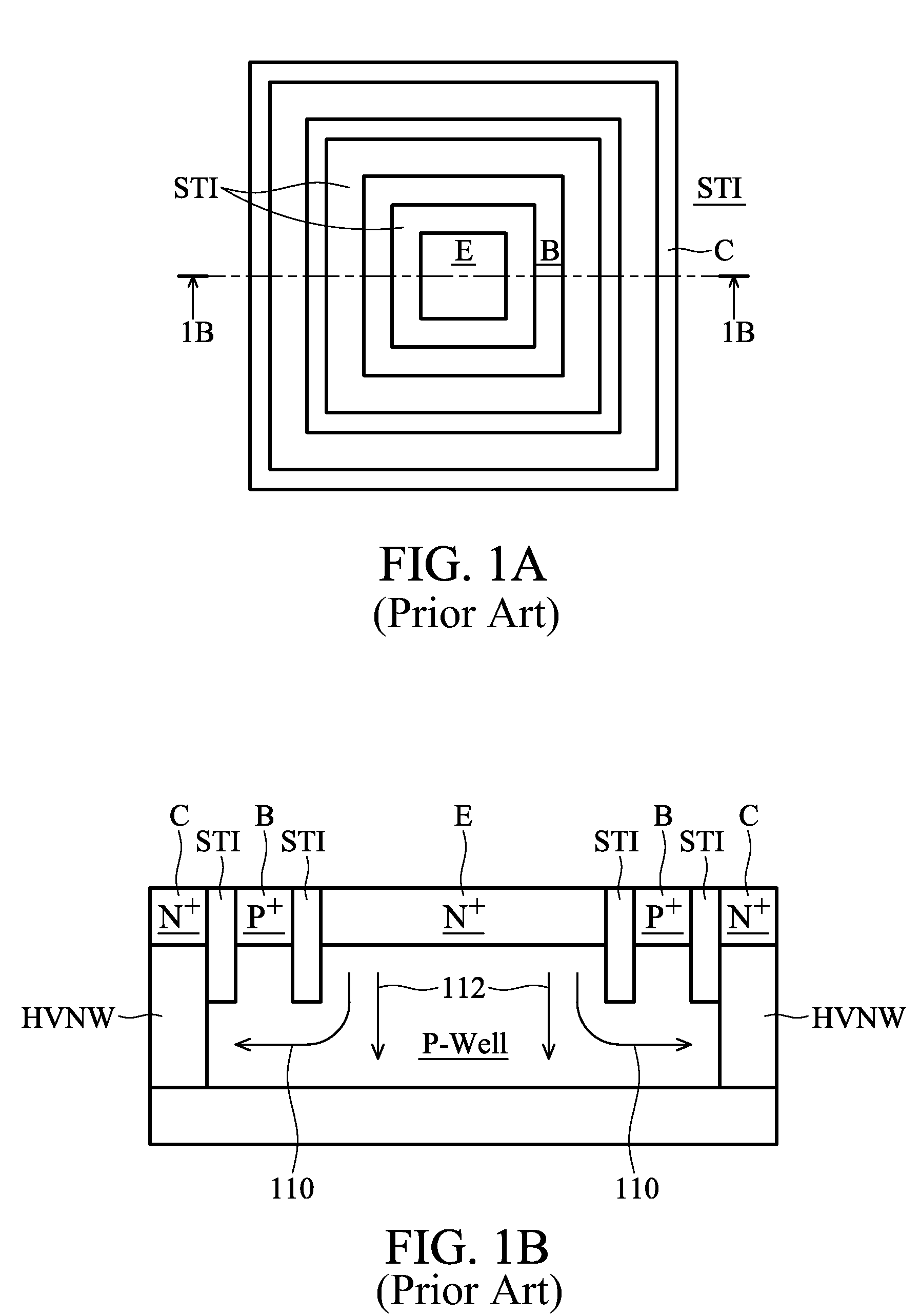

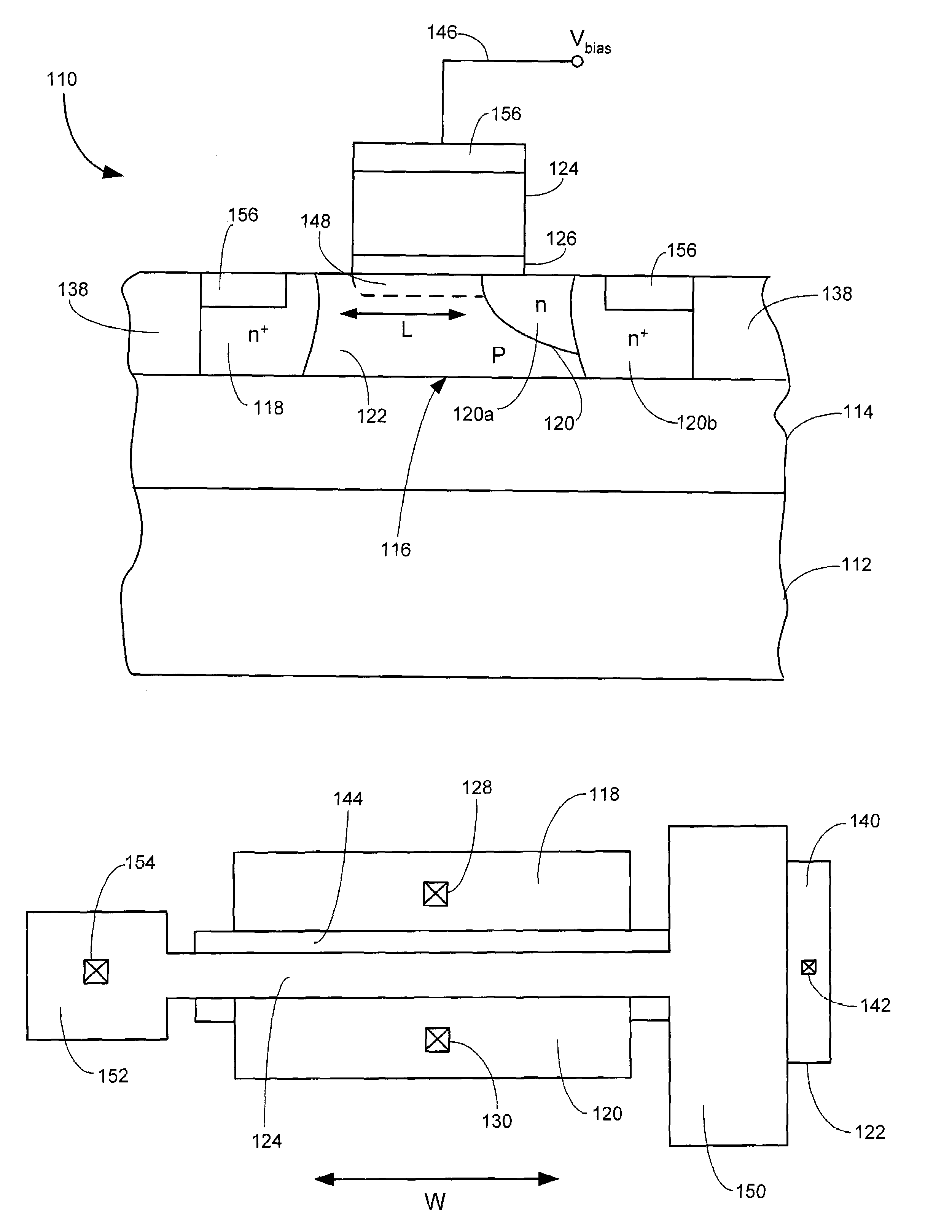

High performance lateral bipolar transistor

InactiveUS7173320B1Reduce contact resistanceLower base resistanceTransistorGalvano-magnetic devicesLow resistanceTransistor

A lateral bipolar transistor includes an emitter region, a base region, a collector region, and a gate disposed over the base region. A bias line is connected to the gate for applying a bias voltage thereto during operation of the transistor. The polarity of the bias voltage is such as to create an accumulation layer in the base under the gate. The accumulation layer provides a low-resistance path for the transistor base current, thus reducing the base resistance of the transistor.

Owner:ALTERA CORP

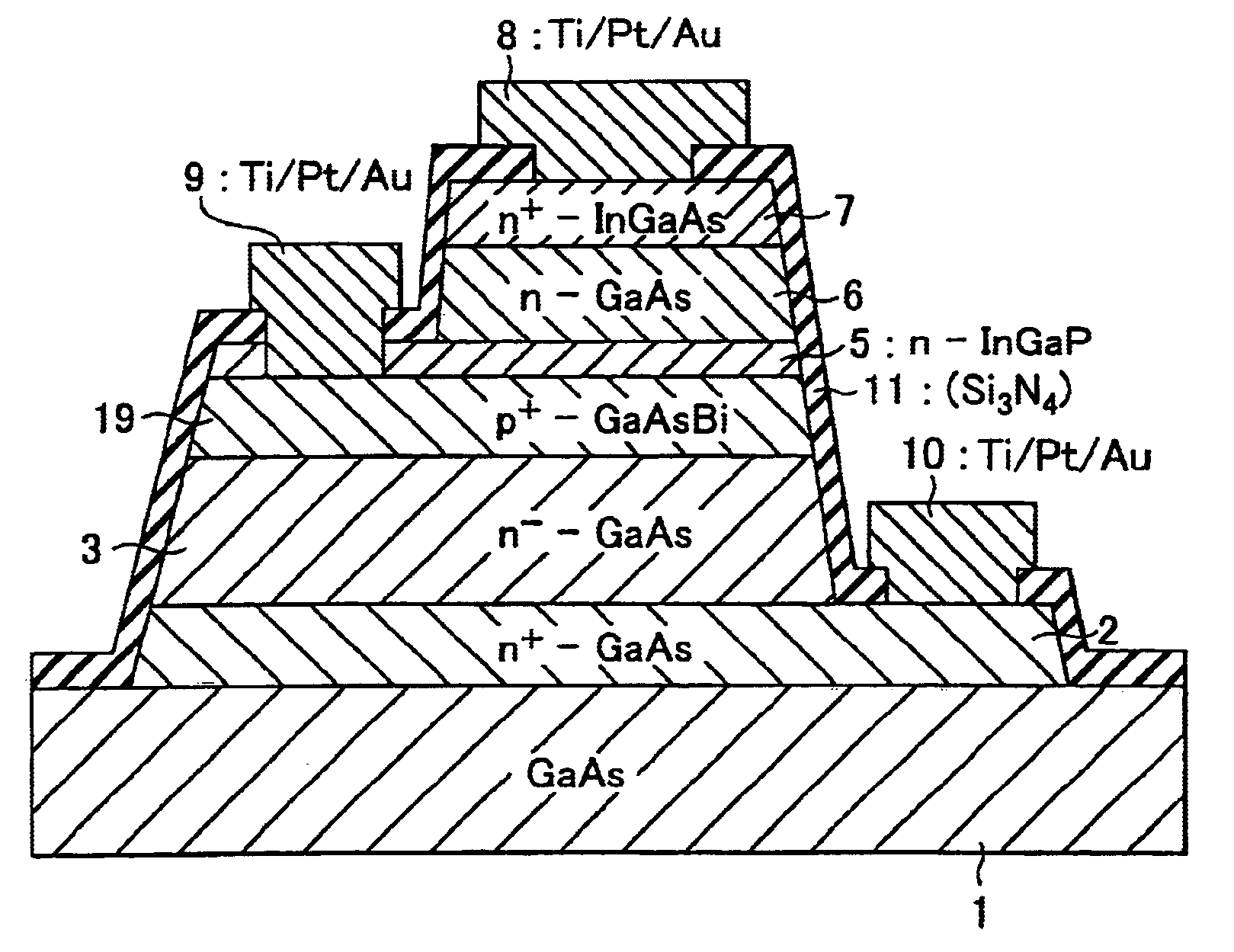

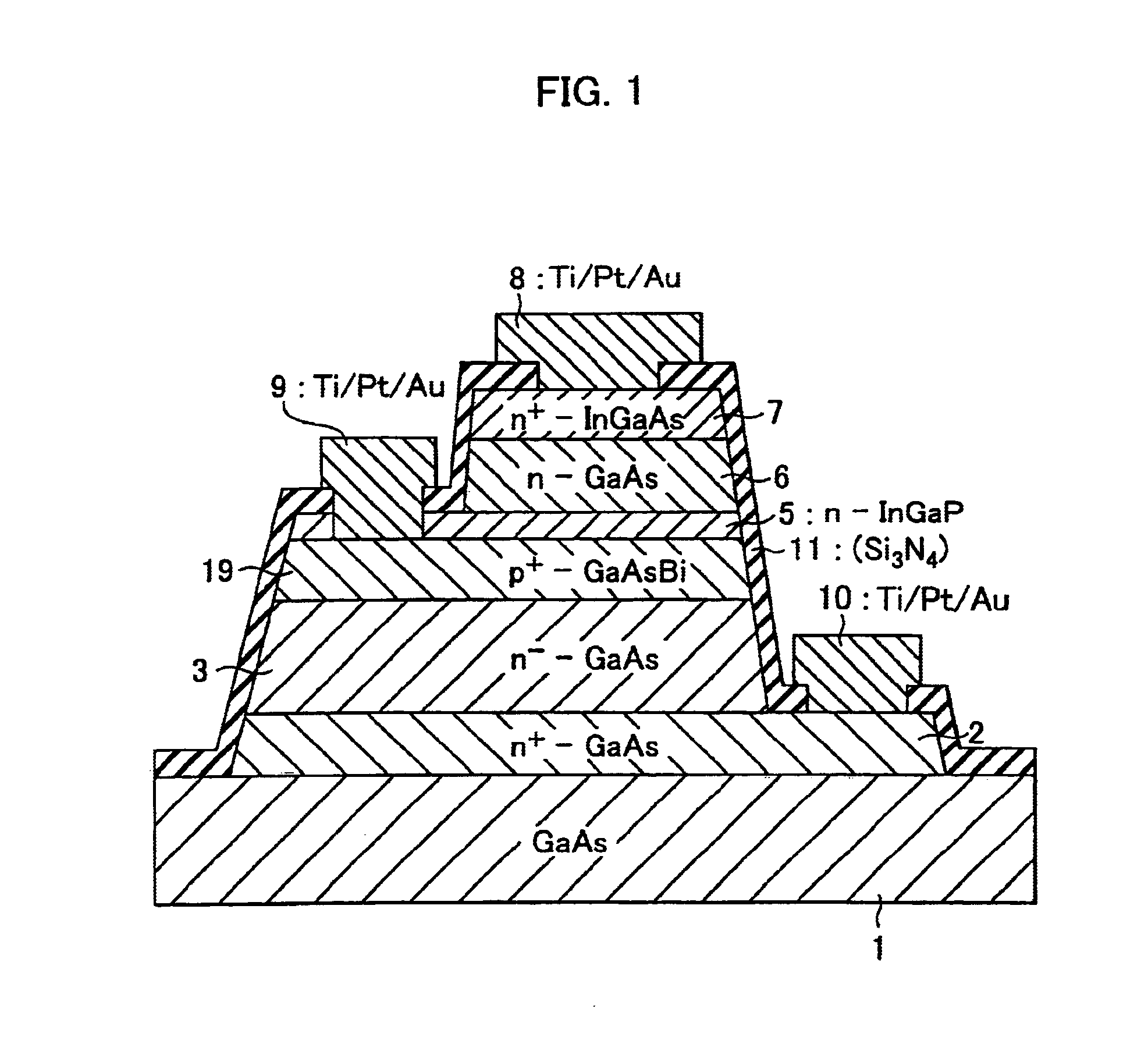

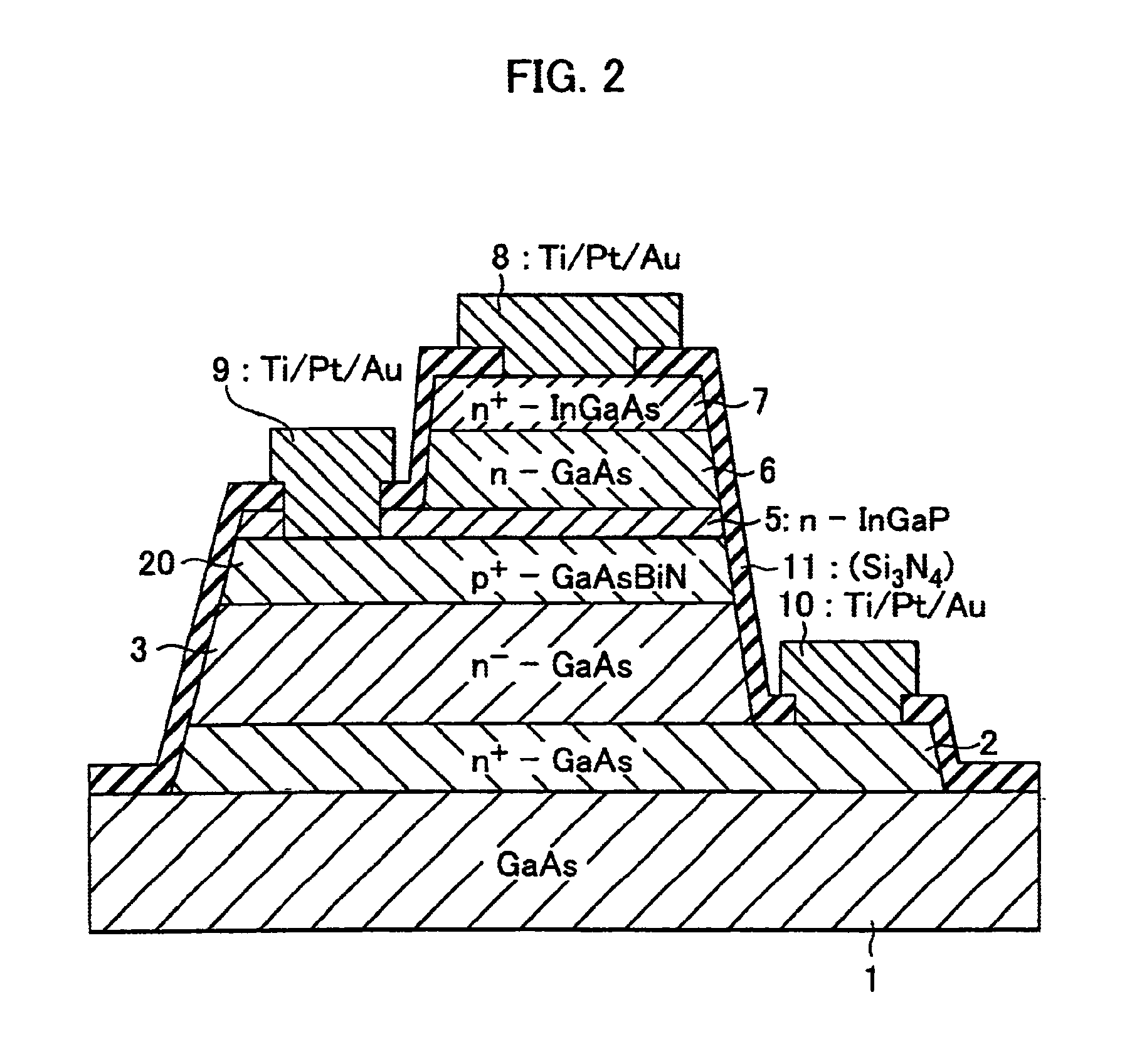

Heterojunction bipolar transistor with a base layer that contains bismuth

InactiveUS6936871B2Improve basic performanceImproved PA characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalAtomic physics

A heterojunction bipolar transistor (HBT) with improved characteristics is provided. A III-V compound semiconductor having Bi added thereto is used for a base layer of a GaAs-based or InP-based HBT. For example, a GaAs-based HBT is formed by successively stacking a subcollector layer made of n+-GaAs, a collector layer made of n−-GaAs, a base layer made of p+-GaAsBi, an emitter layer made of n-InGaP, a first cap layer made of n-GaAs, and a second cap layer made of n+-InGaAs on a substrate 1 made of single crystal GaAs.

Owner:SONY CORP

Heterojunction bipolar transistor using reverse emitter window

ActiveUS7022578B2Improve performanceIncrease speedSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

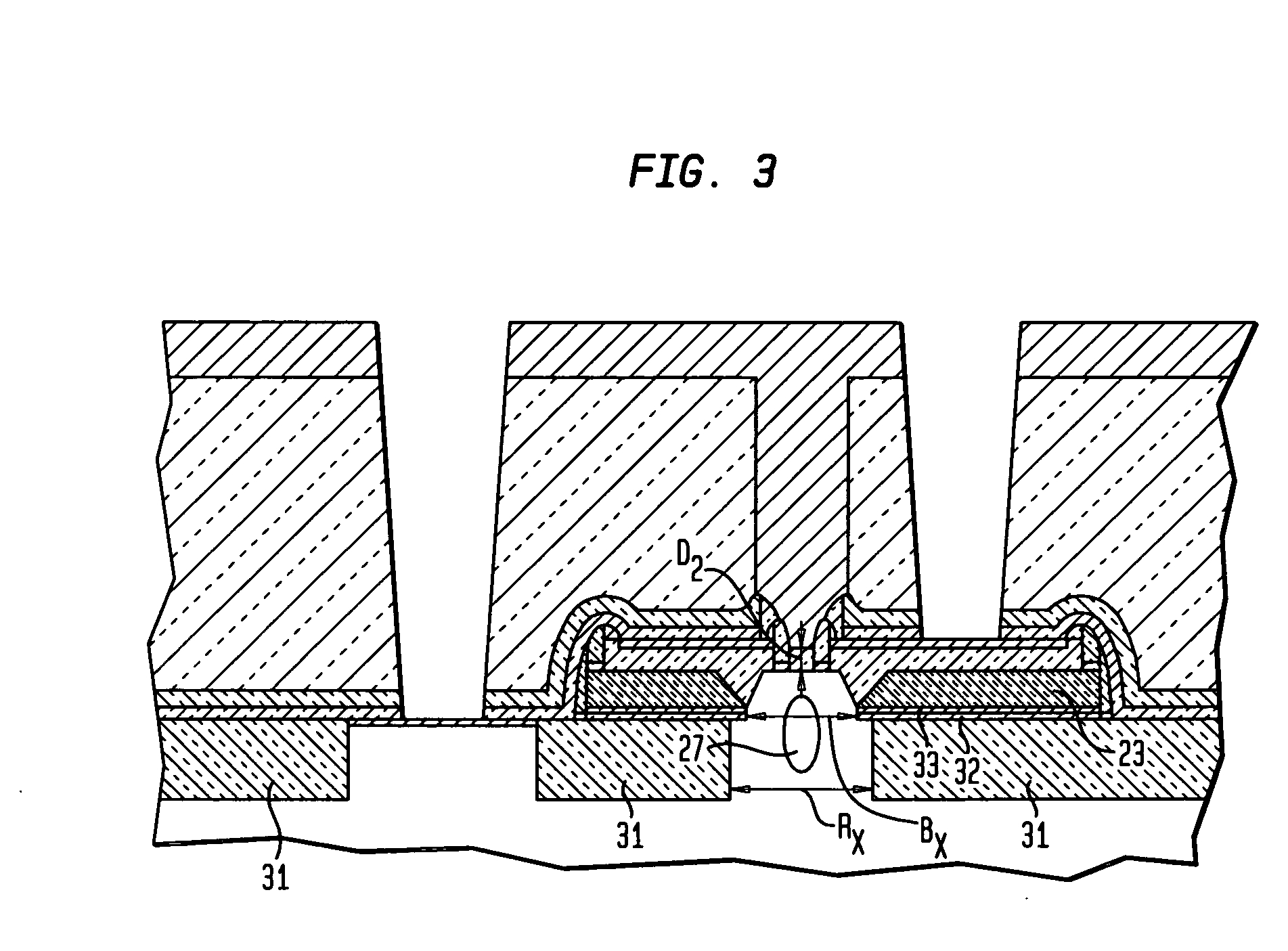

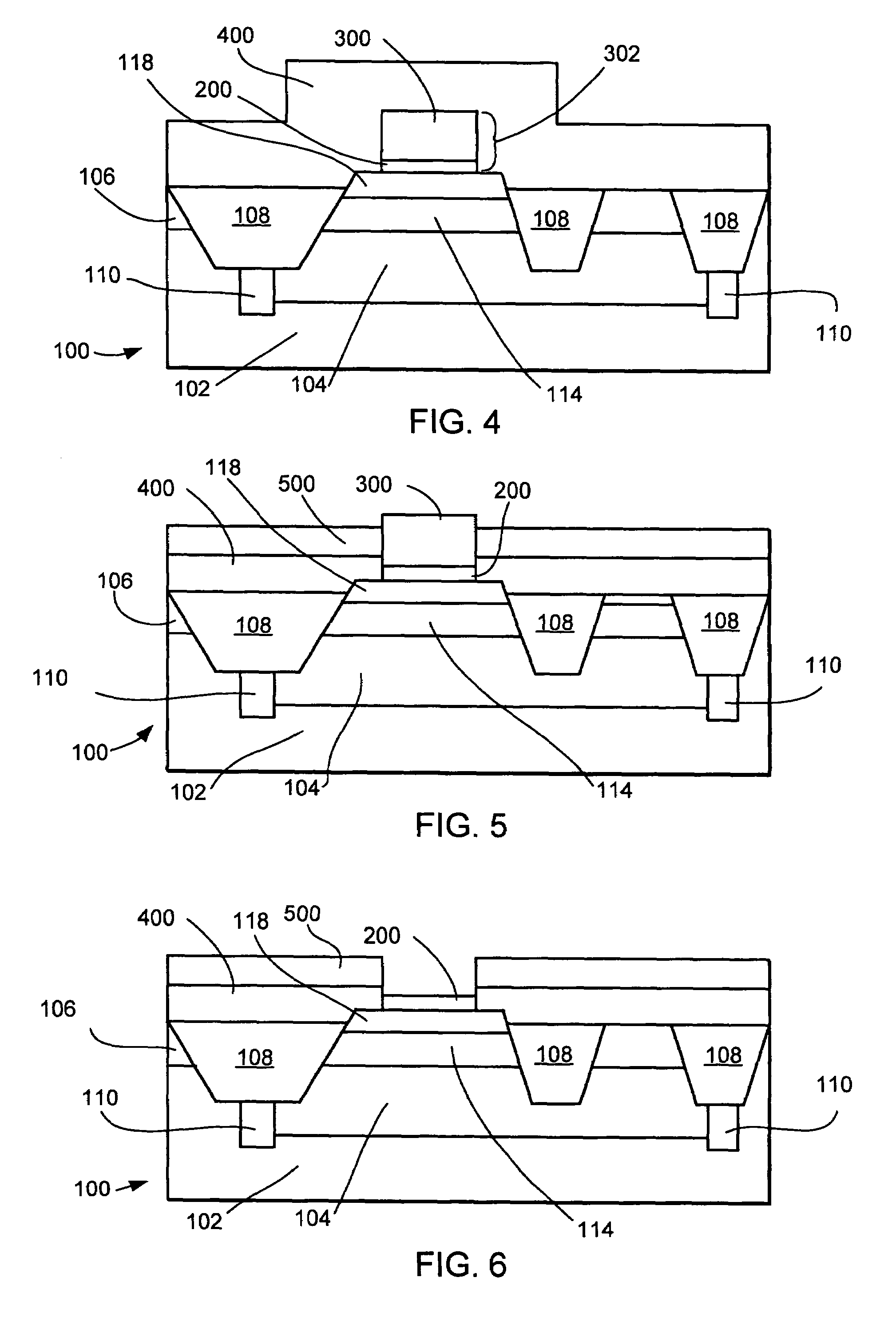

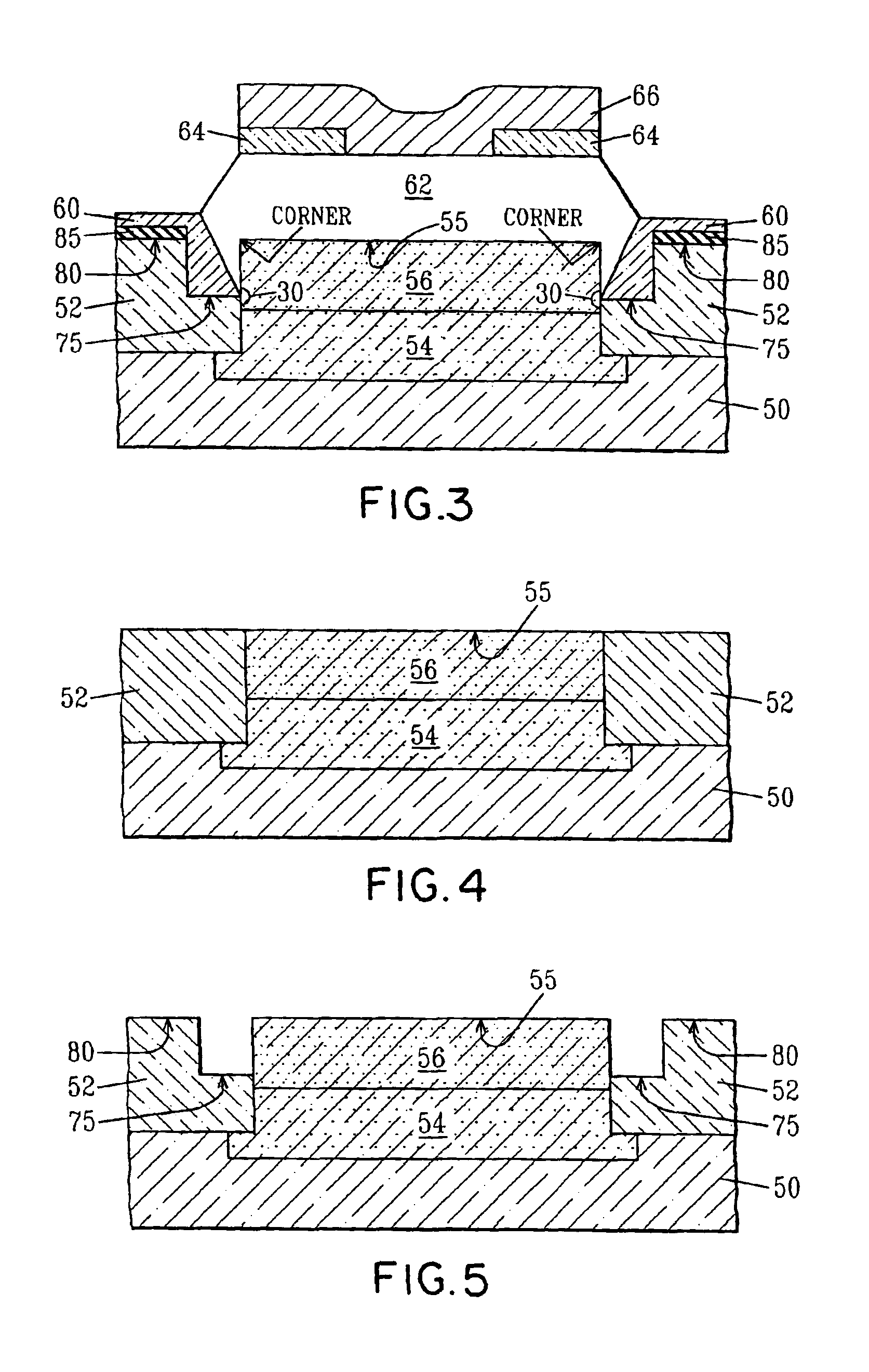

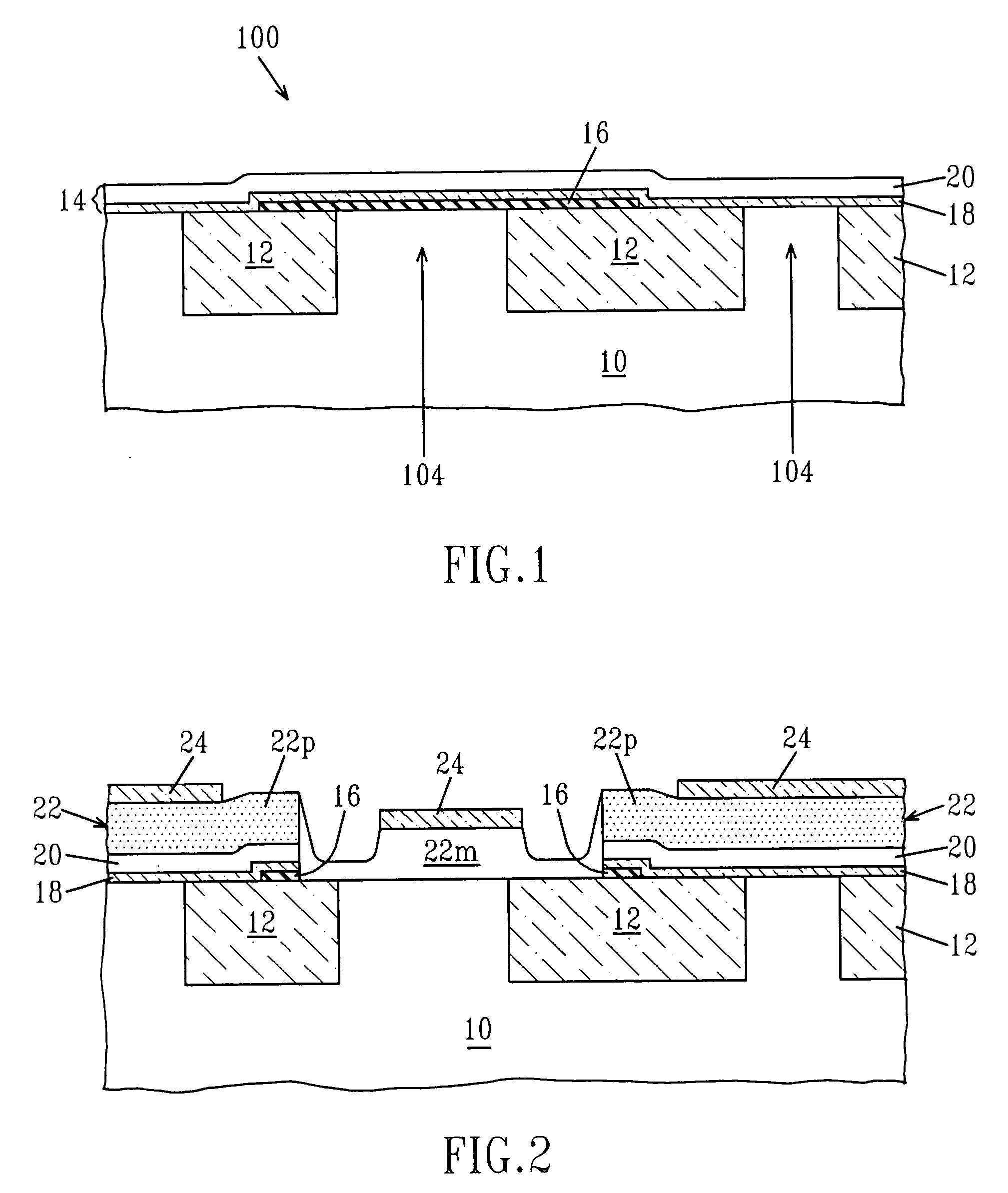

STI pull-down to control SiGe facet growth

InactiveUS6936509B2Lower base resistanceTotal current dropTransistorSemiconductor/solid-state device manufacturingEtchingLithographic artist

A SiGe bipolar transistor including a semiconductor substrate having a collector and sub-collector region formed therein, wherein the collector and sub-collector are formed between isolation regions that are also present in the substrate is provided. Each isolation region includes a recessed surface and a non-recessed surface which are formed utilizing lithography and etching. A SiGe layer is formed on the substrate as well as the recessed non-recessed surfaces of each isolation region, the SiGe layer includes polycrystalline Si regions and a SiGe base region. A patterned insulator layer is formed on the SiGe base region; and an emitter is formed on the patterned insulator layer and in contact with the SiGe base region through an emitter window opening.

Owner:GLOBALFOUNDRIES INC

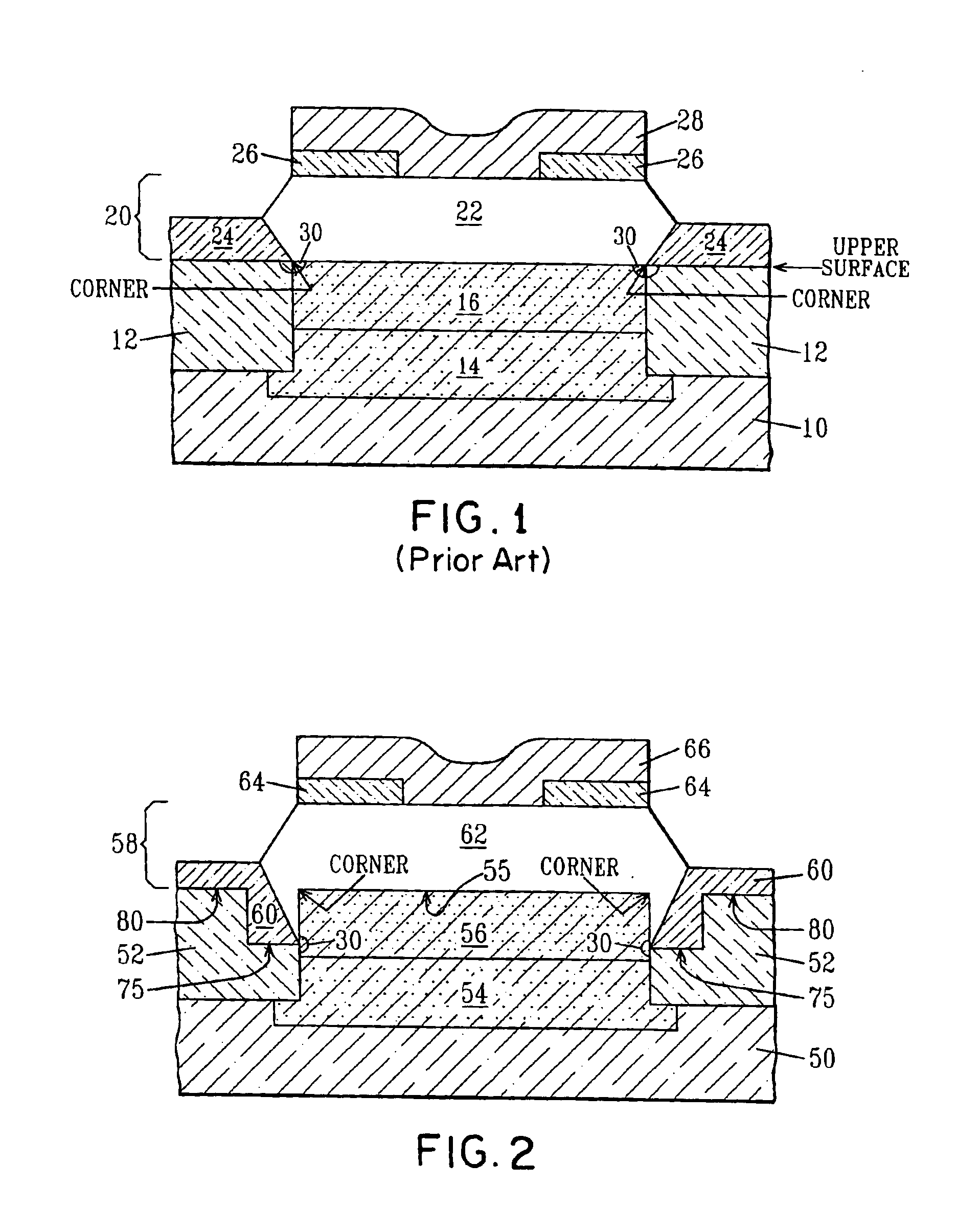

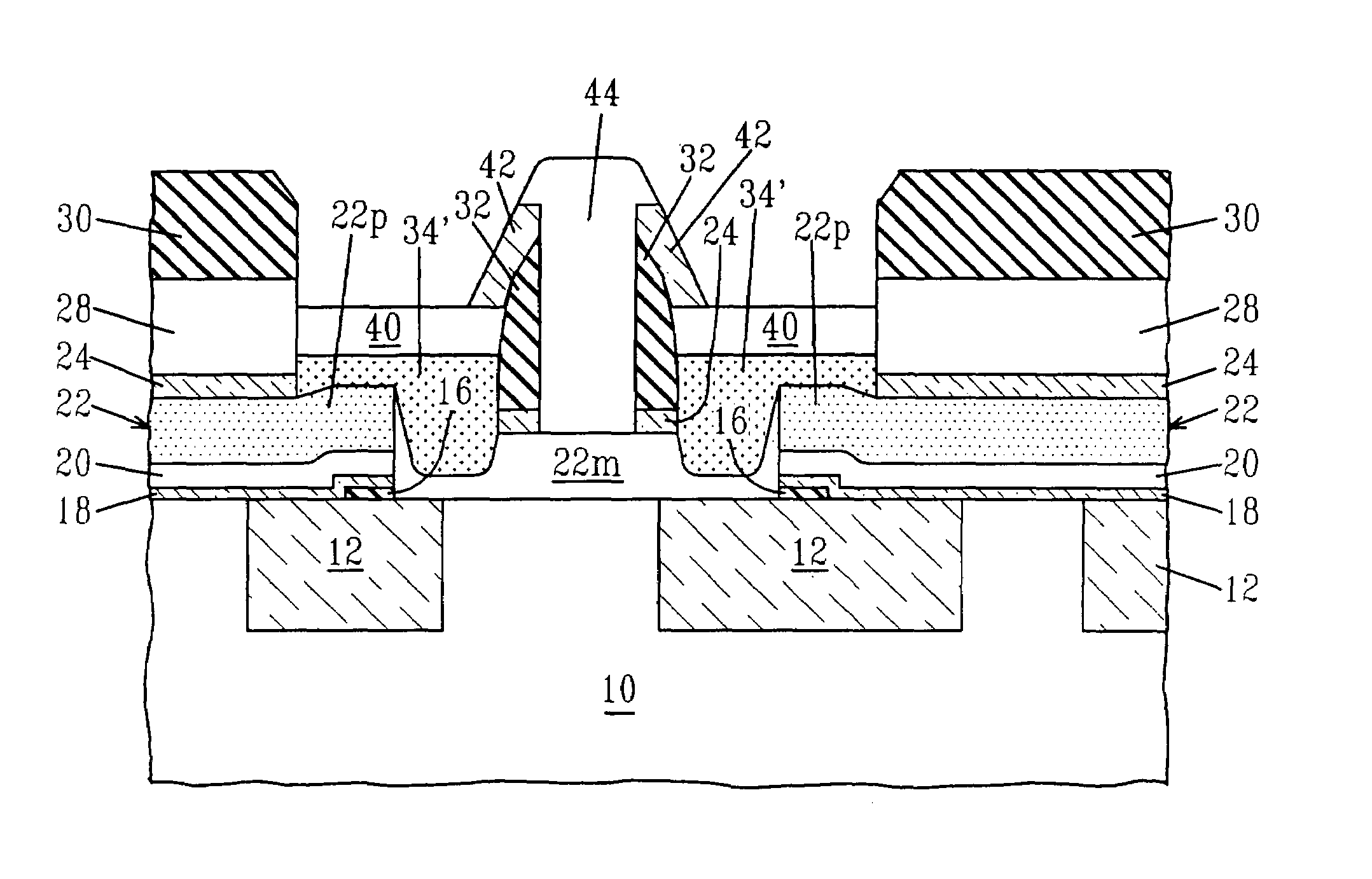

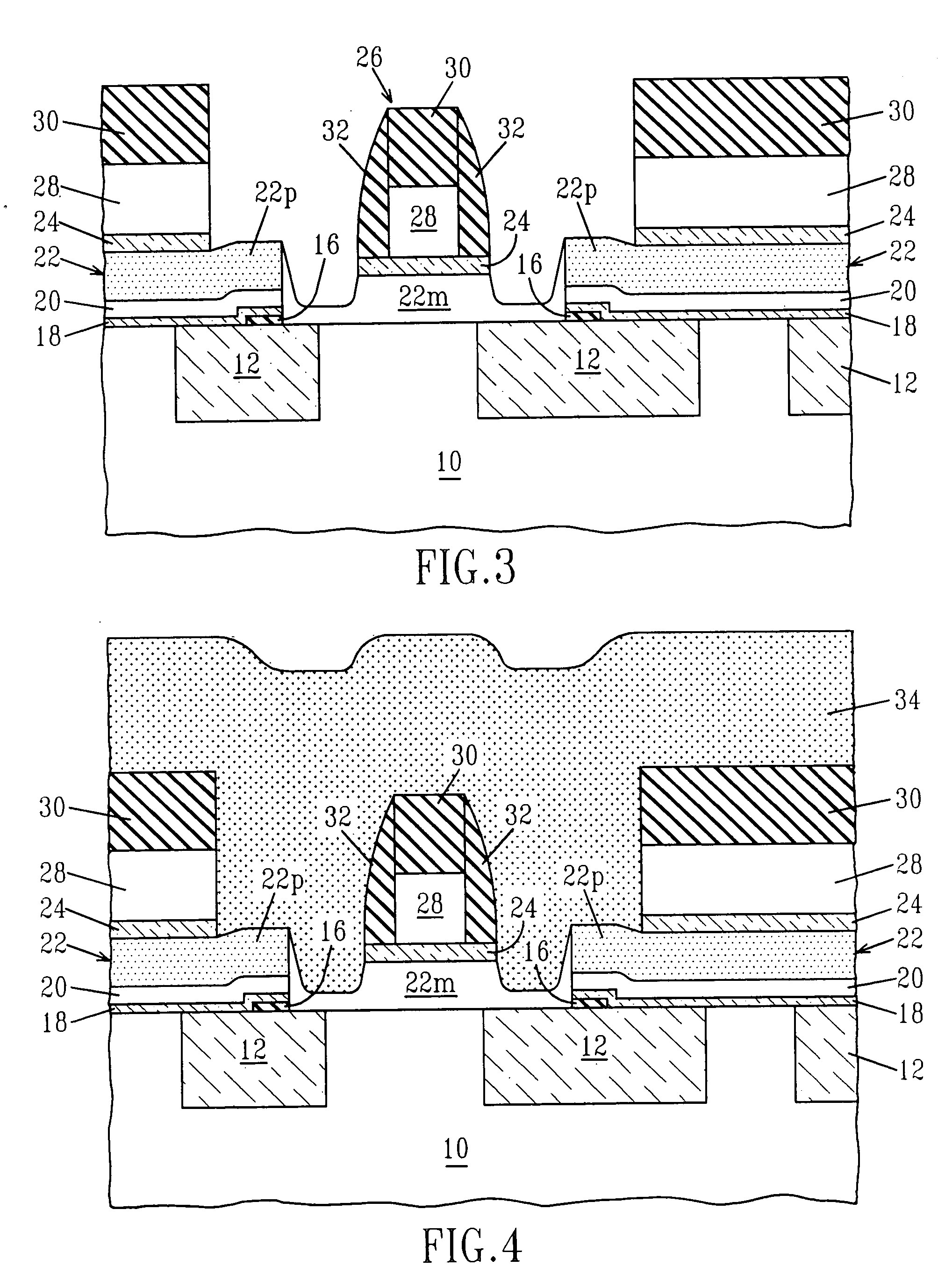

Method of base formation in a BiCMOS process

Methods for fabricating a heterojunction bipolar transistor having a raised extrinsic base is provided in which the base resistance is reduced by forming a silicide atop the raised extrinsic base that extends to the emitter region in a self-aligned manner. The silicide formation is incorporated into a BiCMOS process flow after the raised extrinsic base has been formed. The present invention also provides a heterojunction bipolar transistor having a raised extrinsic base and a silicide located atop the raised extrinsic base. The silicide atop the raised extrinsic base extends to the emitter in a self-aligned manner. The emitter is separated from the silicide by a spacer.

Owner:INT BUSINESS MASCH CORP

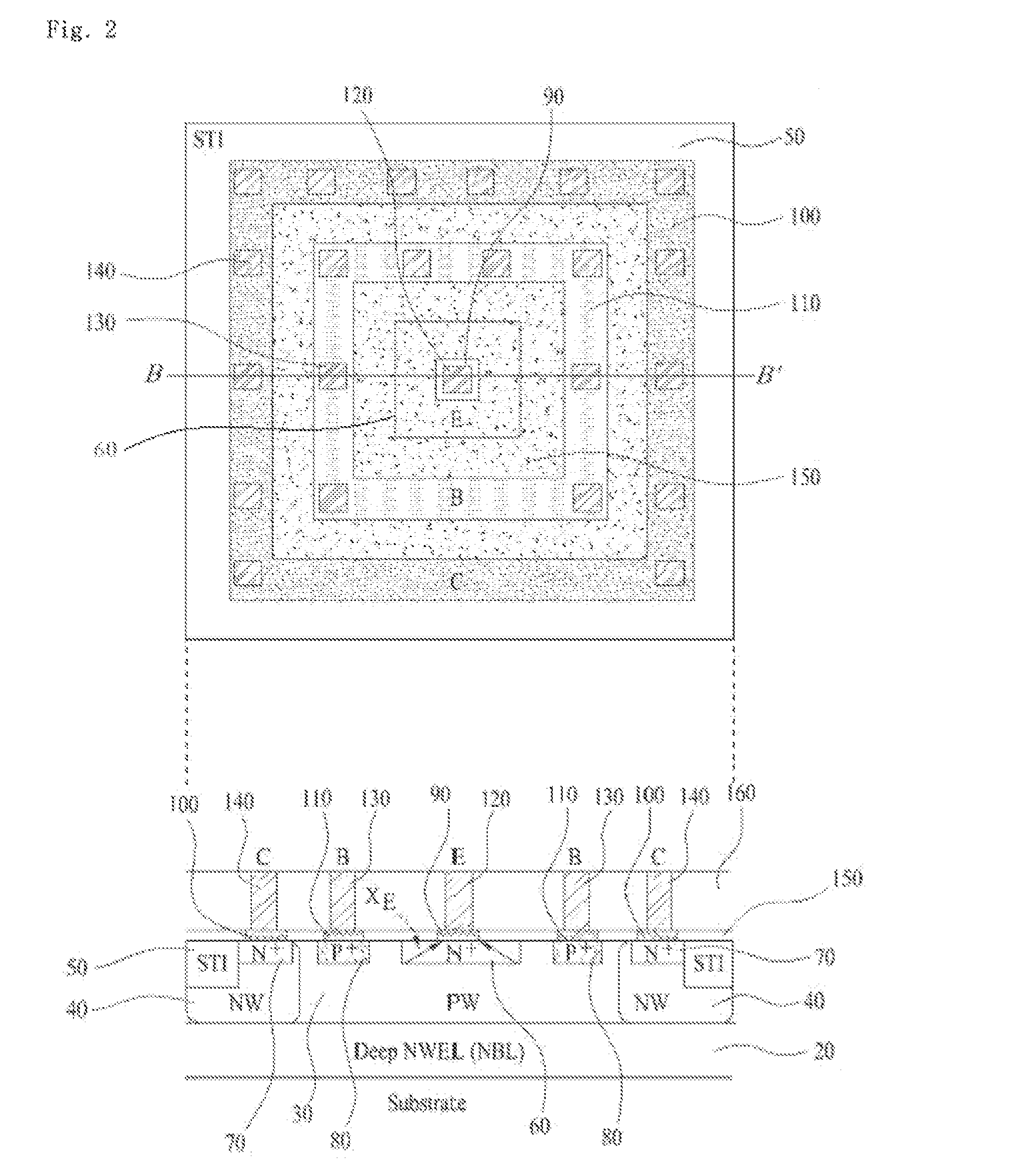

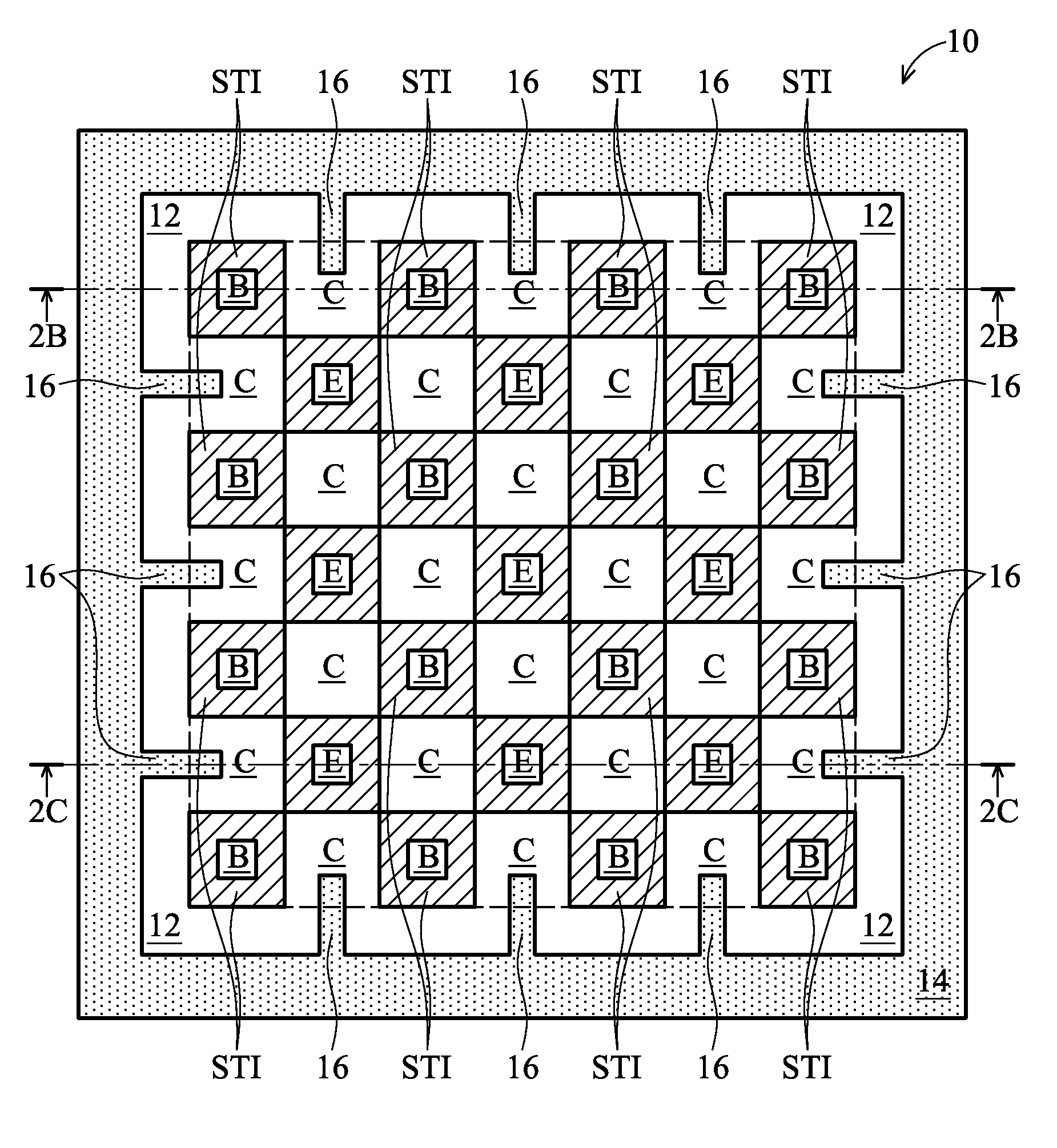

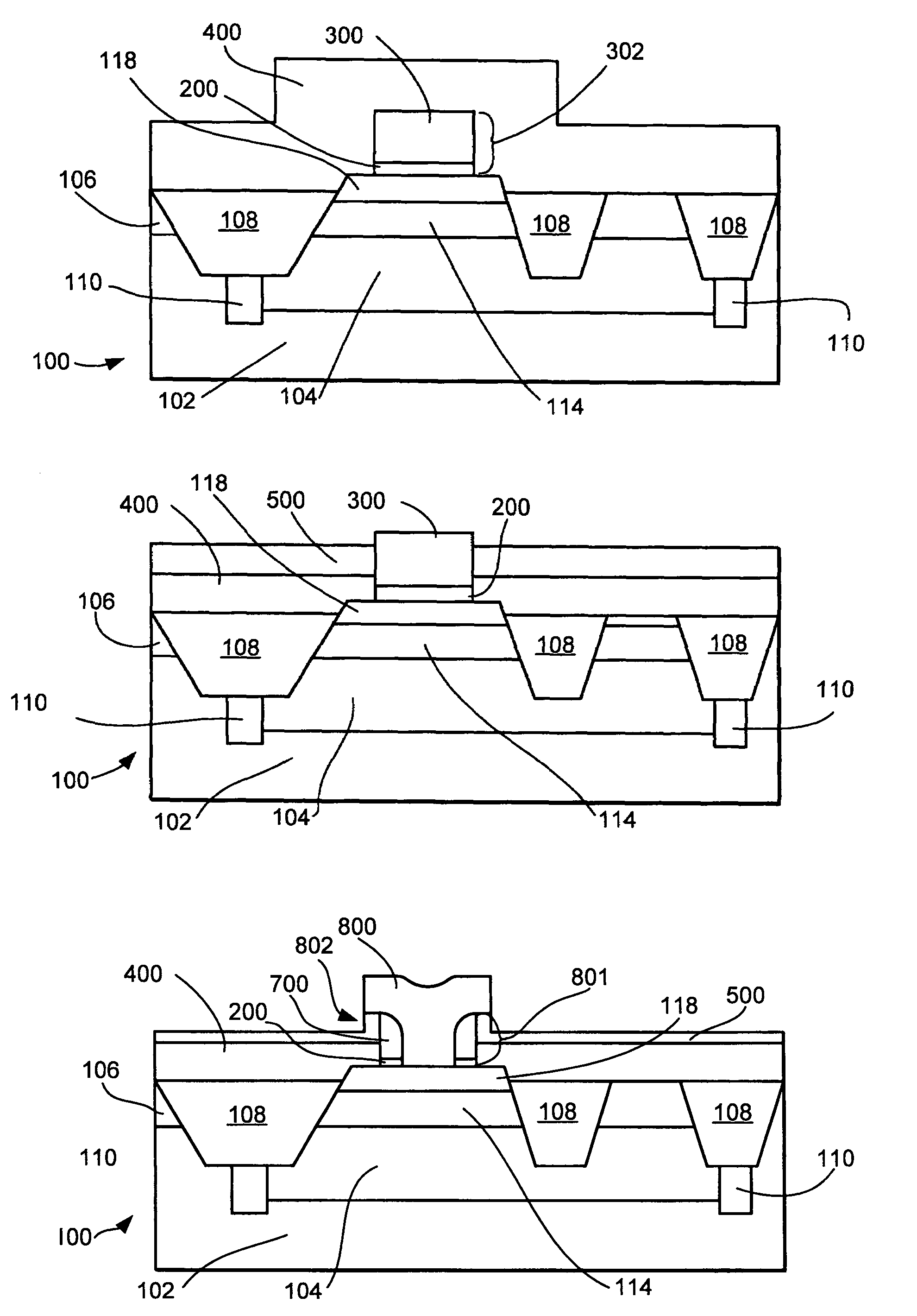

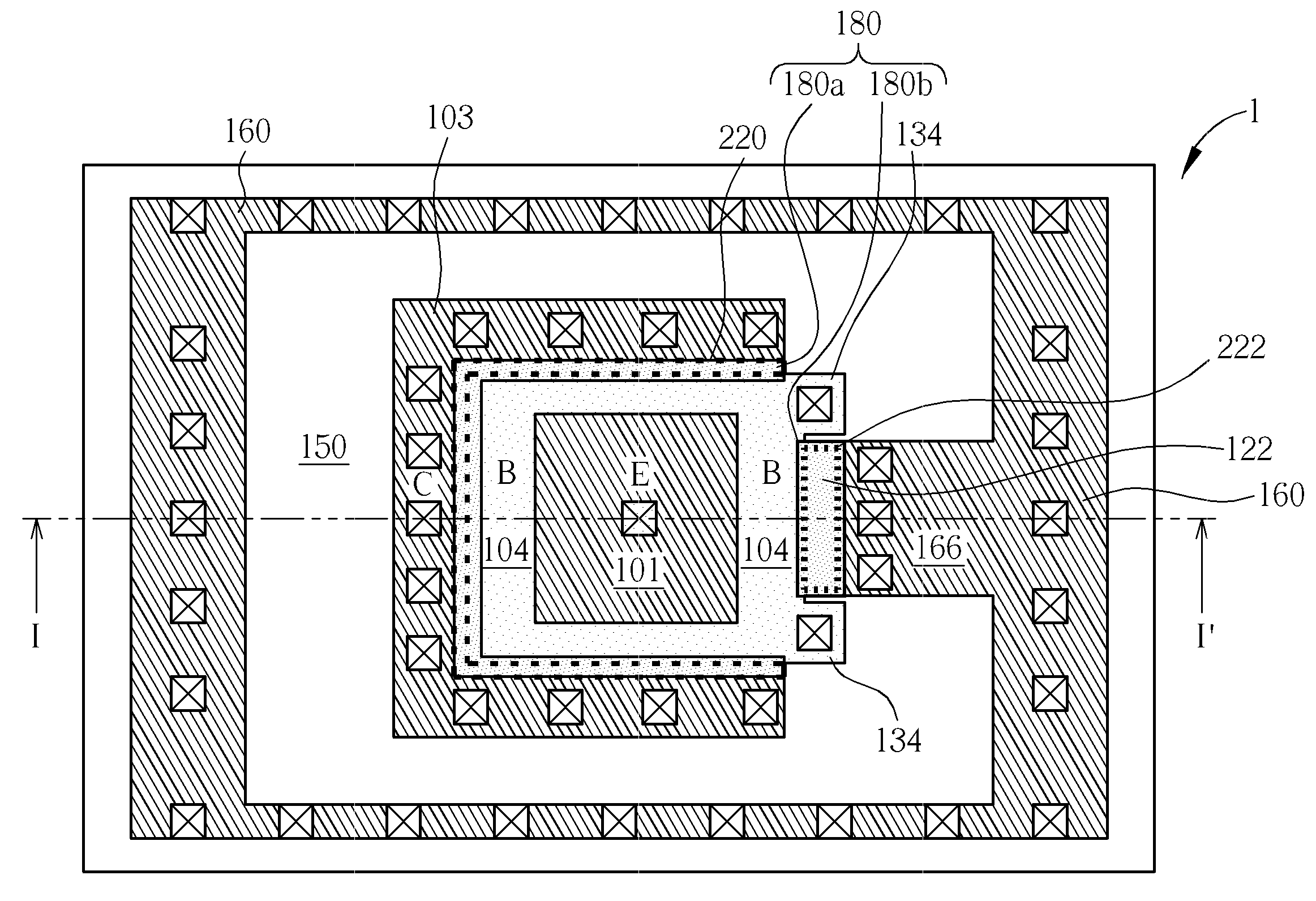

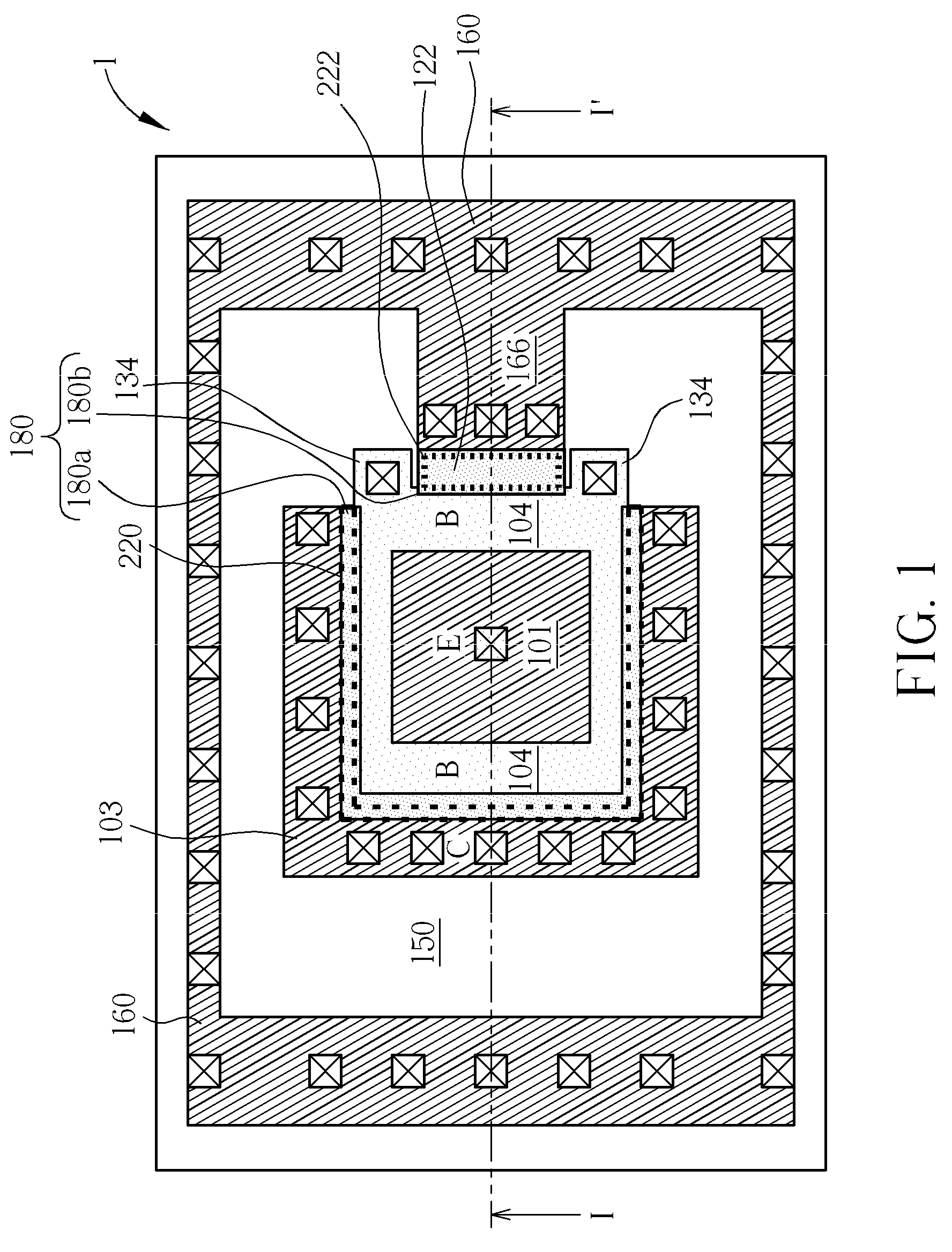

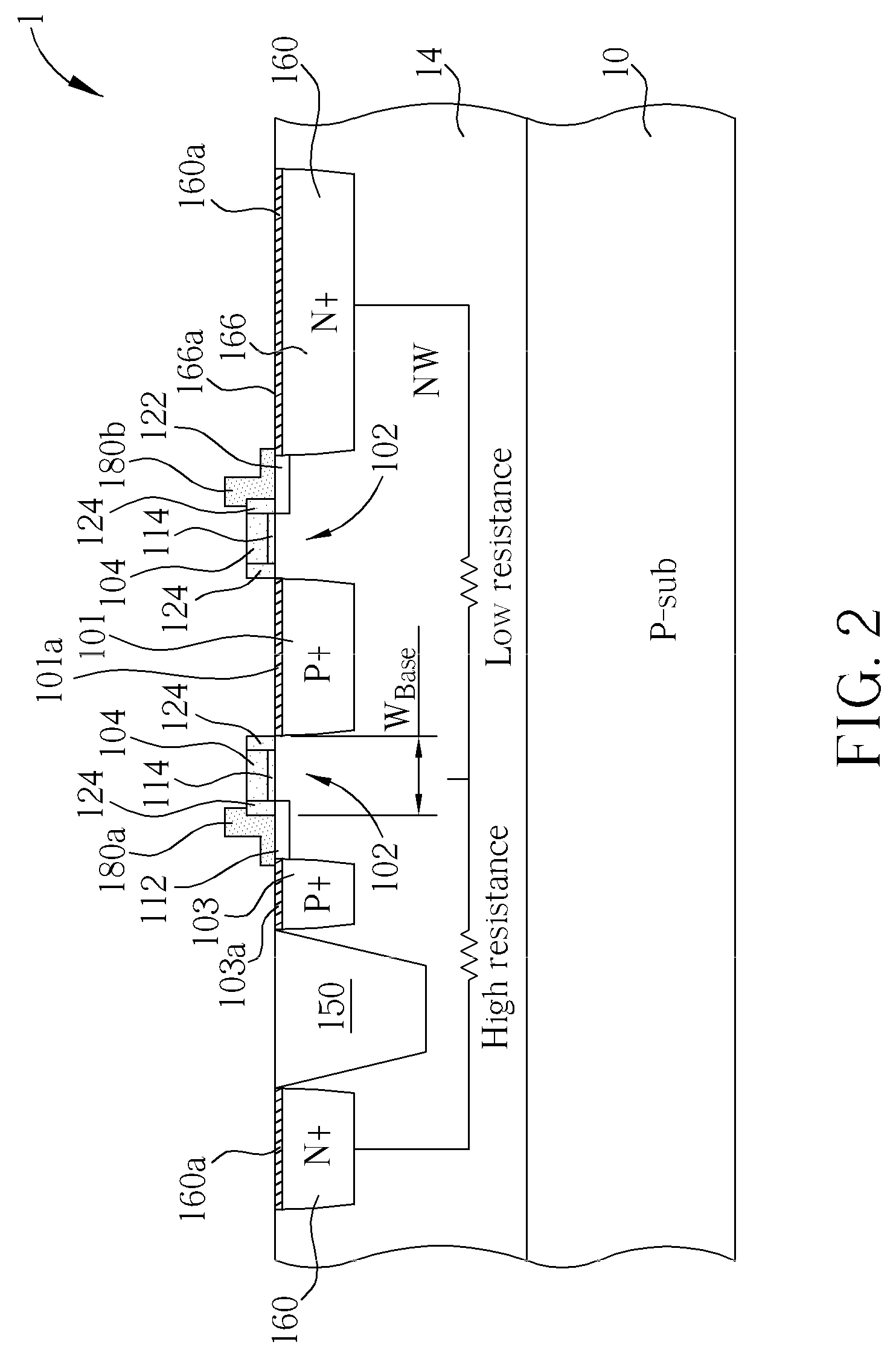

Lateral bipolar junction transistor with reduced base resistance

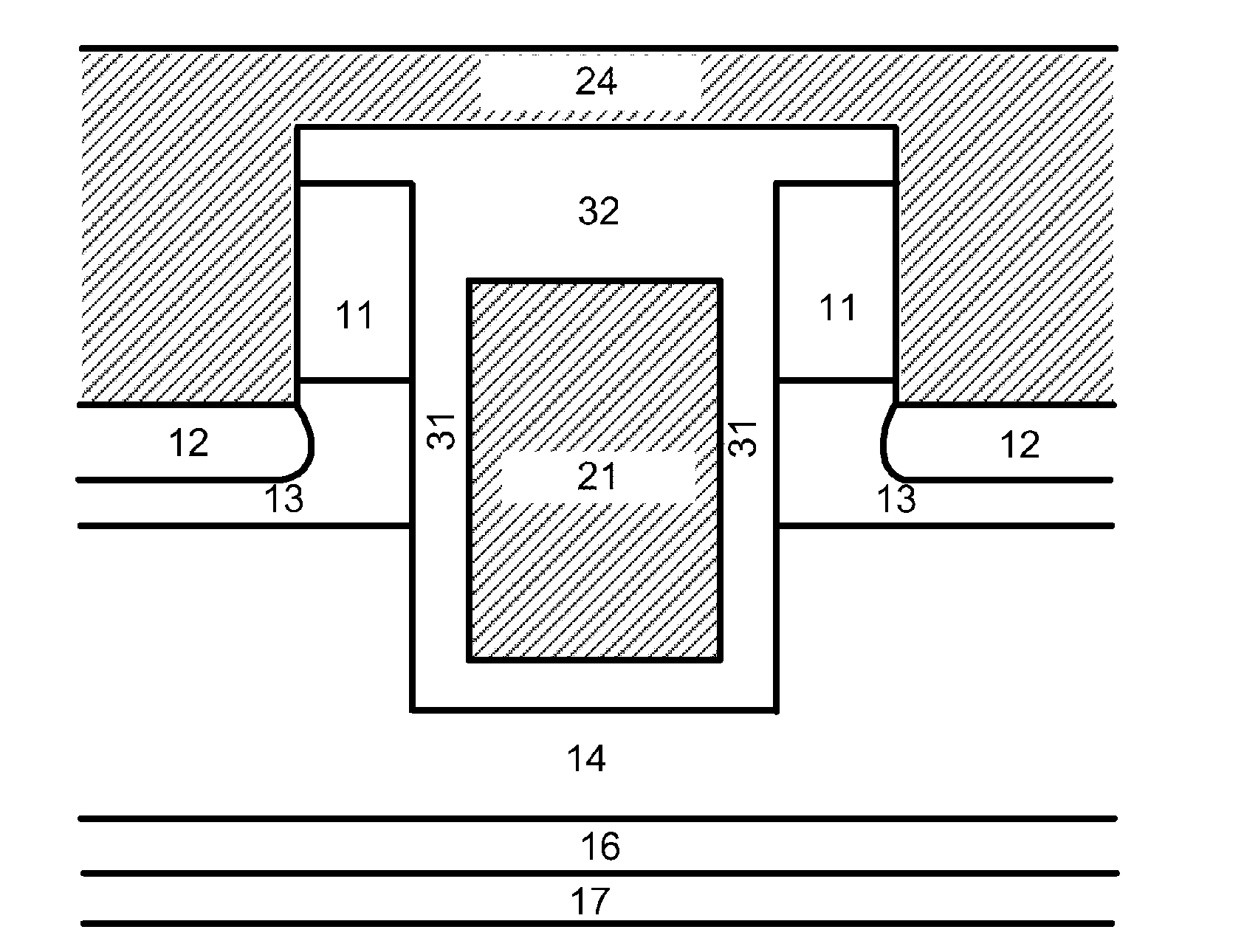

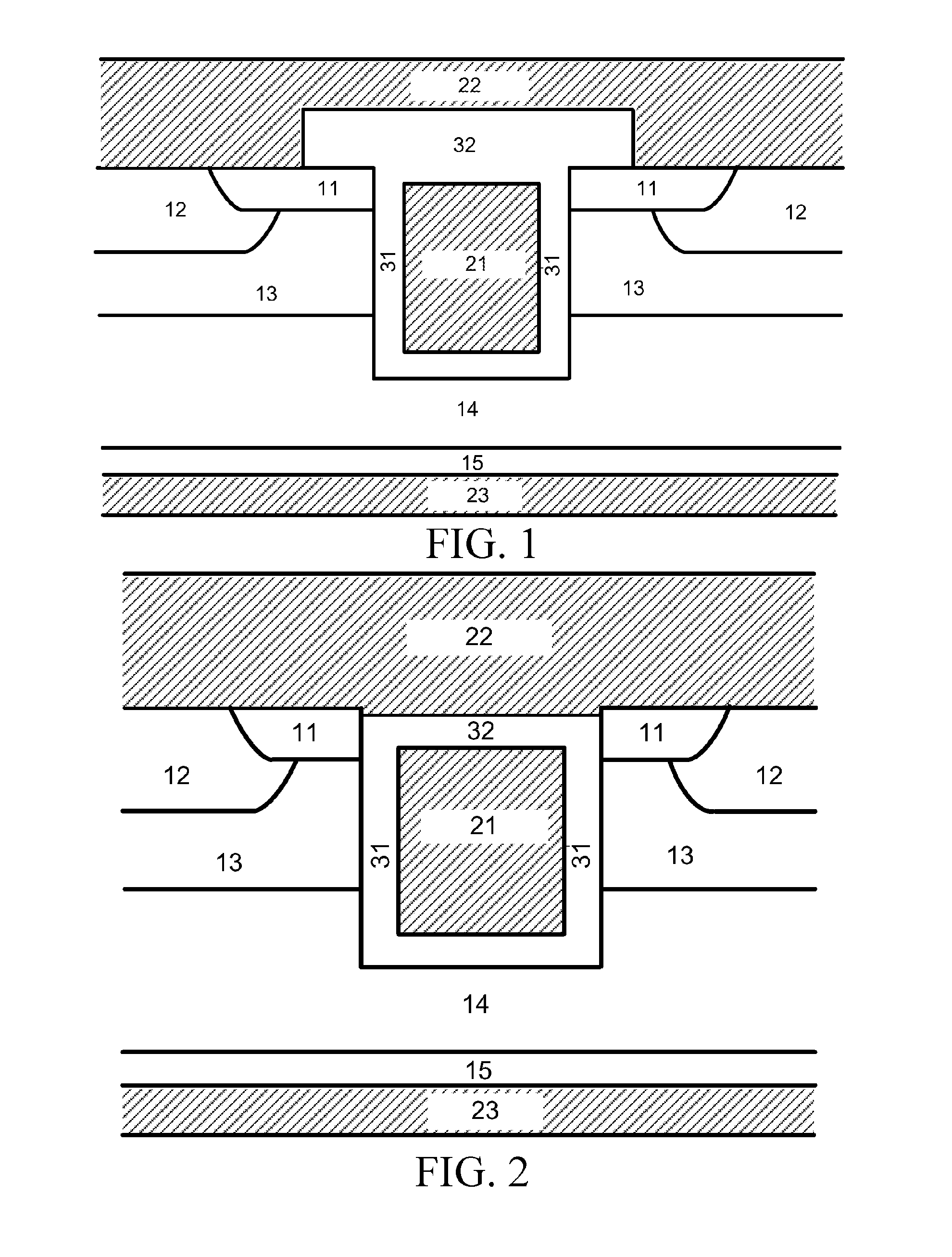

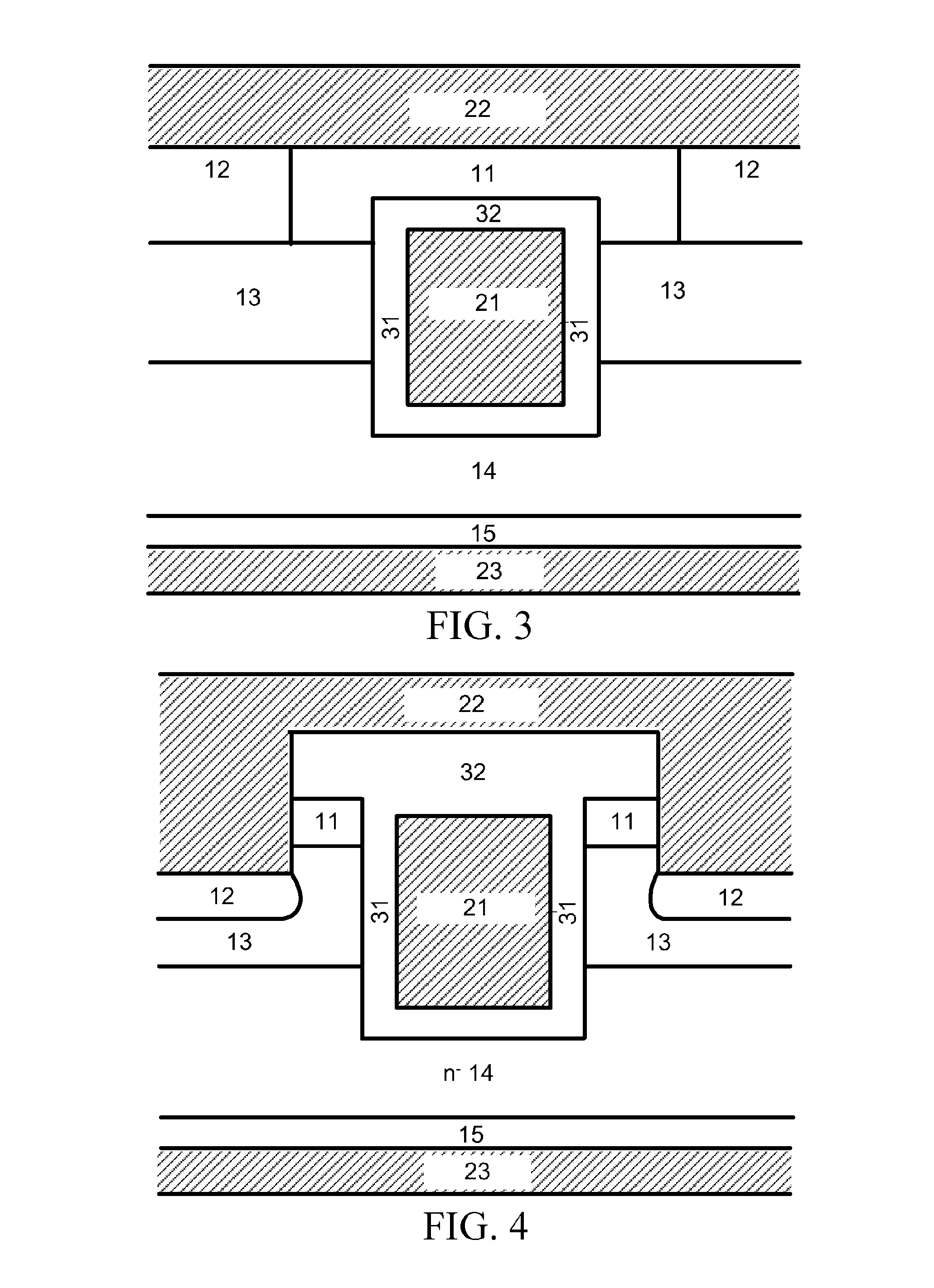

A lateral bipolar junction transistor formed in a semiconductor substrate includes an emitter region; a base region surrounding the emitter region; a gate disposed at least over a portion of the base region; a collector region having at least one open side and being disposed about a periphery of the base region; a shallow trench isolation (STI) region disposed about a periphery of the collector region; a base contact region disposed about a periphery of the STI region; and an extension region merging with the base contact region and laterally extending to the gate on the open side of the collector region.

Owner:MEDIATEK INC

Method of base formation in a bicmos process

Methods for fabricating a heterojunction bipolar transistor having a raised extrinsic base is provided in which the base resistance is reduced by forming a silicide atop the raised extrinsic base that extends to the emitter region in a self-aligned manner. The silicide formation is incorporated into a BiCMOS process flow after the raised extrinsic base has been formed. The present invention also provides a heterojunction bipolar transistor having a raised extrinsic base and a silicide located atop the raised extrinsic base. The silicide atop the raised extrinsic base extends to the emitter in a self-aligned manner. The emitter is separated from the silicide by a spacer.

Owner:IBM CORP

Bipolar transistor having self-adjusted emitter contact

ActiveUS8933537B2Good high-frequency characteristicReduce resistanceTransistorSolid-state devicesChemical compositionSemiconductor materials

Owner:IHP GMBH INNOVATIONS FOR HIGH PERFORMANCE MICROELECTRONICS LEIBNIZ INST FUR INNOVATIVE

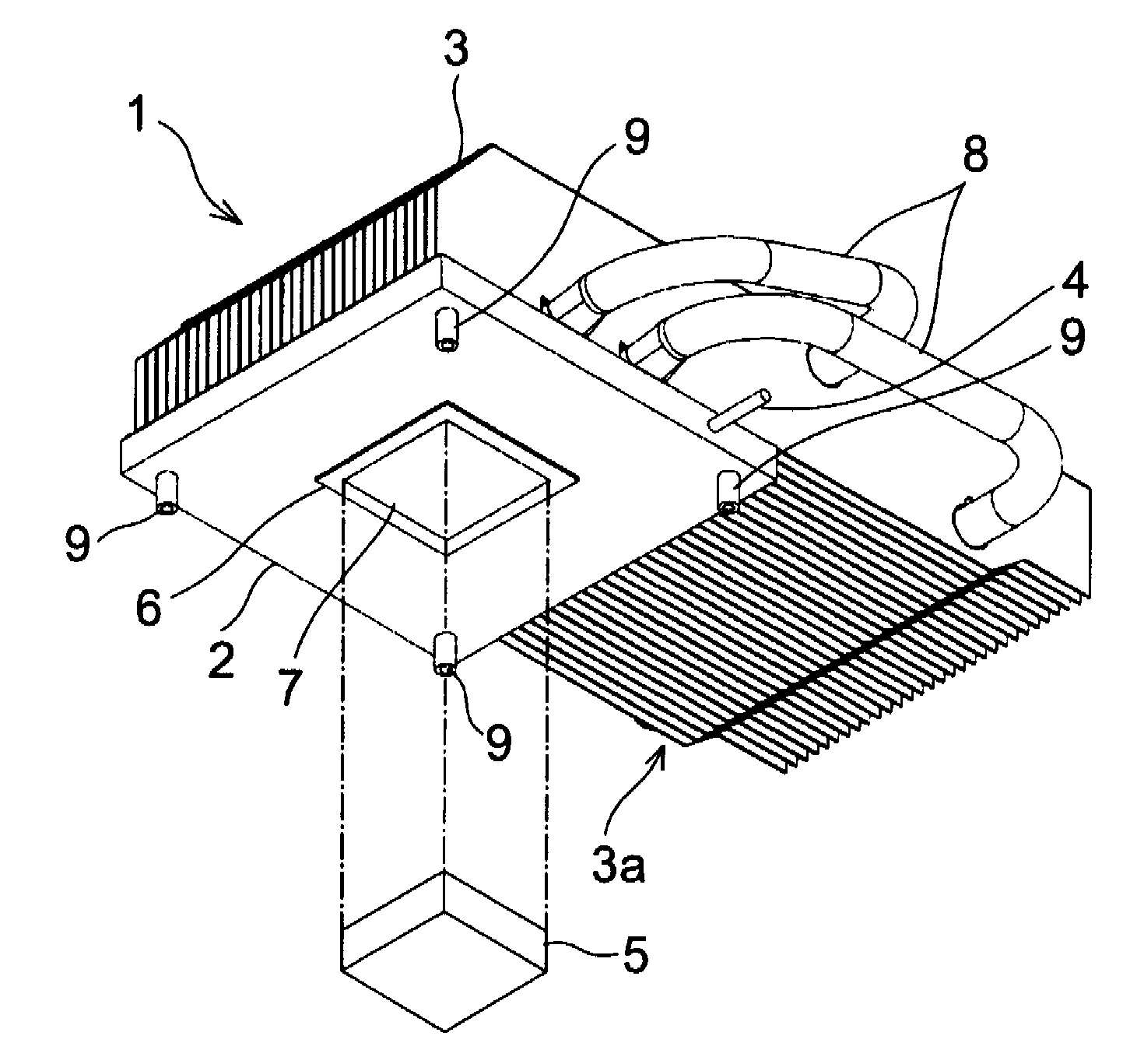

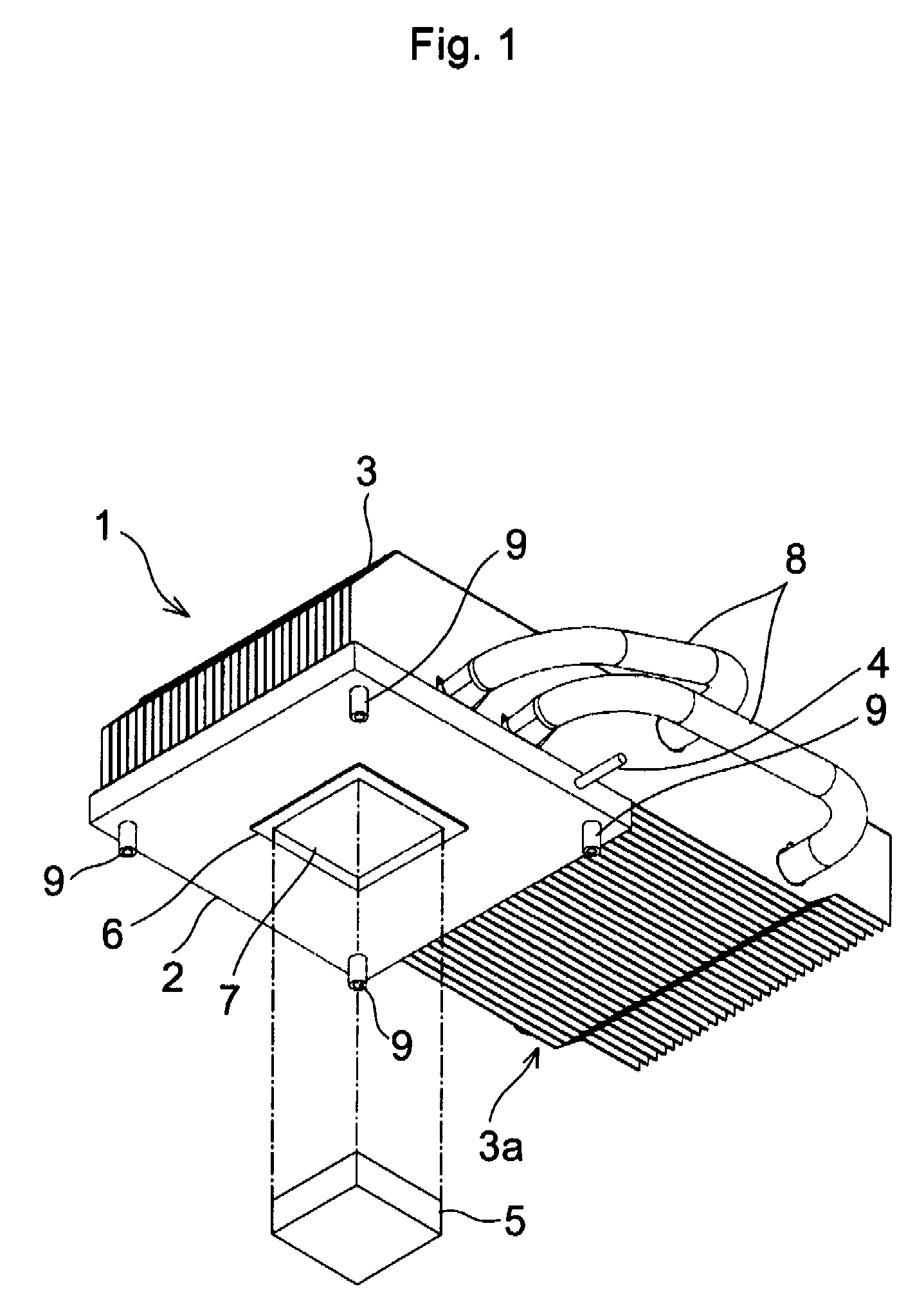

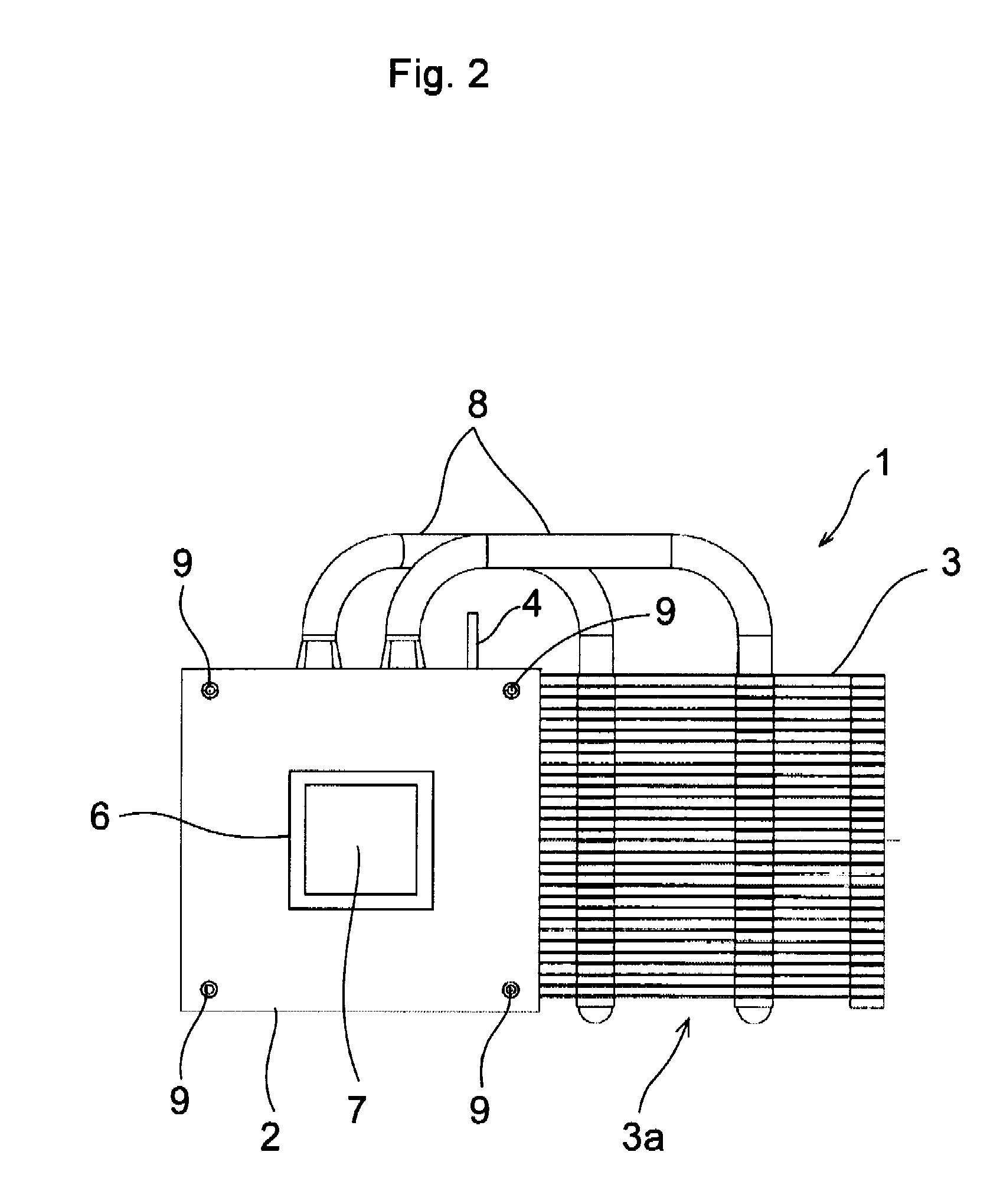

Heat sink

InactiveUS20080251239A1Lower base resistanceImproved heat radiation characteristicSemiconductor/solid-state device detailsSolid-state devicesEngineeringHeat pipe

A heat sink, wherein a plurality of heat radiation fins are mounted on a base plate to which an electron device is attached in a heat transmittable manner. The heat radiation fins are erected vertically and in parallel with each other on the reverse face of the base plate to which the electron device is contacted, and extended laterally from the base plate. The heat sink of the invention comprises a heat pipe for transporting heat between the extended portion of the heat radiation fins and the base plate.

Owner:THE FUJIKURA CABLE WORKS LTD

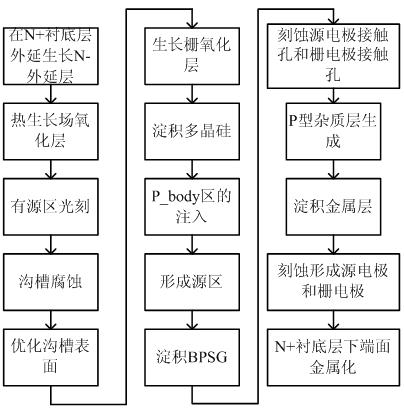

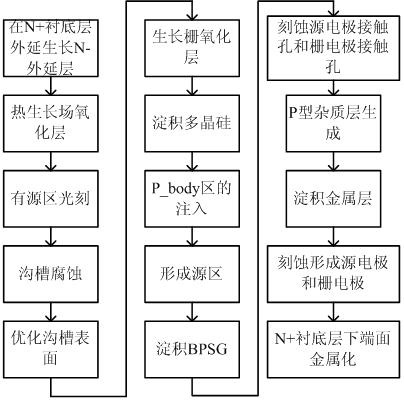

Trench metal oxide semiconductor field effect transistor and manufacturing method thereof

InactiveCN102110717AReduce areaLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField effect

The invention discloses a trench metal oxide semiconductor field effect transistor, which comprises an N+ substrate layer, an N- epitaxial layer, a gate oxide layer, a boron, phosphorus, silicon glass layer, a metal layer and a back metal layer, wherein an annular field oxide layer is arranged on an upper end face of the N- epitaxial layer; the N- epitaxial layer is provided with a trench; a doped polycrystalline silicon layer is filled in the trench; and the N- epitaxial layer comprises a source region layer and a P-body layer which is arranged on a lower end face of the source region layer. The trench metal oxide semiconductor field effect transistor also comprises a source electrode contact hole and a gate electrode contact hole, wherein the source electrode contact hole and the gate electrode contact hole are filled by the metal layer; and the metal layer at the source electrode contact hole is separated from the metal layer at the gate electrode contact hole through an opening. The invention also discloses a method for manufacturing the trench metal oxide semiconductor field effect transistor. Due to the structure and the manufacturing method, the manufacturing cost is saved.

Owner:CHENGDU PROMISING CHIP ELECTRONICS

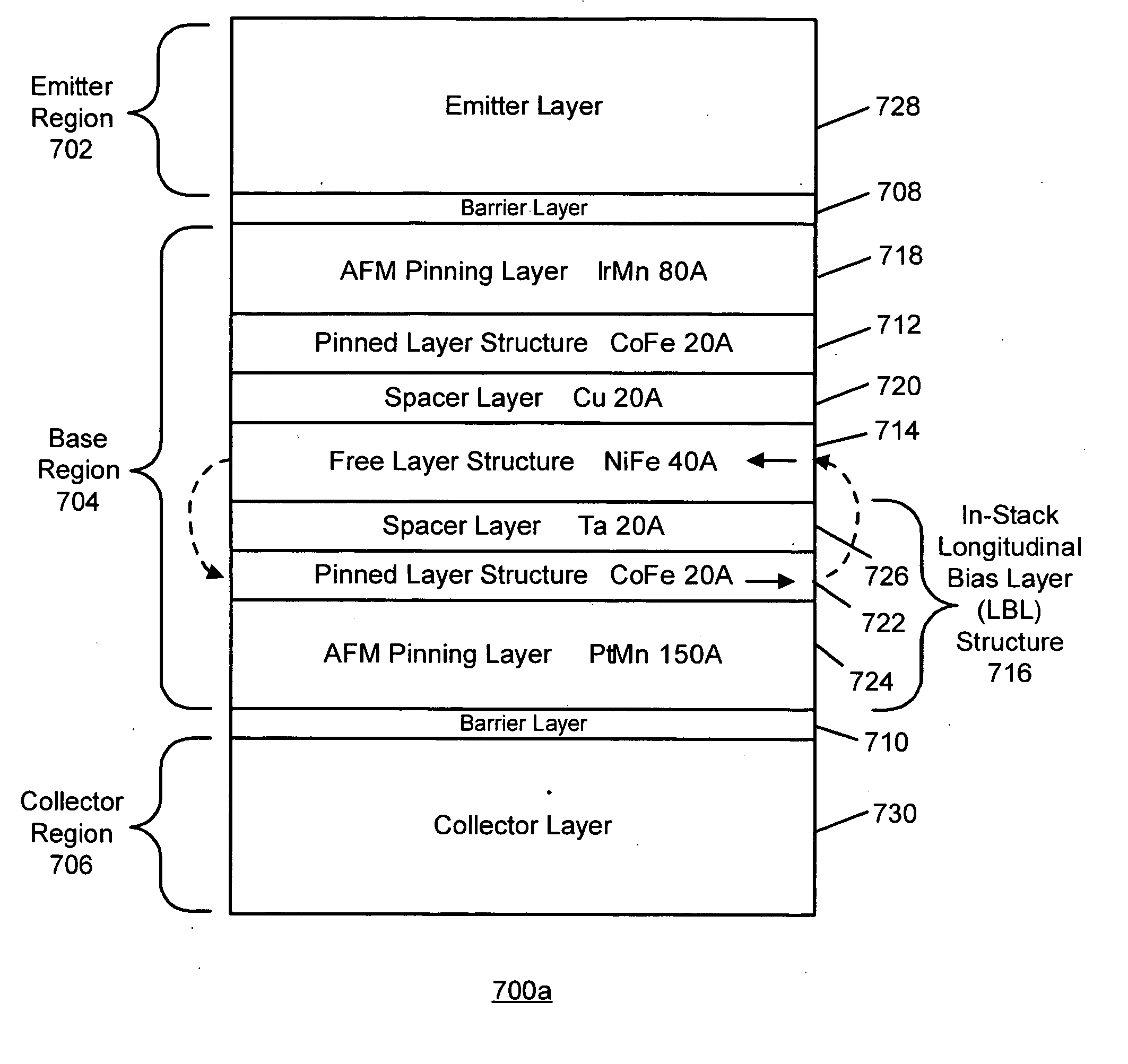

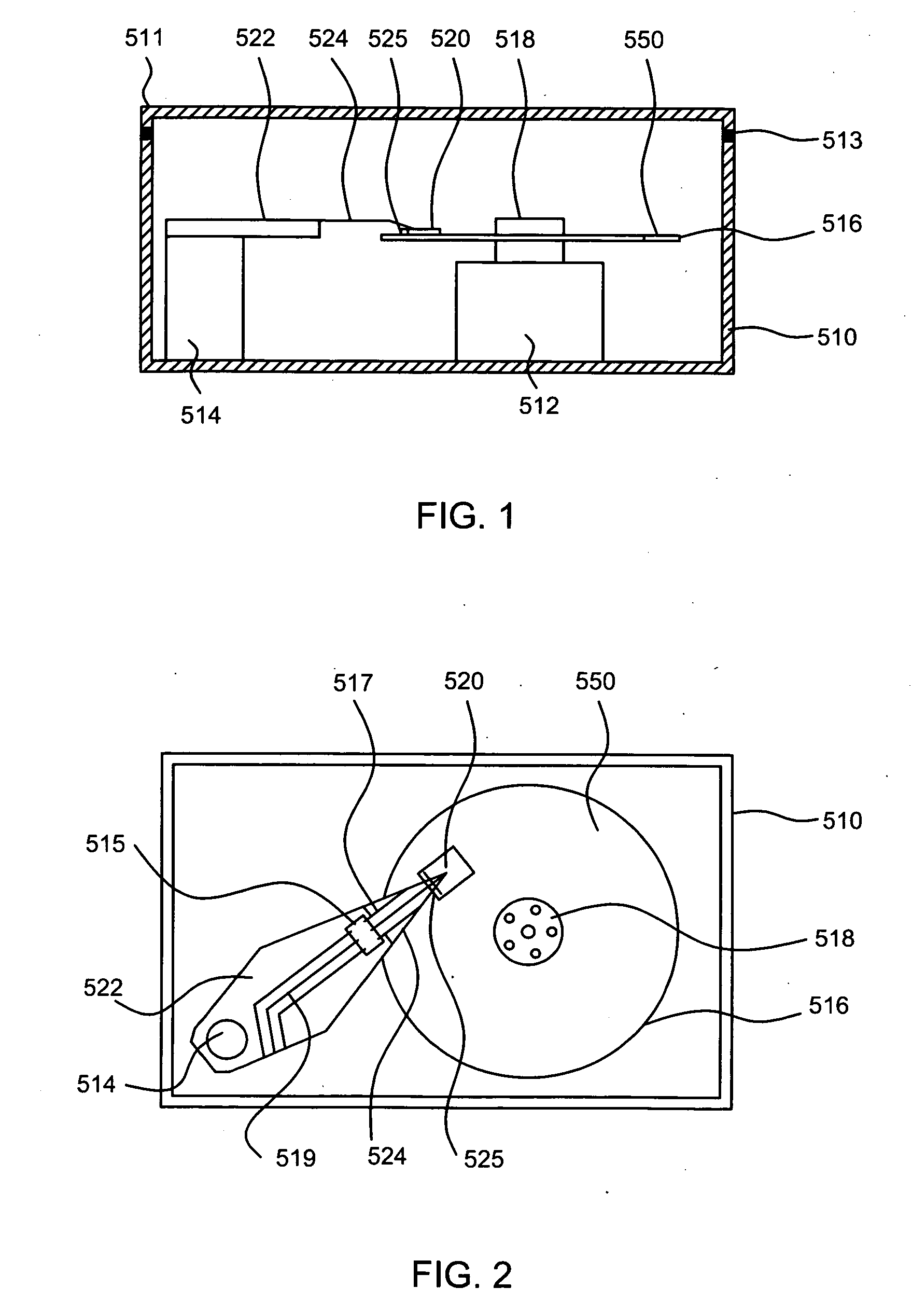

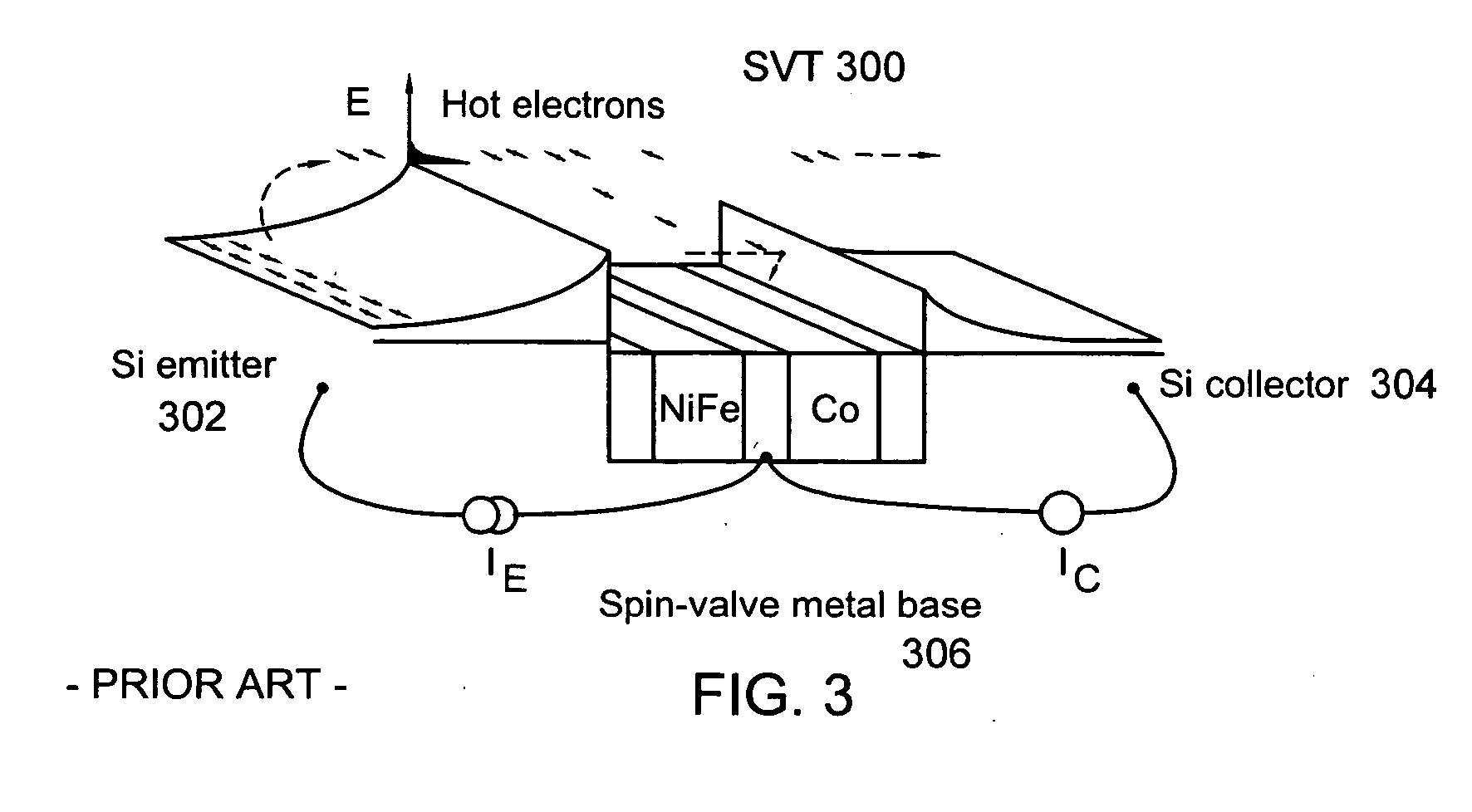

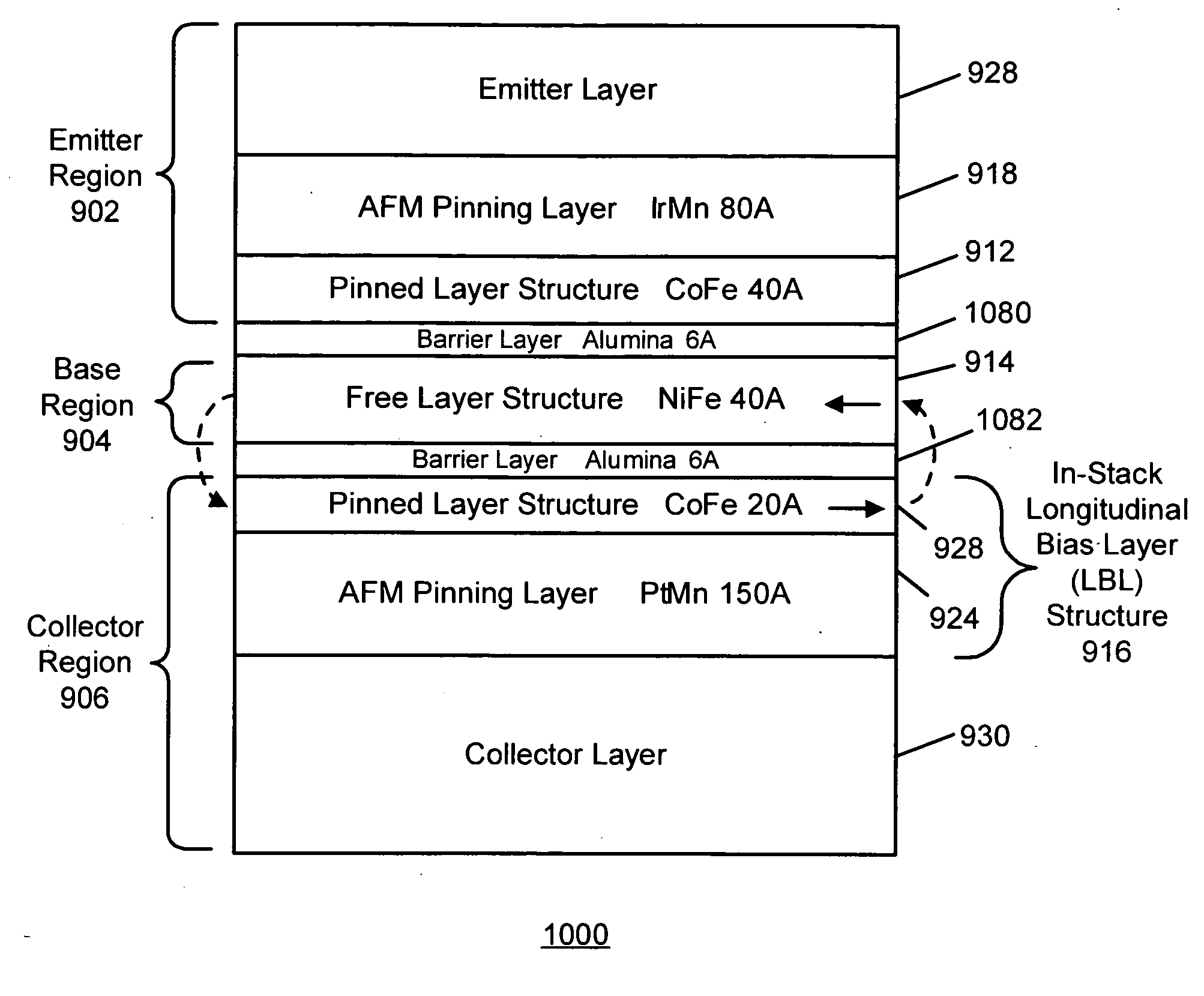

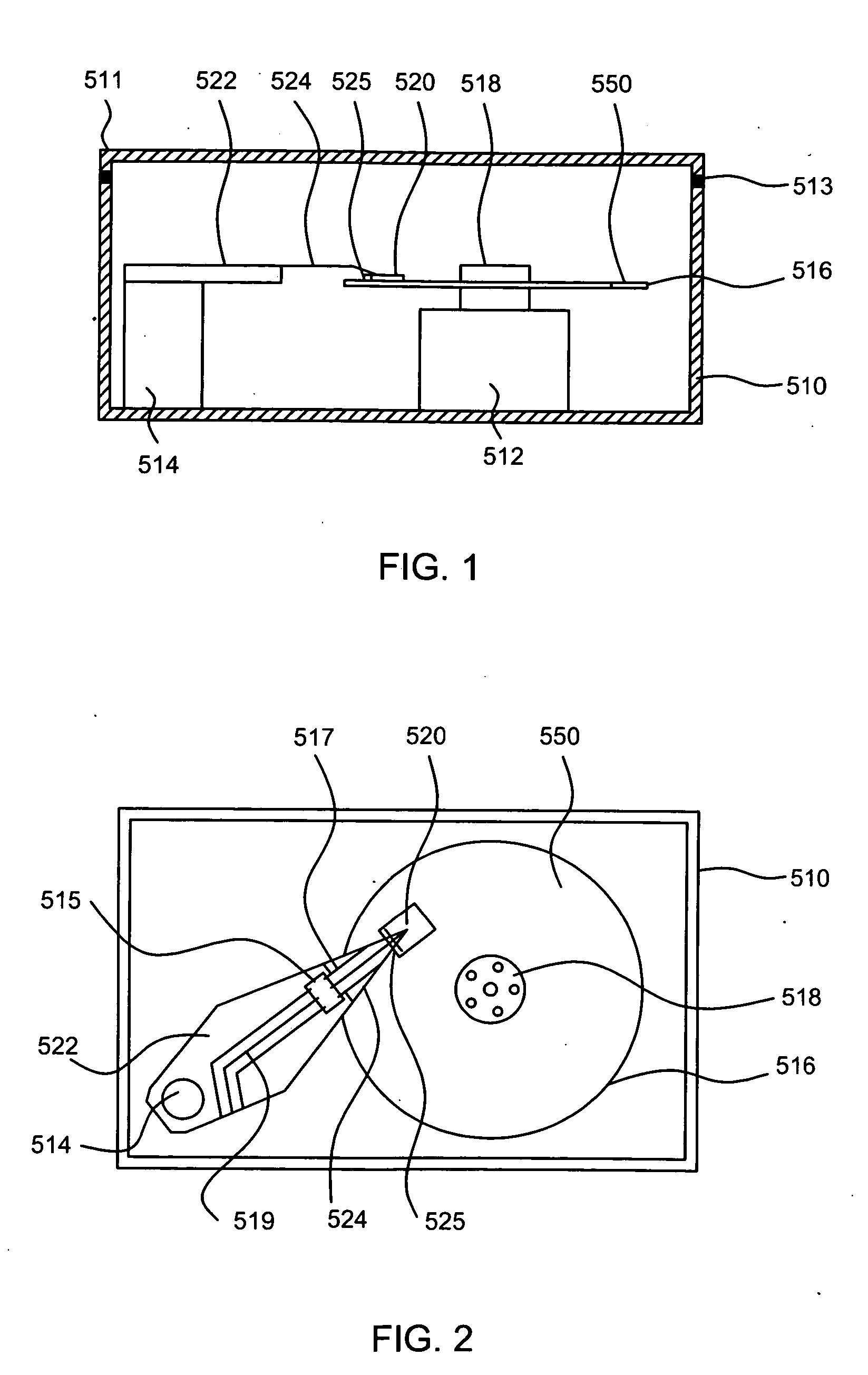

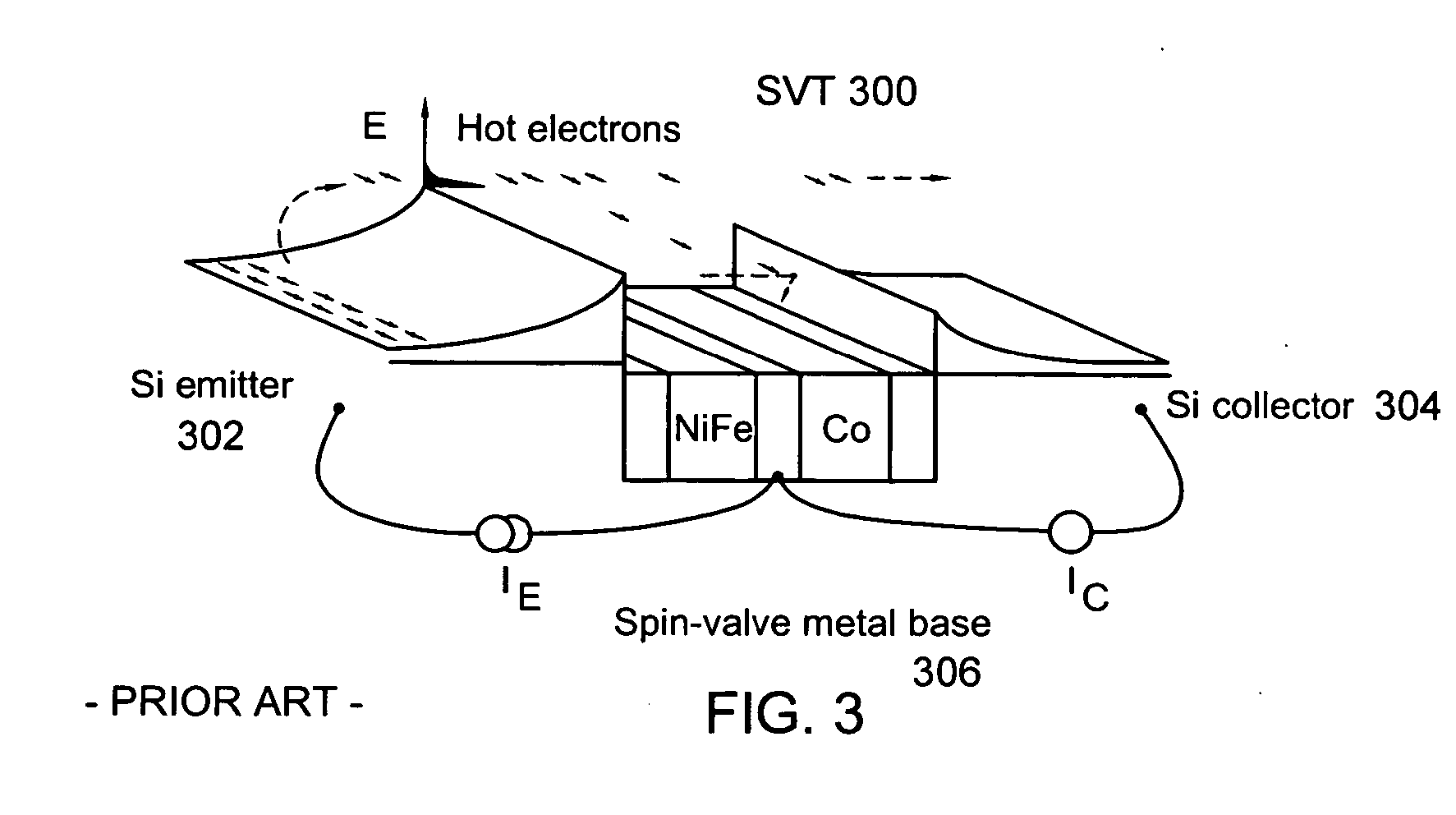

Three terminal magnetic sensor having an in-stack longitudinal biasing layer structure in the collector region and a pinned layer structure in the emitter region

InactiveUS20060152857A1Lower base resistanceReduce emitter resistanceNanomagnetismMagnetic measurementsSpin valveCondensed matter physics

In one illustrative example, a three terminal magnetic sensor (TTM) suitable for use in a magnetic head has a base region, a collector region, and an emitter region. A first barrier layer separates the emitter region from the base region, and a second barrier layer separates the collector region from the base region. A sensing plane is defined along sides of the base region, the collector region, and the emitter region. The base region consists of a free layer structure so as to have a relatively small thickness. A pinned layer structure is made part of the emitter region. An in-stack longitudinal biasing layer (LBL) structure which magnetically biases the free layer structure is made part of the collector region. In one variation, the emitter region has the in-stack LBL structure and the collector region has the pinned layer structure. The TTM may comprise a spin valve transistor (SVT), a magnetic tunnel transistor (MTT), or a double junction structure.

Owner:WESTERN DIGITAL TECH INC

Bipolar transistor having self-aligned silicide and a self-aligned emitter contact border

ActiveUS20050121748A1Reduce capacitanceReduce resistanceTransistorSemiconductor/solid-state device detailsSalicideEngineering

The present invention provides a bipolar transistor having a raised extrinsic base silicide and an emitter contact border that are self-aligned. The bipolar transistor of the present invention exhibit reduced parasitics as compared with bipolar transistors that do not include a self-aligned silicide and a self-aligned emitter contact border. The present invention also is related to methods of fabricating the inventive bipolar transistor structure. In the methods of the present invention, a block emitter polysilicon region replaces a conventional T-shaped emitter polysilicon.

Owner:IBM CORP

Trench gate power semiconductor field effect transistor

ActiveUS20160372572A1Lower on-resistanceReduce contact resistanceTransistorSemiconductor/solid-state device manufacturingSmall cellPower MOSFET

Provided in the present invention is a trench gate power MOSFET (TMOS / UMOS) structure with a heavily doped polysilicon source region. The polysilicon source region is formed by deposition, and a trench-shaped contact hole is used at the source region, in order to attain low contact resistance and small cell pitch. The present invention may also be implemented in an IGBT.

Owner:JSAB TECH LTD

Three terminal magnetic sensor having an in-stack longitudinal biasing layer structure in the collector or emitter region

InactiveUS20060152860A1Lower base resistanceReduce emitter resistanceNanomagnetismMagnetic measurementsSpin valveCrystal

In one illustrative example, a three terminal magnetic sensor (TTM) suitable for use in a magnetic head has a base region, a collector region, and an emitter region. A first barrier layer is located between the emitter region and the base region, and a second barrier layer is located between the collector region and the base region. A sensing plane is defined along sides of the base region, the collector region, and the emitter region. The base region has a free layer structure, a pinned layer structure adjacent the first barrier layer, and a non-magnetic spacer layer located between the free layer structure and the pinned layer structure. The collector region comprises an in-stack longitudinal biasing layer (LBL) structure which magnetically biases the free layer structure, where the second barrier layer serves as a non-magnetic spacer layer for the in-stacking biasing layer structure. In one variation, the layers are inverted such that the emitter region has the in-stack LBL structure. The TTM may comprise a spin valve transistor (SVT), a magnetic tunnel transistor (MTT), or a double junction structure.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

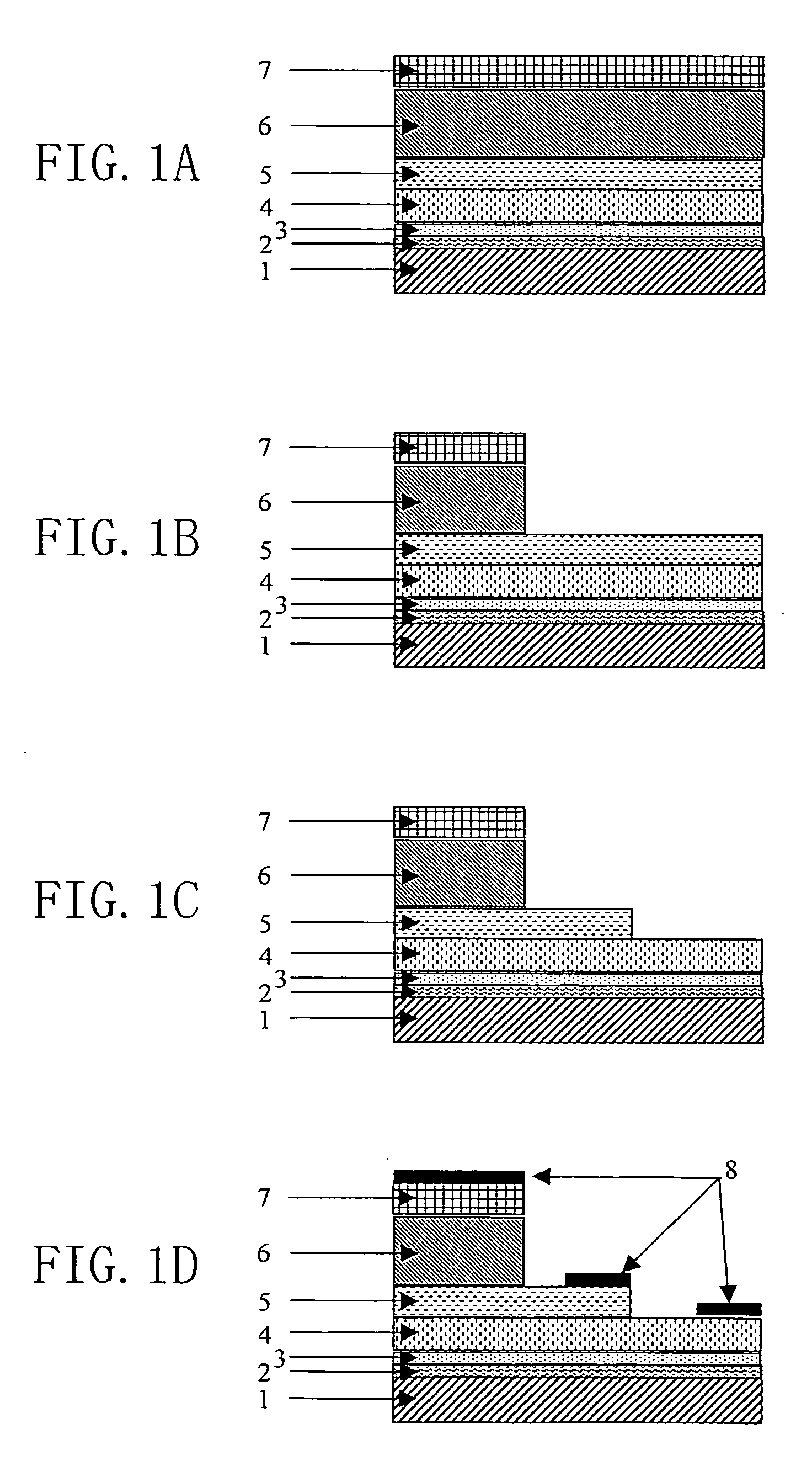

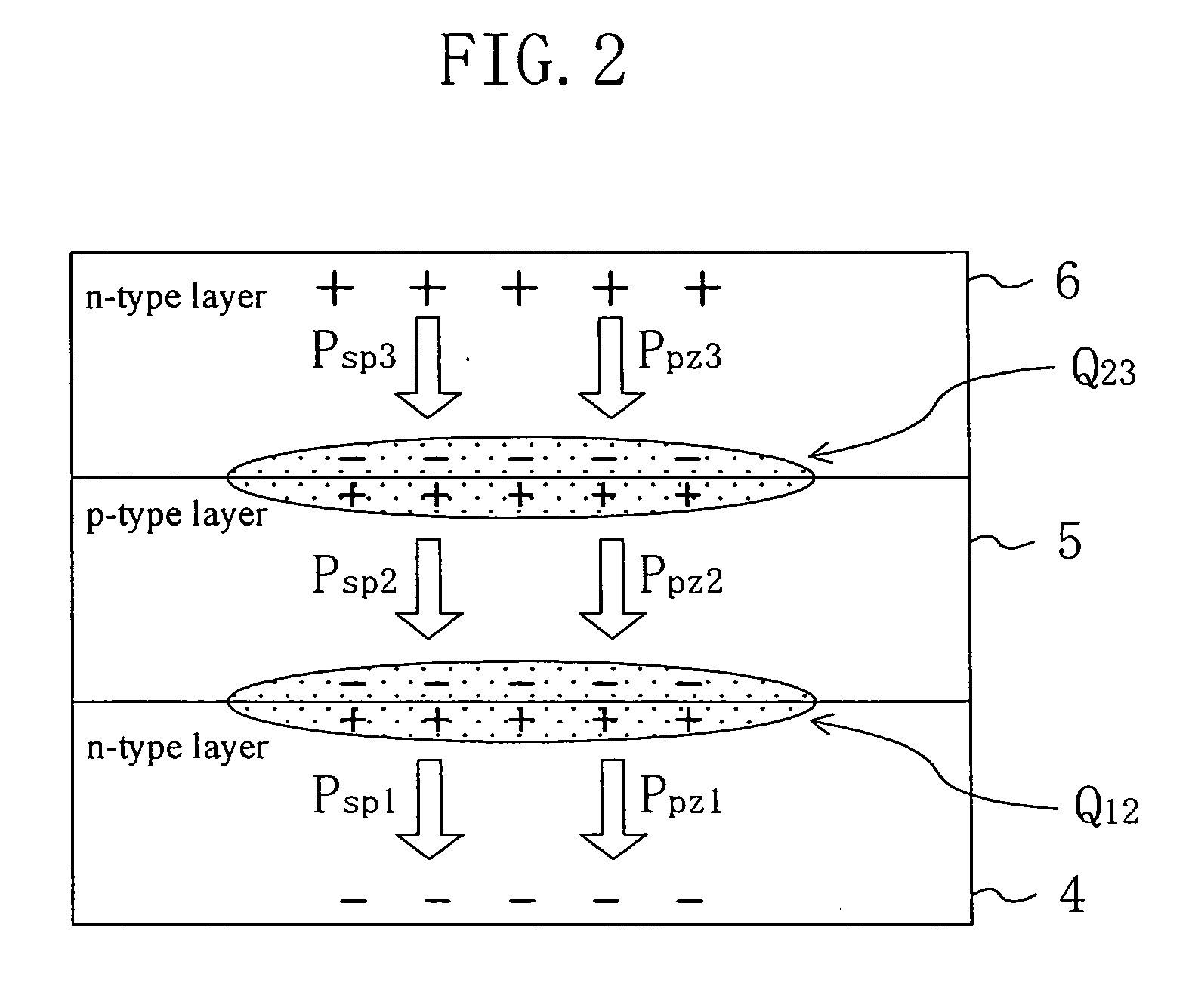

Semiconductor device and hetero-junction bipolar transistor

ActiveUS20050121696A1Reduce resistanceLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesNitrogenElectron

In an npn-type HBT, each of an emitter layer and a collector layer is formed of AlGaN and a base layer is formed of GaN. The emitter layer is in contact with a nitrogen polarity surface of the base layer and the collector layer is in contact with a gallium polarity surface of the base layer. An electric charge is generated at each interface due to a spontaneous polarization and a piezo polarization generated in each of the layers. Because of the electric charge, an internal field is generated so as to accelerate electrons in the base layer.

Owner:PANASONIC CORP