Patents

Literature

2348 results about "Output impedance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The output impedance of an electrical network is the measure of the opposition to current flow (impedance), both static (resistance) and dynamic (reactance), into the load network being connected that is internal to the electrical source. The output impedance is a measure of the source's propensity to drop in voltage when the load draws current, the source network being the portion of the network that transmits and the load network being the portion of the network that consumes.

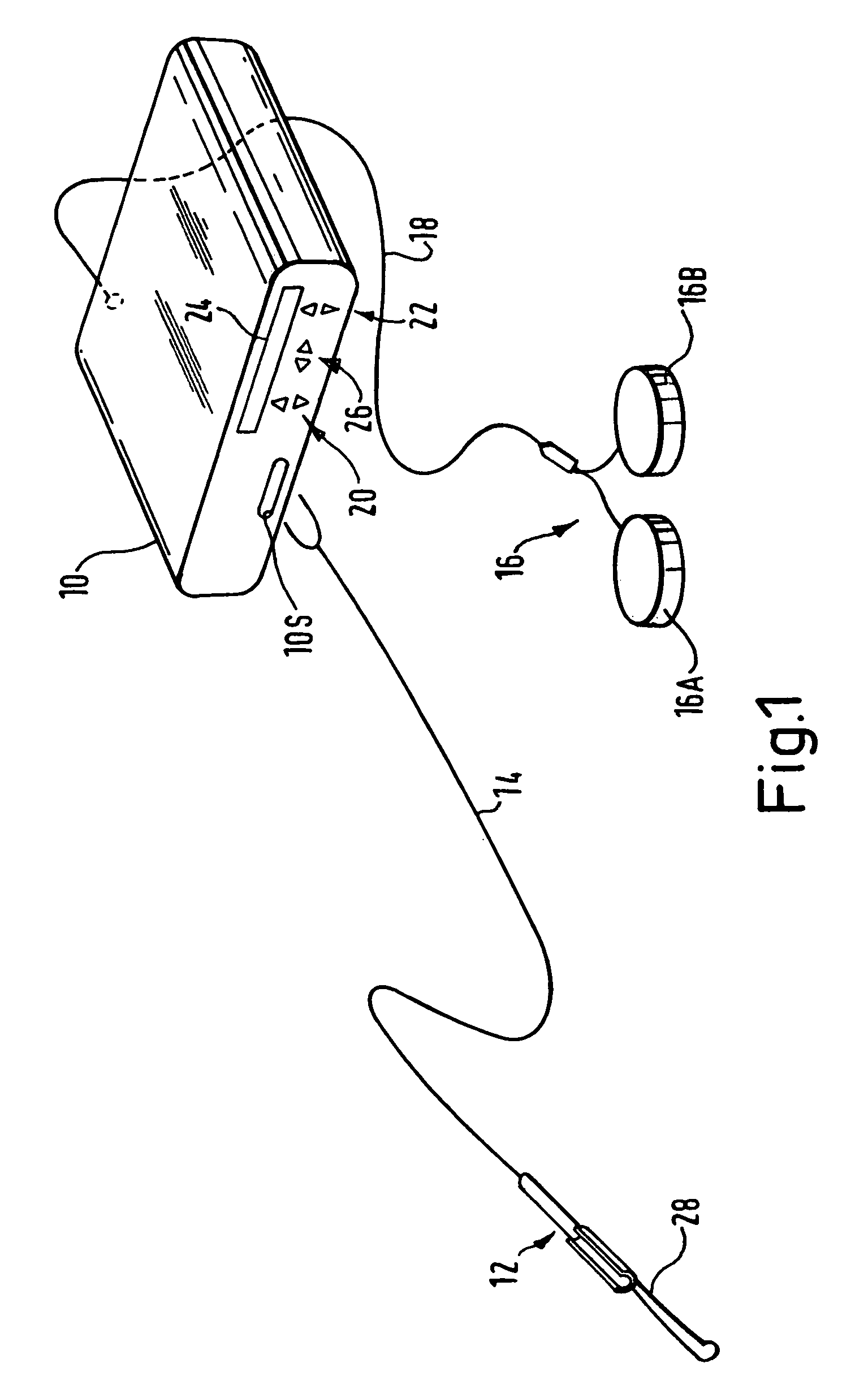

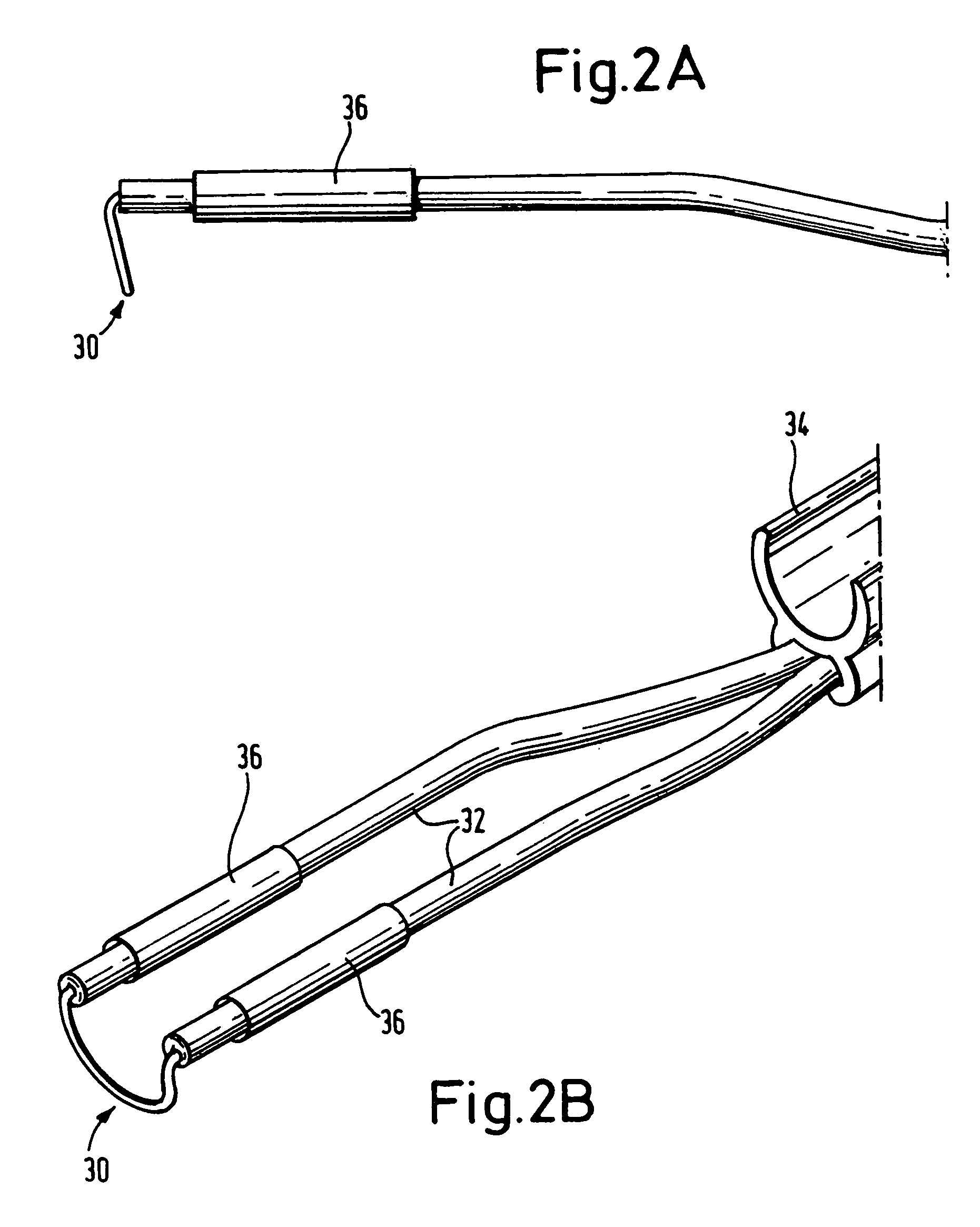

Electrosurgical generator

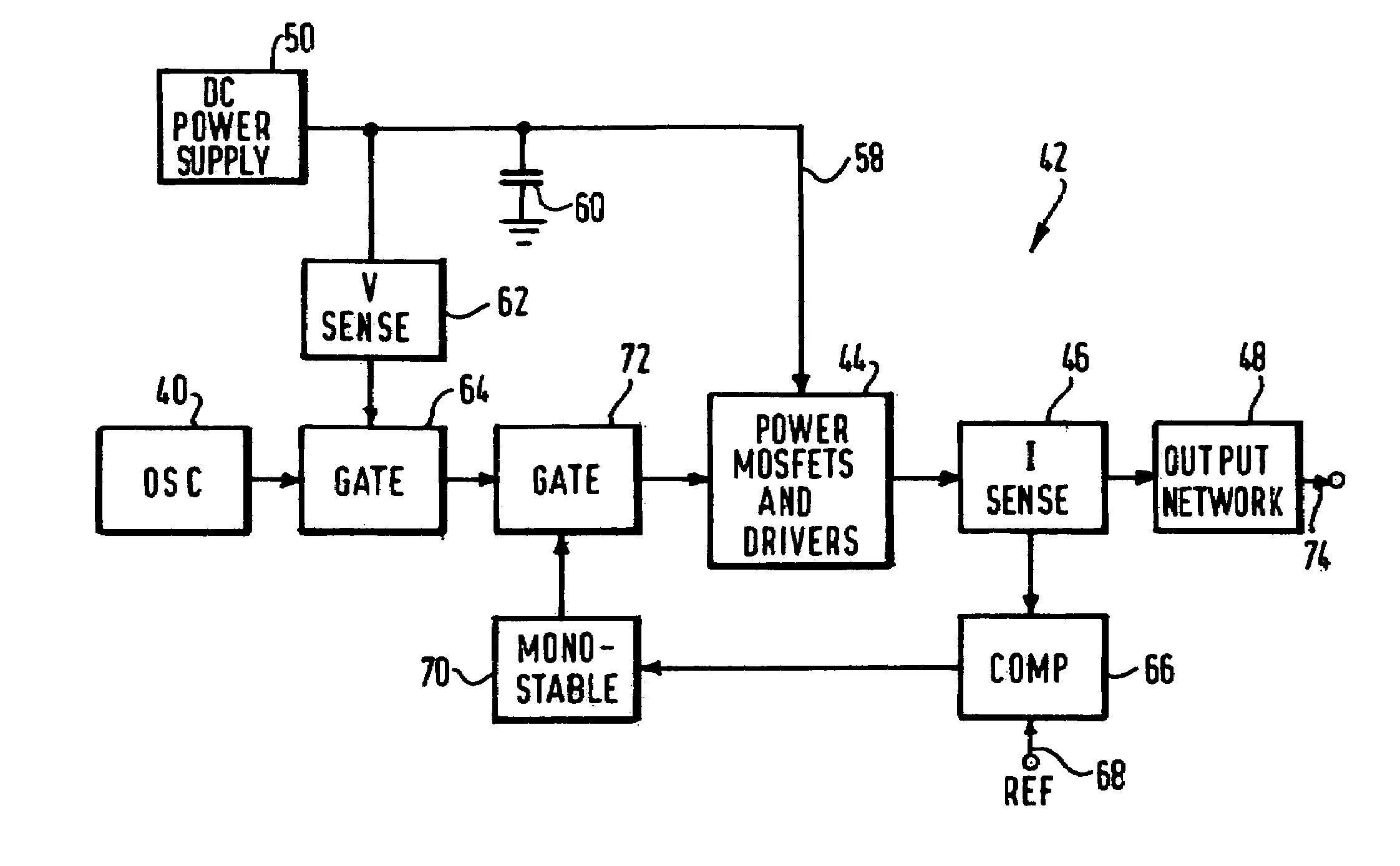

ActiveUS7211081B2Reducing switching transientPromote resultsSurgical instruments for heatingCapacitor voltageEngineering

An electrosurgical generator for supplying RF power to an electrosurgical instrument for cutting or vaporising tissue has an RF output stage (42) with an RF power bridge (Q1, Q2, Q3, Q4), a pair of output lines (74) and a series-resonant output network (48). The output impedance of the output stage (42) at the output lines (74) is less than 200 / √P ohms, where P is the maximum continuous RF output power of the generator. The generator offers improved cutting and vaporising performance, especially in relation to the reliability with which an arc can be struck when presented with an initial low impedance load. Overloading of the output stage is prevented by rapidly operating protection circuitry responsive to a predetermined electrical condition such as a substantial short-circuit across the output lines. In the preferred embodiment, the output stage is capable of maintaining output pulses at least 1kW peak by supplying the power bridge from a large reservoir capacitor (60). Pulsing is dynamically variable in response to load conditions by controlling the maximum energy per pulse in response to the reservoir capacitor voltage.

Owner:GYRUS MEDICAL LTD

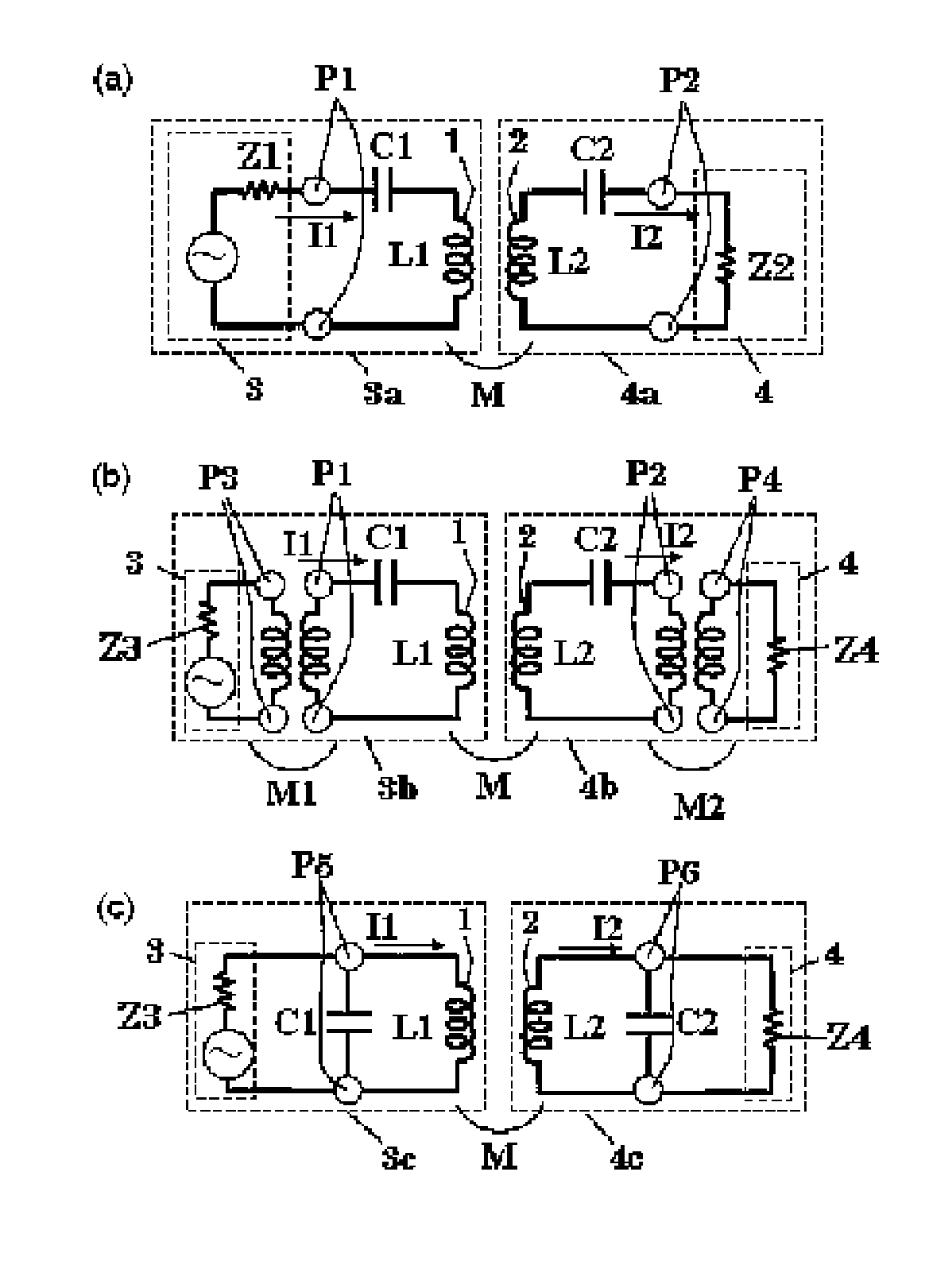

Induced power transmission circuit

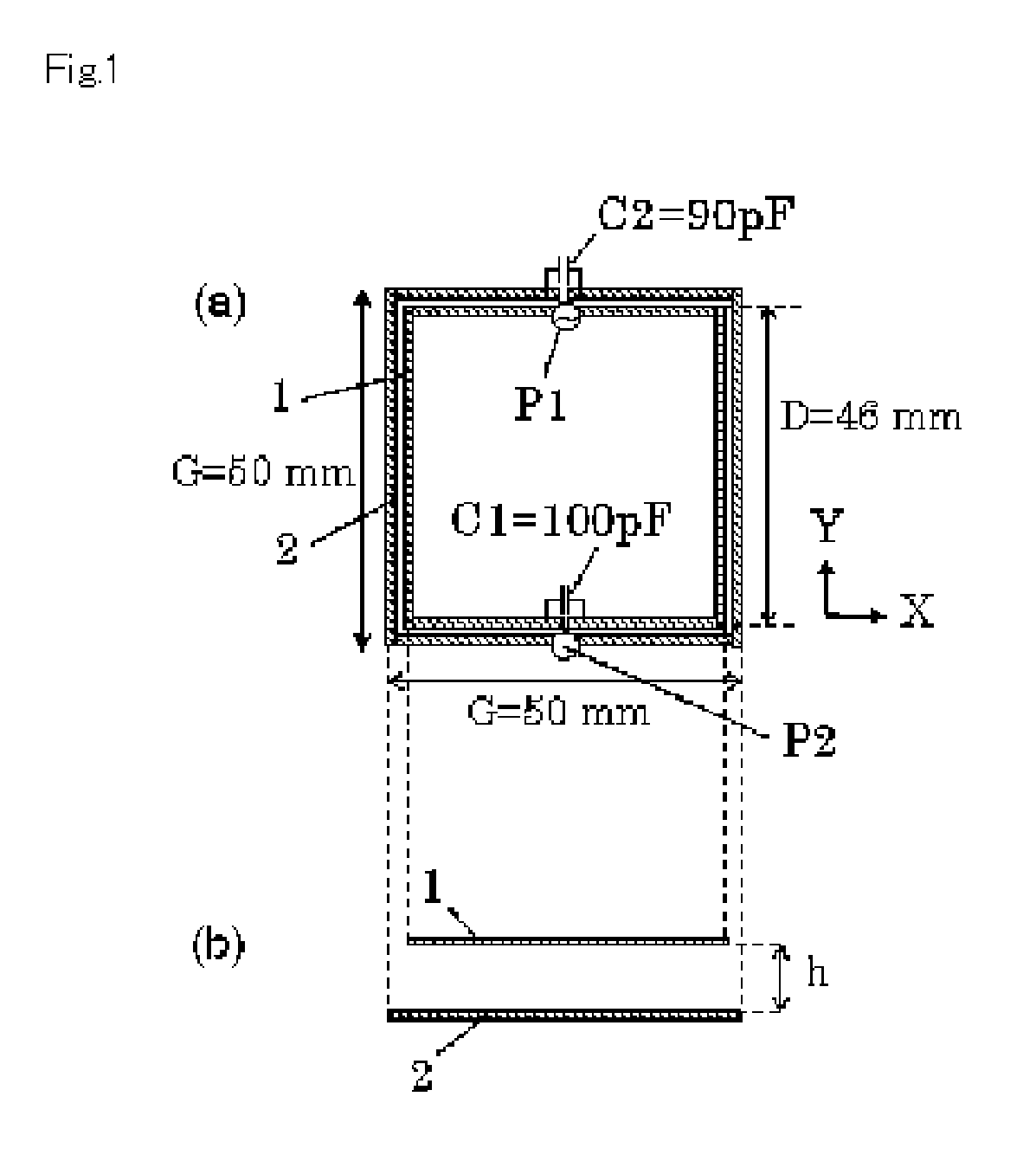

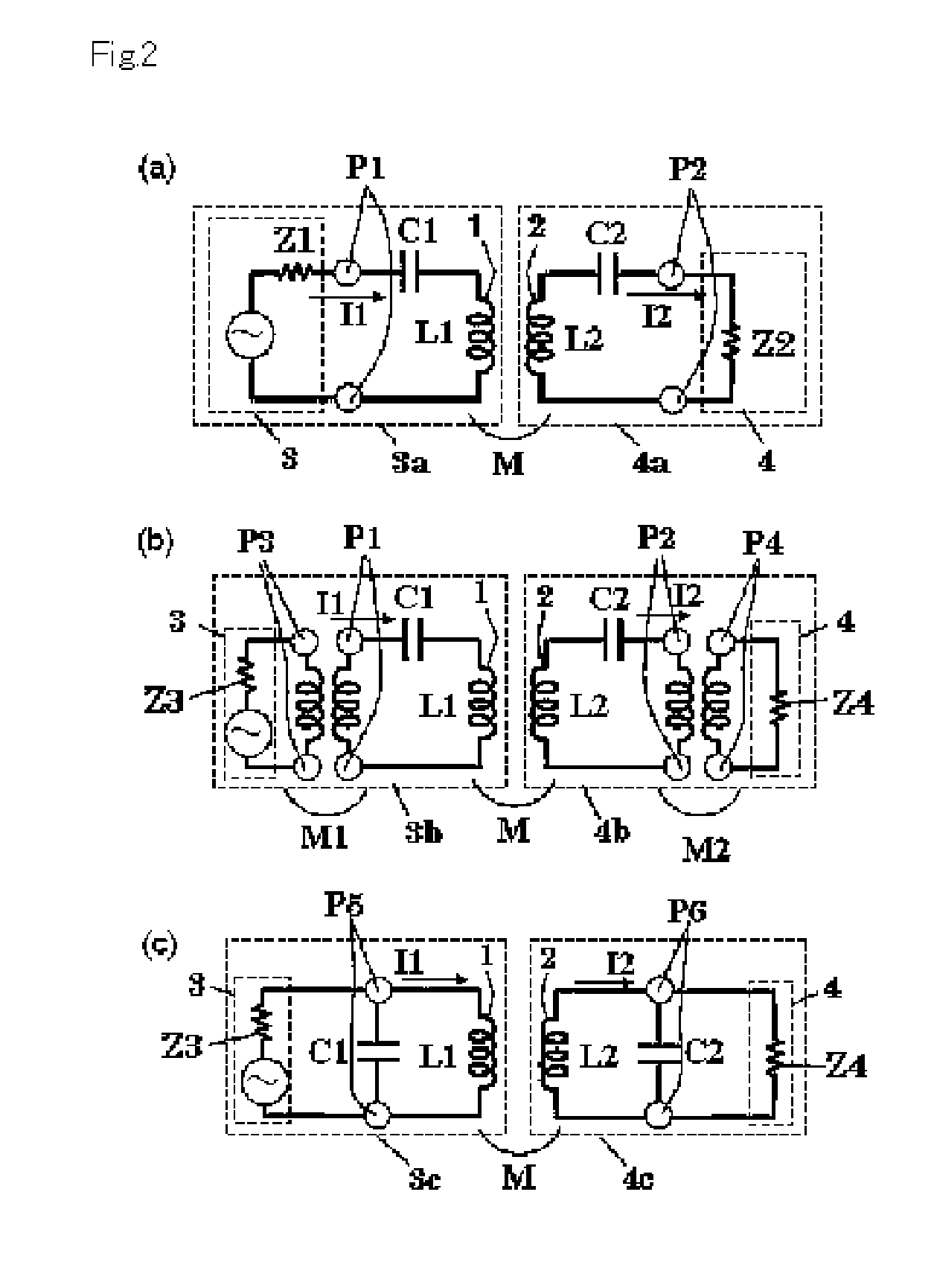

ActiveUS20100213770A1Efficient transferEasy to calculateMultiple-port networksElectromagnetic wave systemElectric power transmissionLoad circuit

To provide an induced power transmission circuit that transmits, from a transmission antenna (1) connected to a power supply circuit, an AC power having an angular frequency ω to a spaced reception antenna (2) with an excellent efficiency, thereby transmitting it to a load circuit. The induced power transmission circuit comprises a circuit the two ends of which are coupled by a capacitor (C1) and in which the power supply circuit is connected in series to a midway port (1) (P1) of the transmission antenna (1) having an effective self-inductance L1; and a circuit the two ends of which are coupled by a capacitor (C2) and in which the load circuit is connected in series to a midway port (2) (P2) of the reception antenna (2) having an effective self-inductance L2; wherein for a coupling coefficient k of the electromagnetic induction between the antennas and for a phase angle β having an arbitrary value, the angular frequency ω is set to the square root of the reciprocal of a value of L2×C2×(1+k*cos (β)), the output impedance of the power supply circuit is set to approximately kωL1*sin (β), and the input impedance of the load circuit is set to approximately kωL2*sin (β). There is also provided an impedance converting circuit that converts the circuit impedances.

Owner:KIKUCHI HIDEO

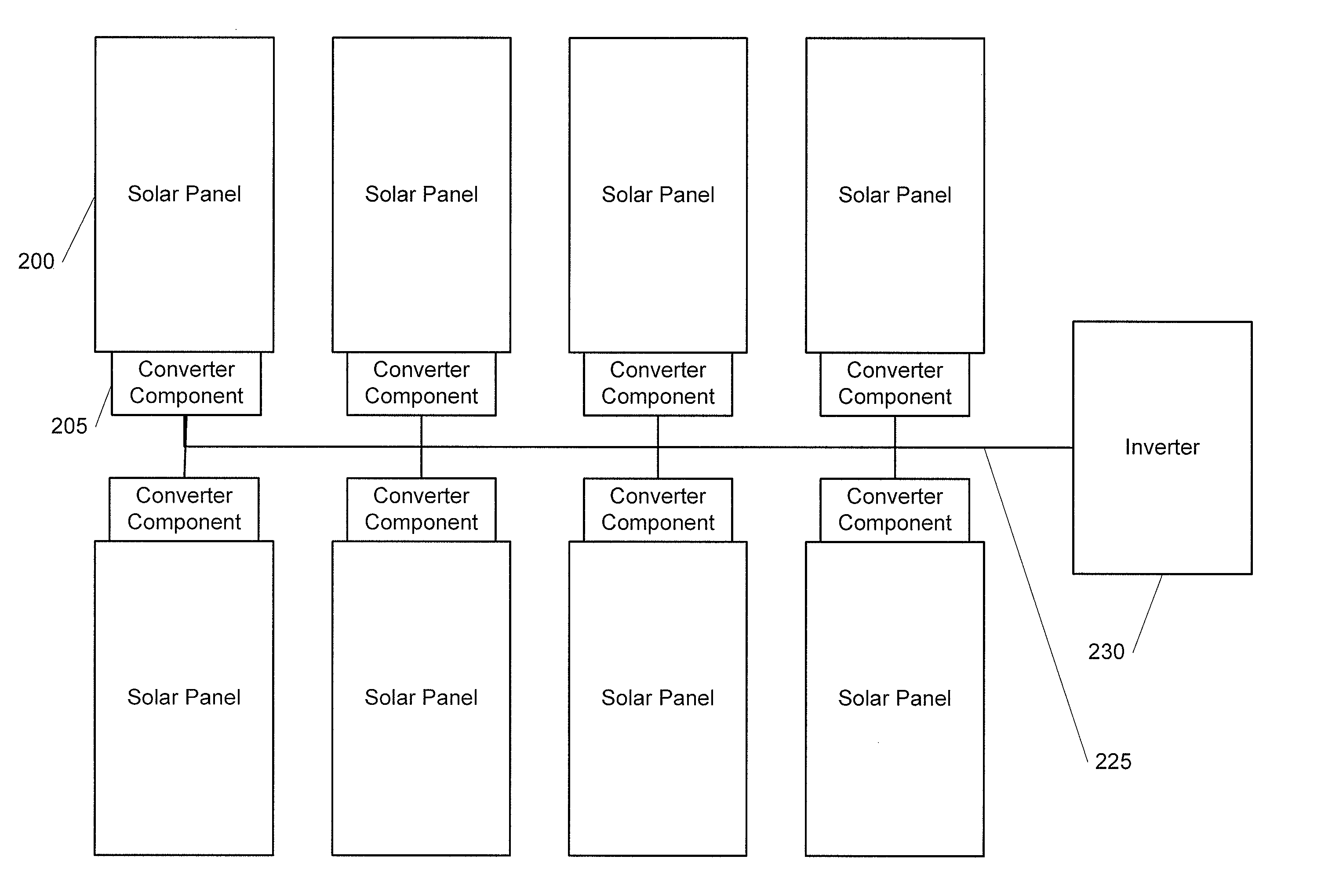

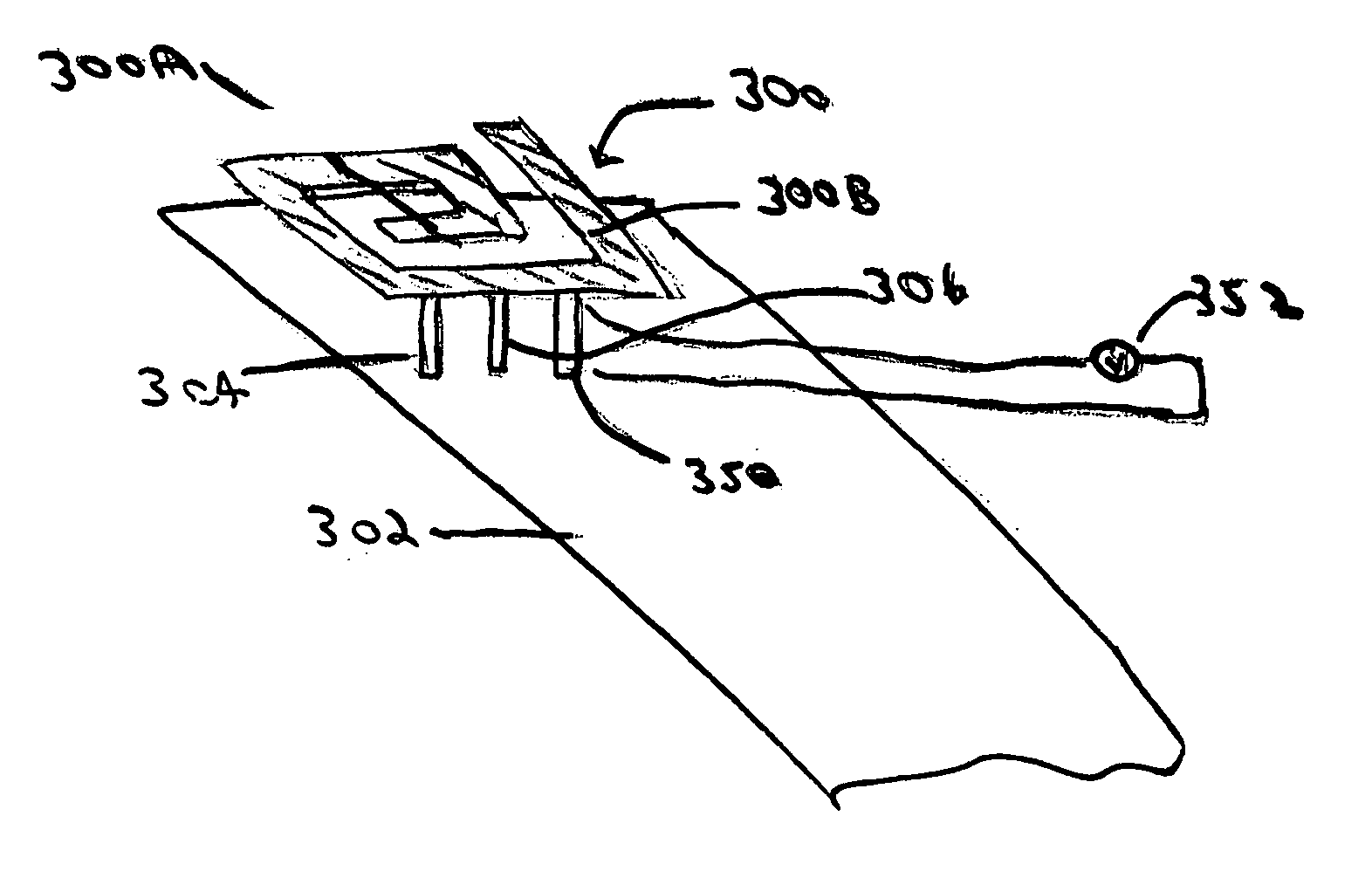

Advanced Renewable Energy Harvesting

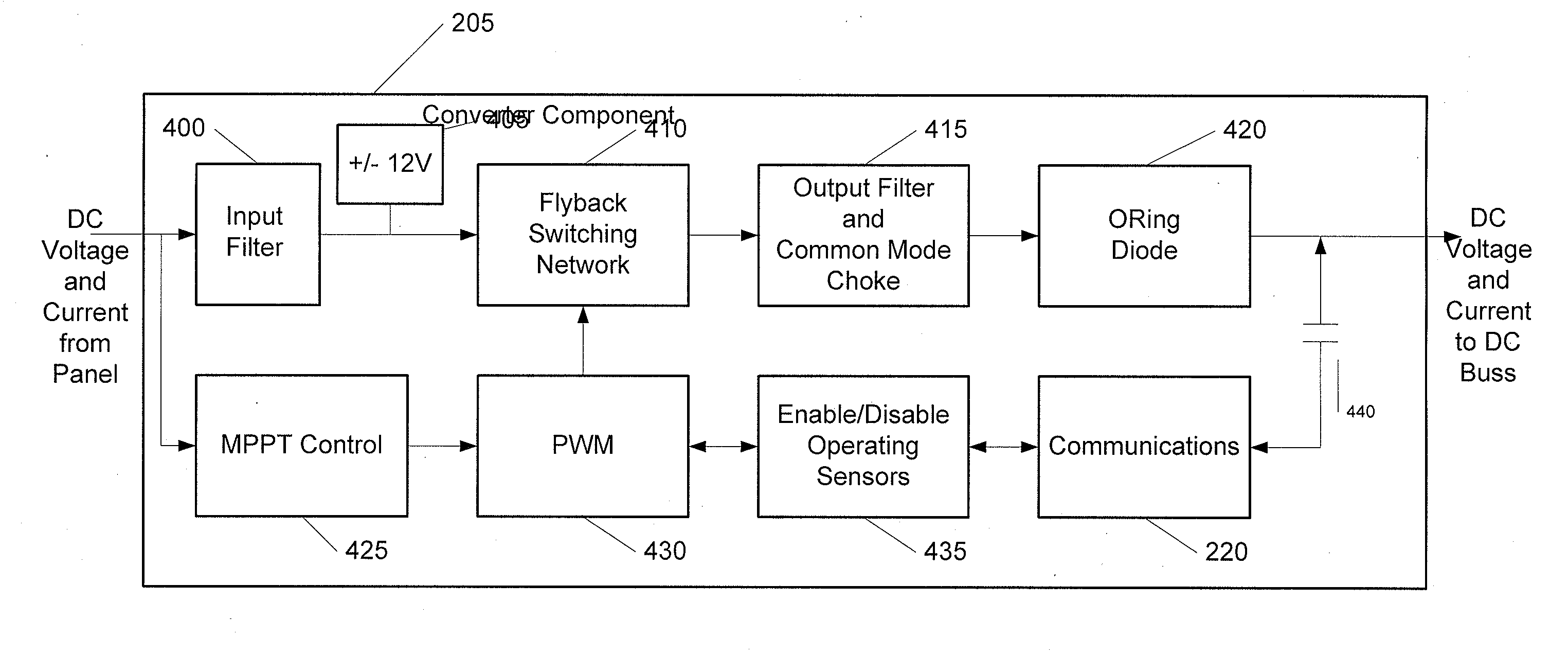

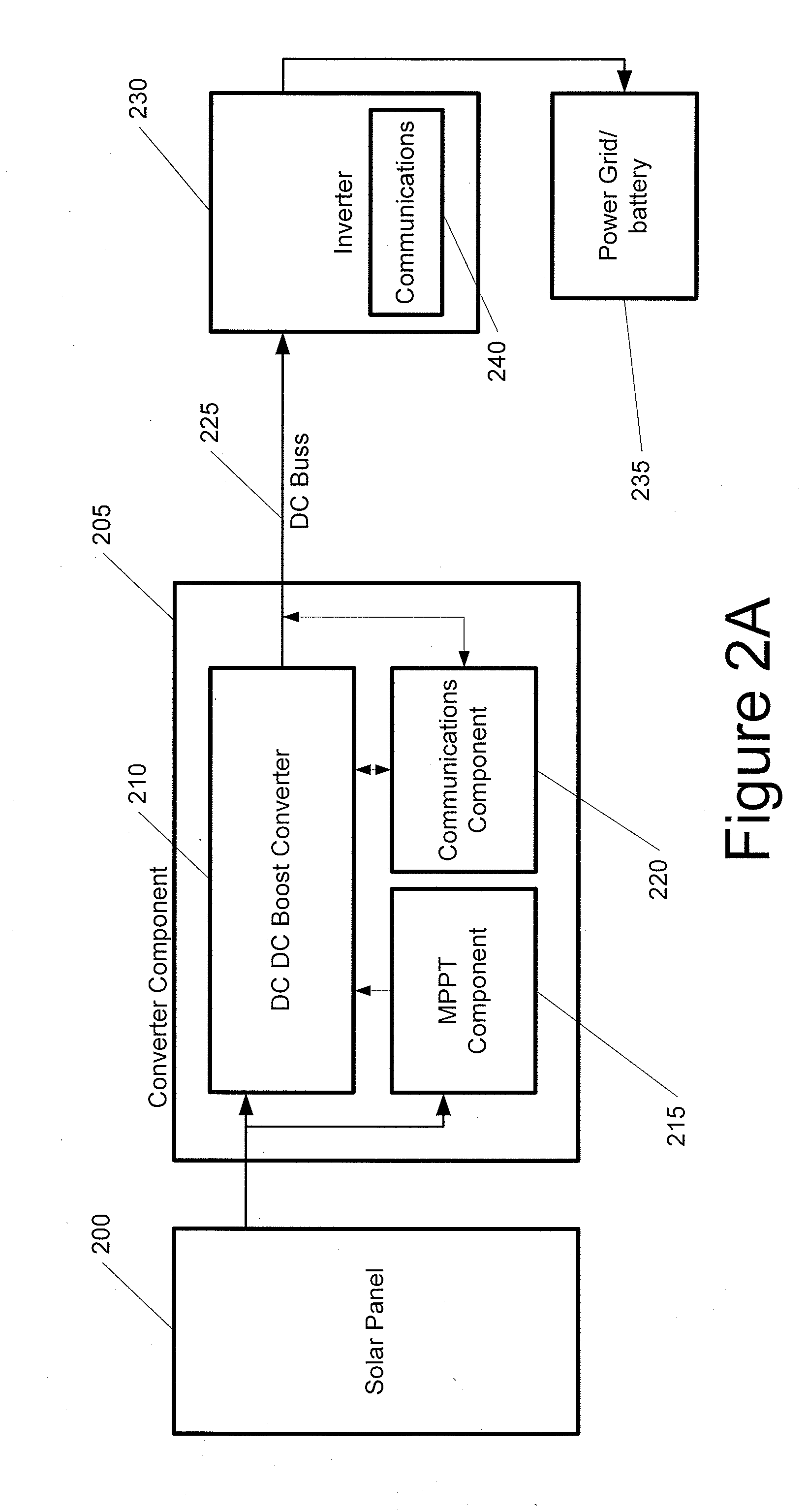

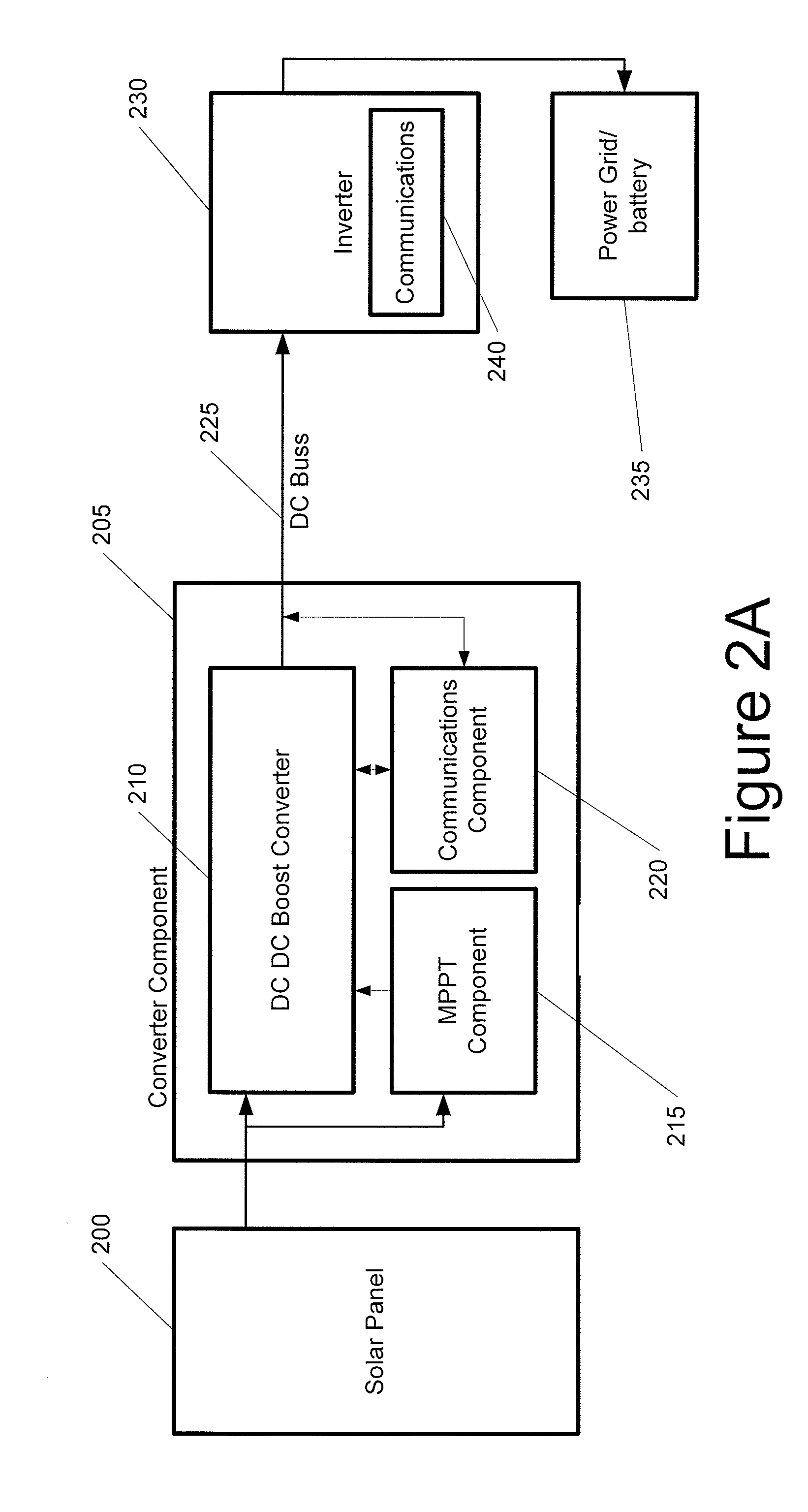

InactiveUS20090160258A1Power maximizationMinimize transmission wire lossBatteries circuit arrangementsSingle network parallel feeding arrangementsTransverterInput impedance

The power of DC electrical sources is combined onto a DC buss, such that each source behaves independently from any other source attached to the buss. In one embodiment, a converter module is attached to each of a plurality of solar photovoltaic panels and its output is attached in a parallel manner to a common buss that forms the input to a DC AC inverter. The converter module includes a Maximum Power Point Tracking component that matches the output impedance of the panels to the input impedance of the converter module. The converter also includes a communication component that provides parametric data and identification to a central inverter. Data generated by each converter module is transmitted over the power line or by wireless means and is collected at the inverter and forwarded to a data collection and reporting system.

Owner:EIQ ENERGY INC

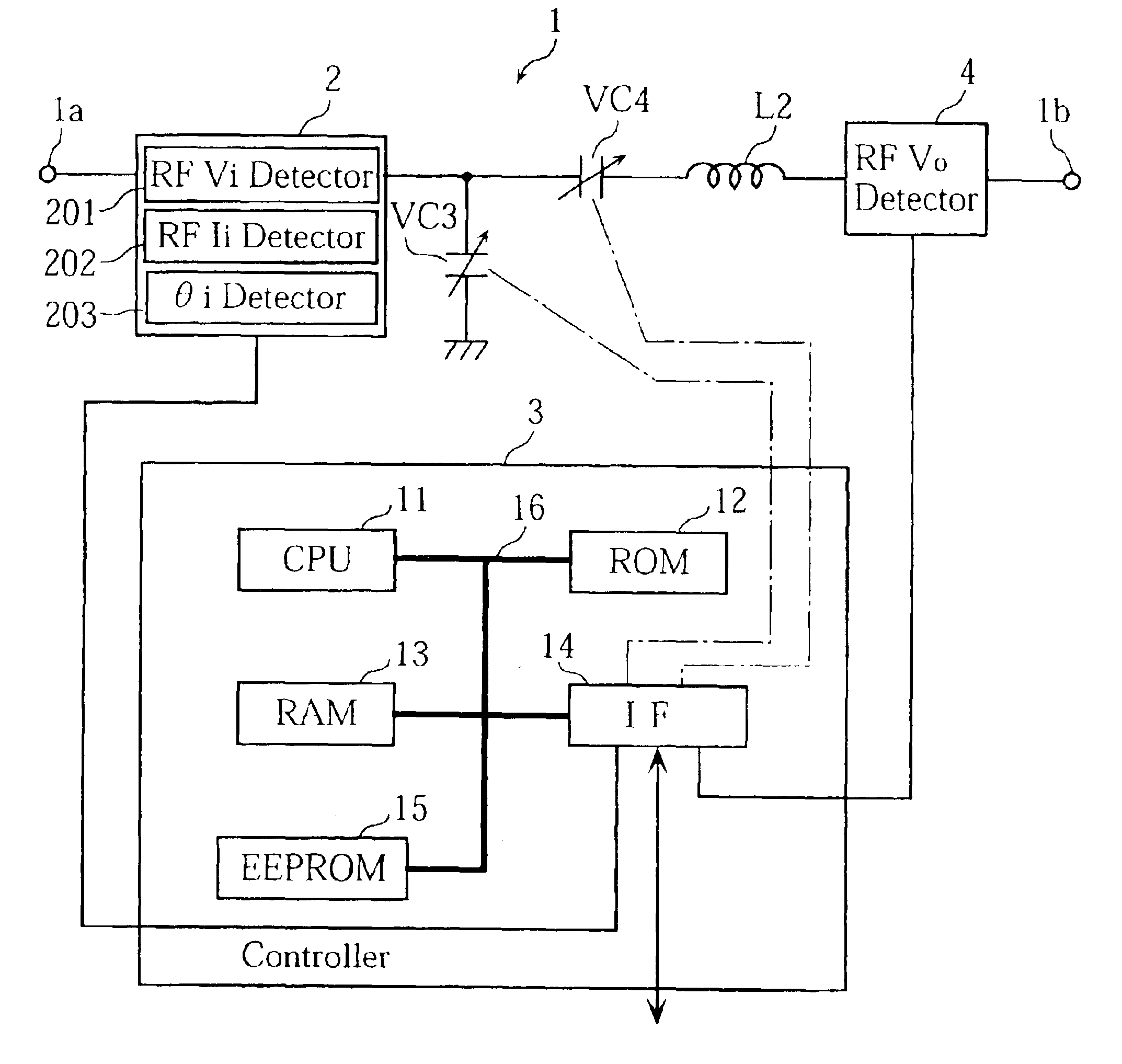

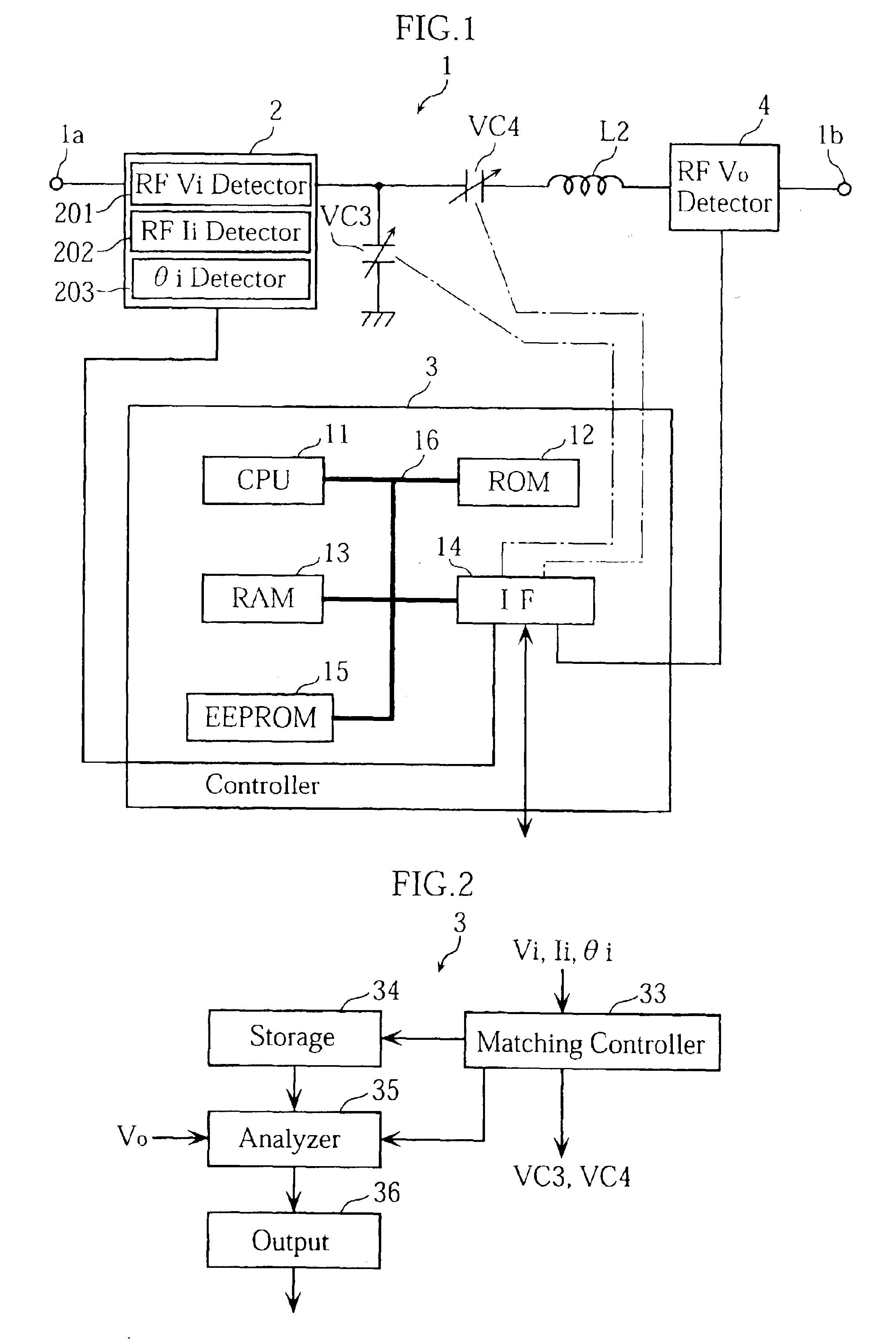

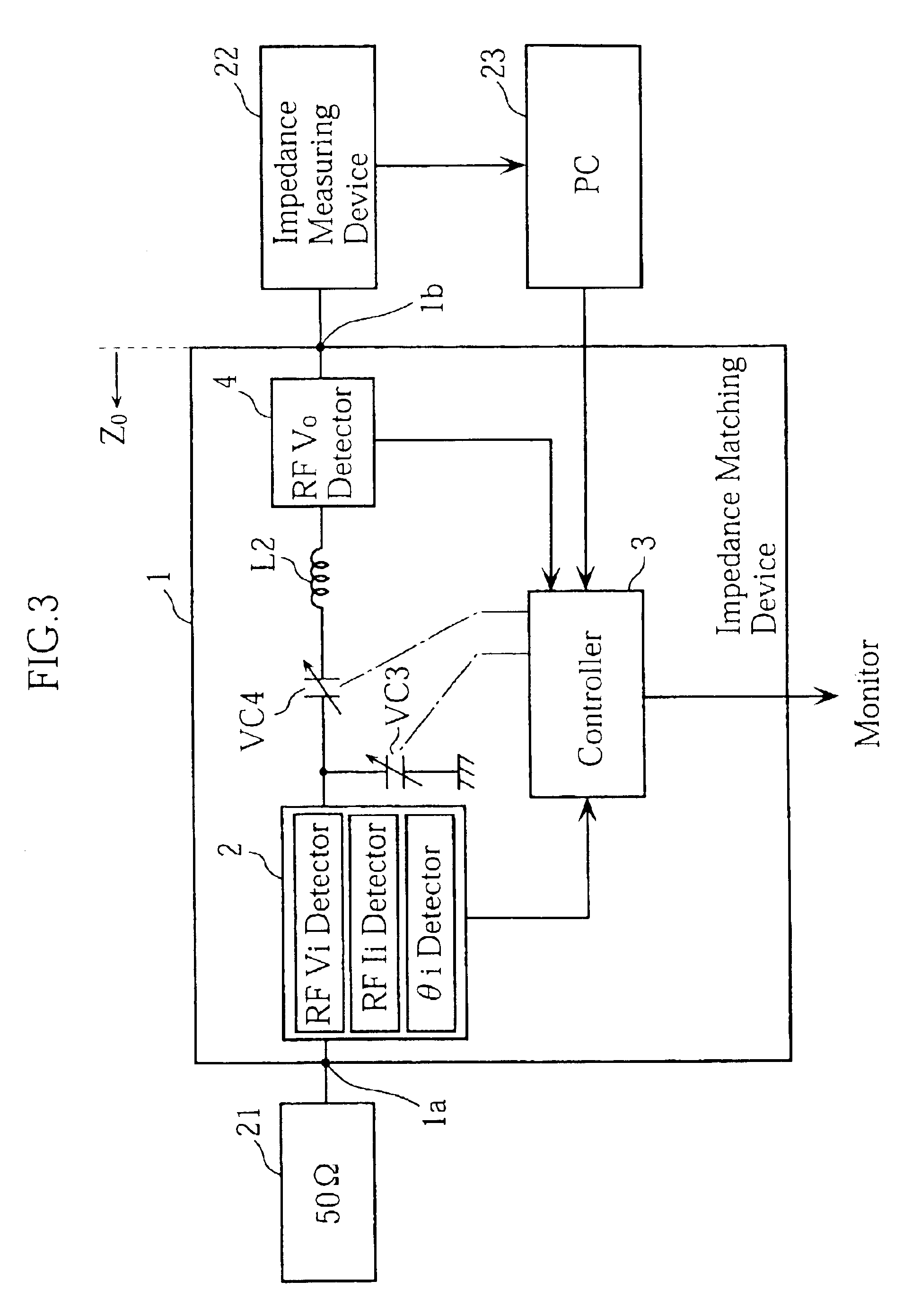

Impedance matching device provided with reactance-impedance table

InactiveUS6946847B2Accurate analysisImpedence matching networksMultiple-port networksCapacitanceElectricity

An impedance matching device is provided, for which the electric characteristics at an output terminal are accurately analyzed. The matching device is provided with an input detector for detecting RF voltage and current at the input terminal, and an output detector for detecting RF voltage outputted from the output terminal. The matching device also includes a controller for achieving impedance matching between a high frequency power source connected to the input terminal and a load connected to the output terminal. The impedance matching is performed by adjusting variable capacitors based on the detection data supplied from the input detector. When the impedance of the power source is matched to that of the load, the controller calculates the output impedance, RF voltage and RF current at the output terminal, based on the adjusted capacitances of the capacitors, a pre-obtained reactance-impedance data and the detection data supplied from the output detector.

Owner:DAIHEN CORP

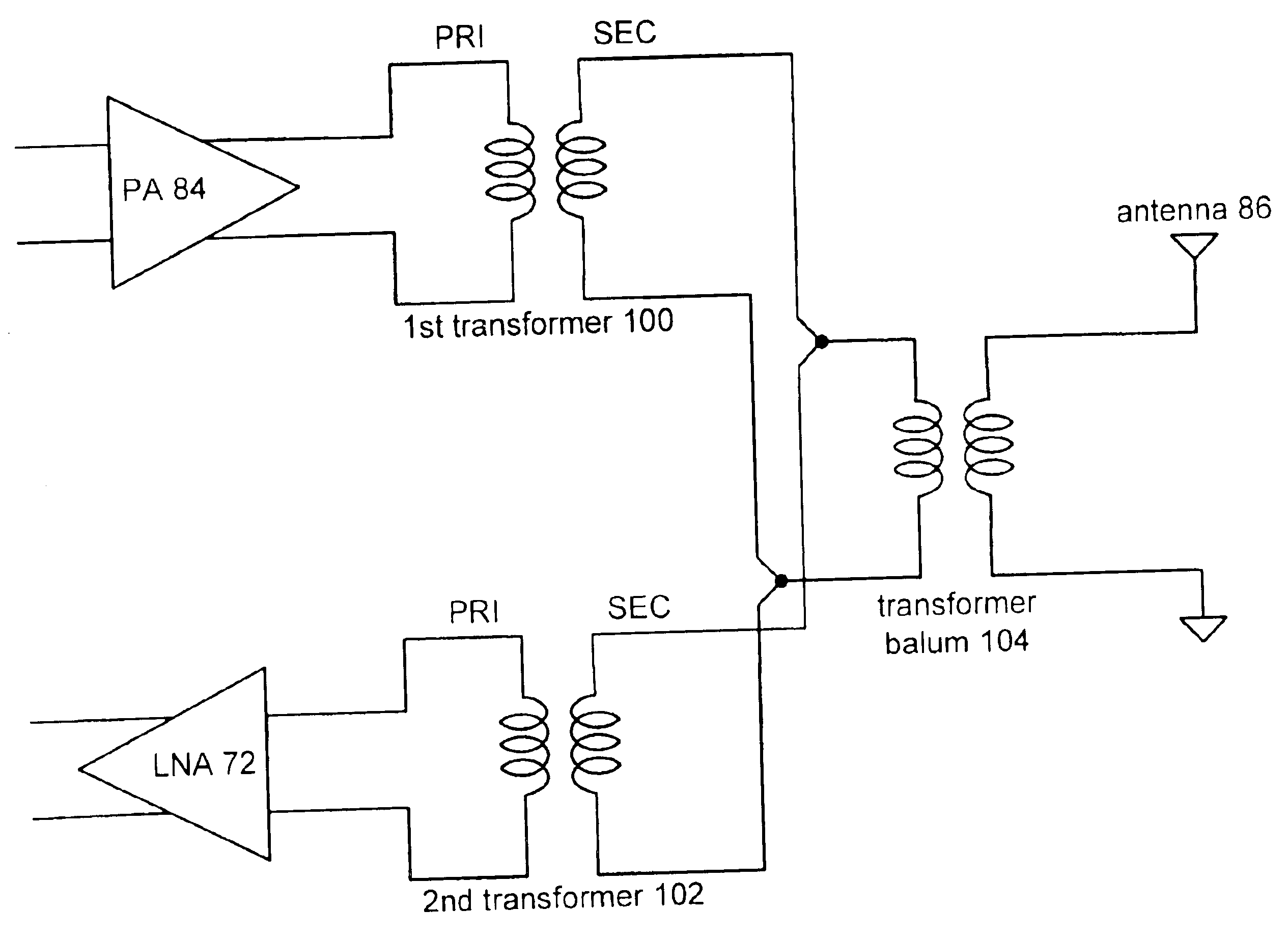

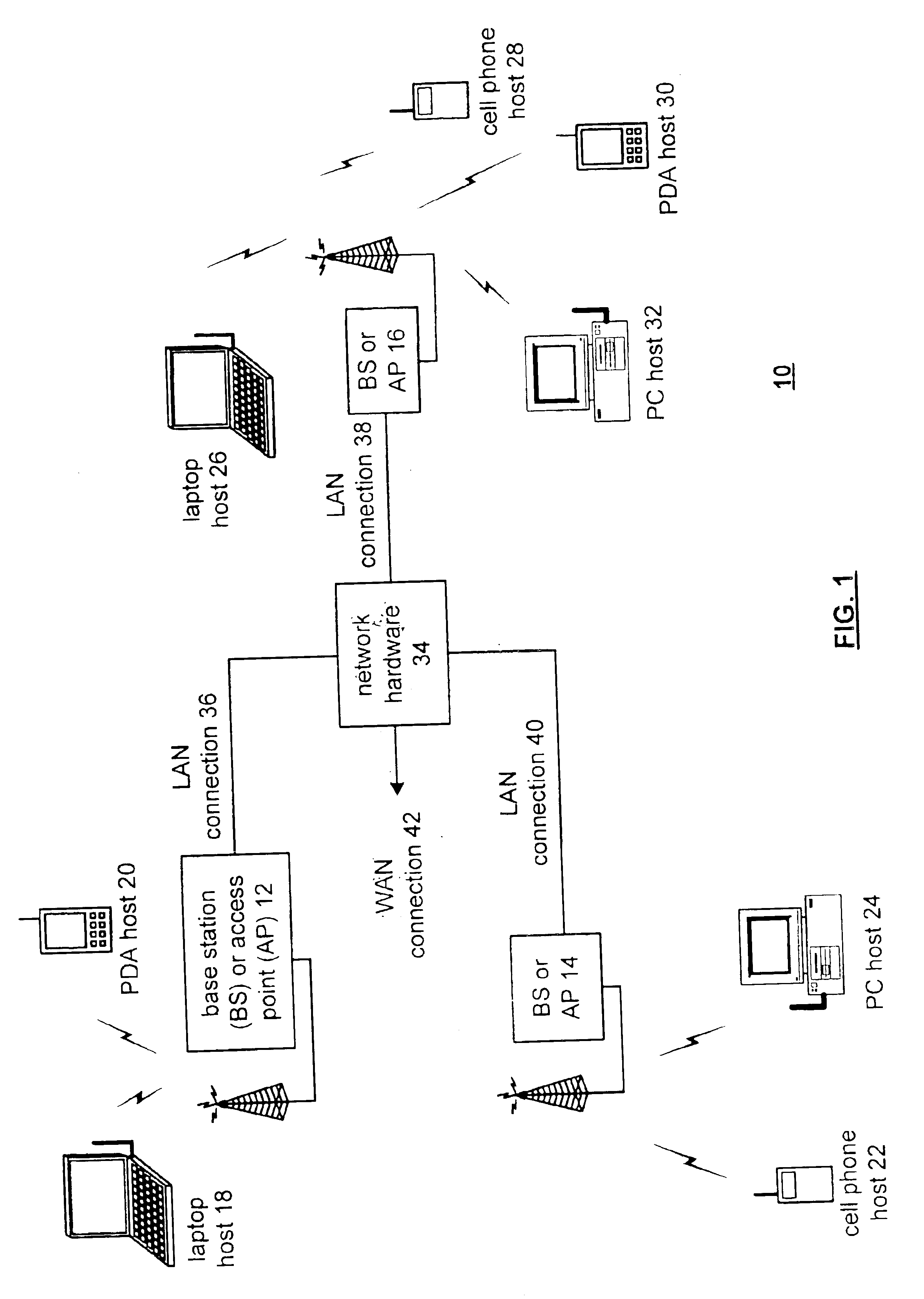

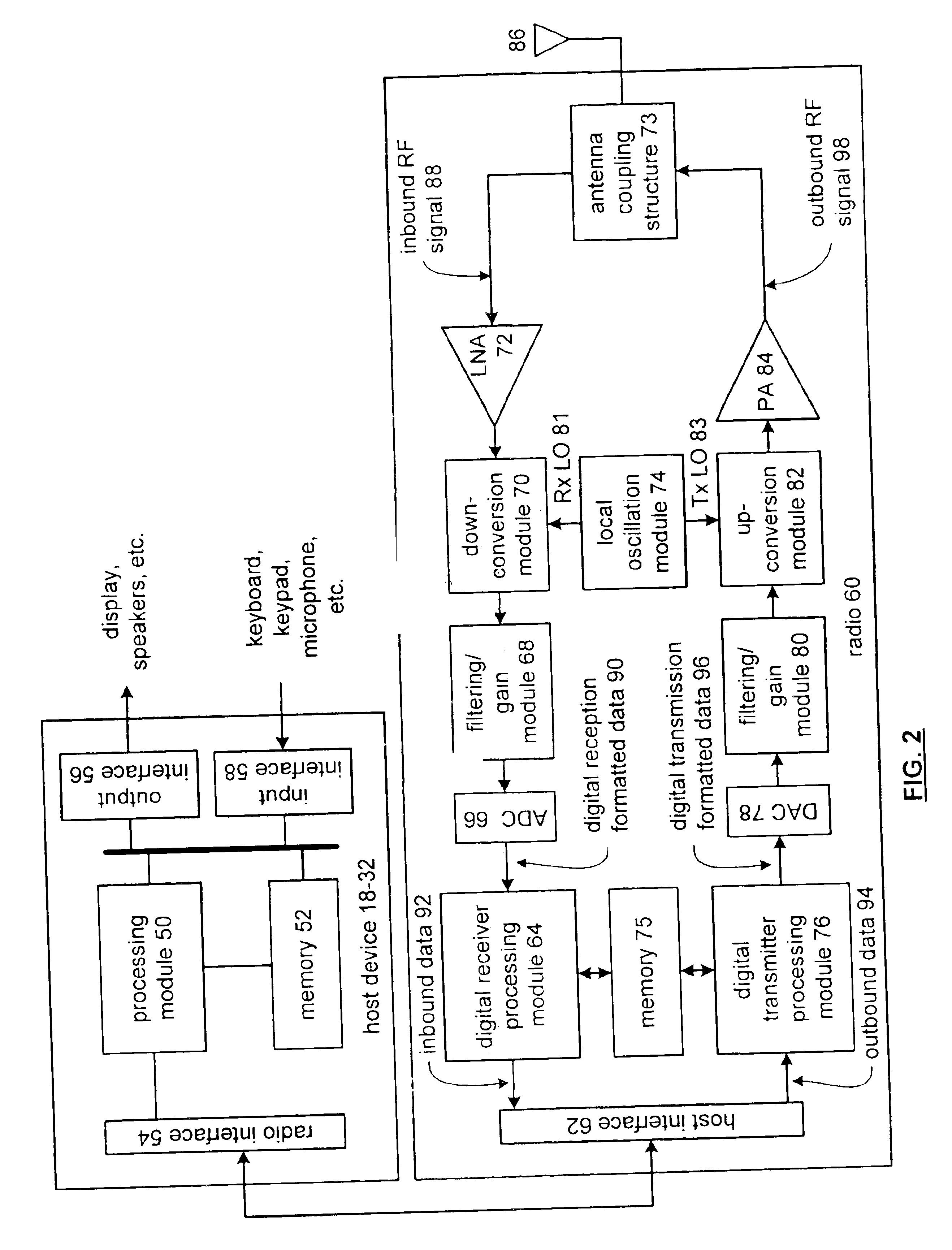

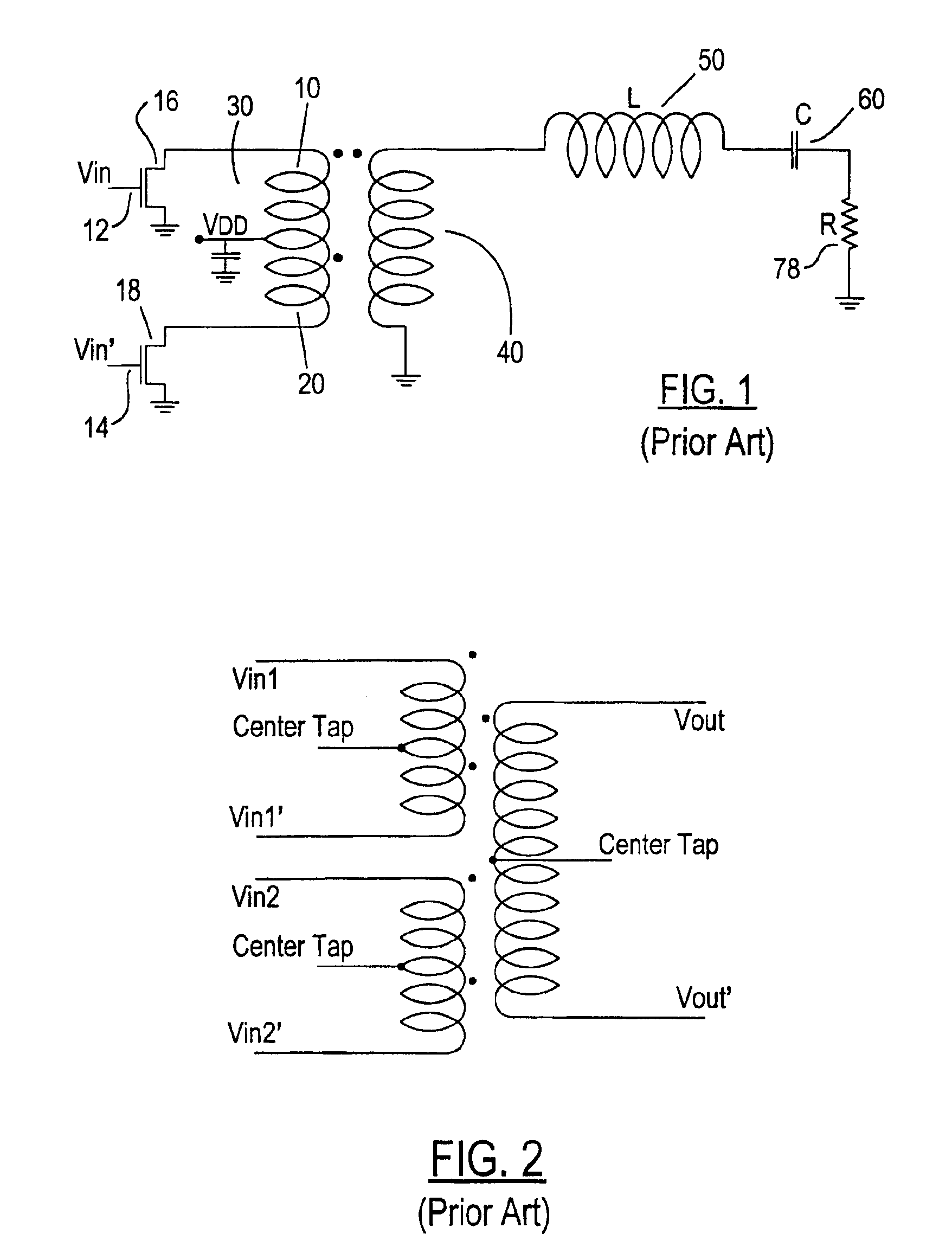

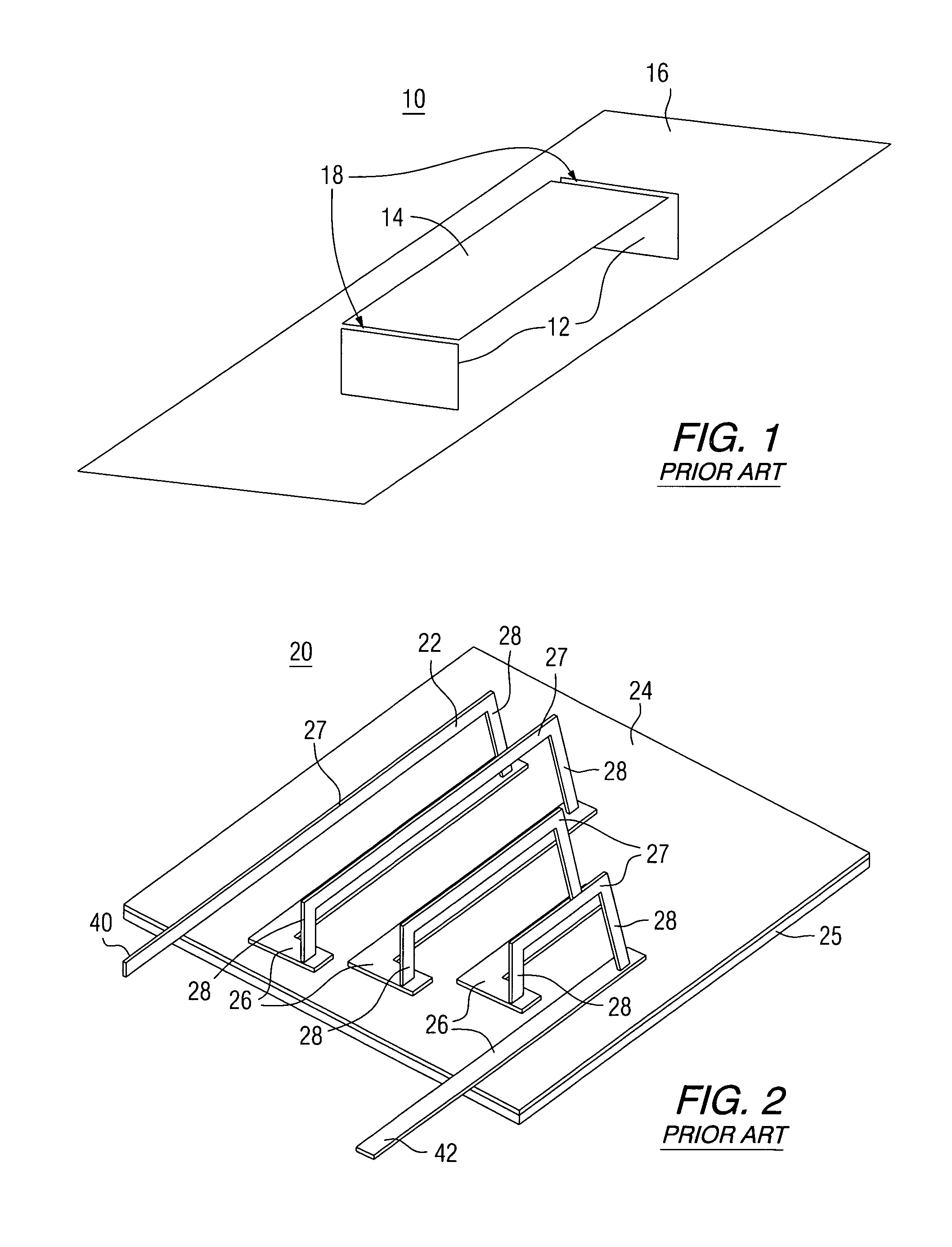

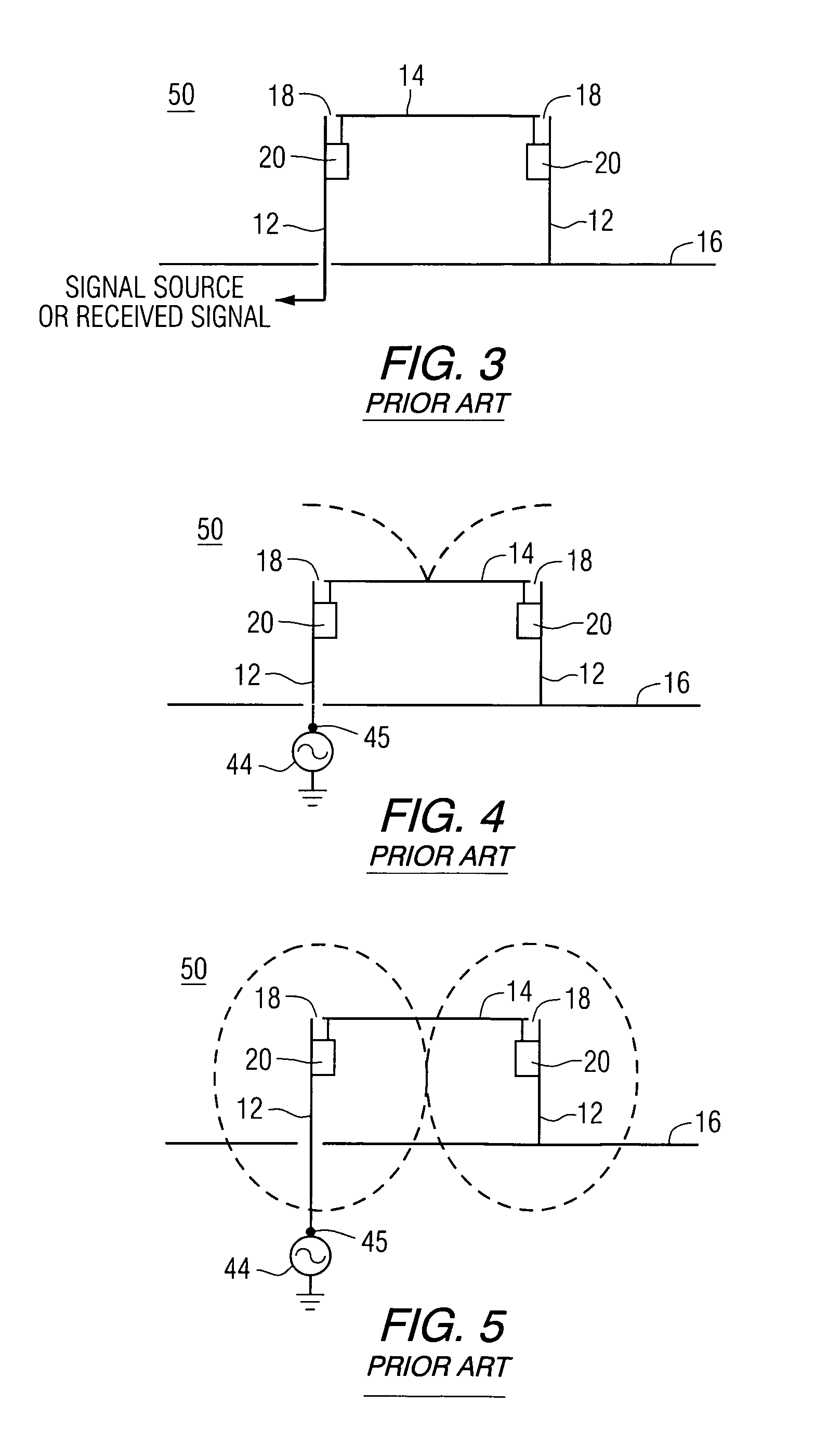

RF antenna coupling structure

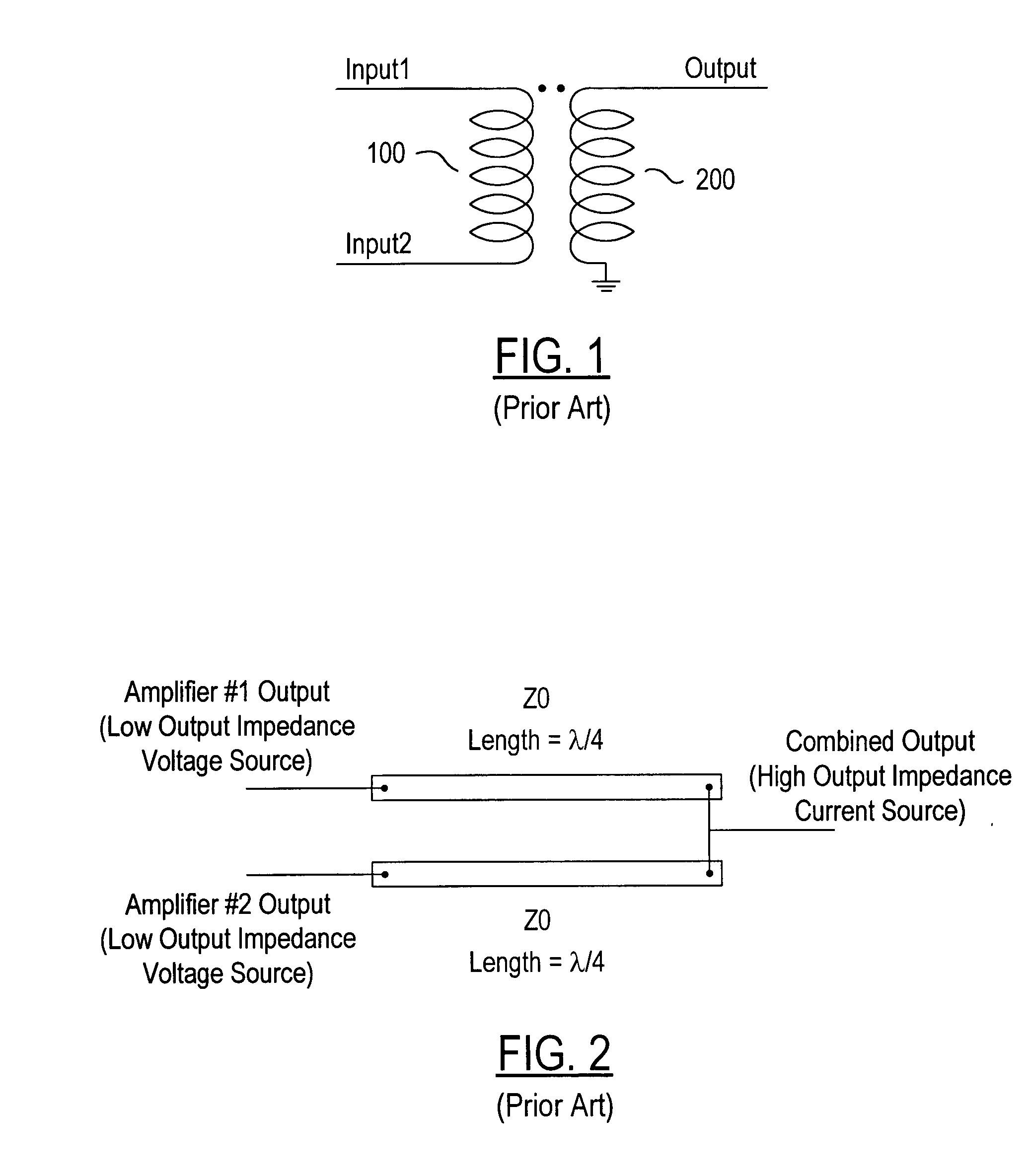

InactiveUS6919858B2Resonant long antennasSimultaneous aerial operationsAudio power amplifierTransformer

An RF antenna coupling structure includes a first transformer, a second transformer, and a transformer balun. The first transformer includes a primary winding and a secondary winding, wherein the primary winding of the first transformer is operably coupled to a power amplifier, and wherein the secondary winding of the first transformer has a desired output impedance corresponding to the operational needs of the power amplifier. The second transformer includes a primary winding and a secondary winding, wherein the primary winding of the second transformer is operably coupled to a low noise amplifier, and wherein the secondary winding of the second transformer has a desired output impedance corresponding to the needs of the low noise amplifier. The transformer balun includes a differential winding and a single-ended winding, wherein the differential winding is operably coupled to the secondary windings of the first and second transformers and the single-ended winding is operably coupled to an antenna.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Advanced renewable energy harvesting

InactiveUS8138631B2Power maximizationEfficiently invertingBatteries circuit arrangementsSingle network parallel feeding arrangementsTransverterInput impedance

The power of DC electrical sources is combined onto a DC buss, such that each source behaves independently from any other source attached to the buss. In one embodiment, a converter module is attached to each of a plurality of solar photovoltaic panels and its output is attached in a parallel manner to a common buss that forms the input to a DC AC inverter. The converter module includes a Maximum Power Point Tracking component that matches the output impedance of the panels to the input impedance of the converter module. The converter also includes a communication component that provides parametric data and identification to a central inverter. Data generated by each converter module is transmitted over the power line or by wireless means and is collected at the inverter and forwarded to a data collection and reporting system.

Owner:EIQ ENERGY INC

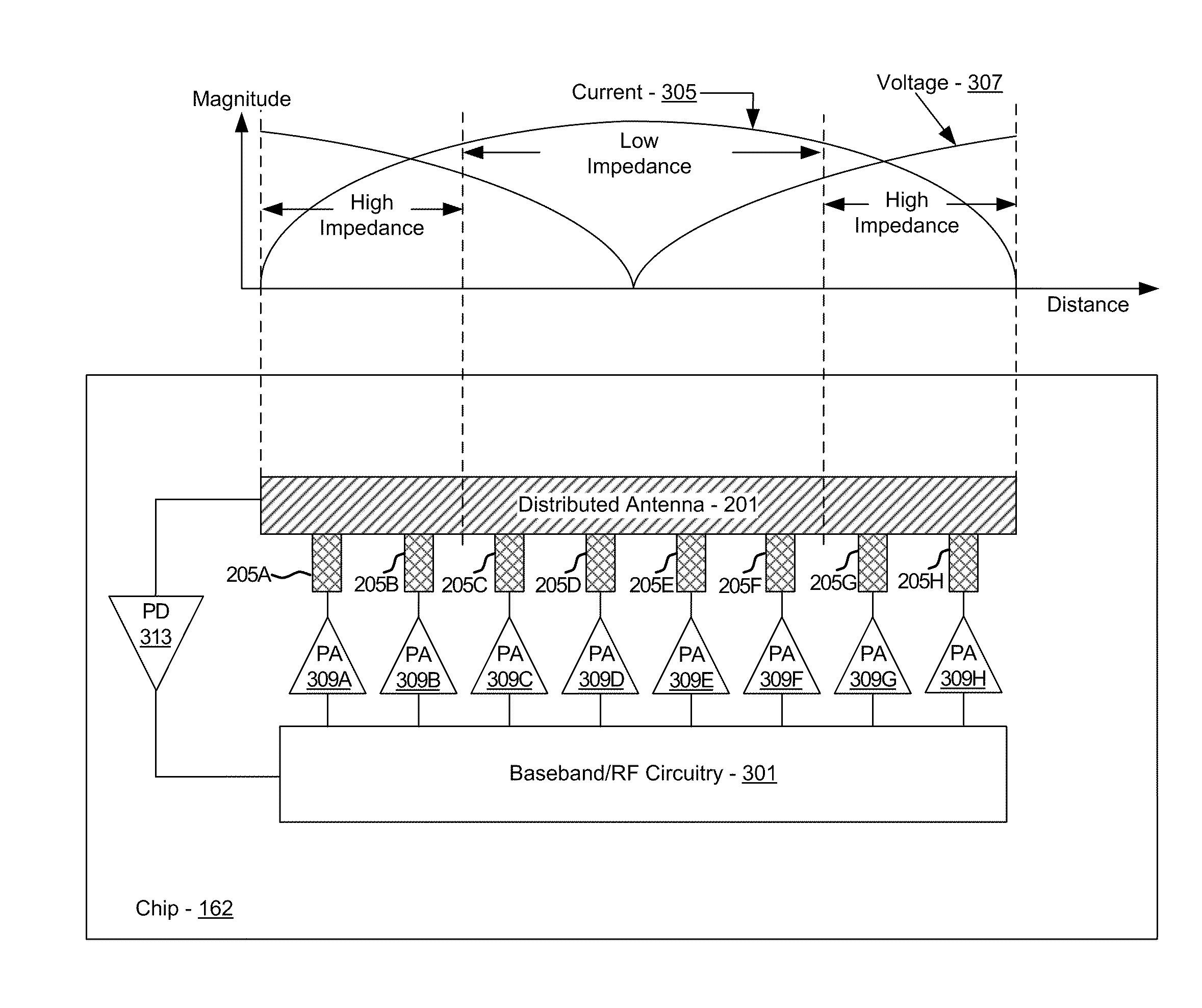

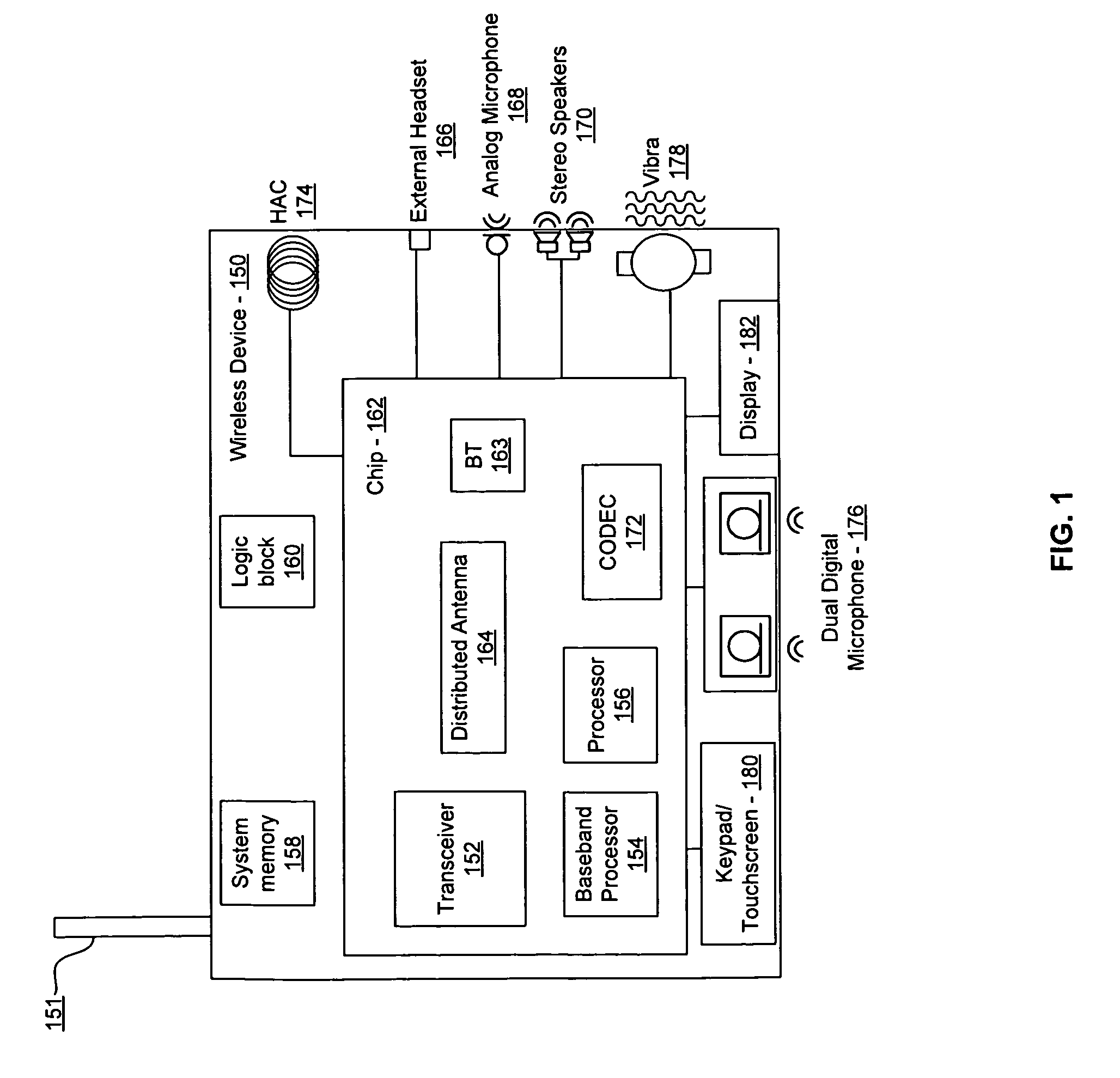

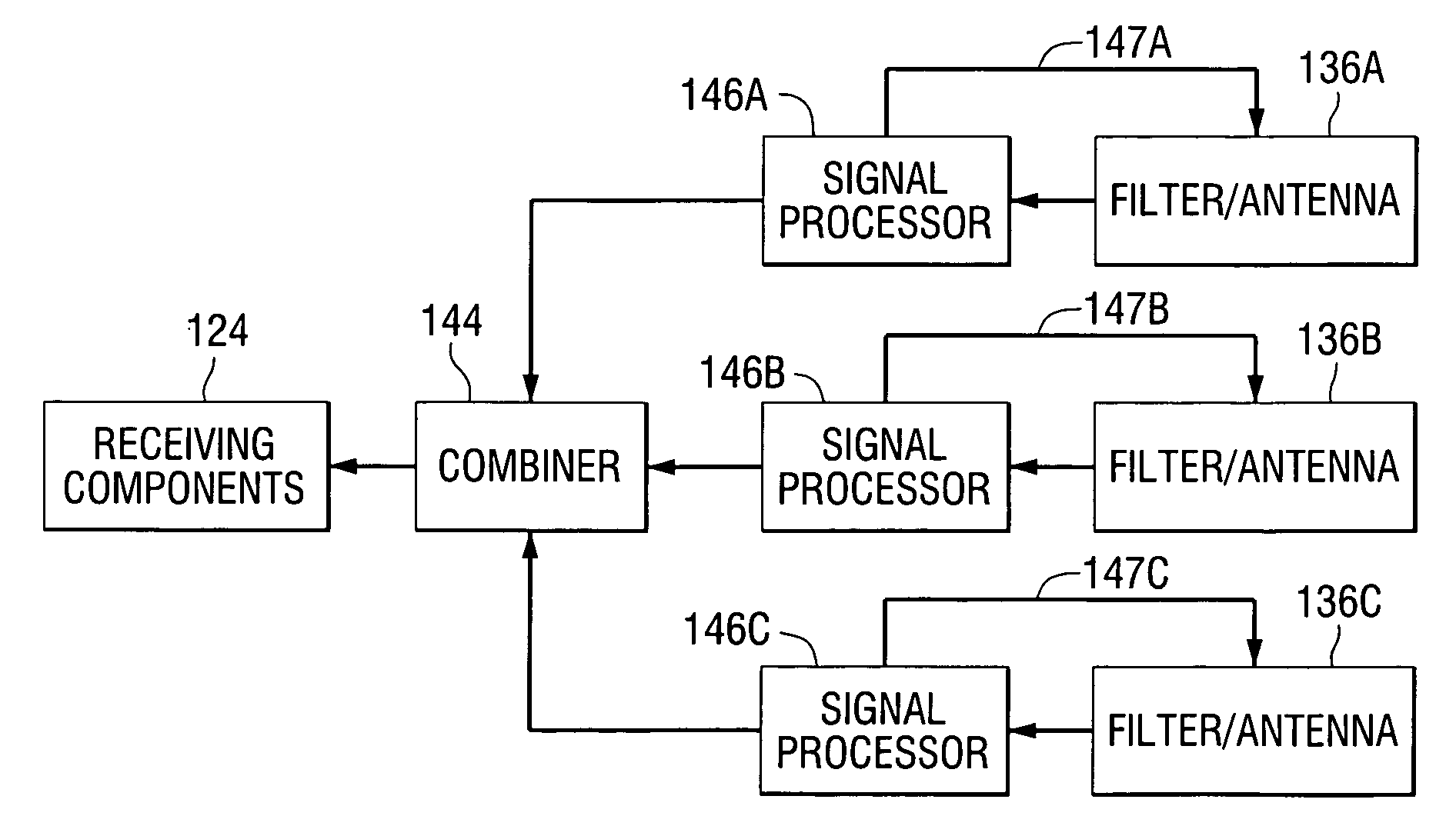

Method and system for power control with optimum power efficiency with a multi-port distributed antenna

Owner:AVAGO TECH INT SALES PTE LTD

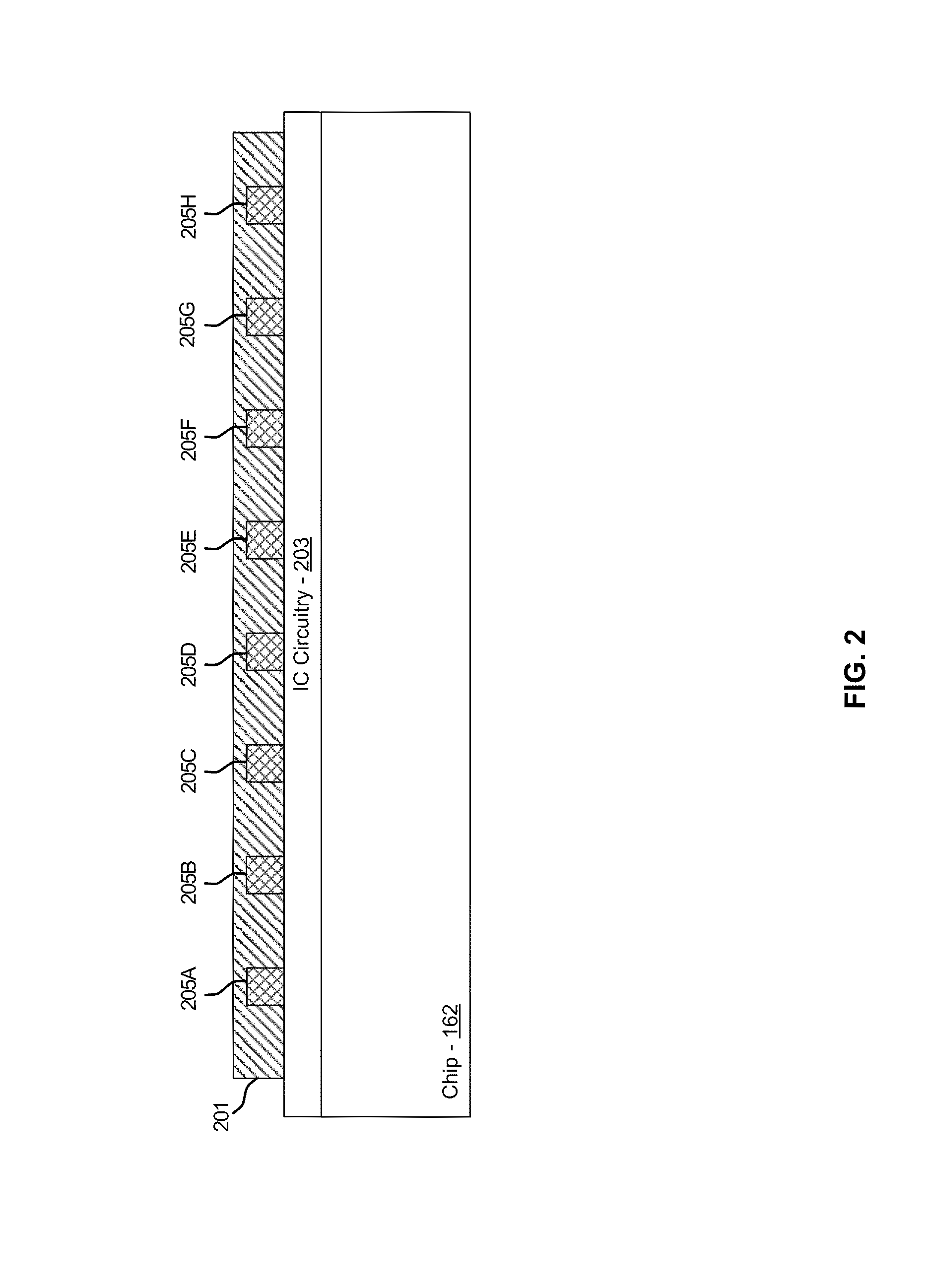

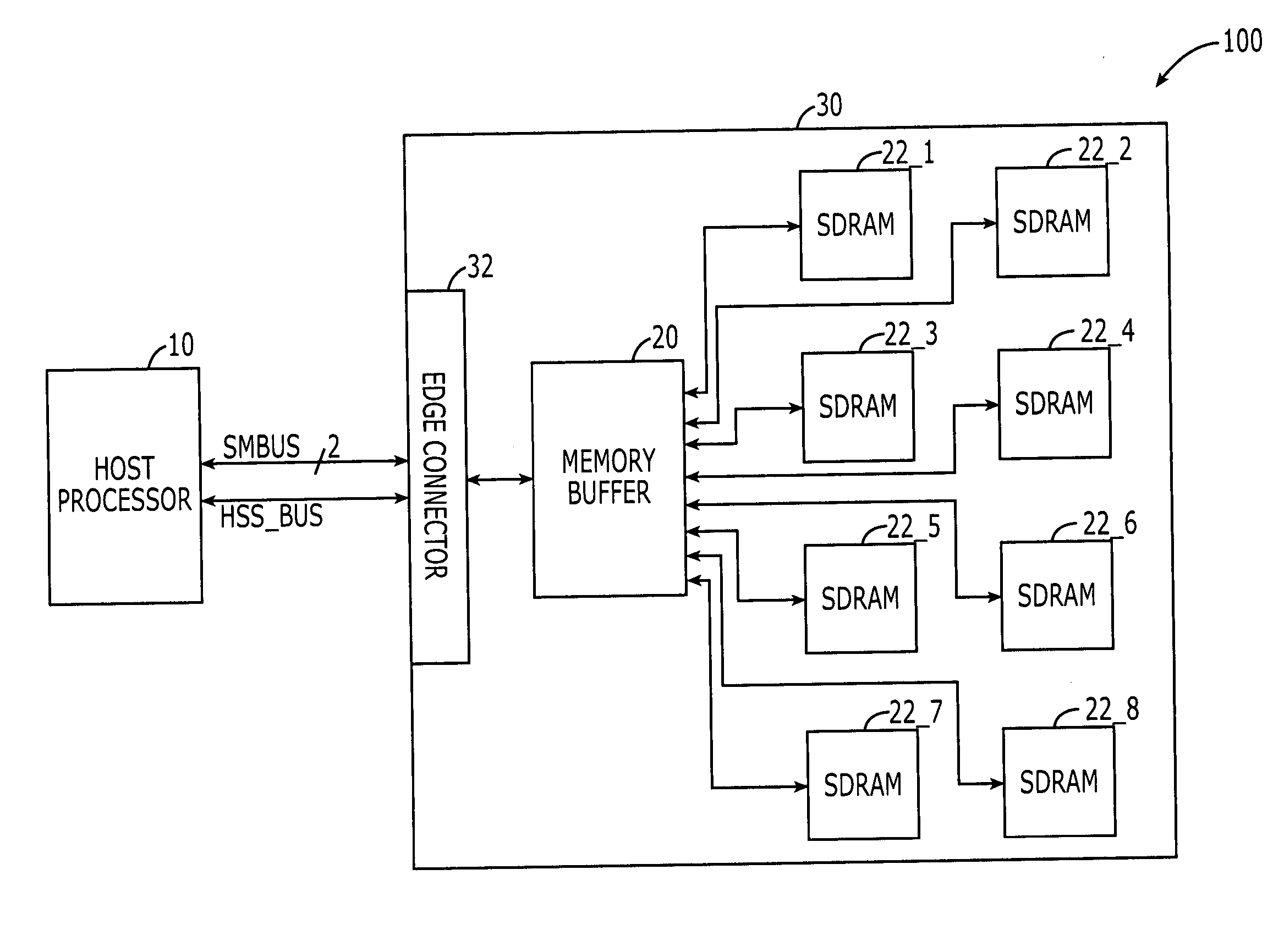

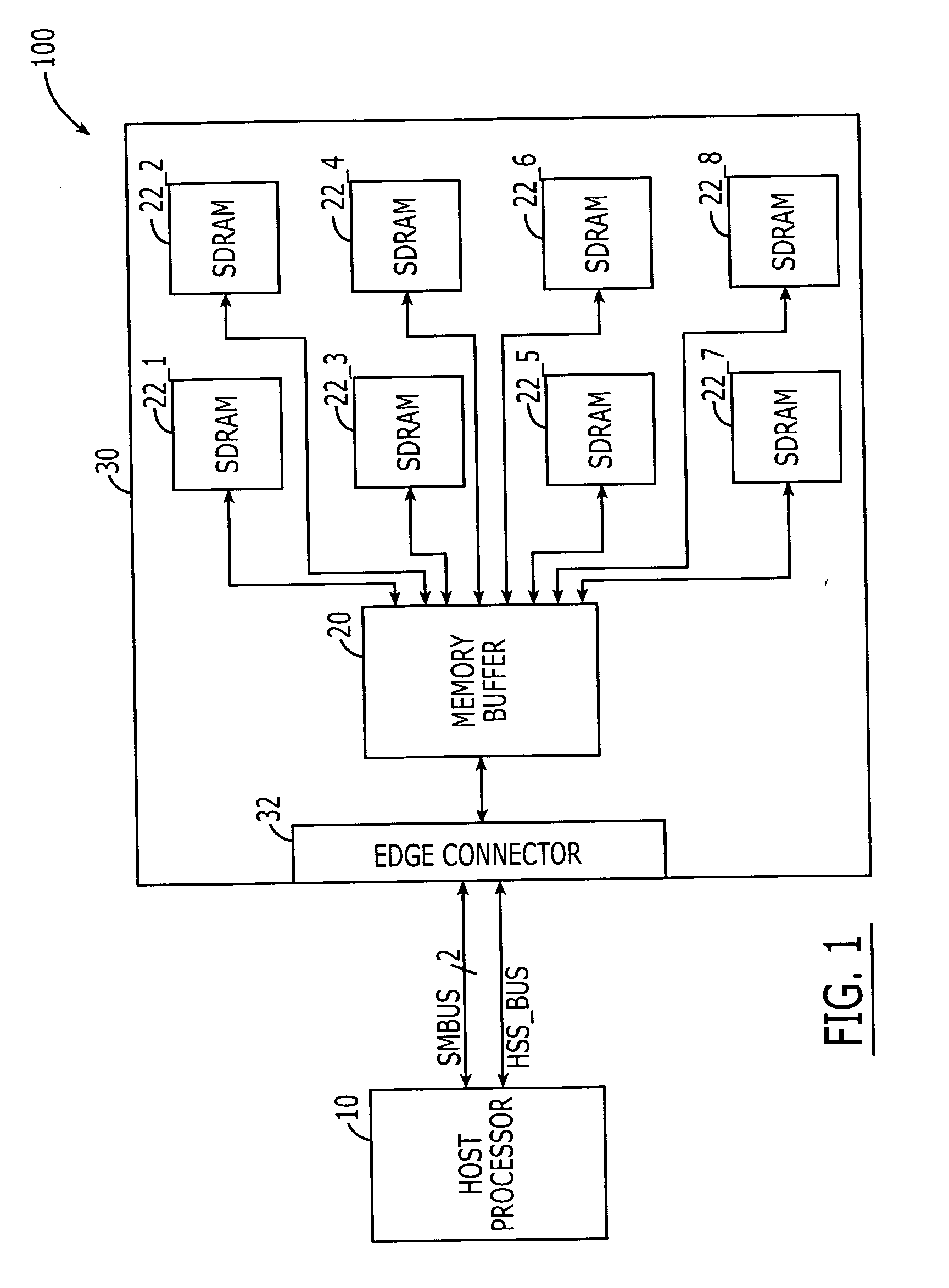

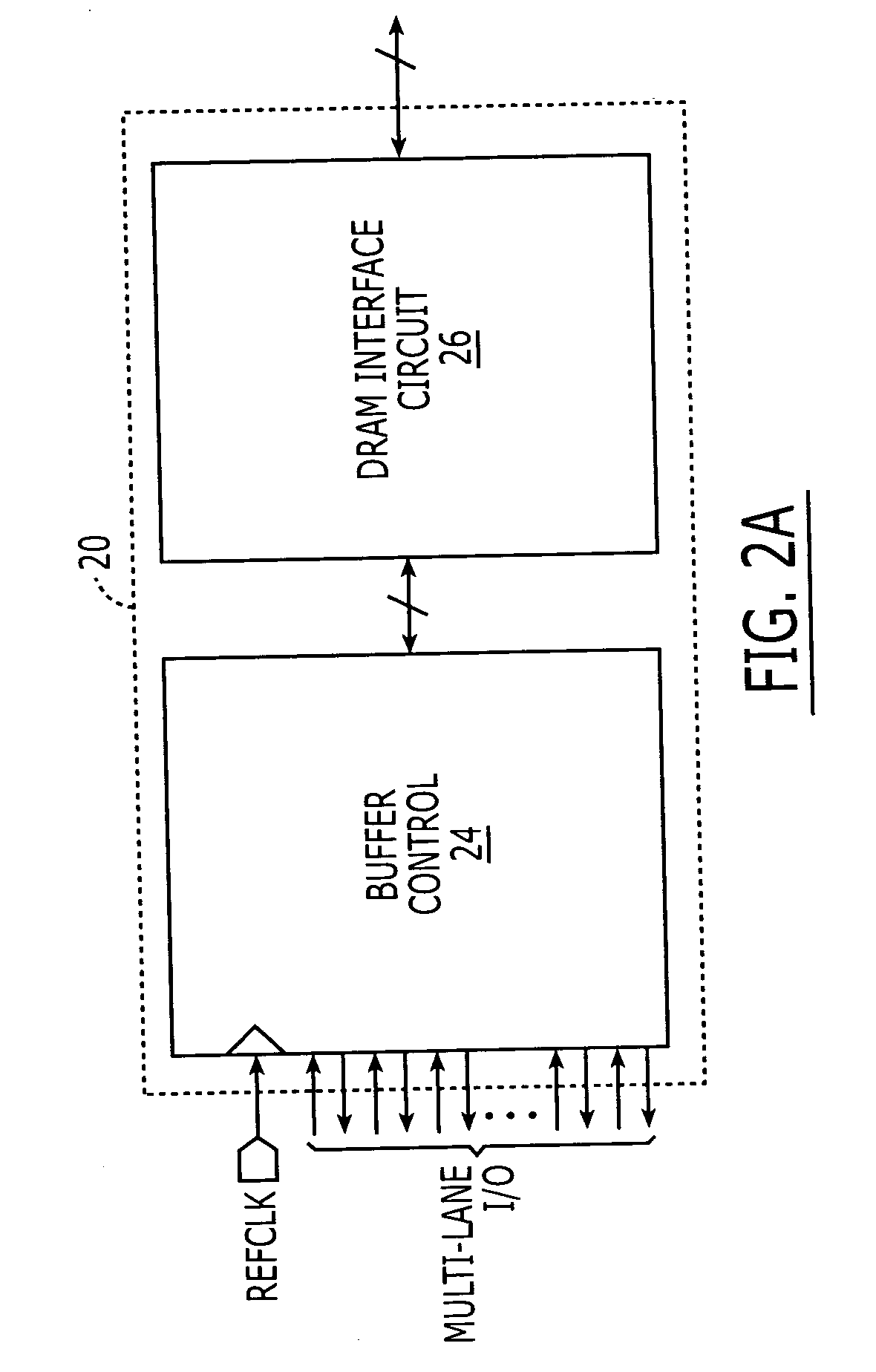

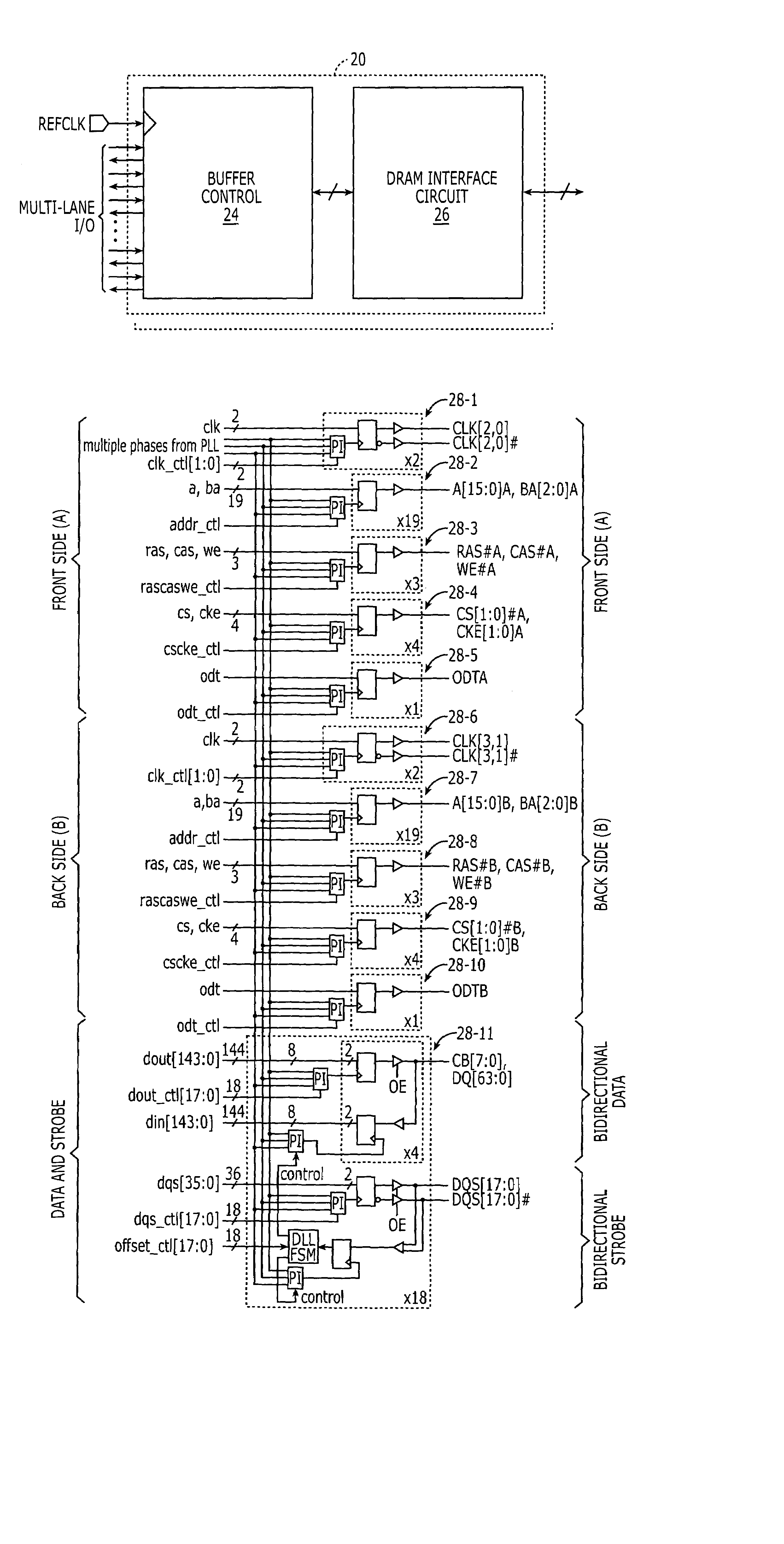

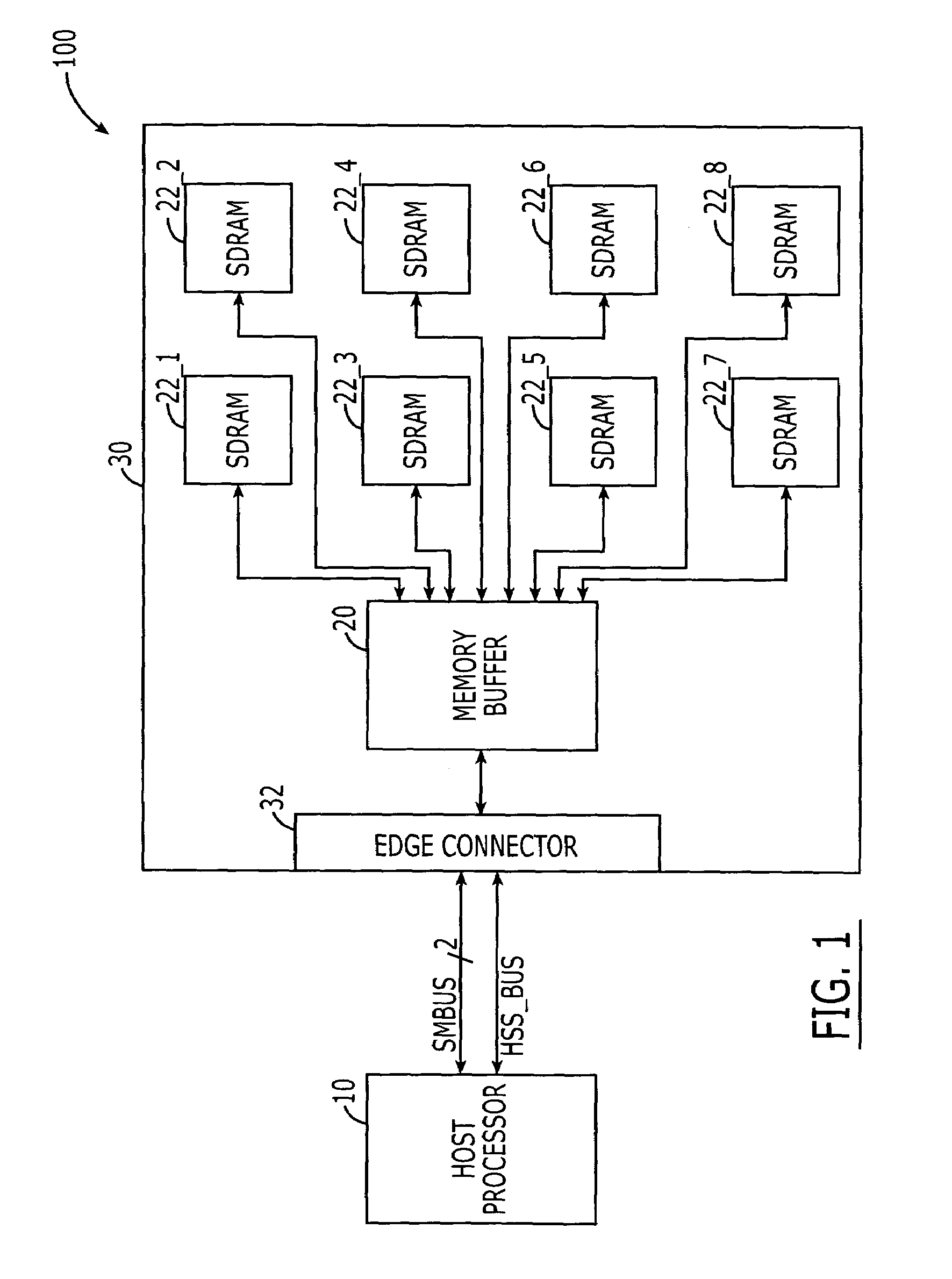

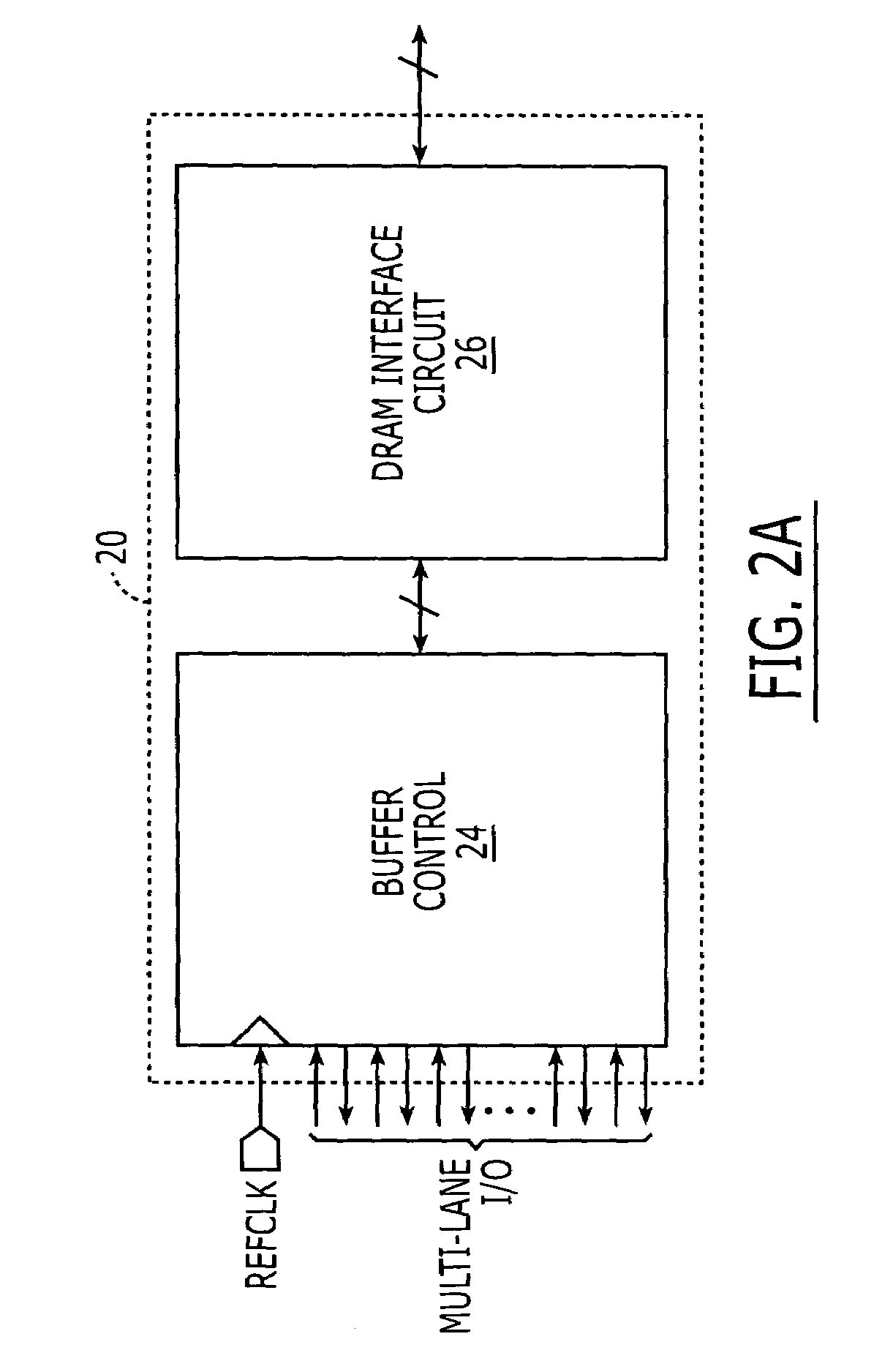

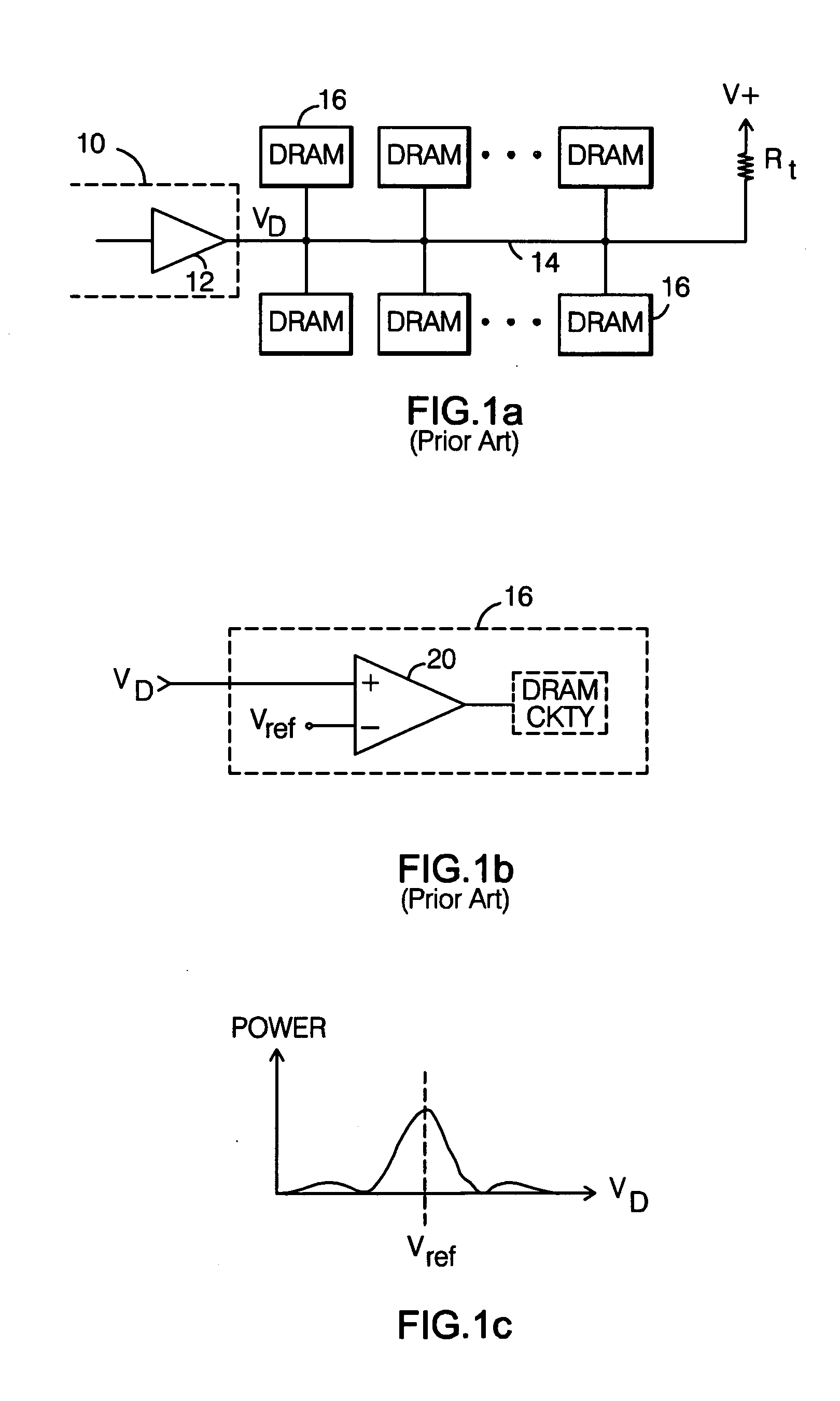

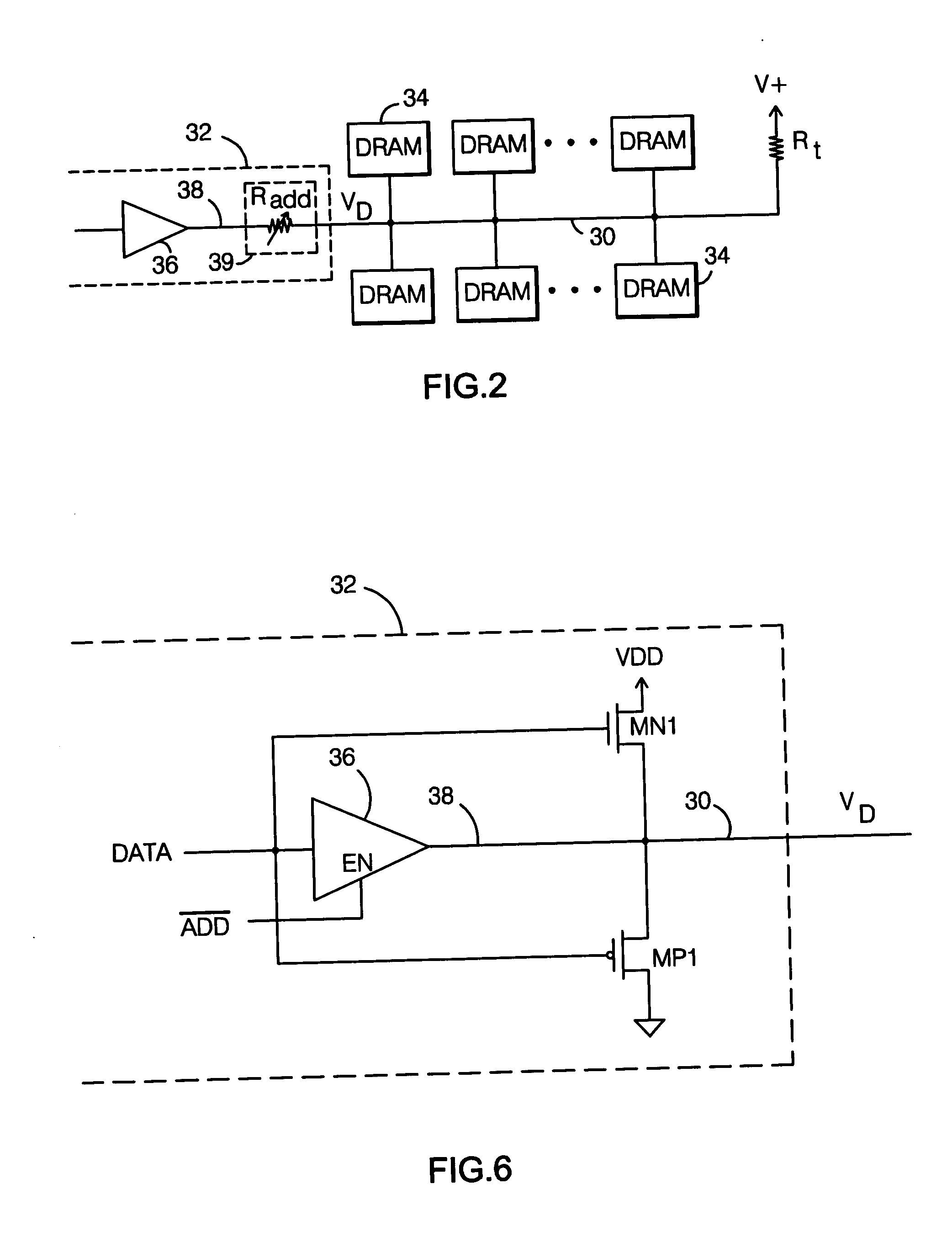

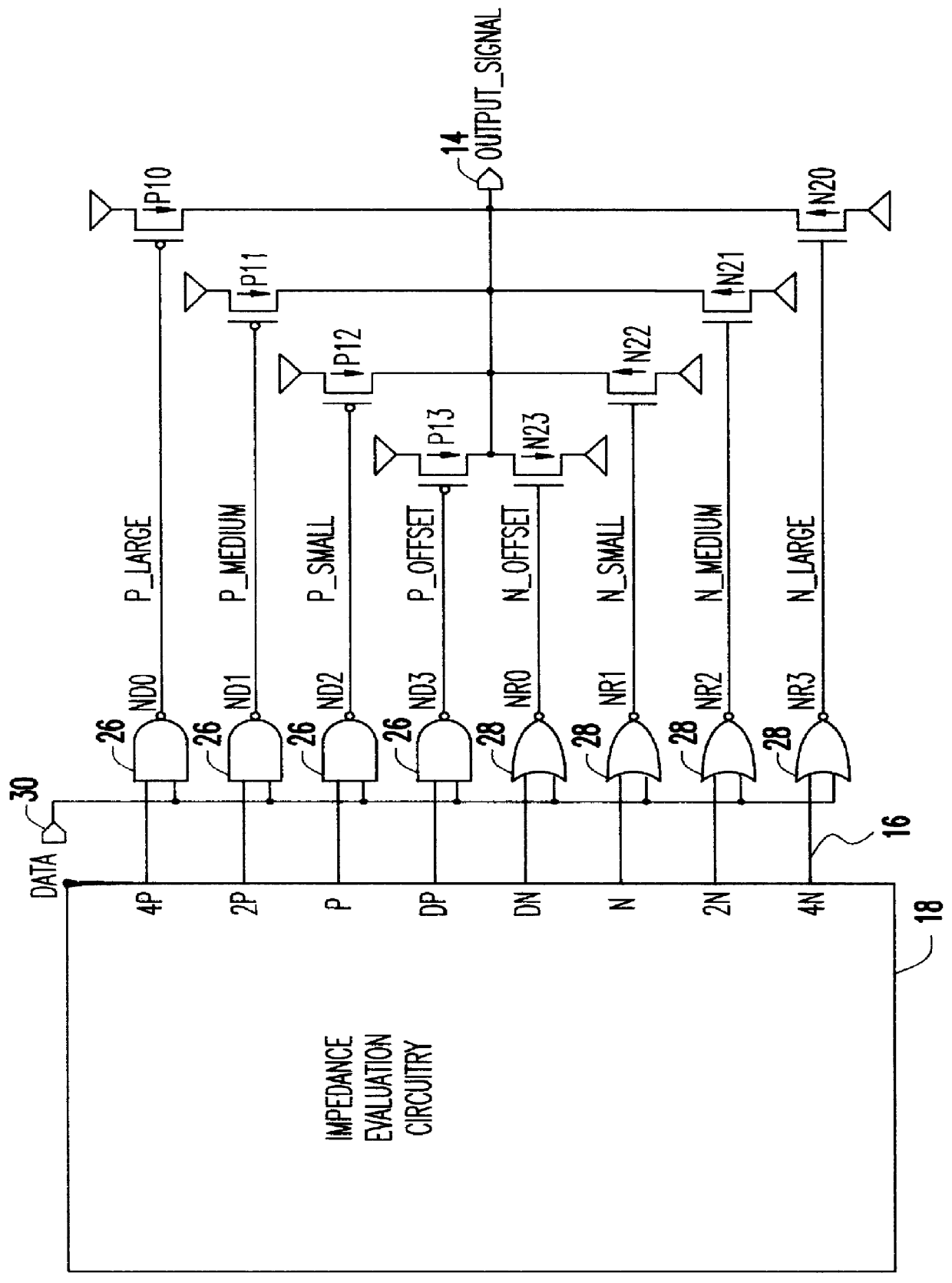

DRAM interface circuits having enhanced skew, slew rate and impedance control

Fully-buffered dual in-line memory modules (FB-DIMM) include advanced memory buffers (AMBs) having enhanced skew, slew rate and output impedance control. The AMB includes user accessible registers that can be programmed to carefully control the edge placement (or phase) of signals generated from the AMB to multiple DRAMs on the module. This control of edge placement, which may be performed independently for each group of signals: clock (CLK, CLK#), command (RAS, CAS, WE), address (including bank address), data (DQ) and data strobe (DQS), provides 360 degrees of control (or one period). This means that any group of signals can be moved independently by one complete period relatively to any other group.

Owner:INTEGRATED DEVICE TECH INC

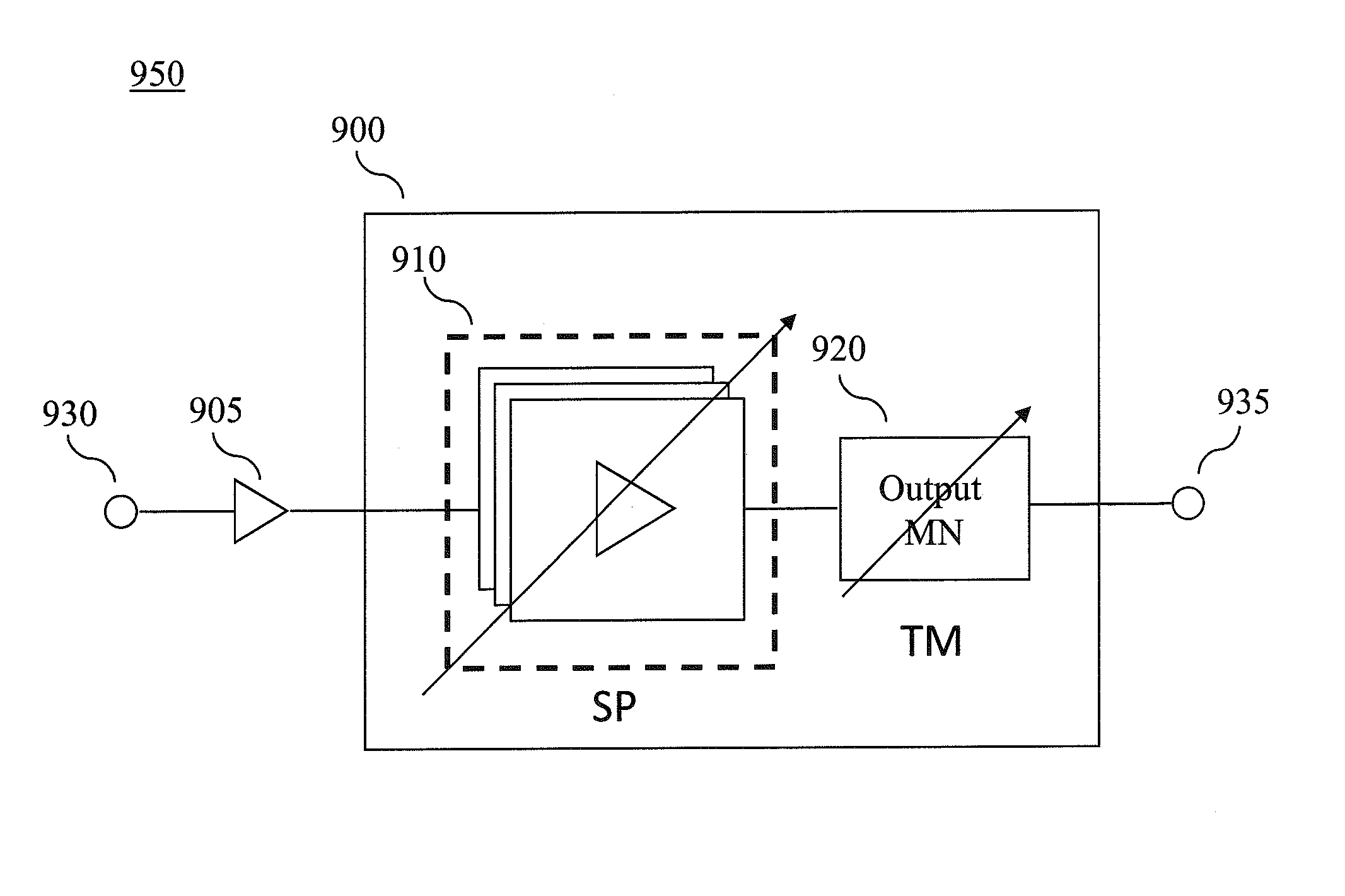

Scalable Periphery Tunable Matching Power Amplifier

A scalable periphery tunable matching power amplifier is presented. Varying power levels can be accommodated by selectively activating or deactivating unit cells of which the scalable periphery tunable matching power amplifier is comprised. Tunable matching allows individual unit cells to see a constant output impedance, reducing need for transforming a low impedance up to a system impedance and attendant power loss. The scalable periphery tunable matching power amplifier can also be tuned for different operating conditions such as different frequencies of operation or different modes.

Owner:PSEMI CORP

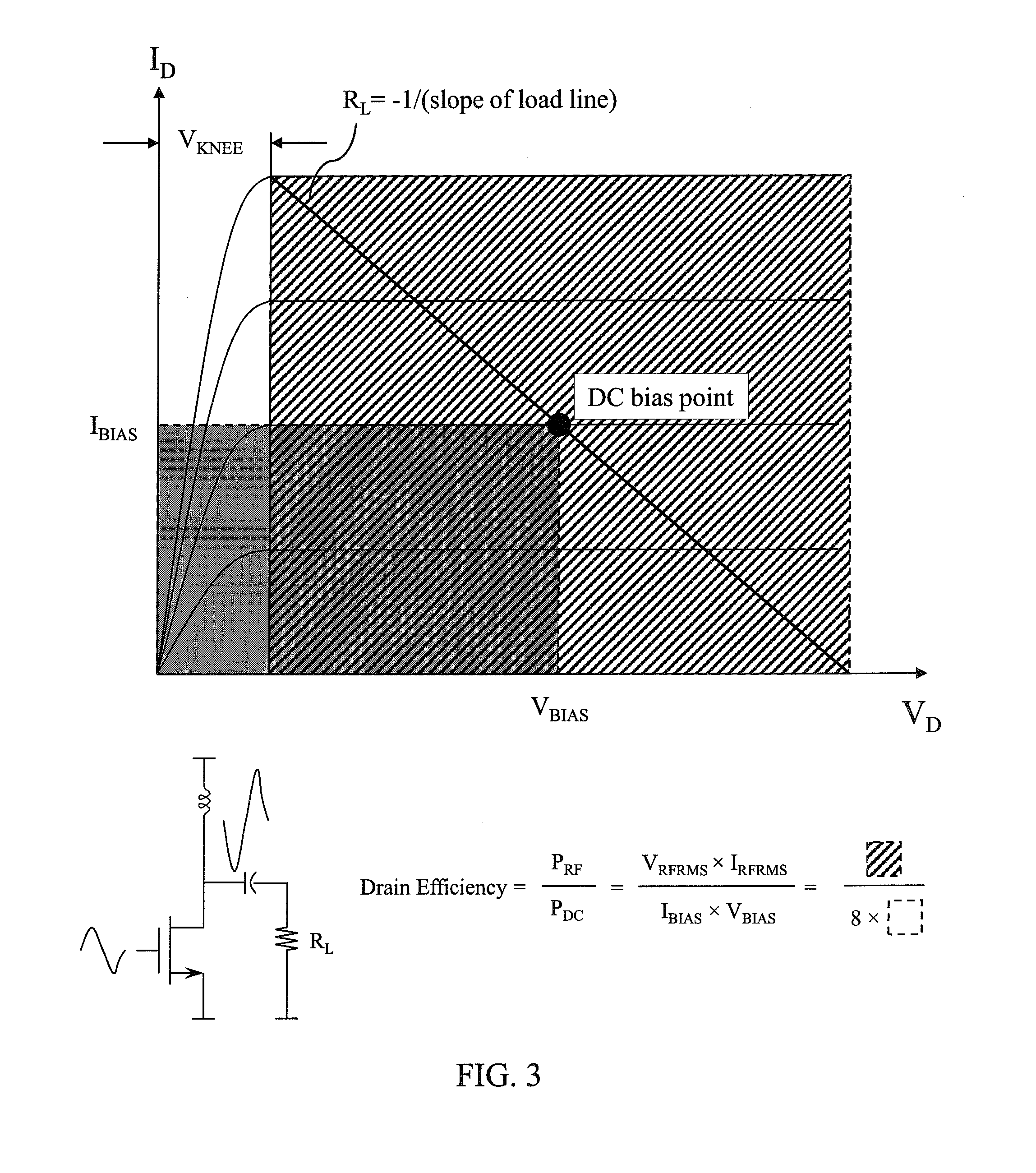

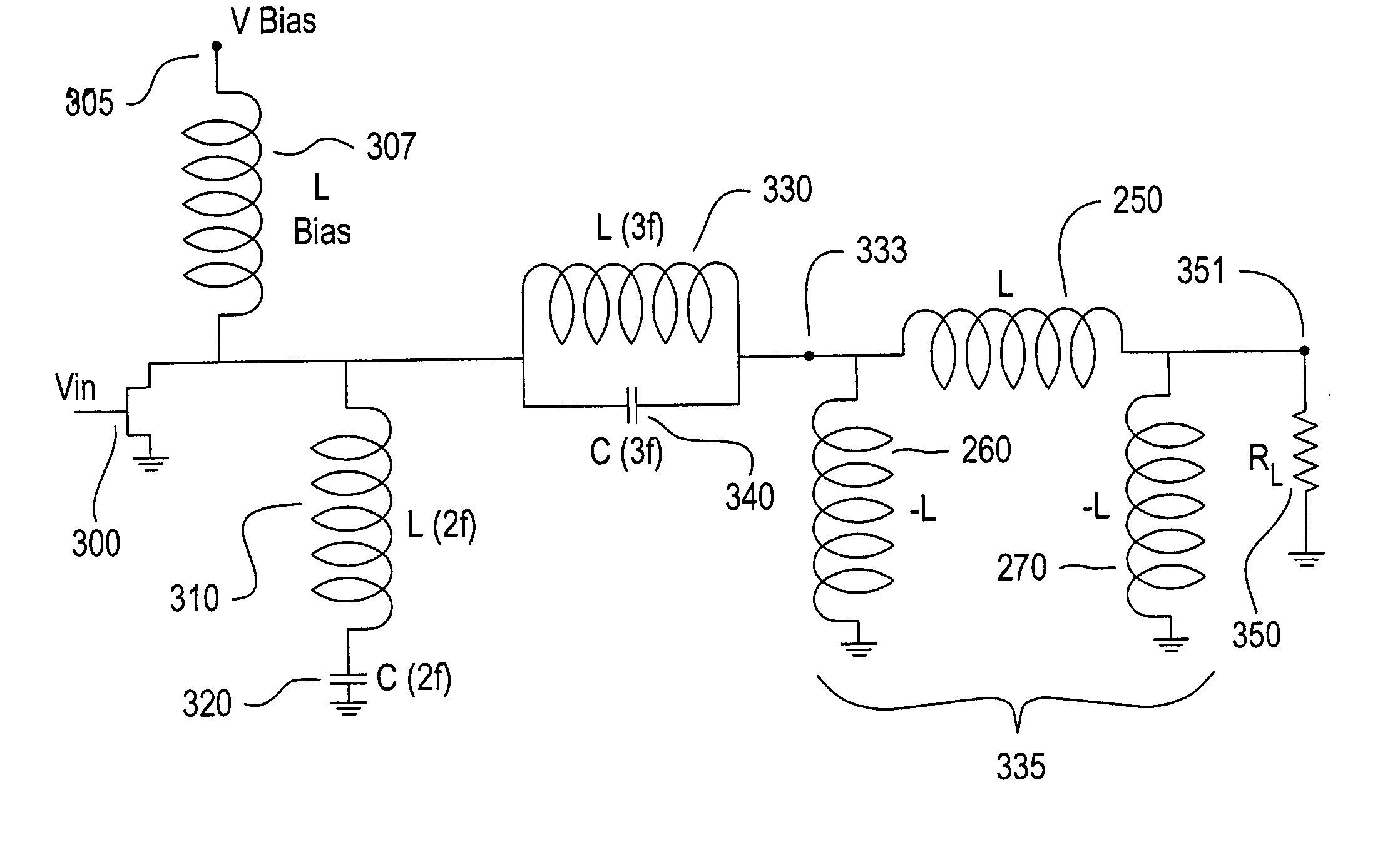

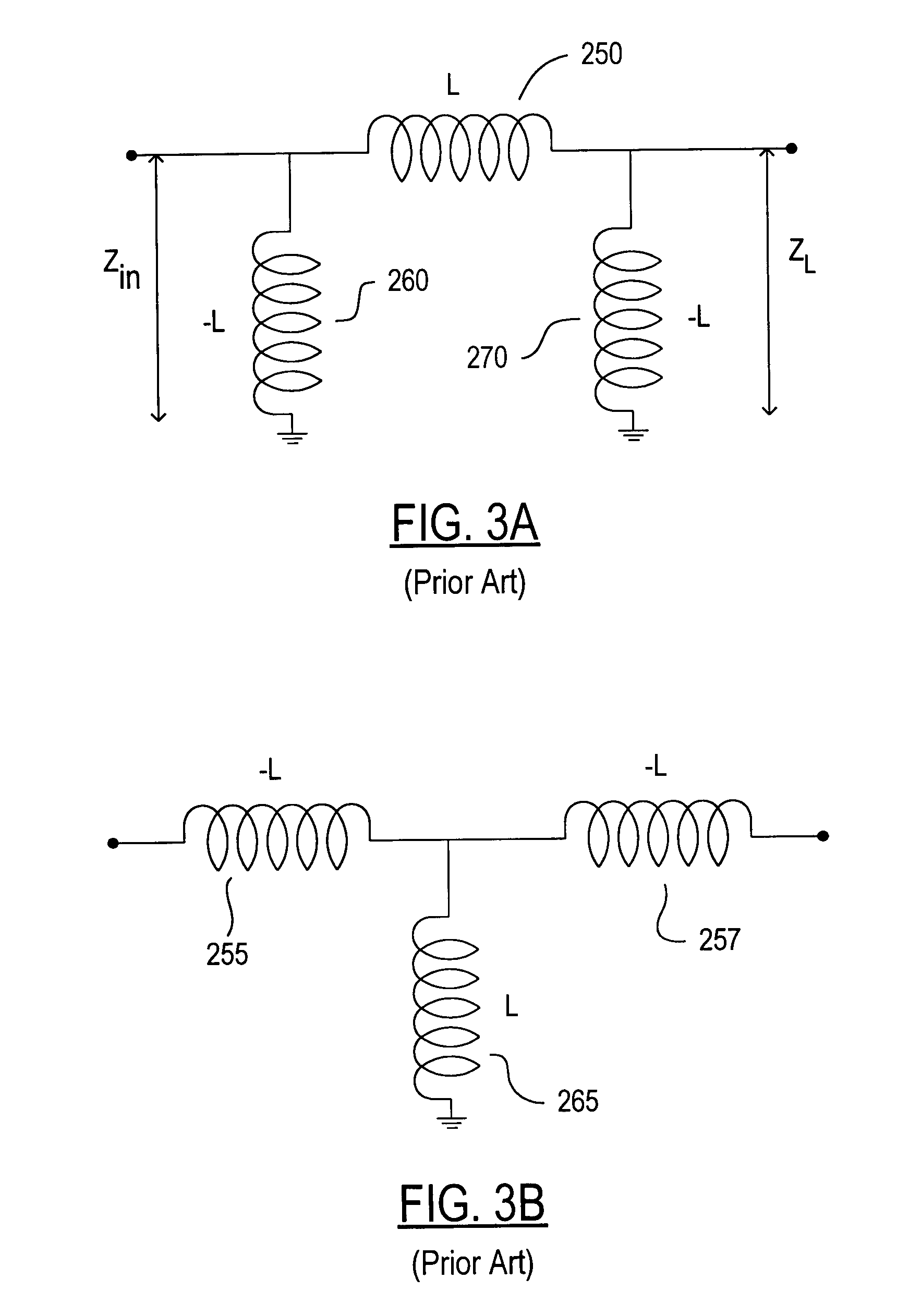

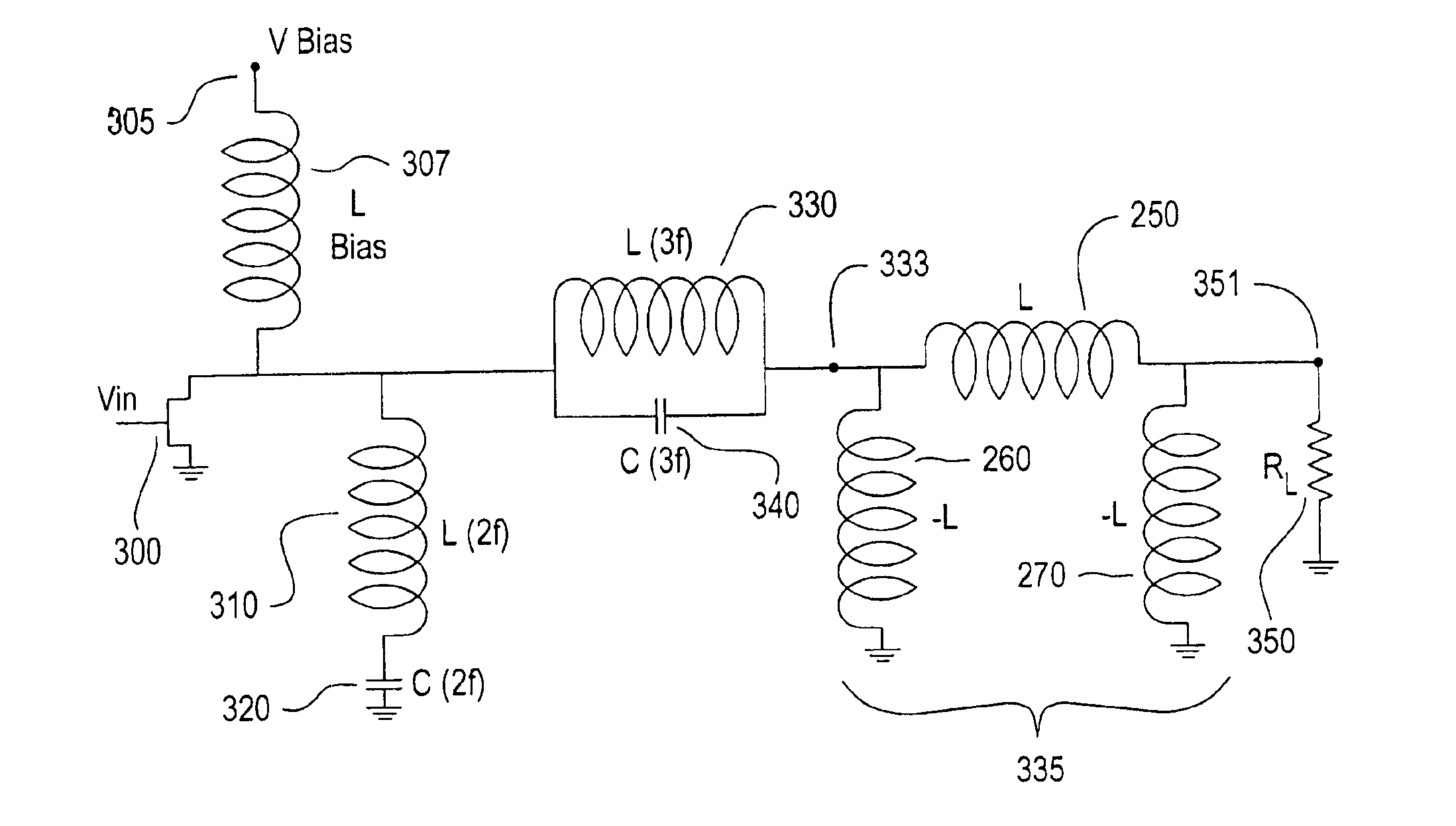

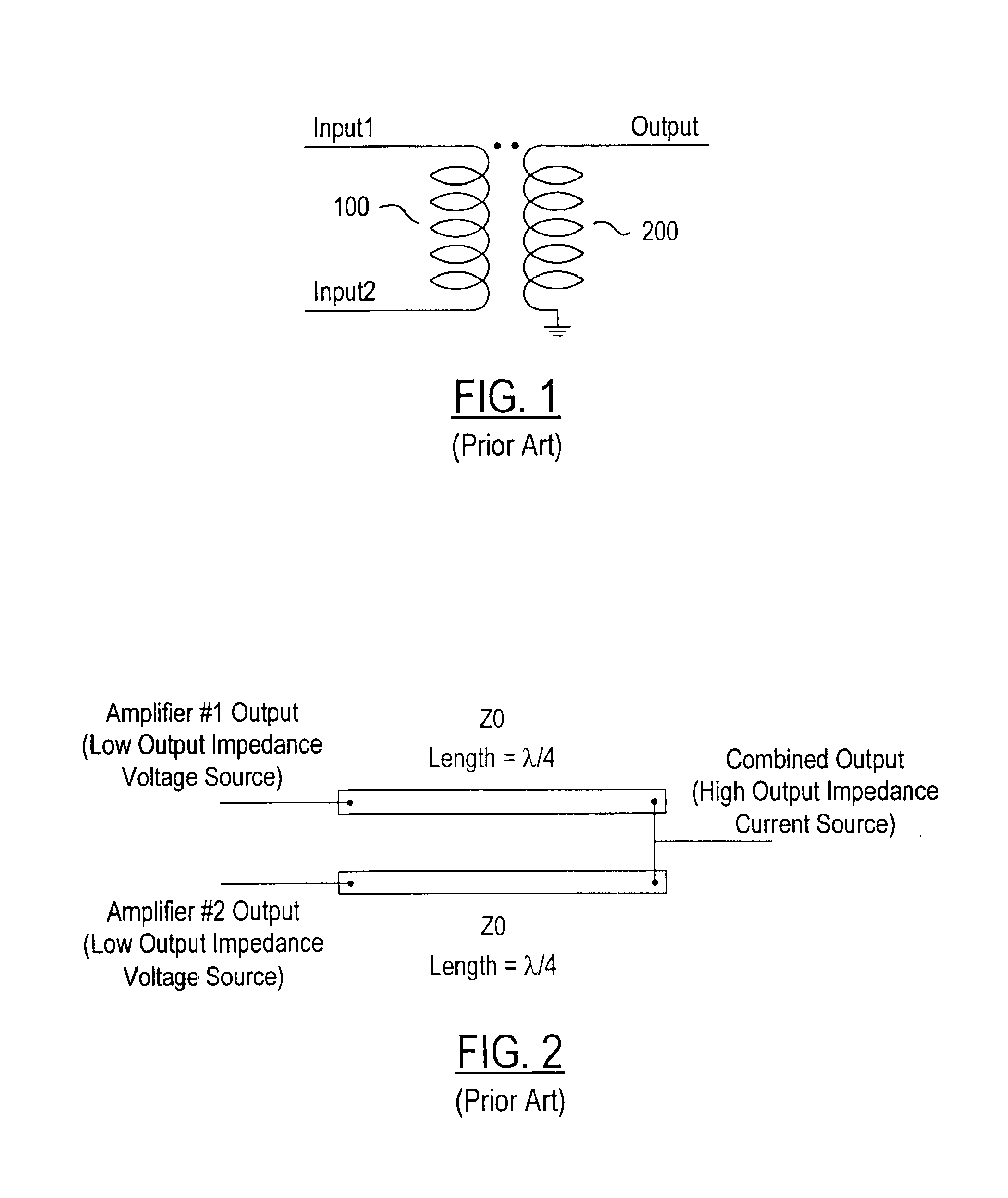

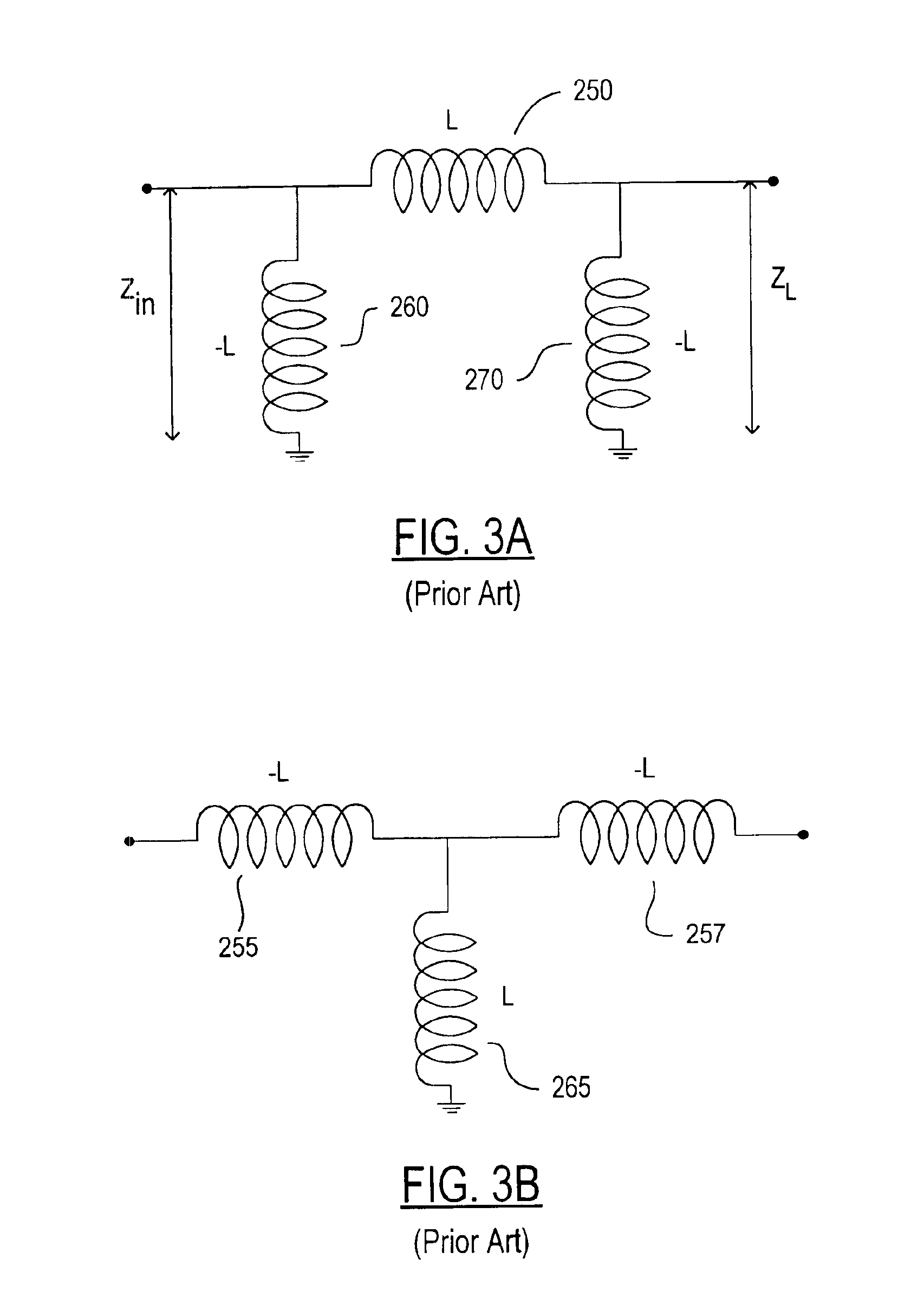

Switched-mode power amplifier using lumped element impedance inverter for parallel combining

InactiveUS20050007194A1Effective compensationAmplifier combinationsAmplifier input/output impedence modificationAudio power amplifierParasitic capacitance

A switched-mode Class F power amplifier is provided for parallel connection with at least one other like amplifier, within a Chireix architecture, for combining the signals output therefrom. An input component includes at least one active device configured to be alternately switched by a signal input thereto to present an amplified signal corresponding to the input signal and constituting a low output impedance voltage source. A lumped element impedance inverter is provided between the input component and an output resonator component, the impedance inverter being configured for transforming the low output impedance voltage source to instead constitute a high output impedance current source configured for said parallel connection. In accordance with the invention, the negative reactive component values required by the impedance inverter are eliminated and effectively provided by incorporating those values into pre-selected reactive components of the input and output components. Further, a source-drain parasitic capacitance across the active device is eliminated by one or more pre-selected reactive components of the input component, the value(s) of which effectively compensate for the parasitic capacitance.

Owner:ZARBANA DIGITAL FUND

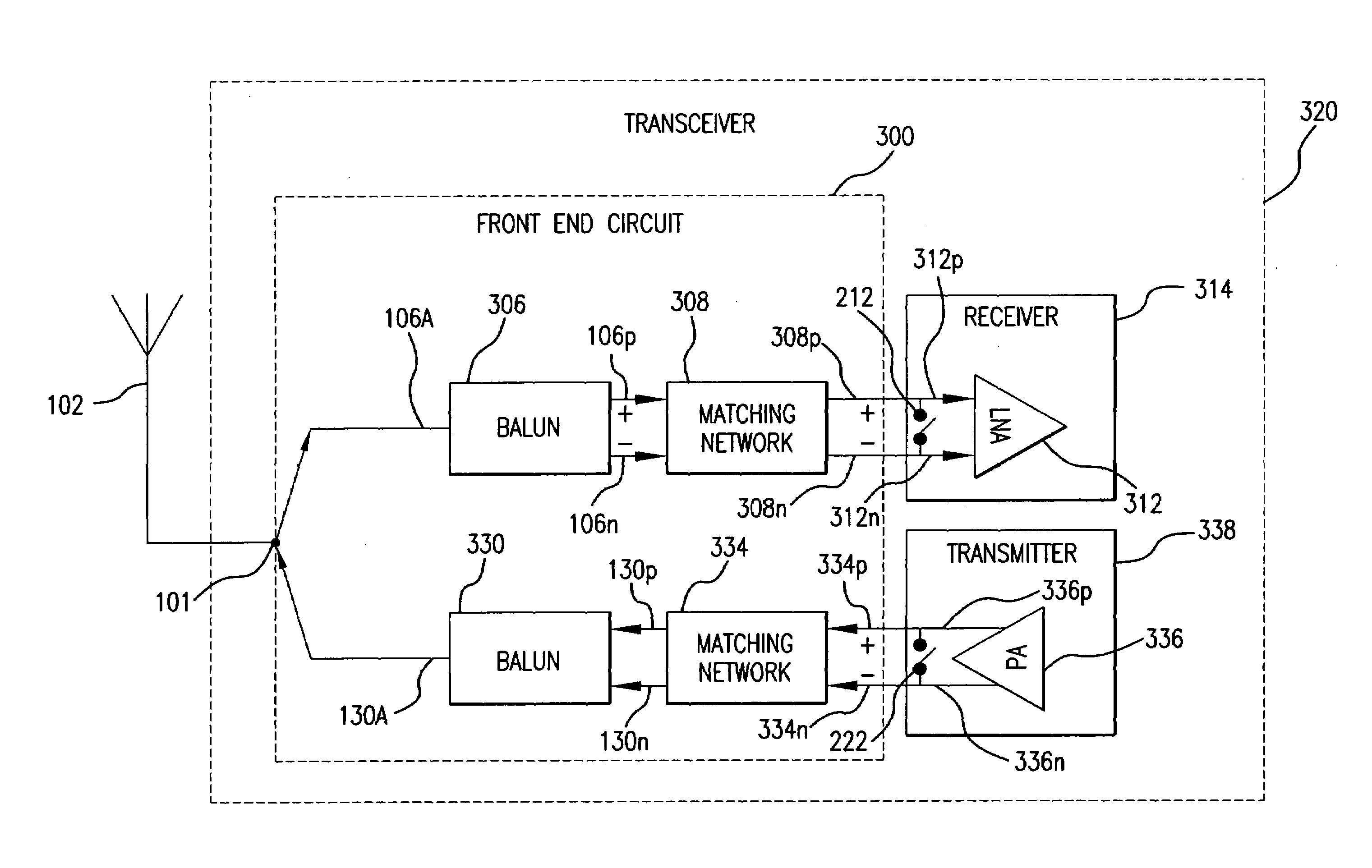

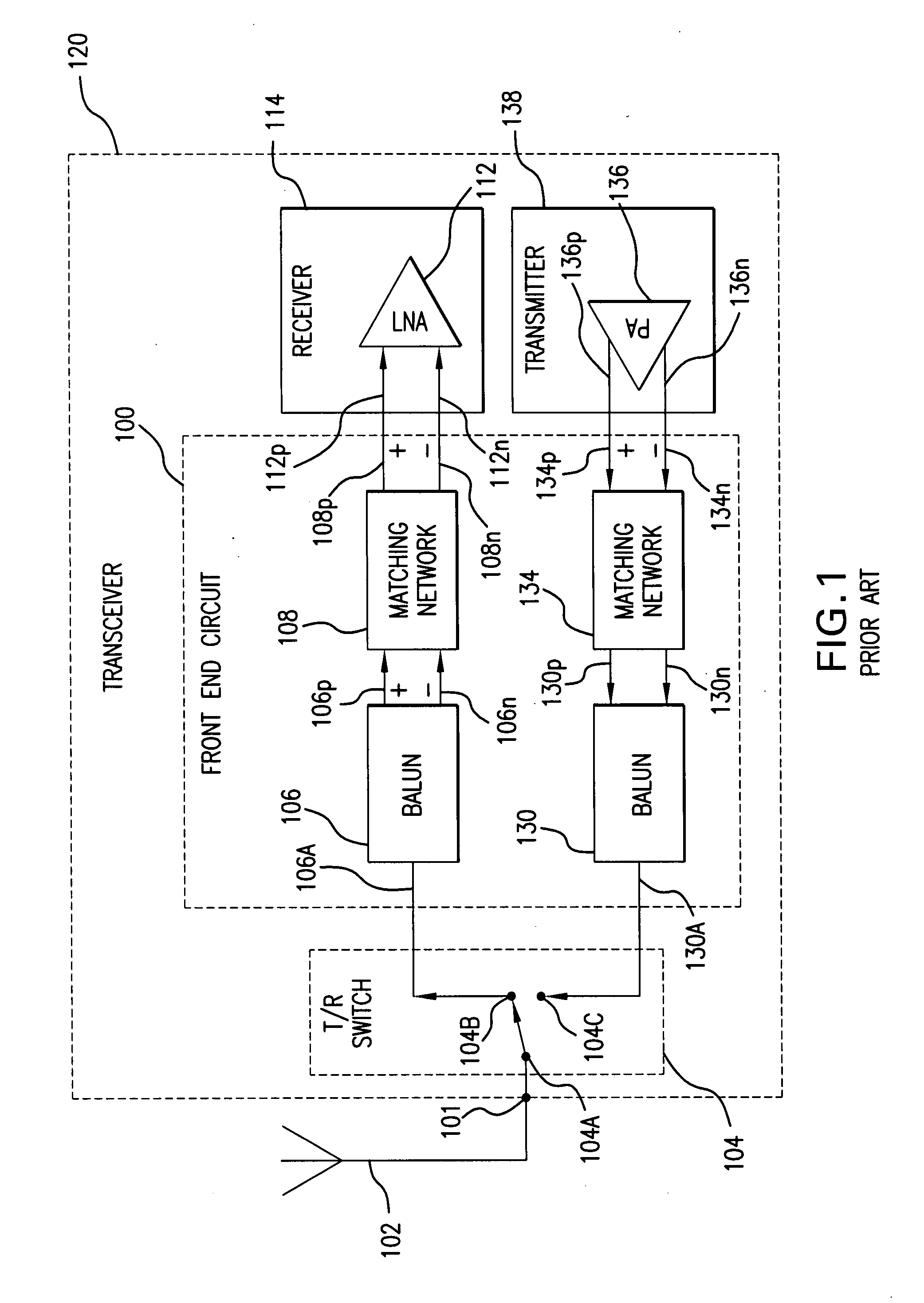

Package filter and combiner network

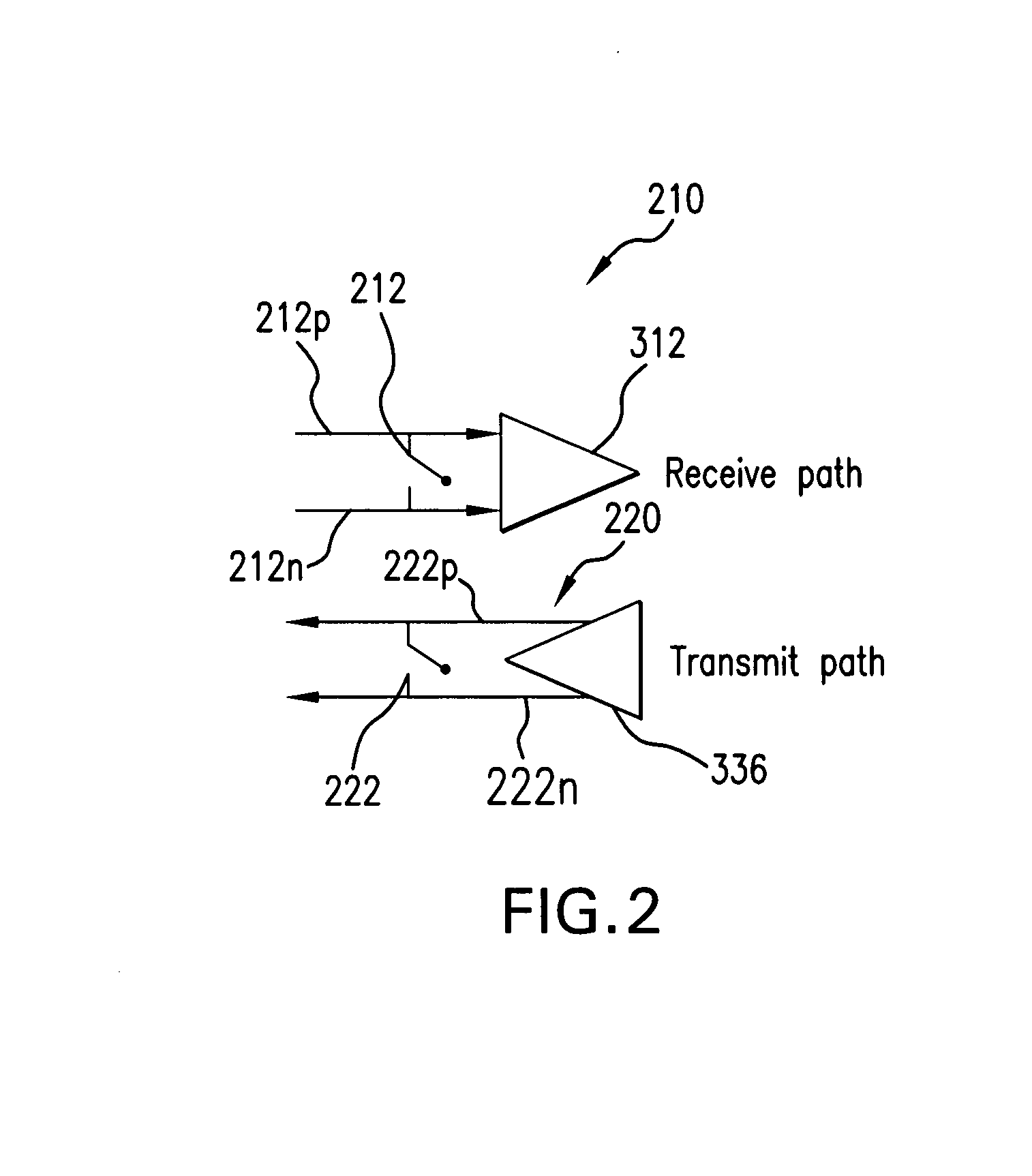

InactiveUS7283793B1Improve powerImprove efficiencyOne-port networksTransmissionPhase shiftedTransceiver

A transceiver front end circuit includes an antenna terminal capable of being coupled to an antenna. A first balun circuit has a single input that is coupled to the antenna terminal, and a pair of balanced outputs coupled to a corresponding pair of balanced receiver inputs. The first balun circuit matches an input impedance of the pair of balanced receiver inputs and substantially phase shifts the input reflection coefficient of the pair of balanced receiver inputs by about 180-degrees. A second balun circuit has a single output coupled to the antenna terminal and a pair of balanced inputs coupled to a corresponding pair of balanced transmitter outputs. The second balun circuit matches an output impedance of the pair of balanced transmitter outputs and substantially phase shifts the output reflection coefficient of the pair of balanced transmitter outputs by about 180-degrees. The first balun circuit and the second balun circuit can be contained within a single package. A first shunt switch can be coupled across the pair of receiver inputs. A second shunt switch can be coupled across the pair of transmitter outputs.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE +1

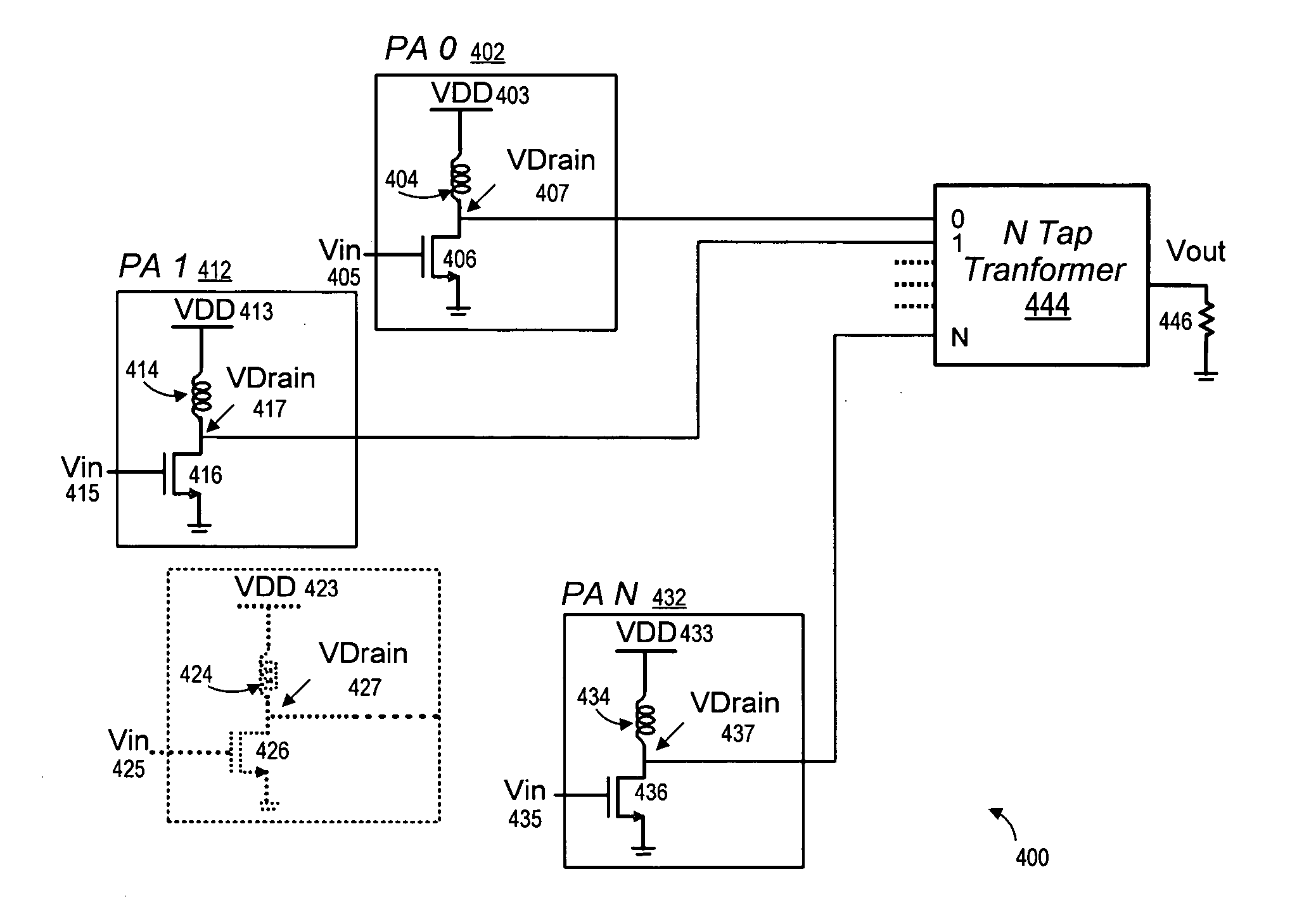

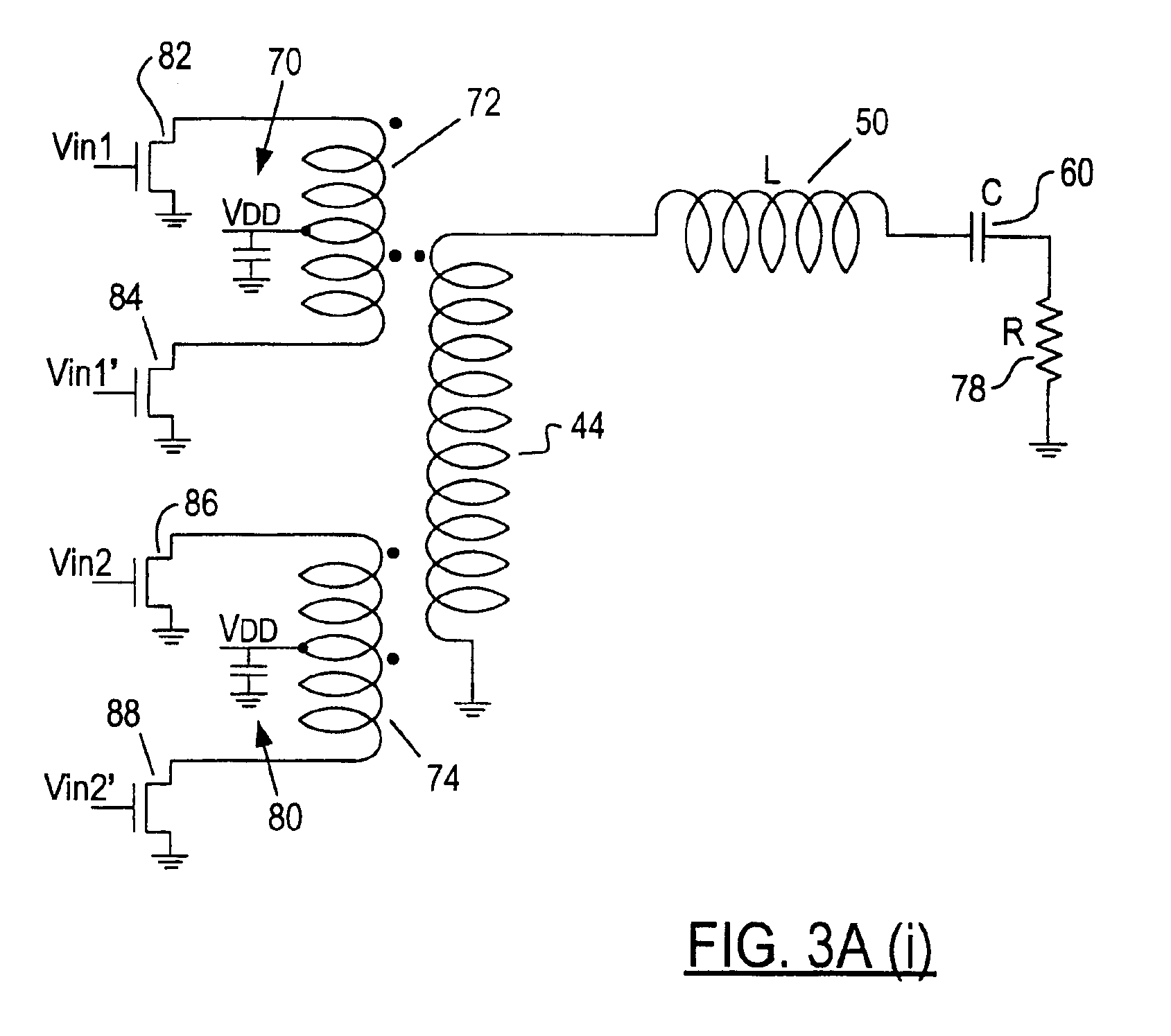

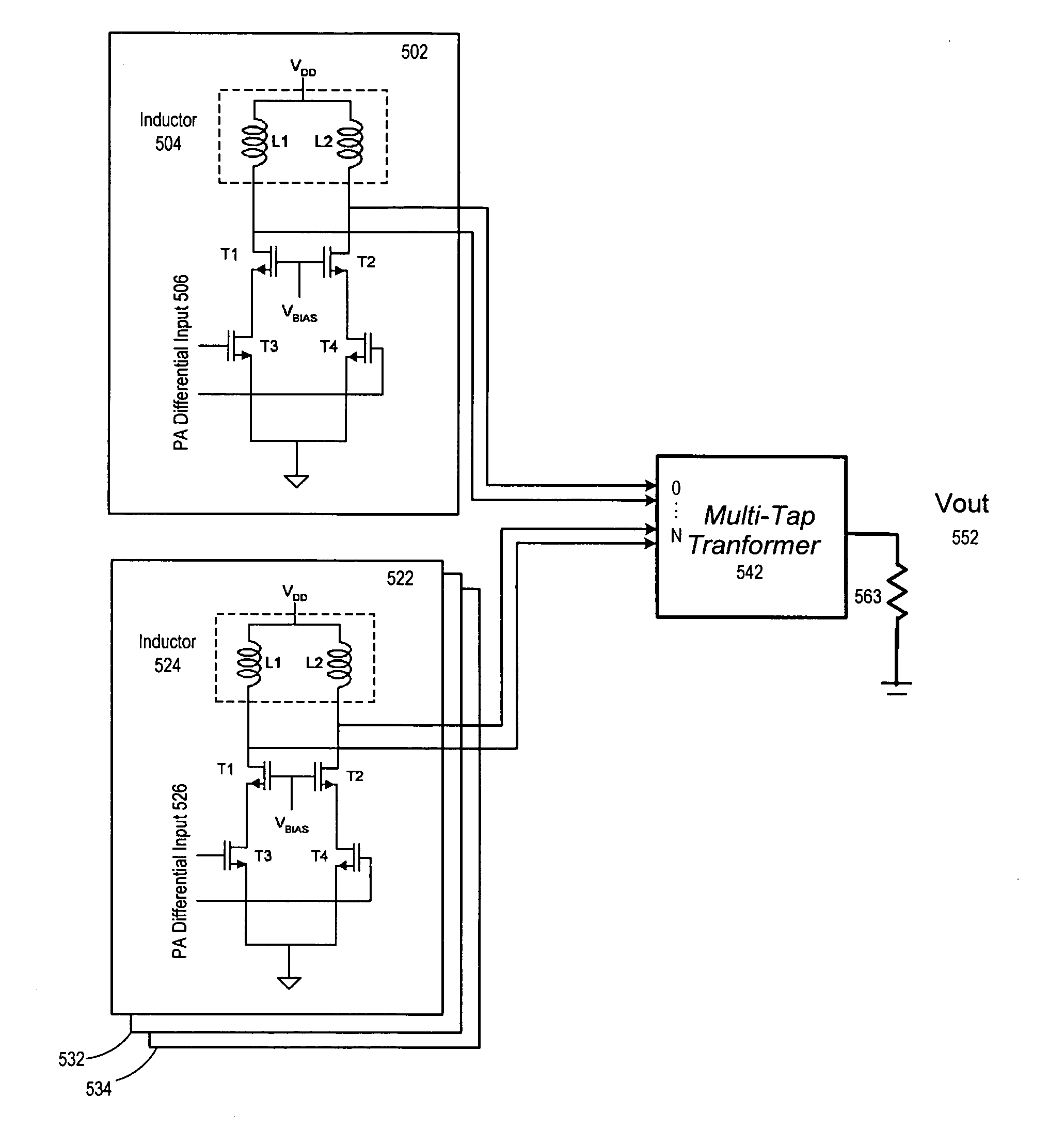

Multilevel power amplifier architecture using multi-tap transformer

InactiveUS20060091958A1Increase powerEffective maintenanceAmplifier combinationsAmplifier detailsCMOSAudio power amplifier

A multi-level power amplifier architecture using a multi-tap transformer implemented on a single CMOS integrated circuit wireless communications device is described. By providing a multi-tap transformer for coupling a plurality of power amplifiers to a shared output impedance, such as an antenna, power transmission may be made at different levels while maintaining efficiency. With a multi-tap transformer having “N” taps featuring “N” different impedance levels, each tap may be connected to an amplifier cell which delivers power into the transformer at the tap for coupling to the output load. Any one of the “N” amplifier cells can be turned on at once along with any combination of the “N” amplifier cells.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

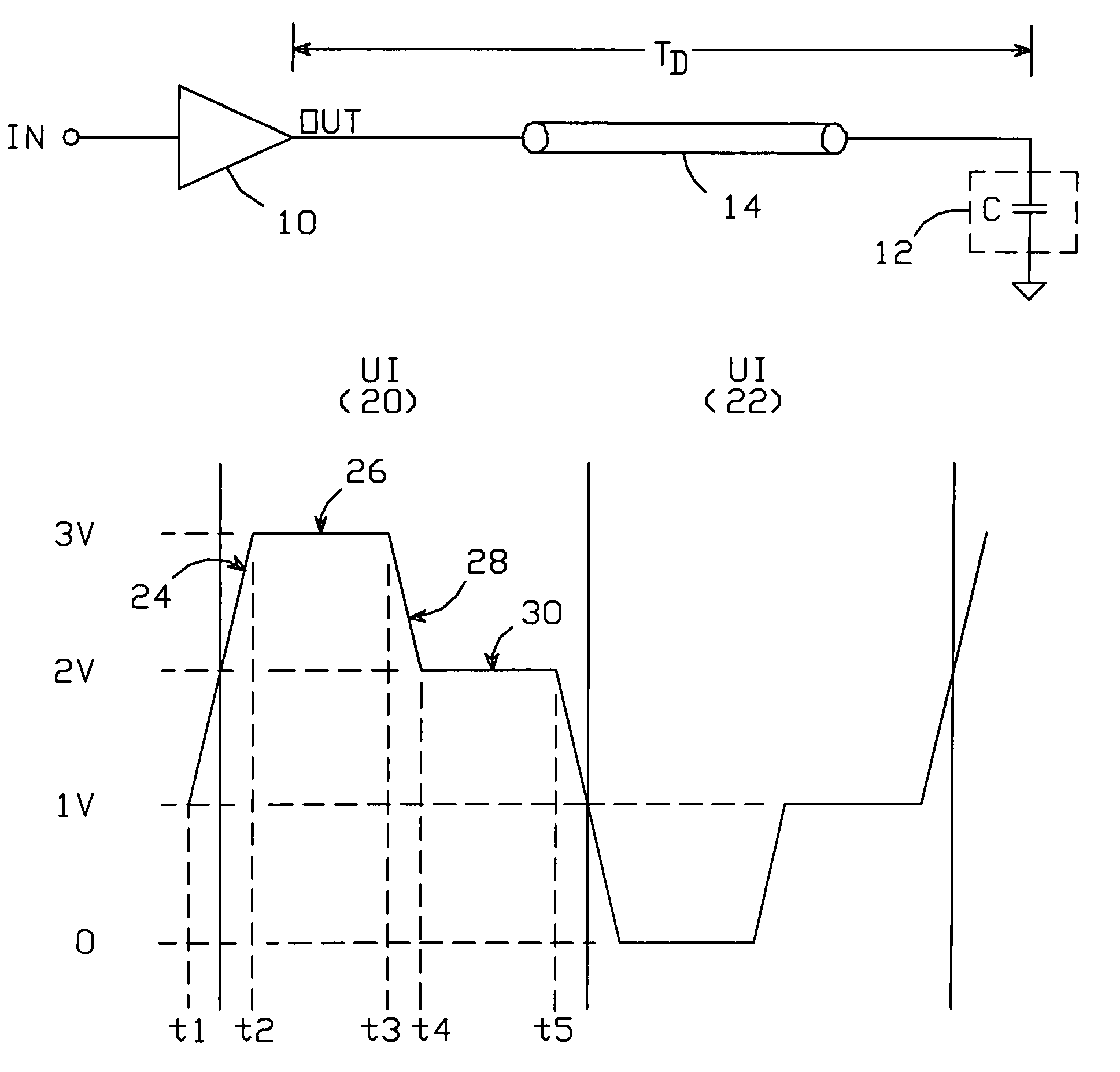

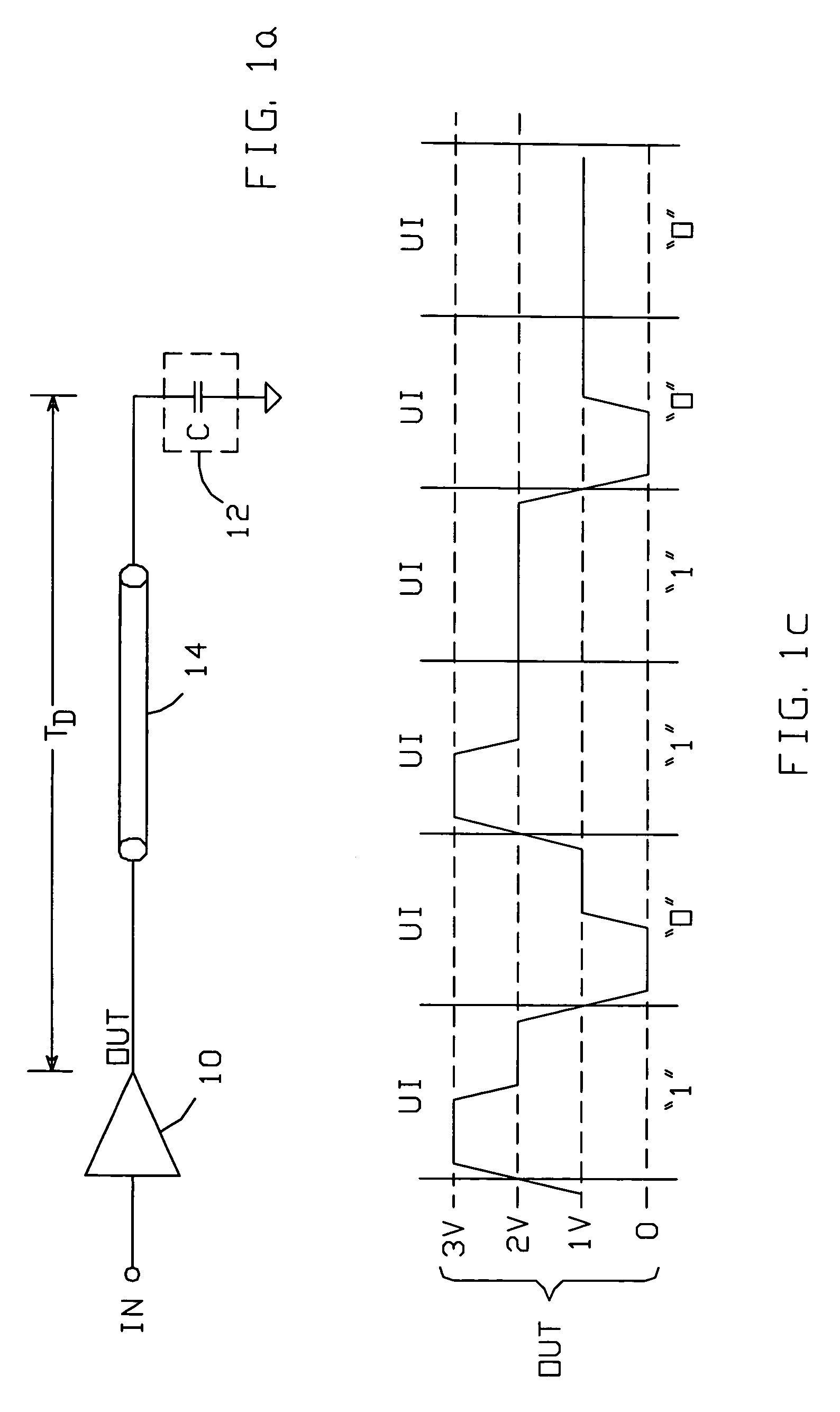

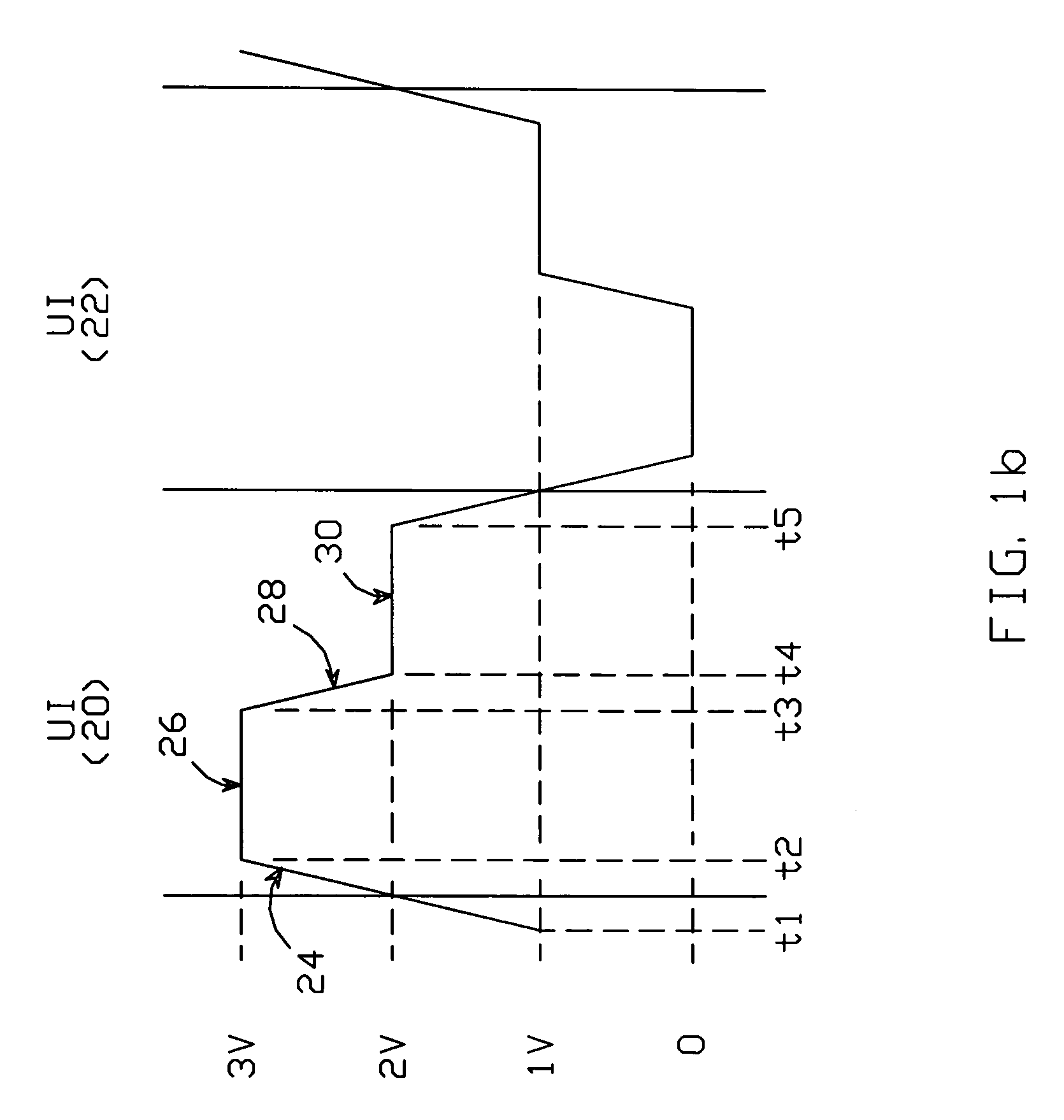

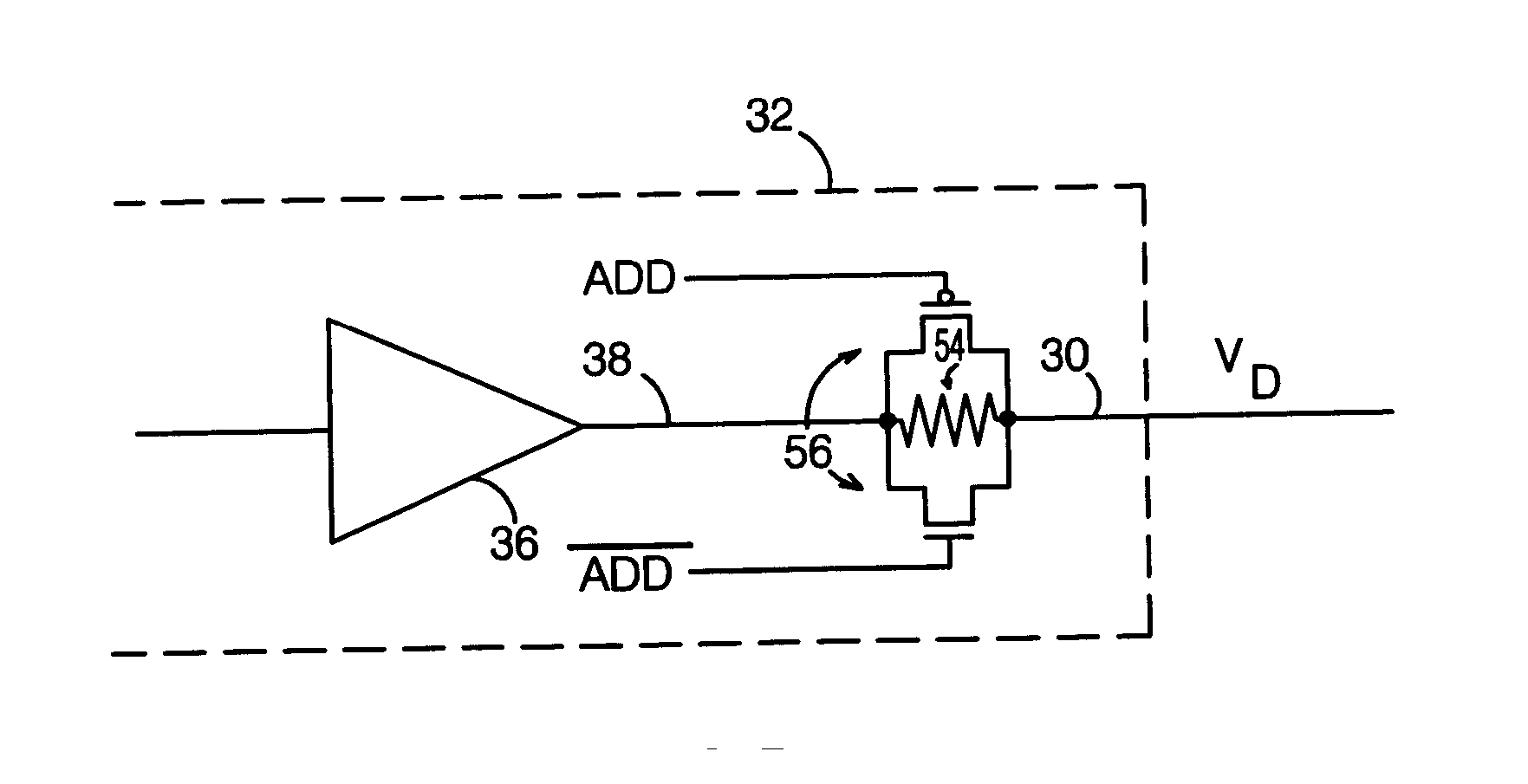

Output buffer with time varying source impedance for driving capacitively-terminated transmission lines

ActiveUS6980021B1Reduce impactFast chargingReliability increasing modificationsLogic circuit coupling arrangementsEngineeringLogic state

An output buffer for driving a capacitively-terminated transmission line produces a waveform which comprises a first portion during which the waveform transitions from a voltage V1 to a voltage V2; a second portion during which it remains fixed at V2; a third portion during which it transitions to a voltage V3; and a fourth portion during which it remains fixed at V3. The waveform is created within a unit interval whenever successive data bits transition between logic states. The first and second portions are generated with circuitry arranged such that V2 is maximized by reducing the buffer's output impedance. The fourth portion is generated with circuitry which has a non-zero output impedance preferably equal to the transmission line's characteristic impedance, to absorb transitions reflected back to the source circuitry by the capacitive termination.

Owner:MARVELL ASIA PTE LTD

DRAM interface circuits having enhanced skew, slew rate and impedance control

Fully-buffered dual in-line memory modules (FB-DIMM) include advanced memory buffers (AMBs) having enhanced skew, slew rate and output impedance control. The AMB includes user accessible registers that can be programmed to carefully control the edge placement (or phase) of signals generated from the AMB to multiple DRAMs on the module. This control of edge placement, which may be performed independently for each group of signals: clock (CLK, CLK#), command (RAS, CAS, WE), address (including bank address), data (DQ) and data strobe (DQS), provides 360 degrees of control (or one period). This means that any group of signals can be moved independently by one complete period relatively to any other group.

Owner:INTEGRATED DEVICE TECH INC

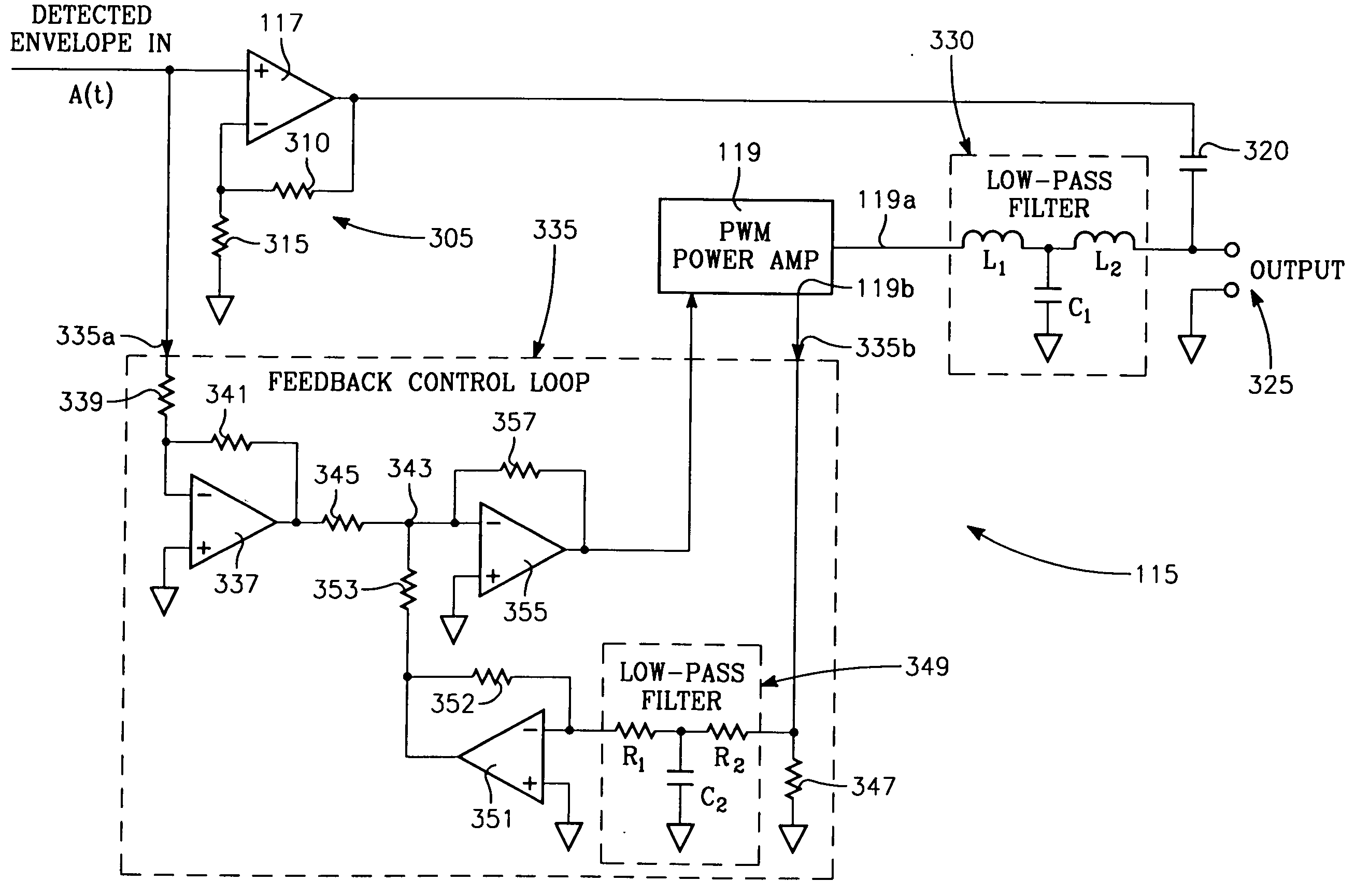

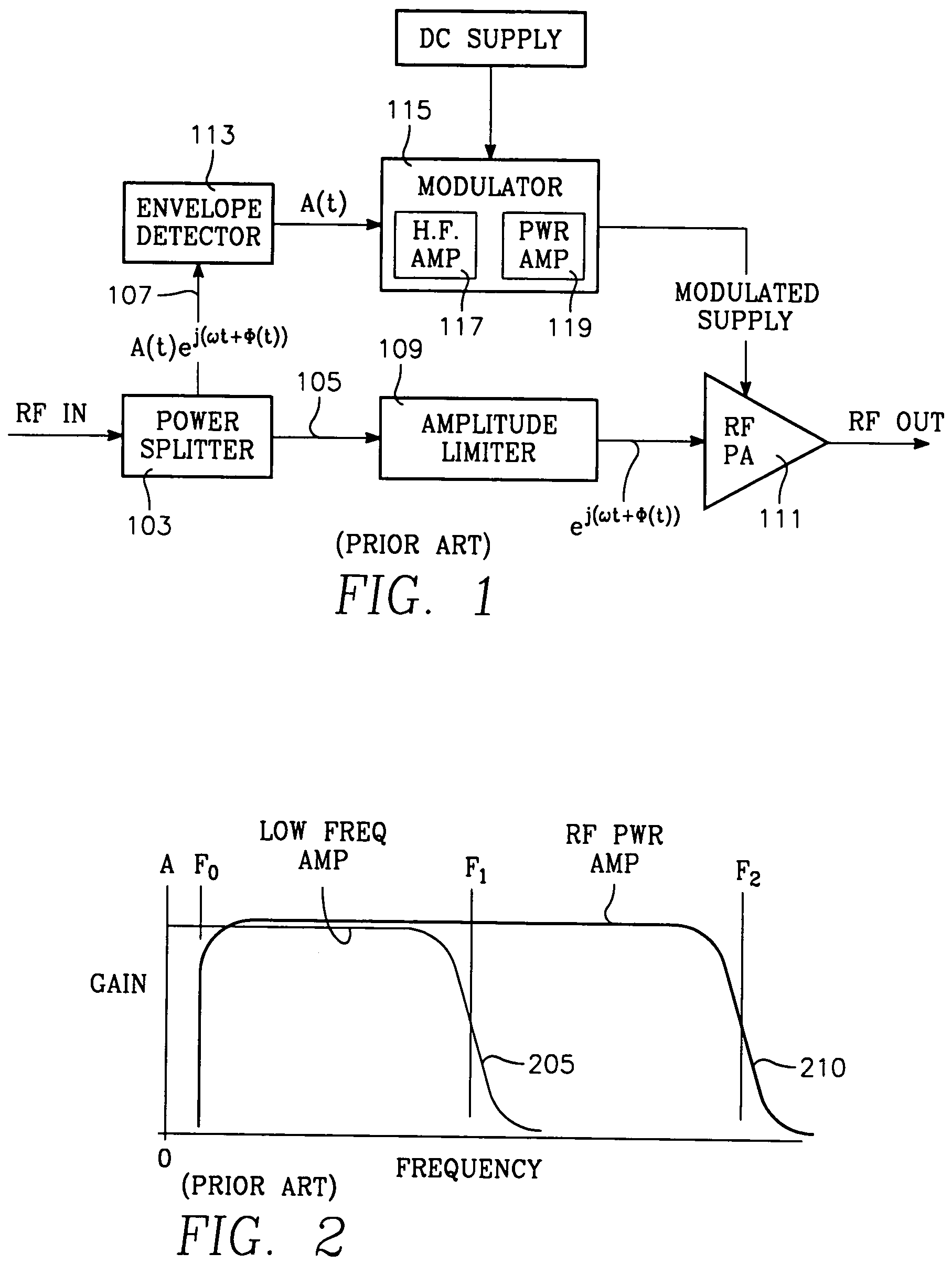

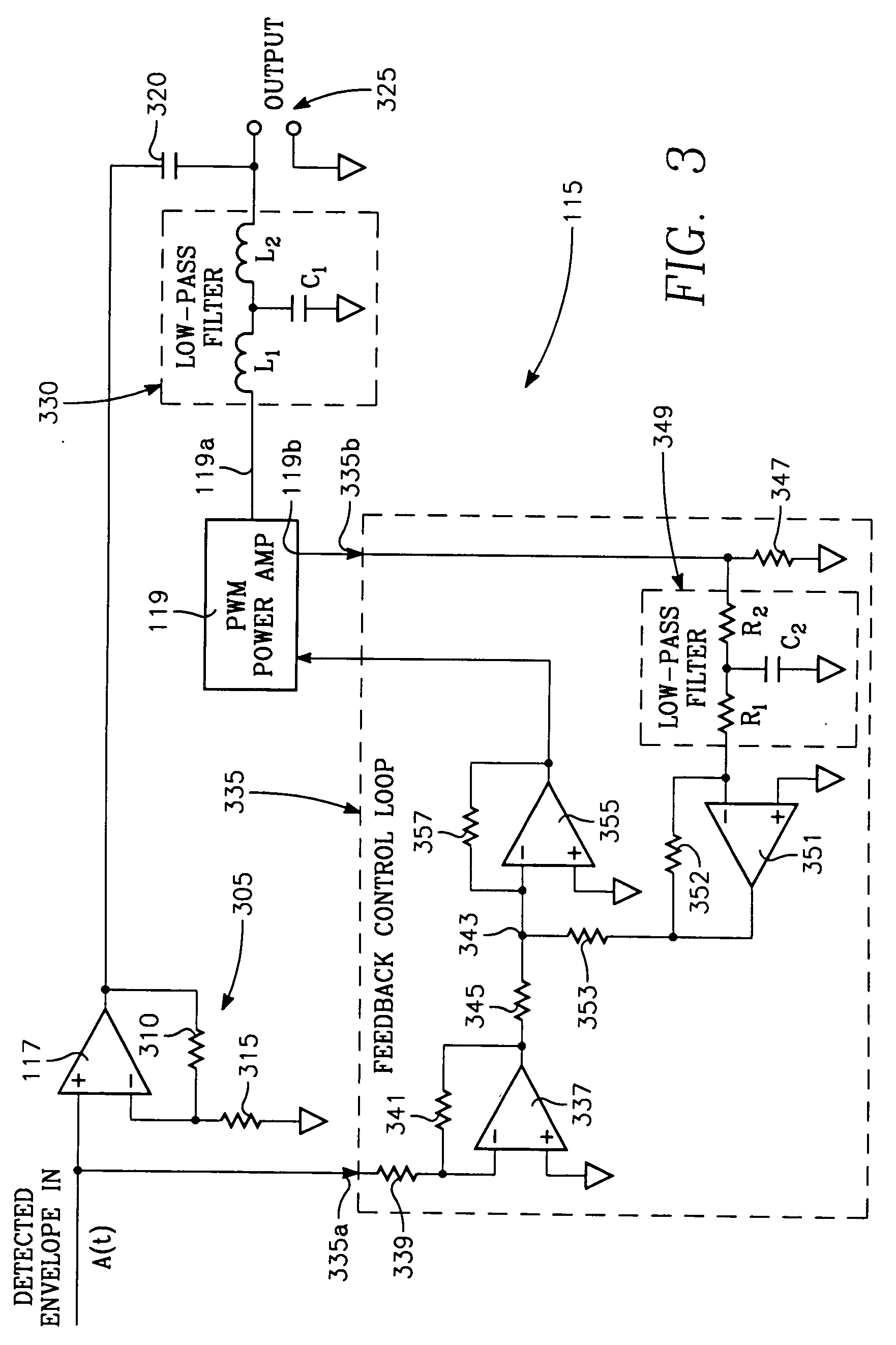

EER modulator with power amplifier having feedback loop providing soft output impedance

ActiveUS20050122163A1Efficient powerImprove efficiencyGain controlAmplifier modifications to raise efficiencyAudio power amplifierEngineering

An EER amplifier for amplifying an RF signal includes: (II) a first RF amplifier for amplifying the phase portion of the signal; (III) an EER modulator for amplifying the envelope or baseband portion of the signal, including: A) a high frequency operational amplifier; B) a power amplifier; C) a feedback control loop including: (1) a current-to-voltage conversion amplifier having an input coupled to a current monitoring output of the power amplifier and an output, (2) an input buffer amplifier having an input coupled to receive the envelope signal and an output; (3) a summing amplifier having: (a) an input coupled to the outputs of: (a) the current-to-voltage conversion amplifier and (b) the input buffer amplifier, and (b) an output coupled to the current control input of the power amplifier.

Owner:NORTHROP GRUMMAN SYST CORP

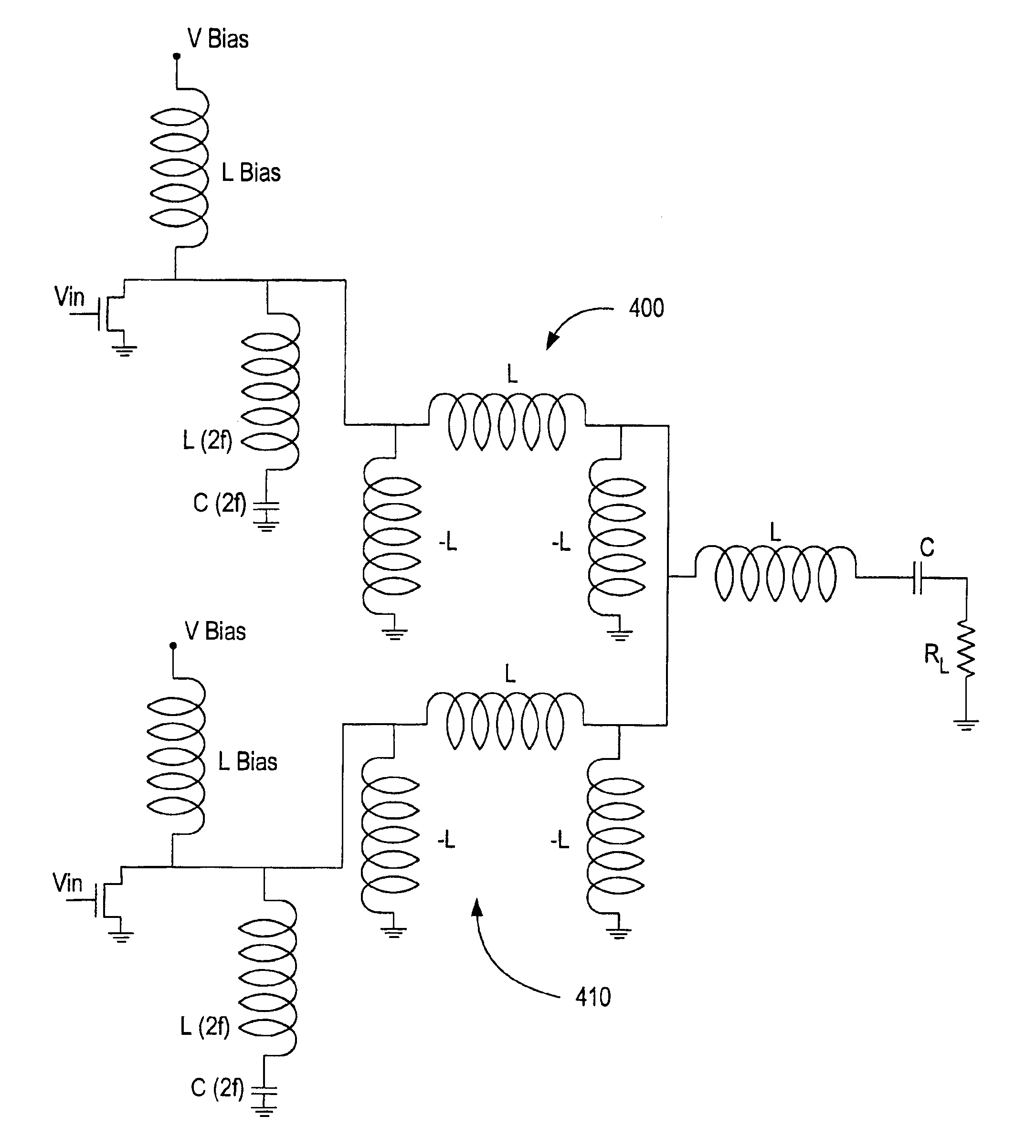

Switched-mode power amplifier integrally performing power combining

InactiveUS6937096B2Negative-feedback-circuit arrangementsPower amplifiersAudio power amplifierImpedance transformer

A switched-mode power amplifier is configured for performing power amplification of a plurality of signals input thereto and integrally summing (combining) those signals. Conceptually, this is achieved by replacing the input winding of the transformer component of a transformer-coupled voltage switching amplifier with separate input components, one for each input signal, in similar manner to the configuration of the input components of a three-port combiner (trifilar). In a first transformer-containing category of embodiments of the invention, the input winding of the amplifier's transformer is comprised of a plurality of series-coupled windings, one for each of the plurality of input components / signals such that the input components constitute a series connection of low output impedance sources applied to the amplifier's resonator and load. This, in turn, provides a high level of isolation between the amplifier input components and results in a low level of loss. In a second non-transformer-containing category of embodiments of the invention, the transformer component is replaced by a transmission line impedance transformer, or a lumped element equivalent circuit, which transforms the low output impedance sources to high output impedance sources and those sources are connected in parallel (rather than in series per the first category of embodiments).

Owner:ZARBANA DIGITAL FUND

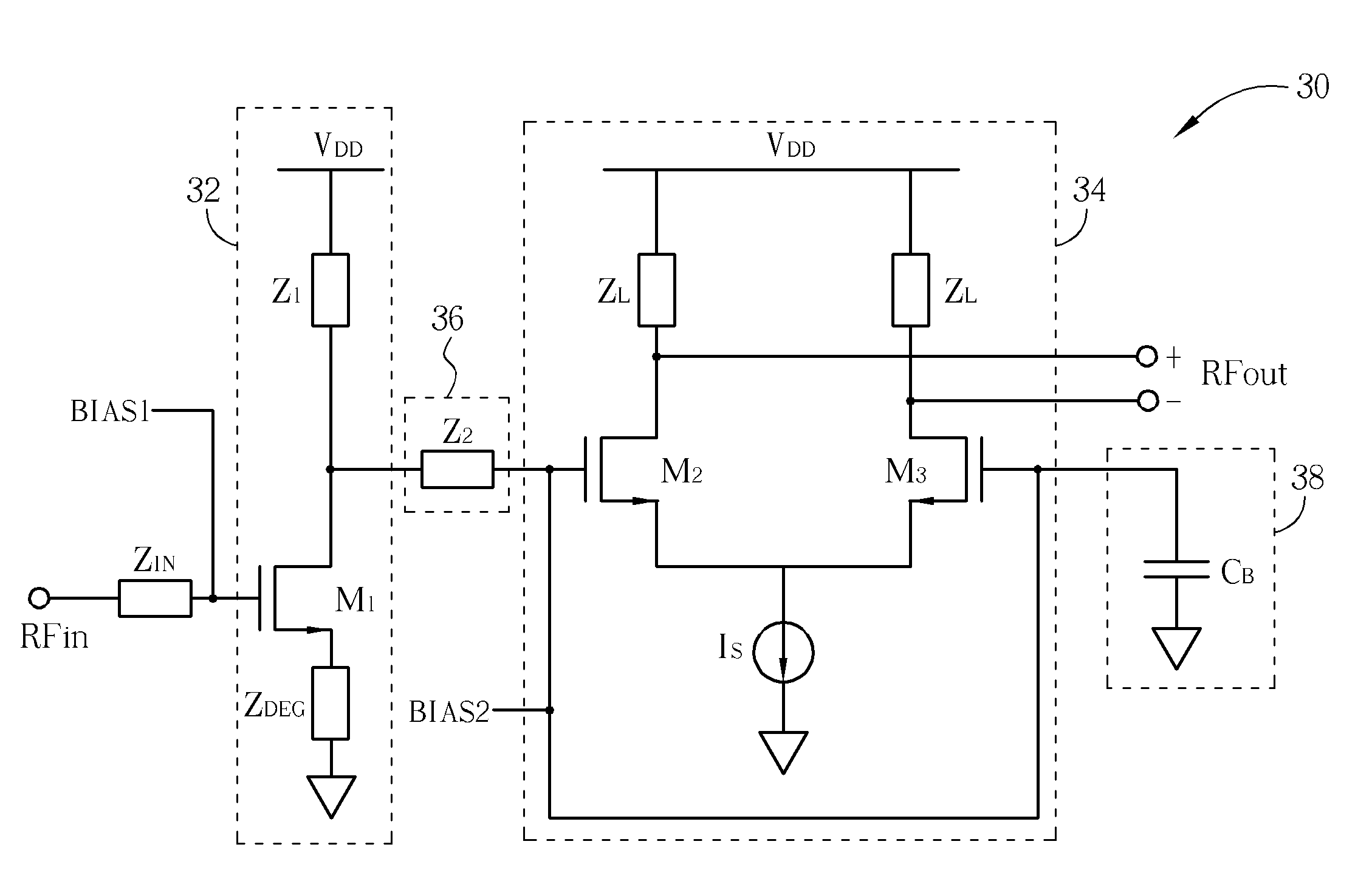

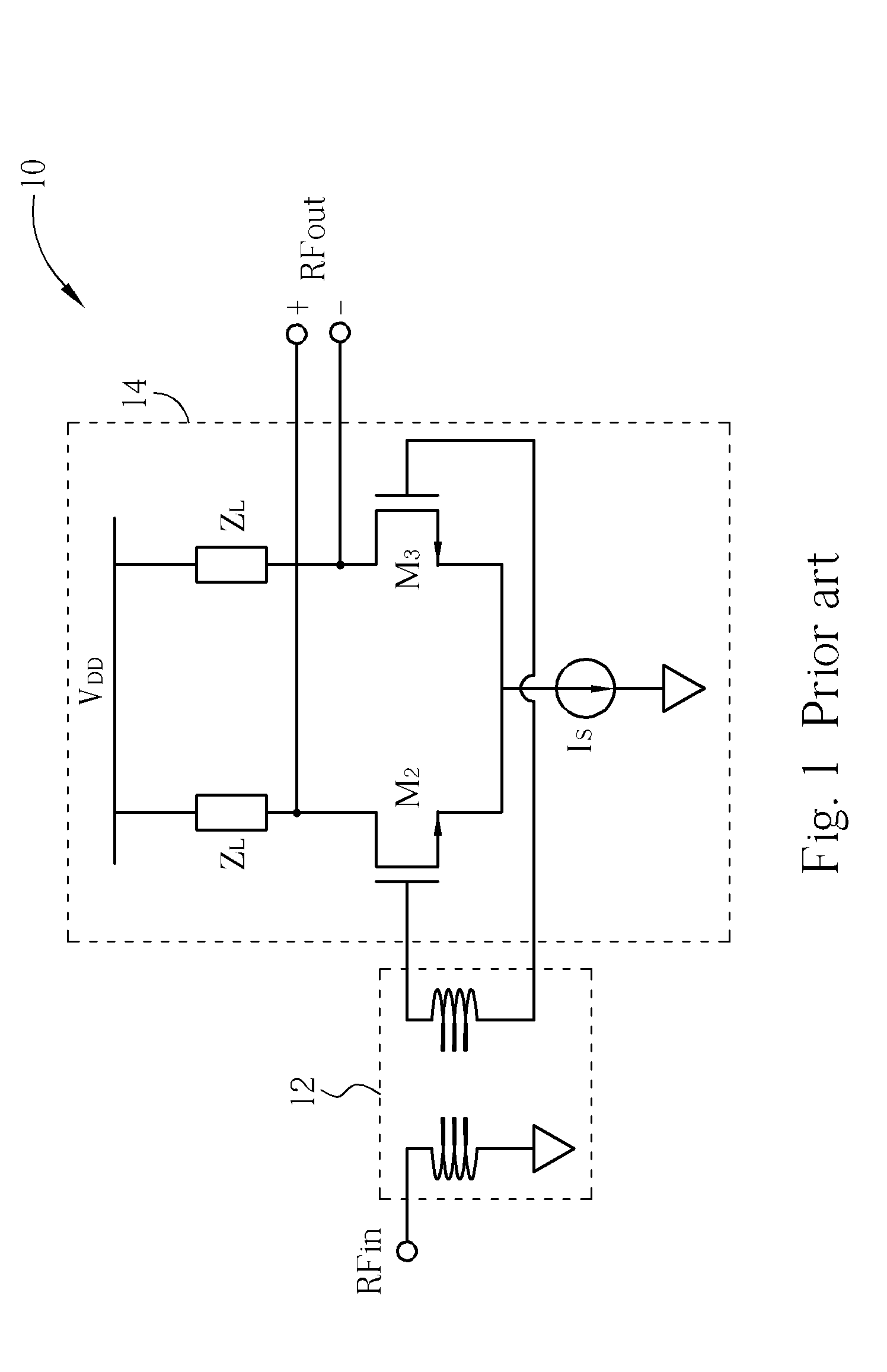

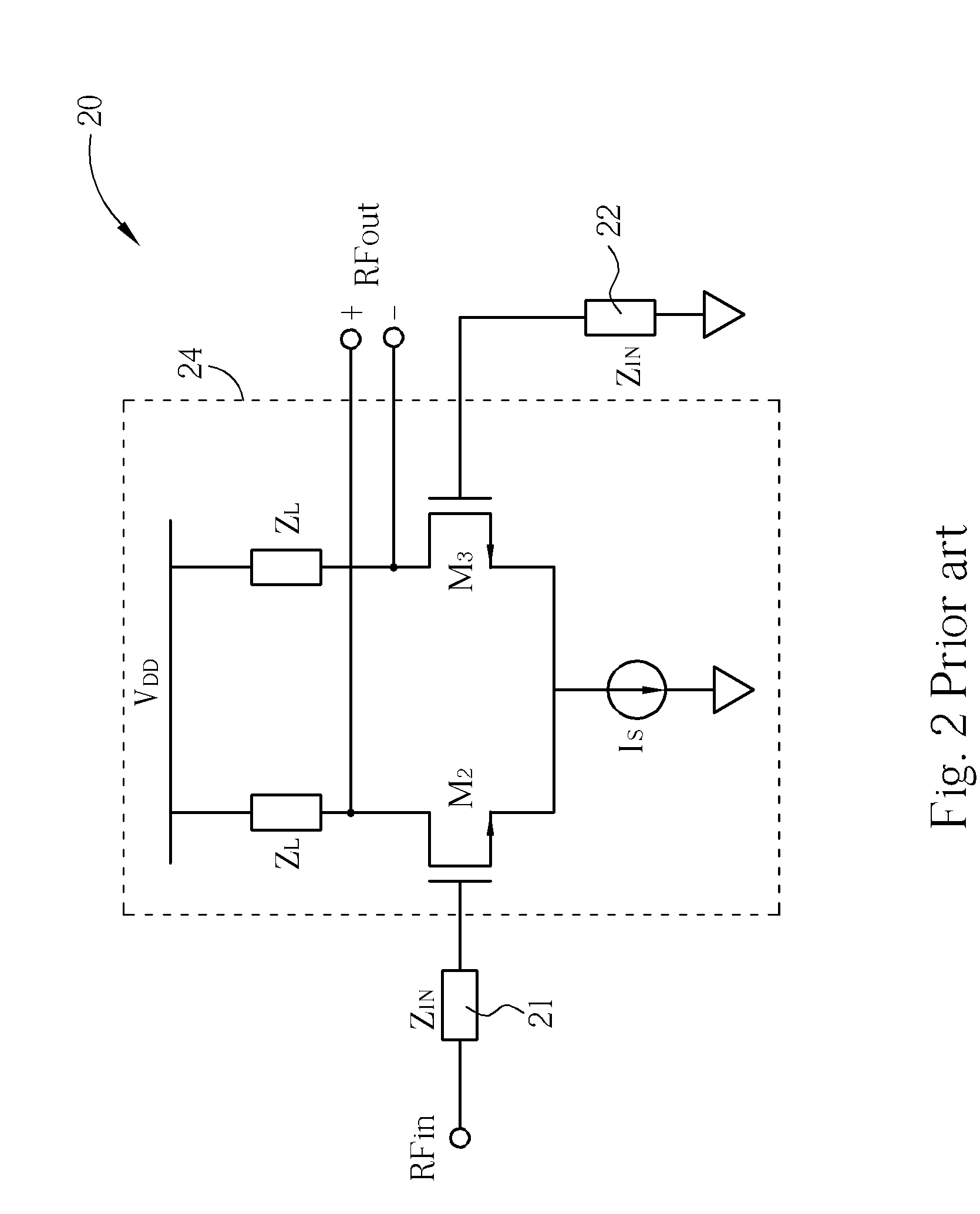

Low noise and high gain low noise amplifier

ActiveUS20060097786A1Low NFIncrease power gainAmplifier modifications to reduce noise influenceDifferential amplifiersLow noiseAudio power amplifier

A high-gain and low-noise low noise amplifier (LNA) includes a differential amplifier, a pre-amplifier and an impedance matching network. The differential amplifier includes a first input end and a second input end coupled to a grounded impedance. The pre-amplifier includes an input end and an output end. The impedance matching network is coupled between the first input end of the differential amplifier and the output end of the pre-amplifier for matching an input impedance of the differential amplifier with an output impedance of the pre-amplifier. The present invention provides a LNA structure with low noise, high gain and easy design.

Owner:RICHWAVE TECH CORP

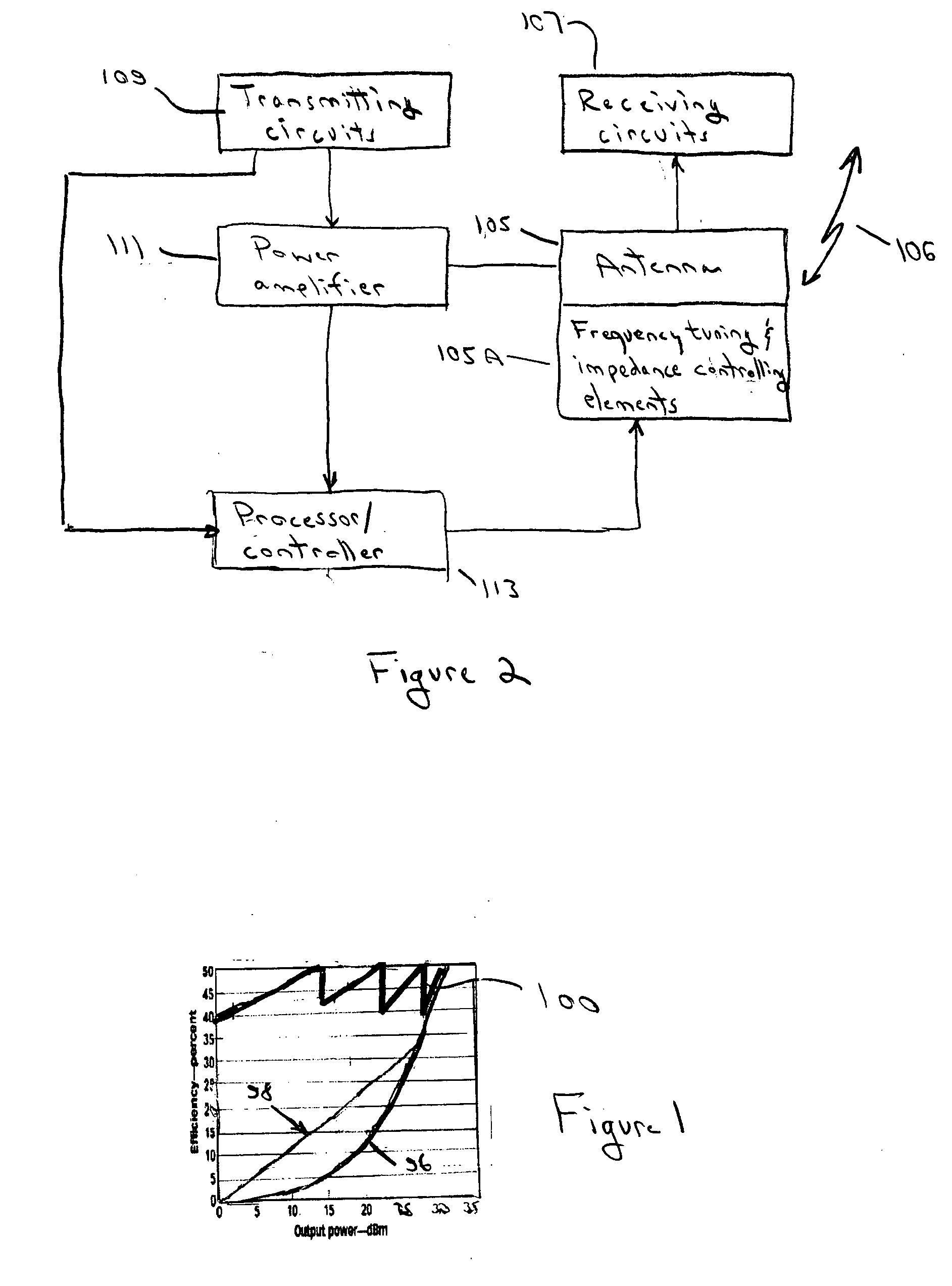

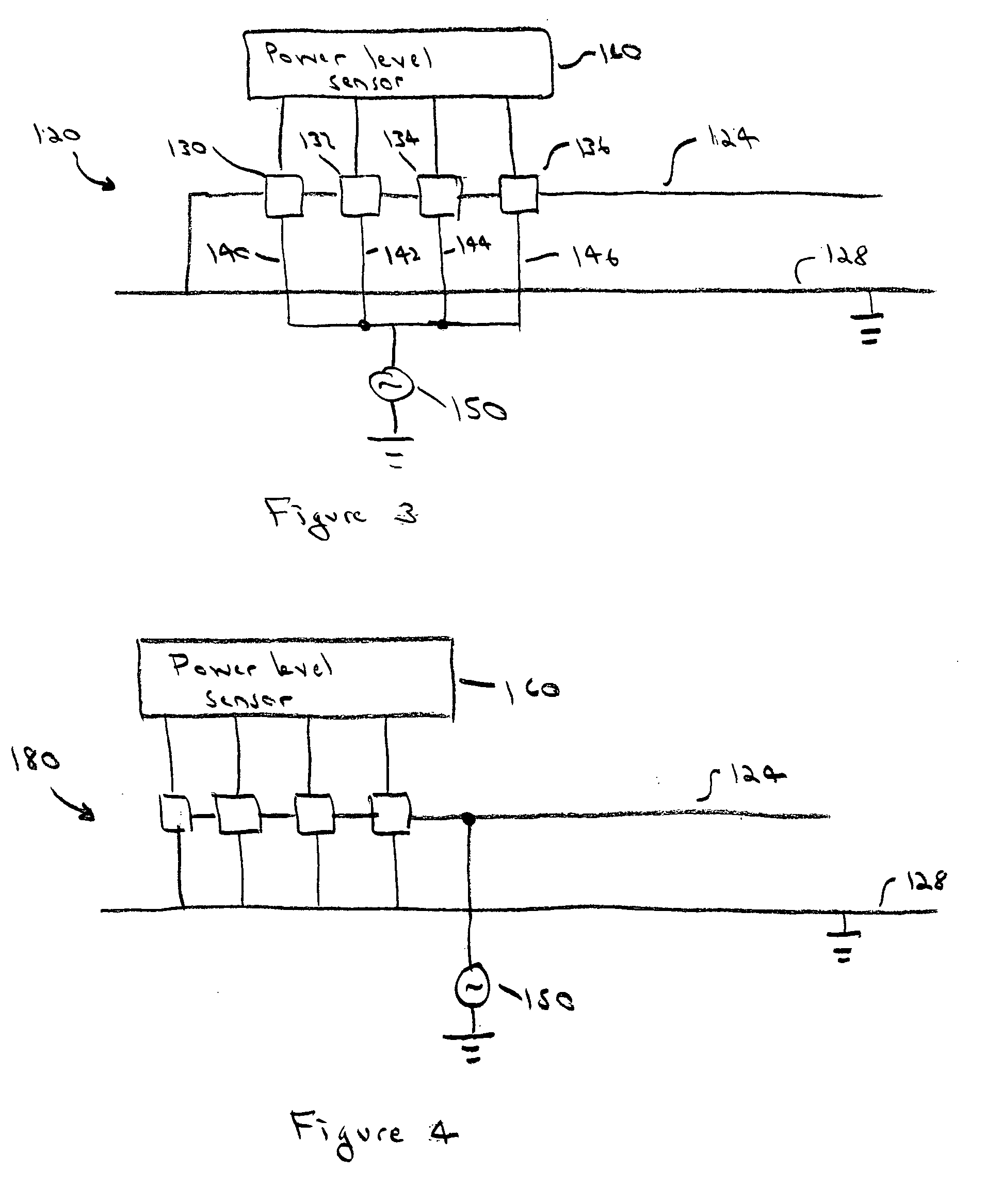

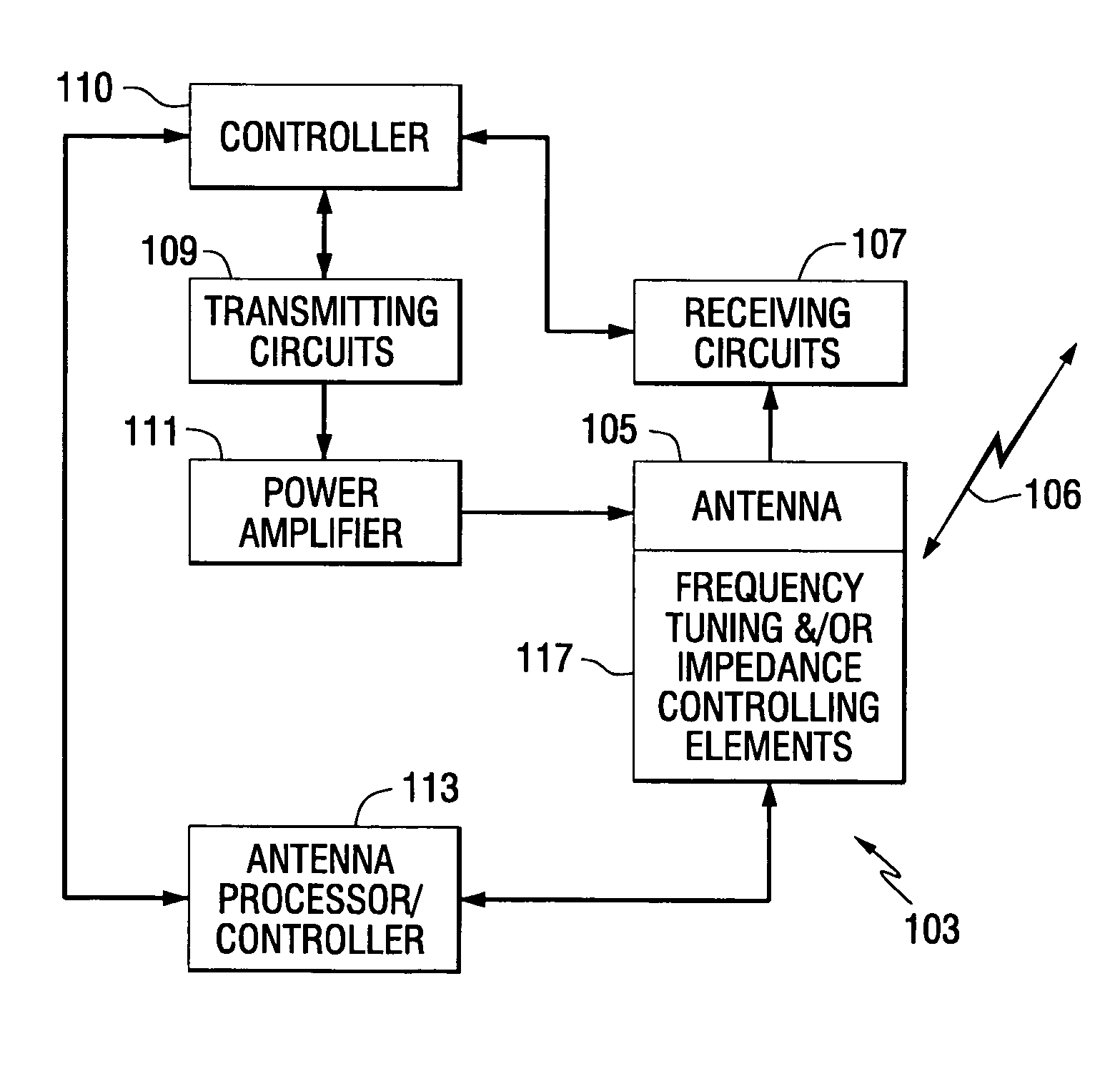

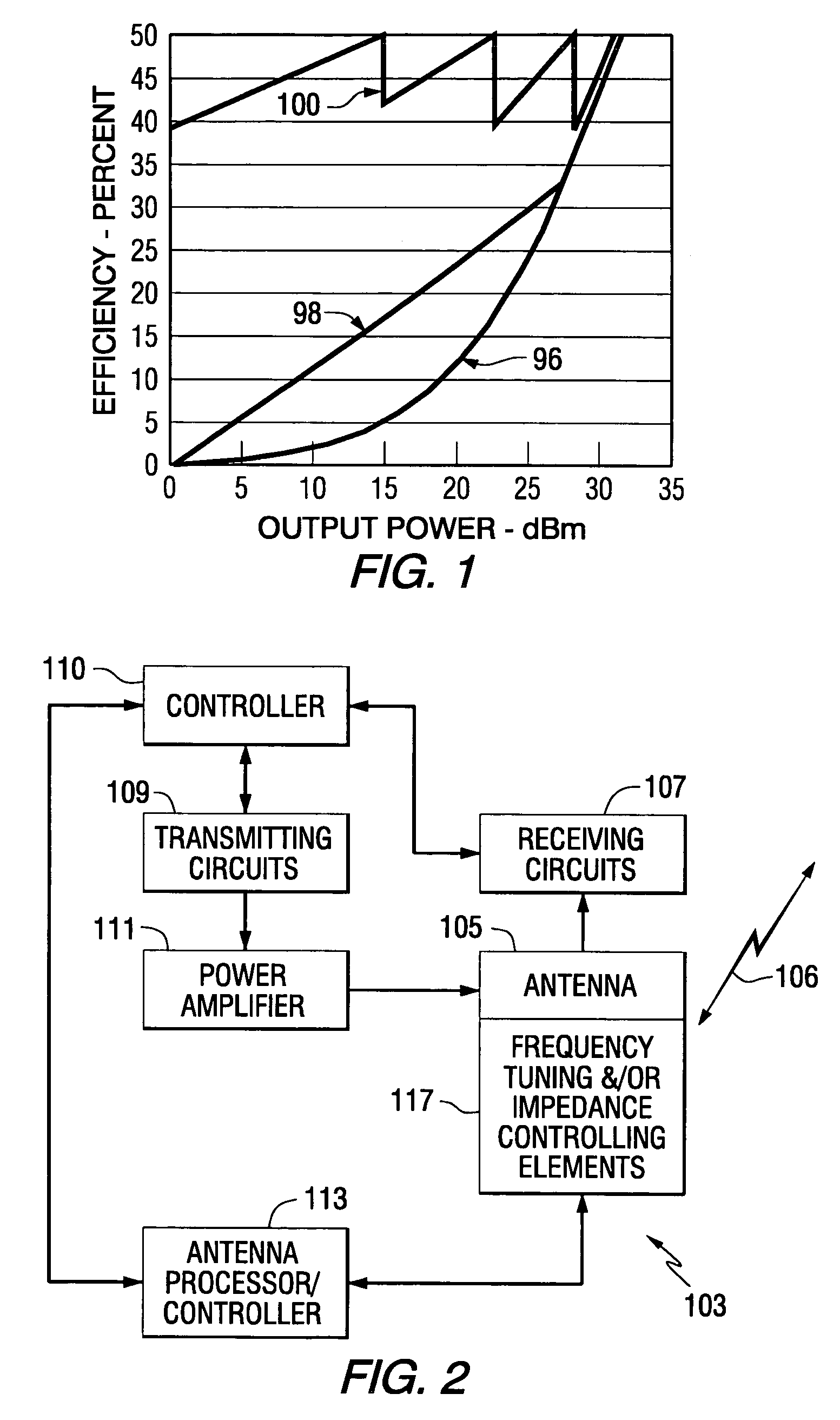

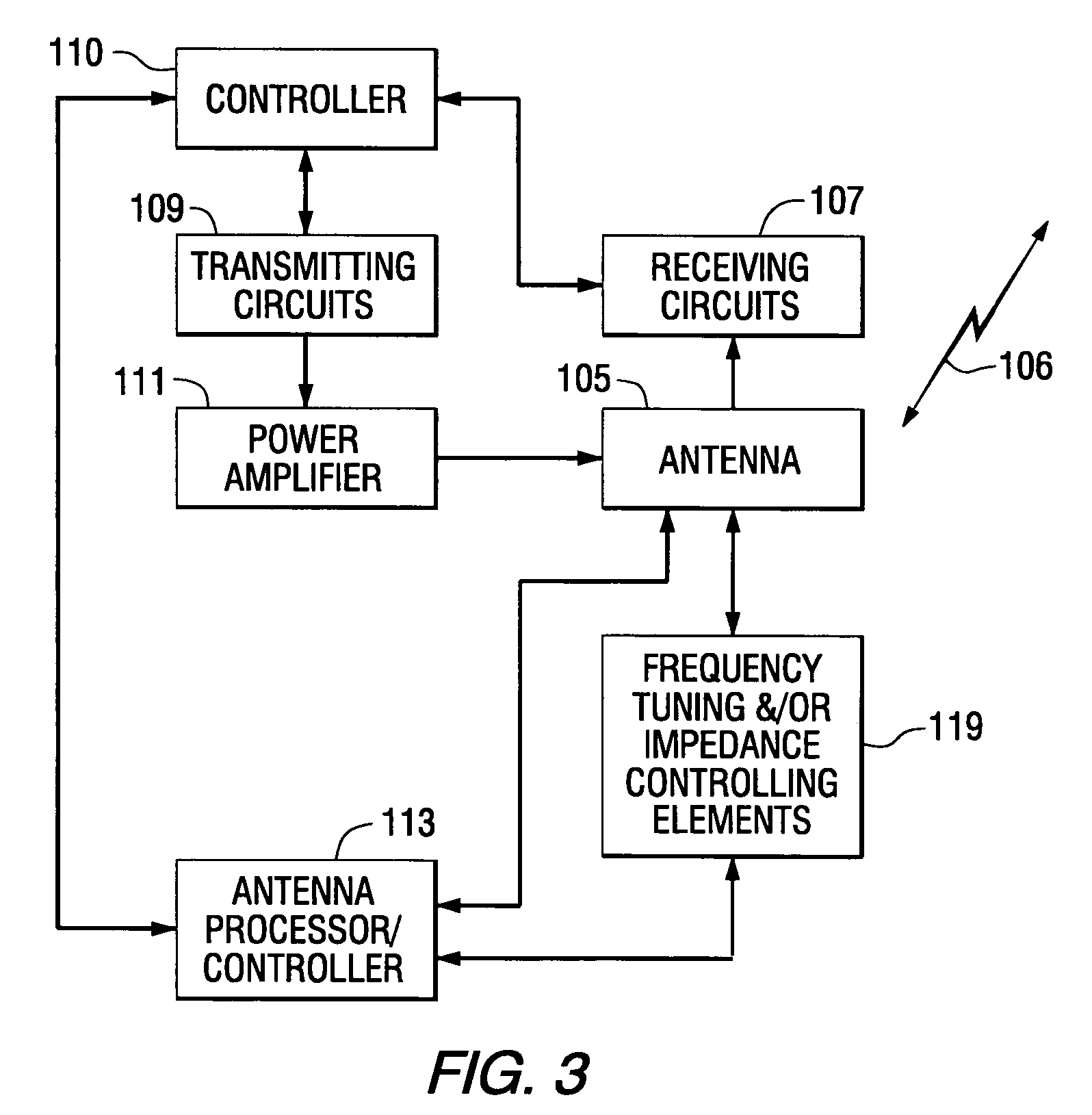

Method and apparatus for adaptively controlling antenna parameters to enhance efficiency and maintain antenna size compactness

InactiveUS20060132360A1Simultaneous aerial operationsAntenna supports/mountingsAntenna impedanceAudio power amplifier

An antenna for a communications device having configurable elements controlled to modify an antenna impedance and / or an antenna resonant frequency to improve performance of the communications device. The antenna impedance is controlled to substantially match to an output impedance of a power amplifier that supplies the antenna with a signal for transmission. The antenna resonant frequency is controlled to overcome the effects of various operating conditions that can detune the antenna or in response to an operable frequency band.

Owner:SKYCROSS INC

Methods and apparatuses for adaptively controlling antenna parameters to enhance efficiency and maintain antenna size compactness

InactiveUS7834813B2Resonant long antennasSimultaneous aerial operationsAudio power amplifierAntenna impedance

An antenna for a communications device having configurable elements controlled to modify an antenna impedance and / or an antenna resonant frequency to improve performance of the communications device. The antenna impedance is controlled to substantially match to an output impedance of a power amplifier that supplies the antenna with a signal for transmission. The antenna resonant frequency is controlled to overcome the effects of various operating conditions that can detune the antenna or in response to an operable frequency band.

Owner:SKYCROSS INC

Switched-mode power amplifier using lumped element impedance inverter for parallel combining

InactiveUS6879209B2Effective compensationNegative-feedback-circuit arrangementsPower amplifiersPower inverterAudio power amplifier

A switched-mode Class F power amplifier is provided for parallel connection with at least one other like amplifier, within a Chireix architecture, for combining the signals output therefrom. An input component includes at least one active device configured to be alternately switched by a signal input thereto to present an amplified signal corresponding to the input signal and constituting a low output impedance voltage source. A lumped element impedance inverter is provided between the input component and an output resonator component, the impedance inverter being configured for transforming the low output impedance voltage source to instead constitute a high output impedance current source configured for said parallel connection. In accordance with the invention, the negative reactive component values required by the impedance inverter are eliminated and effectively provided by incorporating those values into pre-selected reactive components of the input and output components. Further, a source-drain parasitic capacitance across the active device is eliminated by one or more pre-selected reactive components of the input component, the value(s) of which effectively compensate for the parasitic capacitance.

Owner:ZARBANA DIGITAL FUND

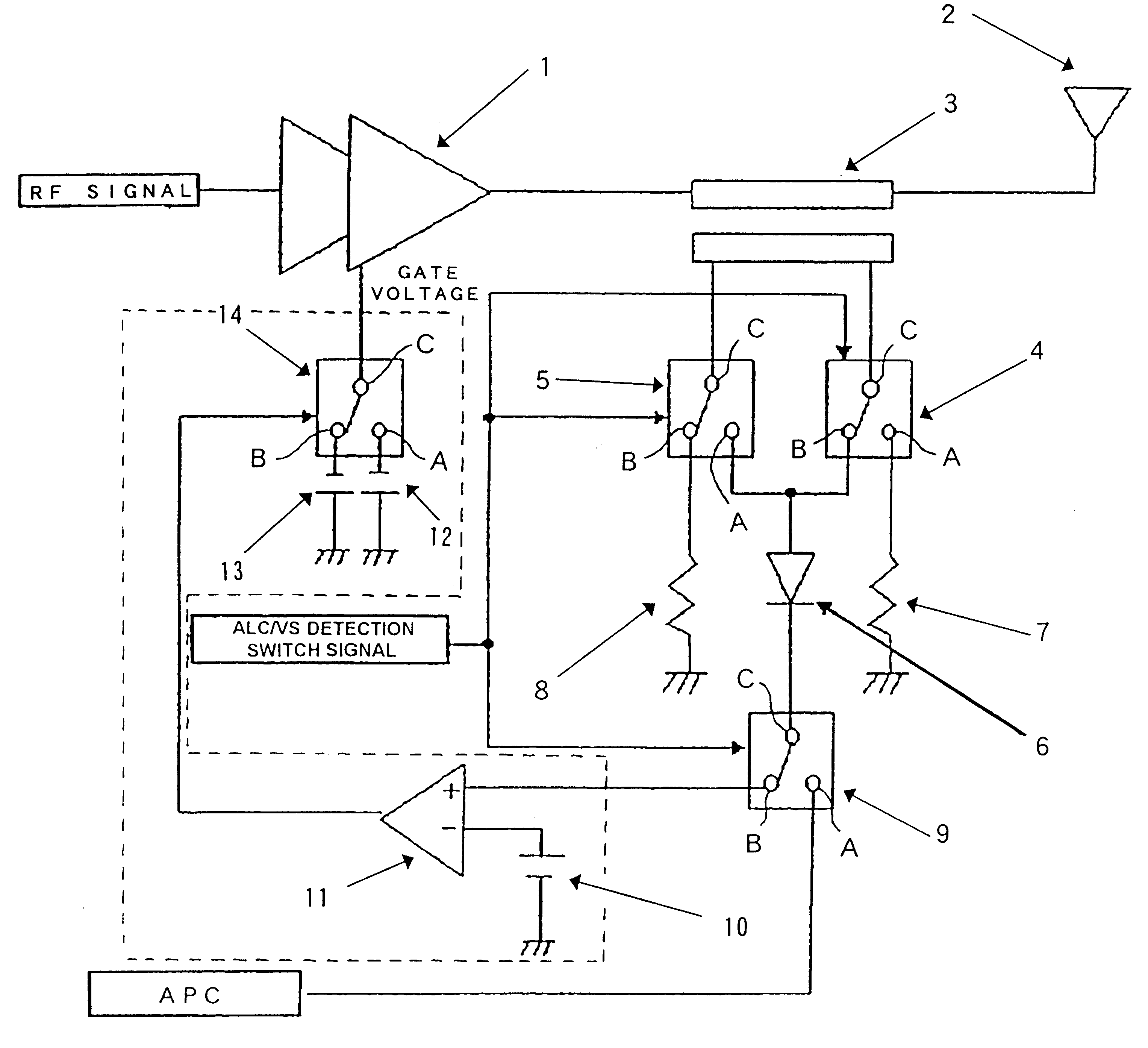

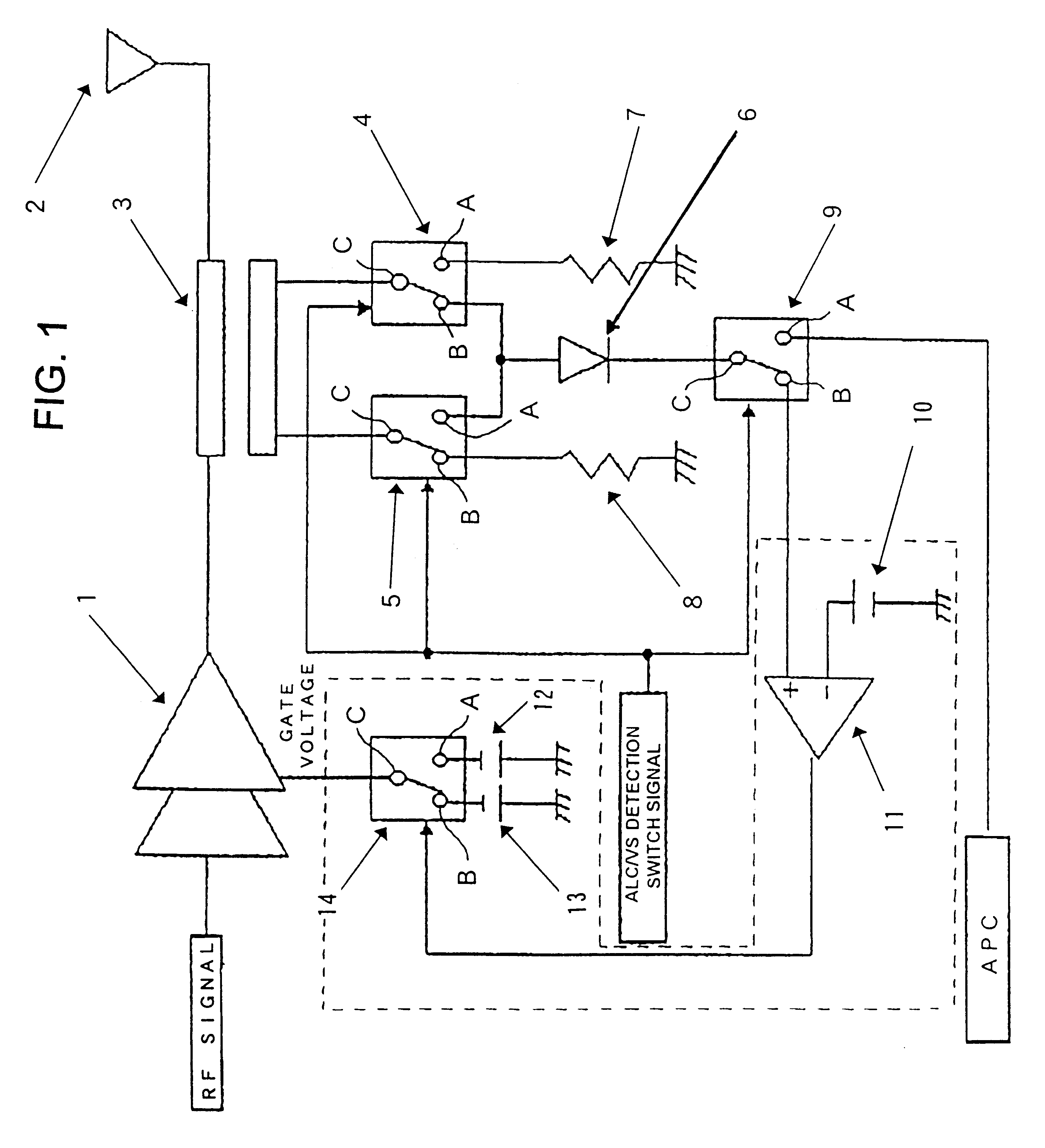

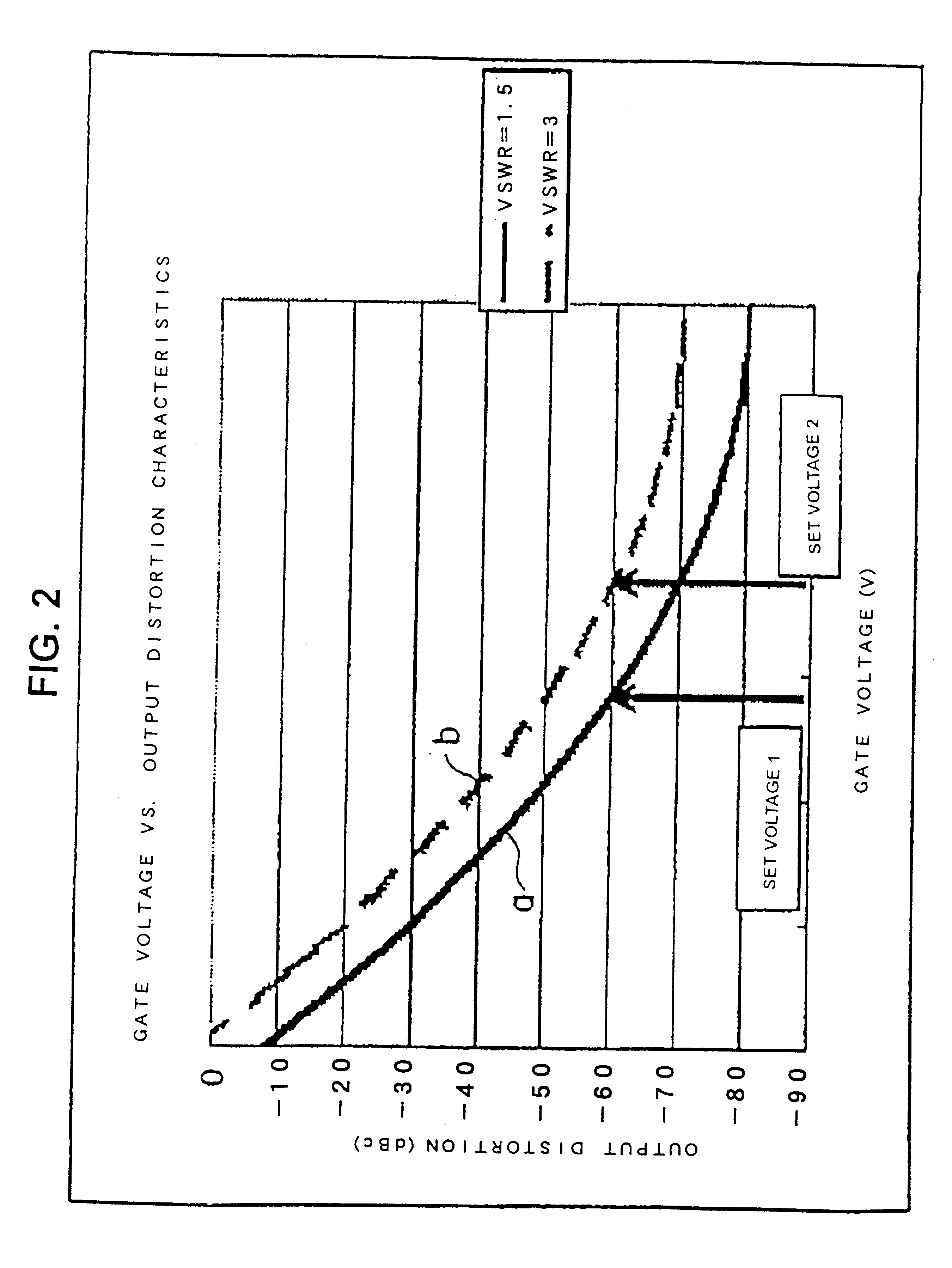

Radio frequency transmitting circuit

InactiveUS6329880B2Excellent electrical propertiesMiniaturize a mobile communication equipmentGain controlEmergency protective circuit arrangementsAudio power amplifierReflected waves

An object of the present invention is to allow the miniaturization of a mobile communication equipment and the reduction of consumption power, and to improve the electrical characteristics of a final stage amplifier. An inputted RF signal is amplified to a specified transmission output by a final stage amplifier, the output power and a reflected wave generated by mismatching between an output impedance of the final stage amplifier and a load impedance connected to an output side of the final stage amplifier are detected by a directional coupler. Two switches are selectively switched in a time division manner, a DC voltage corresponding to the reflected wave is selected, a comparator compares a threshold voltage with the DC voltage, a switch is switched by an output of the comparator outputted in accordance with the comparison, and gate voltages are selectively applied to the final stage amplifier.

Owner:NEC CORP

Multilevel power amplifier architecture using multi-tap transformer

InactiveUS7129784B2Increase powerEffective maintenanceAmplifier combinationsAmplifier detailsCMOSAudio power amplifier

A multi-level power amplifier architecture using a multi-tap transformer implemented on a single CMOS integrated circuit wireless communications device is described. By providing a multi-tap transformer for coupling a plurality of power amplifiers to a shared output impedance, such as an antenna, power transmission may be made at different levels while maintaining efficiency. With a multi-tap transformer having “N” taps featuring “N” different impedance levels, each tap may be connected to an amplifier cell which delivers power into the transformer at the tap for coupling to the output load. Any one of the “N” amplifier cells can be turned on at once along with any combination of the “N” amplifier cells.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Output buffer with switchable output impedance

ActiveUS20070216445A1Reduce power consumptionAvoid unnecessary power consumptionInput/output impedence modificationReliability increasing modificationsDriver circuitNormal mode

An output buffer with a switchable output impedance designed for driving a terminated signal line. The buffer includes a drive circuit, and a means for switching the output impedance of the drive circuit between a first, relatively low output impedance when the output buffer is operated in a ‘normal’ mode, and a second output impedance which is greater than the first output impedance when operated in a ‘standby’ mode. By increasing the drive circuit's output impedance while in ‘standby’ mode, power dissipation due to the termination resistor is reduced. When used in a memory system, additional power savings may be realized by arranging the buffer such that the increased impedance in ‘standby’ mode shifts the signal line voltage so as to avoid the voltage range over which a line receiver's power consumption is greatest.

Owner:MARVELL ASIA PTE LTD

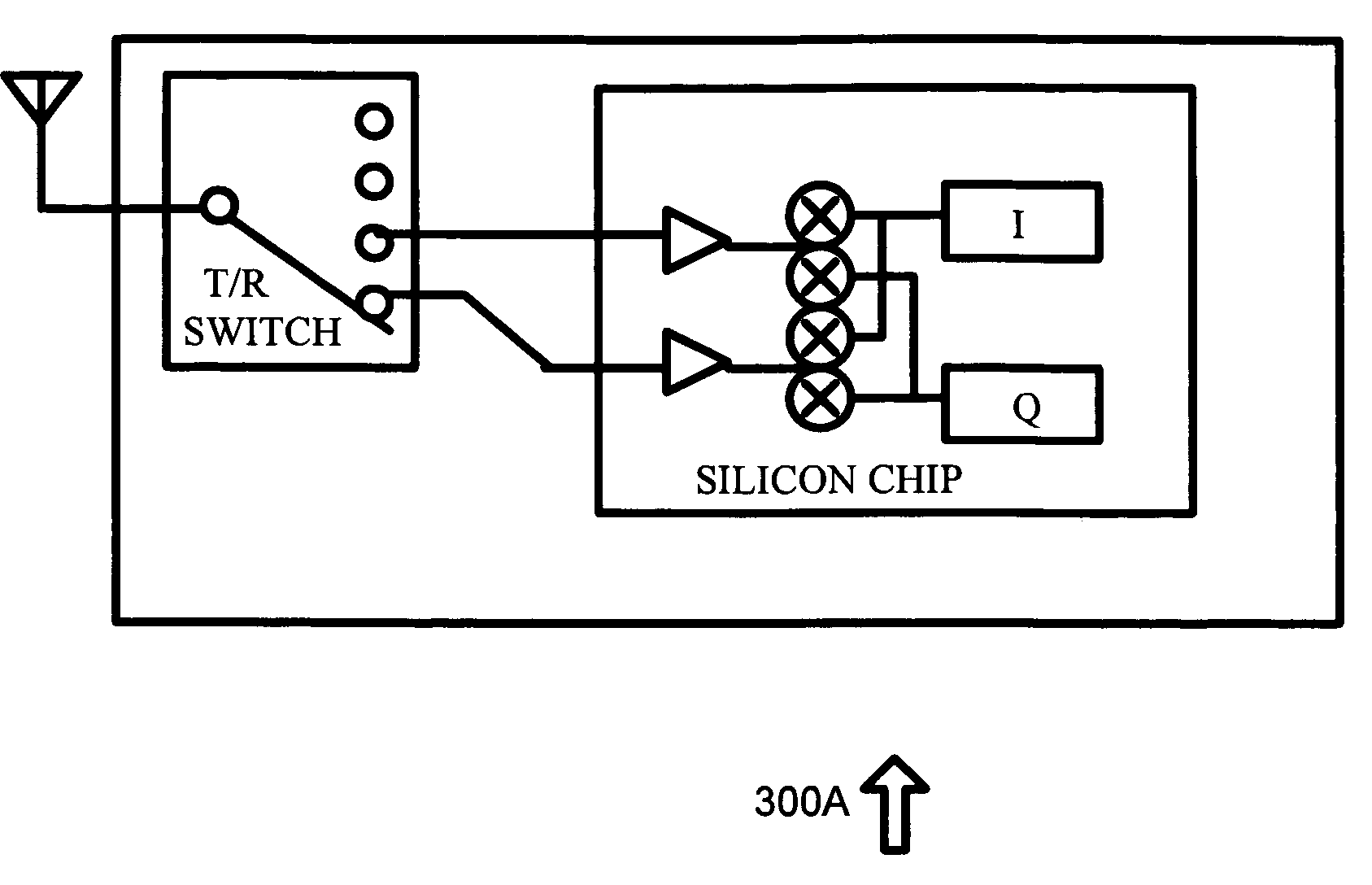

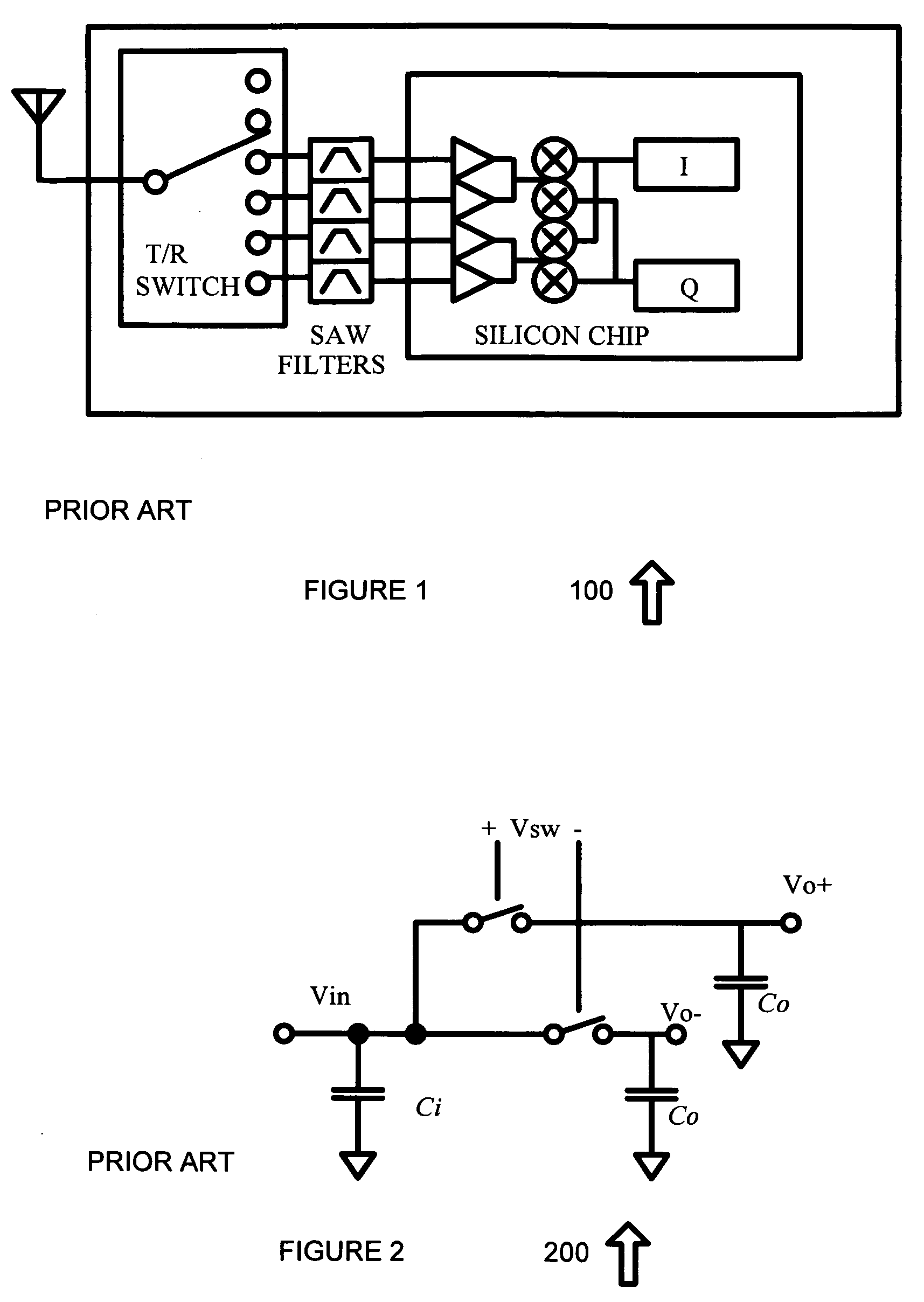

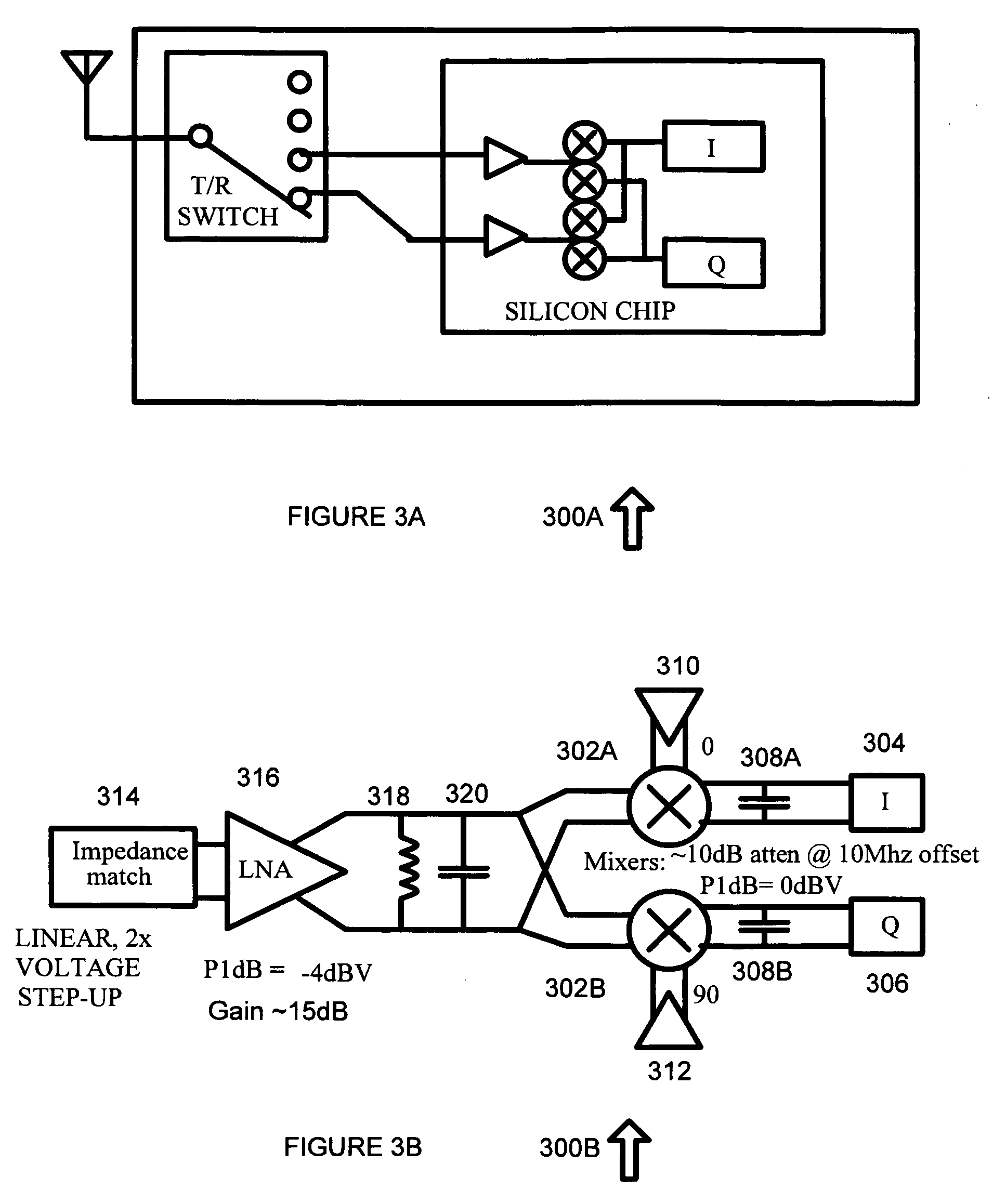

High dynamic range time-varying integrated receiver for elimination of off-chip filters

ActiveUS20050164669A1Improve linearityLow costModulation transference balanced arrangementsSwitched capacitor networksQuadrature mixerOutput impedance

A quadrature mixer with an LO input is provided. The quadrature mixer receives a signal having a frequency FLO and a signal input having a frequency FSIG, and has an output that comprises an output impedance that is high at frequencies of |FLO−FSIG | and |FLO+FSIG| and low at other. A mixer coupled to the output impedance interacts with the output impedance such that an impedance presented at the signal input is high for signals at FSIG if FSIG is a predetermined signal frequency, and low at other frequencies.

Owner:MEDIATEK INC

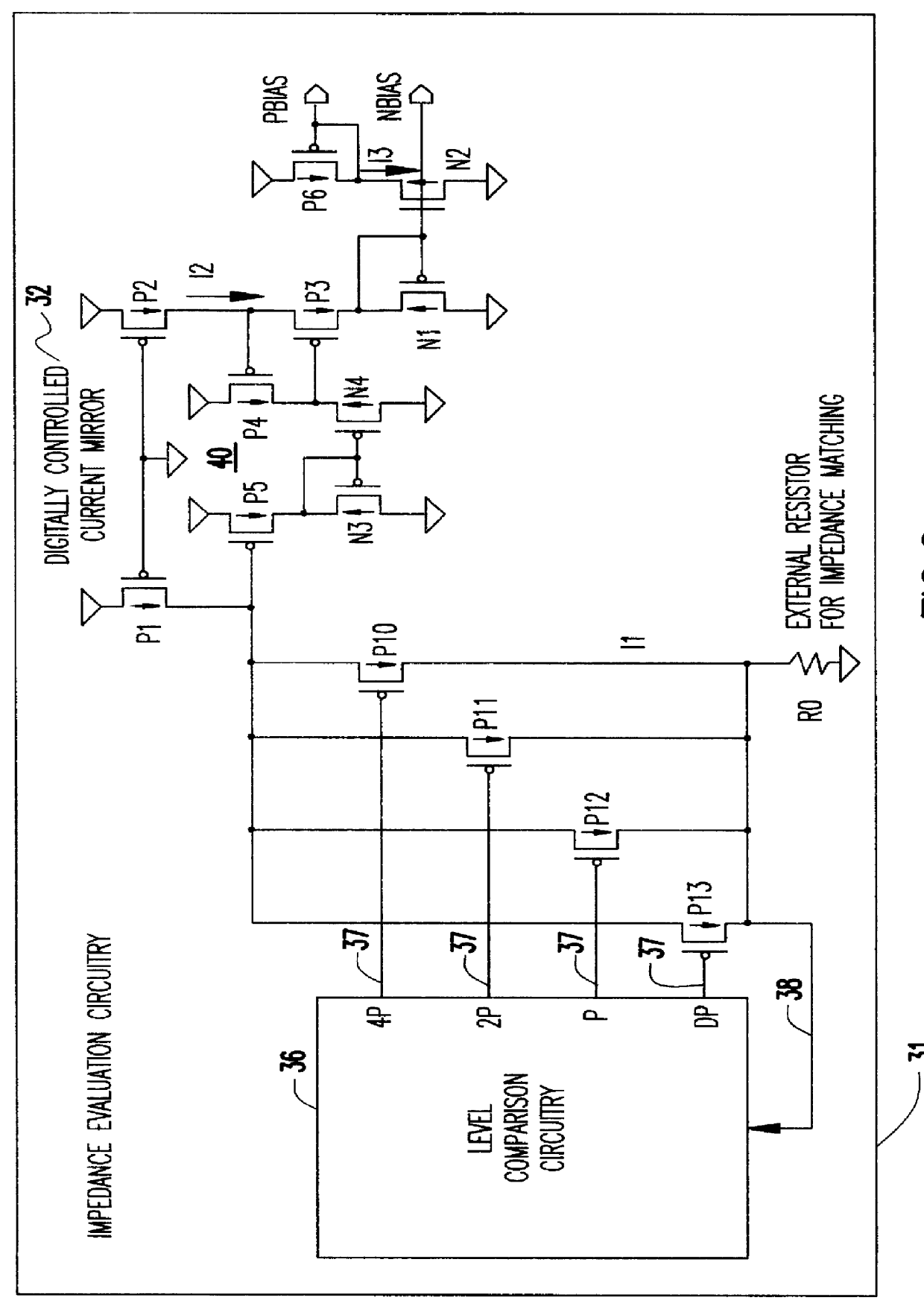

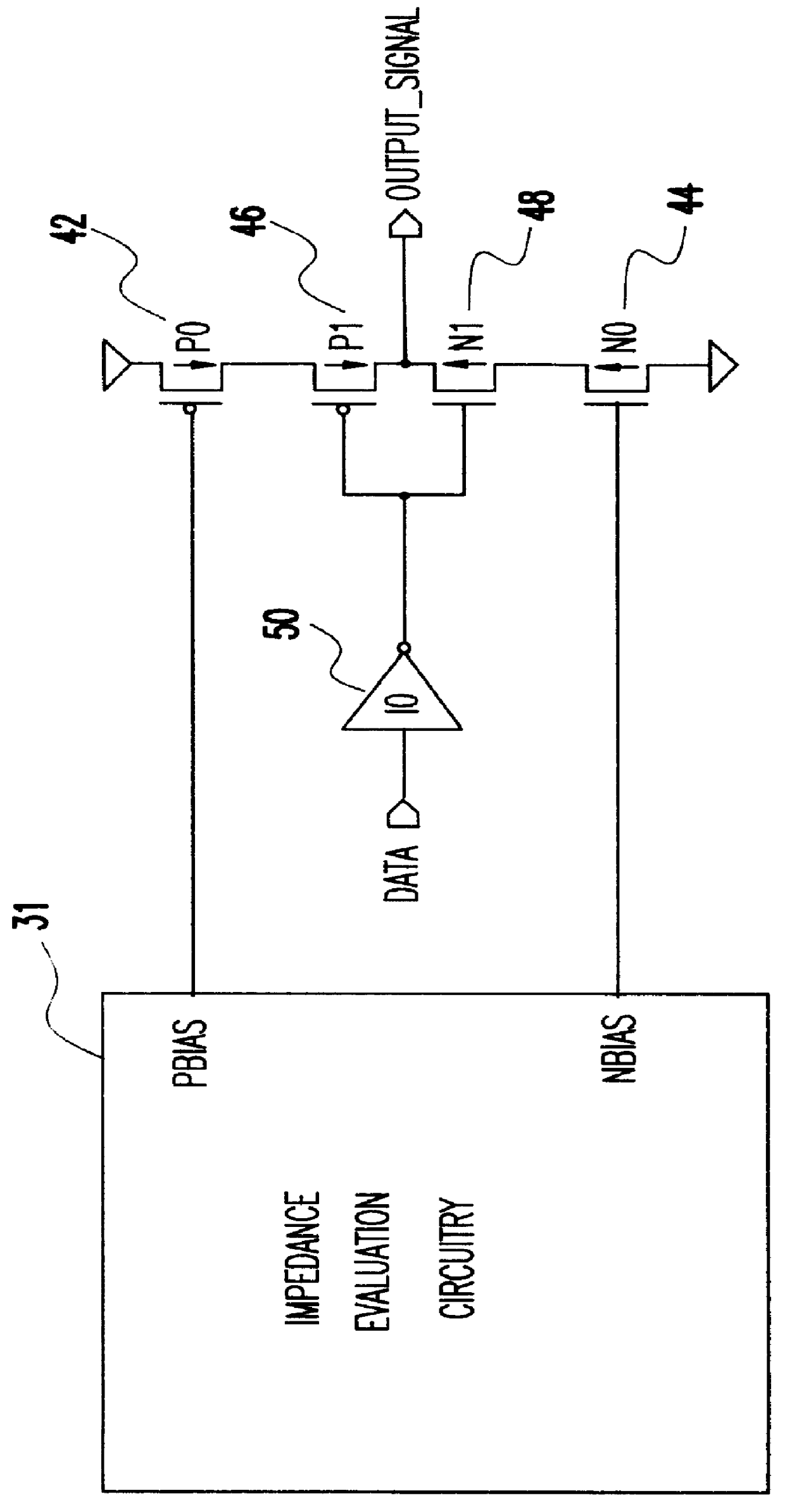

Variable impedance output driver circuit using analog biases to match driver output impedance to load input impedance

InactiveUS6133749AInput/output impedence modificationReliability increasing modificationsDriver circuitElectrical resistance and conductance

A programmable variable impedance output driver circuit uses analog biases to match driver output impedance to load input impedance. A current mirror is used to obtain a measurement of an external resistance value for matching the impedance of a driven load. The mirrored current generates the voltage "NBIAS" when passed through the resistively connected NFET. Similarly, the current is again mirrored and passed through a resistively connected PFET resulting in the voltage "PBIAS". The analog bias voltages, NBIAS and PBIAS are used to vary the impedance of complementary FETs in an impedance matched driver for a high degree of dI / dt control. The driver provides a high degree of flexibility because its turn-on and turn-off characteristics do not depend on a combination of digital control signals connected directly to the driving FETs as in the prior art. Instead, the PBIAS and NBIAS signals provide analog controls which may be applied to single transistors whose impedance changes as PBIAS and NBIAS increase or decrease.

Owner:IBM CORP

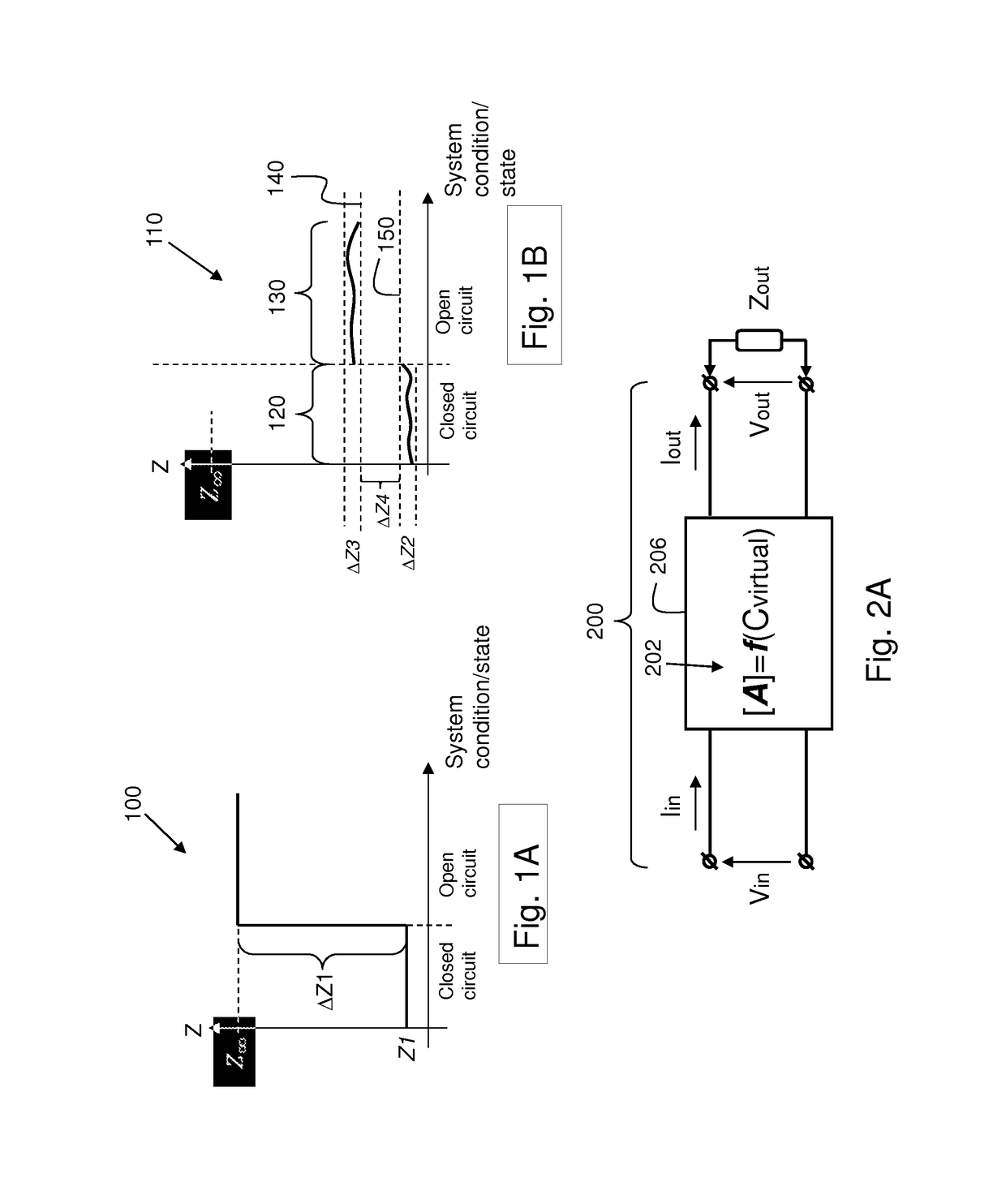

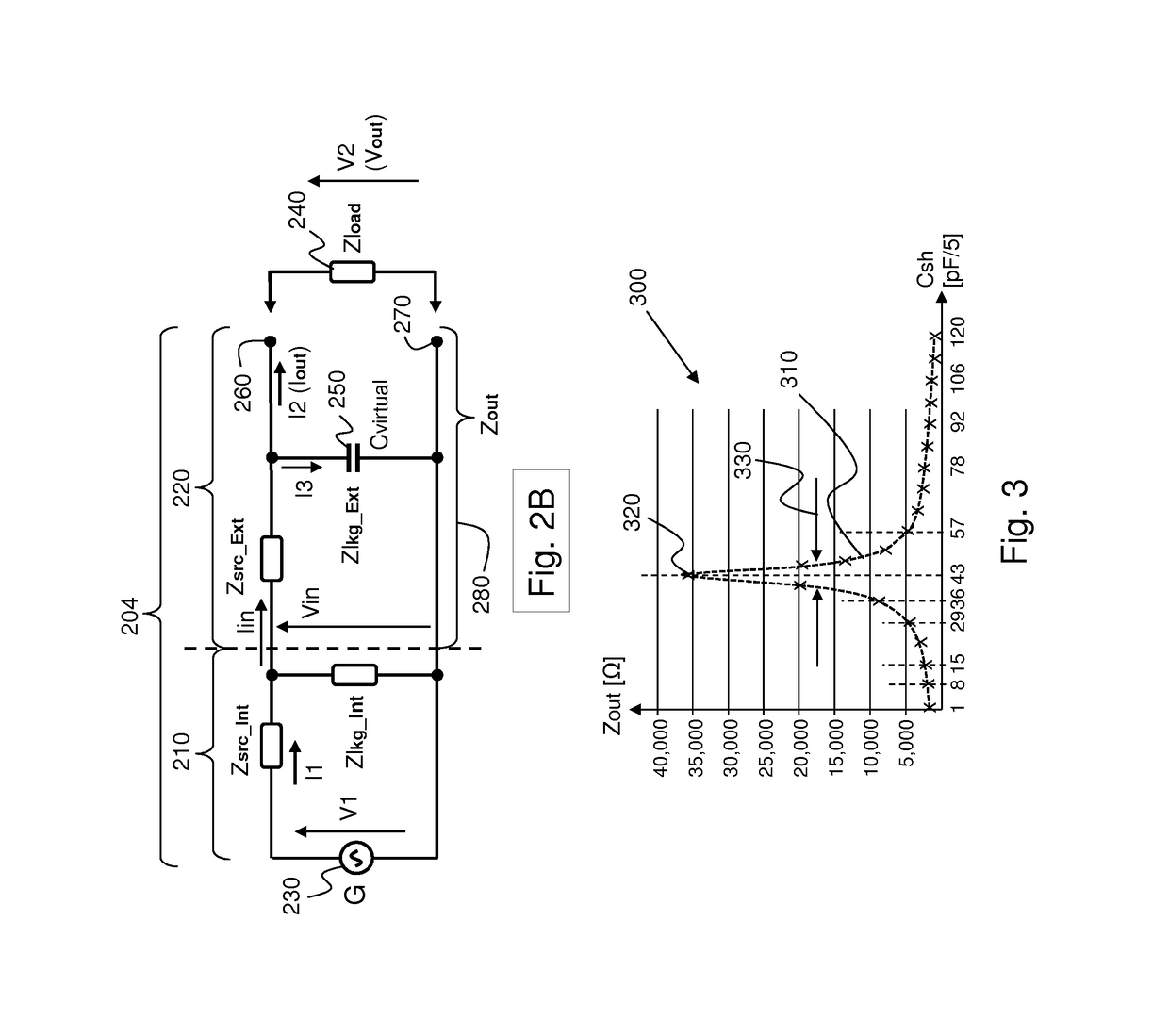

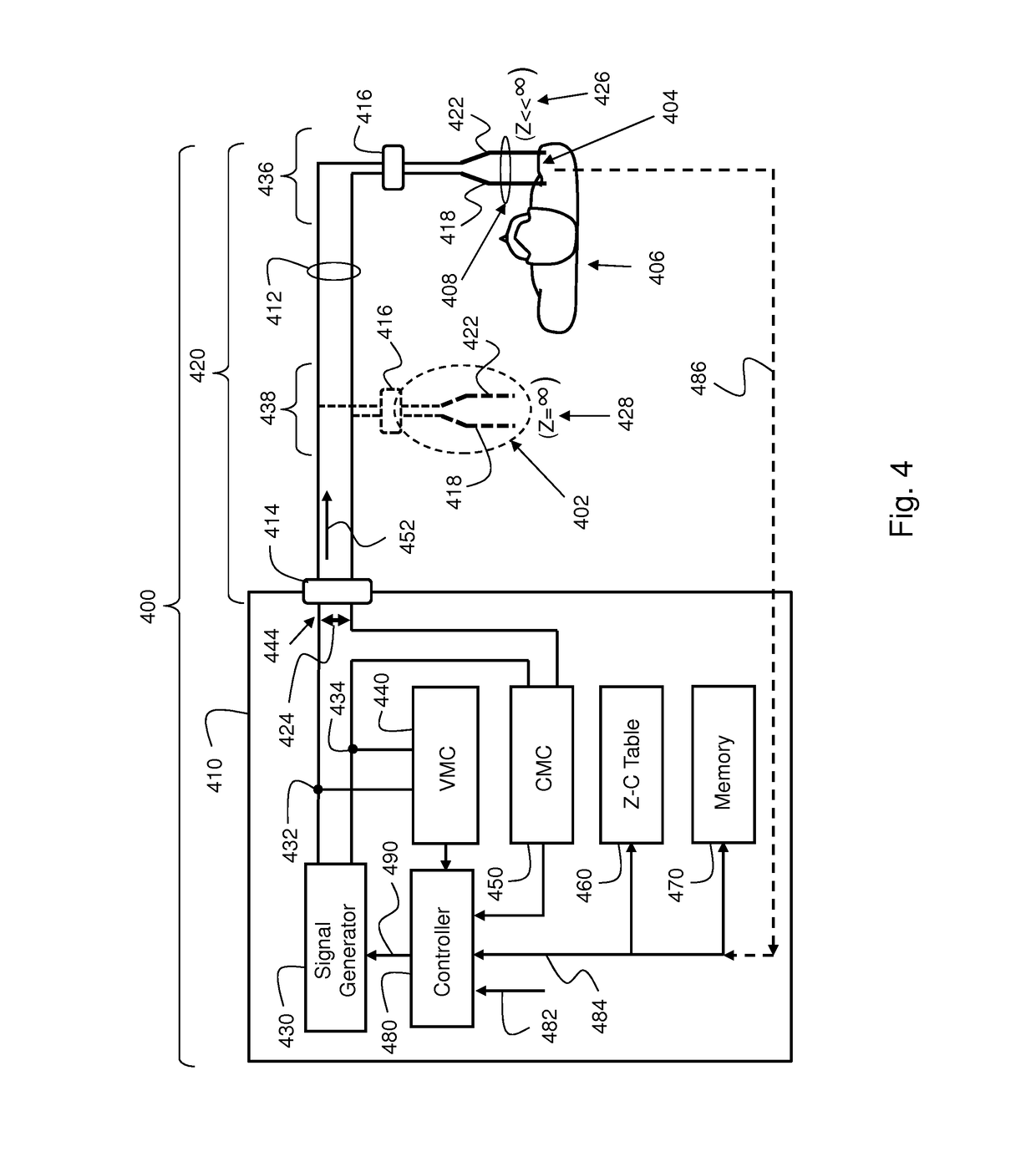

System and method for controlling operation of an electrosurgical system

ActiveUS10172665B2Controlling energy of instrumentSurgical instruments for heatingCapacitancePower flow

An electrosurgical system including or connected to an output circuitry comprising an electrosurgical device and an electrical cable is modelled during a cable interrogation phase using a transfer matrix in order to determine a leakage capacitance in the electrosurgical system. After the leakage capacitance is assigned or set to a virtual capacitor in the transfer matrix, an output parameter of the electrosurgical system, such as output voltage, output current, output impedance or output electrical power, may be determined by applying an actual input voltage to the output circuitry and measuring a resulting input current, and multiplying the input voltage and measured current by the transfer matrix.

Owner:TYCO HEALTHCARE GRP LP

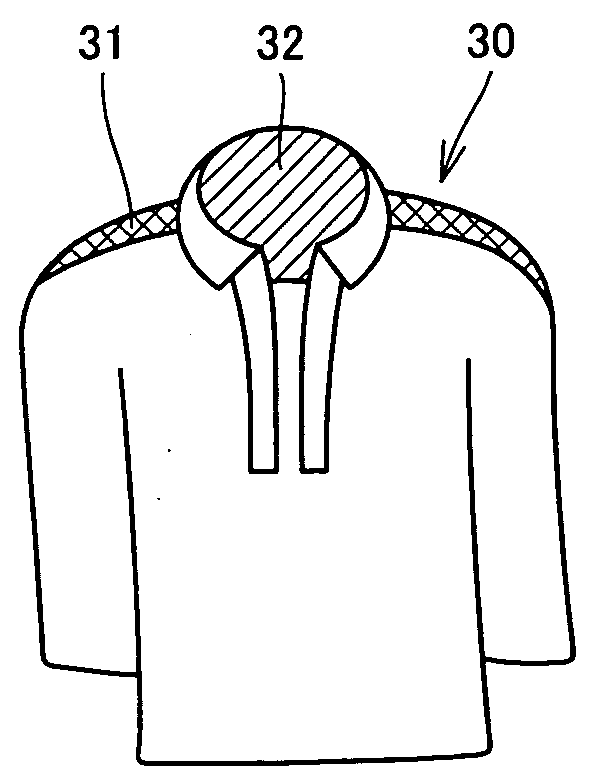

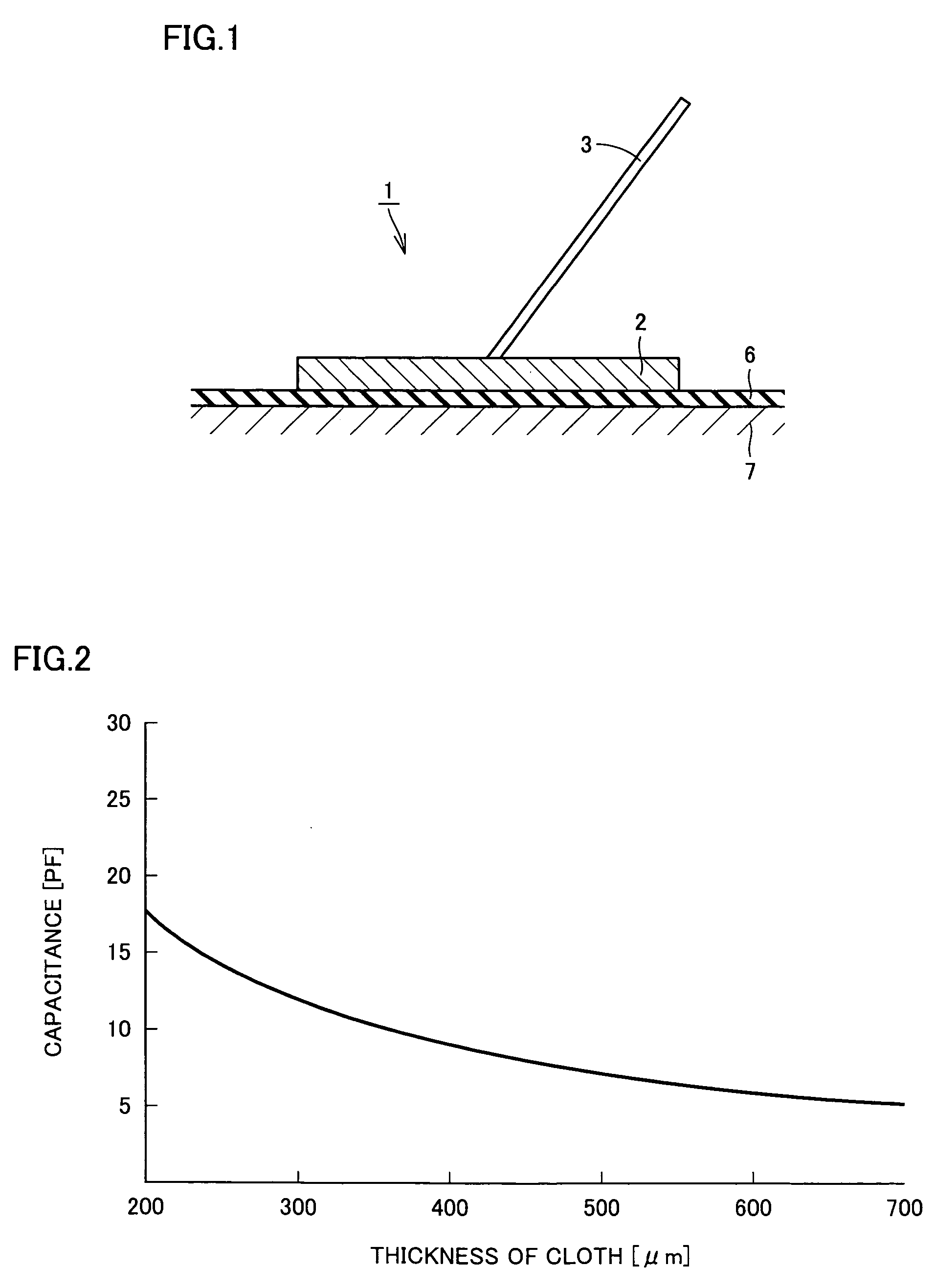

Biometric sensor and biometric method

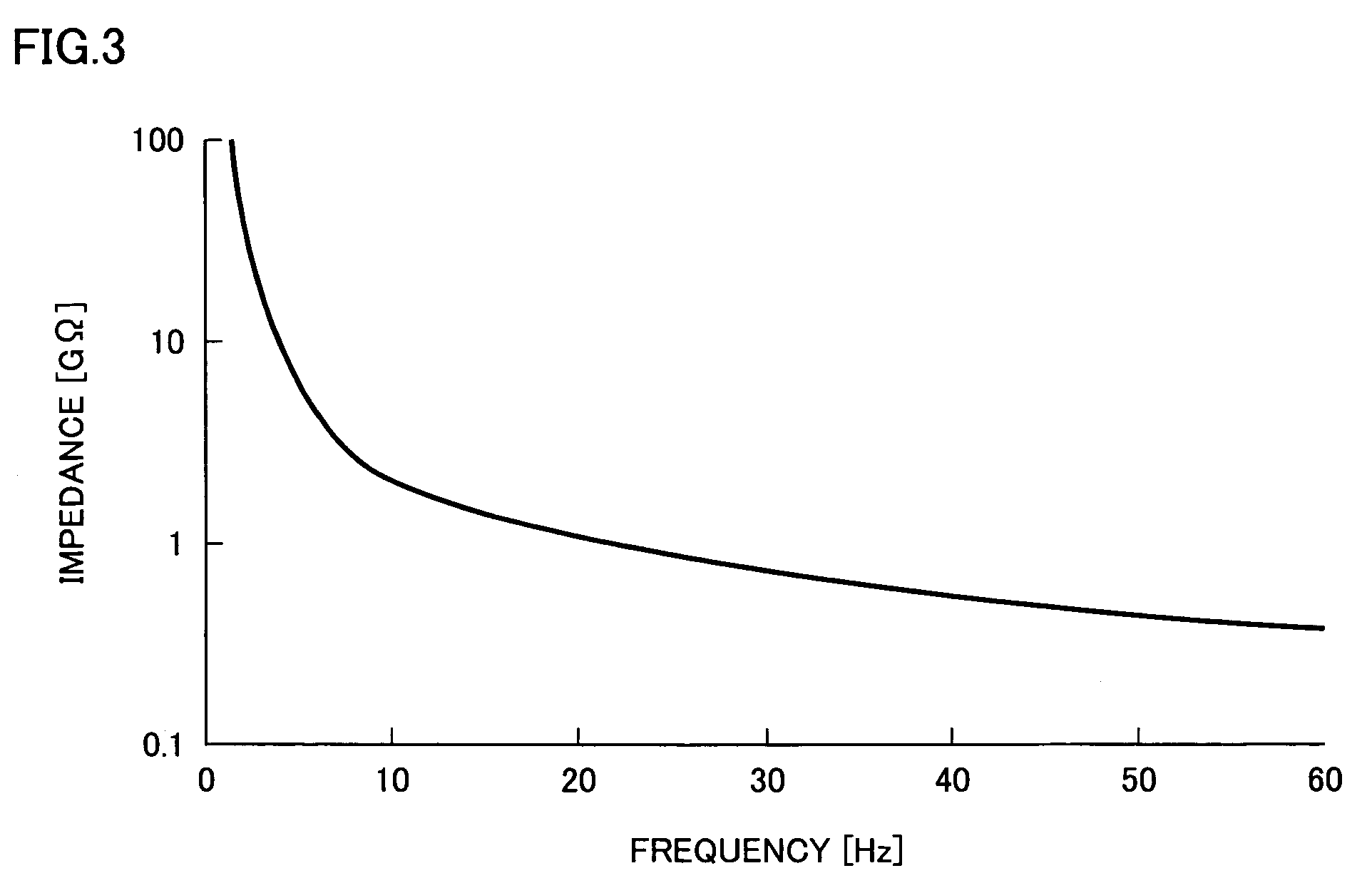

InactiveUS20070010750A1Less invasiveEliminate riskElectrocardiographySensorsCapacitanceImpedance Converter

A living body measuring sensor (1) is made to contact a body surface of a measuring subject through capacitance coupling using a cloth (6) between a metal electrode (2) and the body surface as the capacitance, a living body electric signal is extracted from the metal electrode (2), and an elctrocardiographic waveform is outputted based on an output of the living body measuring sensor (1) using an impedance converter having a high input impedance and a low output impedance.

Owner:GRACO CHILDRENS PROD INC

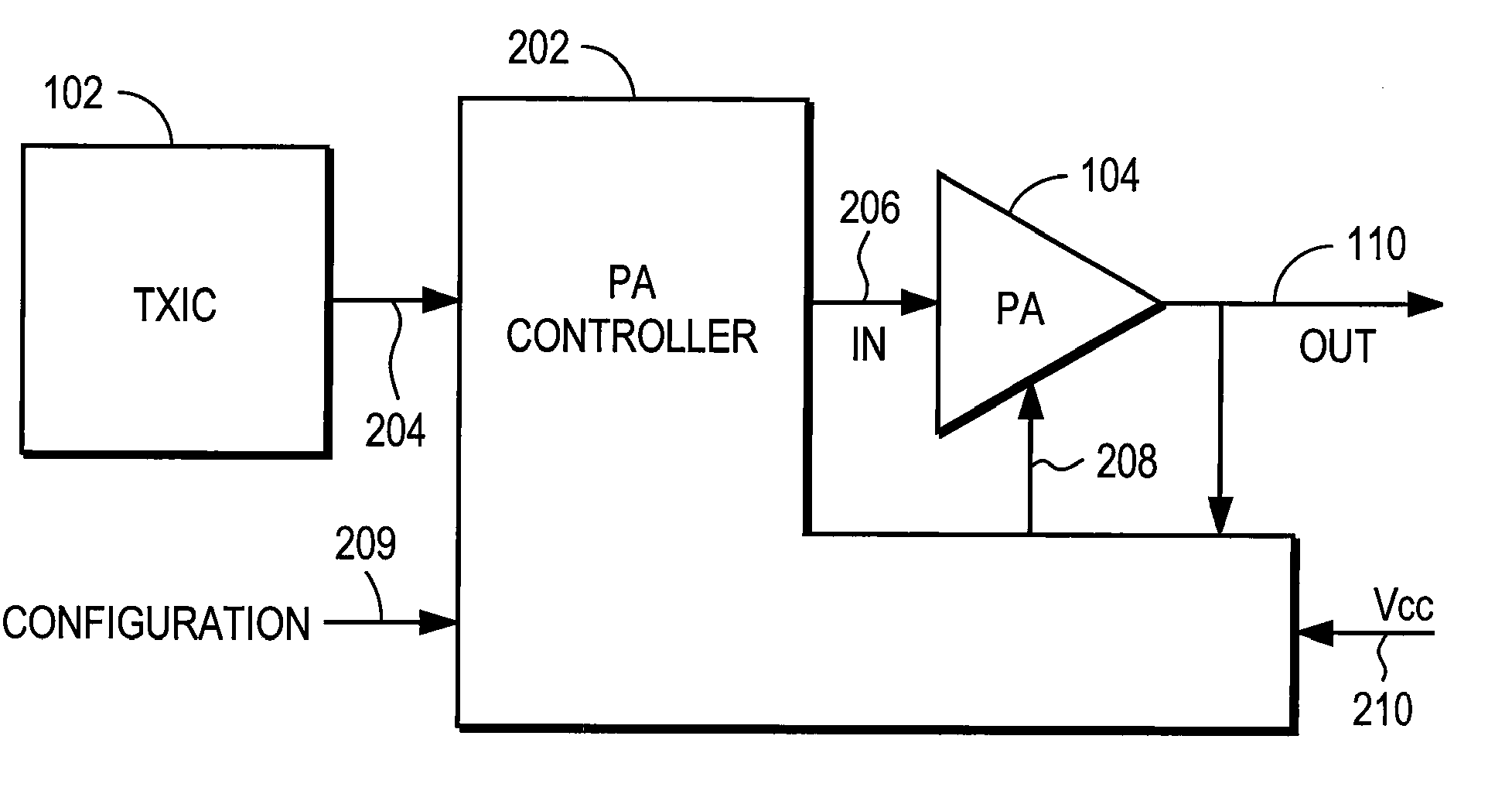

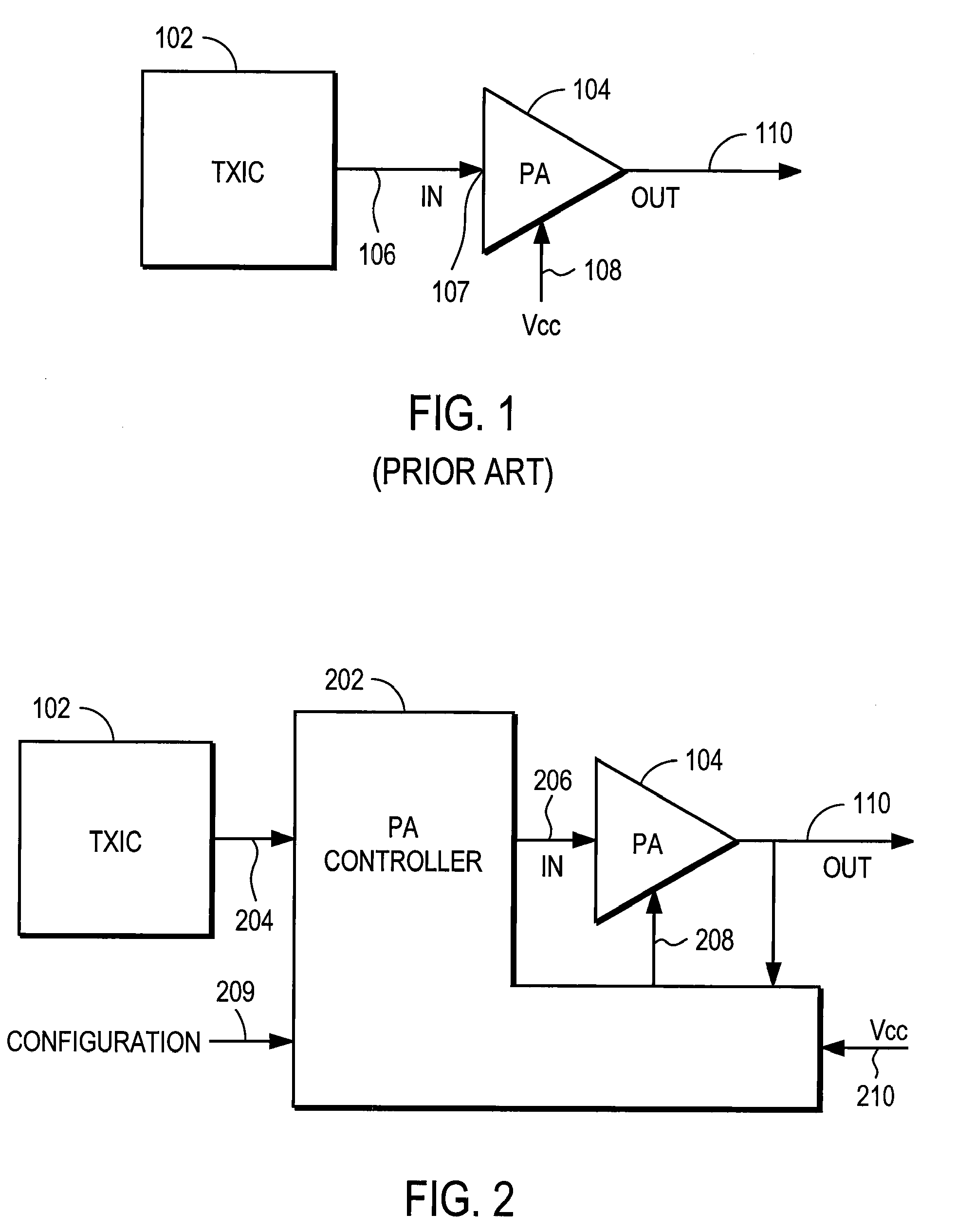

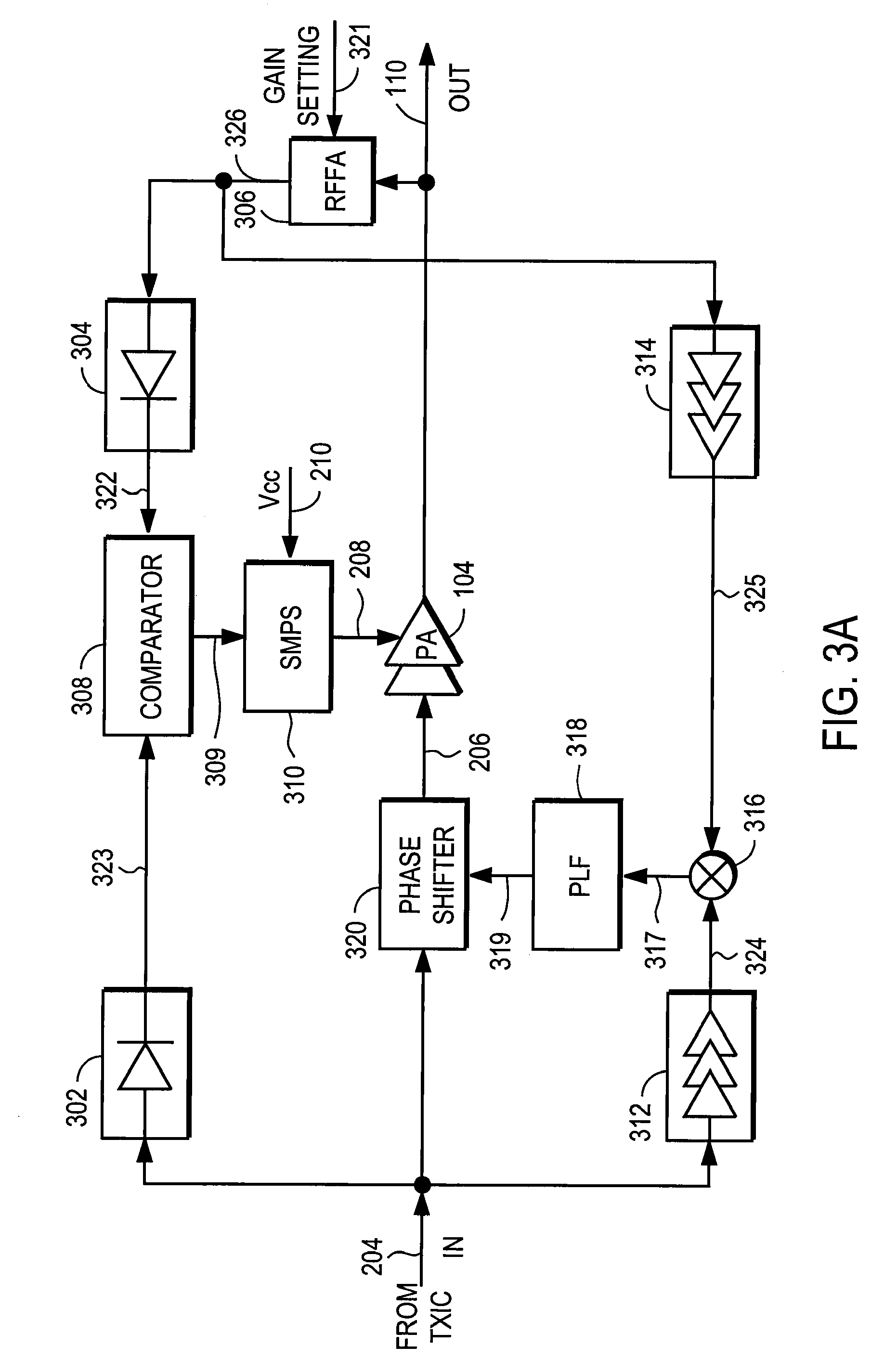

RF Power Amplifier Controller Circuit With Compensation For Output Impedance Mismatch

ActiveUS20070184793A1Narrow bandwidthSacrificing efficiencyResonant long antennasHigh frequency amplifiersAudio power amplifierPhase distortion

A power amplifier controller circuit controls a power amplifier based upon an amplitude correction signal indicating the amplitude difference between the amplitude of the input signal and an attenuated amplitude of the output signal. The power amplifier controller circuit comprises an amplitude control loop and a phase control loop. The amplitude control loop adjusts the supply voltage to the power amplifier based upon the amplitude correction signal. The amplitude control loop may also compensate for impedance mismatch with the load by increasing the power delivered from the power amplifier to the load, or decrease the output power of the power amplifier upon detection of excessive power dissipation in the power amplifier. The phase control loop adjusts the phase of the input signal based upon a phase error signal indicating a phase difference between phases of the input signal and the output signal to reduce phase distortion generated by the power amplifier.

Owner:QUANTANCE

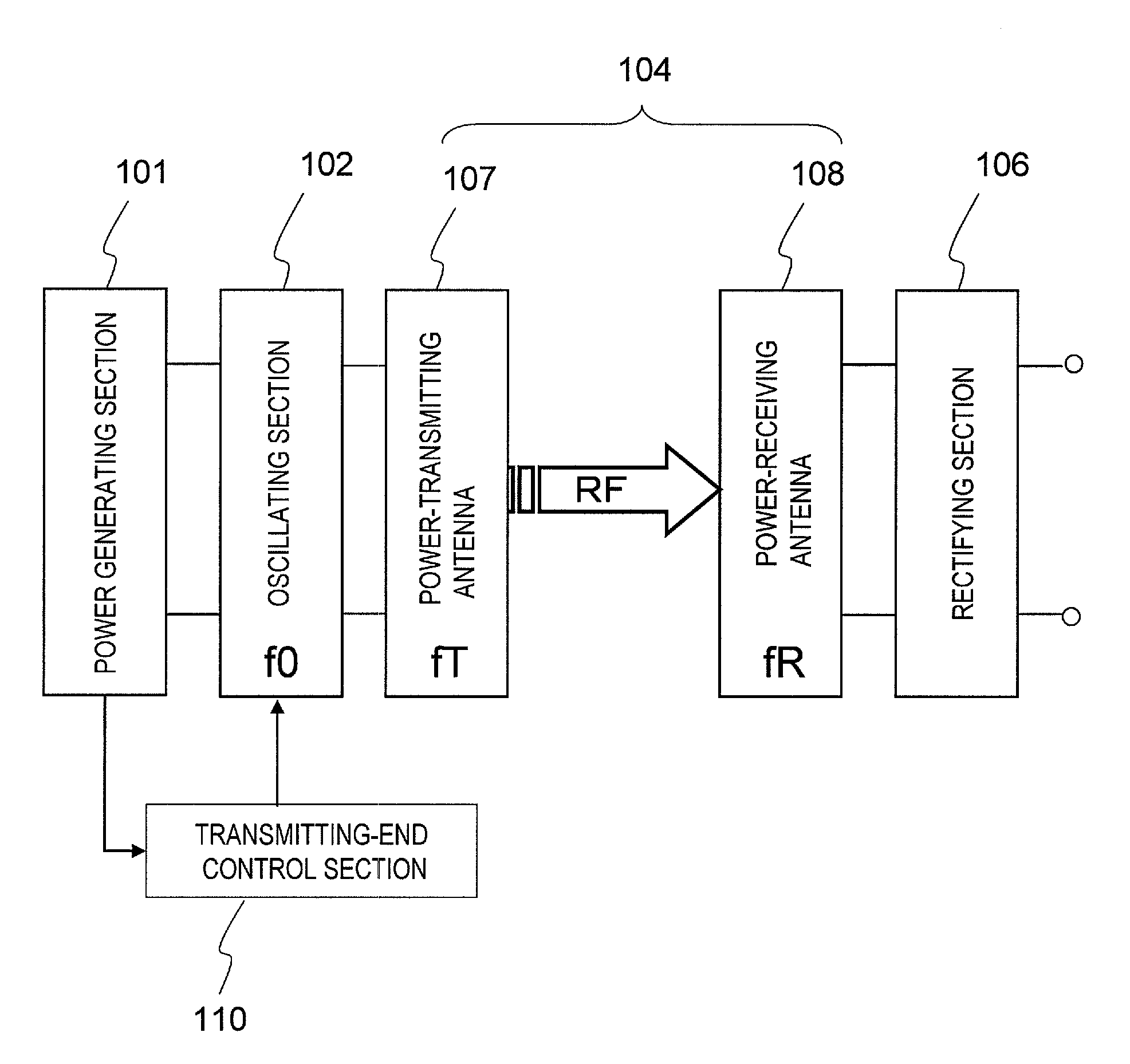

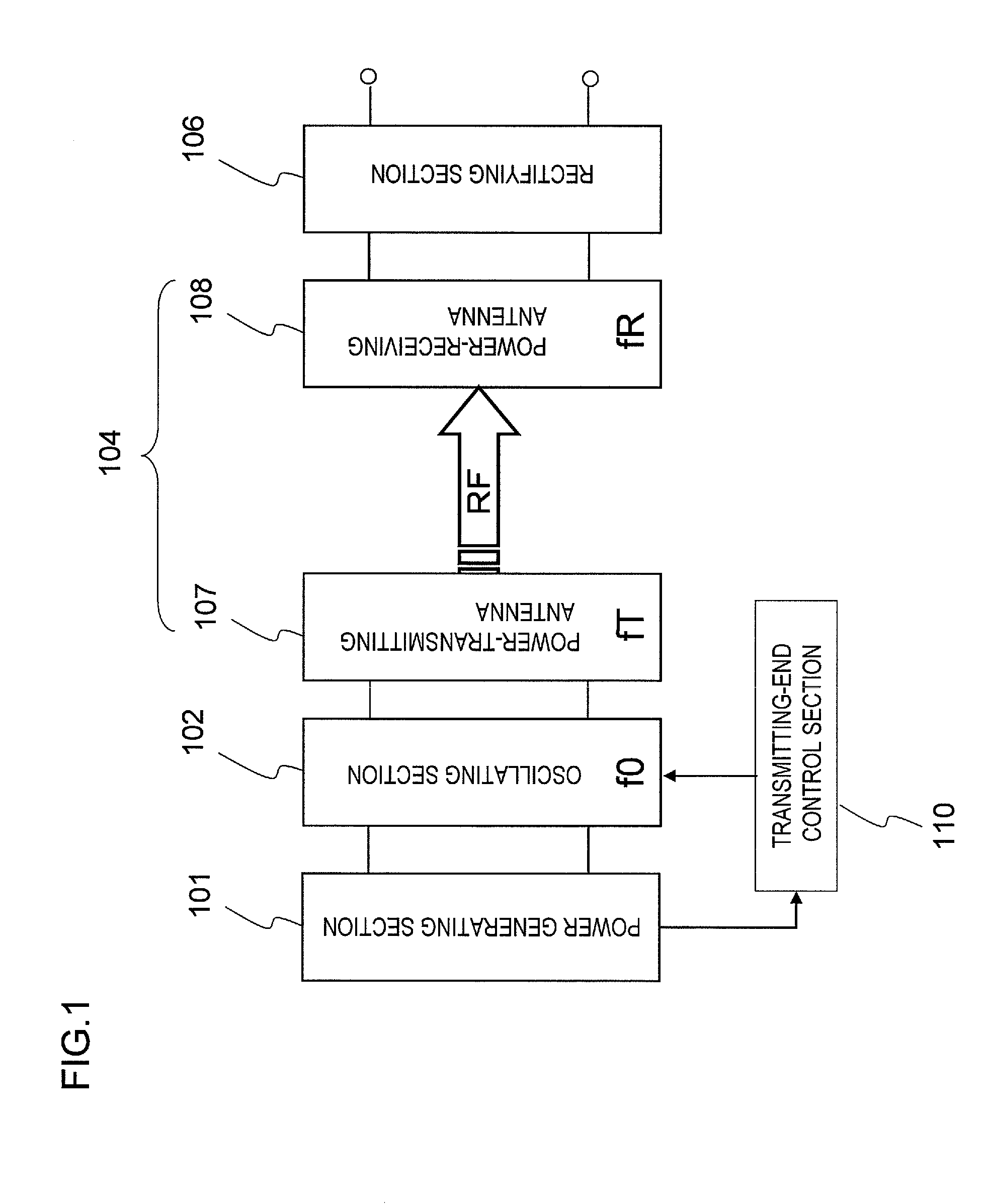

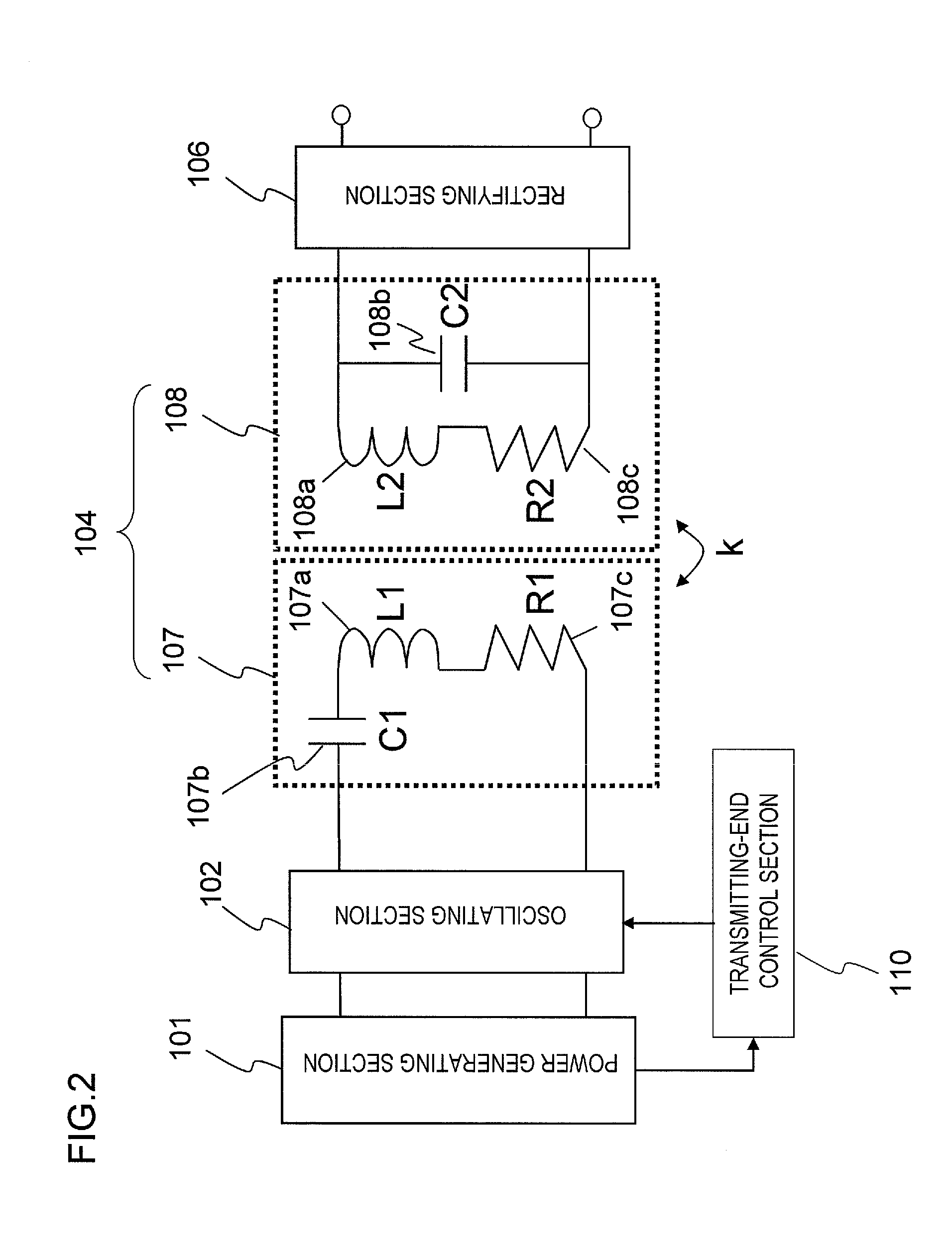

Power generating apparatus, power generating system, and wireless electric power transmission apparatus

ActiveUS20110266882A1Low costWork lessElectromagnetic wave systemTransformersElectric power transmissionInput impedance

A power generator includes: a power generating section 101 that outputs DC energy; an oscillating section 102 that converts the DC energy into RF energy with a frequency f0; a power-transmitting antenna 107 that transmits the RF energy; a power-receiving antenna 108 that receives at least a part of the RF energy that has been transmitted by the power-transmitting antenna 107; and a transmitting-end control section 110 that matches the input impedance of the oscillating section 102 to the output impedance of the power generating section 101 by changing the input impedance of the oscillating section 102 in accordance with a variation in the output impedance of the power generating section 101. The power-transmitting antenna 107 is a series resonant circuit, and the power-receiving antenna 108 is a parallel resonant circuit. And the resonant frequencies fT and fR of the power-transmitting and power-receiving antennas 107 and 108 are both set to be equal to the frequency f0 of the RF energy.

Owner:PANASONIC CORP

Integrated front end antenna

ActiveUS7084823B2Resonant long antennasSimultaneous aerial operationsOutput impedanceRadio frequency

A radio frequency transmitting and receiving apparatus comprising a filter and an antenna, wherein the input reactance of the antenna is substantially equal in magnitude and opposite in sign to the output reactance of the filter. This reactance relationship permits the antenna and filter to be collocated and avoids transformation of the input and output impedances to the conventional 50 ohms such that the filter and antenna can be connected with a conventional 50 ohm transmission line.

Owner:SKYCROSS INC