PNP bipolar transistor in SiGe BiCMOS technology

A bipolar transistor and process technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of long base region width, difficult to reduce the area, difficult to improve the PNP current amplification factor, etc., to achieve the current amplification factor The effect of increasing and reducing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

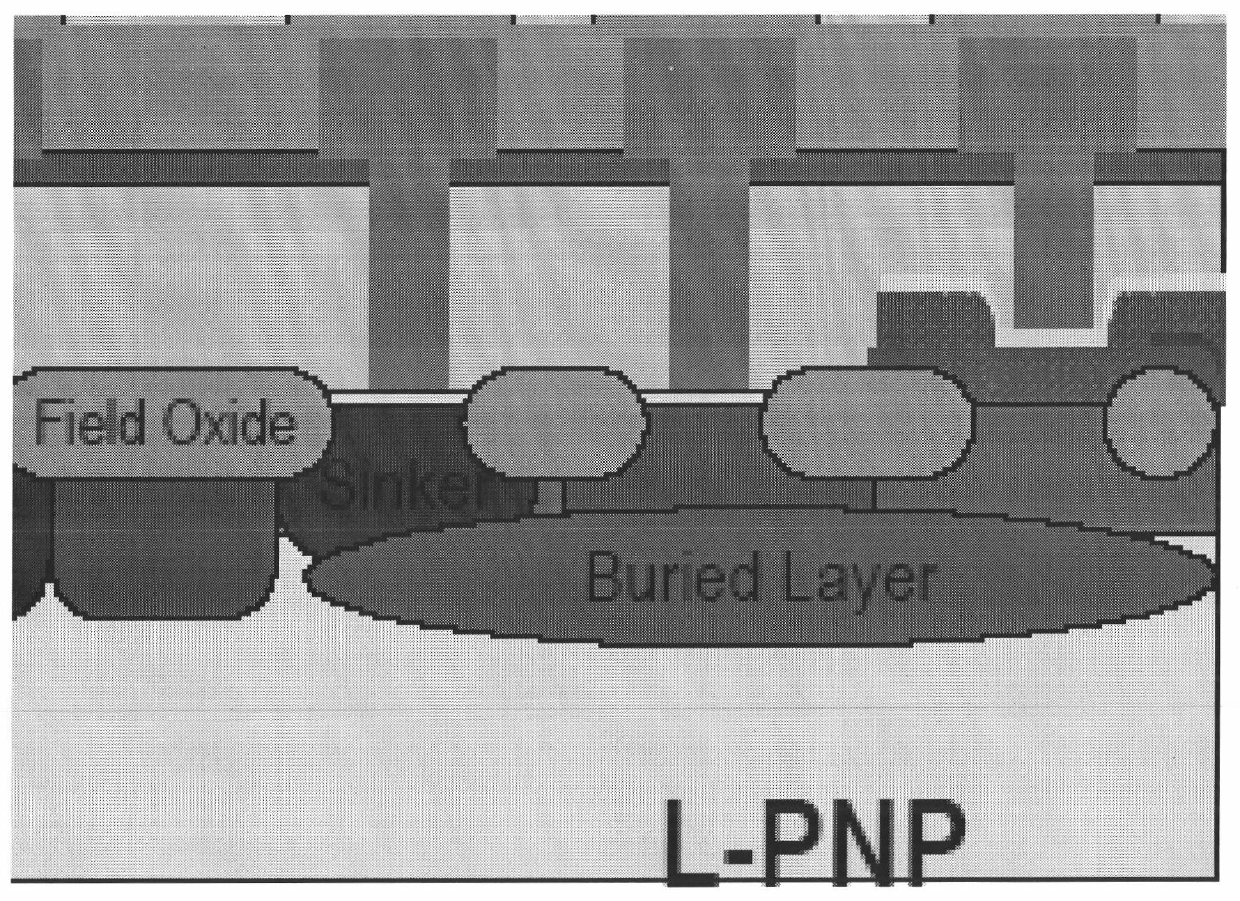

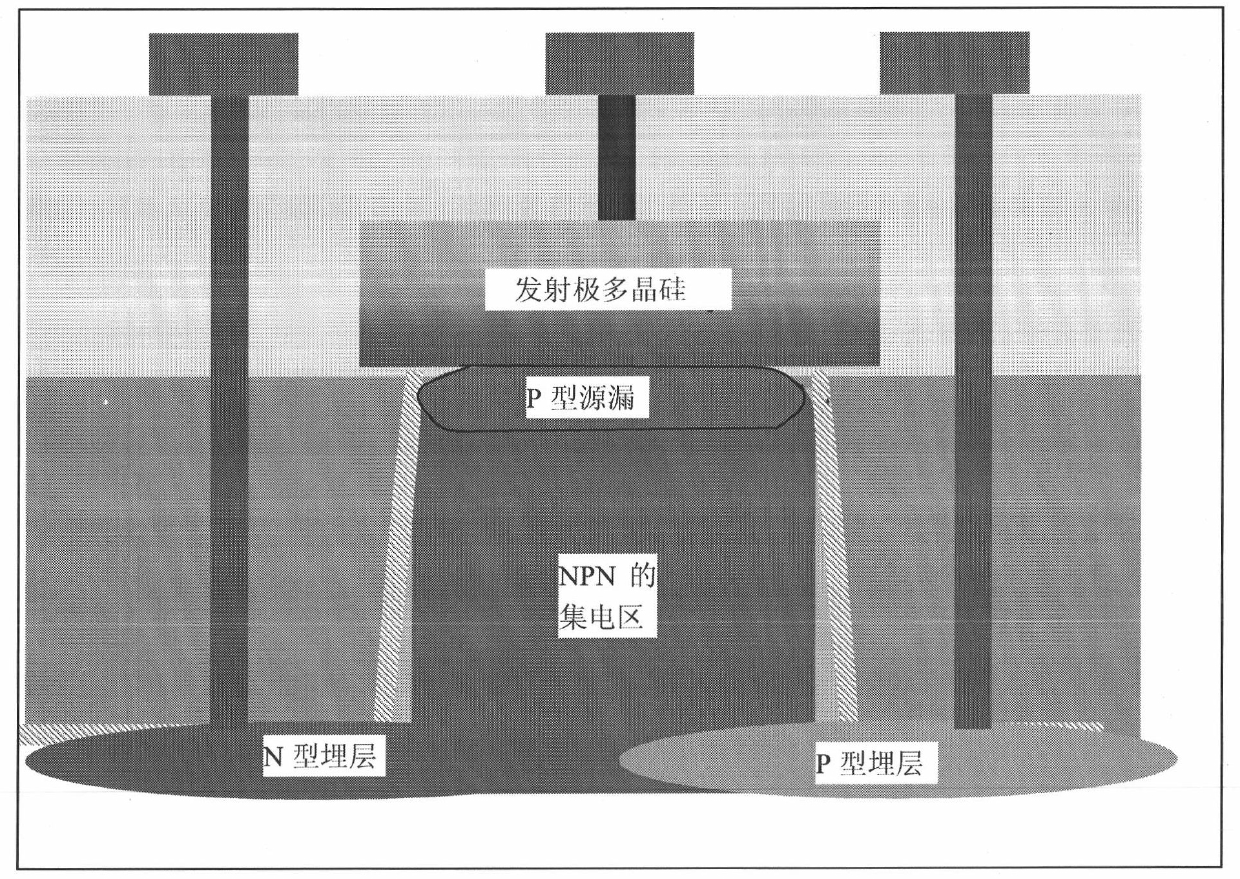

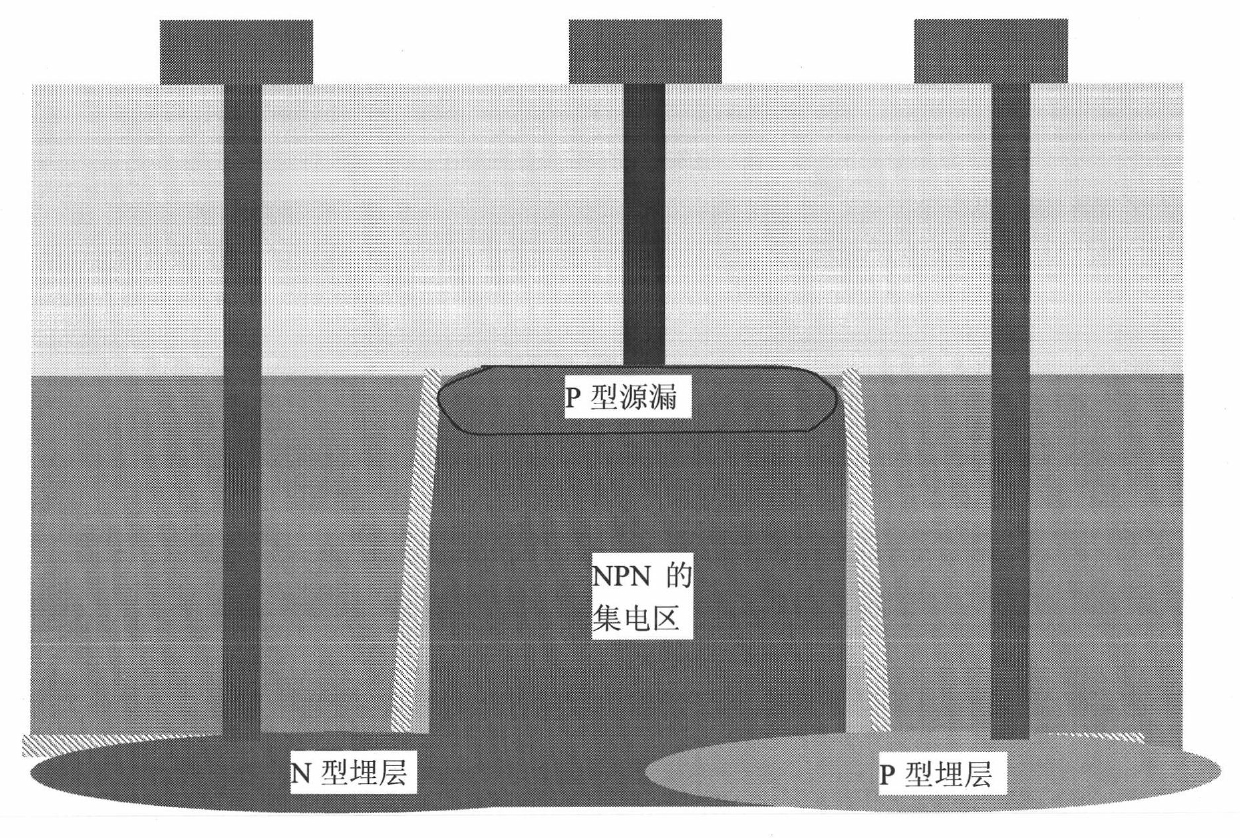

[0016] Such as Figure 2A with Figure 2B Shown is a schematic diagram of the structure of a PNP bipolar transistor in the SiGe BiCMOS process of the present invention. The active region is isolated by a shallow trench field oxide layer, including:

[0017] A collector region is formed by a P-type buried layer located at the bottom of the shallow trench, and the collector region is drawn by forming a deep well contact on the field oxide layer. The P-type buried layer is formed by ion implantation after the shallow trench is formed and before the field oxide layer is filled. The hard mask layer on the active area is locally self-aligned and implanted to ensure that there is no active area. Impurities implanted by the P-type buried layer; B or BF selectively implanted by the P-type buried layer 2 , The injection dose is 1e12~1e14cm -2 , The implant energy is subject to not penetrating the hard mask layer.

[0018] A base area, as Figure 2A with Figure 2B The collector region of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More