Vertical parasitic type precision navigation processor (PNP) device in bipolar complementary metal oxide semiconductor (BiCMOS) technology and manufacture method thereof

一种垂直寄生、工艺条件的技术,应用在半导体/固态器件制造、半导体器件、电气元件等方向,能够解决器件尺寸缩小、器件面积大、集电极连接电阻大等问题,达到减少面积、大电流放大系数、降低生产成本的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment B

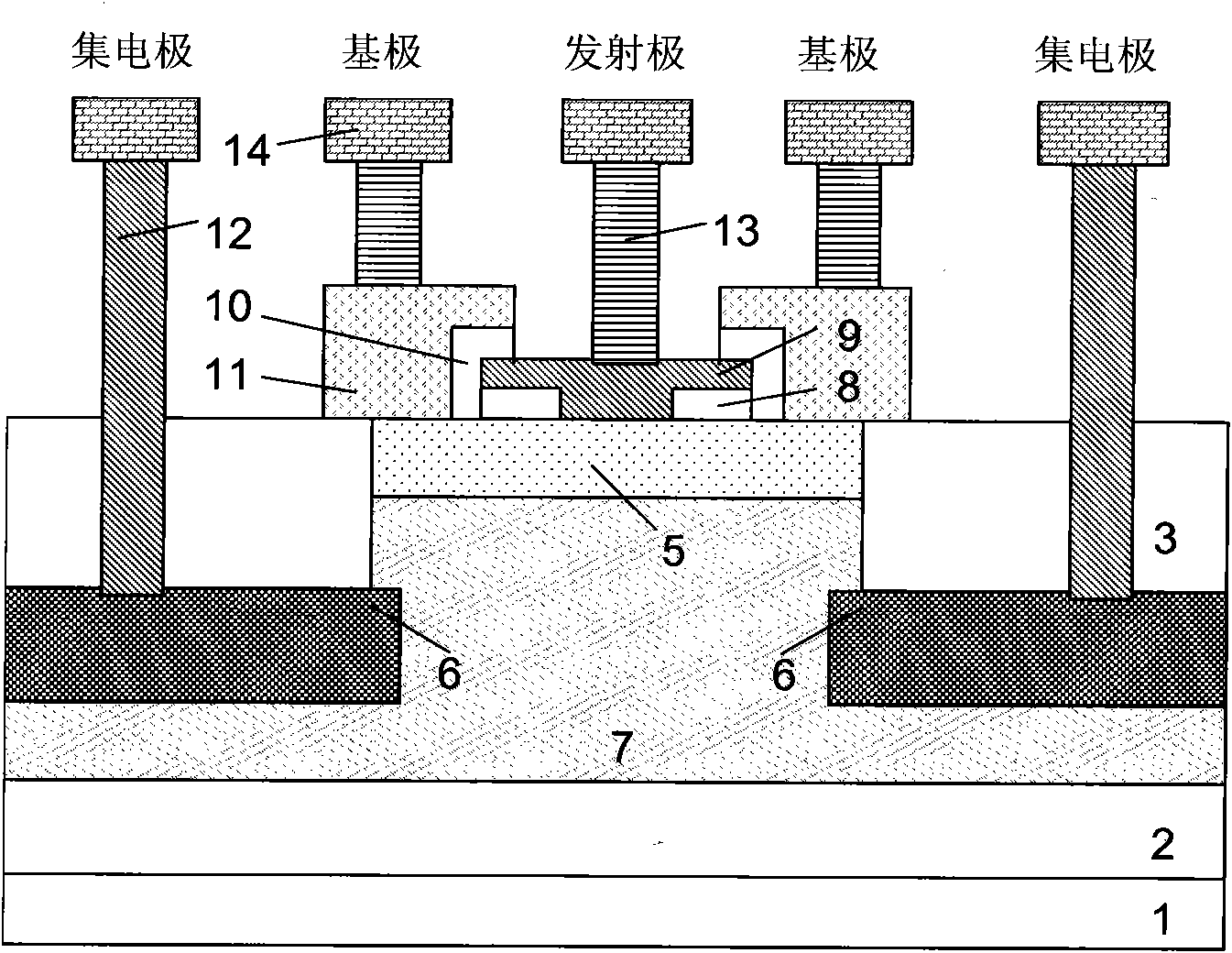

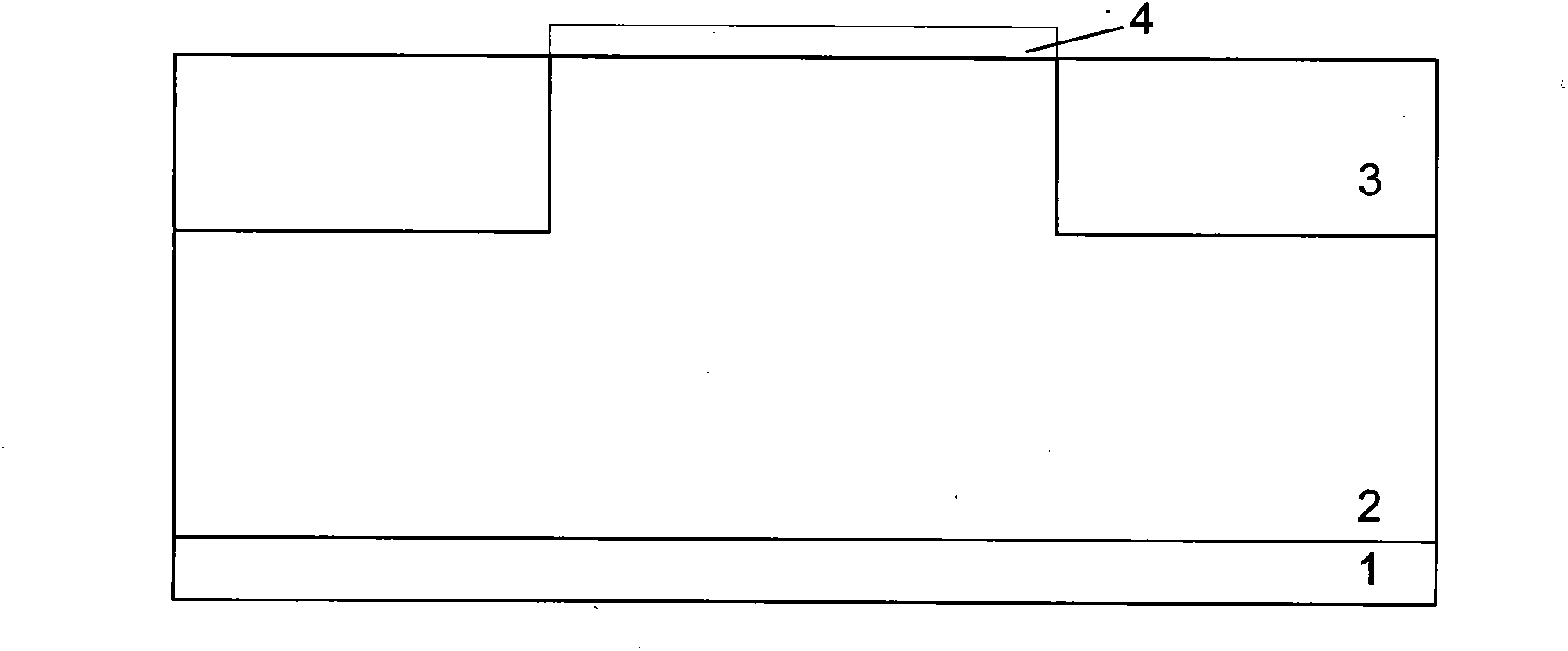

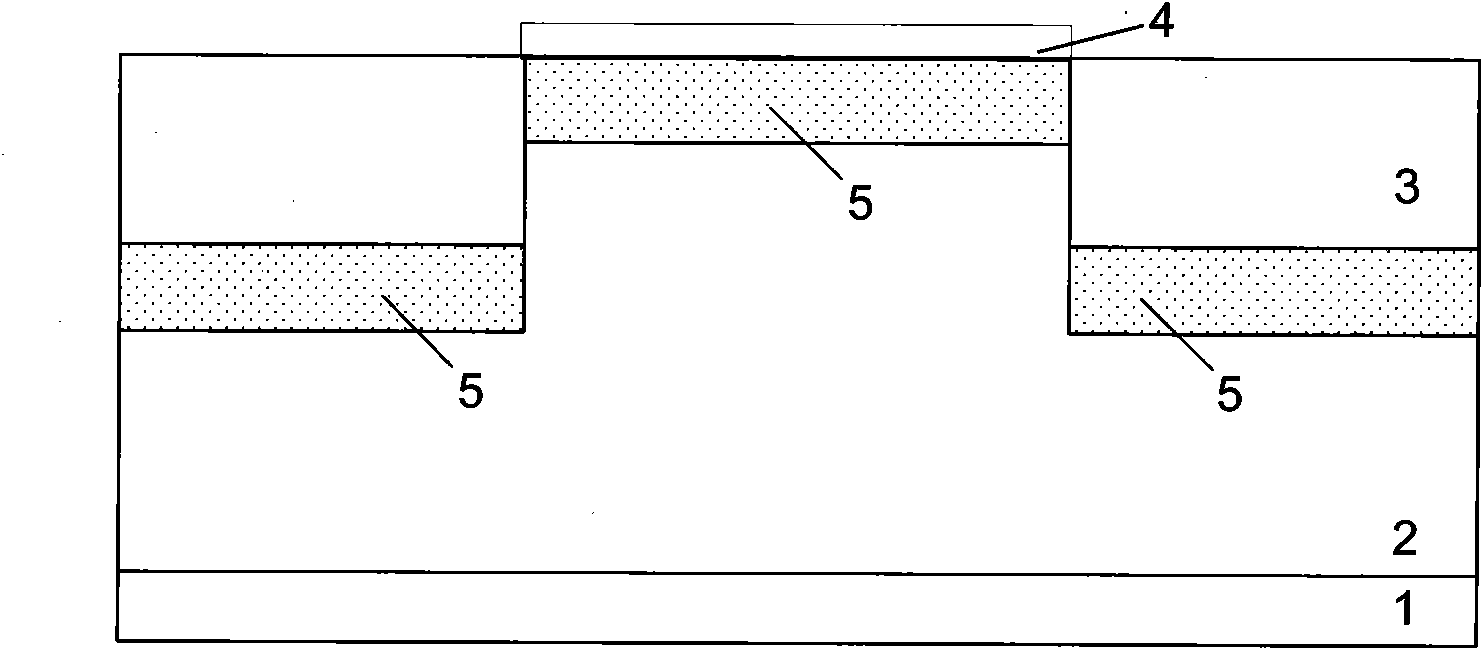

[0027] Such as figure 1 Shown is a schematic structural view of the vertical parasitic PNP device in the BiCMOS process of the embodiment of the present invention. The vertical parasitic PNP device in the BiCMOS process of the embodiment of the present invention is formed on a P-type silicon substrate 1 and placed on the P-type silicon substrate 1. An N-type deep well 2 is formed on a silicon substrate 1, and the active region is isolated by a shallow trench field oxygen 3, which is shallow trench isolation (STI). The vertical parasitic PNP device includes:

[0028] A collector region 7 is composed of a P-type ion implantation region formed in the active region, and the depth of the collector region 7 is greater than or equal to the depth of the bottom of the shallow trench field oxygen 3 . The impurity implanted in the P-type ion implantation of the collector region 7 is boron, which is implemented in two steps: the implantation dose in the first step is 1e11cm -2 ~5e13cm -...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More