Patents

Literature

330 results about "Silicon heterojunction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for preparing silicon thin film heterojunction solar cell

InactiveCN1588649AAvoid damageReduce hydrogen contentFinal product manufacturePhotovoltaic energy generationHeterojunctionSilicon thin film

A prepn. method of silicon thin film heterojunction solar cell includes following steps: cleaning substrate, semiconductor cleaning technology is used to do primary cleaing to substrate surface, then do ultrasonic cleaning in deionized water several times; nitrogen blow drying; prepare nitrinsic amorphous silicon layer by heater chemical vapour phase depositing technology, tungsten filament temp. is measured by pyrometer, temp of heater and sample are determined separately by two electric thermo-couples, temp. is controlled by electric temp. controller; to react and grow thin film on substrate surface; to redeposit a transmitting layer on intrinsic amorphous silicon thin film; front and back electrodes forming, sputtering technology is used to form front and back electrodes; finally to proceed vacuum heat annealing process. The thin film produced by the invention has illumination stability, the photoconduction gain can reach to 10 to the power 6 on Am1.5 100mW / cm2 standard illumination.

Owner:SHANGHAI JIAO TONG UNIV

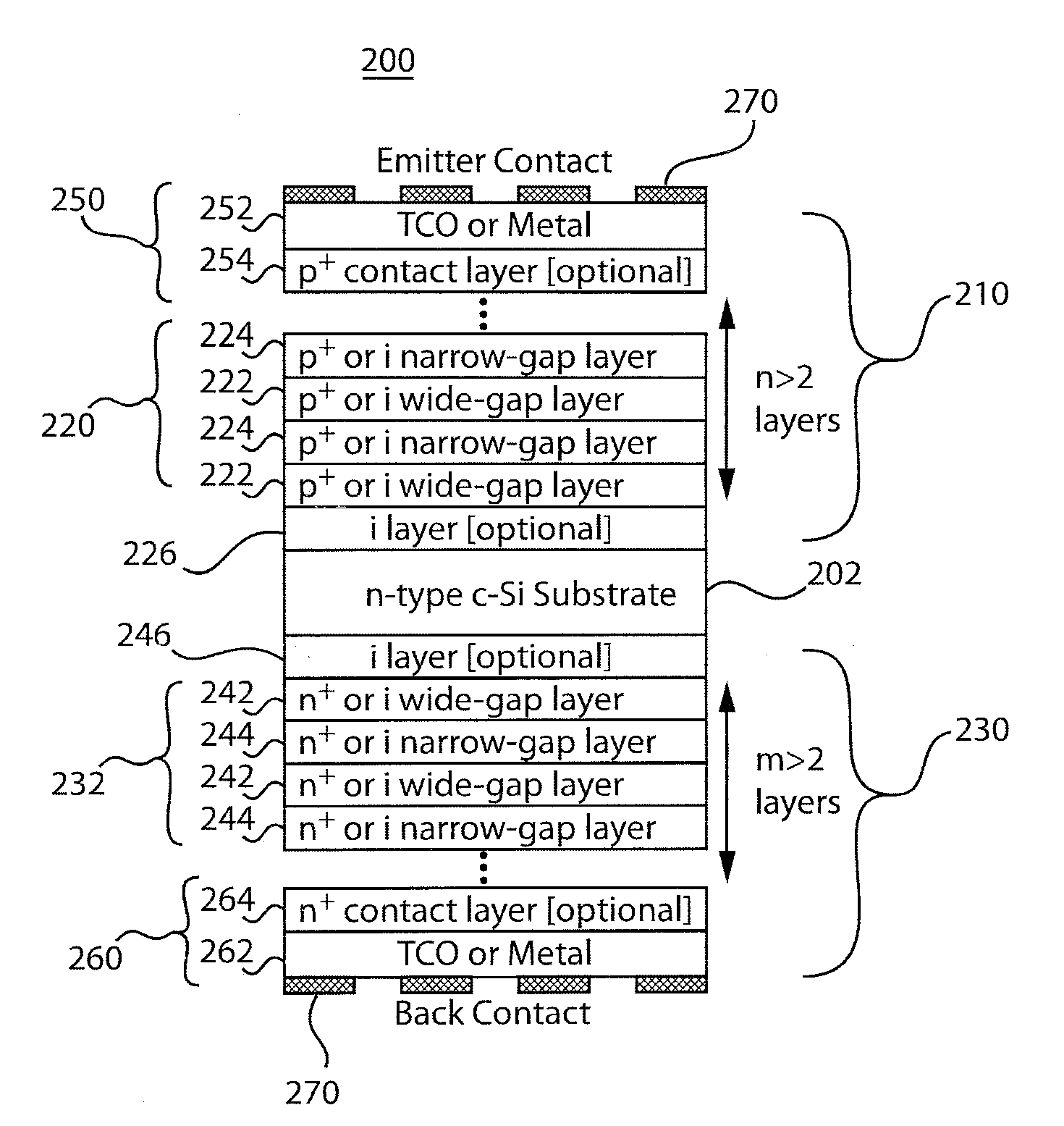

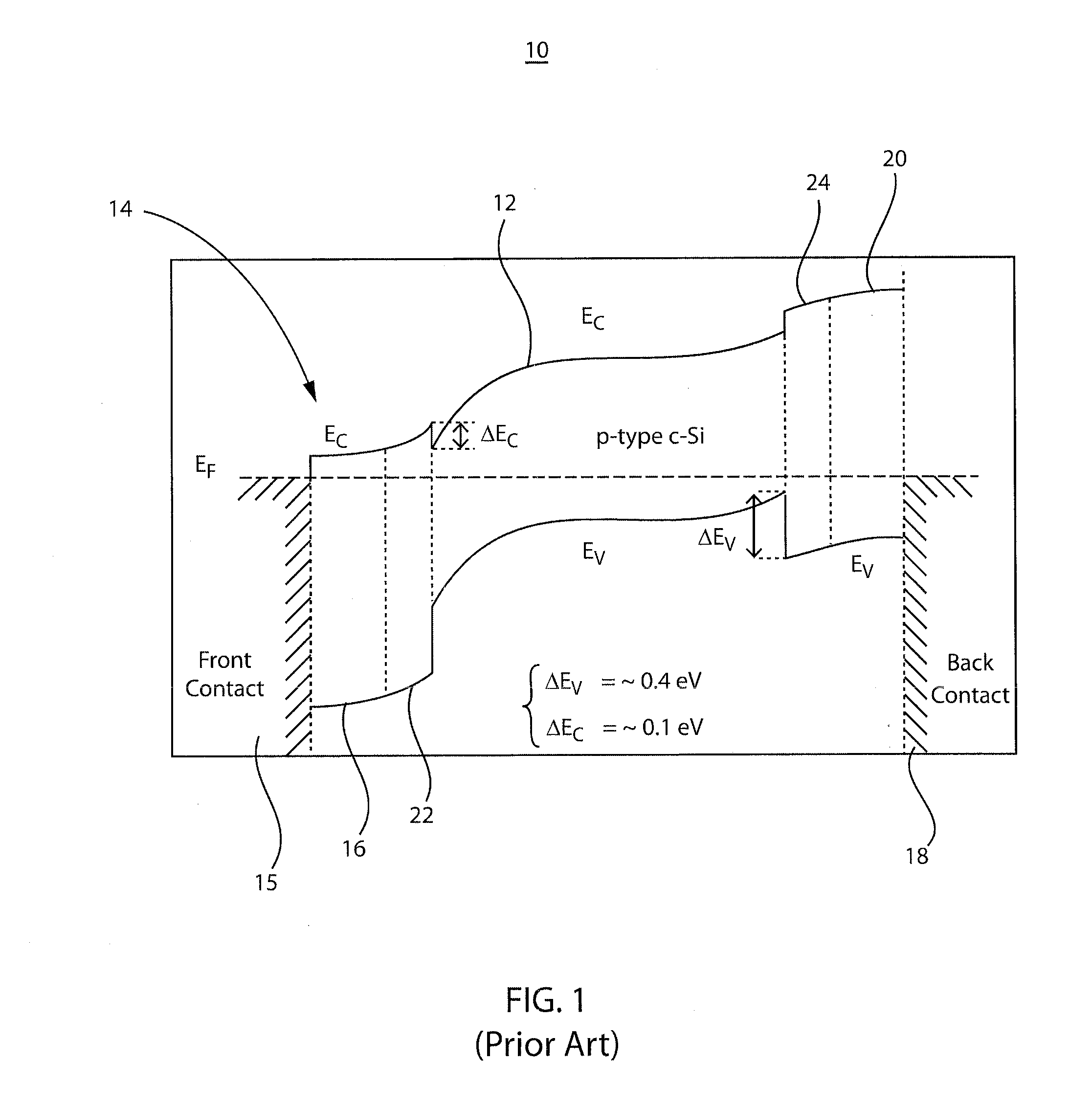

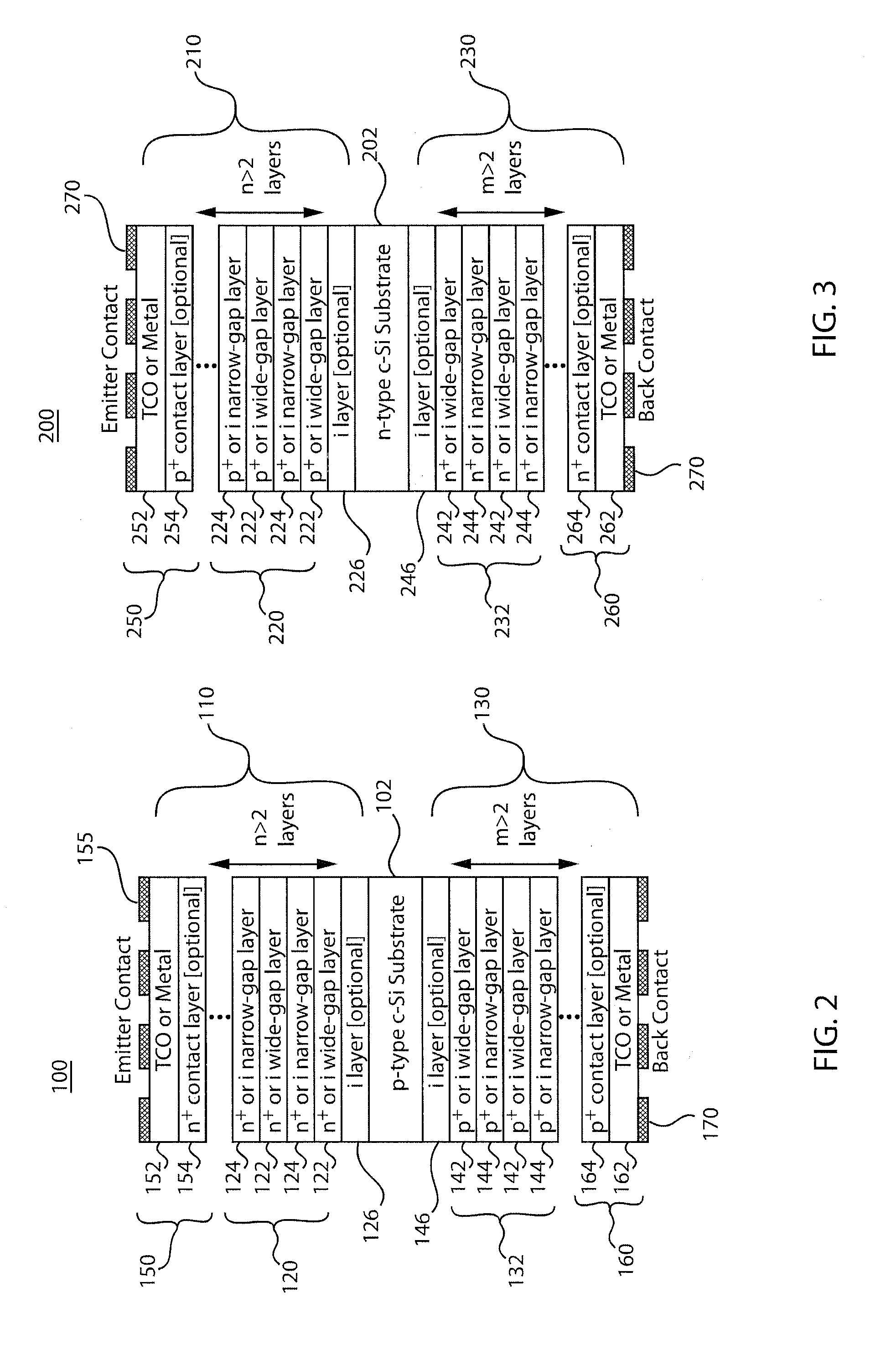

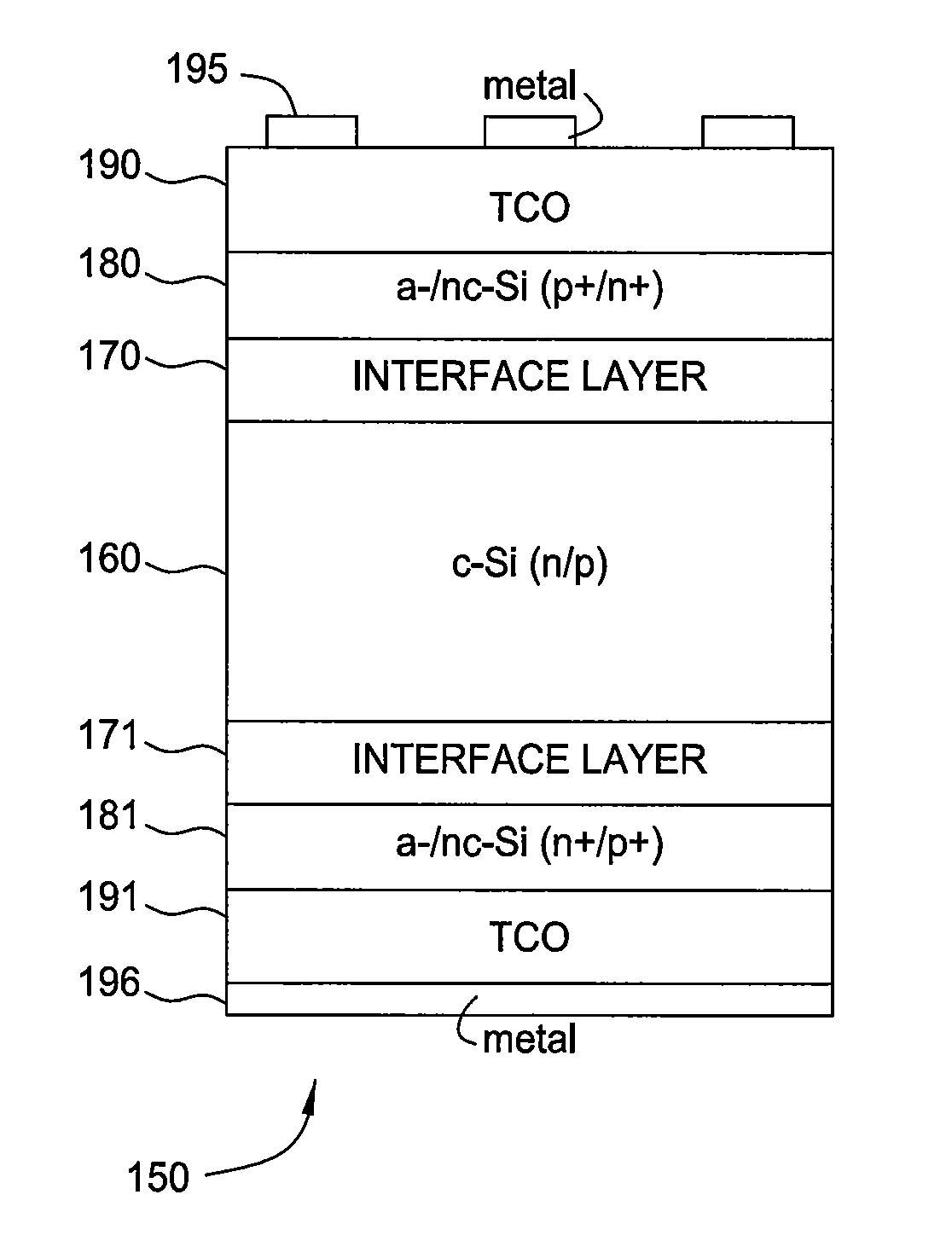

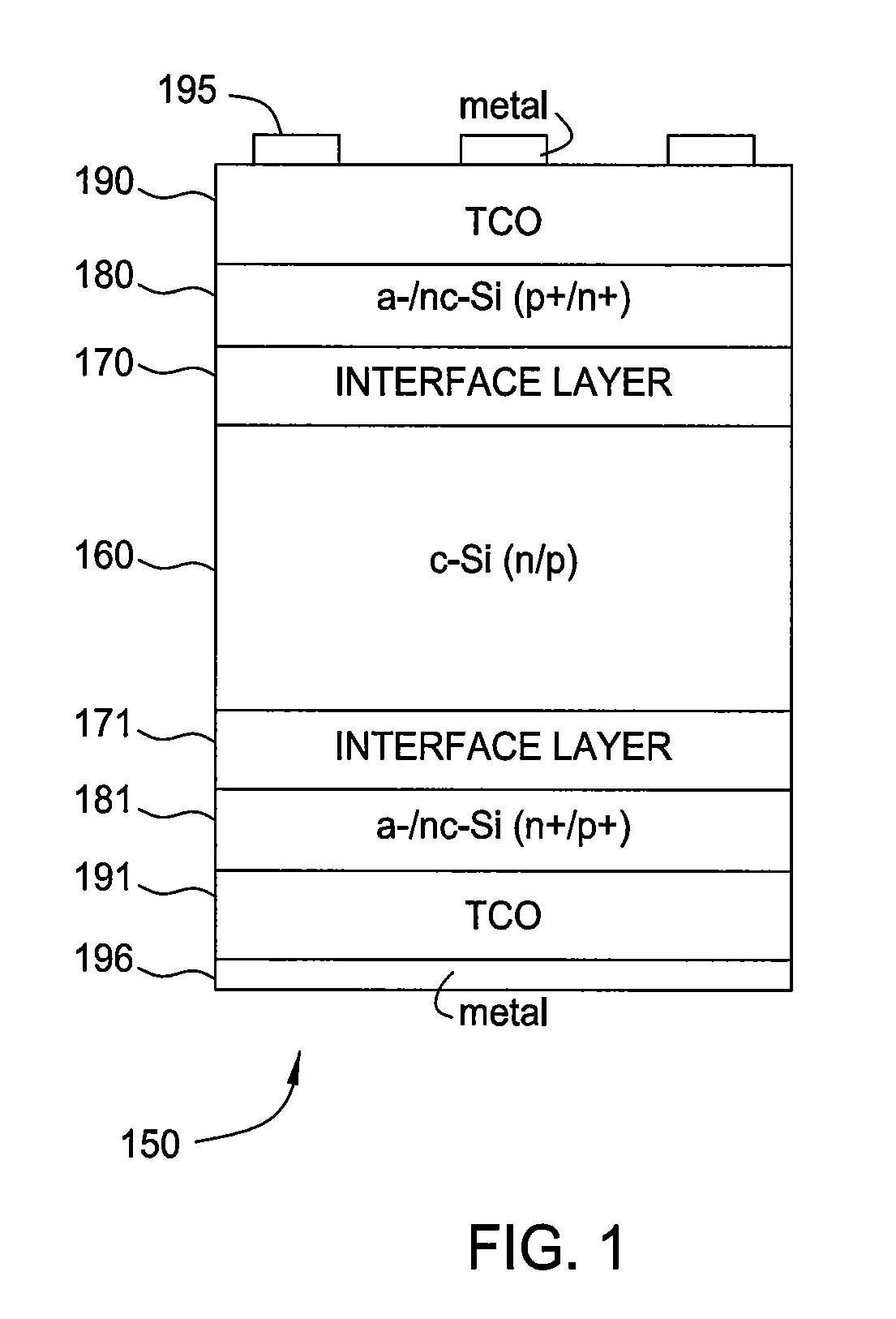

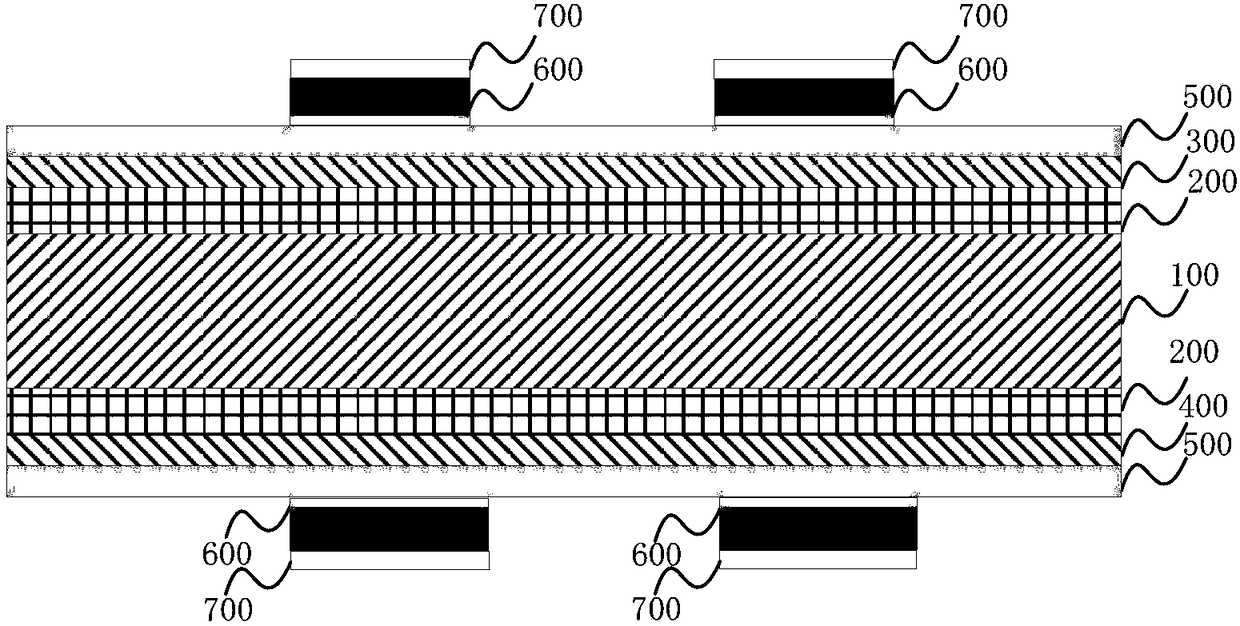

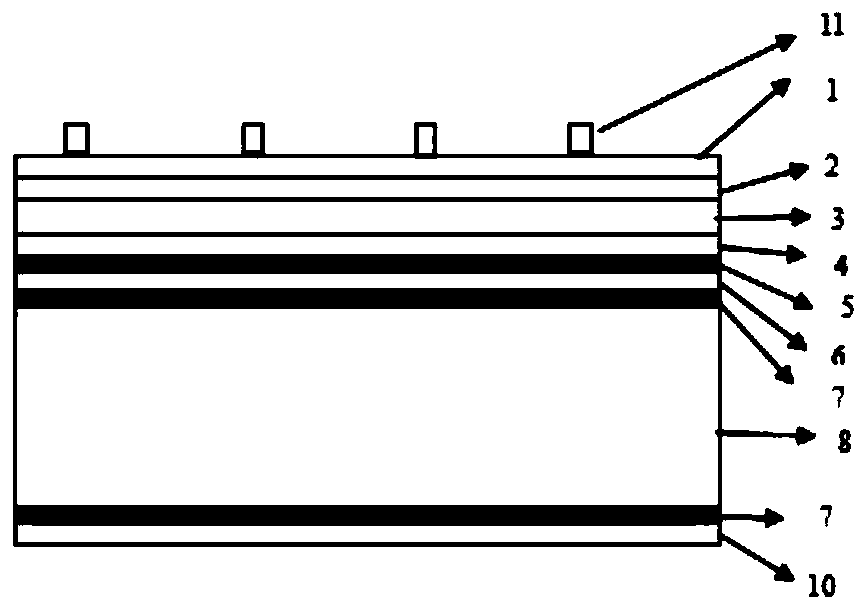

Contact for silicon heterojunction solar cells

InactiveUS20120318336A1Raise the level of dopingSemiconductor/solid-state device manufacturingNanoopticsSolar cellWide band

A photovoltaic device and method include a substrate coupled to an emitter side structure on a first side of the substrate and a back side structure on a side opposite the first side of the substrate. The emitter side structure or the back side structure include layers alternating between wide band gap layers and narrow band gap layers to provide a multilayer contact with an effectively increased band offset with the substrate and / or an effectively higher doping level over a single material contact. An emitter contact is coupled to the emitter side structure on a light collecting end portion of the device. A back contact is coupled to the back side structure opposite the light collecting end portion.

Owner:IBM CORP

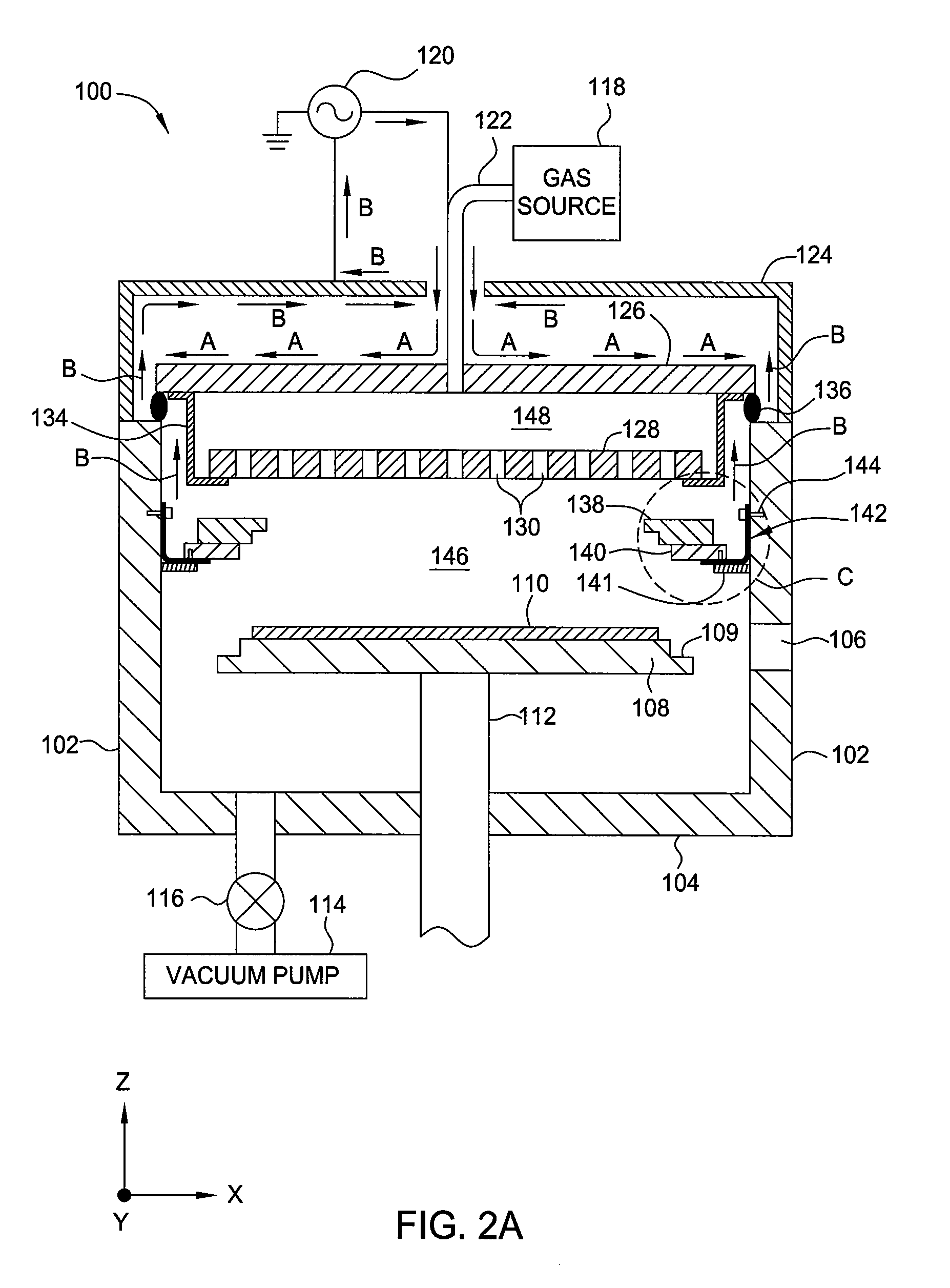

Method and apparatus for fabricating silicon heterojunction solar cells

ActiveUS20130102133A1Low process-induced damageEnhanced vapor depositionElectric discharge tubesFinal product manufactureDopantProcess region

A method for fabricating a semiconductor layer within a plasma enhanced chemical vapor deposition (PECVD) apparatus. The PECVD apparatus includes a plurality of walls defining a processing region, a substrate support, a shadow frame, a gas distribution showerhead, a gas source in fluid communication with the gas distribution showerhead and the processing region, a radio frequency power source coupled to the gas distribution showerhead, and one or more VHF grounding straps electrically coupled to at least one of the plurality of walls. The VHF grounding straps provide a low-impedance current path between at least one of the plurality of walls and at least one of a shadow frame or the substrate support. The method further includes delivering a semiconductor precursor gas and a dopant precursor gas and delivering a very high frequency (VHF) power to generate a plasma to form a first layer on the one or more substrates.

Owner:APPLIED MATERIALS INC

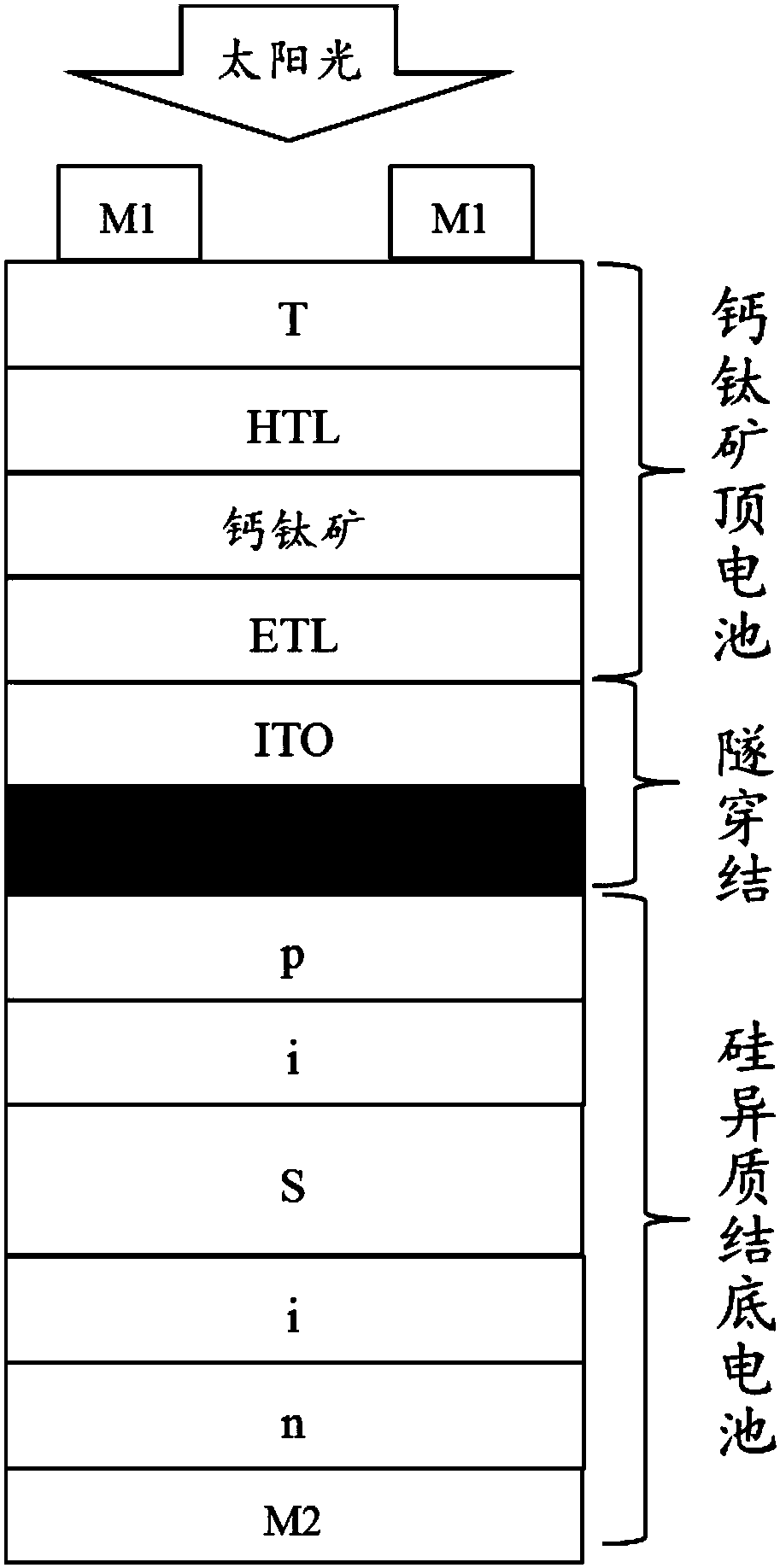

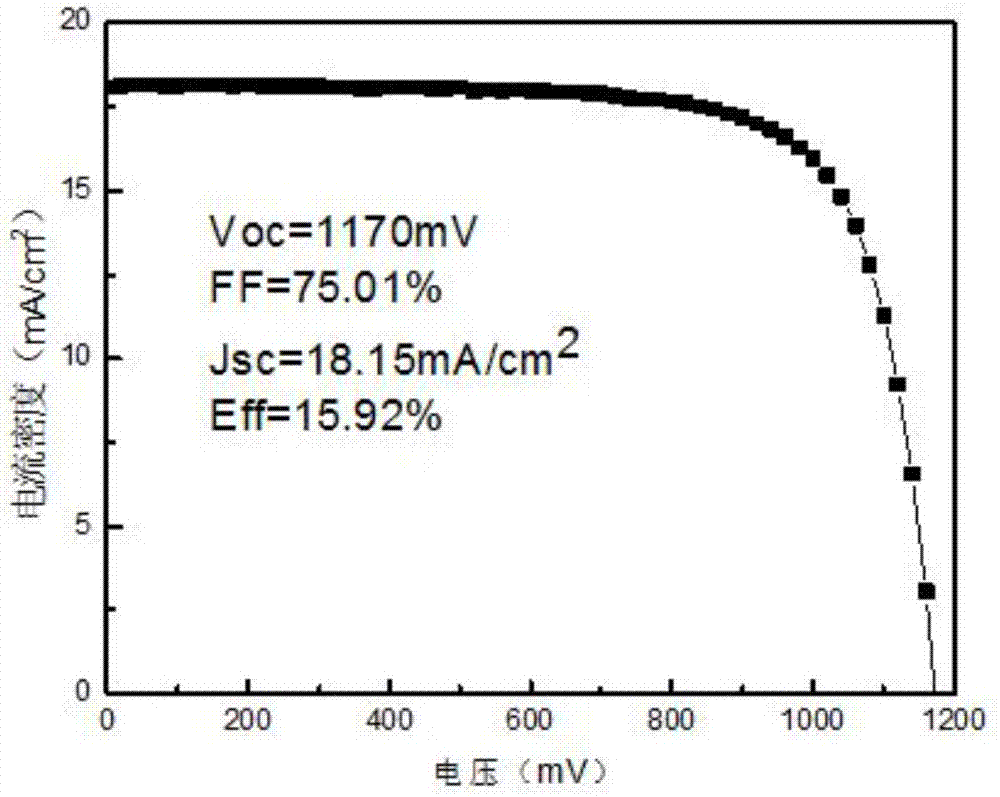

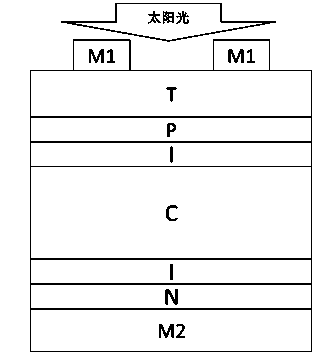

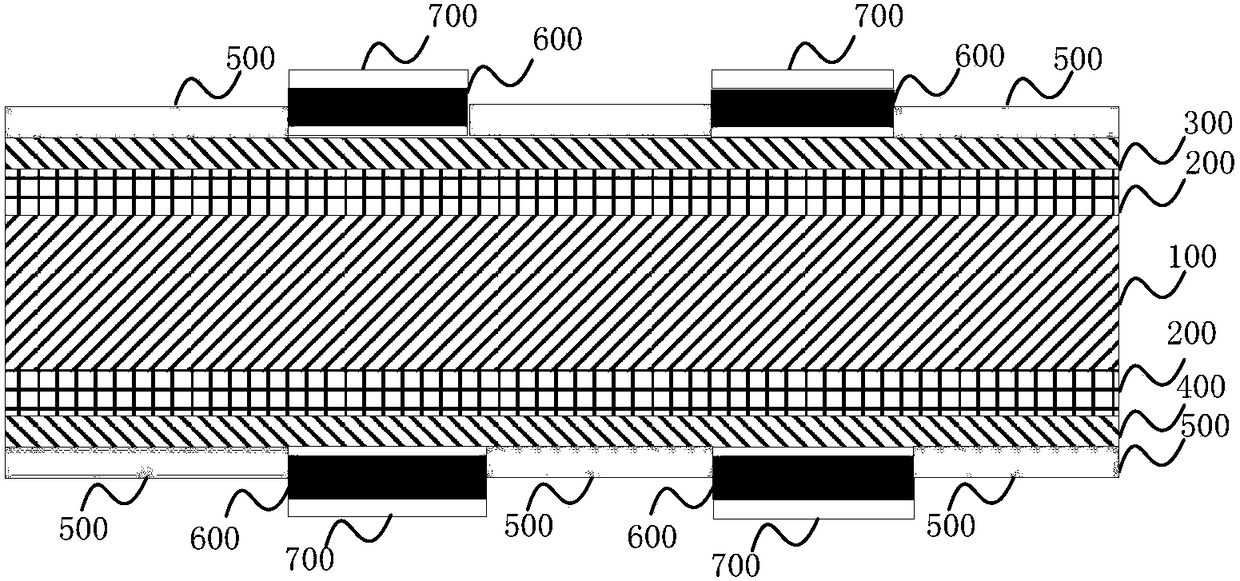

Structure design of tunnel junction in Perovskite/silicon heterojunction lamination solar battery

InactiveCN107564989AFacilitate hole extractionSmall pressure drop lossFinal product manufactureSolid-state devicesHeterojunctionValence band

The invention provides a structure design of tunnel junction in Perovskite / silicon heterojunction lamination solar battery, which relates to the field of solar batteries. A tunneling composite layer TRL with narrow band gap and high doping concentration is added at the junction of the top and bottom part of a lamination battery, and the quite small energy level difference between the conduction band and the valence band can effectively strengthen the carrier recombination at the tunneling junction. The gradient band order at the bottom battery p layer and the tunneling junction can effectivelyenhance the cavity draw-off of the bottom battery and the tunneling junction, and thereby a large amount of charge accumulation among the tunneling junction interfaces can be prevented. After the adding of the TRL having high doping concentration, the defect density of states at the tunneling junction is increased. The electronic cavity assists tunneling through defects, and the probability of recombination and tunneling can be increased. With the adoption of the heterojunction, the spectrum response of the bottom battery can be effectively enhanced, and the opening and pressing loss can be reduced. The preparation method is simple and easy to carry out.

Owner:NANKAI UNIV +1

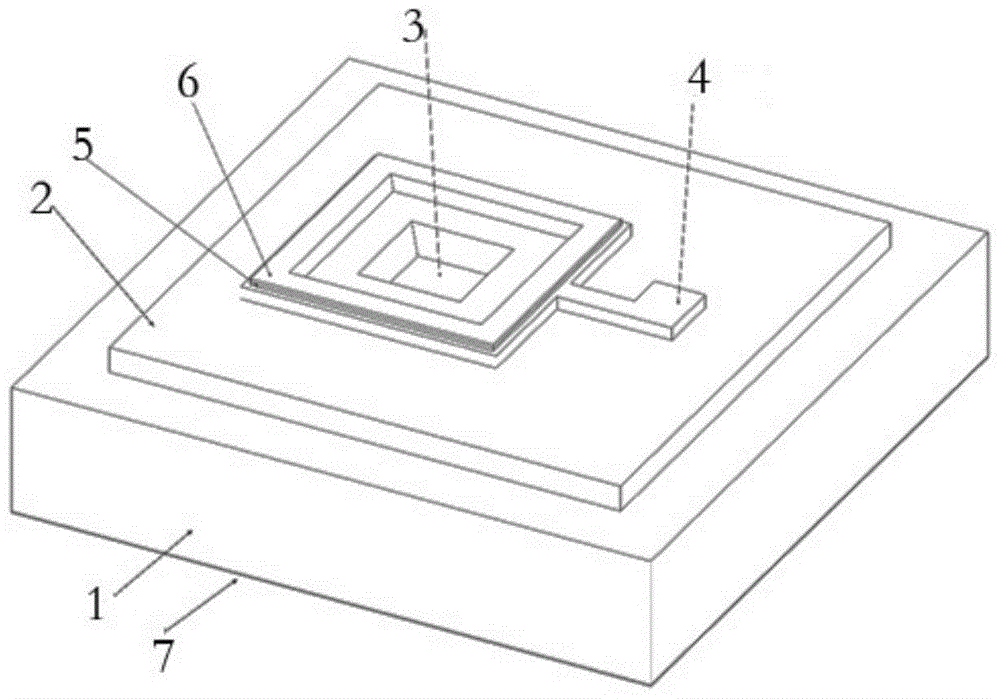

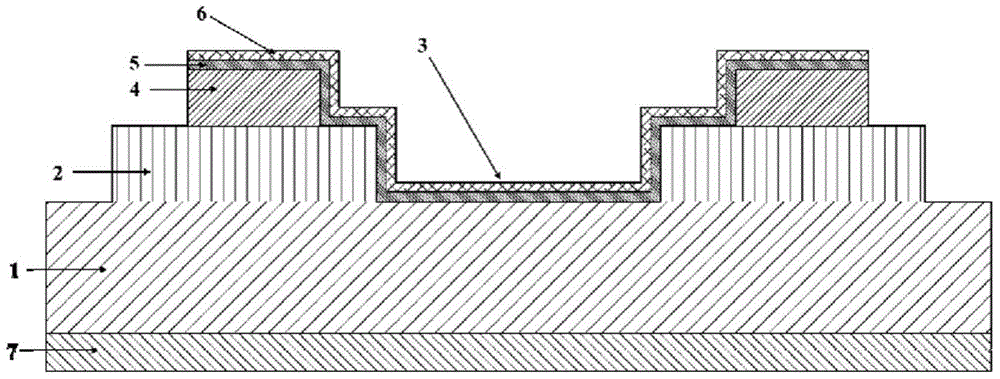

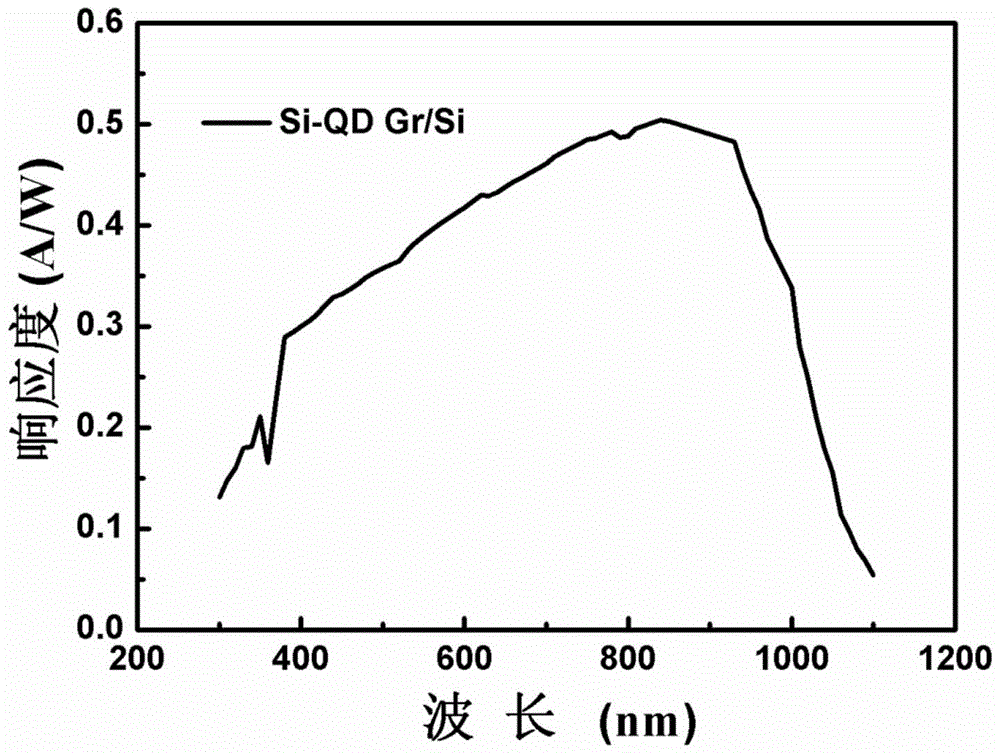

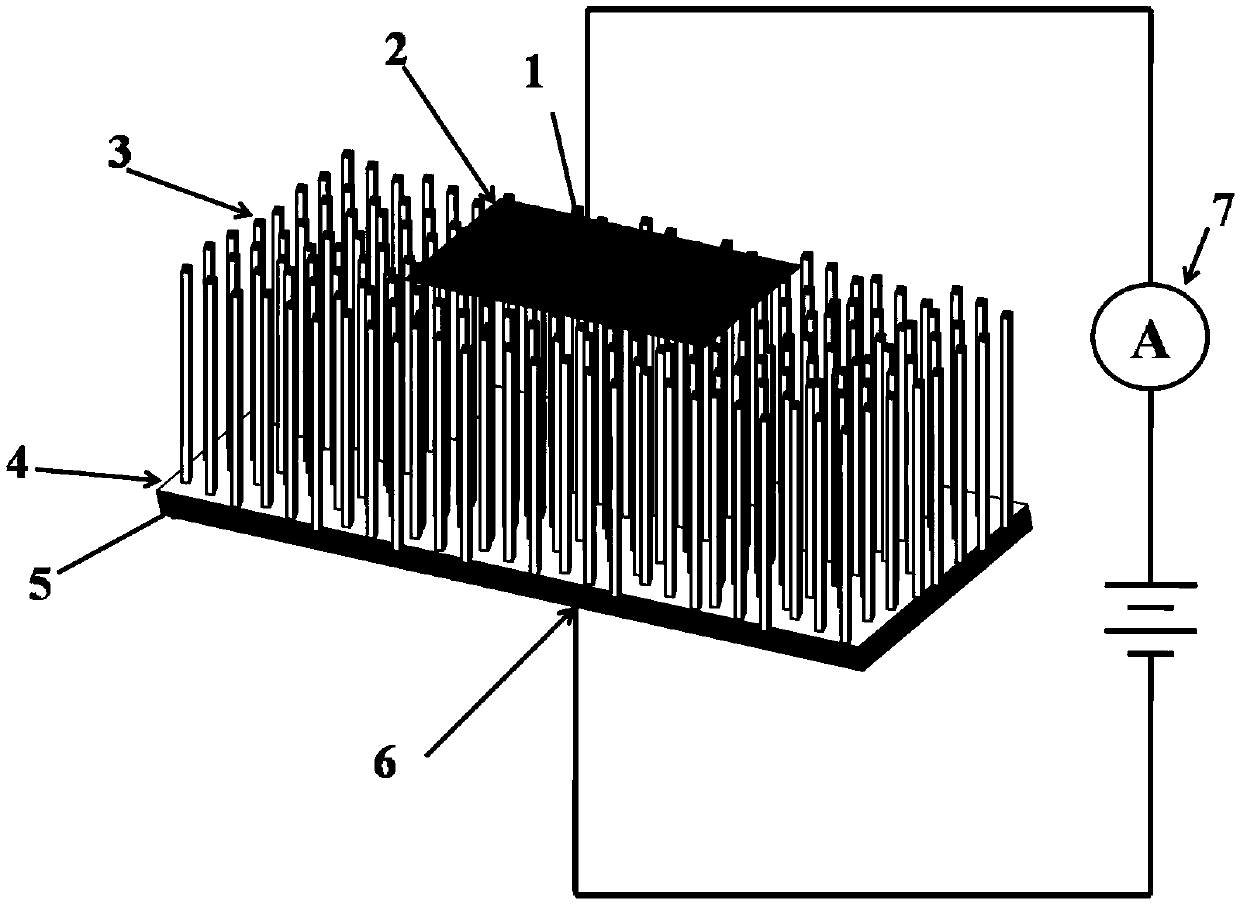

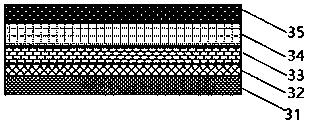

Silicon quantum dot/graphene/silicon heterostructure-based photoelectric sensor

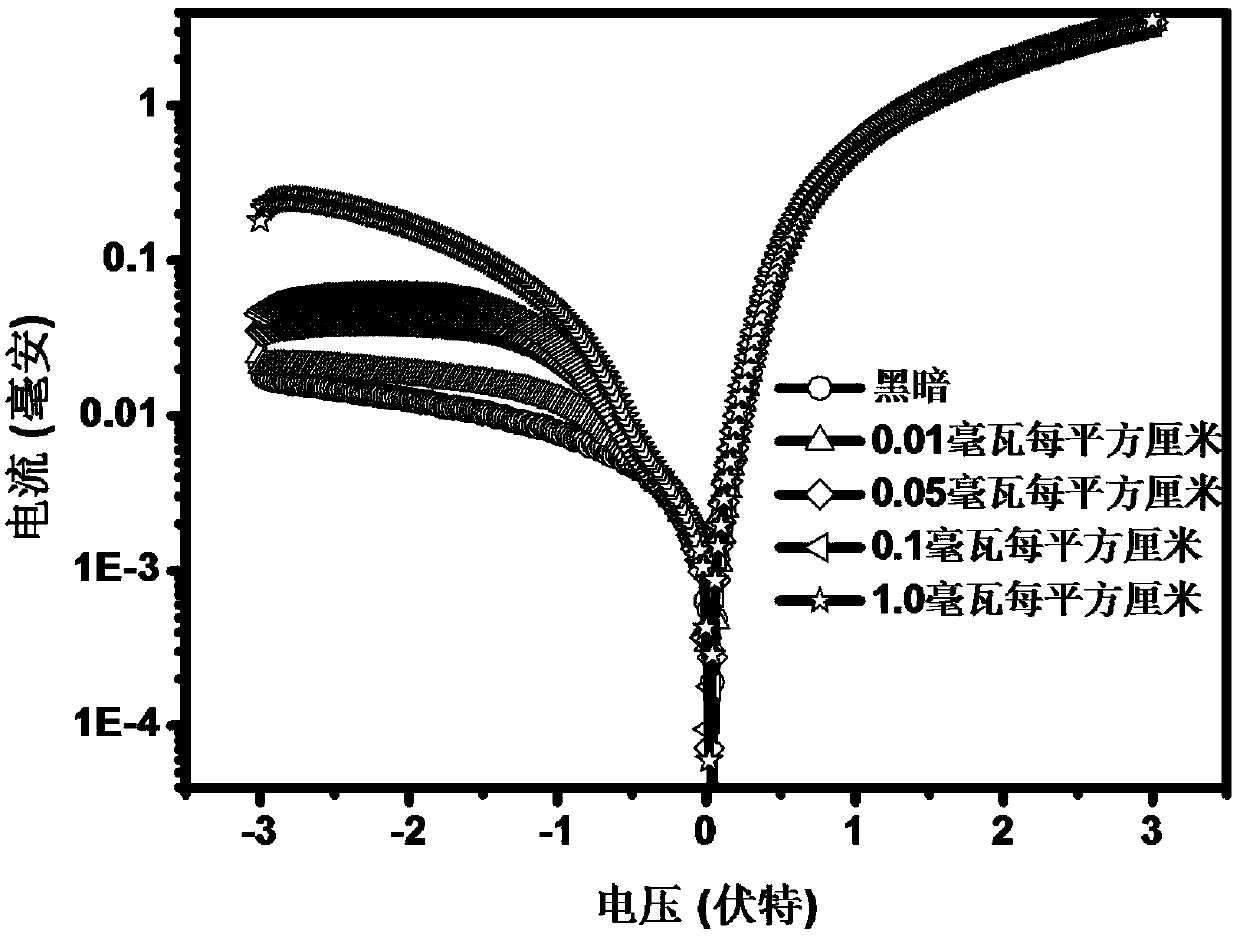

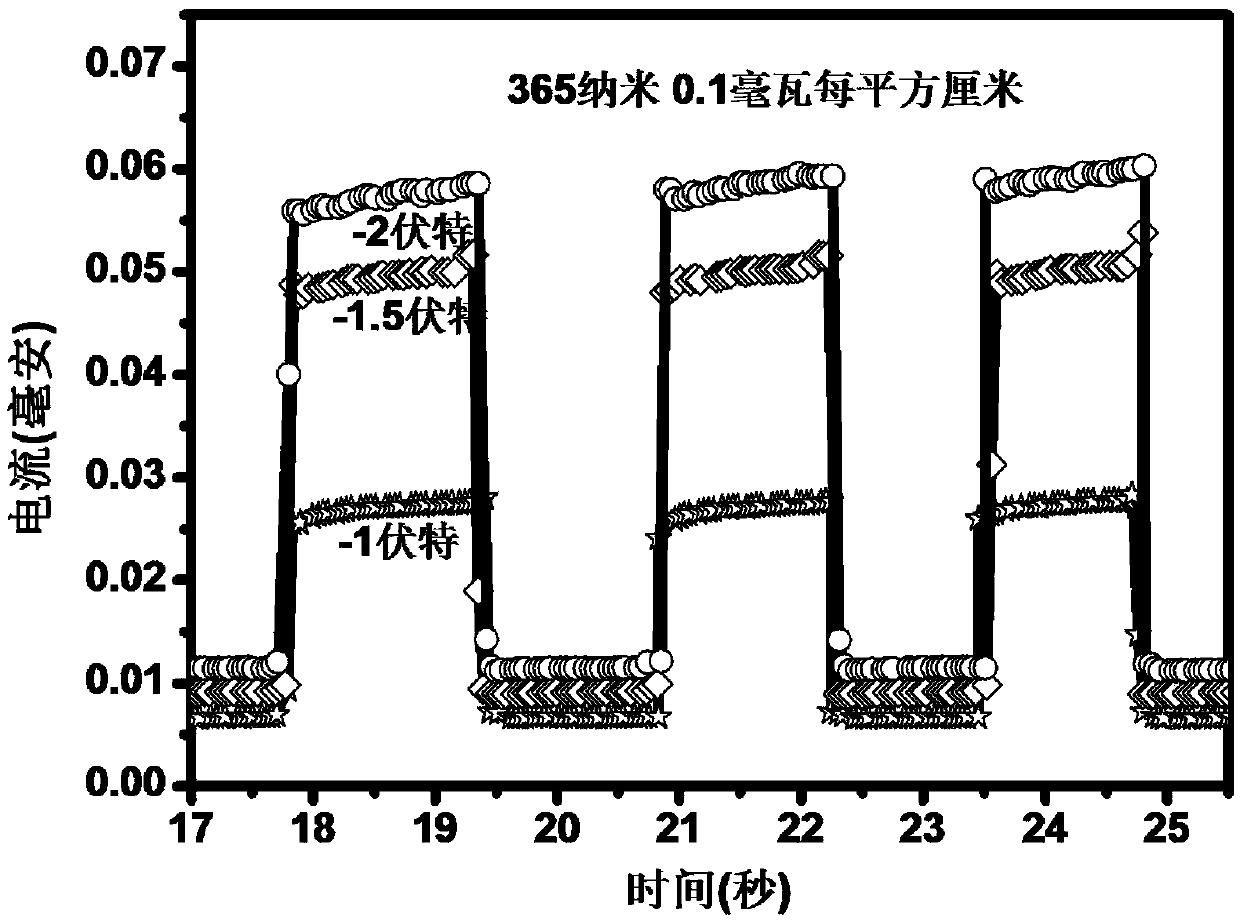

ActiveCN105679857AEasy to manufactureEasy to measureMaterial nanotechnologySemiconductor devicesUltraviolet lightsSilicon dioxide

The invention discloses a silicon quantum dot / graphene / silicon heterostructure-based photoelectric sensor. The photoelectric sensor is sequentially provided with a bottom electrode, an n-type silicon substrate and a silicon dioxide isolation layer from bottom to top, wherein a window is formed in the silicon dioxide isolation layer; the n-type silicon substrate in the window is exposed; the silicon dioxide isolation layer is provided with a top electrode; a single graphene layer and a silicon quantum dot film layer overlay the top electrode; and the single graphene layer is in contact with the n-type silicon substrate in the window to form a graphene / silicon schottky junction. The photoelectric sensor disclosed by the invention is optimization and improvement on the basis of the schottky structure, has the advantages of the schottky junction, utilizes silicon quantum dots as a response increase layer, can effectively improve the responsivity of a device in the whole band, especially the responsivity of ultraviolet and visible parts, and solves the problem that a traditional silicon-based PIN junction is low in response to ultraviolet light detection. The sensor can work at an extremely low reverse bias voltage, and is a low-energy device with a considerable application prospect.

Owner:ZHEJIANG UNIV

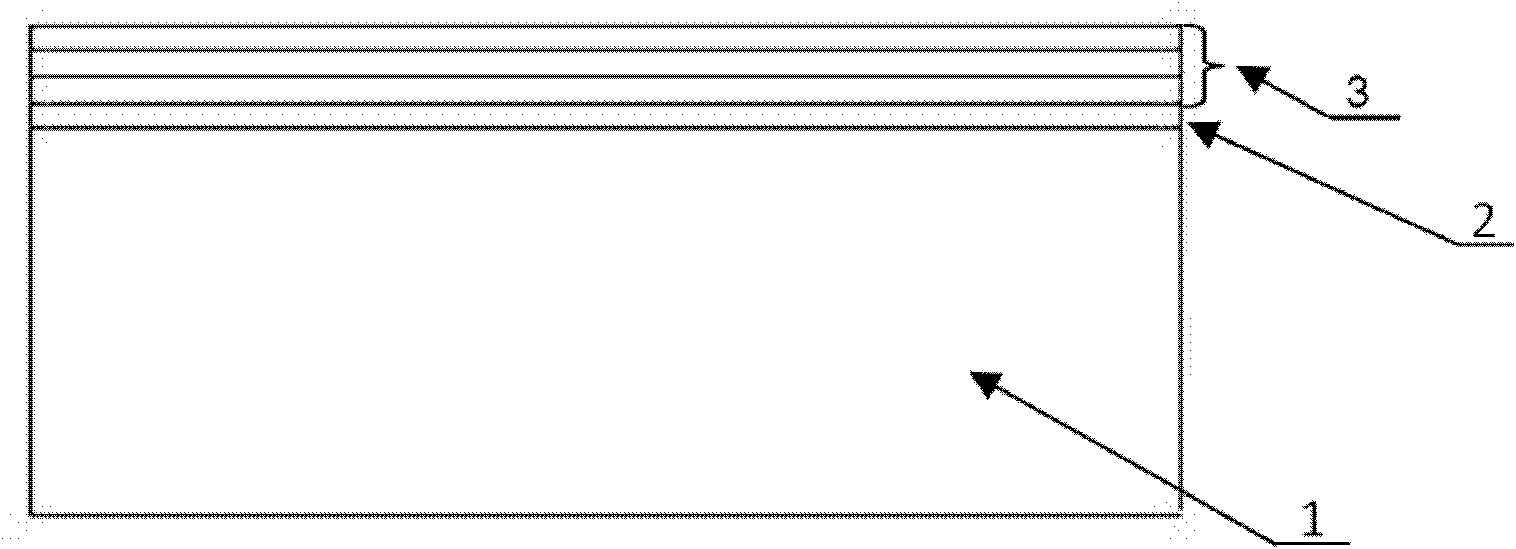

A gradient doped silicon-based heterojunction solar cell and its preparation method

InactiveCN102280502AIncrease collection rateIncrease short circuit currentFinal product manufacturePhotovoltaic energy generationHeterojunctionSilicon heterojunction

The invention discloses a gradient doped silicon-based heterojunction solar cell and a preparation method thereof. A plurality of layers of amorphous silicon membranes of which the doped concentration is increased sequentially are deposited on the surface of crystalline silicon serving as a substrate, and a transparent conductive film with a certain thickness is deposited and an electrode is prepared to prepare the gradient doped silicon-based heterojunction solar cell, wherein the amorphous silicon membranes contact the crystalline silicon to achieve a good passivating effect and obtain highopen-circuit voltage; a plurality of gradient doped amorphous silicon layers can form a strong inner electric field to reduce the composite loss of photo-induced carriers, improve the collection rateof minority carriers and increase short-circuit current; and the doped concentration of the doped amorphous silicon layers contacting the electrode is high, the resistivity is low, and contact resistance between the doped amorphous silicon layers and the electrode can be reduced to improve filling factors of the solar cell. Therefore compared with the conventional silicon-based heterojunction solar cell, the gradient doped silicon-based heterojunction solar cell has high photoelectric conversion efficiency.

Owner:SHANGHAI NORMAL UNIVERSITY

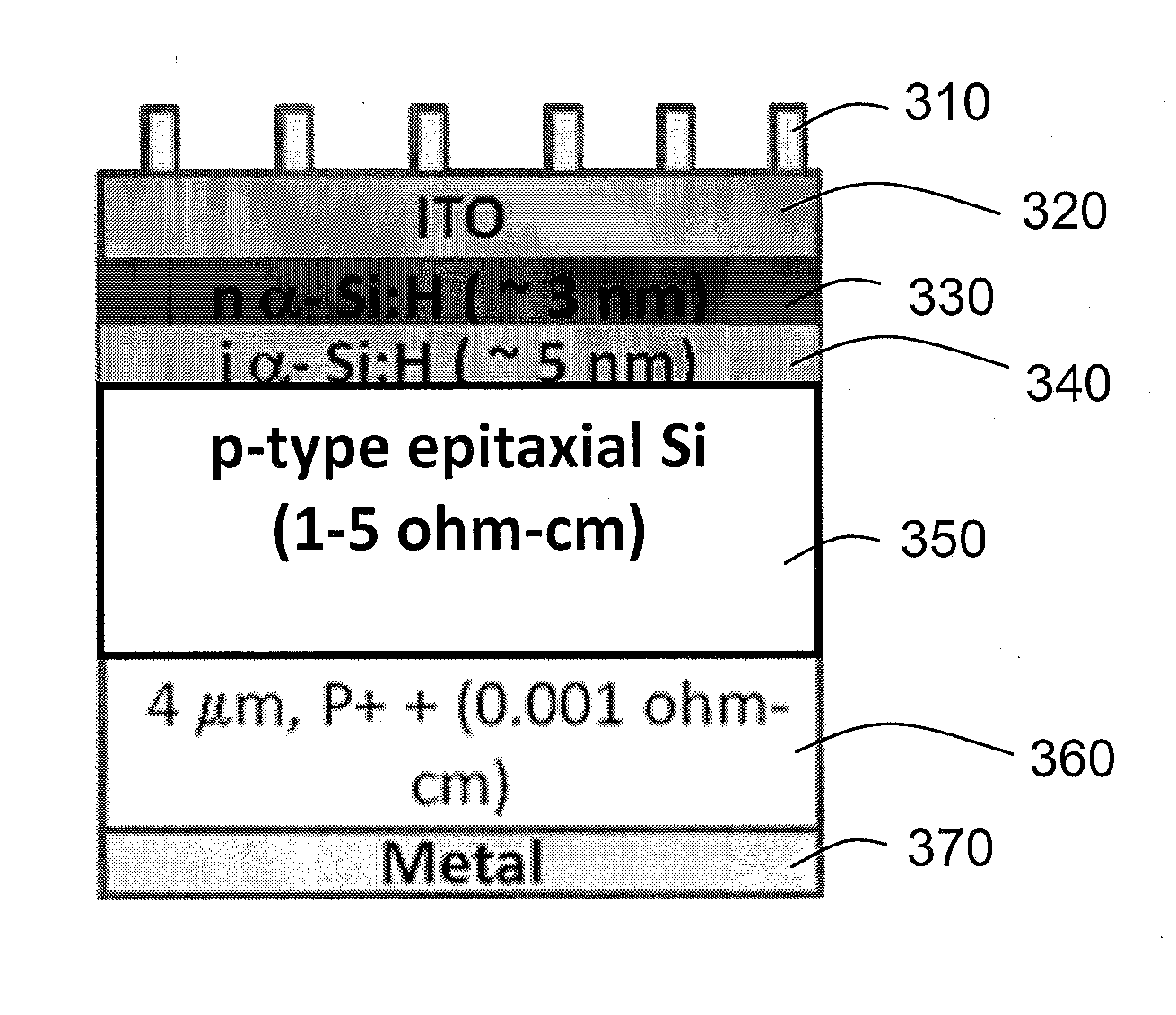

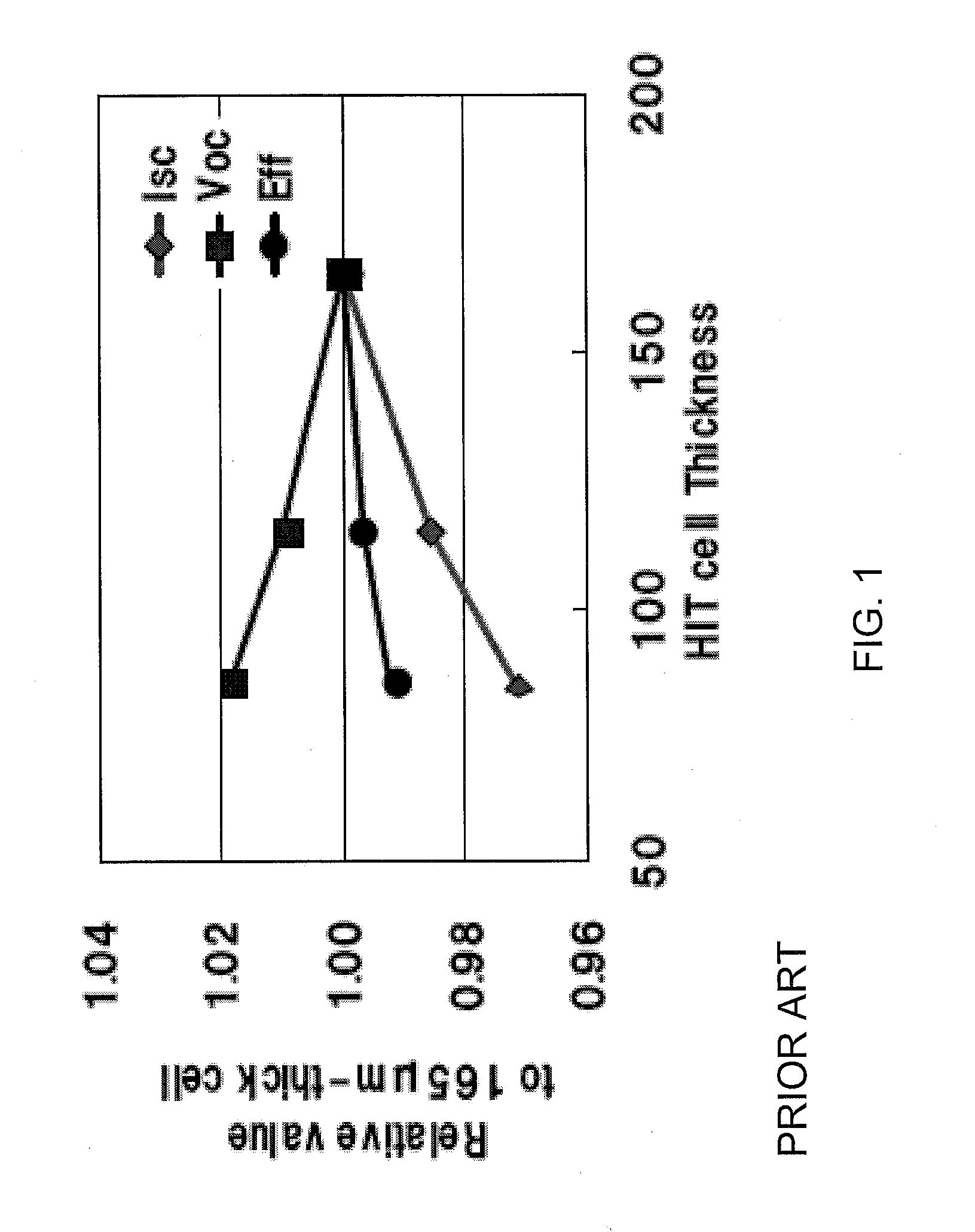

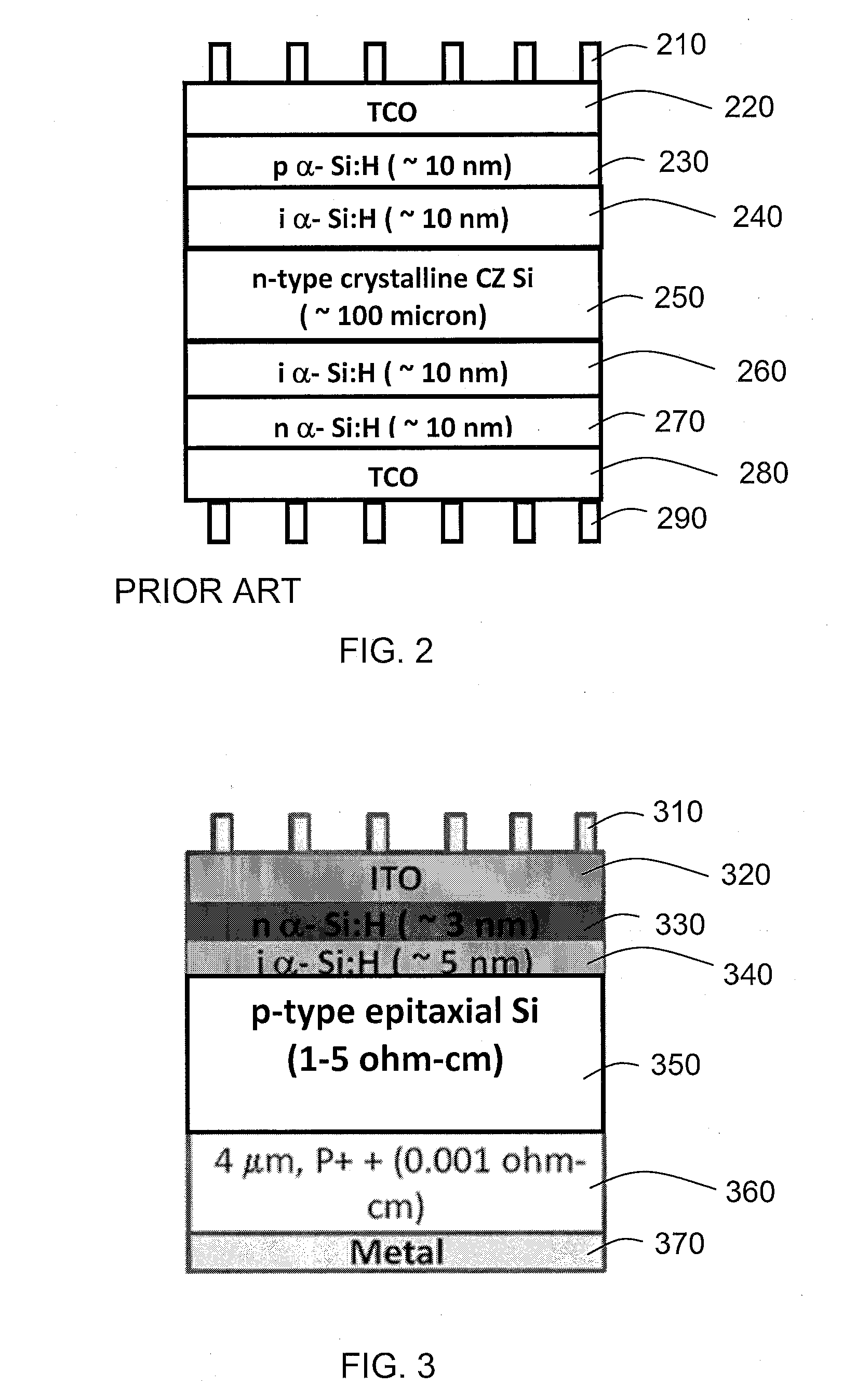

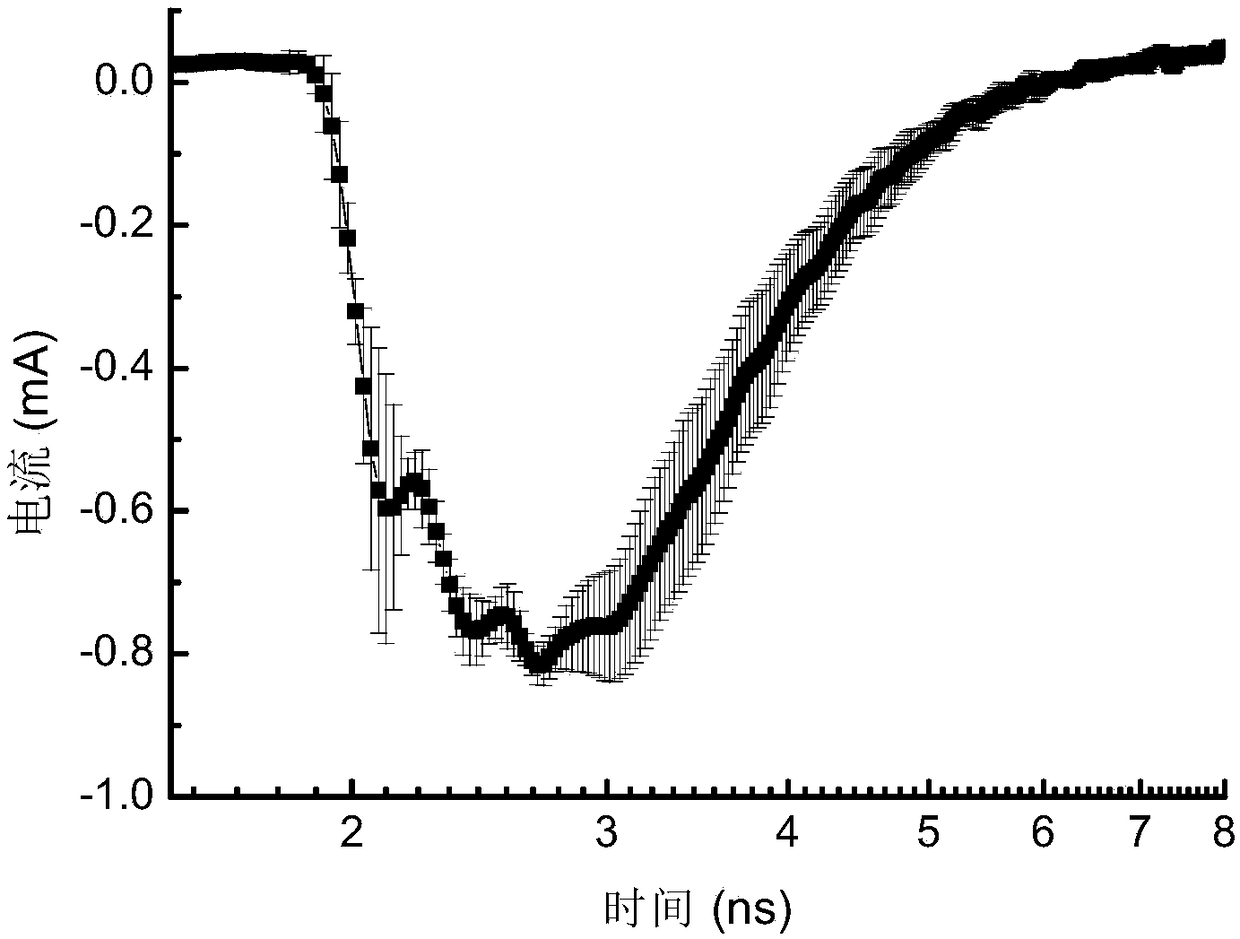

Silicon Heterojunction Solar Cells

InactiveUS20130180578A1Improve device performanceCostSemiconductor/solid-state device manufacturingPhotovoltaic energy generationCell fabricationSolar cell

Methods are described for fabricating HIT solar cells, including double heterojunction and hybrid heterojunction-homojunction solar cells, with very thin single crystal silicon wafers, where the silicon wafer may be less than 80 microns thick, and even less than 50 microns thick. The methods overcome potential issues with handling these very thin wafers by using a process including epitaxial silicon deposition on a growth substrate, partial cell fabrication, attachment to a support substrate and then separation from the growth substrate. Some embodiments of the present invention may include a solar cell device architecture comprising the combination of a heterostructure on the front side of the device with a homojunction at the rear of the device. Furthermore, device performance may be enhanced by including a dielectric stack on the backside of the device for reflecting long wavelength infrared radiation.

Owner:SVAGOS TECHNICK INC

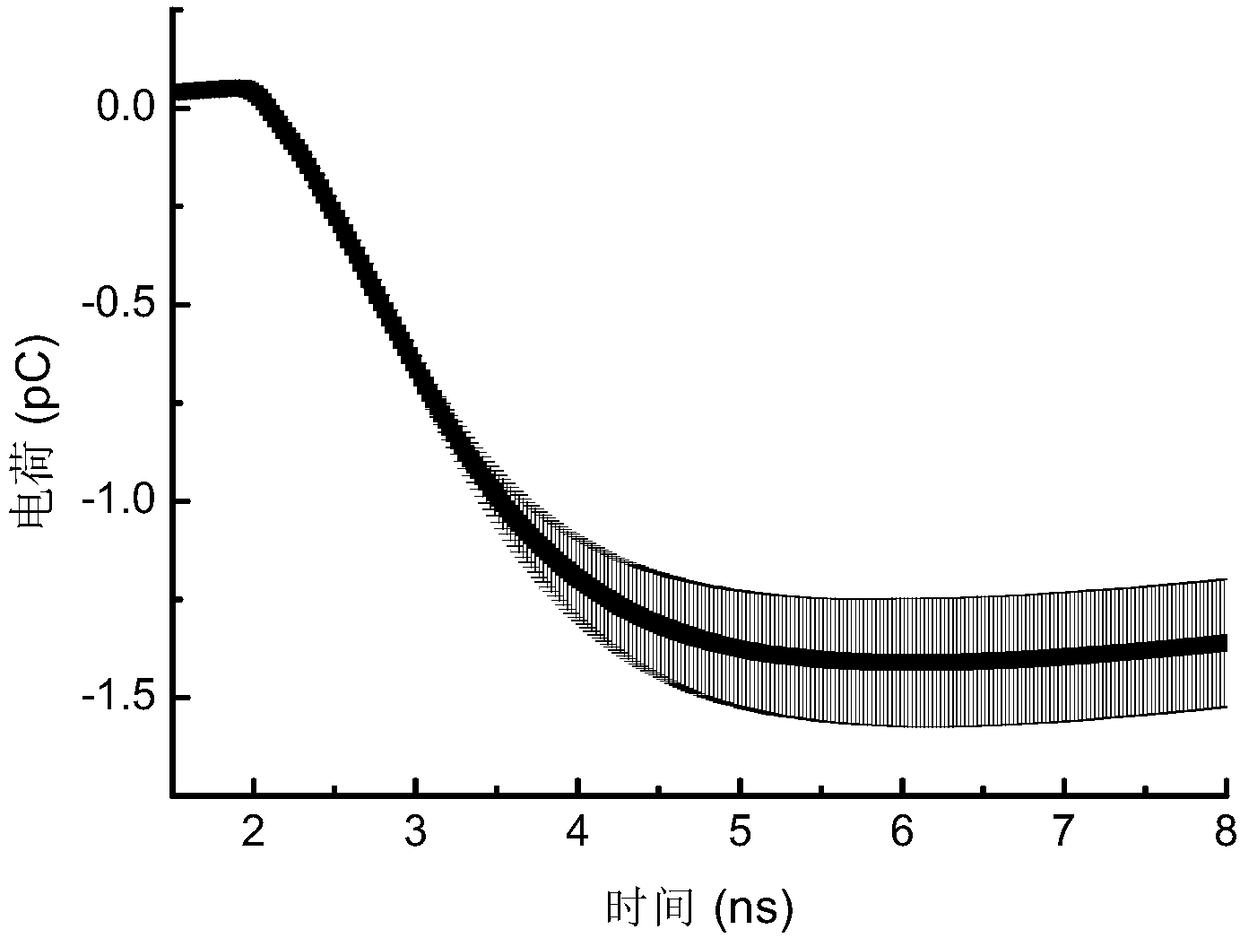

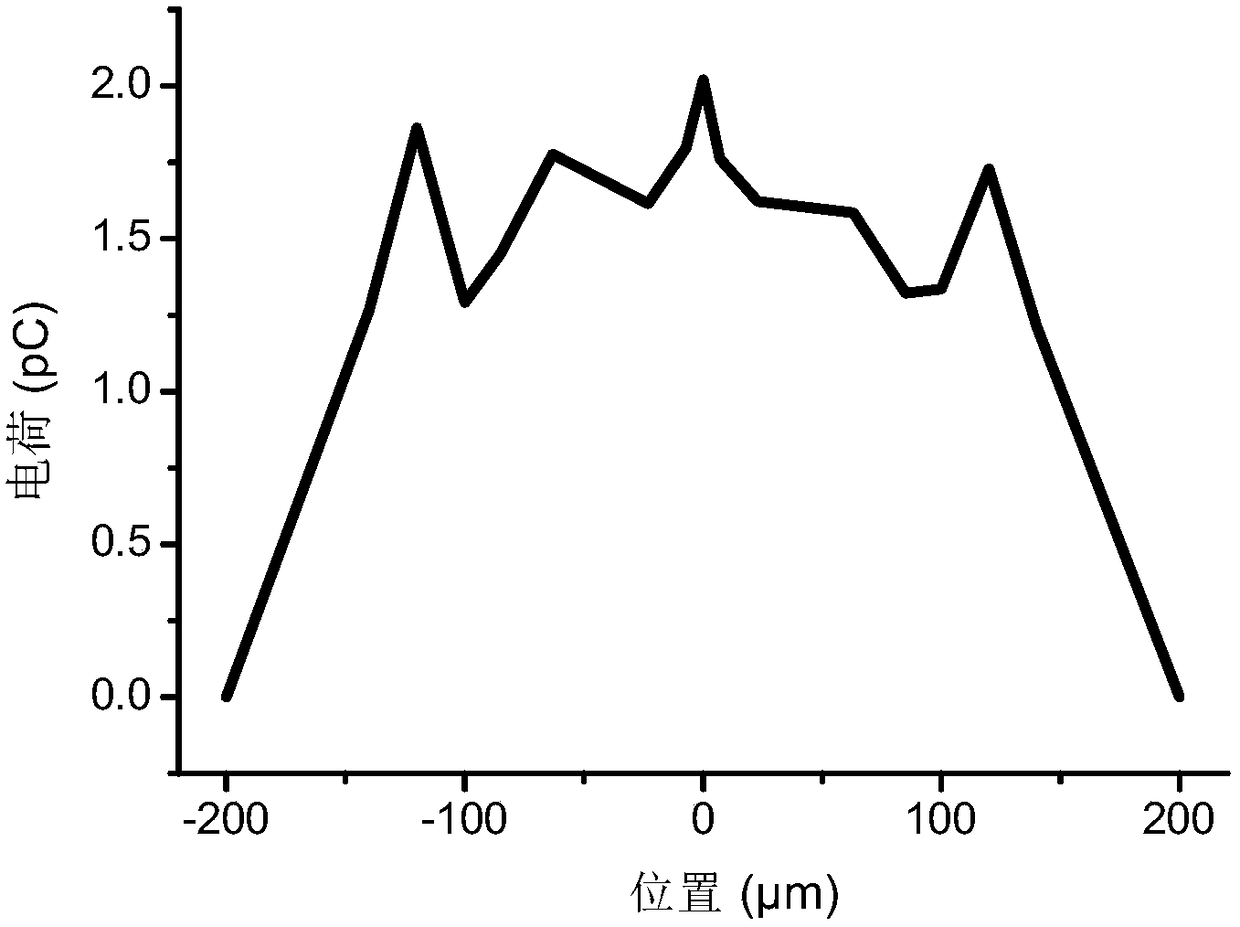

Germanium-silicon heterojunction transistor single event effect test method based on heavy ion microbeam irradiation

ActiveCN108267679AImprove experimental precisionReduce testing costsIndividual semiconductor device testingMicrobeam irradiationIrradiation

The present invention provides a germanium-silicon heterojunction transistor single event effect test method based on heavy ion microbeam irradiation. The problems are mainly solved that a damaging mechanism cannot be directly represented and a sensitive region cannot be accurately located in the prior art. The implementation scheme of the method comprises the steps of: selecting a germanium-silicon heterojunction transistor sample to test electrical properties of the germanium-silicon heterojunction transistor sample; making and testing a PCB test board for irradiation, and performing de-encapsulation processing of a germanium-silicon heterojunction transistor device prior to test; assembling an irradiation platform; setting a test condition of a heavy ion microbeam irradiation test; performing beam ejecting position location of a heavy ion microbeam irradiation device; setting the type and the weight of incident heavy ions; developing the heavy ion microbeam irradiation test; and recoding and processing all the test data, and obtaining a single event effect sensitive region. The method provided by the invention can accurately locate the germanium-silicon heterojunction transistorsingle event effect sensitive region, can improve the experiment precision, can reduce the test cost and can be used for assessment of the astronavigation anti-radiation capacity for microelectronicdevices.

Owner:XIDIAN UNIV

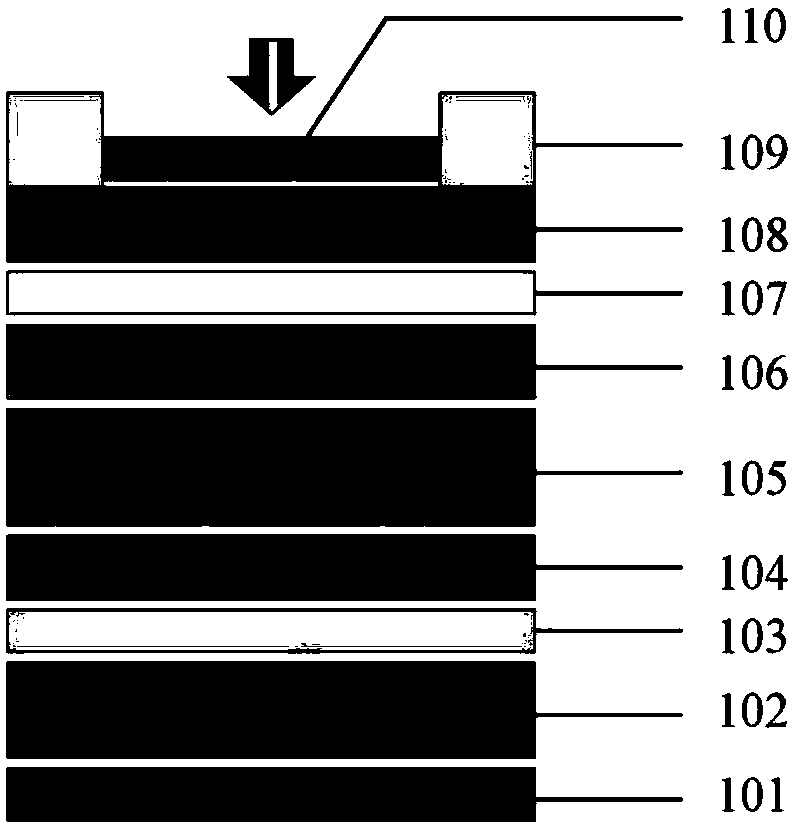

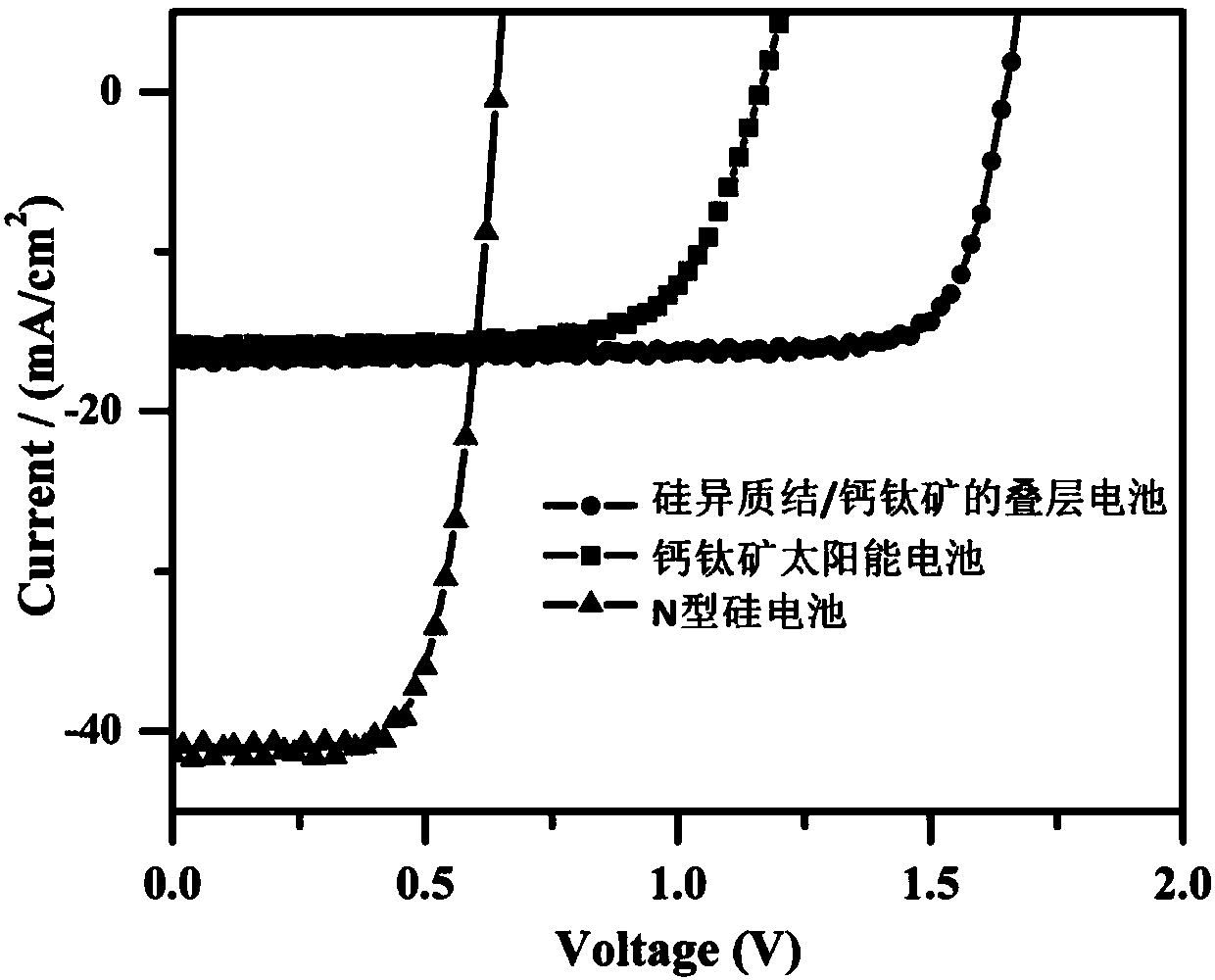

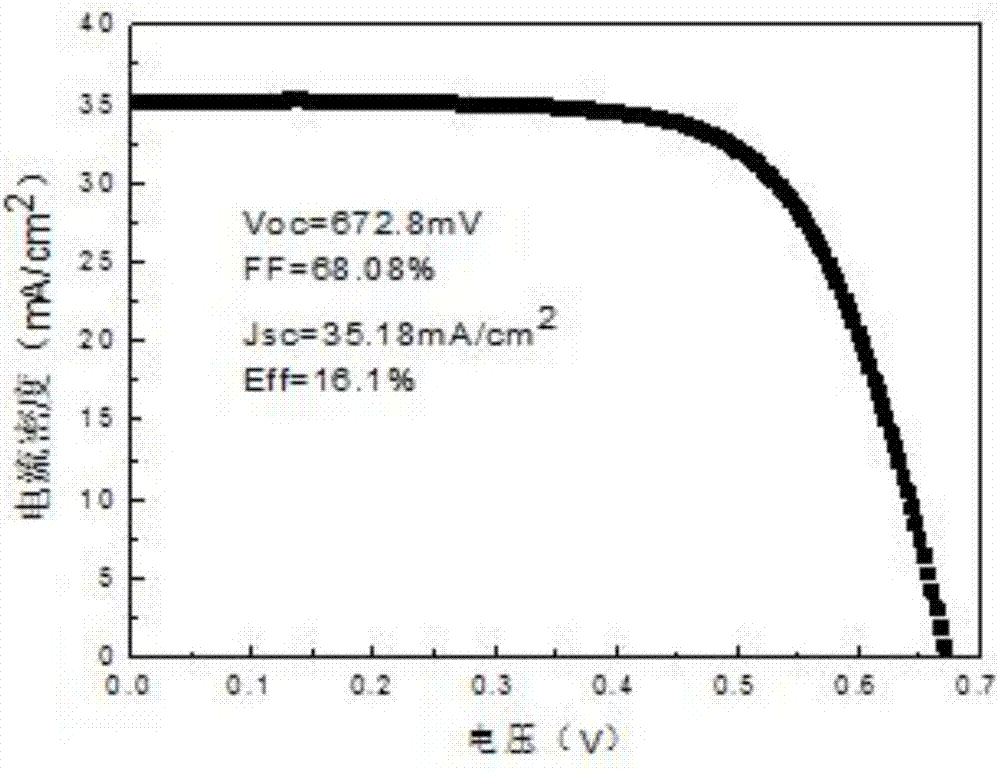

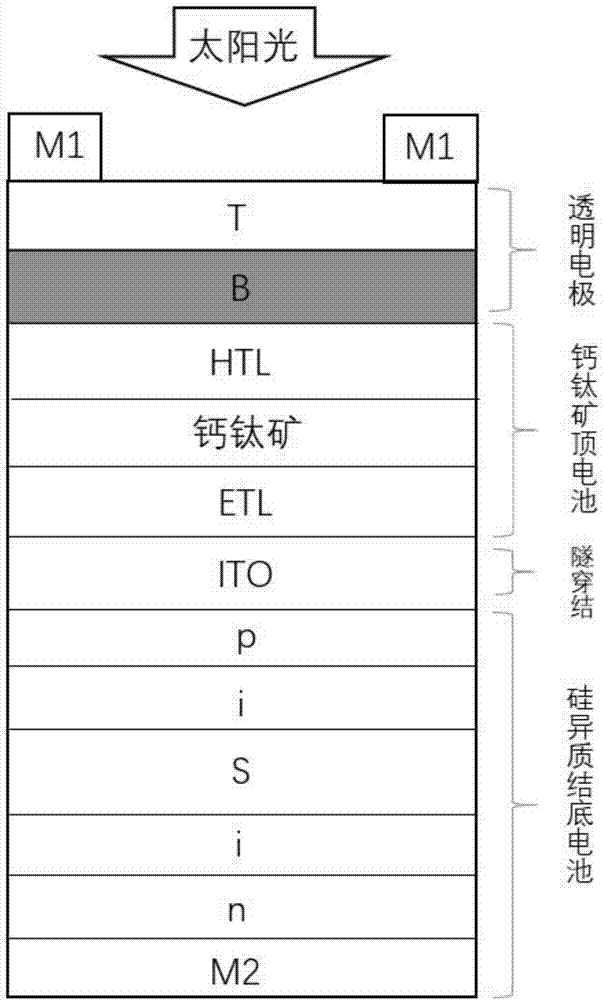

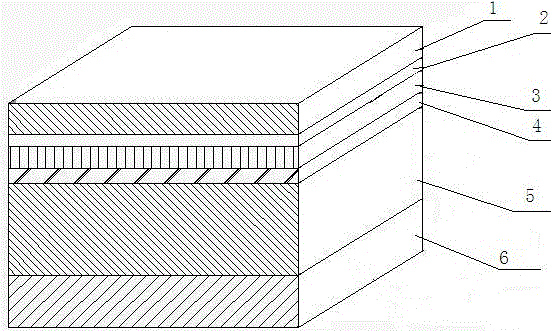

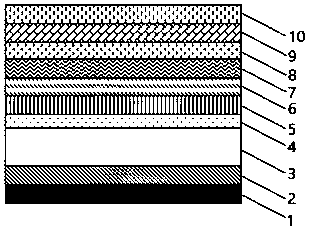

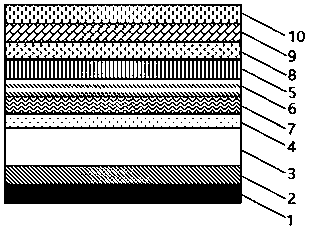

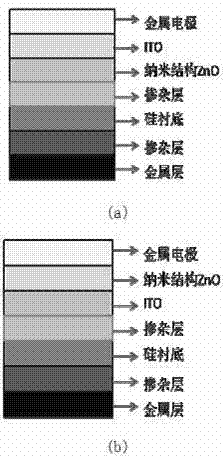

Silicon heterojunction/perovskite based double-electrode laminated solar cell

PendingCN109935690ASolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionMetal electrodes

The invention relates to a preparation method for a silicon heterojunction / perovskite based double-electrode laminated solar cell. Compared with a unijunction solar cell, the laminated solar cell canutilize medium-short wave photons in the sun spectrum more effectively to achieve a higher efficiency. The laminated solar cell based on silicon heterojunction / perovskite electrodes comprises a top wide-band-gap perovskite solar cell and a narrow-band-gap silicon cell, and also comprises an anti-reflecting layer, a transparent top electrode, a protective layer, a perovskite absorbing layer, an electron transmission layer, an intermediate layer, a Si heterojunction battery and a metal electrode successively from top to bottom. The tunnel junction and perovskite absorbing layer are prepared at low temperature. The silicon heterojunction / perovskite double-electrode laminated solar cell prepared by a simple low-cost solution method can reach the efficiency of 22.22% which is in a leading position domestically.

Owner:PEKING UNIV

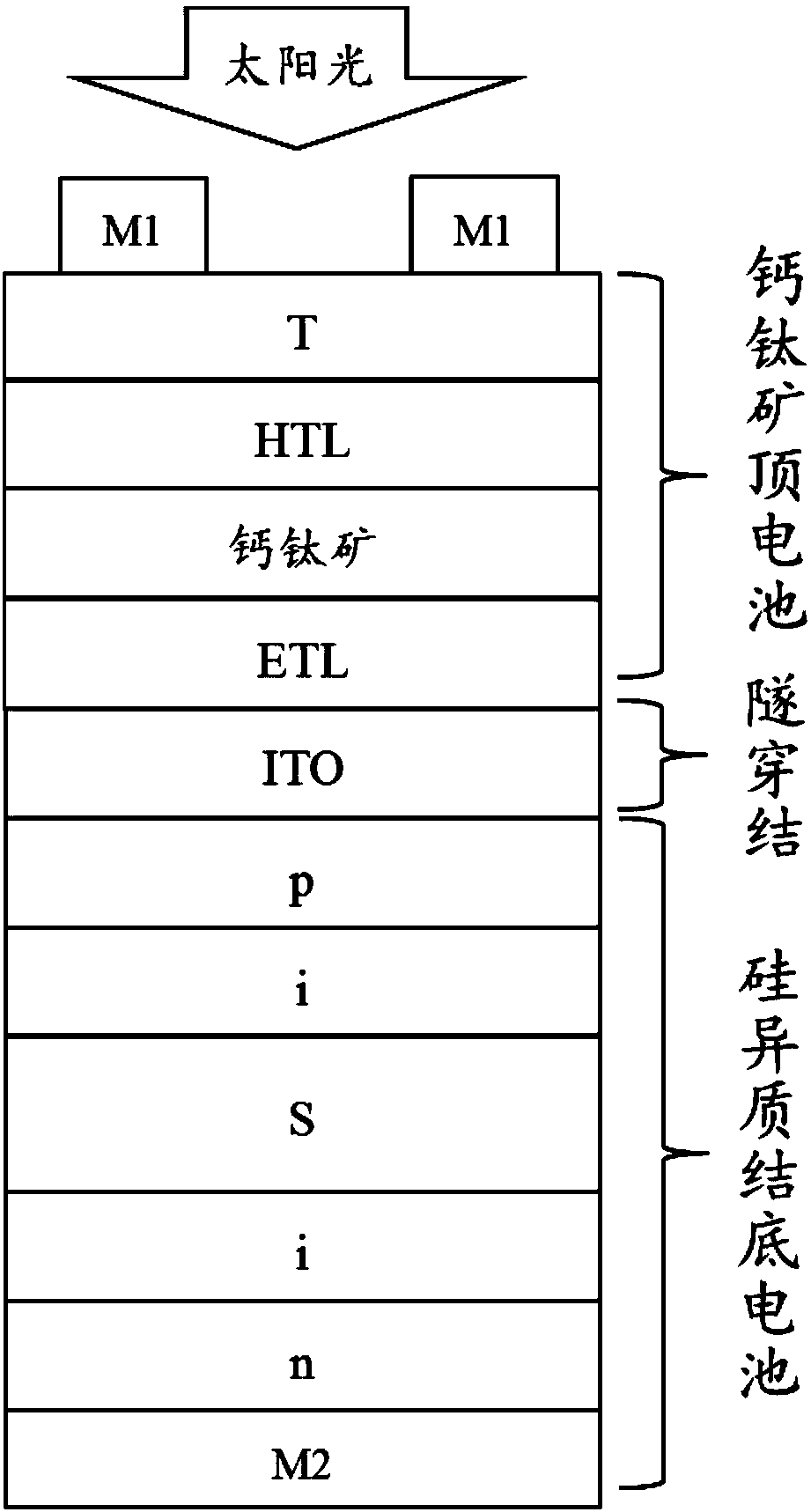

Perovskite/silicon heterojunction two-end laminated solar cell

InactiveCN107369767AReduce compoundingReduce accumulationSolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionPerovskite solar cell

The invention relates to the field of a solar cell, and provides a perovskite / silicon heterojunction two-end laminated solar cell. In the laminated solar cell, the cell with high open voltage and high efficiency is obtained by employing a heterojunction solar cell as a bottom cell, a perovskite solar cell as a top cell and ITO as a tunneling junction and by the matched energy level of a silicon cell and perovskite. By fabricating an intermediate protection layer on a hole transmission layer of the top cell, the laminated solar cell is prevented from being damaged by a subsequent transparent electrode, the structure is prevented from being damaged, the filling factor of the laminated solar cell is improved, and the efficiency is further improved. The preparation method for the material employed by the structure is simple and is easy to implement, and relatively good conversion efficiency can be obtained.

Owner:NANKAI UNIV +1

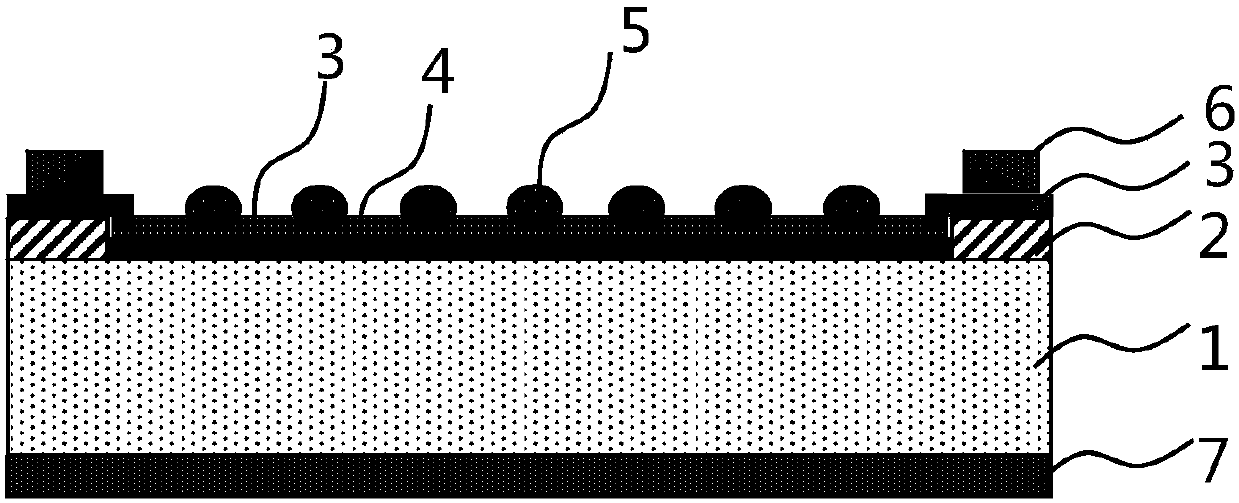

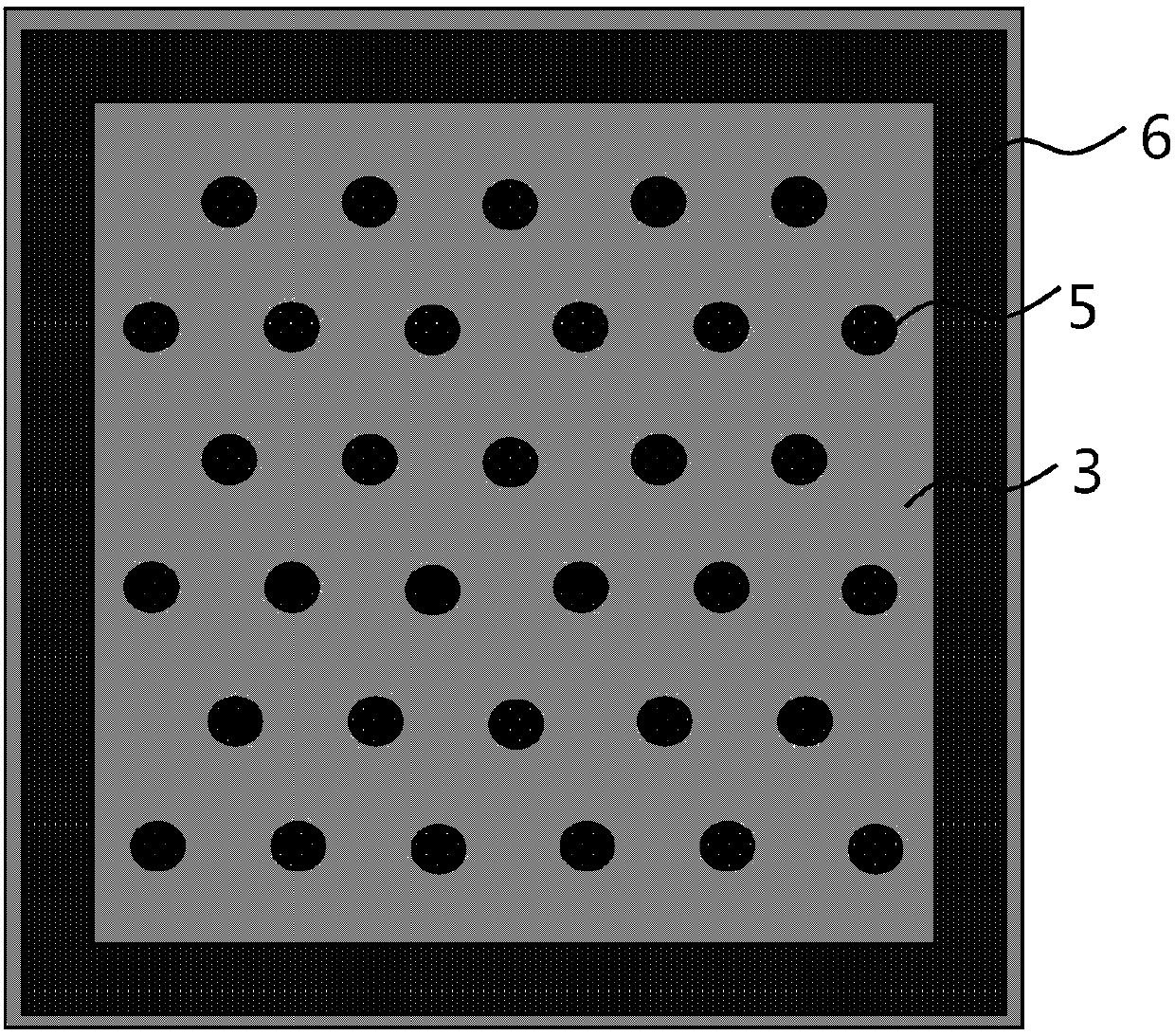

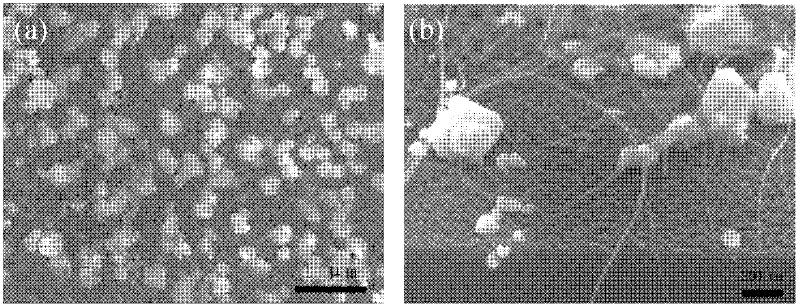

Enhanced graphene-silicon heterojunction photoelectric detection chip and preparation method thereof

InactiveCN107768452AImprove light absorption efficiencyImprove photoresponsivityFinal product manufacturePhotovoltaic energy generationHeterojunctionSpectral response

The invention discloses a graphene-silicon heterojunction photoelectric detection chip and a preparation method thereof. The detection chip includes a silicon substrate, a frame-shaped SiO2 insulatinglayer on the boundary around the silicon substrate, an interface passivation layer on the silicon substrate, a graphene layer on the interface passivation layer, and a metal nanostructure layer on the graphene layer. By introducing the metal nanostructure to the chip structure, on one hand, the light absorption efficiency of the graphene-silicon heterojunction can be significantly improved and the light responsivity and linear light response range of devices can be improved through the localized surface plasmon resonance characteristic of the metal nanostructure. On the other hand, through the ultrafast photoelectric conversion process of the metal nanostructure under light excitation, the spectral response rate and frequency characteristic of the chip can be significantly improved. In addition, by making use of different spectrum resonance characteristics of metal nanoparticles of different materials and sizes, the specific spectrum enhancement characteristic of the detection chip can be significantly improved.

Owner:XIAMEN UNIV

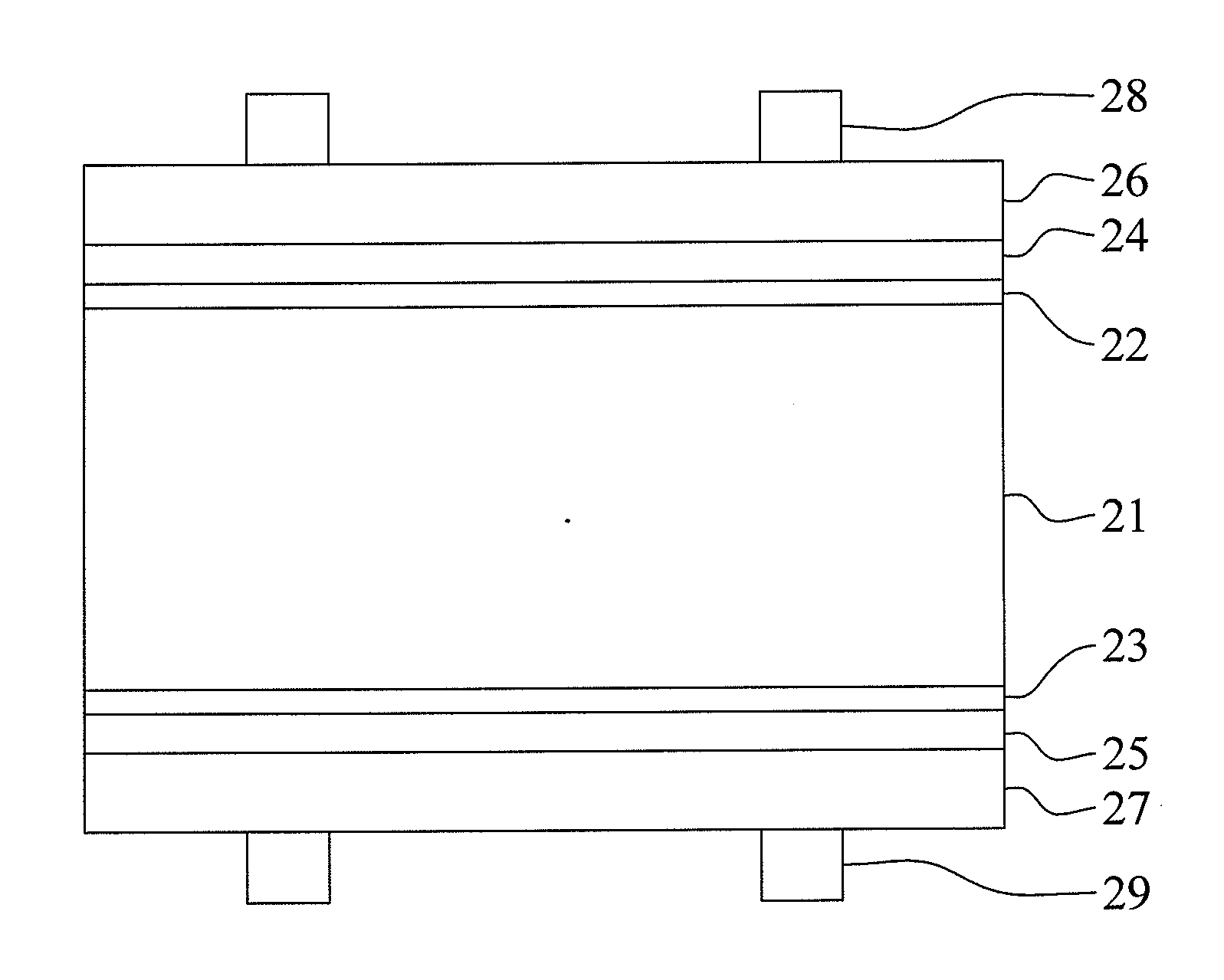

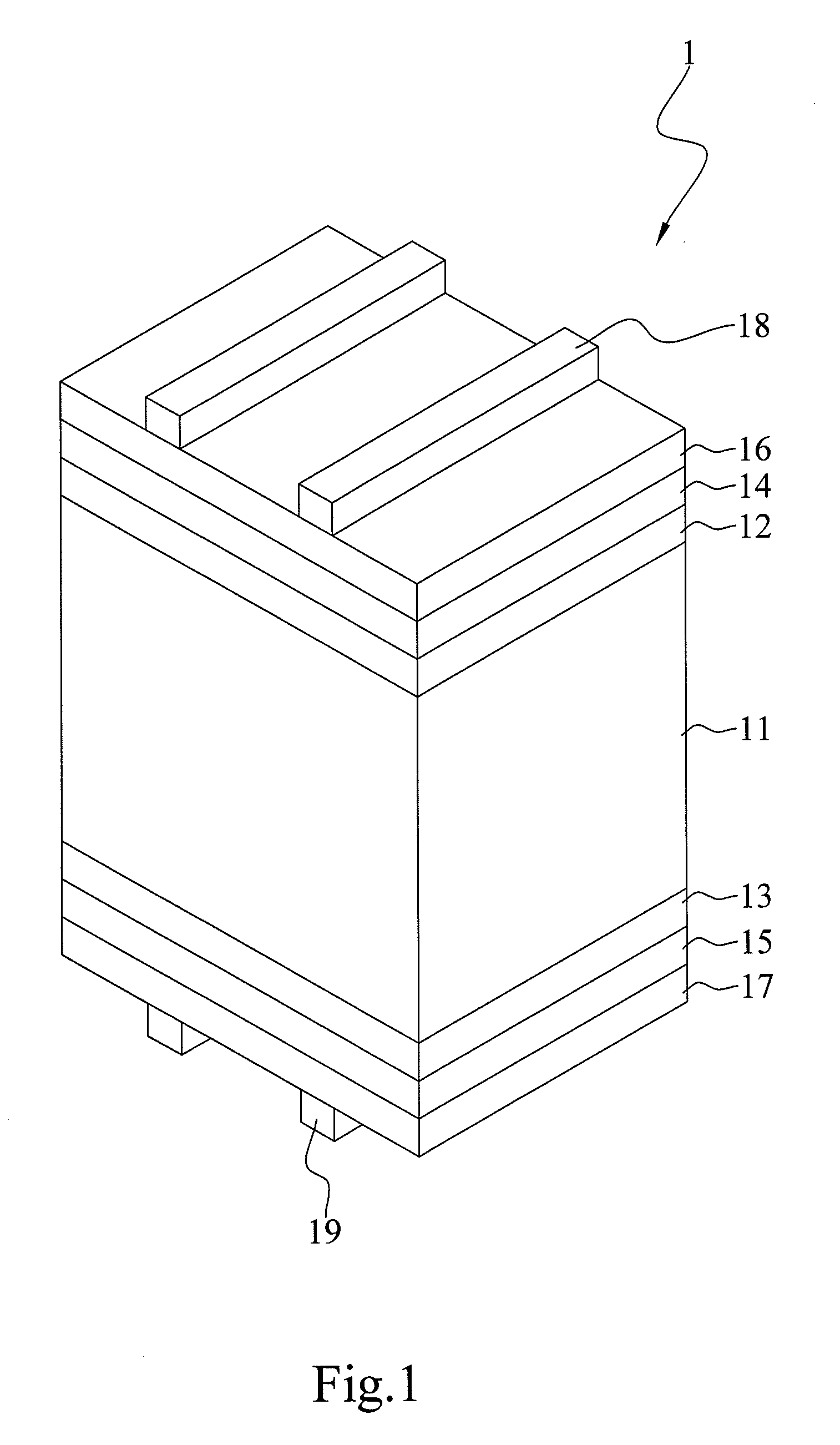

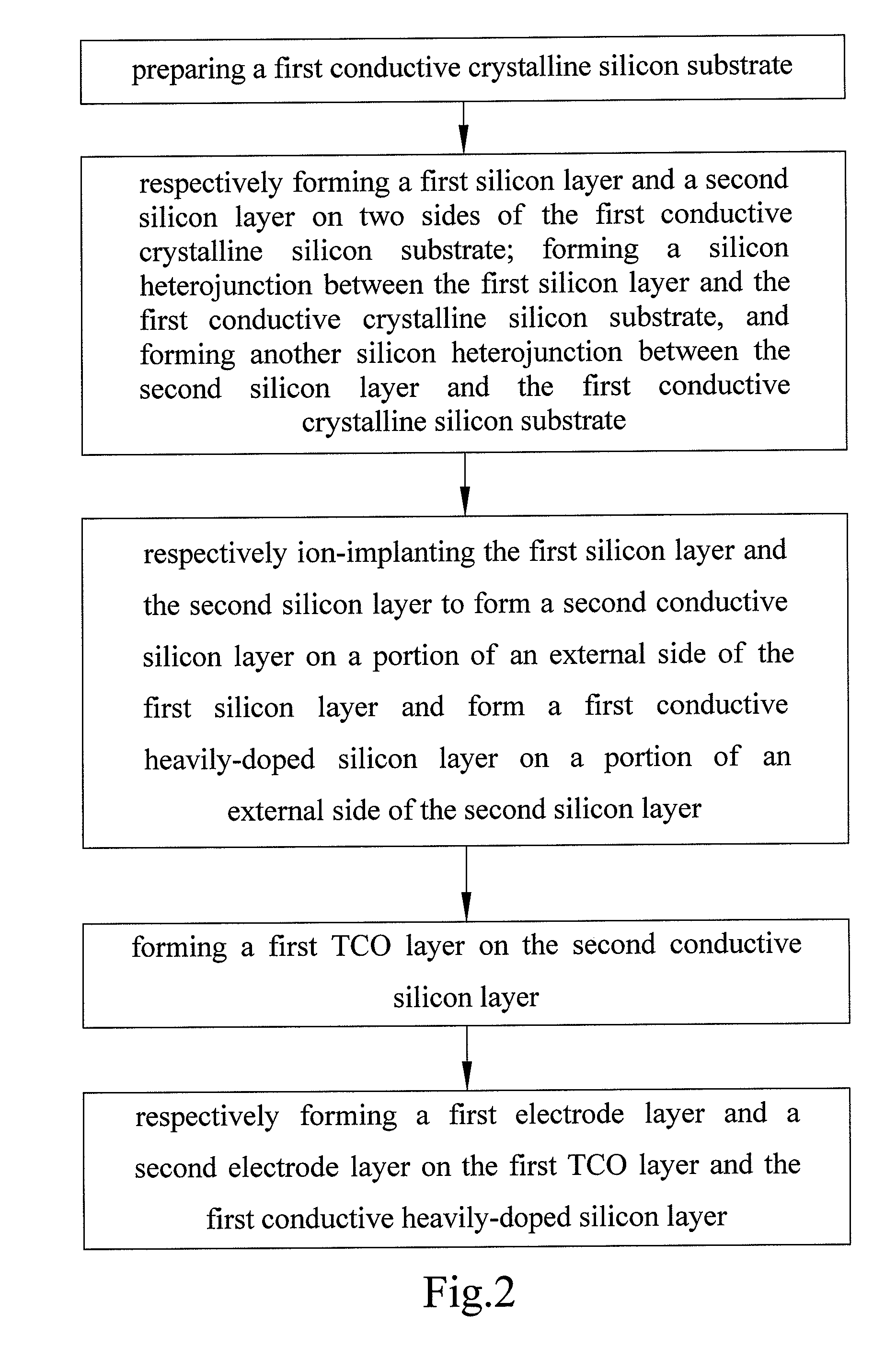

Method for fabricating silicon heterojunction solar cells

InactiveUS20120015474A1Easy to controlThin thicknessSemiconductor/solid-state device manufacturingPhotovoltaic energy generationSolar cellSilicon heterojunction

The present invention discloses a method for fabricating a silicon heterojunction solar cell. The silicon heterojunction solar cell according to the present invention comprises a first conductive silicon substrate; a first intrinsic silicon layer and a second intrinsic silicon layer respectively formed on two sides of the first conductive silicon substrate and jointed with the first conductive silicon substrate to form silicon heterojunctions; a second conductive silicon layer and a first conductive heavily-doped silicon layer respectively formed on the first intrinsic silicon layer and the second intrinsic silicon layer, wherein the second conductive silicon layer and the first conductive heavily-doped silicon layer are formed via an ion implantation method, whereby is optimized the thickness and doped quality of the second conductive silicon layer and the first conductive heavily-doped silicon layer.

Owner:NATIONAL TSING HUA UNIVERSITY

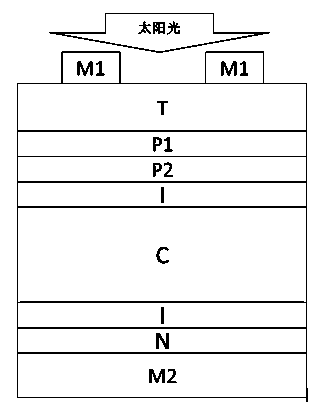

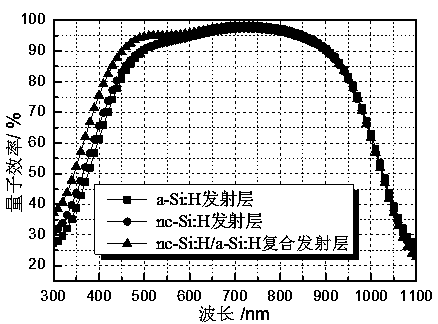

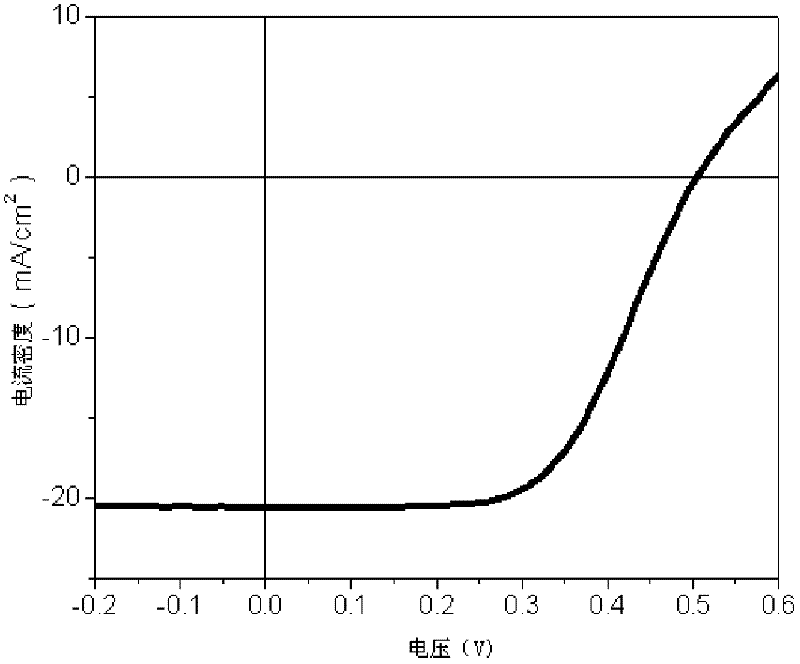

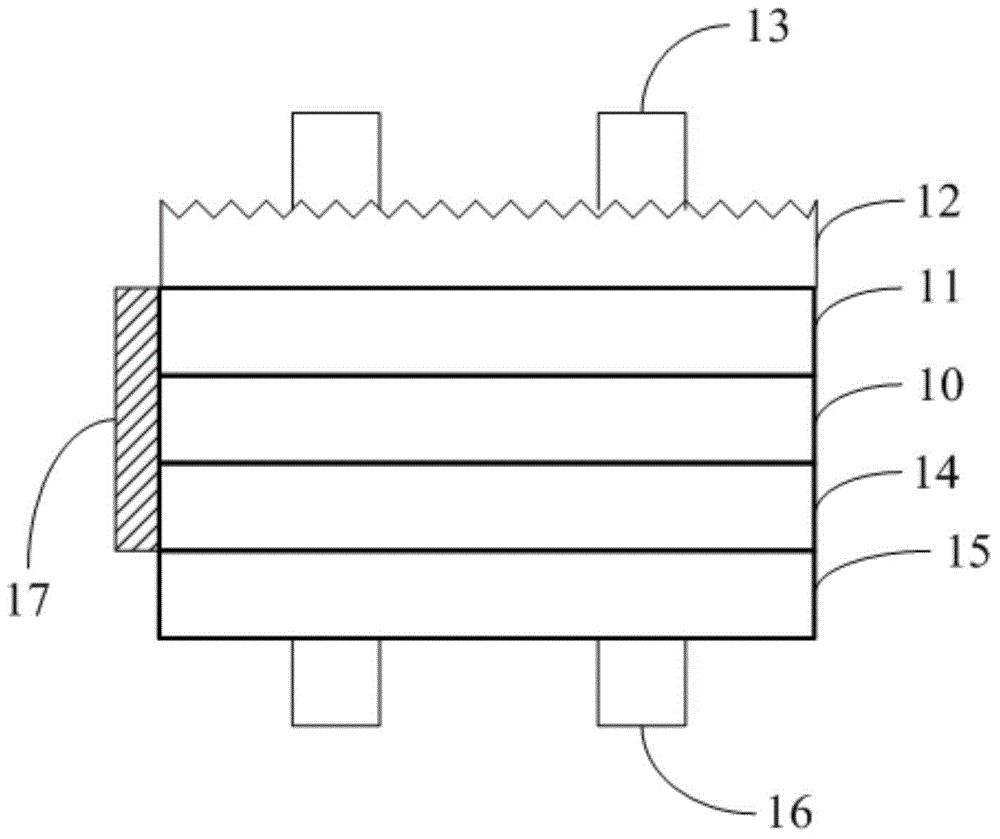

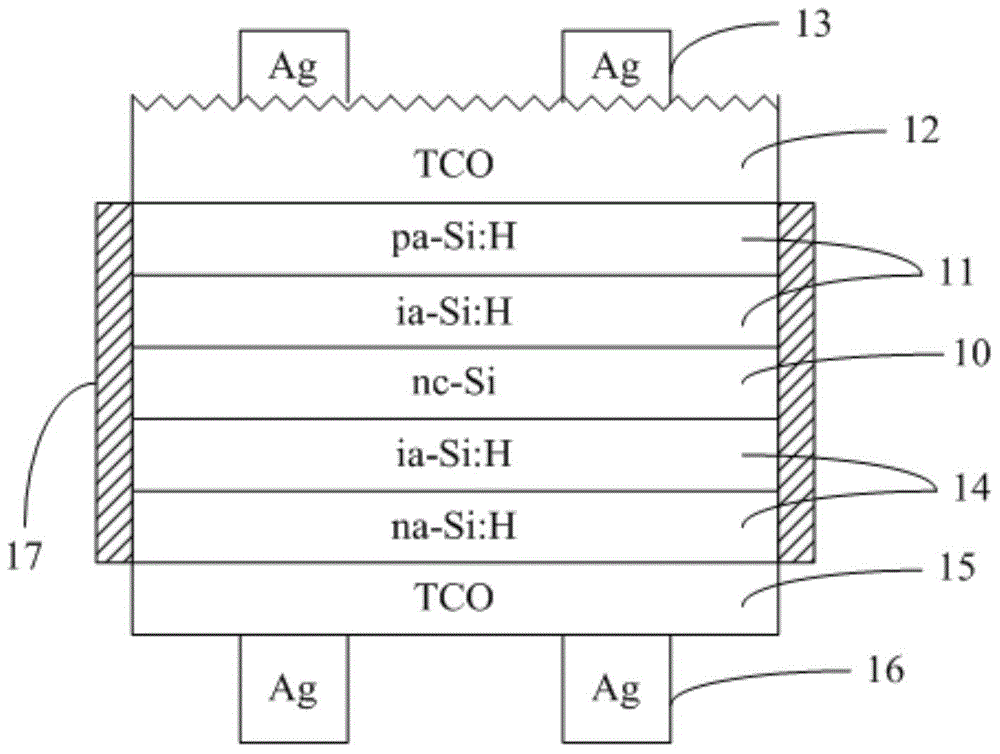

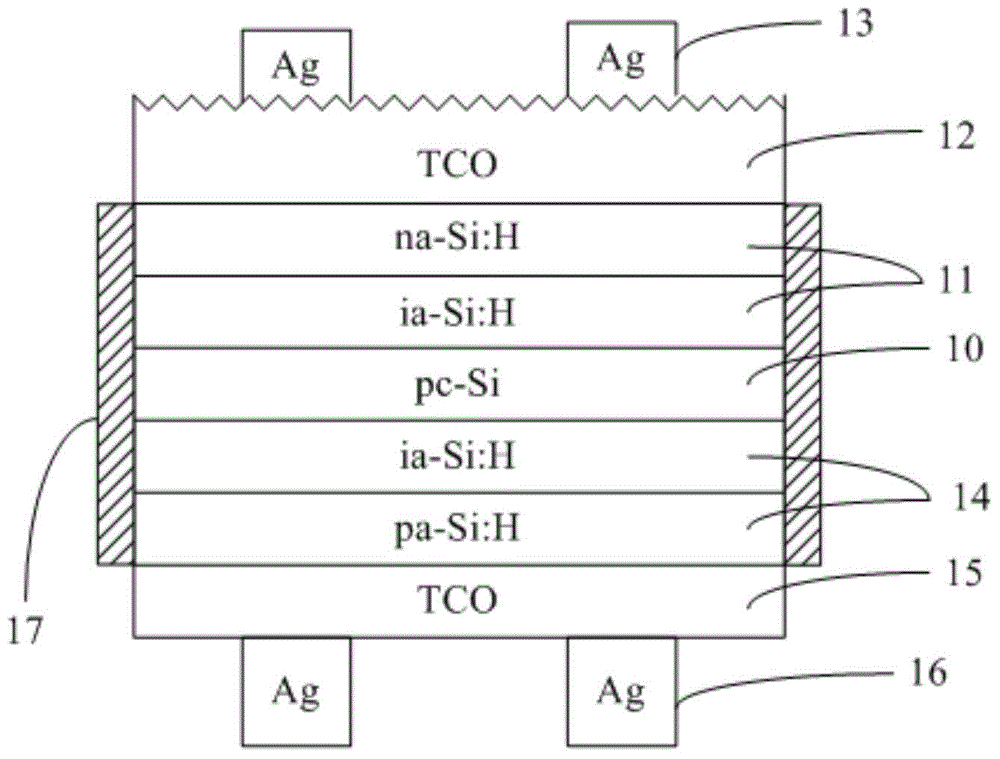

Method for preparing silicon heterojunction solar cell containing composite emission layer

ActiveCN103915523AReduced series resistanceReduce absorptionFinal product manufacturePhotovoltaic energy generationNanocrystalline siliconCrystalline silicon

The invention provides a method for preparing a silicon heterojunction solar cell containing a composite emission layer. The method includes the steps that an amorphous silicon back field N is deposited on one face of a substrate C on which a double-faced intrinsic amorphous silicon passivation layer I is deposited, an amorphous silicon layer P2 with the uniform structure is prepared on the face opposite to the amorphous silicon back field N under the conditions that doping concentration, hydrogen dilution and power density are low, a nanocrystalline silicon layer P1 with the uniform structure is prepared under the conditions that the doping concentration, the hydrogen dilution and the power density are improved, and an amorphous silicon / nanocrystalline silicon composite structure formed by the two silicon films serves as the emission layer of the silicon heterojunction solar cell. Materials have the advantages of being high in transmittance and conductivity through the structure, on the basis, the passivation effect of the surface of crystalline silicon can be improved, short wave response and output characteristics of the cell are improved, and the method for preparing the silicon heterojunction solar cell is simple and easy to carry out.

Owner:捷造科技(宁波)有限公司

Titanium dioxide nanorod array/silicon heterojunction-based ultraviolet light detector and preparation method thereof

PendingCN105514210ASimple processEasy to integrateMaterial nanotechnologyFinal product manufactureHeterojunctionTithonia longiradiata

The invention in particular provides a high performance ultraviolet light detector made from an n-n homotype heterojunction material and formed by a titanium dioxide nanorod array and an n-type silicon substrate. A preparation method of the ultraviolet light detector comprises the following steps: growing a titanium dioxide nano dot film on the n-type silicon substrate by using a sputtering method; then inducing a seed layer to generate the titanium dioxide nanorod array by a water heating method; finally preparing a light transmitting metal layer electrode film by a magnetron sputtering method. The titanium dioxide nanorod array / silicon heterojunction ultraviolet light detector prepared by using the amplification effect of the titanium dioxide nanorod array / silicon heterojunction has the characteristics of being simple in process, low in cost, heater-free, capable of working under room temperature, low in energy consumption, high in sensitivity and short in response and restoration time, has good detection performance to ultraviolet light, and has important application prospect.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

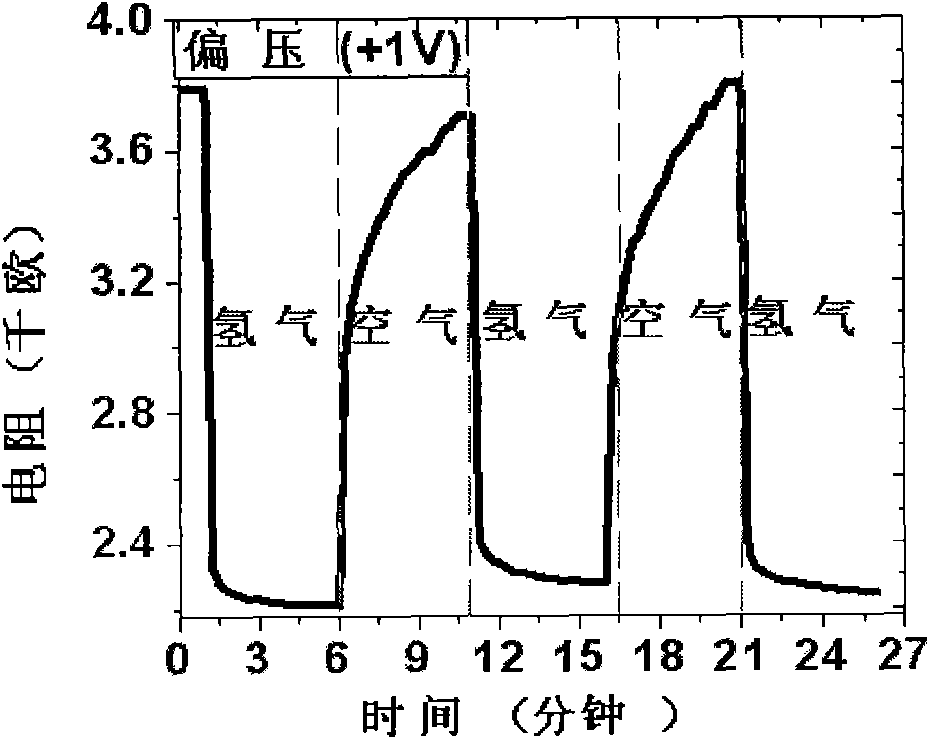

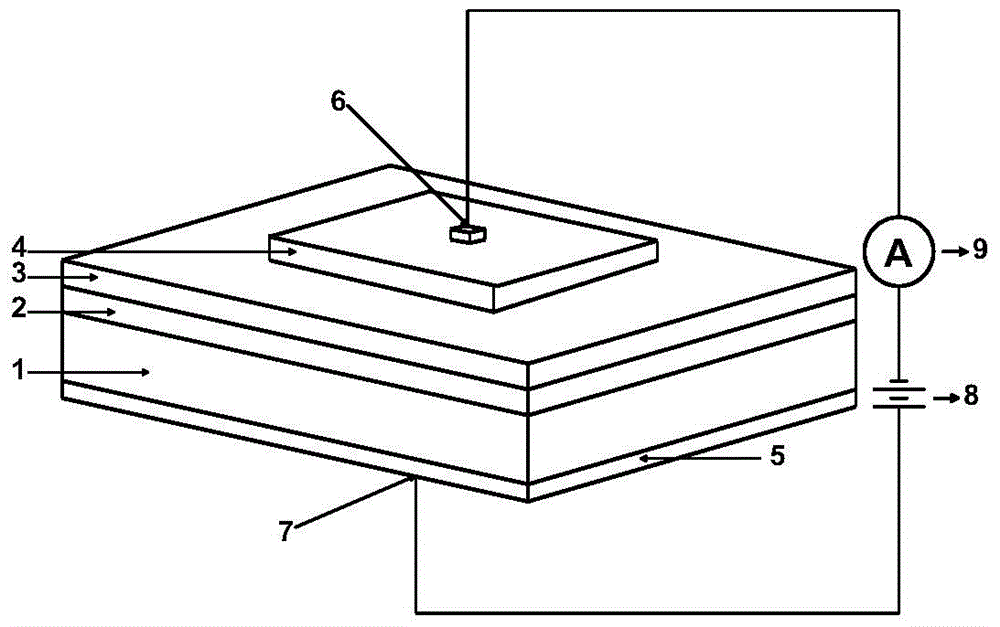

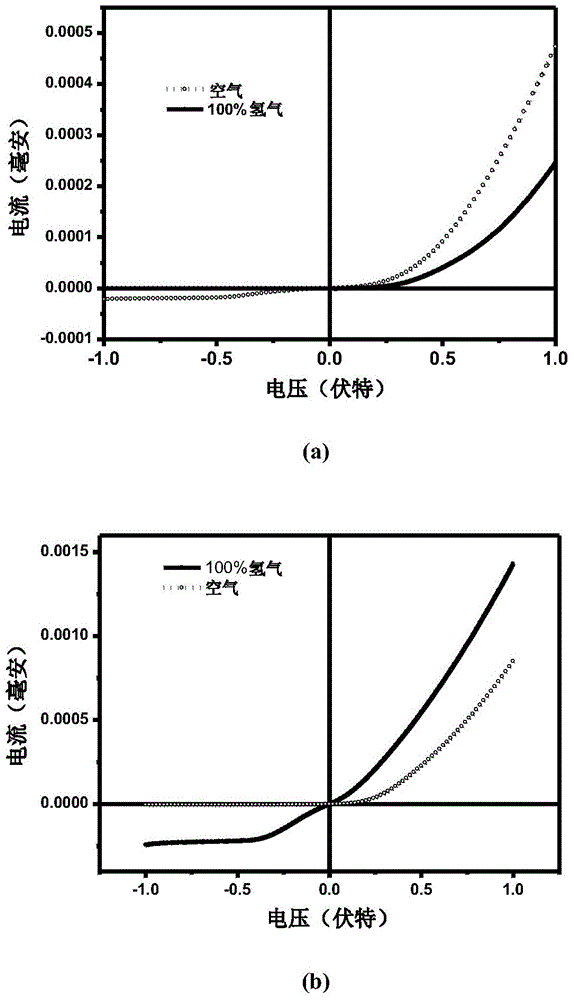

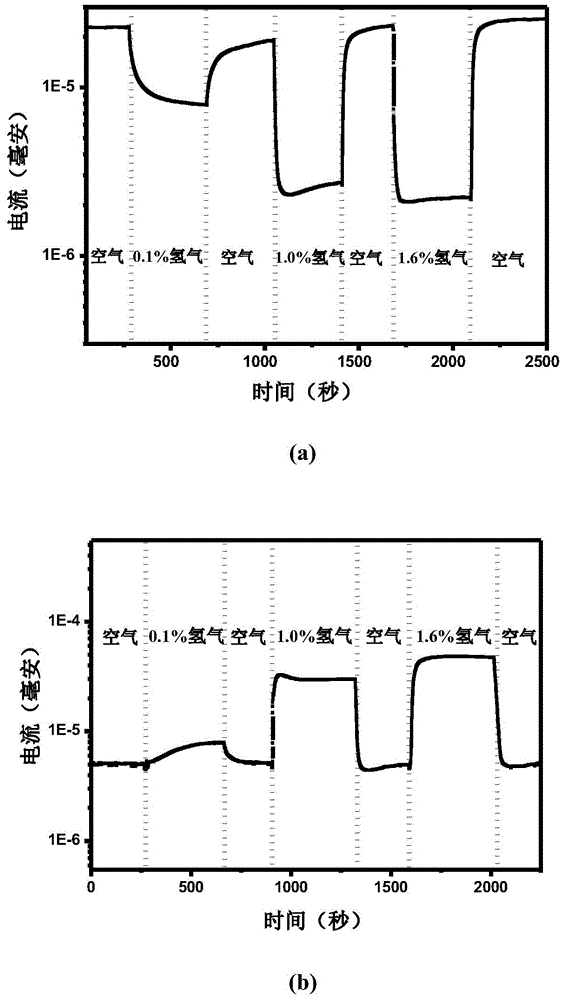

Palladium/carbon/silicon heterojunction material with hydrogen sensitive effect

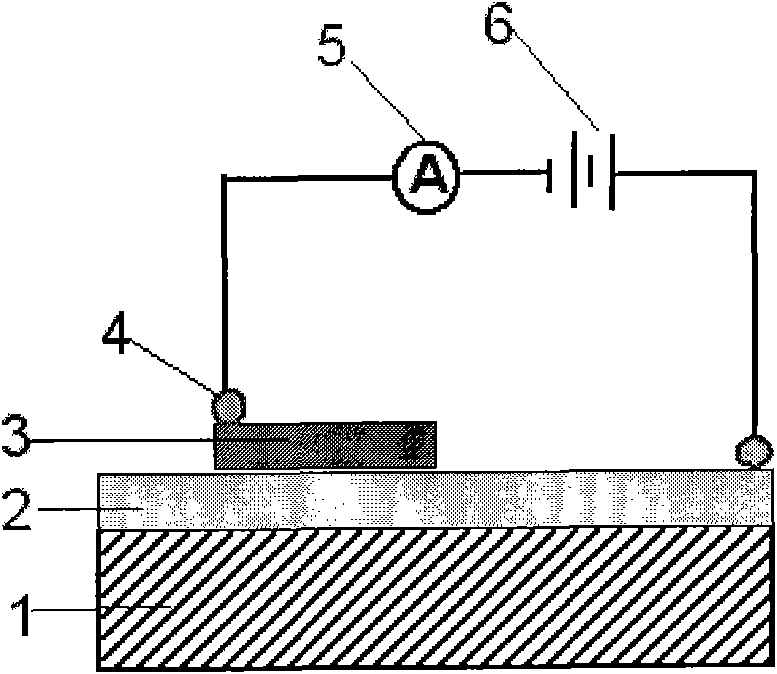

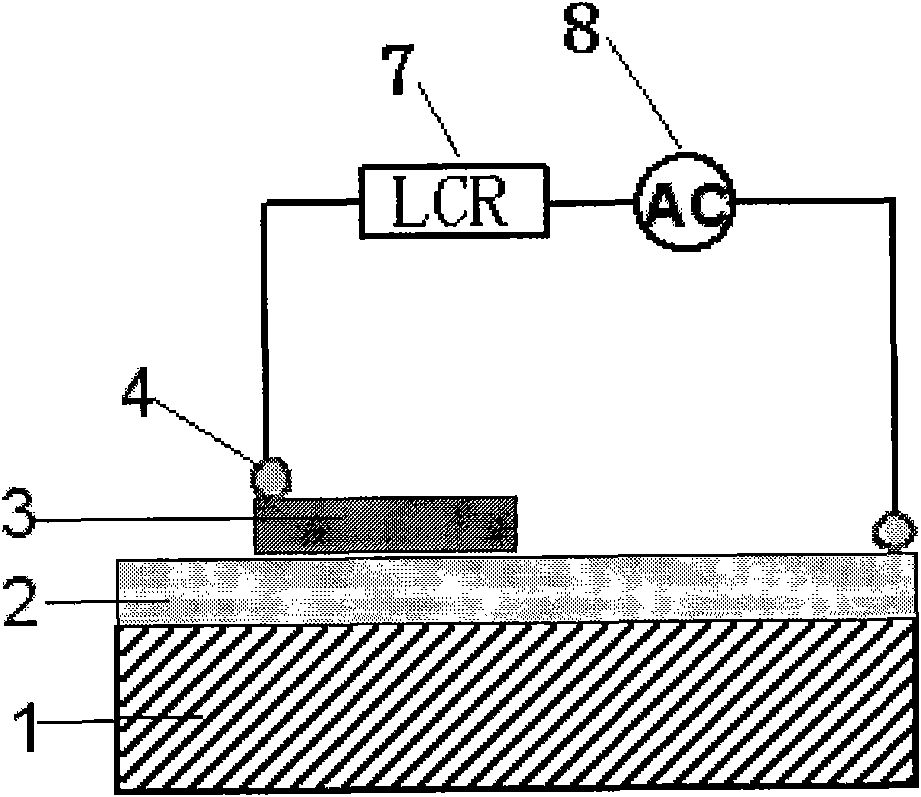

InactiveCN102012385AApparent sensitivity effectMiniaturizationMaterial resistanceMaterial capacitanceCarbon filmHydrogen

The invention provides a palladium film / carbon film / silicon heterojunction material with hydrogen sensitive effect. The material is made by the steps of: sputtering 99.9% graphite palladium on a polished silicon substrate by using a magnetron sputtering method to form a carbon film with 20-20 nm in thickness; and then sputtering a pure palladium film which is 10-30 nm in thickness on the pure carbon film. The palladium film / carbon film / silicon heterojunction material has obvious hydrogen sensitive effect and can be used for preparing a conductive or capacitive hydrogen sensitive sensor. The material works at room temperature and is easy to prepare, the miniaturization and the integration of a device are easy to realize, and the material has high sensitivity, short response time, good stability, simple production process, low cost and broad application prospect.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

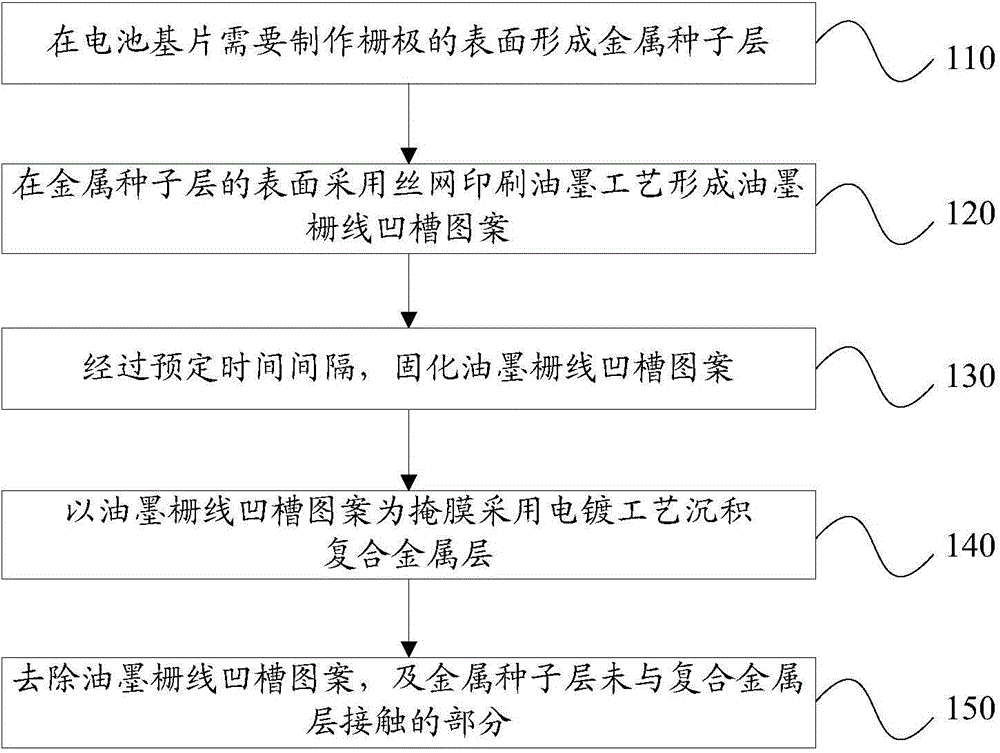

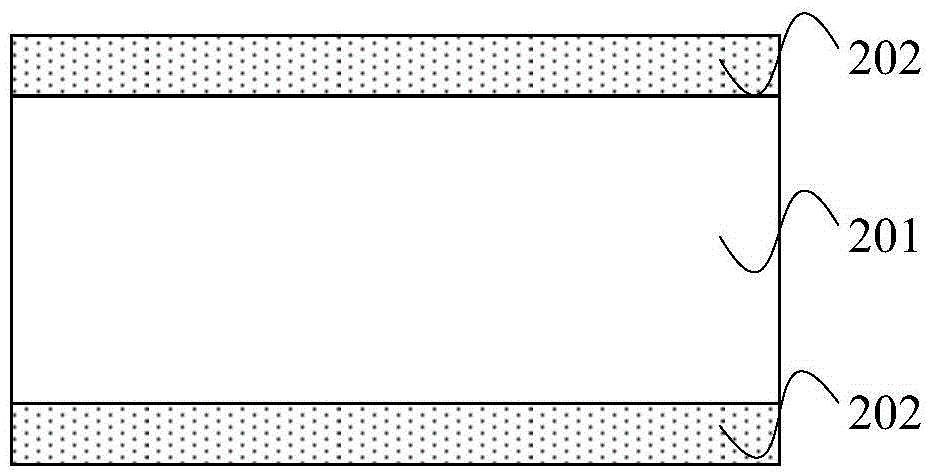

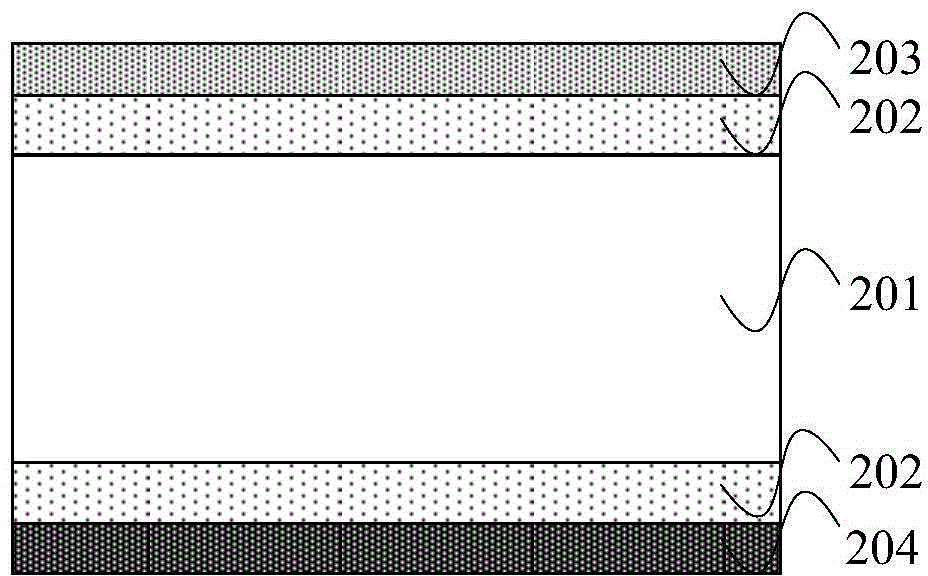

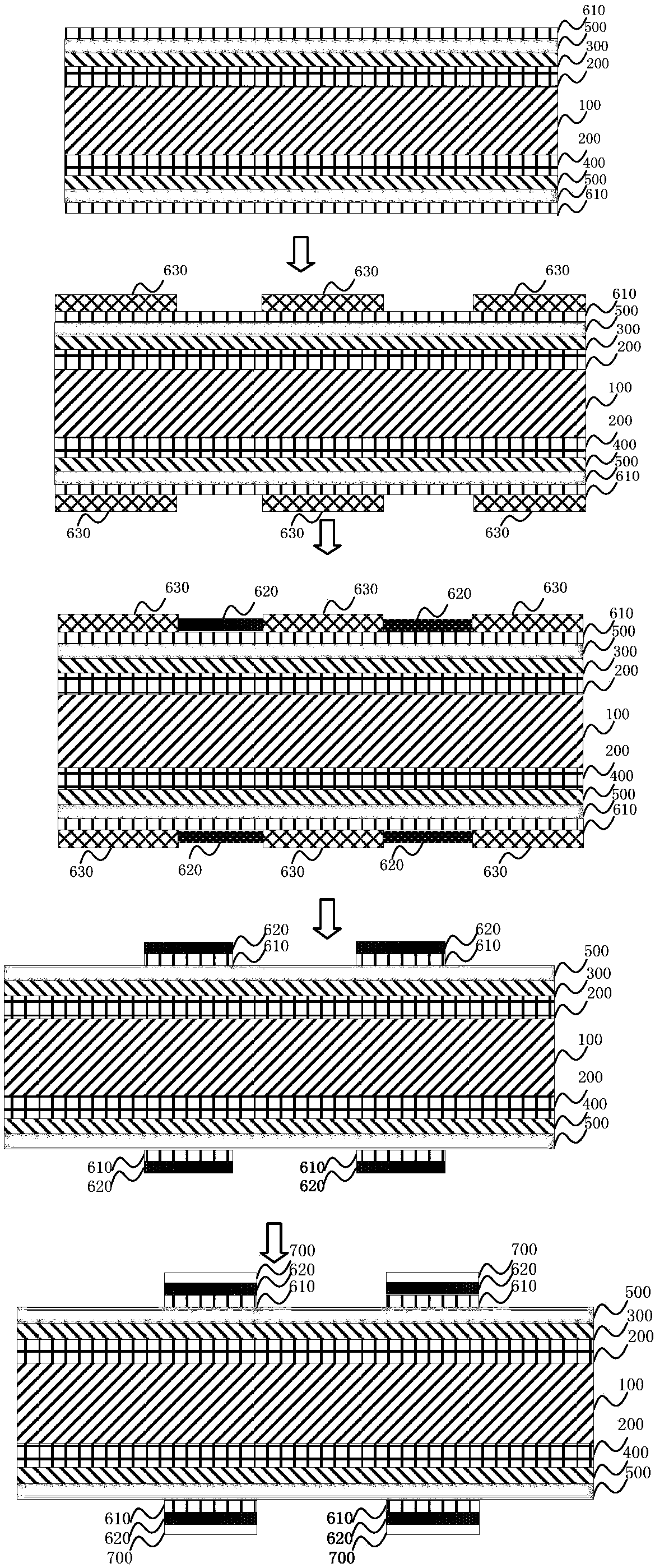

Silicon heterojunction solar cell with electroplating electrode and manufacturing method thereof

InactiveCN104538495AGood removal effectUniform expansion deformationPhotovoltaic energy generationSemiconductor devicesScreen printingManufacturing technology

The embodiment of the invention discloses a silicon heterojunction solar cell with an electroplating electrode and a manufacturing method thereof. The method comprises the steps that a metal seed layer is formed on the surface, where a grid needs to be manufactured, of a cell substrate; a silk-screen printing ink process is used for forming an ink grid line groove pattern on the surface of the metal seed layer; after a preset time interval, the ink grid line groove pattern is cured; the ink grid line groove pattern is used as a mask film, an electroplating process is used for depositing a composite metal layer; the ink grid line groove pattern and the part, which is not in contact with the composite metal layer, of the metal seed layer is removed. The implementation mode for forming the ink grid line groove pattern by the silk-screen printing ink process is simple and controllable, moreover, ink can be removed easily, and the manufacturing technology is simple. In the curing process, the ink can be evenly expanded and deformed, the width of an opening of the obtained ink grid line groove pattern is small, the depth-width ratio of a formed metal grid line is large, the light shading area is small, and the efficiency of the silicon heterojunction solar cell with the electroplating electrode is improved.

Owner:ENN SOLAR ENERGY

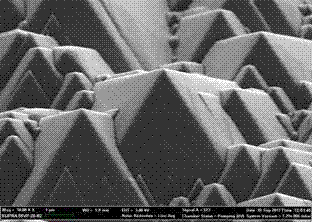

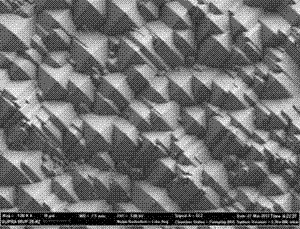

Light trapping structure on silicon substrate surface, preparation method and application thereof

InactiveCN103489929AReduce reflectionPromote absorptionFinal product manufacturePhotovoltaic energy generationSolar cellSilicon heterojunction

The invention relates to a light trapping structure on a silicon substrate surface, which is composed of a texturized monocrystalline silicon layer on the silicon substrate surface and a nano-size small pyramidal ZnO layer on texturized big pyramids, wherein the thickness of the ZnO layer is 300-1000nm, and the average light reflectivity of the light trapping structure for 400-1100nm wavelength is less than 10%. The preparation method comprises the following steps: texturizing on the silicon substrate surface by using sodium hydroxide, isopropanol and sodium silicate, carrying out smoothing treatment by using a mixed solution of hydrofluoric acid, nitric acid and acetic acid, and finally, depositing the nano-size pyramids on the texturized silicon chip by using an MOCVD (metal-organic chemical vapor deposition) technique. The light trapping structure can be used for a HIT cell using monocrystalline silicon as the substrate. The light trapping structure can lower the reflection of the texturized silicon substrate surface etched by a wet process, is used for a silicon geterojunction cell using monocrystalline silicon as the substrate, and can enhance the visible light absorption and utilization of the solar cell.

Owner:NANKAI UNIV

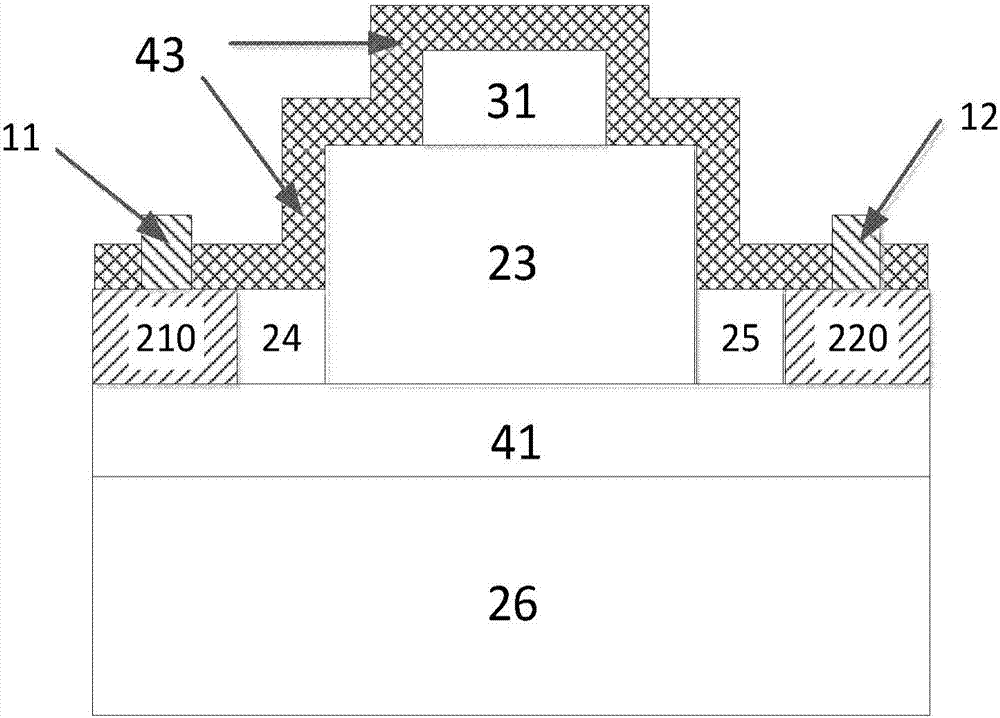

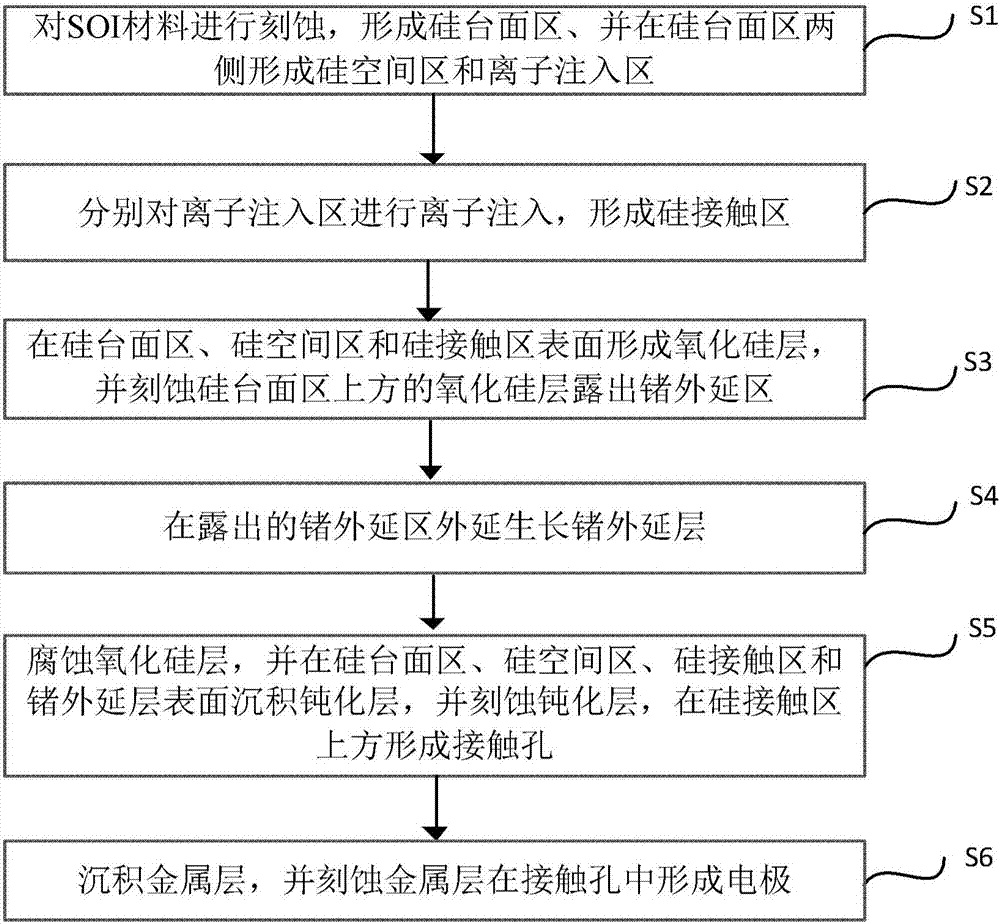

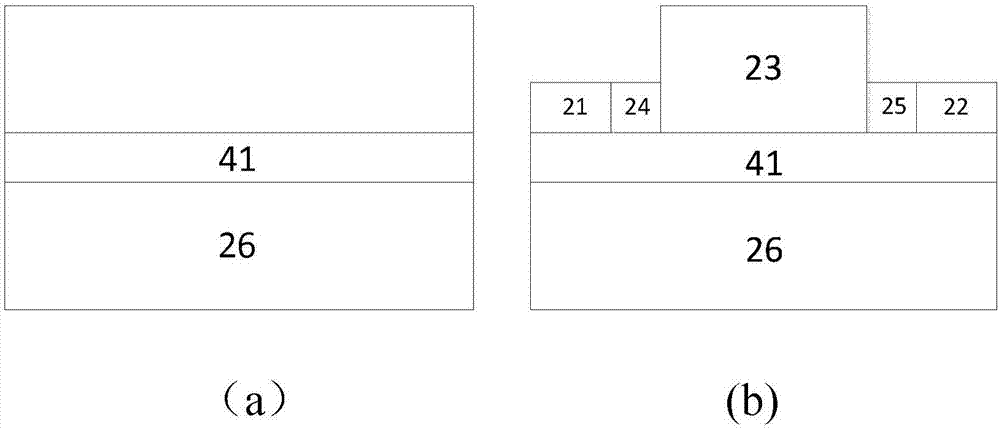

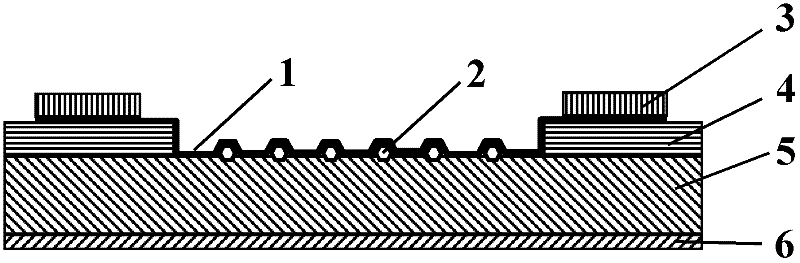

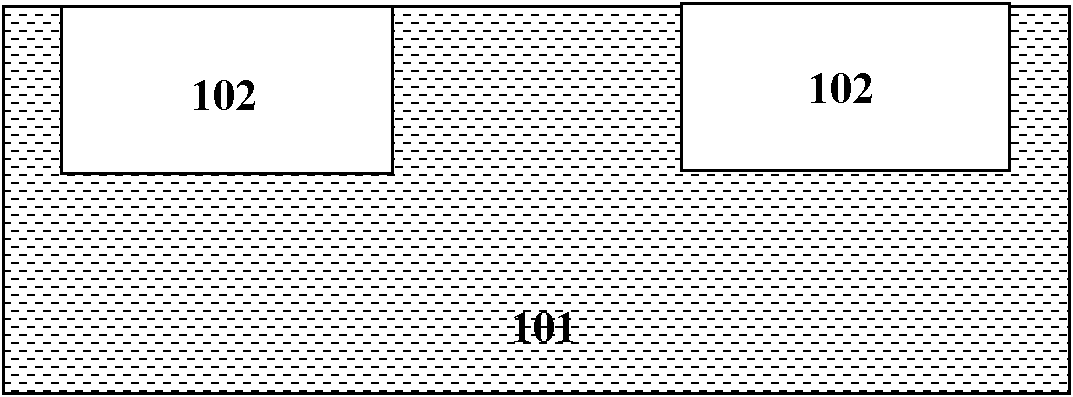

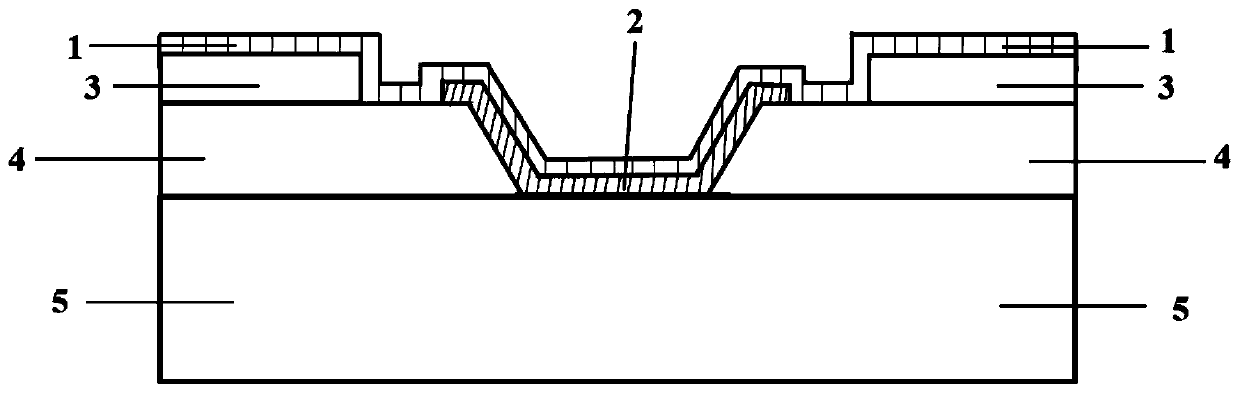

Transverse structure germanium/silicon heterojunction avalanche photoelectric detector and preparation method thereof

ActiveCN107068784AReasonable electric field distributionAchieve separationPhotovoltaic energy generationSemiconductor devicesPhotovoltaic detectorsOhmic contact

The invention discloses a transverse structure germanium / silicon heterojunction avalanche photoelectric detector which is prepared on an SOI (Silicon-on-Insulator) substrate and has a double-tabletop structure. The transverse structure germanium / silicon heterojunction avalanche photoelectric detector comprises a substrate, a buried silicon oxide layer, a silicon tabletop area, silicon space areas, silicon contact areas, electrodes and a germanium epitaxial layer. The buried silicon oxide layer is formed on the silicon substrate. The silicon tabletop area is formed on the buried silicon oxide layer. The silicon space areas are formed on the buried silicon oxide layer at two sides of the silicon tabletop area. The silicon contact areas are formed on the buried silicon oxide layer outside the silicon space areas. The germanium epitaxial layer is formed on the silicon tabletop area. The electrodes are in ohmic contact with the silicon contact areas. The two electrodes are manufactured on a silicon layer. A germanium light absorbing layer is arranged above the silicon layer. A bias voltage which is applied to the two electrodes realize electric fields with different strengths in the light absorbing layer and the silicon layer. Light absorption is realized in the germanium and an avalanche multiplication process is realized in the silicon layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI +1

CNT (carbon nano tube)-silicon heterojunction solar cell and manufacturing method thereof

ActiveCN102368503AEasy to separateReduce compoundingFinal product manufacturePhotovoltaic energy generationIodideCarbon nanotube

The invention discloses a CNT (carbon nano tube)-silicon heterojunction solar cell and a manufacturing method thereof. The solar cell comprises a lower electrode, a silicon wafer arranged on the lower electrode, an annular insulating layer deposited on the silicon wafer, cuprous iodide particles deposited on the silicon wafer and arranged in an annular cavity of the annular insulating layer, a CNT film paved on the insulating layer, the silicon wafer and the cuprous iodide particles, and an annular upper electrode on the CNT. The manufacturing method of the solar cell comprises the following steps of: placing a silicon wafer of which the upper and lower surfaces are provided with the lower electrode and the annular insulating layer in a mixed water solution of Cu (NO3)2 and HF (hydrogen fluoride) to carry out etching so as to obtain a silicon wafer of which the surface is provided with copper particles; placing the silicon wafer with the copper particles in an iodic ethanol solution to carry out halogenation so as to obtain a silicon wafer of which the surface is provided with the cuprous iodide particles; paving the CNT film on the silicon wafer with the cuprous iodide particles; and depositing the upper electrode on the CNT film to obtain the solar cell.

Owner:TSINGHUA UNIV

Silicon heterojunction solar cell and manufacturing method thereof

ActiveCN104538464AIncrease the open circuit voltageImprove fill factorFinal product manufacturePhotovoltaic energy generationSolar cellMetal electrodes

The invention discloses a silicon heterojunction solar cell and a manufacturing method of the silicon heterojunction solar cell to improve the passivation effect of the side face of the silicon heterojunction solar cell and improve the performance of the silicon heterojunction solar cell. The silicon heterojunction solar cell comprises a crystal silicon substrate, a first amorphous silicon passivation layer, a first transparent electrode, a first grid line electrode, a second amorphous silicon passivation layer, a second transparent electrode and a second metal electrode, and further comprises an edge passivation layer, wherein the first amorphous silicon passivation layer, the first transparent electrode and the first grid line electrode are sequentially arranged on the upper surface of the crystal silicon substrate, the second amorphous silicon passivation layer, the second transparent electrode and the second metal electrode are sequentially arranged on the lower surface of the crystal silicon substrate, and the edge passivation layer at least covers the same side faces of the crystal silicon substrate, the first amorphous silicon passivation layer and the second amorphous silicon passivation layer.

Owner:ENN SOLAR ENERGY

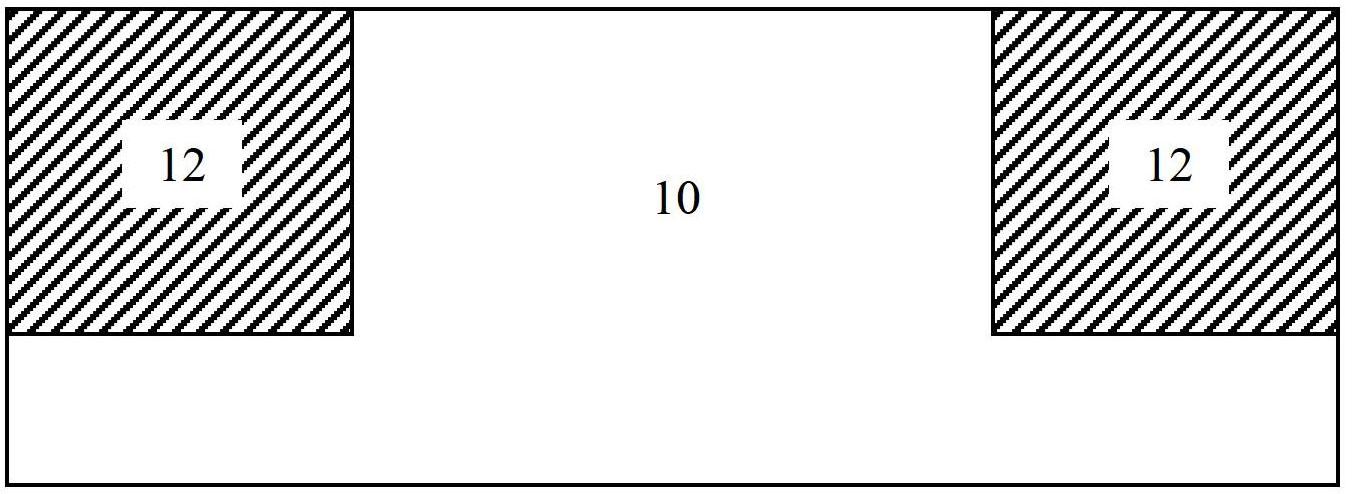

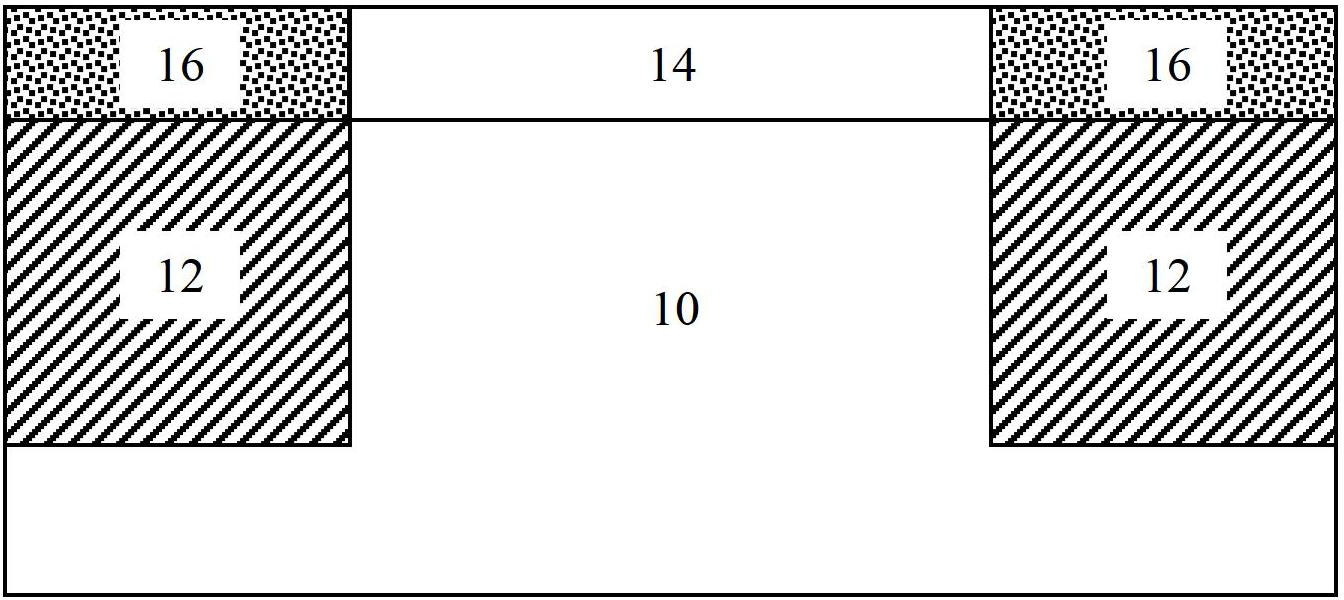

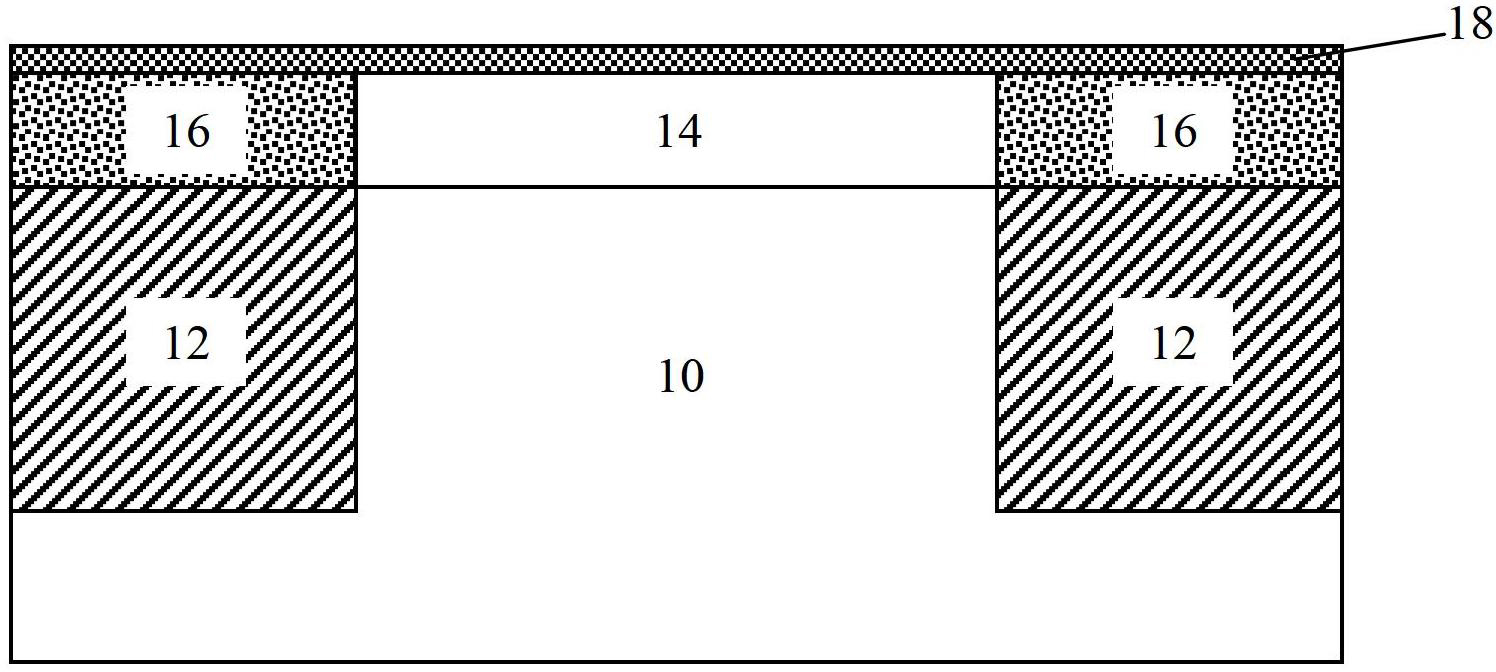

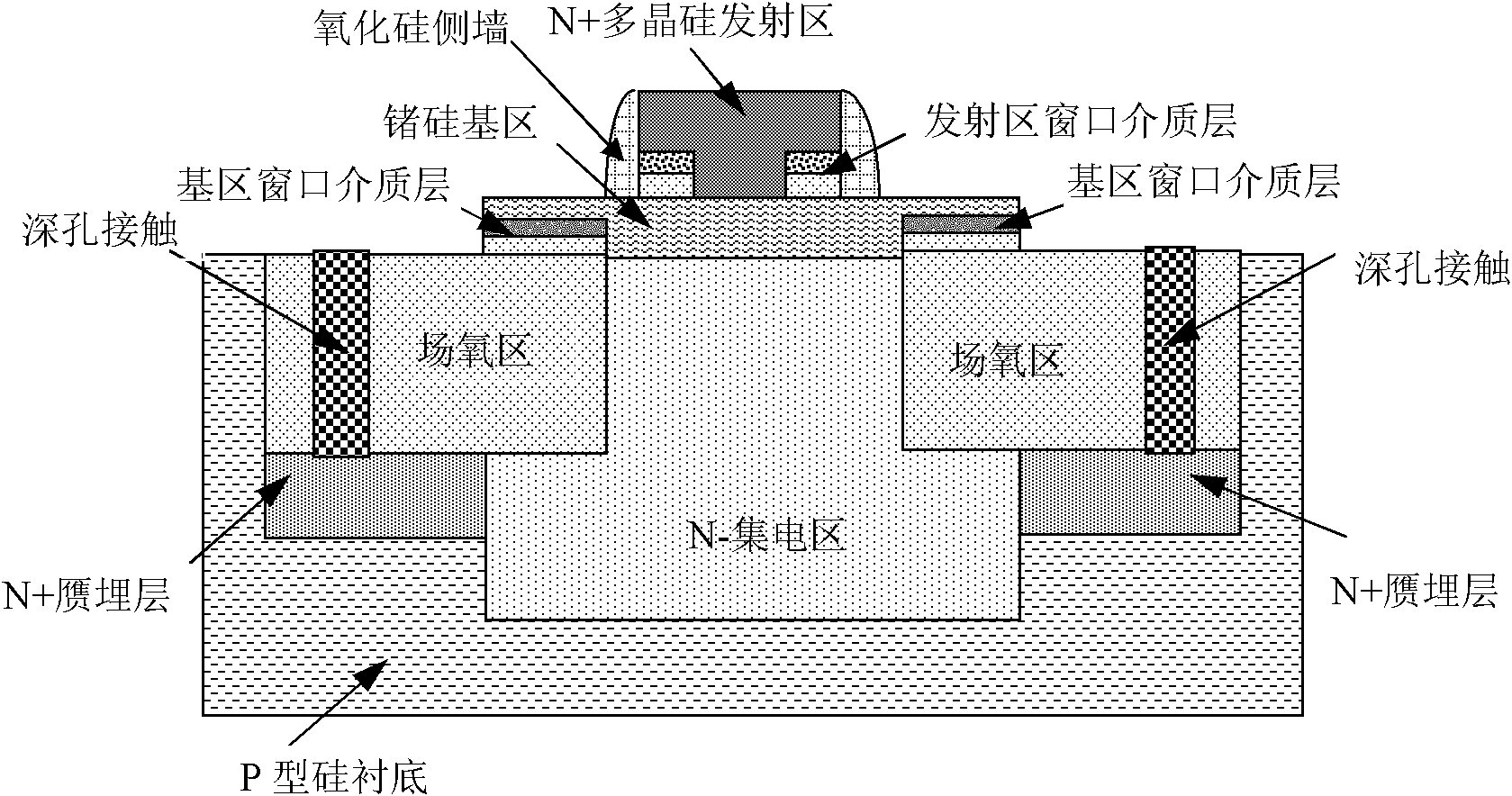

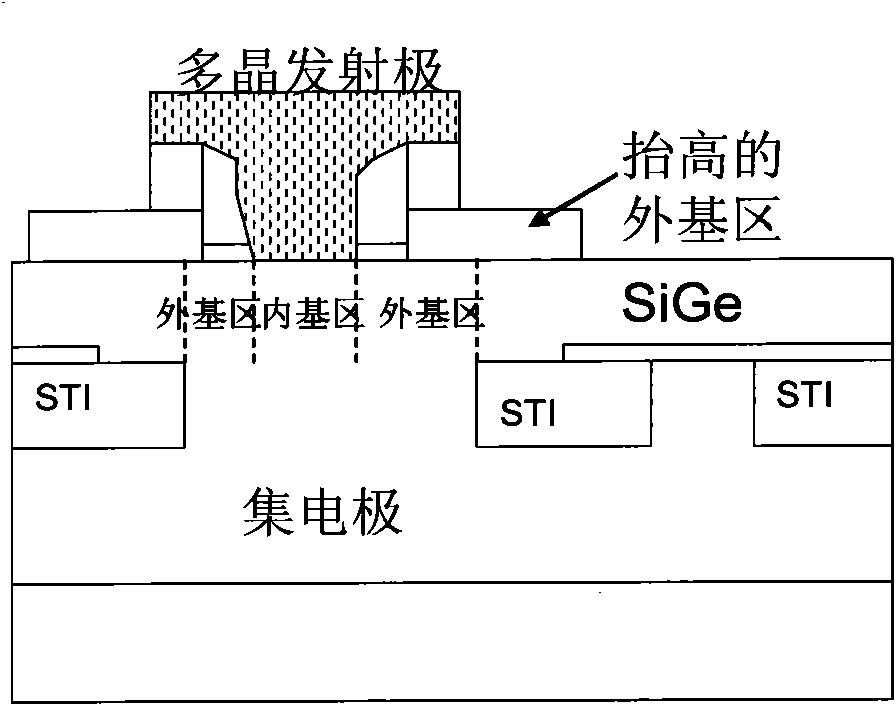

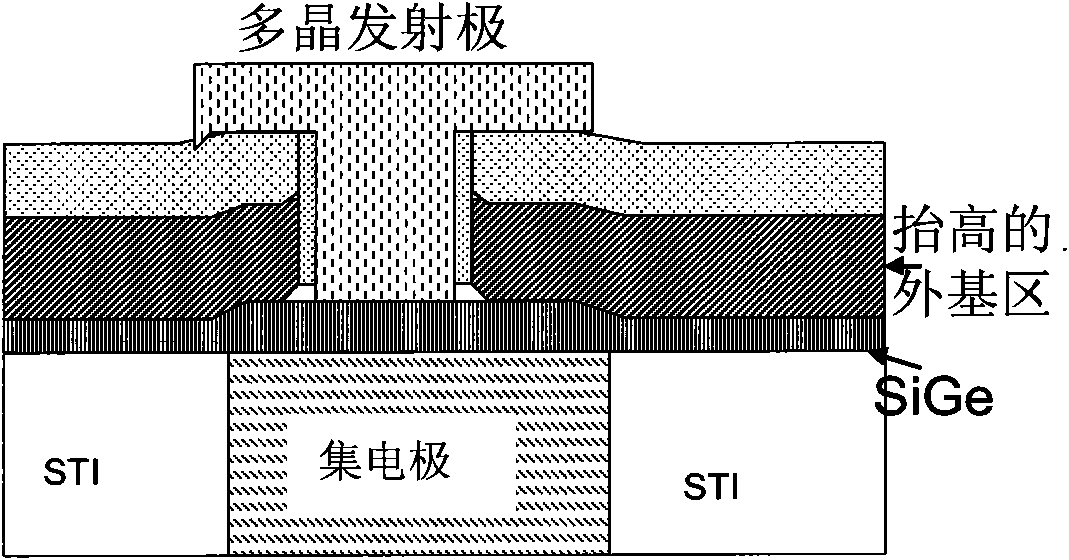

Self-alignment lifting outer base region germanium silicon heterojunction bipolar transistor and preparation method thereof

InactiveCN102683395ALower base resistanceImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideSingle crystal

The invention discloses a self-alignment lifting outer base region germanium silicon heterojunction bipolar transistor which is designed for solving the defects that the existing product base resistance RB is large and the like. The self-alignment lifting outer base region germanium silicon heterojunction bipolar transistor mainly comprises a Si collector region, a local medium region, a base region, a base region low-resistance metal silicide layer, a heavy doping polycrystalline silicon lifting outer base region, an outer base region low-resistance metal silicide layer, a heavy doping polycrystalline silicon emission region, an emission region low-resistance metal silicide layer, an emission region-base region isolation medium region and a heavy doping single-crystal emission region. The base region low-resistance metal silicide layer extends at the outer side of the emission region-base region isolation medium region. The invention discloses a preparation method for the self-alignment lifting outer base region germanium silicon heterojunction bipolar transistor and used for preparing the bipolar transistor. The self-alignment lifting outer base region germanium silicon heterojunction bipolar transistor and the preparation method of the self-alignment lifting outer base region germanium silicon heterojunction bipolar transistor can effectively reduce the base resistance RB, and are simple in process steps and low in cost.

Owner:TSINGHUA UNIV

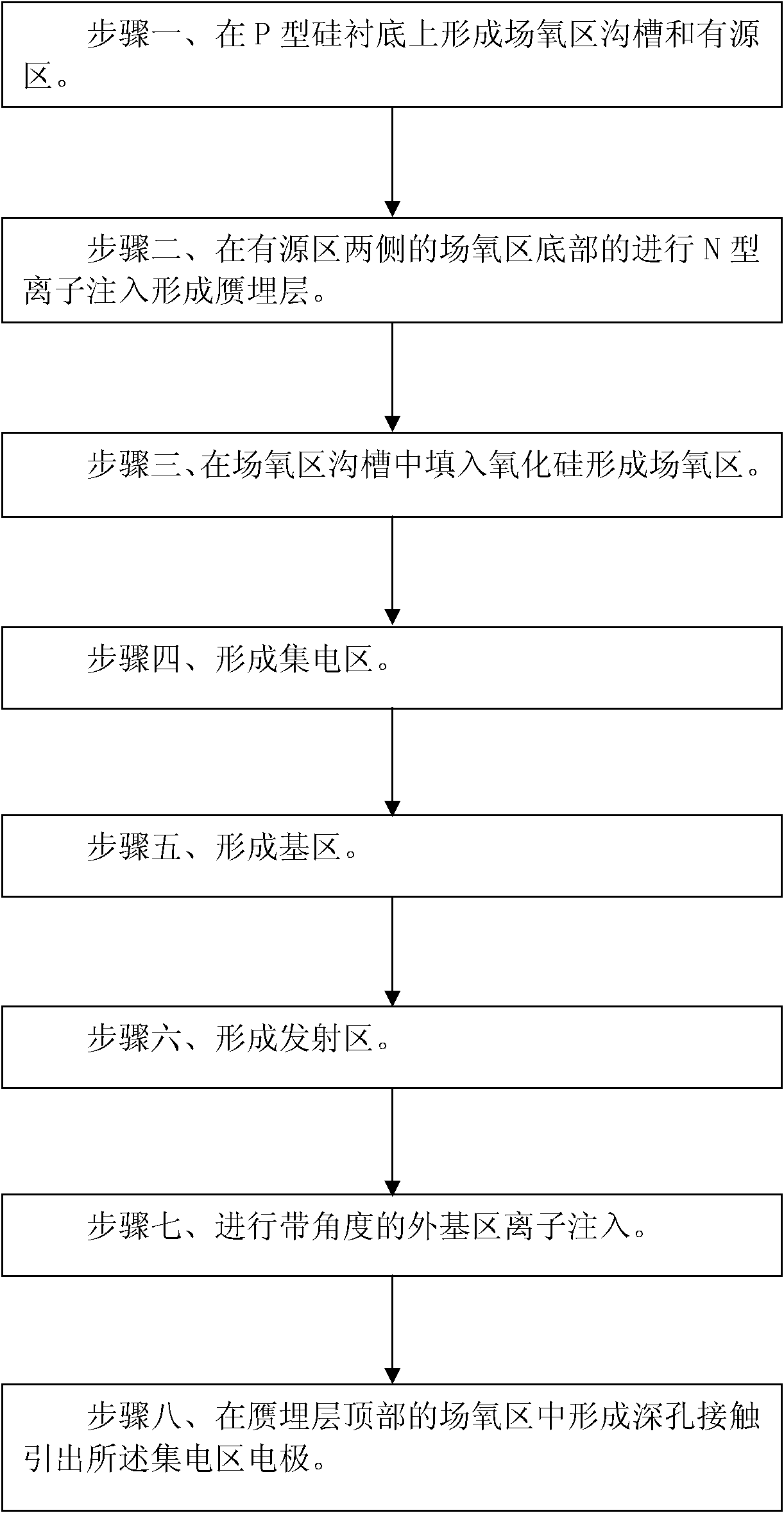

Manufacturing method for silicon germanium heterojunction bipolar transistors

ActiveCN102403222ALower r

<sub>b</sub>Raise F

<sub>max</sub>Semiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSilicon heterojunction

The invention discloses a manufacturing method for silicon germanium heterojunction bipolar transistors. After an emitter region is formed, ion implantation is performed in a base region by means of angular external base region ion implantation process, ions for external base region ion implantation are boron ions, implantation dosage ranges from 1e15cm-2 to 1e16cm-2, implantation energy ranges from 5KeV to 30KeV, and implantation angle ranges from 5 degrees to 30 degrees. Due to the implantation angle of external base region ion implantation, boron impurities can be doped in the base region outside a contact region of the emitter region and the base region. Resistance of the base region of a device can be further reduced without reducing dimension of the device and frequency characteristics of the device can be improved by the manufacturing method for silicon germanium heterojunction bipolar transistors.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

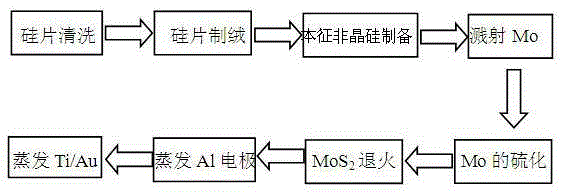

Molybdenum disulfide / silicon heterojunction solar energy cell and preparation method thereof

InactiveCN105244414AHigh crystallinityRealize photoelectric conversionFinal product manufacturePhotovoltaic energy generationHeterojunctionCharge carrier mobility

The invention discloses a molybdenum disulfide / silicon heterojunction solar energy cell and a preparation method thereof. The chemical vapor deposition method can be used in preparing uniform molybdenum disulfide film with large-area and high crystallinity degree. The molybdenum disulfide film has a relatively high carrier mobility and an adjustable band gap. The prepared molybdenum disulfide / silicon heterojunction solar energy cell has characteristics of normal temperature preparation, simple process, low cost and high photoelectric conversion efficiency, and can perform effective conversion of solar energy even when the cell cost is reduced.

Owner:HUAZHONG UNIV OF SCI & TECH

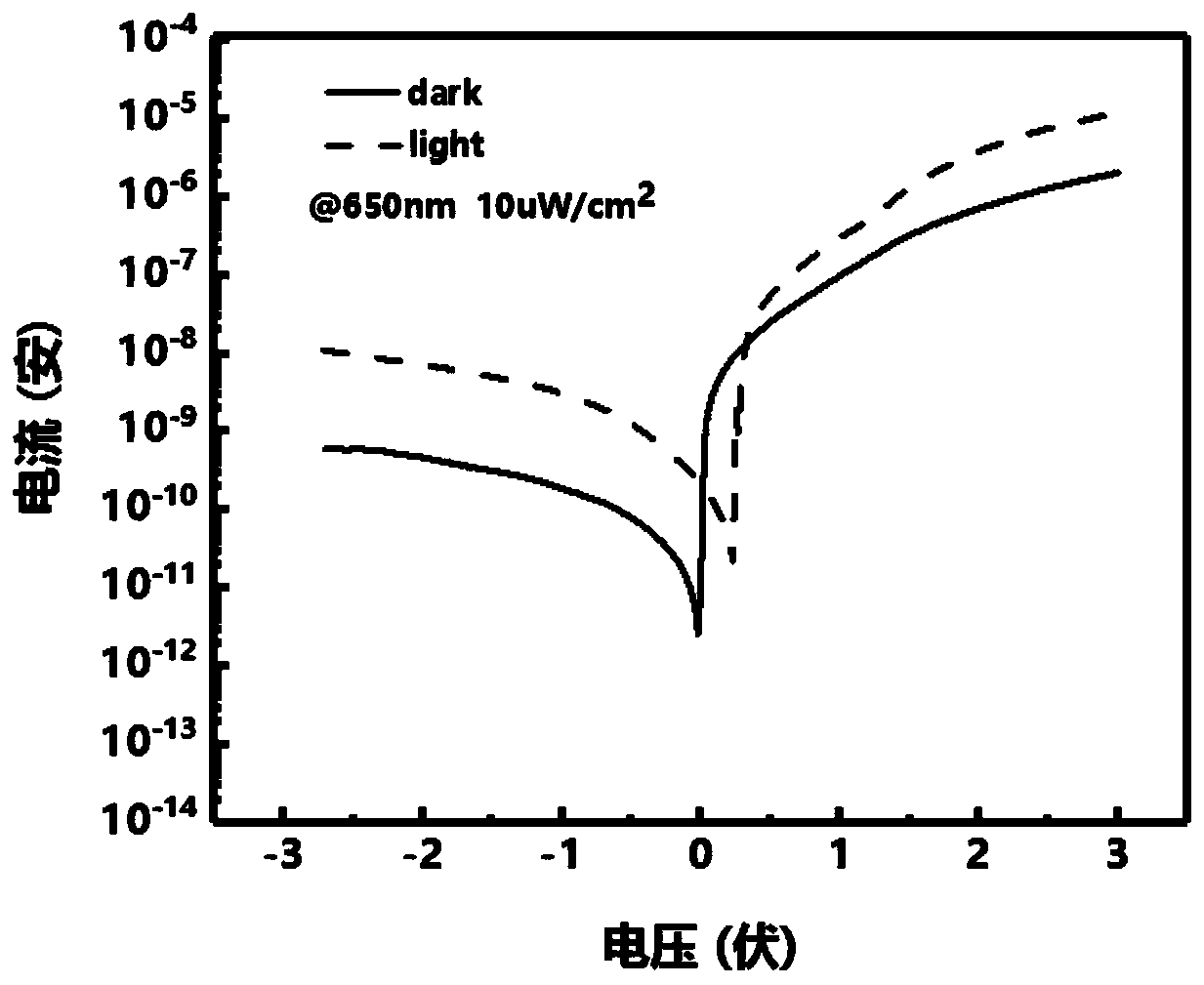

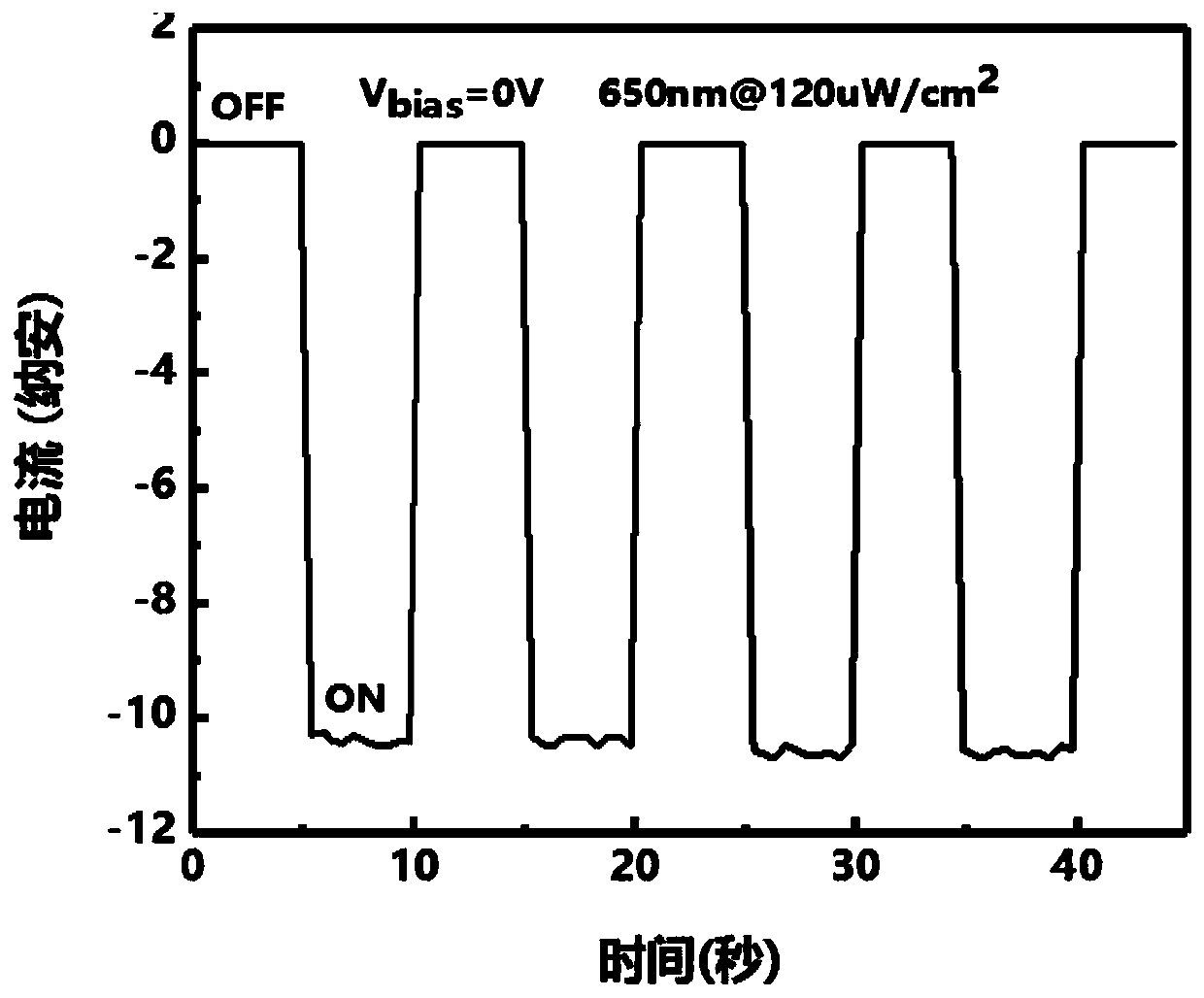

Graphene/palladium diselenide/silicon heterojunction self-driven photoelectric detector

ActiveCN111341875ASelf-driving performanceImprove responsivenessFinal product manufactureSemiconductor devicesHeterojunctionIndium

The invention discloses a graphene / palladium diselenide / silicon heterojunction self-driven photoelectric detector, which is applied to the technical field of photoelectric detection. In view of the problem that the existing photoelectric detector is limited by weak light absorption performance of graphene and low in responsivity, a technical scheme as follows is adopted: firstly, an n-type siliconwindow is exposed on an n-type silicon dioxide / silicon substrate through dry etching; a gold / indium electrode is plated near the silicon window, a palladium diselenide microchip is prepared by adopting mechanical stripping, and palladium diselenide is transferred to the silicon window by utilizing a positioning dry method; and finally, graphene is transferred in a wet transfer mode and covers thesurfaces of palladium diselenide and the electrode, palladium diselenide serves as an interface modification layer between graphene and silicon, and a graphene / palladium diselenide / silicon heterojunction is formed by the graphene layer, the palladium diselenide layer and the n-type silicon substrate corresponding to the single silicon window. The device provided by the invention is simple in preparation process, has self-driving performance, and has excellent performances such as relatively high responsivity in a visible-near-infrared light band.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Silicon heterojunction solar cell and preparation method thereof

PendingCN109148616AImprove the environmentGood welding performanceFinal product manufacturePhotovoltaic energy generationAlloyProtection layer

The invention discloses a silicon heterojunction solar cell and a preparation method thereof. Wherein the solar cell comprises an n-type crystalline silicon substrate layer; a lightly doped an n-typehydrogenated amorphous silicon buffer layer formed on the upper and lower side surfaces of the substrate layer; a heavily doped p-type hydrogenated amorphous silicon emitter layer formed on the surface of one side of lightly doped n-type hydrogenated amorphous silicon buffer layer; a heavily doped n-type hydrogenated amorphous silicon back field layer formed on the surface of the other side of thehydrogenated amorphous silicon buffer layer; transparent conductive oxide layers formed on the surfaces of the hydrogenated amorphous silicon emitter layer and the hydrogenated amorphous silicon backfield layer, respectively; an alloy gate line electrode layer formed on a surface of at least one of the transparent conductive oxide layer, hydrogenated amorphous silicon back field layer, and hydrogenated amorphous silicon emitter layer; and an electrode protection layer formed on the surface of the alloy gate line electrode layer.

Owner:国家电投集团新能源科技有限公司

All-inorganic perovskite layer and preparation method and application thereof

InactiveCN110164998AInhibit migrationEnsure stabilityFinal product manufacturePhotovoltaic energy generationSilicon heterojunctionPerovskite

The invention relates to an all-inorganic perovskite layer, and the all-inorganic perovskite layer is doped with an ammonium salt stabilizer, so that the migration of ions in a perovskite material iseffectively inhibited, and the stability of a perovskite phase is maintained. The invention further discloses a preparation method and application of the perovskite layer doped with the stabilizer. Through the doping of the stabilizer, the stability of a perovskite single-junction solar cell and the stability of a perovskite / silicon heterojunction laminated solar cell are improved, the photoelectric conversion efficiency is further improved, and the highest photoelectric conversion efficiency can reach 25.04%.

Owner:北京宏泰创新科技有限公司

Palladium/titanium dioxide/silicon dioxide/silicon heterojunction-based hydrogen detector

InactiveCN103558253ASimple processEasy to integrateMaterial analysis by electric/magnetic meansTithonia longiradiataRadio frequency magnetron sputtering

The invention specifically provides a high-performance hydrogen detector, which takes a silicon dioxide-covered silicon wafer as a substrate, takes a titanium dioxide semiconductor as a base material, and takes palladium as a catalytic layer. First, a titanium dioxide film is grown on the silicon dioxide-covered silicon substrate by utilizing a radio frequency magnetron sputtering method; and then, a palladium catalytic layer of which the area is smaller than that of the titanium dioxide film is prepared on the film surface by a mask and a direct-current magnetron sputtering method. A palladium / titanium dioxide / silicon dioxide / silicon heterojunction-based hydrogen detector which is disclosed by the invention and utilizes the catalytic effect of the palladium film and the amplification effect of a titanium dioxide / silicon dioxide / silicon heterojunction is simple in process and low in cost, does not need a heater, can work at room temperature, has the characteristics of high sensitivity and short response and recover time, has good detection performance on hydrogen and has an important application prospect.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

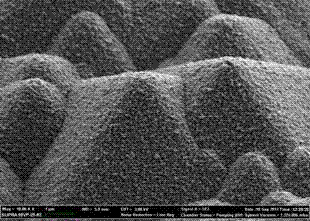

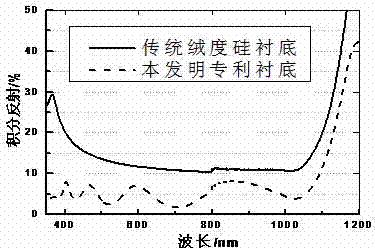

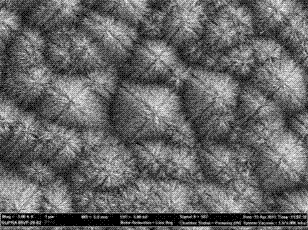

Light trapping structure based on nano-zinc oxide silicon heterojunction battery, and preparation method of the light trapping structure

InactiveCN103489942AReduce reflectivityIntegral reflex reductionFinal product manufacturePhotovoltaic energy generationHeterojunctionEtching

The invention discloses a light trapping structure based on nano-zinc oxide silicon heterojunction battery. The light trapping structure comprises a silicon substrate which has a pyramid appearance and is prepared by wet etching, a ZnO seed layer, and a zinc oxide nano rod or nano cone growing based on the seed layer, wherein the length of the nano rod or nano cone ranges from 200nm to 1,500nm, and the diameter of the nano rod or nano cone is 20-200nm; the preparation method of the light trapping structure comprises the steps of preparing the pyramid appearance by the wet etching, preparing the seed layer by a solution dipping method, and growing the zinc oxide nano rod or nano cone by a hydrothermal method. The light trapping structure has the advantages that when the light trapping structure is used on a Si substrate solar battery, in a range of 400-1,100nm, the average integral reflectivity of the novel light trapping structure on which the zinc oxide nano rod grows is 5.1%, and the average integral reflectivity of the light trapping structure on which the zinc oxide nano cone grows is only 2.5% in comparison with the average integral reflectivity being 10.9% of the conventional light trapping structure with pyramid appearance, so that the integral reflectivity of the novel light trapping structure is lowered obviously.

Owner:NANKAI UNIV

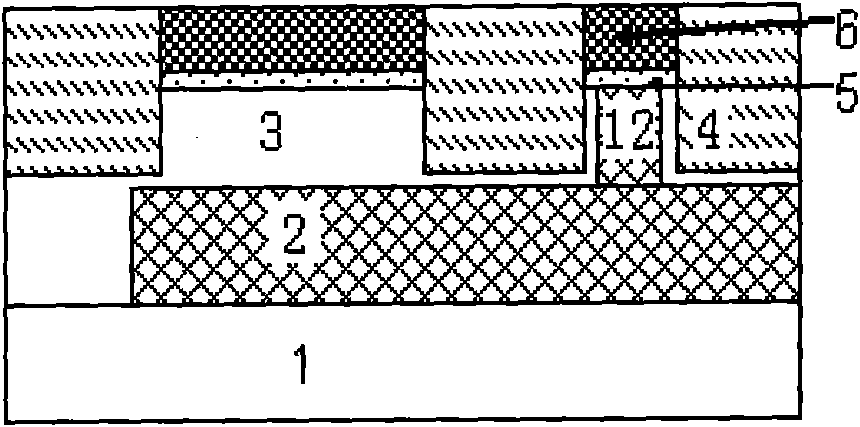

Manufacturing method of SiGe heterojunction bipolar transistor

ActiveCN102054689ASimple structureSemiconductor/solid-state device manufacturingSemiconductor devicesProcess moduleMetallurgy

The invention discloses a manufacturing method of a SiGe heterojunction bipolar transistor. The method comprises the following steps of: forming high P-type doped polycrystalline silicon which raises an outer base region in combination with materials and a process used in a shallow slot isolation process module; forming an inner base region of a germanium-silicon heterojunction bipolar transistor region by using a selective epitaxial process; and depositing an emitter by taking a medium film as an isolation layer between the emitter and the outer base region so as to form a raised outer base region, wherein a self-aligned germanium-silicon heterojunction bipolar transistor is arranged between the outer base region and the emitter. Process steps are reduced, manufacturing time is shortened and manufacturing cost is lowered.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Non-doped crystalline silicon heterojunction perovskite laminated solar cell structure and preparation method thereof

InactiveCN111244278AIncrease the open circuit voltageImprove photoelectric conversion efficiencyFinal product manufactureSolid-state devicesHeterojunctionHole transport layer

The invention belongs to the technical field of solar cells, and particularly relates to a crystalline silicon substrate perovskite laminated heterojunction cell structure and a preparation method. The laminated heterojunction cell sequentially comprises a transparent conductive film (TCO), an electron transport layer, a perovskite layer, a hole transport layer, an interface layer, an electron transport layer, a passivation layer, N-type monocrystalline silicon, a passivation layer, a hole transport layer, a transparent conductive film and a back electrode from the front surface to the back surface. The cell prepared by the invention combines the advantages of a non-doped crystalline silicon heterojunction cell and a perovskite solar cell technology, the generated synergistic effect is fargreater than that of a single technology, and a plurality of problems, such as low crystalline silicon efficiency and poor perovskite stability, generated when the two technologies in the backgroundtechnology are independently adopted are well solved.

Owner:DALIAN INST OF CHEM PHYSICS CHINESE ACAD OF SCI