Patents

Literature

228 results about "Nanocrystalline silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Nanocrystalline silicon (nc-Si), sometimes also known as microcrystalline silicon (μc-Si), is a form of porous silicon. It is an allotropic form of silicon with paracrystalline structure—is similar to amorphous silicon (a-Si), in that it has an amorphous phase. Where they differ, however, is that nc-Si has small grains of crystalline silicon within the amorphous phase. This is in contrast to polycrystalline silicon (poly-Si) which consists solely of crystalline silicon grains, separated by grain boundaries. The difference comes solely from the grain size of the crystalline grains. Most materials with grains in the micrometre range are actually fine-grained polysilicon, so nanocrystalline silicon is a better term. The term Nanocrystalline silicon refers to a range of materials around the transition region from amorphous to microcrystalline phase in the silicon thin film. The crystalline volume fraction (as measured from Raman spectroscopy) is another criterion to describe the materials in this transition zone.

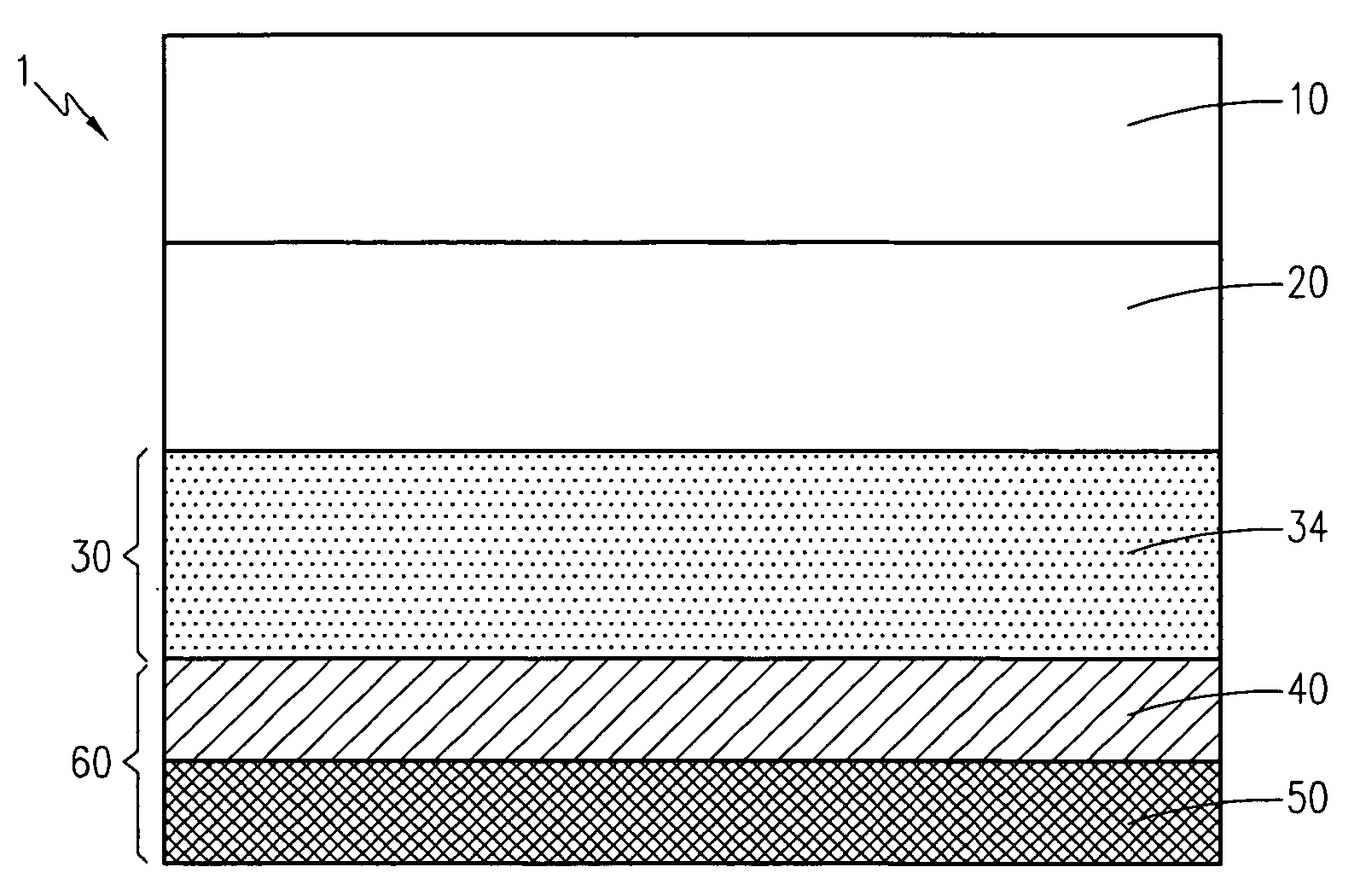

Back contact and back reflector for thin film silicon solar cells

InactiveUS20050172997A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationDielectricBack reflector

A thin film silicon solar cell for use in photovoltaic cells having a carrier substrate, a front transparent conductive oxide contact, a thin film silicon solar cell layer having at least one layer of hydrogenated microcrystalline silicon or nanocrystalline silicon, and a back contact having a transparent conductive oxide contact layer and a back reflective layer comprising a white pigmented dielectric reflective media.

Owner:UNAXIS BALZERS LTD

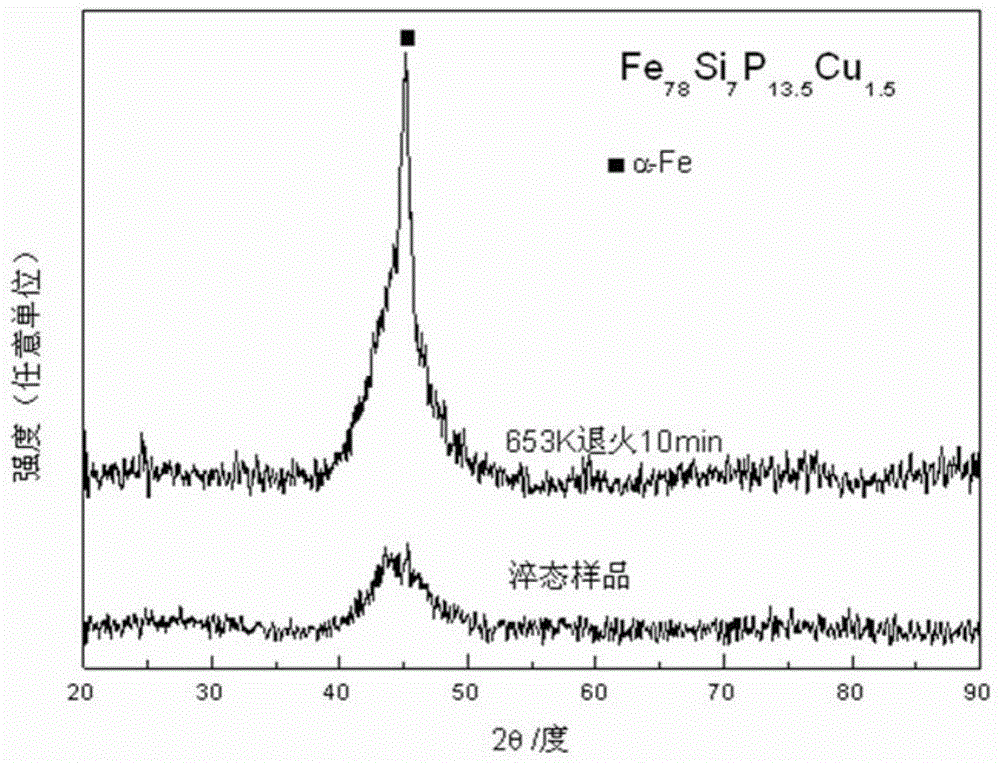

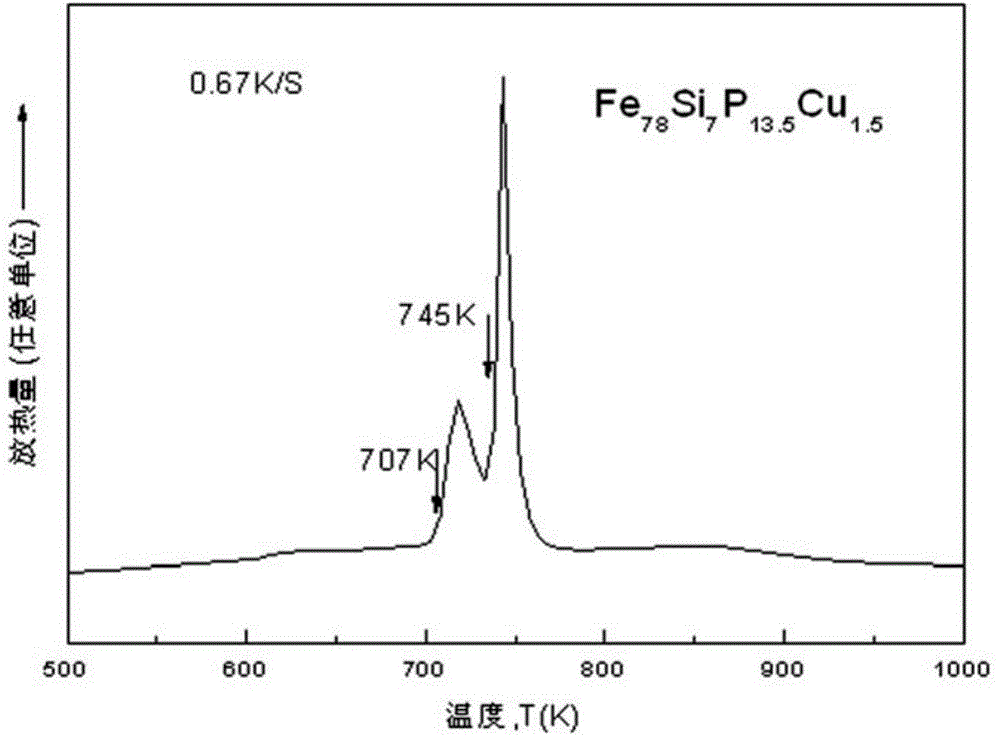

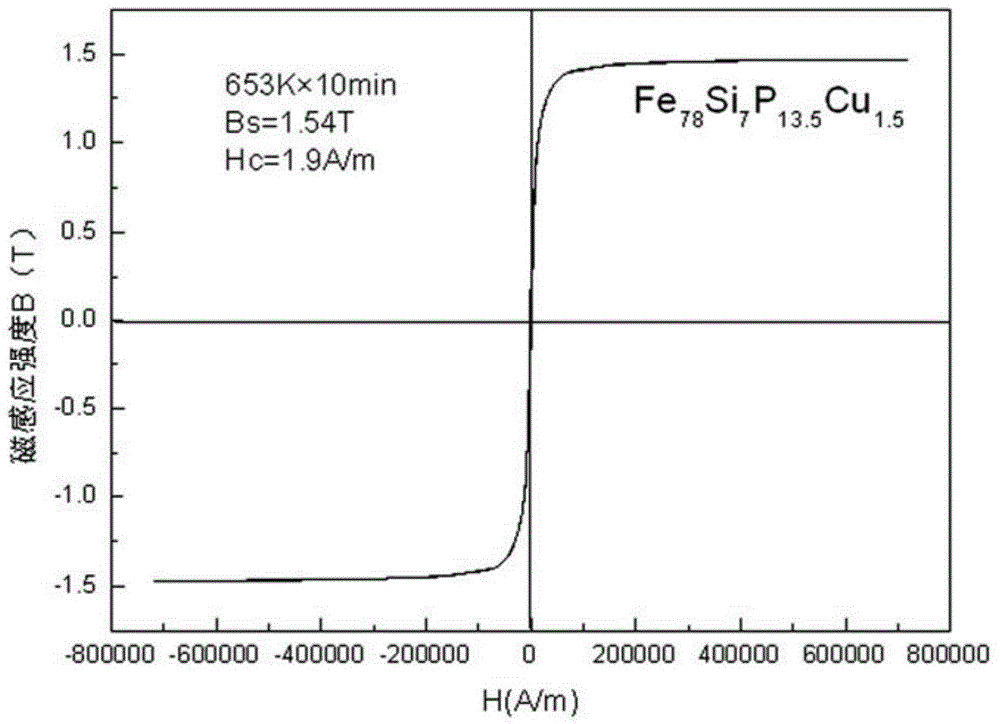

Iron-based nanocrystalline soft-magnetic alloy with excellent high-frequency performance and preparation method thereof

ActiveCN104087833AHigh saturation magnetic inductionImprove thermal stabilityMagnetic materialsRare-earth elementNanocrystalline silicon

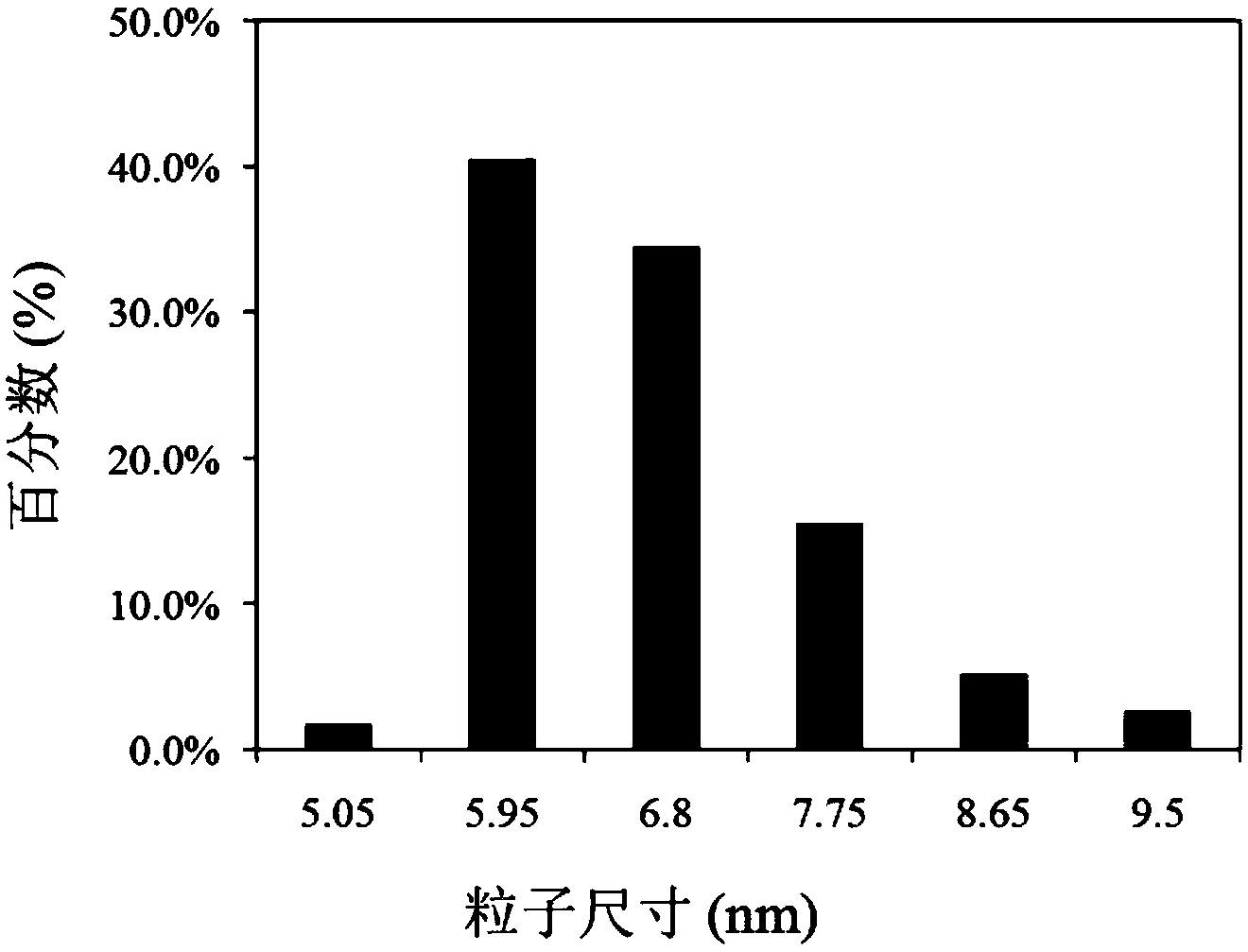

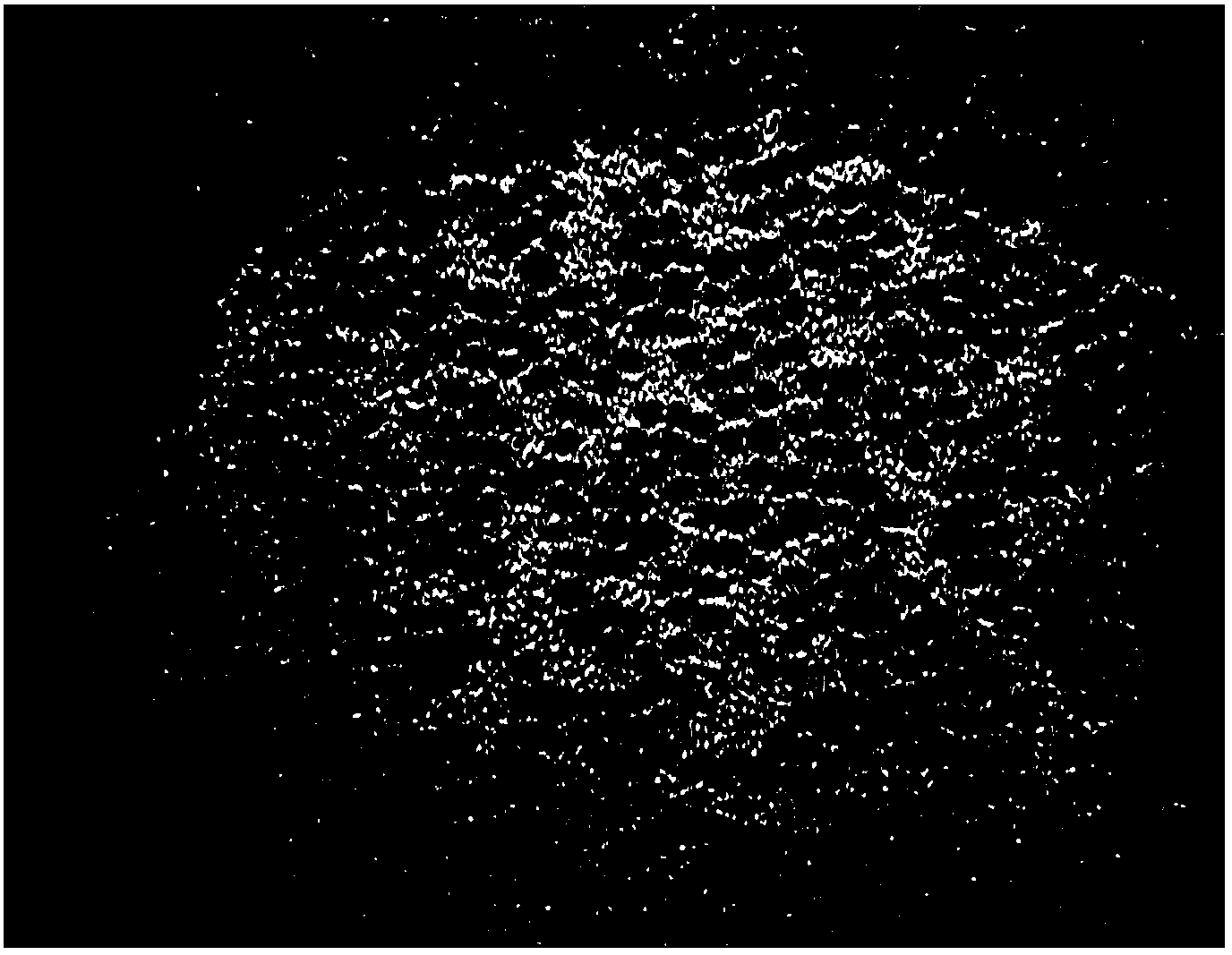

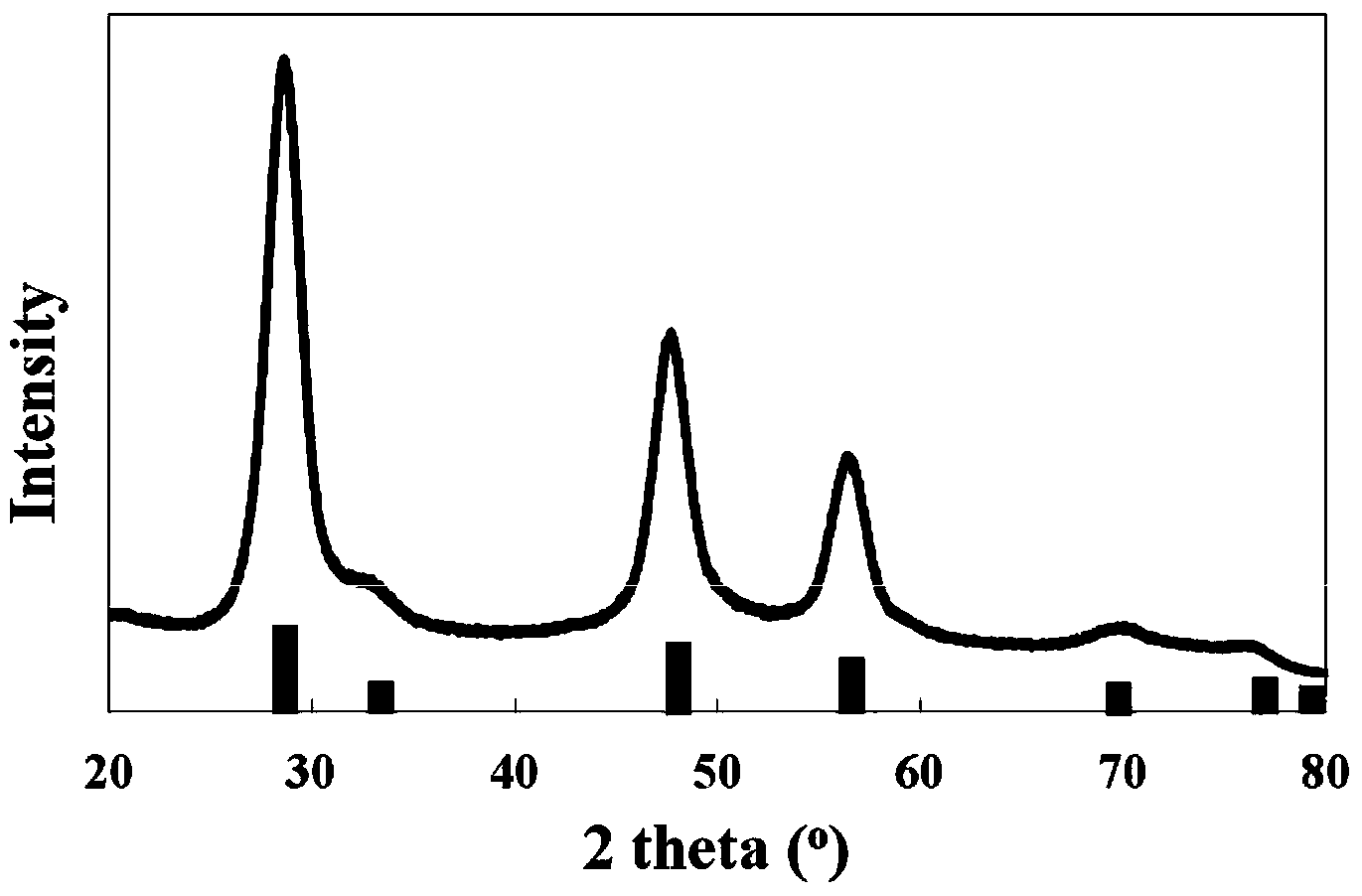

The invention discloses iron-based nanocrystalline soft-magnetic alloy with excellent high-frequency performance and a preparation method thereof. The expression of the alloy is FeaSibPcCuxMy, wherein a, b, c, x and y respectively represent the atomic percent content of corresponding compositions and satisfy the following conditions: 70<=a<=85, 5<=b<=15, 5<=c<=18, 0.0001<=x<=3, 0<=y<=5, a+b+c+x+y=100%, and M is one or more of Zr, Ti, Ta, Hf, Nb, V, W, Mo, Mn, Cr, Re, Zn, In, As, Sb, Bi, Ca, platinum group elements, rare earth elements, N, Sn, Ge, Ga and Al. The alloy is a nanocrystalline soft-magnetic alloy band prepared by employing a single-roller quick-cooling method under the conditions of high vacuum and argon protection. The alloy does not contain B elements, is good in soft magnetic property, high in thermal stability, low in high-frequency loss and low in magnetostriction coefficient.

Owner:ADVANCED TECHNOLOGY & MATERIALS CO LTD

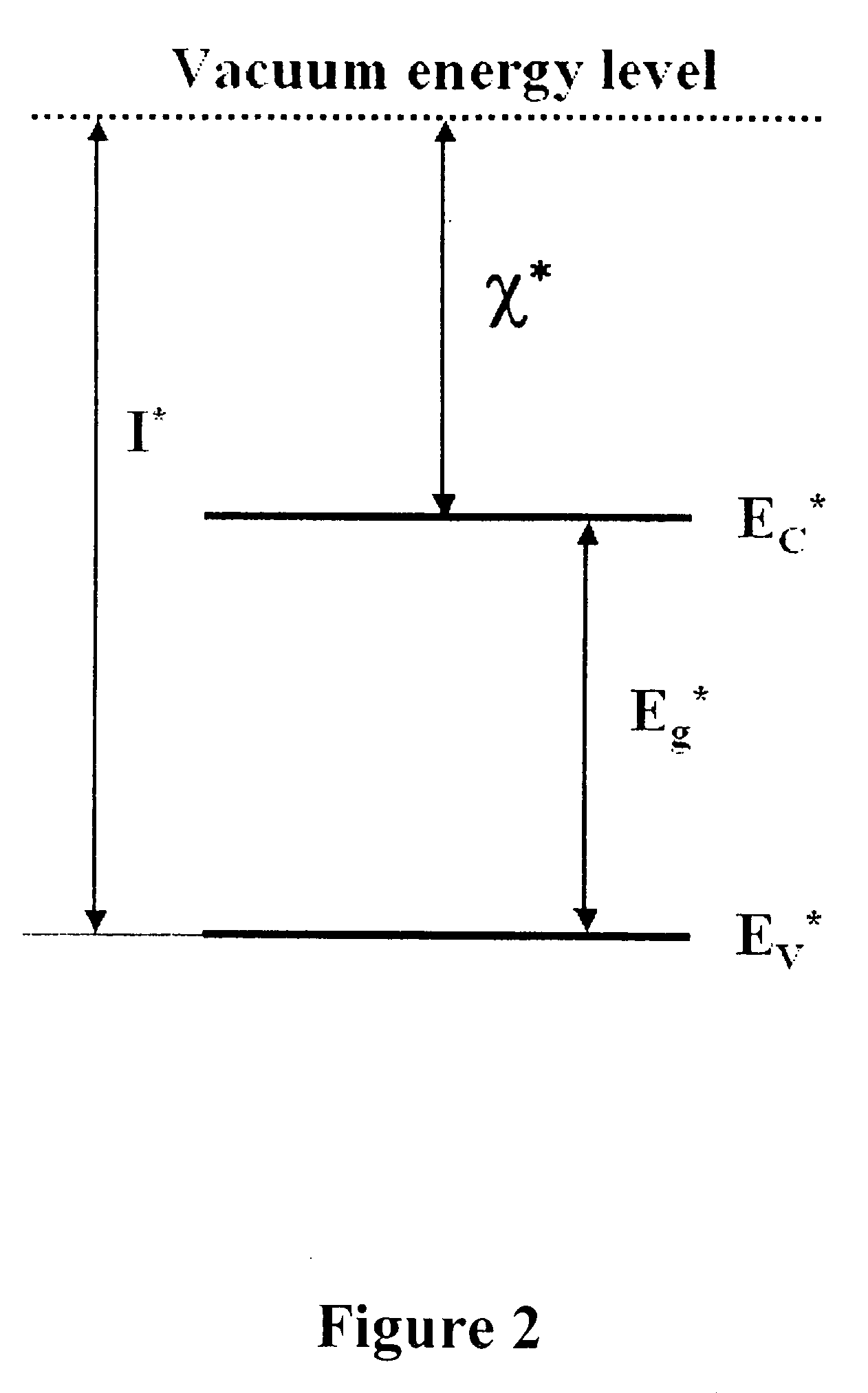

Disordered silicon nanocomposites for photovoltaics, solar cells and light emitting devices

InactiveUS20070272297A1Final product manufacturePhotovoltaic energy generationHeterojunctionNanowire

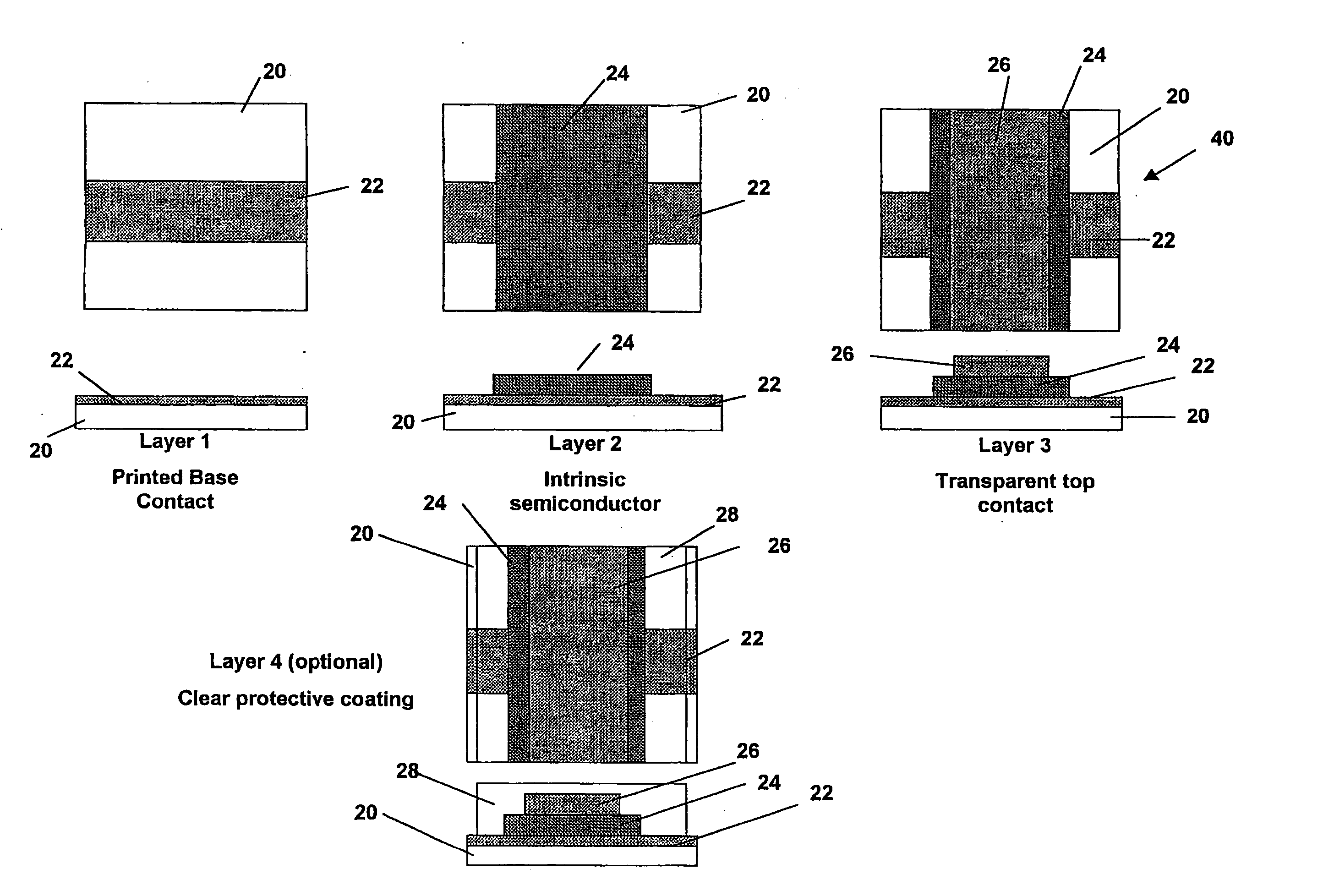

The present invention describes nanocomposite material structures including layers forming p-n and p-i-n homo- and heterojunctions for application in photovoltaics, solar cells, photodetectors, and light emitting devices, comprising semiconductor nanoparticles, such as colloidal semiconductor nanocrystals, nanorods, nanowires, nanotubes, etc., wherein at least one of the layers is made of hydrogenated amorphous or microcrystalline / nanocrystalline silicon or their alloys enabling low-temperature fabrication processes preventing any degradation of physical properties of the nanoparticles.

Owner:ANTEOS

Thin film semiconductor device and method of manufacturing a thin film semiconductor device

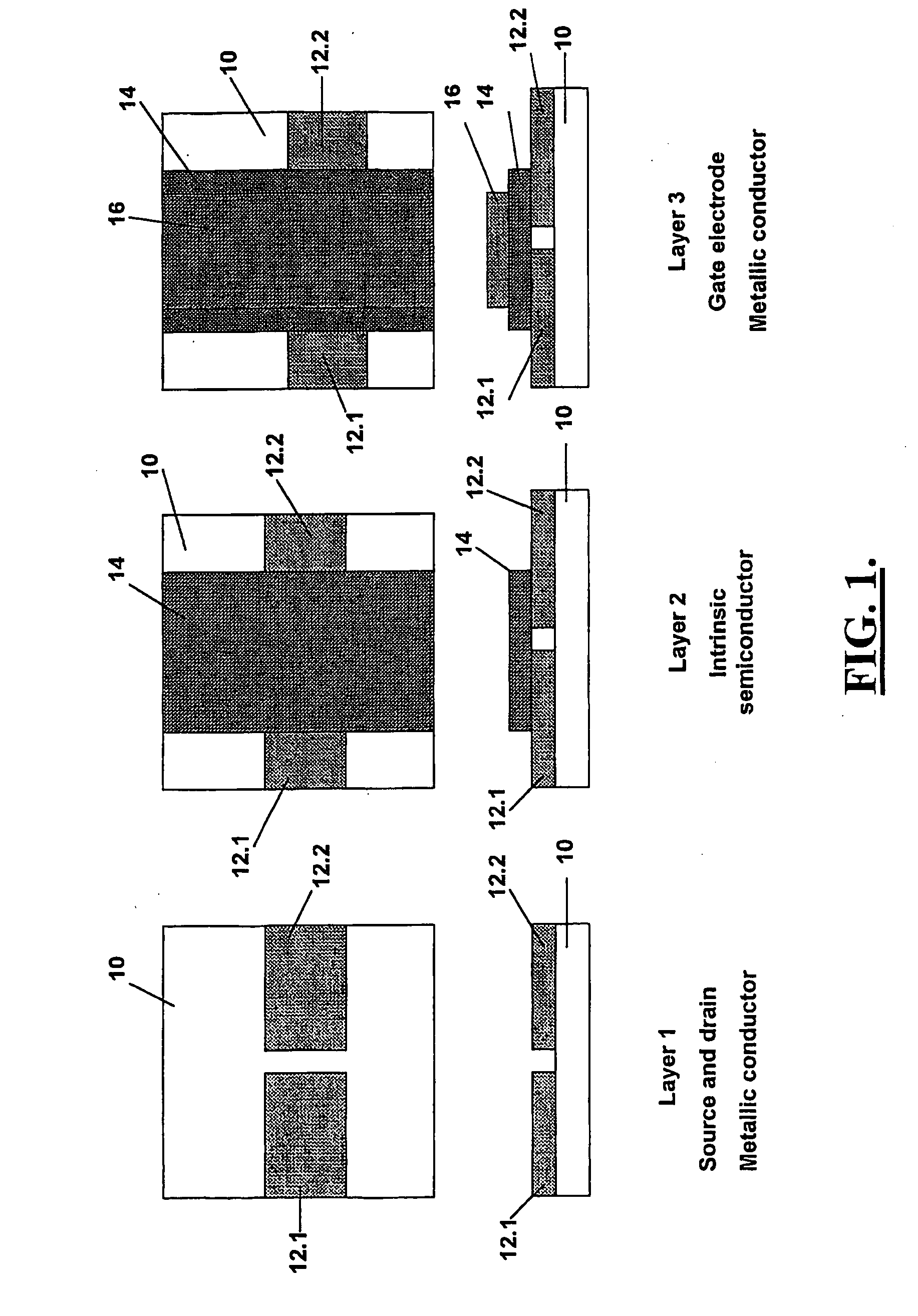

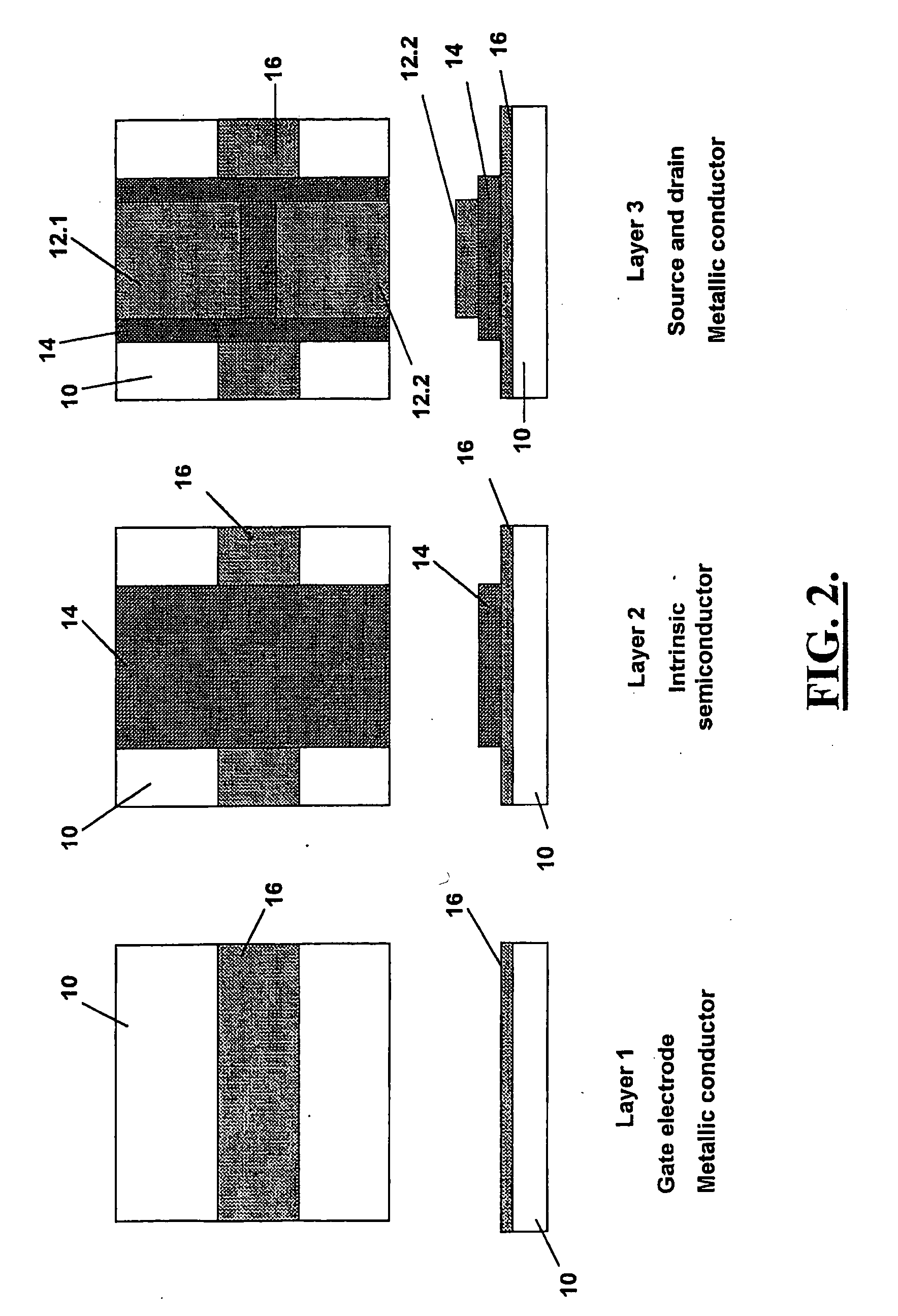

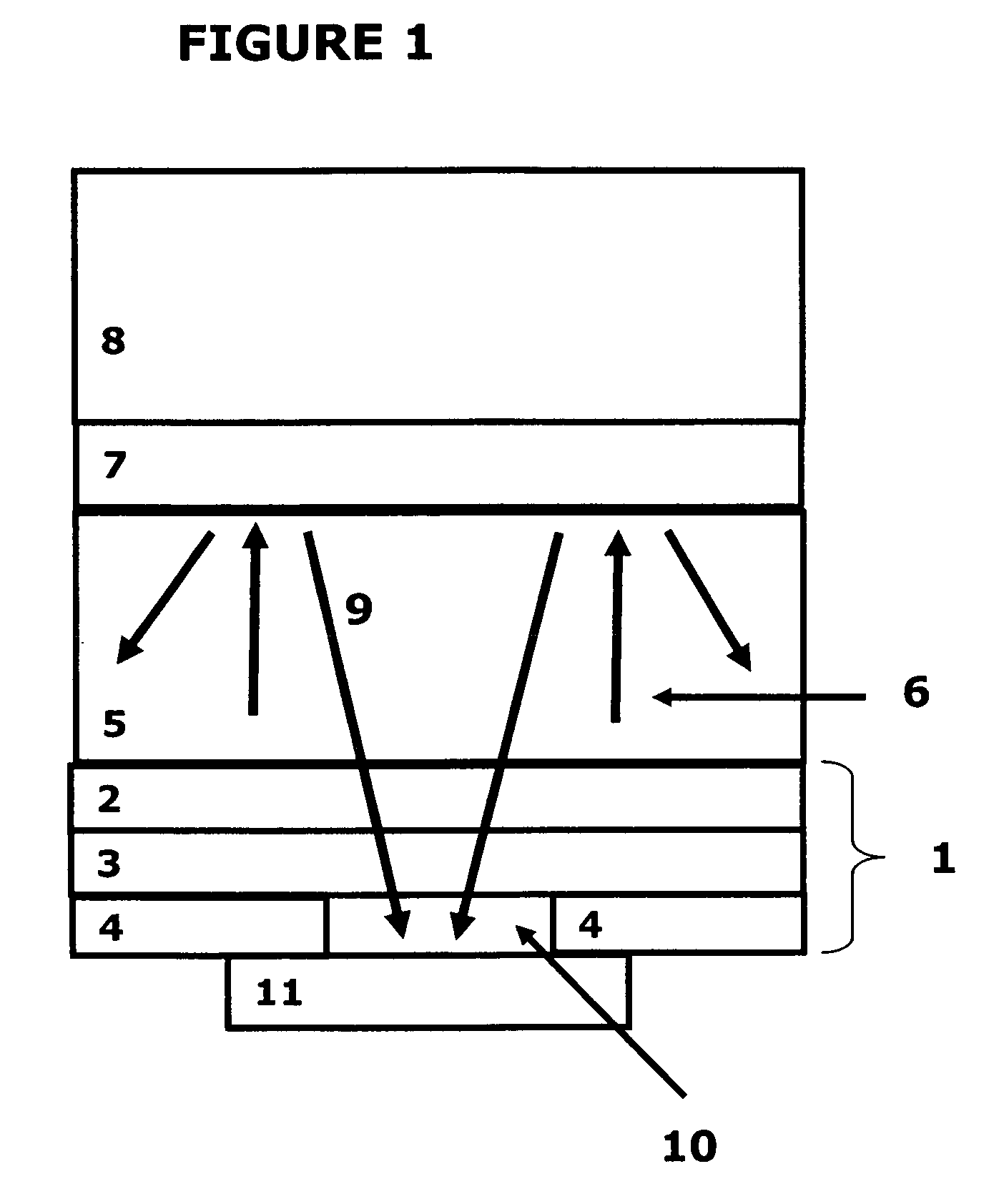

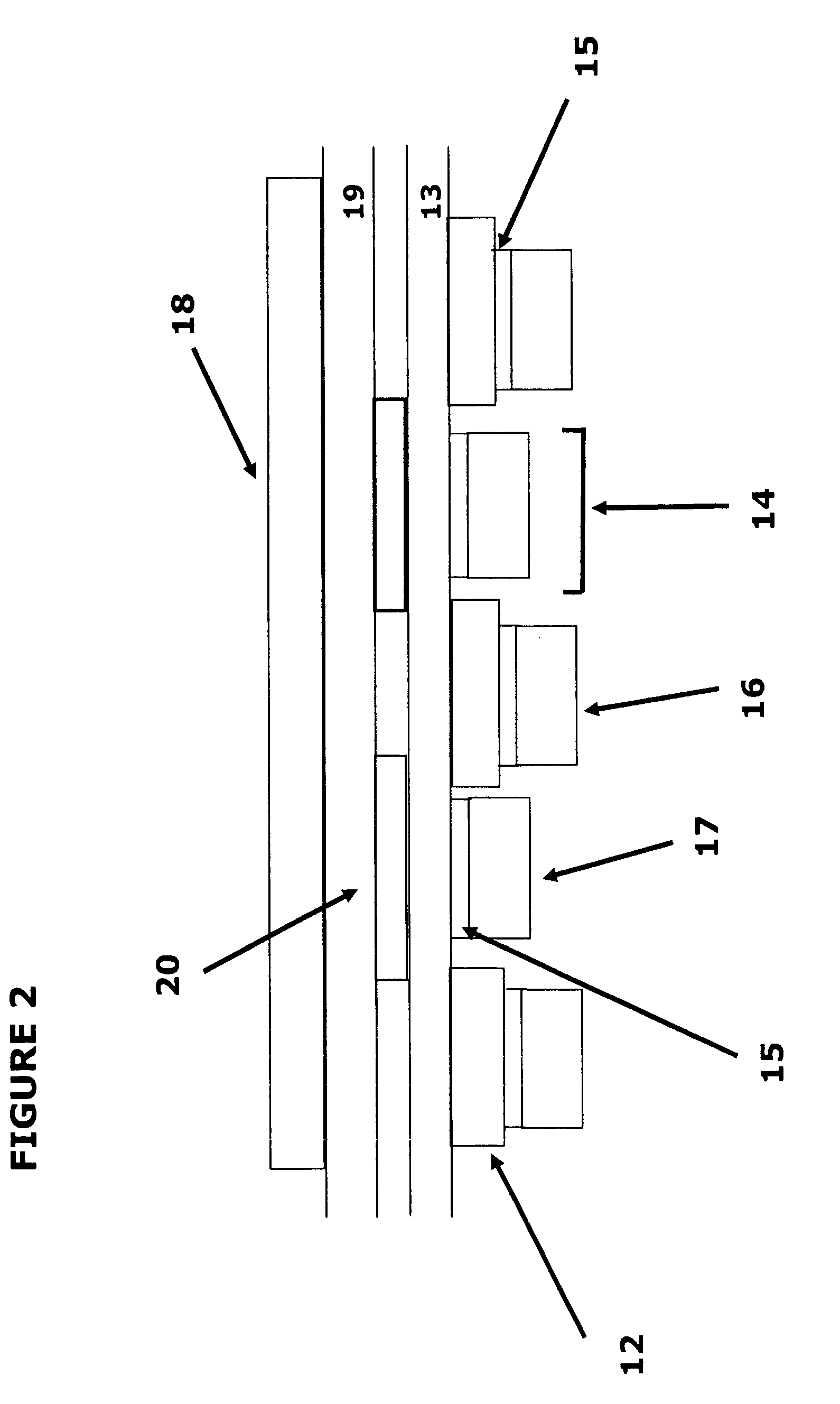

A thin film semiconductor in the form of a metal semiconductor field effect transistor, includes a substrate 10 of paper sheet material and a number of thin film active inorganic layers that are deposited in layers on the substrate. The active layers are printed using an offset lithography printing process. A first active layer comprises source 12.1 and drain 12.2 conductors of colloidal silver ink, that are printed directly onto the paper substrate. A second active layer is an intrinsic semiconductor layer 14 of colloidal nanocrystalline silicon ink which is printed onto the first layer. A third active layer comprises a metallic conductor 16 of colloidal silver which is printed onto the second layer to form a gate electrode. This invention extends to other thin film semiconductors such as photovoltaic cells and to a method of manufacturing semiconductors.

Owner:PST SENSORS

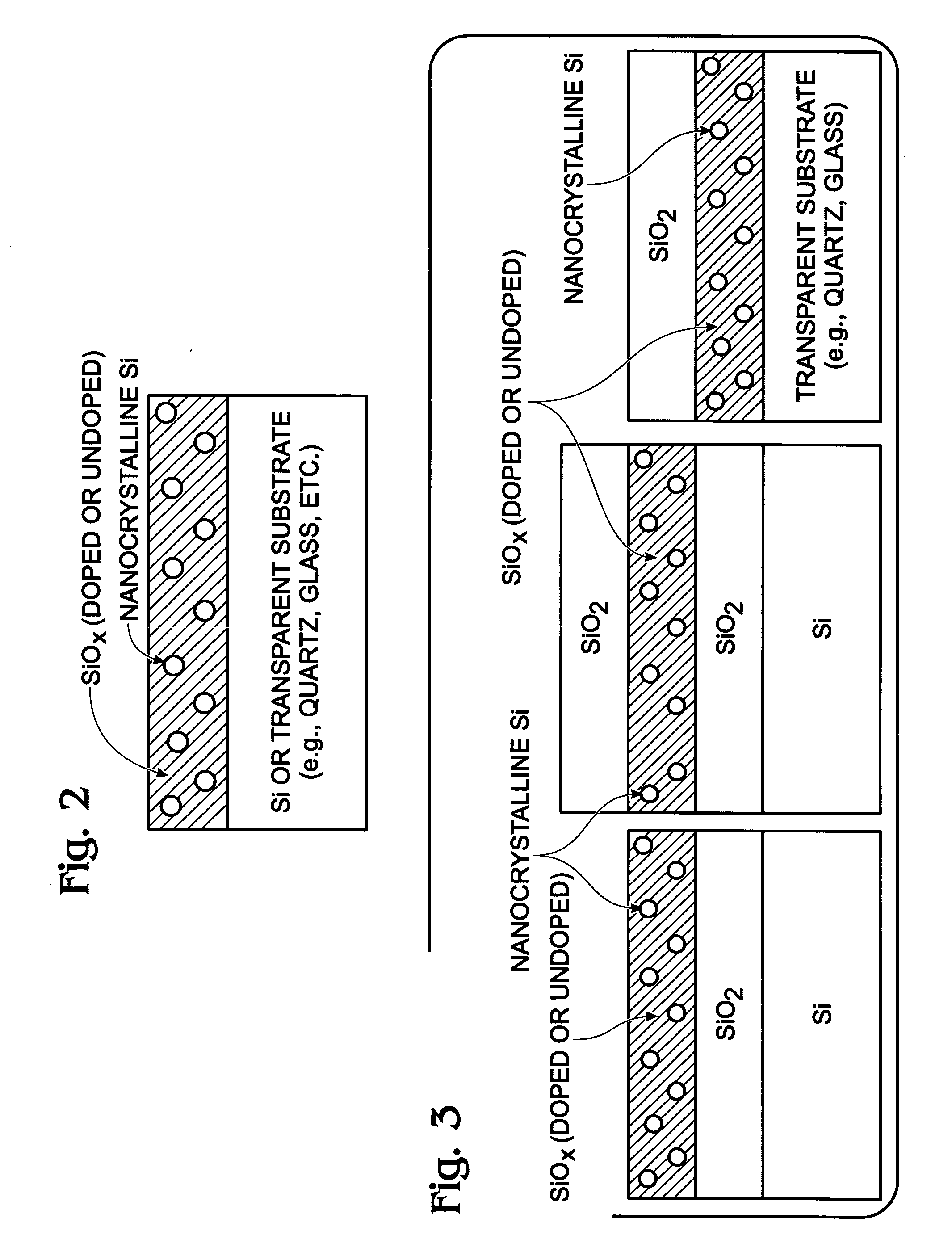

Silicon oxide thin-films with embedded nanocrystalline silicon

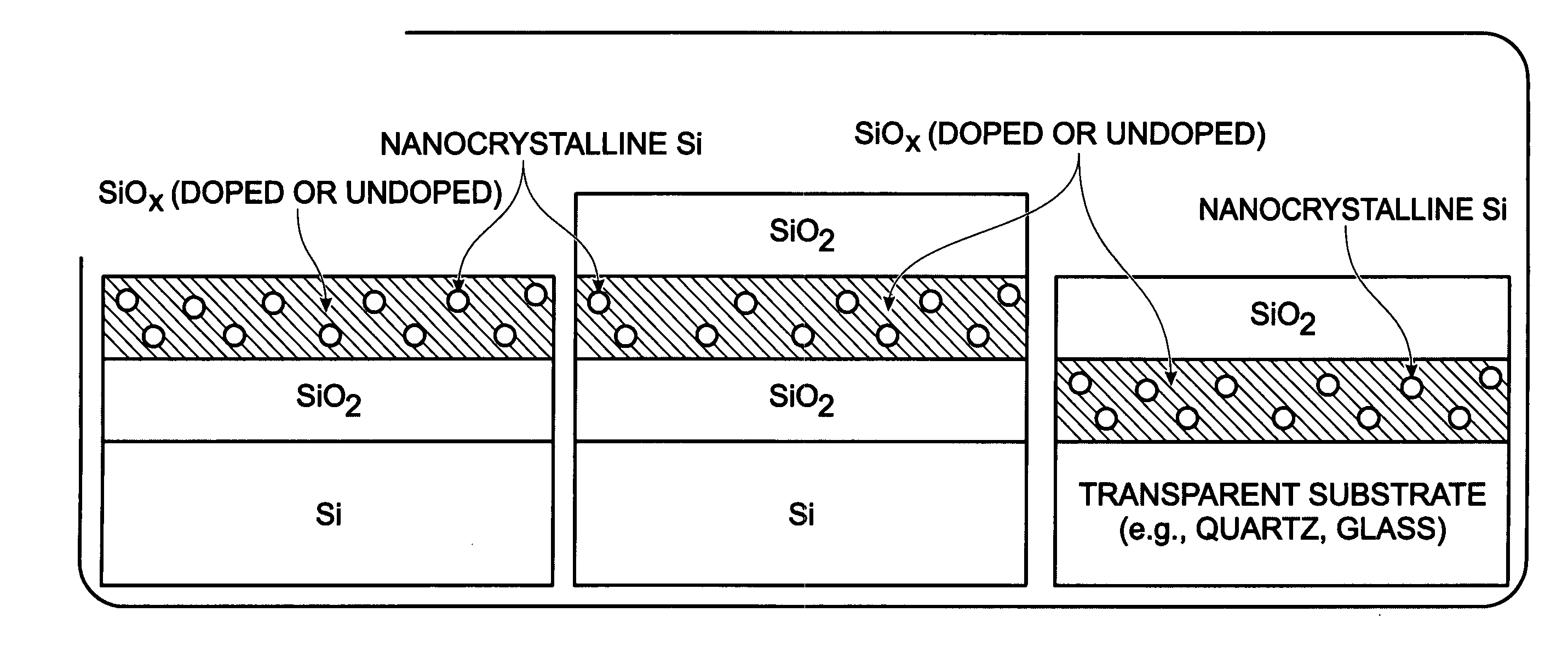

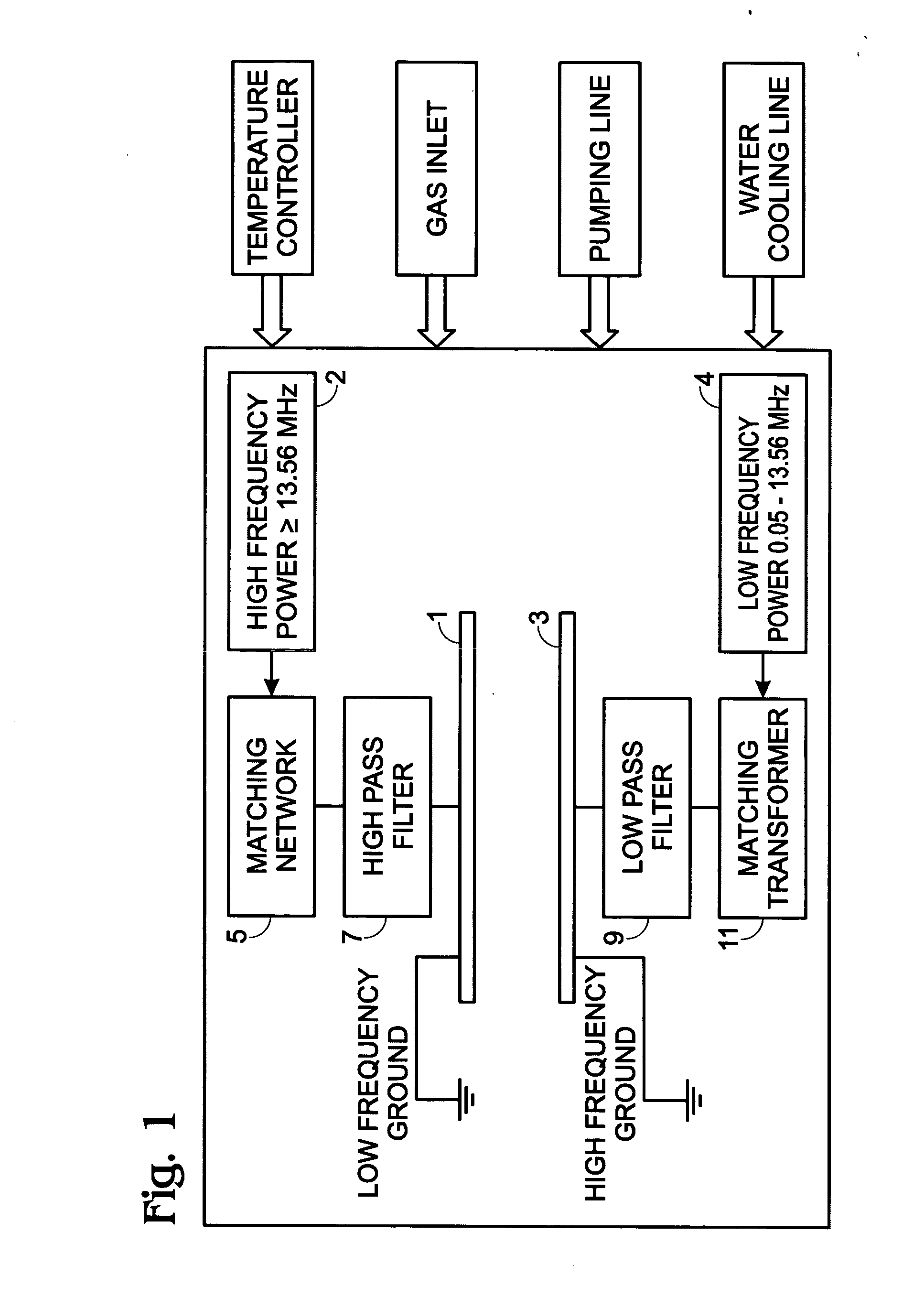

InactiveUS20060211267A1Minimizing plasma induced bulkMinimizing interface damageSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHydrogenHigh density

A method is provided for forming a silicon oxide (SiOx) thin-film with embedded nanocrystalline silicon (Si). The method deposits SiOx, where x is in the range of 1 to 2, overlying a substrate, using a high-density (HD) plasma-enhanced chemical vapor deposition (PECVD) process. As a result, the SiOx thin-film is embedded with nanocrystalline Si. The HD PECVD process may use an inductively coupled plasma (ICP) source, a substrate temperature of less than about 400° C., and an oxygen source gas with a silicon precursor. In one aspect, a hydrogen source gas and an inert gas are used, where the ratio of oxygen source gas to inert gas is in the range of about 0.02 to 5. The SiOx thin-film with embedded nanocrystalline Si typically has a refractive index in the range of about 1.6 to 2.2, with an extinction coefficient in the range of 0 to 0.5.

Owner:SHARP KK

Implantable device using ultra-nanocrystalline diamond

An implantable biocompatible device, that may be either a sensor or stimulator, having electronic circuitry and electrodes formed on a substrate, is uniformly covered with a coating approximately one-micron thick of ultra-nanocrystalline diamond, hermetically sealing the electronic circuitry. Selected electrodes are either left uncovered during coating or uncovered by conventional patterning techniques, allowing the electrodes to be exposed to living tissue and fluids. The ultra-nanocrystalline diamond coating may be doped to create electrically conductive electrodes. These approaches eliminate the need for a hermetically sealed lid or cover to protect hybrid electronic circuitry, and thus allow the device to be thinner than otherwise possible. The conformal ultra-nanocrystalline diamond coating uniformly covers the device, providing relief from sharp edges and producing a strong, uniformly thick hermetic coating around sharp edges and on high aspect-ratio parts.

Owner:SECOND SIGHT MEDICAL PRODS

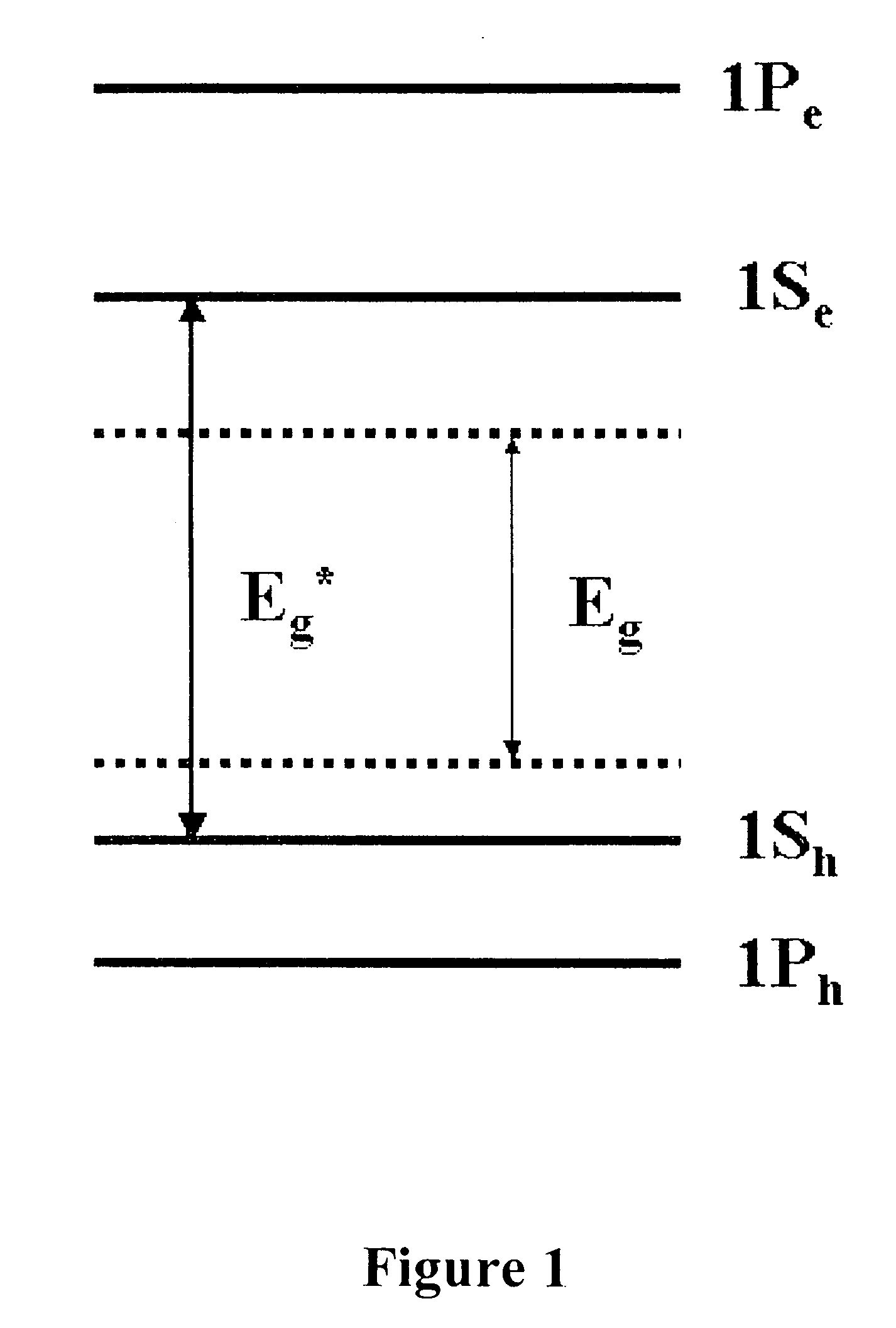

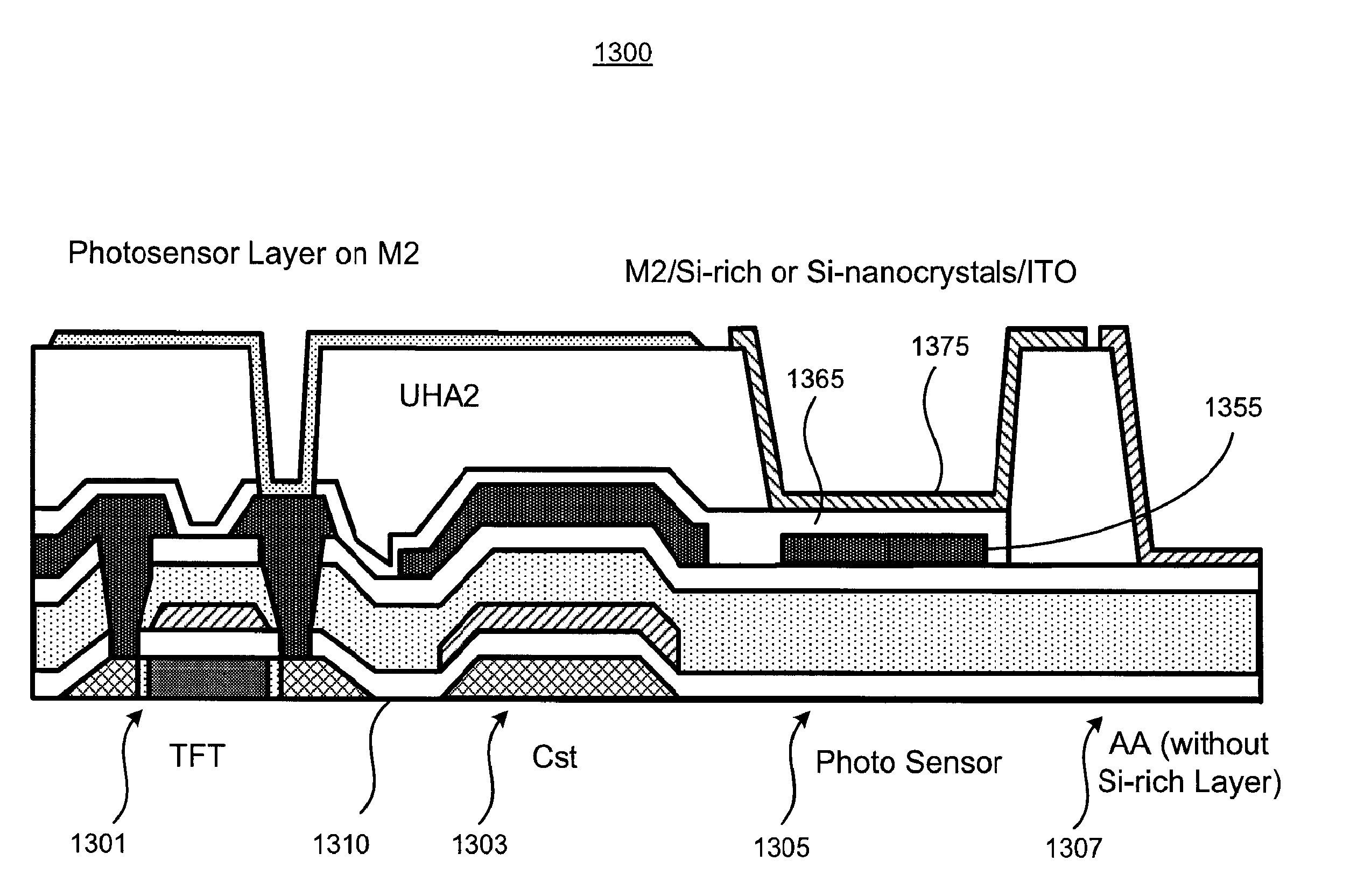

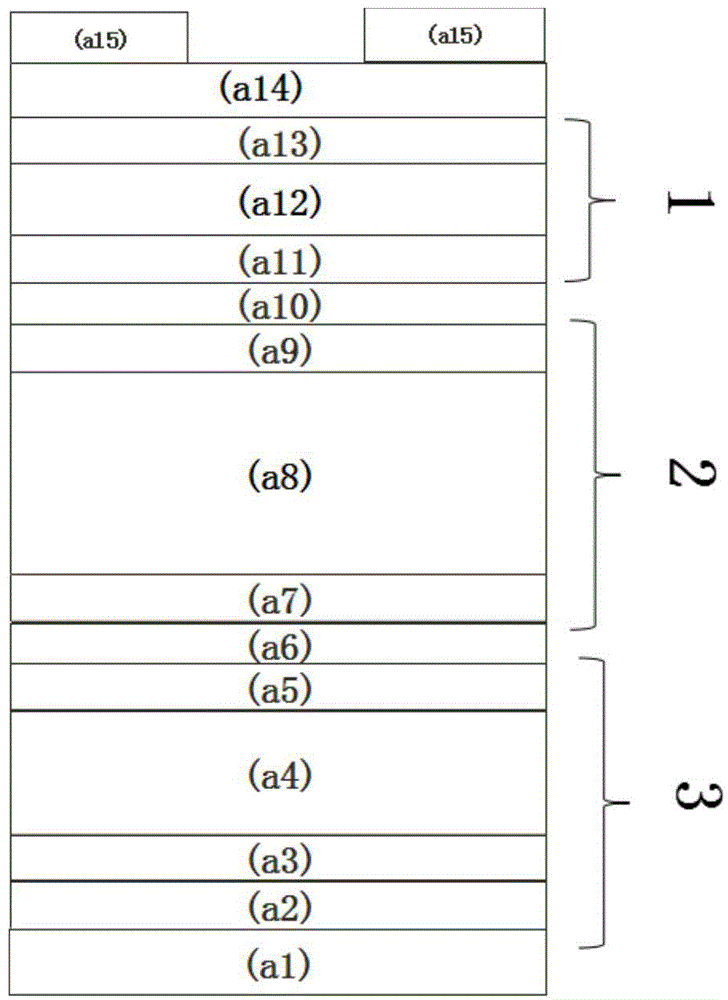

Photovoltaic Cells of Si-Nanocrystals with Multi-Band Gap and Applications in a Low Temperature Polycrystalline Silicon Thin Film Transistor Panel

ActiveUS20090009675A1High photovoltaic efficiencyWavelength tuneabilityFinal product manufacturePhotometryMulti bandNanocrystalline silicon

One aspect of the present invention relates to a photovoltaic cell. In one embodiment, the photovoltaic cell includes a first conductive layer, an N-doped semiconductor layer formed on the first conductive layer, a first silicon layer formed on the N-doped semiconductor layer, a nanocrystalline silicon (nc-Si) layer formed on a first silicon layer, a second silicon layer formed on the nc-Si layer, a P-doped semiconductor layer on the second silicon layer, and a second conductive layer formed on the P-doped semiconductor layer, where one of the first silicon layer and the second silicon layer is formed of amorphous silicon, and the other of the first silicon layer and the second silicon layer formed of polycrystalline silicon.

Owner:AU OPTRONICS CORP

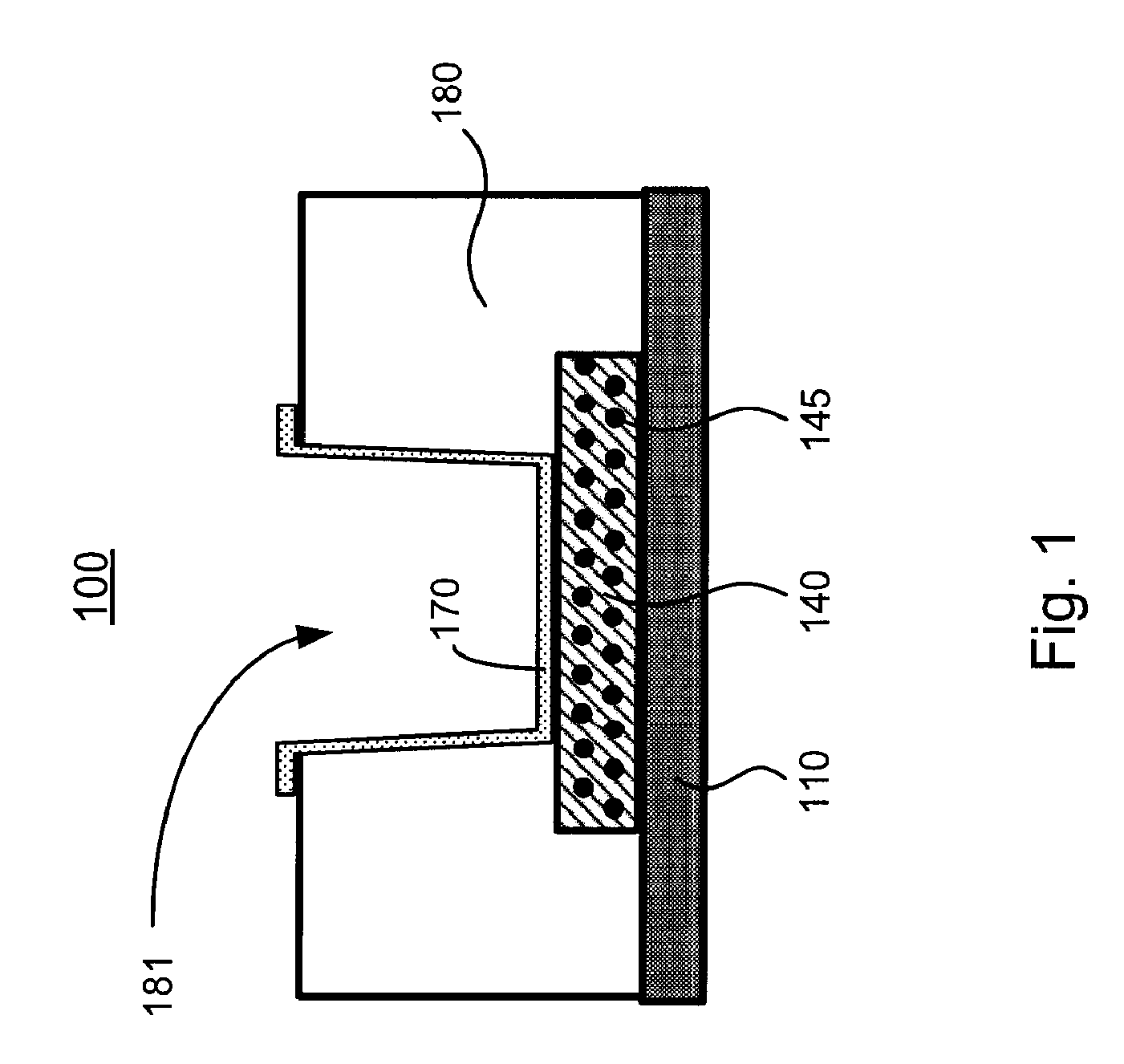

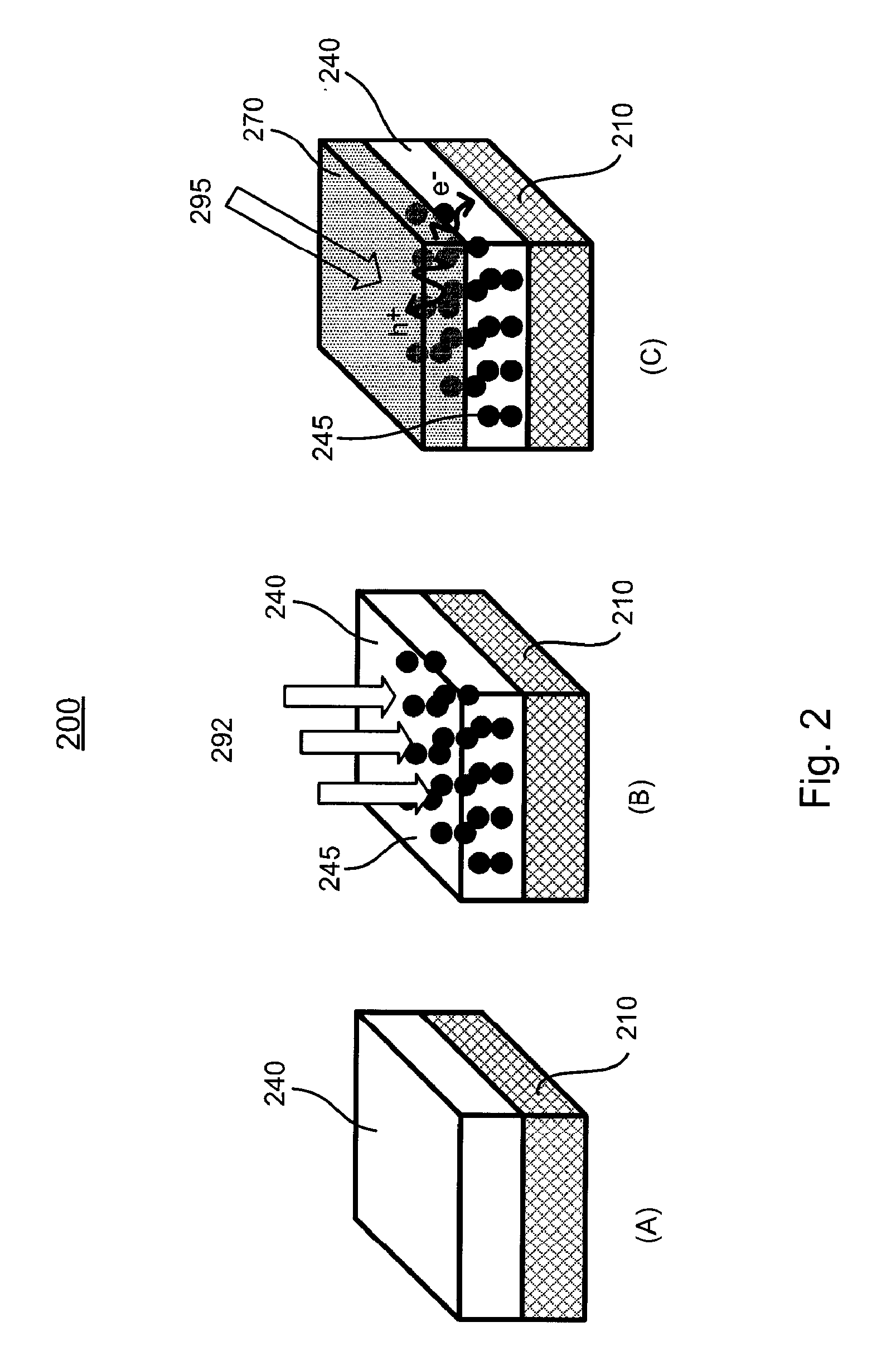

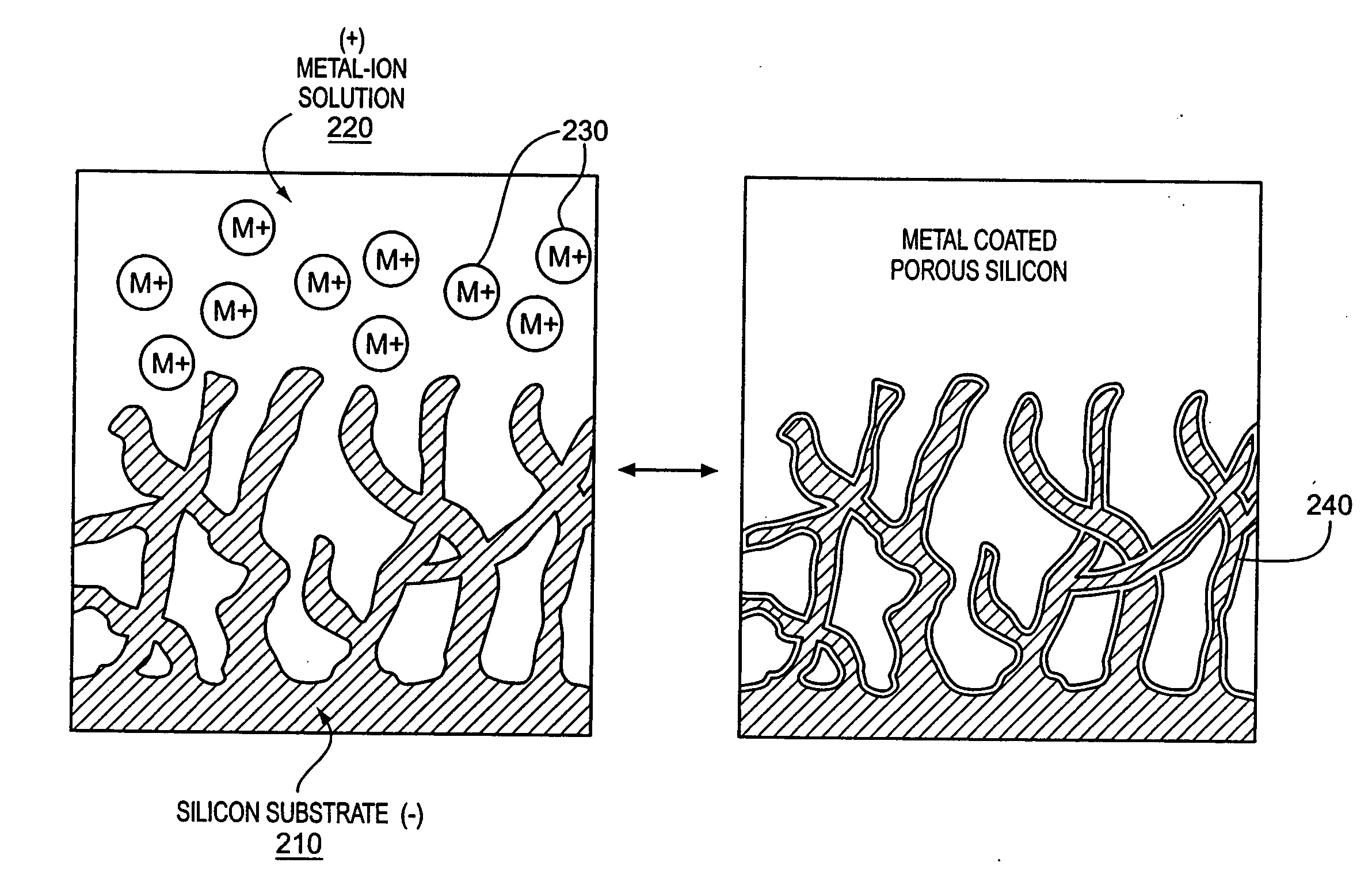

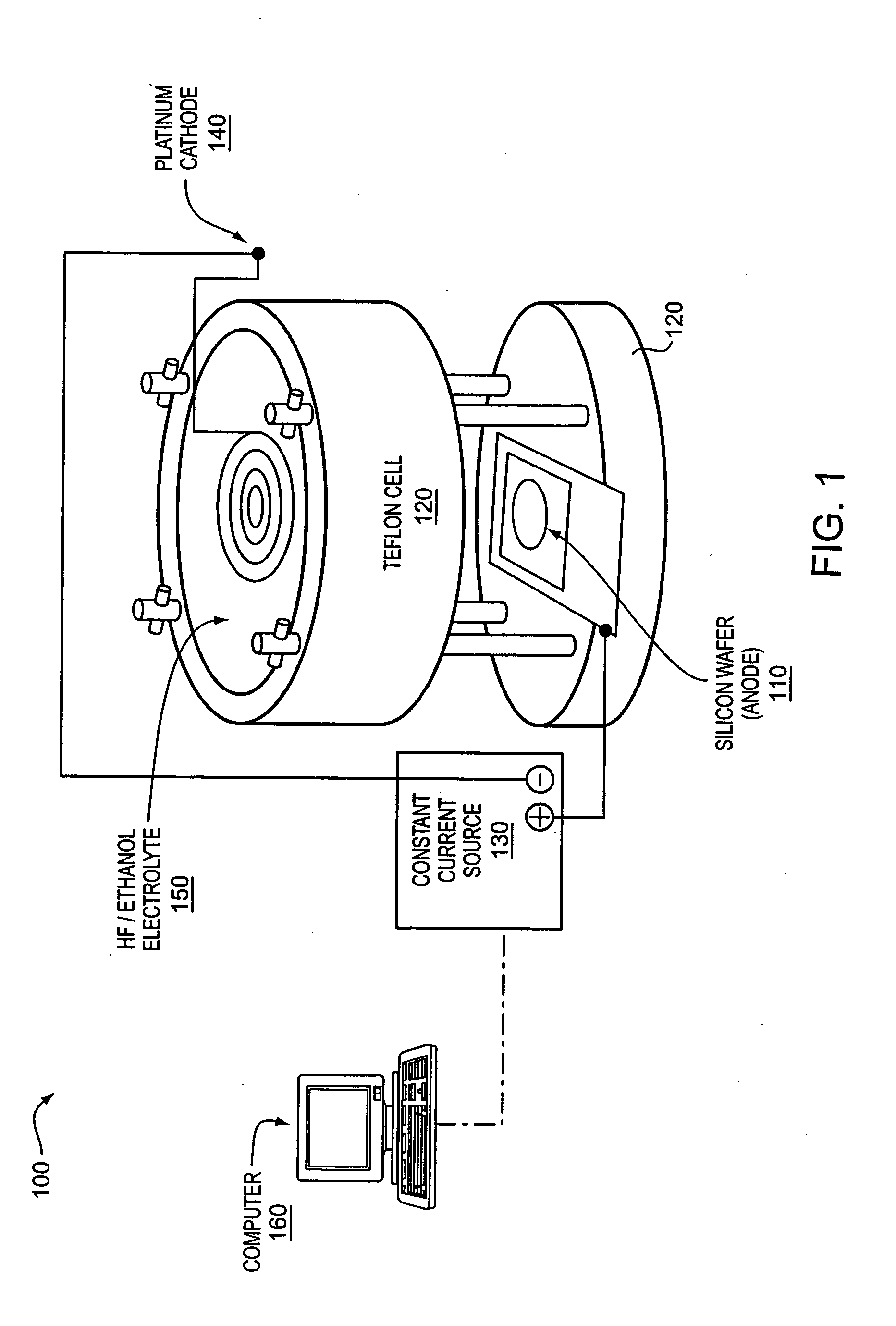

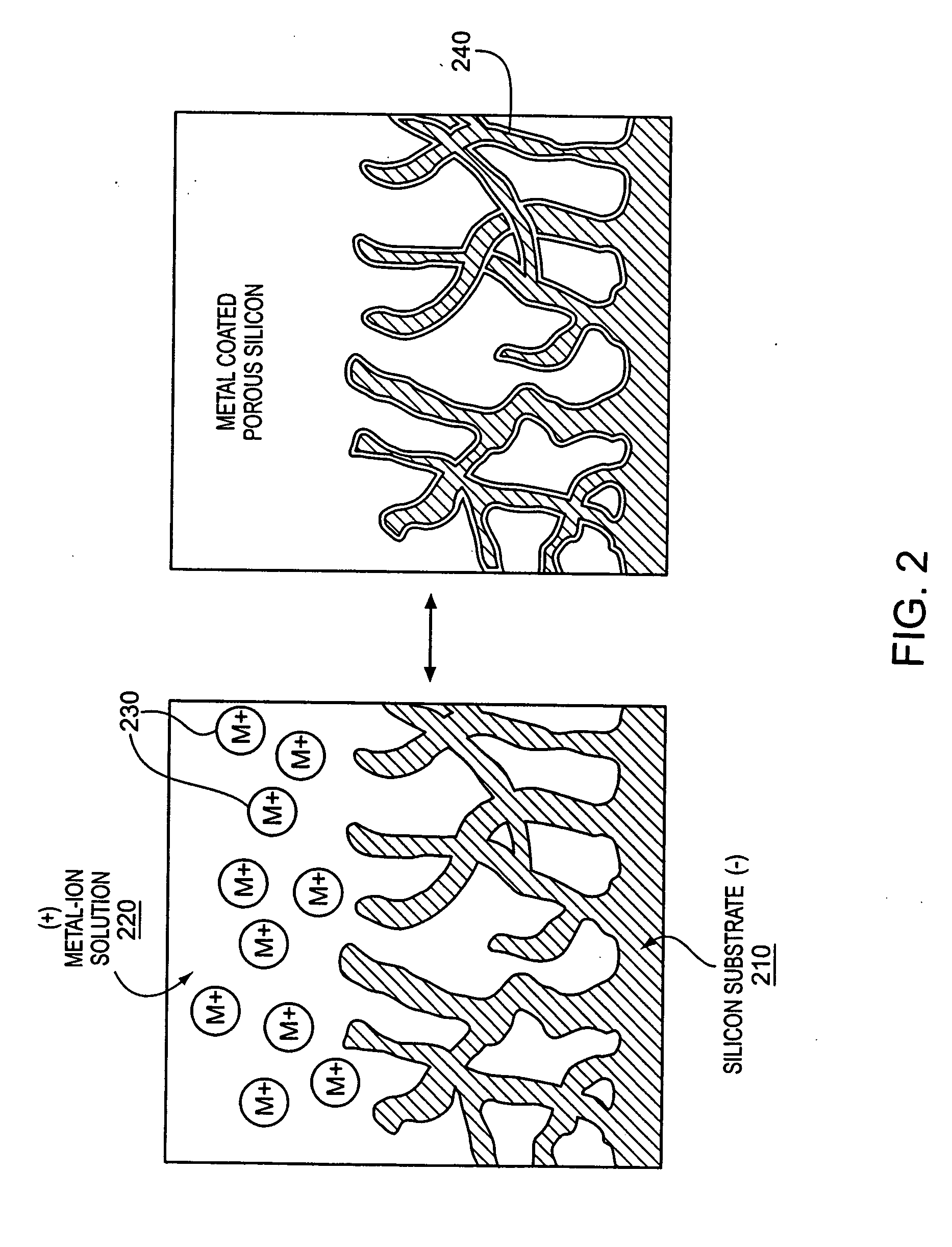

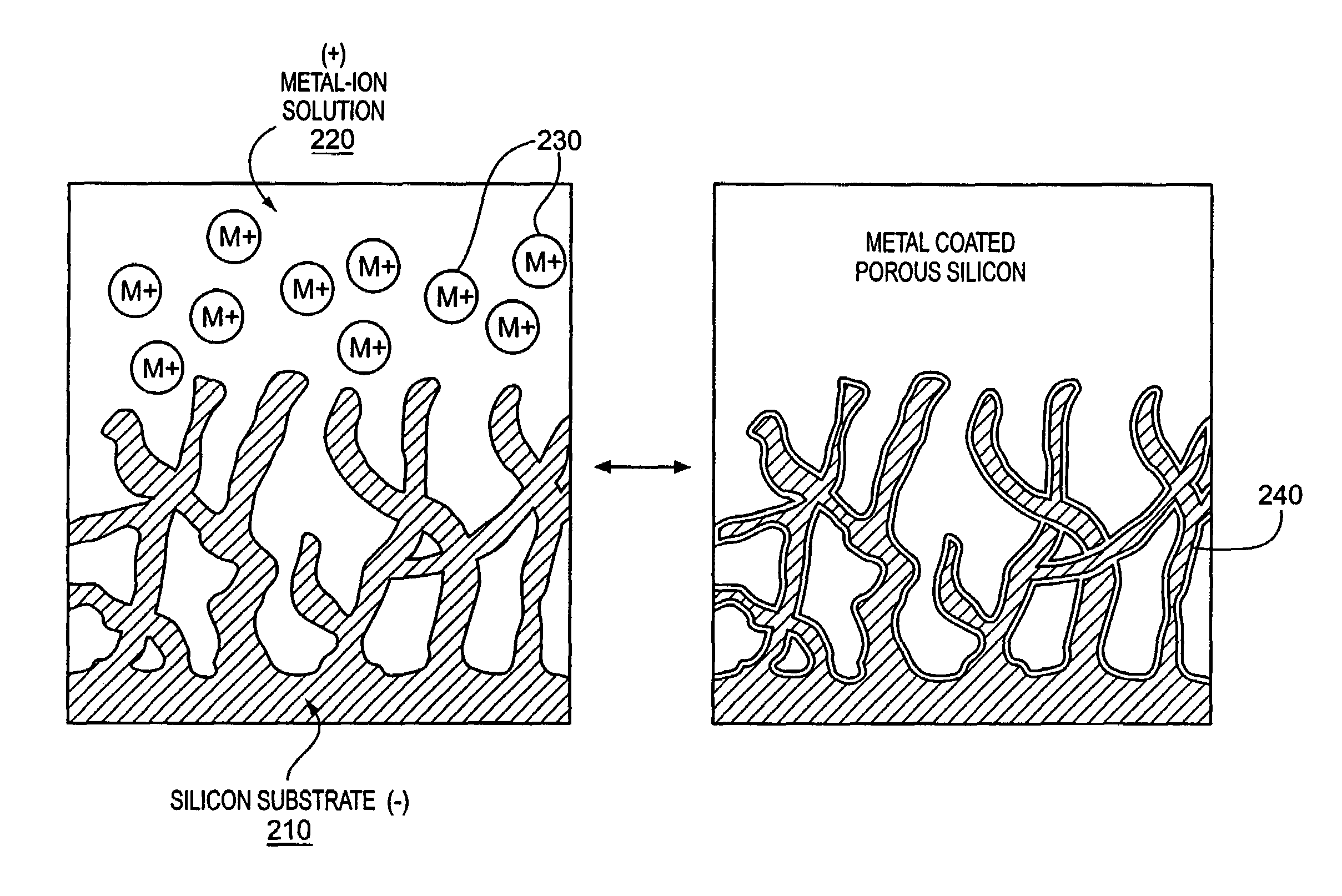

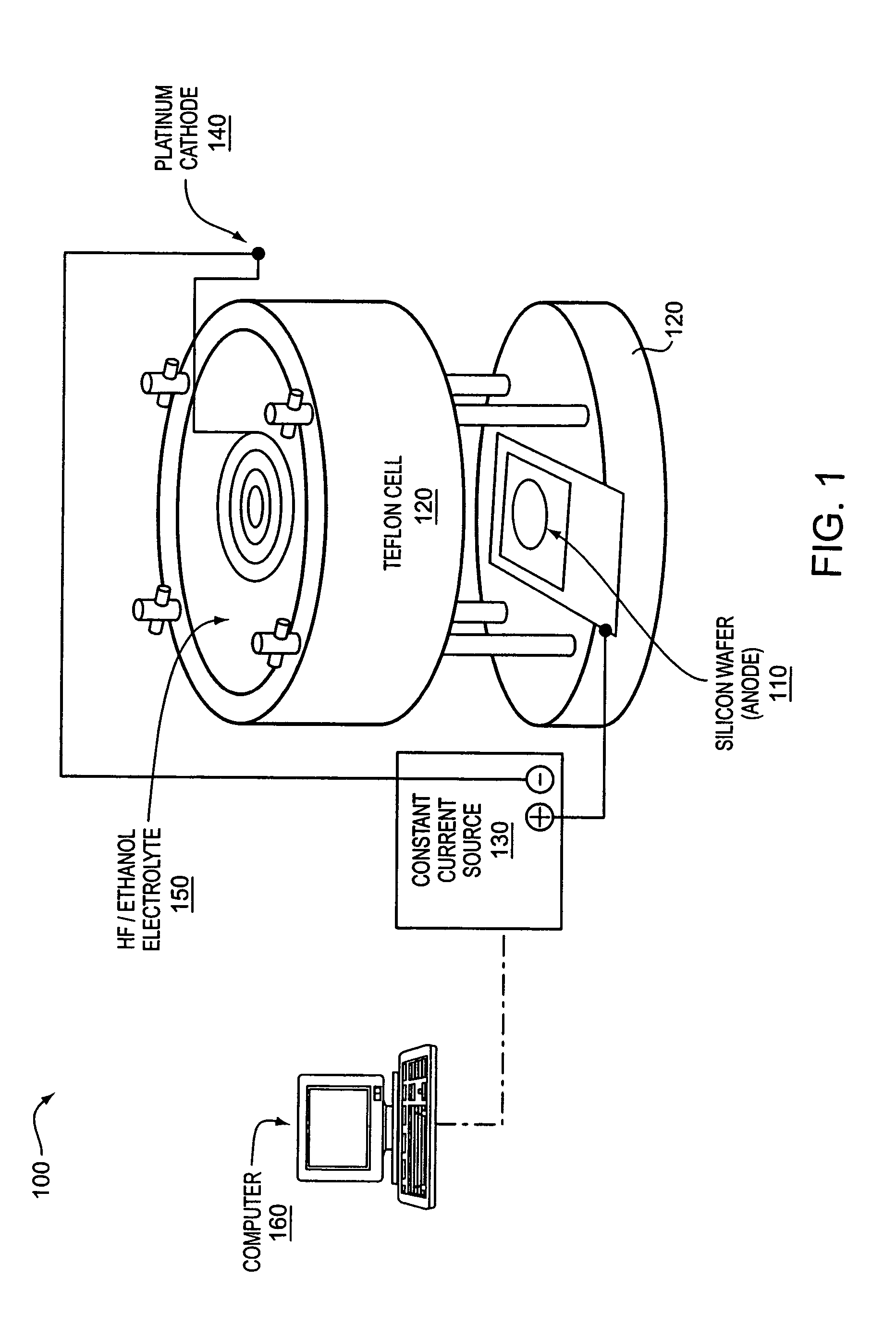

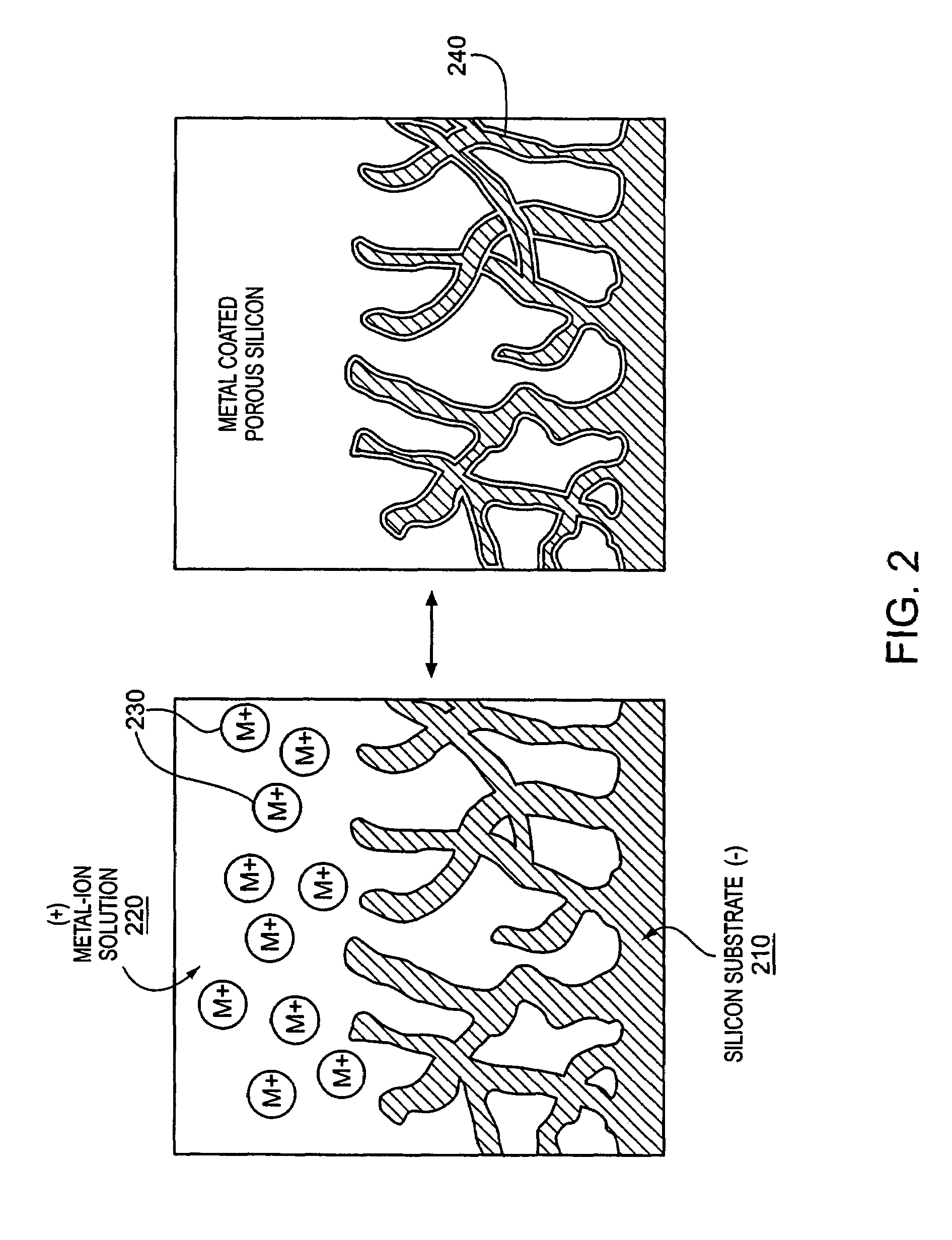

Metal coated nanocrystalline silicon as an active surface enhanced raman spectroscopy (SERS) substrate

The disclosed methods and apparatus concern Raman spectroscopy using metal coated nanocrystalline porous silicon substrates. Porous silicon substrates may be formed by anodic etching in dilute hydrofluoric acid. A thin coating of a Raman active metal, such as gold or silver, may be coated onto the porous silicon by cathodic electromigration or any known technique. In certain alternatives, the metal coated porous silicon substrate comprises a plasma-oxidized, dip and decomposed porous silicon substrate. The metal-coated substrate provides an extensive, metal rich environment for SERS, SERRS, hyper-Raman and / or CARS Raman spectroscopy. In certain alternatives, metal nanoparticles may be added to the metal-coated substrate to further enhance the Raman signals. Raman spectroscopy may be used to detect, identify and / or quantify a wide variety of analytes, using the disclosed methods and apparatus. In some disclosed methods, Raman spectroscopy may be used to detect nucleotides, purines or pyrimidines at the single molecule level.

Owner:INTEL CORP

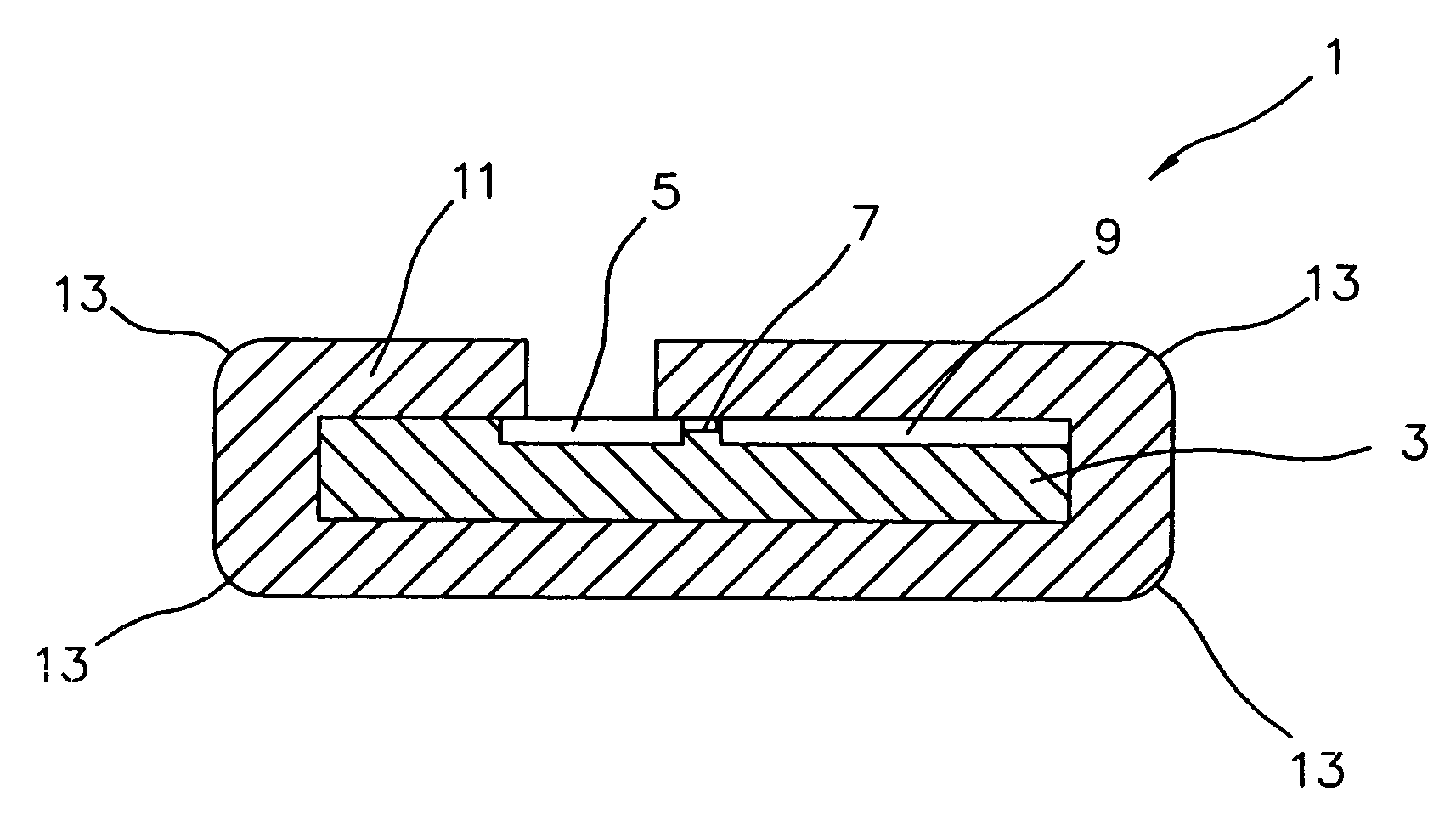

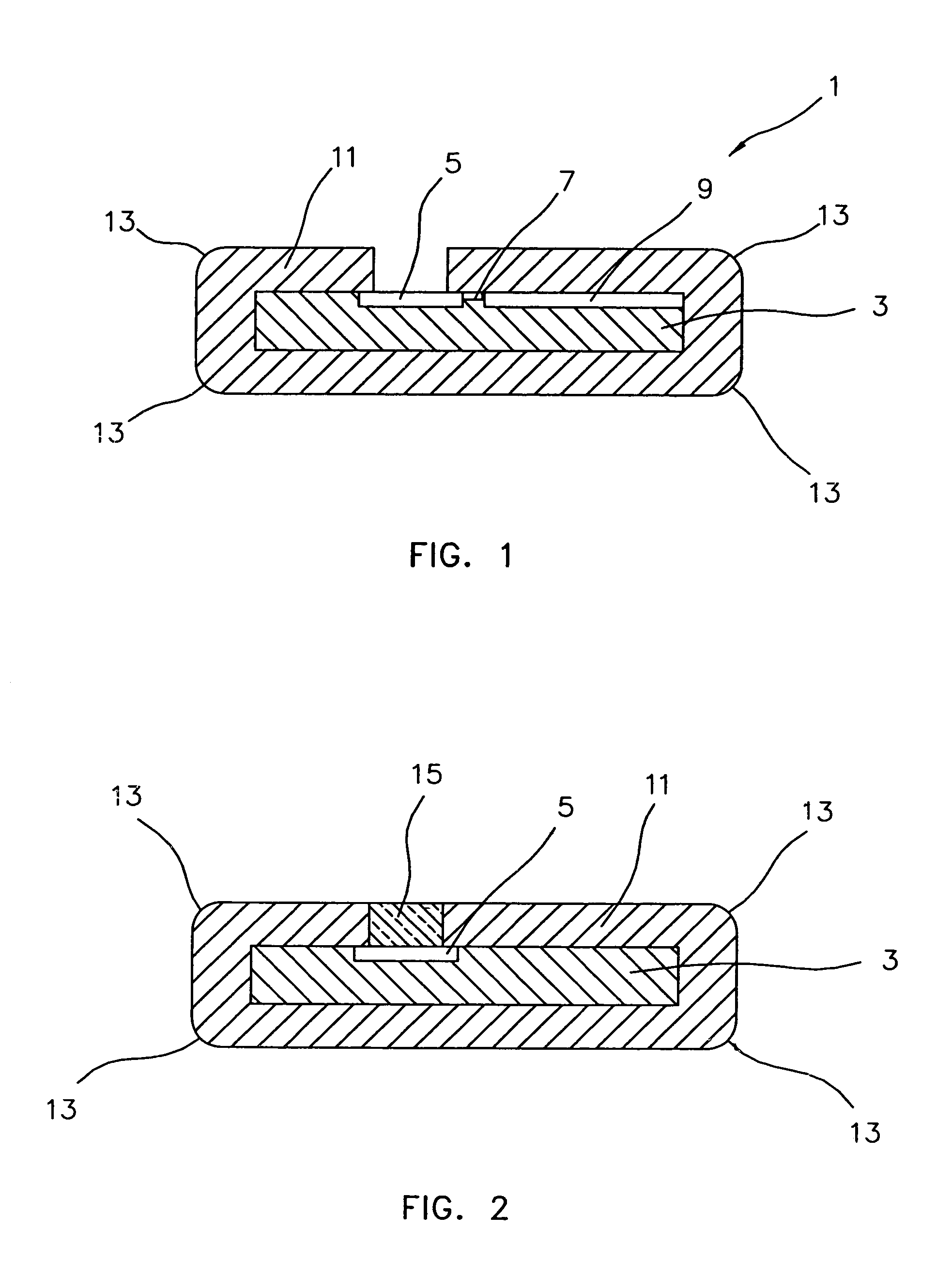

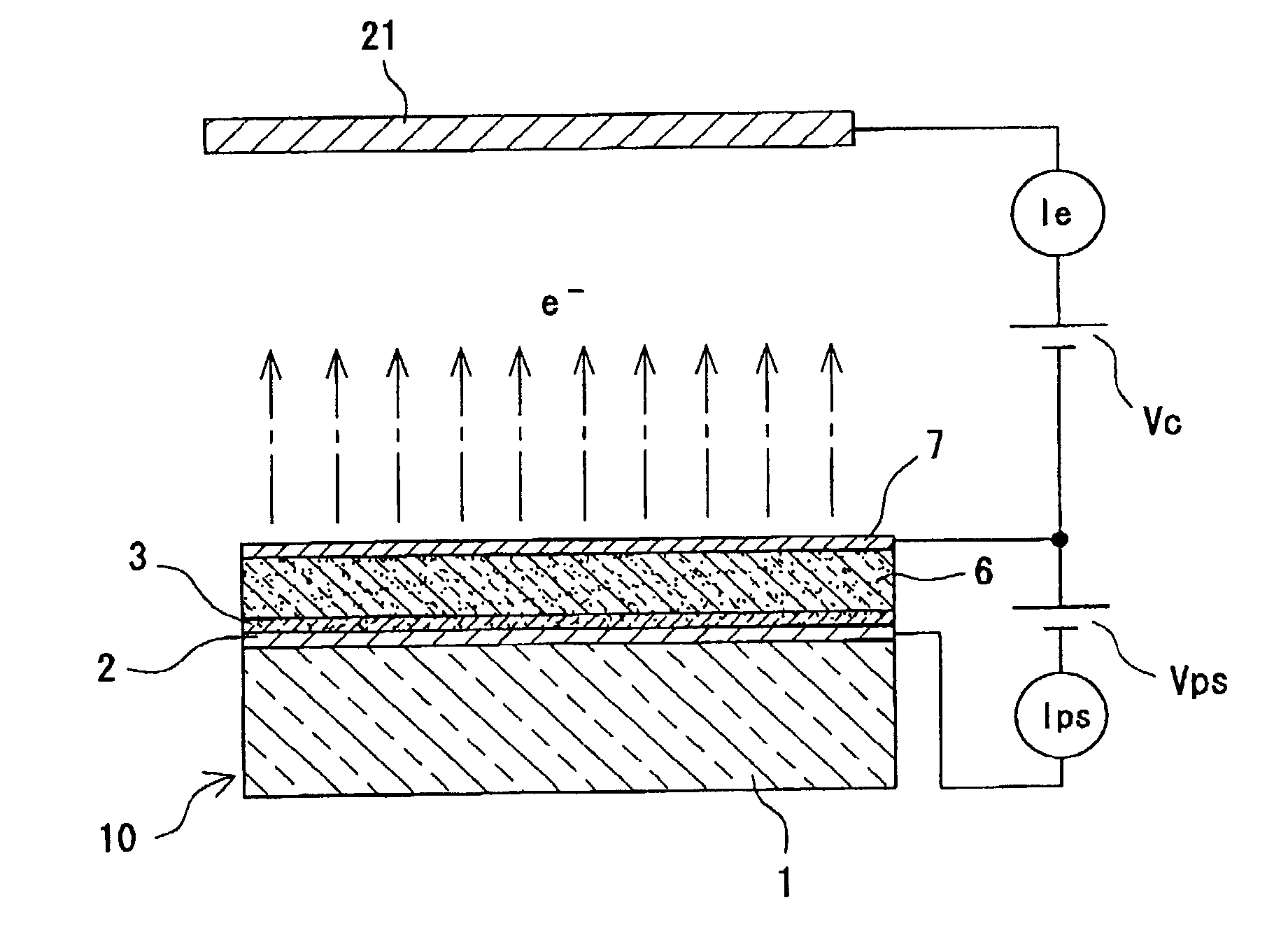

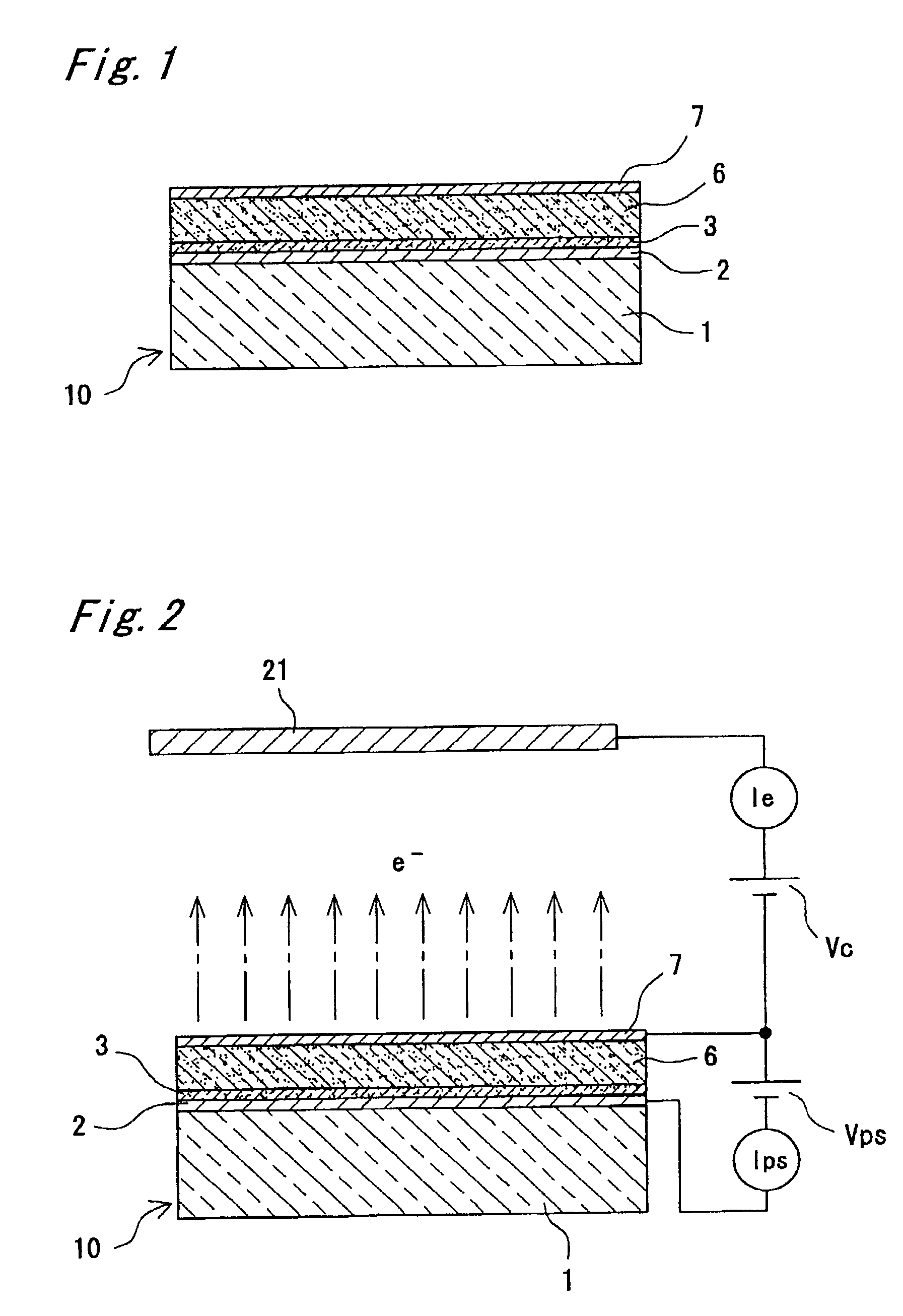

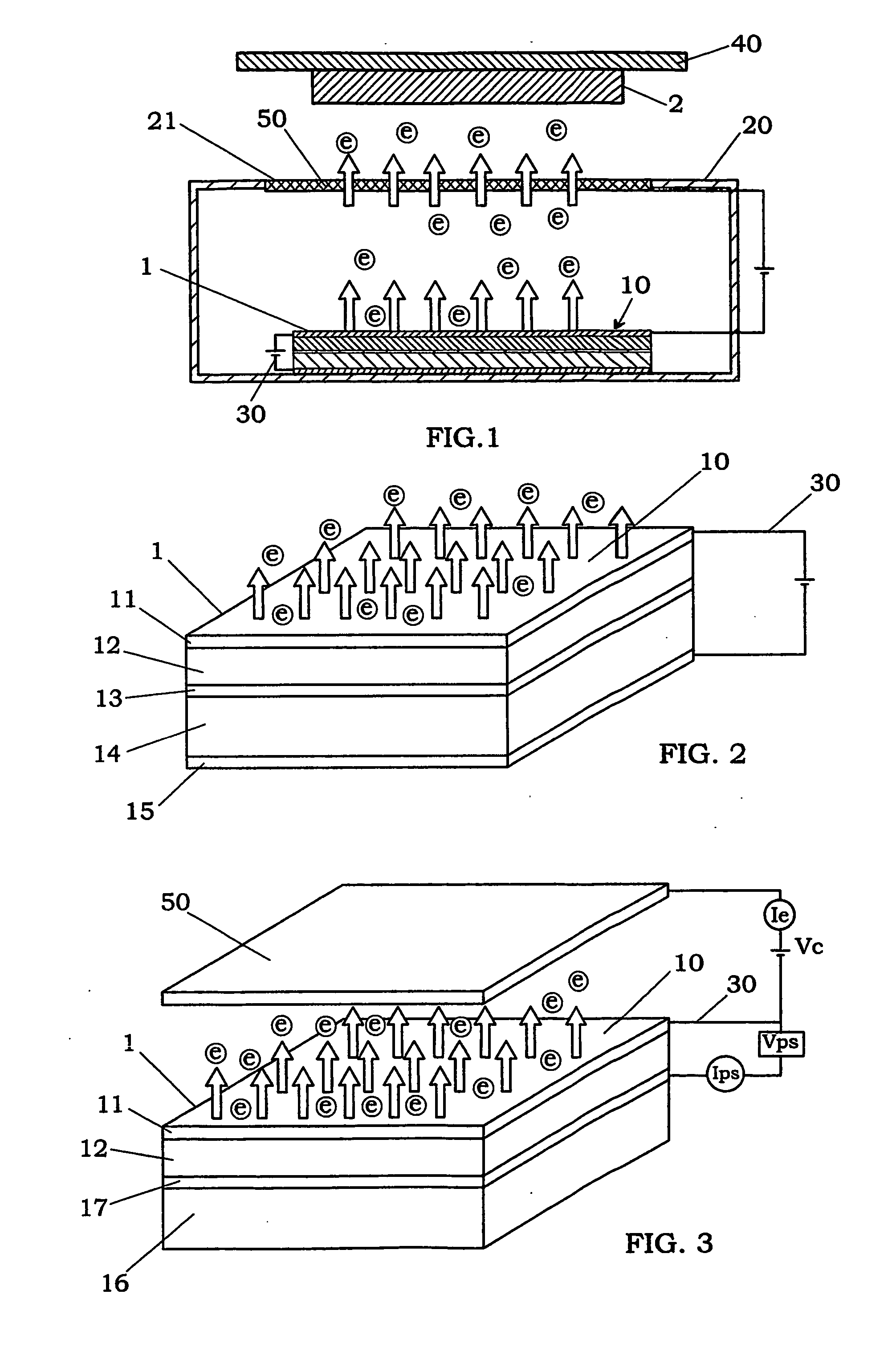

Field emission-type electron source

InactiveUS20030076023A1Increase resistanceImprove featuresDischarge tube luminescnet screensElectric discharge tubesOptoelectronicsNon doped

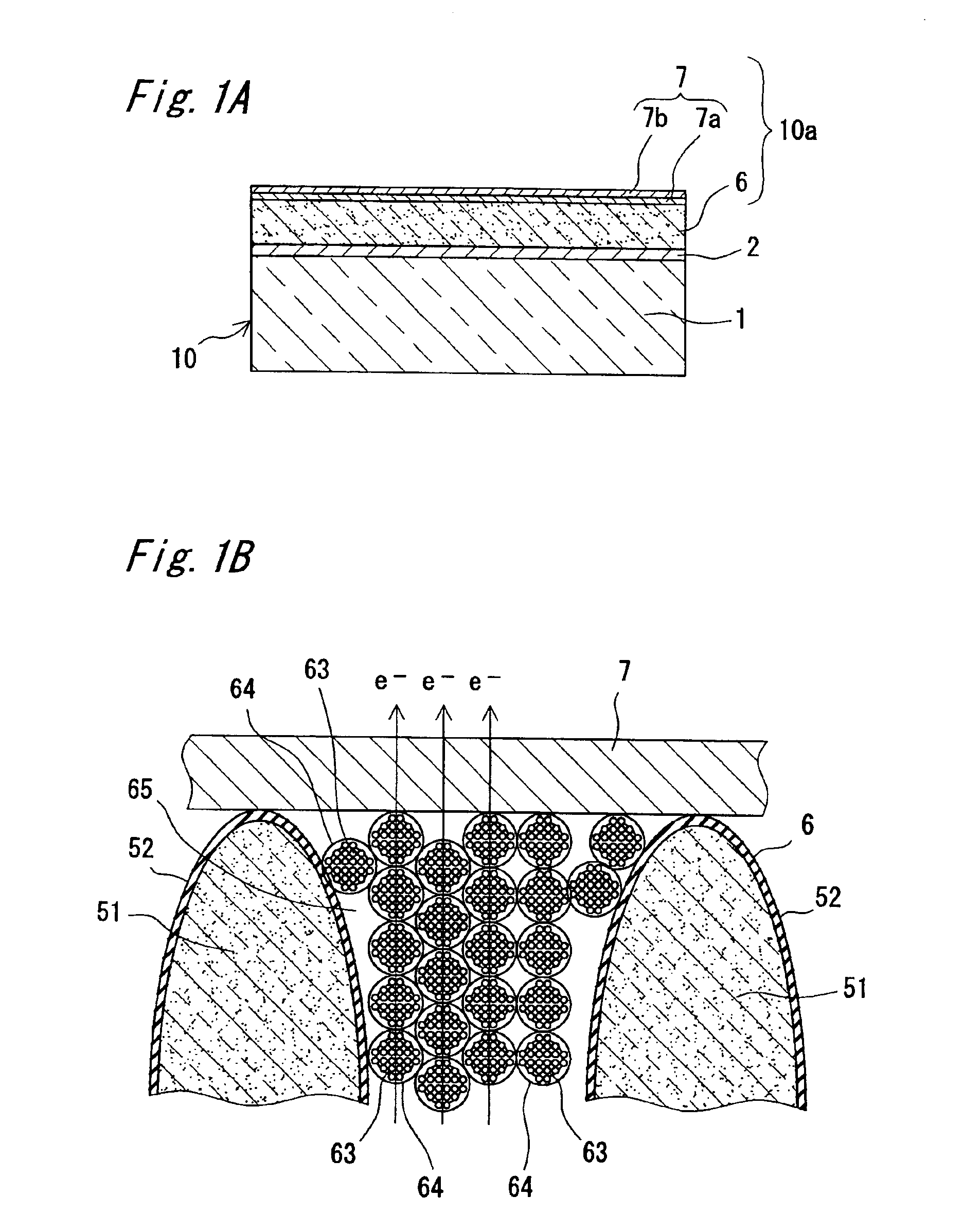

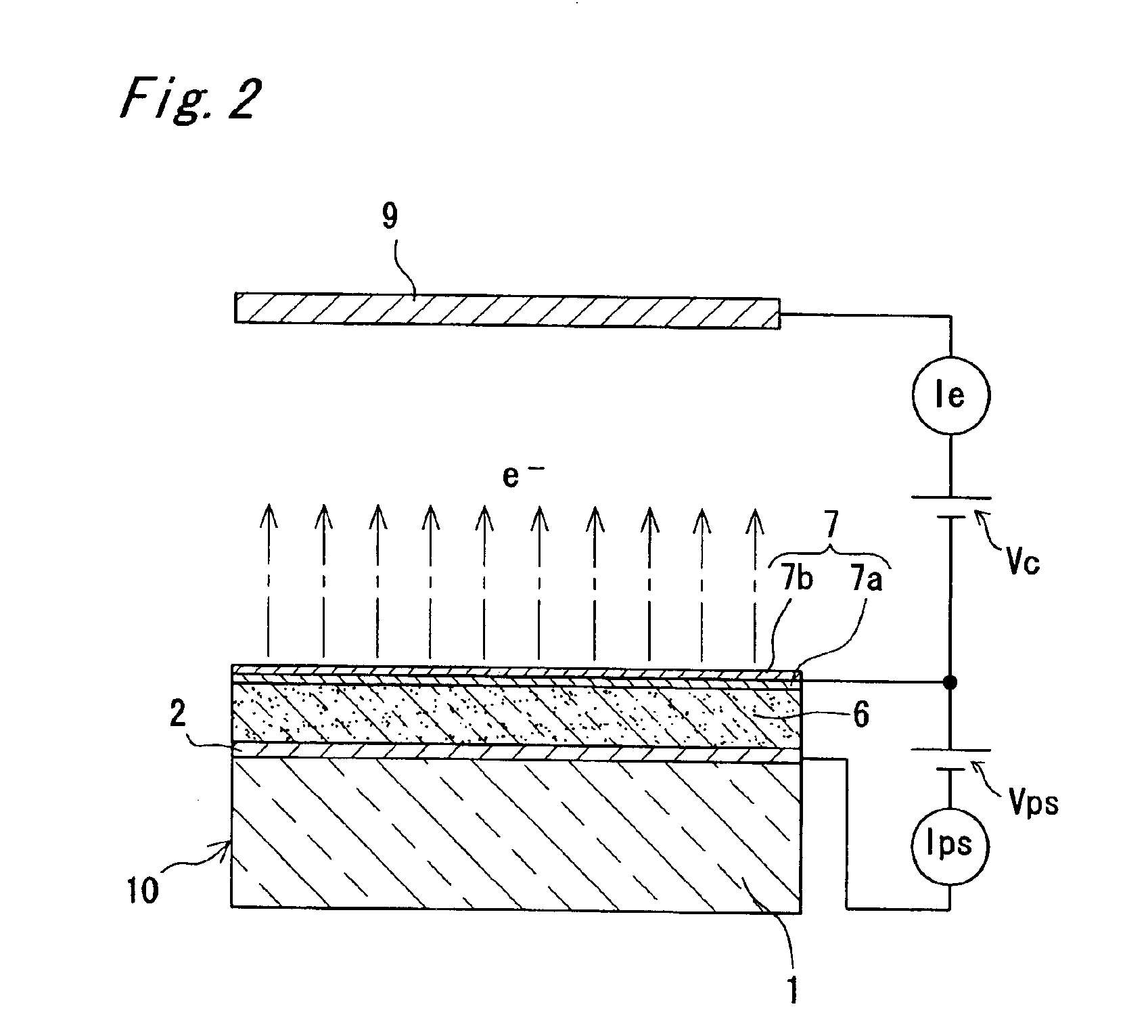

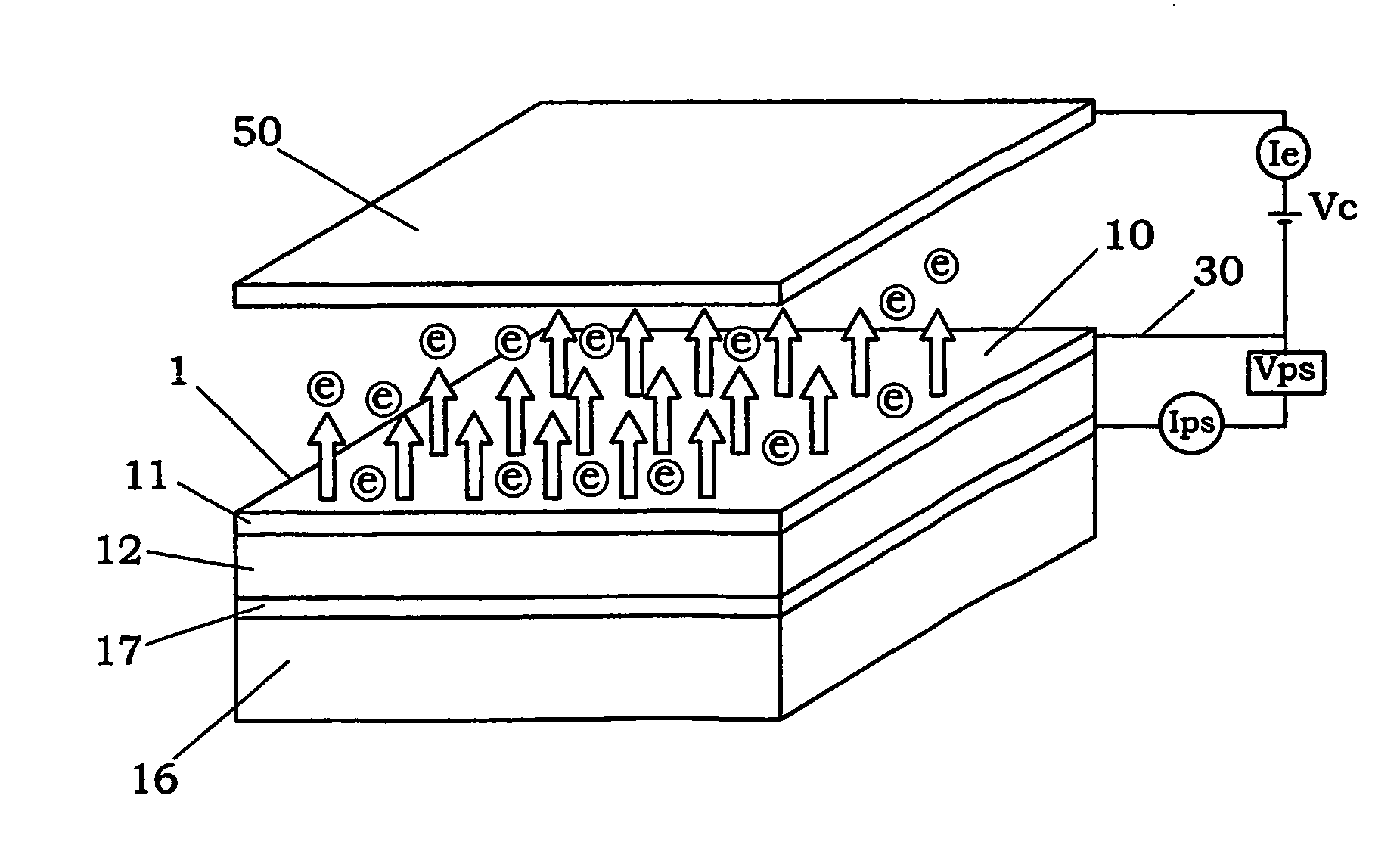

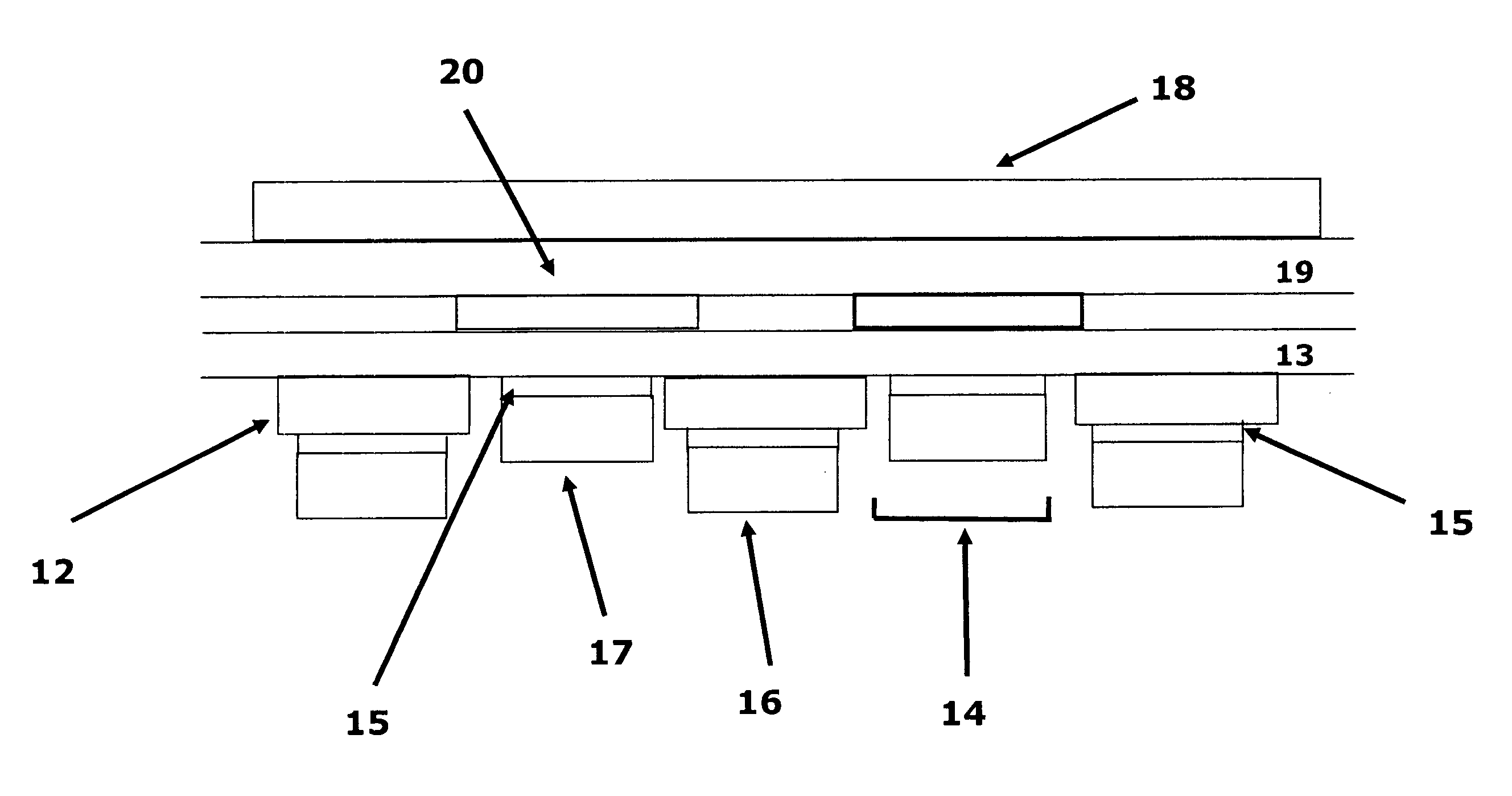

A lower electrode (2) and surface electrode (7) composed of a layer-structured conductive carbide layer is formed on one principal surface side of the substrate (1) composed of an insulative substrate such as a glass or ceramic substrate. A non-doped polycrystalline silicon layer (3) is formed on the lower electrode (2), An electron transit layer (6) composed of an oxidized porous polycrystalline silicon is formed on the polycrystalline silicon layer (3). The electron transit layer (6) is composed of a composite nanocrystal layer including polycrystalline silicon and many nanocrystalline silicons residing adjacent to a grain boundary of the polycrystalline silicon. When voltage is applied between the lower electrode (2) and the surface electrode (7) such that the surface electrode (7) has a higher potential, electrons are injected from the lower electrode (2) toward the surface electrode (7), and emitted through the surface electrode (7) through the electron transit layer (6).

Owner:MATSUSHITA ELECTRIC WORKS LTD

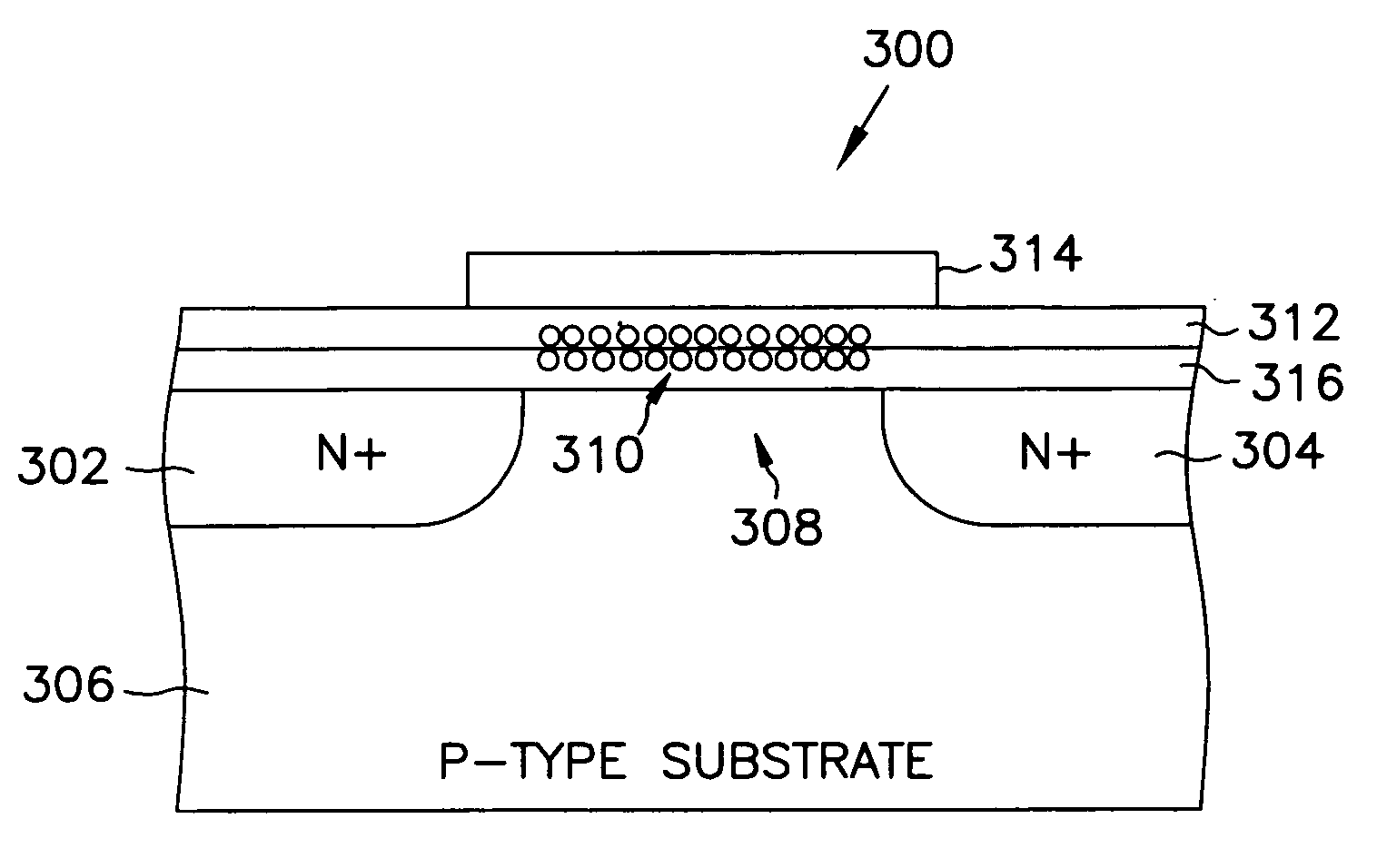

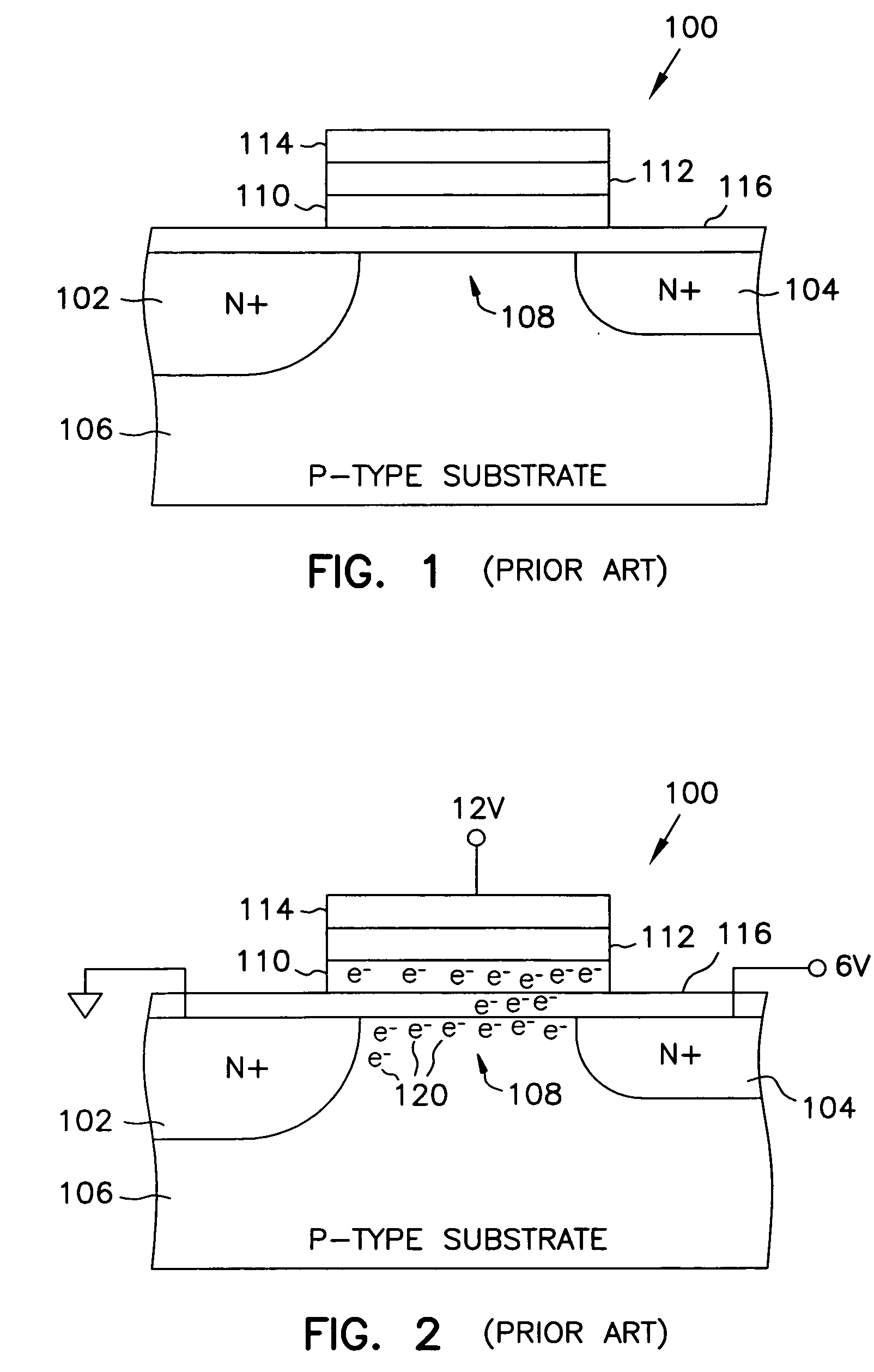

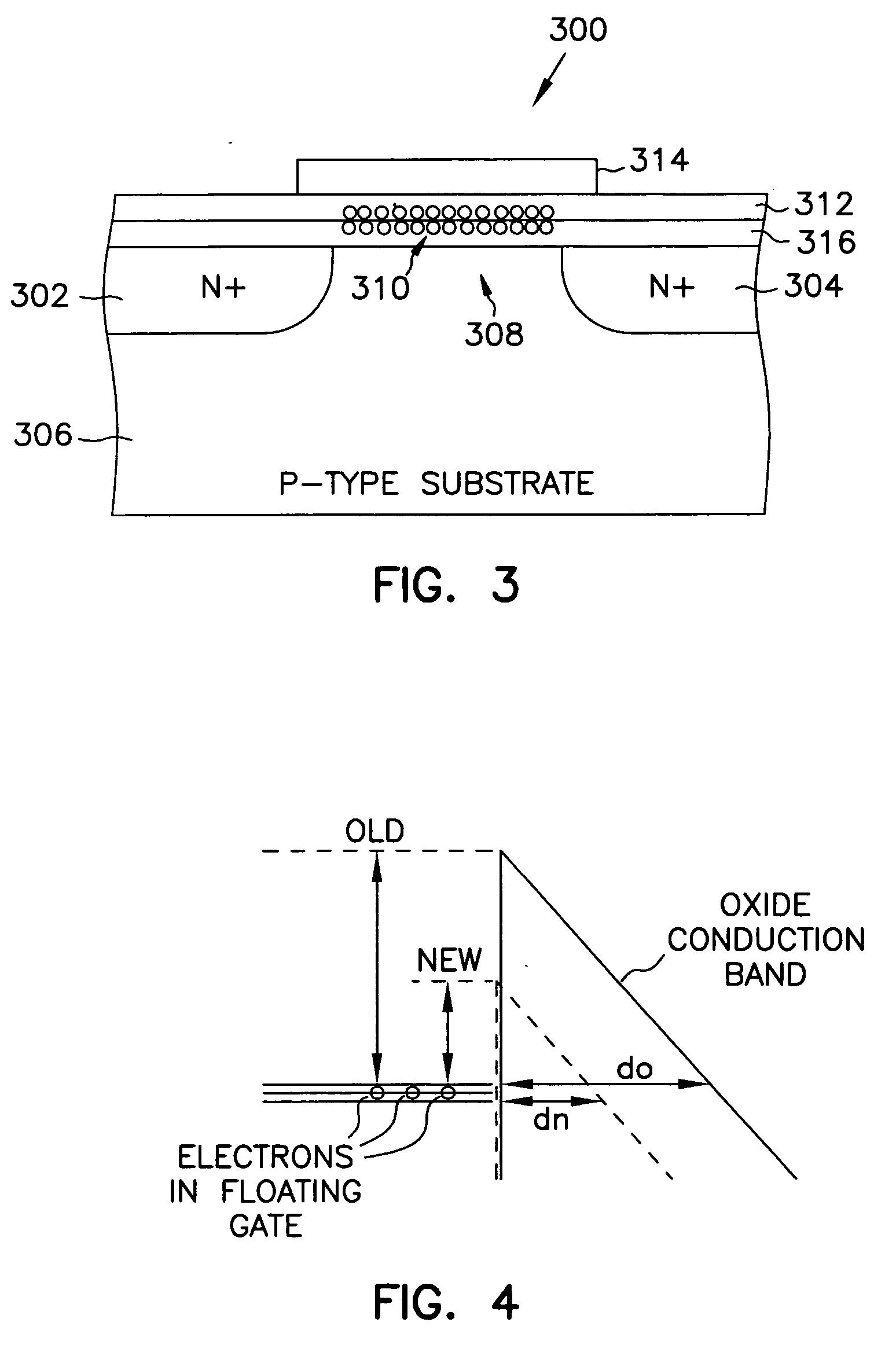

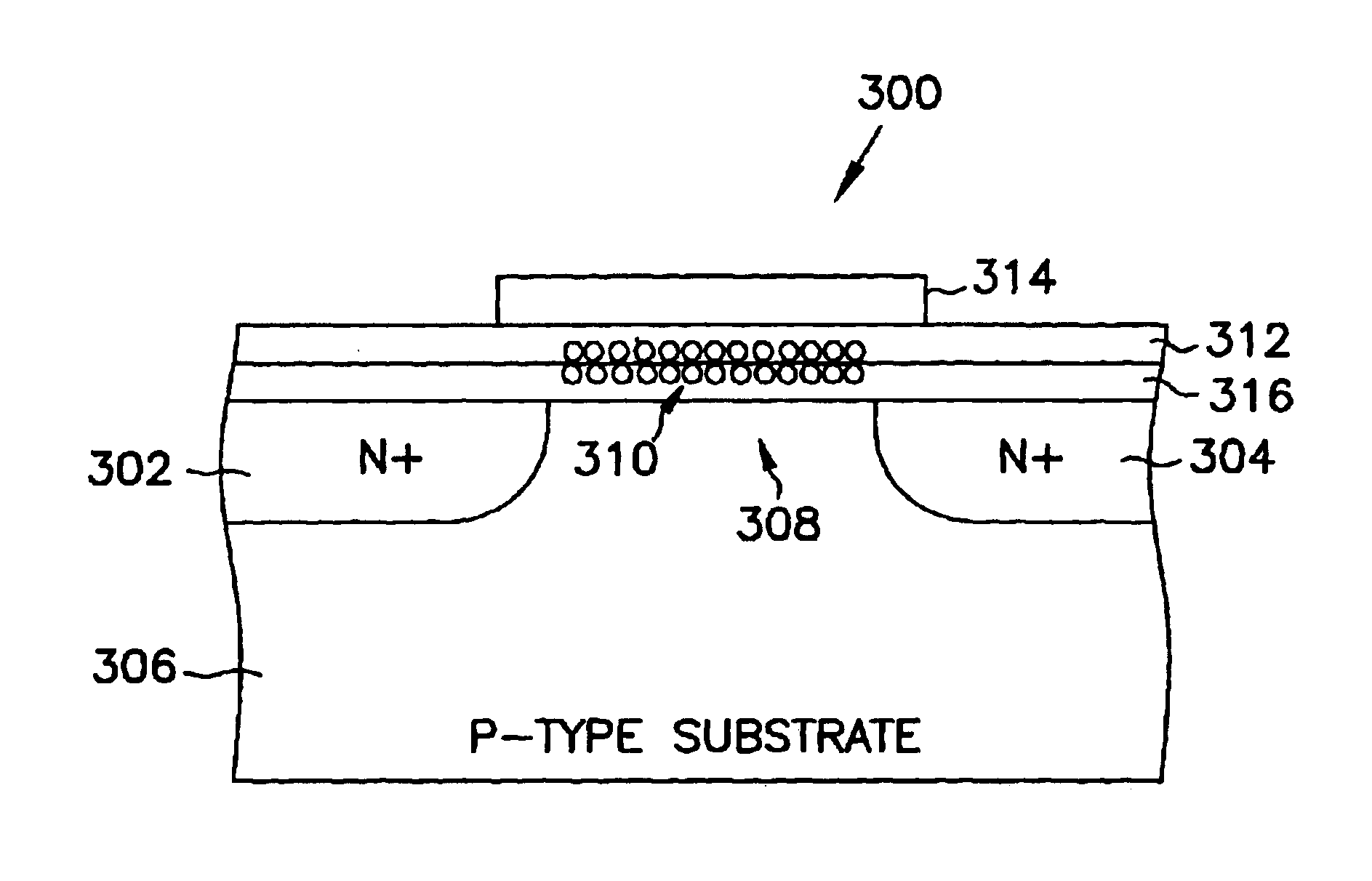

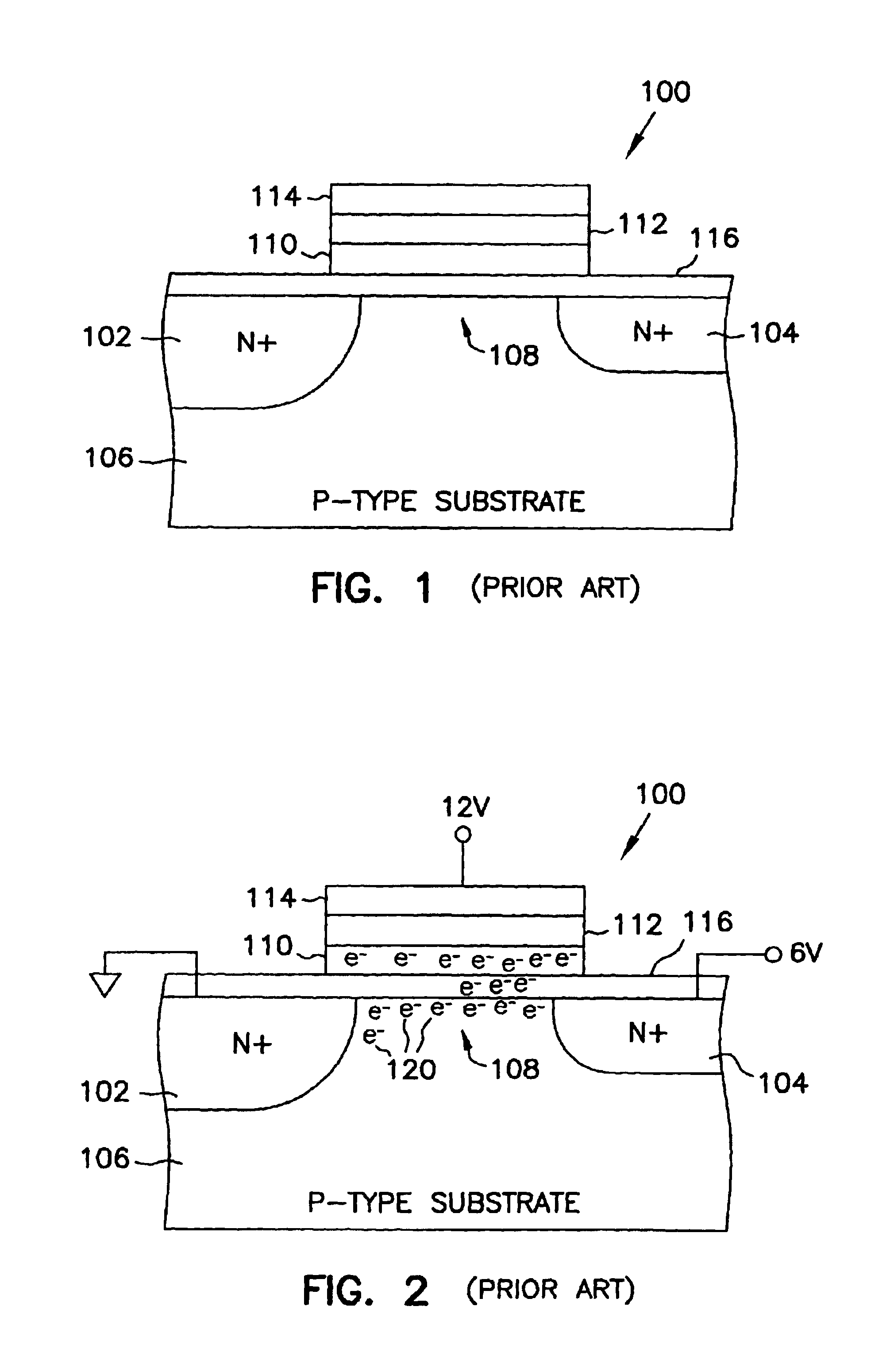

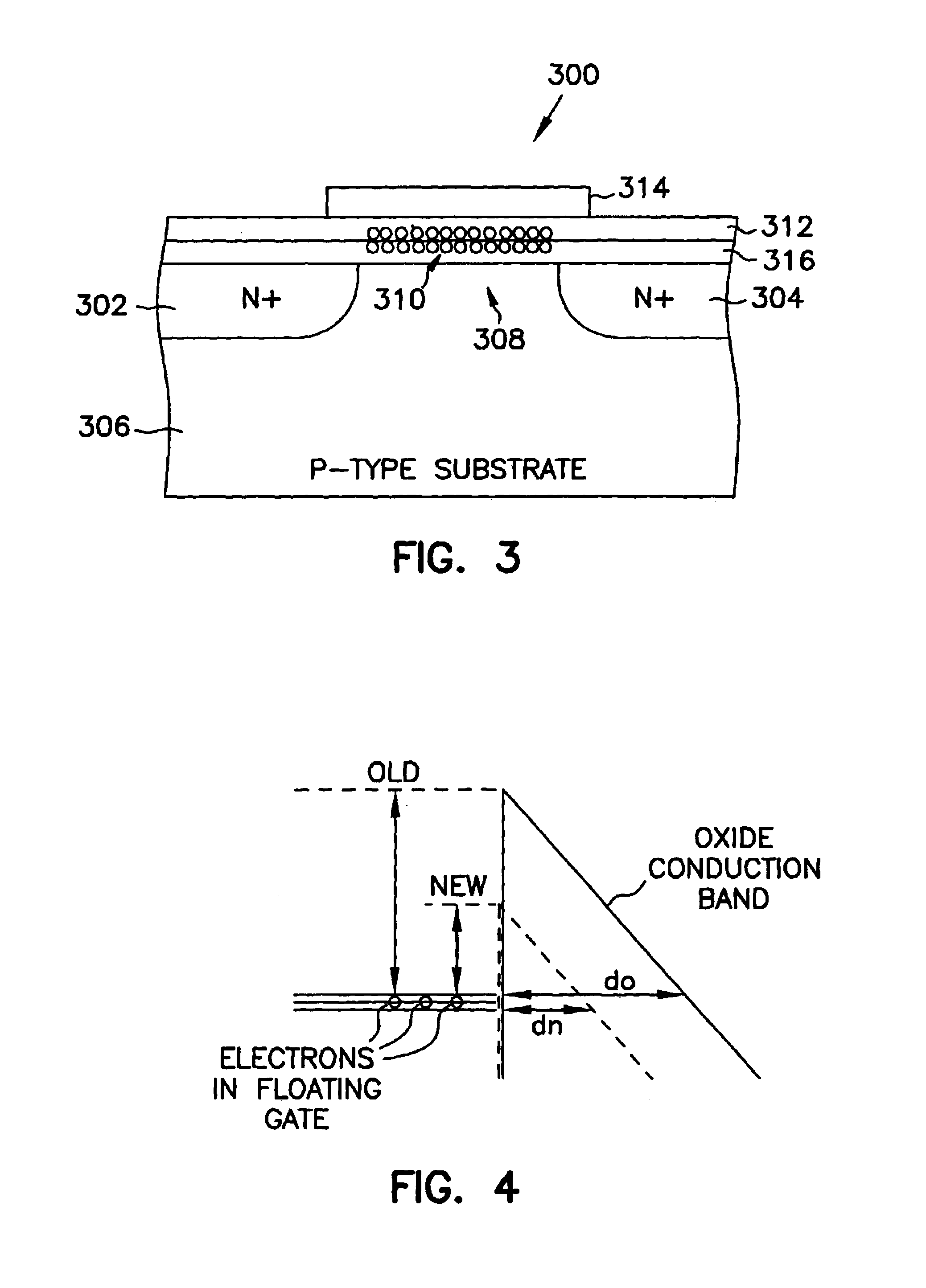

Transistor with nanocrystalline silicon gate structure

A memory is described which has memory cells that store data using hot electron injection. The data is erased through electron tunneling. The memory cells are described as floating gate transistors wherein the floating gate is fabricated using a conductive layer of nanocrystalline silicon particles. Each nanocrystalline silicon particle has a diameter of about 10 Å to 100 Å. The nanocrystalline silicon particles are in contact such that a charge stored on the floating gate is shared between the particles. The floating gate has a reduced electron affinity to allow for data erase operations using lower voltages.

Owner:MICRON TECH INC

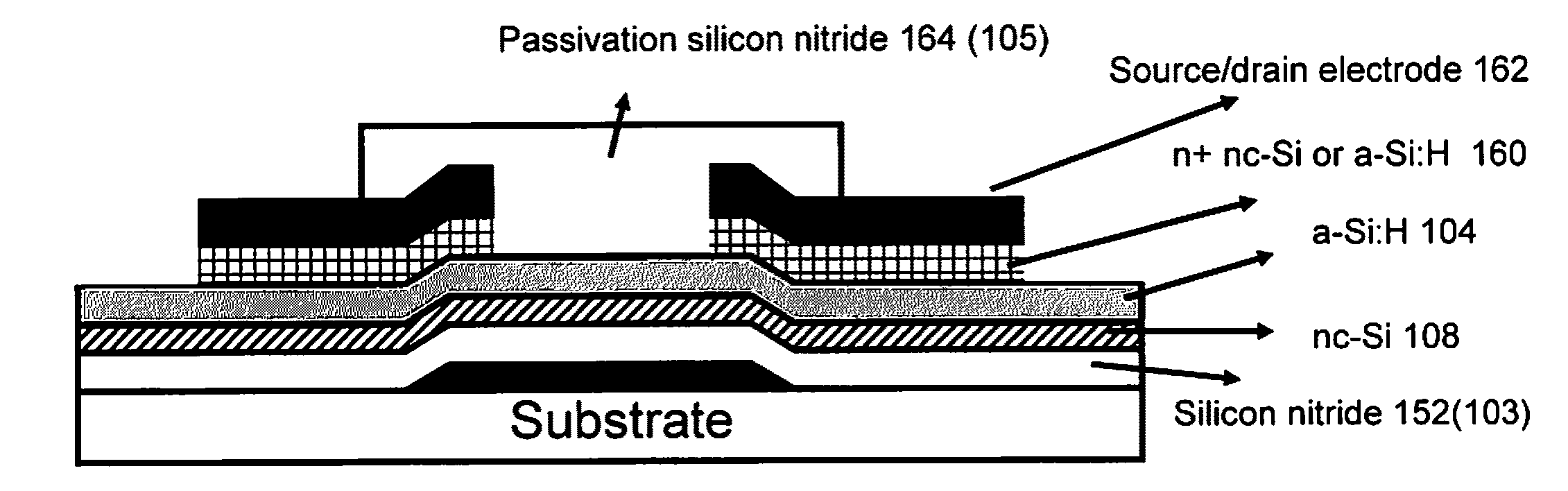

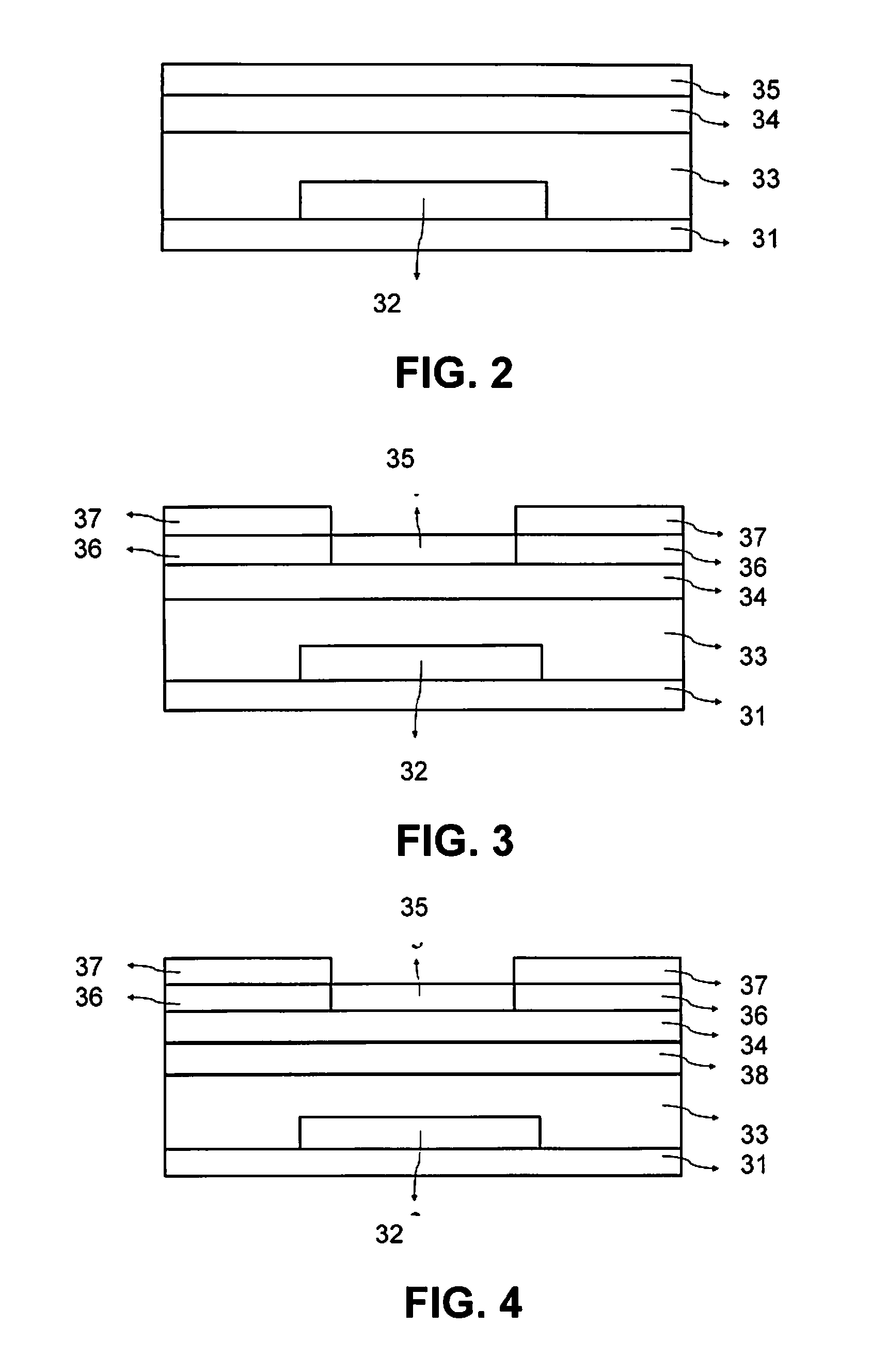

Thin film transistor and method for forming the same

InactiveUS20090212287A1Off-current can be reducedTransistorSemiconductor/solid-state device manufacturingGate dielectricNanocrystalline silicon

A thin film transistor (TFT) and the method of forming the same is provided. The method of forming the TFT on a surface of a substrate, includes the steps of: forming a gate electrode; deposing a gate dielectric on the gate electrode; forming a nanocrystalline silicon (nc-Si) layer and an amorphous silicon (a-Si:H) layer above the gate dielectric, so that the thickness of the nc-Si layer is less than 30 nm thereby reducing off-current; and forming a source / drain electrode. The TFT includes: a gate electrode on a substrate, a gate dielectric on the gate electrode; a nc-Si layer having a thickness less than 30 nm, thereby reducing off-current; an a-Si:H layer; and a source / drain electrode.

Owner:IGNIS INNOVATION

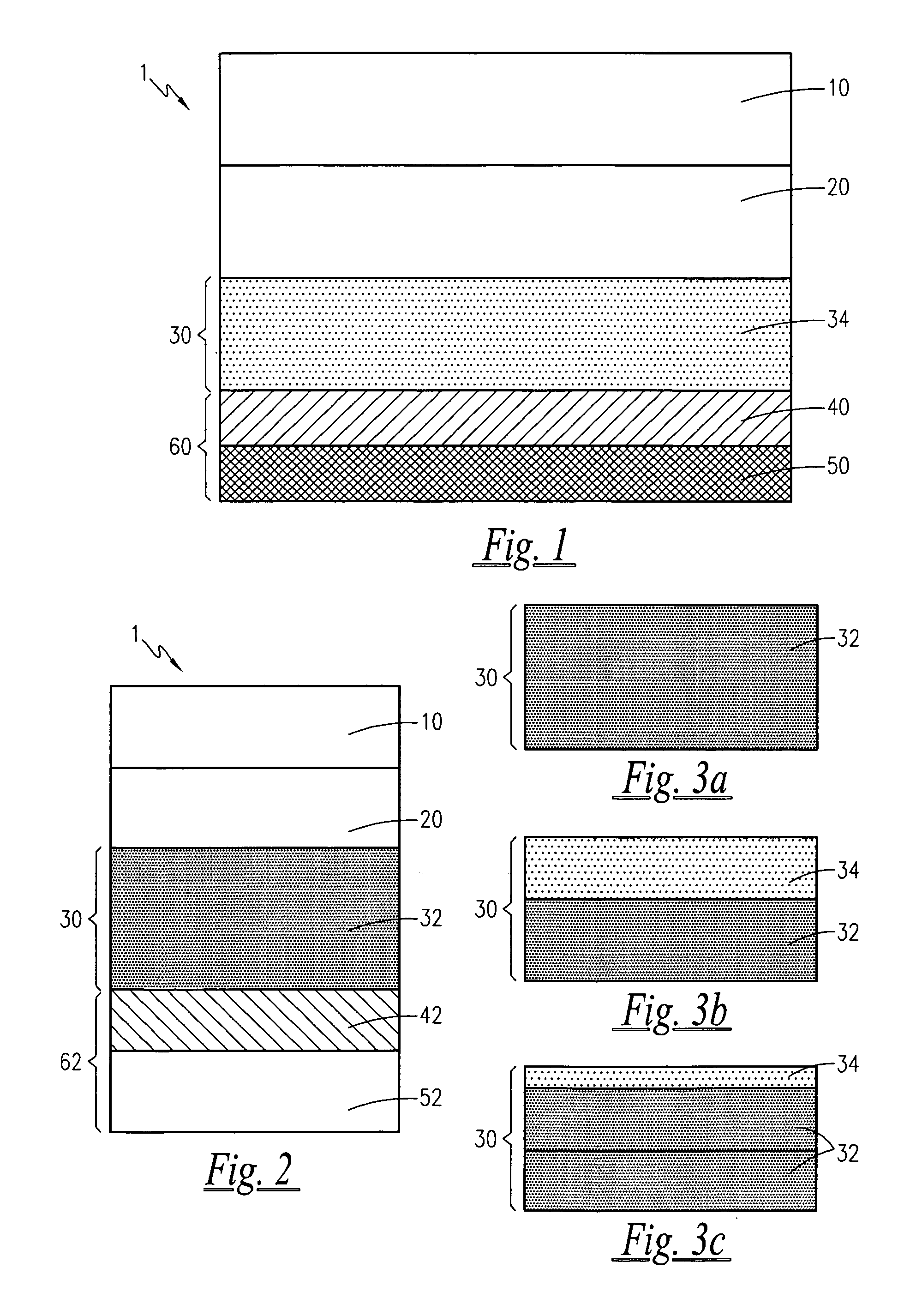

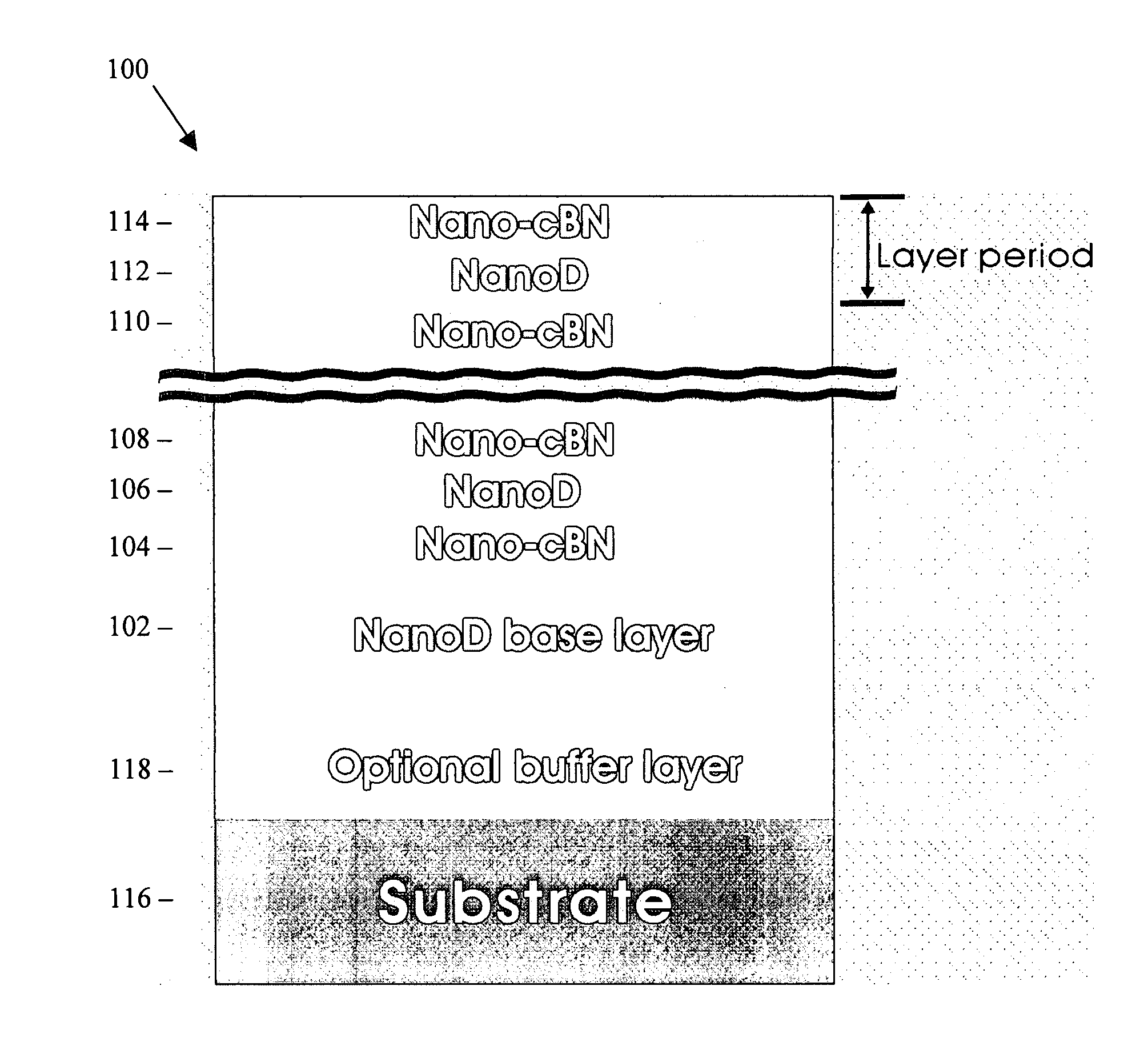

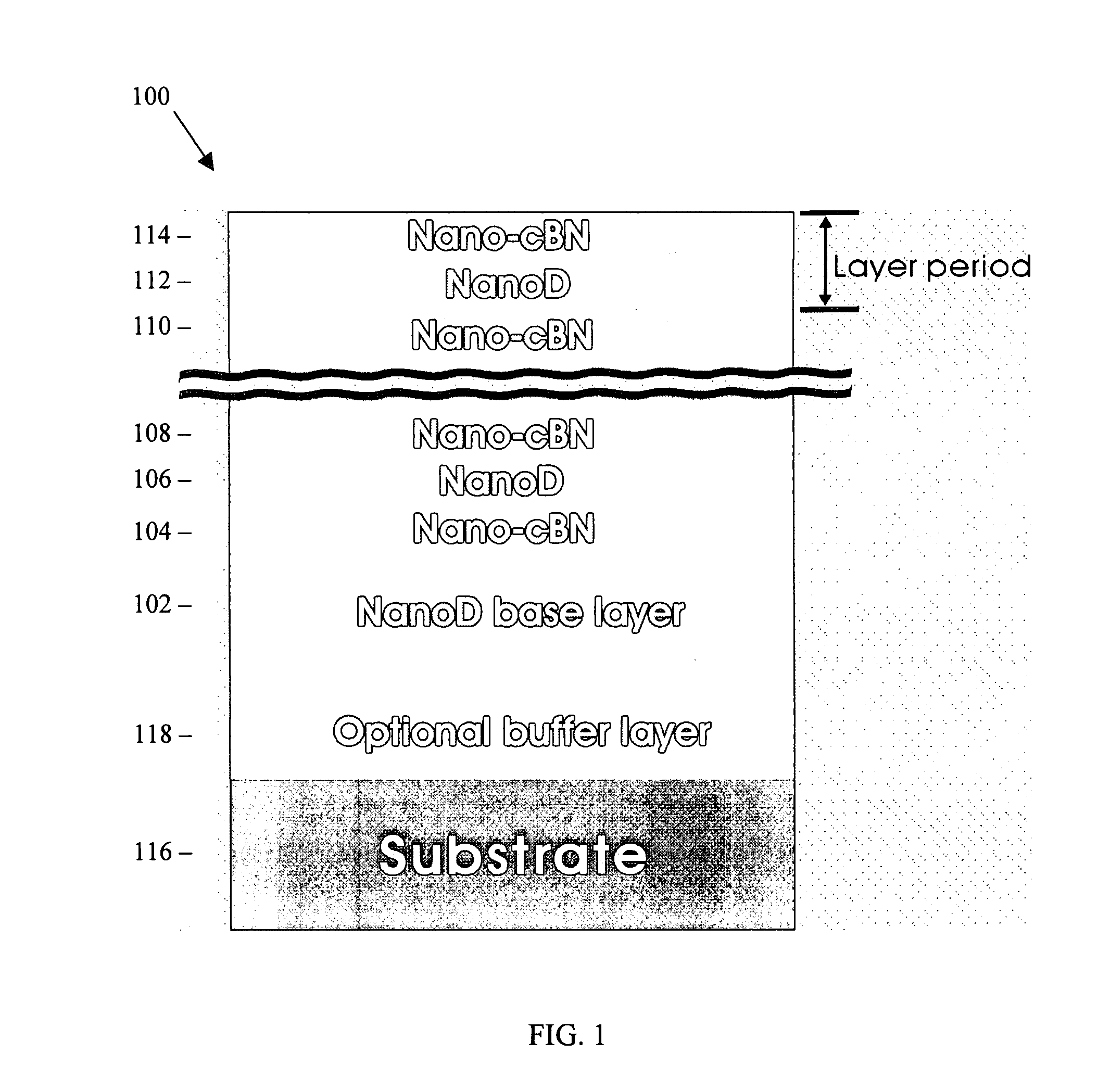

Ultrahard multilayer coating comprising nanocrystalline diamond and nanocrystalline cubic boron nitride

A multilayer coating (MLC) is composed of two chemically different layered nanocrystalline materials, nanodiamond (nanoD) and nano-cubic boron nitride (nono-cBN). The structure of the MLC and fabrication sequence of layered structure are disclosed. The base layer is preferably nanoD and is the first deposited layer serving as an accommodation layer on a pretreated substrate. It can be designed with a larger thickness whereas subsequent alternate nano-cBN and nanoD layers are typically prepared with a thickness of 2 to 100 nm. The thickness of these layers can be engineered for a specific use. The deposition of the nanoD layer, by either cold or thermal plasma CVD, is preceded by diamond nucleation on a pretreated and / or precoated substrate, which has the capacity to accommodate the MLC and provides excellent adhesion. Nano-cBN layers are directly grown on nanodiamond crystallites using ion-assisted physical vapor deposition (PVD) and ion-assisted plasma enhanced chemical vapor deposition (PECVD), again followed by nanodiamond deposition using CVD methods in cycles until the intended number of layers of the MLC is obtained.

Owner:CITY UNIVERSITY OF HONG KONG

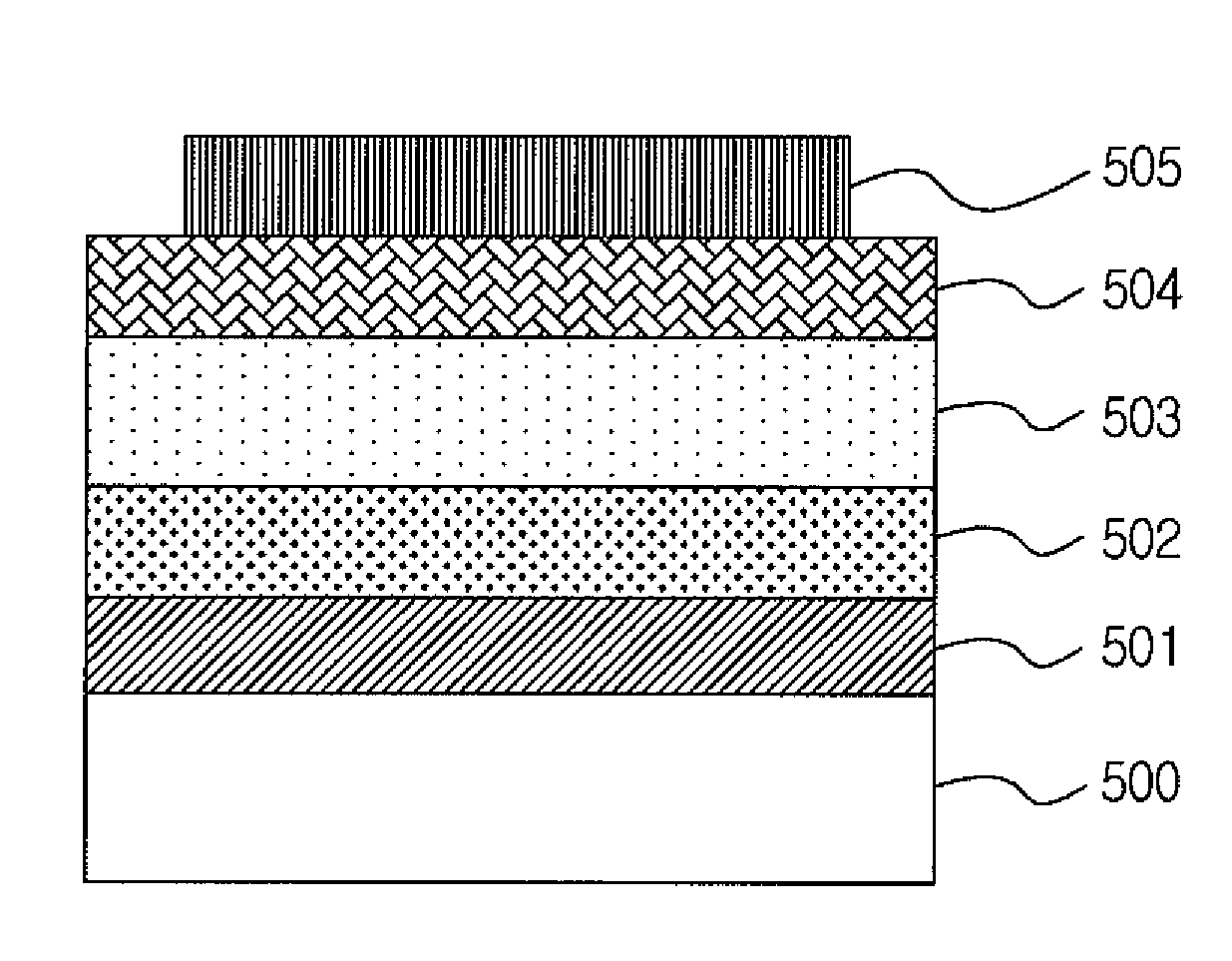

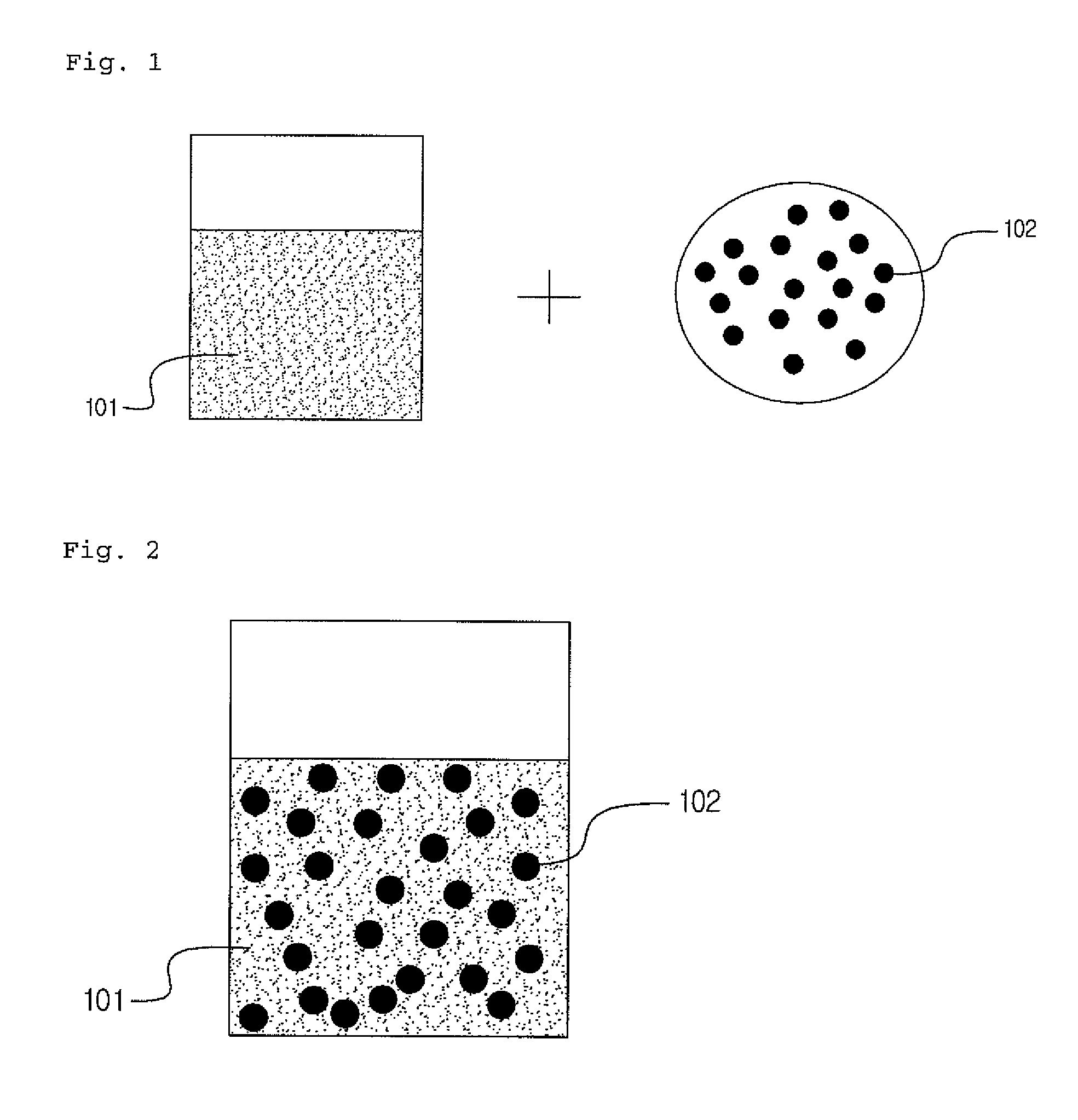

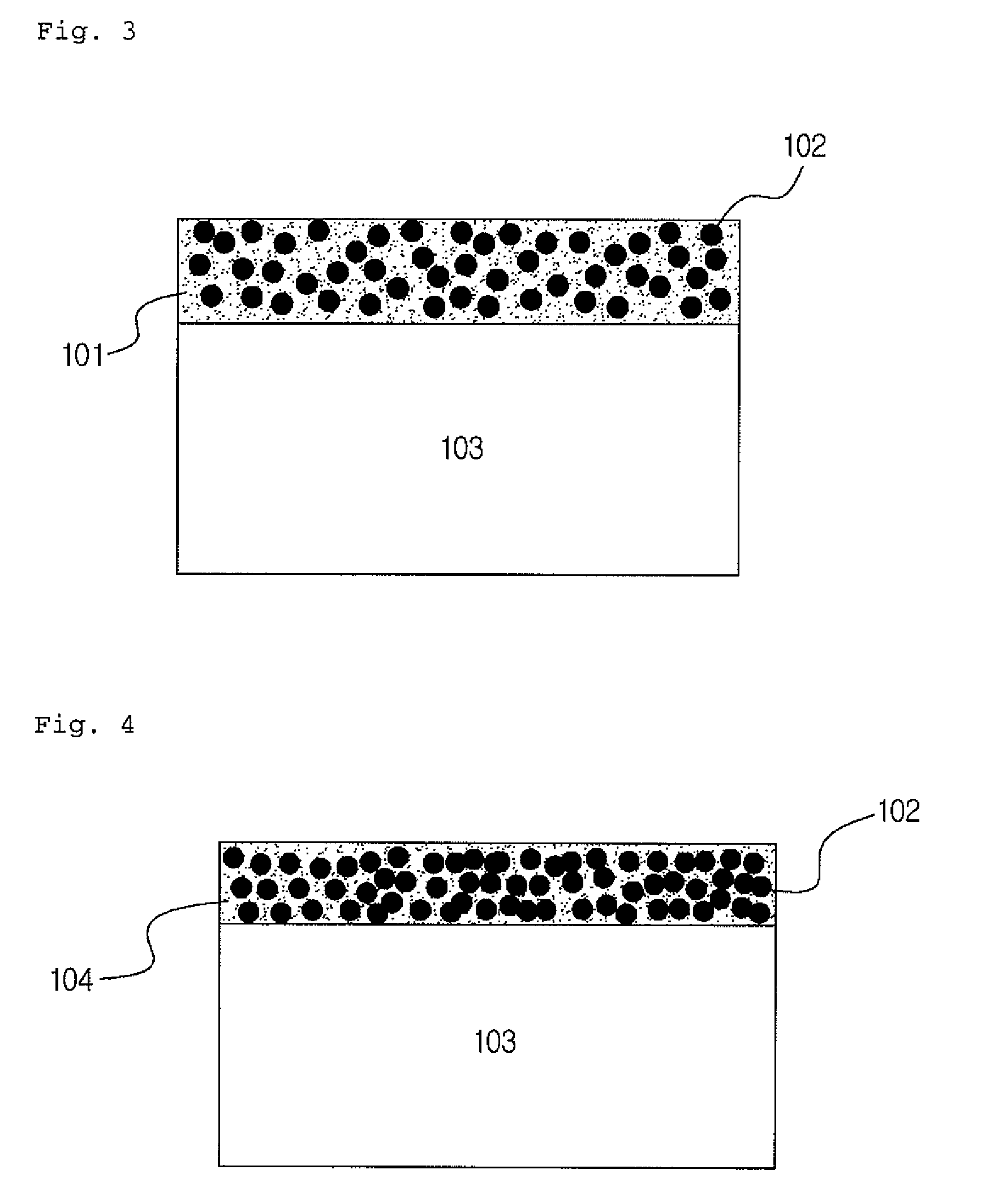

Solar cell manufactured using amorphous and nanocrystalline silicon composite thin film, and process for manufacturing the same

InactiveUS20090071539A1Improve photoelectric conversion efficiencyReduce defectsMaterial nanotechnologyFinal product manufactureComposite filmNanoparticle

Disclosed are a solar cell manufactured using a composite thin film comprising amorphous silicon and nanocrystalline silicon, a method of manufacturing the solar cell, and a composition for the composite thin film used in manufacturing the solar cell. More particularly, a silicon semiconductor layer in the solar cell is fabricated by using the composite thin film comprising the amorphous silicon and the nanocrystalline silicon, the composite thin film being formed by dispersing nanoparticles of the crystalline silicon in a liquid silicon precursor and modifying them.The solar cell of the present invention is manufactured by dispersing the crystalline silicon nanoparticles in the liquid silicon precursor, coating the dispersion on a substrate or printing the substrate with the dispersion, and heating the coated or printed substrate to modify the liquid silicon precursor into the amorphous silicon.According to the present invention, any expensive equipment requiring alternative complicated installations is not needed to form a composite thin film comprising both of amorphous silicon and crystalline silicon. In addition, it is possible to form a composite thin film comprising plural materials with different band gap energy which can remarkably improve conversion efficiency of a solar cell by using a liquid precursor and nanocrystalline particles in a solution process with low production cost.

Owner:LG ELECTRONICS INC

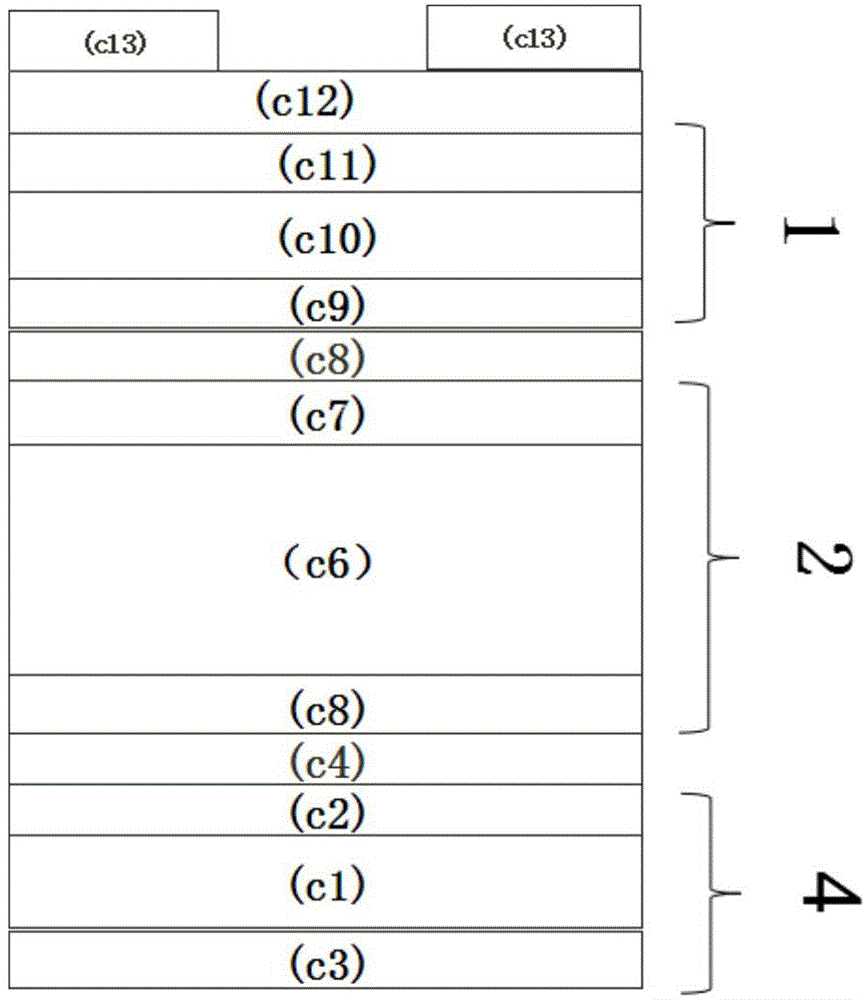

Lamination solar battery

ActiveCN104979421AWide spectral response rangeAct as a barrierPhotovoltaic energy generationSemiconductor devicesUltraviolet lightsNanocrystalline silicon

The invention relates to a lamination solar battery. The lamination solar battery is composed of an amorphous silicon film top battery, a perovskite middle battery and a nanocrystalline silicon bottom battery, or has a double-lamination structure taking an amorphous silicon film battery as a top battery and a perovskite battery as a bottom battery. The optical band gaps of three materials, i.e., amorphous silicon, perovskite and nanocrystalline silicon (crystalline silica) match well (1.75eV, 1.5eV and 1.12eV) so that light of different wavebands can be absorbed segment by segment. The amorphous silicon film top battery and the nanocrystalline silicon bottom battery (or the crystalline silica, nanocrystalline silicon germanium and amorphous silicon germanium) clamp the perovskite therebetween so as to protect the perovskite battery and reduce the influence exerted by atmosphere and water on the perovskite battery. At the same time, the amorphous silicon top battery can absorb ultraviolet light so as to protect a perovskite sub-battery. Besides, an amorphous silicon layer at the top has better UV and blue light response than the perovskite battery so that the defects of the perovskite middle battery are made up for.

Owner:DALIAN INST OF CHEM PHYSICS CHINESE ACAD OF SCI

Transistor with nanocrystalline silicon gate structure

A memory is described which has memory cells that store data using hot electron injection. The data is erased through electron tunneling. The memory cells are described as floating gate transistors wherein the floating gate is fabricated using a conductive layer of nanocrystalline silicon particles. Each nanocrystalline silicon particle has a diameter of about 10 Å to 100 Å. The nanocrystalline silicon particles are in contact such that a charge stored on the floating gate is shared between the particles. The floating gate has a reduced electron affinity to allow for data erase operations using lower voltages.

Owner:MICRON TECH INC

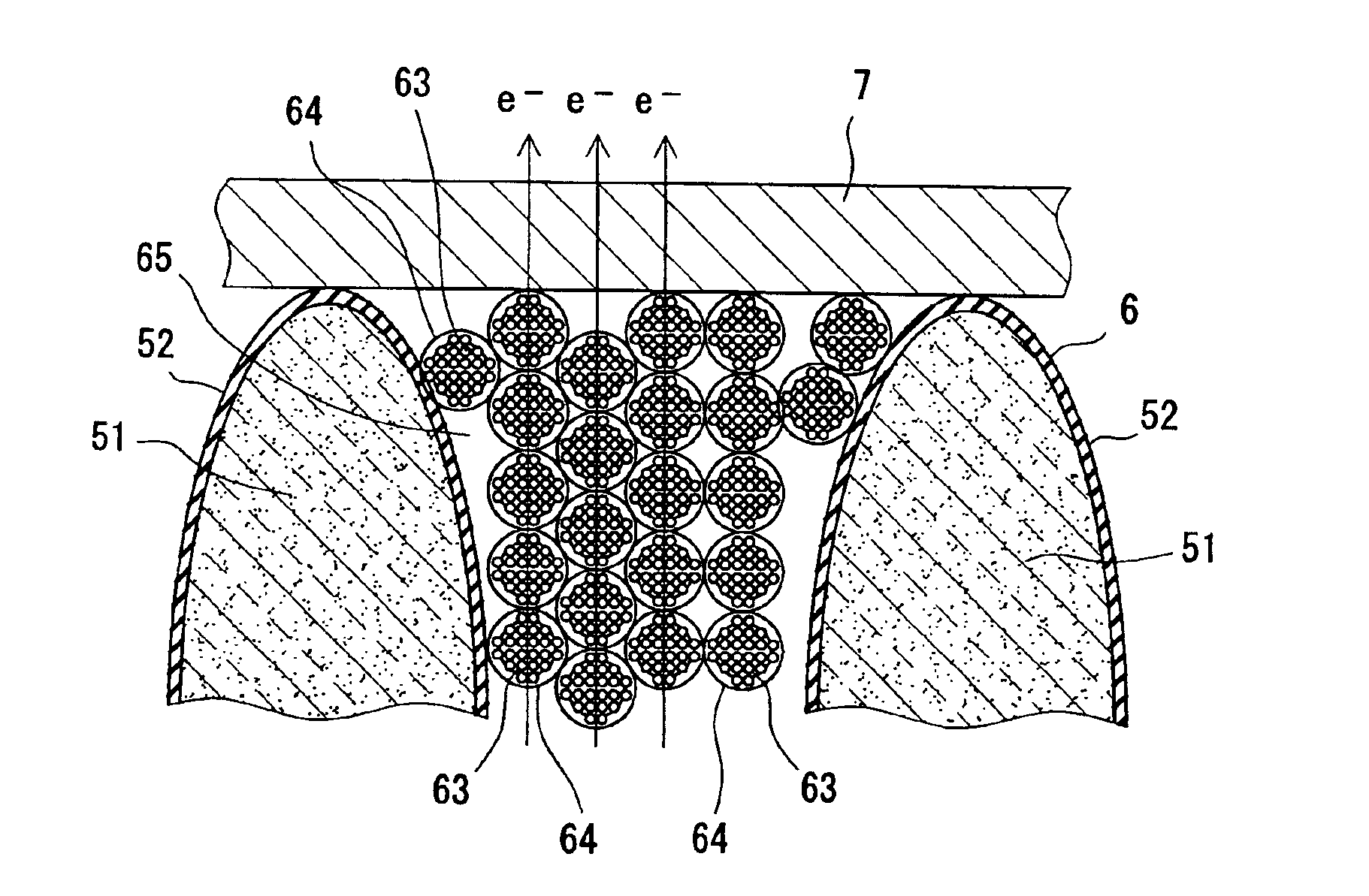

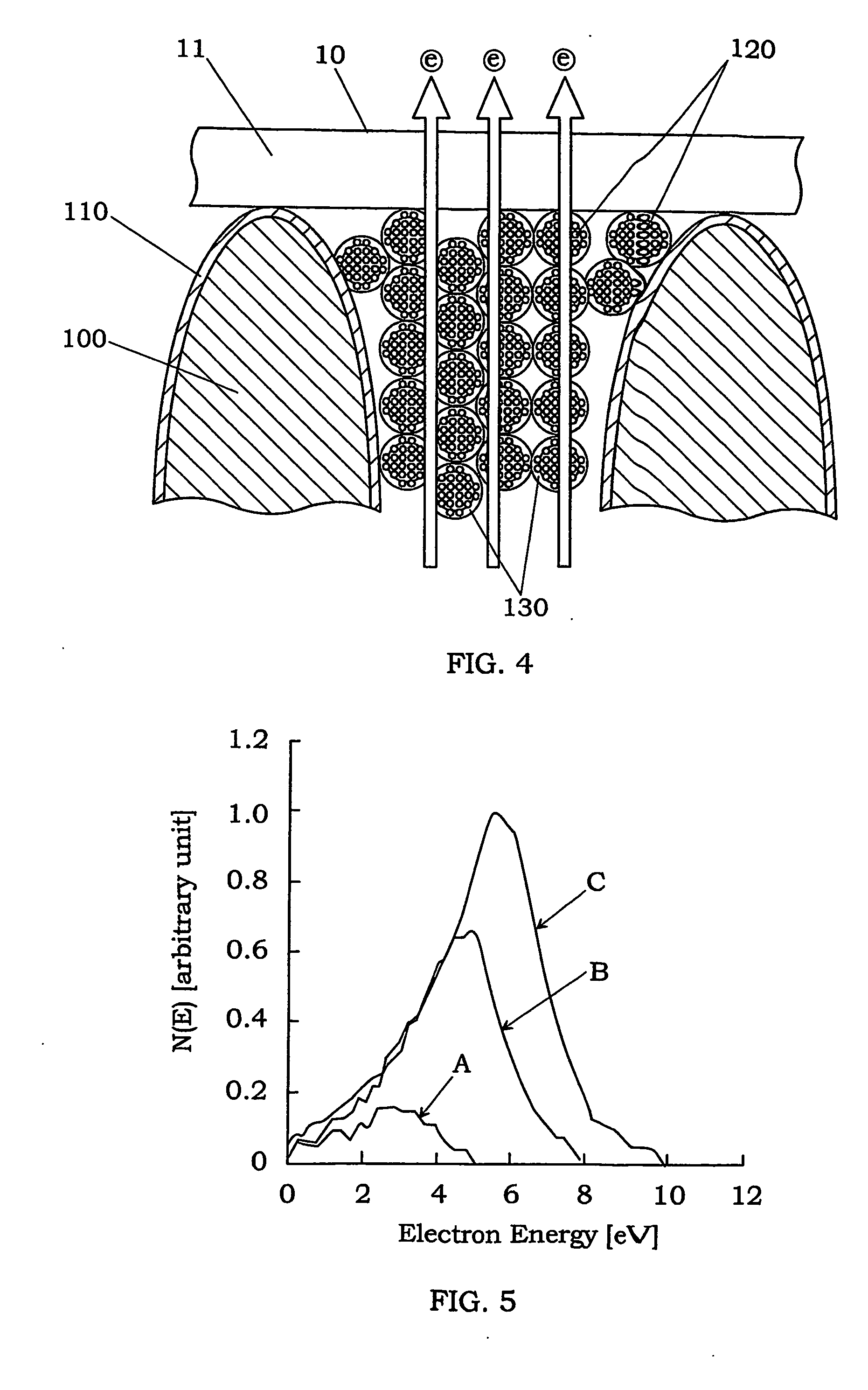

Quantum device

InactiveUS6940087B2Increased durabilityIndividual molecule manipulationNanoinformaticsElectron sourceNanocrystalline silicon

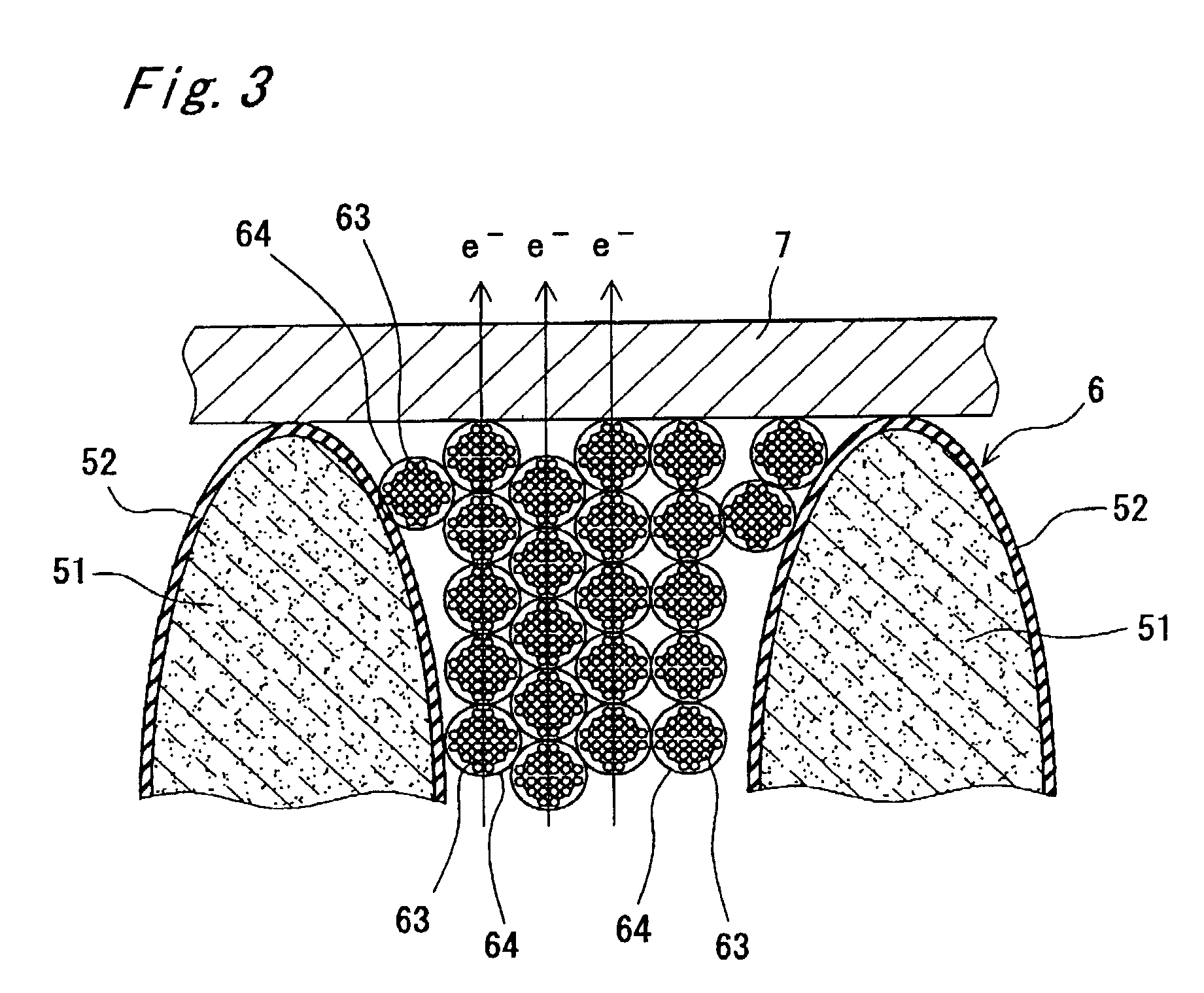

Disclosed is an electron source 10 including an electron source element 10a formed on the side of one surface of an insulative substrate 1. The electron source element 10a includes a lower electrode 2, a composite nanocrystal layer 6 and a surface electrode 7. The composite nanocrystal layer 6 includes a plurality of polycrystalline silicon grains 51, a thin silicon oxide film 52 formed over the surface of each of the grains 51, a number of nanocrystalline silicons 63 residing between the adjacent grains 51, and a silicon oxide film 64 formed over the surface of each of the nanocrystalline silicons 63. The silicon oxide film 64 is an insulating film having a thickness less than the crystal grain size of the nanocrystalline silicon 63. The surface electrode 7 is formed of a carbon thin film 7a laminated on the composite nanocrystal layer 6 while being in contact therewith, and a metal thin film 7b laminated on the carbon thin film 7a.

Owner:MATSUSHITA ELECTRIC WORKS LTD +1

Metal coated nanocrystalline silicon as an active surface enhanced raman spectroscopy (SERS) substrate

Owner:INTEL CORP

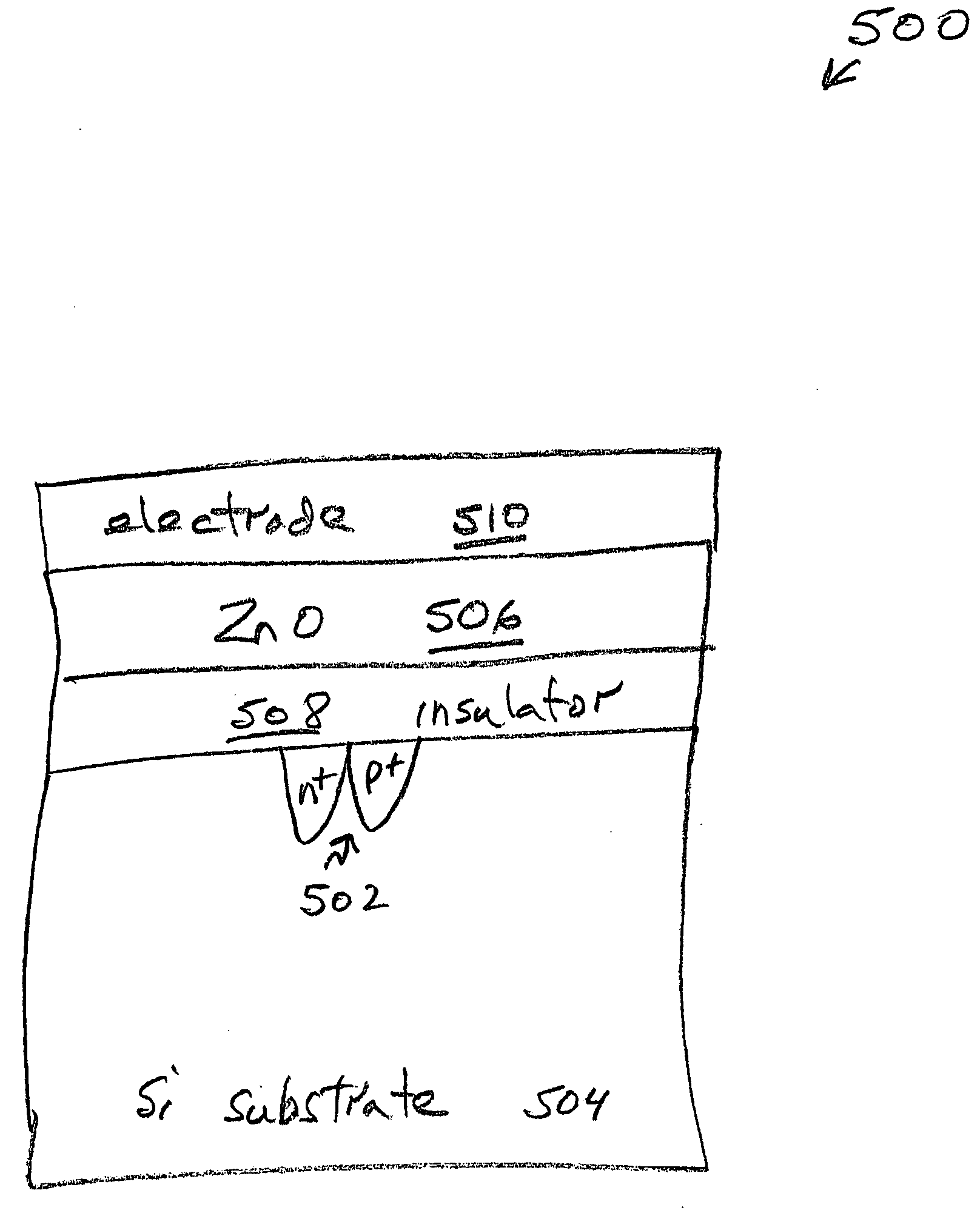

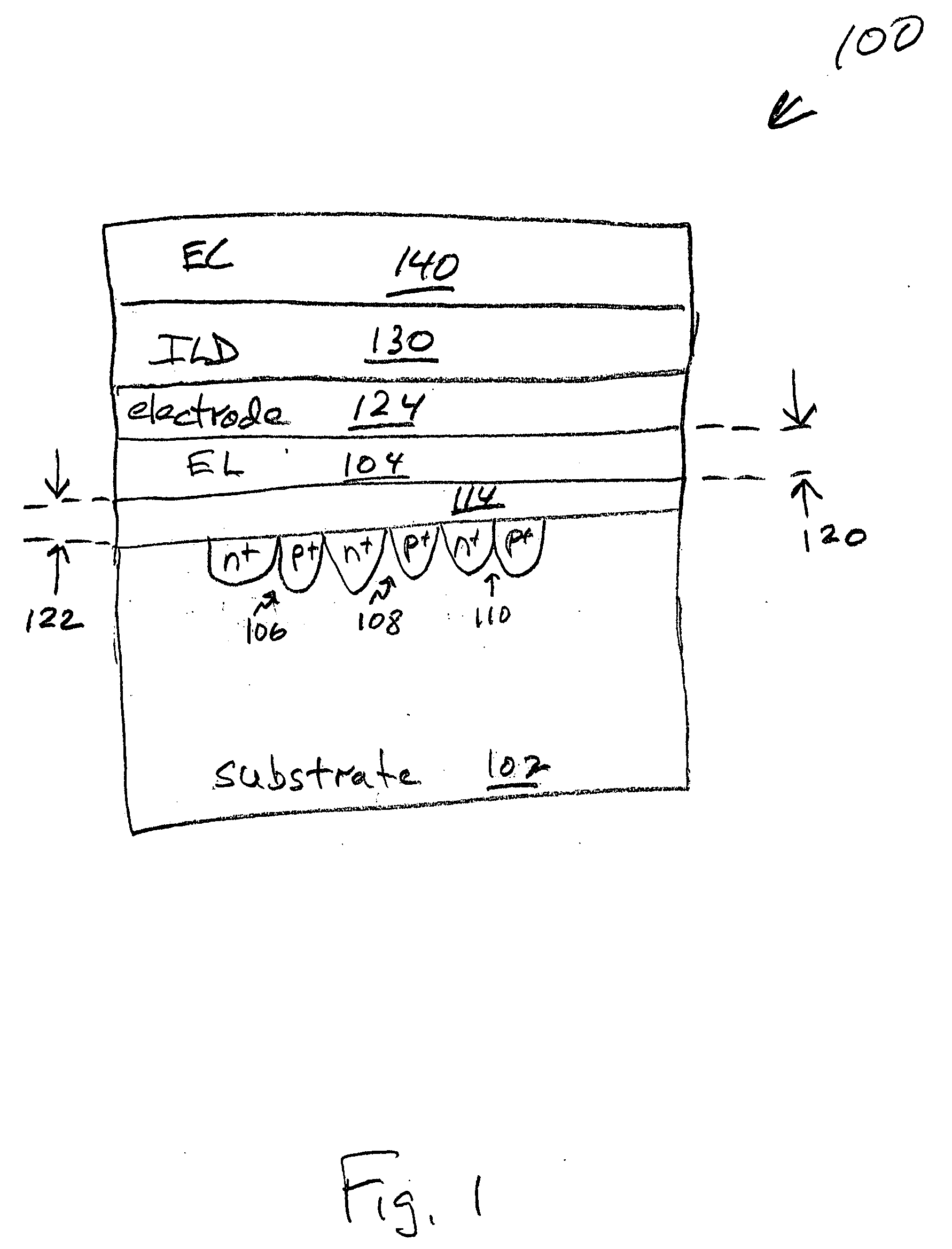

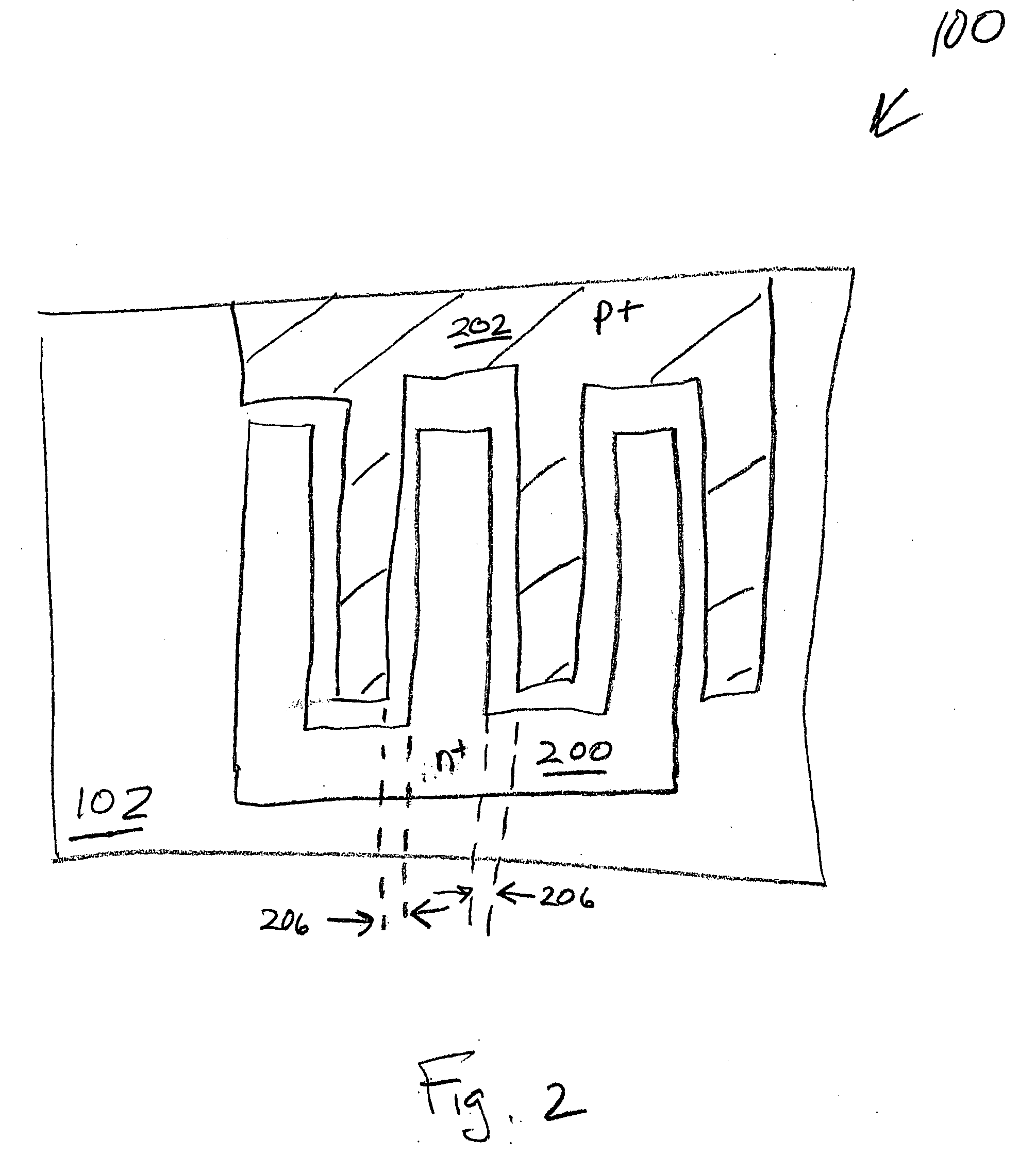

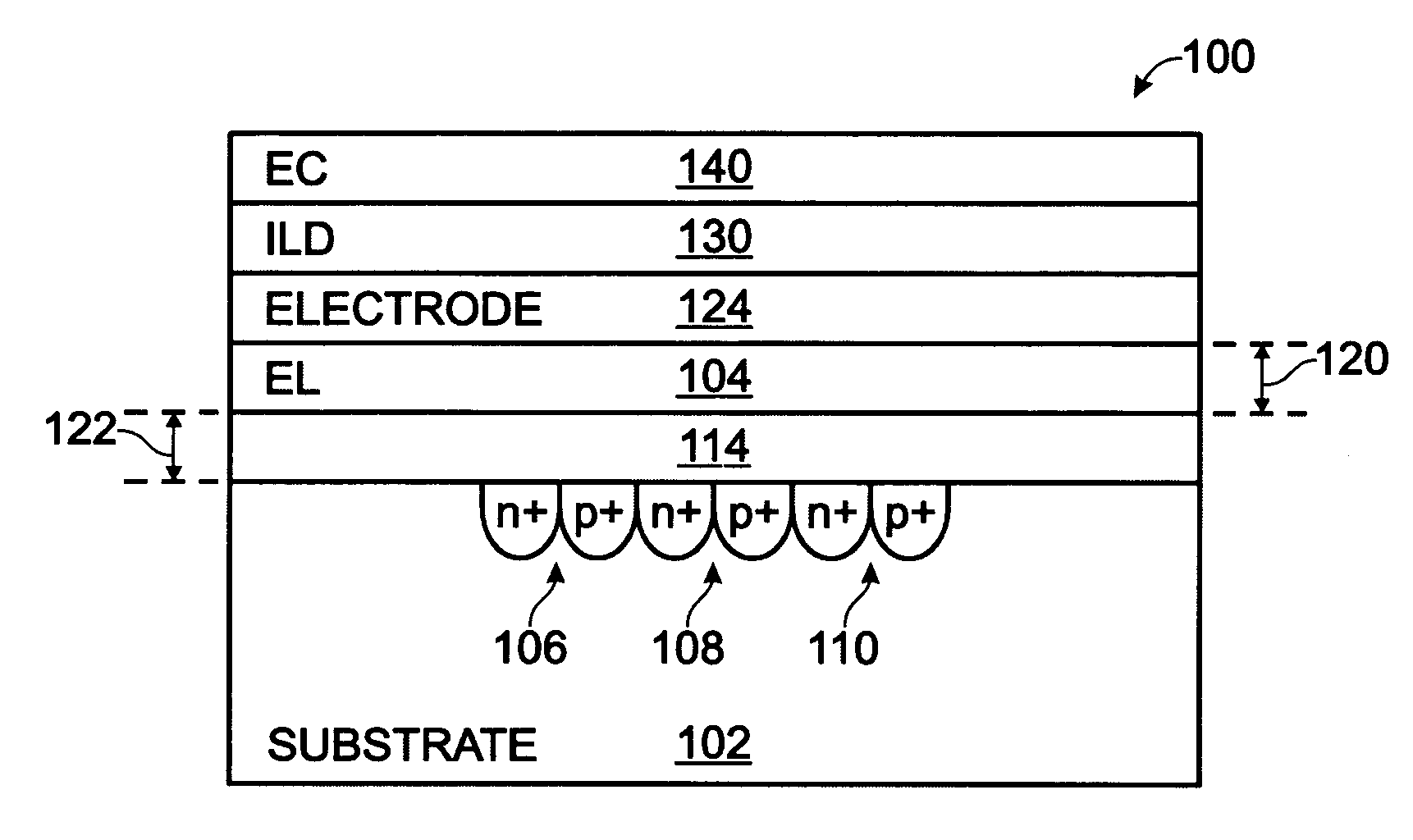

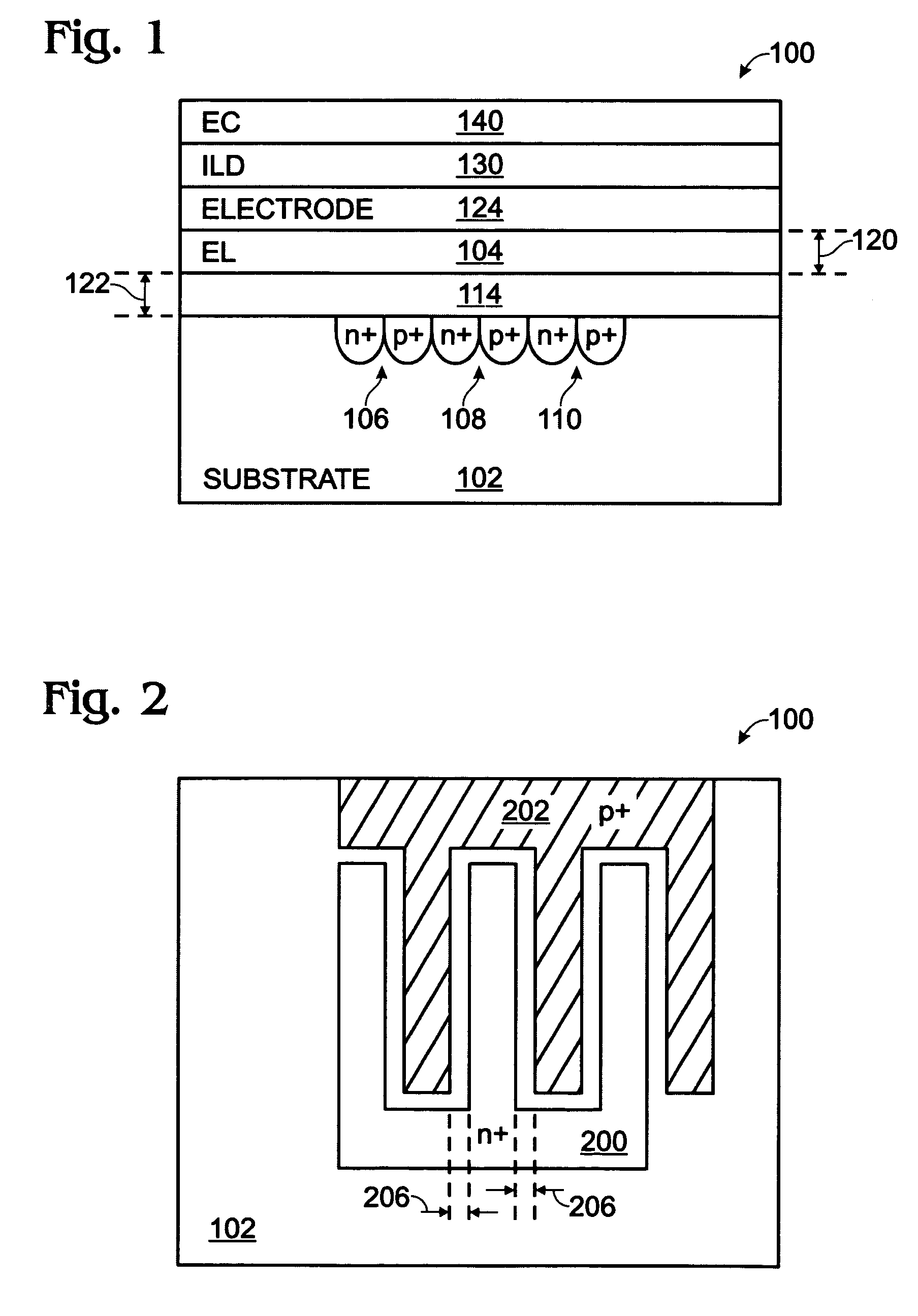

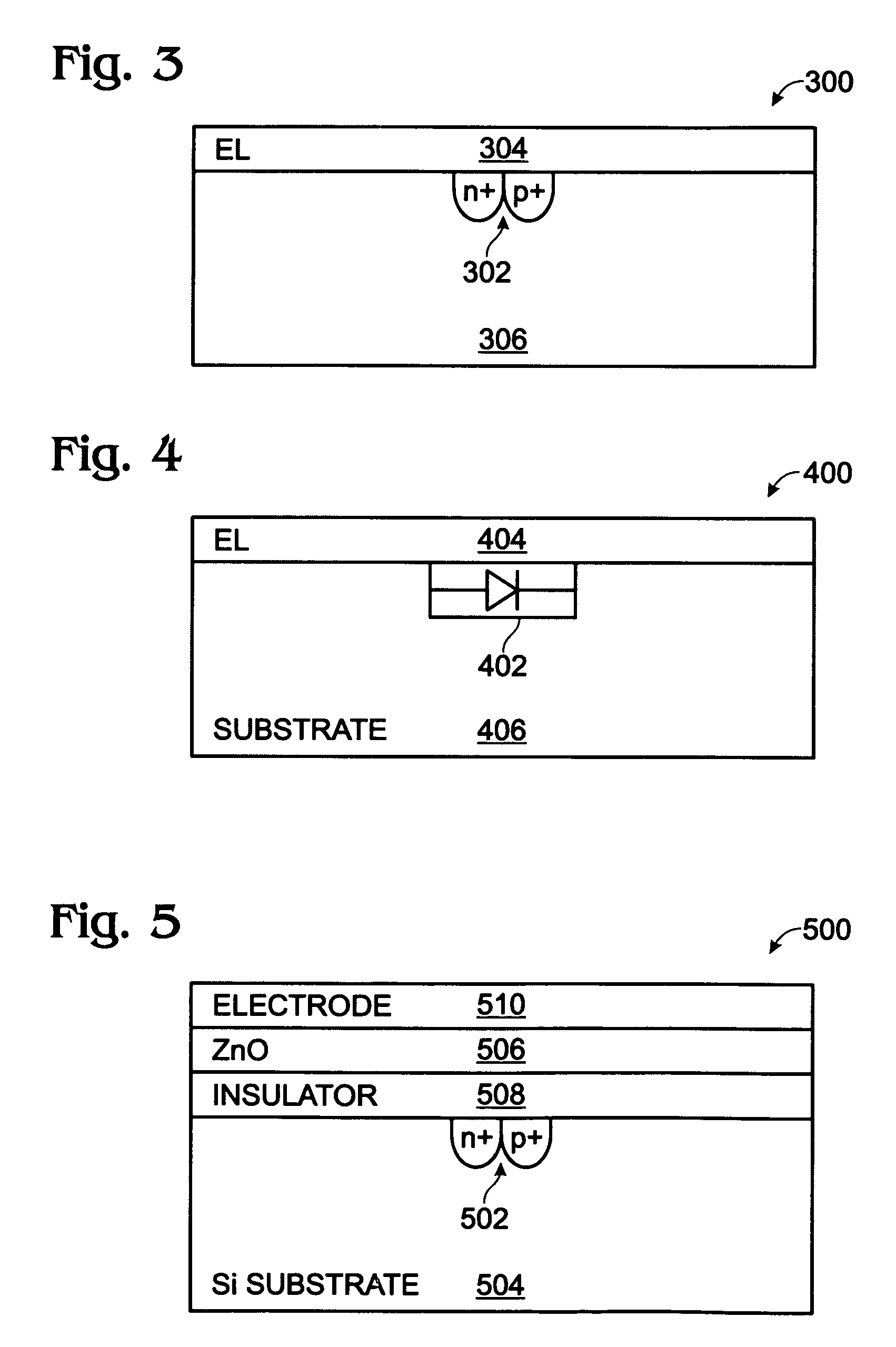

Electroluminescent device

InactiveUS20050253136A1Easy to operateFast fall timeNanotechSolid-state devicesFluorescent polymerSemiconductor materials

A method is provided for forming an electroluminescent device. The method comprises: providing a type IV semiconductor material substrate; forming a p+ / n+ junction in the substrate, typically a plurality of interleaved p+ / n+ junctions are formed; and, forming an electroluminescent layer overlying the p+ / n+ junction(s) in the substrate. The type IV semiconductor material substrate can be Si, C, Ge, SiGe, or SiC. For example, the substrate can be Si on insulator (SOI), bulk Si, Si on glass, or Si on plastic. The electroluminescent layer can be a material such as nanocrystalline Si, nanocrystalline Ge, fluorescent polymers, or type II-VI materials such as ZnO, ZnS, ZnSe, CdSe, and CdS. In some aspect, the method further comprises forming an insulator film interposed between the substrate and the electroluminescent layer. In another aspect, the method comprises forming a conductive electrode overlying the electroluminescent layer.

Owner:SHARP KK

Doped semiconductor nanocrystalline quantum dots having core-shell structure and preparation method thereof

ActiveCN103450904AHigh fluorescence efficiencyImprove quantum efficiencyMaterial nanotechnologyNanoopticsFluorescenceSolar cell

The invention provides a doped semiconductor nanocrystalline quantum dot having a core-shell structure and a preparation method thereof. The quantum dot comprises a nanocrystalline core doped with Mn and a shell layer; the composition of the nanocrystalline core is MnzZn[1-z]SexS[1-x], and the composition of the shell layer is ZnSeyS[1-y], wherein x is greater than 0 or less than or equal to 1, y is greater than or equal to 0 and less than 1 and z is greater than 0 or less than or equal to 0.5; the dimension of the nanocrystalline core is 2-15 nm, and the dimension of the shell layer is 2-15 nm; the emission wavelength of the nanocrystalline quantum dot ranges from 590 to 630 nm. The fluorescence emission wavelength of the quantum dots is continuously adjustable in the range from 590 to 630 nm; as a result, the quantum dots cover the shortage of non-cadmium-doped nanocrystalline in emission wavelength, and have high fluorescence and quantum efficiency, as well as good air, temperature and optical stability; the quantum dots are good in absorption in blue and purple zones and have no self-absorption within other visible light wavelengths; the quantum dots contain no toxic metal and can be widely applied to the fields such as solid-stable lighting, solar cell, biological-medical detection and the like.

Owner:NANJING TECH CORP LTD

Mehtod and apparatus for modifying object with electrons generated from cold cathode electron emitter

InactiveUS20060290291A1Low modification costSave energyStatic indicating devicesNanoinformaticsCold cathodeNanocrystalline silicon

Apparatus and method for modifying an object with electrons are provided, by which the object can be uniformly and efficiently modified with the electrons under a pressure substantially equal to atmospheric pressure even when having a relatively wide surface area to be treated. This method uses a cold-cathode electron emitter having the capability of emitting electrons from a planar electron emitting portion according to tunnel effect, and preferably comprising a pair of electrodes, and a strong field drift layer including nanocrystalline silicon disposed between the electrodes. The object is exposed to electrons emitted from the planar electron emitting portion by applying a voltage between the electrodes. It is preferred that an energy of the emitted electrons is selected from a range of 1 eV to 50 keV, and preferably 1 eV to 100 eV.

Owner:MATSUSHITA ELECTRIC WORKS LTD

Electroluminescent device

InactiveUS7208768B2Easy to operateFast rise and fall timeNanotechSolid-state devicesFluorescent polymerSemiconductor materials

A method is provided for forming an electroluminescent device. The method comprises: providing a type IV semiconductor material substrate; forming a p+ / n+ junction in the substrate, typically a plurality of interleaved p+ / n+ junctions are formed; and, forming an electroluminescent layer overlying the p+ / n+ junction(s) in the substrate. The type IV semiconductor material substrate can be Si, C, Ge, SiGe, or SiC. For example, the substrate can be Si on insulator (SOI), bulk Si, Si on glass, or Si on plastic. The electroluminescent layer can be a material such as nanocrystalline Si, nanocrystalline Ge, fluorescent polymers, or type II–VI materials such as ZnO, ZnS, ZnSe, CdSe, and CdS. In some aspect, the method further comprises forming an insulator film interposed between the substrate and the electroluminescent layer. In another aspect, the method comprises forming a conductive electrode overlying the electroluminescent layer.

Owner:SHARP KK

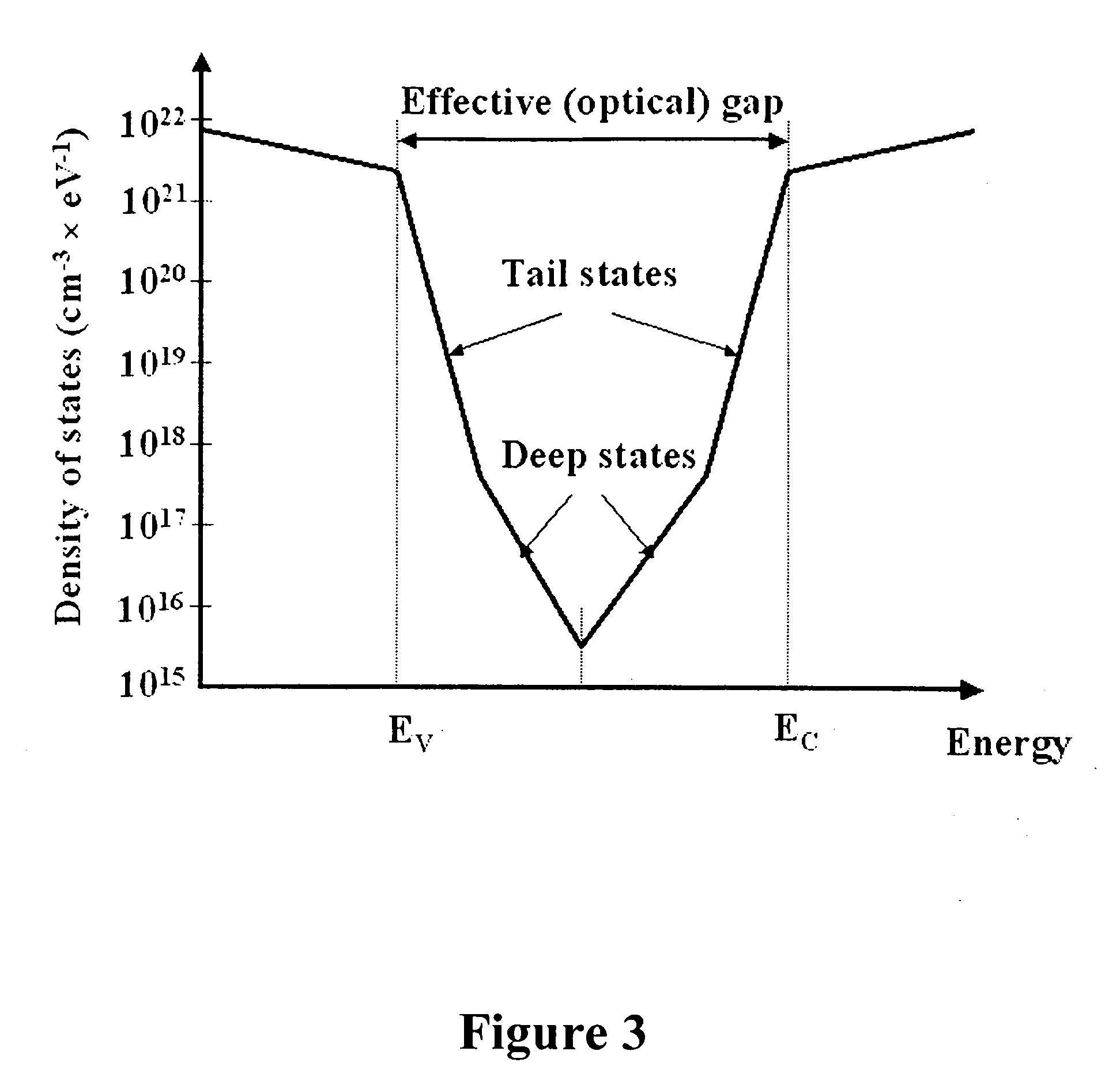

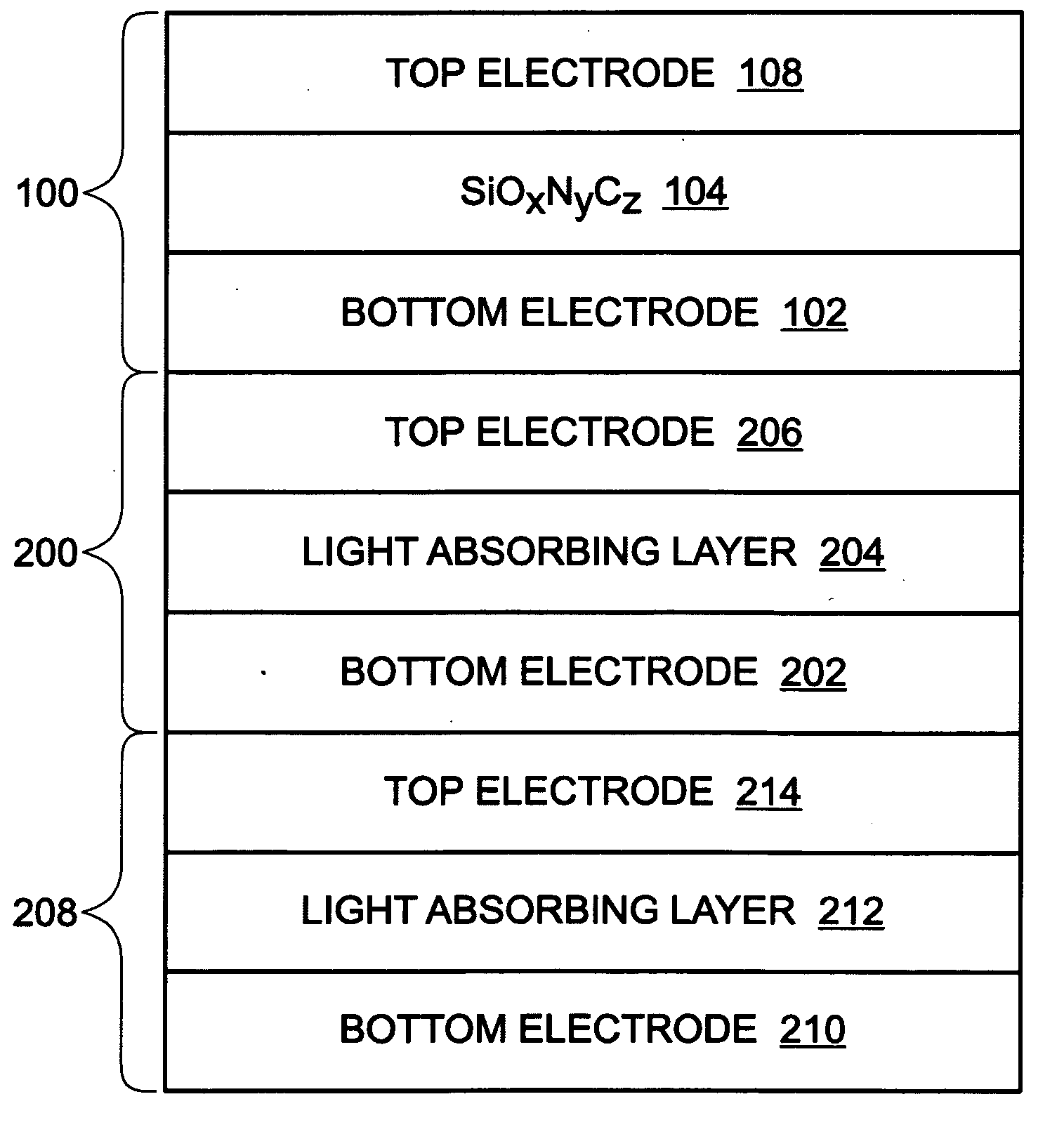

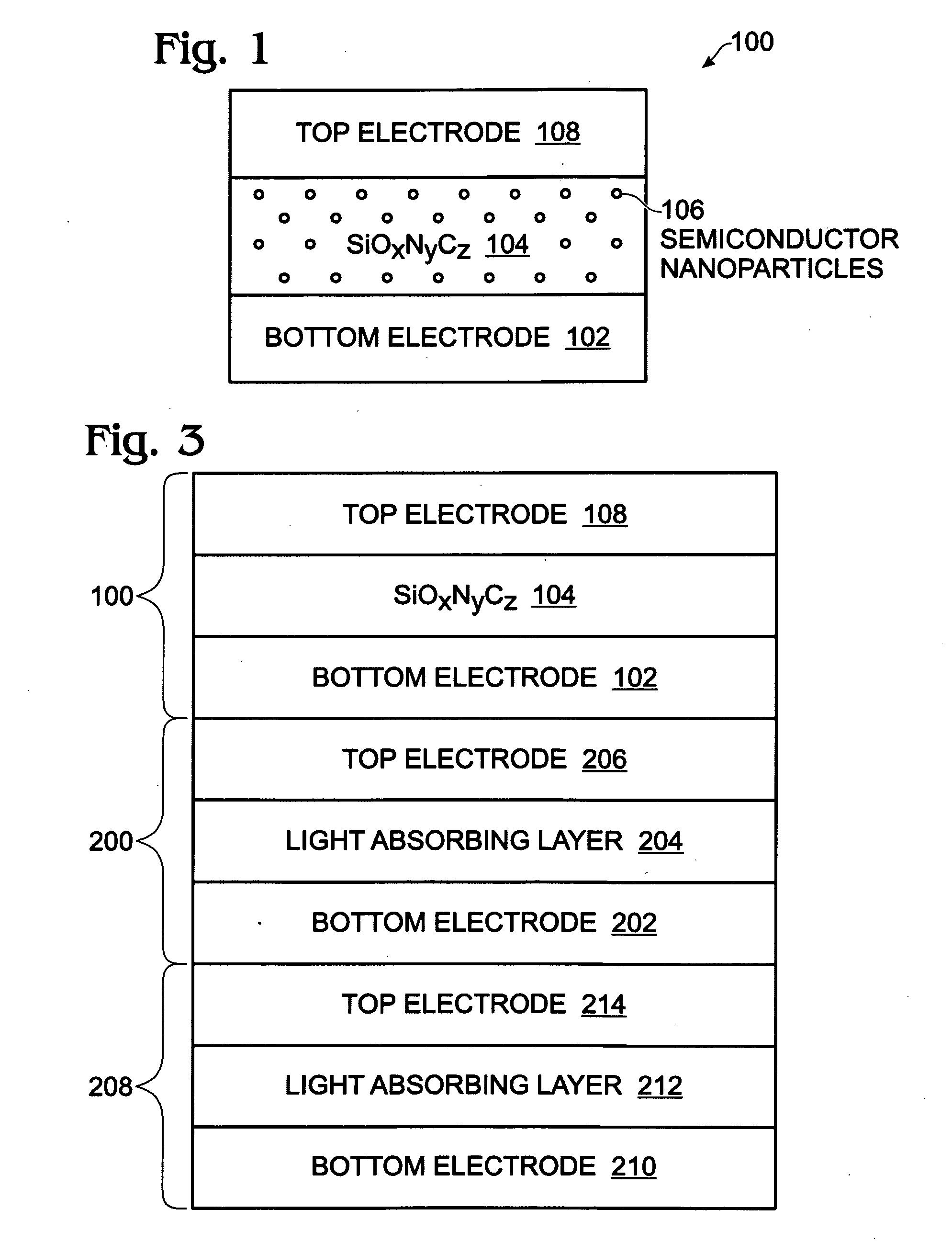

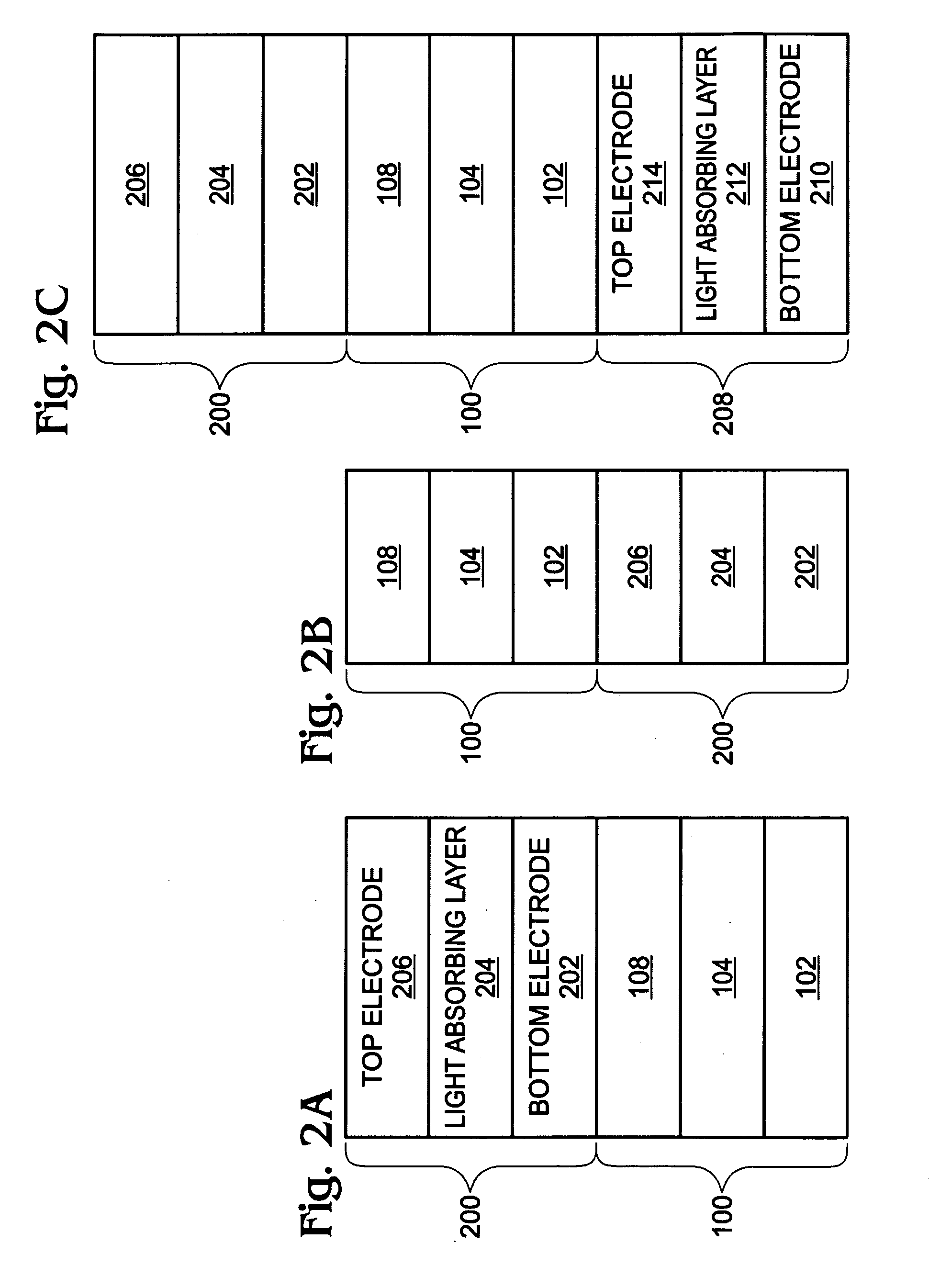

Silicon Oxide-Nitride-Carbide with Embedded Nanocrystalline Semiconductor Particles

InactiveUS20090217968A1Minimizing plasma induced bulkMinimizing interface damagePV power plantsSemiconductor/solid-state device manufacturingSemiconductor materialsSilicon oxide

A solar call is provided along with a method for forming a semiconductor nanocrystalline silicon insulating thin-film with a tunable bandgap. The method provides a substrate and introduces a silicon (Si) source gas with at least one of the following source gases: germanium (Ge), oxygen, nitrogen, or carbon into a high density (HD) plasma-enhanced chemical vapor deposition (PECVD) process. A SiOxNyCz thin-film embedded with a nanocrystalline semiconductor material is deposited overlying the substrate, where x, y, z≧0, and the semiconductor material is Si, Ge, or a combination of Si and Ge. As a result, a bandgap is formed in the SiOxNyCz thin-film, in the range of about 1.9 to 3.0 electron volts (eV). Typically, the semiconductor nanoparticles have a size in a range of 1 to 20 nm.

Owner:SHARP KK

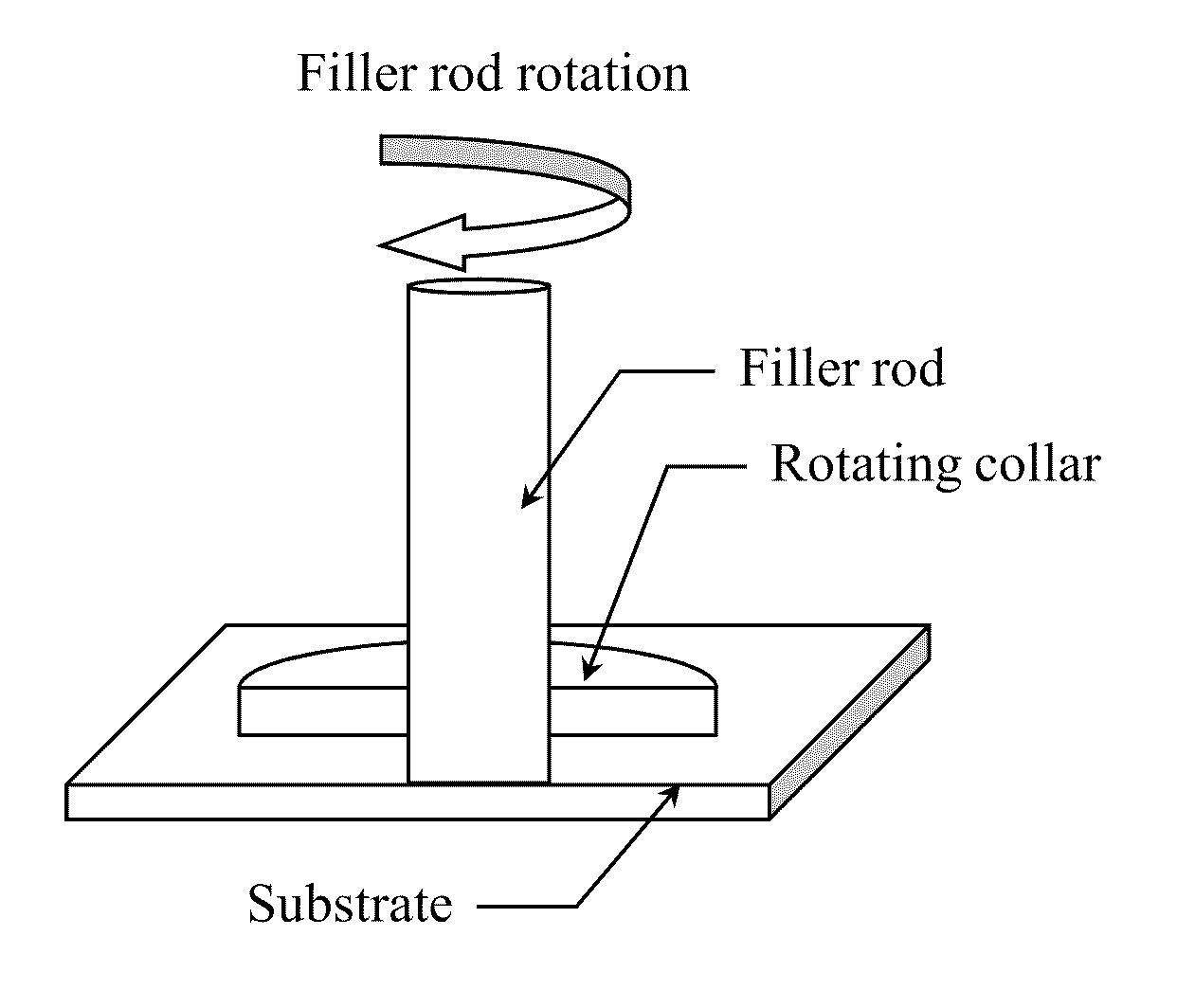

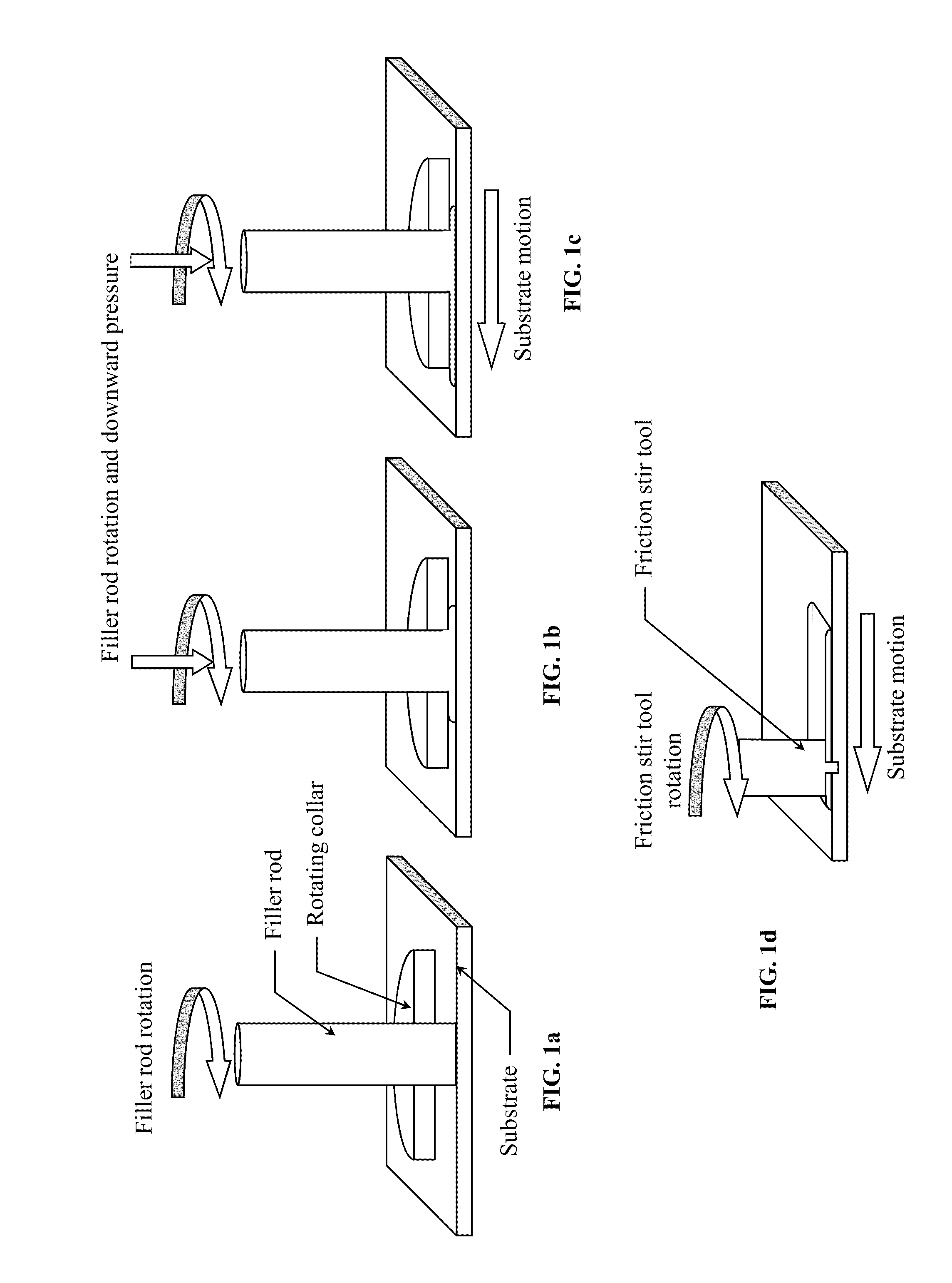

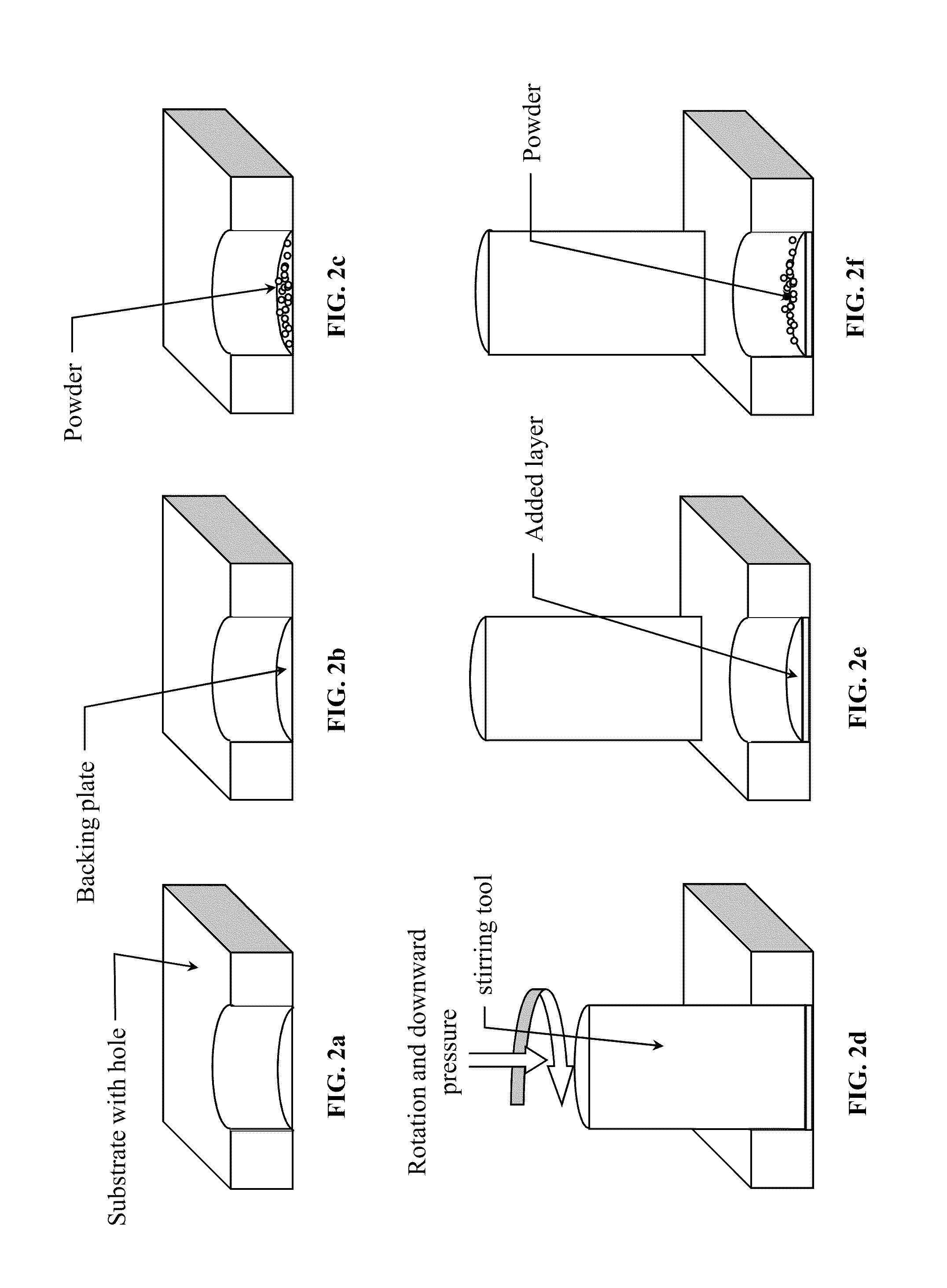

Friction stir fabrication

ActiveUS8636194B2Liquid surface applicatorsWelding/cutting auxillary devicesNanocrystalline siliconMetal matrix composite

A low-temperature friction-based coating method termed friction stir fabrication (FSF) is disclosed, in which material is deposited onto a substrate and subsequently stirred into the substrate using friction stir processing to homogenize and refine the microstructure. This solid-state process is capable of depositing coatings, including nanocrystalline aluminum and / or metal matrix composites and the like, onto substrates such as aluminum at relatively low temperatures. A method of making rod stock for use in the FSF process is also disclosed.

Owner:MELD MFG CORP

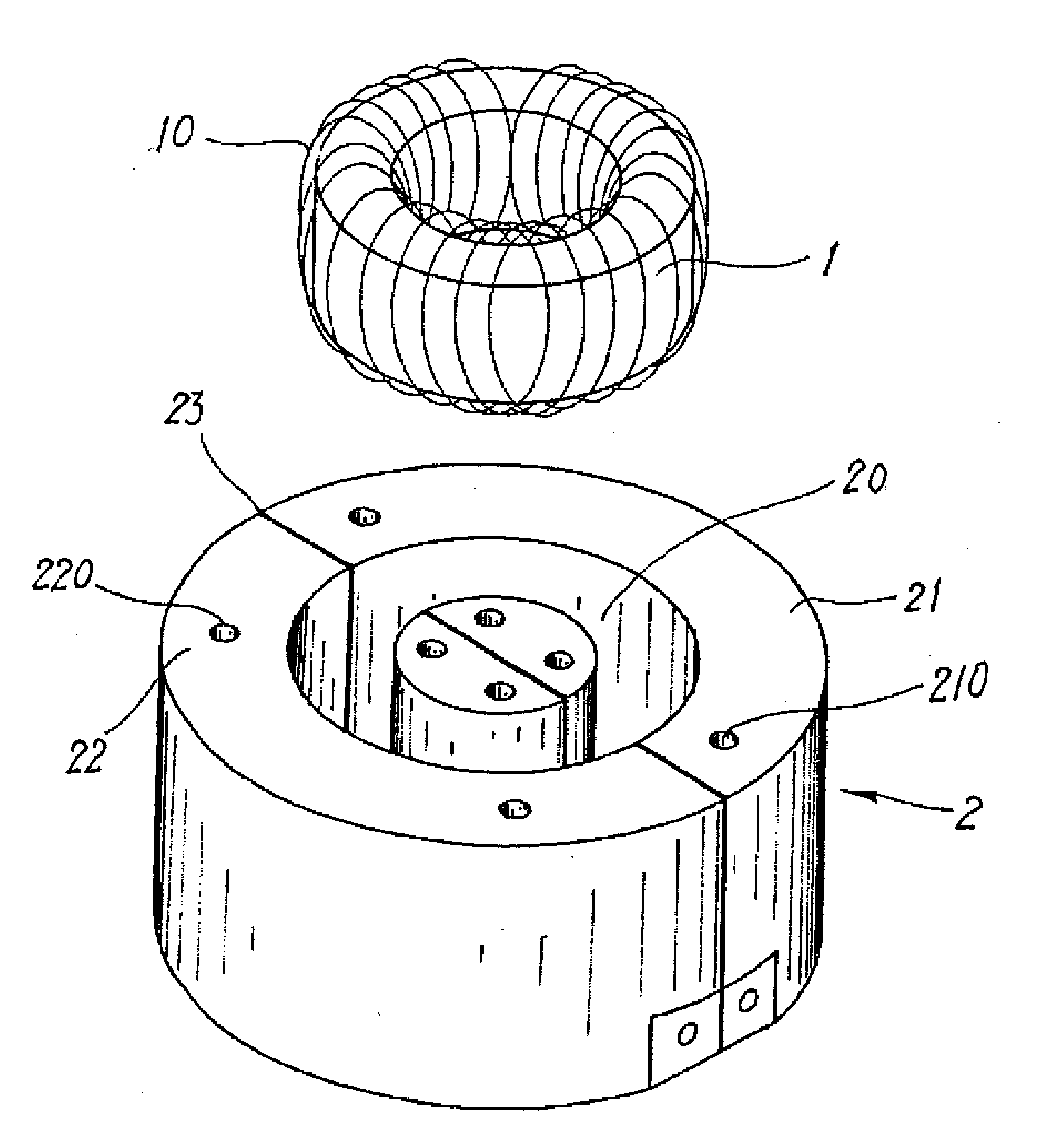

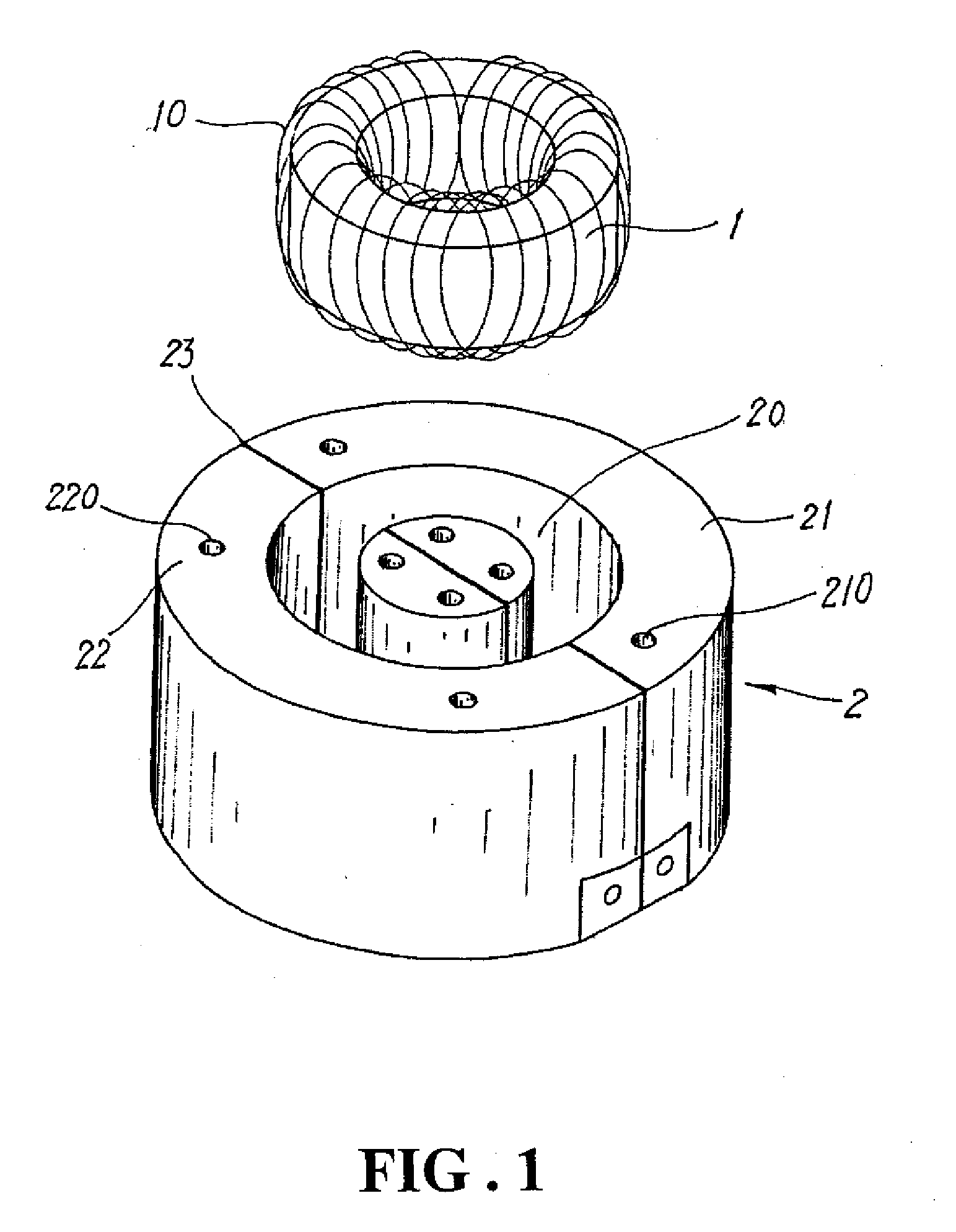

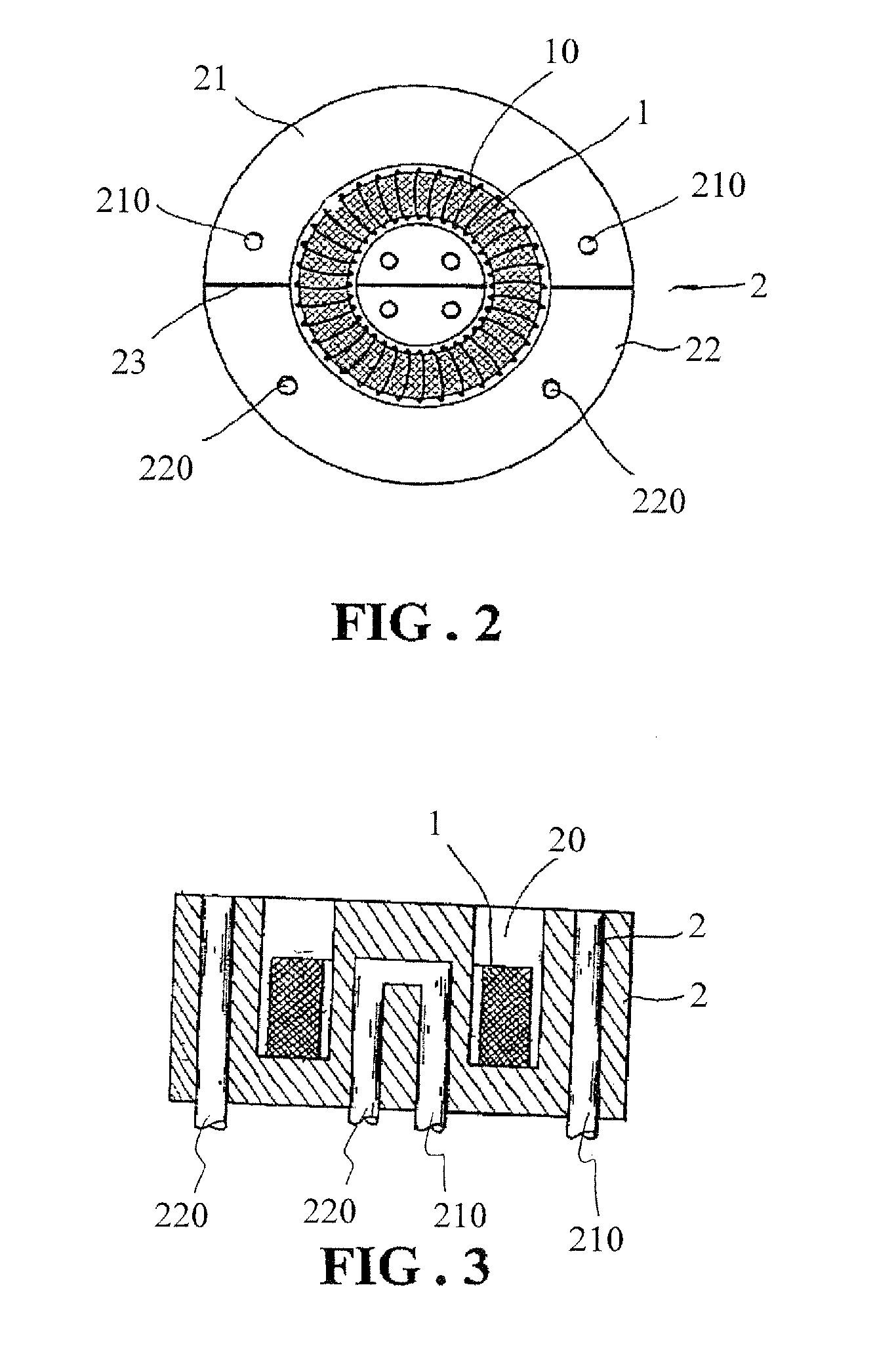

High-frequency switching-type direct-current rectifier

InactiveUS20090322460A1Good lookingImprove performanceTransformers/inductances coolingFixed transformersCopper wireLow voltage

The present invention relates to a novel structure of a transformer for a high-frequency switching-type direct-current (DC) rectifier, and particularly to an improved structure of a transformer applicable to a large-current low-voltage high-frequency switching-type rectifier, wherein the transformer is comprised of a ring-shaped iron core (made of materials such as dust core or nanometer crystalline silicon or amorphous silicone), which is provided with a primary side formed with winding(s) of copper wire(s), coupling with a secondary side that is formed with a newly-developed module or block, which replaces the secondary side that was constructed to provide output with copper wires or copper plate with wire wound thereon. A cooling water tube is arranged in the secondary-side module to remove heat with the water so as to maintain normal temperatures of the transformer in a pollution-free manner with reduced size and weight and easy assembling and reduced costs of the transformer.

Owner:LIN HSUN I

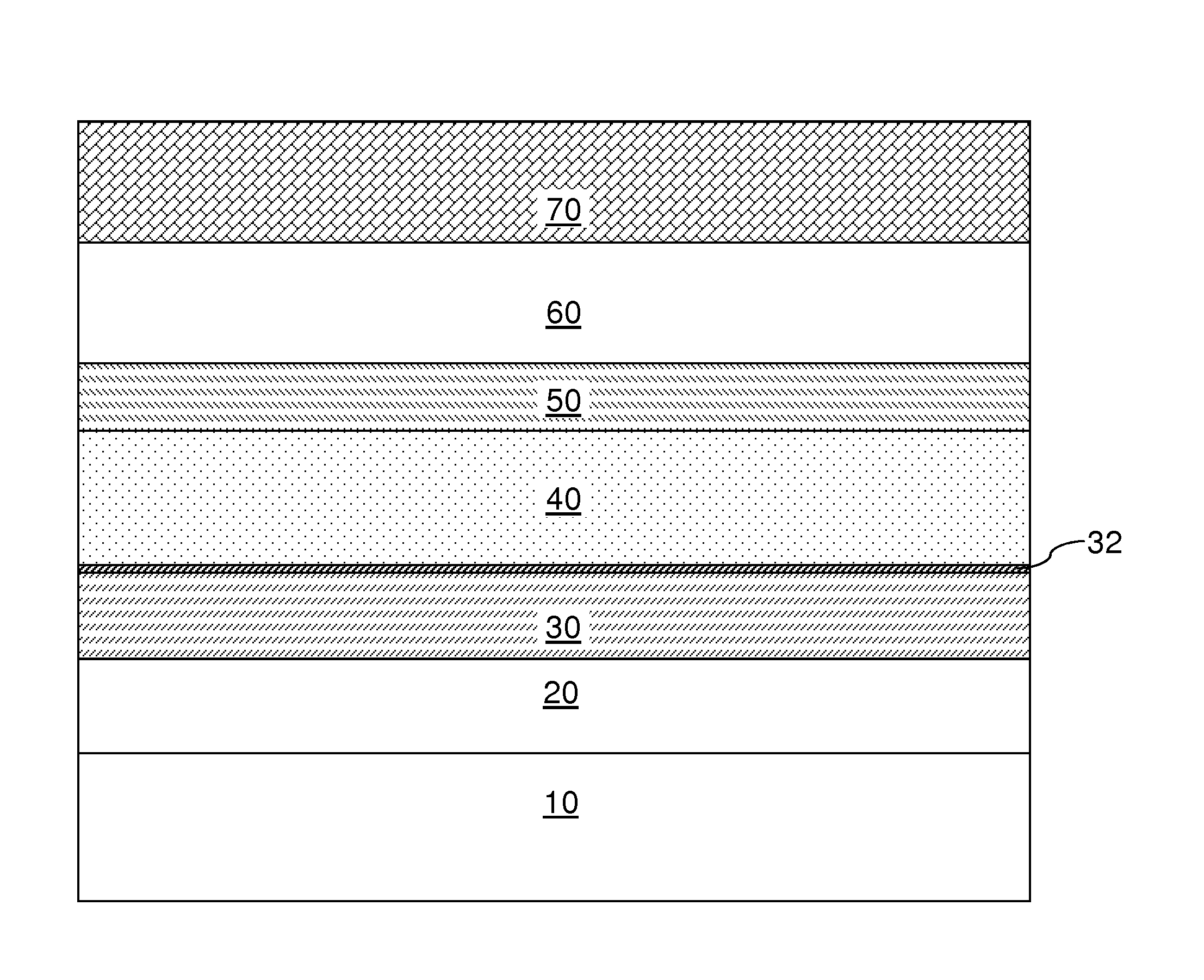

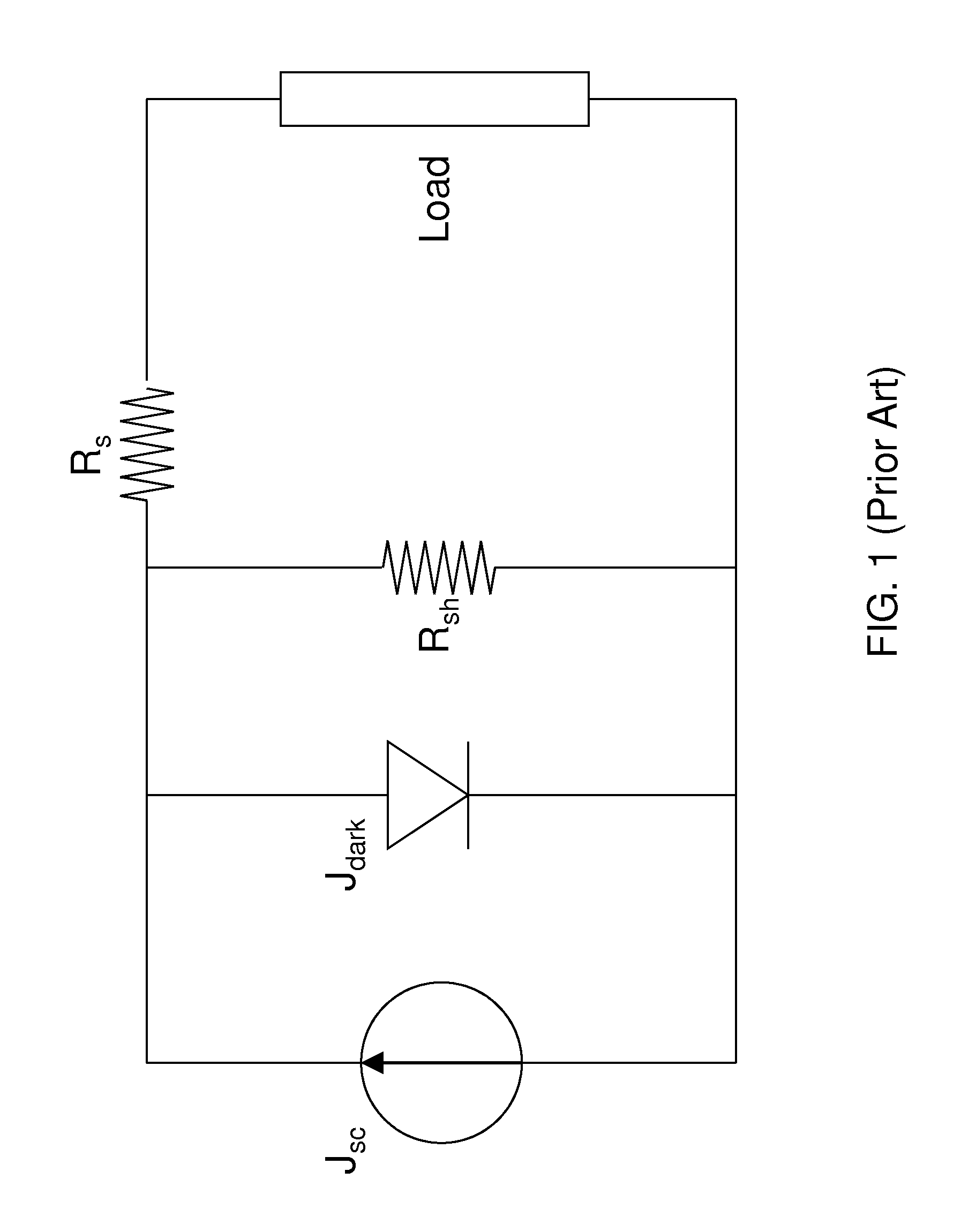

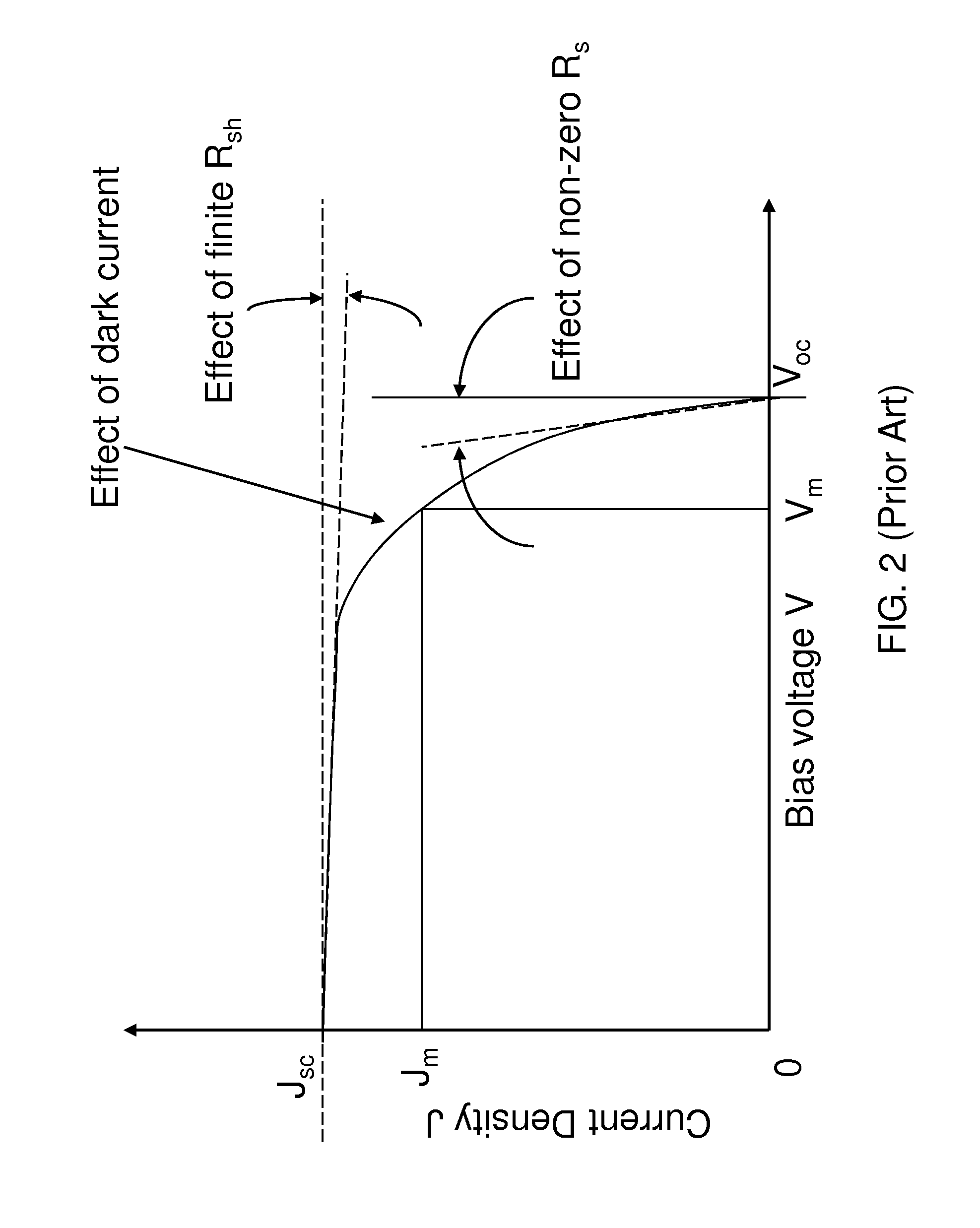

Plasma treatment at a p-i junction for increasing open circuit voltage of a photovoltaic device

InactiveUS20110308583A1Increase the open circuit voltageFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor materialsSurface layer

Open circuit voltage of a photovoltaic device including a p-i-n junction including amorphous silicon-containing semiconductor materials is increased by a high power plasma treatment on an amorphous p-doped silicon-containing semiconductor layer before depositing an amorphous intrinsic silicon-containing semiconductor layer. The high power plasma treatment deposits a thin layer of nanocrystalline silicon-containing semiconductor material or converts a surface layer of the amorphous p-doped silicon containing layer into a thin nanocrystalline silicon-containing semiconductor layer. After deposition of an intrinsic amorphous silicon layer, the thin nanocrystalline silicon-containing semiconductor layer functions as an interfacial nanocrystalline silicon-containing semiconductor layer located at a p-i junction. The increase in the open circuit voltage of the photovoltaic device through the plasma treatment depends on the composition of the interfacial crystalline silicon-containing semiconductor layer, and particularly on the atomic concentration of carbon in the interfacial crystalline silicon-containing semiconductor layer.

Owner:IBM CORP

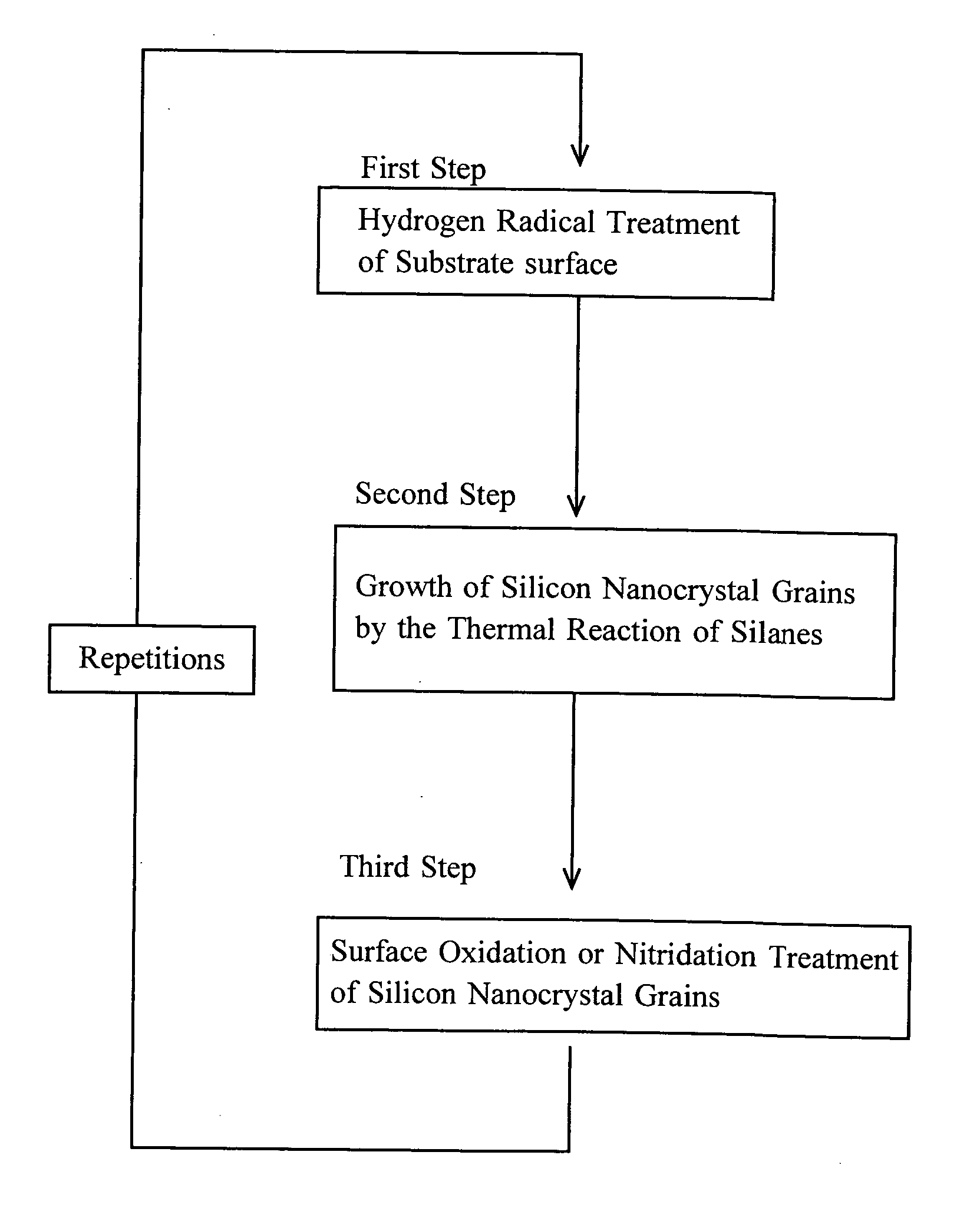

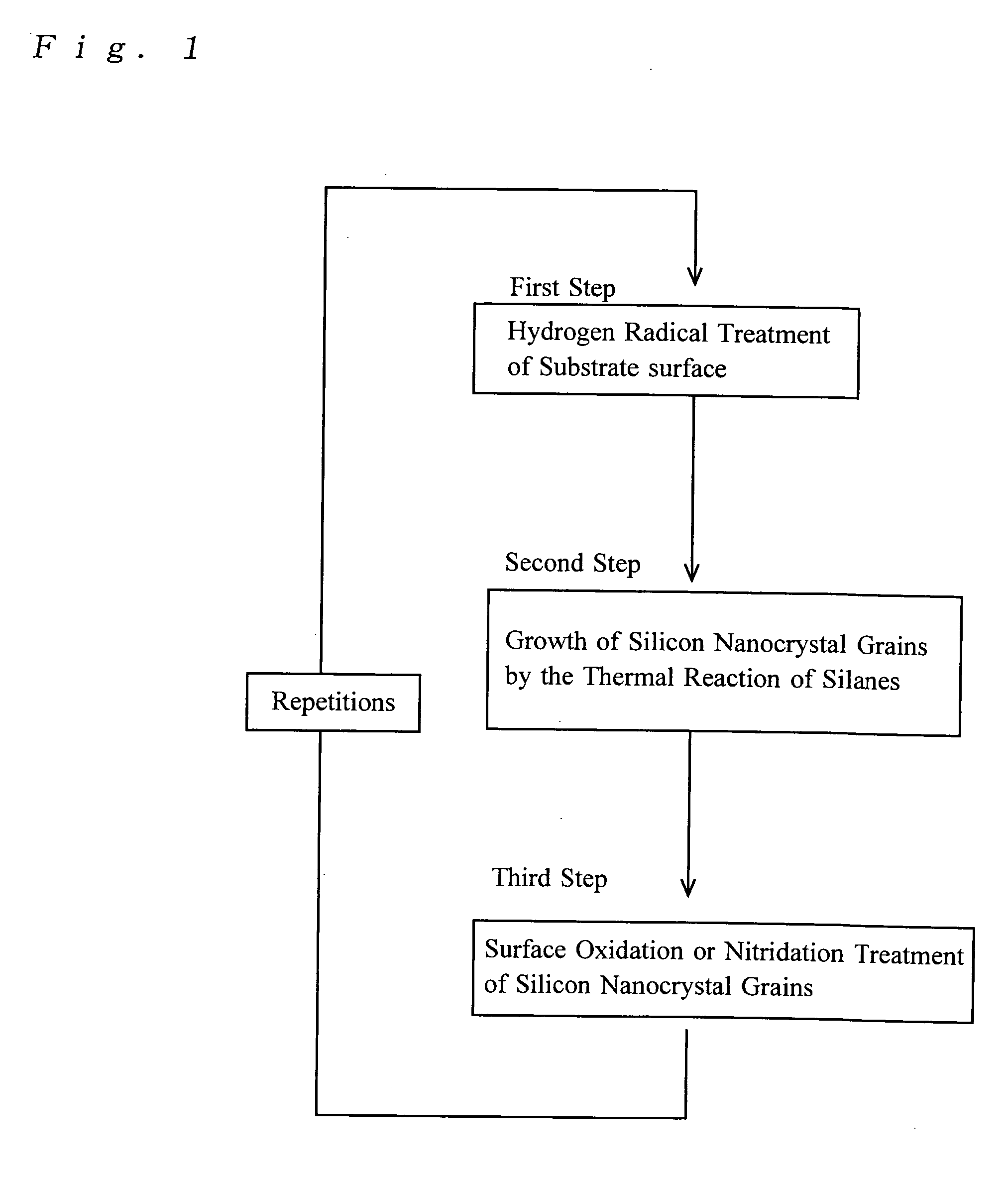

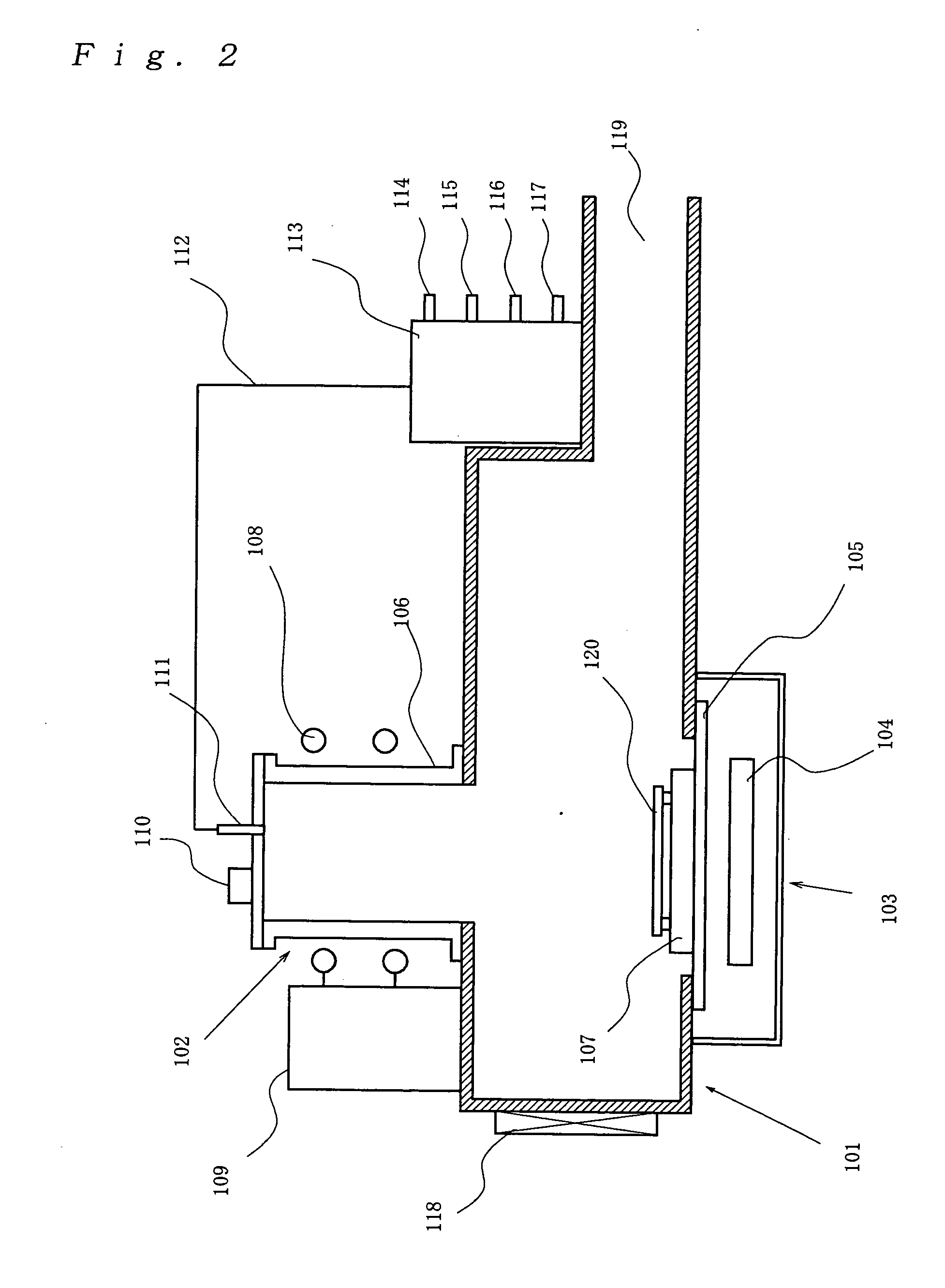

Forming method and a forming apparatus of nanocrystalline silicon structure

InactiveUS20050048796A1Stably terminatedHigh densityMaterial nanotechnologyNanostructure manufactureNitrogenNanocrystalline silicon

A forming method and a forming apparatus of nanocrystalline silicon structure makes it possible to prepare a nanocrystalline silicon structure at a low temperature to have densely packed silicon crystal grains which are stably terminated and to effectively control the grain size in nanometer scale. A forming method and a forming apparatus of nanocrystalline silicon structure with oxide or nitride termination, carry out a first step of treating a surface of a substrate with hydrogen radical; a second step of depositing silicon crystals having a grain size of 10 nm or less by the thermal reaction of a silicon-containing gas; and a third step of terminating the surface of the silicon crystal with oxygen or nitrogen by using one of oxygen gas, oxygen radical and nitrogen radical.

Owner:ANELVA CORP +1

Nanocrystal silicon quantum dot memory device

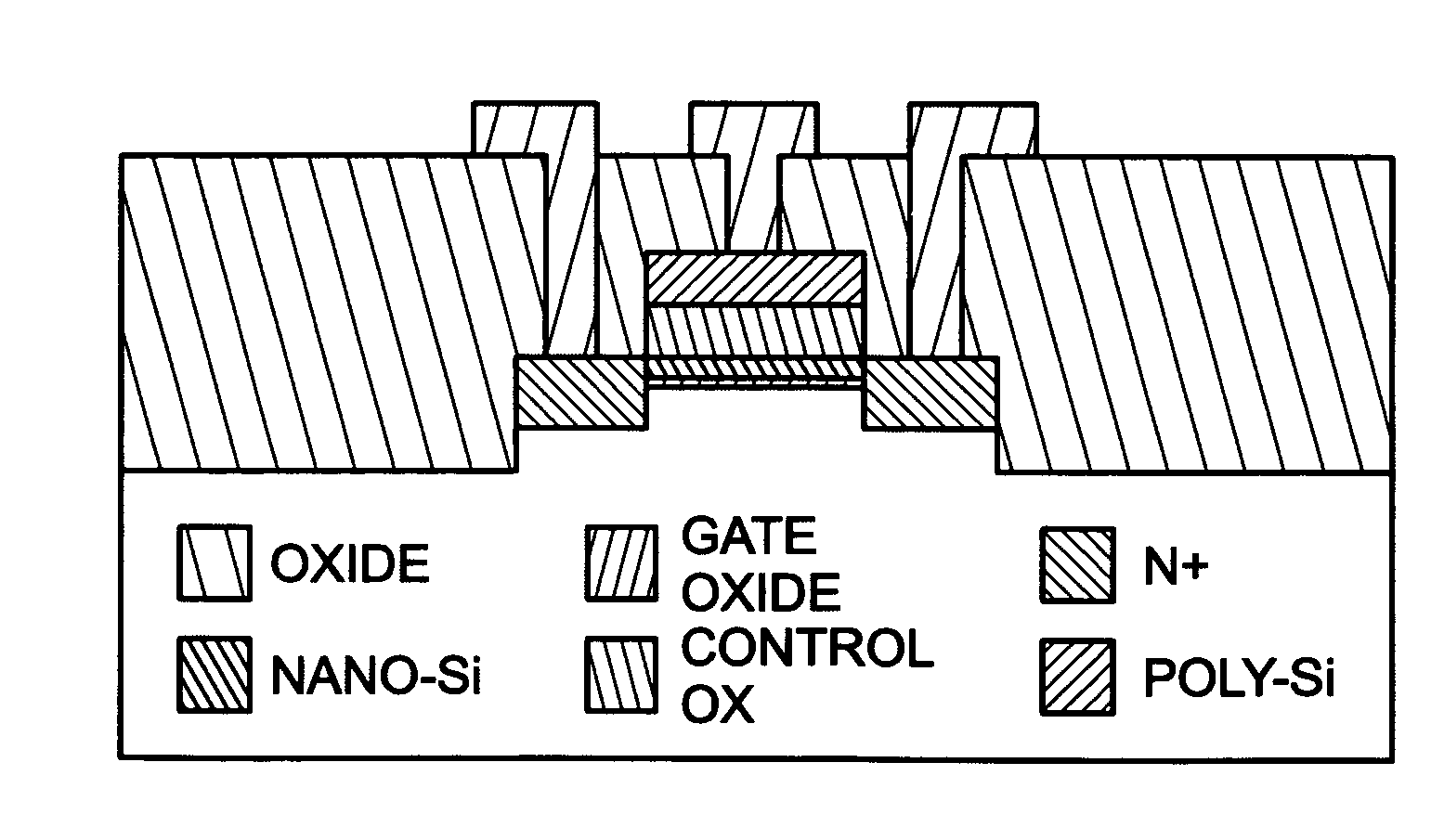

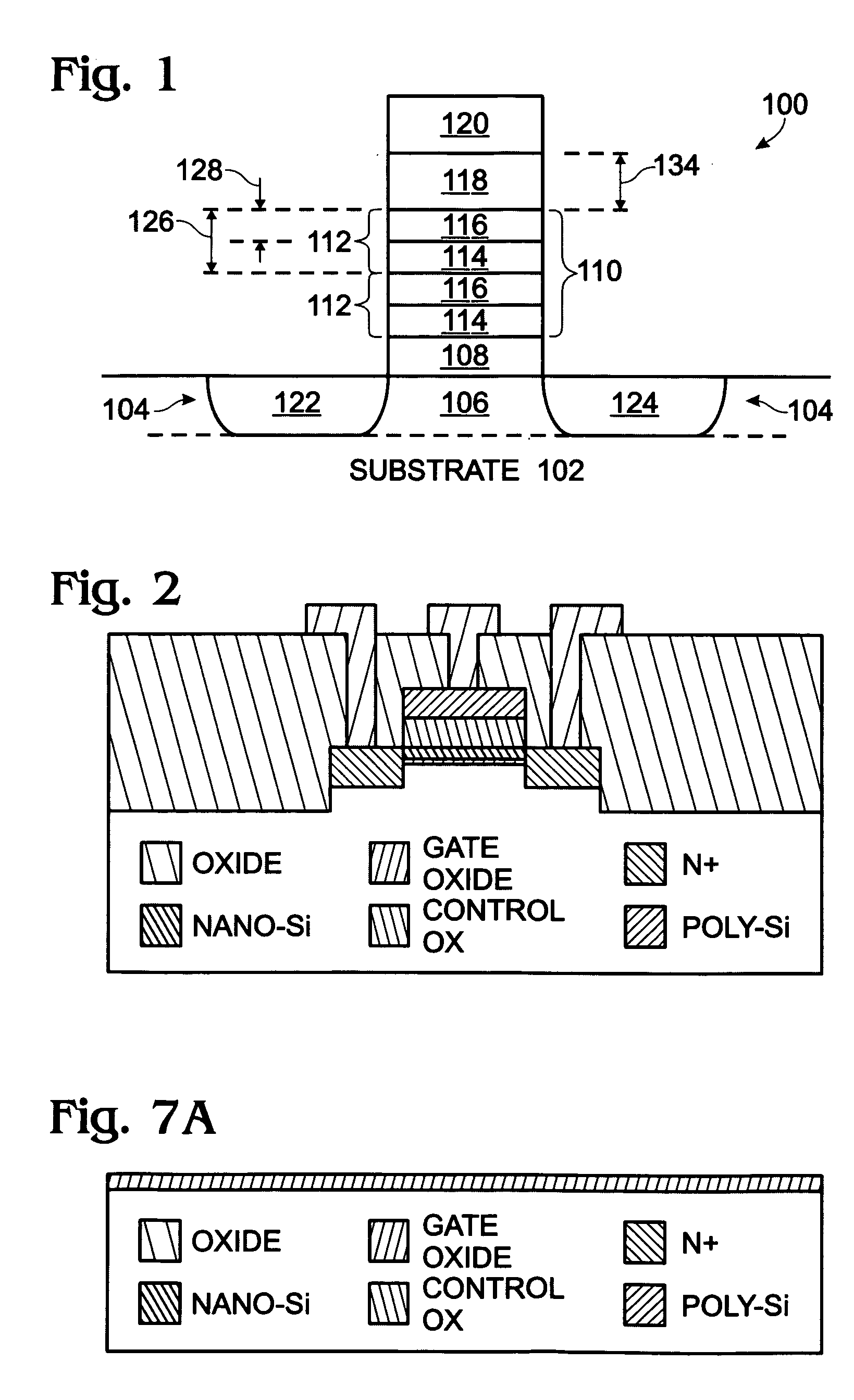

InactiveUS20070108502A1Without sacrificing memory retention timeReduce thicknessTransistorNanoinformaticsControl layerNanocrystalline silicon

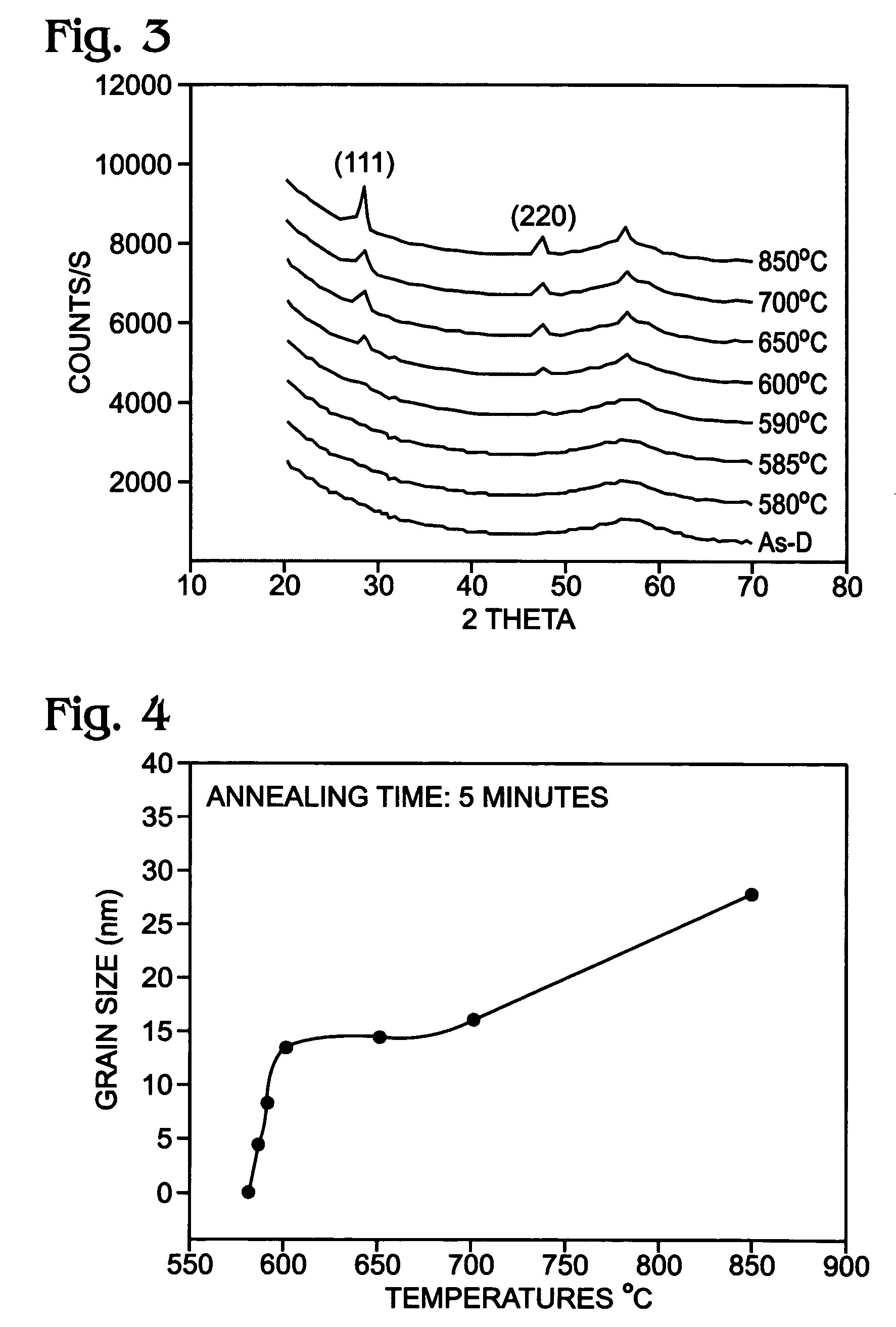

A nanocrystal silicon (Si) quantum dot memory device and associated fabrication method have been provided. The method comprises: forming a gate (tunnel) oxide layer overlying a Si substrate active layer; forming a nanocrystal Si memory film overlying the gate oxide layer, including a polycrystalline Si (poly-Si) / Si dioxide stack; forming a control Si oxide layer overlying the nanocrystal Si memory film; forming a gate electrode overlying the control oxide layer; and, forming source / drain regions in the Si active layer. In one aspect, the nanocrystal Si memory film is formed by depositing a layer of amorphous Si (a-Si) using a chemical vapor deposition (CVD) process, and thermally oxidizing a portion of the a-Si layer. Typically, the a-Si deposition and oxidation processes are repeated, forming a plurality of poly-Si / Si dioxide stacks (i.e., 2 to 5 poly-Si / Si dioxide stacks).

Owner:SHARP LAB OF AMERICA INC

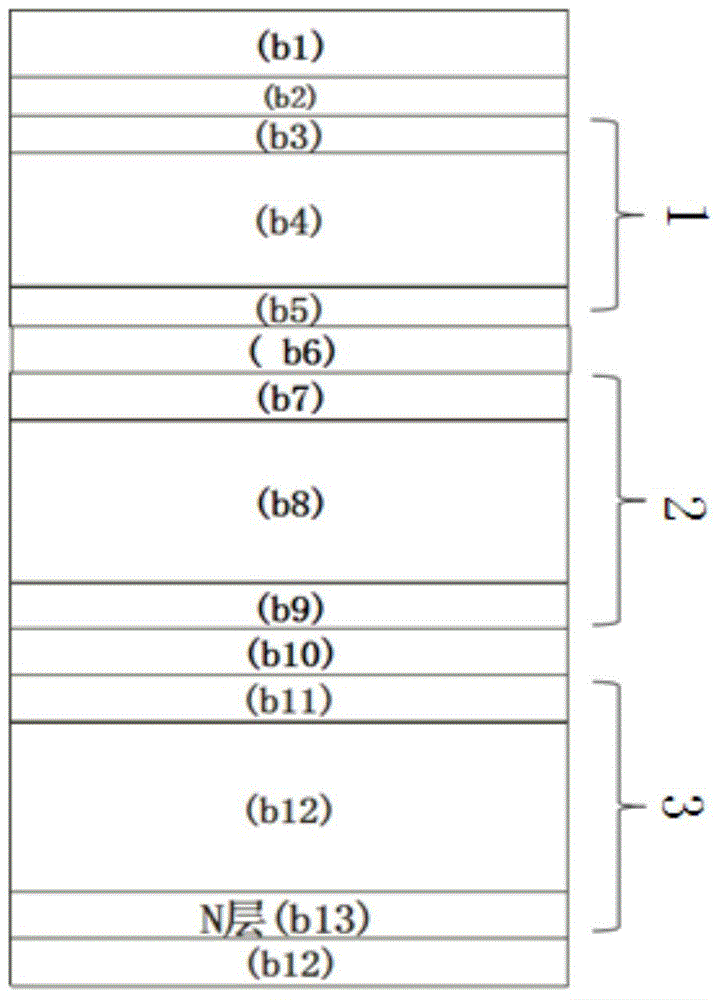

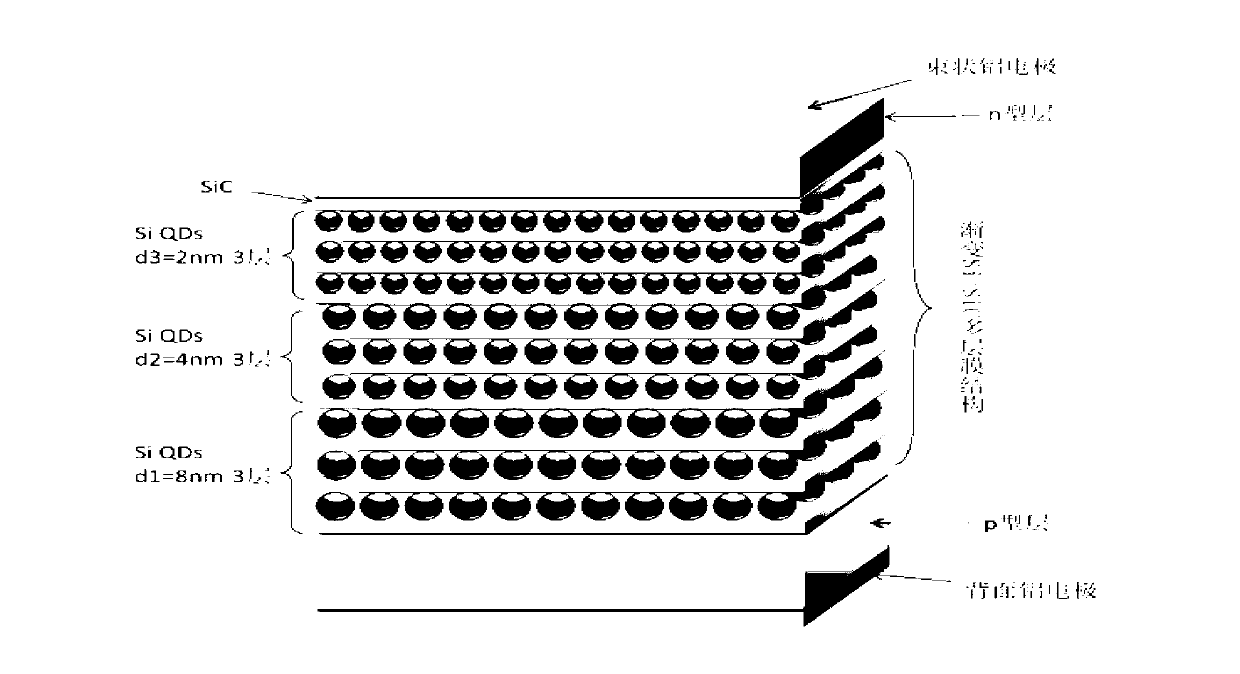

Solar battery with band gap gradual changing silicon quantum dot multilayer film and production method thereof

InactiveCN103000742AExtended photoresponse wavelength rangeIncrease profitFinal product manufacturePhotovoltaic energy generationQuantum dotNanocrystalline silicon

A solar battery with a band gap gradual changing silicon quantum dot multilayer film comprises a p type silicon substrate, wherein a thickness gradual changing multilayer amorphous silicon / silicon carbide film structure, a thickness gradual changing amorphous silicon / silicon carbide grease silicon quantum dot / silicon carbide multilayer film structure and a p-i-n battery structure are arranged on the p type silicon substrate, the p-i-n battery structure is formed by the p type silicon substrate, a silicon carbide intrinsic layer (namely an i layer) and the outermost n type nanocrystalline silicon film, and an electrode is guided out on the surface of the p type silicon substrate to form a battery. The thickness of amorphous silicon sub layers in the period of each hydrogenation amorphous silicon / silicon carbide growing towards the surface of the p type silicon substrate is thinned gradually. The amorphous silicon sub layer growing on the p type silicon substrate or close to the p type silicon substrate is the thickest, and the amorphous silicon sub layer growing towards the surface of the p type silicon substrate is the thinnest.

Owner:NANJING UNIV

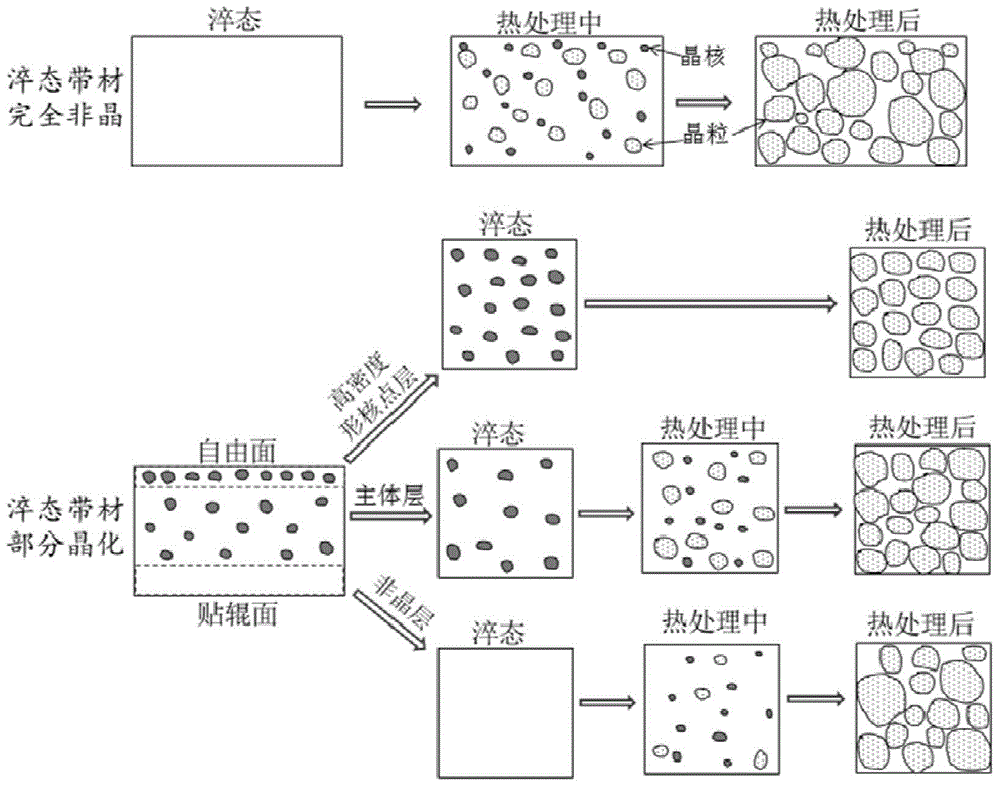

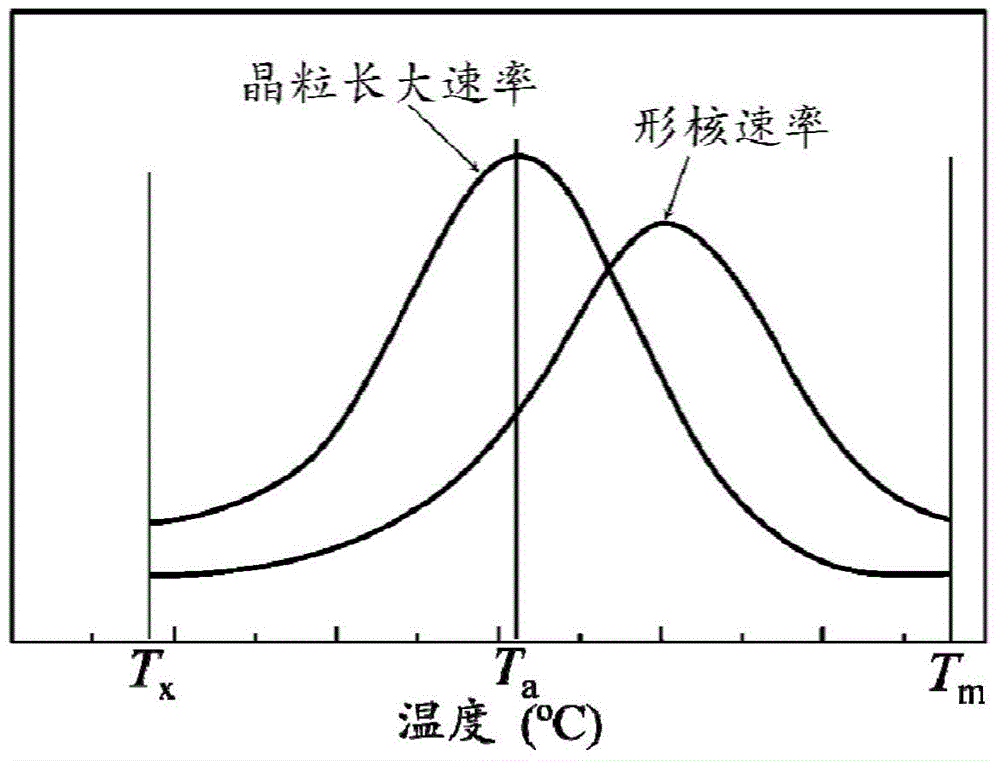

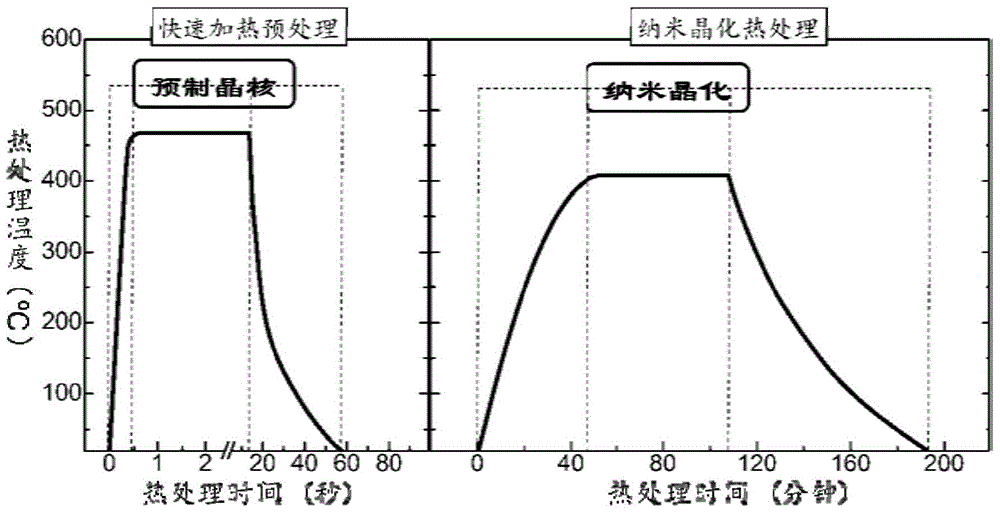

Heat treatment method for preparing nanocrystalline alloy

The invention discloses a heat treatment method for preparing nanocrystalline alloy. According to the method, during the nanocrystalline alloy material preparation by an amorphous crystallization method, a heat treatment process is divided into two steps; in the first step, the characteristics of high heat conductivity and low heat capacity of an amorphous crystallization alloy belt material are used; the fast temperature rise and short-time heat insulation pre-heating treatment is performed; high-density and uniformly-distributed crystal nucleuses are formed in the belt material through excitation; then, in the second step of conventional nano-crystallization heat treatment, high-density crystal particles grow synchronously; the competitive effect between the crystal particles is used for promoting the crystal particle refining. Compared with the existing heat treatment method, the method has the advantages that amorphous crystallization nucleation and crystal particle growth processes are controlled in a separated way; the crystal particle density and the crystallization degree are improved; the crystal particle dimension and the distribution uniformity are improved; in addition, the crystal particles are refined, so that the performance of the alloy is improved.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

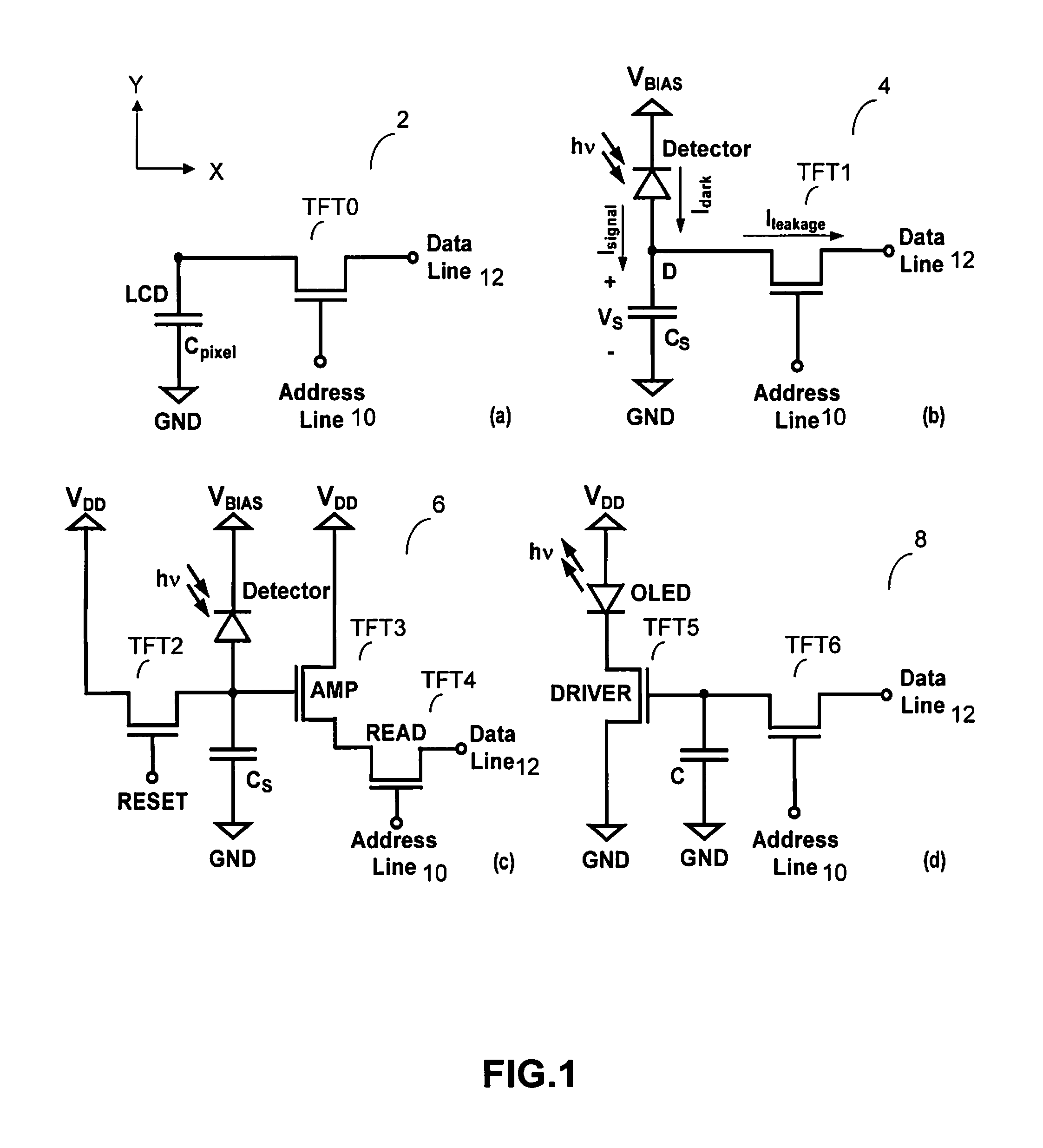

Integrated thin-film sensors and methods

InactiveUS7718130B1Compact and field-deployable deviceChemiluminescene/bioluminescencePhotometryThin film sensorPhotovoltaic detectors

Integrated photoluminescence (PL)-based chemical and biological sensors are provided comprising a photodetector (PD), a long-pass filter, an excitation source, and a sensing element, all based on thin films or structures. In one embodiment the light source is an organic light emitting device (OLED) and the sensing element is based on thin films or solutions in microfluidic channels or wells. The PD and optical filters are based on thin film amorphous or nanocrystalline silicon and related materials. In another embodiment, sensor components are fabricated on transparent substrates, which are attached back-to-back to generate a compact, integrated structure.

Owner:IOWA STATE UNIV RES FOUND