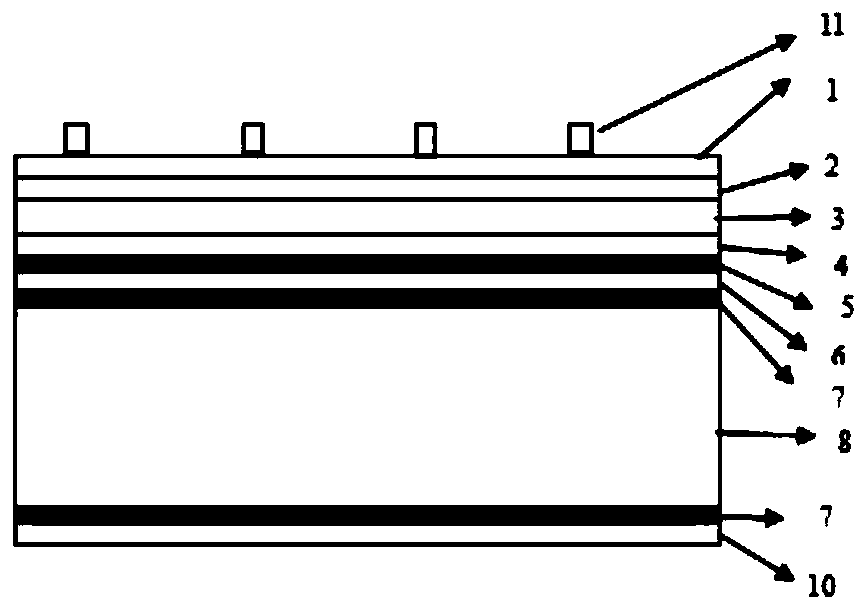

Non-doped crystalline silicon heterojunction perovskite laminated solar cell structure and preparation method thereof

A technology of stacked sun and perovskite, applied in the field of solar cells, can solve the problems of poor stability of perovskite and low efficiency of crystalline silicon, and achieve the effect of improving open circuit voltage and photoelectric conversion efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0045] The non-doped crystalline silicon heterojunction perovskite tandem solar cell of this embodiment is manufactured through the following steps:

[0046] (1) Etch a 180 μm n-type silicon wafer with an n-type crystal orientation in a KOH solution of 80-90 degrees to obtain a pyramid structure, and then use the RCA method to clean it.

[0047] (2) Wet oxidation is adopted, and the cleaned silicon wafer is soaked in concentrated nitric acid at 120 degrees for oxidation to form a silicon dioxide layer for passivation. Minority lifetime 3ms.

[0048] (3) A MgF electron transport layer is deposited on the back of the passivated crystalline silicon by thermal evaporation technology. Thickness is 10nm

[0049] (4) Deposit MoO on the front side of the passivated crystalline silicon by thermal evaporation or magnetron sputtering x Hole transport transport layer. Thickness is 10nm

[0050] (5) Deposit a transparent conductive film ITO on the electron transport layer by thermal ...

Embodiment 2

[0058] (1) Etch a 180 μm n-type silicon wafer with an n-type crystal orientation in a KOH solution of 80-90 degrees to obtain a pyramid structure, and then use the RCA method to clean it.

[0059] (2) Wet oxidation is adopted, and the cleaned silicon wafer is soaked in concentrated nitric acid at 120 degrees for oxidation to form a silicon dioxide layer for passivation. Minority lifetime 3ms.

[0060] (3) Deposit TiO on the back of passivated crystalline silicon by thermal evaporation technology x electron transport layer. Thickness is 10nm

[0061] (4) On the front side of the passivated crystalline silicon, NiO is deposited by thermal evaporation or magnetron sputtering technology x Hole transport transport layer. Thickness is 10nm

[0062] (5) Deposit a transparent conductive film ITO on the electron transport layer by thermal evaporation. On the transparent conductive film ITO, the silver back electrode was deposited by thermal evaporation technology.

[0063] (6) ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More