Patents

Literature

32results about How to "Lower ohmic contact" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

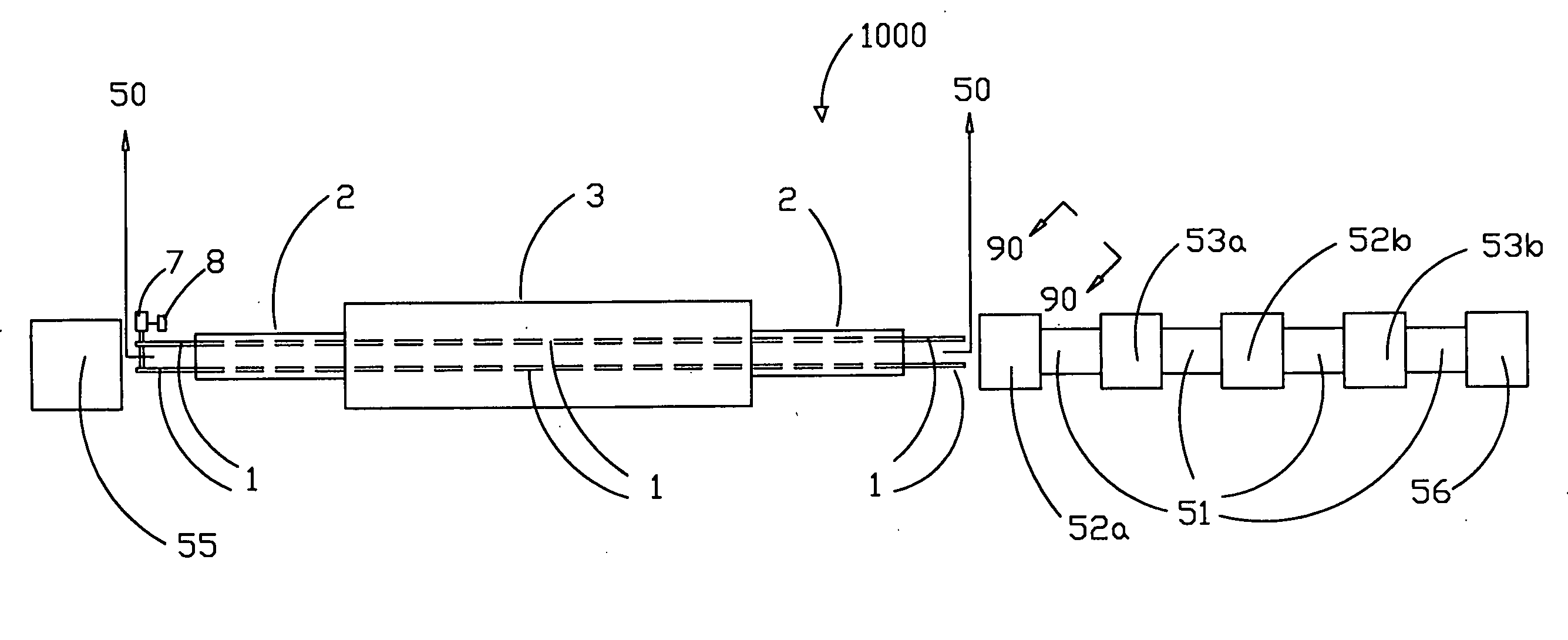

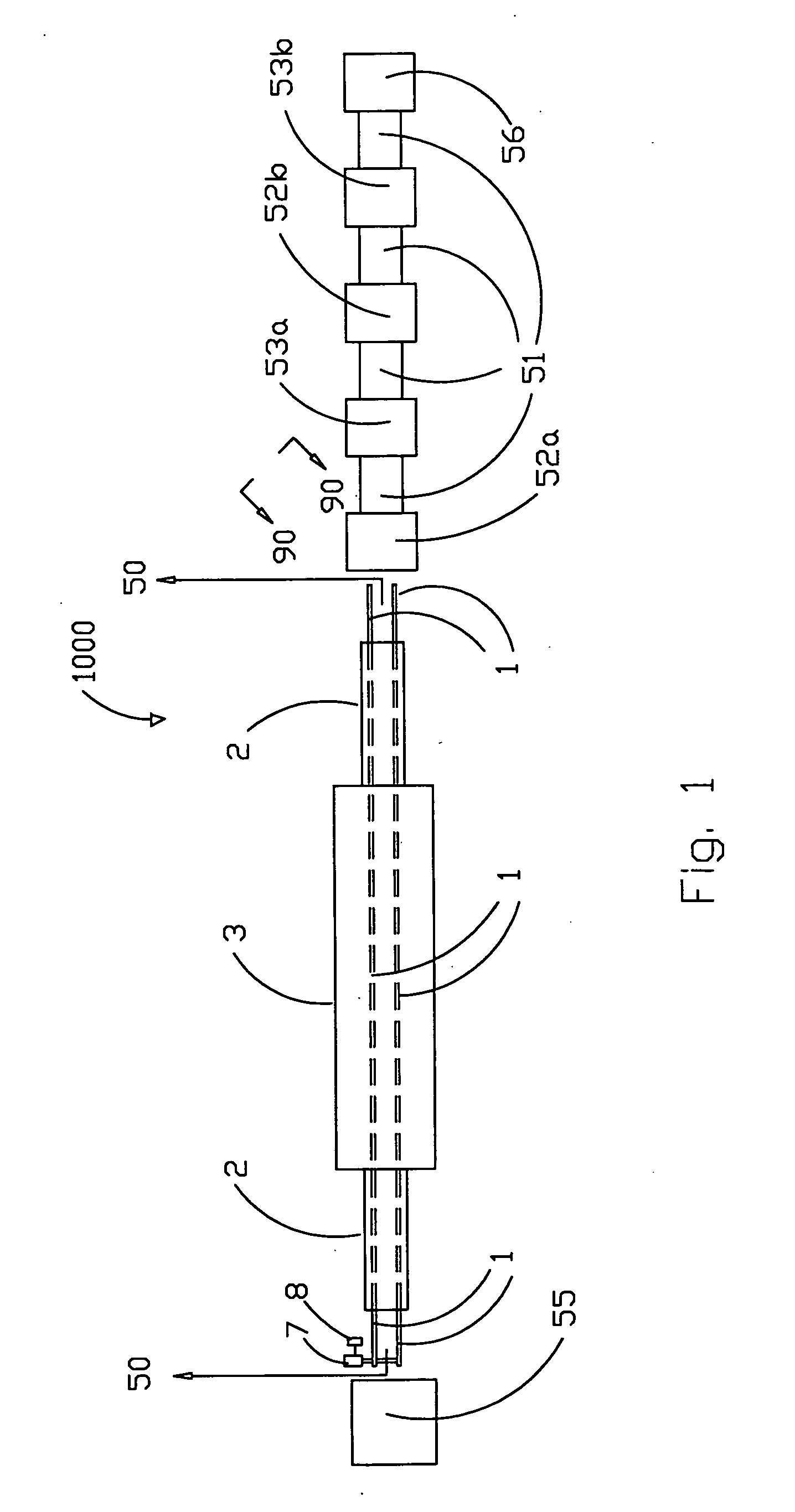

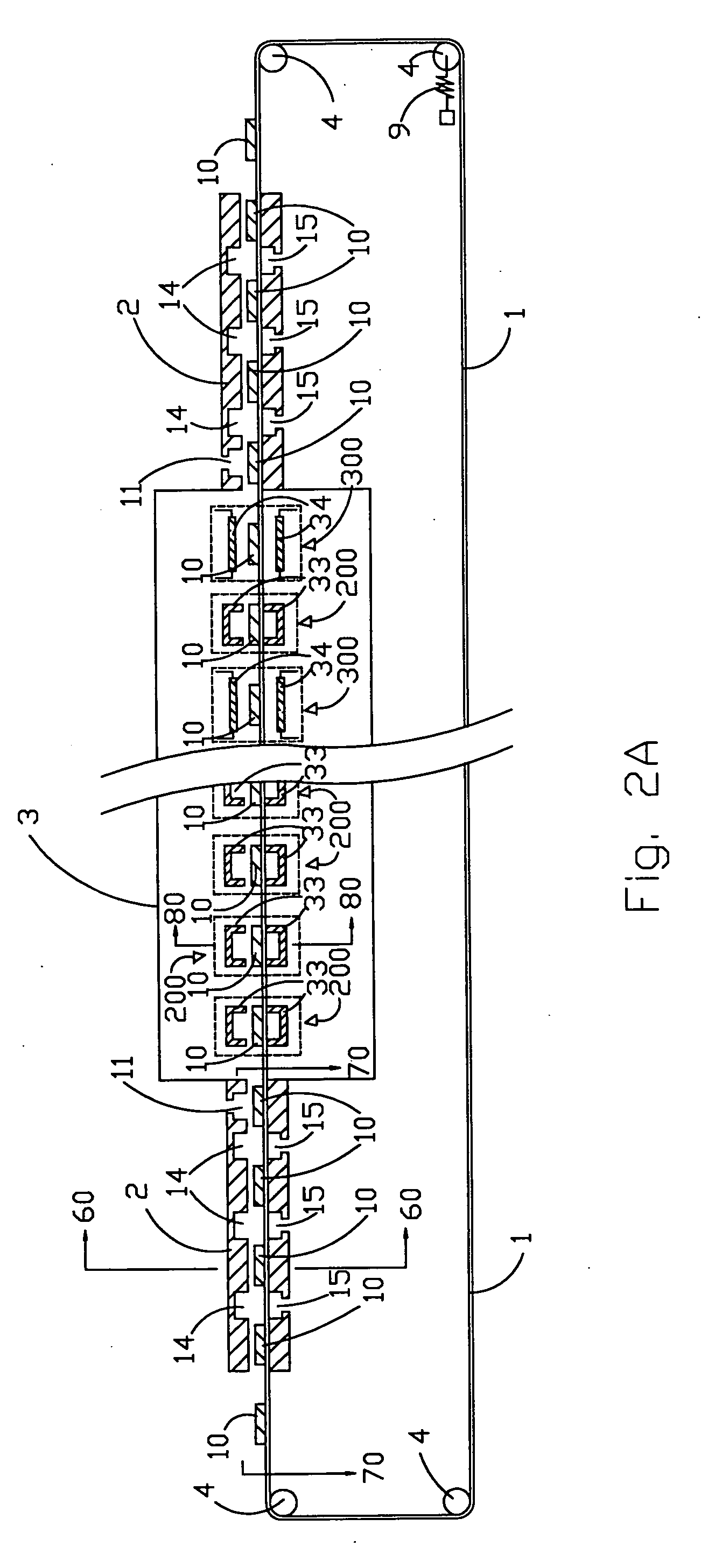

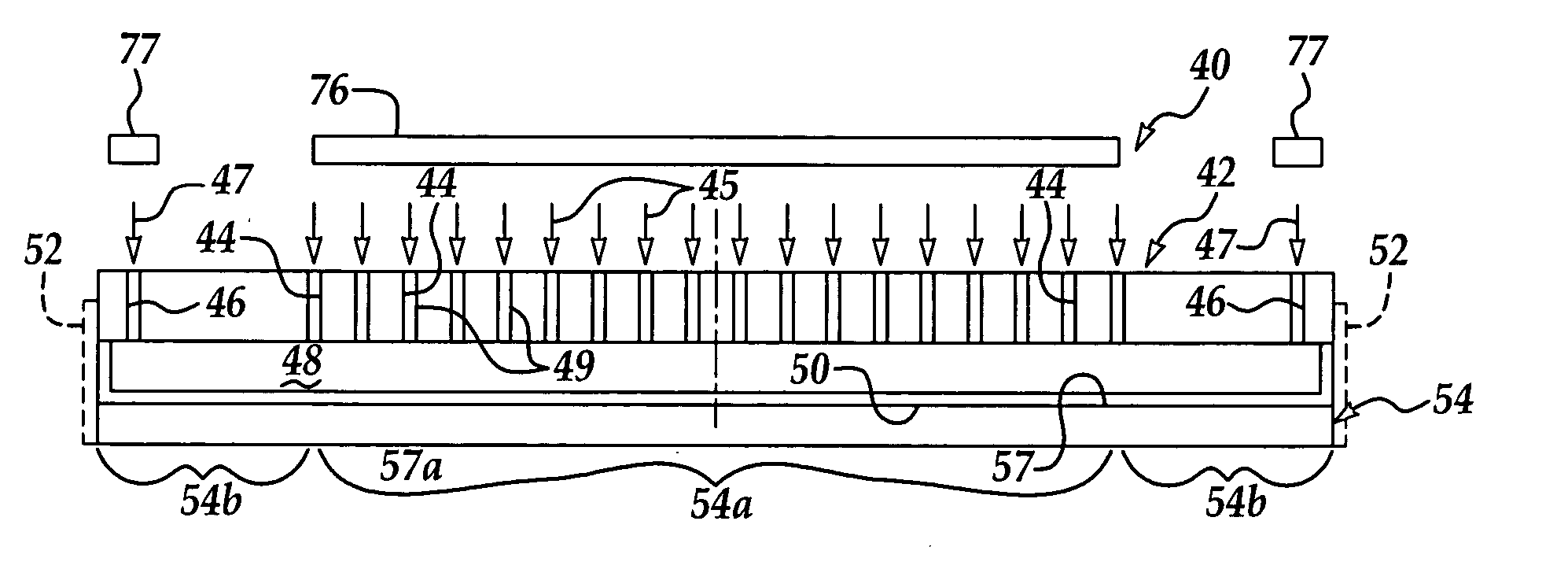

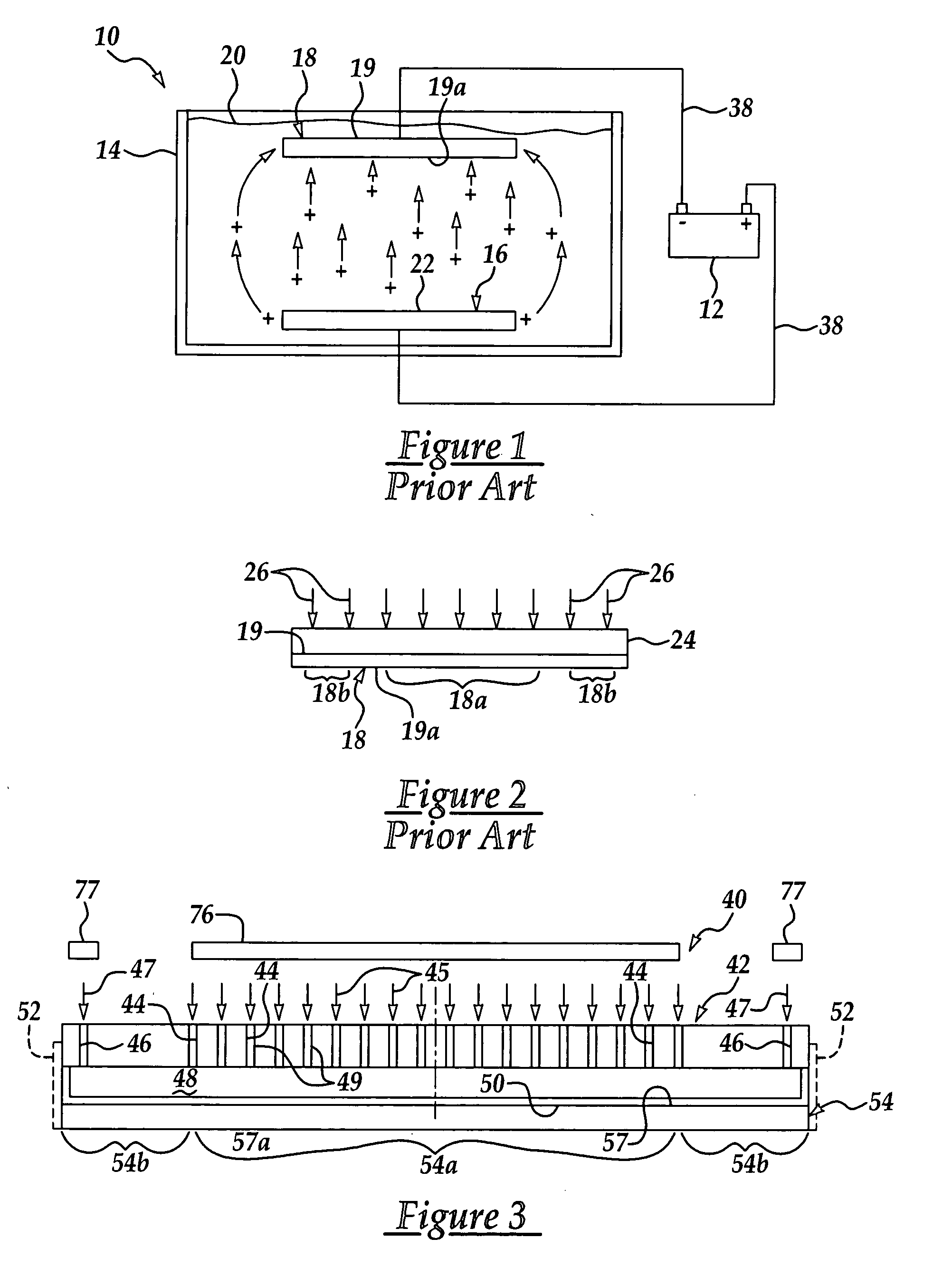

Apparatus and processes for the mass production of photovoltaic modules

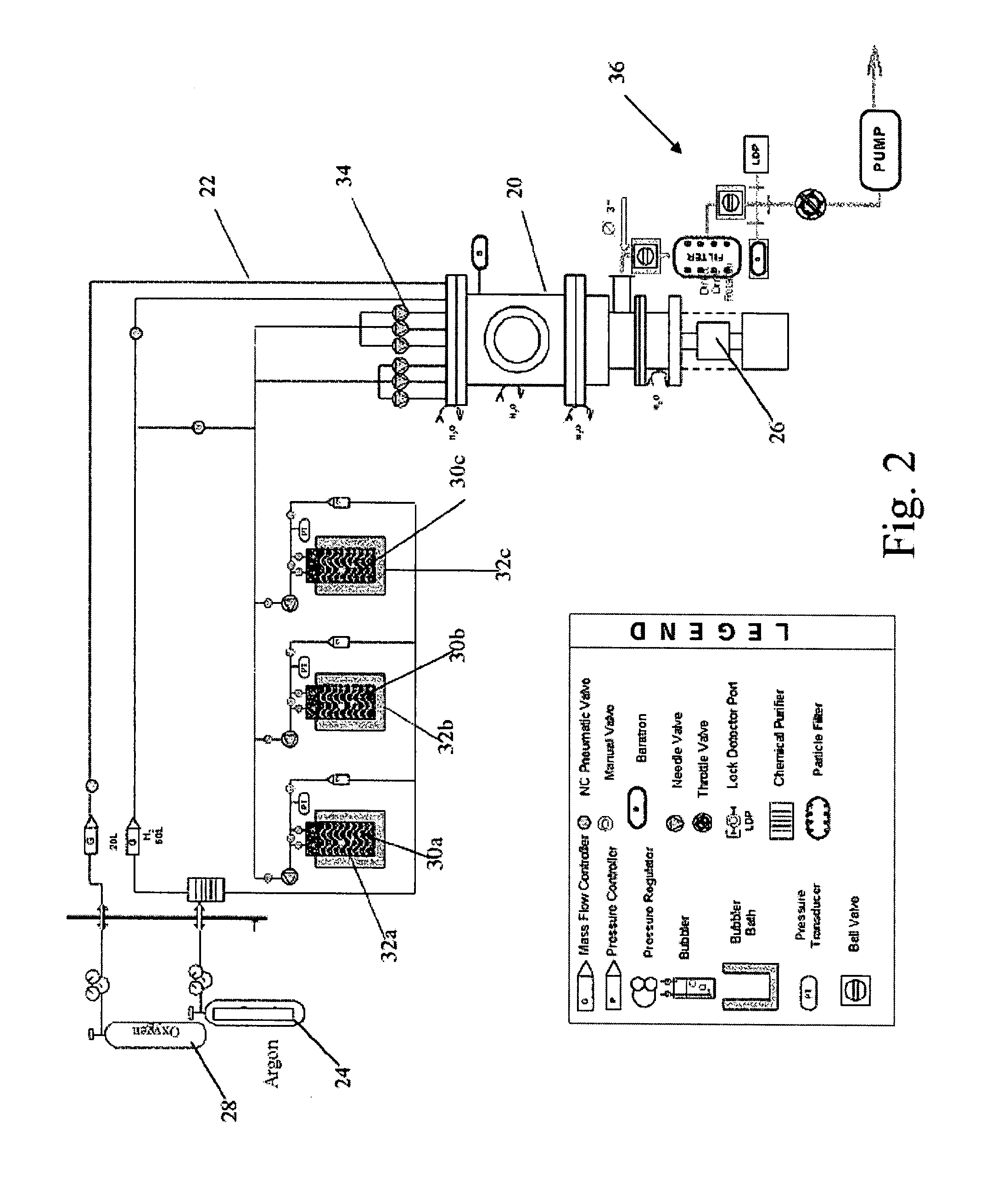

InactiveUS20050158891A1Time stableImprove throughputPolycrystalline material growthSemiconductor/solid-state device manufacturingAbrasive blastingVacuum pressure

An apparatus and processes for large scale inline manufacturing of CdTe photovoltaic modules in which all steps, including rapid substrate heating, deposition of CdS, deposition of CdTe, CdCl2 treatment, and ohmic contact formation, are performed within a single vacuum boundary at modest vacuum pressures. A p+ ohmic contact region is formed by subliming a metal salt onto the CdTe layer. A back electrode is formed by way of a low cost spray process, and module scribing is performed by means of abrasive blasting or mechanical brushing through a mask. The vacuum process apparatus facilitates selective heating of substrates and films, exposure of substrates and films to vapor with minimal vapor leakage, deposition of thin films onto a substrate, and stripping thin films from a substrate. A substrate transport apparatus permits the movement of substrates into and out of vacuum during the thin film deposition processes, while preventing the collection of coatings on the substrate transport apparatus itself.

Owner:COLORADO STATE UNIVERSITY

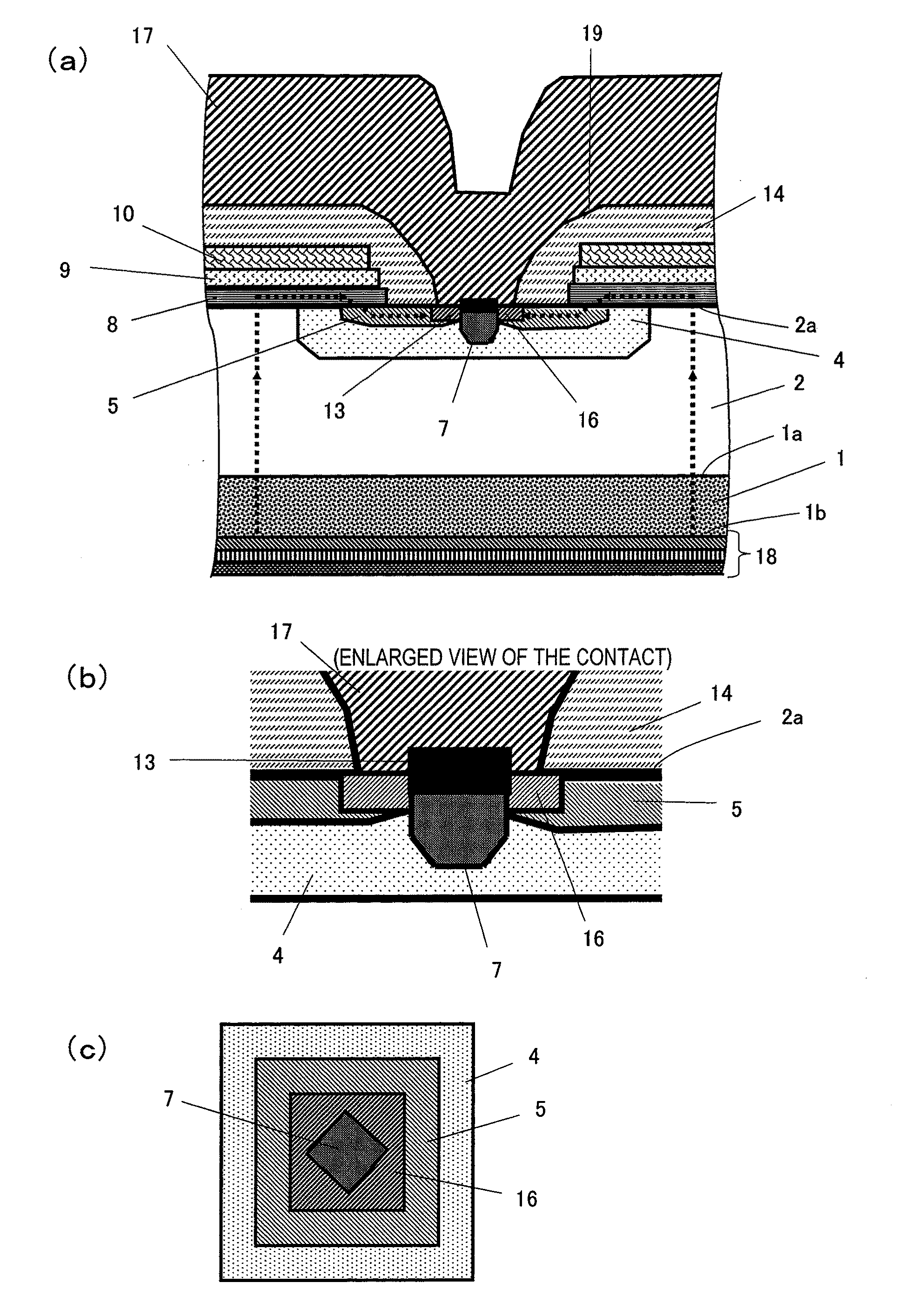

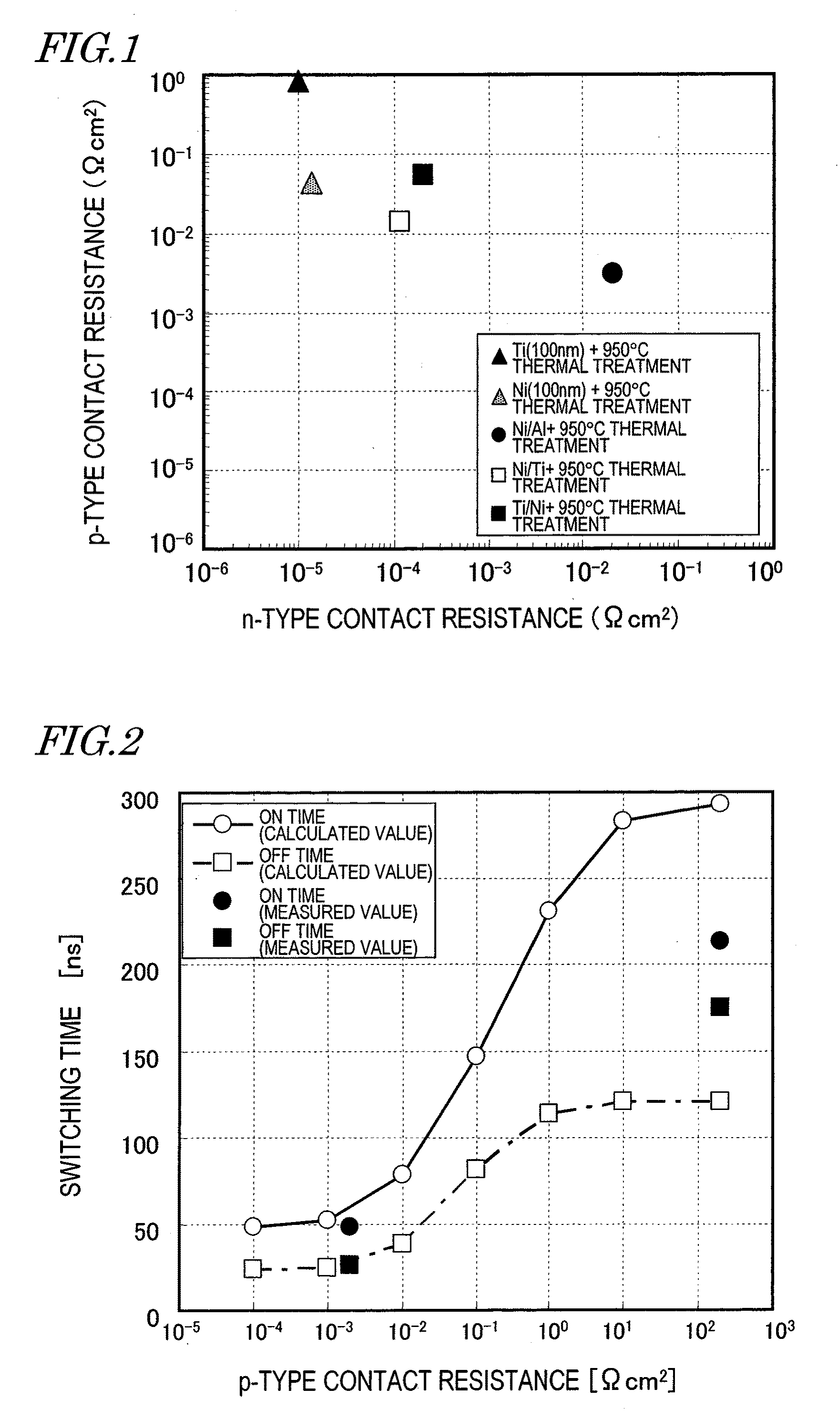

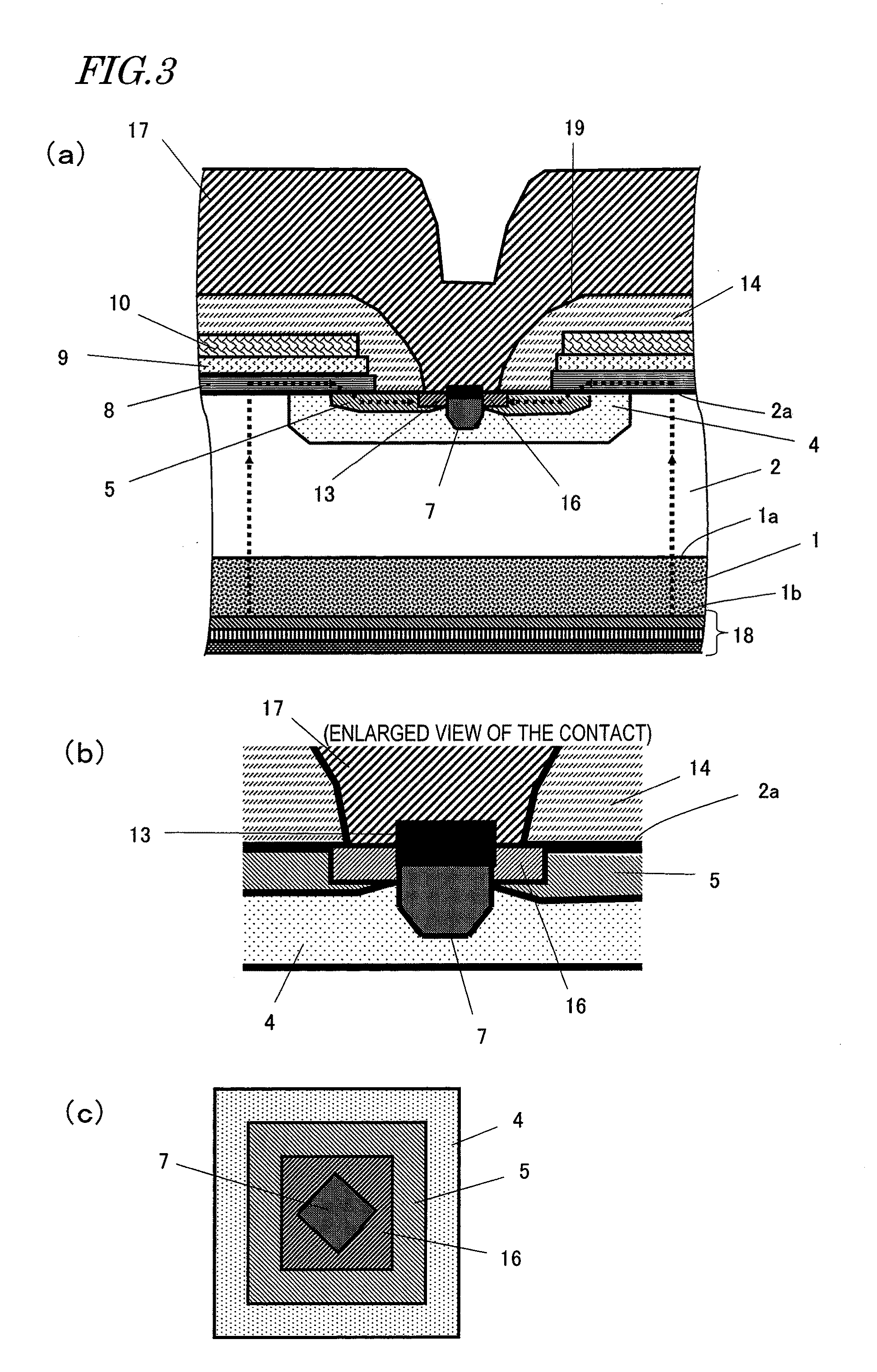

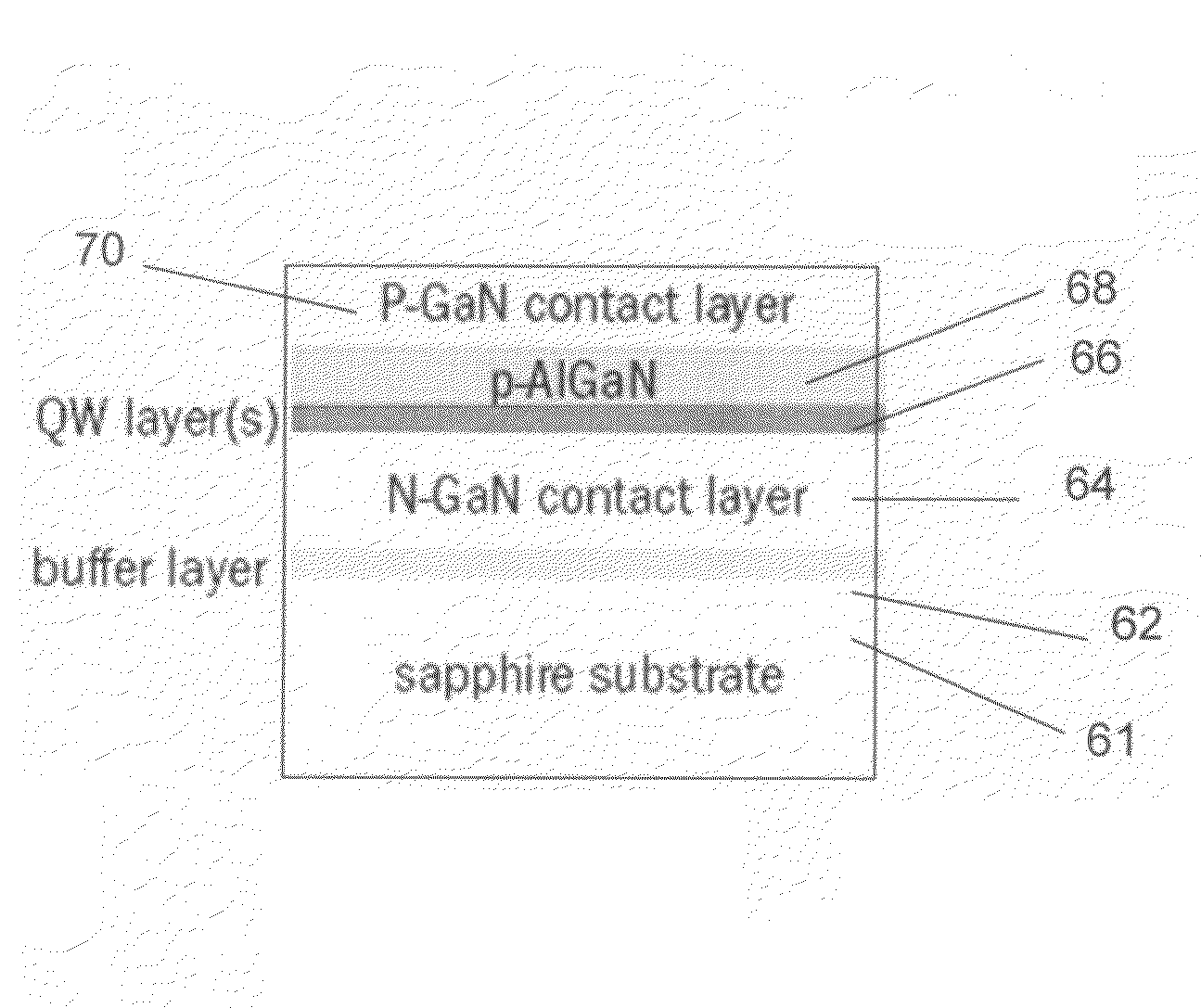

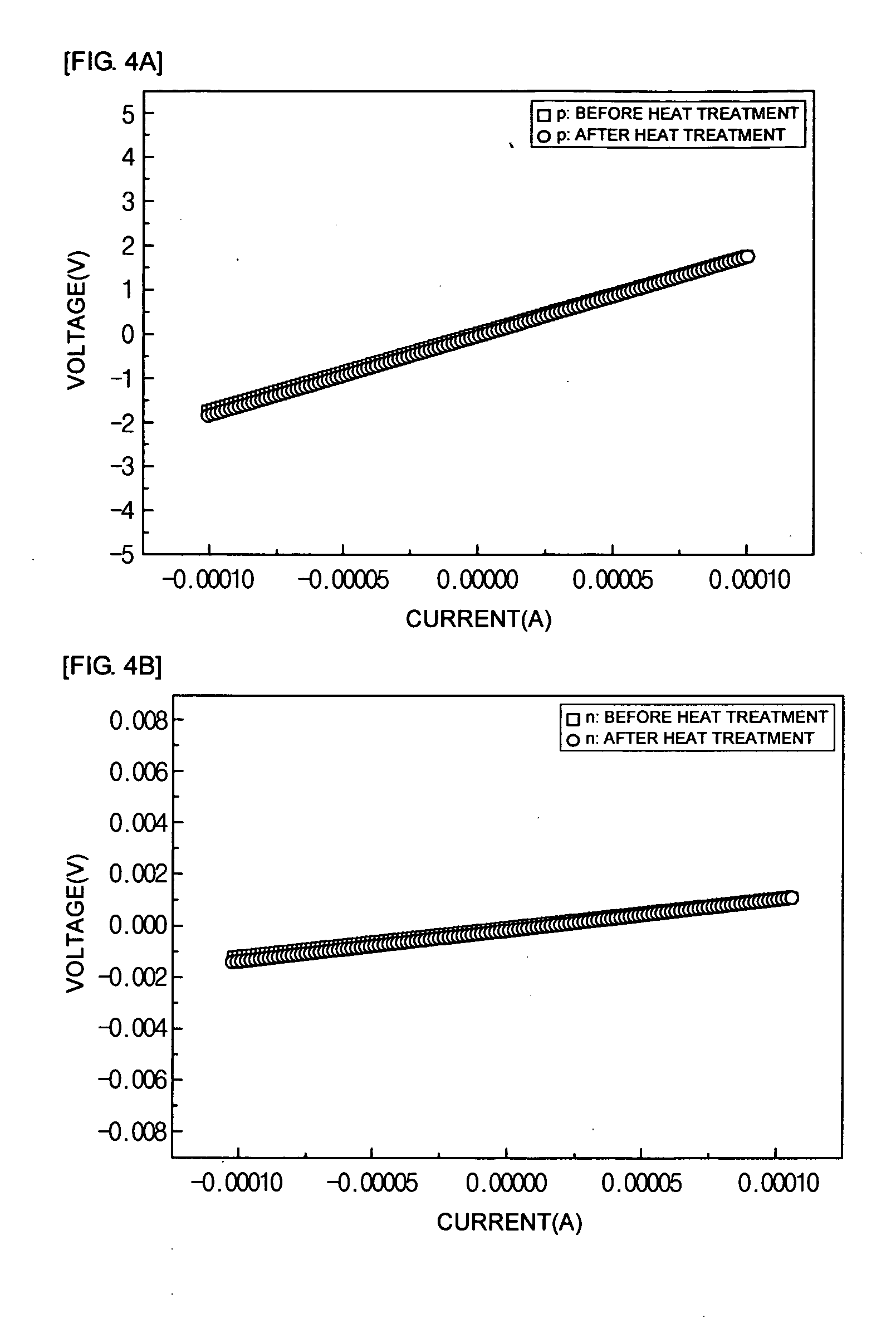

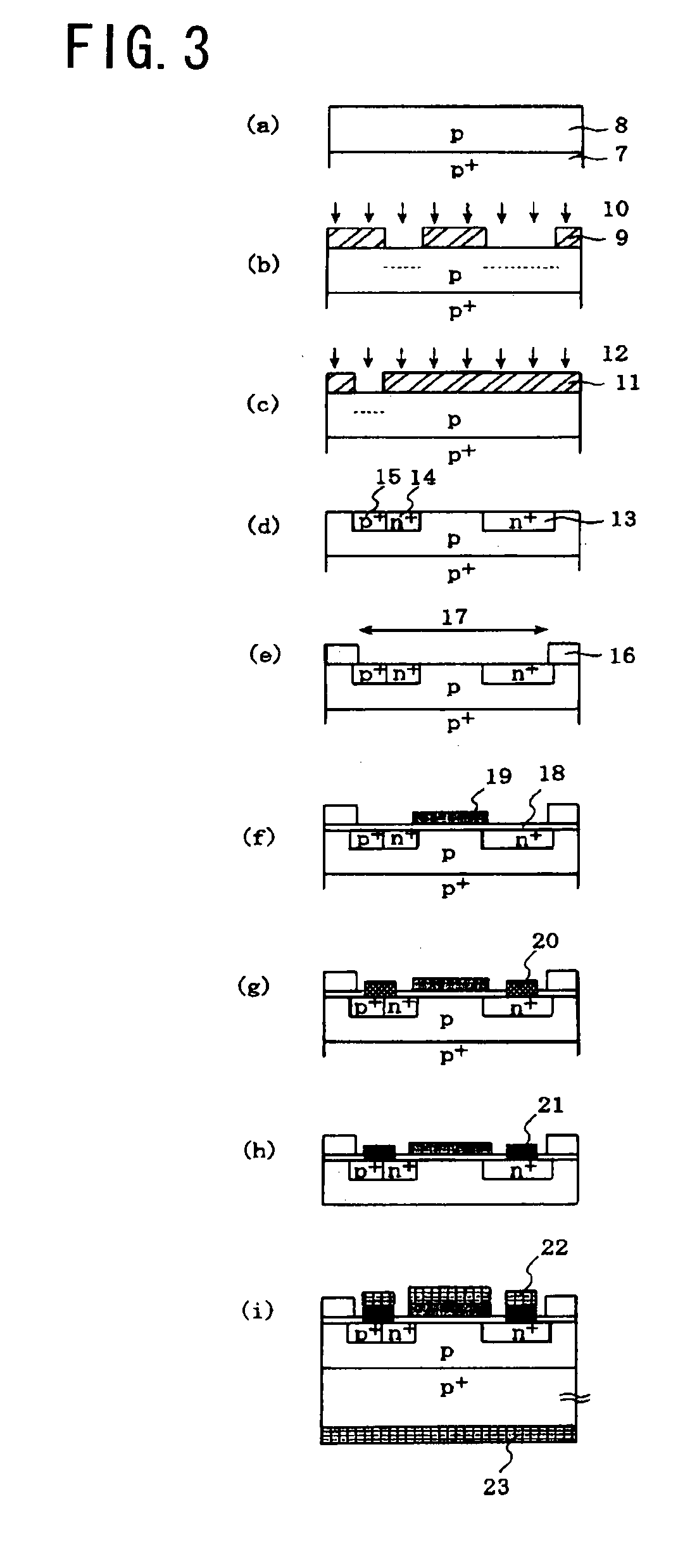

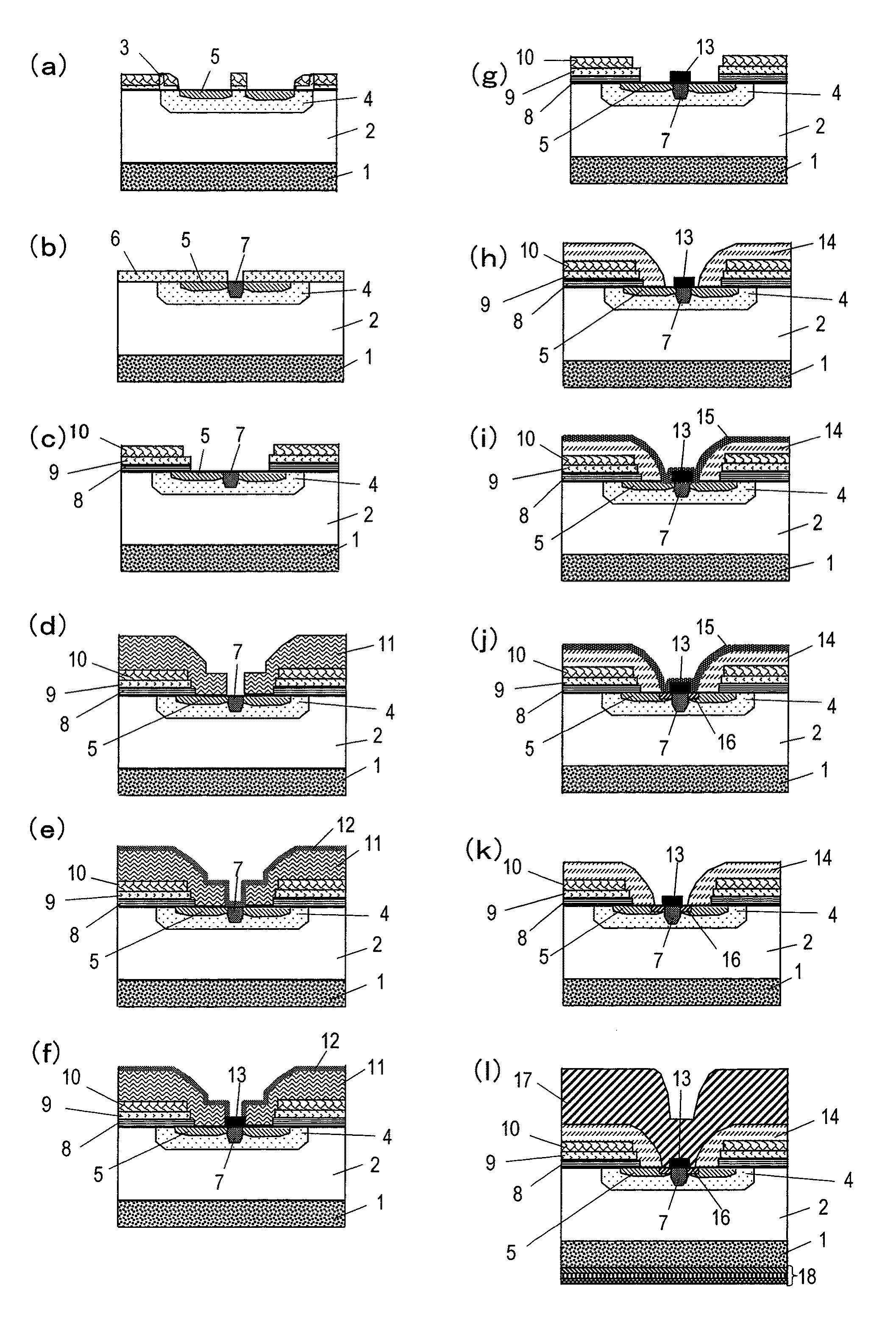

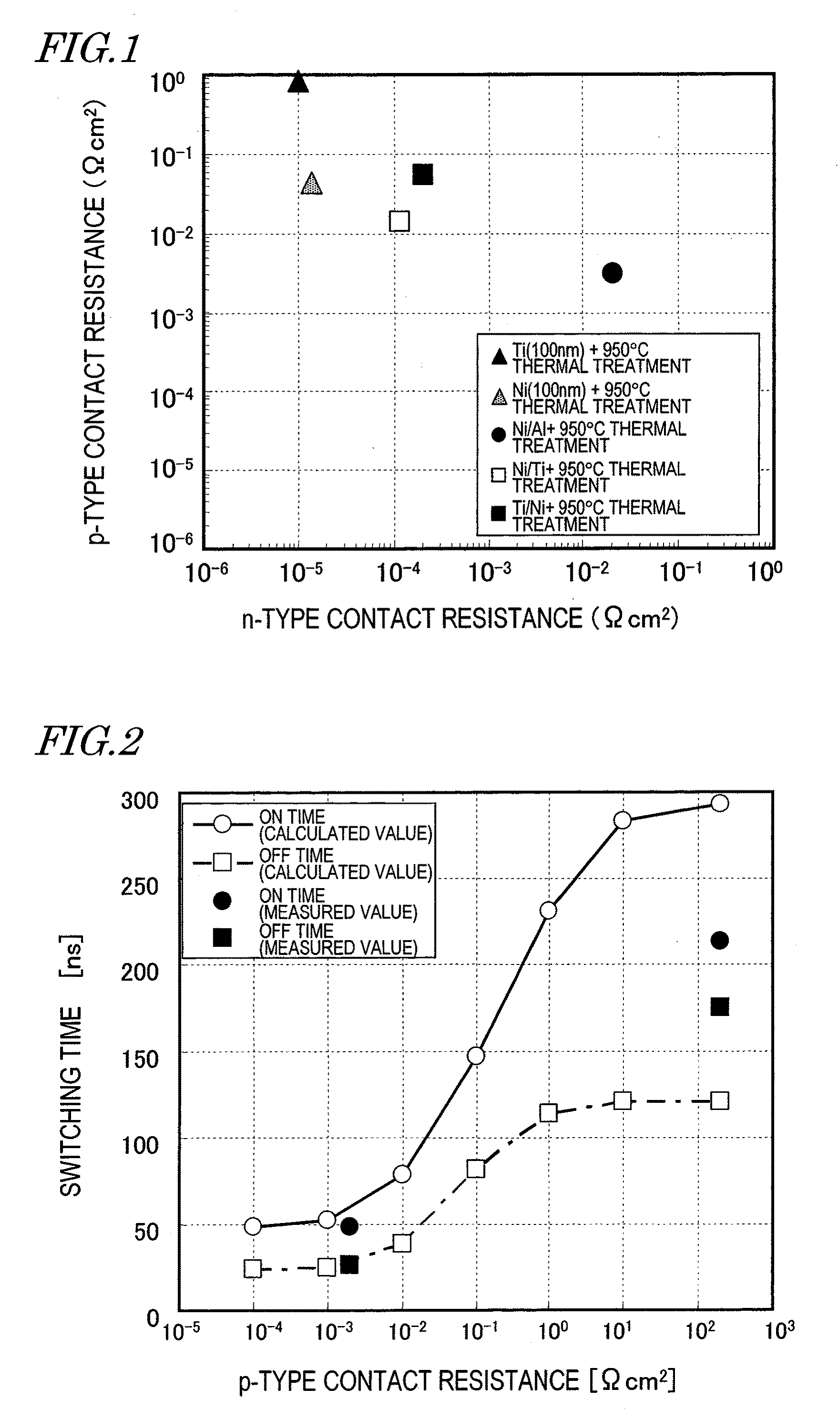

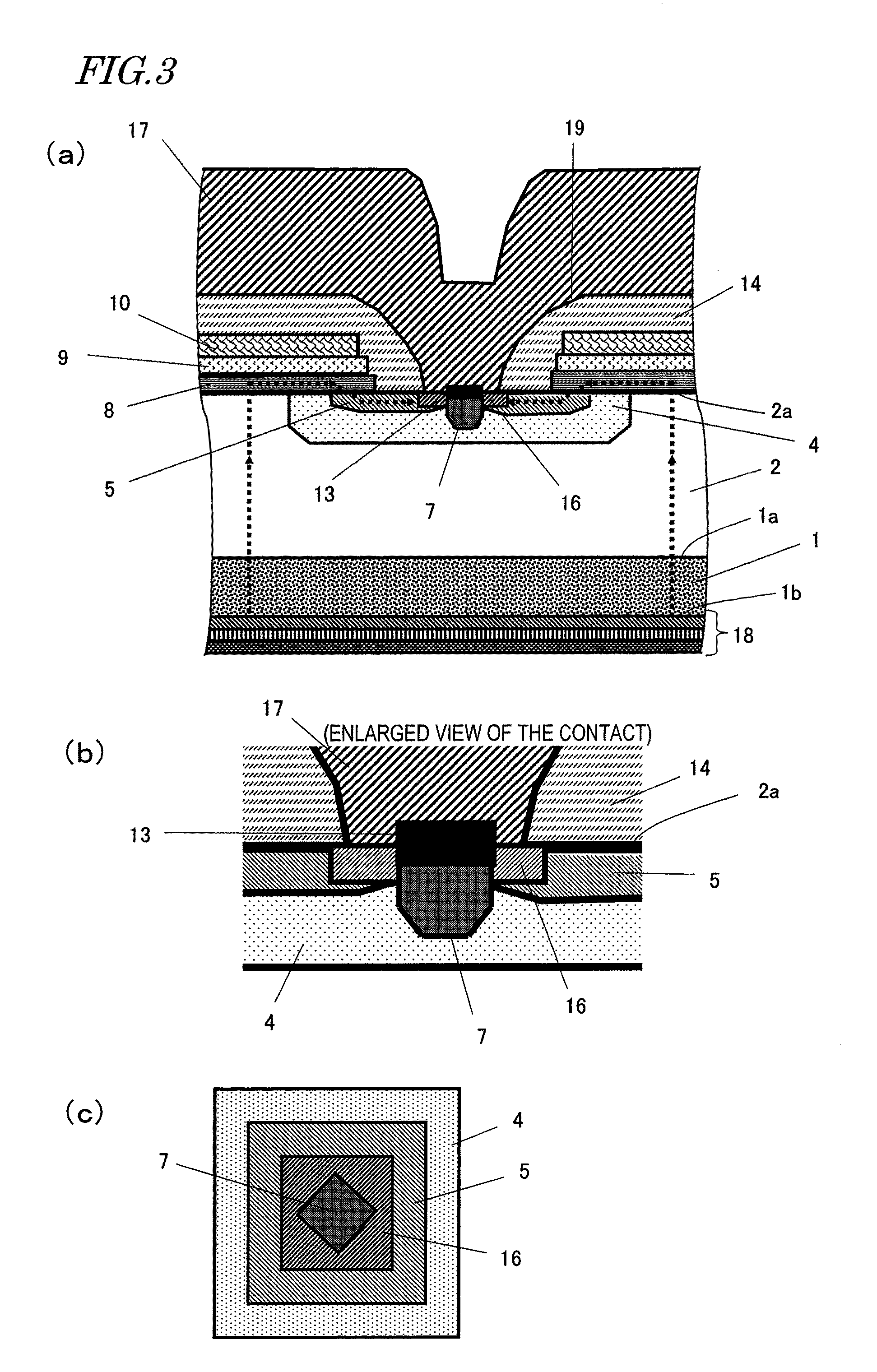

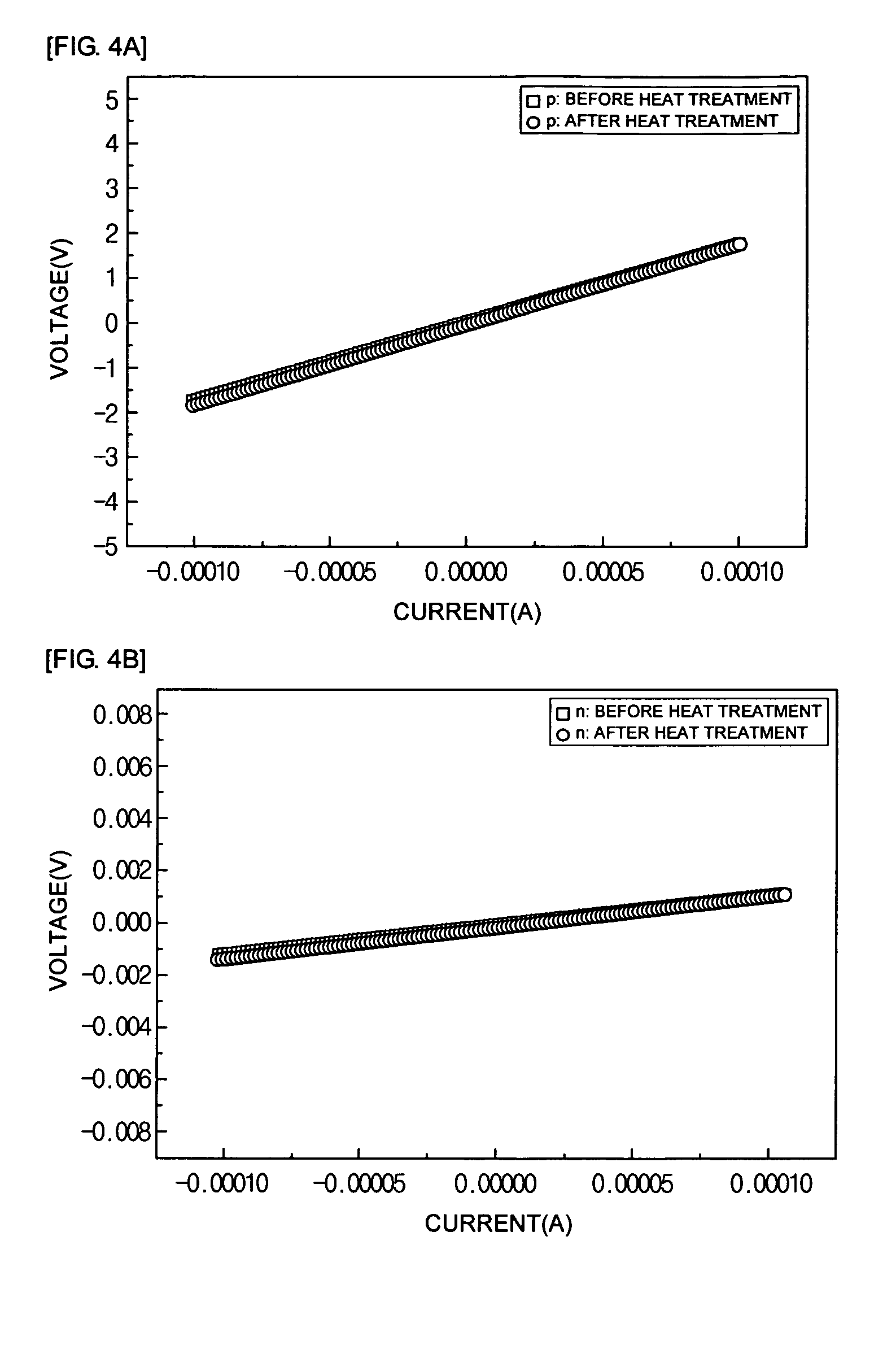

Silicon carbide semiconductor device and method for manufacturing the same

InactiveUS20100055858A1Lower resistanceLower ohmic contactTransistorSolid-state devicesAlloyTitanium

A semiconductor device according to the present invention includes a silicon carbide semiconductor substrate having a silicon carbide semiconductor layer; a p-type impurity region provided in the silicon carbide semiconductor layer and including a p-type impurity; a p-type ohmic electrode electrically connected to the p-type impurity region; an n-type impurity region provided in the silicon carbide semiconductor layer adjacent to the p-type impurity region, and including an n-type impurity; and an n-type ohmic electrode electrically connected to the n-type impurity region. The p-type ohmic electrode contains an alloy of nickel, aluminum, silicon and carbon, and the n-type ohmic electrode contains an alloy of titanium, silicon and carbon.

Owner:PANASONIC CORP

Method for manufacturing silicon solar cell

InactiveCN101783374ALow sheet resistanceLower ohmic contactFinal product manufactureSemiconductor devicesMetallic electrodeOhmic contact

The invention discloses a method for manufacturing a silicon solar cell. In the process of manufacturing a PN junction on a silicon wafer, a selective diffusion technology method is adopted, i,e. laser is utilized to heat a position, on which a positive electrode intends to be manufactured, on the surface of the silicon wafer; and under the action of heating, phosphorus in a phosphorus source uniformly adhered on the surface diffuses towards the inner of the silicon wafer, thus a heavy doping zone with smaller sheet resistance is formed at the position on which the positive electrode intends to be manufactured to effectively reduce the sheet resistance of the silicon solar cell, thereby not only being beneficial for increasing the open-circuit voltage of the silicon solar cell; the increase of the open-circuit voltage effectively improves the conversion efficiency of the silicon solar cell, reduces ohmic contact of a metal electrode and the silicon solar cell, thereby reducing the series resistance of the silicon solar cell, and being capable of meeting the purpose of industrialized production better.

Owner:SUN EARTH SOLAR POWER

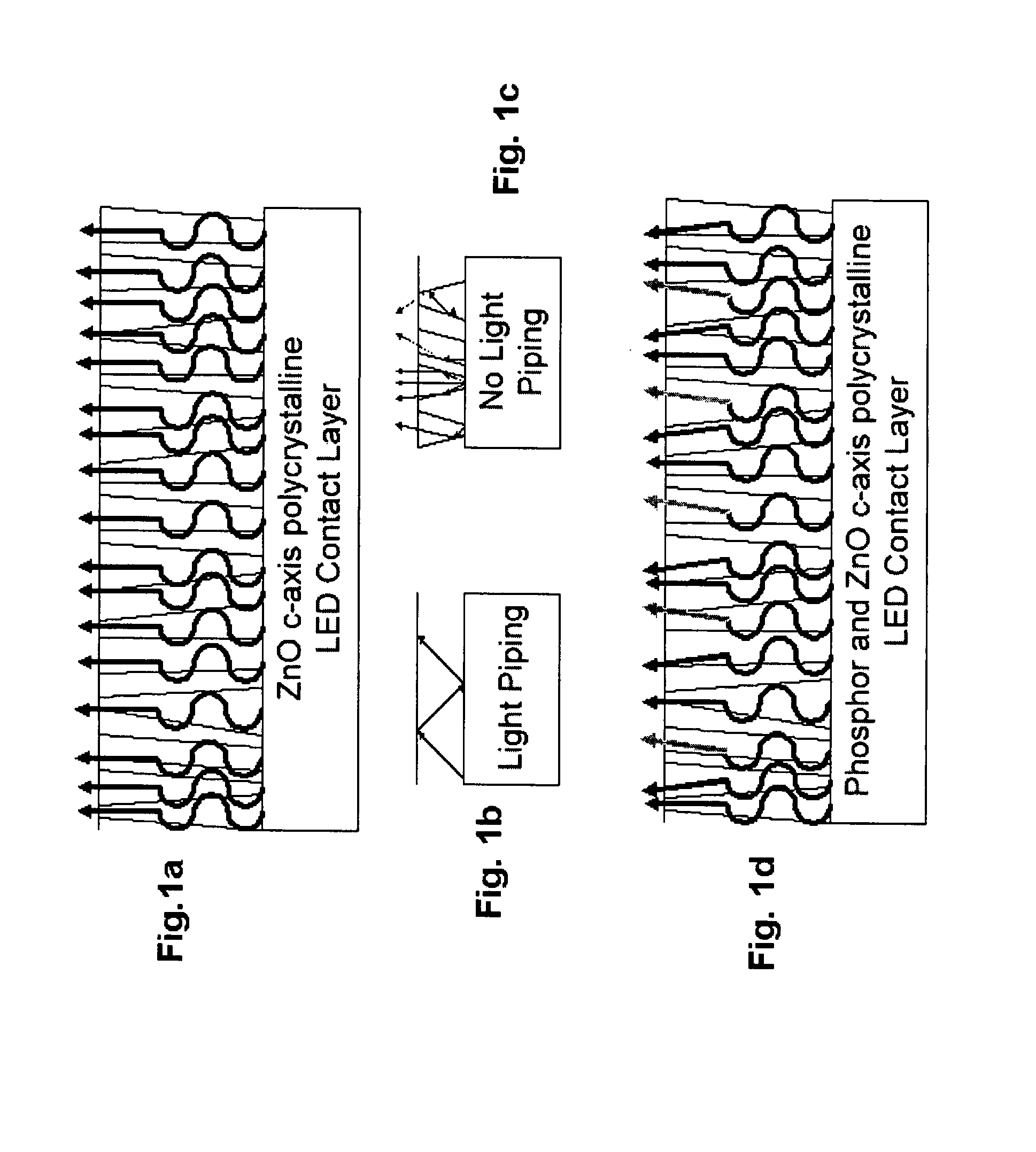

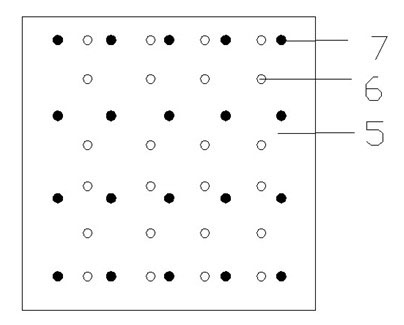

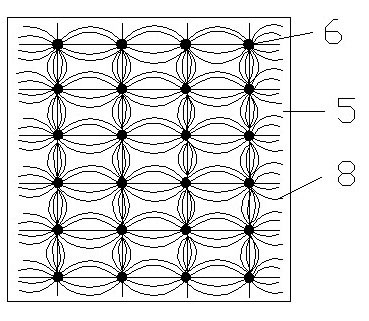

Self assembled controlled luminescent transparent conductive photonic crystals for light emitting devices

InactiveUS20080142810A1Maximize spreadMitigate light trappingPolycrystalline material growthSemiconductor/solid-state device manufacturingPhotonic crystalPhosphor

A transparent conductive oxide contact layer to enhance the spectral output of a light emitting device and a methodology for its deposition. The transparent conductive oxide deposited on the light emitting device so as to have a columnar structure. The transparent conductive oxide contact layer may be preferably ZnO doped with a conductive element. Light emitting phosphors may also be deposited within the transparent conductive oxide contact layer.

Owner:STRUCTURED MATERIALS

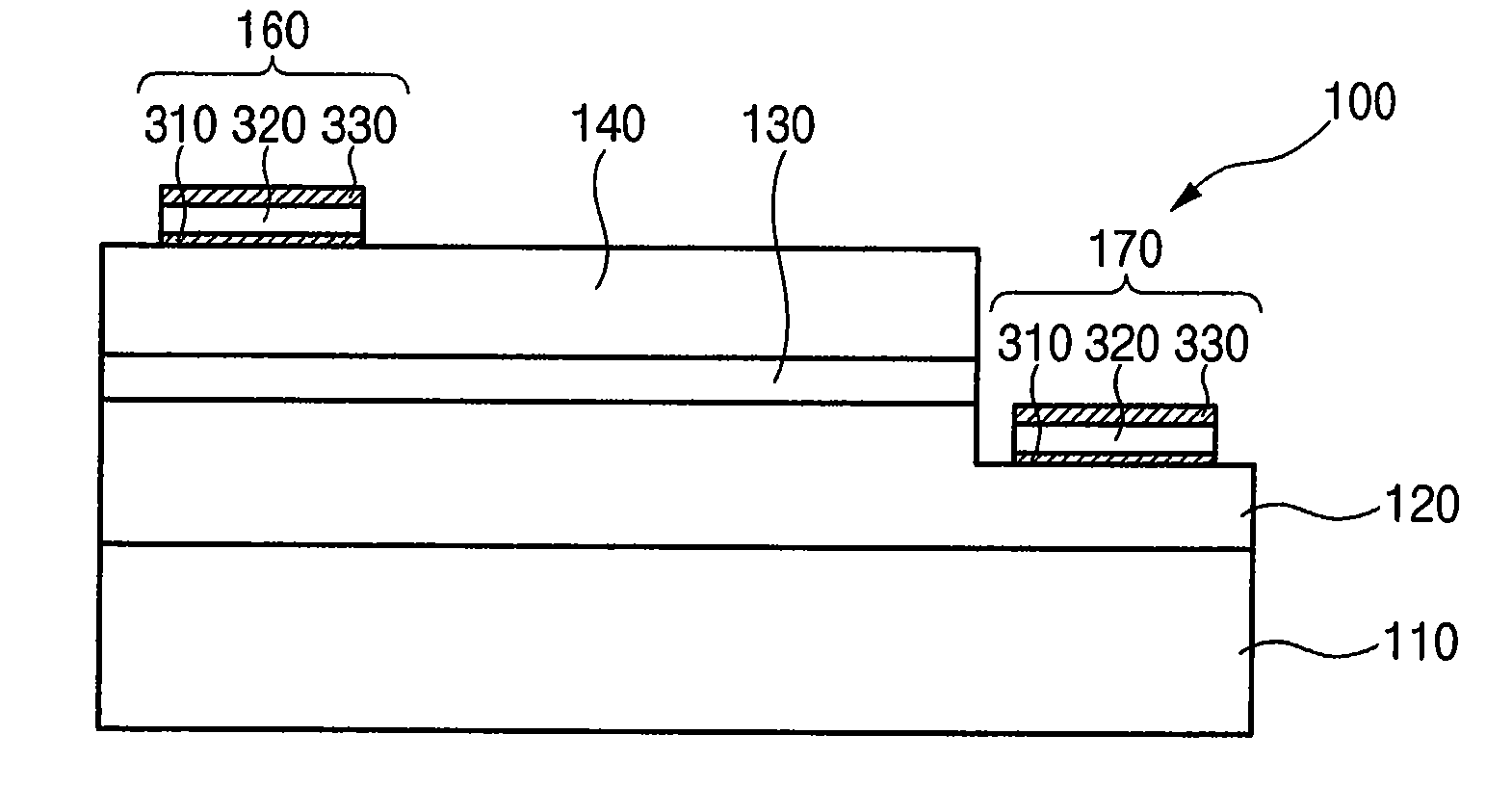

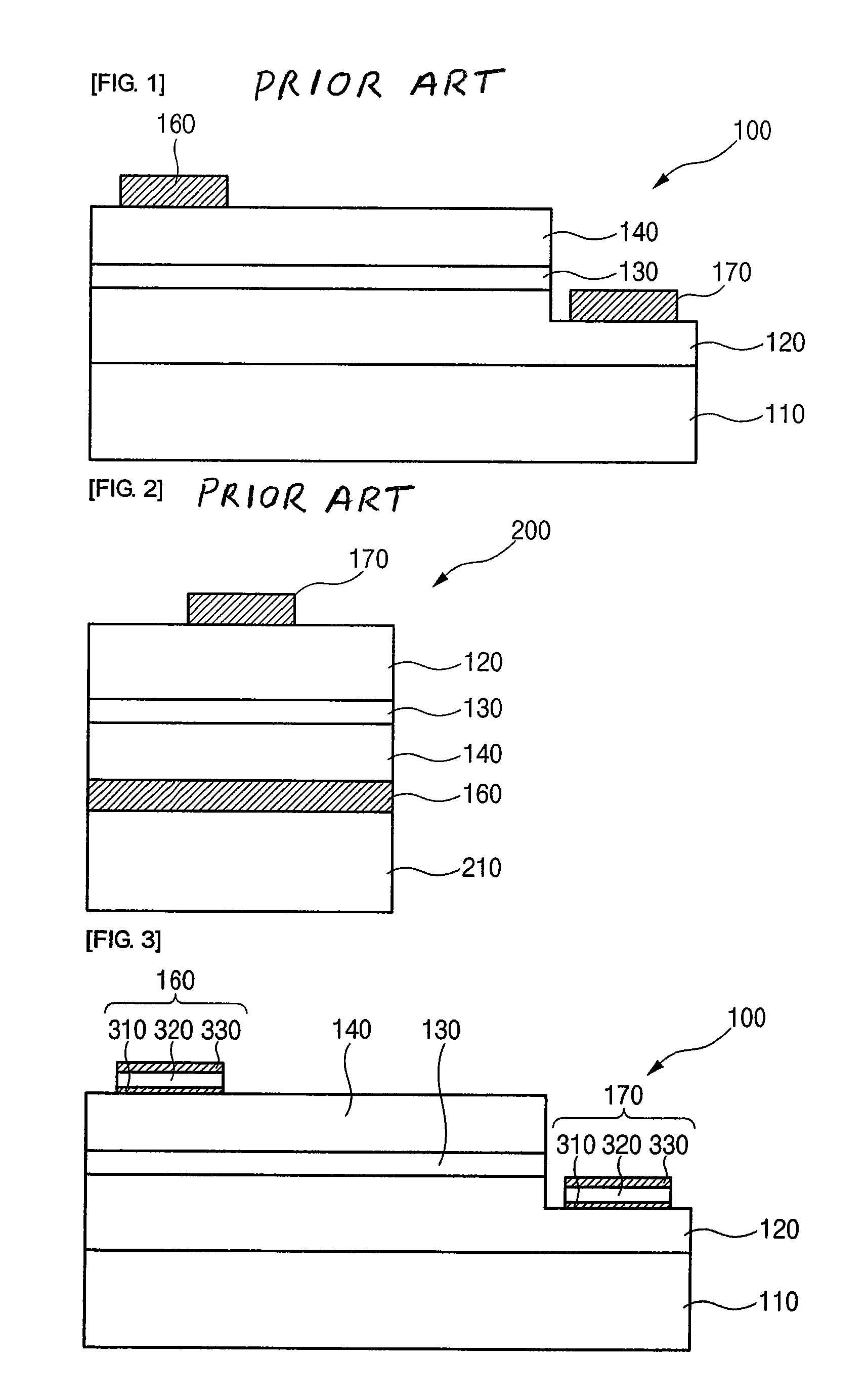

Nitride semiconductor light emitting device including electrodes of a multilayer structure

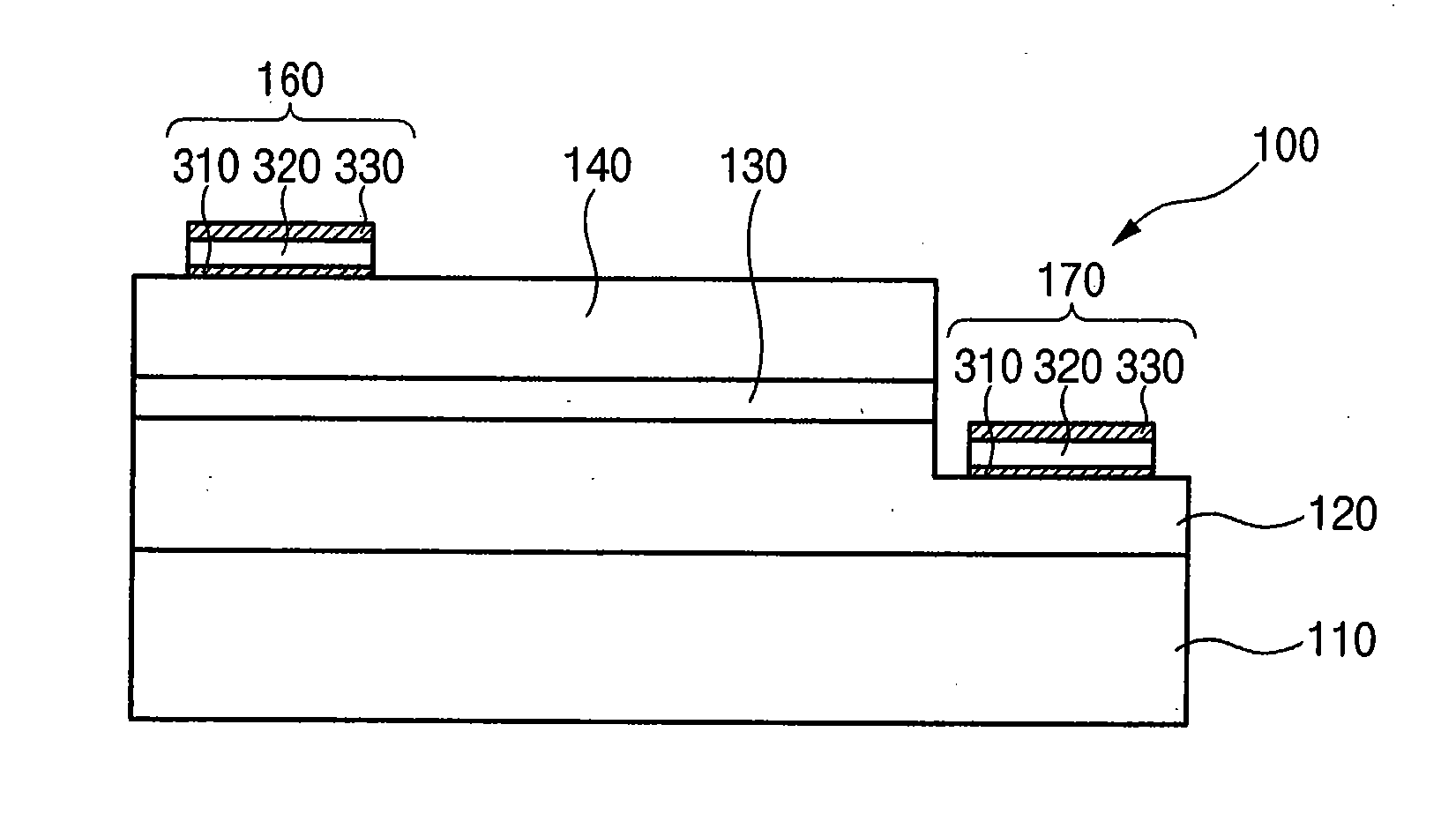

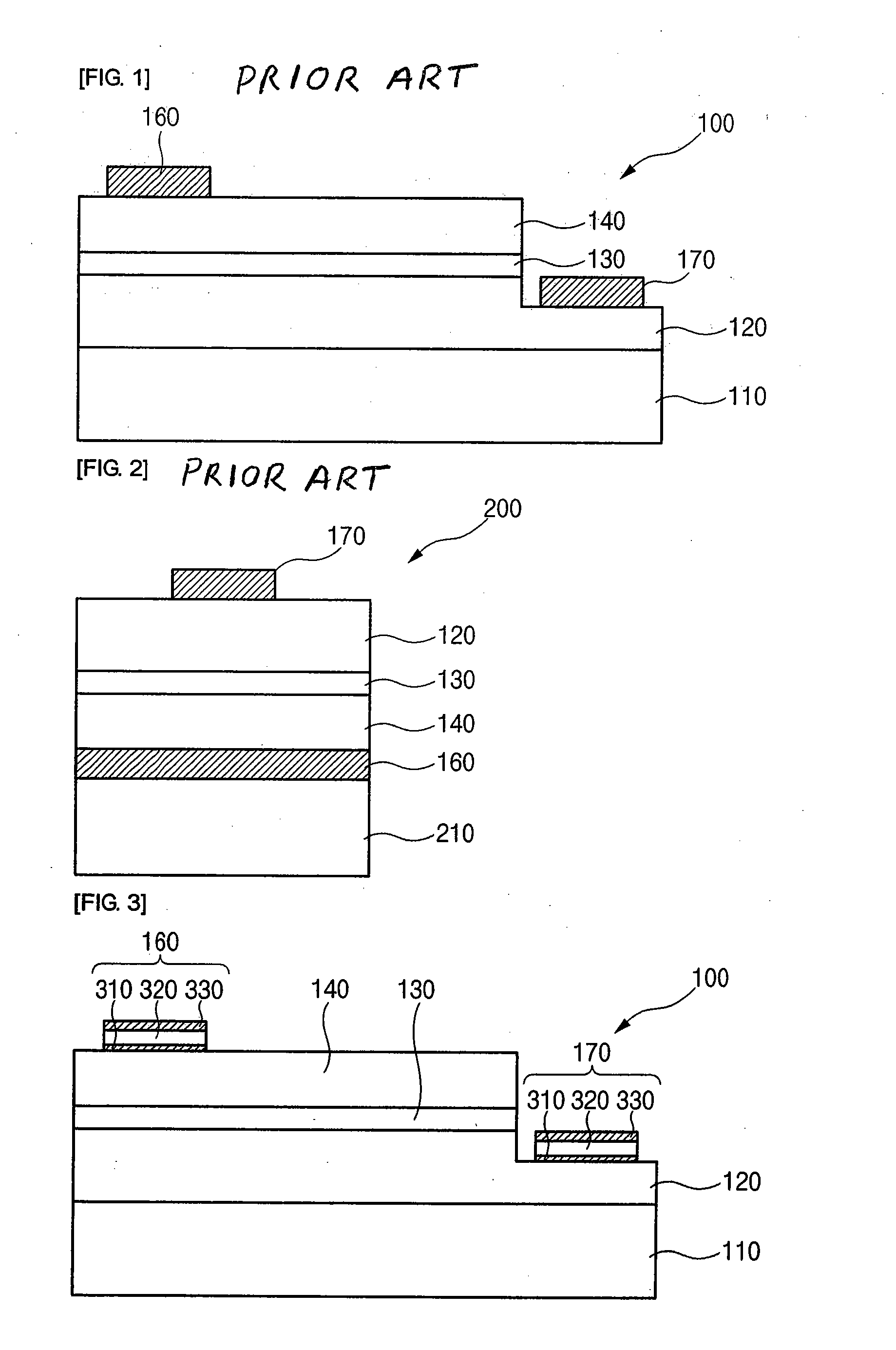

ActiveUS20100308366A1Improve heat resistanceImprove reflectivitySemiconductor devicesOhmic contactActive layer

A nitride semiconductor LED comprises a substrate; an n-type nitride semiconductor layer formed on the substrate; an active layer formed on a predetermined region of the n-type nitride semiconductor layer; a p-type nitride semiconductor layer formed on the active layer; a p-electrode formed on the p-type nitride semiconductor layer; and an n-electrode formed on the n-type nitride semiconductor layer in which the active layer is not formed. The p-electrode and n-electrode are formed to have such a multilayer structure that an ohmic contact layer, a compound layer containing aluminum or silver, and a degradation preventing layer are sequentially laminated.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for manufacturing silicon carbide semiconductor device, and silicon carbide semiconductor device

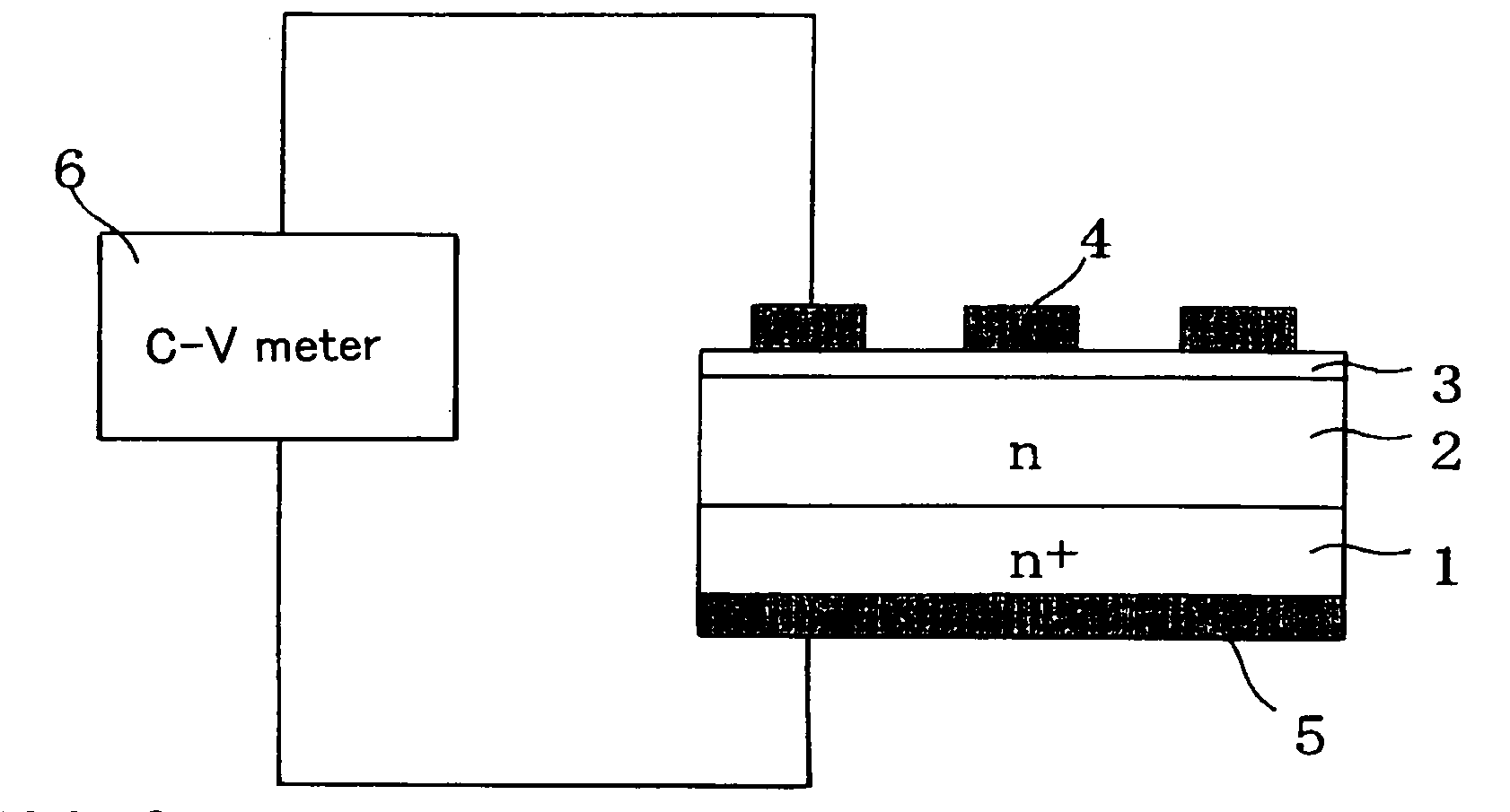

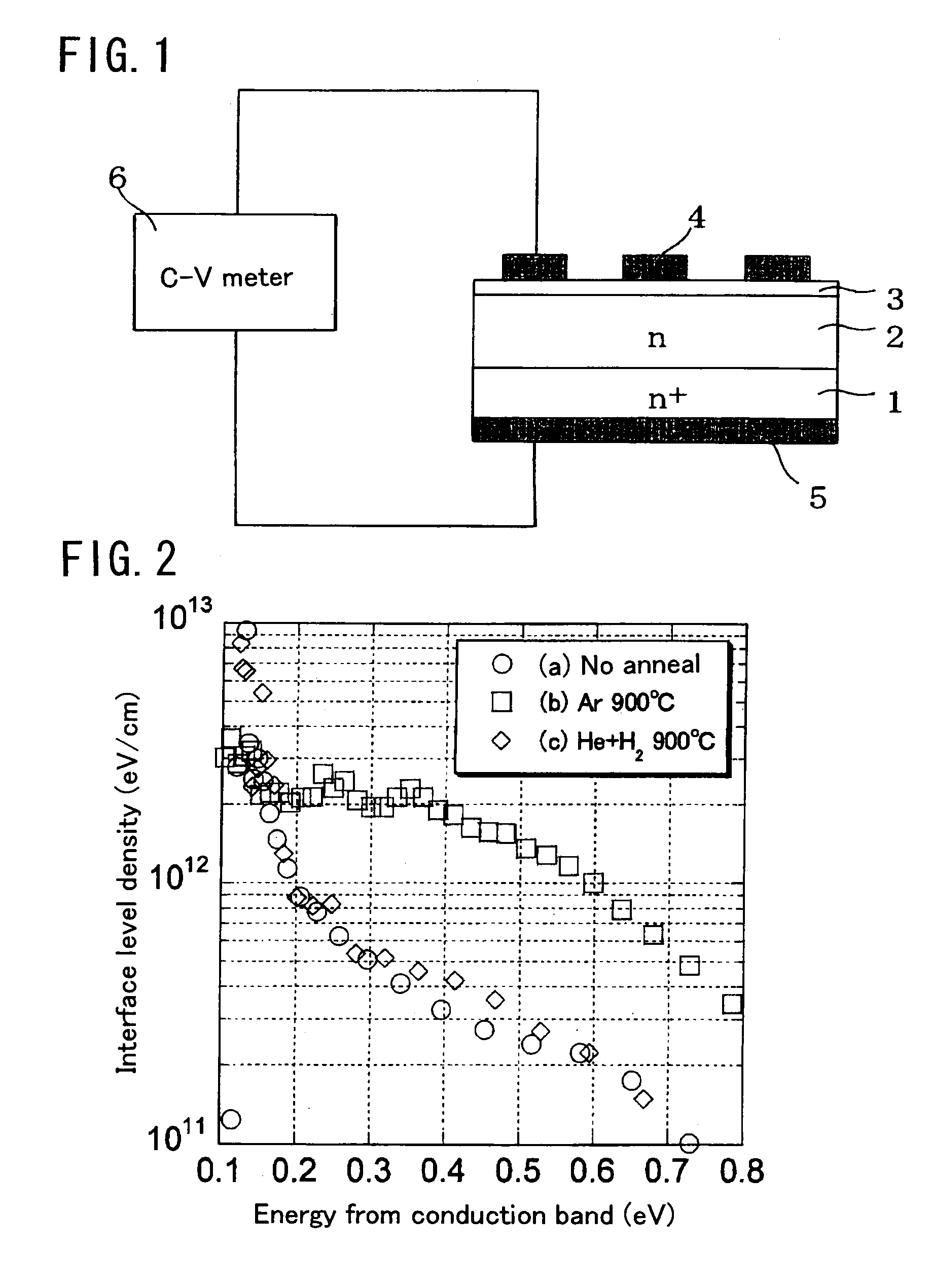

ActiveUS20090072244A1Improve channel mobilityLower ohmic contactSemiconductor/solid-state device manufacturingSemiconductor devicesReaction layerOxygen

The object is to provide a method for the fabrication of a semiconductor device having undergone an anneal treatment for the purpose of forming such ohmic contact as enables decrease of ohmic contact resistance and being provided on the (000-1) plane of silicon carbide with an insulating film and provide the semiconductor device. The method for the fabrication of a silicon carbide semiconductor device includes the steps of performing thermal oxidation on the (000-1) plane of a silicon carbide semiconductor in a gas containing at least oxygen and moisture, thereby forming an insulating film in such a manner as to contact the (000-1) plane of the silicon carbide semiconductor, removing part of the insulating film, thereby forming an opening part therein, depositing contact metal on at least part of the opening part, and performing a heat treatment, thereby forming a reaction layer of the contact metal and silicon carbide, wherein the heat treatment is implemented in a mixed gas of an inert gas and hydrogen.

Owner:NAT INST OF ADVANCED IND SCI & TECH

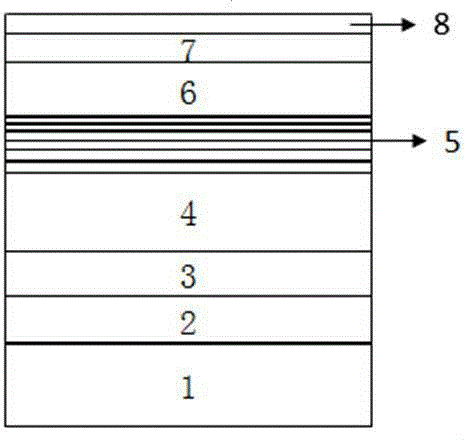

Back contact heterojunction solar battery

InactiveCN102184976AImprove conversion efficiencyReduce shading ratePhotovoltaic energy generationSemiconductor devicesHeterojunctionSilicon solar cell

The invention relates to a solar battery, in particular to a back contact heterojunction solar battery, comprising a transparent conducting film TCO, a P-a-Si amorphous silicon film, an i-a-Si intrinsic amorphous silicon film, an N-C-SiN type crystalline silicon, an i-a-Si intrinsic amorphous silicon film, an N-a-SiN type amorphous silicon film, a penetrative type back electrode and a back electrode which are overlapped in sequence from top to bottom. The solar battery can avoid the photoconduced attenuation phenomenon of the conventional P-type crystalline silicon solar battery, the back contact electrode reduces the contact resistance, and effectively reduces the shading ratio of a light-receiving surface, thereby increasing the current collection rate and improving the conversion efficiency of the solar battery; as the temperature coefficient is low, the back contact heterojunction solar battery is suitable for a high temperature environment; and the low-temperature process simplifies the production process greatly and reduces the production cost, so that the back contact heterojunction solar battery is suitable for industrial development.

Owner:山东力诺太阳能电力股份有限公司

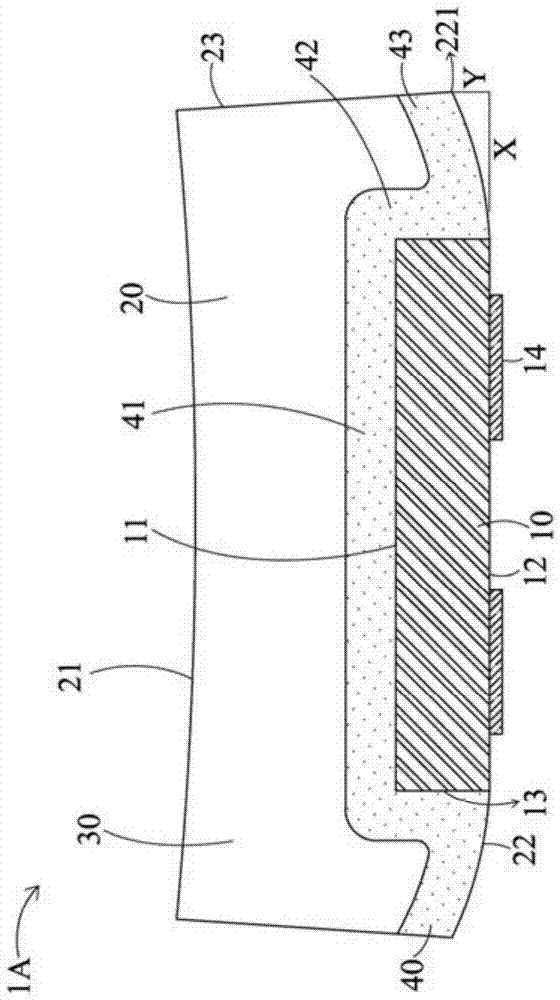

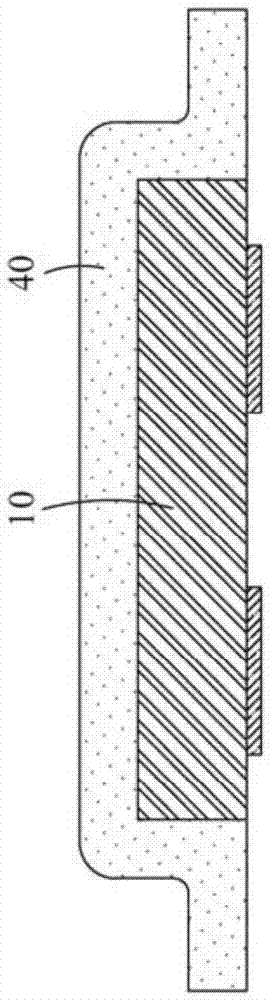

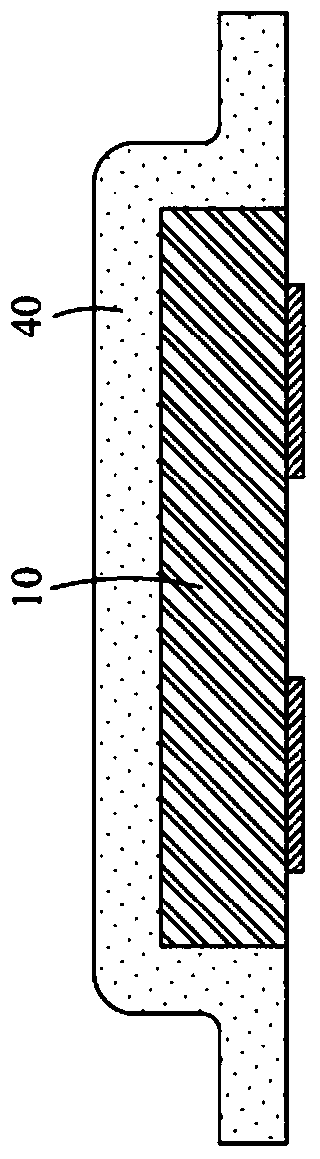

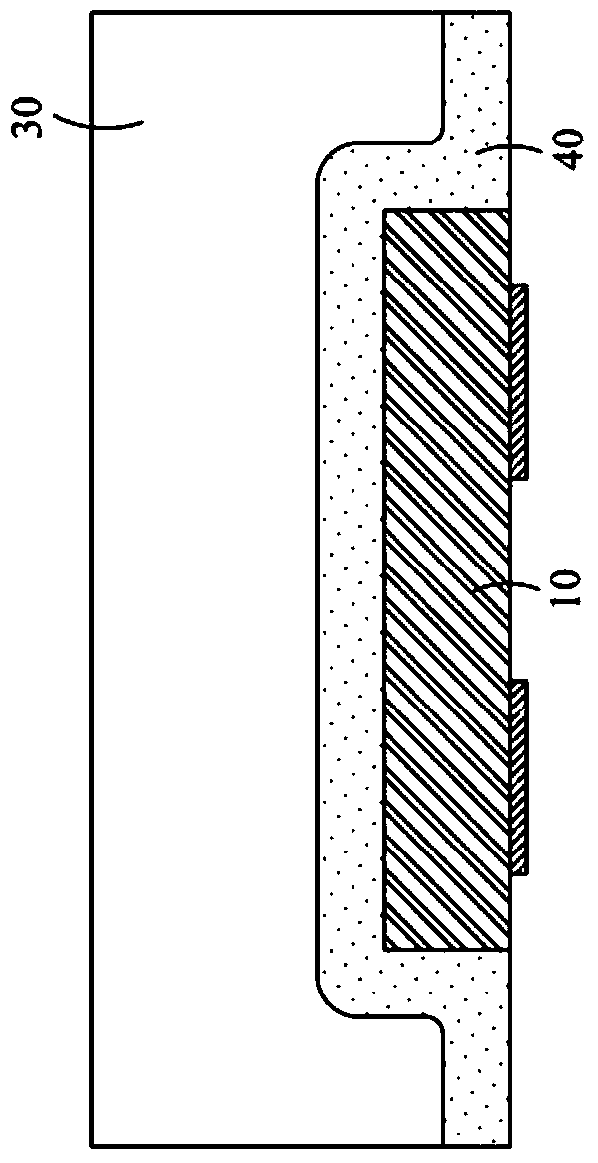

Chip scale package light-emitting apparatus having recessed design and manufacturing method thereof

ActiveCN106981554AAvoid Electrical Connection FailureImprove welding failure or poor welding qualitySemiconductor devicesEutectic bondingReflow soldering

The invention provides a chip scale package light-emitting apparatus having recessed design and a manufacturing method thereof. The chip scale package light-emitting apparatus includes a flip chip type LED chip and a cladding structure. The cladding structure covers the LED chip, and has a bottom surface warps upwardly to for a recessed shape. The invention also provides a manufacturing method for manufacturing the light-emitting apparatus. The apparatus and the method can avoid or improve poor quality of welding points between the light-emitting apparatus and a substrate which is often caused by greater gap between an electrode group of the LED chip and a welding pad of the substrate due to expansion of the cladding structure upon being heated in reflow soldering or eutectic bonding. Therefore, the apparatus and the method can secure the electrode group to the substrate. With excellent welding quality, failure of electrical connection of the light-emitting apparatus can be avoided, the thermal resistance between the light-emitting apparatus and the substrate can be lowered, temperature at the binding point can be lowered when the light-emitting apparatus operates, and light-emitting efficiency and reliability can be improved.

Owner:MAVEN OPTRONICS CO LTD

Silicon carbide semiconductor device and method for manufacturing the same

Owner:PANASONIC CORP

Nitride semiconductor light emitting device including electrodes of a multilayer structure

ActiveUS7868344B2Improve reflectivityIncrease resistanceSemiconductor devicesOhmic contactActive layer

Owner:SAMSUNG ELECTRONICS CO LTD

Method for welding silicon wafer and molybdenum piece in semiconductor device and application of silicon wafer and molybdenum piece

ActiveCN104538321AImprove mechanical propertiesImprove electrical performanceSolid-state devicesSemiconductor/solid-state device manufacturingWeld strengthUltimate tensile strength

The invention discloses a method for welding a silicon wafer and a molybdenum piece in a semiconductor device. The method comprises the following steps that firstly, a first silver layer is arranged on the molybdenum piece; secondly, a second silver layer is arranged on the anode electrode of the silicon wafer; thirdly, a third silver layer is arranged between the first silver layer and the second silver layer; fourthly, the silicon wafer and the molybdenum piece are welded together by welding the first silver layer, the second silver layer and the third silver layer. According to the method, the technology is simple, the yield and the welding strength are high, the voidage of welding layers is low, the deformation is small, and the performance of the product can be greatly improved. The invention further relates to an application of the silicon wafer / molybdenum piece manufactured through the method.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

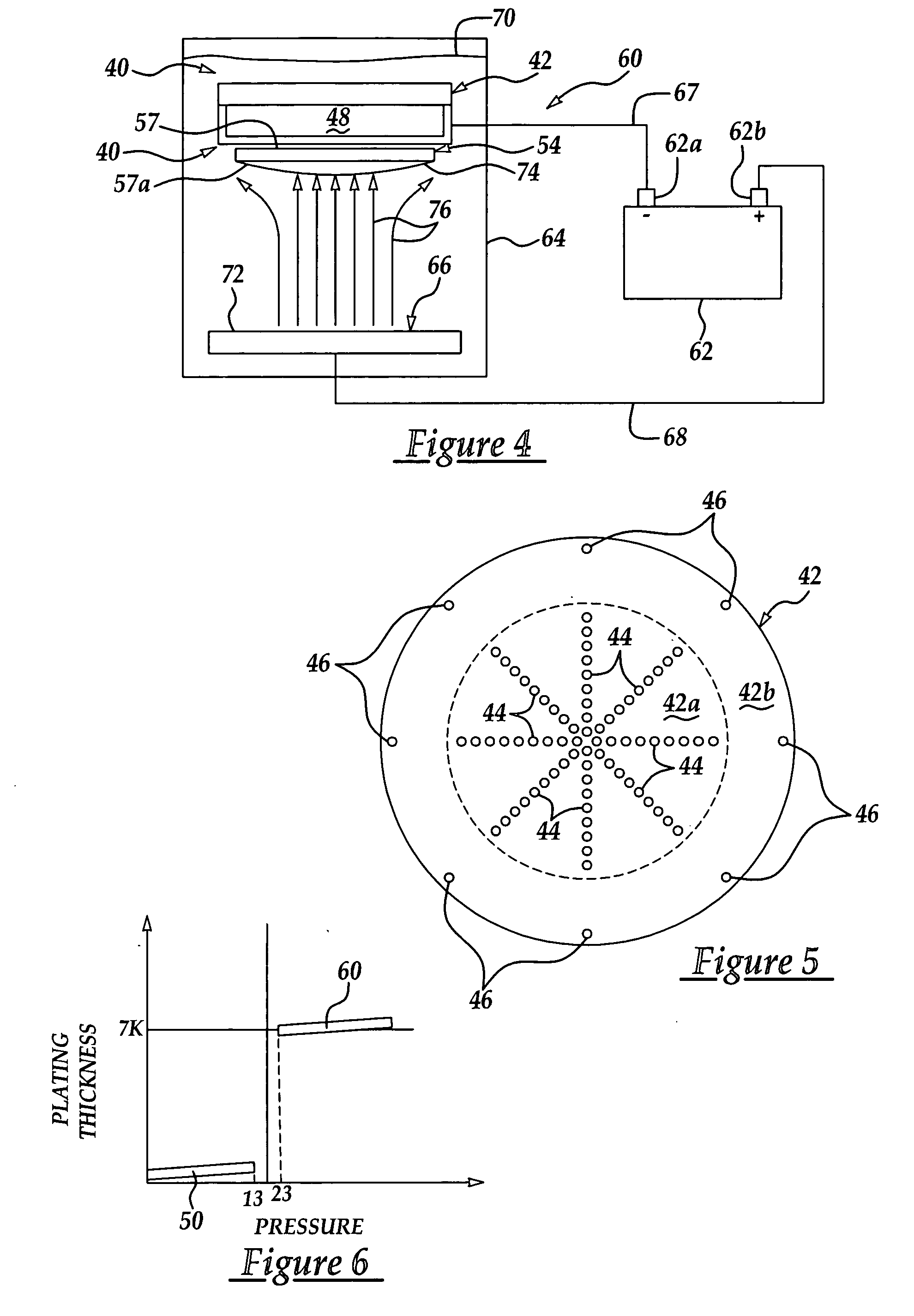

Thrust pad assembly for ECP system

InactiveUS20050121329A1Reduce in quantityReduce and eliminate needSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactVoltage source

A thrust pad assembly which is capable of reducing the quantity of metal electroplated onto the edge region of a substrate to eliminate or reduce the need for edge bevel cleaning or removal of excess metal from the substrate after the electroplating process. The thrust pad assembly includes an air platen through which air is applied at variable pressures to the central and edge regions, respectively, of a thrust pad. The thrust pad applies pressure to a contact ring connected to an electroplating voltage source. The contact ring applies relatively less pressure to the edge region than to the central region of the substrate, thereby reducing the ohmic contact.

Owner:TAIWAN SEMICON MFG CO LTD

Method for manufacturing a semiconductor device by exposing, to a hydrogen plasma atmosphere, a semiconductor substrate

ActiveUS9666676B2Short timeIncrease temperatureSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricHydrogen

A method for manufacturing a semiconductor device having a MOS gate structure includes forming a device structure on a semiconductor substrate; forming an interlayer dielectric to cover the device structure; forming a contact hole through the interlayer dielectric; forming a transition metal film (e.g., Ni) on a portion of the semiconductor substrate exposed by the contact hole; (e) forming a metal film (e.g., Ti) on the entire surface of the semiconductor substrate; forming an oxide film in the surface of the metal film; selectively removing the metal film in which the oxide film has been formed, to thereby expose the transition metal film; and (h) exposing, to a hydrogen plasma atmosphere, the semiconductor substrate in which the transition metal film and the oxide film have been exposed, to thereby cause the transition metal film to generate heat and react with the semiconductor substrate and form an ohmic contact there between.

Owner:FUJI ELECTRIC CO LTD

LED having N type AlInGaN contact layer and preparation method

InactiveCN105161592AReduce blocking effectThe blocking effect is not weakenedSemiconductor devicesValence bandOhmic contact

An LED having an N type AlInGaN contact layer and a preparation method. The structure comprises a substrate, a nucleating layer, a buffer layer, an N type GaN layer, a multi-quantum-well luminous layer and a P type structure in sequence from bottom to top, and the P type structure includes a P type AlGaN layer, a P type GaN layer and an N type AlInGaN contact layer in sequence. The nucleating layer, the buffer layer, the N type GaN layer, the multi-quantum-well luminous layer, the P type AlGaN layer, the P type GaN layer and the N type AlInGaN layer are grown on the substrate in sequence, through regular changes of the doping amount of In in the N type AlInGaN layer arranged in an LED chip, energy band distribution of the N type AlInGaN layer is changed, a blocking effect of a valence band of the N type AlInGaN layer on hole injection is weakened while a blocking effect on electrons is not weakened, surface roughness can be improved to some extent, and ohmic contact of the LED chip can be reduced by about 10%.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

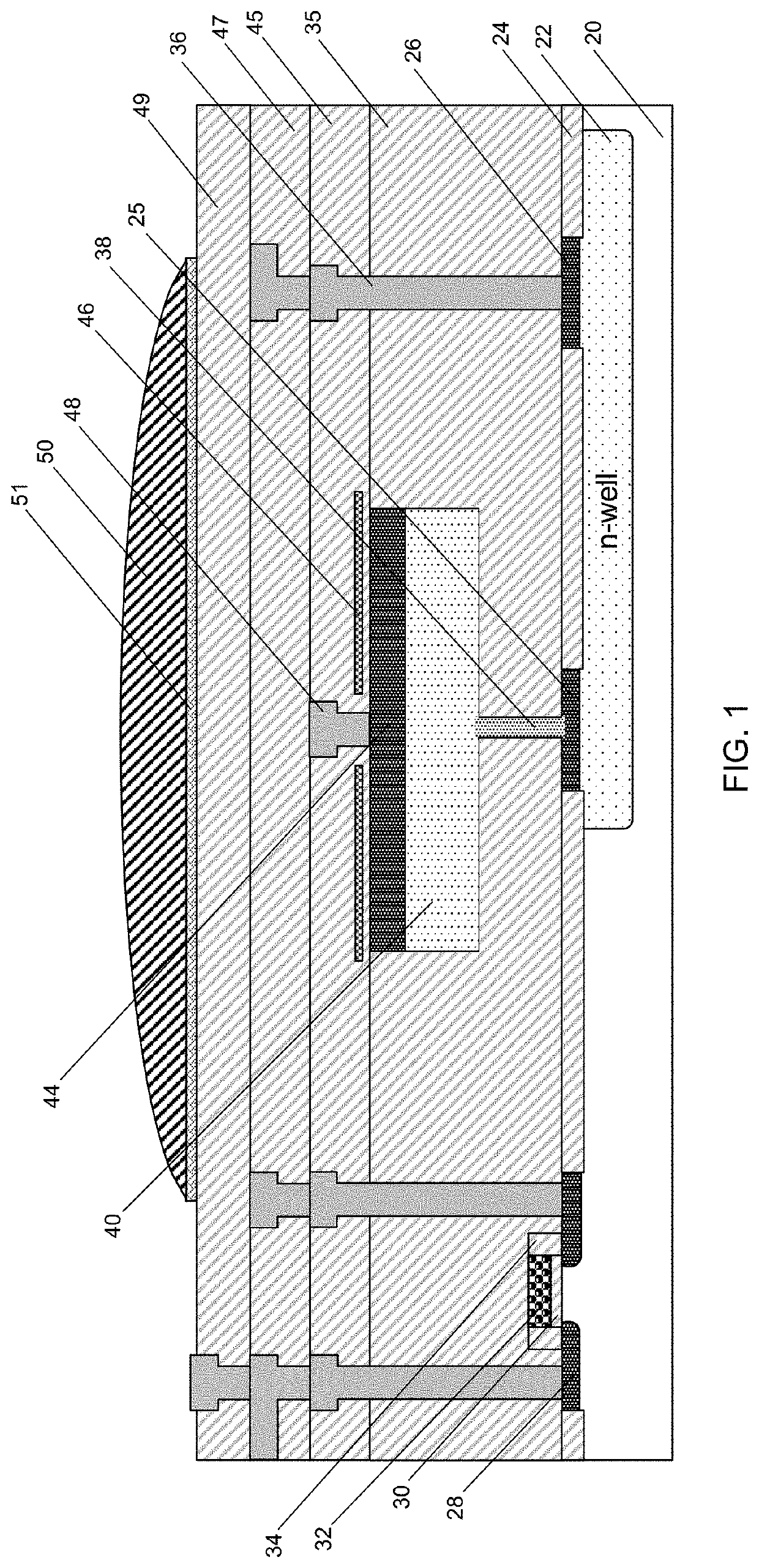

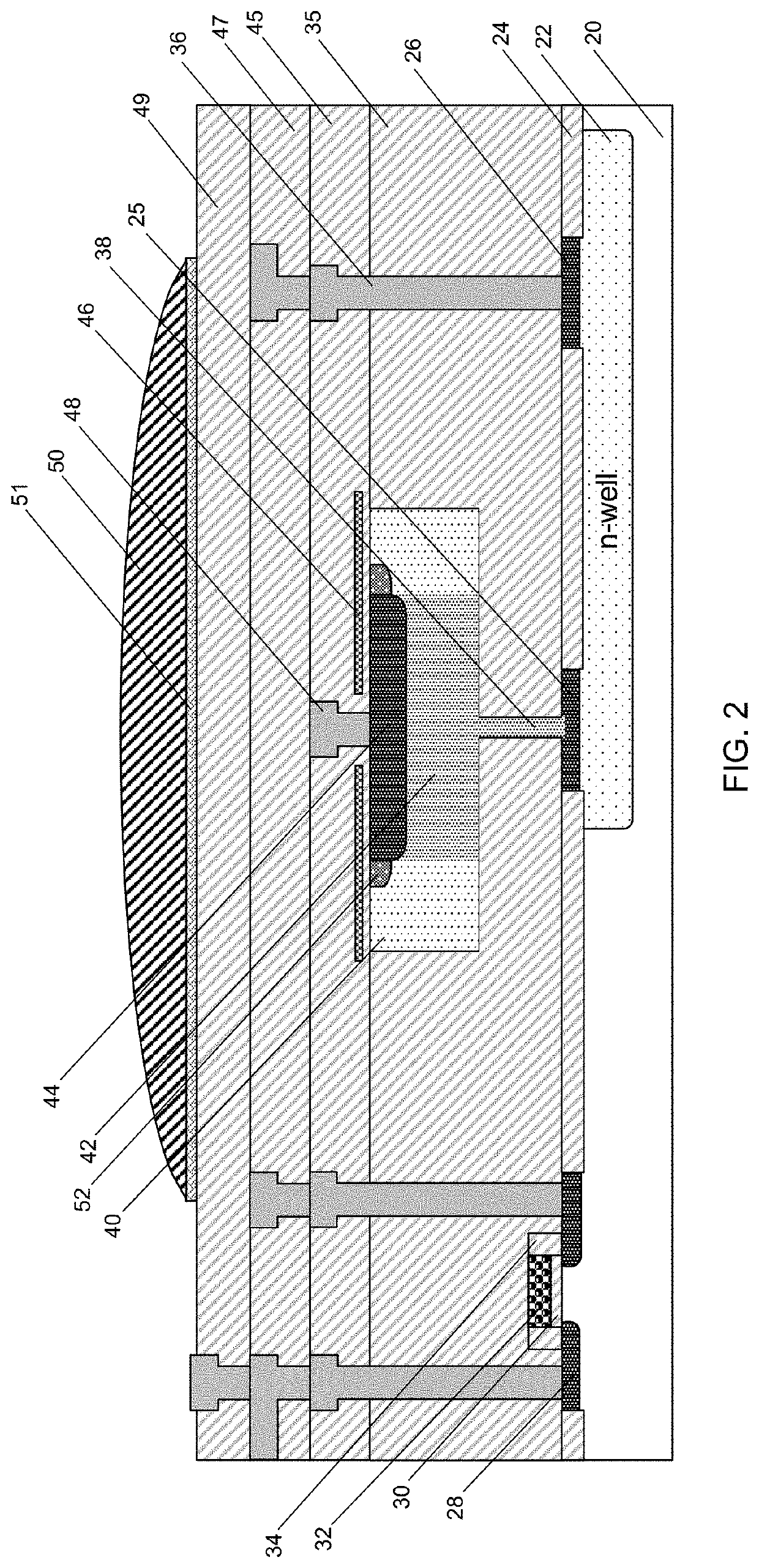

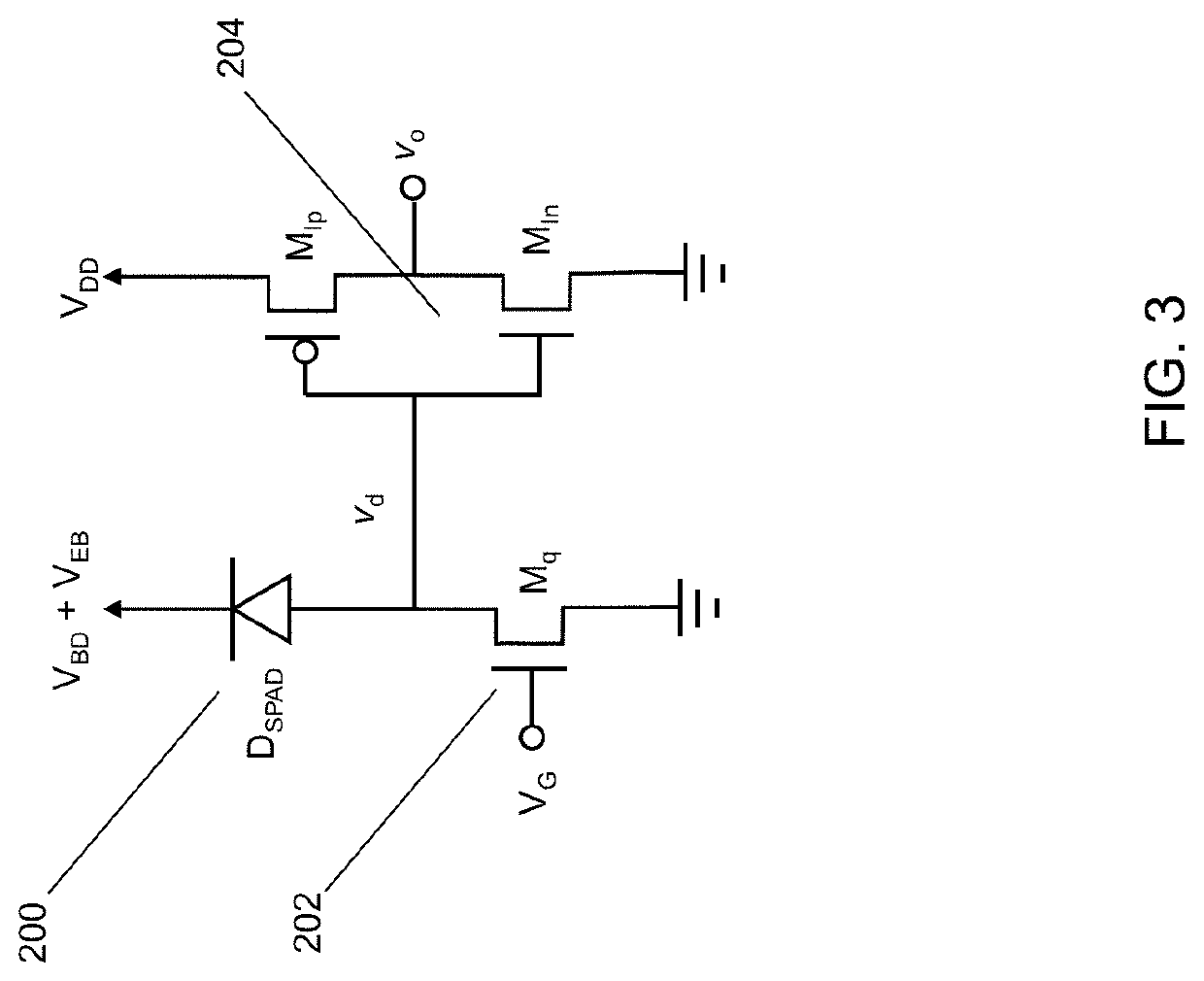

High Dynamic Range Single Photon Avalanche Detector Array on Silicon with Circuitry for Light Detection and Ranging

PendingUS20210341619A1Increase dynamic rangeReduce probabilityTransistorTelevision system detailsImage sensorHigh dynamic range

An image sensor array includes a substrate and a plurality of pixels. Each pixel includes a single photon avalanche detector (SPAD), a quench device coupled to a respective SPAD and configured to quench an avalanche current, and time measurement circuitry configured to measure a time-of-flight of a photon. The SPAD has a trench coupled to the substrate and having a lattice mismatch with the substrate, and a substantially defect-free region coupled to the trench and configured to generate the avalanche current when the photon is detected in the defect-free region, wherein the trench and the defect-free region form an electrode. An imaging system includes an infrared laser configured to provide a pulse of light, and the image sensor array configured to receive the pulse from the infrared laser.

Owner:SEMIKING LLC

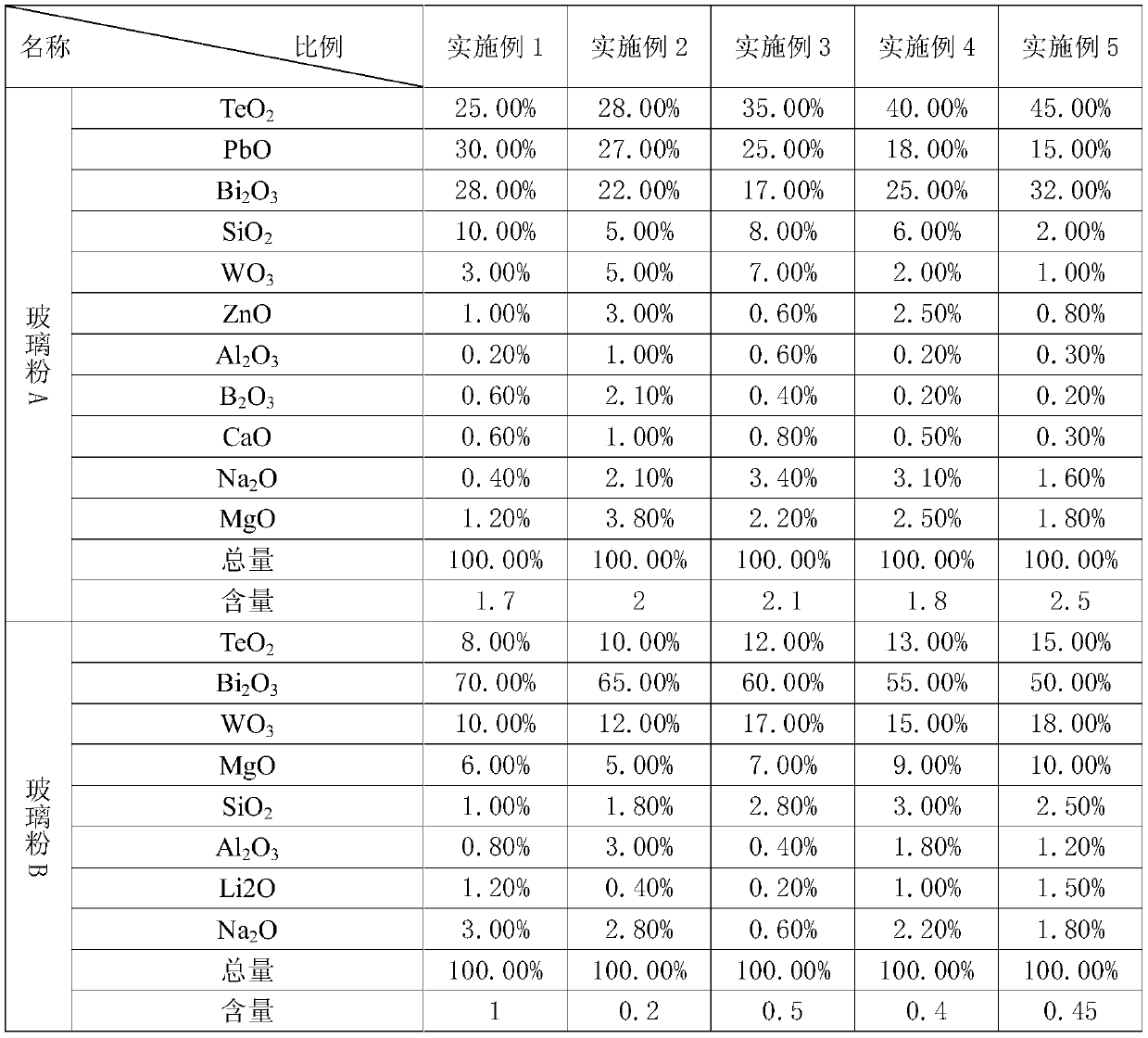

Conductive paste for positive electrode of solar cell as well as preparation method and application thereof

ActiveCN111415766AImprove bonding performanceLower ohmic contactApparatus for manufacturing conducting/semi-conducting layersNon-conductive material with dispersed conductive materialAdhesiveSilver paste

The invention discloses conductive paste for a positive electrode of a solar cell. The conductive paste is added with glass powder A with the mass fraction of 1.7-4% and glass powder B with the mass fraction of 0.1-1%, wherein the glass transition temperature of the glass powder A is 250-350 DEG C, and the glass transition temperature of the glass powder B is 350-450 DEG C. The invention also discloses a preparation method of the conductive silver paste and a solar cell front electrode prepared by applying the conductive silver paste to a silicon wafer cut by a diamond wire. According to the conductive paste for the positive electrode of the solar cell, the glass powder A and the glass powder B with different glass softening temperatures are used as inorganic adhesives of the conductive paste; the bonding performance of the conductive slurry on the surface of a silicon wafer is improved, the degree of etching the surface of the silicon wafer by molten glass powder in the conductive slurry is improved, doping is improved, the ohmic contact of a metal-semiconductor contact layer on the surface of the silicon wafer is reduced, and the unit consumption ratio of a positive electrode ofa solar cell is reduced by 5-10%.

Owner:成都银盛新材料有限公司

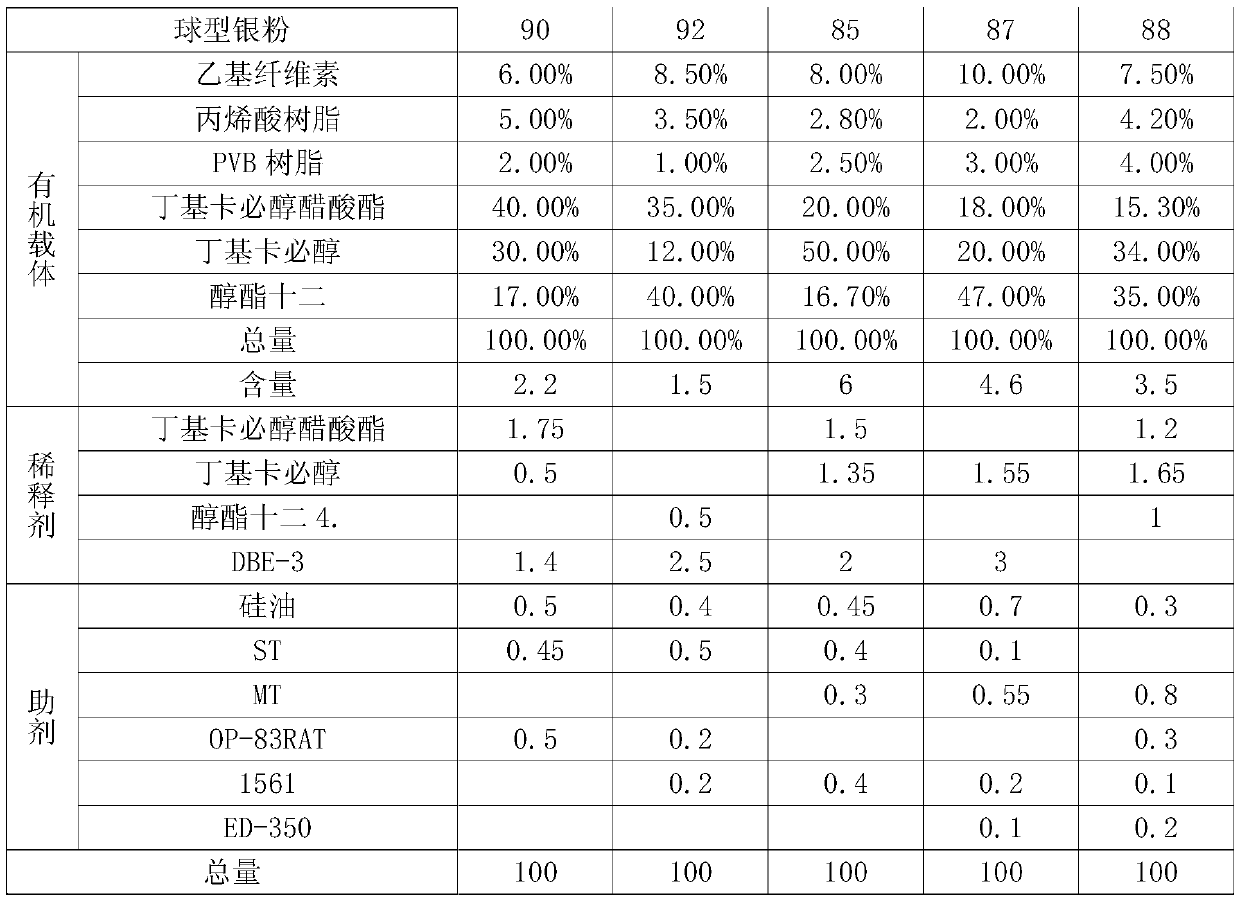

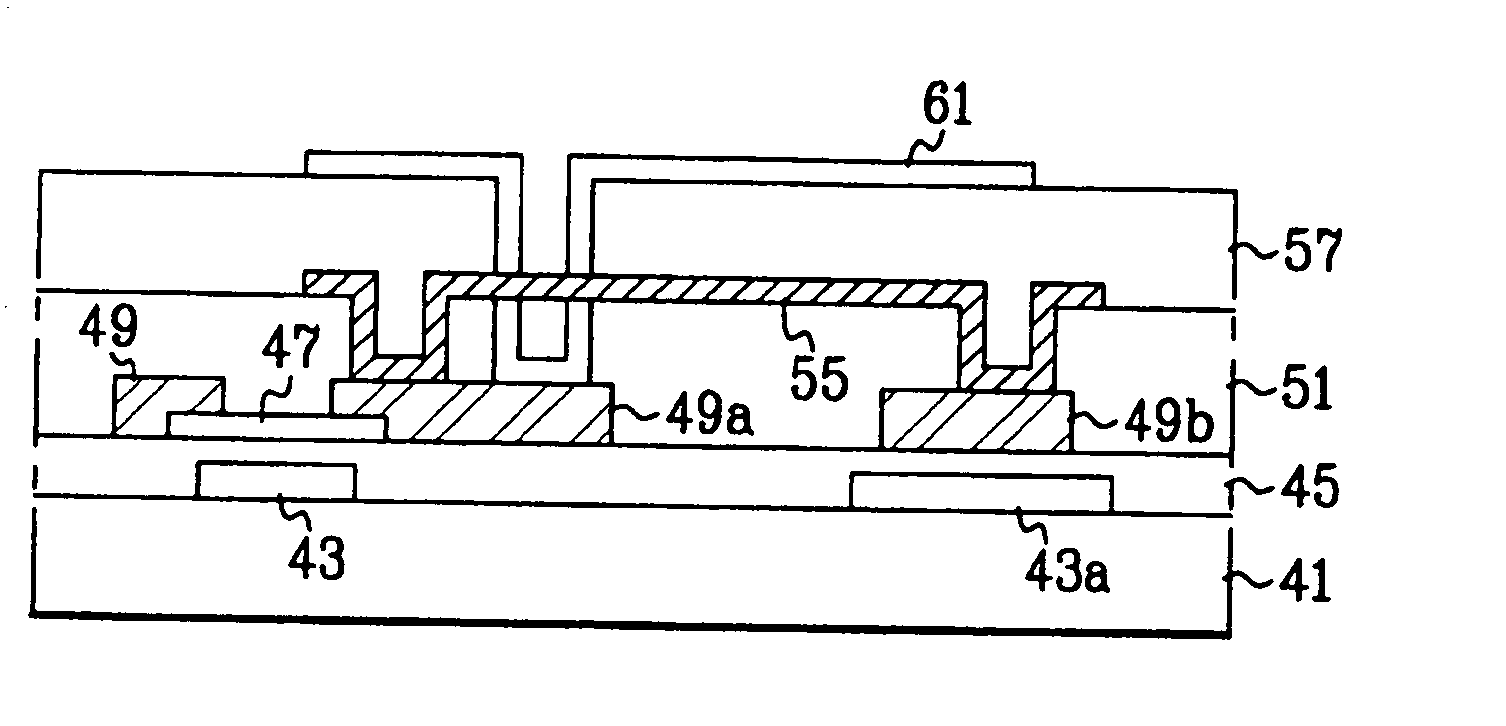

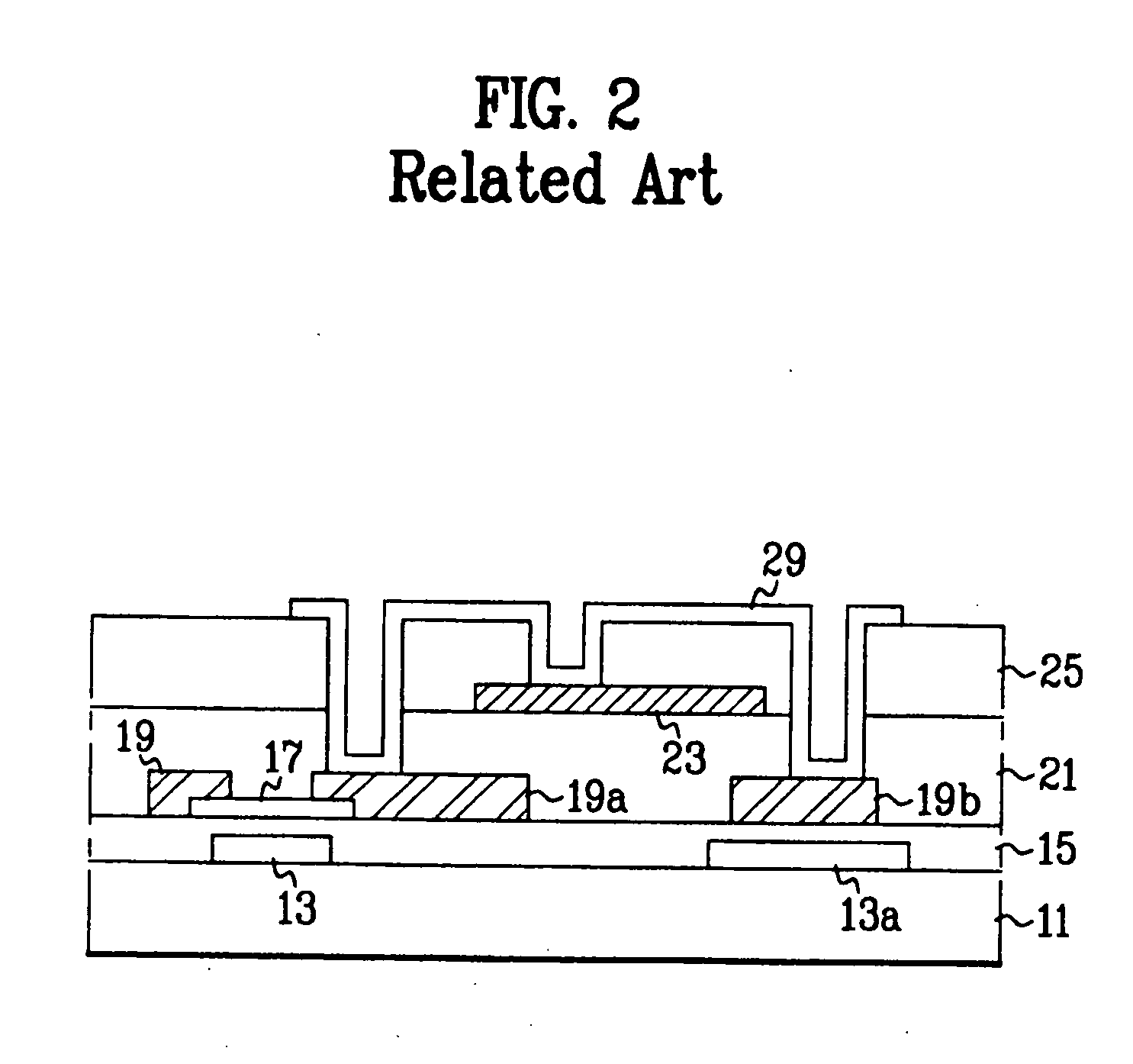

Liquid crystal display device with minimum ohmic contact between reflective and transparent electrodes

InactiveUS20050046770A1The process steps are simpleLower ohmic contactSemiconductor/solid-state device manufacturingNon-linear opticsCapacitanceLiquid-crystal display

An LCD device and a method for manufacturing the same are disclosed, wherein it is possible to reduce an ohmic contact between a reflective electrode and a transparent electrode and to simplify process steps. In the LCD device having first and second substrates and a liquid crystal layer between the first and second substrates, the LCD device includes a gate electrode and a first electrode of a storage capacitor on the first substrate; a first insulating film on the entire surface of the first substrate including the gate electrode; a semiconductor film, source / drain electrodes and a second electrode of the storage capacitor on the first insulating film; a second insulating film on the first insulating film including the source / drain electrodes; a reflective electrode on the second insulating film to connect the drain electrode with the second electrode of the storage capacitor; and a transparent electrode connected with the drain electrode on a third insulating film formed on the second insulating film including the reflective electrode.

Owner:LG DISPLAY CO LTD

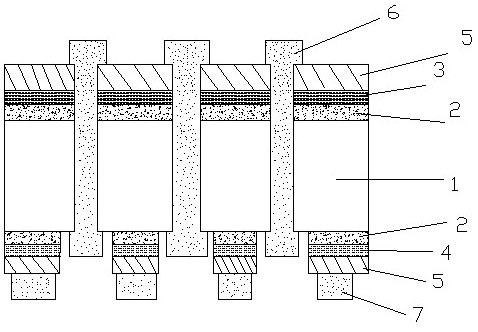

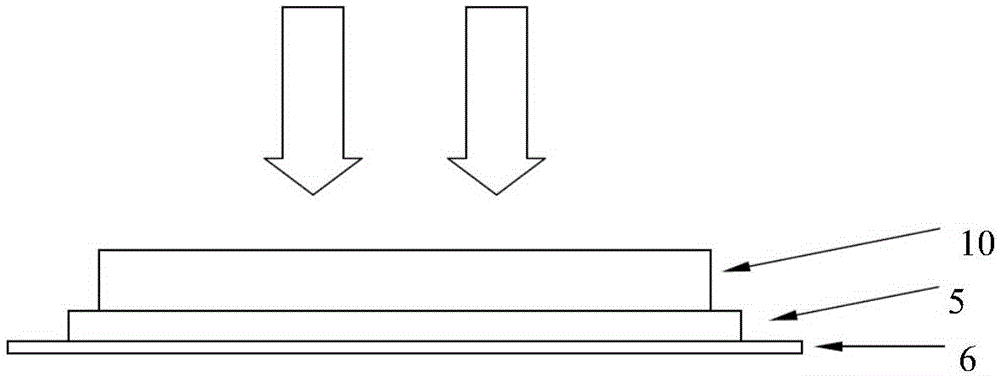

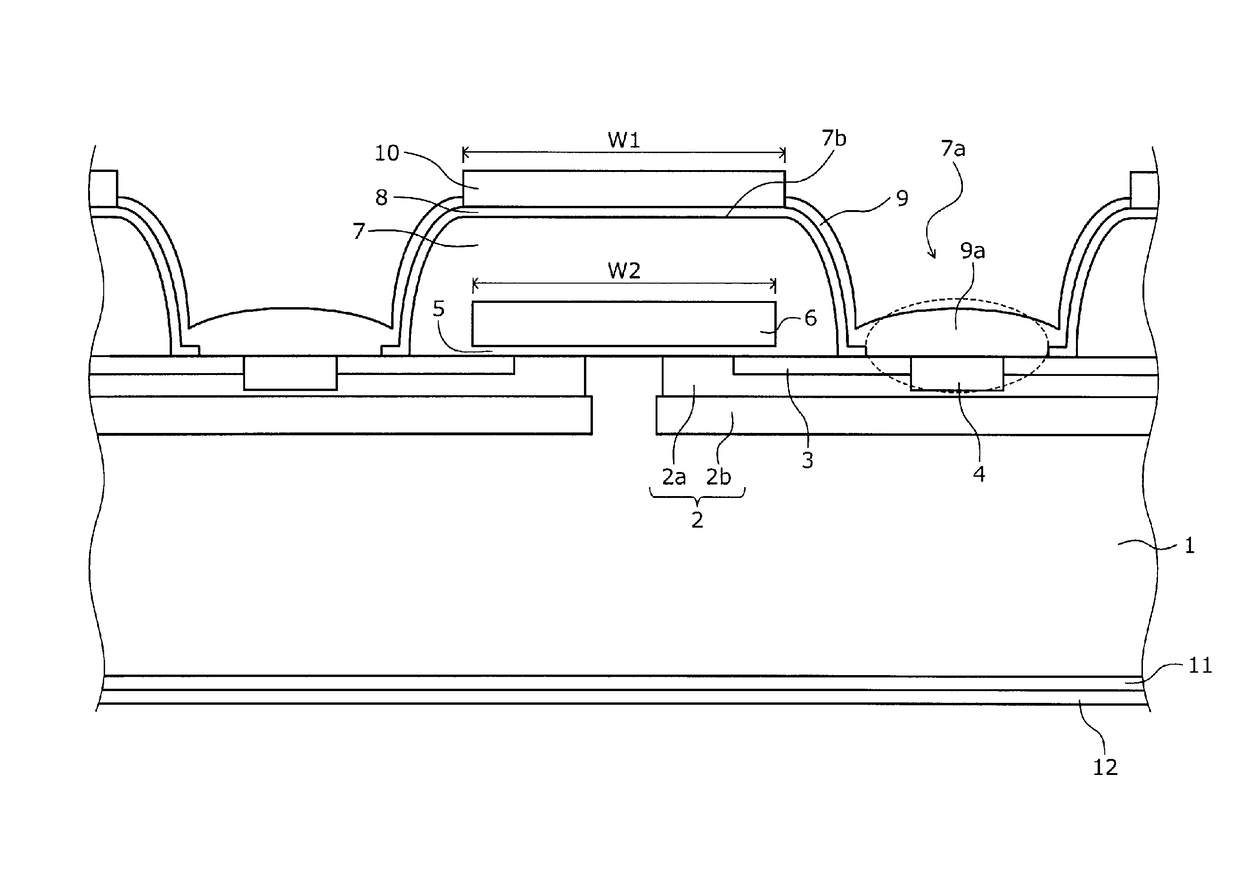

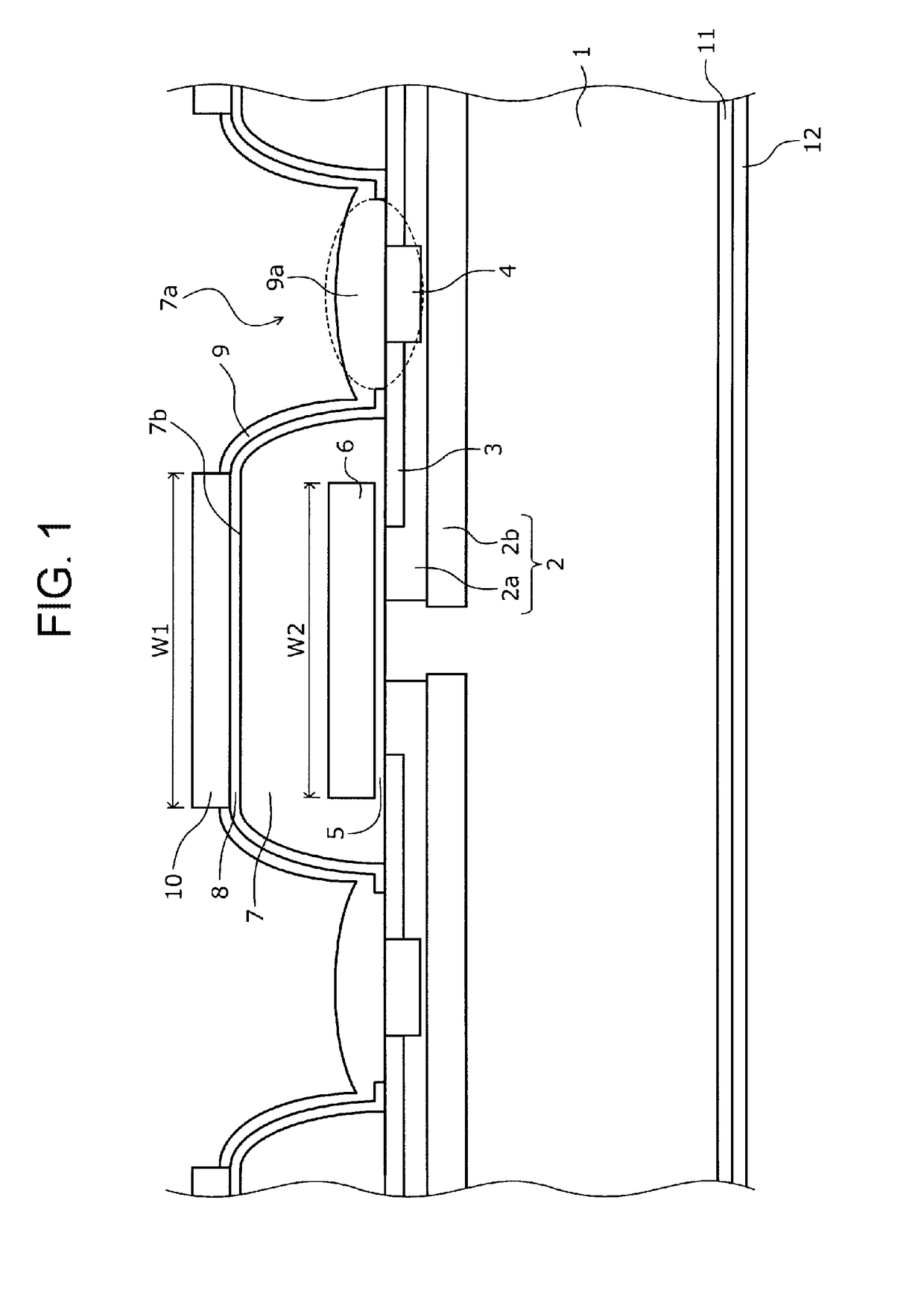

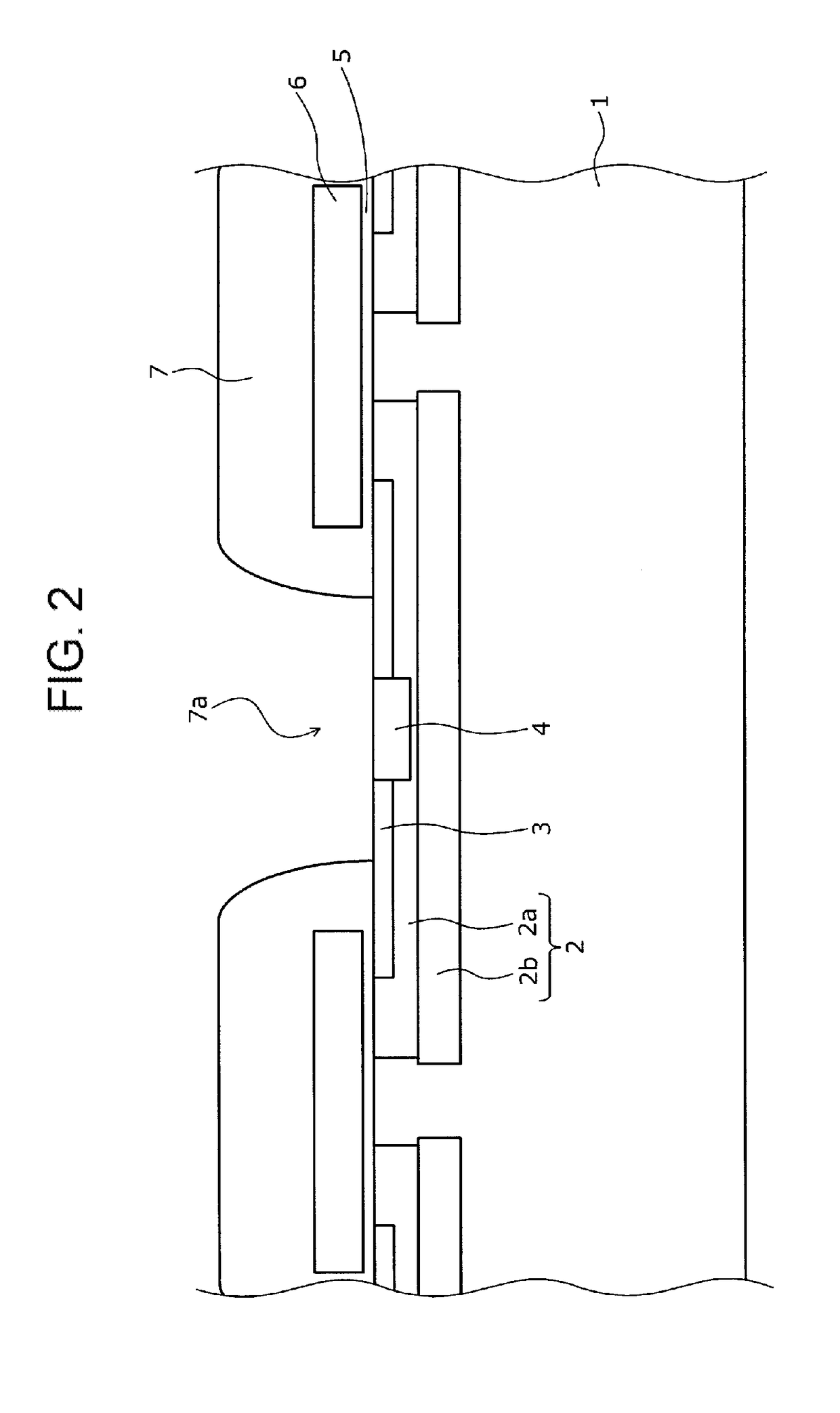

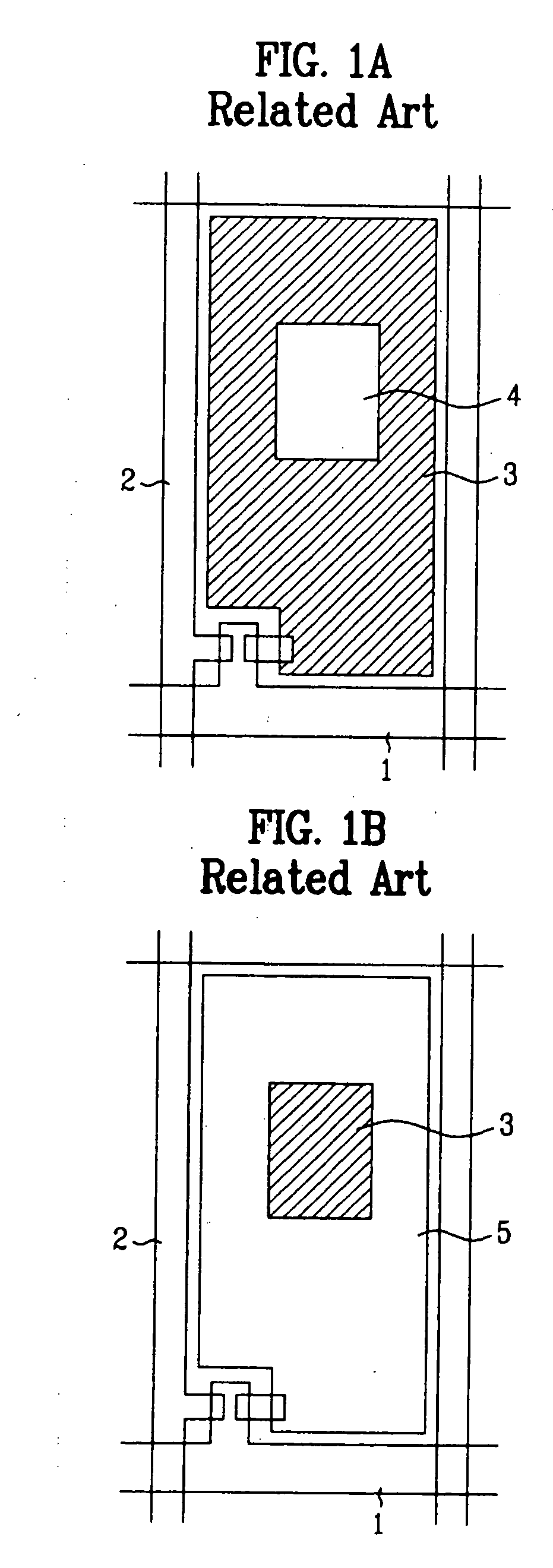

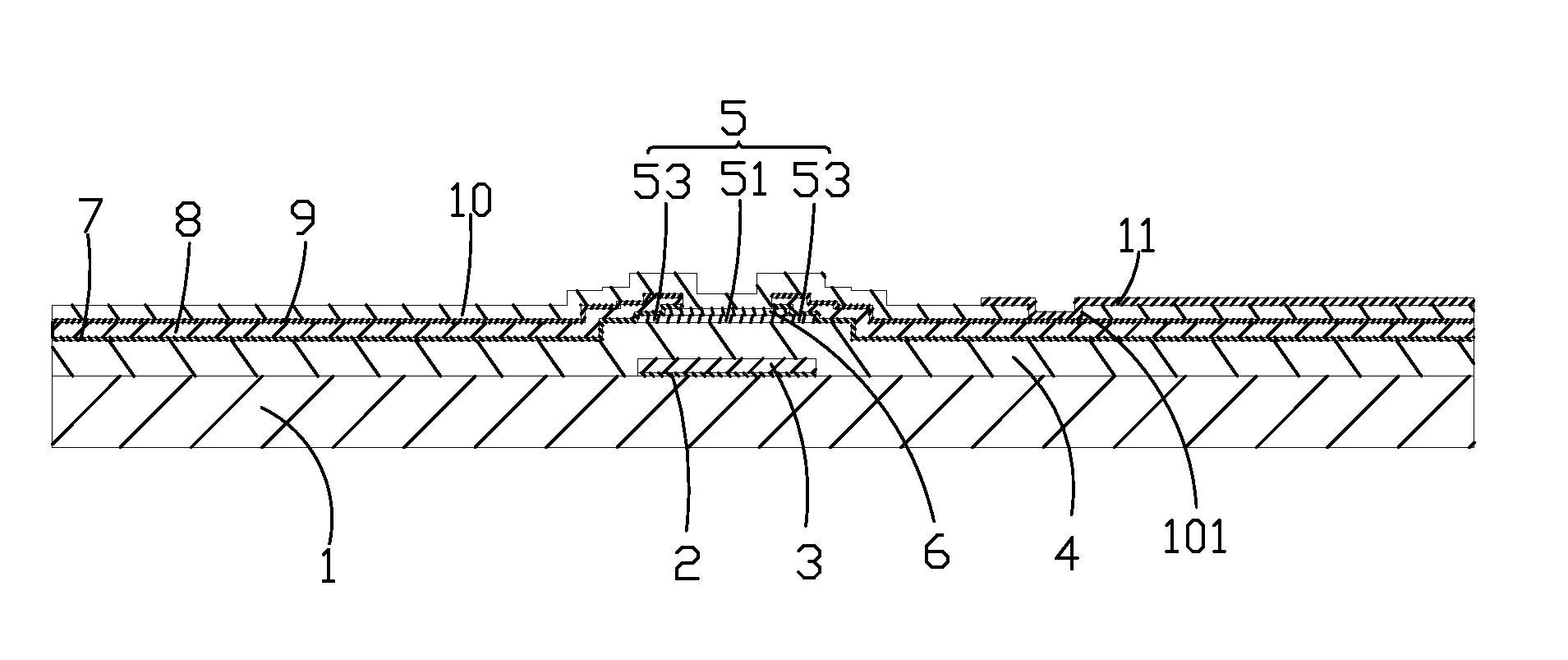

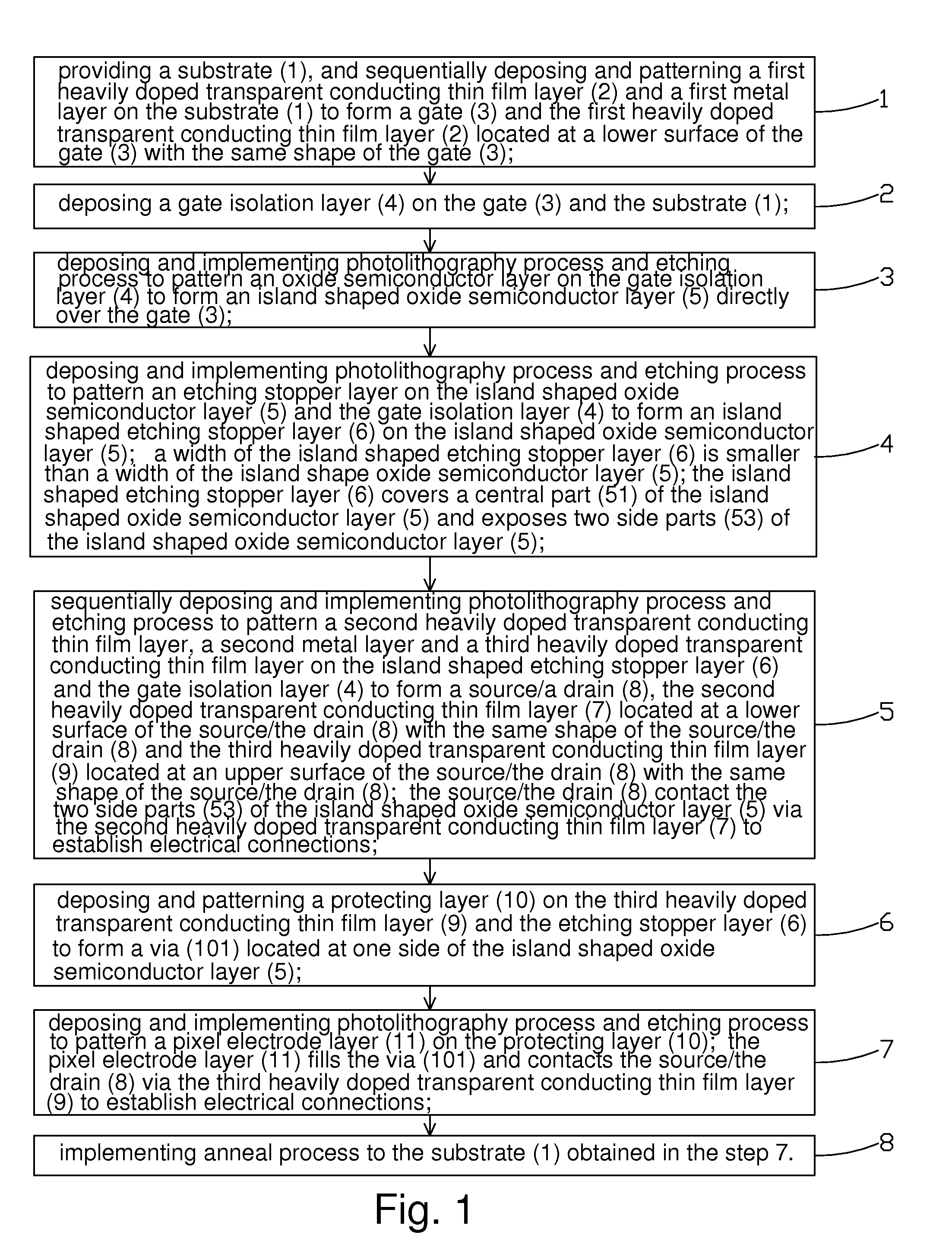

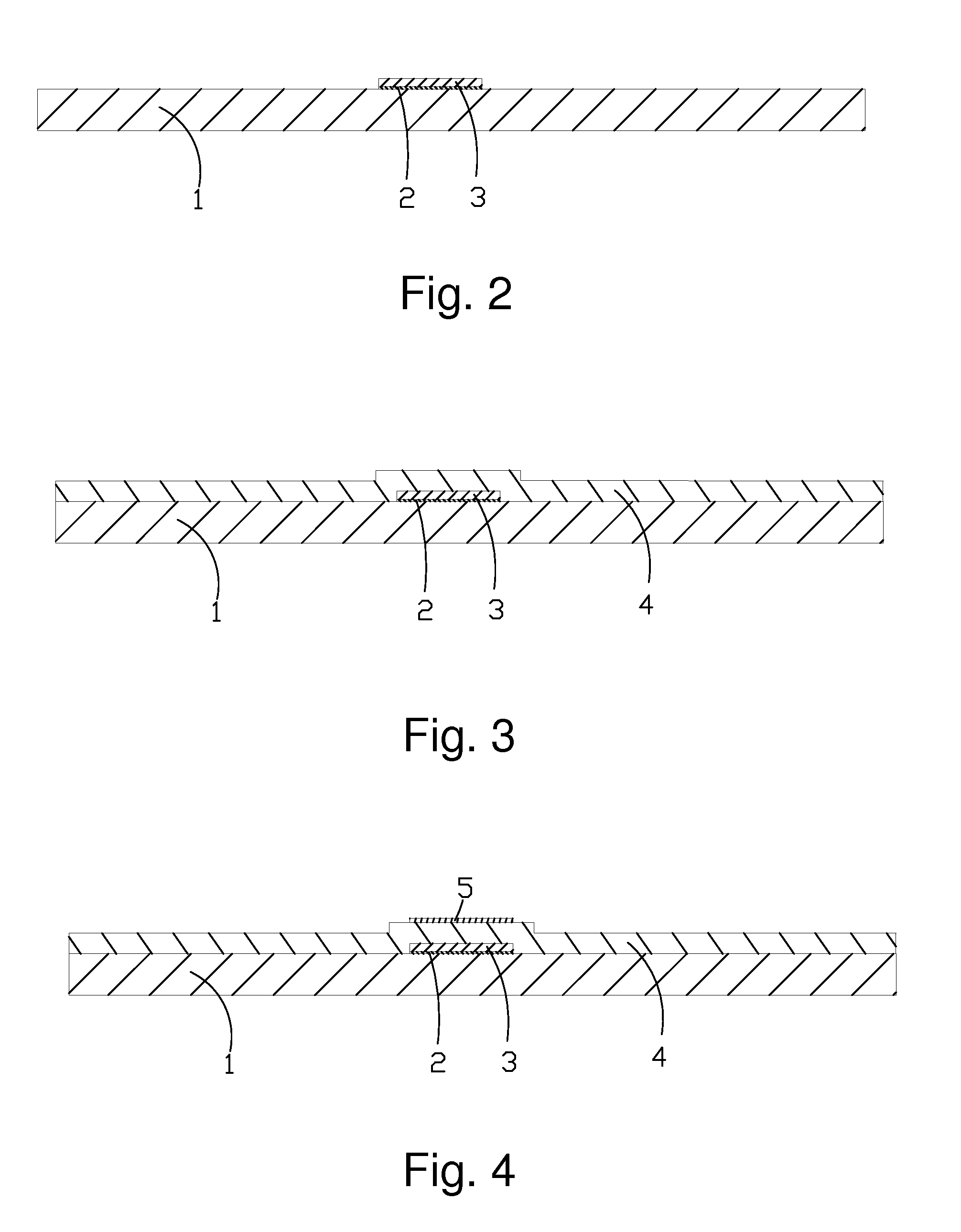

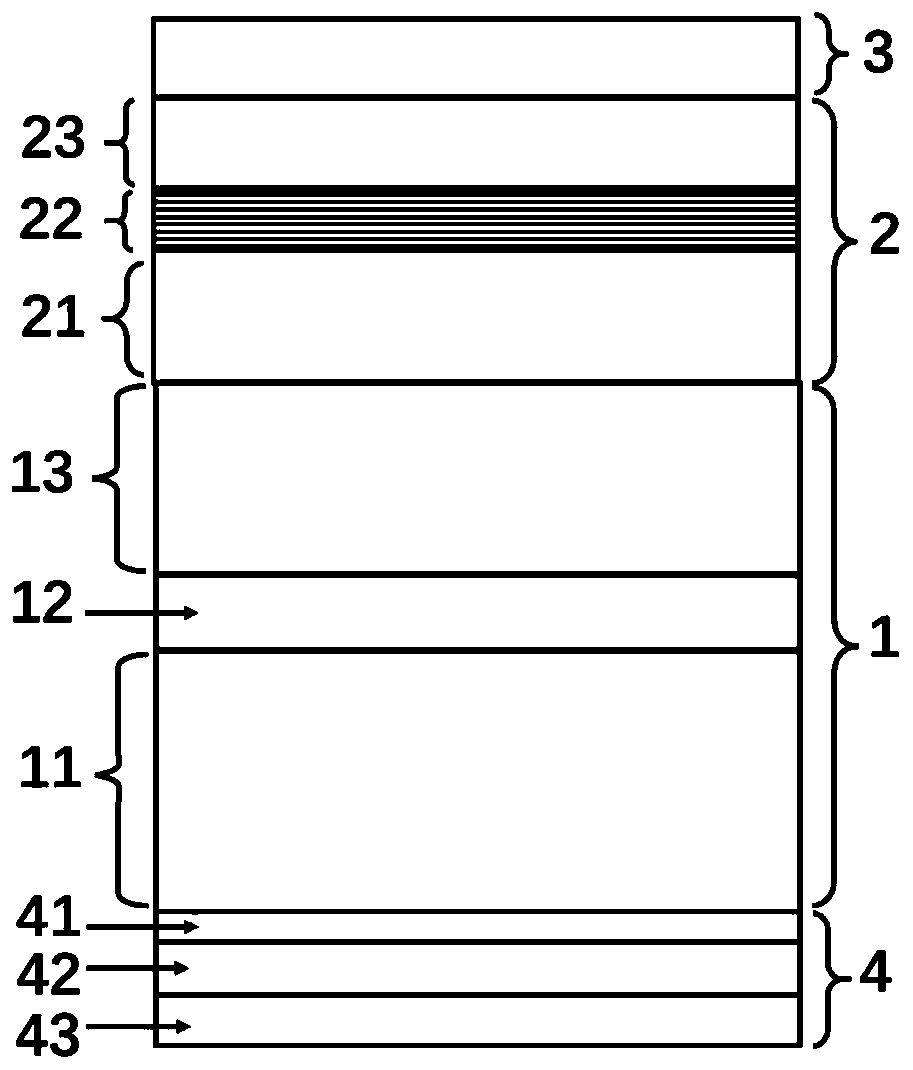

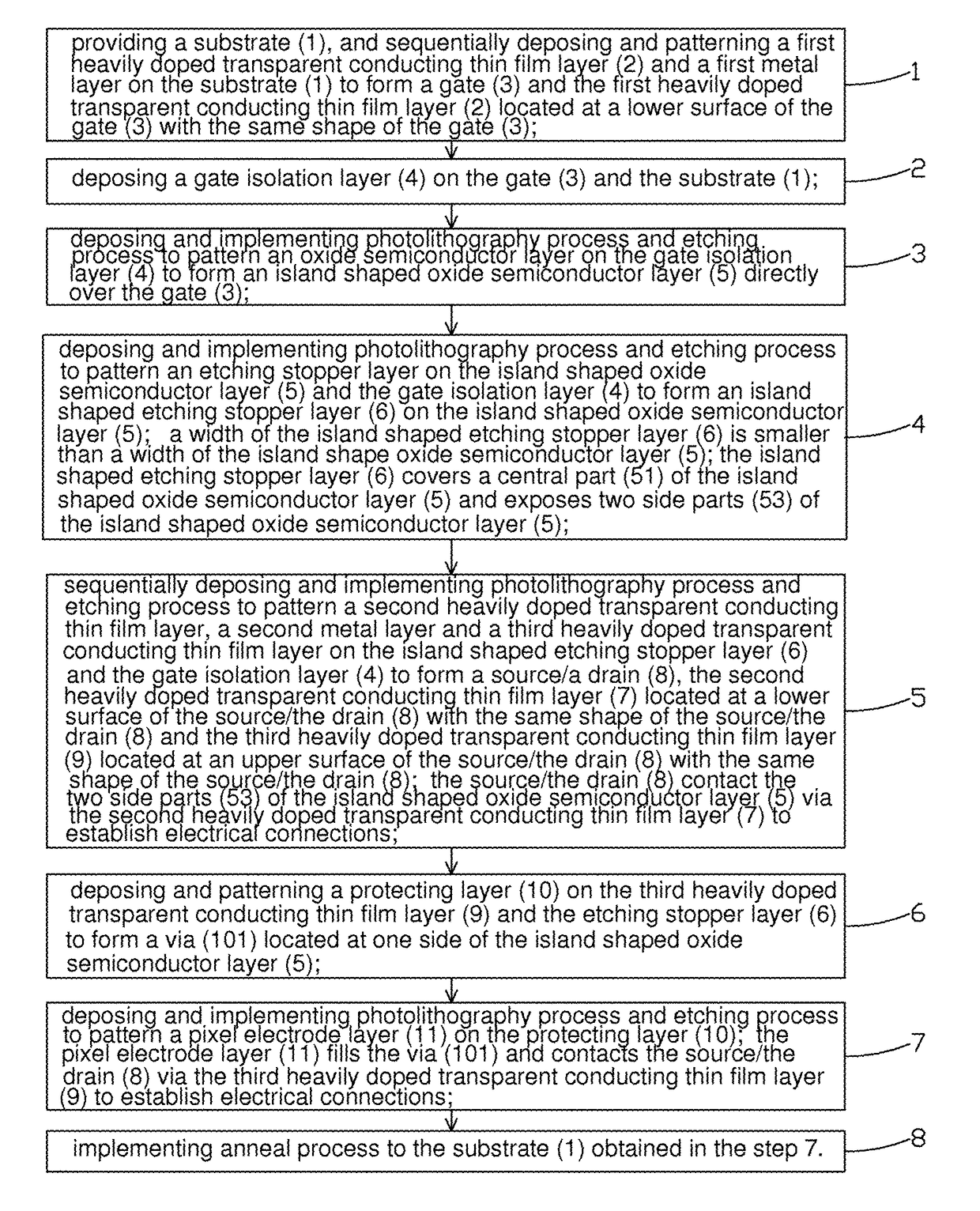

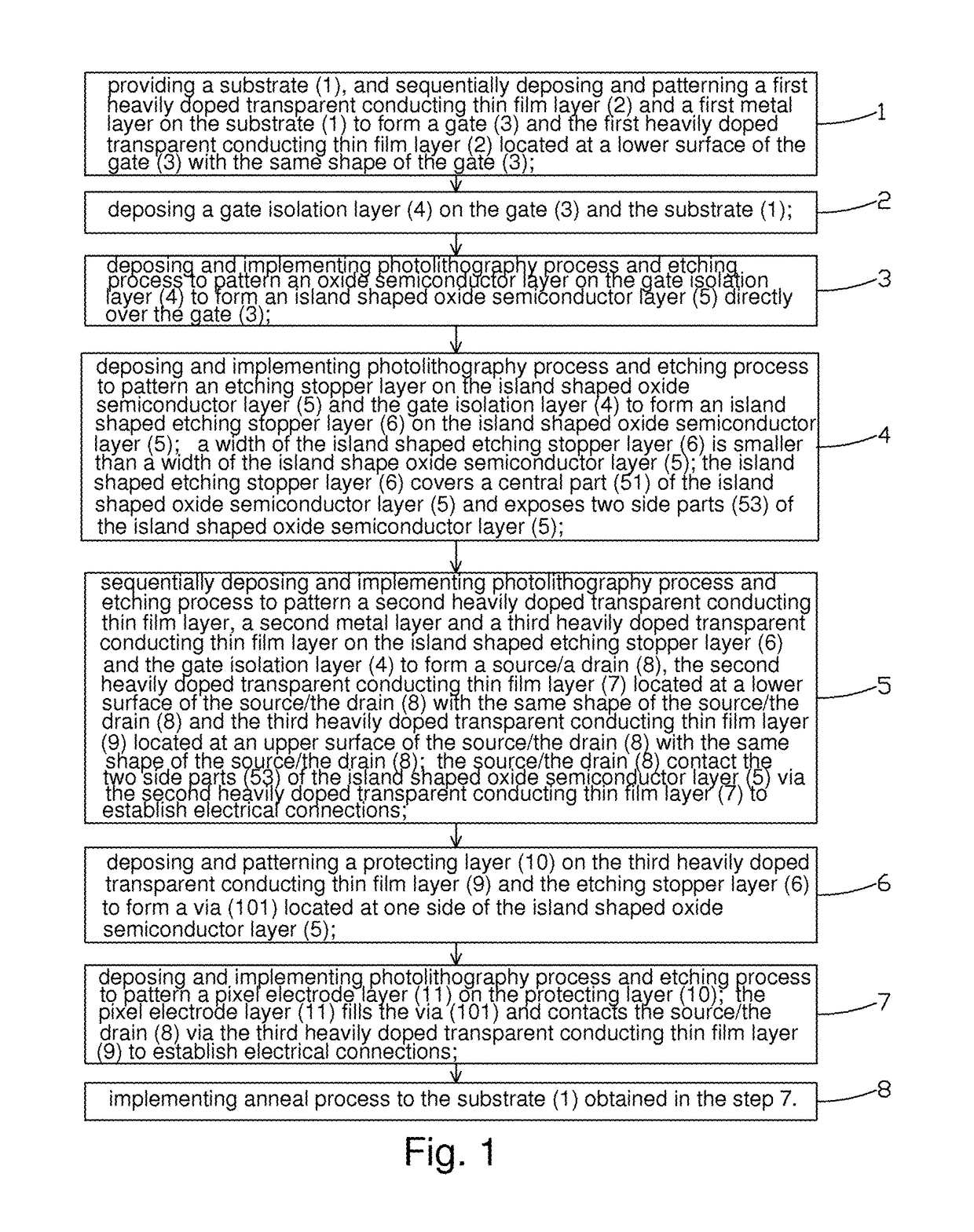

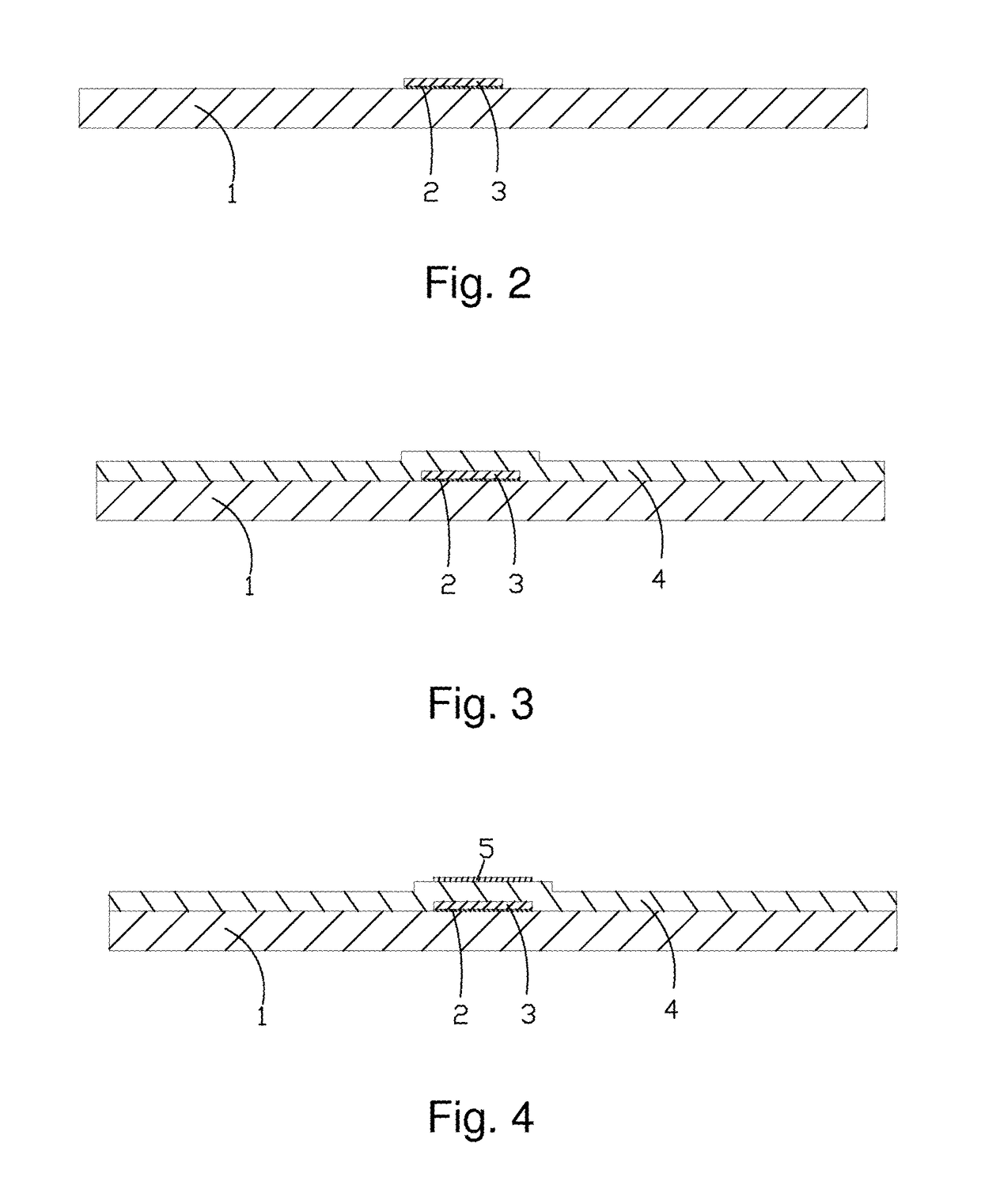

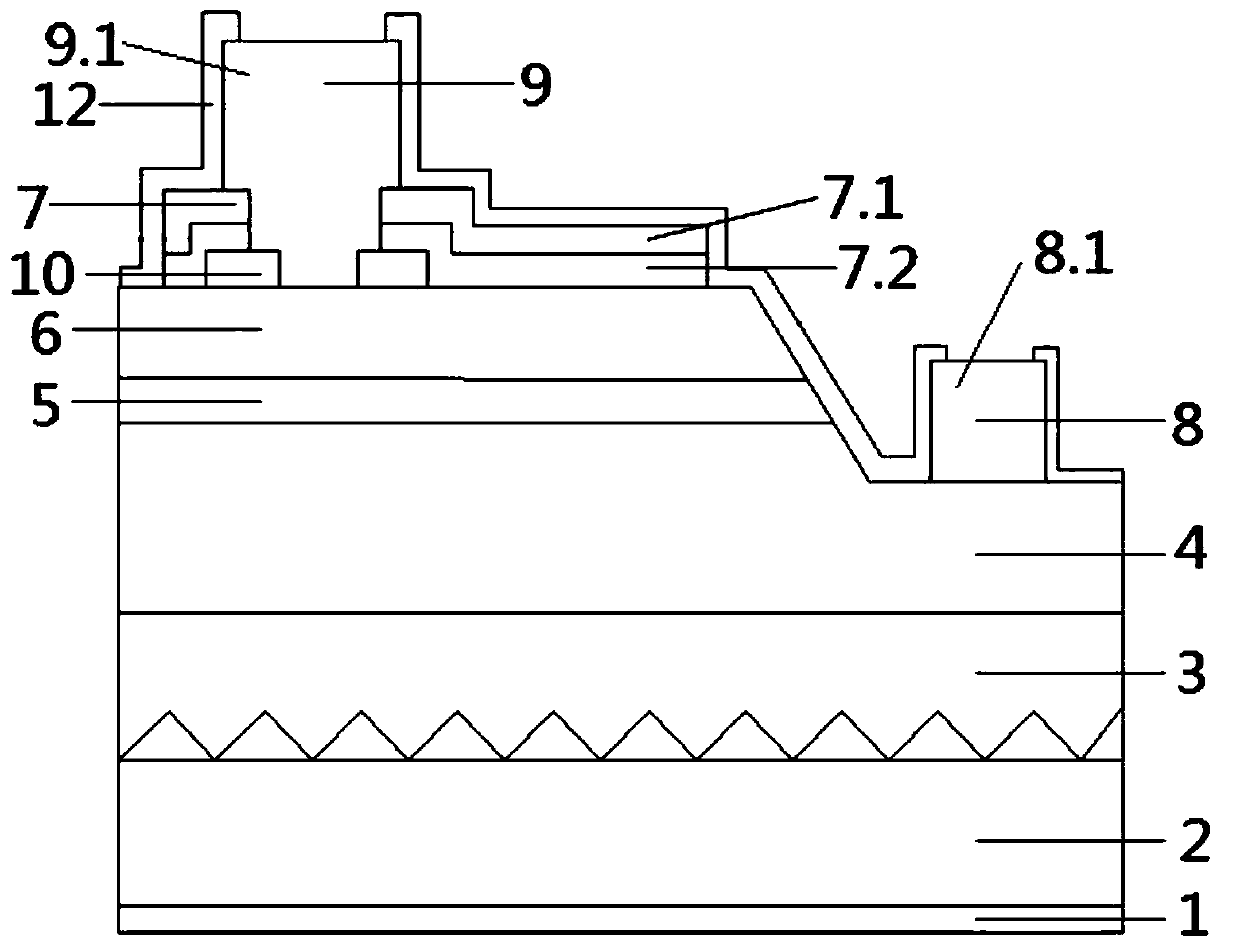

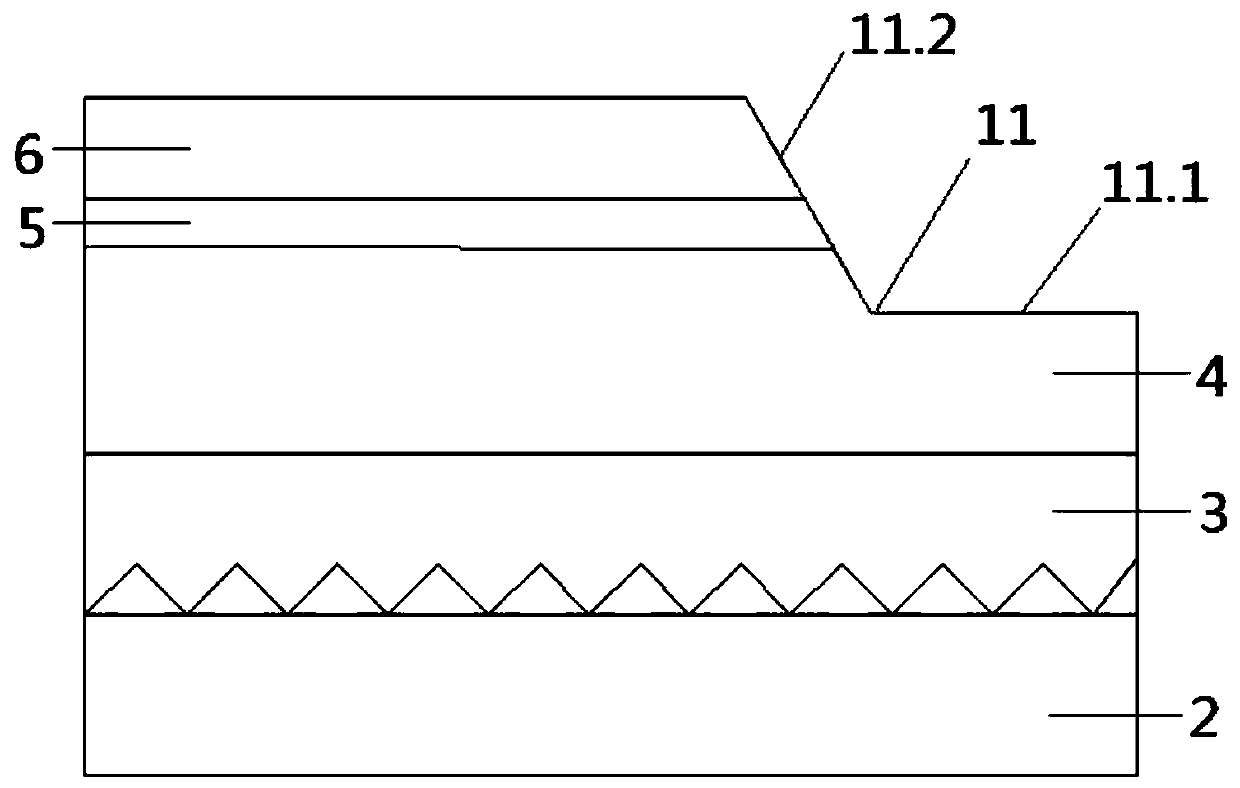

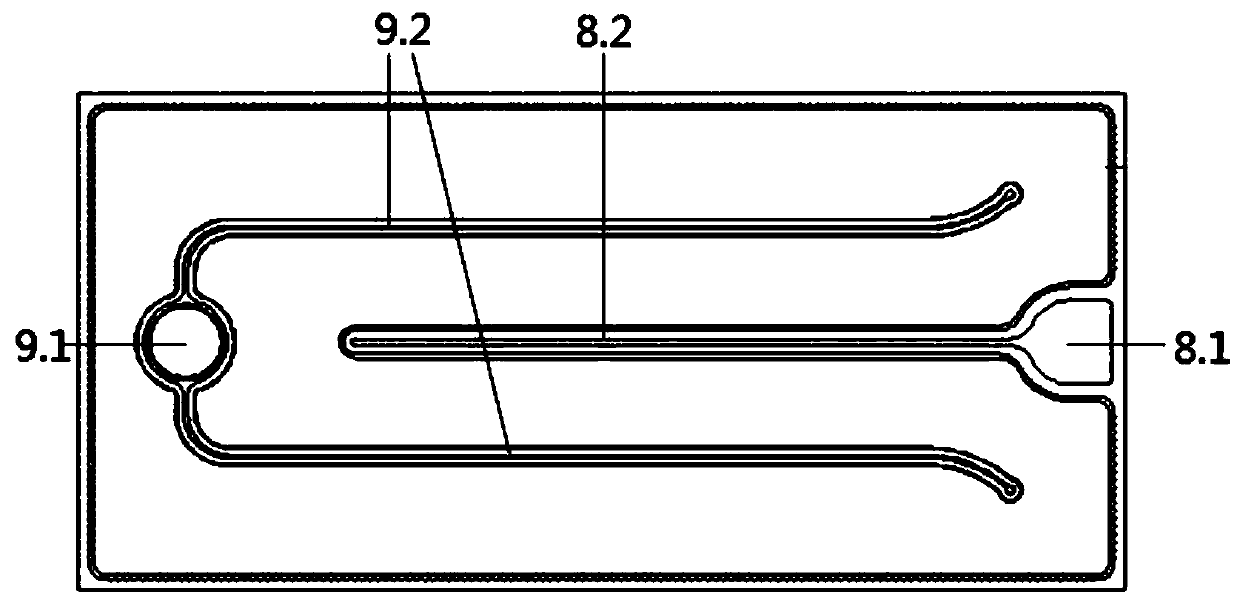

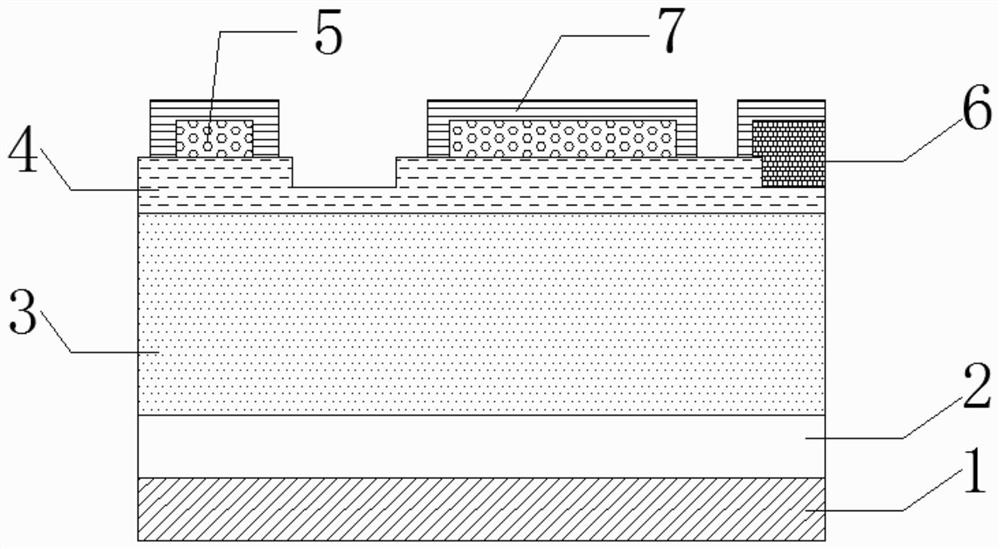

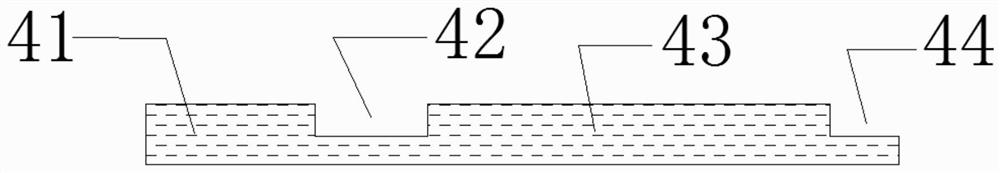

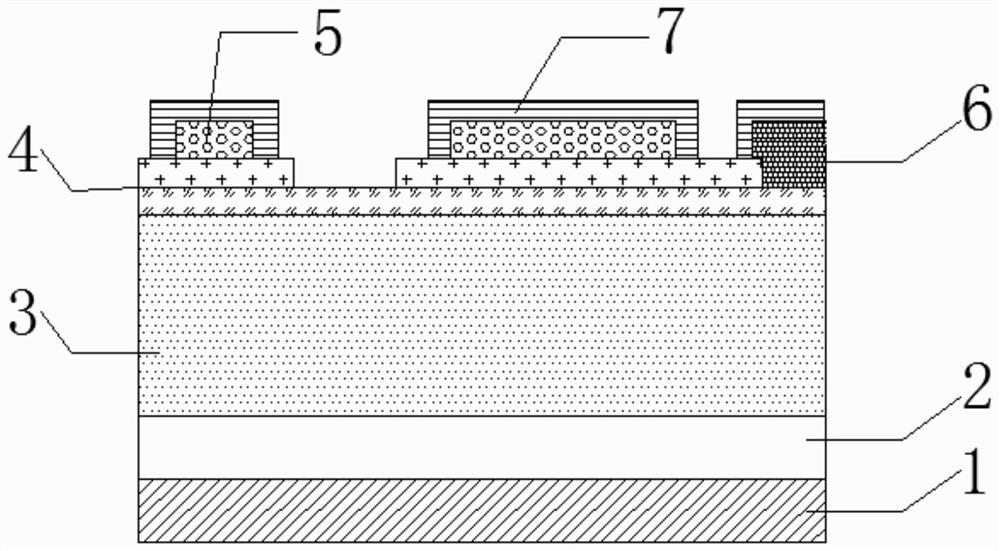

Manufacture method of TFT substrate and sturcture thereof

ActiveUS20160260746A1Reduced ohmic contact resistanceLower threshold voltageTransistorSolid-state devicesPhysicsOxide semiconductor

The present invention provides a manufacture method of an oxide semiconductor TFT substrate, and the method comprises steps of: 1, forming a gate (3) and a first heavily doped transparent conducting thin film layer (2) on a substrate (1); 2, deposing a gate isolation layer (4); 3, forming an island shaped oxide semiconductor layer (5); 4, forming an island shaped photoresistor layer (6); 5, forming a source / a drain (8), and a second, a third heavily doped transparent conducting thin film layer (7, 9), and the source / the drain (8) contact the two side parts (53) of the island shaped oxide semiconductor layer (5) via the second heavily doped transparent conducting thin film layer (7) to establish electrical connections; 6, deposing and patterning a protecting layer (10); 7, deposing and patterning a pixel electrode layer (11) which contacts the source / the drain (8) via the third heavily doped transparent conducting thin film layer (9) to establish electrical connections; 8, implementing anneal process.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Manufacture method of TFT substrate and sturcture thereof

ActiveUS20180166471A1Reduced ohmic contact resistanceLower threshold voltageTransistorSolid-state devicesIsolation layerElectrical connection

An oxide semiconductor TFT substrate includes a substrate, a gate and a first heavily doped transparent conducting layer formed on a substrate and covered by a gate isolation layer. An island shaped oxide semiconductor layer and an island shaped etching stopper layer are sequentially formed on the gate isolation layer with two side parts of the oxide semiconductor layer exposed outside the etching stopper layer. A source and a drain are formed on the two side parts of the oxide semiconductor layer to be in electrical connection therewith with a heavily doped transparent conducting layer therebetween. A protecting layer is formed on the source and the drain and is formed with a via. A pixel electrode extends through the via to electrically connect to the source and the drain with a heavily doped transparent conducting layer interposed therebetween and in direct contact therewith.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

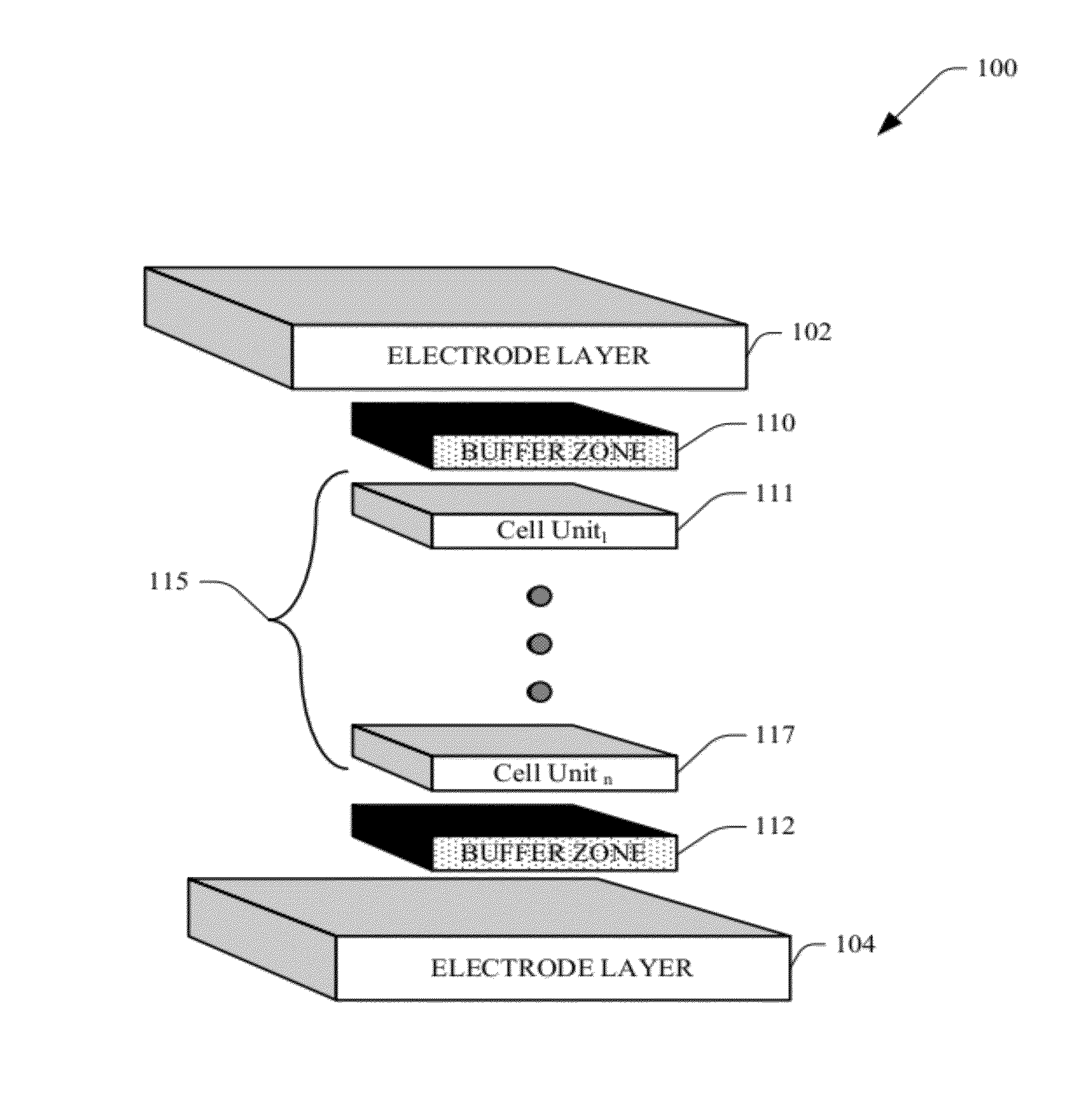

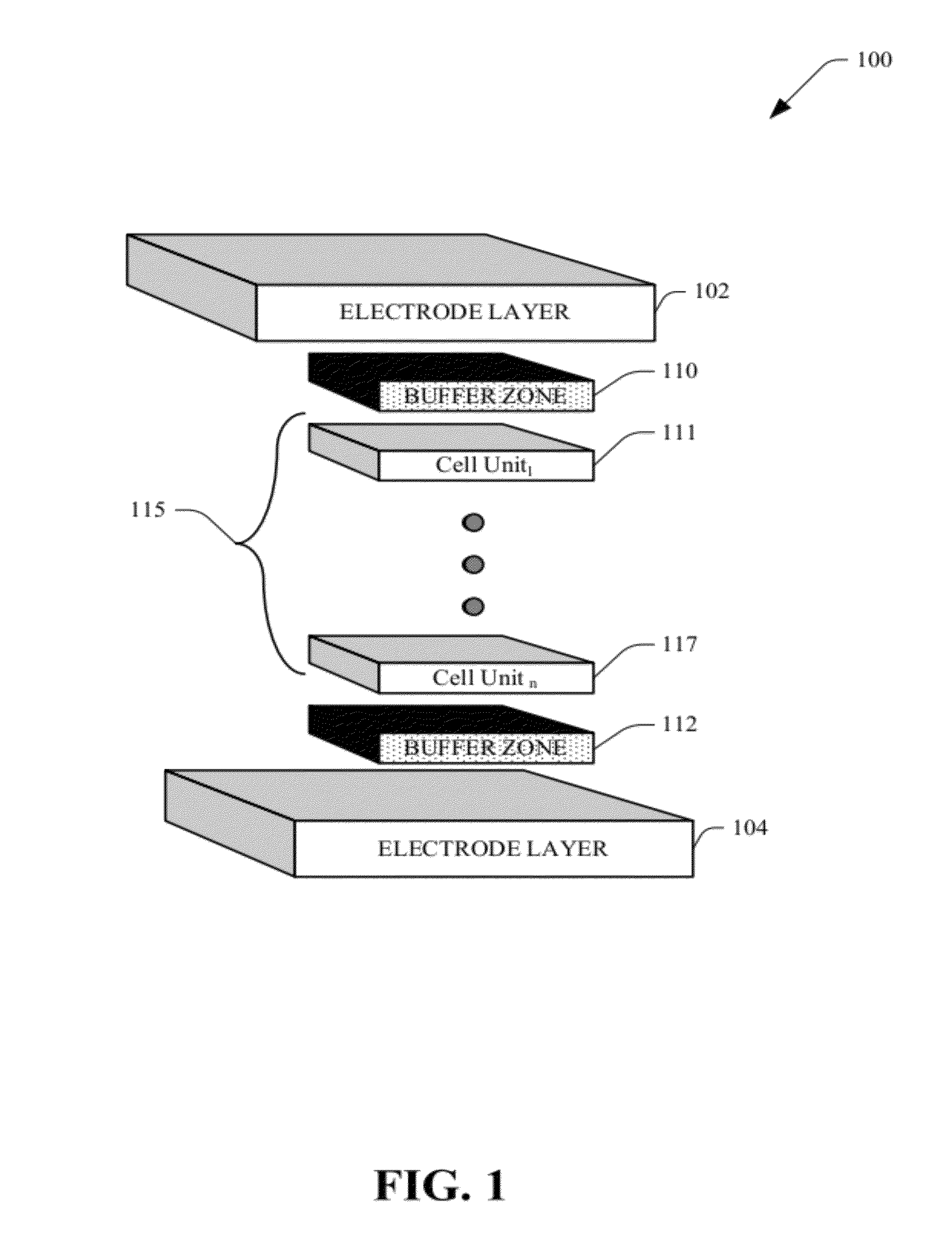

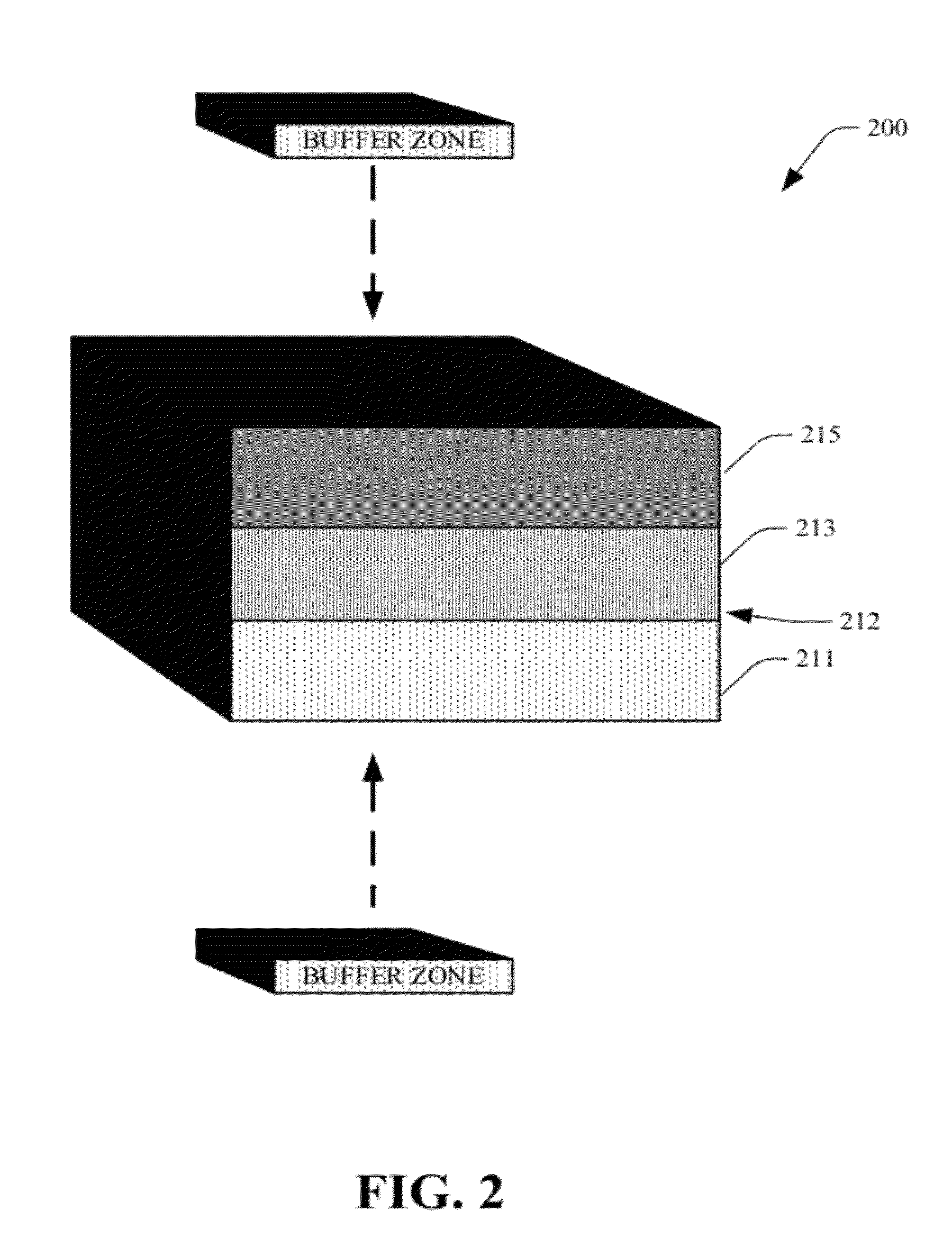

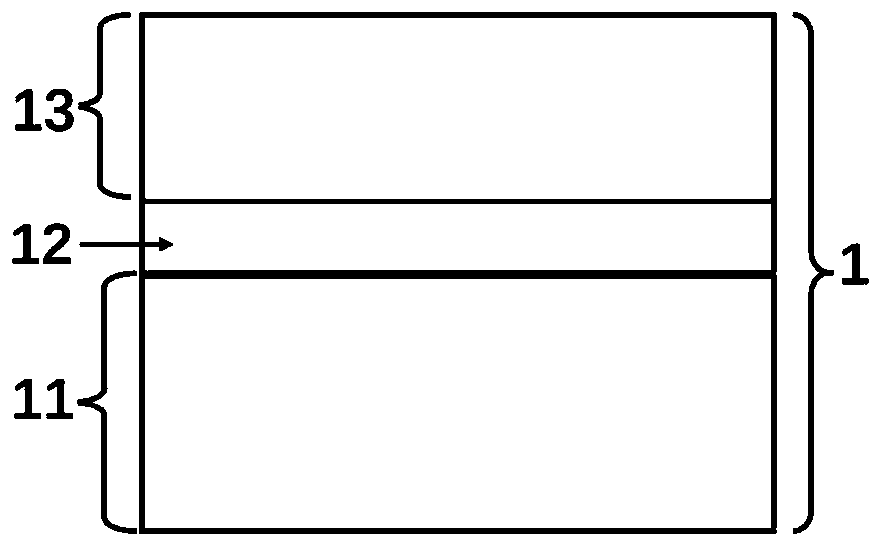

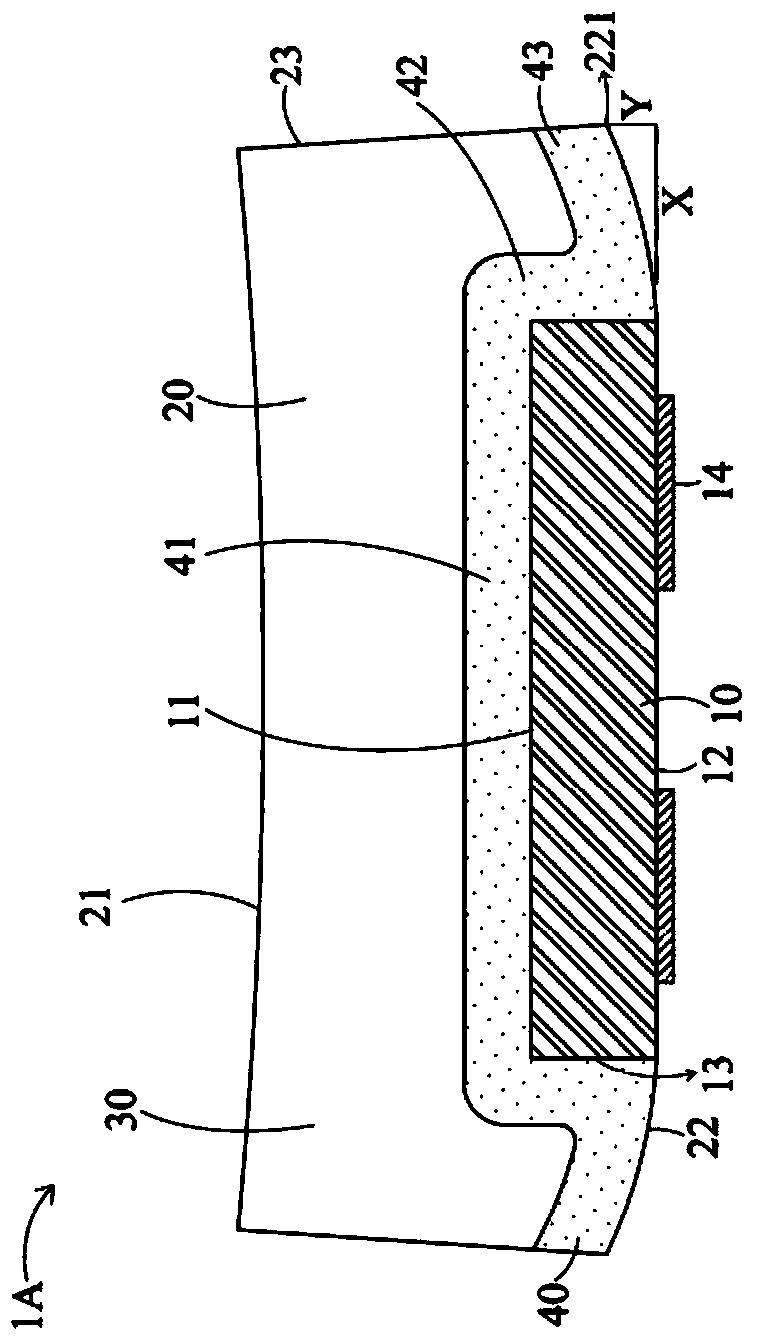

Photovoltaic cell with buffer zone

InactiveUS20120090677A1Easy to moveReduce riskPhotovoltaic energy generationSemiconductor devicesActive layerInduced stress

Systems and methods that provide a barrier for protection of active layers associated with a vertical multi junction (VMJ) photovoltaic cell. Buffer zone(s) in form of an inactive layer(s) arrangement safe guard the active layers against induced stress or strain resulting from external forces / thermal factors (e.g., welding). The buffer zone can be in form of a rim on a surface of an end layer of a cell unit, to act as a protective boundary for such active layer, and to further partially frame the VMJ cell for ease of handling and transportation.

Owner:MH GOPOWER

Silicon-based stress covariant substrate and preparation method thereof, gallium nitride LED and preparation method thereof

PendingCN110931607AOvercoming Large Mismatch Stress ProblemsGood chemical stabilitySemiconductor devicesPhysical chemistrySingle crystal substrate

The invention discloses a silicon-based stress covariant substrate and a preparation method thereof, and a vertical structure gallium nitride LED using the silicon-based stress covariant substrate anda preparation method thereof. The silicon-based stress covariant substrate comprises a double-sided polished silicon single crystal substrate; a thin zirconium nitride conductive reflective stress covariant layer which is formed on the double-sided polished silicon single crystal substrate, and the thickness of the thin zirconium nitride conductive reflective stress covariant layer is 50nm-350nm;and a thin gallium nitride single crystal film template layer which is formed on the thin zirconium nitride conductive reflective stress covariant layer, and the thickness of the thin gallium nitridesingle crystal film template layer is not less than that of the thin zirconium nitride conductive reflective stress covariant layer. The silicon-based stress covariant substrate can overcome and relieve the problem of large mismatch stress during high-quality preparation and growth of GaN materials and LED devices.

Owner:NANJING YOUTIAN METAL TECH +1

Manufacture method of TFT substrate and sturcture thereof

ActiveUS9899421B2Reduce contact resistanceLower threshold voltageTransistorSolid-state devicesIsolation layerElectrical connection

The present invention provides a manufacture method of an oxide semiconductor TFT substrate, and the method comprises steps of: 1, forming a gate (3) and a first heavily doped transparent conducting thin film layer (2) on a substrate (1); 2, deposing a gate isolation layer (4); 3, forming an island shaped oxide semiconductor layer (5); 4, forming an island shaped photoresistor layer (6); 5, forming a source / a drain (8), and a second, a third heavily doped transparent conducting thin film layer (7, 9), and the source / the drain (8) contact the two side parts (53) of the island shaped oxide semiconductor layer (5) via the second heavily doped transparent conducting thin film layer (7) to establish electrical connections; 6, deposing and patterning a protecting layer (10); 7, deposing and patterning a pixel electrode layer (11) which contacts the source / the drain (8) via the third heavily doped transparent conducting thin film layer (9) to establish electrical connections; 8, implementing anneal process.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

LED chip capable of improving external quantum efficiency, and preparation method thereof

PendingCN111463327AImprove luminous efficiencyImprove external quantum efficiencyVacuum evaporation coatingSputtering coatingQuantum efficiencySemiconductor structure

The invention provides an LED chip capable of improving external quantum efficiency. The LED chip comprises a DBR layer, a substrate, a buffer layer, a first semiconductor layer, an active layer, a second semiconductor layer, a transparent conductive layer, an N type electrode and a P type electrode, wherein the N type electrode and the P type electrode are both aluminum-based reflection electrodes, and the aluminum metal layer of the P type electrode is in direct contact with the transparent conductive layer to improve the reflectivity of a reflection electrode and a semiconductor interface.The invention further provides a preparation method of the LED chip capable of improving the external quantum efficiency. The method comprises the following steps: growing a complete LED structure epitaxial wafer on a substrate, and etching to form a semiconductor structure with a step inclined plane; manufacturing a current blocking layer and a transparent conductive layer comprising an AZO layer; preparing a P type electrode, an N type electrode and a passivation layer, and performing back plating of a DBR layer; and preparing the wafer into the LED chip device. According to the invention, the aluminum-based reflecting electrode is adopted, and the insertion layer metal between the P type electrode and the transparent conductive layer is canceled, so that the luminous efficiency of the LED chip is improved, and the external quantum efficiency of the LED chip is improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

Chip scale package light emitting device with concave design and manufacturing method thereof

ActiveCN106981554BAvoid electrical connection failureImprove qualitySemiconductor devicesElectricityElectrical connection

The invention provides a chip scale package light-emitting apparatus having recessed design and a manufacturing method thereof. The chip scale package light-emitting apparatus includes a flip chip type LED chip and a cladding structure. The cladding structure covers the LED chip, and has a bottom surface warps upwardly to for a recessed shape. The invention also provides a manufacturing method for manufacturing the light-emitting apparatus. The apparatus and the method can avoid or improve poor quality of welding points between the light-emitting apparatus and a substrate which is often caused by greater gap between an electrode group of the LED chip and a welding pad of the substrate due to expansion of the cladding structure upon being heated in reflow soldering or eutectic bonding. Therefore, the apparatus and the method can secure the electrode group to the substrate. With excellent welding quality, failure of electrical connection of the light-emitting apparatus can be avoided, the thermal resistance between the light-emitting apparatus and the substrate can be lowered, temperature at the binding point can be lowered when the light-emitting apparatus operates, and light-emitting efficiency and reliability can be improved.

Owner:MAVEN OPTRONICS CO LTD

Method for manufacturing silicon solar cell

InactiveCN101783374BReduce sheet resistanceLower ohmic contactFinal product manufactureSemiconductor devicesElectrical resistance and conductanceOhmic contact

The invention discloses a method for manufacturing a silicon solar cell. In the process of manufacturing a PN junction on a silicon wafer, a selective diffusion technology method is adopted, i,e. laser is utilized to heat a position, on which a positive electrode intends to be manufactured, on the surface of the silicon wafer; and under the action of heating, phosphorus in a phosphorus source uniformly adhered on the surface diffuses towards the inner of the silicon wafer, thus a heavy doping zone with smaller sheet resistance is formed at the position on which the positive electrode intends to be manufactured to effectively reduce the sheet resistance of the silicon solar cell, thereby not only being beneficial for increasing the open-circuit voltage of the silicon solar cell; the increase of the open-circuit voltage effectively improves the conversion efficiency of the silicon solar cell, reduces ohmic contact of a metal electrode and the silicon solar cell, thereby reducing the series resistance of the silicon solar cell, and being capable of meeting the demand of industrialized production better.

Owner:SUN EARTH SOLAR POWER

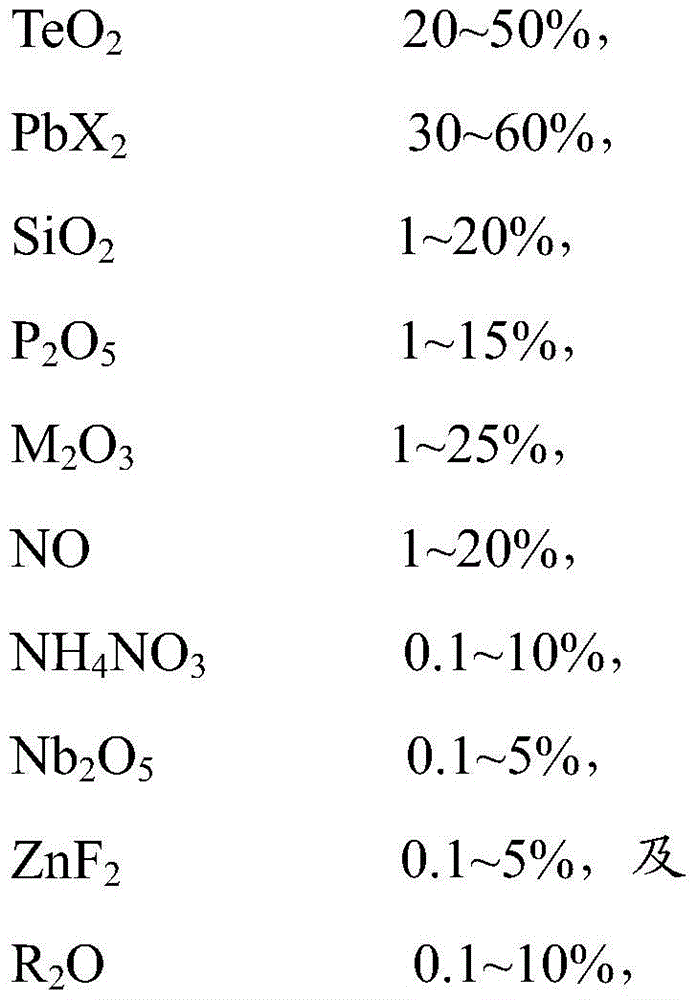

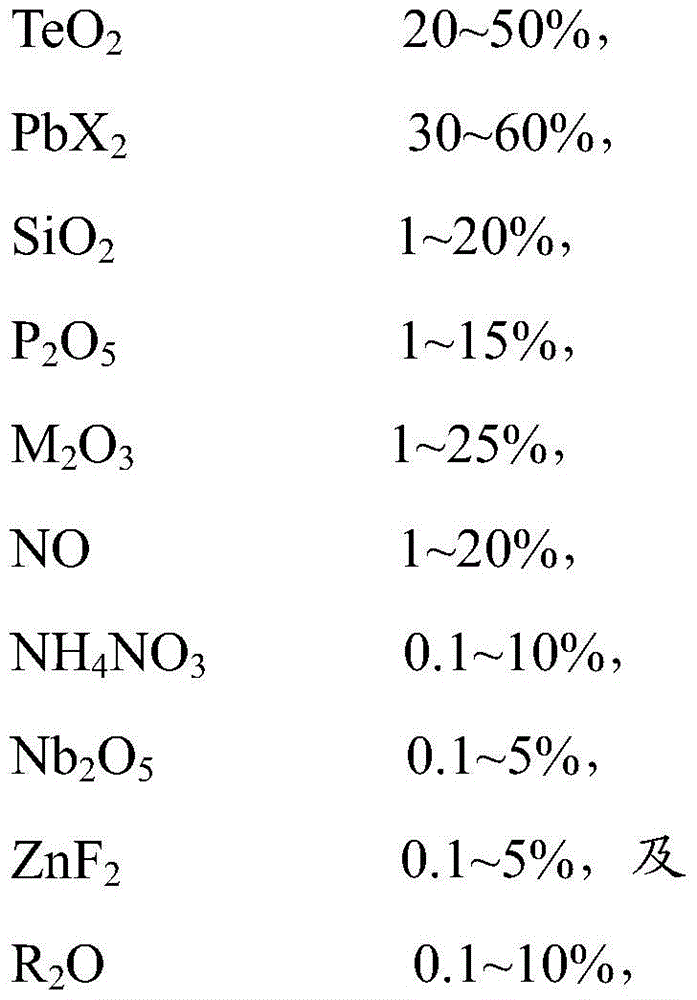

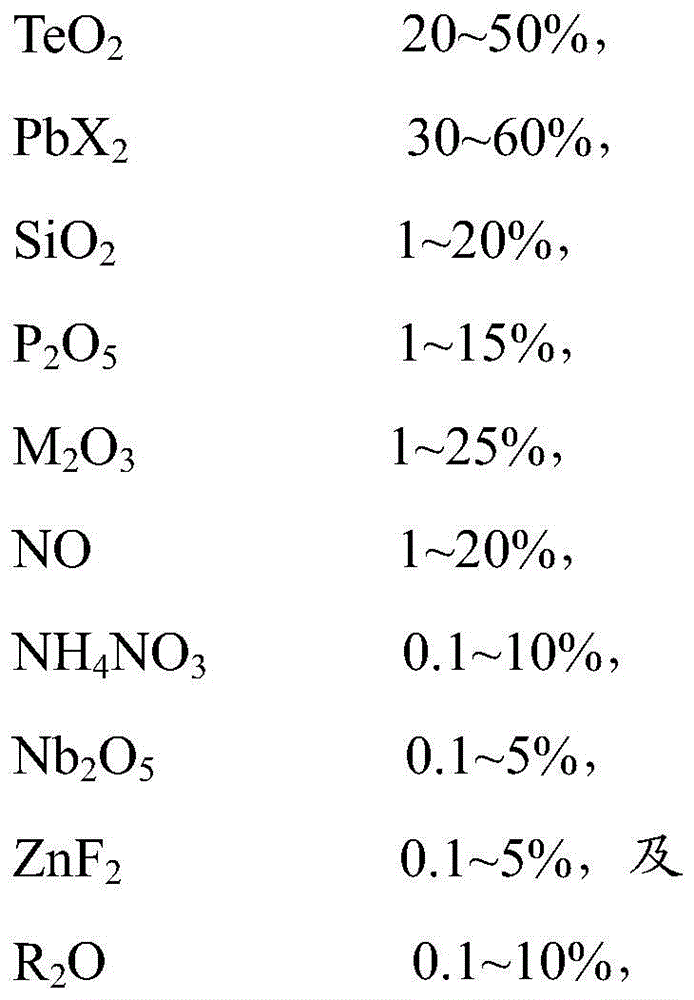

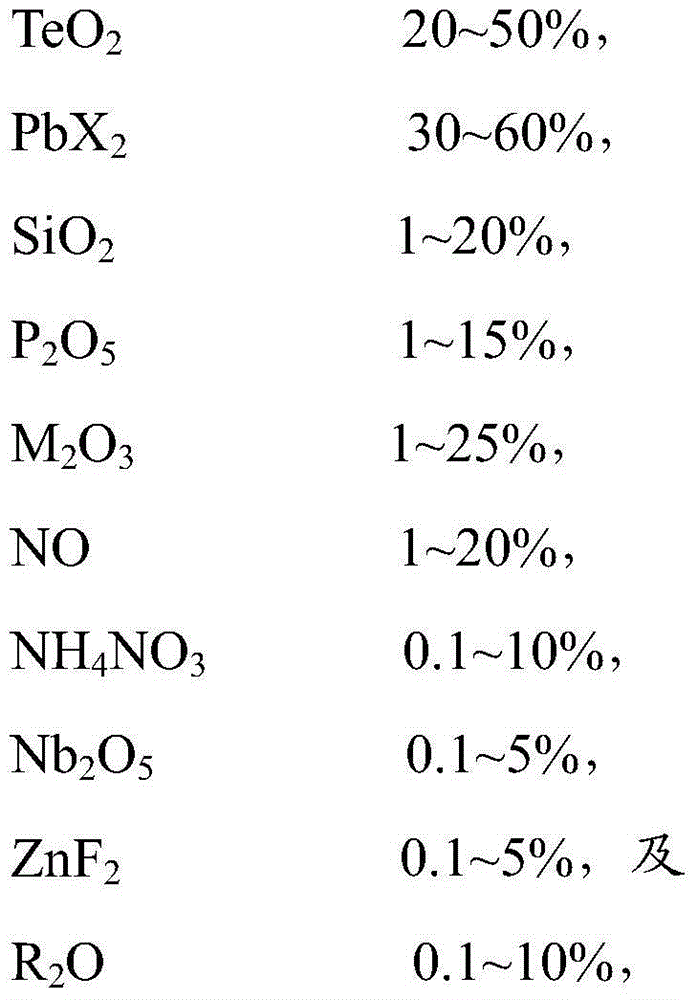

High temperature binder and preparation method thereof

ActiveCN104402227BHigh mechanical strengthHigh fluxPhotovoltaic energy generationSemiconductor devicesTungstatePyrophosphate

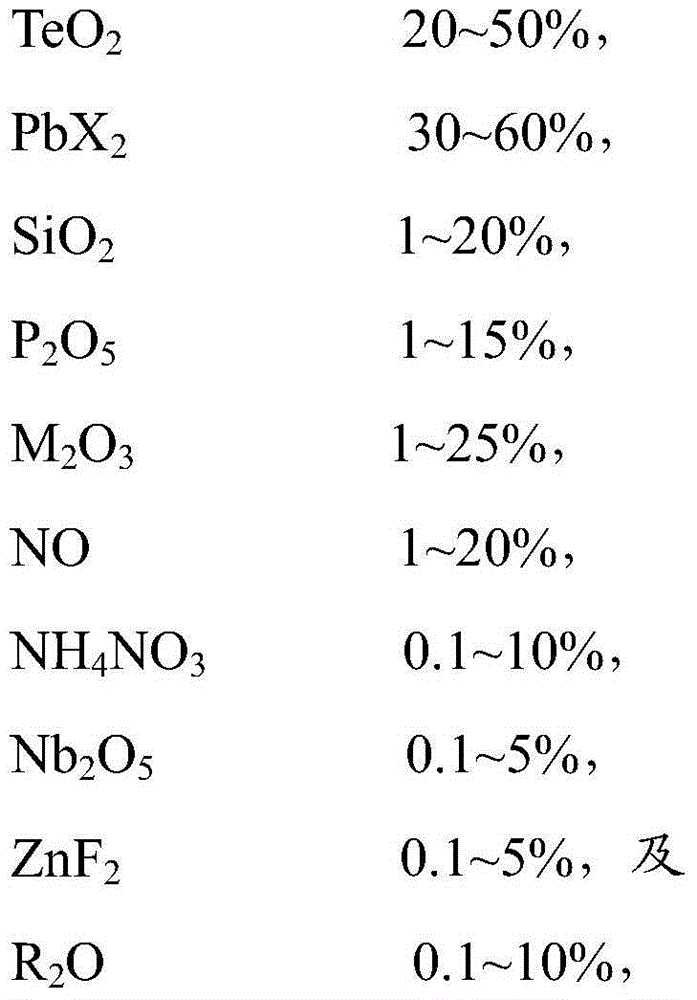

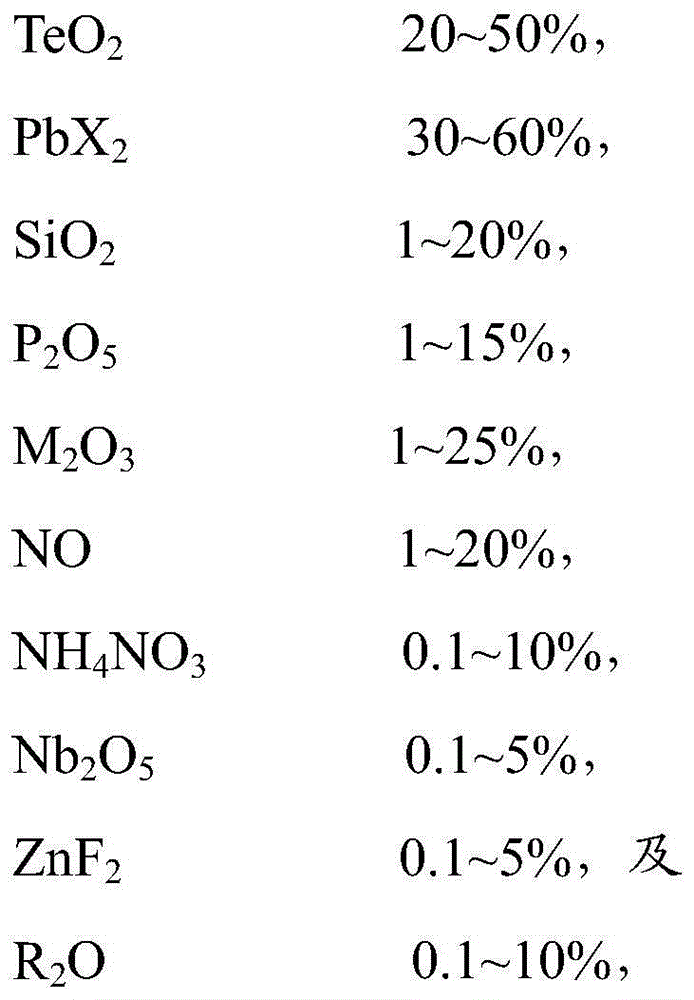

The invention relates to a high-temperature binder for a solar battery electrode and a preparation method thereof. The high-temperature binder for the solar battery electrode comprises a crystal material and an amorphous material, the amorphous material is a glass powder prepared from a mixture, and the mixture comprises the following components by the mass percentage: 20-50% of TeO2, 30-60% of PbX2, 1-20% of SiO2, 1-15% of P2O5, 1-25% of M2O3, 1-20% of NO, 0.1-10% of NH4NO3, 0.1-5% of Nb2O5, 0.1-5% of ZnF2, and 0.1-10% of R2O; the crystal material is selected from at least two of the group consisting of modified beta-spodumene, modified beta-cristobalite, modified cordierite, modified aluminum tungstate and modified titanium pyrophosphate. The high-temperature binder has relatively low thermal expansion coefficient.

Owner:GUANGDONG FENGHUA ADVANCED TECH HLDG

Integrated Gan-based sensor and method for simultaneous monitoring of solution temperature and pH

ActiveCN110927216BRealize online monitoringRealize online monitoring and detectionThermometers using electric/magnetic elementsMaterial analysis by electric/magnetic meansOhmic contactSchottky diode

The invention relates to an integrated GaN-based sensor and a manufacturing method for synchronously monitoring solution temperature and pH. The sensor is characterized in that it includes a substrate layer, a stress buffer layer, a GaN epitaxial layer, an AlGaN barrier layer, an ohmic contact electrode, a Schottky contact electrode and a packaging material layer arranged from bottom to top; the AlGaN barrier layer It includes a first protrusion, a first groove, a second protrusion and a second groove; the ohmic contact electrode is arranged on the surface of the first protrusion and the second protrusion; the Schottky contact electrode Deposition is disposed in the second groove. The sensor can maintain a high two-dimensional electron gas channel concentration while improving the detection sensitivity, so that the response speed is fast, and a Schottky diode is formed on the AlGaN / GaN by using the second groove anode structure to realize online monitoring of the detection solution temperature change.

Owner:宁波铼微半导体有限公司

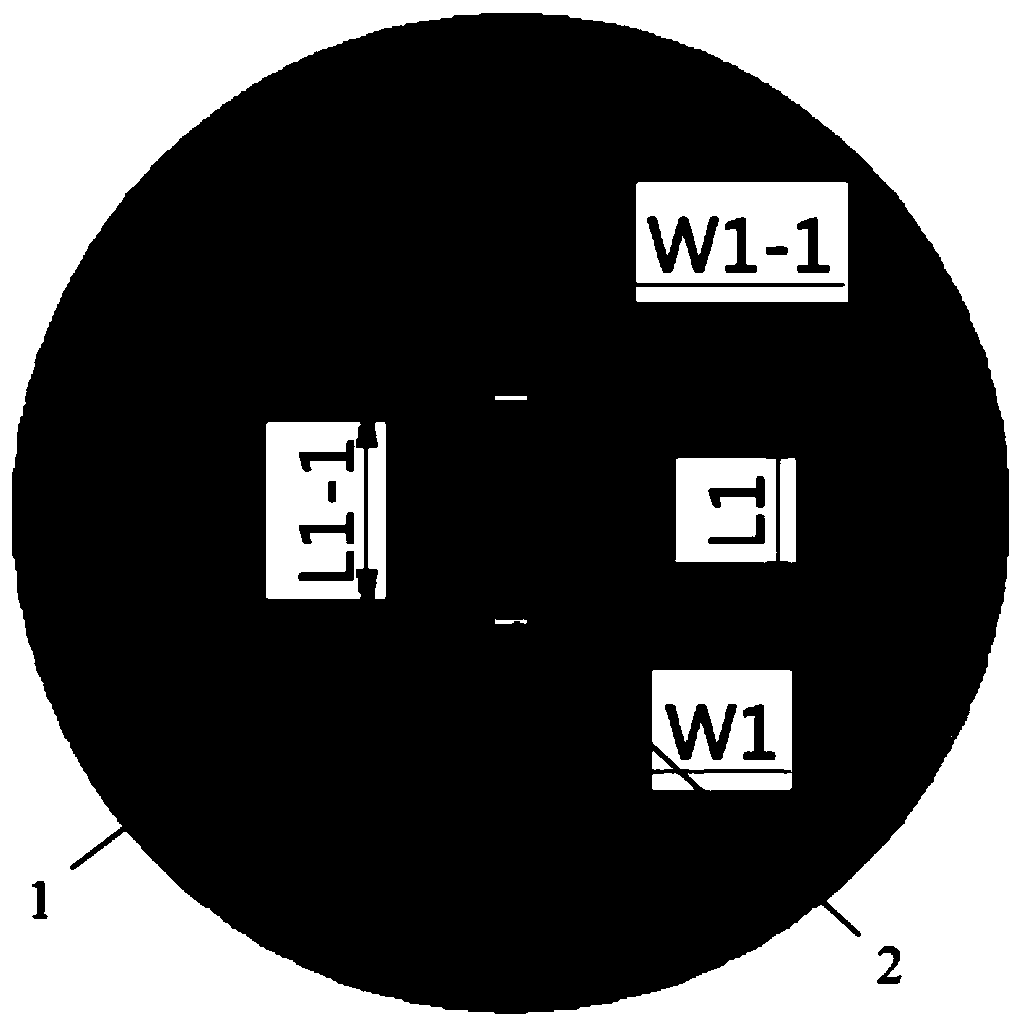

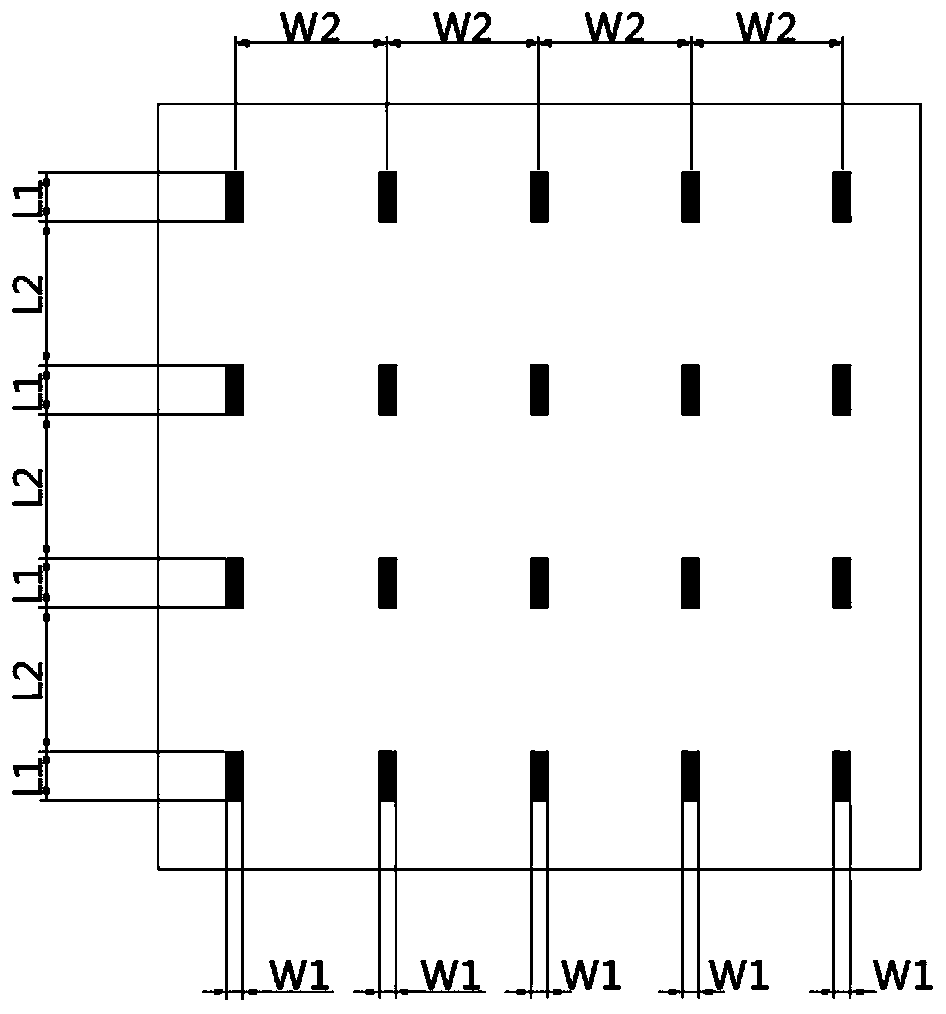

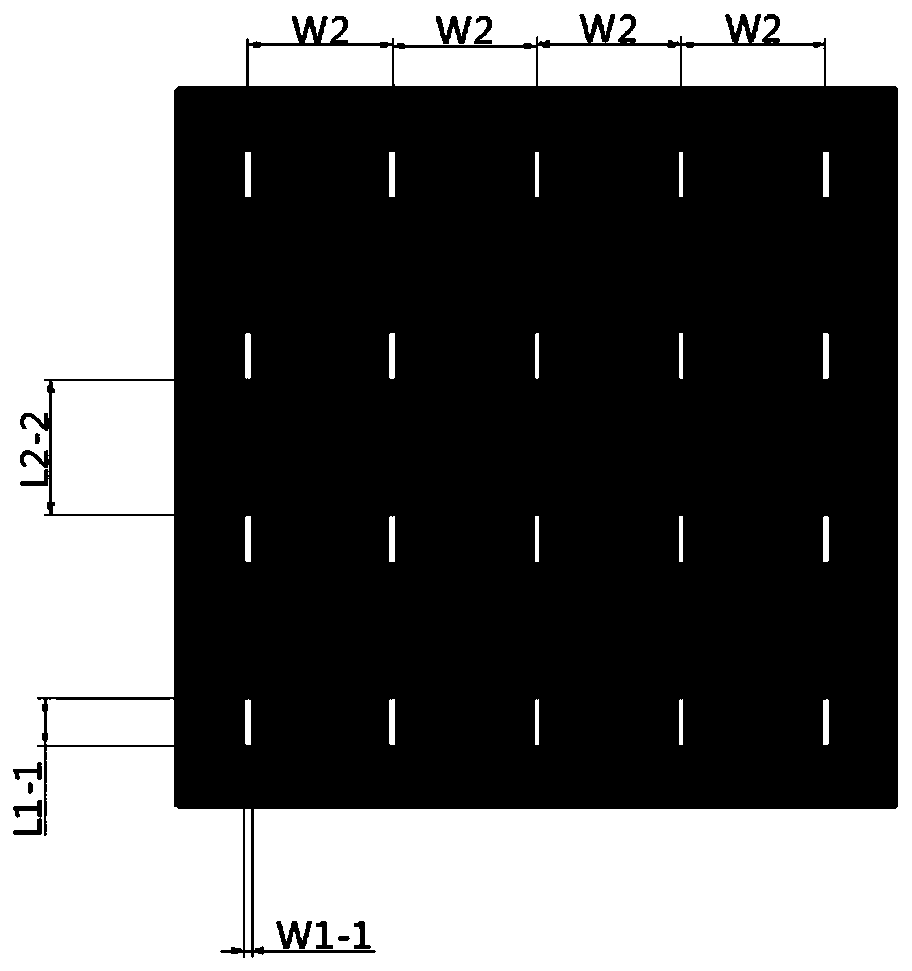

Four-section back electrode back electric field screen printing plate

InactiveCN111009585AShorten the lengthIncrease widthFinal product manufactureScreen printersScreen printingOhmic contact

The invention discloses a four-section back electrode back electric field screen printing plate, which comprises a back electrode of a five-main-grid four-section structure and a back electric field of the five-main-grid four-section structure, and the back electric field correspondingly overprints and covers the back electrode. The back electrode corresponds to the front main grid in position andis divided into four sections by the electrode, and the length of each section is 11 + / -3mm. The length of the back electrode is reduced; the width of the back electrode is increased, and the overlapping area of the back electrode and the back electric field is increased; on the basis of not increasing the consumption of the back silver, the silver-aluminum overlapping area of a junction area isincreased, the conductivity of the back electrode is better improved, ohmic contact of the back silver and the back aluminum is greatly improved, Rs is greatly reduced, longitudinal silicon exposure design is added for a short plate and the back electrode at the welding starting position of an assembly series welding machine, assembly pseudo soldering corresponding to the assembly can be improved,and the assembly tension and the fragment rate are improved.

Owner:JINENG CLEAN ENERGY TECH LTD

Method for preparing TiO2/ conducting polymer thin film

InactiveCN101673621BNo pollution in the processSimple operation processLight-sensitive devicesSolid-state devicesPolymer sciencePolymer thin films

The invention relates to a method for preparing a TiO2 / conducting polymer thin film used in a solar cell. Firstly, TiO2 collosol is prepared; poly <2-(3-thienyl)-ethyoxyl-4-butyl sulfonate solution of which the concentration is 10-15mg / mL is prepared; and then, lower alcohol (one of alcohol, glycol and glycerin) is evenly mixed with PEDT / polyphenyl sulfoacid according to the volume ratio of 1:1;the mixed solution is rotated for film coating on the ITO conductive glass surface at the speed of 50-2500r / min; the ITO conductive glass after film coating is dried for 0.5-5 hours at the temperature of 50-100 DEG C; then, the ITO conductive glass is put in TiO2 collosol for dipping for 15-30 minutes so as to be eluted with high purity water; and the obtained product is dried by N2. ITO conductive glass of which the surface adsorbs PEDT / polyphenyl sulfoacid and TiO2 is dried at the temperature of 450-550 DEG C for 2-4 hours and is then put in polymer 2-(3-thienyl)-ethyoxyl-4-butyl sulfonate solution for dipping for 15-30 minutes; then, the obtained product is eluted with high purity water and dried by N2; the obtained product is dried at the temperature of 150-250 DEG C for 1-3 hours to obtain TiO2 / conducting polymer thin film. The invention has simple technology, low cost and favorable product quality.

Owner:TONGJI UNIV

High-temperature binder and preparation method thereof

ActiveCN104402227AHigh mechanical strengthHigh fluxPhotovoltaic energy generationSemiconductor devicesTungstatePyrophosphate

The invention relates to a high-temperature binder for a solar battery electrode and a preparation method thereof. The high-temperature binder for the solar battery electrode comprises a crystal material and an amorphous material, the amorphous material is a glass powder prepared from a mixture, and the mixture comprises the following components by the mass percentage: 20-50% of TeO2, 30-60% of PbX2, 1-20% of SiO2, 1-15% of P2O5, 1-25% of M2O3, 1-20% of NO, 0.1-10% of NH4NO3, 0.1-5% of Nb2O5, 0.1-5% of ZnF2, and 0.1-10% of R2O; the crystal material is selected from at least two of the group consisting of modified beta-spodumene, modified beta-cristobalite, modified cordierite, modified aluminum tungstate and modified titanium pyrophosphate. The high-temperature binder has relatively low thermal expansion coefficient.

Owner:GUANGDONG FENGHUA ADVANCED TECH HLDG