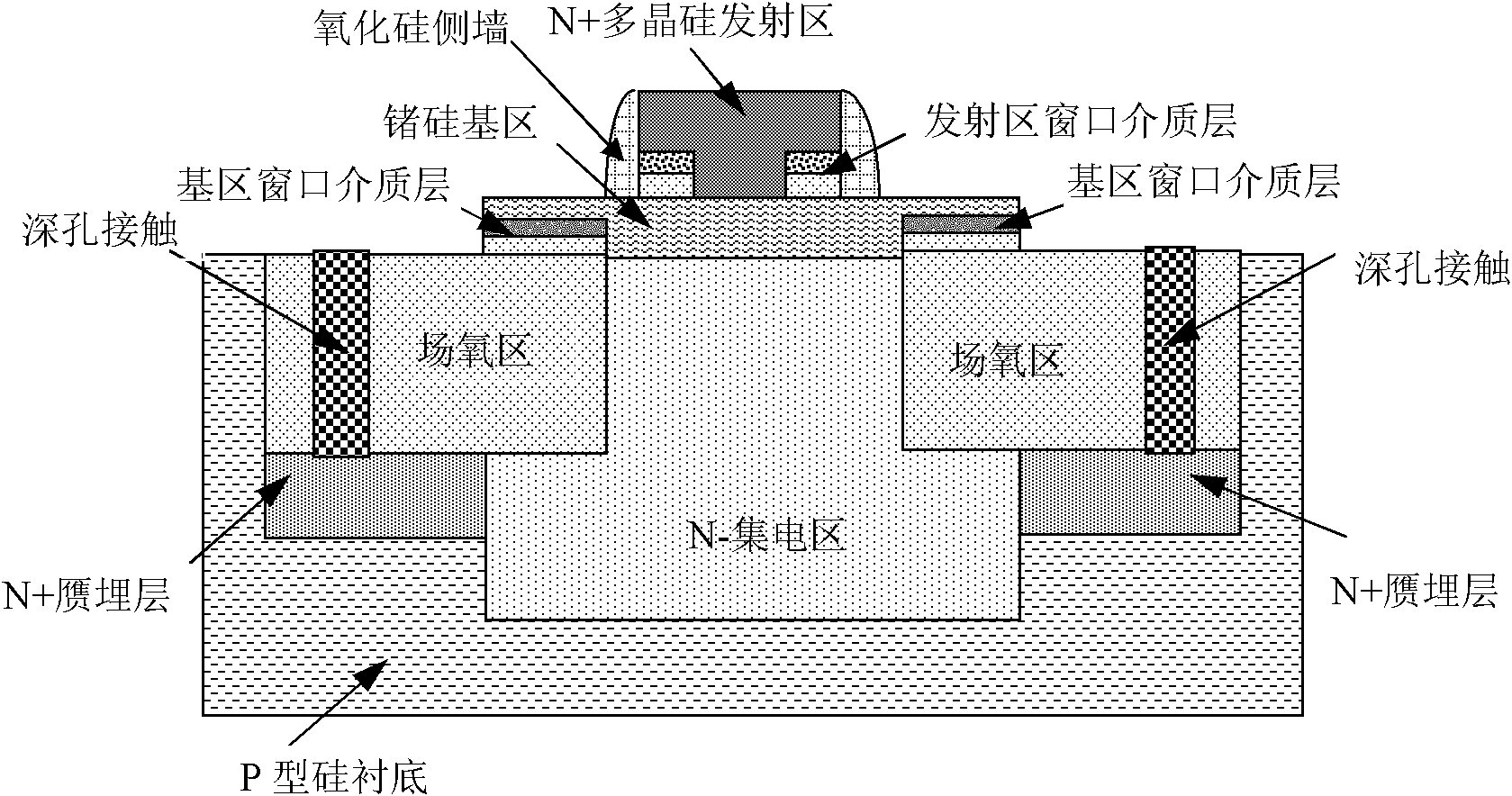

Manufacturing method for silicon germanium heterojunction bipolar transistors

A heterojunction bipolar and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reduced polysilicon emitter size, high quasi-accuracy requirements, and complex processes. The effect of reducing rb and increasing device Fmax

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

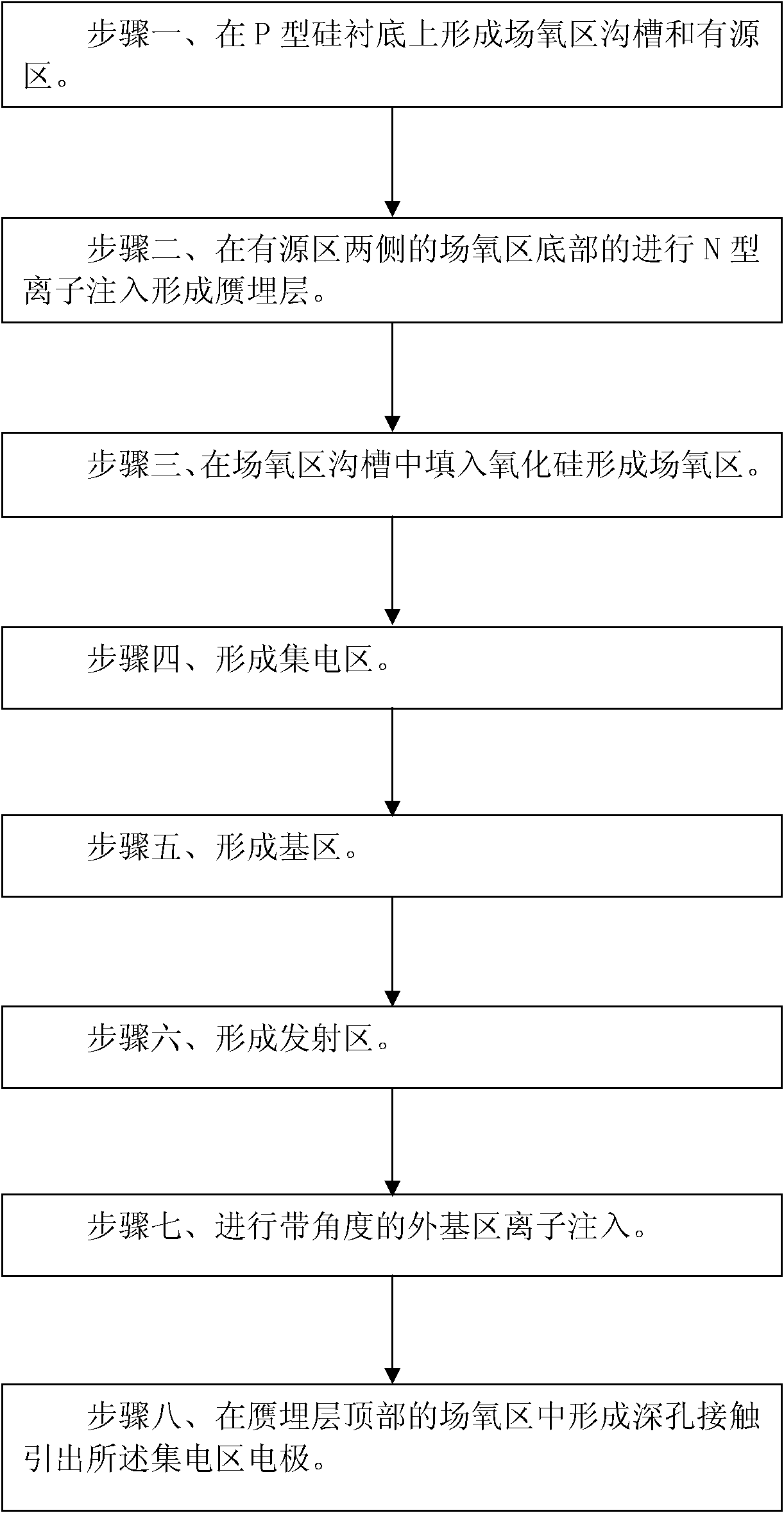

[0027] like figure 2 As shown, it is a flowchart of a method according to an embodiment of the present invention. like Figure 3-Figure 14 As shown, it is a schematic structural diagram of a silicon germanium heterojunction bipolar transistor in each step of the method according to the embodiment of the present invention.

[0028] The manufacturing method of the silicon germanium heterojunction bipolar transistor according to the embodiment of the present invention includes the following steps:

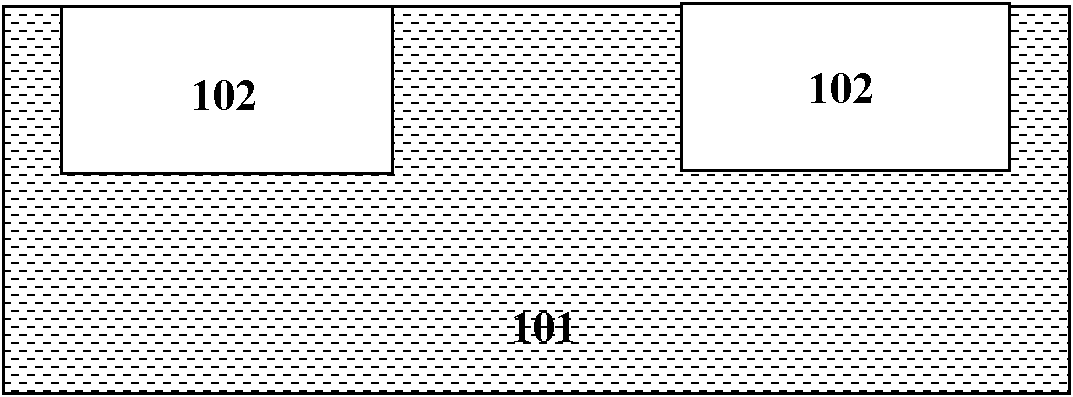

[0029] Step one, as image 3 As shown, trenches and active regions are formed on the P-type silicon substrate 101 for the field oxide region 102 .

[0030] Step 2, forming a pseudo buried layer 103 . First, as Figure 4 As shown, the pseudo-buried layer 103 region is defined by photolithography, that is, photoresist is used to form a pseudo-buried layer protection window during ion implantation of the pseudo-buried layer 103, and the edge of the pseudo-buried layer protection wind...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More