Patents

Literature

478 results about "Boron diffusion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The boron diffusion process consists of two separate reactions. The first reaction is a slow process between the boron and the material that produces a very hard, thin boride layer at the surface. The second reaction involves the diffusion of boron further into the substrate at a much quicker rate.

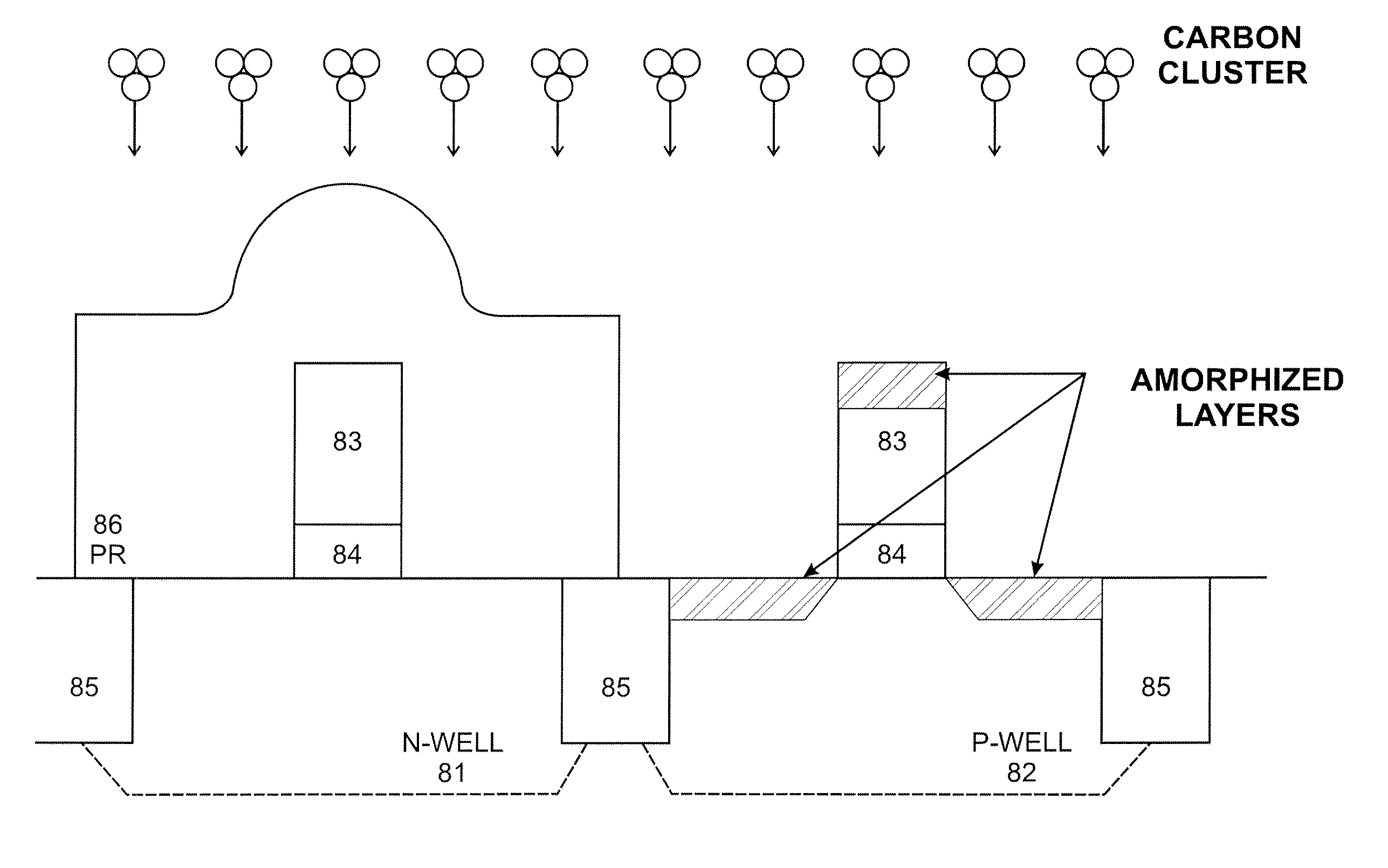

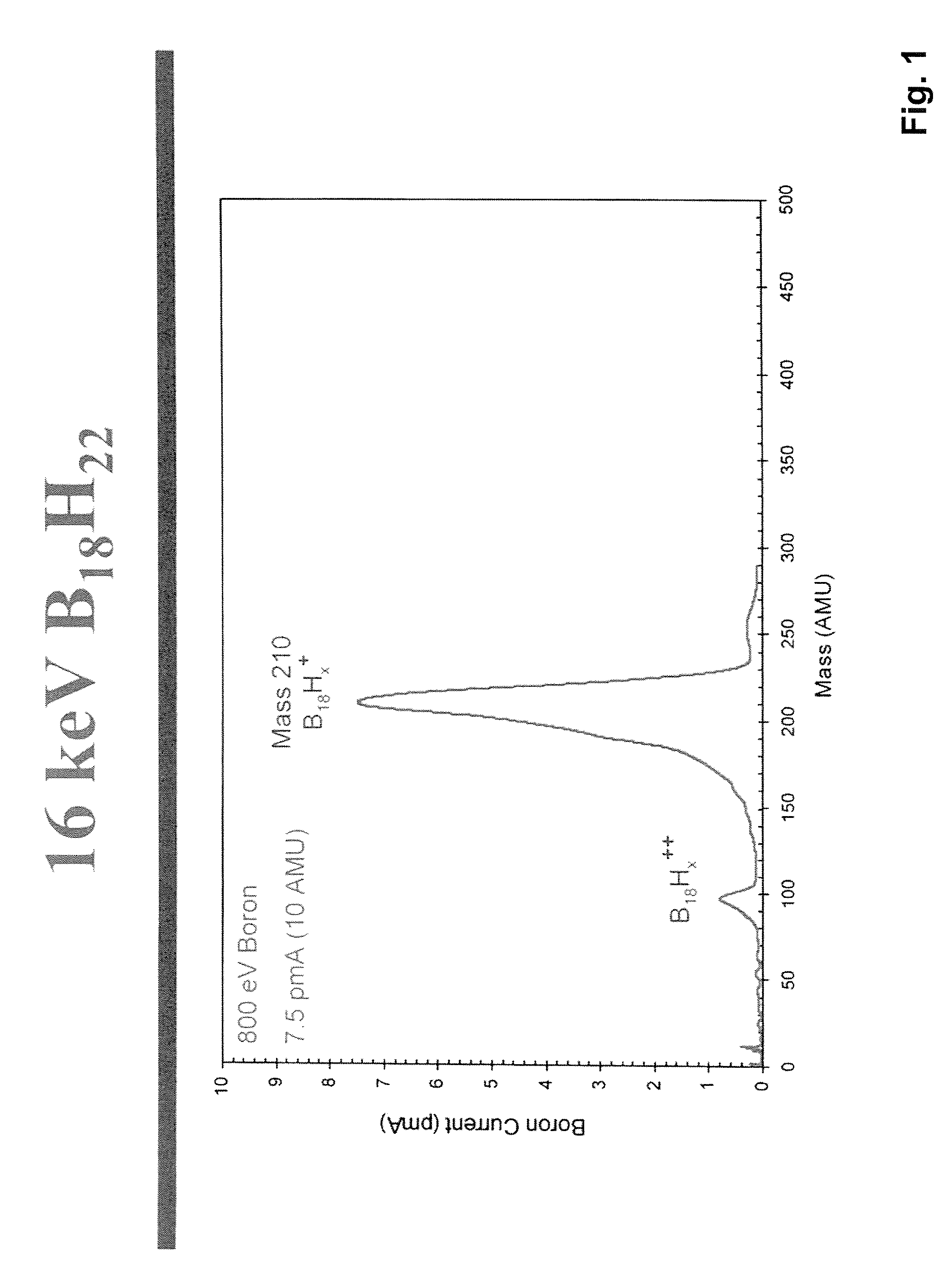

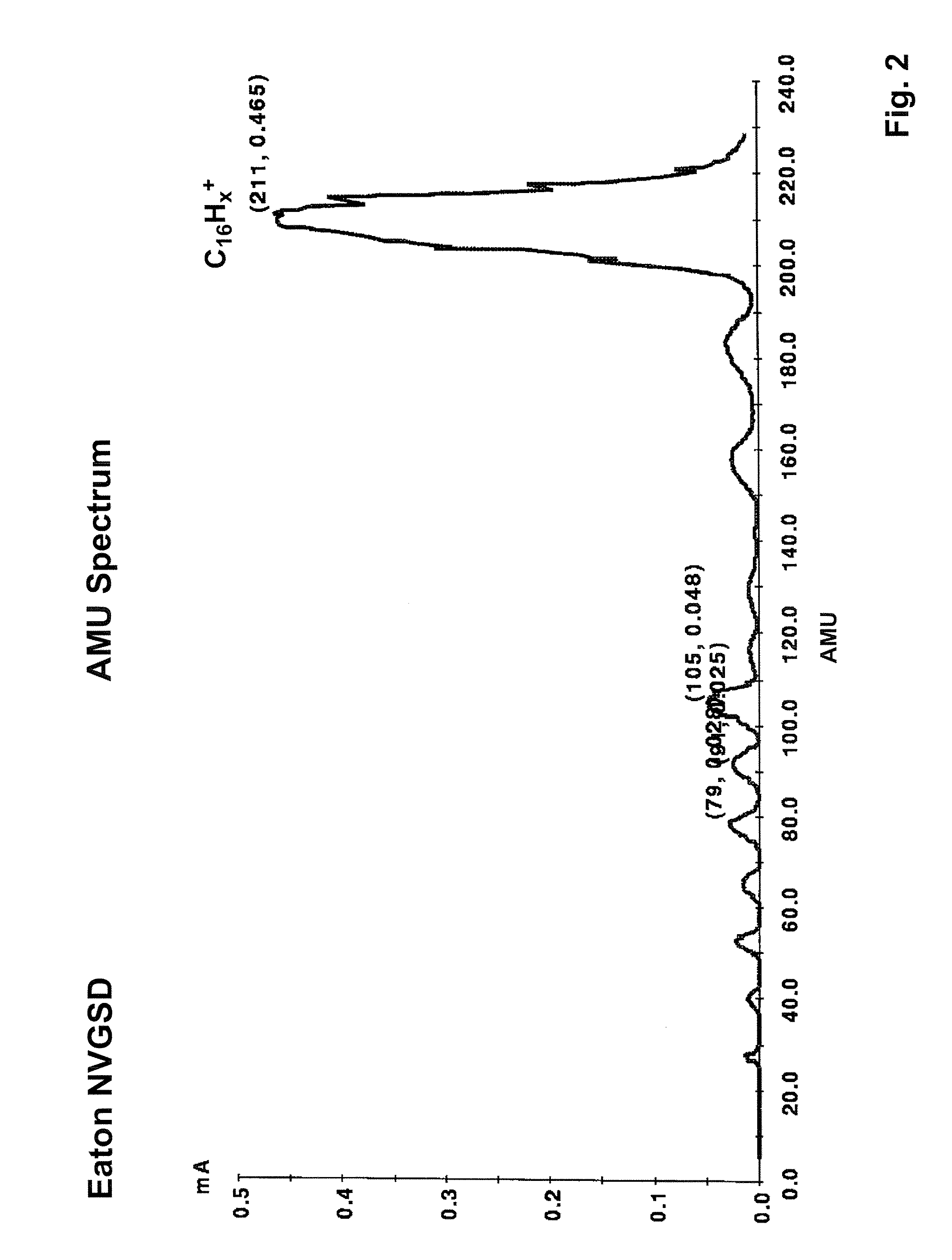

System and method for the manufacture of semiconductor devices by the implantation of carbon clusters

InactiveUS20070148888A1Improve productivityMinimize doseTransistorElectric discharge tubesDevice materialEngineering

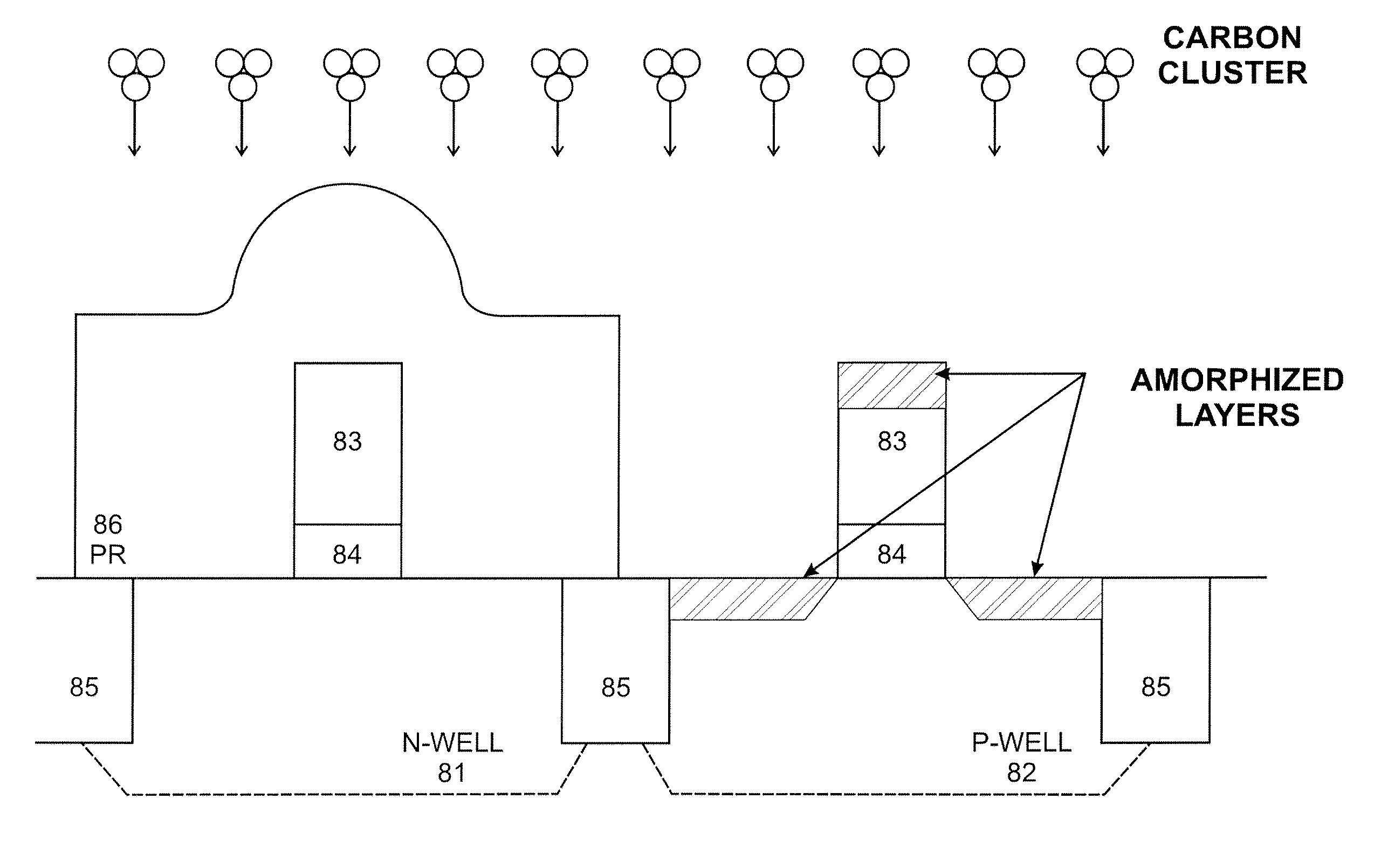

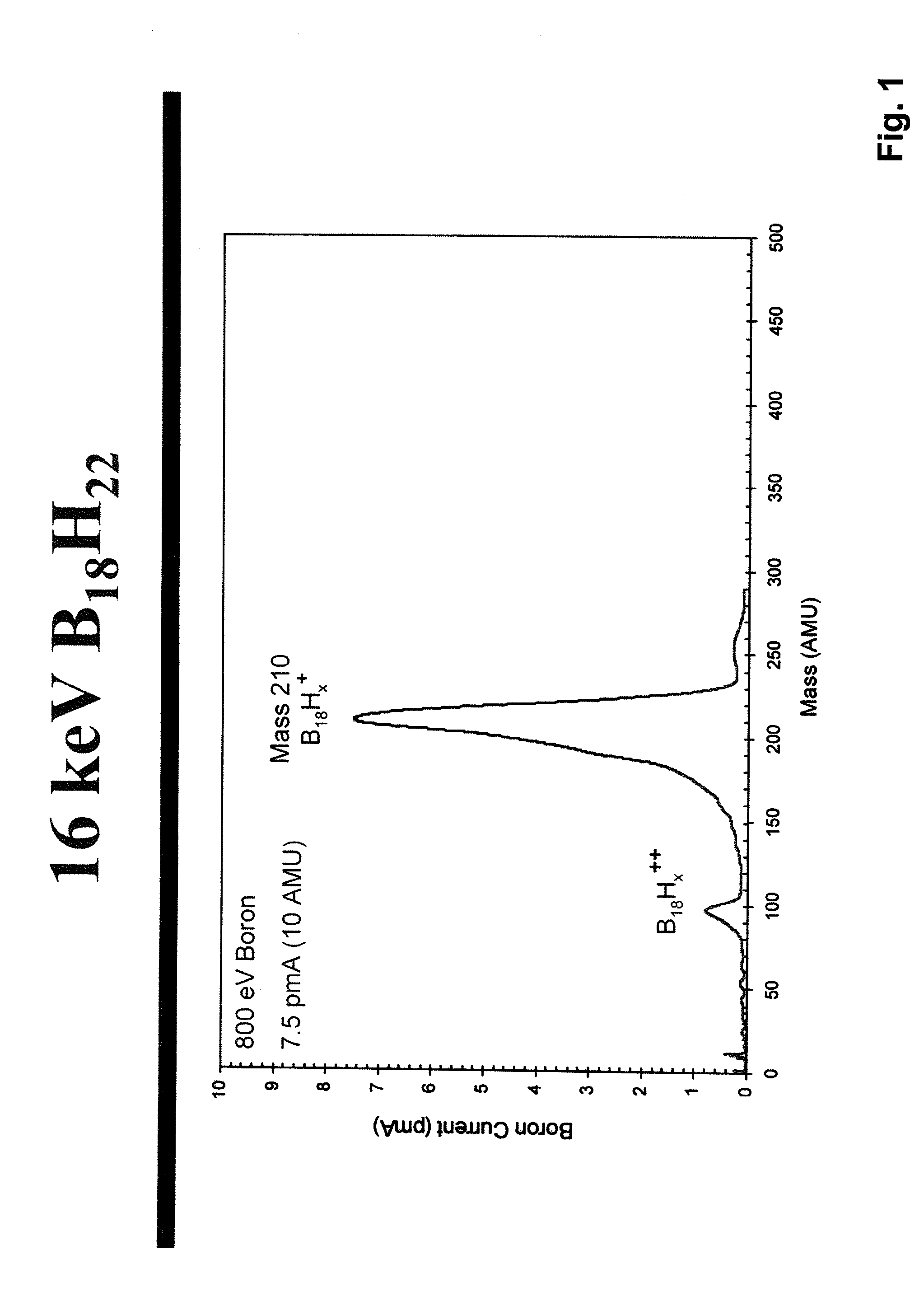

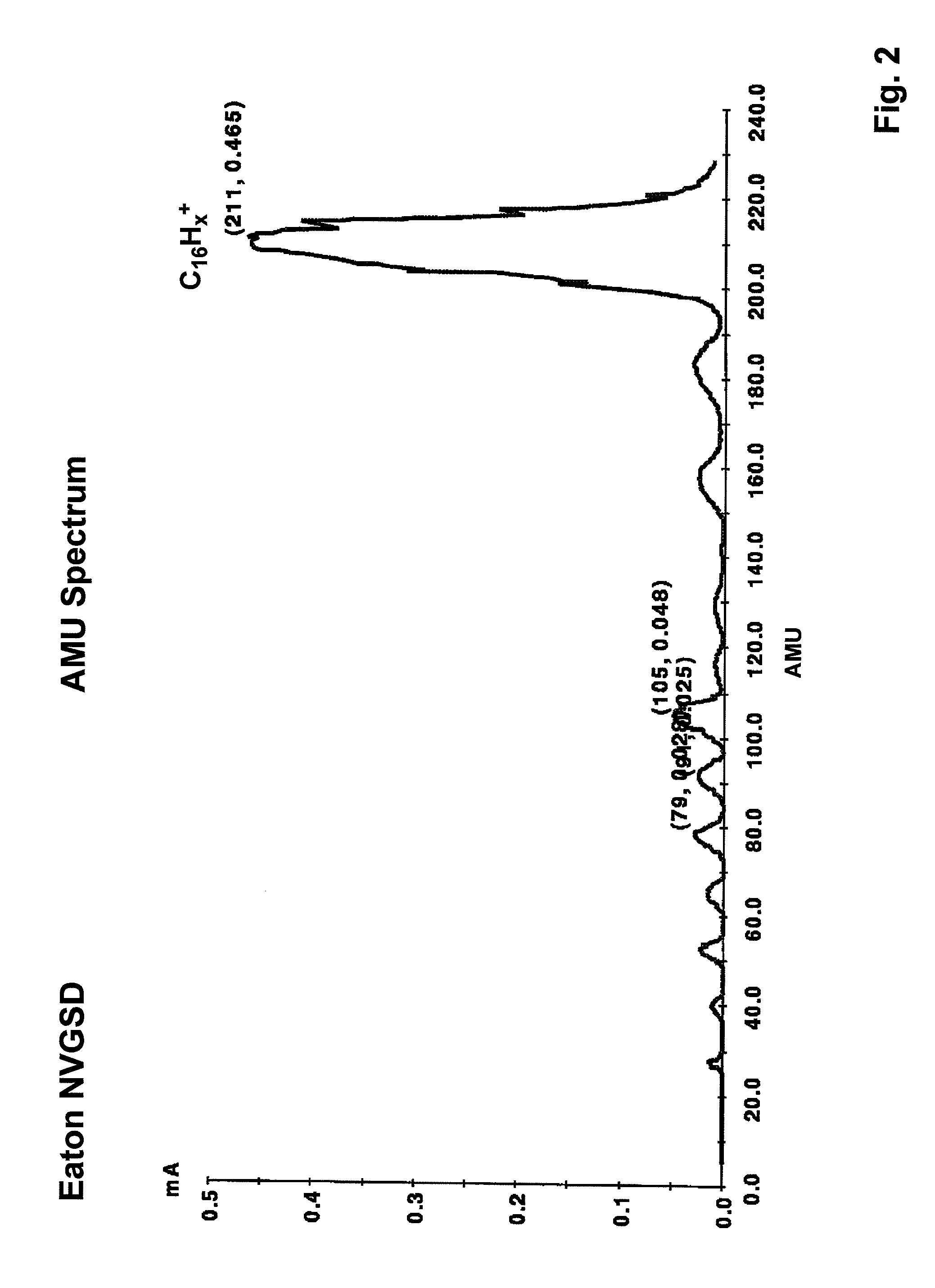

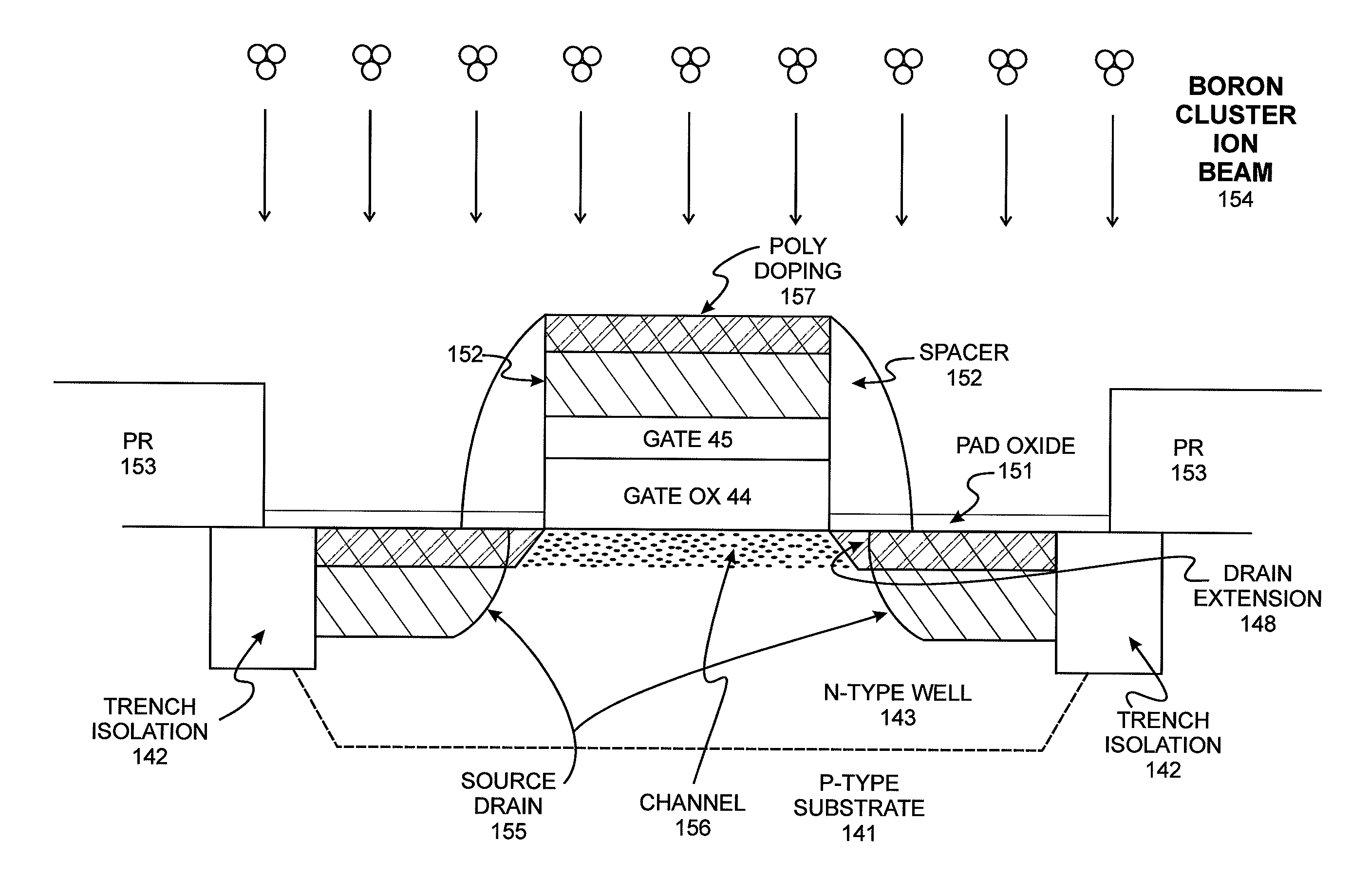

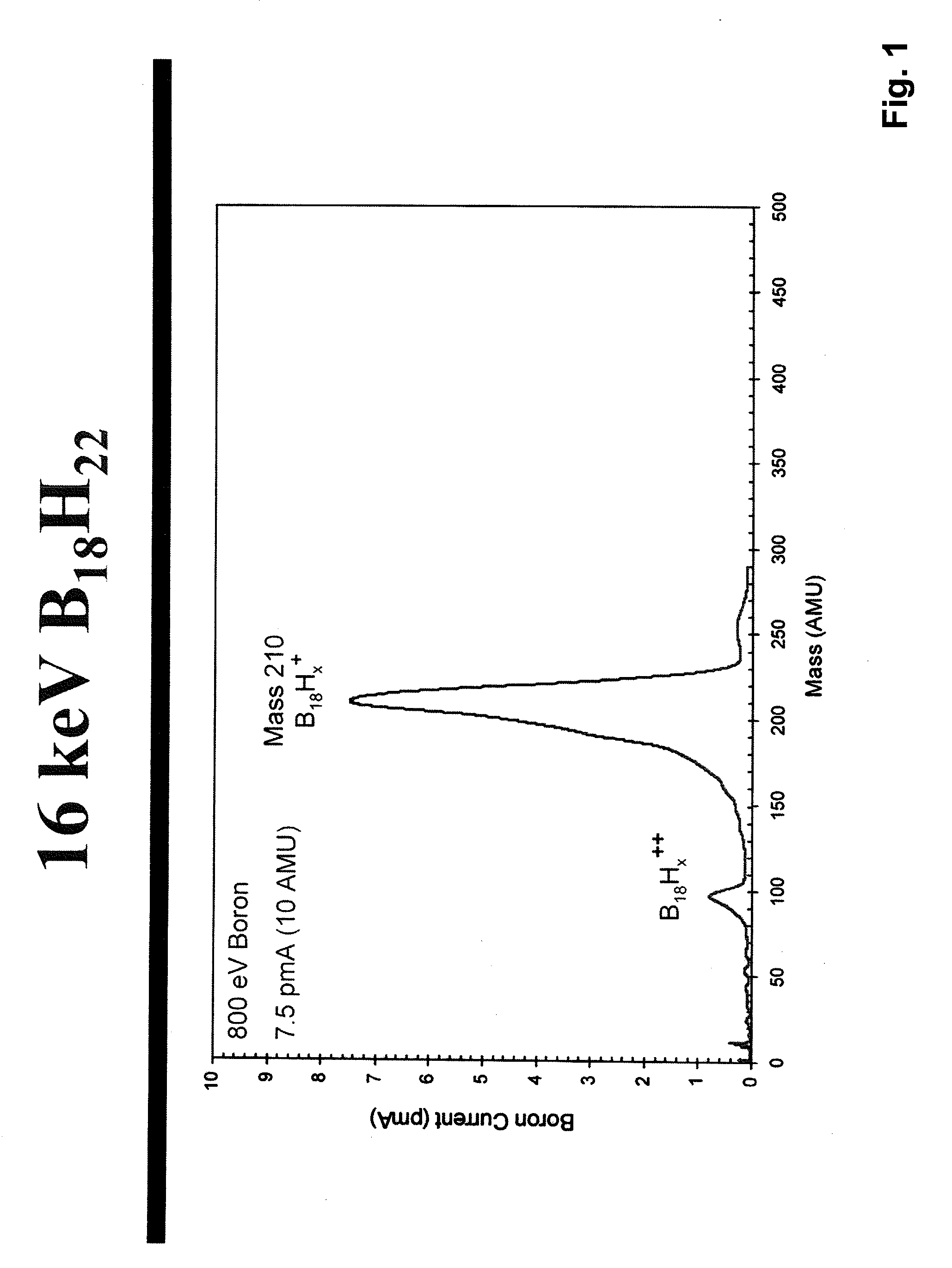

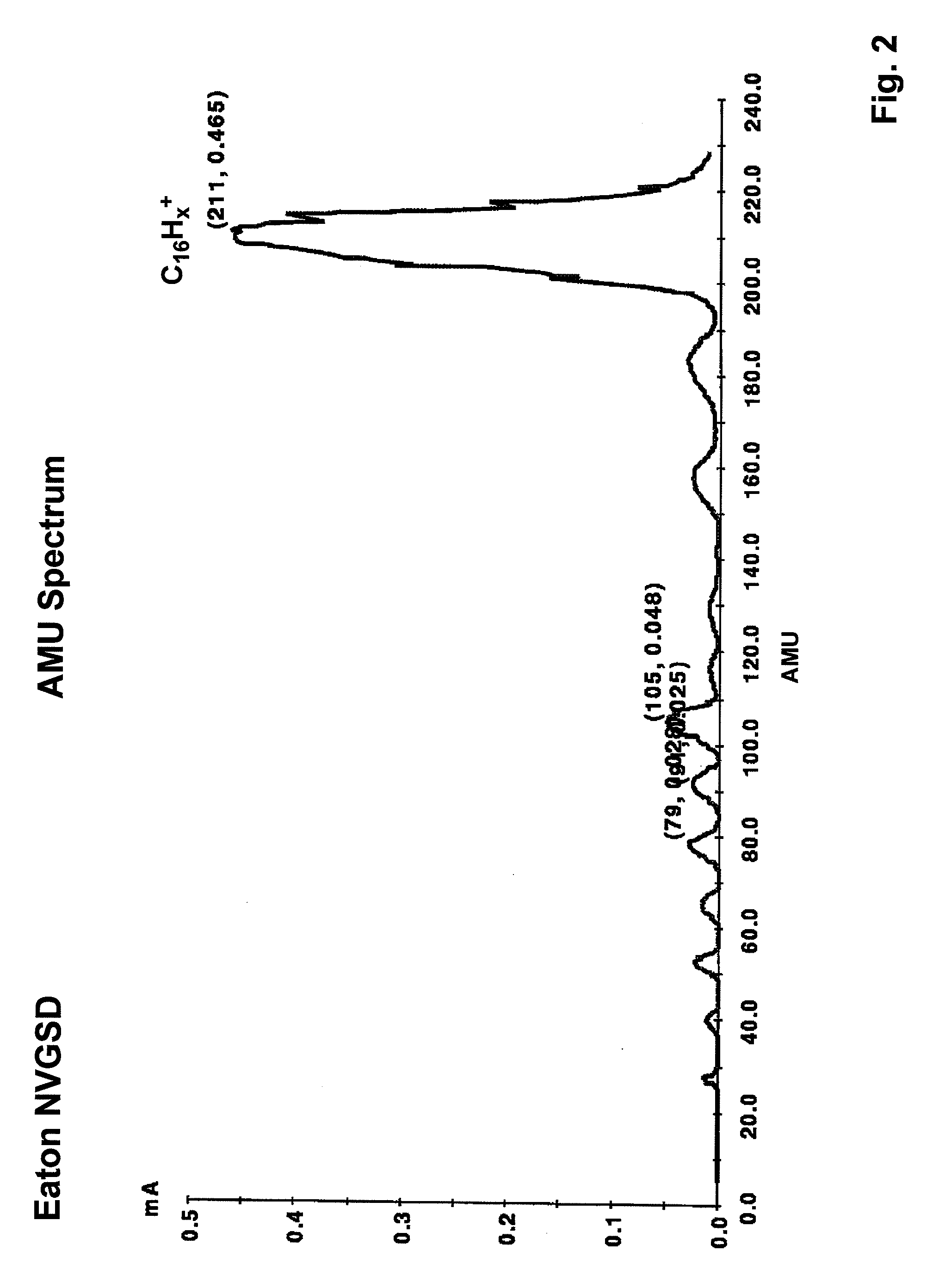

A process is disclosed which incorporates implantation of a carbon cluster into a substrate to improve the characteristics of transistor junctions when the substrates are doped with Boron and Phosphorous in the manufacturing of PMOS transistor structures in integrated circuits. There are two processes which result from this novel approach: (1) diffusion control for USJ formation; and (2) high dose carbon implantation for stress engineering. Diffusion control for USJ formation is demonstrated in conjunction with a boron or shallow boron cluster implant of the source / drain structures in PMOS. More particularly, first, a cluster carbon ion, such as C16Hx+, is implanted into the source / drain region at approximately the same dose as the subsequent boron implant; followed by a shallow boron, boron cluster, phosphorous or phosphorous cluster ion implant to form the source / drain extensions, preferably using a borohydride cluster, such as B18Hx+ or B10Hx+. Upon subsequent annealing and activation, the boron diffusion is reduced, due to the gettering of interstitial defects by the carbon atoms.

Owner:SEMEQUIP

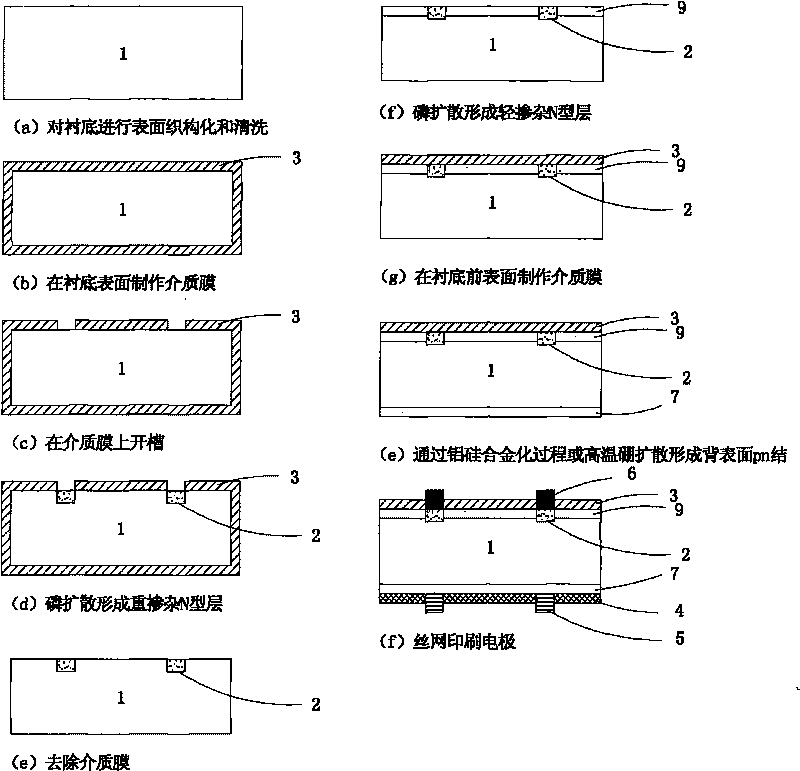

Manufacture method of selective front surface field N-type solar cell

InactiveCN101764179ASimple processLow costFinal product manufactureSemiconductor devicesChemical platingSilicon alloy

The invention discloses a manufacture method of a selective front surface field N-type solar cell, which is characterized in that a back surface p-n junction is formed by utilizing an aluminum-silicon alloying process and a high-temperature boron diffusion process, a front surface lightly doped N-type layer is formed by high-temperature phosphorous diffusion, a front surface local heavily doped N-type region is formed by laser doping, and a front electrode is manufactured on the heavily doped N-type region by utilizing a chemical plating method or an electroplating method. Compared with the traditional manufacture process, the invention has the advantages of simple process and low cost and does not need secondary contraposition.

Owner:SUN YAT SEN UNIV

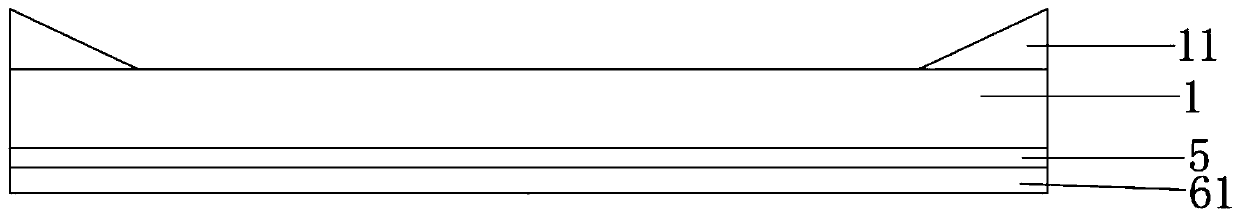

N-type double-sided battery and manufacturing method thereof

InactiveCN104538501AImprove efficiencyIncrease production capacityFinal product manufactureSemiconductor/solid-state device manufacturingScreen printingOptoelectronics

The invention discloses an N-type double-sided battery and a manufacturing method thereof. The manufacturing method comprises the following steps that S1, texturing treatment is performed; S2, a boron source is evenly coated on the upper surface of an N-type silicon wafer in a spin coating or silk-screen printing mode, and boron diffusion is conducted in a furnace tube; S3, a mask is manufactured; S4, phosphorus diffusion is conducted on the lower surface of the N-type silicon wafer, and a high-low-junction structure is formed on the lower surface; S5, phosphorosilicate glass and the mask manufactured in the step S3 are removed; S6, a passivation anti-reflection film made from aluminum oxide and silicon nitride is manufactured on the surface of the diffused boron, and a silicon nitride passivation anti-reflection film is manufactured on the surface of the diffused phosphorus; S7, electrodes are manufactured. The manufacturing method of the N-type double-sided battery is simple in process, and the efficiency of the battery is effectively improved. In addition, a passivation layer manufacturing method of the N-type double-sided battery is a low-temperature process, and a PN junction is not damaged.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

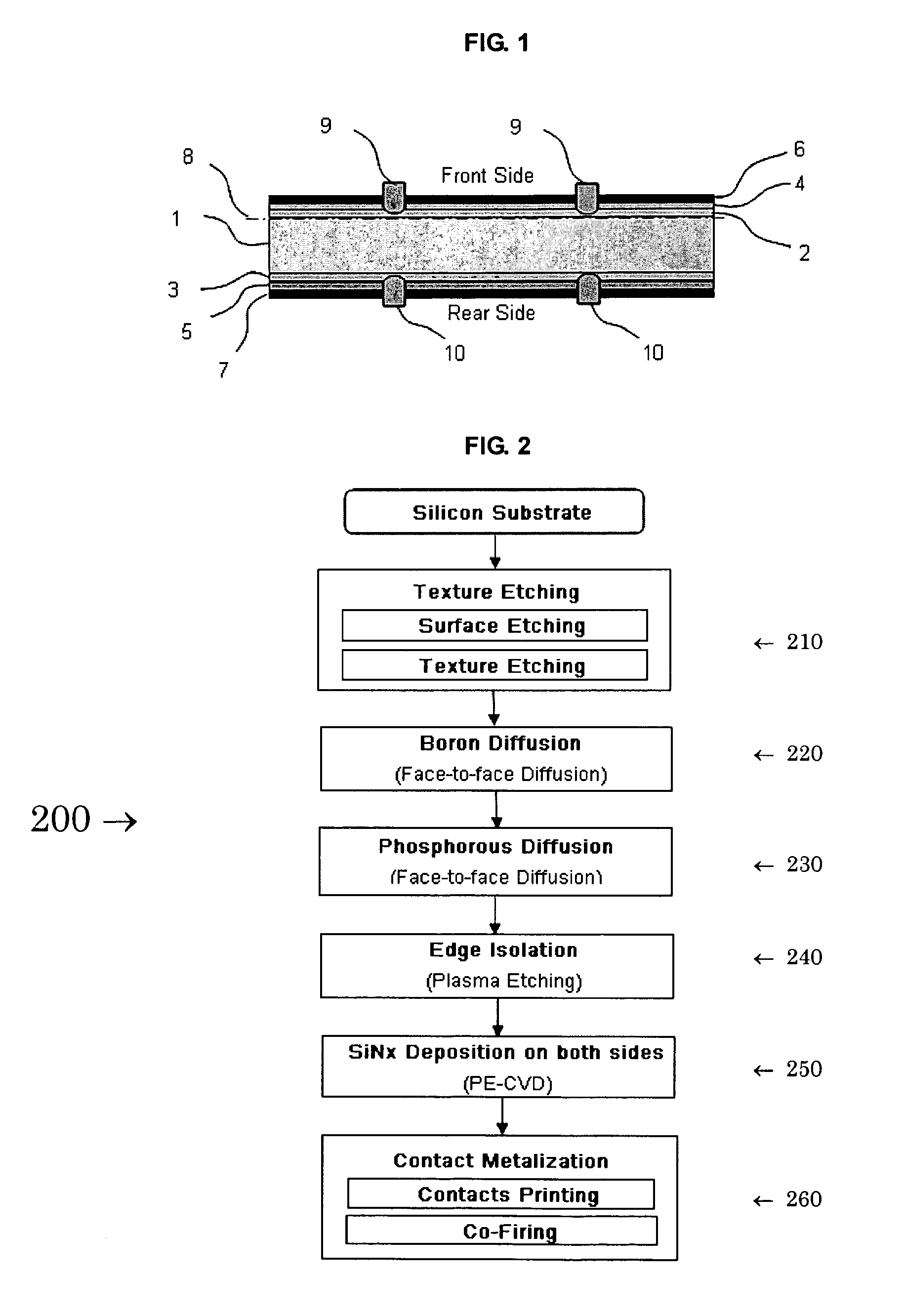

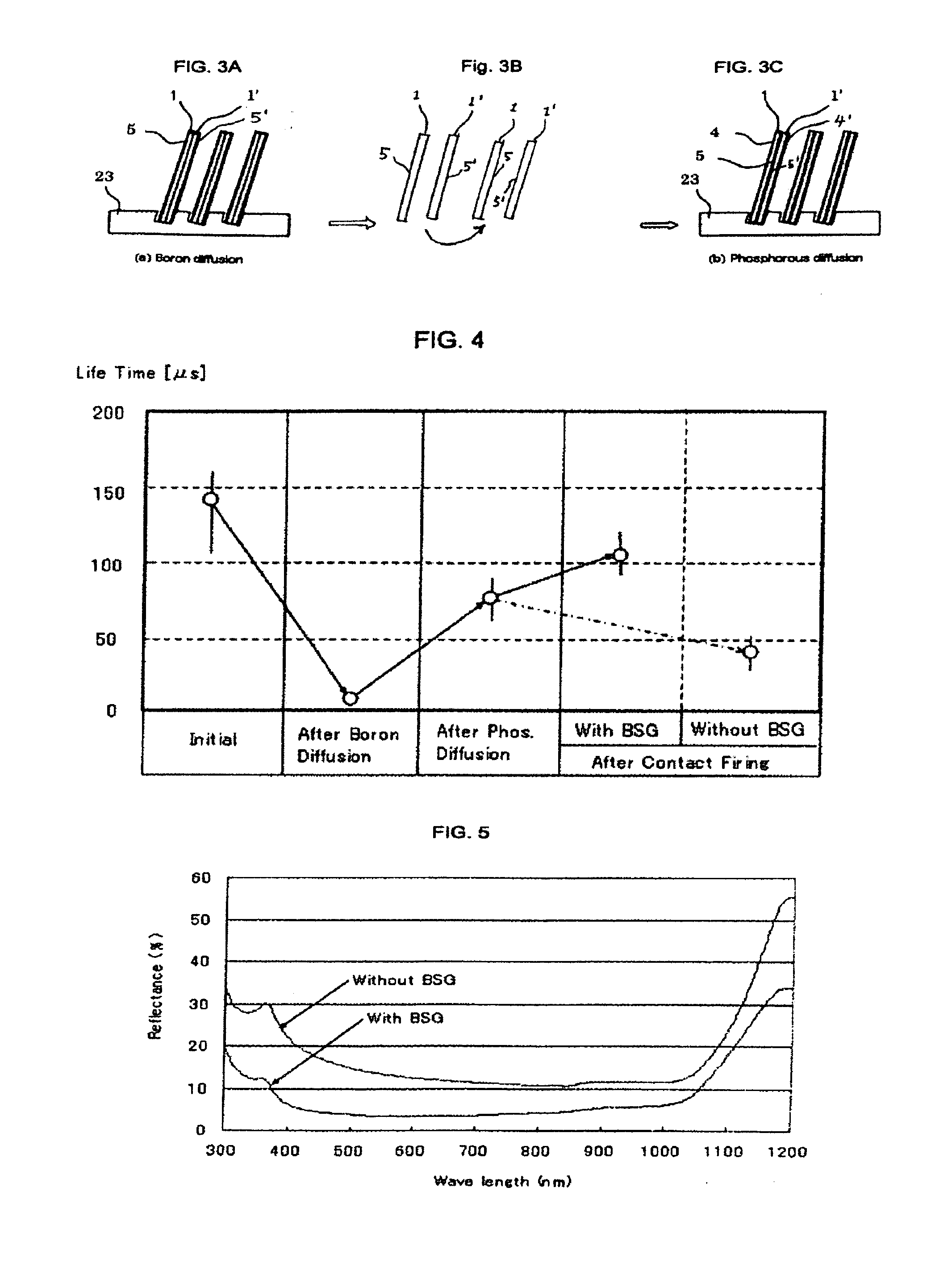

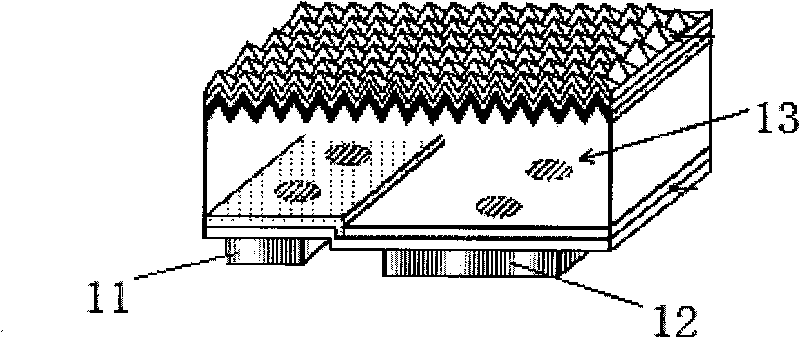

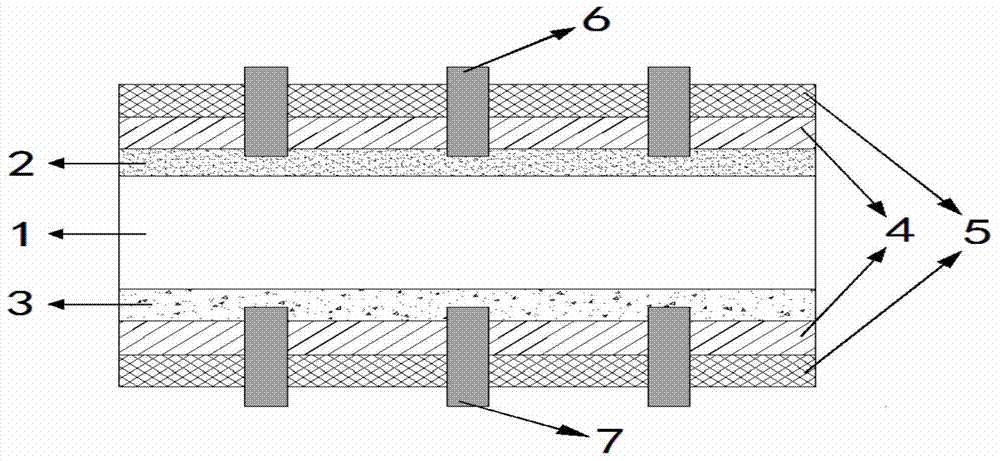

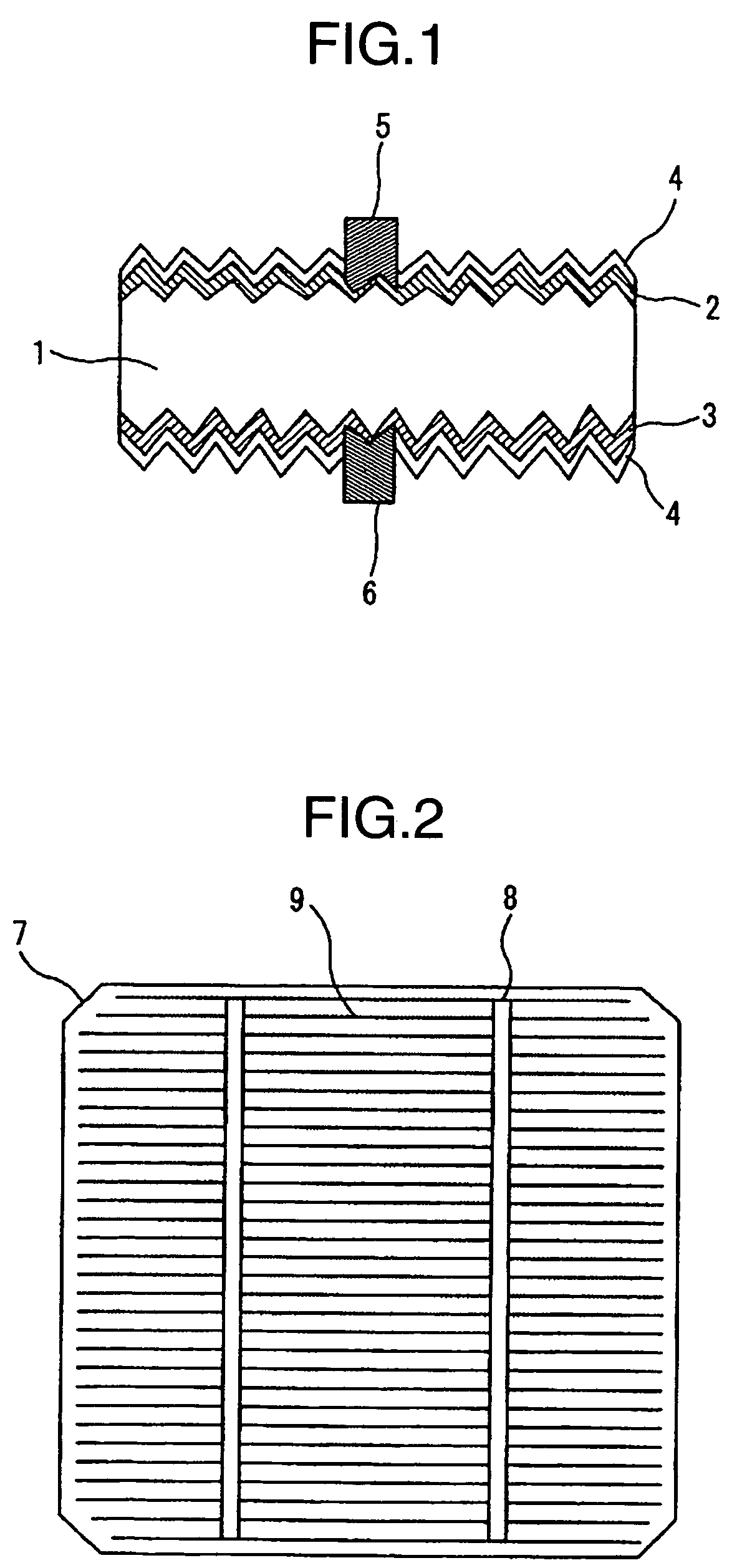

Photovoltaic solar module comprising bifacial solar cells

InactiveUS20110132423A1Without compromising structural integrityLess costly bifacial solar cellsPV power plantsSoldering apparatusDiffusion methodsPhotovoltaic solar energy

A photovoltaic solar cell module comprises a plurality of bifacial solar cells and electrical conductors. Each bifacial solar cell comprises a plurality of bus-bar contacts. A phosphorous silicon glass layer is formed on one side of the bifacial cell by phosphorous diffusion, and a boron silicon glass layer is formed on the other side of the bifacial cell by boron diffusion. The phosphorous diffusion and the boron diffusion are conducted by a face-to-face diffusion method. The combination of the two gettering methods substantially increases the minority carrier life time of the bifacial solar cell.

Owner:GAMMA SOLAR

Method for manufacturing high efficient two-sided N-shaped crystalline silicon solar cell based on silk-screen printing technique

InactiveCN101692466AExtend your lifeImprove conversion efficiencyFinal product manufactureSemiconductor devicesScreen printingProduction line

The invention discloses a method for manufacturing a high efficient two-sided N-shaped crystalline silicon solar cell based on silk-screen printing technique. The preparation steps are: carrying out frontal phosphorous diffusion or partial phosphorous diffusion on the N-shaped silicon chip, growing a passivation layer and an antireflection layer, manufacturing a frontal electrode, carrying out back boron diffusion on the N-shaped silicon chip, growing a passivation layer and an antireflection layer, and manufacturing a back electrode. The inventive method has simple manufacturing technique, low cost, small investment on equipment and high production efficiency, and most part of the manufacturing technique can be carried out on a common conventional cell production line.

Owner:CHINA SUNERGY CO LTD

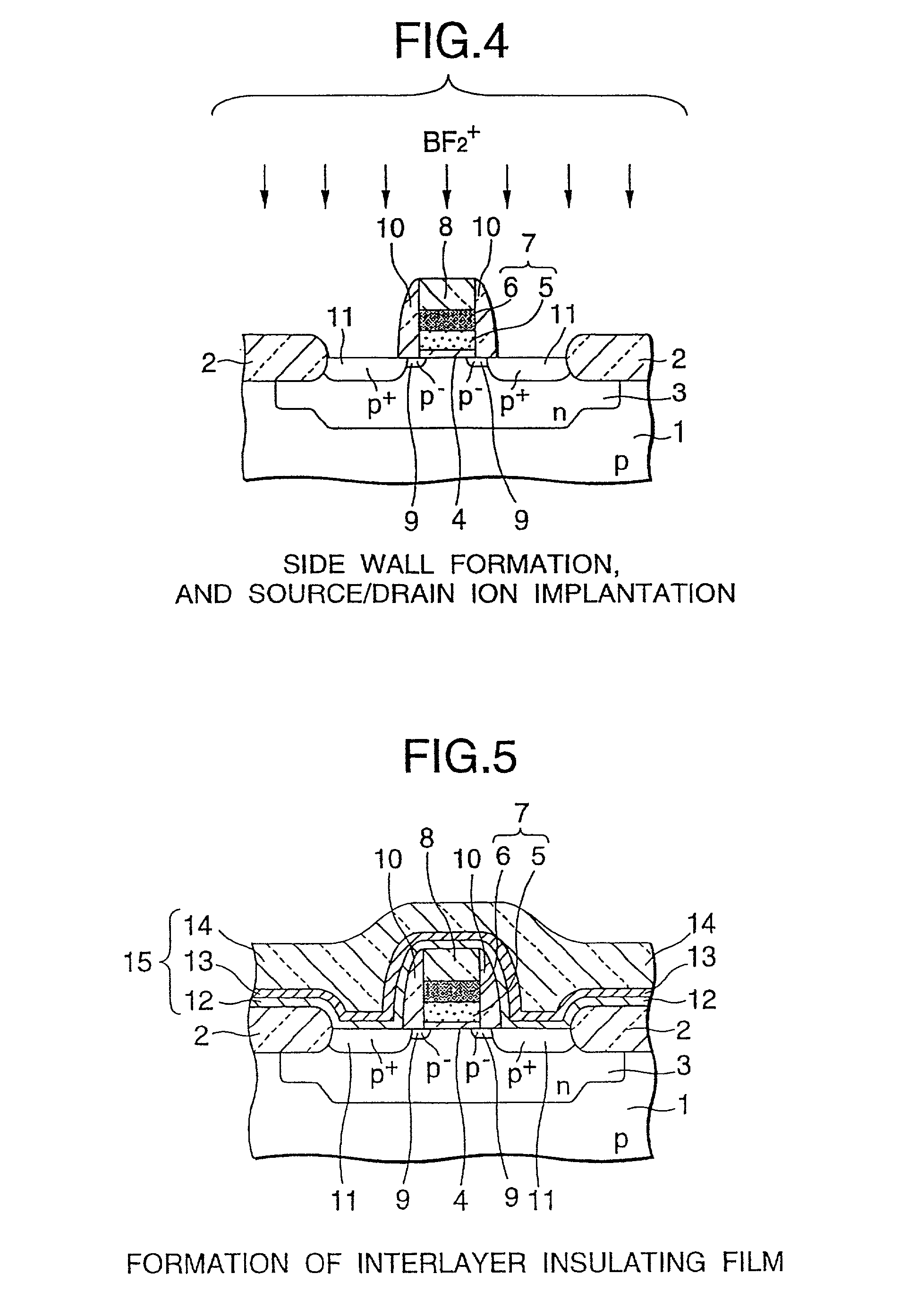

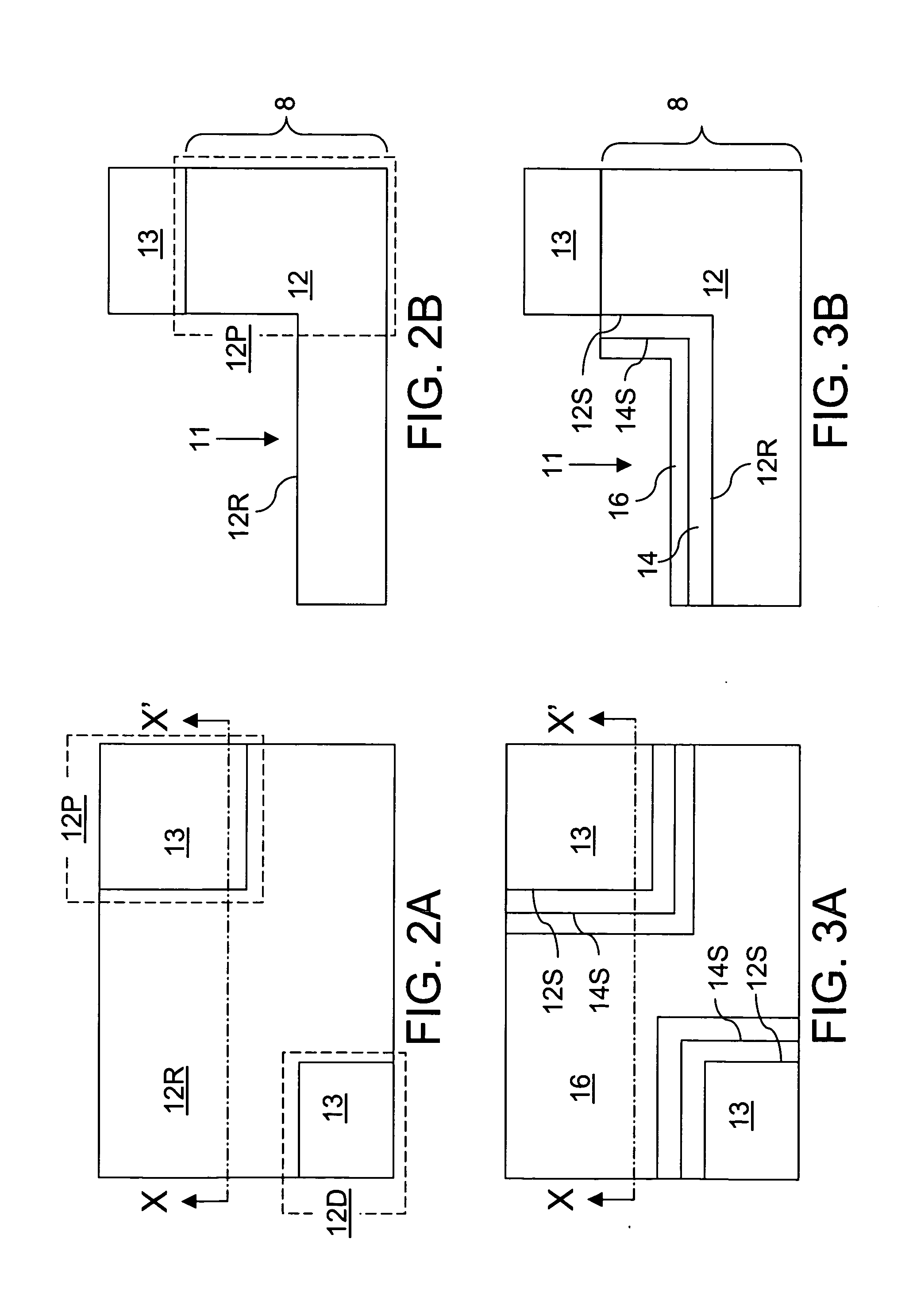

Method for fabricating mos transistors

InactiveUS20010012653A1Inhibited DiffusionTransistorSemiconductor/solid-state device manufacturingHydrogenPunching

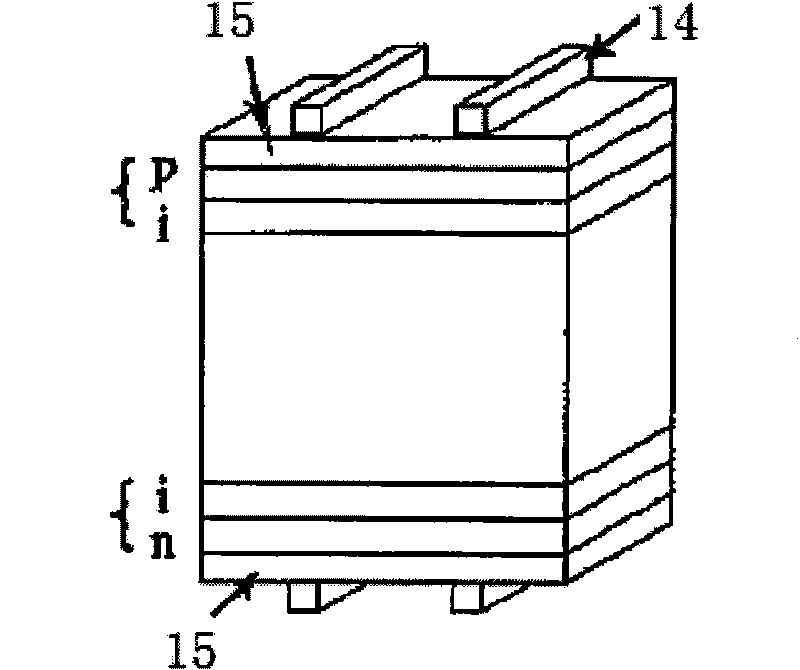

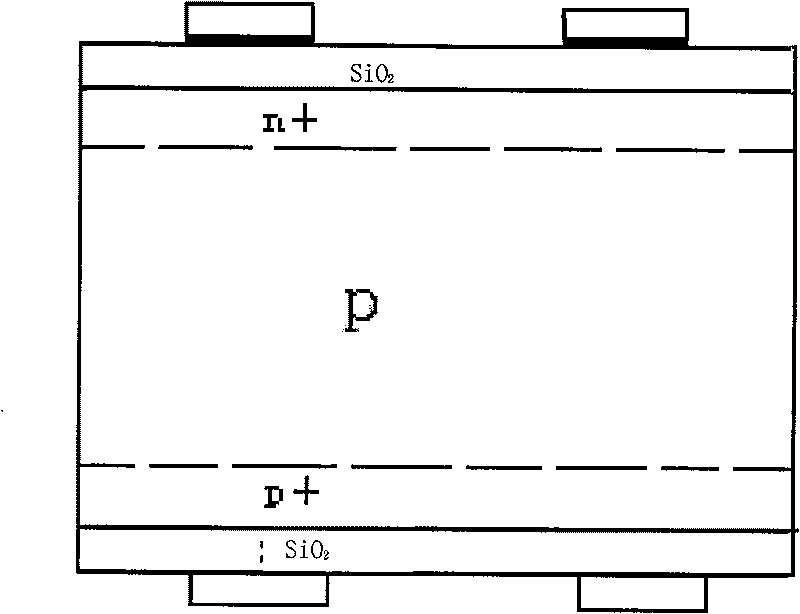

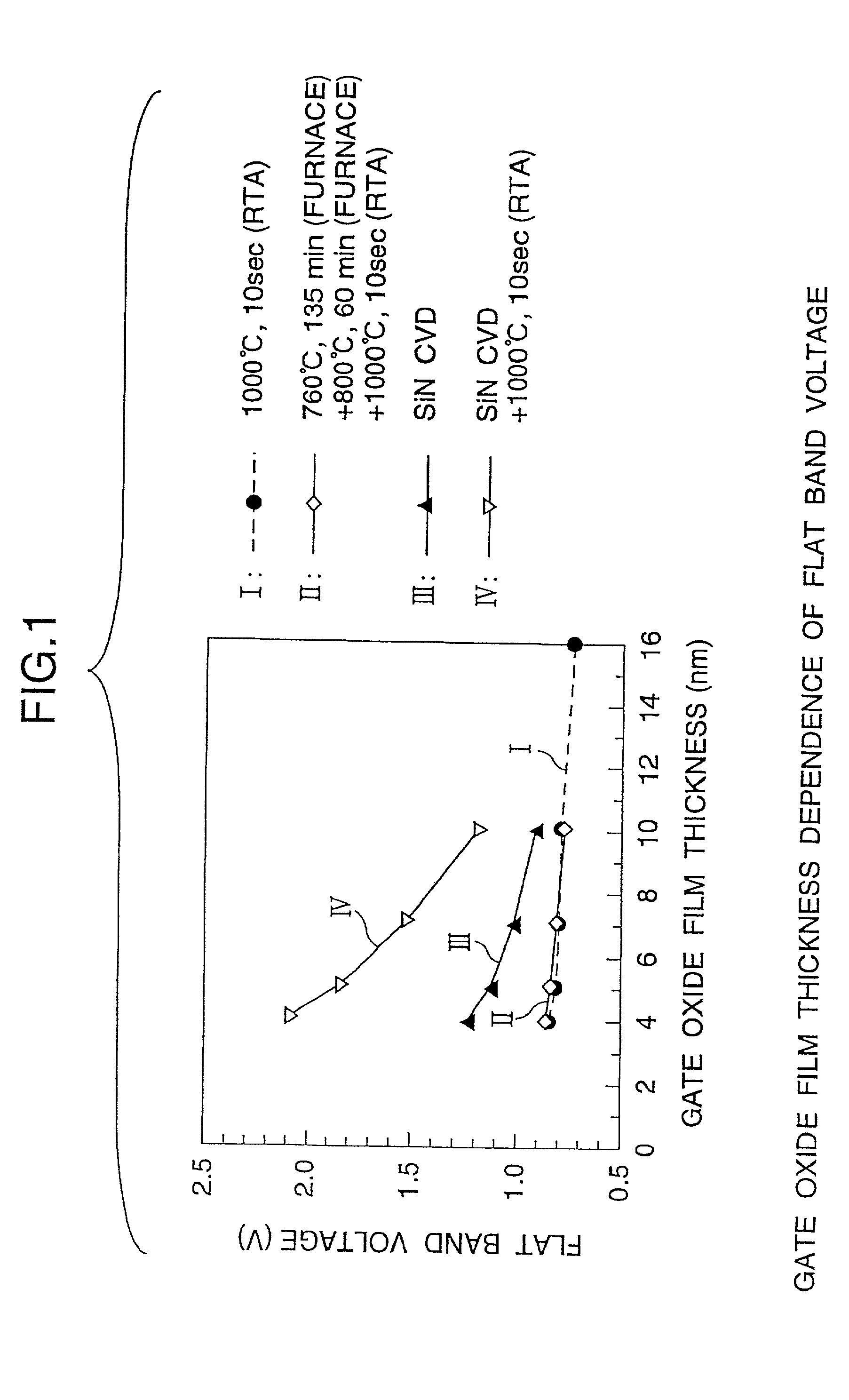

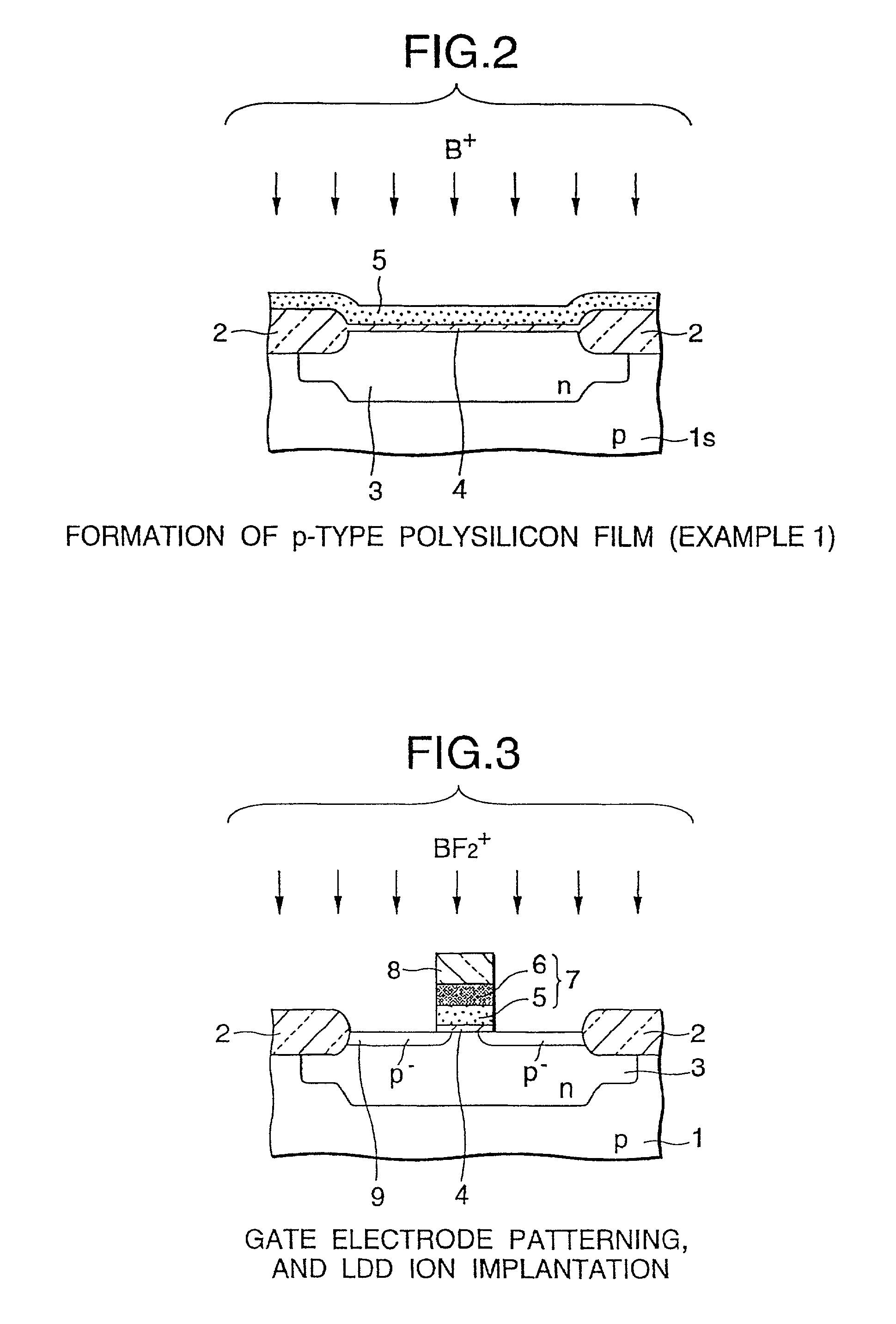

In PMOS having a gate electrode 7 of a p-type polysilicon film 5 along with a silicon nitride film 13, boron diffusion from the p-type polysilicon film 5 and boron punching through the gate oxide film 4 are prevented, thereby stabilizing the properties of the PMOS. Hydrogen existing in the silicon nitride film 13 accelerates boron diffusion from the film 5. To prevent it, all subsequent steps after the step of forming the silicon nitride film 13 are effected within a temperature range within which the boron diffusion is not accelerated by hydrogen. Forming the silicon oxide film 14 through reduced pressure CVD is effected in a furnace at a temperature lower than 850.degree. C. Annealing for dopant activation in the compensation region 17 to be formed on the substrate in the bottom of the contact hole 16 is effected in a manner of RTA (rapid thermal annealing) at a temperature lower than 1000.degree. C.

Owner:SONY CORP

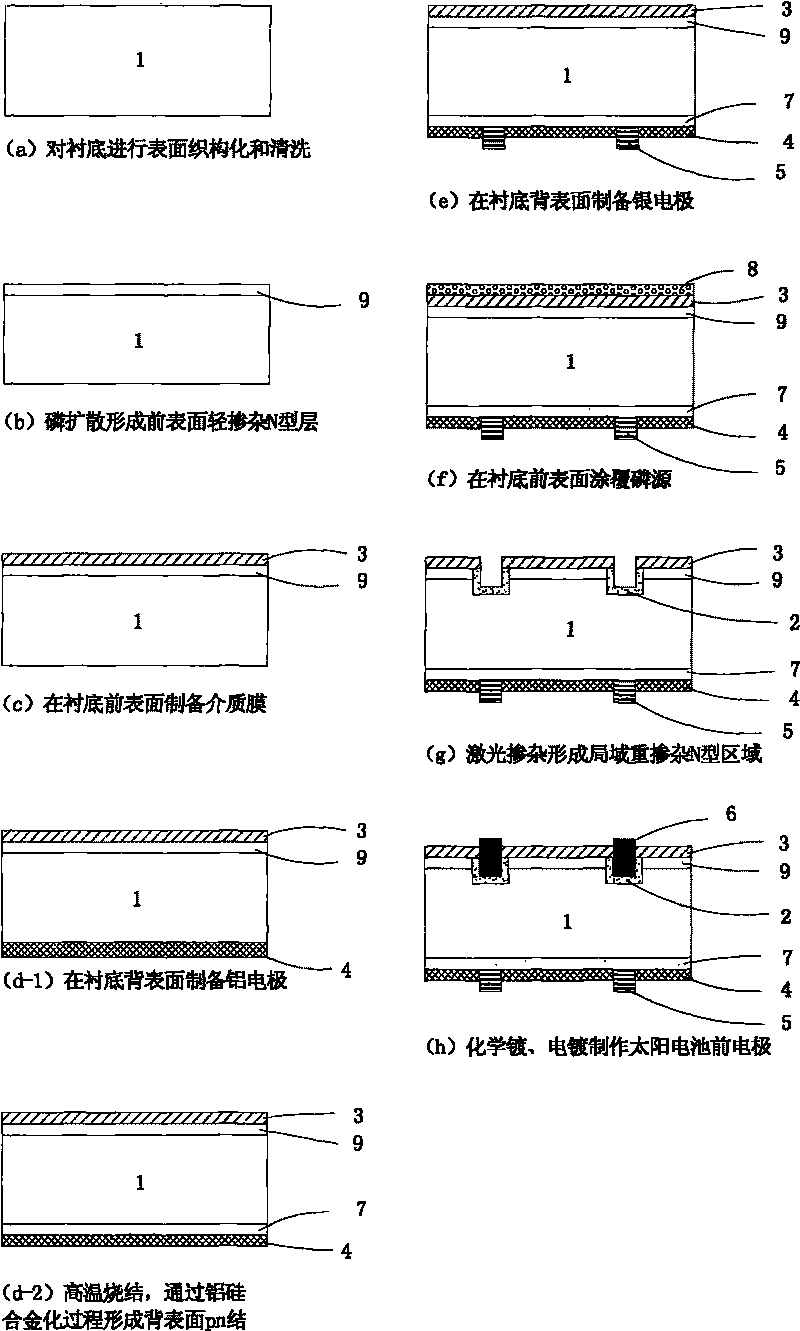

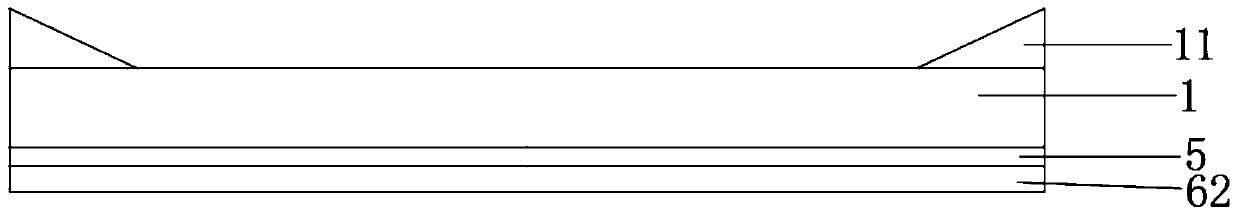

High efficiency N-type double-faced solar cell and preparation method thereof

ActiveCN104733555AIncrease the open circuit voltageInhibited DiffusionFinal product manufacturePhotovoltaic energy generationPhosphorSilicon dioxide

The invention relates to a high efficiency N-type double-faced solar cell and a preparation method thereof. The structure of the solar cell comprises an N-type silicon slice substrate, a front side boron doping layer, a back side phosphor doping layer, double-faced silicon dioxide passivation layers, doubled-faced silicon nitride antireflection layers and double-faced electrodes. The invention further discloses a preparation method for the solar cell, the preparation method particularly comprises the first step that double-faced texturization is conducted; the second step that front side boron diffusion is conducted; the third step that front side film masking is conducted; the fourth step that back side washing is conducted; the fifth step that back side phosphorus diffusion is conducted; the sixth step that a mask film is removed; the seventh step that double-faced passivation is conducted; the eighth step that double-faced film coating is conducted; the ninth step that the front side electrodes and the back side electrodes are formed; the tenth step that laser edge carving is conducted. According to the high efficiency N-type double-faced solar cell and the preparation method thereof, knots are formed on both the front side and the back side of the N-type silicon slice, the front side and the back side both have high photoelectric converting rates, the output power of an assembly of the high efficiency N-type double-faced solar cell is 20% higher than the output power of a common solar cell, and meanwhile the high efficiency N-type double-faced solar cell is applicable to large-scale industrial production due to the fact that the preparation technology is simple and practical.

Owner:常州顺风太阳能科技有限公司

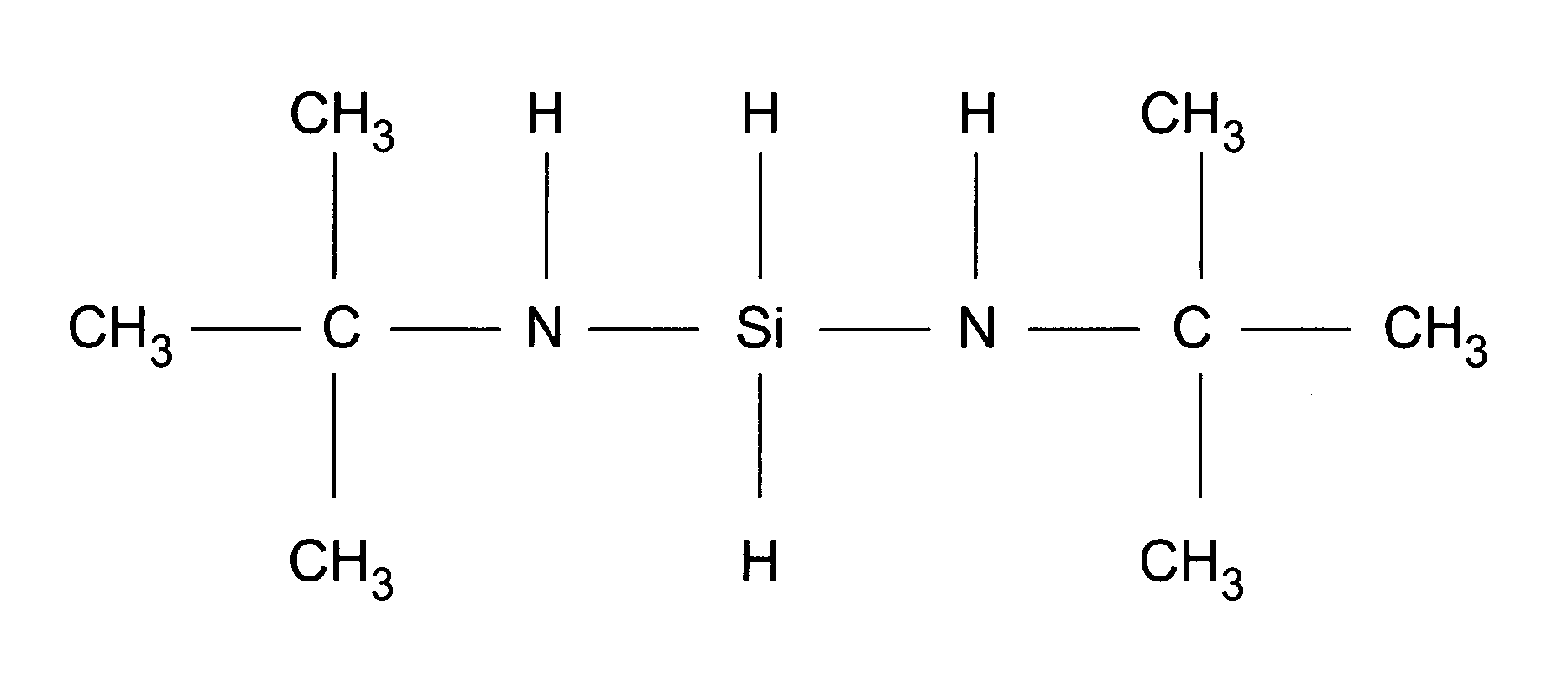

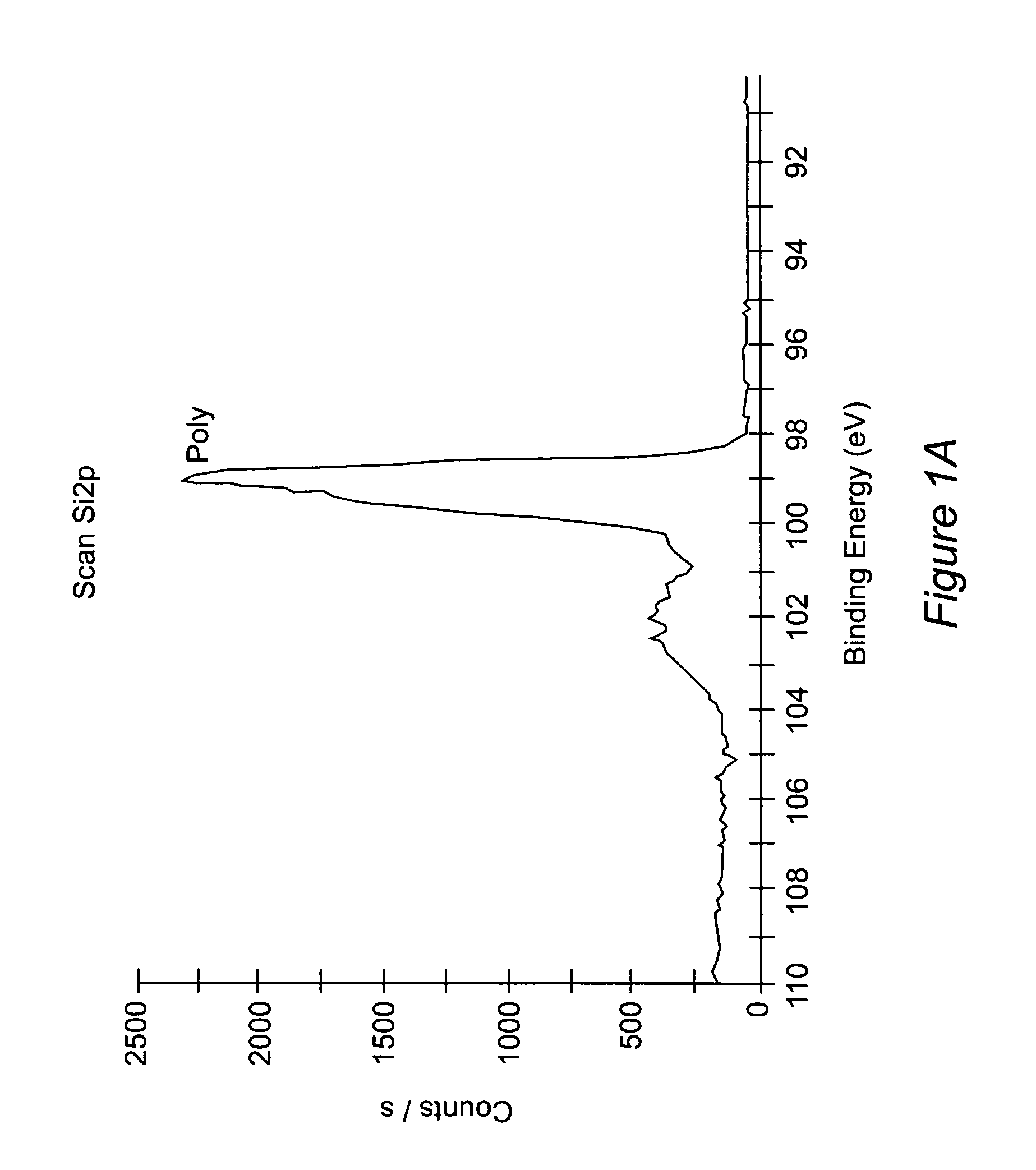

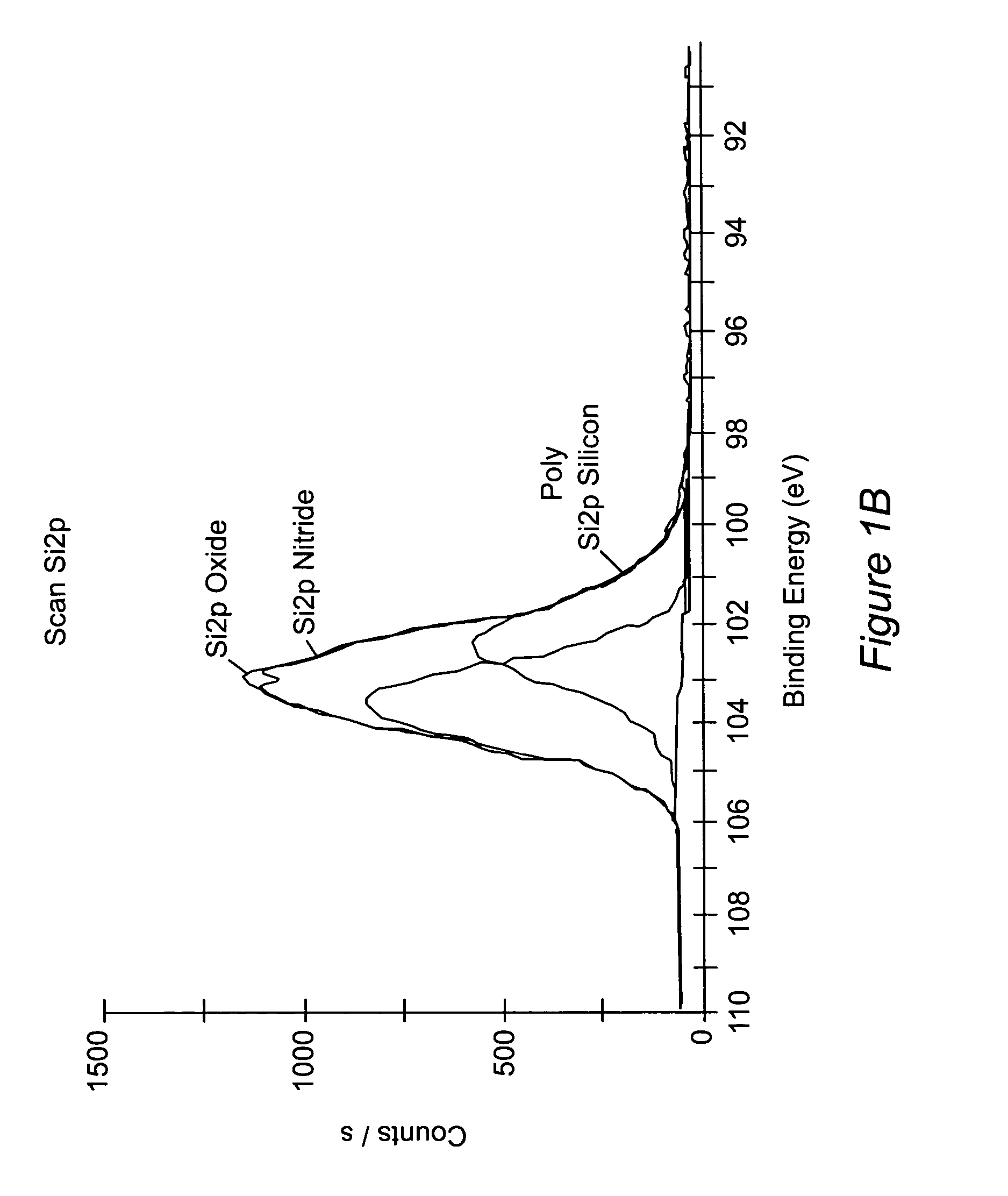

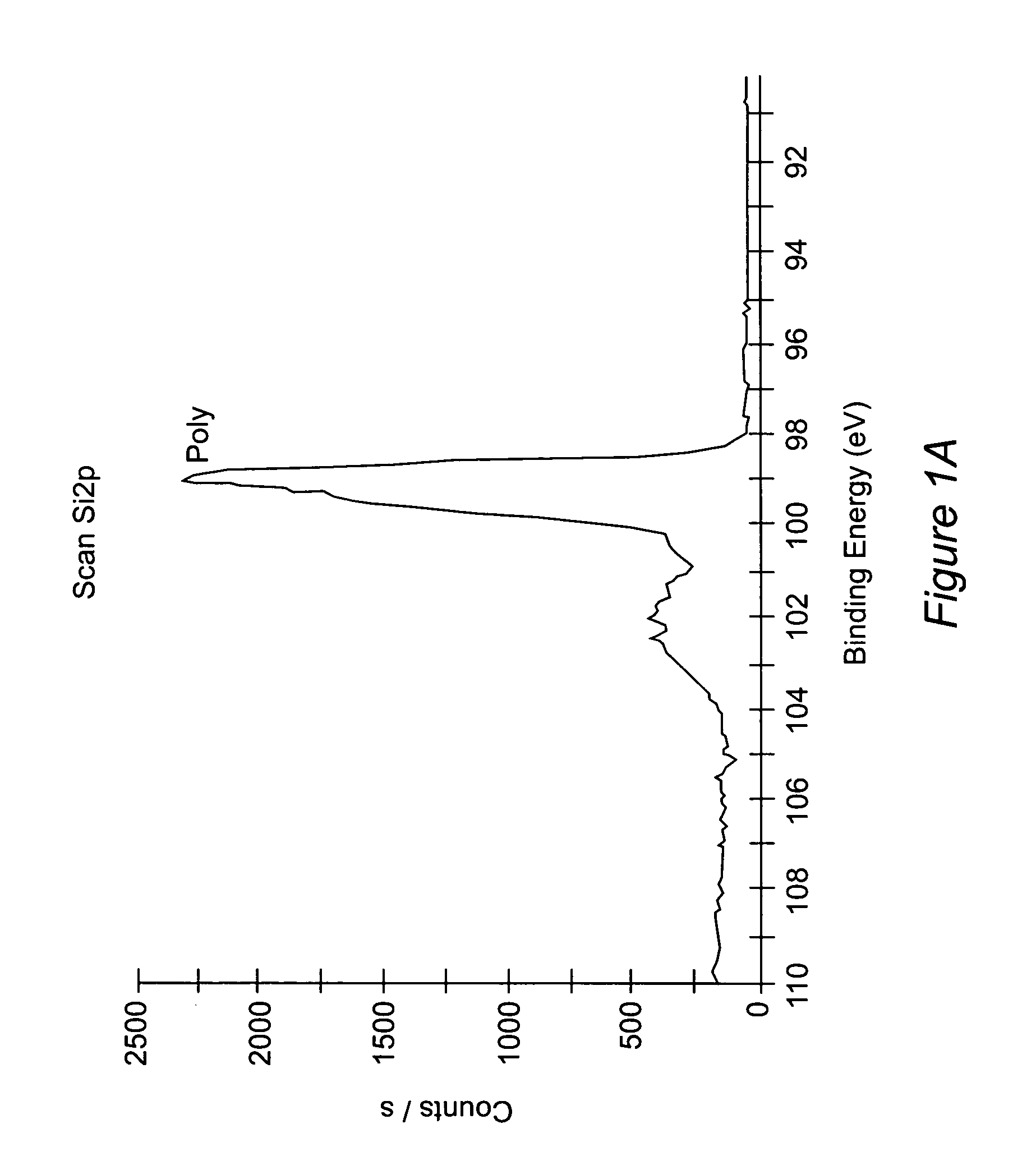

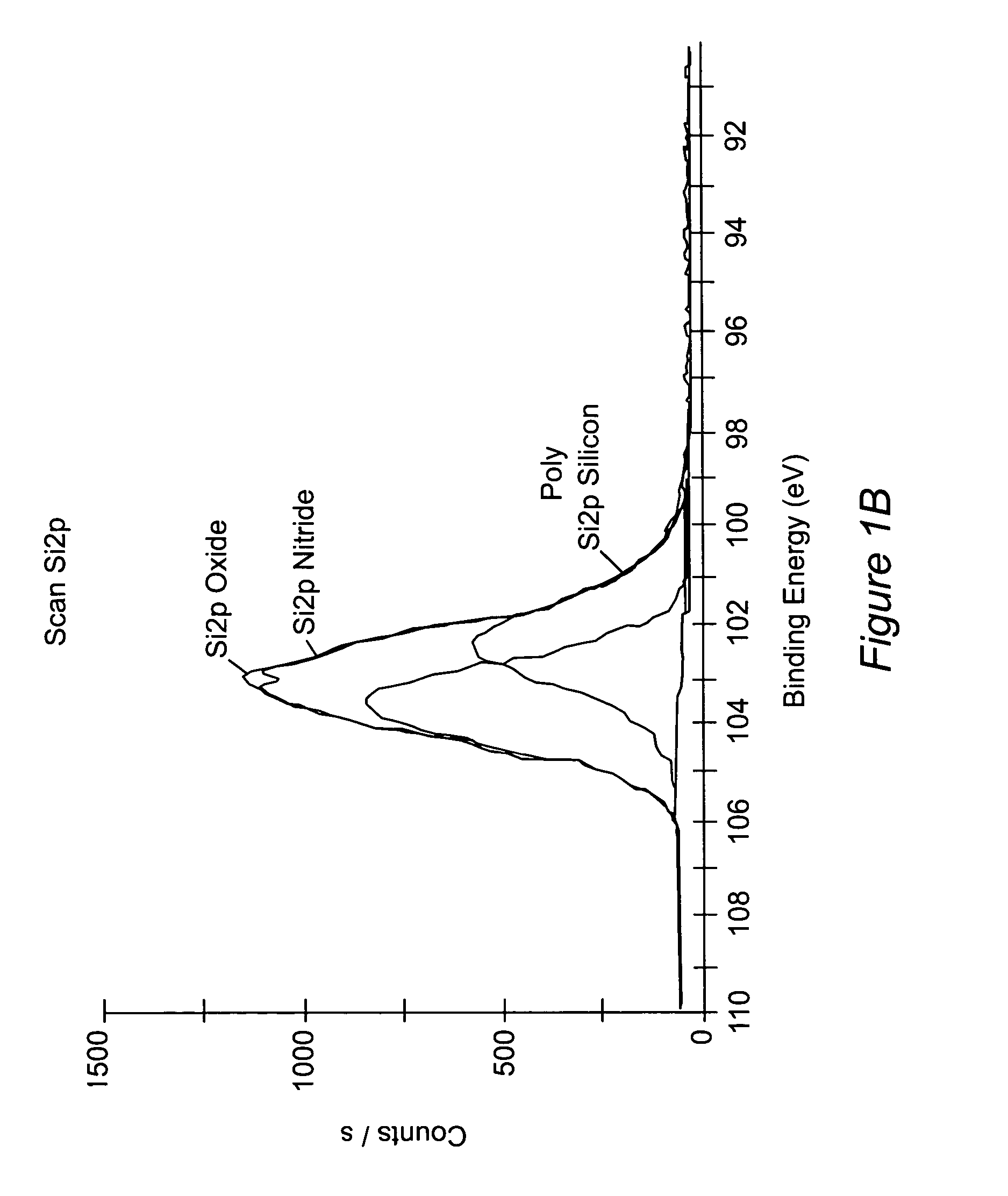

Deposition of carbon and nitrogen doped poly silicon films, and retarded boron diffusion and improved poly depletion

A compound that includes at least Si, N and C in any combination, such as compounds of formula (R—NH)4-nSiXn wherein R is an alkyl group (which may be the same or different), n is 1, 2 or 3, and X is H or halogen (such as, e.g., bis-tertiary butyl amino silane (BTBAS)), may be mixed with silane or a silane derivative to produce a film. A polysilicon silicon film may be grown by mixing silane (SiH4) or a silane derviative and a compound including Si, N and C, such as BTBAS. Films controllably doped with carbon and / or nitrogen (such as layered films) may be grown by varying the reagents and conditions.

Owner:APPLIED MATERIALS INC +1

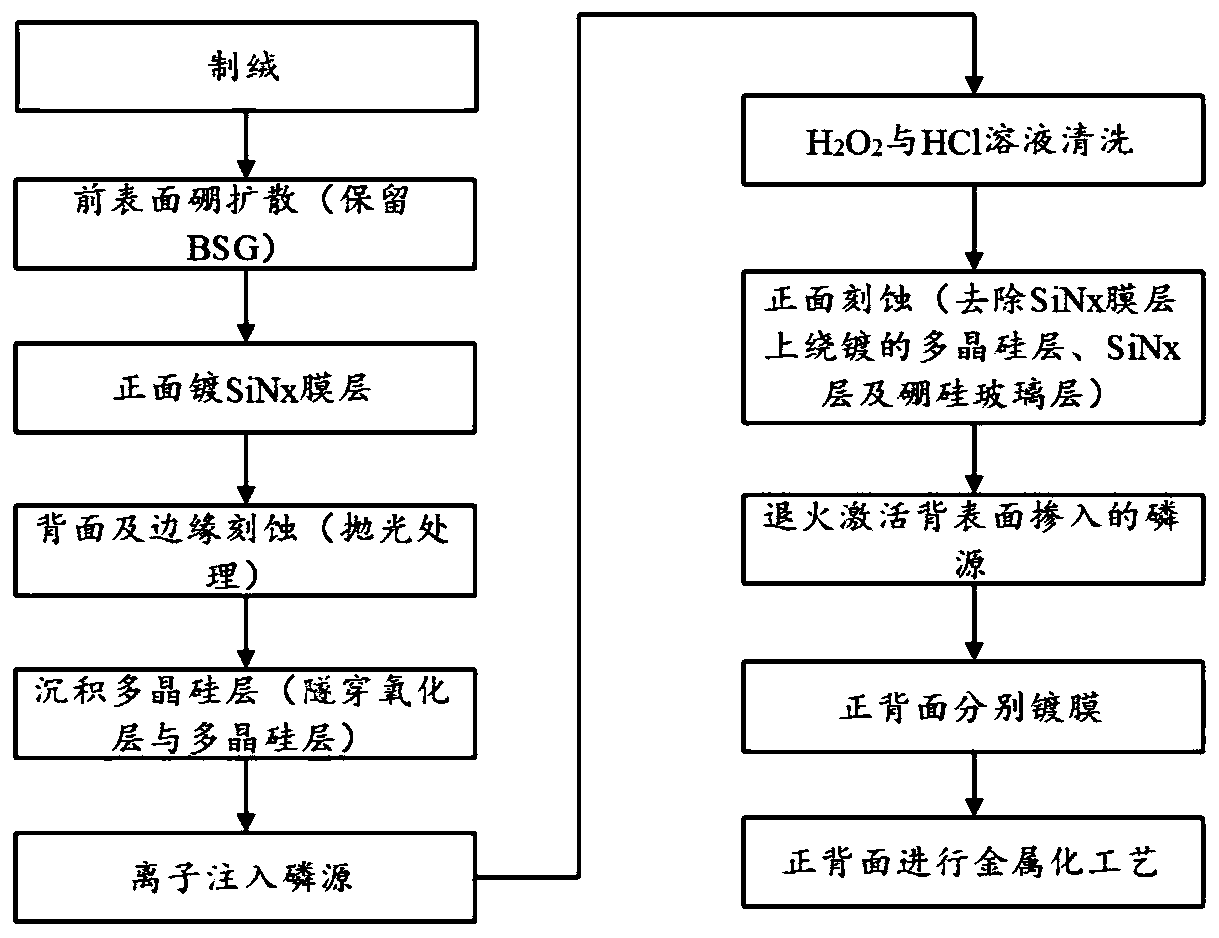

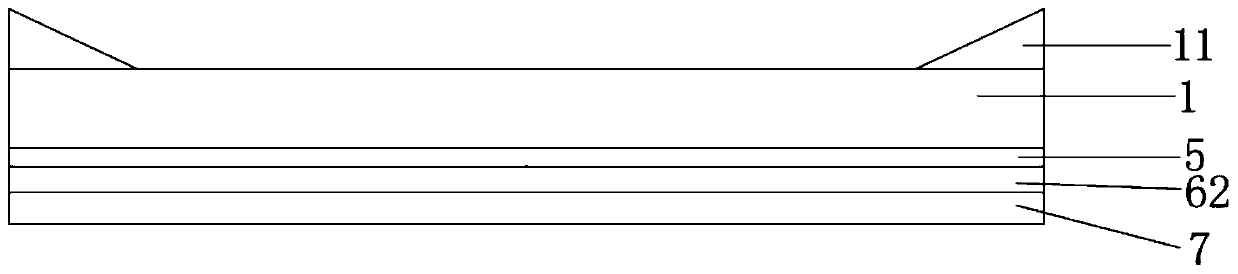

A preparation method of a TOPCon structure battery

InactiveCN109148647AImprove performanceSimple processFinal product manufacturePhotovoltaic energy generationScreen printingTemperature treatment

The invention relates to a preparation method of a TOPCon structure battery, comprising the following steps: (1) cleaning and velvet making; (2) prepare that pn junction by boron diffusion and carrying out high-temperature treatment; (3) After high temperature treatment, the temperature is controlled to 850 DEG C-900 DEG C, a BSG layer with a thickness of 50 nm or more is grown on that surface ofthe silicon wafer by inlet oxygen; (4) carry out acid cleaning and etch on that back side with the boron diffusion layer as the front side; (5) prepare a tunneling oxide layer and a doped thin film silicon layer; (6) carry out alkali cleaning on that front surface to remove the excess polysilicon layer generated by the winding plating on the front surface; (7) Remove BSG / PSG; (8), double-sided passivation; (9) Screen printing sintering. The production process of the invention can remove the wrapping plating, simplifies the process and improves the product performance without separately increasing the preparation process of the mask.

Owner:JIANGSU SHUNFENG PHOTOVOLTAIC TECH CO LTD

System and method for the manufacture of semiconductor devices by the implantation of carbon clusters

InactiveUS7666771B2Increase junction depthReduce leakage currentTransistorElectric discharge tubesDevice materialEngineering

A process is disclosed which incorporates implantation of a carbon cluster into a substrate to improve the characteristics of transistor junctions when the substrates are doped with Boron and Phosphorous in the manufacturing of PMOS transistor structures in integrated circuits. There are two processes which result from this novel approach: (1) diffusion control for USJ formation; and (2) high dose carbon implantation for stress engineering. Diffusion control for USJ formation is demonstrated in conjunction with a boron or shallow boron cluster implant of the source / drain structures in PMOS. More particularly, first, a cluster carbon ion, such as C16Hx+, is implanted into the source / drain region at approximately the same dose as the subsequent boron implant; followed by a shallow boron, boron cluster, phosphorous or phosphorous cluster ion implant to form the source / drain extensions, preferably using a borohydride cluster, such as B18Hx+ or B10Hx+. Upon subsequent annealing and activation, the boron diffusion is reduced, due to the gettering of interstitial defects by the carbon atoms.

Owner:SEMEQUIP

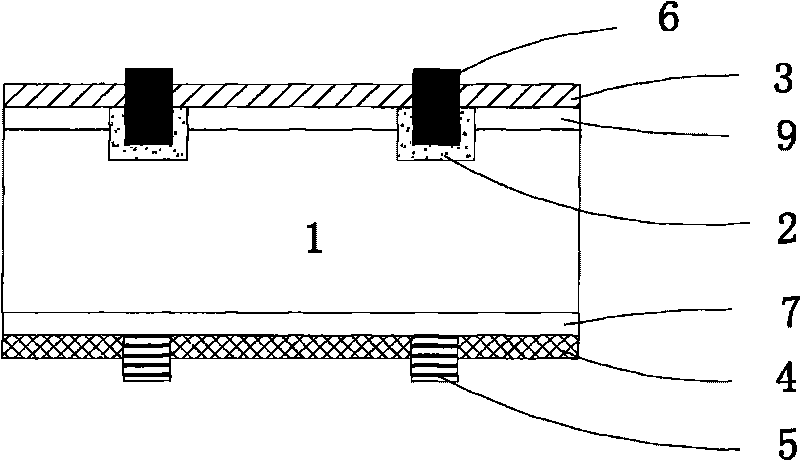

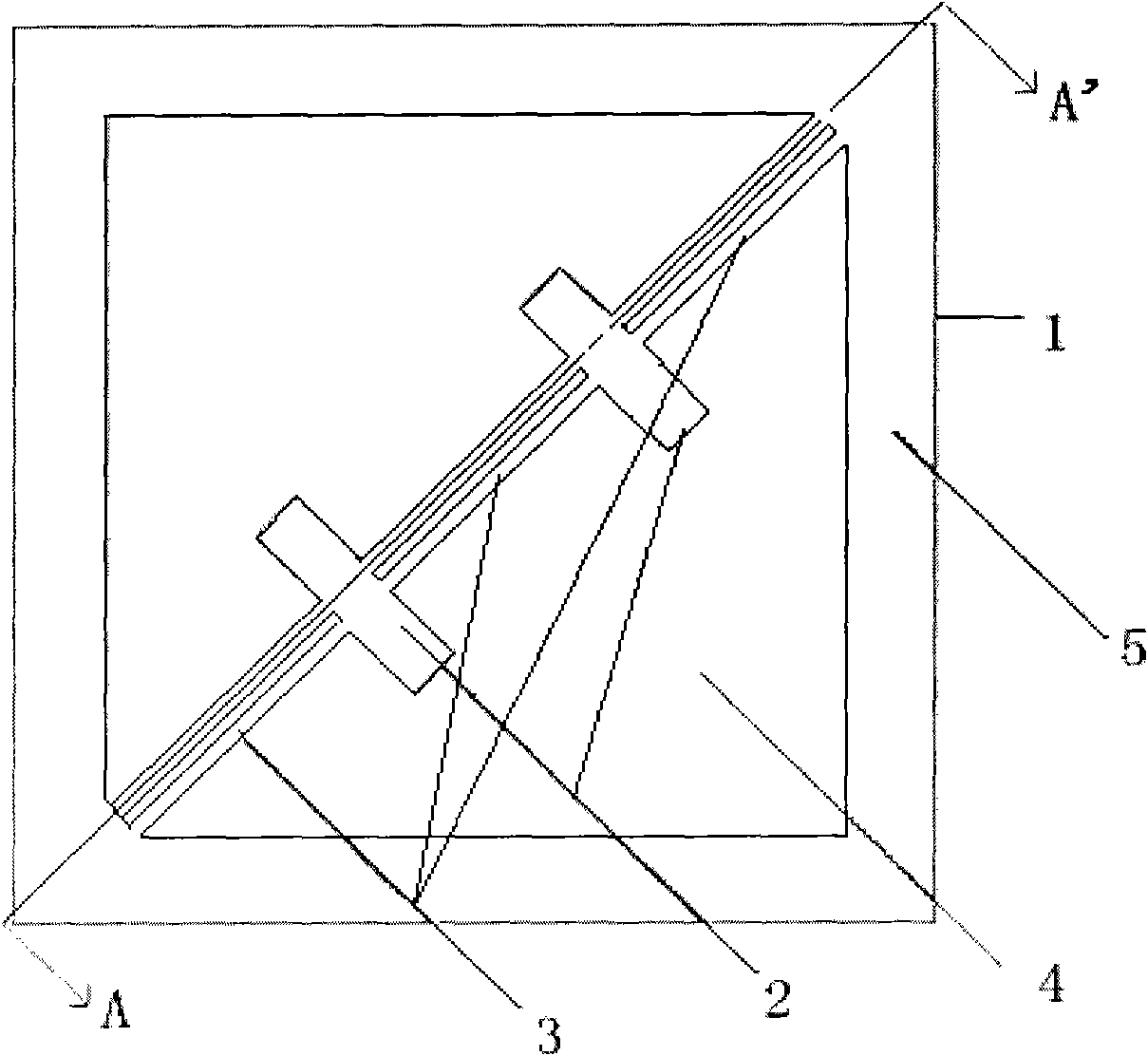

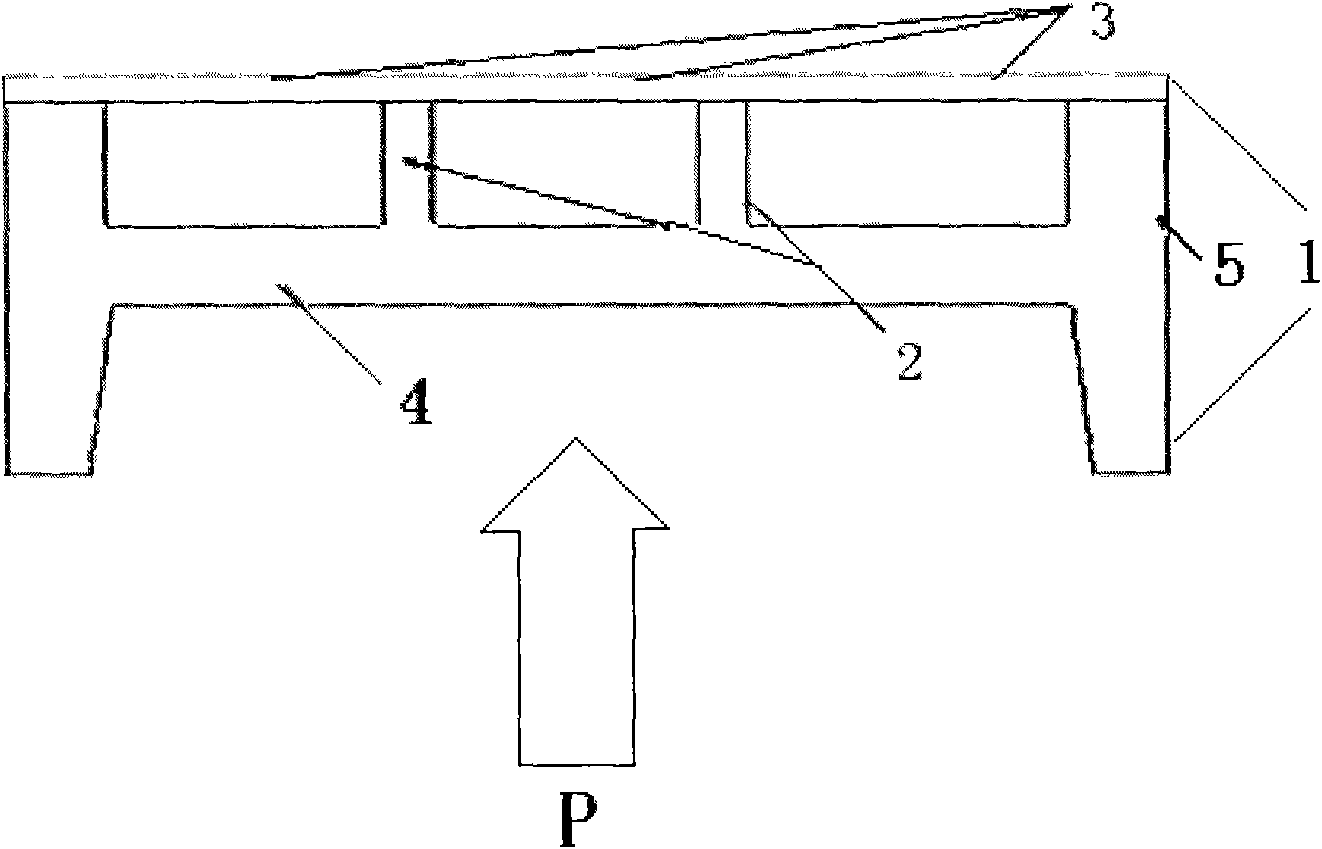

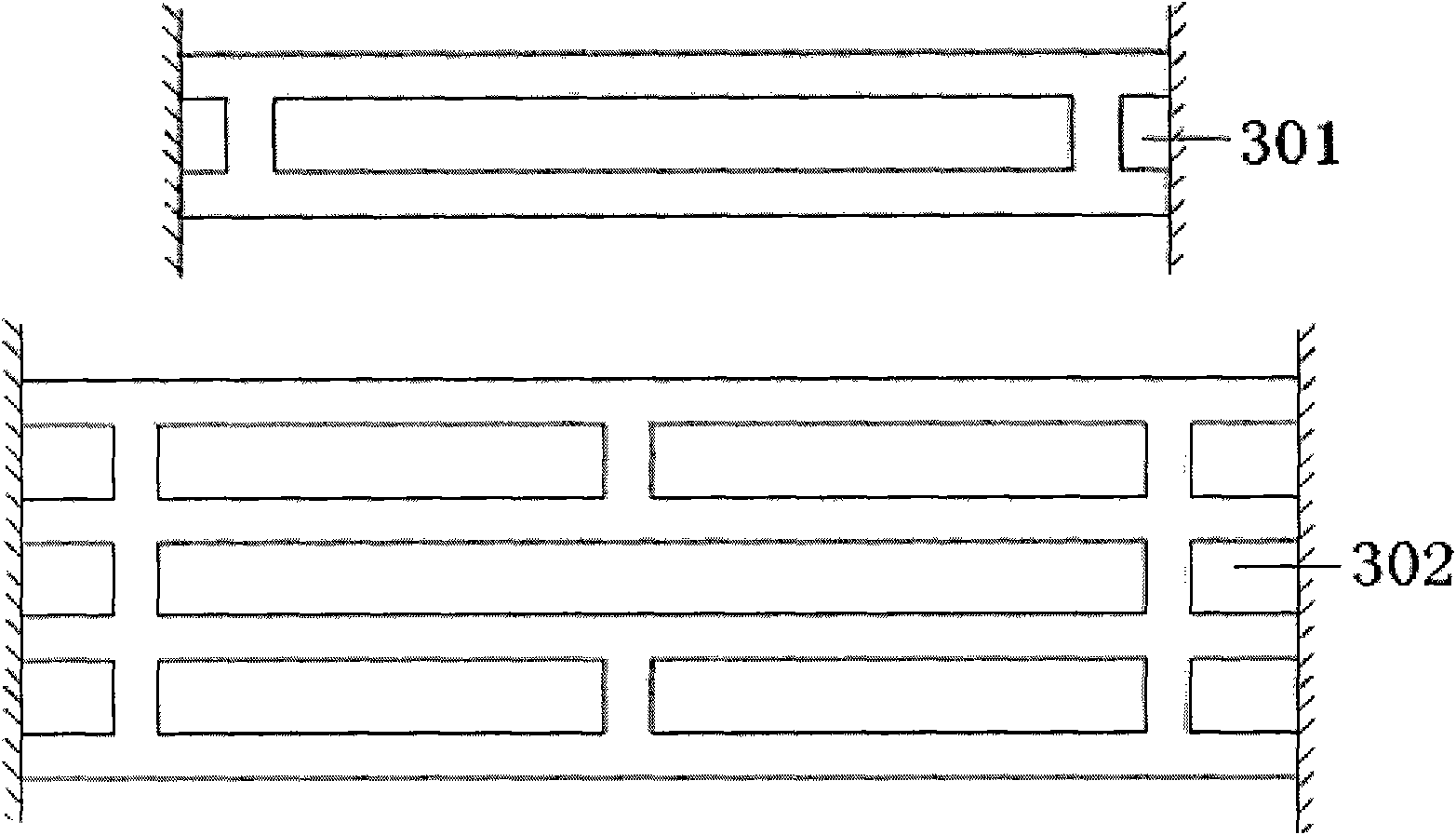

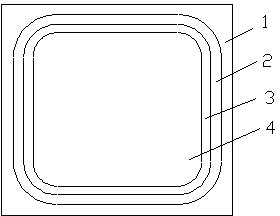

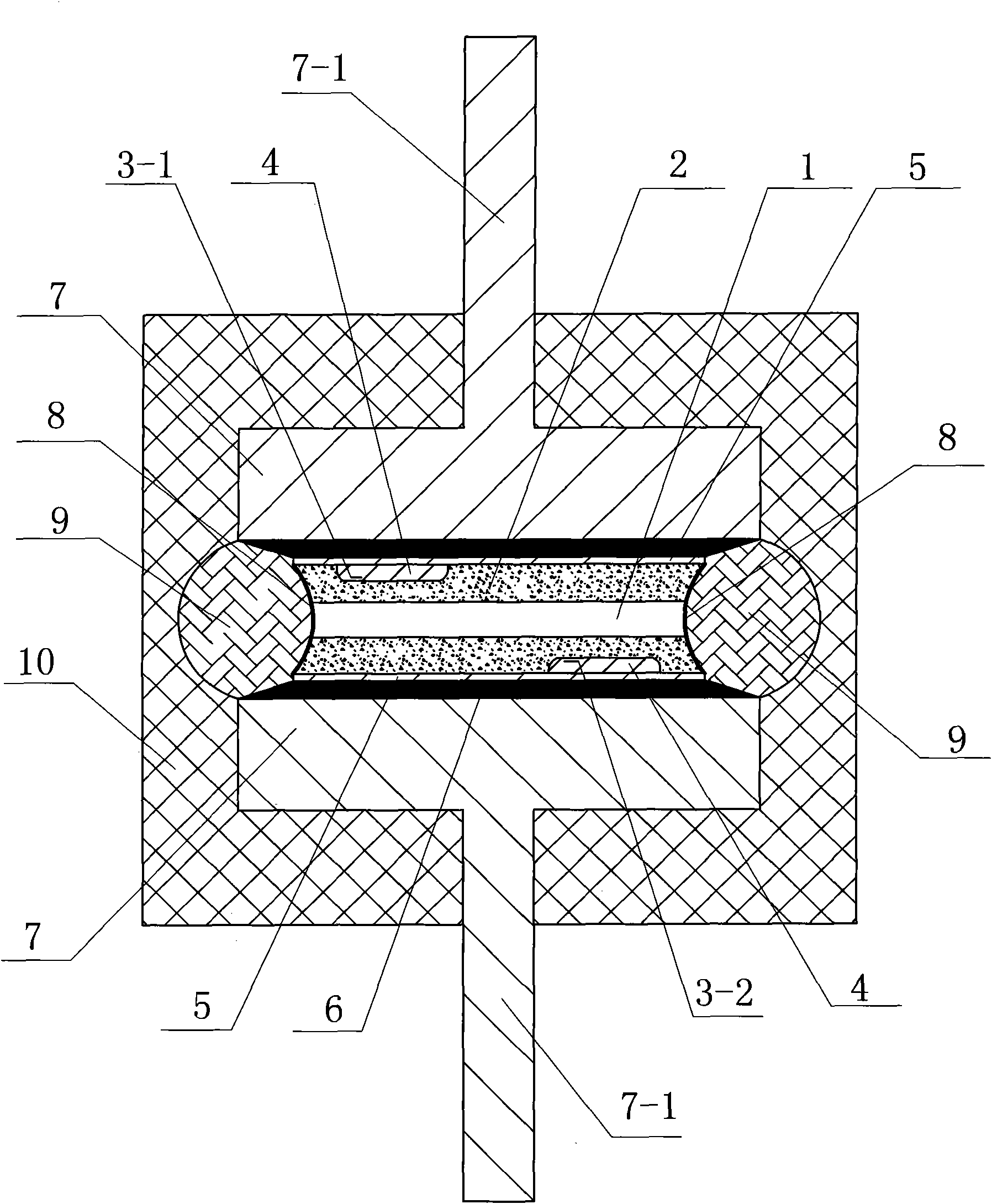

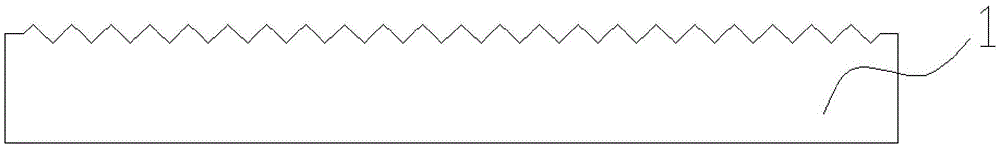

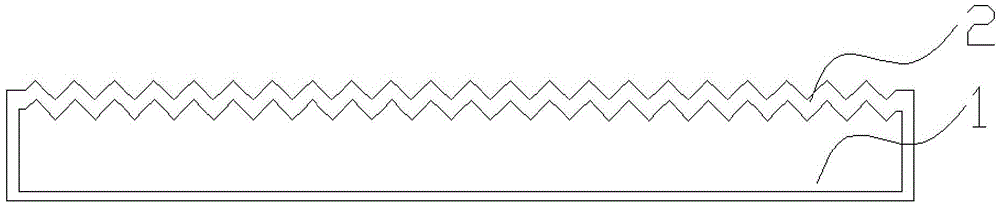

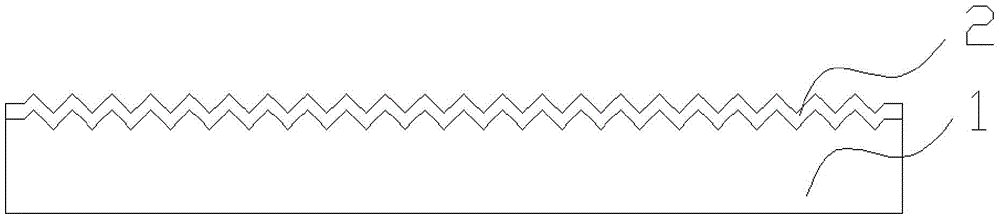

Micromachine-based electromagnetic excitation resonant pressure sensor

InactiveCN102374909AAvoid introducingAvoid bonding processForce measurement by measuring frquency variationsFluid pressure measurement by electric/magnetic elementsThermal expansionAnchor point

The invention discloses a micromachine-based electromagnetic excitation resonant pressure sensor, and relates to a micromachine sensing technology. The sensor is provided with three groups of resonators which are clamped by anchor points on a pressure membrane, arranged on a diagonal line of a frame, and provided with electrodes. The resonators applied with excitation signals are excited by magnetic field force under the action of an external magnetic field; and when pressure to be tested is present outside, the pressure membrane generates strain, and the strain is transmitted to the resonators through the anchor points to change the rigidity of the resonators, so that the natural frequency of the resonators is changed, and the pressure to be tested outside can be measured by detecting the frequency of output signals of vibration pickup electrodes. The sensor has two packaging modes, and is subjected to stress isolation through a ceramic ring of which the coefficient of thermal expansion is basically same as monocrystalline silicon. The resonators of the sensor work in a horizontal vibration mode; the shift caused by external factors such as temperature and the like is inhibited through differential output, and the sensitivity is improved; and the resonators are released by a heavy boron-diffusion self-stop corrosion technology, a process is simple and the consistency is high.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

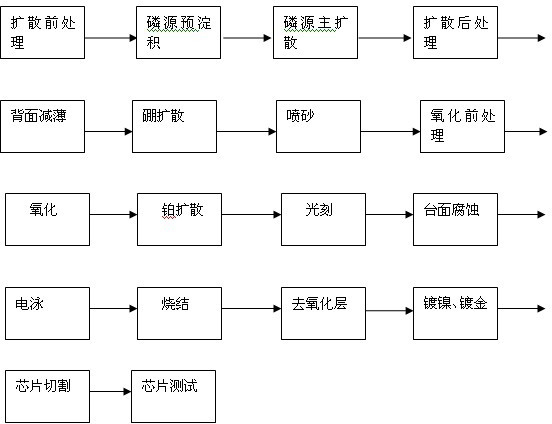

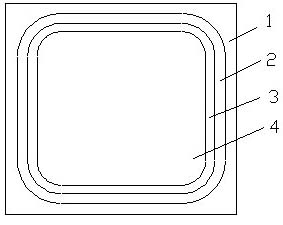

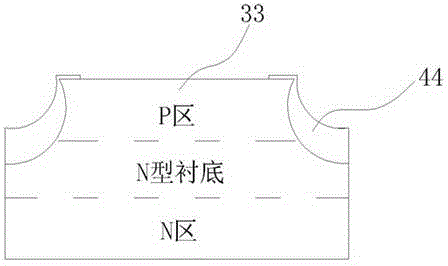

Fast recovery diode (FRD) chip and production process thereof

ActiveCN102087976AImprove anti-surge performanceImprove switching performanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrophoresesEtching

The invention relates to a fast recovery diode (FRD) chip and a production process thereof. A diode with a P+NN+ structure is produced by adopting the process steps of diffusion pretreatment, double diffusion of a liquid source, back thinning, oxidization, platinum diffusion, photoetching, mesa etching, electrophoresis, sintering, scribing and the like. In the chip production process, a method of carrying out deep junction diffusion by carrying a liquid phosphorous source is adopted, so that the flatness of a diffusion junction is improved and the homogeneity and the stability of a breakdown voltage are strengthened; a method of reducing the concentration of a boron diffusion source and improving the purity of the boron diffusion source is adopted, so that the surge resistance capacity of an FRD is improved; and an electrophoresis glassivation process is adopted, so that the voltage withstanding stability and reliability of a bidirectional voltage stabilizing diode are improved. In addition, the production process has the advantages that the reverse recovery time is shortened, the switching speed is improved, the voltage drop is reduced, the power consumption is reduced, the voltage withstanding stability is improved, and the reliability of the diode is improved.

Owner:TIANJIN ZHONGHUAN SEMICON CO LTD

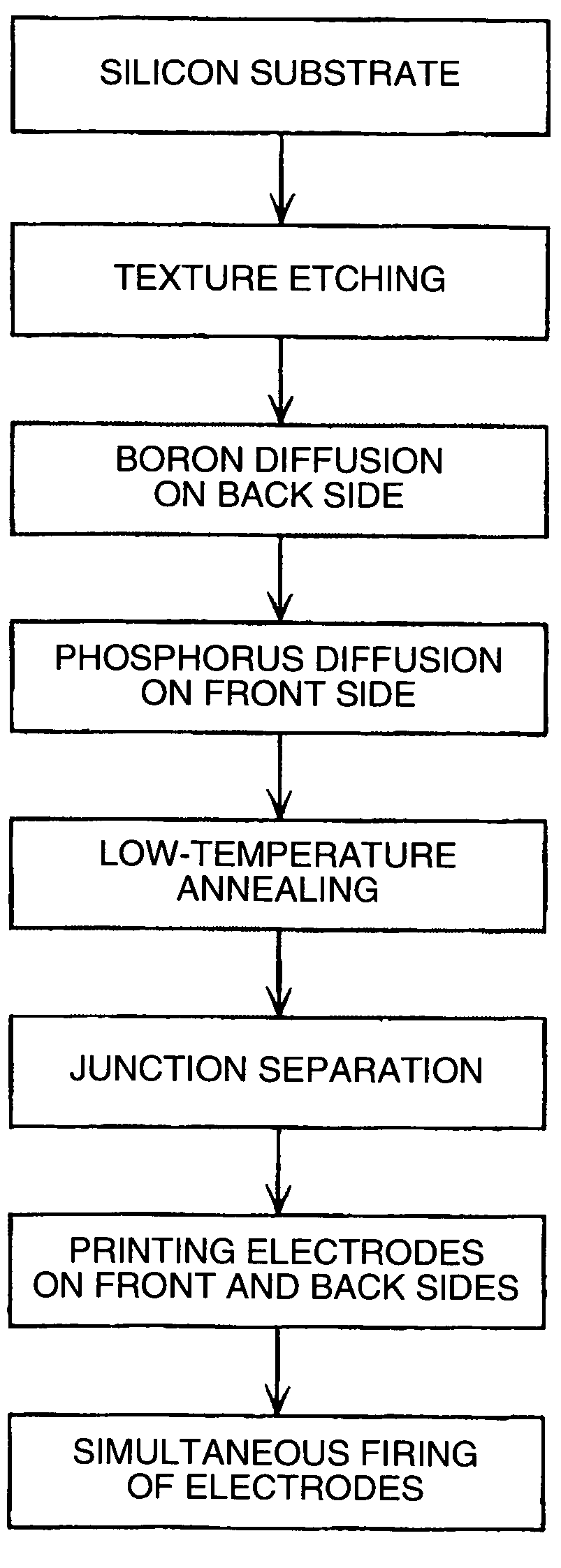

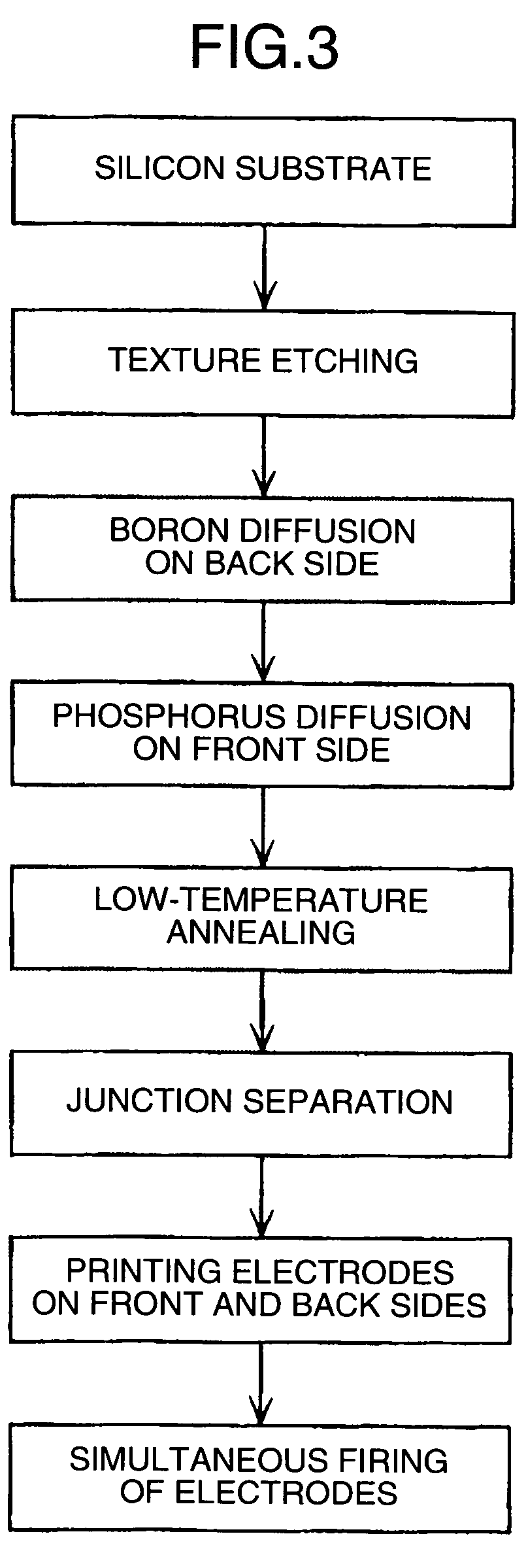

Silicon solar cell and production method thereof

InactiveUS7495167B2Reduces its bulk effective life timeReduced life-timePV power plantsSolid-state devicesPeak valueSilicon solar cell

It is an object of the present invention to provide a silicon solar cell with n+pp+ BSF structure using solar grade silicon substrate, having a life time close to the initial level of the substrate.The solar cell of the present invention is produced by a back side boron diffusion step for diffusing boron on a back side of the substrate, a front side phosphorus diffusion step for diffusing phosphorus on a front side of the substrate, a low-temperature annealing step for annealing the substrate at 600° C. or lower for 1 hour or more, and an electrode firing step carried out at a peak temperature of 700° C. or lower for 1 minute or less, carried out in this order.

Owner:HITACHI LTD

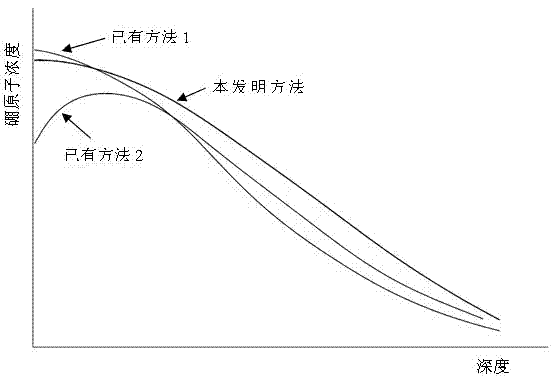

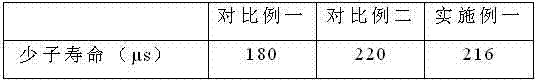

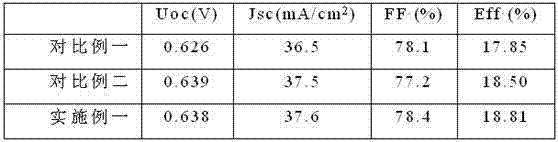

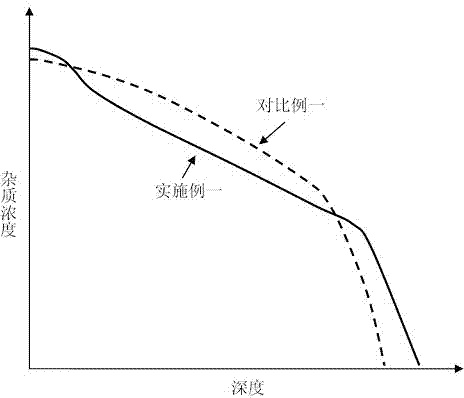

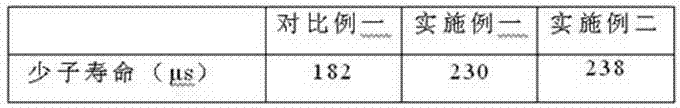

Boron diffusion method of crystalline silicon solar cell

ActiveCN102769069AImprove life expectancyDiffusion avoid or reduceFinal product manufactureDiffusion/dopingHigh surfaceNitrogen gas

The invention discloses a boron diffusion method of a crystalline silicon solar cell. The method comprises the following steps of: (1) putting a silicon chip which is felted and cleaned into a diffusion furnace tube, raising temperature to 800 to 1,000 DEG C, filling oxygen, and oxidizing for 1 to 30 min; (2) keeping the temperature in the step (1), or raising the temperature to 900 to 1,100 DEG C, and filling a boron source, the oxygen and nitrogen for boron diffusion; (3) stopping filling the source, keeping the temperature or reducing the temperature to 800 to 900 DEG C, and keeping the temperature for 5 to 50 min in the nitrogen atmosphere; and (4) reducing the temperature, taking out the silicon chip, and finishing the diffusion process. By adoption of the method, the uniformity of the boron diffusion can be improved, formation of a boron-rich layer is avoided or reduced, and the minority carrier lifetime of the silicon chip is prolonged; and meanwhile, high surface impurity concentration can be kept, and high ohmic contact is formed, so the performance of the cell is improved.

Owner:CSI CELLS CO LTD +1

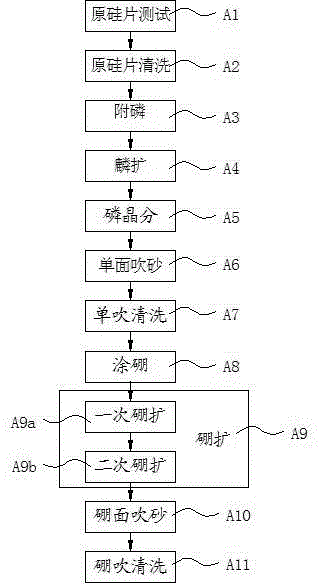

Manufacturing process of transient voltage suppression diode chip

ActiveCN103606521AStress reliefReduce defectsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotoresist

The invention discloses a manufacturing process of a transient voltage suppression diode chip. The manufacturing process of the transient voltage suppression diode chip includes two production processes: a diffusion process and a GPP process. The steps of the diffusion process include original silicon wafer testing, original silicon wafer washing, phosphorus attachment, phosphorus diffusion, phosphorus wafer separation, single side sand blasting, single blasting washing, boron coating, boron diffusion, boron wafer separation, boron side sand blasting, and boron blasting washing, wherein the step of boron diffusion comprises primary boron diffusion and secondary boron diffusion; and the steps of the GPP process sequentially include oxidation, primary photoetching, groove etching, photoresist sintering, groove washing, SIPOS passive film formation, glassivation, secondary photoetching, surface etching, and nickel-gold plating. The manufacturing process of the transient voltage suppression diode chip in the invention reduces defects of the chip, enables voltage distribution to be relatively concentrated, and reduces reverse leakage current at the same time.

Owner:南通康芯半导体科技有限公司

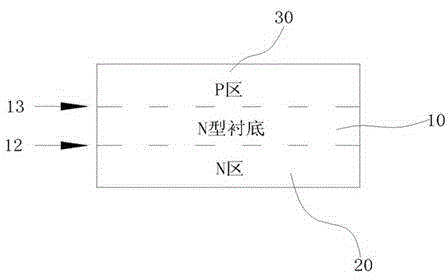

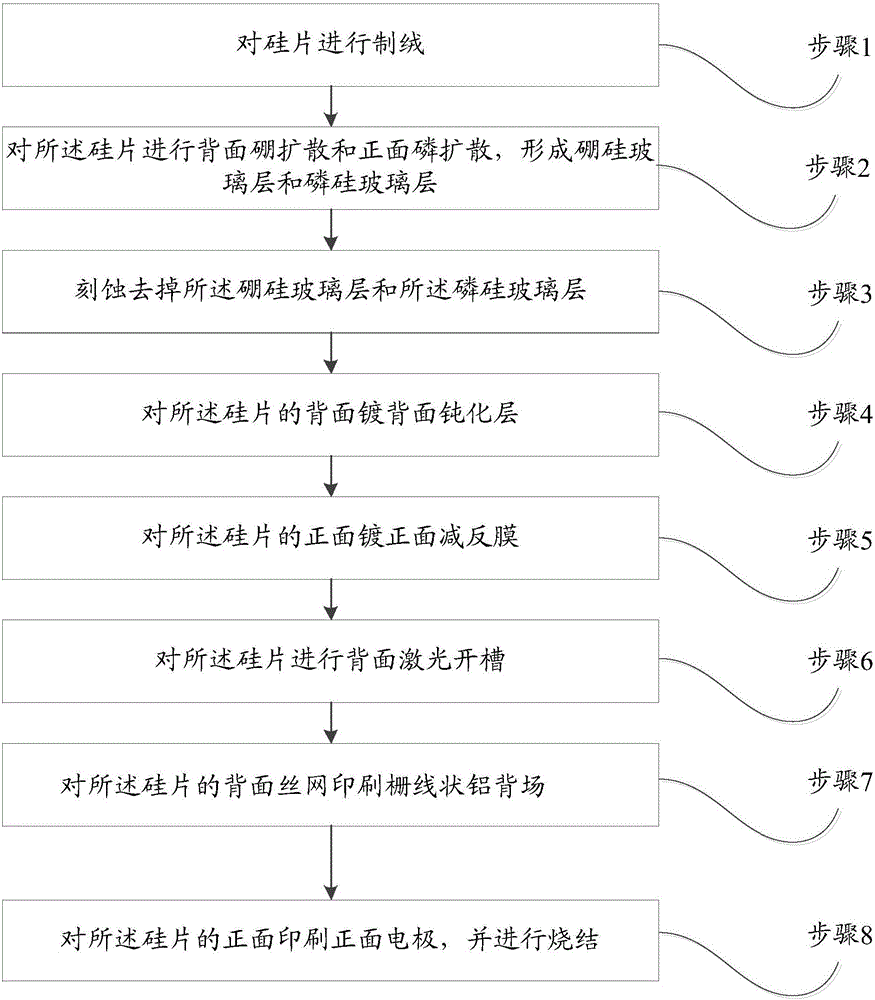

PERC preparation method

InactiveCN106449877AReduce void ratioIncrease powerFinal product manufacturePhotovoltaic energy generationScreen printingBack surface field

The invention discloses a PERC preparation method, which comprises the following steps: 1) carrying out texturing on a silicon wafer; 2) carrying out back-surface boron diffusion and front-surface phosphorus diffusion on the silicon wafer to form a borosilicate glass layer and a phosphorosilicate glass layer; 3) etching the borosilicate glass layer and the phosphorosilicate glass layer; 4) plating a back-surface passivation layer on the back surface of the silicon wafer; 5) plating a front-surface anti-reflection film on the front surface of the silicon wafer; 6) carrying out back-surface laser grooving on the silicon wafer; 7) carrying out grid line aluminum back-surface field silk-screen printing on the back surface of the silicon wafer; and 8) printing a front-surface electrode on the front surface of the silicon wafer and carrying out sintering. By printing a grid line aluminum back-surface field on the back surface, aluminium slurry can be fully extruded and fully fill the whole opening groove body, thereby reducing aluminium silicon cavity proportion, saving aluminium slurry and reducing manufacture cost; and meanwhile, the PERC prepared through double-side diffusion and superposition and printing of the grid line aluminum back-surface field has a double-battery effect, and has a certain power rise for a current novel double-glass assembly.

Owner:ZHEJIANG JINKO SOLAR CO LTD +1

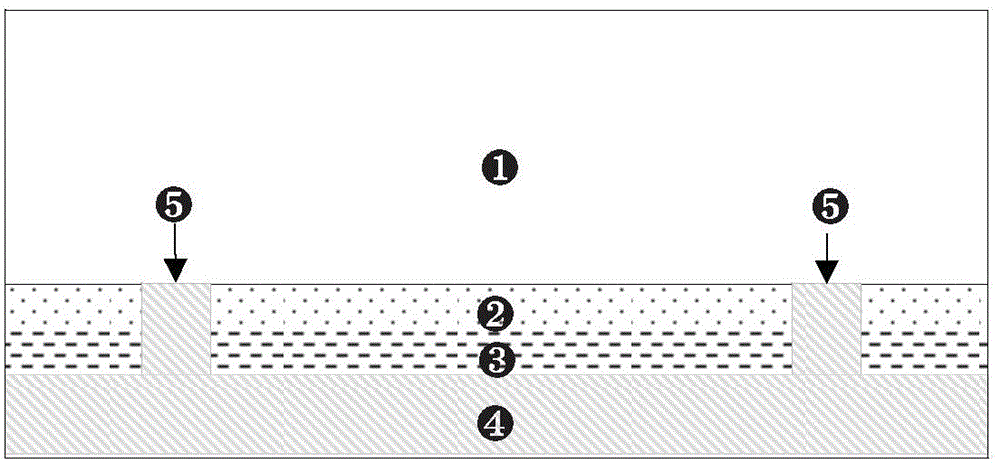

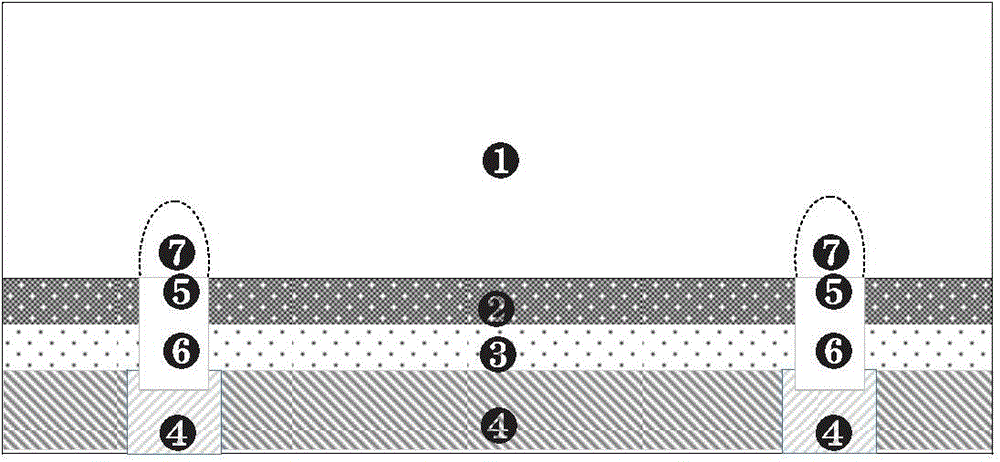

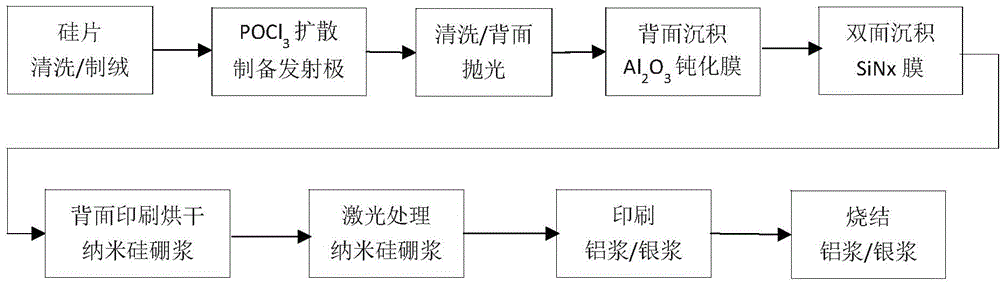

Nano silicon boron slurry and method for preparing PERL solar battery by utilizing nano silicon boron slurry

InactiveCN104638033ALimit industrial mass productionSimple processFinal product manufacturePhotovoltaic energy generationNano siliconScreen printing

The invention discloses nano silicon boron slurry and a method for preparing a PERL solar battery by utilizing the nano silicon boron slurry and a PERL battery structure. A silk screen printing technology which is suitable for the industrialized mass production is adopted, the nano silicon boron slurry is printed on the surface of a silicon chip, and the local boron diffusion is completed by virtue of high temperature diffusion or laser doping process route. A boron tribromide gas diffusion source with high toxicity is avoided, and the corresponding complicated technological procedures such as masking, etching, washing and the like for realizing the local boron diffusion is avoided. Compared with a produced PERC battery, the upgrading of the PERC battery can be completed, and the battery efficiency can be improved by only adding a printer and a drying furnace to the production process of the PERL battery.

Owner:苏州金瑞晨科技有限公司

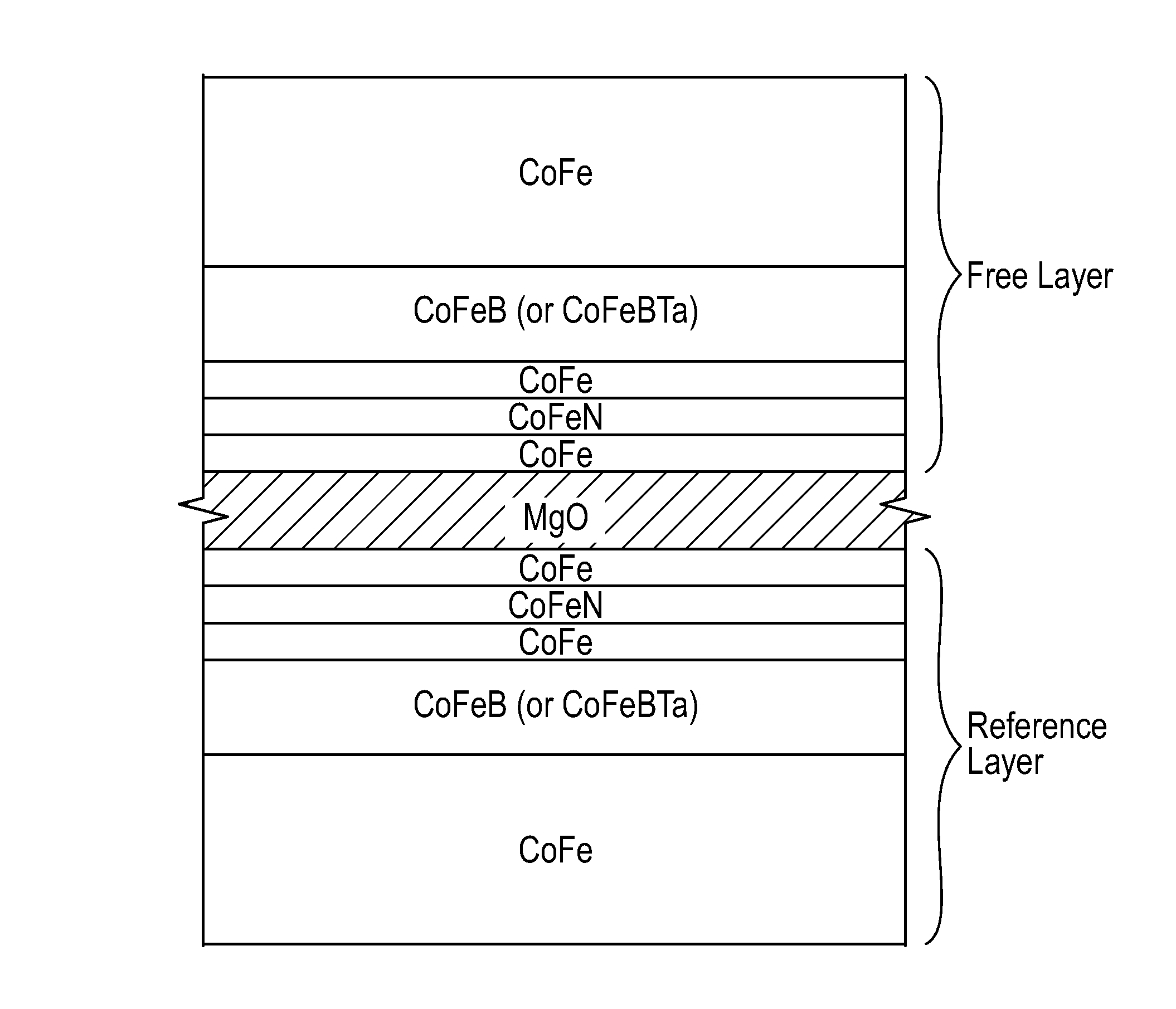

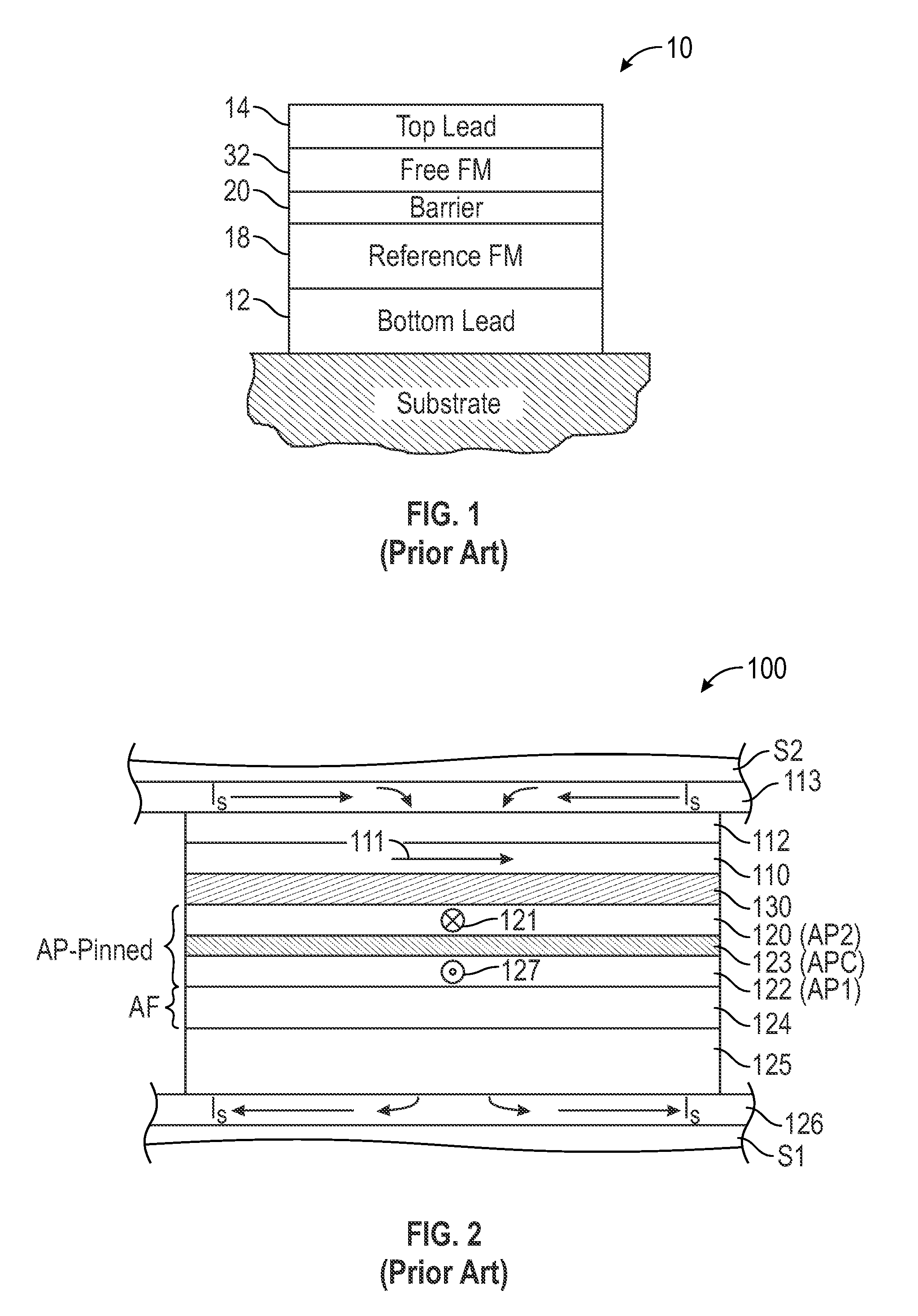

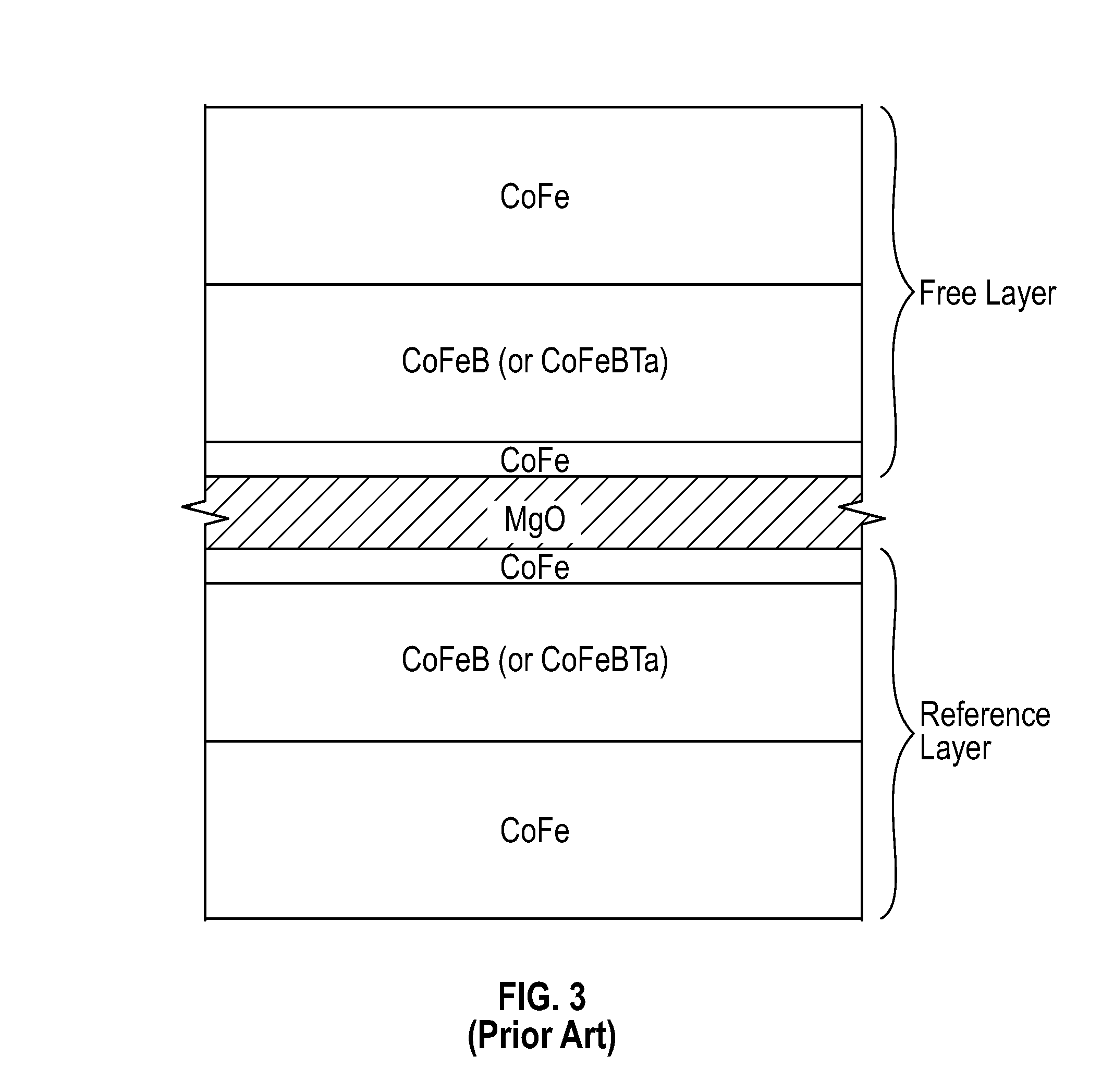

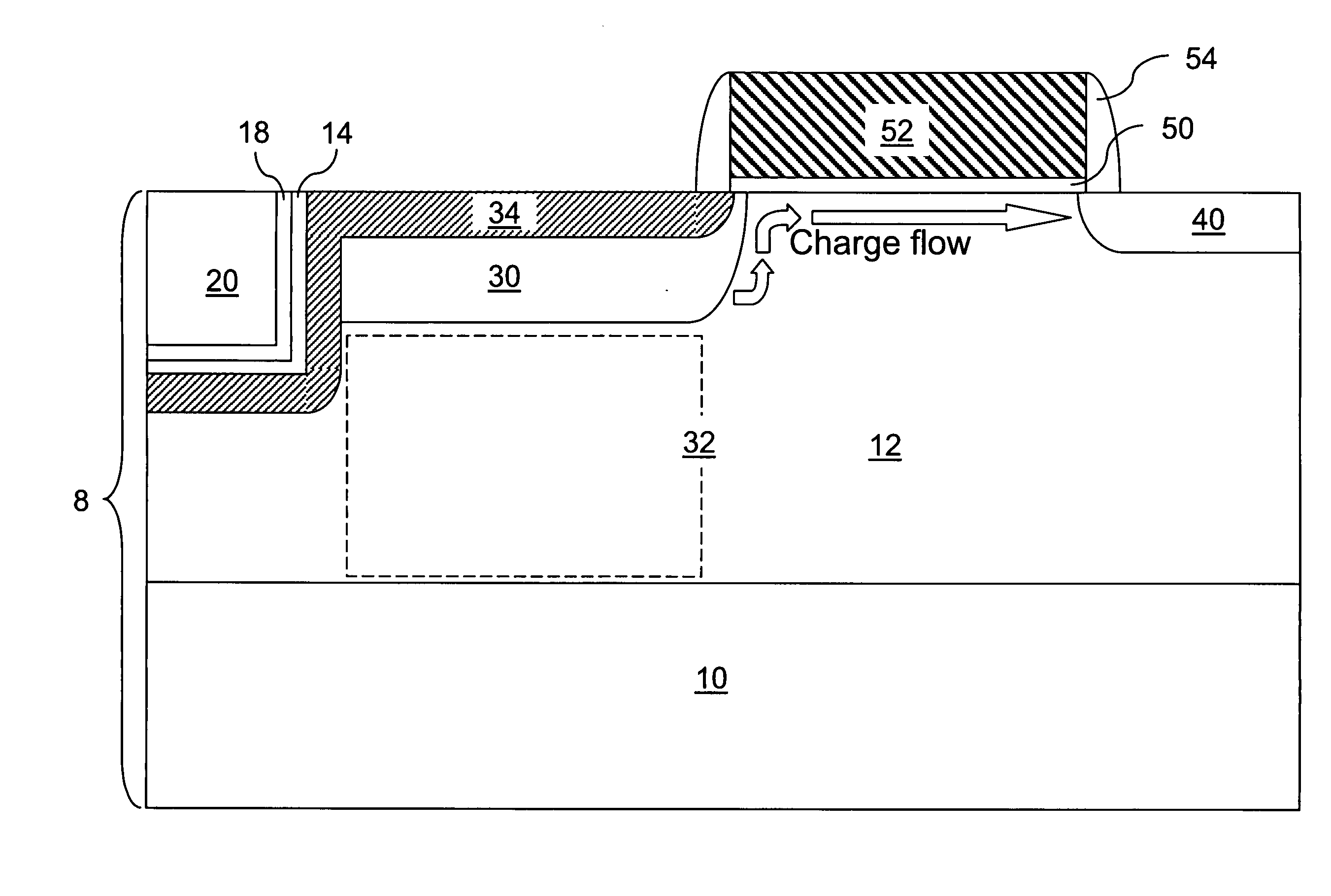

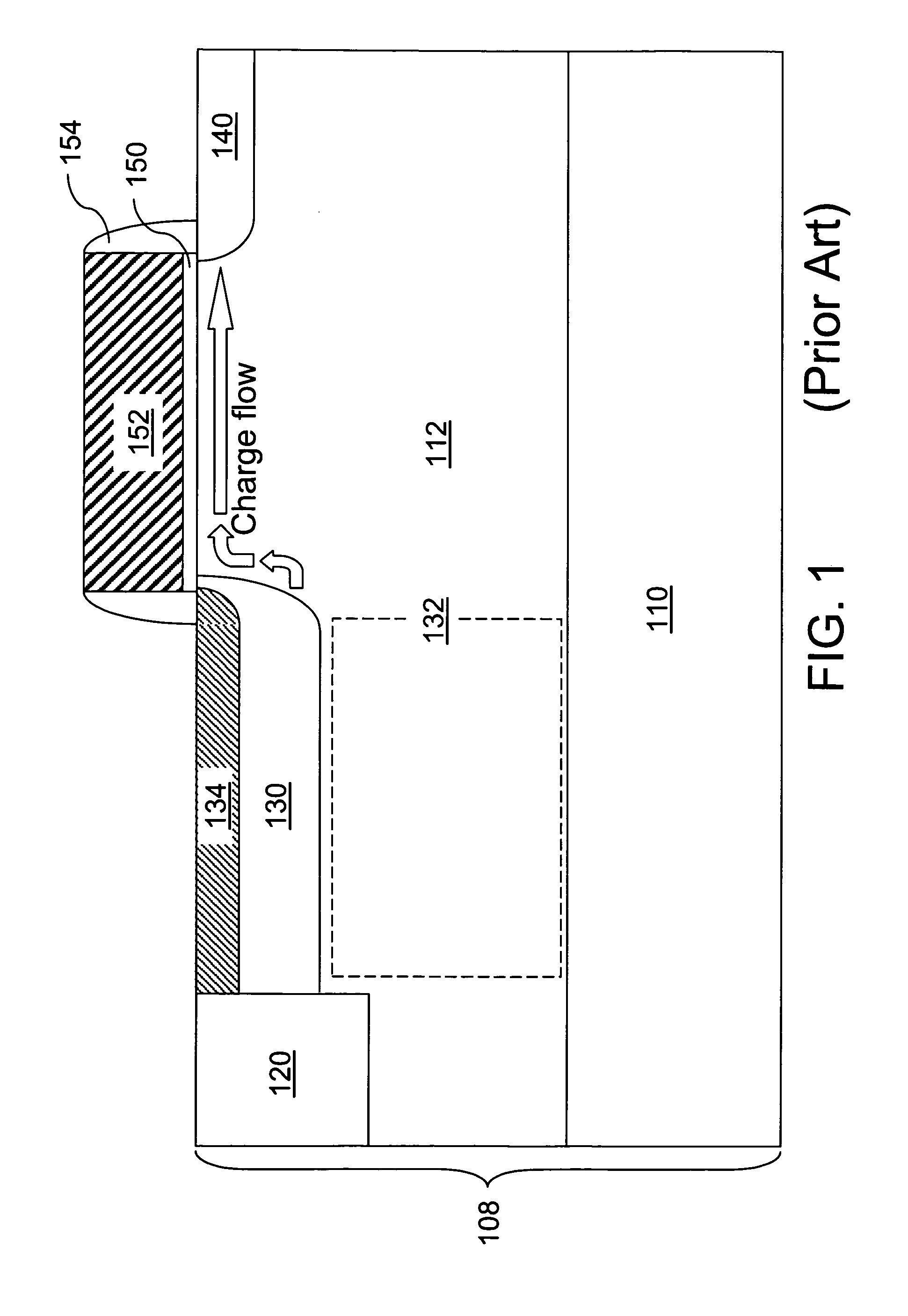

Tunneling magnetoresistive (TMR) device with MgO tunneling barrier layer and nitrogen-containing layer for minimization of boron diffusion

A tunneling magnetoresistance (TMR) device, like a magnetic recording disk drive read head, has a nitrogen-containing layer between the MgO barrier layer and the free and / or reference ferromagnetic layers that contain boron. In one embodiment the free ferromagnetic layer includes a boron-containing layer and a trilayer nanolayer structure between the MgO barrier layer and the boron-containing layer. The trilayer nanolayer structure includes a thin Co, Fe or CoFe first nanolayer in contact with the MgO layer, a thin FeN or CoFeN second nanolayer on the first nanolayer and a thin Co, Fe or CoFe third nanolayer on the FeN or CoFeN nanolayer between the FeN or CoFeN nanolayer and the boron-containing layer. If the reference ferromagnetic layer also includes a boron-containing layer then a similar trilayer nanolayer structure may be located between the boron-containing layer and the MgO barrier layer.

Owner:WESTERN DIGITAL TECH INC

CMOS image sensor with reduced dark current

ActiveUS20090242949A1Improve performanceTotal current dropSolid-state devicesSemiconductor/solid-state device manufacturingCMOSPhotodiode

A carbon-containing semiconductor layer is formed on exposed surfaces of a p-doped semiconductor layer abutting sidewalls of a shallow trench. Following formation of a dielectric layer on the carbon-containing semiconductor layer, a surface pinning layer having a p-type doping is formed underneath the carbon-containing semiconductor layer. A shallow trench isolation structure and a photodiode are subsequently formed. Diffusion of defects directly beneath the shallow trench isolation structure, now contained in the carbon-containing semiconductor layer, is suppressed. Further, boron diffusion into the shallow trench isolation structure and into the photodiode is also suppressed by the carbon-containing semiconductor layer, providing reduction in dark current and enhancement of performance of the photodiode.

Owner:GLOBALFOUNDRIES US INC

Method for removing poly-Si winding plating for manufacturing Topcon battery

ActiveCN110197855ASolve the difficulty of removalEasy to industrializeFinal product manufactureSemiconductor devicesScreen printingComposite film

The invention discloses a method for removing poly-Si winding plating for manufacturing a Topcon battery. The method comprises the steps of: 1) removing a damaged layer from an original silicon wafer,and performing double-sided texturing; 2) finishing the front surface boron diffusion doping process of the obtained textured silicon wafer, and reserving a borosilicate glass layer on the front surface; 3) coating the front surface of a coating film to grow a layer of SiNx film on the borosilicate glass layer; 4) polishing the back surface and etching the edges of the back surface, removing a boron doped layer, and insulating the front surface and the back surface of the boron doped layer; 5) growing a tunnel oxide layer and a polycrystalline silicon layer on the back surface; 6) injecting aphosphorus source into the polycrystalline silicon layer; 7) removing organic matters and surface metal ion pollution; 8) removing the SiNx film, the poly-Si layer and the borosilicate glass layer; 9) annealing the back surface to form N+ doping on the poly-Si layer; 10) plating the SiNx film on the back surface, and plating a composite film layer of Al2O3 and SiNx on the front surface; and 11) respectively performing silk-screen printing on the front and back surfaces of the battery structure coated with the film, and performing sintering to complete metallization of the front and back surfaces of the battery structure. The method is good in stability and easy to operate, and is beneficial to industrialized production.

Owner:XIAN UNIV OF TECH

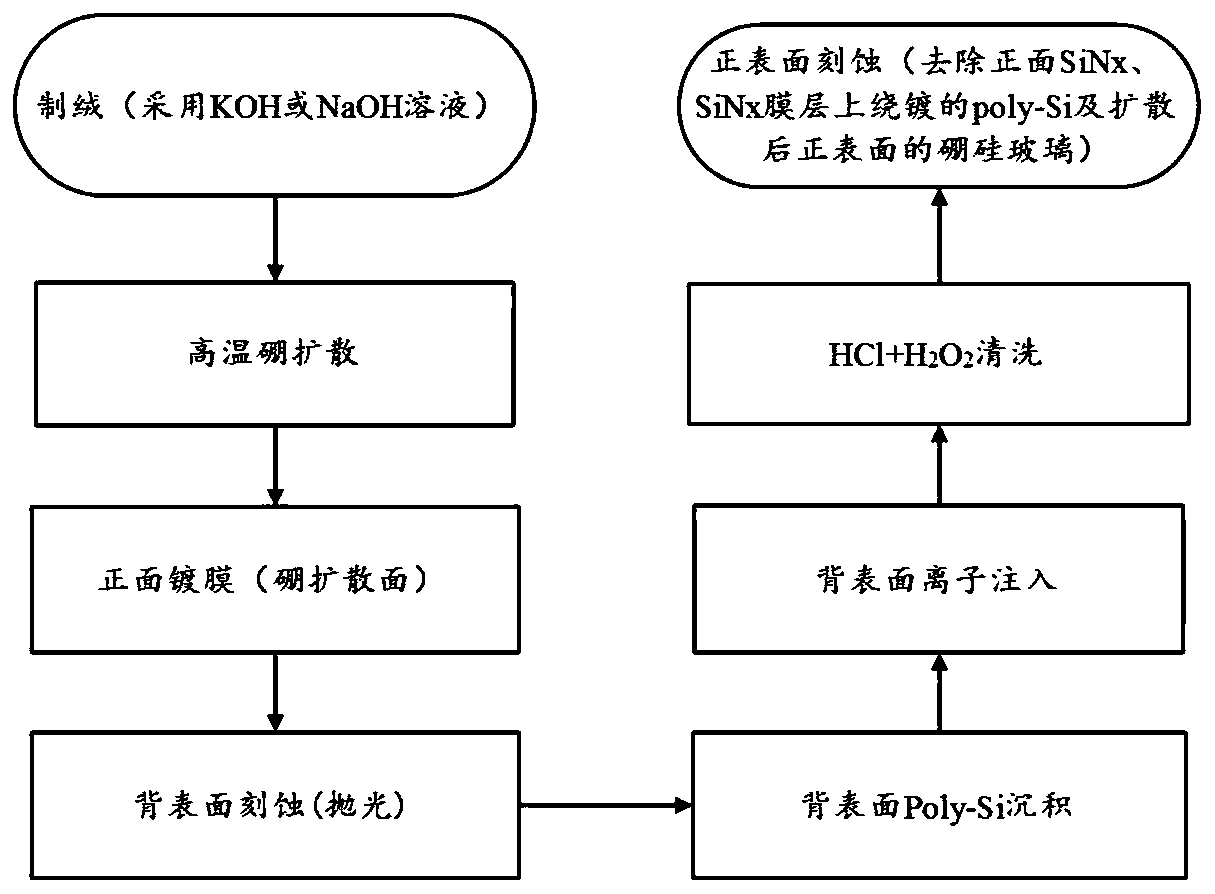

Double-sided N-type crystalline silicon cell and preparation method thereof

InactiveCN105047742AIncrease the open circuit voltageImprove current efficiencyFinal product manufacturePhotovoltaic energy generationChemical solutionBack surface field

The invention discloses a double-sided N-type crystalline silicon cell comprising a front AgAl electrode, a front antireflection film, a boron emitter passivation layer, a boron emitter p+ layer, an N-type silicon wafer, a phosphorus diffusion n+ back surface field layer, a back passivation layer, a back antireflection film, and a back Ag electrode. The front and the back of the cell are textured surfaces, and both sides can receive light and generate electricity. The boron emitter passivation layer and the back passivation layer are prepared at the same time by growing SiO2 layers through thermal oxidation in a low-temperature dry method, which reduces the interface-state density and the rate of interface recombination. A laminated film composed of a borosilicate glass layer and a silicon nitride layer formed in the diffusion process is used as a boron emitter protection layer. Therefore, boron diffusion surface etching and phosphorous diffusion cross contamination caused by chemical solution are prevented effectively, multiple times of etching and mask deposition in the process are reduced, and the technological process is simplified.

Owner:中国东方电气集团有限公司

Deposition of carbon and nitrogen doped poly silicon films, and retarded boron diffusion and improved poly depletion

A compound that includes at least Si, N and C in any combination, such as compounds of formula (R—NH)4-nSiXn wherein R is an alkyl group (which may be the same or different), n is 1, 2 or 3, and X is H or halogen (such as, e.g., bis-tertiary butyl amino silane (BTBAS)), may be mixed with silane or a silane derivative to produce a film. A polysilicon silicon film may be grown by mixing silane (SiH4) or a silane derviative and a compound including Si, N and C, such as BTBAS. Films controllably doped with carbon and / or nitrogen (such as layered films) may be grown by varying the reagents and conditions.

Owner:APPLIED MATERIALS INC +1

System and method for the manufacture of semiconductor devices by the implantation of carbon clusters

InactiveUS20090286367A1Increase junction depthReduce leakage currentTransistorElectric discharge tubesCarbon ionHigh doses

A process is disclosed which incorporates implantation of a carbon cluster into a substrate to improve the characteristics of transistor junctions when the substrates are doped with Boron and Phosphorous in the manufacturing of PMOS transistor structures in integrated circuits. There are two processes which result from this novel approach: (1) diffusion control for USJ formation; and (2) high dose carbon implantation for stress engineering. Diffusion control for USJ formation is demonstrated in conjunction with a boron or shallow boron cluster implant of the source / drain structures in PMOS. More particularly, first, a cluster carbon ion, such as C16Hx+, is implanted into the source / drain region at approximately the same dose as the subsequent boron implant; followed by a shallow boron, boron cluster, phosphorous or phosphorous cluster ion implant to form the source / drain extensions, preferably using a borohydride cluster, such as B18Hx+ or B10Hx+. Upon subsequent annealing and activation, the boron diffusion is reduced, due to the gettering of interstitial defects by the carbon atoms.

Owner:SEMEQUIP

IBC cell manufacturing method

InactiveCN106340568AThe production process is simpleReduce manufacturing costFinal product manufactureSemiconductor/solid-state device manufacturingPhosphorSlurry

The invention discloses an IBC cell manufacturing method. The method comprises the following steps of carrying out texture surface making; depositing a diffusion mask layer; making a back side P+ definition area; carrying out P+ area boron diffusion to form a back junction; removing a residual diffusion mask layer on a silicon chip surface; printing a phosphor doping slurry on an N+ doped area defined on a silicon chip back side; manufacturing a front surface field; under a high temperature condition, using POCL3 to form the front surface field on an upper surface of the silicon chip, wherein the phosphor doping slurry enters into a substrate to form an N+ area under the high temperature condition during a process that the POCL3 is used to carry out phosphorous diffusion so as to form the front surface field; depositing a passivation reduction reflecting layer on a front side and a back side of the silicon chip; and making a metal electrode. In the method, a phosphorus diffusion technology only needs to be performed once and front field and back field areas possessing different doped concentrations can be synchronously manufactured; and a making technology process of an IBC cell is simplified and production cost is reduced, which is convenient for large-scale popularization.

Owner:YINGLI ENERGY CHINA

Boron diffusion method of crystalline silicon solar cell

ActiveCN102766908AIncrease impurity concentrationReduce impurity concentrationFinal product manufactureDiffusion/dopingMetallurgyNitrogen gas

The invention discloses a boron diffusion method of a crystalline silicon solar cell, wherein the method comprises the following steps: (1), arranging a silicon chip subjected to felting and cleaning processes in a diffusion furnace pipe, heating to 900 DEG C to 1100 DEG C, introducing nitrogen, a relatively large amount of boron source and oxygen, and performing boron diffusion, wherein the diffusion time is 5min to 60min; (2), keeping the temperature in the step (1), introducing nitrogen, a relatively small amount of boron source and oxygen, and performing boron diffusion, wherein the diffusion time is 15min to 80min; (3), keeping the temperature in the step (1) or heating to 910 DEG C to 1100 DEG C, introducing nitrogen, a relatively large amount of boron source and oxygen, and performing boron diffusion, wherein the diffusion time is 2min to 30min; and (4) finishing the diffusion process. With the adoption of the boron diffusion method, the high impurity concentration is formed within small depth range of the surface of the silicon chip, so as to be beneficial to forming of excellent ohm contact; the impurity concentration of the large depth range of a diffusion layer is reduced; the auger recombination and combination generated by nudged defect are reduced, the minority carrier lifetime is prolonged, so the property of the cell is enhanced.

Owner:CSI CELLS CO LTD +1

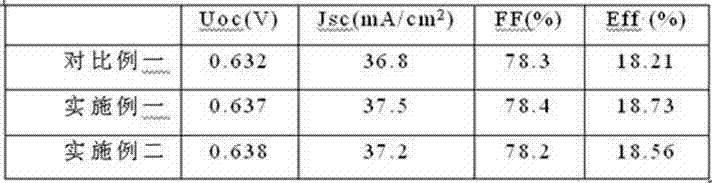

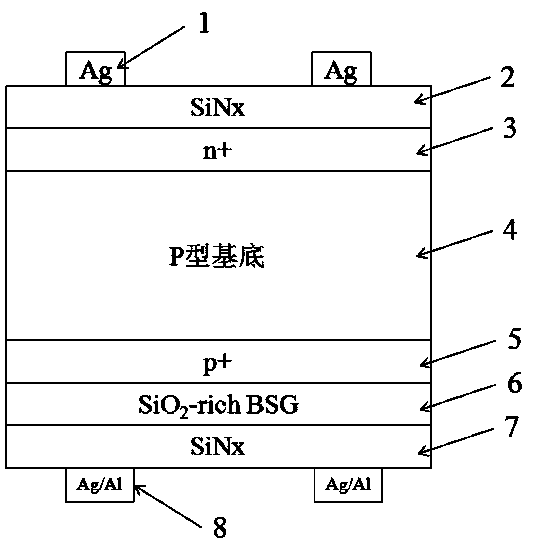

Double-face P-type crystalline silicon battery structure and manufacturing method thereof

ActiveCN103887347AAchieve passivationReduce concentrationFinal product manufacturePhotovoltaic energy generationElectrical batteryMaterials science

The invention discloses a double-face P-type crystalline silicon battery structure and a manufacturing method thereof. The double-face P-type crystalline silicon battery structure formed through the method comprises a back face passivation anti-reflecting composite film, the anti-reflecting composite film comprises a borosilicate glass layer containing SiO2 and a silicon nitride layer, the borosilicate glass layer is arranged on a double-face crystalline silicon battery boron diffusion layer, and the silicon nitride layer is deposited on the borosilicate glass layer; the battery structure can reduce the interface state density and the interface compounding rate and realize the passivation effect on the boron diffusion layer; a BSG / SiNx laminated structure formed by the borosilicate glass layer and the silicon nitride layer can realize the functions such as passivation, diffusion masking and reflection resisting, and can increase the open-circuit voltage of a battery, the short-circuit current of the battery and the photo-electric conversion efficiency of the battery; the BSG(SiO2-rich) / SiNx laminated structure is adopted in the back face to serve as the back face passivation layer, the diffusion masking layer and the back face anti-reflection layer of the battery, therefore, the technology is greatly simplified, the production efficiency is increased and the production technology cost is lowered.

Owner:中国东方电气集团有限公司

Preparation method of N-type passivation contact solar cell

ActiveCN111029438ASolve the leakAvoid damageFinal product manufacturePhotovoltaic energy generationElectrical batterySolar battery

The invention discloses a preparation method of an N-type passivation contact solar cell. The method sequentially comprises the following steps: performing double-sided polishing on an N-type crystalline silicon substrate; sequentially growing a tunneling oxide layer and an intrinsic amorphous silicon layer on the back surface; doping the intrinsic amorphous silicon layer; depositing a silicon nitride film on the back surface; performing texturing and boron diffusion on the front surface; removing the front surface and a borosilicate glass layer wound and expanded to the back surface; preparation of a passivation anti-reflection on the front surface; silver paste printing on the back surface; silver-aluminum paste printing on the front surface; and sintering and like so that preparation ofthe N-type passivation contact solar cell is completed. The problem of electric leakage caused by adopting a phosphorus diffusion process in the conventional process is solved, the step of activatingthe back doping source by high-temperature annealing is omitted, damage to the silicon substrate is reduced, process steps are reduced, production cost is reduced, and the silicon nitride passivationfilm is prepared by plate-type PECVD (plasma enhanced chemical vapor deposition) equipment and thus poor appearance caused by texturing of a clamping groove mark position during front texturing is avoided.

Owner:江苏杰太光电技术有限公司

Method for preparing high-voltage diac

ActiveCN101593693ANo damageImprove anti-ablation performanceSemiconductor/solid-state device manufacturingDIACAcid washing

The invention relates to a method for preparing a high-voltage diac. In the method, a raw material silicon chip is processed in sequence by the following steps: chemical polishing, boron diffusion, oxidation of a mask, double-sided primary photoetching, phosphorous diffusion, nickel plating and alloying, scribing, welding, acid washing, protection, and packaging to obtain a finished product of the high-voltage diac, wherein the chemical polishing step is that the raw material silicon chip is evenly corroded in corrosion solution at the normal temperature for 3 to 5 minutes, washed for multiple times and dried to obtain a silicon chip (1) with the matt surface, and the corrosion solution is formed by mixing hydrofluoric acid, glacial acetic acid and nitric acid according to the volume ratio of 1:1 to 3:25 to 30; and the acid washing step is that a corrosion layer (8) is formed on the periphery of the silicon chip (1) obtained by soaking by mixed acid liquor, corroding and welding so as to obtain the electric performance, and the mixed acid solution is formed by mixing the hydrofluoric acid, the nitric acid, acetic acid and sulfuric acid according to the volume ratio of 9: 9: 9 to 15:4. The method has the advantages of simplified working procedure, low cost, reliable performance and corrosion resistance.

Owner:常州银河电器有限公司

N-type double-sided solar cell and preparation method thereof

InactiveCN105489671AImprove photoelectric conversion efficiencyConcentrated efficiency distributionFinal product manufacturePhotovoltaic energy generationScreen printingEtching

The invention relates to an N-type double-sided solar cell and a preparation method thereof. According to the preparation method of the N-type double-sided solar cell, fabrication of a p+ doped region on the front surface of a silicon substrate and an n+ doped region on the back surface of the silicon substrate is achieved by a technique of combining boron diffusion and phosphorus ion implantation; passivation of the front surface and the rear surface of the silicon substrate and antireflection of the front surface are achieved by a composite dielectric film of two or three of SiO<2>, Al<2>O<3> and SiN<x>; and finally metal contact of the p+ doped region on the front surface of the silicon substrate and the n+ doped region on the back surface is achieved through silk-screen printing and co-sintering technologies, and fabrication of the N-type double-sided solar cell is facilitated. According to the preparation method provided by the invention, an ion implantation technique is introduced into a fabrication technology of the N-type double-sided solar cell, so that a mask technology can be omitted; edge etching is not required; and the N-type double-sided solar cell fabricated by the ion implantation technique is high in photoelectric conversion efficiency, relatively concentrated in efficiency distribution and high in yield.

Owner:JOLYWOOD SUZHOU SUNWATT

A making method for quick recovery silicon rectifying diode chip

InactiveCN101188199AImprove performanceGuaranteed reliabilitySemiconductor/solid-state device manufacturingEvaporationShock resistance

The invention discloses a manufacturing method of rapidly recovering a silicon rectifier diode chip, which relates to a silicon rectifier diode, in particular to the manufacturing method of the chips. The method comprises processes as follows: silicon single crystal wafer selection, silicon wafer cleaning, phosphorus diffusion, lapping, boron diffusion, second phosphorus diffusion, phosphorus surface evaporation gold, gold diffusion, boron surface light sand blasting and aluminum evaporation. Three processes of the second phosphorus diffusion, the phosphorus surface evaporation gold and the gold diffusion are added into a technological process to cause the concentration of diffusion impurities in N -type silicon to change and the contact of the N -type silicon and the aluminum to form an almost complete ohmic contact, and the performance of the produced chip is improved. Under large current, when the forward voltage obtains decrease simultaneously, the recovery time of a glass passivation rapid recovering silicon rectifier diode ship which is manufactured by the method can reach below 30ns, and the reliability of the product obtains assurance, which causes the forward voltage to be smaller than o.875V. The produced chip has the advantages of small volume, light weight and high reliability, and temperature shock resistance.

Owner:CHINA ZHENHUA GRP YONGGUANG ELECTRONICS CO LTD STATE OWNED NO 873 FACTORY