Patents

Literature

126results about How to "Increase impurity concentration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

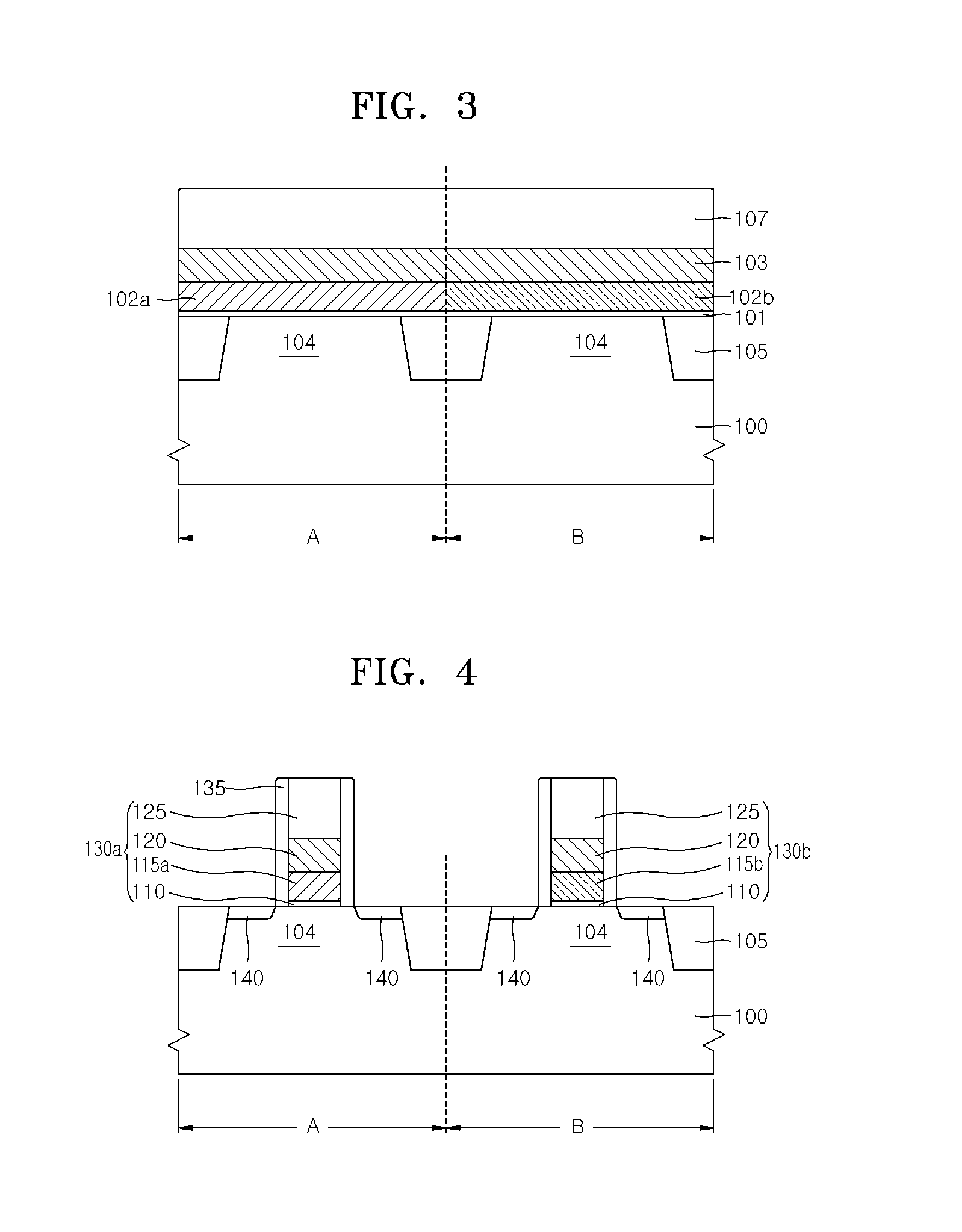

Method of manufacturing semiconductor device, and semiconductor device

ActiveUS20070254414A1Sufficient carrier mobilityImpurity will diffuseSemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerConcentration gradient

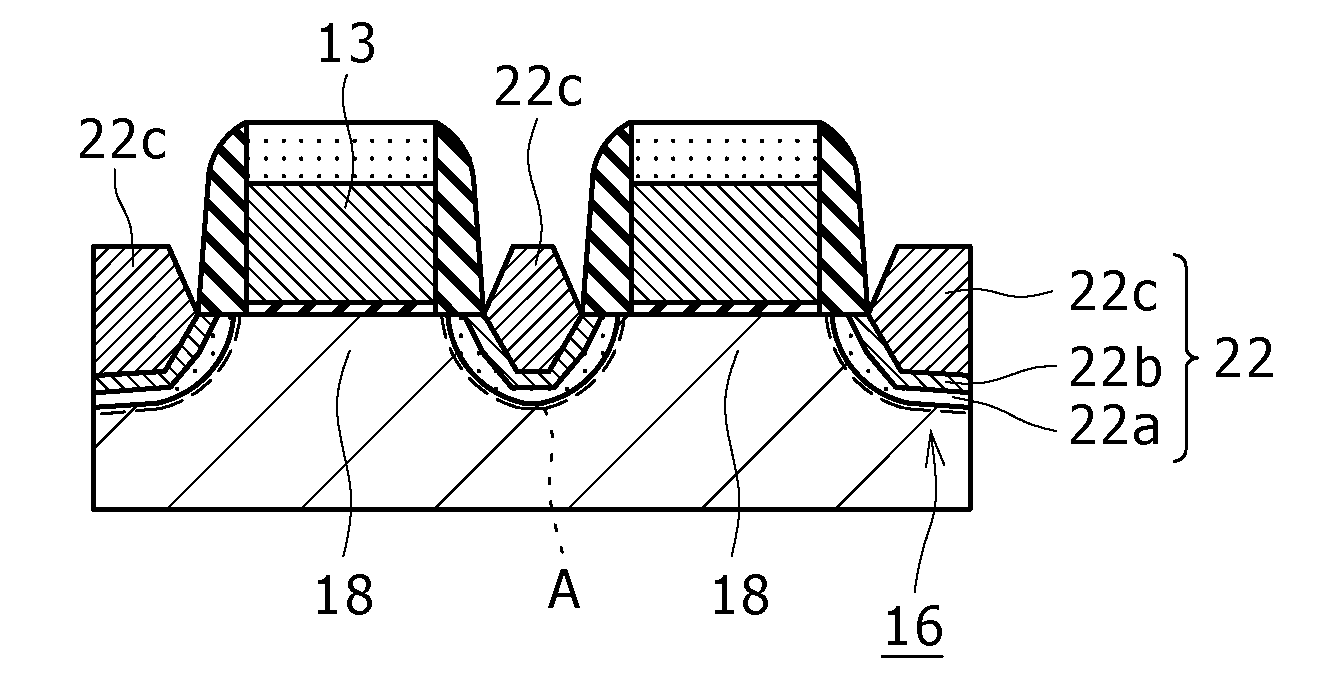

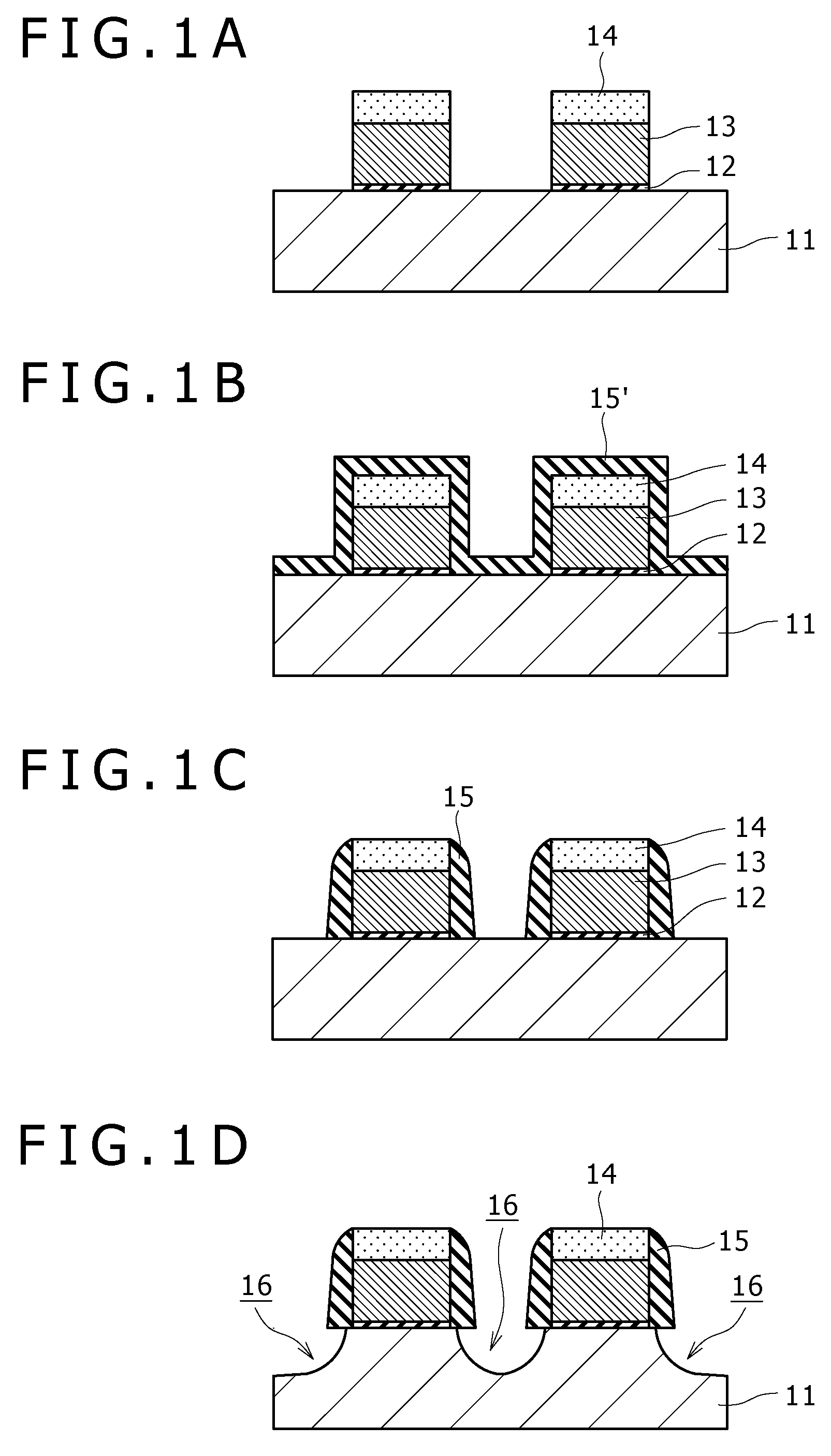

A method of manufacturing a semiconductor device includes: the first step of forming a gate electrode over a silicon substrate, with a gate insulating film; and the second step of digging down a surface layer of the silicon substrate by etching conducted with the gate electrode as a mask. The method of manufacturing the semiconductor device further includes the third step of epitaxially growing, on the surface of the dug-down portion of the silicon substrate, a mixed crystal layer including silicon and atoms different in lattice constant from silicon so that the mixed crystal layer contains an impurity with such a concentration gradient that the impurity concentration increases along the direction from the silicon substrate side toward the surface of the mixed crystal layer.

Owner:SONY CORP

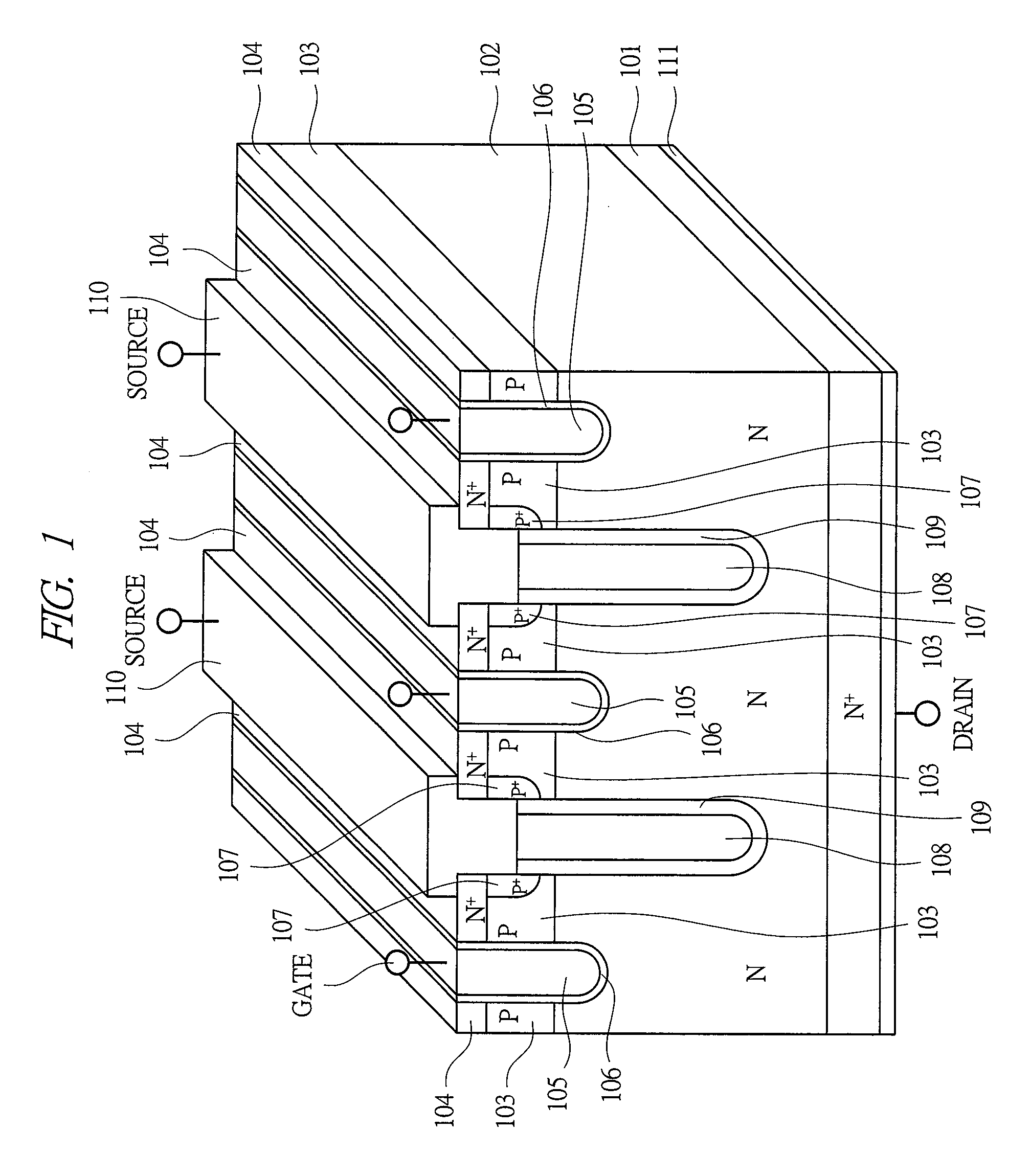

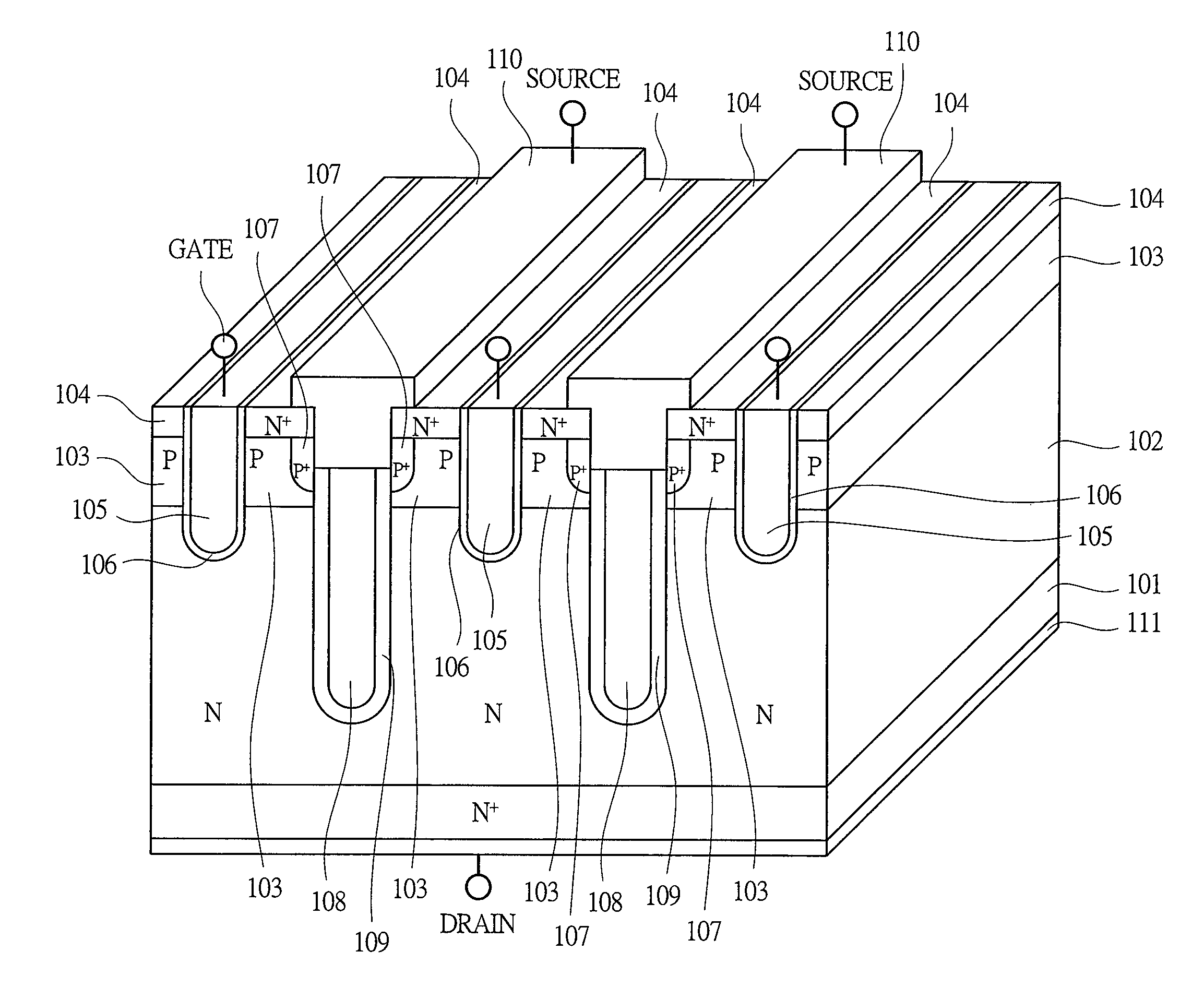

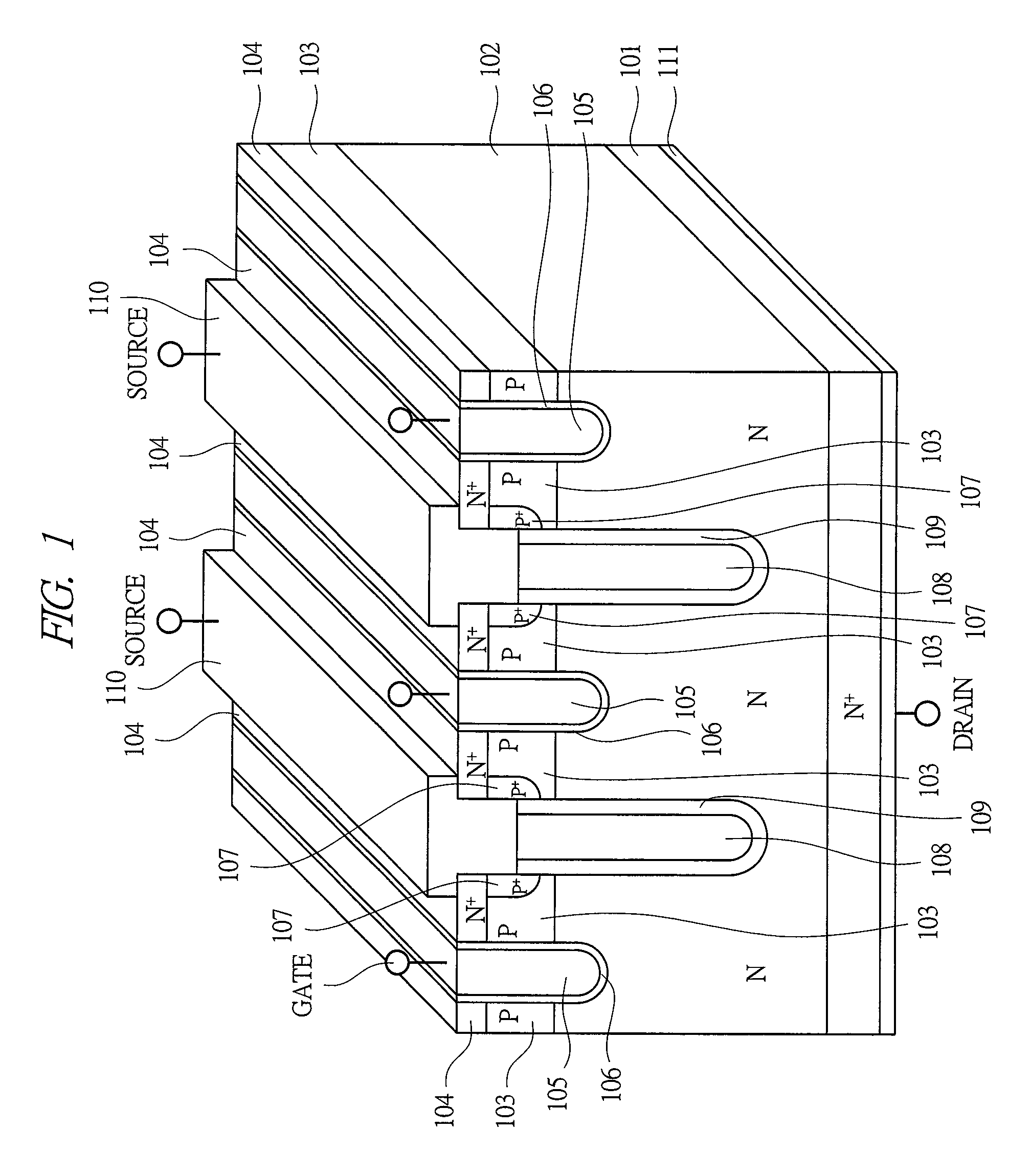

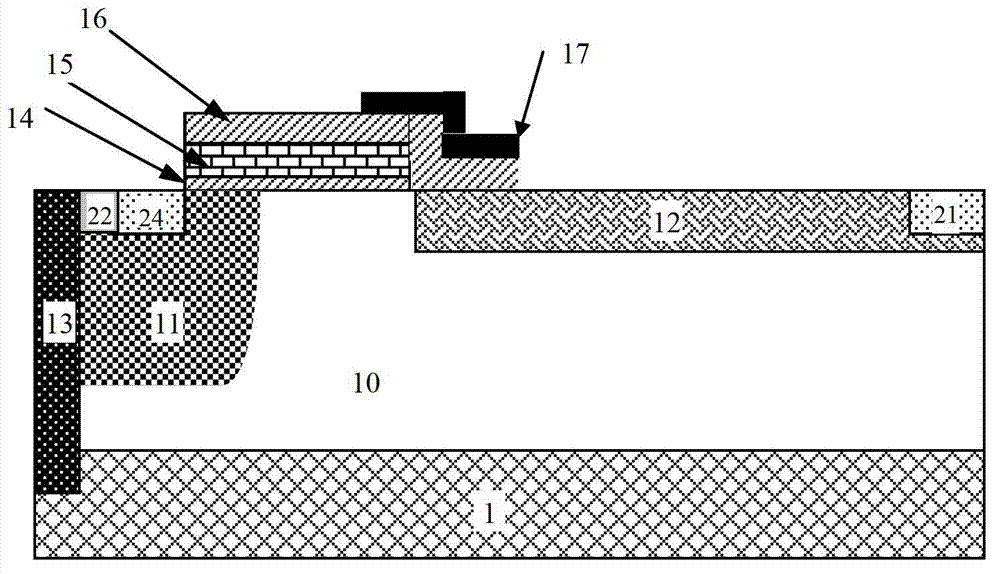

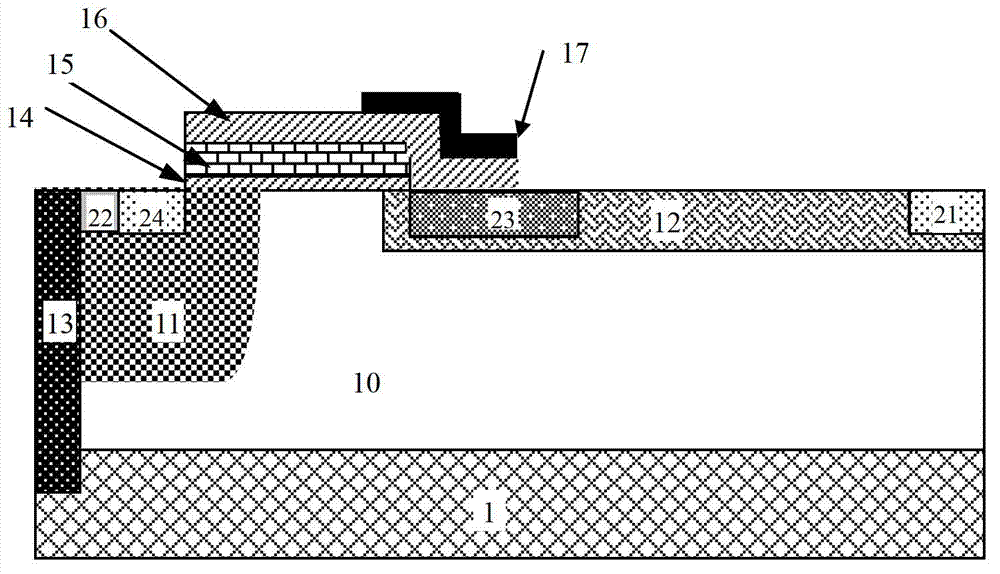

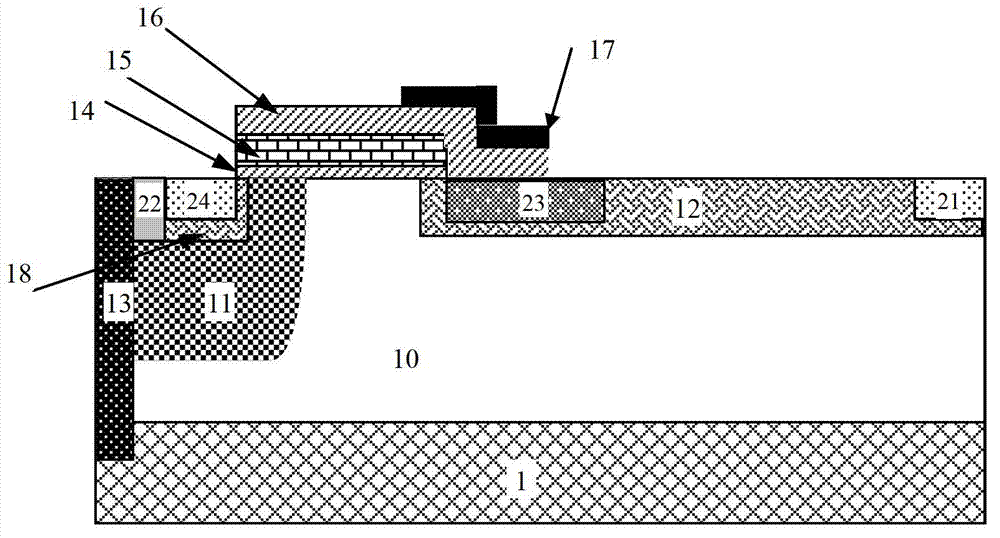

Semiconductor device and manufacturing method of the same

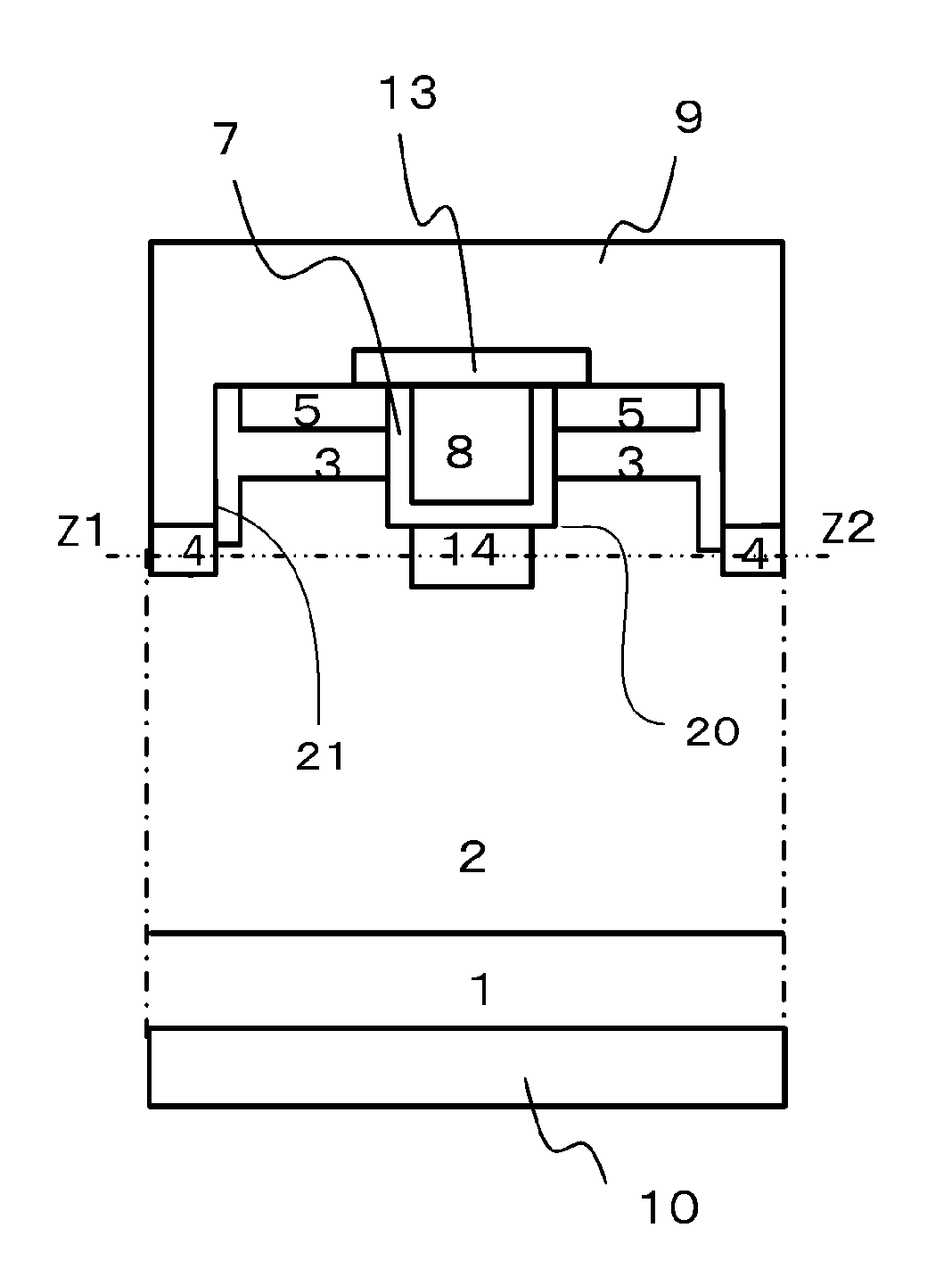

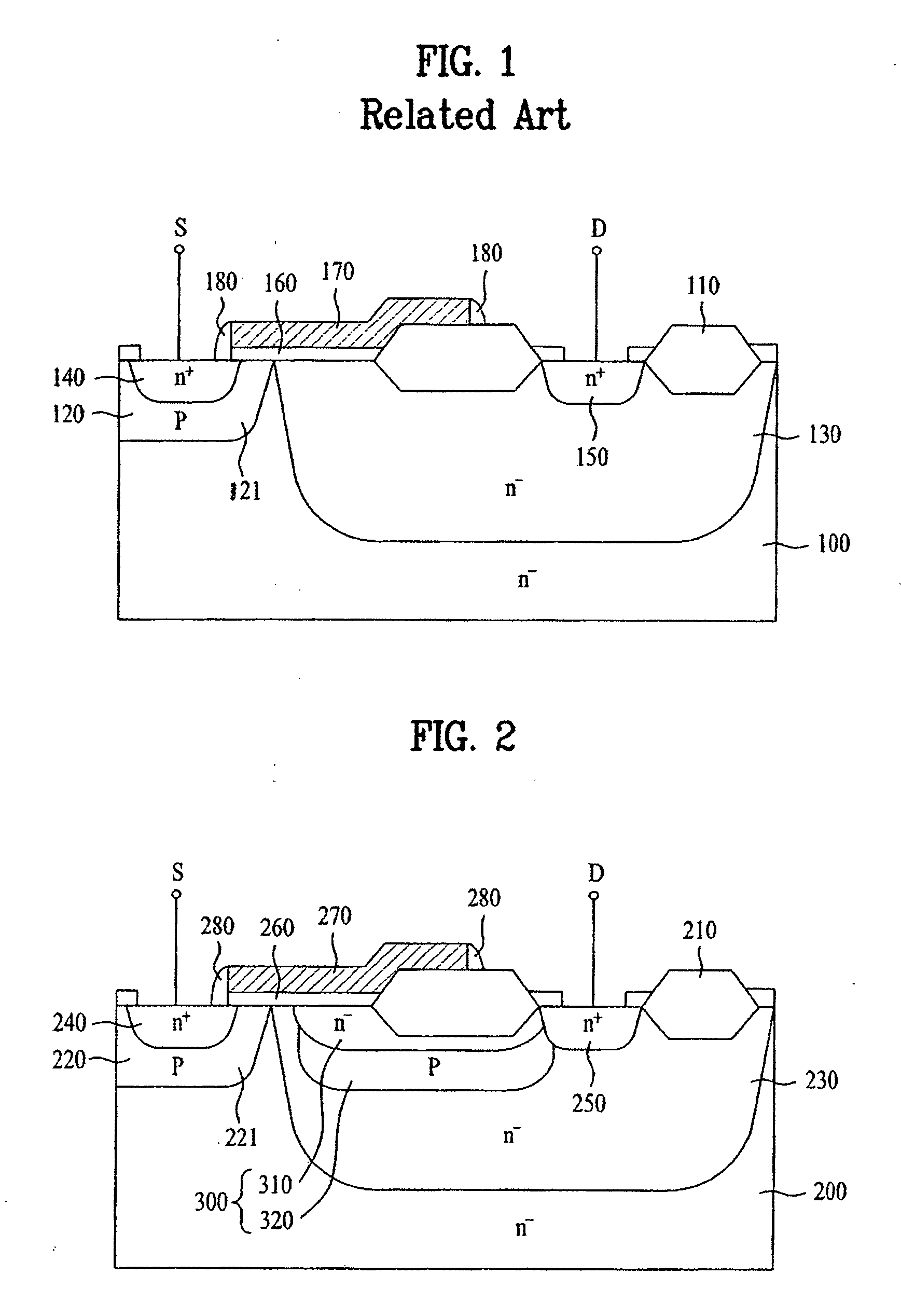

InactiveUS20090140327A1Increase impurity concentrationLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetElectrode Contact

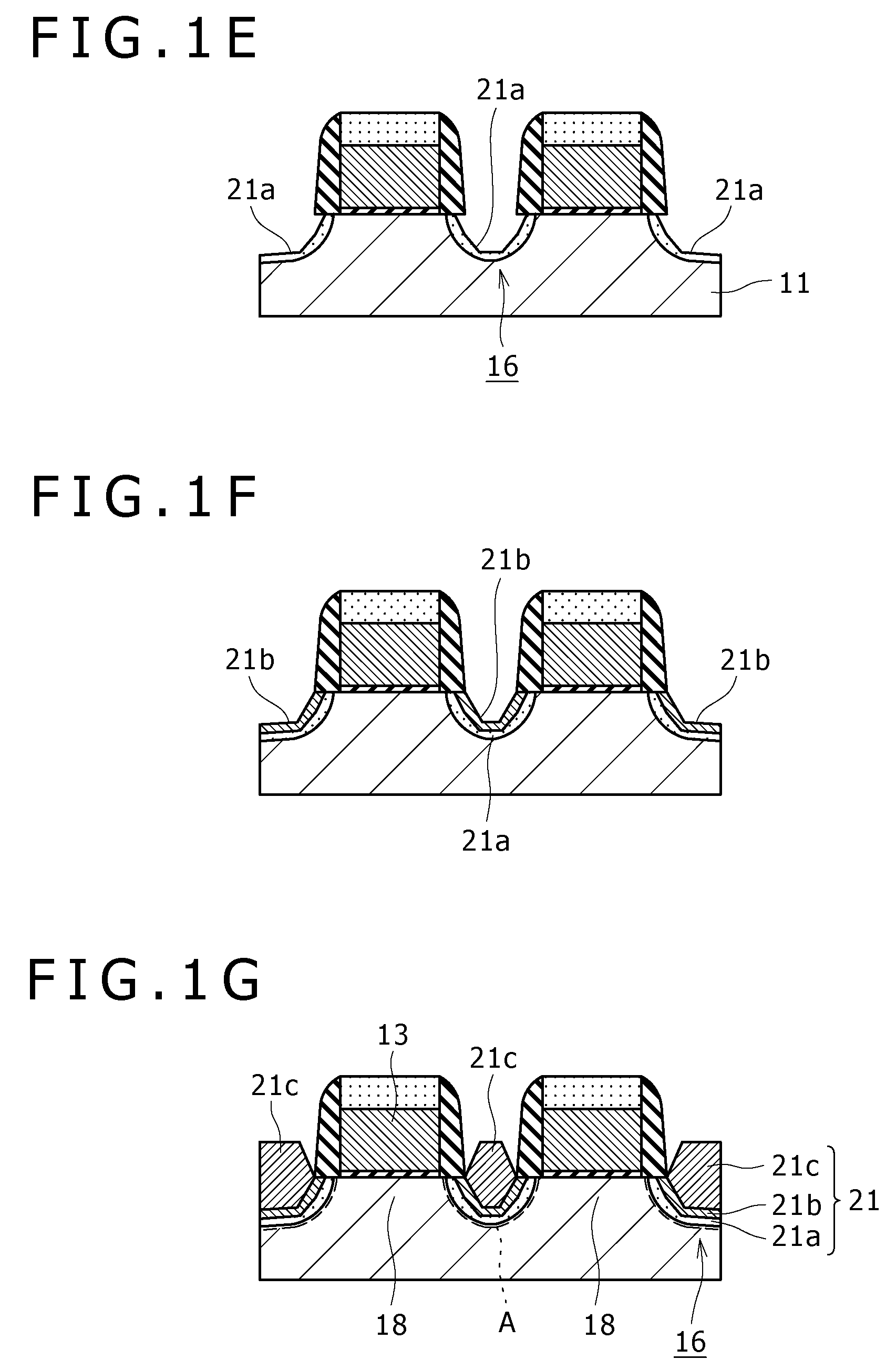

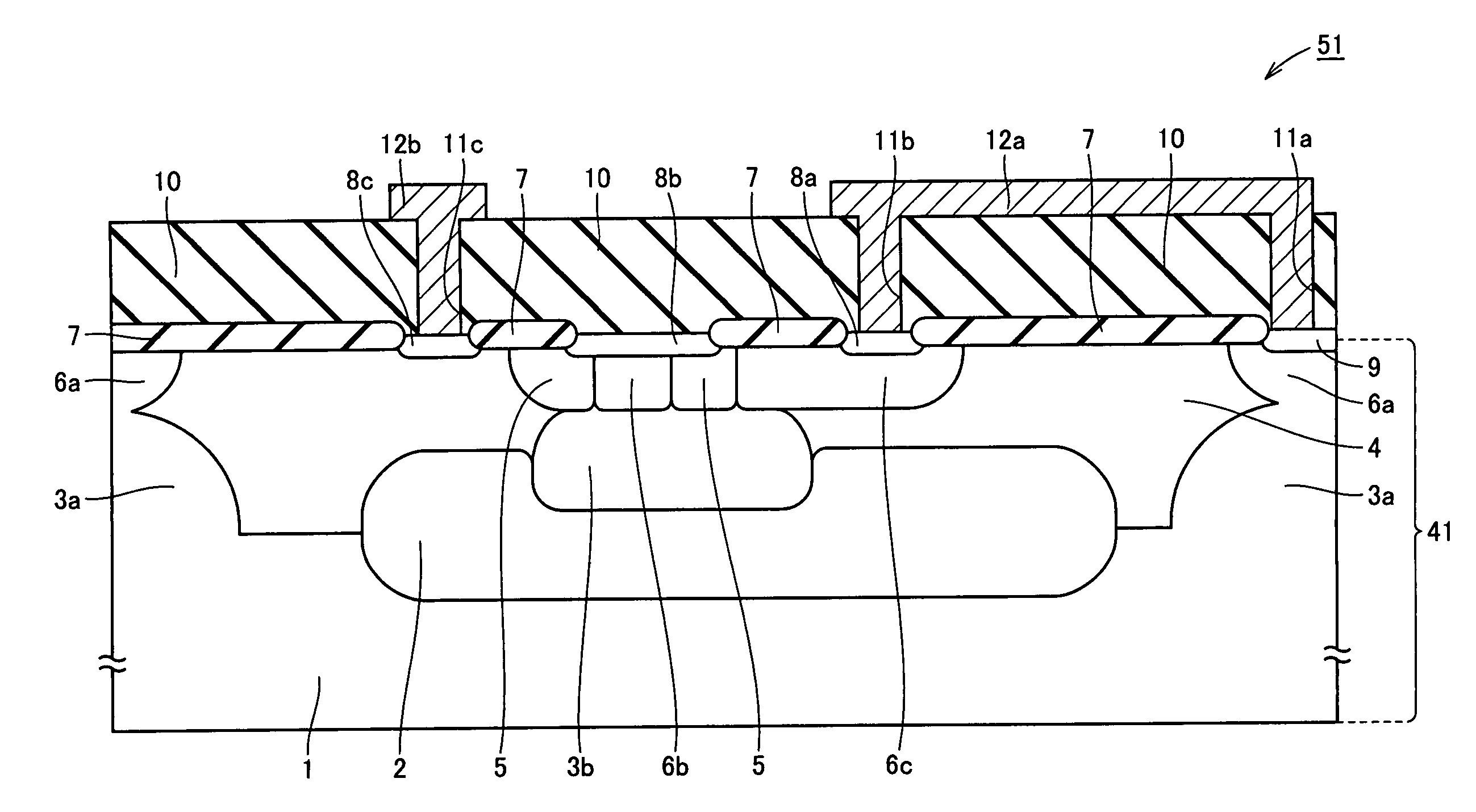

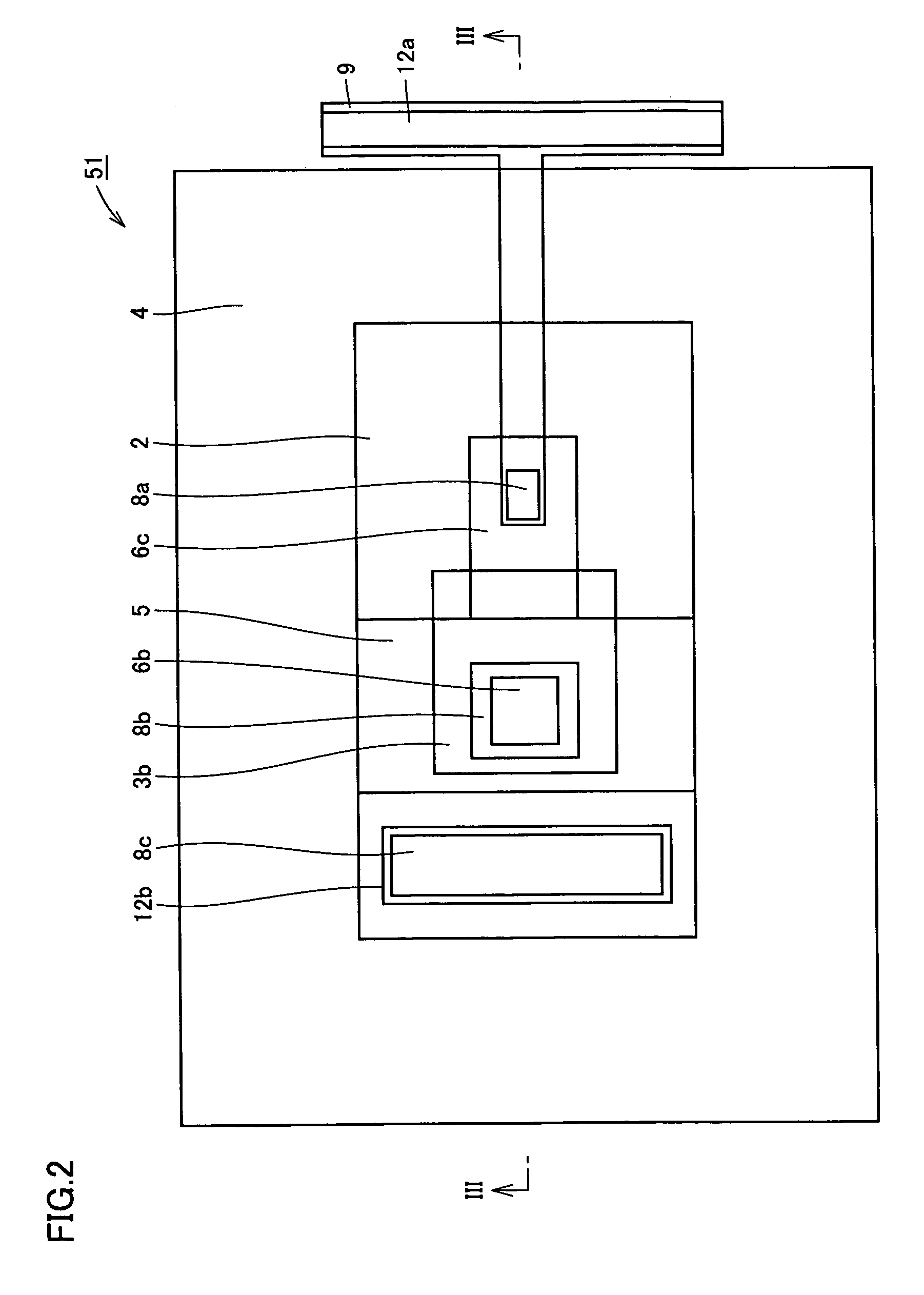

The vertical trench MOSFET comprises: an N type epitaxial region formed on an upper surface of an N+ type substrate having a drain electrode on a lower surface thereof; a gate trench extending from a front surface into the N type epitaxial region; a gate electrode positioned in the gate trench so as to interpose an insulator; a channel region formed on the N type epitaxial region; a source region formed on the channel region; a source electrode formed on the source region; a source trench extending from the front surface into the N type epitaxial region; and a trench-buried source electrode positioned in the source trench so as to interpose an insulator, wherein the source electrode contacts with the trench-buried source electrode.

Owner:RENESAS ELECTRONICS CORP

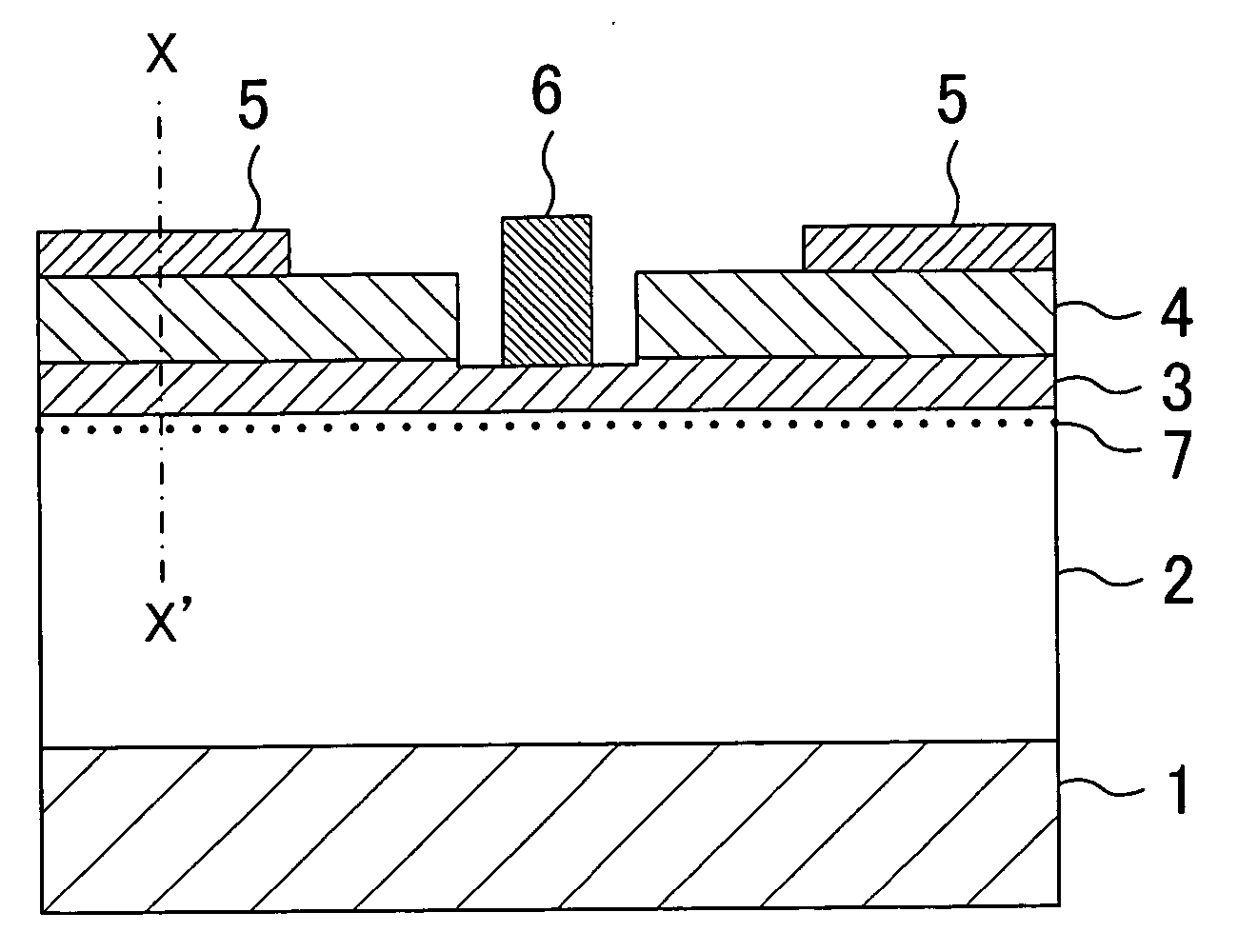

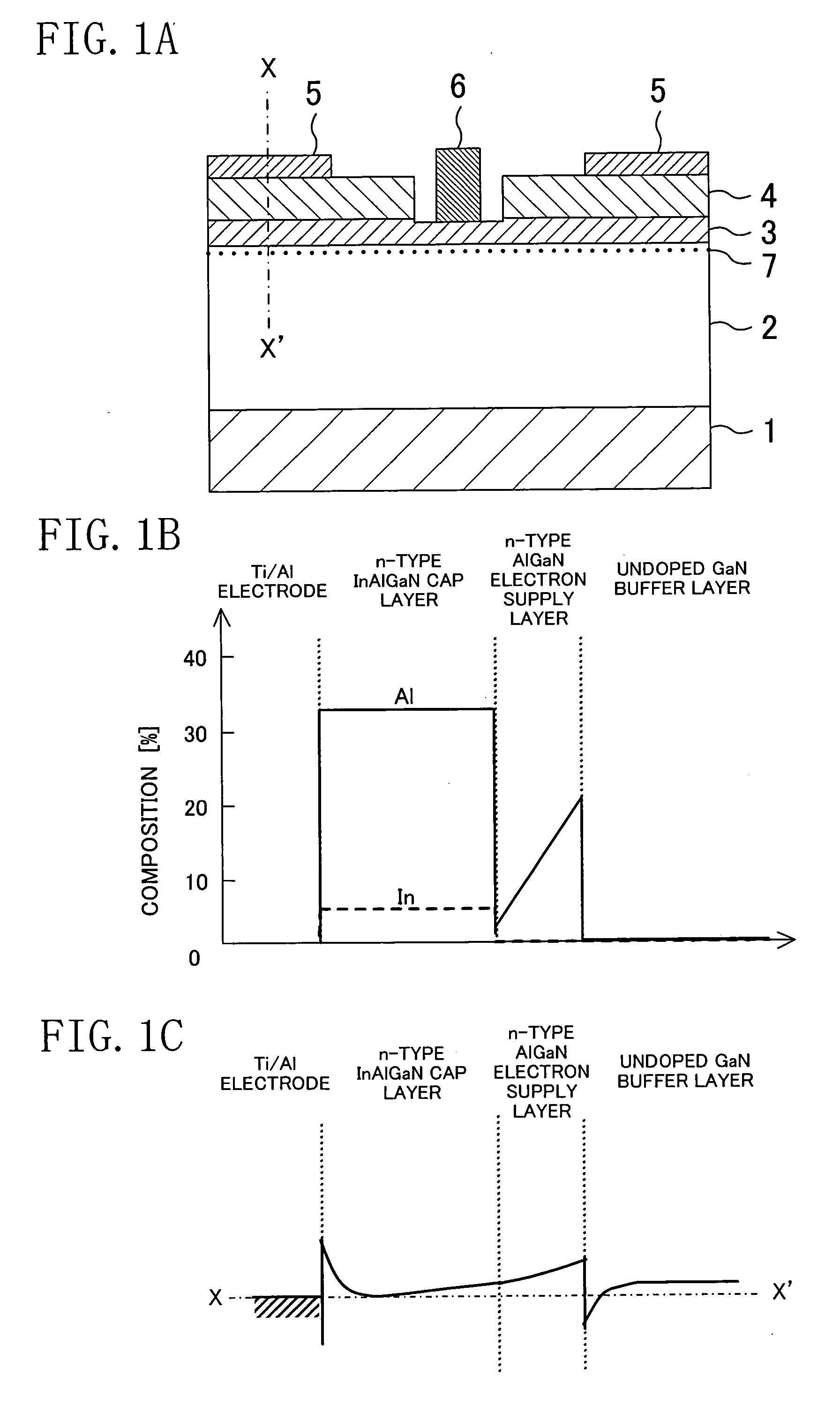

Field effect transistor and method for fabricating the same

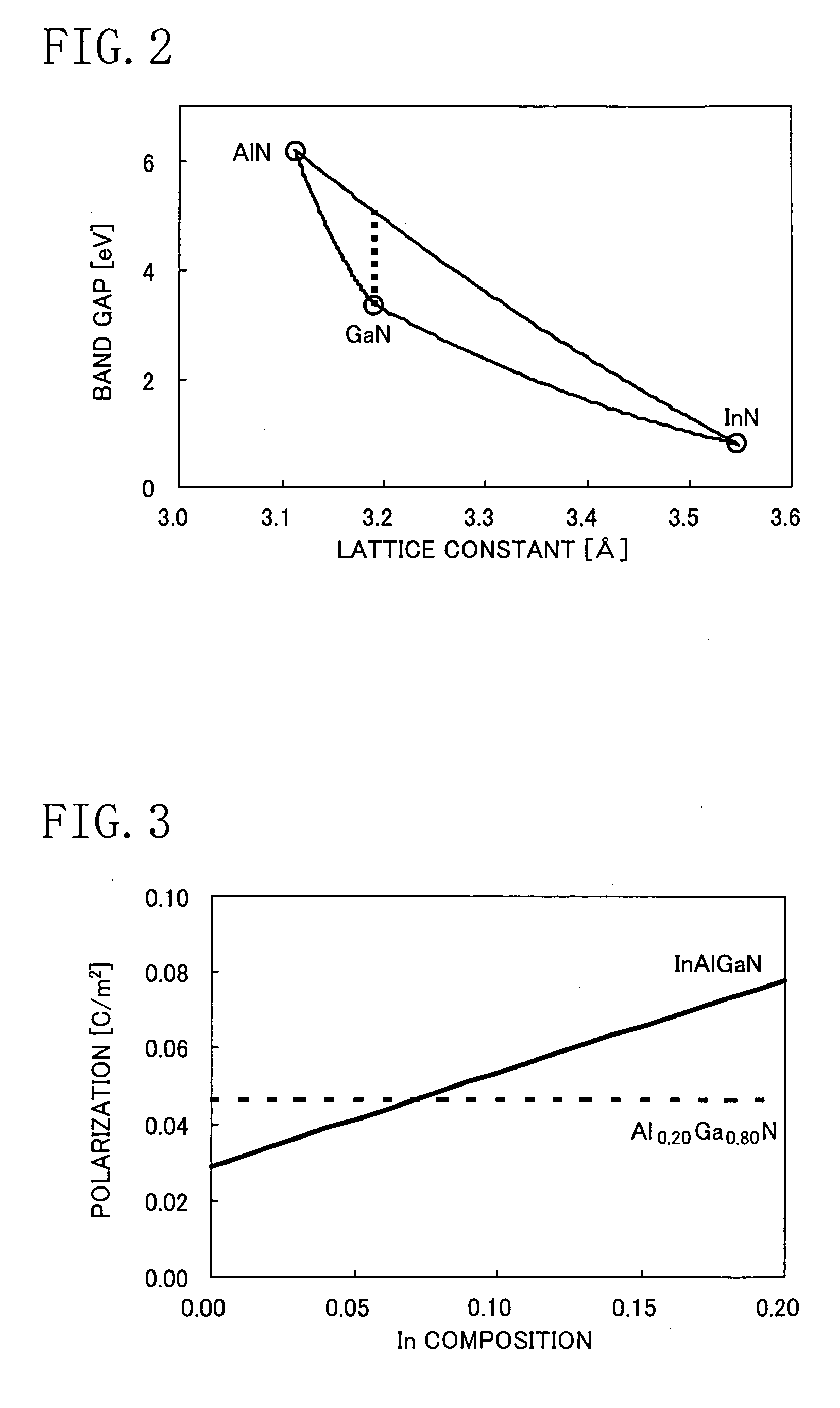

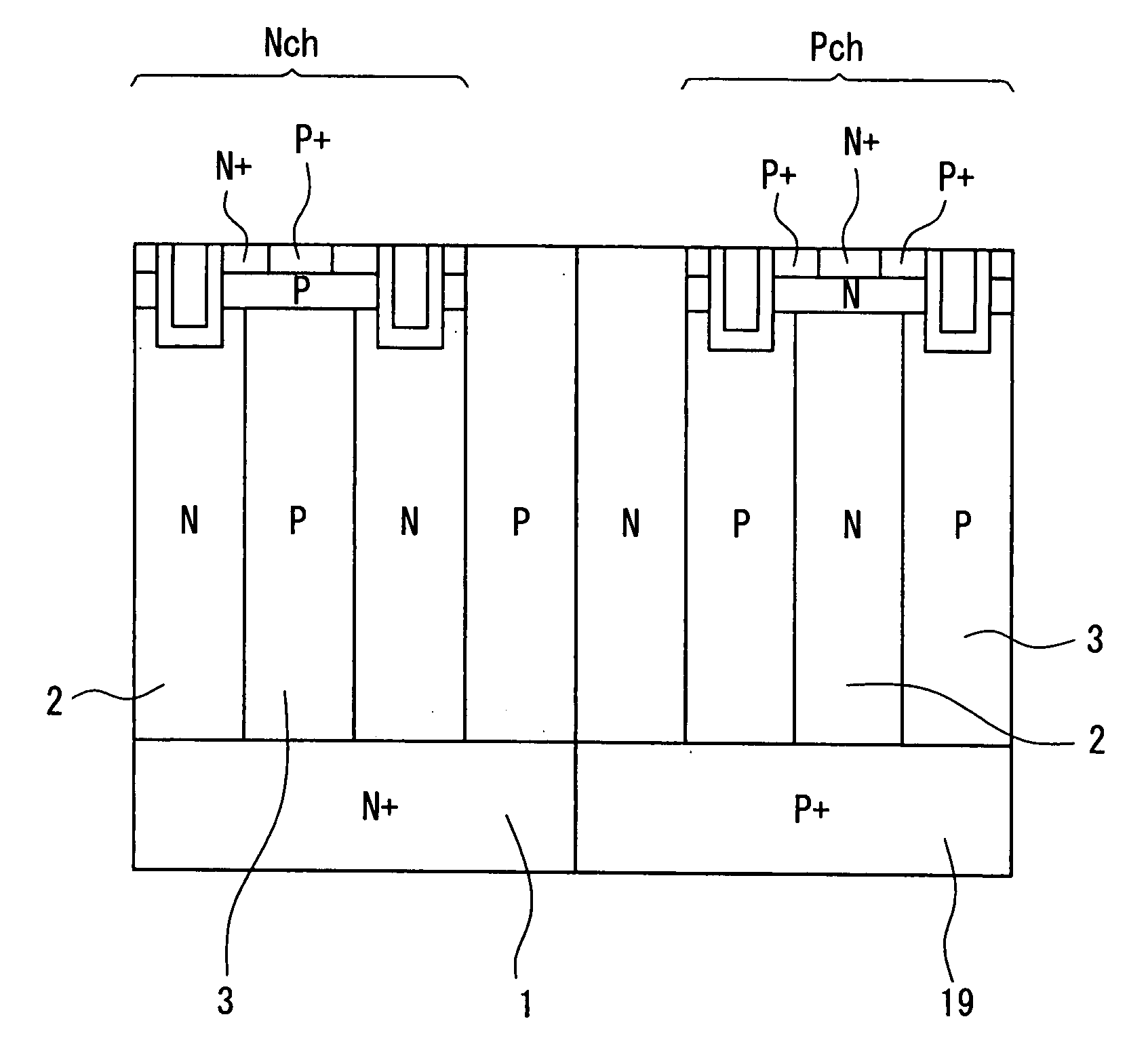

ActiveUS20060180831A1High crystallinityIncrease parasitic resistanceSemiconductor devicesConduction bandField-effect transistor

A field effect transistor includes a nitride semiconductor layer; an InxAlyGa1-x-yN layer (wherein 0<x<1, 0<y<1 and 0<x+y<1) formed on the nitride semiconductor layer; and a source electrode and a drain electrode formed on and in contact with the InxAlyGa1-x-yN layer. The lower ends of the conduction bands of the nitride semiconductor layer and the InxAlyGa1-x-yN layer are substantially continuous on the interface therebetween.

Owner:PANASONIC CORP

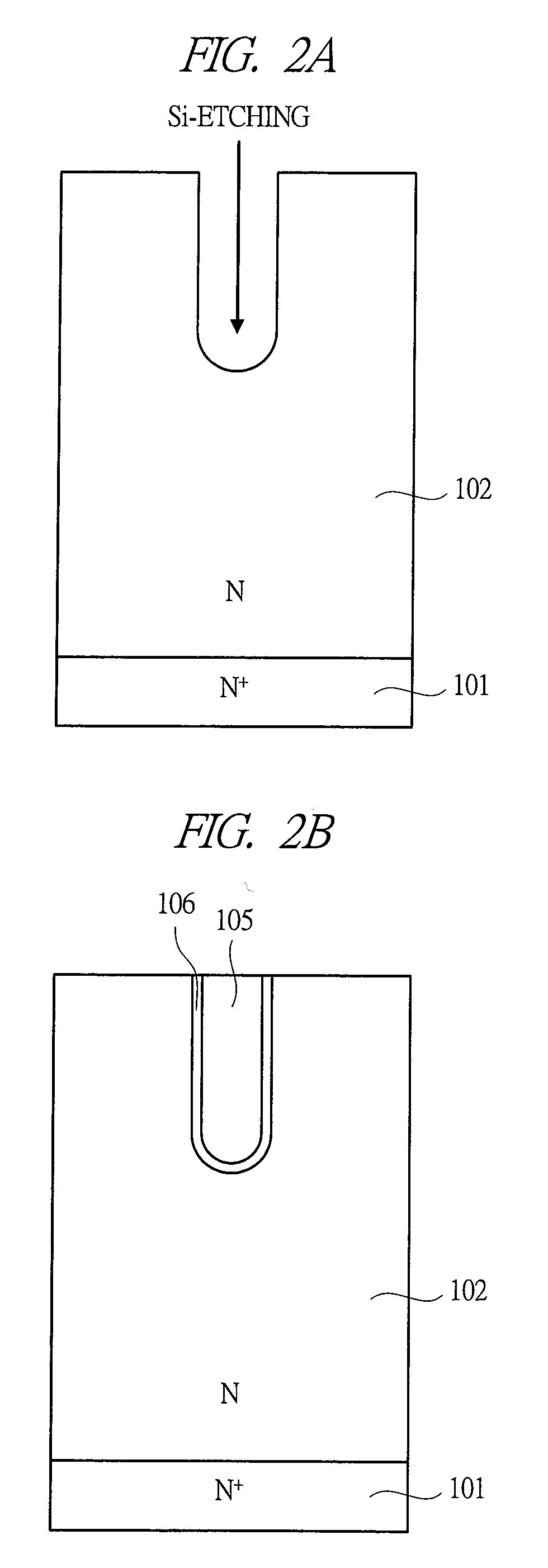

Method for manufacturing semiconductor device

ActiveUS20080038850A1Reduce manufacturing costReduce time costSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringSemiconductor

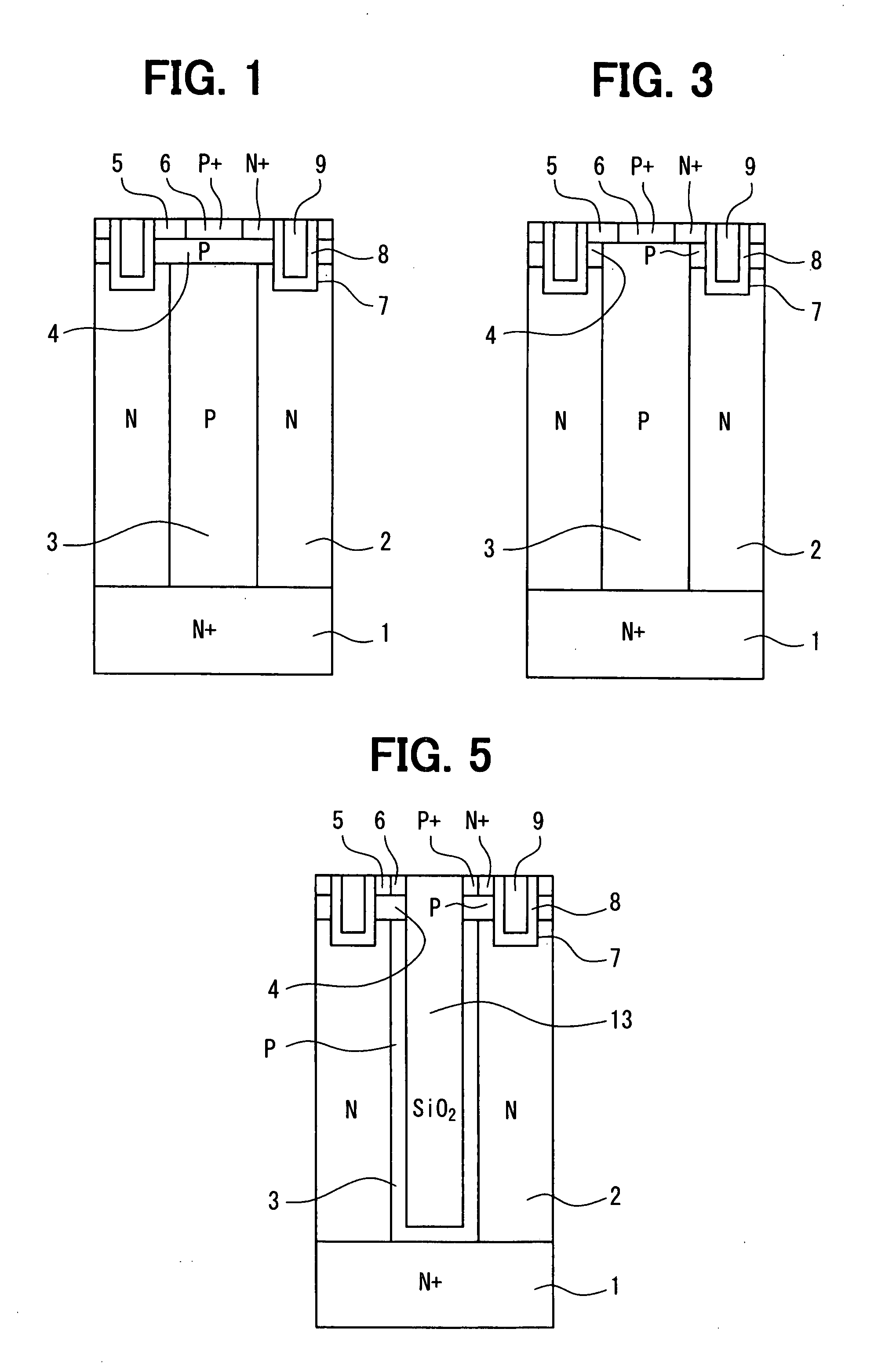

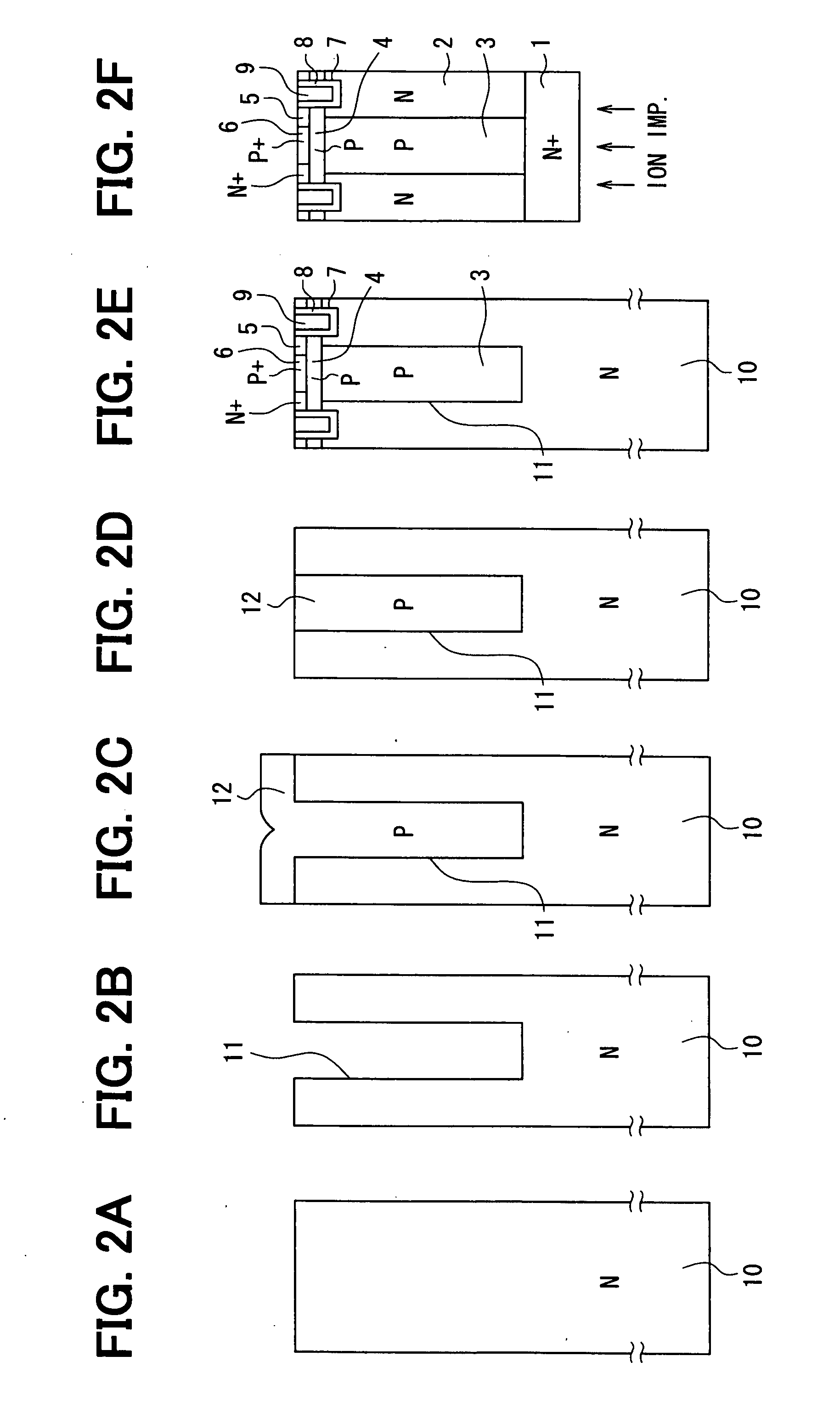

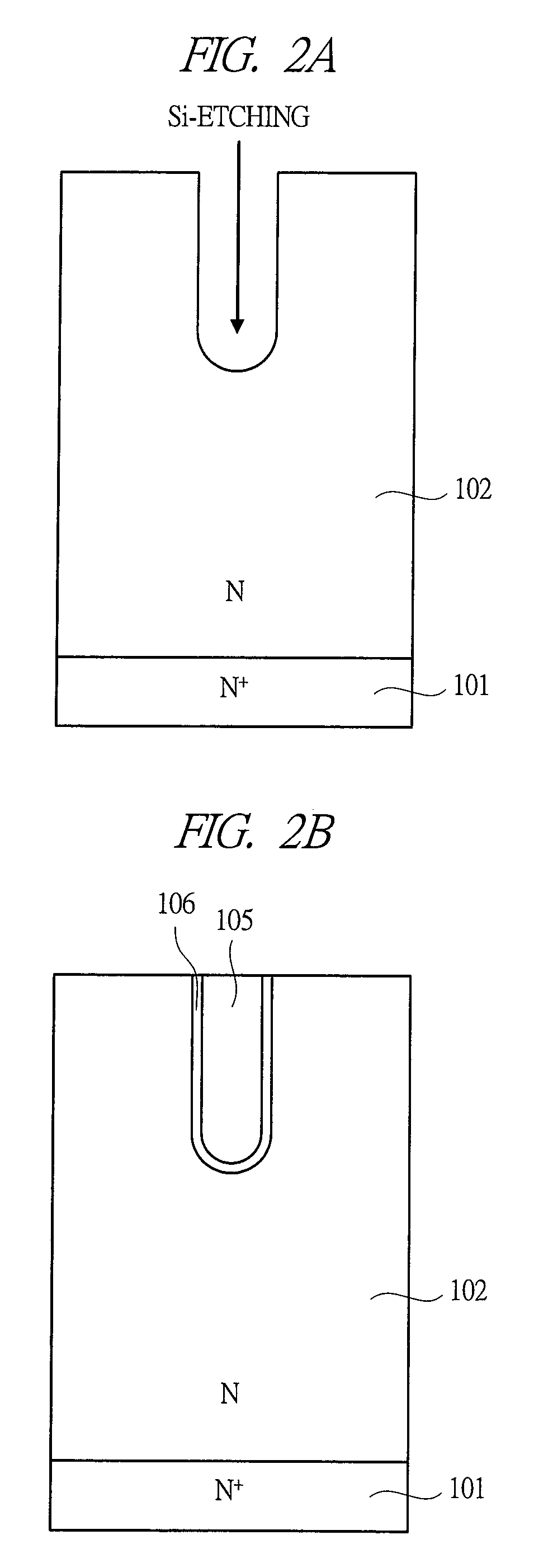

A manufacturing method of a semiconductor device includes: forming multiple trenches on a semiconductor substrate; forming a second conductive type semiconductor film in each trench to provide a first column with the substrate between two trenches and a second column with the second conductive type semiconductor film in the trench, the first and second columns alternately repeated along with a predetermined direction; thinning a second side of the substrate; and increasing an impurity concentration in a thinned second side so that a first conductive type layer is provided. The impurity concentration of the first conductive type layer is higher than the first column. The first column provides a drift layer so that a vertical type first-conductive-type channel transistor is formed.

Owner:DENSO CORP

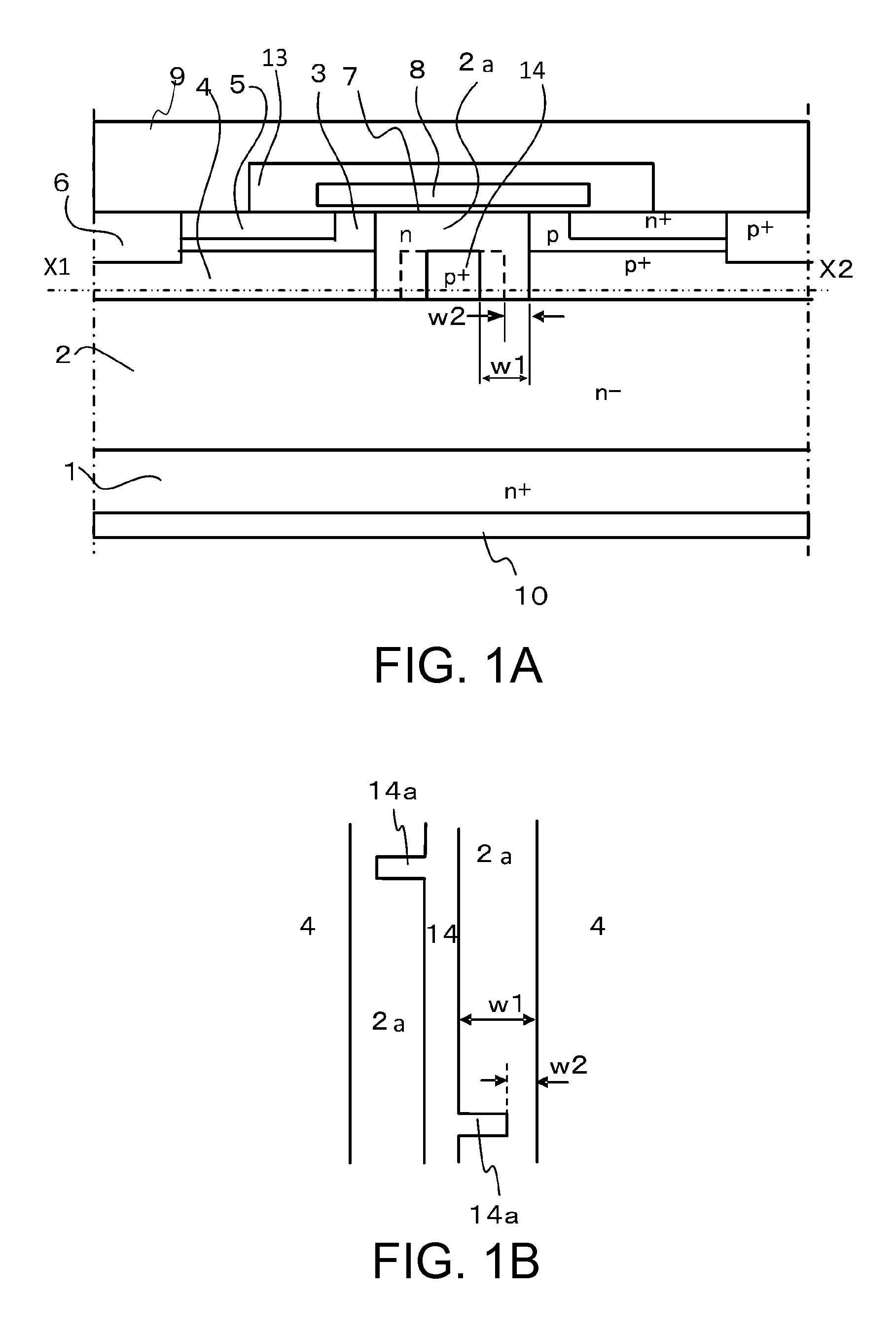

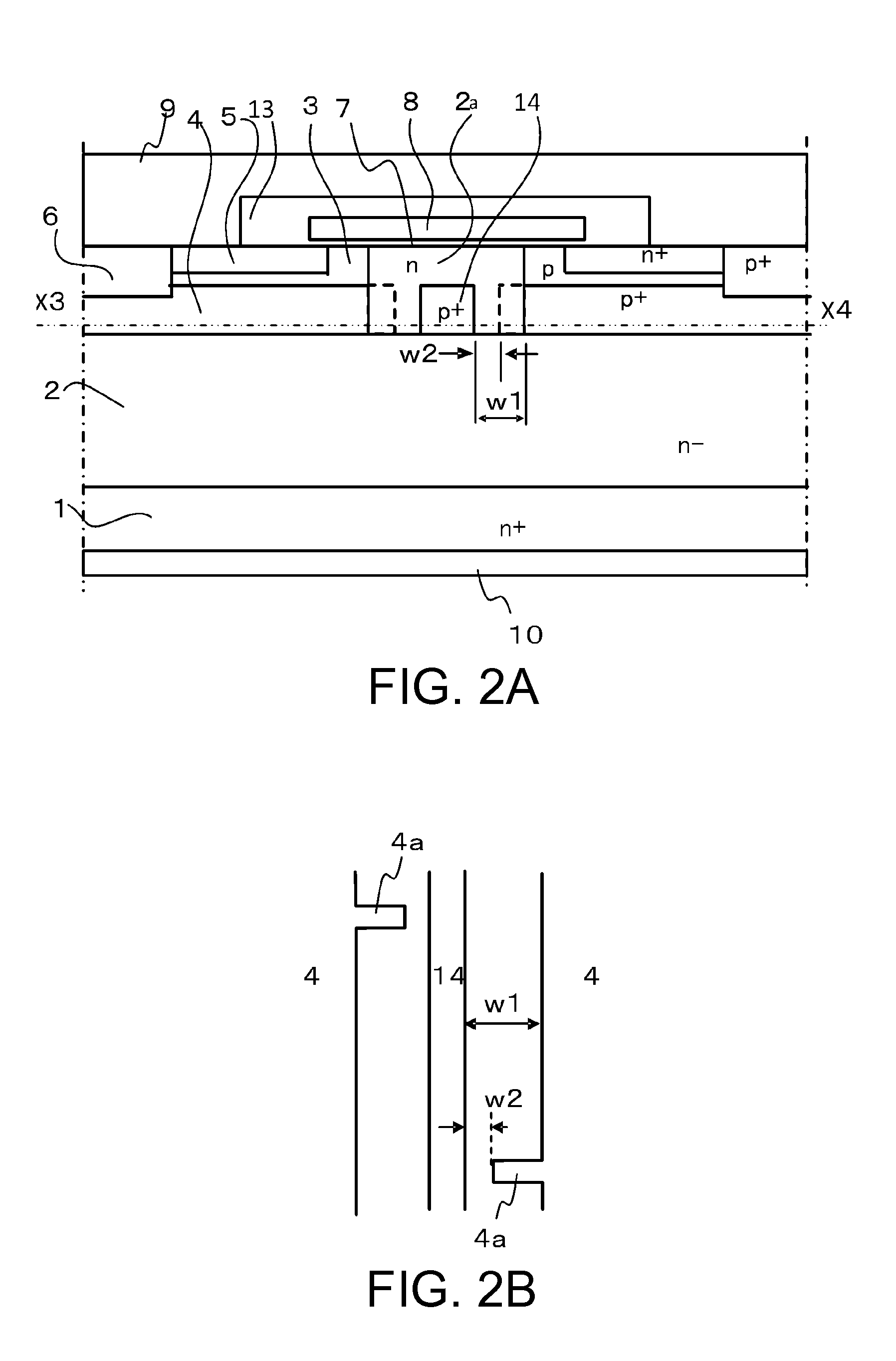

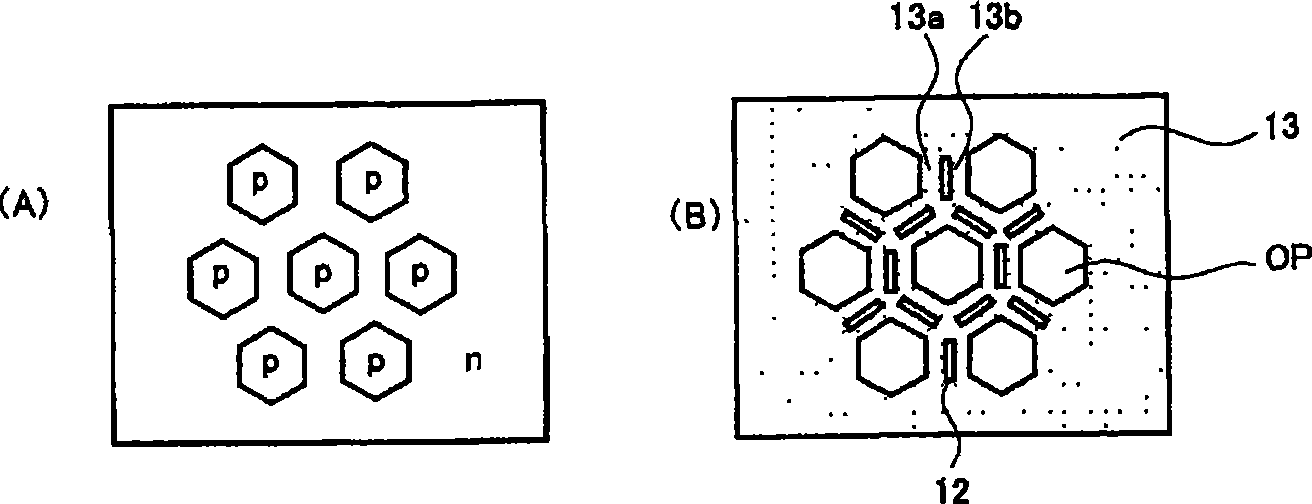

Wide bandgap insulated gate semiconductor device

ActiveUS20150053999A1Increase impurity concentrationReduce thicknessSemiconductor devicesDevice materialEngineering

A wide bandgap insulated gate semiconductor device includes a semiconductor substrate made of semiconductor having a bandgap wider than silicon; n− drift layer over the semiconductor substrate; p-channel regions selectively disposed over the drift layer; n+ semiconductor regions selectively disposed in respective surfaces in the channel regions; a plurality of p+ base regions in contact with bottoms of the respective channel regions; a protruding drift layer portion that is n-type region interposed between the p-channel regions and the p+ base regions thereunder; a gate electrode formed, through a gate insulating film, on the protruding drift layer portion and on respective surfaces of the p-channel regions; a source electrode in contact with the n+ semiconductor regions in the channel regions; and a p+ floating region inside the protruding drift layer portion, having side faces respectively facing side faces of the second conductivity type base regions, wherein respective gaps between the p+ base regions and the p+ floating region defined by the respective side faces have a wide portion and a narrow portion.

Owner:FUJI ELECTRIC CO LTD

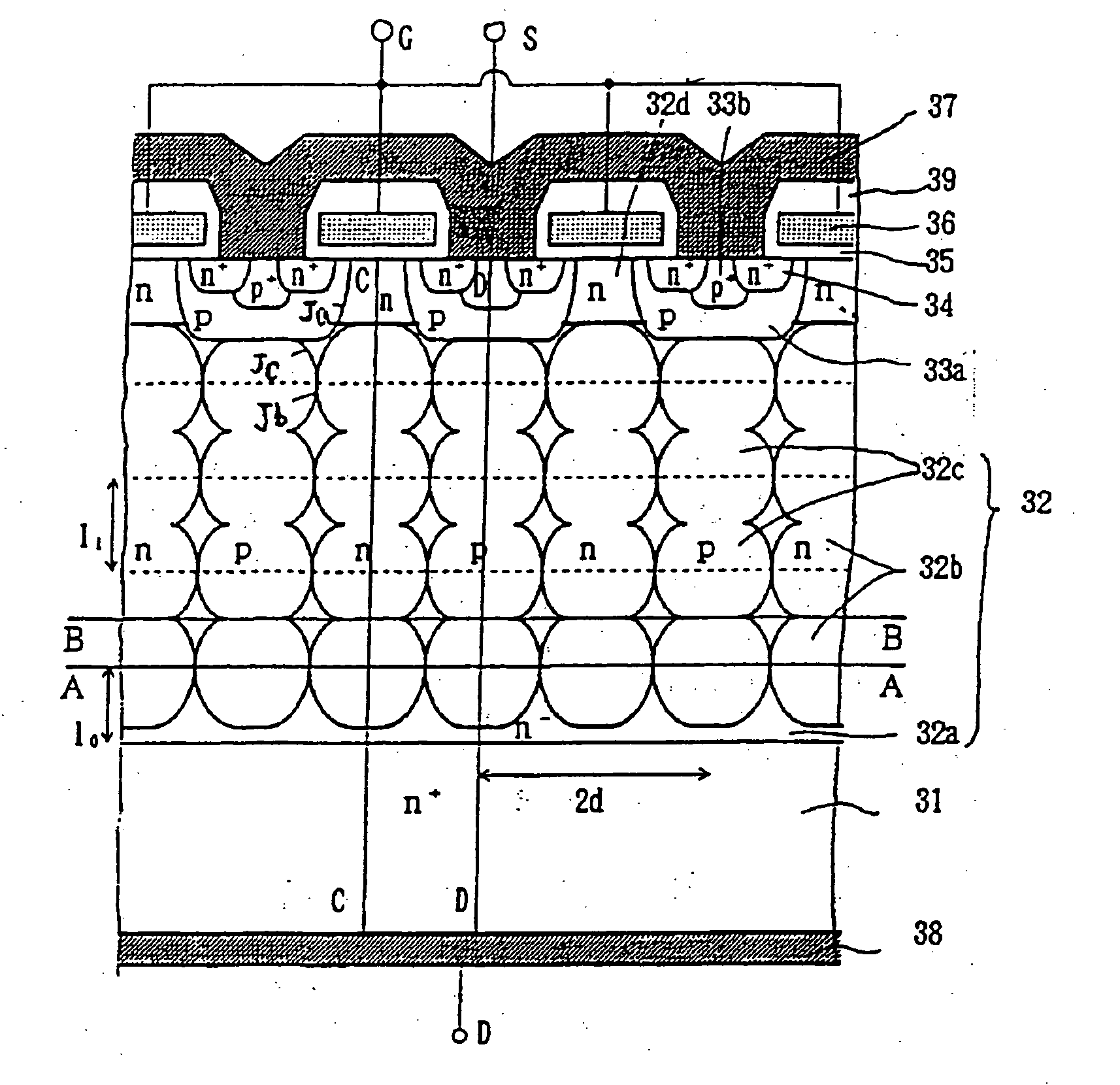

Semiconductor device with alternating conductivity type layer and method of manufacturing the same

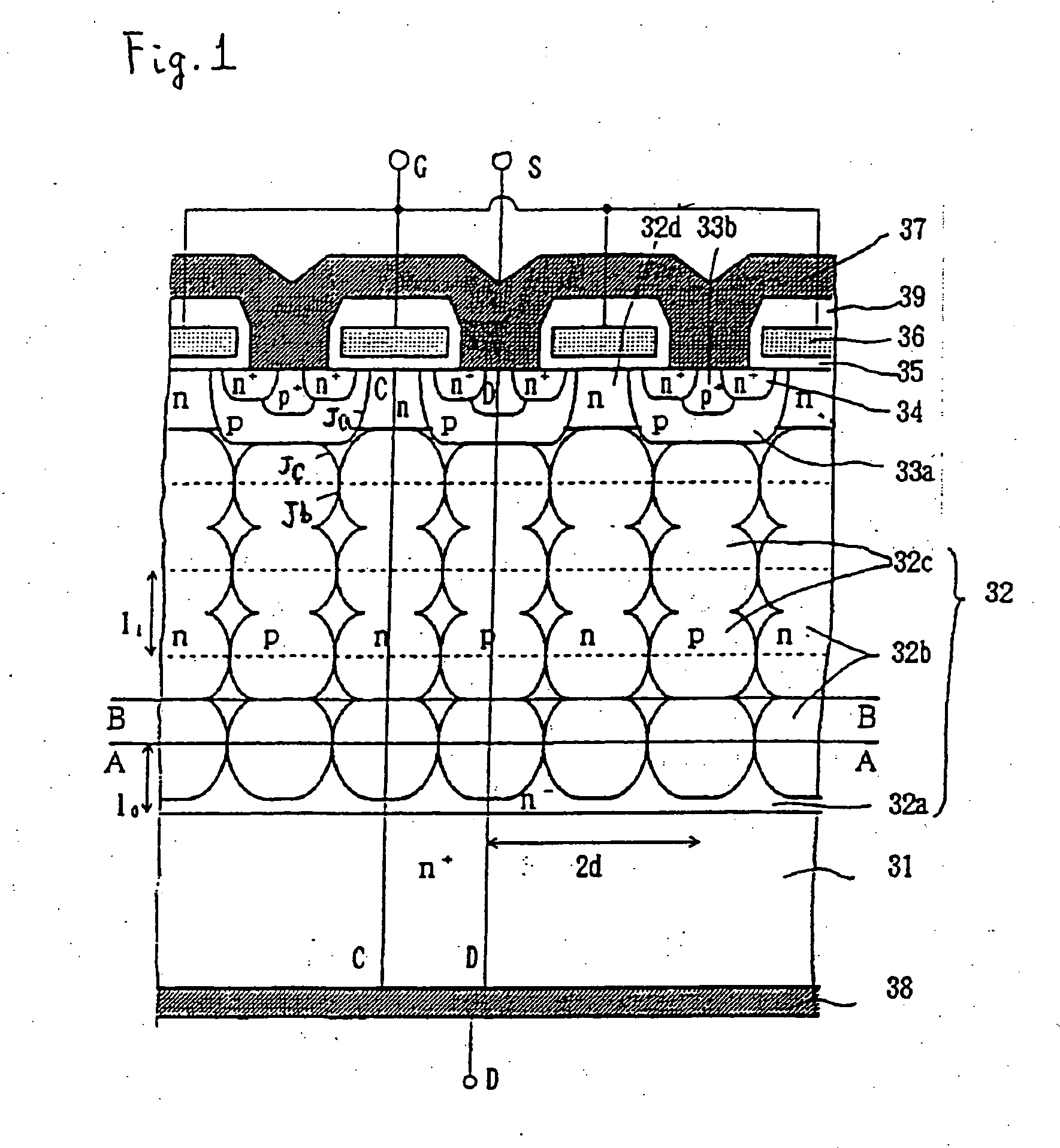

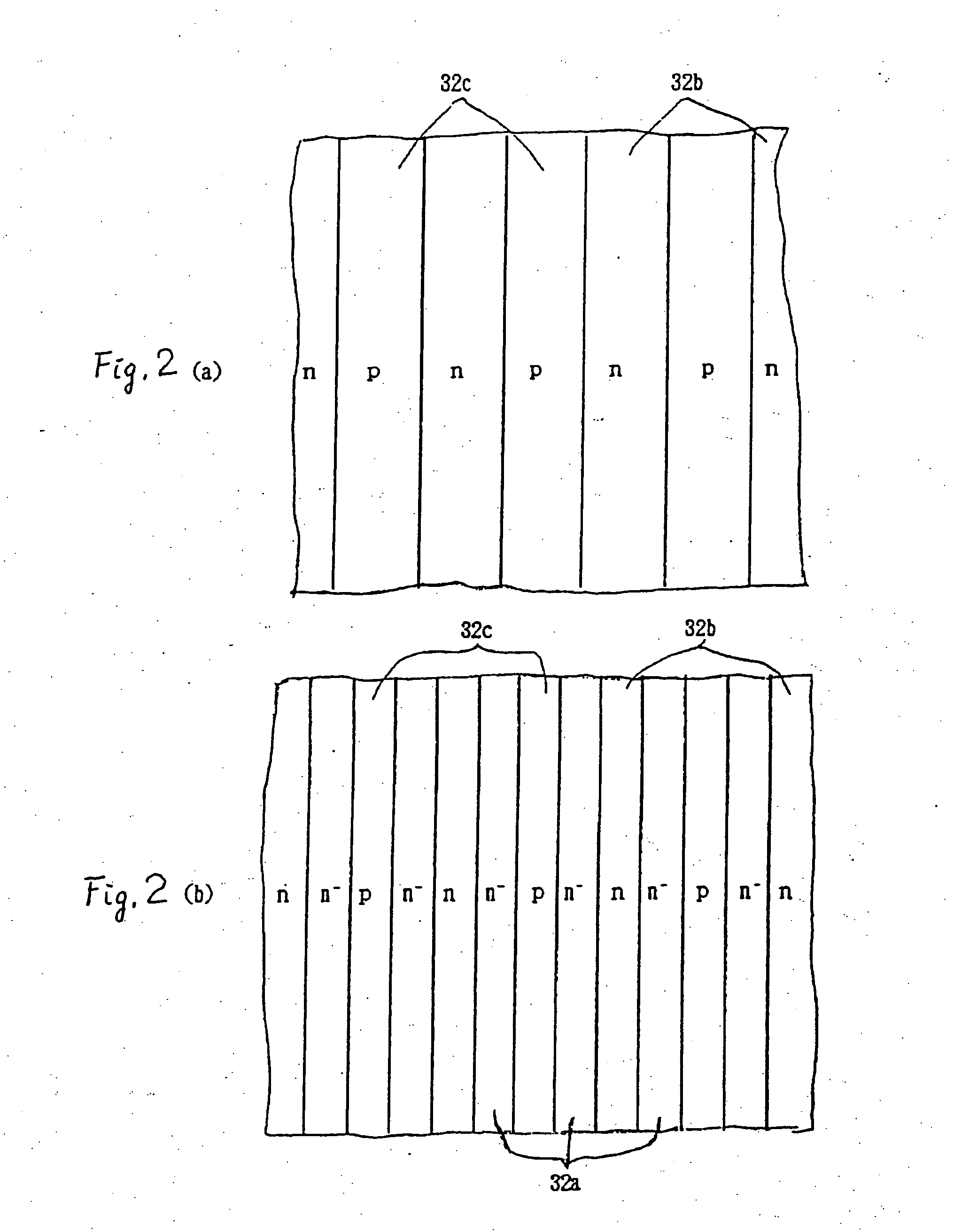

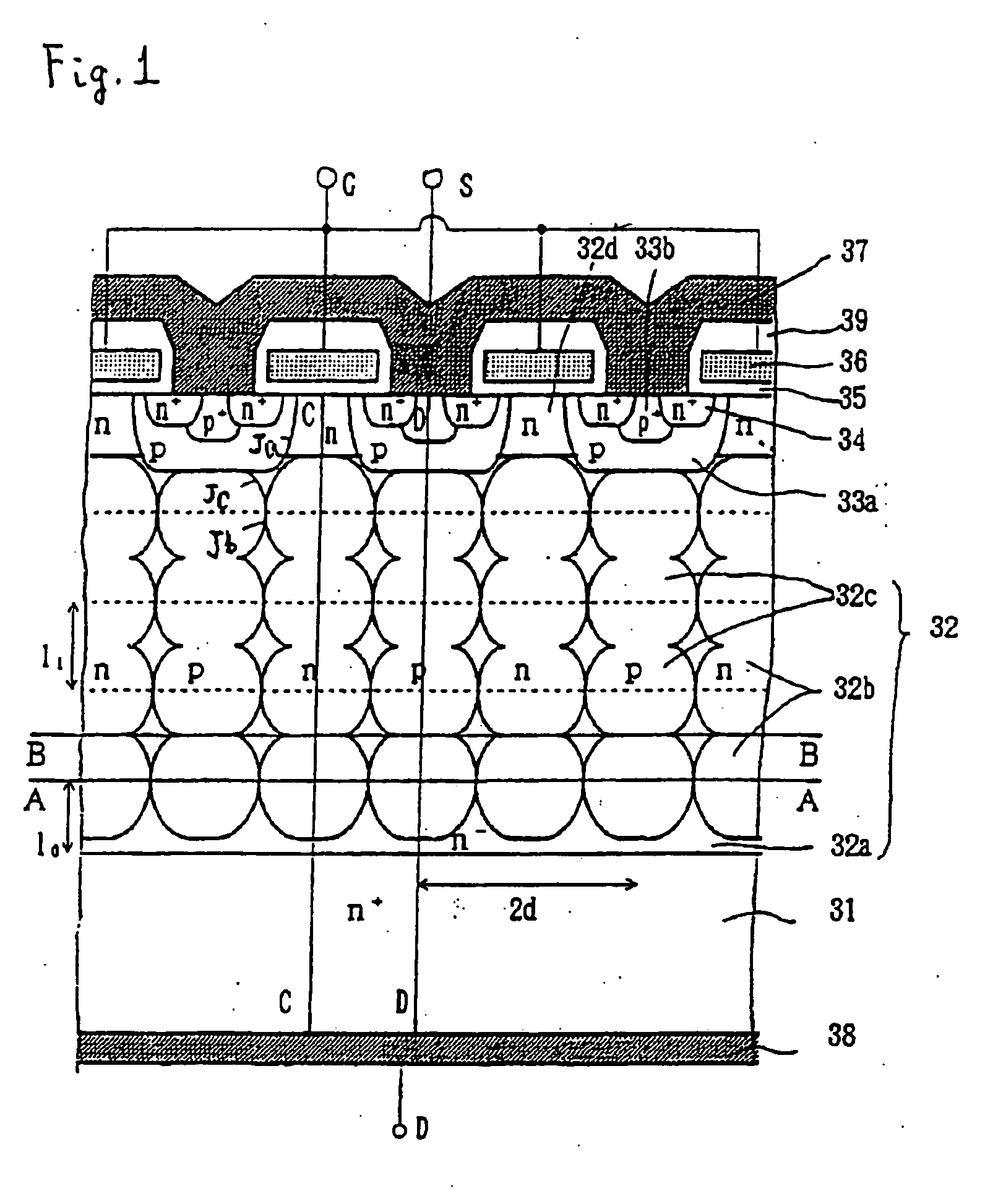

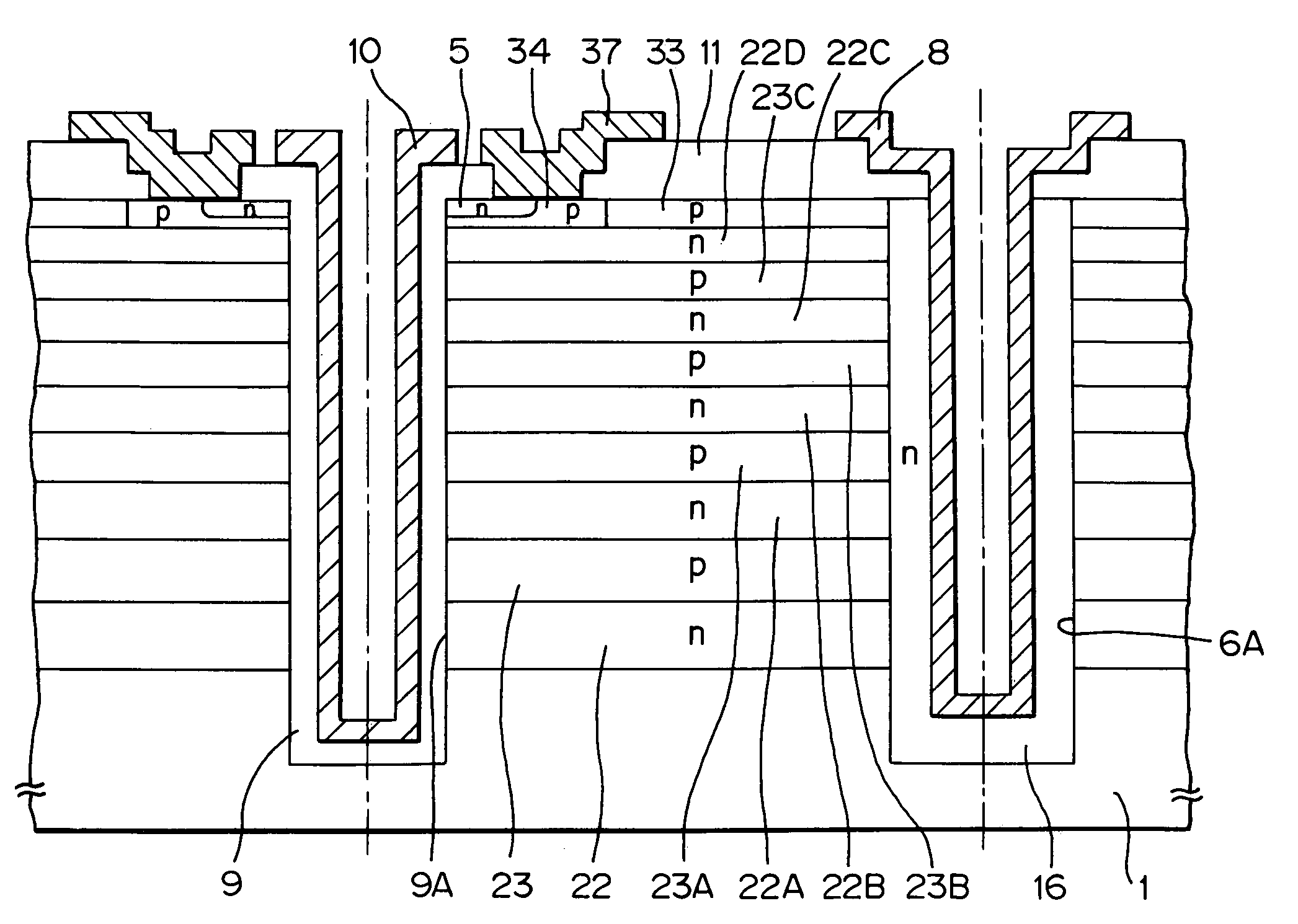

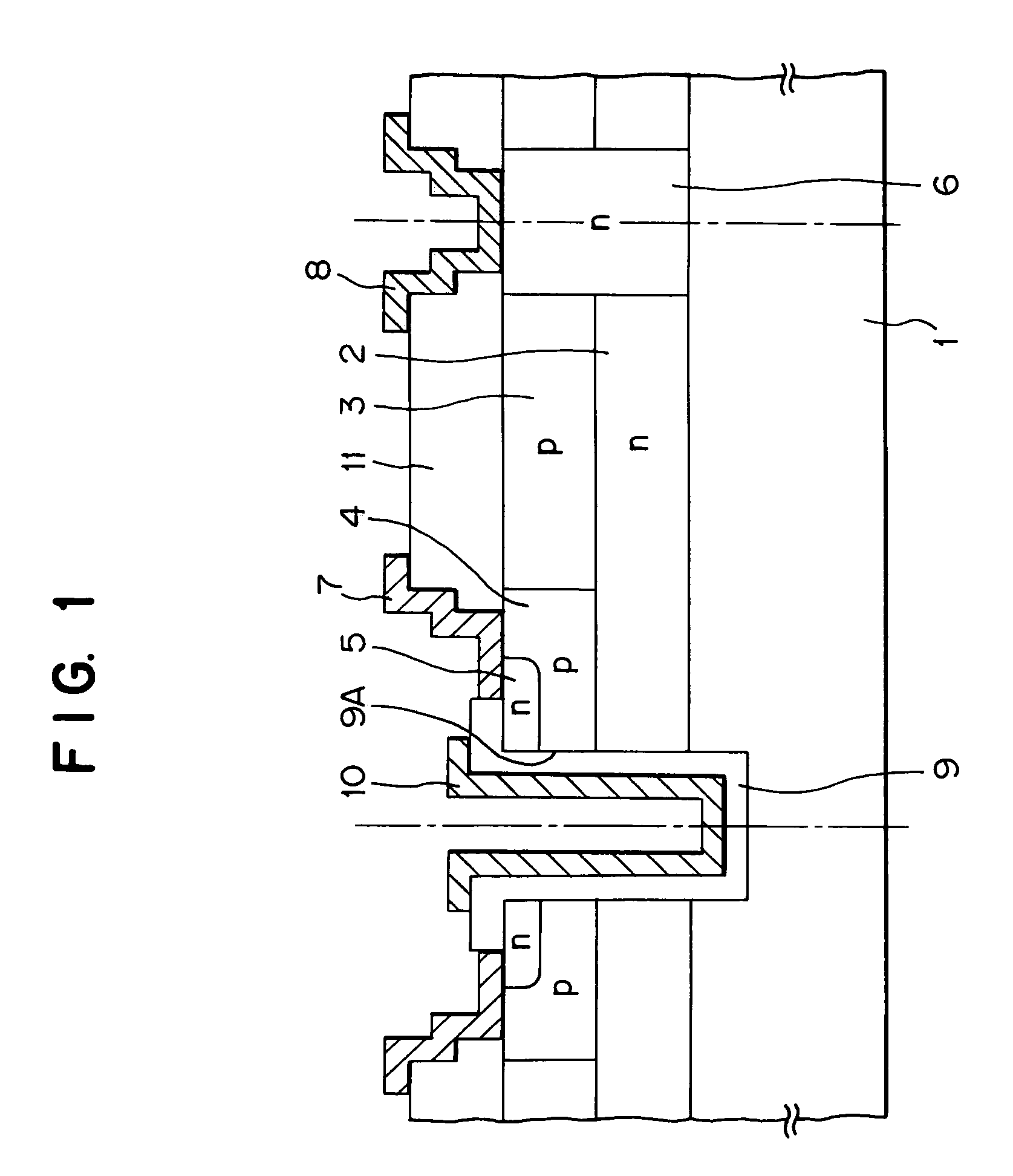

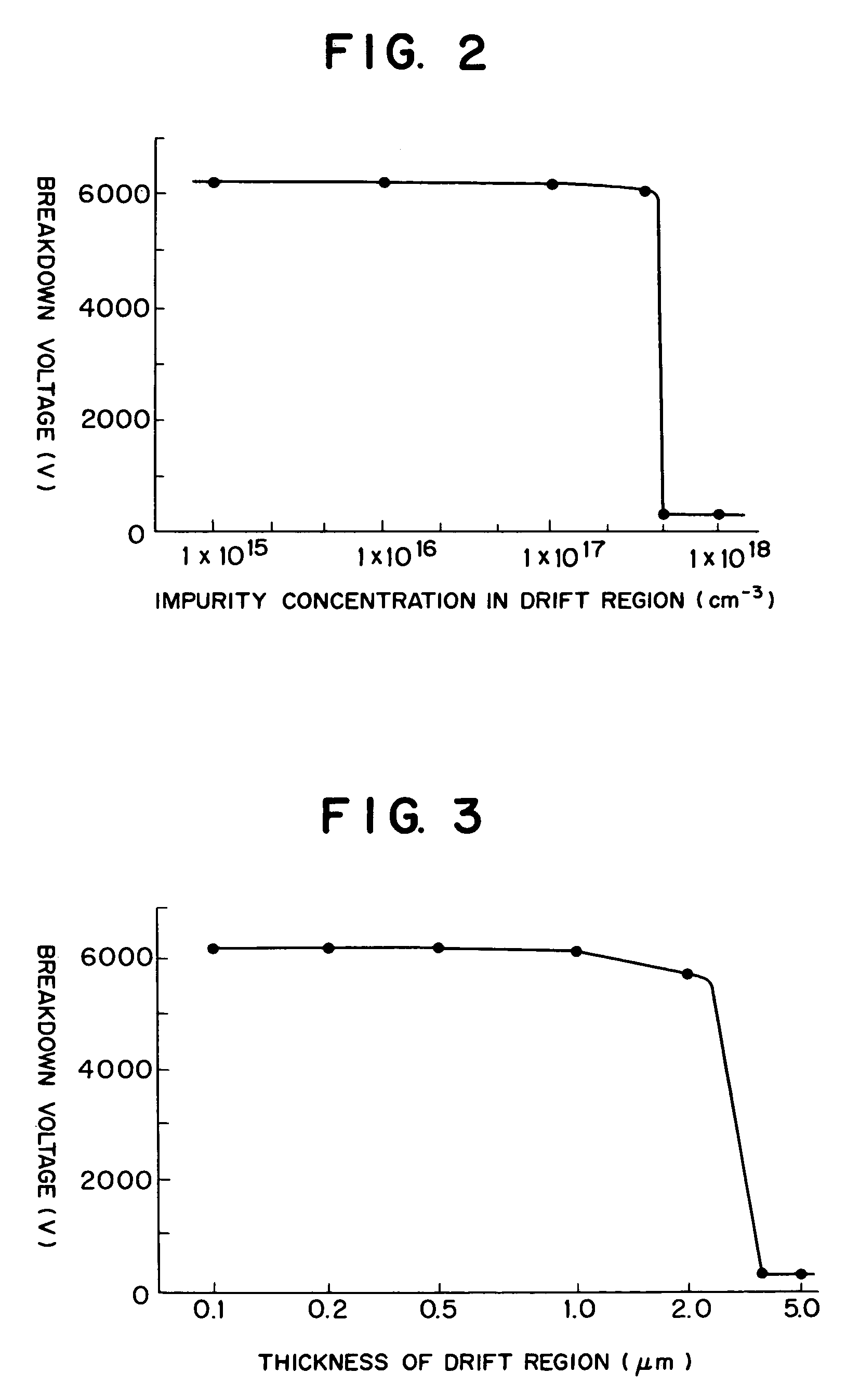

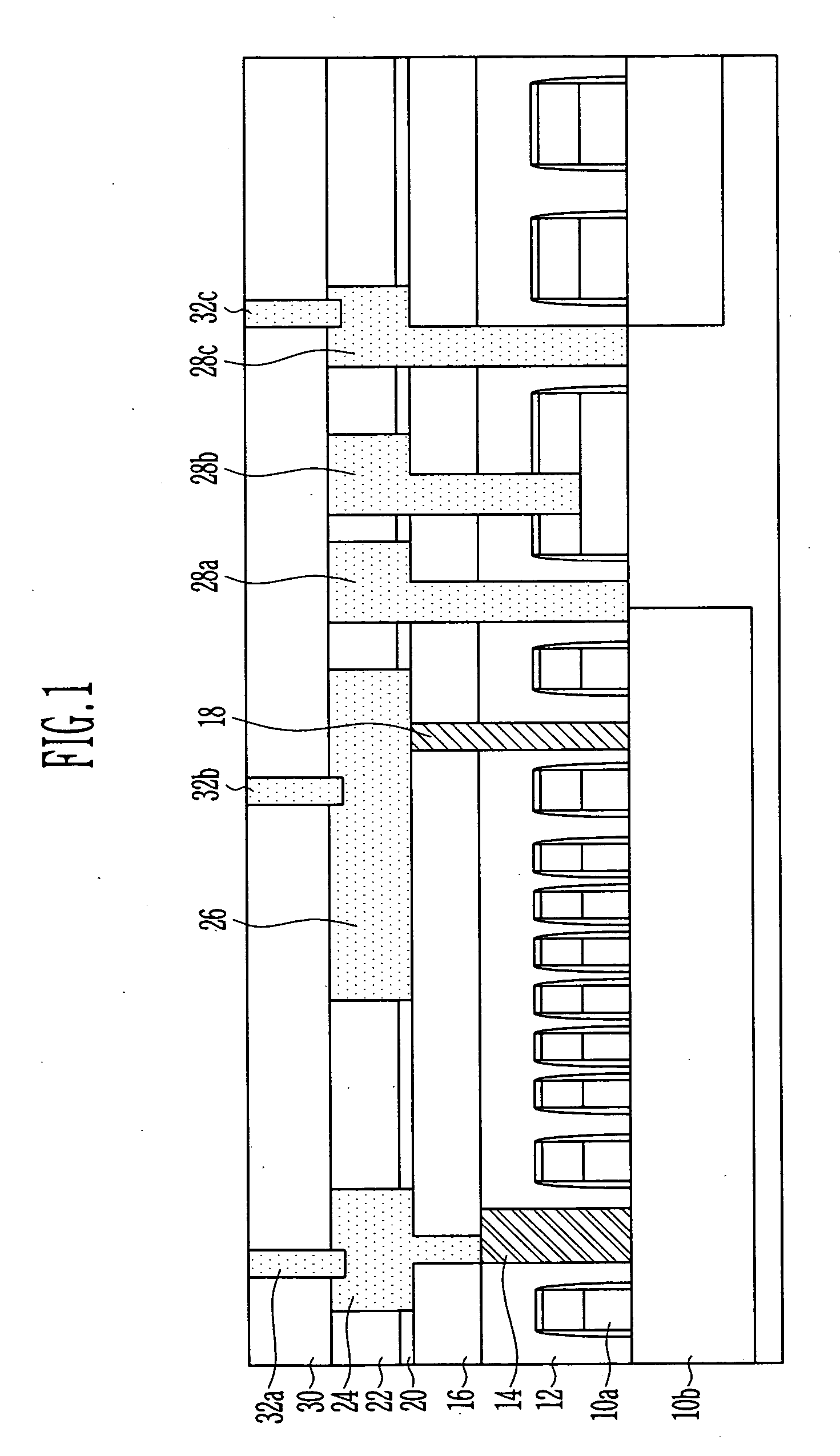

InactiveUS20050035371A1Easily manufactureLow resistanceTransistorSemiconductor/solid-state device manufacturingSemiconductorDevice material

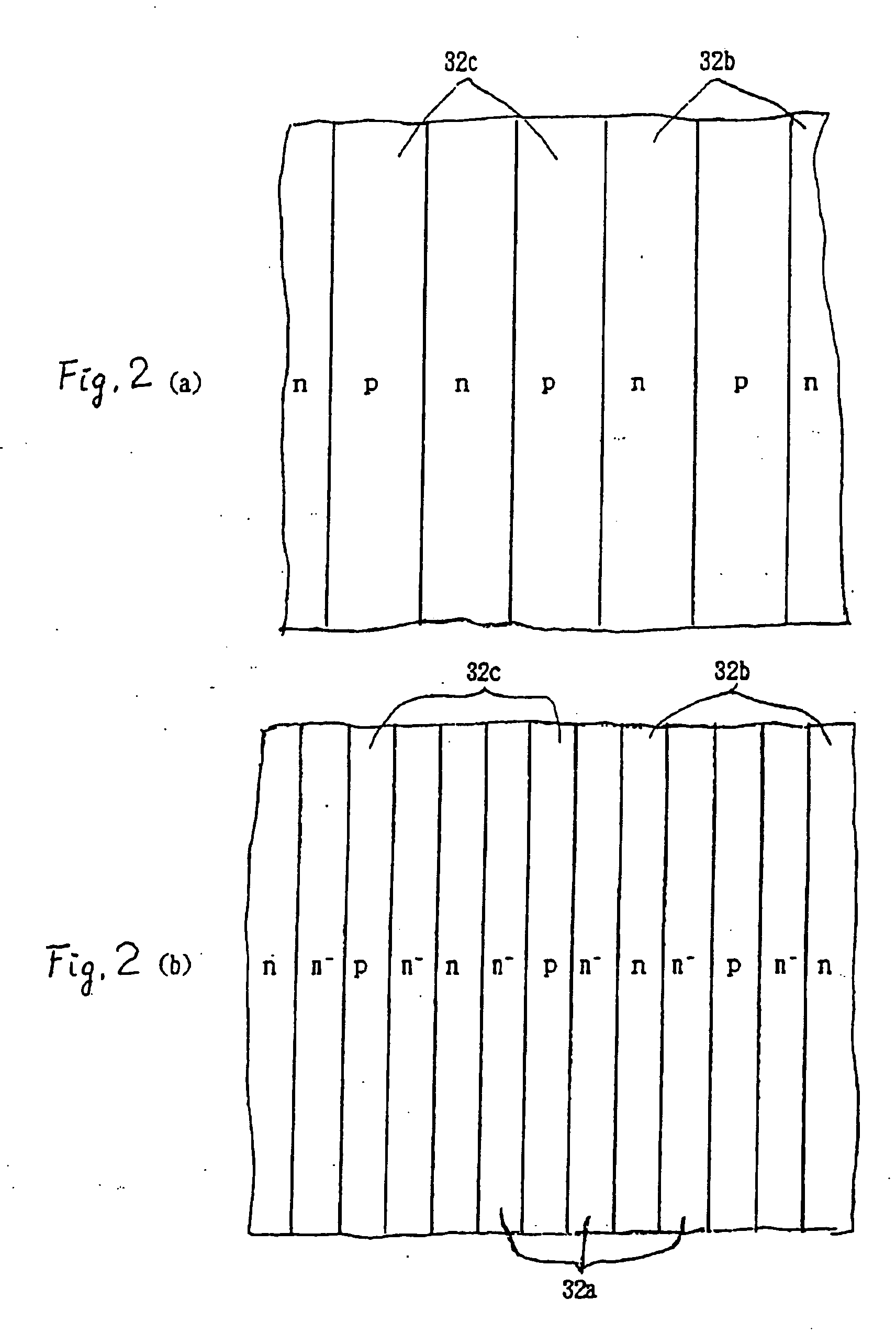

A semiconductor device having an alternating conductivity type layer improves the tradeoff between the on-resistance and the breakdown voltage and facilitates increasing the current capacity by reducing the on-resistance while maintaining a high breakdown voltage. The semiconductor device includes a semiconductive substrate region, through which a current flows in the ON-state of the device and that is depleted in the OFF-state. The semiconductive substrate region includes a plurality of vertical alignments of n-type buried regions 32 and a plurality of vertical alignments of p-type buried regions. The vertically aligned n-type buried regions and the vertically aligned p-type buried regions are alternately arranged horizontally. The n-type buried regions and p-type buried regions are formed by diffusing respective impurities into highly resistive n-type layers 32a laminated one by one epitaxially.

Owner:FUJI ELECTRIC CO LTD

Semiconductor device with alternating conductivity type layer and method of manufacturing the same

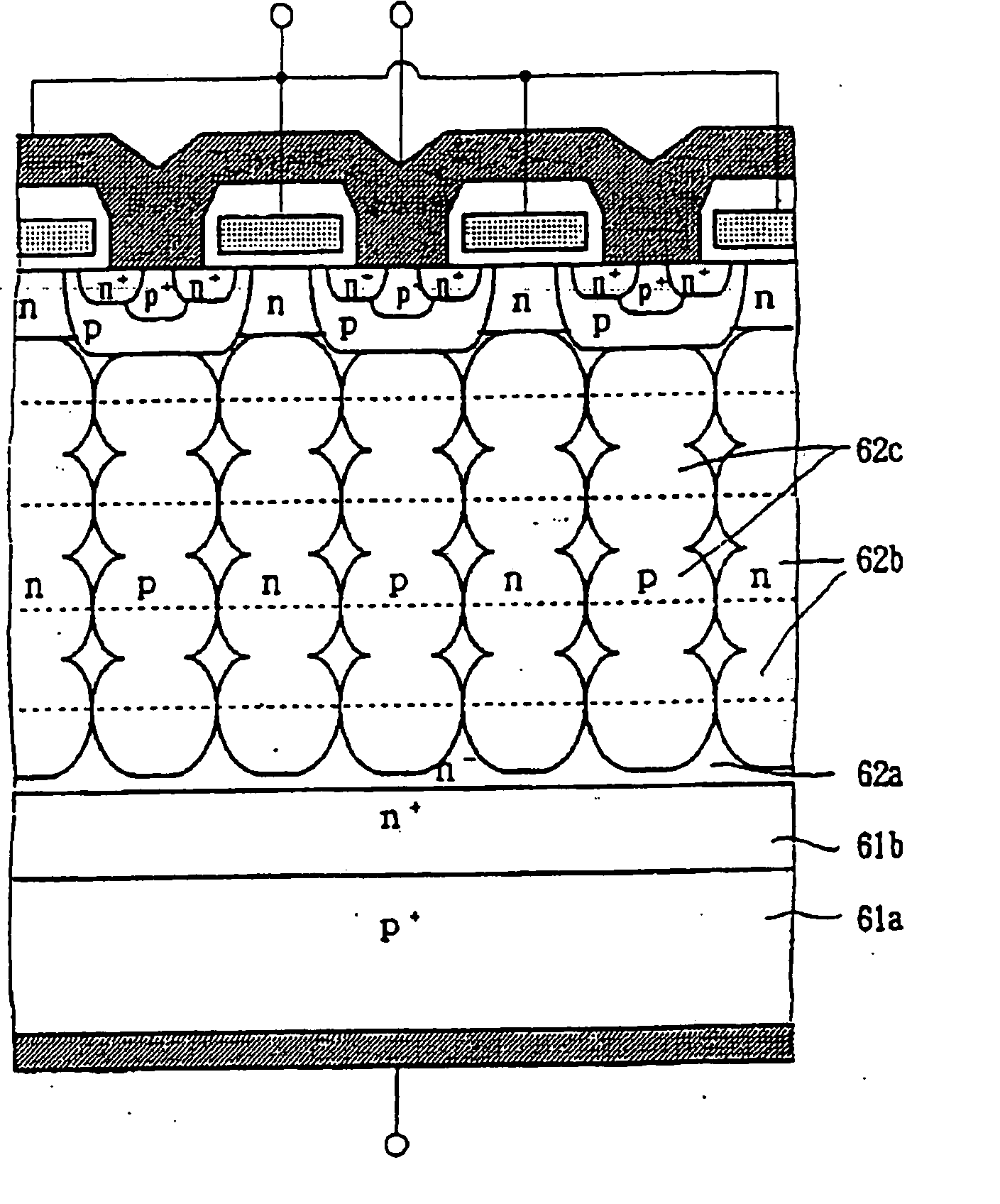

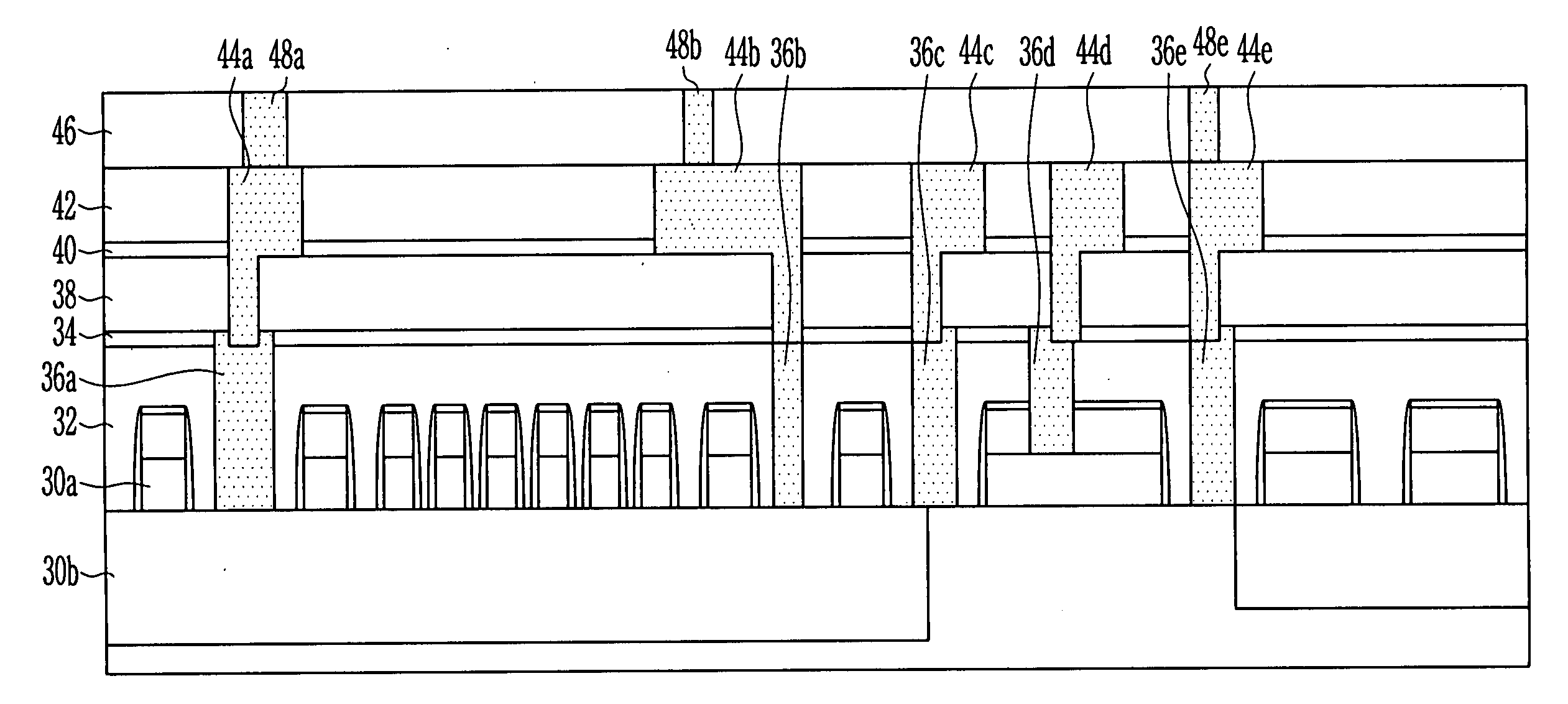

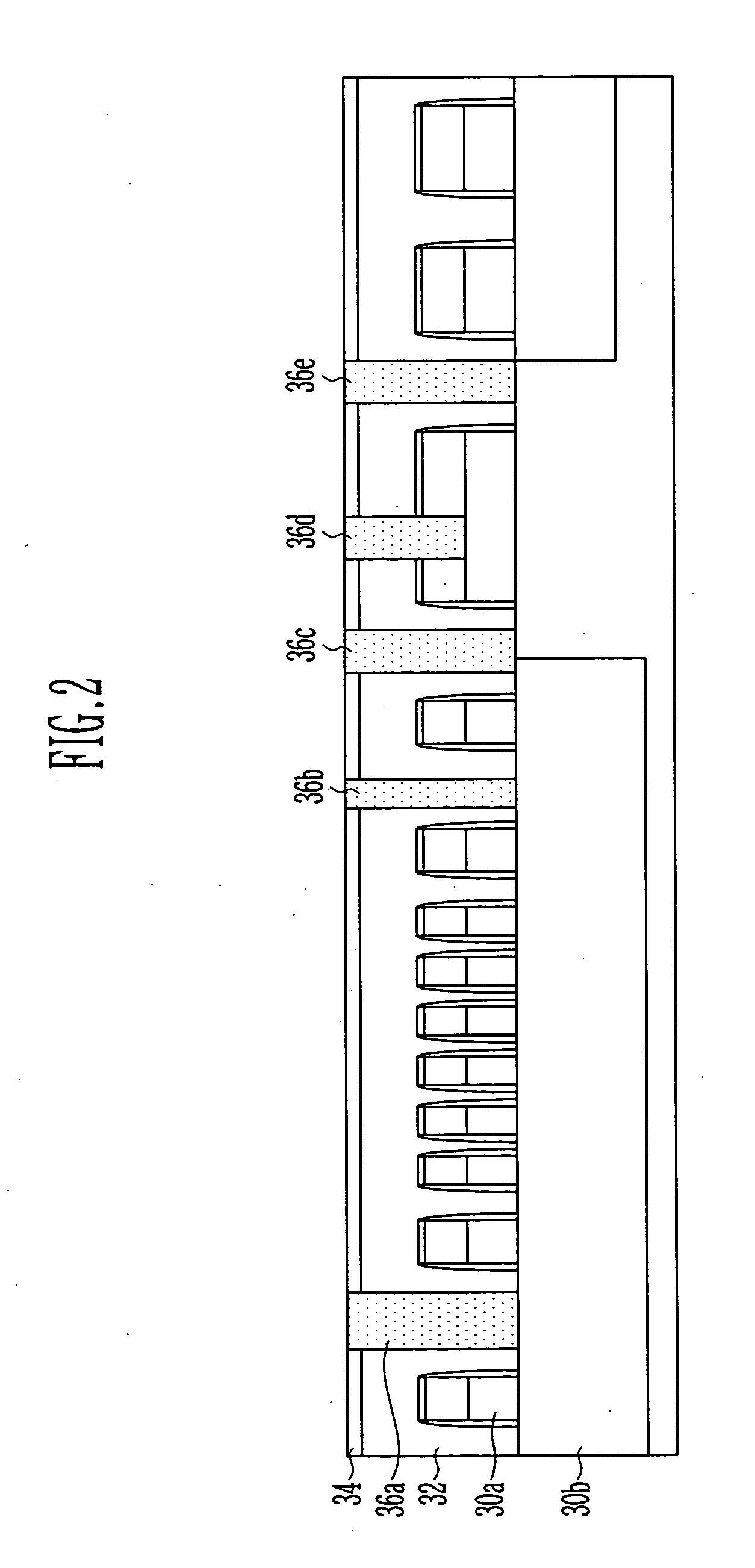

InactiveUS20050156235A1Reduces tradeoff relationImprove batch productivityTransistorSemiconductor/solid-state device manufacturingDevice materialVertical alignment

A semiconductor device having an alternating conductivity type layer improves the tradeoff between the on-resistance and the breakdown voltage and facilitates increasing the current capacity by reducing the on- resistance while maintaining a high breakdown voltage. The semiconductor device includes a semiconductive substrate region, through which a current flows in the ON-state of the device and that is depleted in the OFF-state. The semiconductive substrate region includes a plurality of vertical alignments of n-type buried regions 32 and a plurality of vertical alignments of p-type buried regions. The vertically aligned n-type buried regions and the vertically aligned p-type buried regions are alternately arranged horizontally. The n-type buried regions and p-type buried regions are formed by diffusing respective impurities into highly resistive n-type layers 32a laminated one by one epitaxially.

Owner:FUJI ELECTRIC CO LTD

Method of manufacturing a semiconductor device with a vertical drain drift layer of the alternating-conductivity-type

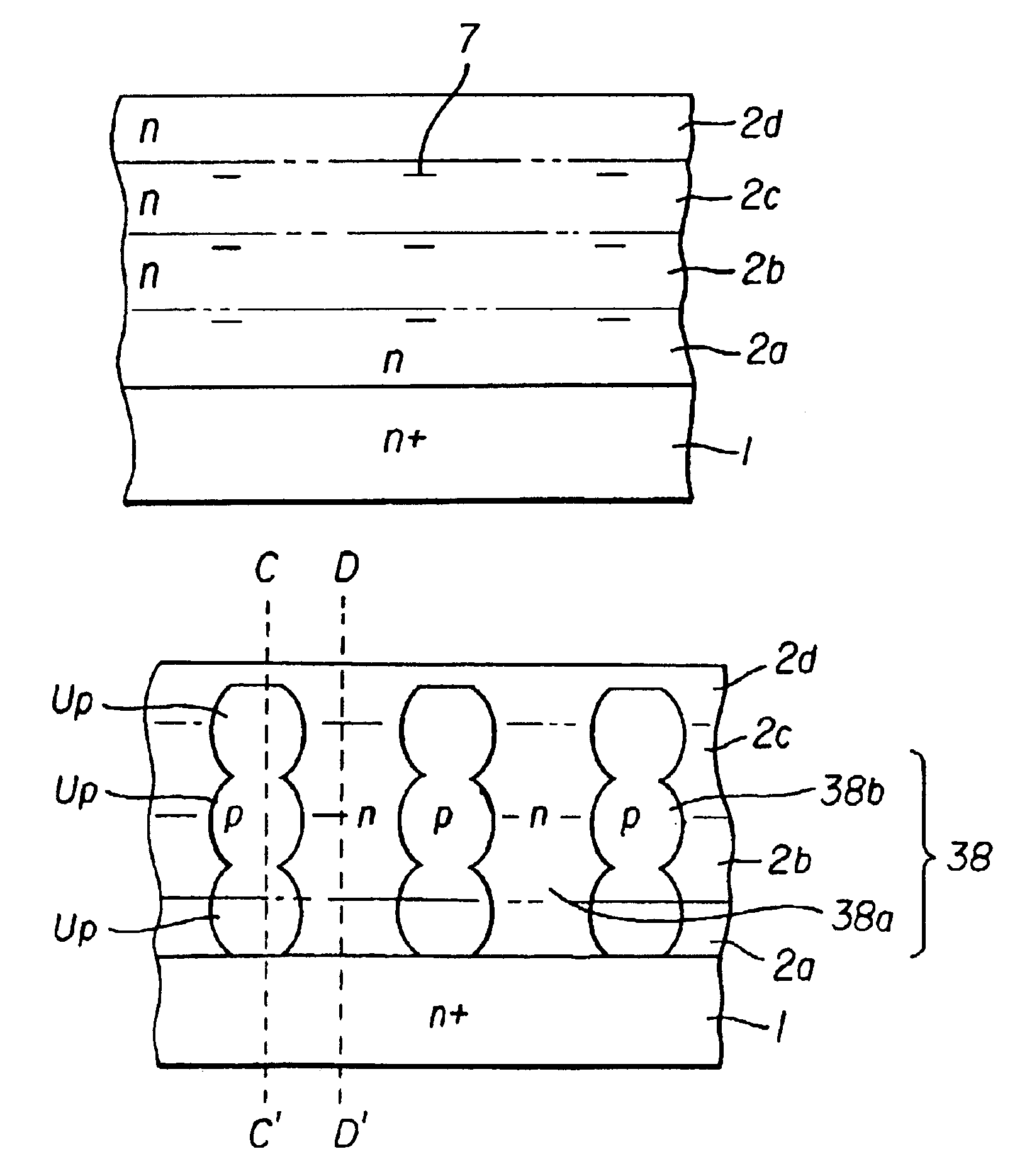

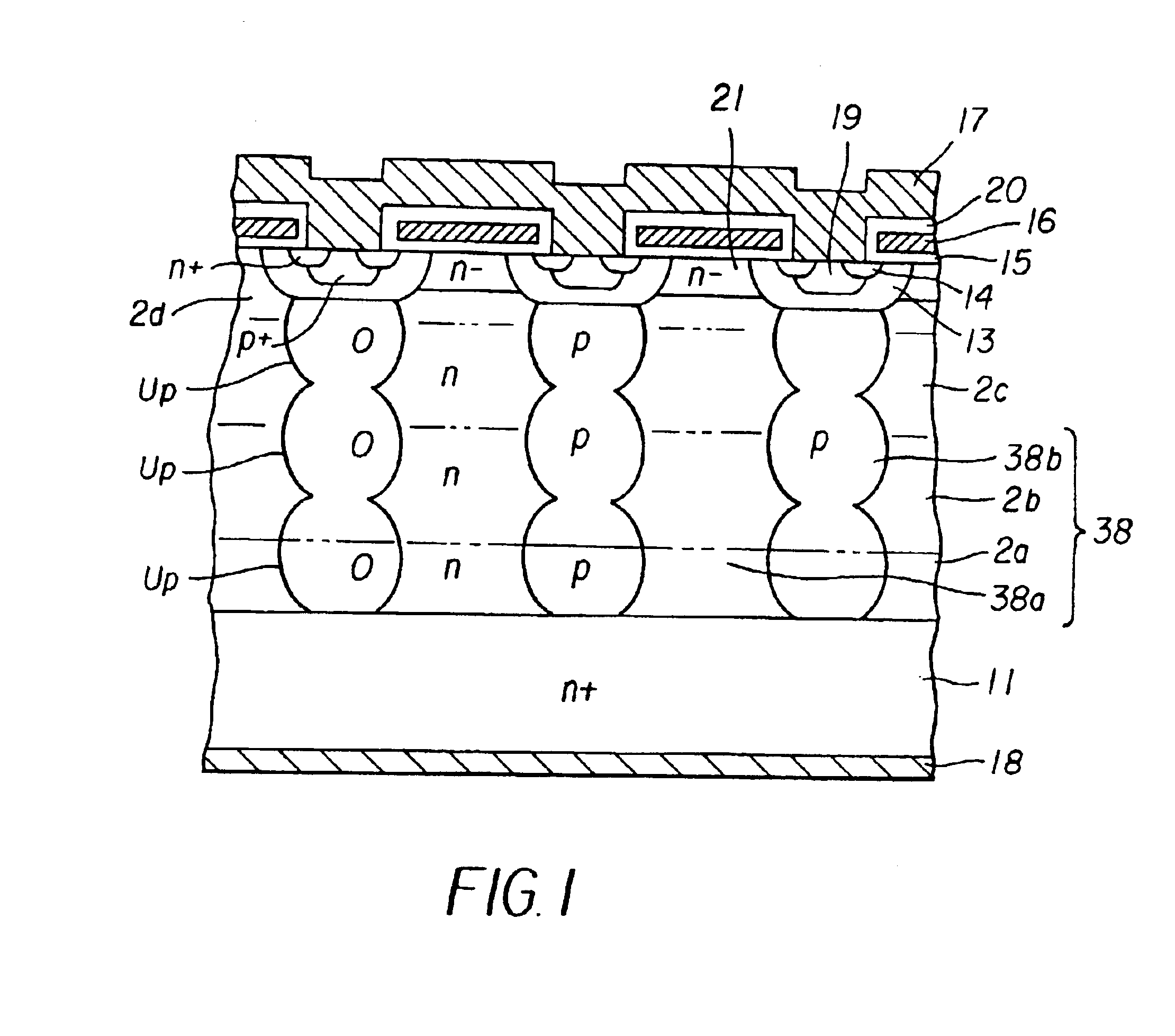

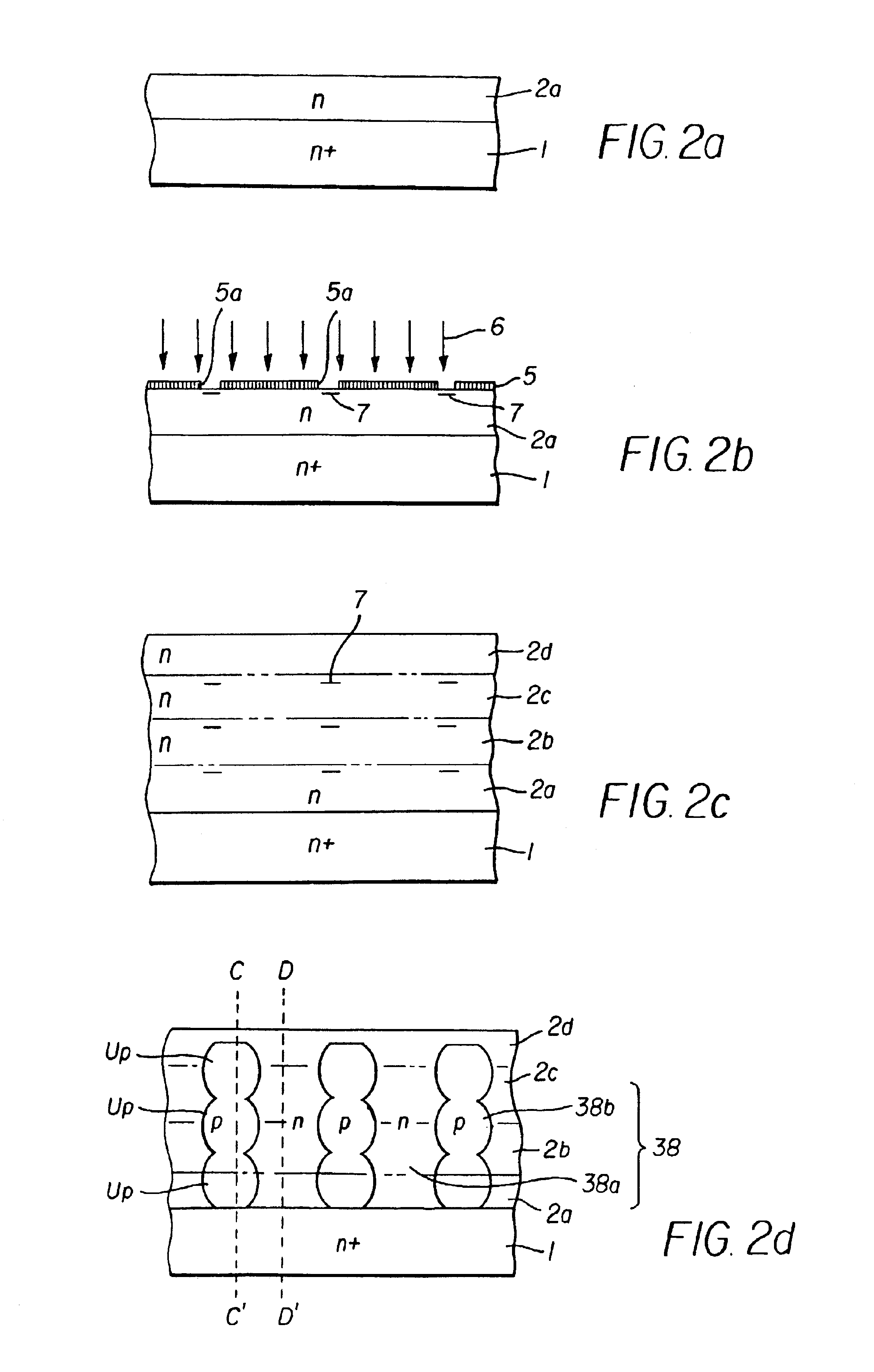

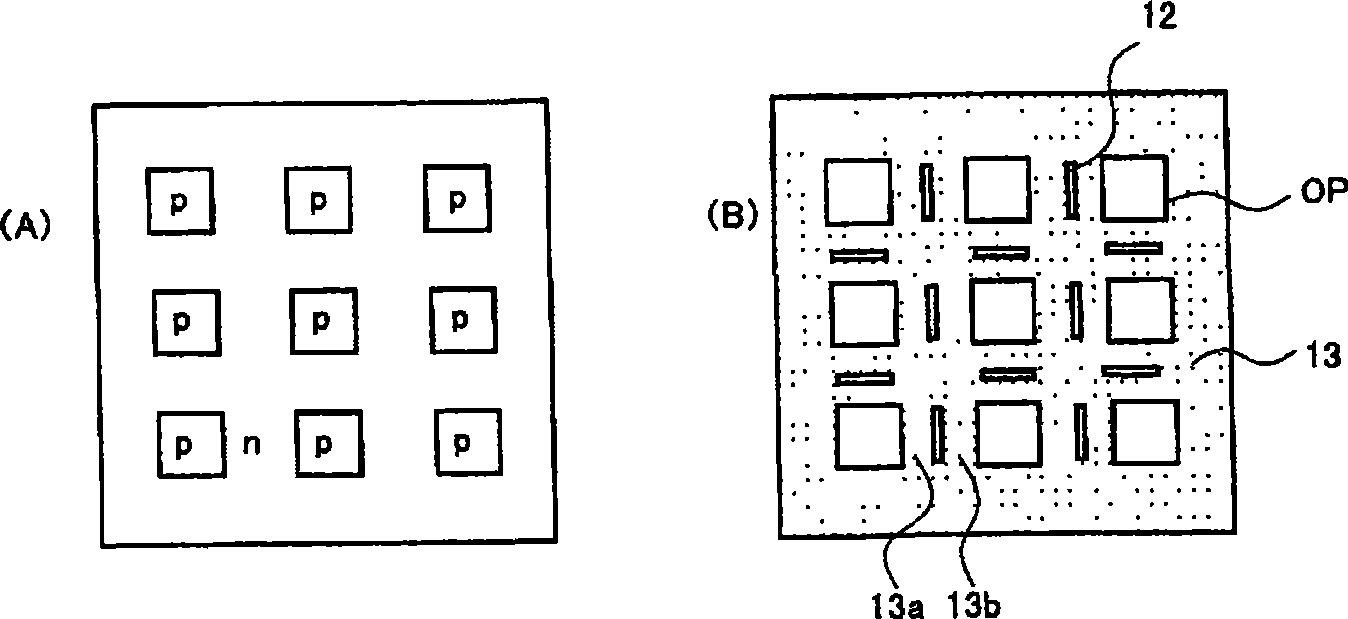

InactiveUS6900109B2High densityImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETImpurity ions

A semiconductor device includes an improved drain drift layer structure of alternating conductivity types, that is easy to manufacture, and that facilitates realizing a high current capacity and a high breakdown voltage and to provide a method of manufacturing the semiconductor device. The vertical MOSFET according to the invention includes an alternating-conductivity-type drain drift layer on an n+-type drain layer as a substrate. The alternating-conductivity-type drain drift layer is formed of n-type drift current path regions and p-type partition regions alternately arranged laterally with each other. The n-type drift current path regions and p-type partition regions extend in perpendicular to n+-type drain layer. Each p-type partition region is formed by vertically connecting p-type buried diffusion unit regions Up. The n-type drift current path regions are residual regions, left after connecting p-type buried diffusion unit regions Up, with the conductivity type thereof unchanged. The alternating-conductivity-type drain drift layer is formed by repeating the step of epitaxial layer growth and the step of implanting p-type impurity ions and by diffusing the impurity ions at once from the impurity sources located on multiple levels.

Owner:FUJI ELECTRIC CO LTD

High-voltage power semiconductor device with body regions of alternating conductivity and decreasing thickness

InactiveUS7470960B1Improve pressure resistanceLower on-resistanceTransistorThyristorPower semiconductor deviceElectrical resistance and conductance

A semiconductor device which eases an electric field at a drift portion without a reduction in impurity concentrations, and has a high withstand voltage and a low on-resistance, wherein, when a rated voltage is applied between a body region and a drain region formed on an insulating semiconductor substrate, the thicknesses of two, p-type and n-type, drift regions sandwiched between the body and drain regions are selected so as to completely deplete the drift regions.

Owner:THE KANSAI ELECTRIC POWER CO

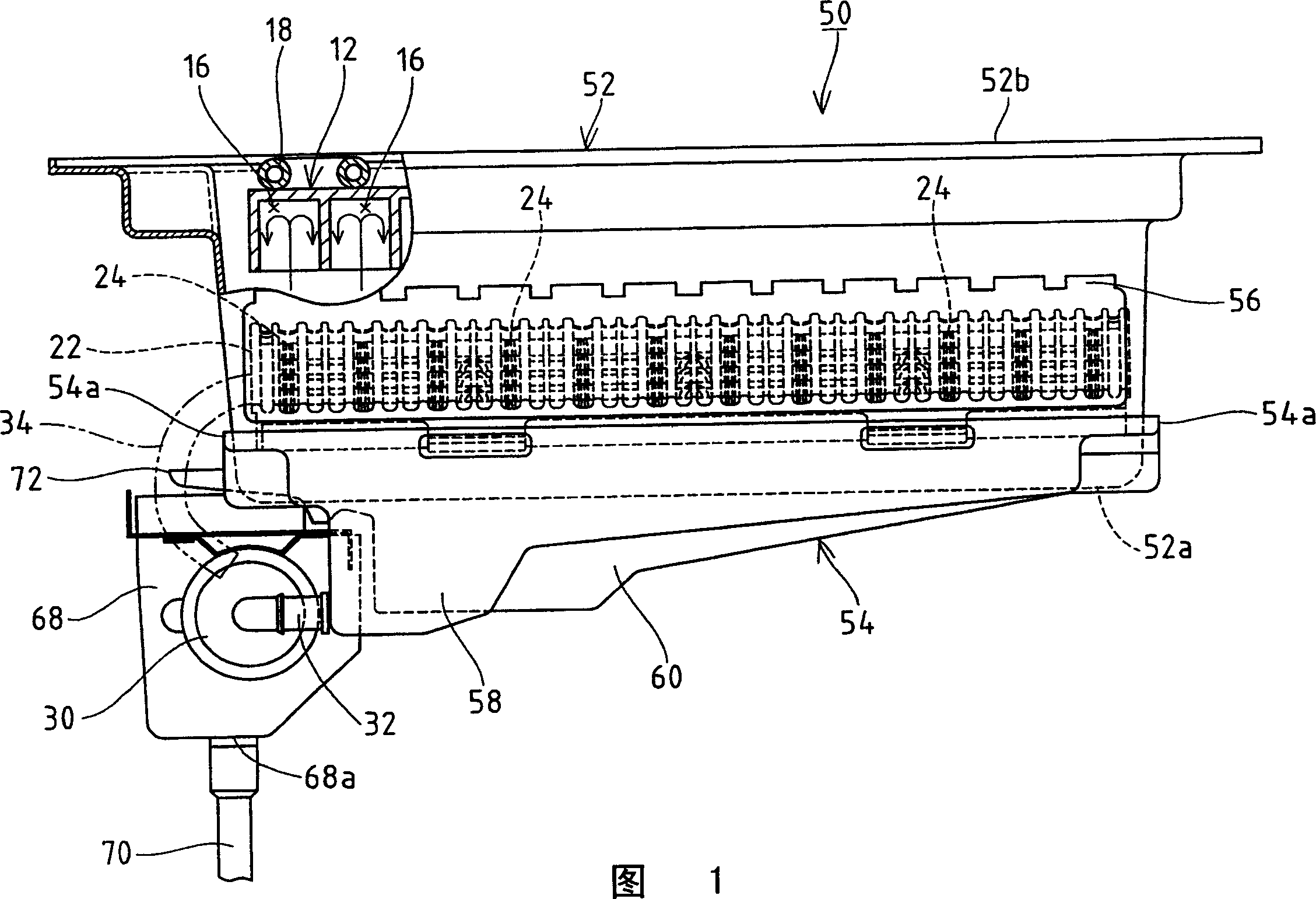

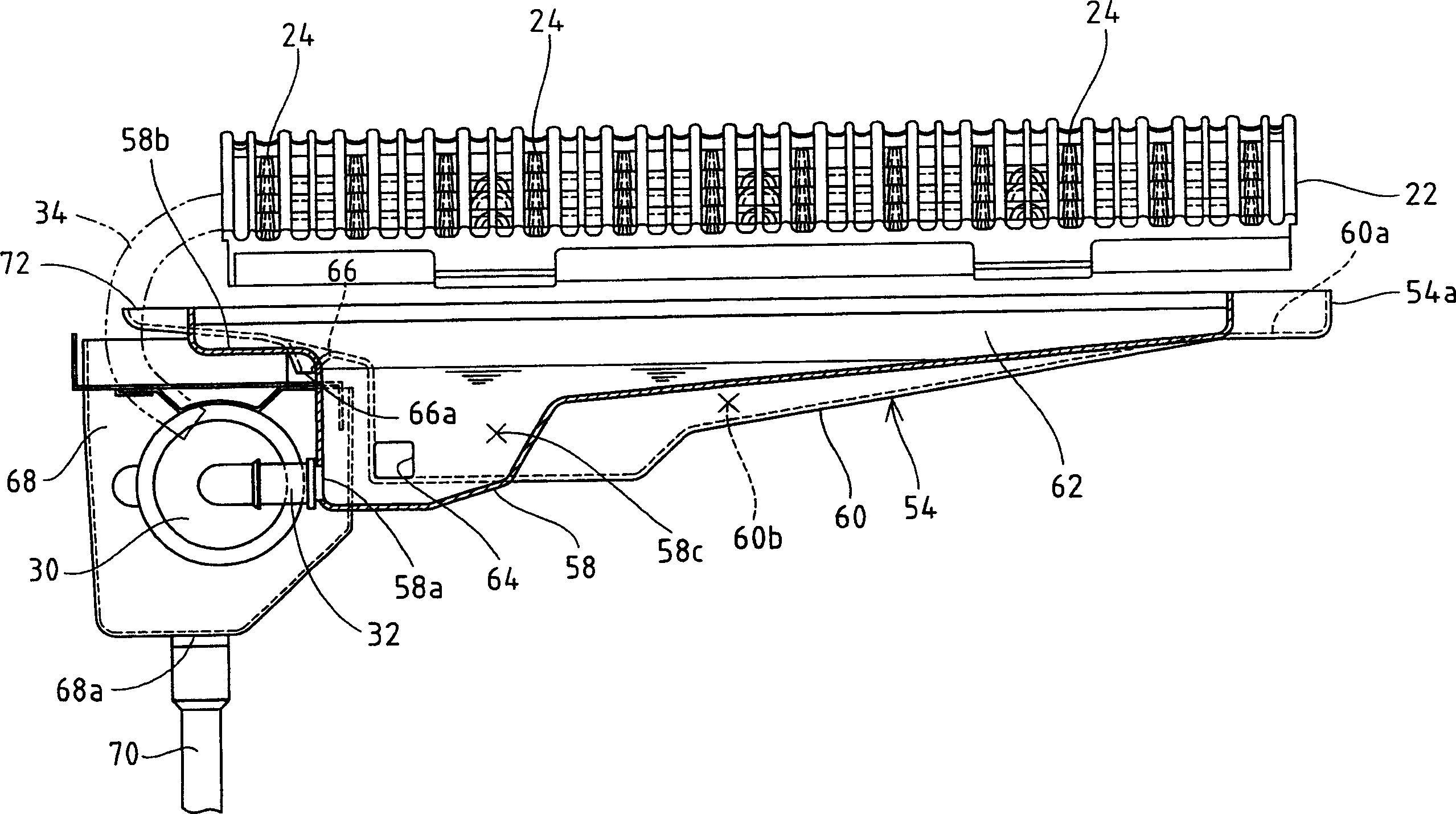

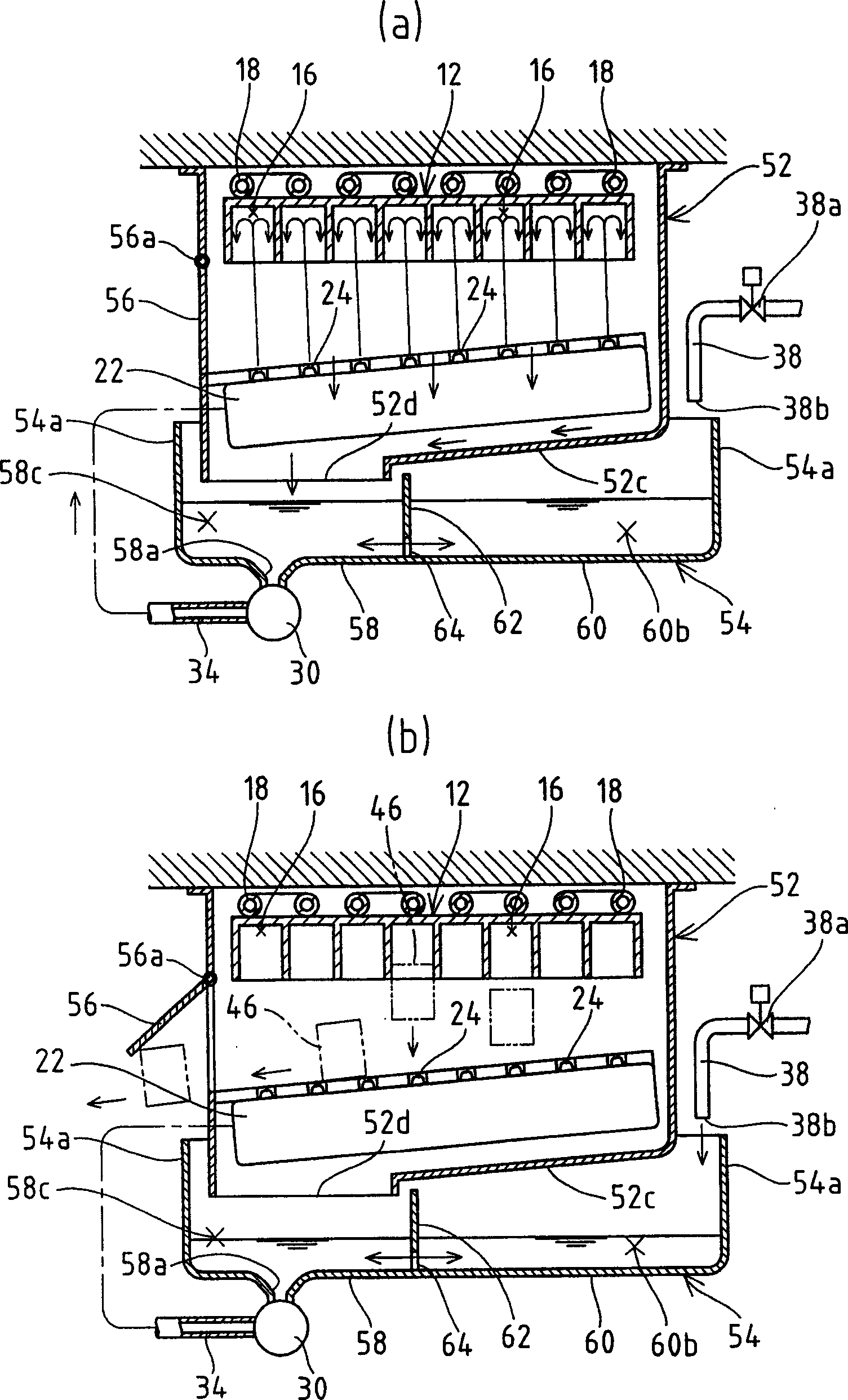

Ice making mechanism for ice maker

InactiveCN1621767AIncrease impurity concentrationImproved ice production efficiencyLighting and heating apparatusIce productionIce waterImpurity

An ice-making water tank (54) can improve ice-making efficiency by preventing the concentration of impurities contained in ice-making water from increasing. The ice-making water tank (54) is divided into a circulation tank part (58) and a storage tank part (60) by a partition (62). The ice-making water stored in the circulation tank part (58) and the ice-making water stored in the storage tank part (60) can convect each other through a communication hole (64). The storage tank section (60) has a capacity greater than that of the circulation tank section (58). Above said sump part (60) is covered with a guide plate (52c) of the machine base (52), the unfrozen water cooled during ice making operation is only collected into the circulation tank through an opening (52d) (58). The opening (52d) opens downward above the circulation tank (58).

Owner:HOSHIZAKI ELECTRIC CO LTD

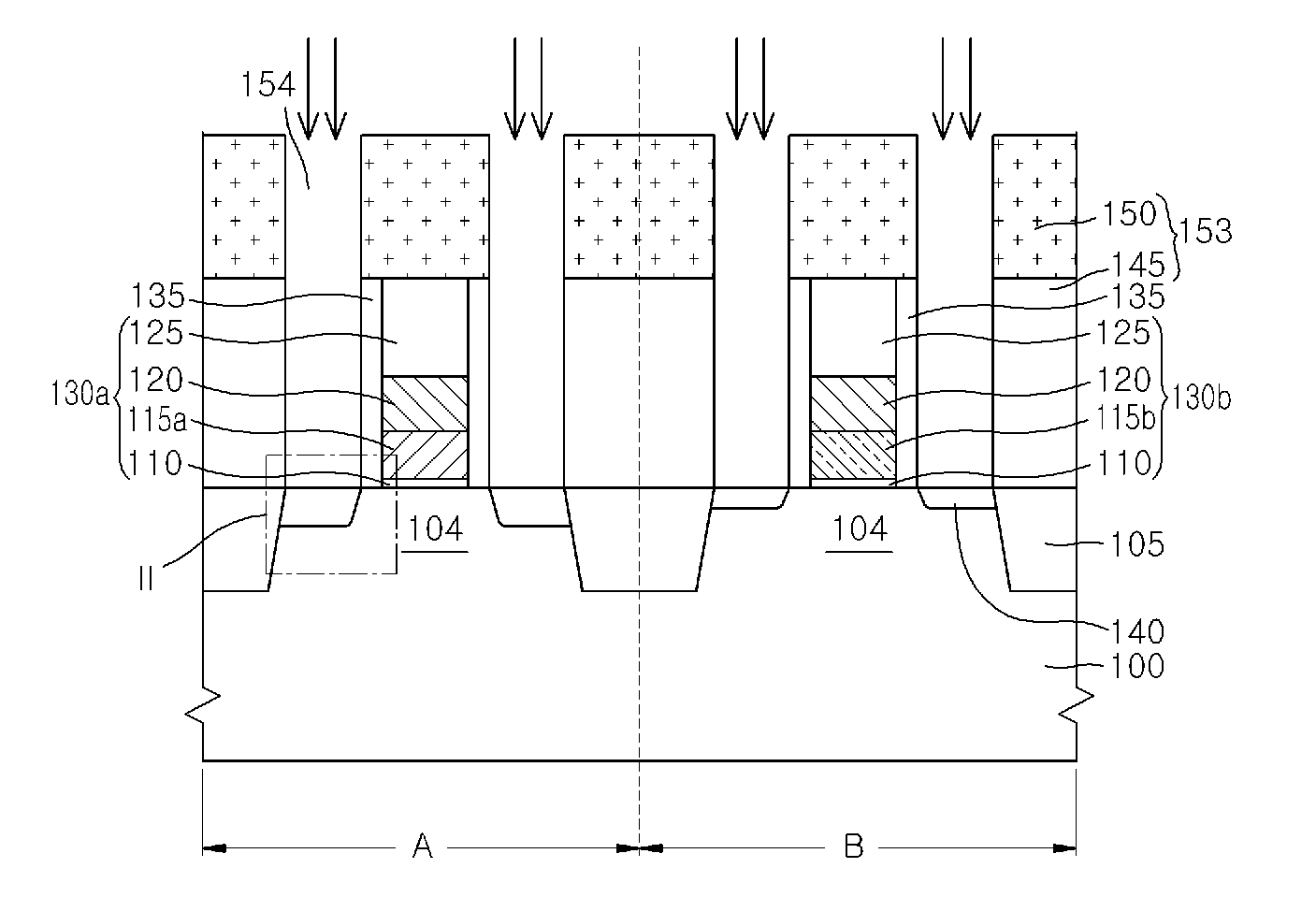

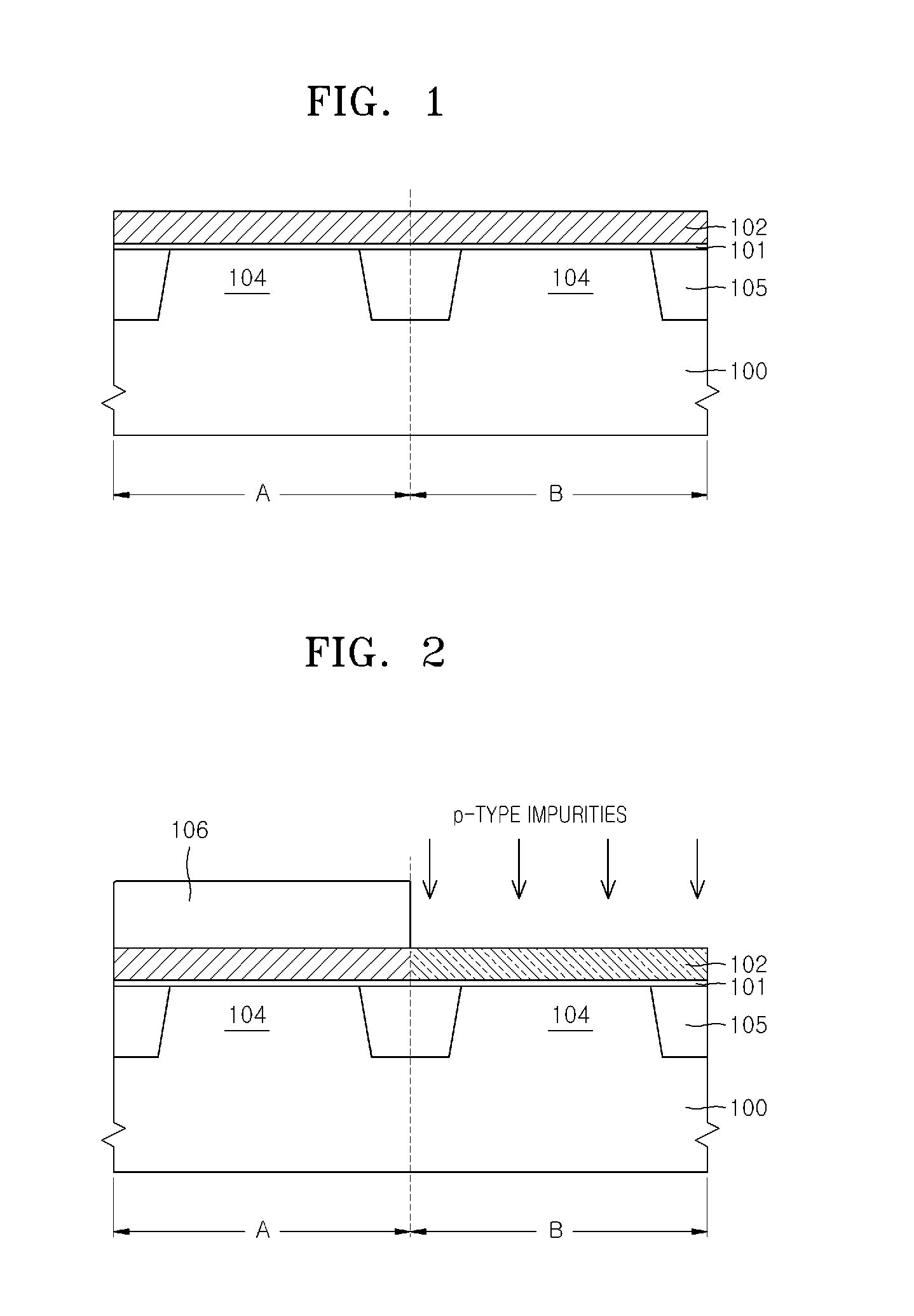

Method for fabricating semiconductor device

InactiveUS20120208333A1Improve featuresMinimized contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

A method for fabricating a semiconductor device includes: forming an impurity junction area within an area of the semiconductor substrate; forming a contact hole which partially exposes a surface the impurity junction area; and performing an additional ion implant process to implant impurity ions into the impurity junction area exposed through the contact hole, thereby increasing an impurity concentration of a surface portion of the impurity junction area.

Owner:SK HYNIX INC

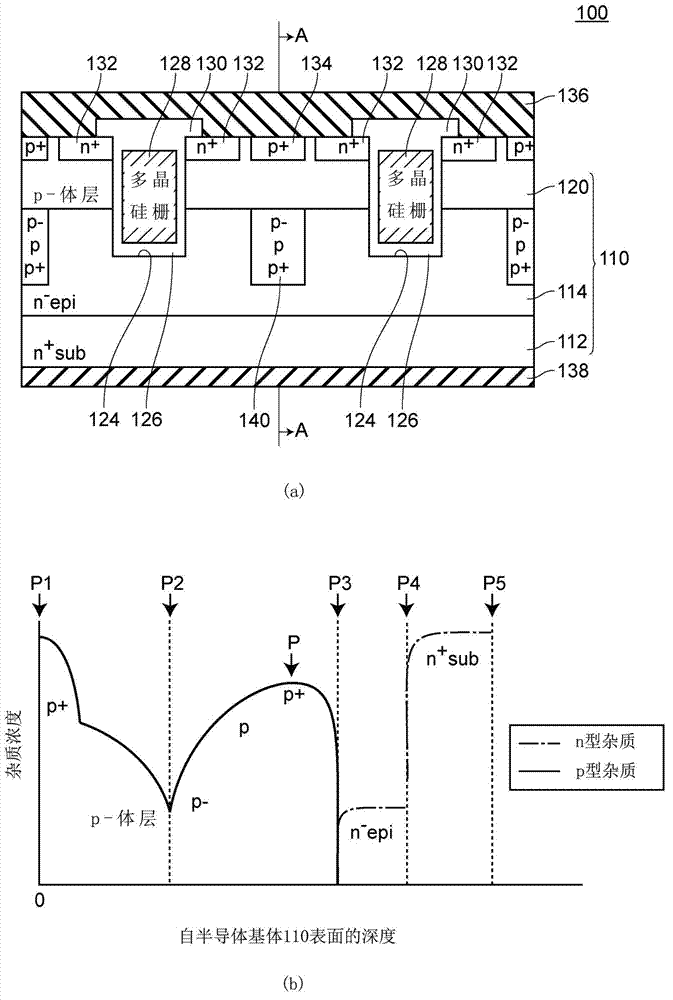

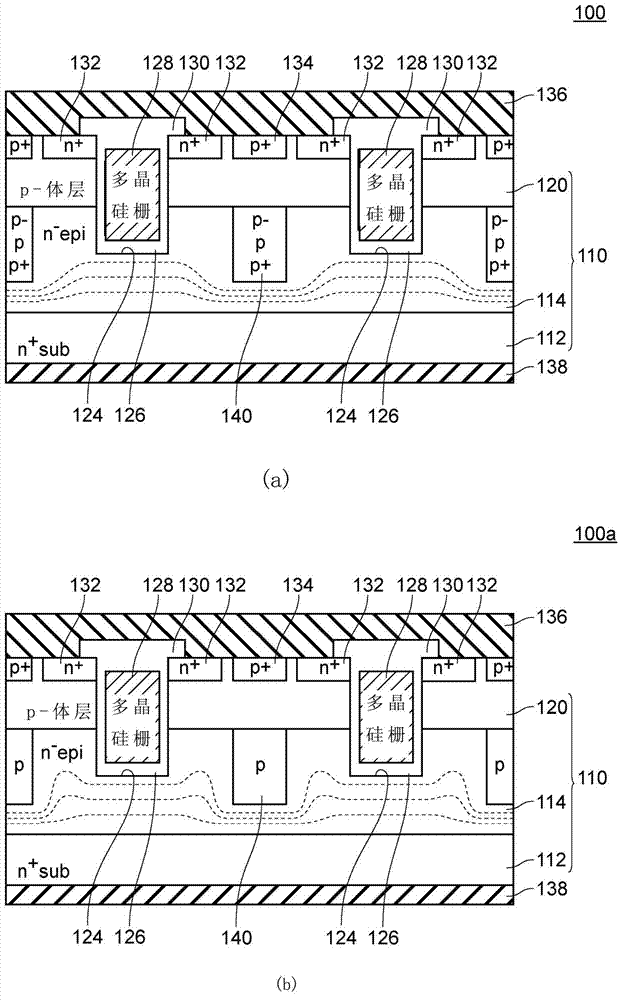

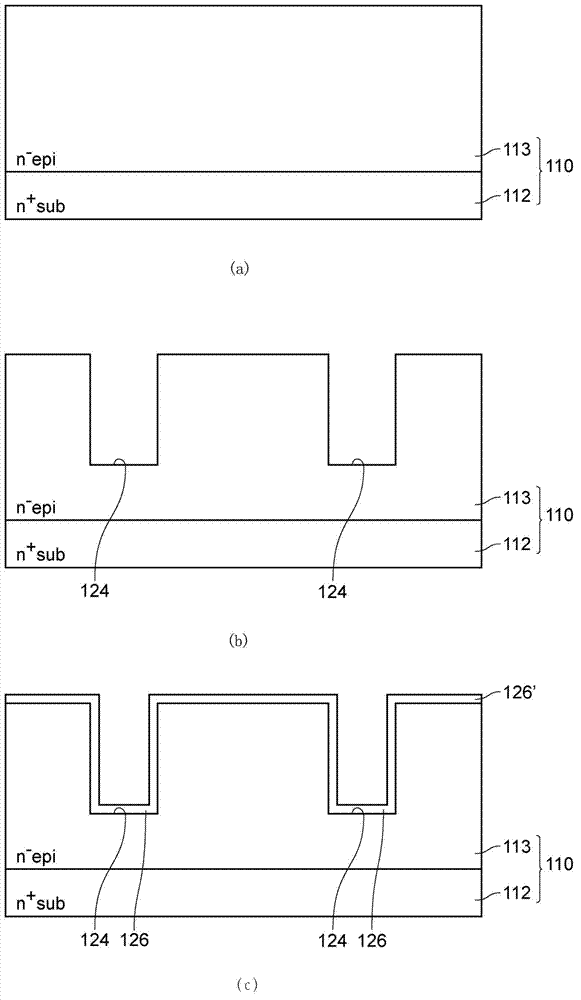

Trench gate power semiconductor device and method for manufacturing same

ActiveCN103250254AImprove reverse withstand voltageIncrease impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

A trench gate power semiconductor device (100) of the present invention is provided with: an n--type drift layer (114); a p-type body layer (120); a groove (124); an n+-type source region (132); a gate insulating film (126) that is formed on the inner peripheral surface of the groove (124); a gate electrode film (128) that is formed on the inner peripheral surface of the gate insulating film (126); and a source electrode layer (136) that is formed to be in contact with the source region (132), while being insulated from the gate electrode film (128). In the drift layer (114), a region sandwiched between two adjacent grooves (124) is provided with a p-type buried region (140) that is in contact with the body layer (120) and extends deeper than the grooves (124). In the buried region (140), the depth position at which the p-type impurity concentration is maximum is located deeper than the midway between the bottom surface (P2) of the body layer (120) and the bottom surface (P3) of the buried region (140). This trench gate power semiconductor device (100) has high reverse breakdown voltage and further lower on-resistance.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

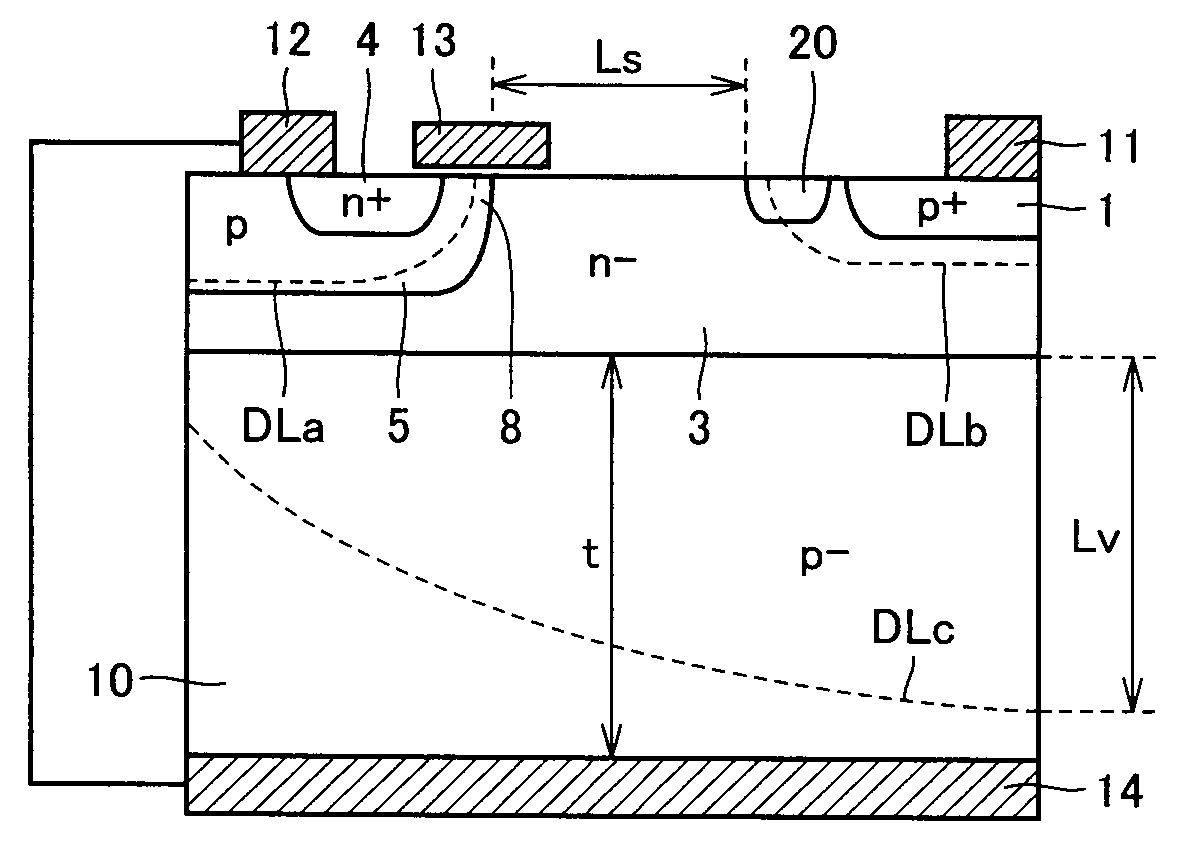

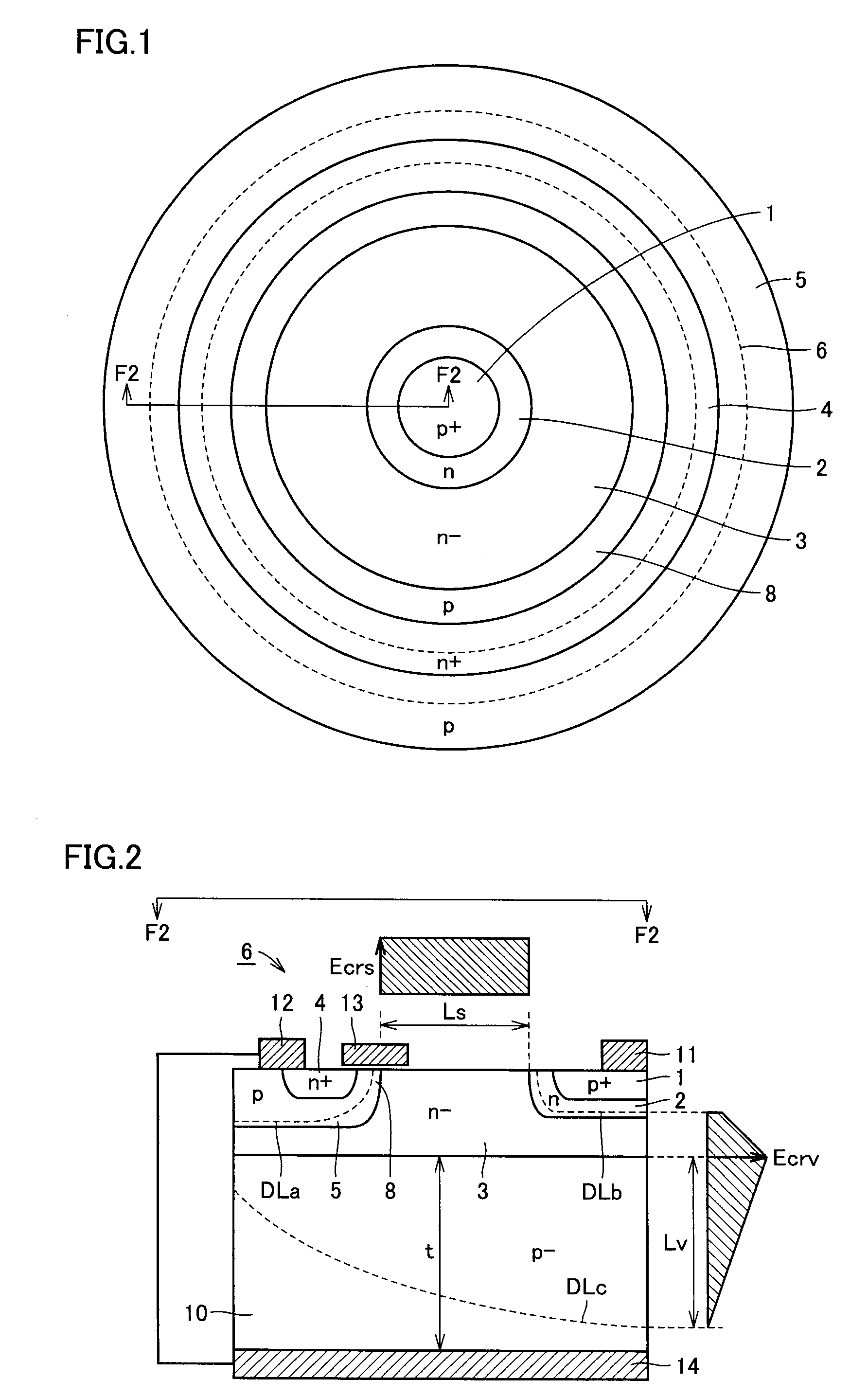

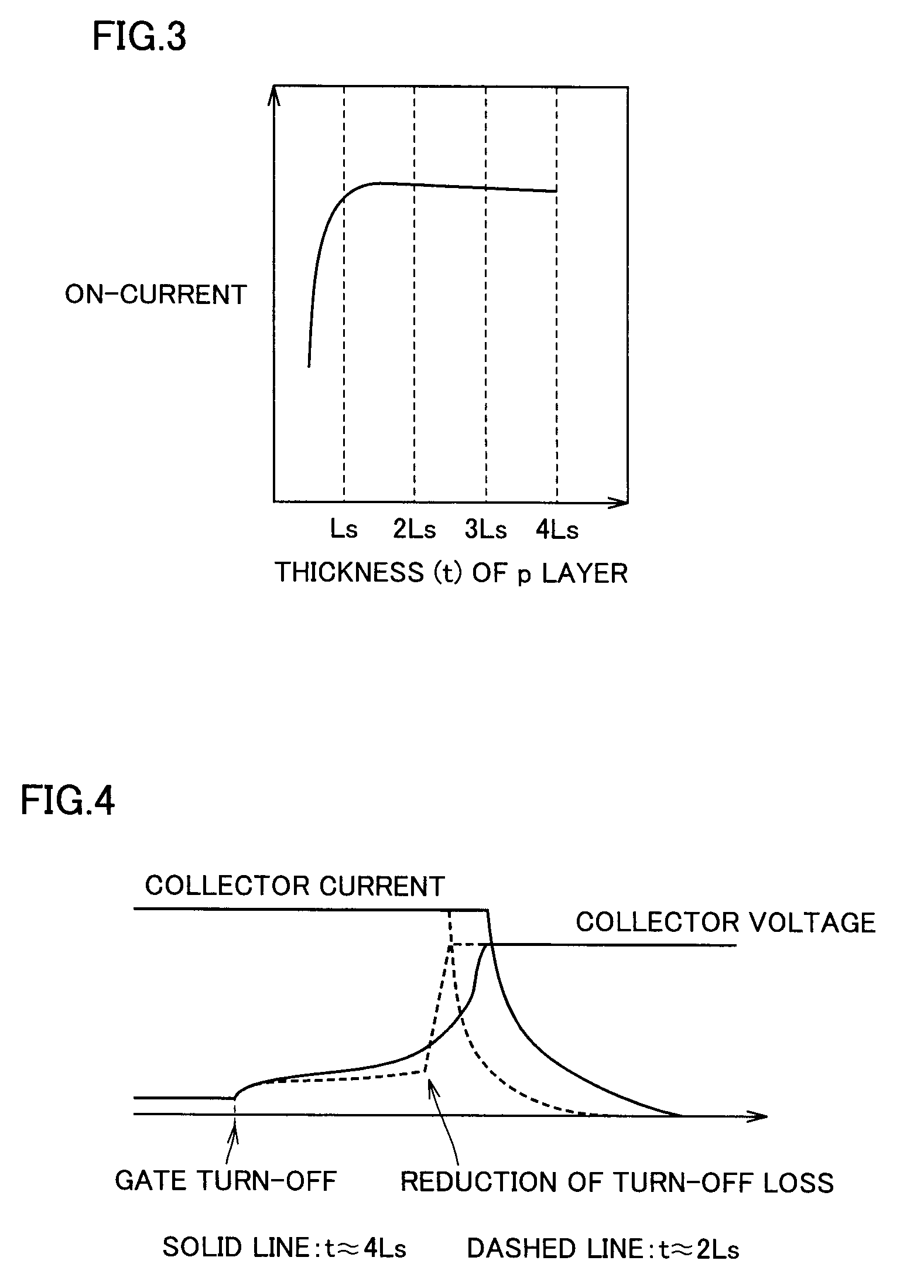

Semiconductor device

ActiveUS20080179663A1Prevent lockoutWithout increasing number of manufacturing stepTransistorSolid-state devicesDevice materialSemiconductor

The relationship between a distance Ls between a base layer and an n type buffer layer formed on the surface of a drift layer and the thickness t of a semiconductor substrate in contact with the drift layer is set to Ls≦t≦2×Ls. A loss upon turn-off of a high breakdown voltage semiconductor device can be reduced without deteriorating breakdown voltage characteristics.

Owner:MITSUBISHI ELECTRIC CORP

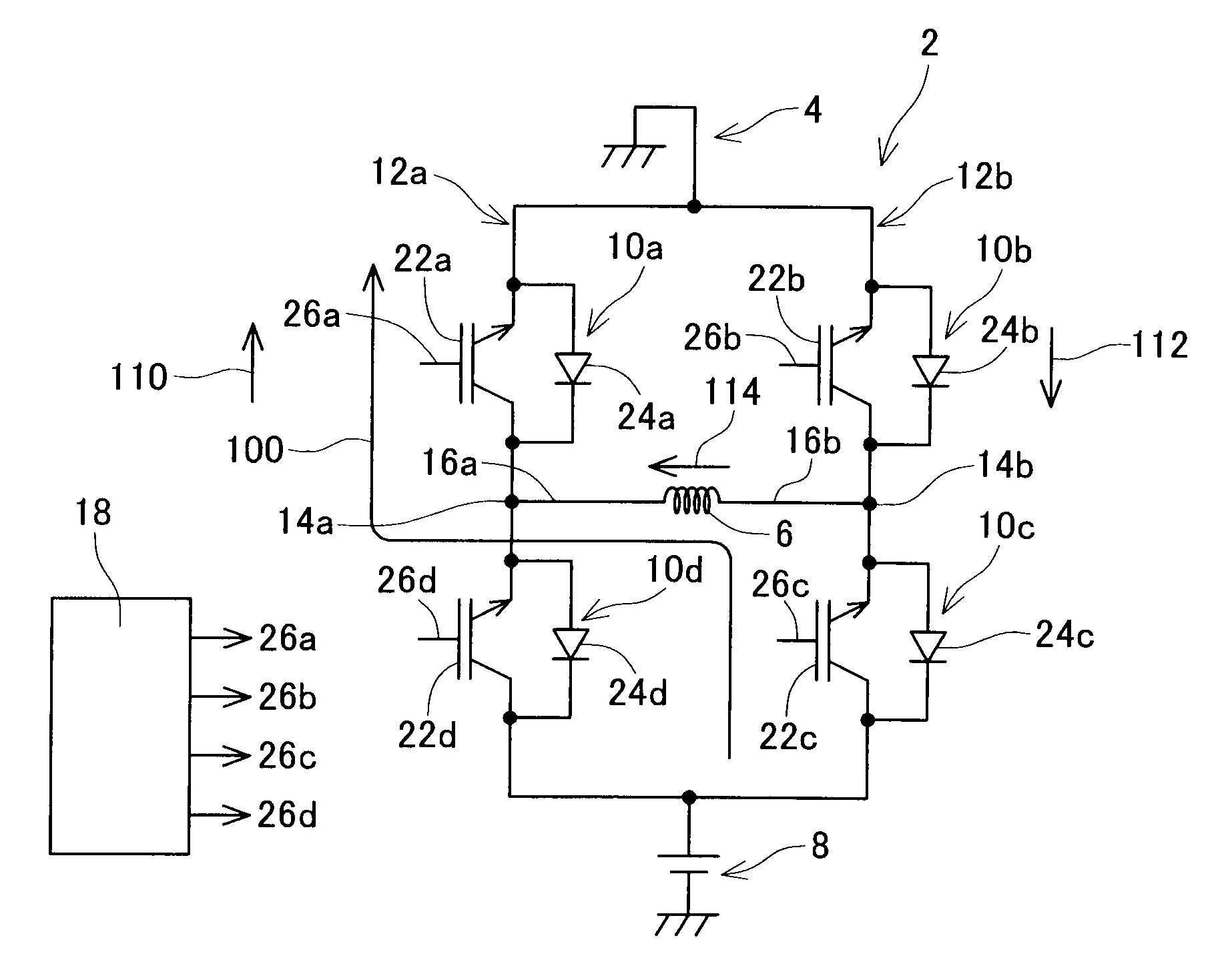

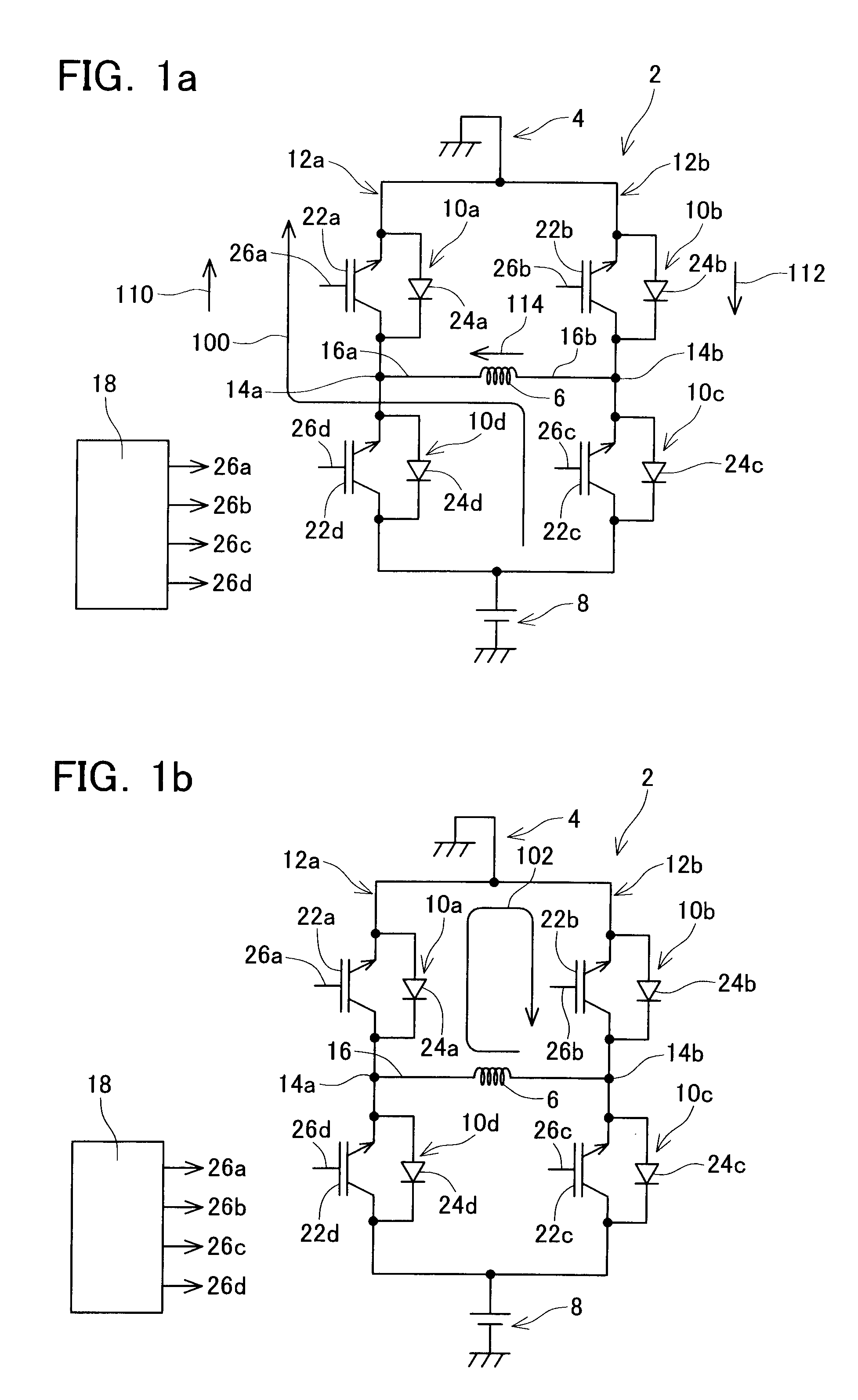

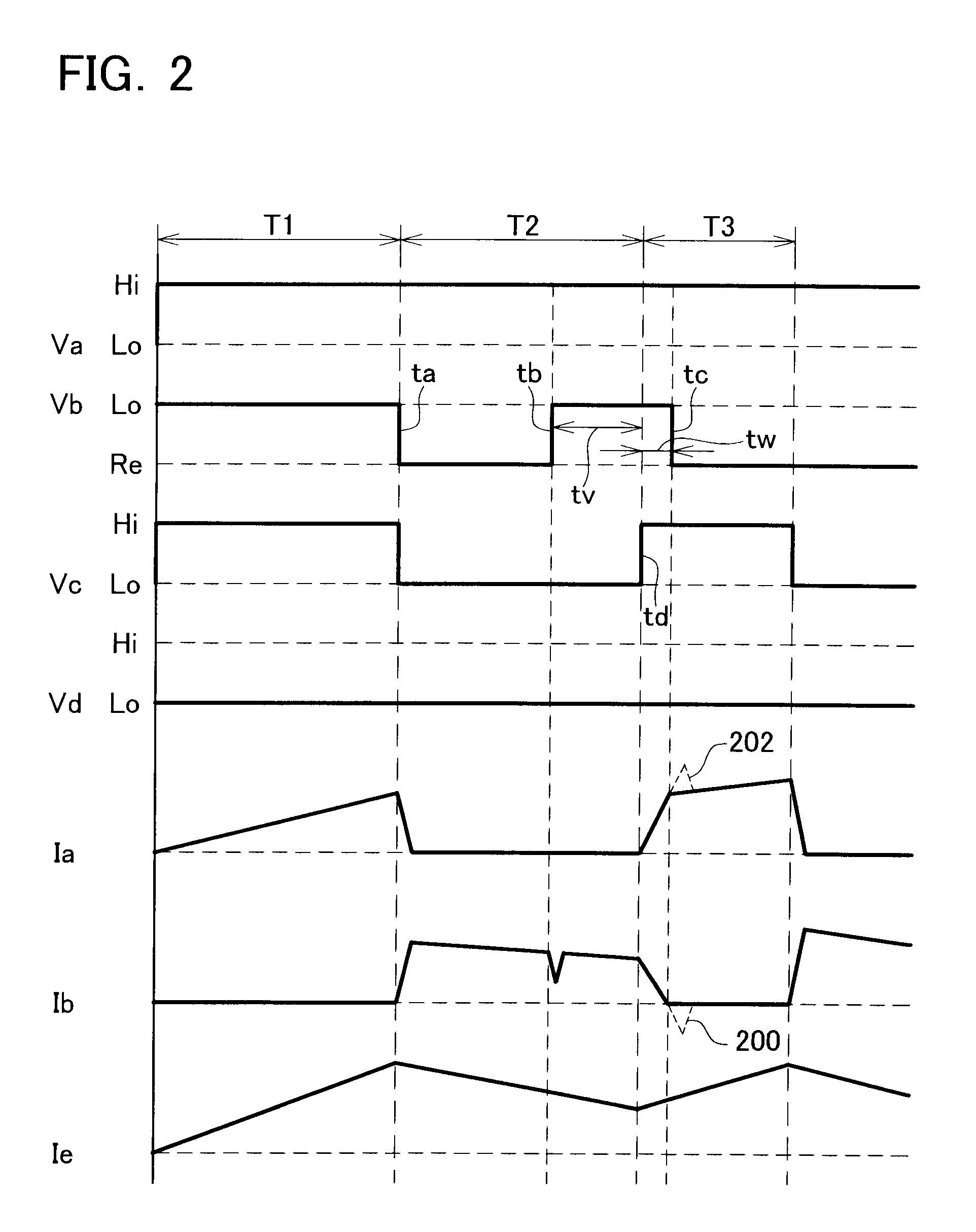

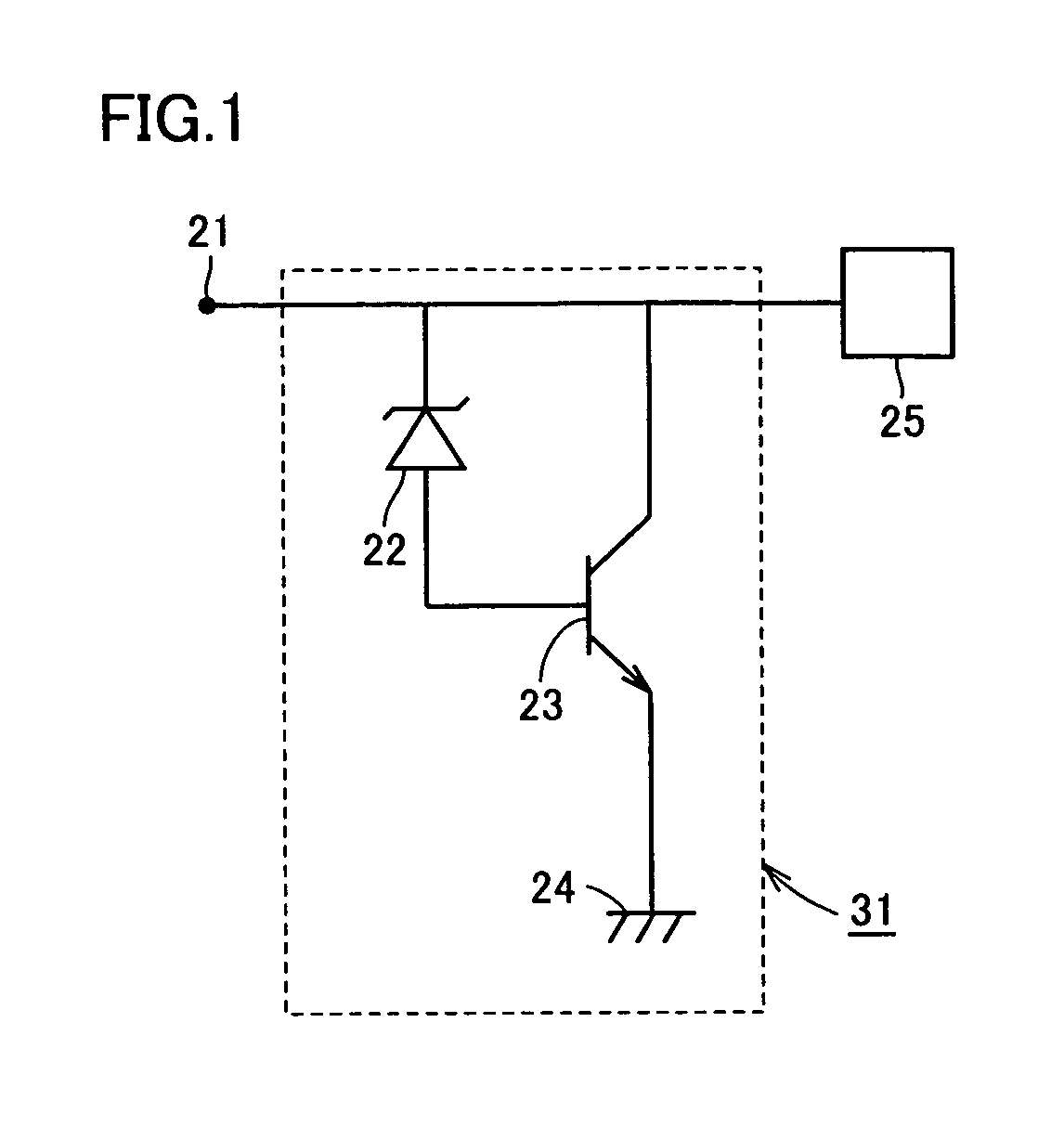

Power supply device and method for driving the same

ActiveUS20100283514A1Lower forward voltage dropGain is not constantAc-dc conversionElectronic switchingBody contactEngineering

In a reverse conducting semiconductor device, which forms a composition circuit, a positive voltage that is higher than a positive voltage of a collector electrode may be applied to an emitter electrode. In this case, in a region of the reverse conducting semiconductor device in which a return diode is formed, a body contact region functions as an anode, a drift contact region functions as a cathode, and current flows from the anode to the cathode. When a voltage having a lower electric potential than the collector electrode is applied to the trench gate electrode at that time, p-type carriers are generated within the cathode and a quantity of carriers increases within the return diode. As a result, a forward voltage drop of the return diode lowers, and constant loss of electric power can be reduced. Electric power loss can be reduced in a power supply device that uses such a composition circuit in which a switching element and the return diode are connected in reverse parallel.

Owner:DENSO CORP

Semiconductor device with vertical trench and lightly doped region

InactiveUS7928505B2Improve breakdown voltageReduction in epi-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceTrench mosfet

The vertical trench MOSFET comprises: an N type epitaxial region formed on an upper surface of an N+ type substrate having a drain electrode on a lower surface thereof; a gate trench extending from a front surface into the N type epitaxial region; a gate electrode positioned in the gate trench so as to interpose an insulator; a channel region formed on the N type epitaxial region; a source region formed on the channel region; a source electrode formed on the source region; a source trench extending from the front surface into the N type epitaxial region; and a trench-buried source electrode positioned in the source trench so as to interpose an insulator, wherein the source electrode contacts with the trench-buried source electrode.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device with surge protection circuit capable of preventing current leakage

InactiveUS7026705B2Reduce contact resistanceInhibit currentTransistorSemiconductor/solid-state device detailsDiffusion layerSemiconductor

A semiconductor device has a surge protection circuit electrically connected to a signal input terminal and including a diode and a transistor. The diode has its cathode region constituted of an n+ diffusion layer, an n− epitaxial layer, an n-type diffusion layer and an n+ diffusion layer. The n+ diffusion layer is electrically connected to a conductive layer and formed at a main surface of a semiconductor substrate. The n+ diffusion layer constitutes, together with a p-type diffusion layer, a pn junction where Zener breakdown occurs, and the pn junction with the Zener breakdown occurring therein is distant from a field oxide film. Then, the semiconductor device with the surge protection circuit without suffering from current leakage and thus normally operating can be achieved.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method of fabricating the same

InactiveUS20050082603A1Desirable levelReduce resistanceTransistorSemiconductor/solid-state device detailsEngineeringBody region

The present invention is aimed at providing a DMOSFET and a method of fabricating the same, capable of keeping a desirable level of drain voltage resistance and, at the same time, of reducing the drain resistance. In a DMOSFET configured as having a drain region composed of an epitaxial layer formed on a P-type semiconductor substrate while placing an N-type buried layer in between, and as having, in the drain region, a P-type body region having an N-type source region nested therein and a drain extraction region, formation of N-type, heavily-doped buried layers prior to the epitaxial growth is proceeded so as not to form them at least in the region under the P-type body region, and so as to make an impurity concentration in the region under the P-type body region smaller than that in the region under a drift region when viewed after the impurity is diffused by the succeeding annealing. This makes it possible to suppress breakdown and thereby to suppress lowering in the drain voltage resistance, and at the same time to reduce the drain resistance by raising the impurity concentration of the N-type buried layer in the region under the drift region.

Owner:RENESAS ELECTRONICS CORP

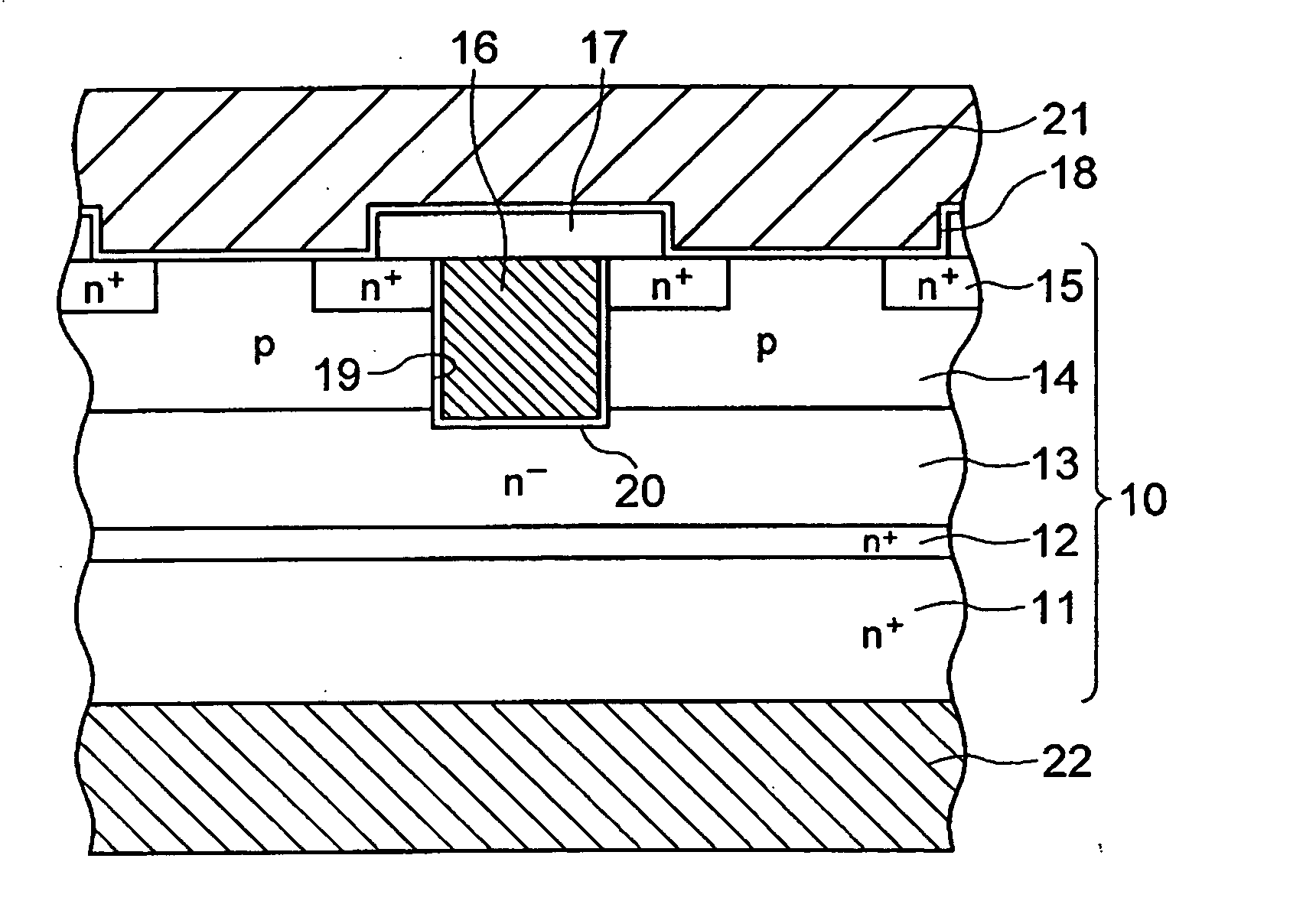

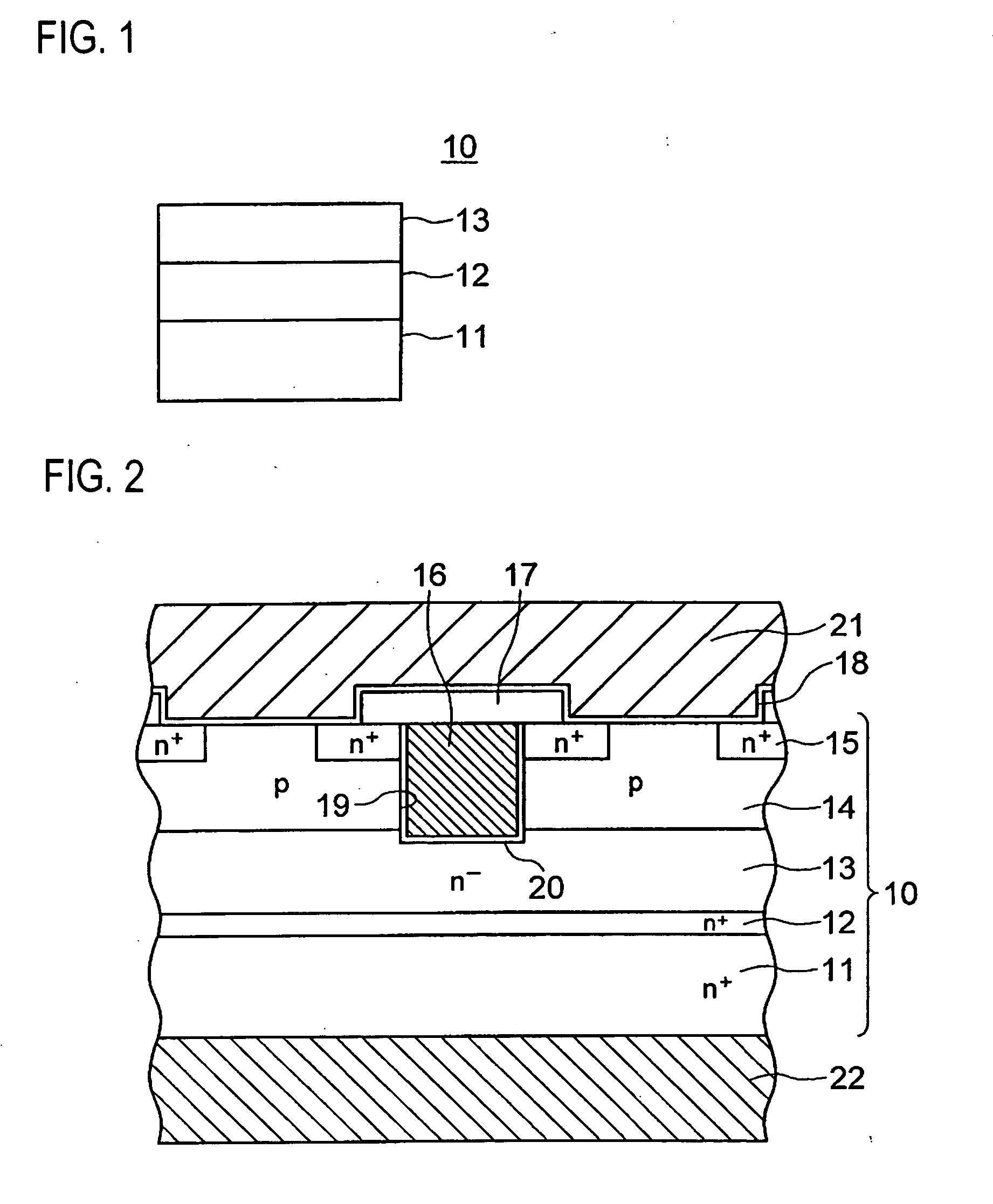

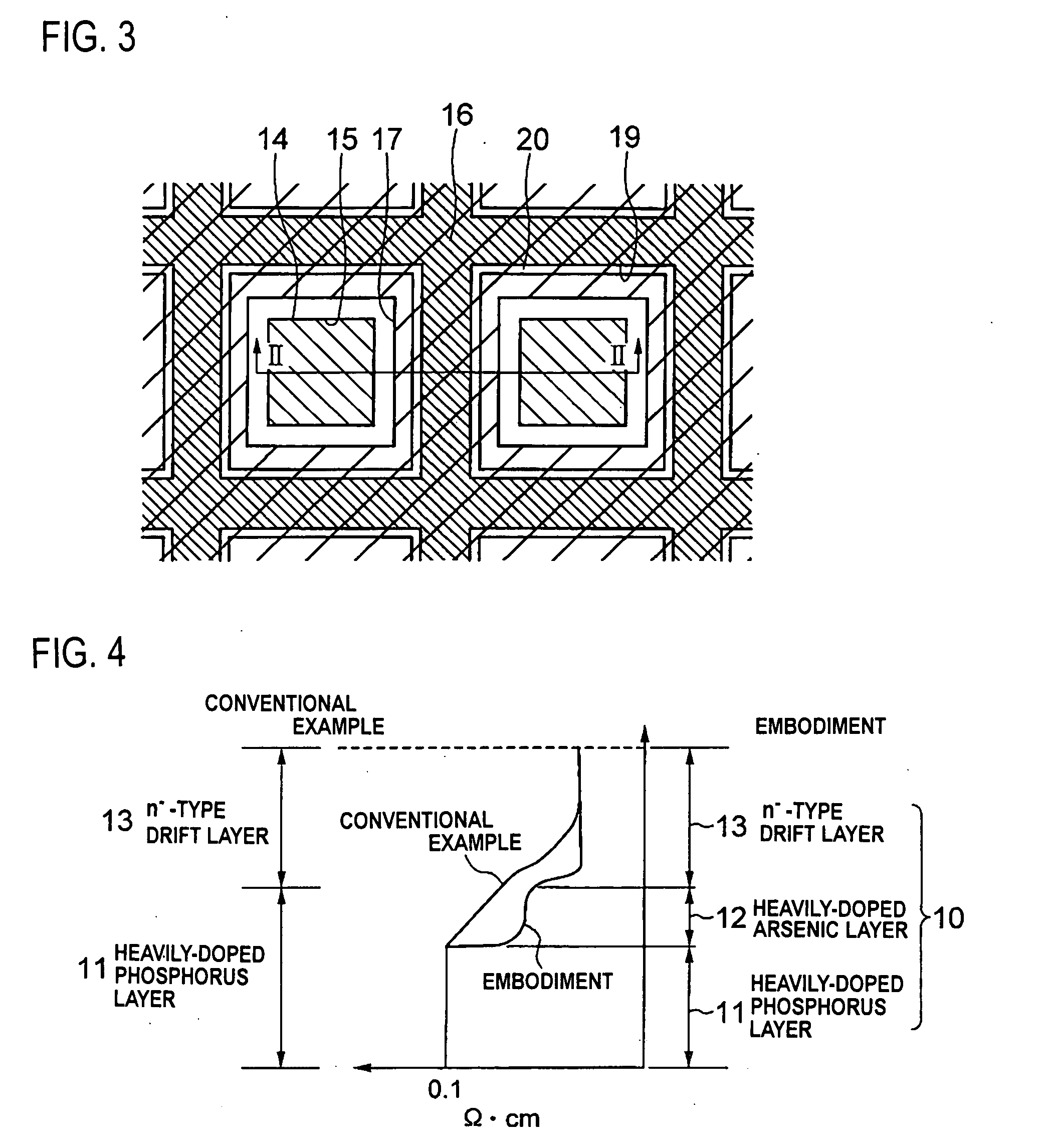

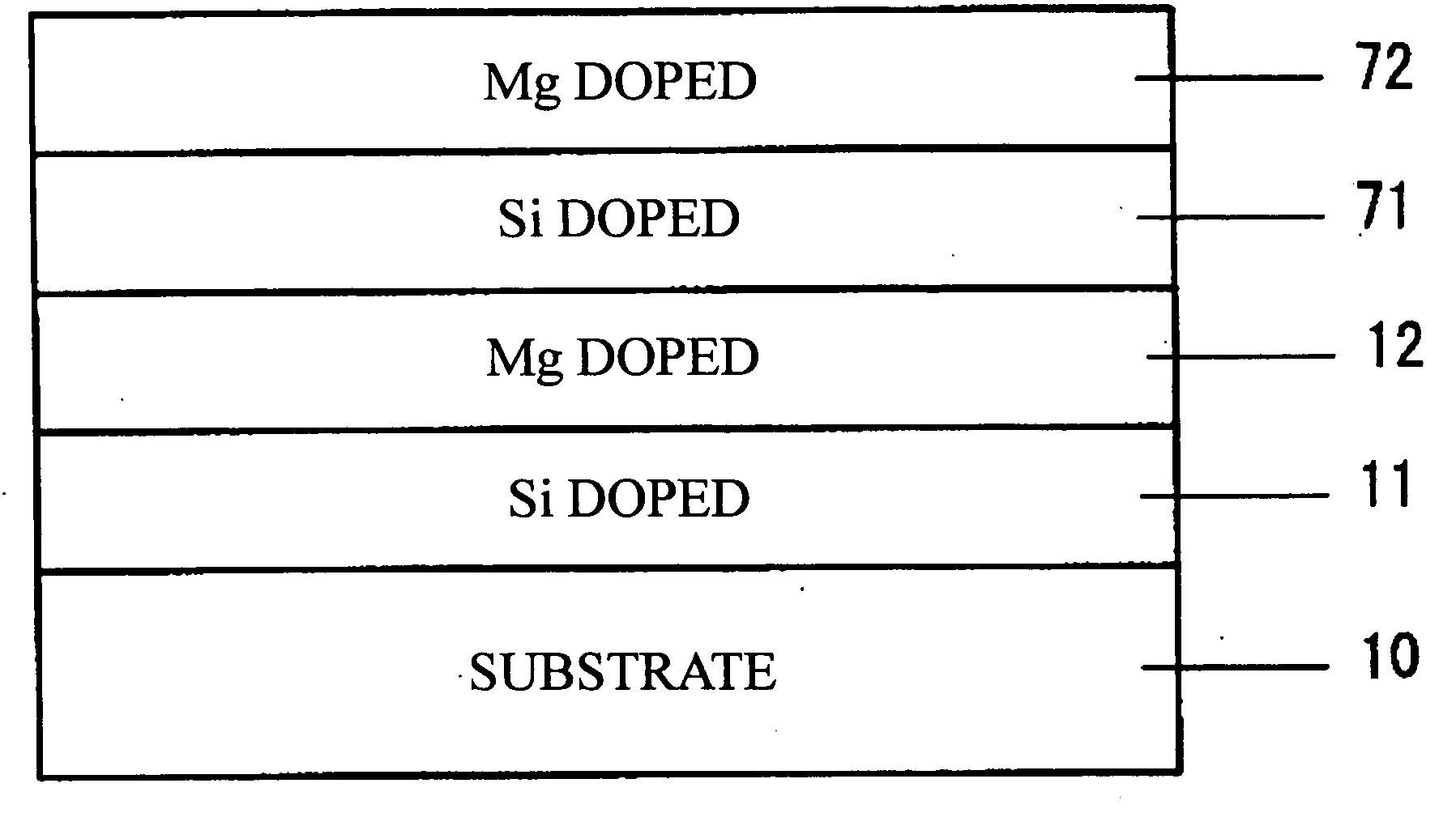

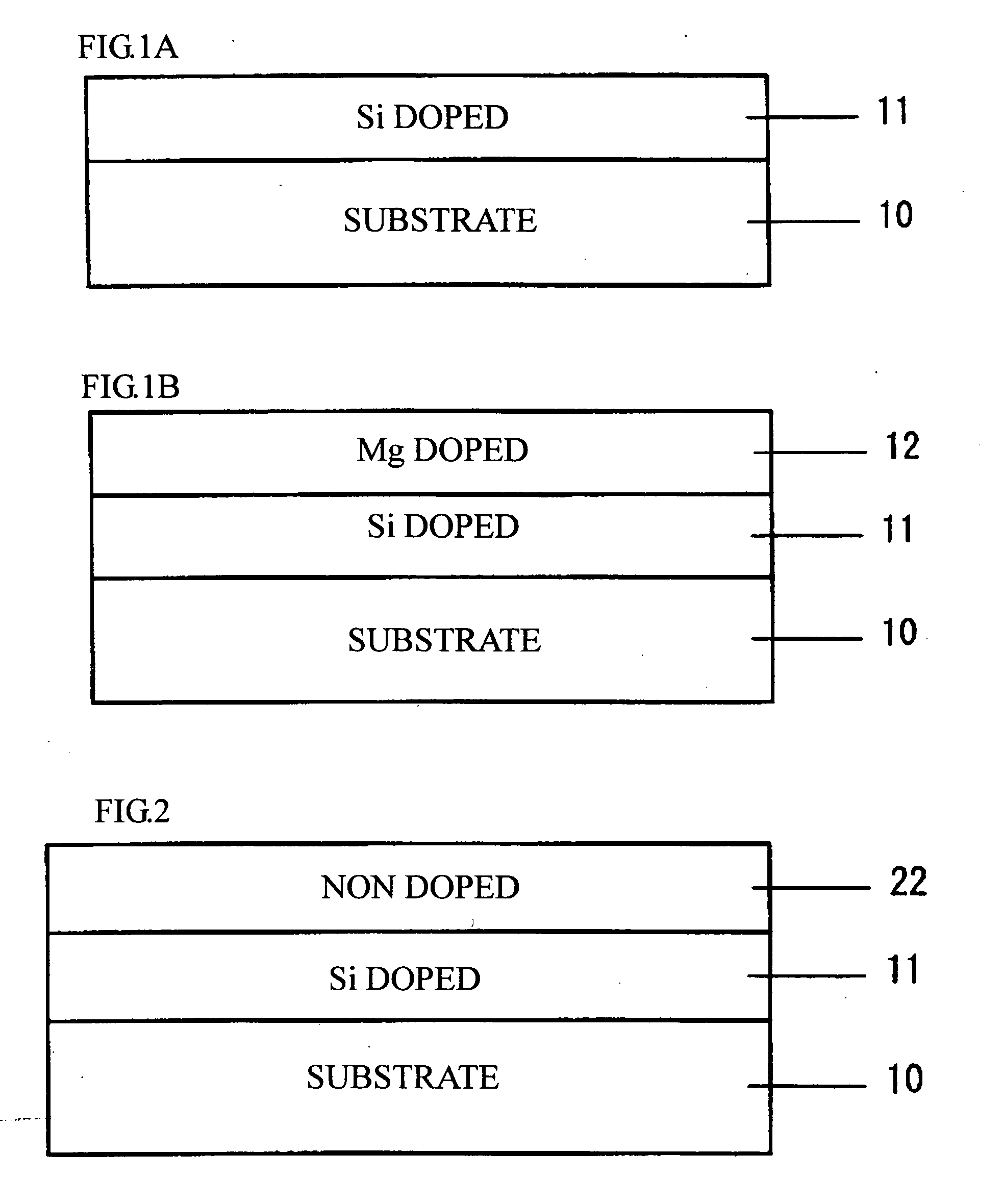

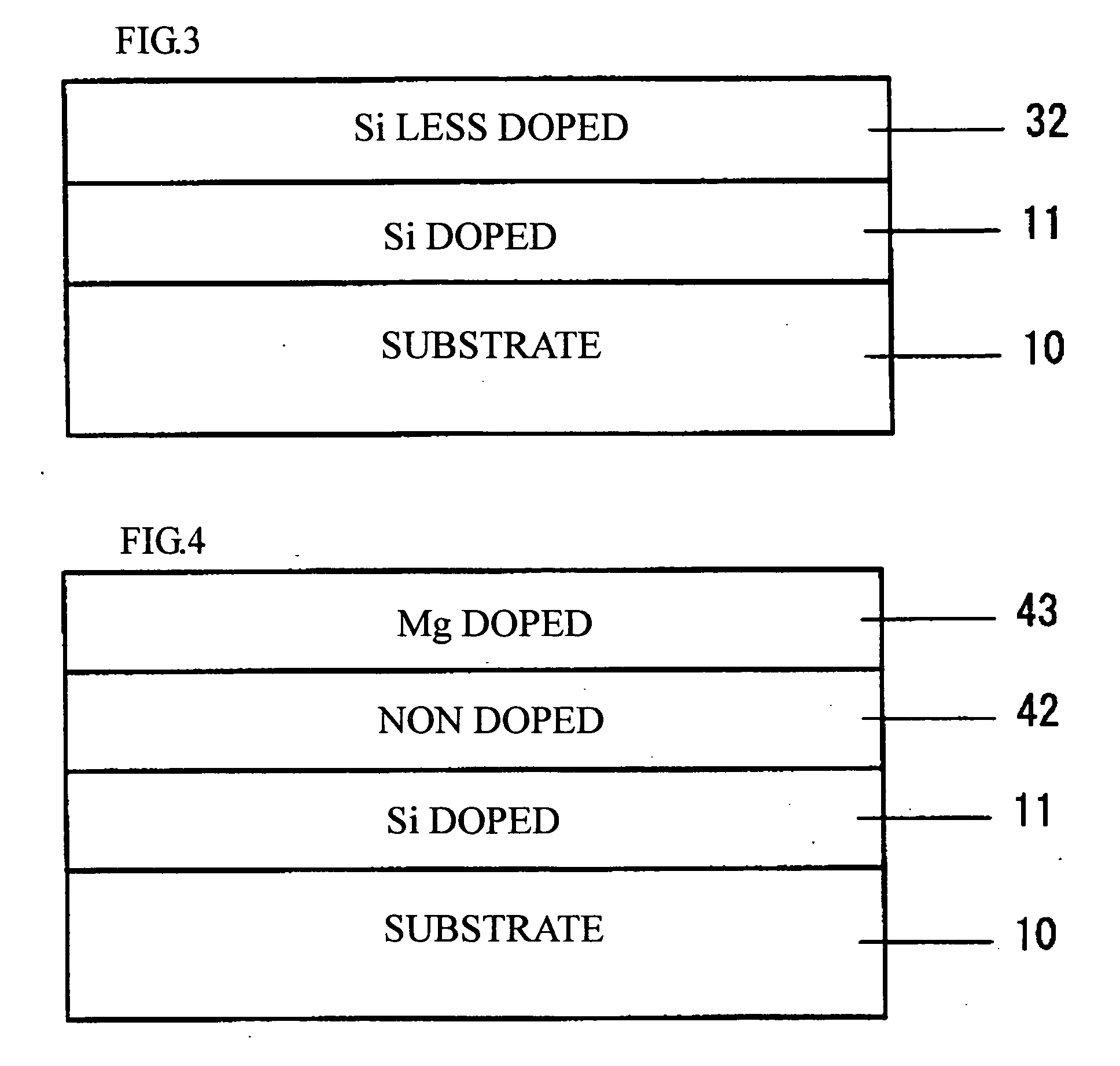

Semiconductor substrate and semiconductor device using the same

InactiveUS20050151221A1Inhibited DiffusionAdequate levelSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDevice material

A semiconductor substrate used for fabricating vertical devices, such as vertical MOSFET, capable of maintaining low ON-stage resistance and of ensuring a necessary level of OFF-stage breakdown voltage is provided. A heavily-doped arsenic layer of 0.5 to 3.0 μm thick is inserted between a heavily-doped phosphorus layer 11 composing the drain of a vertical MOSFET and an n−-type drift layer. The heavily-doped arsenic layer functions as a barrier layer which prevents phosphorus from diffusing from the heavily-doped phosphorus layer into the n−-type drift layer. This is successful in maintaining spreading of the depletion layer during OFF time of the vertical MOSFET to thereby improve the OFF-stage breakdown voltage, and in maintaining the low ON-stage resistance.

Owner:RENESAS ELECTRONICS CORP

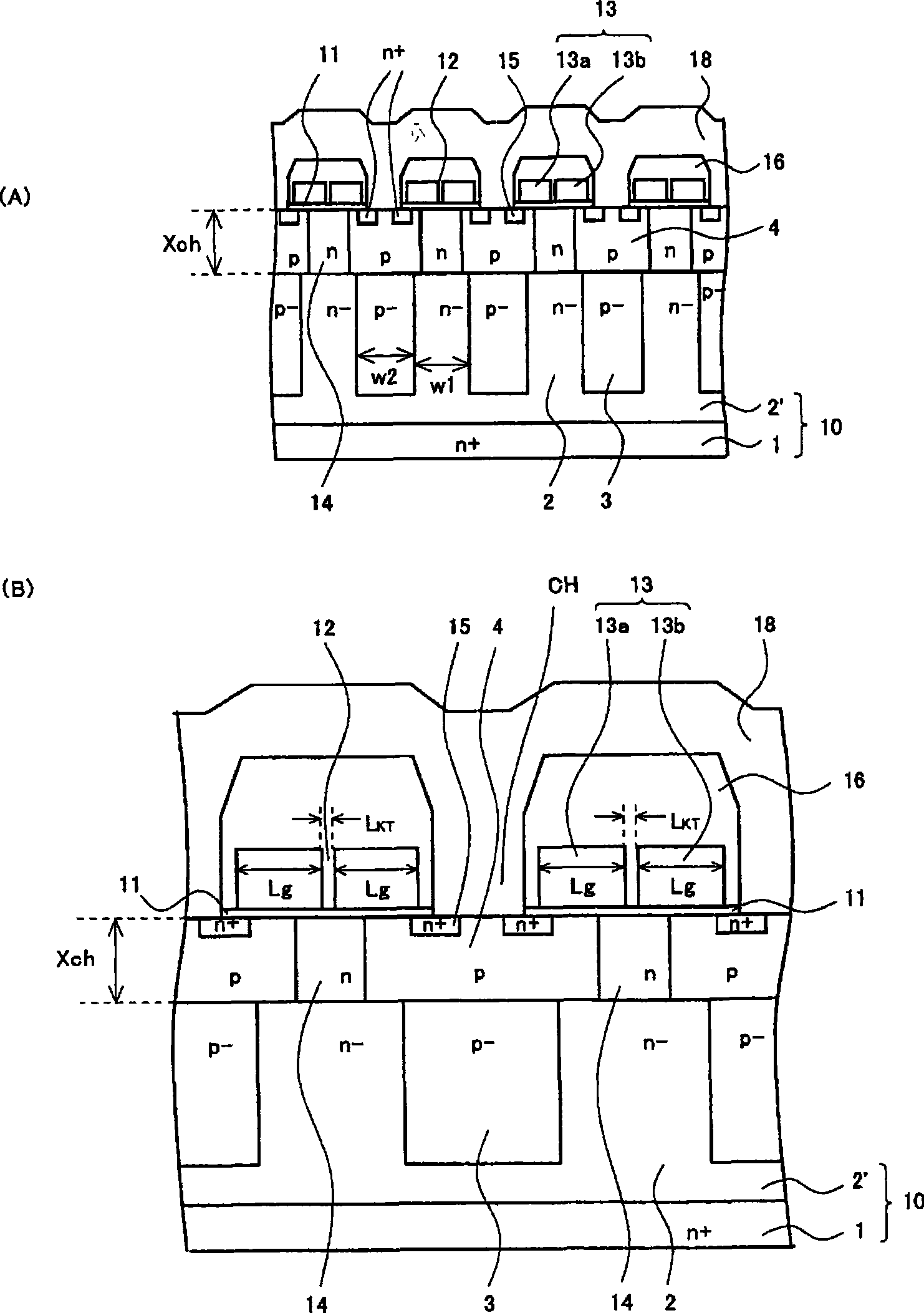

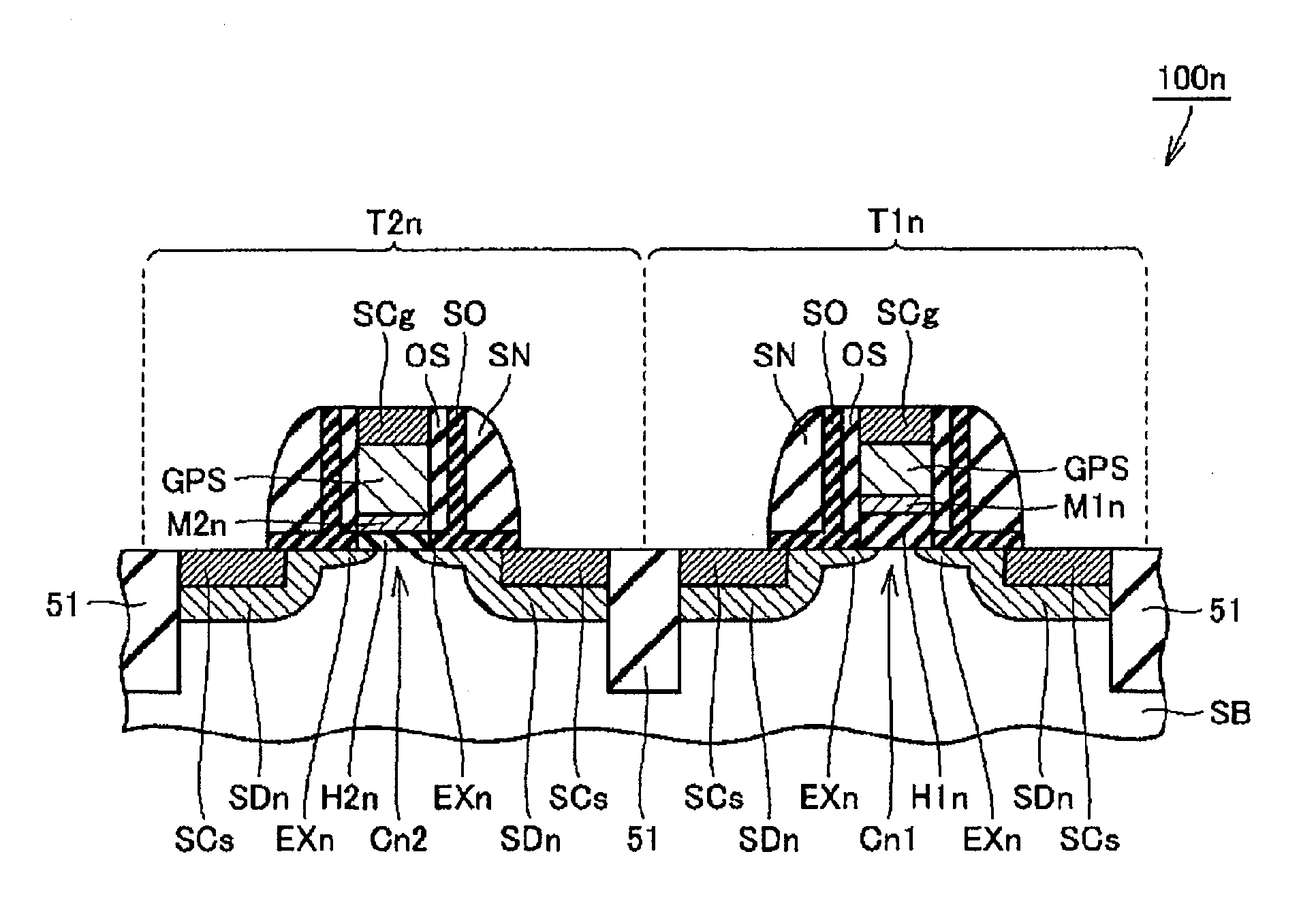

Semiconductor device and method of manufacturing the same

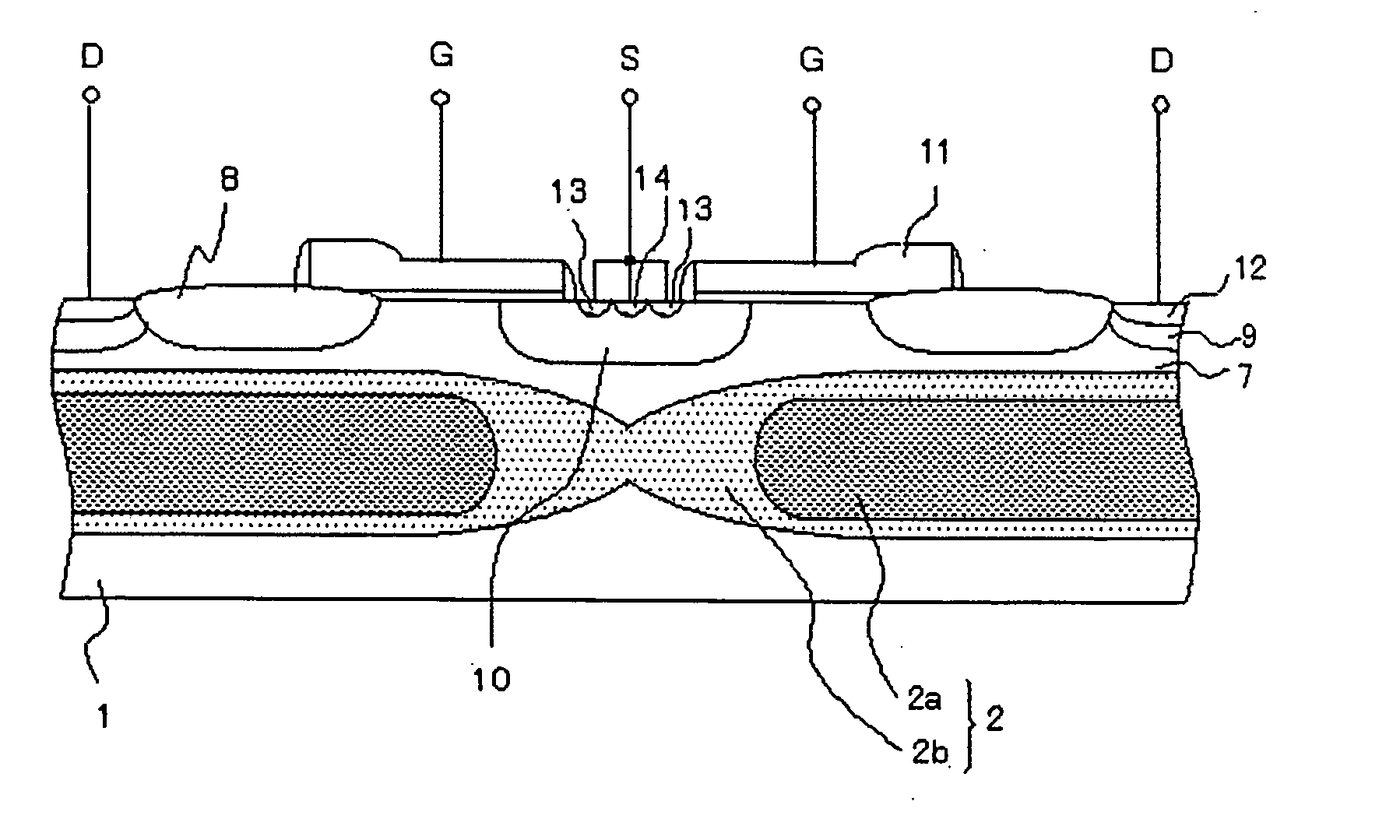

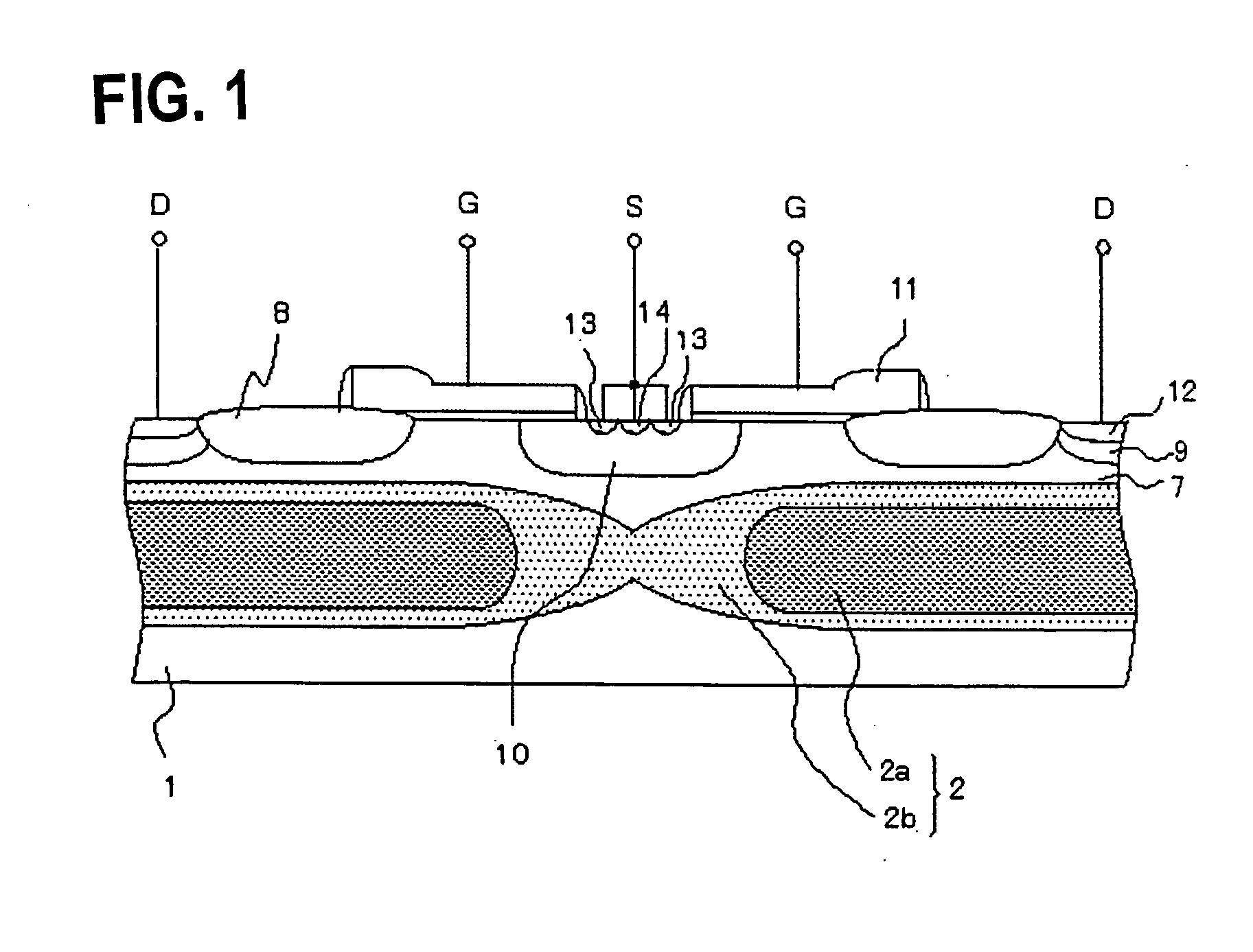

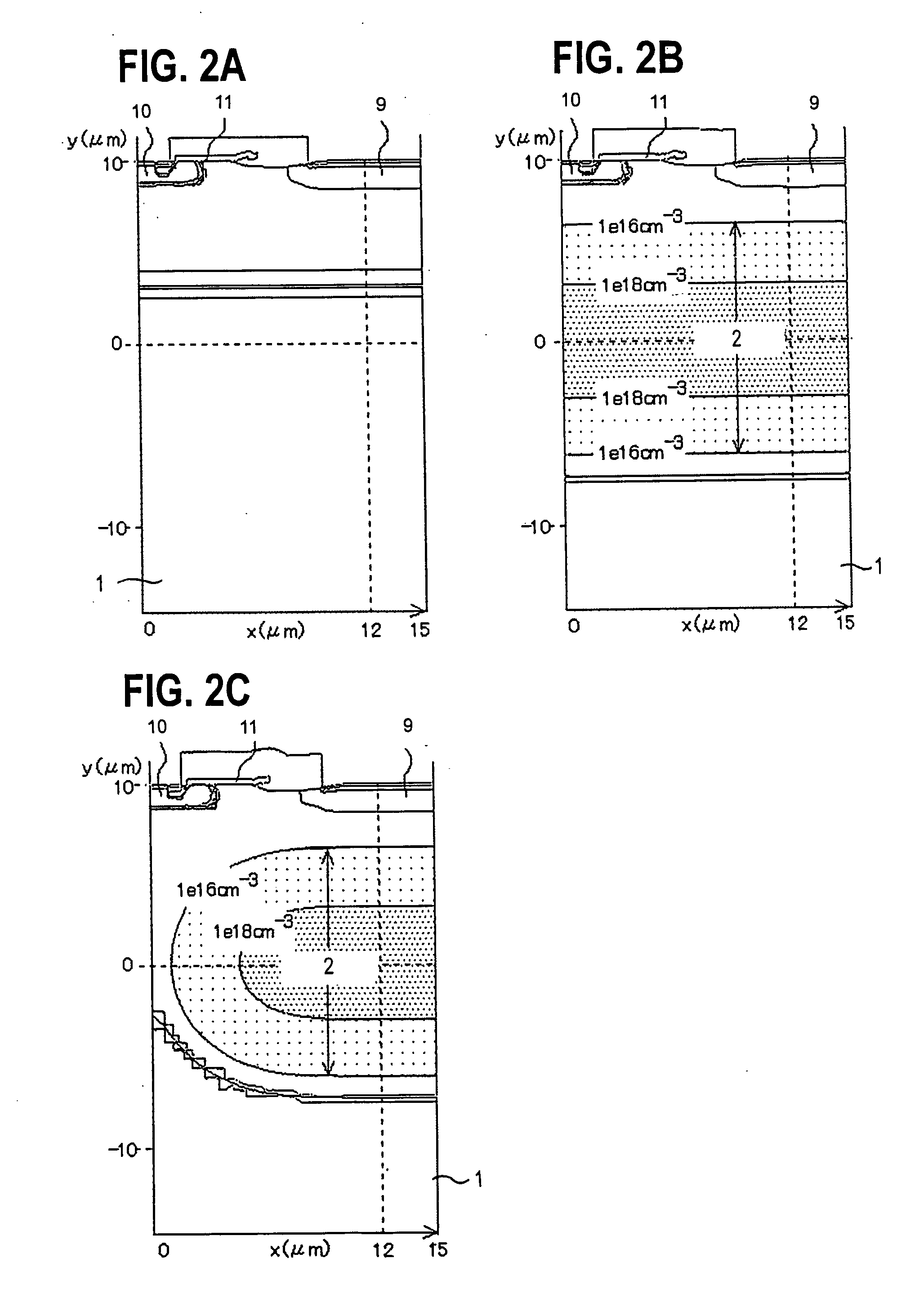

InactiveCN101399268AAvoid lateral spreadLower resistanceTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceHigh concentration

Provided is a semiconductor device and a method of manufacturing a semiconductor device. In the semiconductor device, high-concentration n type impurity regions are formed respectively below gate electrodes. By setting a gate length to be smaller than a depth of channel regions, pn junction interfaces formed of adjacent side faces of the n type impurity regions and the channel regions can be substantially vertical to a top surface of a base. With this configuration, even when reduction in size is achieved in a super junction structure, a distance between the channel regions (i.e. a current path below the gate electrode) is not reduced unnecessarily. Accordingly, an increase in resistance can be prevented. In addition, depletion layers uniformly expand in the n type semiconductor regions, and impurity concentration of the regions can be increased consequently. Accordingly, reduction in resistance can be achieved.

Owner:SANYO ELECTRIC CO LTD +1

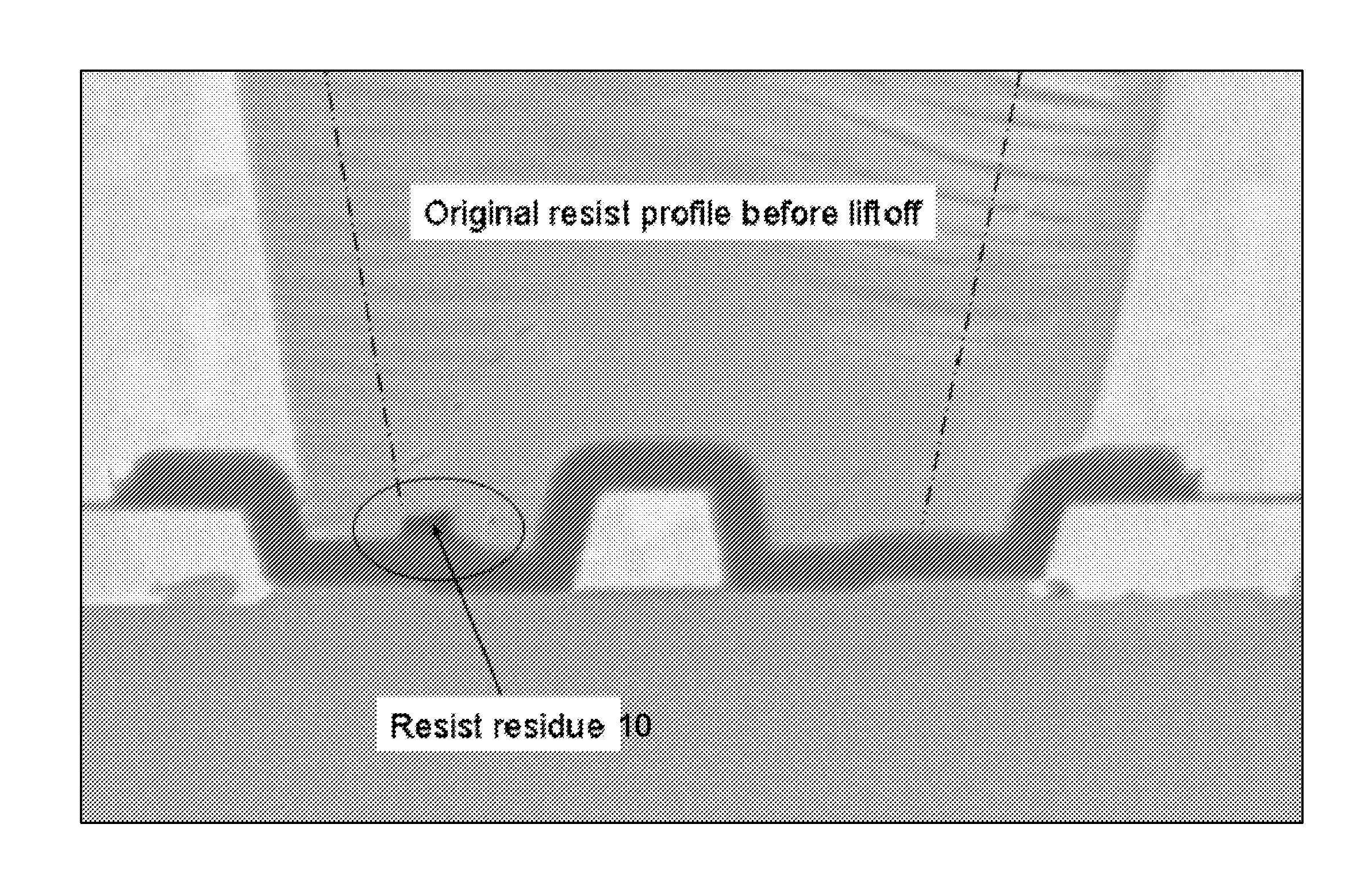

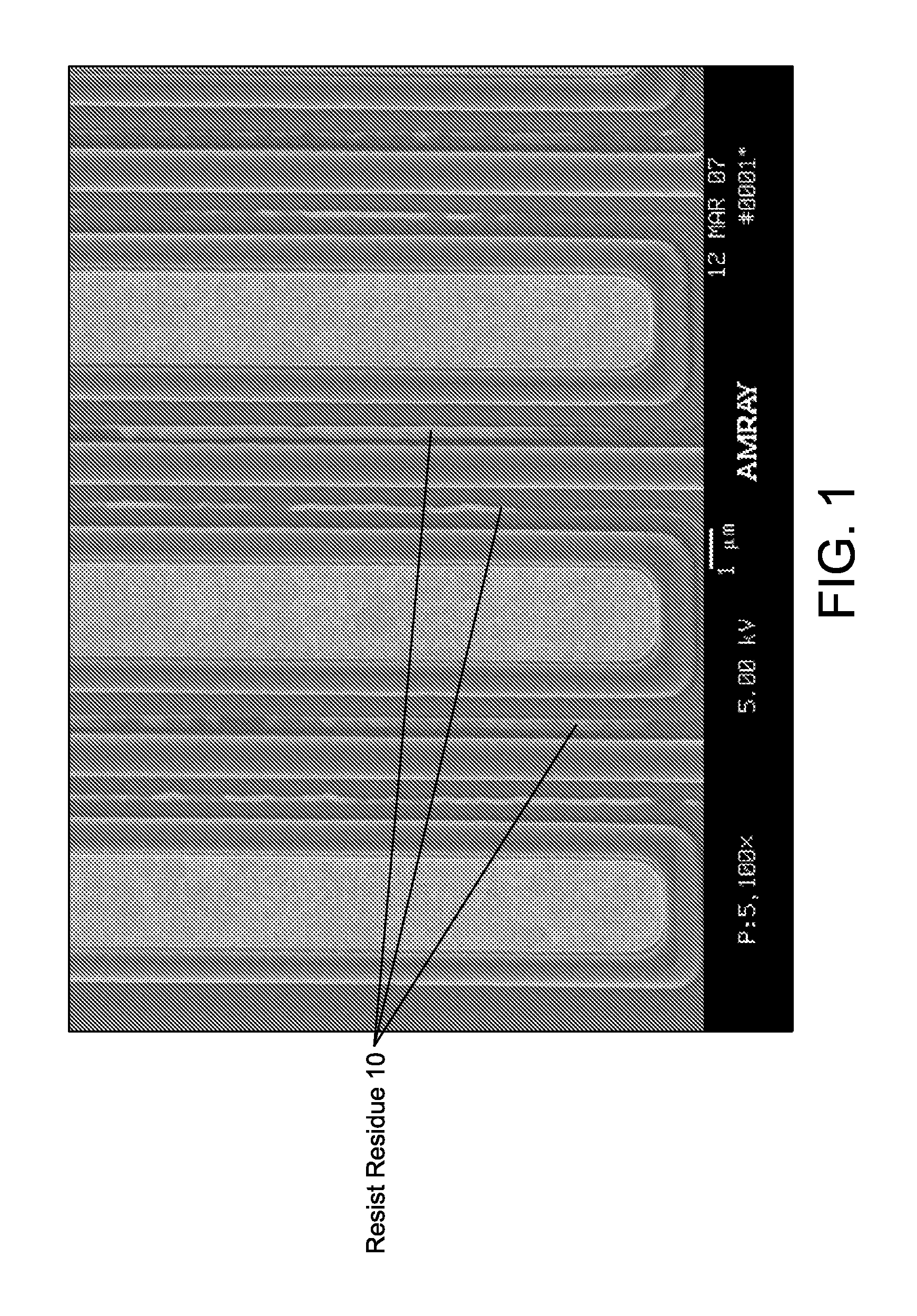

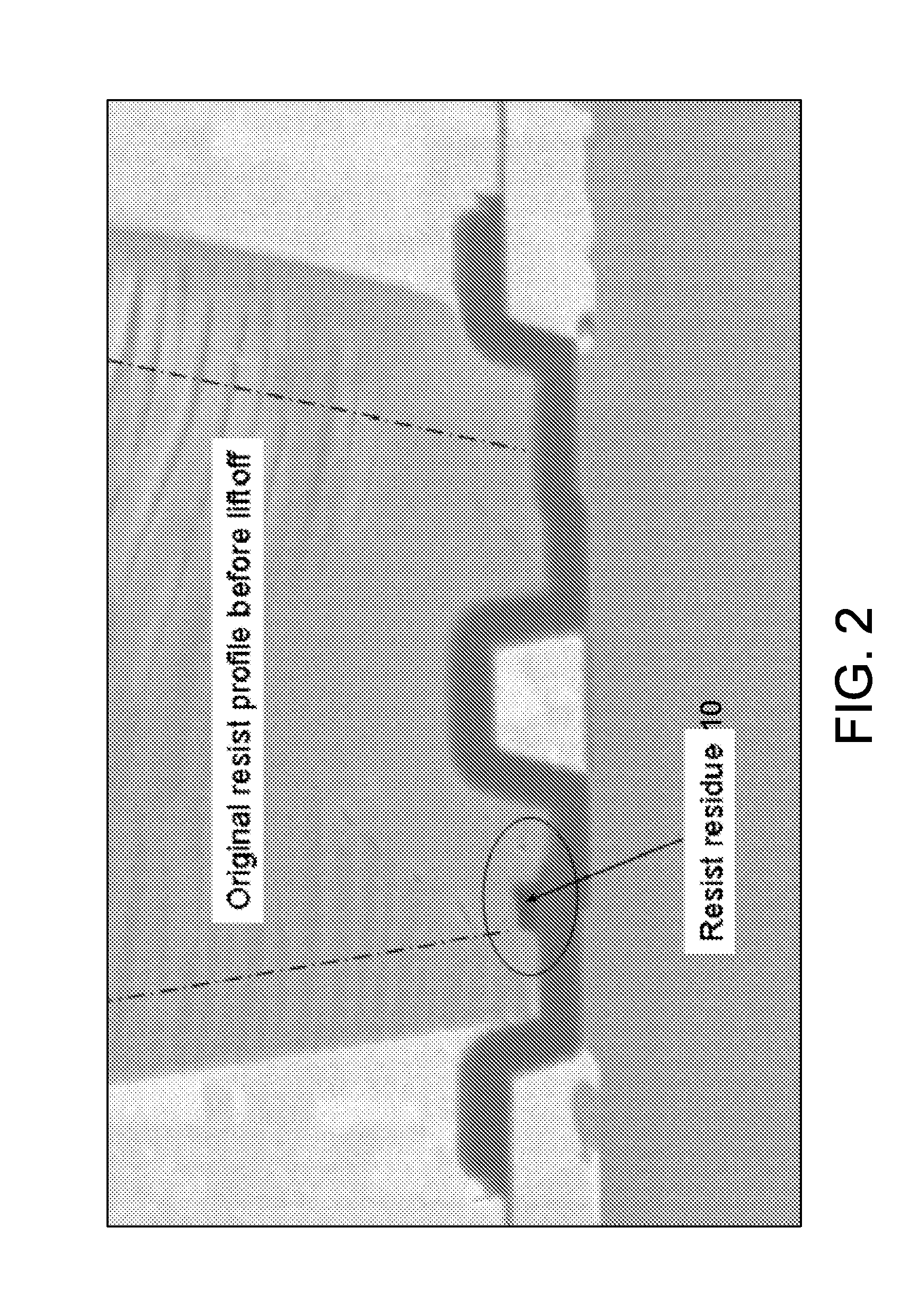

Electron radiation monitoring system to prevent gold spitting and resist cross-linking during evaporation

ActiveUS20110193576A1Increase productionReduce in quantitySemiconductor/solid-state device testing/measurementResistance/reactance/impedenceCross-linkElectron radiation

Disclosed herein are systems and methods for in-situ measurement of impurities on metal slugs utilized in electron-beam metal evaporation / deposition systems, and for increasing the production yield of a semiconductor manufacturing processes utilizing electron-beam metal evaporation / deposition systems. A voltage and / or a current level on an electrode disposed in a deposition chamber of an electron-beam metal evaporation / deposition system is monitored and used to measure contamination of the metal slug. Should the voltage or current reach a certain level, to the deposition is completed and the system is inspected for contamination.

Owner:SKYWORKS SOLUTIONS INC

Semiconductor device and method for fabricating the same

InactiveUS20050093020A1Improve featuresSmall body currentTransistorSolid-state devicesDevice formSilicon oxide

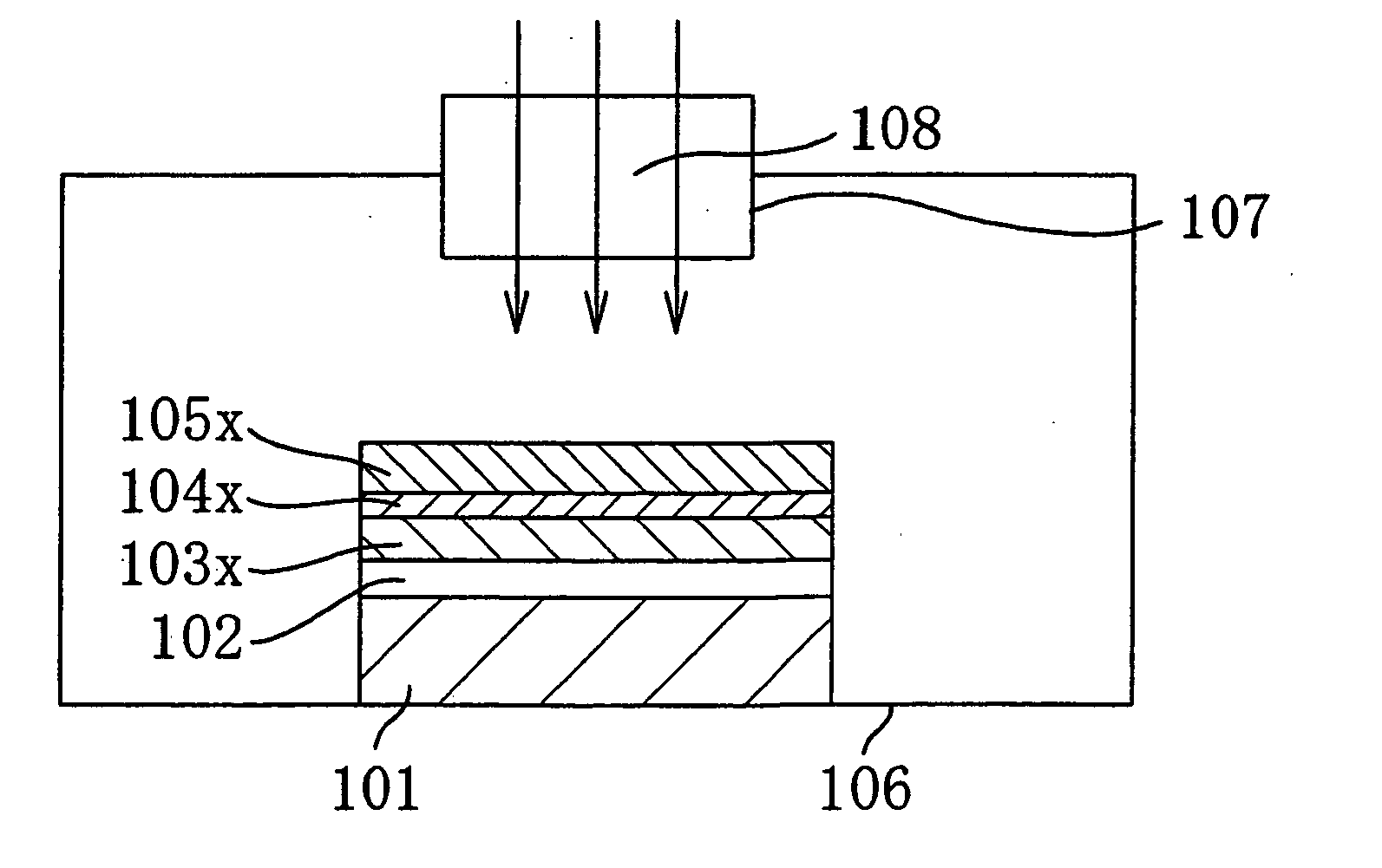

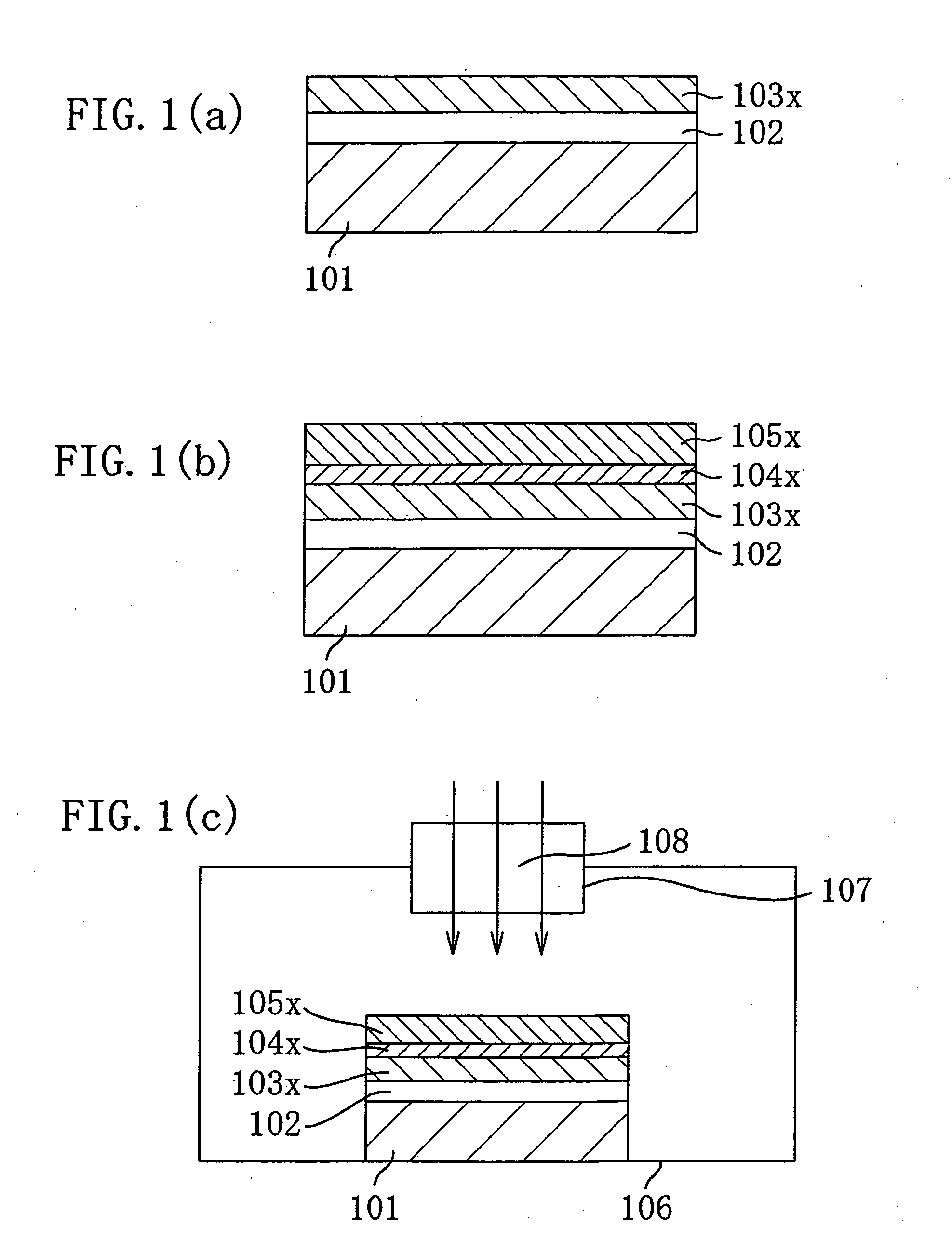

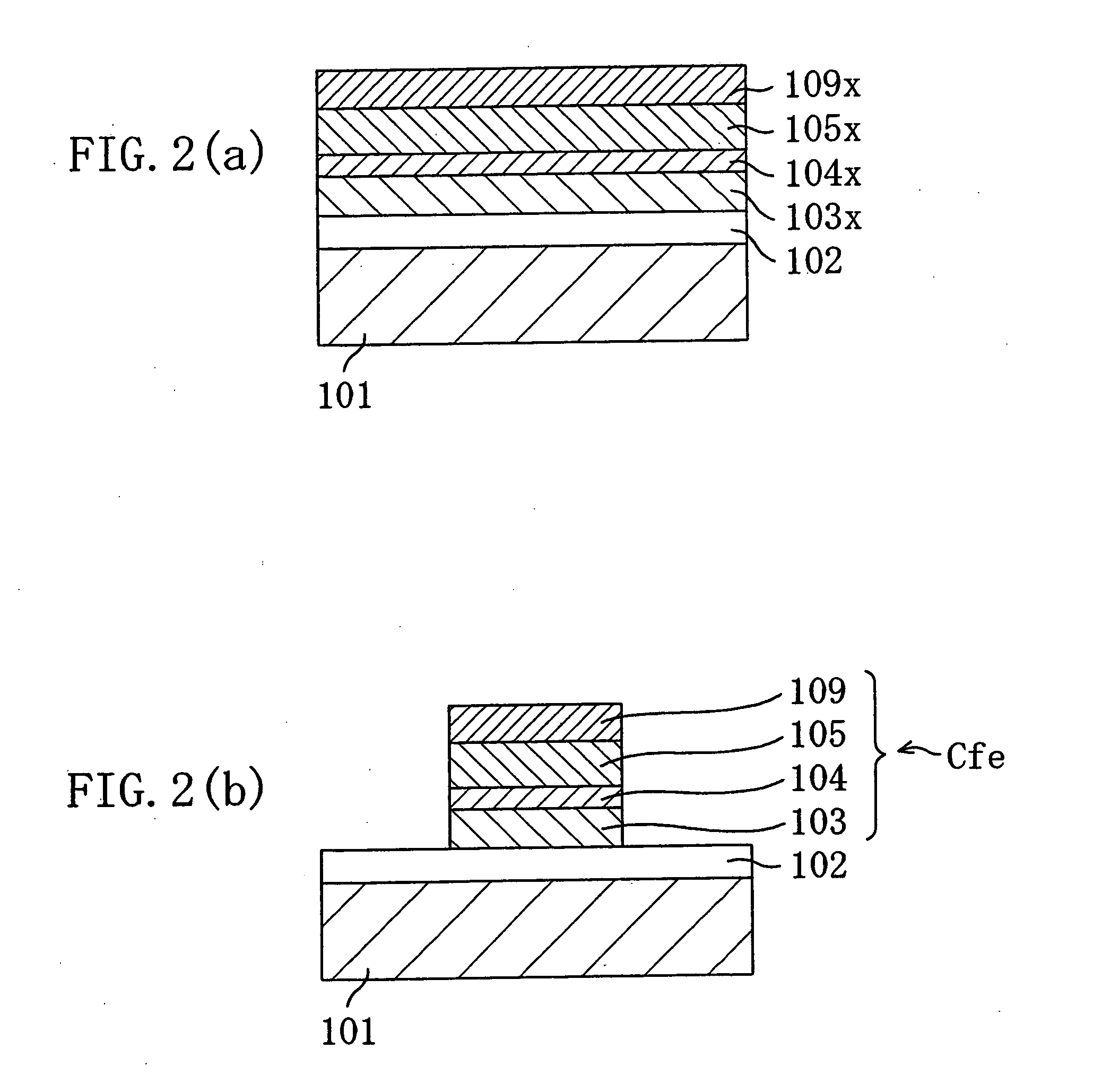

A silicon oxide film 102, a Pt film 103x, a Ti film 104x and a PZT film 105x are deposited in this order over a Si substrate 101. The Si substrate 101 is placed in a chamber 106 so that the PZT film 105x is irradiated with an EHF wave 108. The irradiation with the EHF wave locally heats a dielectric film such as the PZT film. As a result, it is possible to improve, for example, the leakage property of the dielectric film without adversely affecting a device formed on the Si substrate 101.

Owner:PANASONIC CORP

Method for manufacturing semiconductor device

InactiveUS20050095838A1Efficient fillingReduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

The present invention discloses a method for manufacturing a semiconductor device, comprising the steps of: providing a semiconductor substrate on which cell strings are formed and in which a plurality of conductive regions are formed; sequentially forming a first interlayer insulation film and a first etch barrier film on the semiconductor substrate; forming a plurality of contact holes by exposing the plurality of conductive regions formed in the semiconductor substrate, wherein an impurity concentration of the conductive regions is reduced due to the process for forming the contact holes; filling a metal material in the contact holes and forming a plurality of contact plugs; sequentially forming a second interlayer insulation film, a second etch barrier film and a third interlayer insulation film over a resulting structure including the contact plugs; forming a plurality of metal line patterns, wherein the metal line patterns pass through the third interlayer insulation film, the second etch barrier film and the second interlayer insulation film and contact to the contact plugs; forming a fourth interlayer insulation film over a resulting structure including the plurality of metal line patterns; forming a plurality of metal line contact holes by patterning the fourth interlayer insulation film; and forming a plurality of metal line contact plugs in the plurality of metal line contact holes by filling a metal material in the metal line contact holes.

Owner:STMICROELECTRONICS SRL +1

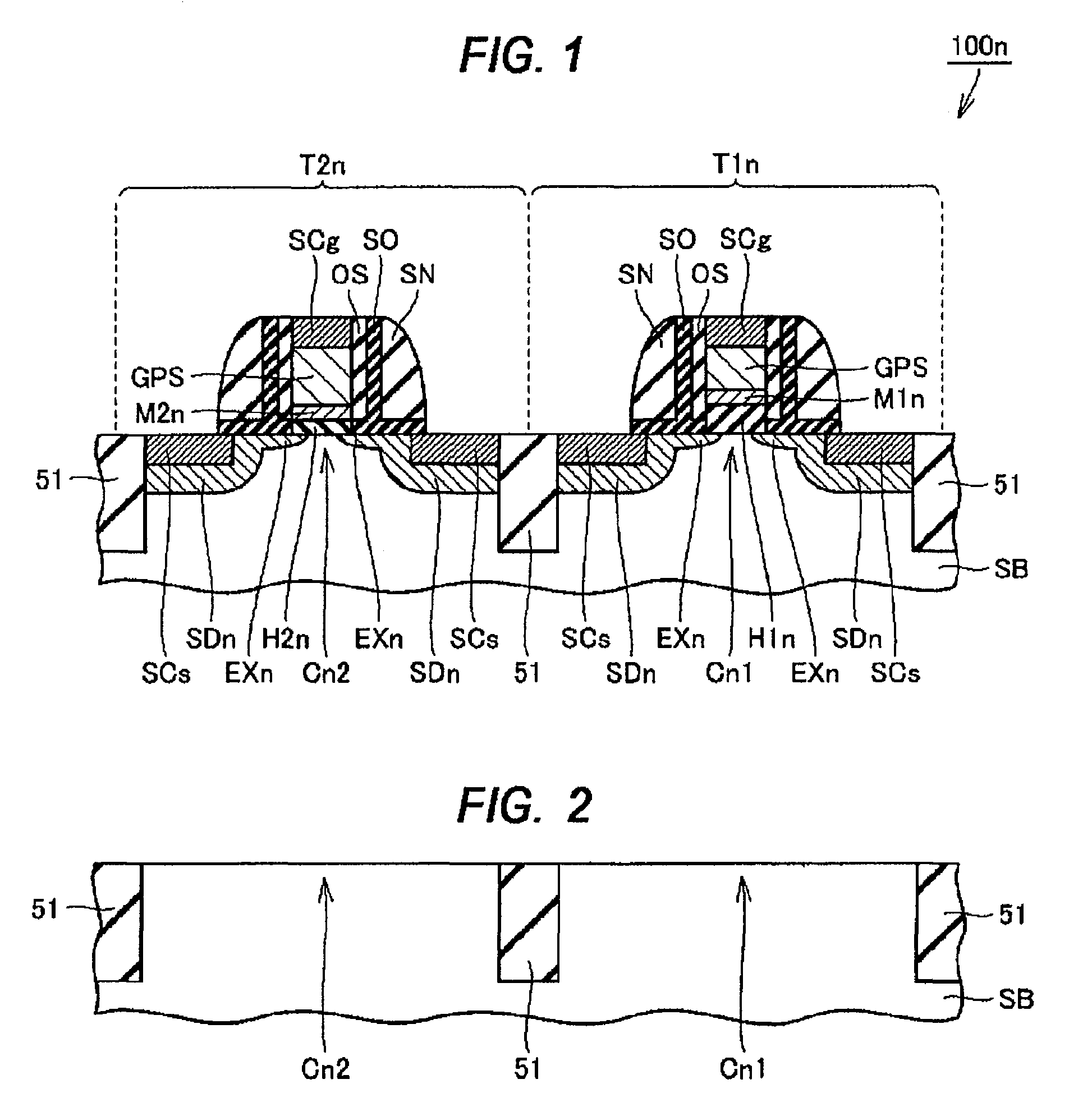

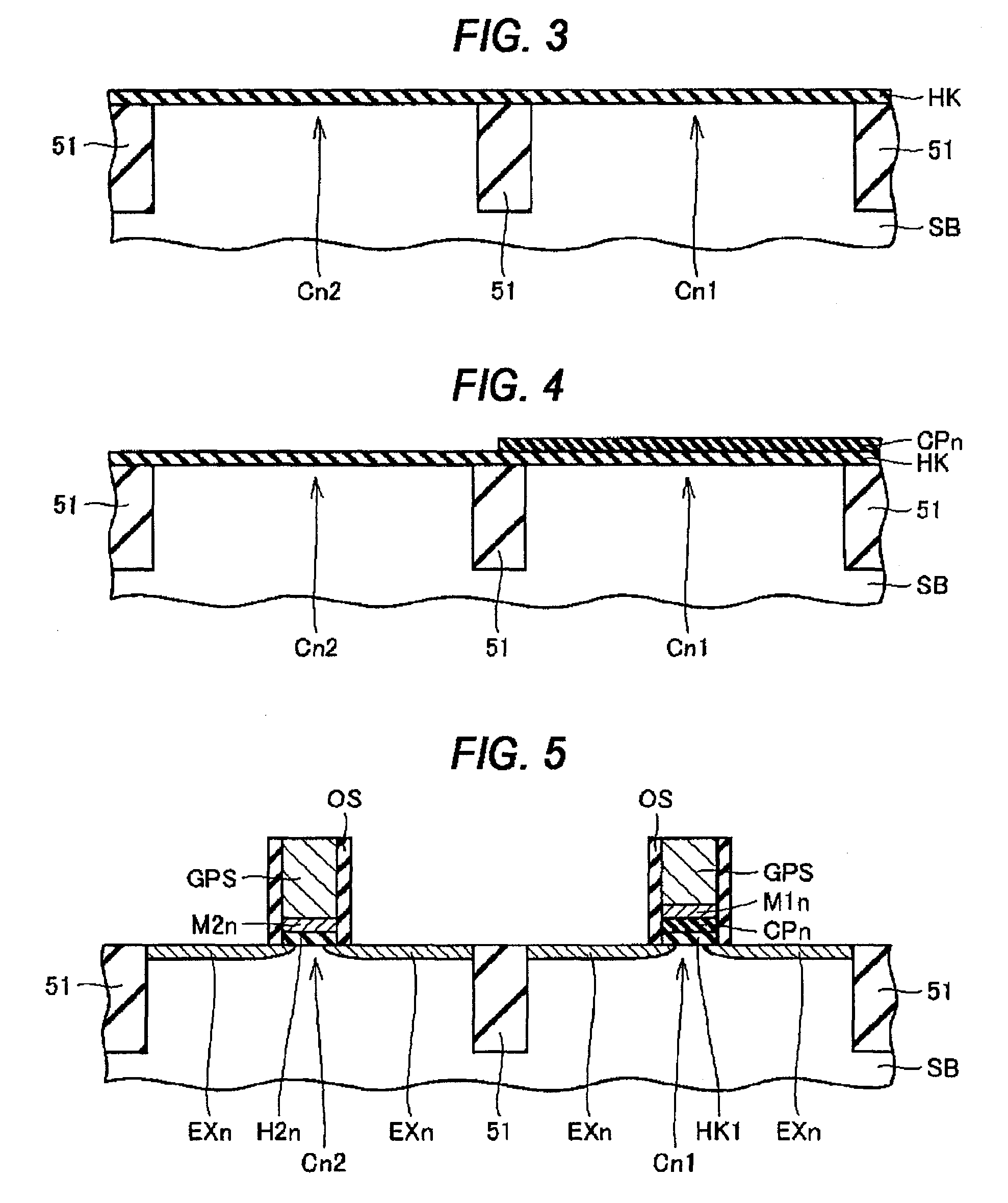

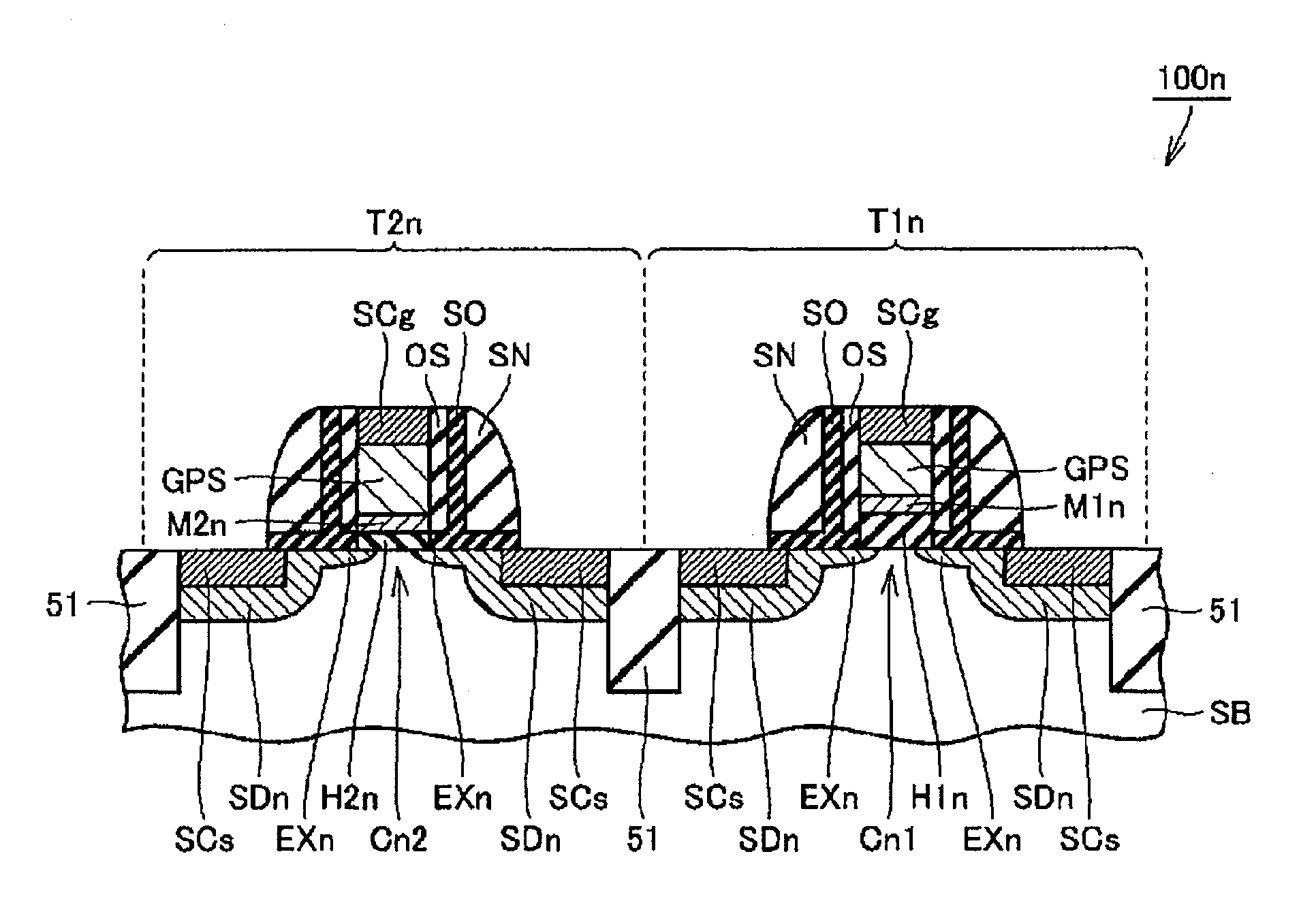

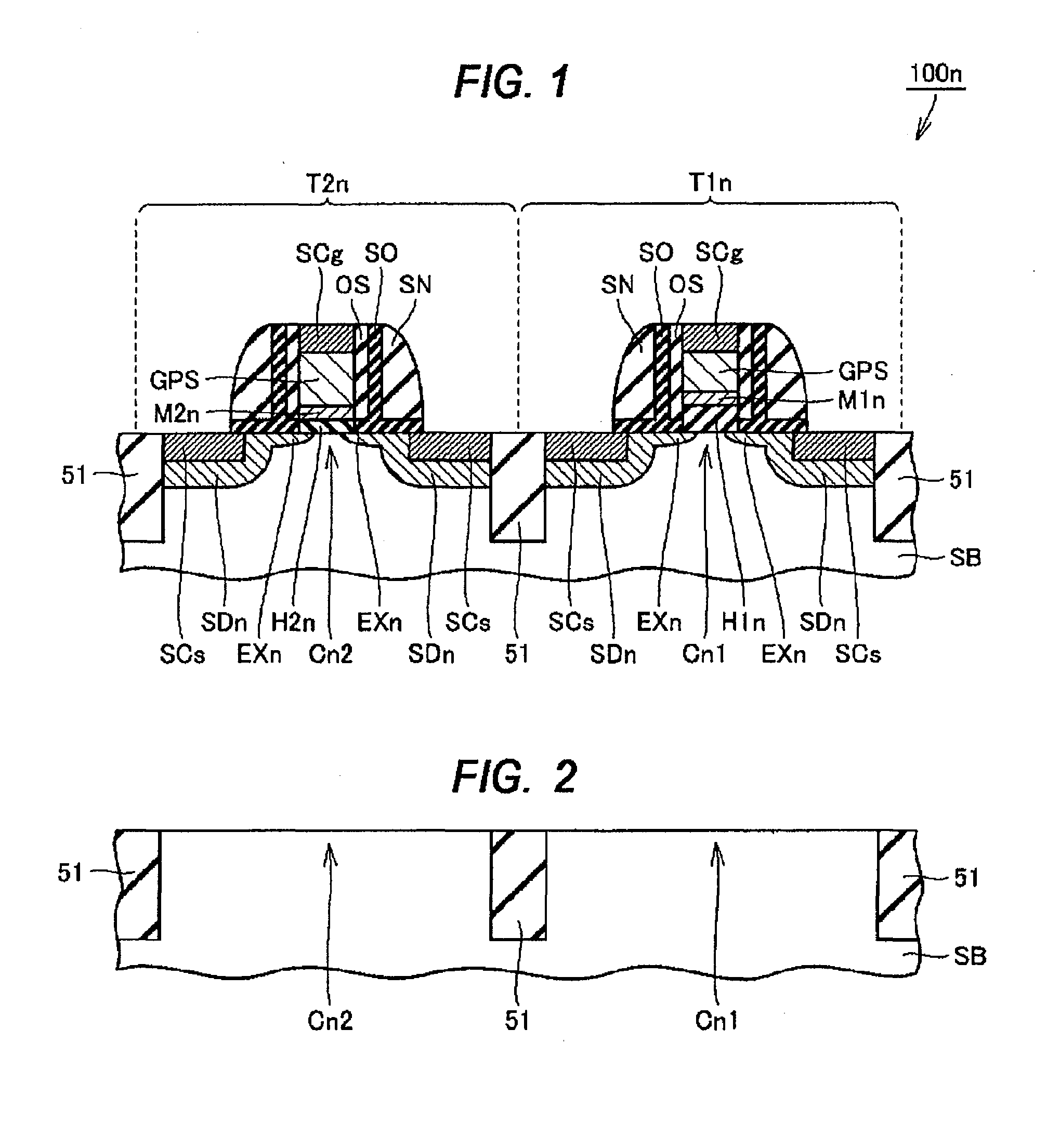

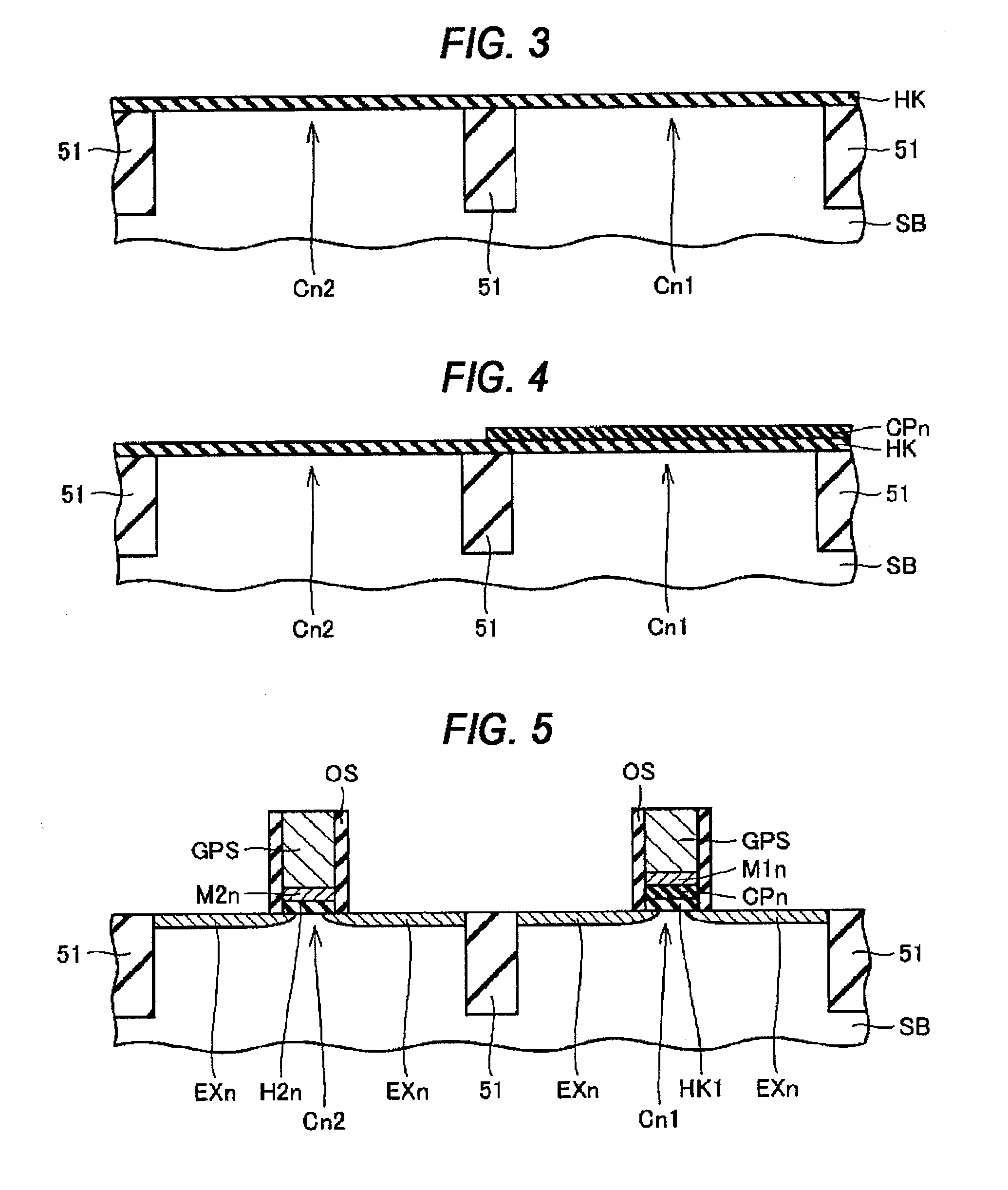

Semiconductor device and method of manufacturing same

ActiveUS8384160B2Increase valueInhibition decreasedTransistorSolid-state devicesDriving currentPower semiconductor device

To provide a semiconductor device and a method of manufacturing the same capable of suppressing, when a plurality of MIS transistors having different absolute values of threshold voltage is used, the reduction of the drive current of a MIS transistor having a greater absolute value of threshold voltage. The threshold voltage of a second nMIS transistor is greater than the threshold voltage of a first nMIS transistor and the sum of the concentration of lanthanum atom and the concentration of magnesium atom in a second nMIS high-k film included in the second nMIS transistor is lower than the sum of the concentration of lanthanum atom and the concentration of magnesium atom in a first nMIS high-k film included in the first nMIS transistor.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method of manufacturing same

ActiveUS20100164007A1Increase value of threshold voltageInhibition decreasedTransistorSolid-state devicesDriving currentEngineering

To provide a semiconductor device and a method of manufacturing the same capable of suppressing, when a plurality of MIS transistors having different absolute values of threshold voltage is used, the reduction of the drive current of a MIS transistor having a greater absolute value of threshold voltage.The threshold voltage of a second nMIS transistor is greater than the threshold voltage of a first nMIS transistor and the sum of the concentration of lanthanum atom and the concentration of magnesium atom in a second nMIS high-k film included in the second nMIS transistor is lower than the sum of the concentration of lanthanum atom and the concentration of magnesium atom in a first nMIS high-k film included in the first nMIS transistor.

Owner:RENESAS ELECTRONICS CORP

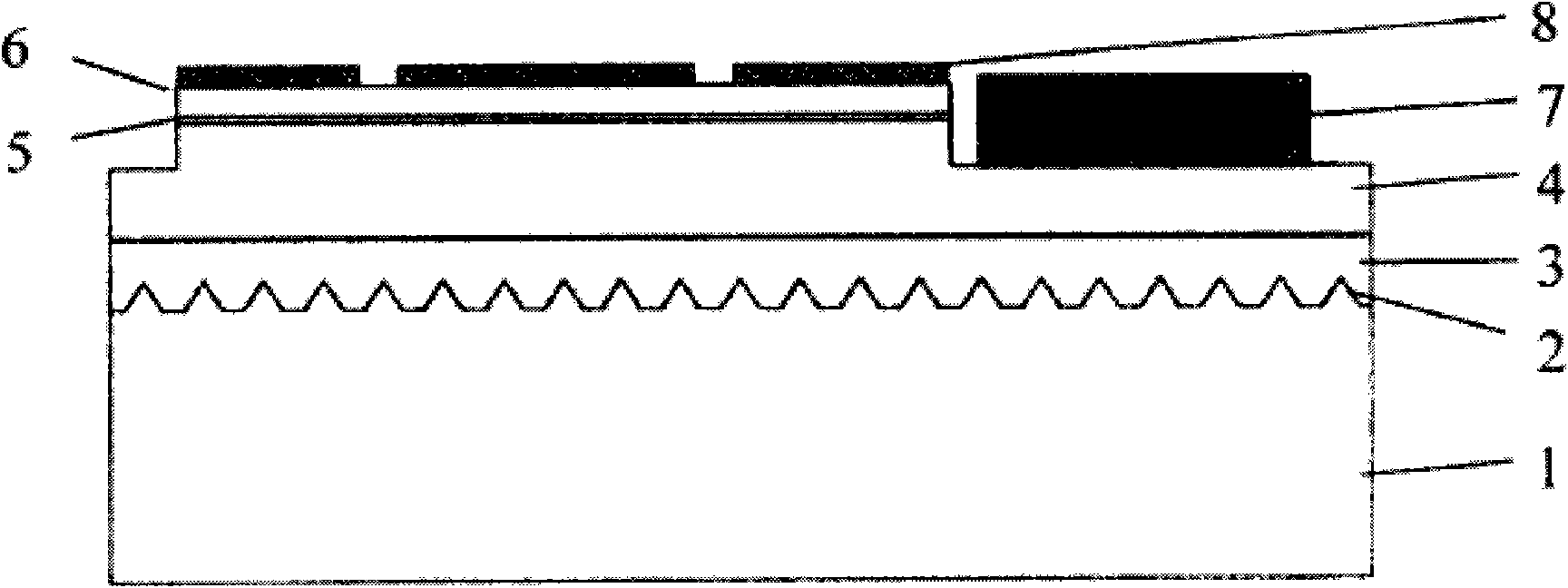

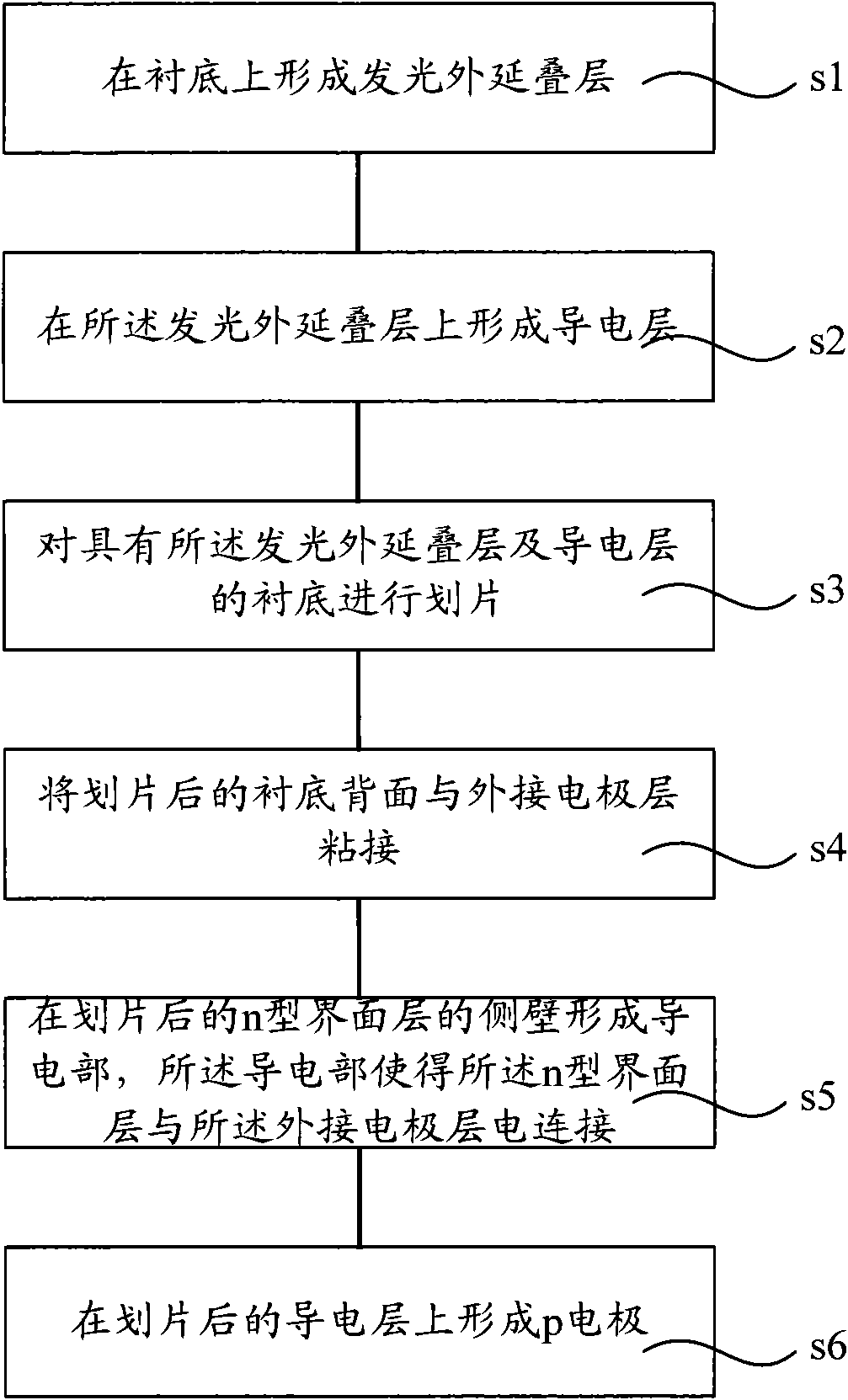

LED chip and manufacturing method thereof

ActiveCN101887938AIncrease light emitting areaReduce manufacturing costSemiconductor devicesInterface layerLight-emitting diode

The invention relates to an LED chip and a manufacturing method thereof. The LED chip comprises a substrate and a luminous epitaxial stack on the substrate, wherein the luminous epitaxial stack sequentially comprises an n-shaped interface layer, a luminous layer on the n-shaped interface layer and a p-shaped interface layer on the luminous layer. The area of the p-shaped interface layer is same as that of the luminous layer and the n-shaped interface layer; the p-shaped interface layer is provided with a p electrode; the back surface of the substrate is provided with an external electrode layer; and the side wall of the n-shaped interface layer is electrically connected with the external electrode layer by a conductive part.

Owner:JADE BIRD DISPLAY SHANGHAI LTD

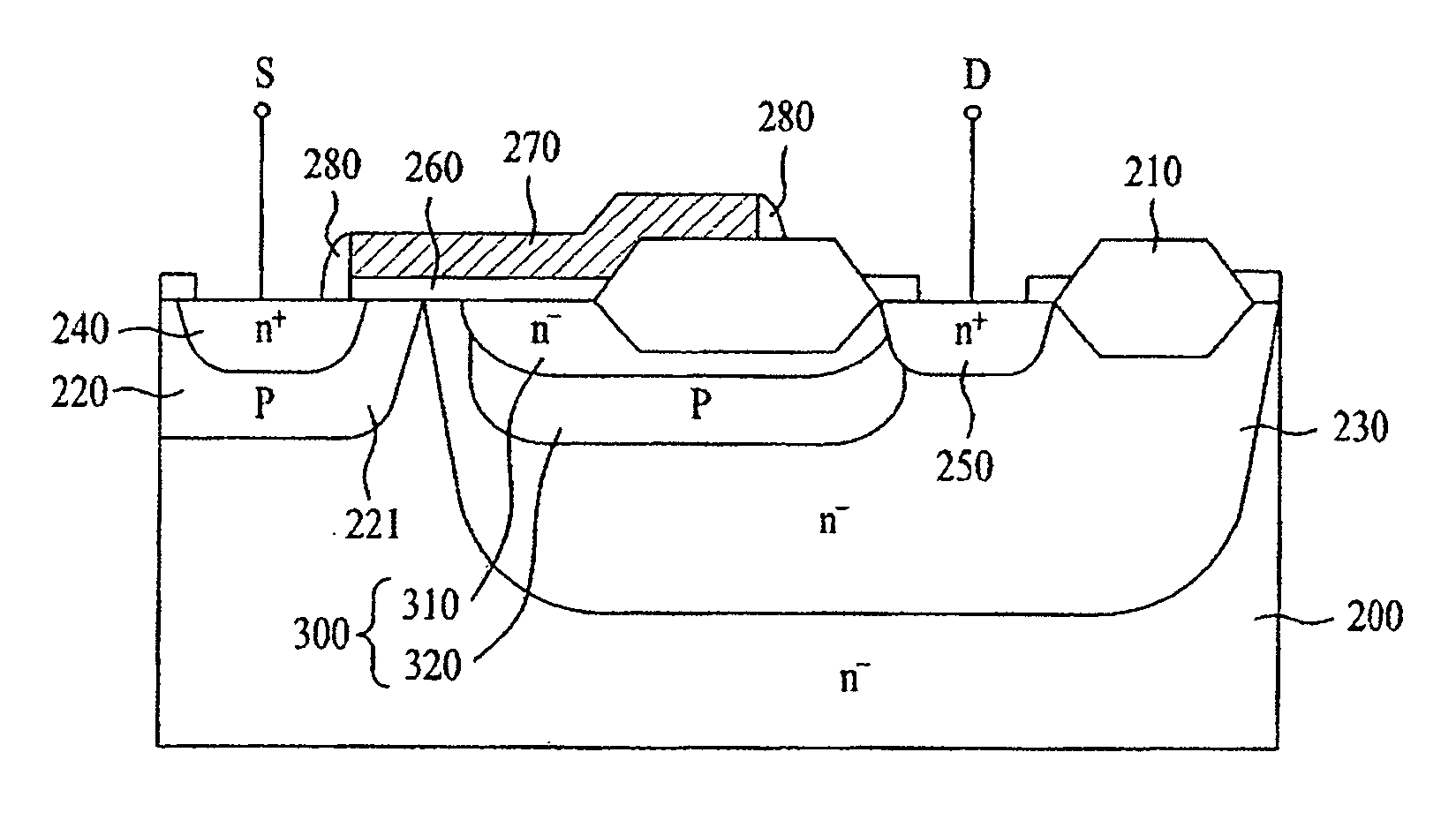

LDMOS transistor

InactiveUS20060145249A1Increase impurity densityIncrease impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorEngineering

A lateral double-diffused metal oxide semiconductor transistor (LDMOS) transistor includes a semiconductor substrate of a first conductivity; an extended drain region of the first conductivity formed in a surface region of the semiconductor substrate; and a depletion region, formed in the extended drain region, including first and second impurity regions sequentially embedded below a surface of the extended drain region, the first embedded impurity region being of a second conductivity and the second embedded impurity region being of the first conductivity.

Owner:DONGBU ELECTRONICS CO LTD

Manufacturing method of group III nitride semiconductor

ActiveUS20100248455A1Quality improvementControl surface flatnessPolycrystalline material growthLamination ancillary operationsOptoelectronicsSURFACTANT BLEND

A manufacturing method of a group III nitride semiconductor comprising: preparing a substrate including a buffer layer; forming a first layer on the buffer layer from a group III nitride semiconductor by MOCVD while doping an anti-surfactant, wherein a thickness of the first layer is equal to or thinner than 2 μm; forming a second layer on the first layer from a group III nitride semiconductor by MOCVD while doping at least one of surfactant and an anti-surfactant; and controlling a crystalline quality and a surface flatness of the second layer by adjusting an amount of the anti-surfactant and the surfactant doped during the formation of the second layer.

Owner:TOYODA GOSEI CO LTD

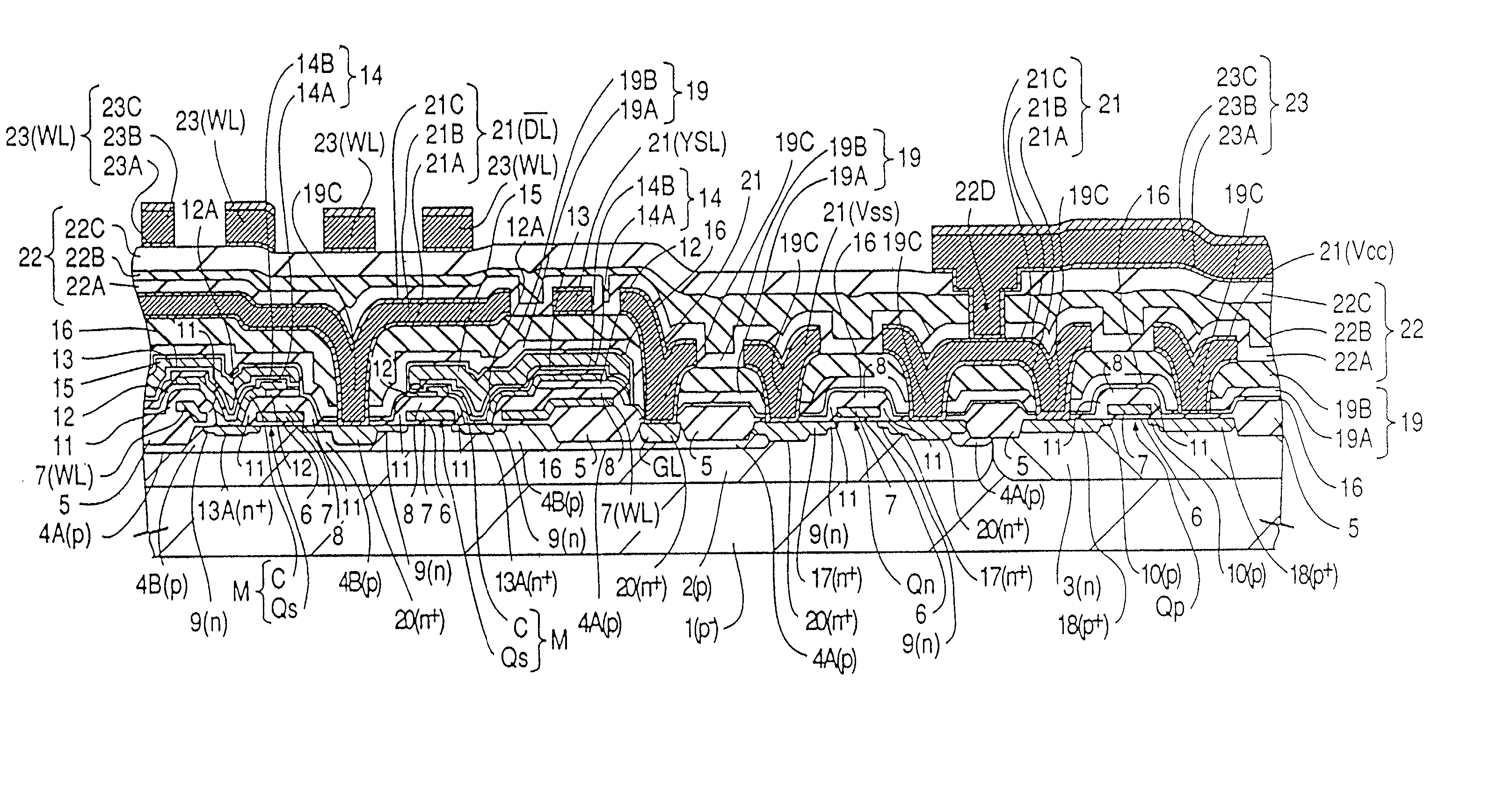

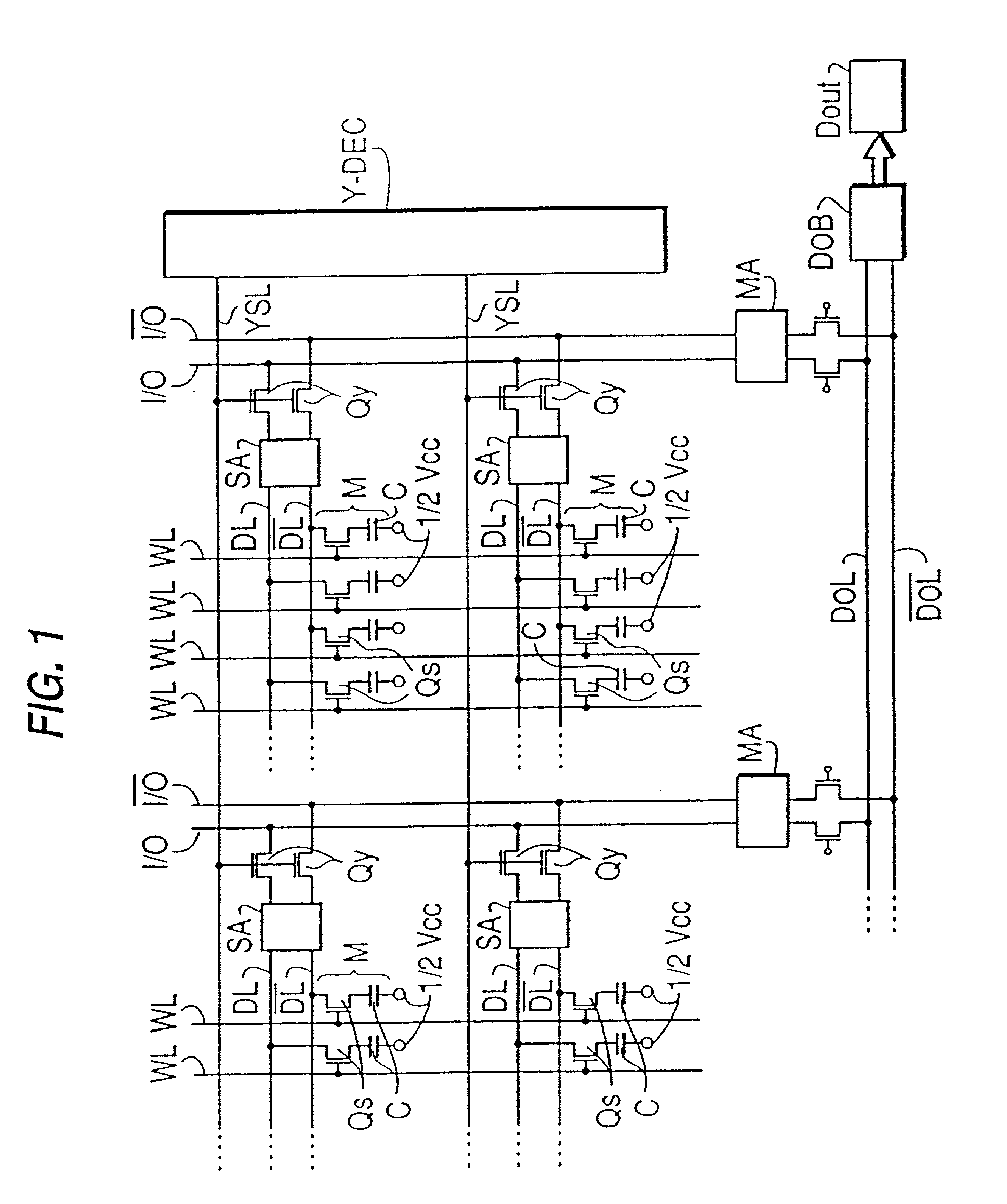

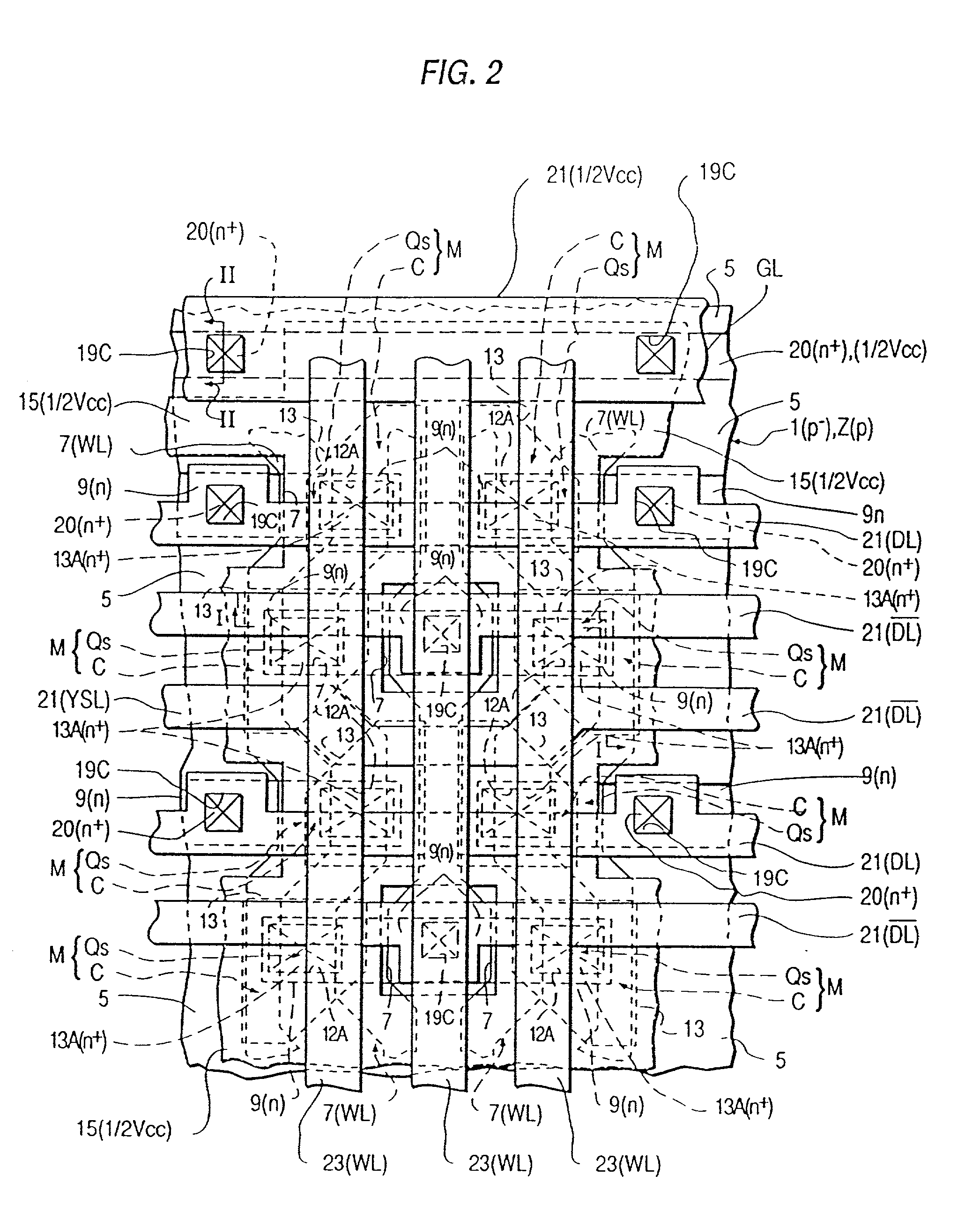

Semiconductor integrated circuit device having switching misfet and capacitor element and method of producing the same, including wiring therefor and method of producing such wiring

InactiveUS20020127793A1Reduce contact resistanceElectrical connectionTransistorSolid-state devicesDielectricSilicon oxide

A semiconductor integrated circuit device having a switching MISFET, and a capacitor element formed over the semiconductor substrate, such as a DRAM, is disclosed. In a first aspect of the present invention, the impurity concentration of the semiconductor region of the switching MISFET to which the capacitor element is connected is less than the impurity concentration of semiconductor regions of MISFETs of peripheral circuitry. In a second aspect, the Y-select signal line overlaps the lower electrode layer of the capacitor element. In a third aspect, a potential barrier layer, provided at least under the semiconductor region of the switching MISFET to which the capacitor element is connected, is formed by diffusion of an impurity for a channel stopper region. In a fourth aspect, the dielectric film of the capacitor element is co-extensive with the capacitor electrode layer over it. In a fifth aspect, the capacitor dielectric film is a silicon nitride film having a silicon oxide layer thereon, the silicon oxide layer being formed by oxidizing a surface layer of the silicon nitride under high pressure. In sixth and seventh aspects, wiring is provided. In the sixth aspect, an aluminum wiring layer and a protective (and / or barrier) layer are formed by sputtering in the same vacuum sputtering chamber without breaking the vacuum between forming the layers; in the seventh aspect, a refractory metal, or a refractory metal suicide QSi.sub.x, where Q is a refractory metal and 0<x<2, is used as a protective layer, for an aluminum wiring containing an added element (e.g., Cu) to prevent migration.

Owner:HITACHI LTD

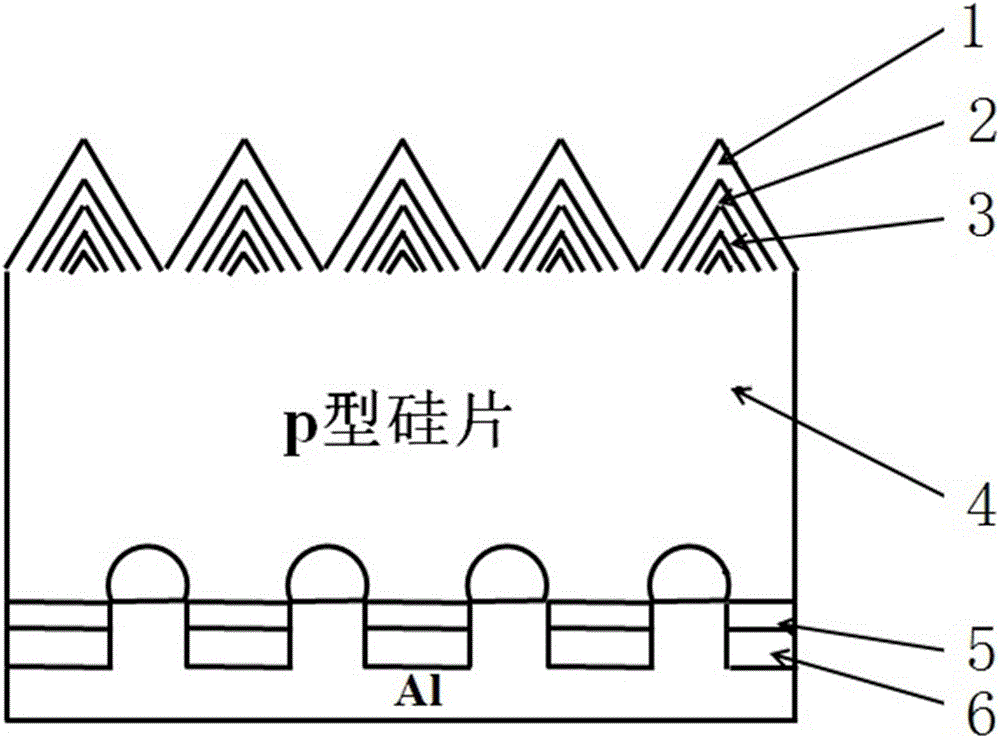

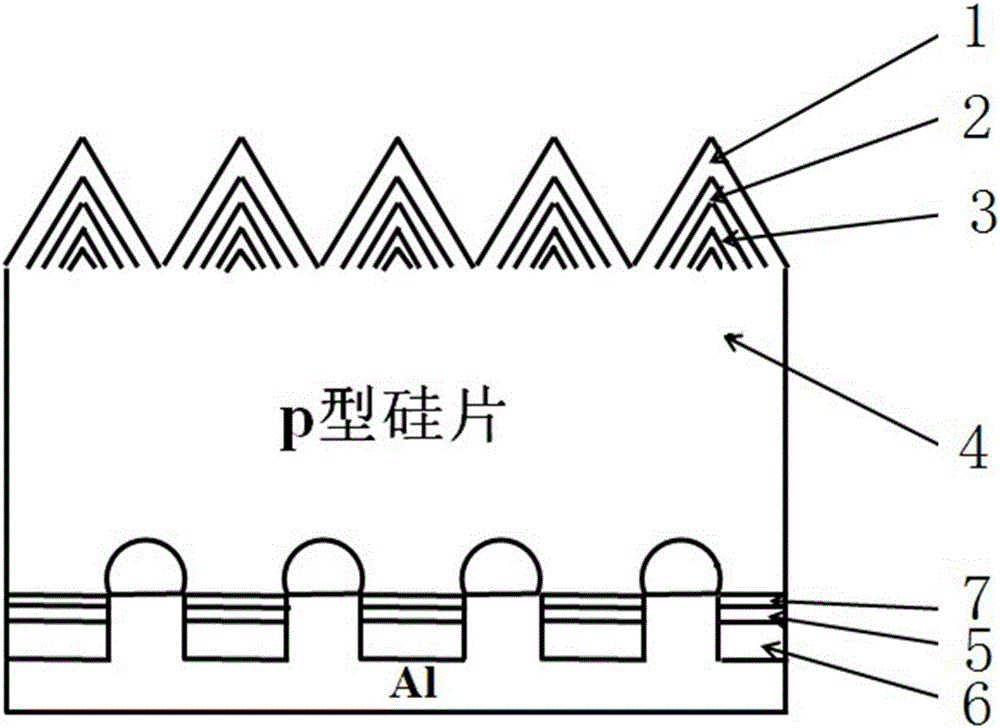

PERC solar cell structure and preparation process thereof

ActiveCN106653871AIncrease impurity concentrationImprove conversion efficiencyFinal product manufacturePhotovoltaic energy generationElectrical batteryEngineering

The invention discloses a PERC solar cell structure and a preparation process thereof. The PERC solar cell structure comprises a cell piece body. A SiO2 layer, an anti-reflection layer and an AlOx layer are successively deposited / grown on the front surface of the cell piece body. An AlOx layer and a SiNx layer are successively deposited on the back surface of the cell piece body. On the basis of a conventional PERC cell preparation process, a surface oxidation doping process is used. In addition, the PERC battery process is adjusted. A unique surface passivation layer deposition process is also used. The beneficial effect of the preparation process is that effective doping in an oxidation process improves the surface impurity concentration of the cell, improves the FF of the cell, compensate the deterioration of the FF due to the local contact on the back surface; and the adjustment of the PERC cell process solves edge electric leakage due to doping process so as to simply the process, thereby improving the conversion efficiency of the cell and providing a better hydrogenation effect for the subsequent photonic recovery process of the PERC battery so as to achieve anti-LID.

Owner:HENGDIAN GRP DMEGC MAGNETICS CO LTD

Radio frequency (RF) laterally diffused metal oxide semiconductor (LDMOS) component and manufacture method

ActiveCN103035678AImprove breakdown voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSRadio frequency

The invention discloses a radio frequency (RF) laterally diffused metal oxide semiconductor (LDMOS) component. A structure of the RF LDMOS component is that a P trap is formed on the left of a P epitaxy, a drain terminal N type light dope region is formed on the right of the P epitaxy, a drain terminal N type heavy dope region is formed on the right of the drain terminal N type light dope region, an N type middle dope region is formed on the left of the drain terminal N type light dope region, and the drain terminal N type heavy dope region is not contacted with the N type middle dope region. The drain terminal N type light dope region of the RF LDMOS component is horizontally and unevenly N doped, the doping concentration of one side close to a polycrystalline silicon gate is high, the doping concentration close to the portion of a drain terminal is low, the component has high breakdown voltage, and simultaneously on resistance of the component is effectively reduced. The invention further discloses a manufacture method of the RF LDMOS component.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP