Semiconductor device and method of manufacturing same

a semiconductor and device technology, applied in semiconductor devices, digital storage, instruments, etc., can solve the problem of low drive current, achieve the effect of suppressing the reduction of drive current, increasing the absolute value of threshold voltage, and increasing the impurity concentration of the channel region

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

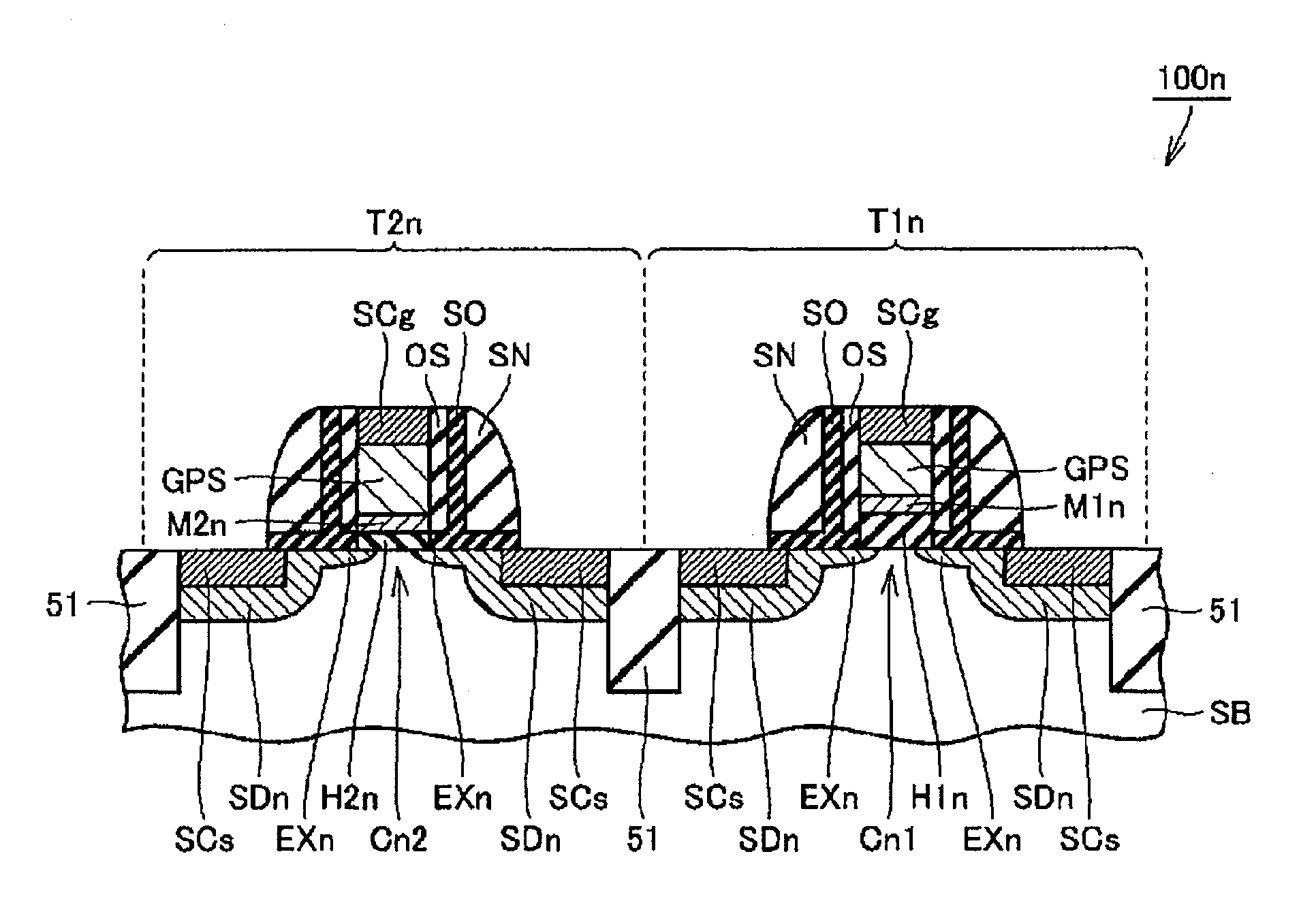

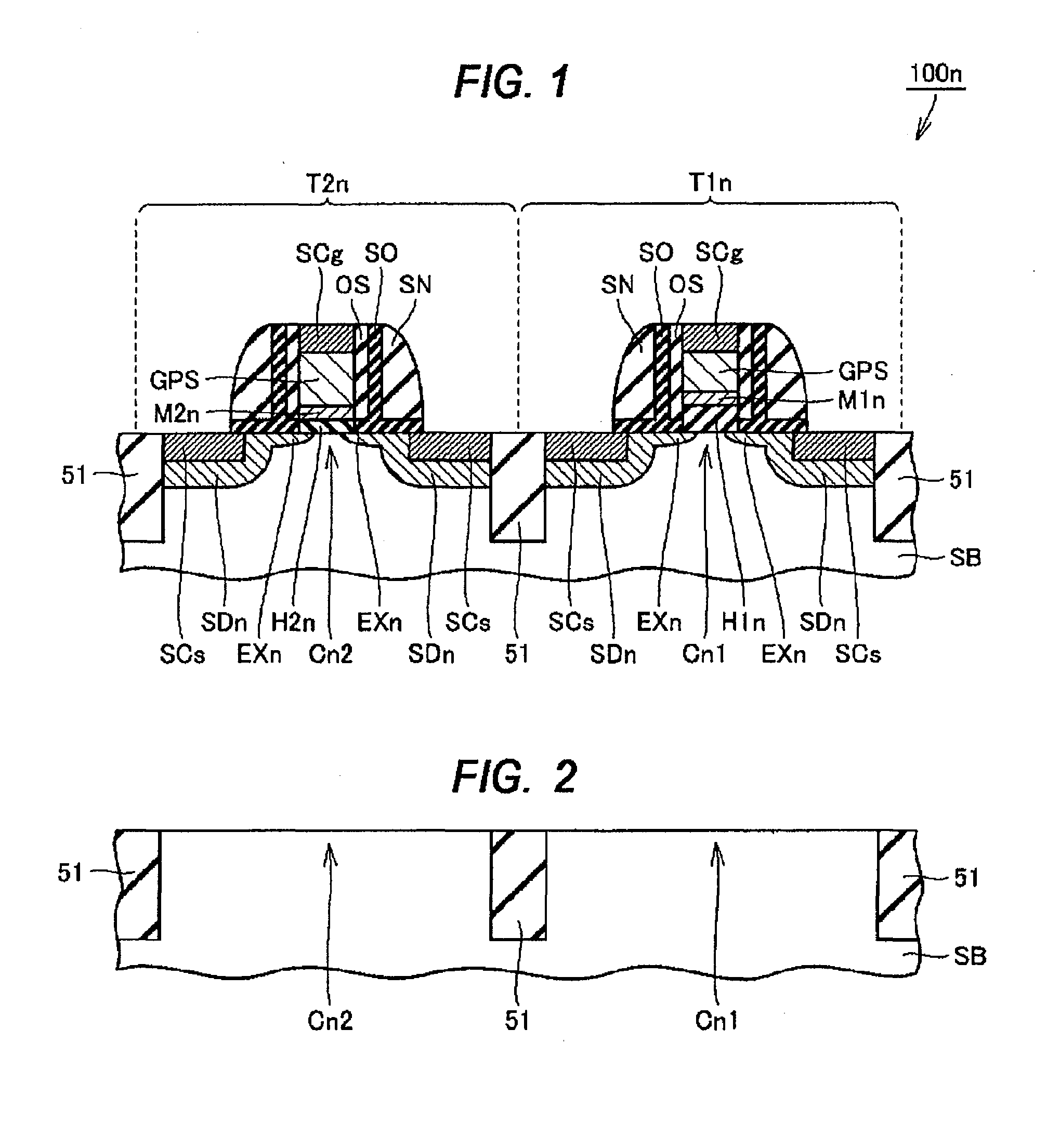

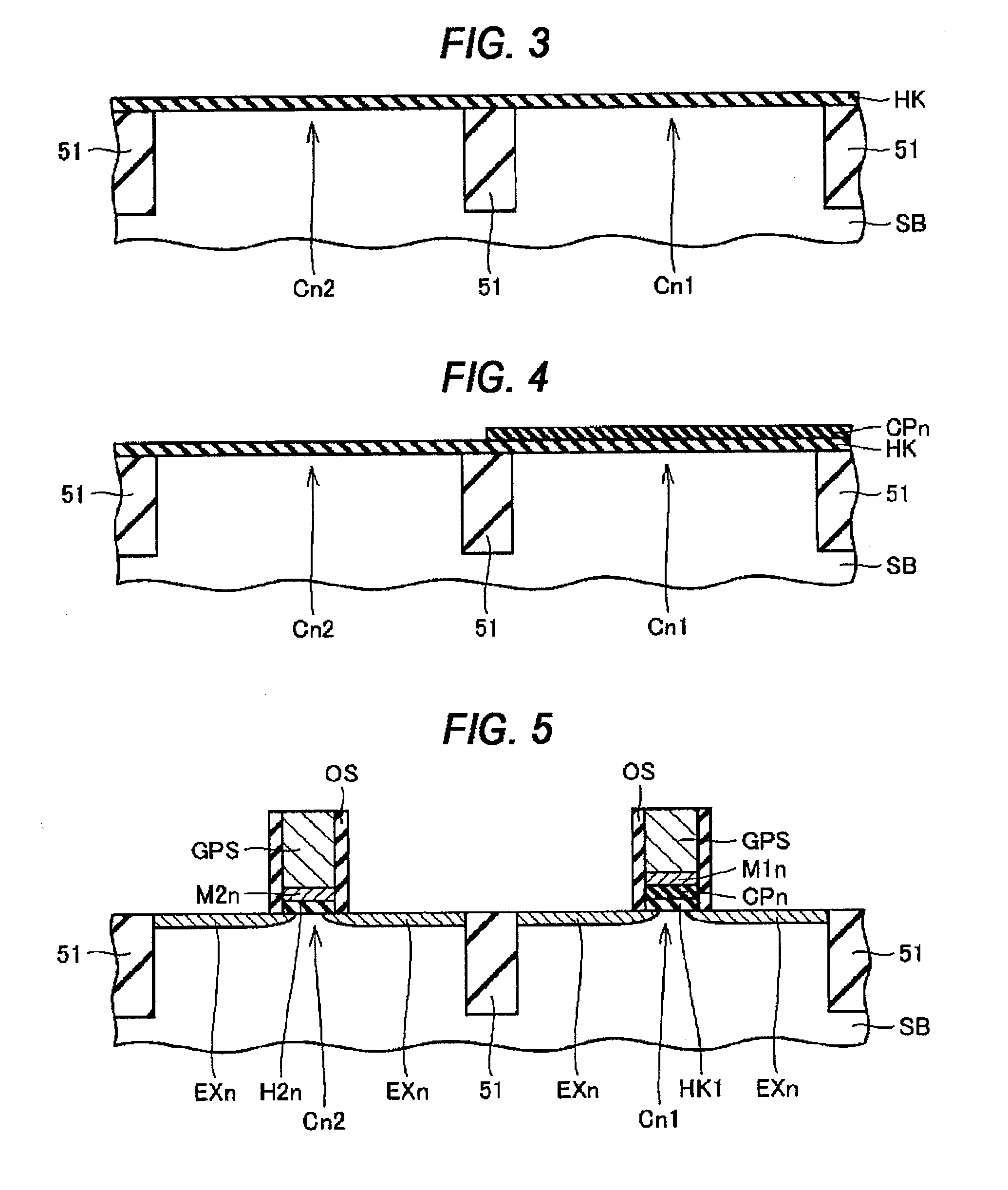

[0032]FIG. 1 is a partial section view schematically showing a configuration of a semiconductor device in a first embodiment of the present invention.

[0033]Referring to FIG. 1, a semiconductor device 100n in the present embodiment has a first nMIS transistor T1n and a second nMIS transistor T2n. The first and second nMIS transistors T1n, T2n are separated from each other by a silicon oxide film 51 configured to separate elements over a semiconductor substrate SB. The first and second nMIS transistors T1n, T2n have a first and a second nMIS threshold voltage, respectively. The absolute value of the second nMIS threshold voltage is greater than that of the first nMIS threshold voltage.

[0034]The first nMIS transistor T1n has a first nMIS channel region Cn1, a first nMIS high-k film H1n, a first nMIS metal electrode M1n, a gate polysilicon layer GPS, a pair of n-type source / drain regions SDn, an n-type source / drain extension EXn, nickel silicide layers SCg, SCs, an offset spacer OS, a s...

second embodiment

[0052]FIG. 7 is a partial section view schematically showing a configuration of a semiconductor device in a second embodiment of the present invention.

[0053]Referring to FIG. 7, a semiconductor device 100p in the present embodiment has a first pMIS transistor T1p and a second pMIS transistor T2p. The first and second pMIS transistors T1p, T2p are separated from each other by the silicon oxide film 51 configured to separate elements over the semiconductor substrate SB. The first and second pMIS transistors T1p, T2p have a first and a second pMIS threshold voltage, respectively. The absolute value of the second pMIS threshold voltage is greater than that of the first pMIS threshold voltage.

[0054]The first pMIS transistor T1p has a first pMIS channel region Cp1, a first pMIS high-k film H1p, a first pMIS metal electrode M1p, the gate polysilicon layer GPS, a pair of p-type source / drain regions SDp, a p-type source / drain extension EXp, the nickel silicide layers SCg, SCs, the offset spa...

third embodiment

[0072]FIG. 12 is a partial section view schematically showing a configuration of a semiconductor device in a third embodiment of the present invention. Referring to FIG. 12, a semiconductor device 100c in the present embodiment further has the first and second nMIS transistors T1n, T2n in addition to the configuration of the semiconductor device 100p in the second embodiment.

[0073]Configurations other than those described above are substantially the same as those in the above-described first or second embodiment, and therefore, the same symbols are assigned to the same or corresponding elements and their description is not repeated.

[0074]According to the present embodiment, the same effects as those in the first and second embodiments, respectively, can be obtained. Further, it is possible to form a CMIS structure having both the nMIS structure and the pMIS structure.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More