Patents

Literature

104results about How to "Avoid lateral spread" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

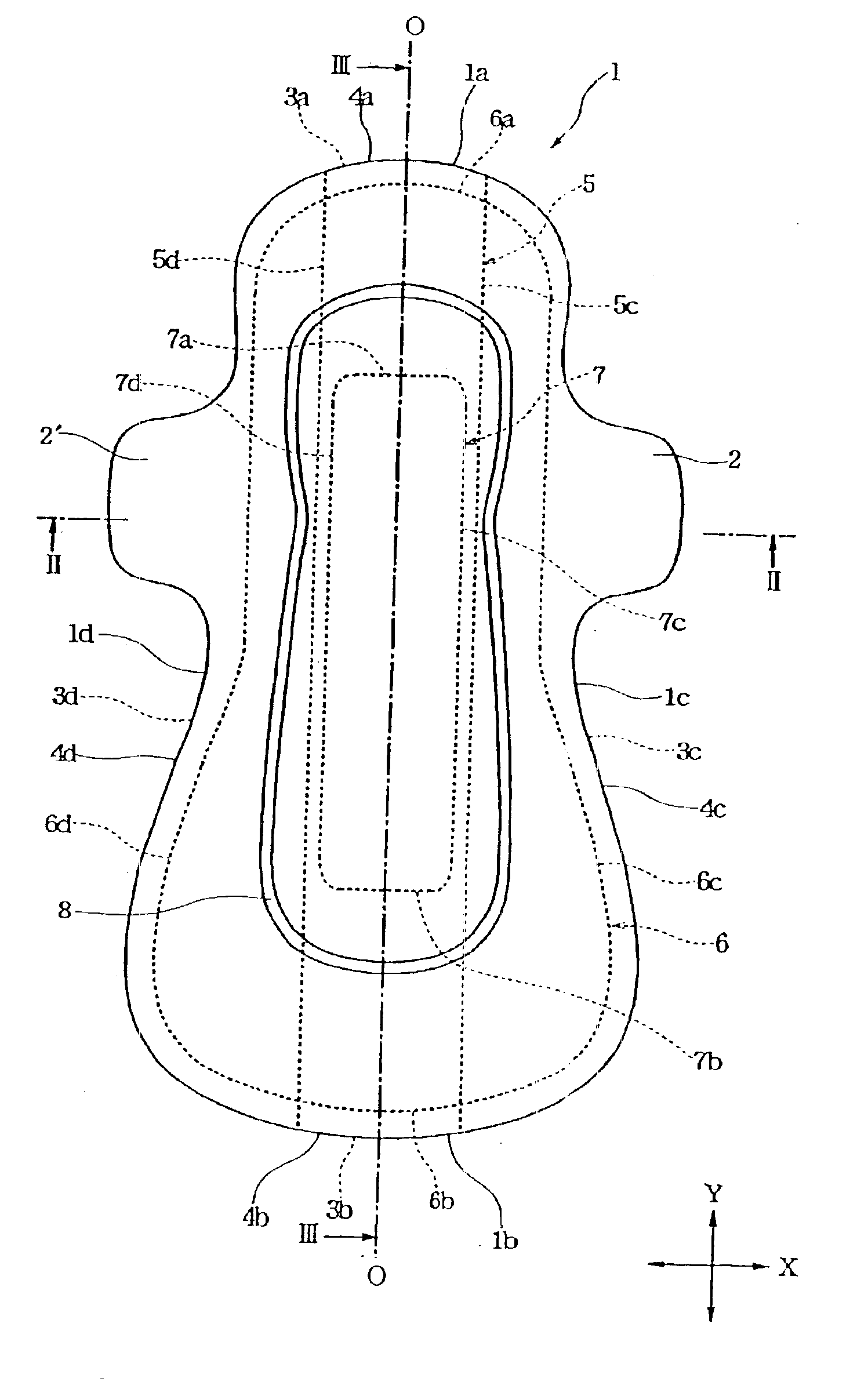

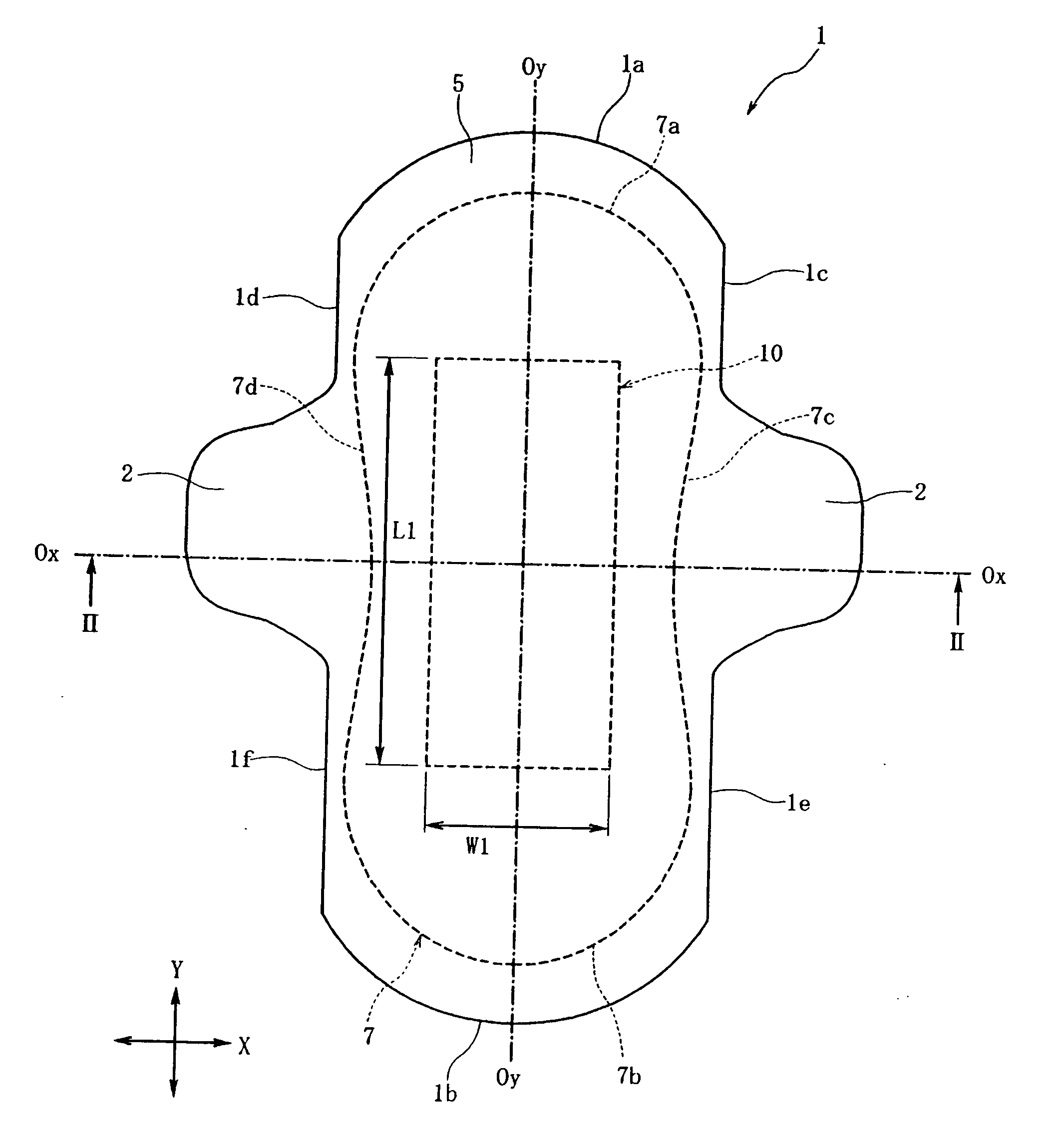

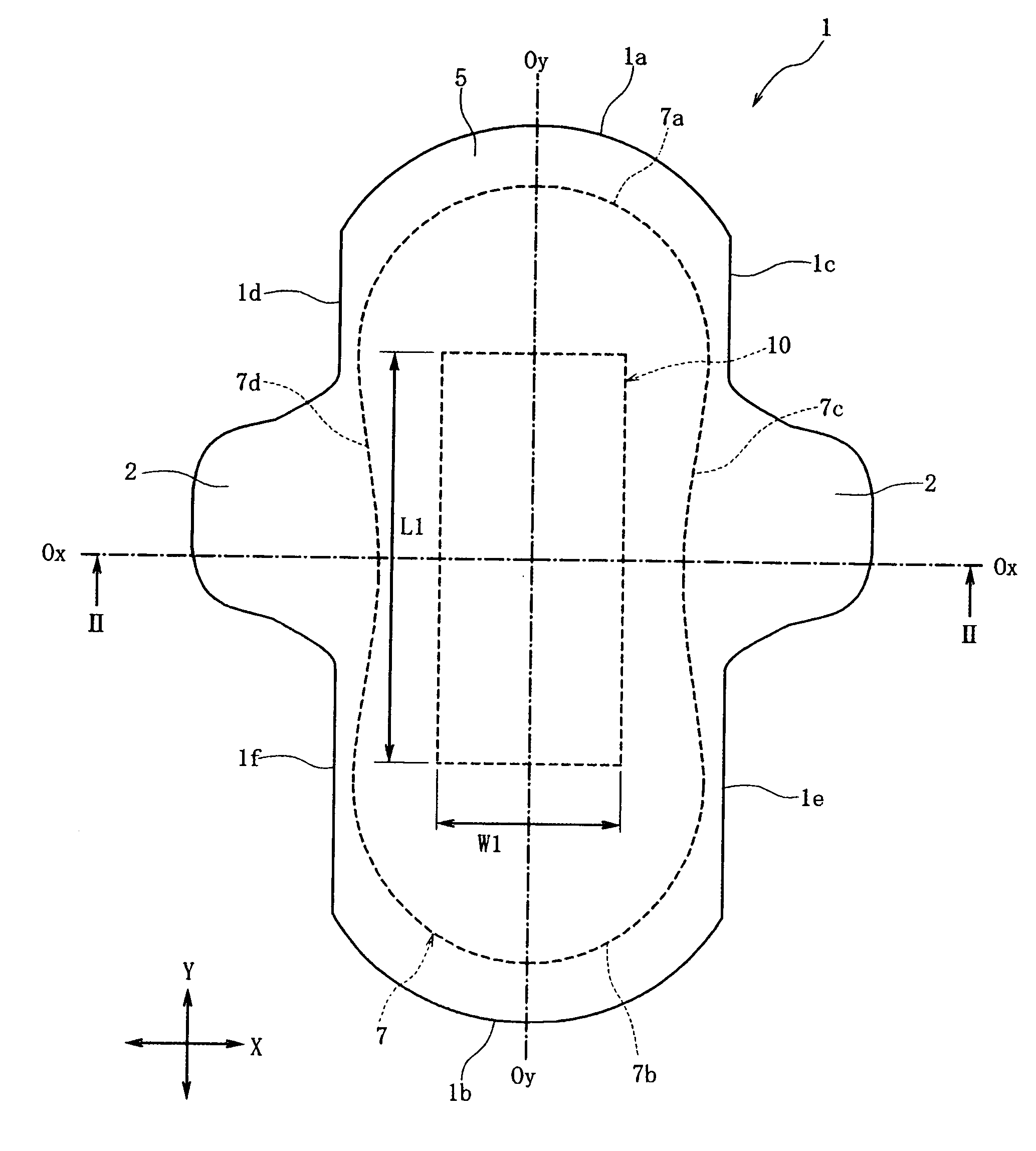

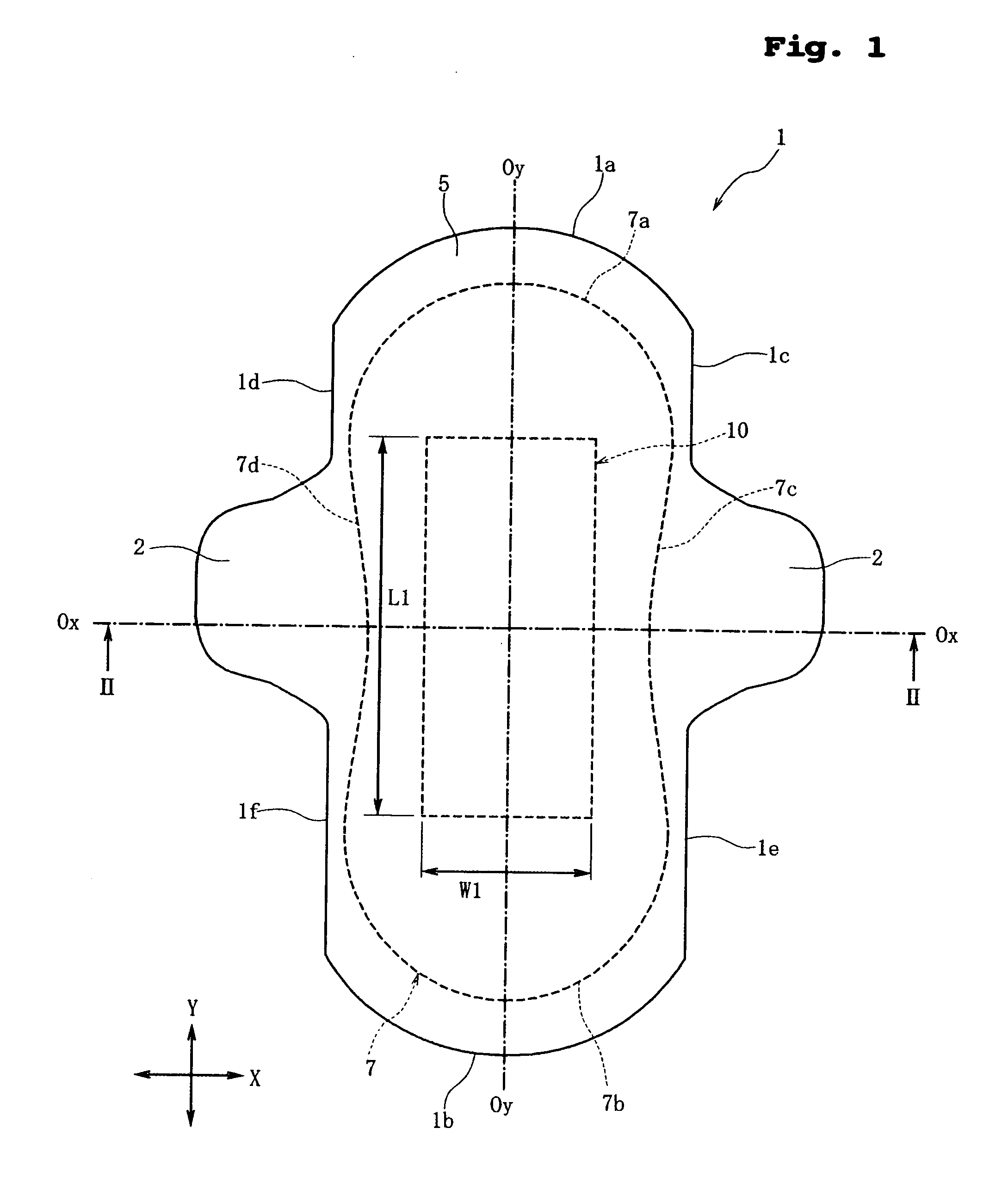

Absorbent article with compressed grooves

InactiveUS6858771B2Avoid lateral spreadConvenient guidanceSanitary towelsBaby linensEngineeringRetention ratio

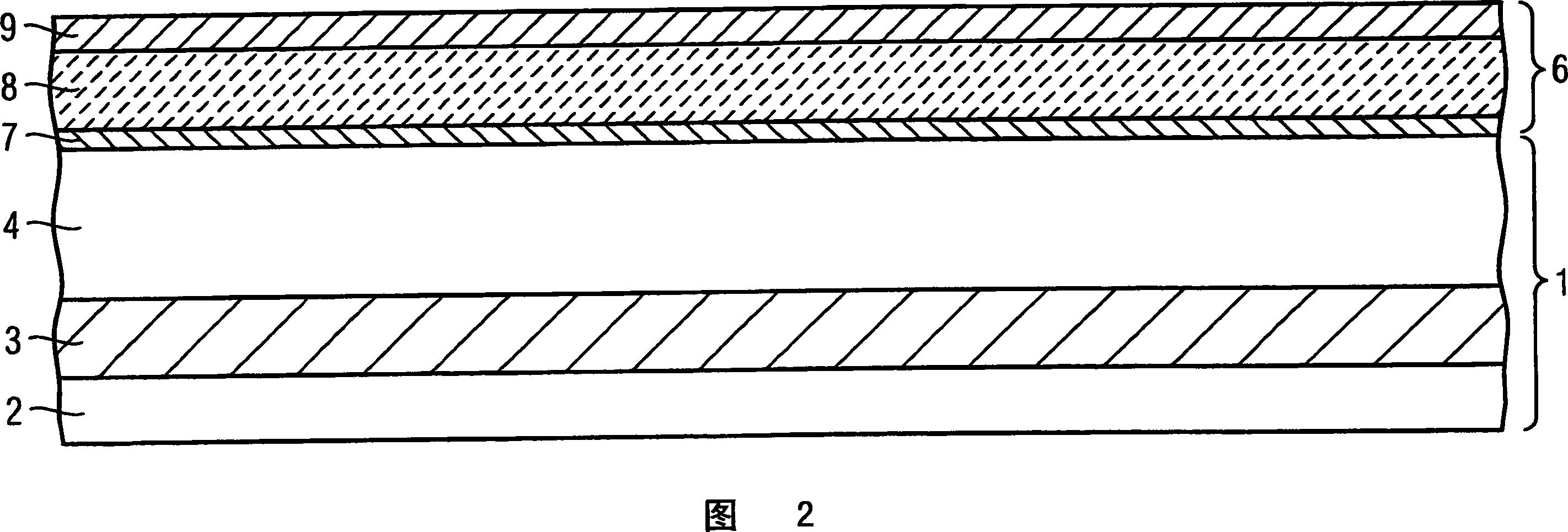

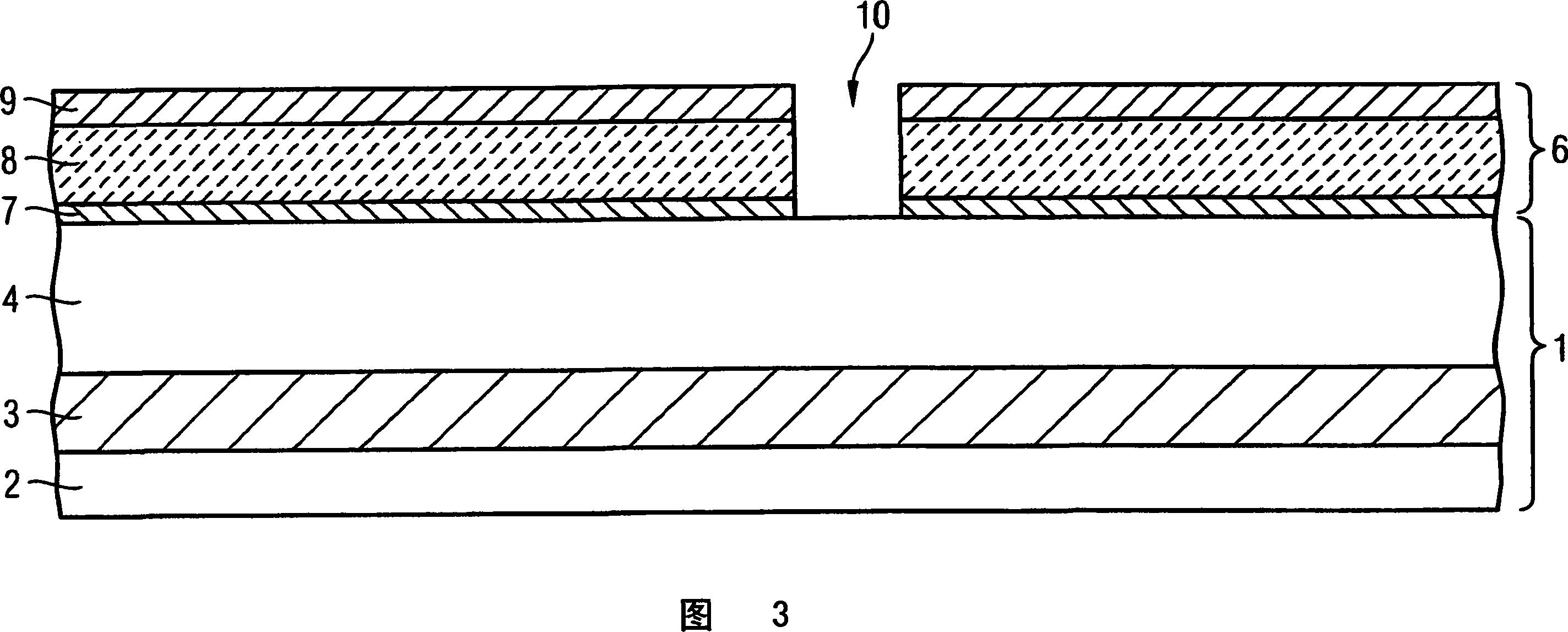

Disclosed is an absorbent article including a backsheet, an absorbent storage layer, a liquid guide layer, and a top layer. The absorbent storage layer, the liquid guide layer and the top layer satisfy the following relationships: the liquid guide layer>the absorbent storage layer>the top layer with respect to a water absorbency due to capillary phenomenon; the liquid guide layer>the absorbent storage layer>the top layer with respect to a retention ratio of a liquid dropped onto the top layer in an amount less than a maximum water absorption amount of the liquid guide layer; and the absorbent storage layer>the liquid guide layer>the top layer with respect to a retention ratio of a liquid dropped onto the top layer in an amount more than the maximum water absorption amount of the liquid guide layer.

Owner:UNI CHARM CORP

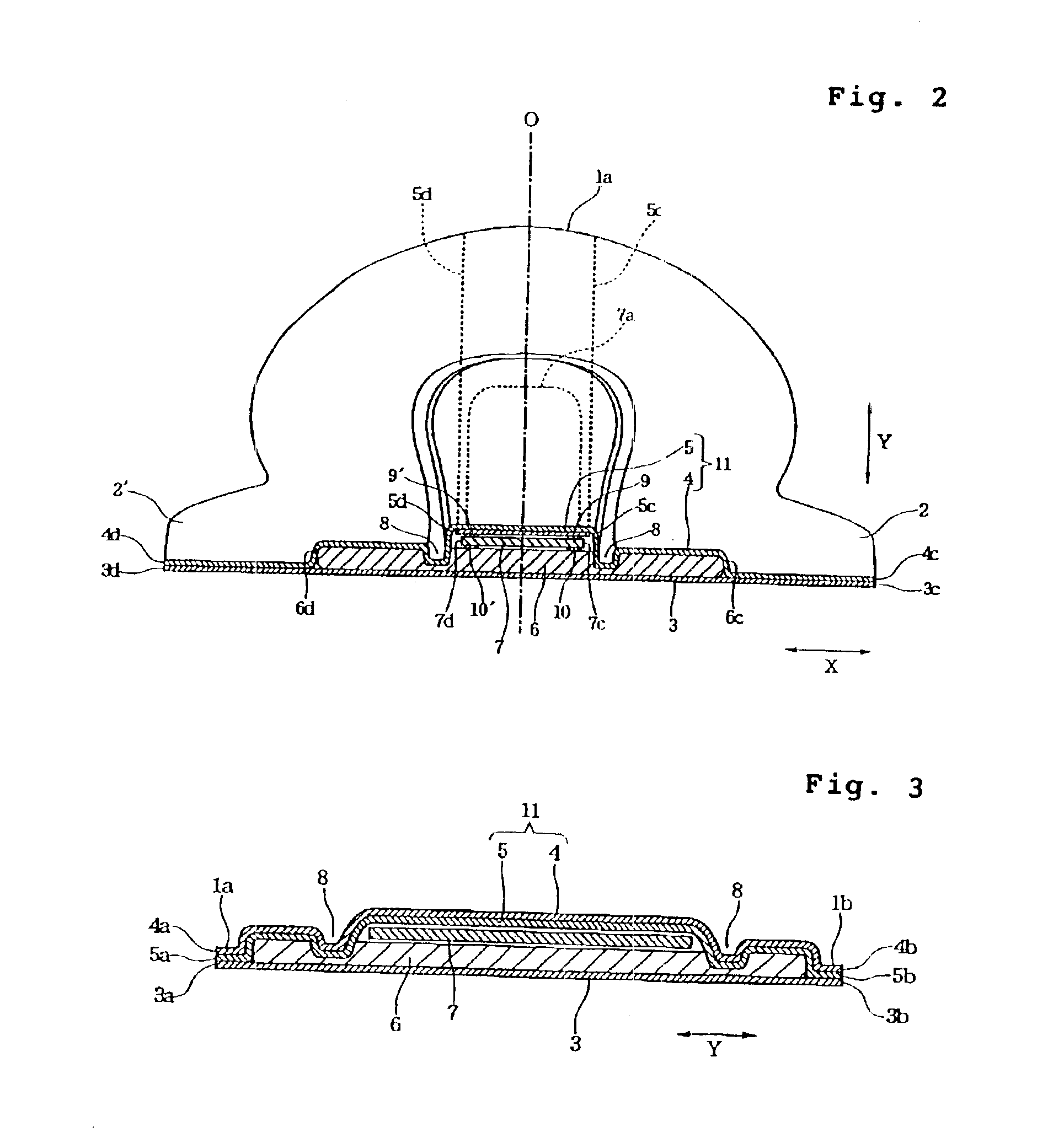

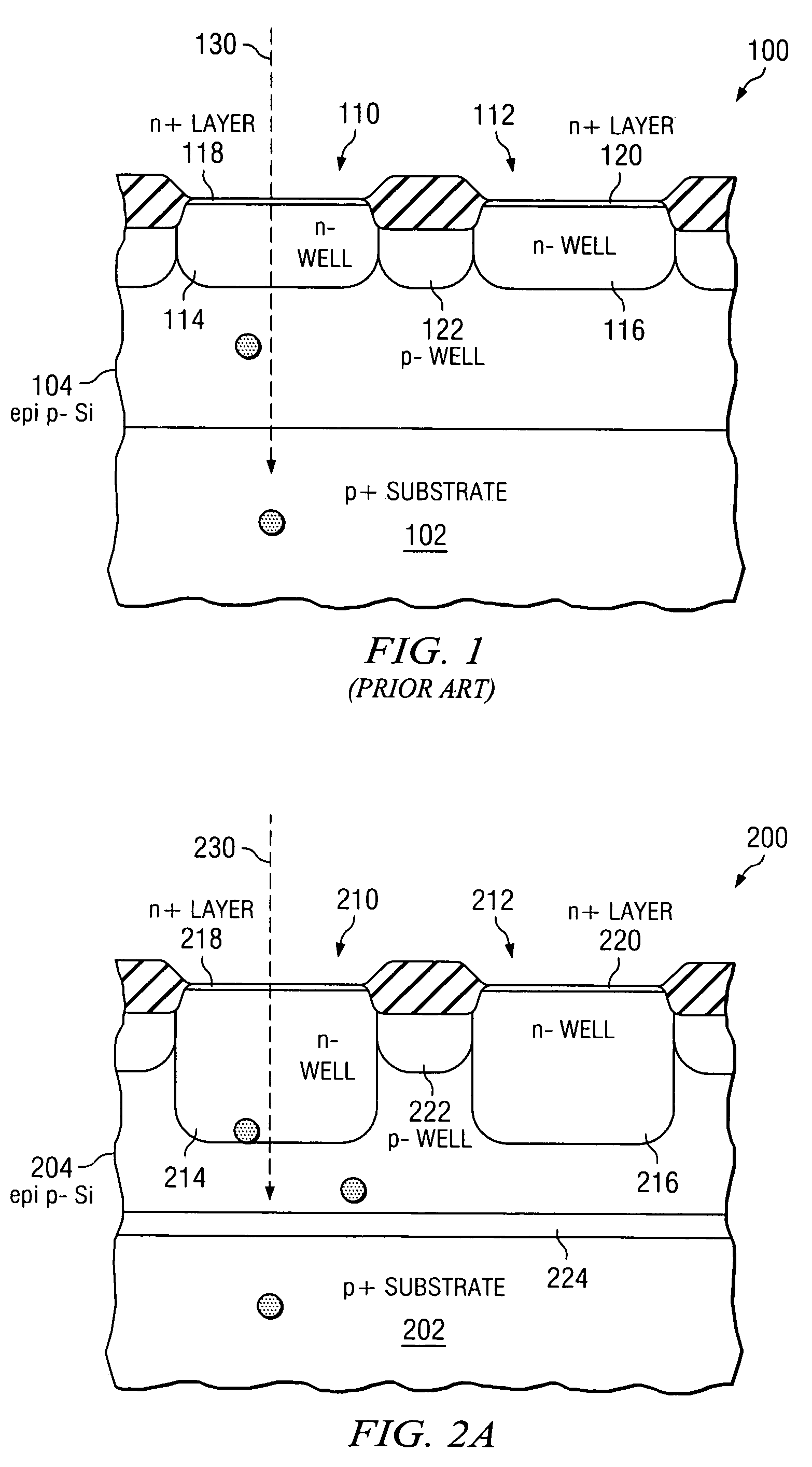

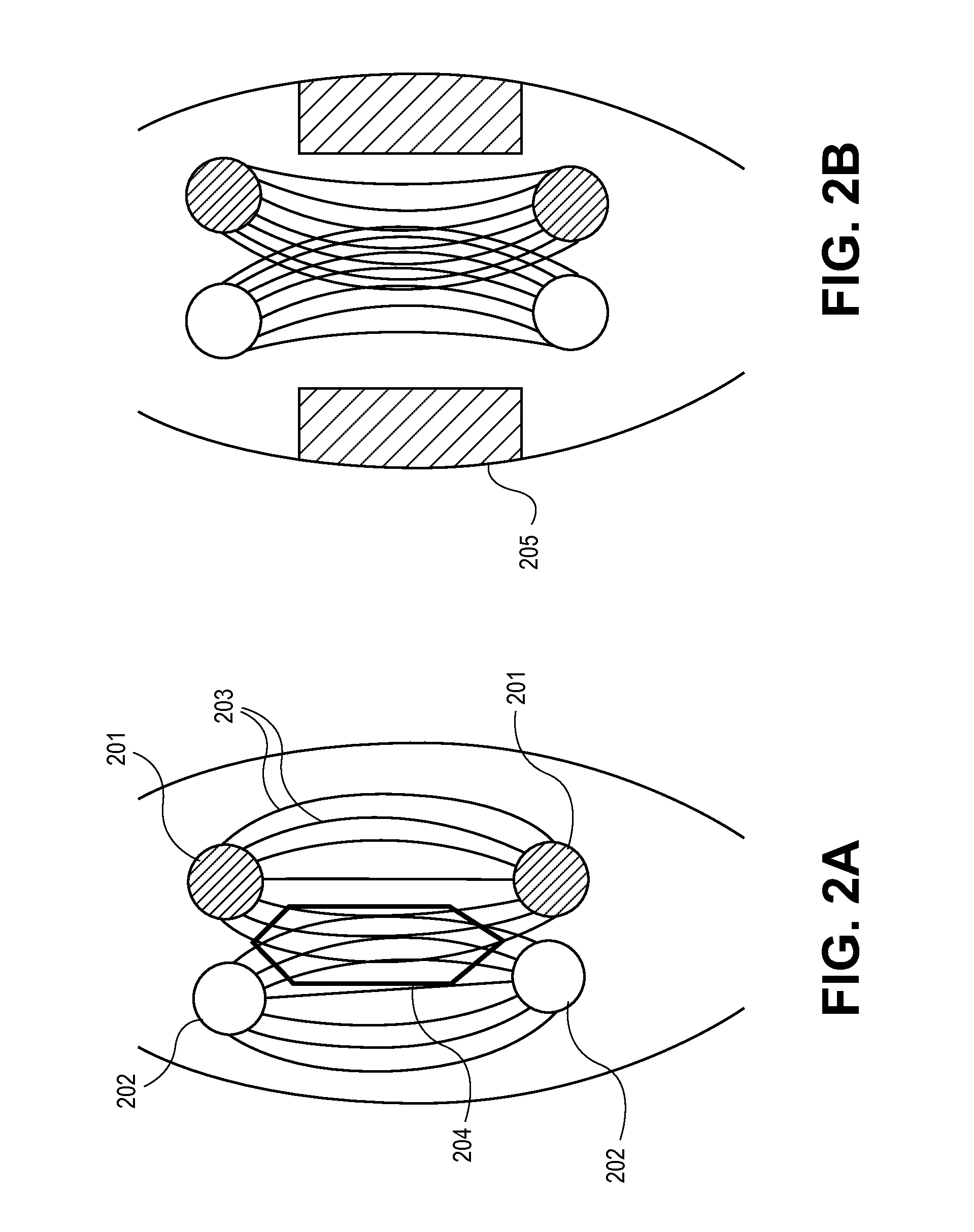

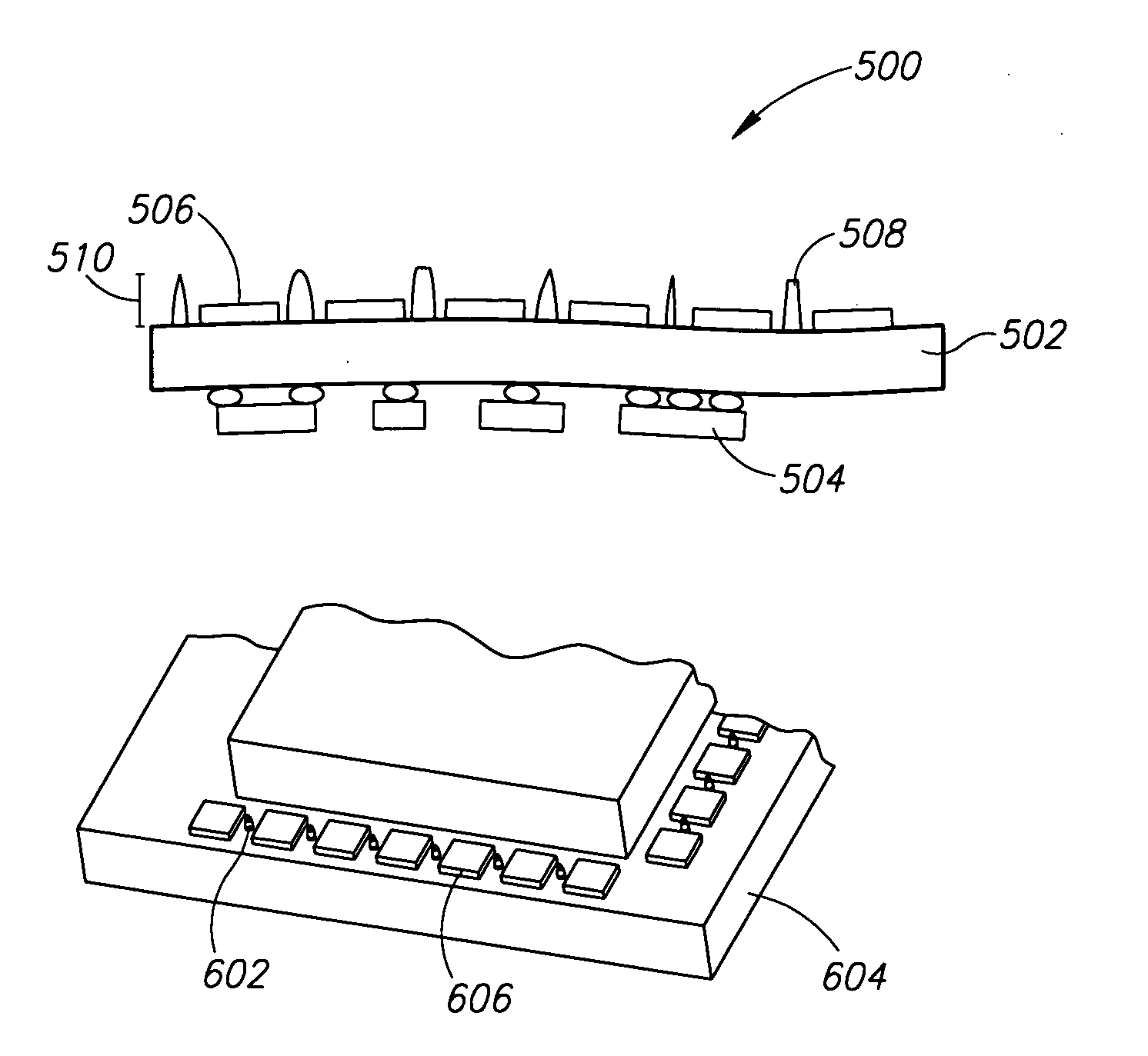

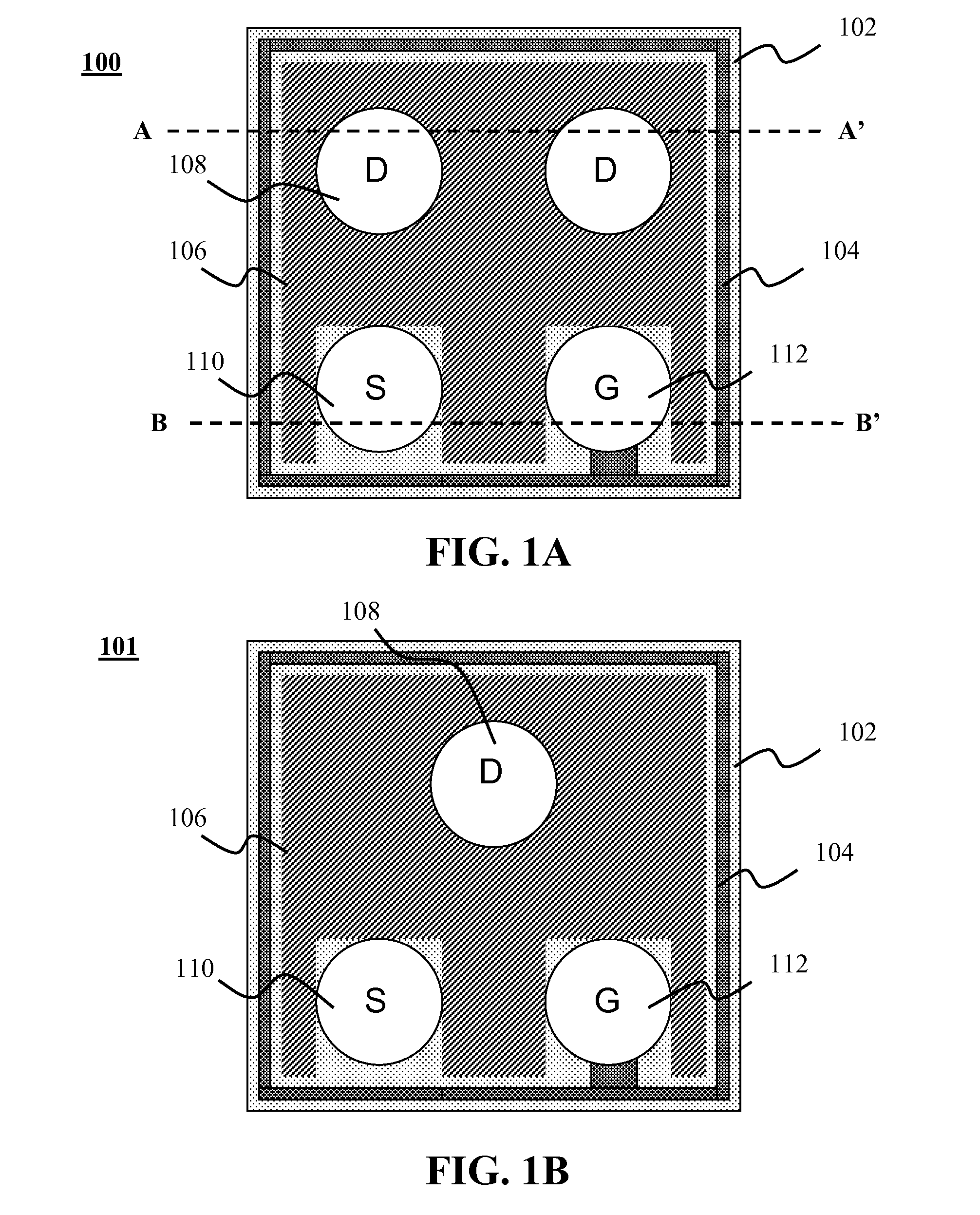

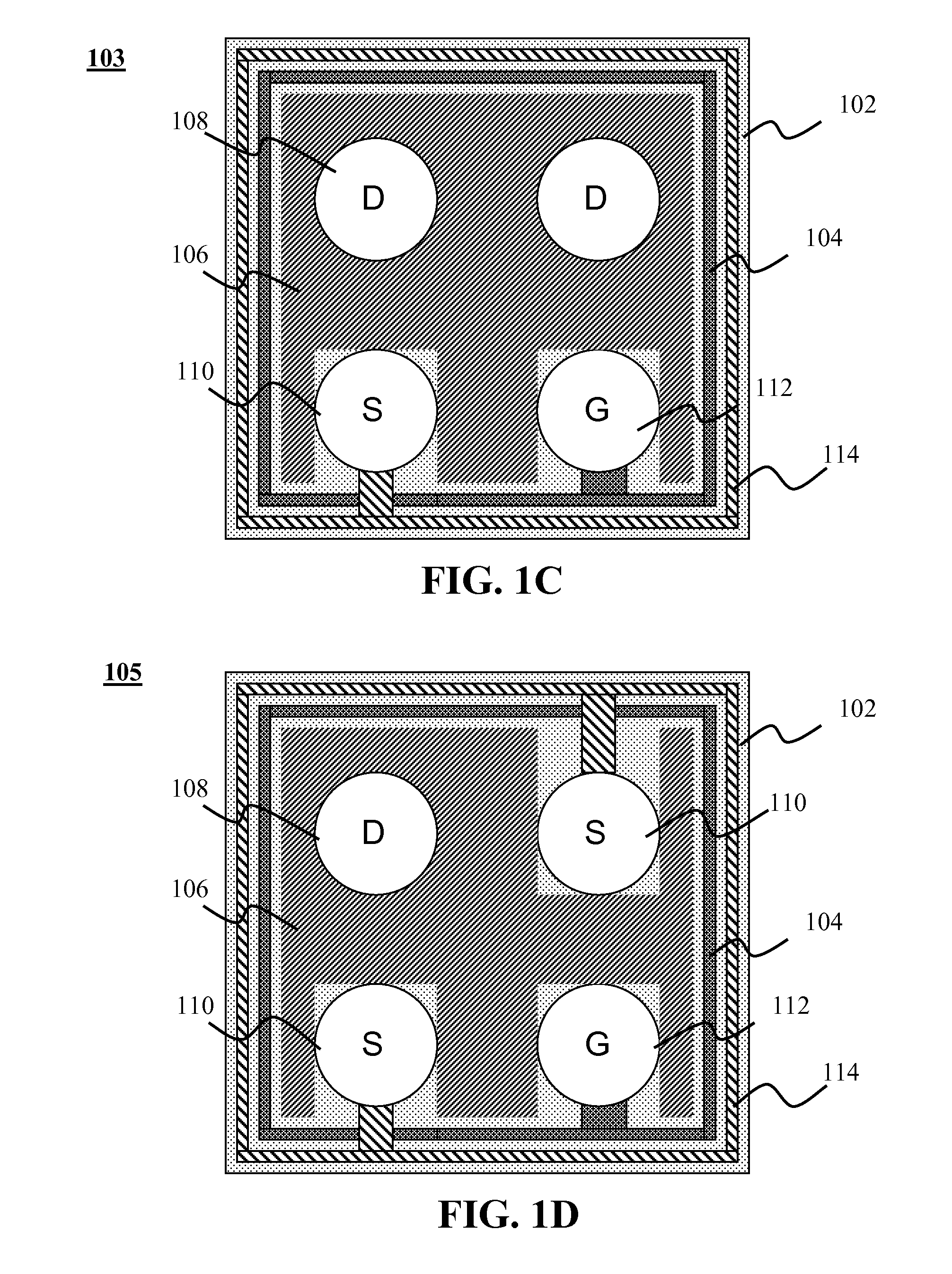

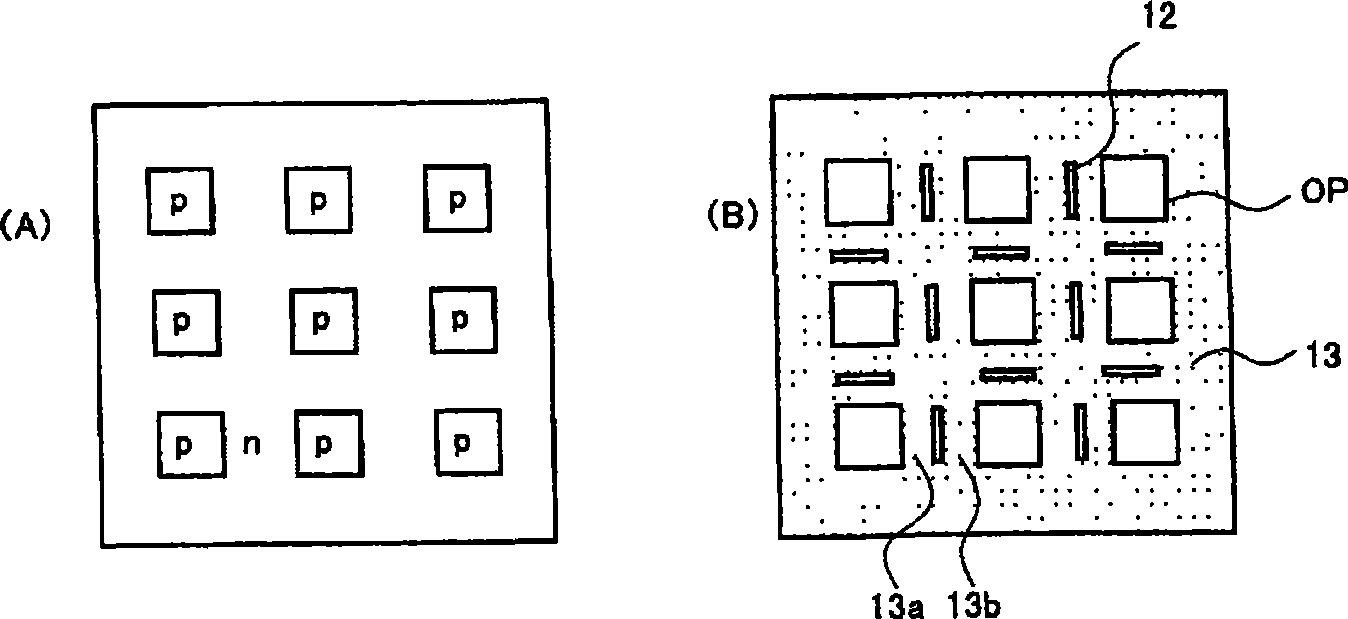

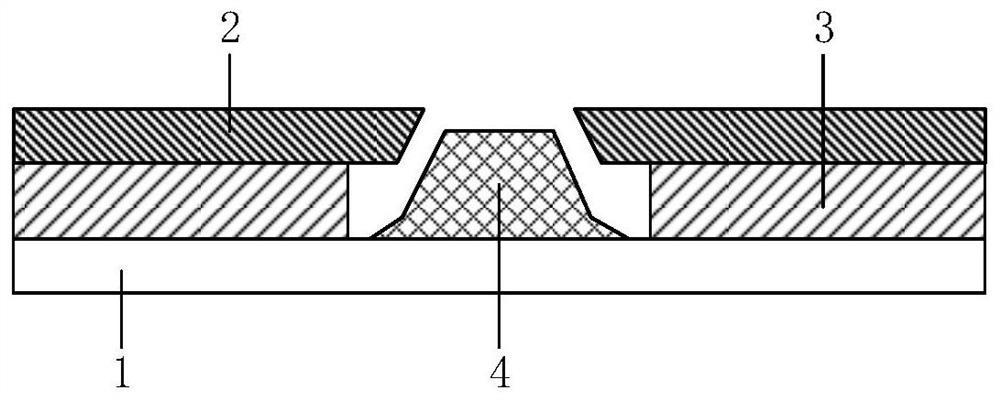

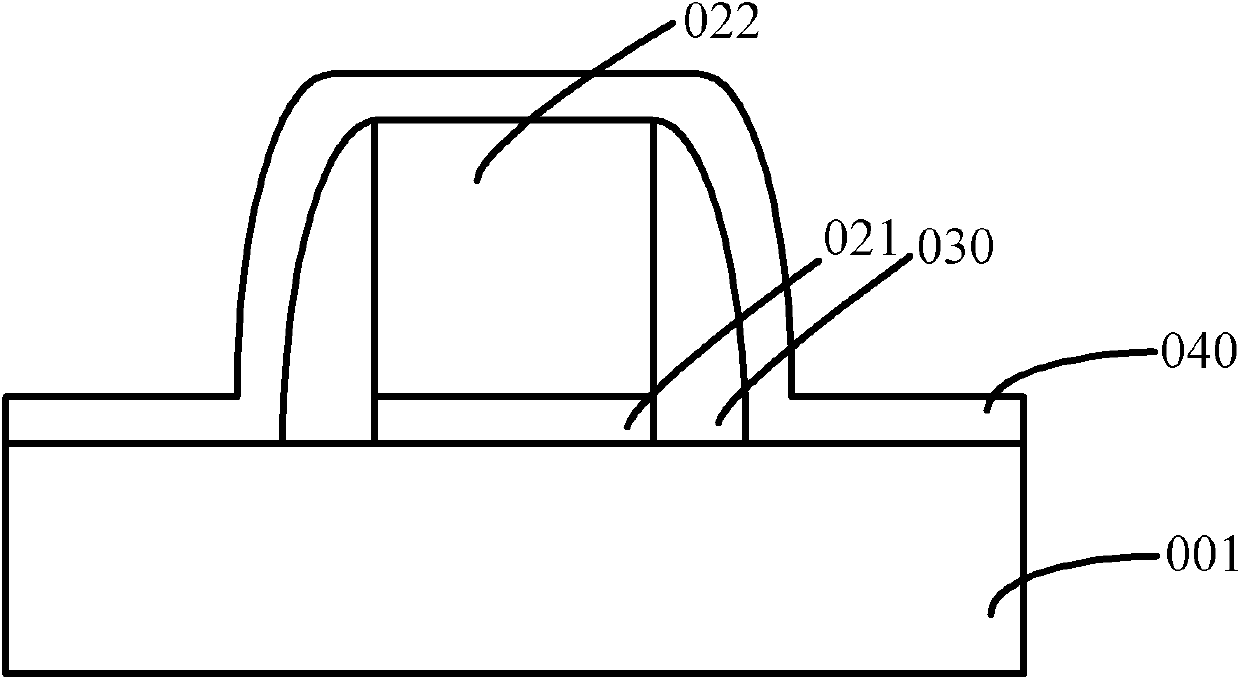

Reduced crosstalk CMOS image sensors

ActiveUS7307327B2High sensitivityReduce crosstalkSolid-state devicesRadiation controlled devicesCMOSCharge carrier

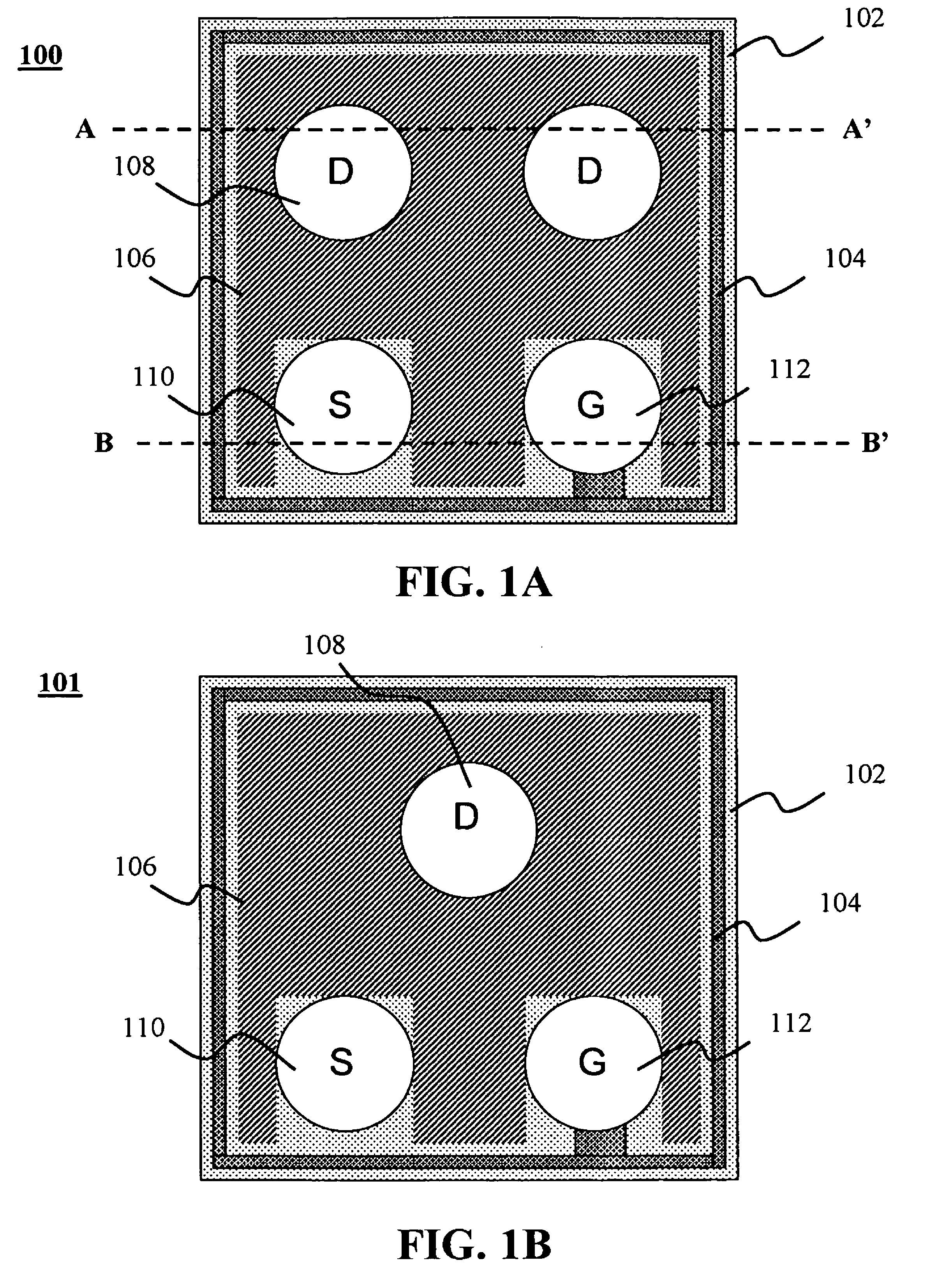

CMOS image sensor having high sensitivity and low crosstalk, particularly at far-red to infrared wavelengths, and a method for fabricating a CMOS image sensor. A CMOS image sensor has a substrate, an epitaxial layer above the substrate, and a plurality of pixels extending into the epitaxial layer for receiving light. The image sensor also includes at least one of a horizontal barrier layer between the substrate and the epitaxial layer for preventing carriers generated in the substrate from moving to the epitaxial layer, and a plurality of lateral barrier layers between adjacent ones of the plurality of pixels for preventing lateral diffusion of electrons in the epitaxial layer.

Owner:APTINA IMAGING CORP

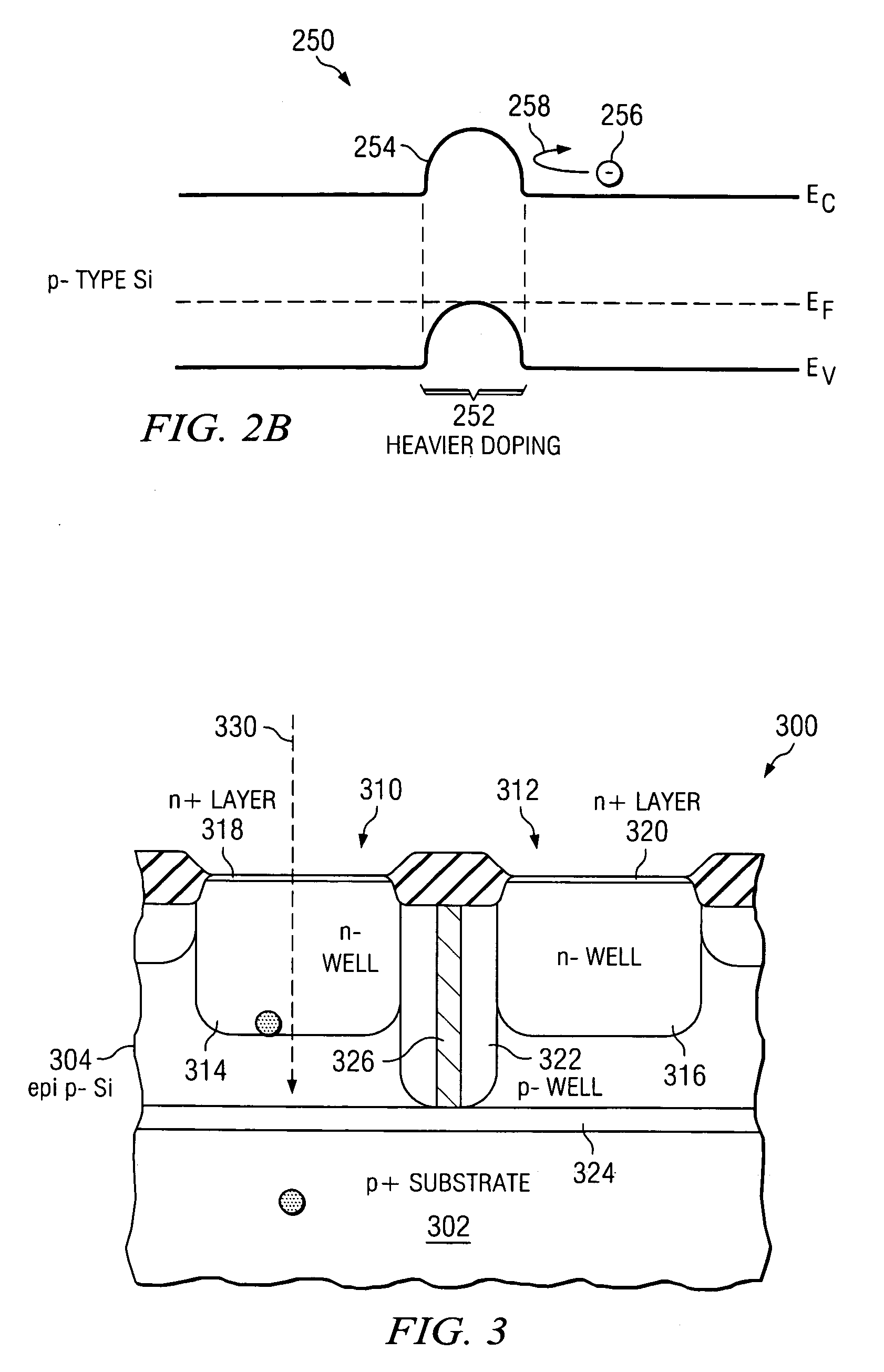

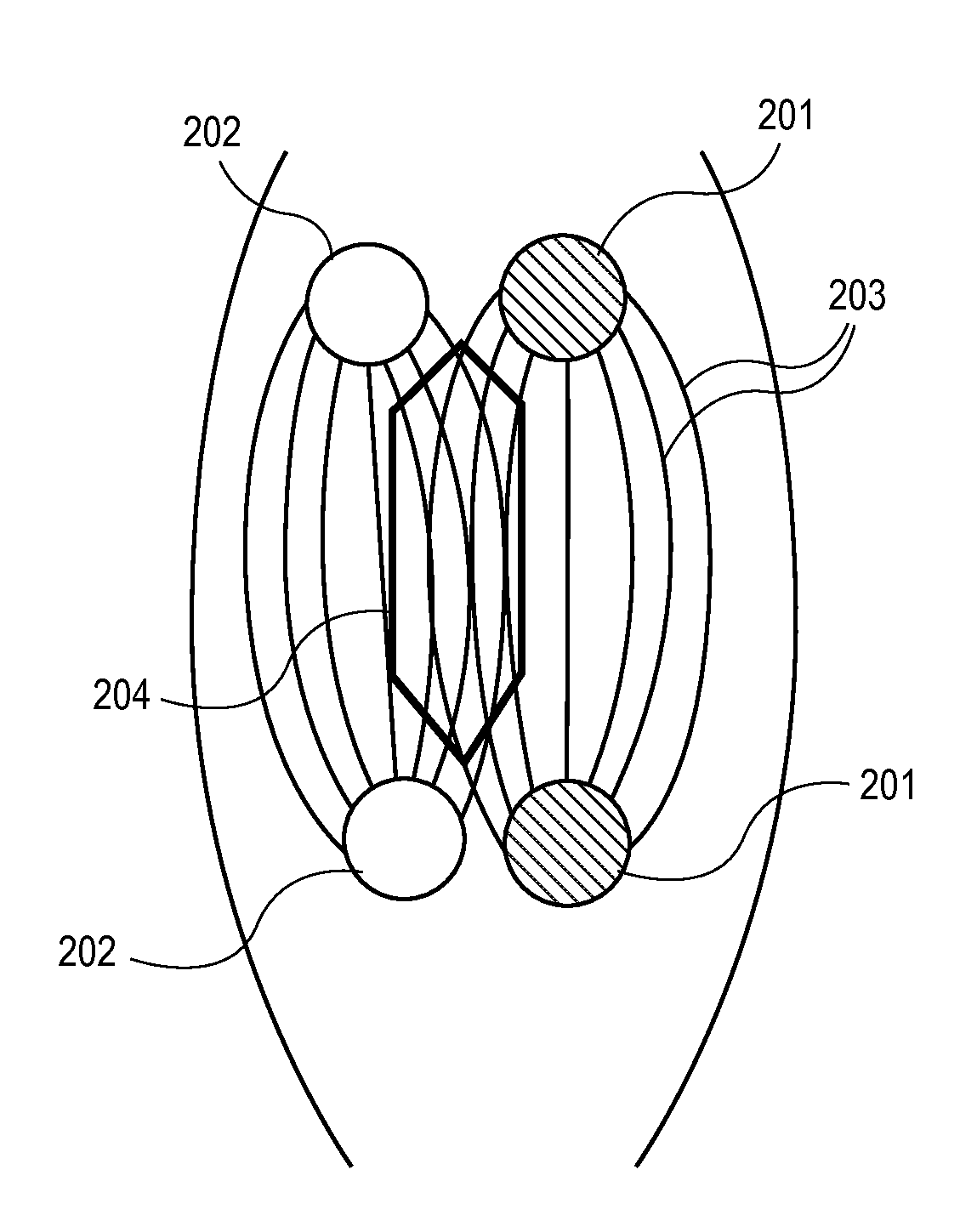

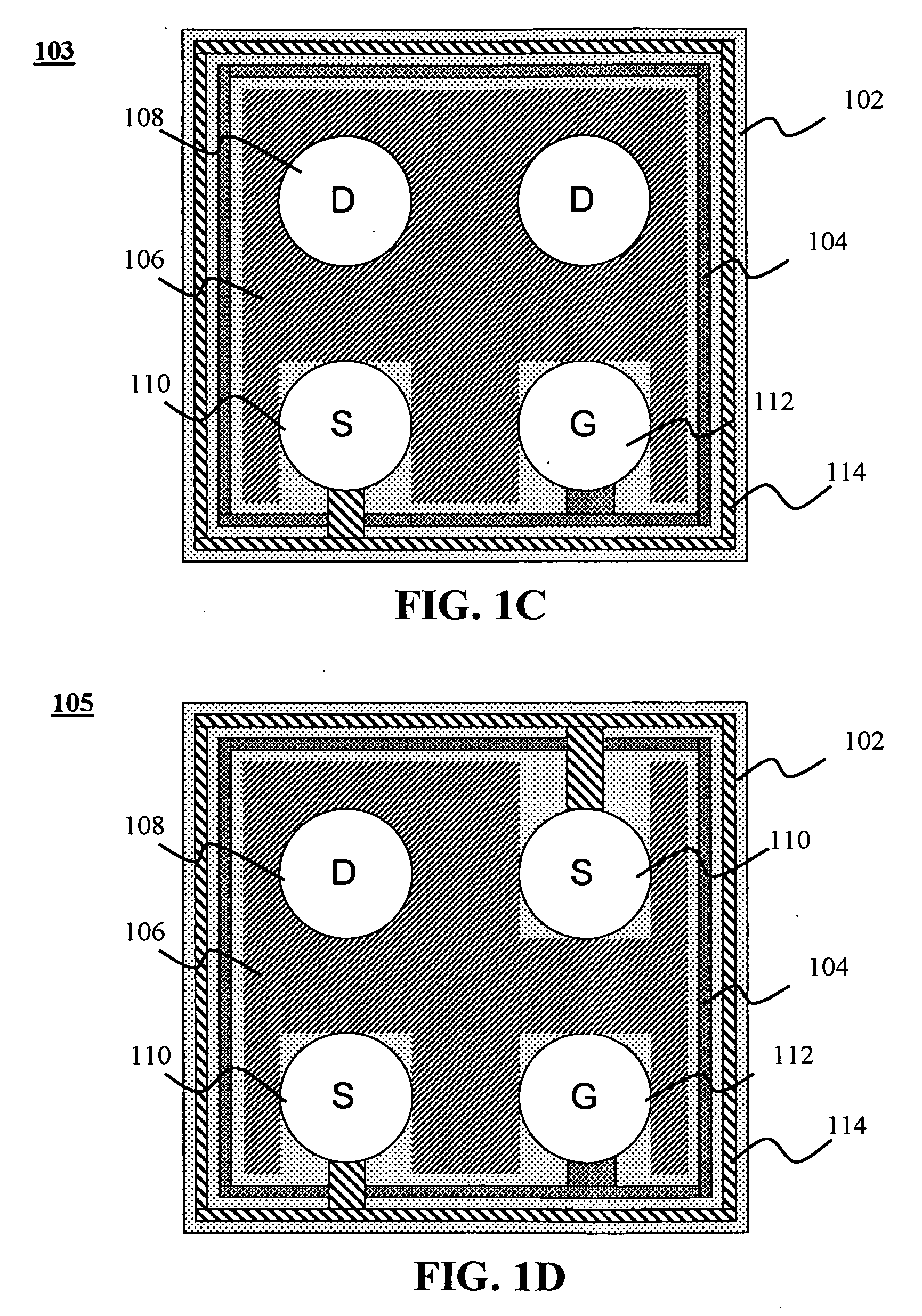

Synergistic Muscle Activation Device

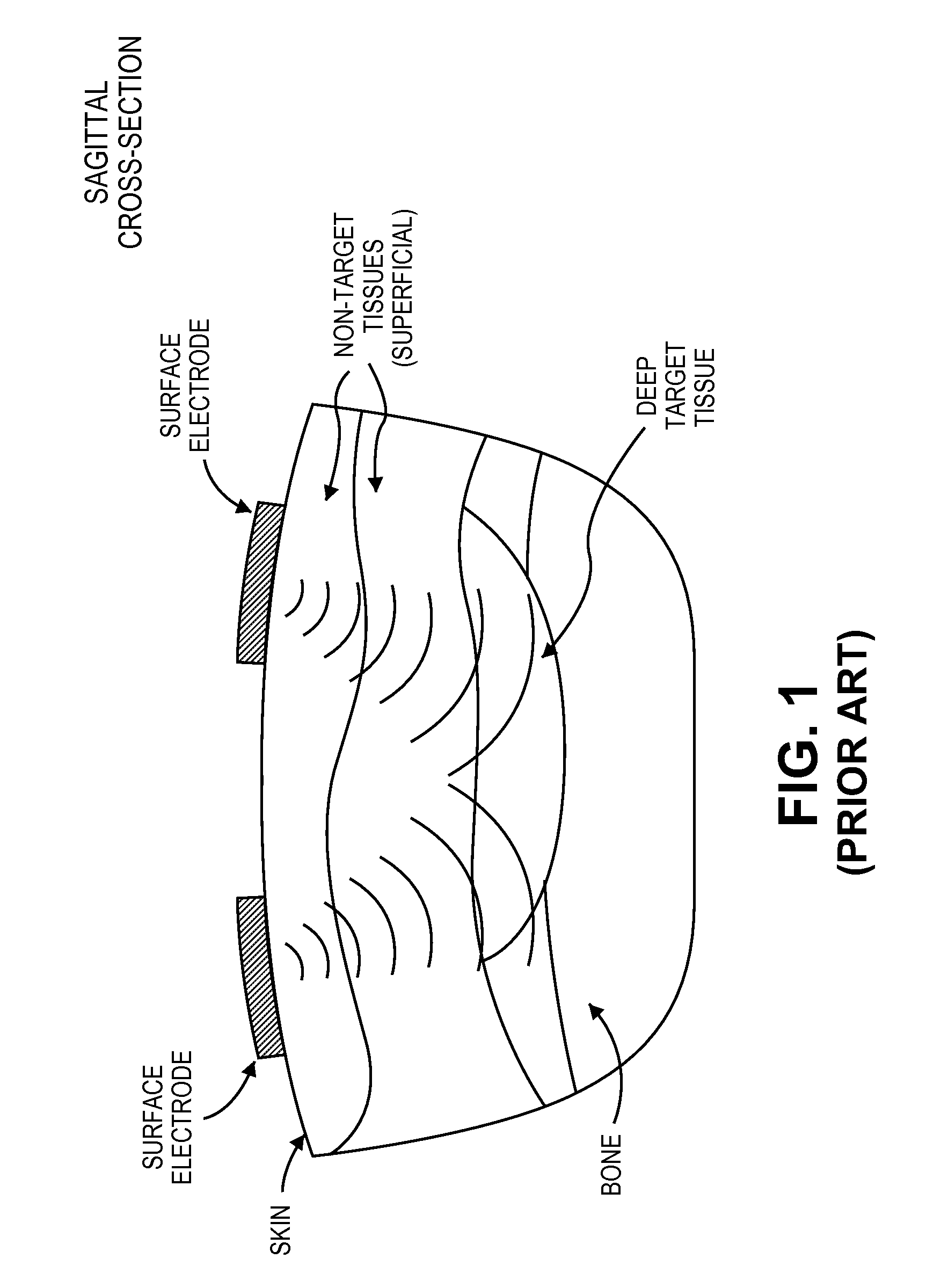

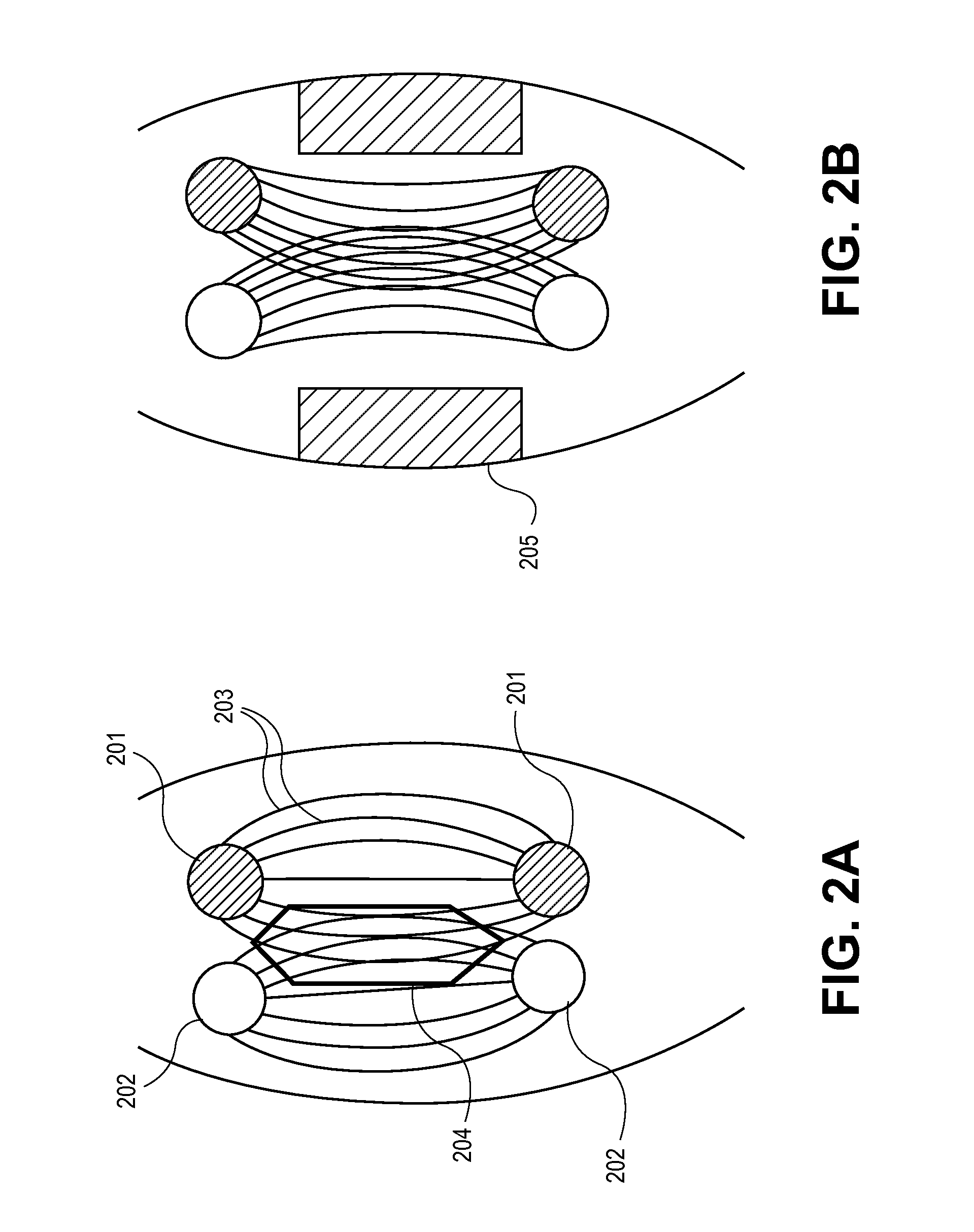

ActiveUS20110112605A1Reduce amountUse energy savingElectrotherapyTherapeutic coolingAnesthesiaMuscle activation

Owner:SAGE PRODS

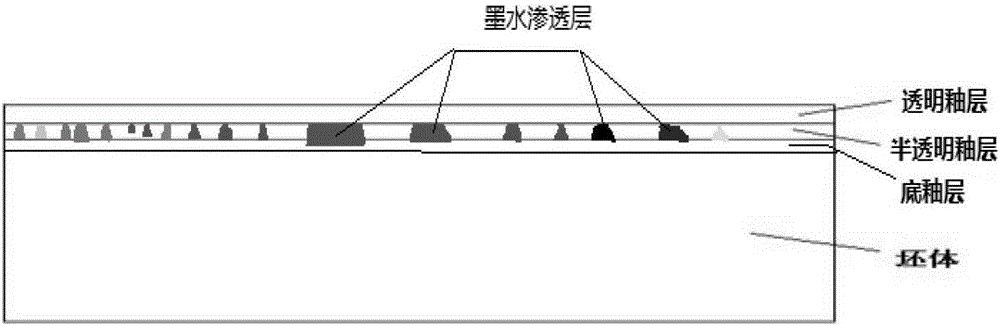

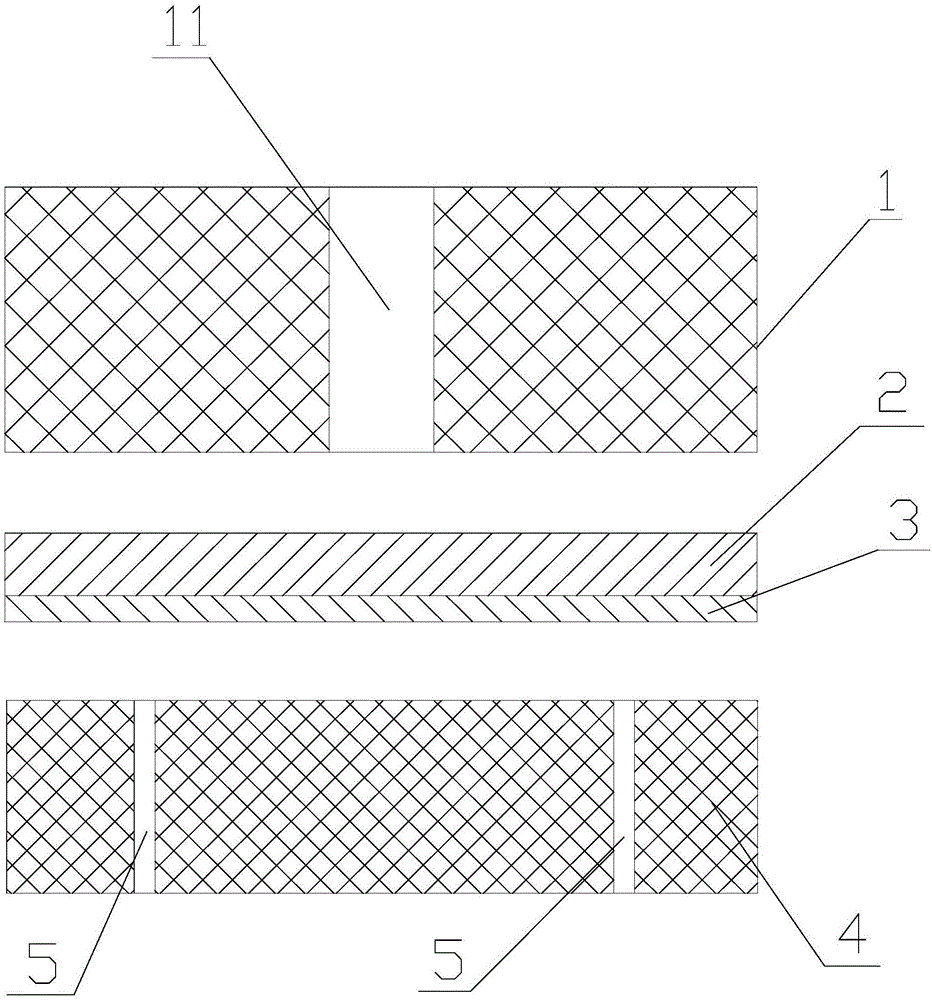

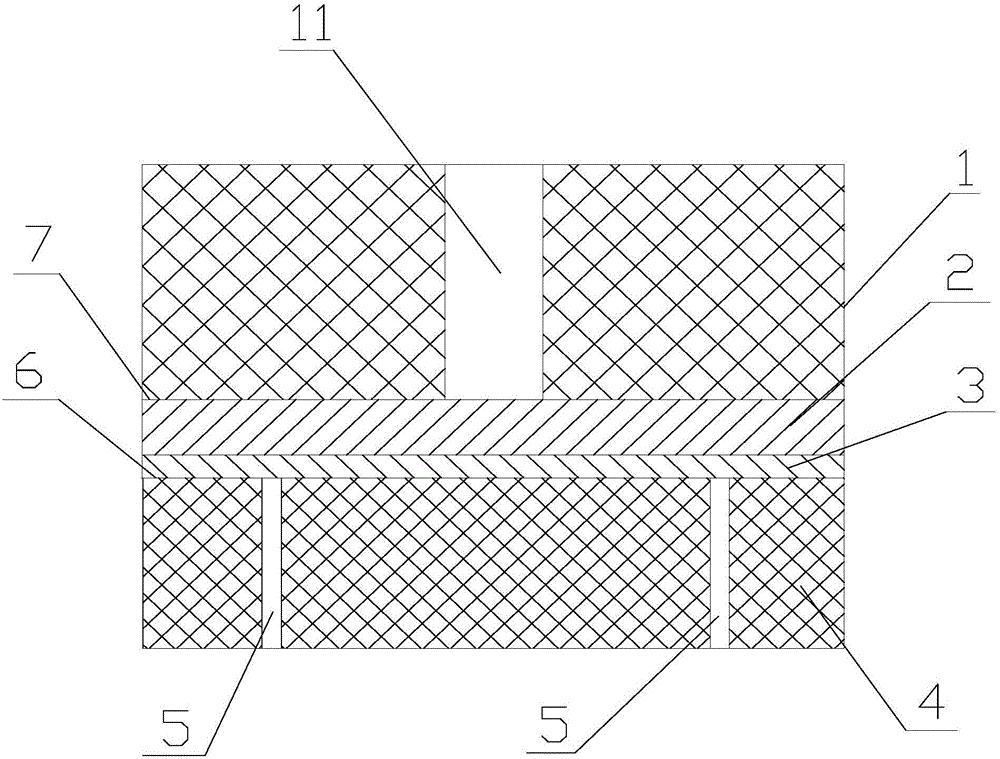

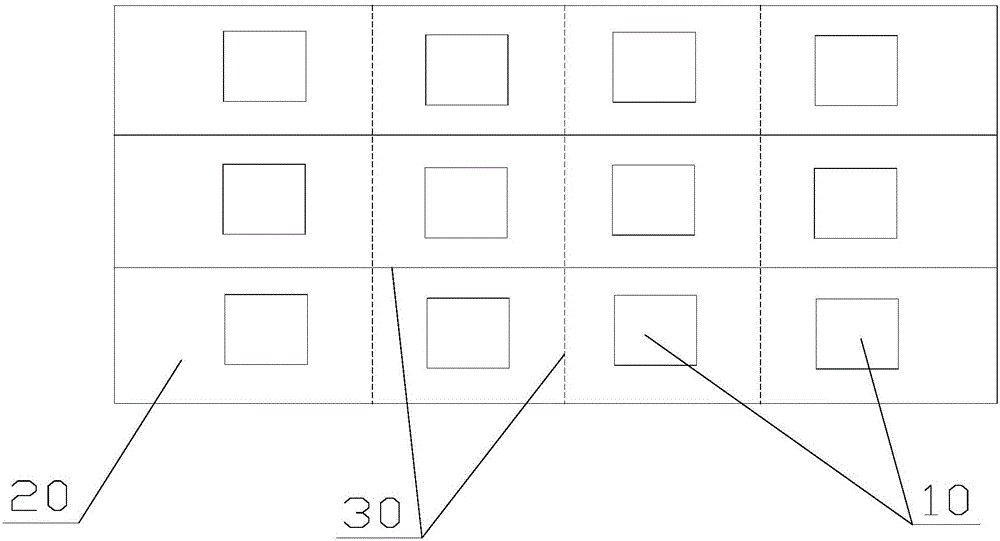

One-time sintered super-flat ink-jet penetrating porcelain tiles with three-dimensional decorative effects, and manufacturing method thereof

The invention relates to one-time sintered super-flat ink-jet penetrating porcelain tiles with three-dimensional decorative effects, and a manufacturing method thereof. According to the manufacturing method, a bottom green brick layer, a priming glaze slurry, a semitransparent glaze slurry, and a transparent glaze slurry are prepared respectively; the bottom green brick layer is subjected to following treatment respectively: a priming glaze layer is formed via priming glaze slurry pouring, jet printing of decorative patterns is carried out, a semitransparent glaze layer is formed via semitransparent glaze slurry pouring, and drying is carried out; obtained green bricks are printed with decorative patterns with ink-jet of penetrating ink and jet printing of a permeation promoter, and are allowed to stand for more than 5min; the obtained green bricks are printed with isolation glaze with water isolating performance via silk-screen printing, and are dried and cooled; the green bricks are coated with the transparent glaze slurry via pouring; the green bricks are subjected to one time sintering so as to obtain one-time sintered ink-jet penetrating porcelain tile semi-finished products with three-dimensional decorative effects; the semi-finished products are subjected to polishing via inelastic module technology so as to obtain the one-time sintered super-flat ink-jet penetrating porcelain tiles with three-dimensional decorative effects.

Owner:MONALISA GRP CO LTD

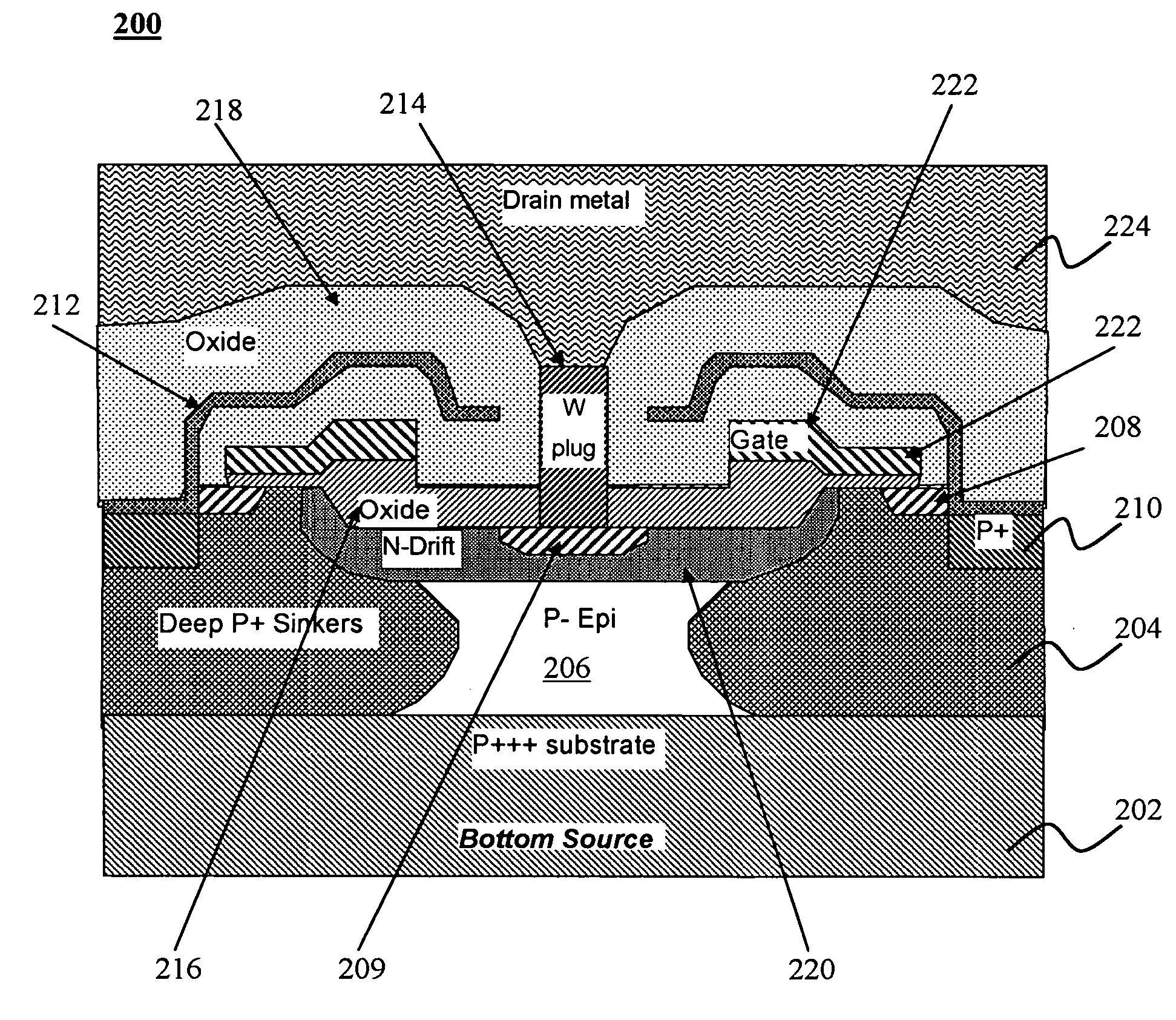

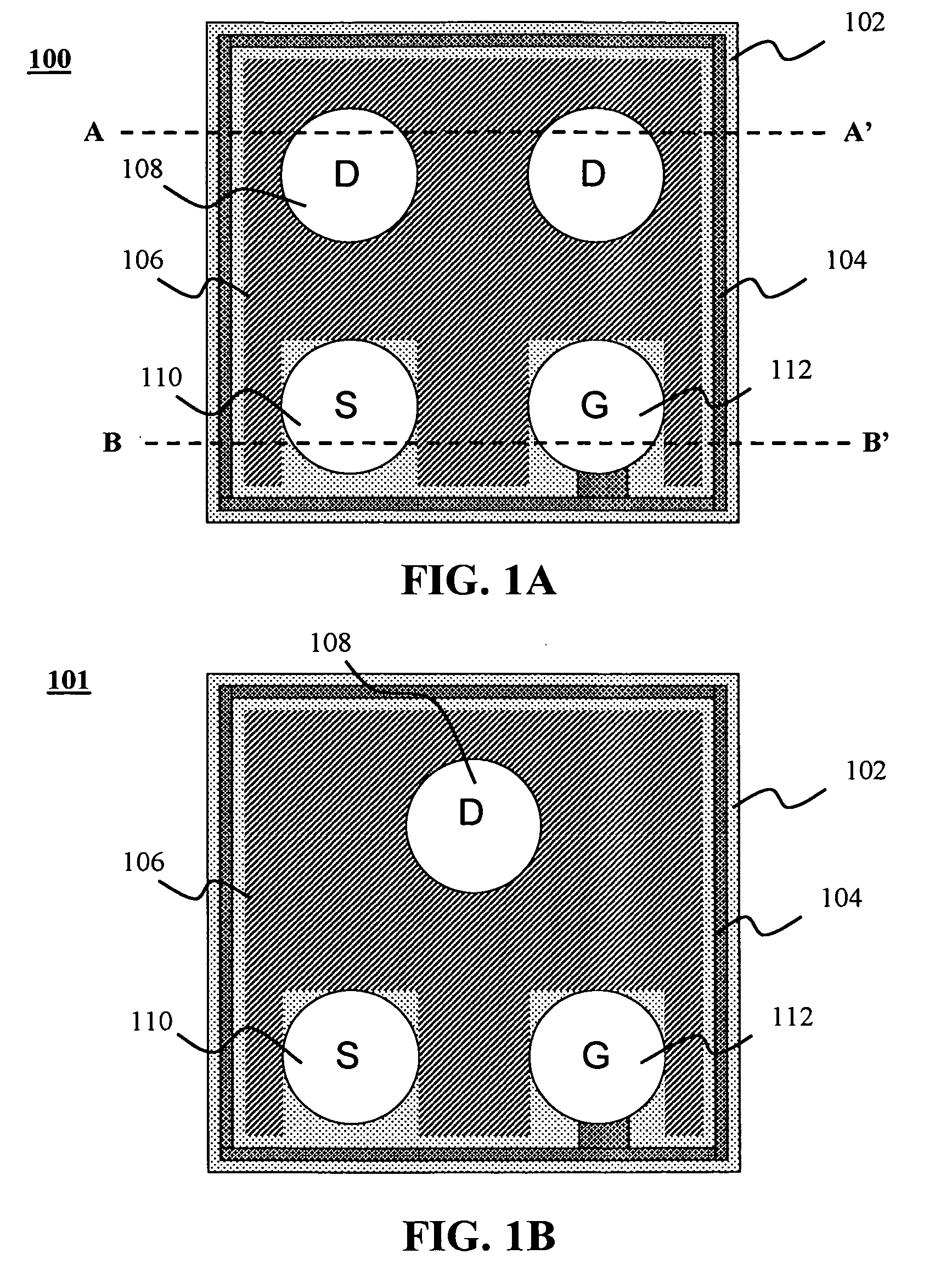

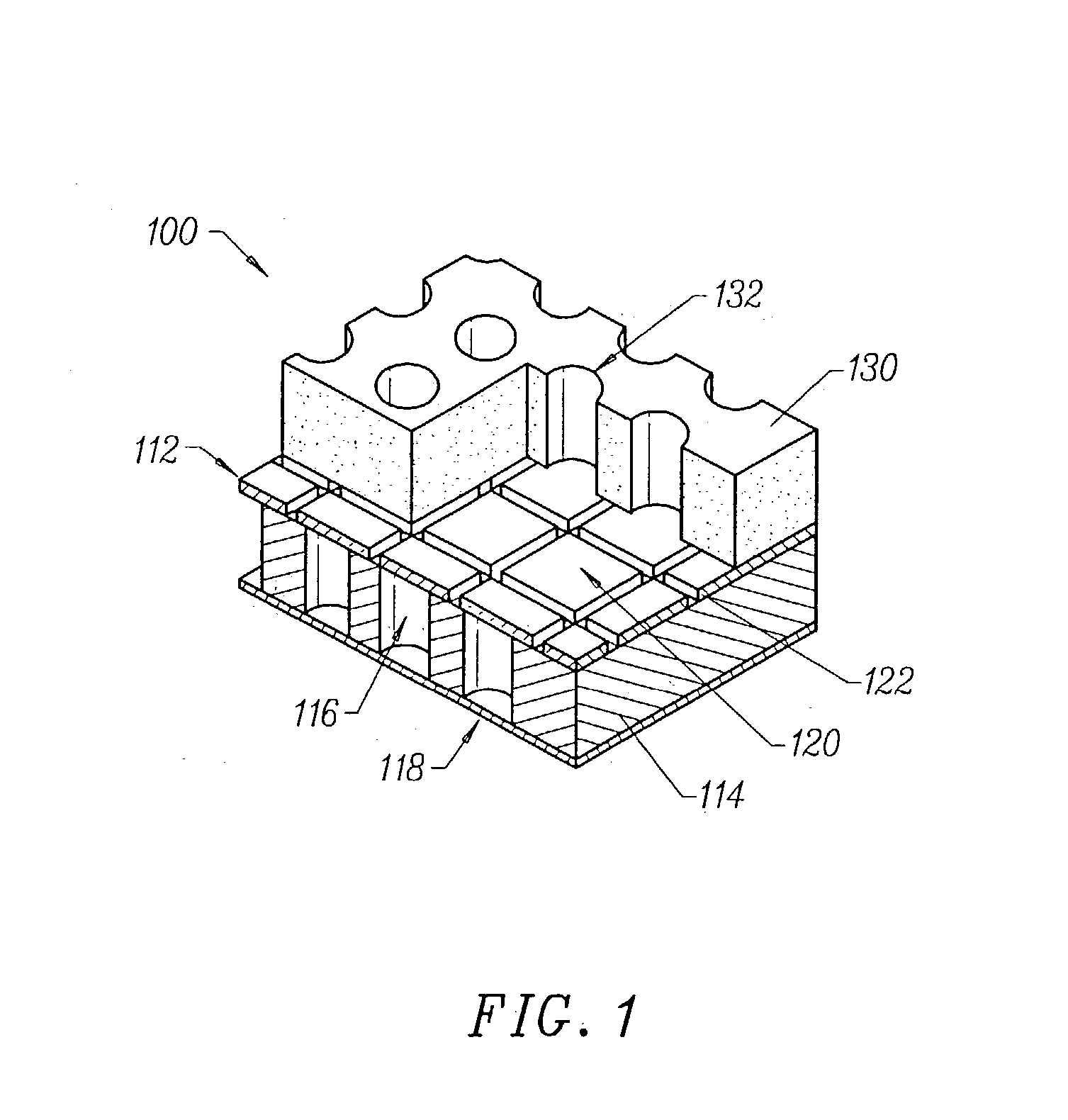

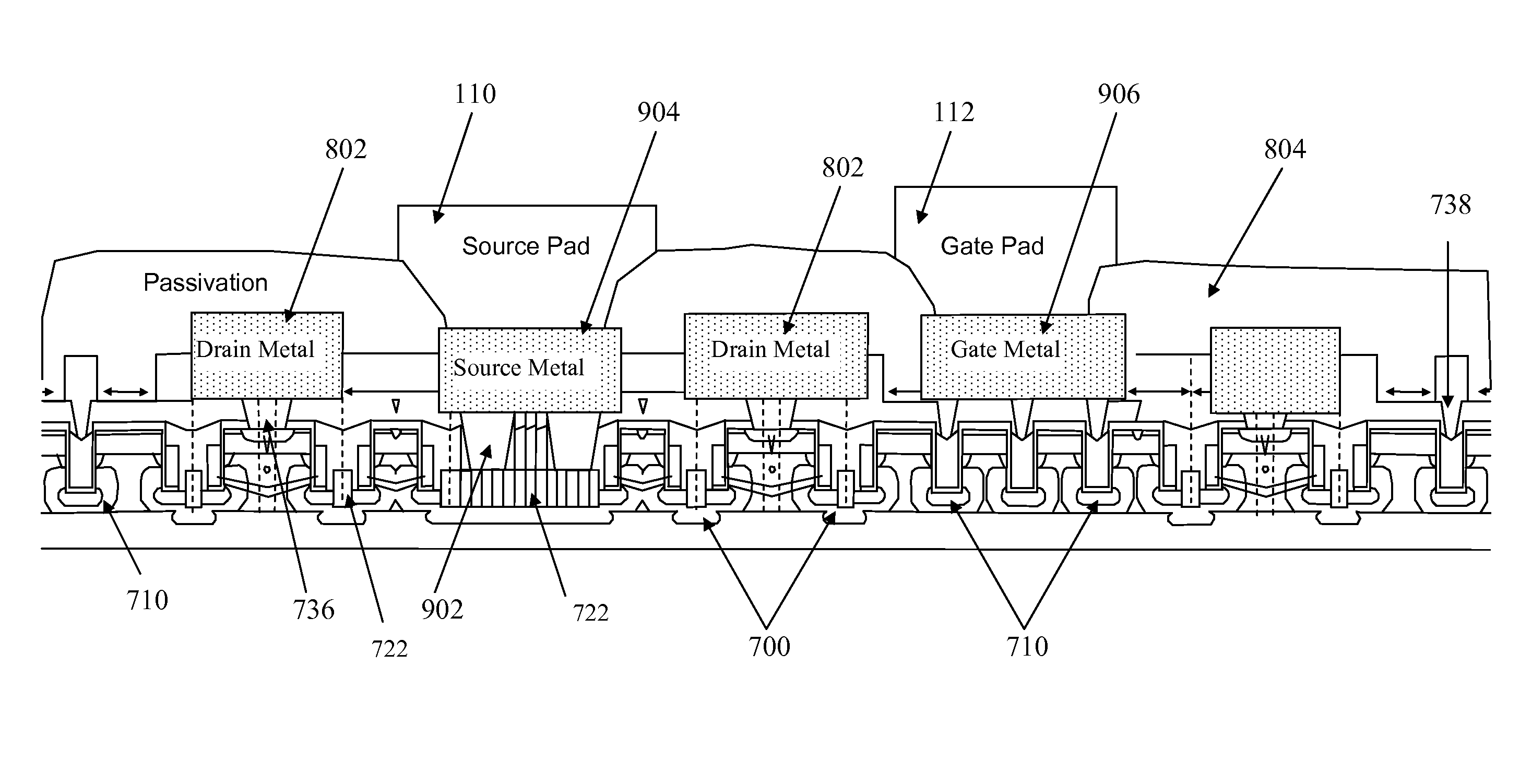

True csp power mosfet based on bottom-source ldmos

ActiveUS20100163979A1Reduce resistanceReduce inductanceTransistorSolid-state devicesLDMOSSemiconductor package

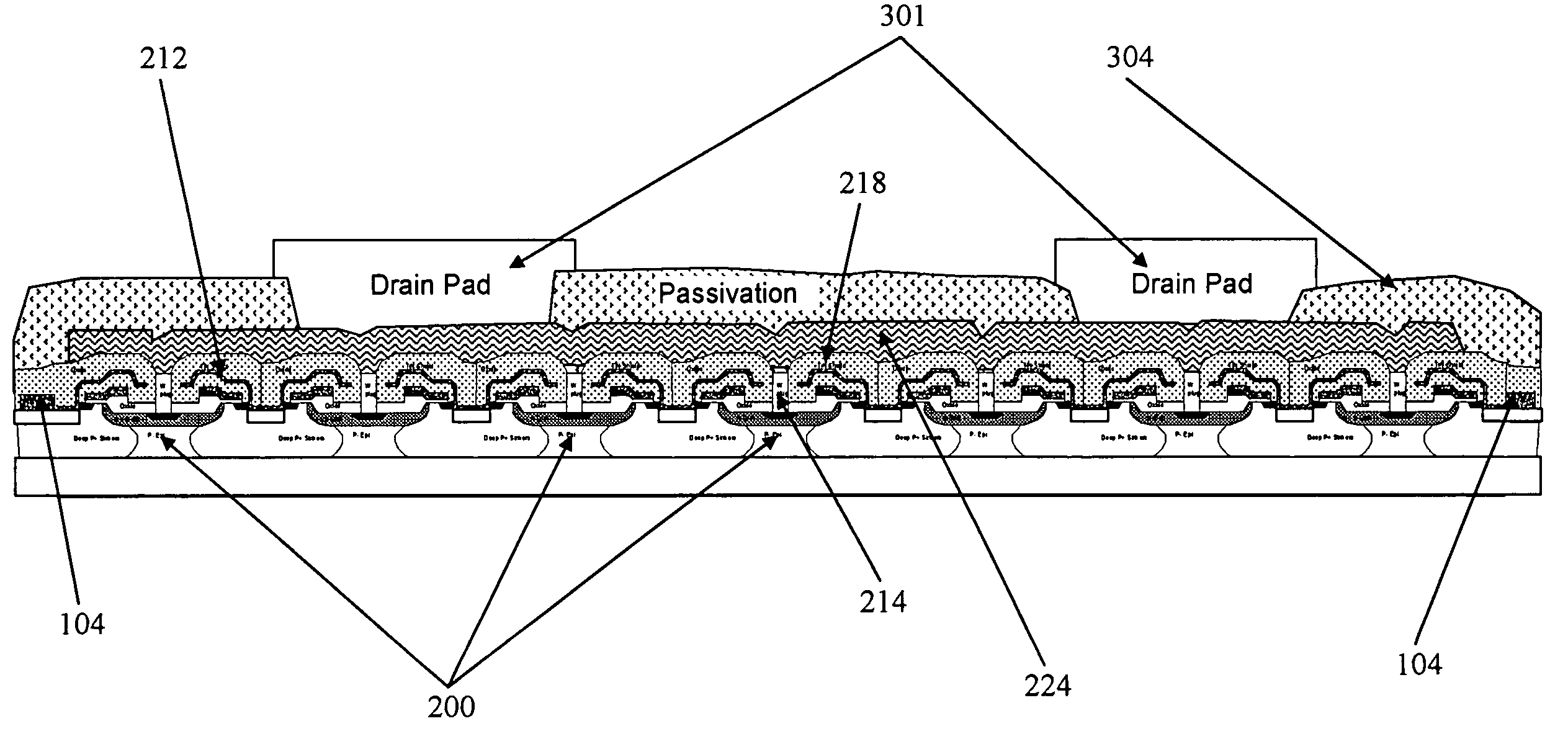

A semiconductor package may comprise a semiconductor substrate, a MOSFET device having a plurality cells formed on the substrate, and a source region common to all cells disposed on a bottom of the substrate. Each cell comprises a drain region on a top of the semiconductor device, a gate to control a flow of electrical current between the source and drain regions, a source contact proximate the gate; and an electrical connection between the source contact and source region. At least one drain connection is electrically coupled to the drain region. Source, drain and gate pads are electrically connected to the source region, drain region and gates of the devices. The drain, source and gate pads are formed on one surface of the semiconductor package. The cells are distributed across the substrate, whereby the electrical connections between the source contact of each device and the source region are distributed across the substrate.

Owner:ALPHA & OMEGA SEMICON LTD

Synergistic muscle activation device

ActiveUS8588901B2Reduce amountUse energy savingInternal electrodesExternal electrodesAnesthesiaMuscle activation

Owner:SAGE PRODS

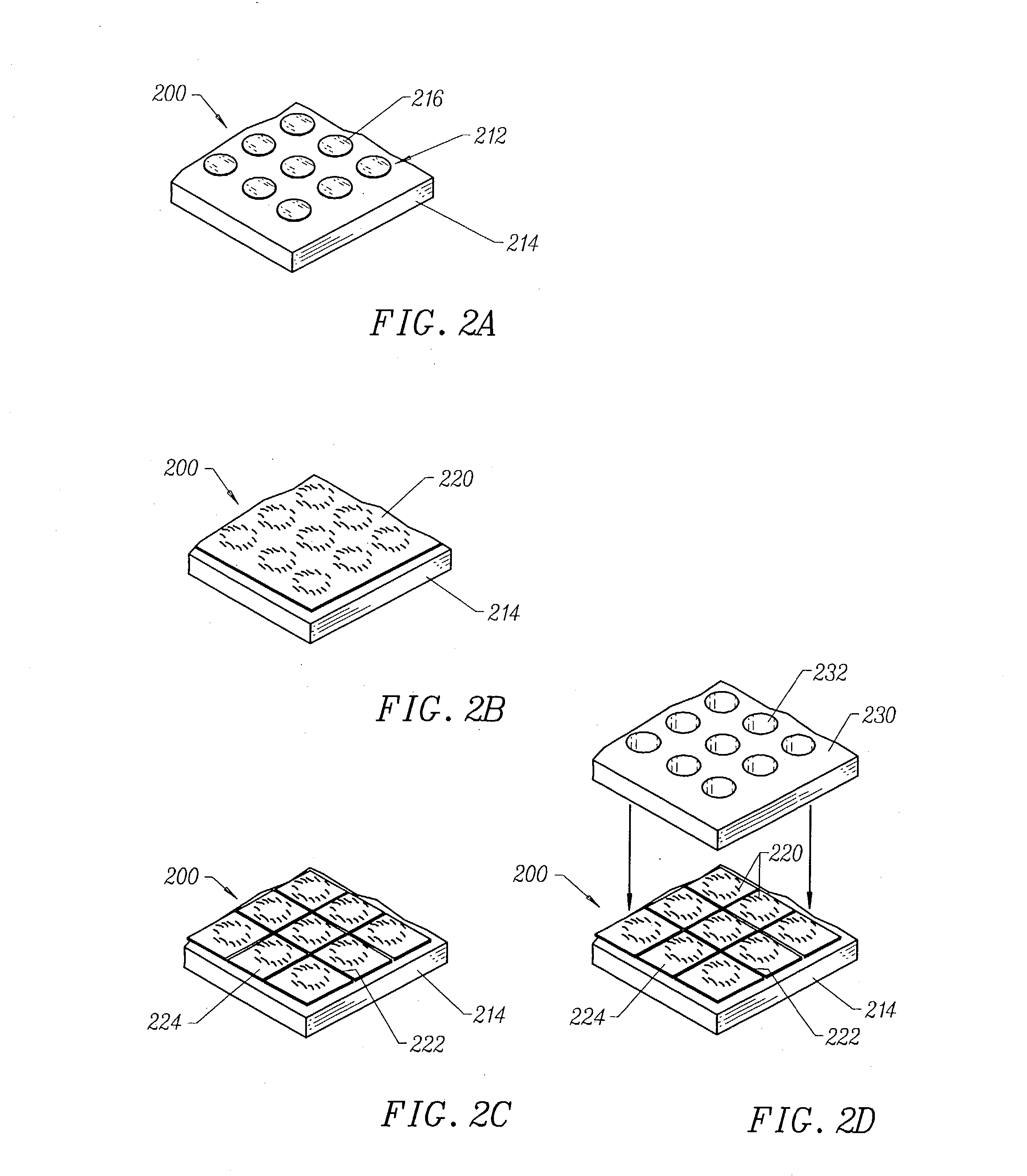

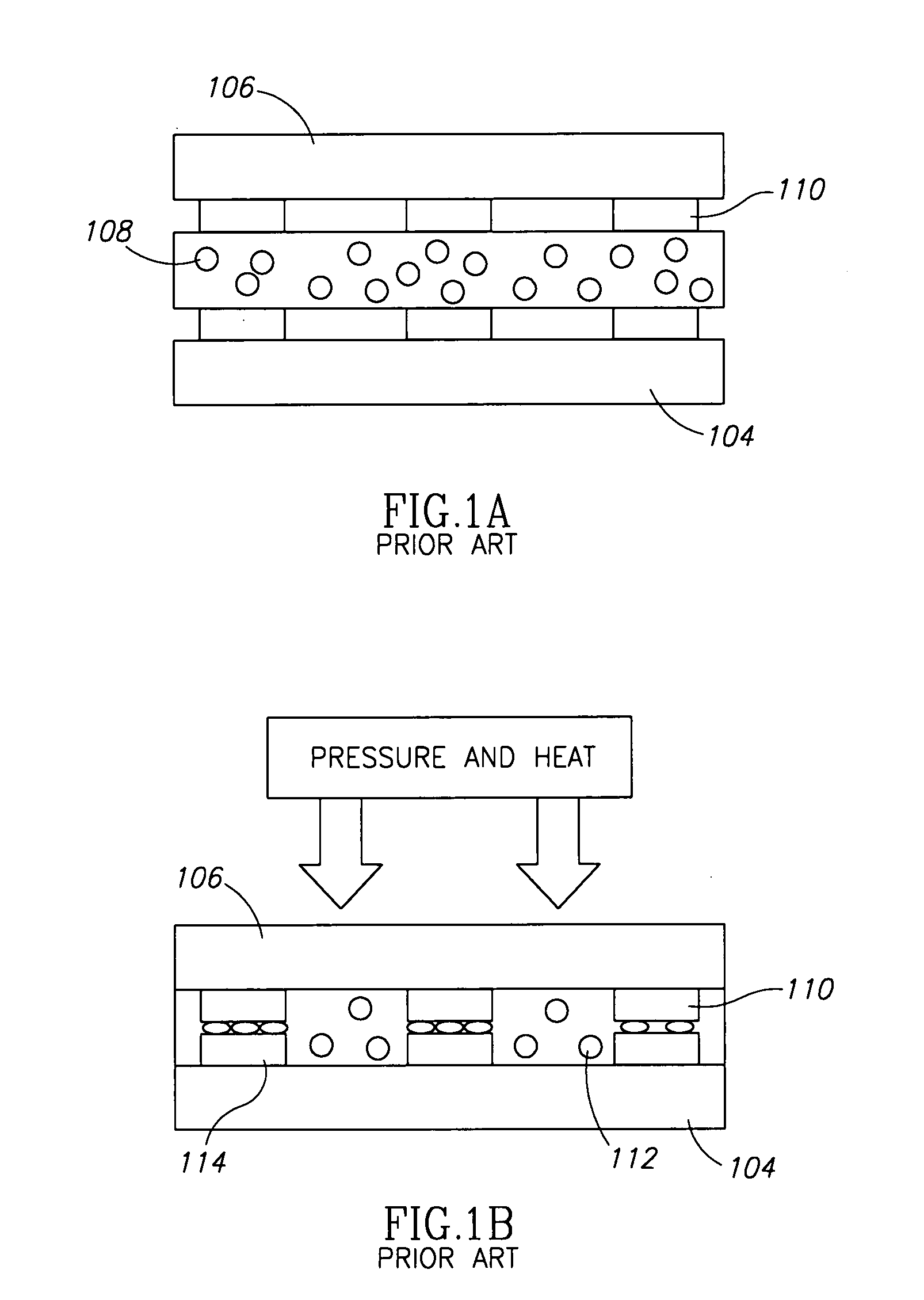

System and method for optimizing tissue barrier transfer of compounds

InactiveUS20030170610A1Avoid lateral spreadMinimize cytotoxicityBioreactor/fermenter combinationsBiological substance pretreatmentsChemical compoundPharmaceutical drug

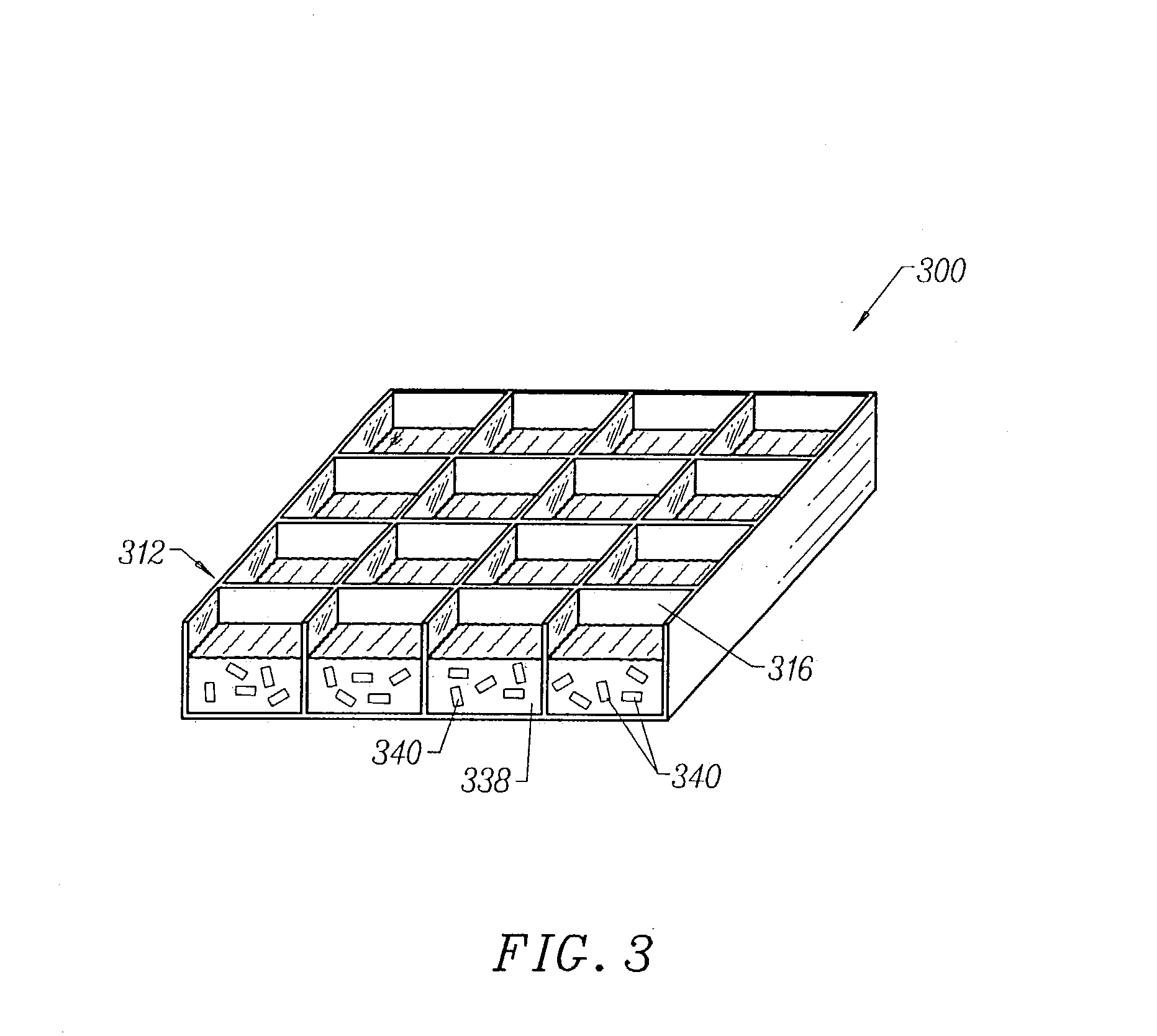

The present invention relates to high-throughput systems and methods to prepare a large number of component combinations, at varying concentrations and identities, at the same time, and high-throughput methods to test tissue barrier transfer, such as transdermal transfer, of components in each combination. The methods of the present invention allow determination of the effects of inactive components, such as solvents, excipients, enhancers, adhesives and additives, on tissue barrier transfer of active components, such as pharmaceuticals. The invention thus encompasses the high-throughput testing of pharmaceutical compositions or formulations in order to determine the overall optimal composition or formulation for improved tissue transport, such as transdermal transport.

Owner:TRANSFORM PHARMACEUTICALS INC

True CSP power MOSFET based on bottom-source LDMOS

ActiveUS7851856B2Reduces the source inductanceReduce degradationTransistorSolid-state devicesLDMOSSemiconductor package

Owner:ALPHA & OMEGA SEMICON LTD

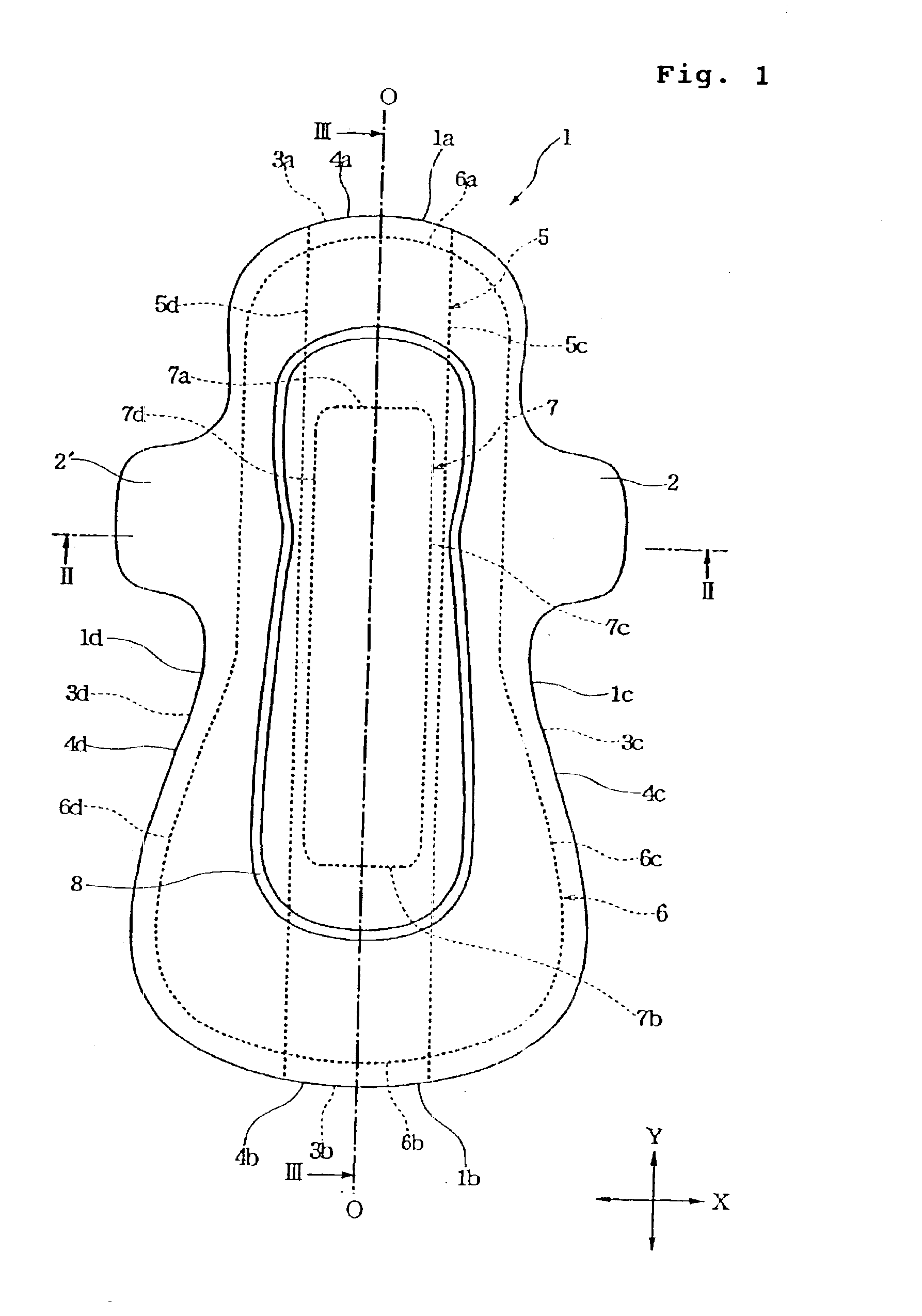

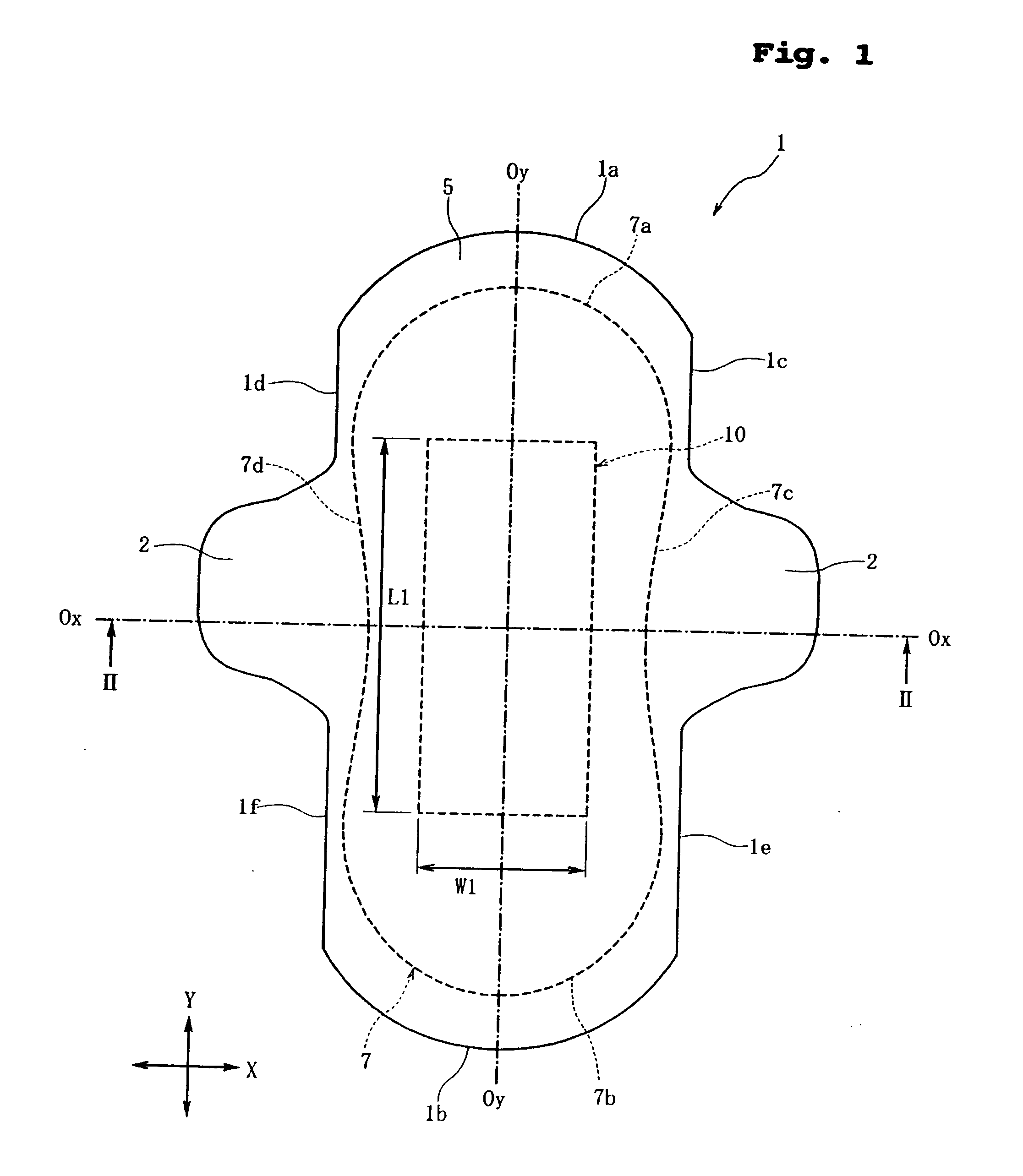

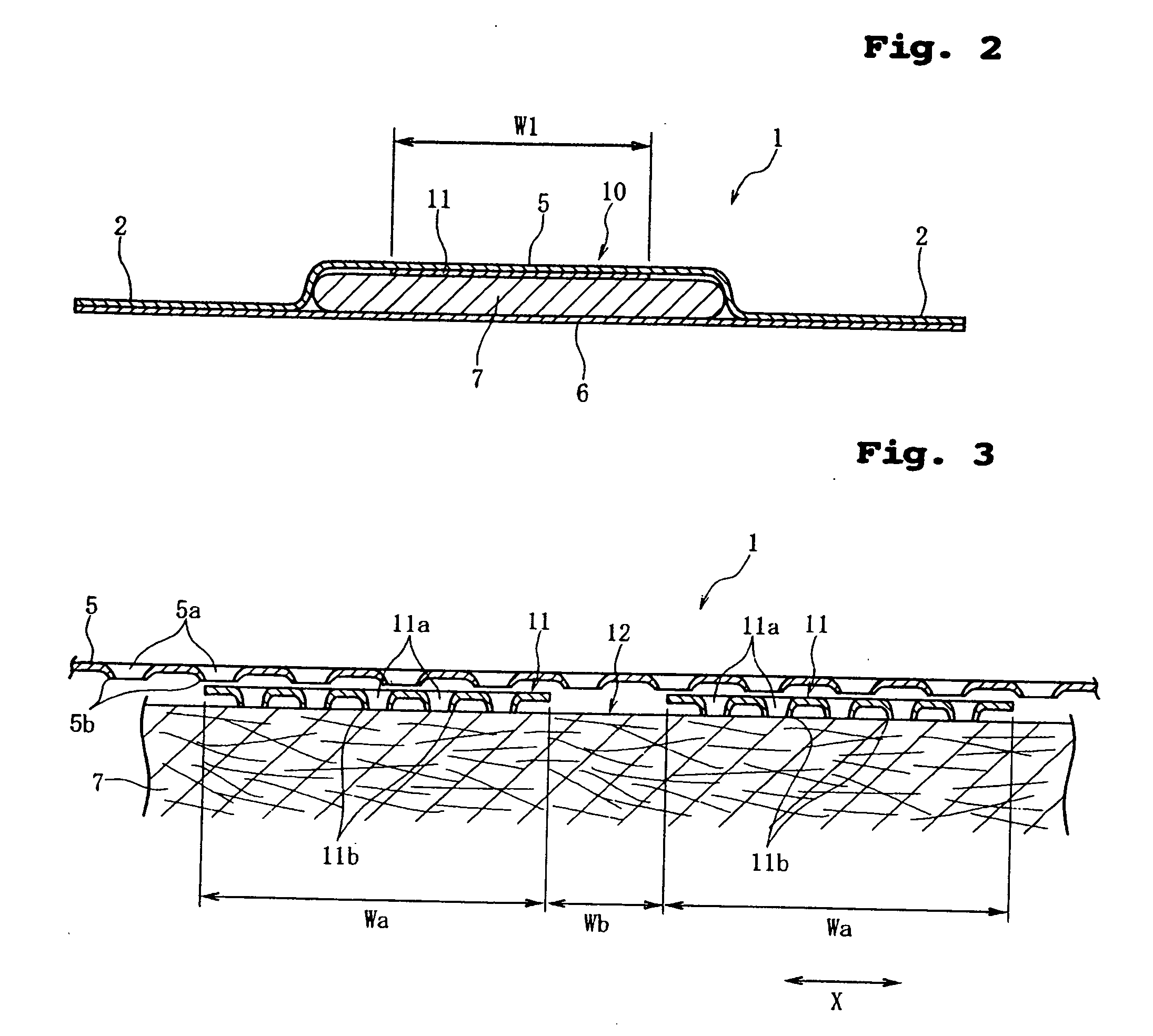

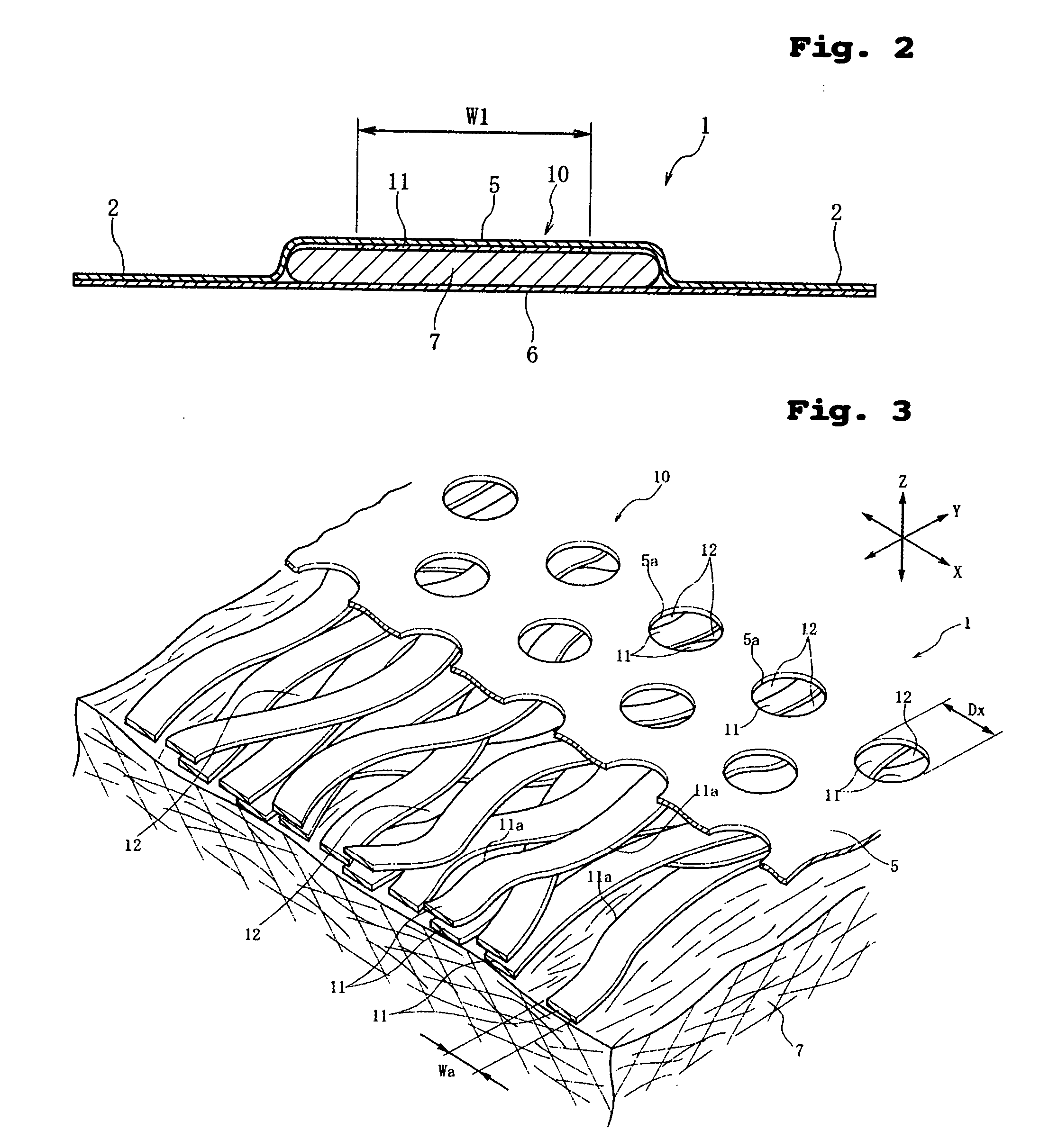

Sanitary napkin

Disclosed is a sanitary napkin which is allowed to quickly absorb menstrual blood and also effective in preventing absorbed menstrual blood from returning to the skin-side surface under pressure and in concealing the color of absorbed menstrual blood from the outside. Between a liquid absorbent layer and a topsheet formed of a resin film having a large number of liquid passage apertures, there is disposed a barrier layer formed of a resin film having a large number of liquid passage apertures. The barrier layer is composed of a plurality of strip-shaped elements, and liquid passage regions are defined between adjacent elements of the barrier layer. After passing through the liquid passage apertures of the topsheet, menstrual blood tends to be absorbed by the liquid absorbent layer through the liquid passage regions. The barrier layer functions to prevent liquid return and conceal the color of menstrual blood.

Owner:UNI CHARM CORP

Methods for Manufacturing a Sensor Assembly

ActiveUS20070292983A1Reduce riskAvoiding any lateral conductancePrinted circuit assemblingElectrically conductive connectionsEngineeringConductive materials

Owner:MICROSOFT TECH LICENSING LLC

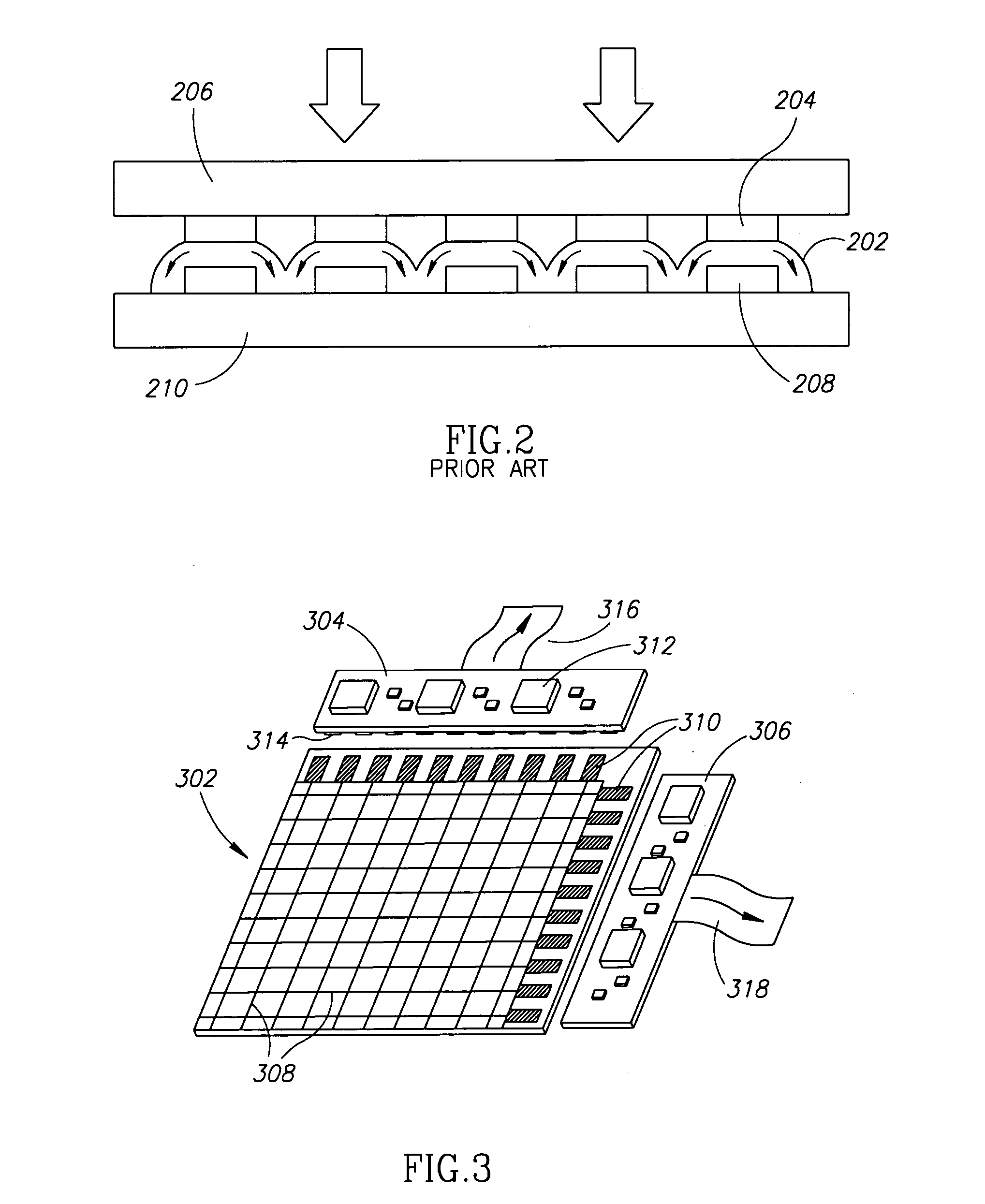

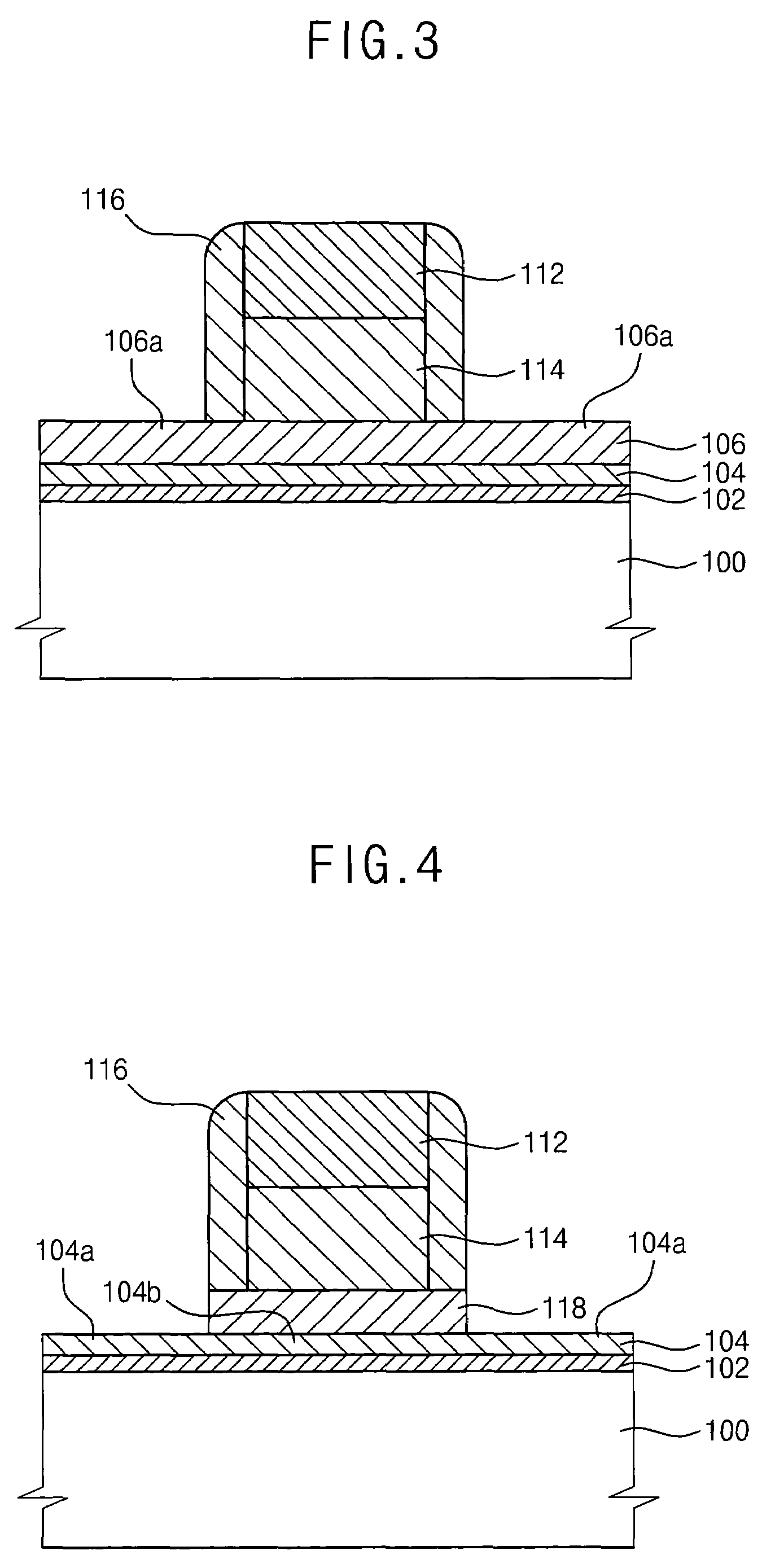

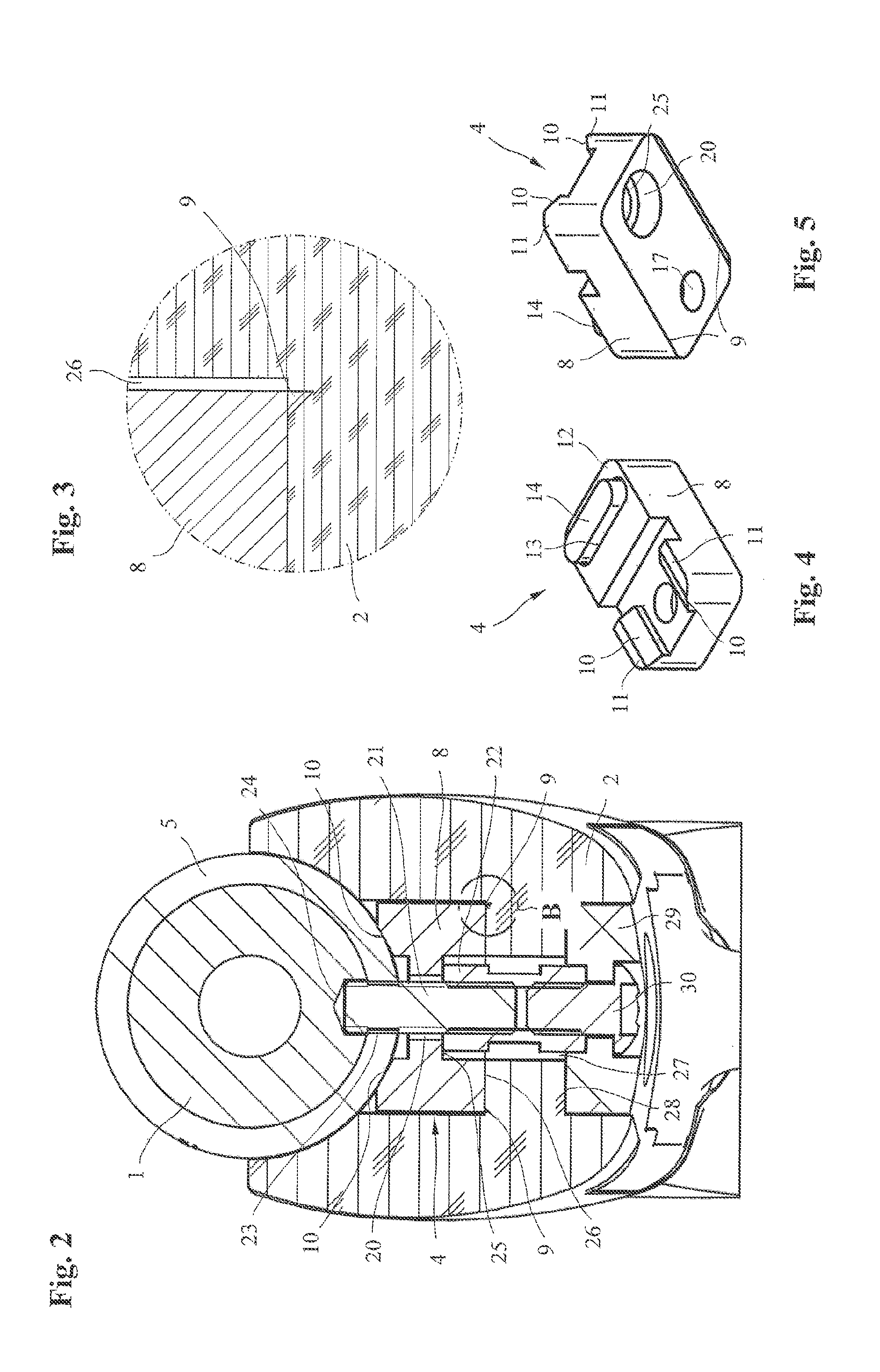

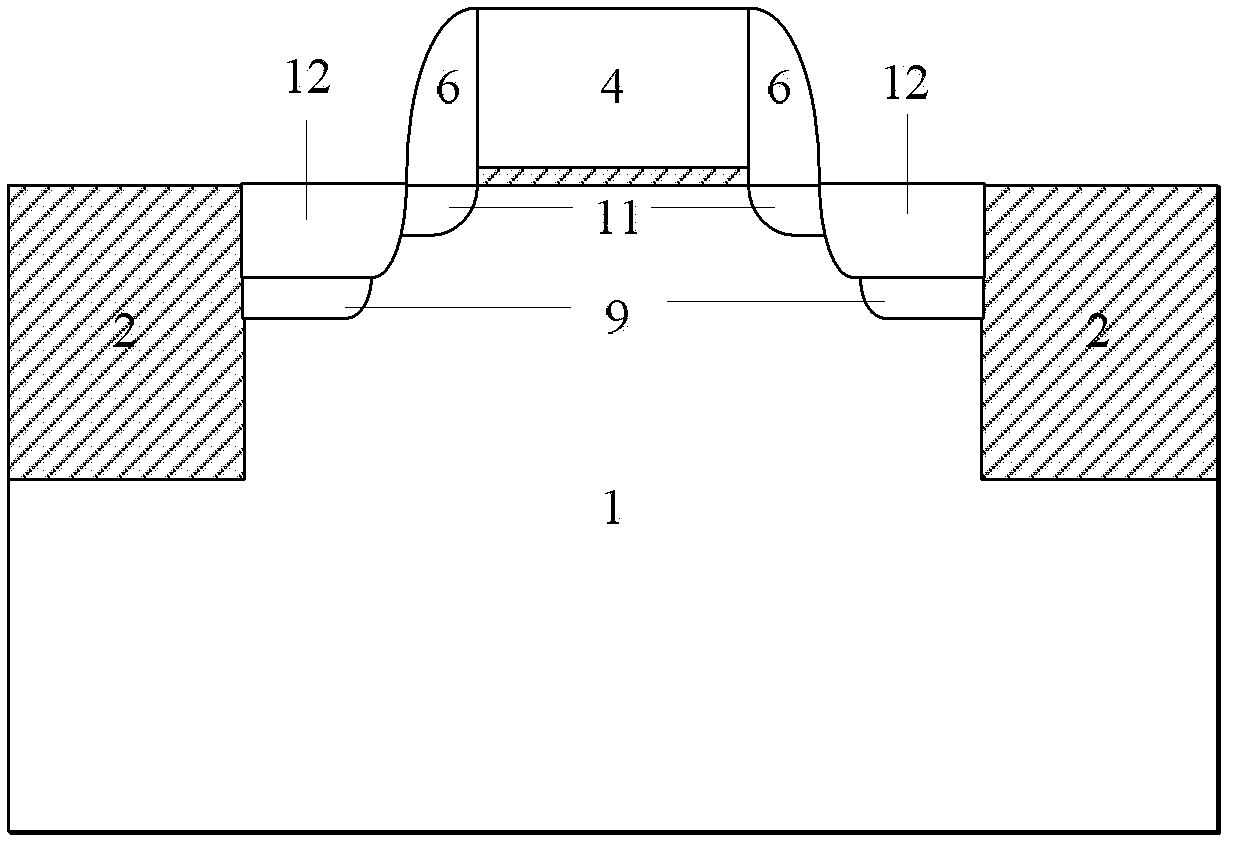

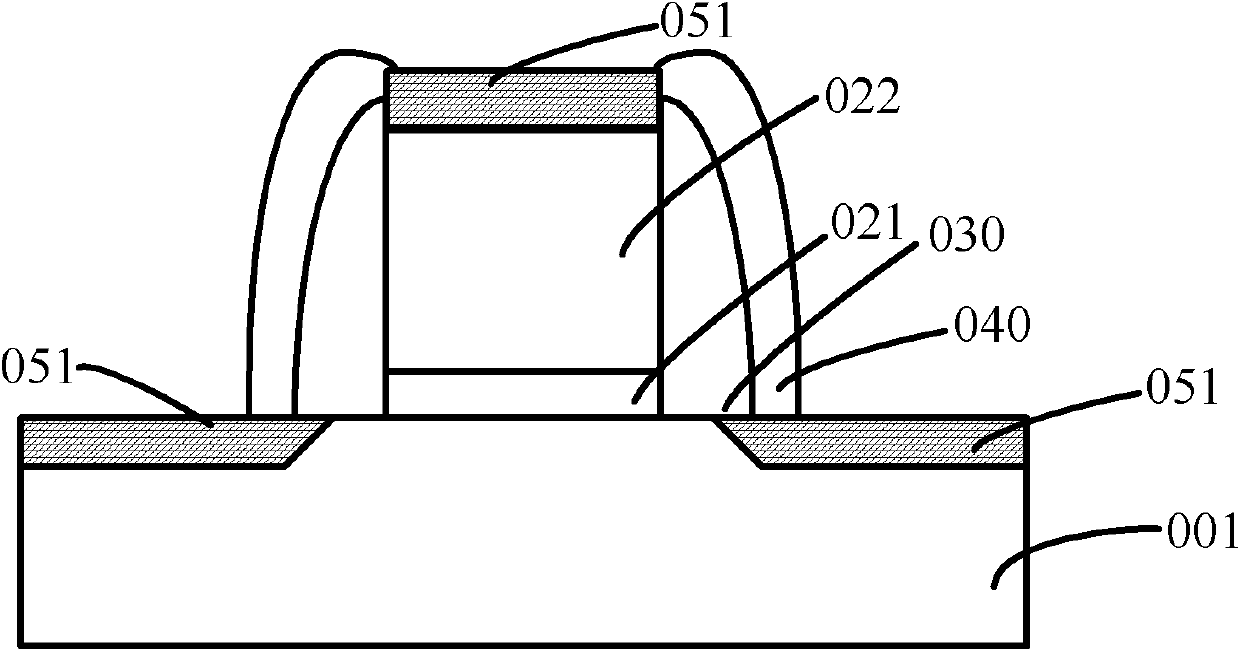

Non-volatile memory devices and methods of manufacturing the same

ActiveUS7564094B2Controlled diffusionAvoid lateral spreadNanoinformaticsSemiconductor/solid-state device manufacturingTrappingLateral diffusion

Non-volatile memory devices include a tunnel insulating layer on a channel region of a substrate, a charge-trapping layer pattern on the tunnel insulating layer and a first blocking layer pattern on the charge-trapping layer pattern. Second blocking layer patterns are on the tunnel insulating layer proximate sidewalls of the charge-trapping layer pattern. The second blocking layer patterns are configured to limit lateral diffusion of electrons trapped in the charge-trapping layer pattern. A gate electrode is on the first blocking layer pattern. The second blocking layer patterns may prevent lateral diffusion of the electrons trapped in the charge-trapping layer pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

True csp power mosfet based on bottom-source ldmos

ActiveUS20110073943A1Reduces the source inductanceReduce degradationTransistorSolid-state devicesLDMOSElectrical connection

A semiconductor package may comprise a semiconductor substrate, a MOSFET device having a plurality cells formed on the substrate, and a source region common to all cells disposed on a bottom of the substrate. Each cell comprises a drain region on a top of the semiconductor device, a gate to control a flow of electrical current between the source and drain regions, a source contact proximate the gate; and an electrical connection between the source contact and source region. At least one drain connection is electrically coupled to the drain region. Source, drain and gate pads are electrically connected to the source region, drain region and gates of the devices. The drain, source and gate pads are formed on one surface of the semiconductor package. The cells are distributed across the substrate, whereby the electrical connections between the source contact of each device and the source region are distributed across the substrate.

Owner:ALPHA & OMEGA SEMICON INC

Matt color ink jet printer paper paint and preparation method thereof

InactiveCN101446055AImprove adsorption capacityLow costPaper coatingCoatingsRoom temperatureSilicon dioxide

The invention relates to matt color ink jet printer paper paint and a preparation method thereof. The preparation method is characterized in that the method comprises the following steps: adding dispersant into deionized water to be dissolved at the room temperature; adding modified bentonitic clay to the dissolved deionized water and dispersing at the room temperature; adding silicon dioxide to the modified bentonitic clay dispersion liquid for dispersion, and obtaining mixed dispersion liquid; adding an adhesion agent to the mixed dispersion liquid while stirring; adding a silicone antifoaming agent, PDMDAAC and carboxymenthyl cellulose in sequence, and obtaining paint liquid after evenly blending and stirring. Because the modified bentonitic clay is utilized as the pigment to prepare the paint for the matt color ink jet printer paper, good water absorption performance, good color fixation performance, high color density, good color reductibility and no infiltration of the matt color ink jet printer paper can be ensured, and the purpose of reducing the cost of the matt color ink jet printer paper can be achieved.

Owner:JIANGNAN UNIV

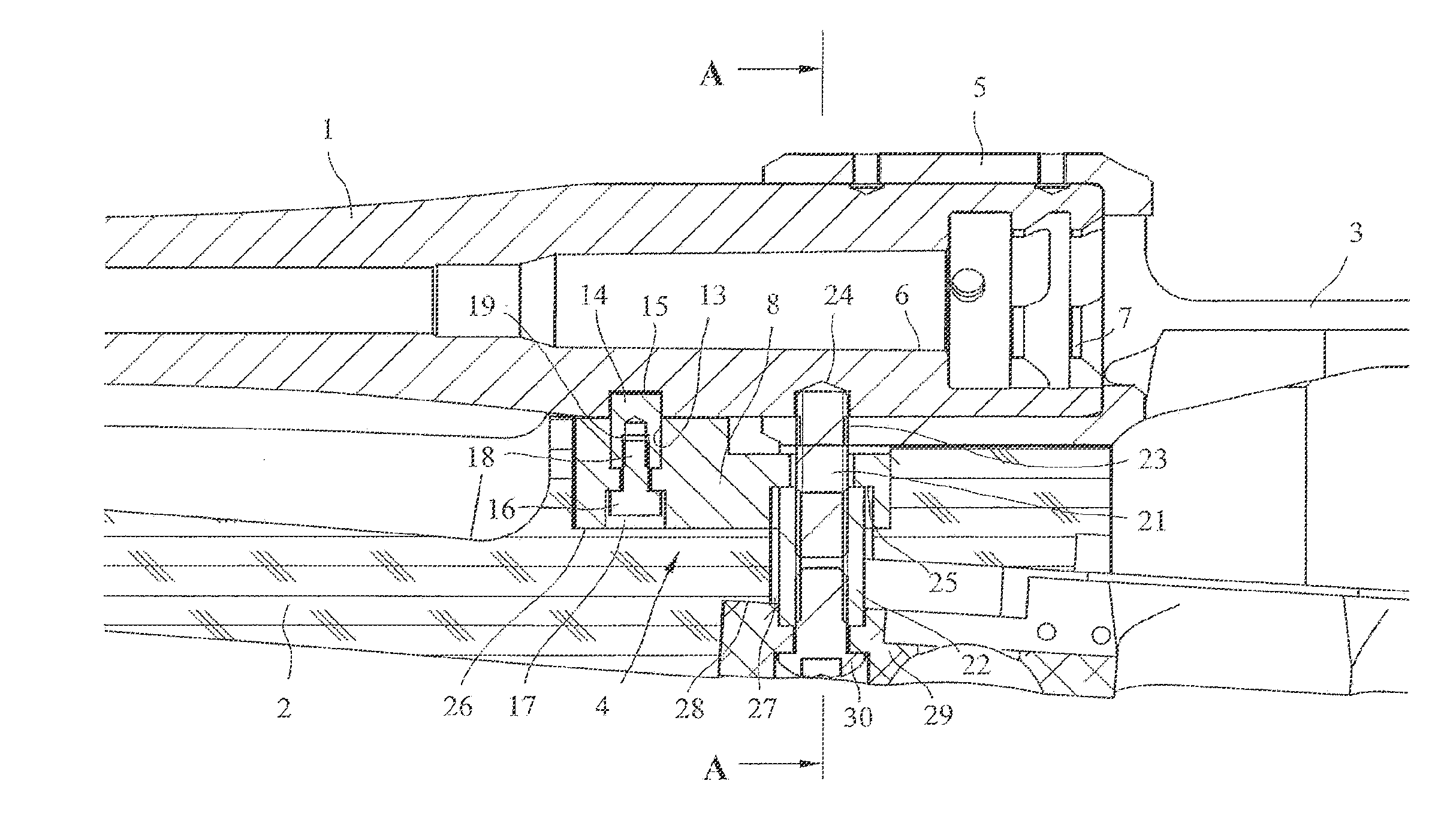

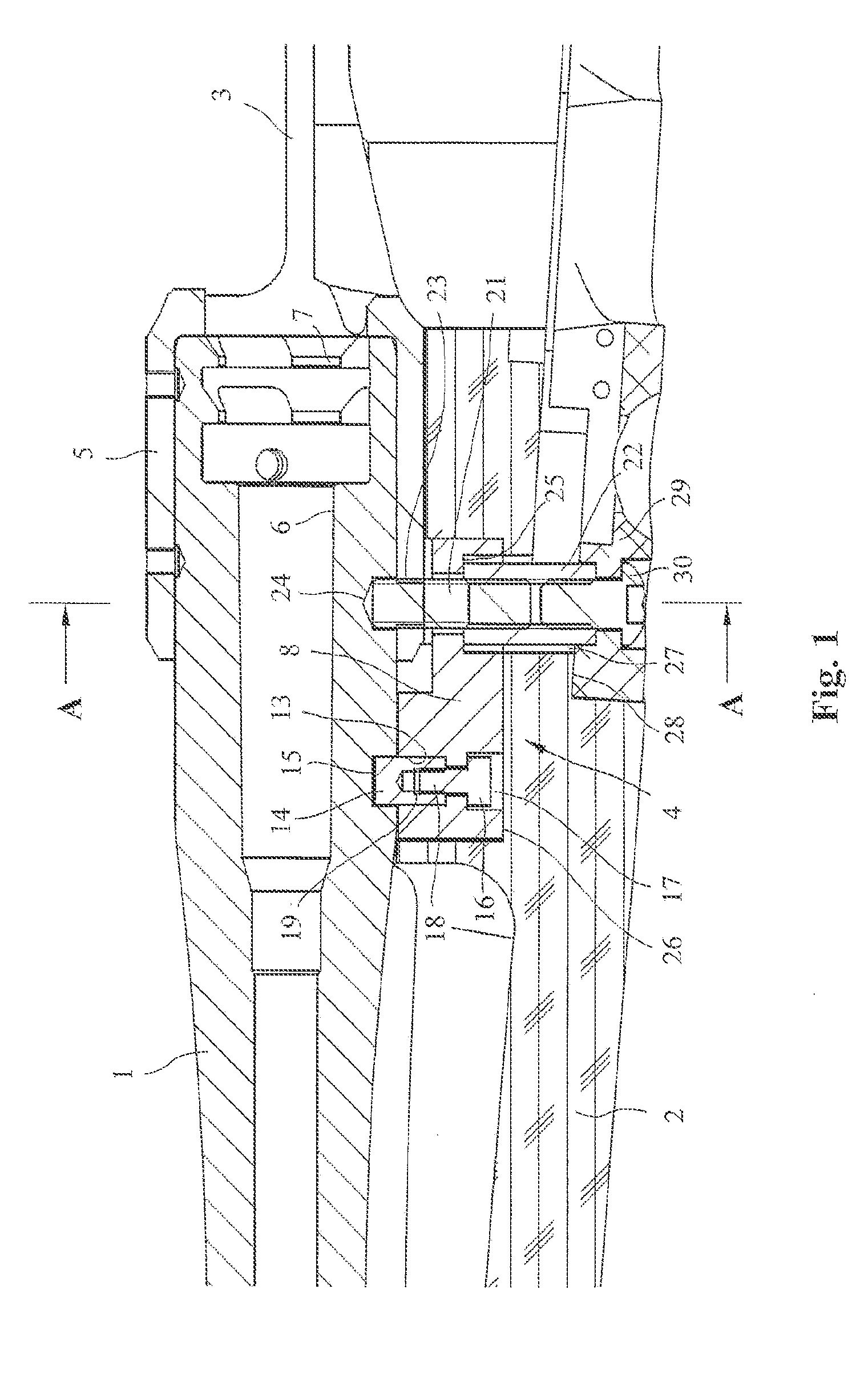

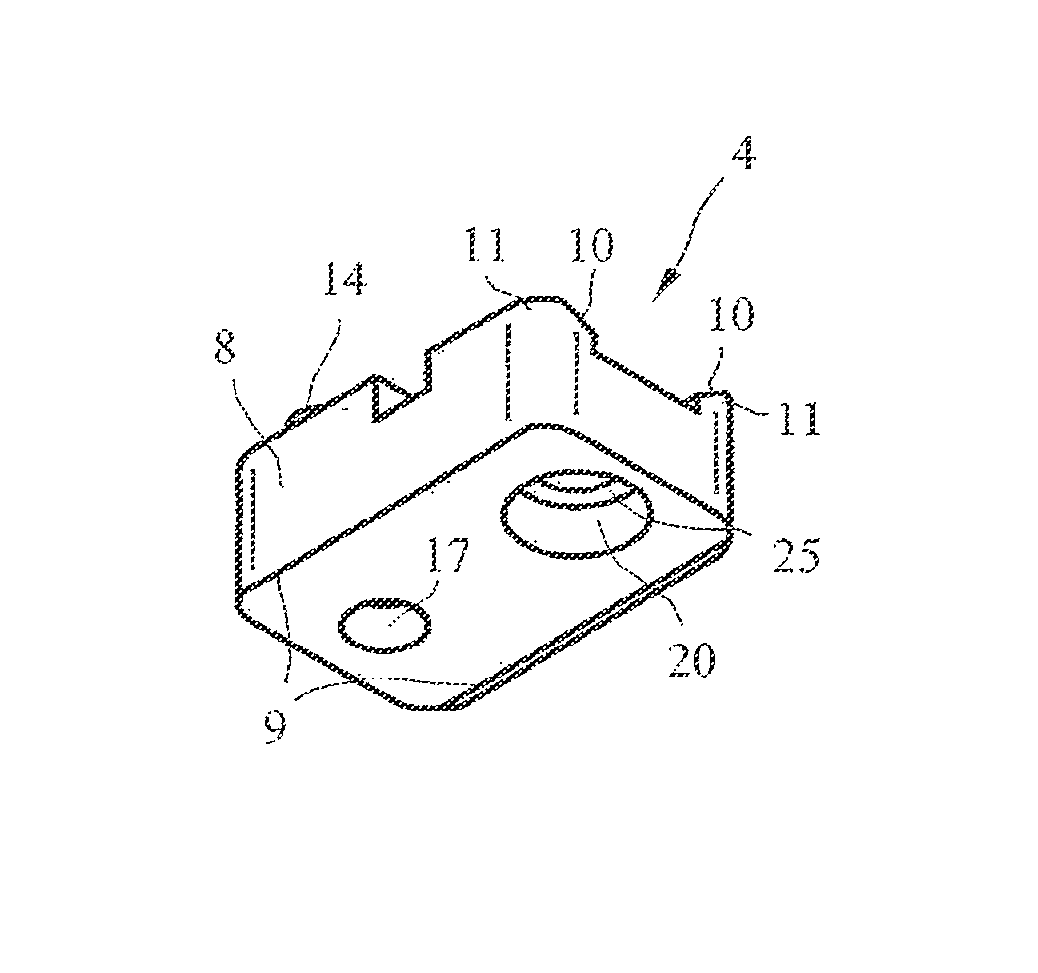

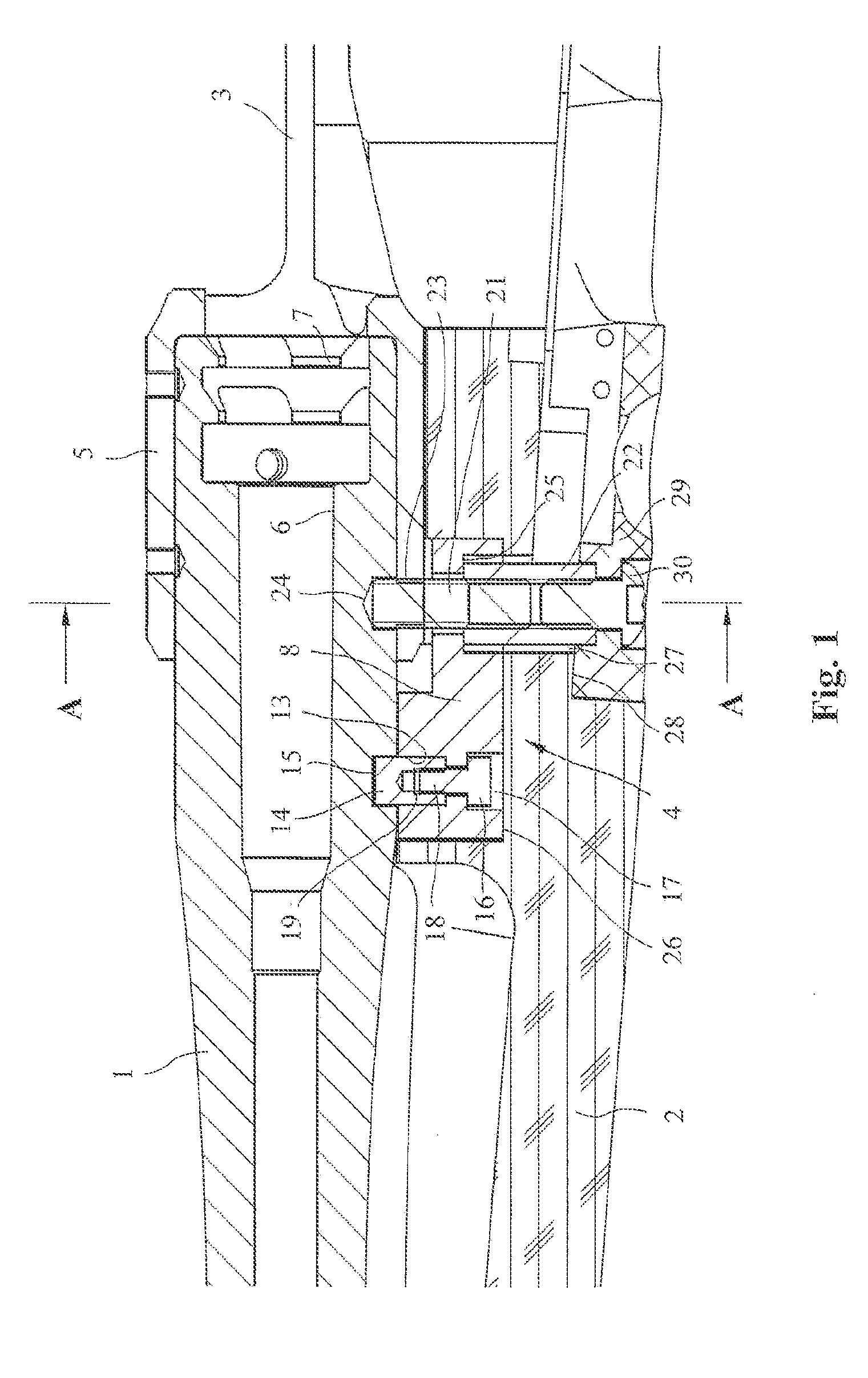

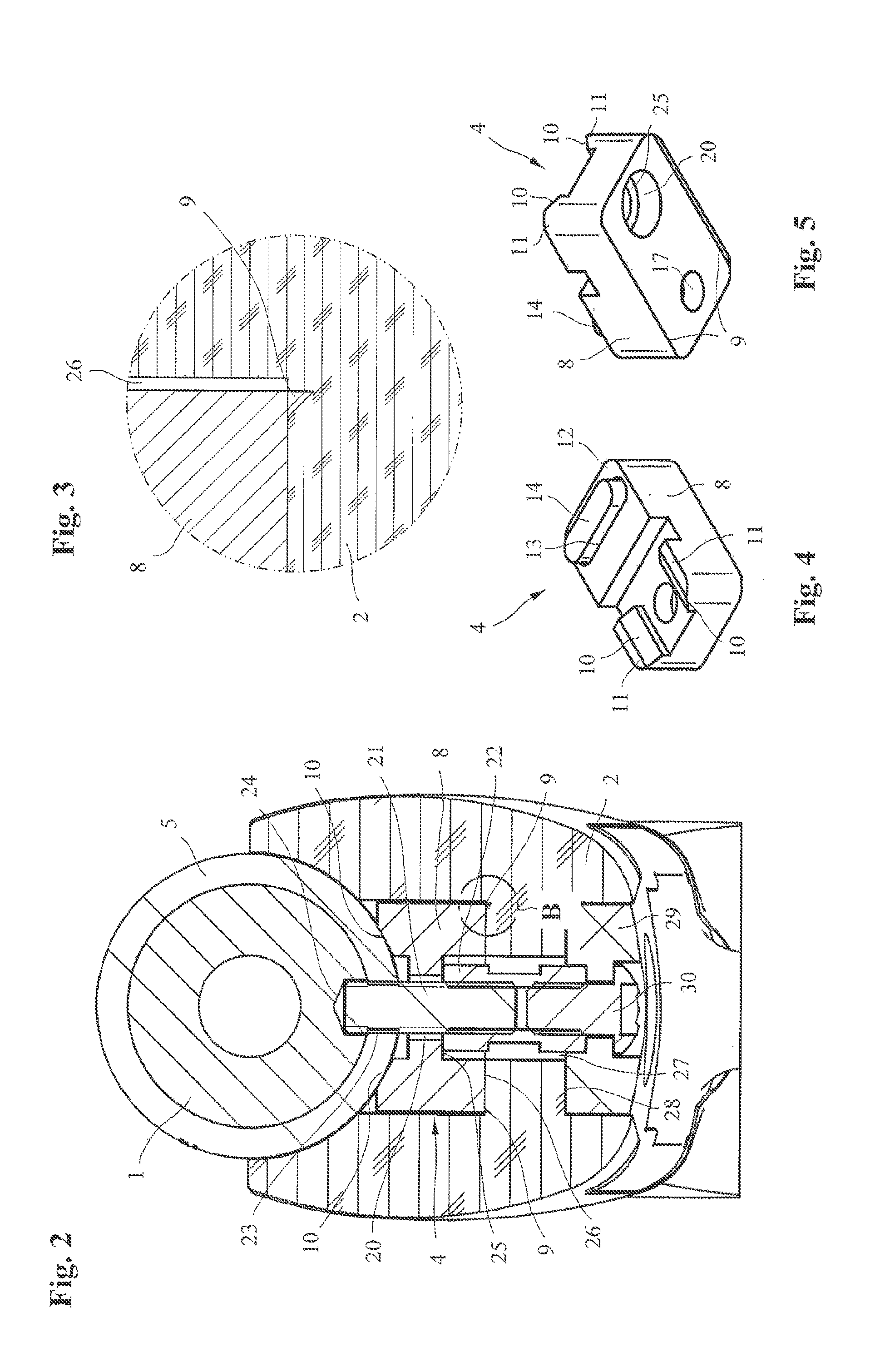

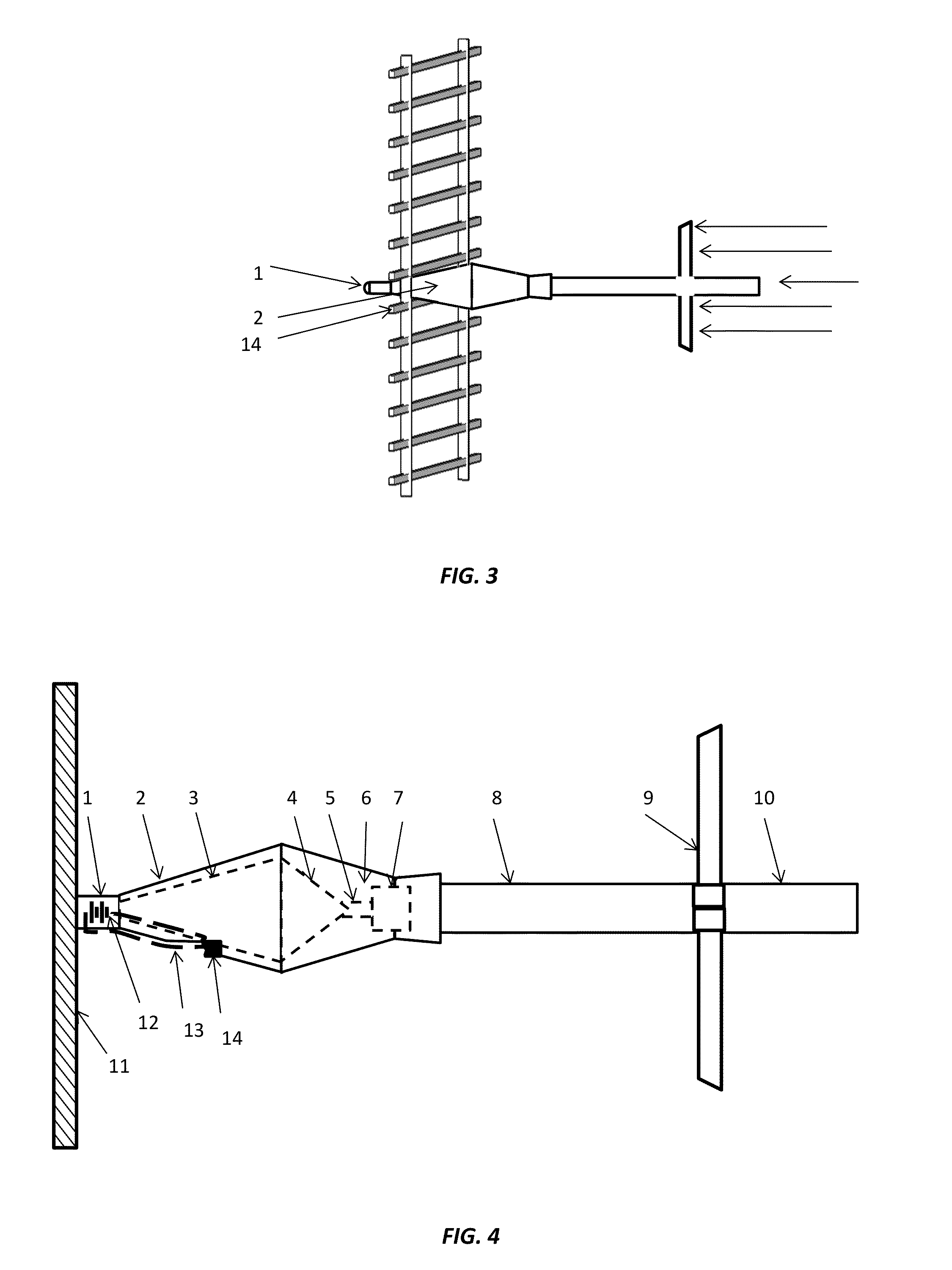

Mechanism for bedding a receiver frame and/or a barrel in a stock of a firearm

The present invention relates to a mechanism for bedding a receiver frame (3) and / or a barrel (1) in a stock (2) of a firearm, the mechanism having a bearing component (8) which can be attached to the stock (2) and which, on its upper surface, has a bearing surface (10,11) for bearing the receiver frame (3) and / or the barrel (1). To ensure permanent and reproducibly accurate positioning, the lower surface of the bearing component (8) comprises a guide profile (9) for seating the bearing component (8) free from play in the stock (2).

Owner:BLASER FINANZHLDG

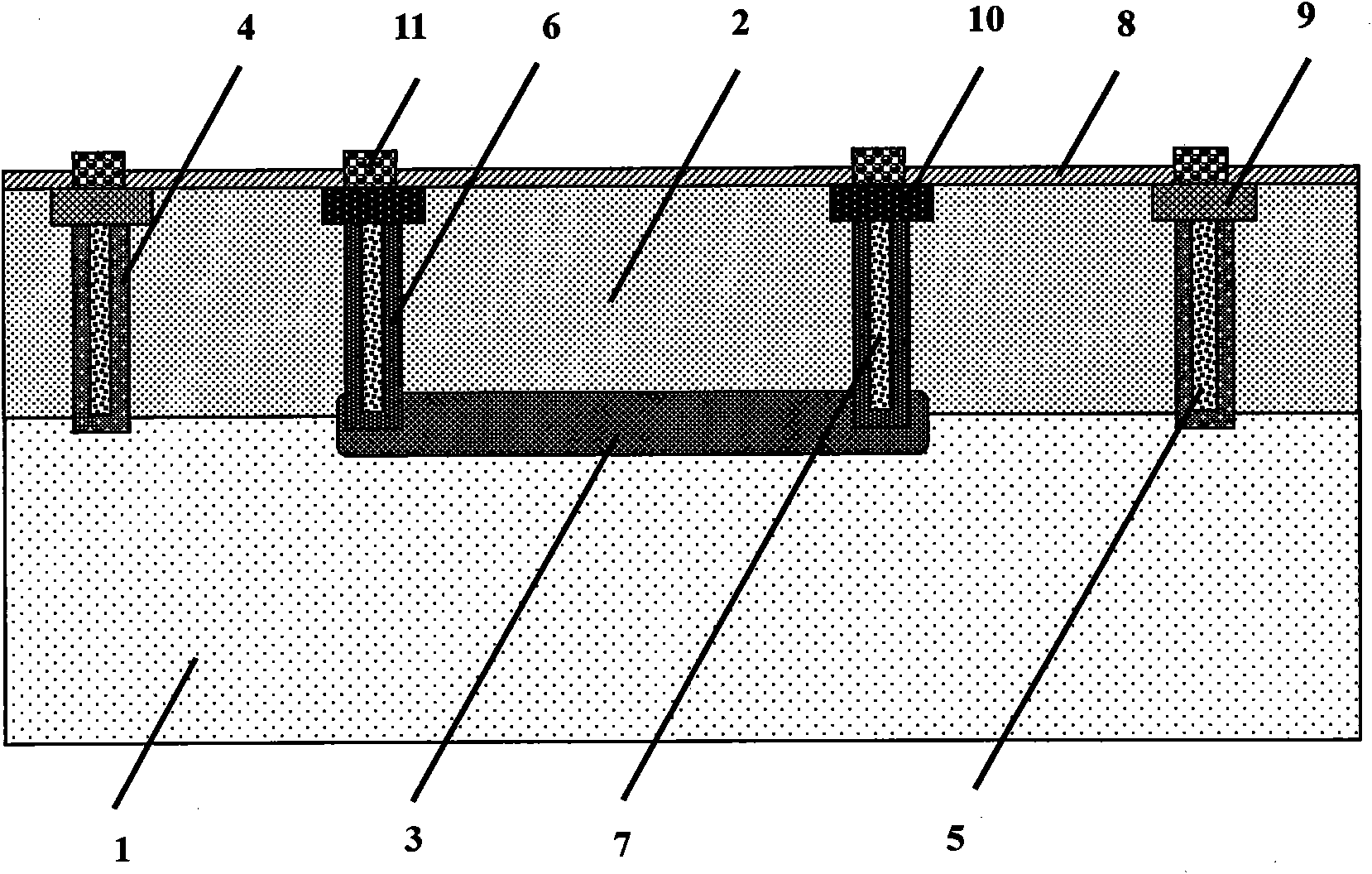

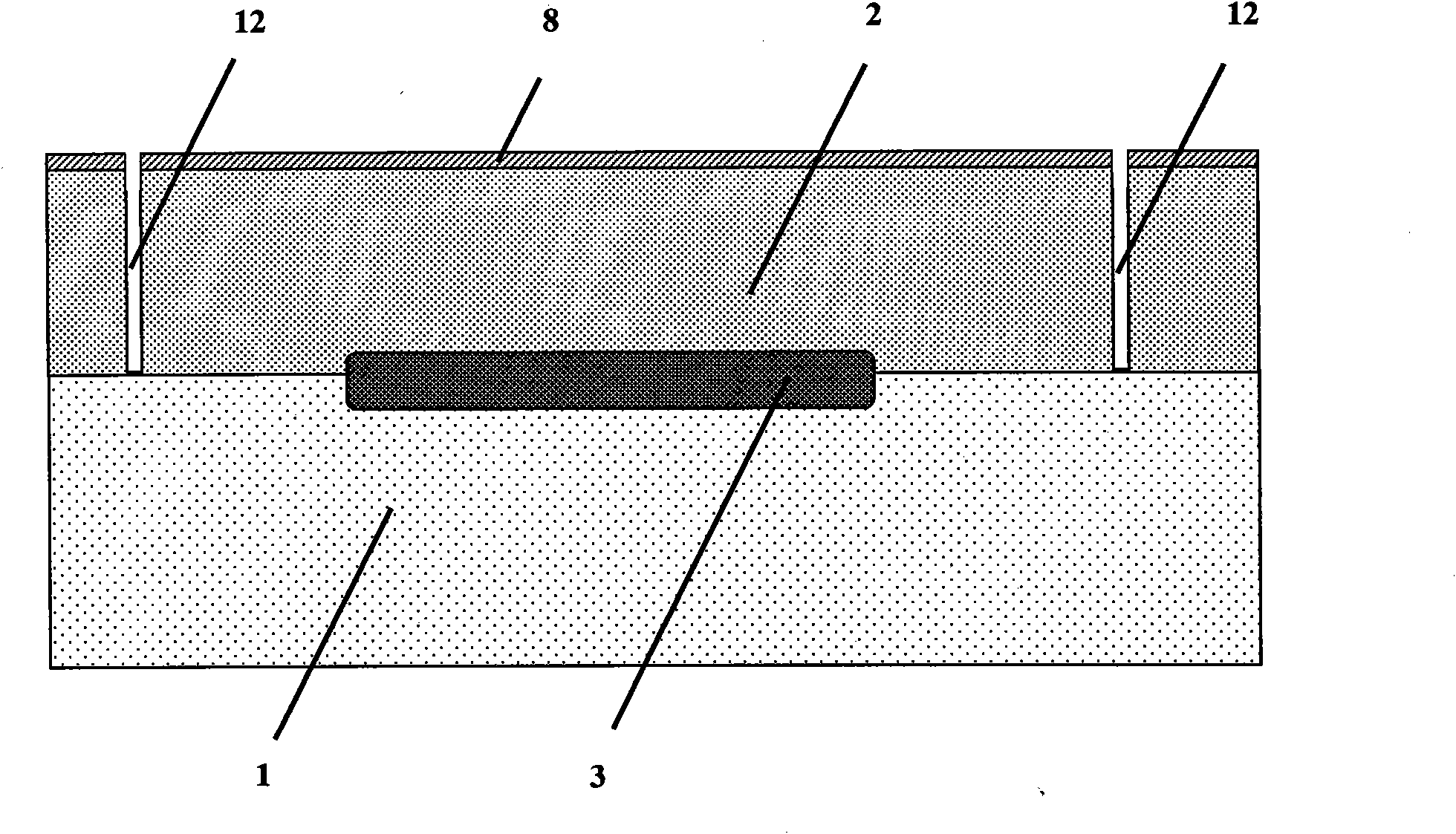

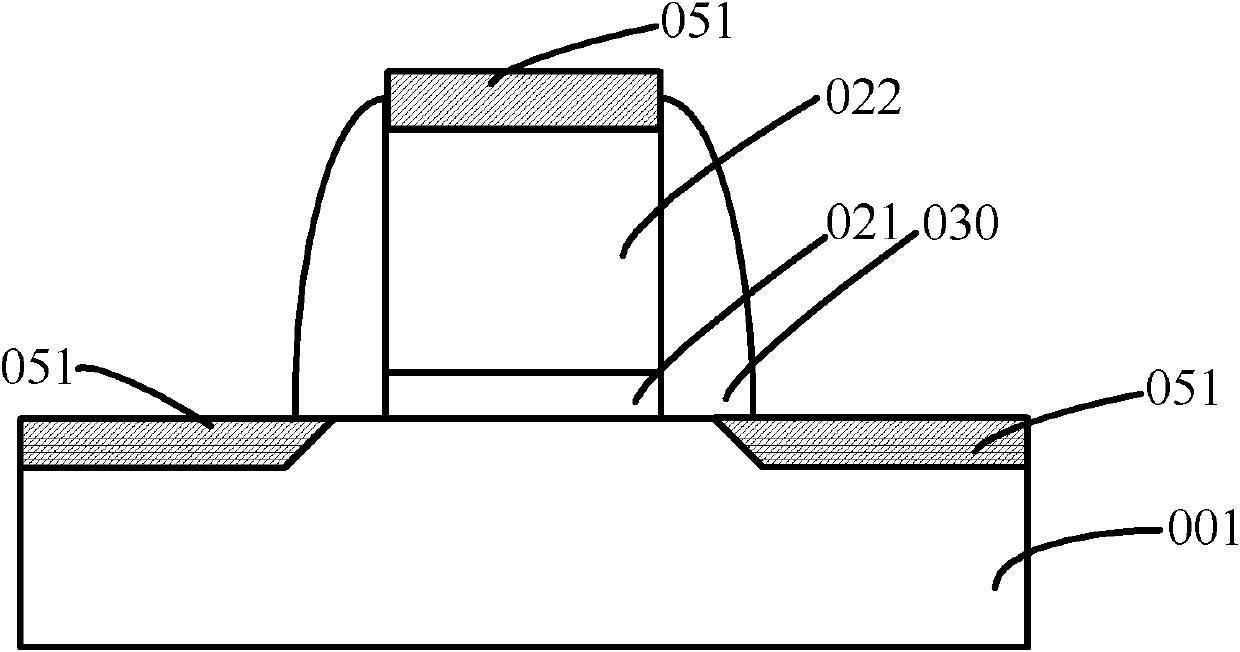

Semiconductor component and method for manufacturing semiconductor component

ActiveCN101097919AAvoid lateral spreadSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

The present invention relates to a semiconductor component and a method for manufacturing the same. The semiconductor component comprises a semiconductor body, which includes a substrate of a first conducting type, a buried semiconductor layer of a second conducting type being arranged on the substrate, a functional cell semiconductor layer of a third conducting type being arranged on the buried semiconductor layer. The functional cell semiconductor layer provides at least two semiconductor functional cells being arranged landscape orientation in a row. The buried semiconductor layer is part of at least one semiconductor functional cell. The semiconductor functional cells are electrically insulated with each other by means of the functional semiconductor layer, the buried semiconductor layer and the separating structure of the substrate. The separating structure comprises at least a trench and a conducting contact with the substrate, the contact is electrically insulated with the functional cell semiconductor layer and the buried layer by means of at least one trench.

Owner:INFINEON TECH AG

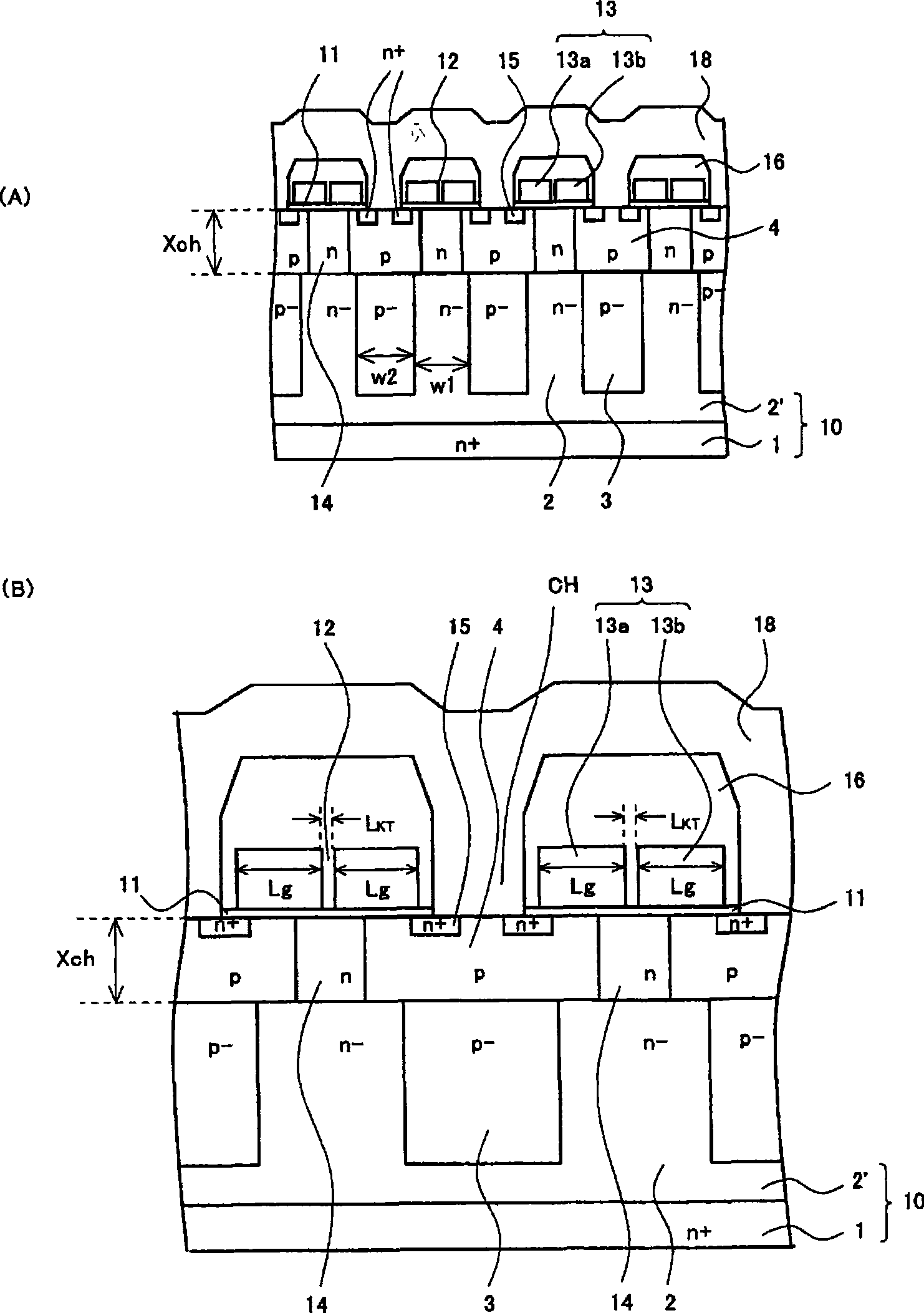

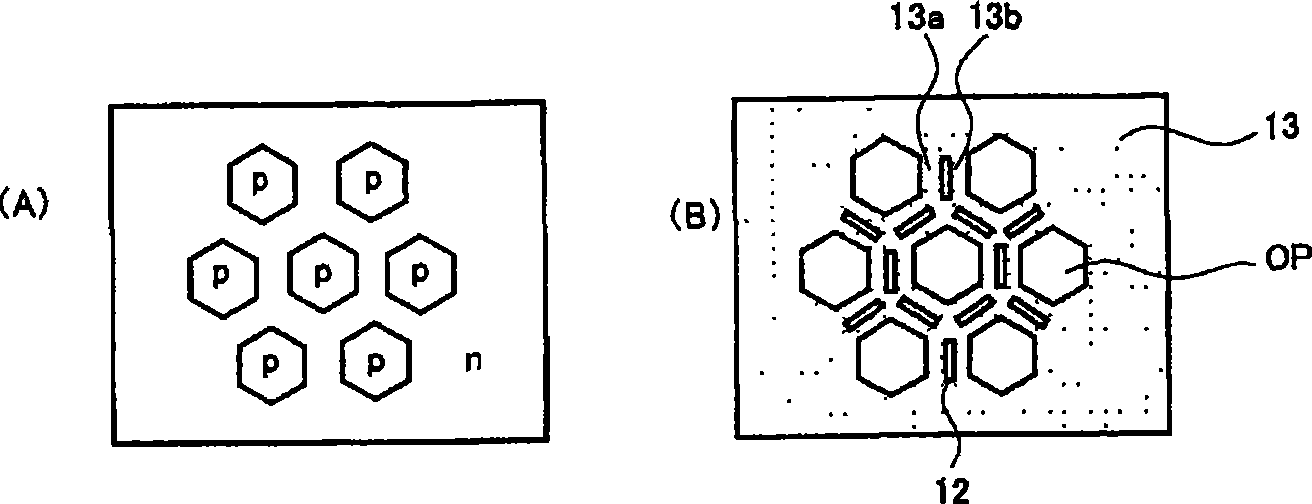

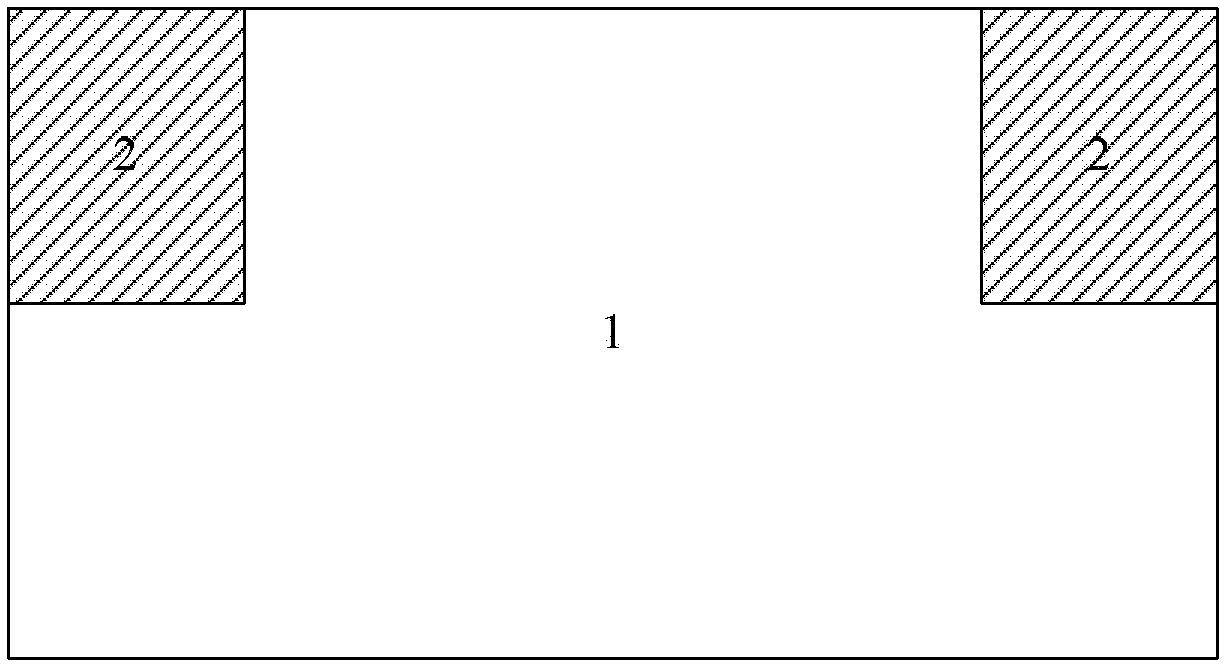

Semiconductor device and method of manufacturing the same

InactiveCN101399268AAvoid lateral spreadLower resistanceTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceHigh concentration

Provided is a semiconductor device and a method of manufacturing a semiconductor device. In the semiconductor device, high-concentration n type impurity regions are formed respectively below gate electrodes. By setting a gate length to be smaller than a depth of channel regions, pn junction interfaces formed of adjacent side faces of the n type impurity regions and the channel regions can be substantially vertical to a top surface of a base. With this configuration, even when reduction in size is achieved in a super junction structure, a distance between the channel regions (i.e. a current path below the gate electrode) is not reduced unnecessarily. Accordingly, an increase in resistance can be prevented. In addition, depletion layers uniformly expand in the n type semiconductor regions, and impurity concentration of the regions can be increased consequently. Accordingly, reduction in resistance can be achieved.

Owner:SANYO ELECTRIC CO LTD +1

Sanitary napkin

Disclosed is a sanitary napkin which is allowed to quickly absorb menstrual blood and also effective in preventing absorbed menstrual blood from returning to the skin-side surface under pressure and in concealing the color of absorbed menstrual blood from the outside. Between a liquid absorbent layer and a topsheet formed of a resin film having a large number of liquid passage apertures, there is disposed a large number of barrier members having a small width. The barrier members are strips formed of a resin film, and gaps are left between adjacent barrier members. After passing through the liquid passage apertures of the topsheet, menstrual blood tends to be absorbed by the liquid absorbent layer through the gaps. The barrier members also function to prevent liquid return and conceal the color of menstrual blood.

Owner:UNI CHARM CORP

Mechanism for bedding a receiver frame and/or a barrel in a stock of a firearm

The present invention relates to a mechanism for bedding a receiver frame (3) and / or a barrel (1) in a stock (2) of a firearm, the mechanism having a bearing component (8) which can be attached to the stock (2) and which, on its upper surface, has a bearing surface (10,11) for bearing the receiver frame (3) and / or the barrel (1). To ensure permanent and reproducibly accurate positioning, the lower surface of the bearing component (8) comprises a guide profile (9) for seating the bearing component (8) free from play in the stock (2).

Owner:BLASER FINANZHLDG

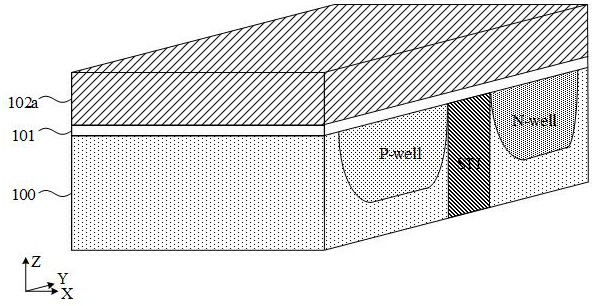

Semiconductor structure for increasing integration density of high-voltage integrated circuit device and manufacturing method

ActiveCN101976680AImprove integration densityLower process temperatureSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

The invention relates to a semiconductor structure for increasing integration density of a high-voltage integrated circuit device and a manufacturing method. Aiming at the problems of large occupation area of PN junction isolation and penetration diffusion adopted in a high-voltage integrated circuit and high step, high electric field, high stress and poor clamping hidden trouble of conventional deep slot isolation, a deep slot diffusion isolation and deep slot penetration diffusion structure is adopted to realize improvement on the integration density of the high-voltage device and promotion on the performance of the device. The method can reduce over 35 percent of high-voltage integrated circuit area at most, improve the integration density of the high-voltage integrated circuit, thin the thickness of an epitaxial layer compared with the common penetration structure, simplify the process design of the high-voltage integrated circuit device structure and effectively solve the high step, high electric field, high stress and poor clamping hidden trouble of the conventional deep slot isolation structure. The method is applied in the fields of structure design and manufacture of high-voltage semiconductor devices and integrated circuits.

Owner:NO 24 RES INST OF CETC

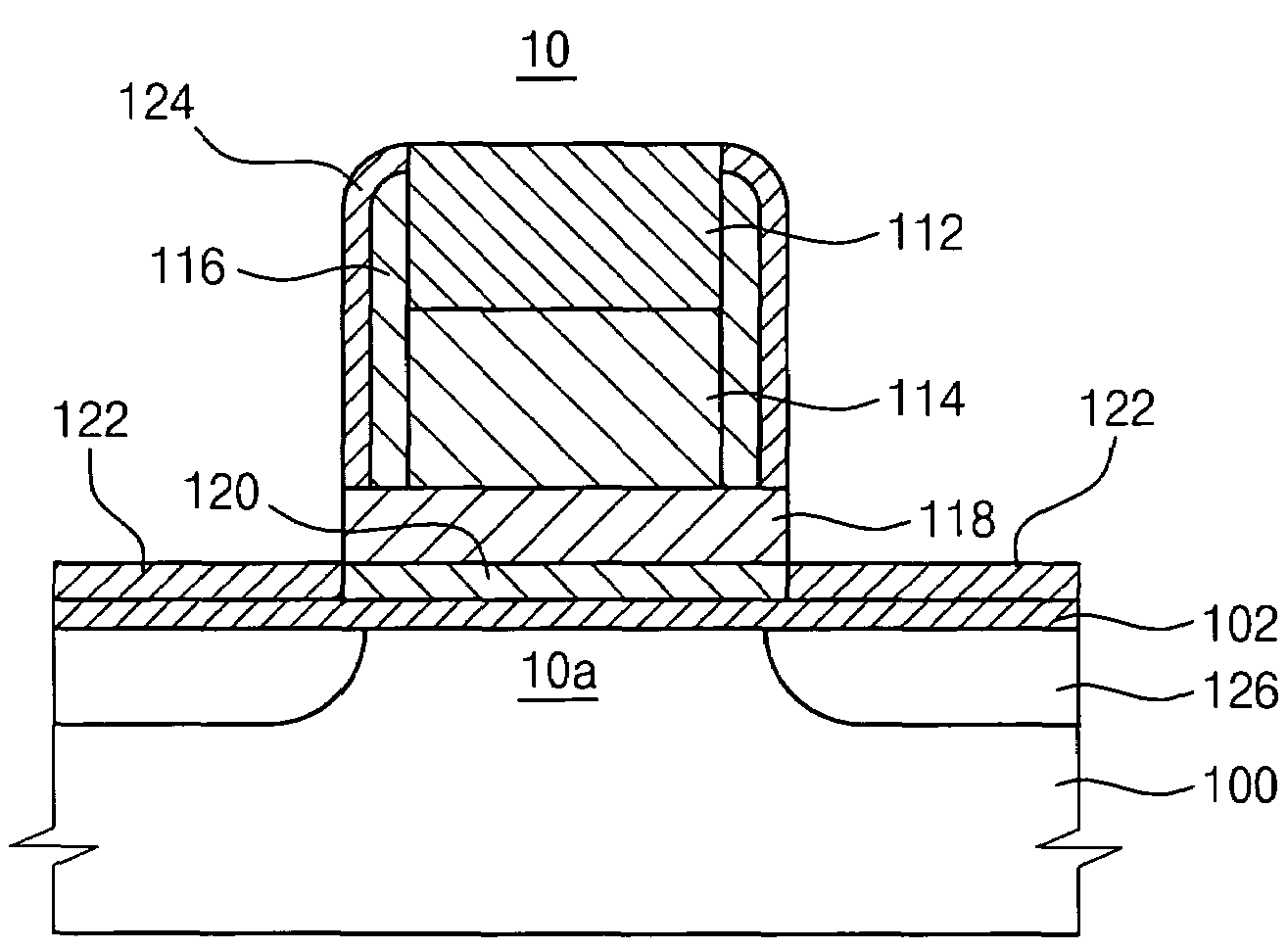

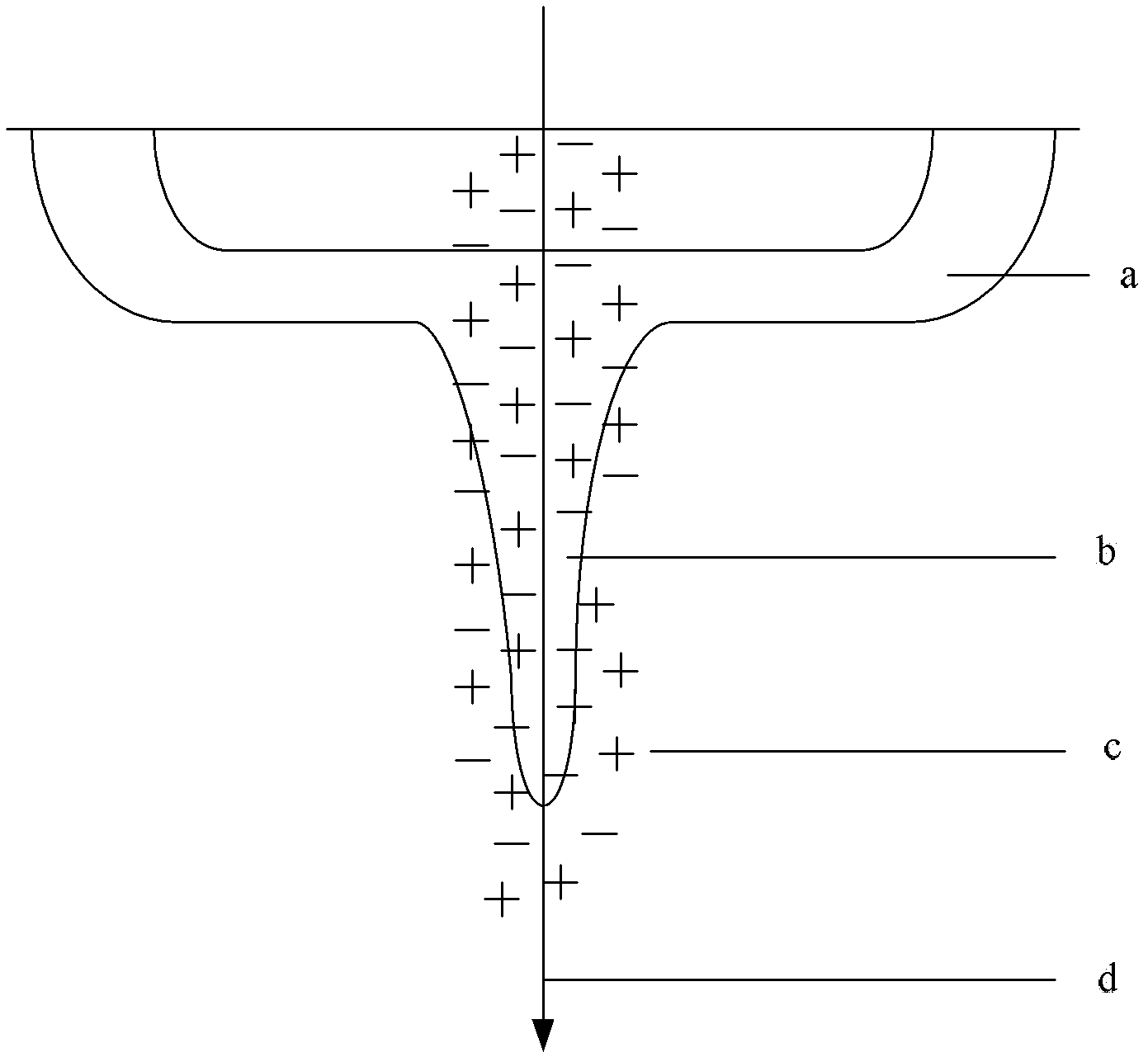

CMOS (complementary metal oxide semiconductor) device capable of reducing charge collection generated by radiation and preparation method thereof

ActiveCN102386186AAvoid lateral spreadTransistorSemiconductor/solid-state device manufacturingCMOSElectron hole

The invention discloses a CMOS (complementary metal oxide semiconductor) device capable of reducing charge collection generated by radiation and a preparation method thereof. The CMOS device provided by the invention is provided with a heavily doped charge restriction collecting region vertically below a source region and a drain region, the doping type of the charge restriction collecting region is opposite to those of the source region and the drain region, and the doping concentration is greater than or equal to those of the source region and the drain source. The transverse range of the charge restriction collecting region is slightly less than or equal to those of the source region and the drain region, and the transverse position of a channel is not more than the edges of the source region and the drain region. The CMOS device provided by the invention can greatly decrease the 'hopper' range generated under the action of independent particles so that the instantaneously collected charge can be decreased under the action of the electric field. As the width of a depletion layer is narrowed, an electron hole in the 'hopper' range is more difficult to diffuse to the edge of the depletion layer, thus the charge collected by a sensitive node can be greatly reduced and the influence of the transient independent particles on the integrated circuit can be effectively restrained.

Owner:PEKING UNIV

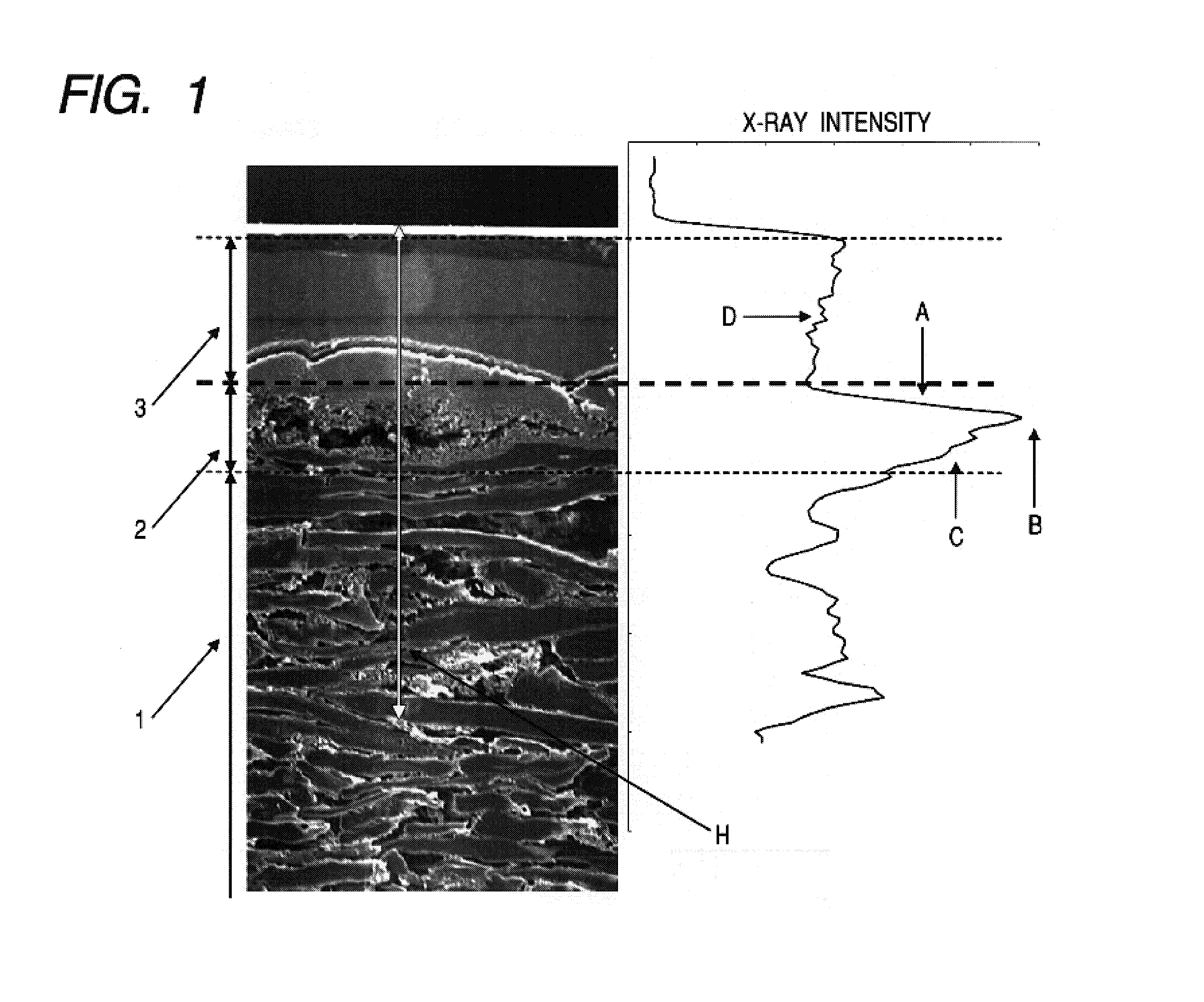

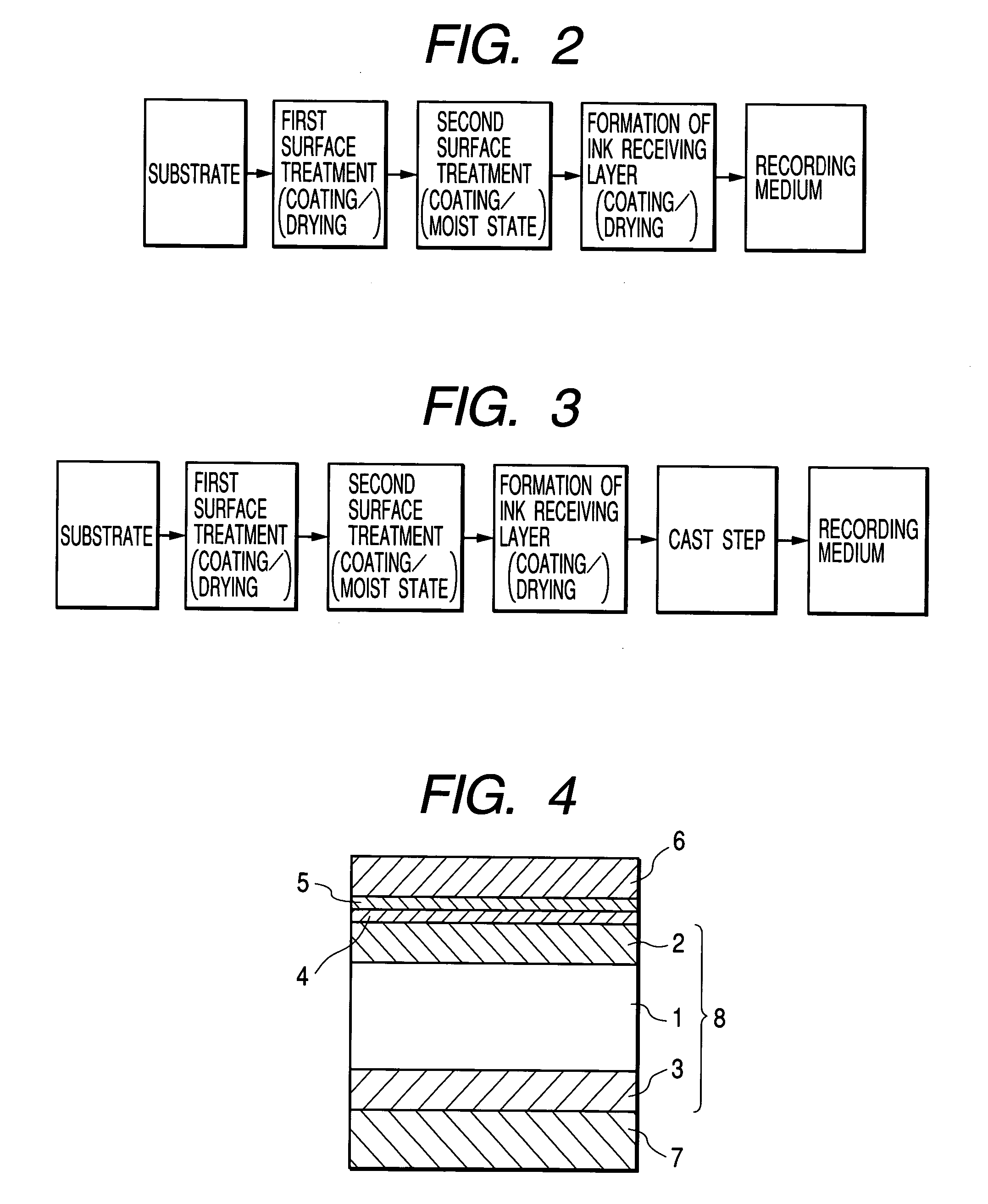

Recording medium for ink and method for producing the same

InactiveUS7255901B2Prevent image deteriorationFast absorptionCoatingsThermographyAlumina hydratePhotochemistry

Owner:CANON KK

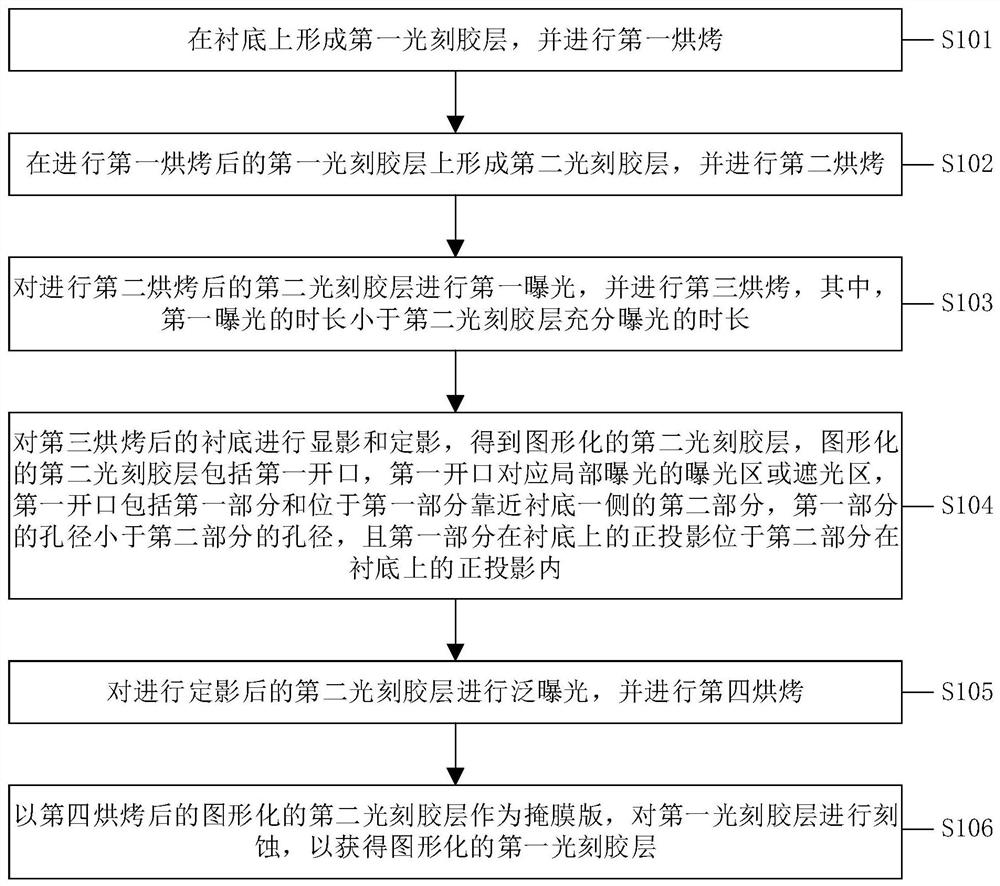

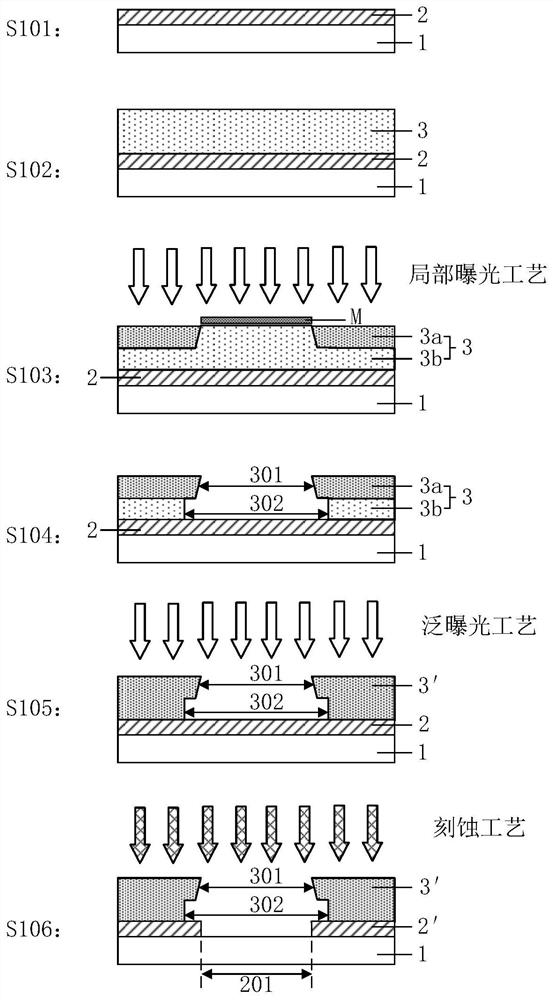

Photoresist structure, graphical deposition layer, semiconductor chip, and manufacturing methodd of photoresist structure, graphical deposition layer and semiconductor chip

ActiveCN112652522AGood lookingAvoid corrosion damageSemiconductor/solid-state device manufacturingPhotosensitive material processingSemiconductor chipEngineering

The embodiment of the invention provides a photoresist structure, a graphical deposition layer, a semiconductor chip, and manufacturing methods of the photoresist structure, the graphical deposition layer and the semiconductor chip. According to the manufacturing method of the photoresist structure, a single photoresist is utilized, the second photoresist layer containing the undercut can be obtained only by using a single developing solution for one-time development, and the size of the undercut can be controlled through the development time, so the problems of stripping difficulty and the like caused by adhesion of a deposition material and the side wall of the photoresist structure in a traditional stripping process are avoided; the first photoresist layer is used as a protective adhesive layer, so that corrosion damage of a developing solution to a substrate material during development can be avoided; and the first photoresist layer is etched, so that the first photoresist layer serving as a protective adhesive layer is converted into a pattern limiting adhesive layer, lateral diffusion at the bottom of a deposition material can be effectively prevented in the material deposition process, and the deposition layer with good morphology is obtained.

Owner:TENCENT TECH (SHENZHEN) CO LTD

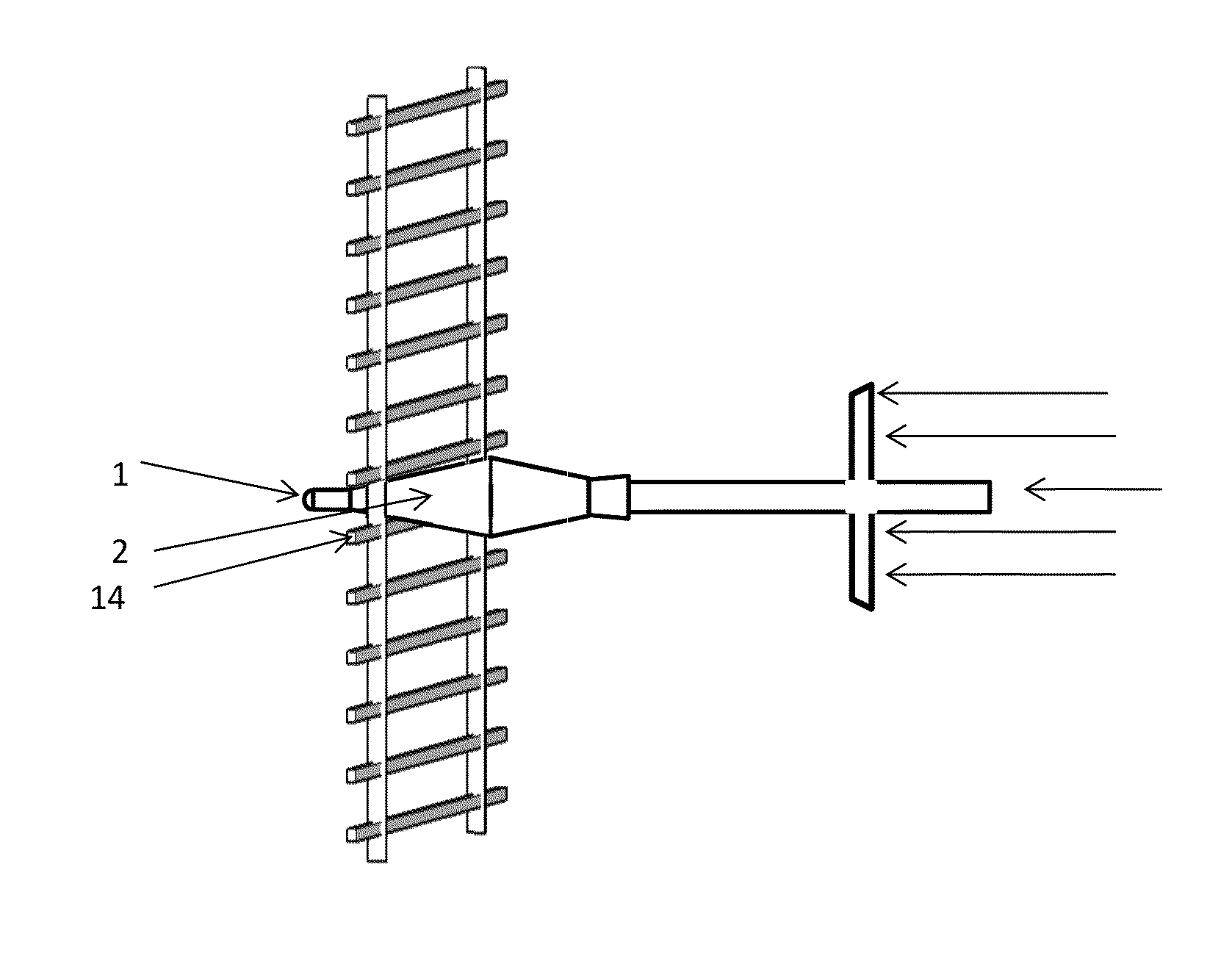

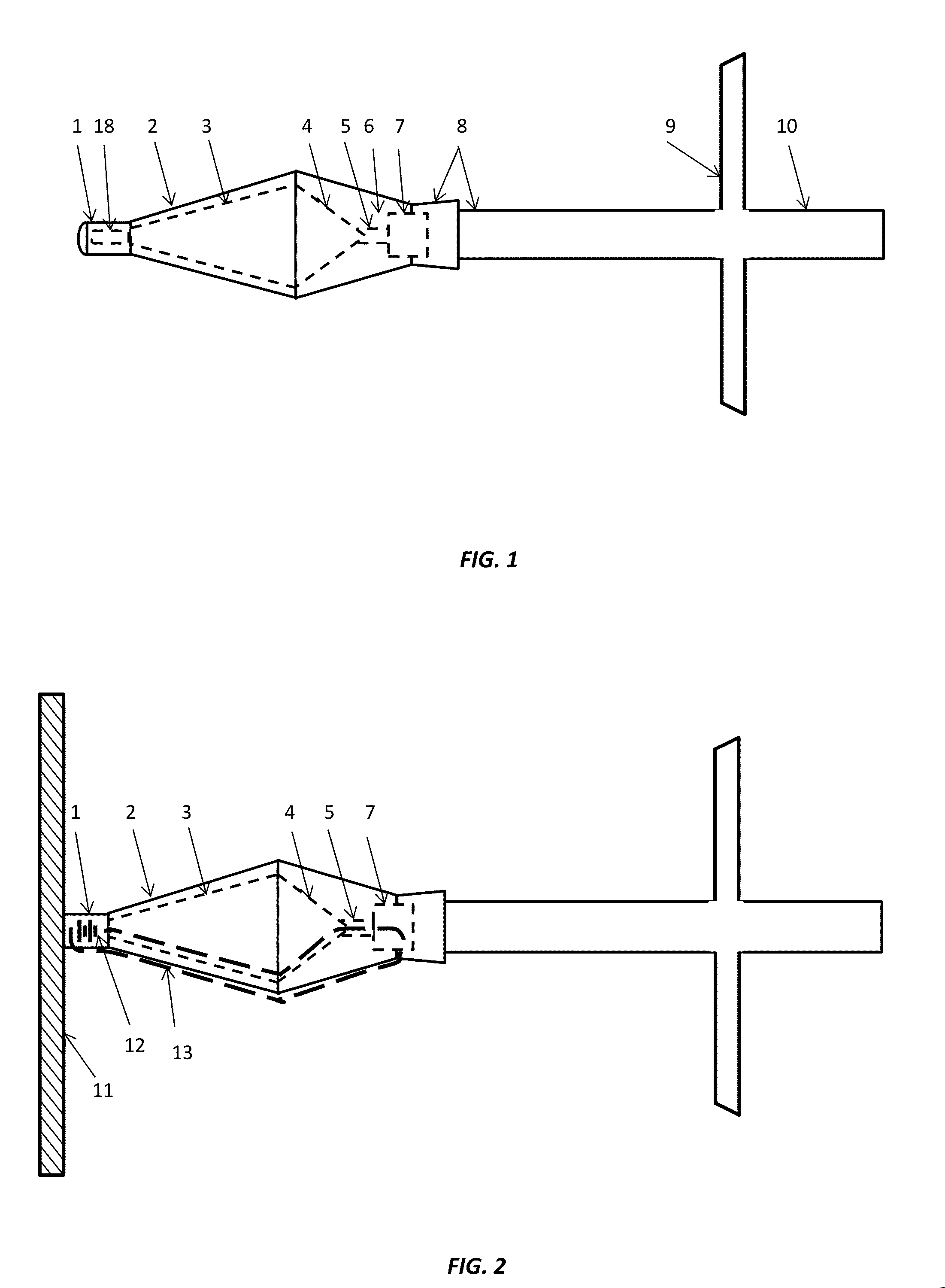

Ultra Light Bar Armor

InactiveUS20150020678A1High strengthAvoid spreadingArmoured vehiclesArmour platesElectricityCross connection

Bar armor currently provides a means of providing partial protection of vehicles and structures against certain types of Rocket Propelled Grenades (RPGs). However, the individual bars must provide enough strength to cut through or deform the outer ogive of an RPG and cause electrical contact with the inner ogive. This in turn imposes constraints on the overall effectiveness of the system and how light it can be made. These constraints can be eased by providing cross-attachments for the bars, provided that the cross-attachments themselves are of low enough density and sufficient frangibility to avoid detonating the RPG when they are struck by the RPG nosepiece, which contains a piezoelectric element that causes the fuse of the RPG to function. Through this means, bar armor can be made lighter, more effective, and easier to see through.

Owner:HAFER THOMAS FREDERICK

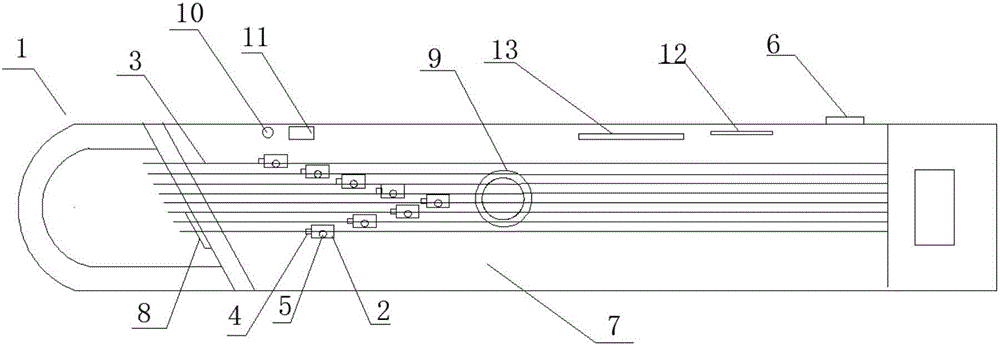

Guzheng (a 21-or 25-stringed plucked instrument) with teaching function

InactiveCN106531127AImprove accuracyRaise the pitchStringed musical instrumentsMusicBiomedical engineeringPressure sensor

Owner:刘可

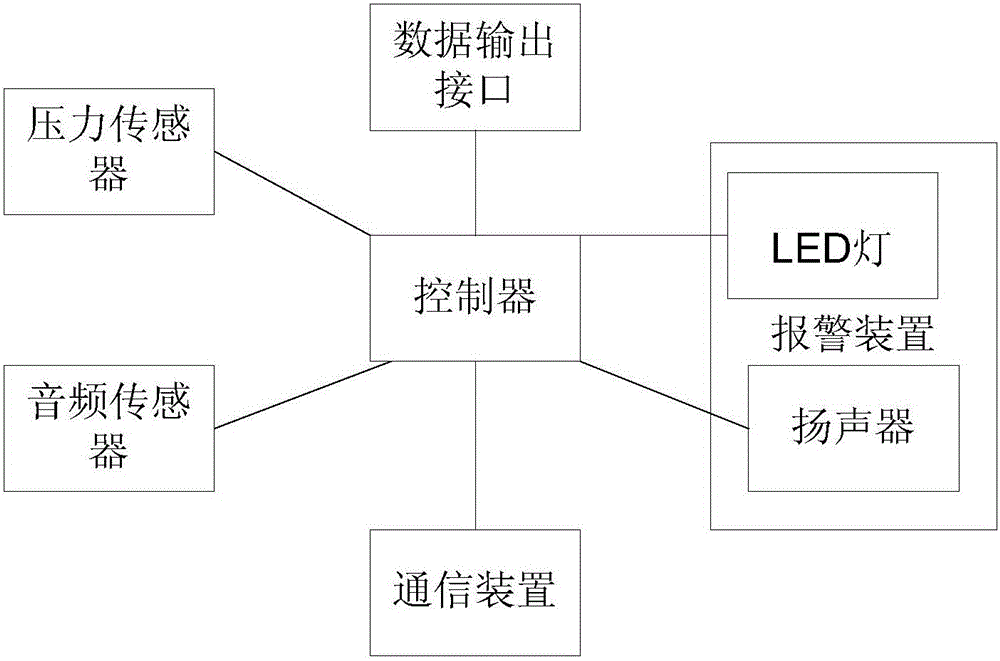

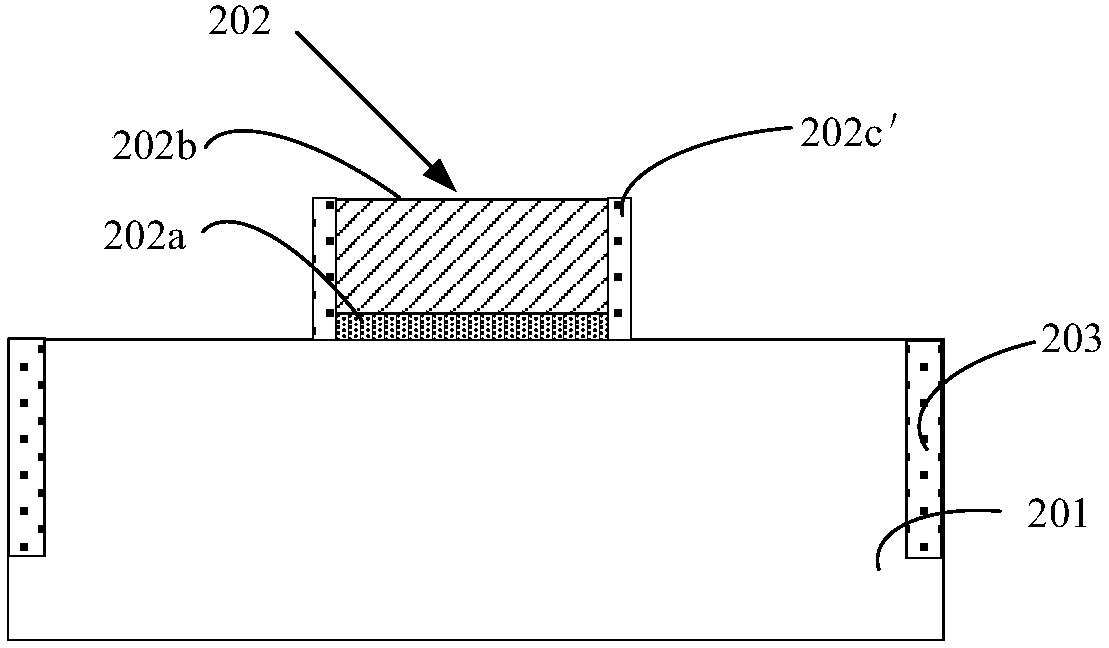

Slapper energy change element structure and preparation method thereof

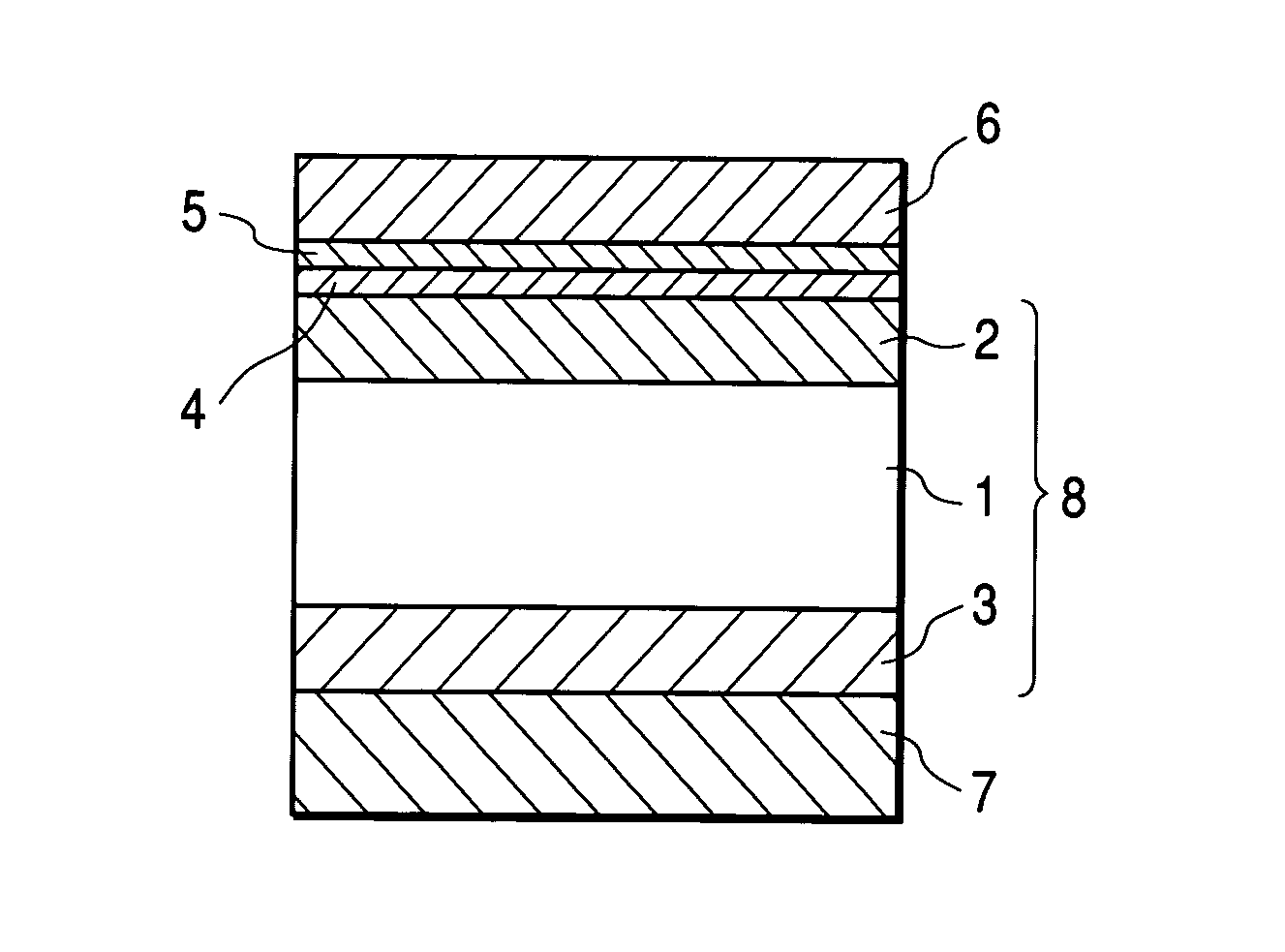

ActiveCN106482591AAvoid lateral spreadImprove conversion efficiencyLamination ancillary operationsSynthetic resin layered productsEngineeringEnergy conversion efficiency

The invention discloses a slapper energy change element structure and a preparation method thereof. The slapper energy change element structure comprises a shear layer, a fly layer, an explosive foil and a substrate, wherein the shear layer, the fly layer, the explosive foil and the substrate are laminated and bonded in sequence from top to bottom; a plurality of conductive through holes are formed in the substrate in a penetrating manner; the hole surfaces of the upper ends of the conductive through holes are in contact with the lower surface of the explosive foil; the hole surfaces of the lower ends of the conductive through holes are flush with the lower surface of the substrate; a shear through hole is formed in the center of the shear layer in a penetrating manner; the upper hole surface of the shear through hole is flush with the upper surface of the shear layer; the lower hole surface of the shear through hole is in contact with the upper surface of the fly layer; and the fly layer is made of a polyimide material. By lamination and bonding of the shear layer, the fly layer, the explosive foil and the substrate in sequence from top to bottom, contact of the molecular layers of the substrate, the explosive foil and the fly layer is realized, and transverse diffusion of plasmas is prevented, so that the energy conversion efficiency is improved.

Owner:INST OF CHEM MATERIAL CHINA ACADEMY OF ENG PHYSICS

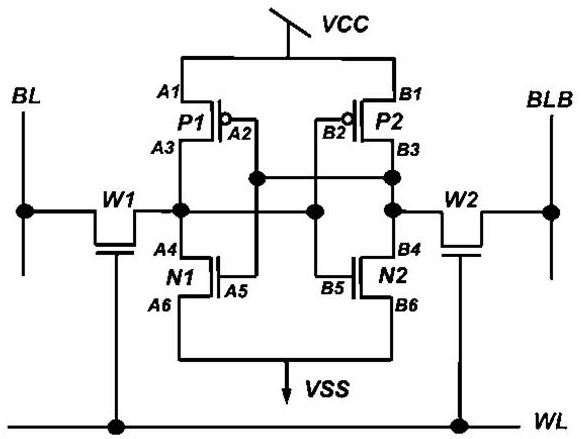

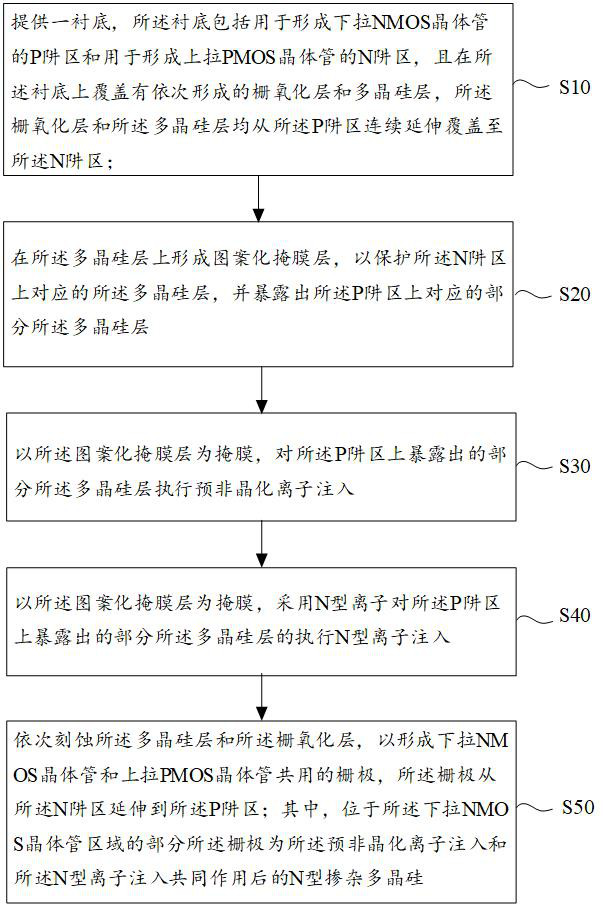

Preparation method of static random access memory

ActiveCN112635403AEnhanced inhibitory effectImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryPhysical chemistry

The invention provides a preparation method of a static random access memory. According to the preparation method, pre-amorphization ion implantation is performed on a part of a polycrystalline silicon layer before N-type ion implantation is performed, so that the condition that implanted ions longitudinally diffuse, penetrates a gate oxide layer and enters a P well region due to overlarge grain size in the polycrystalline silicon layer in the N-type ion implantation process can be prevented, so that the reduction of the threshold voltage of a subsequently formed pull-down NMOS transistor caused by the above condition can be avoided, and the voltage mismatch can be avoided; meanwhile, the inhibition effect of N-type ion implantation on a polycrystalline depletion effect is improved; and besides, a pull-up PMOS transistor and a pull-down NMOS transistor which are formed subsequently share the same gate structure, so that transverse diffusion of ions in the N-type ion implantation can be inhibited by executing the pre-amorphization ion implantation, the influence of the N-type ion implantation on the threshold voltage of the pull-up PMOS transistor formed subsequently is avoided, and the problem of voltage mismatch is relieved, and device performance can be improved. The same mask is used for two times of ion implantation, and therefore, the preparation cost is low, and the process is simple.

Owner:晶芯成(北京)科技有限公司

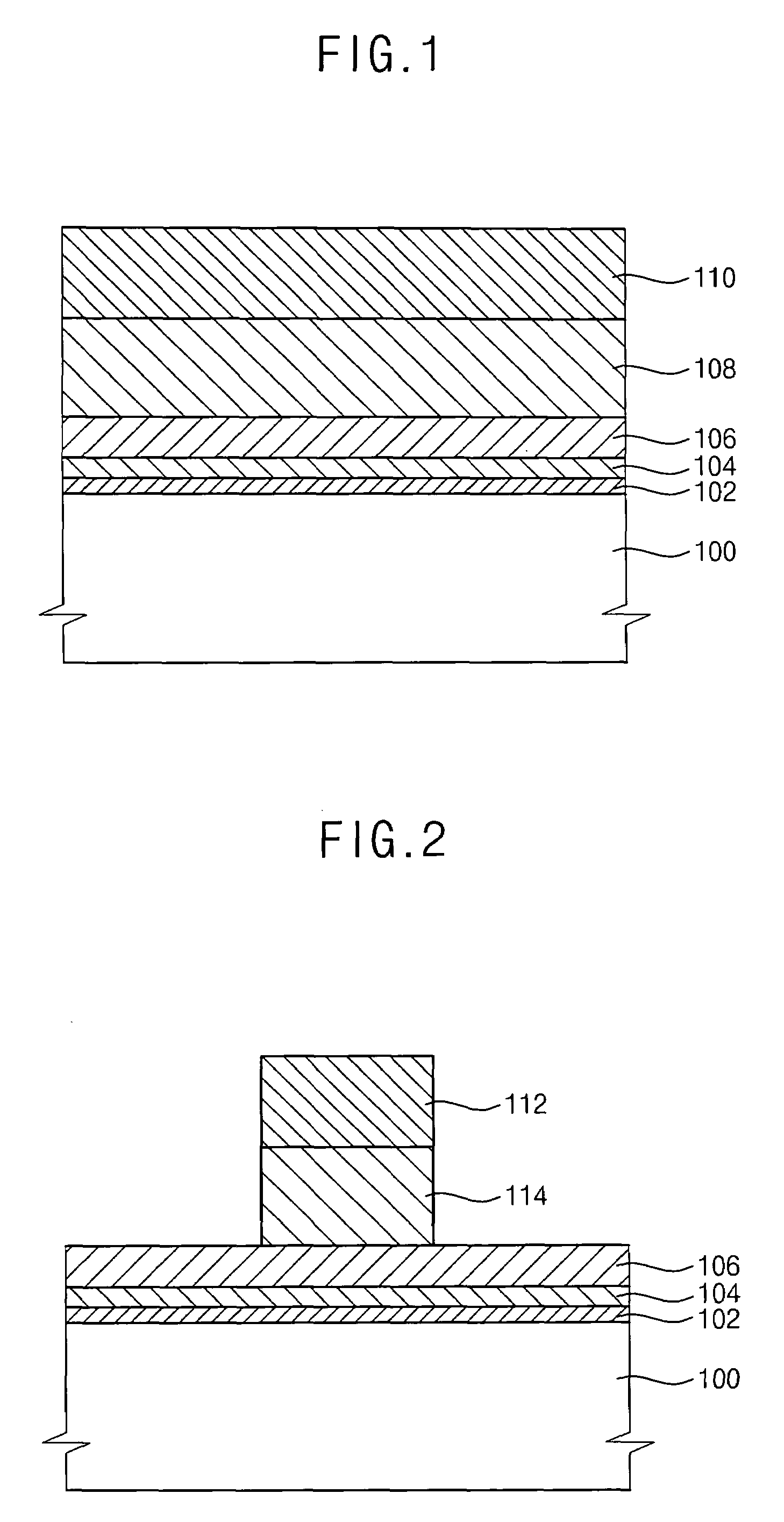

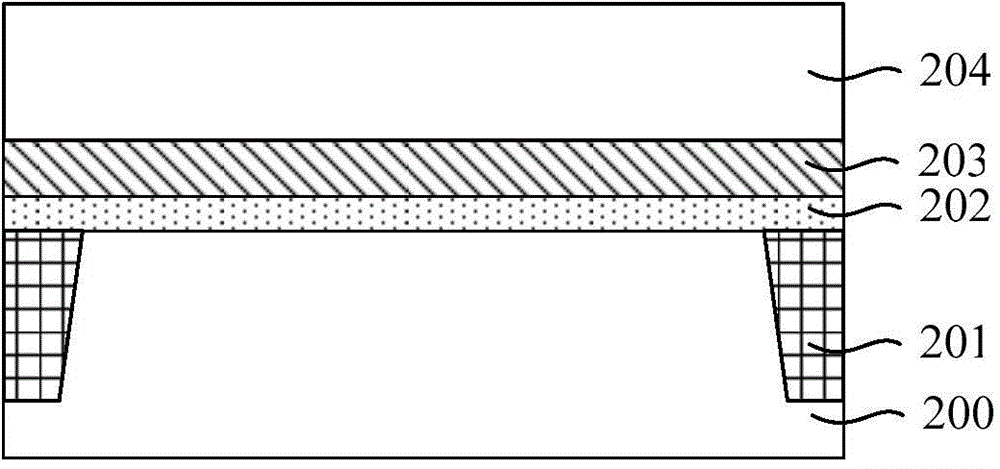

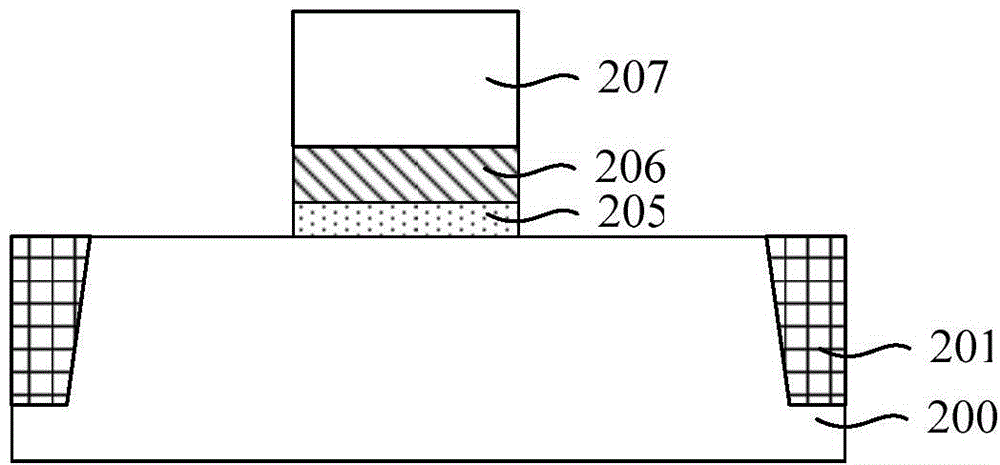

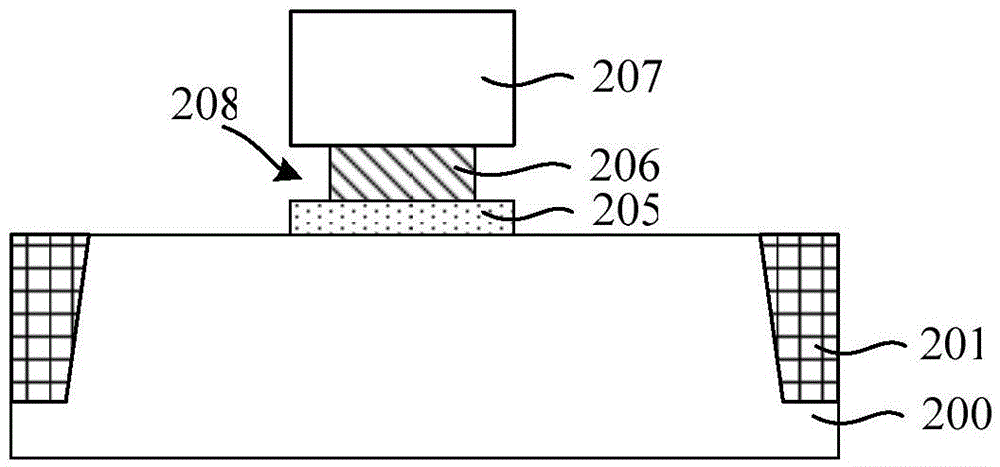

Formation method of transistor

InactiveCN106033730AHigh positioning accuracyAvoid lateral spreadSemiconductor/solid-state device manufacturingPhysicsShort-channel effect

A method for forming a transistor, comprising: providing a semiconductor substrate, forming a gate dielectric layer and a gate electrode on the gate dielectric layer on the semiconductor substrate, and the gate electrode includes a first gate electrode on the gate dielectric layer layer and a second gate layer located on the first gate layer, the material of the first gate layer is different from the material of the second gate layer; a part of the width is etched along the sidewall of the first gate layer Openings are formed on both sides of the remaining first gate layer at the bottom of the second gate layer; after the openings are formed, the first ion implantation is performed using the gate electrode as a mask, and on both sides of the gate electrode A lightly doped region is formed in the semiconductor substrate; after the opening is formed, the gate electrode is used as a mask to perform an angled second ion implantation, and a pocket-shaped implanted region is formed in the semiconductor substrate at the bottom of the gate electrode. The pocket-shaped implanted region The doping type of the region is opposite to that of the shallowly doped region. The transistor formed by the method of the invention can better prevent the generation of short channel effect.

Owner:SEMICON MFG INT (SHANGHAI) CORP

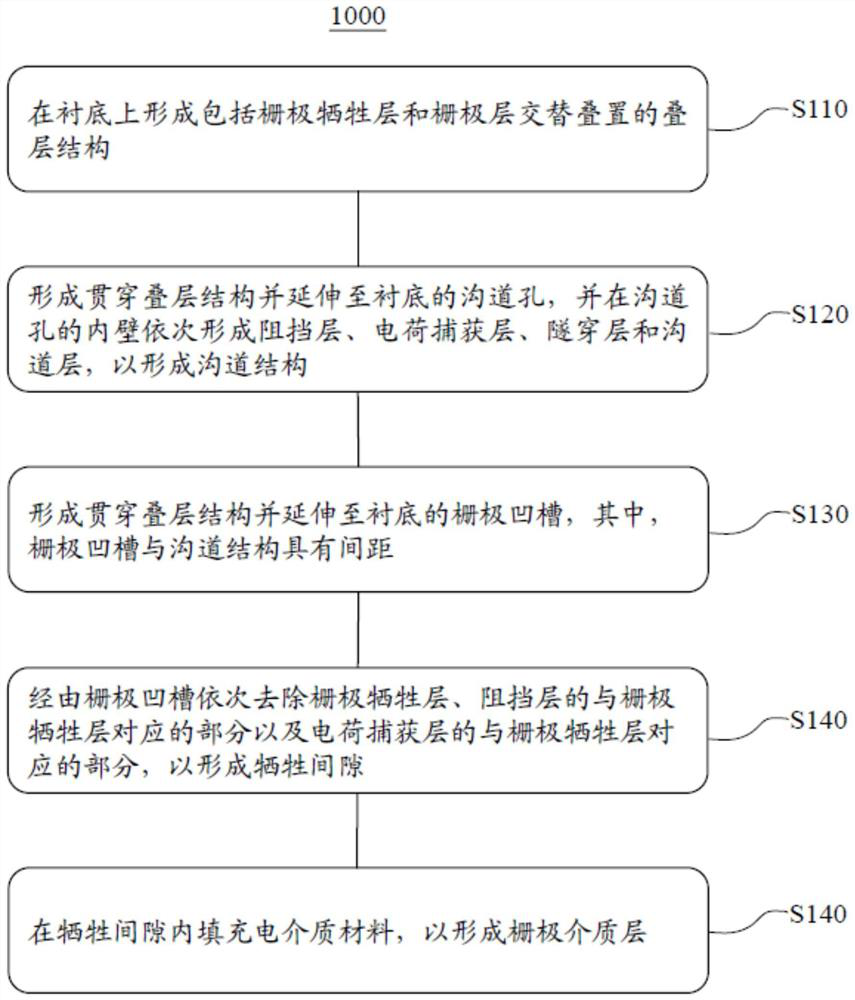

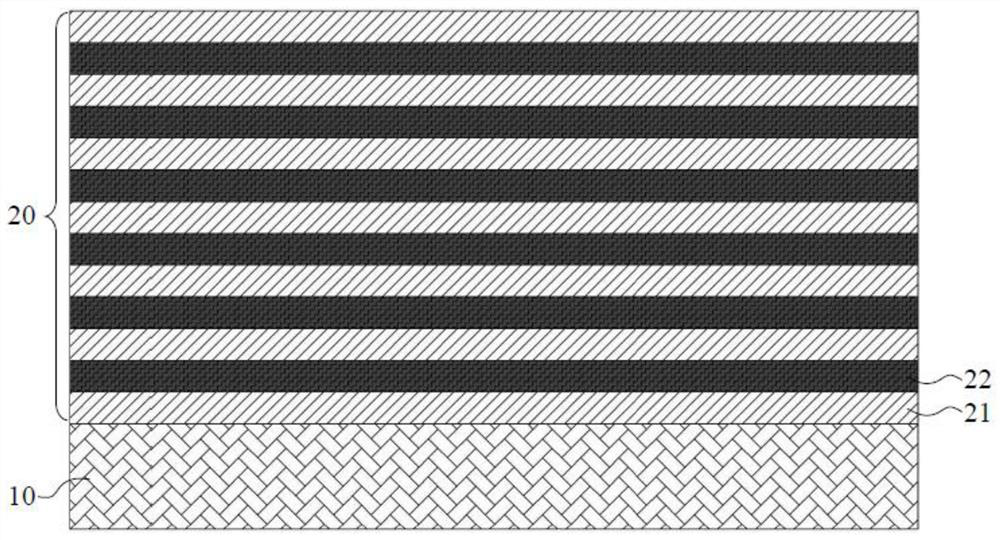

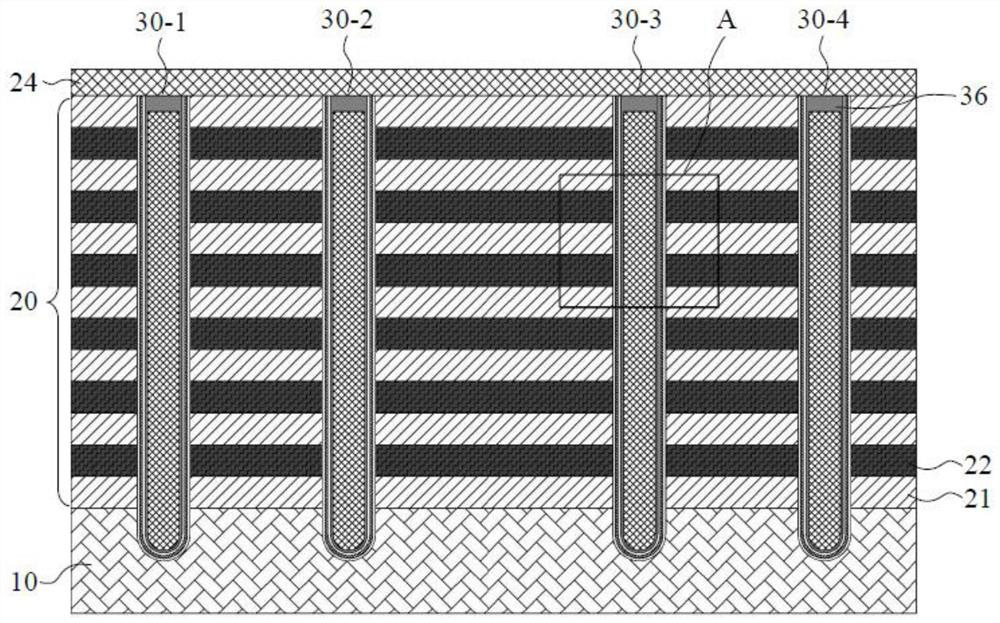

Three-dimensional memory and preparation method thereof

PendingCN112820736AImprove storage retention characteristicsAvoid lateral spreadSolid-state devicesSemiconductor devicesGate dielectricPhysics

The invention provides a three-dimensional memory and a preparation method thereof. The method comprises the following steps: forming a laminated structure on a substrate, wherein the laminated structure comprises gate sacrificial layers and gate layers which are alternately laminated; forming a channel hole penetrating through the laminated structure and extending to the substrate, and sequentially forming a barrier layer, a charge capture layer, a tunneling layer and a channel layer on the inner wall of the channel hole to form a channel structure; forming a gate groove penetrating through the laminated structure and extending to the substrate, and forming a gap between the gate groove and the channel structure; sequentially removing the gate sacrificial layer, the part, corresponding to the gate sacrificial layer, of the barrier layer and the part, corresponding to the gate sacrificial layer, of the charge trapping layer through the gate groove to form a sacrificial gap; and filling a dielectric material in the sacrificial gap to form a gate dielectric layer. According to the preparation method, lateral diffusion of the charge trapping layer corresponding to each gate layer can be effectively inhibited, and the storage reliability of the charge trapping layer is improved, so that the storage retention characteristic of the prepared three-dimensional memory is improved.

Owner:YANGTZE MEMORY TECH CO LTD

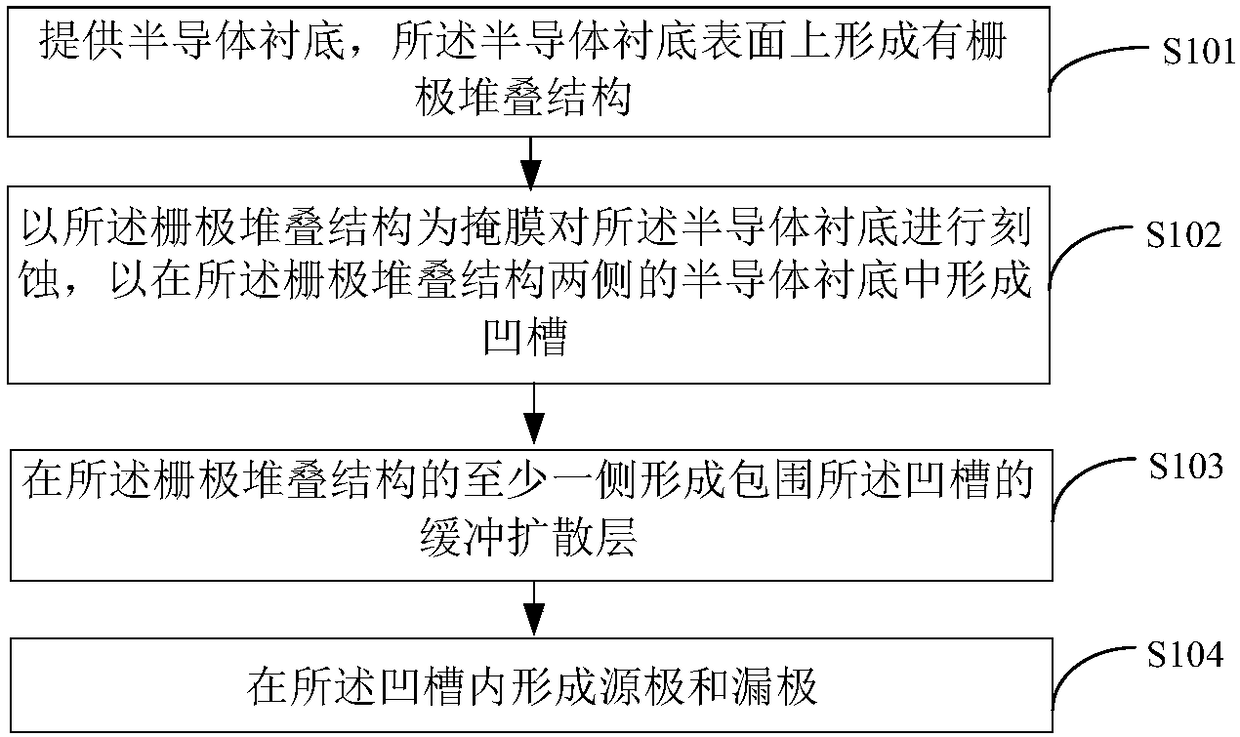

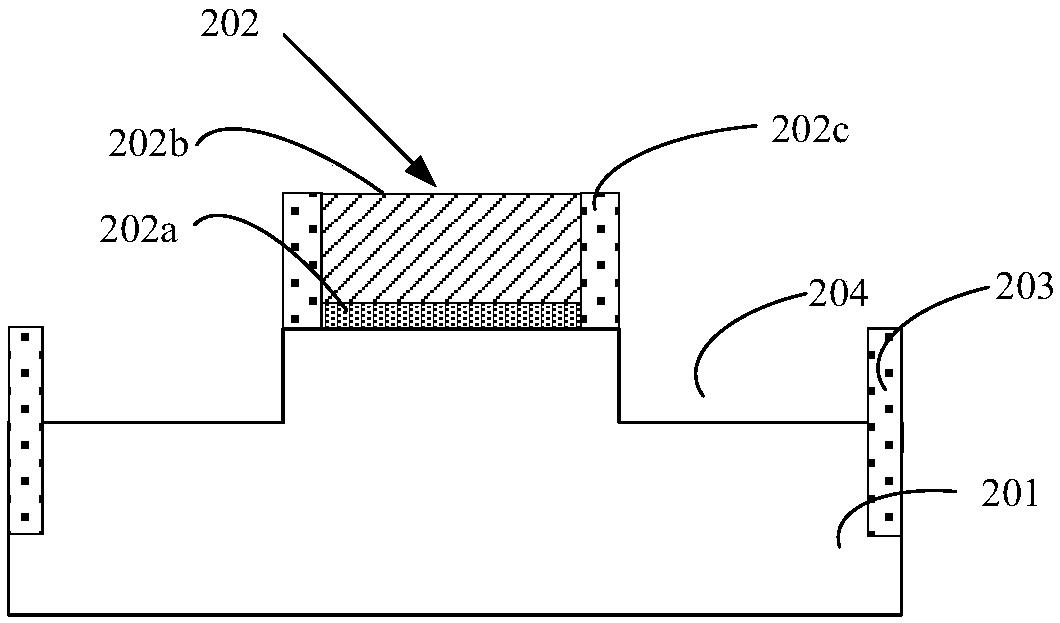

Manufacturing method of semiconductor device

ActiveCN109087859AEvenly distributedAvoid lateral spreadSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

The invention provides a manufacturing method of a semiconductor device. The method includes the following steps: providing a semiconductor substrate, and forming a gate stacking structure on the surface of the semiconductor substrate; etching the semiconductor substrate by using the gate stacking structure as a mask so as to form grooves in the semiconductor substrate on the two sides of the gatestacking structure; forming buffer diffusion layers surrounding the corresponding grooves on at least one side of the gate stacking structure; and forming a source electrode and a drain electrode inthe grooves. According to the method of the invention, the buffer diffusion layers are formed before forming the source electrode and the drain electrode, diffusion of impurities in the buffer diffusion layers drives diffusion of impurities in the source electrode and drain electrode regions in a subsequent annealing process, and so the distribution of the impurities in the source electrode and the drain electrode regions more uniform, the electric field distribution of PN junctions of the source electrode and the drain electrode regions is reduced, lateral diffusion of the impurities can be avoided, lateral short channel effect is controlled, the junction capacitance and the junction leakage current of the source electrode and the drain electrode regions are reduced, and the yield rate and performance of the semiconductor device are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor device forming method

ActiveCN102569089AIncrease spacingImprove leakage performanceSemiconductor/solid-state device manufacturingMetal silicideSemiconductor

The invention provides a semiconductor device forming method, which comprises the steps that: a substrate, a grid structure positioned on the substrate and side walls positioned at two sides of the grid structure are provided; an auxiliary side wall is formed on the surface of the side walls; a metal layer is formed on the surface of the auxiliary side wall and the exposed substrate; and the metal layer is subjected to annealing, metal silicide is formed in the substrate, the auxiliary side wall is used for preventing the metal layer from transversely diffusing into the side walls, and the formation of the metal silicide on the side walls is avoided. The semiconductor device forming method has the advantages that the auxiliary side wall is formed on the side walls, the gap of the metal silicide in the substrate positioned at two sides of the grid structure is enlarged, the electric leakage performance in an enhancement channel of the metal silicide formed through the metal diffusion is avoided, and the electric connection of a source / drain region and a grid electrode is further avoided, so the performance of a semiconductor device is improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP