Patents

Literature

31results about How to "Improve leakage performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

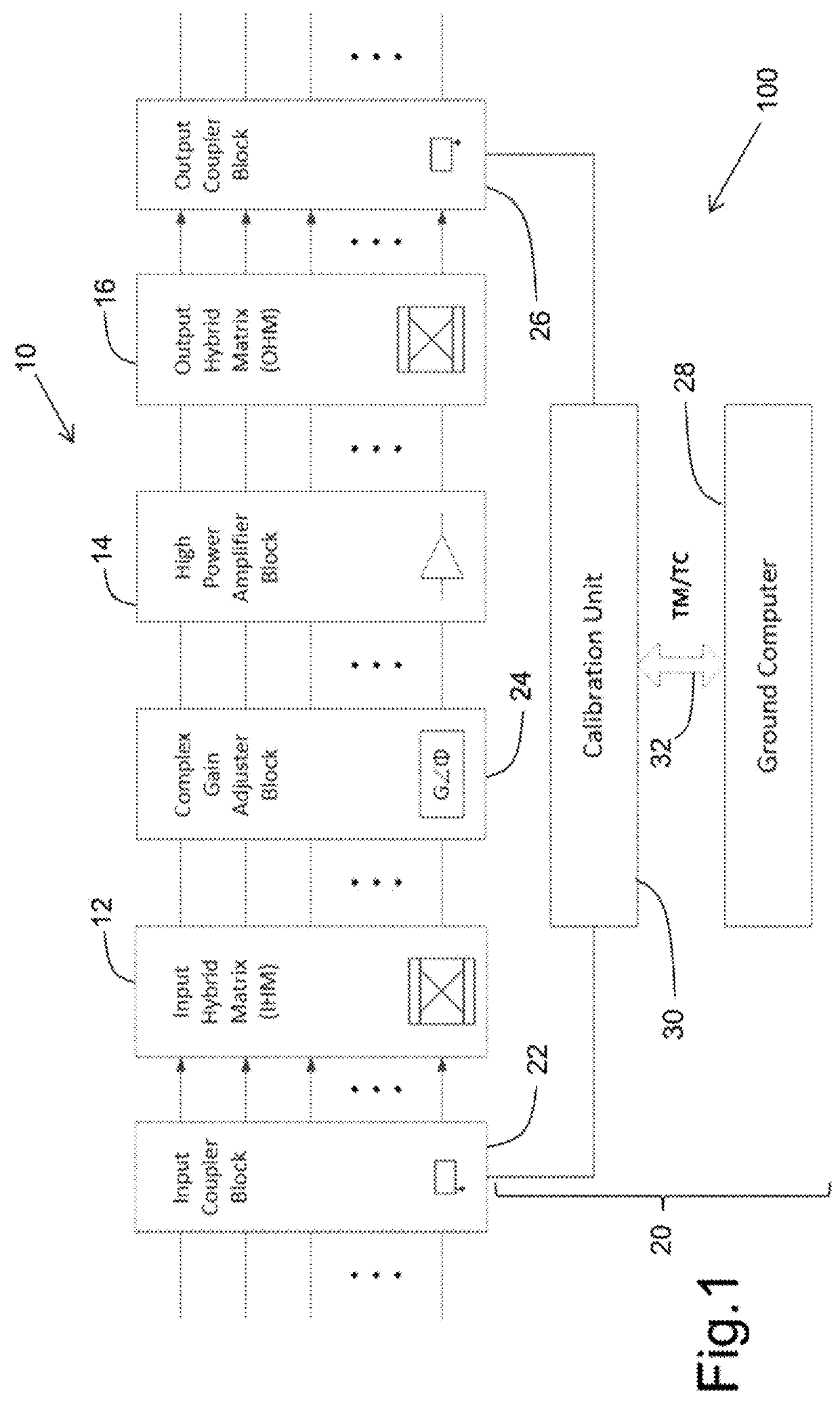

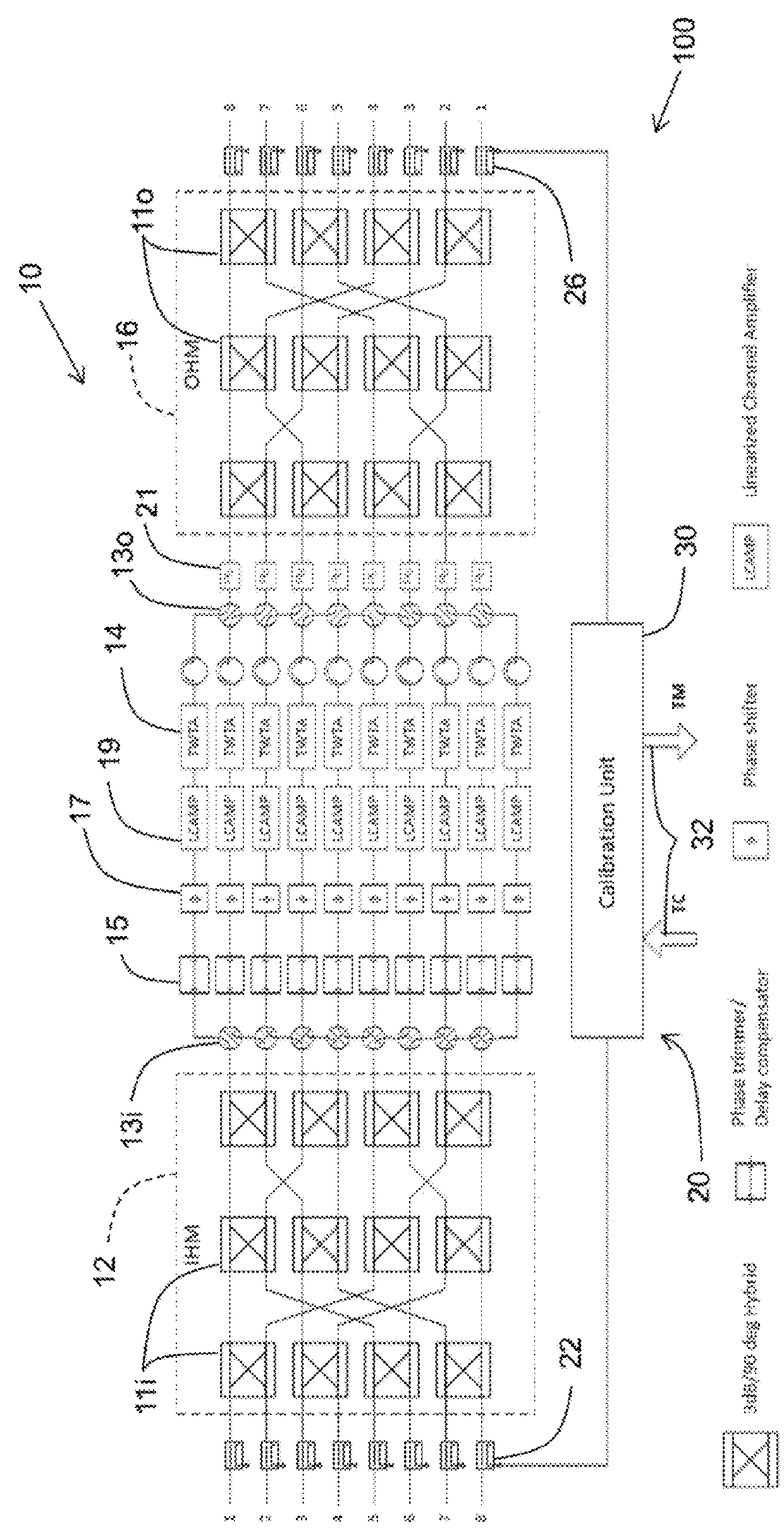

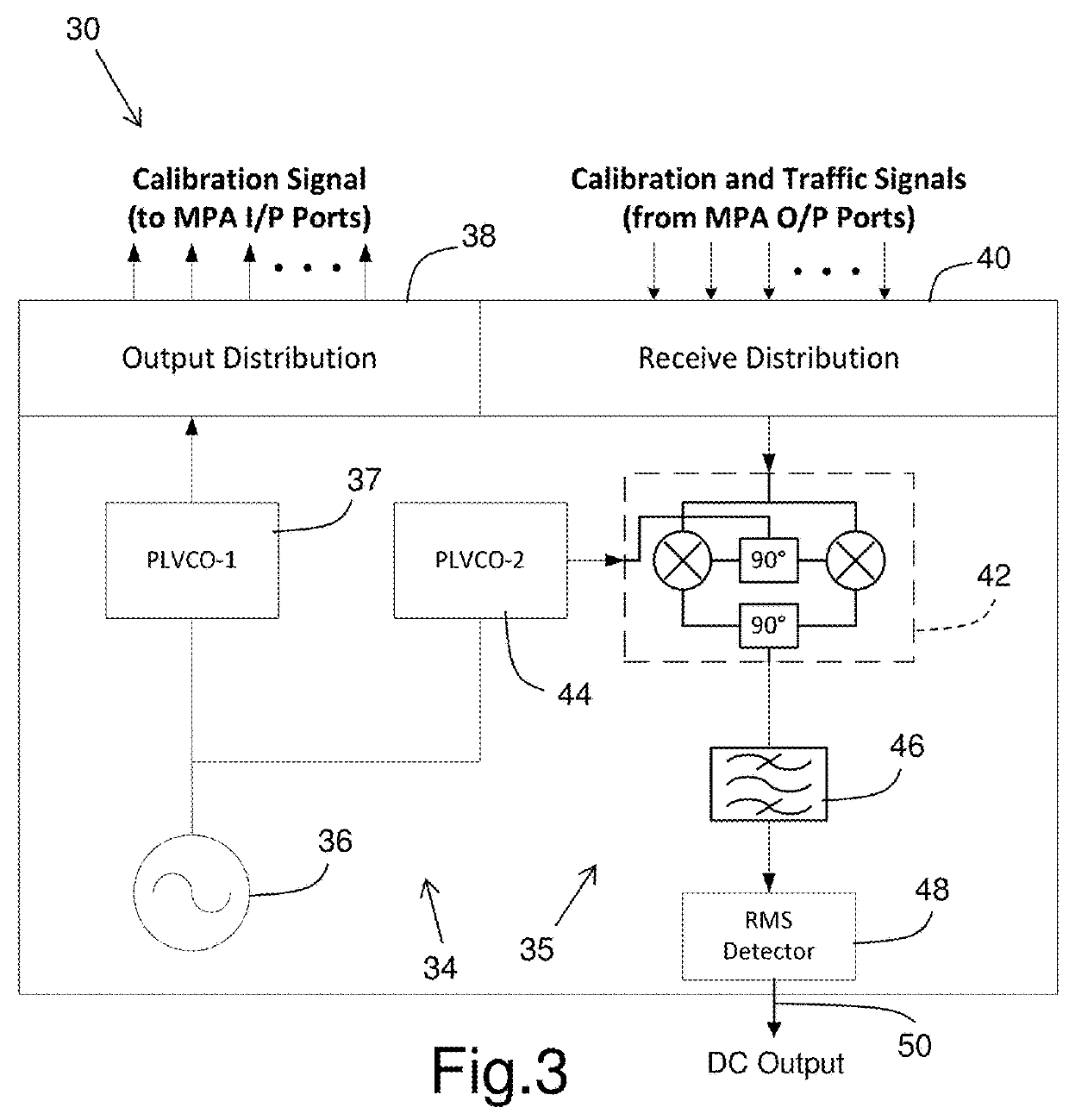

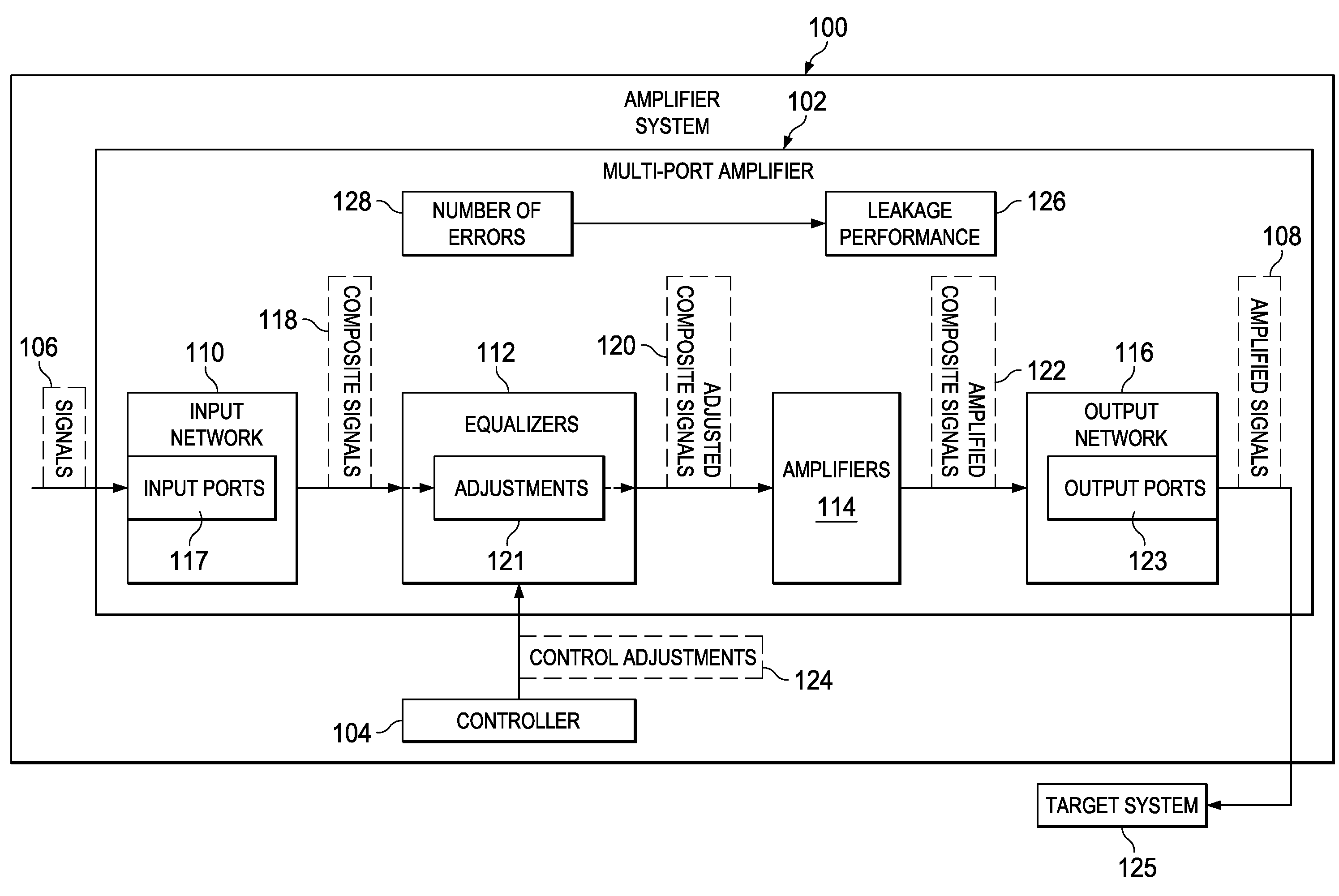

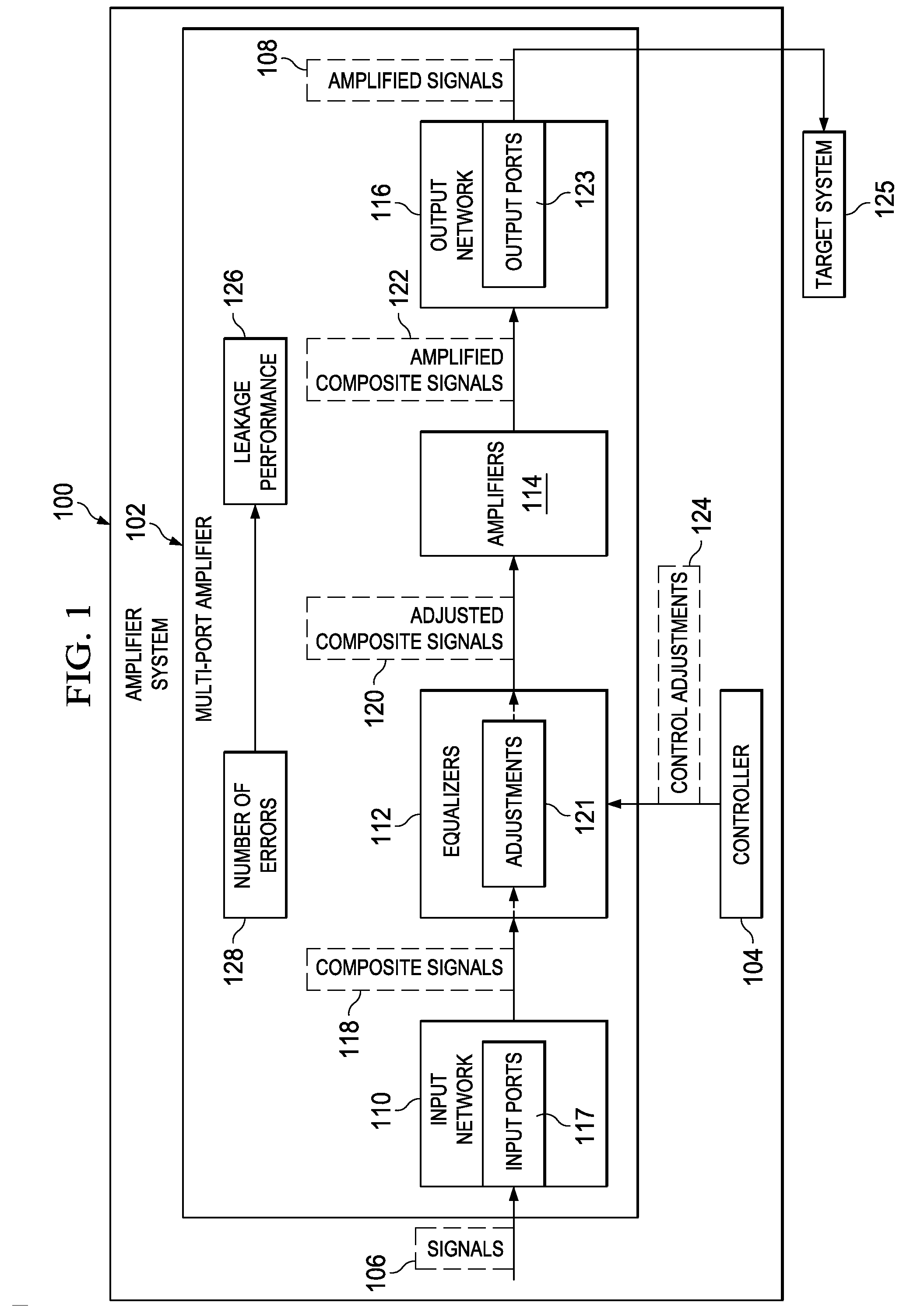

Calibration system and method for optimizing leakage performance of a multi-port amplifier

ActiveUS20180183397A1Improve leakage performanceEliminate the problemAmplifier modifications to reduce non-linear distortionHigh frequency amplifiersAudio power amplifierEngineering

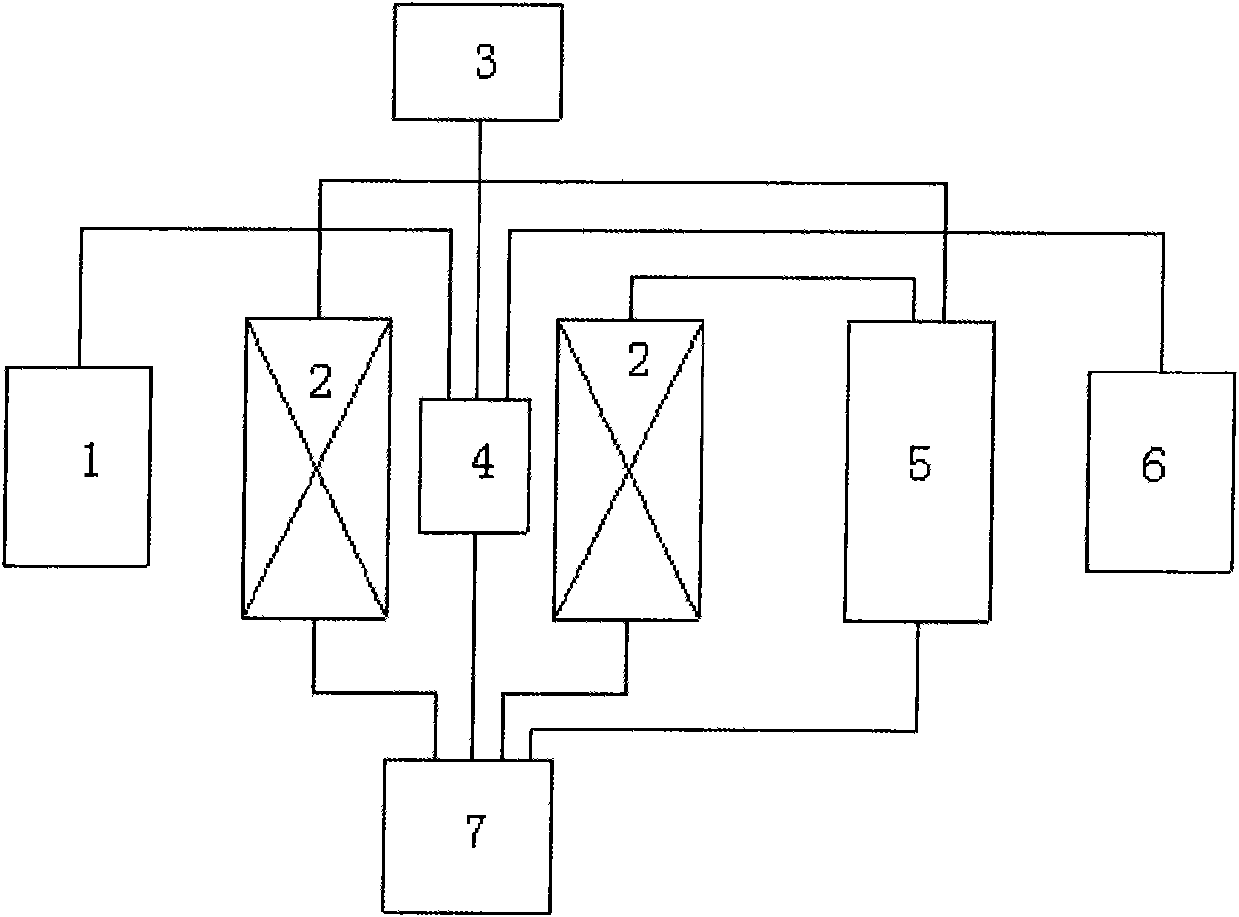

A calibration system of architecture, apparatus, algorithms and method for optimizing leakage performance of a multi-port amplifier (MPA) for satellite communications. The calibration system comprises simple onboard apparatus and generally on-ground algorithms implementation connected via telecommand and telemetry links. The isolation performance of the MPA is monitored by using a commandable frequency generator and a flexible narrowband receiver. The high performance is achieved by direct and efficient optimization of the aggregate leakage of the MPA. The calibration system may be applied but not limited to Ku and Ka-band high throughput satellite systems.

Owner:MACDONALD DETTWILER & ASSOC INC

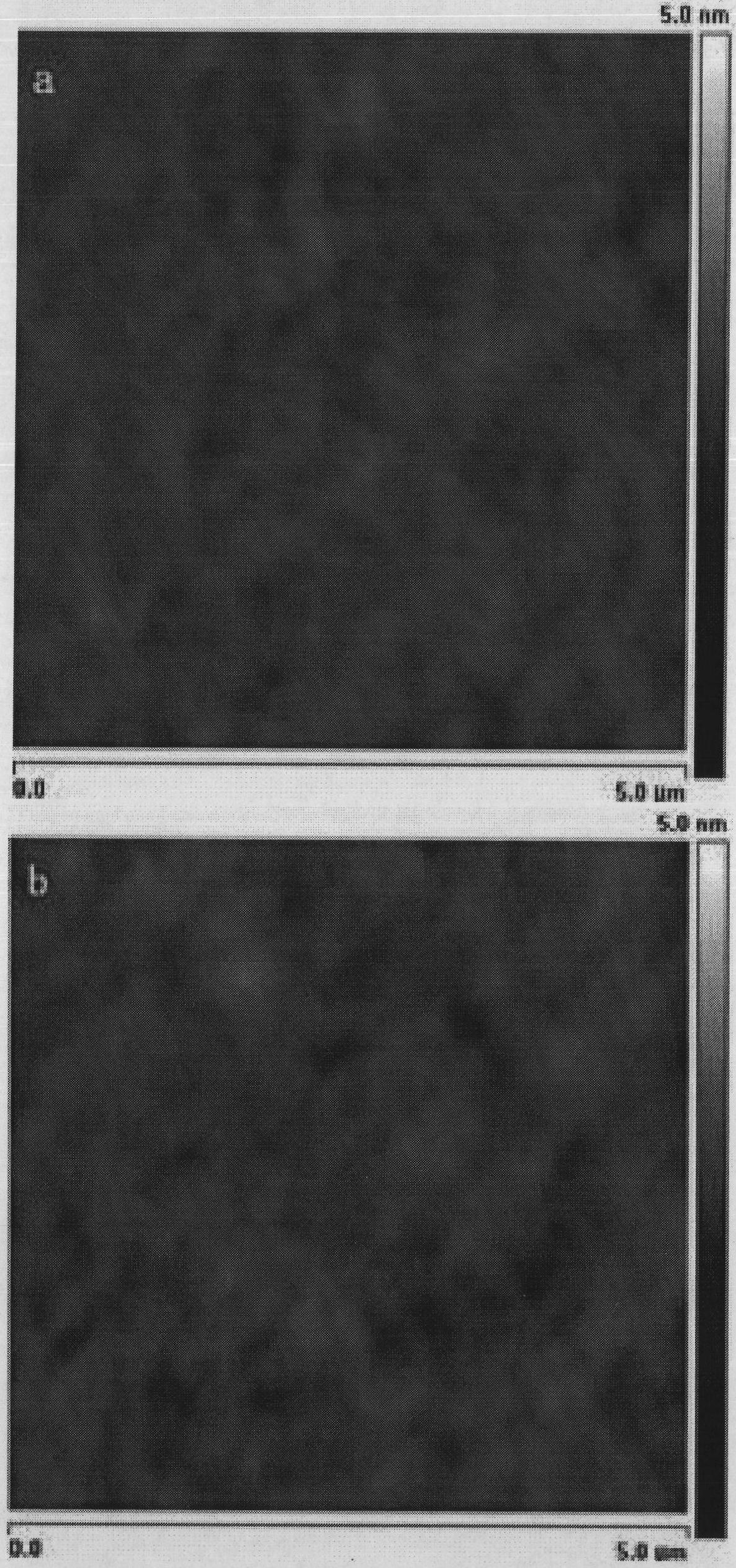

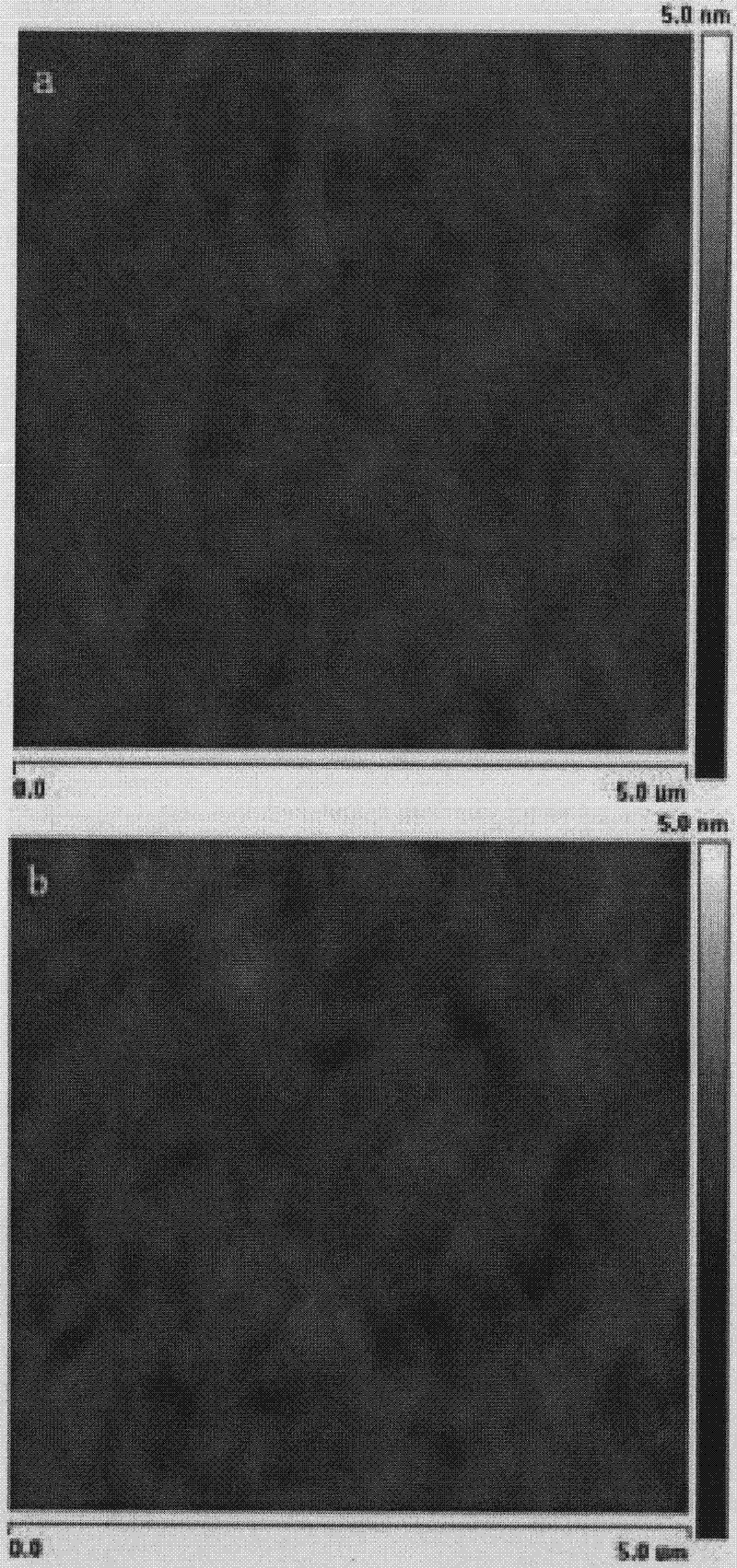

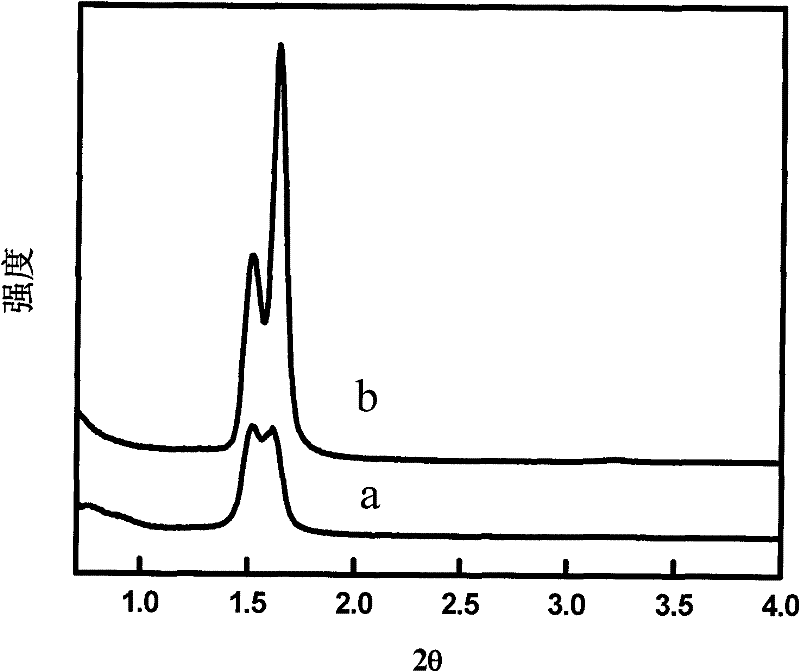

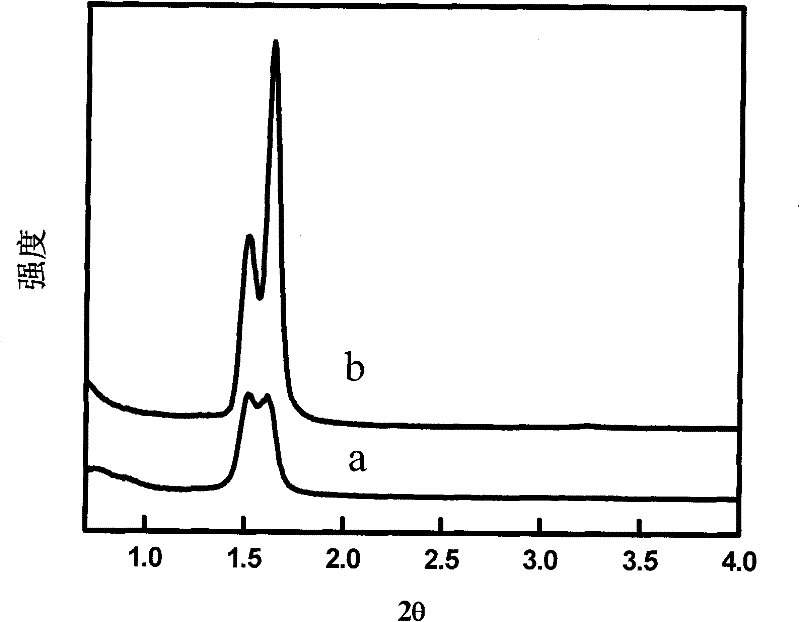

Porous ultra-low dielectric constant material film and preparation method thereof

InactiveCN101789418AReduce roughnessLow dielectric constantSemiconductor/solid-state device detailsSolid-state devicesLeakage current densityThermal stability

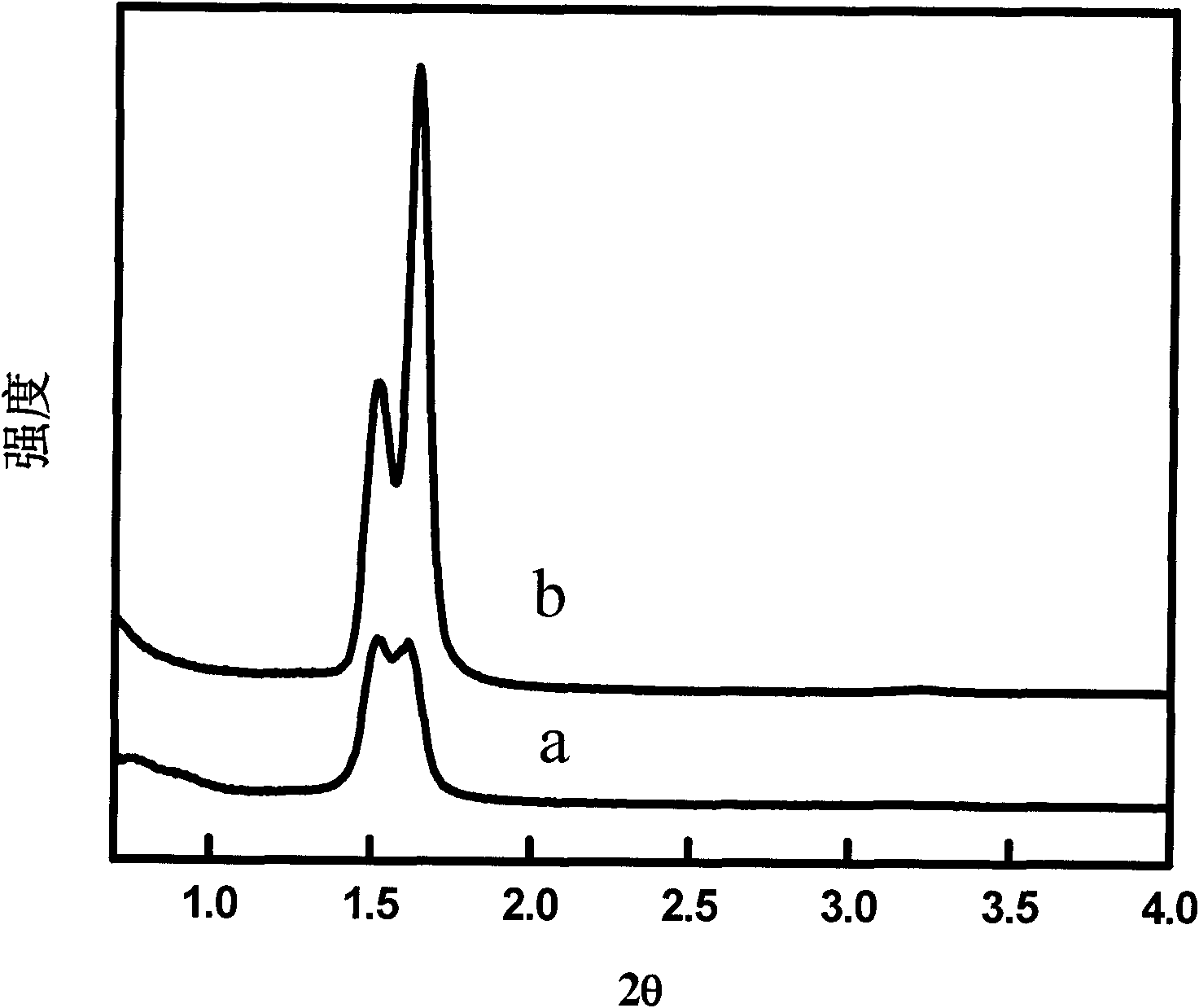

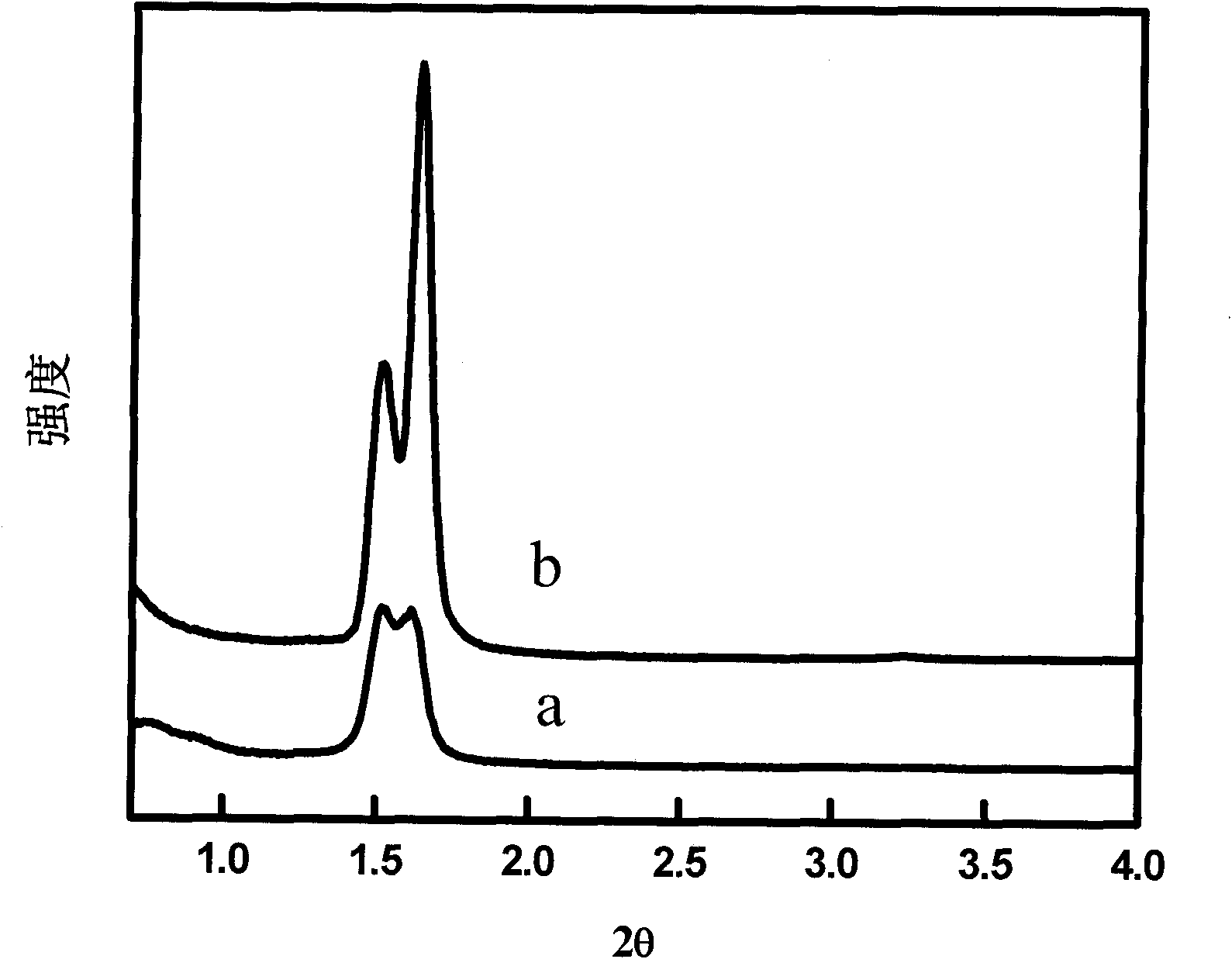

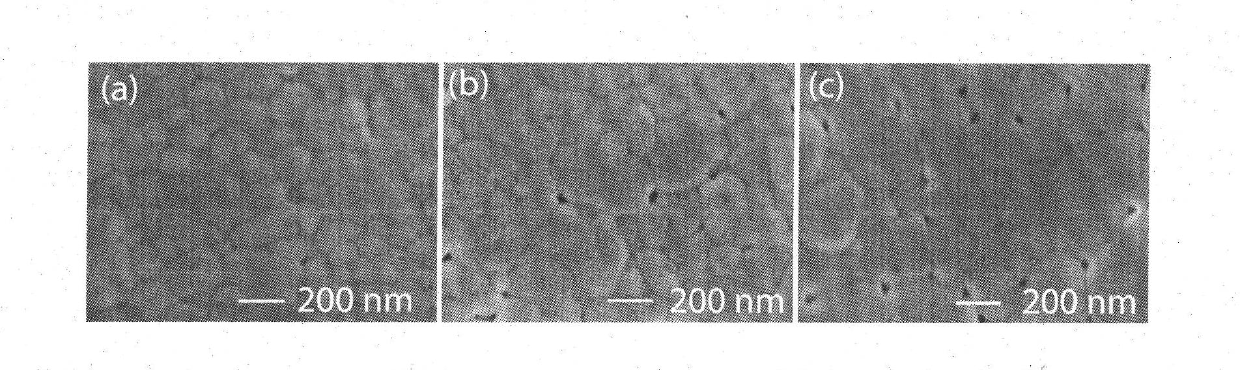

The invention belongs to the technical field of integrated circuit manufacture, in particular to a porous ultra-low dielectric constant material film and a preparation method thereof. The preparation procedures of the invention are as follows: using the sol-gel process, taking organo-siloxane as a precursor, and preparing the porous ultra-low dielectric constant material by controlling the ratio of the precursor to a pore forming agent, a catalyst and a solvent, the solution concentration, and the synthesis, post-treatment and annealing temperatures and the like. The process has simple procedures, and the prepared film has ordered nano-pores, even surface, low roughness and good thermal stability, the dielectric constant is 1.9-2.0, and the leakage current density is from10-8 to10-9A / cm<2>order of magnitude at 1MV / cm.

Owner:FUDAN UNIV

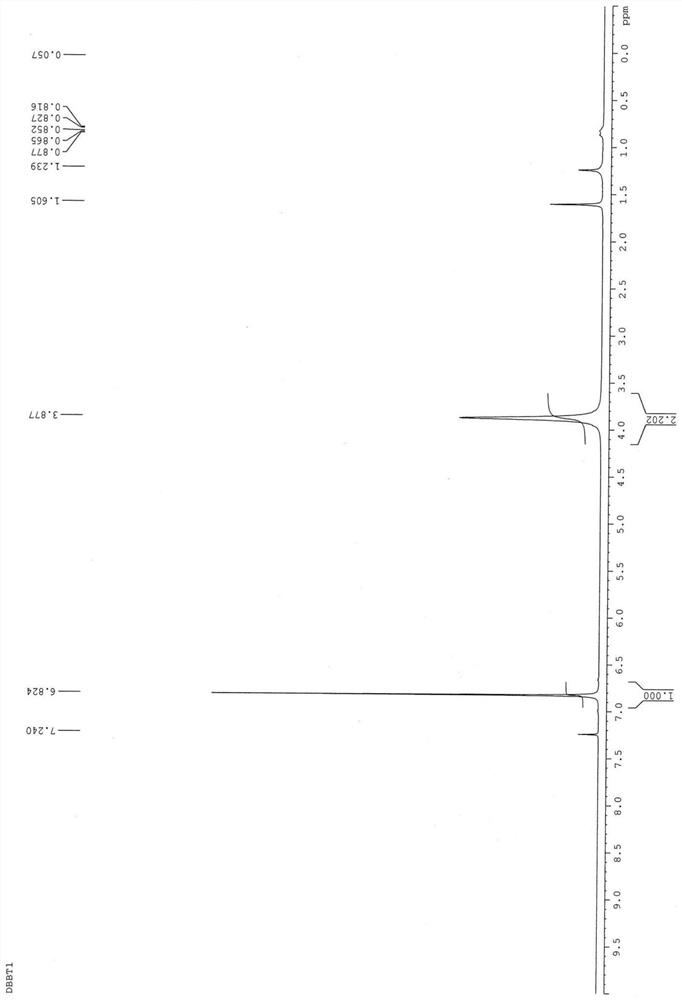

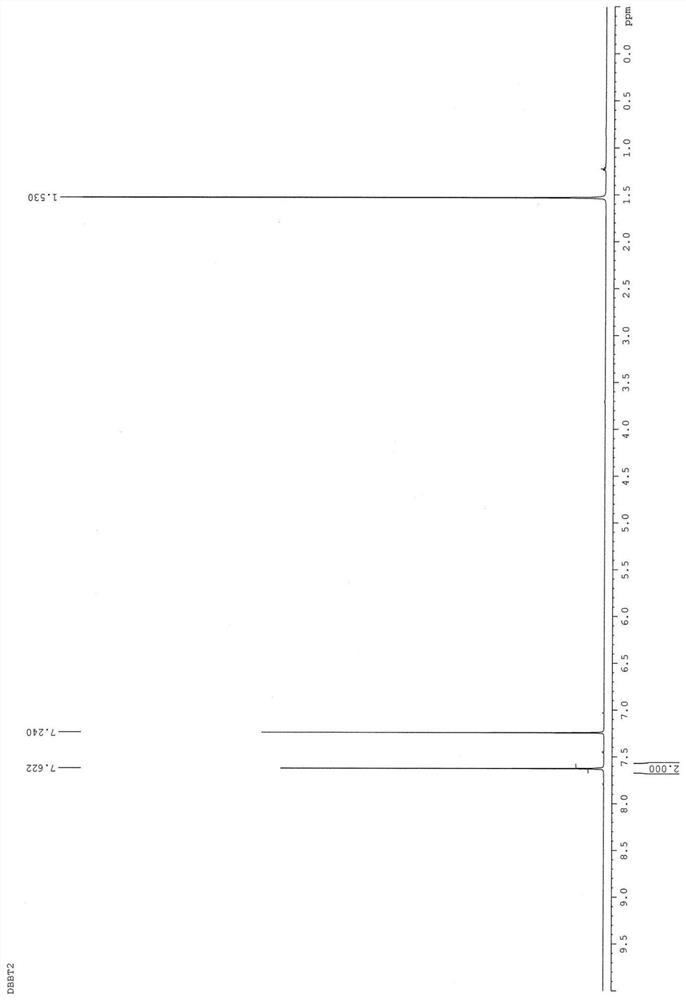

Super-low dielectric constant (k) material thin film and preparation method thereof

InactiveCN102683275AImprove leakage performanceImprove breakdown performanceSemiconductor/solid-state device detailsSolid-state devicesYoung's modulusSolvent

The invention belongs to the technical field of super-large-scale integrated circuits and particularly relates to a super-low k material thin film and a preparation method thereof. The preparation method comprises the following steps of: preparing a sol solution by taking 1,2-bi(triethoxy silicon substrate) ethane (BTEE) as a precursor and adding surfactant P123, HCl, ethanol and deionized water; and then obtaining the super-low k material thin film by adopting a spin coating technology and carrying out post annealing treatment. By virtue of the control on the proportions of the precursor, the surfactant, catalyst and solvent, as well as the control on spin coating film-forming conditions and post treatment conditions, the super-low k material SiCOH thin film, which has the characteristics that the k value is 2.1-2.5, the leakage current density under electric field intensity of 1MV / cm is 1.5*10<-6> to 3.4*10<-9> A / cm<2>, and the Young modulus is 21.05-24.15 Gpa, is obtained.

Owner:FUDAN UNIV

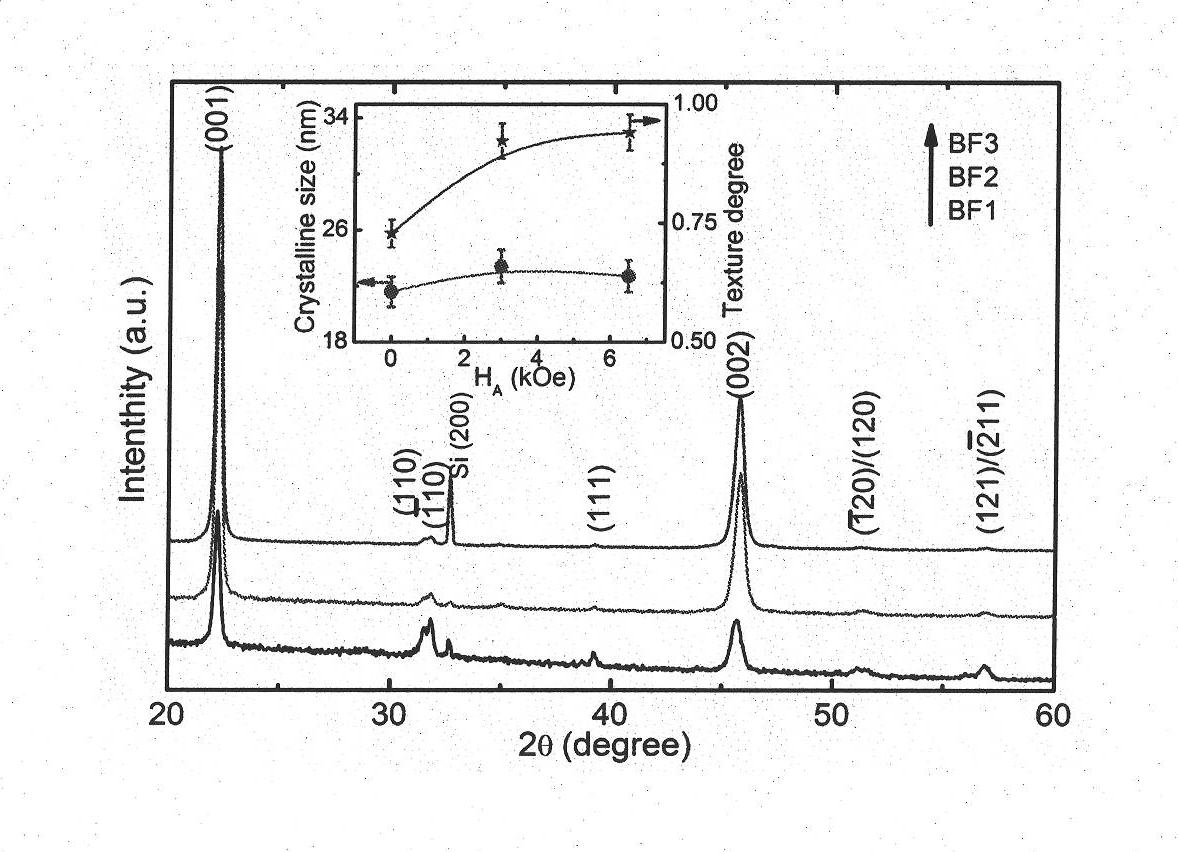

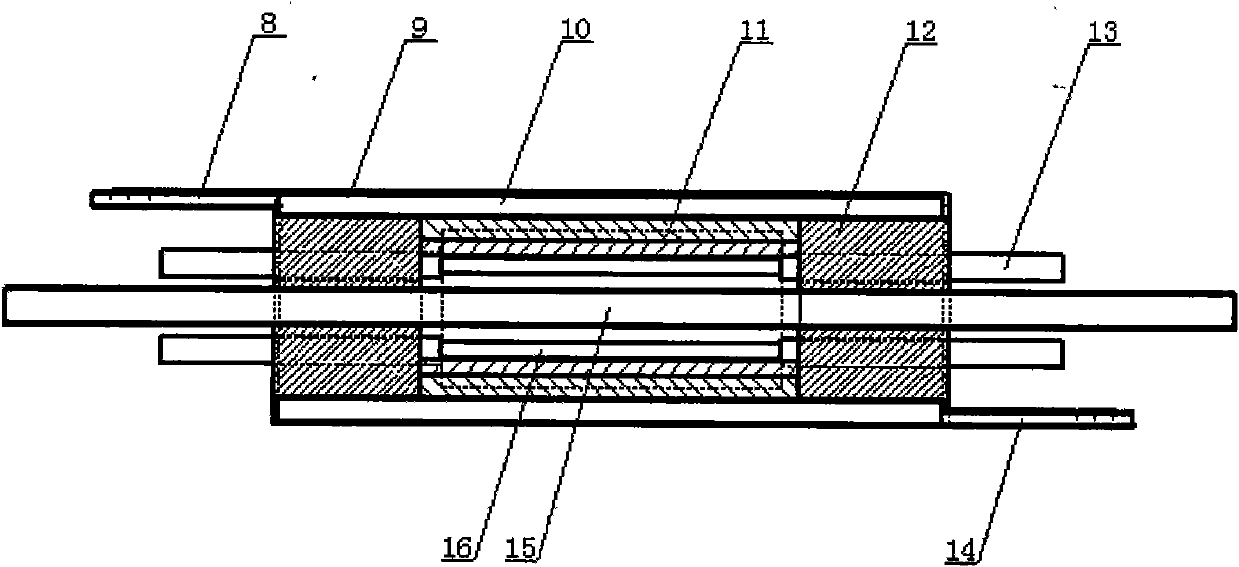

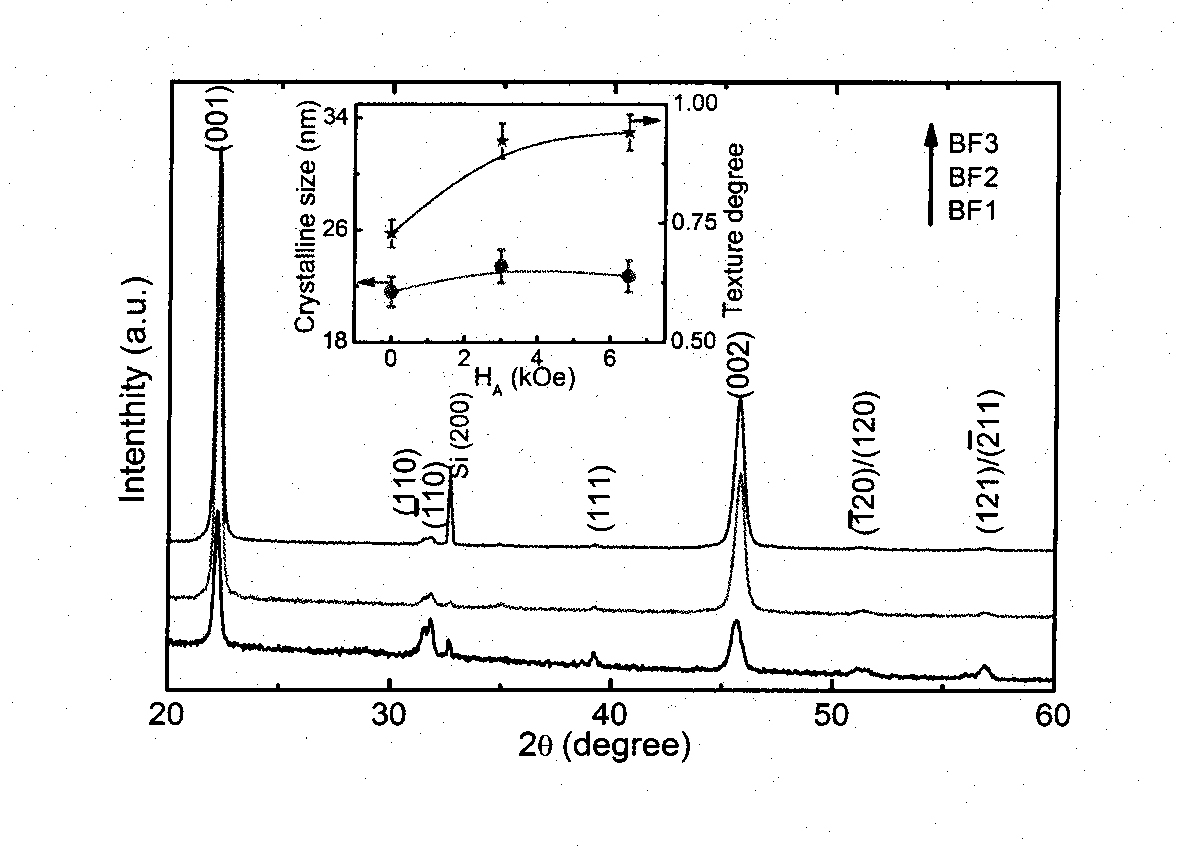

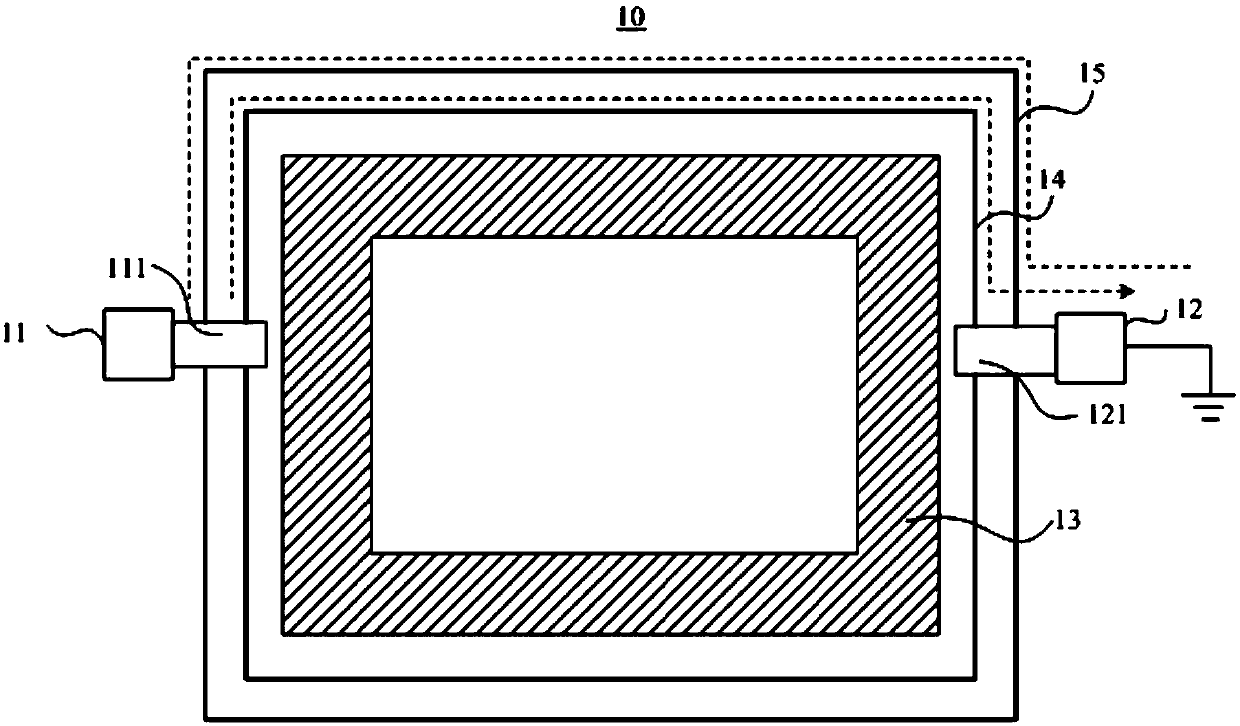

High-temperature heat treatment device under magnetic field and method thereof for preparing bismuth ferrite film

The invention provides a high-temperature heat treatment device under a magnetic field and a method thereof for preparing a bismuth ferrite film. The device comprises a tube type heating furnace, wherein the tube type heating furnace is arranged between magnet pole heads of a direct current water-cooling magnet, the direct current water-cooling magnet is connected with a direct-current magnet power supply and a circulating water-cooling system, the heating cavity of the tube type heating furnace is communicated with a vacuumizing system and an atmosphere control system; the tube type heating furnace is also connected with a temperature controller; the water-cooling cavity is formed by adopting a double-layer nonmagnetic stainless steel material by the shell of the tube type heating furnace; heating bodies are connected in series by four silicon carbide rods; a high-temperature resistant aluminum oxide heat insulating fiber material is used as a heat insulating material; and a high-temperature aluminum oxide ceramic tube or a quartz glass tube is used as a furnace tube. The device has the characteristics of small volume, high magnetic field utilization ratio and heating efficiency,and the like, can be used for carrying out the synthesis and the heat treatment on materials below 2 Tesla of the magnetic field and under the condition of vacuum or atmosphere. The microstructure and the properties of the bismuth ferrite film prepared by the device are improved.

Owner:HEFEI INSTITUTES OF PHYSICAL SCIENCE - CHINESE ACAD OF SCI +1

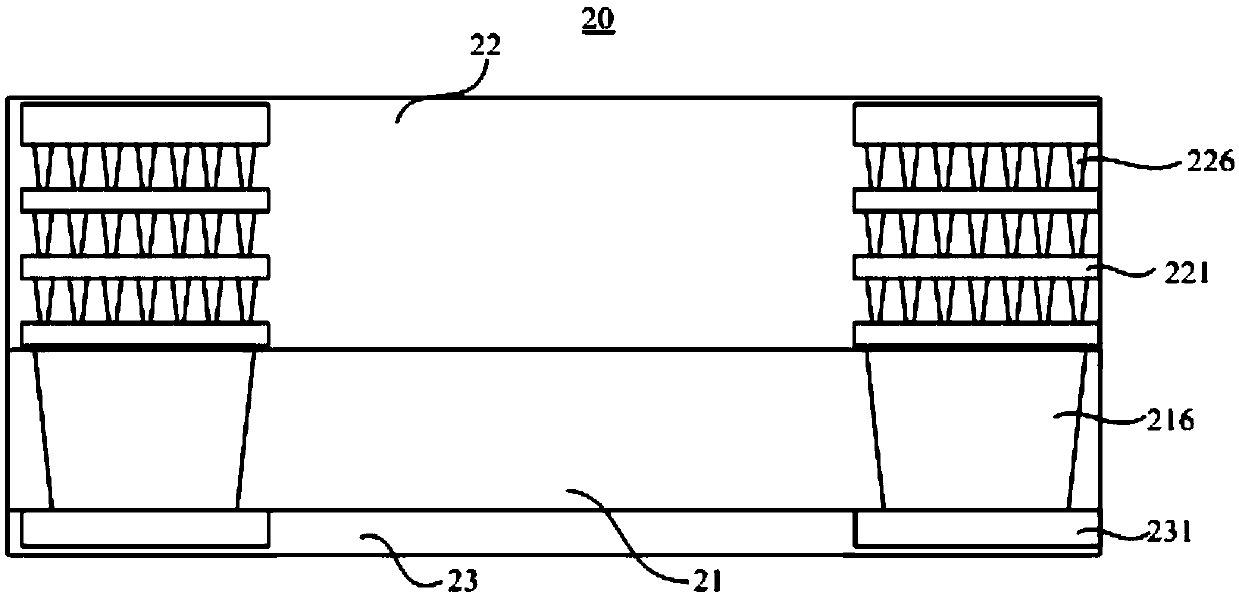

Multi-quantum well layer growing method of micro LED

The invention provides a multi-quantum well layer growing method of a micro LED. A multi-quantum well layer comprises a GaN barrier layer and an In<x>Ga<1-x>N well layer, wherein 0<X<1. Hydrogen is introduced in the process of forming the GaN barrier layer and hydrogen is not introduced in the process of forming the In<x>Ga<1-x>N well layer. According to the invention, by independently introducingthe hydrogen in the GaN barrier layer, the crystallization quality of the barrier layer is improved; stress between the GaN barrier layer and the In<x>Ga<1-x>N well layer; dislocation density is reduced; anti-static electricity ability and anti-electricity leakage performance of an epitaxial layer are improved; by further inserting a blocking layer between the GaN barrier layer and the In<x>Ga<1-x>N well layer, hydrogen possibly generated in the switching processes of growing the GaN barrier layer and the In<x>Ga<1-x>N well layer can be effectively prevented from overflowing to the In<x>Ga<1-x>N well layer to damage the In components; and the blocking layer is capable of allowing the In components to be quite uniformly distributed.

Owner:HEFEI HUIKE JINYANG TECH

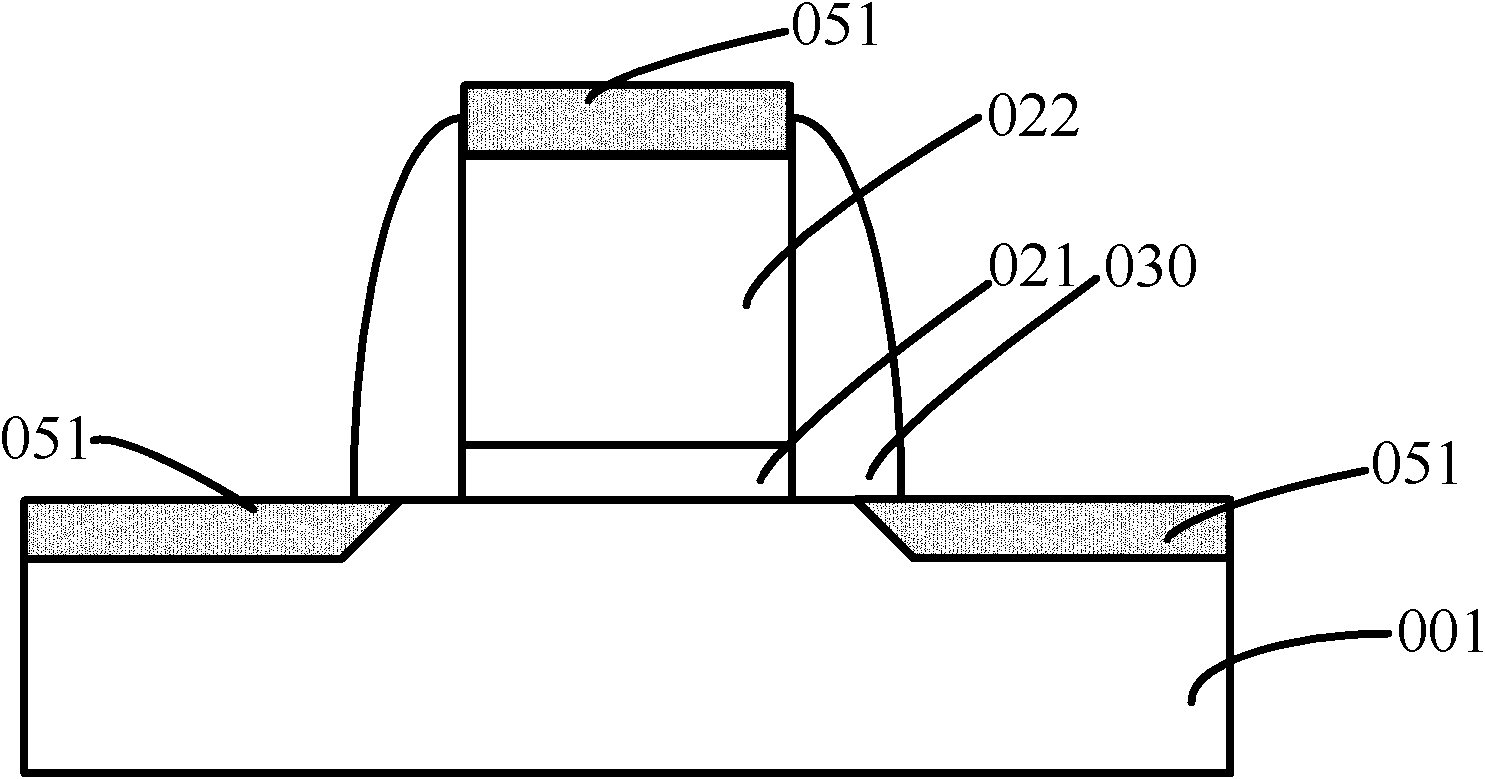

Method for forming semiconductor device

ActiveCN102468150AImprove diffusion abilityPrevent proliferationSemiconductor/solid-state device manufacturingSemiconductor devicesSource areaNickel silicide

The invention provides a method for forming a semiconductor device, comprising the following steps: providing a substrate, a grid structure positioned on the substrate and a source area and a drain area which are both positioned in two side substrates of the grid structure; forming a nickel alloy layer on the exposed substrate surface containing nickel and at least one of other metals and having the thickness of 150-400 angstrom; and annealing the nickel alloy layer to form a nickel silicide in the substrate. According to the method, the diffusing capacity of the subsequently-formed nickel silicide in platinum is improved through improving the thickness of the nickel alloy layer which is in the range of 150-400 angstrom to enhance the diffusion barrier performance of the platinum element to the nickel element, thereby avoiding the diffusion of nickel to channel regions below a gate oxidation layer, reducing the generation of NiSi2 layers and improving the problem of deteriorating the electric leakage performance due to the development of the NiSi2 layer to channels.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

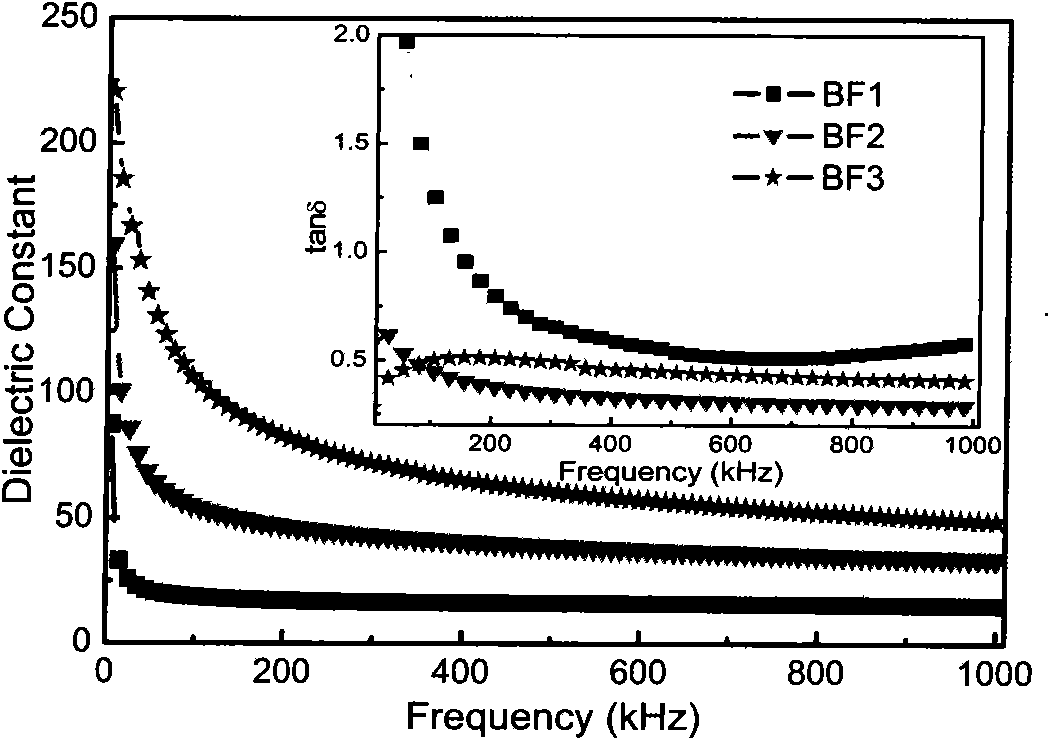

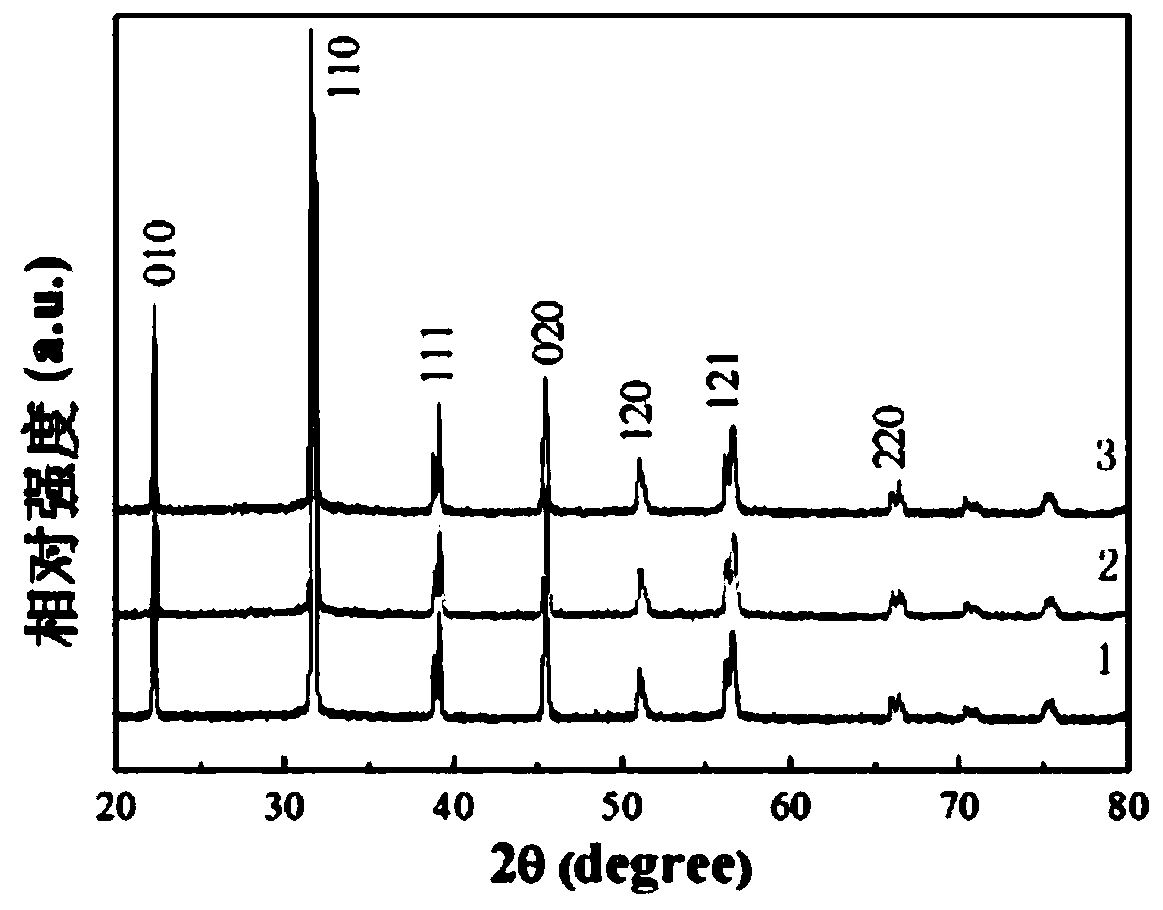

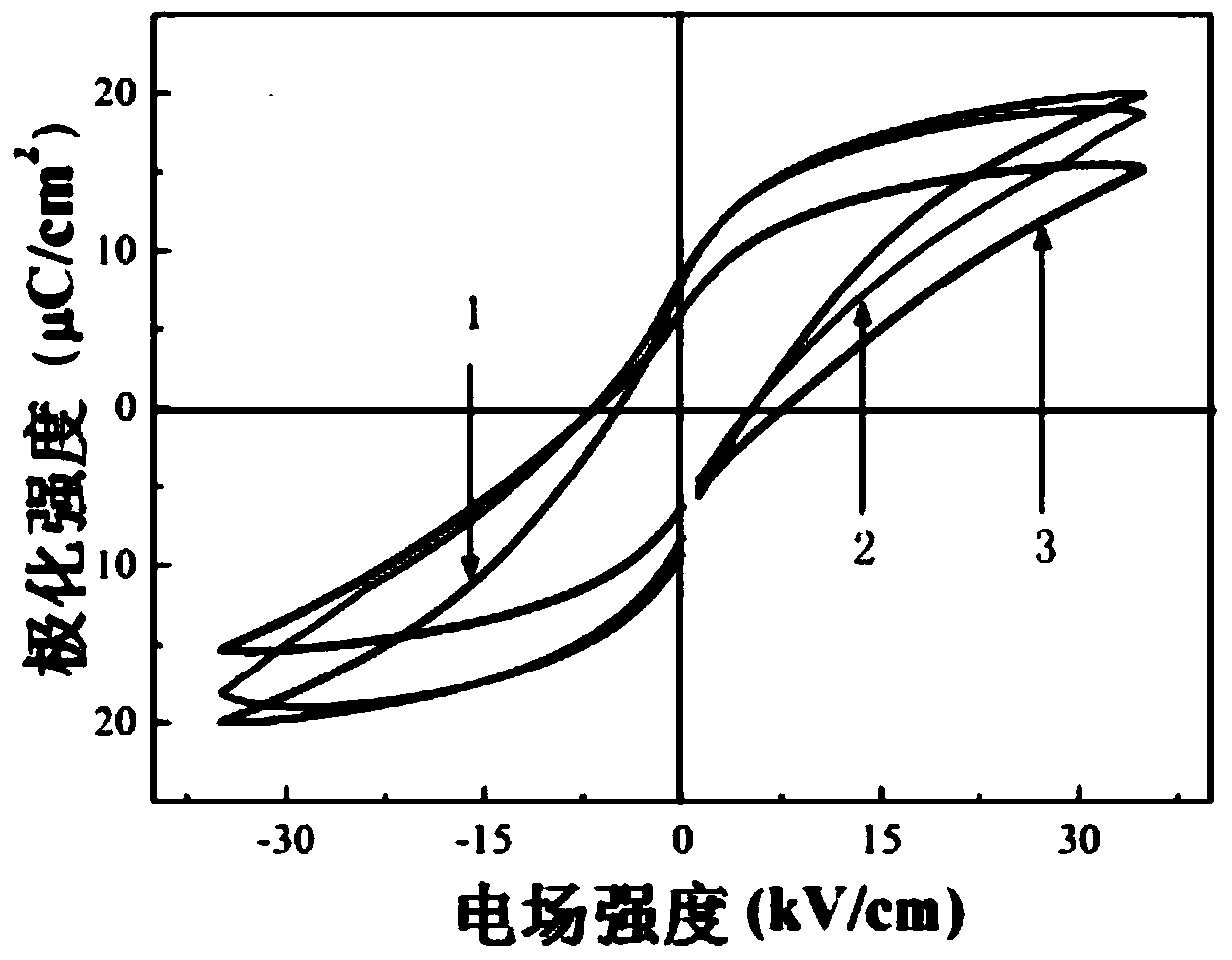

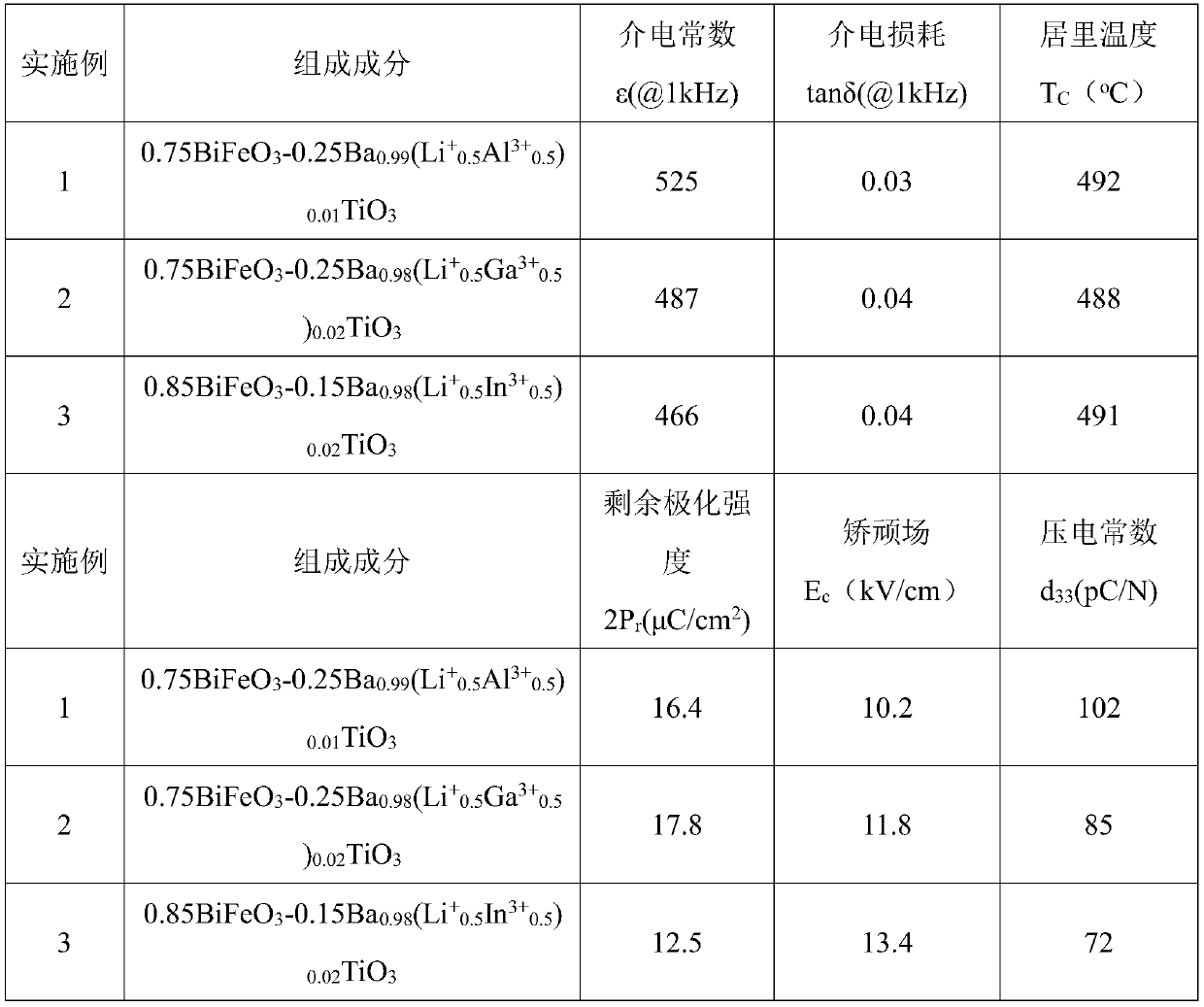

Composite doped bismuth ferrite-barium titanate binary lead-free ferroelectric ceramic material, preparation method and application thereof

InactiveCN110015893AHigh curie temperatureThe preparation process is stableFixed capacitor dielectricCurie temperaturePerovskite

The invention discloses a composite doped bismuth ferrite-barium titanate binary lead-free ferroelectric ceramic material, a preparation method and application thereof, belongs to the field of lead-free ferroelectric ceramic materials, particularly relates to the composite doped bismuth ferrite-barium titanate binary lead-free ferroelectric ceramic material, the preparation method and applicationthereof, and aims to solve the problem that the BFO ceramic prepared by the conventional solid phase synthesis method has poor ferroelectric performance and serious electric leakage. The chemical general formula of the ceramic material is (1-y)BiFeO<3-y>Ba<1-x>(Li<0.5><+>A<0.5><3+>)<x>TiO3. The ceramic material is obtained by adopting a sintering manner combining SPS rapid low-temperature sintering and solid phase synthesis, the system is a perovskite phase, and has no impurity phase, the prepared ceramic material has excellent electrical properties and relatively high Curie temperature, the preparation process of the material is stable, and the material has a relatively good application prospect. The prepared ceramic material is used as an electronic component in fields of temperature-stable capacitors and high-temperature applications.

Owner:HARBIN UNIV OF SCI & TECH

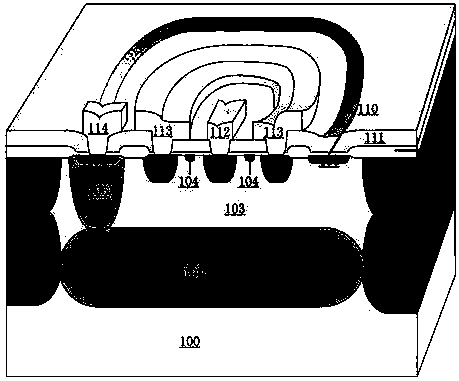

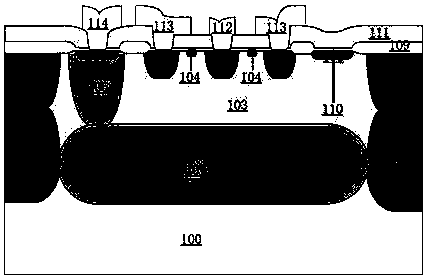

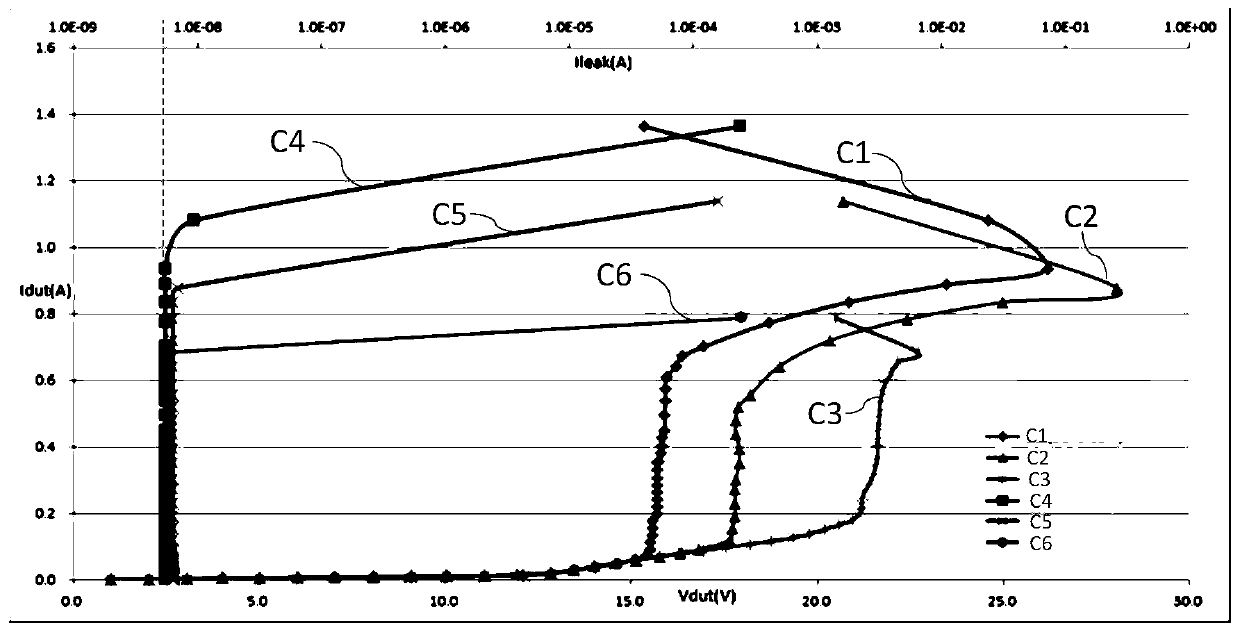

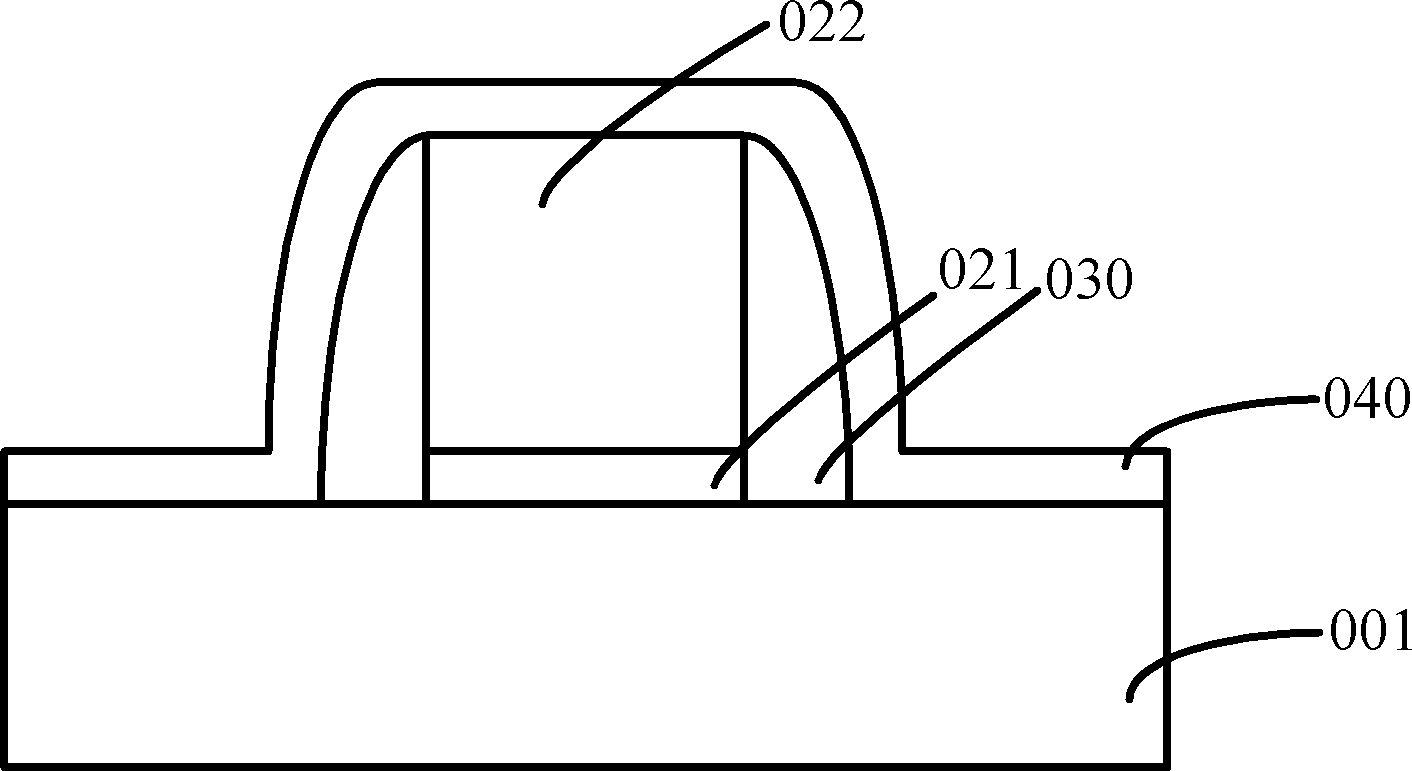

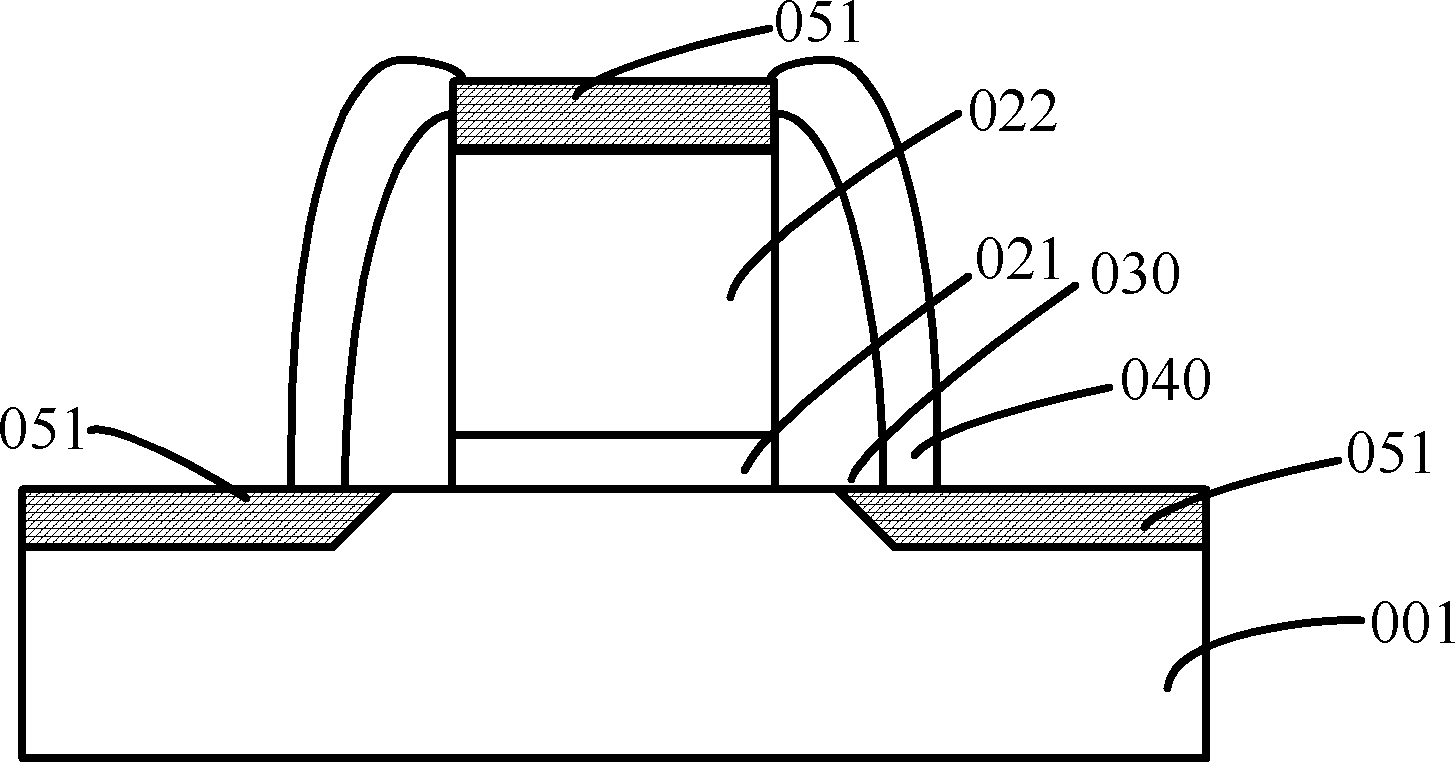

Transverse high-voltage bipolar junction transistor and manufacturing method thereof

PendingCN107946355AReduce leakage currentCurvature effect reducedSemiconductor/solid-state device manufacturingSemiconductor devicesHigh pressureFlow sheet

The invention discloses a transverse high-voltage bipolar junction transistor and a manufacturing method thereof. The transverse high-voltage bipolar junction transistor includes a P-type substrate, an N-type buried layer, a P-type buried layer, an N-type epitaxial layer, a P-type isolation penetration region, an N-type punch-through region, a P-type body region, an N-type heavily doped region, anN-type heavily doped ring region, a pre-oxidized layer, a field oxygen layer, a TEOS pre-metal dielectric layer, emitter metal, collector metal and base metal. Based on a conventional transverse power bipolar junction transistor, N-type ring injection is added between a collector region and an emitter region, the layout of a first layer of metal is optimized to enable all metal to completely cover the collector region, and the size is more than twice the junction depth of the collector region. Simulation and the actual tape-out result show that the transverse high-voltage bipolar junction transistor has the advantage that under the condition of little influence of the remaining parameters, BVcbo is improved by over 40%, BVceo is improved by over 30%, and the leakage capacity is improved by one order of magnitude. The invention provides a transverse high-voltage bipolar junction transistor.

Owner:CHONGQING ZHONGKE YUXIN ELECTRONICS

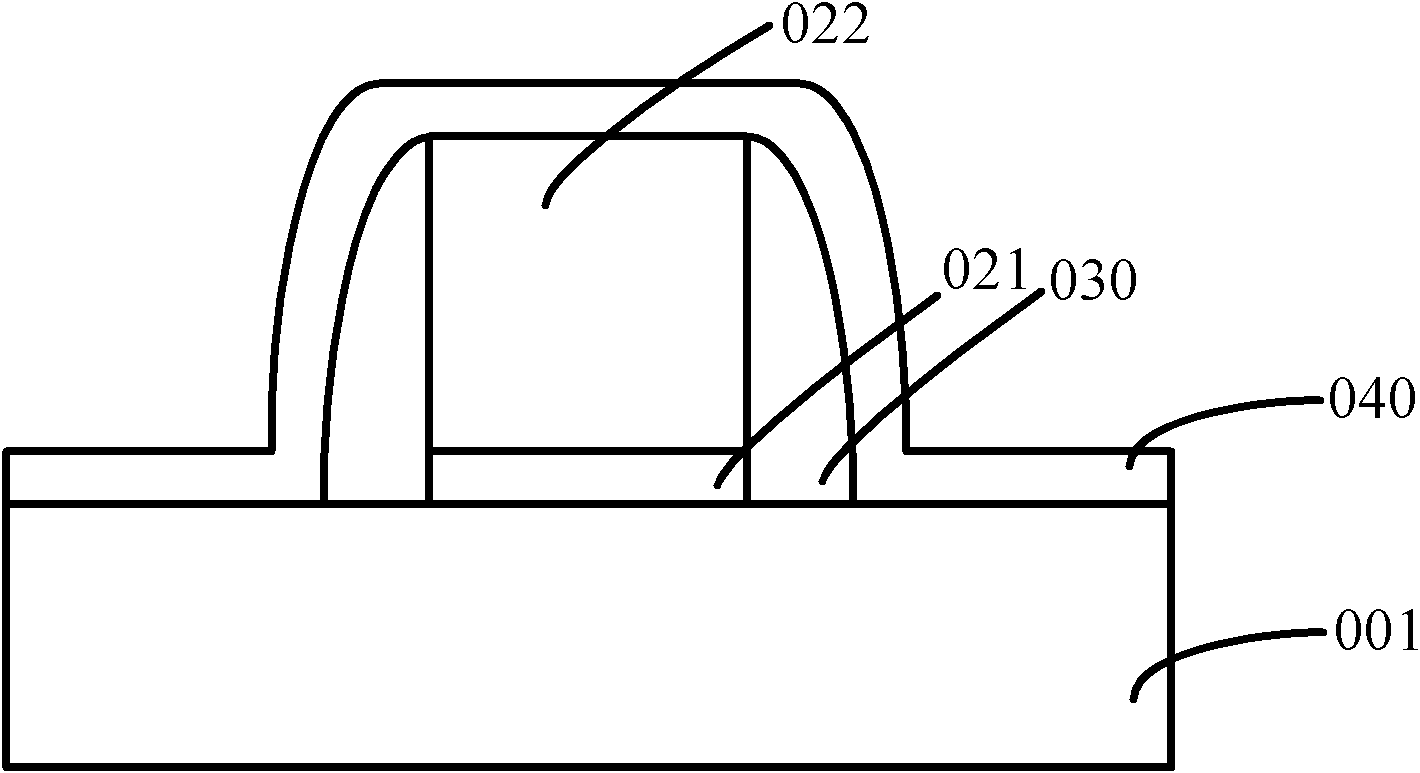

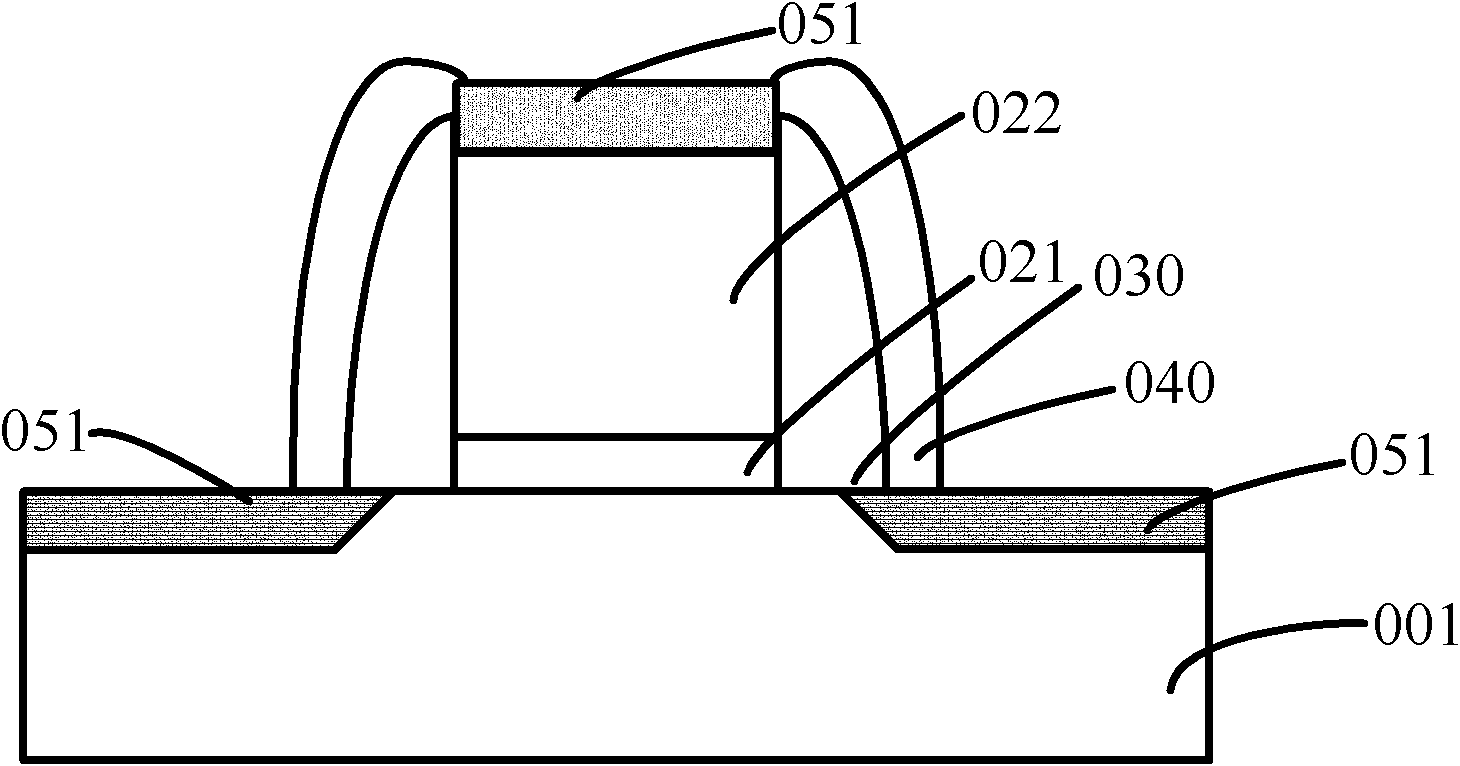

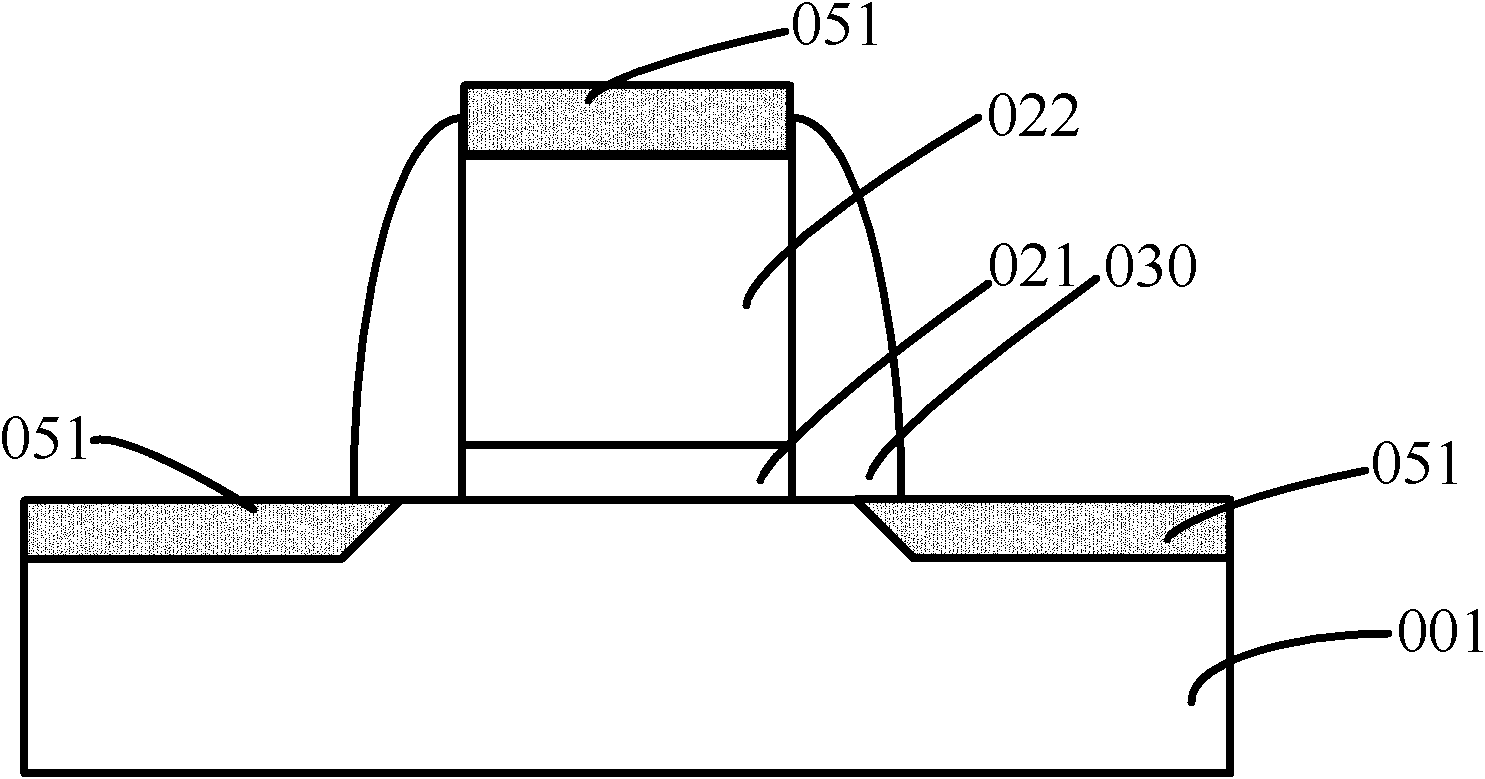

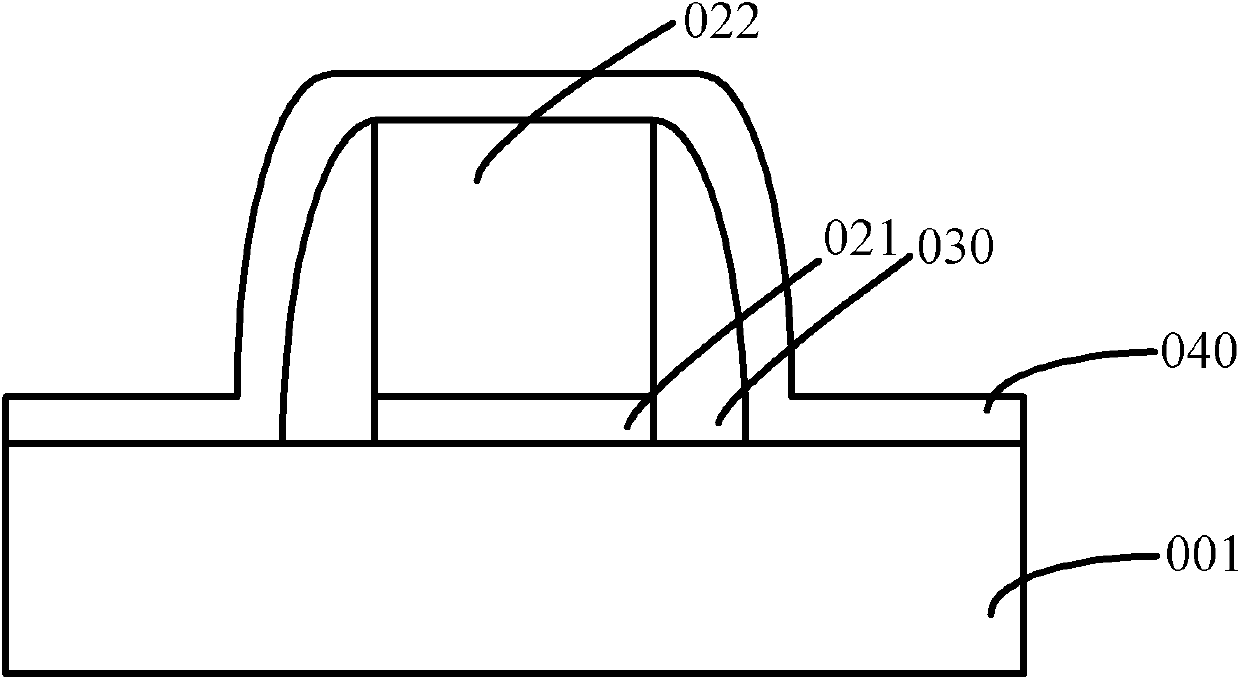

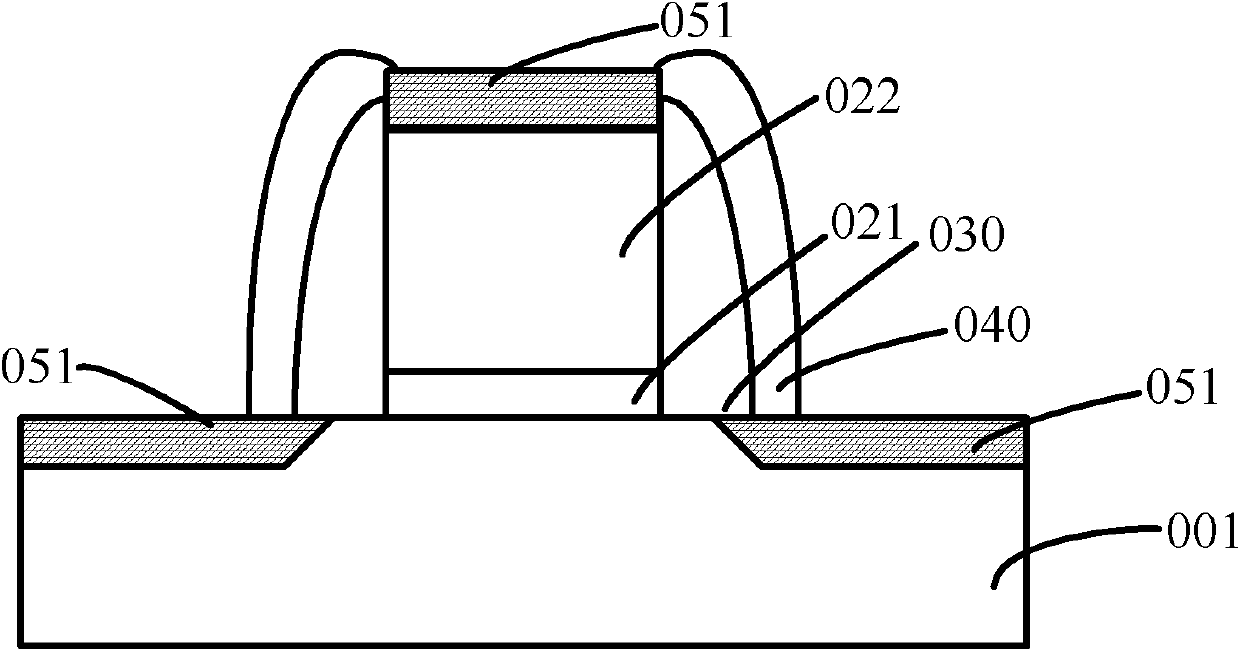

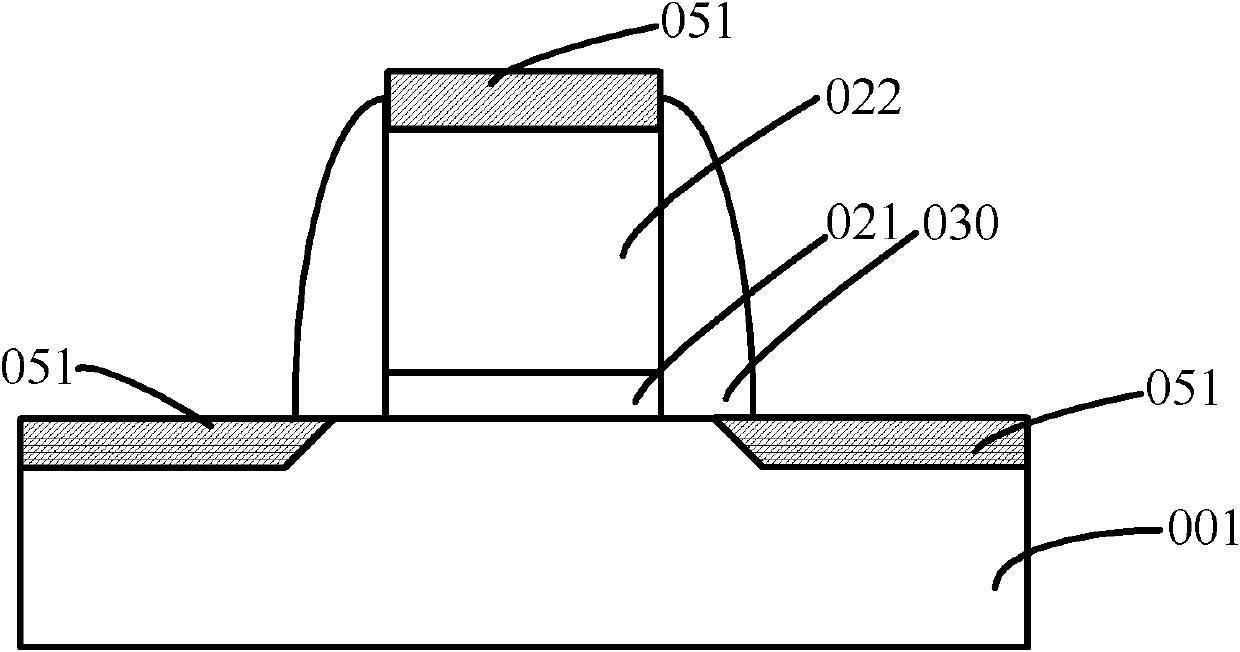

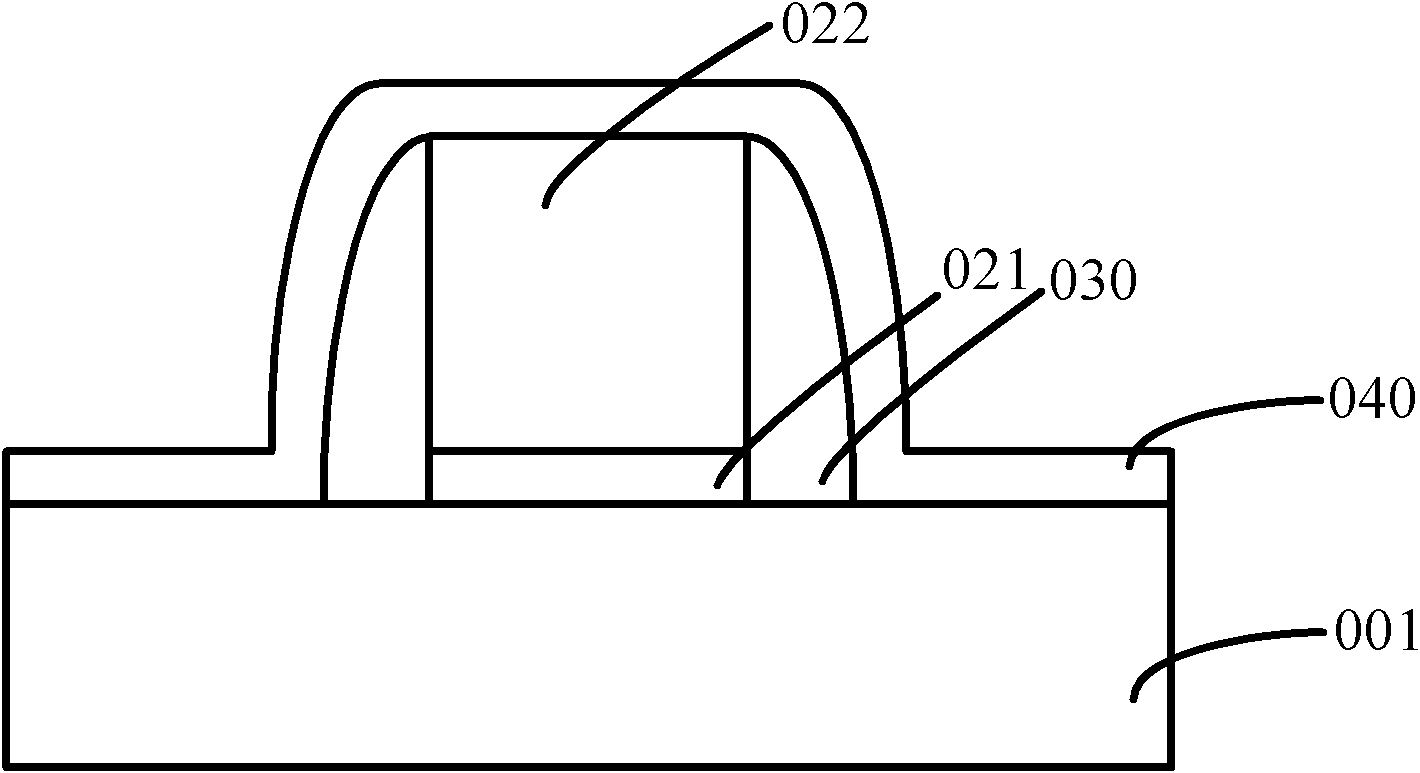

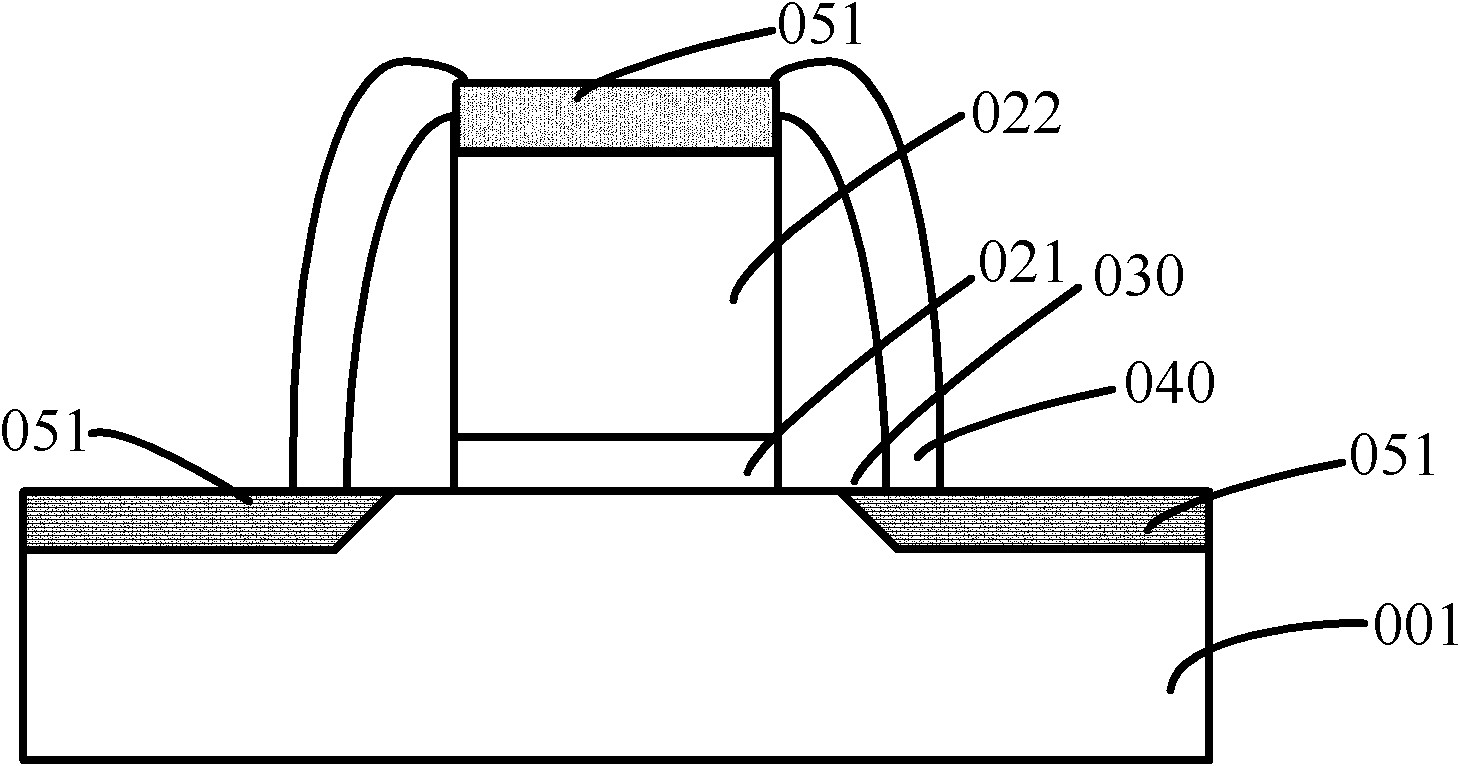

Semiconductor device forming method

ActiveCN102569089AIncrease spacingImprove leakage performanceSemiconductor/solid-state device manufacturingMetal silicideSemiconductor

The invention provides a semiconductor device forming method, which comprises the steps that: a substrate, a grid structure positioned on the substrate and side walls positioned at two sides of the grid structure are provided; an auxiliary side wall is formed on the surface of the side walls; a metal layer is formed on the surface of the auxiliary side wall and the exposed substrate; and the metal layer is subjected to annealing, metal silicide is formed in the substrate, the auxiliary side wall is used for preventing the metal layer from transversely diffusing into the side walls, and the formation of the metal silicide on the side walls is avoided. The semiconductor device forming method has the advantages that the auxiliary side wall is formed on the side walls, the gap of the metal silicide in the substrate positioned at two sides of the grid structure is enlarged, the electric leakage performance in an enhancement channel of the metal silicide formed through the metal diffusion is avoided, and the electric connection of a source / drain region and a grid electrode is further avoided, so the performance of a semiconductor device is improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

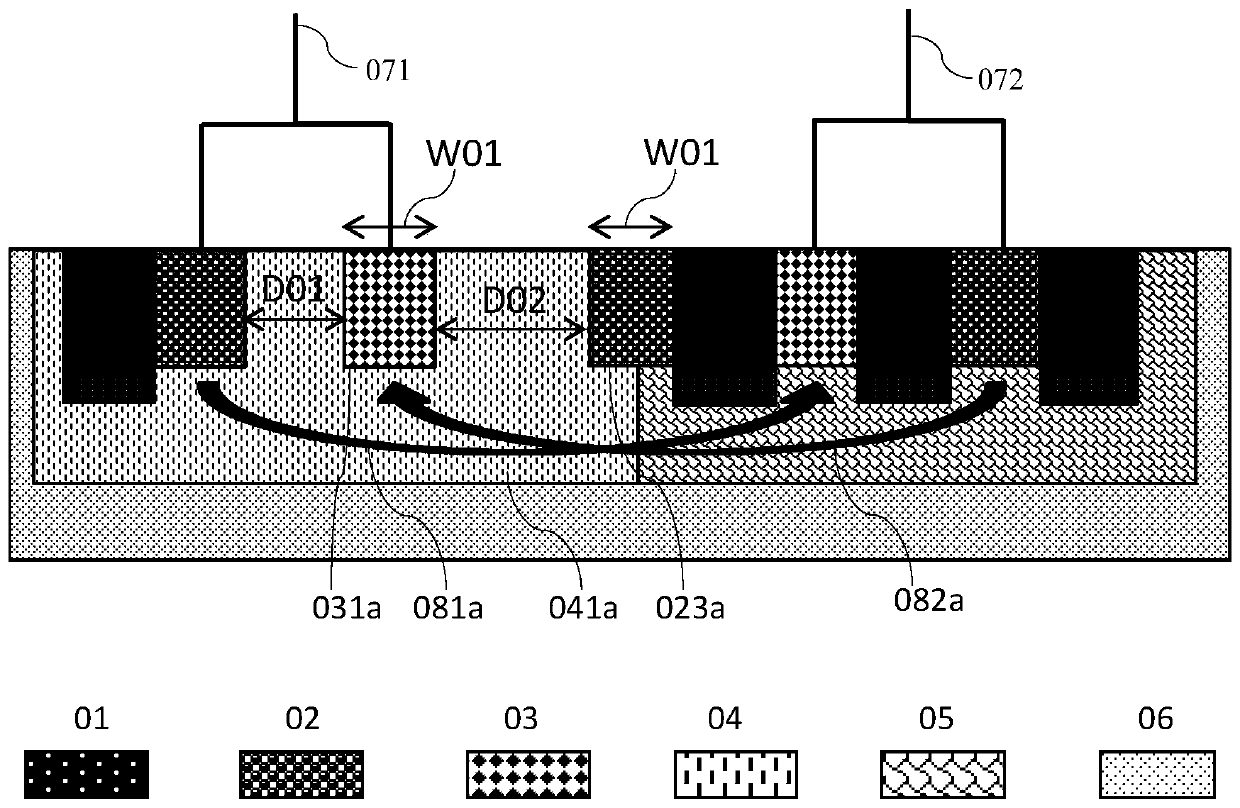

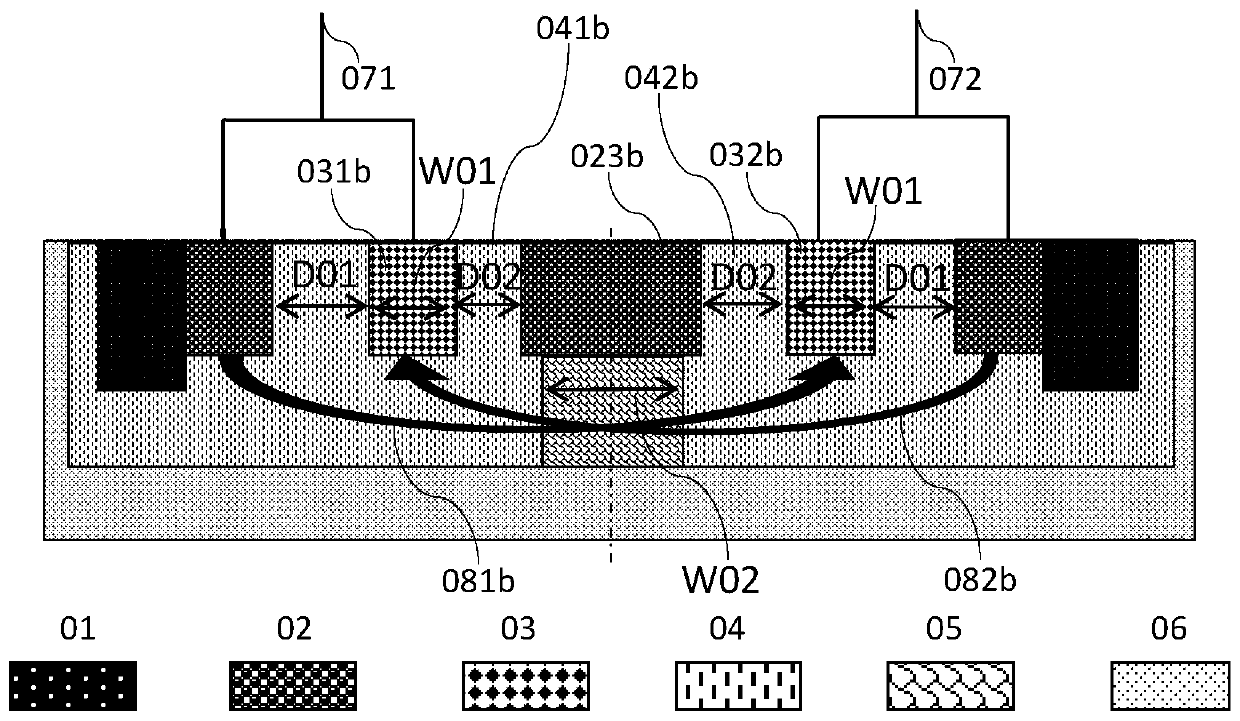

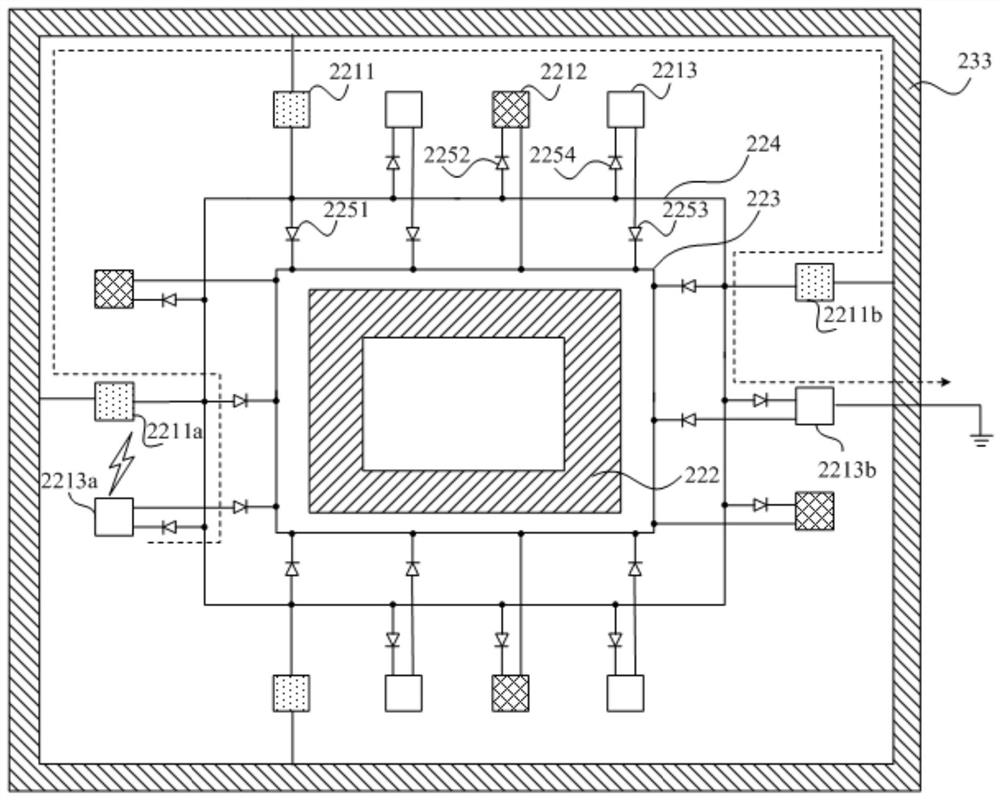

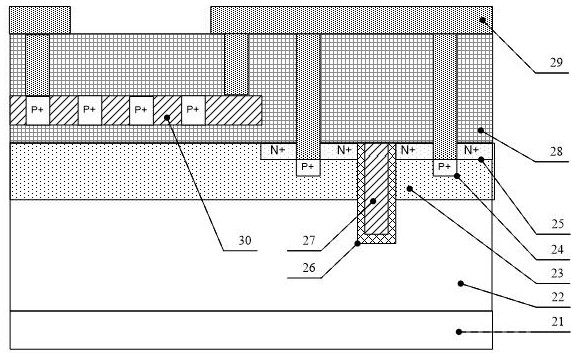

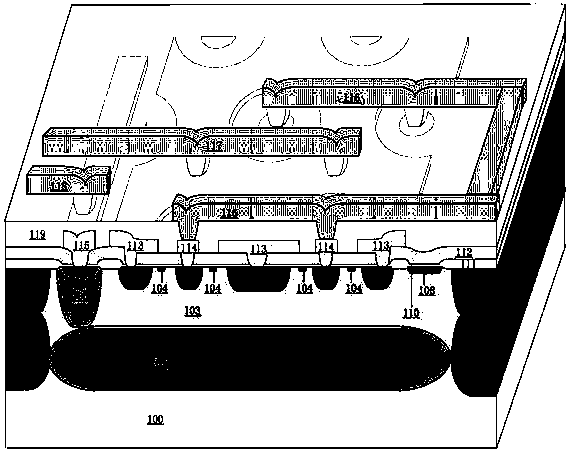

Silicon-controlled rectifier and manufacturing method thereof

PendingCN110854181AImprove leakage performanceSolid-state devicesSemiconductor devicesHigh concentrationHemt circuits

The invention provides a silicon-controlled rectifier and a manufacturing method thereof. The silicon-controlled rectifier comprises a semiconductor substrate, a first N well, a P well, a second N well, first / second high-concentration P-type doping, first / second high-concentration N-type doping and third high-concentration P-type doping, wherein the first N well, the P well and the second N well are adjacent in sequence; the first / second high-concentration P-type doping and the first / second high-concentration N-type doping are located on the upper part of the first / second N well; the third high-concentration P-type doping is located at the upper part of the P well; a first / second grid electrode is arranged above the first / second N well between the first / second high-concentration N-type doping and the third high-concentration P-type doping; and the first / second high-concentration P-type doping, the first / second high-concentration N-type doping and the first / second grid electrode are connected to form a first / second device pole. Accordingly, the first / second device pole is connected with the input and output end of the positive / negative high voltage, PNPN channels without a conduction condition are formed, a bidirectional anti-static protection function suitable for the positive / negative high voltage at the same time is achieved in an applied circuit, and good electric leakage performance is achieved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

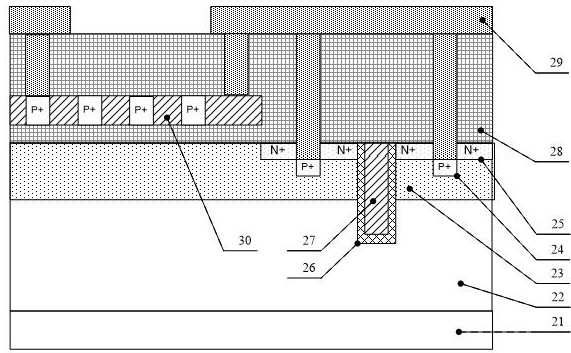

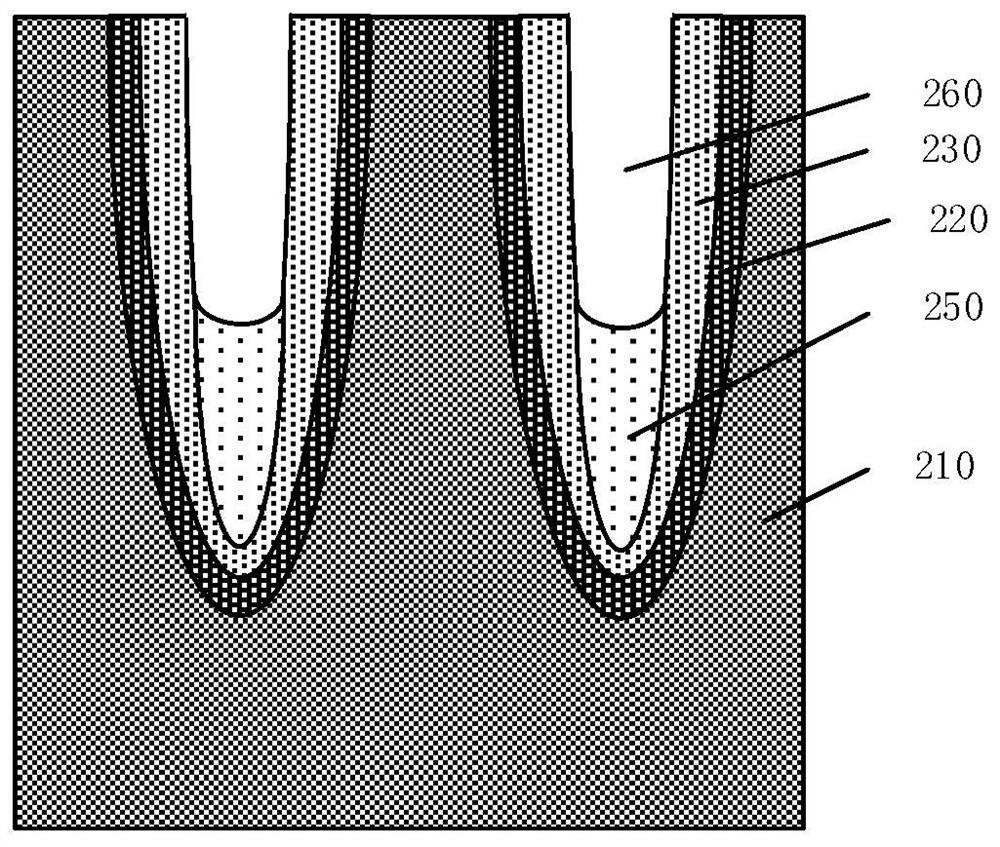

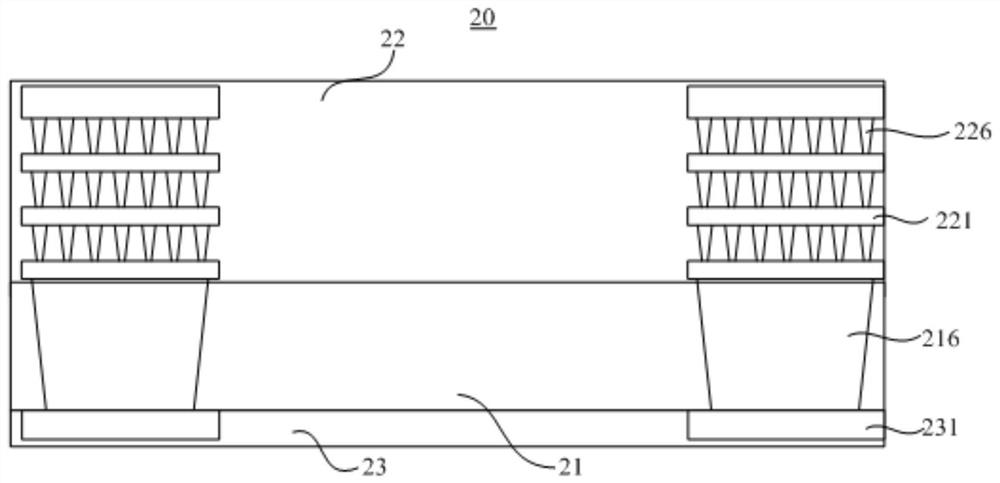

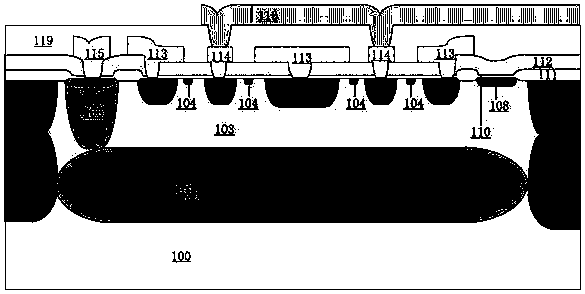

Power device structure with ESD and preparation method thereof

ActiveCN113421829AReduce manufacturing costImprove leakage performanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringMetal electrodes

The invention provides a power device structure with an ESD and a preparation method thereof. The device comprises an N-type substrate, an N-type epitaxial layer, a first groove, a second groove, a P-type body region, a P-type active region, an N-type active region, a dielectric layer and a metal electrode, wherein the first groove and the second groove are distributed in the N-type epitaxial layer at intervals, a gate oxide layer and polycrystalline silicon ESD are arranged in the first groove, and a P-type doped region is formed in the polycrystalline silicon ESD; a gate oxide layer and a polycrystalline silicon gate are arranged in the second groove; the P-type body region is located in the N-type epitaxial layer between the grooves; the dielectric layer covers the first groove, the second groove and the P-type body region; the hole leading-out region is positioned in the dielectric layer and is electrically contacted with a P-type doped region and a P-type active region of the polycrystalline silicon ESD and an N-type active region in a P-type body region between the first groove and the second groove; and the metal electrode is located on the dielectric layer. The area of the ESD structure can be effectively reduced, the process planarization is facilitated, the device preparation cost is reduced, and the ESD leakage performance is improved.

Owner:SHANGHAI NATLINEAR ELECTRONICS CO LTD +1

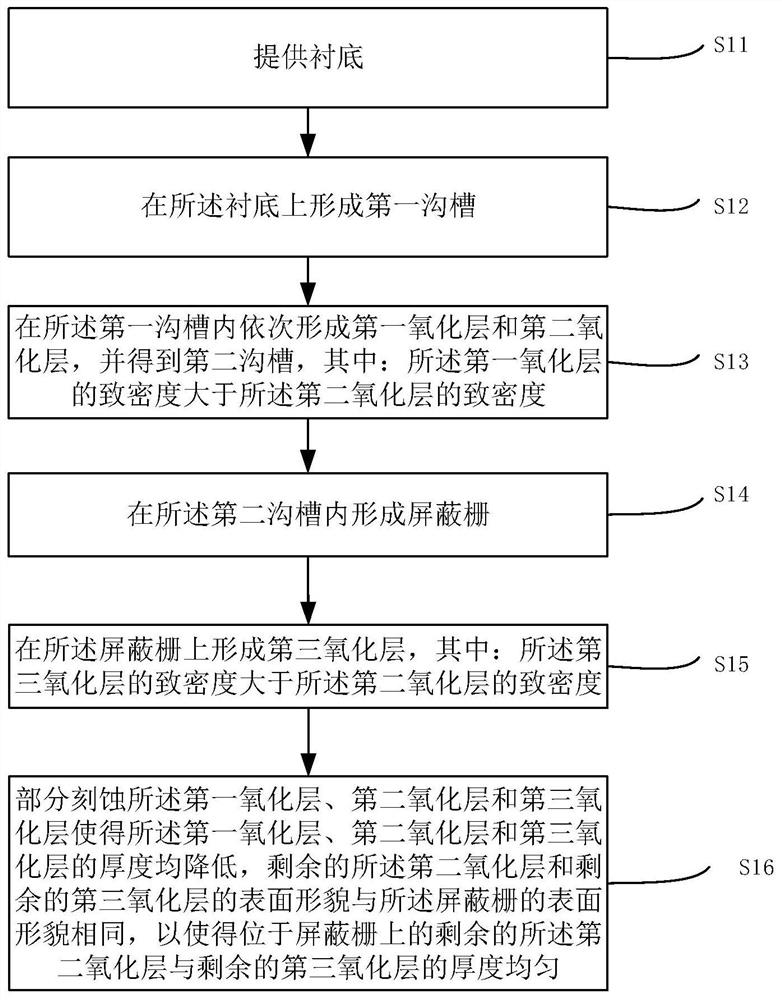

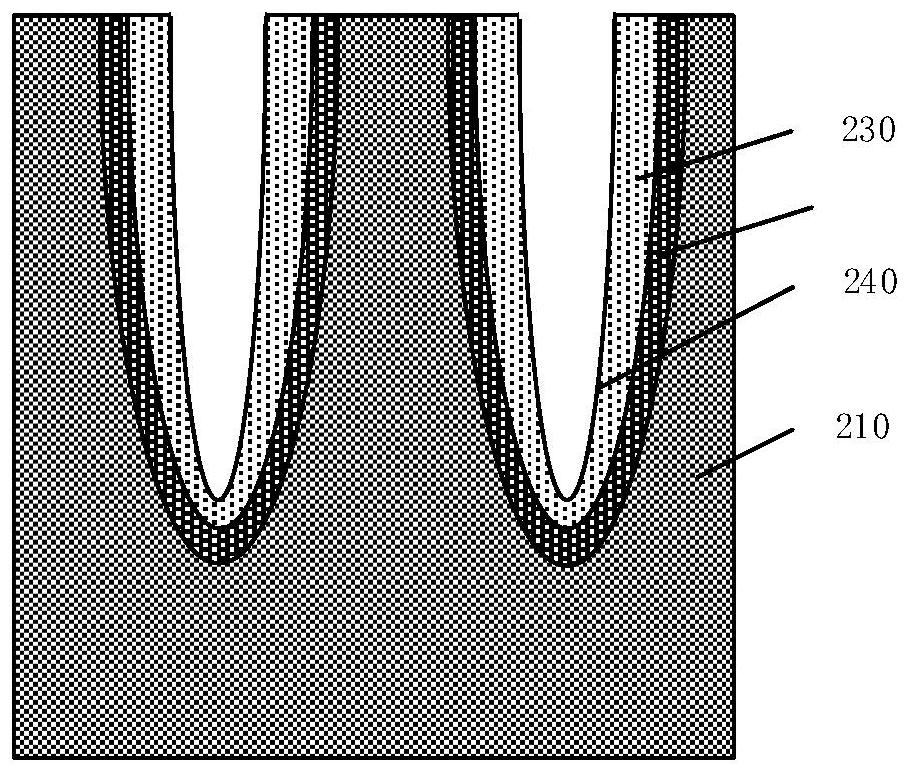

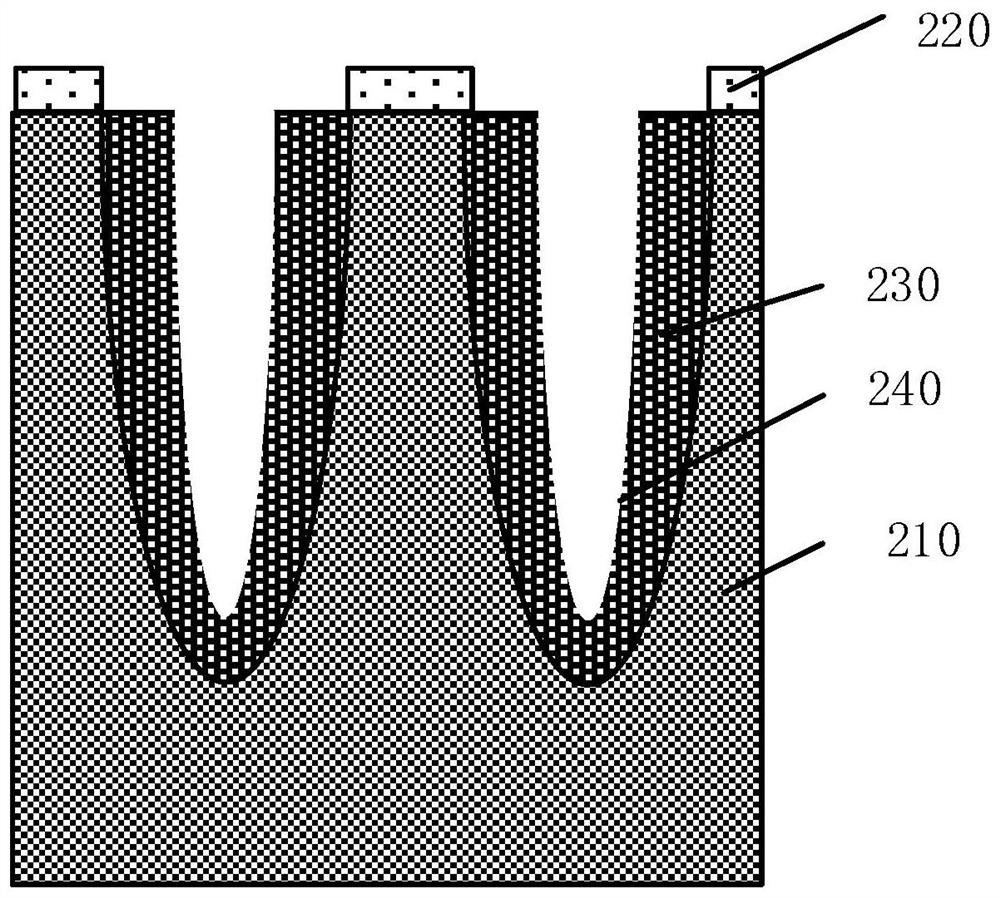

Process method of shielding gate trench type device

ActiveCN112133627AReduce thicknessUniform thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryEngineering

The invention provides a process method of a shielding gate trench type device. The process method comprises the steps of providing a substrate; forming a first trench on the substrate; sequentially forming a first oxide layer and a second oxide layer in the first trench, and obtaining a second trench, wherein the density of the first oxide layer is greater than that of the second oxide layer; forming a shielding gate in the second trench; forming a third oxide layer on the shielding gate, wherein the density of the third oxide layer is greater than that of the second oxide layer; and partially etching the first oxide layer, the second oxide layer and the third oxide layer to enable the thicknesses of the first oxide layer, the second oxide layer and the third oxide layer to be reduced, enabling the surface topography of the remaining second oxide layer and the remaining third oxide layer to be the same as the surface topography of the shielding gate, and enabling the thickness of thecombination formed by the remaining first oxide layer, the second oxide layer and the third oxide layer to be uniform, and thus improving the electric leakage performance between a control gate and the shielding gate.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

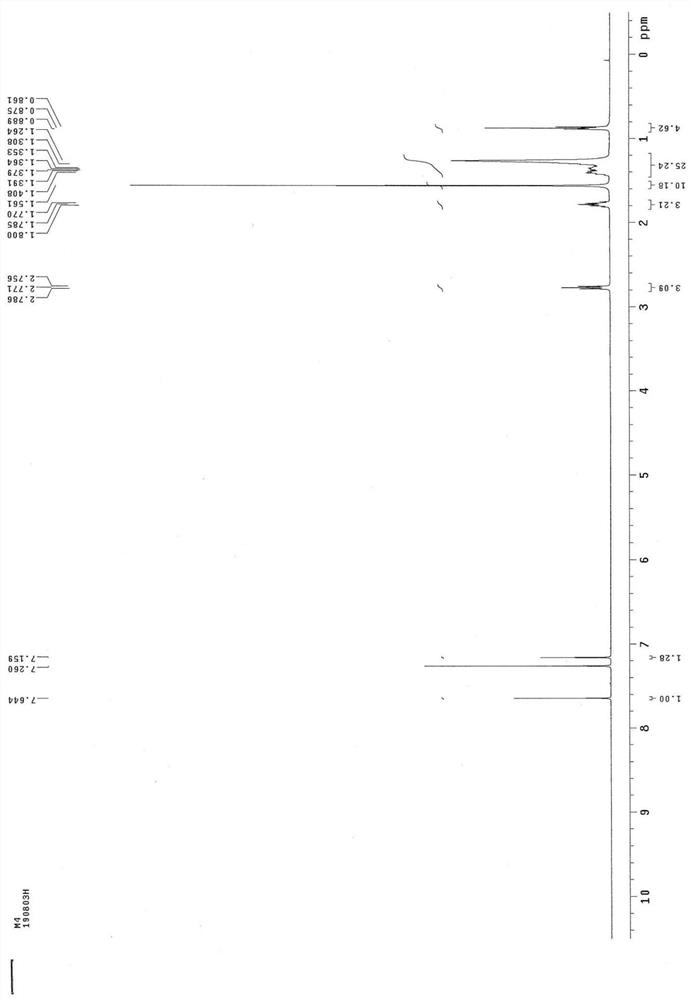

Non-fullerene acceptor compound containing benzoselenadiazole and organic optoelectronic element comprising the same

PendingCN113135941AImprove leakage performanceHOMO value increasedOrganic chemistrySolid-state devicesKetonePerylene derivatives

The present invention relates to a non-fullerene acceptor compound containing benzoselenadiazole and an organic photoelectric element comprising the same. The non-fullerene acceptor compound containing benzoselenadiazole has a structure as shown in the following formula shown in the description, wherein Ar1 is a penta-heterocycles; Ar2 is a monocyclic or polycyclic aromatic heterocyclic derivative of C5-C20; pi is a C5-C20 monocyclic or polycyclic aromatic heterocyclic derivative, and m is equal to 0-5; and EG is a monocyclic or polycyclic derivative containing ketones and electron withdrawing groups. The organic photoelectric element, such as OPD or OPV, containing the benzoselenadiazole-containing non-fullerene acceptor compound can provide better light absorption wavelength range and photoelectric conversion efficiency during use.

Owner:RAYNERGY TEK INC

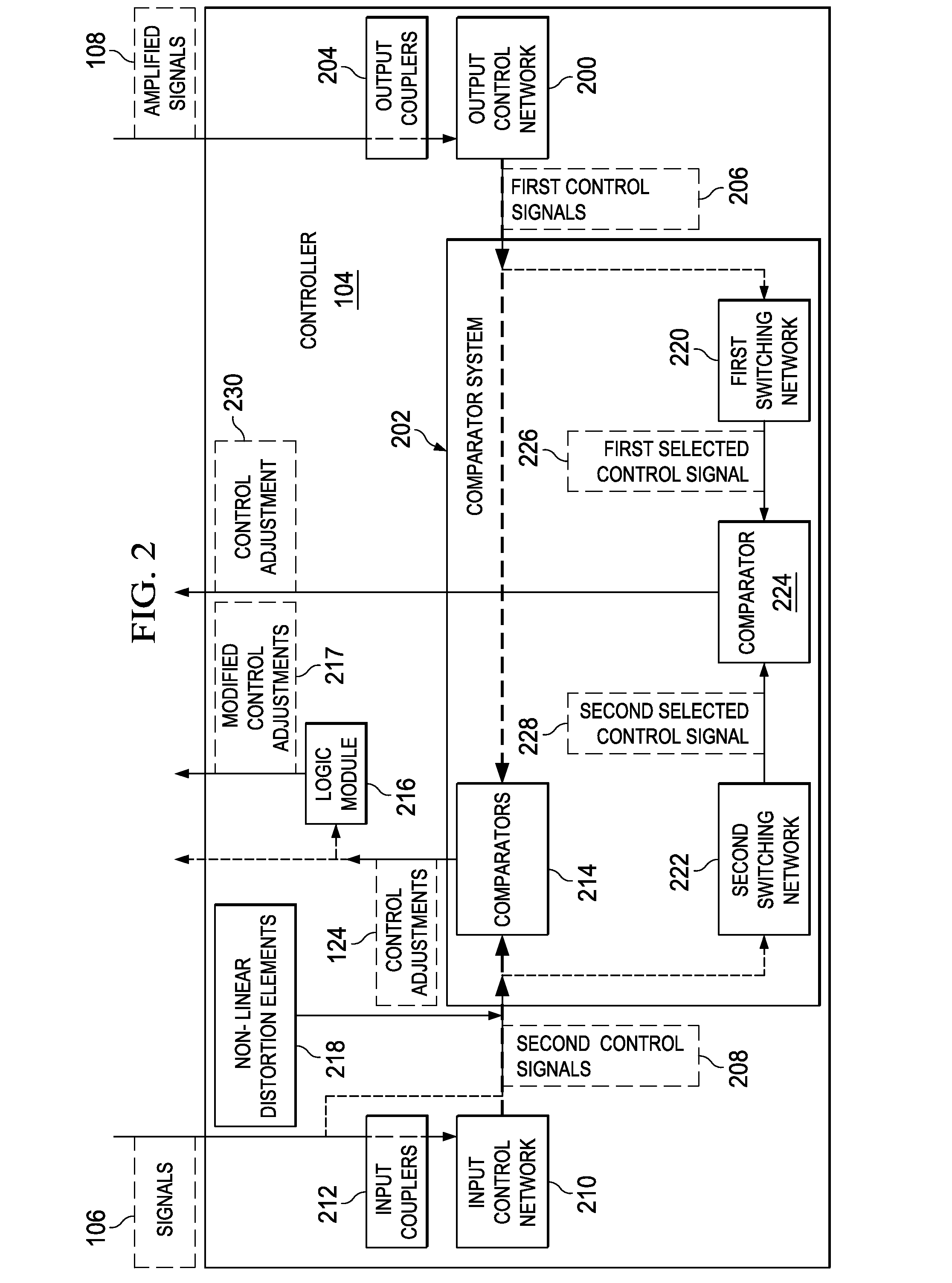

Method and Apparatus for Improving Leakage Performance of a Multi-Port Amplifier

ActiveUS20150035594A1Improve leakage performanceImprove performanceHigh frequency amplifiersPower amplifiersAudio power amplifierEngineering

A method and apparatus for managing a multi-port amplifier. In one illustrative embodiment, an apparatus comprises the multi-port amplifier and a controller. The multi-port amplifier is configured to amplify a plurality of signals to form a plurality of amplified signals. The controller is configured to send a plurality of control adjustments to a plurality of equalizers in the multi-port amplifier to improve leakage performance of the multi-port amplifier.

Owner:THE BOEING CO

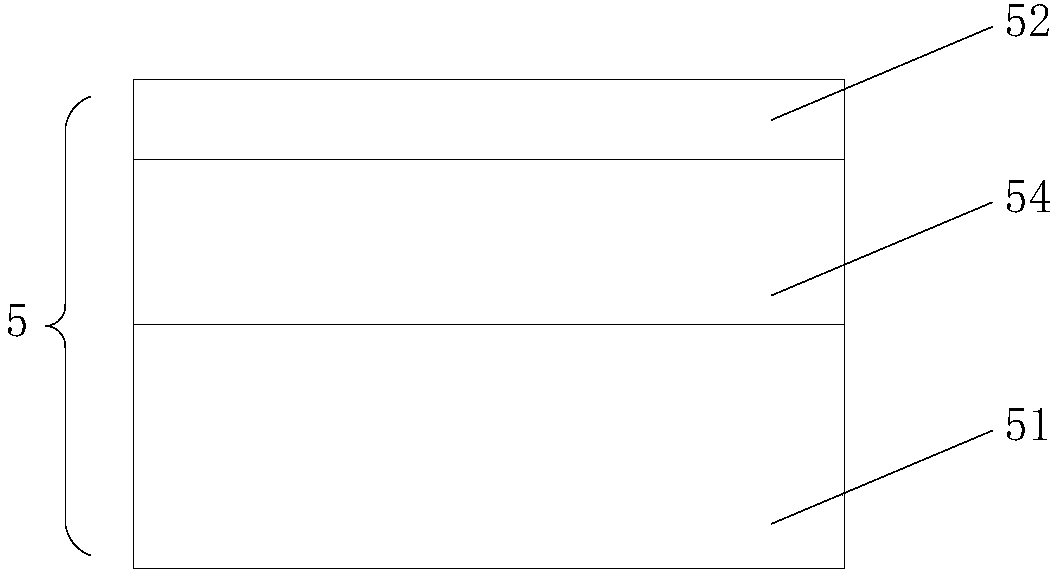

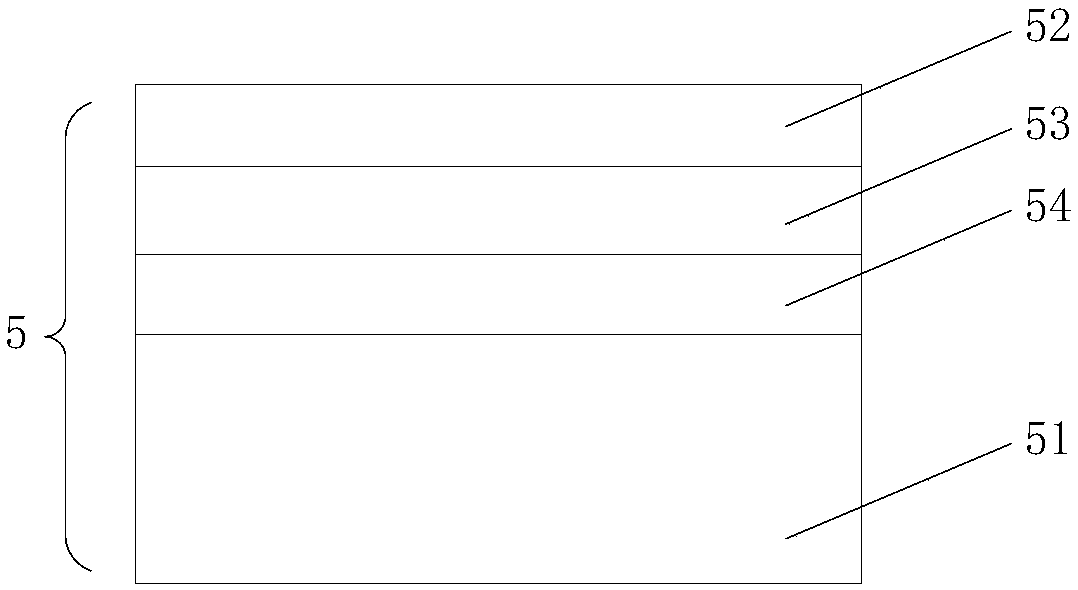

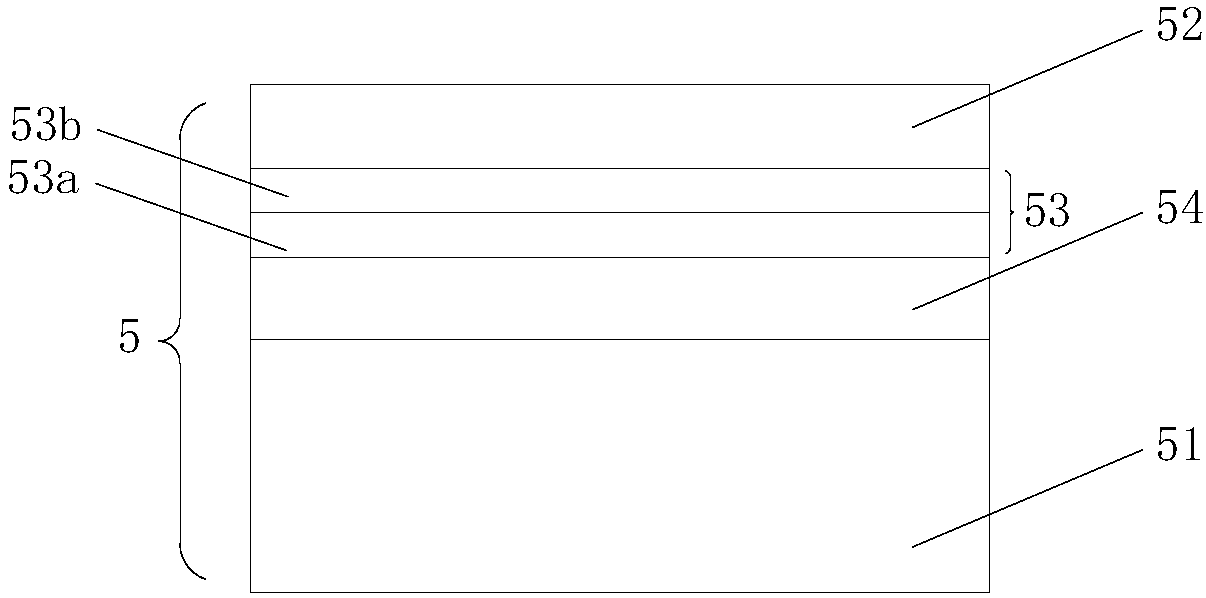

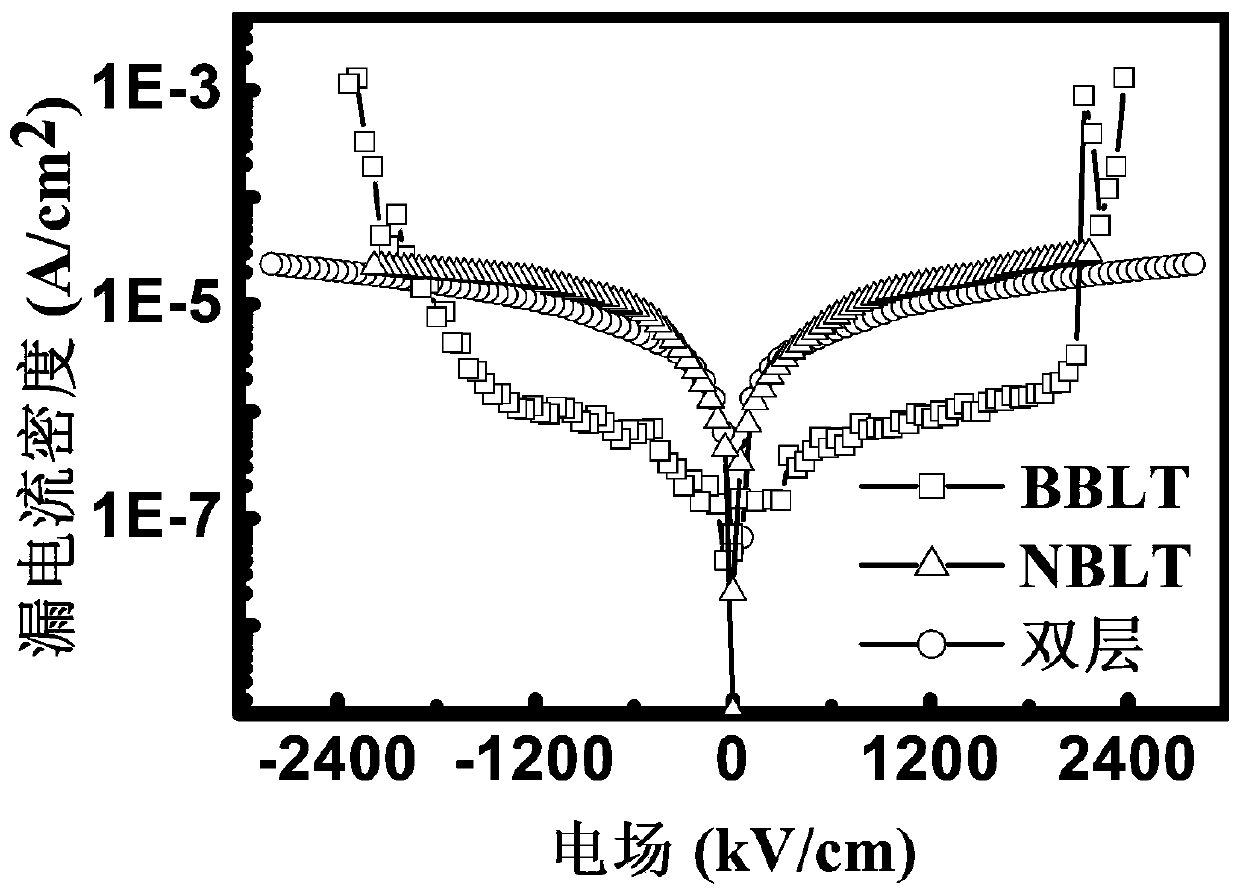

Dielectric film and preparation method thereof

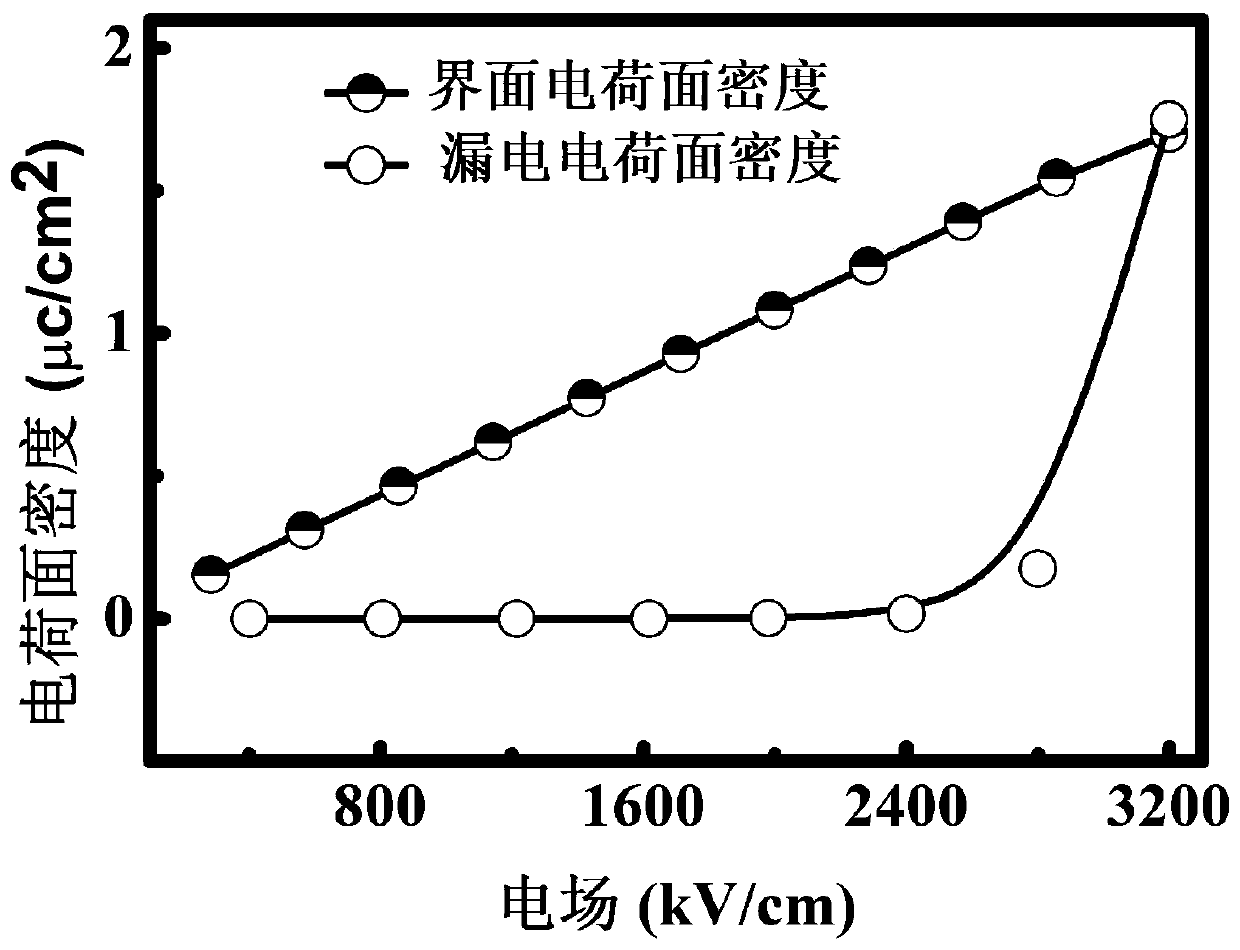

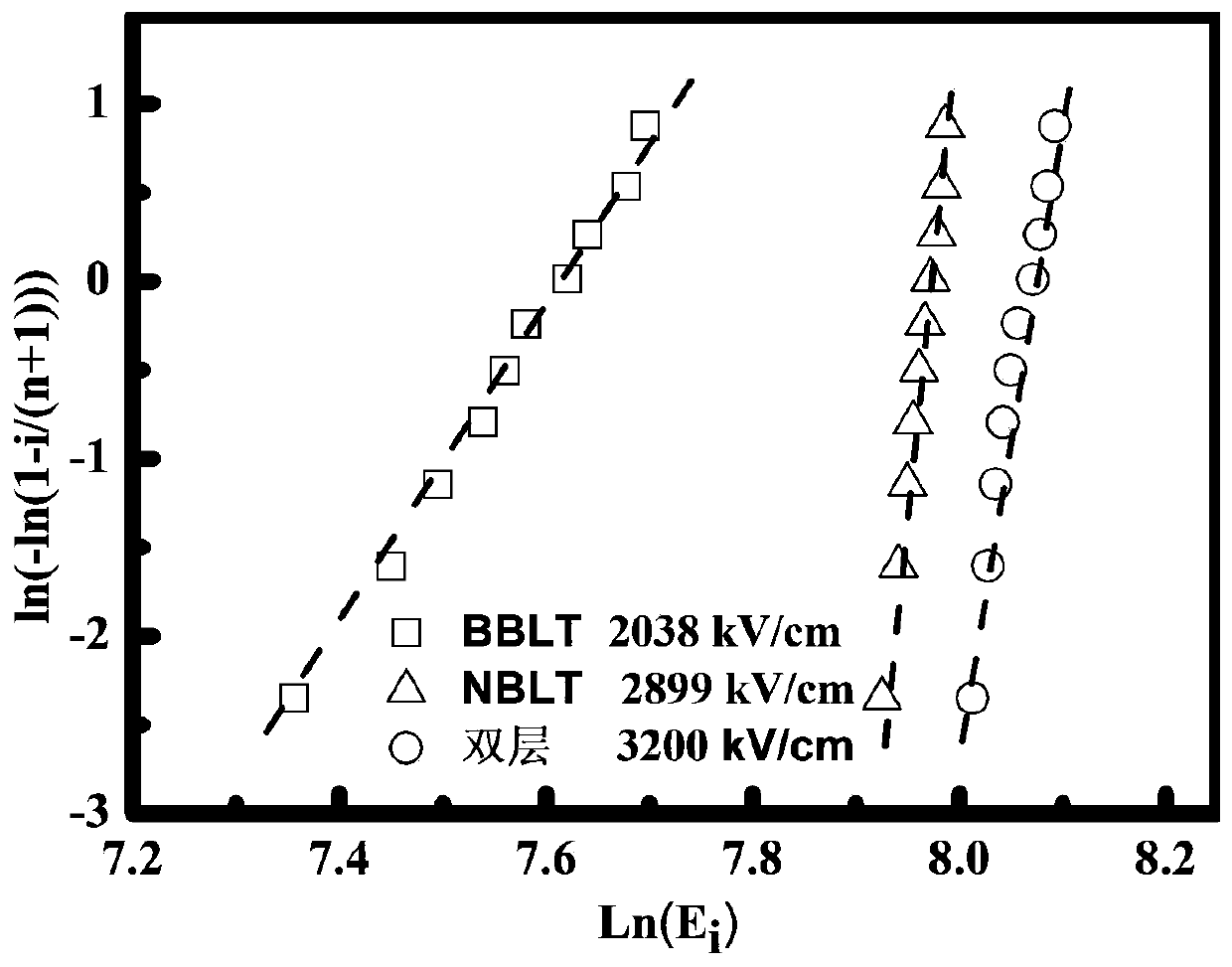

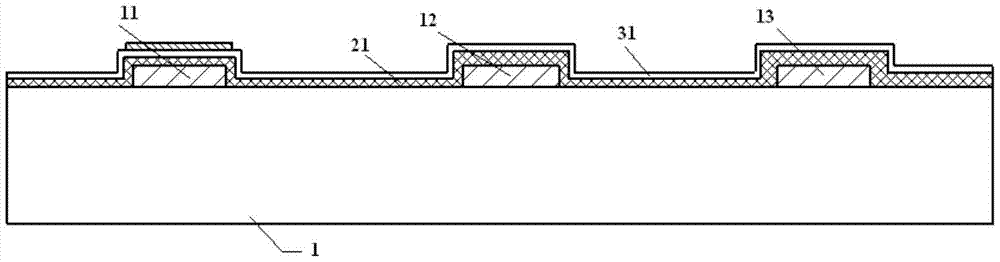

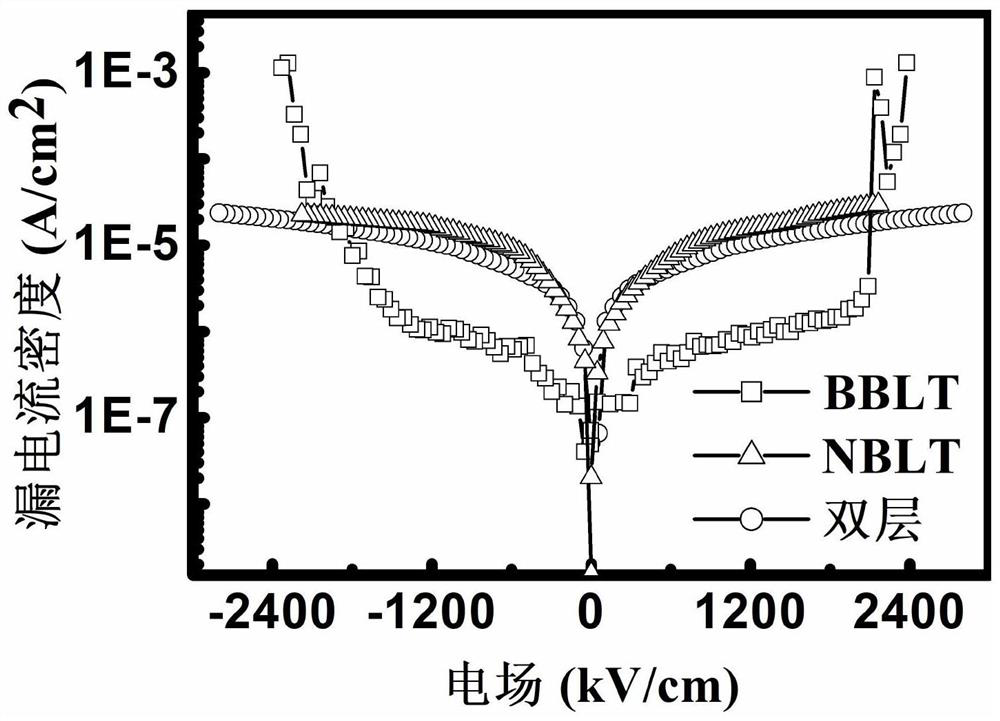

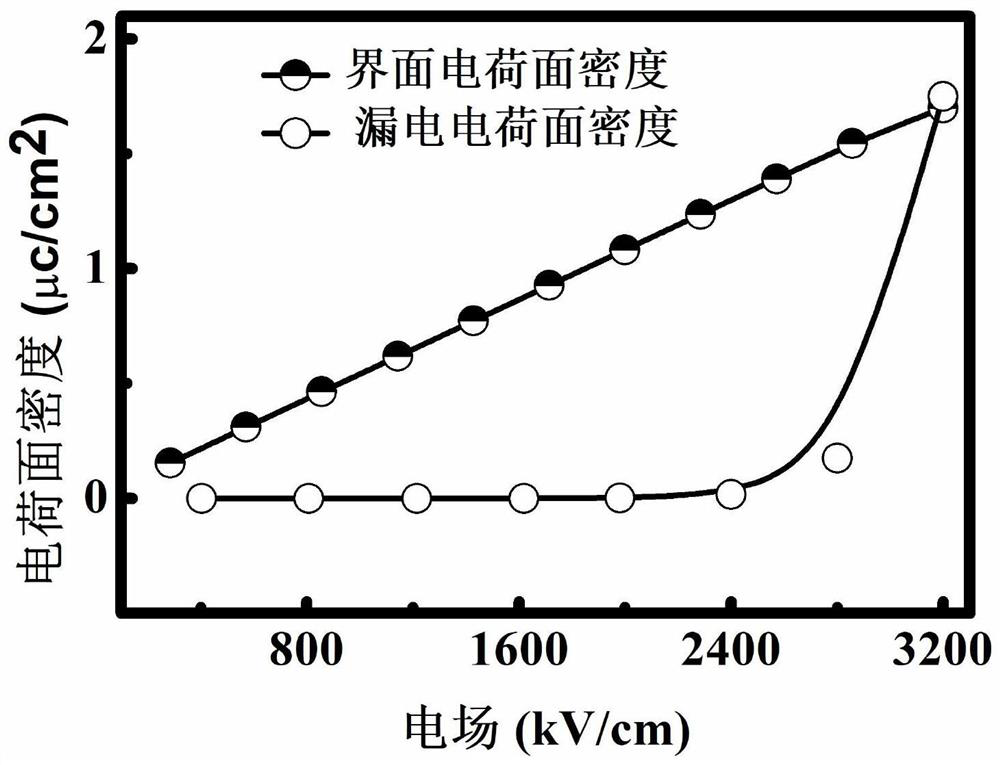

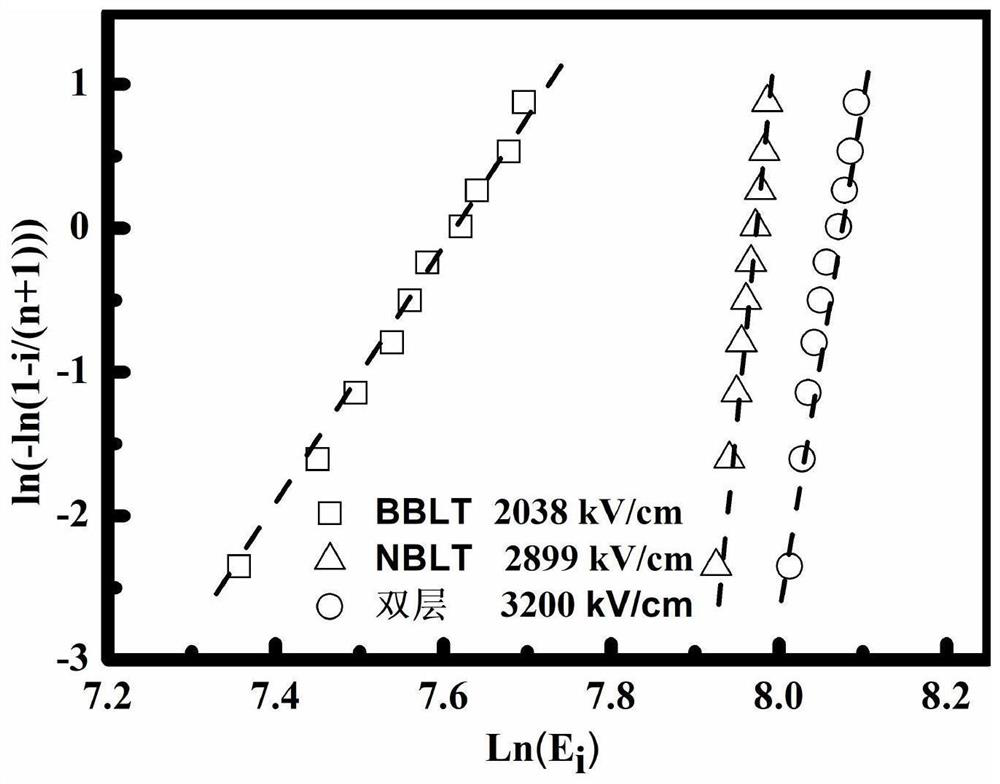

ActiveCN110783103AImprove energy storage characteristicsIncrease the breakdown electric fieldThin/thick film capacitorFixed capacitor dielectricDielectric membraneThin membrane

The invention relates to a dielectric film and a preparation method thereof. The preparation method comprises the steps: adopting an interface charge accumulation model of the first material and the second material and obtaining a thickness ratio of the first material and the second material and a leakage charge surface density of the interface between the first material and the second material; and preparing the dielectric film formed of the first material and the second material of the thickness ratio. Compared with the original film, the dielectric film effectively improves the leakage performance, reduces energy loss and improves breakdown electric field so as to improve the energy storage characteristics.

Owner:INNER MONGOLIA UNIVERSITY

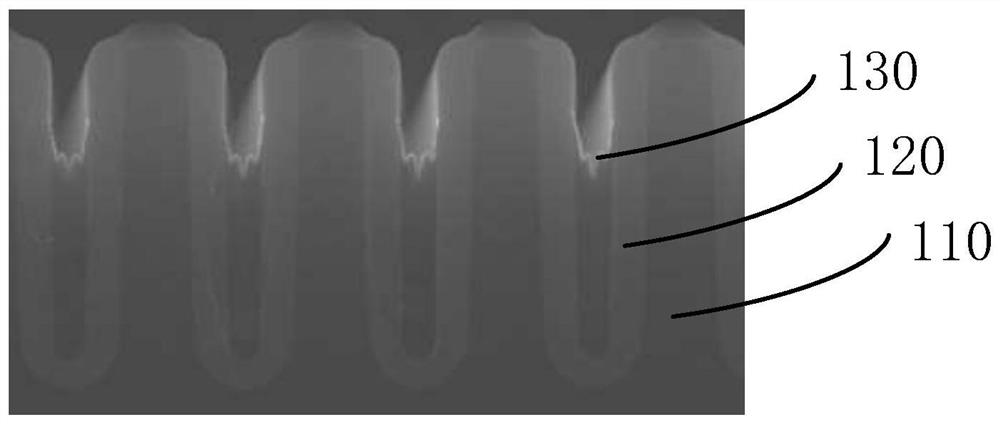

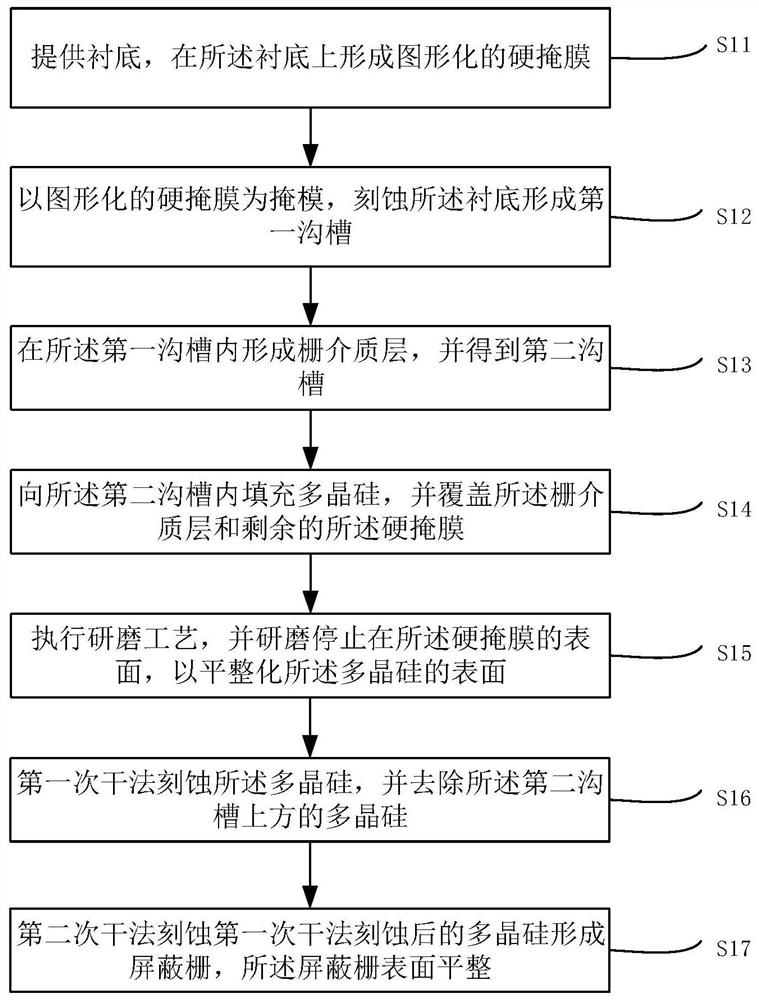

Method for improving surface roughness of shielding gate

PendingCN112133628AImprove leakage performanceIncreased process windowSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSurface roughness

The invention provides a method for improving the surface roughness of a shielding gate. The method comprises the steps of providing a substrate, and forming a graphical hard mask on the substrate; taking the graphical hard mask as a mask, and etching the substrate to form a first trench; forming a gate dielectric layer in the first trench, and obtaining a second trench; filling the second trenchwith polycrystalline silicon, and covering the gate dielectric layer and the residual hard mask; executing a grinding process, and stopping grinding on the surface of the hard mask to flatten the surface of the polycrystalline silicon; performing dry etching on the polycrystalline silicon for the first time, and removing the polycrystalline silicon above the second trench; and carrying out seconddry etching on the polycrystalline silicon subjected to the first dry etching to form a shielding gate, wherein the surface of the shielding gate is flat. The problem that the surface of the formed shielding gate is rough can be solved, so that a process window of a dielectric layer formed between the shielding gate and the control gate is increased, and the electric leakage performance between the control gate and the shielding gate is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

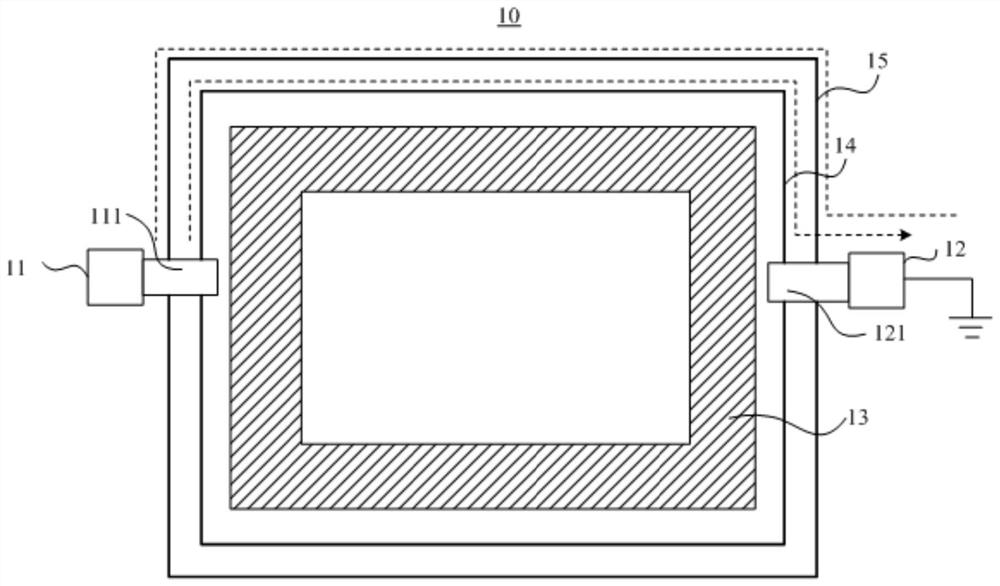

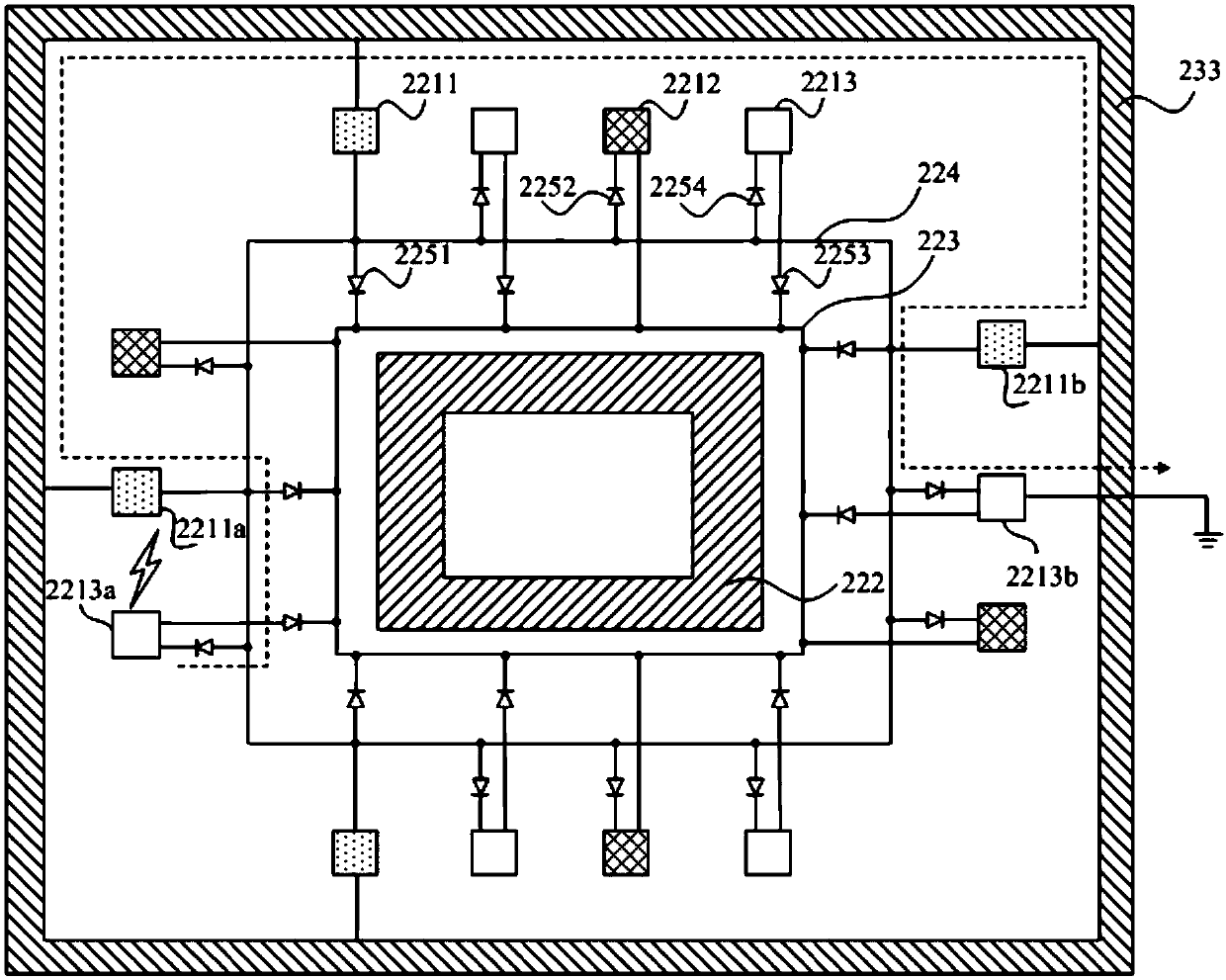

Electrostatic protection structure of image sensor and image sensor

ActiveCN109638011BImprove electrostatic discharge performanceLower resistanceSolid-state devicesDiodeMetal interconnectHemt circuits

Owner:北京诚博锐芯科技有限公司

High-temperature heat treatment device under magnetic field and method thereof for preparing bismuth ferrite film

The invention provides a high-temperature heat treatment device under a magnetic field and a method thereof for preparing a bismuth ferrite film. The device comprises a tube type heating furnace, wherein the tube type heating furnace is arranged between magnet pole heads of a direct current water-cooling magnet, the direct current water-cooling magnet is connected with a direct-current magnet power supply and a circulating water-cooling system, the heating cavity of the tube type heating furnace is communicated with a vacuumizing system and an atmosphere control system; the tube type heating furnace is also connected with a temperature controller; the water-cooling cavity is formed by adopting a double-layer nonmagnetic stainless steel material by the shell of the tube type heating furnace; heating bodies are connected in series by four silicon carbide rods; a high-temperature resistant aluminum oxide heat insulating fiber material is used as a heat insulating material; and a high-temperature aluminum oxide ceramic tube or a quartz glass tube is used as a furnace tube. The device has the characteristics of small volume, high magnetic field utilization ratio and heating efficiency,and the like, can be used for carrying out the synthesis and the heat treatment on materials below 2 Tesla of the magnetic field and under the condition of vacuum or atmosphere. The microstructure and the properties of the bismuth ferrite film prepared by the device are improved.

Owner:HEFEI INSTITUTES OF PHYSICAL SCIENCE - CHINESE ACAD OF SCI +1

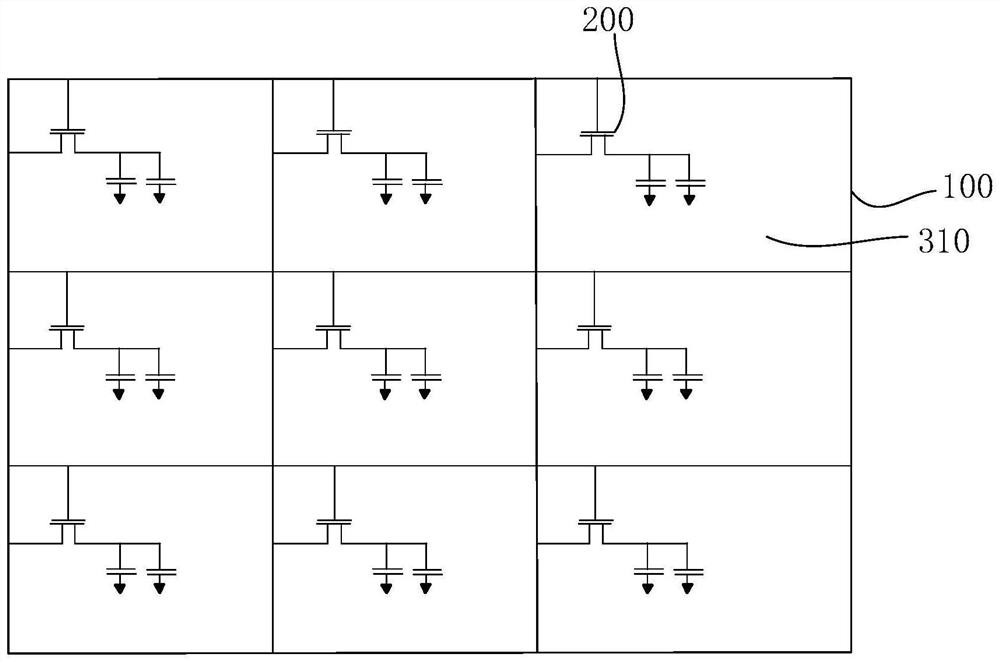

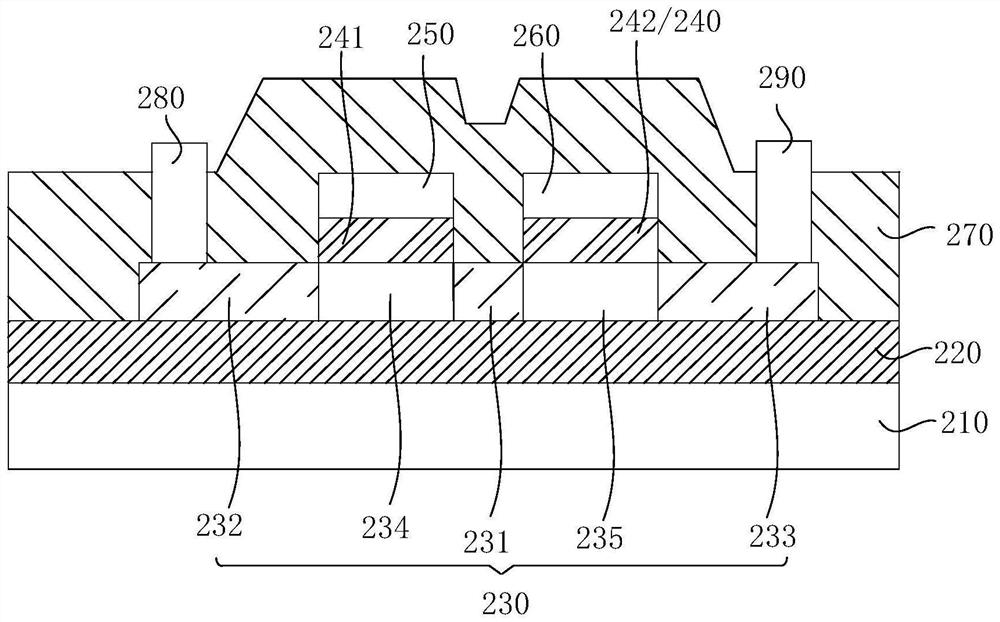

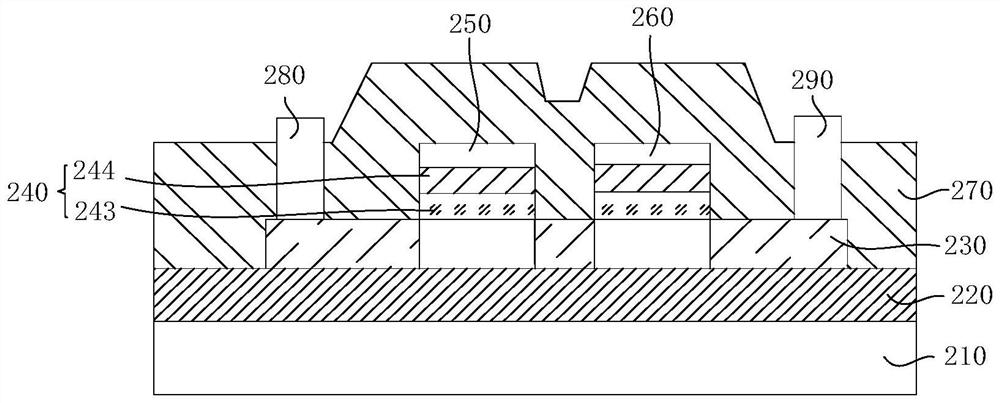

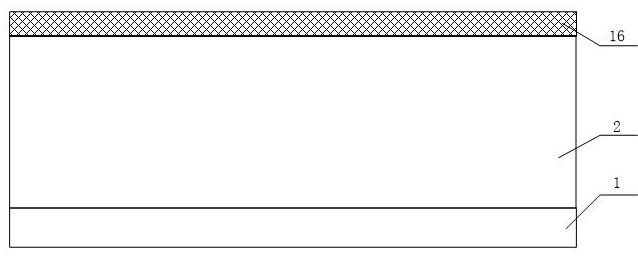

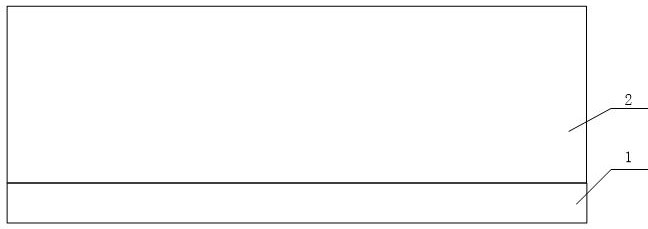

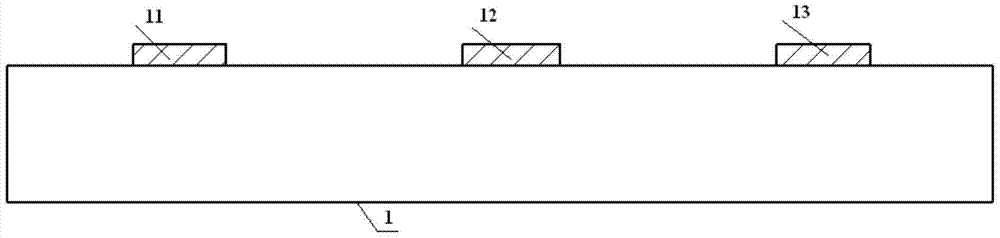

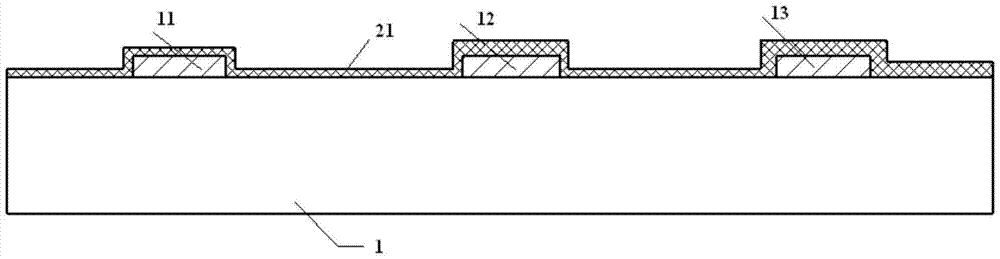

Active switch, manufacturing method thereof and display panel

PendingCN112542516AImprove controlImprove leakage performanceTransistorSolid-state devicesInsulation layerIndium gallium zinc oxide

The invention discloses an active switch, a manufacturing method thereof and a display panel. The active switch comprises a substrate, a buffer layer, an active layer, a gate insulation layer, a firstgate, a second gate, a passivation layer, a source electrode and a drain electrode which are stacked in sequence; the active layer is composed of indium gallium zinc oxide; the first gate and the second gate are arranged in parallel. and is located between the source electrode and the drain electrode; the source electrode and the drain electrode penetrate through the passivation layer and are connected with the two ends of the active layer respectively. With the active switch with the double-top-gate structure adopted, the parallel double top gates are equivalent to two cascaded active switches which are controlled by the same gate signal; with the double-top-gate structure adopted, the off-state leakage current can be obviously reduced without influencing on-state current, so that the gate control capability can be improved, the electric leakage effect of a TFT is improved, and the stability of the indium gallium zinc oxide type active layer is improved.

Owner:BEIHAI HKC OPTOELECTRONICS TECH CO LTD +1

Semiconductor device forming method

ActiveCN102569089BIncrease spacingImprove leakage performanceSemiconductor/solid-state device manufacturingMetal silicideEngineering

The invention provides a semiconductor device forming method, which comprises the steps that: a substrate, a grid structure positioned on the substrate and side walls positioned at two sides of the grid structure are provided; an auxiliary side wall is formed on the surface of the side walls; a metal layer is formed on the surface of the auxiliary side wall and the exposed substrate; and the metal layer is subjected to annealing, metal silicide is formed in the substrate, the auxiliary side wall is used for preventing the metal layer from transversely diffusing into the side walls, and the formation of the metal silicide on the side walls is avoided. The semiconductor device forming method has the advantages that the auxiliary side wall is formed on the side walls, the gap of the metal silicide in the substrate positioned at two sides of the grid structure is enlarged, the electric leakage performance in an enhancement channel of the metal silicide formed through the metal diffusion is avoided, and the electric connection of a source / drain region and a grid electrode is further avoided, so the performance of a semiconductor device is improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

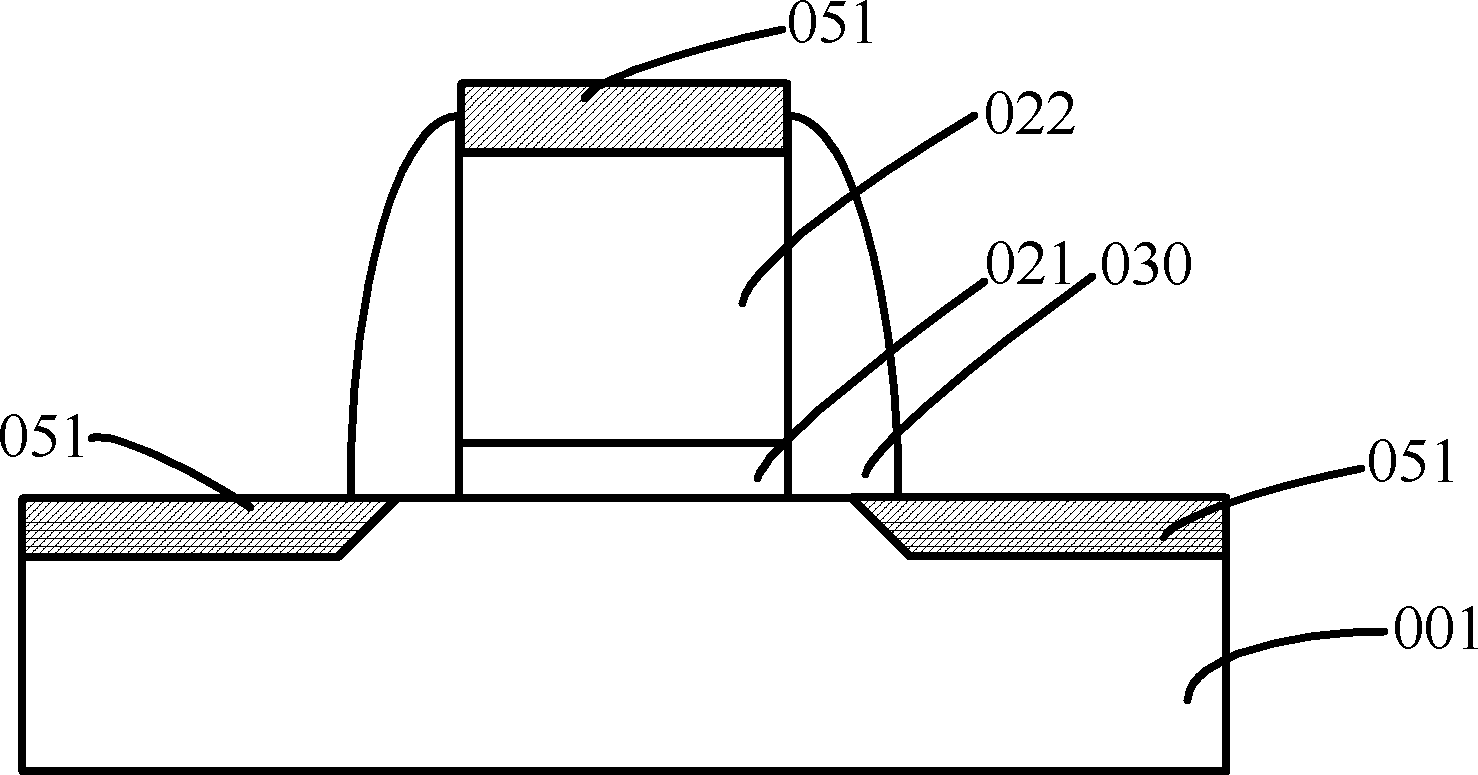

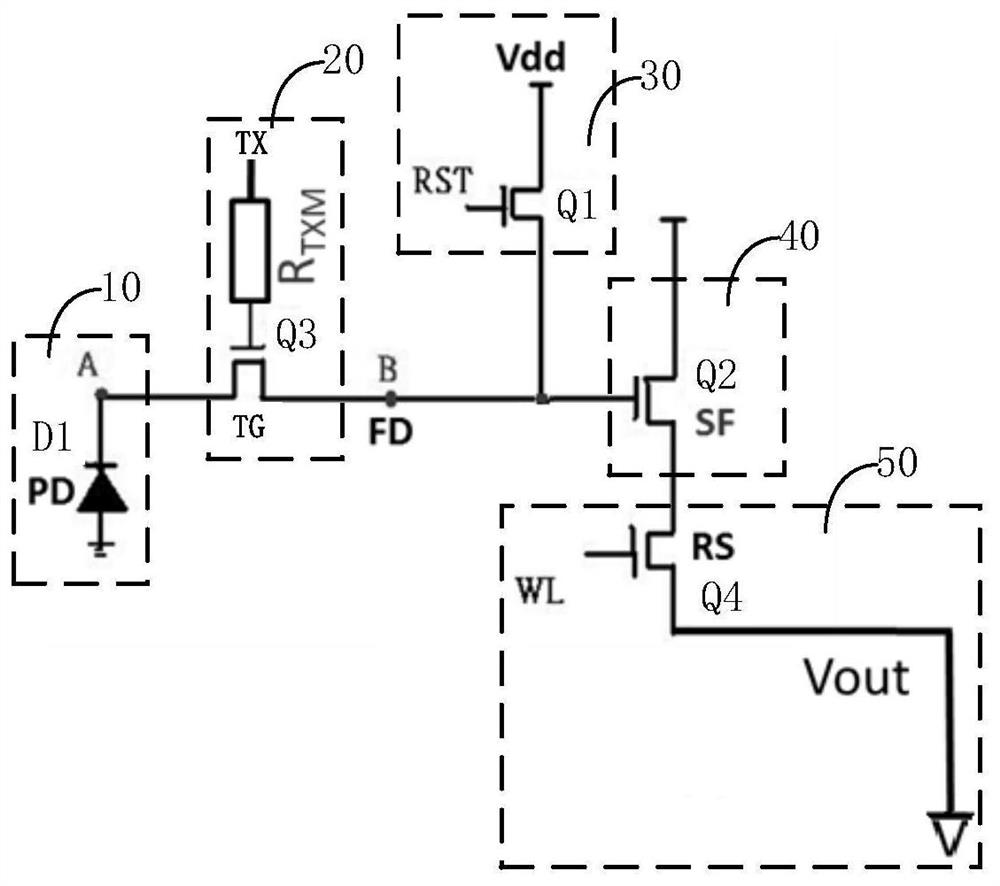

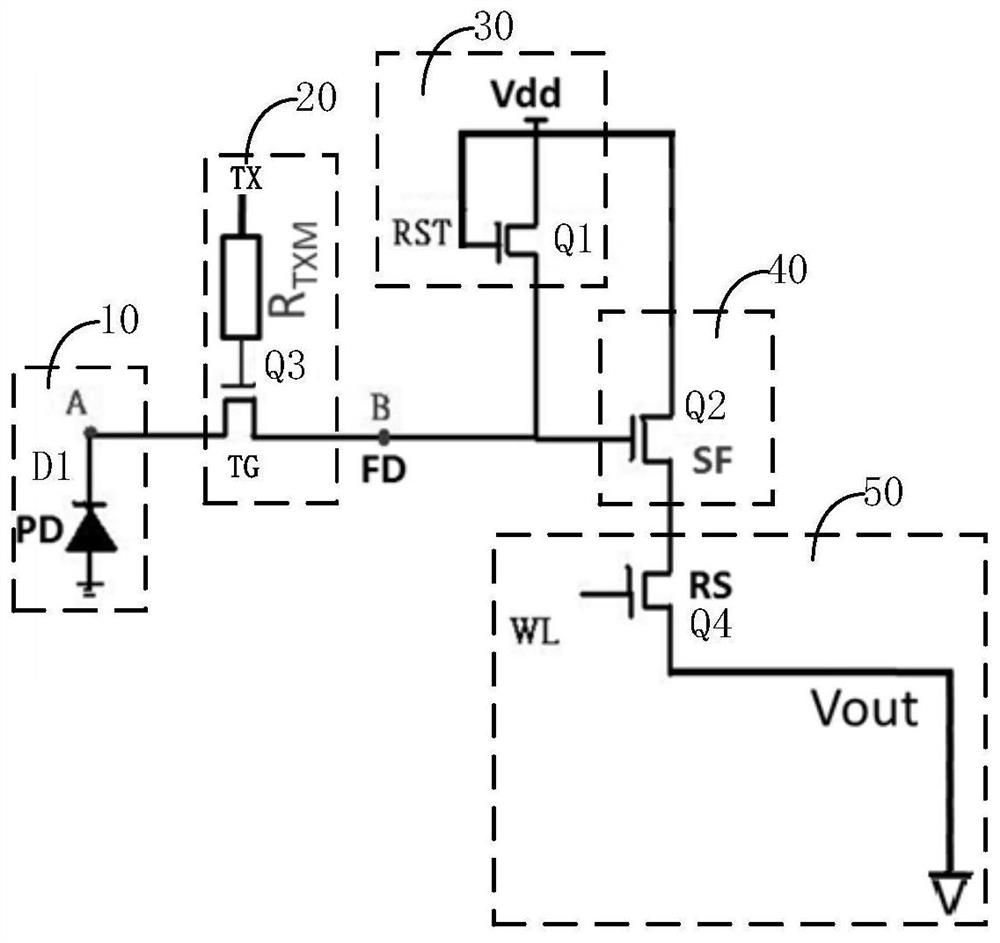

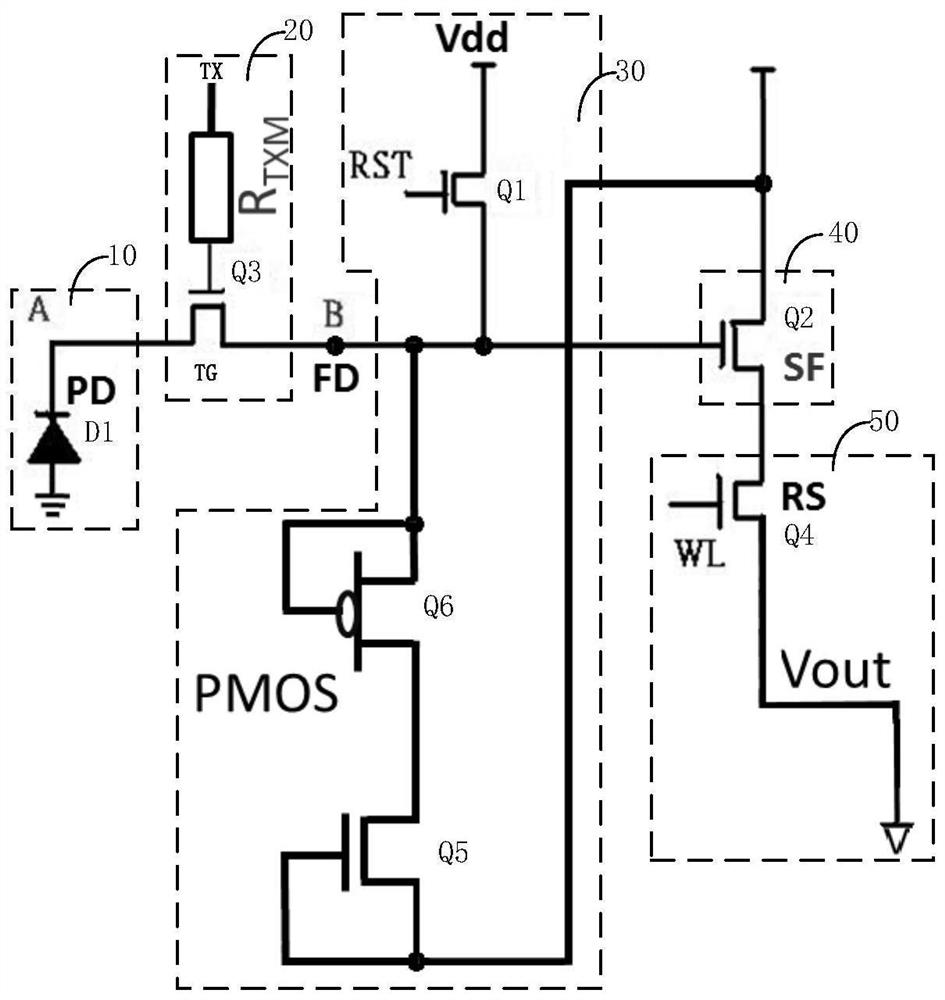

CIS sensor having linear logarithm output

ActiveCN112565642ASmall pixel sizeIncrease light sensitivityTelevision system detailsColor television detailsControl signalHemt circuits

The invention discloses a CIS sensor with linear logarithm output. The sensor comprises a photoelectric induction module which is used for converting an optical signal into a photoelectric signal; a charge transmission module used for transmitting the photoelectric signal generated by the photoelectric sensing module to a floating node FD under the control of a transmission control signal TX; a linear logarithm module used for outputting a linear signal level or a logarithm signal level under the control of a memory resistor, and maintaining the memory of illumination so as to maintain the linear or logarithm output of illumination intensity selection; a source follower module used for isolating and outputting charges of the floating node FD; and a selection module used for transmitting the photoelectric signal isolated and output by the source follower module to a subsequent circuit under the control of an output word line WL of a decoding circuit.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Electrostatic protection structure of image sensor and image sensor

ActiveCN109638011AImprove electrostatic discharge performanceLower resistanceSolid-state devicesDiodeInterconnectionElectrical impedance

The present invention provides an electrostatic protection structure of an image sensor and an image sensor, the image sensor comprises: a substrate including a plurality of pixel regions; a first metal interconnection layer arranged on one side of the substrate, including a pixel peripheral circuit; and a second metal layer arranged on the other side of the substrate. The electrostatic protectionstructure comprises: a first electrostatic discharge protection circuit arranged on the first metal interconnection layer and a second electrostatic discharge protection circuit arranged on the second metal layer; wherein the impedance of the second electrostatic discharge protection circuit is smaller than that of the first electrostatic discharge protection circuit, and the second electrostaticdischarge protection circuit and the first electrostatic discharge protection circuit have at least one access point. The electrostatic protection structure can reduce the resistance of a leakage path and improve the electrostatic discharge performance of a chip under the premise of not increasing the chip area.

Owner:北京诚博锐芯科技有限公司

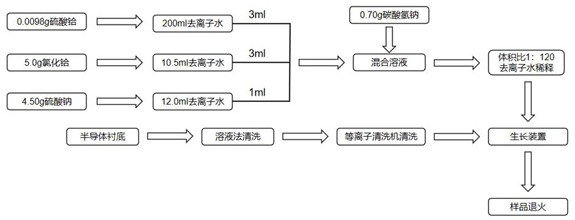

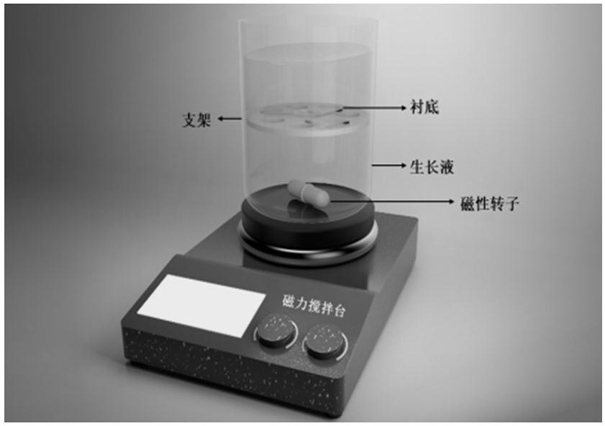

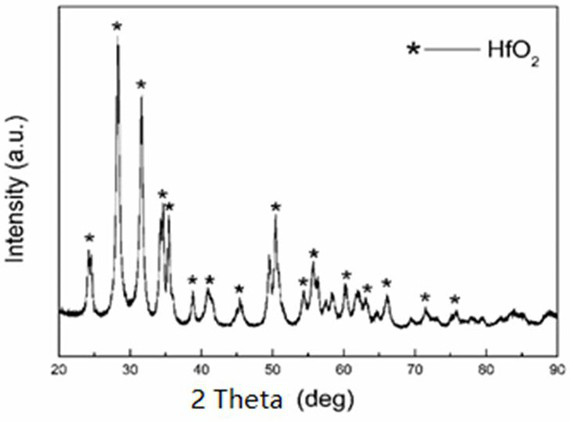

Method for preparing hafnium oxide film by chemical liquid phase deposition method

ActiveCN114411124AImprove transmittanceLow costLiquid/solution decomposition chemical coatingInorganic saltsSulfate radicals

The invention discloses a method for preparing a hafnium oxide film by a chemical liquid phase deposition method, which mainly comprises the following steps: carrying out double hydrolysis reaction on inorganic salt of hafnium and strong-alkali weak-acid salt, adding sulfate ions capable of promoting hydrolysis reaction and coagulation, and regulating the pH value of the solution by controlling the amount of the strong-alkali weak-acid salt to prepare the hafnium oxide film. According to the present invention, the deposition is slowly separated out and deposited on the surface of the substrate, and annealing treatment is performed to obtain the compact and continuous hafnium oxide film with characteristics of good electric leakage and high transmittance, such that the novel hafnium oxide film preparation method can be used as the low-cost and simple-process novel hafnium oxide film preparation method, and can be used in optical and electrical devices.

Owner:FUZHOU UNIV

Method for forming semiconductor device

ActiveCN102468150BImprove diffusion abilityPrevent proliferationSemiconductor/solid-state device manufacturingSemiconductor devicesSource areaNickel silicide

The invention provides a method for forming a semiconductor device, comprising the following steps: providing a substrate, a grid structure positioned on the substrate and a source area and a drain area which are both positioned in two side substrates of the grid structure; forming a nickel alloy layer on the exposed substrate surface containing nickel and at least one of other metals and having the thickness of 150-400 angstrom; and annealing the nickel alloy layer to form a nickel silicide in the substrate. According to the method, the diffusing capacity of the subsequently-formed nickel silicide in platinum is improved through improving the thickness of the nickel alloy layer which is in the range of 150-400 angstrom to enhance the diffusion barrier performance of the platinum element to the nickel element, thereby avoiding the diffusion of nickel to channel regions below a gate oxidation layer, reducing the generation of NiSi2 layers and improving the problem of deteriorating the electric leakage performance due to the development of the NiSi2 layer to channels.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A kind of porous ultra-low dielectric constant material film and preparation method thereof

InactiveCN101789418BReduce roughnessLow dielectric constantSemiconductor/solid-state device detailsSolid-state devicesPower flowSurface roughness

The invention belongs to the technical field of integrated circuit manufacturing, and in particular relates to a porous ultra-low dielectric constant film material and a preparation method thereof. The preparation process of the present invention adopts a sol-gel process, using organosiloxane as a precursor, by controlling the ratio of the precursor, pore-forming agent, catalyst and solvent, the concentration of the solution, and conditions such as synthesis, post-treatment and annealing temperature , prepared an ultra-low dielectric constant porous thin film material. The process is simple, the prepared film contains ordered nanopores, the surface of the film is uniform, the roughness is low, and the thermal stability is good, the dielectric constant is 1.9-2.0, and the leakage current density is 10-8 at 1MV / cm ~10-9A / cm2 order of magnitude.

Owner:FUDAN UNIV

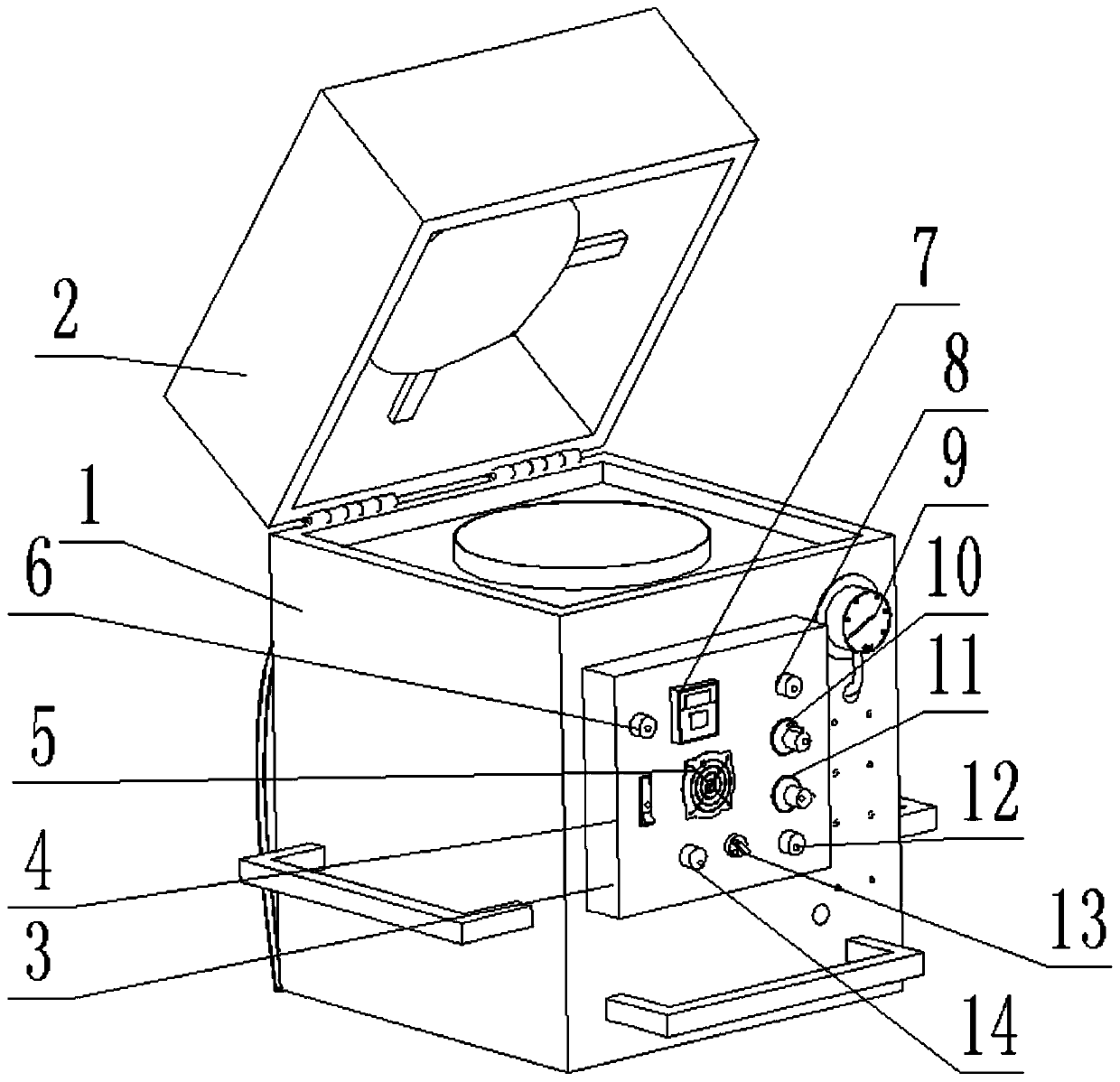

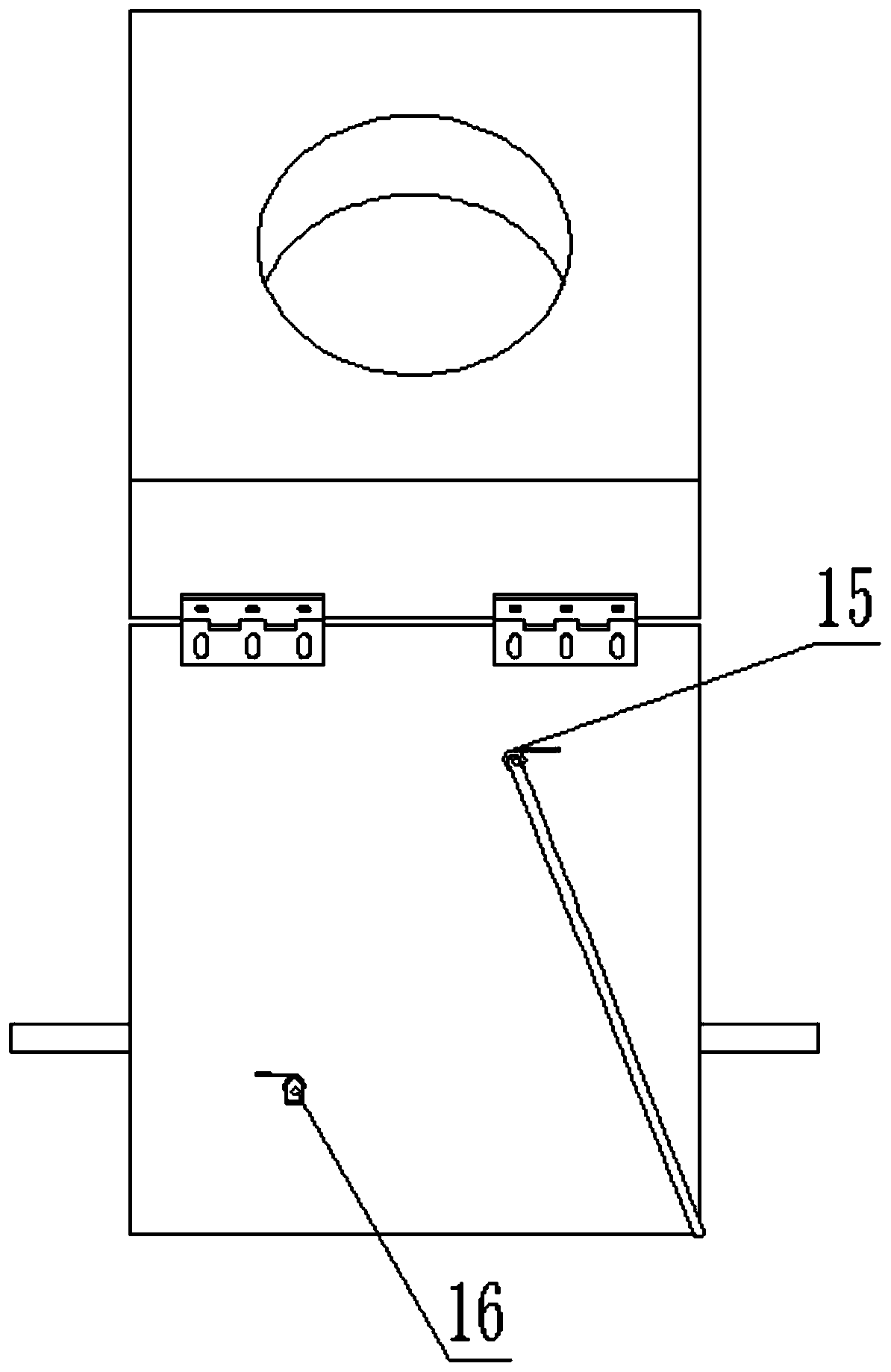

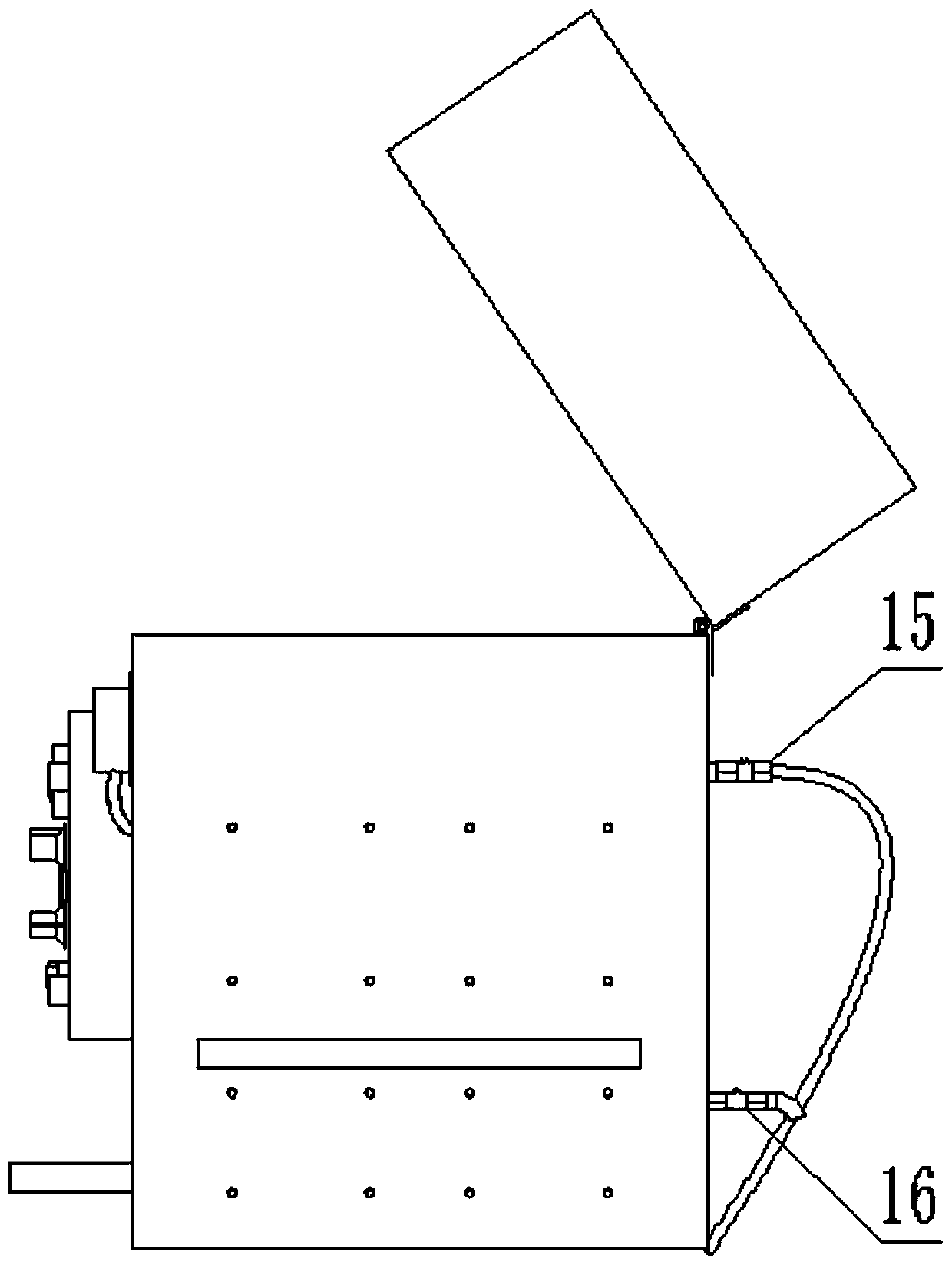

Fast wine brewing machine

InactiveCN110093222AMellow tasteFast processingAlcoholic beverage preparationElectric dischargeRapid processing

The invention discloses a fast wine brewing machine comprising a case; a case lid is arranged on the top of the case, and the case lid and the case are rotatingly connected through a hinge shaft. Theinterior of the case is a wine brewing chamber, and the wine brewing chamber is 70 cm in depth; a control panel is arranged on the front side face of the case and has a lip opening switch, a first heat generating pipe switch, a second heat generating pipe switch and a pot bottom switch; two heat generating pipes are arranged in the wine brewing chamber, one of the heat generating pipes has a powerof 6 kW, the other one of the heat generating pipes has a power of 3 kW, and the two heat generating pipes are connected with the first heat generating pipe switch and the second heat generating pipeswitch respectively. The first heat generating pipe switch is connected with a second switch indication lamp, and the second heat generating pipe switch is connected with a third switch indication lamp. The device has the advantages of rapid processing, high output, and mellow taste of produced wine, overall sealing, good electric discharge and leakage effects and the like.

Owner:杨聪芸

Power device structure with esd and preparation method thereof

ActiveCN113421829BReduce manufacturing costImprove leakage performanceSolid-state devicesSemiconductor/solid-state device manufacturingMetal electrodesDielectric layer

The invention provides a power device structure with ESD and a preparation method thereof. The device includes an N-type substrate, an N-type epitaxial layer, a first groove, a second groove, a P-type body region, a P-type active region, an N-type active region, a dielectric layer and a metal electrode, the first groove and the The second trenches are distributed at intervals in the N-type epitaxial layer. The first trench includes a gate oxide layer and a polysilicon ESD, and a P-type doped region is formed in the polysilicon ESD; the second trench includes a gate oxide layer and a polysilicon gate. The P-type body region is located in the N-type epitaxial layer between the trenches; the dielectric layer covers the first trench, the second trench and the P-type body region; the hole lead-out region is located in the dielectric layer and is connected to the polysilicon ESD The P-type doping region, the P-type active region, and the N-type active region in the P-type body region between the first trench and the second trench are in electrical contact; the metal electrode is located on the dielectric layer. The invention can effectively reduce the area of the ESD structure, is beneficial to process planarization and reduces device manufacturing cost, and helps to improve ESD leakage performance.

Owner:SHANGHAI NATLINEAR ELECTRONICS CO LTD +1

Manufacturing method of array substrate, array substrate and display device

ActiveCN104465516BReduce parasitic capacitanceExcellent electrical propertiesTransistorSolid-state devicesParasitic capacitanceDisplay device

The invention provides a manufacturing method of an array substrate, an array substrate and a display device. The manufacturing method of the array substrate includes the step of arranging a grid metal layer on the substrate and the step of arranging a source drain metal layer on the substrate, the grid metal layer comprises a grid electrode of a thin film transistor and a first pole plate of a storage capacitor, and the source drain metal layer comprises a source electrode and a drain electrode of the thin film transistor and a second pole plate of the storage capacitor; between the step of arranging the grid metal layer and the step of arranging the source drain metal layer, the manufacturing method of the array substrate further includes the steps that at least one non-channel contact interface grid insulating layer is arranged on the substrate, the part, corresponding to the grid electrode and / or the first pole plate, of the non-channel contact interface grid insulating layer is graphed and wholly or partially thinned; a channel contact interface grid insulating layer which is not graphed is arranged on the substrate, and a channel layer of the thin film transistor is arranged on the channel contact interface grid insulating layer. The electrical properties and the storage capacitance of the thin film transistor are improved, and stray capacitance is reduced.

Owner:BOE TECH GRP CO LTD

Dielectric film and its preparation method

ActiveCN110783103BImprove leakage performanceReduce lossThin/thick film capacitorFixed capacitor dielectricPolymer scienceDielectric membrane

Owner:INNER MONGOLIA UNIVERSITY

Transverse high-voltage power bipolar junction transistor and manufacturing method thereof

PendingCN107946356ACurvature effect reducedReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesEdge effectsEngineering

The invention discloses a transverse high-voltage power bipolar junction transistor and a manufacturing method thereof. Based on a conventional transverse power bipolar junction transistor, N-type ring injection is added between all collector regions and emitter regions, the layout of all metal in a first layer is optimized to enable a first layer of metal of a collector to completely cover the collector regions, the size is more than twice the junction depth of the collector regions, and the metal of an emitter is led out via a through hole and a second layer of metal. Theoretical analysis shows that when the device is in a reverse voltage withstanding working state, as the edges of all collector junctions are covered by a metal field plate, the curvature effect of the edge curved surfacejunction is greatly reduced and the withstanding voltage is increased sharply when the depletion region is diffused, while the introduction of N ring can greatly reduce the drain current between thecollector and the emitter of the device. Simulation and the actual tape-out result show that the transverse high-voltage power bipolar junction transistor has the advantage that under the condition oflittle influence of the remaining parameters, BVcbo is improved by over 40%, BVceo is improved by over 40%, and the leakage capacity is improved by one order of magnitude.

Owner:CHONGQING ZHONGKE YUXIN ELECTRONICS