Manufacturing method of array substrate, array substrate and display device

A technology of an array substrate and a manufacturing method, which is applied in the field of manufacturing array substrates, can solve the problems of insufficient charging of thin film transistors, increased parasitic capacitance, problems with images of display devices, etc., so as to enhance the anti-static breakdown and leakage capabilities, and reduce parasitics. Capacitance, improving electrical properties and the effect of storage capacitors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

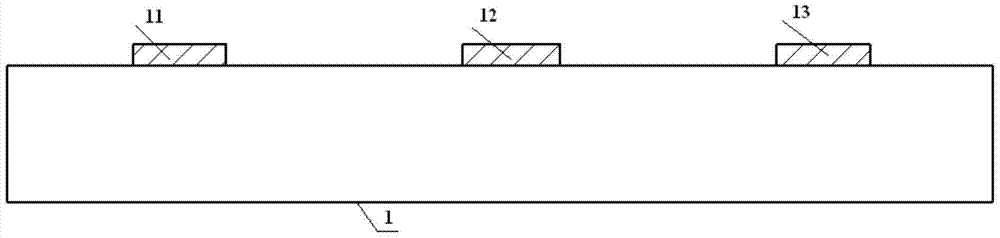

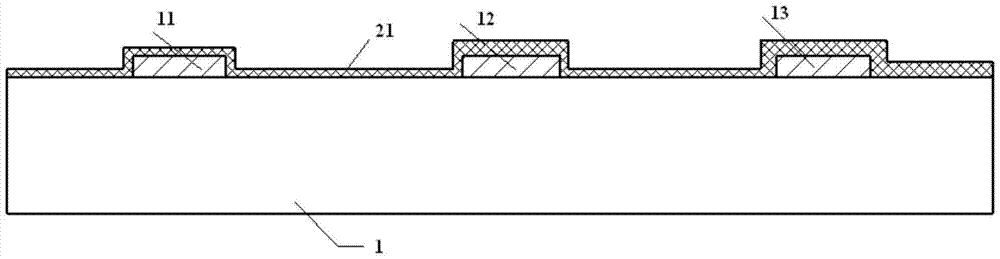

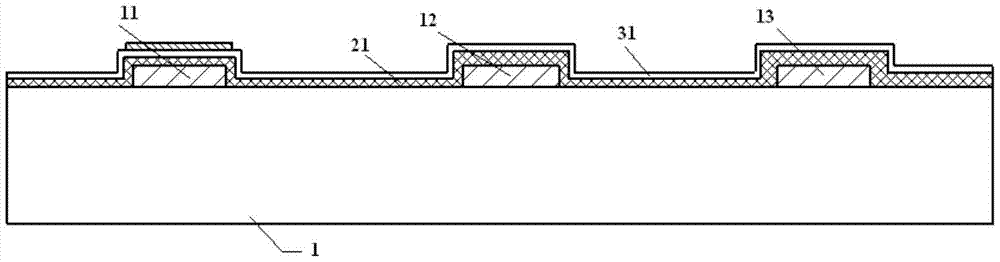

[0038] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0039] The method for manufacturing an array substrate according to an embodiment of the present invention includes the steps of providing a gate metal layer and a source-drain metal layer on the substrate, the gate metal layer including the gate of the thin film transistor and the first electrode of the storage capacitor plate, the source and drain metal layer includes the source of the thin film transistor, the drain of the thin film transistor and the second...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More