Patents

Literature

856 results about "Hafnium oxide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Apparatuses and methods for atomic layer deposition of hafnium-containing high-k dielectric materials

InactiveUS20050271813A1Steam generation heating methodsDecorative surface effectsGas phaseWater vapor

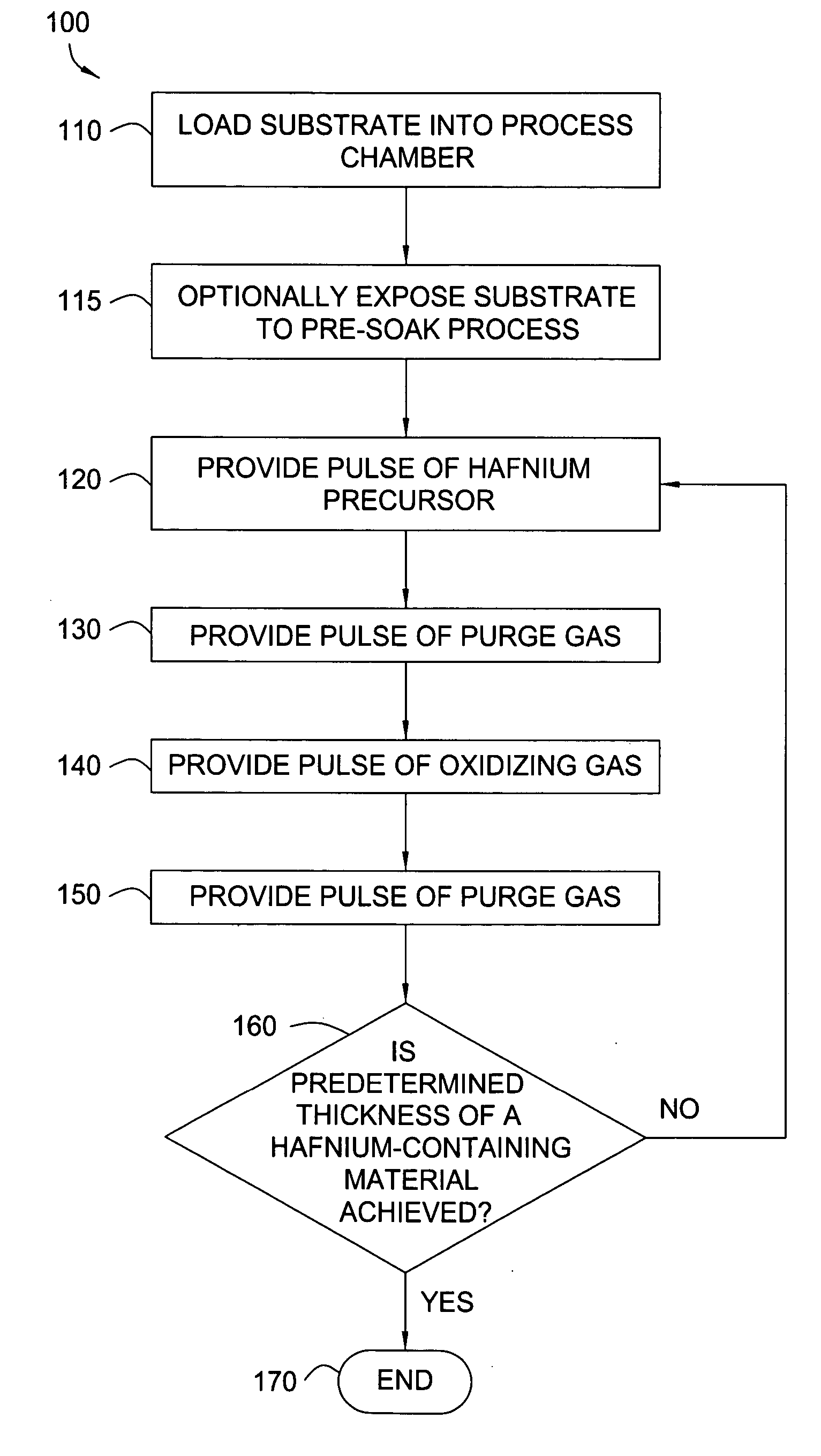

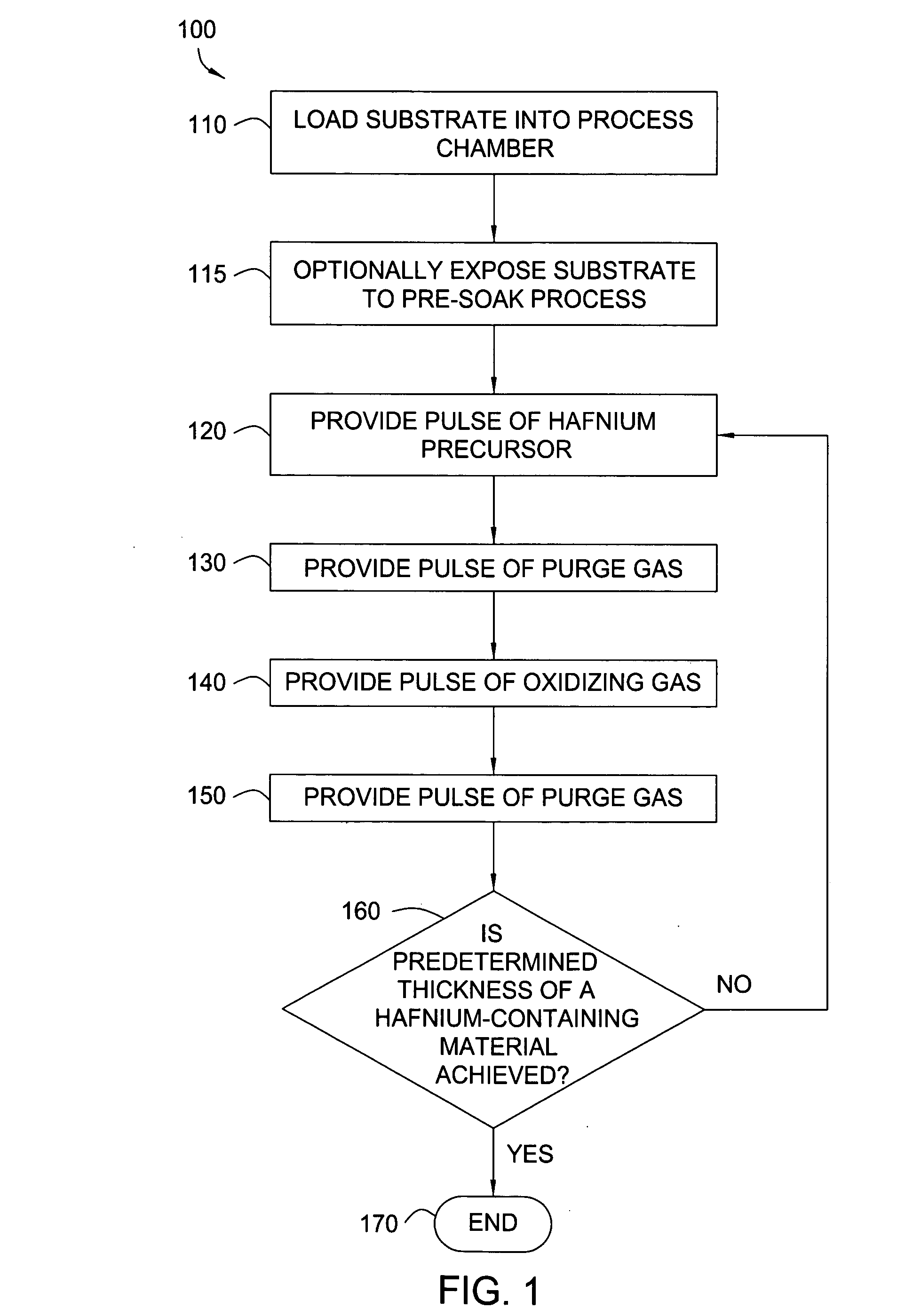

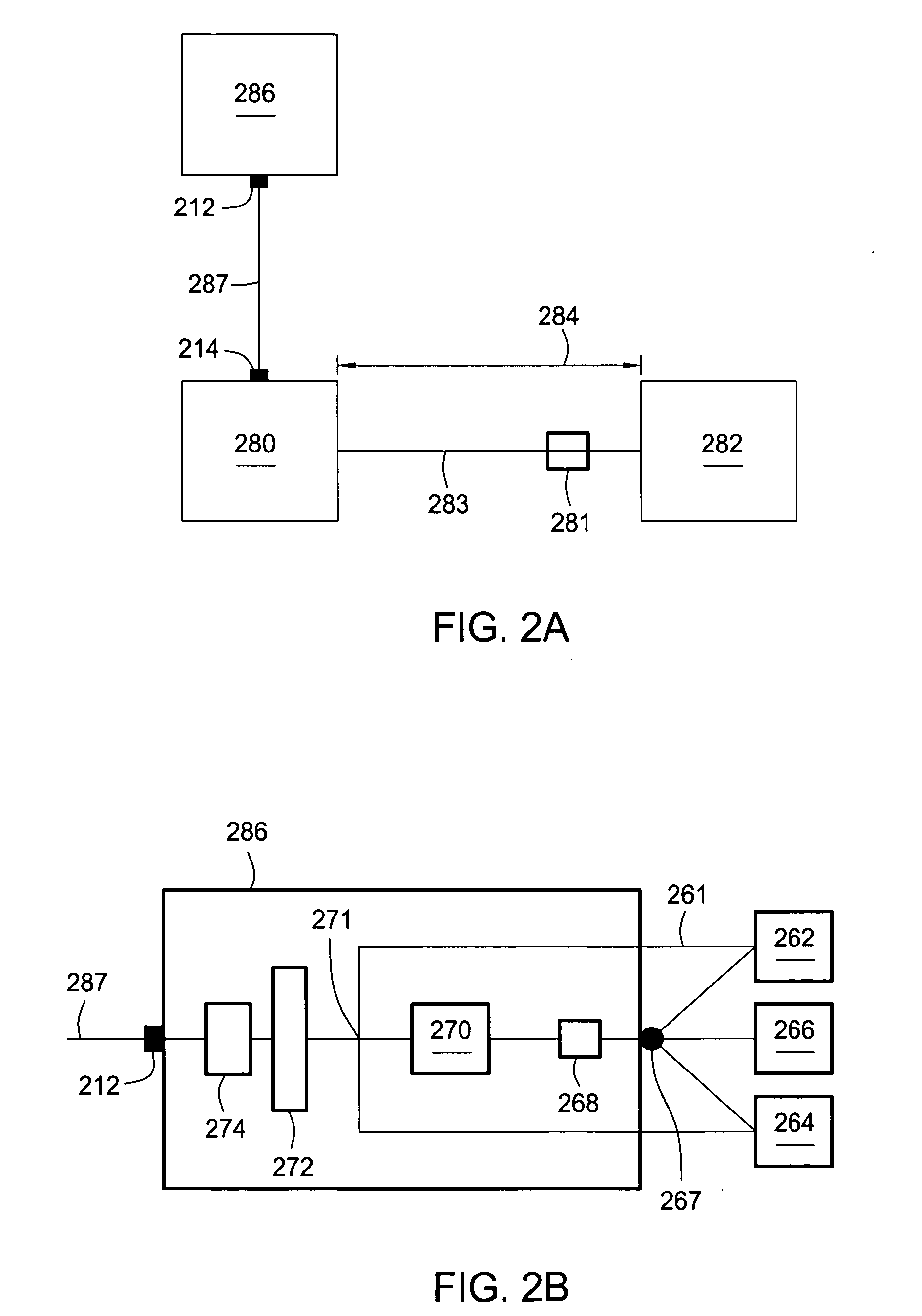

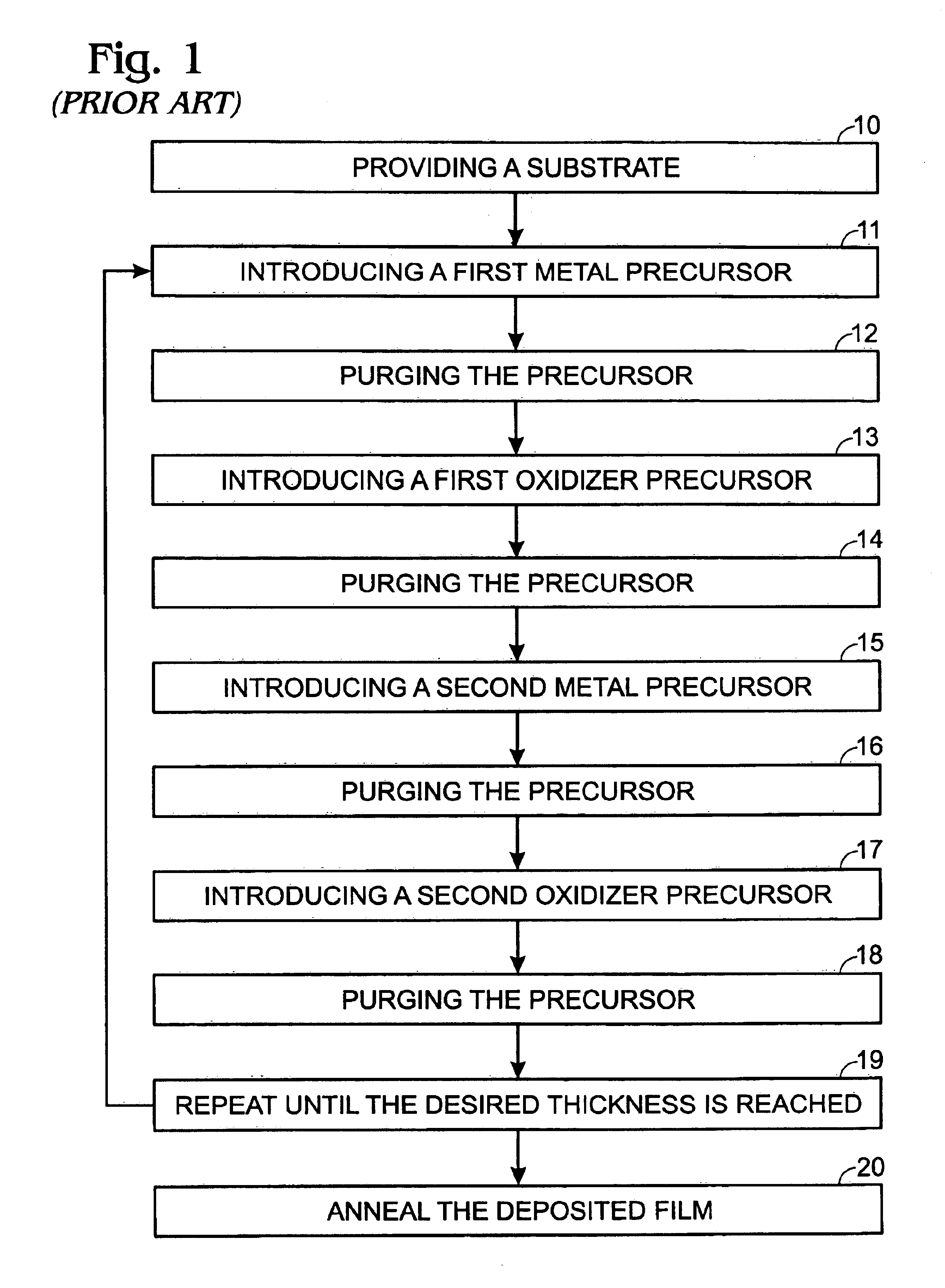

Embodiments of the invention provide methods for depositing dielectric materials on substrates during vapor deposition processes, such as atomic layer deposition (ALD). In one example, a method includes sequentially exposing a substrate to a hafnium precursor and an oxidizing gas to deposit a hafnium oxide material thereon. In another example, a hafnium silicate material is deposited by sequentially exposing a substrate to the oxidizing gas and a process gas containing a hafnium precursor and a silicon precursor. The oxidizing gas usually contains water vapor formed by flowing a hydrogen source gas and an oxygen source gas through a water vapor generator. In another example, a method includes sequentially exposing a substrate to the oxidizing gas and at least one precursor to deposit hafnium oxide, zirconium oxide, lanthanum oxide, tantalum oxide, titanium oxide, aluminum oxide, silicon oxide, aluminates thereof, silicates thereof, derivatives thereof or combinations thereof.

Owner:APPLIED MATERIALS INC

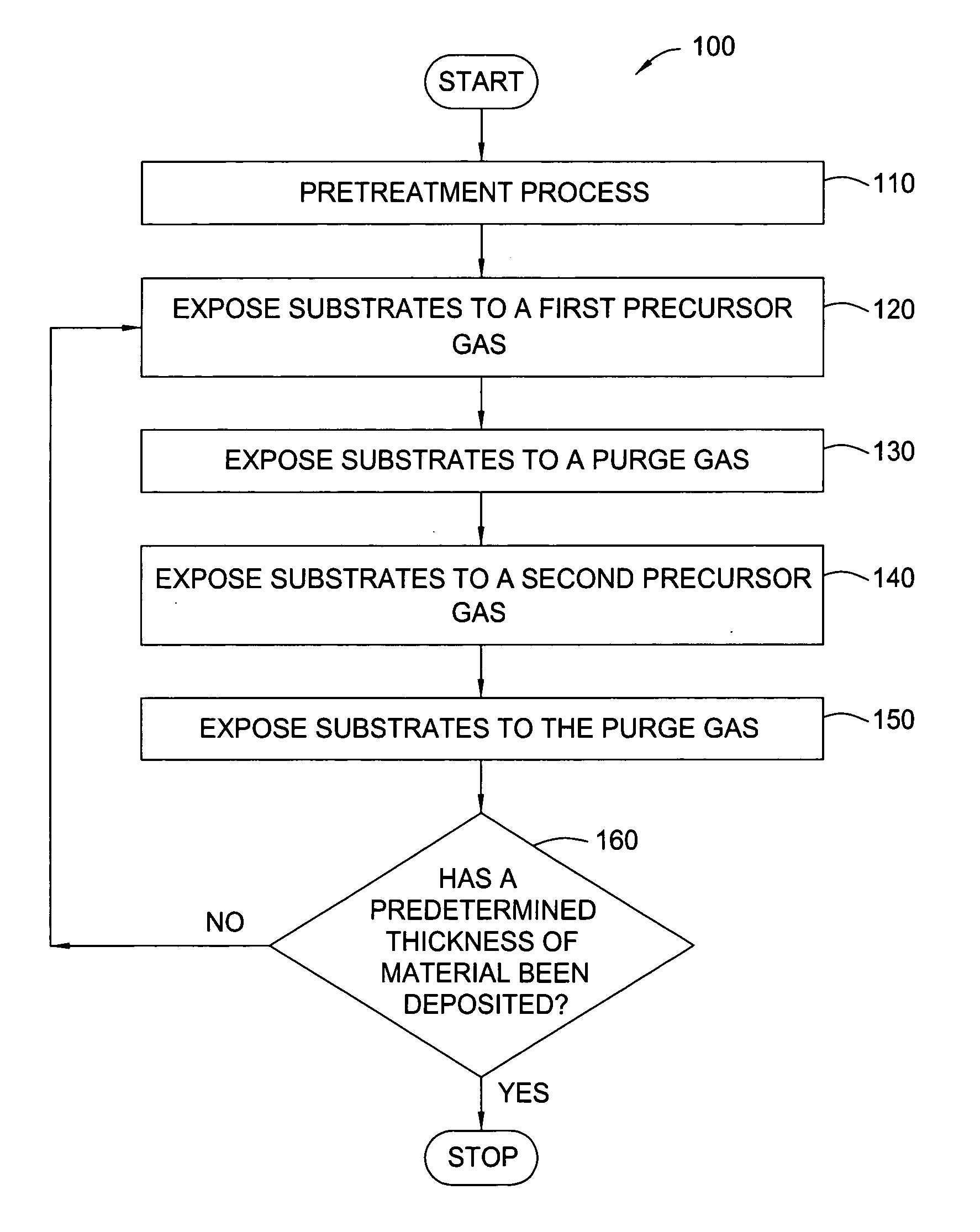

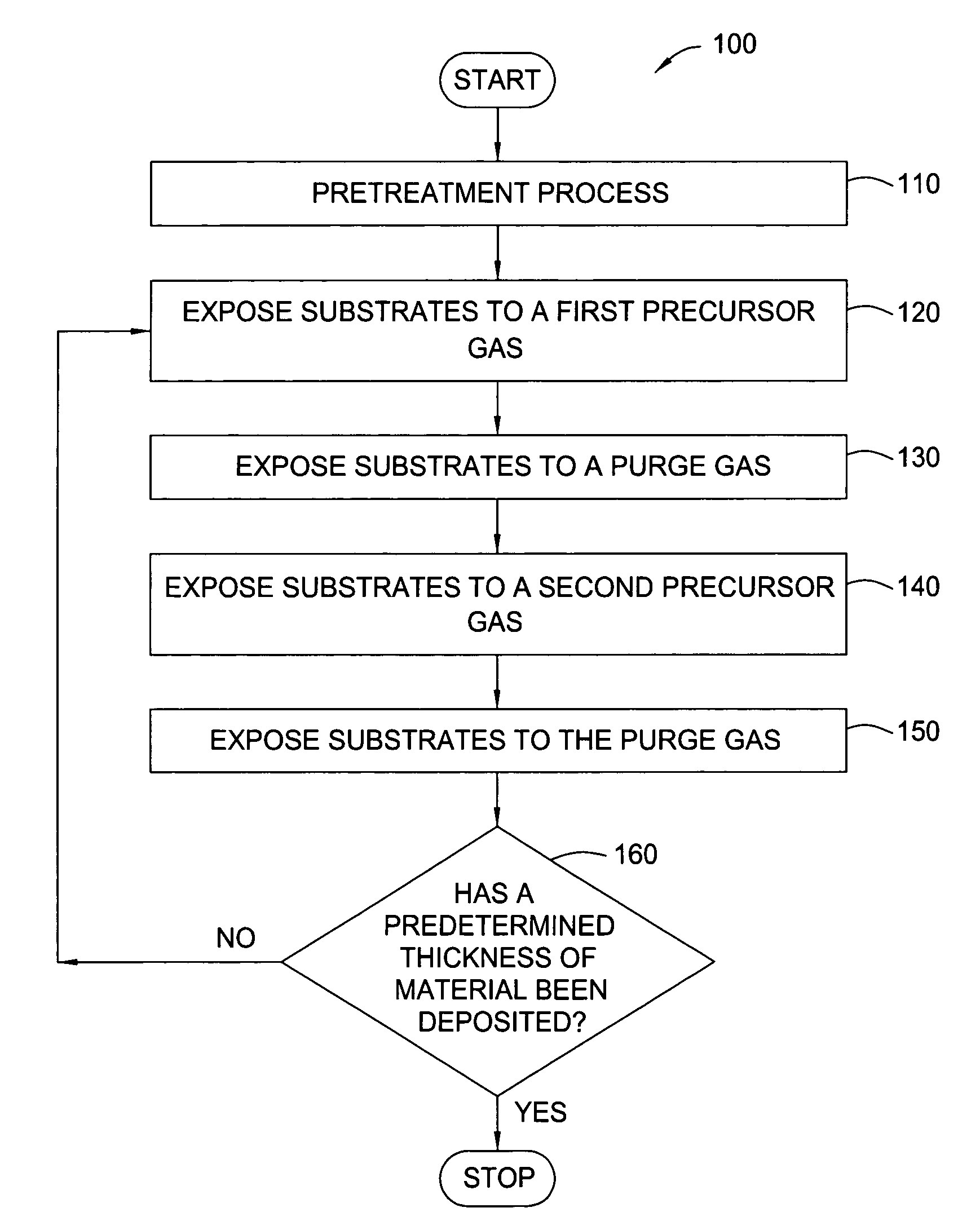

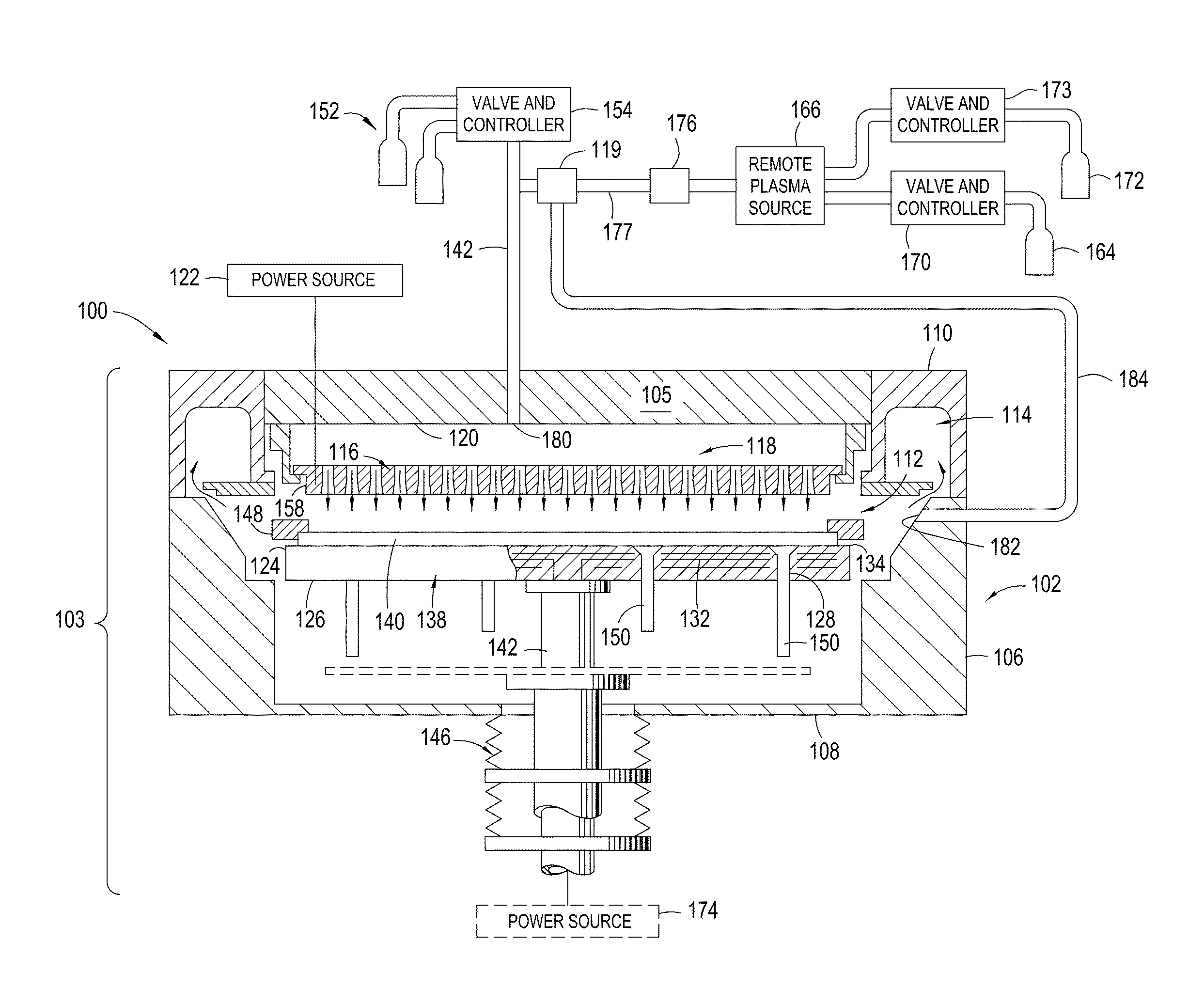

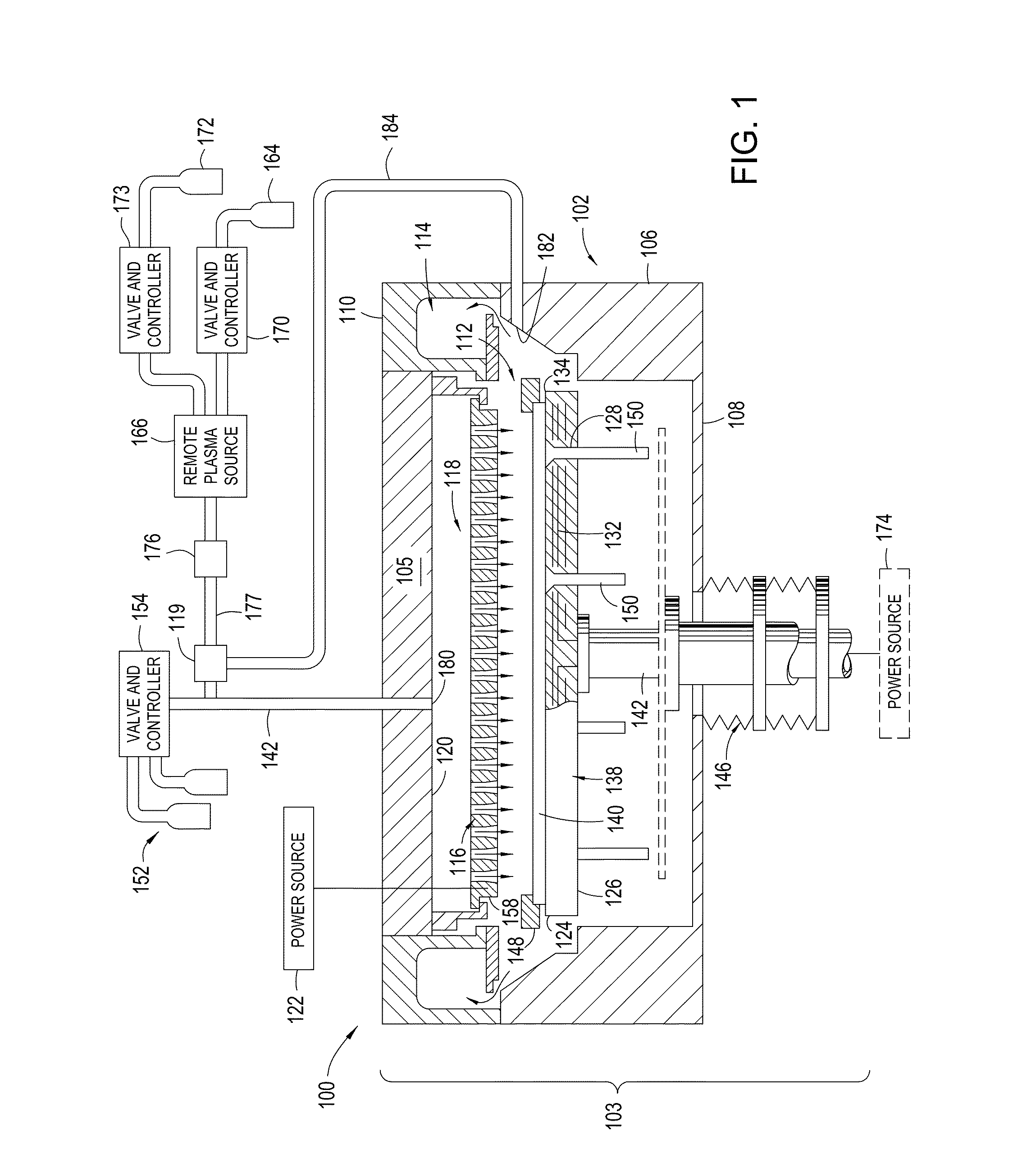

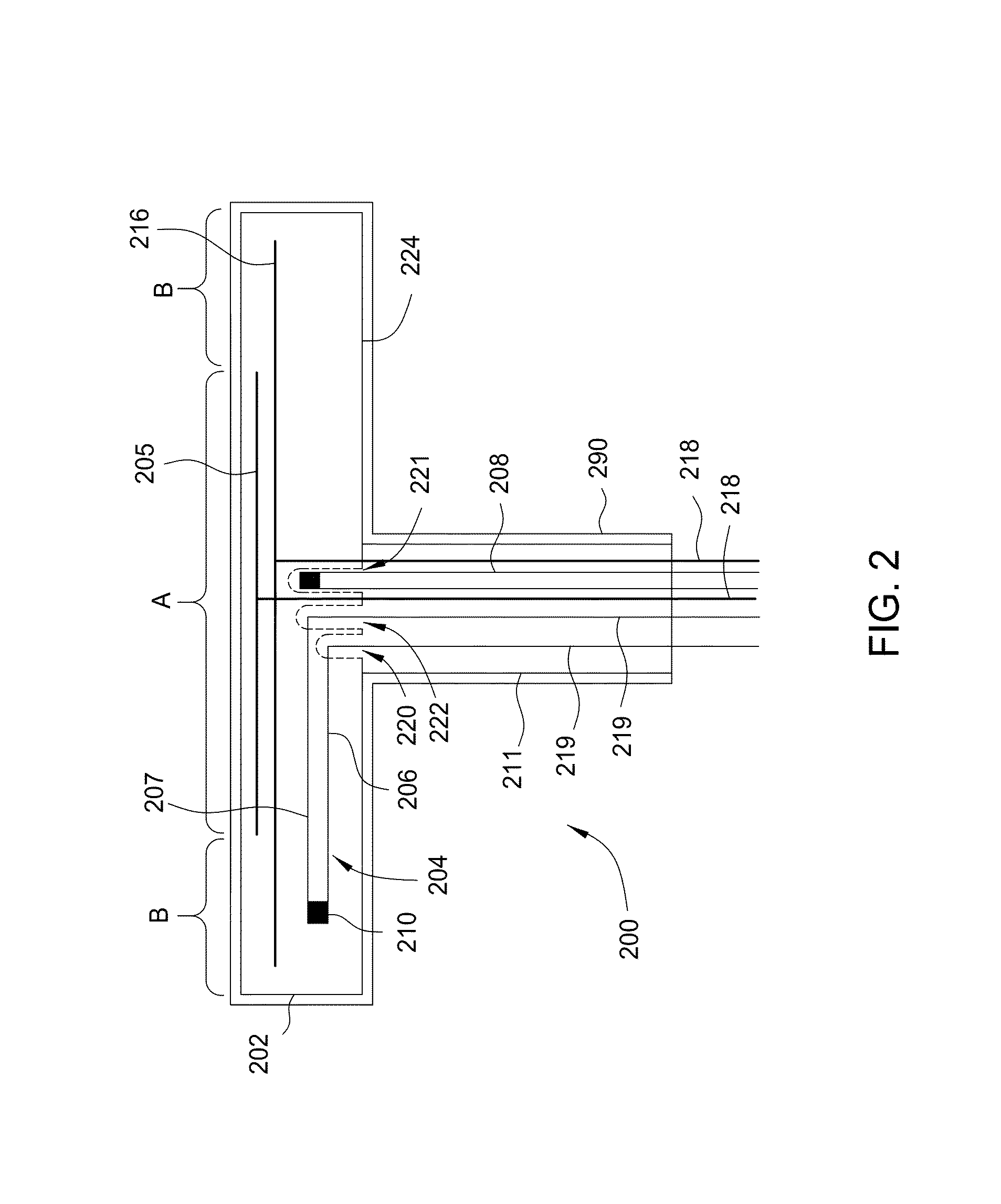

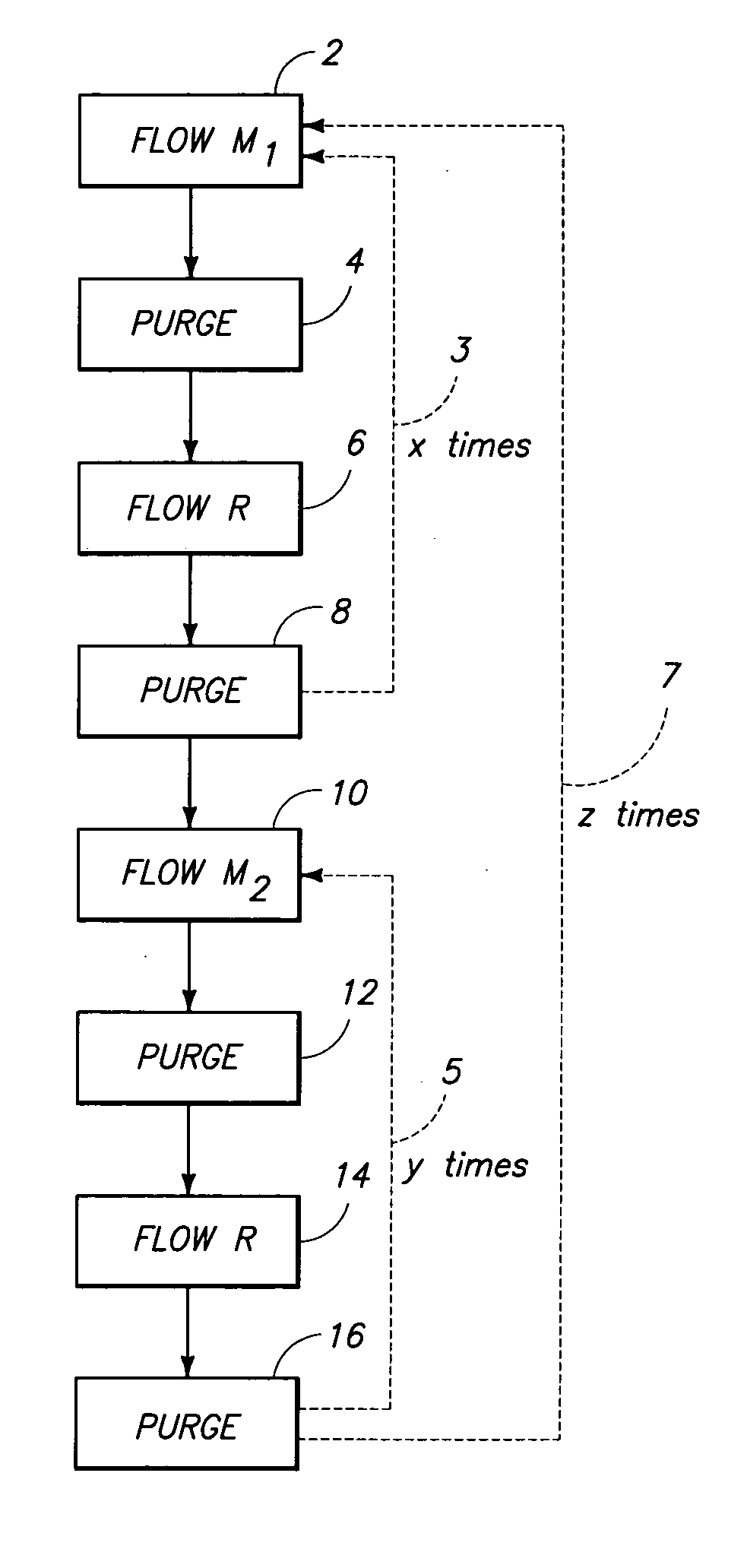

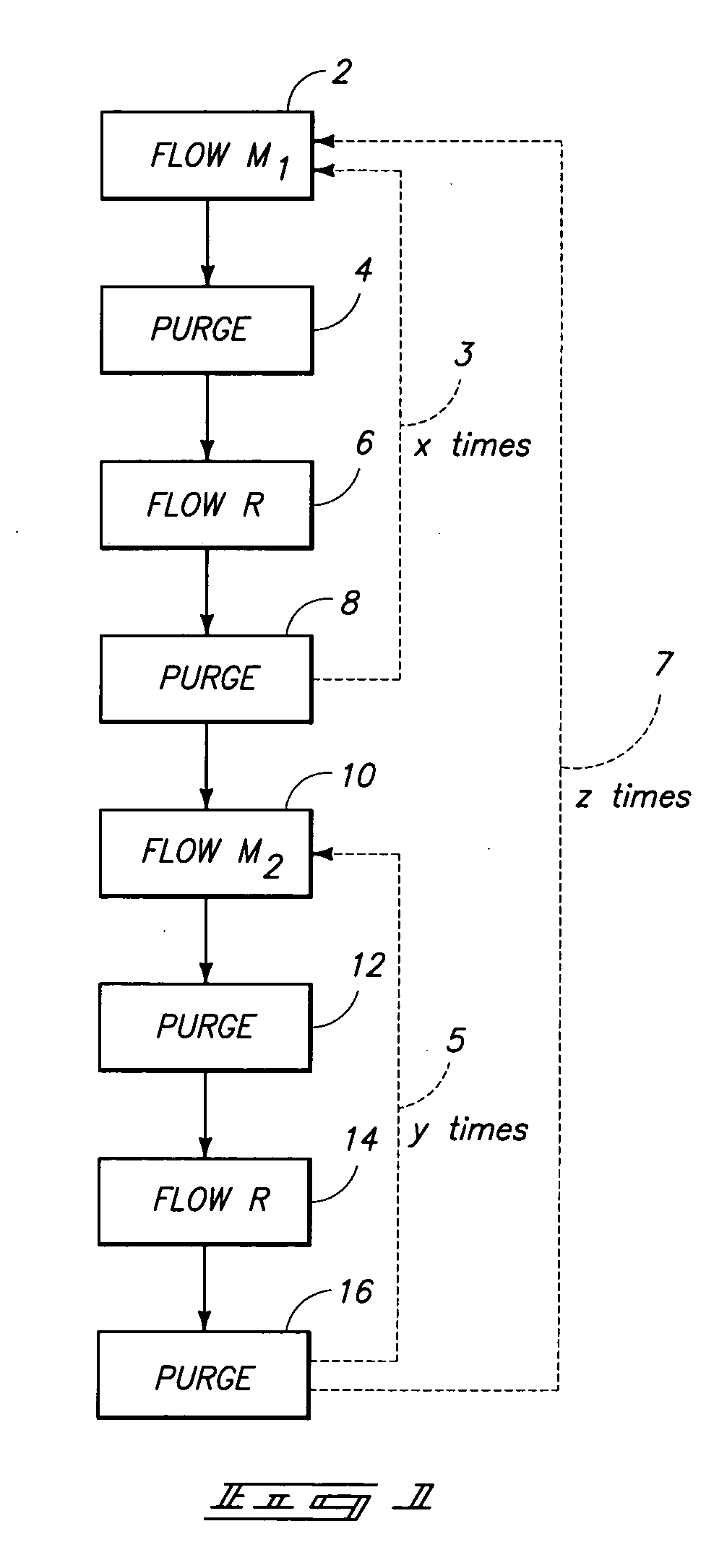

Treatment processes for a batch ALD reactor

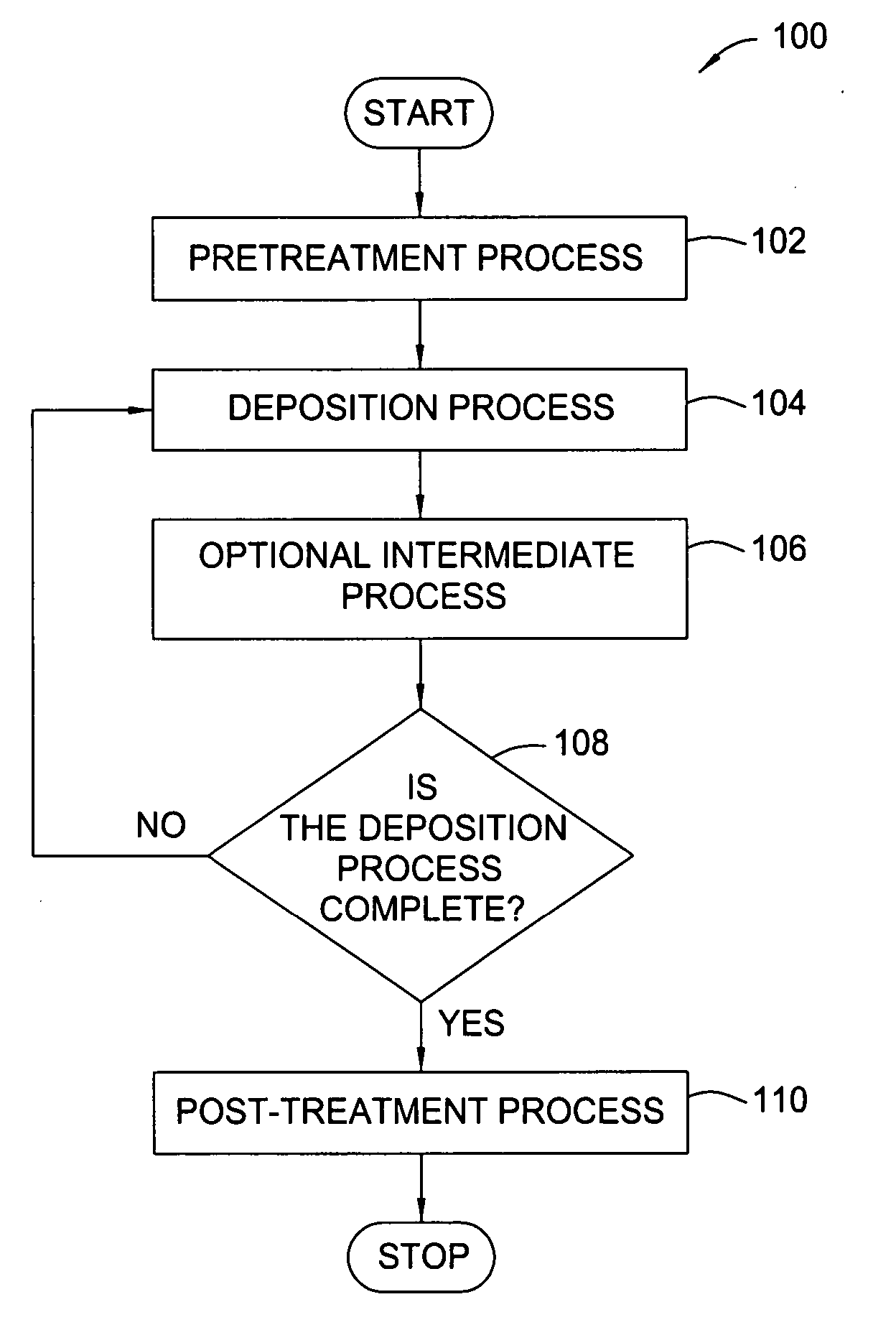

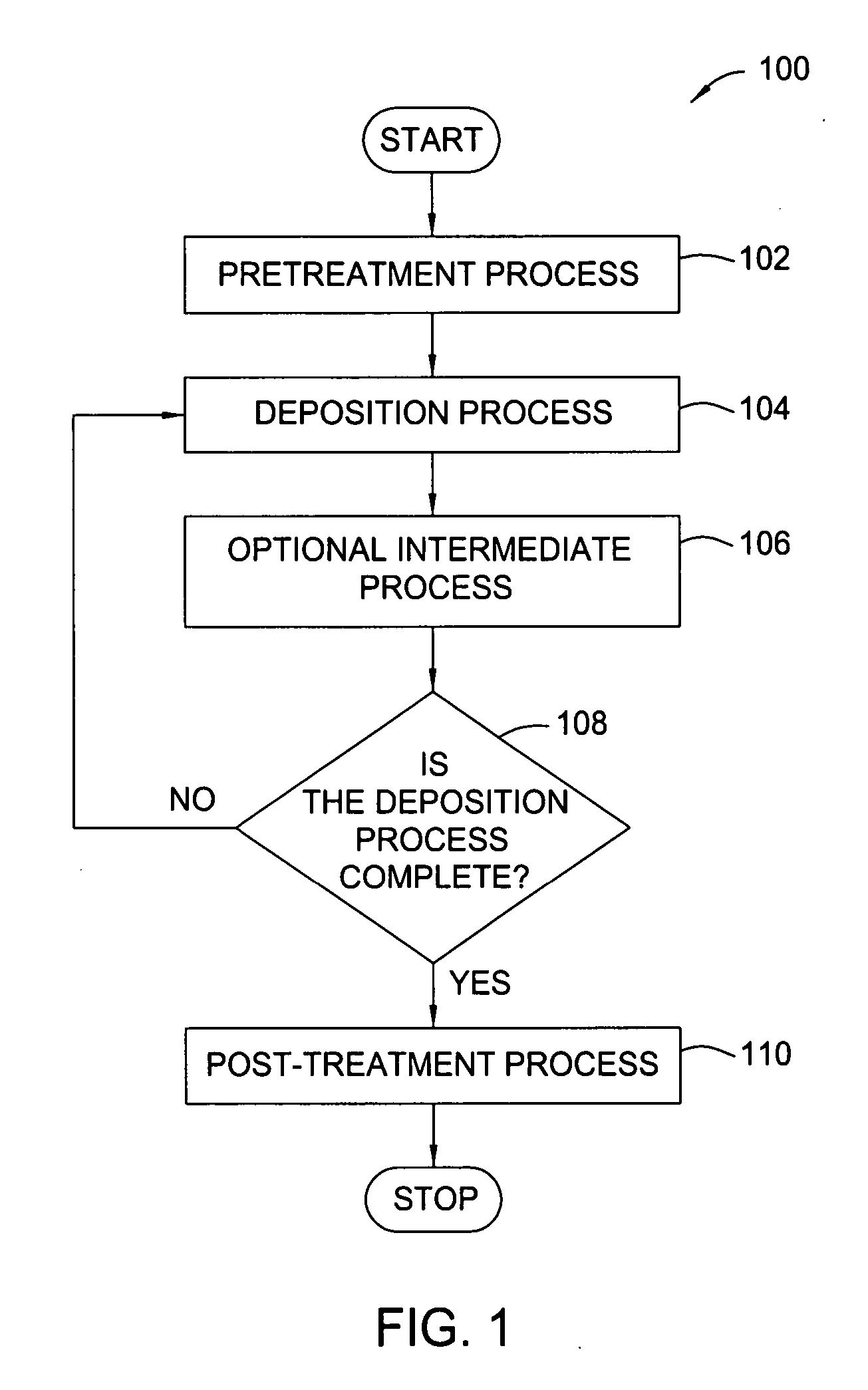

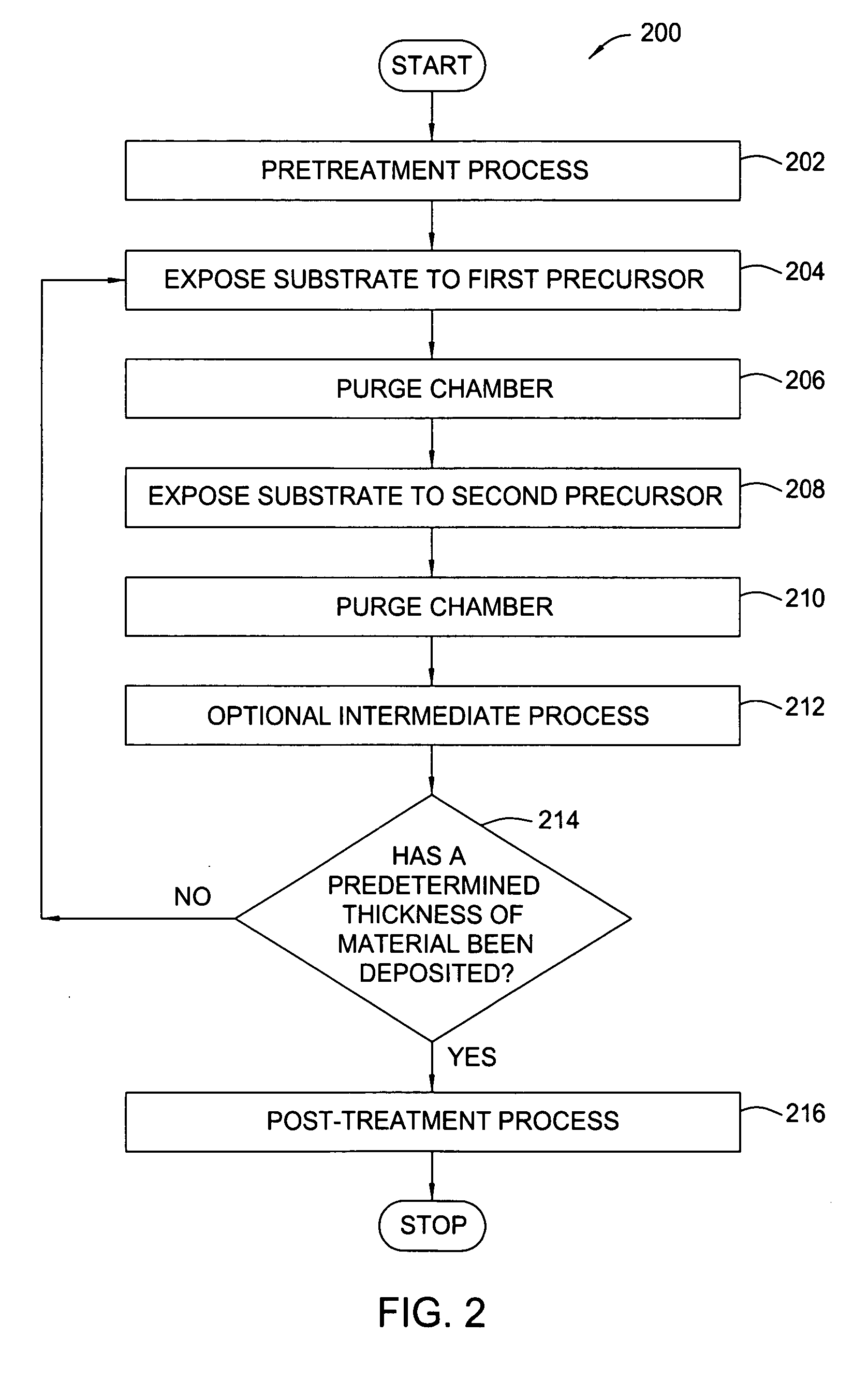

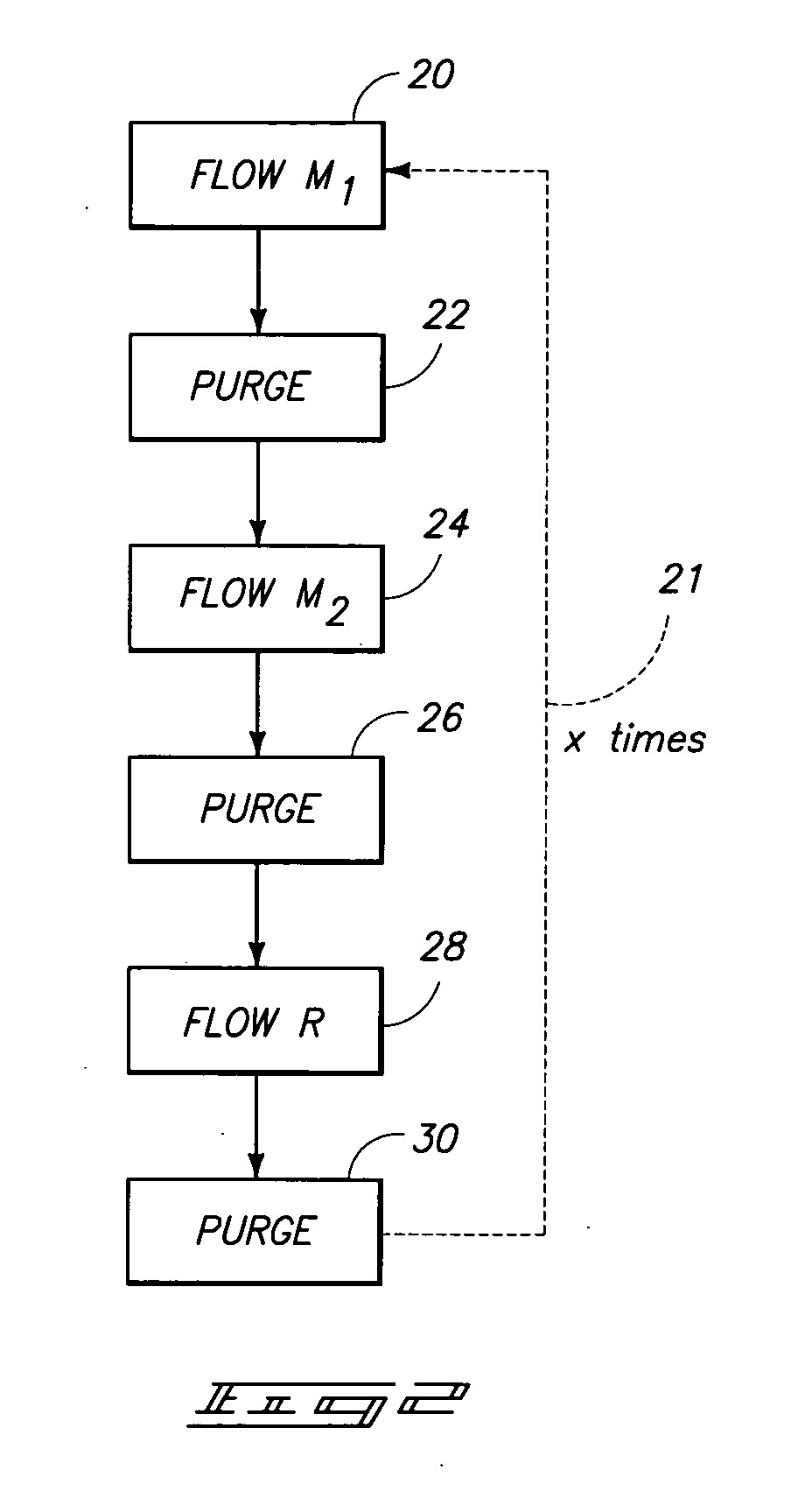

Embodiments of the invention provide treatment processes to reduce substrate contamination during a fabrication process within a vapor deposition chamber. A treatment process may be conducted before, during or after a vapor deposition process, such as an atomic layer deposition (ALD) process. In one example of an ALD process, a process cycle, containing an intermediate treatment step and a predetermined number of ALD cycles, is repeated until the deposited material has a desired thickness. The chamber and substrates may be exposed to an inert gas, an oxidizing gas, a nitriding gas, a reducing gas or plasmas thereof during the treatment processes. In some examples, the treatment gas contains ozone, water, ammonia, nitrogen, argon or hydrogen. In one example, a process for depositing a hafnium oxide material within a batch process chamber includes a pretreatment step, an intermediate step during an ALD process and a post-treatment step.

Owner:APPLIED MATERIALS INC

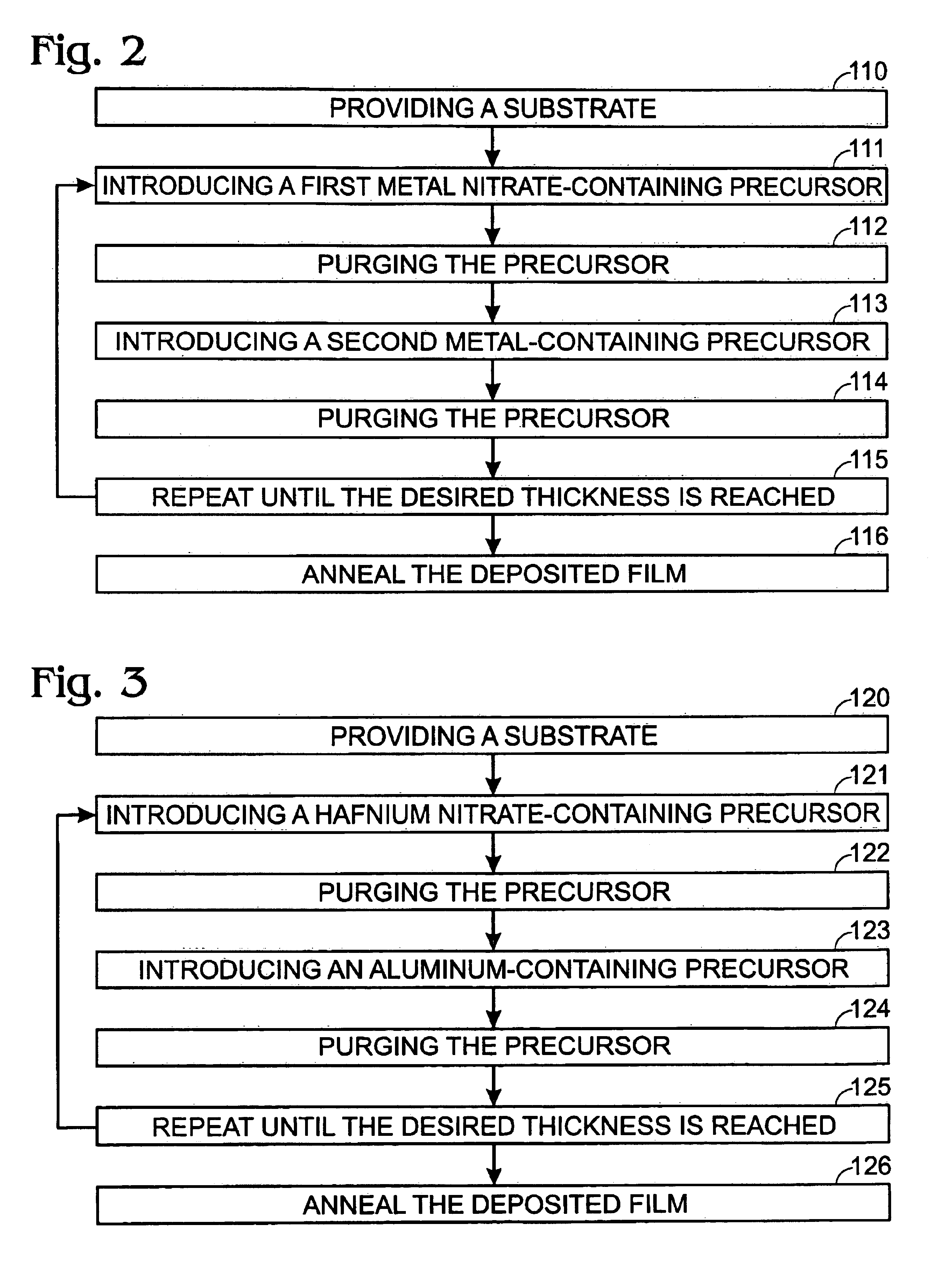

Method for depositing a nanolaminate film by atomic layer deposition

InactiveUS6930059B2Simple methodQuality improvementTransistorSemiconductor/solid-state device manufacturingGate dielectricHafnium

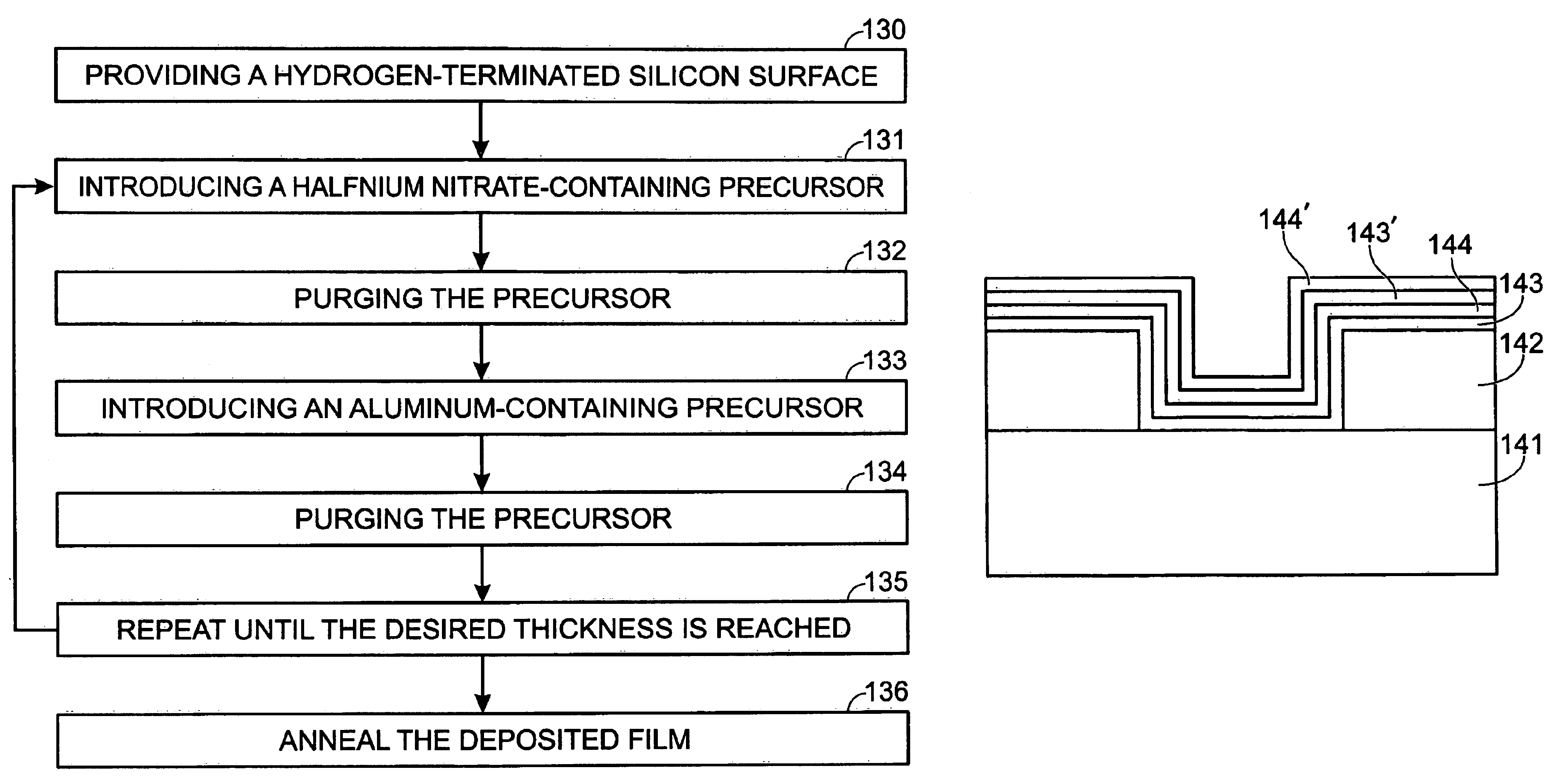

An atomic layer deposition method to deposit an oxide nanolaminate thin film is provided. The method employs a nitrate ligand in a first precursor as an oxidizer for a second precursor to form the oxide nanolaminates. Using a hafnium nitrate precursor and an aluminum precursor, the method is well suited for the deposition of a high k hafnium oxide / aluminum oxide nanolaminate dielectric for gate dielectric or capacitor dielectric applications on a hydrogen-terminated silicon surface.

Owner:SHARP LAB OF AMERICA INC

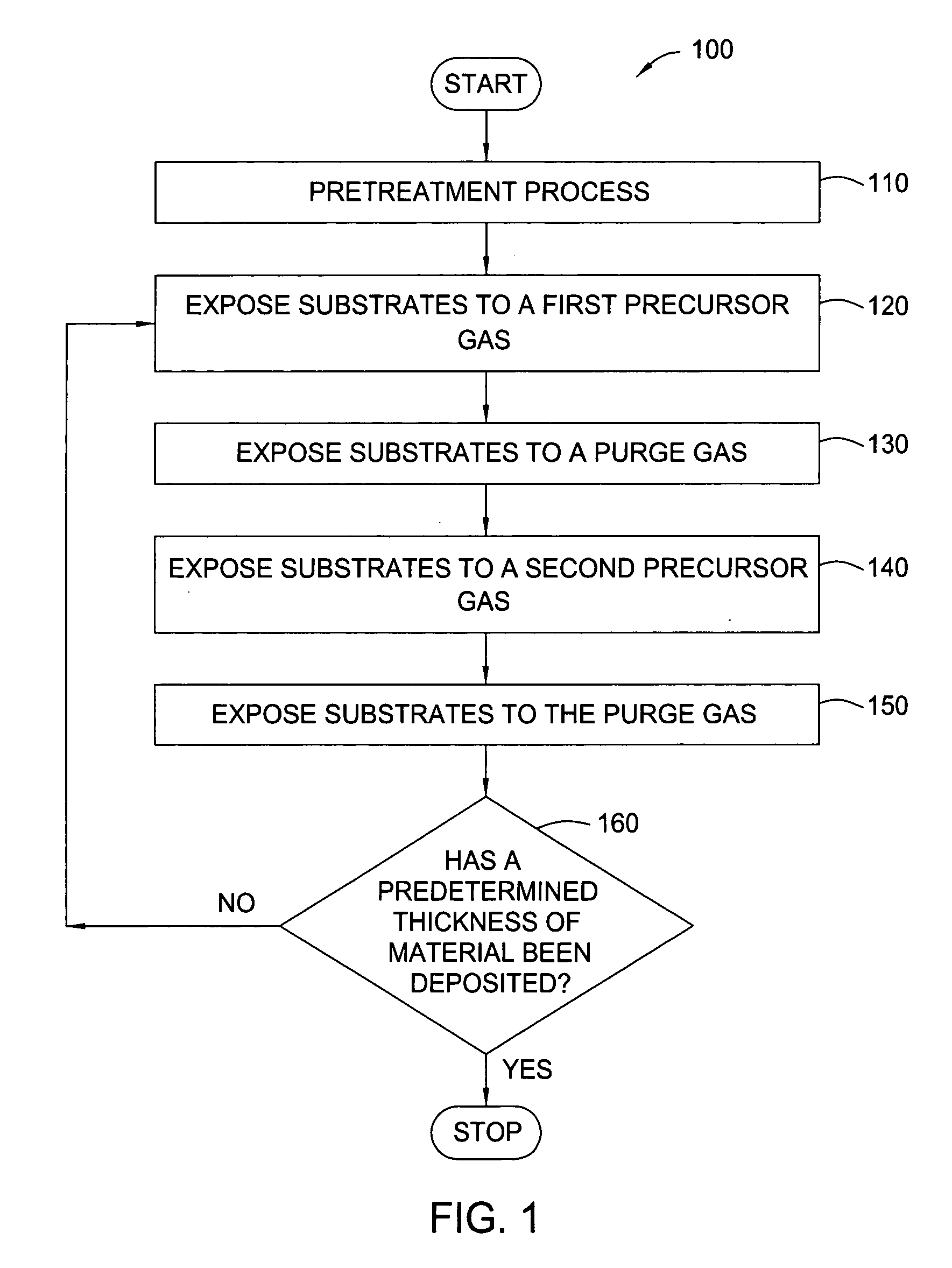

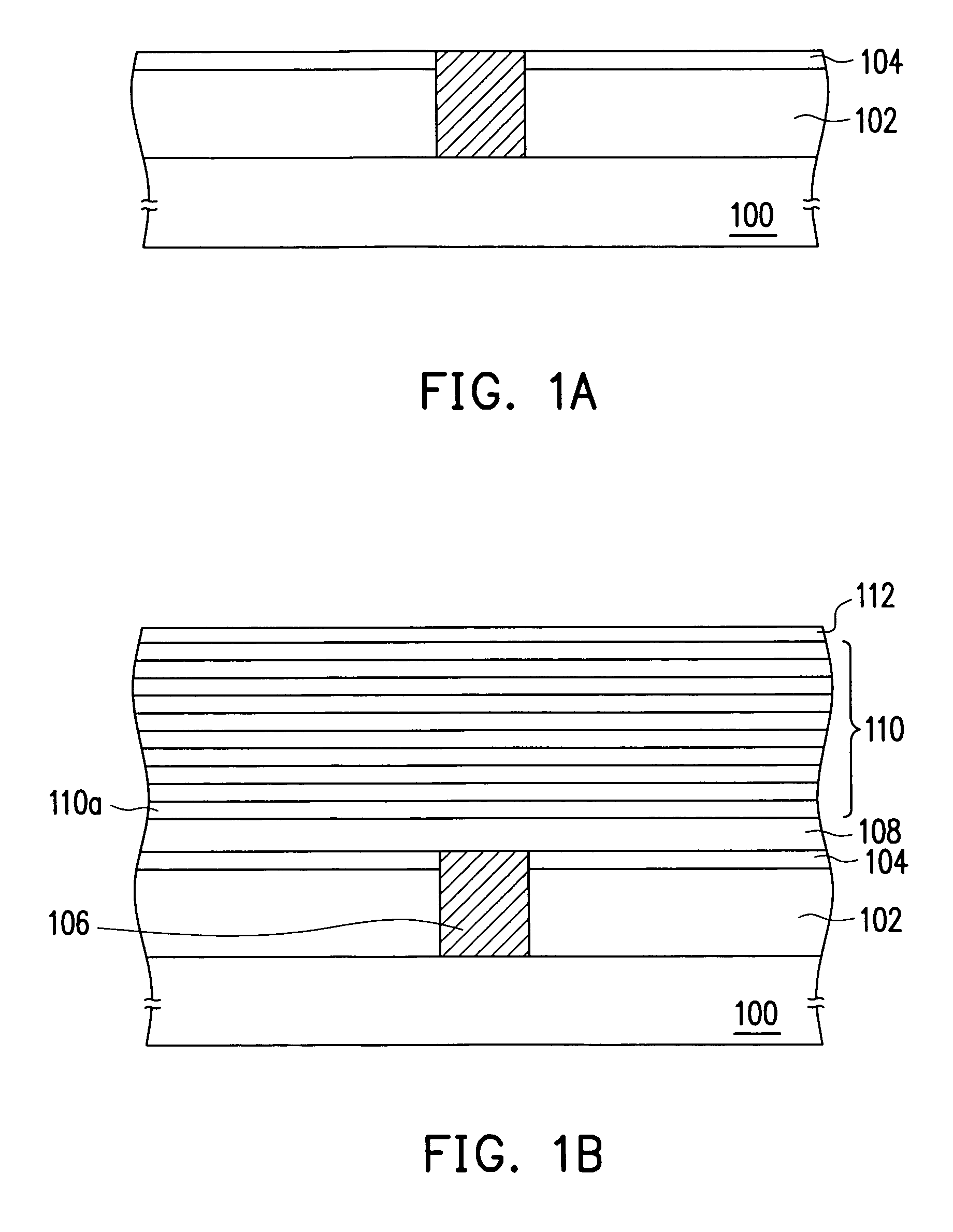

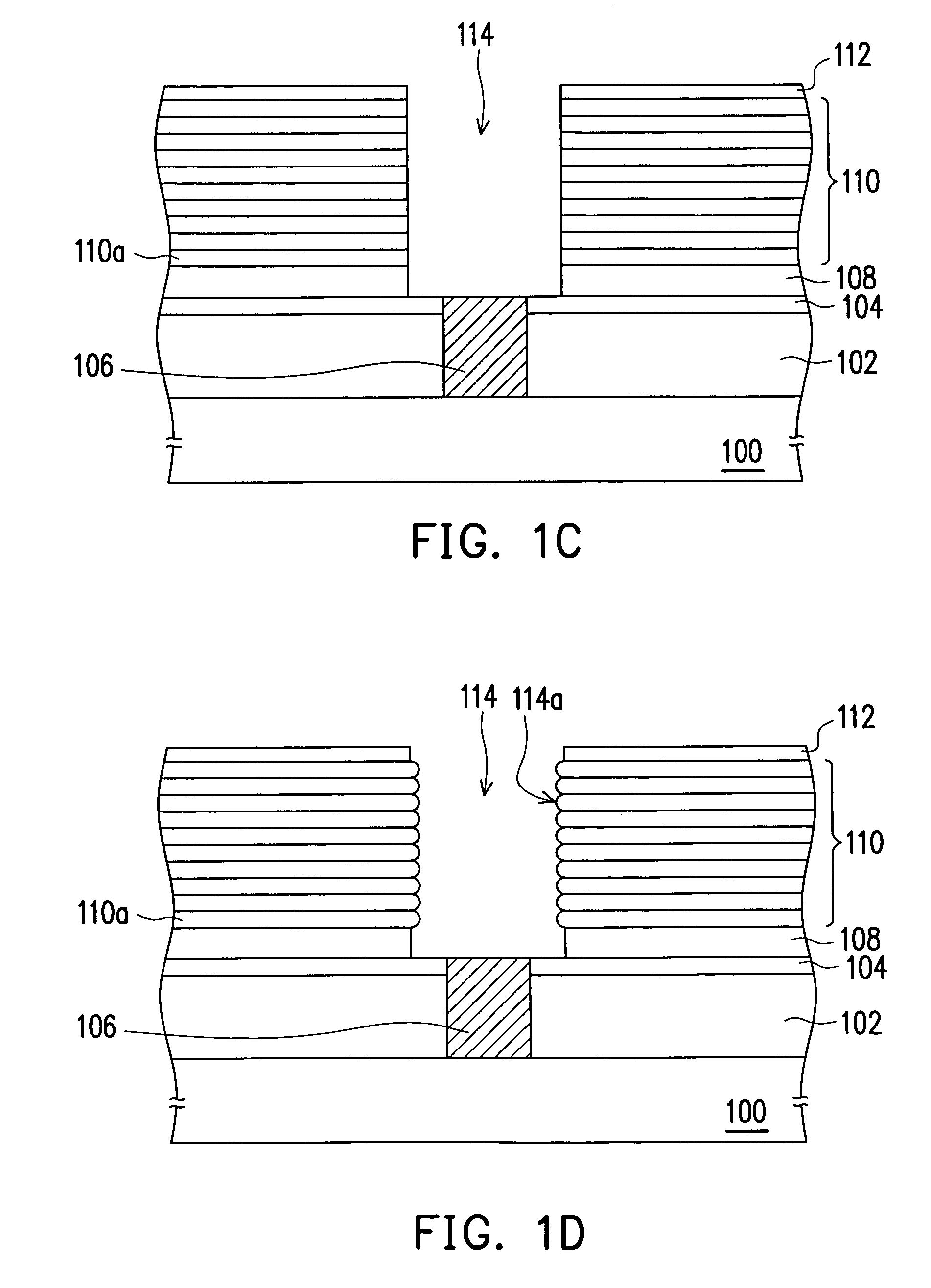

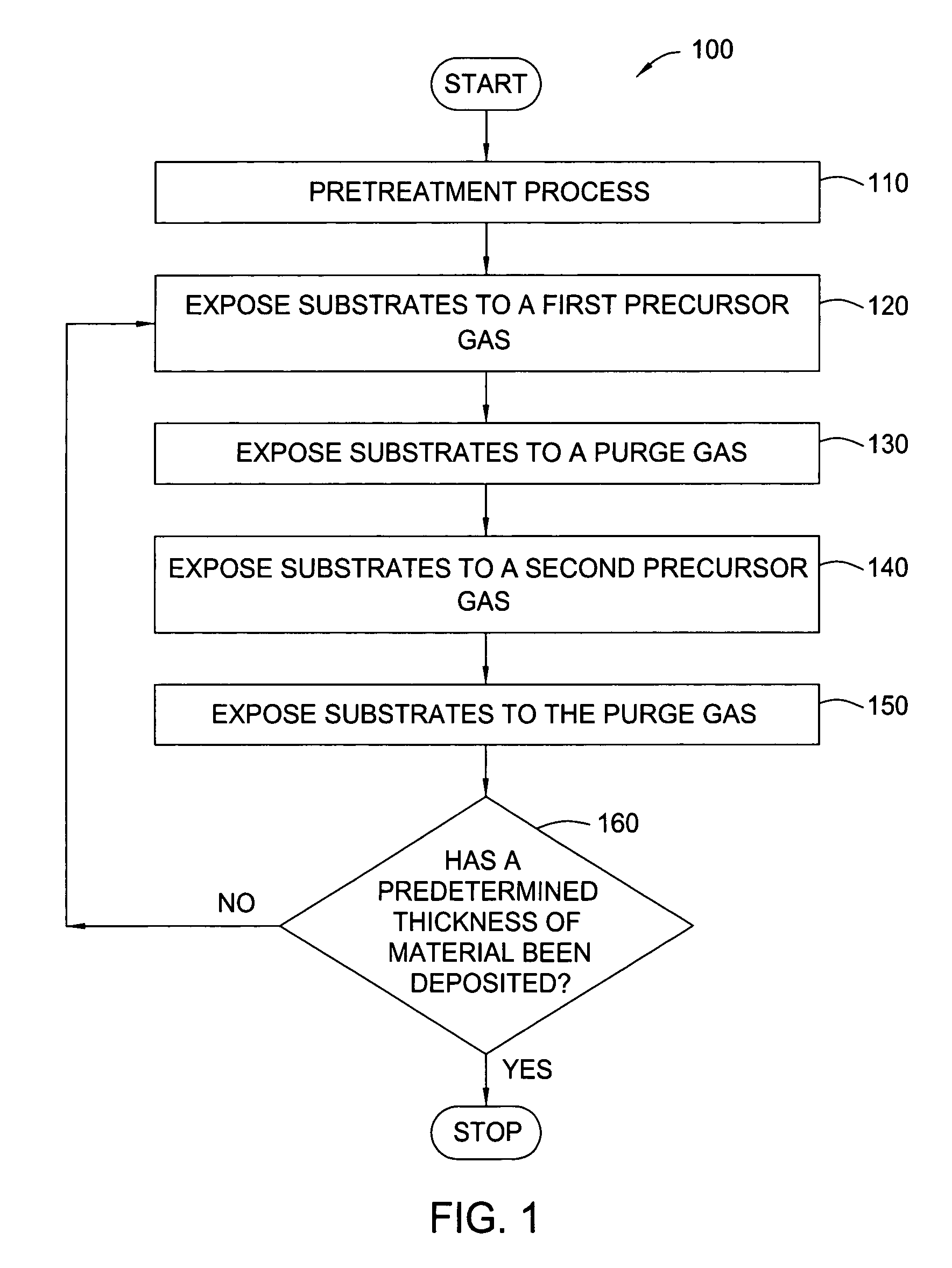

Pretreatment processes within a batch ALD reactor

InactiveUS20070049053A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingWater vaporHafnium

Embodiments of the invention provide methods for forming a material on a substrate which includes exposing a plurality of substrates within a batch process chamber to a first oxidizing gas during a pretreatment process, exposing the substrates sequentially to a precursor and a second oxidizing gas during an ALD cycle and repeating the ALD cycle to form a material on the substrates. In a preferred example, a hafnium precursor is used during the ALD process to form a hafnium-containing material, such as hafnium oxide. In one example, the first and second oxidizing gases are the same oxidizing gases. In a preferred example, the first and second oxidizing gases are different oxidizing gases, such that the pretreatment process contains ozone and the ALD process contains water vapor.

Owner:APPLIED MATERIALS INC

Method of manufacturing charge storage device

InactiveUS7405166B2Increase electrode areaEasy to produceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceHydrogen fluoride

Owner:IND TECH RES INST

Pretreatment processes within a batch ALD reactor

InactiveUS7402534B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingBatch processingWater vapor

Embodiments of the invention provide methods for forming a material on a substrate which includes exposing a plurality of substrates within a batch process chamber to a first oxidizing gas during a pretreatment process, exposing the substrates sequentially to a precursor and a second oxidizing gas during an ALD cycle and repeating the ALD cycle to form a material on the substrates. In a preferred example, a hafnium precursor is used during the ALD process to form a hafnium-containing material, such as hafnium oxide. In one example, the first and second oxidizing gases are the same oxidizing gases. In a preferred example, the first and second oxidizing gases are different oxidizing gases, such that the pretreatment process contains ozone and the ALD process contains water vapor.

Owner:APPLIED MATERIALS INC

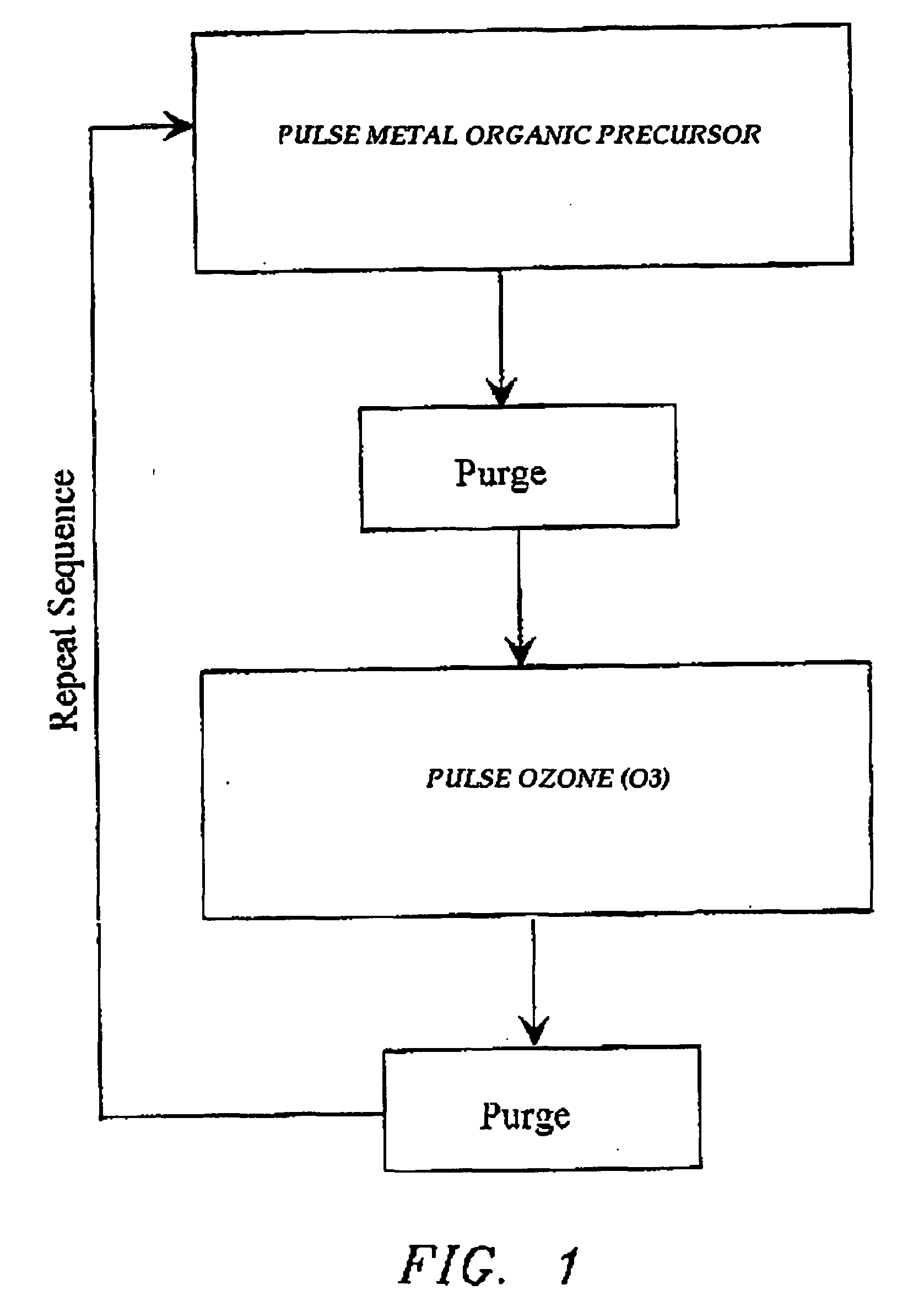

Atomic layer deposition of high-k metal oxides

InactiveUS20060258078A1Improve thermal stabilityLess growthSolid-state devicesSemiconductor/solid-state device manufacturingDielectric layerTitanium oxide

The present invention relates to the atomic layer deposition (“ALD”) of high k dielectric layers of metal oxides containing Group 4 metals, including hafnium oxide, zirconium oxide, and titanium oxide. More particularly, the present invention relates to the ALD formation of Group 4 metal oxide films using an metal alkyl amide as a metal organic precursor and ozone as a co-reactant.

Owner:AVIZA TECHNOLOGY INC +1

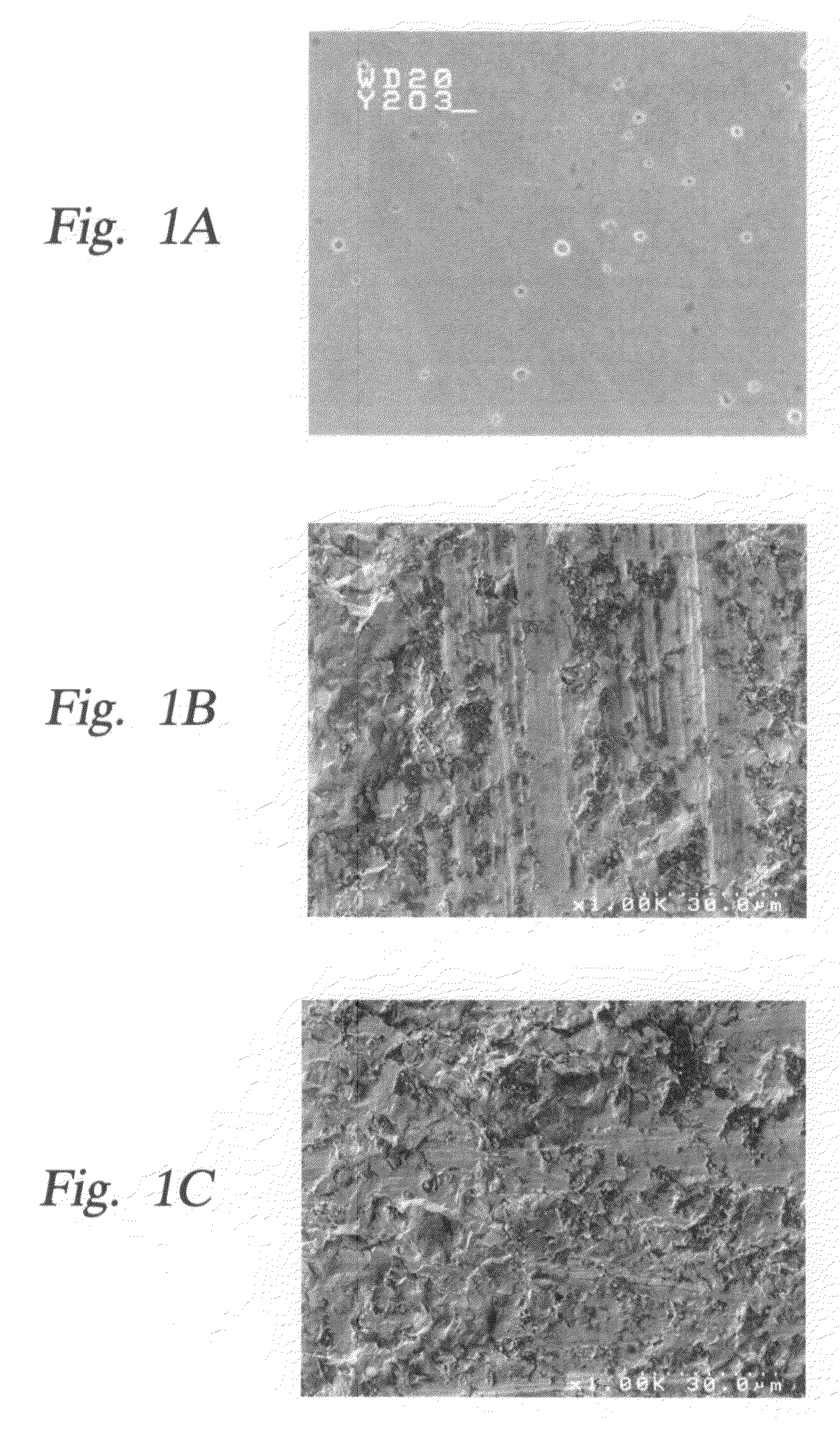

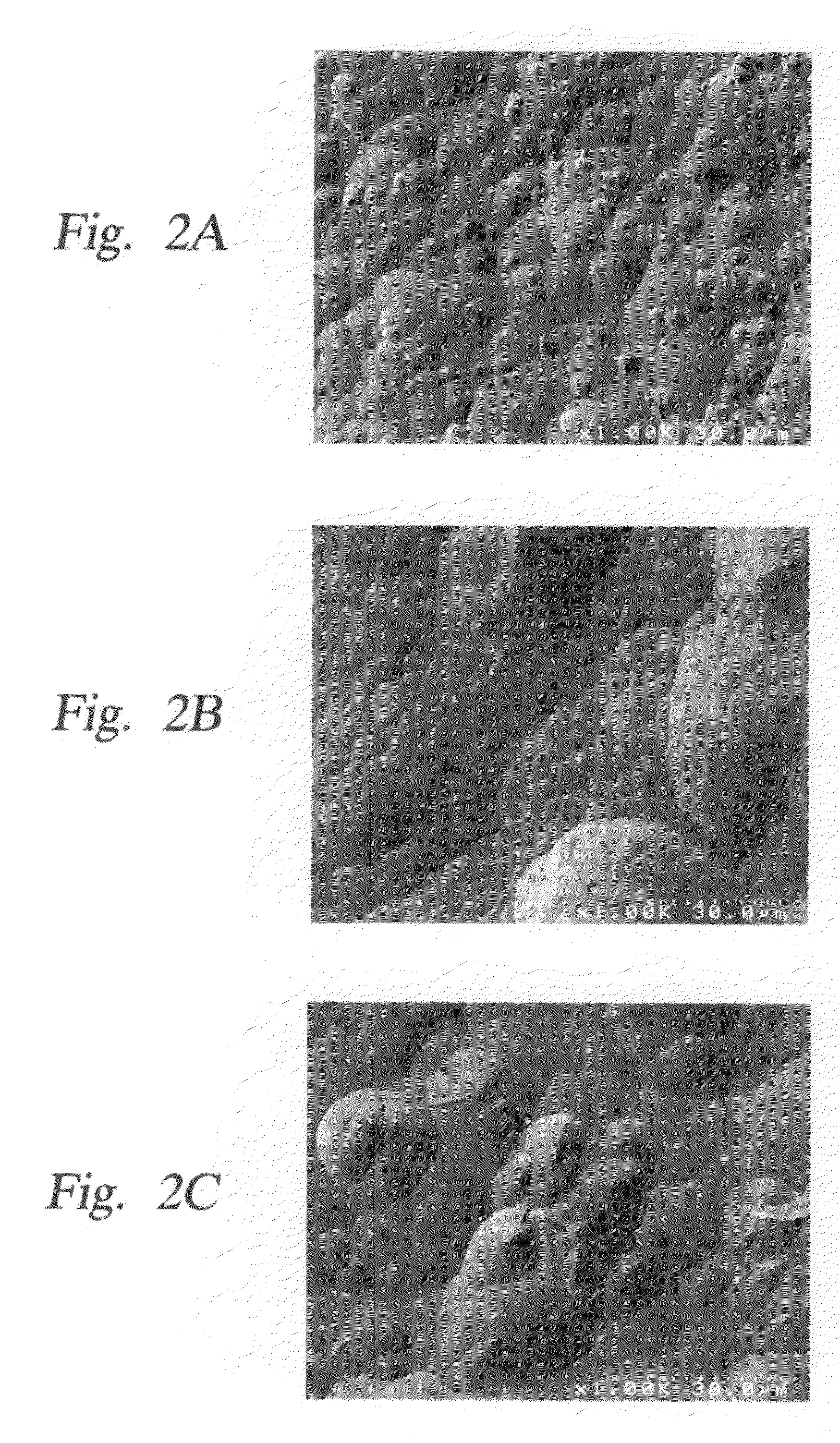

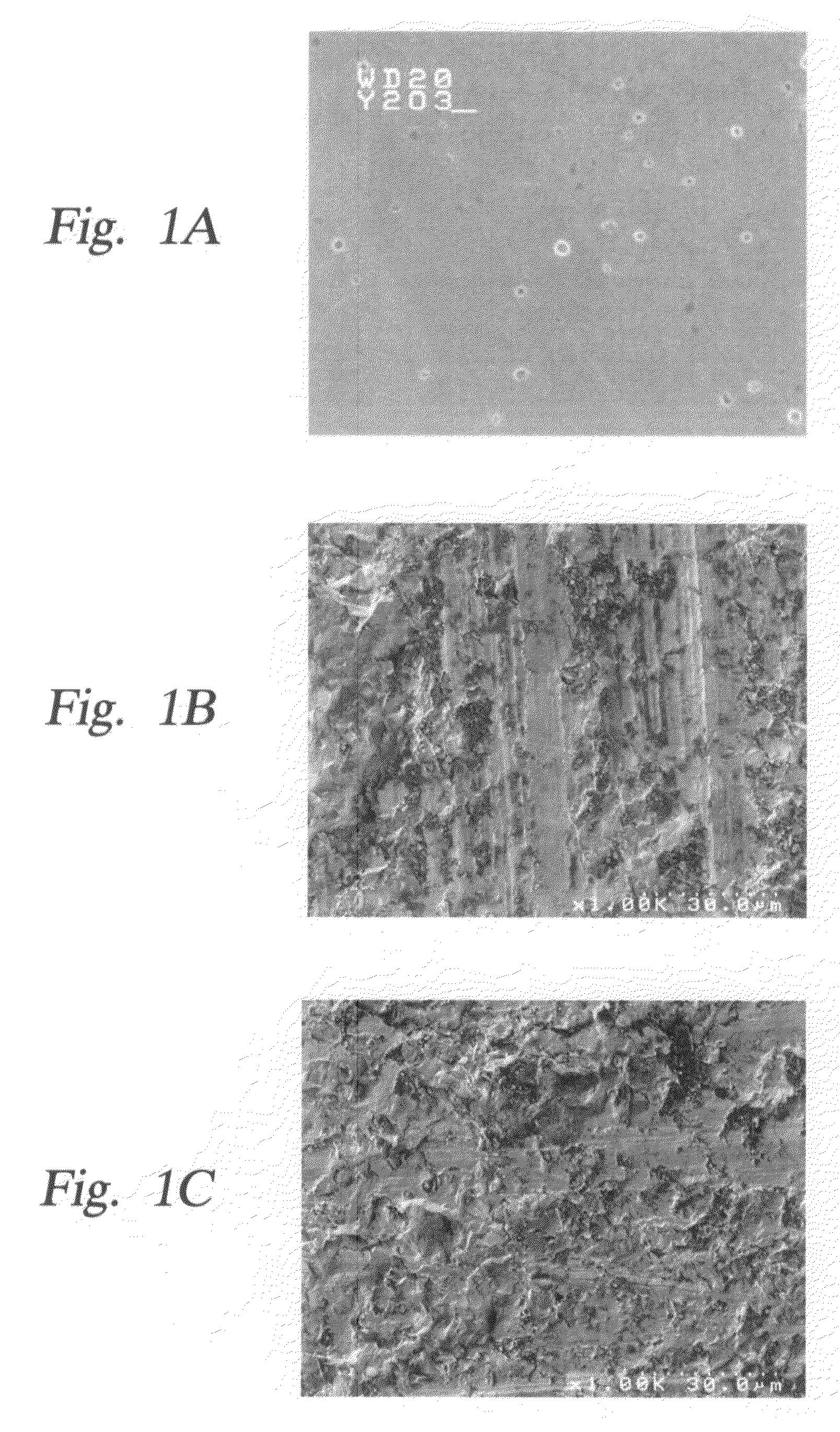

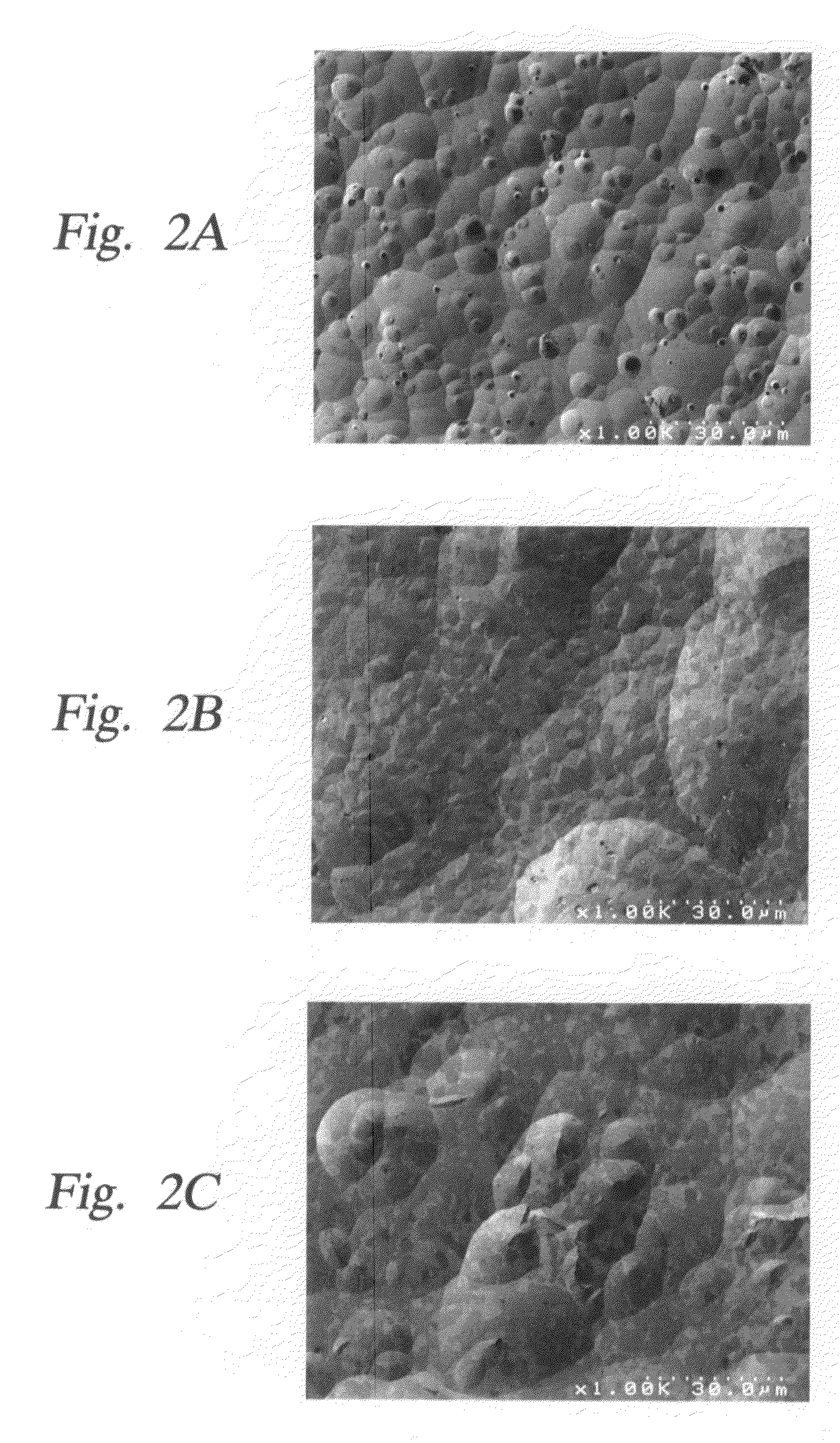

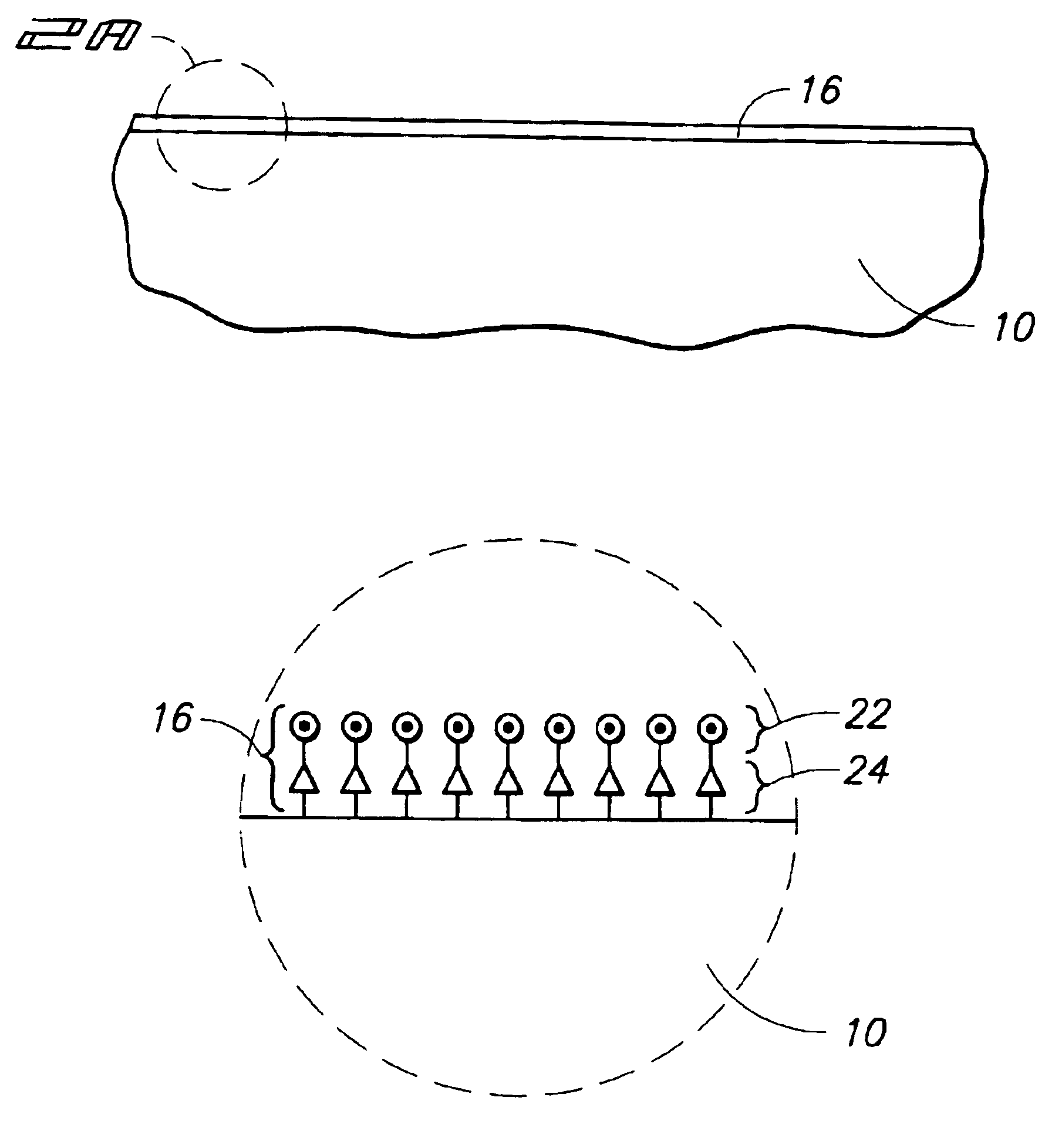

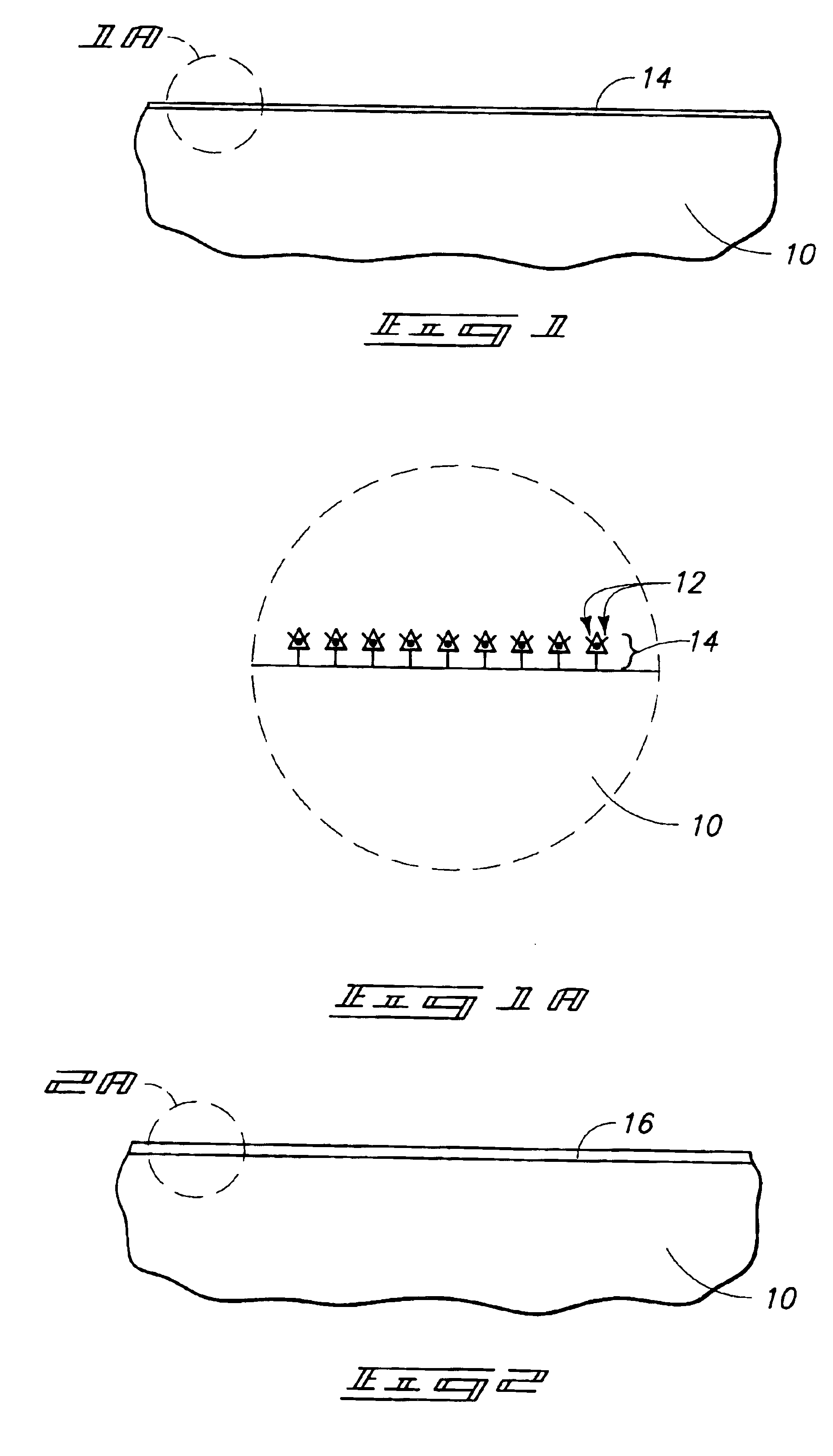

Yttria-based material coated chemical vapor deposition chamber heater

ActiveUS20140263272A1Improve wear resistanceImprove flexural strengthLiquid surface applicatorsMolten spray coatingYTTERBIUM OXIDEFlexural strength

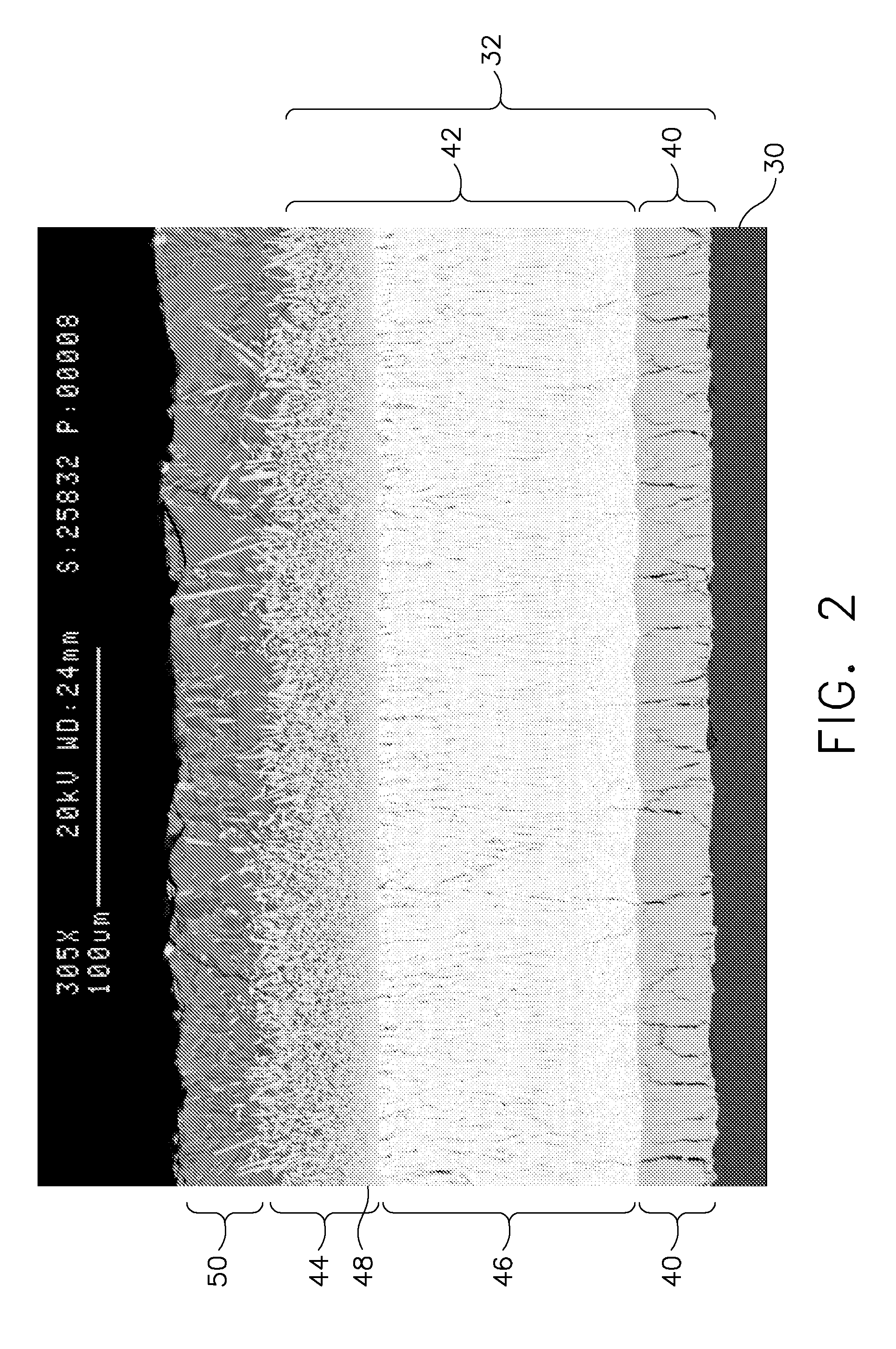

Embodiments of the present invention generally relate to heated substrate supports having a protective coating thereon. The protective coating is formed from yttrium oxide at a molar concentration ranging from about 50 mole percent to about 75 mole percent; zirconium oxide at a molar concentration ranging from about 10 mole percent to about 30 mole percent; and at least one other component, selected from the group consisting of aluminum oxide, hafnium oxide, scandium oxide, neodymium oxide, niobium oxide, samarium oxide, ytterbium oxide, erbium oxide, cerium oxide, and combinations thereof, at a molar concentration ranging from about 10 mole percent to about 30 mole percent. The alloying of yttrium oxide with a compatible oxide improves wear resistance, flexural strength, and fracture toughness of the protective coating, relative to pure yttrium oxide.

Owner:APPLIED MATERIALS INC

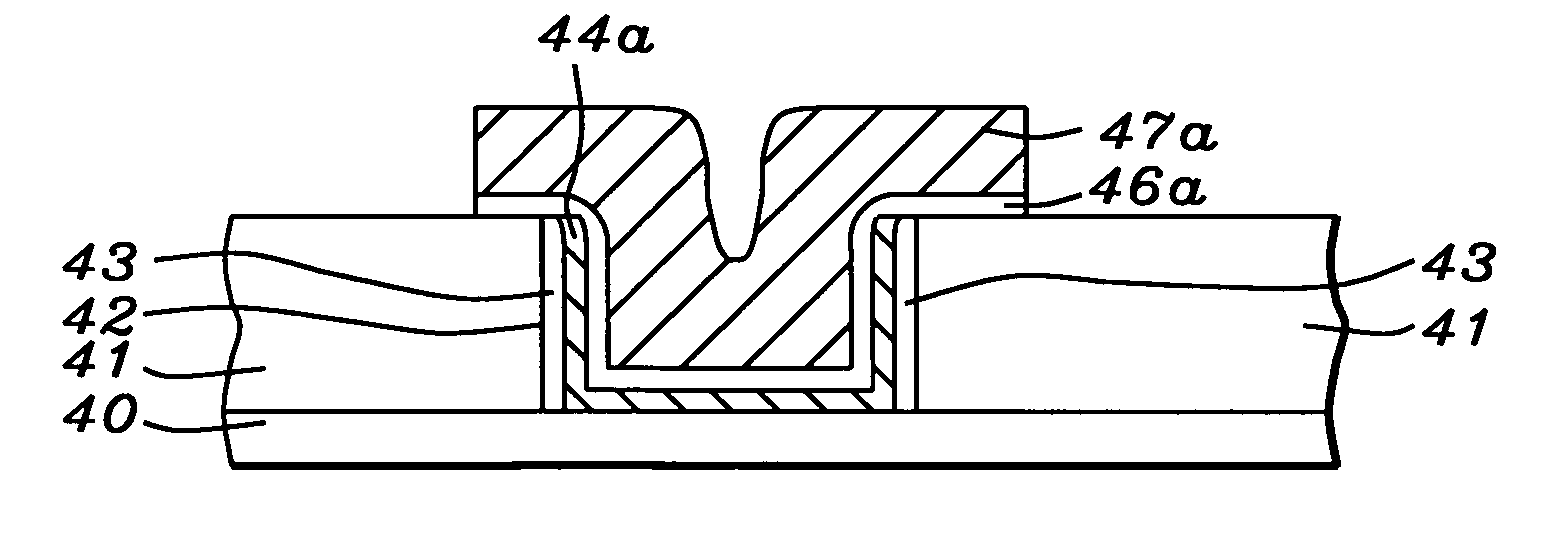

Manufacturing method of semiconductor device

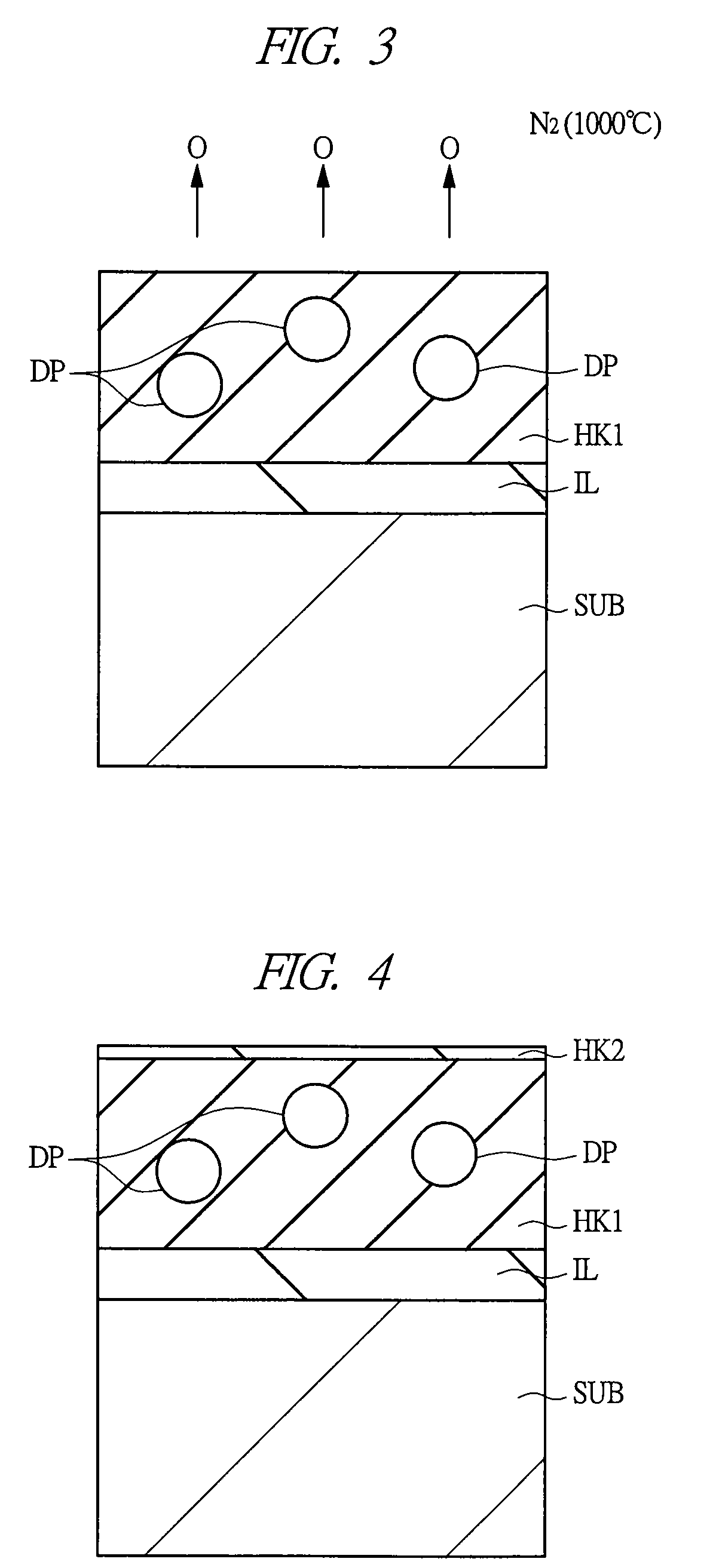

InactiveUS20090011608A1Reduce hypoxiaSuppression of interface silicon oxide growthSemiconductor/solid-state device manufacturingSemiconductor devicesTantalum nitrideSilicon oxide

The transistor characteristics of a MIS transistor provided with a gate insulating film formed to contain oxide with a relative dielectric constant higher than that of silicon oxide are improved. After a high dielectric layer made of hafnium oxide is formed on a main surface of a semiconductor substrate, the main surface of the semiconductor substrate is heat-treated in a non-oxidation atmosphere. Next, an oxygen supplying layer made of hafnium oxide deposited by ALD and having a thickness smaller than that of the high dielectric layer is formed on the high dielectric layer, and a cap layer made of tantalum nitride is formed. Thereafter, the main surface of the semiconductor substrate is heat-treated.

Owner:RENESAS TECH CORP

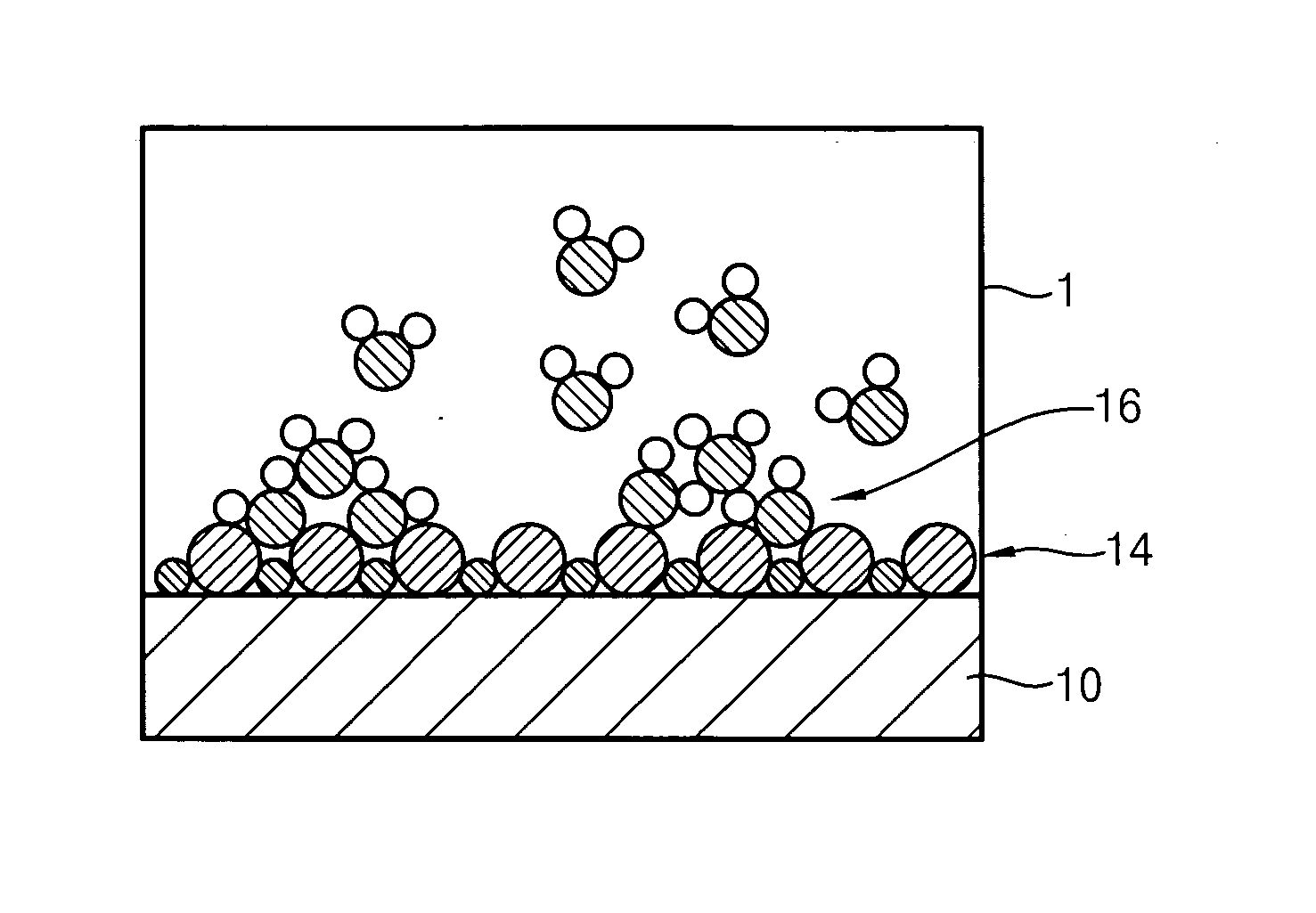

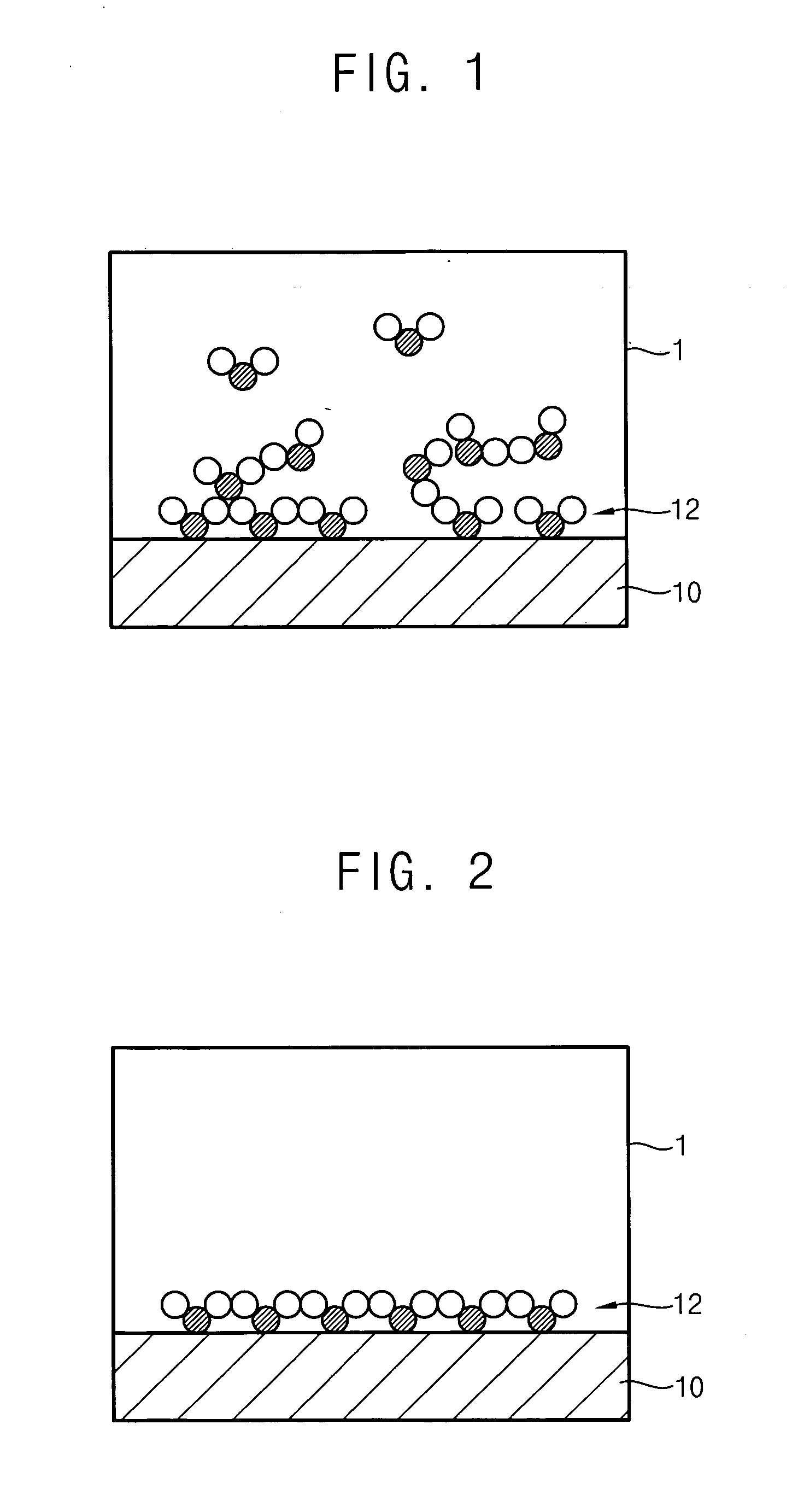

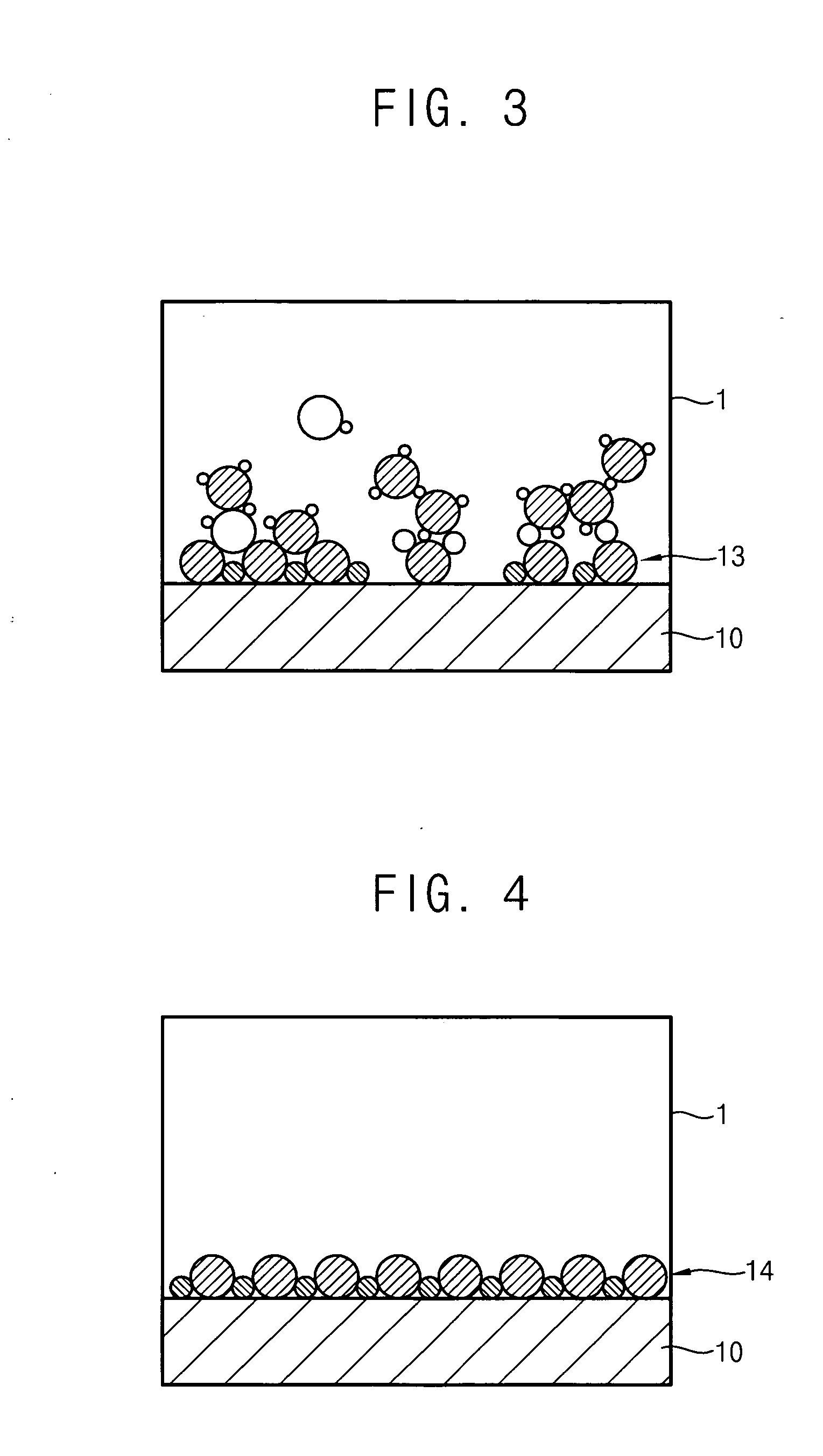

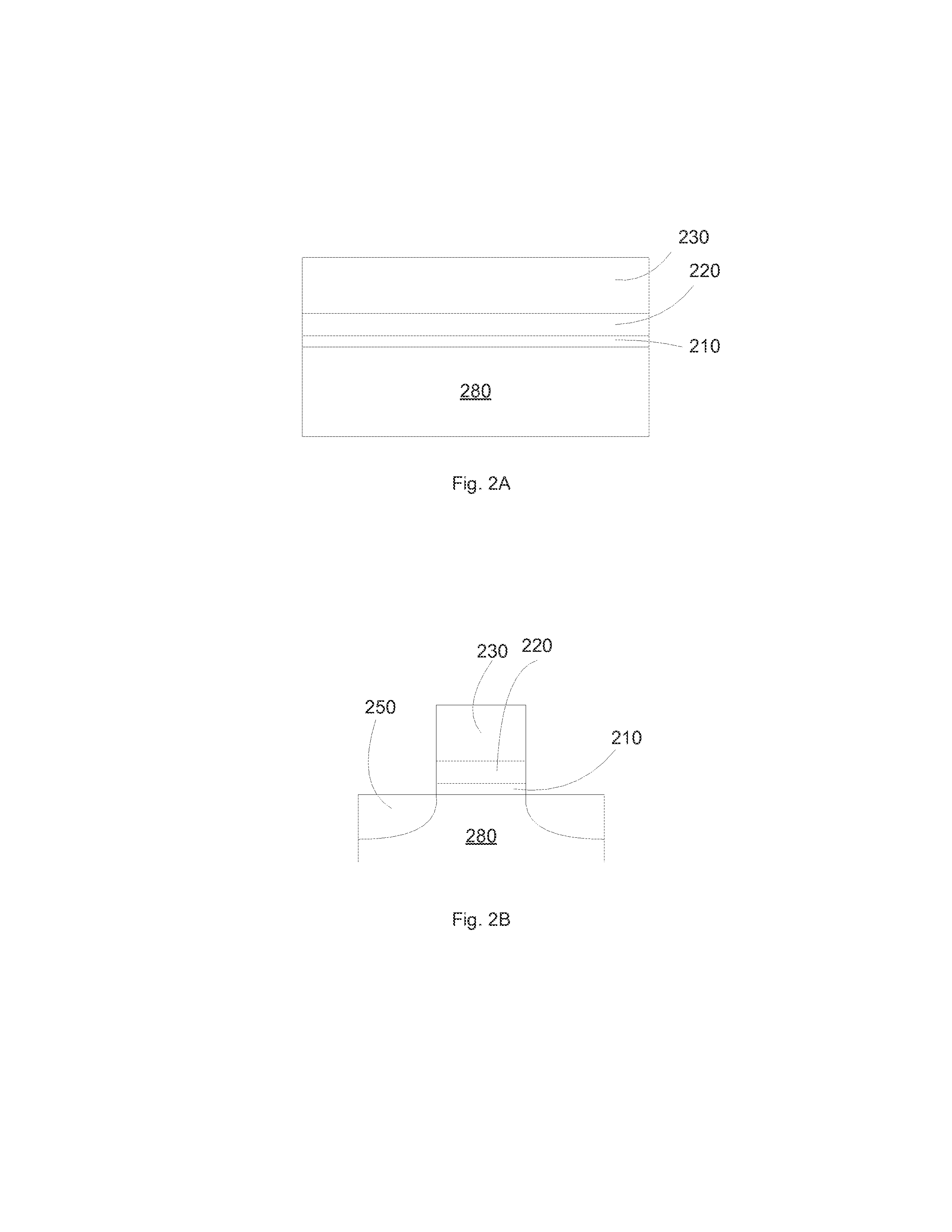

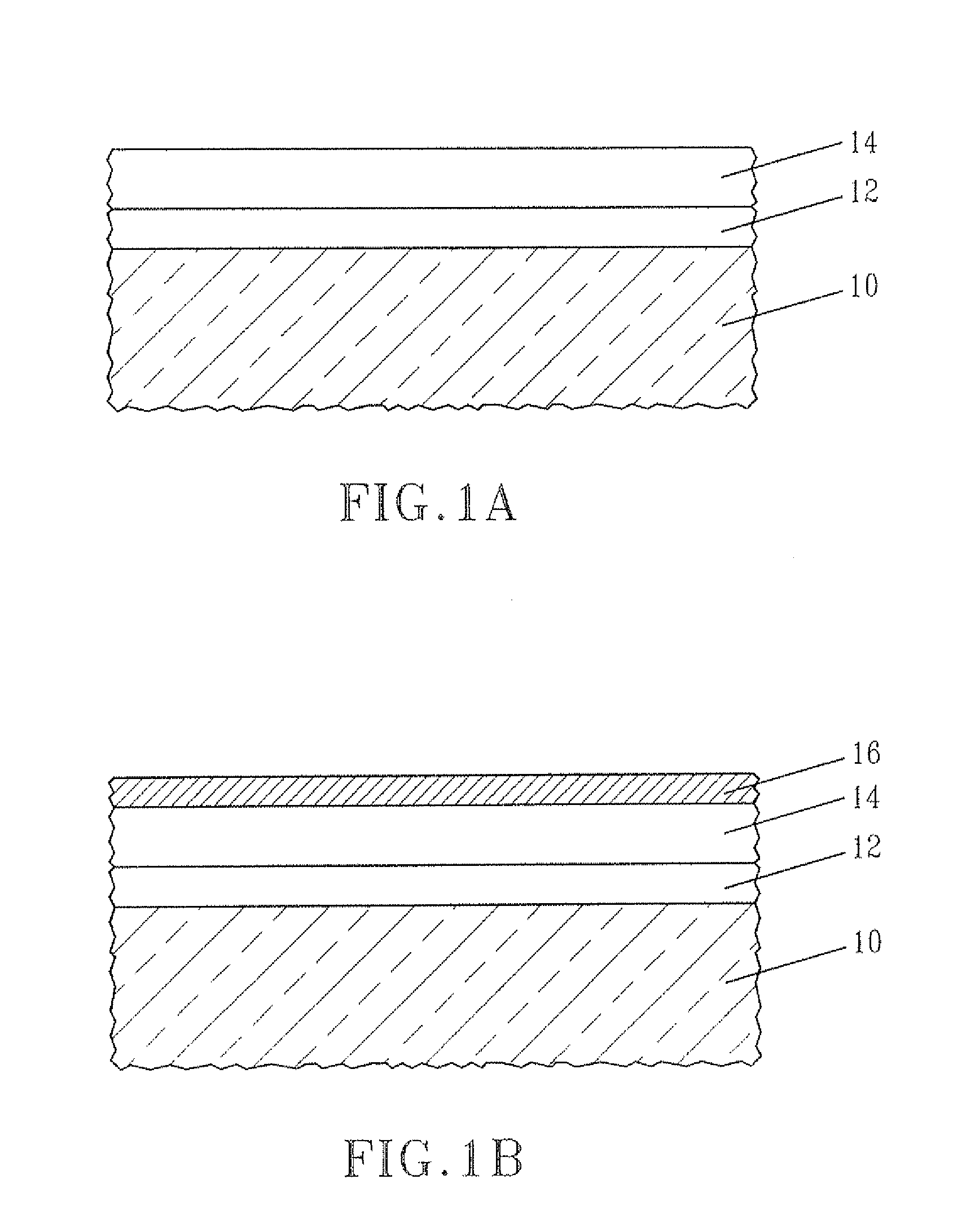

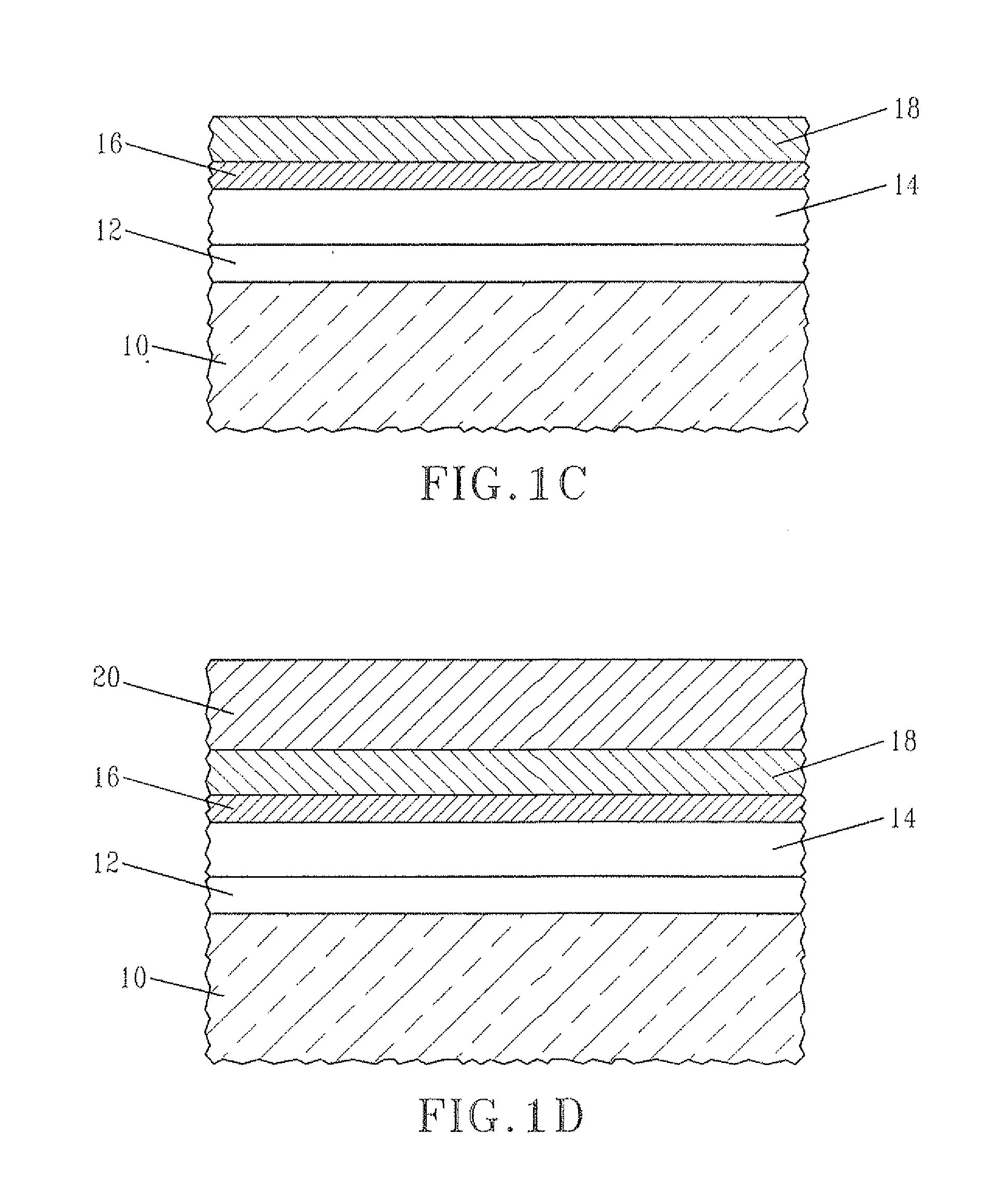

Methods of forming a thin film structure, and a gate structure and a capacitor including the thin film structure

InactiveUS20060013946A1Well formedHigh dielectric constantSemiconductor/solid-state device manufacturingSpecial surfacesChemical reactionSilicon oxide

A thin film structure is formed that includes hafnium silicon oxide using an atomic layer deposition process. A first reactant including tetrakis ethyl methyl amino hafnium (TEMAH) is introduced onto a substrate. A first portion of the first reactant is chemisorbed to the substrate, whereas a second portion of the first reactant is physorbed to the first portion of the first reactant. A first oxidant is provided onto the substrate. A first thin film including hafnium oxide is formed on the substrate by chemically reacting the first oxidant with the first portion of the first reactant. A second reactant including amino propyl tri ethoxy silane (APTES) is introduced onto the first thin film. A first portion of the second reactant is chemisorbed to the first thin film, whereas a second portion of the second reactant is physorbed to the first portion of the second reactant. A second oxidant is provided onto the first thin film. A second thin film including silicon oxide is formed on the first thin film by chemically reacting the second oxidant with the first portion of the second reactant.

Owner:SAMSUNG ELECTRONICS CO LTD

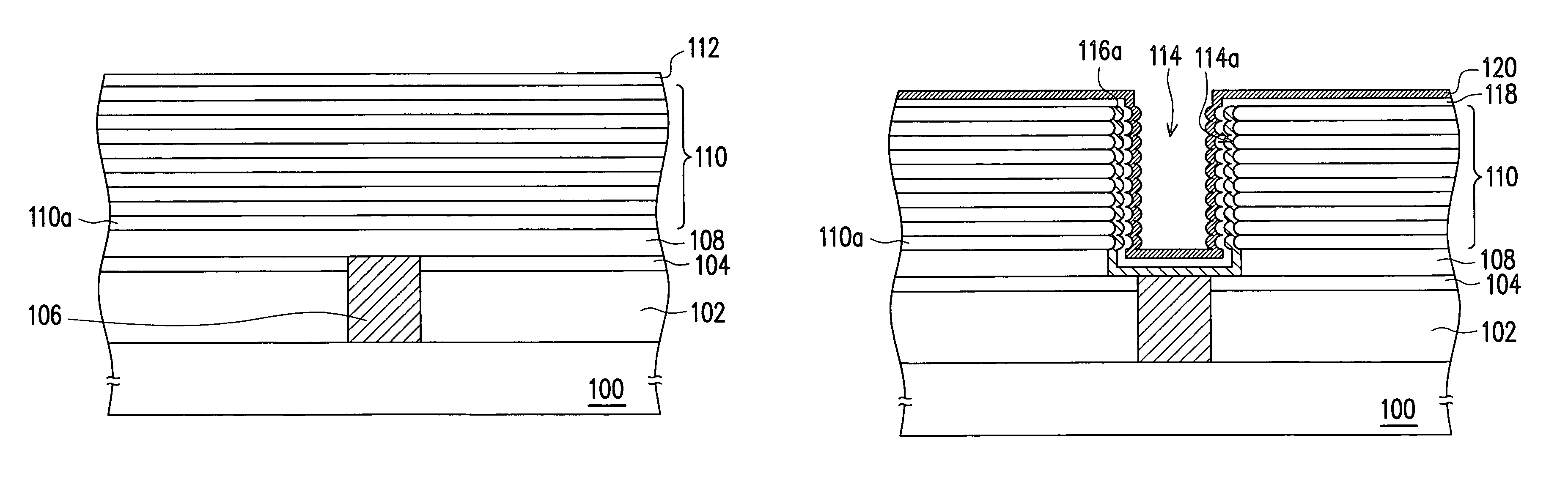

Hafnium oxide and aluminium oxide alloyed dielectric layer and method for fabricating the same

InactiveUS20050110069A1Preventing break down voltageReduce voltageTransistorSolid-state devicesAtomic layer depositionDielectric layer

The present invention relates to a dielectric layer alloyed with hafnium oxide and aluminum oxide and a method for fabricating the same. At this time, the dielectric layer is deposited by an atomic layer deposition technique. The method for fabricating the hafnium oxide and aluminum oxide alloyed dielectric layer includes the steps of: depositing a single atomic layer of hafnium oxide by repeatedly performing a first cycle of an atomic layer deposition technique; depositing a single atomic layer of aluminum oxide by repeatedly performing a second cycle of the atomic layer deposition technique; and depositing a dielectric layer alloyed with the single atomic layer of hafnium oxide and the single atomic layer of aluminum oxide by repeatedly performing a third cycle including the admixed first and second cycles.

Owner:SK HYNIX INC

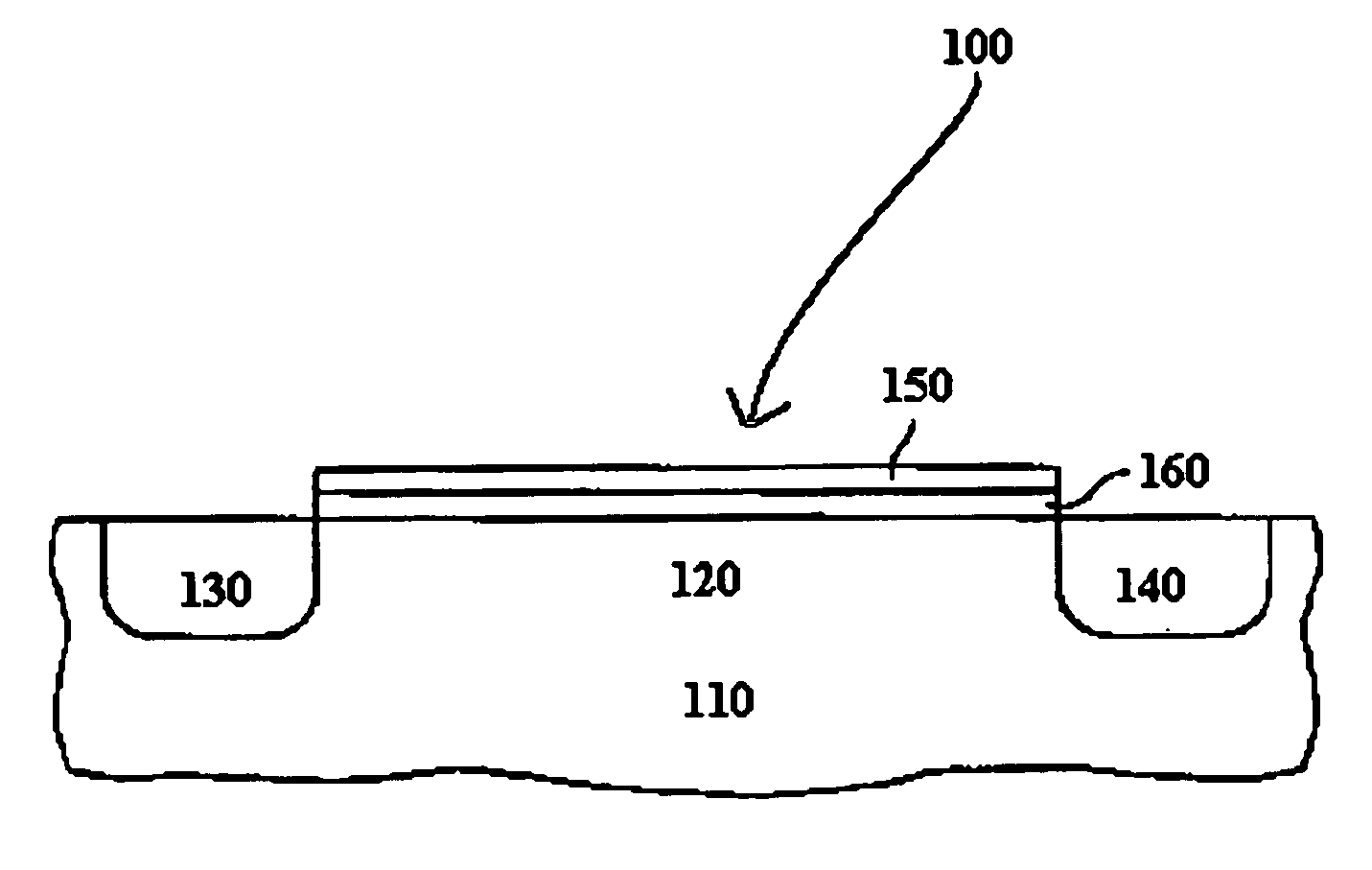

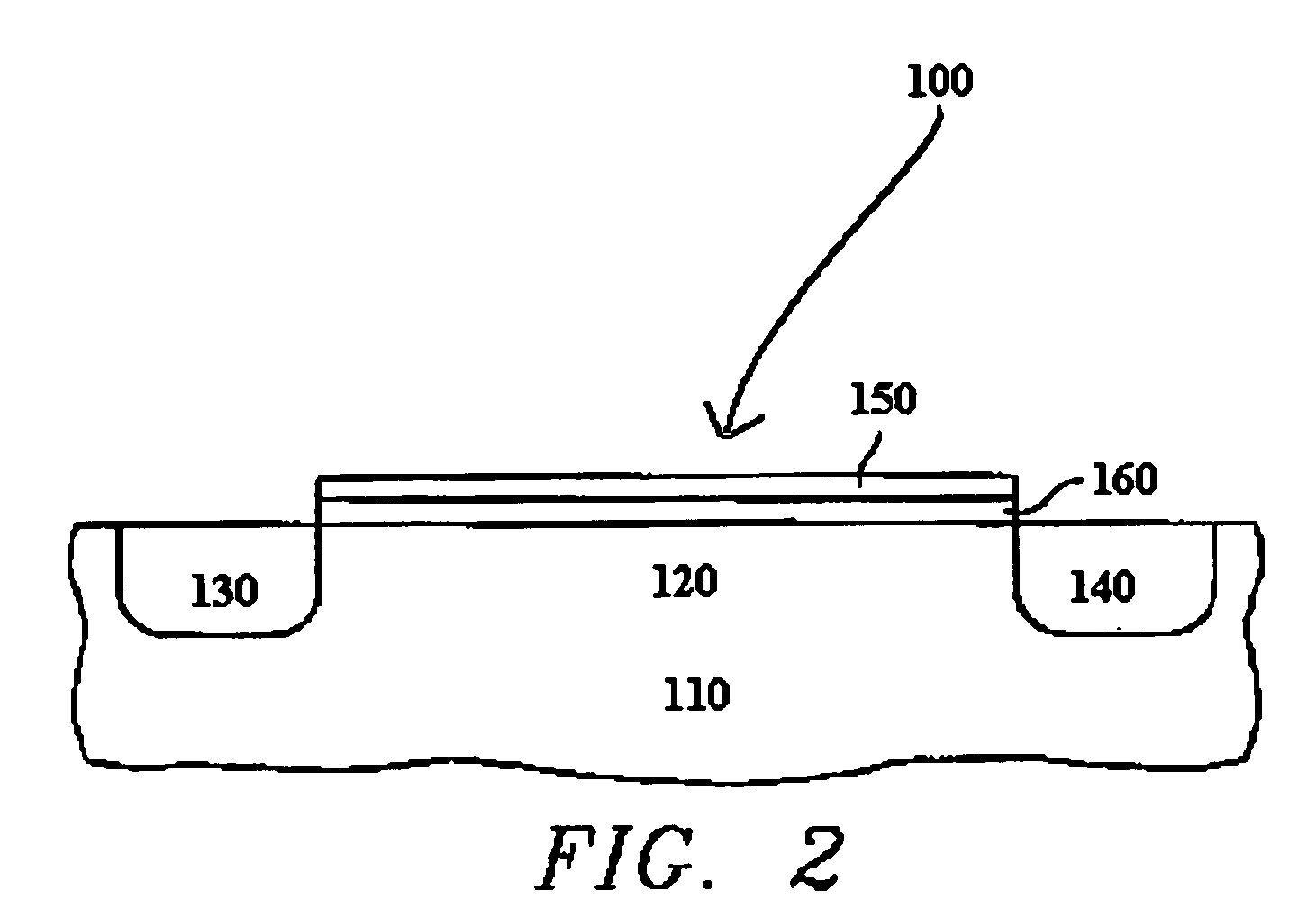

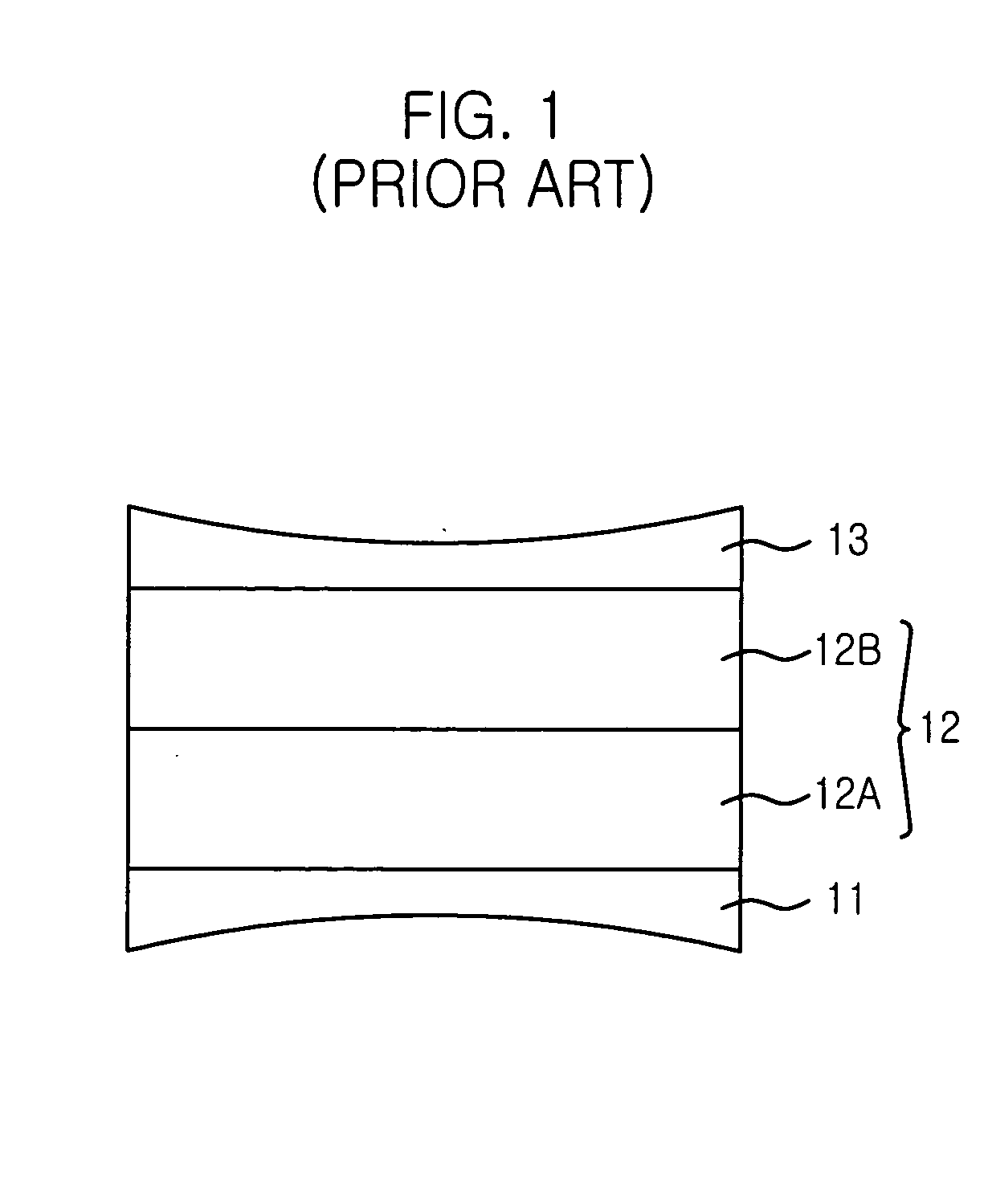

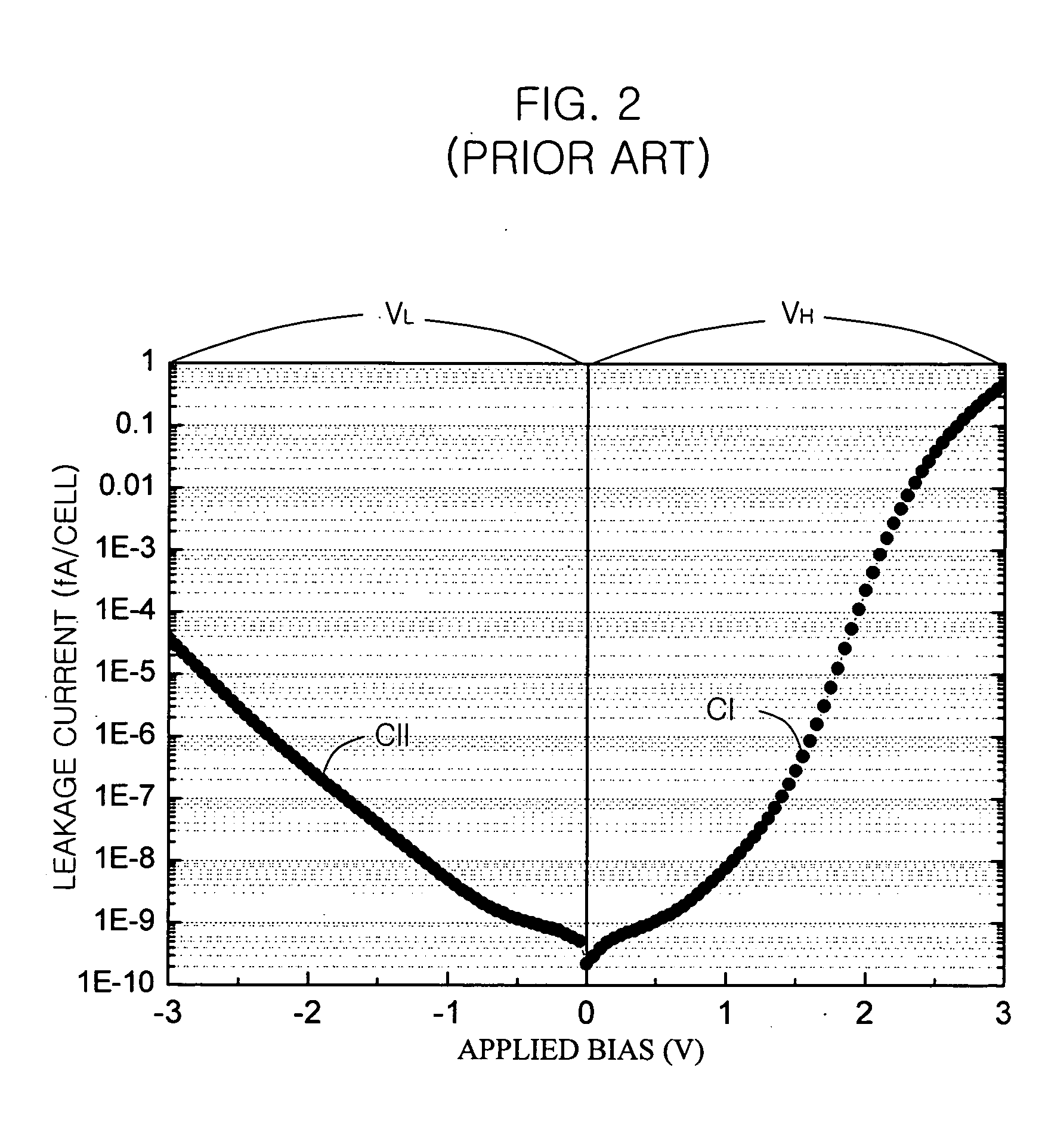

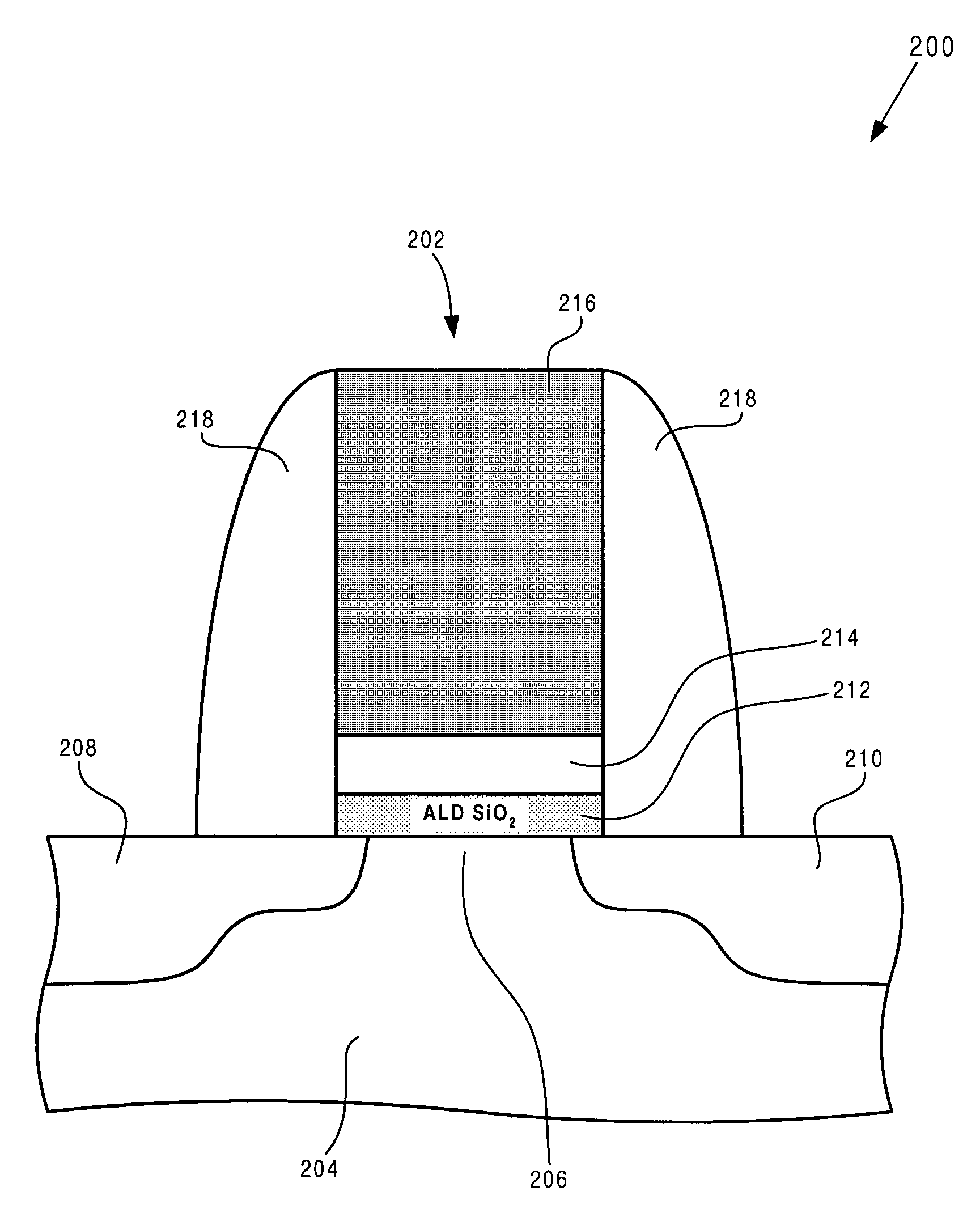

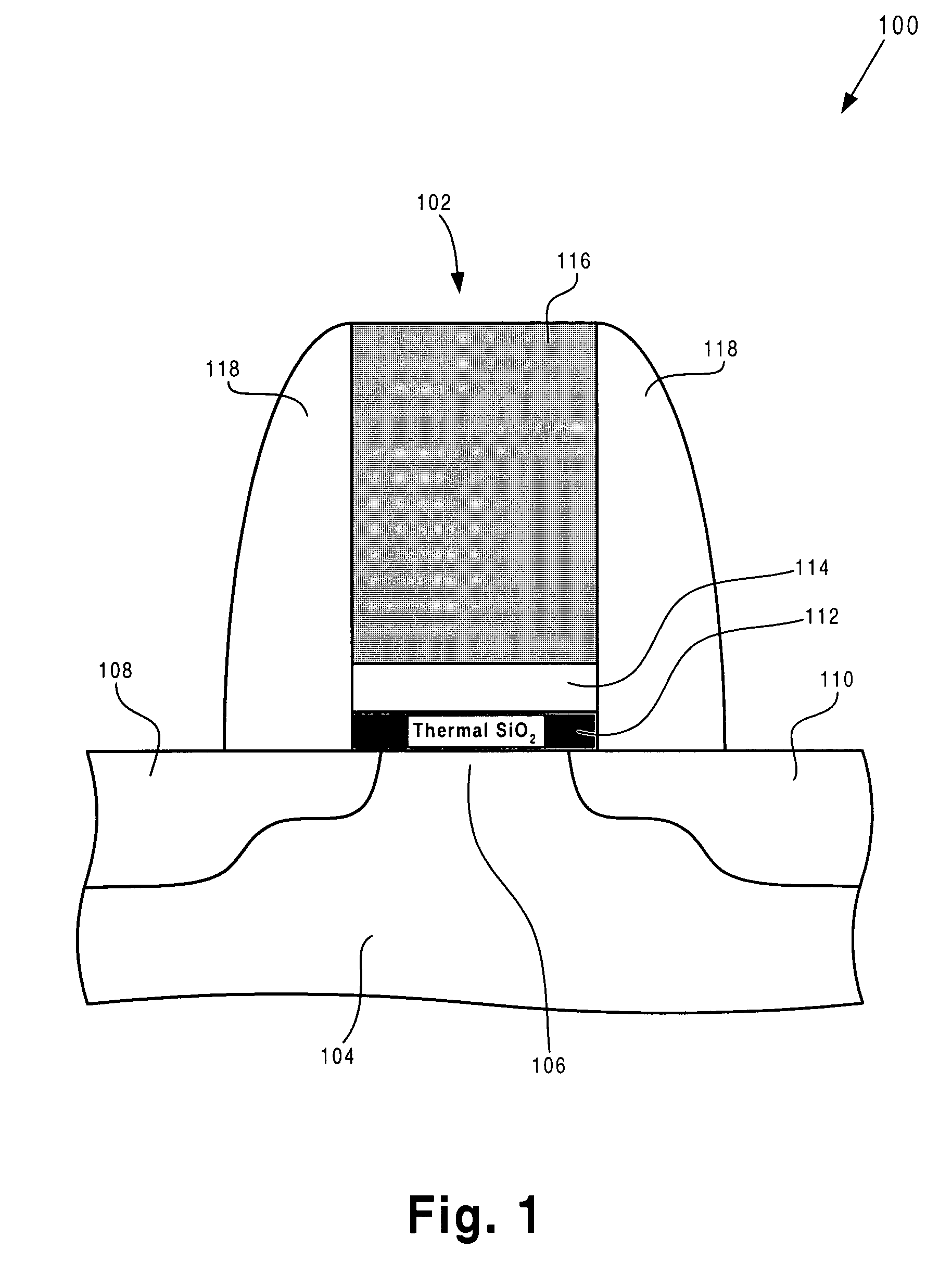

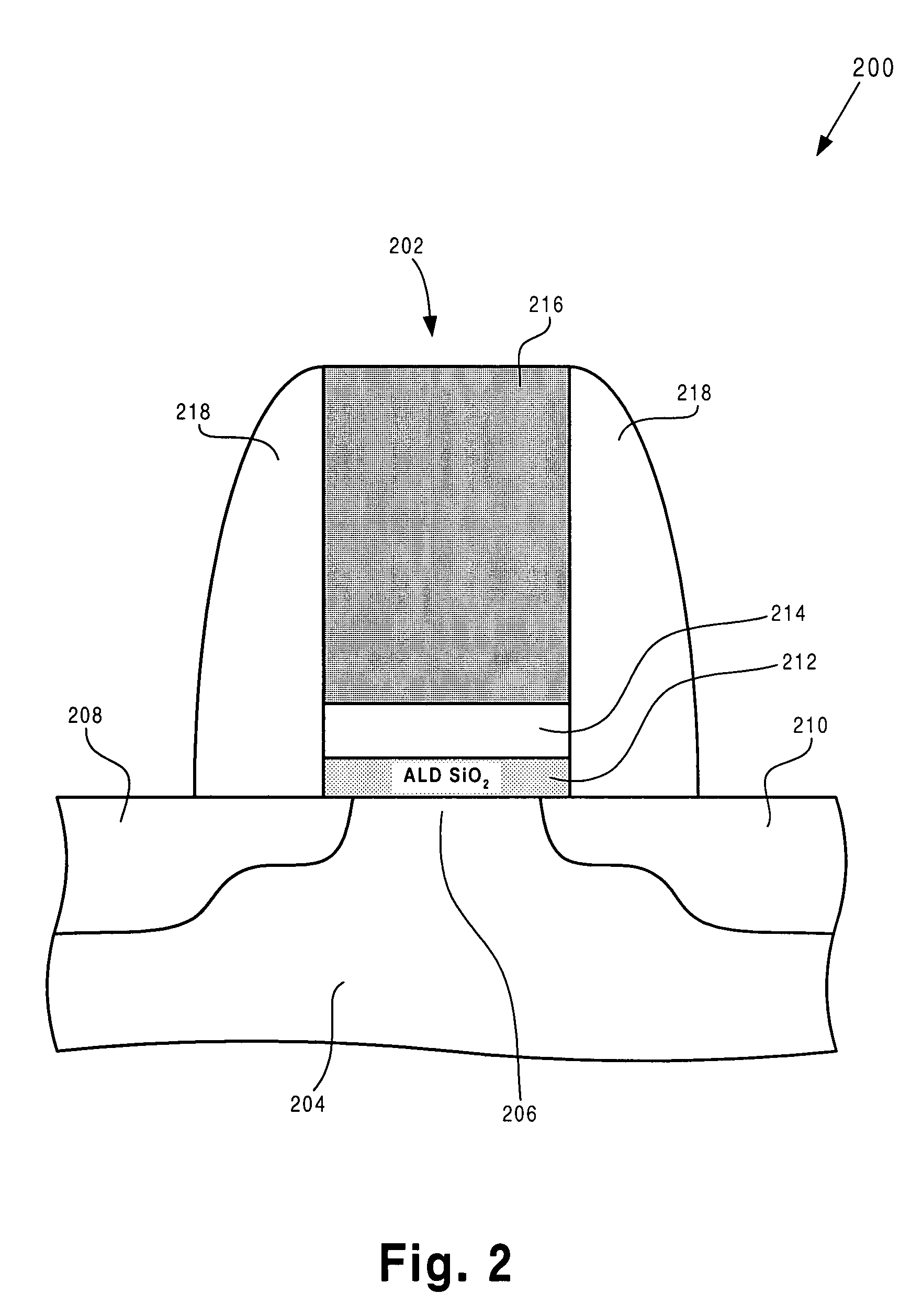

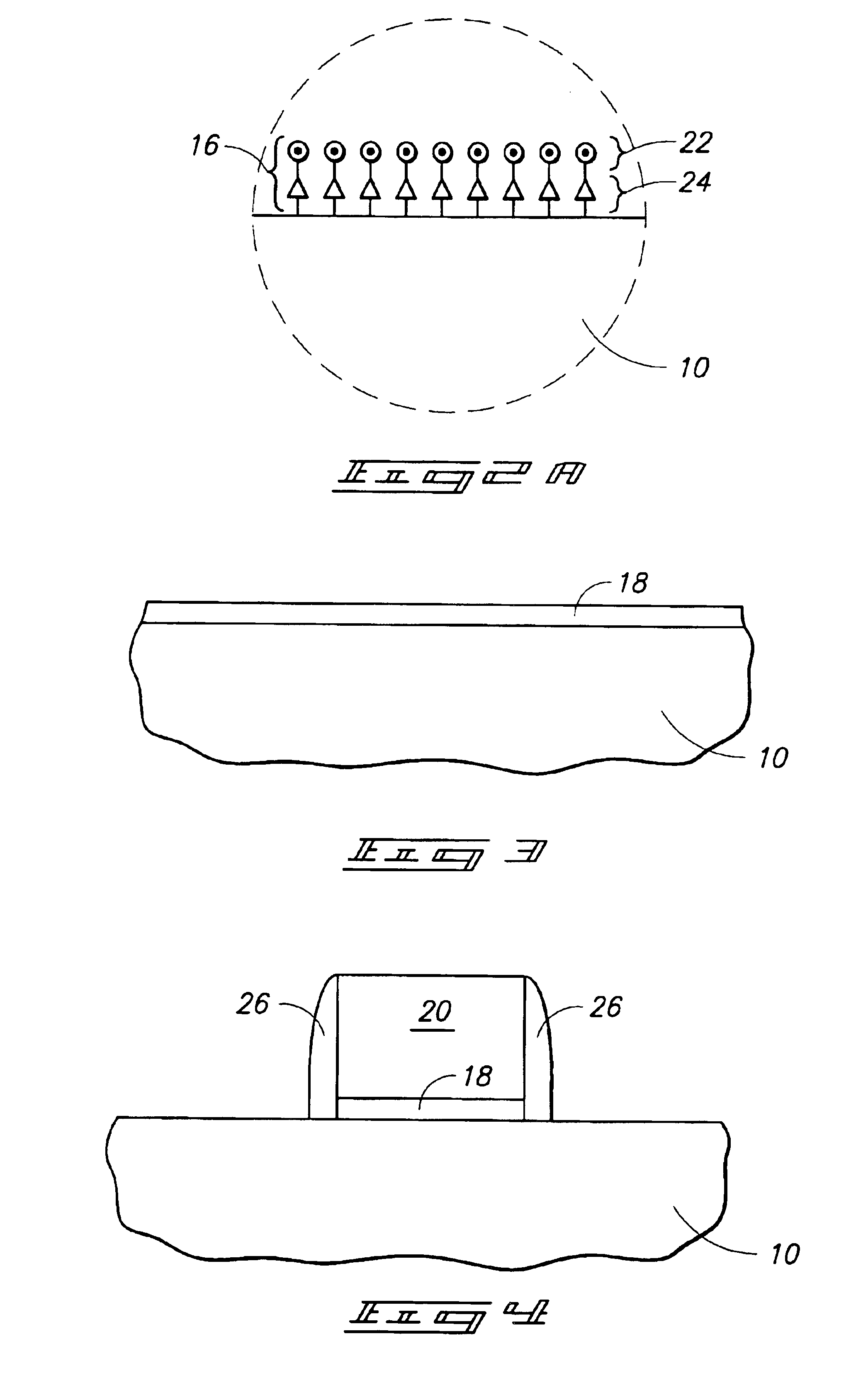

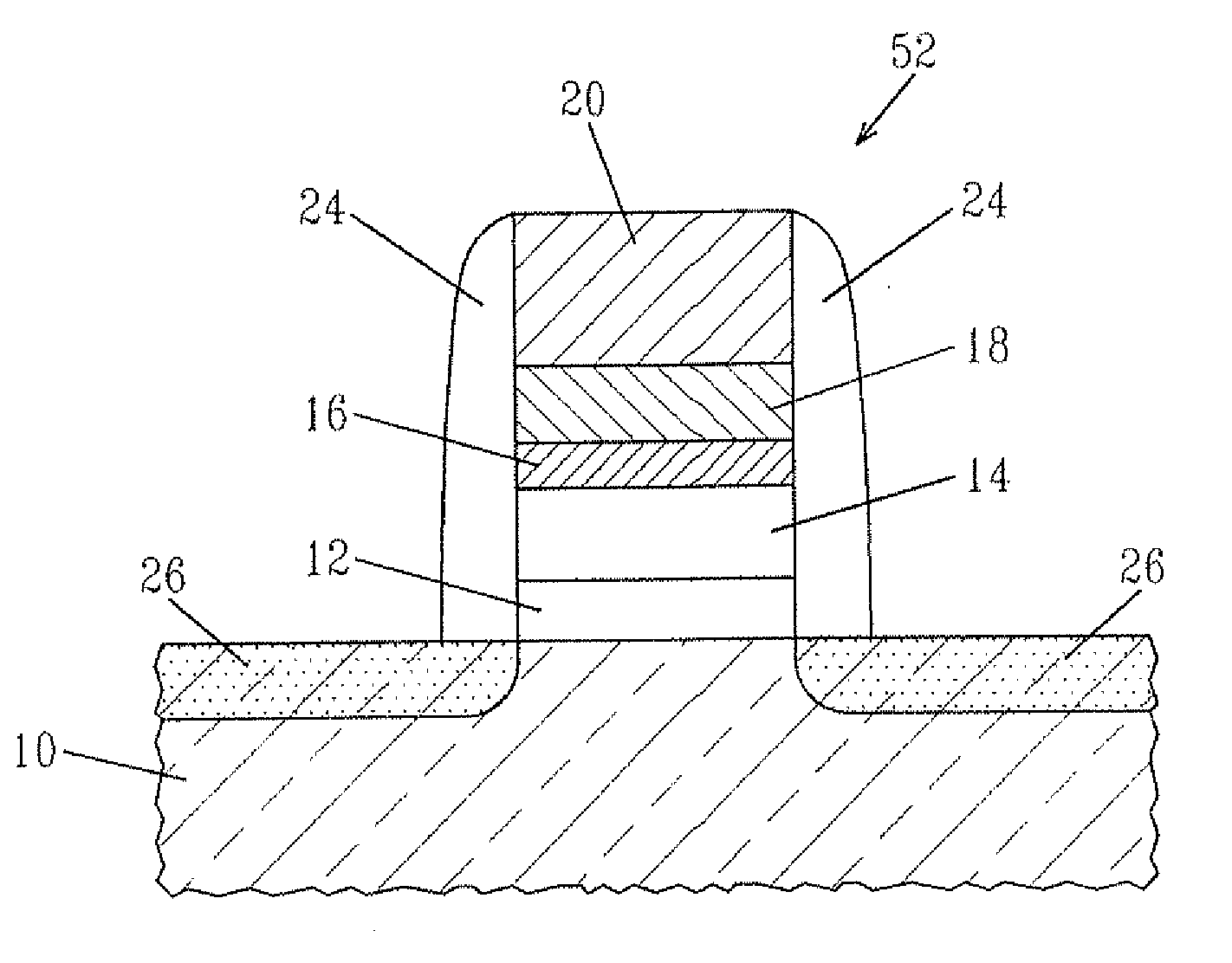

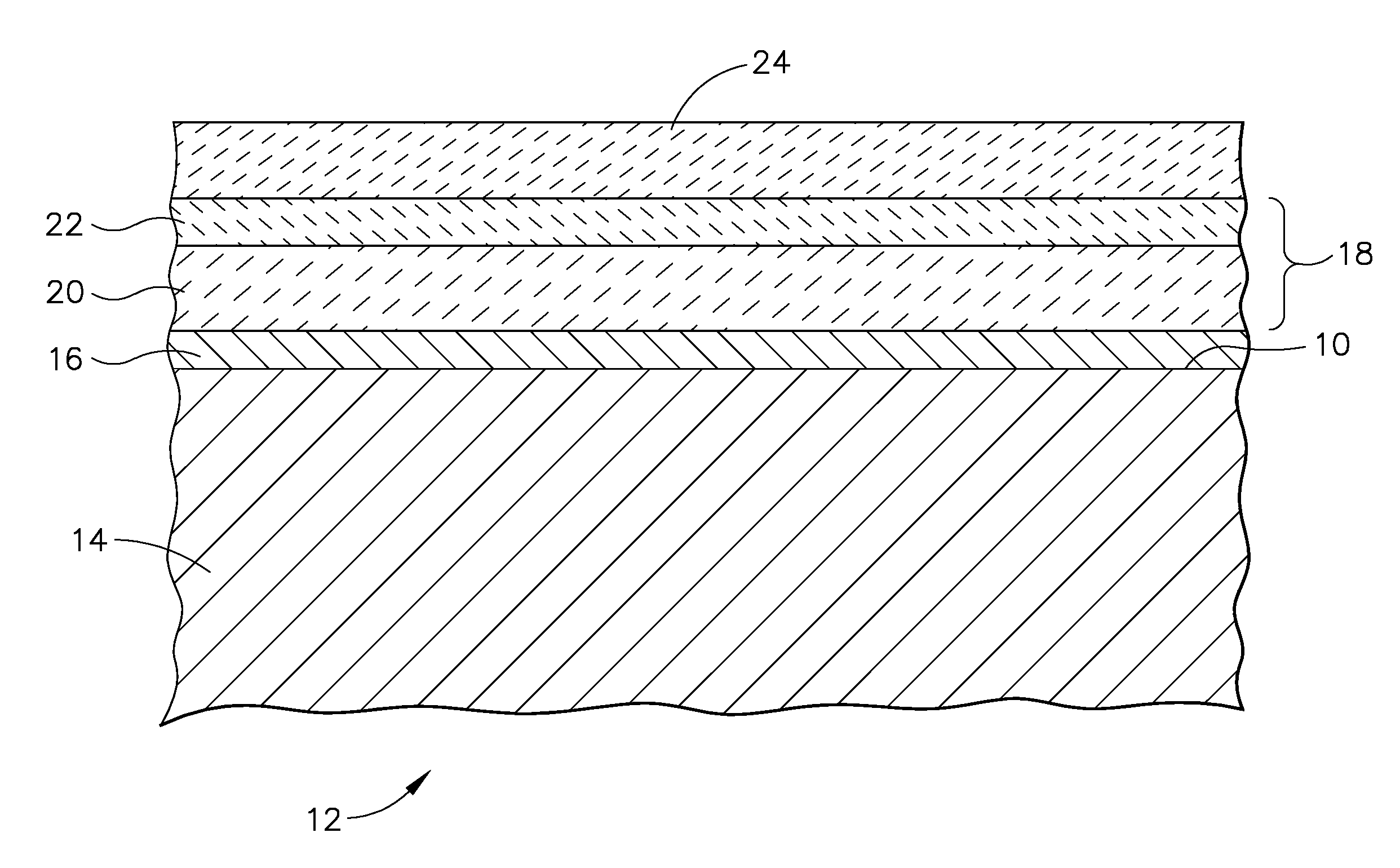

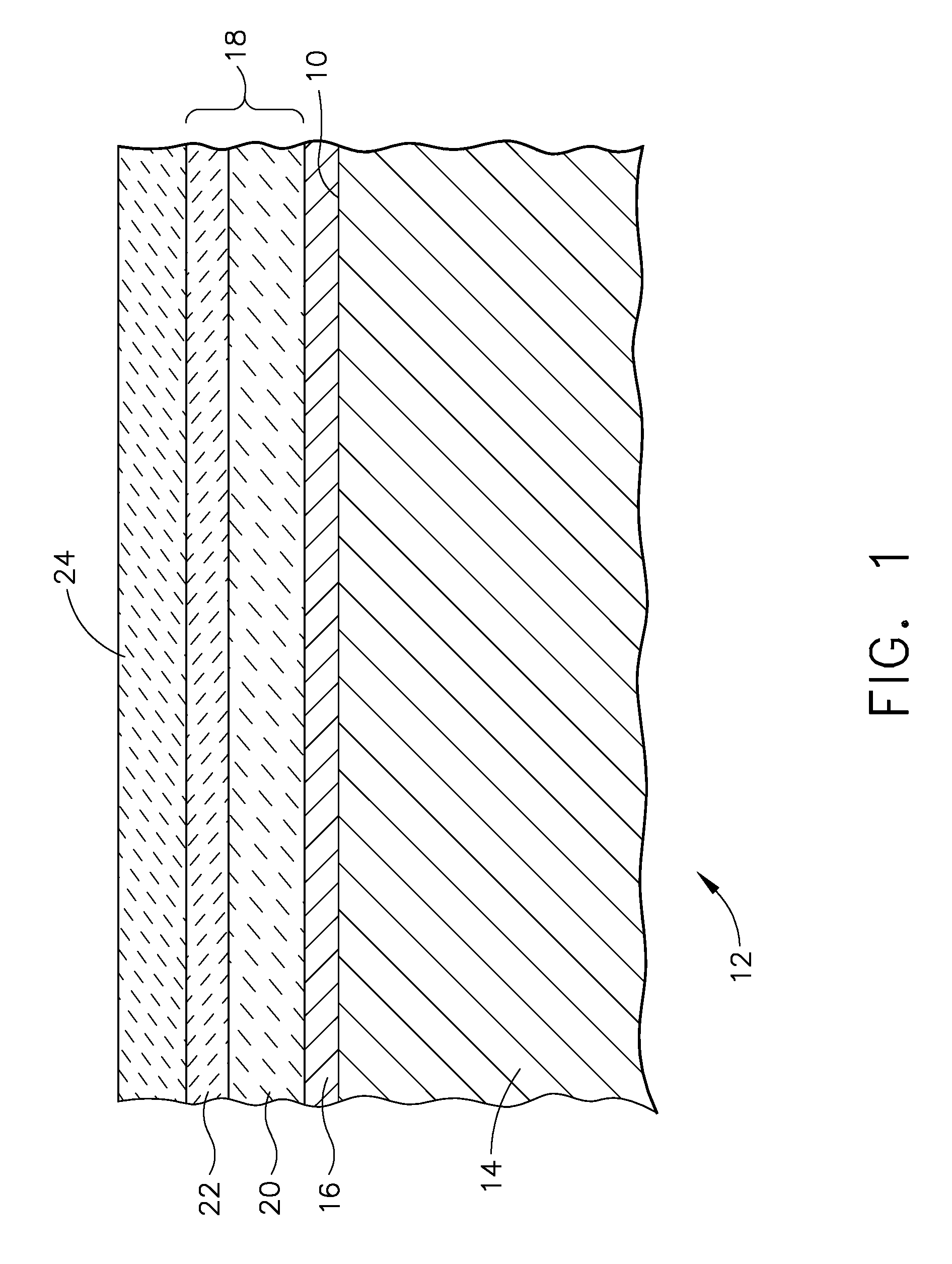

Method for forming a thin, high quality buffer layer in a field effect transistor and related structure

ActiveUS7071051B1Readily apparentSemiconductor/solid-state device manufacturingSemiconductor devicesOrganic field-effect transistorOptoelectronics

According to one exemplary embodiment, a method for forming a field-effect transistor on a substrate comprises a step of forming a buffer layer on the substrate, where the buffer layer comprises ALD silicon dioxide. The buffer layer can be formed by utilizing a silicon tetrachloride precursor in an atomic layer deposition process, for example. The buffer layer comprises substantially no pin-hole defects and may have a thickness, for example, that is less than approximately 5.0 Angstroms. The method further comprises forming a high-k dielectric layer over the buffer layer. The high-k dielectric layer may be, for example, hafnium oxide, zirconium oxide, or aluminum oxide. According to this exemplary embodiment, the method further comprises forming a gate electrode layer over the high-k dielectric layer. The gate electrode layer may be polycrystalline silicon, for example.

Owner:GLOBALFOUNDRIES US INC

Methods of forming material over substrates

InactiveUS20070252244A1Speed up pressure saturationSemiconductor/solid-state device detailsSolid-state devicesHafnium oxideAnalytical chemistry

The invention includes ALD-type methods in which two or more different precursors are utilized with one or more reactants to form a material. In particular aspects, the precursors are hafnium and aluminum, the only reactant is ozone, and the material is hafnium oxide predominantly in a tetragonal crystalline phase.

Owner:ROUND ROCK RES LLC

Methods of atomic layer deposition of hafnium oxide / erbium oxide bi-layer as advanced gate dielectrics

InactiveUS20130313656A1Improve electrical performanceFew defectSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricHafnium

Provided is a two-step ALD deposition process for forming a gate dielectric involving an erbium oxide layer deposition followed by a hafnium oxide layer deposition. Hafnium oxide can provide a high dielectric constant, high density, large bandgap and good thermal stability. Erbium oxide can act as a barrier against oxygen diffusion, which can lead to increasing an effective oxide thickness of the gate dielectric and preventing hafnium-silicon reactions that may lead to higher leakage current.

Owner:INTERMOLECULAR

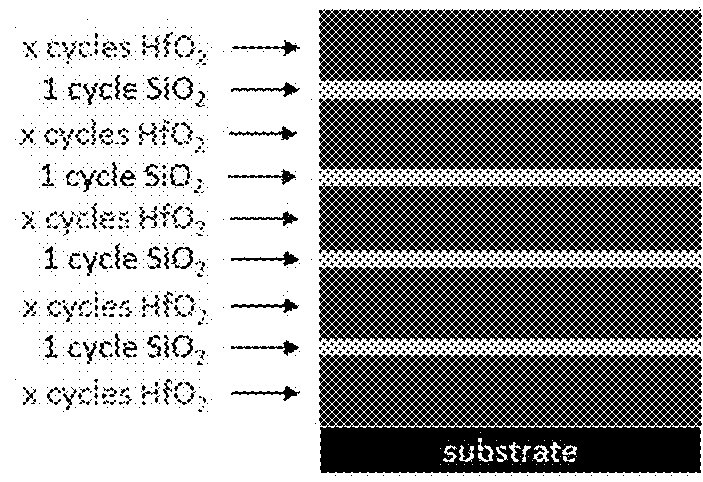

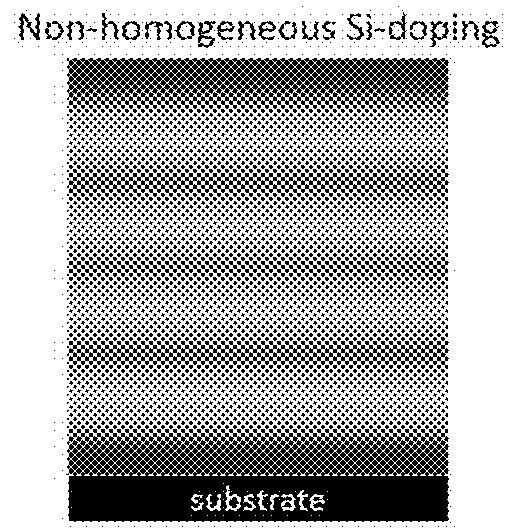

Formulation for Deposition of Silicon Doped Hafnium Oxide as Ferroelectric Materials

ActiveUS20180269057A1Reduce and increase reactivityEasy to controlSolid-state devicesSemiconductor/solid-state device manufacturingHafniumSilicon

In one aspect, the invention is formulations comprising both organoaminohafnium and organoaminosilane precursors that allows anchoring both silicon-containing fragments and hafnium-containing fragments onto a given surface having hydroxyl groups to deposit silicon doped hafnium oxide having a silicon doping level ranging from 0.5 to 8 mol %, preferably 2 to 6 mol %, most preferably 3 to 5 mol %, suitable as ferroelectric material. In another aspect, the invention is methods and systems for depositing the silicon doped hafnium oxide films using the formulations.

Owner:VERSUM MATERIALS US LLC

Zirconium oxide and hafnium oxide etching using halogen containing chemicals

ActiveUS20050164479A1Effective meanSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricHafnium

A method is described for selectively etching a high k dielectric layer that is preferably a hafnium or zirconium oxide, silicate, nitride, or oxynitride with a selectivity of greater than 2:1 relative to silicon oxide, polysilicon, or silicon. The plasma etch chemistry is comprised of one or more halogen containing gases such as CF4, CHF3, CH2F2, CH3F, C4F8, C4F6, C5F6, BCl3, Br2, HF, HCl, HBr, HI, and NF3 and leaves no etch residues. An inert gas or an inert gas and oxidant gas may be added to the halogen containing gas. In one embodiment, a high k gate dielectric layer is removed on portions of an active area in a MOS transistor. Alternatively, the high k dielectric layer is used in a capacitor between two conducting layers and is selectively removed from portions of an ILD layer.

Owner:TAIWAN SEMICON MFG CO LTD

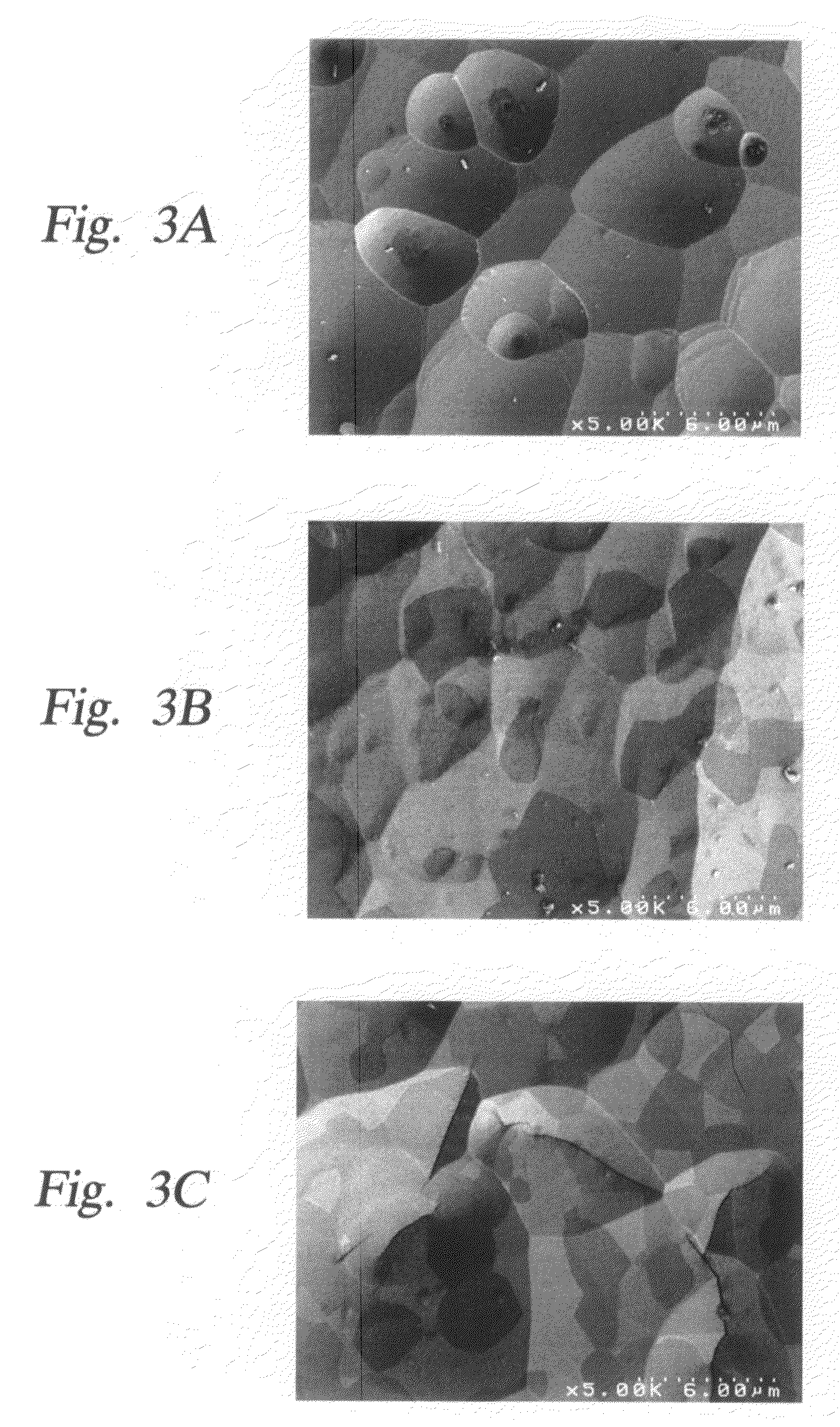

Method and apparatus which reduce the erosion rate of surfaces exposed to halogen-containing plasmas

ActiveUS20080264565A1Improve plasma resistanceImprove corrosion resistanceElectric discharge tubesSemiconductor/solid-state device manufacturingYTTERBIUM OXIDEErosion rate

A ceramic article which is resistant to erosion by halogen-containing plasmas used in semiconductor processing. The ceramic article includes ceramic which is multi-phased, typically including two phase to three phases. The ceramic is formed from yttrium oxide at a molar concentration ranging from about 50 mole % to about 75 mole %; zirconium oxide at a molar concentration ranging from about 10 mole % to about 30 mole %; and at least one other component, selected from the group consisting of aluminum oxide, hafnium oxide, scandium oxide, neodymium oxide, niobium oxide, samarium oxide, ytterbium oxide, erbium oxide, cerium oxide, and combinations thereof, at a molar concentration ranging from about 10 mole % to about 30 mole %.

Owner:APPLIED MATERIALS INC

Composite dielectric forming methods and composite dielectrics

InactiveUS20050009370A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricCapacitor

A composite dielectric forming method includes atomic layer depositing alternate layers of hafnium oxide and lanthanum oxide over a substrate. The hafnium oxide can be thermally stable, crystalline hafnium oxide and the lanthanum oxide can be thermally stable, crystalline lanthanum oxide. A transistor may comprise the composite dielectric as a gate dielectric. A capacitor may comprise the composite dielectric as a capacitor dielectric.

Owner:MICRON TECH INC

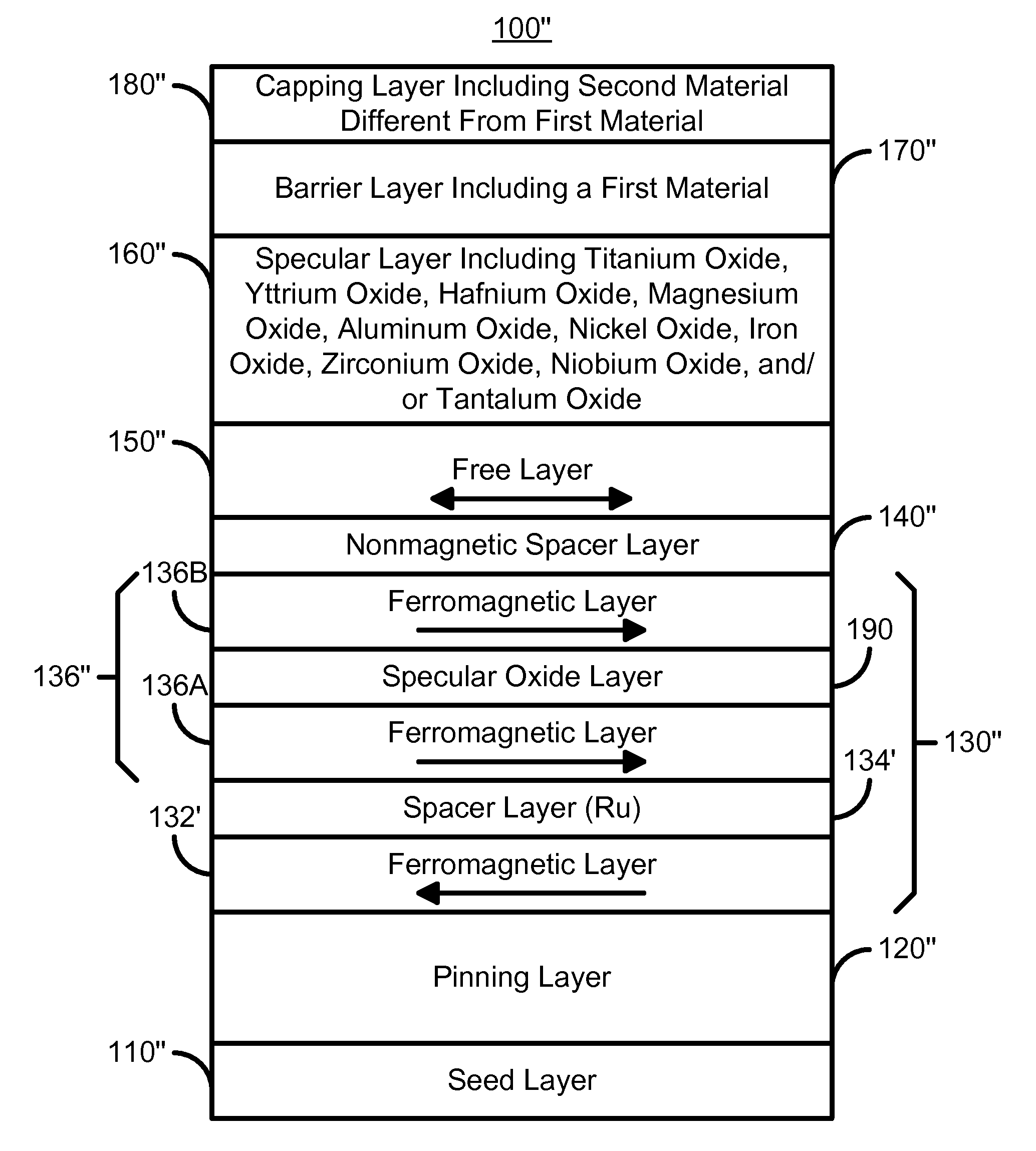

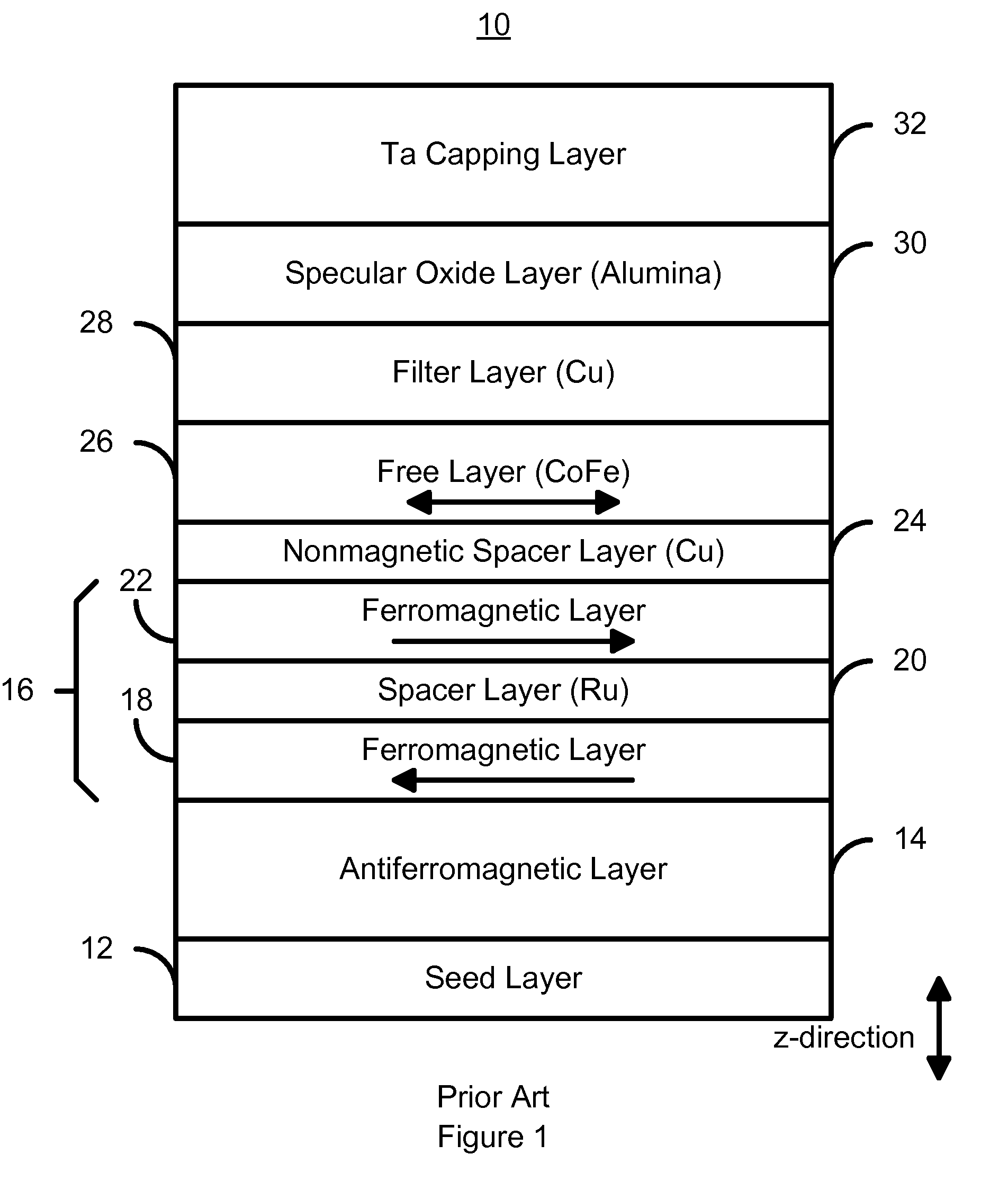

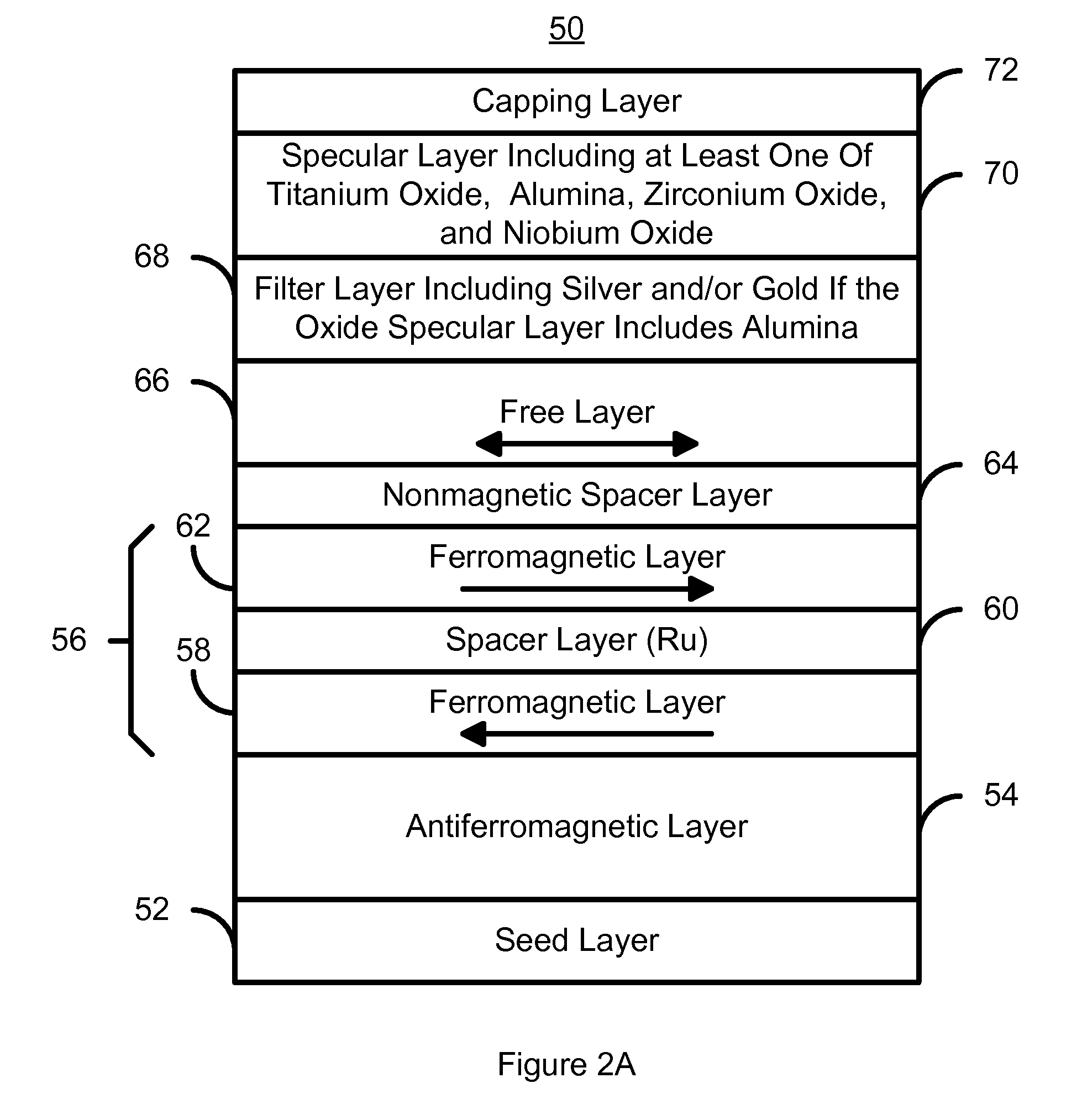

Magnetoresistive structure having a novel specular and barrier layer combination

InactiveUS7684160B1Magnetic-field-controlled resistorsConductive/insulating/magnetic material on magnetic film applicationYttriumTitanium oxide

A method and system for providing a magnetoresistive structure is disclosed. The magnetoresistive structure includes a pinned layer, a nonmagnetic spacer layer, a free layer, a specular layer, a barrier layer, and a capping layer. The spacer layer resides between the pinned layer and the free layer. The free layer is electrically conductive and resides between the specular layer and the nonmagnetic spacer layer. The specular layer is adjacent to the free layer and includes at least one of titanium oxide, yttrium oxide, hafnium oxide, magnesium oxide, aluminum oxide, nickel oxide, iron oxide, zirconium oxide, niobium oxide, and tantalum oxide. The barrier layer resides between the specular layer and the capping layer. The barrier layer is nonmagnetic and includes a first material. The capping layer includes a second material different from the first material.

Owner:WESTERN DIGITAL TECH INC

Method and apparatus which reduce the erosion rate of surfaces exposed to halogen-containing plasmas

ActiveUS7696117B2Reduce erosion rateImprove mechanical propertiesElectric discharge tubesSemiconductor/solid-state device manufacturingErosion rateYttrium

A ceramic article which is resistant to erosion by halogen-containing plasmas used in semiconductor processing. The ceramic article includes ceramic which is multi-phased, typically including two phase to three phases. The ceramic is formed from yttrium oxide at a molar concentration ranging from about 50 mole % to about 75 mole %; zirconium oxide at a molar concentration ranging from about 10 mole % to about 30 mole %; and at least one other component, selected from the group consisting of aluminum oxide, hafnium oxide, scandium oxide, neodymium oxide, niobium oxide, samarium oxide, ytterbium oxide, erbium oxide, cerium oxide, and combinations thereof, at a molar concentration ranging from about 10 mole % to about 30 mole %.

Owner:APPLIED MATERIALS INC

Composite dielectric forming methods and composite dielectrics

InactiveUS6960538B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricCapacitor

A composite dielectric forming method includes atomic layer depositing alternate layers of hafnium oxide and lanthanum oxide over a substrate. The hafnium oxide can be thermally stable, crystalline hafnium oxide and the lanthanum oxide can be thermally stable, crystalline lanthanum oxide. A transistor may comprise the composite dielectric as a gate dielectric. A capacitor may comprise the composite dielectric as a capacitor dielectric.

Owner:MICRON TECH INC

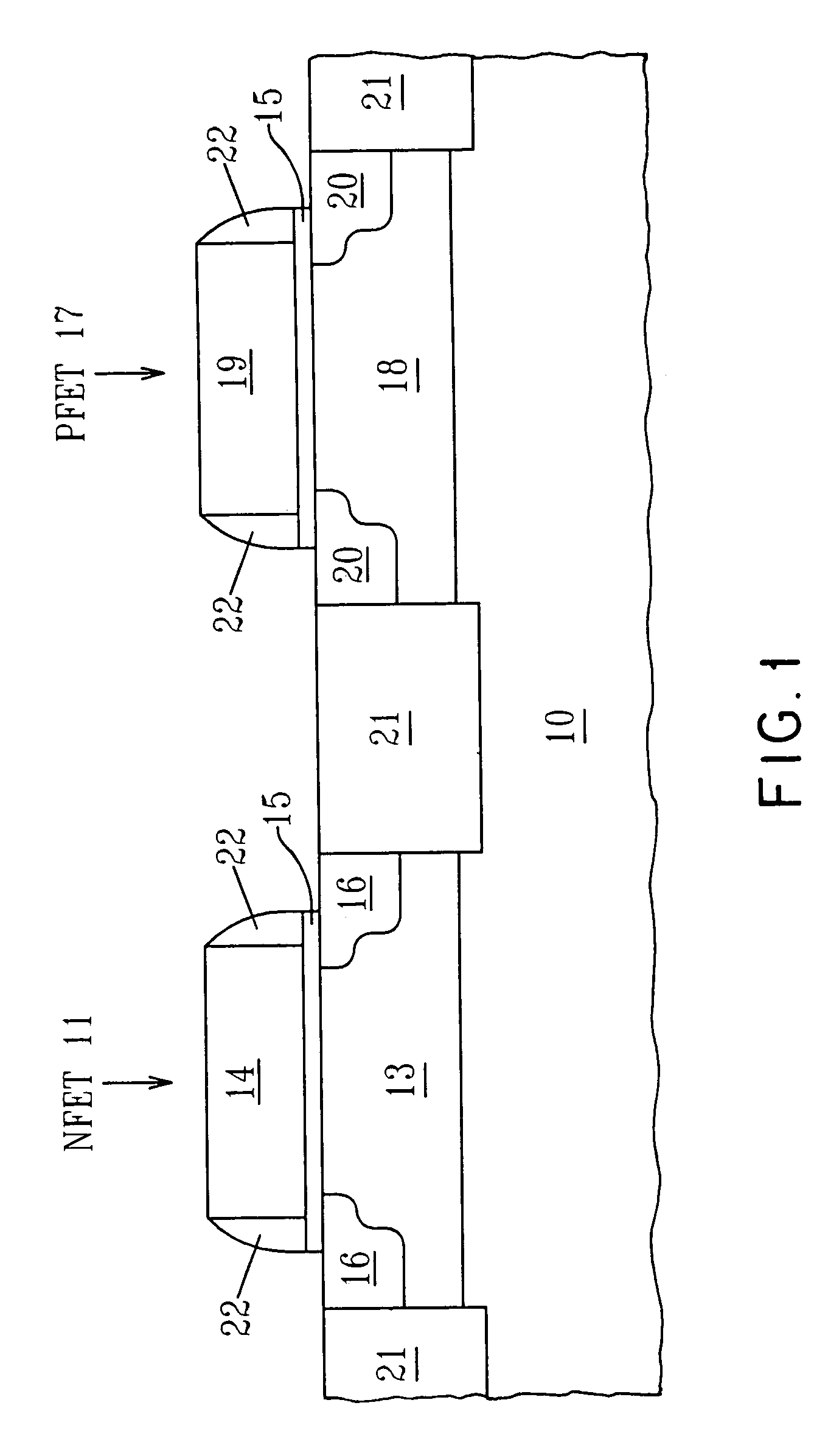

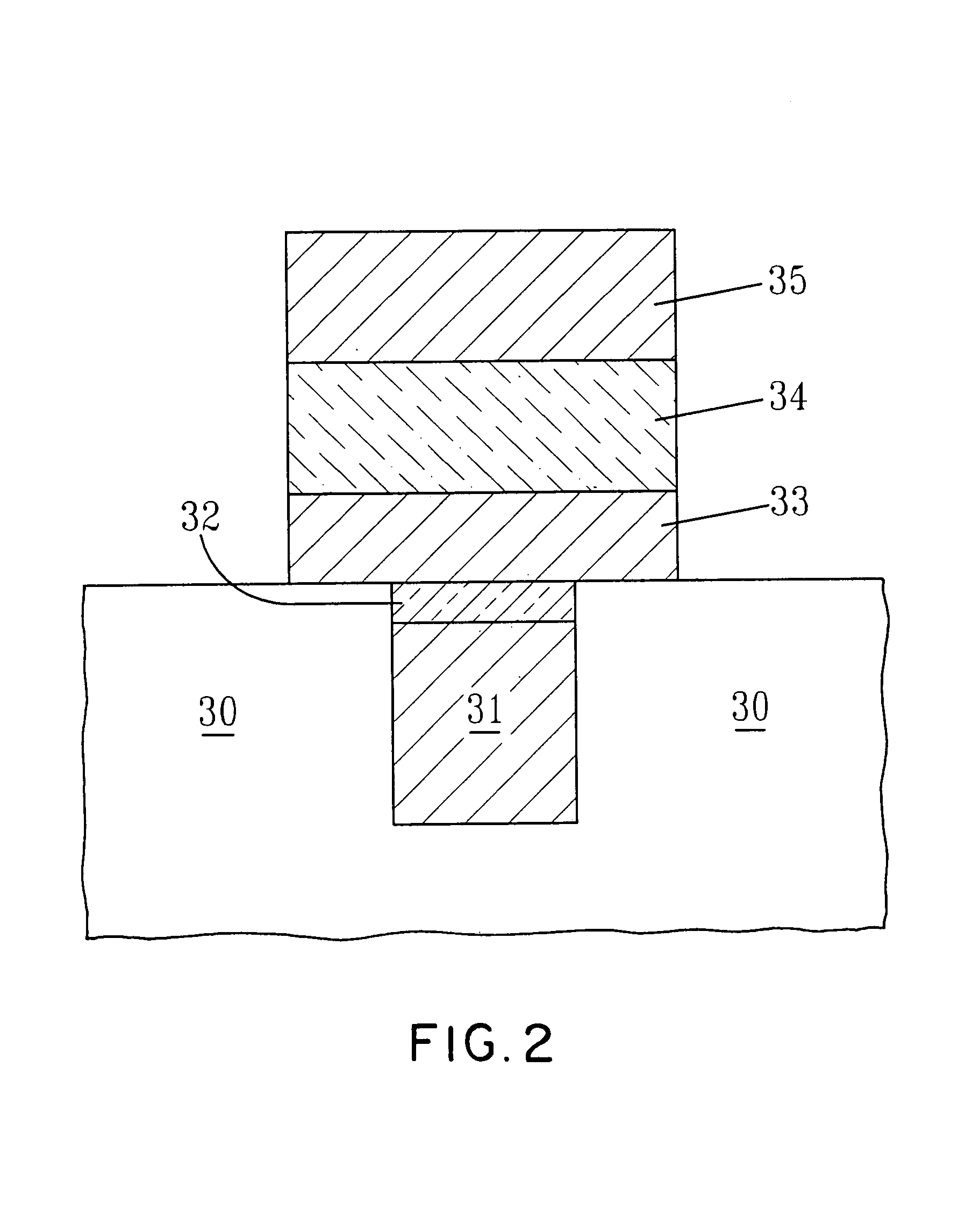

Stabilization of flatband voltages and threshold voltages in hafnium oxide based silicon transistors for CMOS

InactiveUS20080258198A1Promoting the necessary flatband voltage shiftEffective alignmentSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSElectrical conductor

The present invention provides a metal stack structure that stabilizes the flatband voltage and threshold voltages of material stacks that include a Si-containing conductor and a Hf-based dielectric. This present invention stabilizes the flatband voltages and the threshold voltages by introducing a rare earth metal-containing layer into the material stack that introduces, via electronegativity differences, a shift in the threshold voltage to the desired voltage. Specifically, the present invention provides a metal stack comprising:a hafnium-based dielectric; a rare earth metal-containing layer located atop of, or within, said hafnium-based dielectric; an electrically conductive capping layer located above said hafnium-based dielectric; and a Si-containing conductor.

Owner:AURIGA INNOVATIONS INC

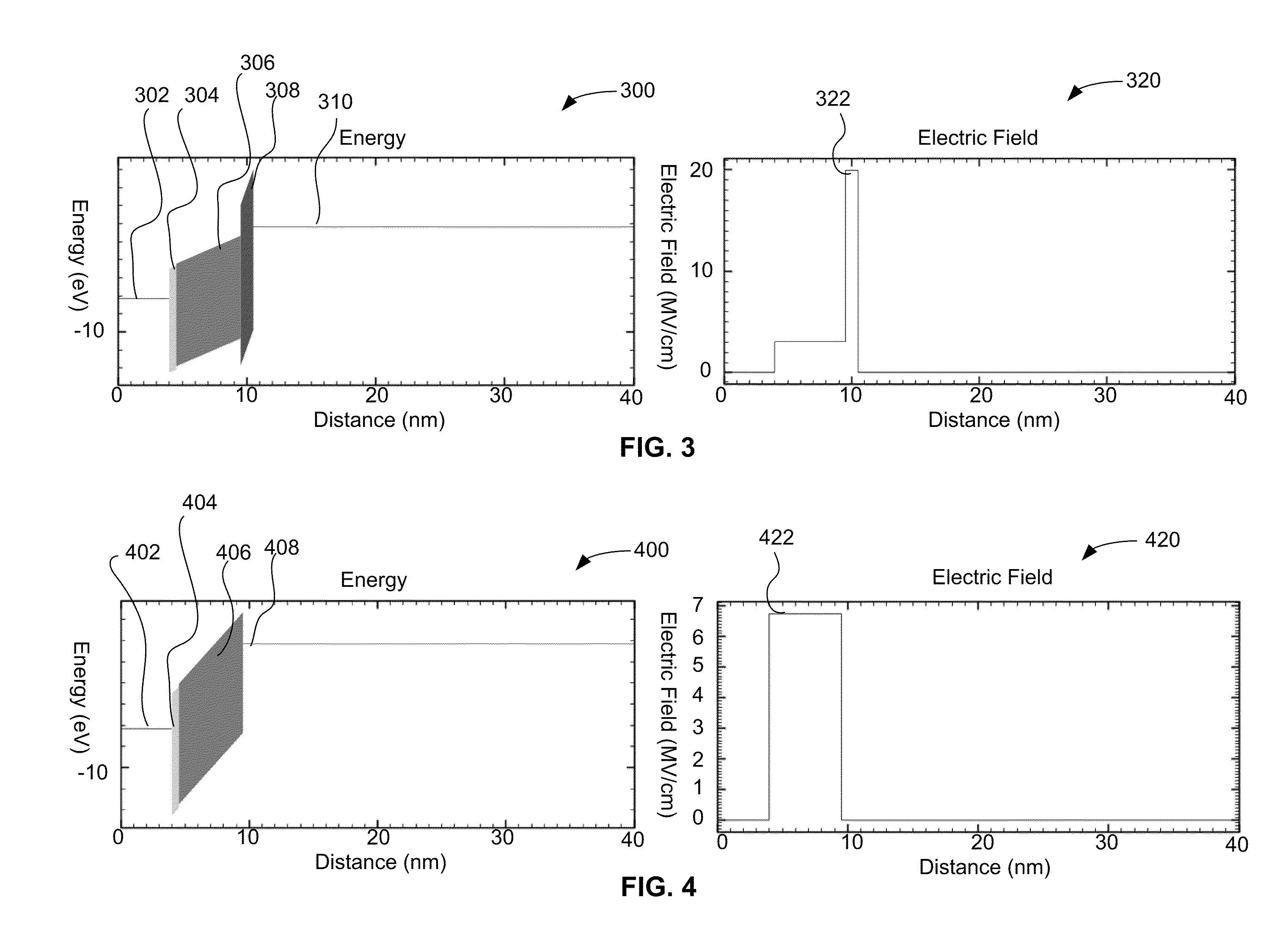

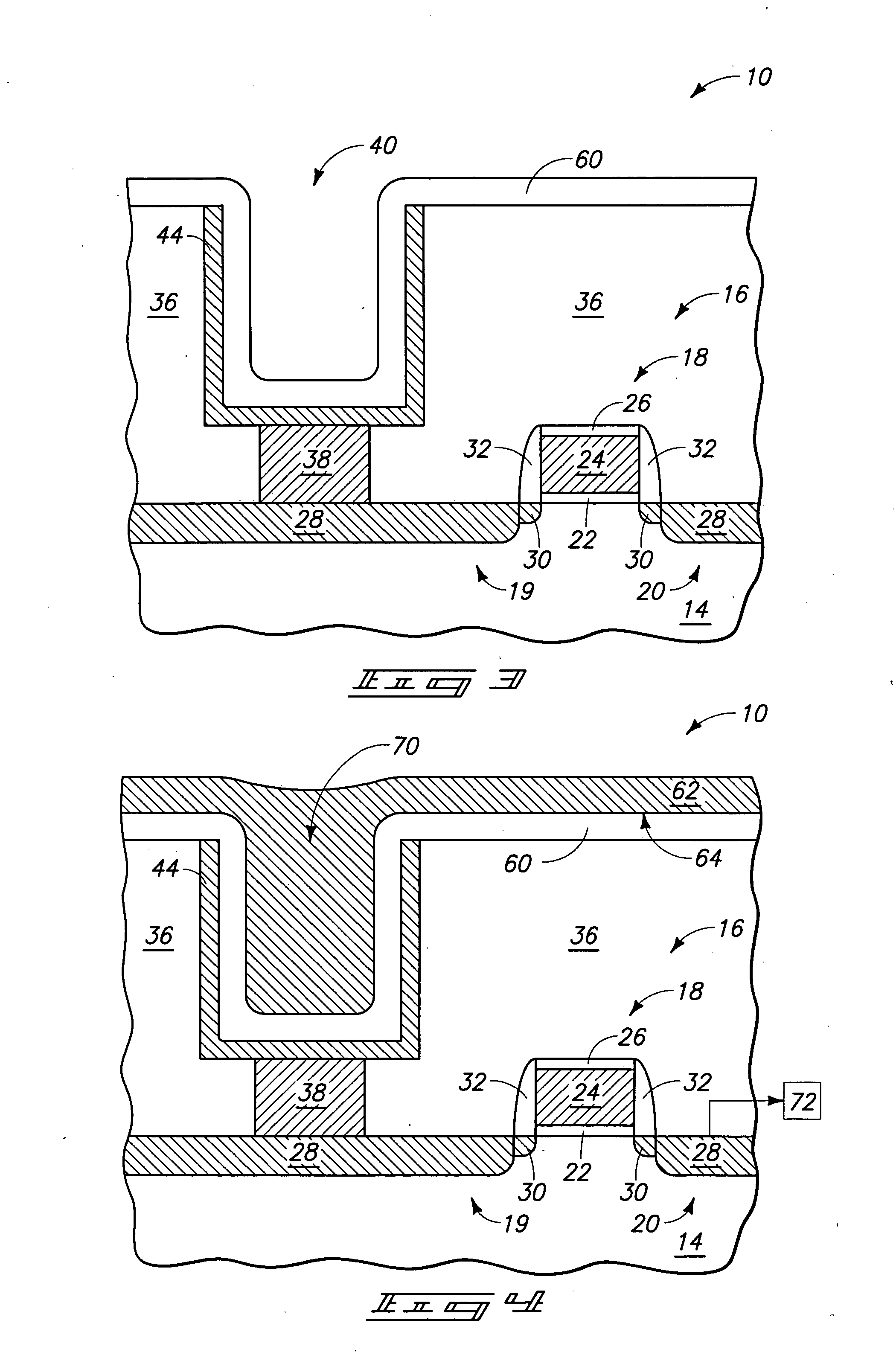

Resistive-switching memory elements having improved switching characteristics

ActiveUS20100258782A1Solid-state devicesSemiconductor/solid-state device manufacturingCouplingTitanium

Resistive-switching memory elements having improved switching characteristics are described, including a memory element having a first electrode and a second electrode, a switching layer between the first electrode and the second electrode comprising hafnium oxide and having a first thickness, and a coupling layer between the switching layer and the second electrode, the coupling layer comprising a material including metal titanium and having a second thickness that is less than 25 percent of the first thickness.

Owner:INTERMOLECULAR

Deposition of hafnium oxide and/or zirconium oxide and fabrication of passivated electronic structures

InactiveUS6982230B2Stable to reducing condition necessaryImprove electrical performanceSolid-state devicesSemiconductor/solid-state device manufacturingElectronic structureHydrogen

A method of fabricating hafnium oxide and / or zirconium oxide films is provided. The methods include providing a mixture of Hf and / or Zr alkoxide dissolved, emulsified or suspended in a liquid; vaporizing at least the alkoxide and depositing the vaporized component at a temperature of greater than 400° C. The resultant film is dense, microcrystalline and is capable of self-passivation when treated in a hydrogen plasma or forming gas anneal.

Owner:GLOBALFOUNDRIES INC

Layered thermal barrier coatings containing lanthanide series oxides for improved resistance to CMAS degradation

InactiveUS20070160859A1Avoid damageElimination of expensiveBlade accessoriesEfficient propulsion technologiesReaction layerCerium

A coating applied as a two layer system. The outer layer is an oxide of a group IV metal selected from the group consisting of zirconium oxide, hafnium oxide and combinations thereof, which are doped with an effective amount of a lanthanum series oxide. These metal oxides doped with a lanthanum series addition comprises a high weight percentage of the outer coating. As used herein, lanthanum series means an element selected from the group consisting of lanthanum (La), cerium (Ce), praseodymium (Pr), neodymium (Nd), promethium (Pm), samarium (Sm), europium (Eu), gadolinium (Gd), terbium (Tb), dysprosium (Dy), holmium (Ho), erbium (Er), thulium (Tm), ytterbium (Yb), lutetium (Lu) and combinations thereof, and lanthanum series oxides are oxides of these elements. When the zirconium oxide is doped with an effective amount of a lanthanum series oxide, a dense reaction layer is formed at the interface of the outer layer of TBC and the CMAS. This dense reaction layer prevents CMAS infiltration below it. The second layer, or inner layer underlying the outer layer, comprises a layer of partially stabilized zirconium oxide.

Owner:GENERAL ELECTRIC CO

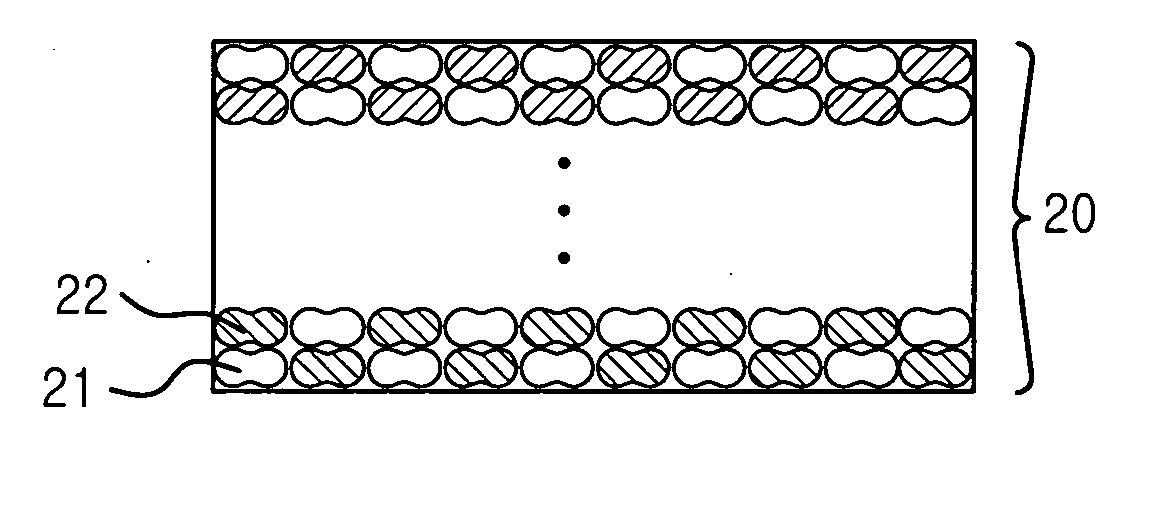

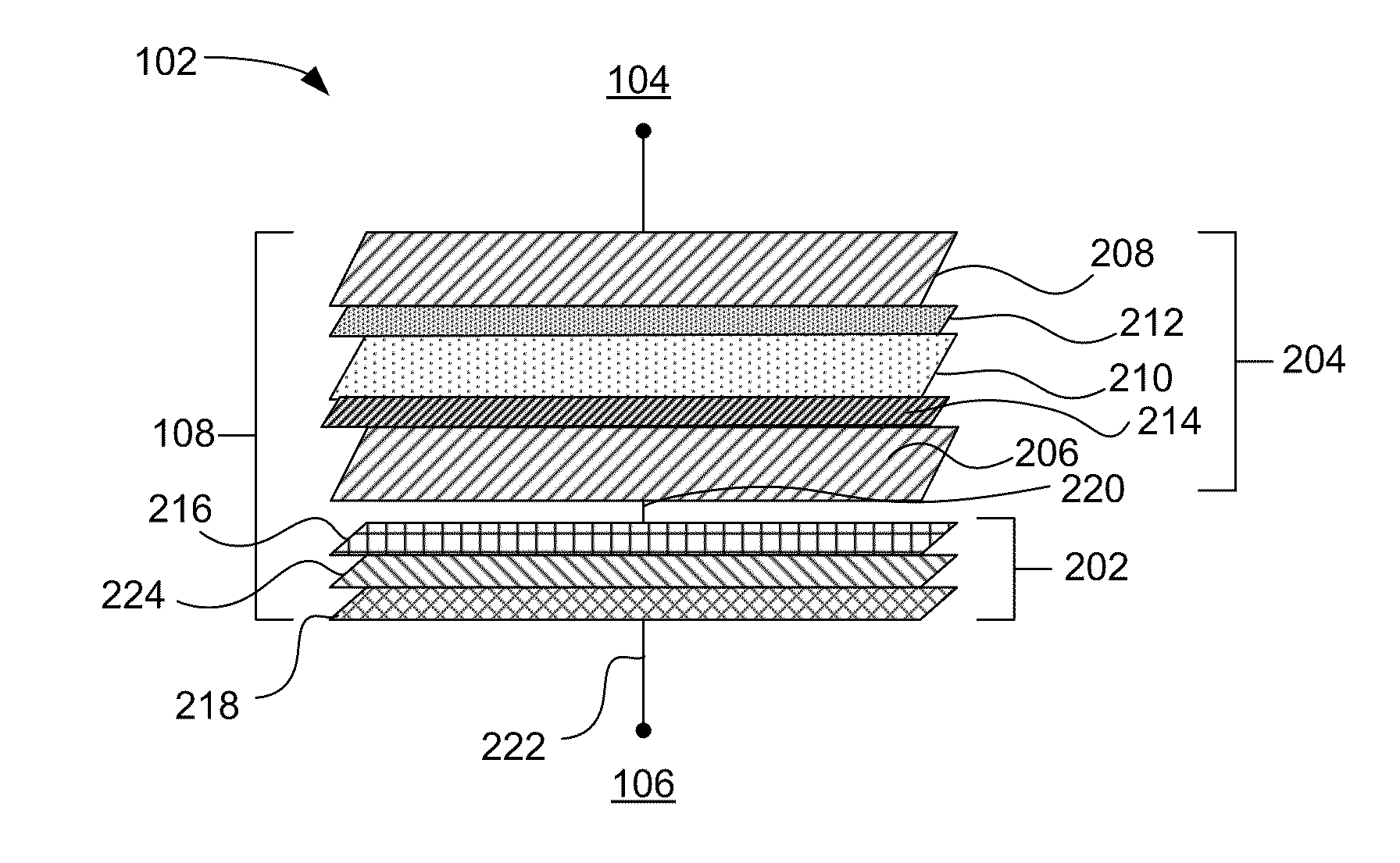

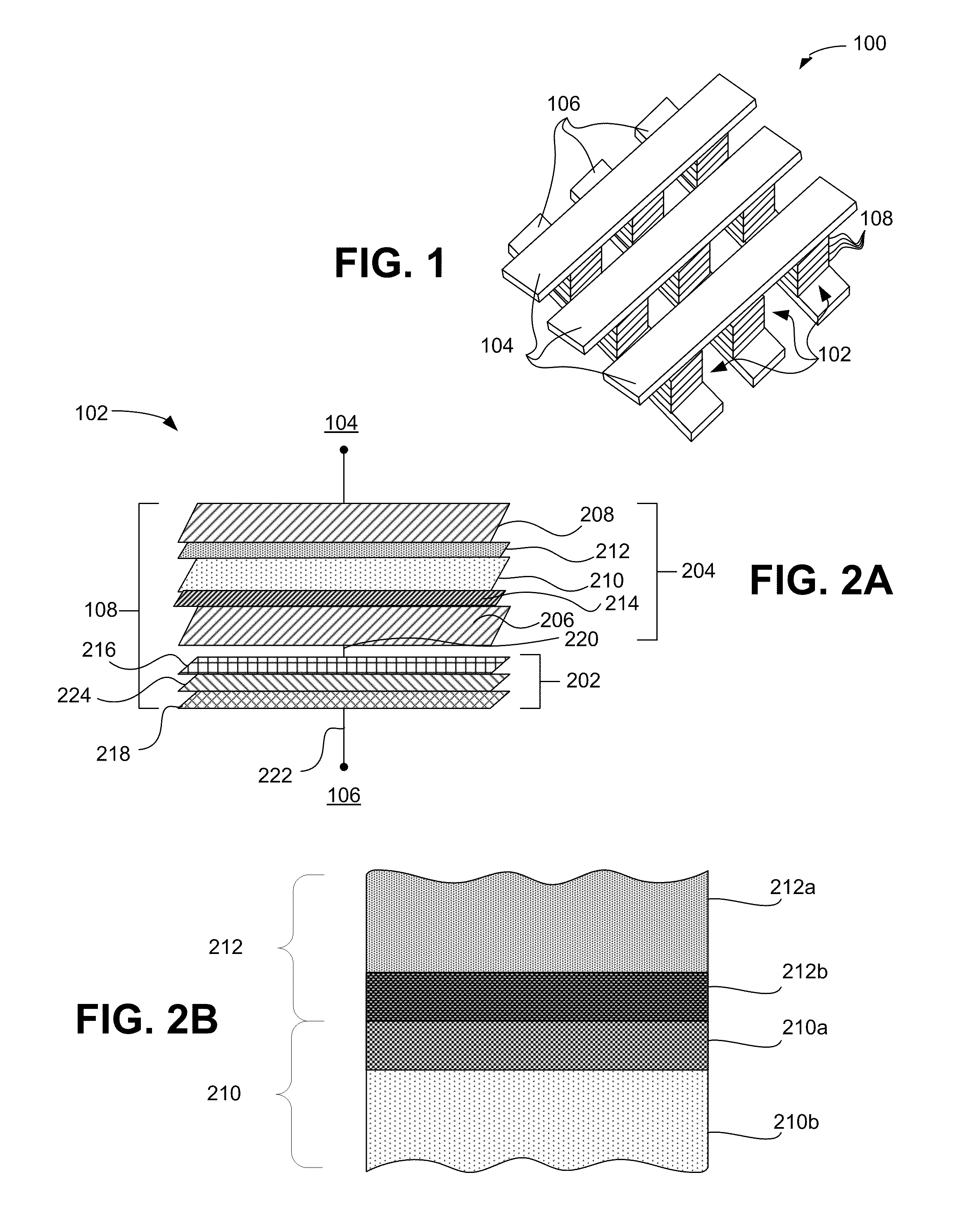

Electron blocking layers for electronic devices

InactiveUS20080150003A1Improve performanceEnhancement of charge retention propertySemiconductor/solid-state device manufacturingSemiconductor devicesCharge retentionHafnium

Methods and apparatuses for electronic devices such as non-volatile memory devices are described. The memory devices include a multi-layer control dielectric, such as a double or triple layer. The multi-layer control dielectric includes a combination of high-k dielectric materials such as aluminum oxide (Al2O3), hafnium oxide (HfO2), and / or hybrid films of hafnium aluminum oxide. The multi-layer control dielectric provides enhanced characteristics, including increased charge retention, enhanced memory program / erase window, improved reliability and stability, with feasibility for single or multistate (e.g., two, three or four bit) operation.

Owner:SANDISK TECH LLC

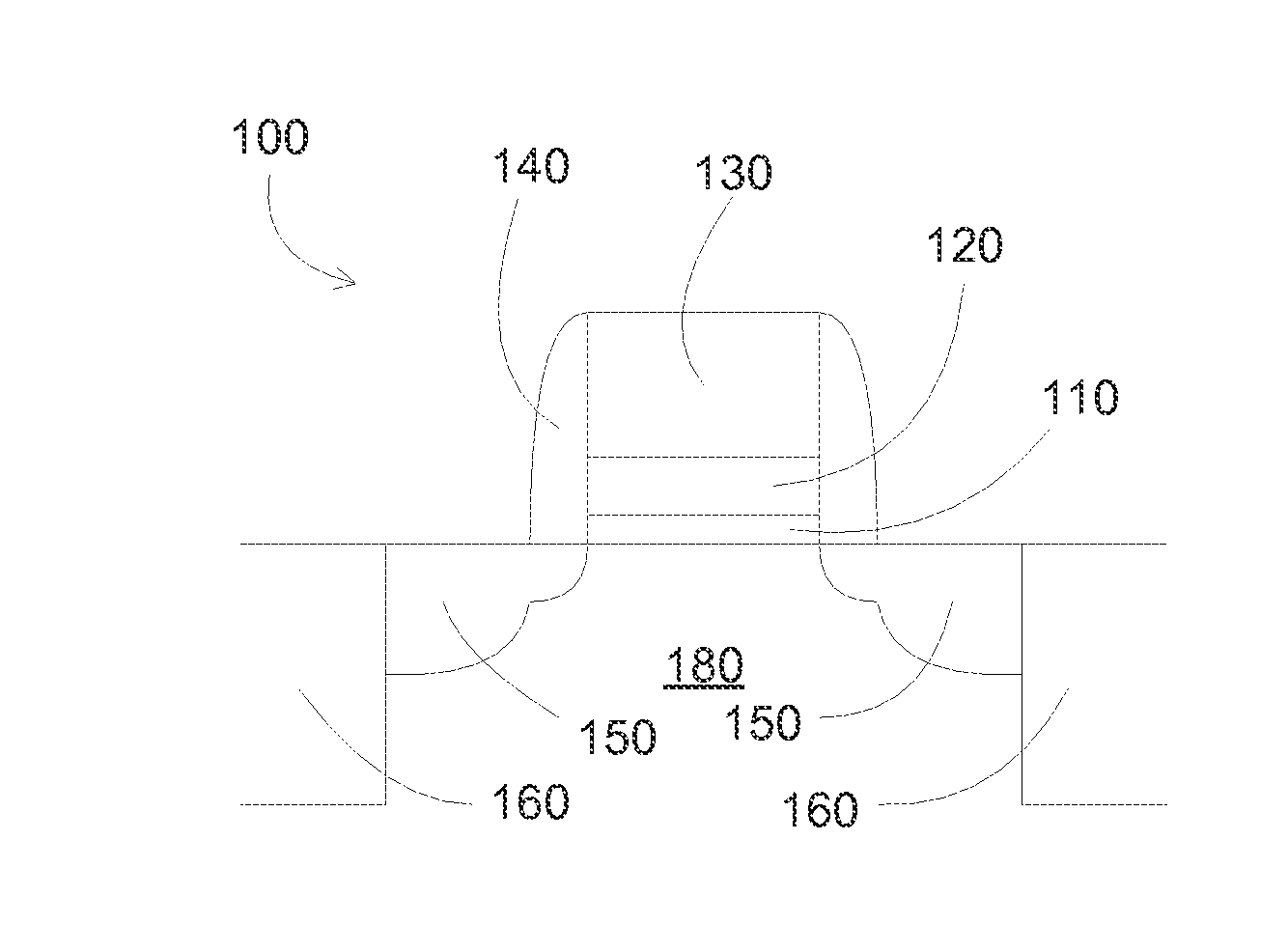

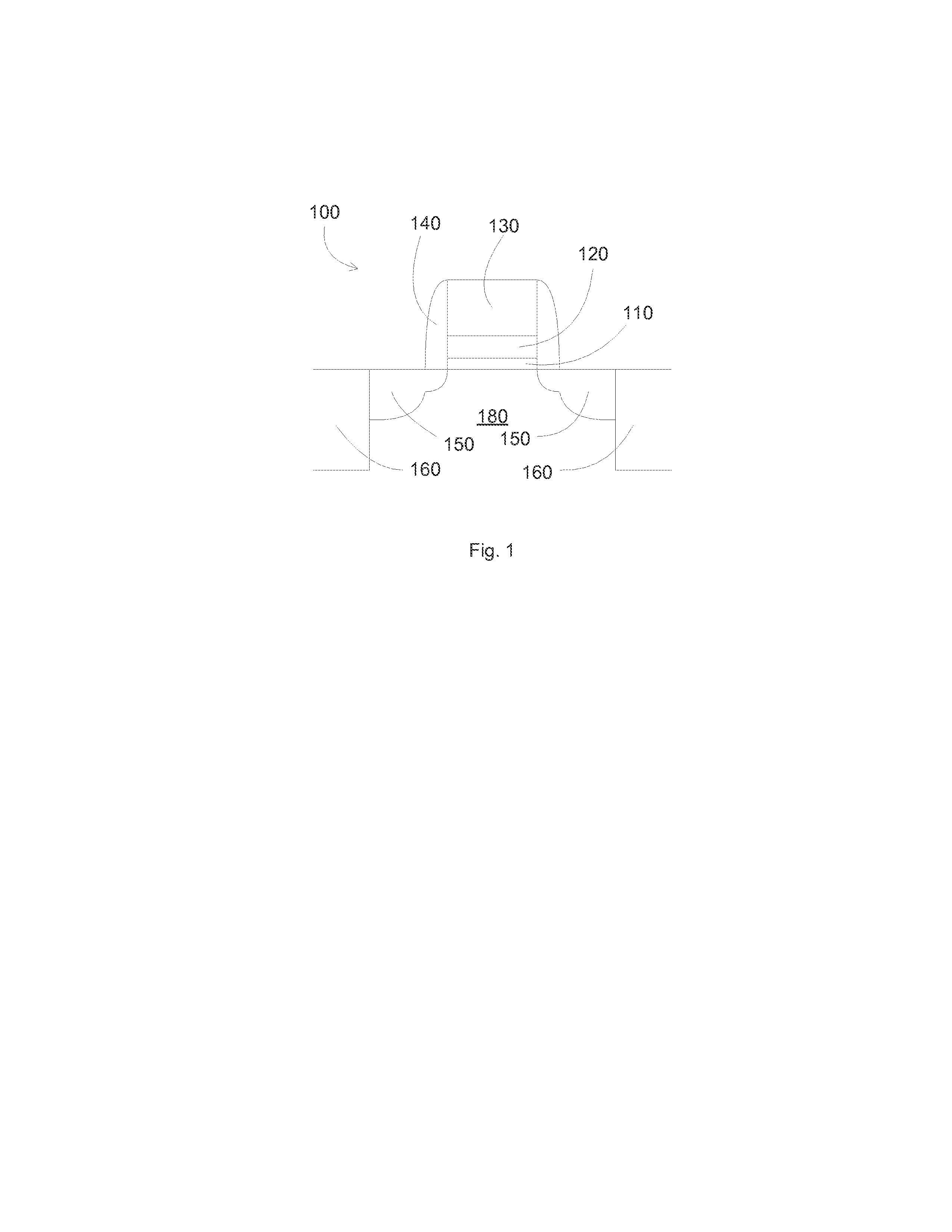

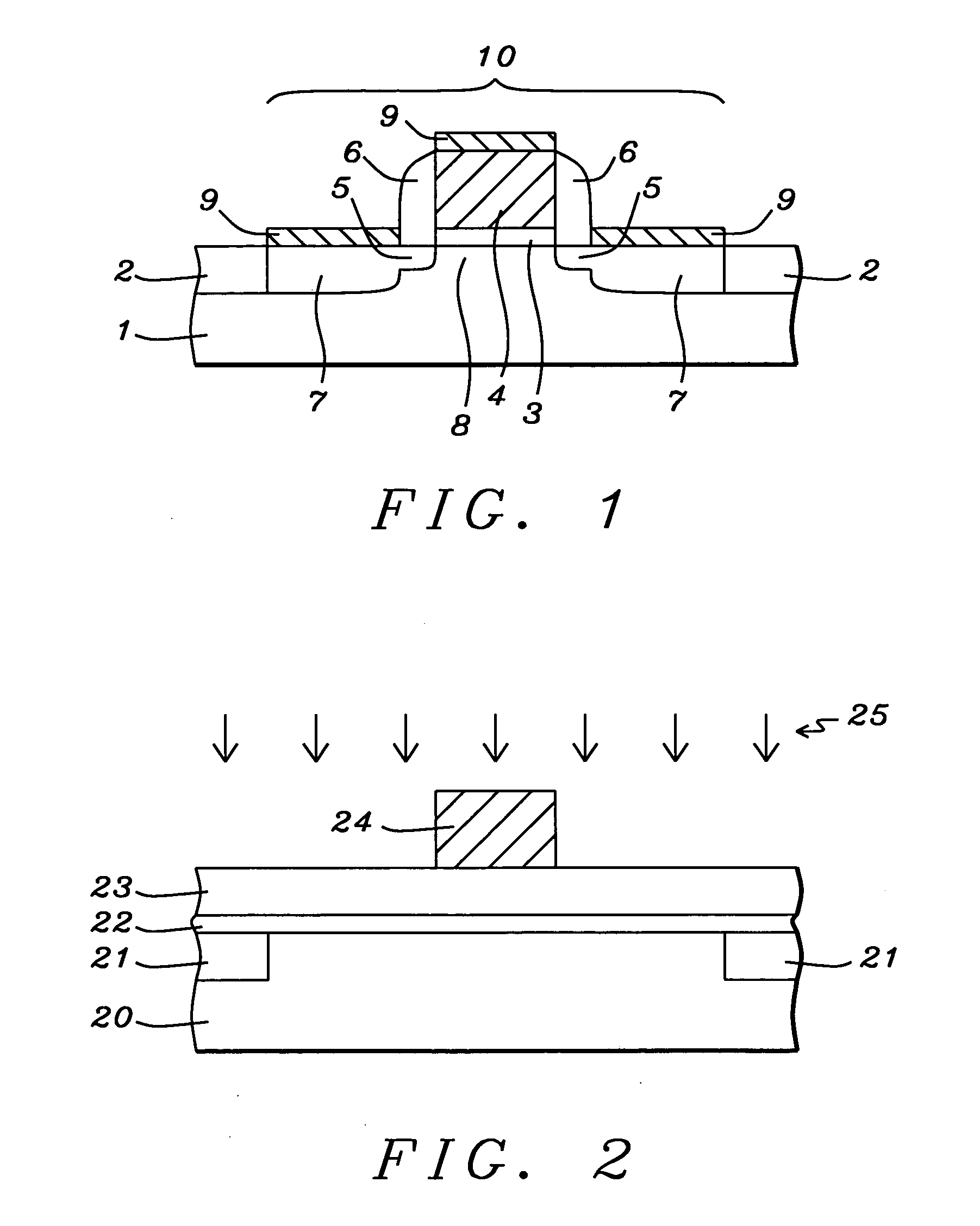

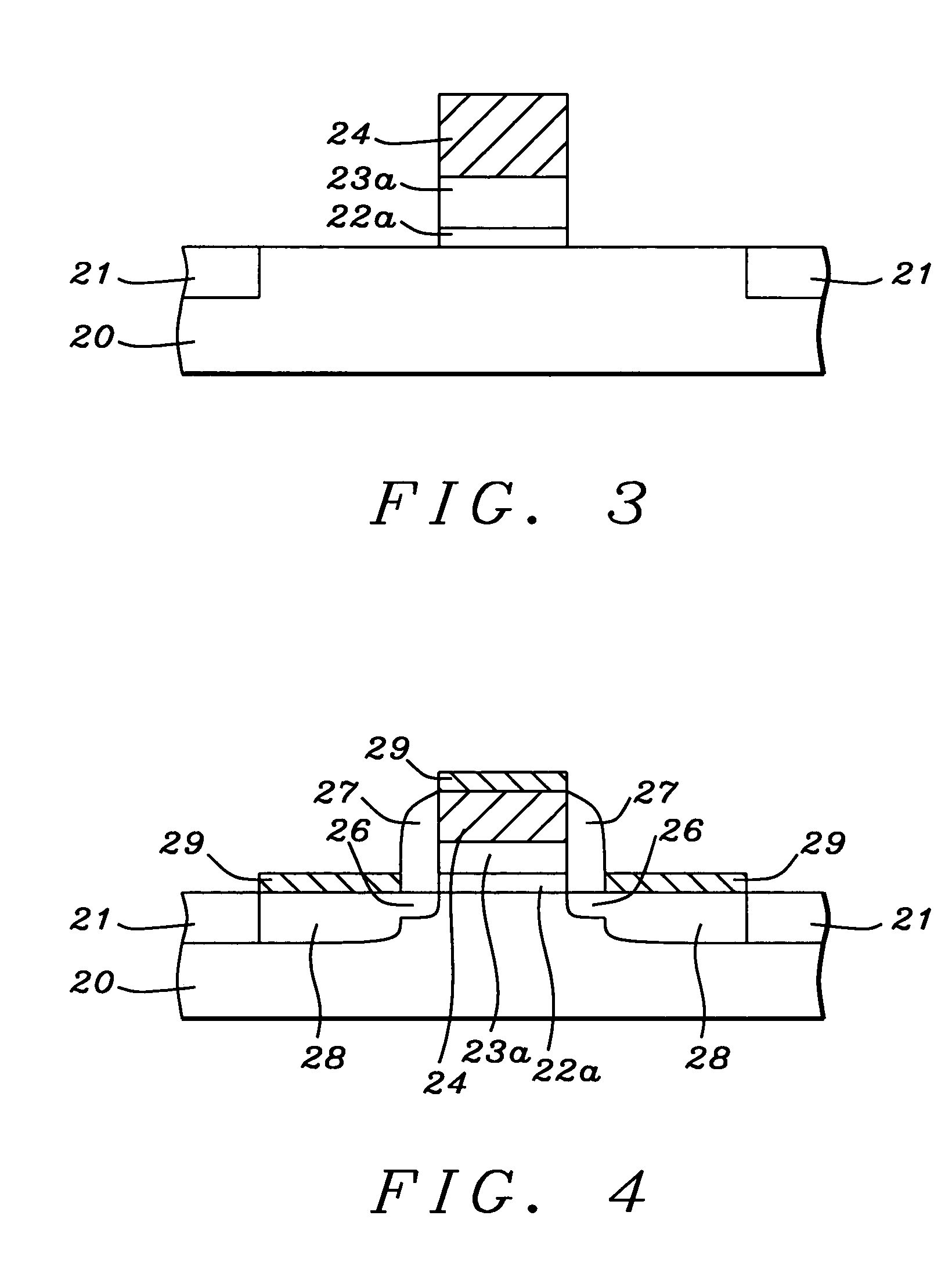

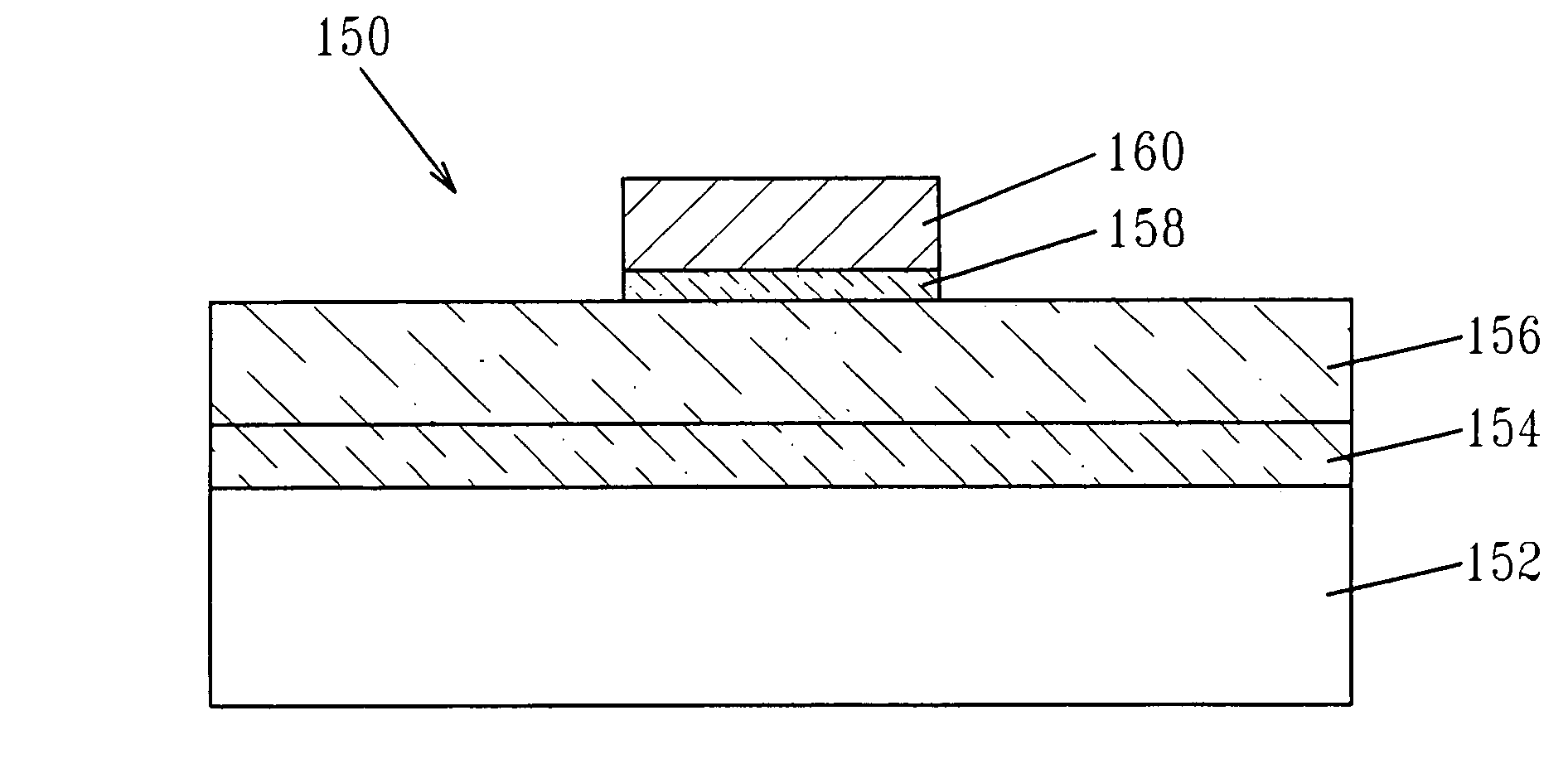

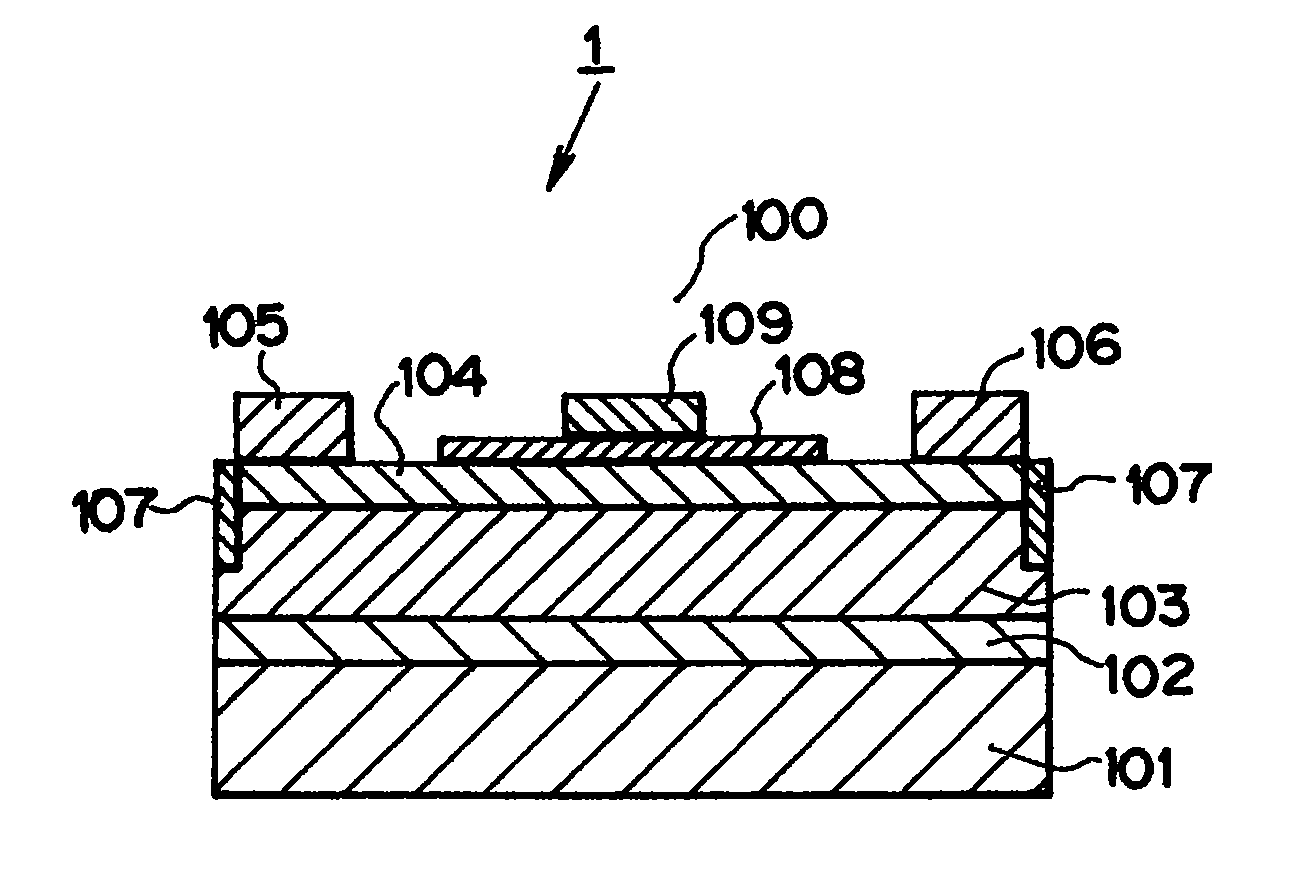

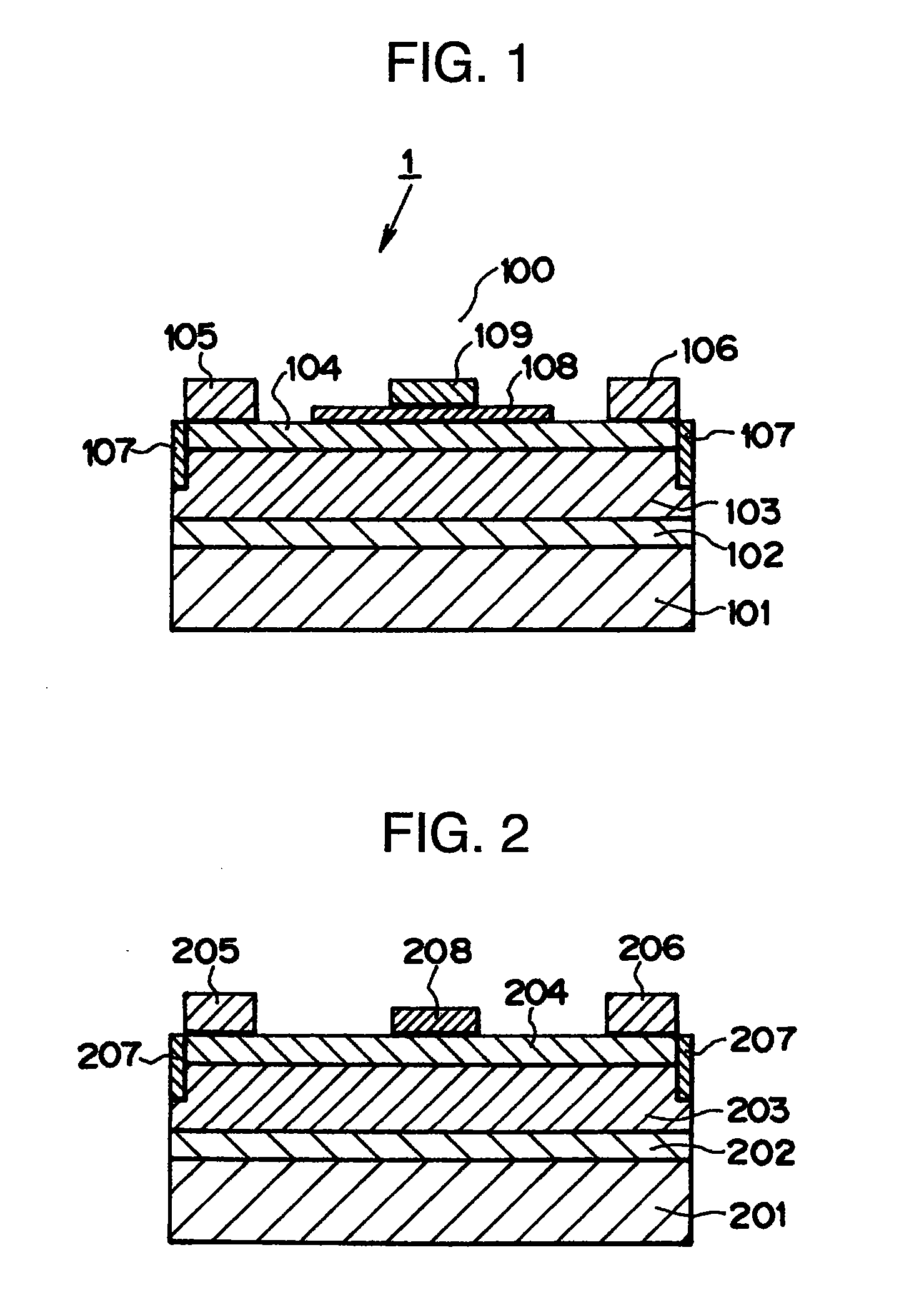

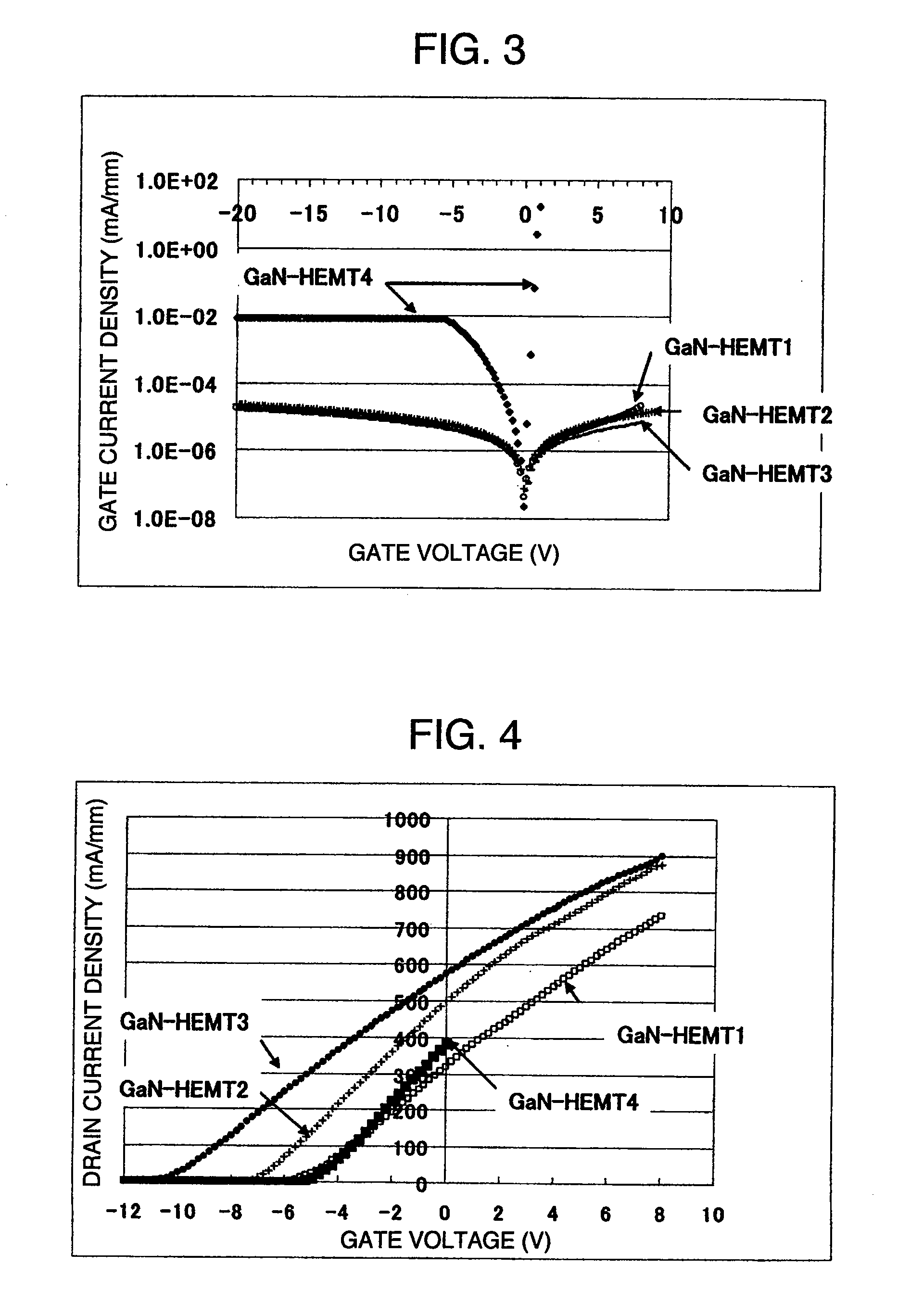

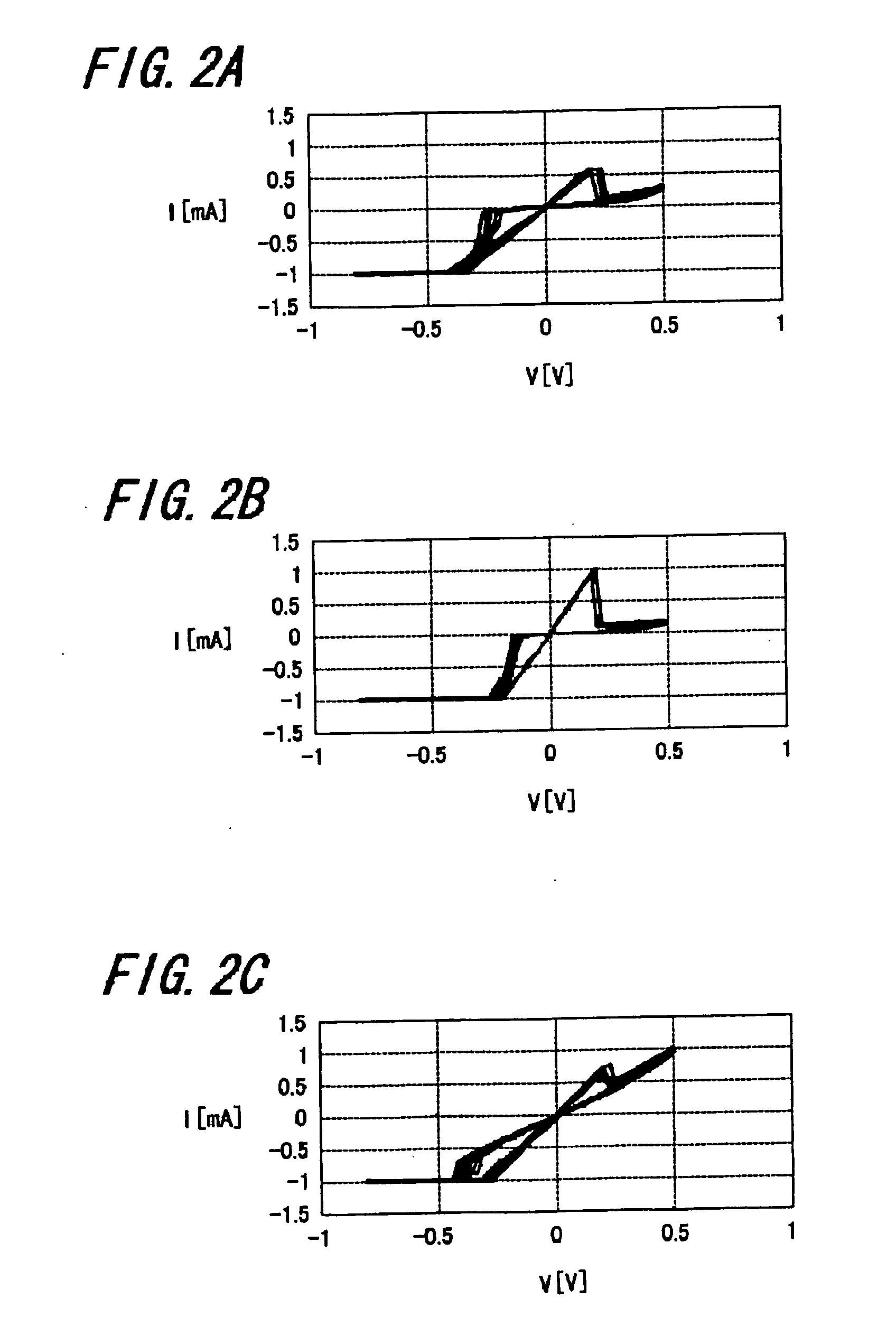

Semiconductor field effect transistor and method for fabricating the same

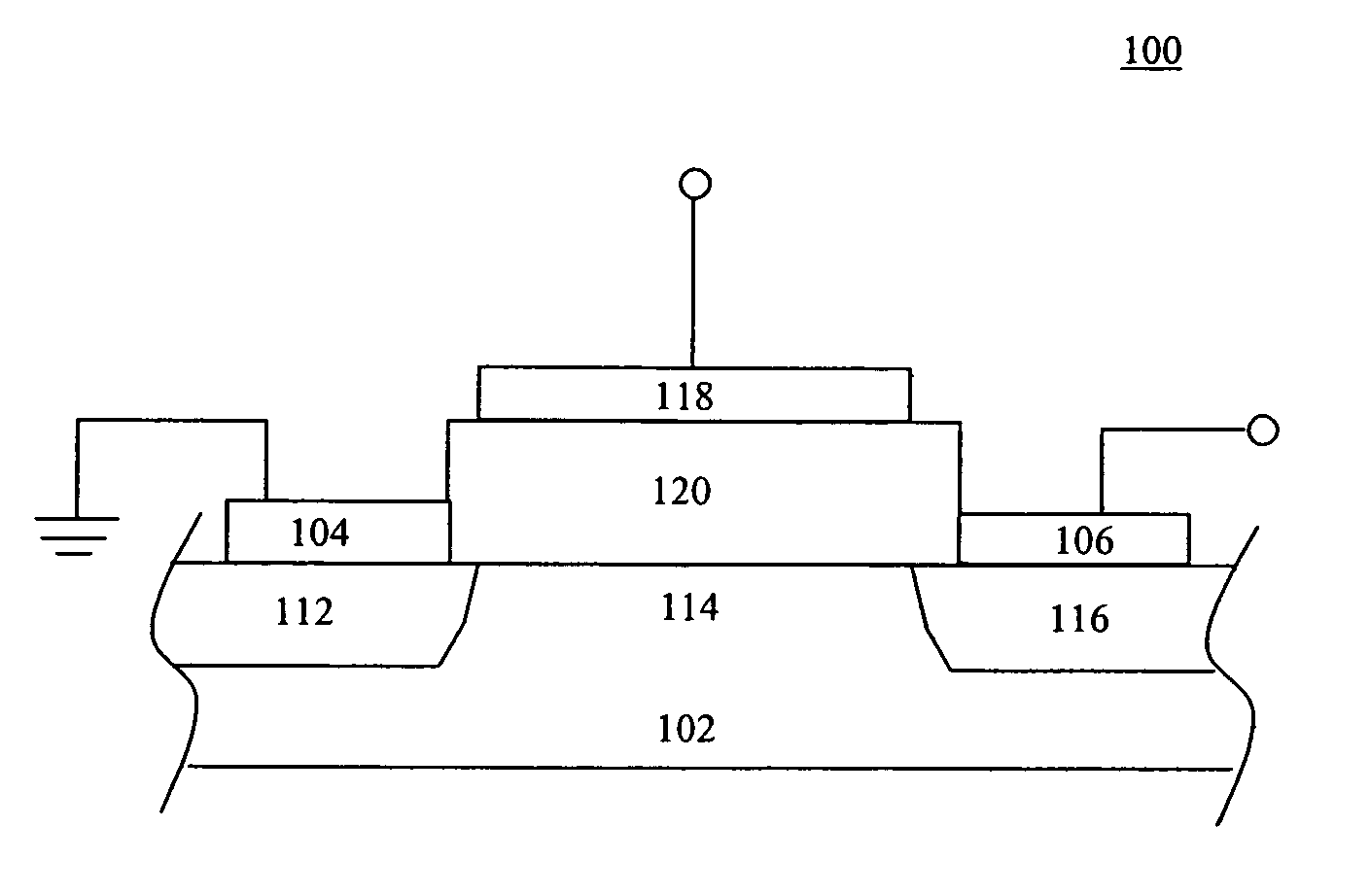

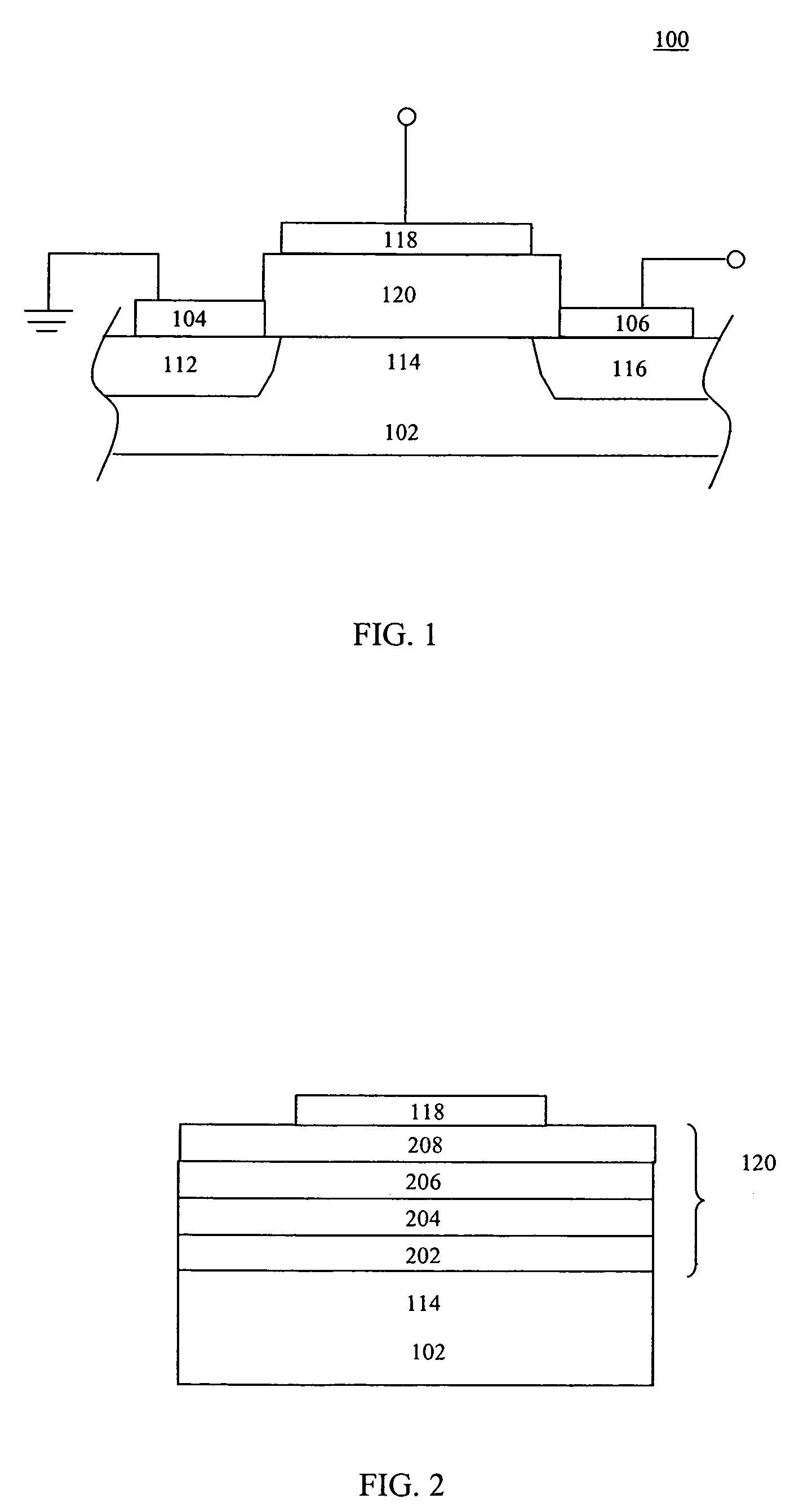

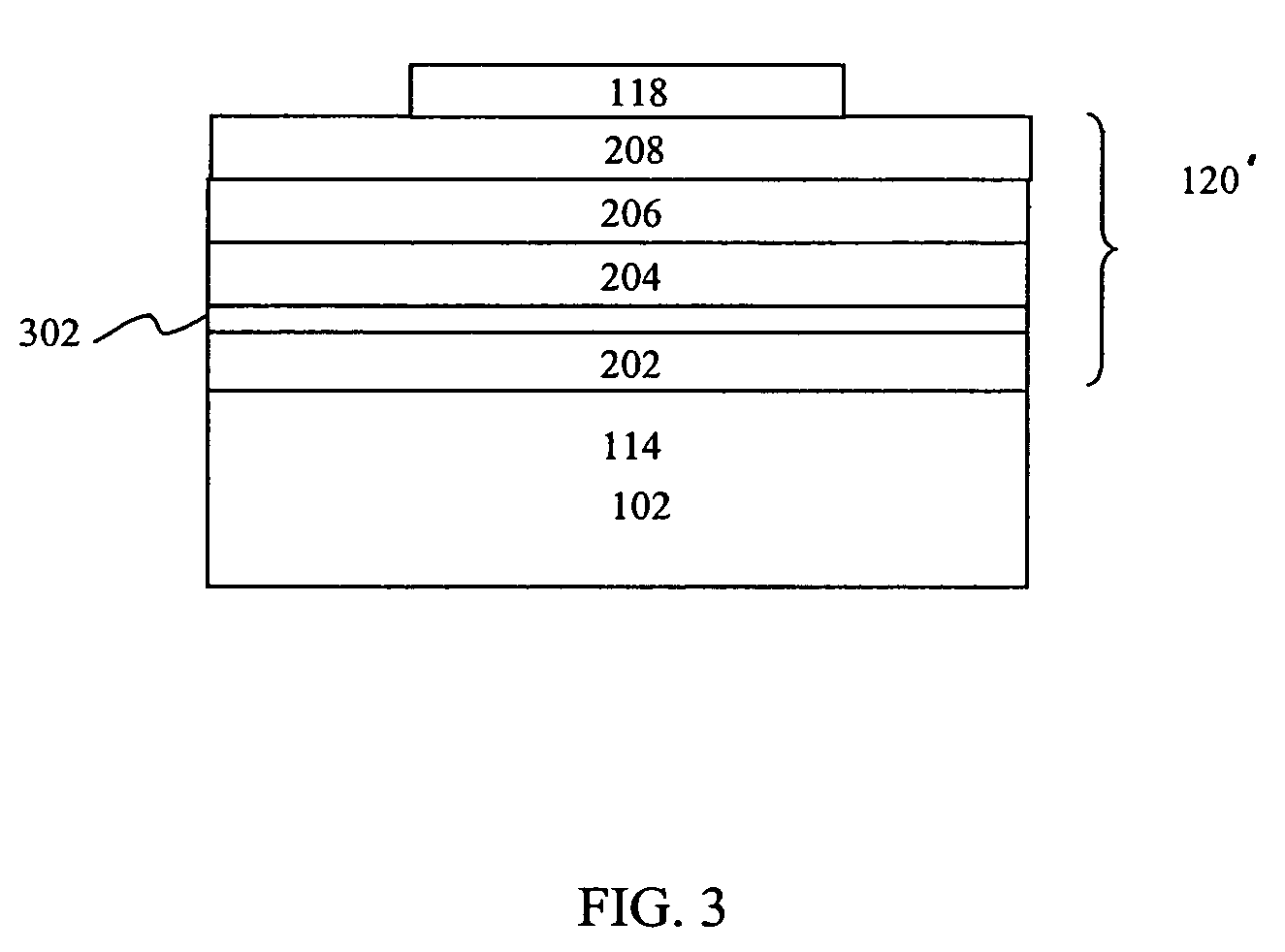

InactiveUS20110012110A1Improve mobilityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesHysteresisGallium nitride

A gallium nitride based field effect transistor having good current hysteresis characteristics in which forward gate leakage can be reduced. In a gallium nitride-based field effect transistor (100) having a gate insulation film (108), part or all of a material constituting the gate insulation film (108) is a dielectric material having a relative dielectric constant of 9-22, and a semiconductor crystal layer A (104) in contact with the gate insulation film (108) and a semiconductor crystal layer B (103) in the vicinity of the semiconductor crystal layer A (104) and having a larger electron affinity than the semiconductor crystal layer A (104) constitute a hetero junction. A hafnium oxide such as HfO2, HfAlO, HfAlON or HfSiO is preferably contained, at least partially, in the material constituting the gate insulation film (108).

Owner:SUMITOMO CHEM CO LTD +1

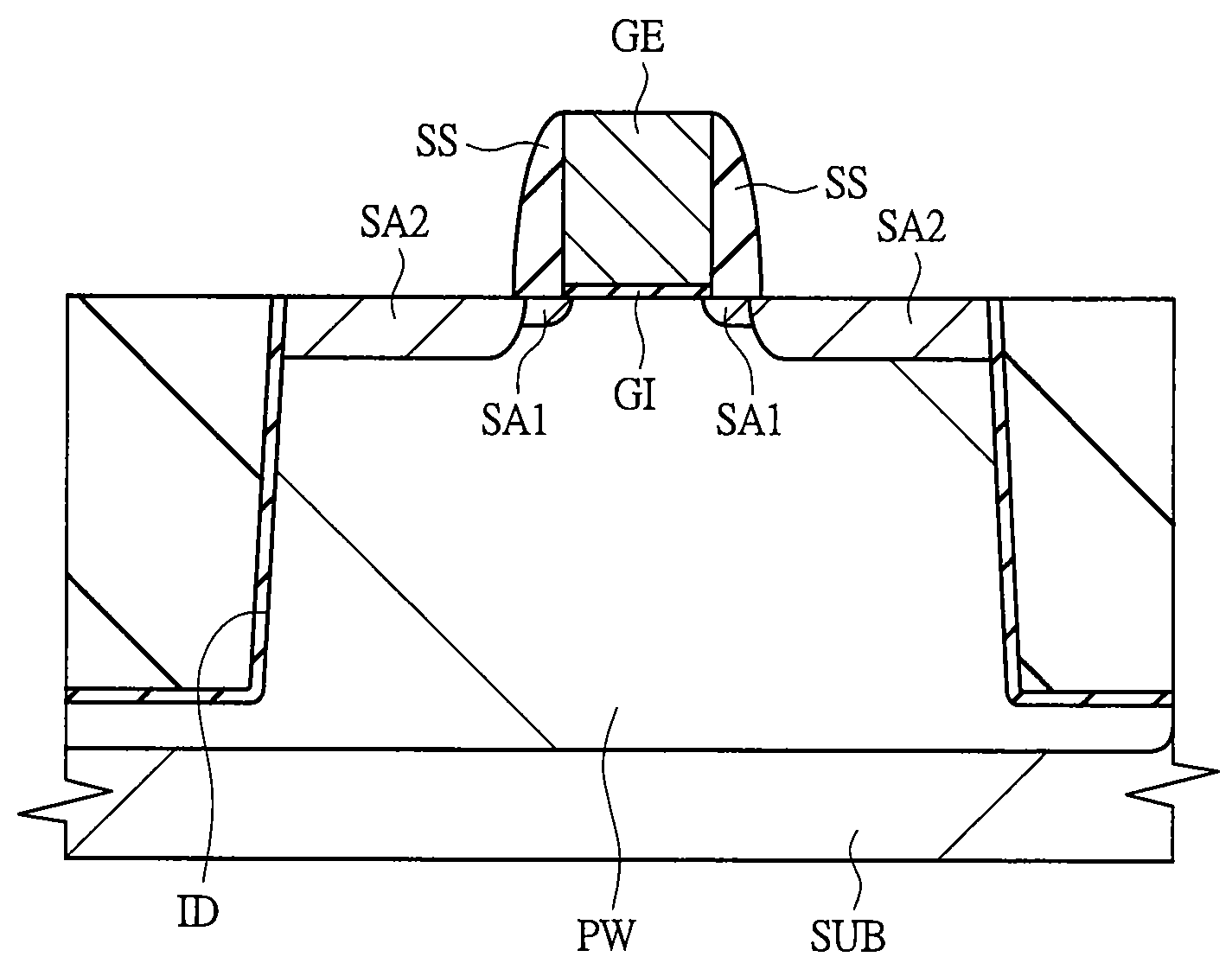

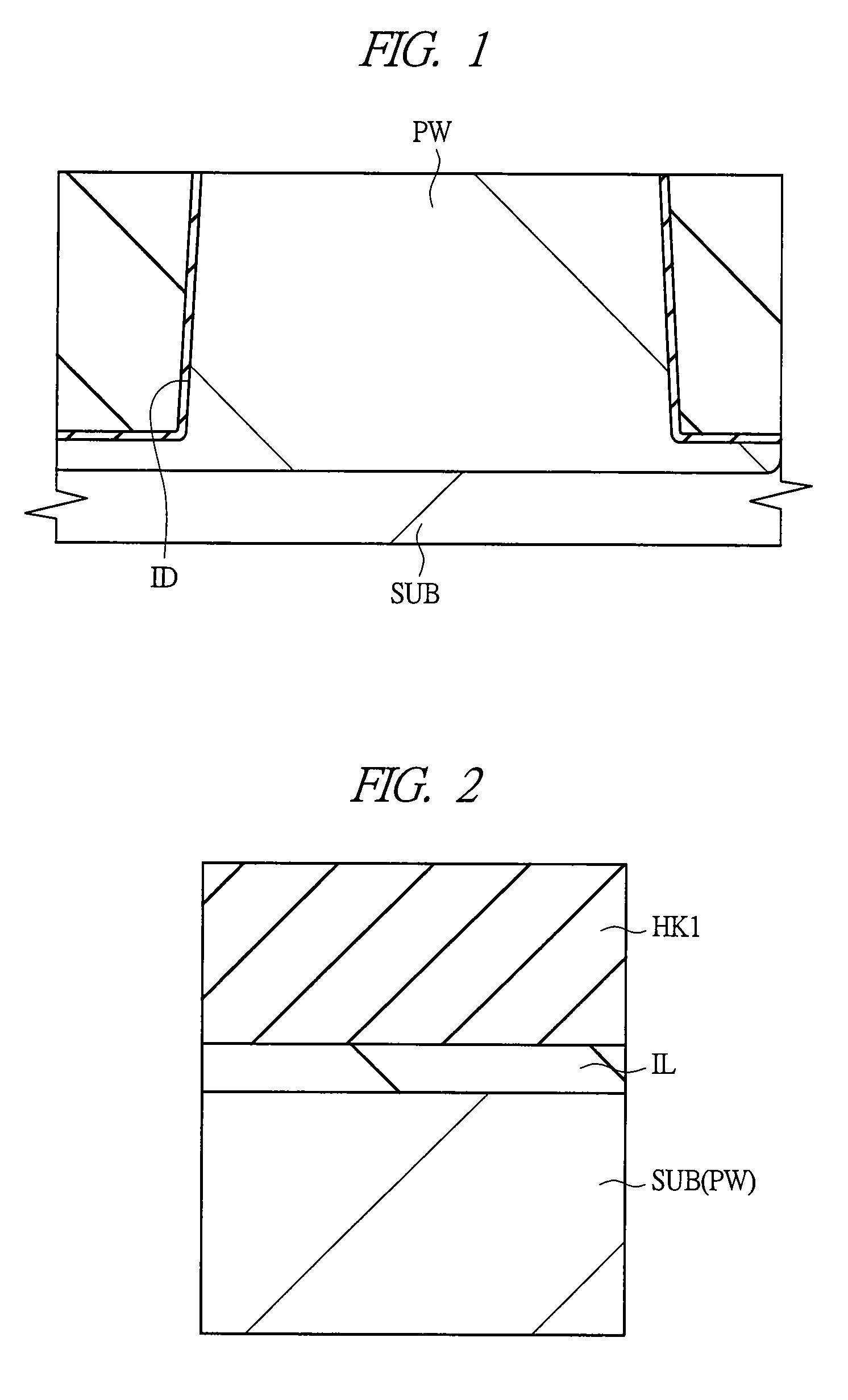

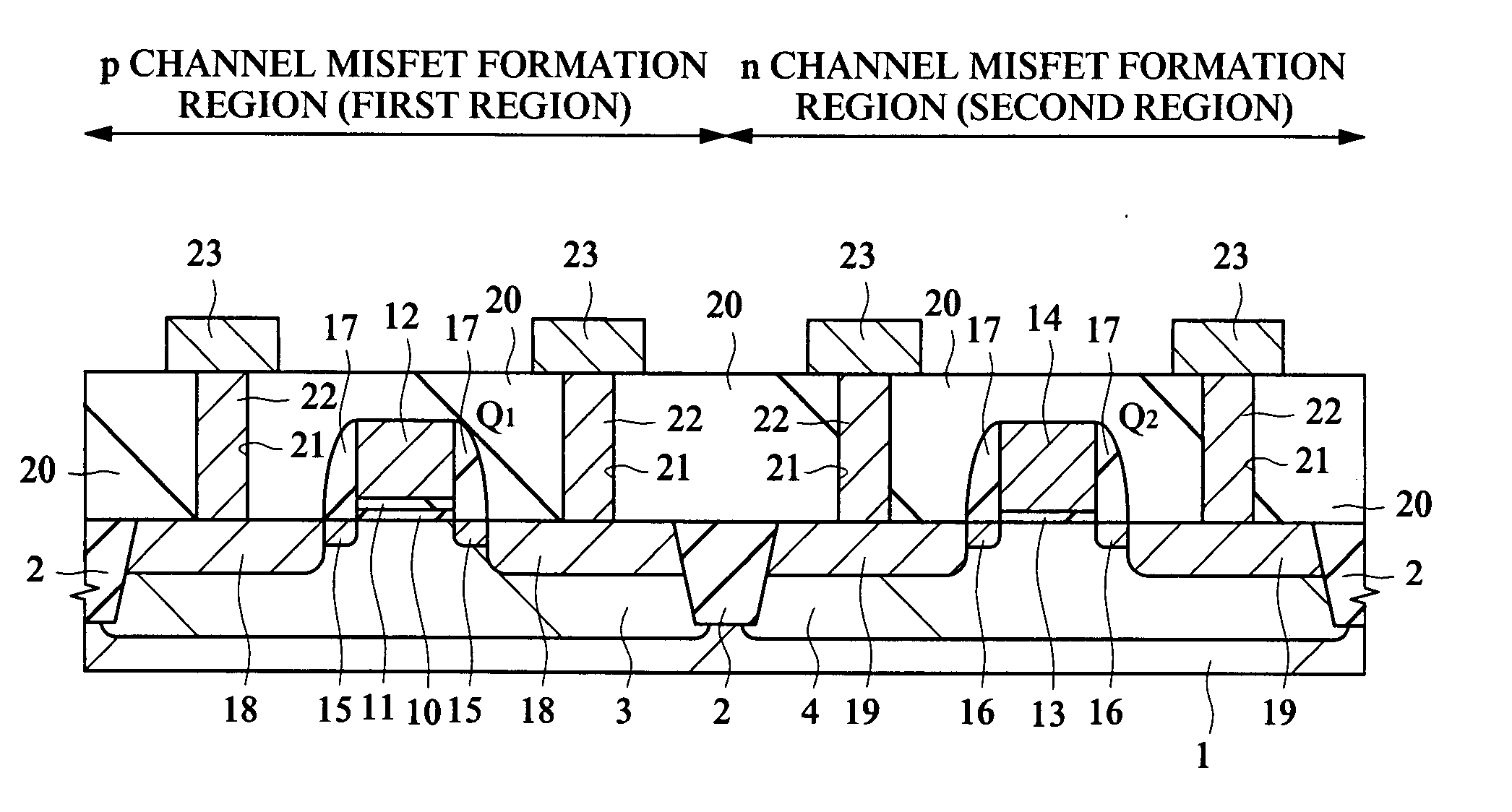

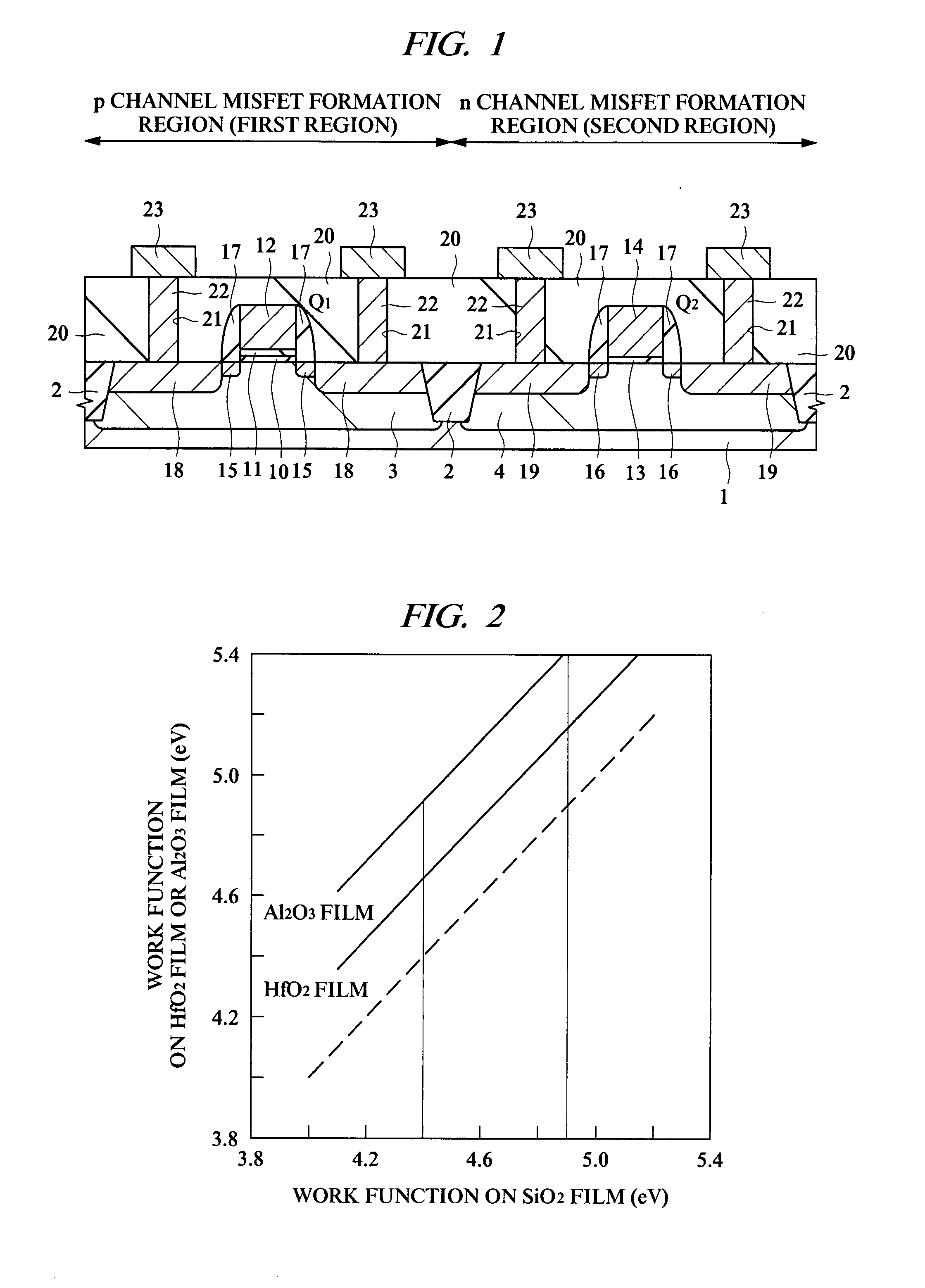

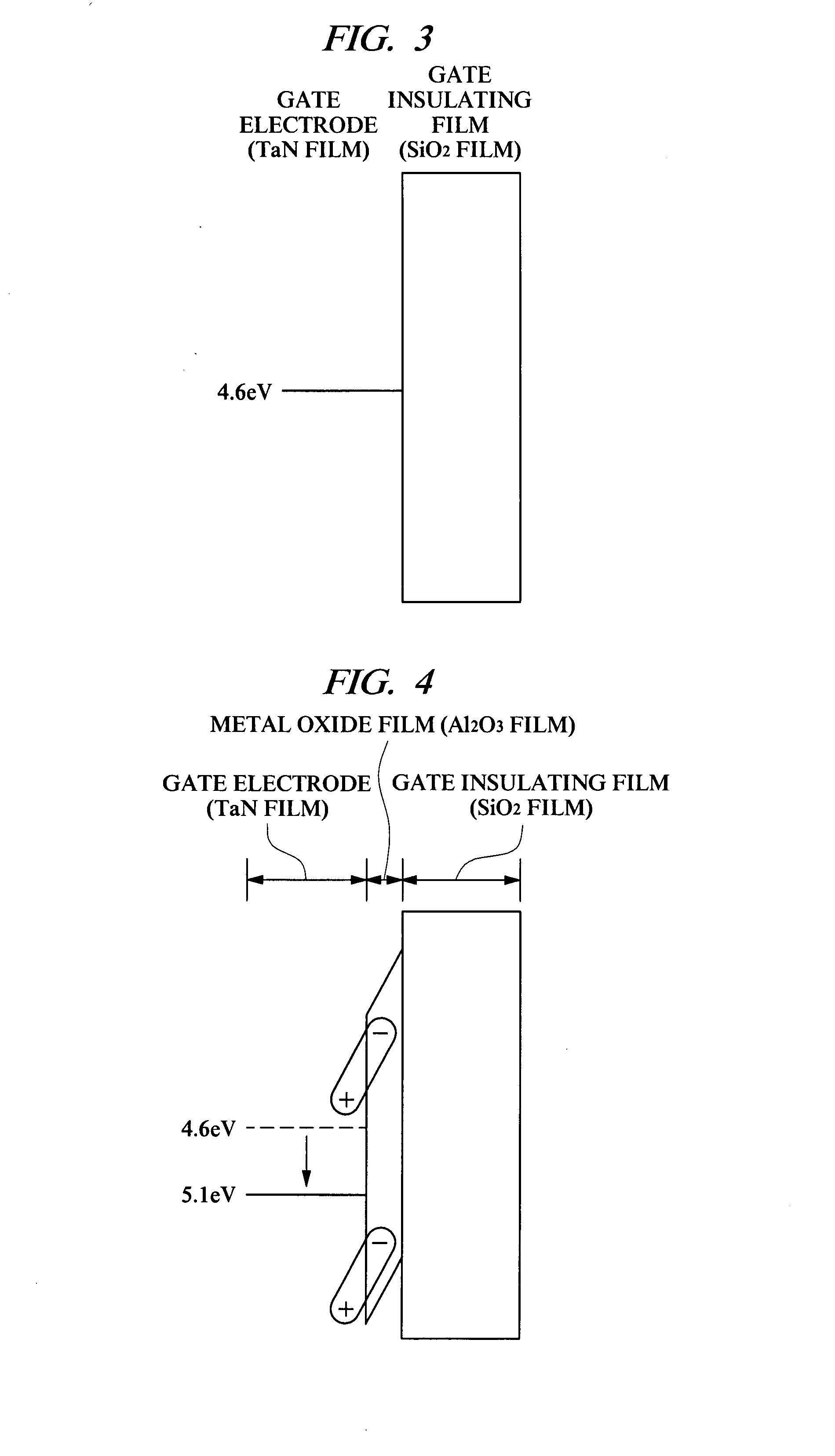

Semiconductor device and semiconductor device manufacturing method

InactiveUS20070210354A1Increased physical film thicknessReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSilicon oxide

Provided is a technology capable of improving the productivity of a p channel MISFET using a high dielectric-constant film as a gate insulating film and a conductive film containing metal as a gate electrode. In this technology, a threshold voltage of the p channel MISFET can be decreased even if a work function value of the conductive film containing metal at the time of contacting a silicon oxide film is away from a value near a valence band of silicon. A p channel MISFET formed on a semiconductor substrate has a gate insulating film formed of a hafnium oxide film, a metal oxide film formed of an aluminum oxide film on this gate insulating film, and a gate electrode formed of a tantalum nitride film on this metal oxide film. The metal oxide film has a function to shift a work function value of the gate electrode.

Owner:RENESAS TECH CORP

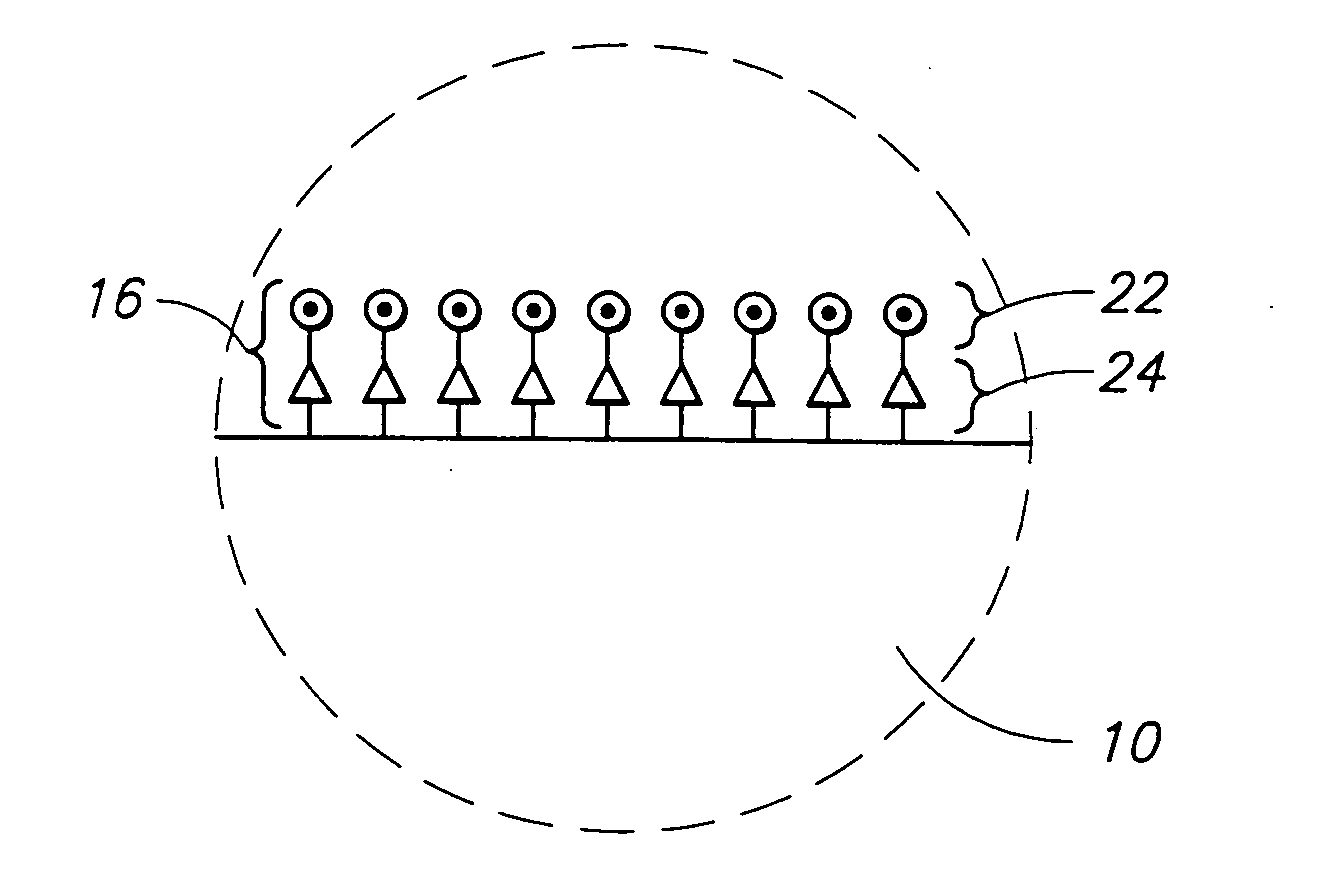

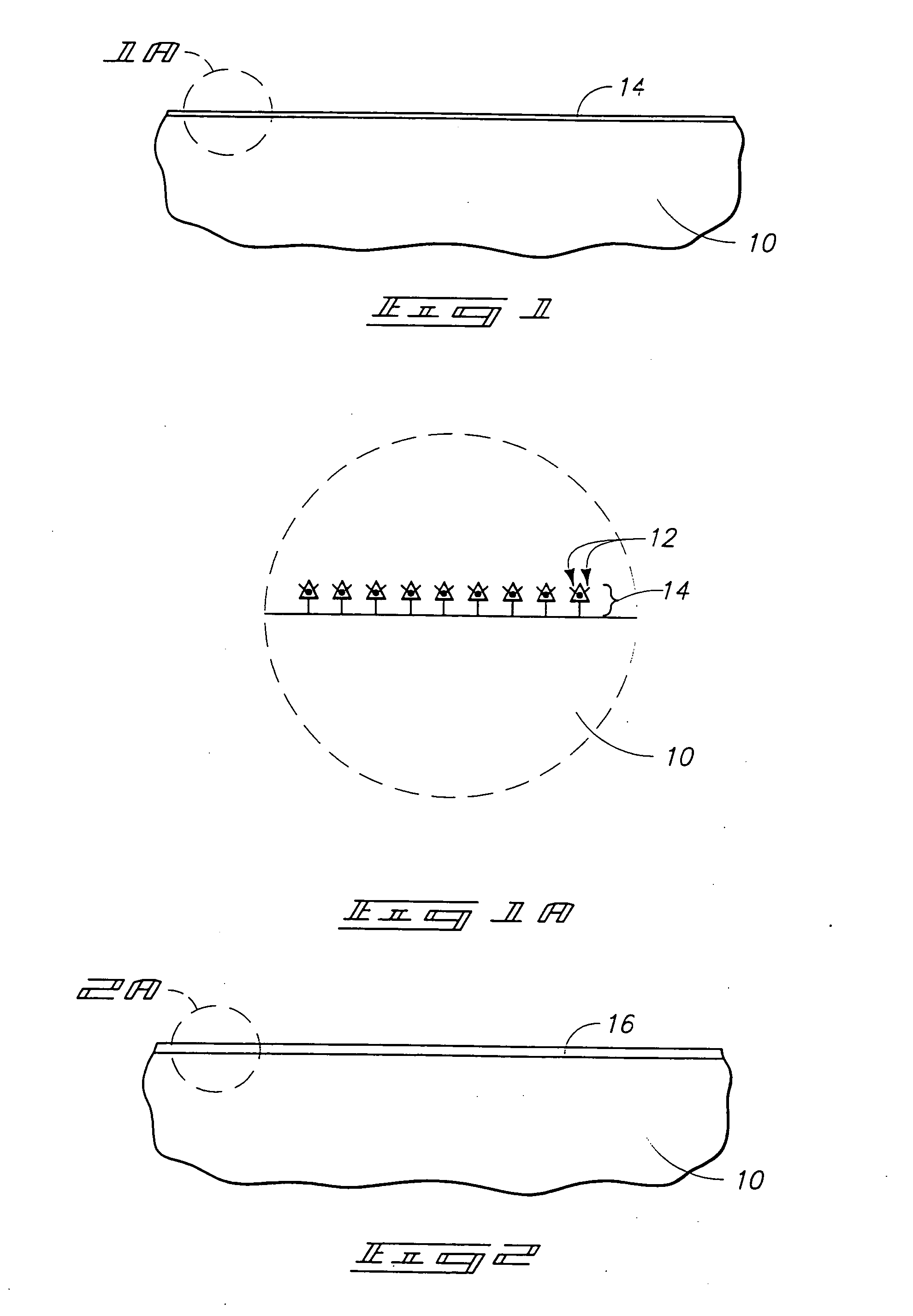

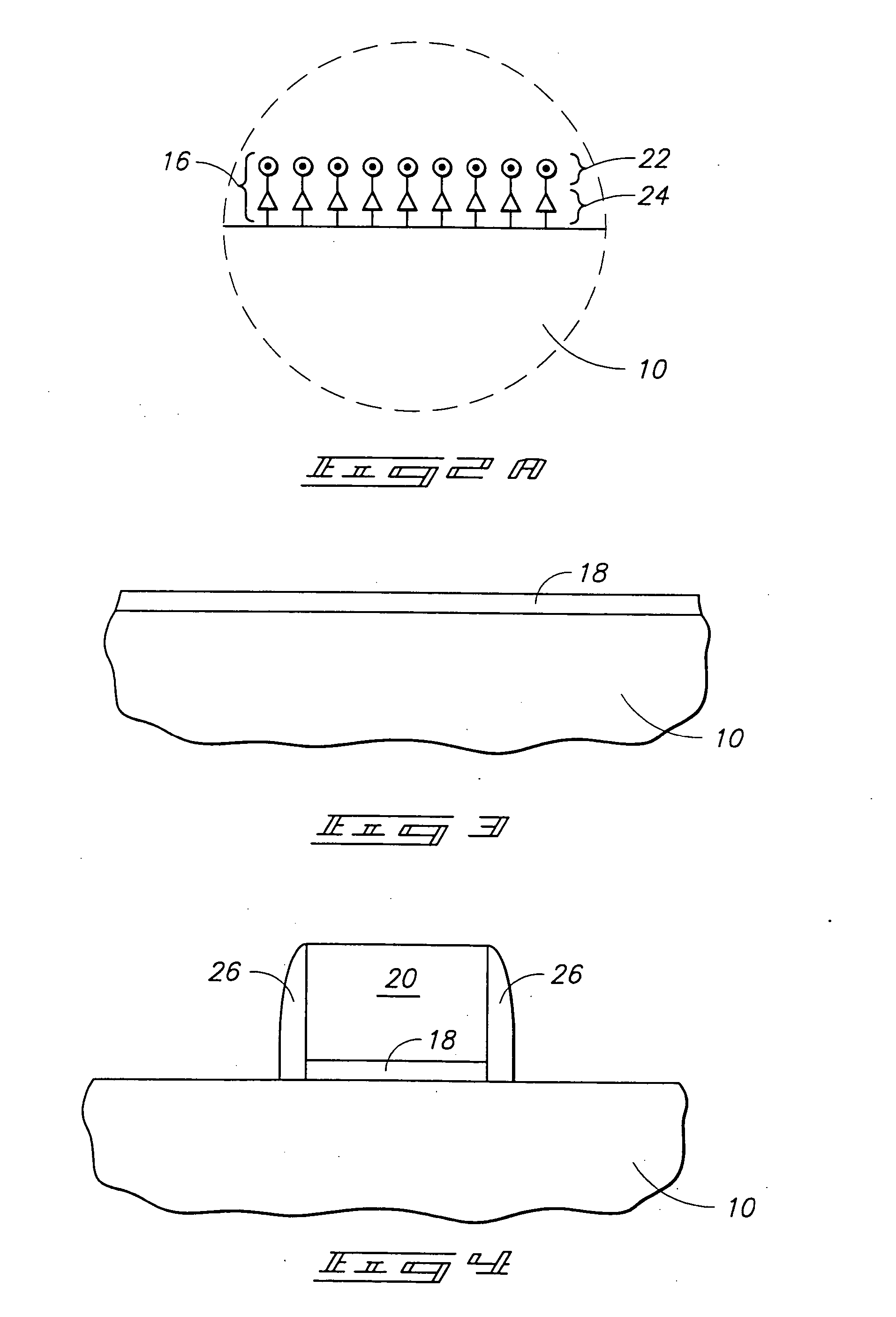

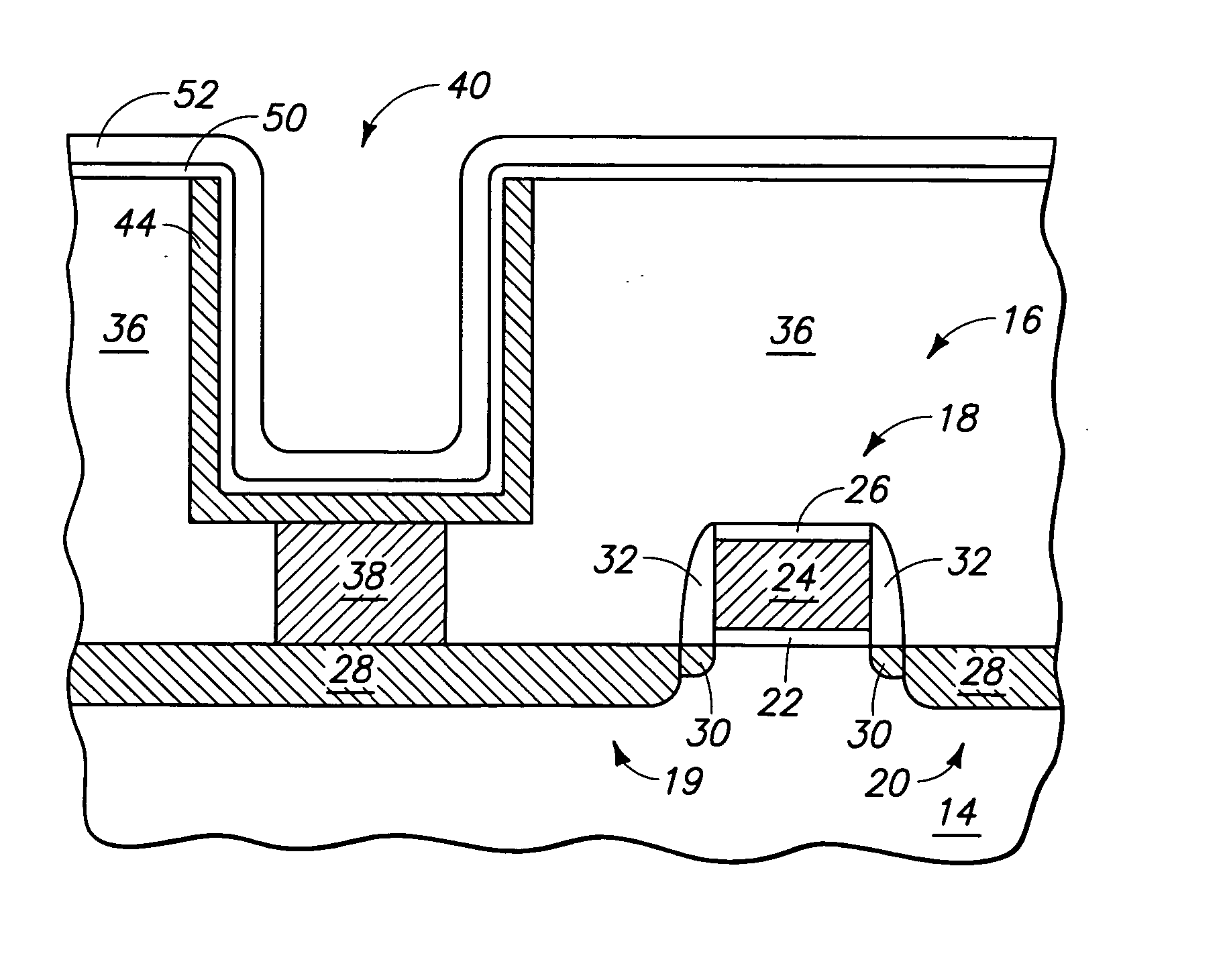

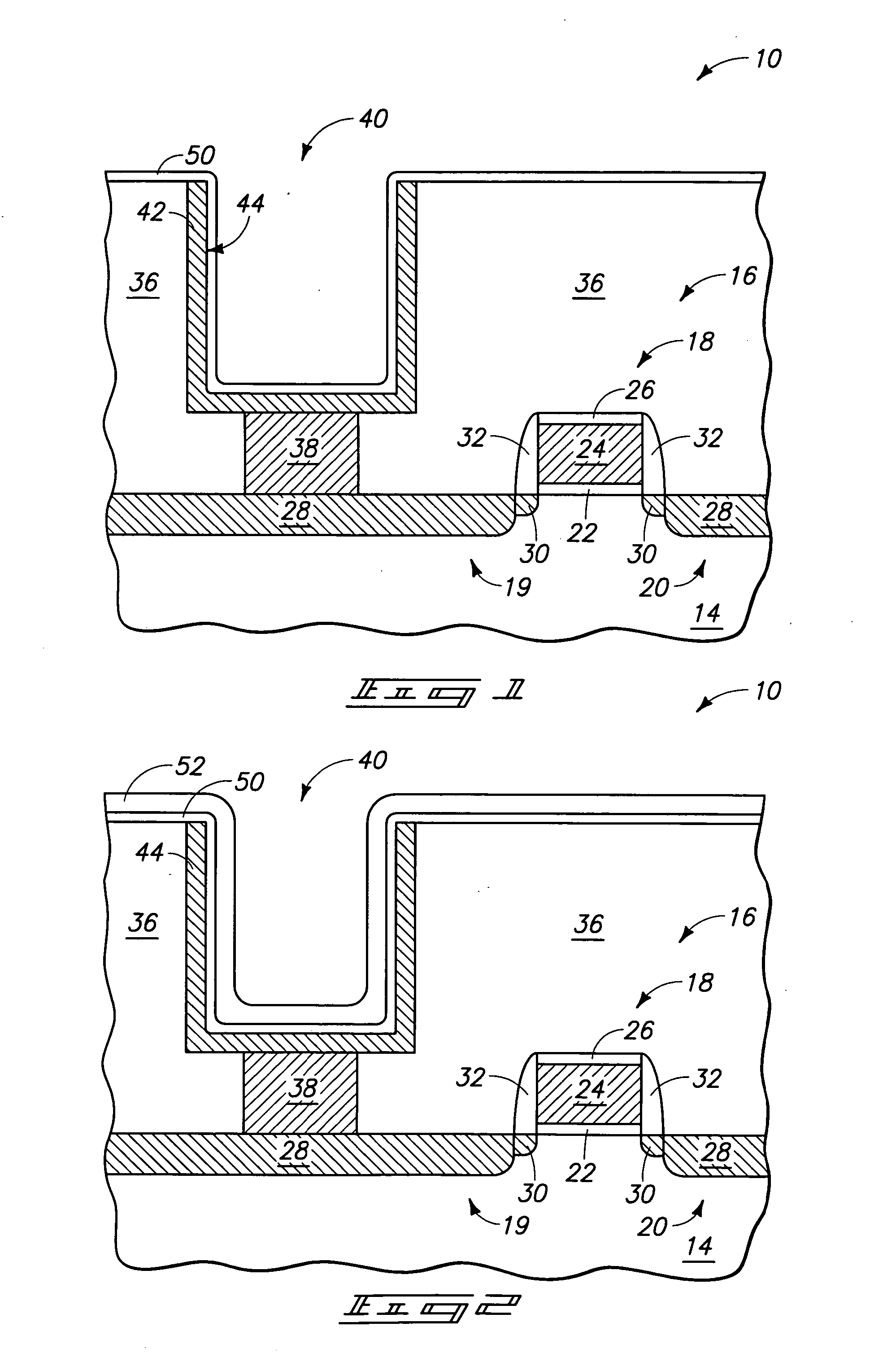

Methods of forming hafnium-containing materials, methods of forming hafnium oxide, and constructions comprising hafnium oxide

The invention includes methods of forming hafnium-containing materials, such as, for example, hafnium oxide. In one aspect, a semiconductor substrate is provided, and first reaction conditions are utilized to form hafnium-containing seed material in a desired crystalline phase and orientation over the substrate. Subsequently, second reaction conditions are utilized to grow second hafnium-containing material over the seed material. The second hafnium-containing material is in a crystalline phase and / or orientation different from the crystalline phase and orientation of the hafnium-containing seed material. The second hafnium-containing material can be, for example, in an amorphous phase. The seed material is then utilized to induce a desired crystalline phase and orientation in the second hafnium-containing material. The invention also includes capacitor constructions utilizing hafnium-containing materials, and circuit assemblies comprising the capacitor constructions.

Owner:MICRON TECH INC

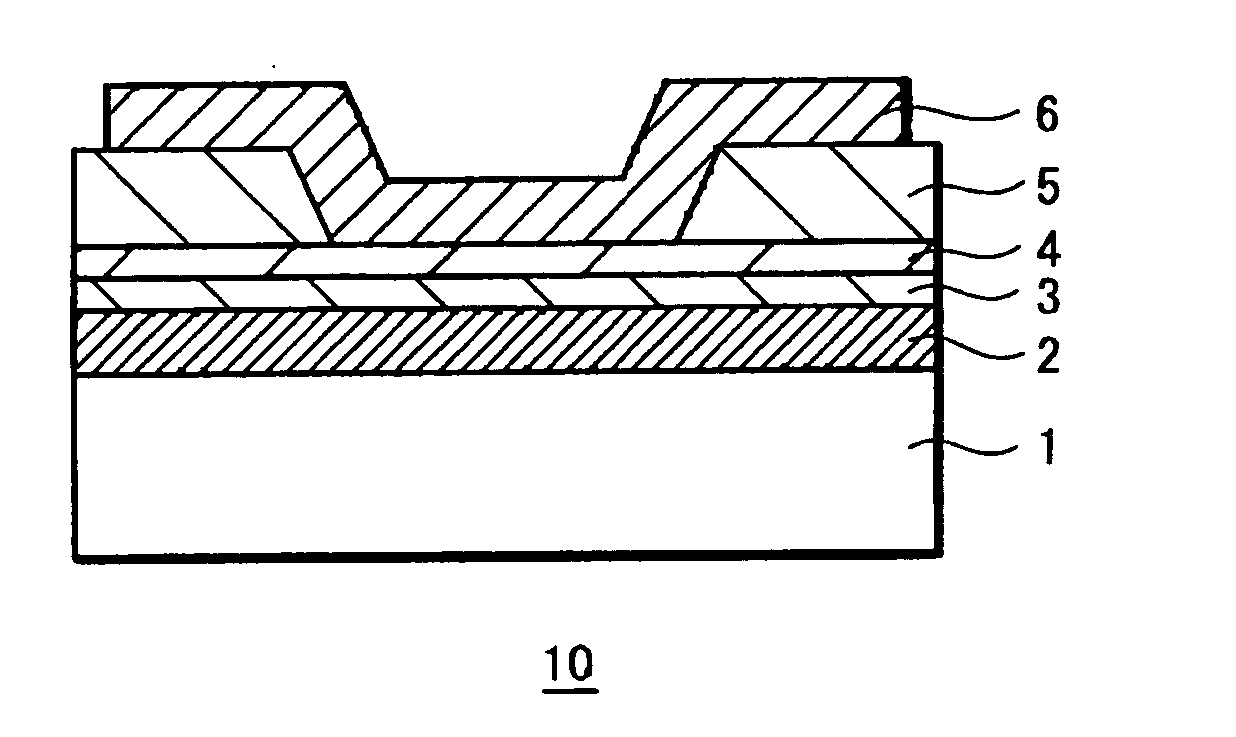

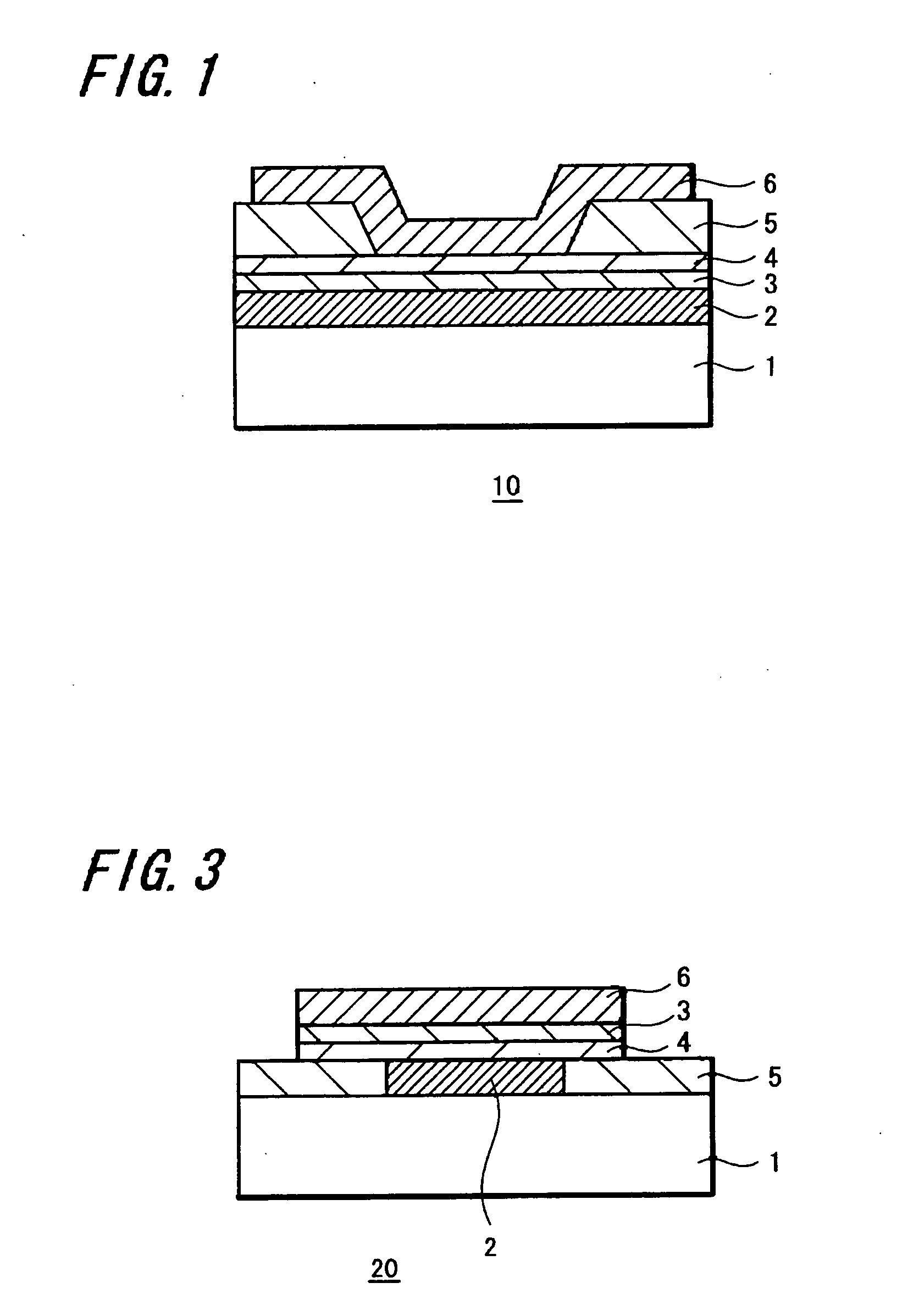

Memory element and memory device

ActiveUS20060126423A1Deterioration of characteristic can be preventedDeterioration of characteristicSolid-state devicesDigital storageData recordingNiobium oxide

A memory element which stably performs operations such as data recording and which has a stable structure with respect to heat is provided. A memory element 10 includes a memory layer 4 and an ion source layer 3 positioned between the first electrode 2 and second electrode 6, in which the ion source layer 3 contains any of elements selected from Cu, Ag and Zn, and any of elements selected from Te, S and Se, and the memory layer 4 is made of any of tantalum oxide, niobium oxide, aluminum oxide, hafnium oxide and zirconium oxide, or is made of mixed materials thereof.

Owner:SONY CORP