Semiconductor device forming method

A semiconductor and device technology, which is applied in the field of semiconductor device formation, can solve the problems that nickel silicide cannot be completely removed and affects the conductivity of semiconductor devices, and achieve the effect of improving electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

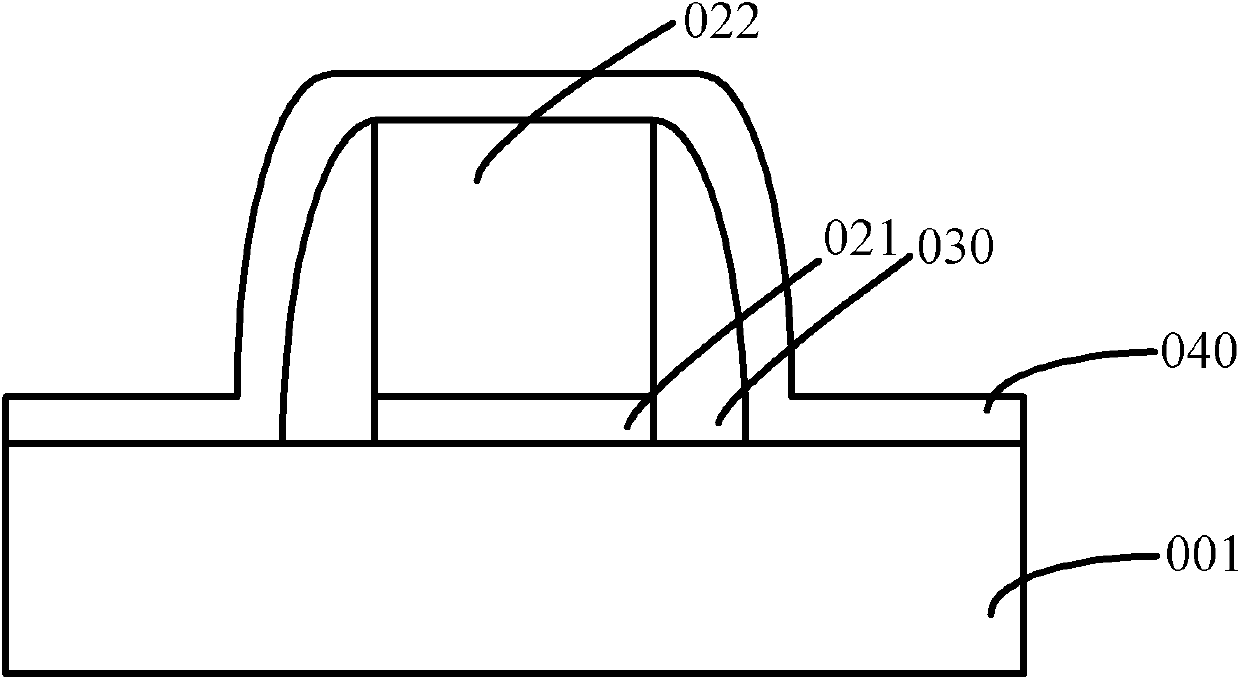

[0035] refer to Figure 1 to Figure 4 , in the process of forming metal silicide in the prior art, because the metal silicide formed by metal diffusion will enhance the leakage phenomenon between the source and drain regions, and the source / drain region and the The gate is electrically connected, which seriously reduces the reliability of the semiconductor's conductive performance.

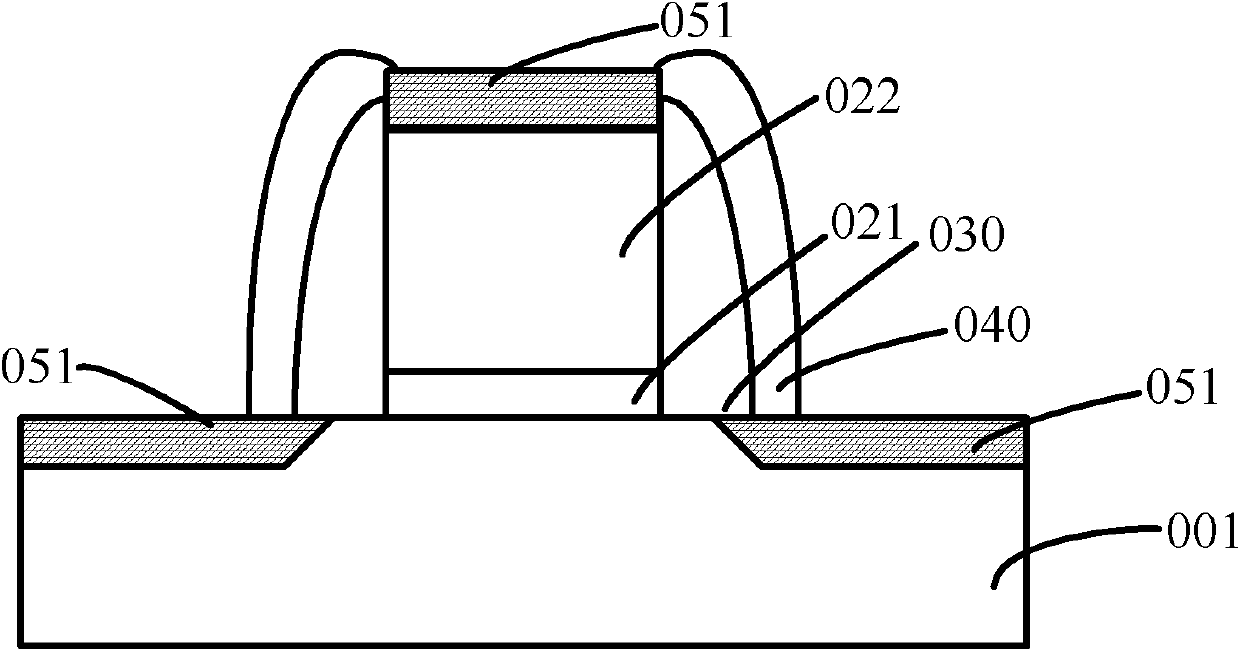

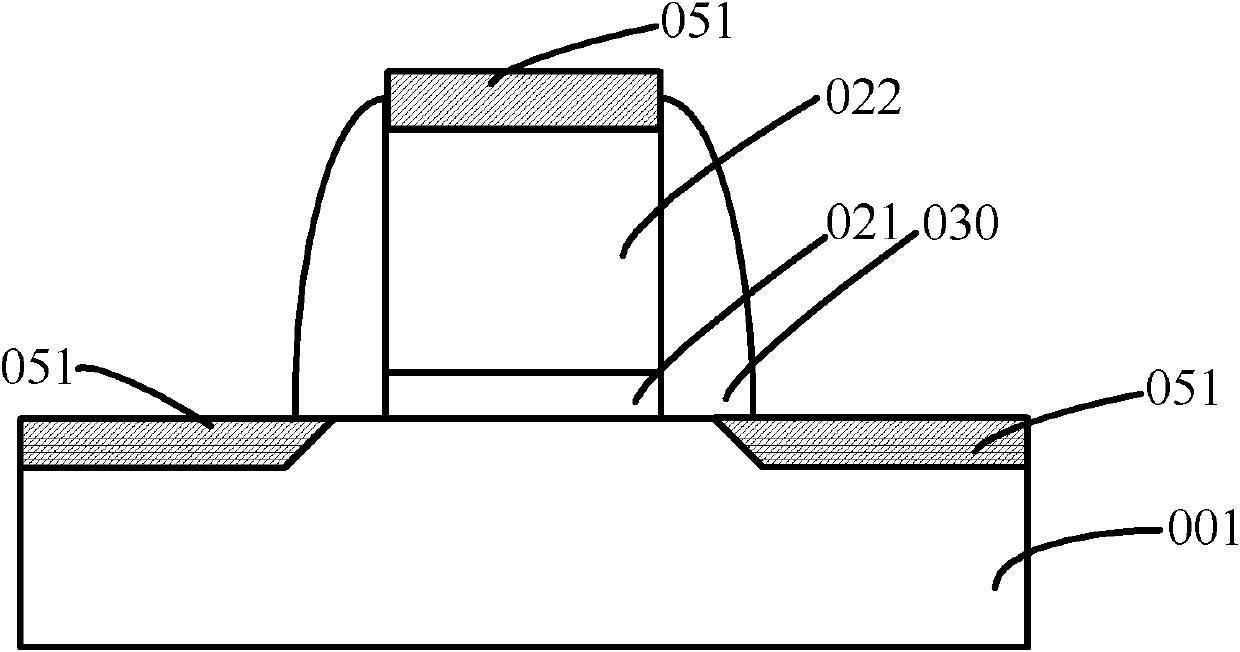

[0036] In order to solve the above problems, the present invention provides a method for forming a semiconductor device, comprising: providing a substrate, a gate structure on the substrate, and sidewalls on both sides of the gate structure; forming an auxiliary spacer on the surface; forming a metal layer on the exposed surface of the substrate and the auxiliary side wall; annealing the metal layer to form a metal silicide in the substrate, and the auxiliary side wall is used to prevent metal The layer is diffused laterally into the sidewalls to avoid the formation of metal silicides on the sidew...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More