Patents

Literature

71results about How to "Low phase noise" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Laser based frequency standards and their applications

InactiveUS20070086713A1Minimize lossLow phase noiseLaser detailsCoupling light guidesFrequency standardLight source

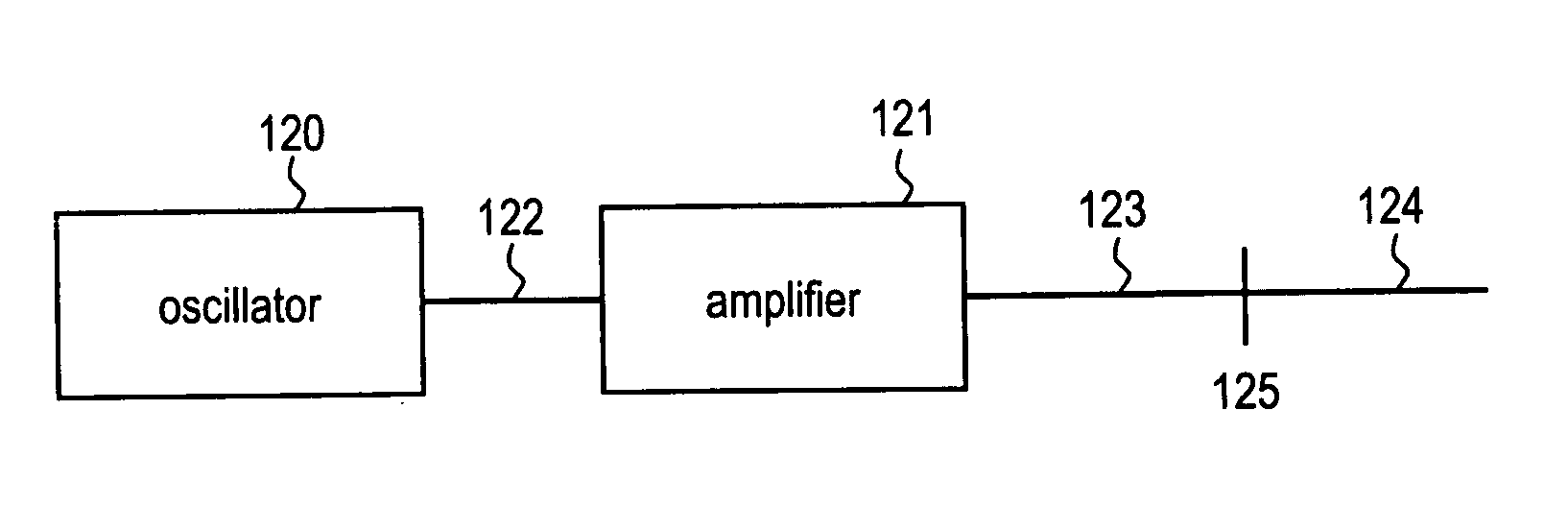

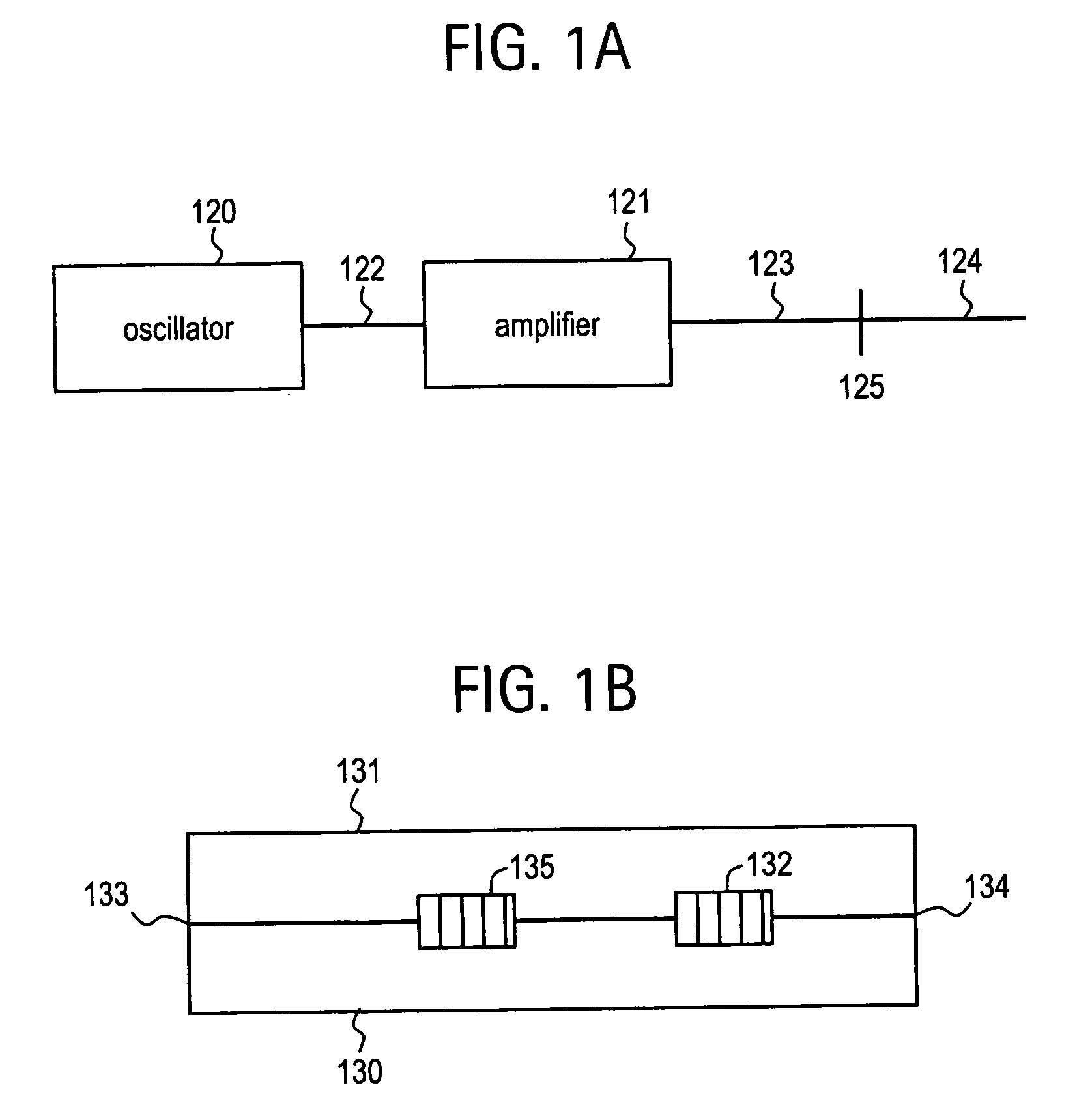

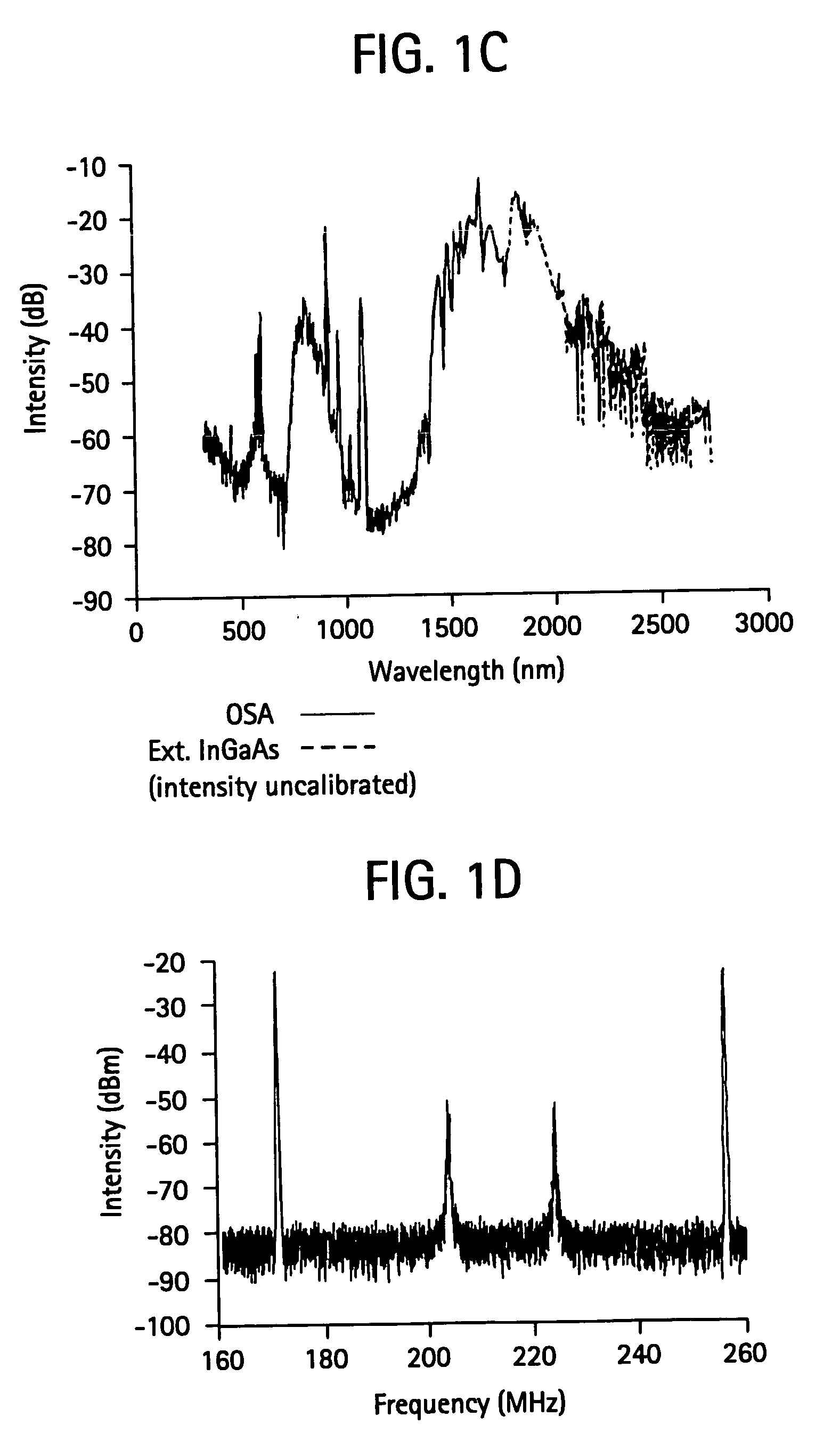

Frequency standards based on mode-locked fiber lasers, fiber amplifiers and fiber-based ultra-broad bandwidth light sources, and applications of the same.

Owner:IMRA AMERICA

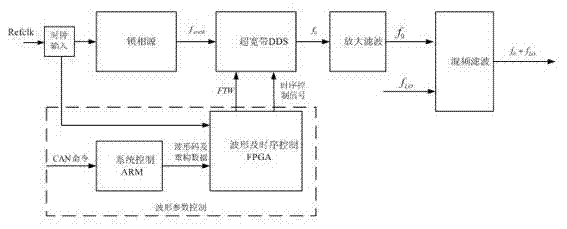

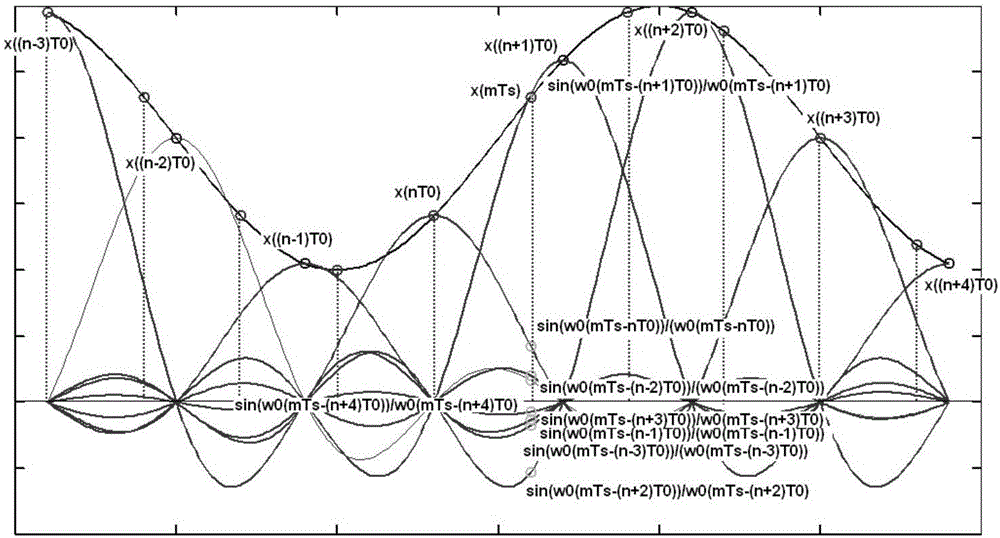

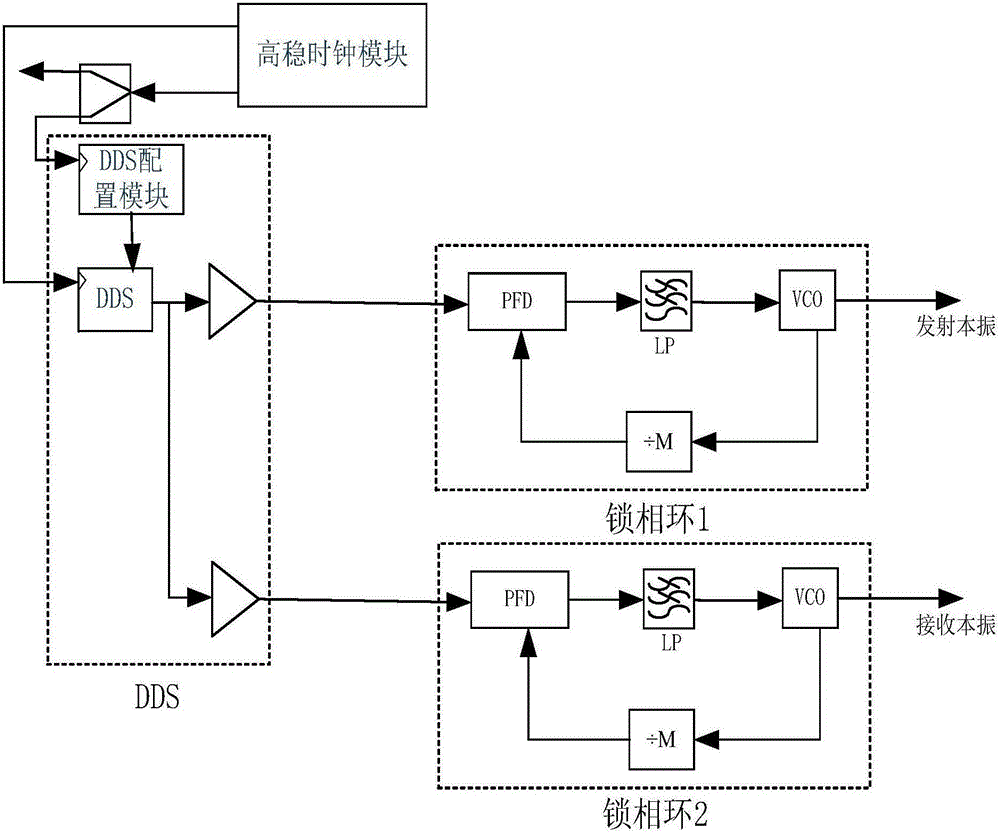

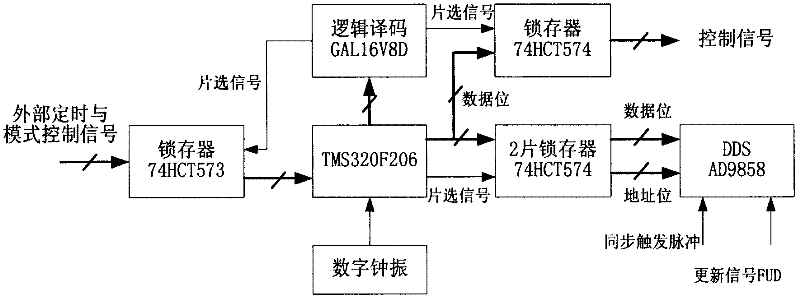

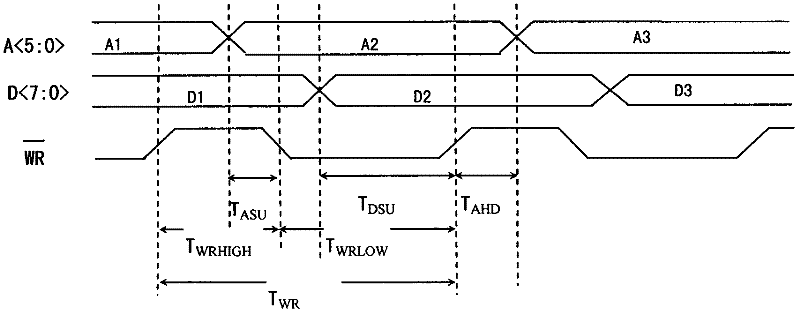

Method for generating stepped frequency signals based on combination of direct digital synthesis (DDS) and ping-pong phase locked loop

InactiveCN102185608AImprove combat skill indicatorsTechnical indicators leapWave based measurement systemsPulse automatic controlPhase noiseEngineering

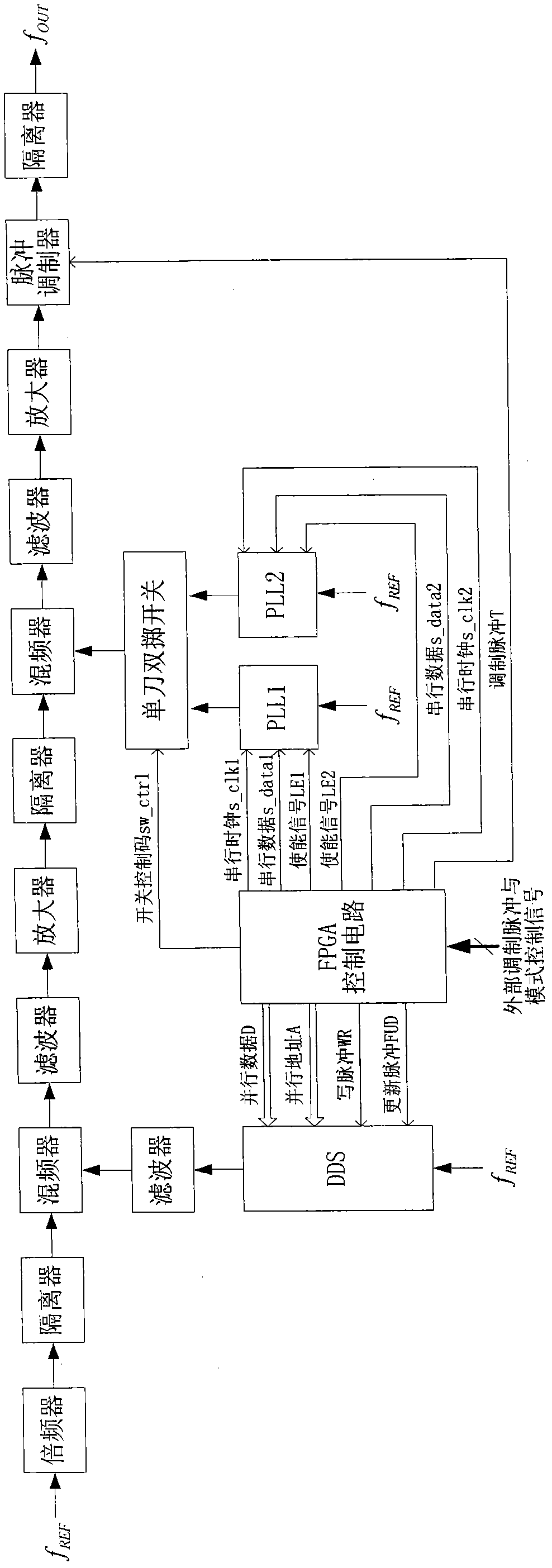

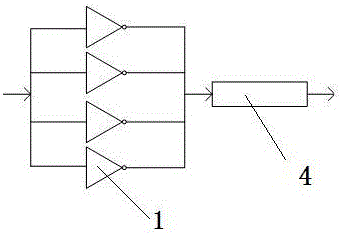

The invention discloses a method for generating stepped frequency signals based on the combination of direct digital synthesis (DDS) and a ping-pong phase locked loop. DDS has the advantages of high narrowband application performance and capability of easily realizing extremely small frequency step, and the phase locked loop has the advantages of easily realizing broadband application and ensuring high comprehensive performance particularly in broadband great-step application. In the method, advantage complementarity between the DDS and the phase locked loop is utilized, a ping-pong phase locked loop is formed by combining two identical phase locked loops and a microwave single-pole double-throw switch, frequency synthesis is performed by combining the DDS and the ping-pong phase locked loop, the DDS is used for synthesizing narrowband small-step signals, the ping-pong phase locked loop is used for synthesizing broadband great-step signals, and the broadband great-step signal and the narrowband small-step signals are combined together in a frequency shifting way, thereby generating broadband radar stepped frequency signals with low phase noise, low stray, small step and frequency agility. Therefore, tactical and technical indexes of a radar frequency synthesizer are greatly increased, and qualitative leaps in technical indexes of the radar stepped frequency signals are achieved.

Owner:中国兵器工业第二0六研究所

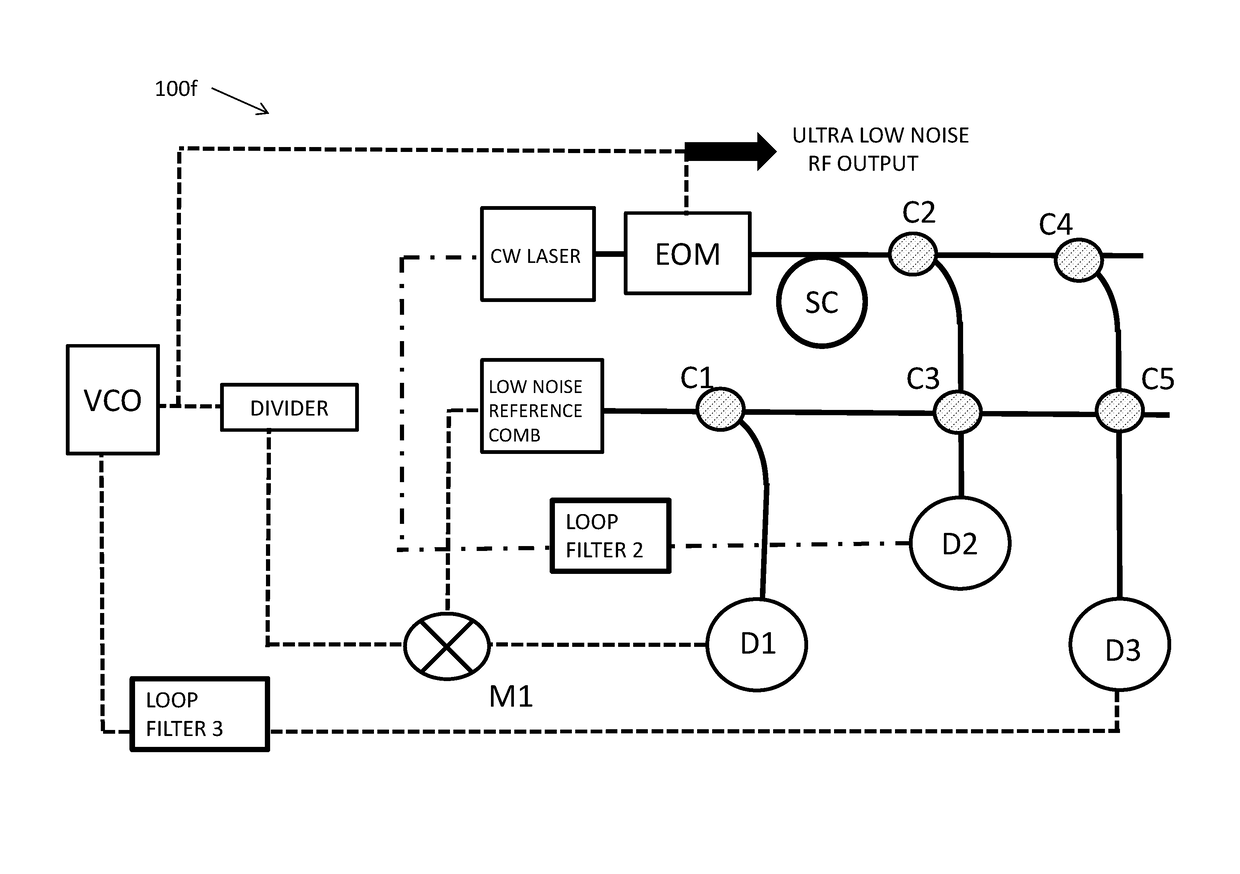

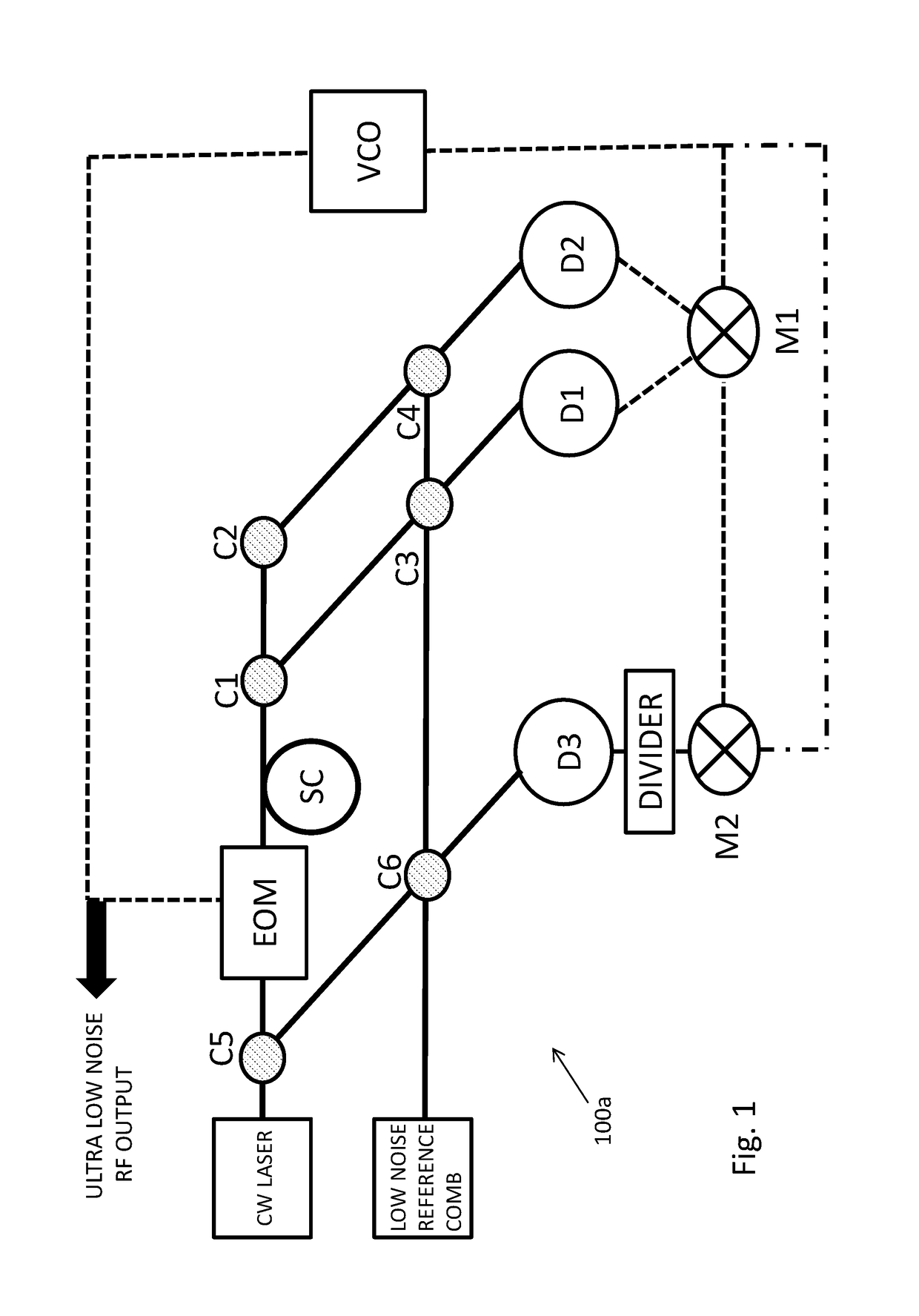

Systems and methods for low noise frequency multiplication, division, and synchronization

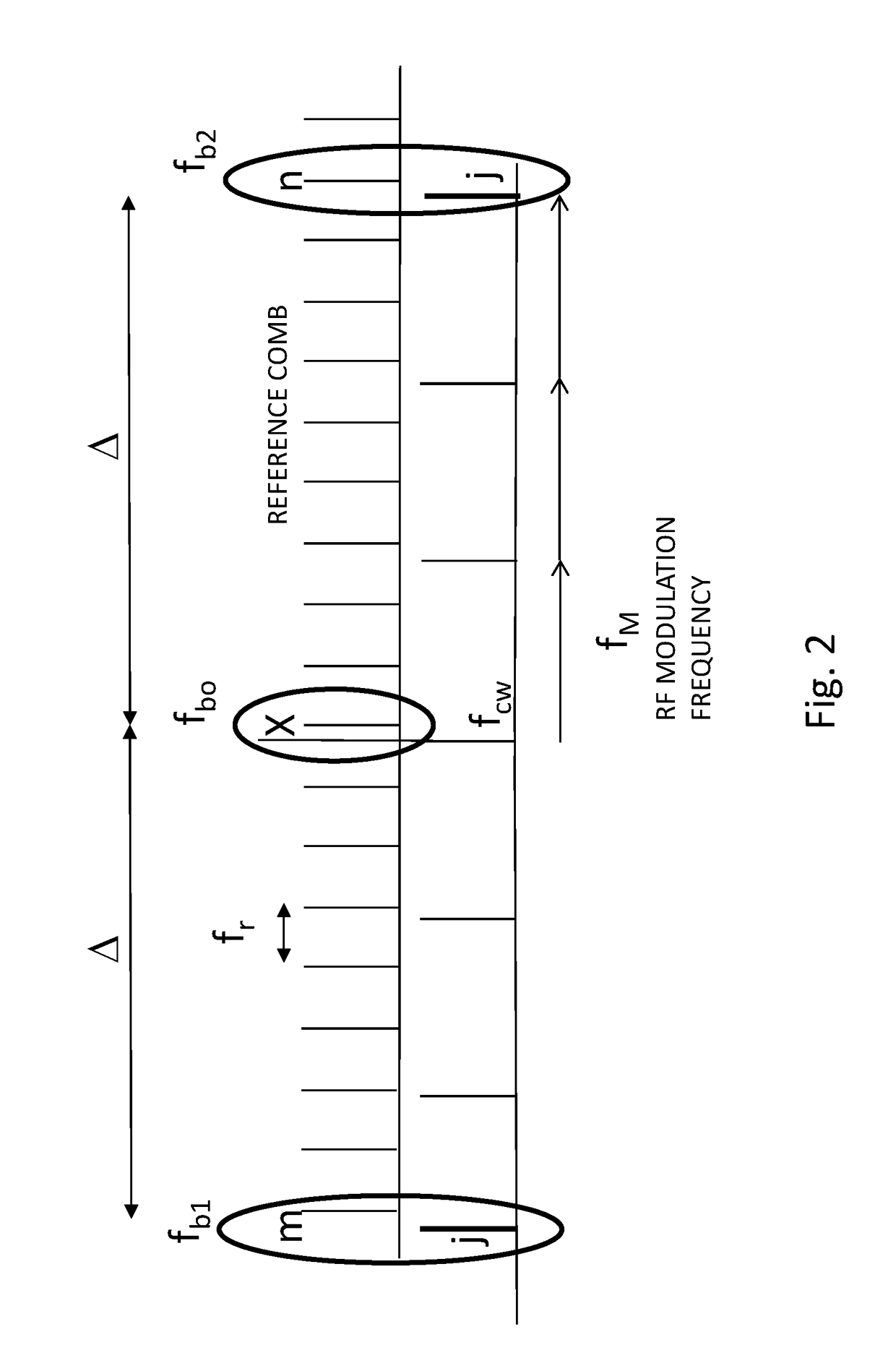

ActiveUS20180048113A1Reduce phase noiseLow phase noiseModulation transference balanced arrangementsPulse automatic controlRadio frequencySideband

Low phase noise radio frequency (RF) sources generated by voltage controlled oscillators (VCOs) are described. Optical modulators driven by a VCO may be used to generate optical side-bands to cw lasers. The spectral extent of said side-bands can be increased via frequency broadening in highly nonlinear waveguides. Free running mode locked low phase noise comb oscillators can be used as reference oscillators to generate beat signals between those side-bands and individual comb modes at distal spectral regions, thereby creating an error signal used to reduce the phase noise of VCOs and the generation of low phase noise RF signals. VCO phase noise may be reduced by using free-running modelocked comb lasers phase locked to external frequency references, by omitting a reference comb and using a nonlinear interferometer for generating an error signal, or by locking a slave comb to the modulation frequency of an intra-cavity modulator driven by the VCO.

Owner:IMRA AMERICA

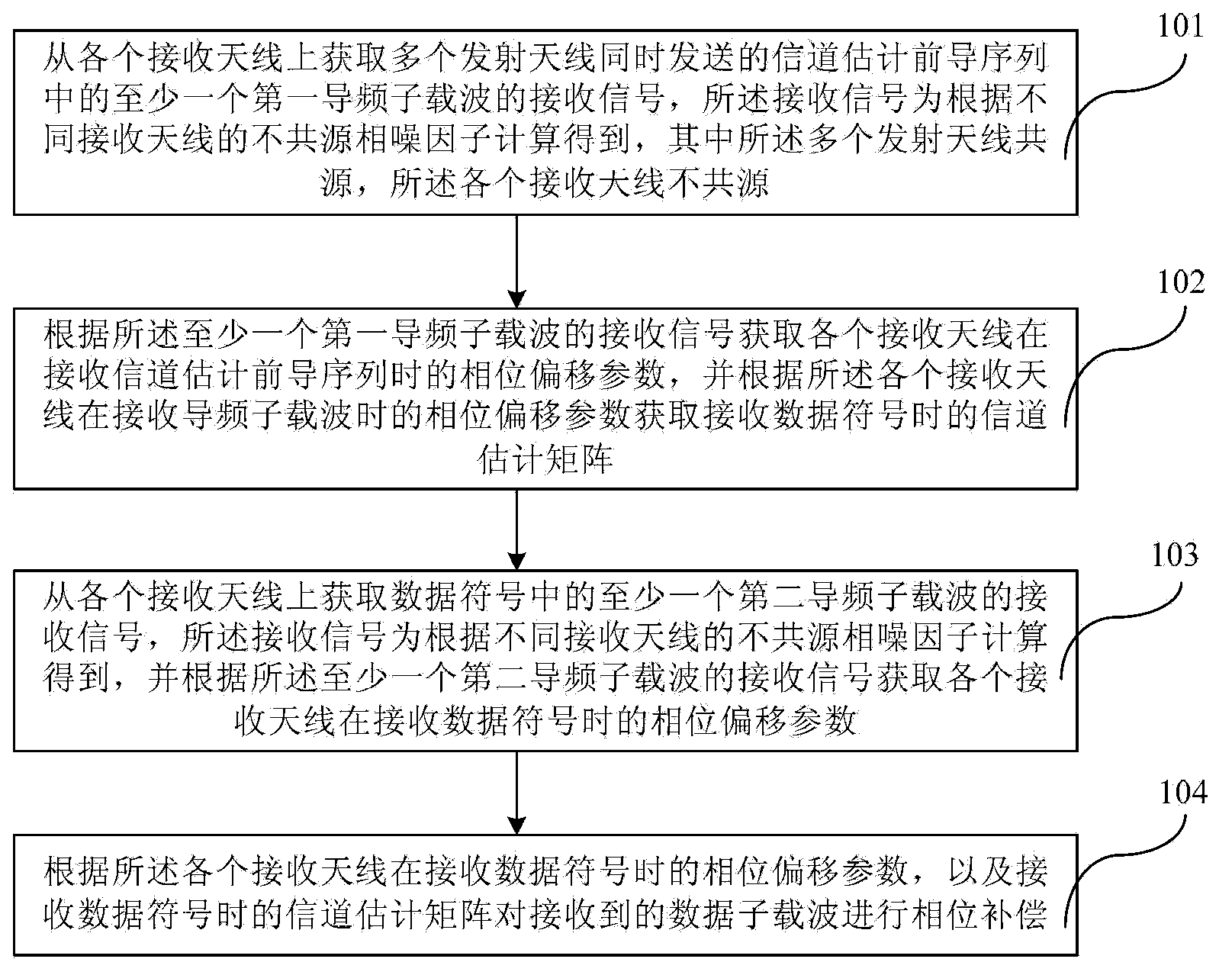

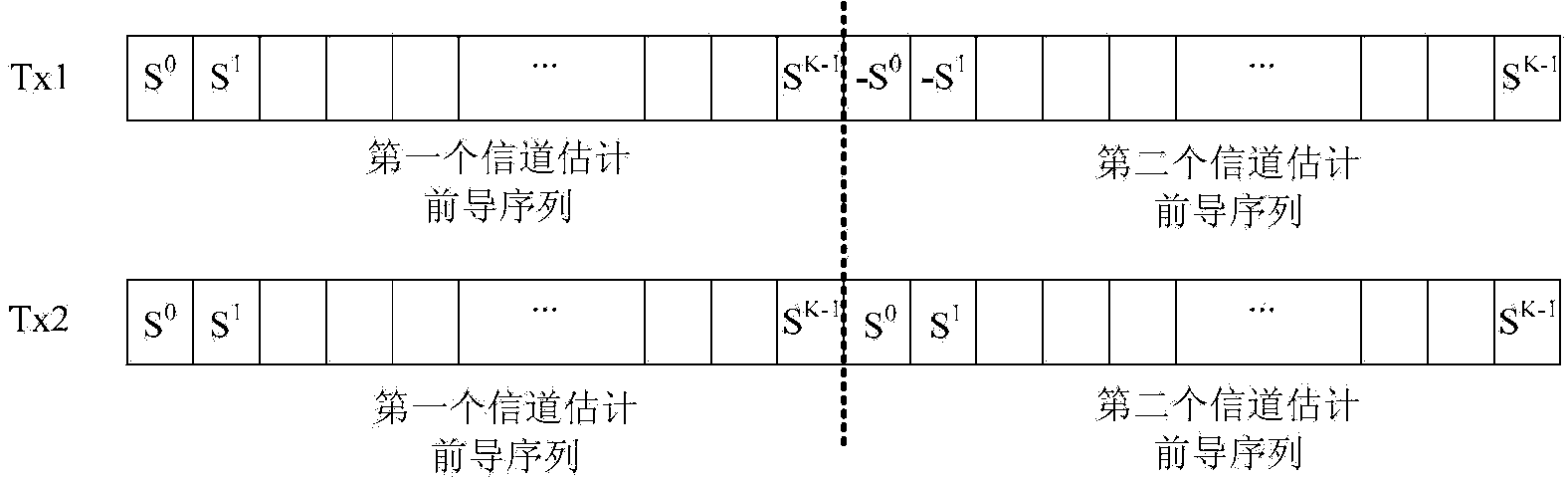

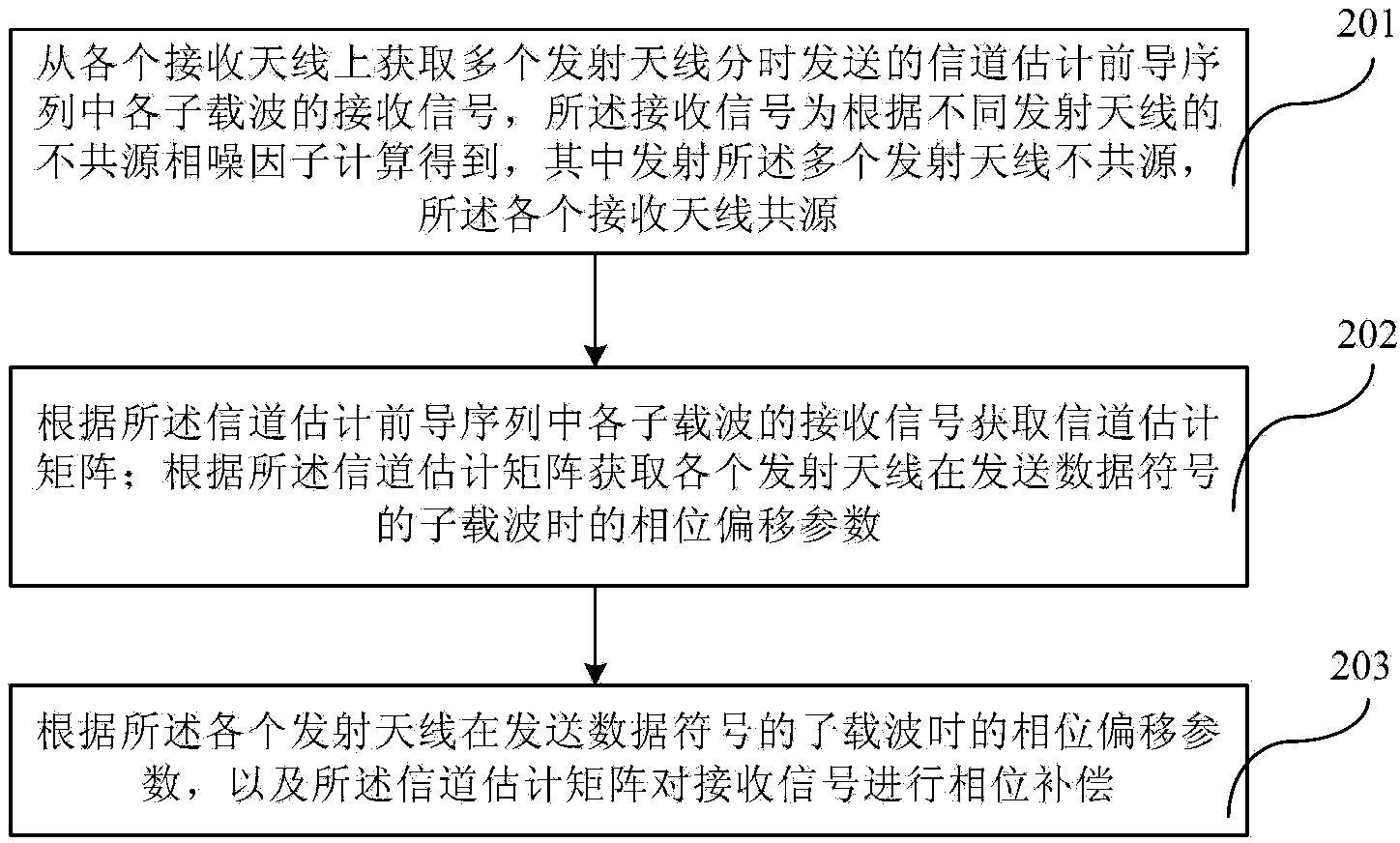

Channel estimation processing method, device and communication equipment thereof

Provided in the present invention are a channel estimation processing method, apparatus and communication device, wherein a phase compensation processing method comprises: obtaining from various receiving antennae a reception signal of at least one first pilot frequency subcarrier in channel estimation preamble sequences transmitted simultaneously by a plurality of transmitting antennae; according to the reception signal of the at least one first pilot frequency subcarrier, obtaining the phase shift parameters of the various receiving antennae during the reception of the channel estimation preamble sequences, and obtaining a channel estimation matrix during the reception of data symbols; obtaining from the various receiving antennae a reception signal of at least one second pilot frequency subcarrier in the data symbols, the reception signal being obtained by calculation on the basis of non-common source phase noise factors of different receiving antennae, and obtaining the phase shift parameters of the various receiving antennae during the reception of the data symbols; and performing phase compensation on the received data subcarrier according to the phase shift parameters as well as the channel estimation matrix during the reception of the data symbols. The technical solution of the present invention can reduce the influence of phase noise and frequency offset effectively.

Owner:HUAWEI TECH CO LTD

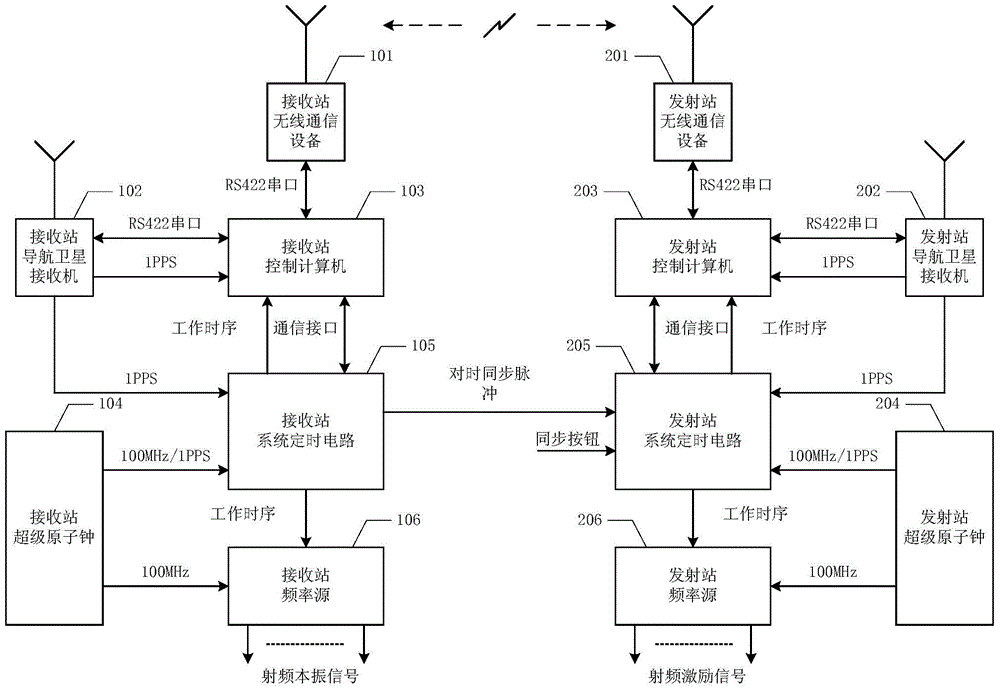

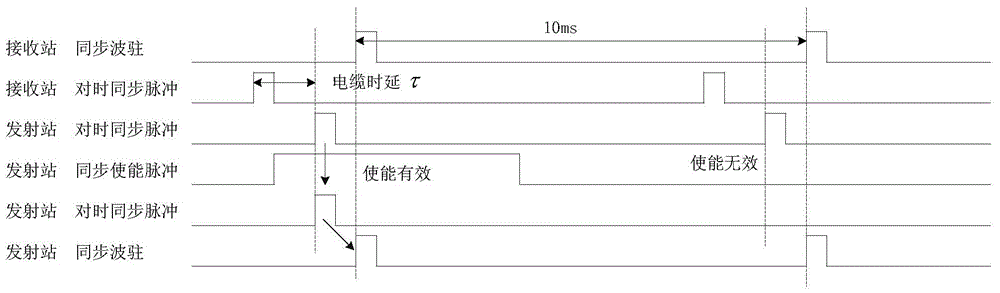

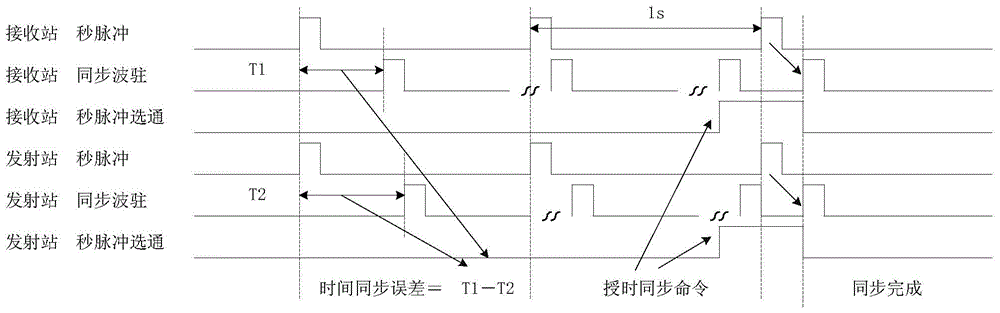

Method for synchronizing time and frequency of motor-driven configured bistatic radar

ActiveCN104569965ASync indirect frequencyLow phase noiseRadio wave reradiation/reflectionMotor drivePhase noise

The invention relates to a method for synchronizing the time and the frequency of a motor-driven configured bistatic radar. The frequency and the time between a receiving station and a transmitting station of the bistatic radar can be realized by utilizing the characteristics of long-term stability, low phase noise and low stray; when the receiving station and the transmitting station are deployed separately, the real-time statistics of time synchronization errors of the receiving station and the transmitting station are completed on the basis of pulses per second of a navigation satellite; when the time synchronization errors exceed a limit value and the state of the pulses per second of the navigation satellite is normal, time resynchronization between the receiving station and the transmitting station is completed in a navigation satellite time service synchronization mode; the receiving station and the transmitting station enter a timekeeping synchronization state again. The method is applicable to synchronizing the time and the frequency of the motor-driven configured bistatic radar, and has the advantages of short erecting and withdrawing time, high maneuverability, high working stability and the like. Before the receiving station and the transmitting station are deployed separately, the modes of direct time contrast synchronization and long-time autonomous timekeeping maintenance are adopted, and have the advantages of being not limited by the navigation satellite and not impacted by electromagnetic environment in wartime.

Owner:CNGC INST NO 206 OF CHINA ARMS IND GRP

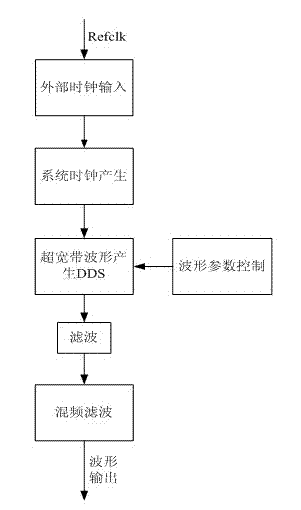

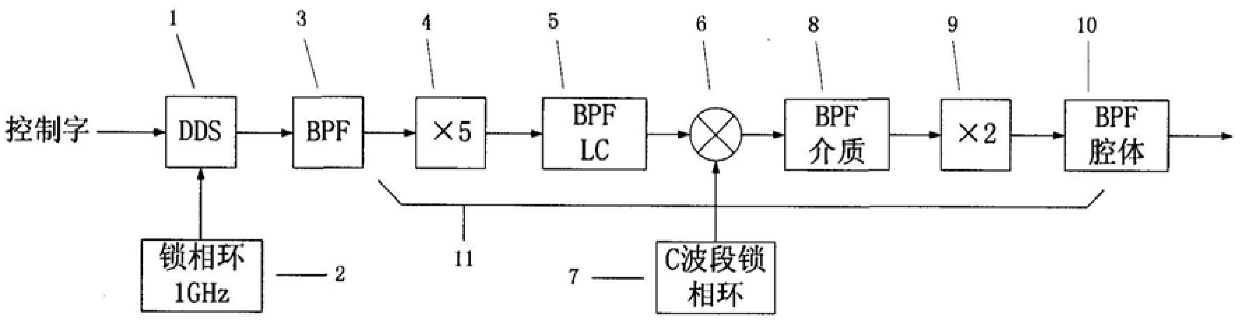

DDS (direct digital synthesis) type ultra-wide band frequency-modulated signal generating circuit and method

InactiveCN102780490AHigh resolutionLow spuriousPulse automatic controlFrequency synthesisRadio frequency

The invention belongs to the technical field of radar wideband frequency synthesis and in particular relates to an ultra-wide band frequency-modulated signal generating method which is based on the combination of wideband DDS (direct digital synthesis) and an analog frequency synthesis technique. According to the invention, a wideband DDS chip is used for directly generating a wideband linear frequency-modulated, non-linear frequency-modulated or special phase-coded signal, and waveform signal parameters can be configured online by an upper computer. A radio frequency microwave band datum reference signal is generated by utilizing an analog phase-locked loop and a frequency synthesis technique, and the wideband linear frequency-modulated, non-linear frequency-modulated or special phase-coded signal and the radio frequency microwave band datum reference signal are combined by virtue of frequency spectrum shifting, thus an ultra-wide band frequency-modulated signal with low spur, low phase noise and high resolution is generated, a microwave direct frequency synthesizer with high resolution and low phase noise is realized and is simple in structure and easy to integrate.

Owner:WUHAN BINHU ELECTRONICS

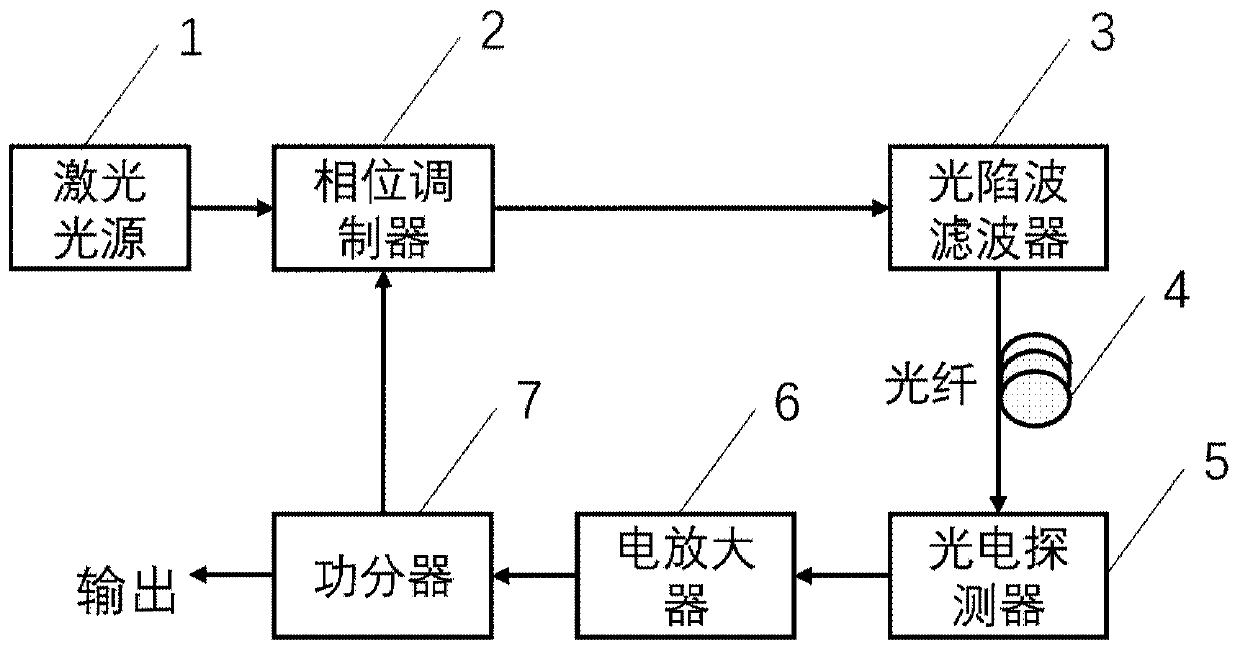

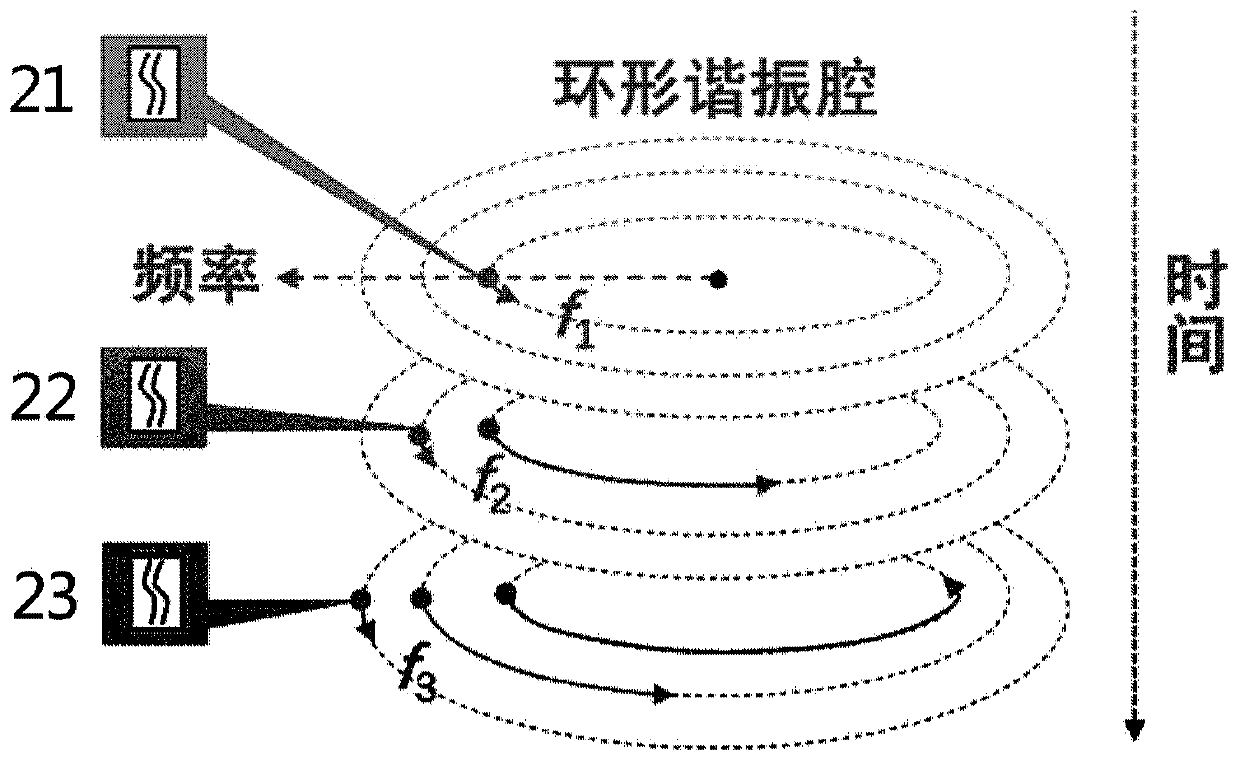

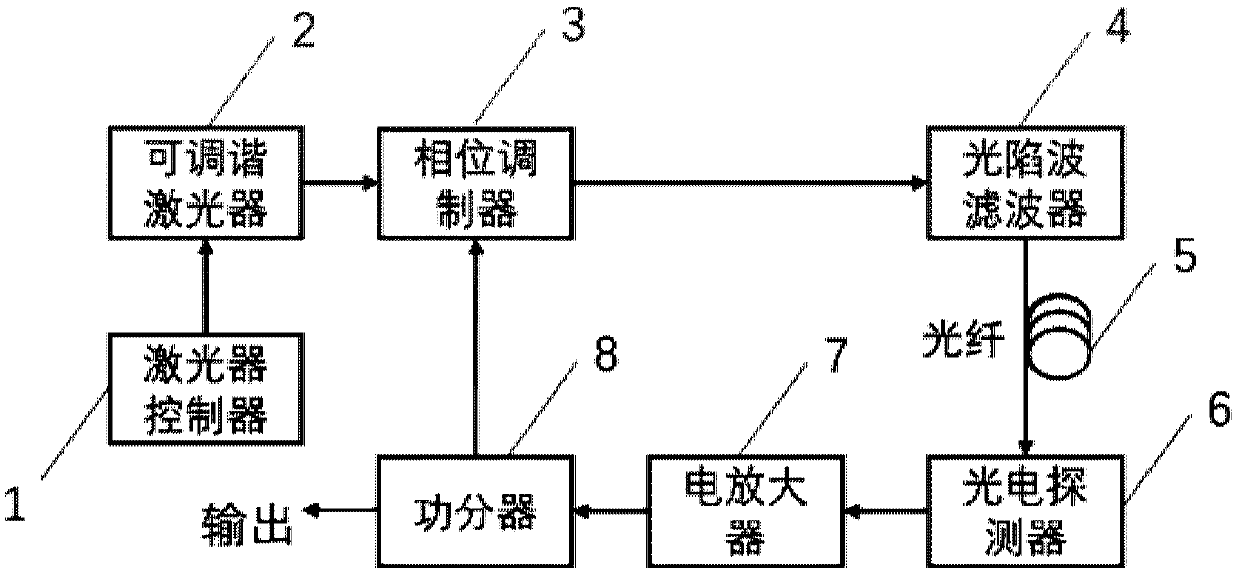

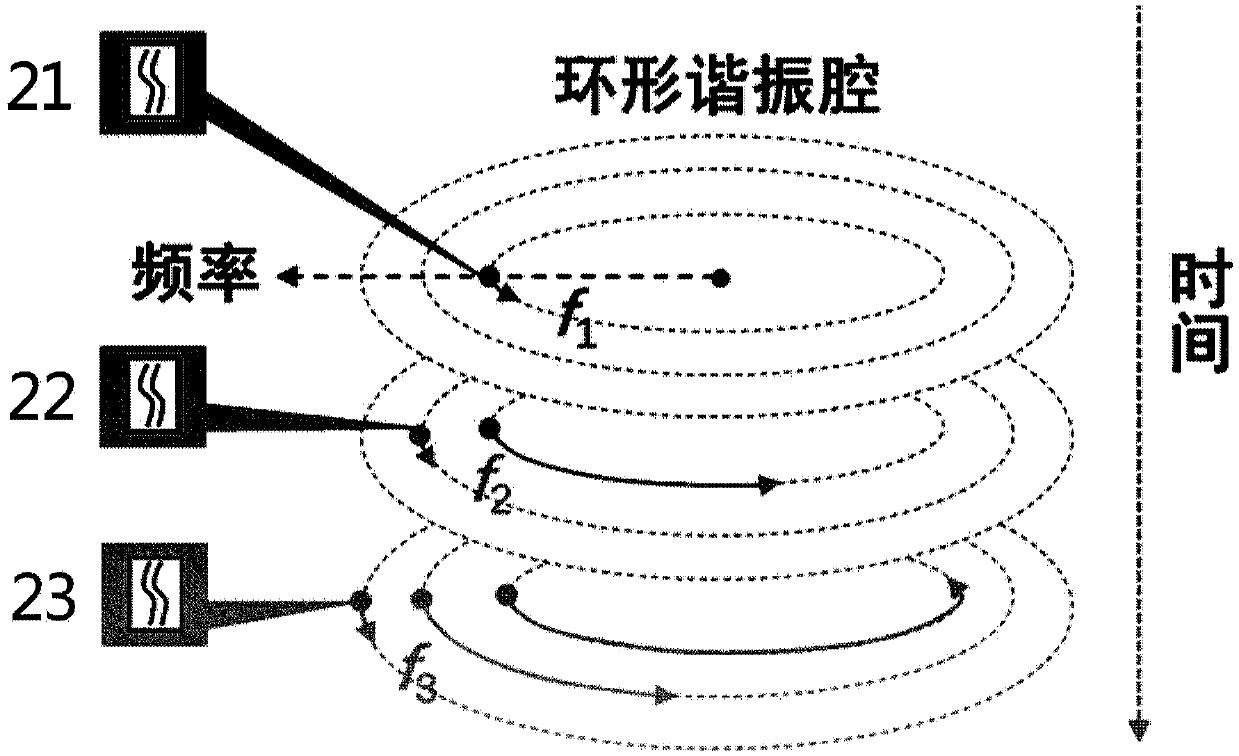

Fourier domain mode-locked photoelectric oscillator

InactiveCN110504613AFrequency broadband adjustableLow phase noiseSolid masersOscillations generatorsBroadbandOpto-electronic oscillator

The invention discloses a Fourier domain mode-locked photoelectric oscillator. The Fourier domain mode-locked photoelectric oscillator comprises a laser source, a phase modulator, a light notching filter, a photoelectric detector, a power amplifier and a power divider; the laser source, the phase modulator, the light notching filter and the photoelectric detector form a sweeping frequency microwave photon filter; a transmission band of the sweeping frequency microwave photon filter is decided by the difference of the laser source and the light notching filter notching location corresponding wavelength, the sweeping frequency of the microwave photon filter transmission band is realized through the sweeping frequency of the laser source or the light notching filter, and the change of the filter transmission band and the signal are matched with the in the time delay for transmitting a circle in a photoelectric oscillator loop; the Fourier domain mode-locking is realized, and the bandwidth-adjustable chirp microwave signal can be output.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

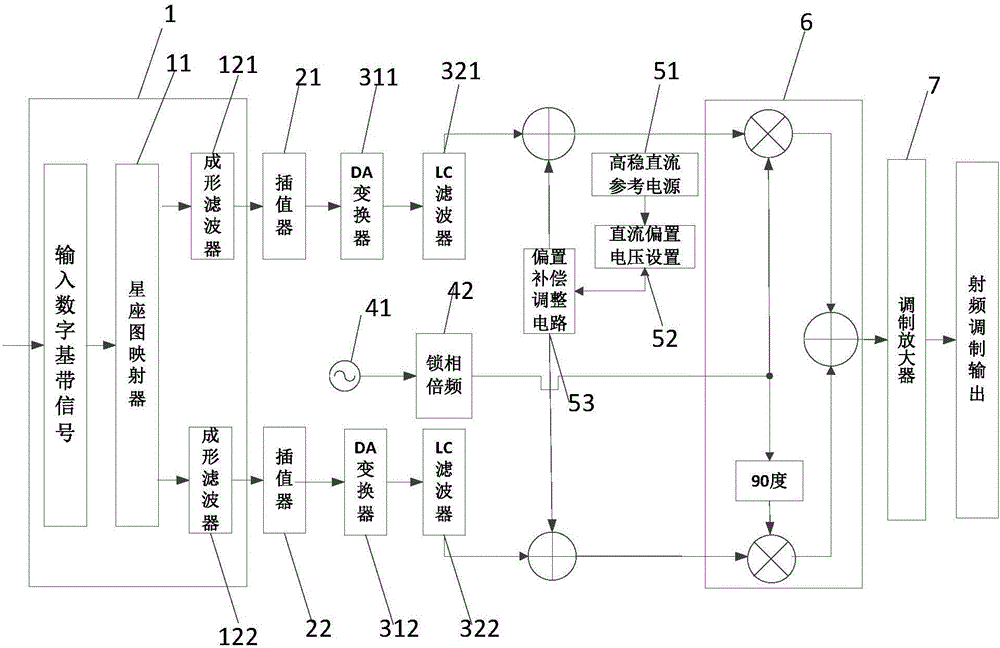

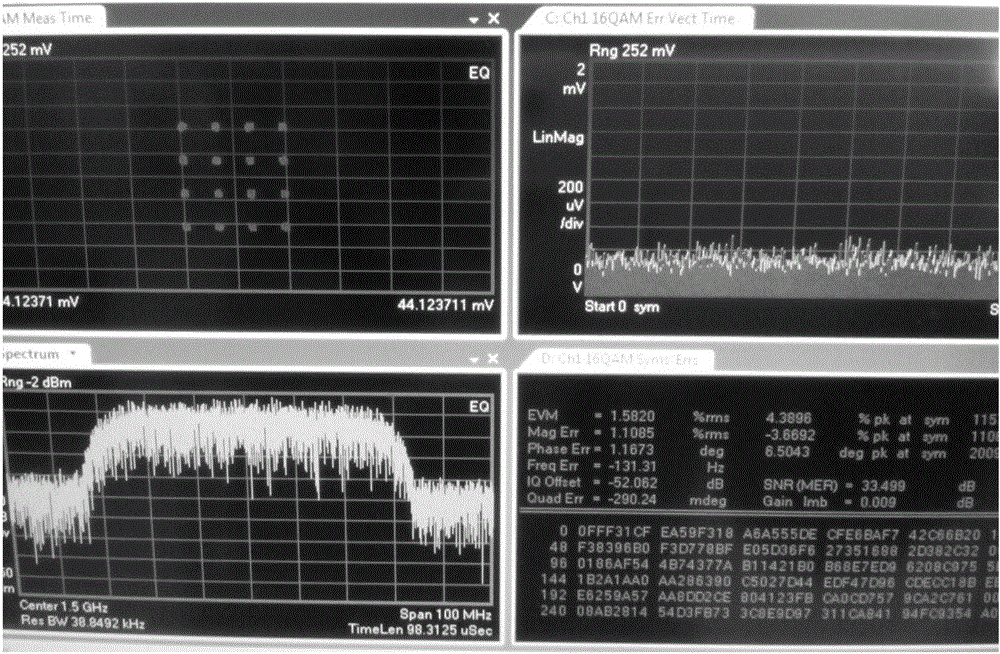

Ka waveband radio frequency modulation system and method

InactiveCN106160755AImprove performance indicatorsSimple forming methodMultiple carrier systemsCarrier signalRadio frequency signal

The present invention proposes a Ka-band radio frequency modulation system and method, including: a baseband signal processing module, which receives a digital baseband signal, and performs constellation mapping on it according to a corresponding modulation mode, and performs shaping and filtering on the generated constellation mapping symbols Output; the digital-to-analog conversion processing module is connected to the baseband signal processing module to perform digital-to-analog conversion and filtering on the shaped and filtered data signal, and output the analog baseband signal; the carrier source generation module is used to generate and output modulation Carrier signal; quadrature analog modulator, connected to the digital-to-analog conversion processing module and the carrier source generation module, for performing quadrature analog modulation on the analog baseband signal according to the carrier signal, and outputting a modulated radio frequency signal. It solves the problems of poor performance index and flexibility of common modulation systems, and achieves the characteristics of simple circuit, small footprint, low power consumption, excellent modulation performance index, and strong flexibility.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

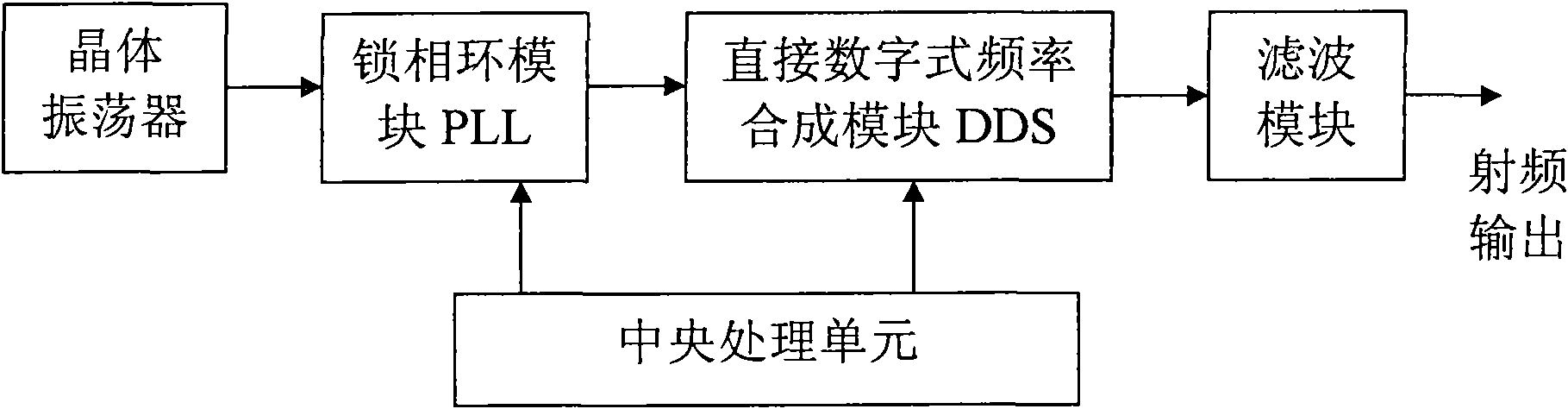

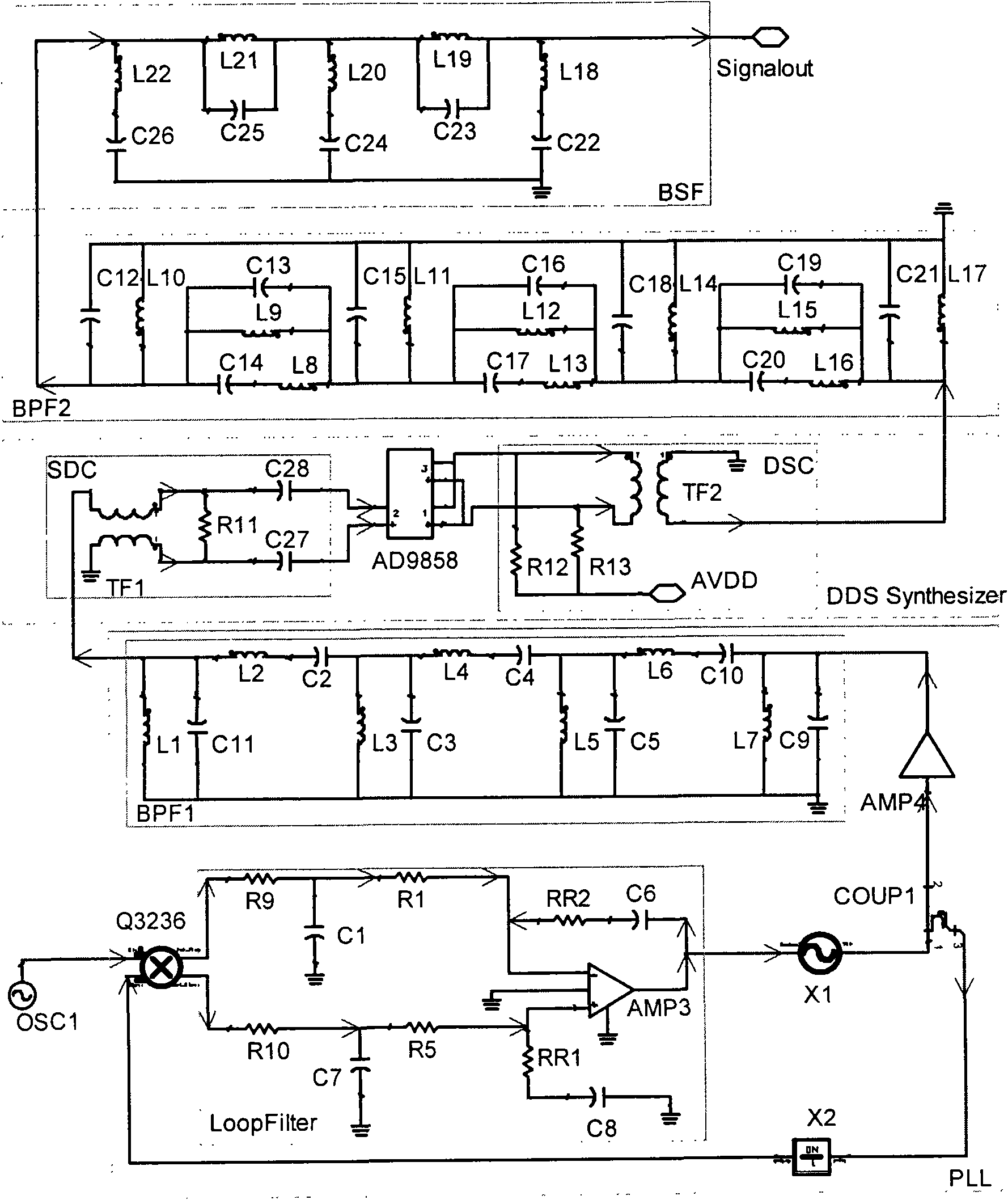

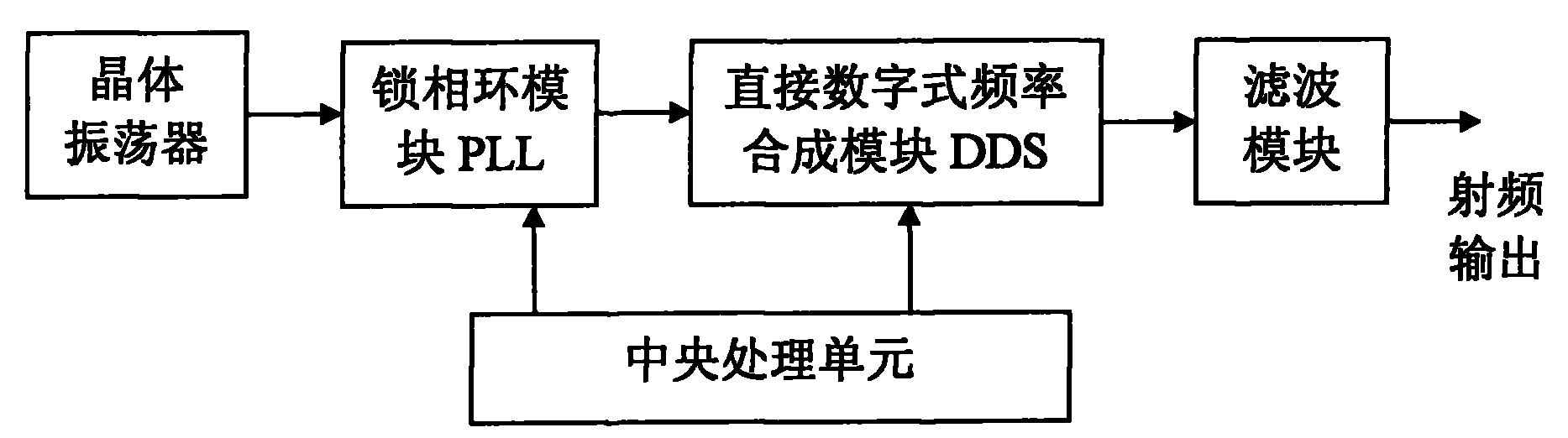

Frequency synthesis system for enhancing spectrum purity of direct digital frequency synthesizer

InactiveCN101847992AHigh quality signal synthesisReduce noisePulse automatic controlFrequency synthesisSignal frequency

The invention relates to a frequency synthesis system for enhancing spectrum purity of a direct digital frequency synthesizer, which comprises a crystal oscillator, a phase-locked loop module (PLL), a direct digital frequency synthesis module (DDS), a filter module and a central processing unit, wherein the system uses the phase-locked loop module (PLL) to provide a variable clock for the direct digital frequency synthesis module (DDS), and the clock frequency of the variable clock provided by the phase-locked loop module (PLL) is an integral multiple of the frequency of the output signal. By changing the clock frequency of the direct digital frequency synthesizer, the noise generated in the quantization process is minimized, thereby improving the stray indexes of the output signal and enhancing the spectrum purity of the output signal.

Owner:NANJING GUORUI ANTAIXIN TECH

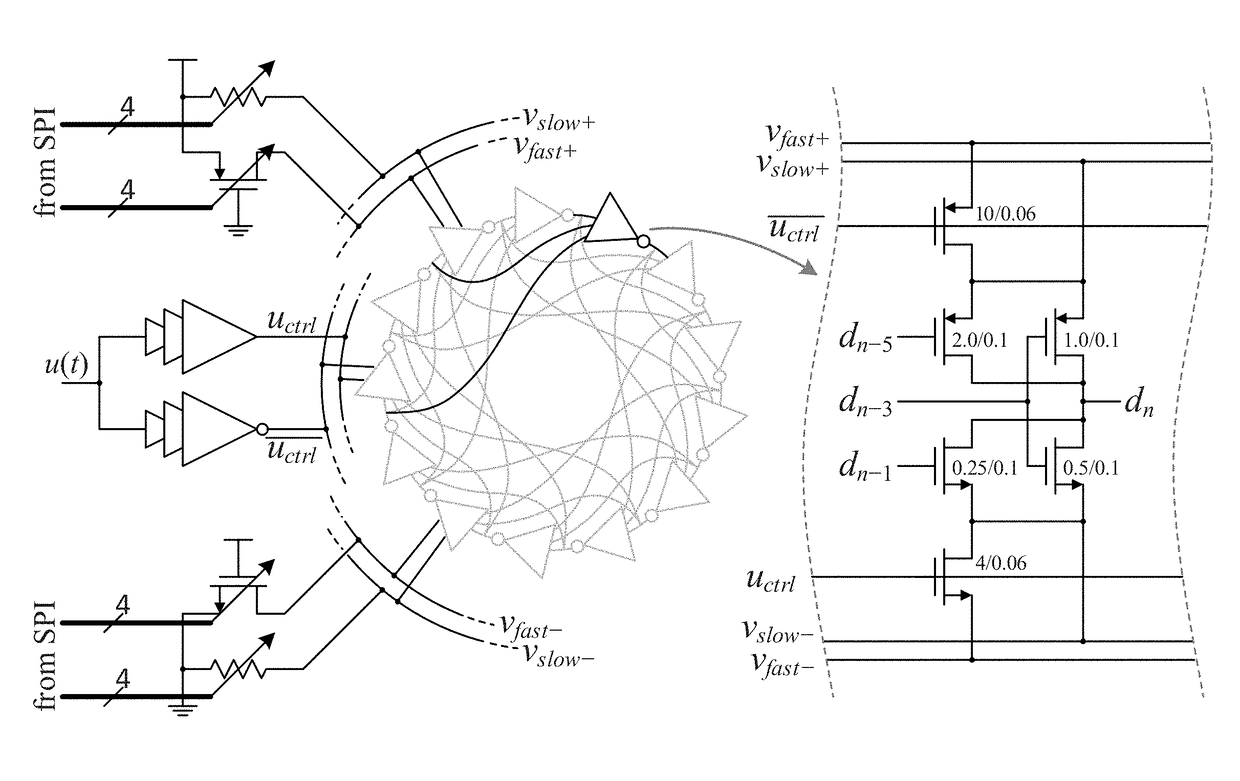

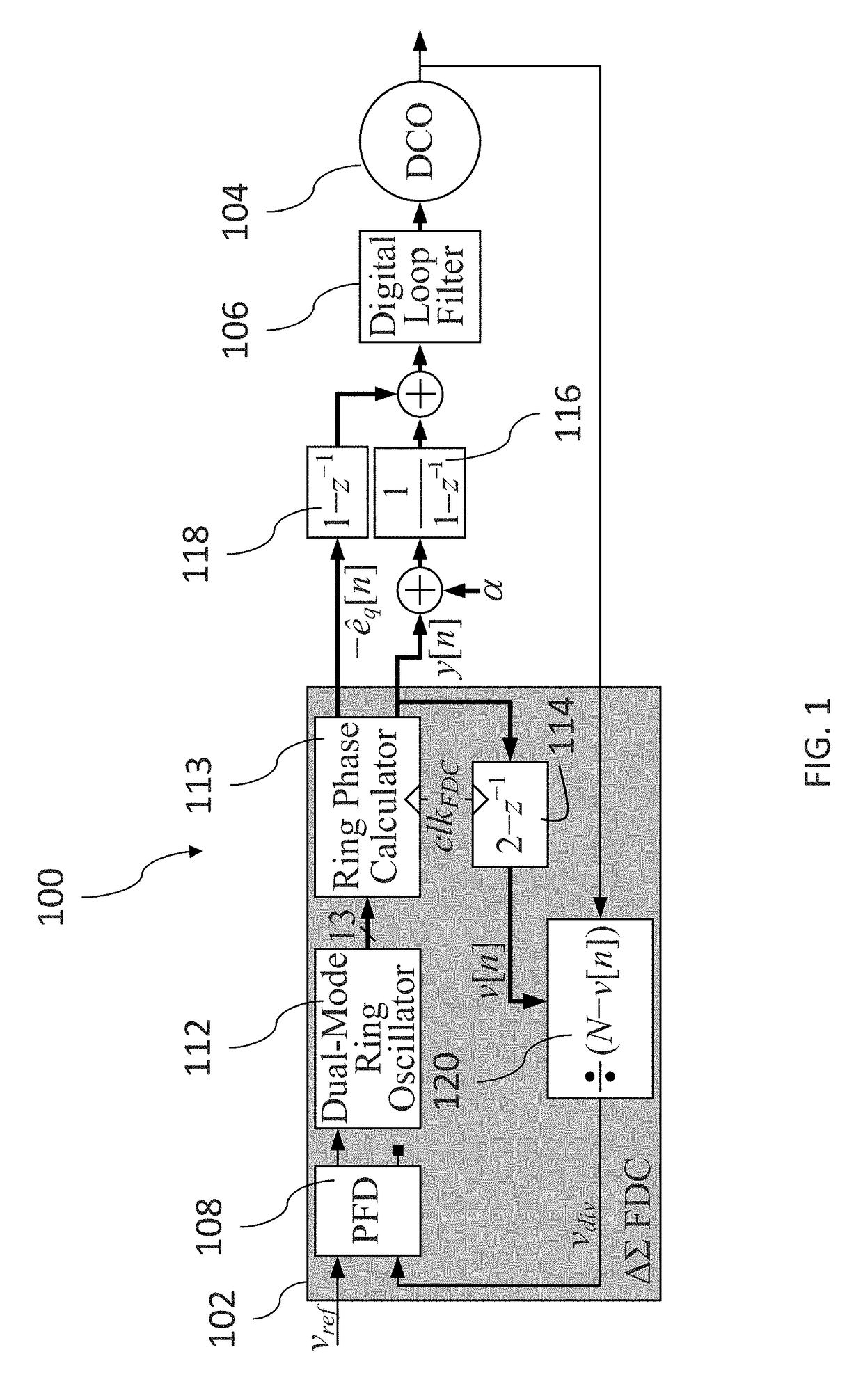

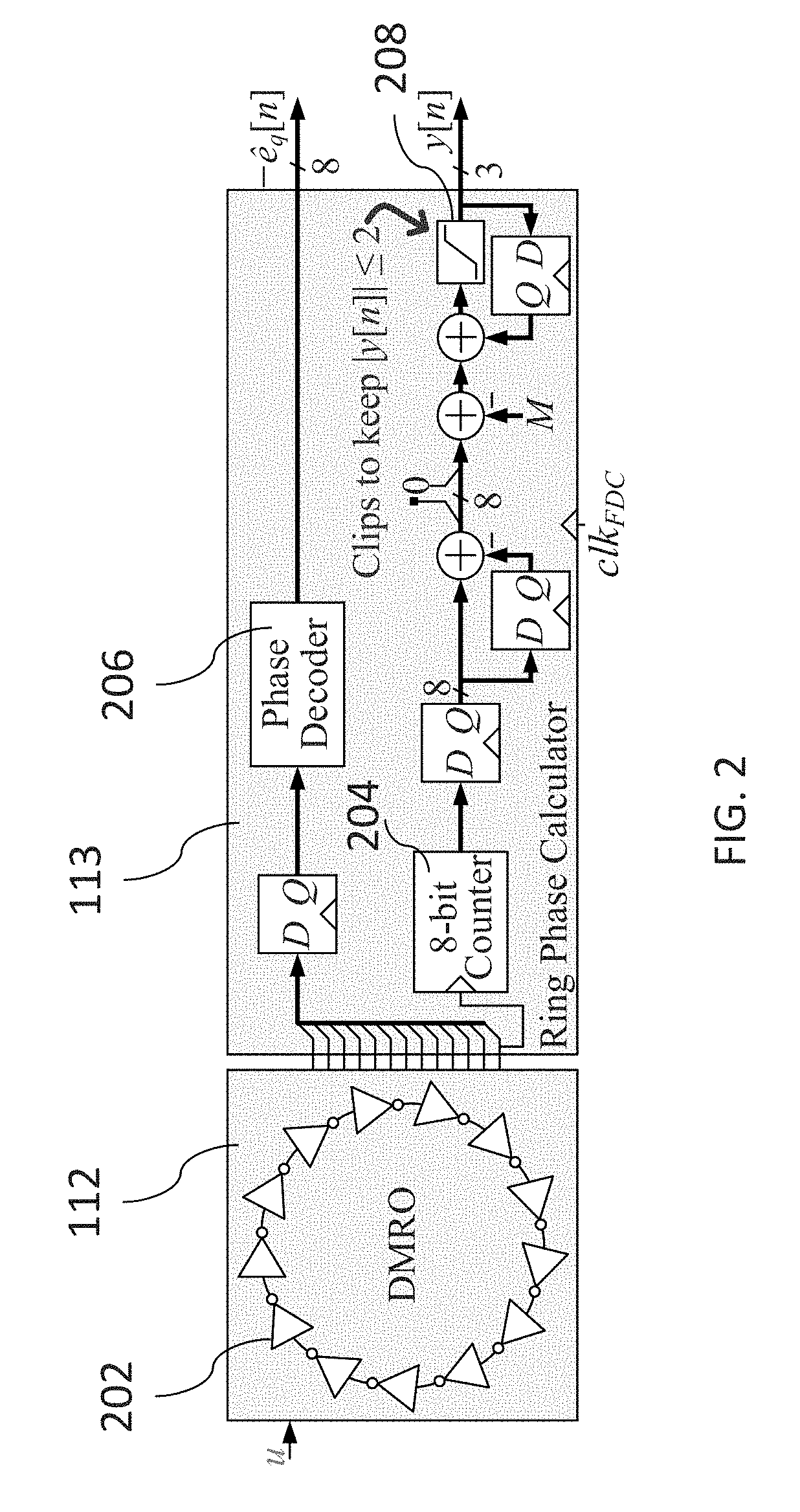

Digital fractional-n pll based upon ring oscillator delta-sigma frequency conversion

ActiveUS20170244544A1Well spurious tone performanceLow phase noisePulse automatic controlSynchronising arrangementA d converterGreek letter sigma

A frequency-to-digital-converter based PLL (FDC-PLL) that implements the functionality of a charge pump and analog-to-digital converter (ADC) with a dual-mode ring oscillator (DMRO) and digital logic. Preferred embodiments of the invention include circuit-level techniques that provide better spurious tone performance and very low phase noise with lower power dissipation and supply voltage than prior digital PLLs known to the inventors

Owner:RGT UNIV OF CALIFORNIA

Broadband low-noise frequency modulation signal source

ActiveCN105223555ALow phase noiseImprove signal-to-noise ratioWave based measurement systemsLow noisePhase noise

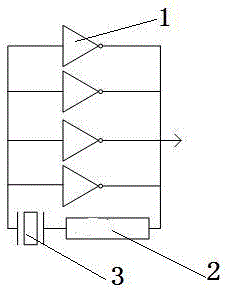

The invention discloses a broadband low-noise frequency modulation signal source. A high-stability clock module has two clock signals as output, the first clock signal as output is directly connected with the reference clock end of a DDS module, and the second clock signal is connected with the input end of a power divider; the power divider divides the second clock signal into haves and respectively outputs the two haves through two output ends, wherein one half is output to a DDS configuration module; the DDS configuration module outputs a configuration signal to the DDS module, the DDS module, after receiving the configuration signal, generates a frequency modulation signal by use of a phase synthesis and table look-up method and outputs the frequency modulation signal through a waveform output end; the waveform output end is respectively connected with a first phase-locked loop circuit and a second phase-locked loop circuit through a low-noise amplifier; output of the first phase-locked loop circuit is taken as an emission local oscillator; and output of the second phase-locked loop circuit is taken as a receiving local oscillator. The signal source provided by the invention can meet the demands for high linearity and low phase noise of a broadband frequency modulation signal source.

Owner:北京理工雷科电子信息技术有限公司

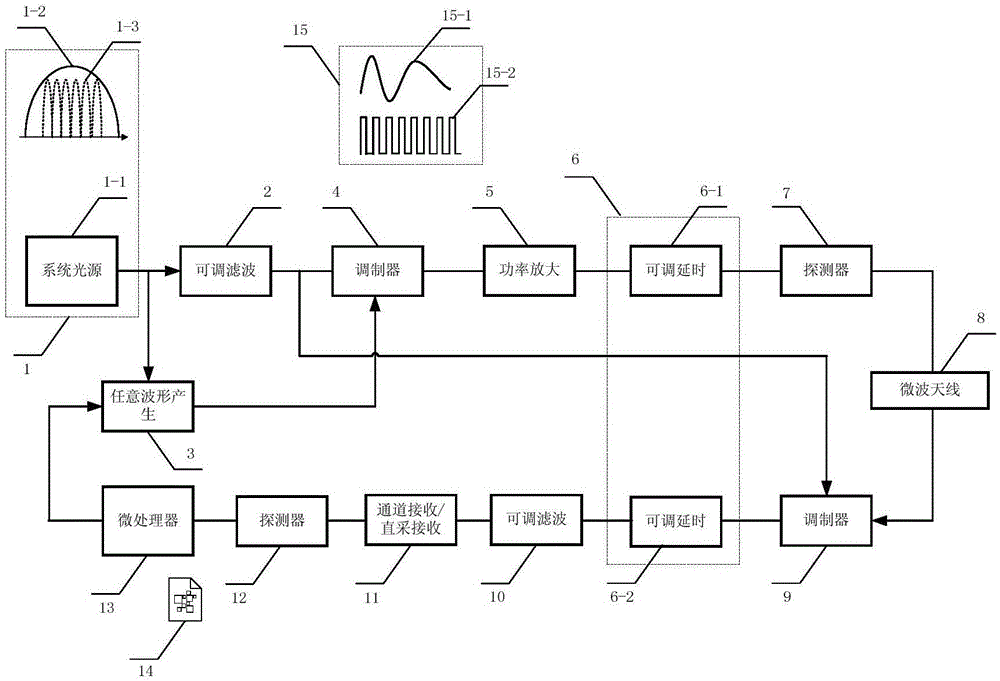

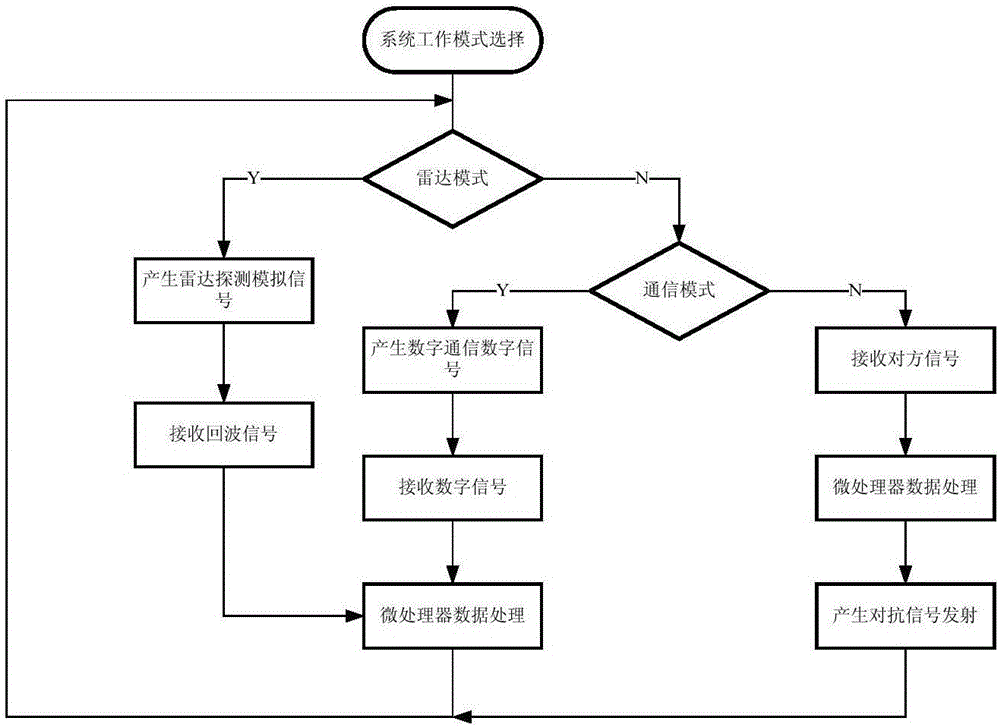

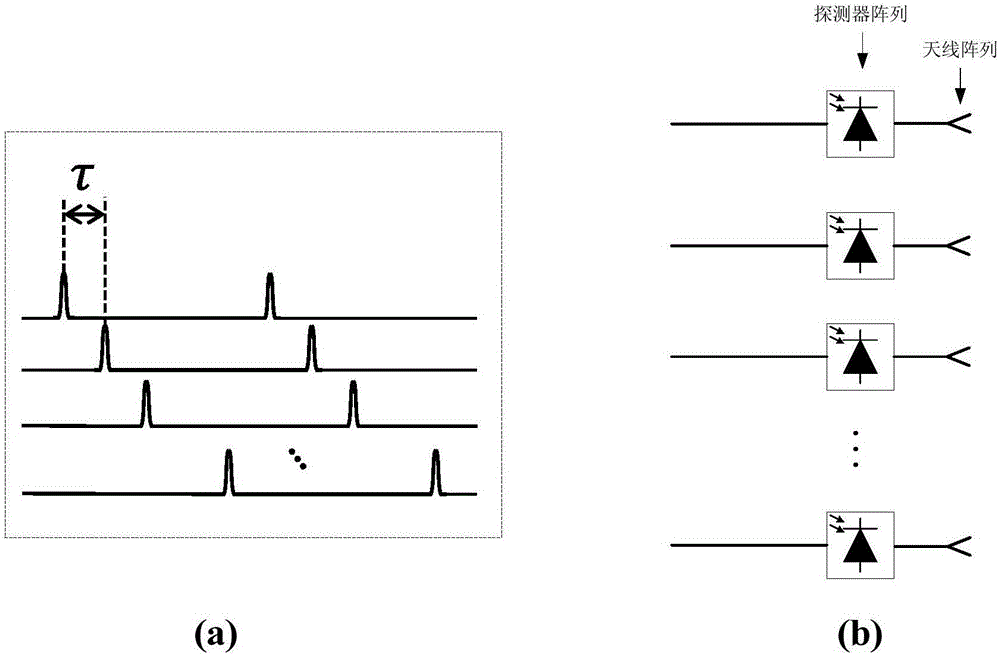

Radar communication countermeasure integration system based on microwave photonics

ActiveCN106230516ARealize integrated designImprove coherencePhotonic quantum communicationRadio wave reradiation/reflectionLow noiseEngineering

The invention relates to a radar communication countermeasure integration design based on microwave photonics. The radar communication countermeasure integration design comprises a system light source, an emitting and receiving end adjustable filtering module, an any waveform generating module, an emitting and receiving end modulator module, a light power amplifier module, a system time delay module, an emitting and receiving end end-detection module, a microwave antenna module, a passage receiving / direct collection receiving module, a microprocessor module and the like. The system can realize the function switching of three kinds of information systems of radar detection, digital communication and electronic countermeasure through parameter configuration and chip configuration; through the any waveform generating module, analog signals or digital signals used for three kinds of systems can be generated; the system comprises an emitting loop and a receiving loop; the emitting loop and the receiving loop use identical light sources, so that the system coherence is ensured; meanwhile, the microwave signals are processed in the photonic filed, so that the advantages of high bandwidth and low noise performance are realized. The system can realize the functional integration of the information system; the environment adaptability and reconfigurability of the system can be improved; the system can be widely used in the information technology fields such as ultra-wide band radar, digital communication and electronic countermeasure.

Owner:SHANGHAI JIAO TONG UNIV

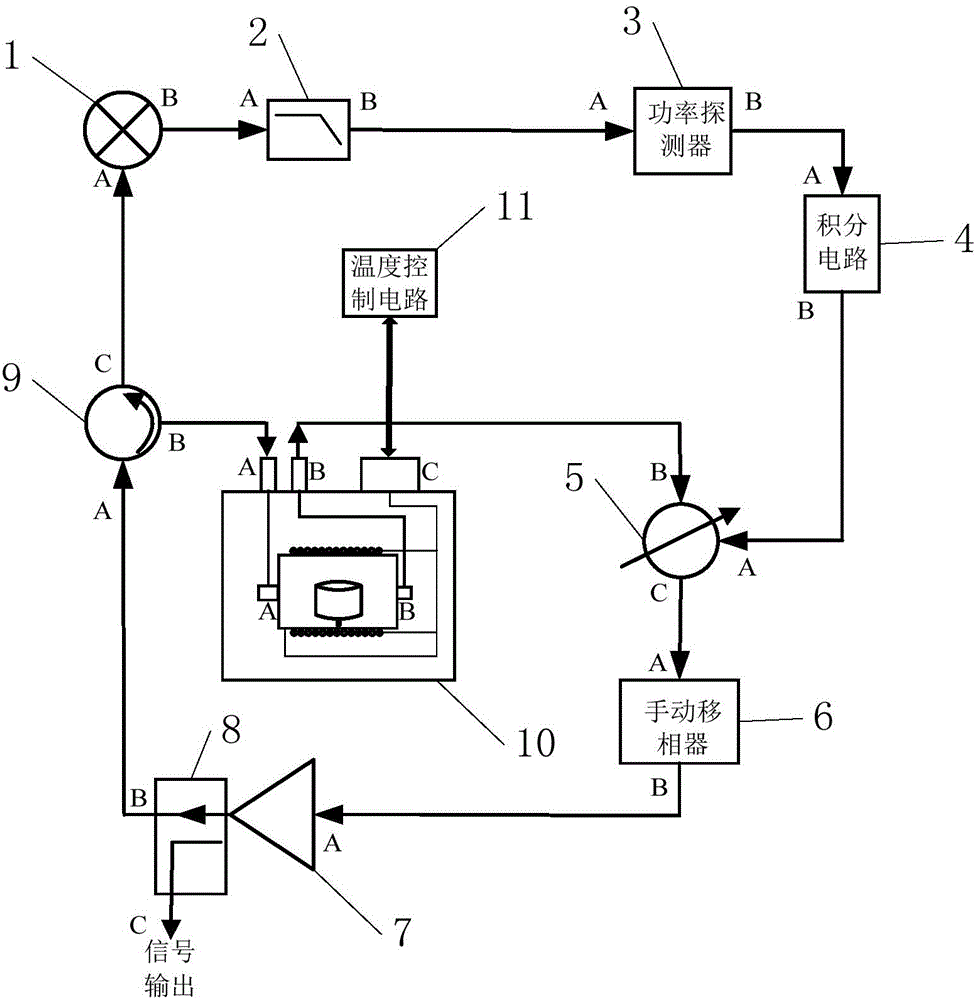

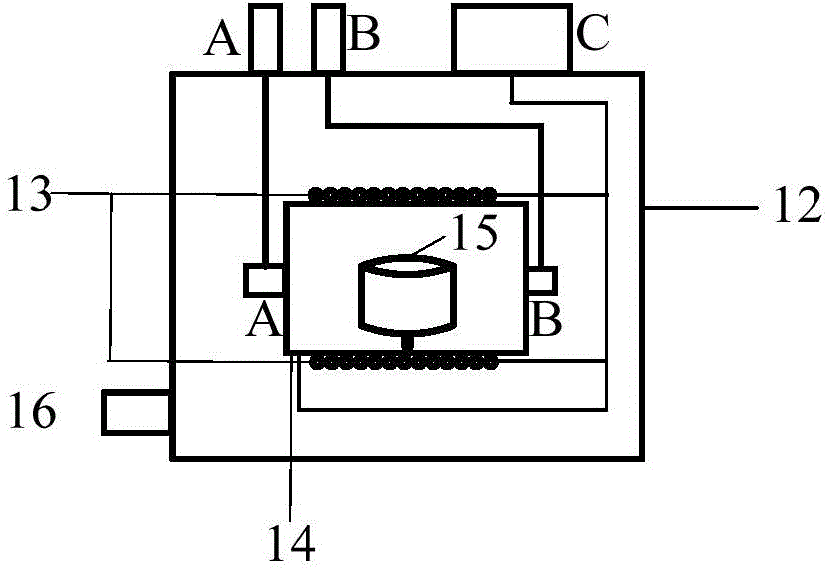

Sapphire microwave oscillator with low phase noise

The invention discloses a sapphire microwave oscillator with low phase noise. The sapphire microwave oscillator comprises a mixer, a low pass filter, a power detector, a integral circuit, a voltage controlled phase shifter, a manual phase shifter, a microwave amplifier, a power coupler, a microwave circulator, a sapphire filter and a temperature control circuit, wherein the sapphire filter comprises an evacuated enclosure, a heating wire 13, a metallic shield chamber, a sapphire crystal and a vacuum maintaining subassembly. The microwave oscillator of the invention could obtain a stable high-frequency microwave signal with low phase noise under room temperature, and the phase noise of the microwave signal at the far-end is far higher than the index reached by crystal oscillator frequency doubling.

Owner:BEIJING INST OF RADIO METROLOGY & MEASUREMENT

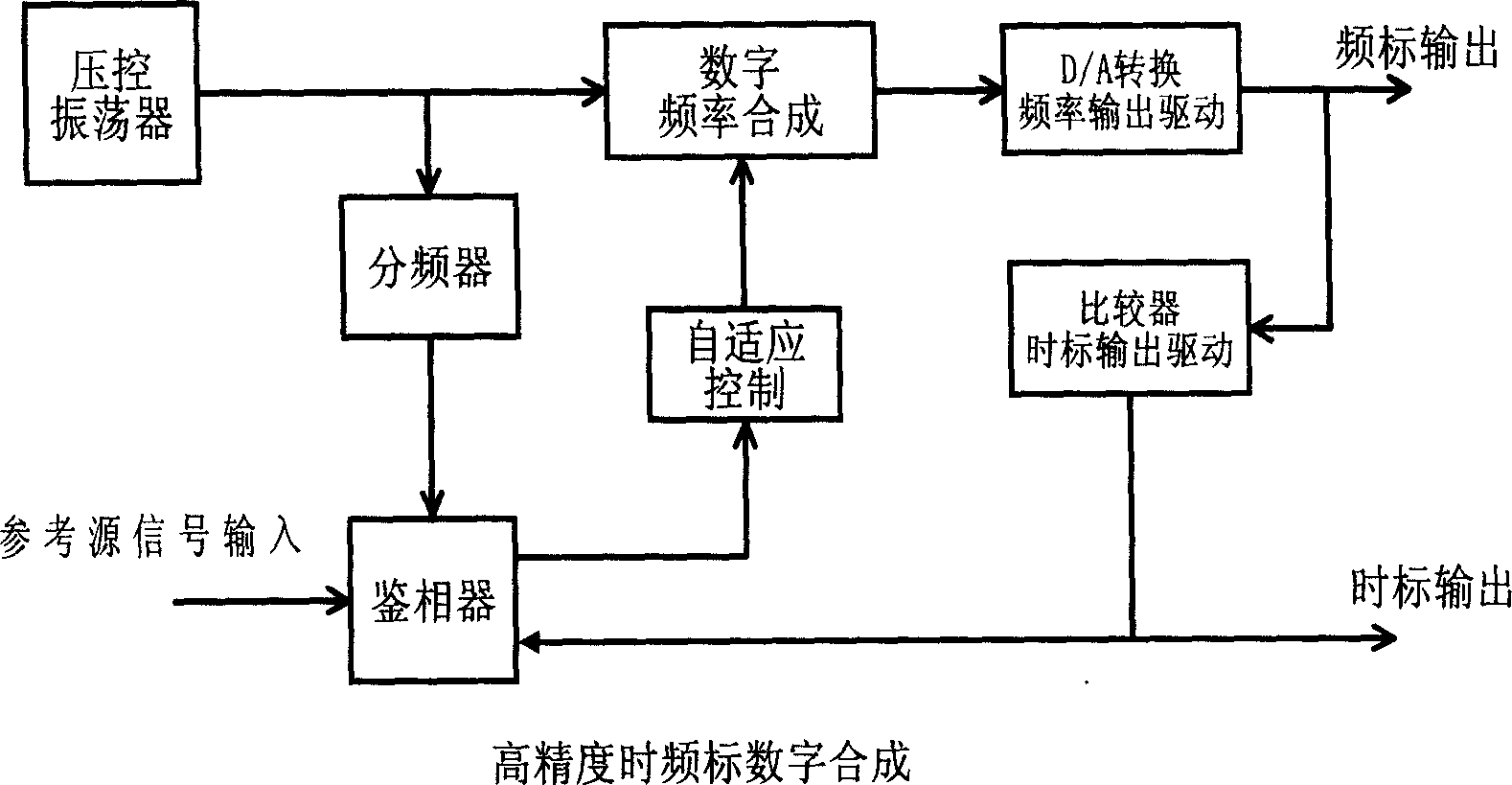

Method for synthesizing high accuracy digital time-frequency standard

InactiveCN1992529ATroubleshoot Control Coupling ProblemsLow phase noisePulse automatic controlFrequency synthesisPhysics

The invention discloses a high precision digital time frequency standard synthesis method, the method being: A. using full digital distinguishing phase and frequency synthesis, and separating the frequency generation and correction; the oscillator working in a free oscillation mode; B. using high-precision phase cumulative method to achieve frequency synthesis, and after combining with the DA converting, outputting to the filter to process noise reduction; C. using digital filtering method to process the distinguishing phase data, and getting the oscillator frequency deviation; D. using the output frequency signal dividing frequency and sending into distinguishing phase device, to achieve the monitor of the frequency synthesizer quality. This invention uses full digital distinguishing phase and frequency synthesis, separates the frequency generation and the correction, and solves control coupling problem; the oscillator works in a free oscillation mode, phase noise being lower, stability being good; meanwhile it supports multiple reference sources to parallel process, very suited to the high-precision time frequency standard synthesis cases, such as satellite timing and others.

Owner:郑州威科姆电子科技有限公司

Method and apparatus for providing a dual-loop phase lock loop

ActiveUS20090111408A1Wider frequency lock rangeLow phase noisePulse automatic controlRadio transmissionDual loopRadio frequency

A method and apparatus for providing a dual-loop phase lock loop (PLL) for a radio-frequency (RF) receiver is provided. The dual-loop PLL may include coarse tuning circuitry and fine tuning circuitry. The coarse turning circuitry and fine tuning circuitry may be arranged in parallel. Both of the coarse tuning circuitry and fine tuning circuitry provide respective tuning signals to a voltage-controlled oscillator (e.g., a varactor tuned VCO). The coarse tuning circuitry and the fine tuning circuitry may provide the respective tuning signals simultaneously. In addition, coarse and fine tuning circuitry may be formed monolithically with other elements of the dual-loop PLL so as to provide a highly-integratable having a wide frequency lock range and high sensitivity.

Owner:AVAGO TECH INT SALES PTE LTD

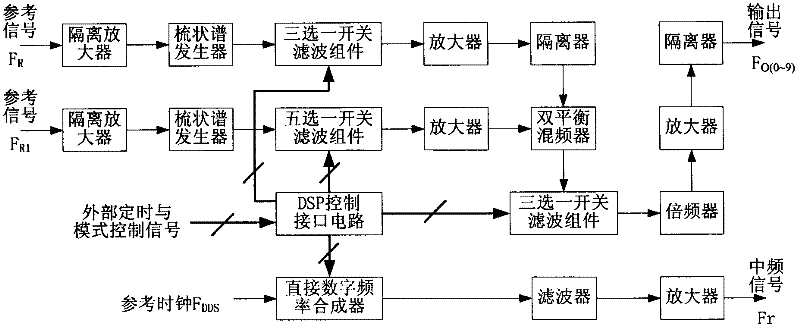

Frequency agility synthesis method compatible with microwave large band width and mid-frequency small stepping and device thereof

InactiveCN102394645AImproved technical indicatorsImprove scalabilityProgramme controlPulse automatic controlIntermediate frequencySynthesis methods

The invention relates to a frequency agility synthesis method compatible with microwave large band width and mid-frequency small step and a device thereof. The invention is characterized in that direct simulation type frequency synthesis, direct digital frequency synthesis, and DSP(digital signal processor) technology are combined to perform frequency synthesis, so as to make the best of the advantages of the mentioned technologies, avoid technical defects, realize the optimization of all technical indexes of the frequency synthesizer, has a better expandability on the design of frequency band width and at the same time is compatible with large band width microwave frequency agility and mid-frequency small stepping frequency agility signal functions.

Owner:中国兵器工业第二〇六研究所

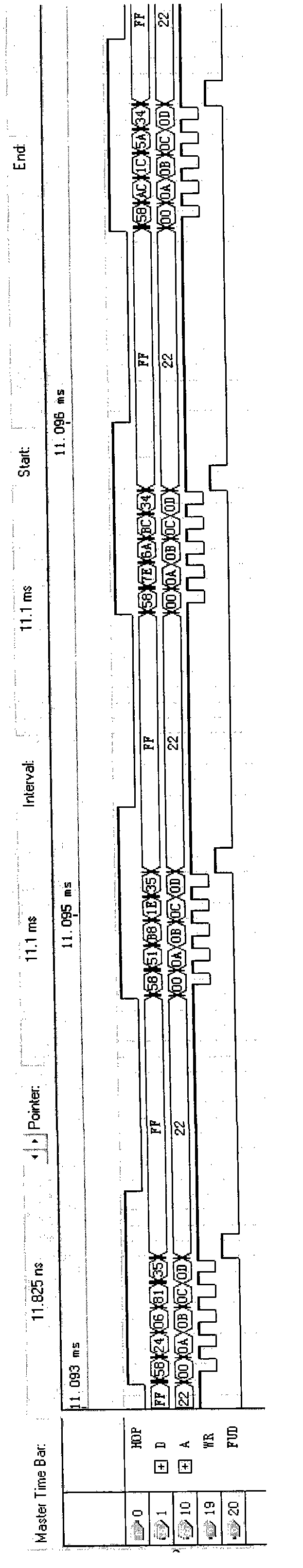

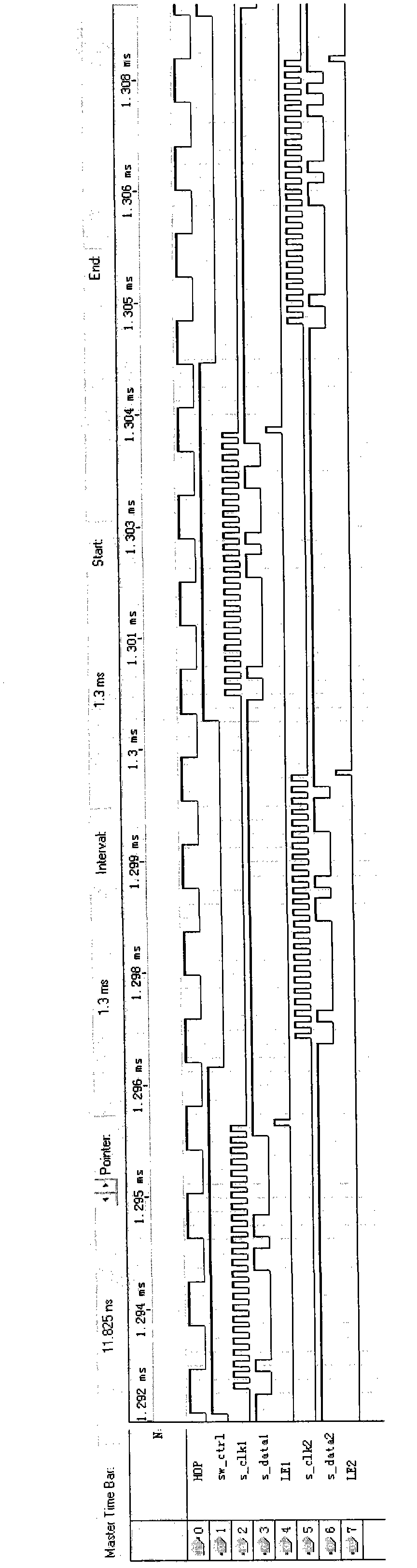

Online synchronous regulating circuit and method for use in distributed waveform generation

InactiveCN103630881AFlexible waveformHigh synchronization accuracyWave based measurement systemsLeading edgeControl communications

The invention belongs to the technical field of synchronous comprehensive design for radar distributed waveform generation, and particularly relates to an online synchronous regulating circuit and method for use in distributed waveform generation. A main control terminal completes controlled communication with a waveform generation part in a receiving-transmitting assembly, and setting and adjustment of relevant parameters such as the leading edge and lagging edge of waveform output and initial frequency are realized according to a preset communication protocol. The online synchronous regulating circuit has the advantages of low cost, convenience and rapidness in operation, high accuracy, simple structure and easiness in integration.

Owner:WUHAN BINHU ELECTRONICS

Fourier domain mode-locked photoelectric oscillator

A Fourier domain mode-locked photoelectric oscillator comprises a laser controller, a tunable laser, a phase modulator, an optical notch filter, an optical fiber, a photoelectric detector, an electricamplifier and a power divider, wherein the tunable laser, the phase modulator, the optical notch filter and the photoelectric detector form a microwave photonic filter together, and the transmissionband of the microwave photonic filter is determined by the difference value of wavelengths corresponding to the notch positions of the tunable laser and the optical notch filter. According to the invention, the tunable laser, the phase modulator, the optical notch filter and the photoelectric detector form a quickly tuned microwave photon filter, the rapid tuning of the transmission band of the microwave photonic filter is realized through the rapid tuning of the laser, and the change of the transmission band of the filter is matched with the time delay of a signal transmitted for a circle ina photoelectric oscillator loop, so that the Fourier domain mode locking is realized, and a chirp microwave signal with an adjustable broadband can be outputted.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

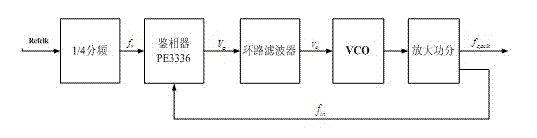

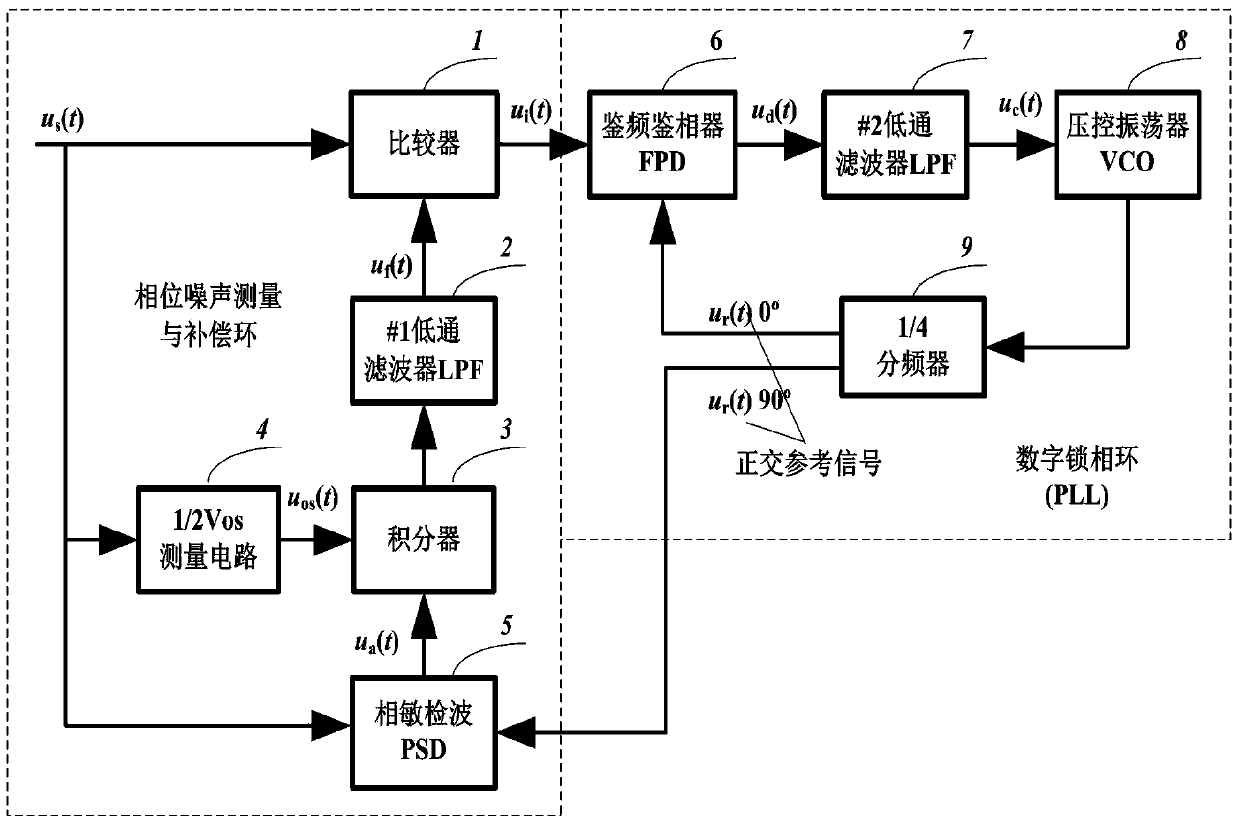

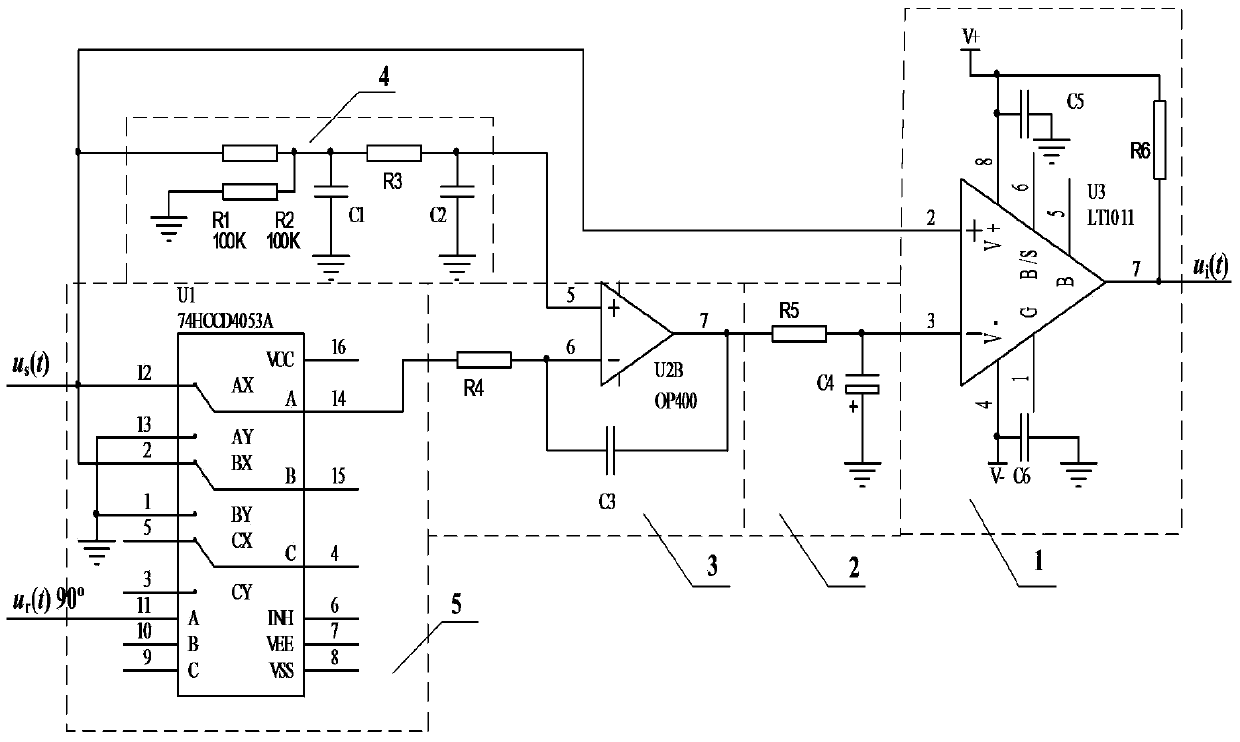

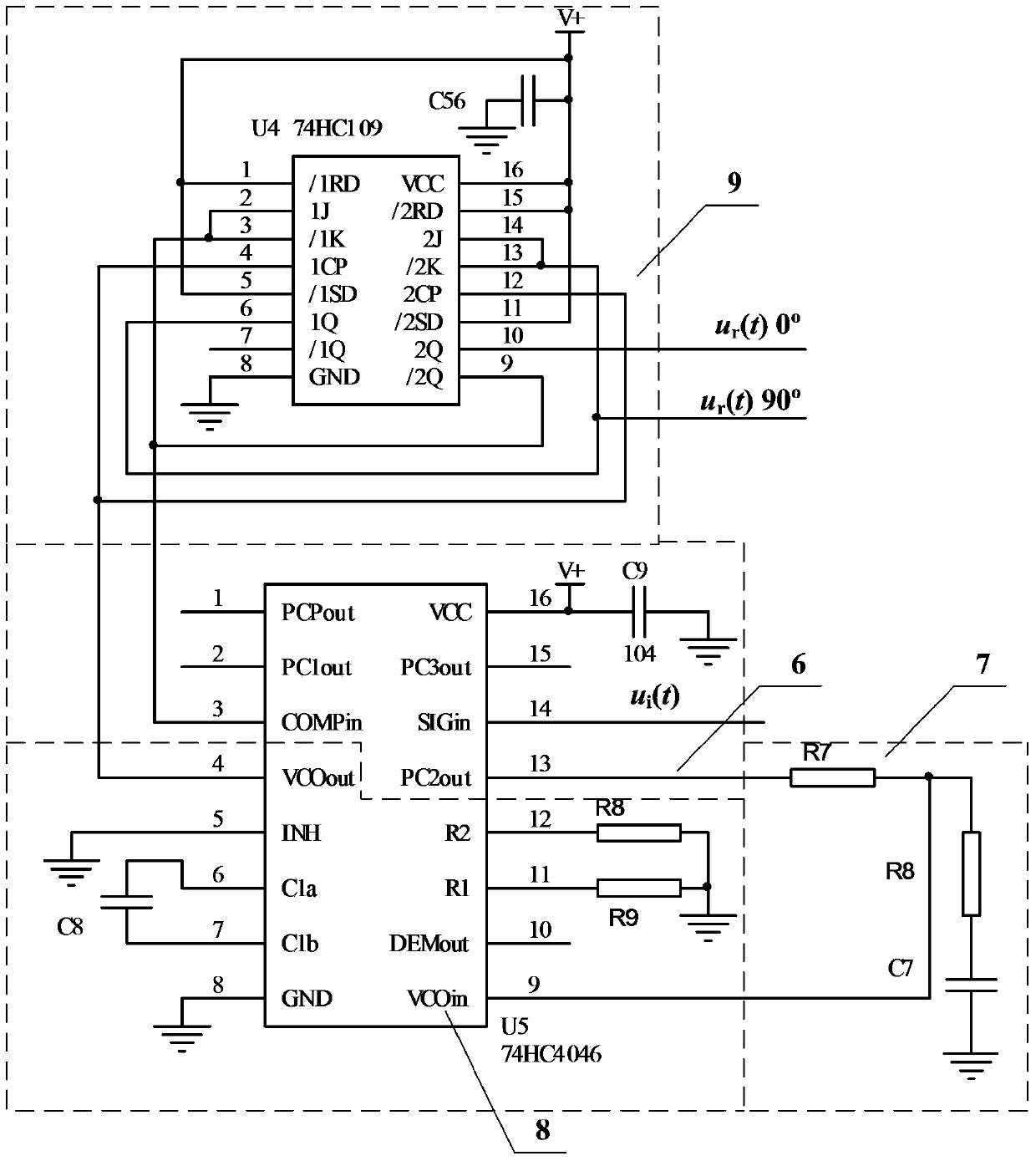

Dual-loop compensation orthogonal signal source phase noise restraining circuit based on lock-in amplifier

ActiveCN104201992ASuppress phase noiseLow phase noiseAmplifier modifications to reduce noise influencePhase detectorPhase sensitive

The invention discloses a dual-loop compensation orthogonal signal source phase noise restraining circuit based on a lock-in amplifier. An output orthogonal component of a quarter frequency divider is connected with the input side of a phase sensitive detector, and the output side of the phase sensitive detector is connected with the input negative terminal of an integrator. The output side of a half Vos measuring circuit is connected with the input positive terminal of the integrator. The output side of the integrator is connected with the input side of a #1 low pass filter. The output side of the low pass filter is connected the negative terminal of a comparator, and the output side of the comparator is connected with the input side of a phase frequency detector. The cophase component output side of the quarter frequency divider is connected with the input side of the phase frequency detector, the output side of the phase frequency detector is connected with the input side of a #2 low pass filter, the output side of the #2 low pass filter is connected with the input side of a voltage-controlled oscillator, and the output side of the voltage-controlled oscillator is connected with the input side of the quarter frequency divider. A signal source is connected with the input side of the phase sensitive detector, the input side of the half Vos measuring circuit and the input side of the comparator. The dual-loop compensation orthogonal signal source phase noise restraining circuit compensates for the phase offset caused by phase noise, and can effectively restrain the phase noise and ensure the eddy measuring accuracy.

Owner:JIANGSU SMART TECH

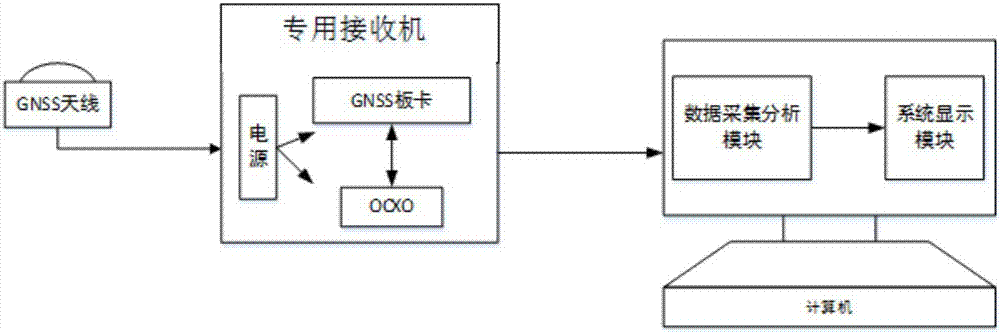

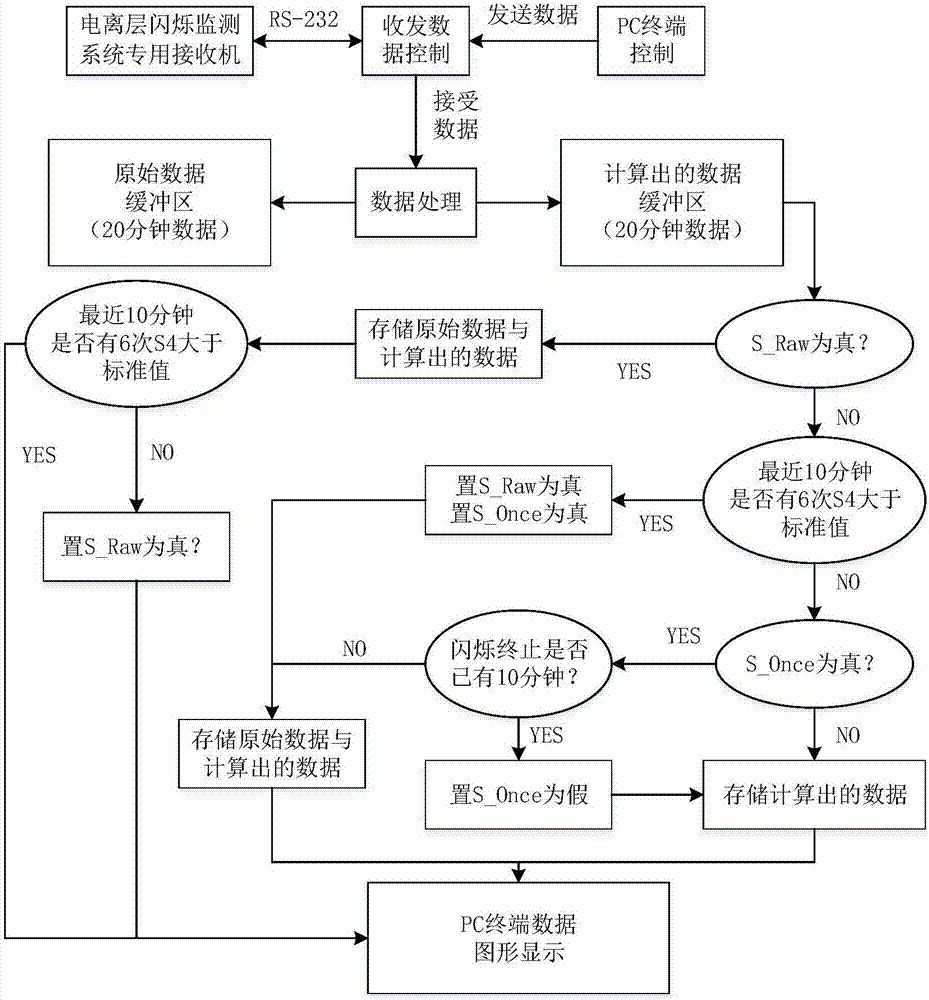

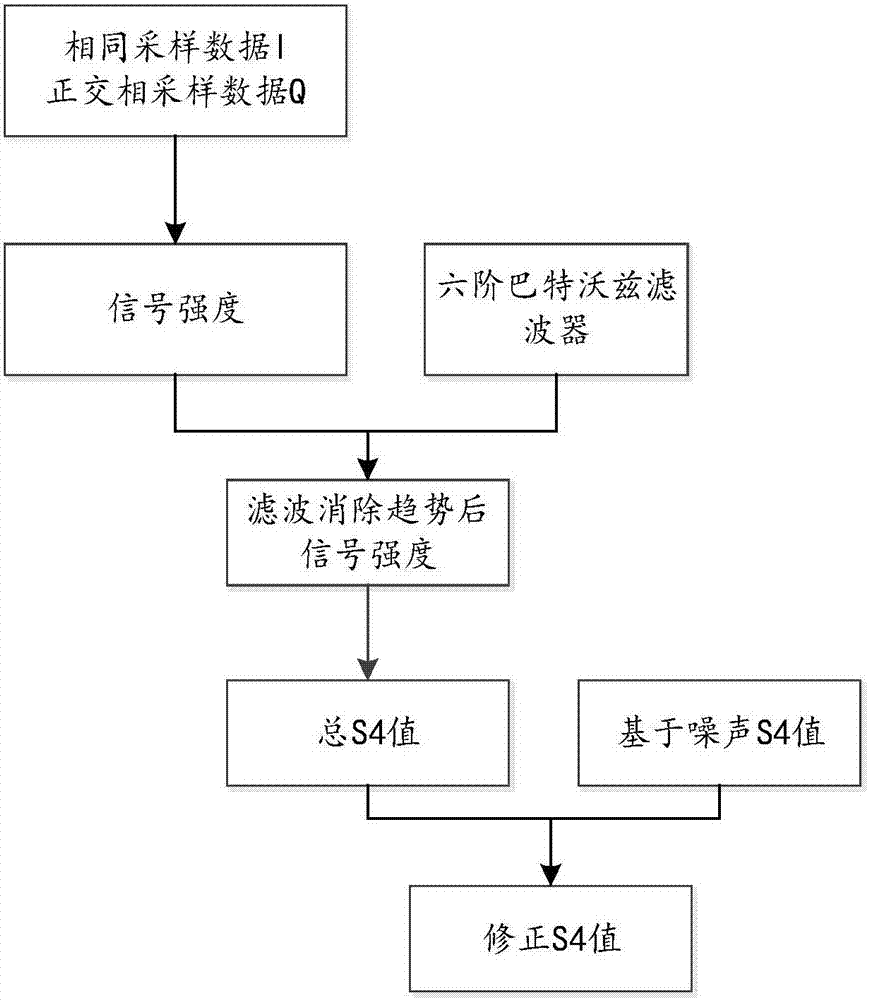

Ionospheric scintillation monitoring system based on Beidou navigation

InactiveCN107219538ATo achieve the effect of real-time monitoringReasonable software architectureSatellite radio beaconingData displayFrequency stabilization

The invention discloses an ionospheric scintillation monitoring system based on Beidou navigation, comprising: an antenna for receiving Beidou satellite signals, and transmitting the Beidou satellite signals to the receiver for processing; and carrier phase φ information are transmitted to the computer; the computer includes a data acquisition and analysis module and a system display module, and the data analysis module processes the satellite signal strength SI and carrier phase φ information output by the hardware, and performs data display through the system display module. Beneficial effects: this embodiment adopts an internal crystal oscillator source, which has stable frequency and low phase noise, and has strong anti-interference ability. The computer directly outputs the signal strength SI and carrier phase φ information of the satellite signal, which can be used to calculate the scintillation of the ionosphere, which is more convenient, simple, stable and reliable than the original equipment.

Owner:JIANGSU PROVINCE SURVEYING & MAPPING ENG INST +1

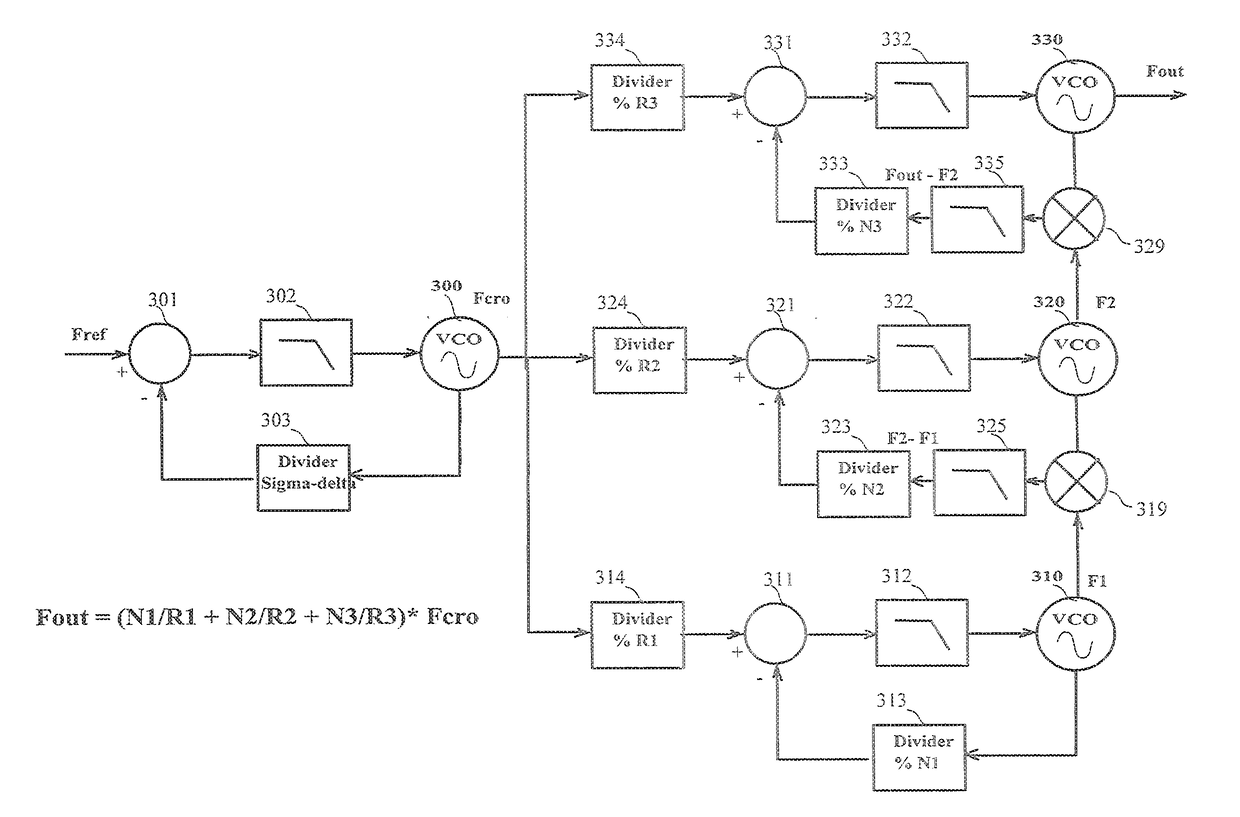

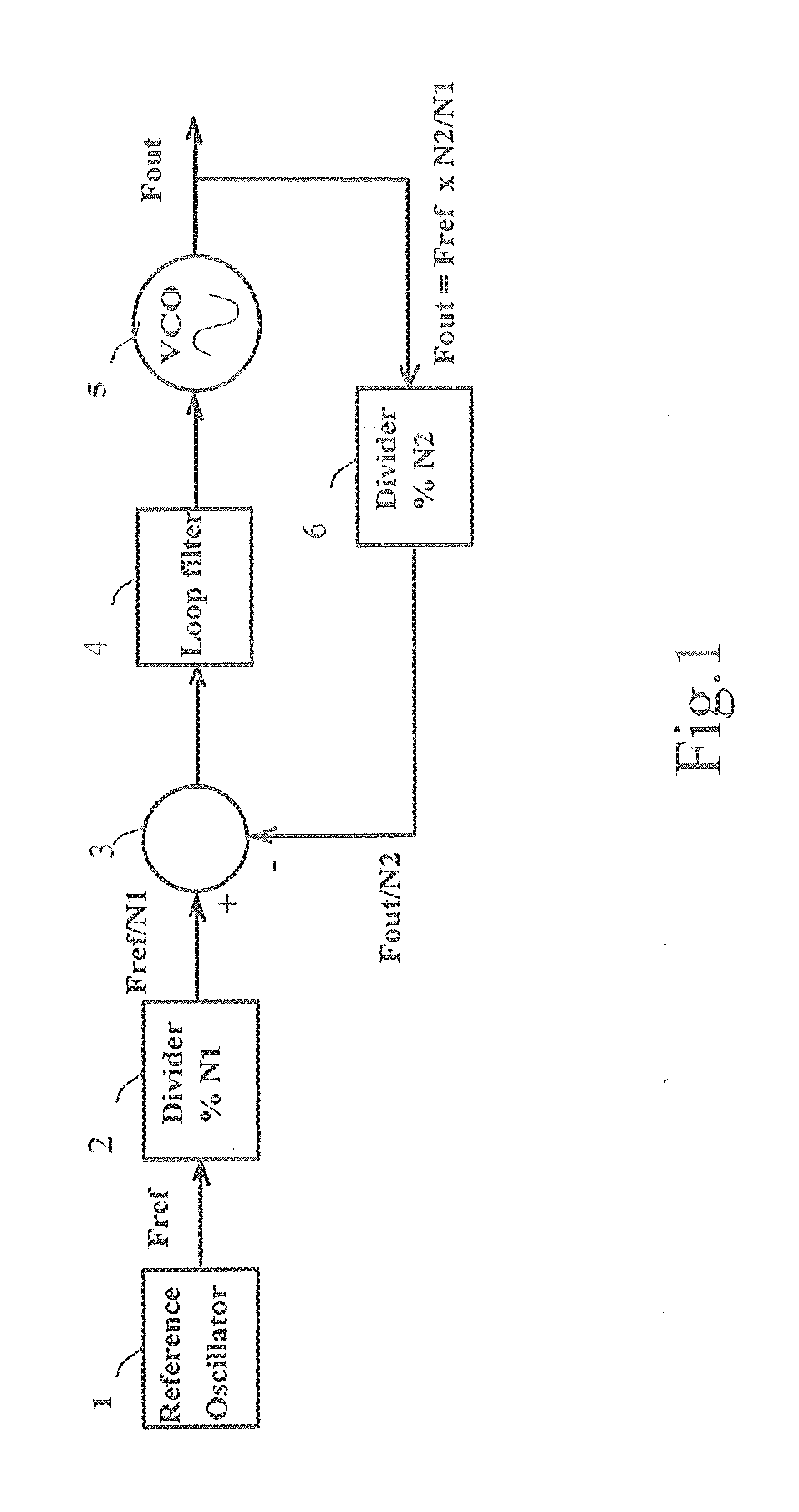

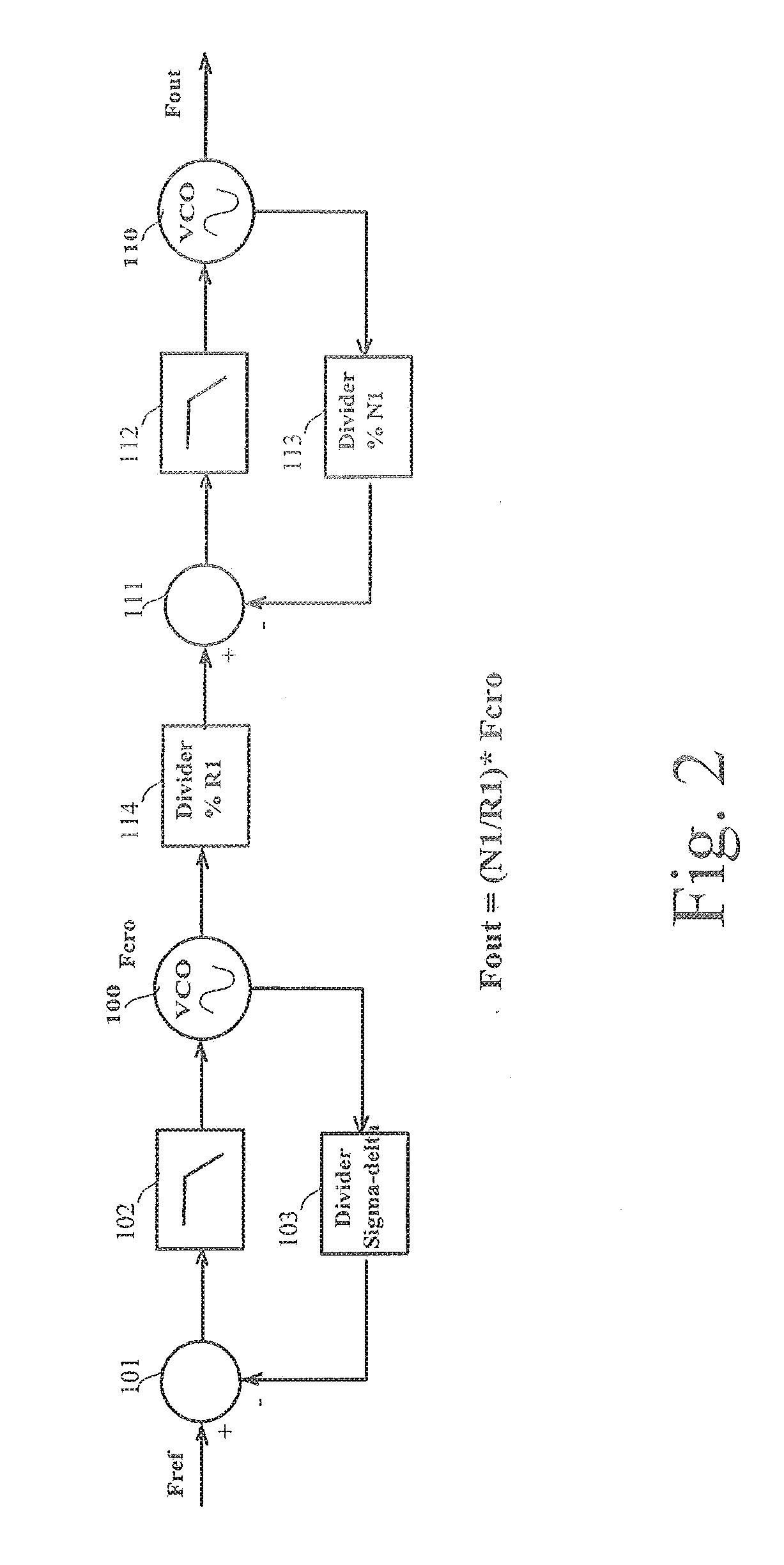

Multi-loop pll structure for generating an accurate and stable frequency over a wide range of frequencies

InactiveUS20170201262A1Low phase noiseImprove accuracyPulse automatic controlPhase detectorFrequency mixer

A multiloop PLL circuit comprising:a first PLL loop comprising a first VCO, a first phase detector having a first input receiving a reference frequency (Fref) and a second input receiving the output of a first programmable divider, which input receives the signal generated by the first VCO and a first loop filter connected between said first phase detector and said first VCO;at least one auxiliary PLL loop comprising a second VCO, a second phase detector, a second (R1) and a third (N1) programmable dividers, and a second loop filtera main loop for generating a desired output frequency Fout comprising a third VCO, a third phase detector, a fourth (Rn) and a fifth (Nn) programmable divider, a main loop filter and a mixeradditional possible auxiliary PLL loop each comprising a forth VCO, a forth phase detector, a sixth (Ri) and a seventh (Ni) programmable divider, a third auxiliary loop filter and a mixerwhereby the desired output frequency Fout is generated in accordance with the relation:Fout=(N1 / R1+ . . . +Nn / Rn)*Fcro where N1 and R1 are the dividing values of the first auxiliary loop and Ni and Ri with i=2 . . . n−1 being the dividing ratios of any possible further auxiliary loop; and Fcro is the frequency generated by VCO,whereby the multiloop circuit is configured with dividing values which optimizes a cost function F.

Owner:SDRF EURL

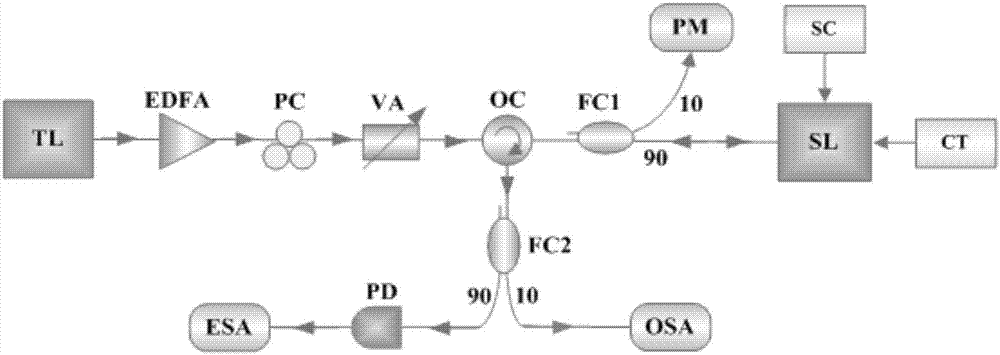

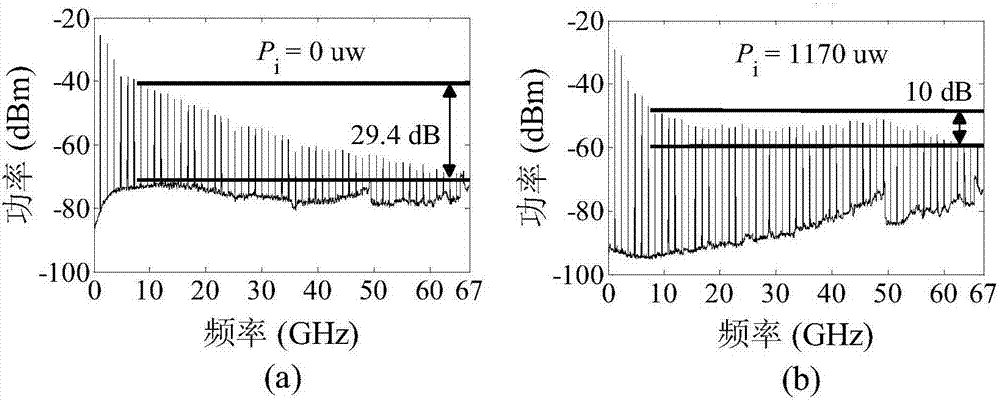

Method for generating tunable ultra-wideband microwave frequency comb based on semiconductor laser

InactiveCN106981814AOvercoming Bandwidth LimitationsFrequency stabilitySolid masersUltra-widebandContinuous light

The invention discloses a method for generating a tunable ultra-wideband (UWB) microwave frequency comb based on a semiconductor laser. The method comprises steps of: using a semiconductor laser to produce the tunable UWB microwave frequency comb, wherein the temperature and the current of the semiconductor laser are controlled by a current temperature control source; using an external signal source to modulate the driving current of the semiconductor laser, causing the semiconductor laser to output a seed source of the microwave frequency comb by adjusting the modulation frequency fm and the modulation power Pm of an signal source output signal; injecting continuous light output by an adjustable laser source into the current-modulated semiconductor laser, using a bandwidth enhancement effect caused by light injection to cause the semiconductor laser (SL) to produce the high-quality tunable UWB microwave frequency comb. The method can produce the microwave frequency combs with a continuously variable comb distance from 0.5GHz to 10GHz. The high-quality microwave frequency comb obtained in two adjustable comb distance ranges from 1.1GHz to 1.2GHz and from 3.3GHz to 8.0GHz can achieve a bandwidth up to 59GHz (within 10dB flatness amplitude).

Owner:SOUTHWEST UNIV

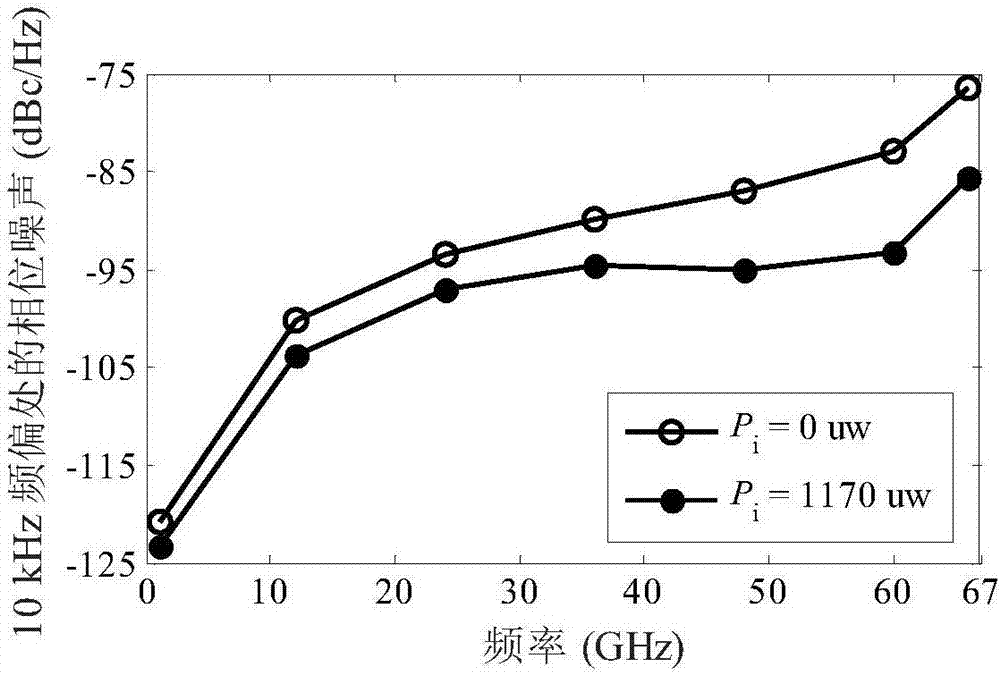

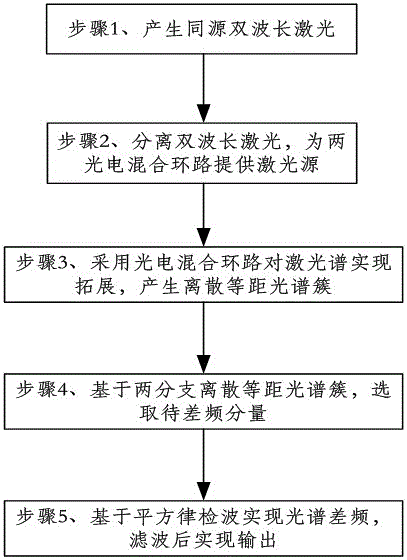

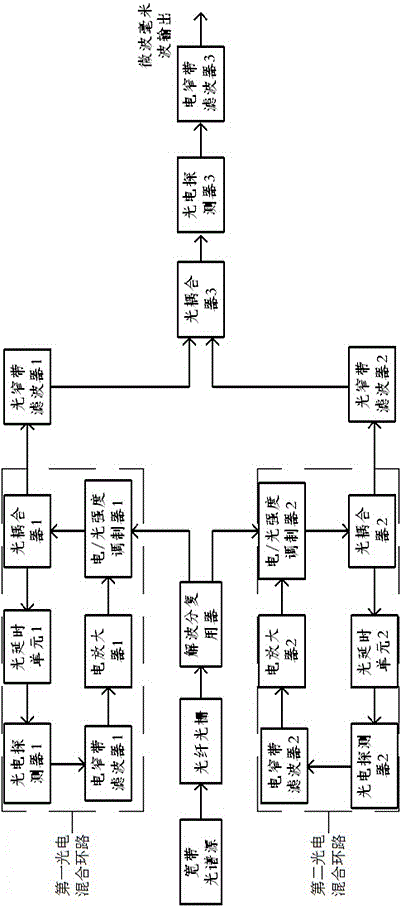

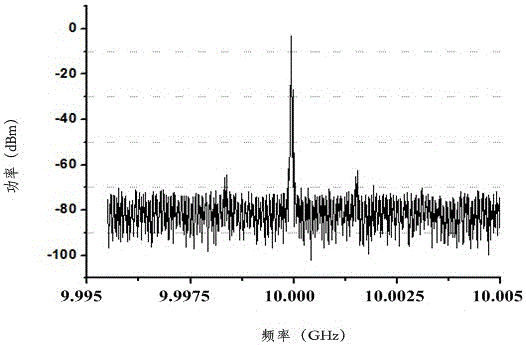

Method and device for generating high-stability microwave millimeter wave source

The invention provides a method and a device for generating a high-stability microwave millimeter wave source and relates to the technical field of photoelectron and microwave millimeter wave. The method is mainly based on the conception as follows: adopting a fiber bragg grating to perform spectrum cutting on a broadband spectrum source signal, thereby acquiring homologous dual-wavelength laser; adopting a photoelectric hybrid loop is respectively used for performing frequency spectrum expansion on two laser signals, thereby realizing dispersing equidistant spectrum cluster taking an optical carrier wave as a center; lastly, selecting a target dispersing equidistant spectrum cluster for performing square-law detection, performing narrow-band filtering after the beat frequency treatment, thereby realizing the output of a low-phase noise microwave millimeter single-frequency point signal. The microwave millimeter wave source generated by the method and the device has the advantages of (1) low phase noise and (2) full-band adjustability.

Owner:HUNAN INST OF TECH

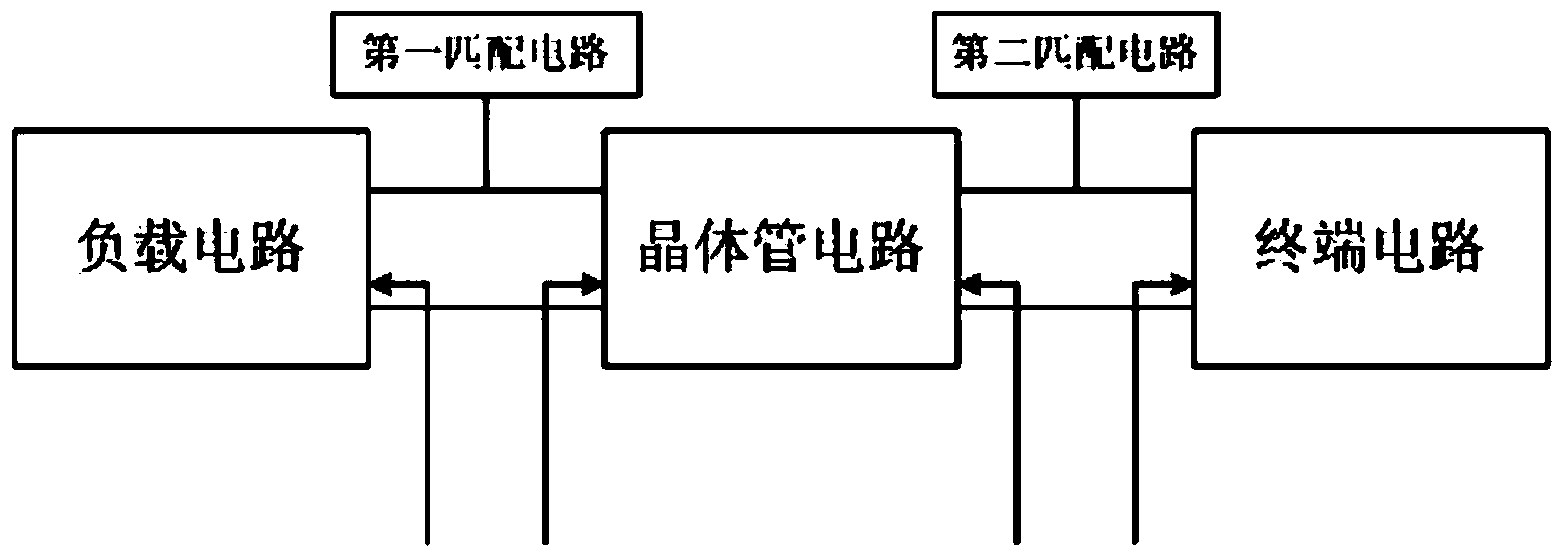

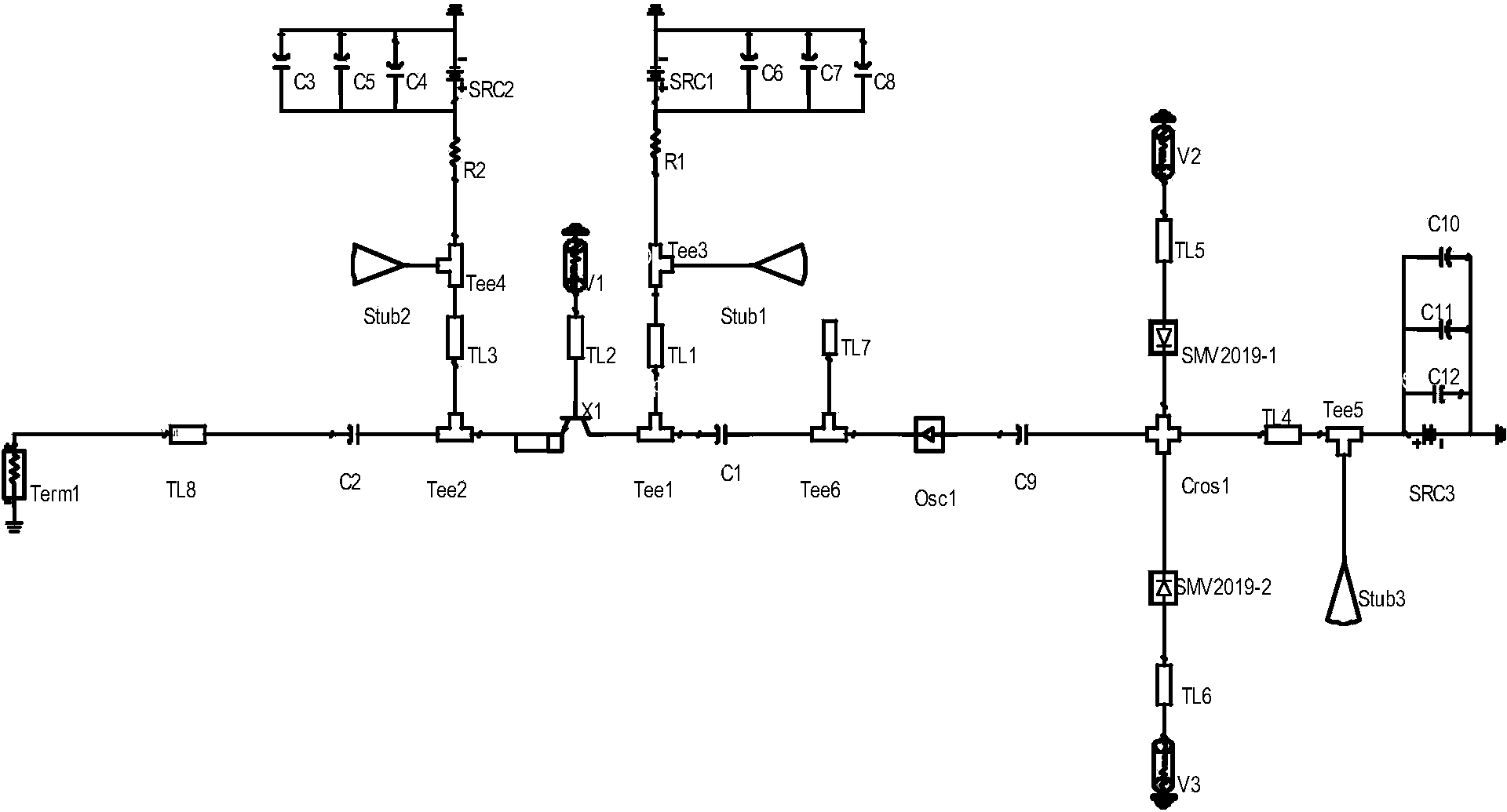

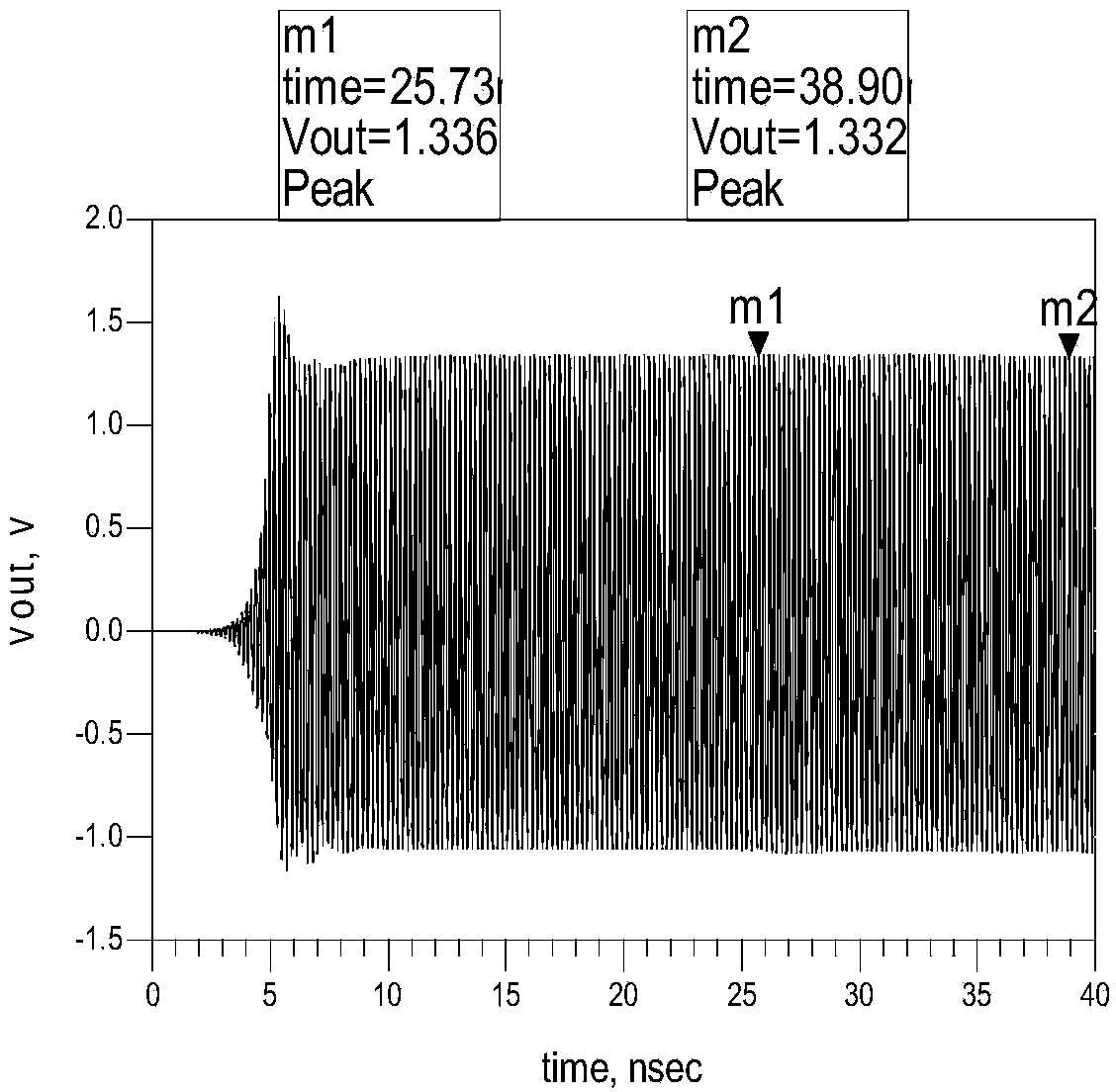

C wave band voltage-controlled oscillator

The invention discloses a C wave band voltage-controlled oscillator. The C wave band voltage-controlled oscillator comprises a load circuit for changing the resonant frequency, a transistor circuit for enabling the whole circuit to oscillate, a terminal circuit for meeting the oscillation condition, a first match circuit and a second match circuit. The load circuit is connected with the transistor circuit through the first match circuit, and the transistor circuit is connected with the terminal circuit through the second match circuit. According to the voltage-controlled oscillator with the center frequency being any frequency point in a C wave band, the circuit is simple in structural design, cost is low, the requirement for the machining precision is not high, high cost performance is achieved, and the C wave band voltage-controlled oscillator has the advantages of being low in phase noise, wide in tuning range, good in linearity, high in output power, stable in in-band power and the like.

Owner:江苏晶曌半导体有限公司

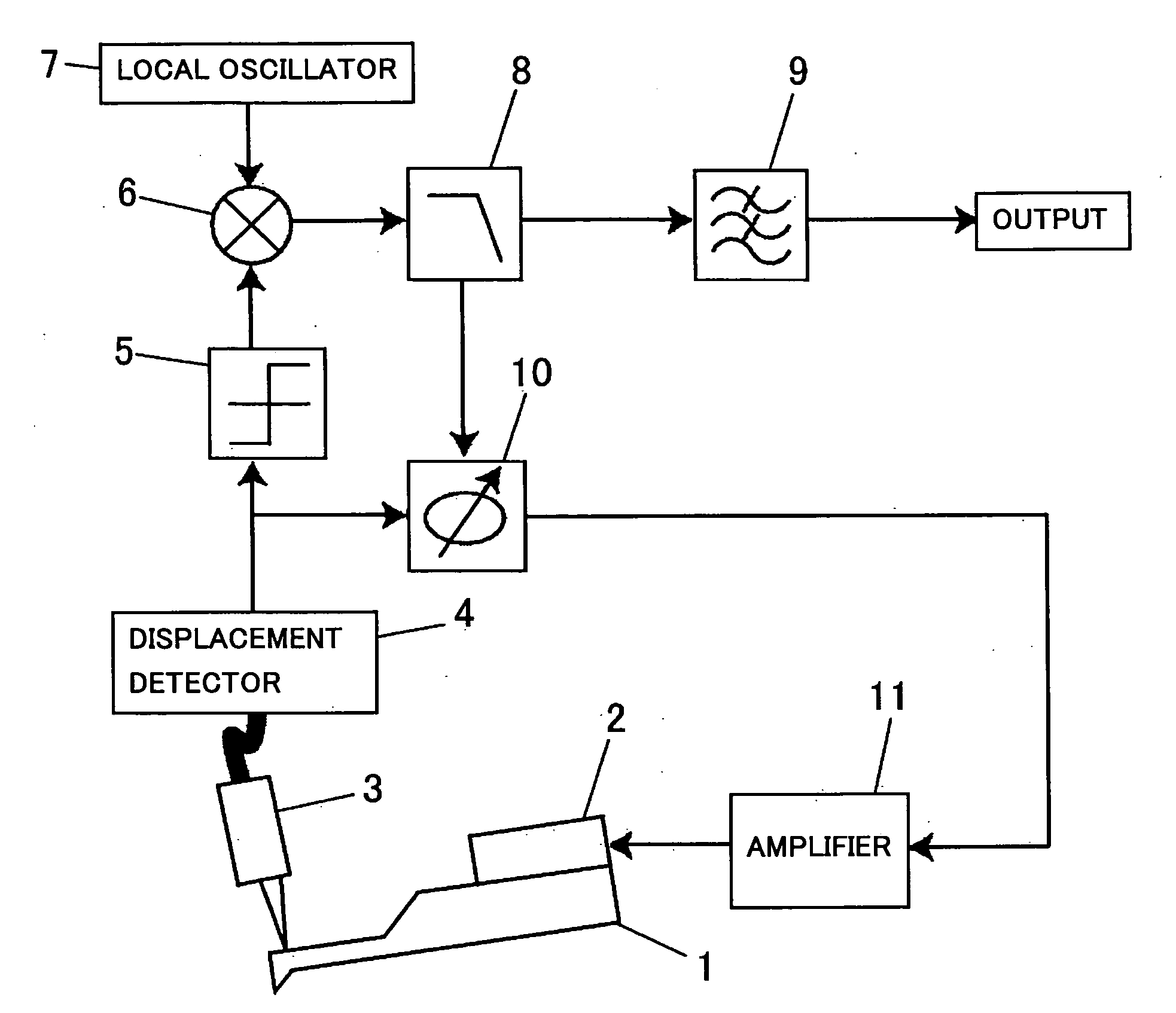

Highly Sensitive Force/Mass Detection Method and Device Using Phase Synchronization Circuit

InactiveUS20080252385A1Low phase noiseHigh purityVibration measurement in solidsForce measurement by measuring frquency variationsPhysicsHighly sensitive

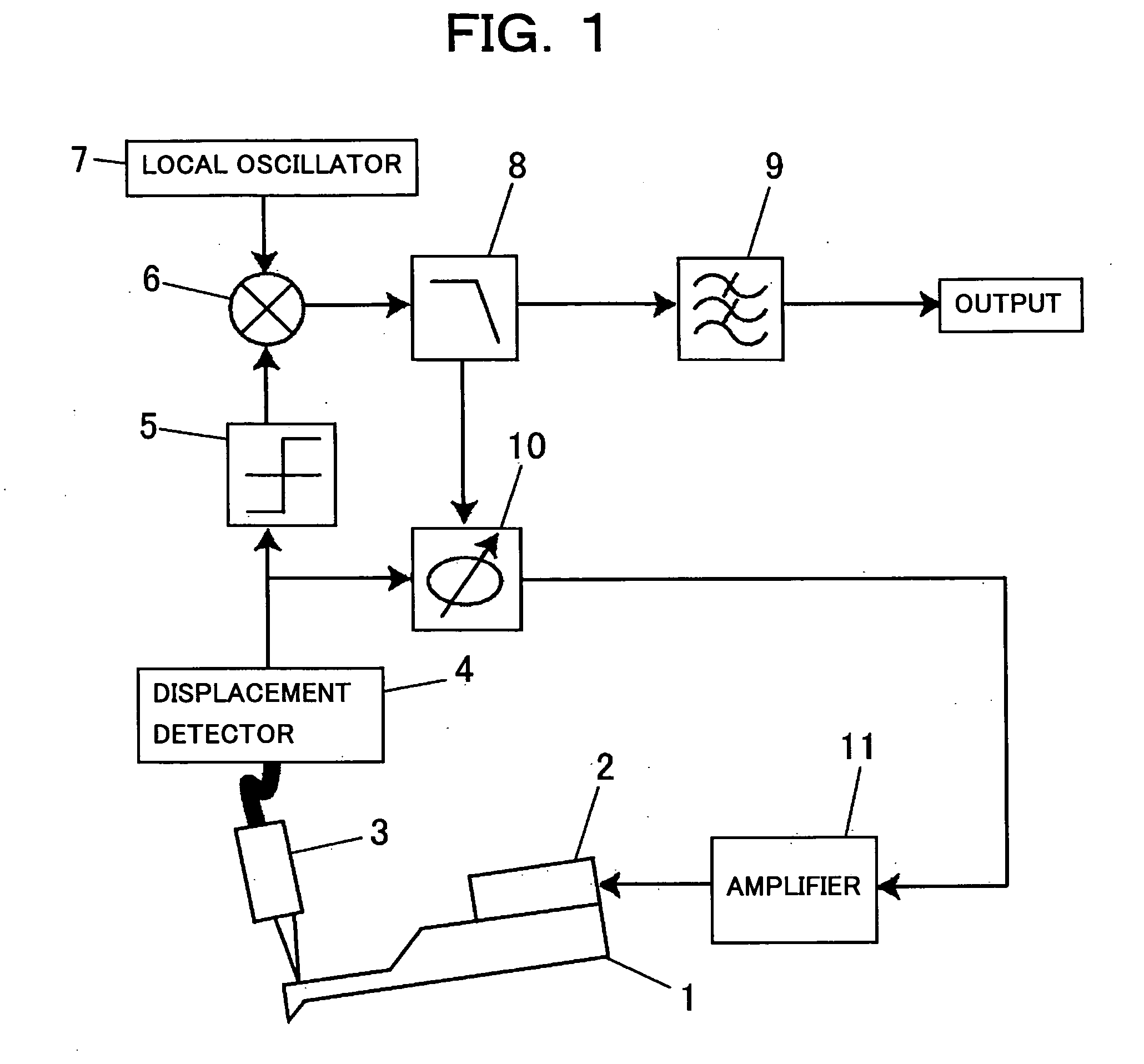

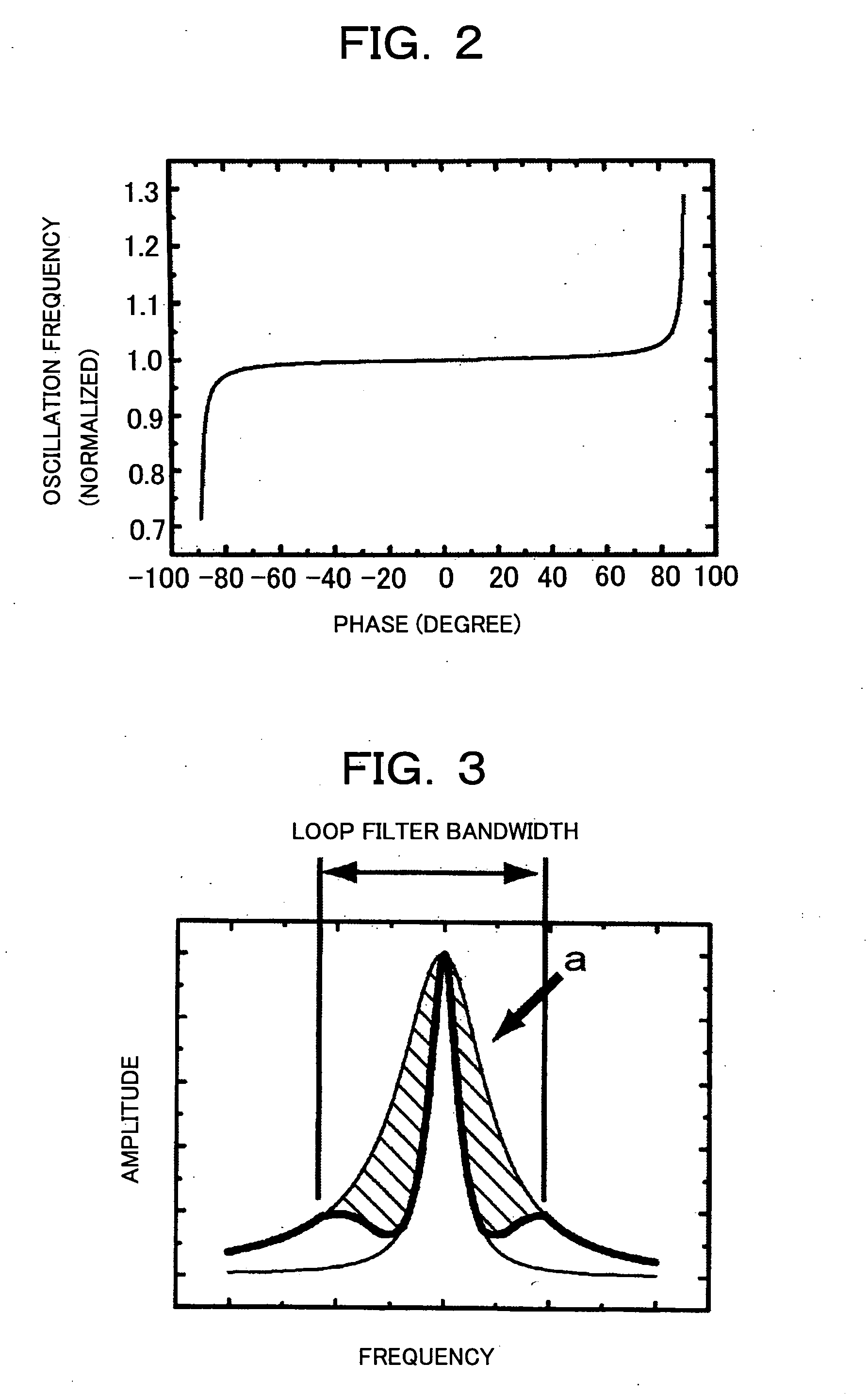

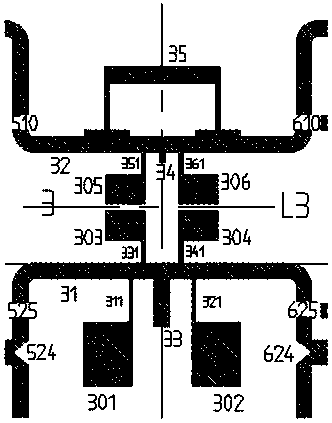

There are provided a highly sensitive force / mass detection method and device using a phase-locked loop, in which a phase noise of the mechanical element can be reduced using the phase-locked loop, by synchronizing a vibration signal of a mechanical element to an oscillation signal from a local oscillator which has a low phase noise and a high purity property. In the highly sensitive force / mass detection device using the phase-locked loop, an oscillation circuit of a mechanical vibrator 1 including a phase adjuster 10, a binarization circuit 5 for detecting a phase of an oscillation signal of the oscillation circuit, a local oscillator 7 having a low phase noise and a high purity property, a phase comparator 6 for comparing the phase of the oscillation signal of the mechanical vibrator 1 with a phase of an oscillation signal from the local oscillator 7, and a loop filter 8 connected to the phase comparator 7, are provided. An output of the phase comparator 6 is fed back to the phase adjuster 10 through the loop filter 8, and a phase noise of the mechanical vibrator 1 is reduced.

Owner:JAPAN SCI & TECH CORP

Push-push type oscillator based on microstrip differential band-pass filter

ActiveCN110380688ALow phase noiseGood frequency selectivityOscillations generatorsCoupling devicesPhysicsDielectric substrate

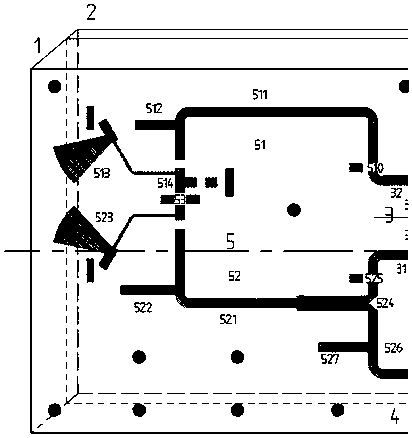

The invention discloses a push-push type oscillator based on a microstrip differential band-pass filter. The push-push type oscillator comprises a rectangular dielectric substrate (1), a metal grounding layer (2) attached to the lower surface of the dielectric substrate (1), a differential filter (3) arranged on the upper surface of the dielectric substrate (1), a power combiner (4), a first amplifier input and output matching circuit (5) and a second amplifier input and output matching circuit (6). And the power combiner (4) is connected with the differential filter (3) through the first andsecond amplifier input and output matching circuits (5, 6). The push-push type oscillator based on microstrip differential band-pass filter is low in phase noise, high in fundamental wave suppressionlevel, high in quality factor and good in selectivity.

Owner:NANJING UNIV OF SCI & TECH

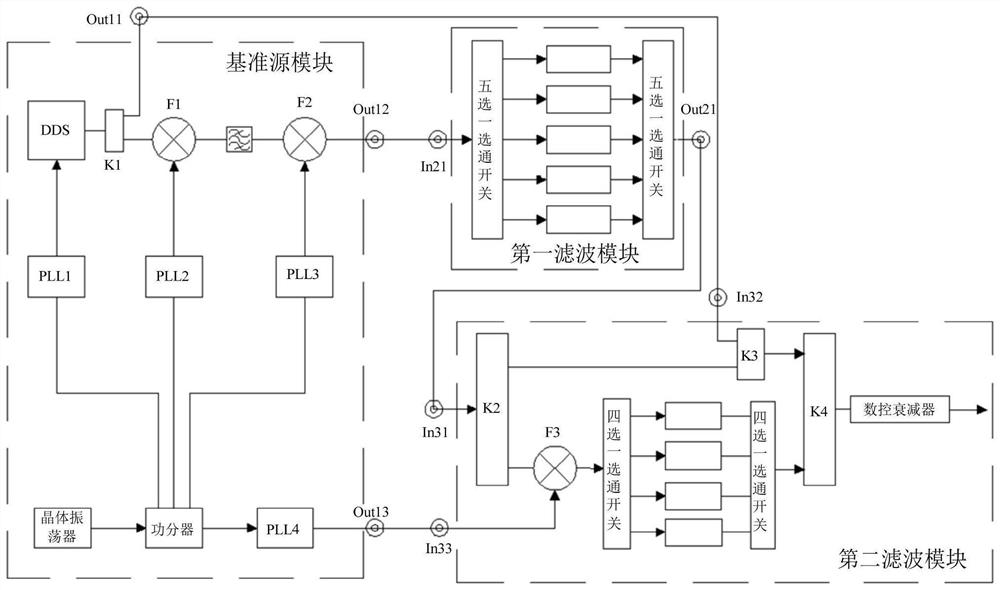

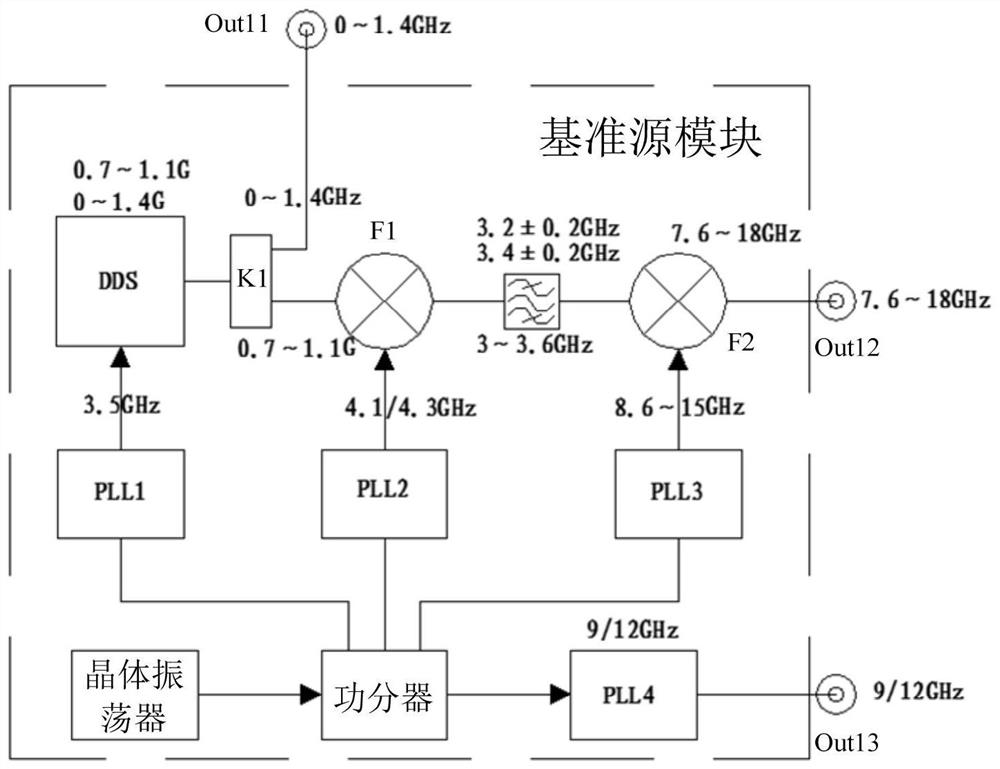

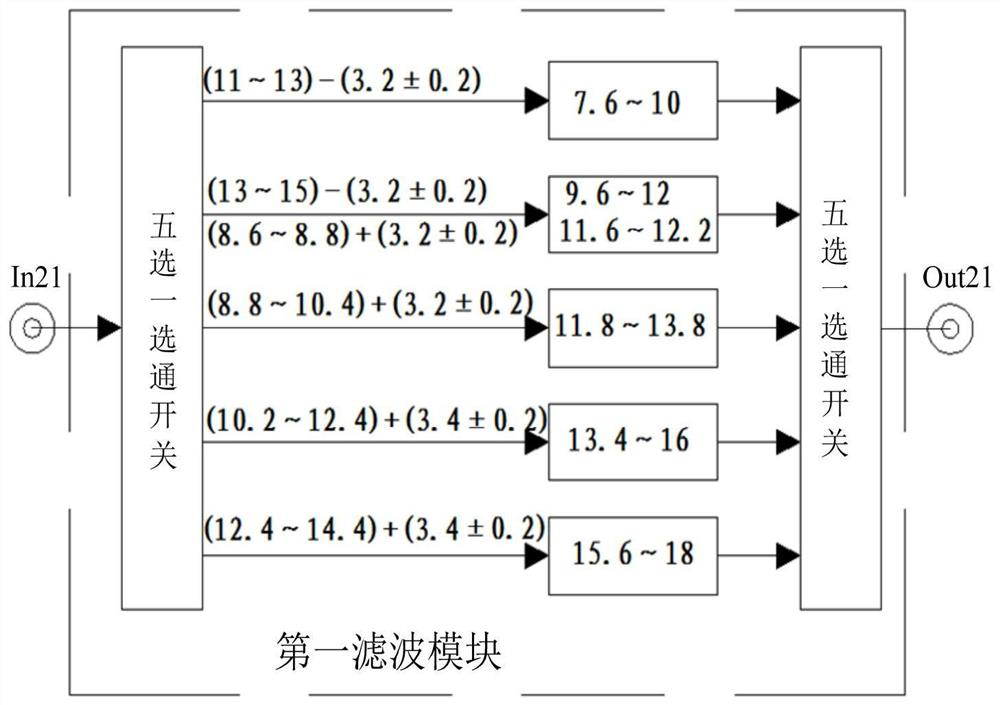

0-18GHz ultra wide band frequency sweep source

ActiveCN111740720ASmall sizeMeet performance indicatorsWave based measurement systemsImpedence networksUltra-widebandLow noise

The invention discloses a 0-18 GHz ultra wide band frequency sweep source and relates to the technical field of microwave. The 0-18 GHz ultra wide band frequency sweep source comprises a reference source module, a first filtering module and a second filtering module, wherein the reference source module generates any point frequency or linear frequency modulation signal of 0-1.4 GHz by using a high-speed DDS technology, and uses an ultra-wideband low-noise PLL technology integrated with a VCO generating a 8.6-15GHz ultra-wideband frequency hopping high local oscillation signal with low phase noise and low stray and other y point frequency local oscillation and excitation signals. Compared with a direct synthesis technology, the frequency sweep source has the advantages that the size can beeffectively reduced, through careful design of a frequency conversion scheme and application of two filtering modules to a broadband switch filtering technology, the frequency sweep source can achieveultra wide band through a simplified structure, and the size requirement is met while the performance index is met.

Owner:WUXI HUACE ELECTRONICS SYST

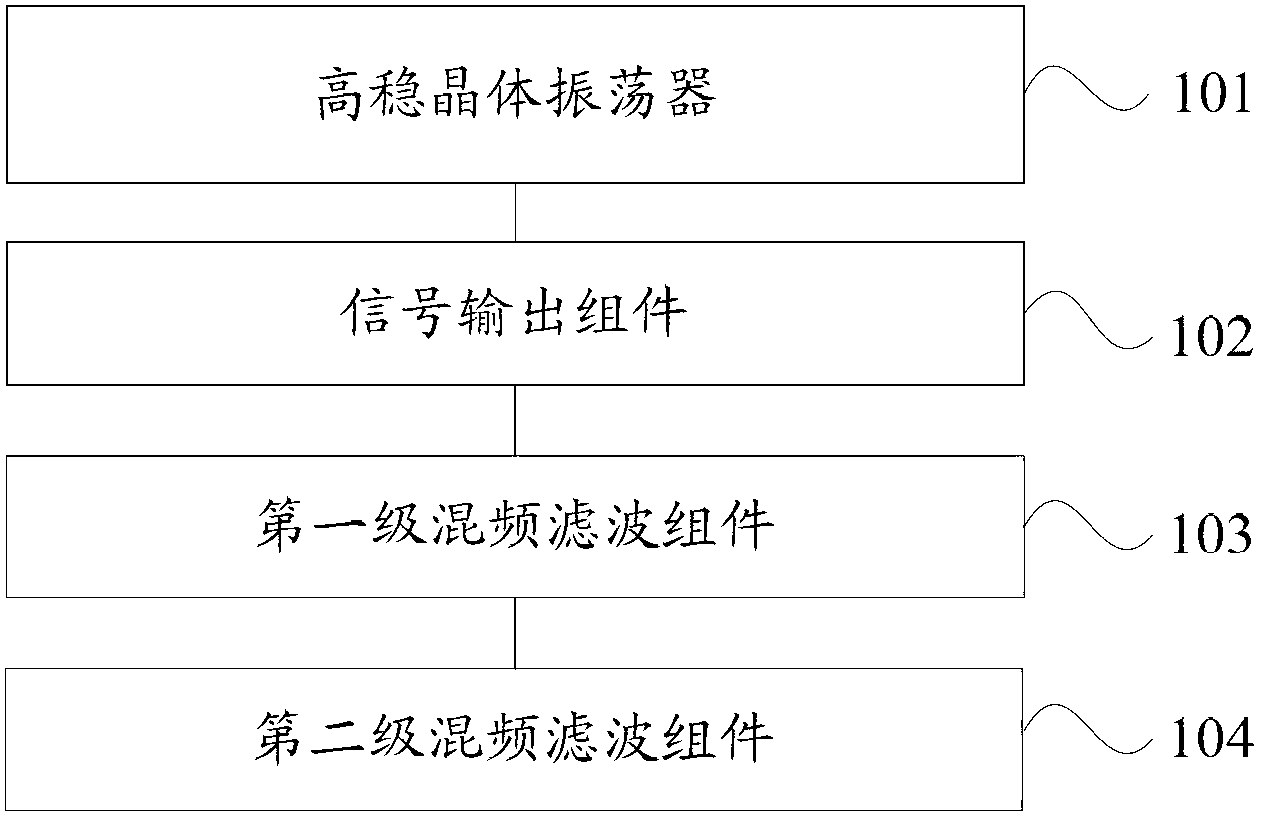

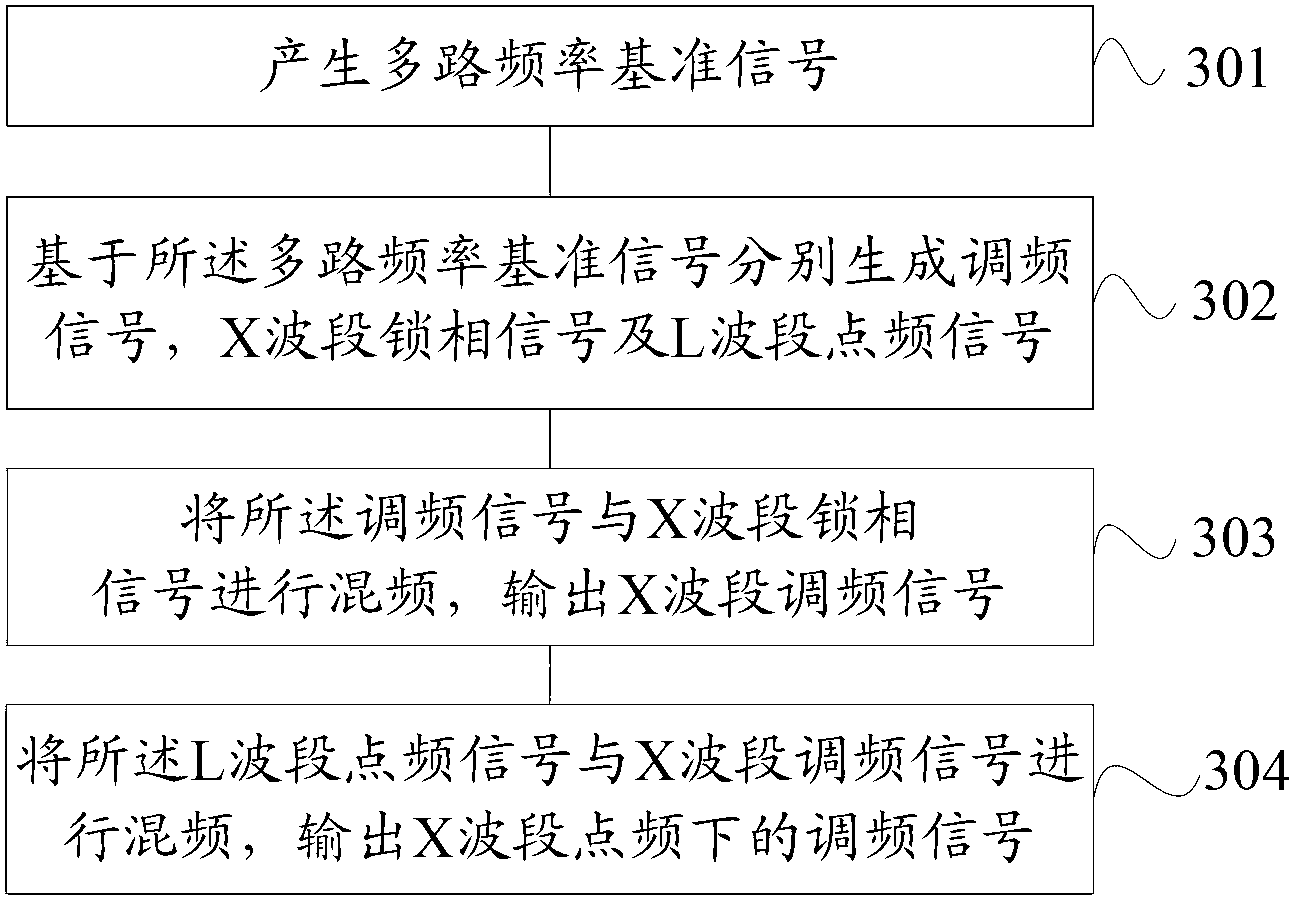

Microwave signal source and method for producing microwave signal

The invention provides a microwave signal source and a method for producing a microwave signal. The microwave signal source comprises a highly-stable crystal oscillator, a signal output assembly, a first-stage mixing smoothing assembly and a second-stage mixing smoothing assembly, wherein the highly-stable crystal oscillator is used for producing multiple ways of frequency reference signals, the signal output assembly used for producing a frequency modulated signal, an X-band lock phase signal and an L-band dot frequency signal respectively based on the multiple ways of frequency reference signals, the first-stage mixing smoothing assembly used for mixing the frequency modulated signal with the X-band lock phase signal and outputting an X-band frequency modulated signal, and the second-stage mixing smoothing assembly used for mixing the L-band dot frequency signal with the X-band frequency modulated signal and outputting an X-band dot frequency modulated signal. According to the microwave signal source and the method for producing the microwave signal, the requirements of fixation of frequency offset of frequency modulation deviation under multipledot frequency and low phase noise can be met in production practice.

Owner:中国人民解放军95989部队

A X-band ultra-high-speed frequency hopping source

ActiveCN106342404BGood harmonic spuriousOutput frequency band adjustablePulse automatic controlPhysicsWave band

The invention belongs to microwave technology and relates to an X-band ultra-high-speed frequency hopping source. The X-band ultra-high-speed frequency hopping source of the present invention includes a DDS module, a local oscillator phase-locked loop and a frequency-mixing frequency multiplication chain. Wherein, the DDS module is composed of a DDS and a frequency reference phase-locked loop, and the frequency mixing and multiplication chain includes a first band-pass filter, a first frequency multiplier, a second band-pass filter, a mixer, The third bandpass filter, the second frequency multiplier and the fourth bandpass filter, the frequency reference phase-locked loop is connected with the DDS to form a DDS module, and the DDS module is connected to the first bandpass of the frequency mixing and multiplication link After passing through the first frequency multiplier and the second band-pass filter in sequence, the filter is connected with the mixer. The local oscillator phase-locked loop is also connected to a mixer connected to a third bandpass filter, a second frequency multiplier and a fourth bandpass filter connected in sequence. The invention can realize nanosecond-level frequency hopping, good harmonic spuriousness, low phase noise, and adjustable X-band output frequency range.

Owner:CHINA AIR TO AIR MISSILE INST

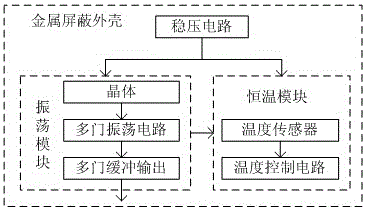

Multi-gate oscillation low-phase-noise constant-temperature crystal oscillator

InactiveCN106533363AReduce volumeReduce phase noiseOscillations generatorsTemperature controlLow noise

The invention discloses a multi-gate oscillation low-phase-noise constant-temperature crystal oscillator. The crystal oscillator comprises a metal shielding housing, an oscillation module arranged in the metal shielding housing, a constant-temperature module and a voltage stabilizing circuit used for providing a stable working power supply for the whole circuit, wherein the voltage stabilizing circuit is respectively connected to the oscillation module and the constant-temperature module; the oscillation module comprises a crystal for generating a stable low-noise oscillation signal, a multi-gate oscillation circuit and a multi-gate buffer output circuit used for realizing signal buffer and amplification output of the multi-gate oscillation circuit; the crystal, the multi-gate oscillation circuit and the multi-gate buffer output circuit are connected in sequence; the constant-temperature module used for providing constant temperature for the whole circuit comprises a temperature sensor and a temperature control circuit connected to the temperature sensor, and the temperature sensor is arranged on the crystal. The crystal oscillator has small volume, reliable circuit, simple debugging and good consistency and is suitable for mass production.