Method for generating stepped frequency signals based on combination of direct digital synthesis (DDS) and ping-pong phase locked loop

A signal generation and phase-locked loop technology, applied in the field of radar, can solve the problems of frequency hopping time, minimum step phase noise, spurious level volume and cost constraints, and achieve good performance, large bandwidth and small step advanced effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

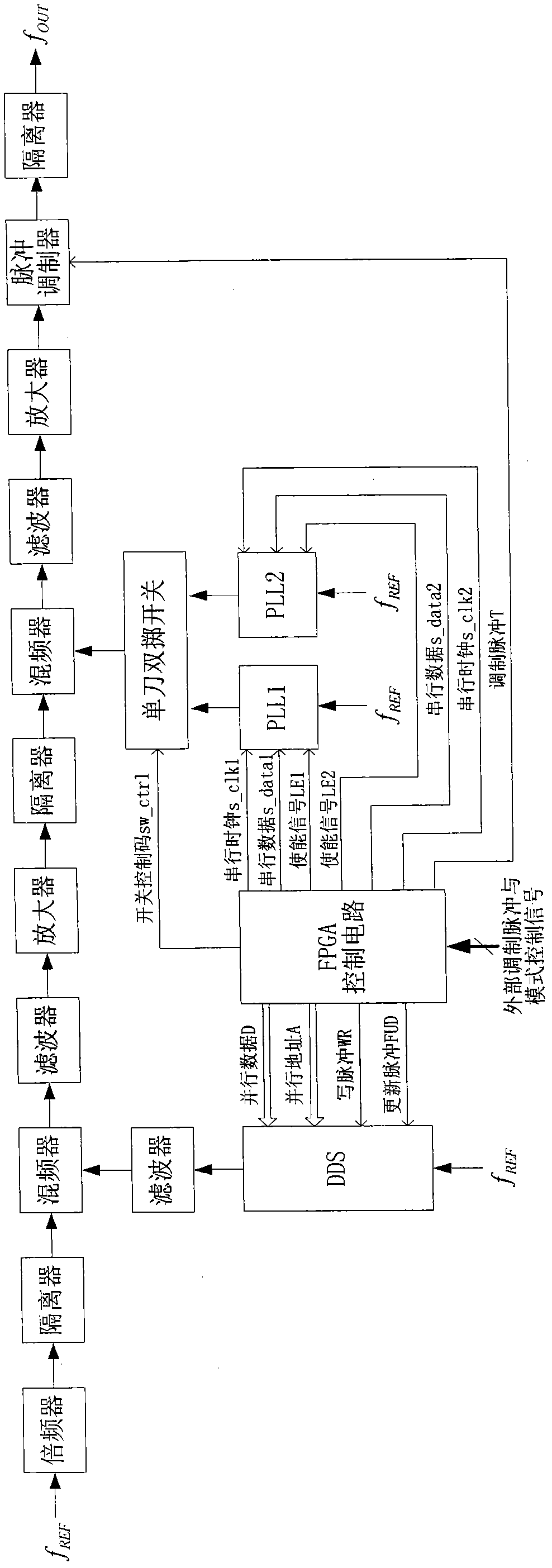

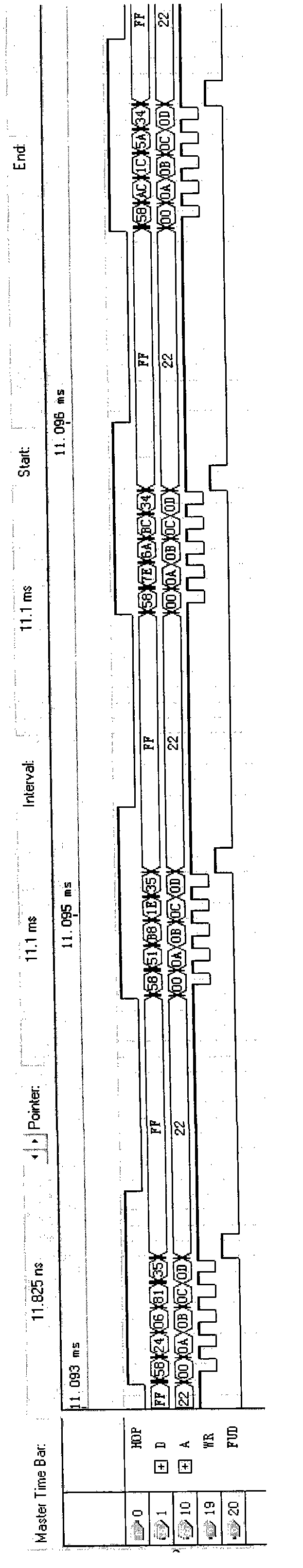

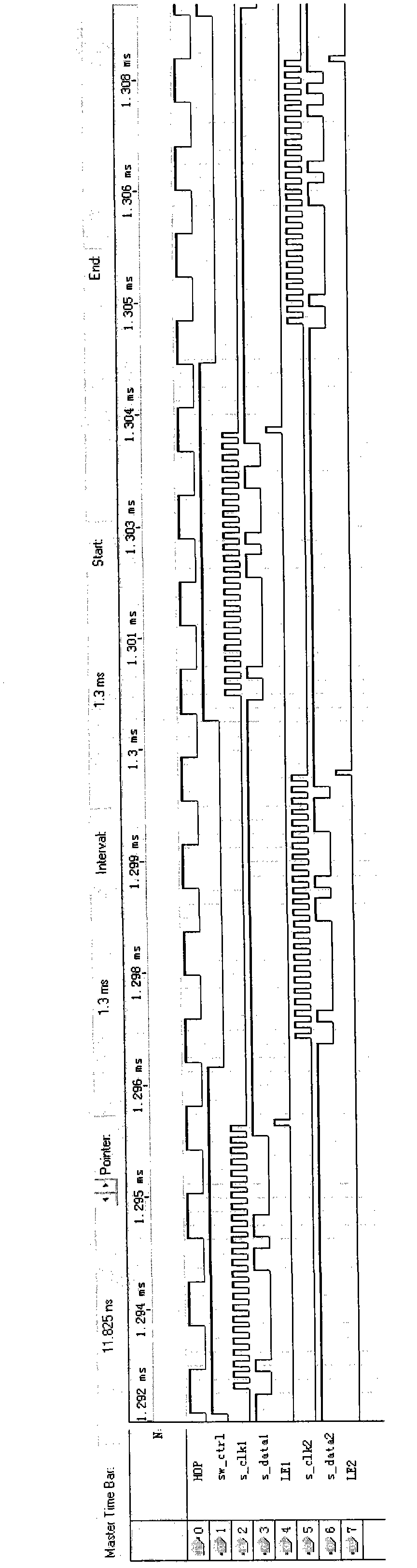

[0028] figure 1 A hardware realization block diagram of the preferred embodiment of the present invention is given. Two phase-locked loops (PLL1 and PLL2) working in the L-band and single-pole double-throw switches form a ping-pong phase-locked loop. The frequency step of the phase-locked loop is set to 6MHz, which is controlled by FPGA to generate a step It is a 6MHz L-band broadband signal; DDS generates P-band small step signals under the control of FPGA. Since DDS is mainly used to realize the small steps between 6MHz large steps of the ping-pong phase-locked loop, the work of DDS The bandwidth is set to 6MHz, realizes the seamless combination with the ping-pong phase-locked loop, and under the situation of not making any changes to the hardware circuit, only through software programming, the DDS can realize multiple different frequency steps at the same time (this embodiment We have achieved 2MHz, 1.5MHz, 1MHz, 0.75MHz, 0.5MHz and other steps at the same time), in additi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More