Patents

Literature

572 results about "Dual loop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Dual-loop is a method of electrical circuit termination used in electronic security applications, particularly modern intruder alarms. It is called 'dual-loop' because two circuits (alarm and anti-tamper) are combined into one using resistors. Its use became widespread in the early 21st century, replacing the basic closed-circuit system, mainly because of changes in international standards and practices.

Dual loop voltage regulation circuit of power supply chip

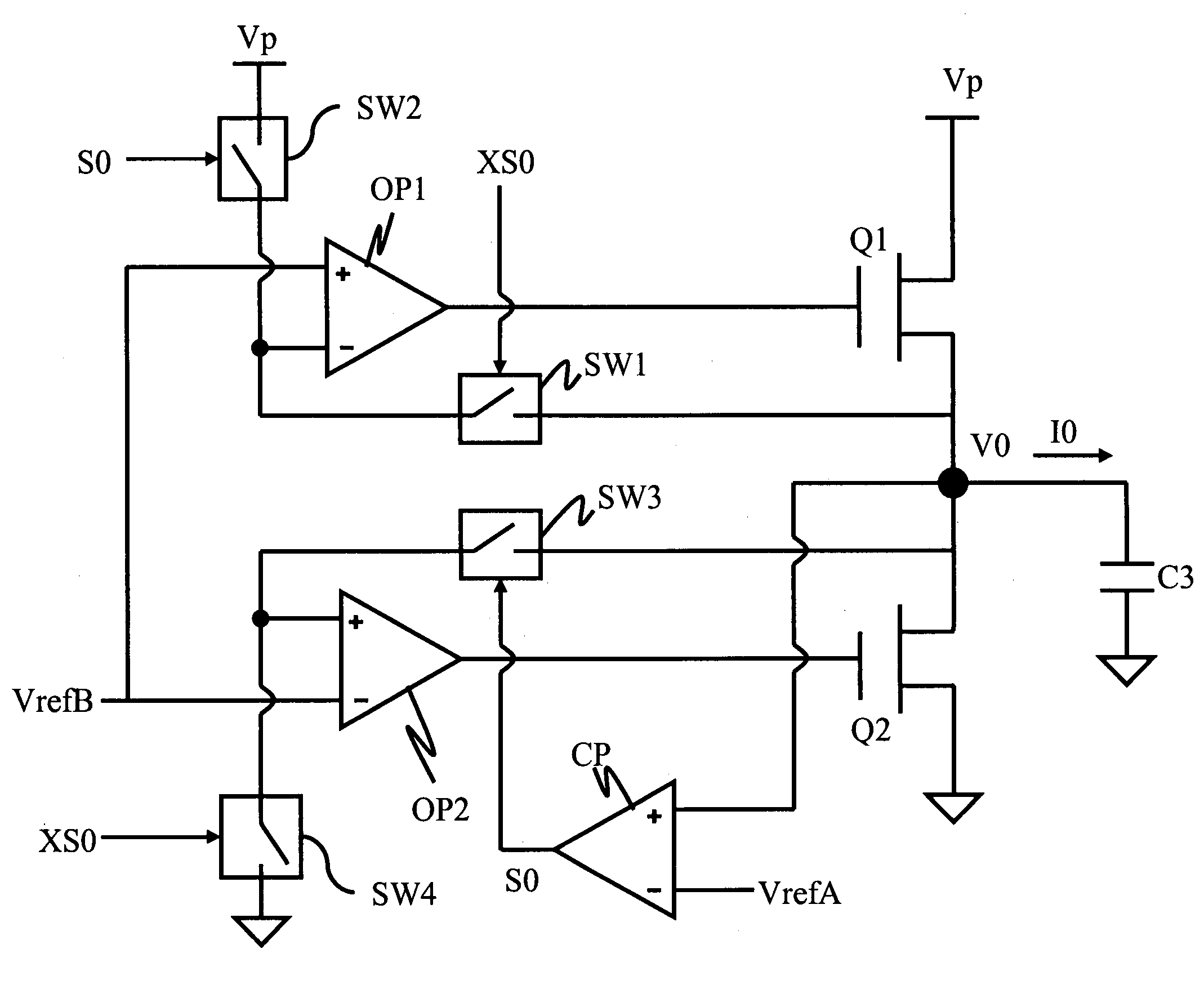

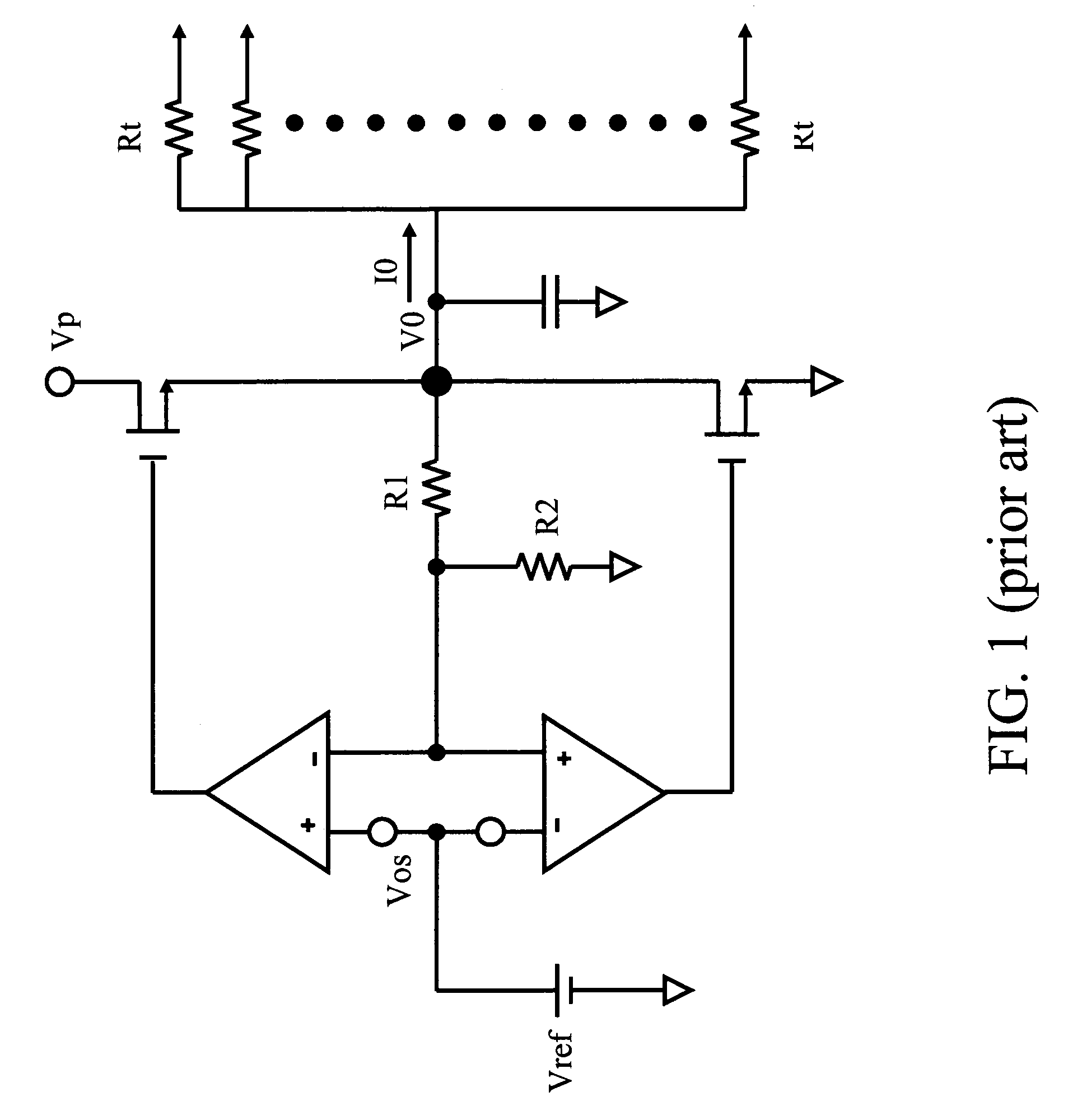

InactiveUS7193453B2Increase jitterShorten the timeTransistorElectronic switchingAudio power amplifierVoltage regulation

A dual loop voltage regulation circuit of power supply chip is provided, comprising a capacitor for providing a voltage signal, a comparator for comparing a first reference voltage signal and the voltage signal to output forward or backward trigger signal, a first switch triggered by a forward trigger signal, a second switch triggered by a backward trigger signal, a first operational amplifier generating a first drive signal while the first and second switches are on, a first transistor switch triggered to be on by a first drive signal to provide a current source loop, a third switch triggered by a forward trigger signal, a fourth switch triggered by a backward trigger signal, a second operational amplifier generating a second drive signal while the third and fourth switches are on, and a second transistor switch triggered to be on by a second drive signal to provide a current sink loop.

Owner:LEADTREND TECH

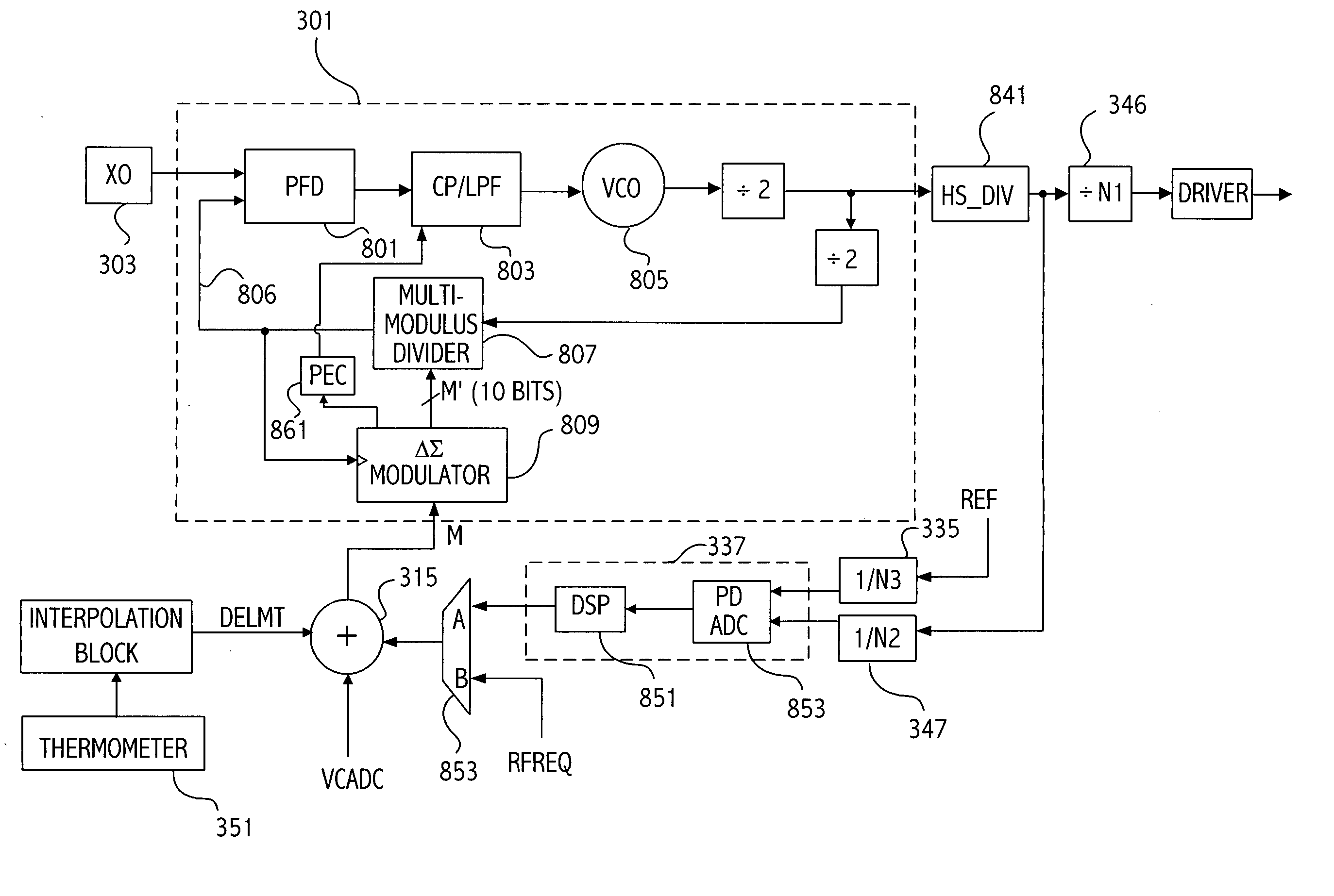

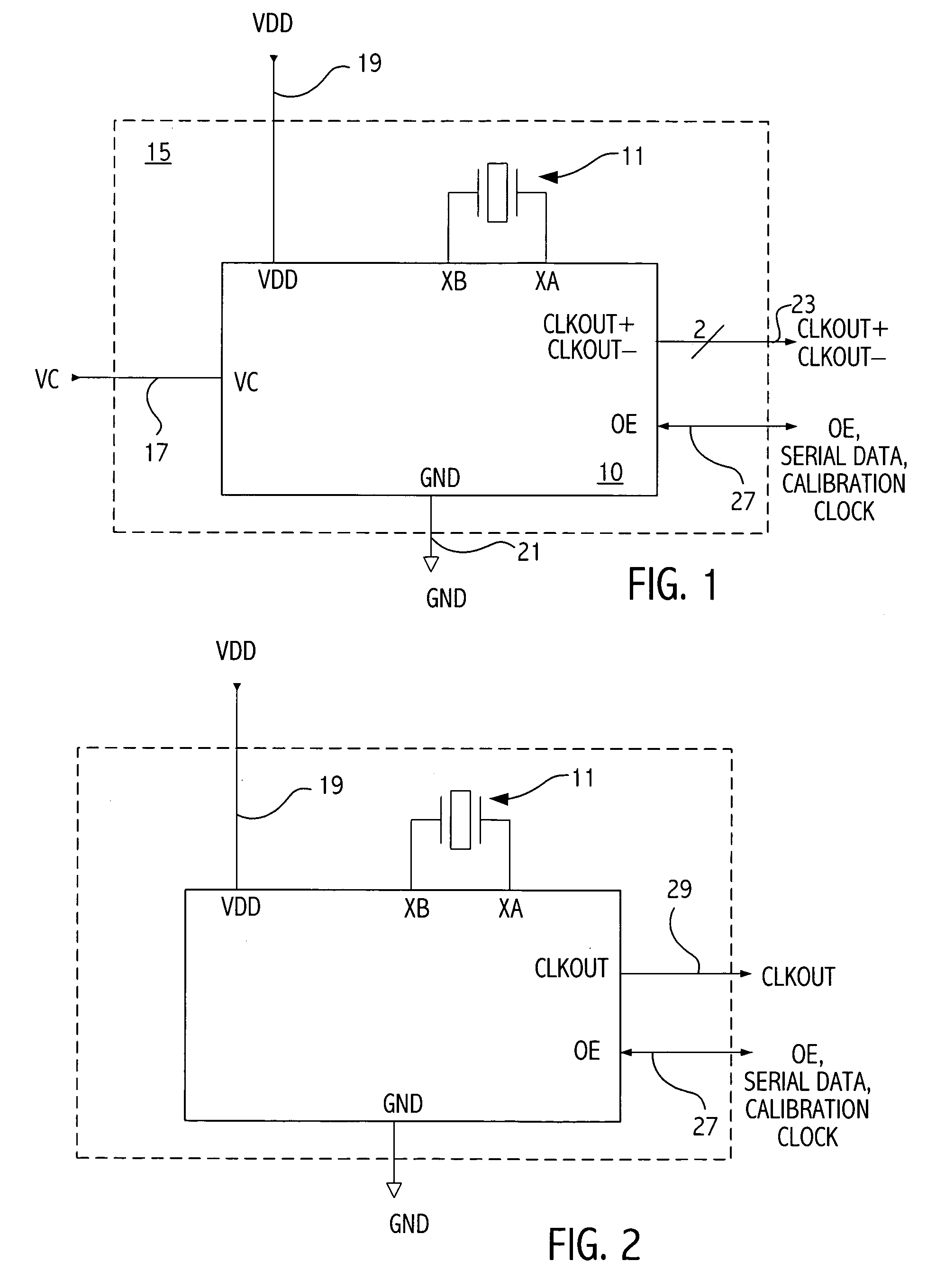

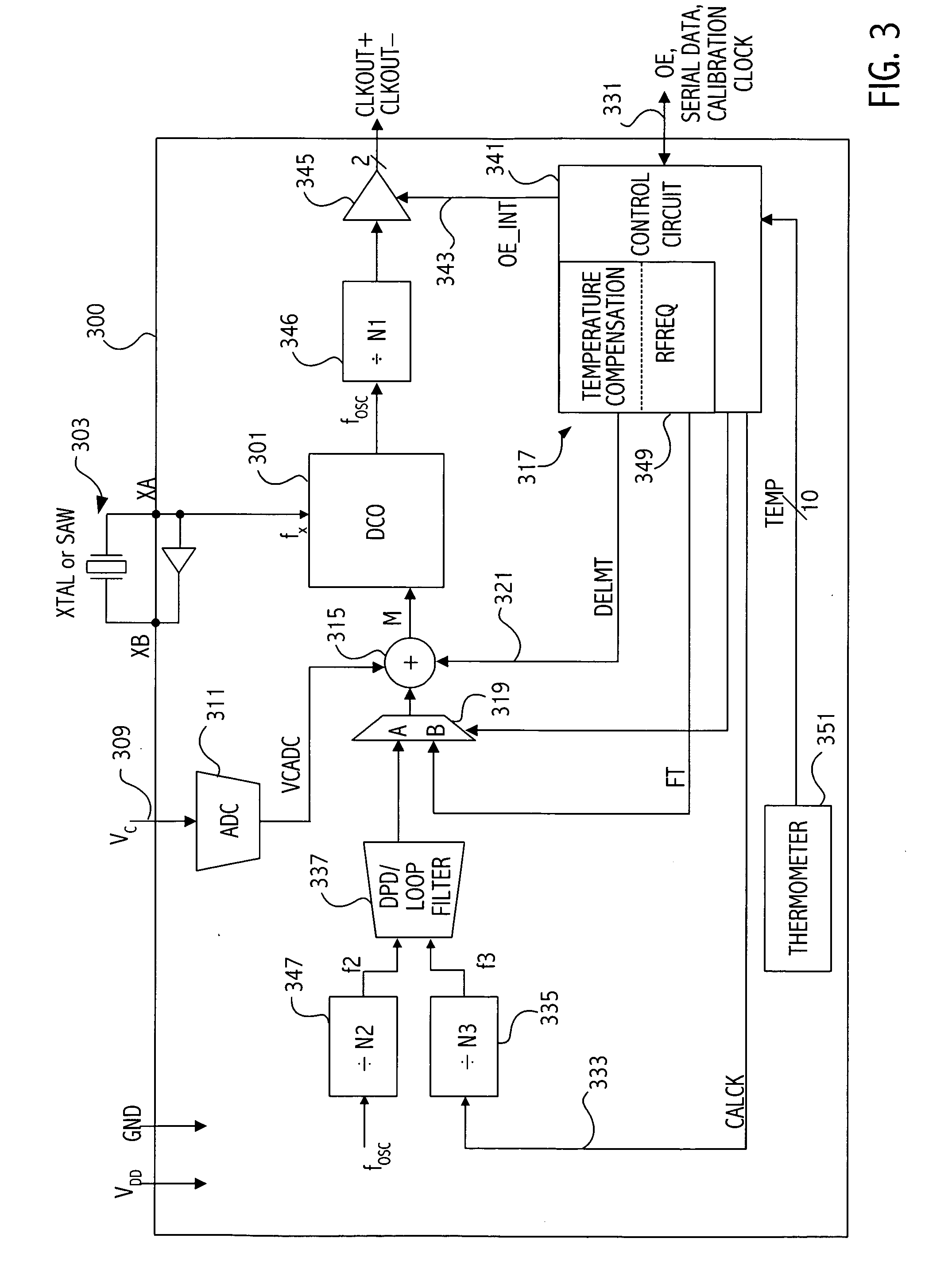

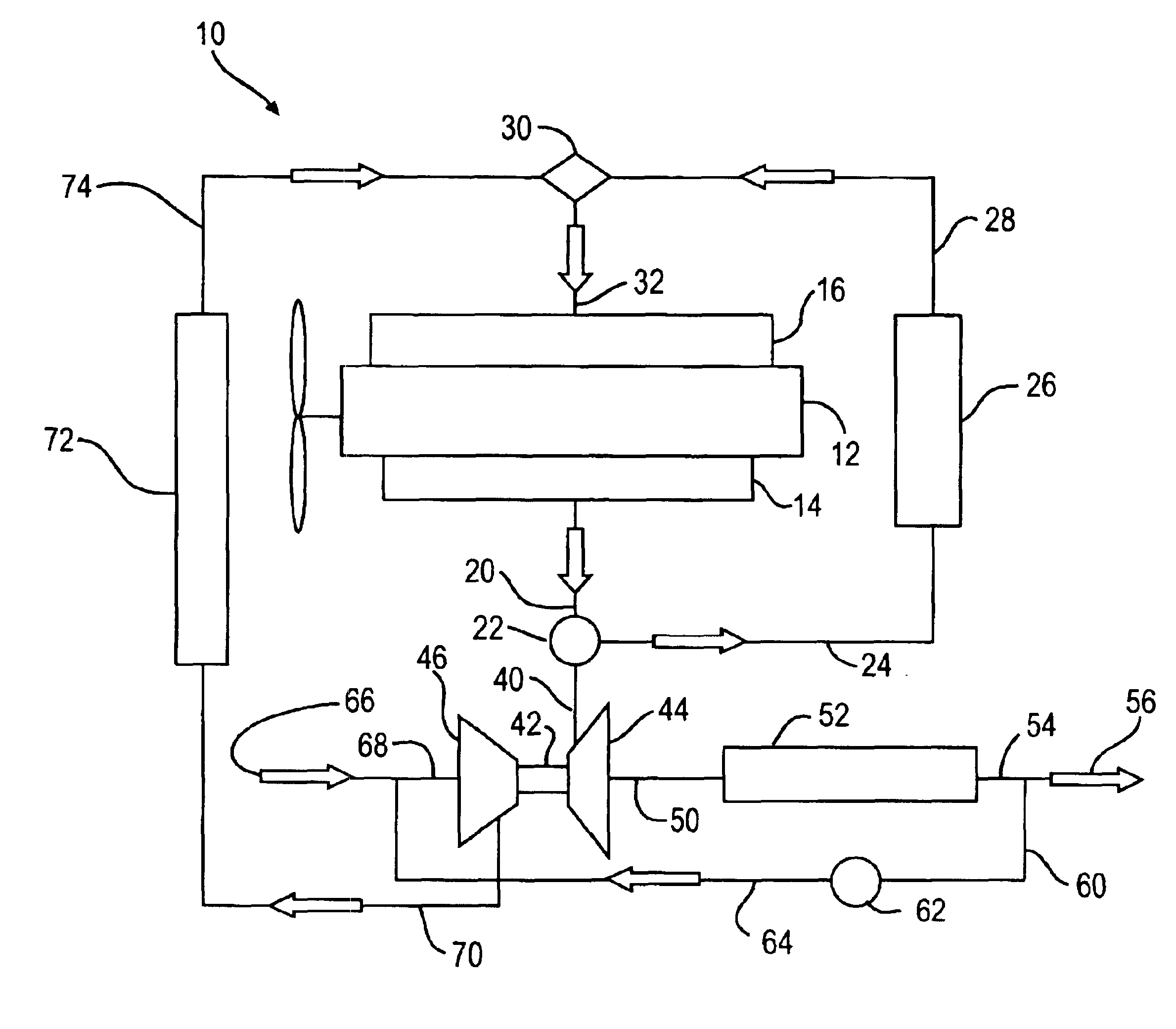

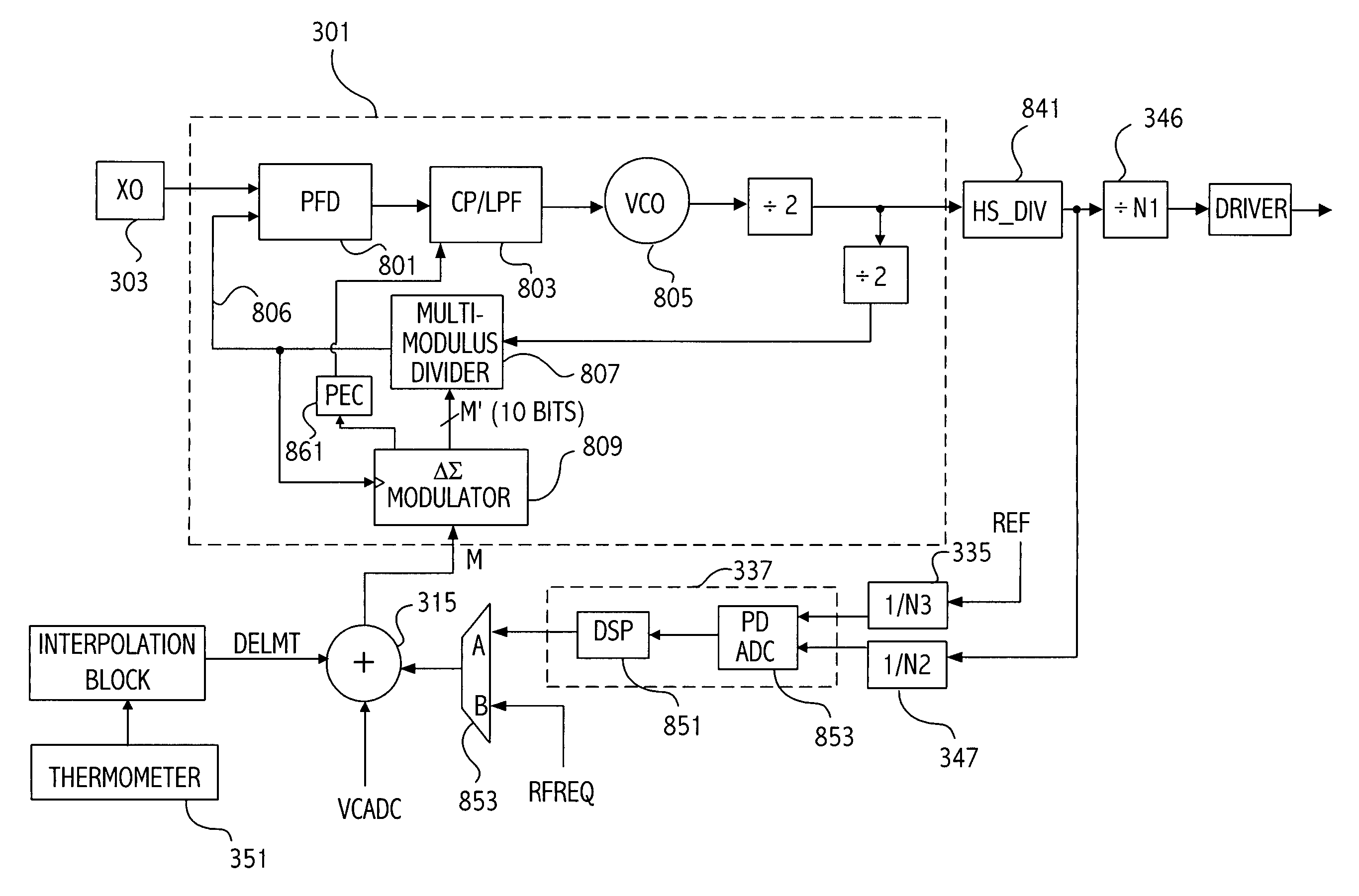

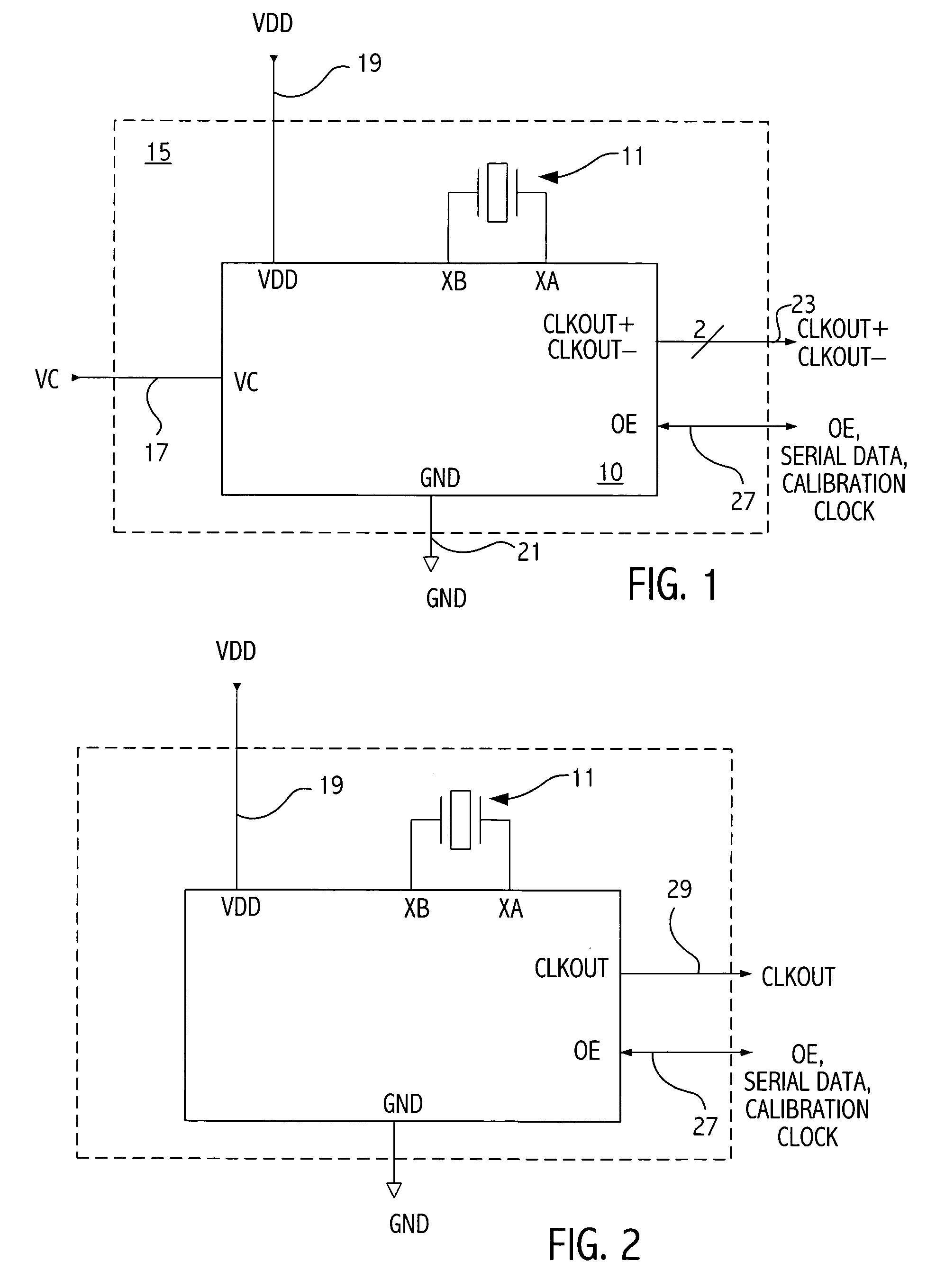

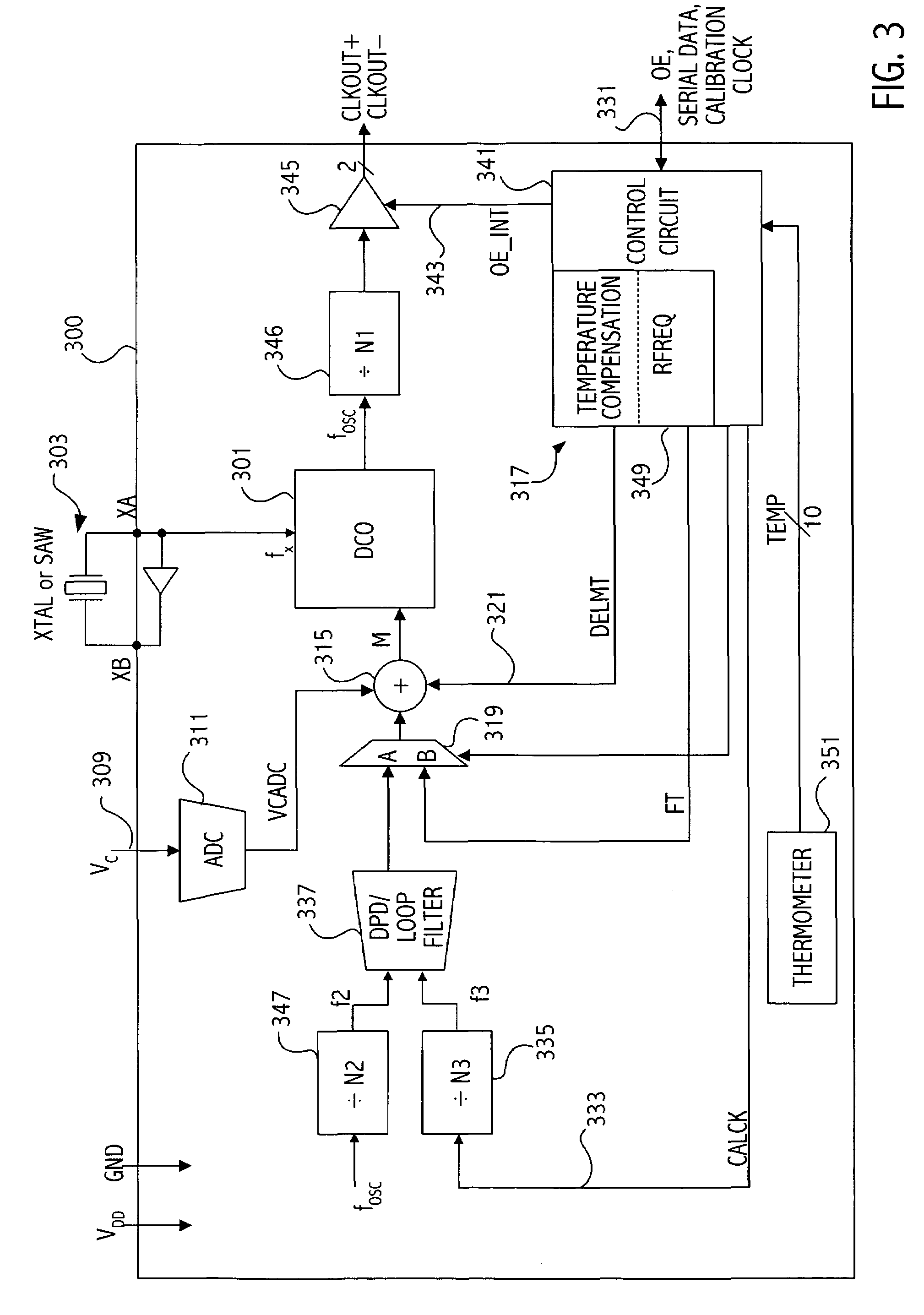

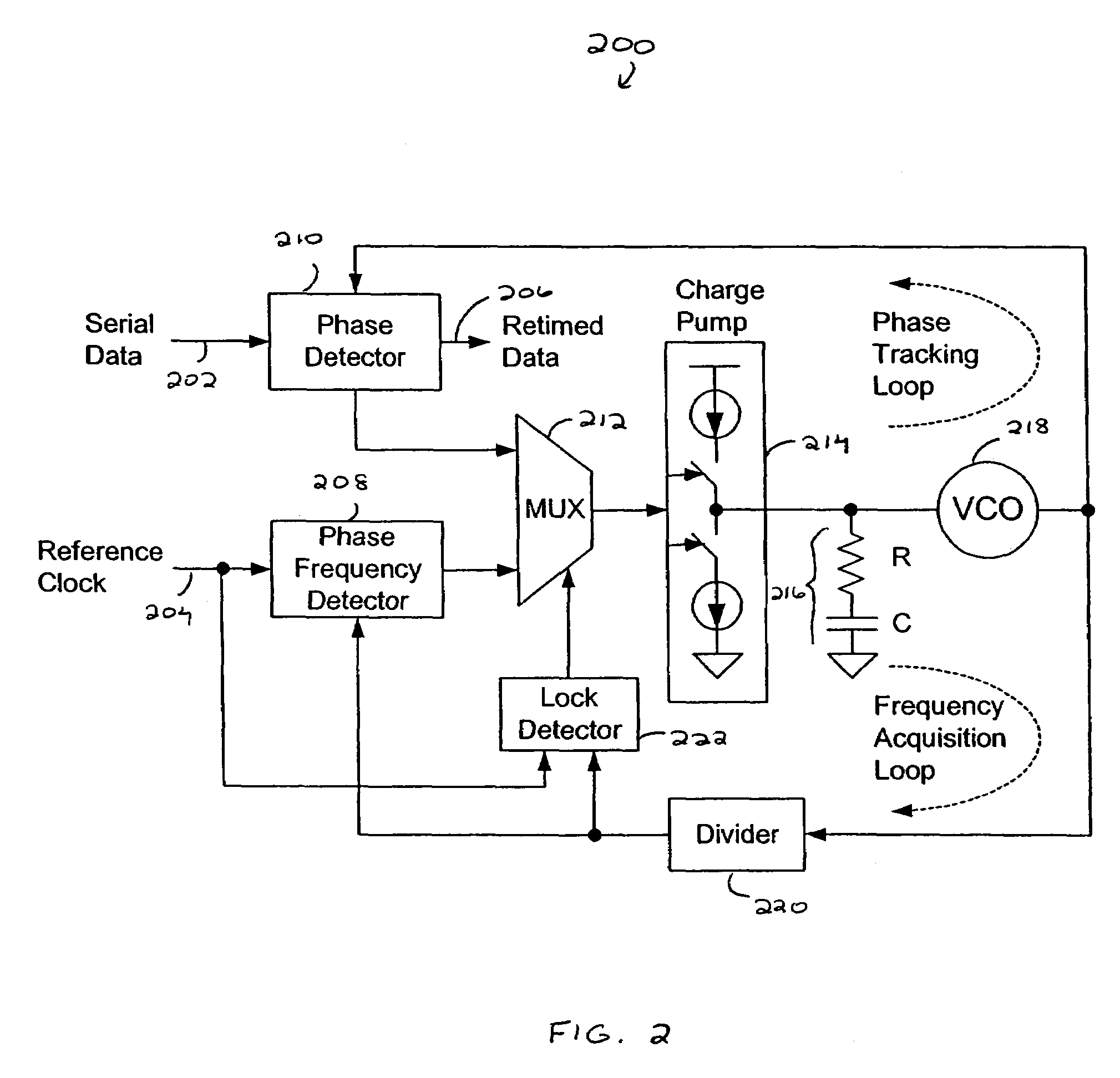

Dual loop architecture useful for a programmable clock source and clock multiplier applications

InactiveUS20040232995A1Pulse automatic controlGenerator stabilizationFrequency multiplierDigital control

A first phase-locked loop (PLL) circuit includes an input for receiving a timing reference signal from an oscillator, a controllable oscillator circuit supplying an oscillator output signal, and a multi-modulus feedback divider circuit. A second control loop circuit is selectably coupled through a select circuit to supply a digital control value (M) to the multi-modulus feedback divider circuit of the first loop circuit to thereby control the oscillator output signal. While the second control loop is coupled to supply the control value to the feedback divider circuit, the control value is determined according to a detected difference between the oscillator output signal and a reference signal coupled to the second control loop circuit at a divider circuit. While the second control loop circuit is not coupled to control the first PLL circuit, the first PLL circuit receives a digital control value to control a divide ratio of the feedback divider, the digital control value is determined at least in part according to a stored control value stored in nonvolatile storage, the stored control value corresponding to a desired frequency of the oscillator output signal.

Owner:SKYWORKS SOLUTIONS INC

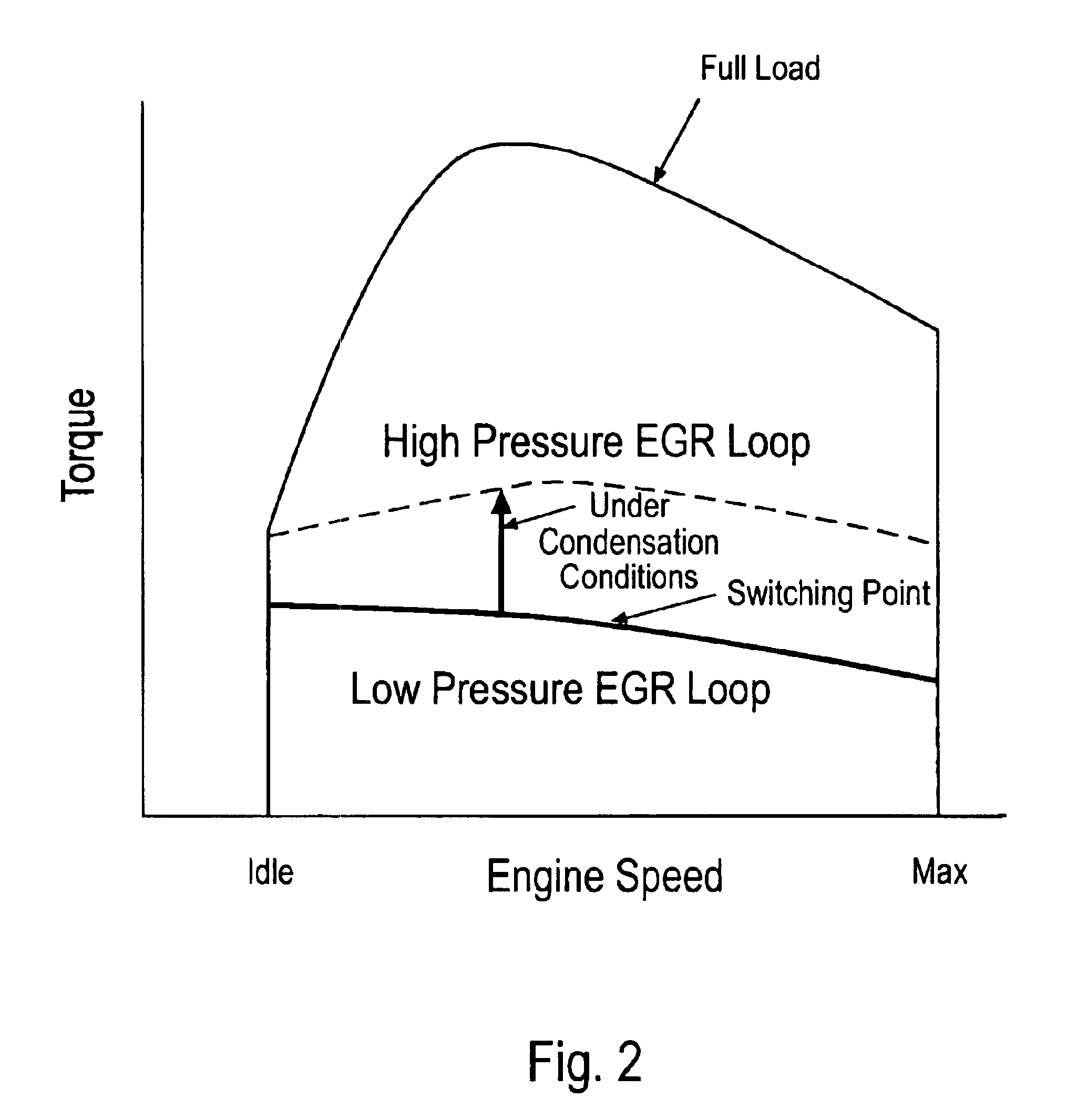

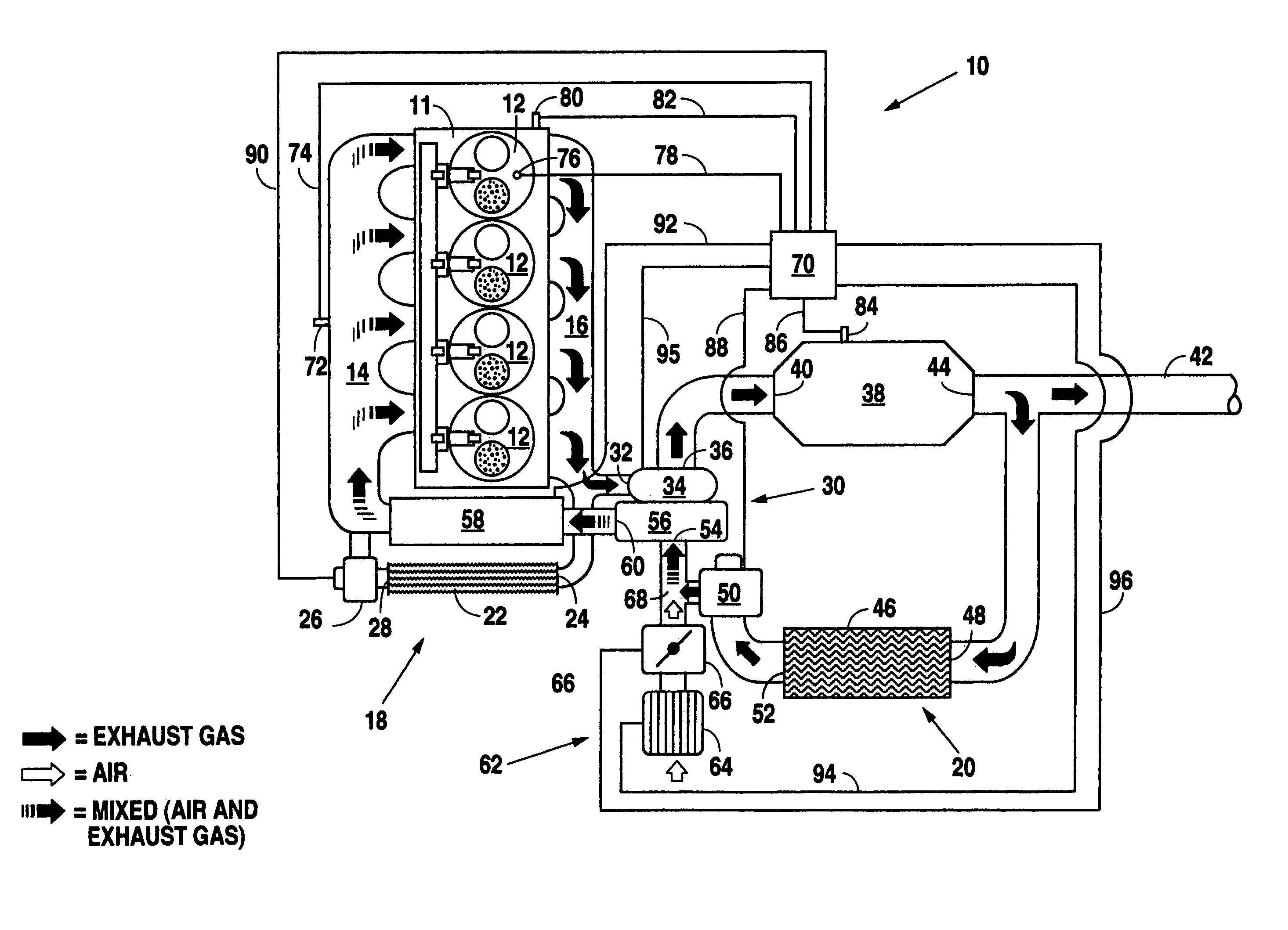

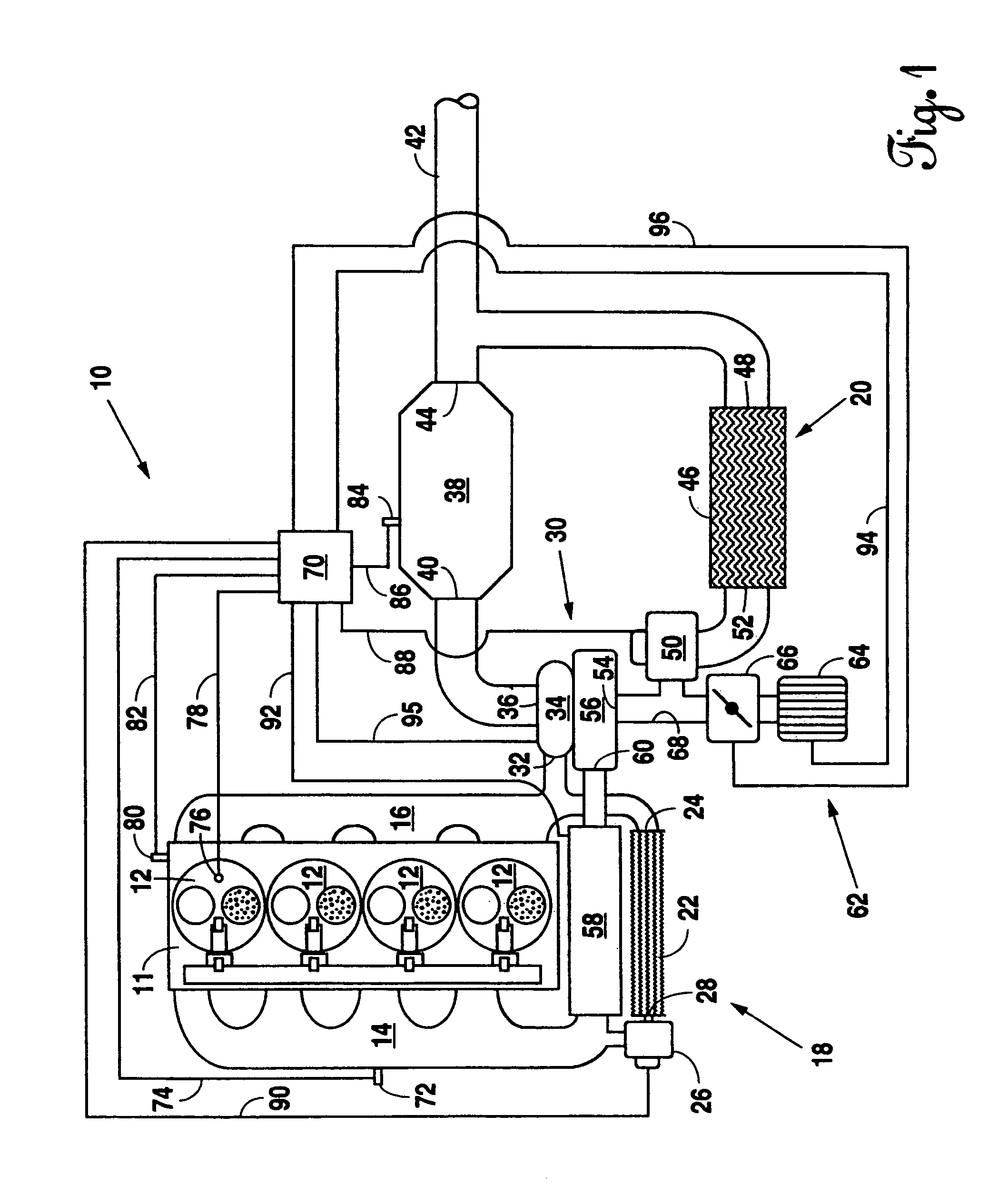

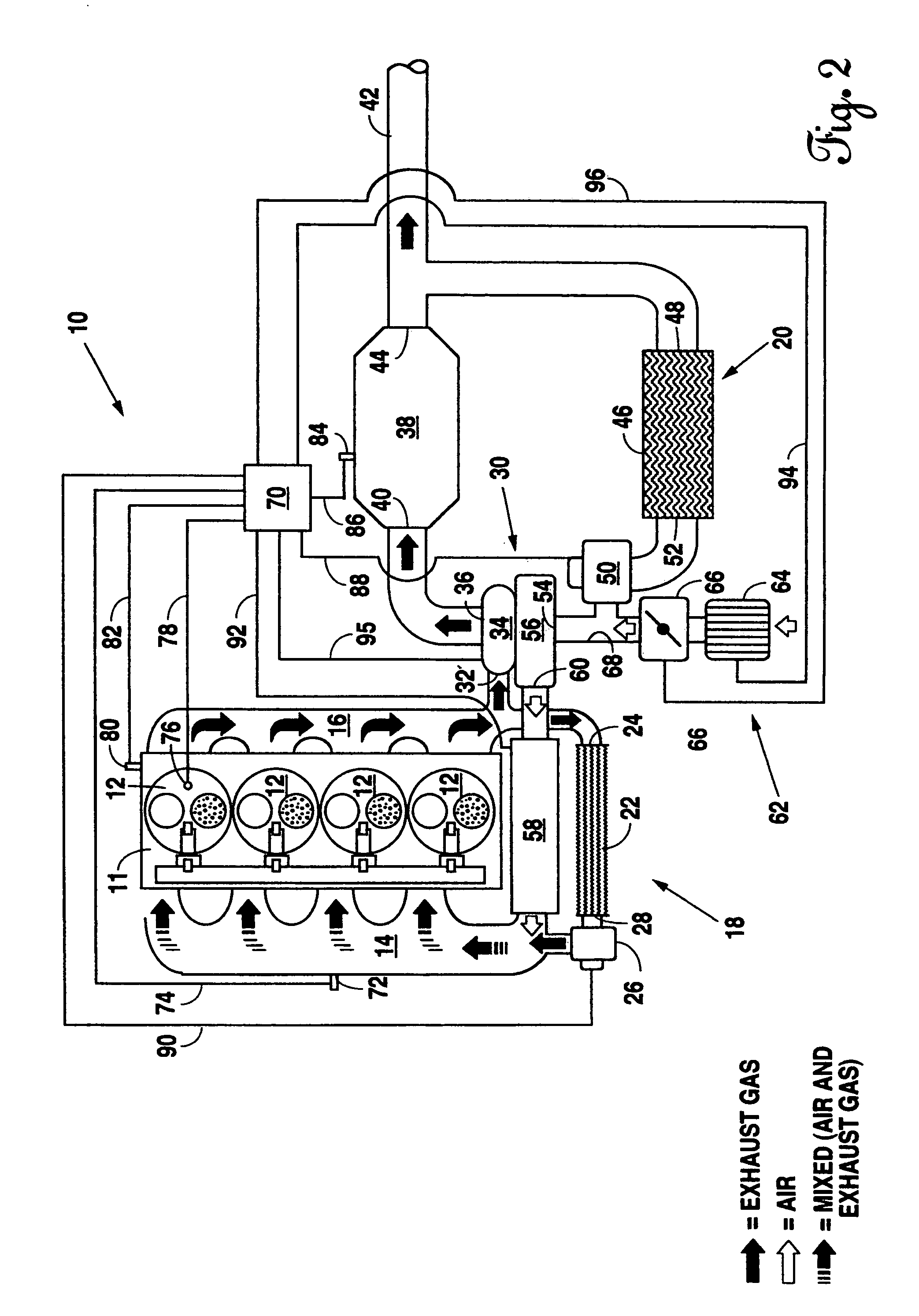

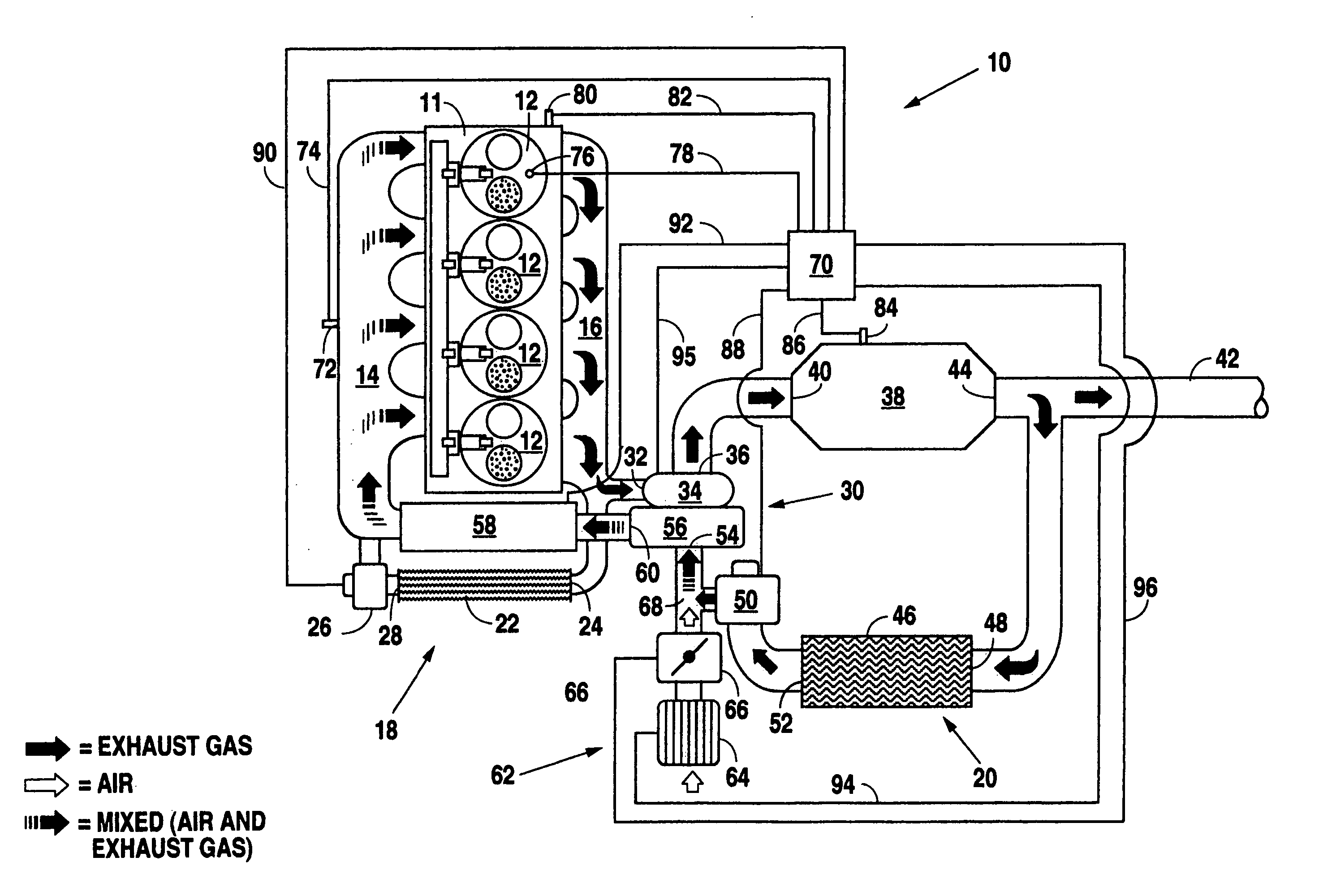

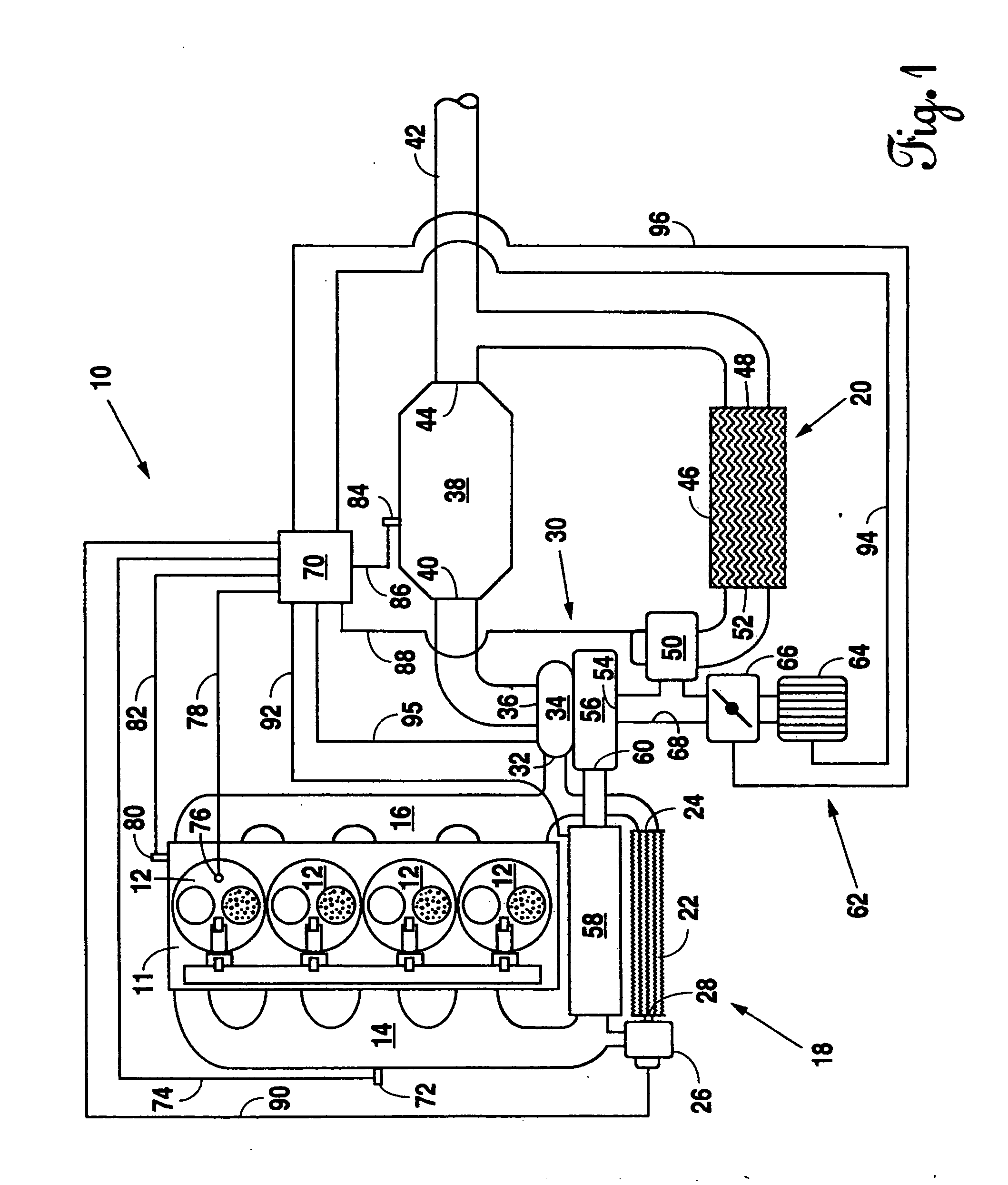

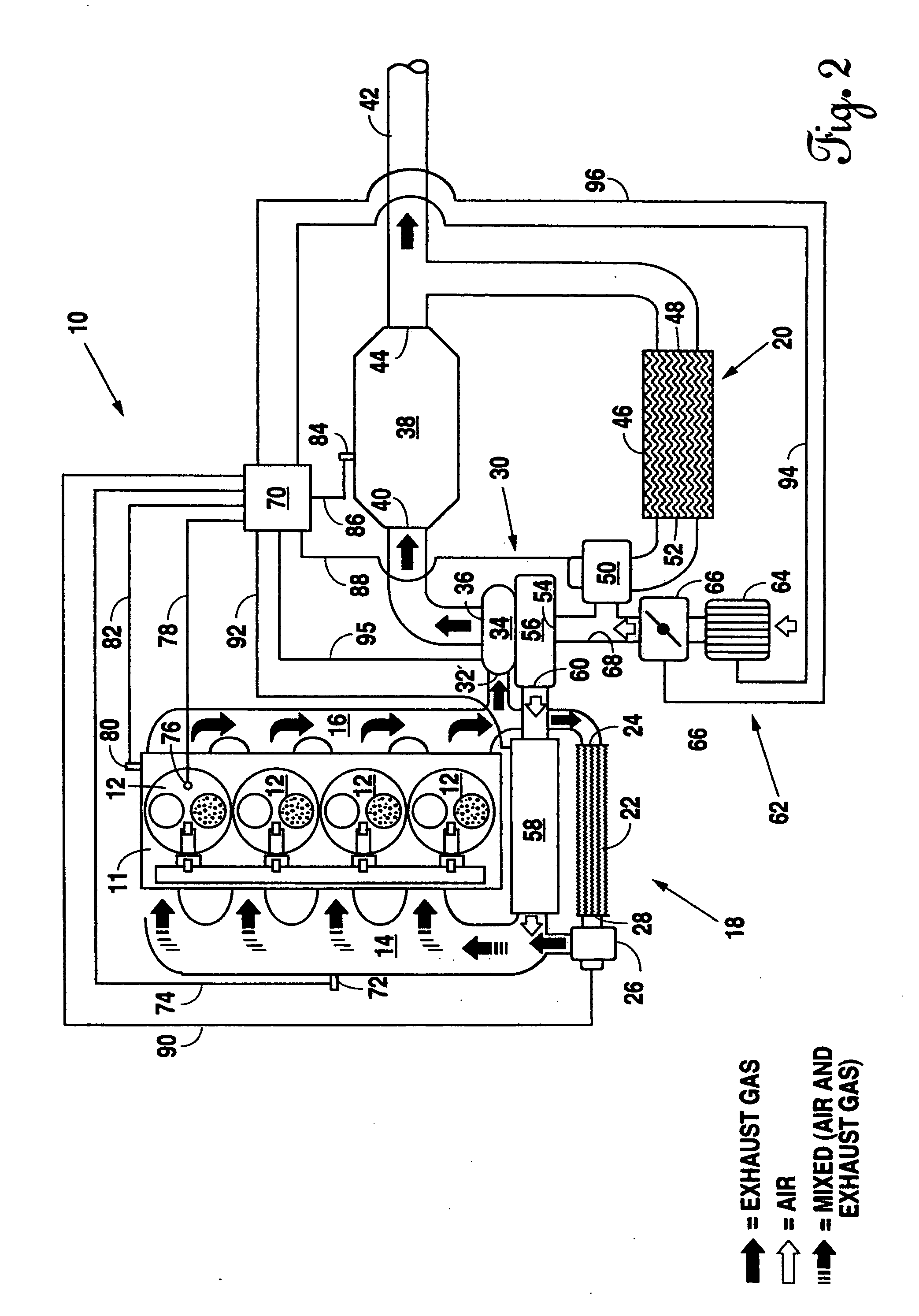

Dual path EGR system and methods

InactiveUS6899090B2Reduce condensationElectrical controlInternal combustion piston enginesFresh airHigh pressure

An internal combustion engine system, dual loop EGR system and method is provided, with a high pressure EGR loop, controlled by a control valve, in fluidic connection with the exhaust outlet of the exhaust manifold and the air inlet of the intake manifold, and a low pressure EGR loop, wherein exhaust, in proportions controlled by a control valve, enters a compressor from a point downstream of an exhaust emissions controller, together with fresh air, the low pressure EGR loop being in fluidic connection with an output of the compressor and the air inlet of the intake manifold.

Owner:GARRETT TRANSPORATION I INC

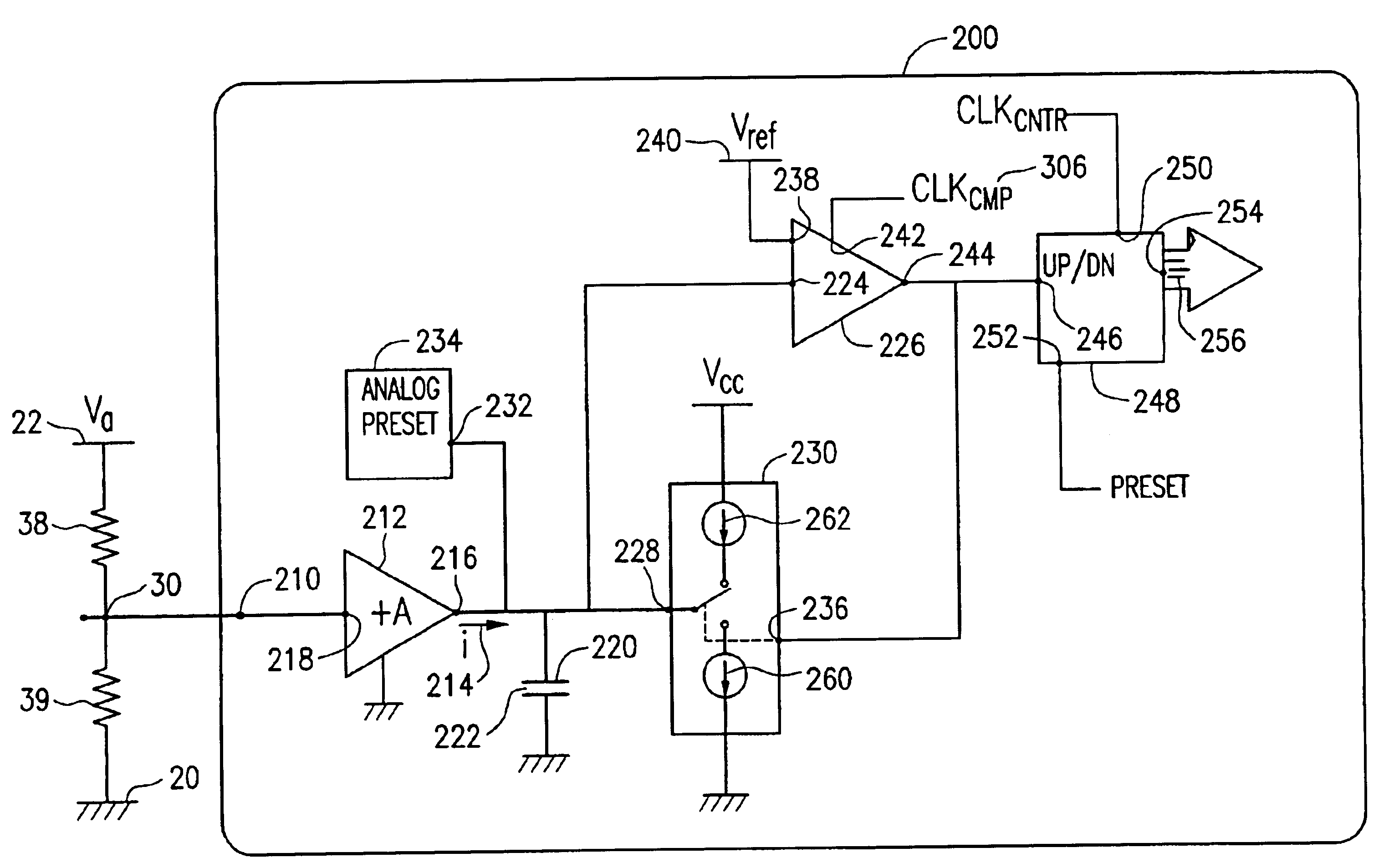

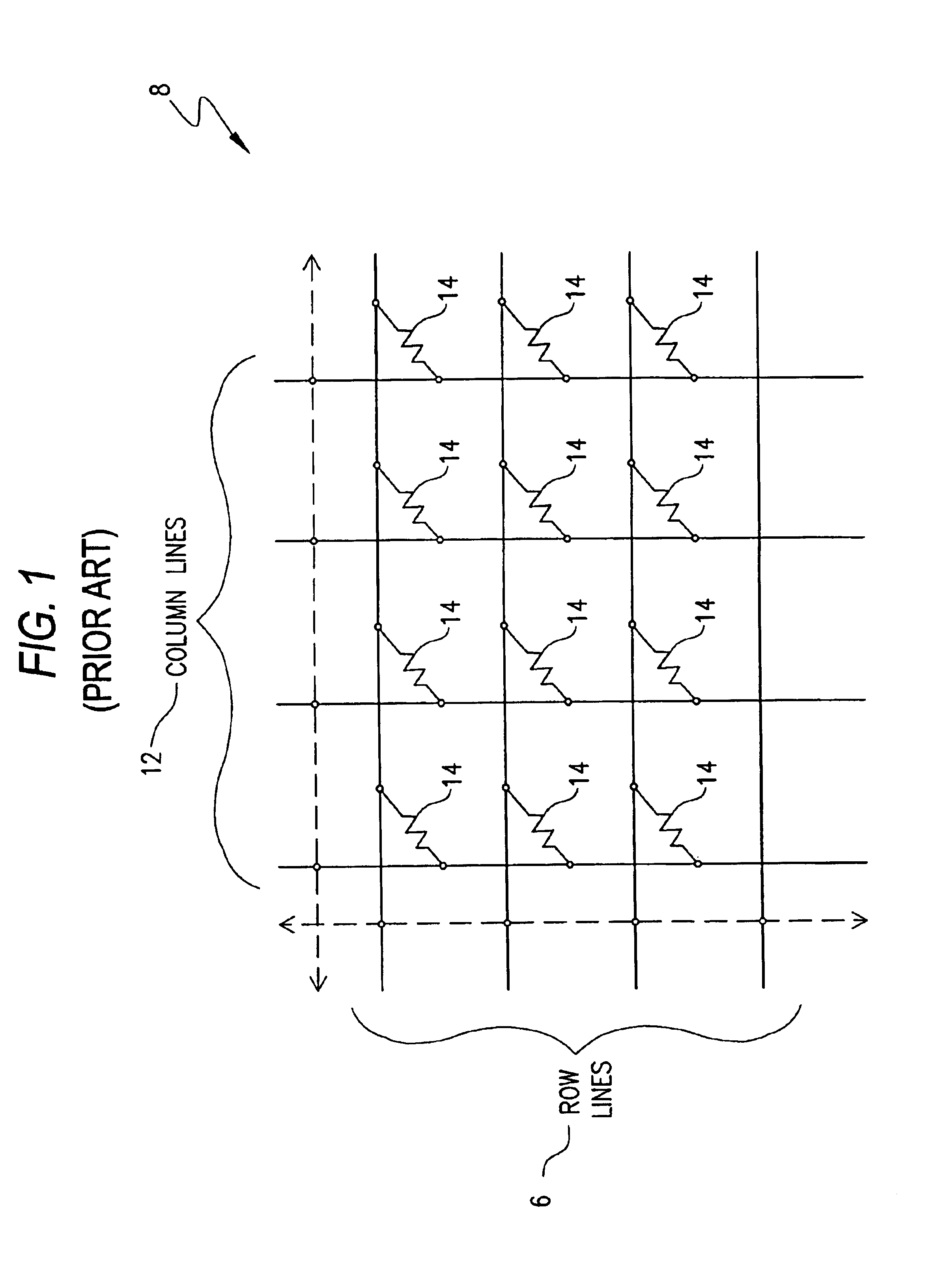

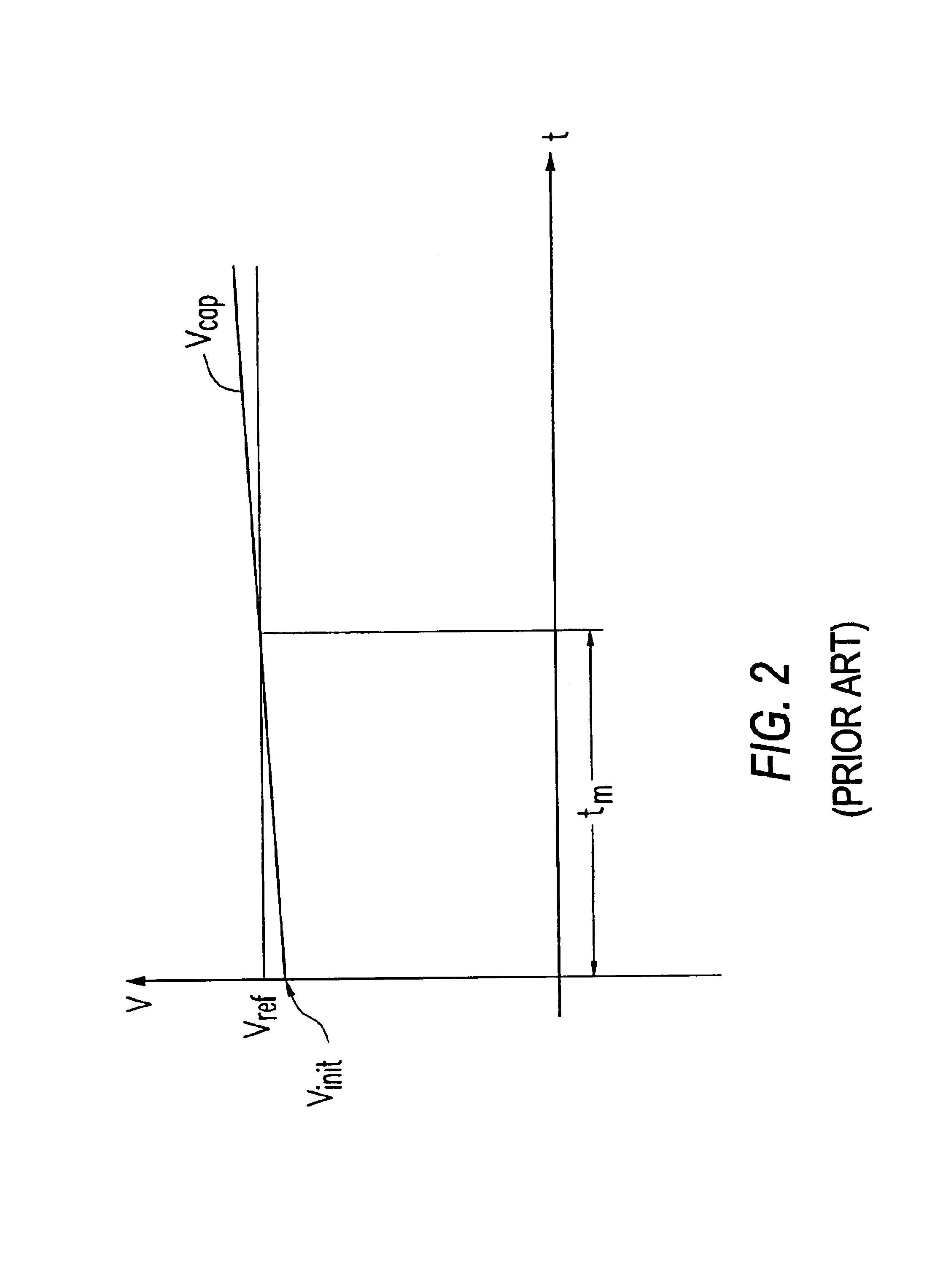

Dual loop sensing scheme for resistive memory elements

A method and apparatus for sensing a resistive state of a resistive memory element includes producing a first current related to a resistance of a memory cell. The first current is added to a second current during a first sensing time and subtracted from a third current during a second sensing time. The first, second and third currents are integrated over time using a capacitor, and a resulting voltage signal on the capacitor is timed using a clocked counter. A time average value of a digital output of the clocked counter is then related to the resistance of the memory cell, and hence to the resistive state of the resistive memory element.

Owner:OVONYX MEMORY TECH LLC

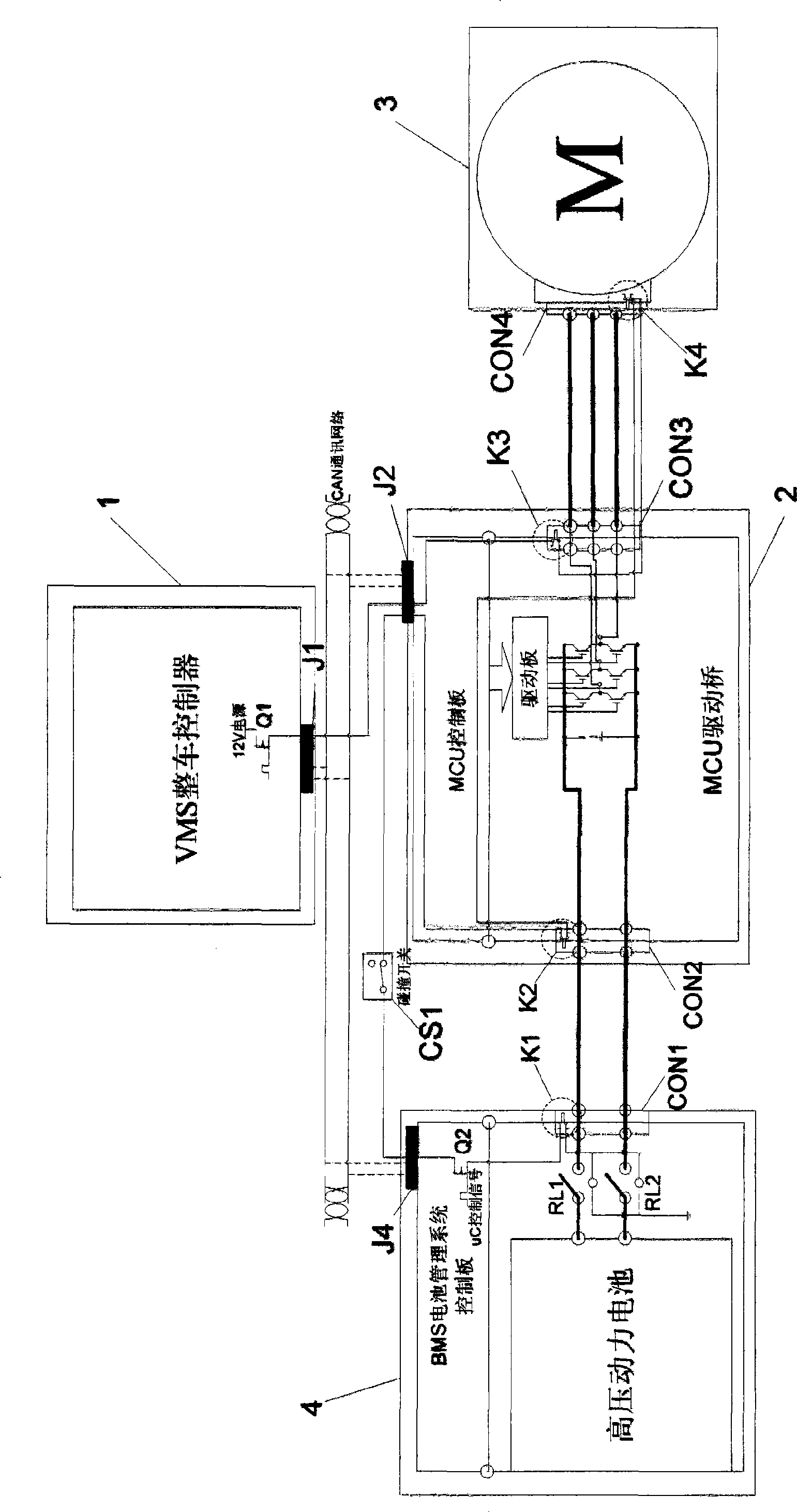

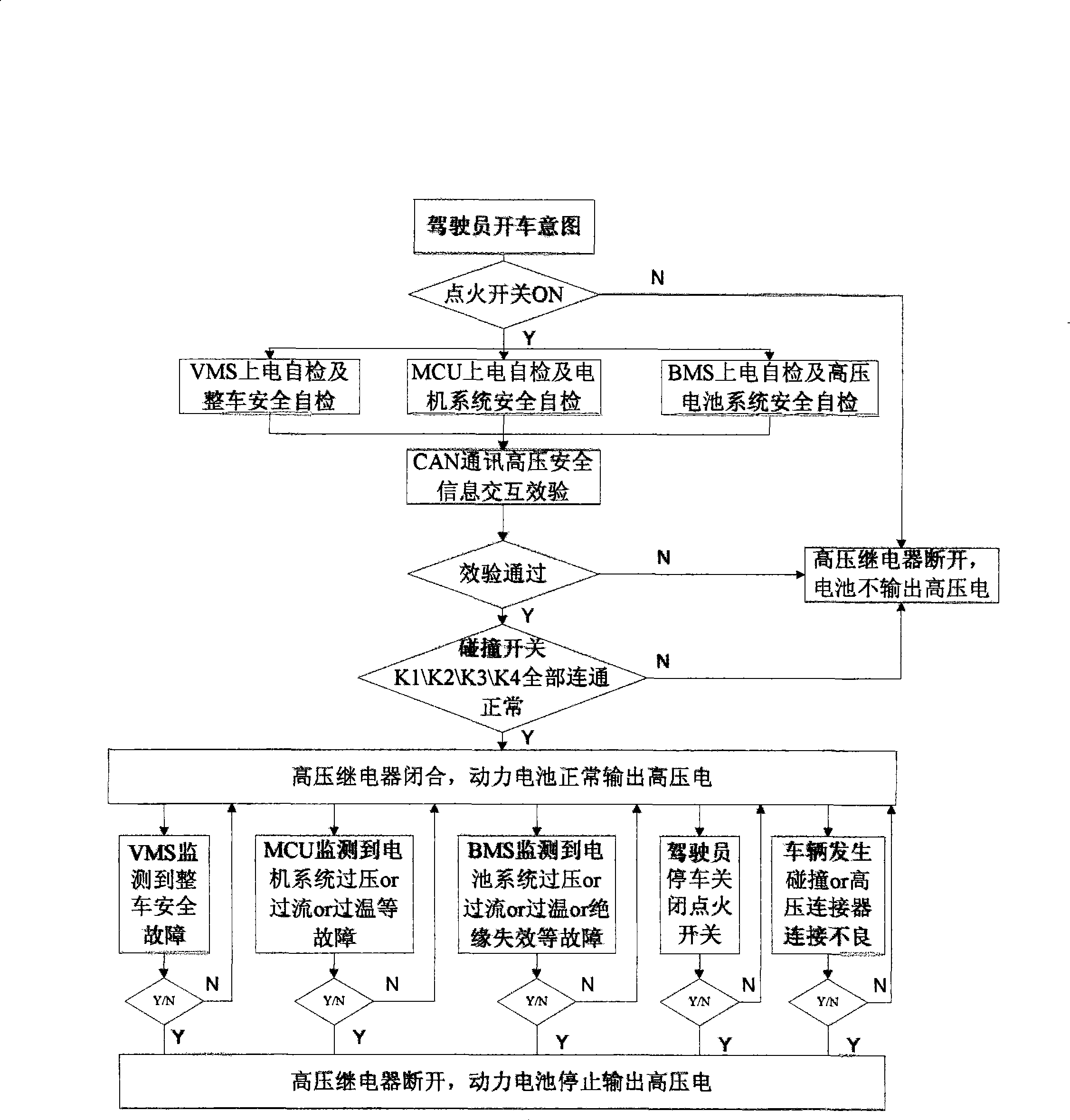

High-voltage double-loop safety system of electric vehicle and method thereof

ActiveCN101544215AProtection securityImprove securityElectric devicesElectric vehicle charging technologyElectrical batteryDrive motor

The present invention discloses a high-voltage double-loop safety system of electric vehicle and a method thereof. The high-voltage double-loop safety system of electric vehicle comprises a hardwired control loop which is composed of a VMS vehicle controller, a motor controller assembly, a driving motor and a high-voltage power battery pack assembly through hardwired connection in series, a VMS vehicle controller which is connected in parallel in the vehicle CAN network, and a communication network control loop composed of an MCU control plate in the motor controller assembly and a BMS battery management system in the high-voltage power battery pack assembly. The control method of the invention mainly determines whether the power battery outputs high-voltage electricity through the self testing of each control system and the safety information interaction checking of CAN communication network. The high-voltage double-loop safety system of electric vehicle according to the invention can reliably realize the purpose of protection of electric vehicle or the high-voltage electric device and high-voltage power transmission line in a hybrid power vehicle and the operator safety. The safety and reliability of high-voltage electricity can be greatly increased.

Owner:CHERY AUTOMOBILE CO LTD

Dual loop architecture useful for a programmable clock source and clock multiplier applications

A first phase-locked loop (PLL) circuit includes an input for receiving a timing reference signal from an oscillator, a controllable oscillator circuit supplying an oscillator output signal, and a multi-modulus feedback divider circuit. A second control loop circuit is selectably coupled through a select circuit to supply a digital control value (M) to the multi-modulus feedback divider circuit of the first loop circuit to thereby control the oscillator output signal. While the second control loop is coupled to supply the control value to the feedback divider circuit, the control value is determined according to a detected difference between the oscillator output signal and a reference signal coupled to the second control loop circuit at a divider circuit. While the second control loop circuit is not coupled to control the first PLL circuit, the first PLL circuit receives a digital control value to control a divide ratio of the feedback divider, the digital control value is determined at least in part according to a stored control value stored in nonvolatile storage, the stored control value corresponding to a desired frequency of the oscillator output signal.

Owner:SKYWORKS SOLUTIONS INC

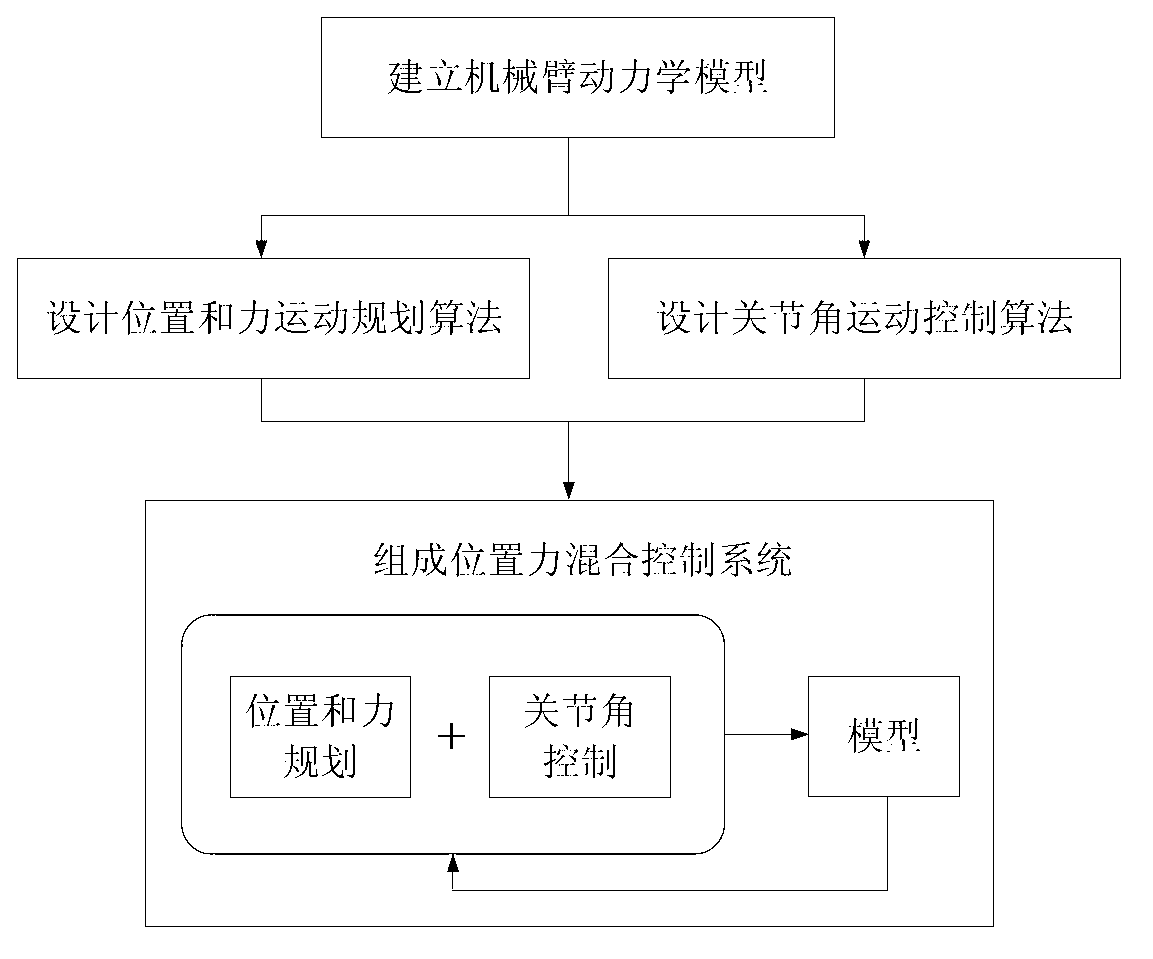

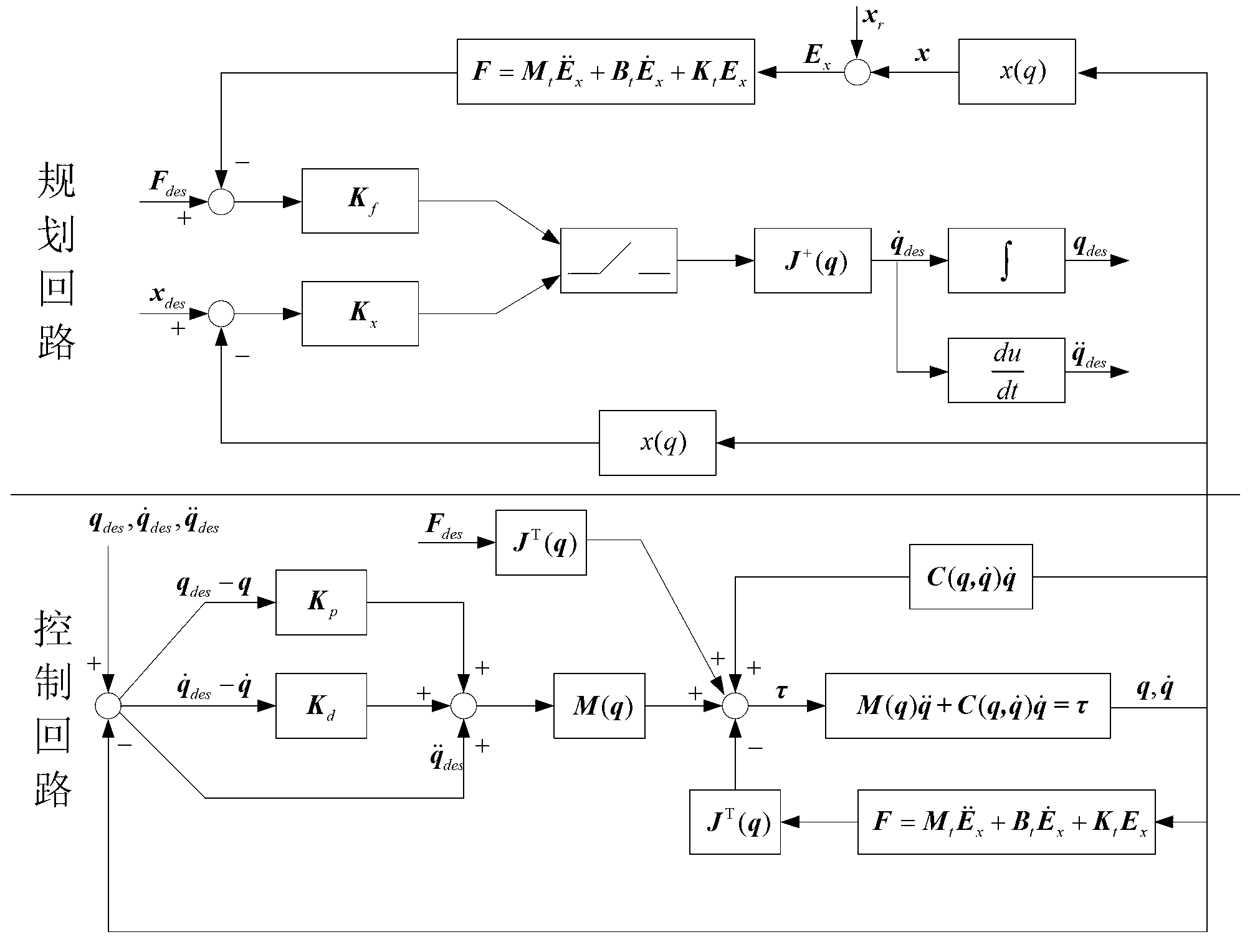

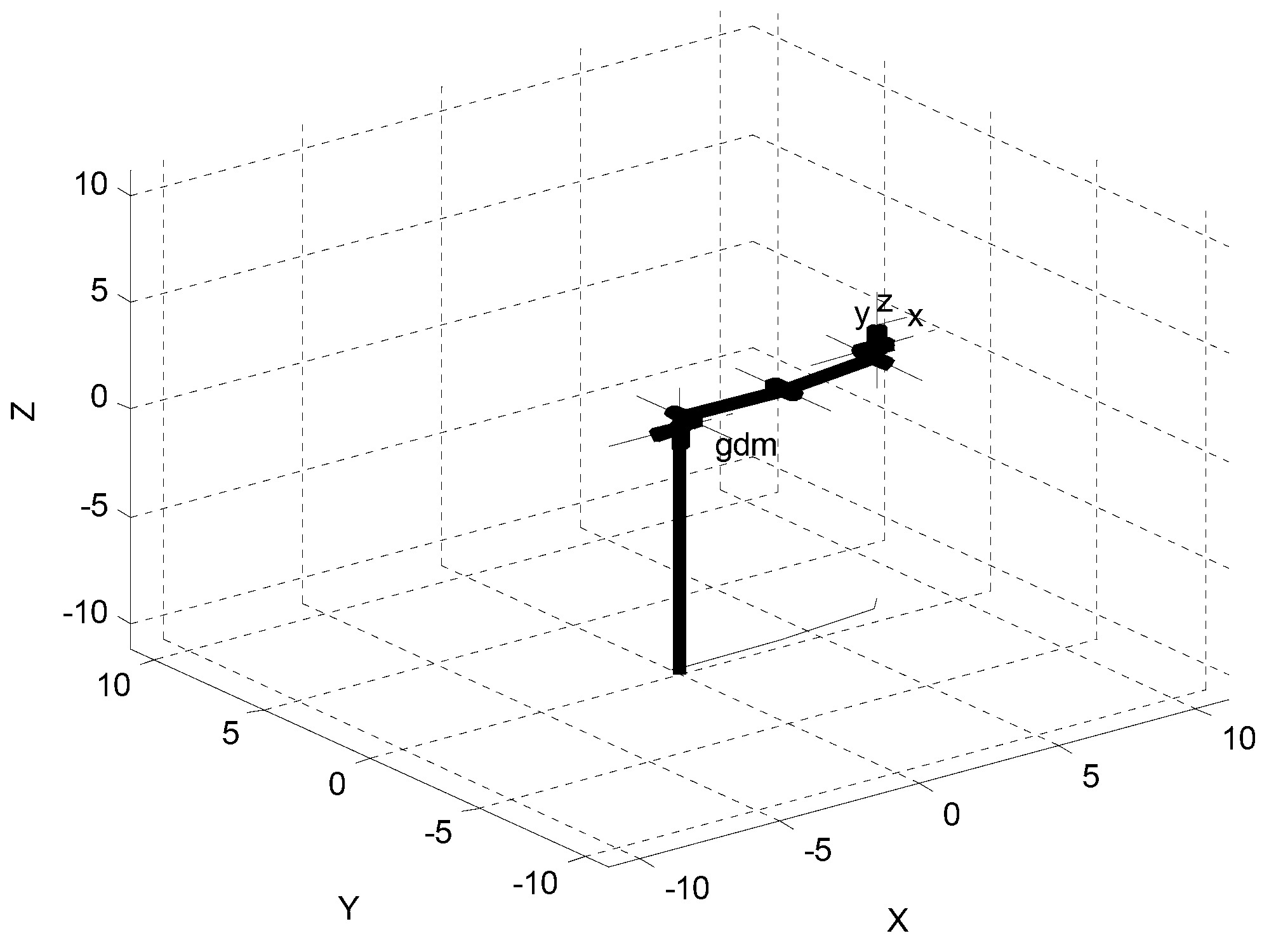

Position/force hybrid control method for space manipulator

ActiveCN103213129ASmooth transitionPosition/force hybrid control for precise trackingProgramme-controlled manipulatorLoop controlContact force

The invention relates to a position / force hybrid control method for a space manipulator, which is a double-loop control method combining a Cartesian space and a joint space. Compared with a conventional control method on the basis of an integral model, which has the problems of oscillation of the transition process and algorithm complexity, the position / force hybrid control method for the space manipulator has the advantages that the position / force hybrid control problem is decomposed into the planning problem of the Cartesian space and the control problem of the joint space; a position / force kinematic plan from the Cartesian space to the joint space and kinematic control of the joint space are given out; an internal and external loop control system is formed; and position control on a free space at the tail end of the manipulator and contact force control in a space restrained by the environment are implemented. A simulation result for a SDOF ( Seven Degrees of Freedom) redundant manipulator proves that the method disclosed by the invention is simple to operate, is effective and is easy for engineering realization.

Owner:BEIJING INST OF SPACECRAFT SYST ENG

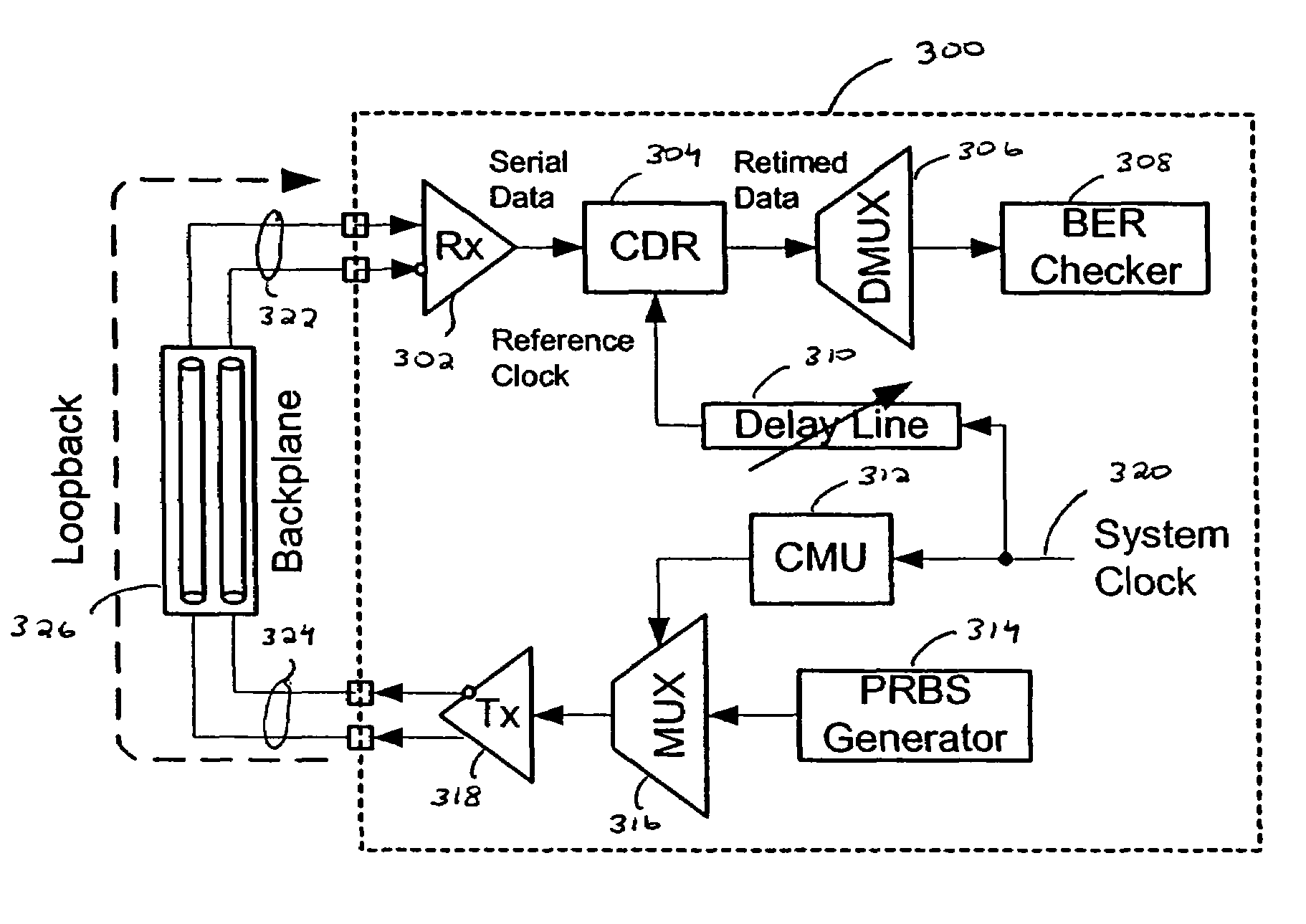

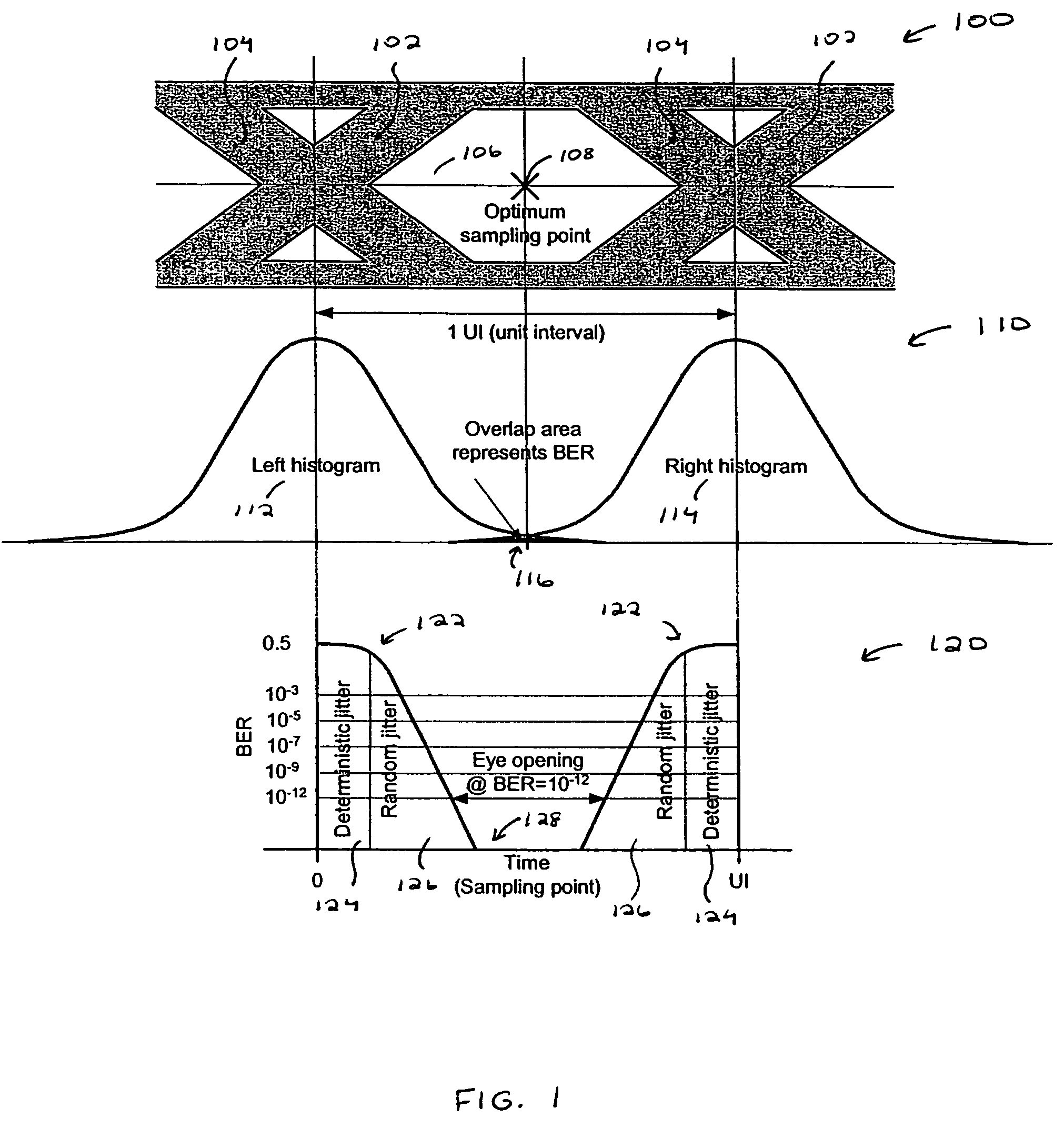

Built-in at-speed bit error ratio tester

InactiveUS7743288B1Low-cost solutionEfficient testingError preventionTransmission systemsEqualizationBuilt-in self-test

A built-in, at-speed BERT is provided that may be part of high-speed serial interface circuitry implemented on an integrated circuit. The built-in, at-speed BERT takes advantage of an existing clock data recovery (CDR) dual-loop architecture and built-in self test (BIST) circuitry. The built-in, at-speed BERT provides a low-cost solution for production testing of high-speed serial links, facilitating jitter analysis and evaluation of pre-emphasis and equalization performance. This further allows adaptation of pre-emphasis and equalization.

Owner:ALTERA CORP

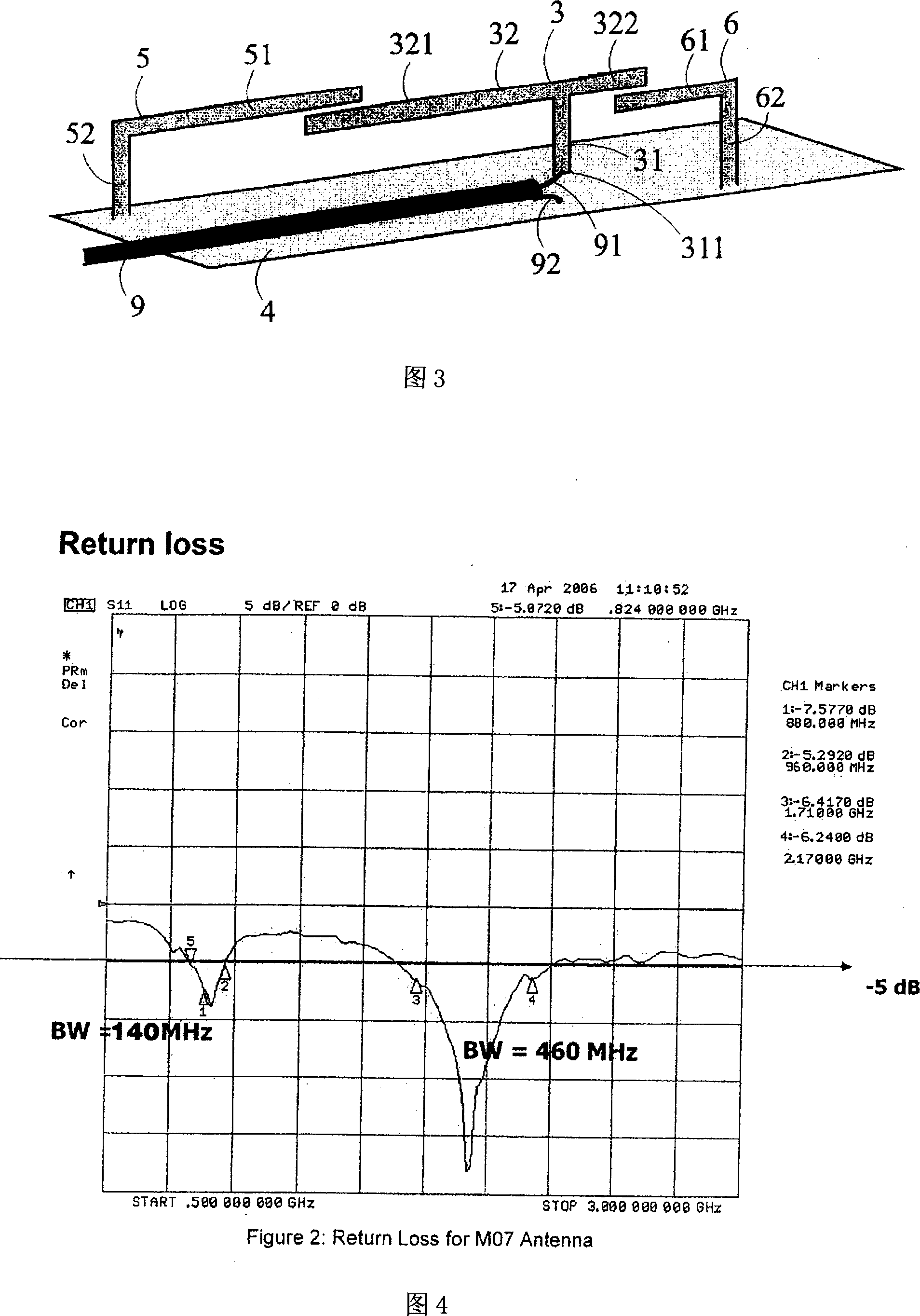

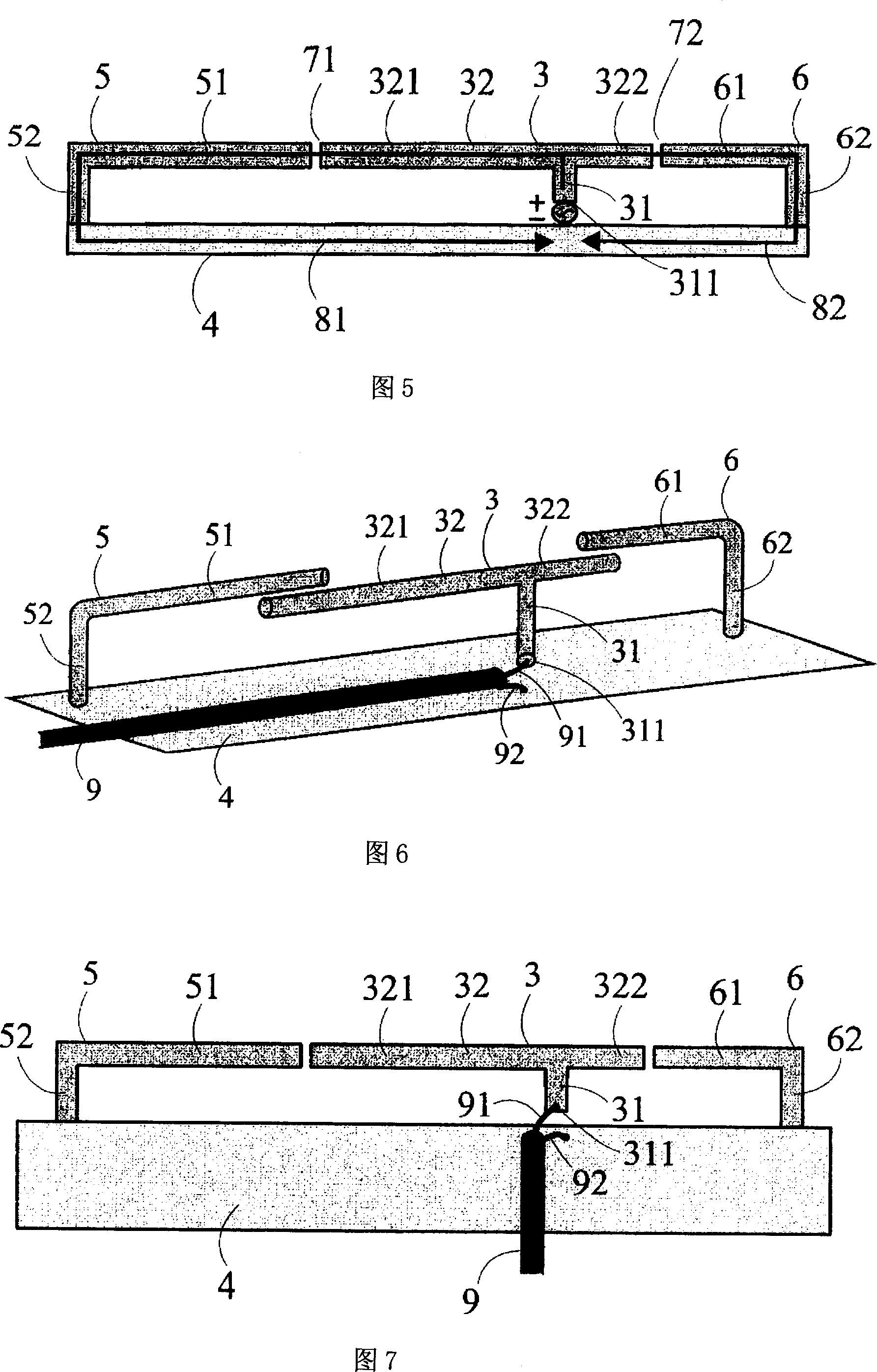

Dual loop multi-frequency antenna

ActiveCN101106211AHigh bandwidthSignificant frequency reduction effectAntenna arraysSimultaneous aerial operationsSystem requirementsOperation mode

The invention relates to a double-loop multi-frequency antenna, with a T-shaped metal radiator provided with long sides at different lengths acting as a main body and two L-shaped metal radiators connected with the ground cooperated to form two loop antennas, which can respectively generate high-frequency and low-frequency operation modes. The invention utilizes a bidirectional structure to allow multi-frequency antenna to have enough frequency width at high frequency, and at the same time, to meet the usage demands at low frequency, so as to meet the system requirements of the frequency bands of DCS / PCS / UMTS high frequency and AMPS / GSM low frequency.

Owner:昆山展腾电子科技有限公司

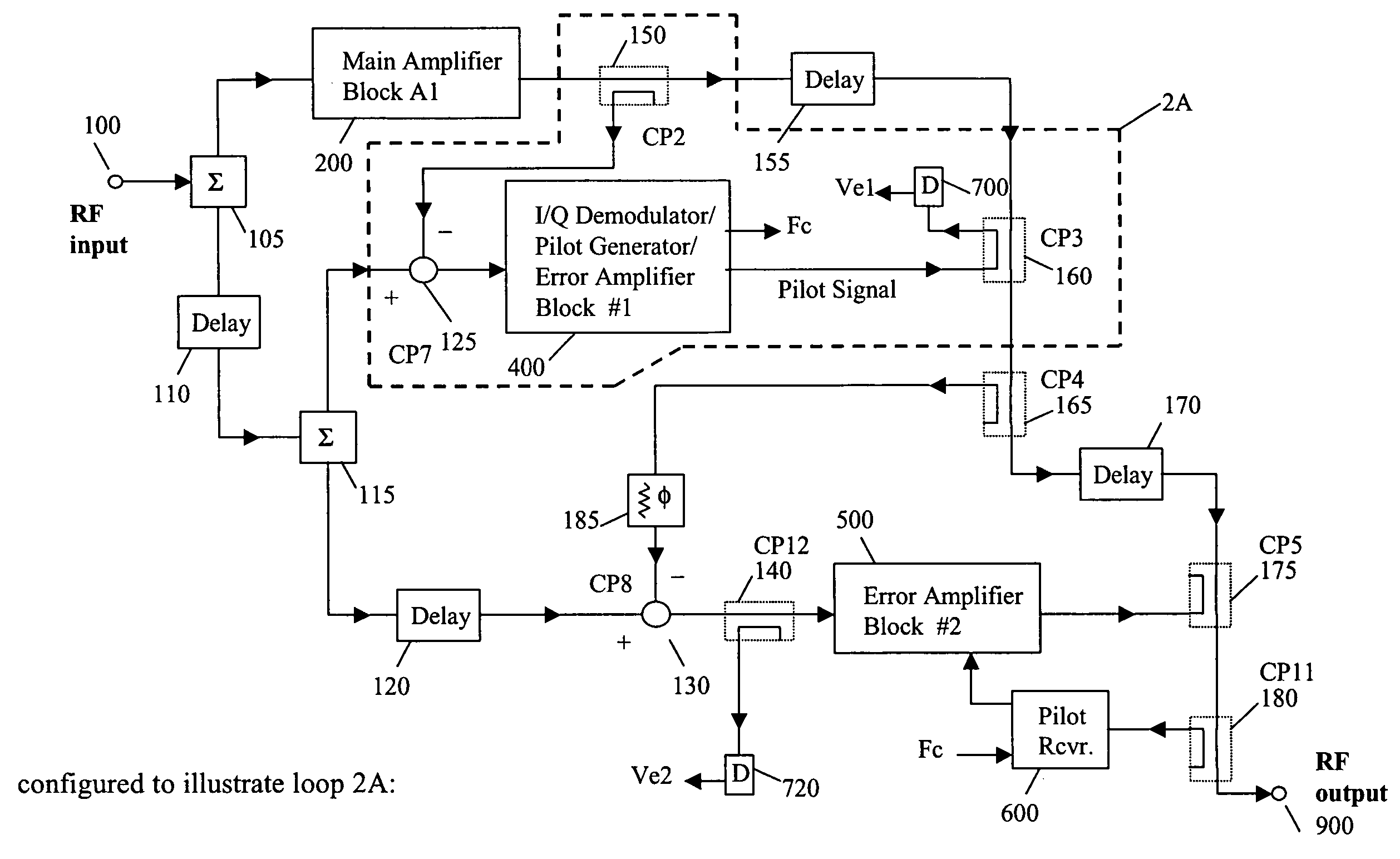

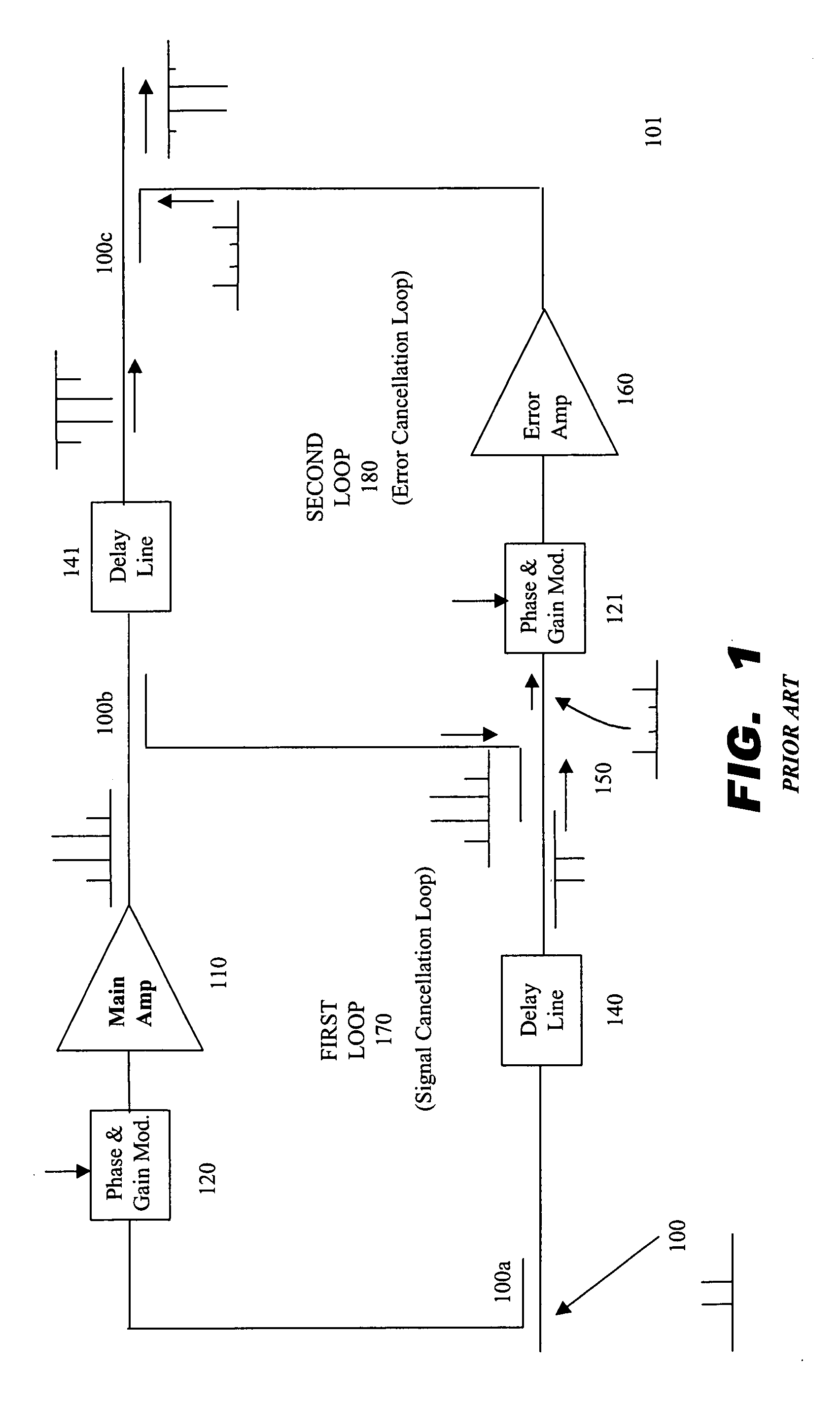

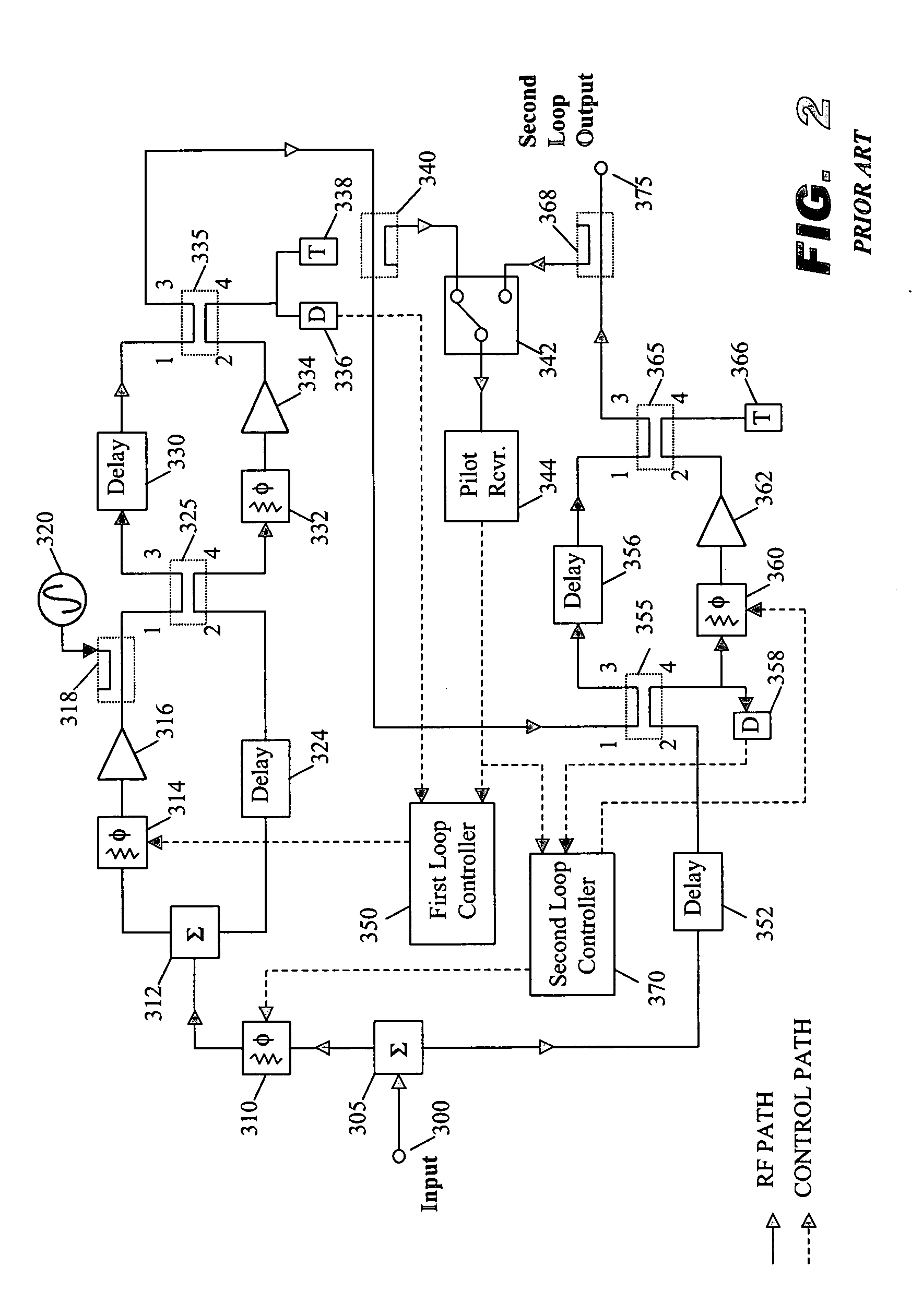

System and method of carrier reinjection in a feedforward amplifier

InactiveUS20050113052A1Signal distortion is smallAmplifier modifications to reduce non-linear distortionAmplifier modifications to reduce noise influenceAudio power amplifierCarrier signal

A dual loop feedforward power amplifier. A dual loop feedforward power amplifier, comprising an input that provides a multicarrier signal; a first feedforward power amplifier; and a second feedforward power amplifier, wherein the first feedforward power amplifier serves as a main amplifier gain block in the second feedforward power amplifier, wherein the first feedforward power amplifier comprises a carrier cancellation loop and a first error amplifier loop, and wherein the second feedforward power amplifier comprises a third loop and a fourth loop that cancel small signal distortions that are not reduced by the first feedforward amplifier.

Owner:INTEL CORP

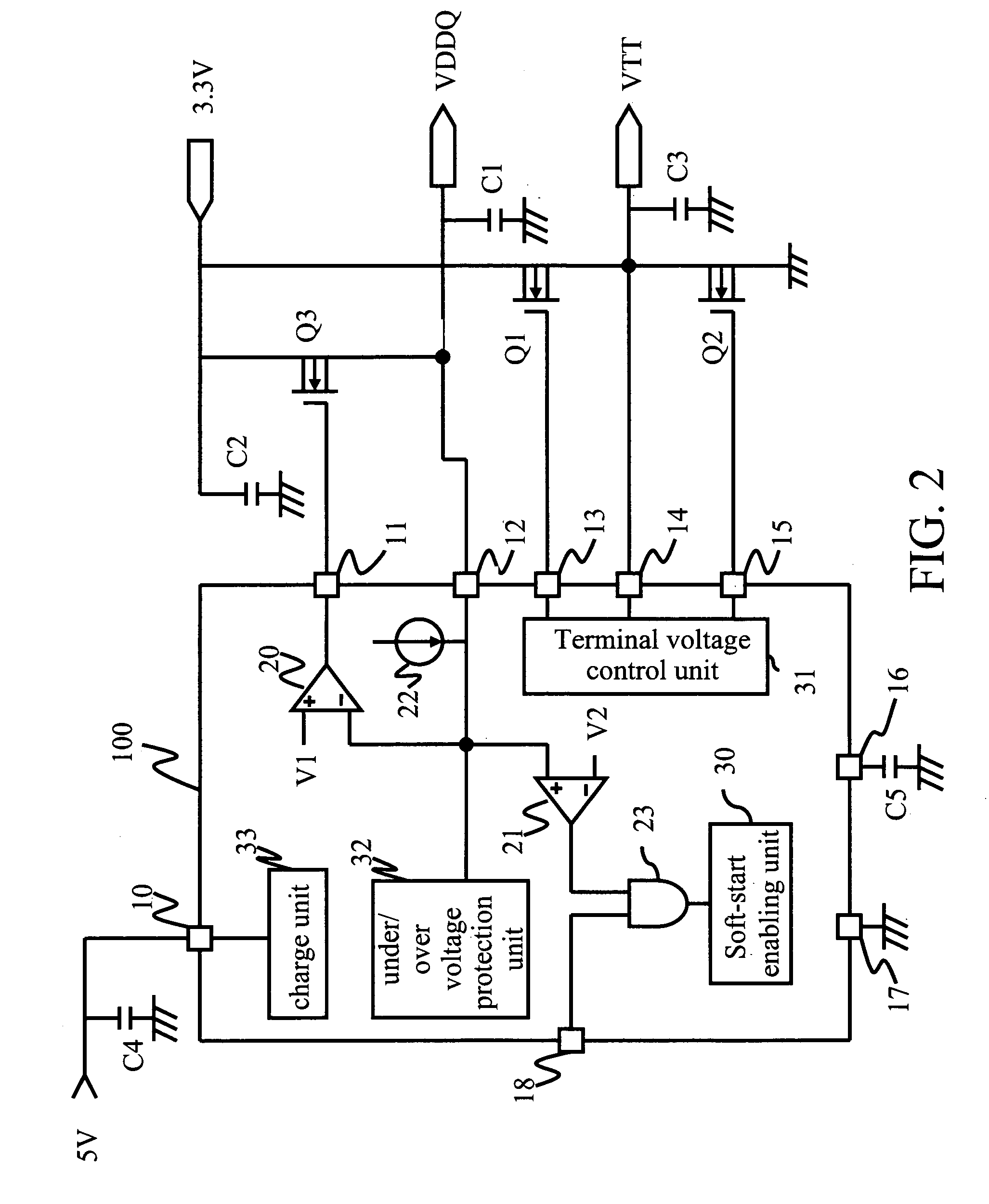

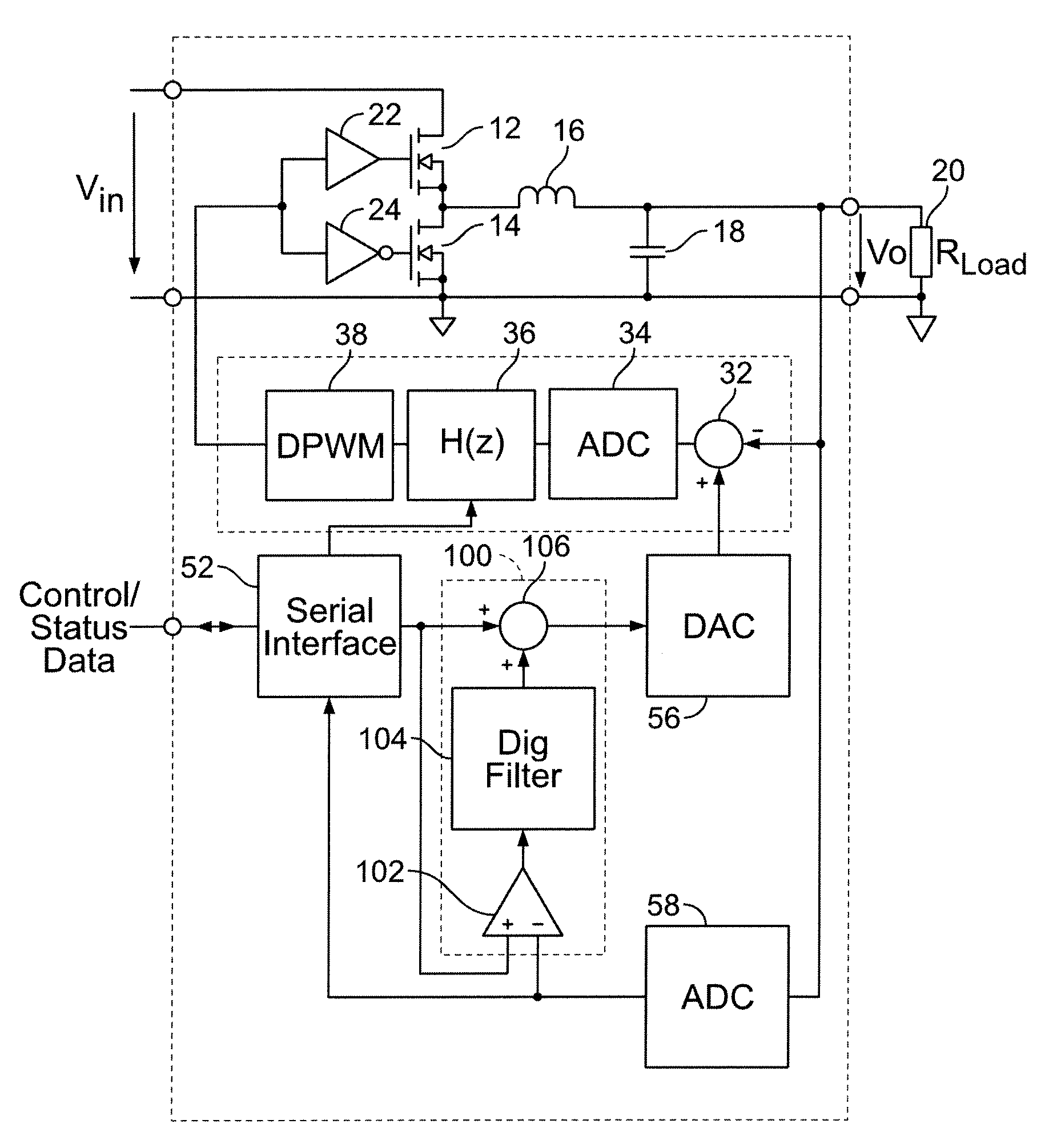

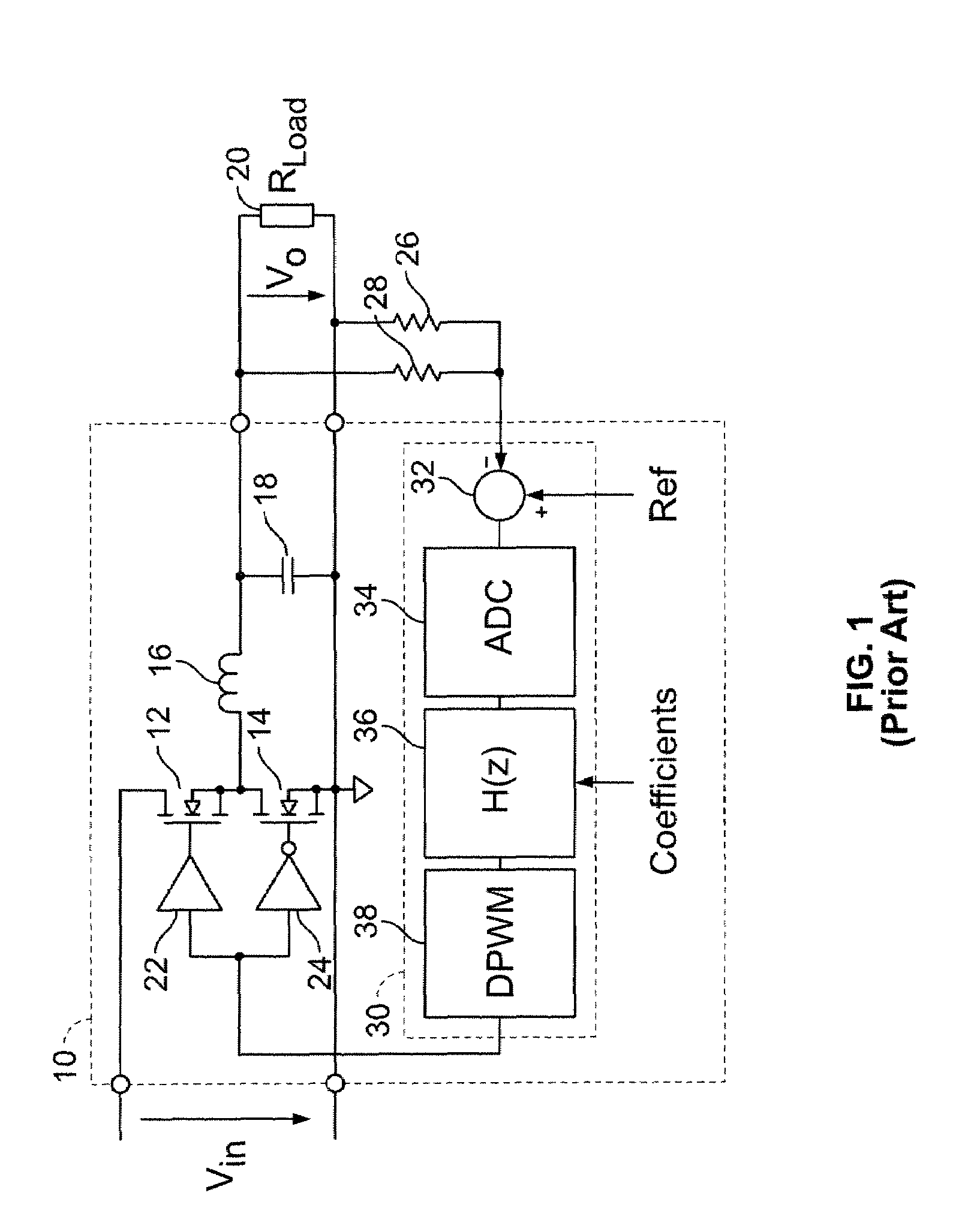

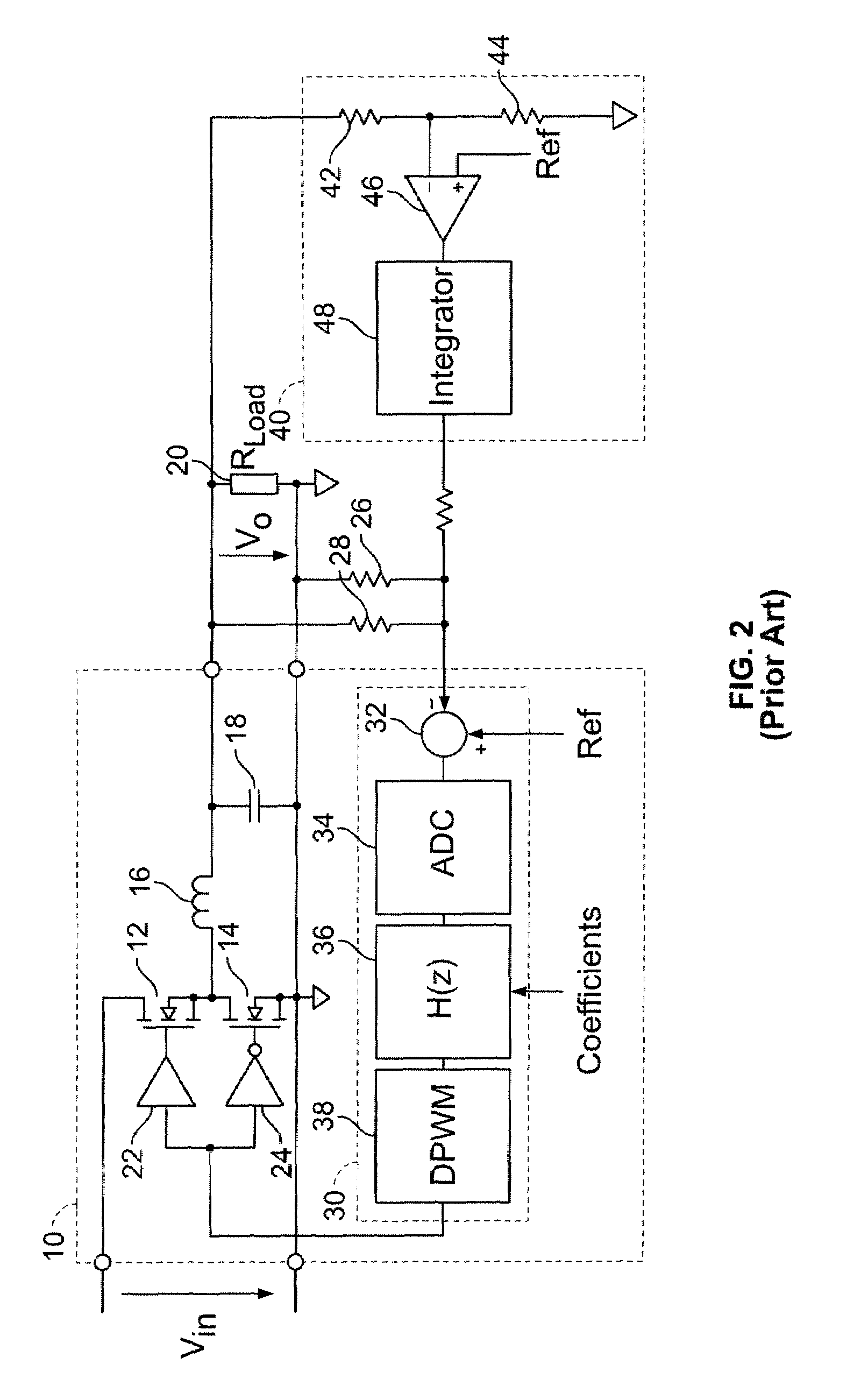

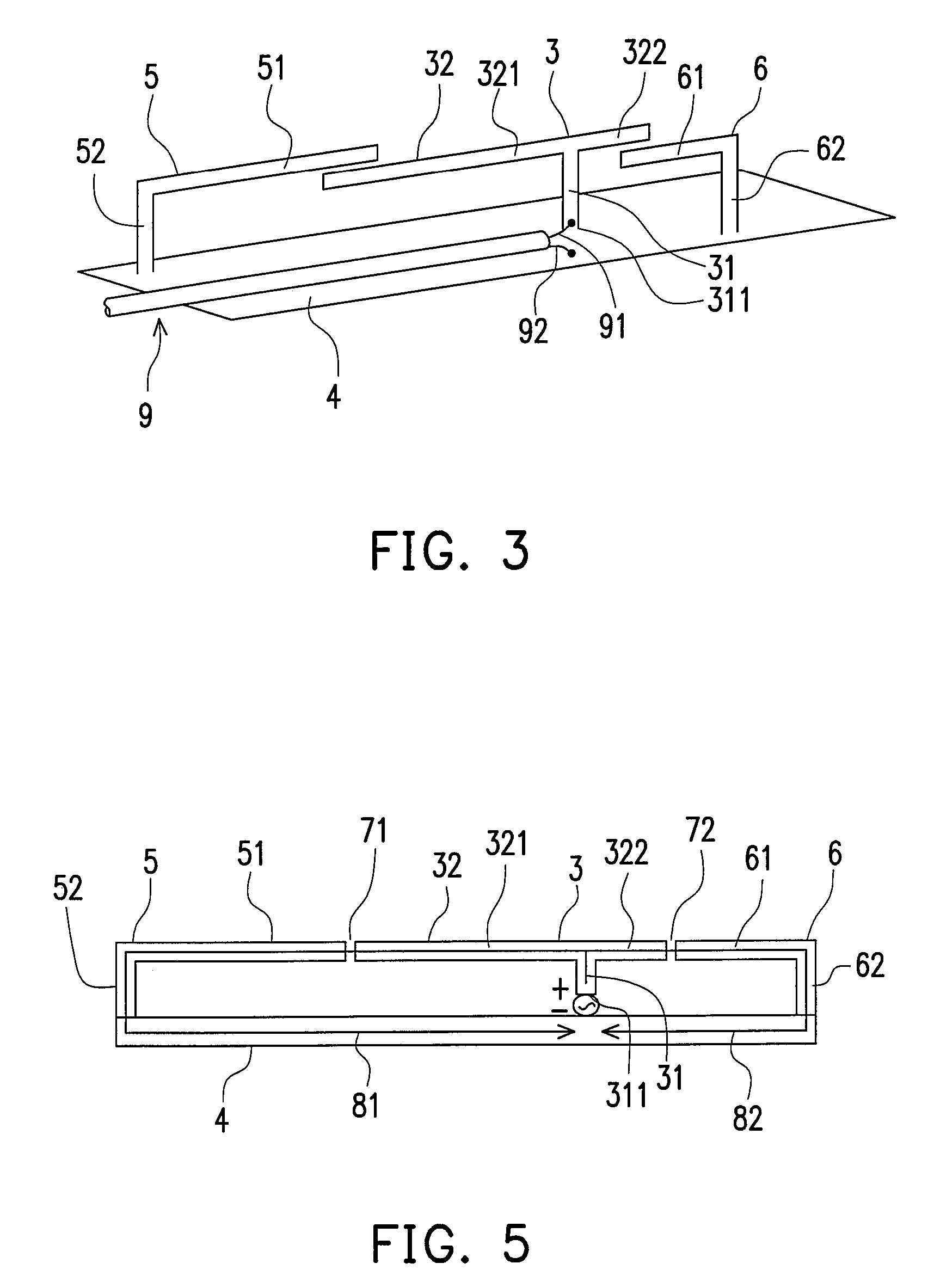

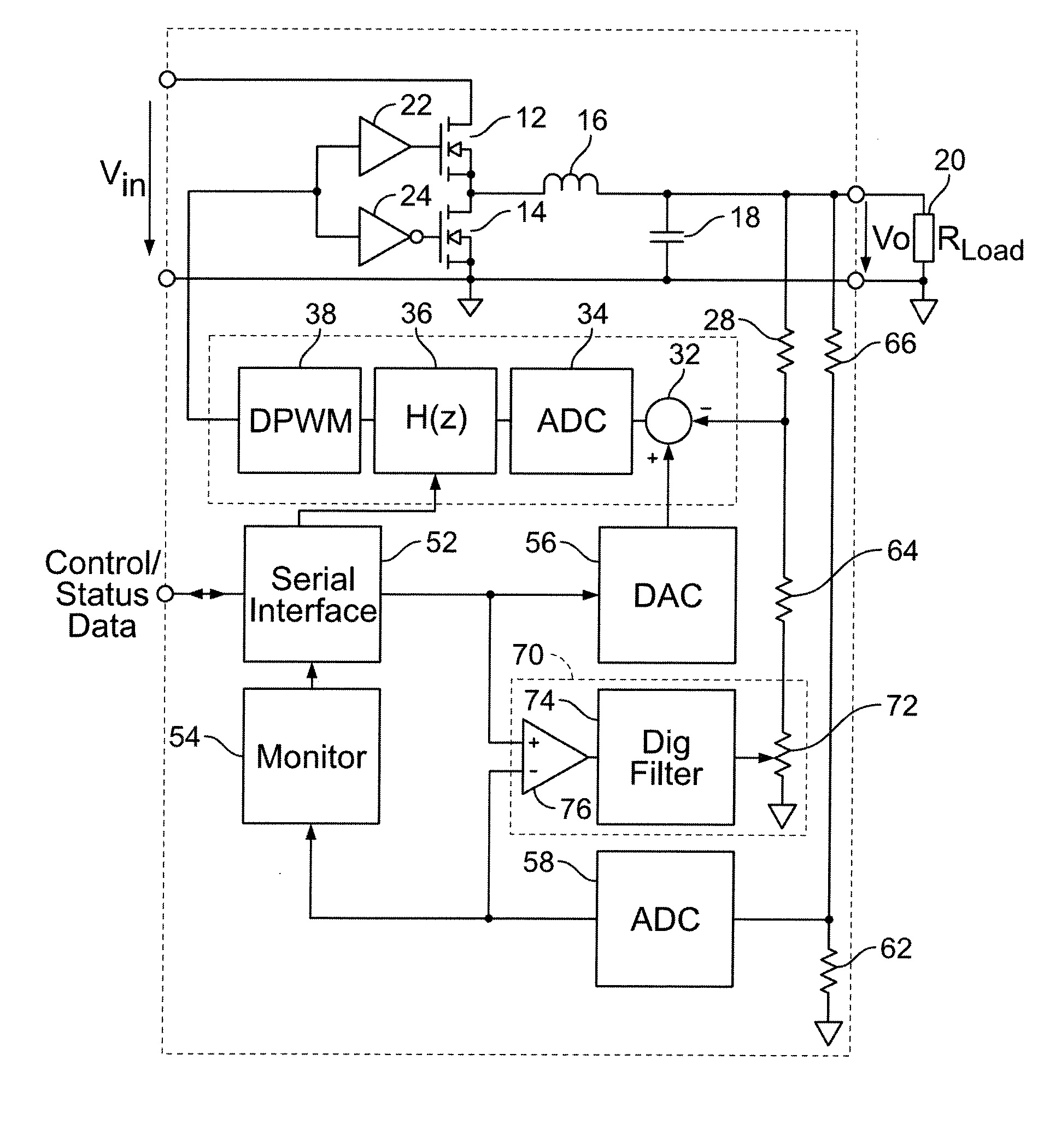

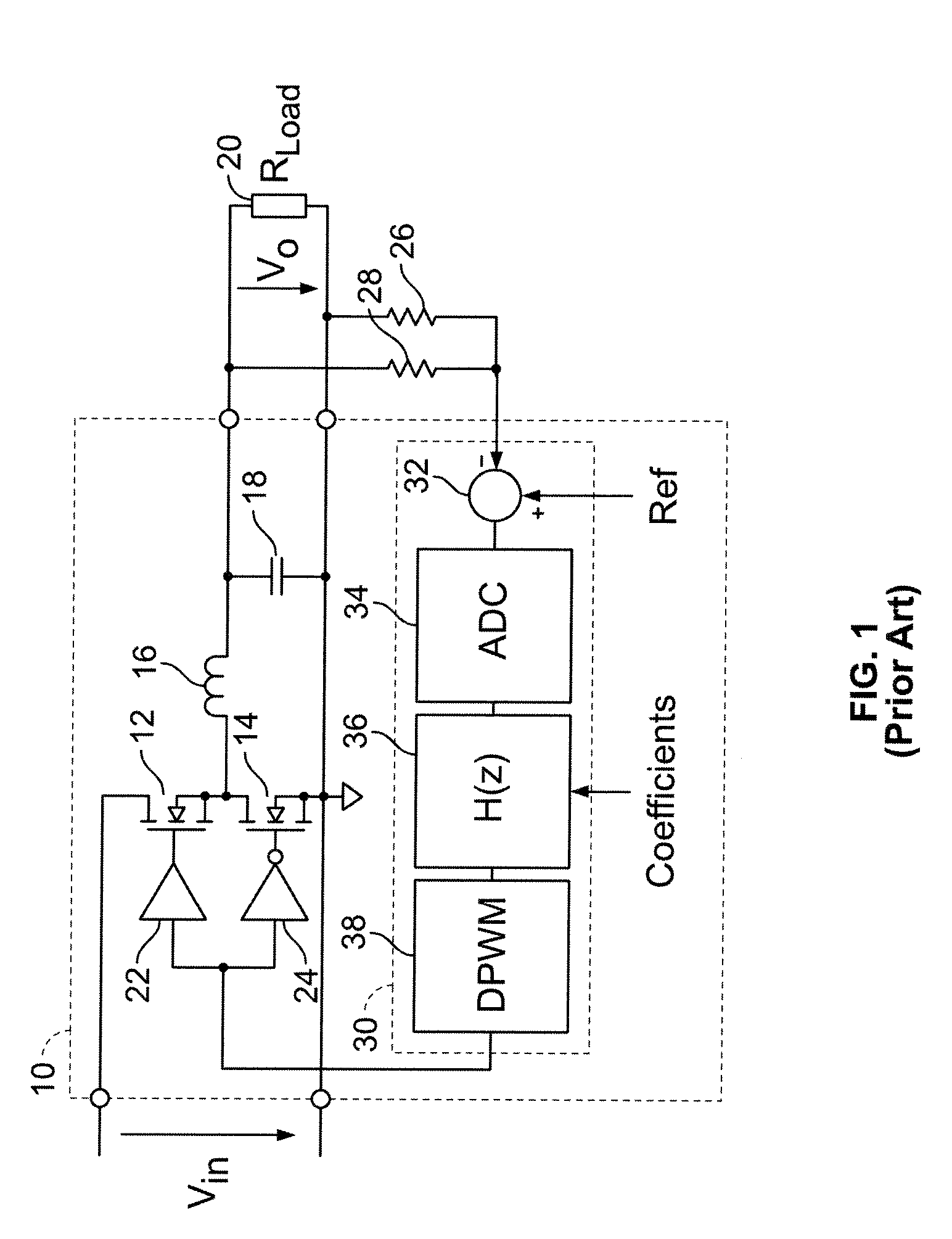

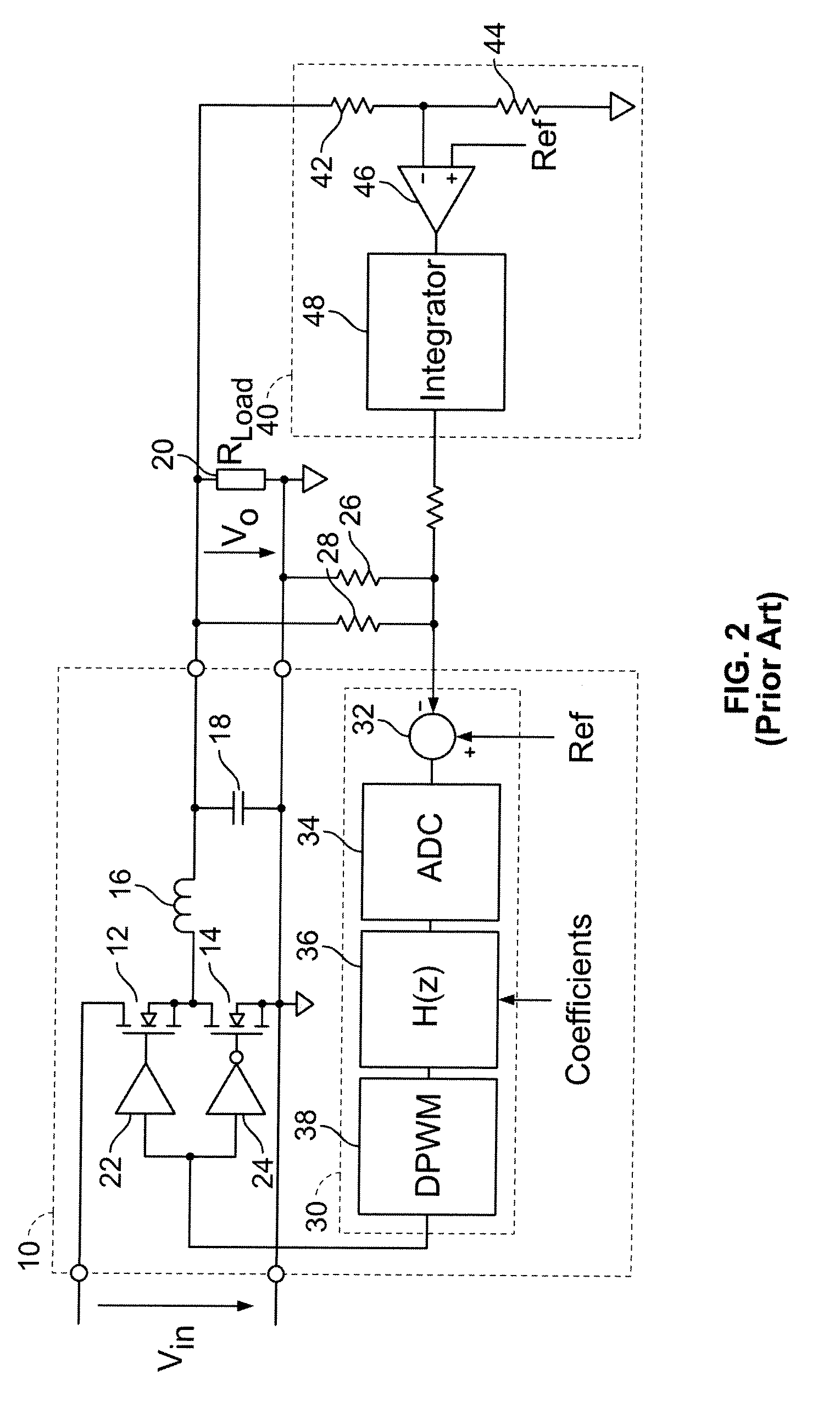

Digital double-loop output voltage regulation

ActiveUS7554310B2Increase speedImprove accuracyAnalogue/digital conversionElectric signal transmission systemsLow speedControl system

A switched mode voltage regulator has a digital control system that includes dual digital control loops. The voltage regulator comprises at least one power switch adapted to convey power between respective input and output terminals of the voltage regulator and a digital controller adapted to control operation of the power switches responsive to an output of the voltage regulator. The digital controller further comprises dual digital control loops in which a first control loop provides high speed with lower regulation accuracy and a second control loop has high accuracy with lower speed. Thus, the digital control system provides the advantages of both high speed and high regulation accuracy.

Owner:BEL POWER SOLUTIONS INC +1

Multi-frequency antenna with dual loops

ActiveUS7425924B2Increase capacityWide bandSimultaneous aerial operationsAntenna supports/mountingsOperation modeGSM

Owner:ADVANCED CONNECTEK INC

Digital double-loop output voltage regulation

ActiveUS20070182391A1Increase speedLow regulation accuracyAnalogue/digital conversionElectric signal transmission systemsLow speedControl system

A switched mode voltage regulator has a digital control system that includes dual digital control loops. The voltage regulator comprises at least one power switch adapted to convey power between respective input and output terminals of the voltage regulator and a digital controller adapted to control operation of the power switches responsive to an output of the voltage regulator. The digital controller further comprises dual digital control loops in which a first control loop provides high speed with lower regulation accuracy and a second control loop has high accuracy with lower speed. Thus, the digital control system provides the advantages of both high speed and high regulation accuracy.

Owner:BEL POWER SOLUTIONS INC +1

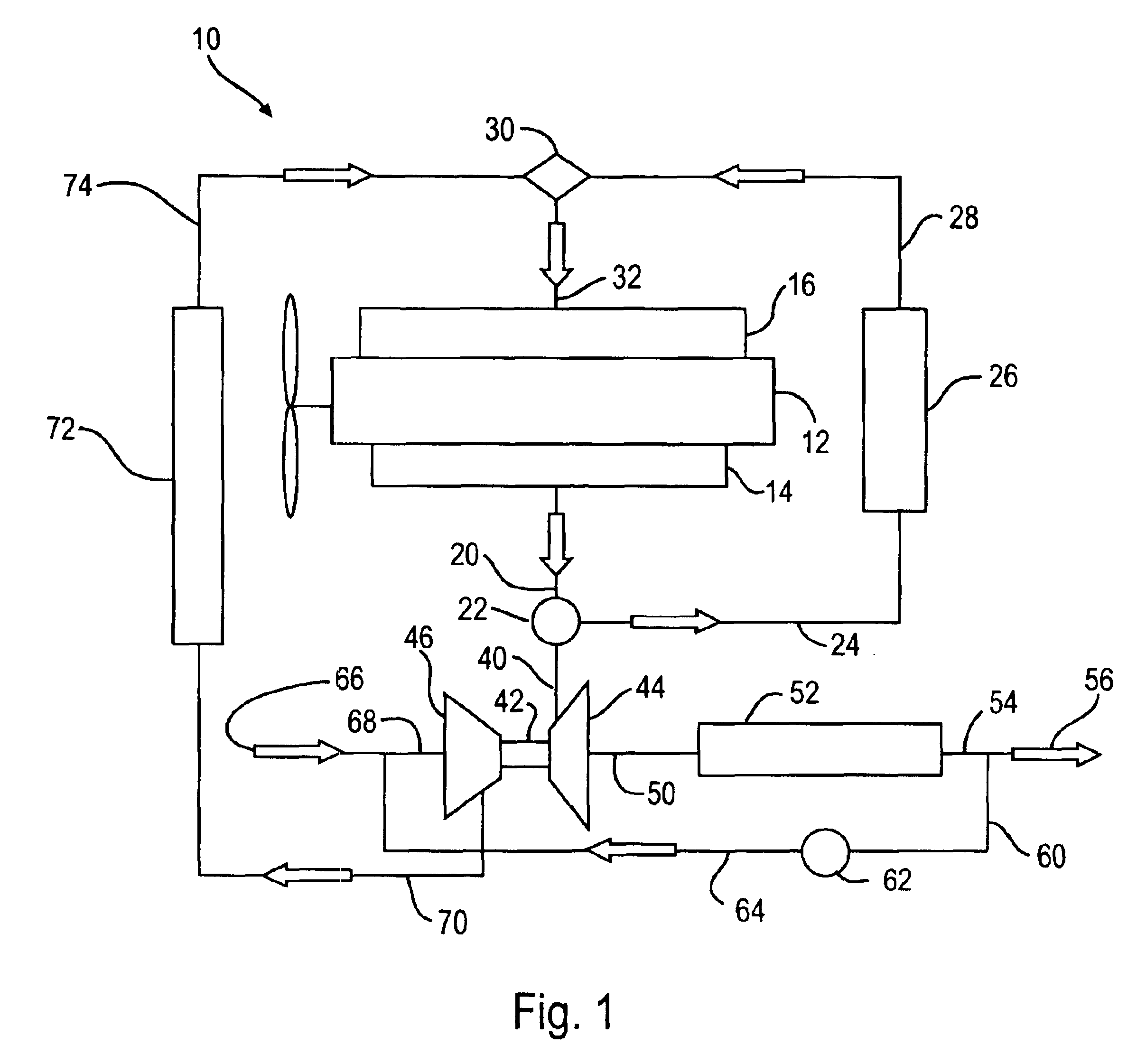

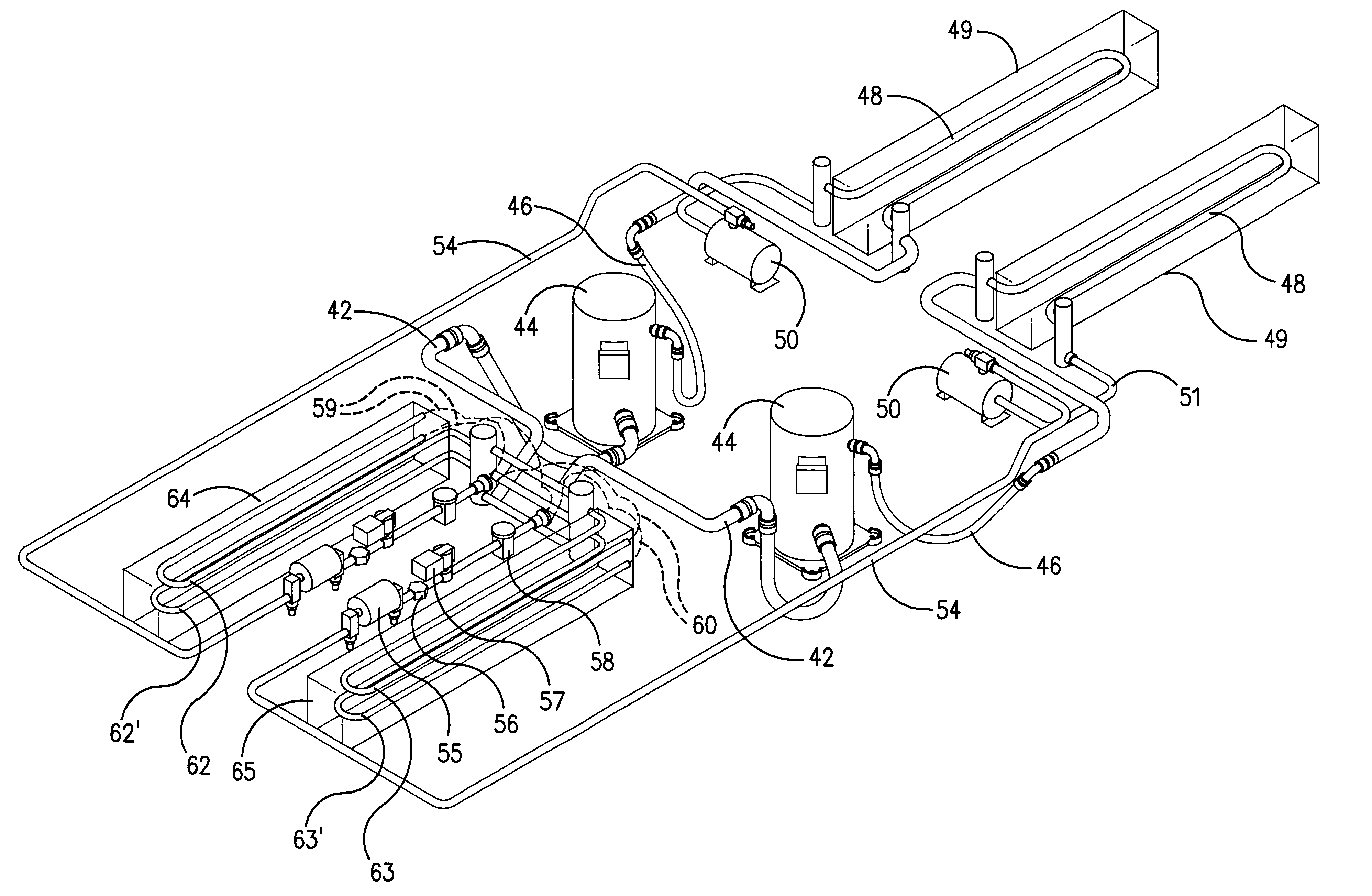

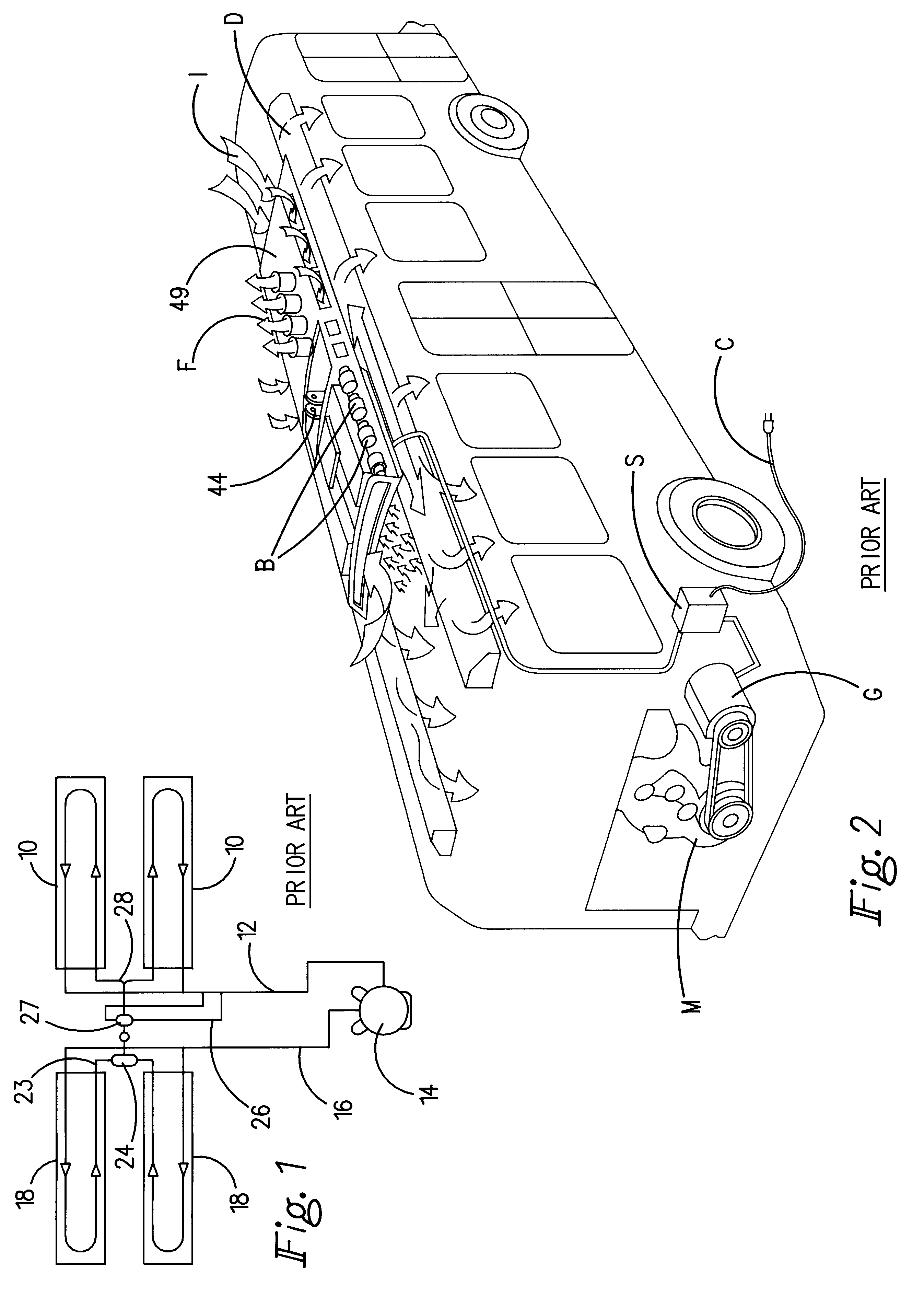

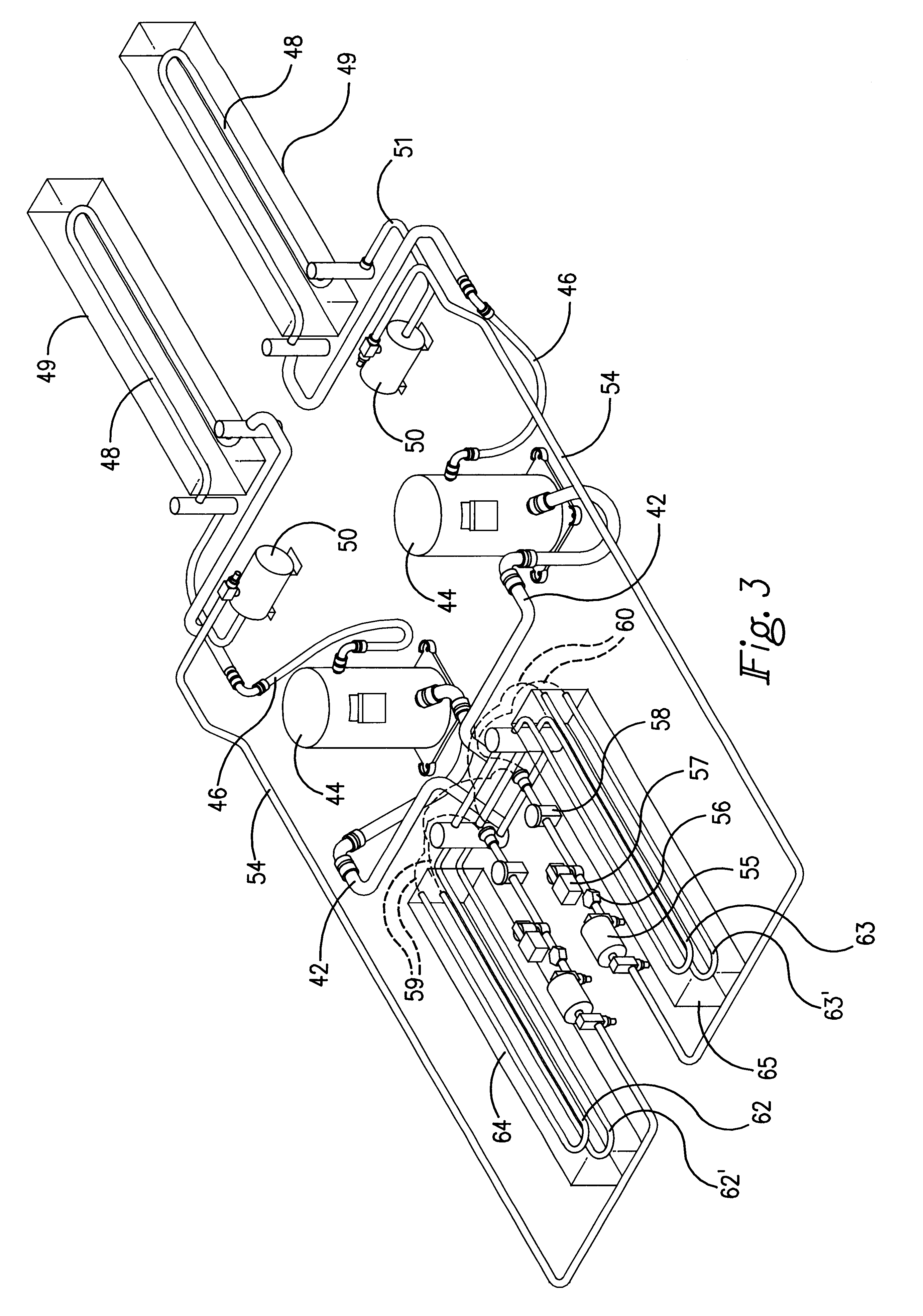

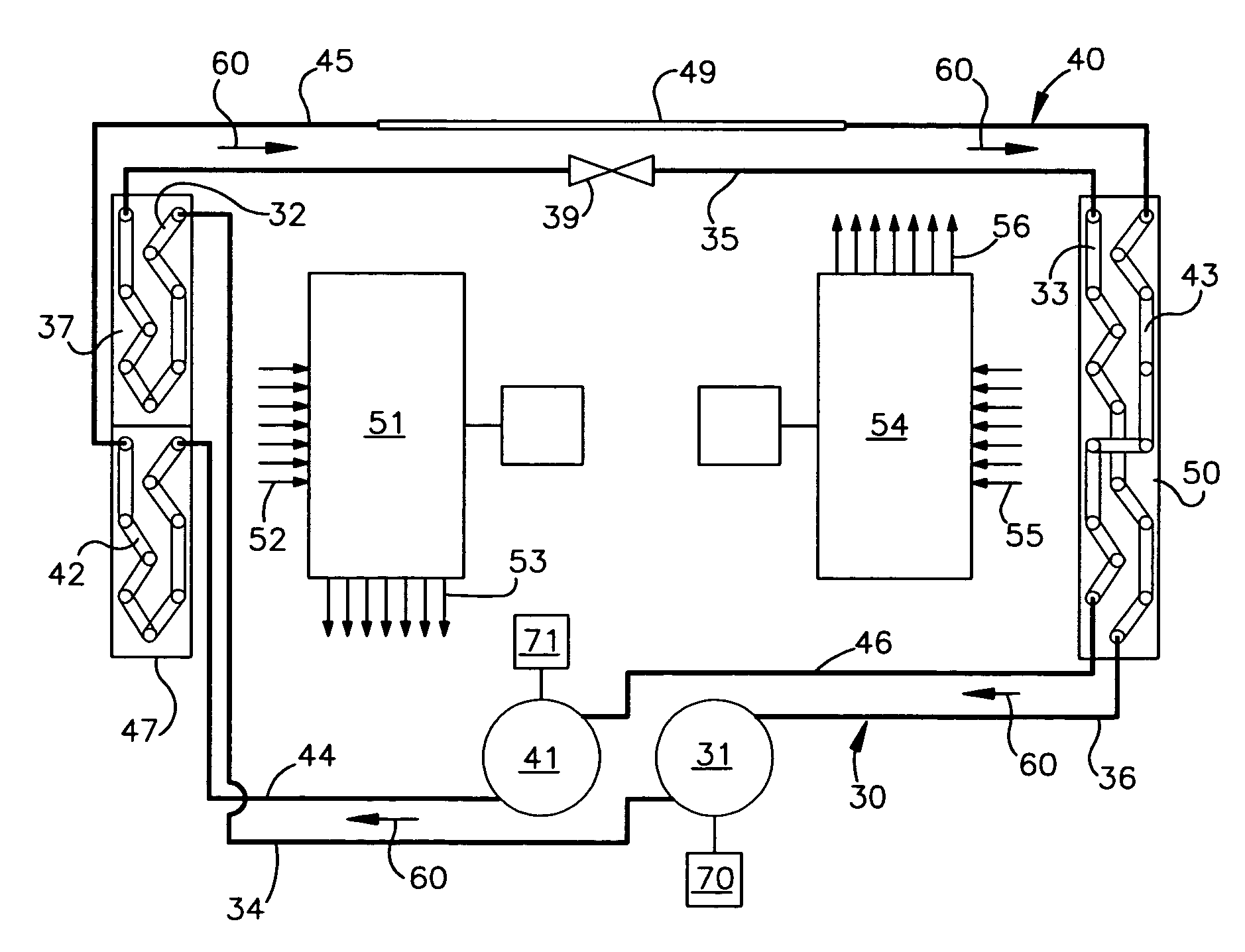

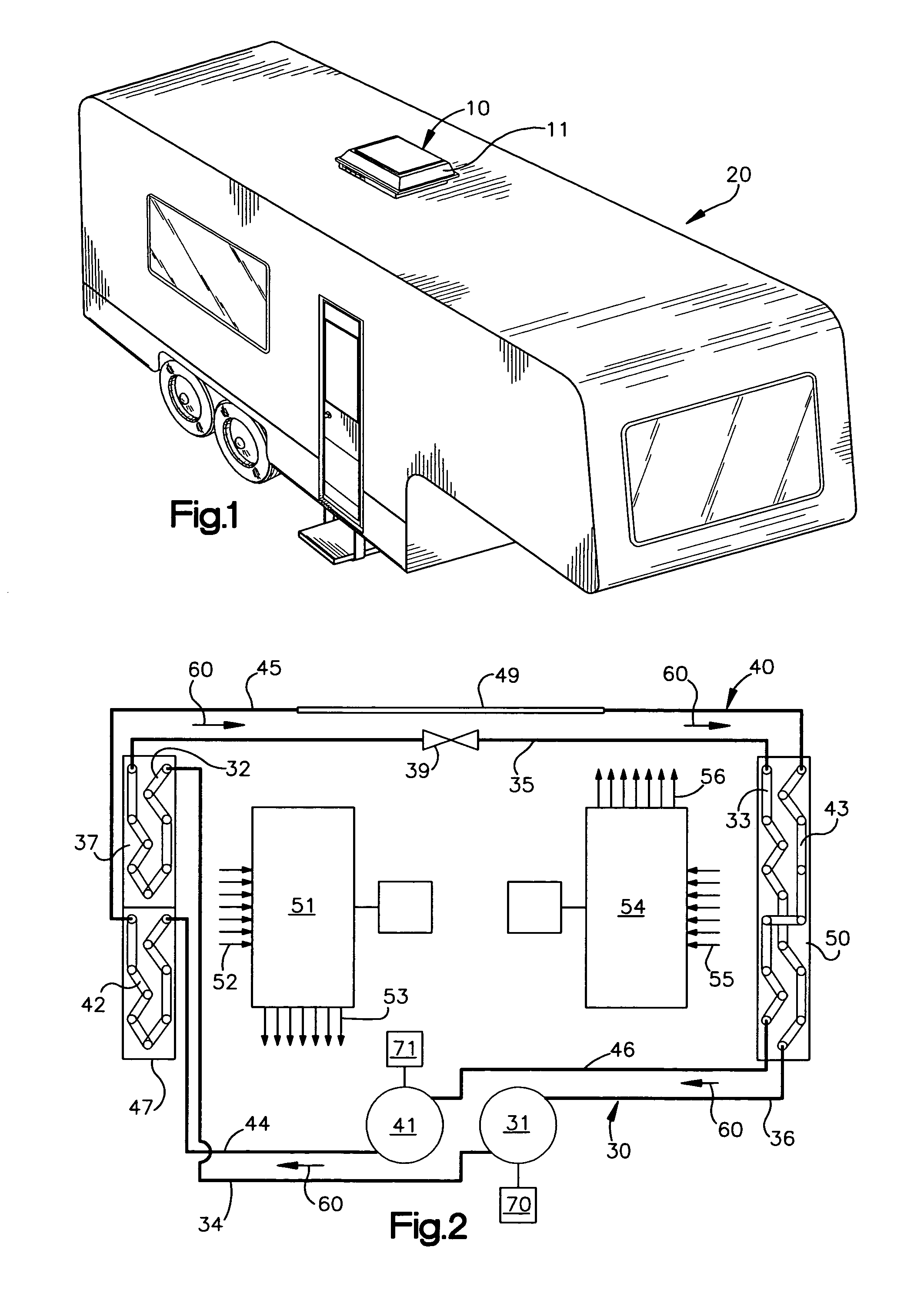

Dual loop vehicle air conditioning system

A vehicle air conditioning system is specifically adaptable for mounting on the roof of a bus and is made up of condenser sections in which air is circulated across each of the condensor sections, a pair of evaporator sections with air circulated across the evaporator sections in the usual manner, and a pair of compressors are arranged in a double loop refrigerant system between the condenser and evaporator sections in such a way that each compressor delivers refrigerant to one of the condensor sections from which the refrigerant is then advanced to one or more evaporator coils in each of the evaporator sections.

Owner:FERDOWS HOUSHANG K

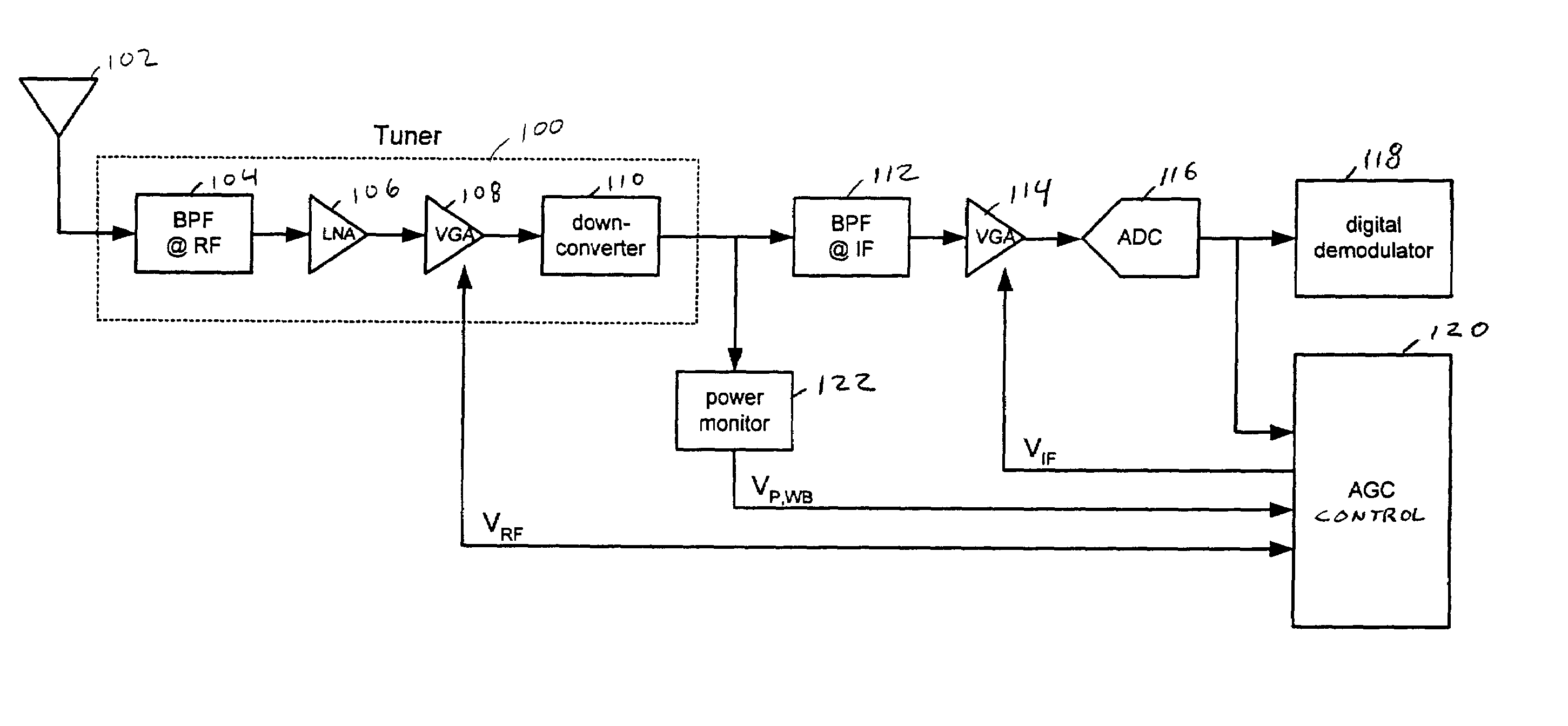

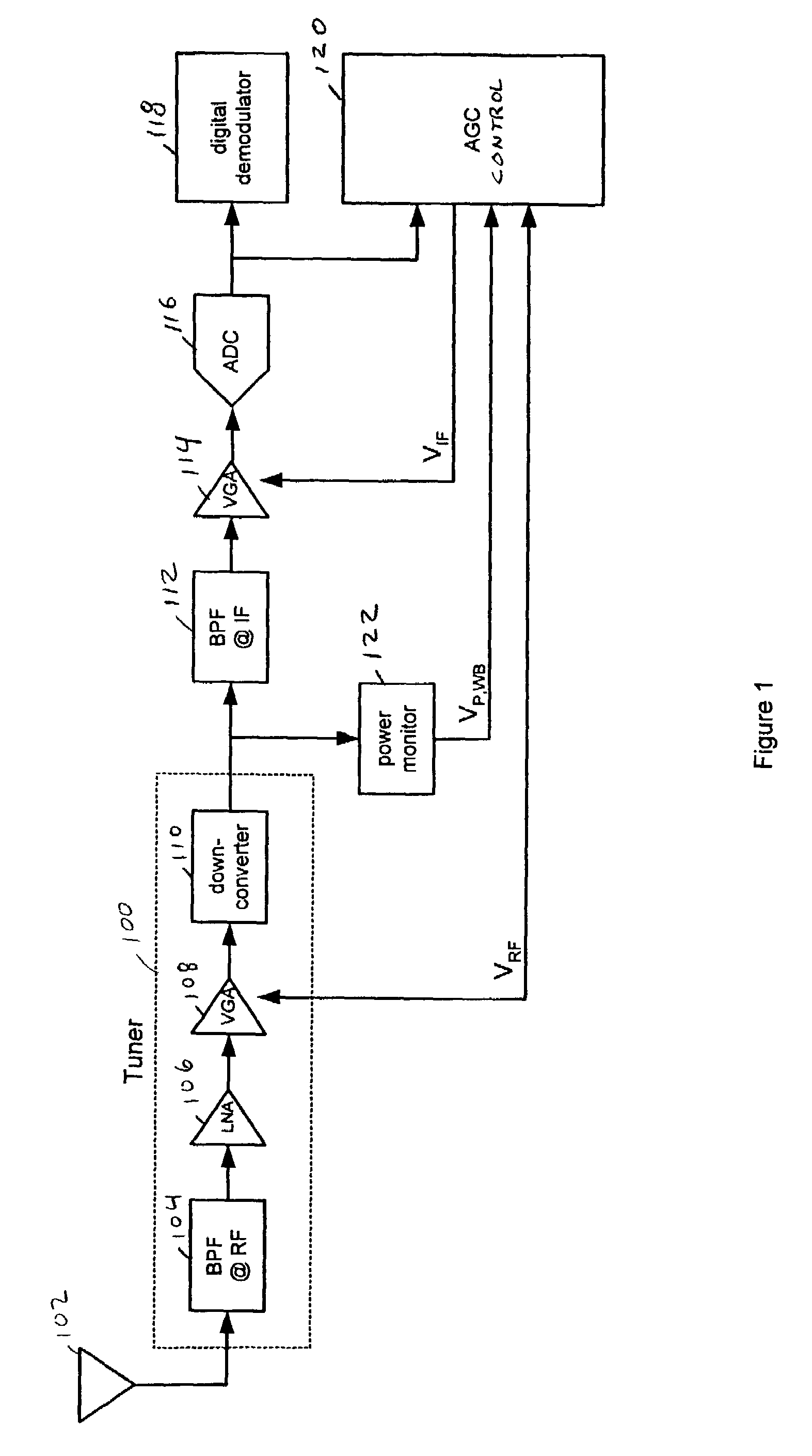

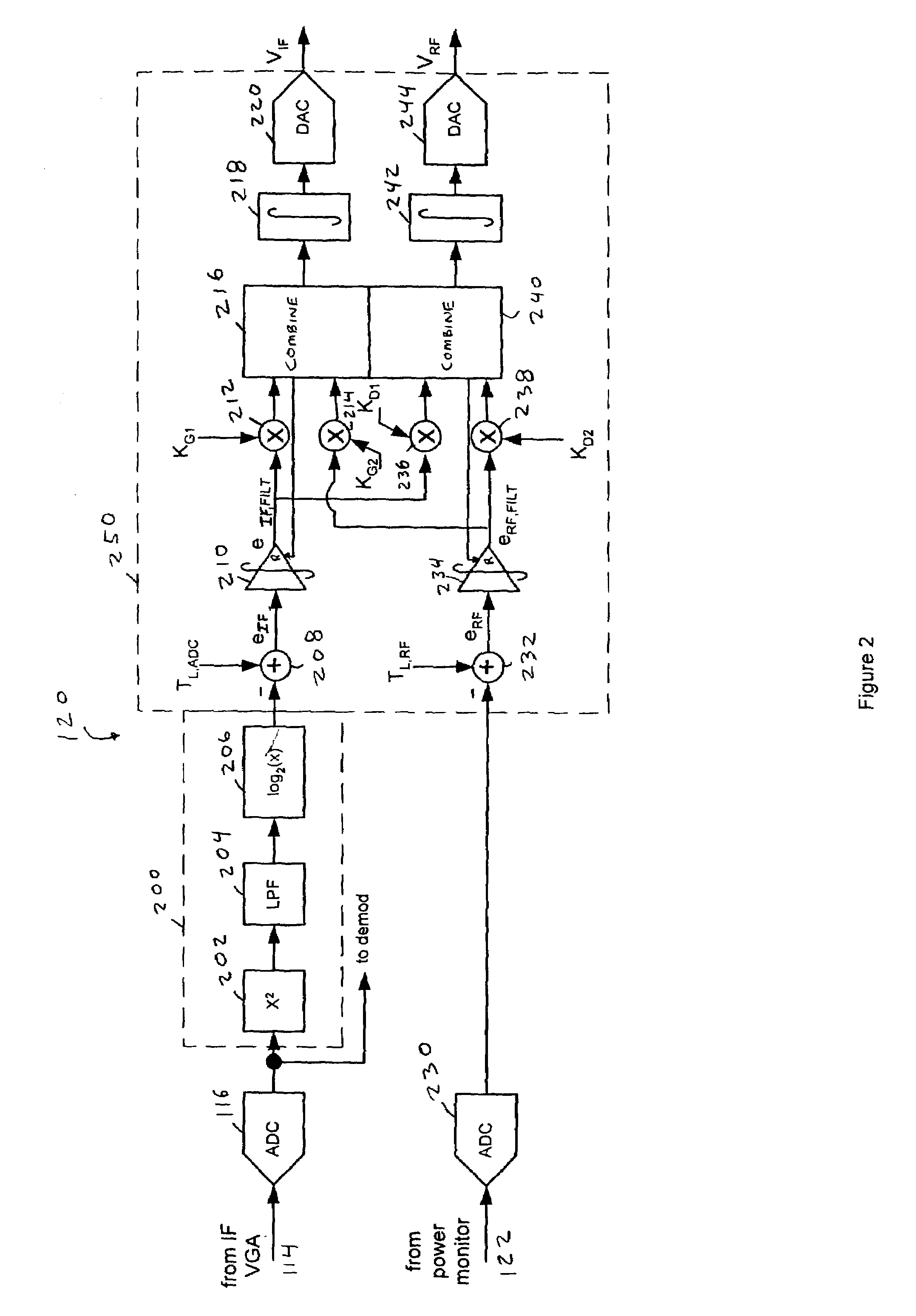

Dual loop automatic gain control

An AGC circuit includes both wide-band and narrow-band VGAs. Two power monitors monitor the power level of the two VGAs. Based upon the signals provided by the power monitors, the AGC circuit derives two error terms. The AGC circuit filters and combines the error terms to determine a desired adjustment to the total gain and a desired adjustment to the distribution of the gain between the wide-band VGA and the narrow-band VGA. The AGC circuit also minimizes the noise figure of the narrow-band VGA subject to linearity constraints.

Owner:BROADCOM CORP

Dual loop exhaust gas recirculation system for diesel engines and method of operation

ActiveUS6988365B2Internal combustion piston enginesNon-fuel substance addition to fuelTurbochargerExhaust fumes

A catalyst bed temperature of an aftertreatment device is maintained and the operational regime for stable and smokeless rich combustion is expanded by use of a dual loop exhaust gas recirculation system. Under light load conditions, at least a portion of the exhaust gas is recirculated through a relatively high pressure exhaust gas recirculation loop, wherein there is no substantial reduction in recirculated exhaust gas temperature or pressure. When operating in relatively medium or higher load operating regimes of the engine, at least a portion of the exhaust gas is passed through a relatively low pressure recirculation mode in which work is extracted from the recirculated gas by the turbine stage of a turbocharger and an exhaust gas recirculation cooler prior to reintroduction into the intake manifold of the engine.

Owner:SOUTHWEST RES INST

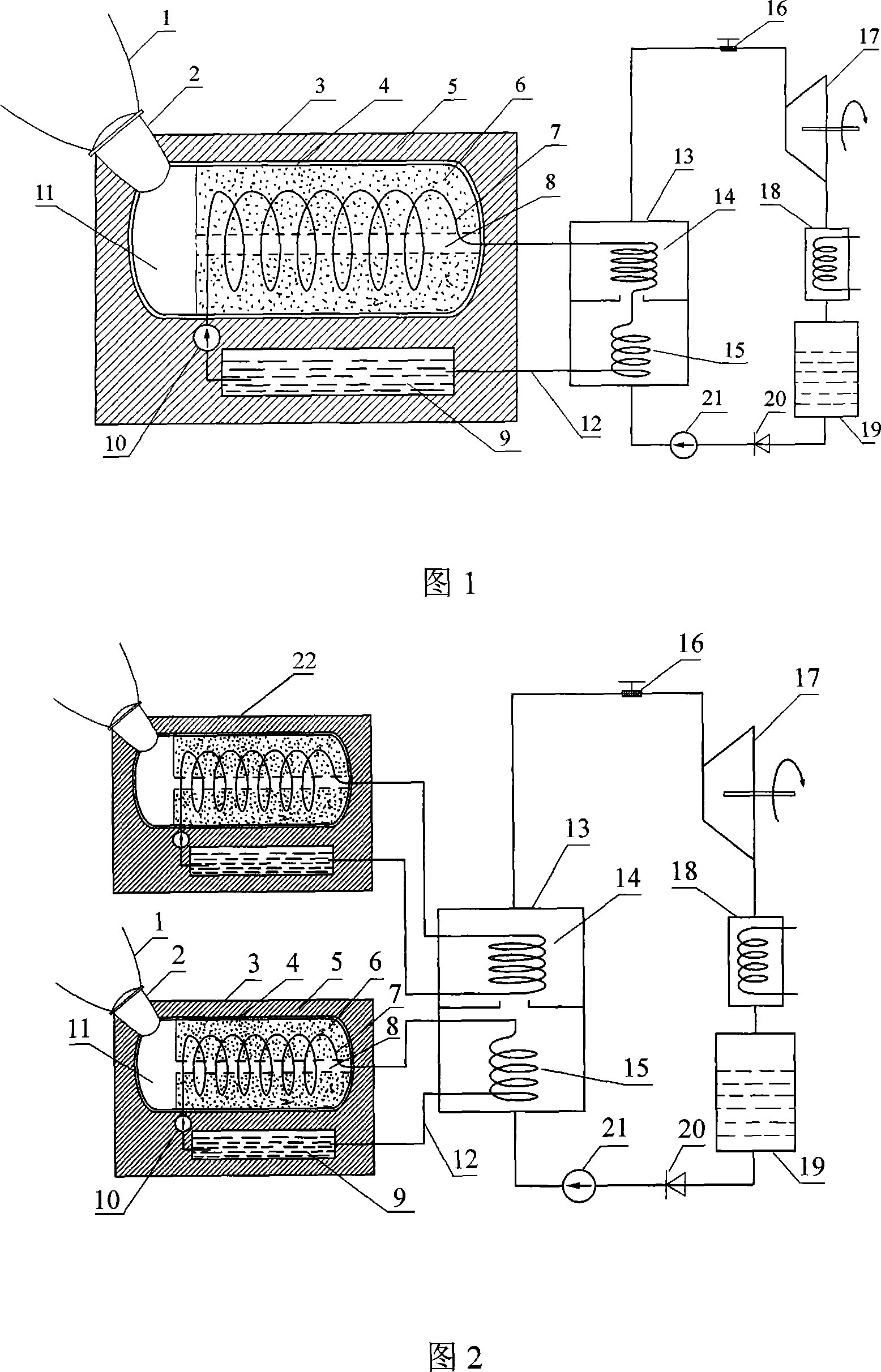

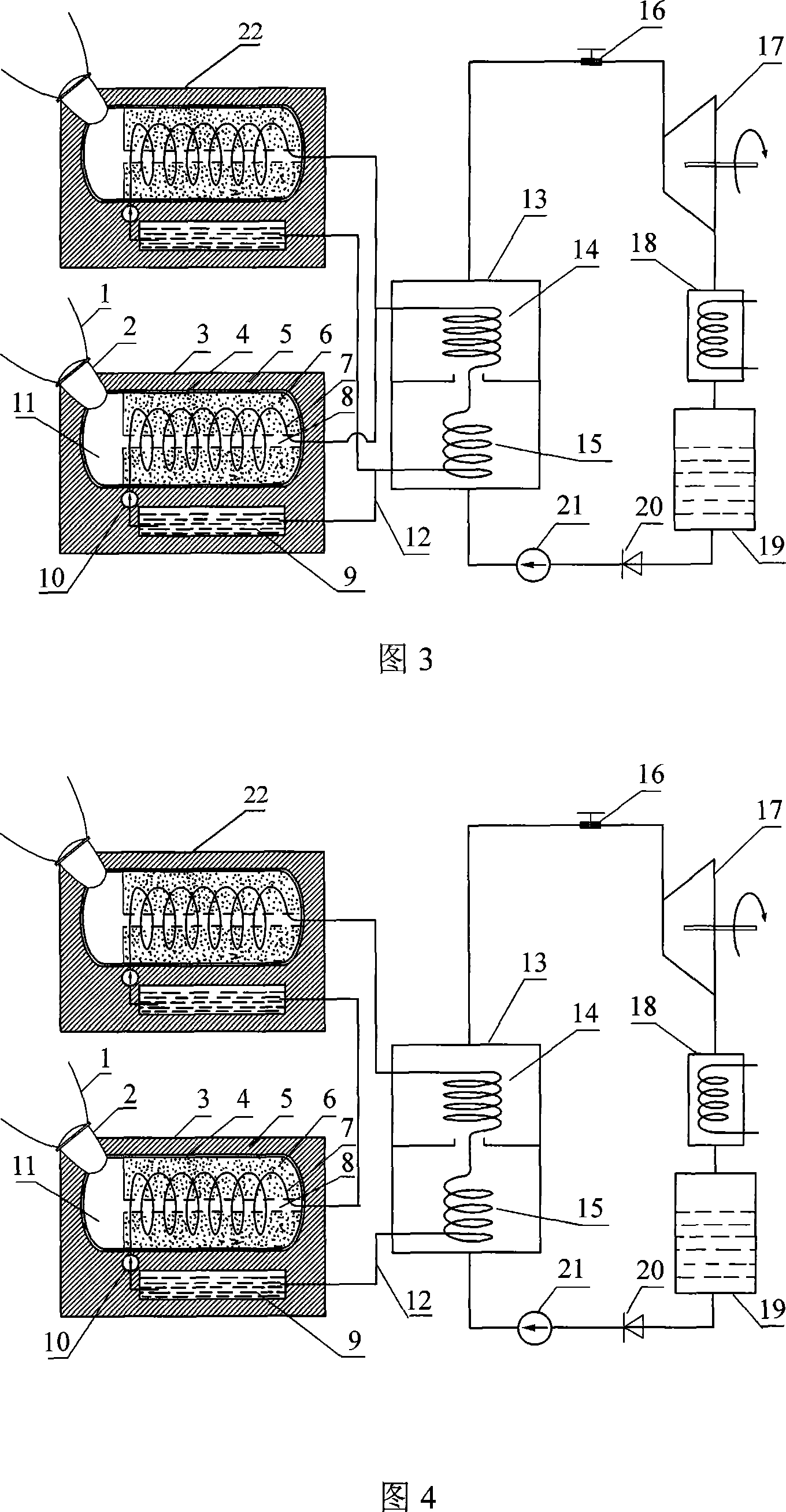

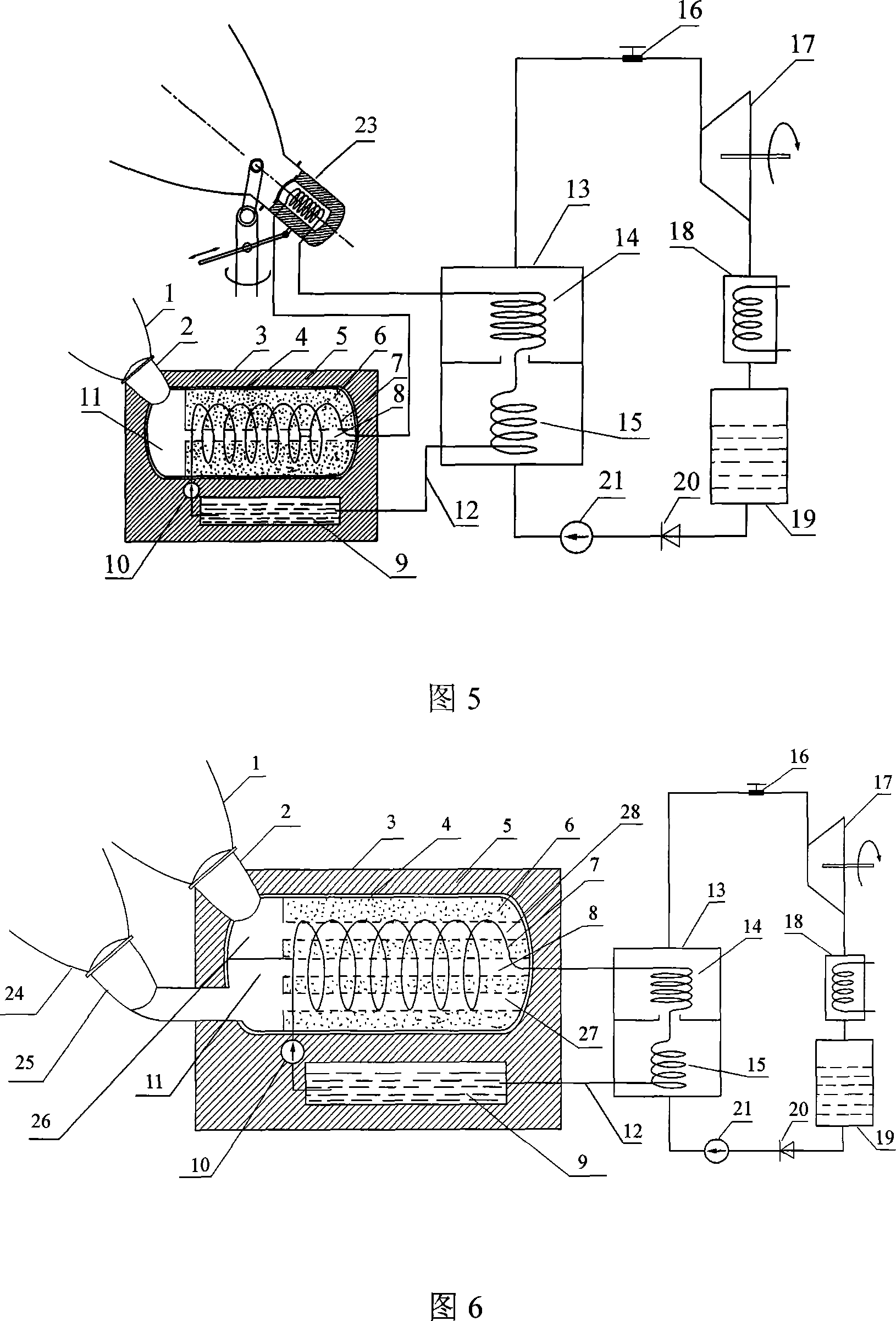

Convergence type condensation high temperature energy-concentrated heat-stored double loop driven solar energy heat power device

InactiveCN101105342AUniform and more rapid incomingEven and faster exportSolar heating energyFrom solar energyHigh temperature storageThermal energy

The invention relates to a converging type solar thermal power device capable of condensing sunlight, storing heat using high temperature phase change energy storage material and driving double loops, belonging to the technical field of solar energy collection and solar energy heat utilization. The device comprises a funnel-shaped converging type solar energy condenser, a transparent light transmitting window, an energy accumulator, a high temperature heat-conducting oil heat supply circulating system, a superheated steam generator, and a Rankine cycle-based heat-power converting system. The sunlight is condensed by the funnel-shaped converging type solar energy condenser, and entered into the energy accumulator through the transparent light transmitting window to realize high temperature storage therein, the high temperature heat-conducting oil heat supply circulating system transmits the high temperature in the energy accumulator to the superheated steam generator to heat working fluid to generate high pressure high temperature superheated steam therein, and converts heat energy to power through thermodynamic cycle. The invention is a device for supplying power or electric energy for user by condensing sunlight, storing heat using high temperature phase change energy storage material, and driving heat-power converting system using high temperature heat energy.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

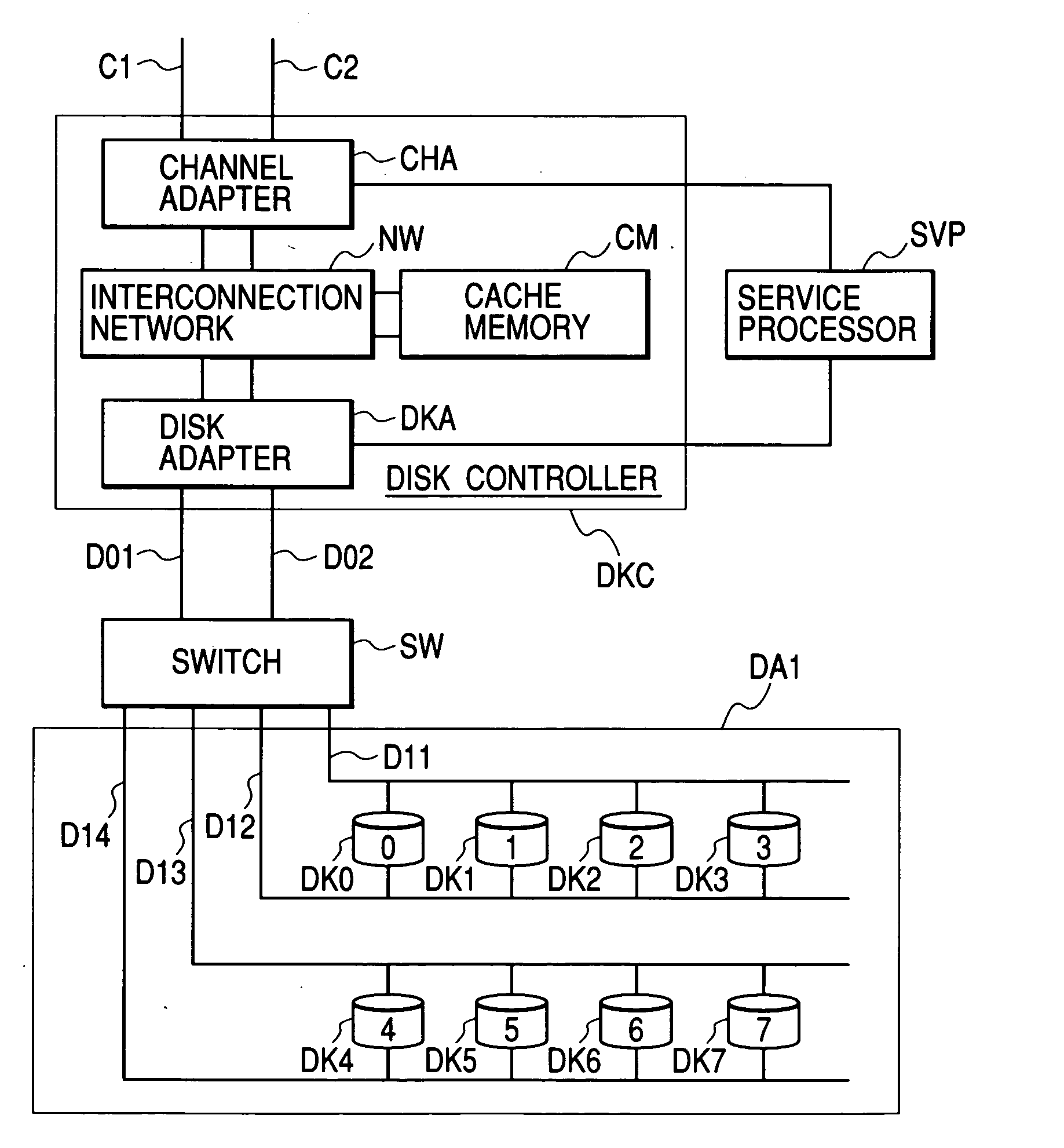

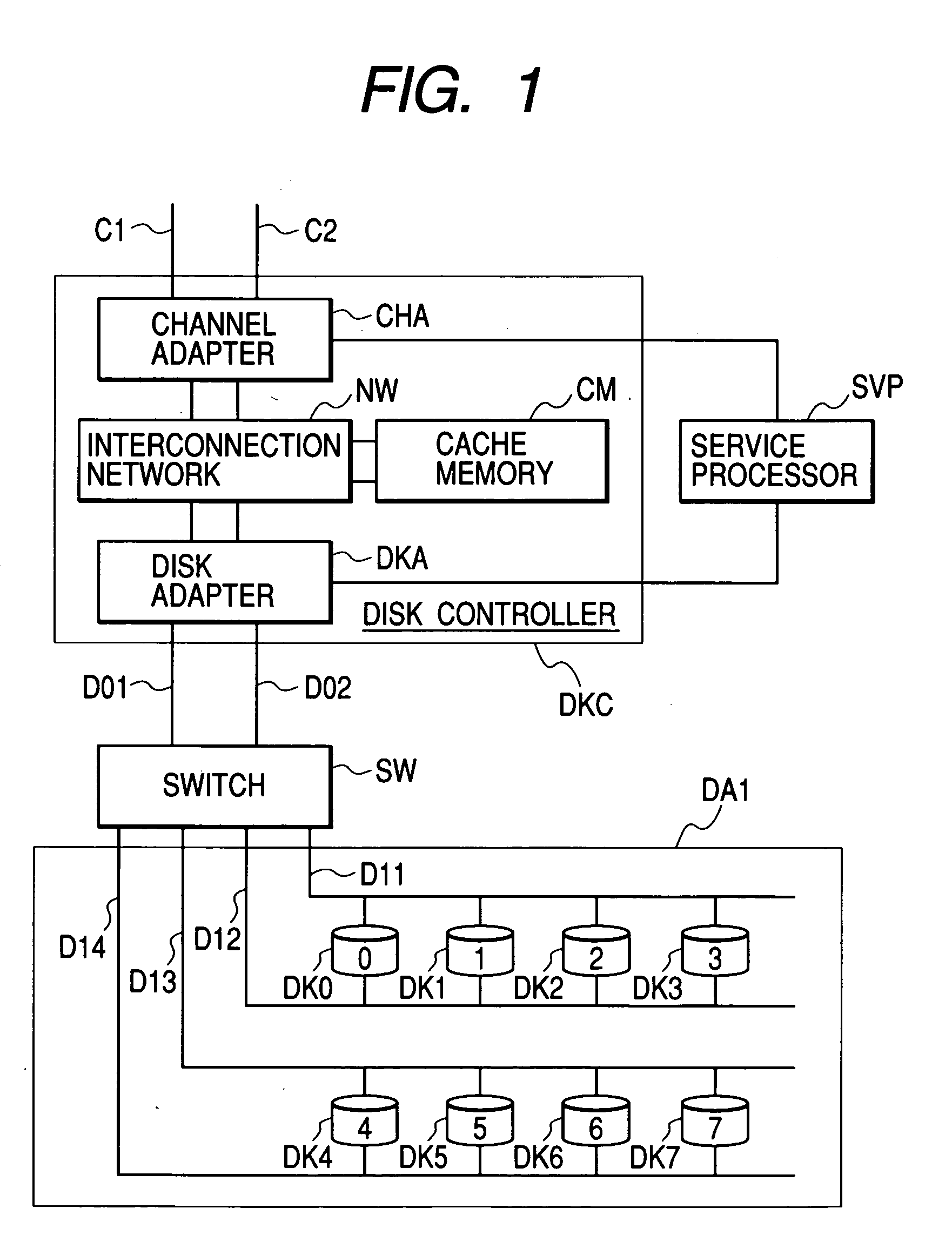

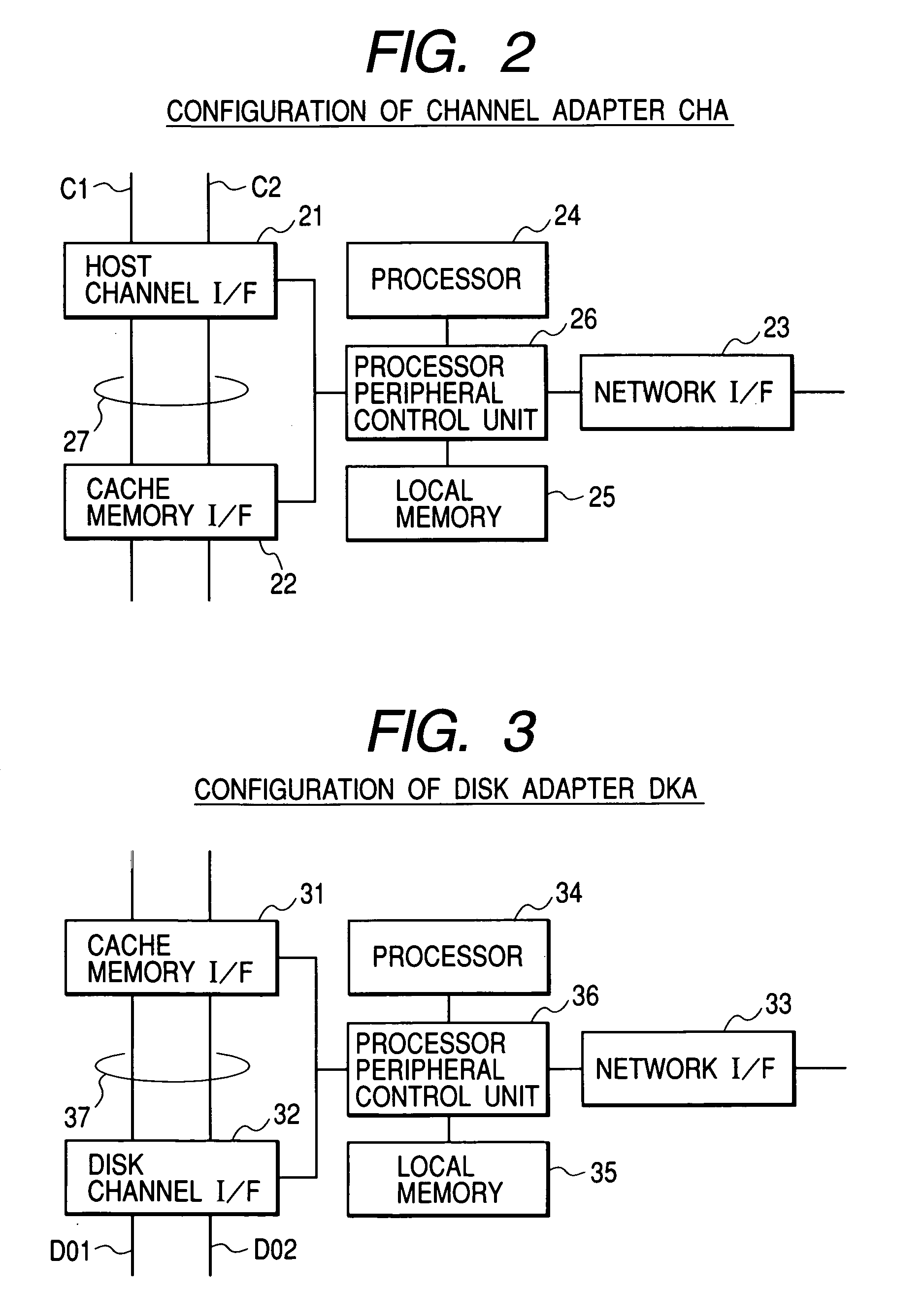

Storage device and controlling method thereof

InactiveUS20050108476A1Improve reliabilityInput/output to record carriersTransmissionOperating systemDual loop

Owner:HITACHI LTD

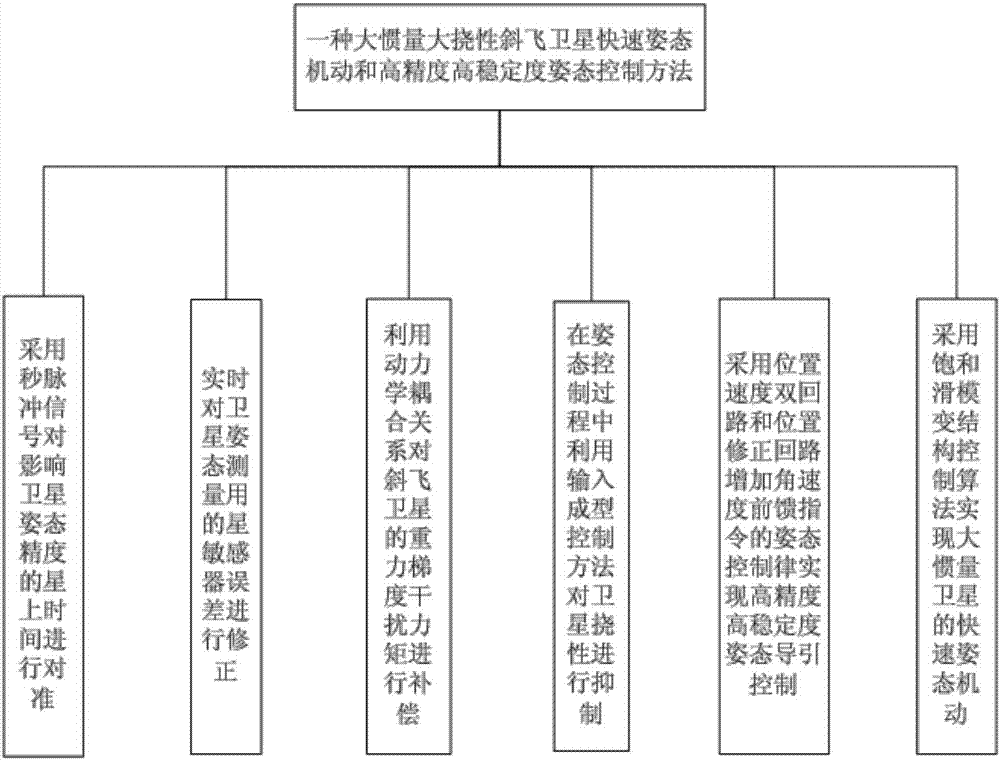

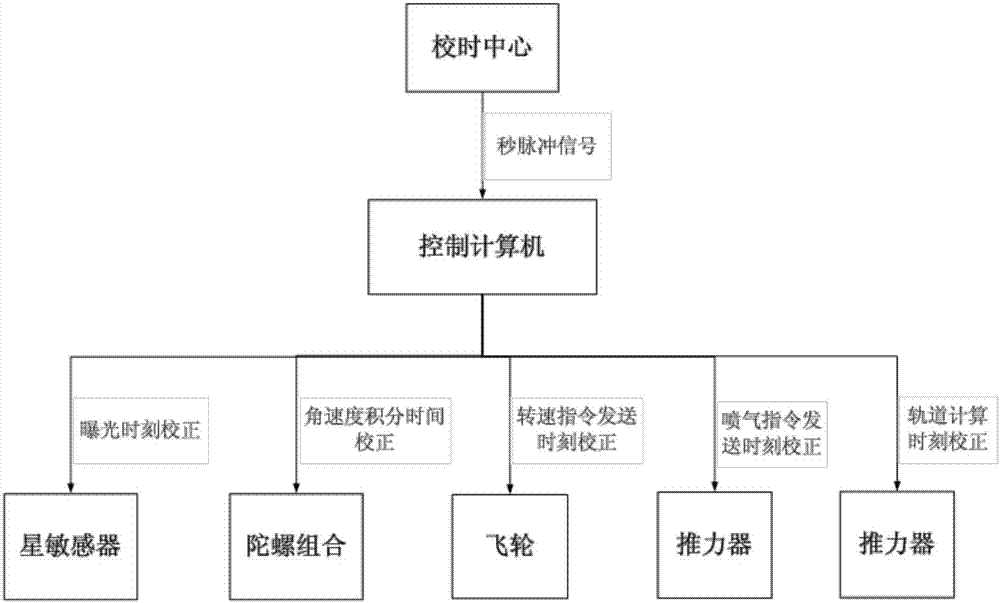

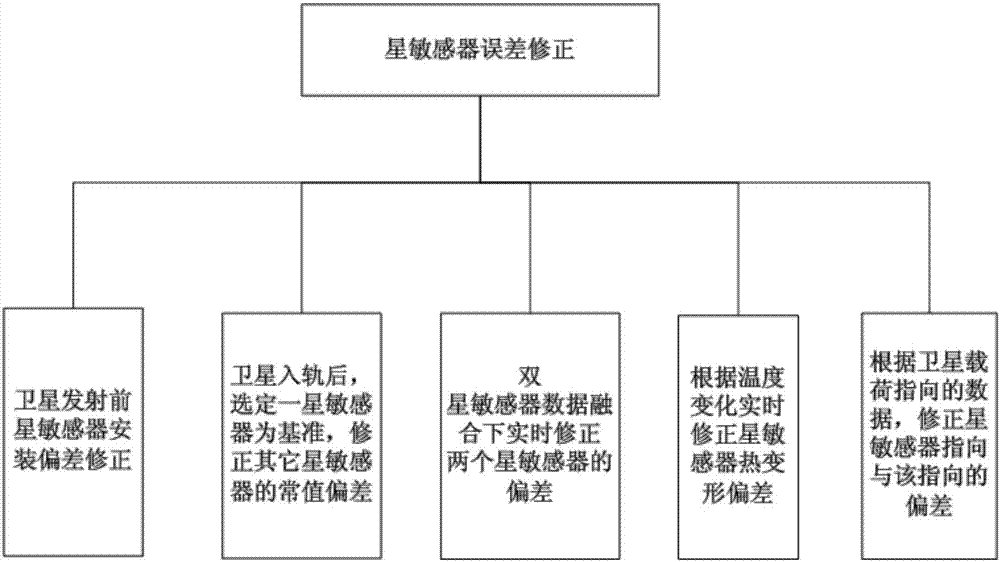

Attitude control method

ActiveCN106915477AImprove performanceReduce development costsCosmonautic vehiclesAttitude controlAttitude controlGuidance control

The invention discloses an attitude control method. The attitude control method comprises the following procedures that the on-satellite time influencing the satellite attitude precision is aligned through a second pulse signal; a satellite sensor error used for satellite attitude measurement is corrected in real time; the gravity gradient disturbance torque of an oblique flying satellite is compensated through a dynamics coupling relationship; the satellite flexibility is restrained through an input forming control method in the attitude controlling process; the attitude control law of an angular velocity feedforward instruction is increased through position and speed double loops and a position correcting loop to achieve high-precision and high-stability attitude guidance control; and quick attitude maneuver of the large-inertia satellite is achieved through a saturated sliding mold structural control algorithm. The attitude control method has the advantages that the computing method is simple, control is flexible, the attitude control method can be applied to attitude control of the large-inertia large-flexible oblique flying satellite, the property of the satellite is greatly improved, and researching and manufacturing cost of satellite hardware is reduced.

Owner:SHANGHAI AEROSPACE CONTROL TECH INST

Dual-circuit refrigeration system

ActiveUS6978630B2Air-treating devicesCompression machines with non-reversible cycleEngineeringAir conditioning

A refrigeration system and method of refrigeration employ dual refrigeration circuits. Each circuit has an independent compressor, condenser and evaporator. In one refrigeration circuit, the flow of the refrigerant from the condenser to the evaporator is regulated in response to variations in the heat load at the evaporator while, in the other refrigeration circuit, the refrigerant is passed from the condenser to the evaporator at a substantially constant rate of flow. The refrigeration system can be used as a cooling system, including an air conditioning system, and as a heat pump. The evaporator in both circuits may be incorporated within a common heat exchanger as may the two condensers. Additionally, the flow of the refrigerant from the condenser to the evaporator in one refrigeration circuit may be regulated in response to variations in the heat load in the evaporator in that refrigeration circuit by a thermal expansion valve.

Owner:DOMETIC CORP

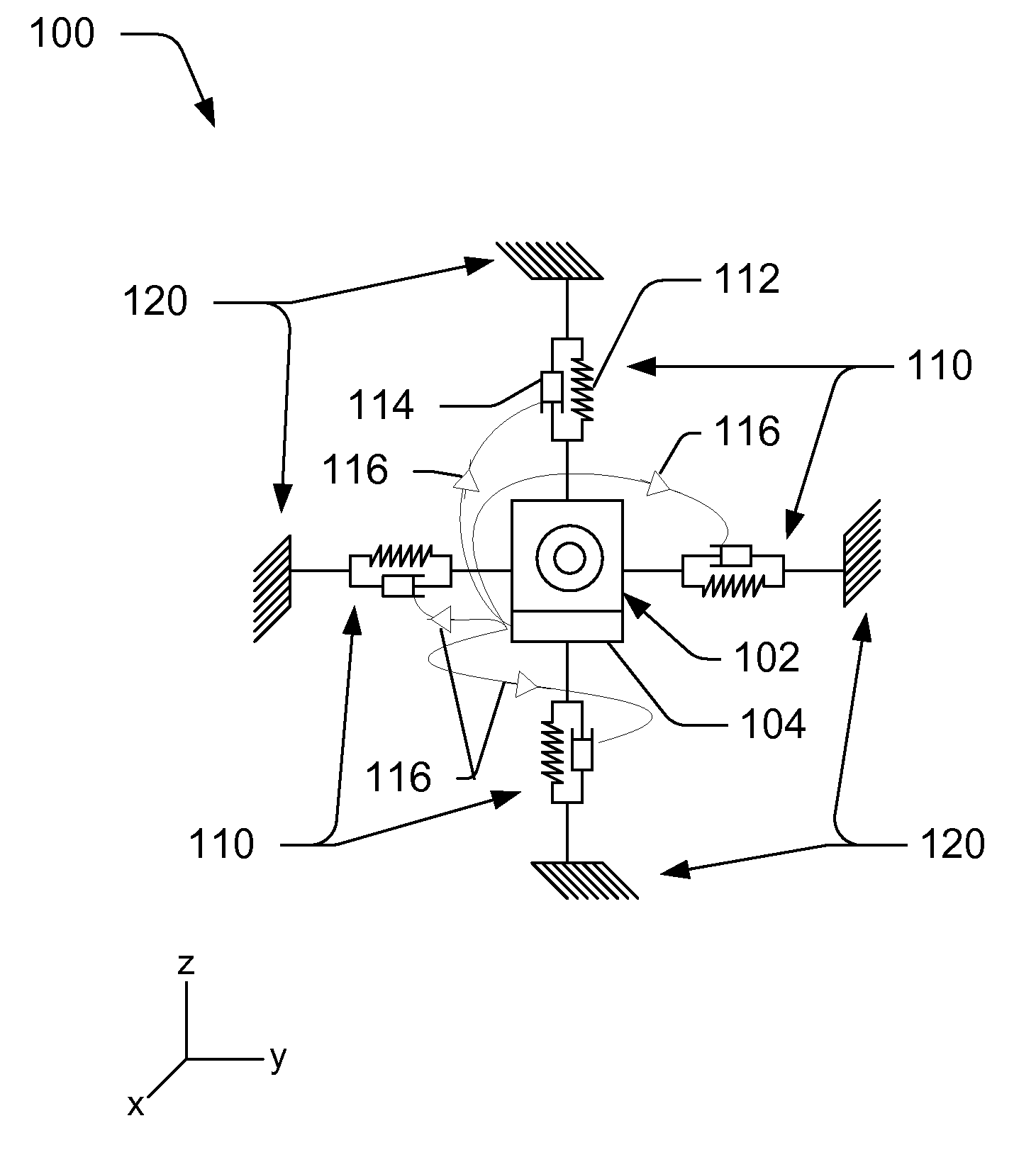

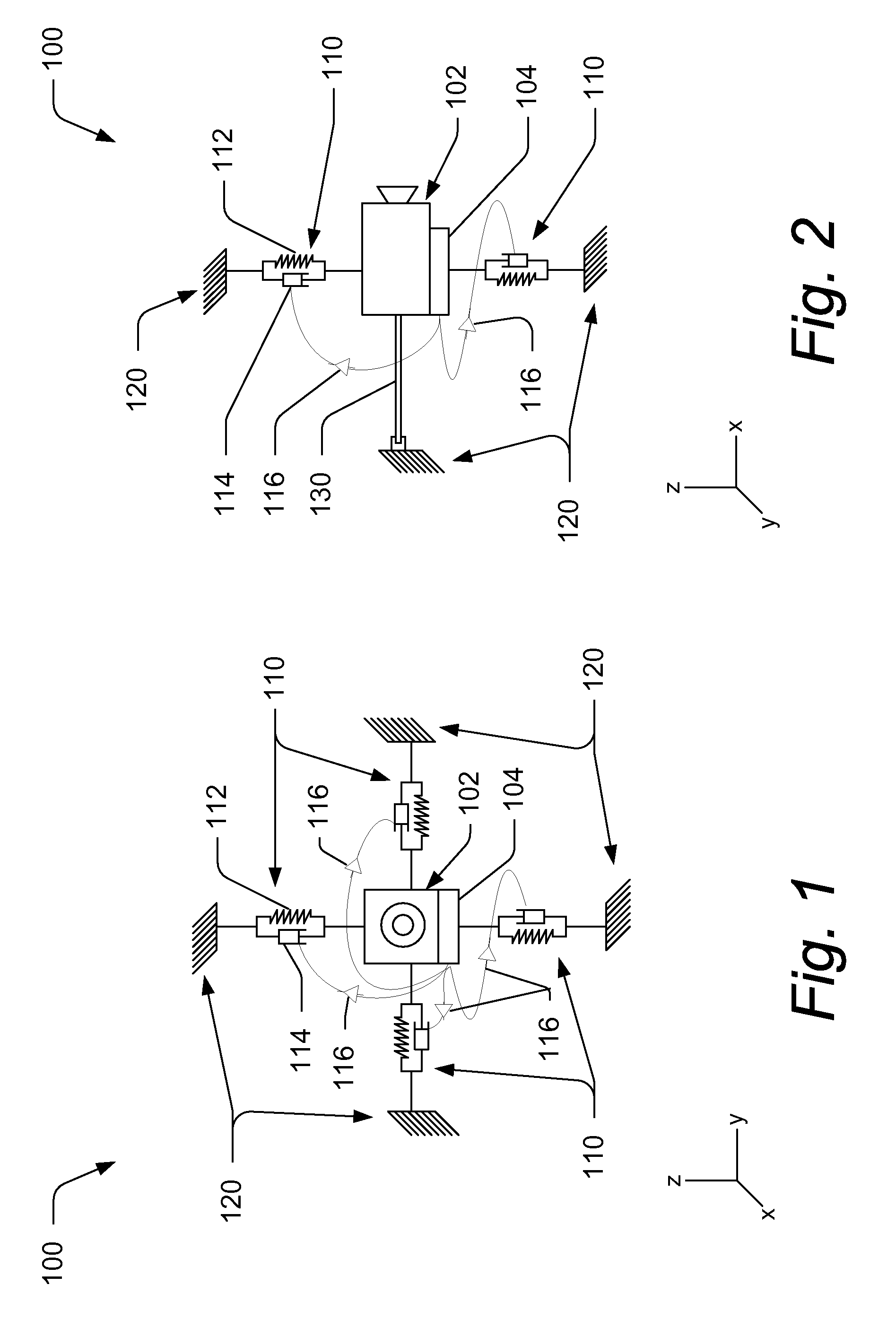

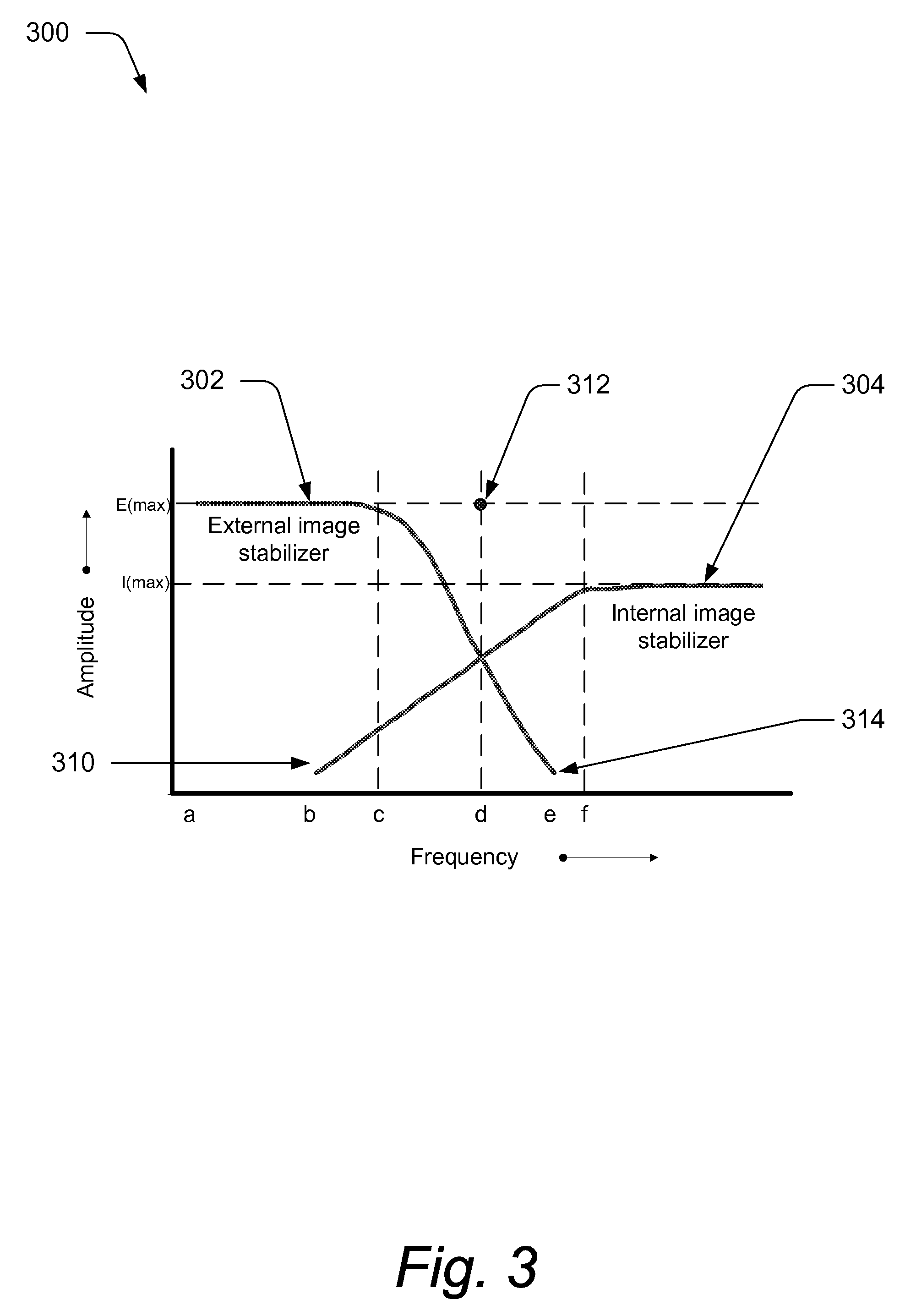

Dual Loop Stabilization of Video Camera Images

InactiveUS20080158371A1Improve stabilityReduce the impactTelevision system detailsColor television detailsControl signalMotion sensing

Dual loop stabilization of video images is disclosed. In one embodiment, an apparatus includes a video camera having a first image stability control component configured to stabilize a video image in a first motion environment. A second image stability control component is coupled between the video camera and a moveable platform and is configured to stabilize the video image in a second motion environment. A motion sensing device detects movement of the video camera and transmits a control signal to adjust a stabilization response of the second image stability control component according to the movement. In some embodiments, a first amplitude range of the first motion environment is at least partially lower than a second amplitude range of the second motion environment, and a first frequency range of the first motion environment is at least partially higher than a second frequency range of the second motion environment.

Owner:THE BOEING CO

Dual loop exhaust gas recirculation system for diesel engines and method of operation

ActiveUS20050103014A1Internal combustion piston enginesNon-fuel substance addition to fuelTurbochargerExhaust fumes

A catalyst bed temperature of an aftertreatment device is maintained and the operational regime for stable and smokeless rich combustion is expanded by use of a dual loop exhaust gas recirculation system. Under light load conditions, at least a portion of the exhaust gas is recirculated through a relatively high pressure exhaust gas recirculation loop, wherein there is no substantial reduction in recirculated exhaust gas temperature or pressure. When operating in relatively medium or higher load operating regimes of the engine, at least a portion of the exhaust gas is passed through a relatively low pressure recirculation mode in which work is extracted from the recirculated gas by the turbine stage of a turbocharger and an exhaust gas recirculation cooler prior to reintroduction into the intake manifold of the engine.

Owner:SOUTHWEST RES INST

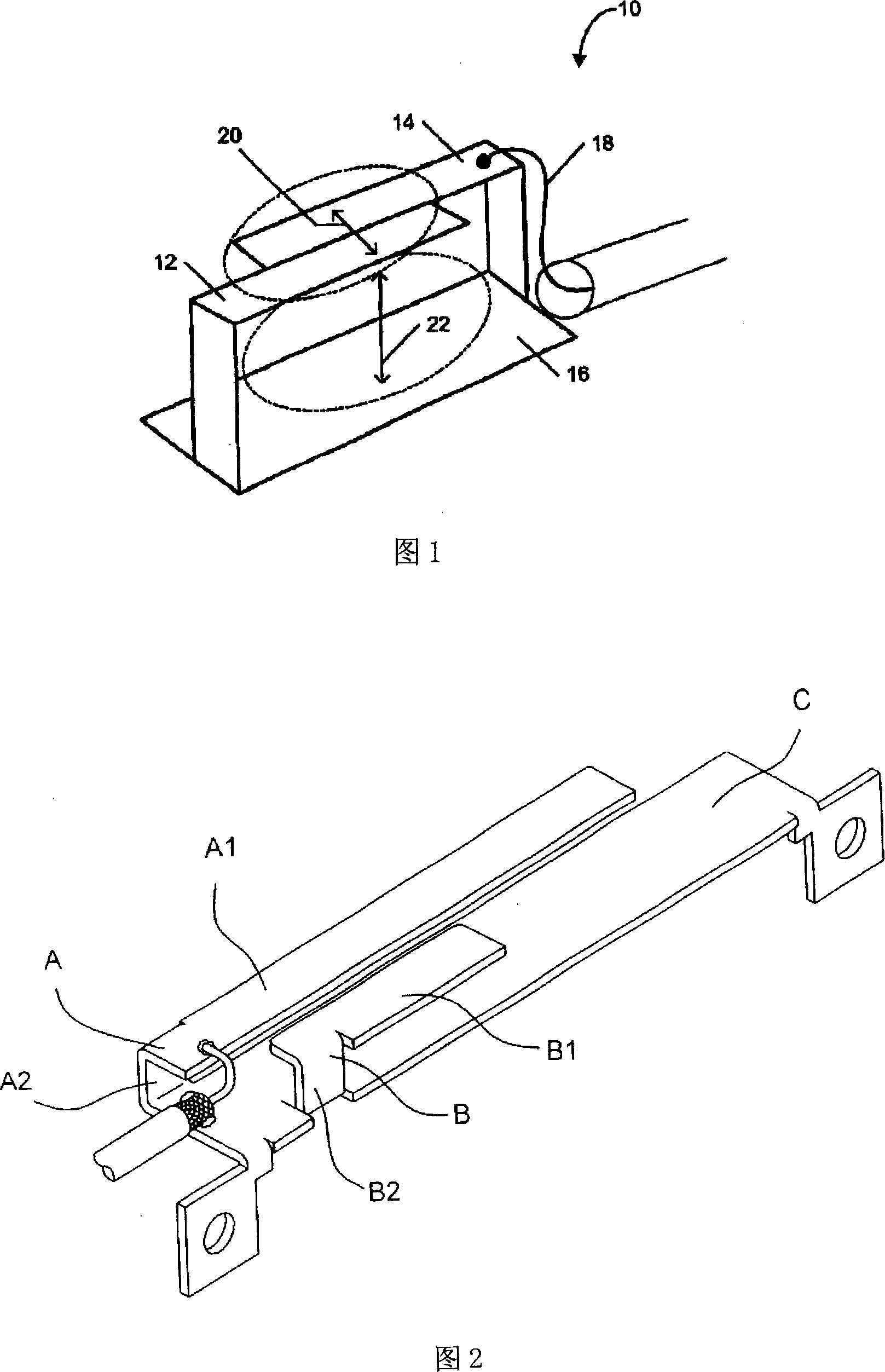

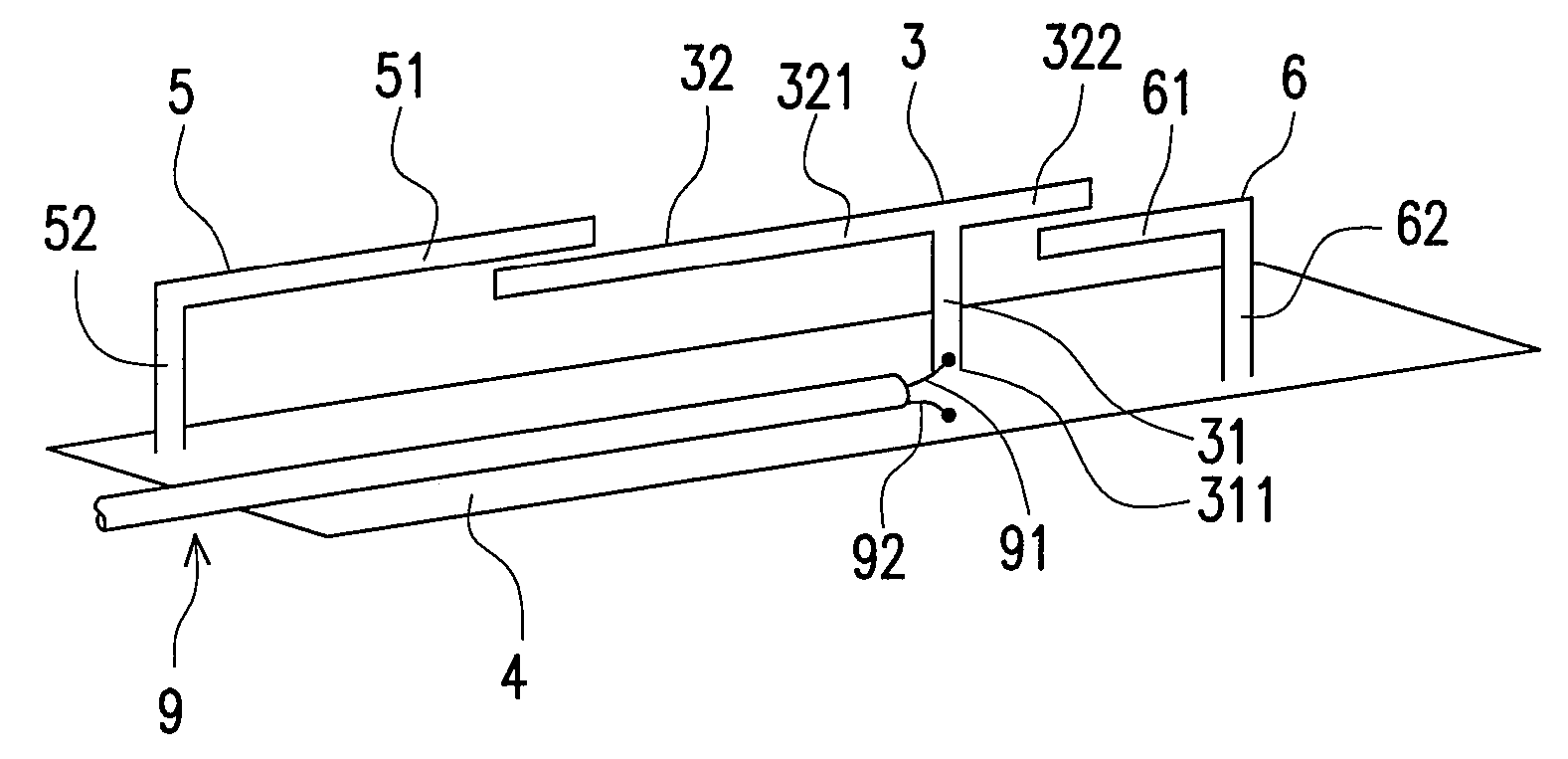

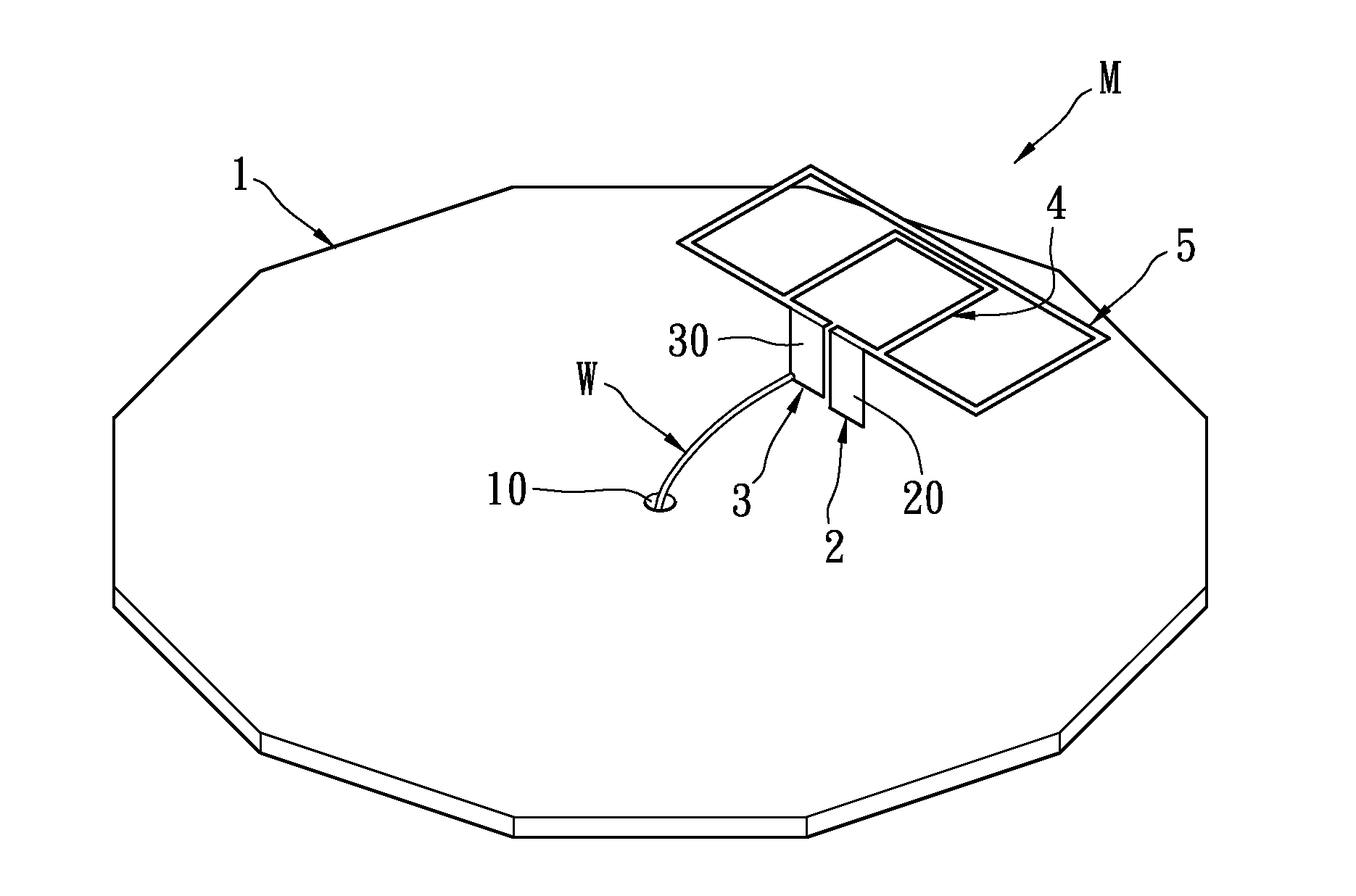

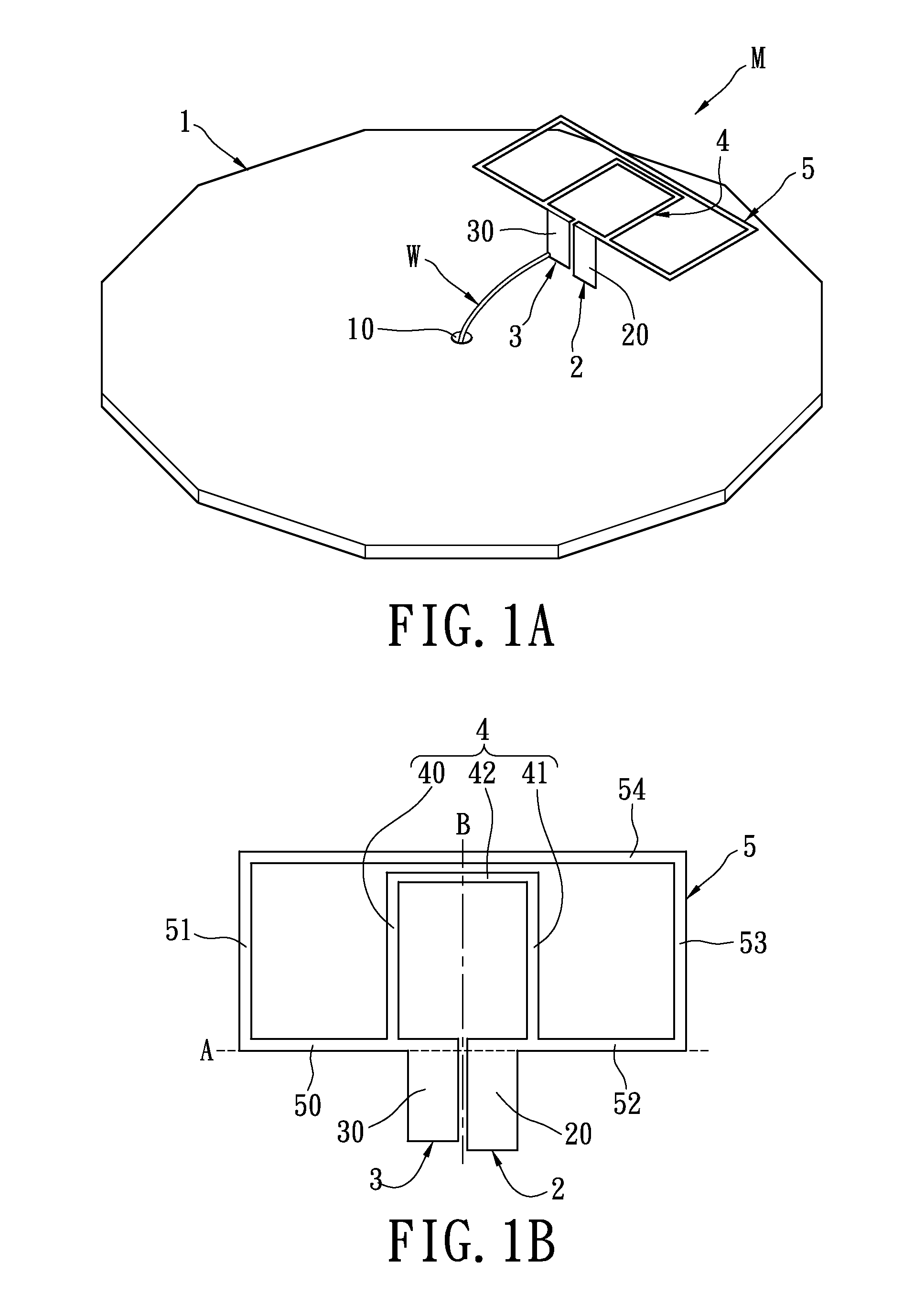

Dual-loop antenna and multi-frequency multi-antenna module

ActiveUS20110063180A1Small sizeLow profileResonant long antennasSimultaneous aerial operationsDual loopMulti antenna

A dual-loop antenna includes a grounding unit, a shorting unit, a feeding unit, a first loop radiating unit and a second loop radiating unit. The shorting unit has at least one shorting pin disposed on the grounding unit. The feeding unit has at least one feeding pin separated from the shorting pin by a predetermined distance and suspended above the grounding unit at a predetermined distance. The first loop radiating unit is disposed above the grounding unit at a predetermined distance. The first loop radiating unit has two ends respectively electrically connected to the shorting unit and the feeding unit. The second loop radiating unit is disposed above the grounding unit at a predetermined distance and around the first loop radiating unit. The second loop radiating unit has two ends respectively electrically connected to the shorting unit and the feeding unit.

Owner:LITE ON ELECTRONICS (GUANGZHOU) LTD +1

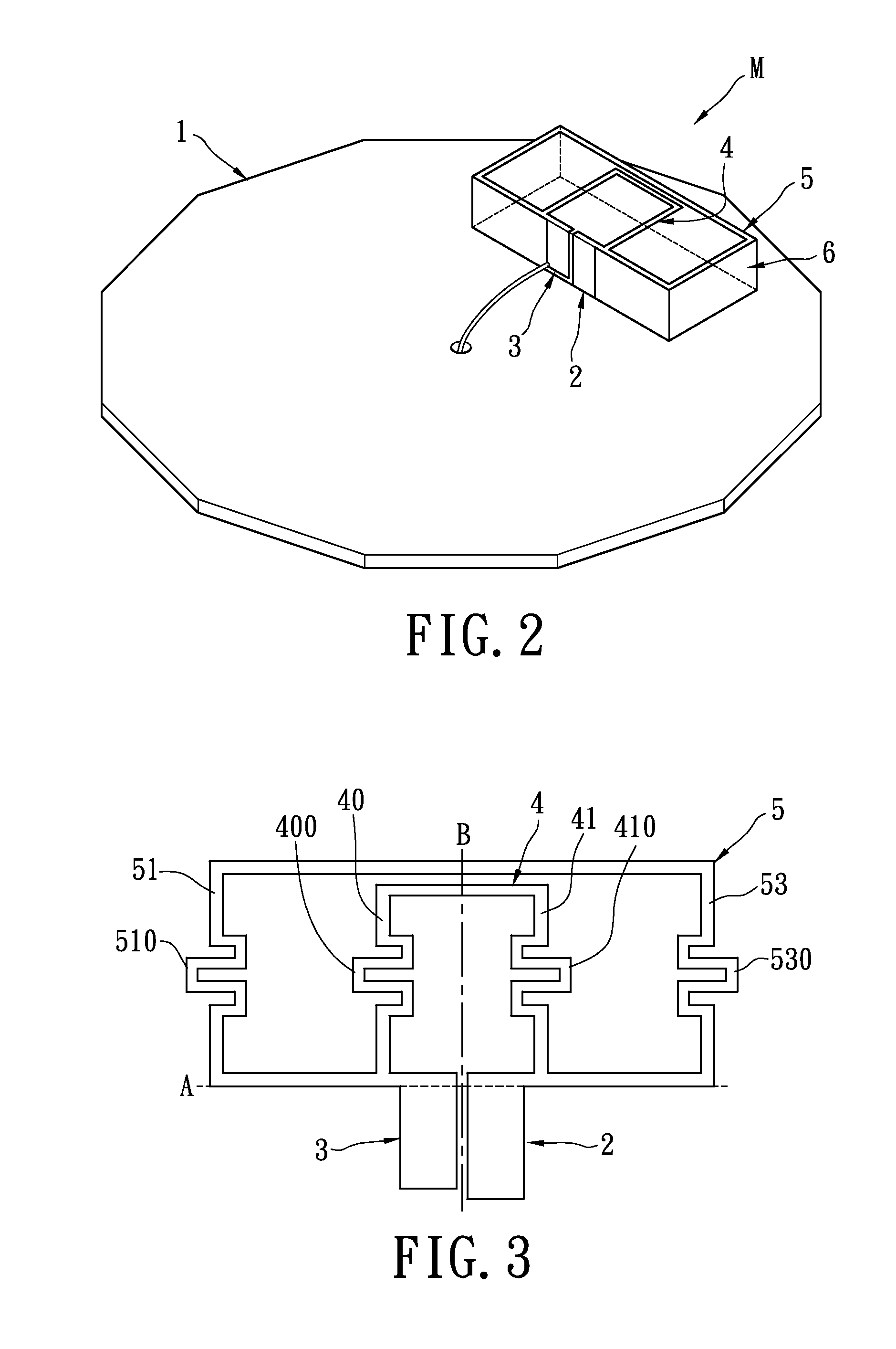

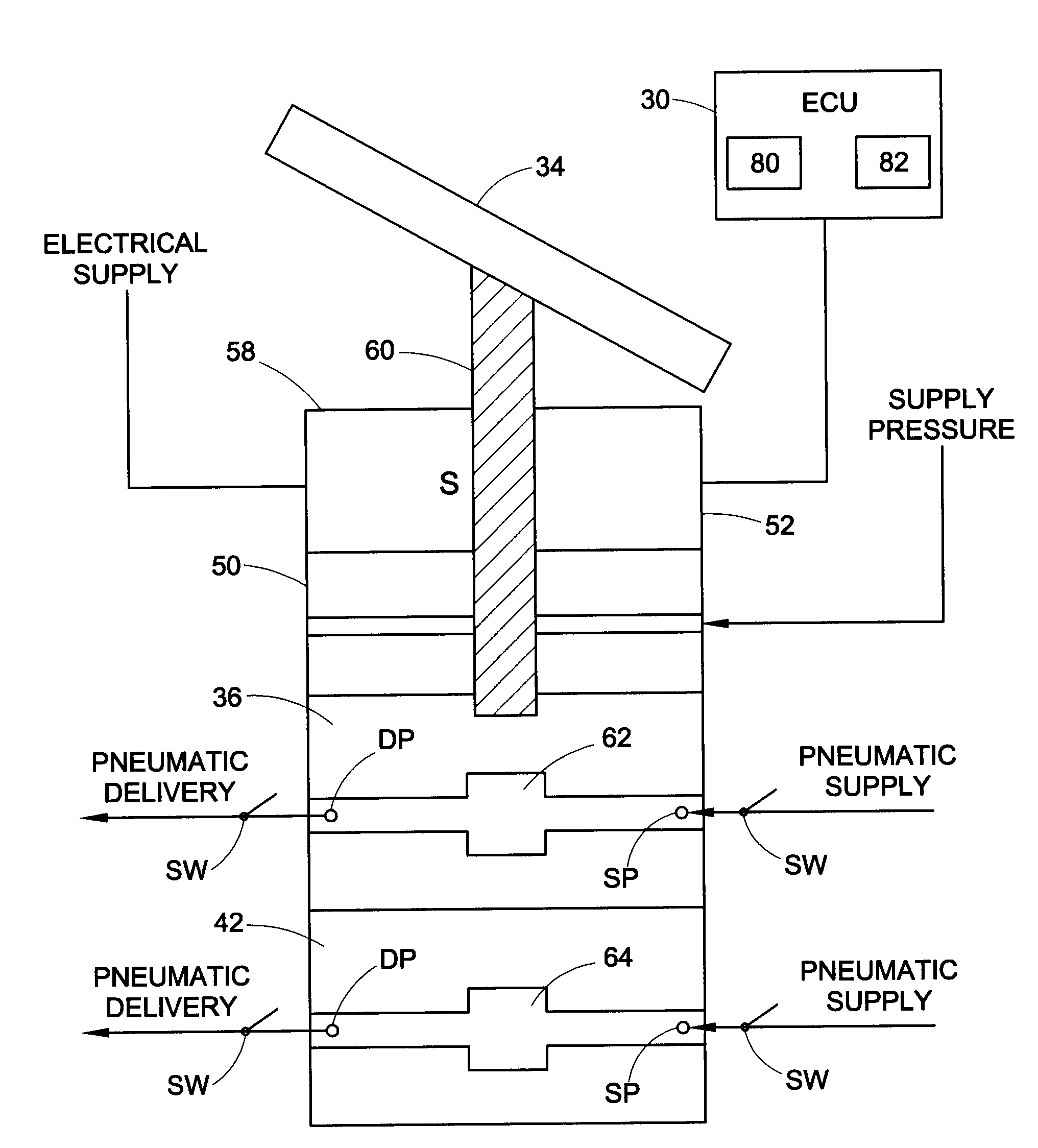

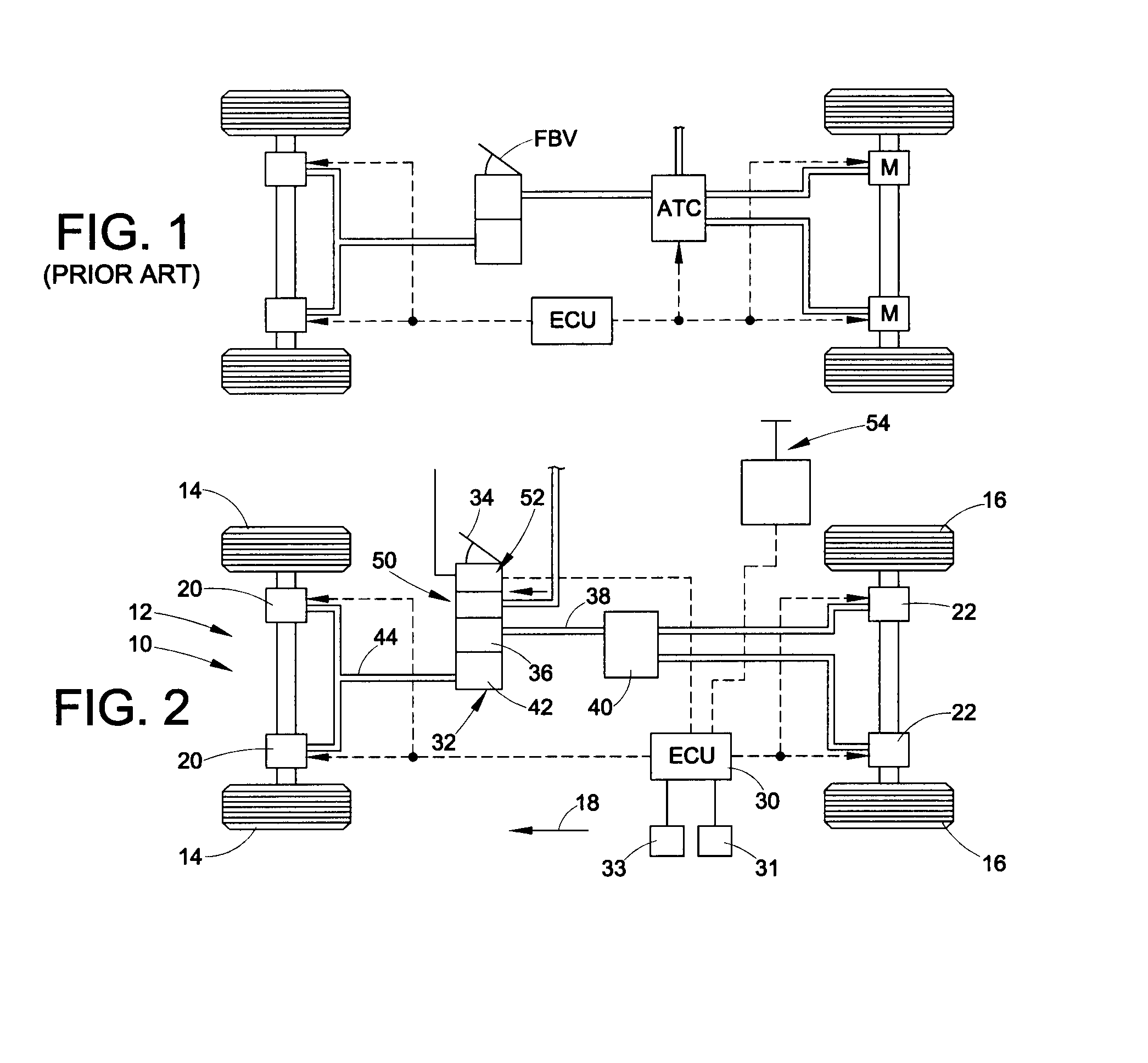

Dual circuit pneumatic foot valve with electronically controlled proportional modulator (ECPM) and operator input sensing

ActiveUS20130320751A1Analogue computers for trafficFoot actuated initiationsEngineeringBraking system

A foot valve that can be activated either by the driver or an electronic control unit, wherein the foot valve can be the central driving device for automated braking applications such as Hill Start Aid and Work Brake Systems. Pneumatic pressure delivered by an electronically controlled proportional modulator to the foot valve activates either primary and / or secondary portions of the brake valve. The driver can mechanically override the electronic intervention when he presses on the brake pedal. For applications such as ESC and ATC, driver demand can be sensed by sensors in the foot valve and transmitted to the braking system electronic controller on the vehicle.

Owner:BENDIX COMML VEHICLE SYST LLC

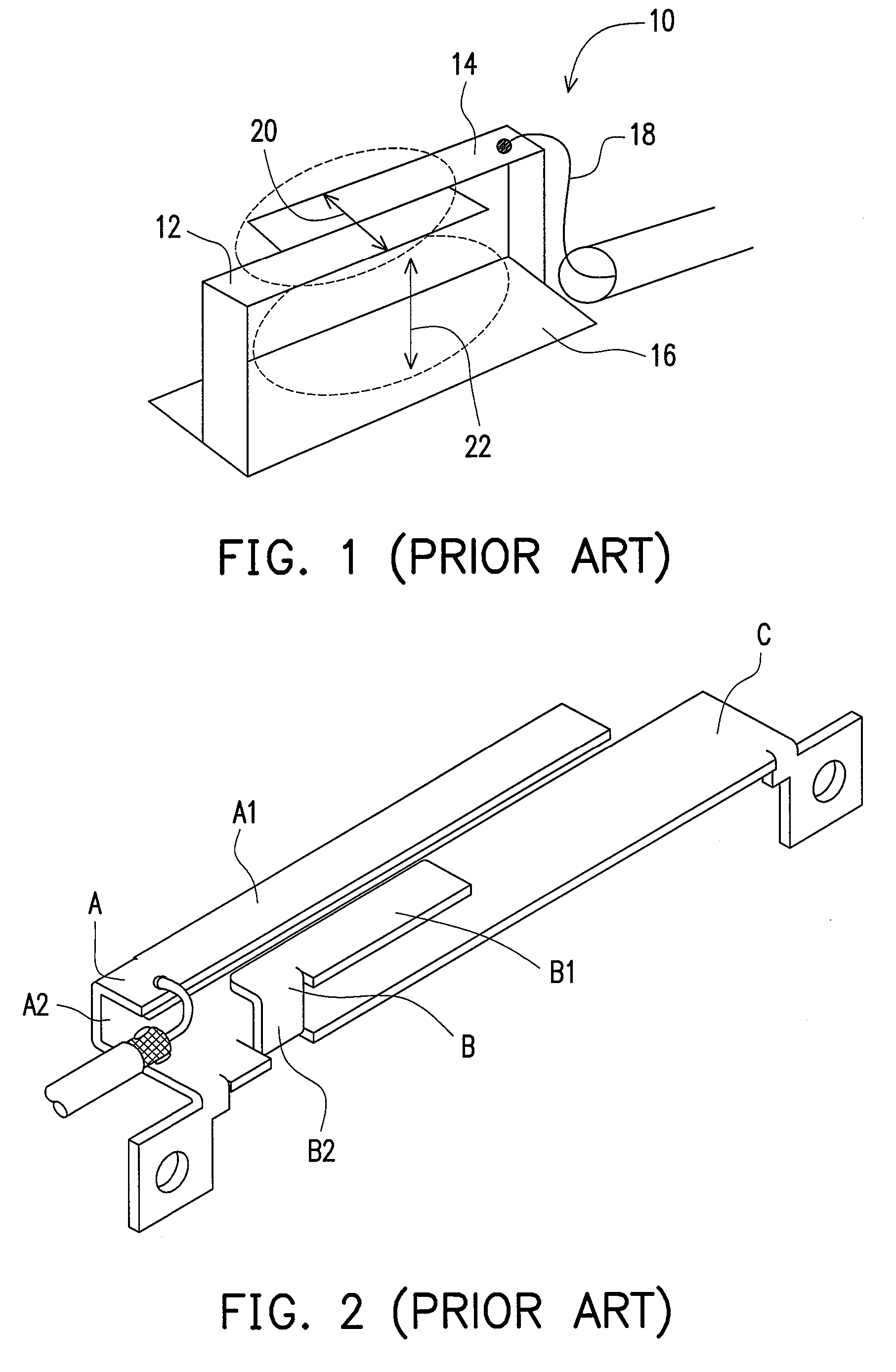

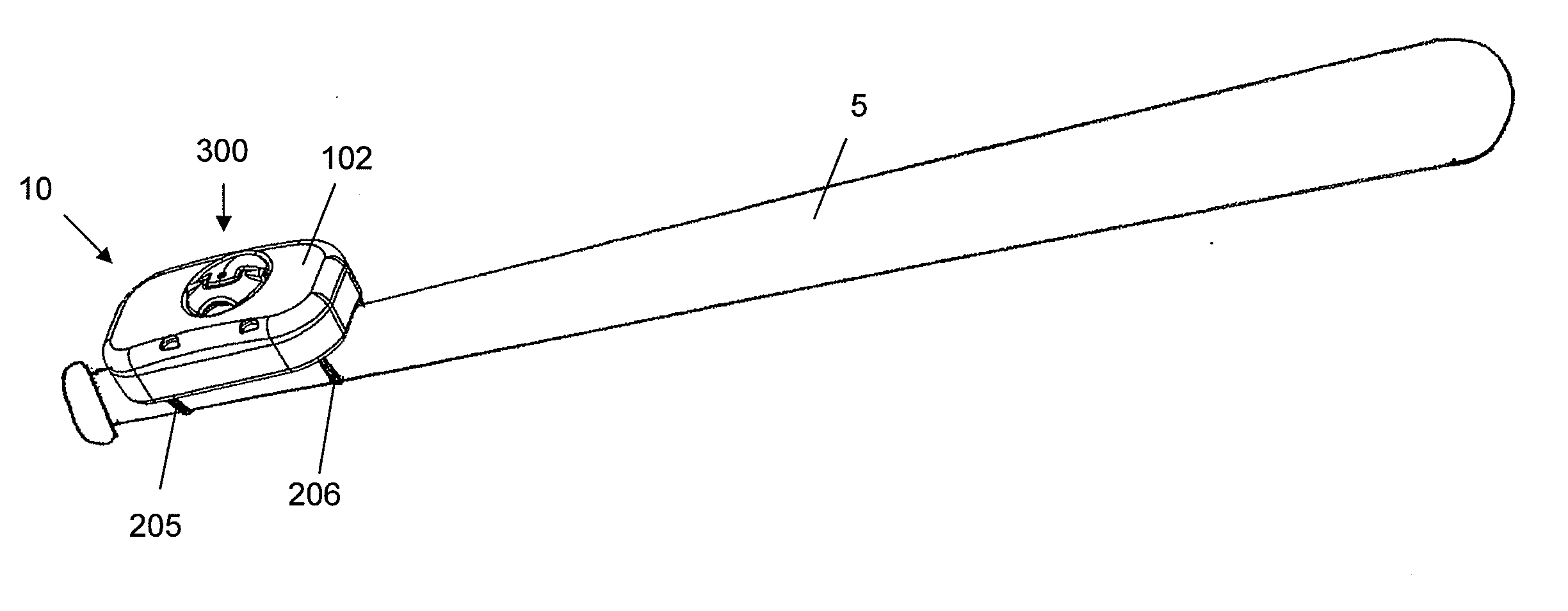

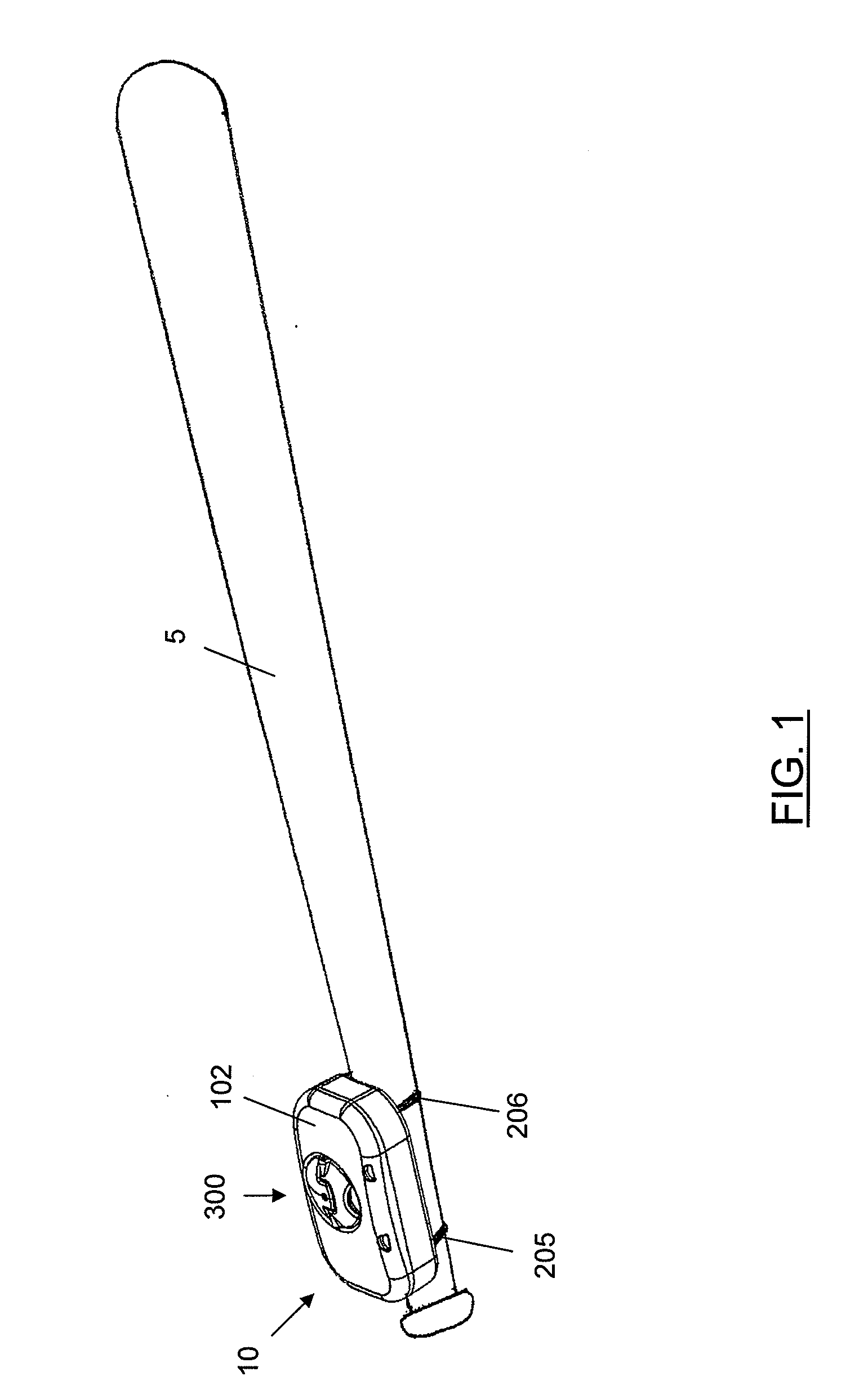

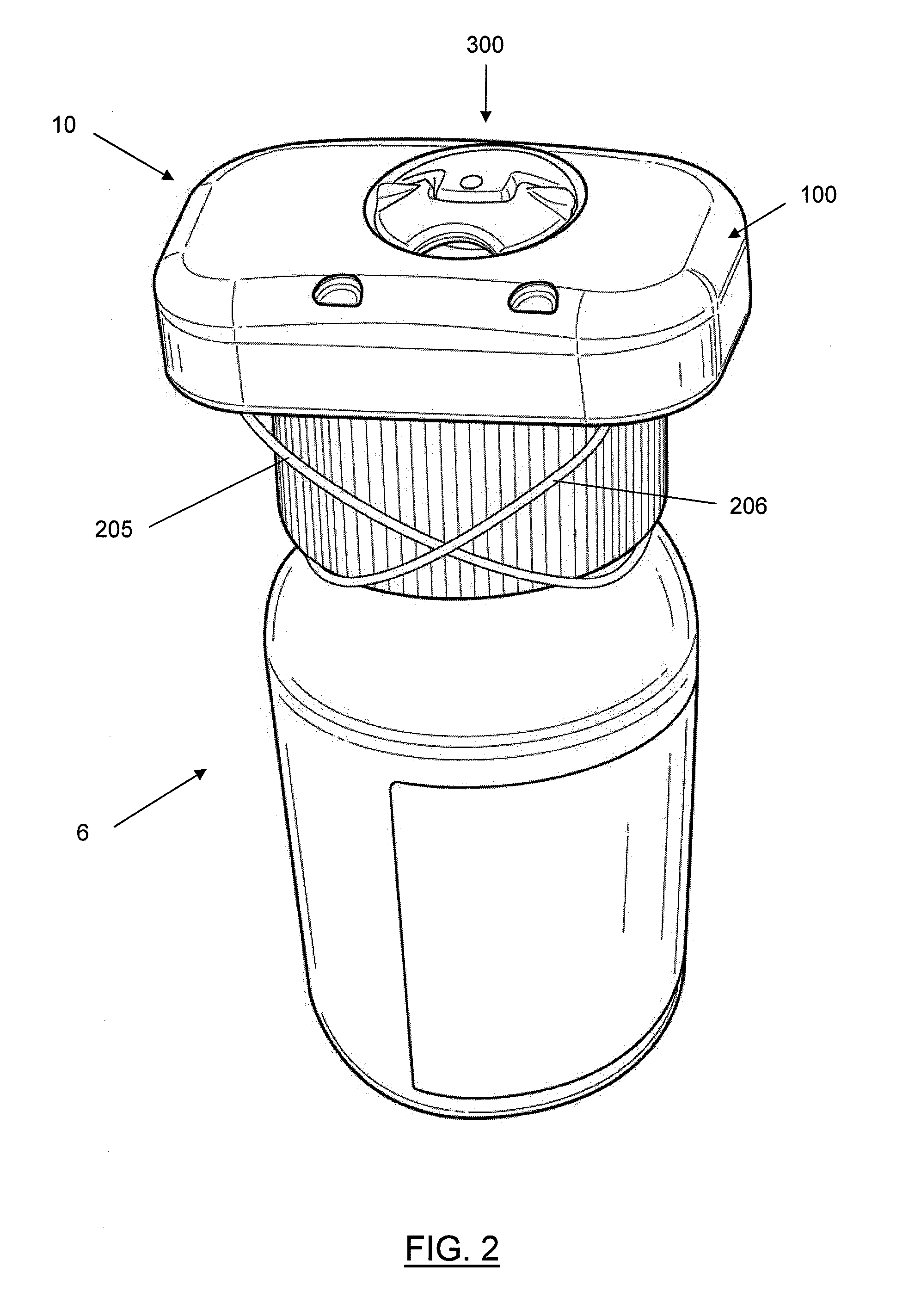

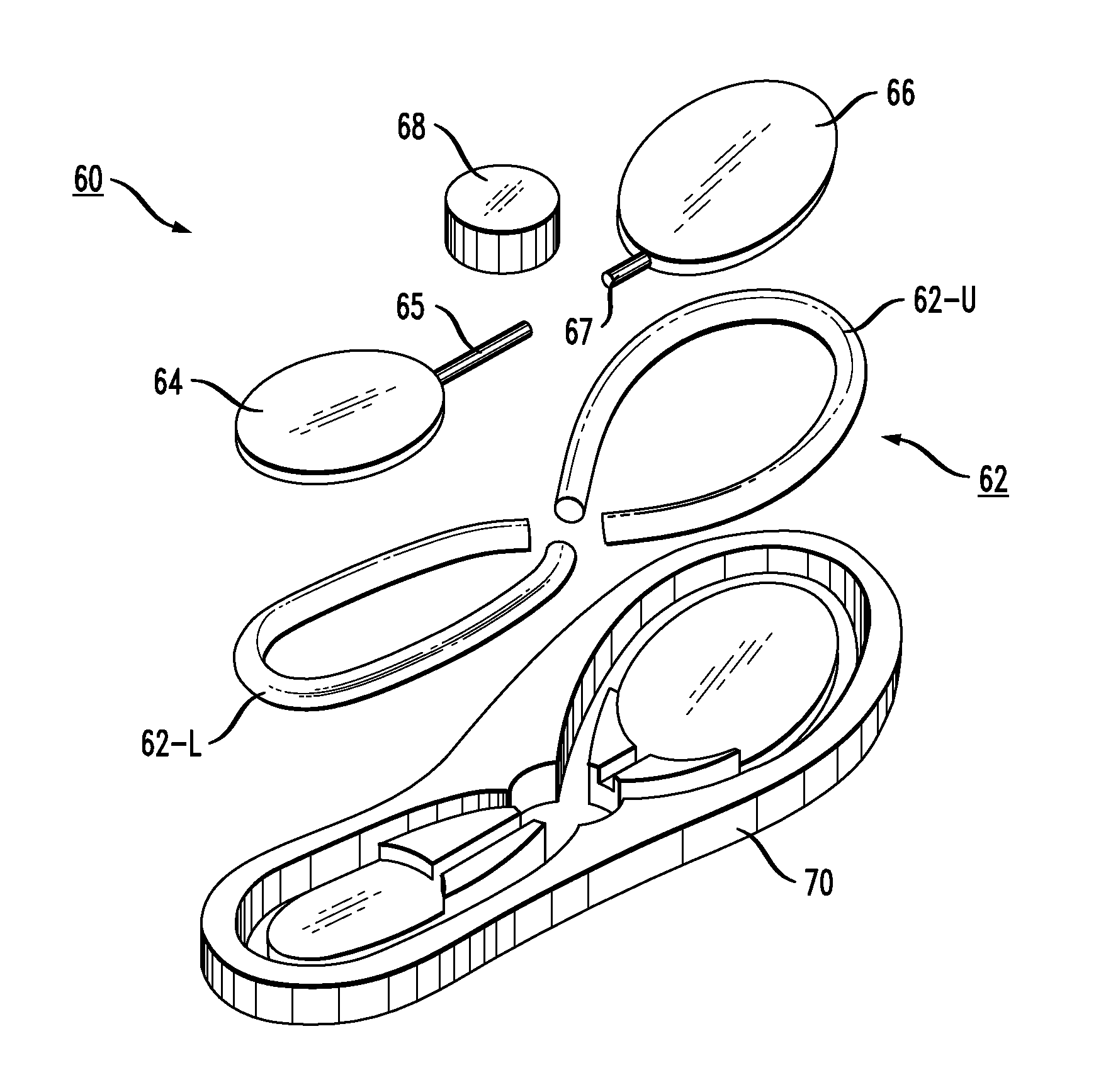

Adjustable dual loop cable security device

InactiveUS20110102179A1Reduce tampering with and disablingLocks for portable objectsBurglar alarm by hand-portable articles removalEngineeringMechanical engineering

Various embodiments of the invention may be directed to a security device comprising a housing, a rotatable assembly, a locking assembly, and a cable. The rotatable assembly may include a plurality of locking teeth, a spool, and an engagement portion configured to facilitate rotation the rotatable assembly. The locking assembly may include biasing elements configured to apply a biasing force so that the locking assembly and the rotatable assembly may be configured in a locked position. Further, the locking assembly may include magnetically attractive elements configured to counteract the biasing force when a specifically configured key is applied to the housing of the security device. The security device may further include a security element, an alarm, and other components.

Owner:CHECKPOINT SYST INC

Method and apparatus for jitter reduction

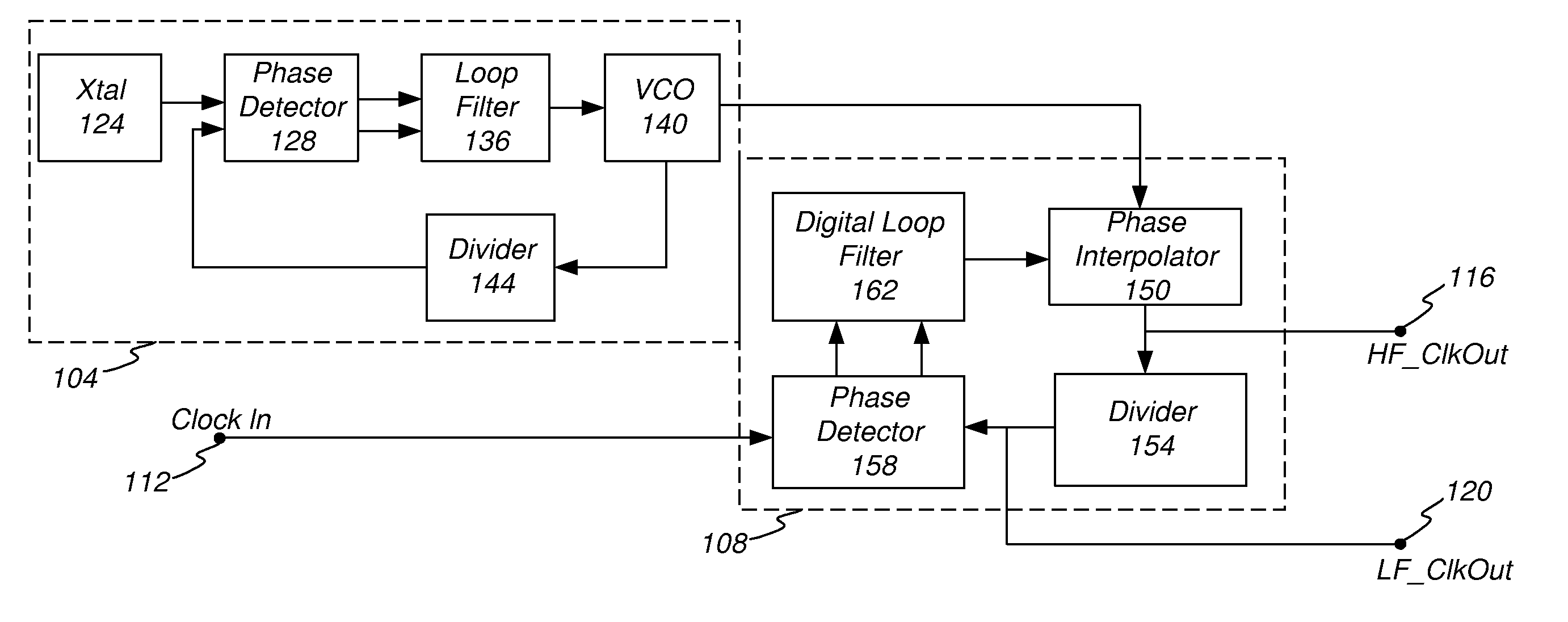

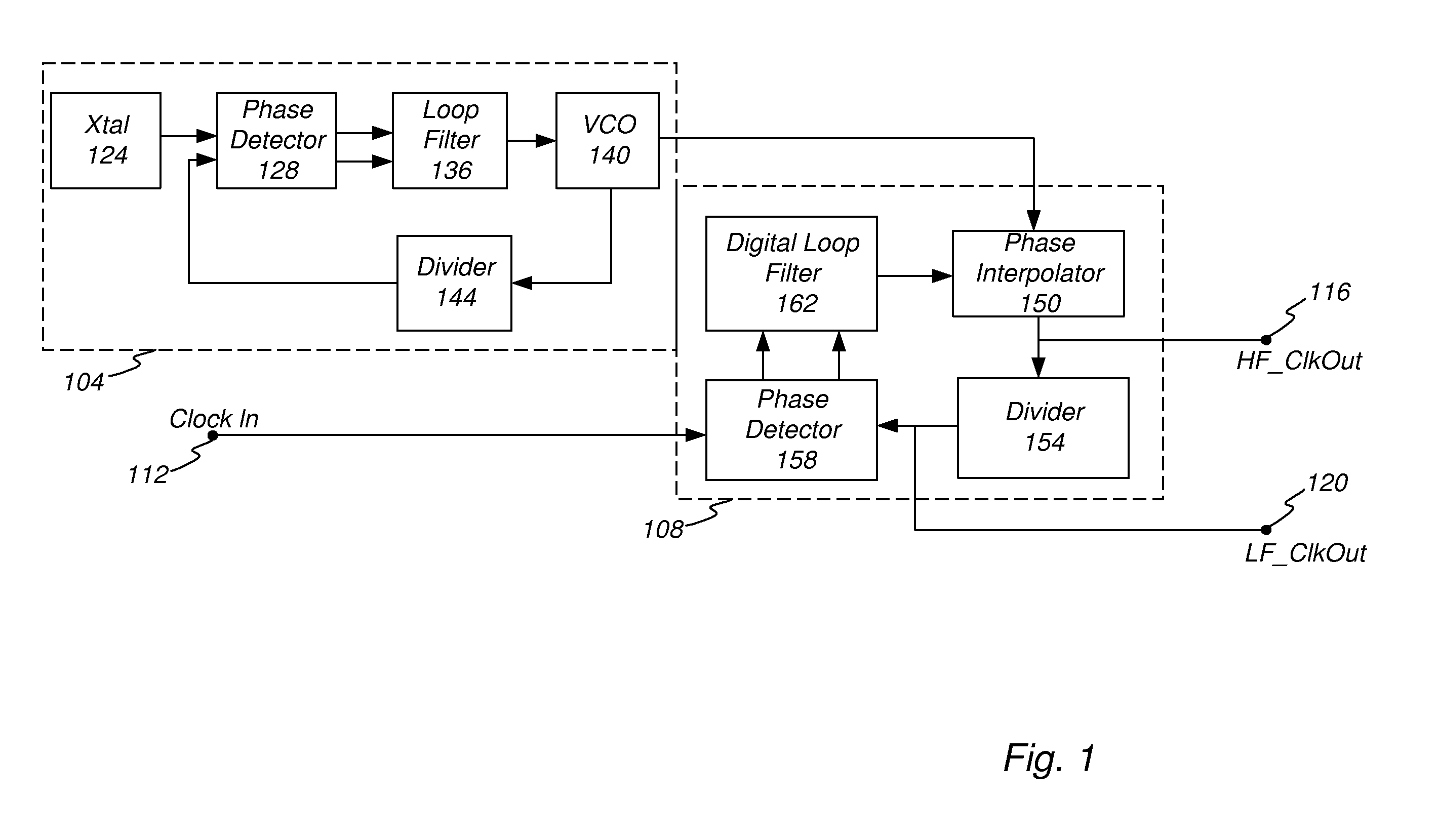

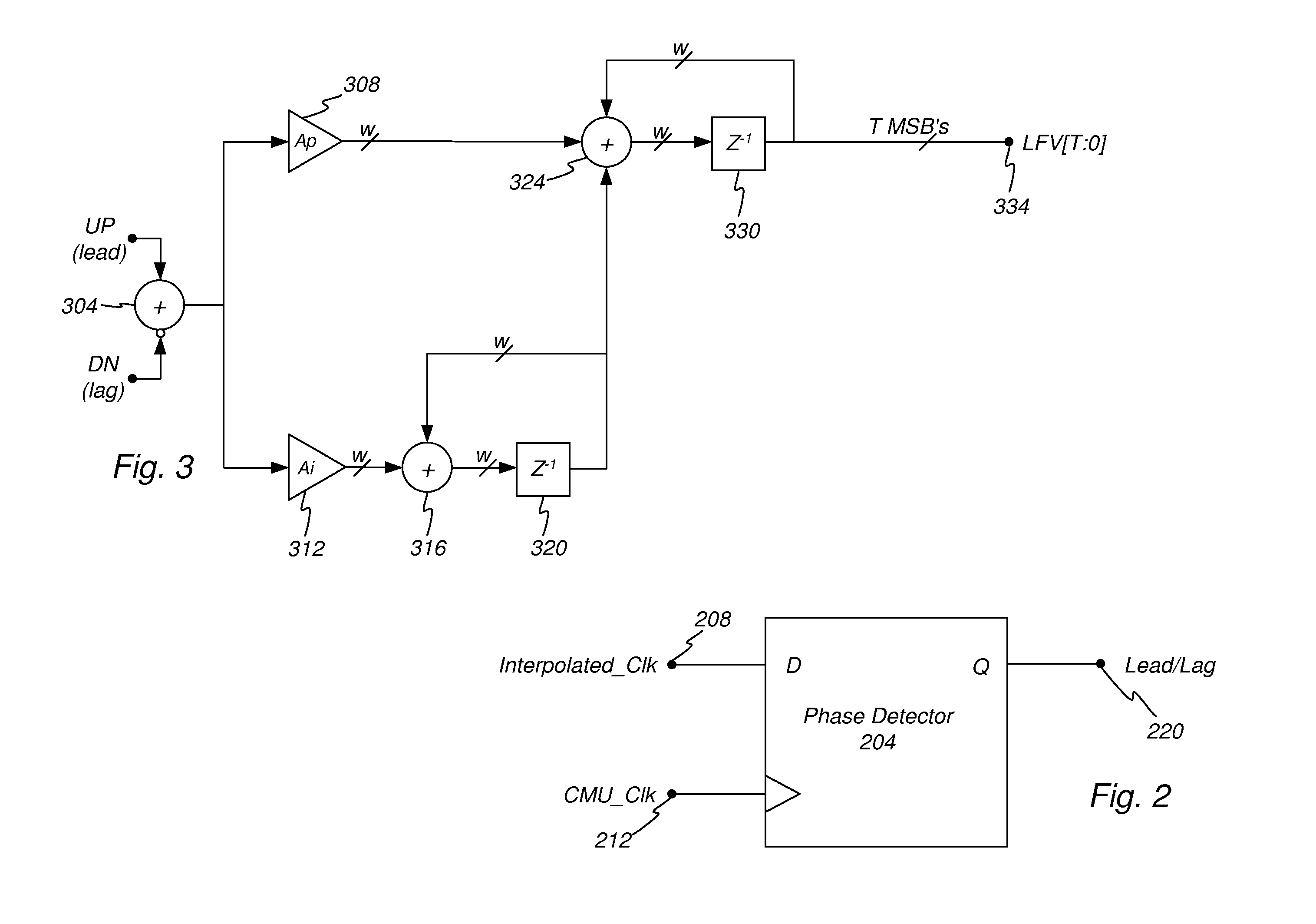

A low bandwidth phase lock loop (PLL) arranged in a dual-loop configuration is disclosed. The first loop is a standard loop configuration using a crystal oscillator as a reference clock. The loop parameters for this first PLL can be optimized to work over a wide range of output frequencies, and with a minimum amount of jitter. The first loop outputs a reference signal, which is a VCO output. The second loop comprises a bang-bang detector configured to drive a digital loop filter, which then drives a phase interpolator. The phase interpolator manipulates the output phase. Since phase and frequency are related, where frequency is the derivative of phase, small frequency offsets can be made using a phase control signal, generated within the second loop based on the relation between the reference signal and the clock input signal. The second loop sets the jitter transfer bandwidth of the system.

Owner:MACOM TECH SOLUTIONS HLDG INC

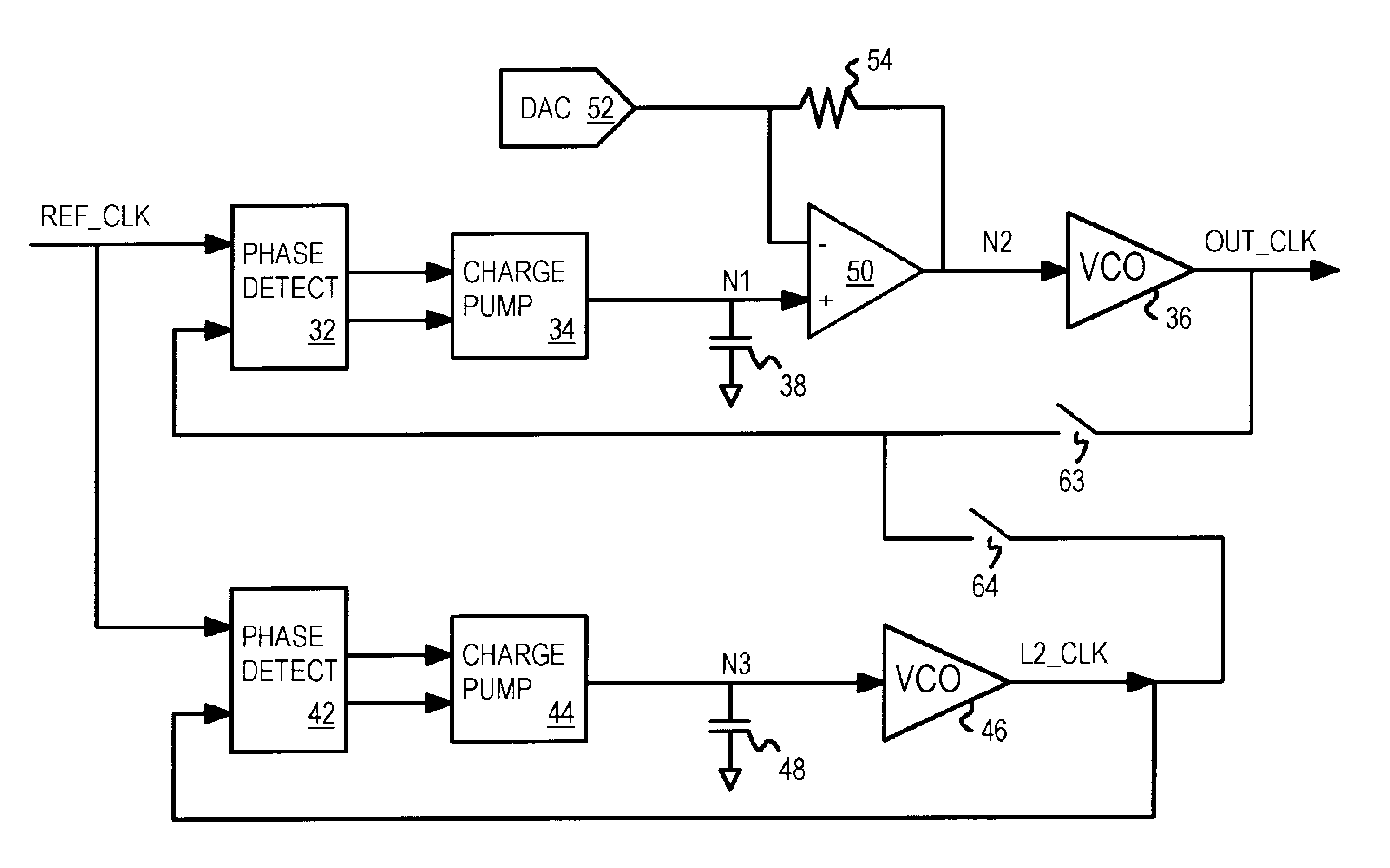

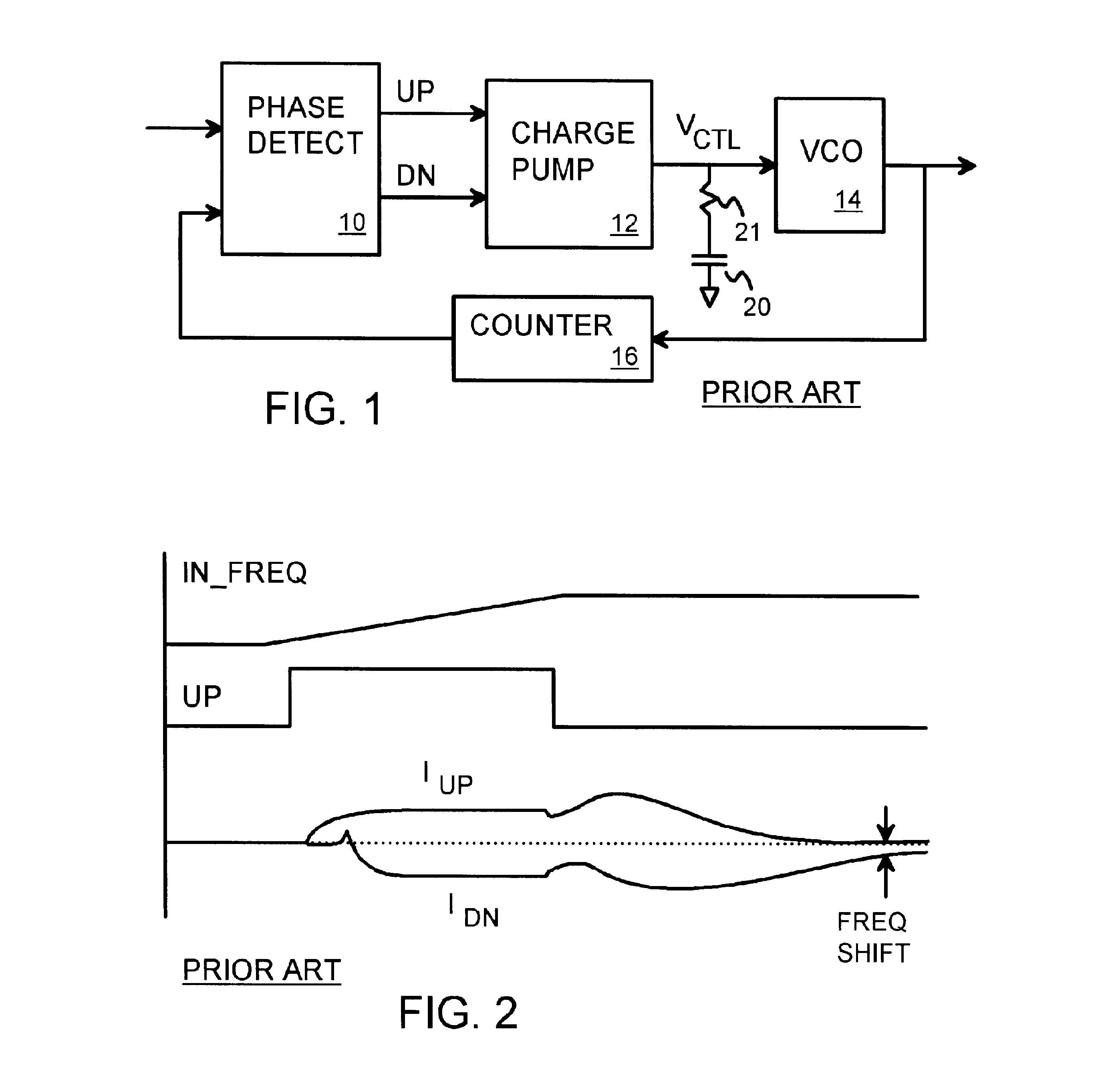

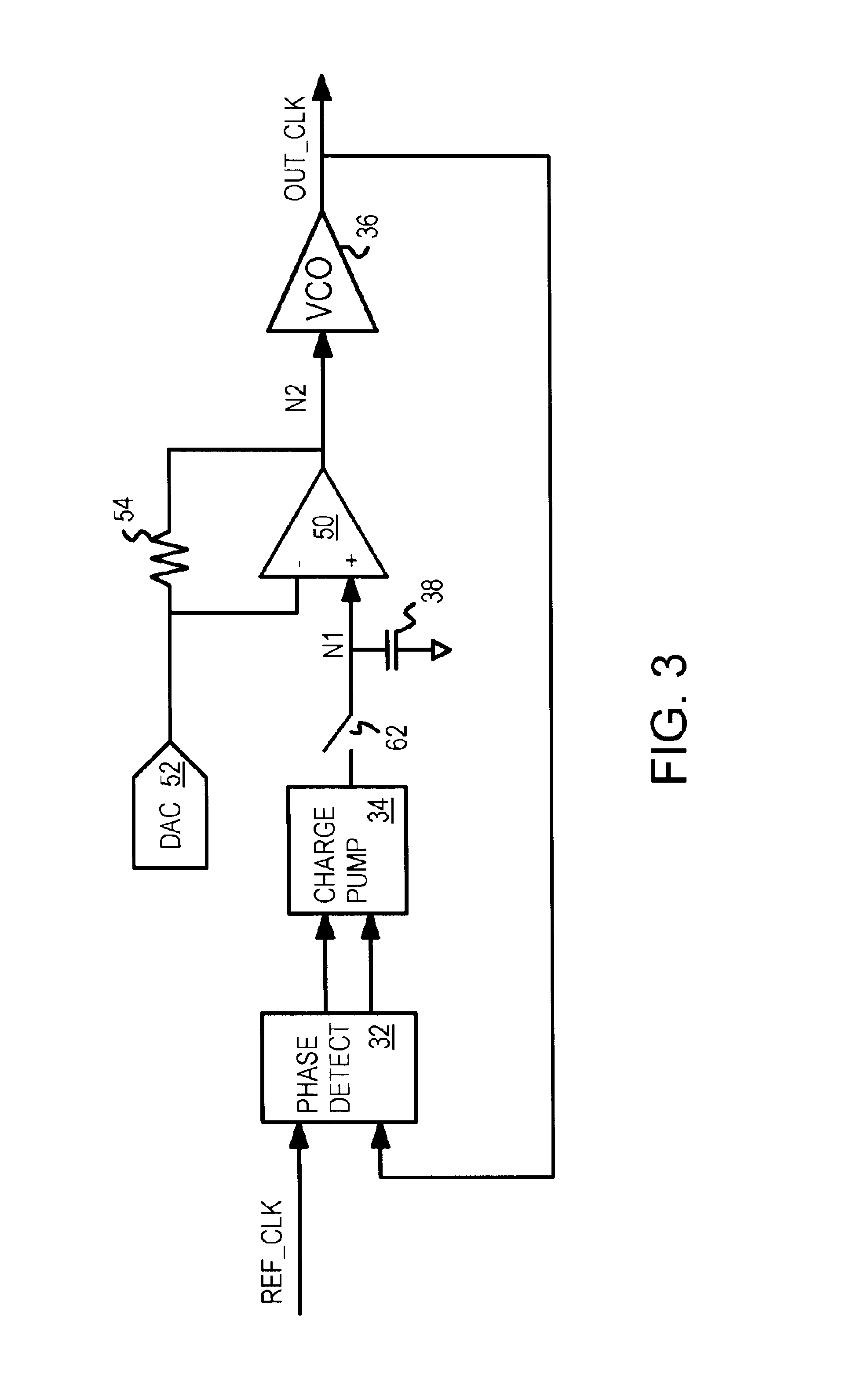

Dual-loop PLL with DAC offset for frequency shift while maintaining input tracking

A phase-locked loop (PLL) keeps tracking a reference clock when a frequency offset is introduced. The PLL has primary and secondary PLL loops. A digital-to-analog converter (DAC) generates a current that is passed through an offset resistor to generate an offset voltage. An op amp is inserted in the primary loop between a filter capacitor and a voltage-controlled oscillator (VCO). The offset resistor is coupled between the inverting input of the op amp and the op amp's output. When the DAC offset occurs, the voltage to the VCO and the frequency of the primary loop change and the primary loop loses tracking of the reference clock. The secondary loop keeps tracking the reference clock during the DAC offset while the primary loop is open. Then the output clock of the secondary loop is applied as the feedback clock to the phase comparator of the primary loop.

Owner:DIODES INC

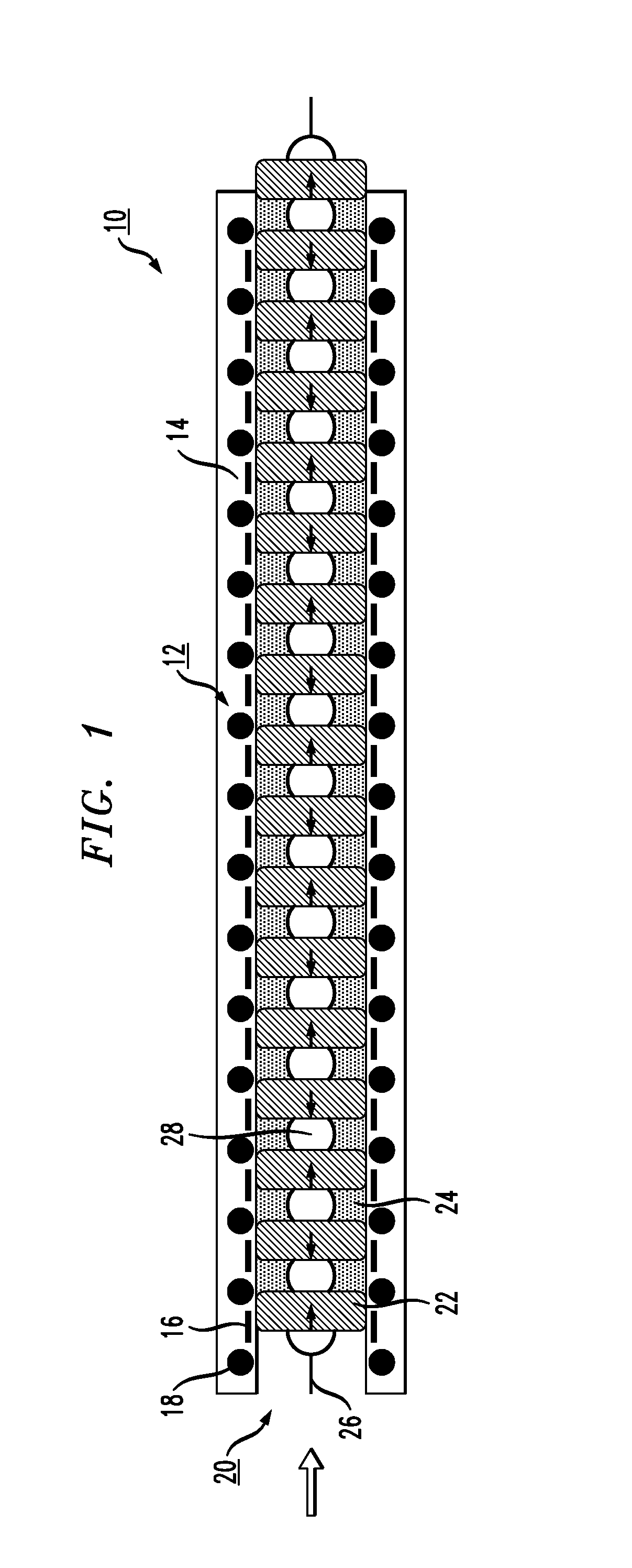

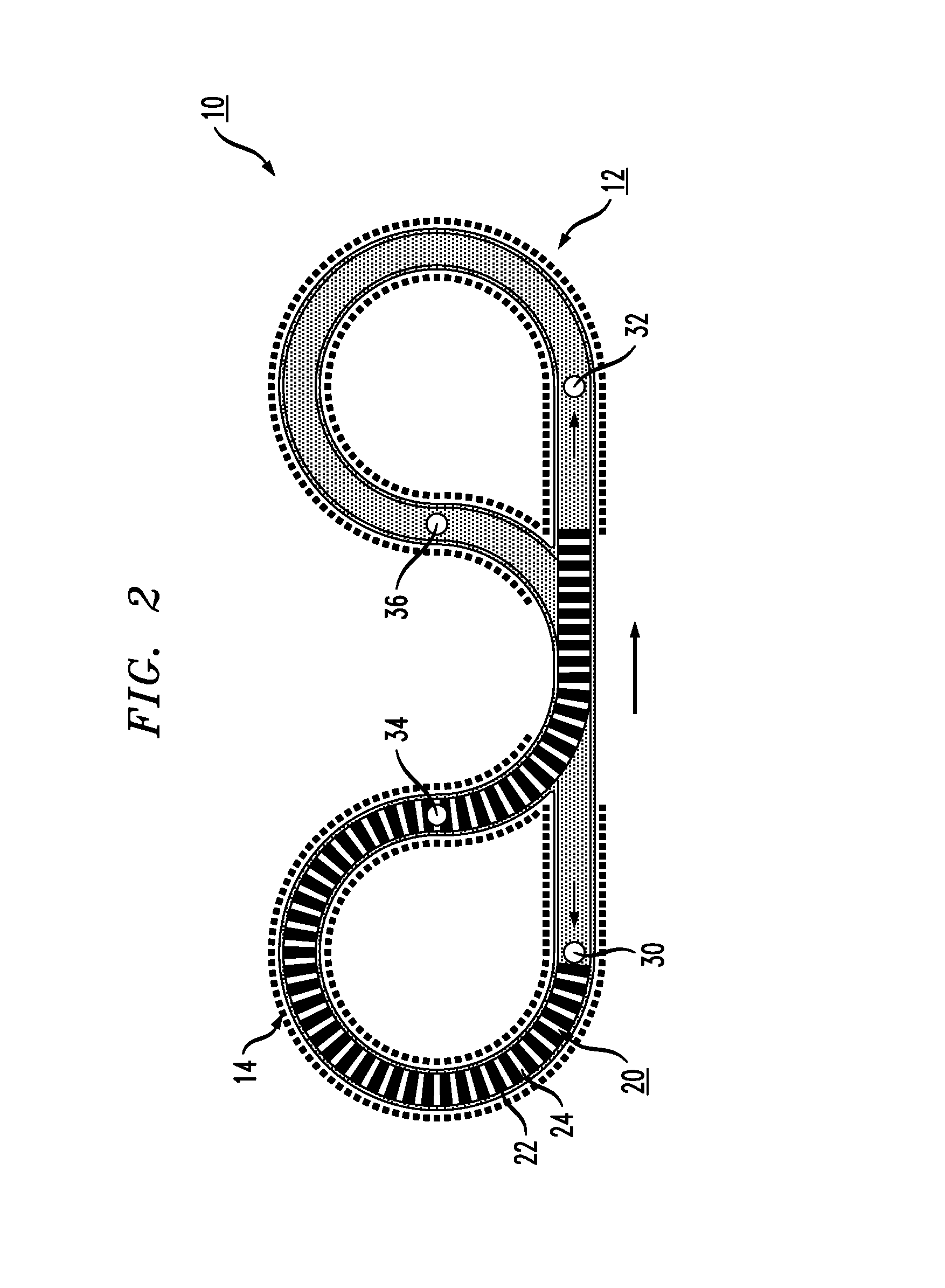

Apparatus For Footwear-Embedded Mechanical Energy Harvesting System Based On Dual-Loop Channel

An energy harvesting apparatus is described that utilizes hydraulic actuation and creates a continuous, revolving motion of a chain of energy-producing elements within an energy-producing channel (the channel being in the form of a tube, for example). In particular, the arrangement of the present invention is based upon a specially-designed dual-loop channel topology that allows for efficient conversion of a unidirectional flow of a fluid entering the energy-producing channel into a smooth, continuous revolving motion of a chain of energy-producing elements within the channel.

Owner:KRUPENKIN THOMAS NIKITA +1

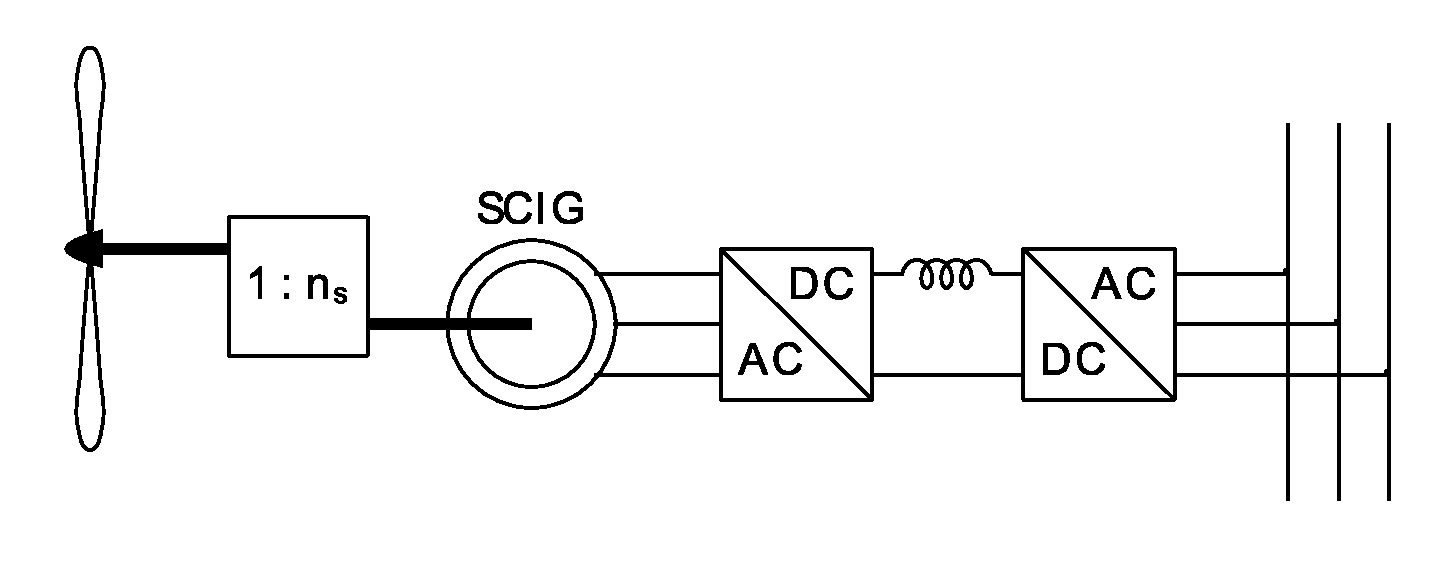

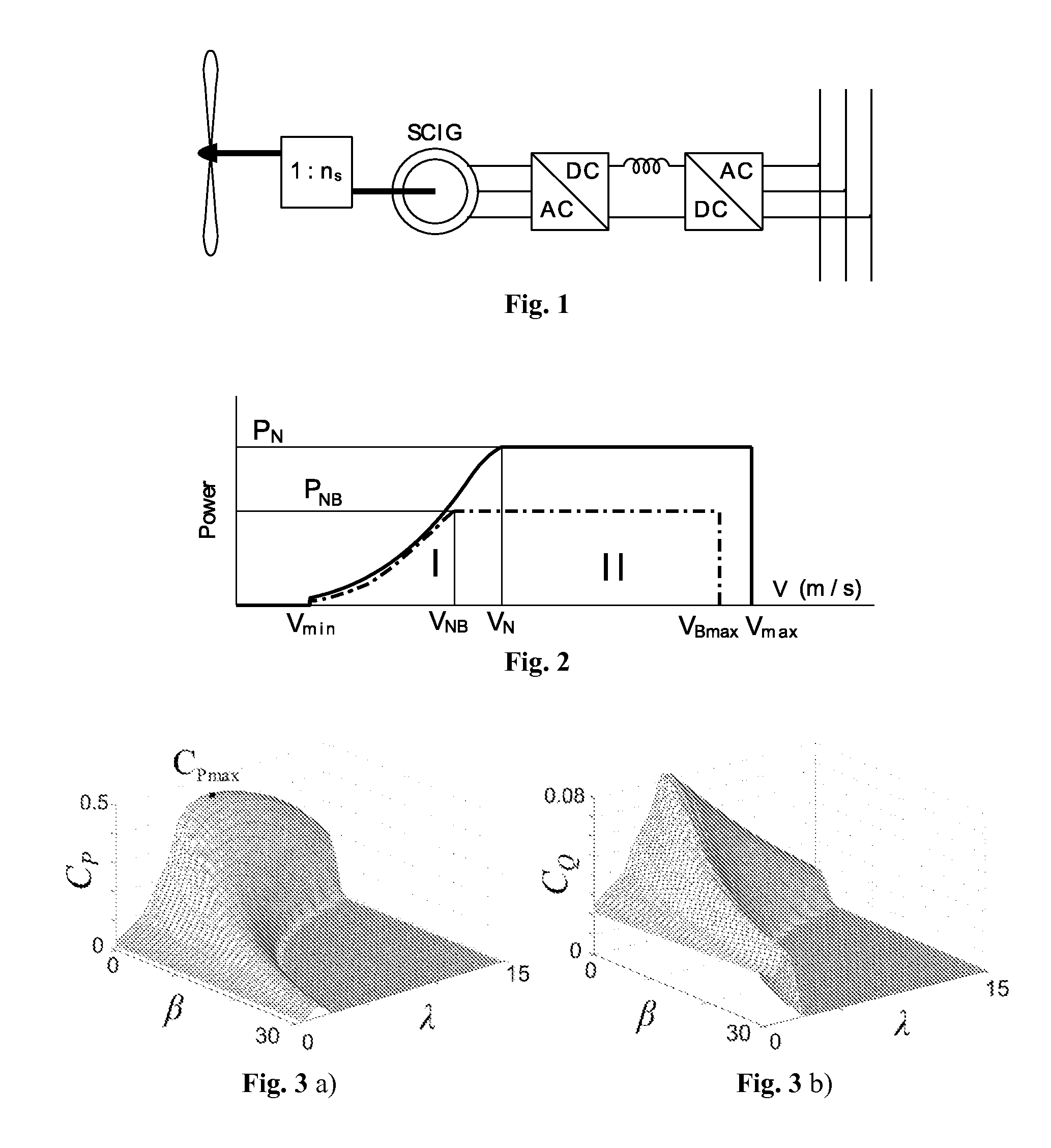

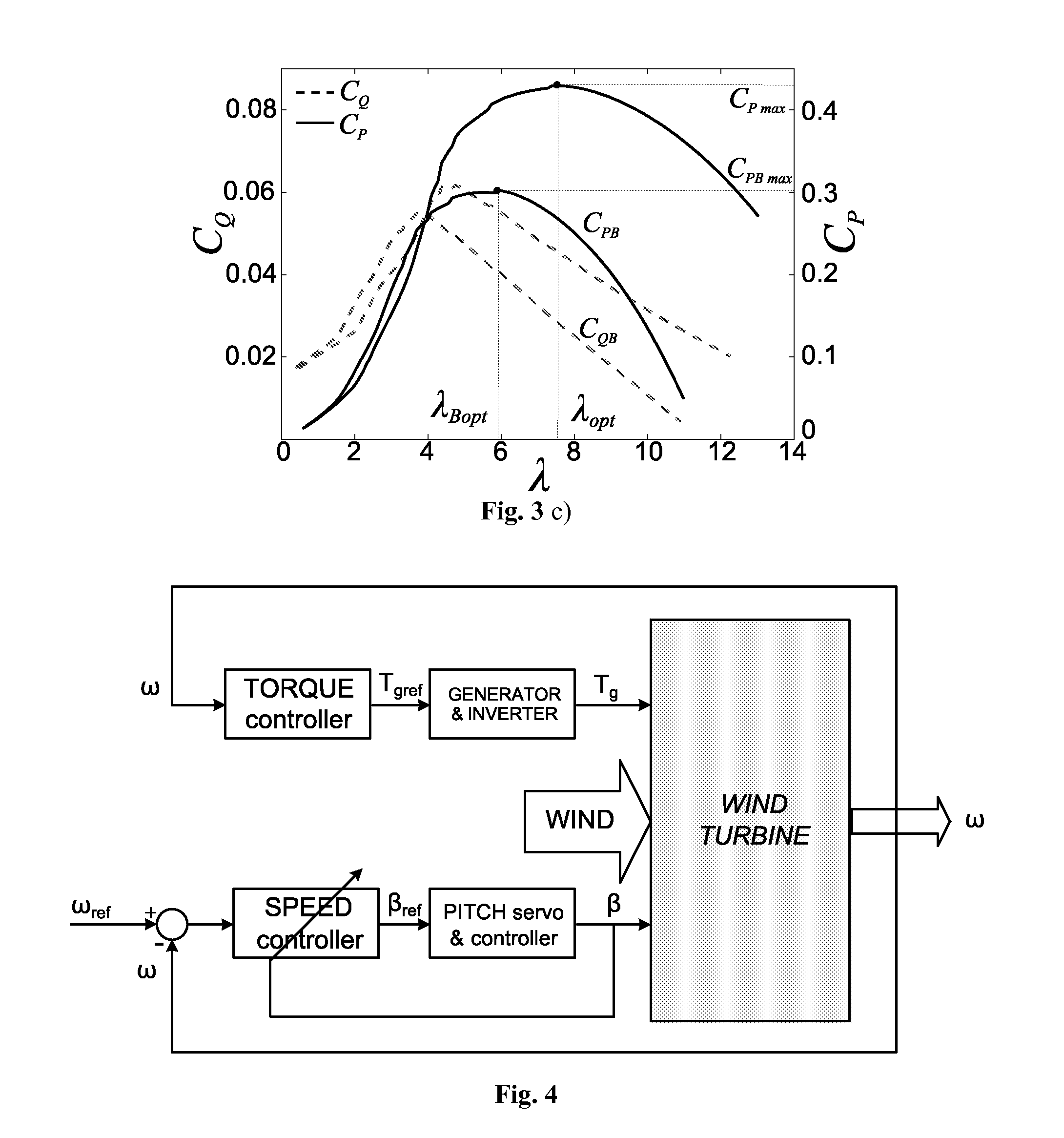

Generator-Fault-Tolerant Control for a Variable-Speed Variable-Pitch Wind Turbine

InactiveUS20140246855A1Reduce resistanceTorque modulationElectric motor controlWind motor controlLoop controlDual loop control

A fault-tolerant control system and method for variable-speed variable-pitch wind turbines with an inverter-fed generator. When generator faults are detected, the generator torque and / or flux is limited to prevent propagation of the faults and possible failure and shutdown of the generator. The control system and method improves on two-loop control methods for variable-speed variable-pitch wind turbines and provides improved power delivery under fault conditions.

Owner:UNIV OF ZAGREB FACULTY OF ELECTRICAL ENG & COMPUTING

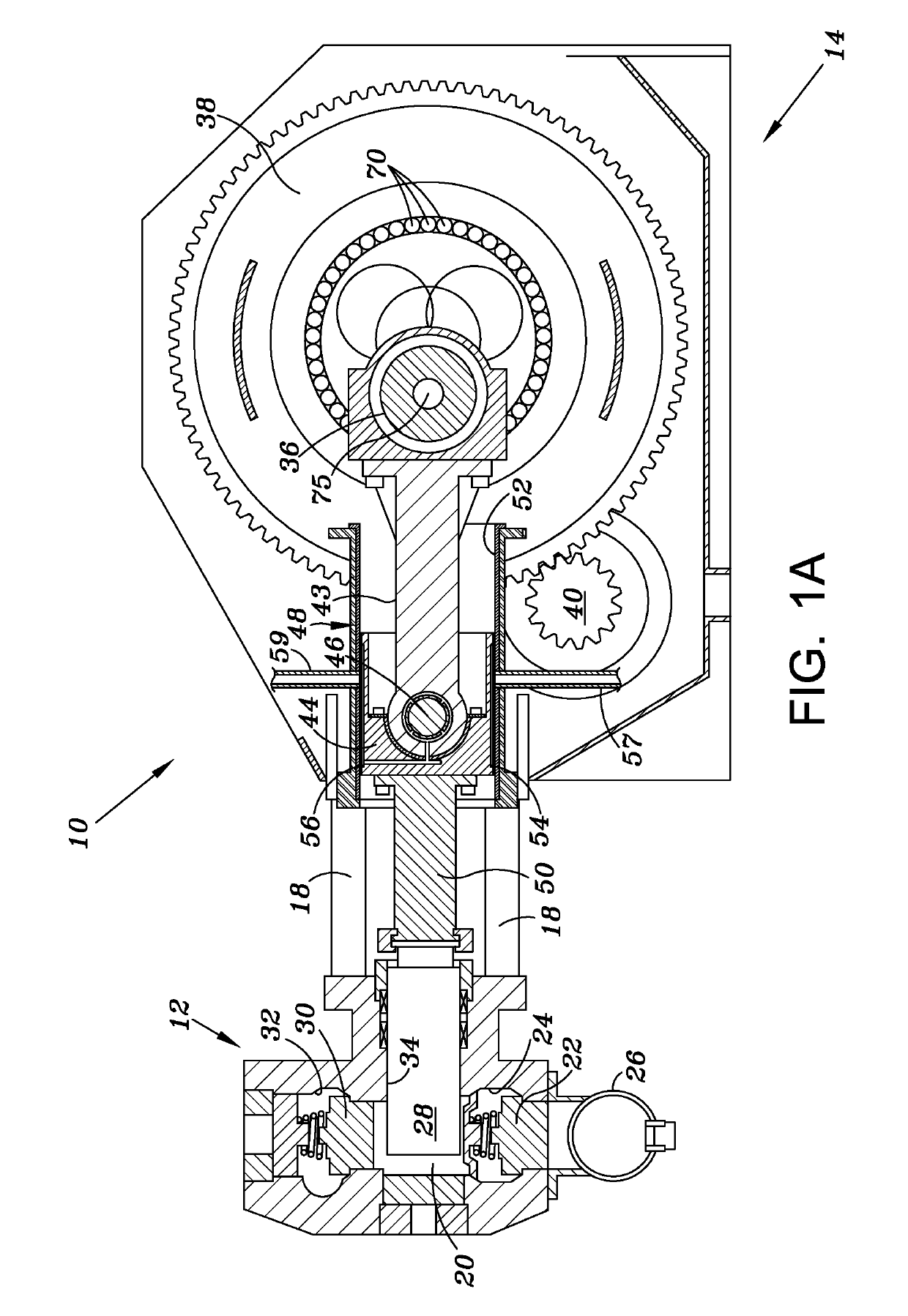

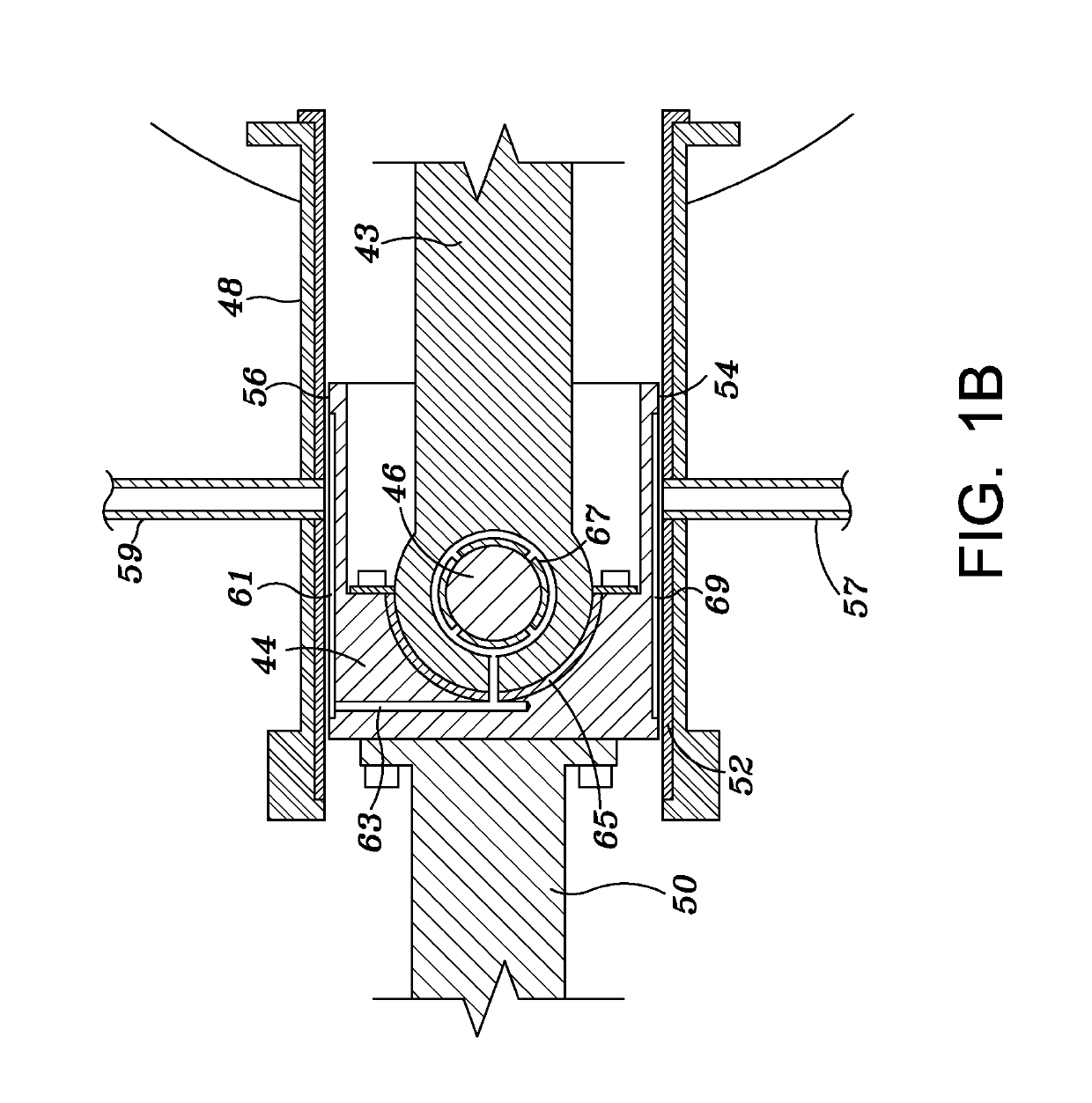

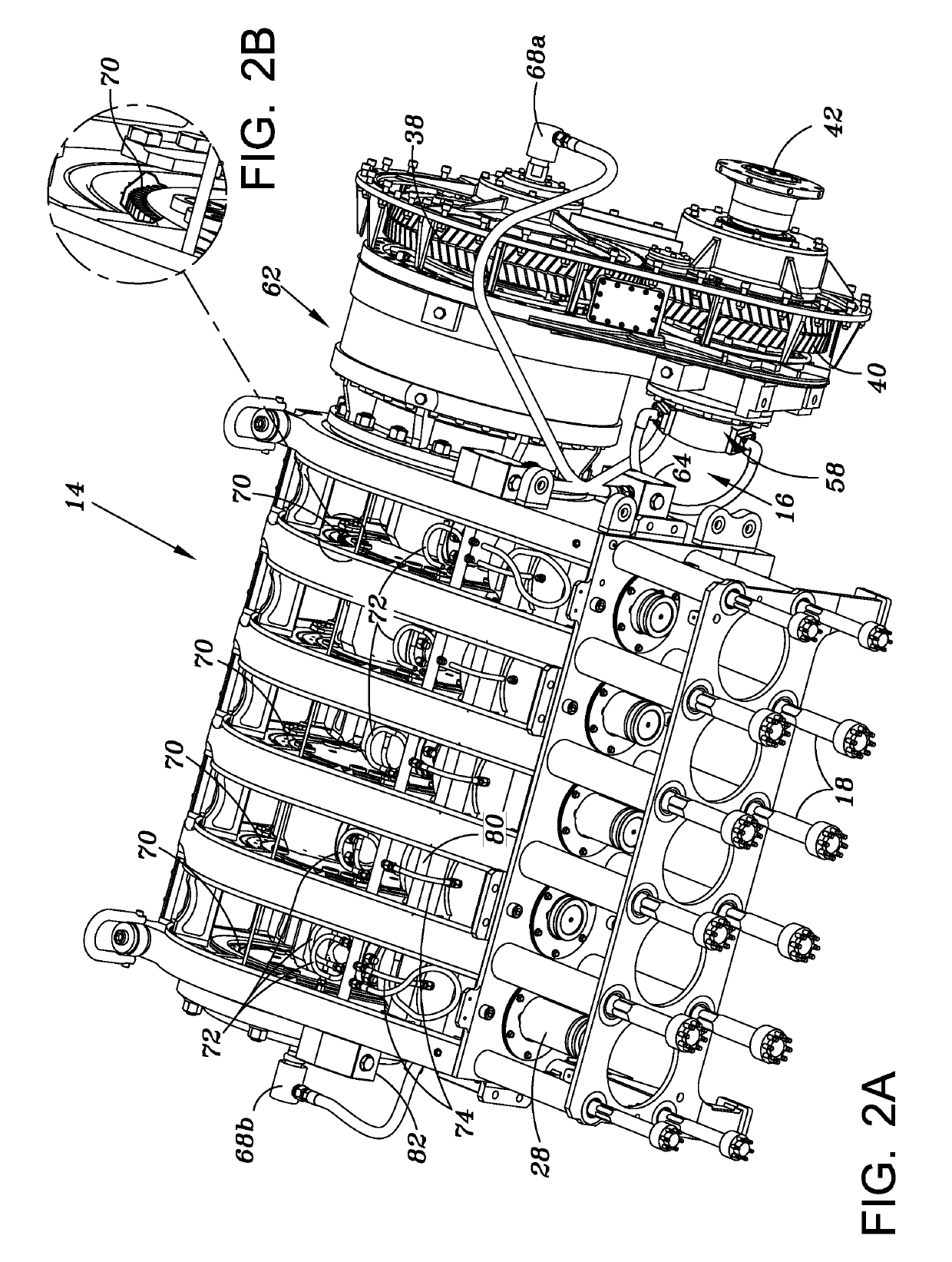

Reciprocating pump with dual circuit power end lubrication system

ActiveUS10352321B2Positive displacement pump componentsRotary/oscillating piston combinationsEngineeringHigh pressure

A dual circuit lubrication system for a power end of a reciprocating pump that includes a lubrication pump that supplies lubrication fluid to a high pressure lubrication circuit and a low pressure lubrication circuit. The high pressure lubrication circuit is fluidly coupled to a crankshaft to supply lubrication fluid to sliding surfaces associated with the crankshaft at a first lubrication fluid pressure. The crankshaft drives a crosshead coupled to a plunger to displace fluid from a fluid end of the reciprocating pump. The low pressure lubrication circuit is fluidly coupled to supply the lubrication fluid to a plurality of rolling surfaces associated with the crankshaft at a second lubrication fluid pressure. The first lubrication fluid pressure is greater than the second lubrication fluid pressure.

Owner:SPM OIL & GAS INC