Patents

Literature

641 results about "Constant rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A constant rate in math is the absence of acceleration. In general, a function with a constant rate is one with a second derivative of 0. If you were to plot the function on standard graph paper, it would be a straight line, as the change in y (or rate) would be constant.

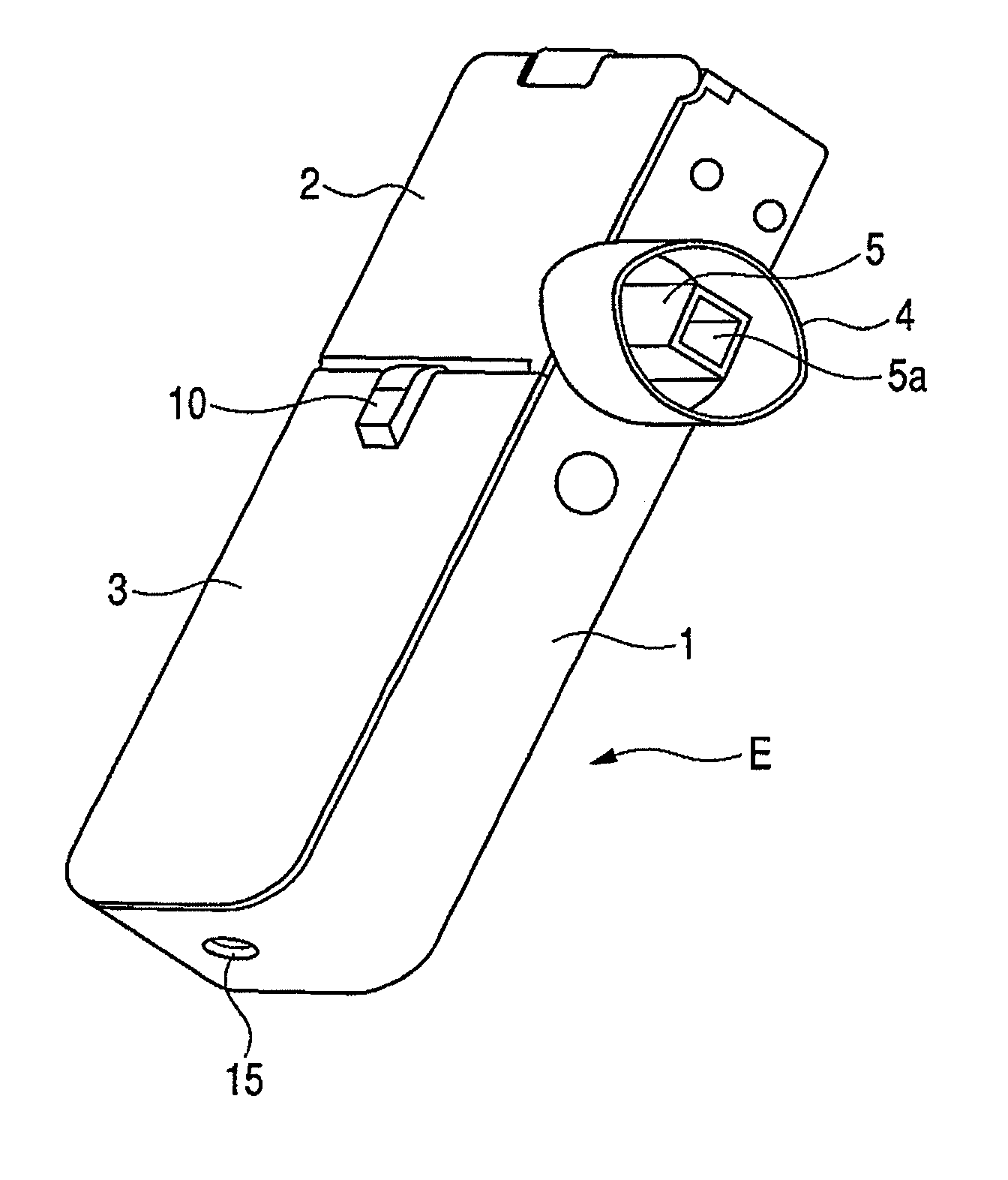

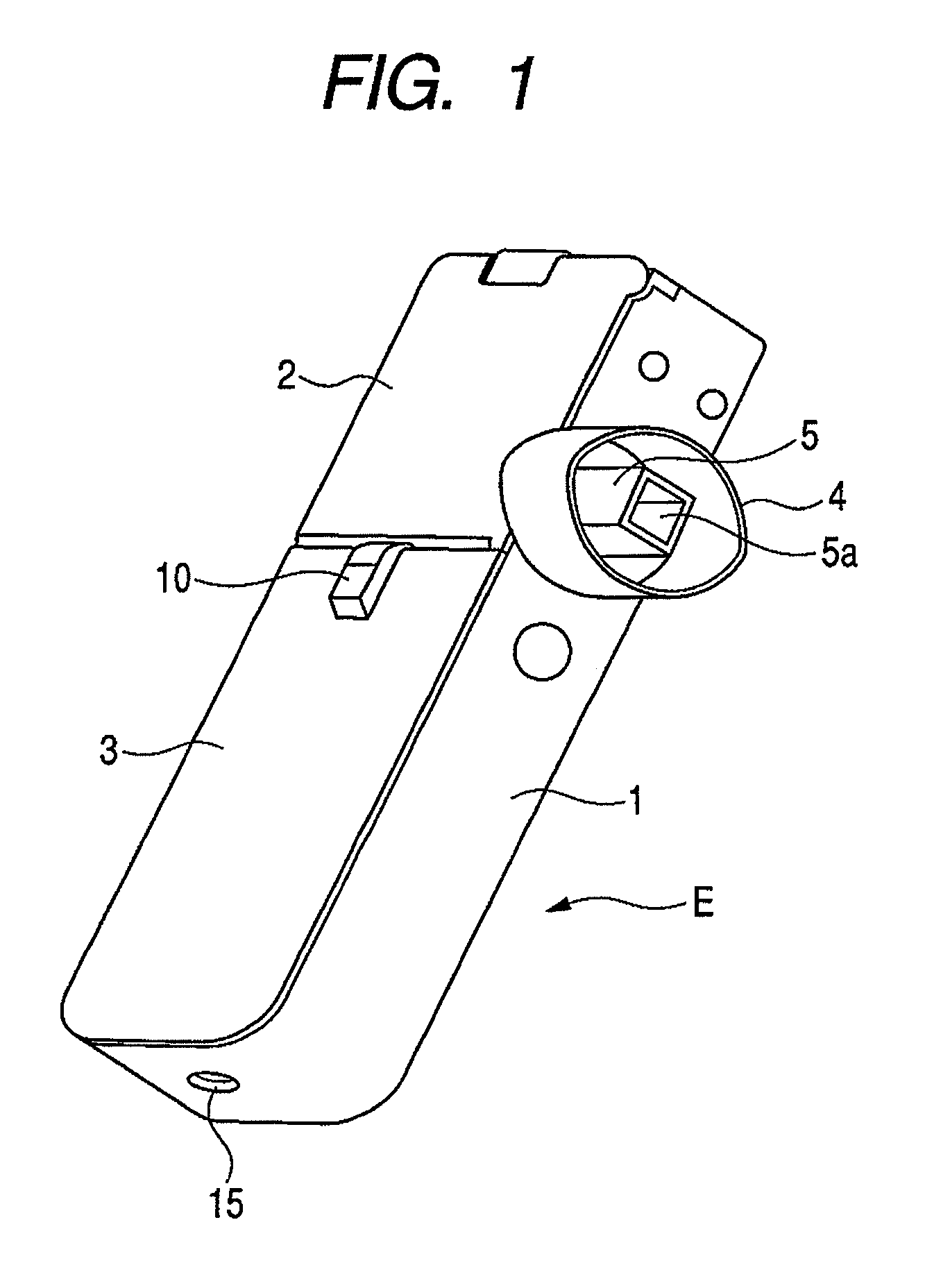

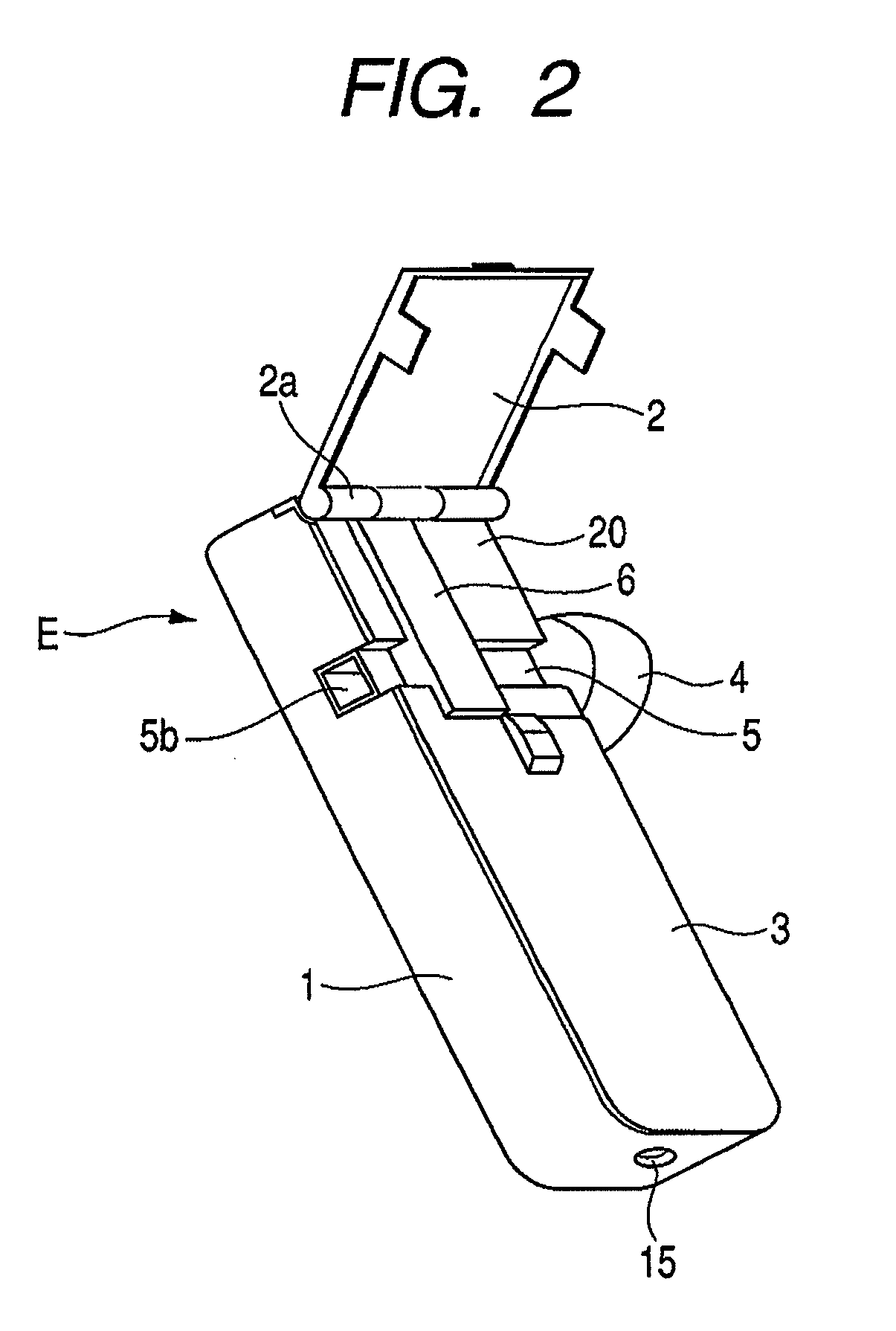

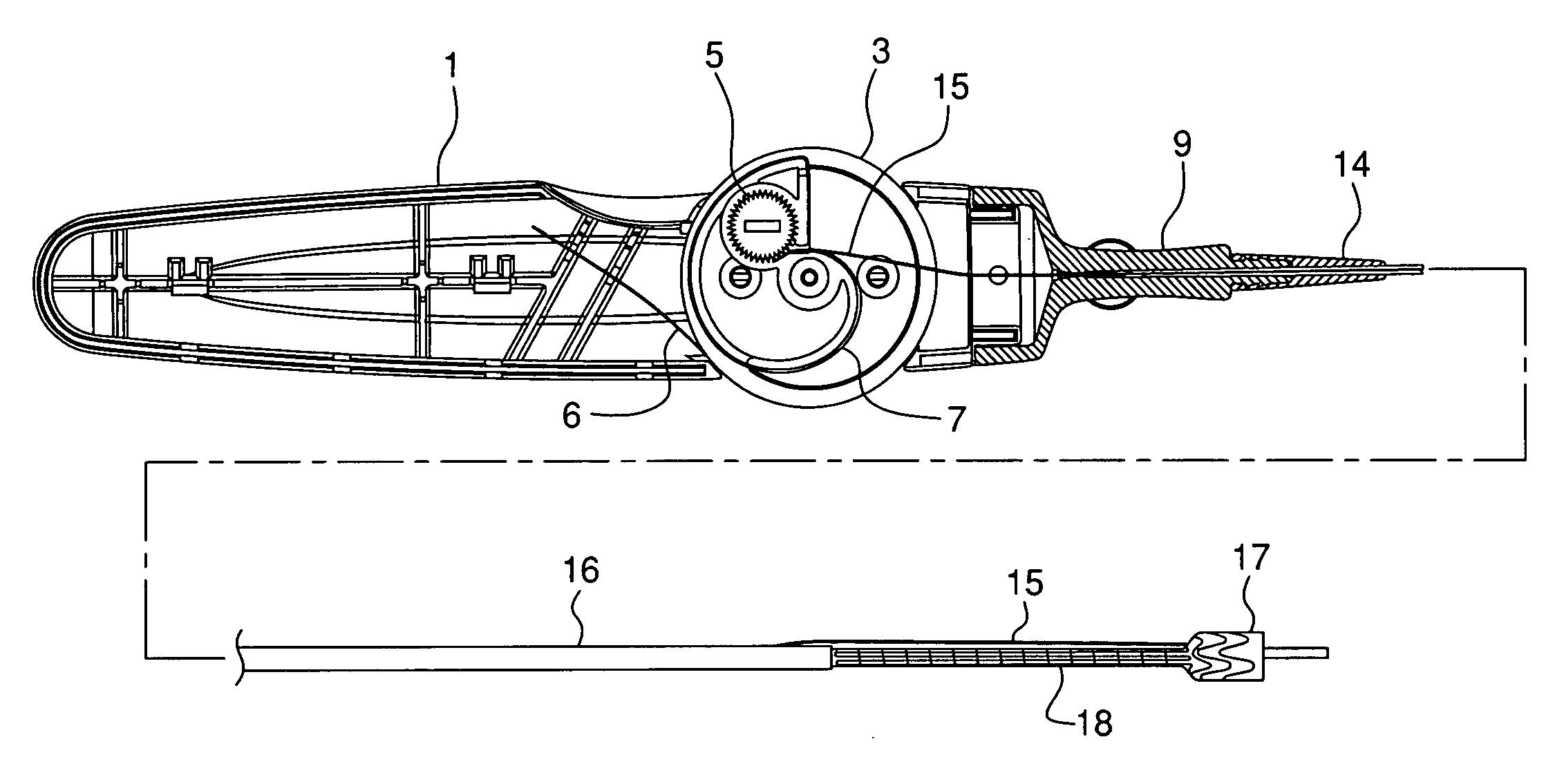

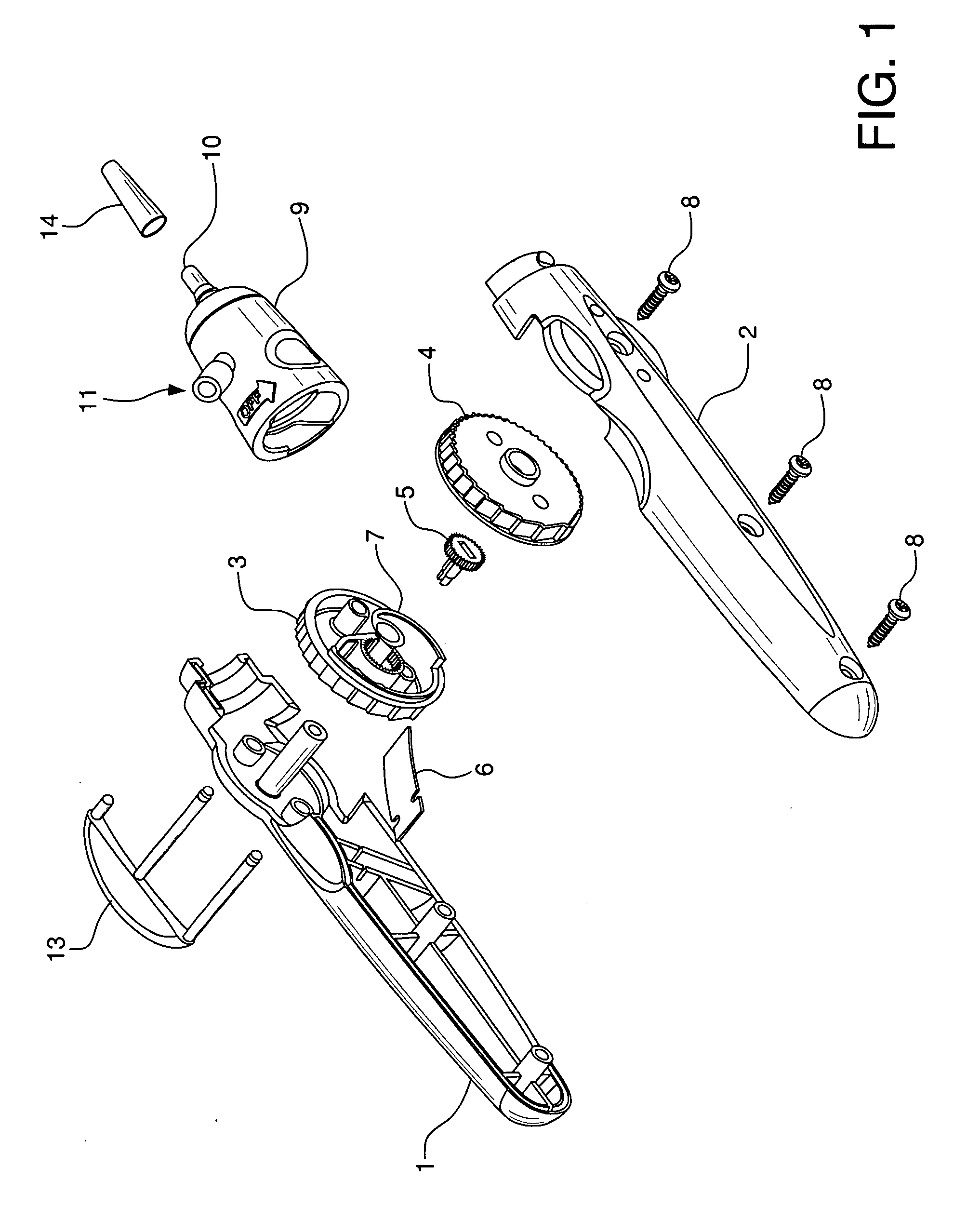

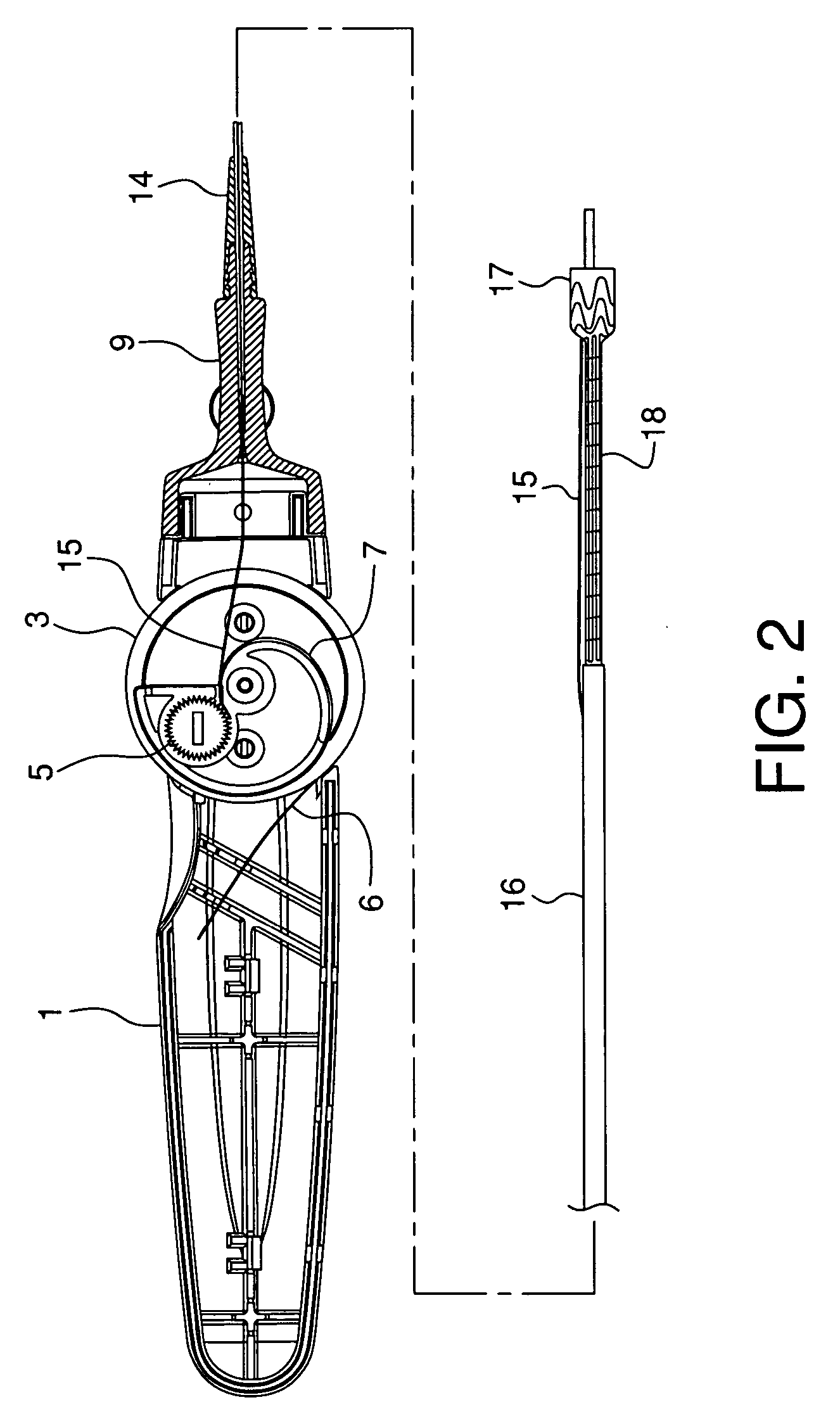

Medicine inhaler and medicine ejection method

InactiveUS7896006B2Efficiently inhaledAccurate doseRespiratorsOperating means/releasing devices for valvesOpen air environmentBiomedical engineering

A medicine ejection device is provided allowing a medicine with a desired droplet diameter to be inhaled at a constant rate. The medicine ejection device has a decision part at which the ejection operating conditions of a medicine ejection part for ejecting the medicine are decided in accordance with at least one of an open-air environment or a state of the medicine during use of the device. The device ejects the medicine according to the ejection operating conditions decided by the decision part.

Owner:CANON KK

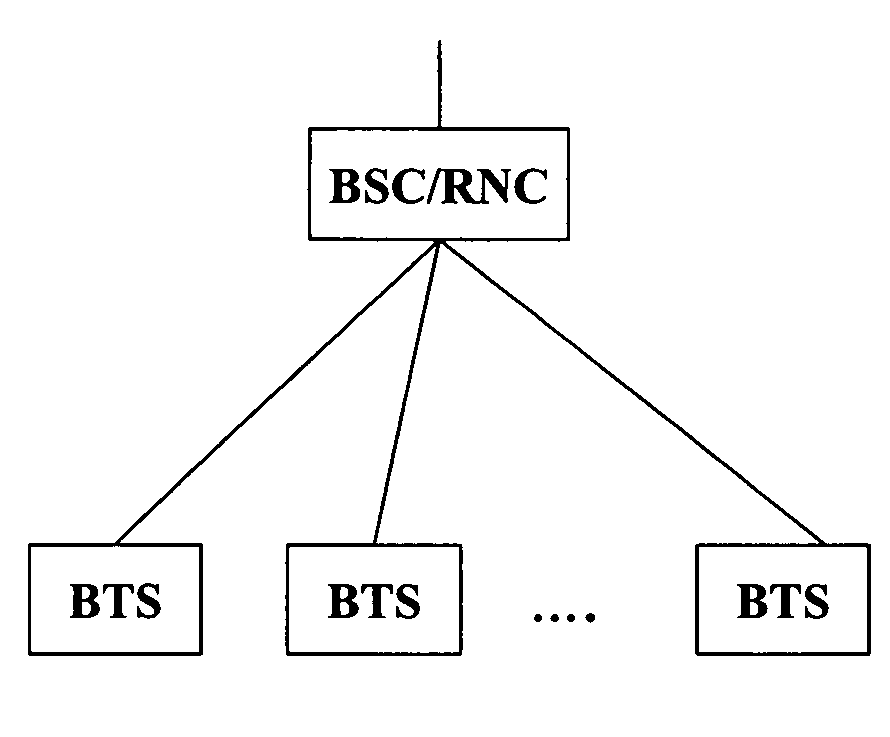

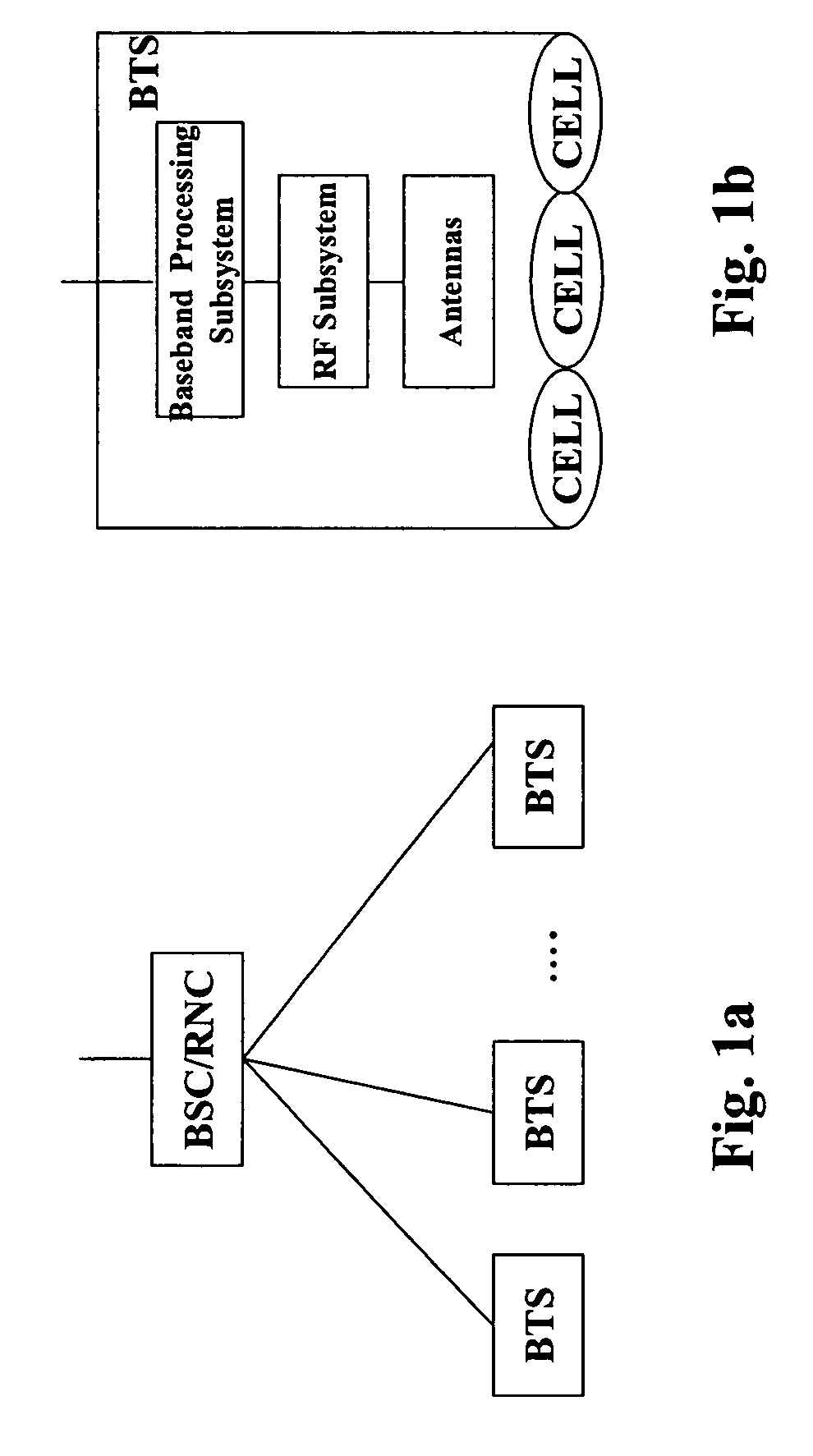

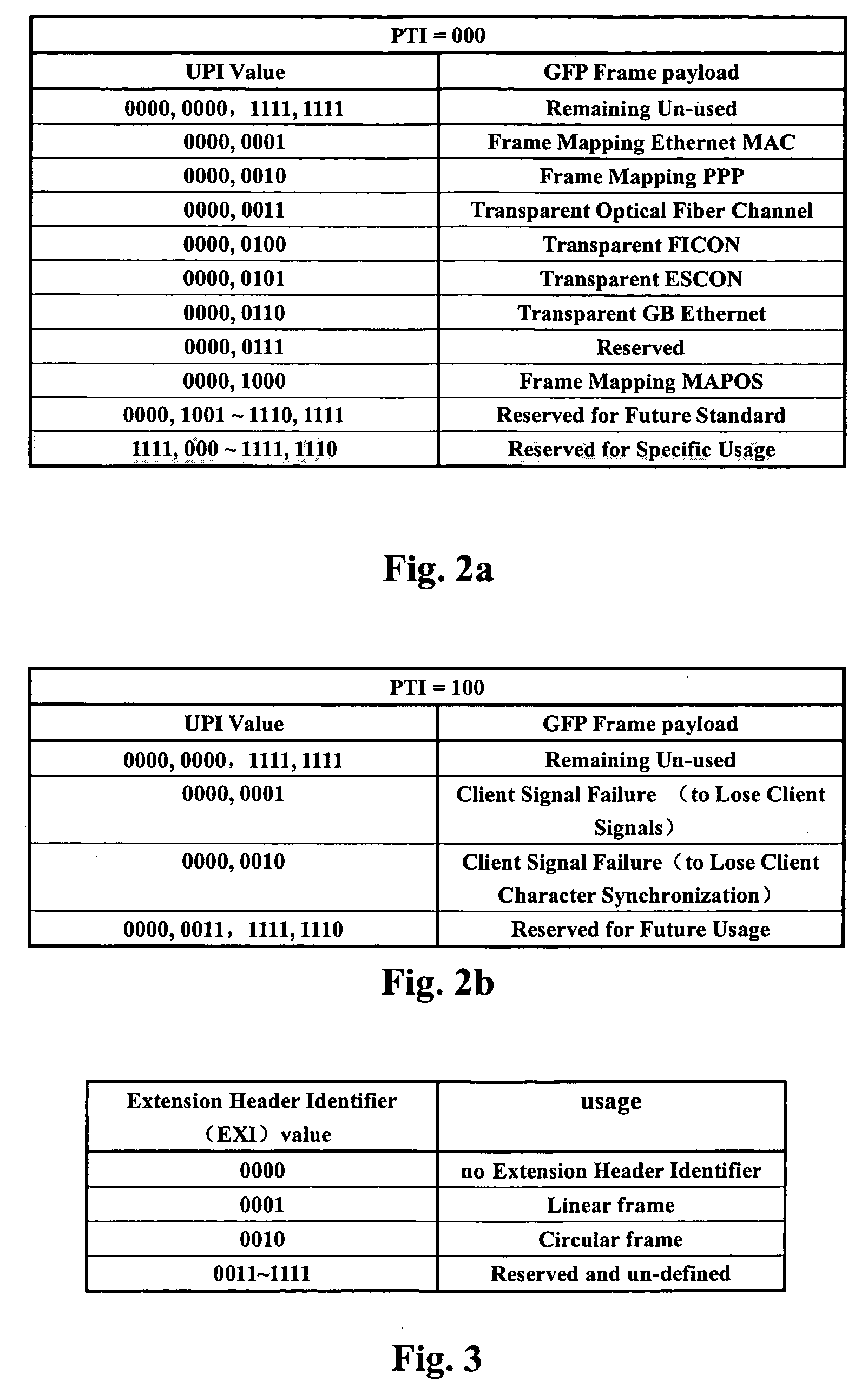

CPRI-based multiprotocol signal transmission method and apparatus in distributed base station system

InactiveUS20070091896A1EffectiveNetwork traffic/resource managementNetwork topologiesSTM-1Interface protocol

The present invention provides a method for realizing transmission of multiprotocol client signals in a distributed base station subsystem, comprising: encapsulating client signals by a GFP-T frame; and mapping said GFP-T frame into a lower-layer transmission link to realize the transmission of client signals. Said lower-layer transmission link is a common public radio interface CPRI link. Said client signals are one of the following: baseband I / Q signals of WCDMA supported by CPRI protocol, baseband I / Q signals of radio interface protocols other than WCDMA, structured signals of E1 / T1, STM-1 and other constant-rate links, structured variable-rate link signals such as Ethernet MAC frame signals, PPP / HDLC frame signals, etc. This method is also applicable to other types of synchronous transmission links between a remote radio unit and a primary baseband processing unit, e.g., the links as specified by OBSAI (Open Base Station Architecture Initiative).

Owner:UTSTARCOM TELECOM CO LTD

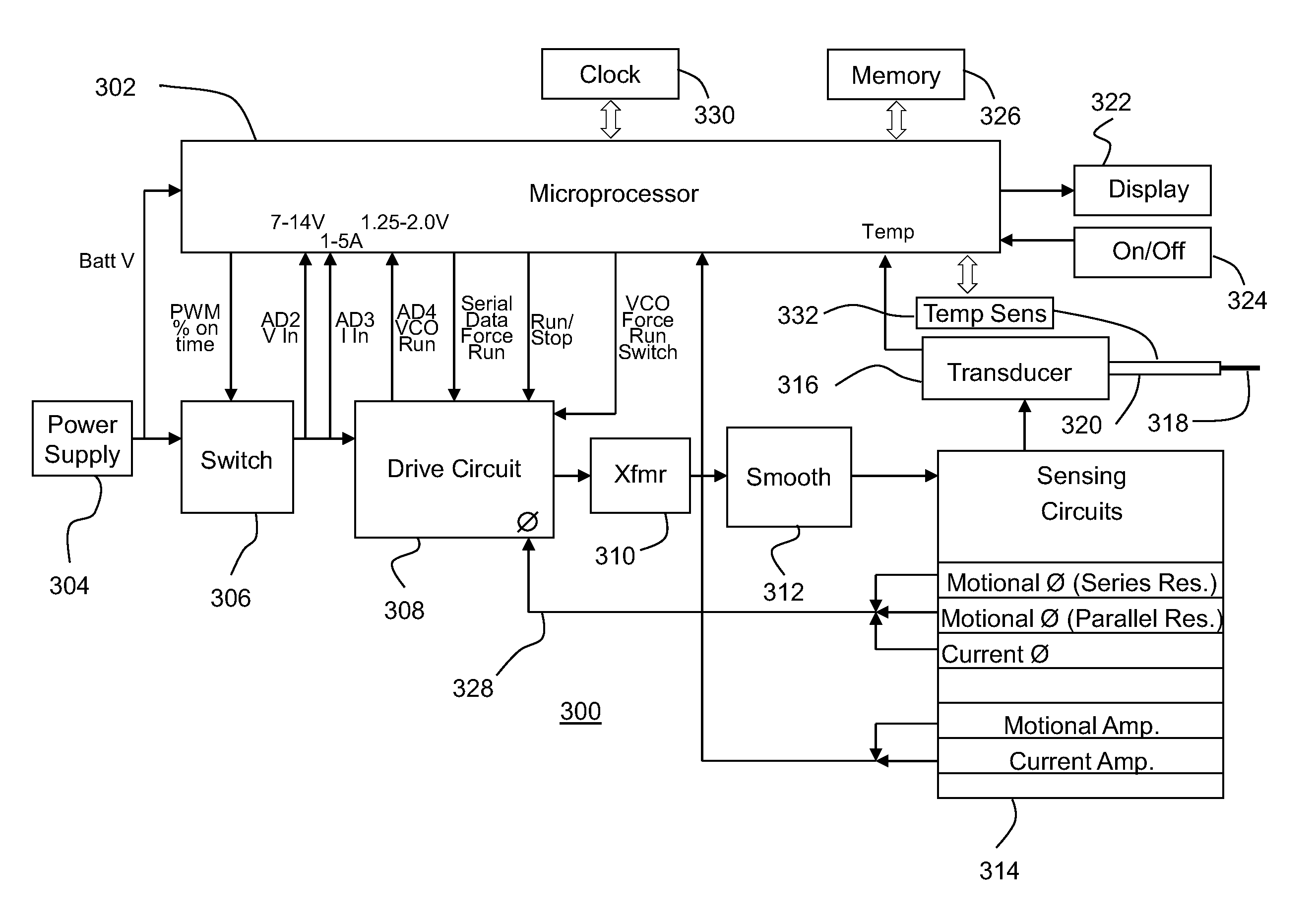

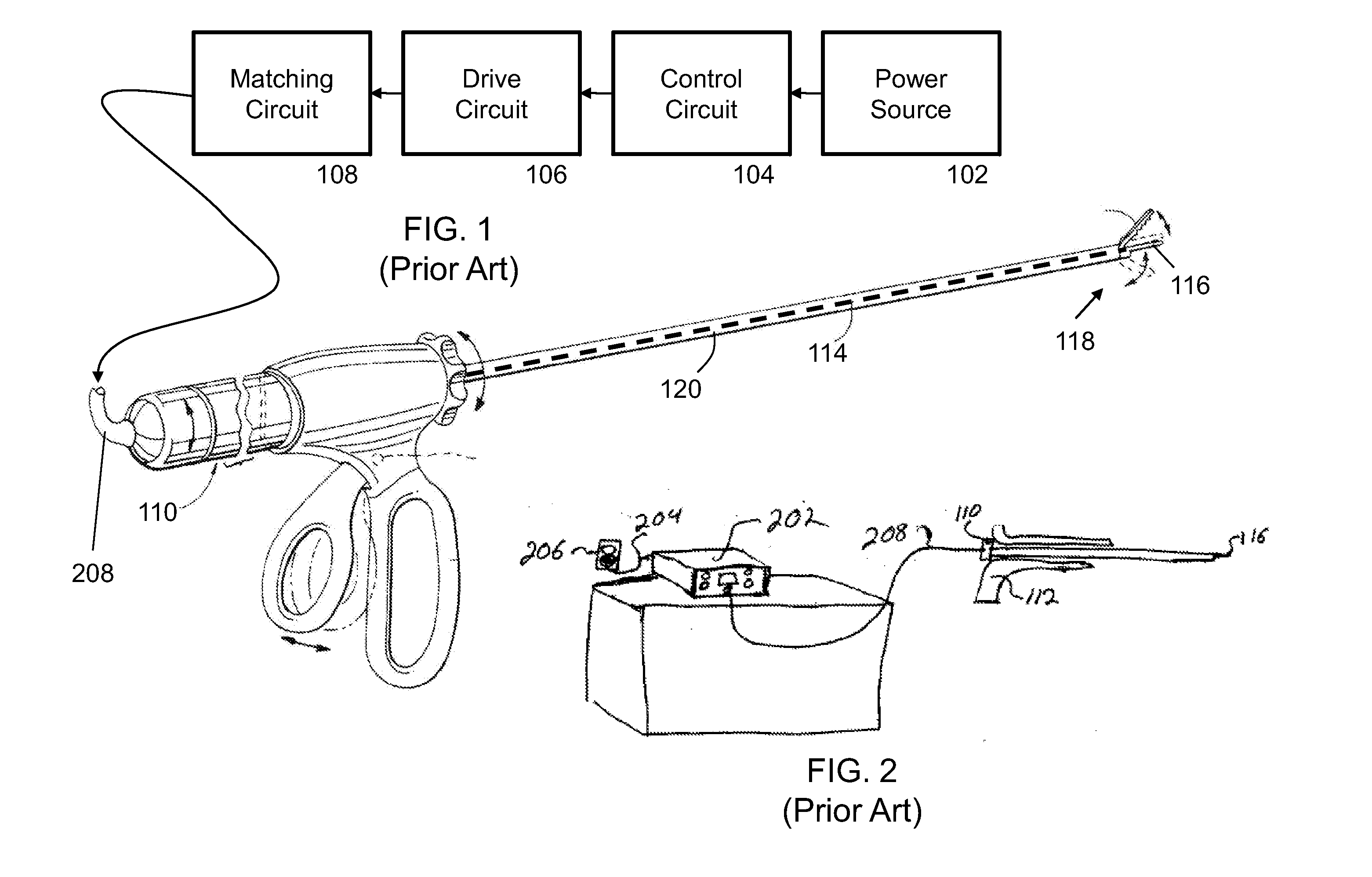

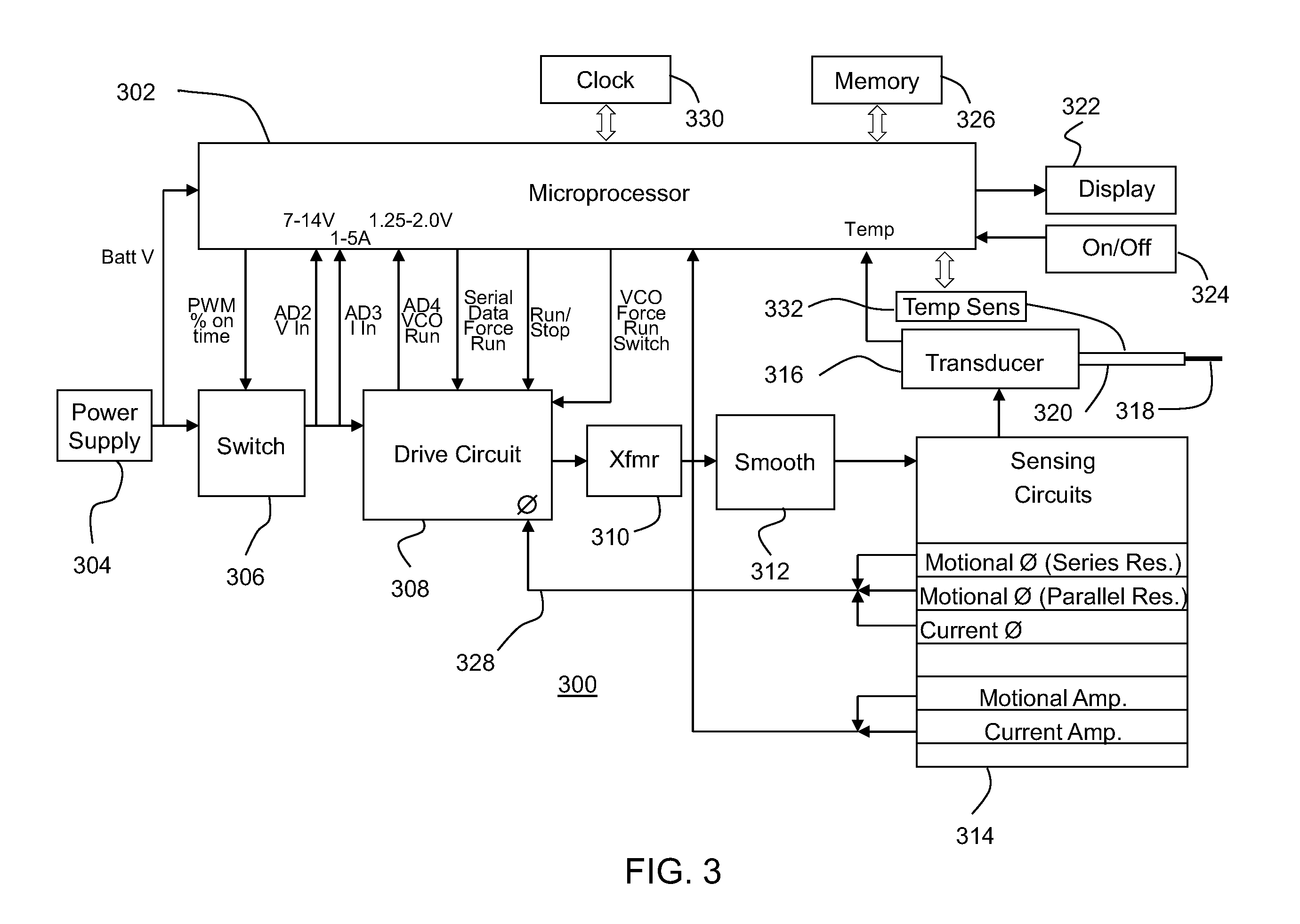

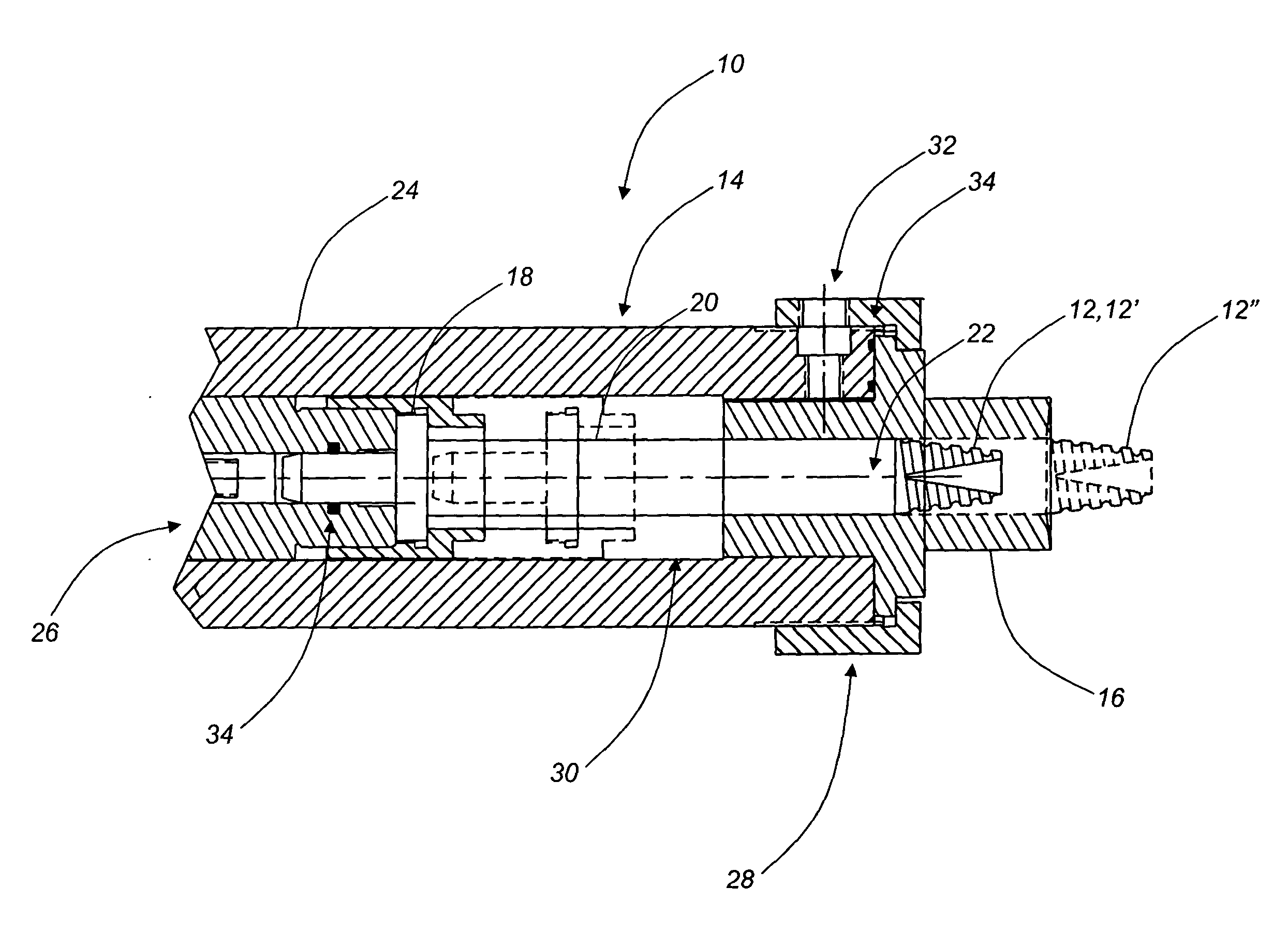

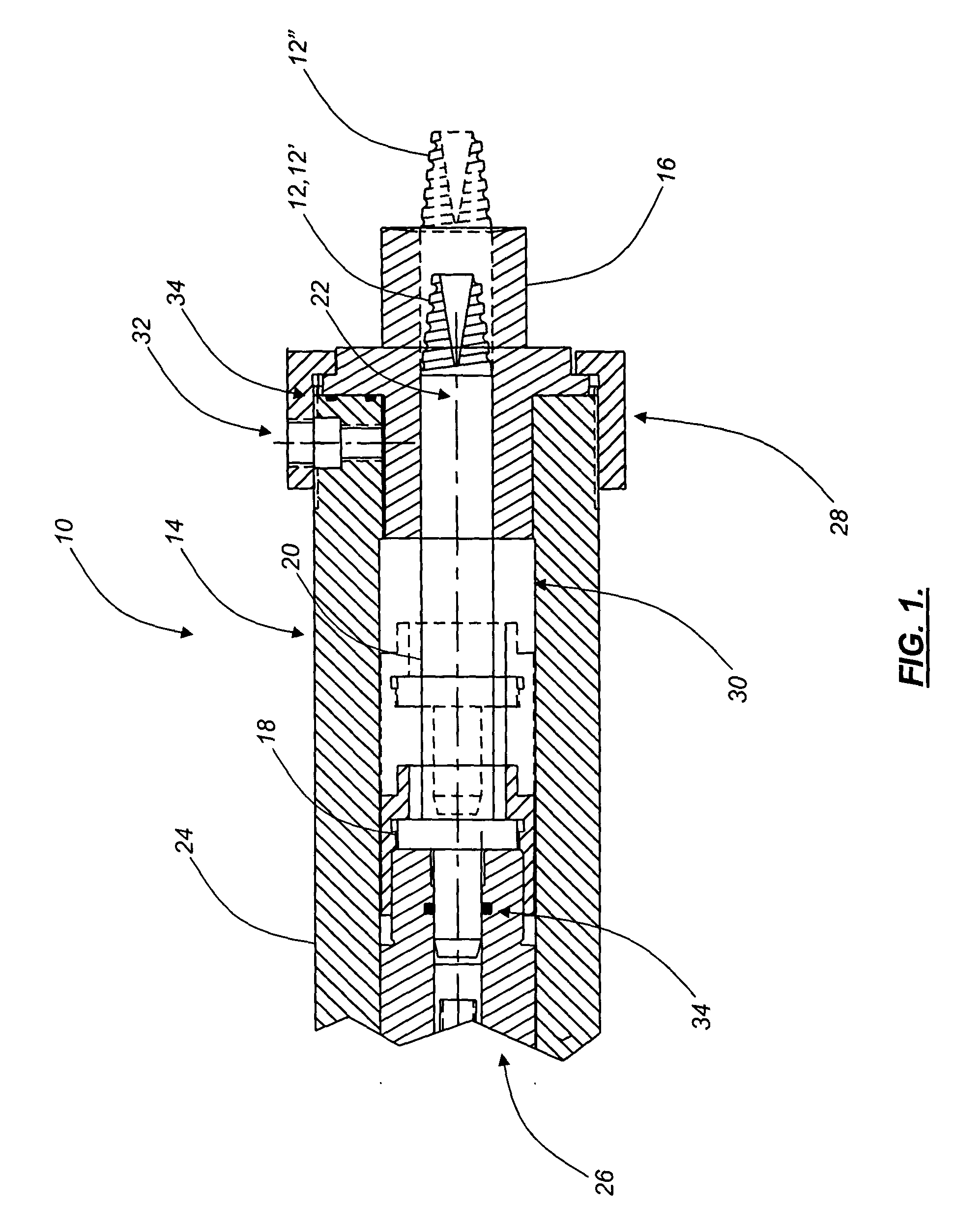

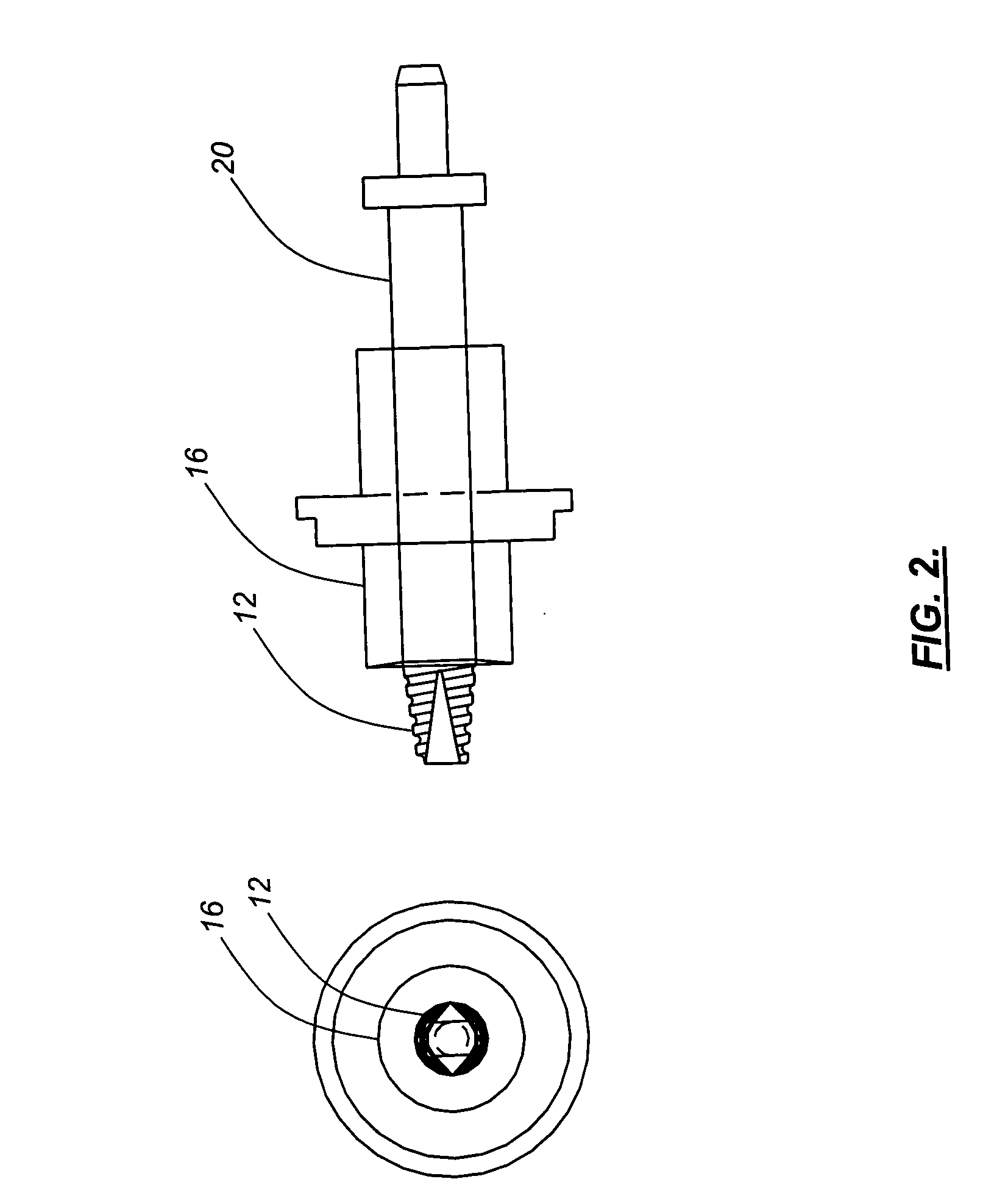

Cordless Hand-Held Ultrasonic Cautery Cutting Device

ActiveUS20110167619A1Alter functionAlter performanceElectrical transducersSurgeryUltrasonic sensorHand held

An ultrasonic surgical assembly includes an ultrasonic transducer operable to convert a received motional current into a movement of a cutting blade of an ultrasonic waveguide, a measurement circuit connected in a parallel configuration with the ultrasonic transducer, a variable power source operable to supply current through a set of connection points to the parallel configuration and thereby create the motional current in the ultrasonic transducer, and a current controller operable to regulate the motional current by varying an output of the variable power source, thereby maintaining a substantially constant rate of movement of the cutting blade across a variety of cutting loads.

Owner:COVIDIEN AG

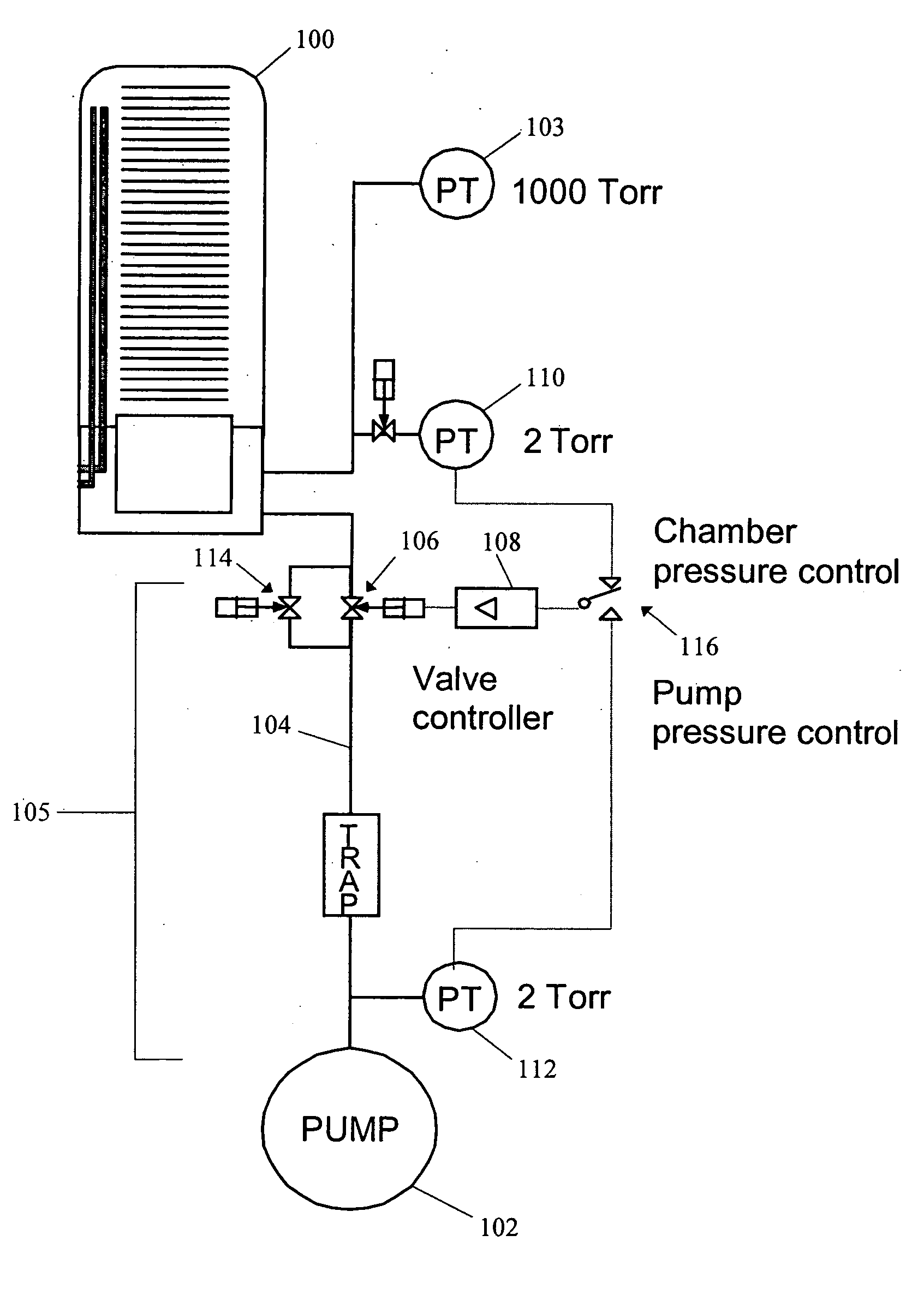

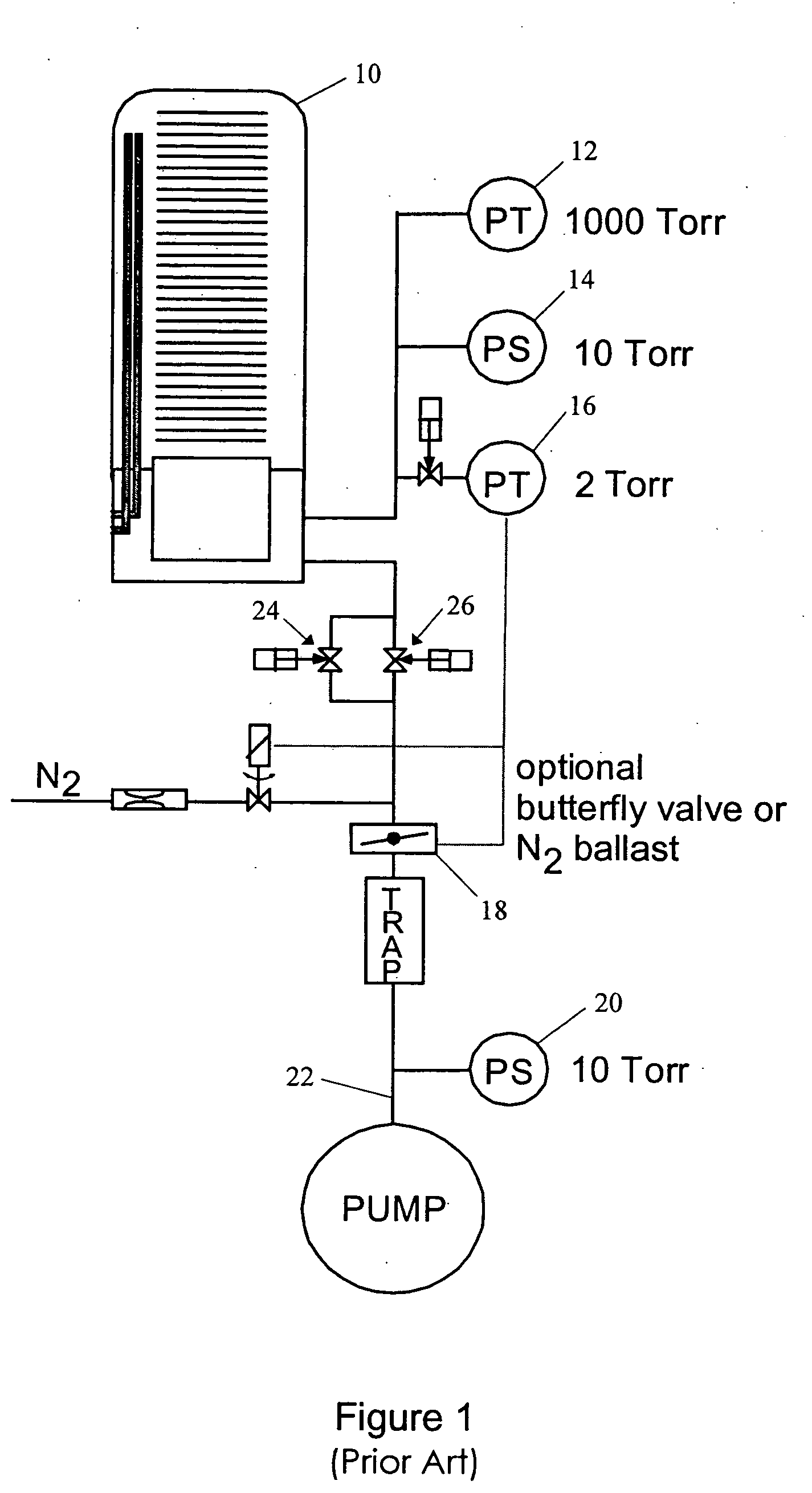

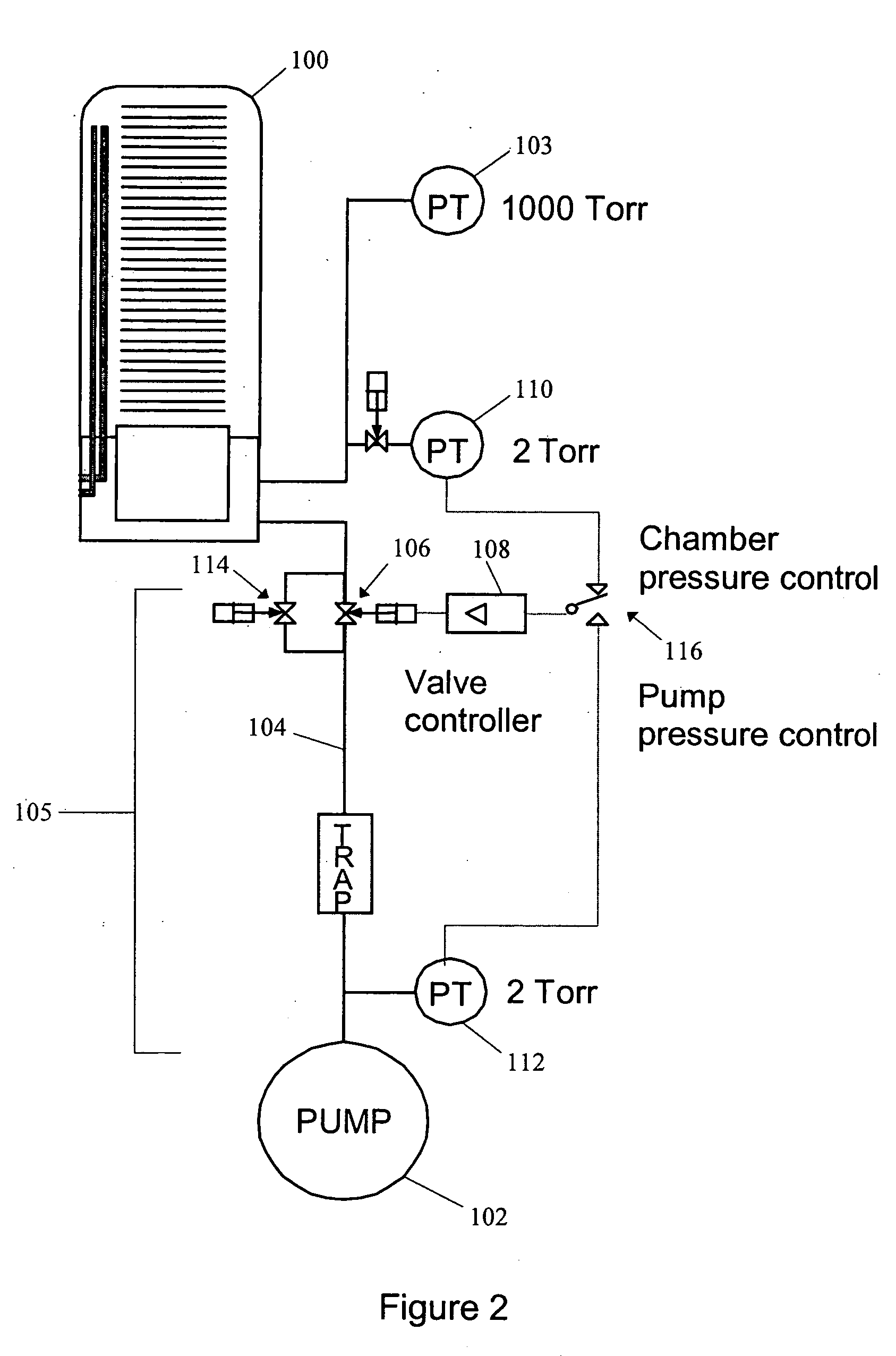

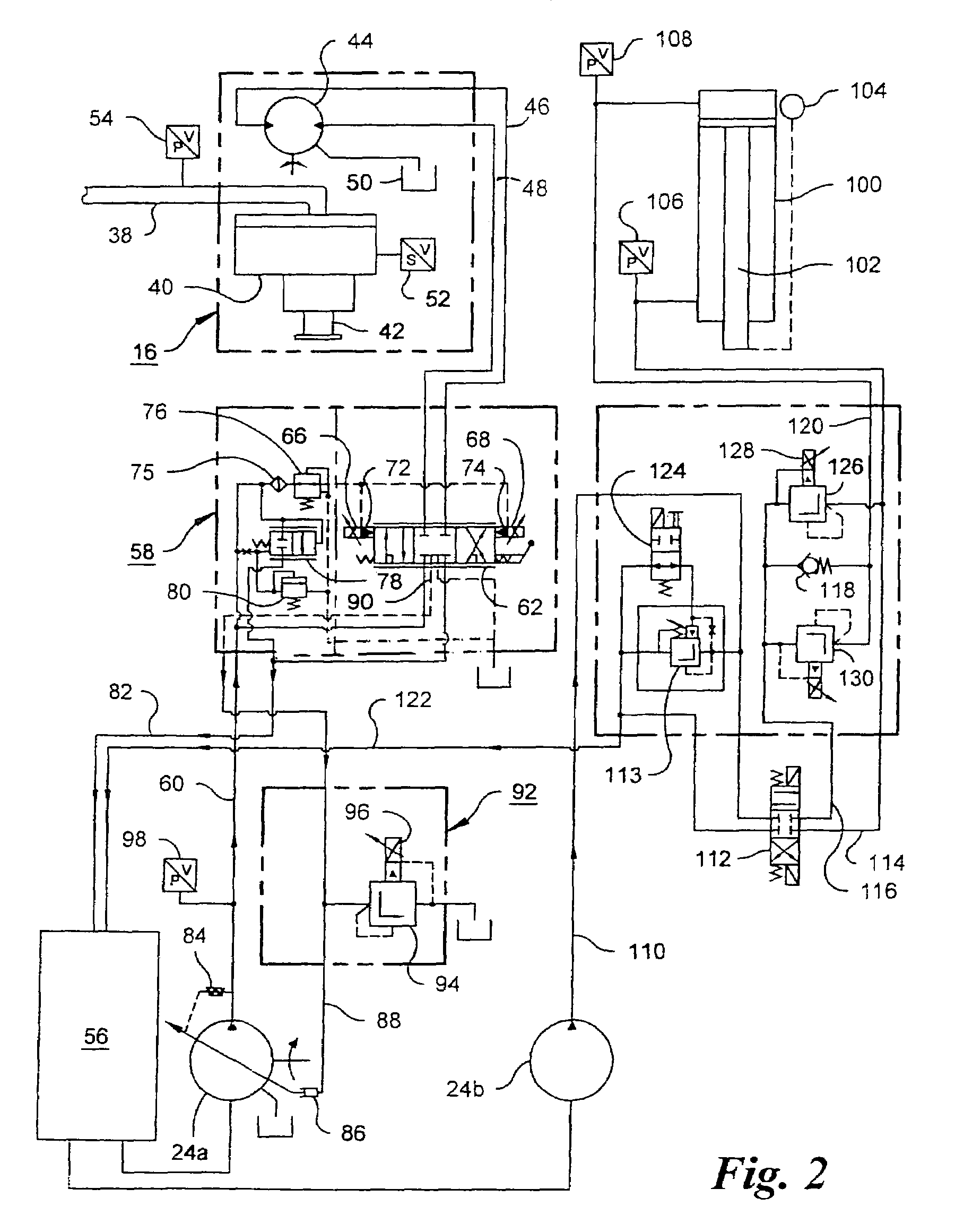

Pressure control system

ActiveUS20050279454A1Semiconductor/solid-state device manufacturingFluid pressure control using electric meansControl systemVacuum pump

A pressure control system allows gas to be evacuated out of a semiconductor process chamber at a substantially constant rate of mass flow. A gas line connects the process chamber to a vacuum pump. A controllable valve having a variable sized opening is positioned between the process chamber and the vacuum pump. A pressure sensor is in turn positioned between the valve and the vacuum pump, proximate the inlet to the vacuum pump. The size of the variable sized opening is regulated based upon the pressure in the gas line measured by the pressure sensor. The size of the valve opening is varied to maintain the pressure measured by the pressure sensor at a constant value. As a result, because the quantity of gas flowing through the gas line is proportional to the gas pressure, a substantially constant mass flow of gas out of the chamber and into the pump can be achieved.

Owner:ASM INTERNATIONAL

Electrically heated/phase change probe temperature control

ActiveUS20050171582A1Reduce temperature differenceSurgical instruments for heatingTherapeutic coolingTemperature controlSurface cooling

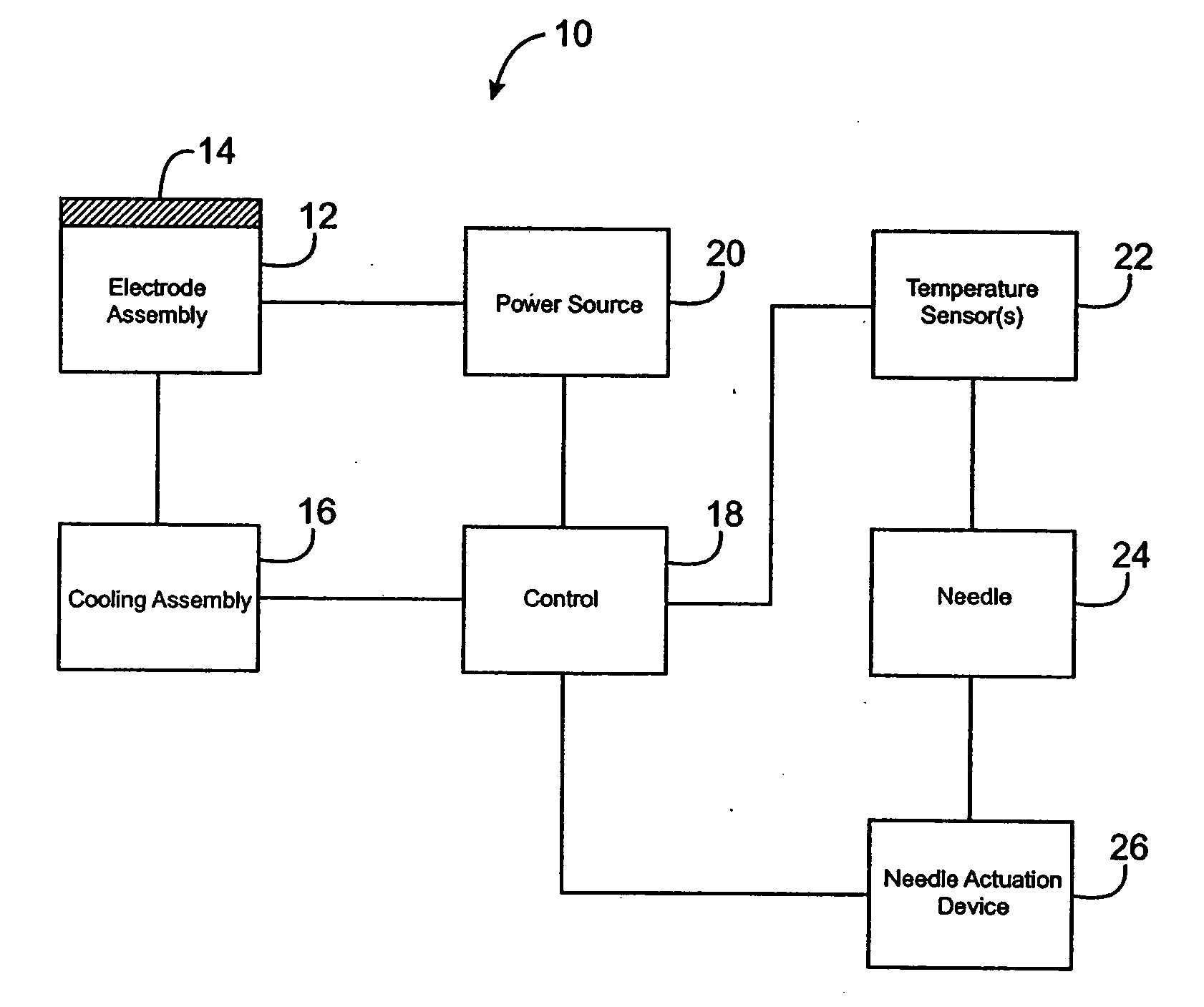

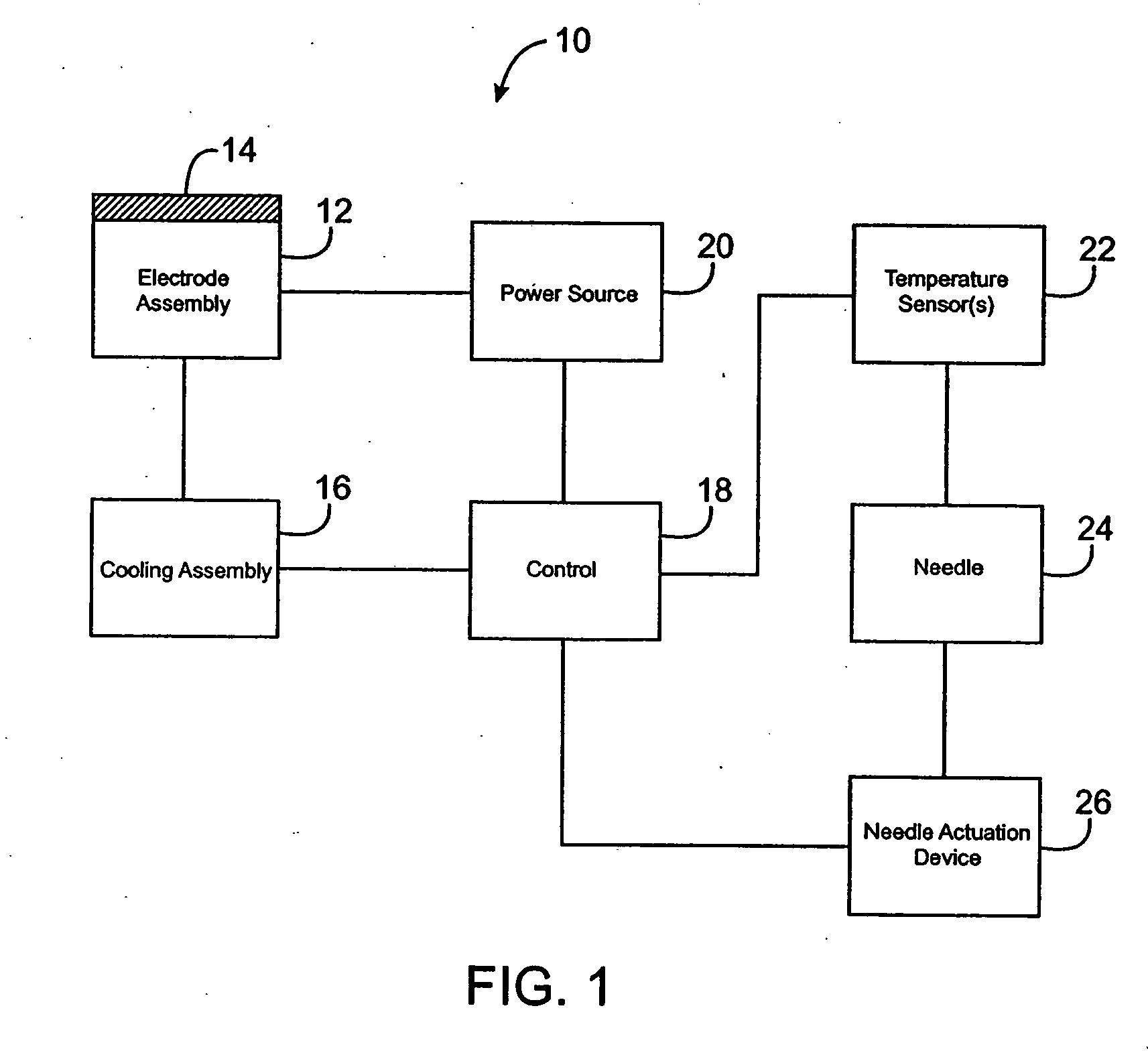

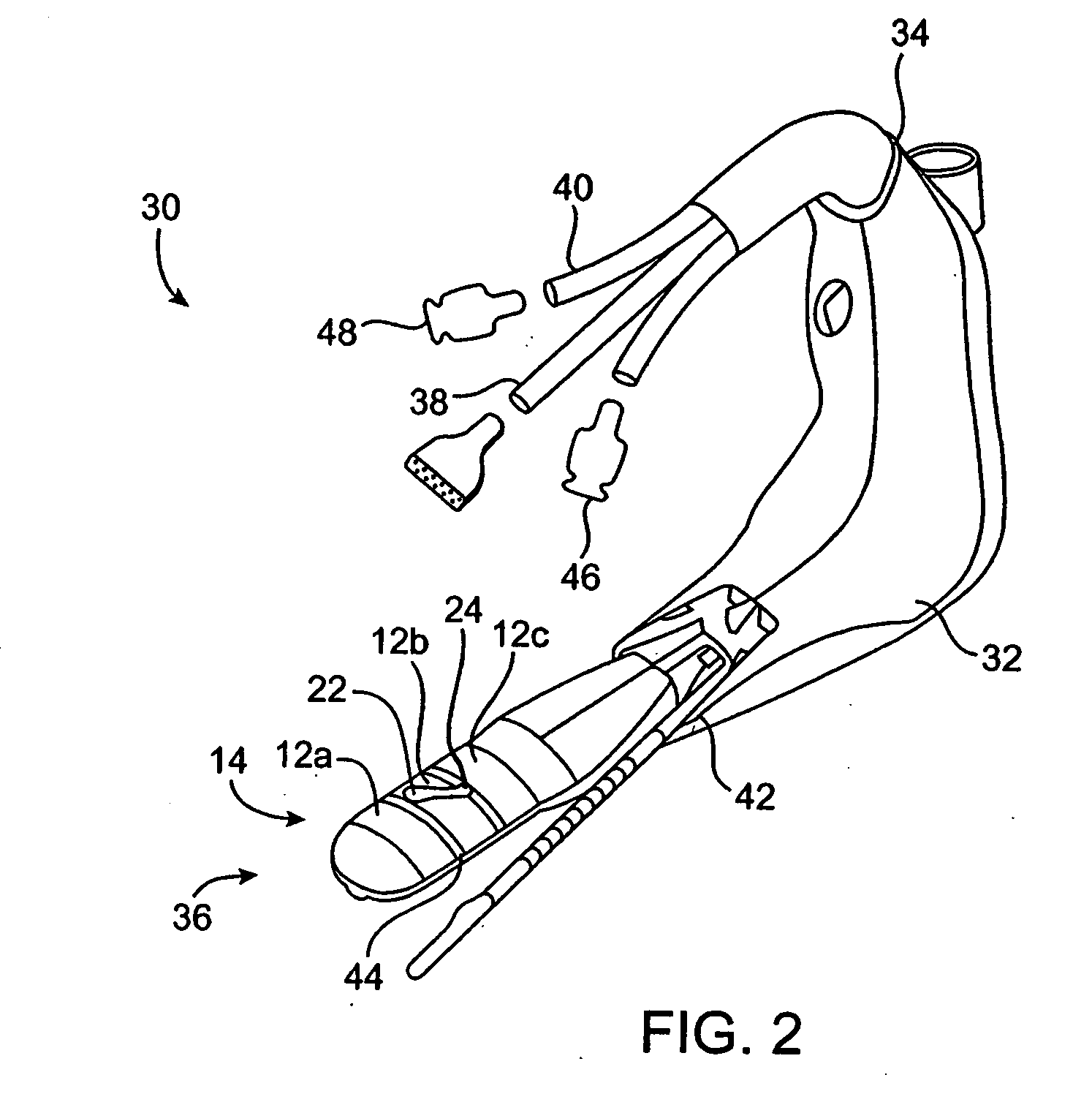

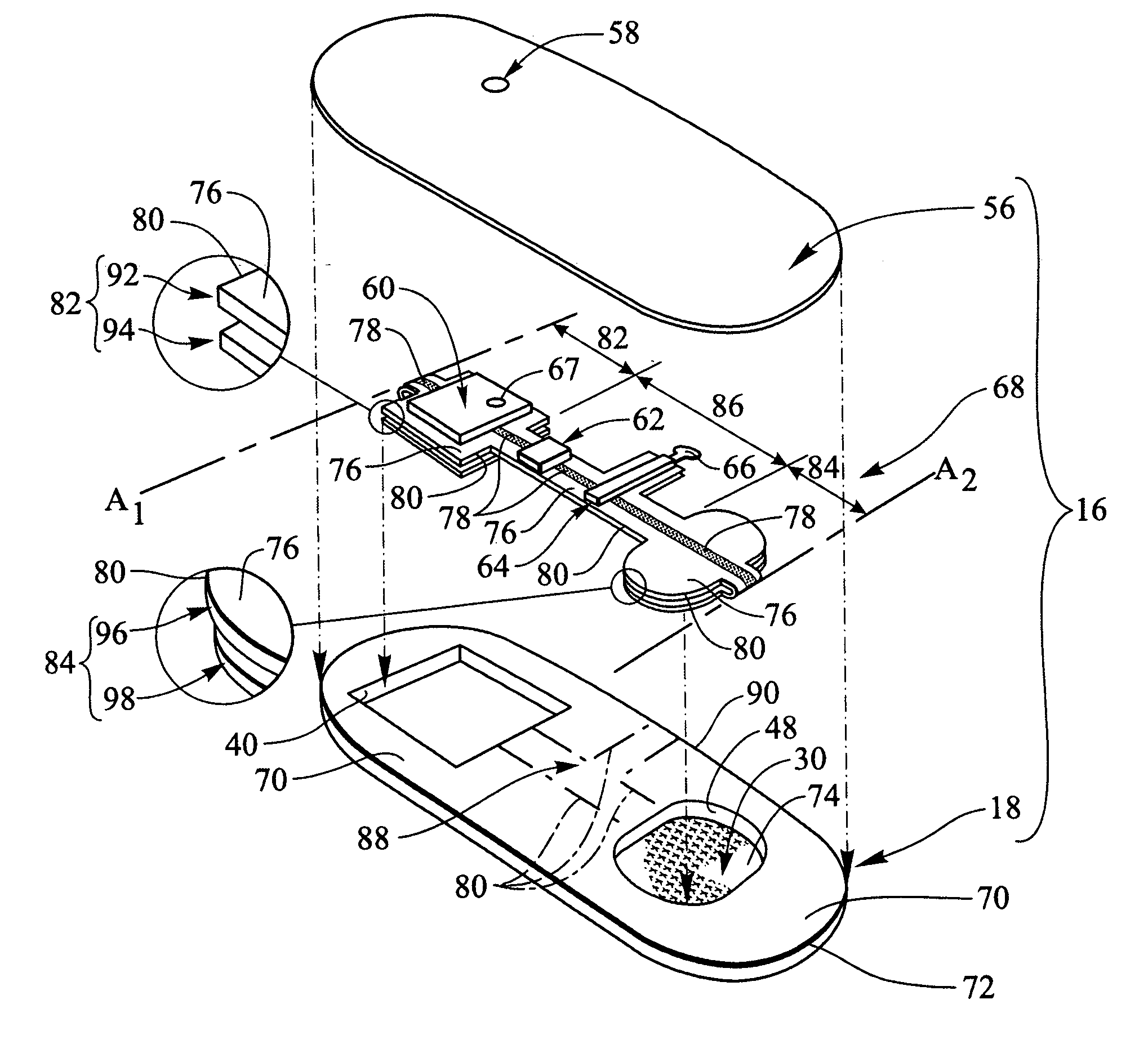

The present invention provides devices and methods for treating tissue. In one embodiment the present invention provides a method of controlling a temperature of an applicator body, the method comprising providing an applicator body that comprises at least one contact surface A coolant is delivered through at least a portion of the applicator body at a substantially constant rate. Energy is delivered to the coolant through a heating element so that the contact surface of the applicator body is cooled to a desired temperature.

Owner:ASTORA WOMENS HEALTH

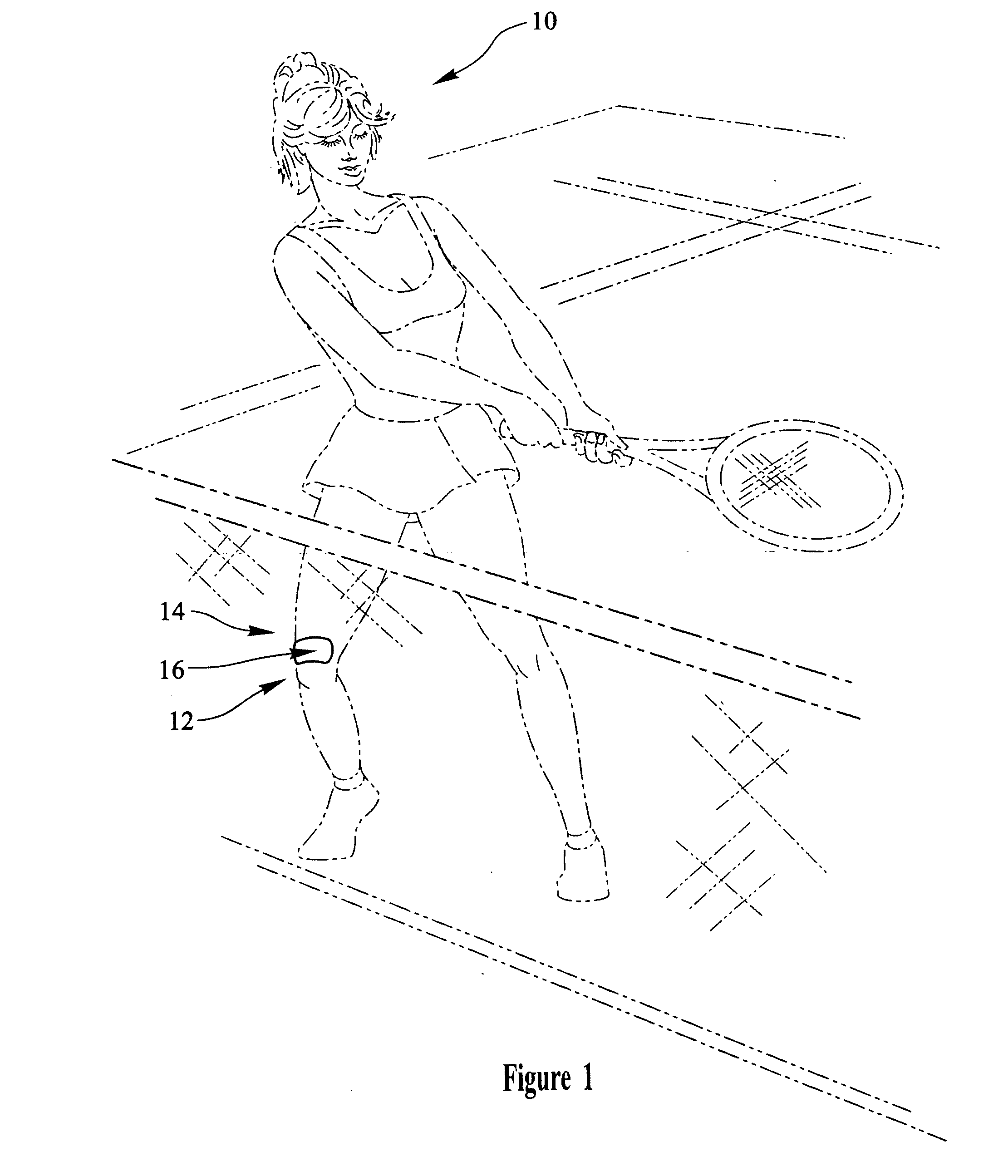

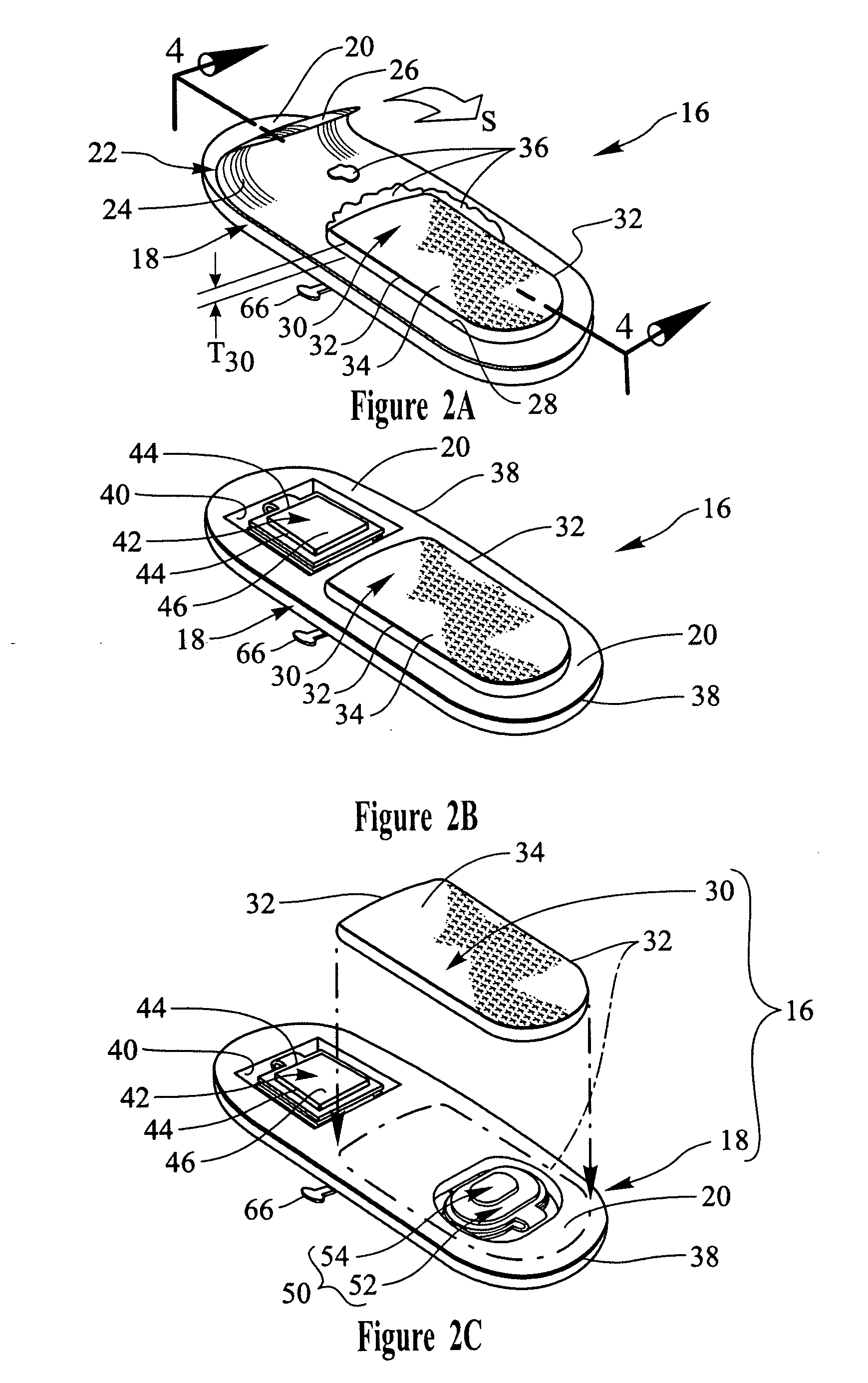

Active transdermal medicament patch

InactiveUS20080214985A1Improve securityReduce technical difficultyElectrotherapySheet deliveryPlanar substrateTransdermal medication

An active transdermal medicament patch includes a planar substrate with a therapeutic face releasably retainable against the skin of a patient. A return electrode and a medicament matrix susceptible to permeation by medicament are secured at separated locations on the therapeutic face. Each electrically conductively engages the skin, when the substrate is retained thereon. A power source carried on the substrate is electrically coupled between the medicament matrix and a programmed microprocessor also carried on the substrate. A substantially invariant voltage presented at an output contact of the microprocessor is applied during a predetermined therapy period across the skin between the medicament matrix and the return electrode, inducing transcutaneous migration of medicament into the skin at a substantially constant rate. A light-emitting diode carried on the substrate and coupled to the microprocessor communicates that the patch is operating.

Owner:ACTIVATEK

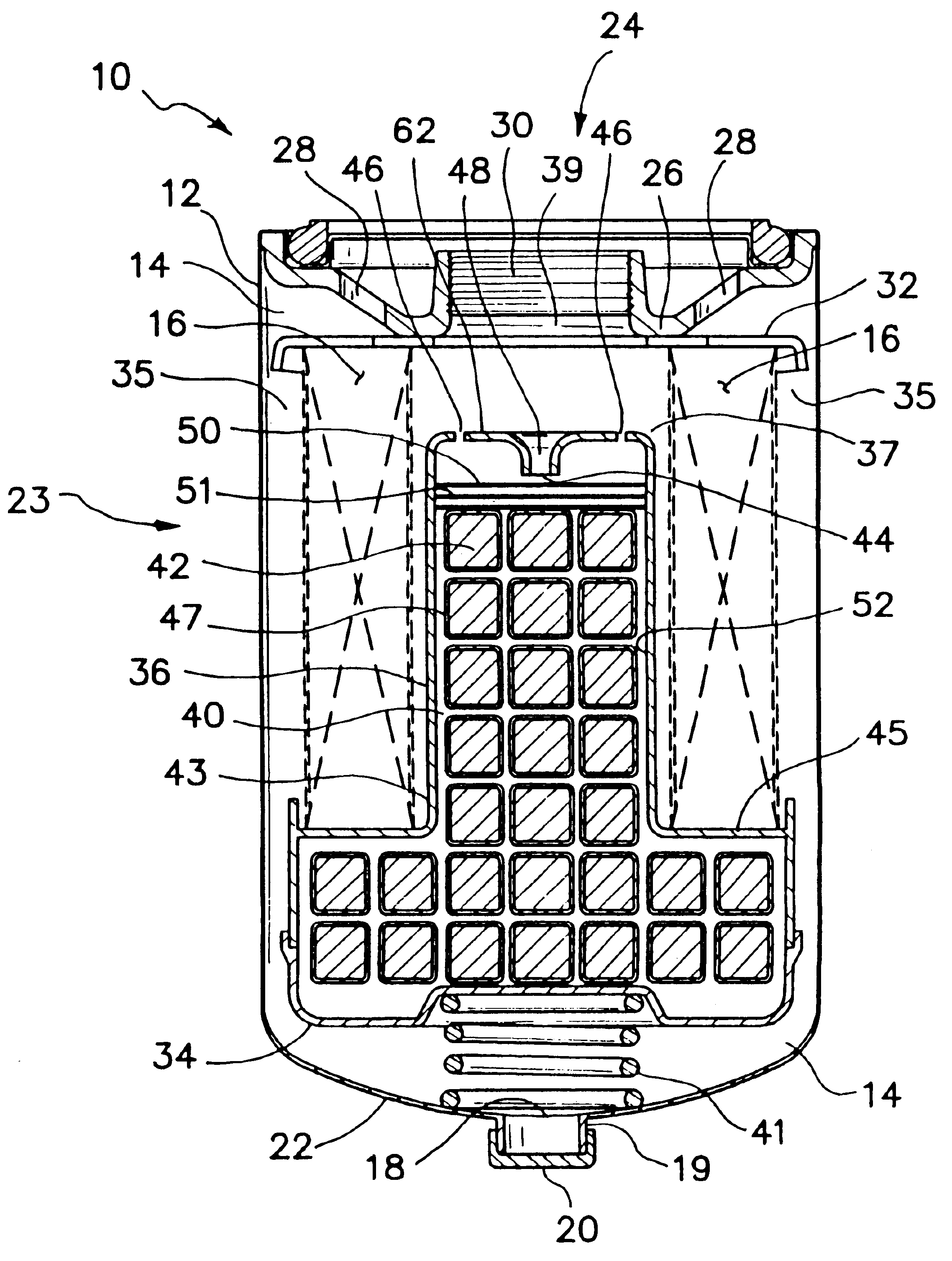

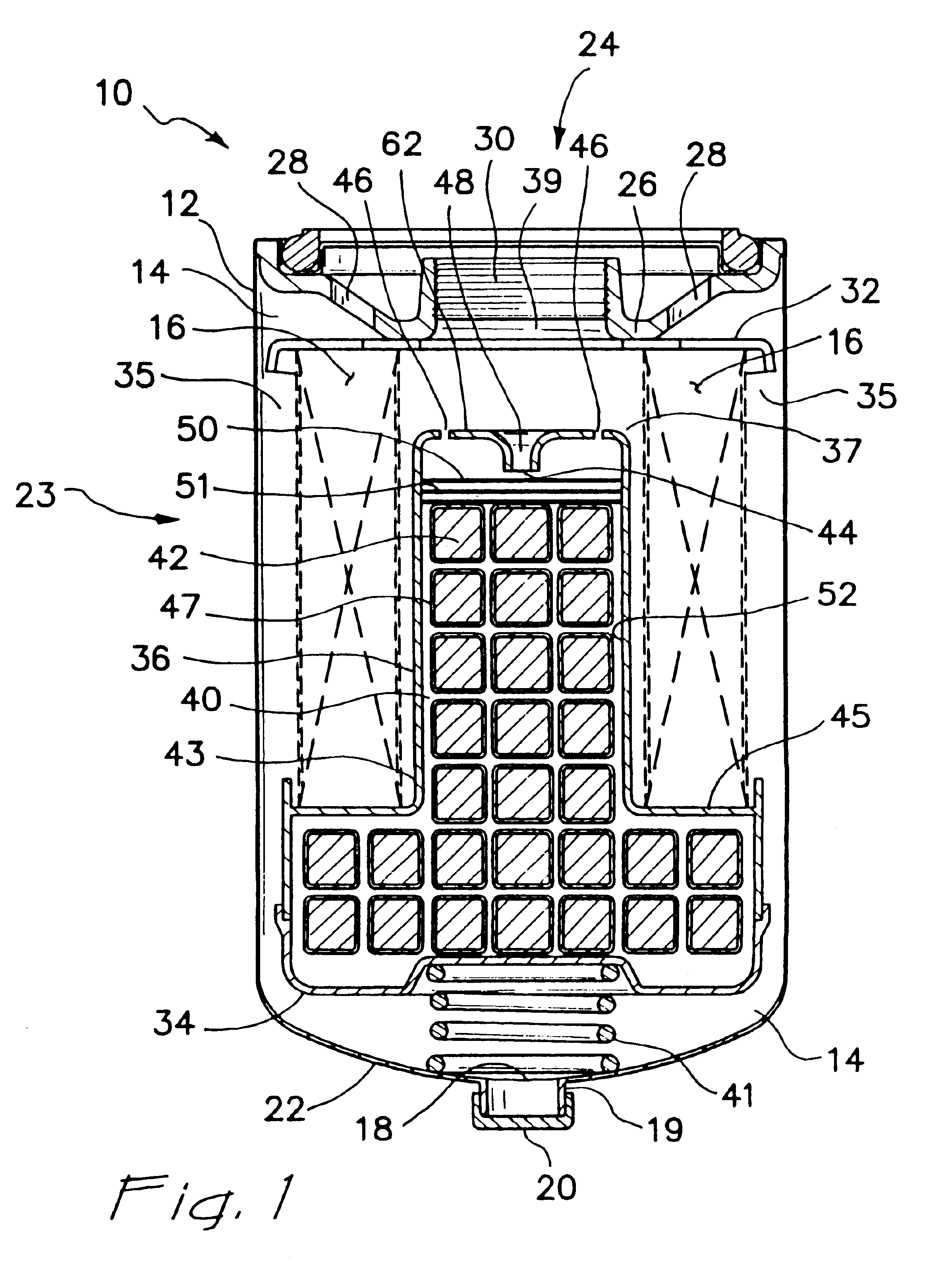

Fuel filter including slow release additive

This invention relates to a fuel filter for use with internal combustion engines. The fuel filter includes a fuel additive that can be released into fuel. The rate of release for the fuel can be controlled. In one form the fuel additive can be mixed with a matrix material and released at a substantially constant rate to maintain a uniform level of fuel additive in the fuel. Use of the present invention provides a fuel filter having an extended life span that is longer than fuel filters typically used with combustion engines.

Owner:DOBER CHEMICAL CORPORATION +1

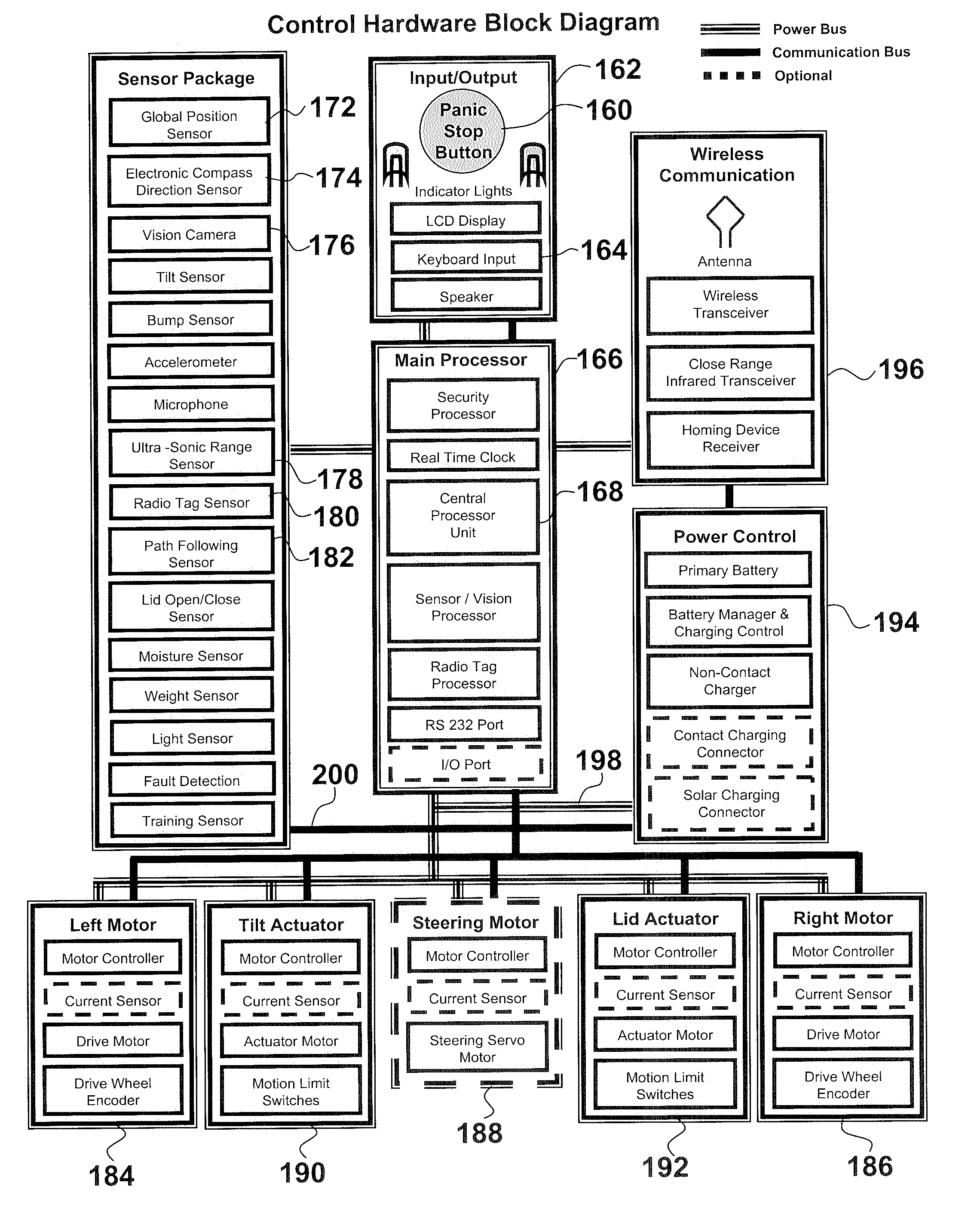

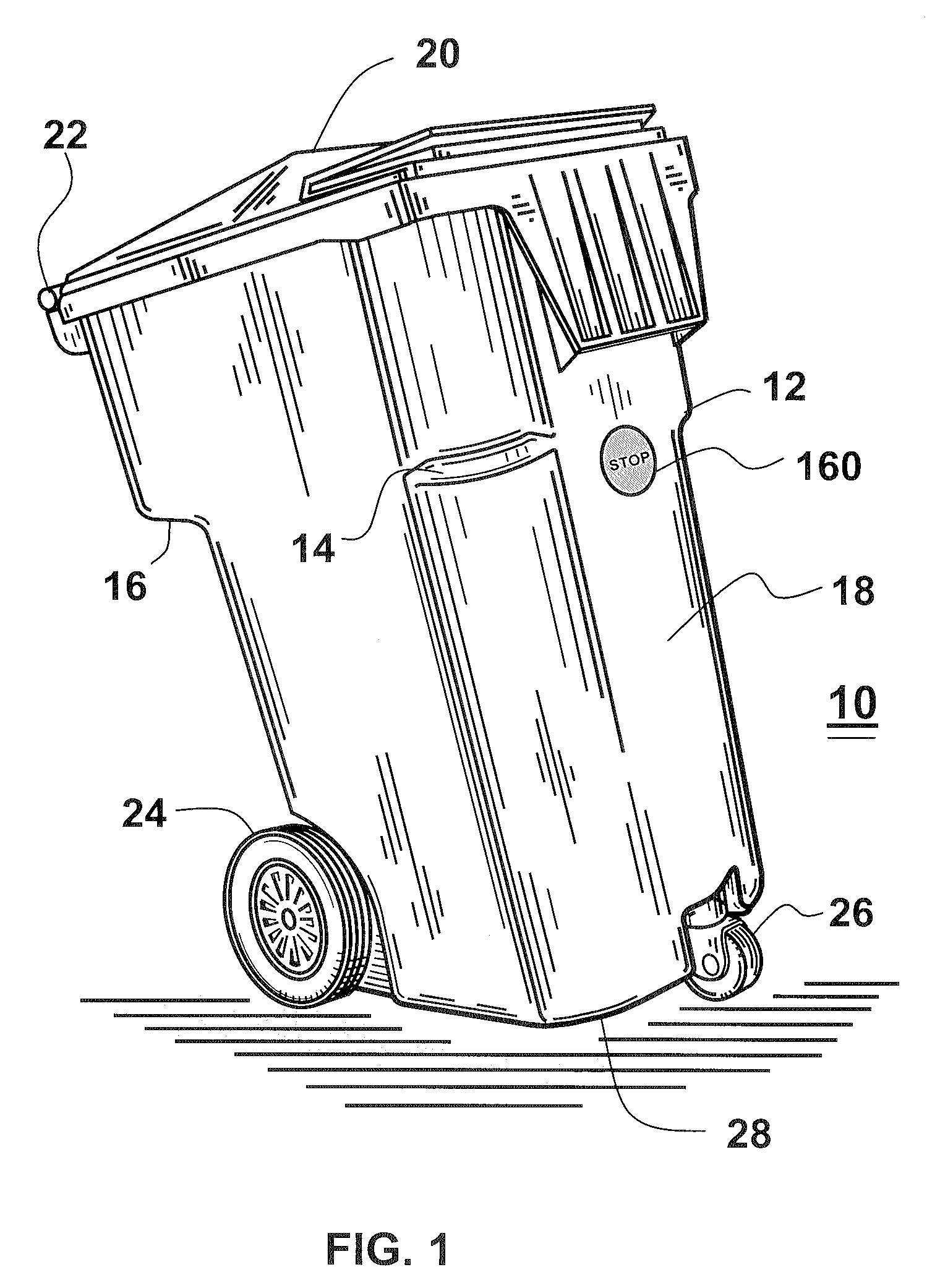

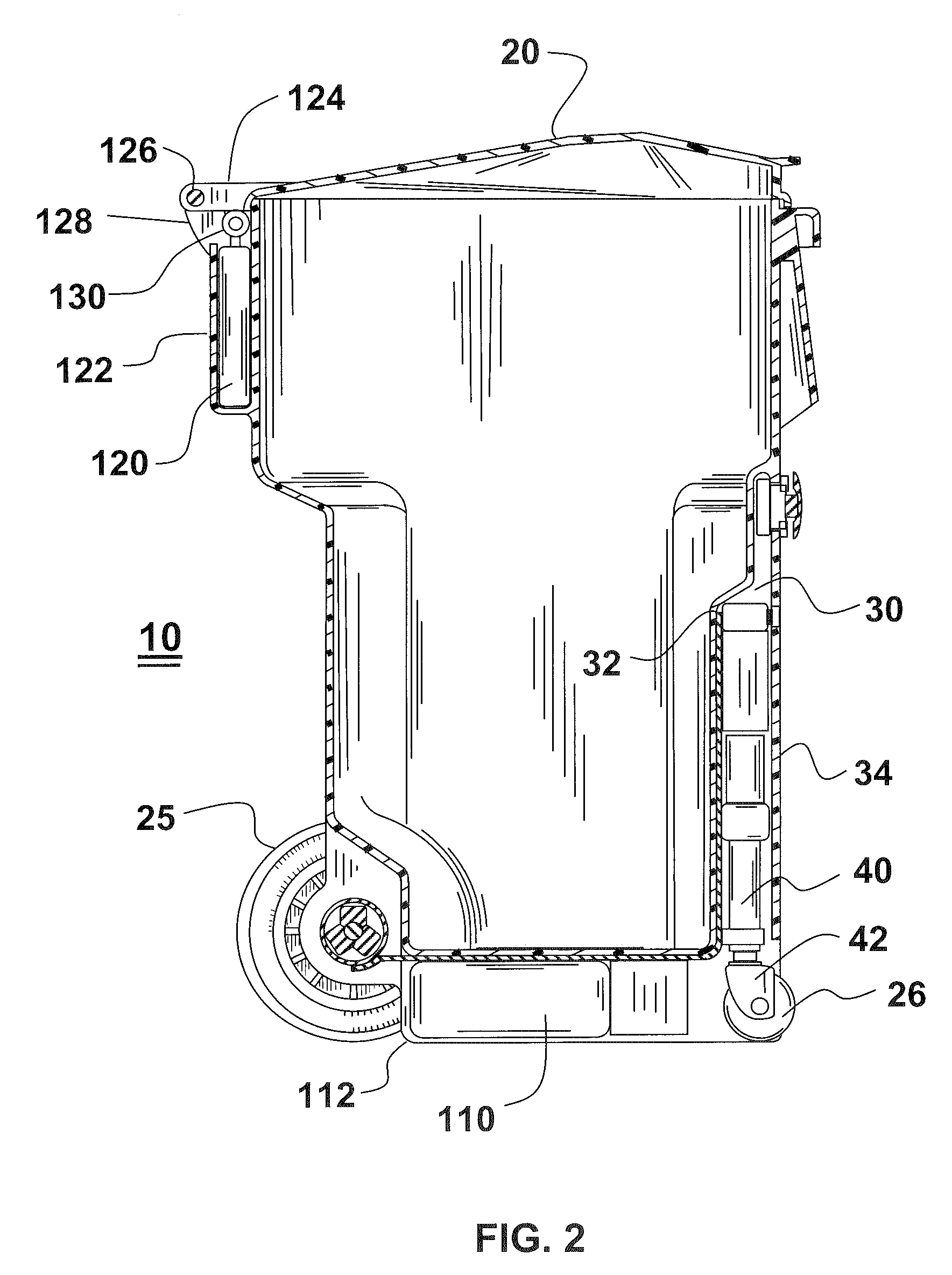

Automated self powered waste container

InactiveUS20080140253A1Increase the footprintReduce the possibilityRefuse receptaclesVehicle position/course/altitude controlDrive wheelSteering wheel

An automated self propelled refuse container travels from a parking or storage location to a refuse discharge location and return in response to a control unit cooperating with a tracking unit to control the direction of travel. Power is provided by an electric motor associated with each of two driving wheels rotating at the same rate and a third steering wheel provides stability and control over the direction of travel. The two driving wheels may rotate at a constant rate for straight line travel or charge direction, respectively, and a castering wheel provides stability and accommodates the direction of travel. Alternatively, a single wheel can provide both motive power and steering capability under control of a control unit responsive to the tracking unit and a pair of free wheeling wheels provide stability.

Owner:SONY CORP

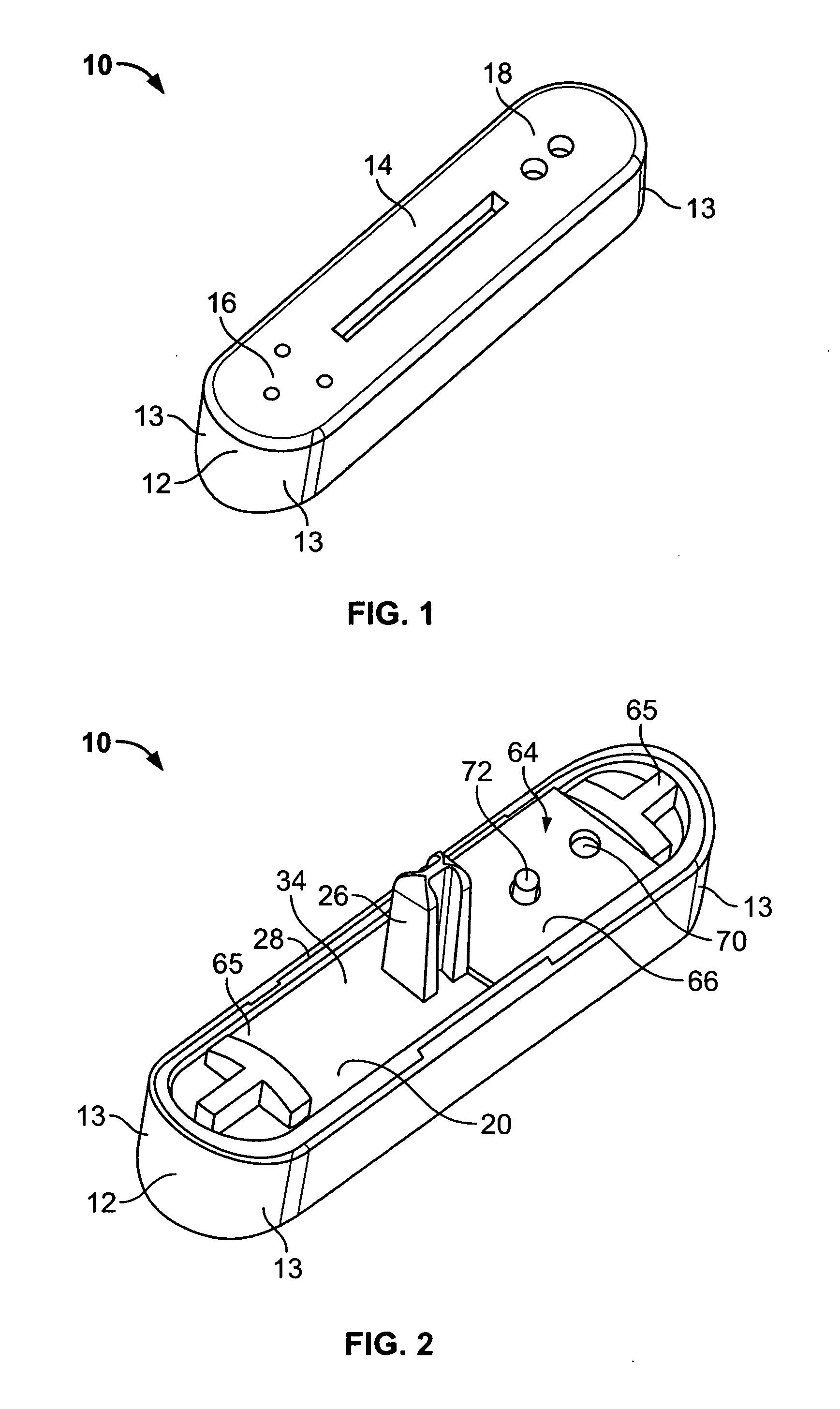

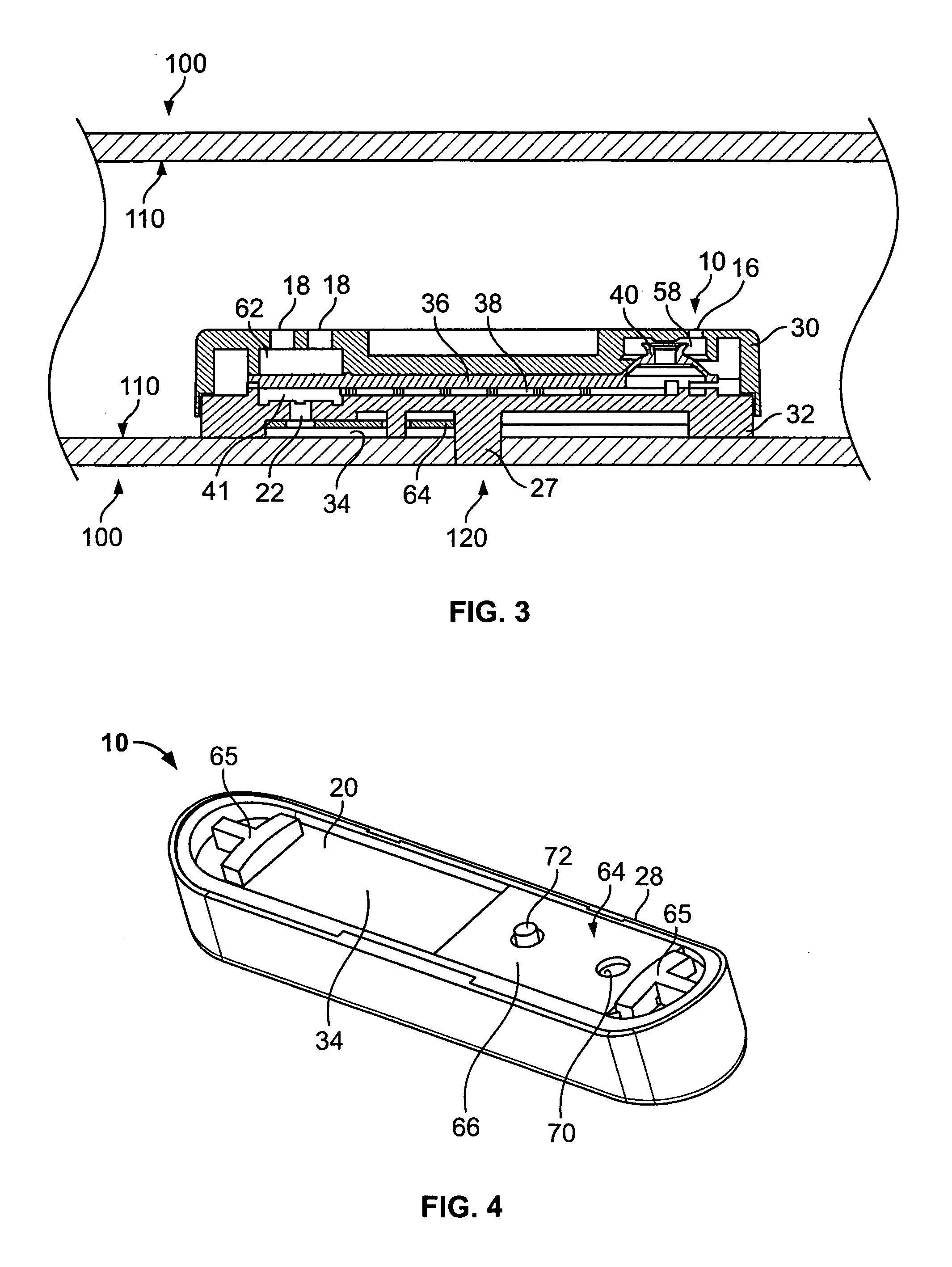

Device for deploying an implantable medical device

Owner:WL GORE & ASSOC INC

Drip emitter

A drip emitter is provided for delivering irrigation water from a supply tube to an emitter outlet at a reduced and relatively constant flow rate. Water enters the emitter through a first inlet and proceeds into a first chamber. When the water pressure is above a predetermined level, a one-directional valve opens to allow fluid flow past the first chamber, through a tortuous path flow channel, and through an emitter outlet. A second inlet is used to compensate for water pressure fluctuations in the supply tube to maintain output flow at a relatively constant rate. Water enters the second inlet and presses a flexible diaphragm toward a water metering surface to provide pressure-dependent control of the output flow. A copper member is mounted to the emitter over the emitter outlet to prevent plant root intrusion into the emitter outlet.

Owner:RAIN BIRD CORP

Large volume bolus device and method

A device and method for the infusion of medicinal fluid at a controlled flow rate to a wound site or the blood stream of a patient is disclosed. A pump delivers fluid under pressure from a fluid source through a continuous and substantially constant flow path and through a supplemental bolus dose flow path. A large volume bolus dose reservoir accumulates a large quantity of fluid from the bolus dose flow path and holds the fluid under pressure. A flow regulator controls the fill rate of the large volume bolus reservoir. The large volume supplemental bolus dose is released from the bolus reservoir upon patient activation of a valve. The release rate of the bolus dose is controlled by the decompression of an elastomeric sphere or spring chamber, by the pressure gradient at the valve and / or by optional flow control tubing. In one embodiment, a source of fluid under pressure is pumped at a continuous and substantially constant rate to a wound site or the blood stream of a patient and into a bolus syringe, which is capable of holding a large quantity of fluid under pressure. A plunger on the bolus syringe may be depressed to release a bolus dose of fluid into a chamber accumulator and then to the patient at a controlled release rate.

Owner:AVENT INC

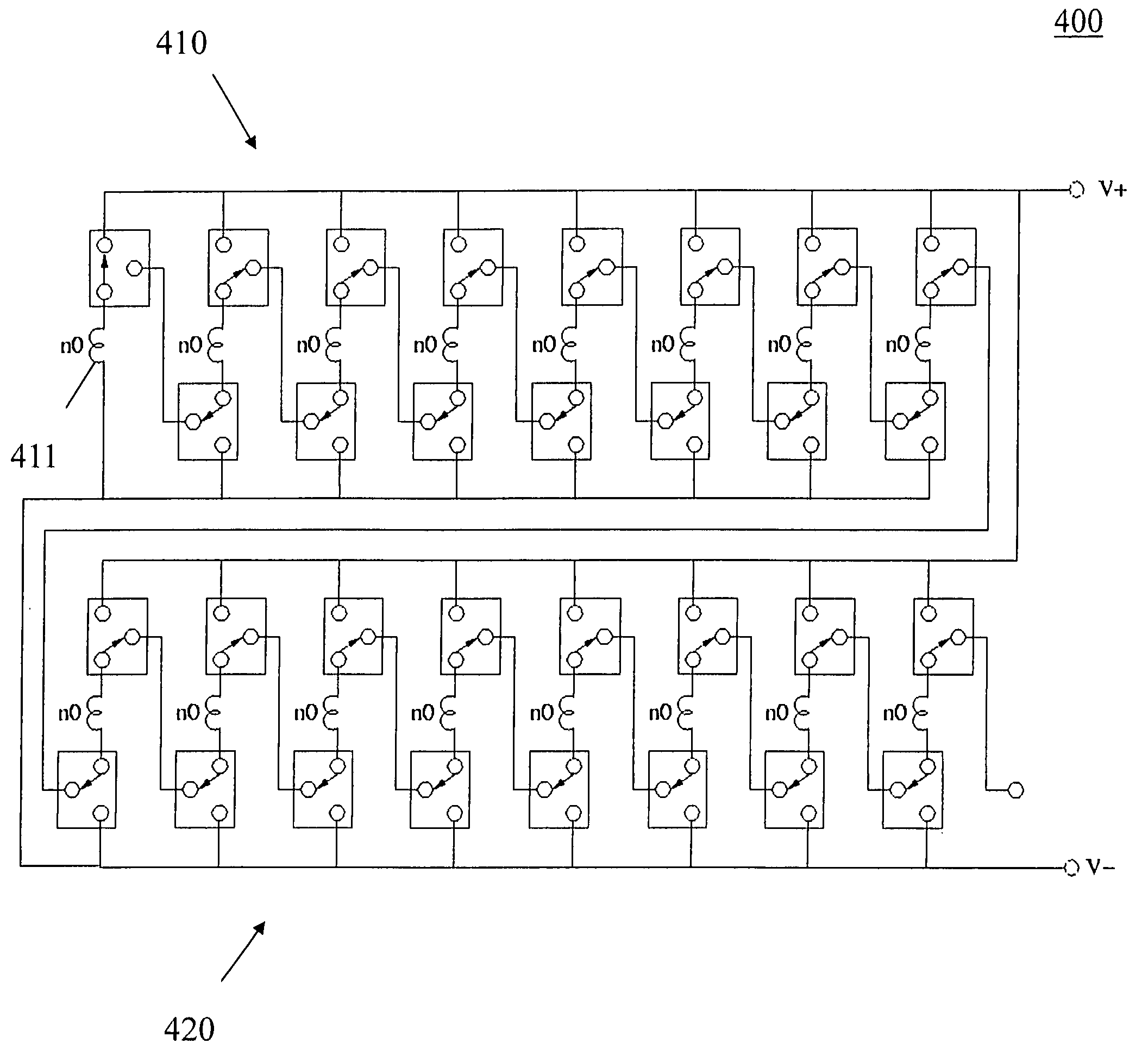

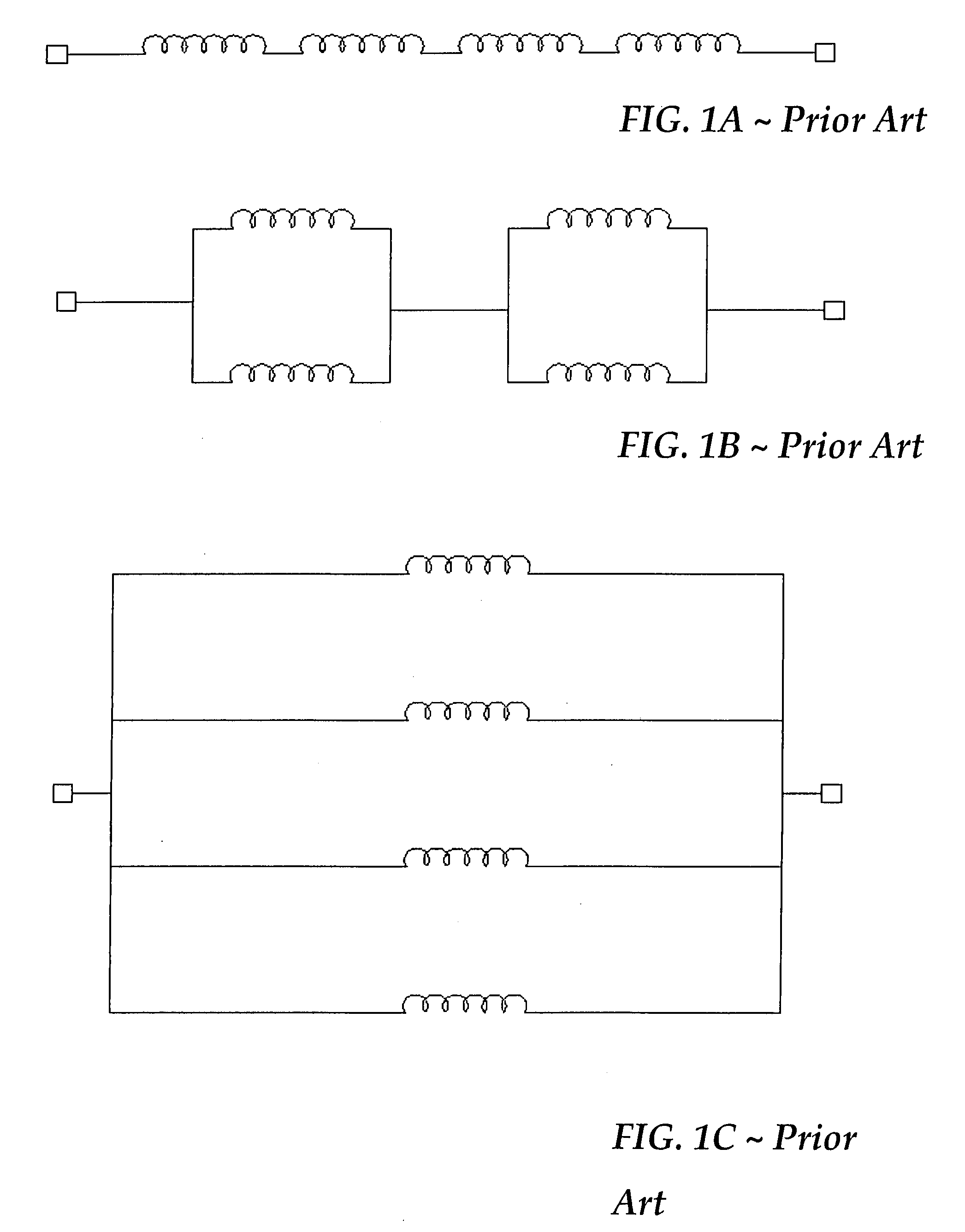

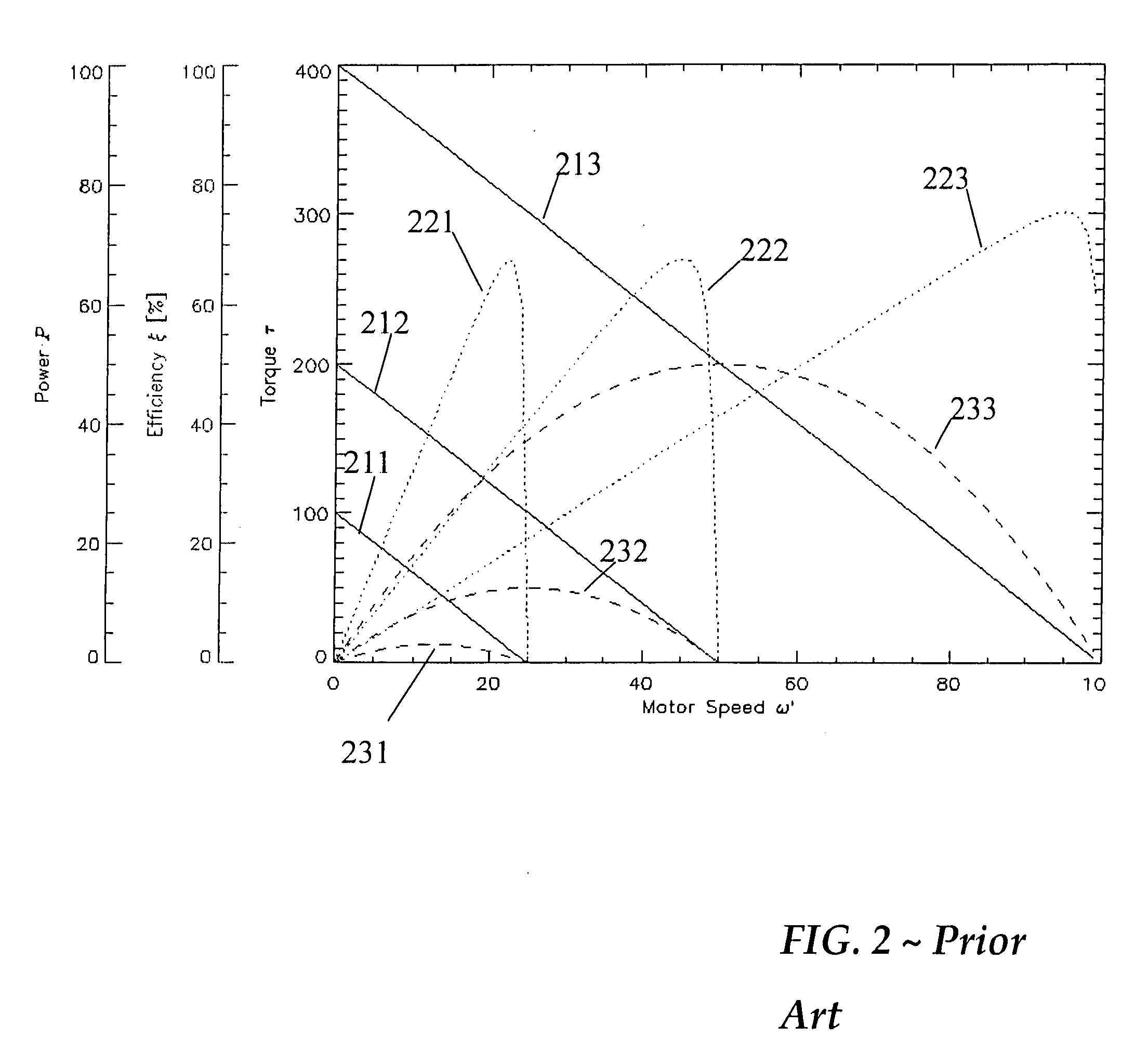

Adaptive winding system and control method for electric machines

ActiveUS20080116759A1Improve efficiencyWide speed rangeSynchronous generatorsAC motor controlElectric machineEngineering

An adaptive winding configurations and control method is disclosed for the electromagnetic poles of electric machines, including motors and generators. Motors utilizing the inventive adaptive winding configuration and control method are able to dynamically adjust their operating characteristics to maintain a constant rated power over a large operating speed range with high efficiency. Generators employing the inventive adaptive winding configuration and control method are able to dynamically adjust their operating characteristics in response to a variable driving force to achieve maximum power conversion efficiency. These generators are also able to dynamically change their output voltage and current (thus charging speed) when charging batteries depending on the charged state of the battery, and on the expected duration of the input power.

Owner:LIN PANCHIEN

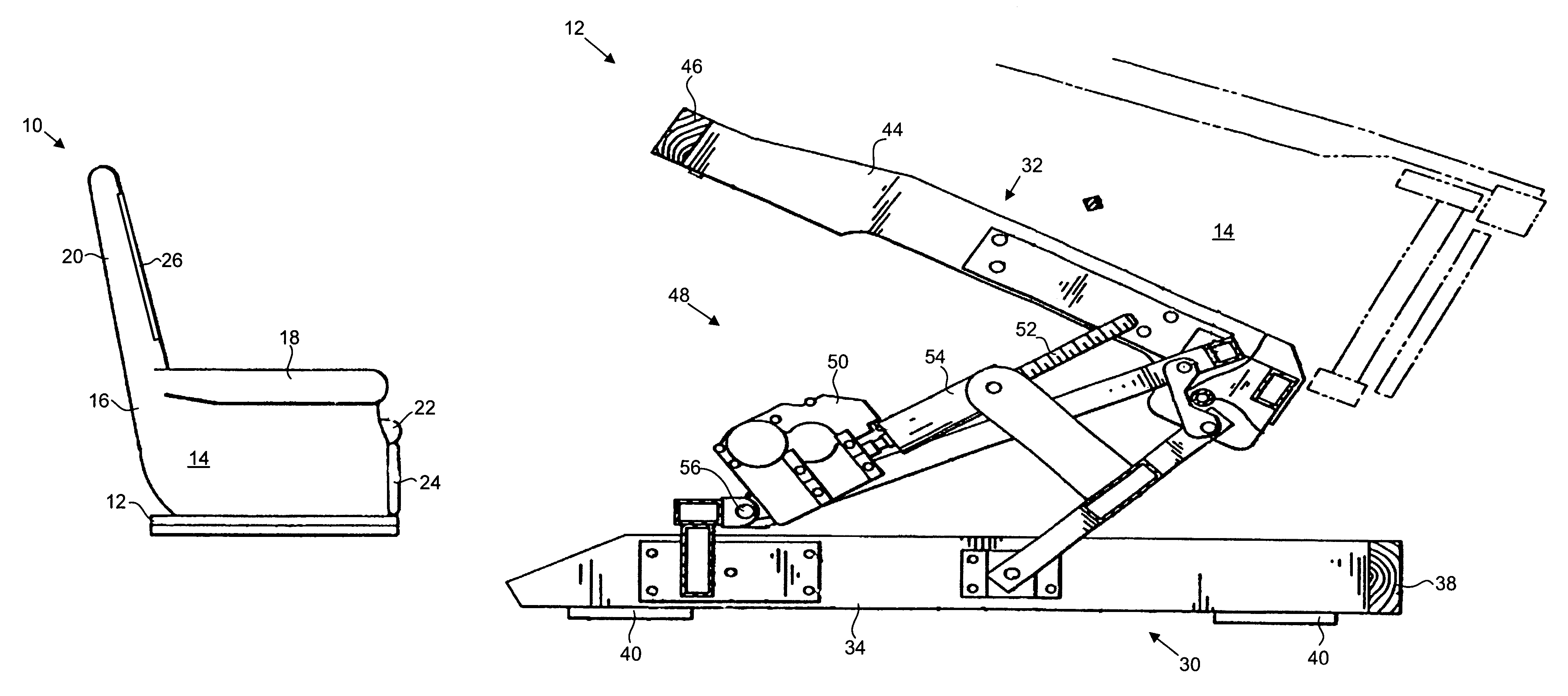

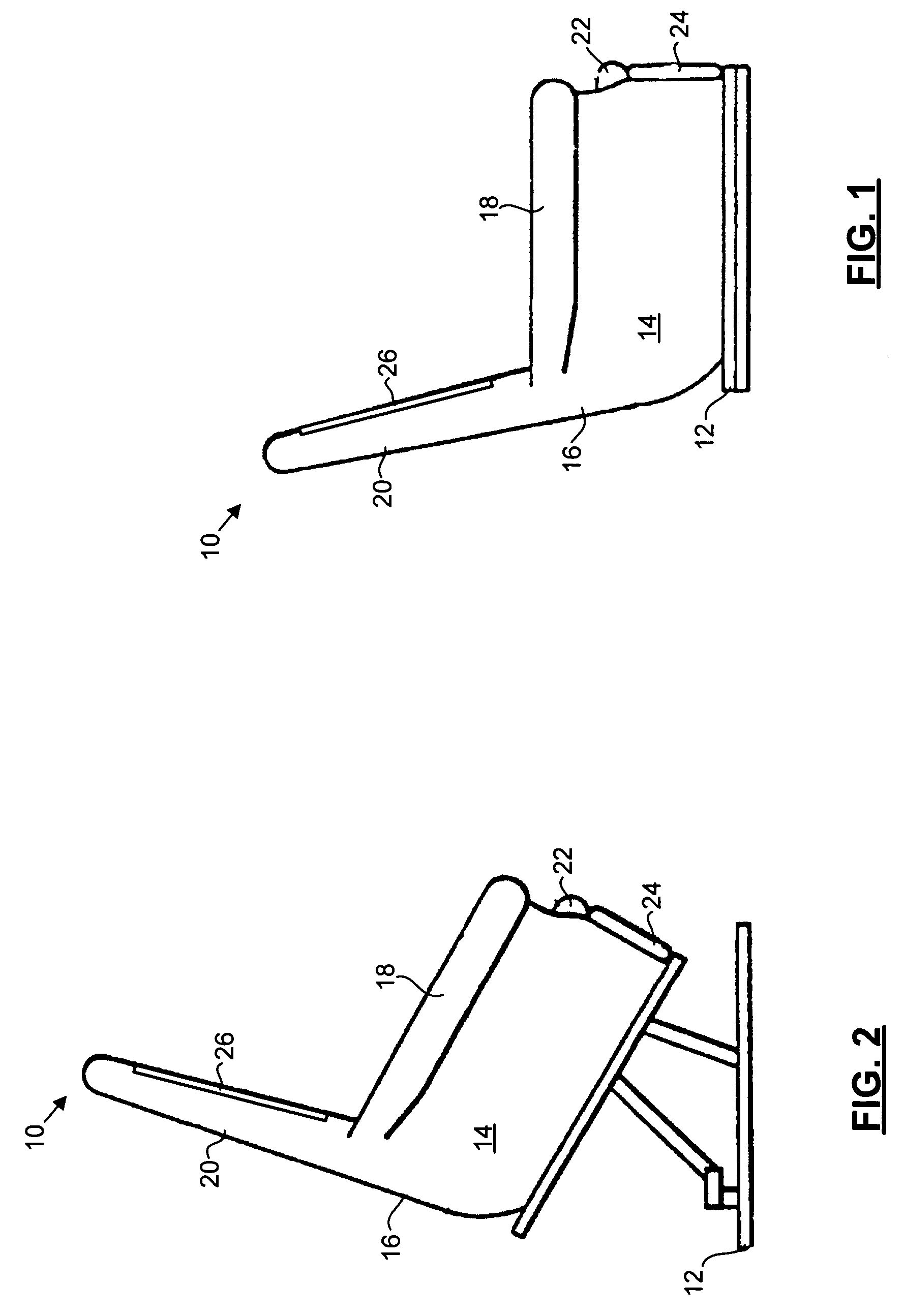

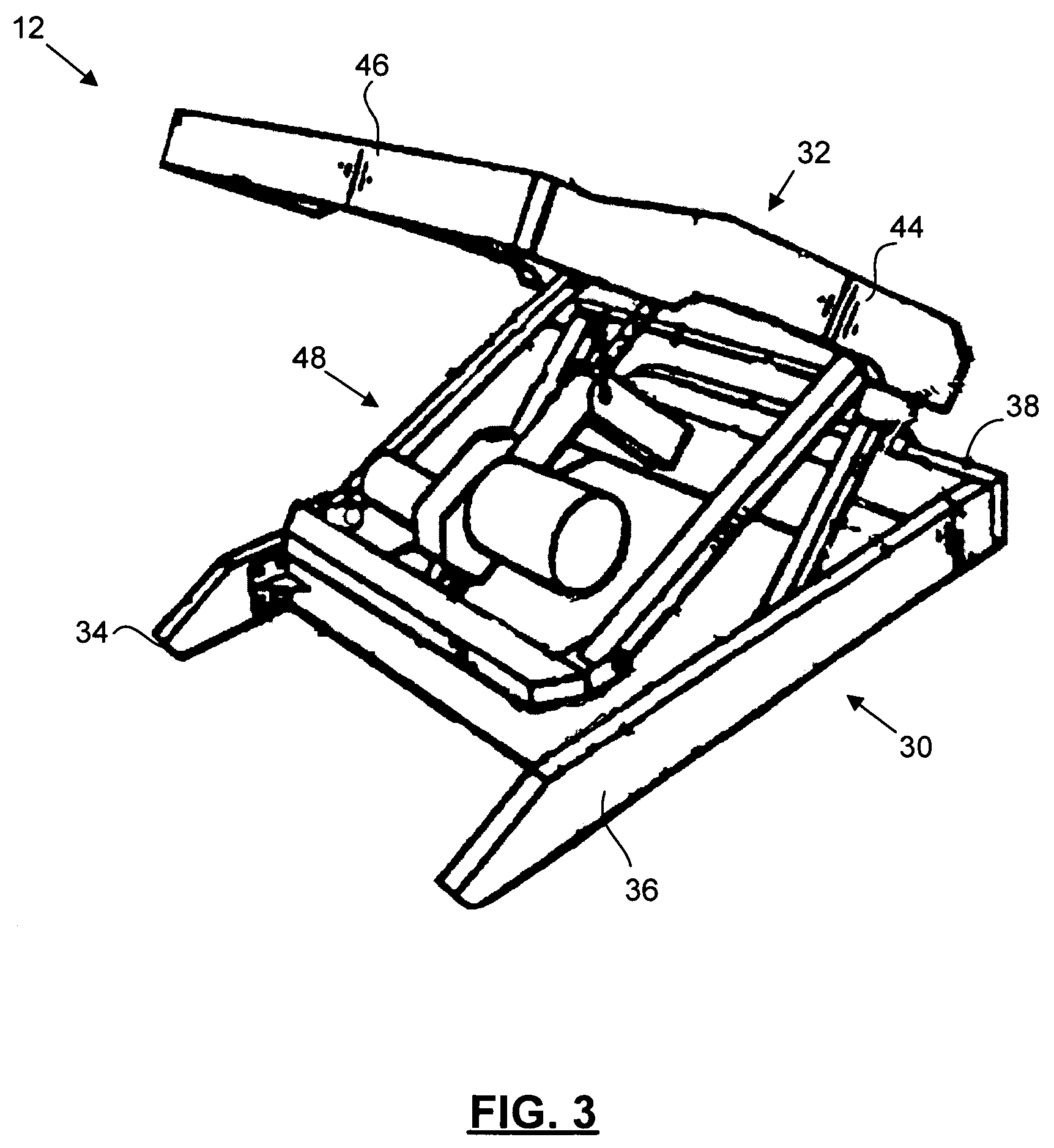

Heavy lift chair

A power-assisted heavy lift chair comprises a base assembly. A chair frame is supported on the base assembly. A lift mechanism communicates with the base assembly and the chair frame, and is operable to actuate the chair frame between first and second positions. A transformer provides electrical power to an electric motor. The electric motor provides rotational power to the lift mechanism at a first rate to lift and / or lower the chair frame. The electric motor draws current from the transformer according to a load upon the chair frame. The rate that the electric motor lifts and / or lowers the chair frame depends upon the voltage provided by the transformer. The transformer is operable to provide a generally constant voltage regardless of the current draw of the electric motor. Therefore, the electric motor lifts and / or lowers the chair at a constant rate independent of the load on the chair.

Owner:LA-Z-BOY

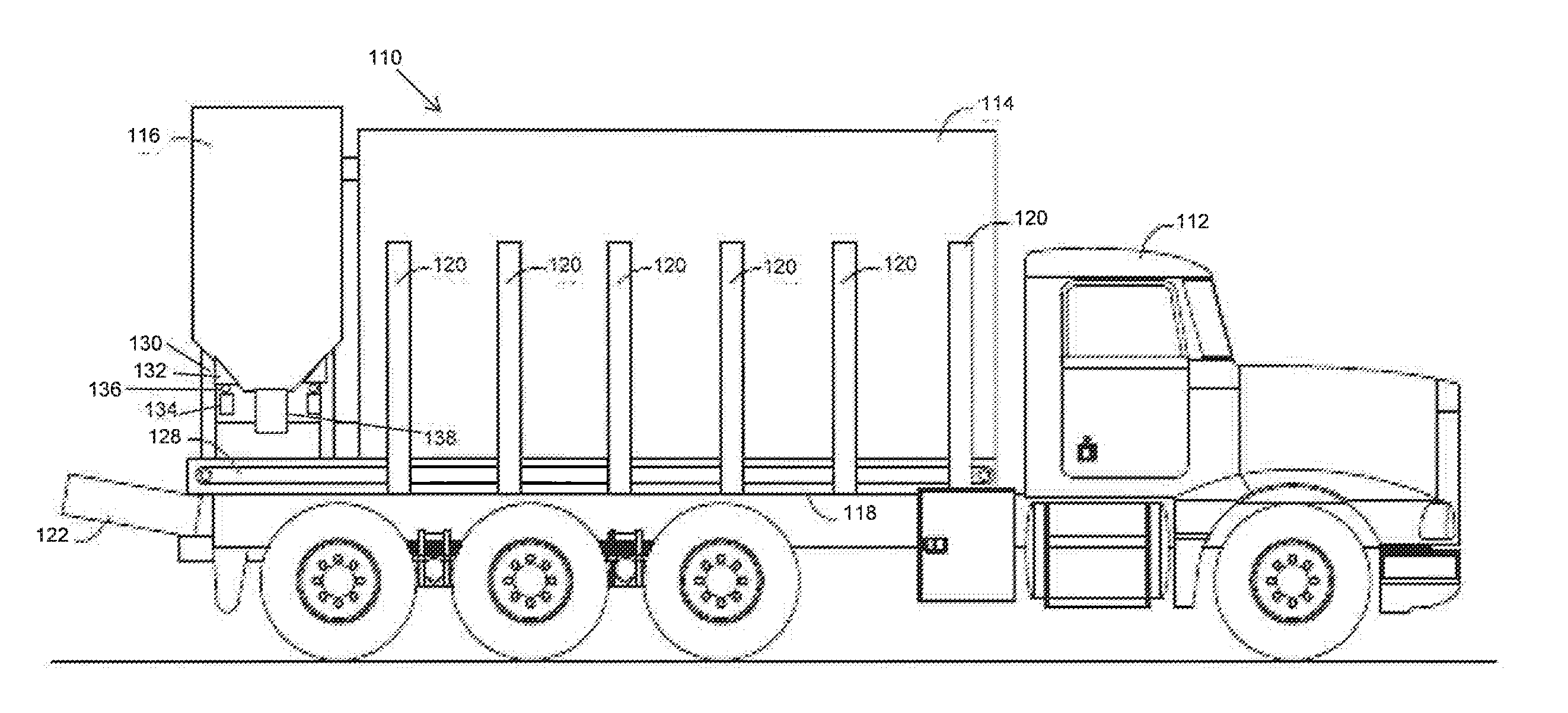

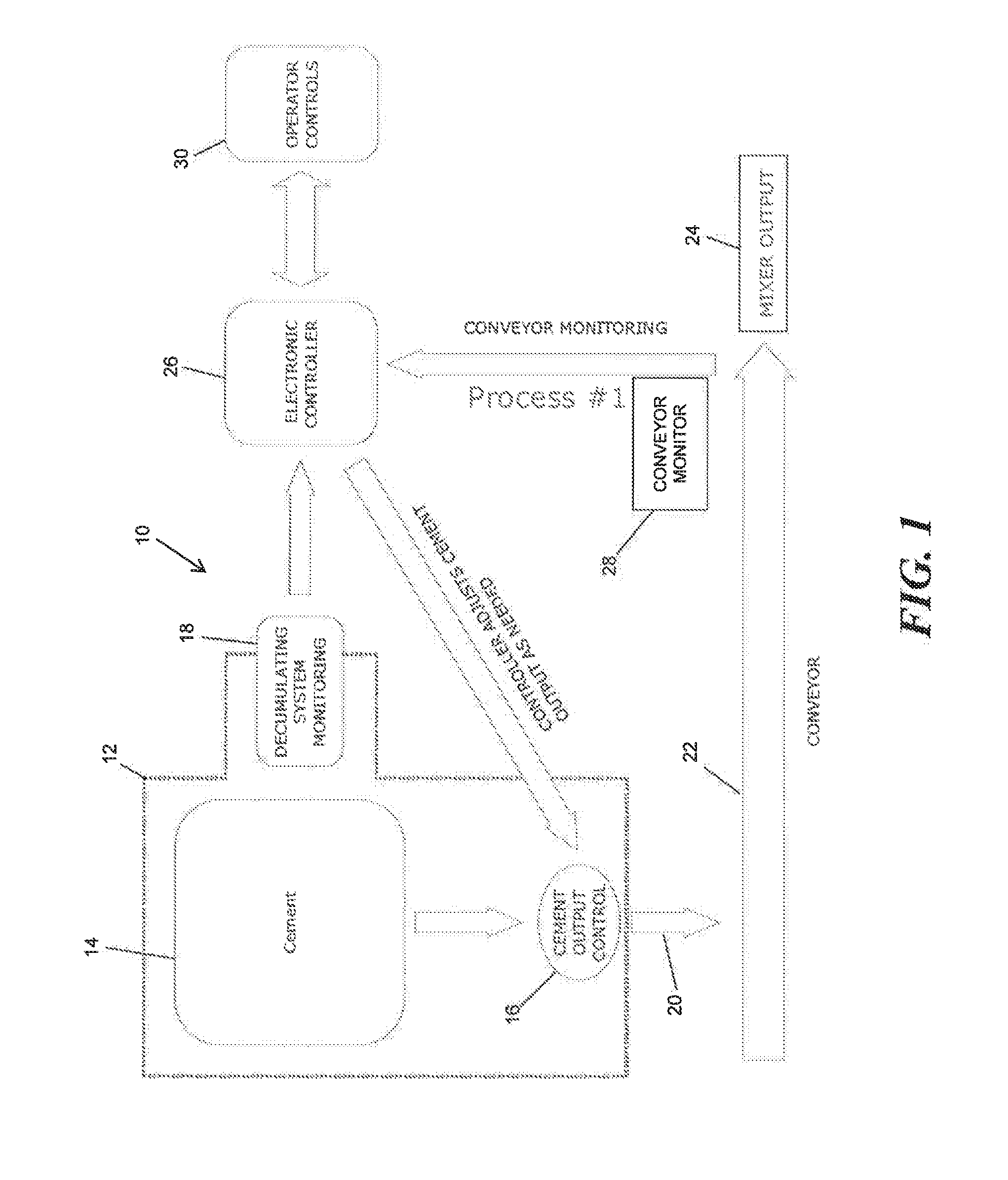

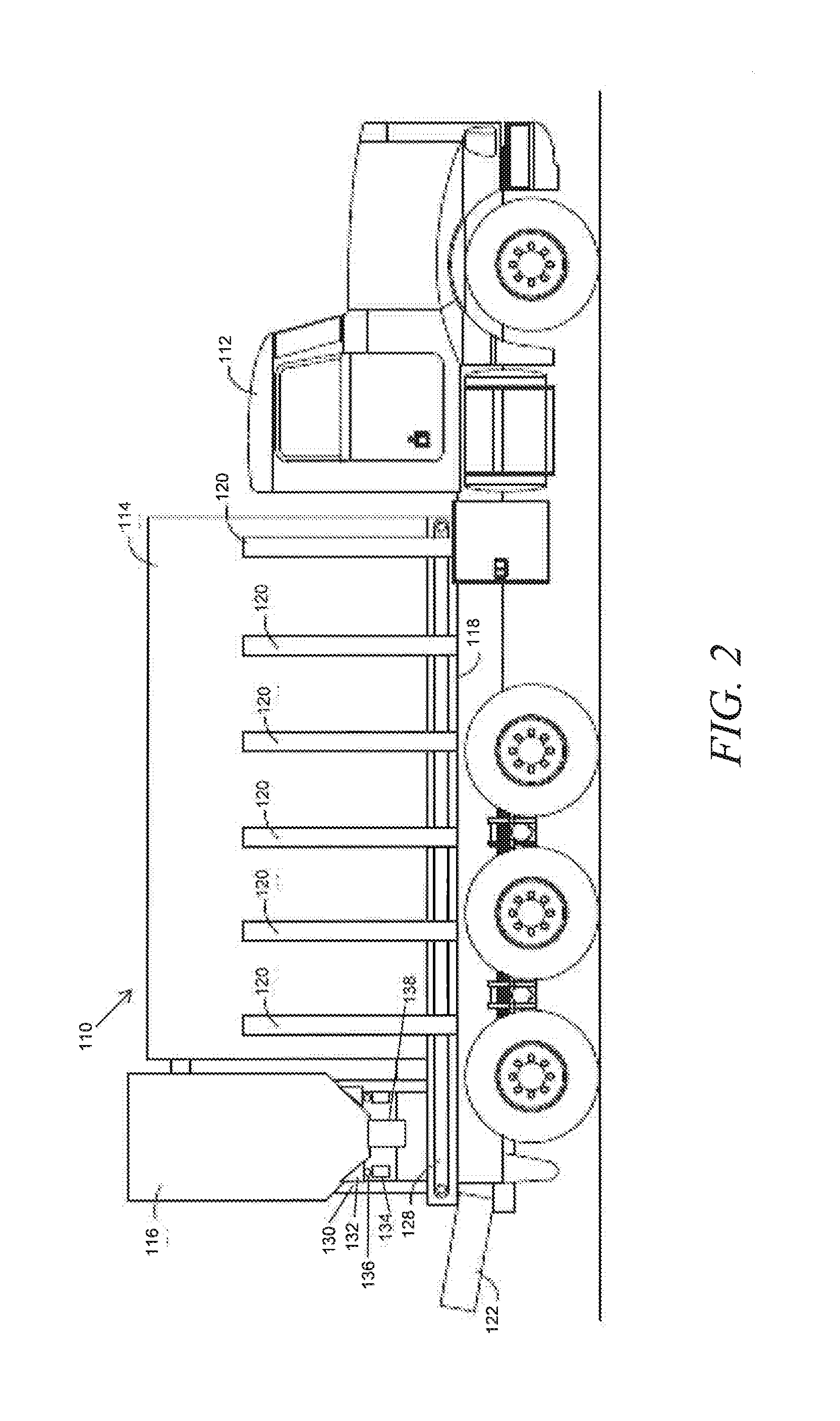

Volumetric mixer with monitoring system and control system

InactiveUS20160221220A1Uniform ratioEasy to controlIngredients proportioning apparatusCement mixing apparatusControl systemMonitoring system

A volumetric concrete mixer includes a monitoring and control system that assures a uniform amount of cement per unit of aggregate. A processor is in communication to receive an input of a weight of a cement bin from a cement bin load cell and in communication to receive an input of a number of rotations of a conveyor from an aggregate sensor. The processor is adapted to determine a rate of change of weight of the cement bin over a set number of rotations of the conveyor, and to instruct the cement dispenser to adjust the cement dispenser speed to maintain a constant rate of cement being dispensed from the dispenser bin to the mixing area per the set number of rotations of the conveyor.

Owner:OMEGA CM DELTA LLC

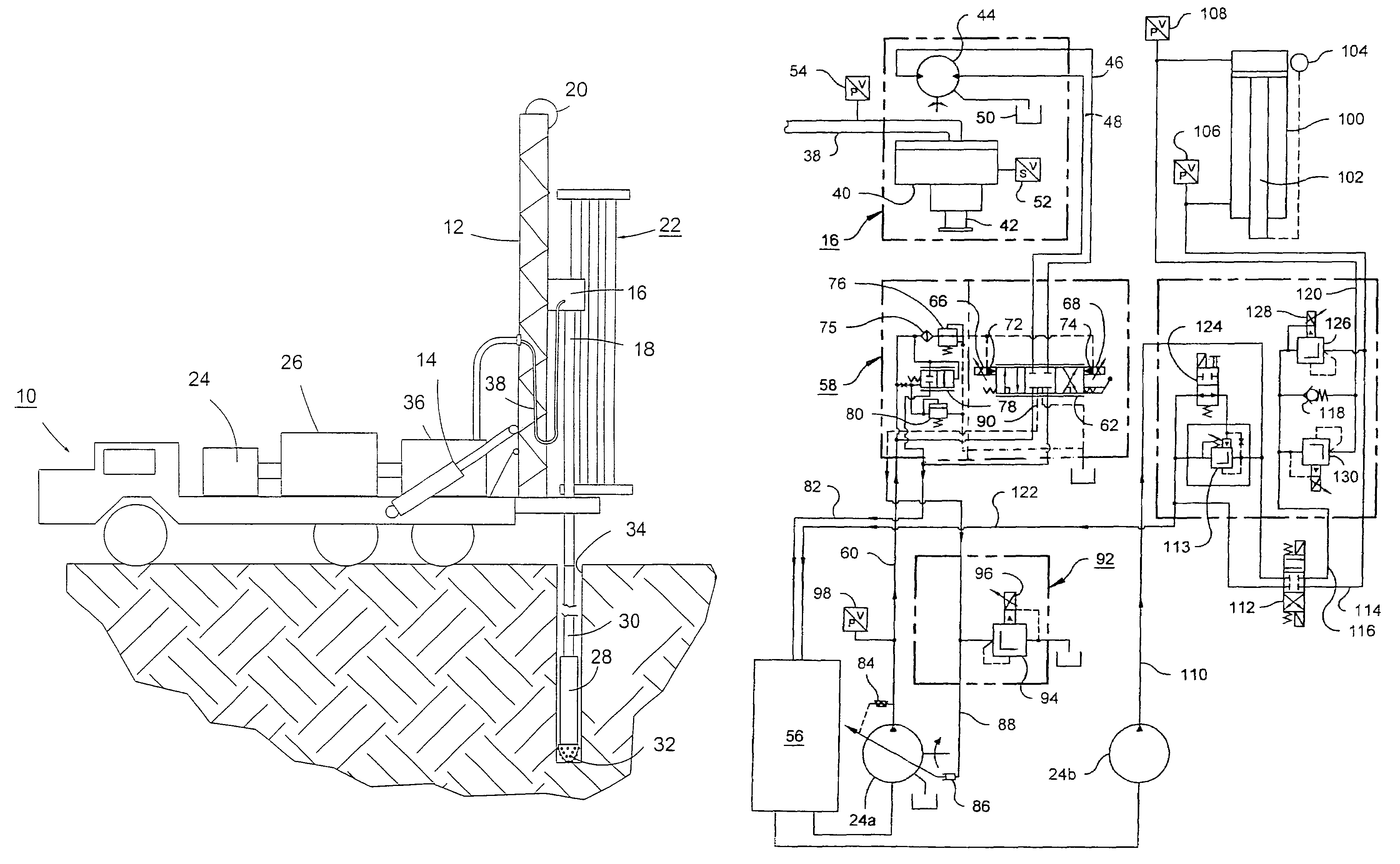

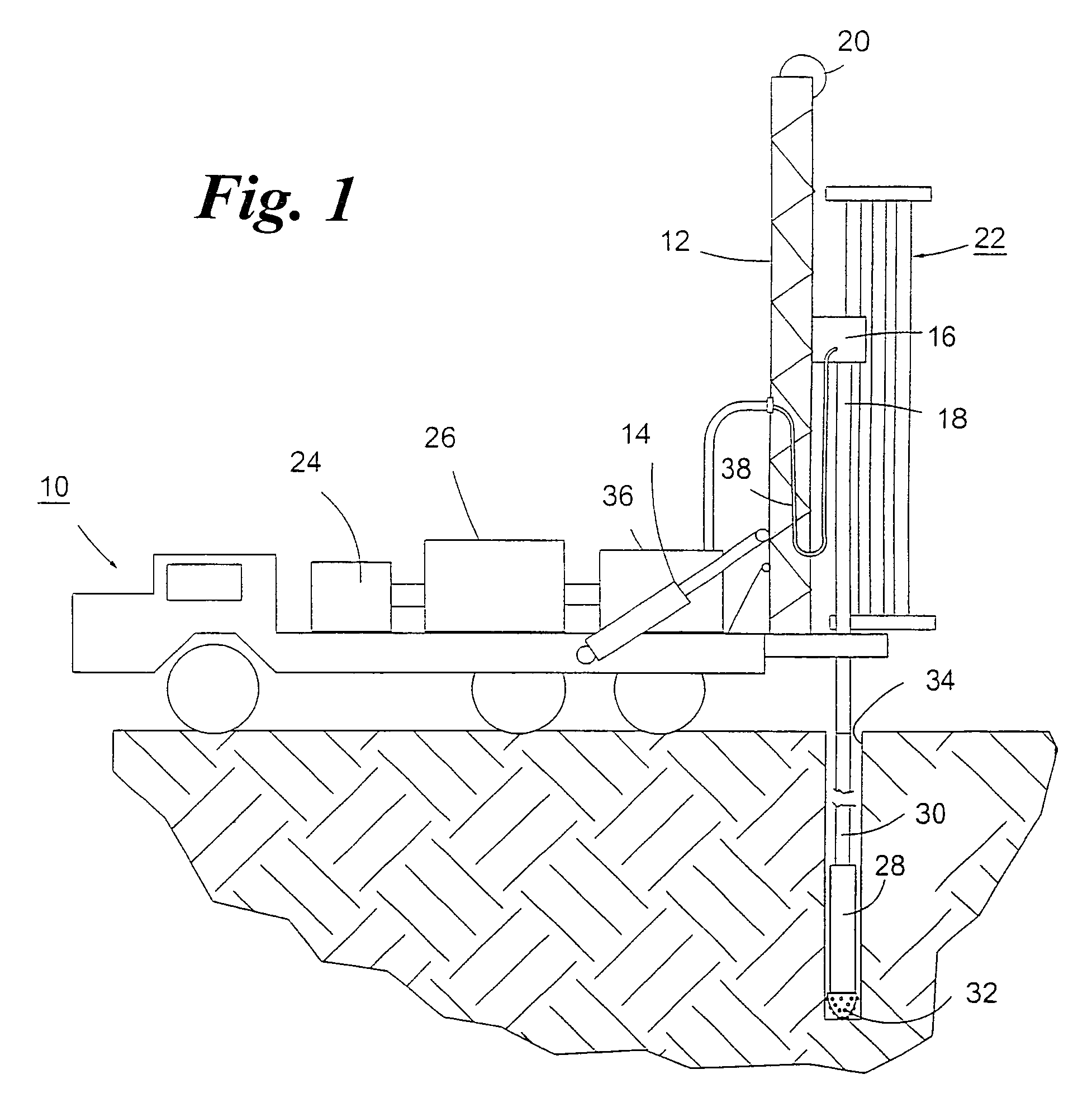

Electronically controlled earth drilling rig

ActiveUS7350593B1Effective maintenanceConstant rate of penetrationAutomatic control devicesSurveyLower limitShortest distance

An electronic control, for automated earth drilling using a pneumatic hammer-operated bit, preliminarily weighs a drill string, and, during drilling, automatically maintains a desired weight on the bit, and also maintains a constant rate of drilling progress by regulating drill string rotation speed. The weight on the bit is automatically maintained at a fraction of the pre-established desired weight as the air pressure in the supply to the pneumatic hammer builds up to an operating level. The control detects voids and broken formations by monitoring air pressure and torque respectively, and responds by reducing the weight on the bit. The control automatically raises the drill bit though a short distance as the drill head reaches the lower limit of its travel, pauses until the air pressure drops, and then raises the drill string to a position for insertion of a new length of pipe.

Owner:SCHRAMM INC

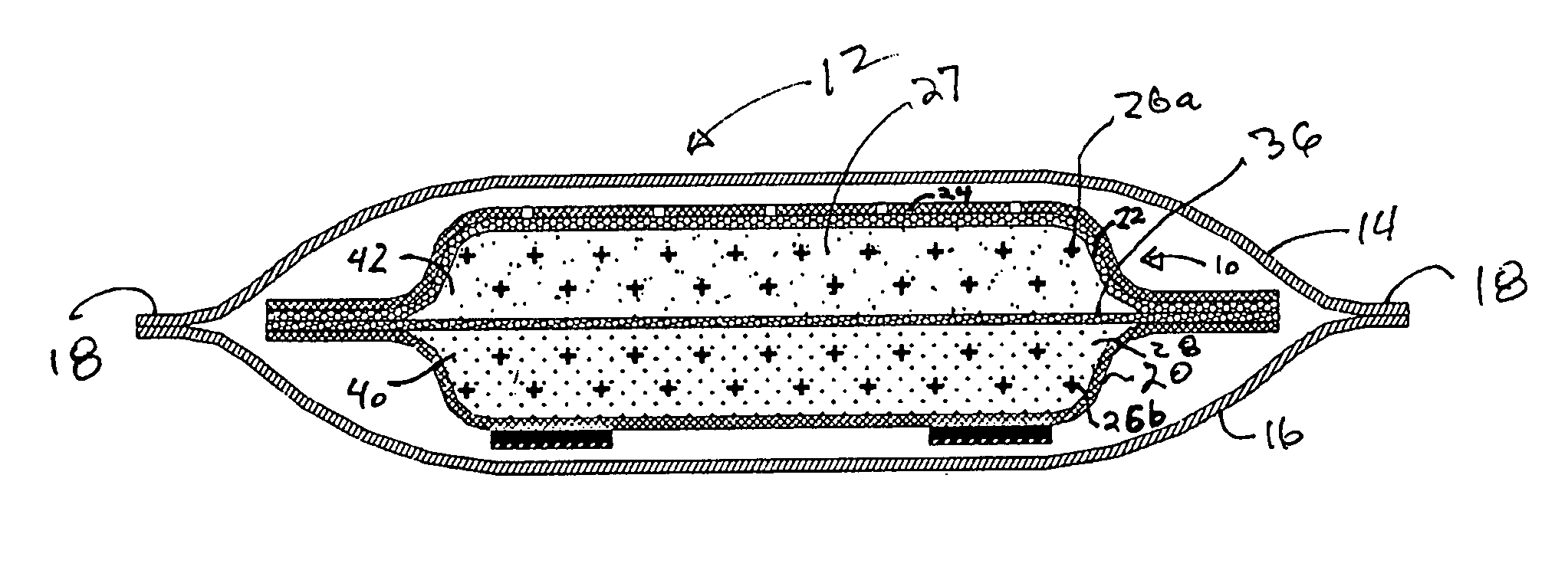

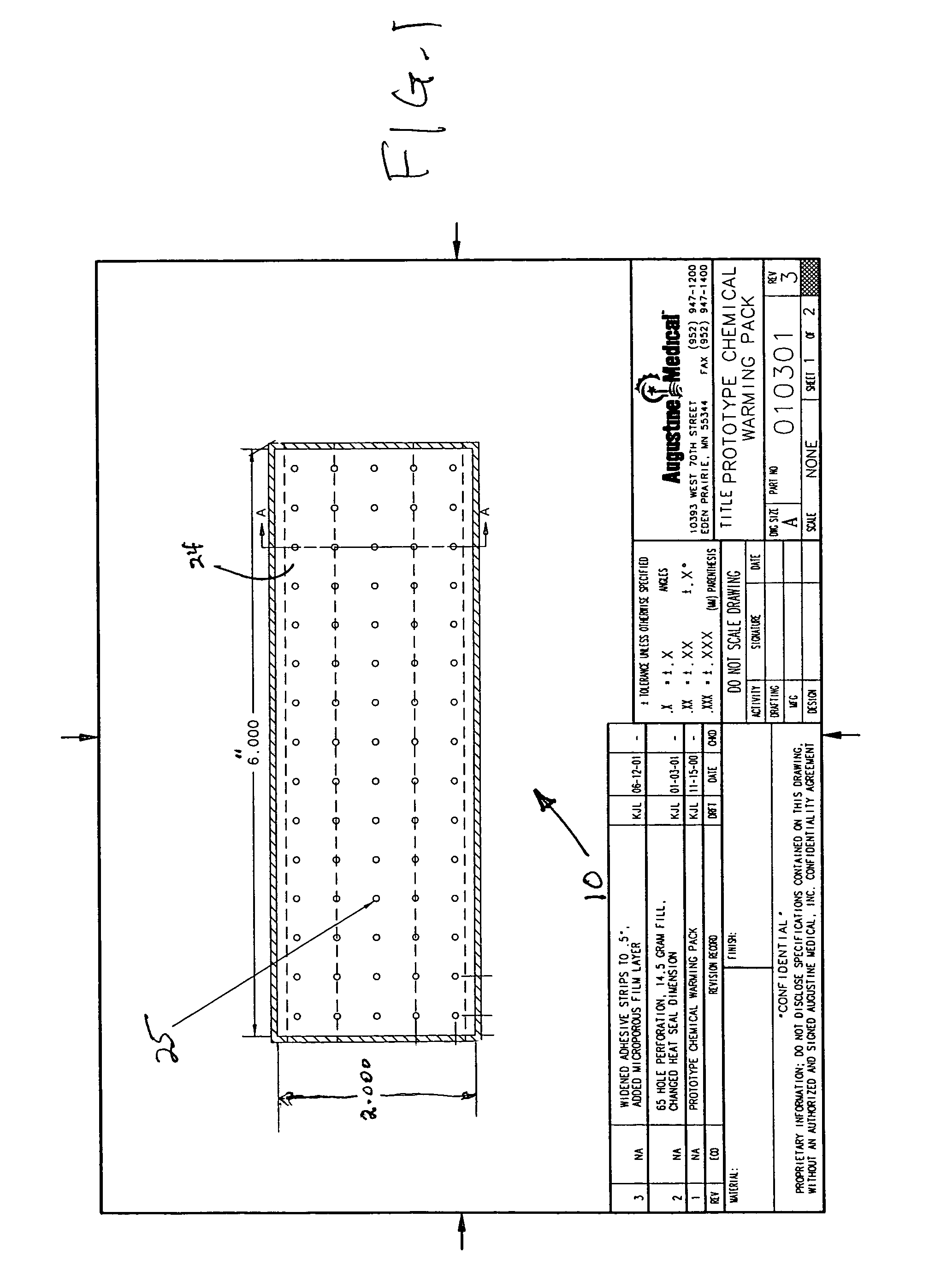

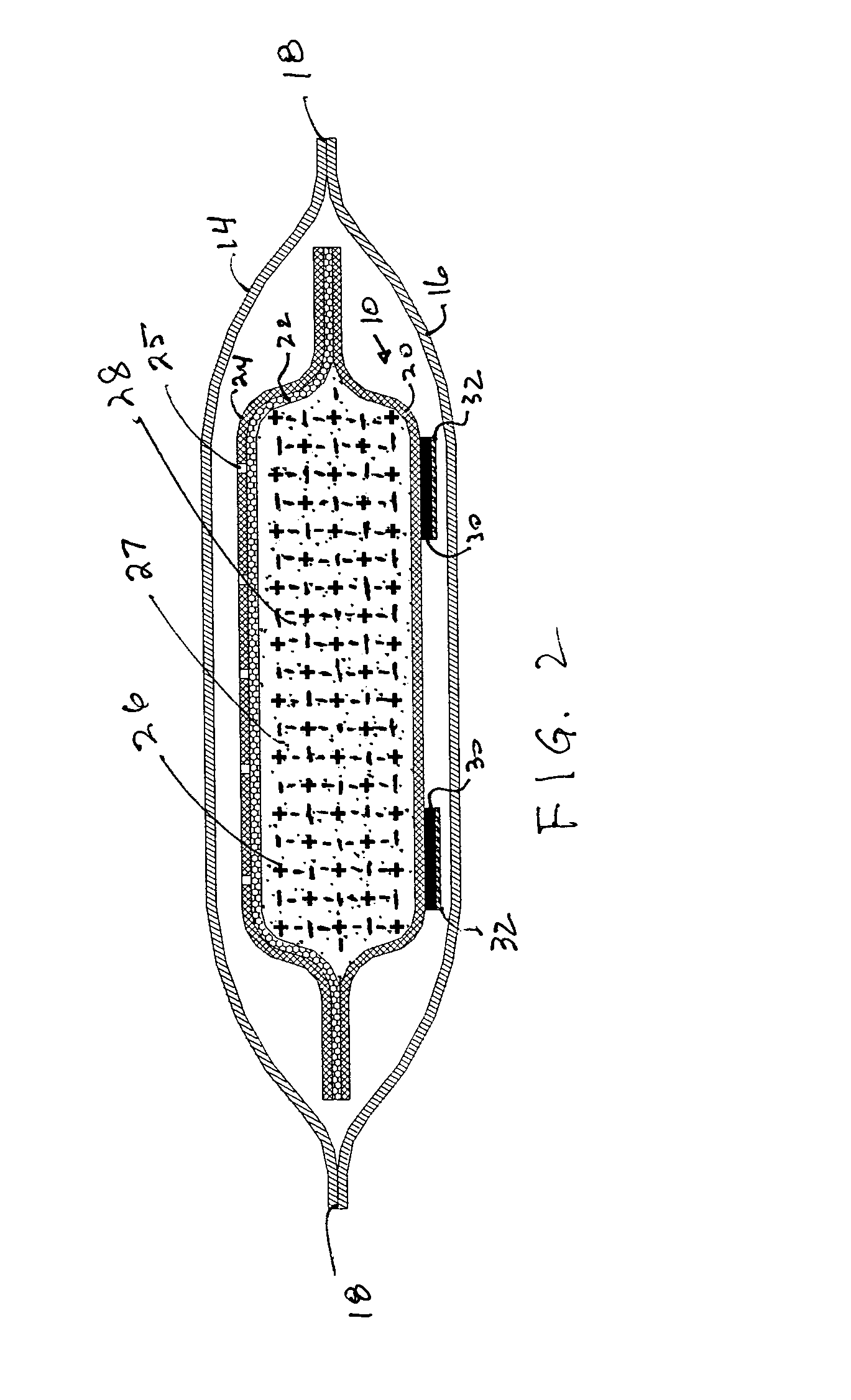

Warming pack with temperature uniformity and temperature stabilization

InactiveUS7041123B2Reduce the temperatureReduce temperature changesExothermal chemical reaction heat productionDomestic cooling apparatusChemical reactionConstant rate

A warming pack includes a container in the form of a pack, pouch, or bag in which reactants for an exothermic chemical reaction are distributed in one or more flexible matrixes that prevent them from shifting. The rate of the reaction is controlled and the reaction is thermally buffered in order that heat be produced at a constant rate.

Owner:GEN ELECTRIC CAPITAL +1

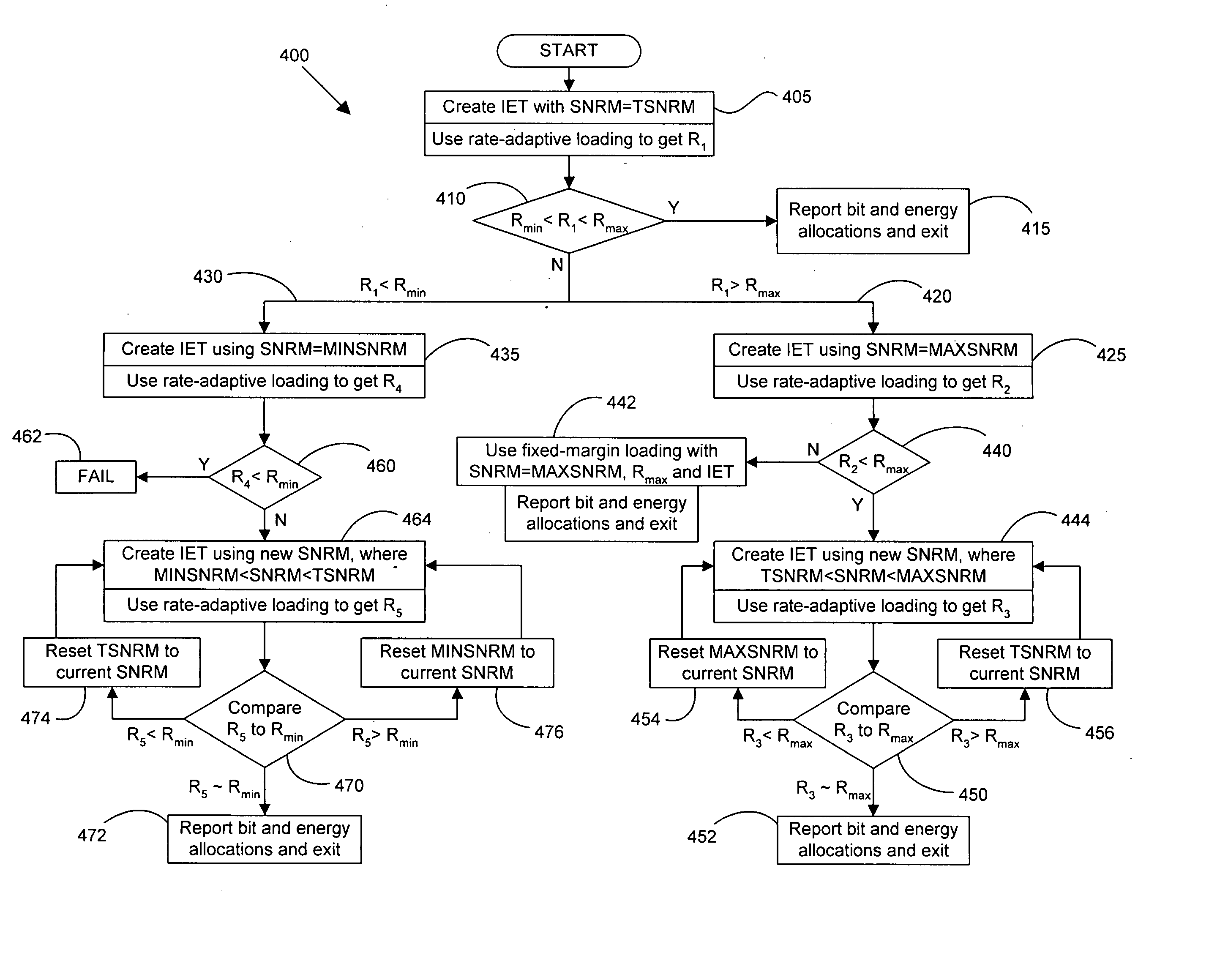

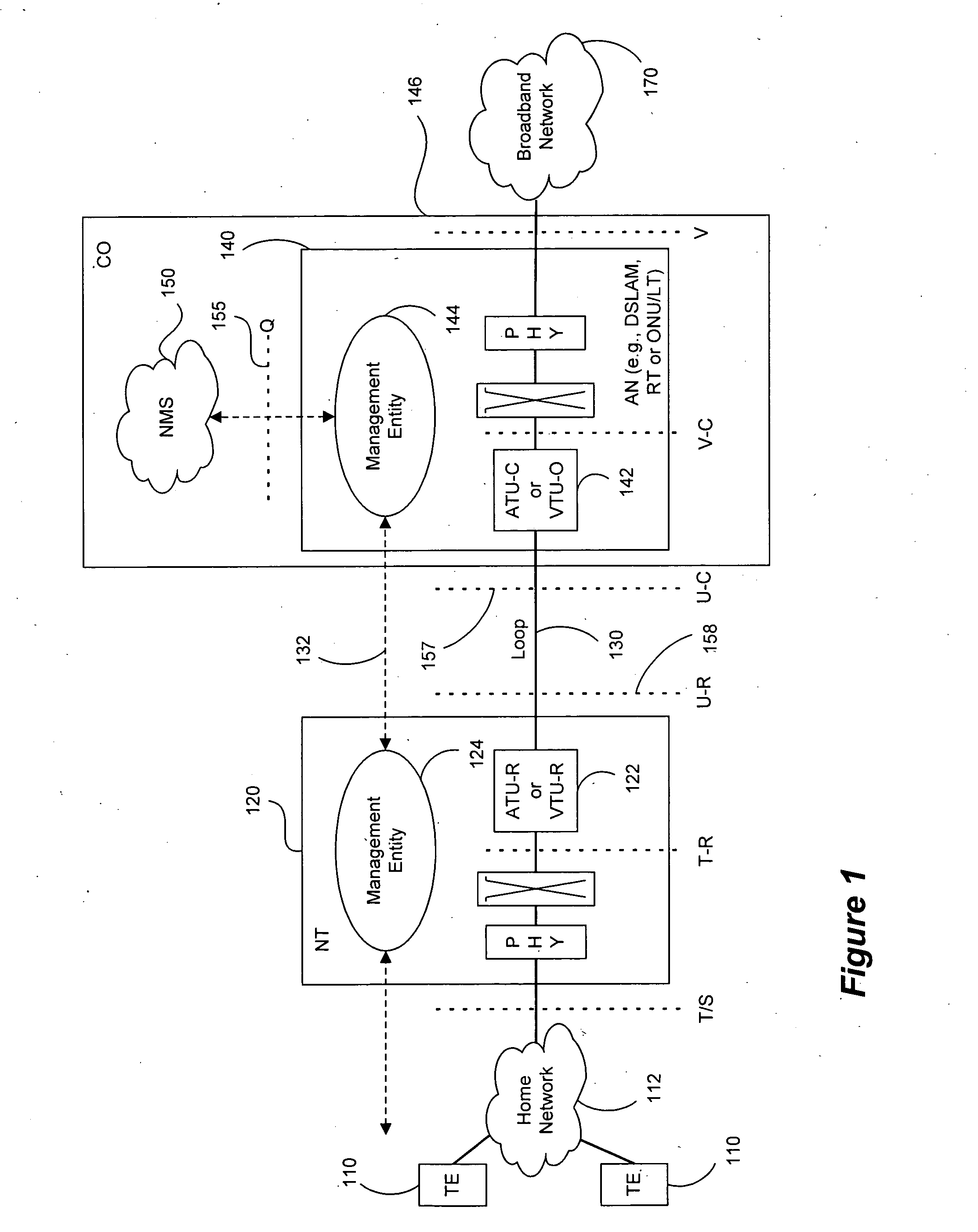

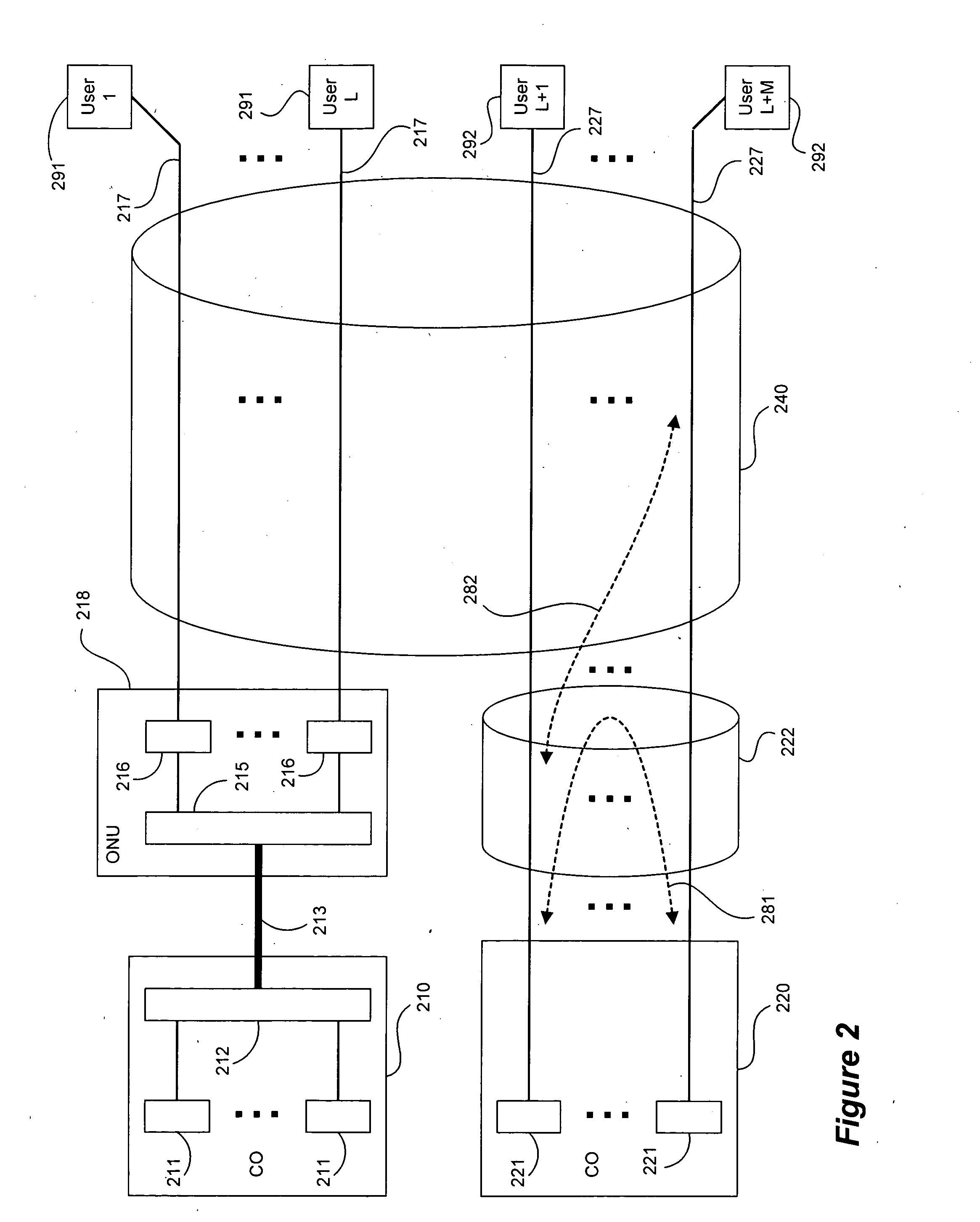

DSL system loading and ordering

ActiveUS20060280237A1Favorable vector of rateReduce complexityTransmission path divisionCriteria allocationBit allocationEngineering

Loading and ordering techniques are provided for one-sided and two-sided vectored line groups, as well as loading methodologies that also can be used on a single line, in communication systems such as DSL binders. For single-user lines, bits and energy are optimally allocated for a given set of parameters, which may include maximum rate, minimum rate, maximum margin, target margin, minimum margin and PSD mask of any shape. Iterations, bit-swapping during loading or adaptive margin update during loading can be used in single-user loading, which has low complexity and can be used for a variety of loading objectives and / or goals, such as rate-adaptive, margin-adaptive and fixed-margin objectives. For multi-user vectoring systems, ordering as well as loading is provided for a supplied rate-tuple within a rate region, determining acceptable user loadings and orderings so that the rate-tuple can be implemented. For one-sided vectored DSL, some loading and ordering determines acceptable allocations of bits, energy and decoding / precoding ordering(s) for each tone of each user for a specified set of rates on the vectored lines. PSD determination, ordering and bit allocation can be iteratively used in multi-user loading and ordering and can augment and alter the criteria used for bit swapping procedures used in single lines (or in bonded multiple lines for a single user) so that a favorable vector of rates is achieved for all users. Order swapping can adjust a bit vector and / or rate vector within a constant-rate-sum convex subset of a hyperplane towards the desired vector of user rates for each of the lines.

Owner:ASSIA SPE LLC CO THE CORP TRUST CO

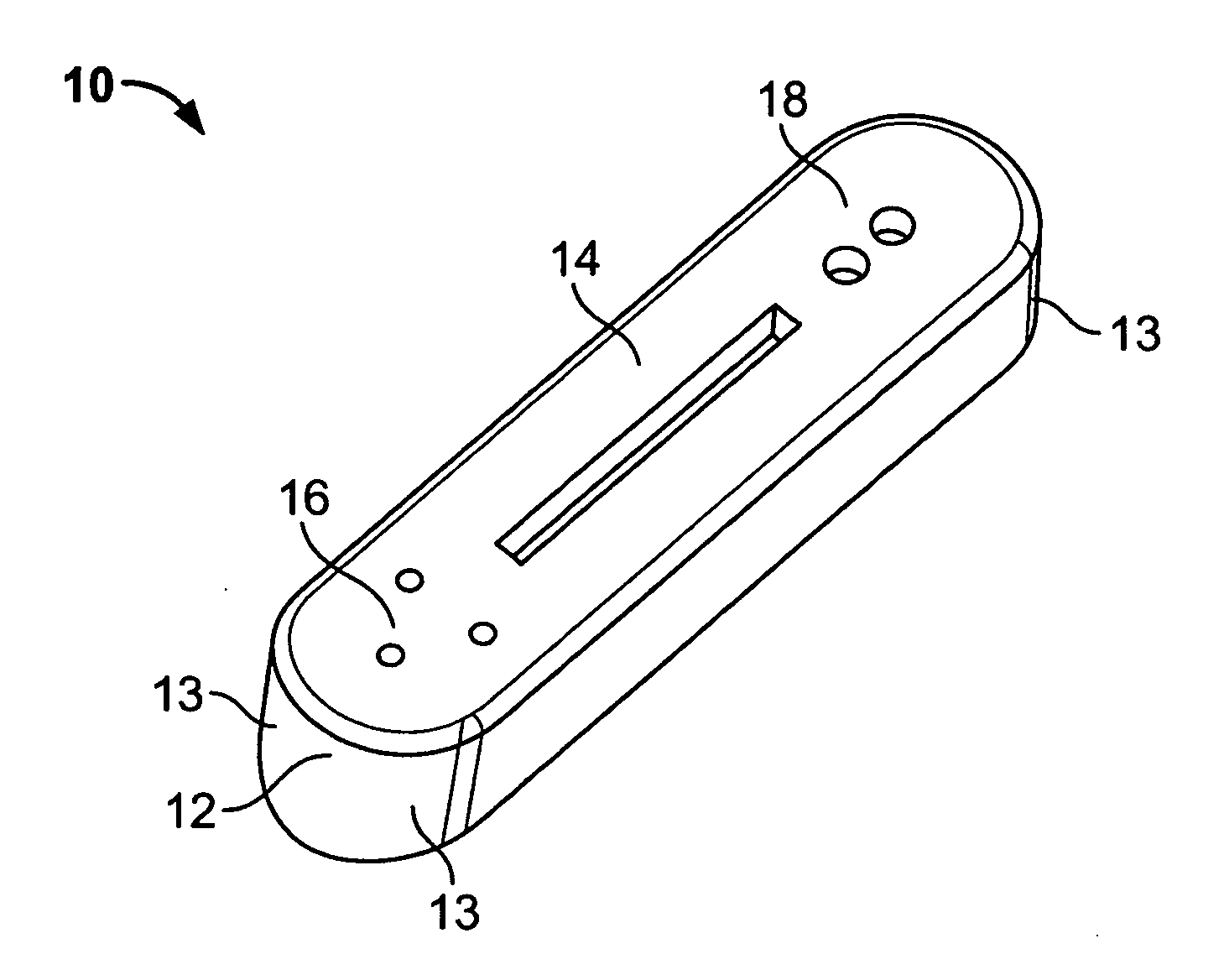

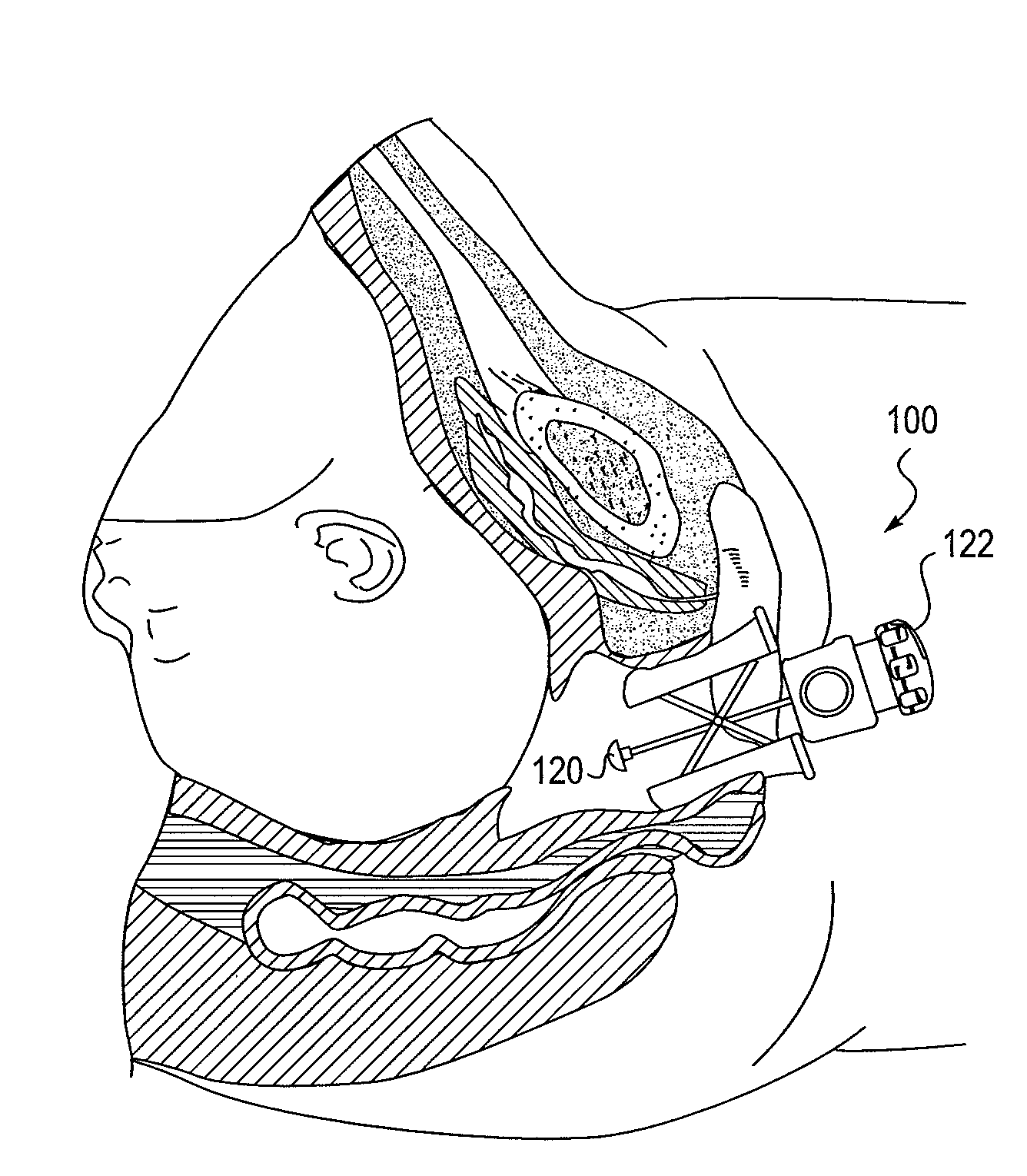

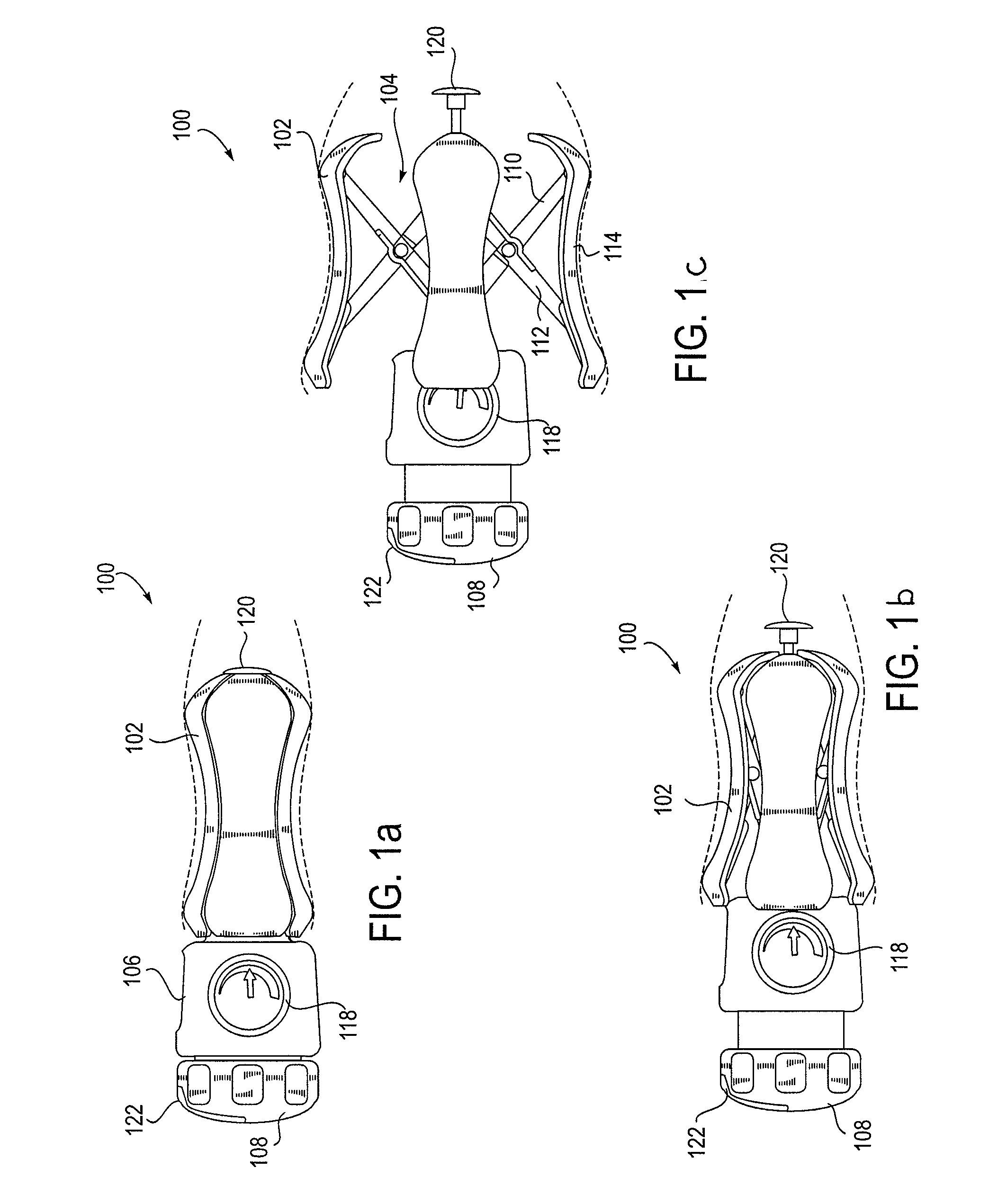

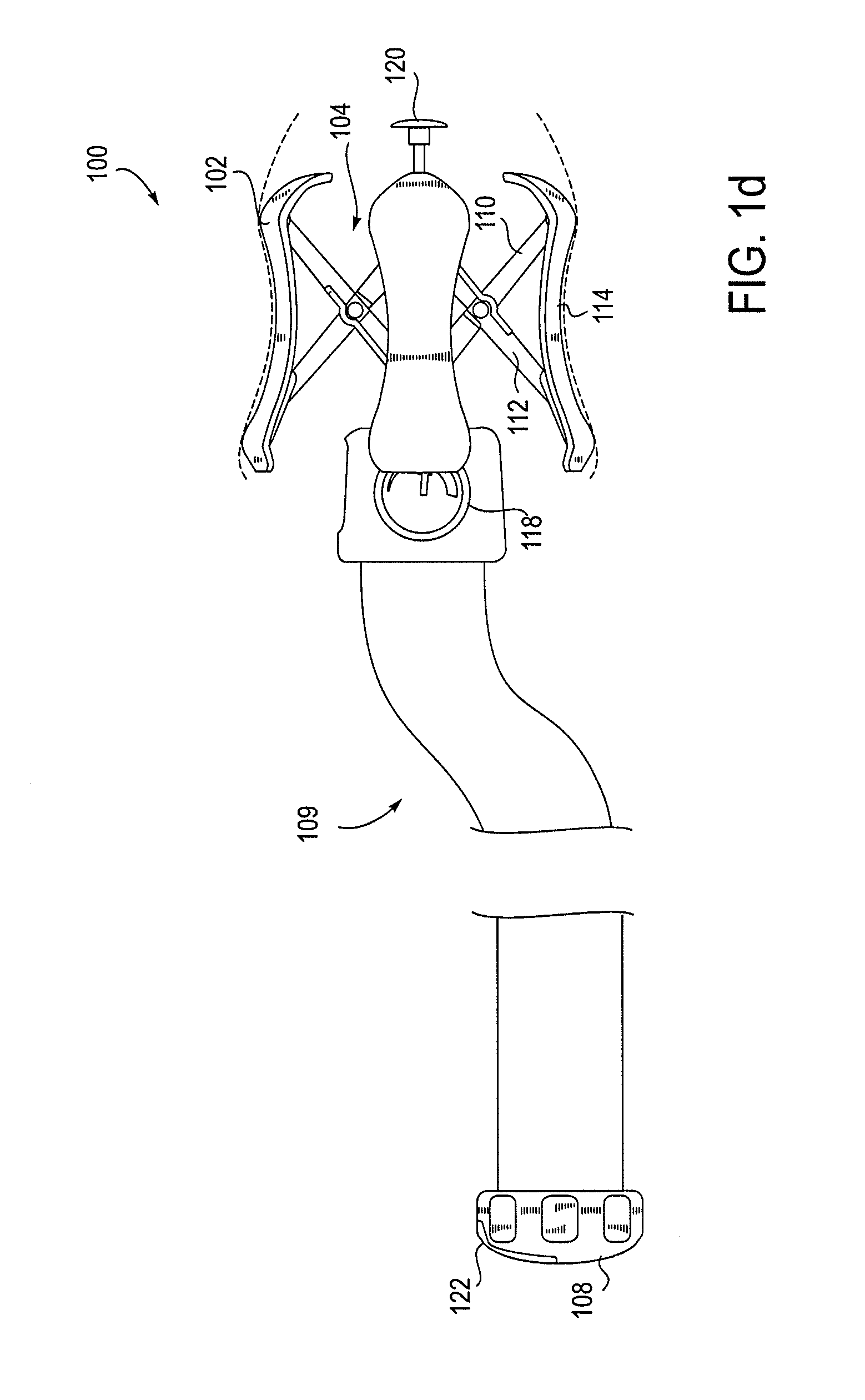

Methods and apparatus for preventing vaginal lacerations during childbirth

ActiveUS20130053863A1Avoid overexpansionPrevent pressureCannulasDilatorsVaginal dilationAutomatic control

A vaginal dilation device is provided that may include any of a number of features. One feature of the vaginal dilation device is that it is configured to dilate vaginal tissue during labor to prevent tissue damage. Another feature of the vaginal dilation device is that it can be manually controlled to dilate vaginal tissue, or can be automatically controlled to dilate vaginal tissue. In some embodiments, the vaginal dilation device is configured to measure a force applied by the device to tissue. In other embodiments, the vaginal dilation device is configured to apply a constant force to tissue. In other embodiments, the vaginal dilation device is configured to expand at a constant rate. Methods associated with use of the vaginal dilation device are also provided.

Owner:MATERNA MEDICAL

Apparatus and method for friction stir welding using a consumable pin tool

InactiveUS20050045695A1Improve mechanical propertiesImprove joint efficiencyNon-electric welding apparatusMulti materialMetal alloy

The present invention provides a friction stir welding apparatus operable for welding one or more metals, metal alloys, or other materials. The friction stir welding apparatus includes a pin tool holder, a shoulder having a surface coupled to the pin tool holder, and a pin tool coupled to the pin tool holder, the pin tool at least partially protruding from the surface of the shoulder, wherein the pin tool is made of a consumable pin tool material. Optionally, the shoulder rotates at a predetermined rotational speed and is retractable into / extendable from the pin tool holder at a substantially constant rate. Optionally, the shoulder is also made of a consumable shoulder material that is at least partially incorporated into the volume of a joint to be welded. The consumable shoulder material comprises a material that is the same as, similar to, or dissimilar from one or more materials comprising a workpiece to be friction stir welded. Preferably, the pin tool rotates at a predetermined rotational speed and is retractable into / extendable from the surface of the shoulder at a substantially constant rate. The consumable pin tool material is at least partially incorporated into the volume of the joint to be welded. The consumable pin tool material comprises a material that is the same as, similar to, or dissimilar from one or more materials comprising the workpiece to be friction stir welded.

Owner:GENERAL ELECTRIC CO

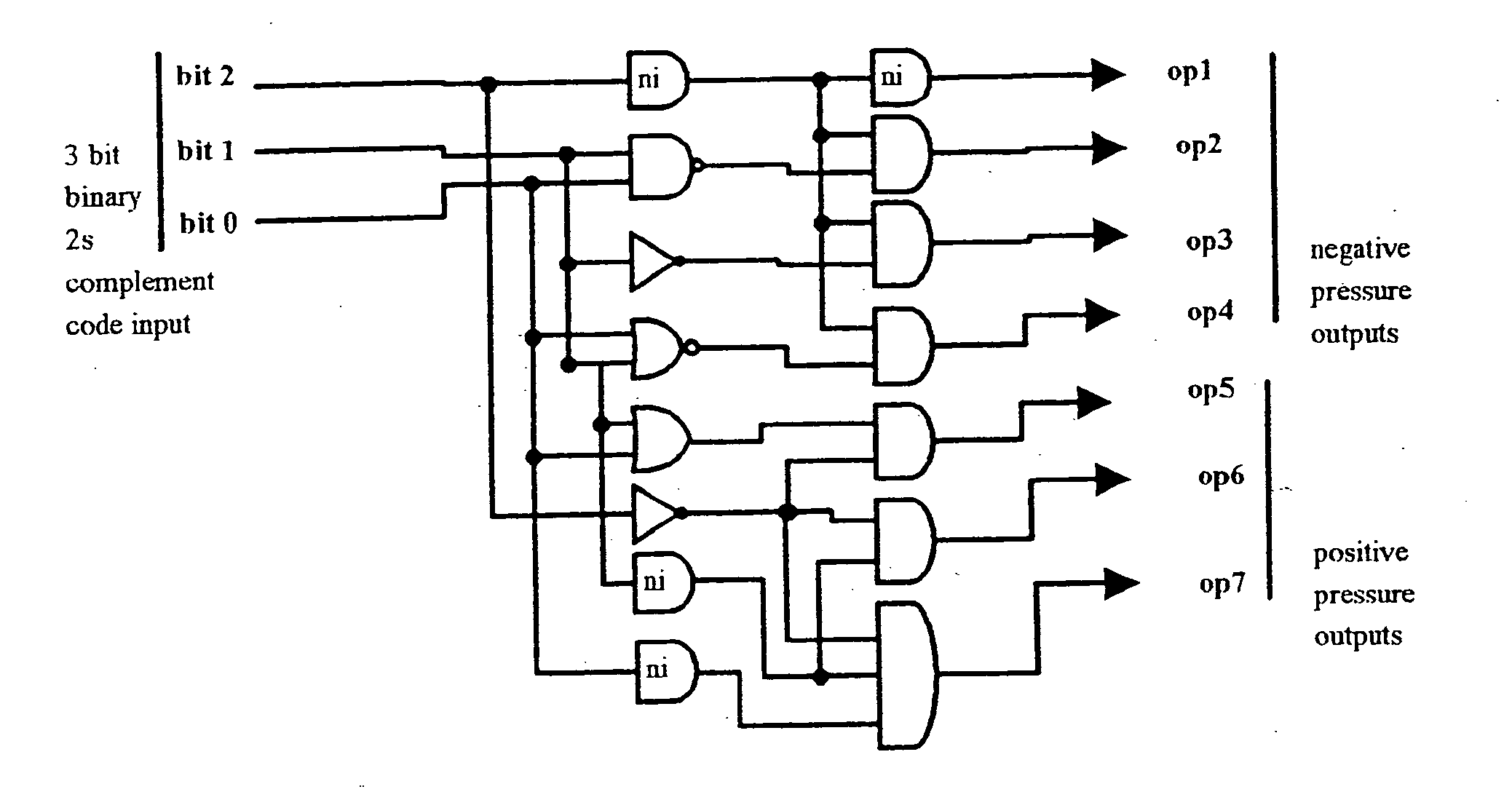

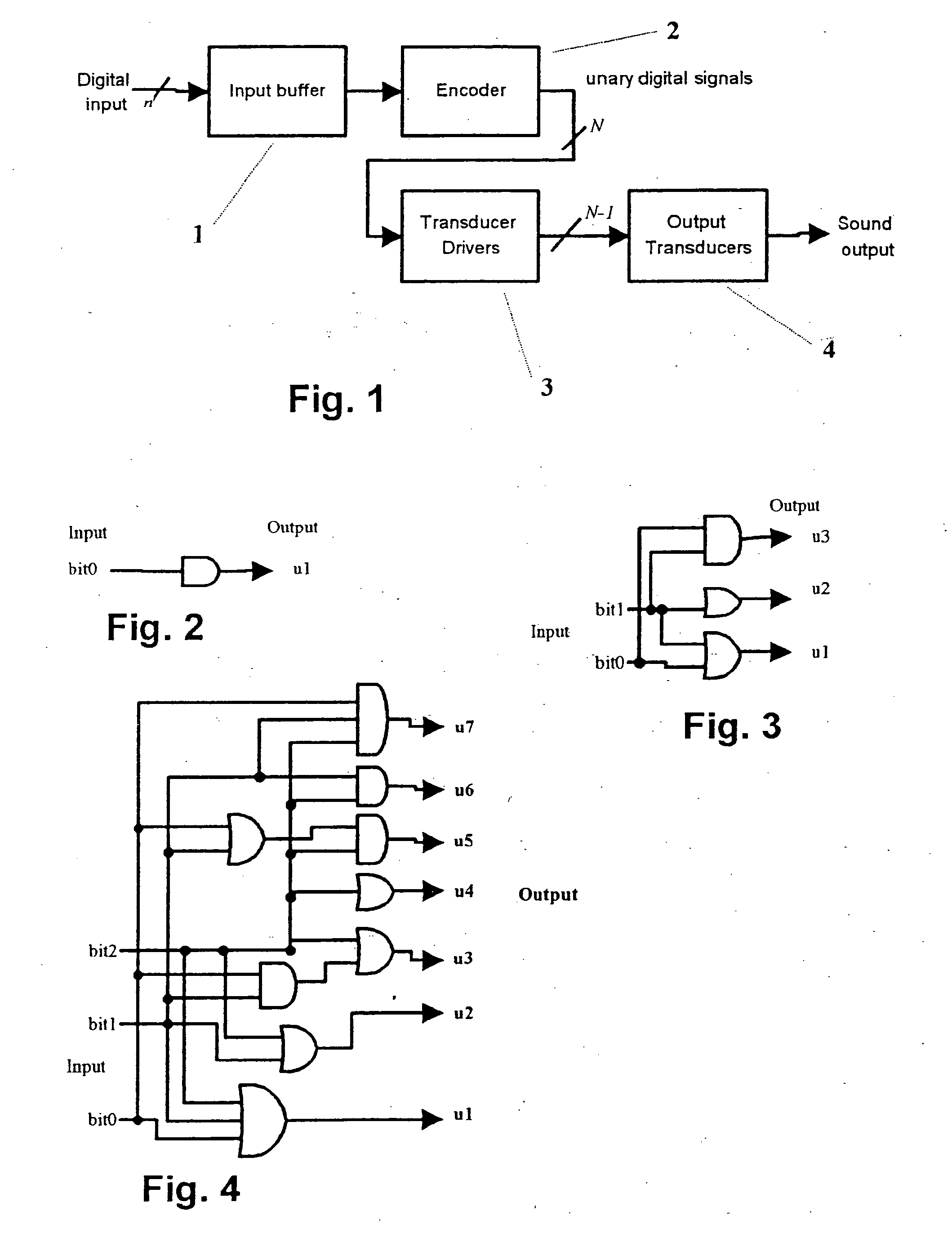

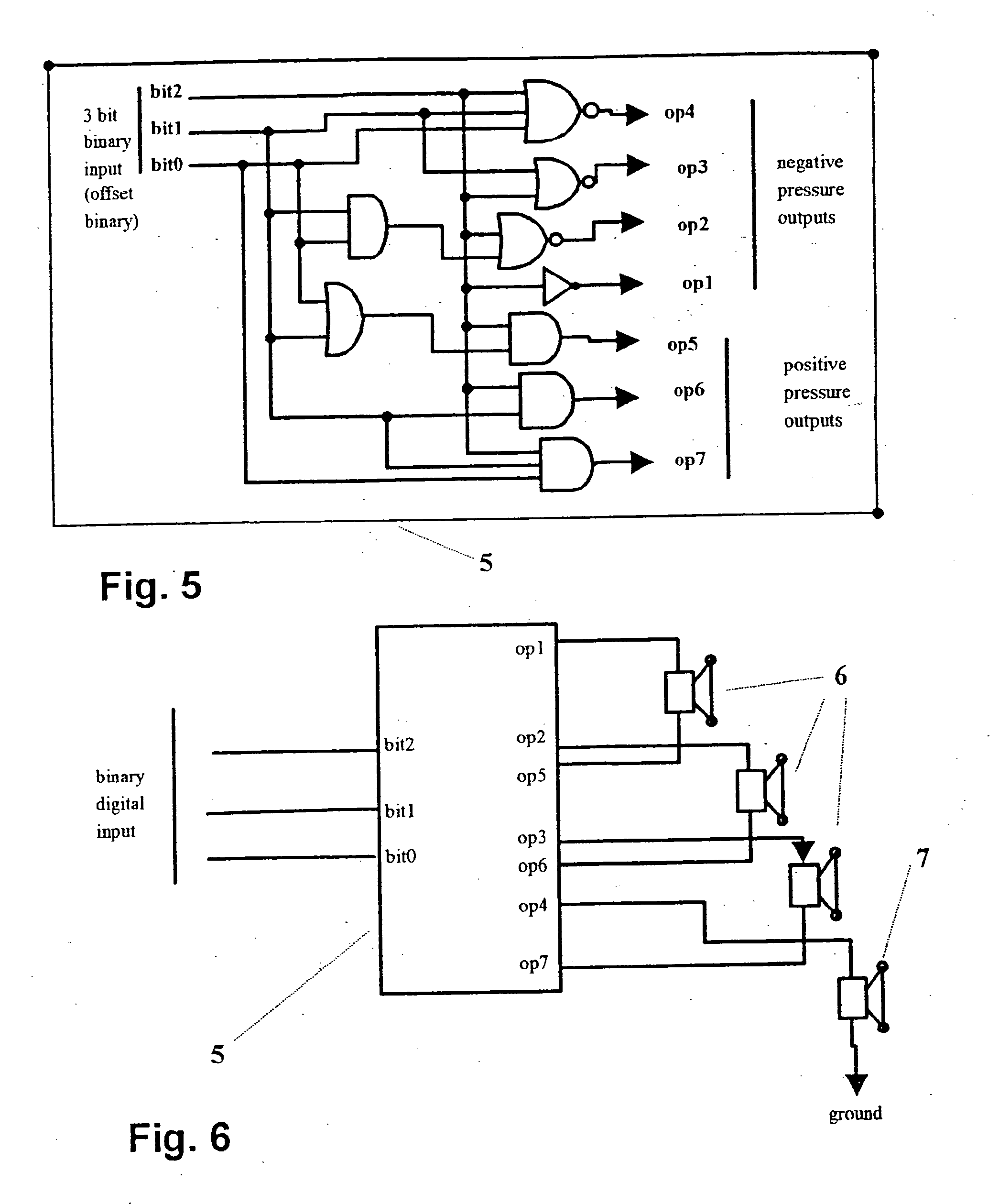

Digital pulse-width-modulation generator

A digital pulse-width-modulation (PWM) generator comprising: an n bit digital magnitude comparator having first and second n bit inputs and an output indicative of the relative values of the signals applied at the first and second inputs; a first n bit digital up / down counter having a count direction input coupled to receive a sign bit of a digital unary input signal, an n bit parallel binary count output connected to the first n bit input of the magnitude comparator, and a clock input; a second n bit counter having a clock input coupled to receive a constant rate clock signal and an n bit parallel binary count output connected to the second n bit input of the magnitude comparator; an AND gate having a first input coupled to receive the constant rate clock signal in frequency divided form and a second input coupled to receive a magnitude portion of the digital unary input signal, and further having an output connected to the clock input of the first counter; and wherein the comparator continually generates an output signal indicative of the relative magnitudes of the counts of the first and second counters, whereby said output signal is a PWM output signal with an average value representing a ramp voltage having a slope determined by magnitude portion of the digital unary input signal with a direction of a slope of the output signal being determined by the polarity of the sign bit.

Owner:YAMAHA CORP

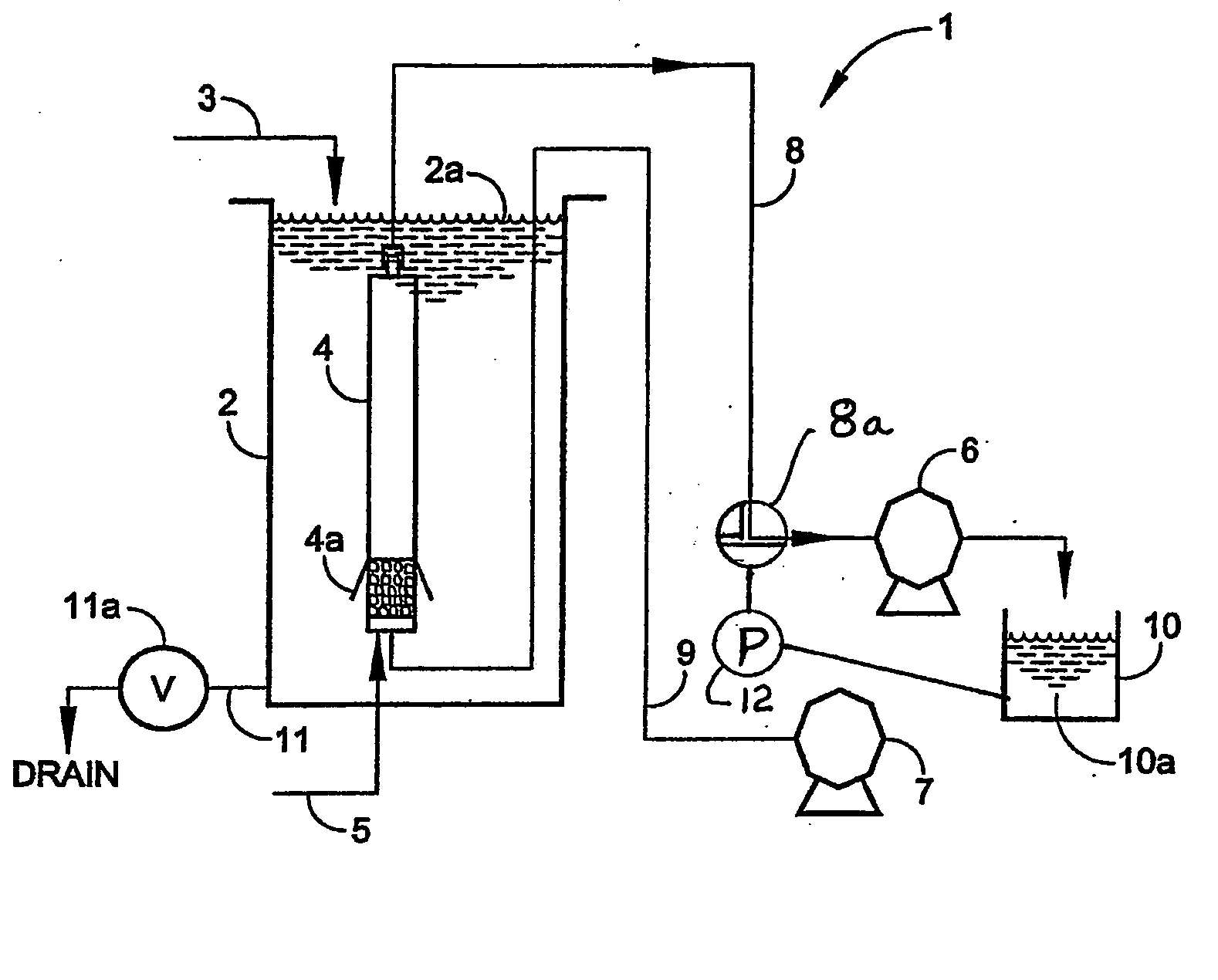

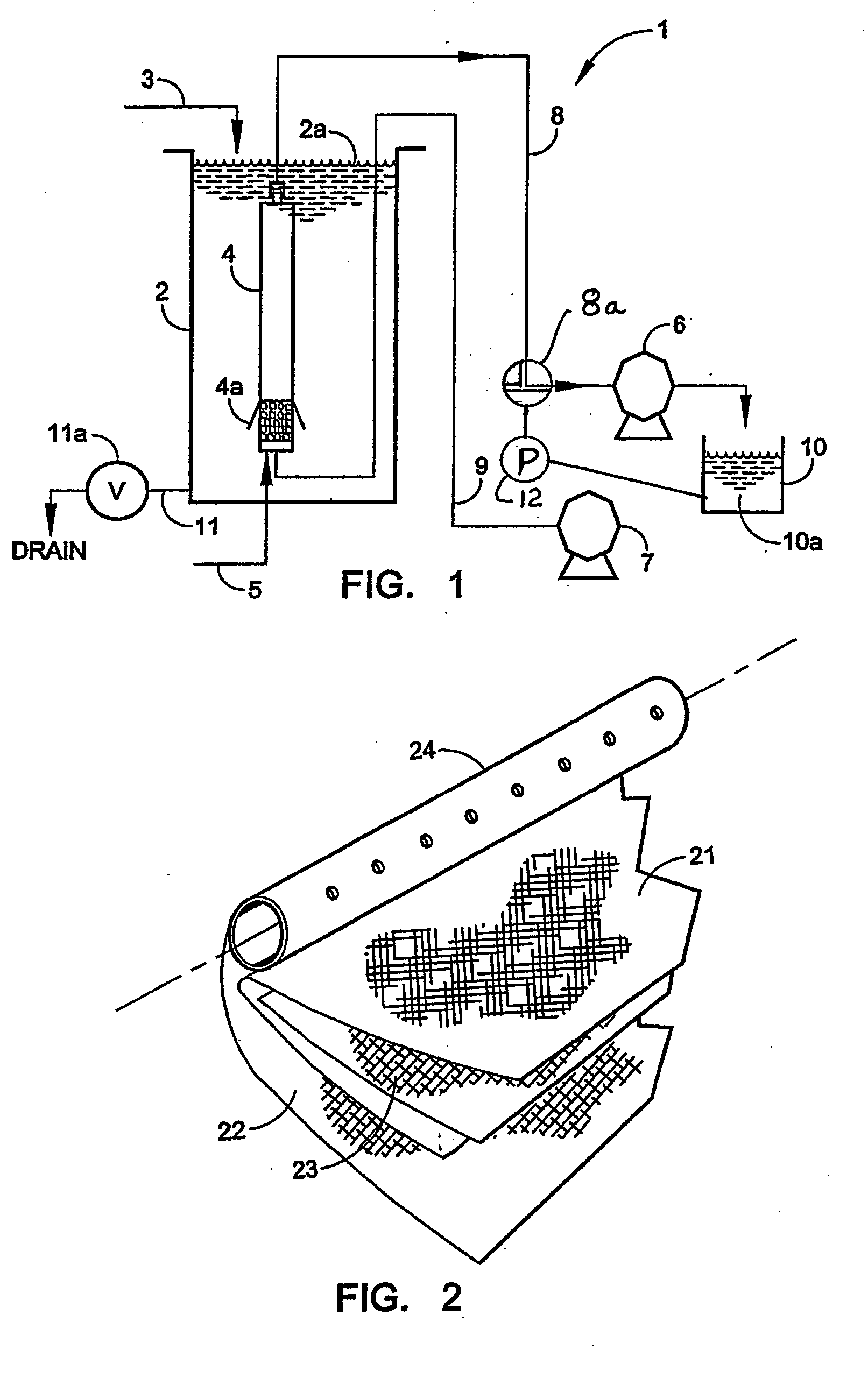

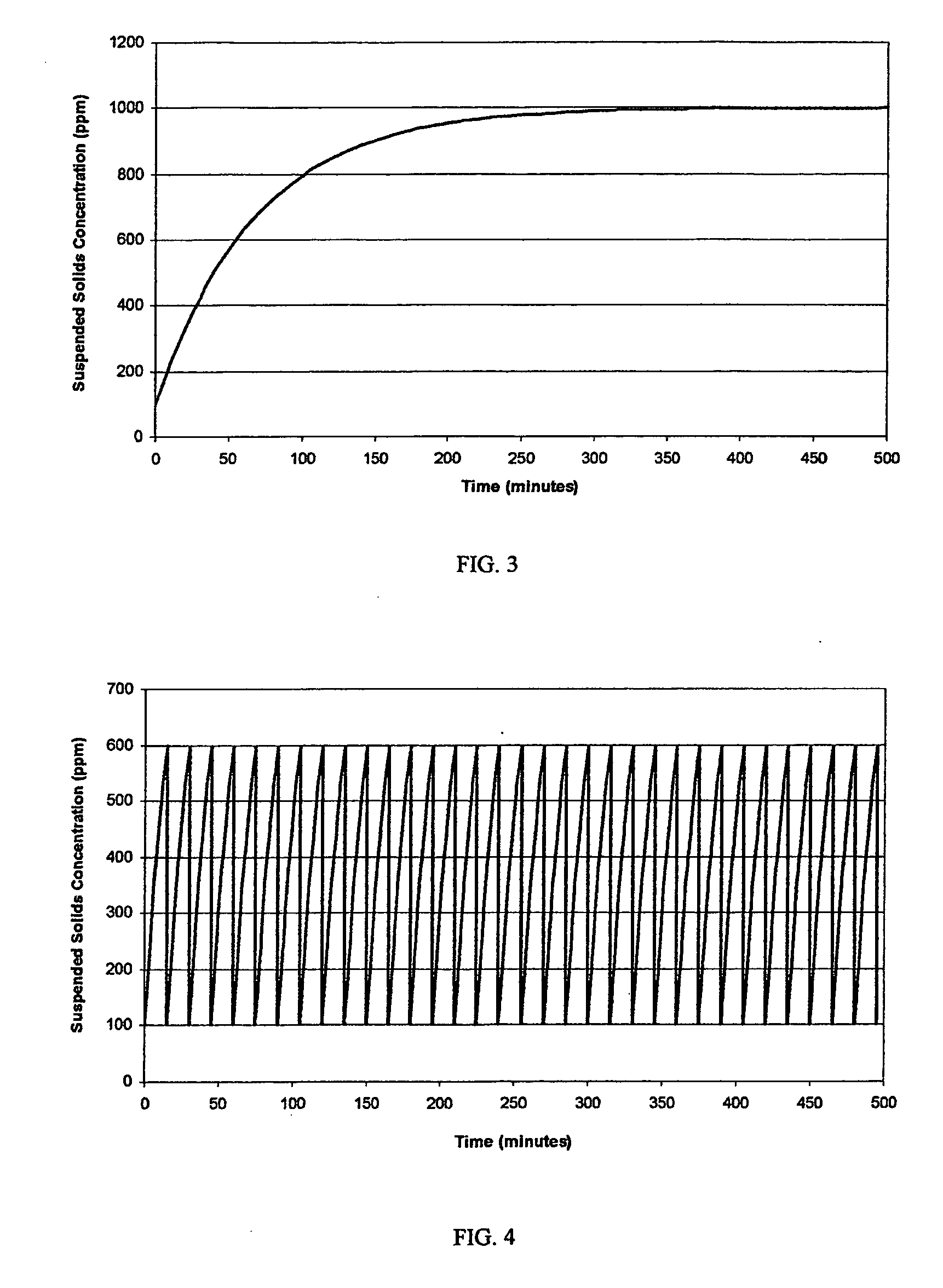

Low pressure filtration

ActiveUS20070131614A1Produced economicallyReduce energy consumptionMembranesUltrafiltrationFiltrationStreamflow

High flow, low-pressure ultrafiltration or microfiltration spiral wound membrane cartridges are used in filtration of liquid feedstocks having high suspended solids. Applications may utilize either vacuum or pumping for transmembrane drive pressure (TMP), and gas may optionally be bubbled up through the cartridges with certain feedstocks. Water permeate flux rates as high as 90 gallons per square foot per day (gfd) can be obtained at TMPs below 5 pounds per square inch. By locating each spiral wound cartridge in its own casing and supplying liquid feedstock to an open lower end of the casing, as opposed to submerging such cartridges in a tank filled with feedstock, overall low pressure performance is greatly improved. High permeate flow can be maintained for long periods of time between shutdowns for intensive cleaning. TMP is gradually increased to maintain a substantially constant rate of permeate discharge until a target is reached, indicative of solids accumulation on the membrane surface to an undesirable extent; then backflushing is effected for a short time. Discarding the hold-up volume of feedstock in the cartridge, the backflushing fluid and dislodged solids, allows production to be promptly resumed with fresh feedstock at performance at near original levels.

Owner:MANNHUMMEL WATER & FLUID SOLUTIONS GMBH

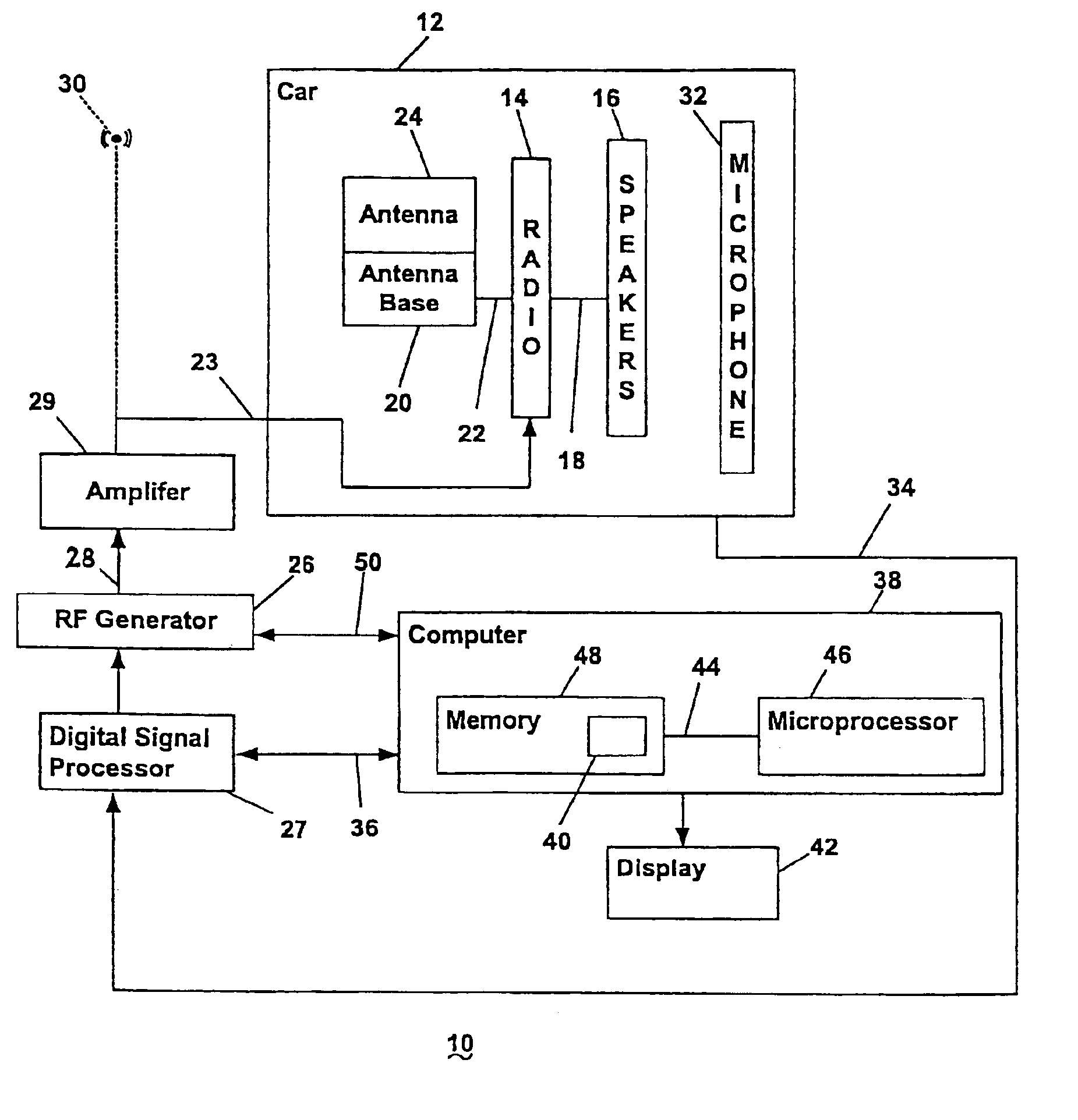

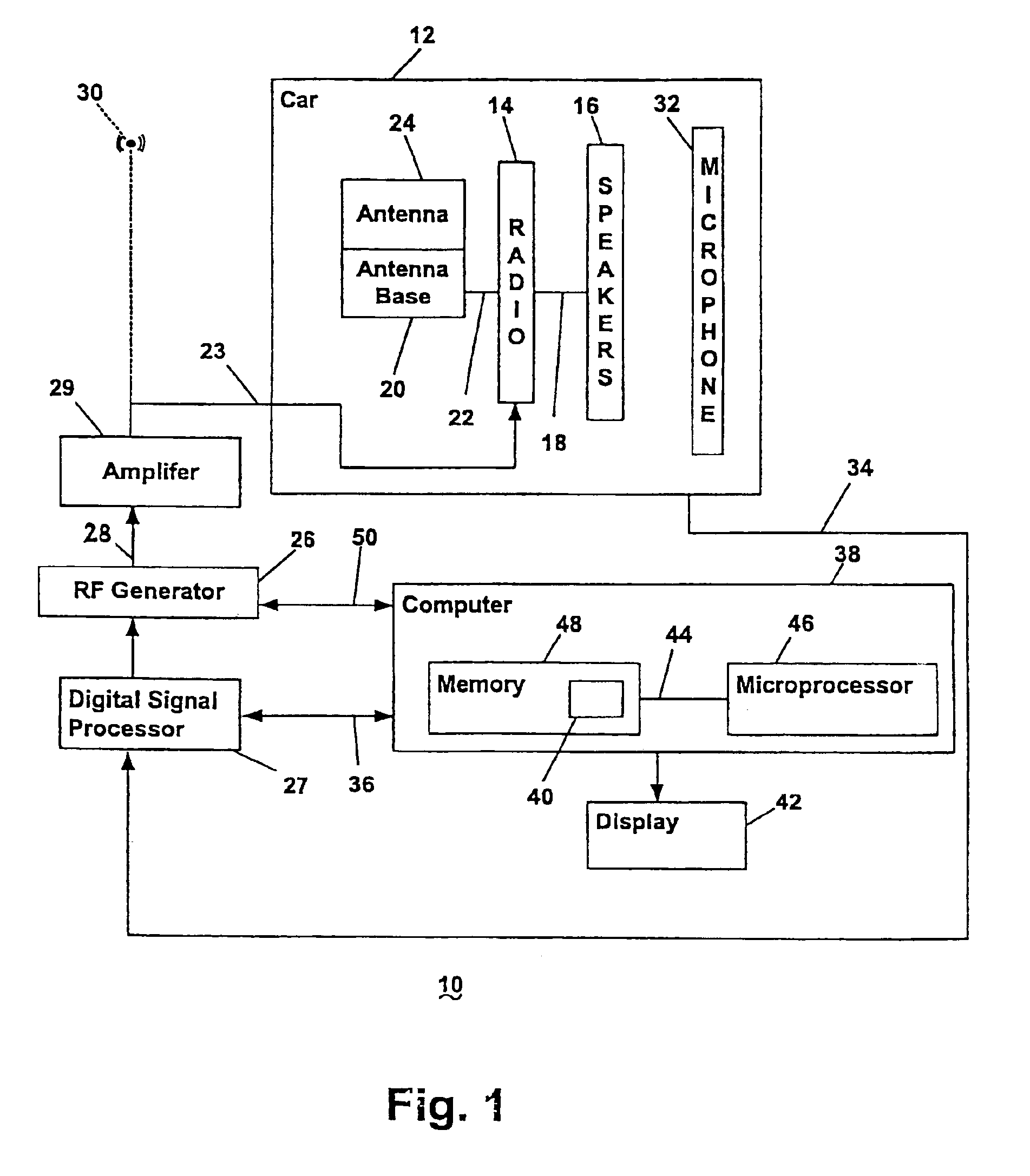

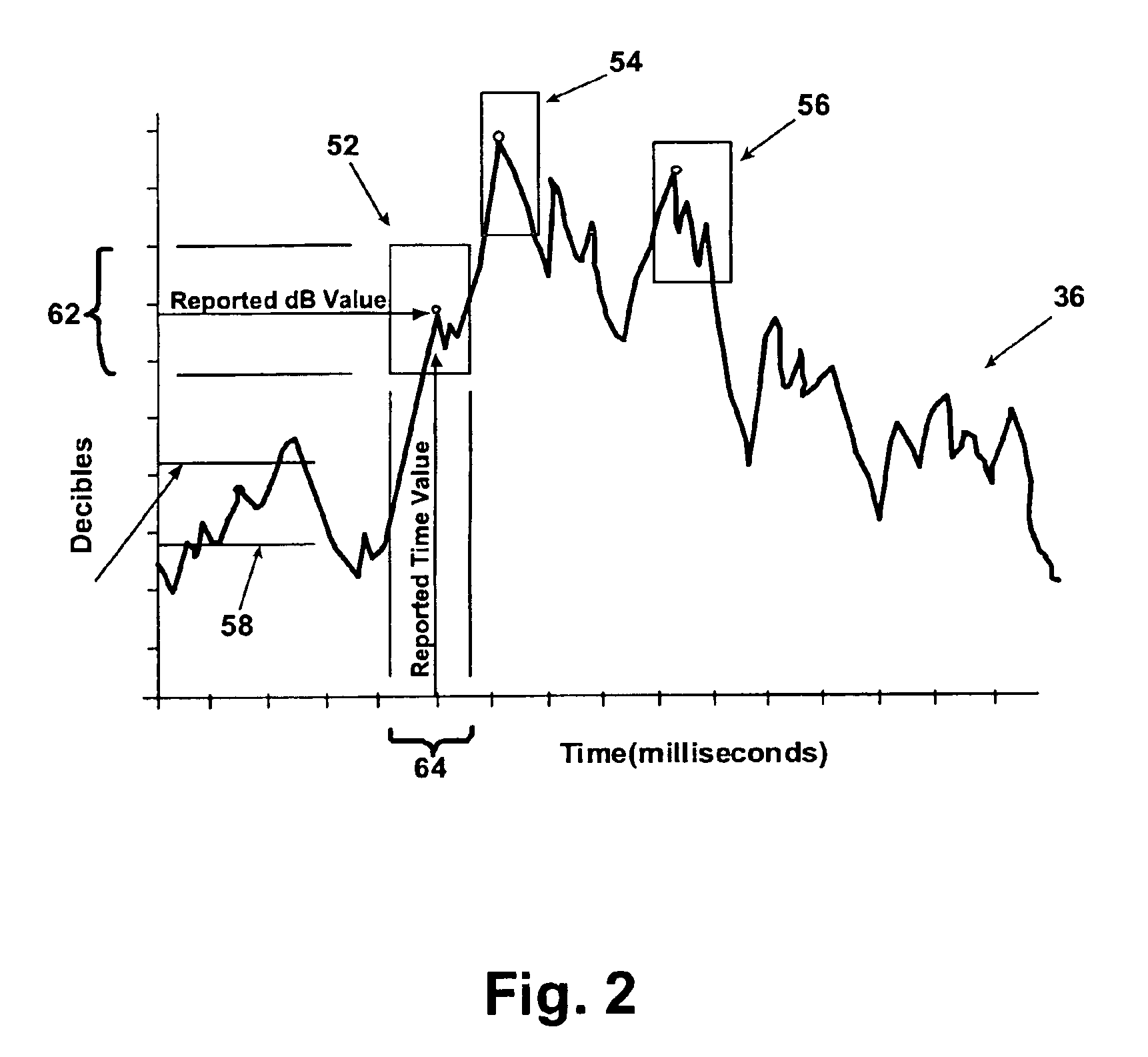

Automated system and method for automotive time-based audio verification

ActiveUS6950525B2High incidenceImproved audio product informationElectrical testingTransmission monitoringVerification systemLoudspeaker

A time-based audio verification system used to verify the correct installation of an audio system in a vehicle is based on the principle that the distances between a pick-up microphone and each speaker within the vehicle are different. Sound travels at a constant rate, and the wave is measured that provides the time it takes the sound emanating from each speaker to travel to the microphone. Once it is determined where in the wave each speaker is located, the presence of each speaker in the vehicle can be determined. Additionally, the level of each speaker in the curve can be analyzed to determine individual speaker output quality.

Owner:GM GLOBAL TECH OPERATIONS LLC

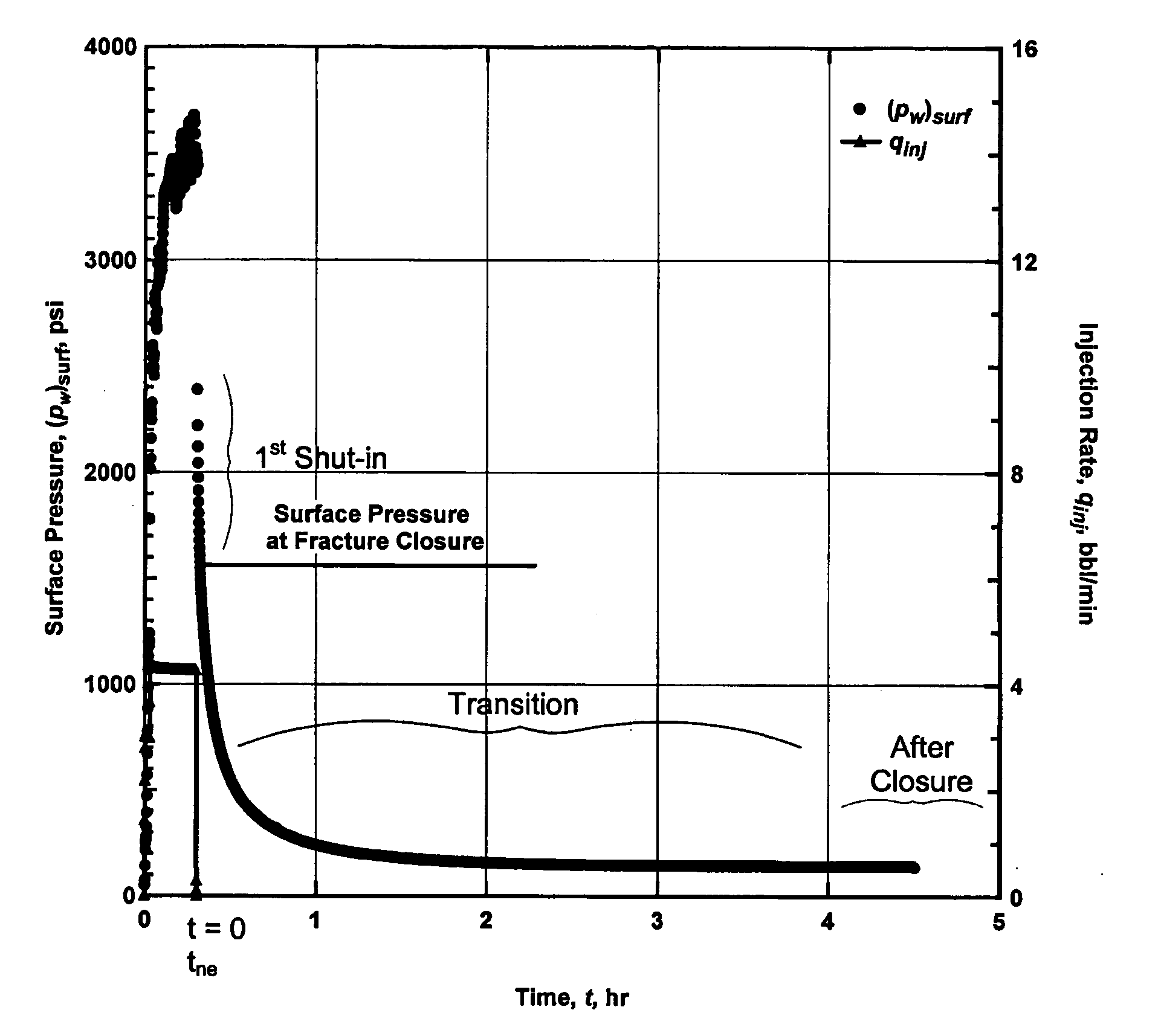

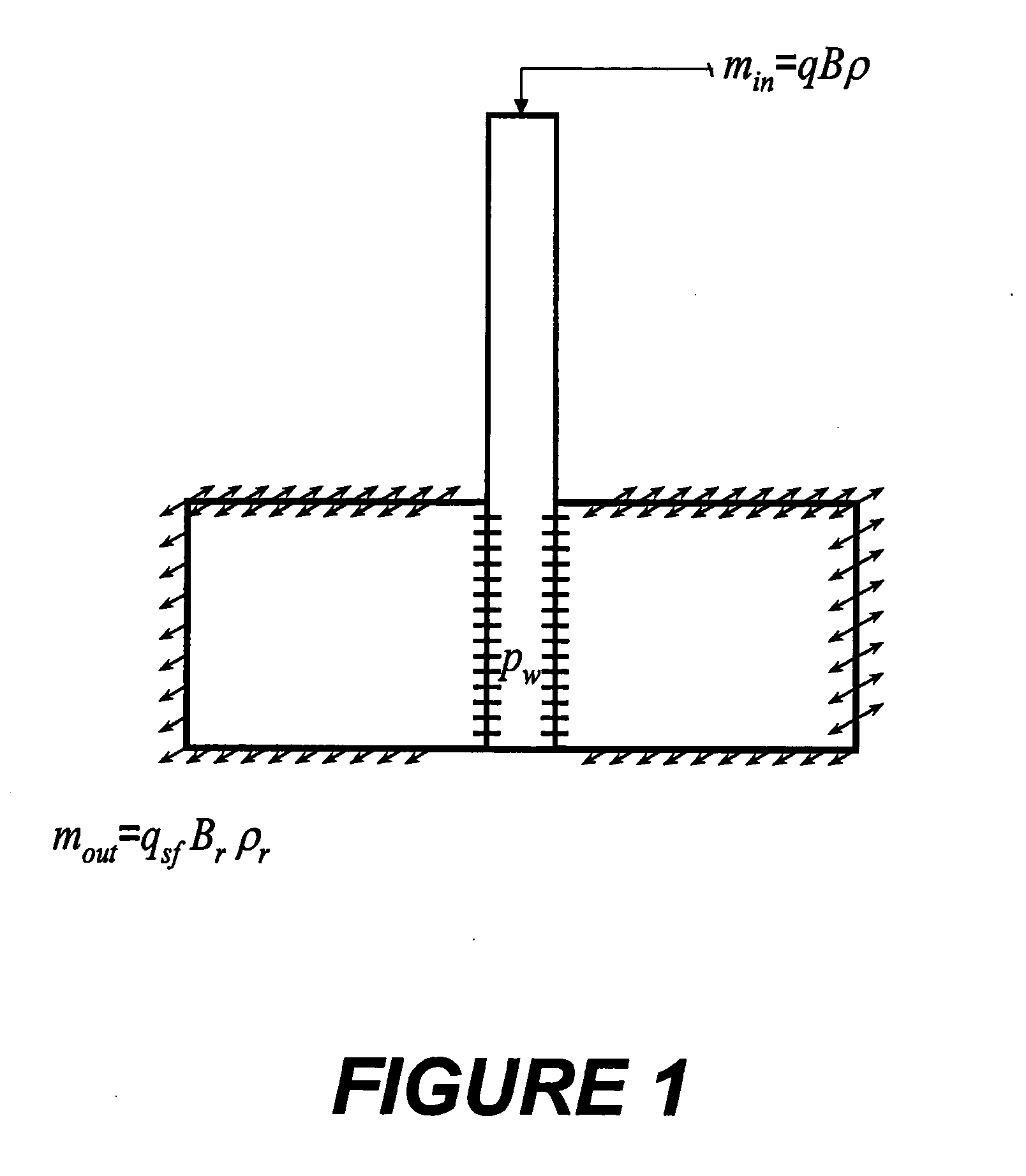

Method and an apparatus for detecting fracture with significant residual width from previous treatments

ActiveUS20050222852A1Rapid determinationElectric/magnetic detection for well-loggingSurveyDual unitMedicine

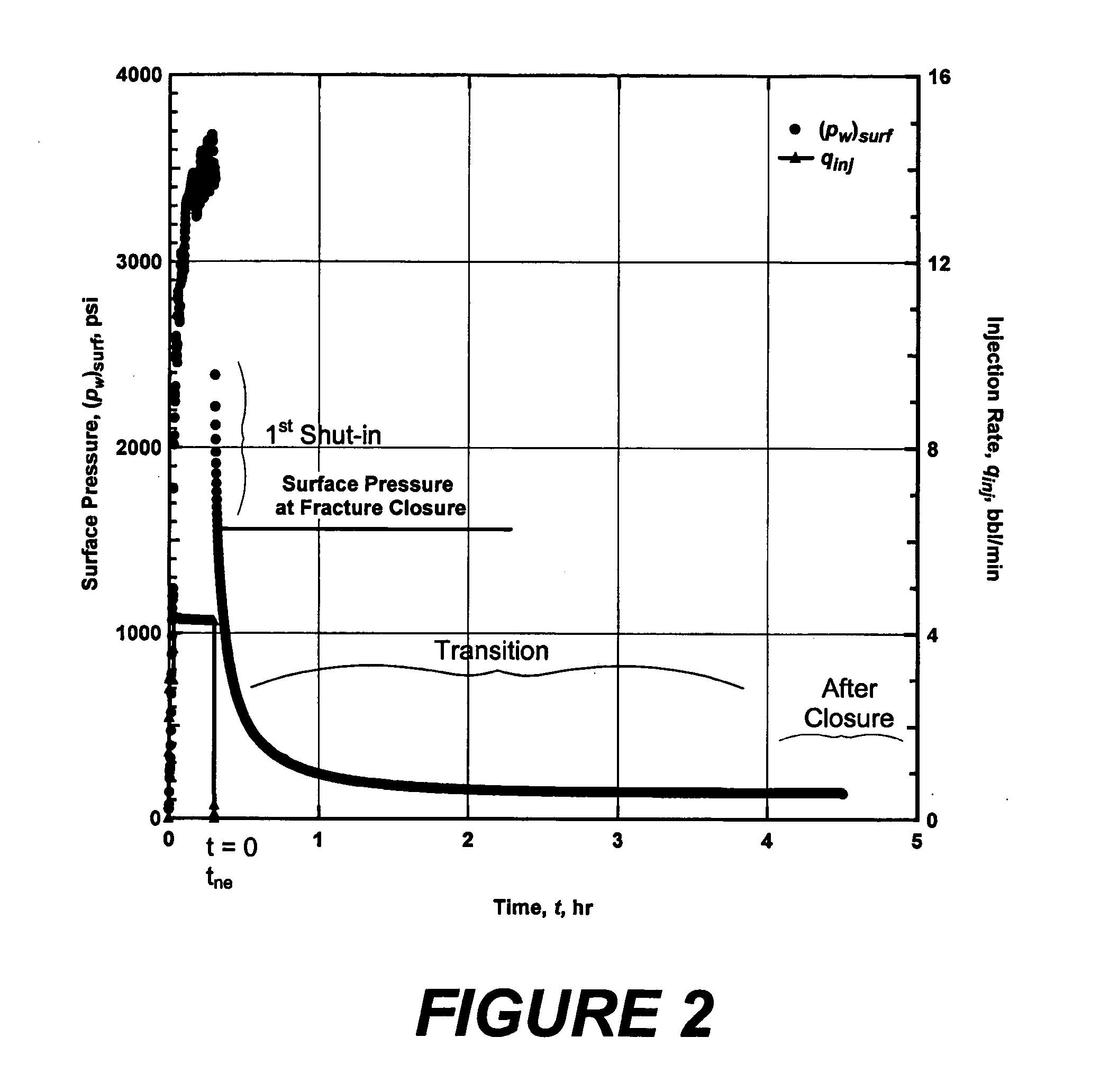

A refracture-candidate diagnostic test is an injection of compressible or slightly compressible fluid such as liquid, gas, or combination at pressures in excess of minimum in-situ stress and formation fracture pressure with pressure decline following injection test recorded to detect a fracture retaining residual width from previous stimulation treatments. The diagnostic consists of small volume injections with injection time being a small fraction of time required for compressible or slightly compressible reservoir fluid to exhibit pseudoradial flow. The fracture-injection portion of a test can be considered as occurring instantaneously, and the results obtained in an open infinite-conductivity hydraulic fracture with pressures above fracture closure stress during before-closure portion of pressure falloff and with pressures less than fracture closure stress during after-closure portion of pressure falloff. Data measurements are transformed into a constant rate equivalent pressure transformation to obtain adjusted pressures or adjusted pseudovariables which are analyzed to identify dual unit-slope before and after closure periods confirming a residual retaining width.

Owner:HALLIBURTON ENERGY SERVICES INC

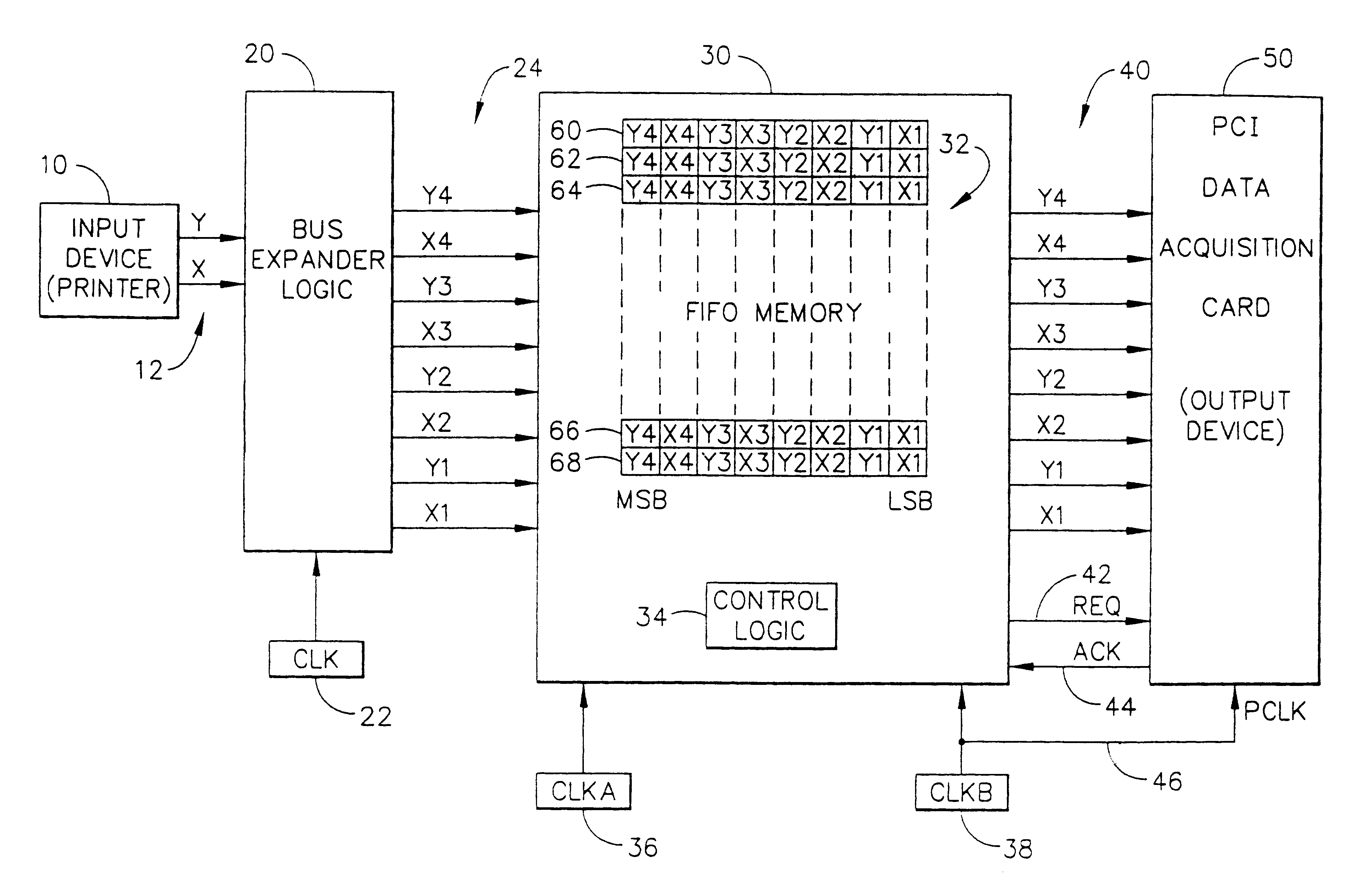

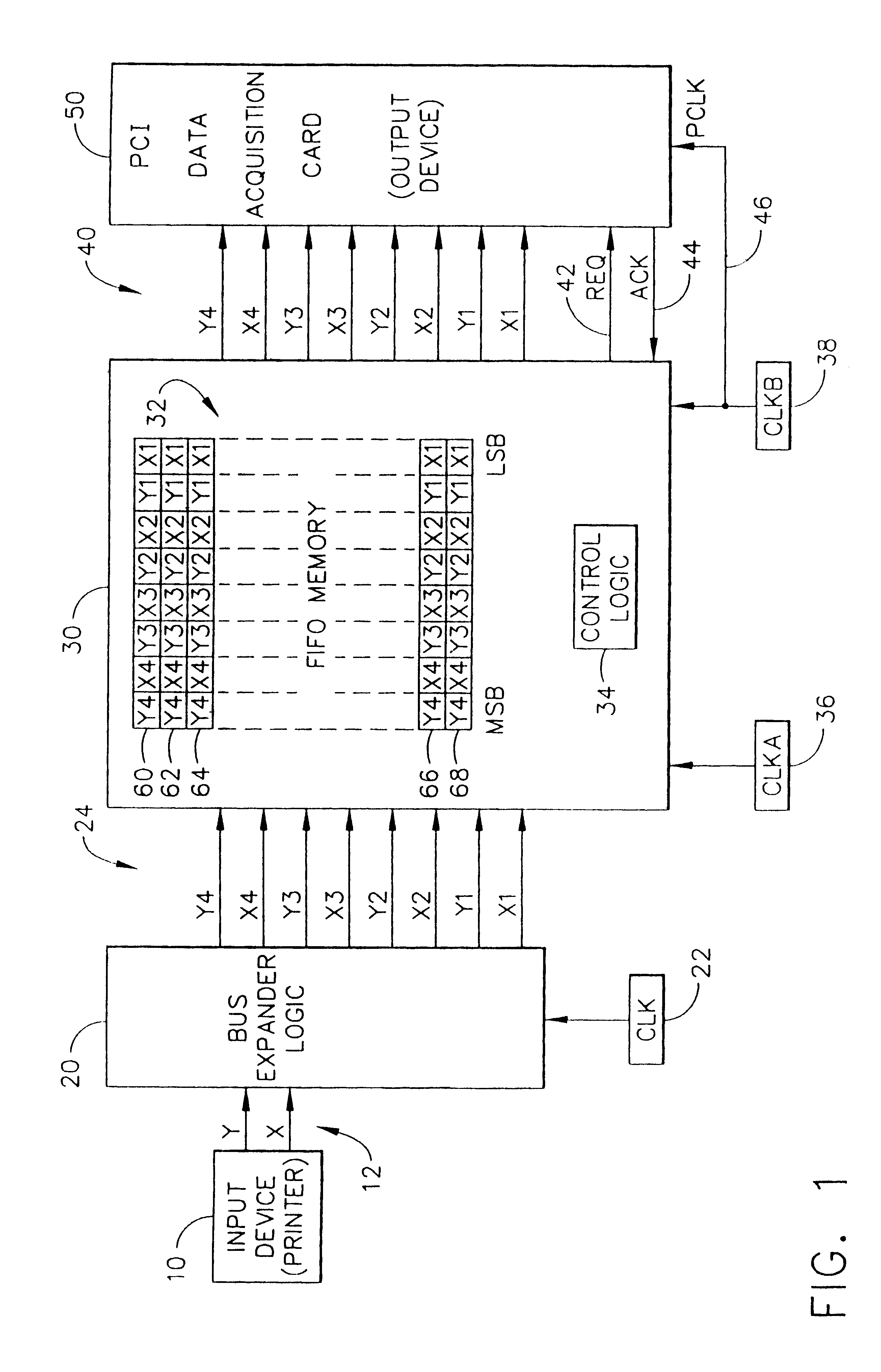

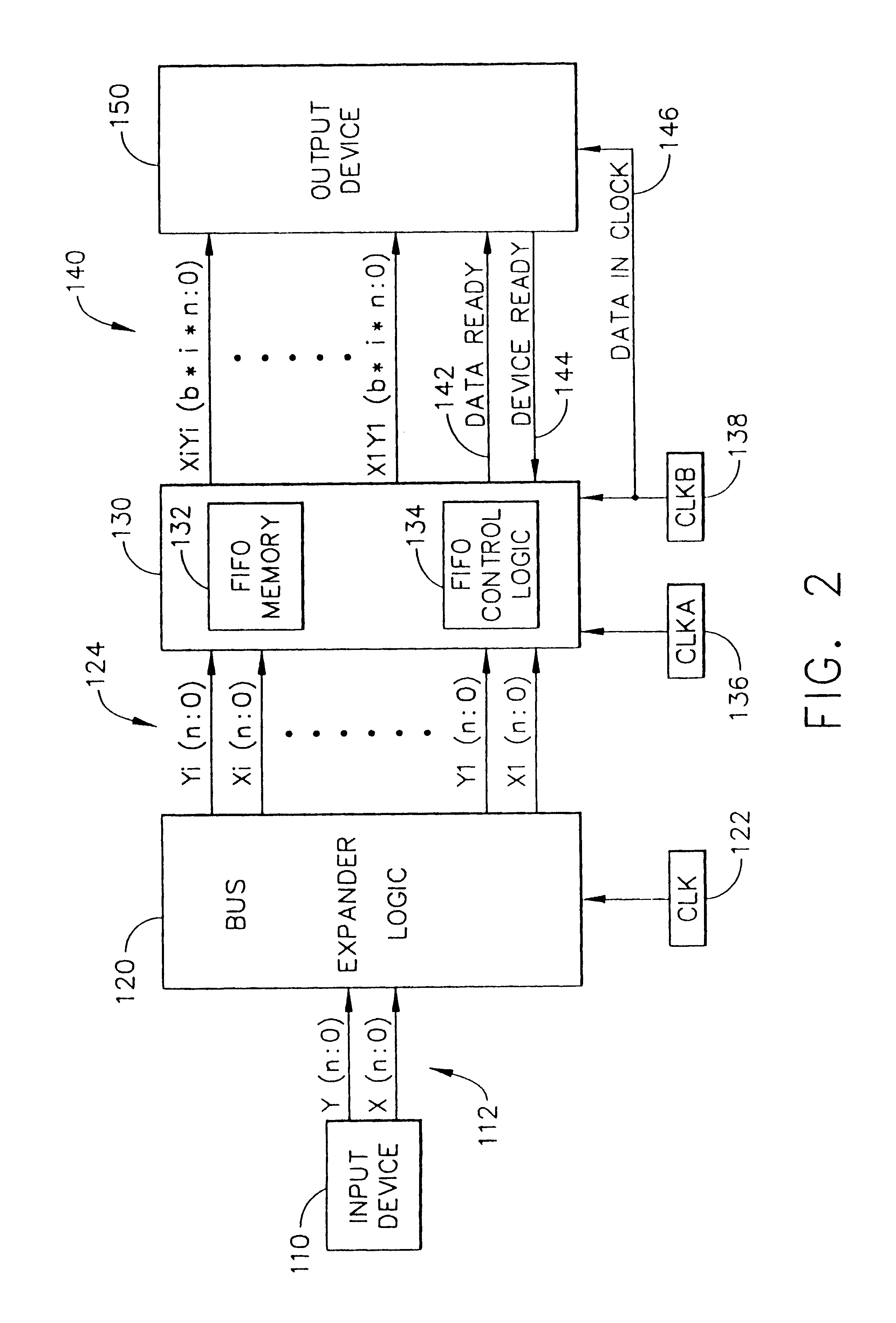

Method and apparatus for sampling digital data at a virtually constant rate, and transferring that data into a non-constant sampling rate device

InactiveUS6865241B1Faster data rateImprove data throughputElectric digital data processingSynchronising arrangementDigital dataConstant frequency

An improved data acquisition system interface provides virtually constant sampling of input signals and provides those signals in a digitized format to a data acquisition unit that may not be able to sample at a constant rate without missing or “losing” some of the samples. The present invention acts as a front end interface that temporarily latches the sampled data, expands the data into multiple parallel signals, then stores the multiple parallel signals in a dual-port FIFO memory unit. Finally, the multiple parallel signals are transferred into the data acquisition unit at a lower frequency, and the transfer operations take place only when the data acquisition unit is ready to accept data. Since the front end misses no sampling intervals (i.e., it always takes a sample according to an extremely constant frequency crystal clock), then the data acquisition unit will be provided with all of these samples without losing any data. The only requirement is that the data throughput of the multiple parallel signals into the data acquisition unit be greater than or equal to the data sampling rate of the original signal at the front end. The present invention can be used with pure digital signals to capture their precise times of logic state transitions, or with serial data signals in which the precise moments of transition can be used to decipher the serial data. Moreover, the interface can be used with analog signals that are digitized using an analog-to-digital converter.

Owner:LEXMARK INT INC

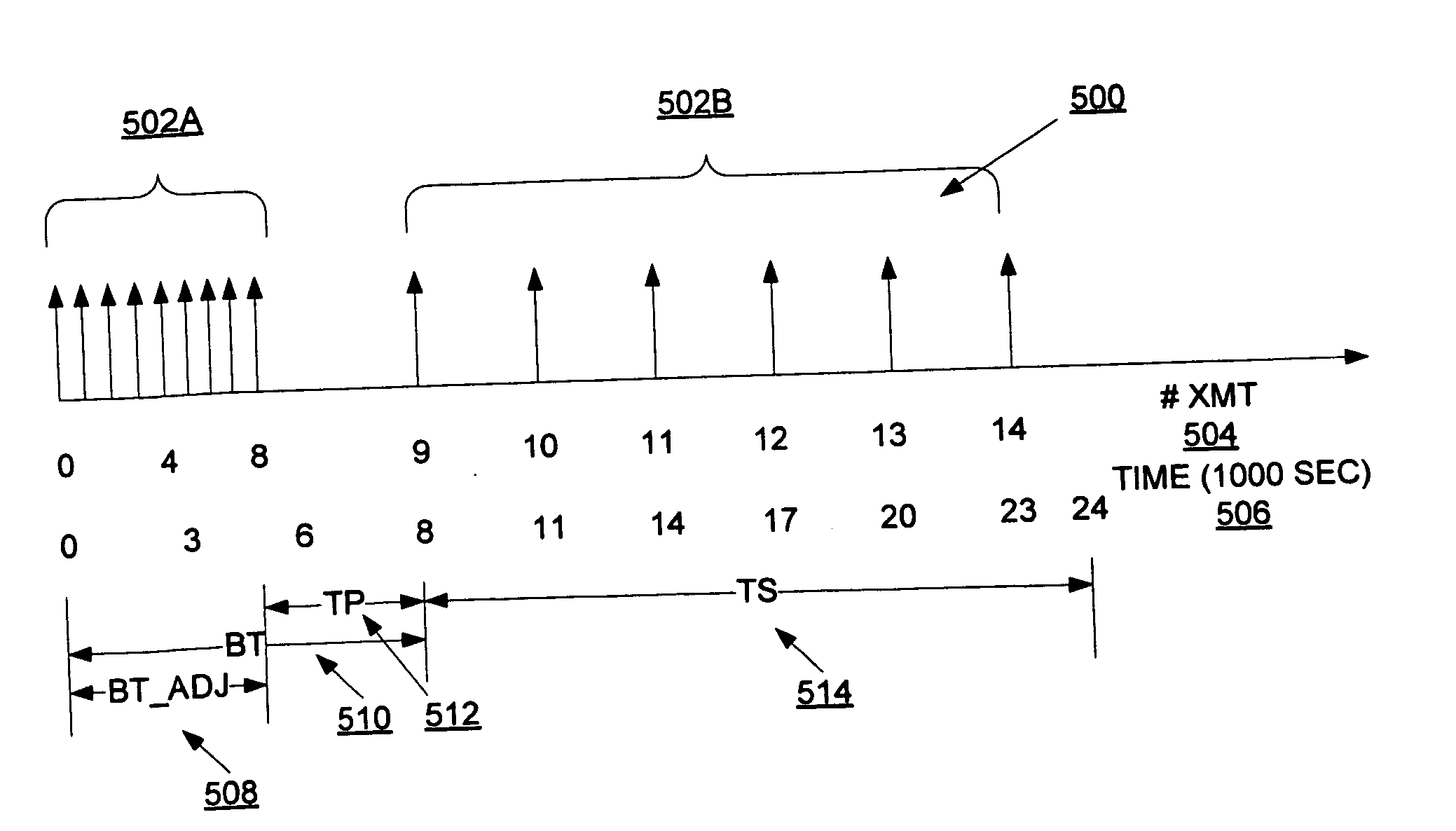

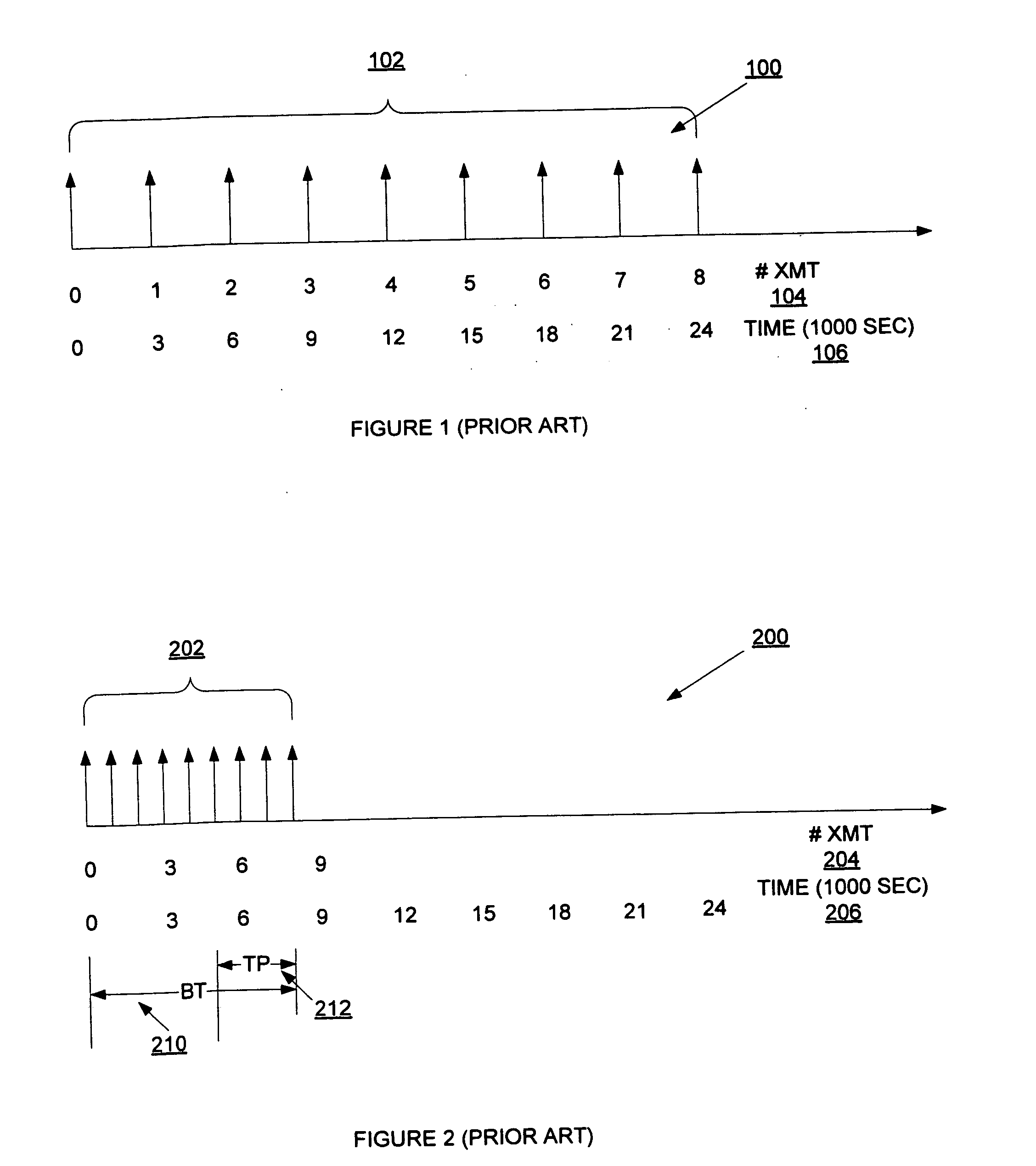

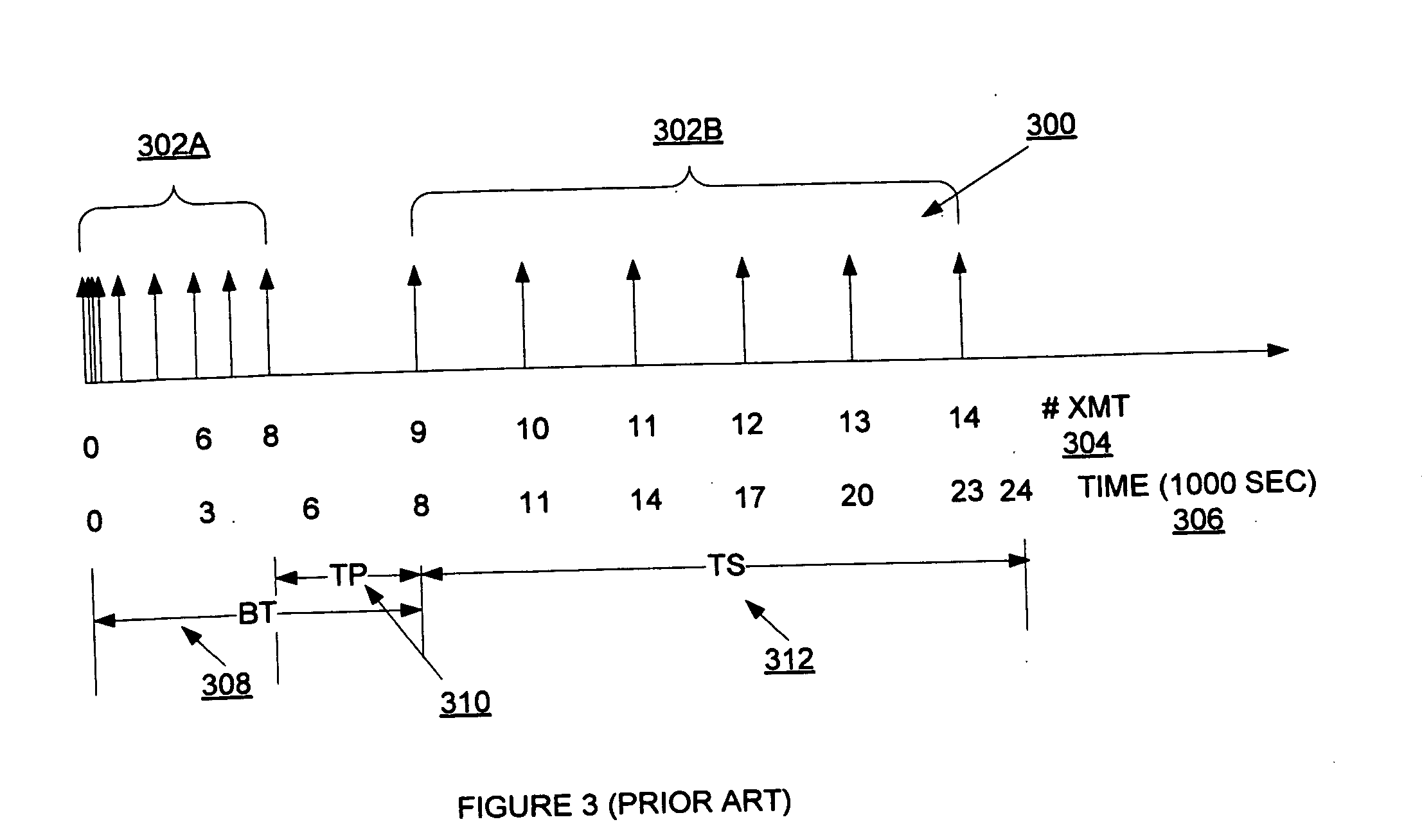

Method and apparatus for traffic shaping

A method and apparatus for a traffic shaper that uses a traffic shaping algorithm based on a sustained rate token bucket and a constant rate emitter. The sustained rate token bucket uses a plurality of tokens based on the sustained rate and the sustained burst size. The constant rate emitter allows transmission of traffic at an adjusted transmission rate, where the adjusted transmission rate is derived from the peak rate, peak burst size, sustained rate and sustained burst size.

Owner:TELEFON AB LM ERICSSON (PUBL)

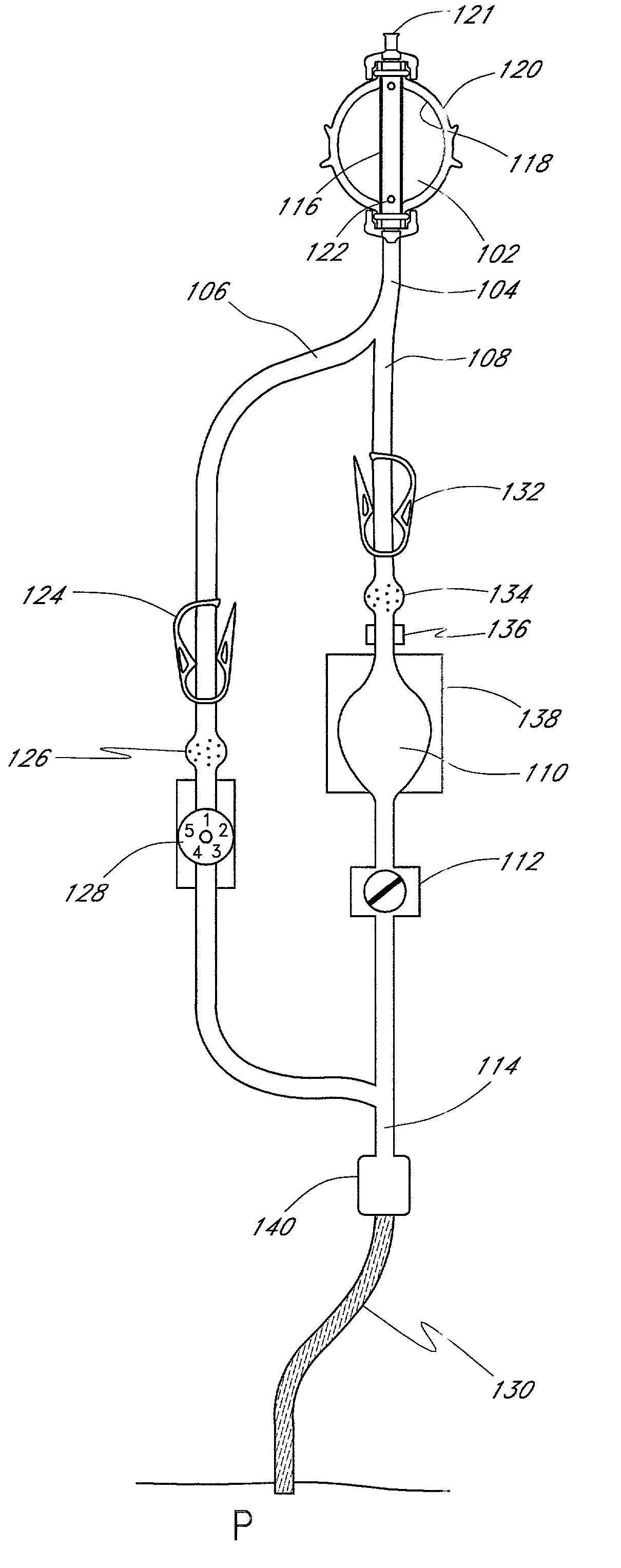

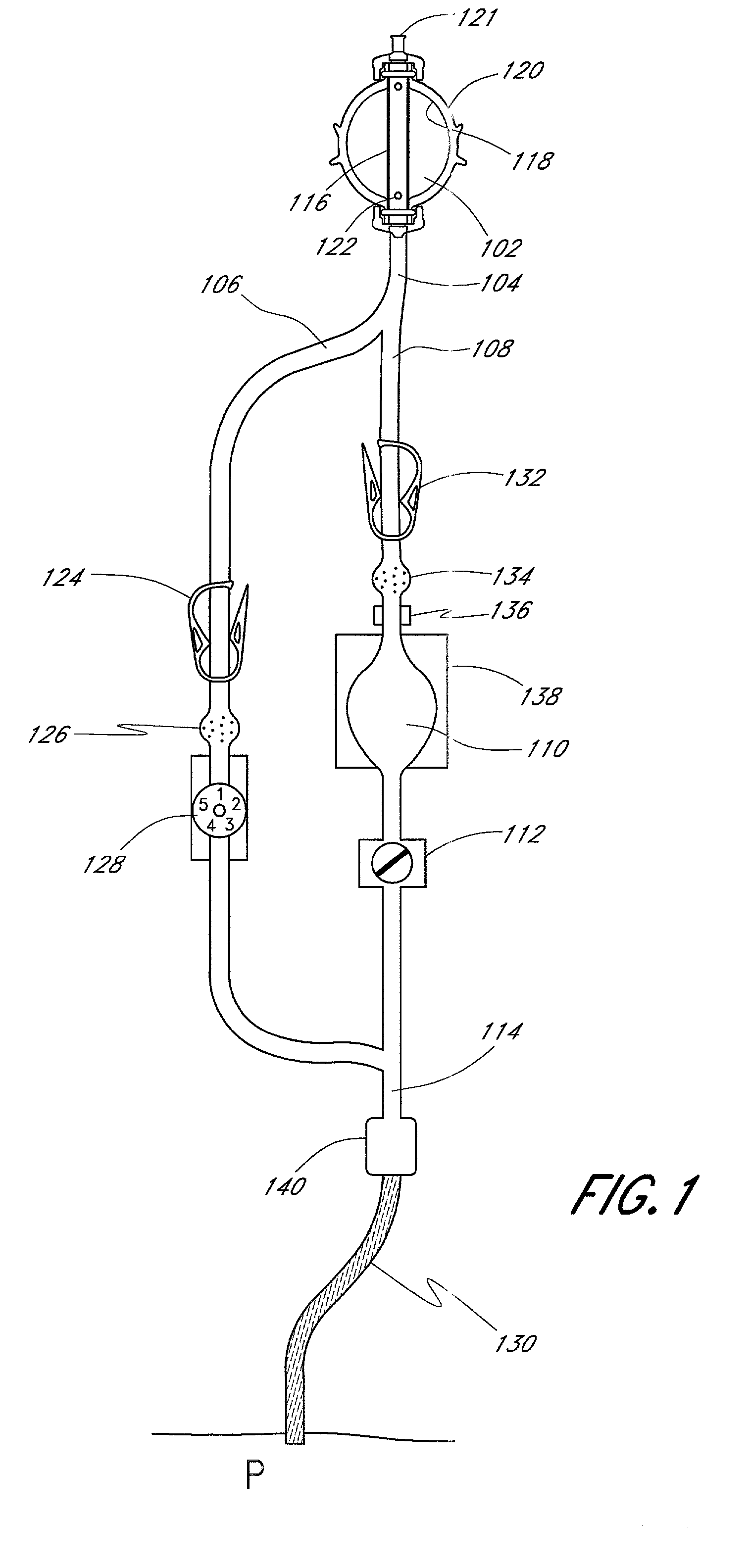

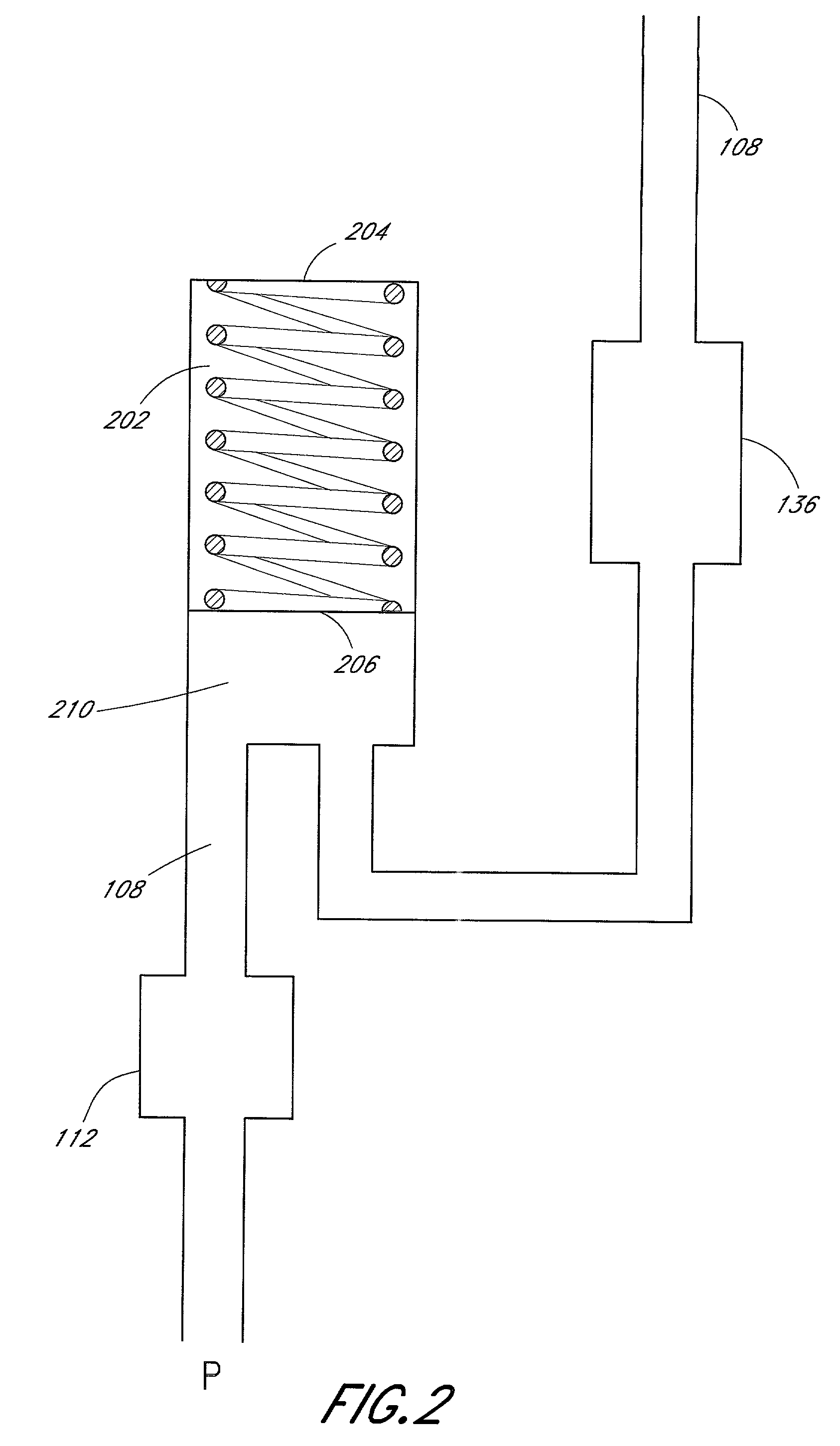

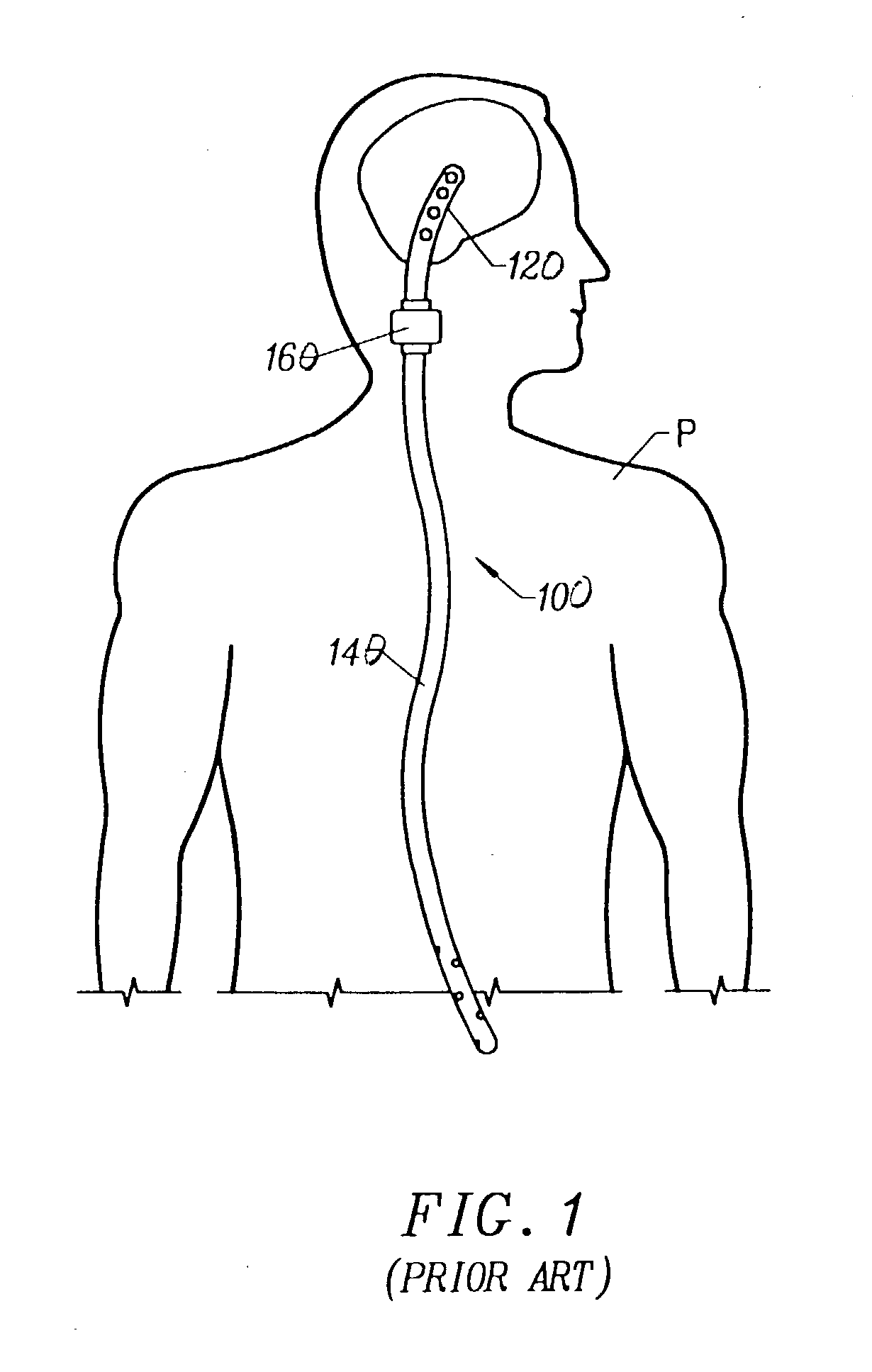

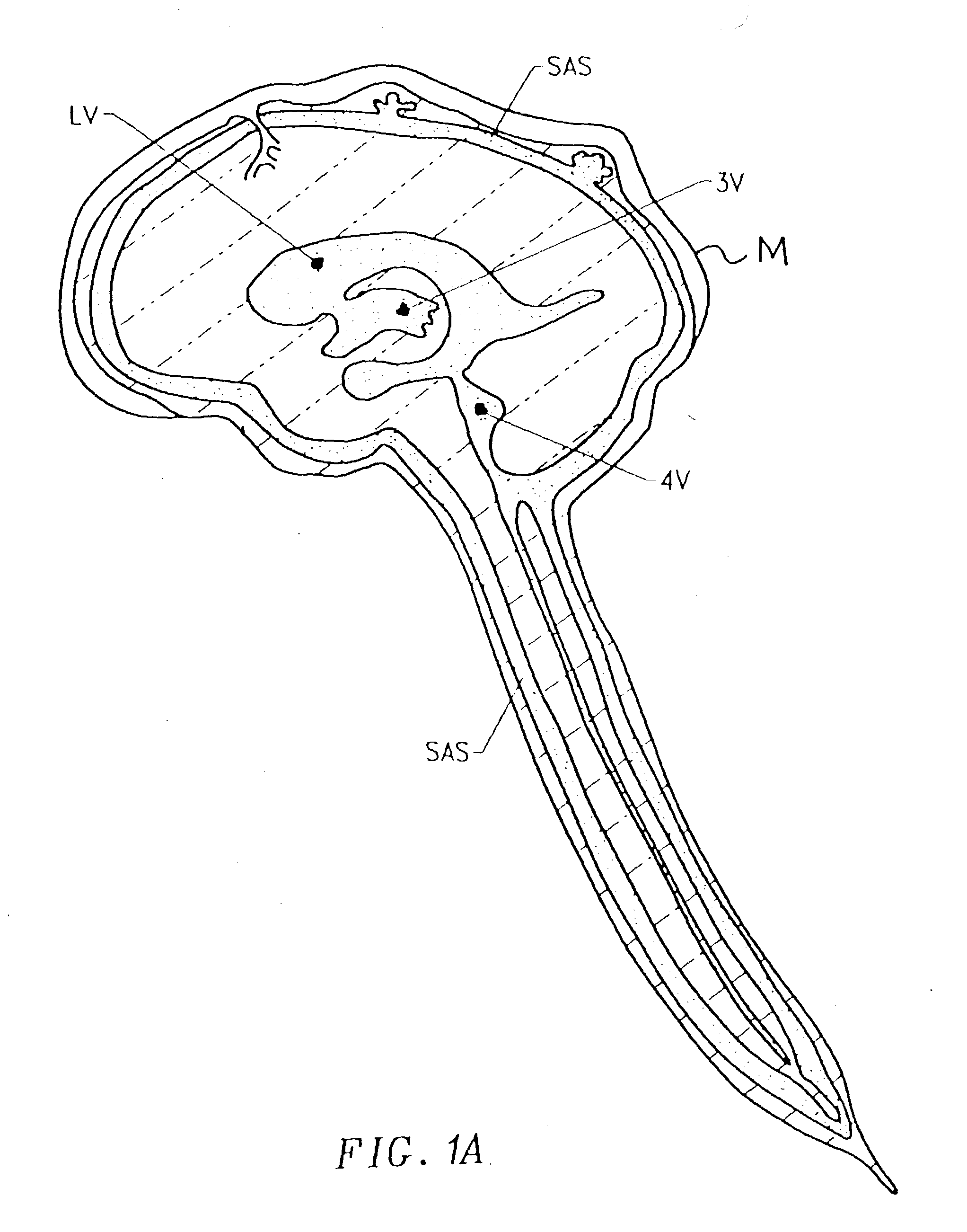

Systems and methods for flow detection and measurement in CSF shunts

InactiveUS20040068201A1Reduce concentrationIncrease productionWound drainsDiagnostic recording/measuringNormal intracranial pressureCsf shunt

Devices and methods for removing cerebrospinal fluid (CSF) from a CSF space of a patient at relatively constant flow rates for patients having normal intracranial pressures, e.g. patients not suffering from hydrocephalus. The devices and methods provide drainage paths which permit the removal of CSF at relatively low flow rates, usually below 0.2 ml / day, at normal intracranial pressures, e.g. an intracranial pressure between -170 mm of H2O in upright patients and 200 mm of H2O in reclining patients. The removal of CSF at relatively low, constant rates is particularly suitable for treating Alzheimer's disease and other conditions related to the presence of toxic and / or pathogenic substances in the CSF.

Owner:INTEGRA LIFESCI

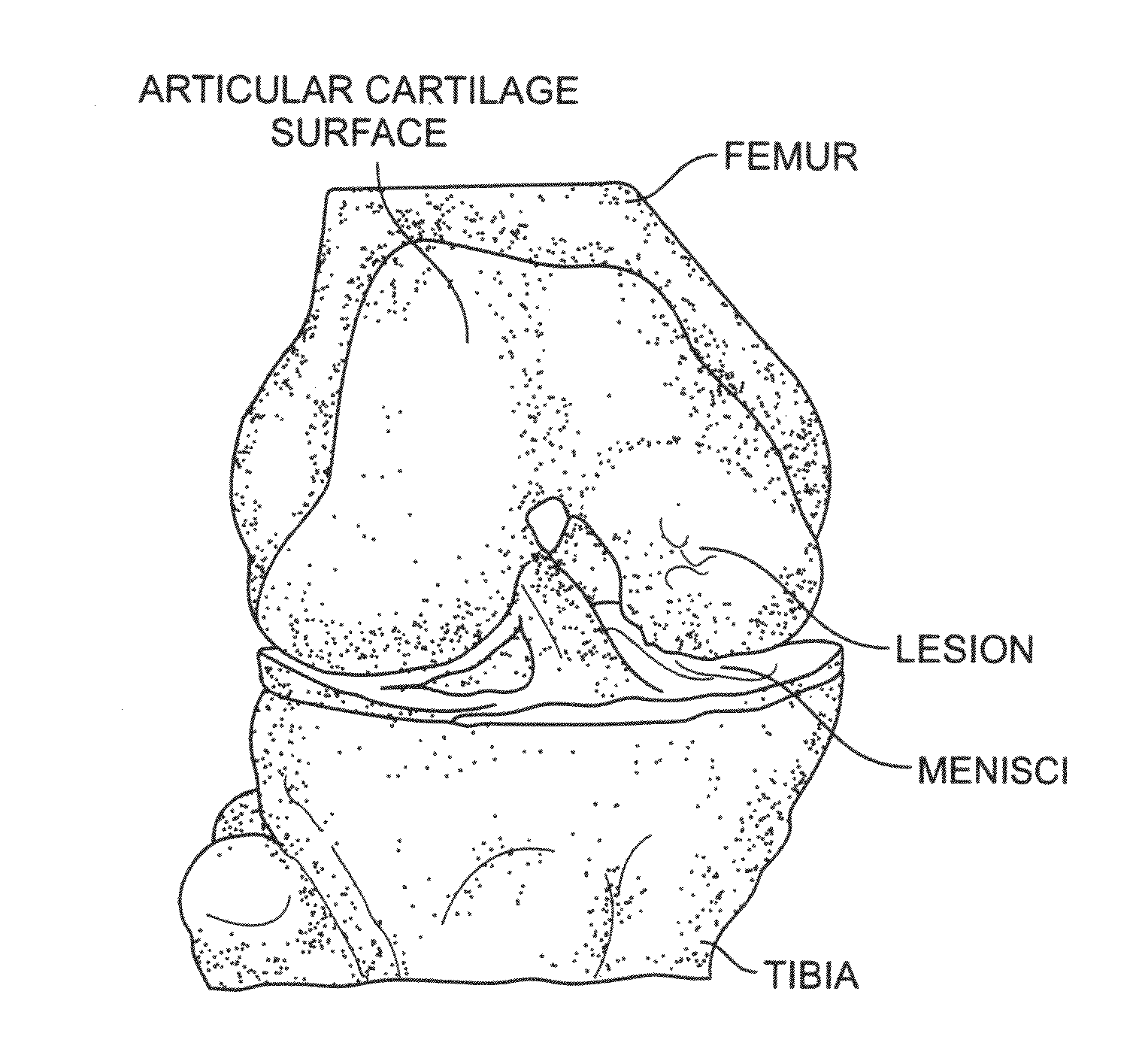

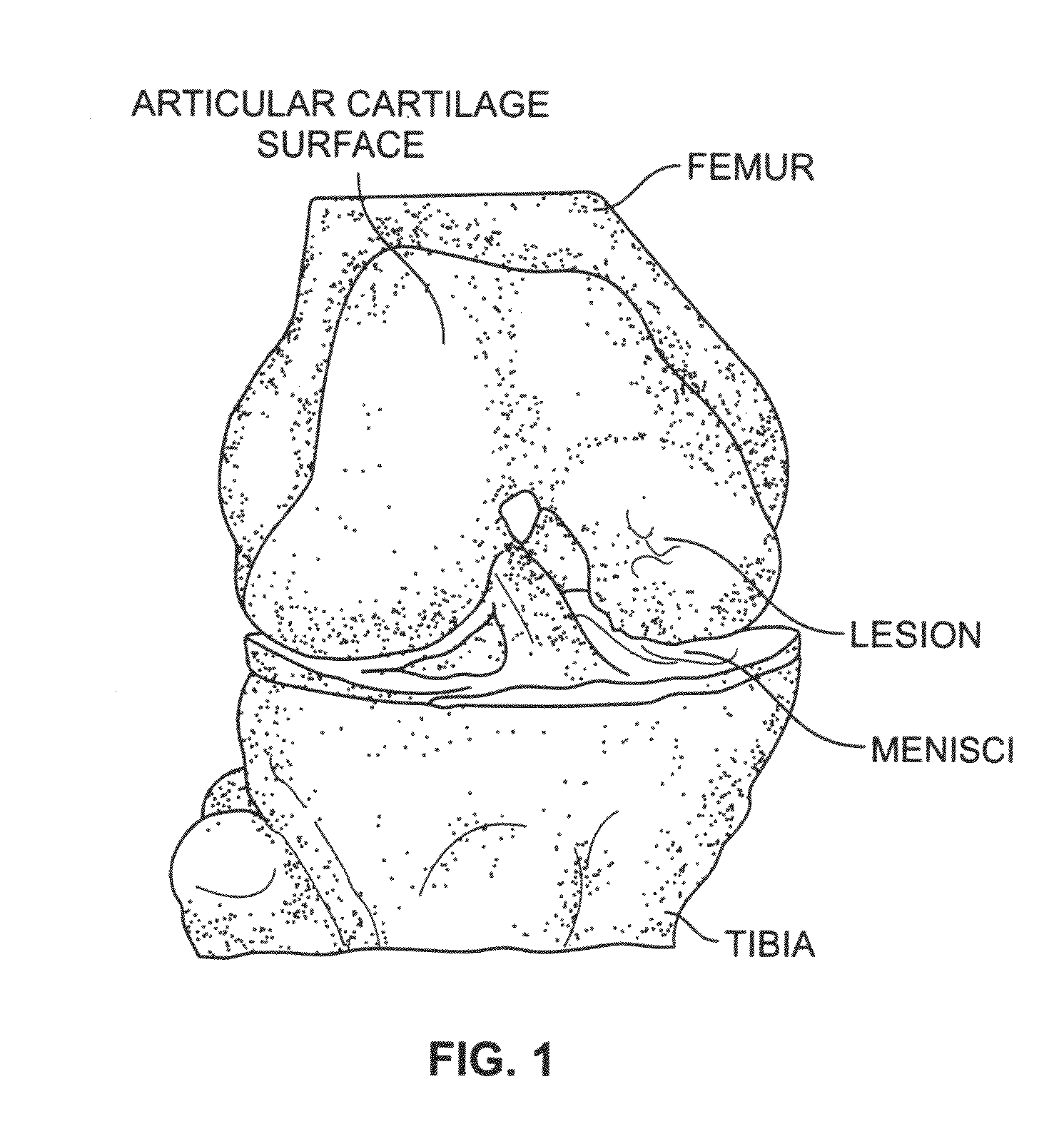

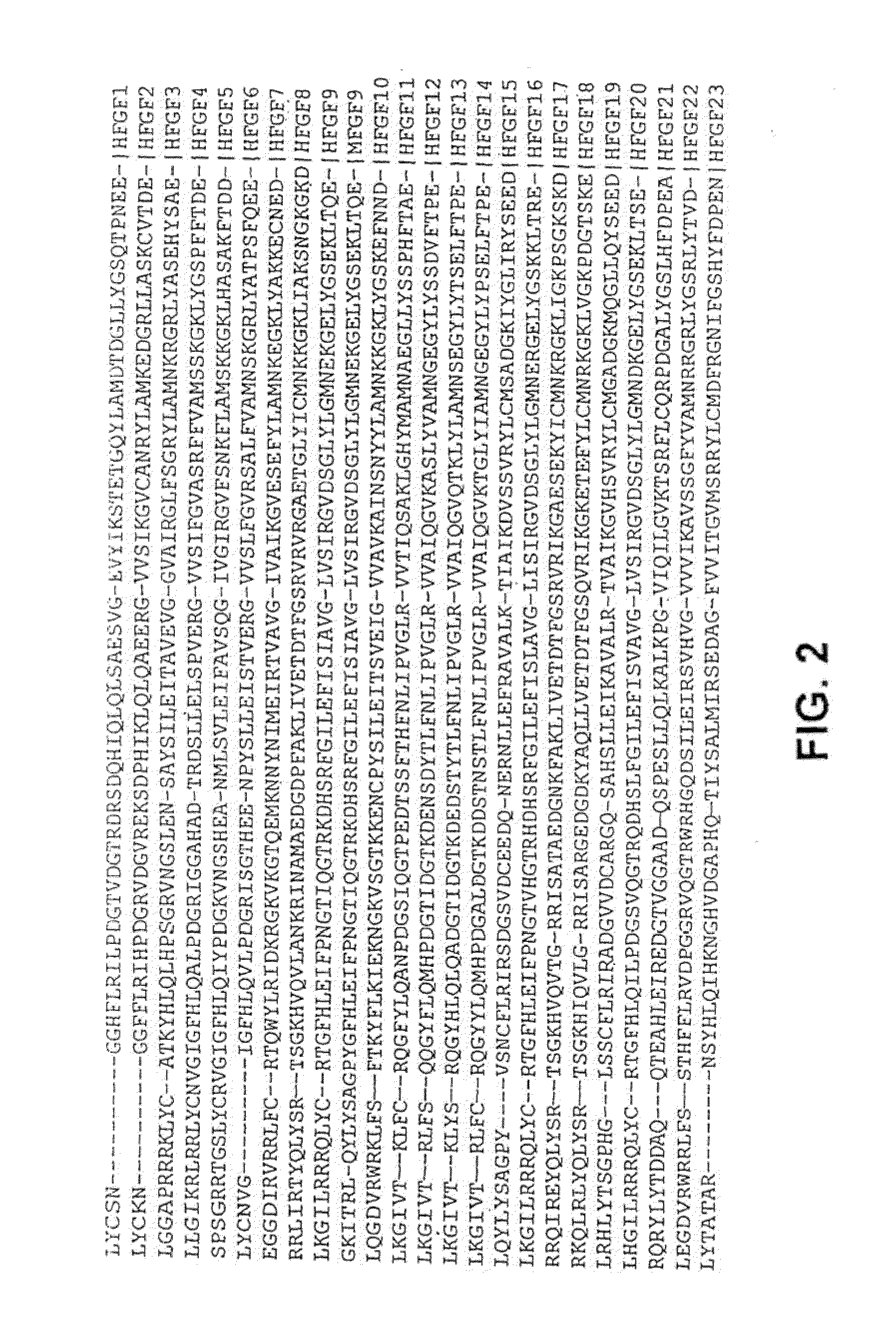

Cartilage particle tissue mixtures optionally combined with a cancellous construct

Mixtures, such as gels or pastes, comprising freeze-milled cartilage particles and exogenous growth factors are used for repairing chondral defects. Such mixtures may be applied to constructs comprising cancellous bone for implantation at the defect site. Suitable growth factors include variants of FGF-2, particularly variants that include a sole amino acid substitution for asparagine at amino acid 111 of the β8-β9 loop of the FGF-2 peptide. Such FGF-2 variants are released slowly and continuously at a constant rate from cartilage pastes. In other embodiments, the amino acid substituted for asparigine is glycine. Other variants that may be used include FGF-9 variants having truncated chains and a sole amino acid substitution in the β8-β9 loop of the FGF-9 peptide either for tryptophan at amino acid 144 or for asparagine at amino acid 143.

Owner:MUSCULOSKELETAL TRANSPLANT FOUND INC +1

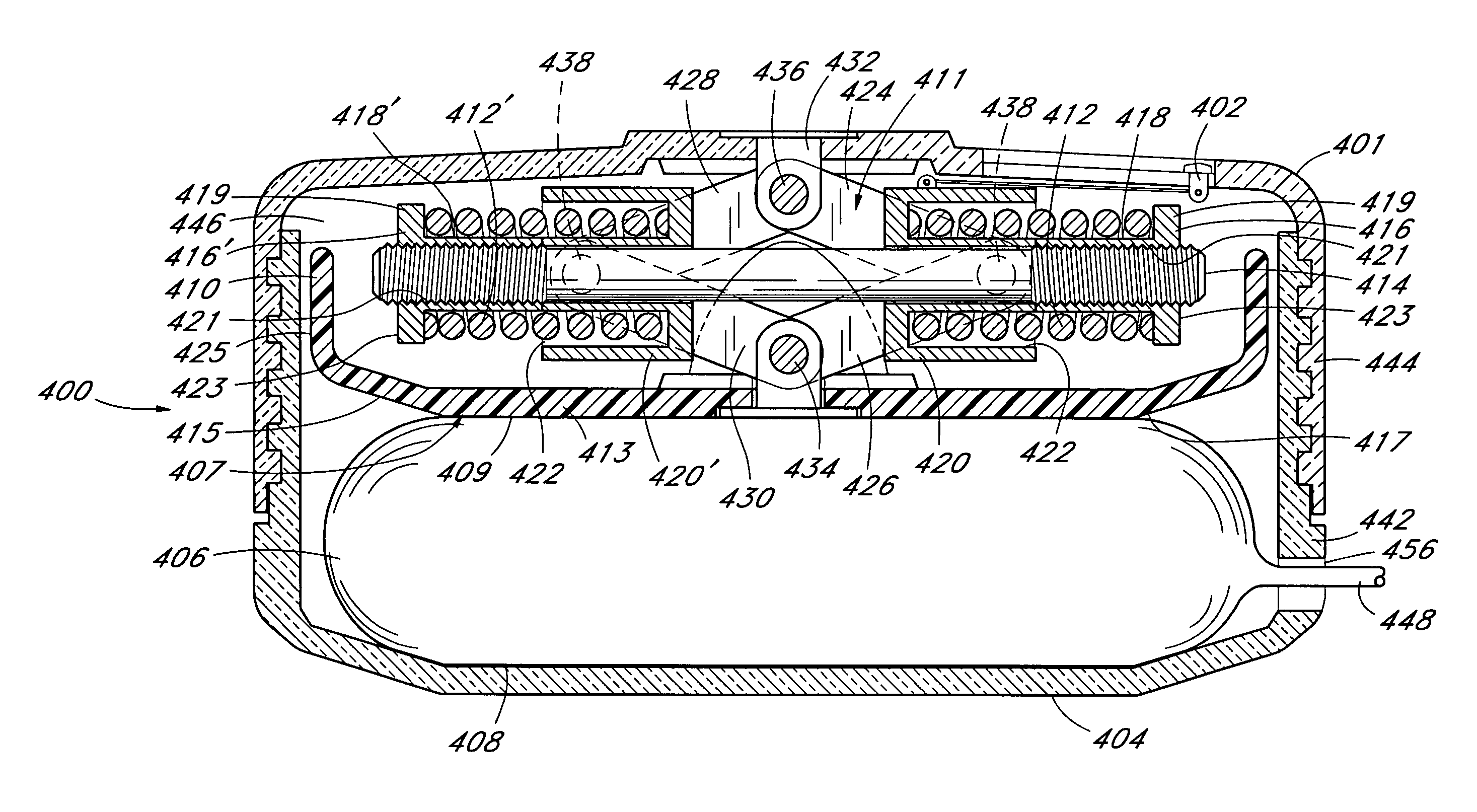

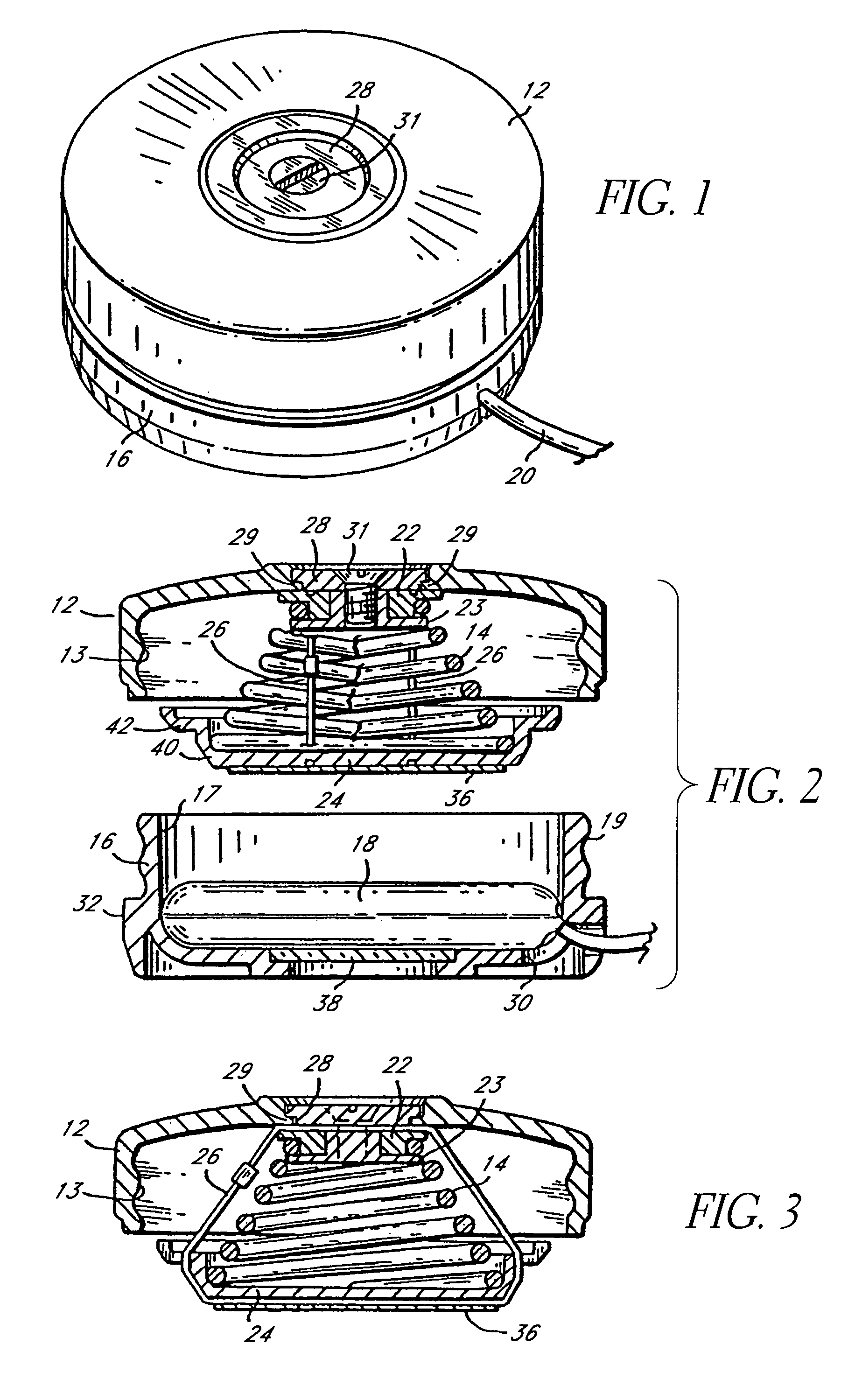

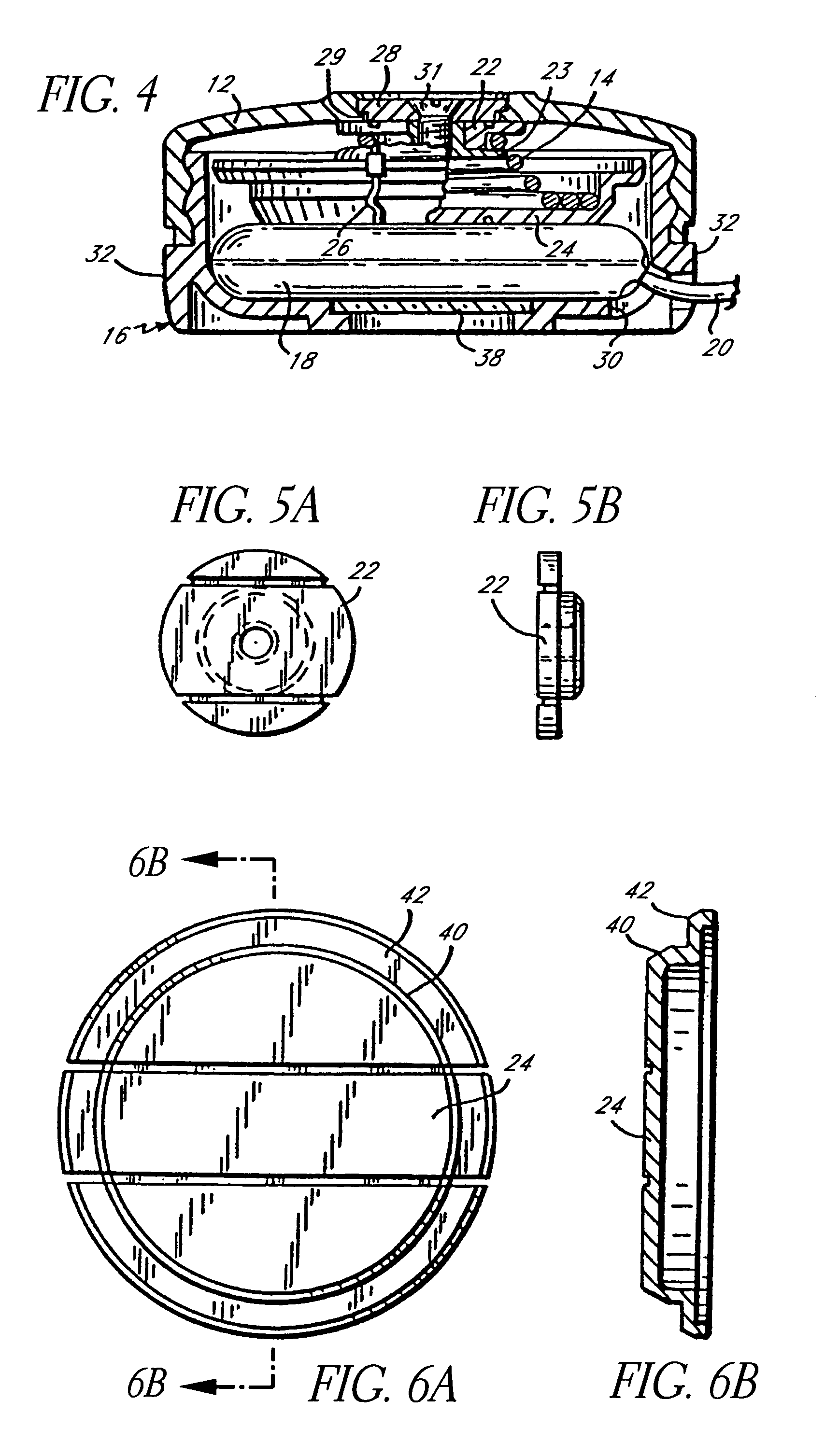

Platen pump

An infusion pump for expelling a fluid from a collapsible fluid reservoir to a patient. The pump includes a housing having a chamber therein for receiving the fluid reservoir. A first wall is provided on the housing for contacting the fluid reservoir, and a second wall is movable from a first position distanced from the first wall to form the chamber therebetween, and a second position relatively closer to the first wall. Advancing the movable wall from the first position to the second position expels fluid from the collapsible reservoir at a substantially constant rate by applying increasing force on the fluid reservoir through the dispensation cycle. Preferably, the first and second walls are provided with non-planar complementary surface configurations for contacting the collapsible reservoir. Retraction mechanisms for retracting the movable wall from the second position to the first position, and user readable indicium of the status of the dispensation cycle are also disclosed.

Owner:BMR MEDICAL LTDA

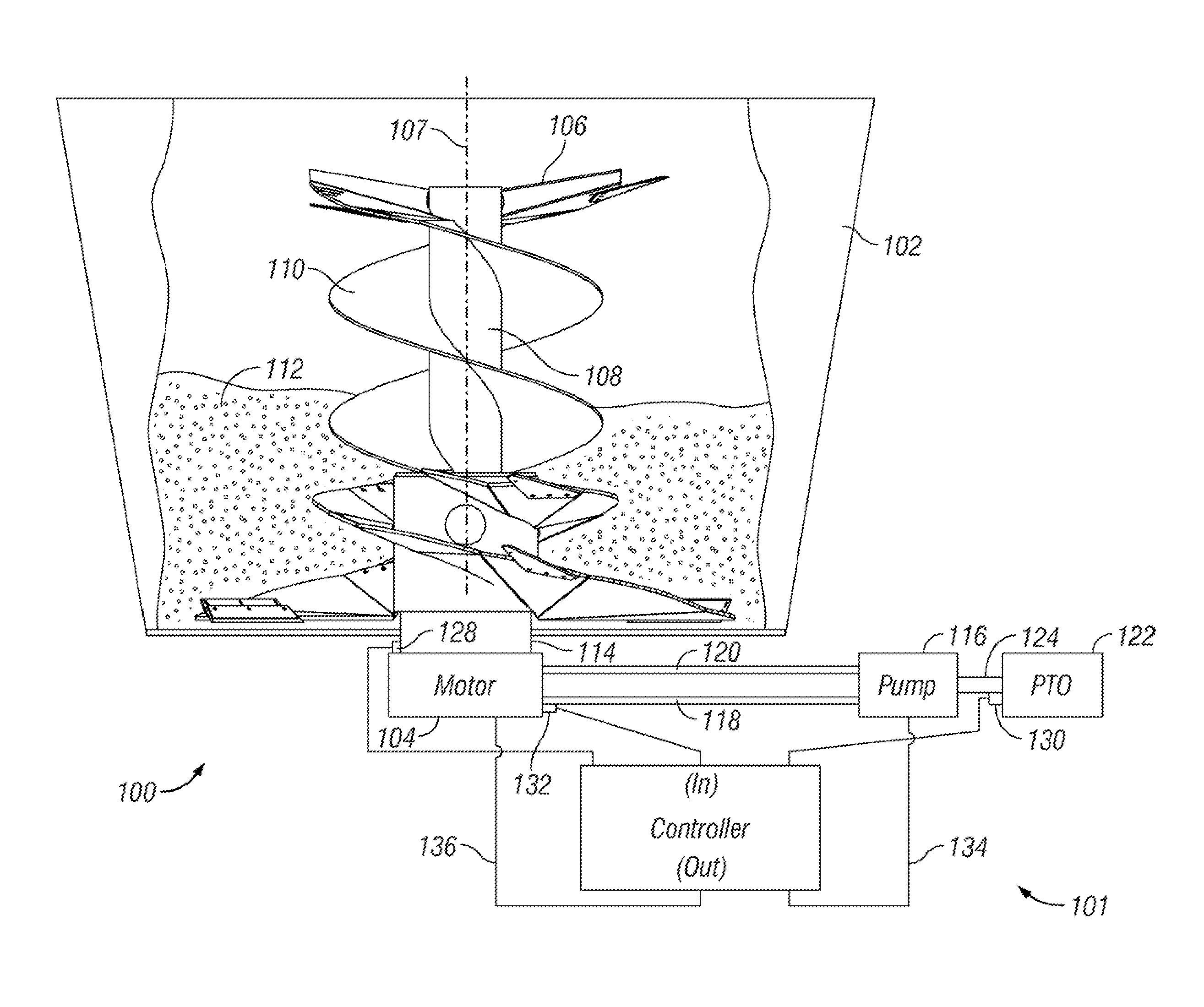

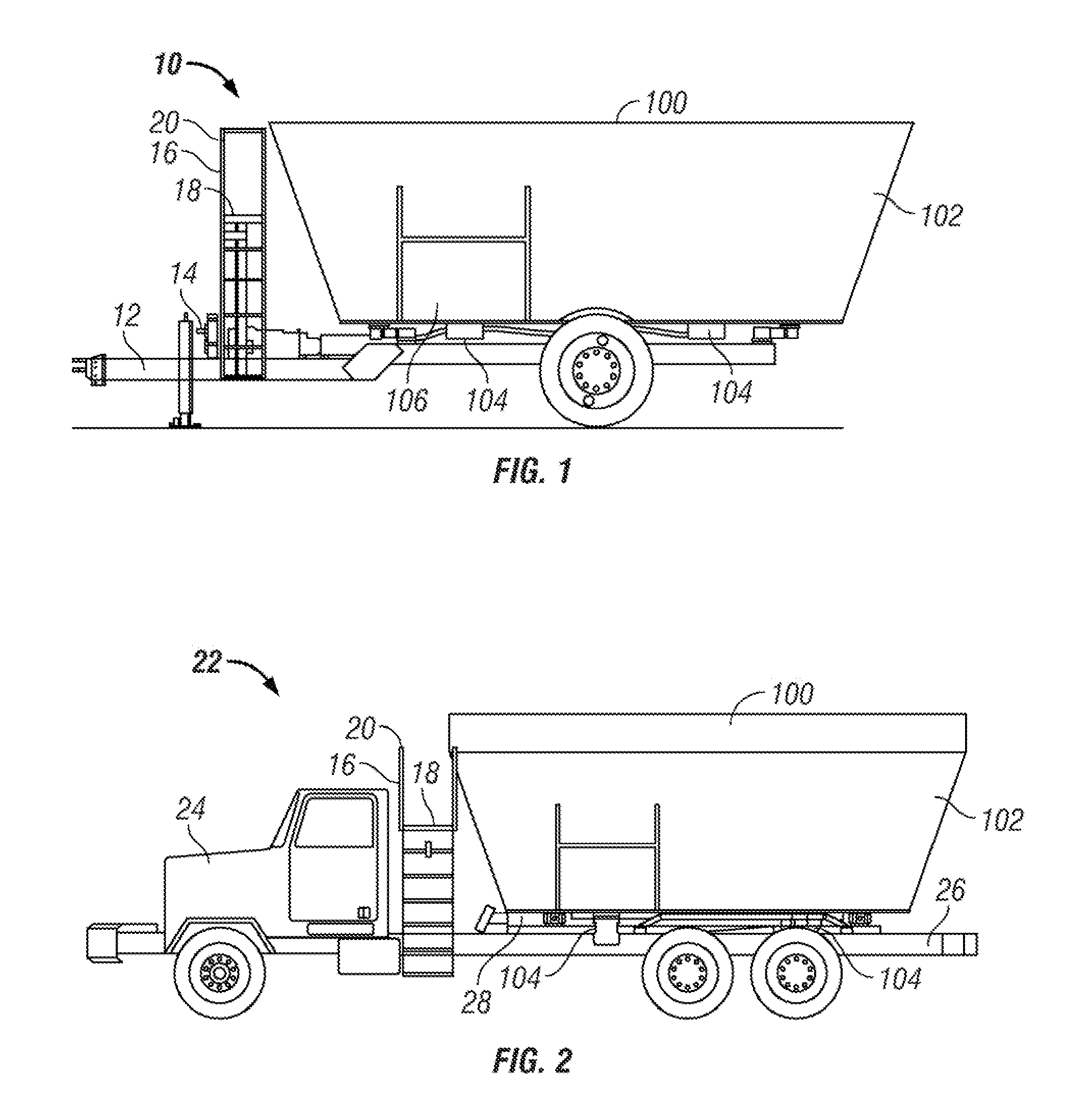

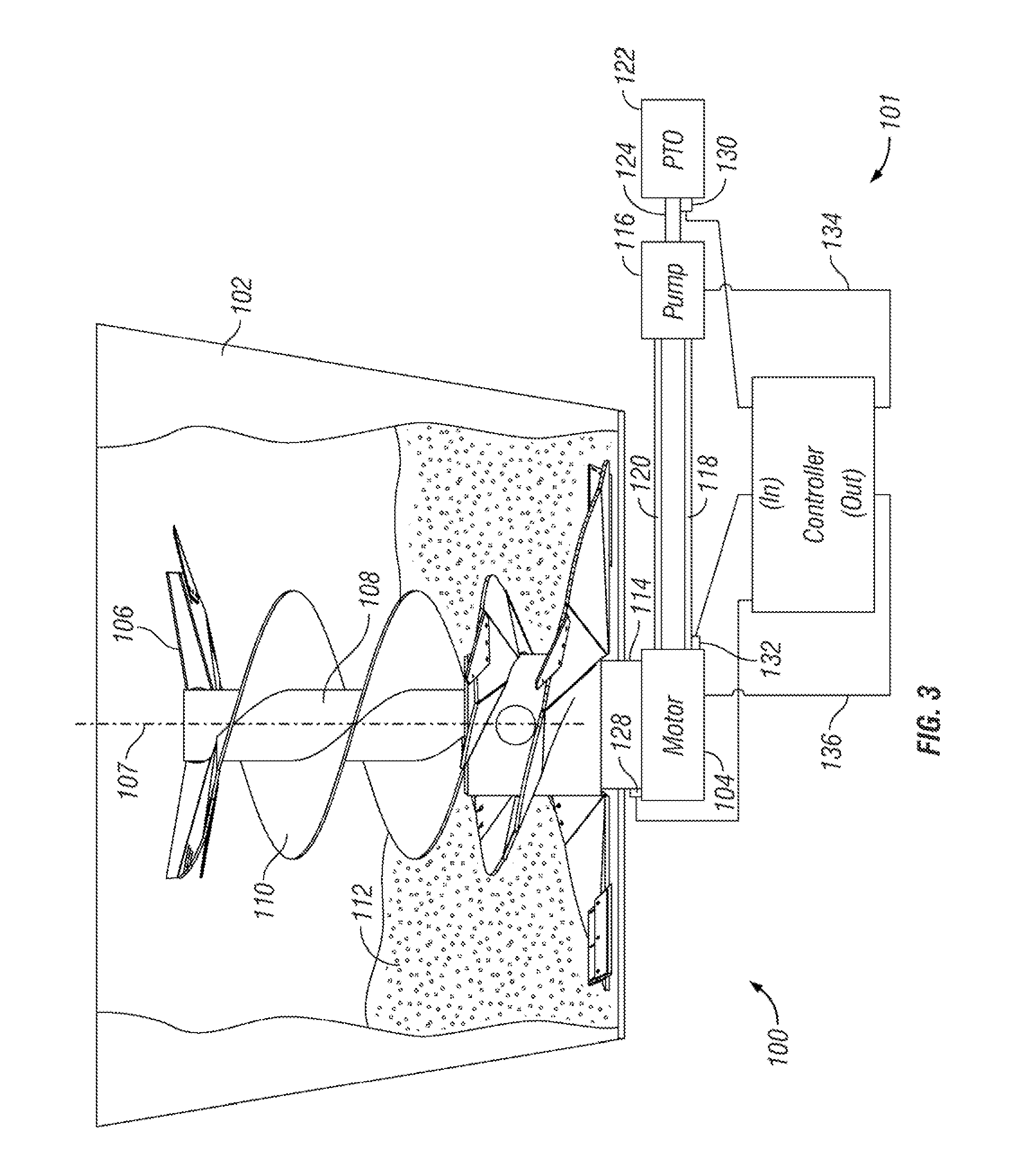

Agricultural mixer with drive system and method of using same

InactiveUS20120008457A1Easy to operateFlow mixersRotary stirring mixersRotation velocityControl theory

An agricultural mixer includes a hydraulic drive system. The mixer includes an automatic jam-resolving feature, whereby if an auger becomes jammed, the drive system will cause the auger to rotate in a reverse direction for a period of time to resolve the jam. The hydraulic drive system will maintain a speed of rotation of the auger at a relatively constant rate during mixing while choosing an efficient displacement setting for the hydraulic motor. The auger is maintained at a constant speed during a discharge mode by maintaining the motor in a maximum displacement setting. A clean-out mode is provided wherein the auger is rotated at a maximum speed to aid in cleaning out the last remaining feed mixture in the mixer.

Owner:ROTO MIX

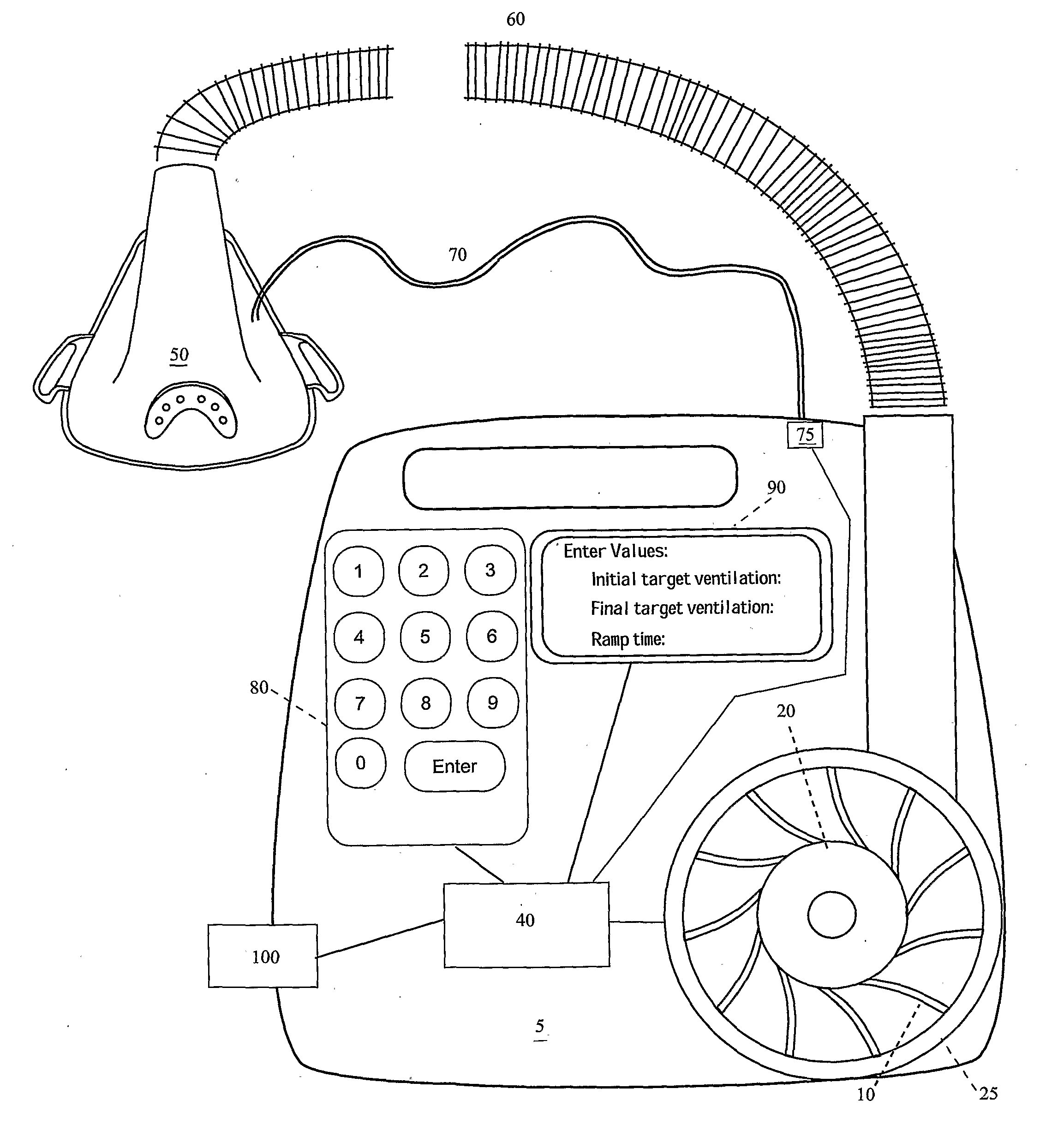

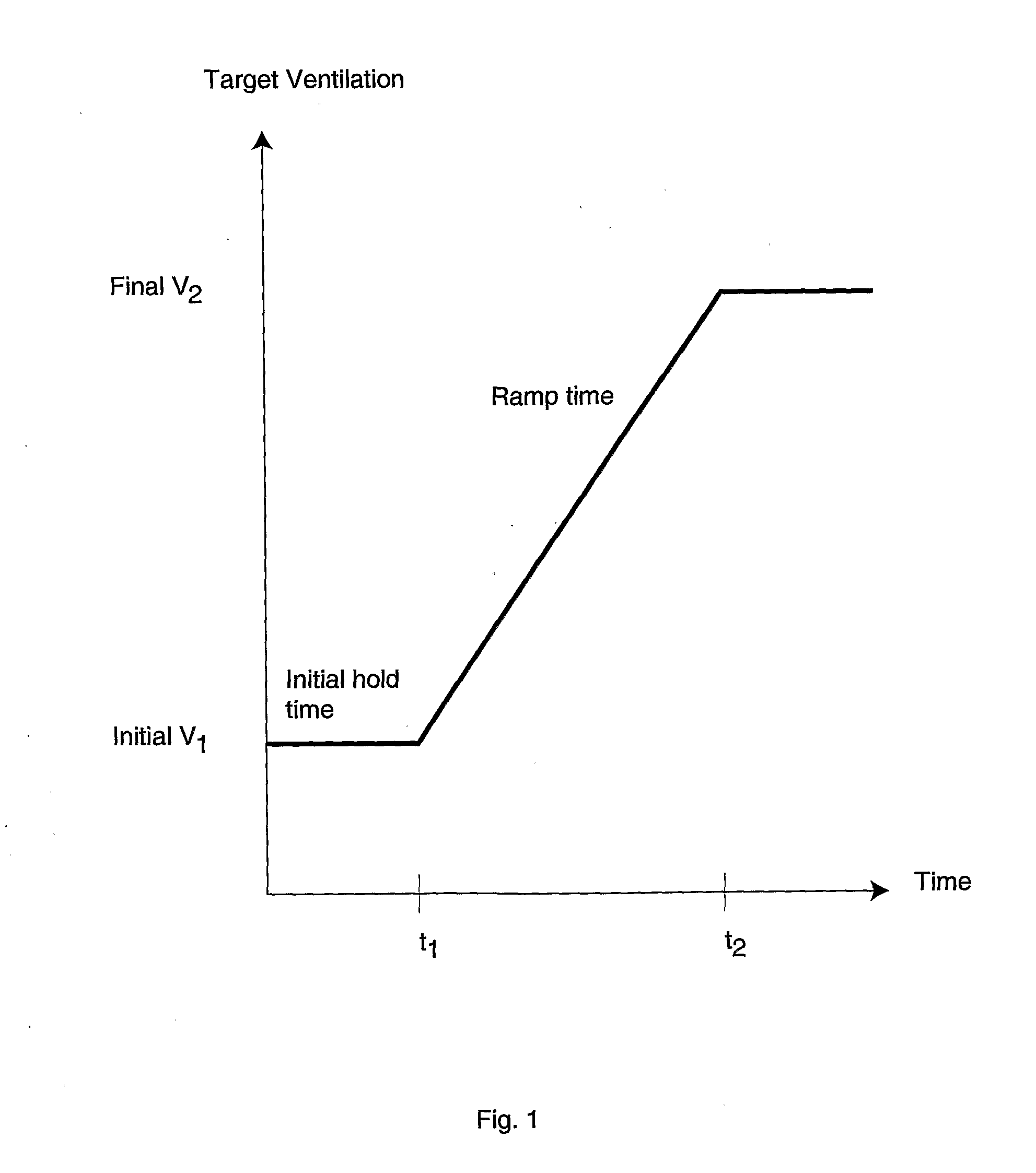

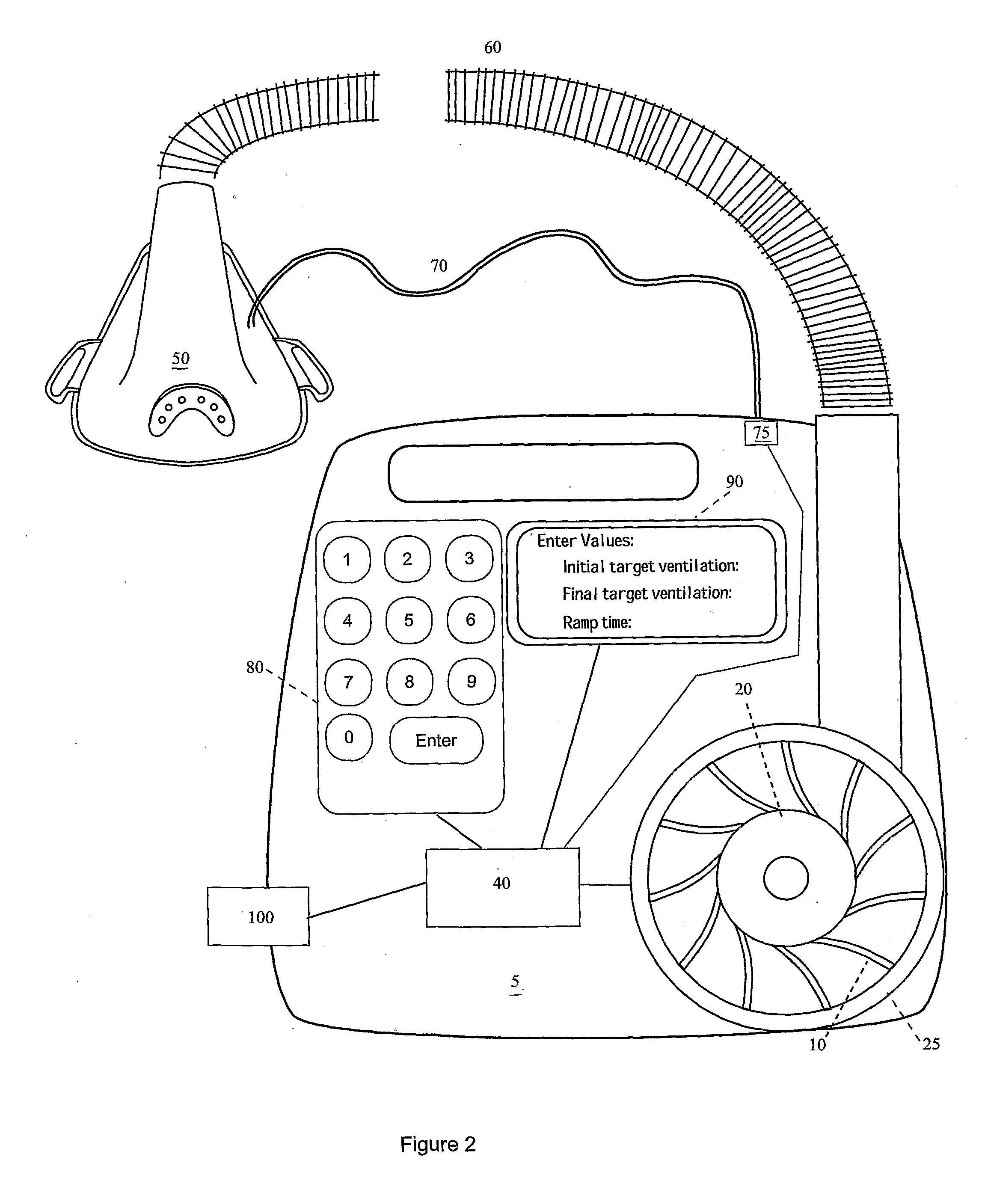

Adjustment of target ventilation in a servoventilator

ActiveUS20090013999A1Improve degradation rateRespiratorsOperating means/releasing devices for valvesVentilation volumeEngineering

A servoventilator control slowly changes the target ventilation over a period of time, according to a preprogrammed schedule adapted to be set by the physician. Preferably, the target ventilation stays constant at an initial target ventilation for an initial hold time, and then increases at a constant rate until it reaches a final target ventilation, whereupon it stays constant thereafter. If the pressure support level is too high, possibly indicating glottic or upper airway closure, the rate of increase of target ventilation may be lowered or the final target ventilation not reached.

Owner:RESMED LTD