Patents

Literature

738 results about "Hold time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The amount of time spent in a phone queue on hold (telephone) Hold Time, by M. Ward; See also. Holding time (disambiguation) This disambiguation page lists articles associated with the title Hold time. If an internal link led you here, you may wish to change the link to point directly to the intended ...

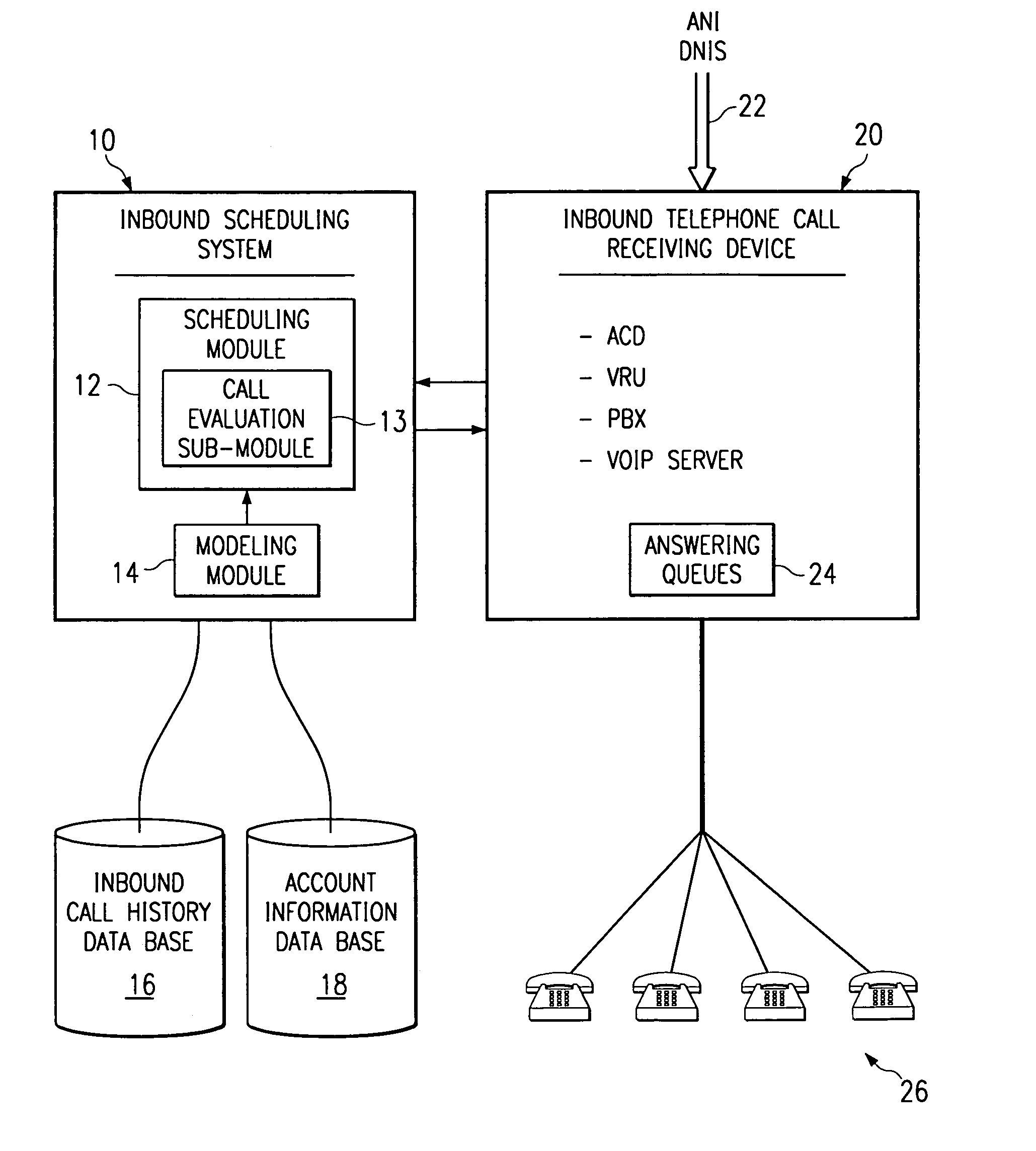

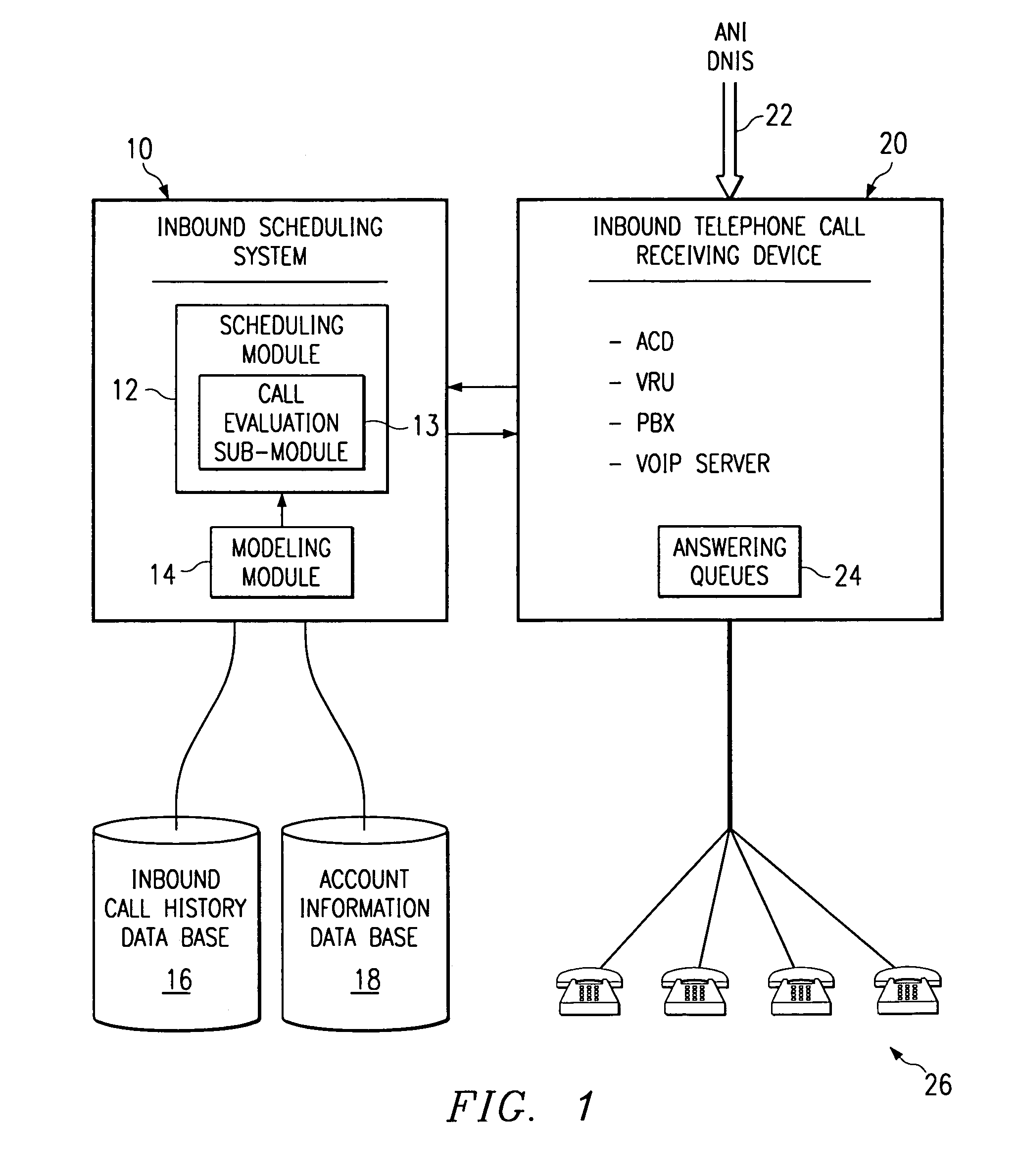

Method and system for scheduling inbound inquiries

InactiveUS6956941B1Accurate modelingMaximize useSpecial service for subscribersManual exchangesStatistical analysisRegression analysis

A method and system schedules inbound inquiries, such as inbound telephone calls, for response by agents in an order that is based in part on the forecasted outcome of the inbound inquiries. A scheduling module applies inquiry information to a model to forecast the outcome of an inbound inquiry. The forecasted outcome is used to set a priority value for ordering the inquiry. The priority value may be determined by solving a constrained optimization problem that seeks to maximize an objective function, such as maximizing an agent's productivity to produce sales or to minimize inbound call attrition. The inbound call may be placed on a virtual hold or be responded to on a real-time basis based on the inbound inquiry's priority value. A modeling module generates models that forecast inquiry outcomes based on a history and inquiry information. Statistical analysis such as regression analysis determines the model with the outcome related to the nature of the inquiry. Forecasted outcomes are based on the goal of the inbound calls and include factors such as probability an inbound caller will hang up, probability that an inbound caller will alter a business relationship based on hold time, probability that an inbound caller will make a purchase, and the relative probable reward of responding to an inbound call.

Owner:UNWIRED BROADBAND INC

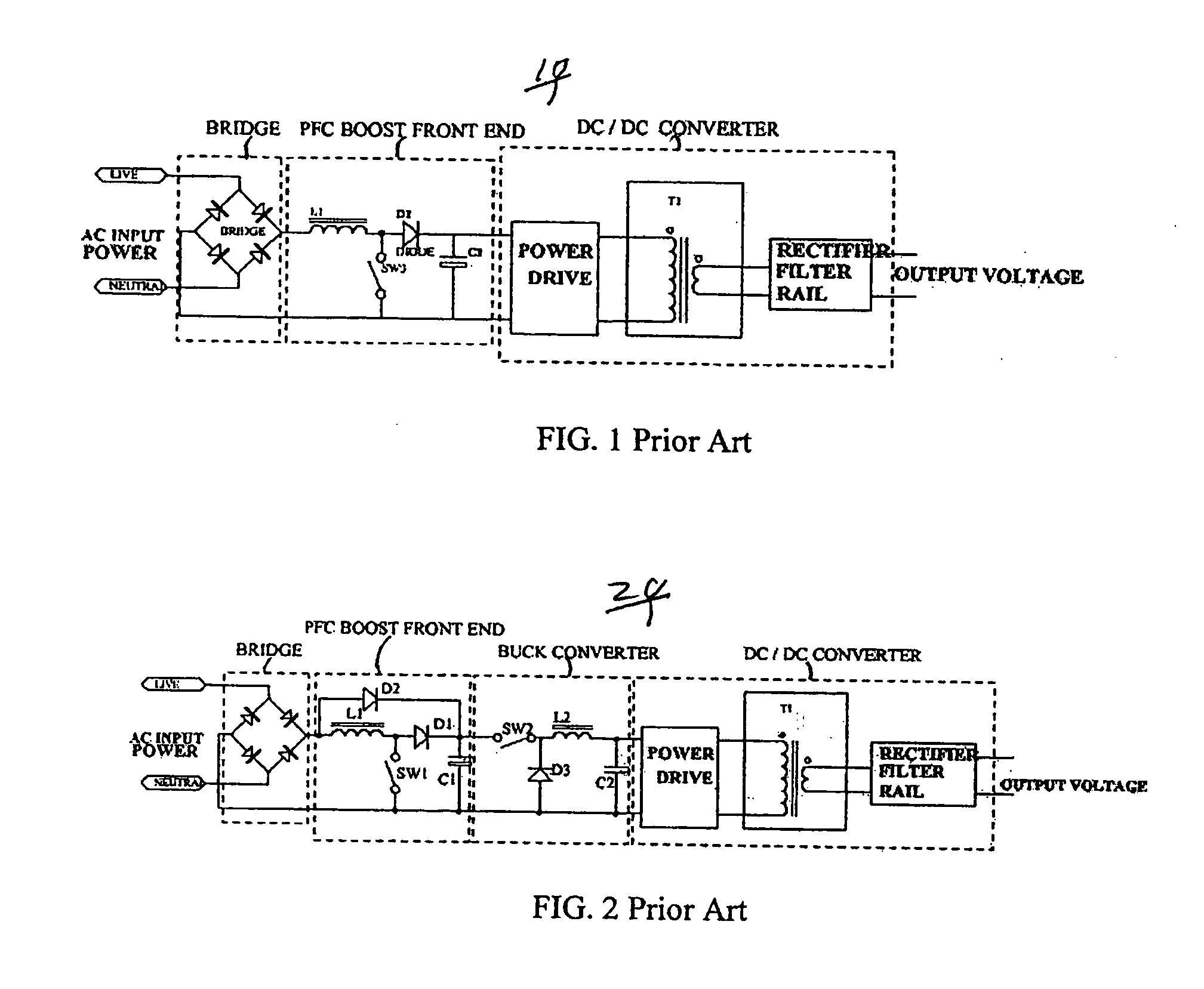

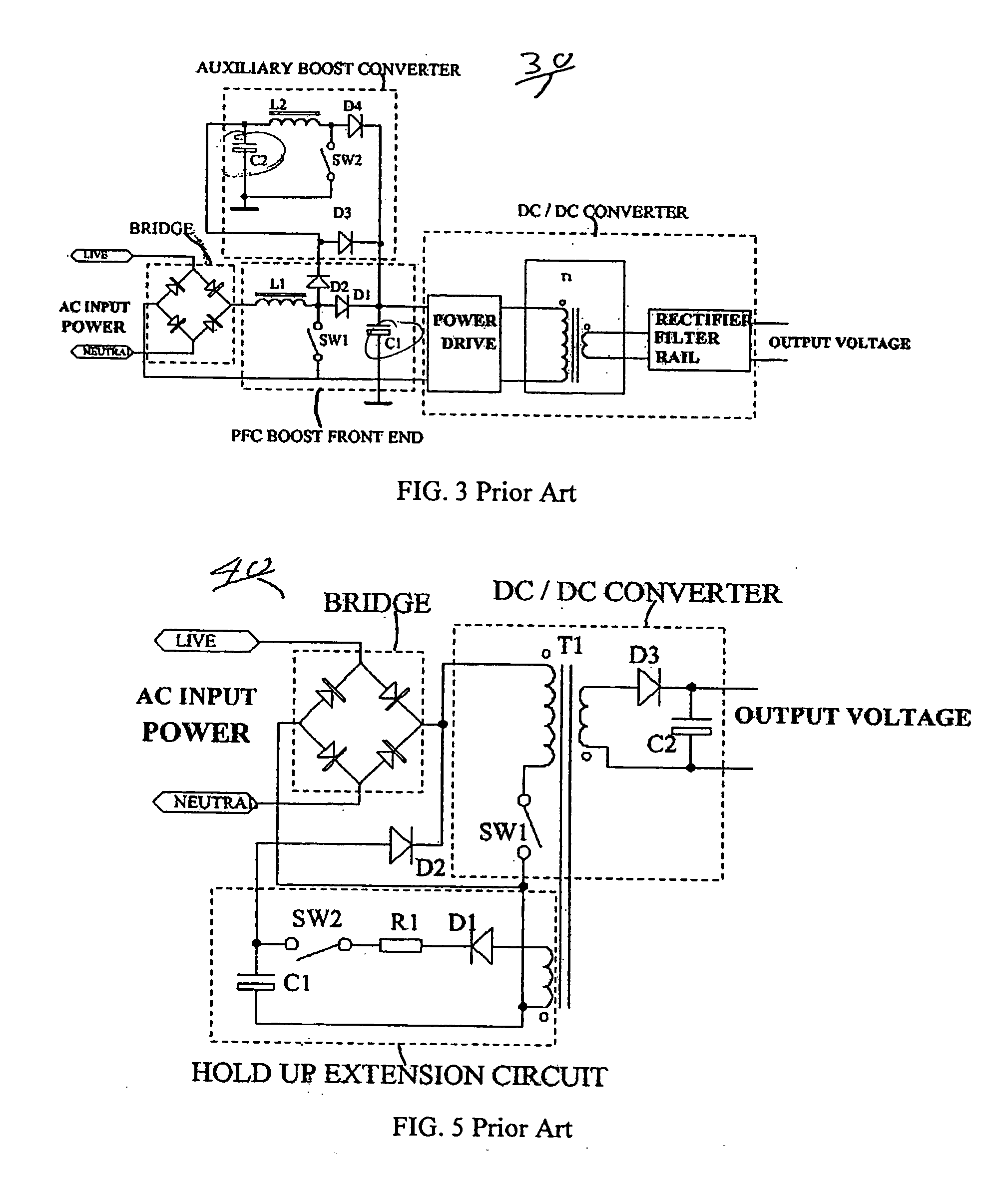

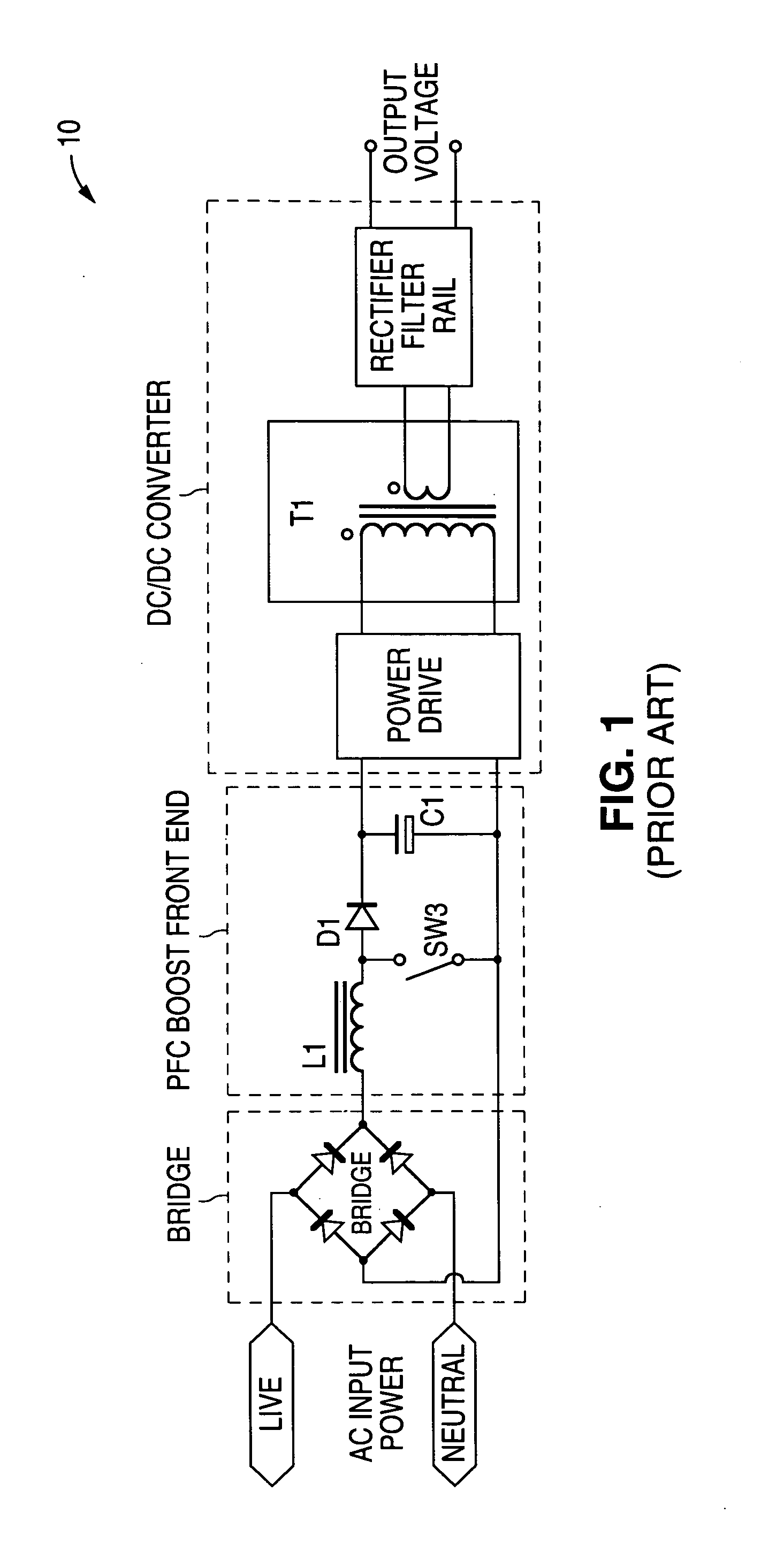

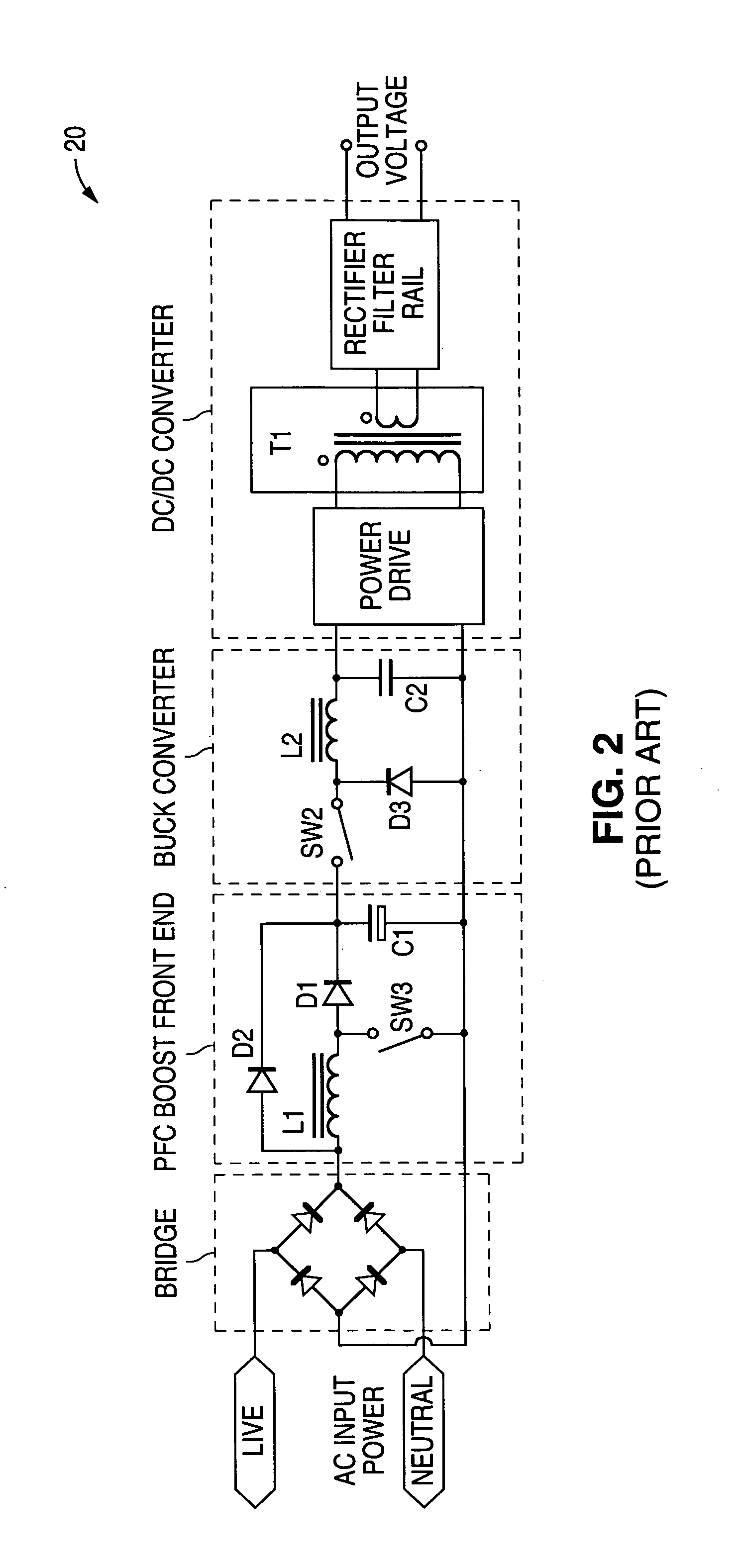

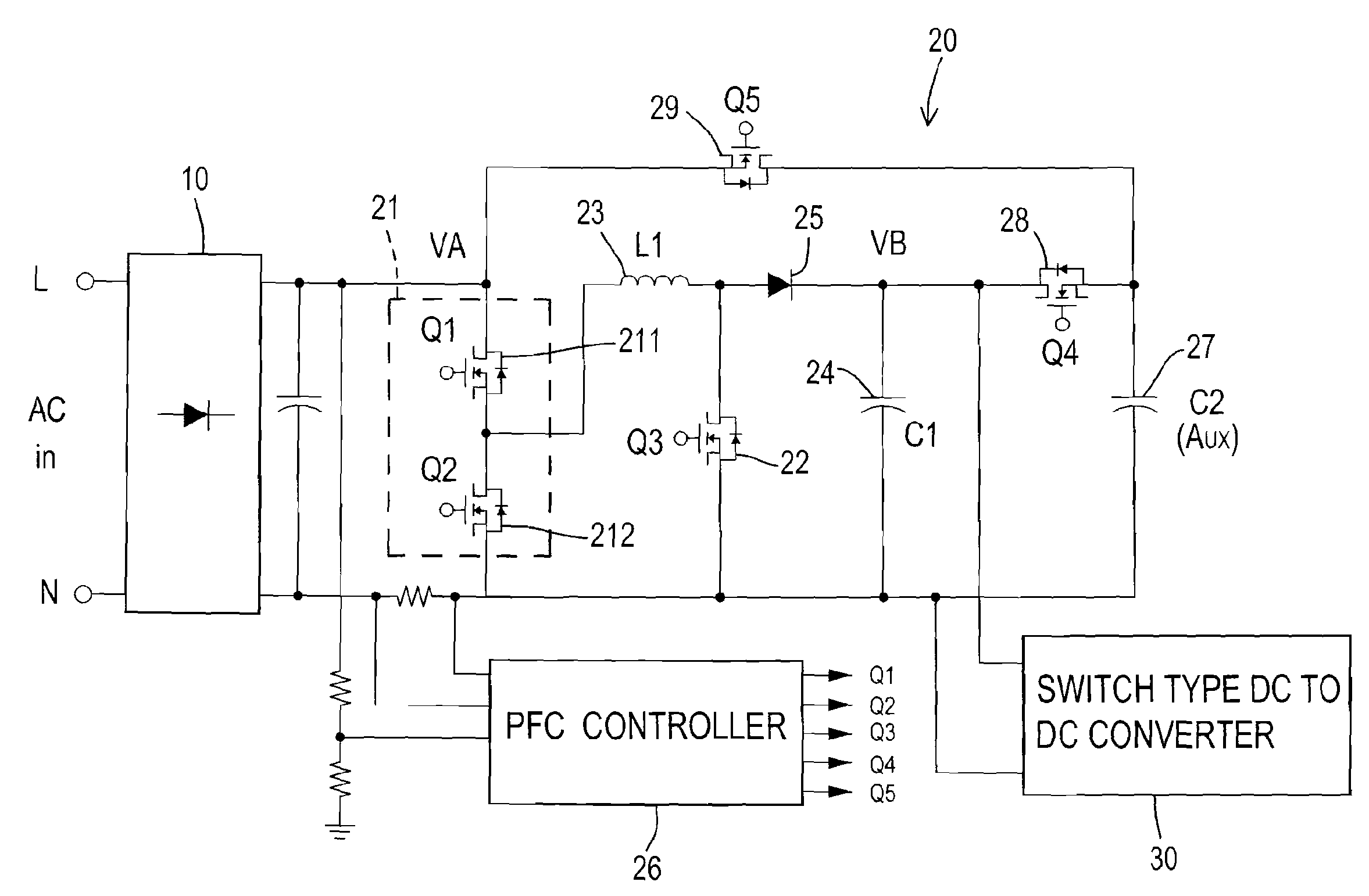

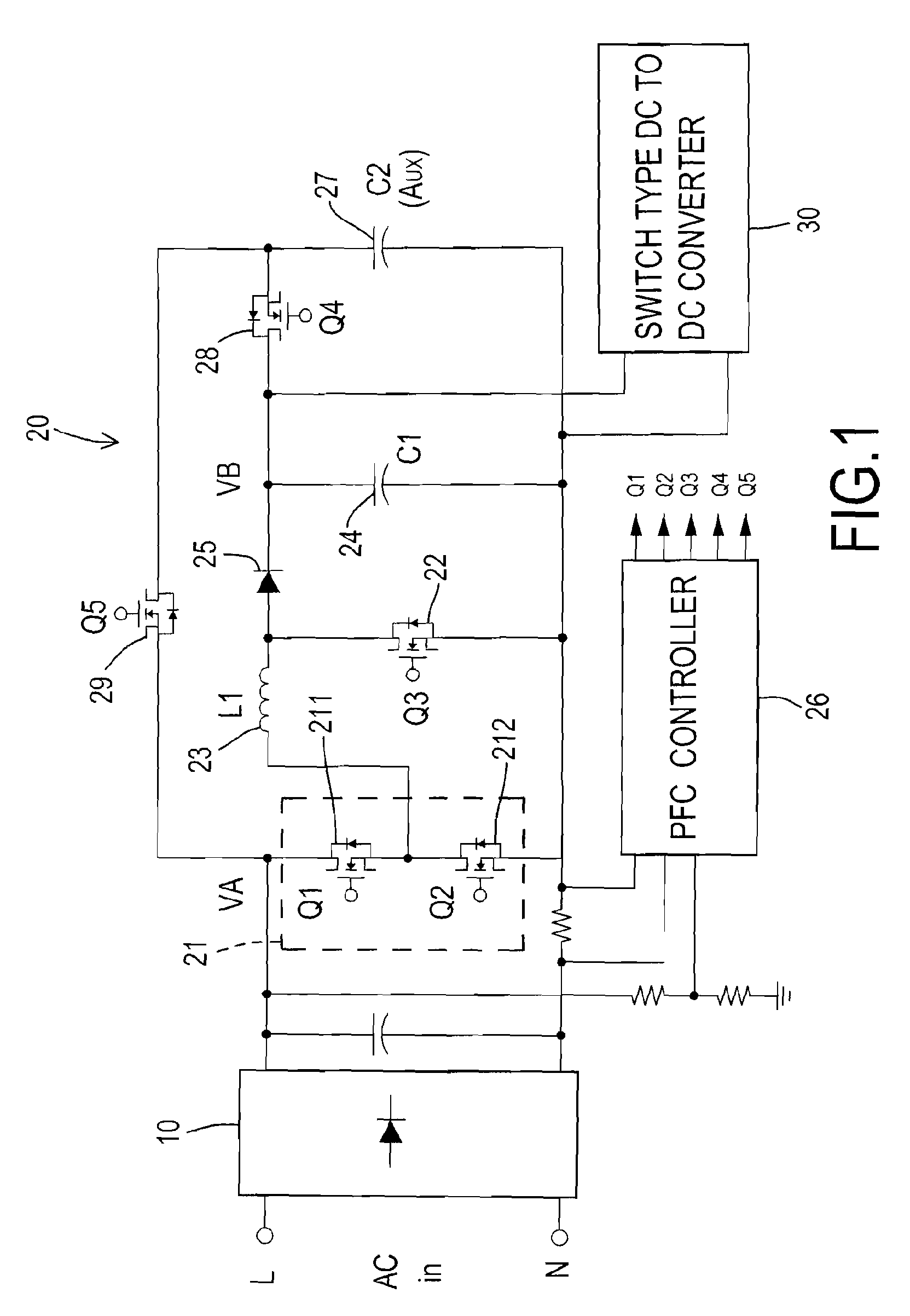

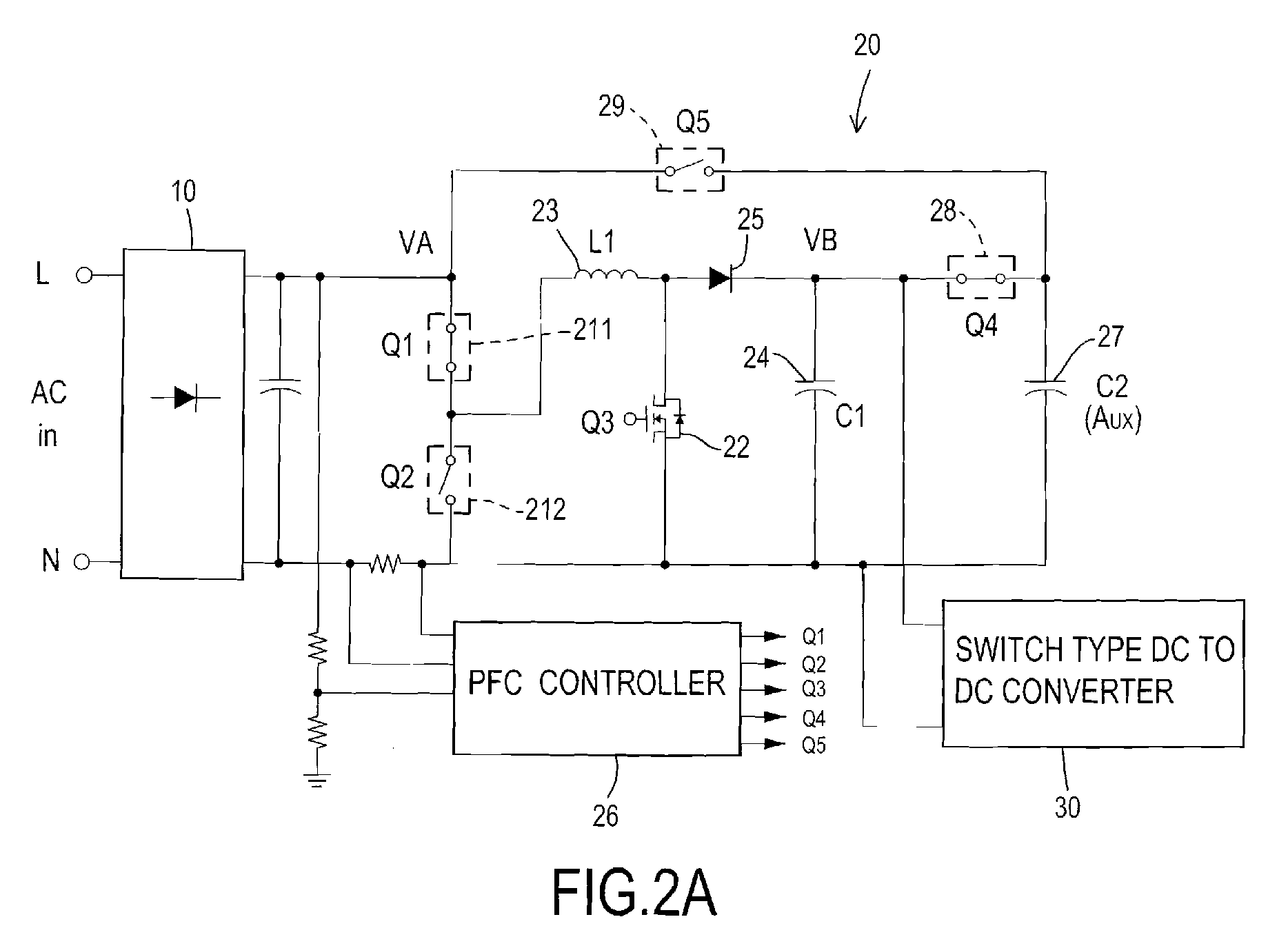

Circuit for maintaining hold-up time while reducing bulk capacitor size and improving efficiency in a power supply

InactiveUS20050030772A1Improve efficiencyReducing voltage operating rangeEfficient power electronics conversionApparatus with intermediate ac conversionCapacitanceDc dc converter

Owner:ASTEC INT LTD

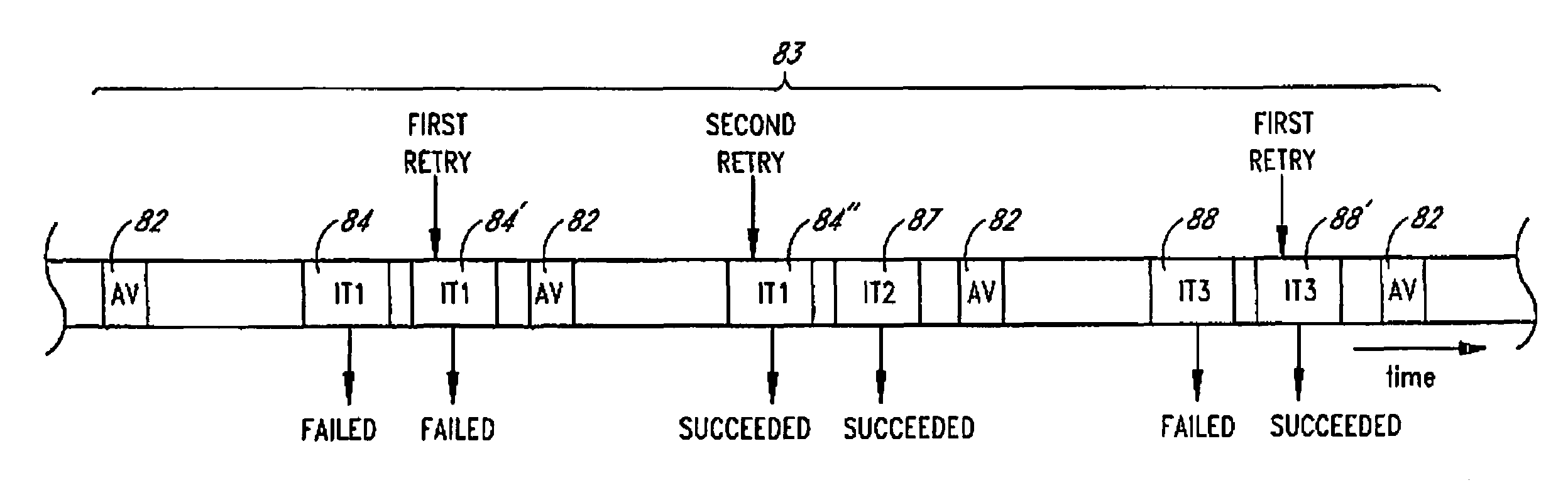

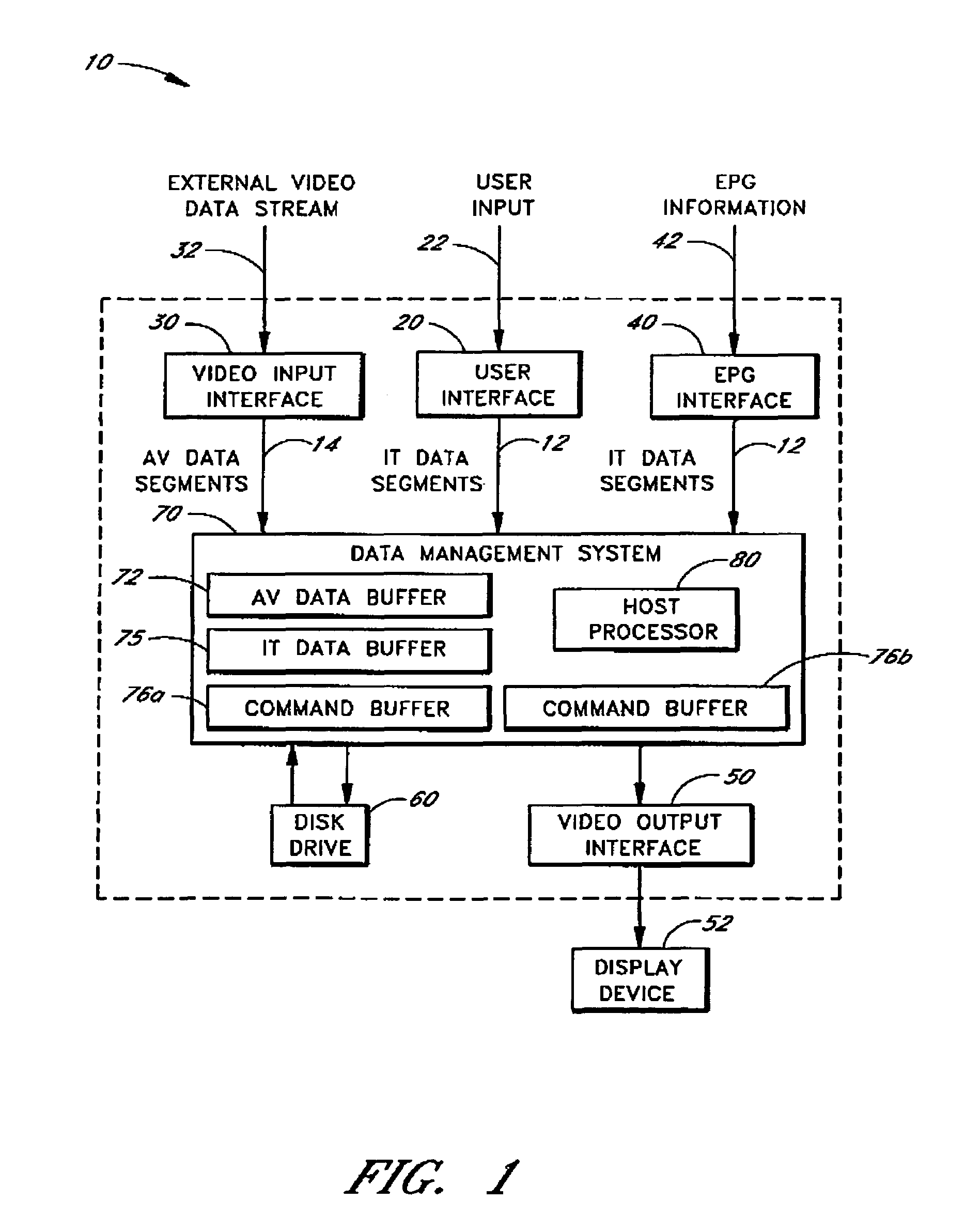

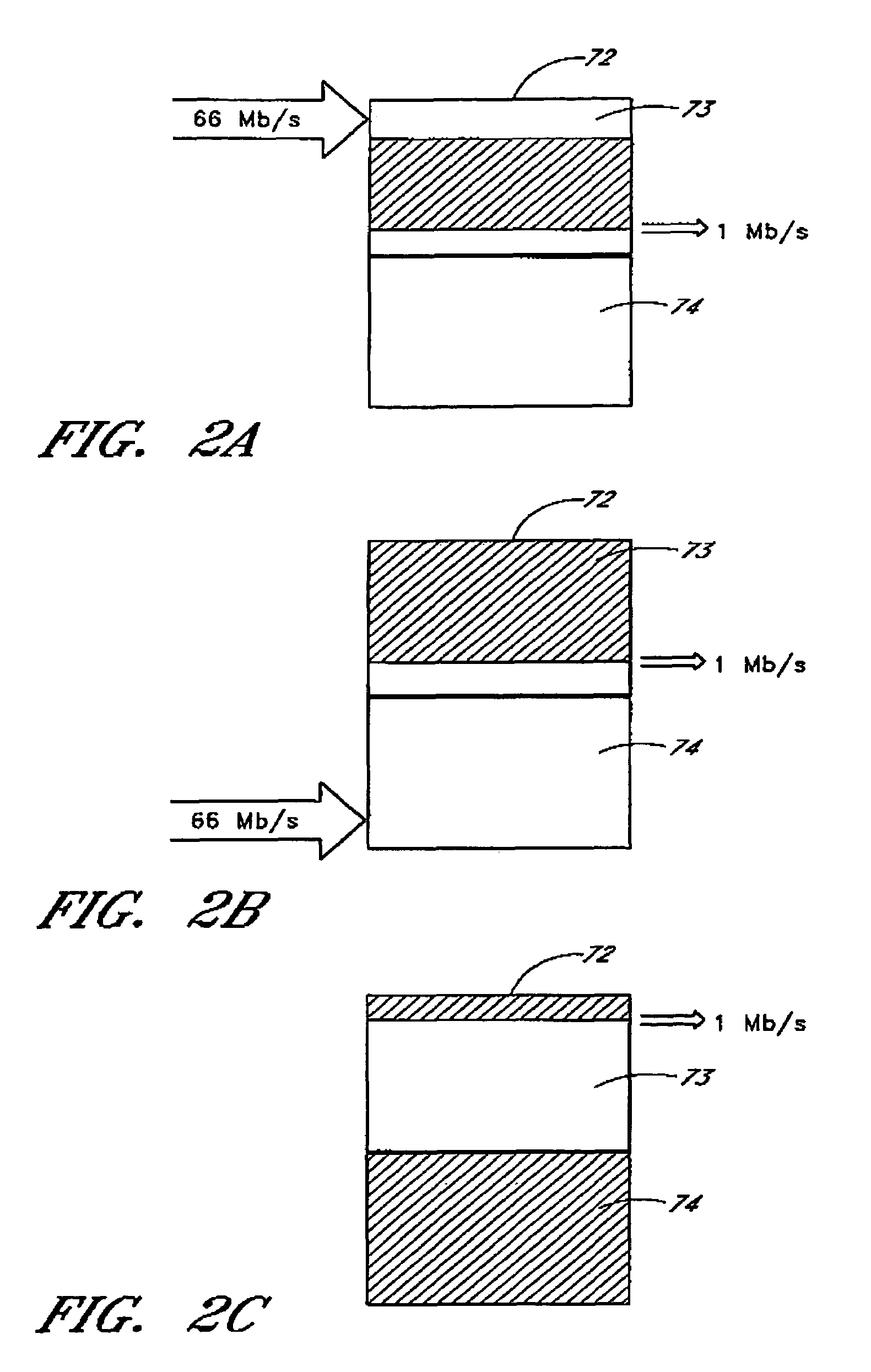

Video recording system utilizing storage redundancy to transfer non-time-critical, error-intolerant data segments while transferring time-critical, error-tolerant streaming data segments at a required data transfer rate

InactiveUS7133600B1Maintaining data transfer bandwidthEasy transferTelevision system detailsRecording carrier detailsStreaming dataData segment

The present invention may be regarded as a video recording system and method of transferring a non-time-critical, error-intolerant data segment stored on a disk drive, which is responsive to a set of data transfer commands generated by a host processor and which is operating in a mode optimized for transferring time-critical, error-tolerant streaming data segments stored or to be stored on the disk drive. The method includes sending a sequence of data transfer commands generated by the host processor to the disk drive to transfer a respective sequence of time-critical, error-tolerant streaming data segments at a required data transfer rate. The method further includes selectively interposing a first data transfer command into the sequence of data transfer commands, the first data transfer command initiating a first transfer of the non-time-critical, error-intolerant data segment from a first storage location. The method further includes transmitting a data transfer error signal generated by the disk drive to the host processor, the data transfer error signal having a state that indicates whether any data transfer errors have occurred with respect to the first transfer of the non-time-critical, error-intolerant data segment. The method further includes selectively interposing a second data transfer command into the sequence of data transfer commands, the second data transfer command initiating a second transfer of the non-time-critical, error-intolerant data segment from a second storage location, thereby utilizing storage redundancy to achieve an accuracy required for the non-time-critical, error-intolerant data segment while maintaining the required data transfer rate of the sequence of time-critical, error-tolerant data segments.

Owner:KEEN PERSONAL MEDIA +1

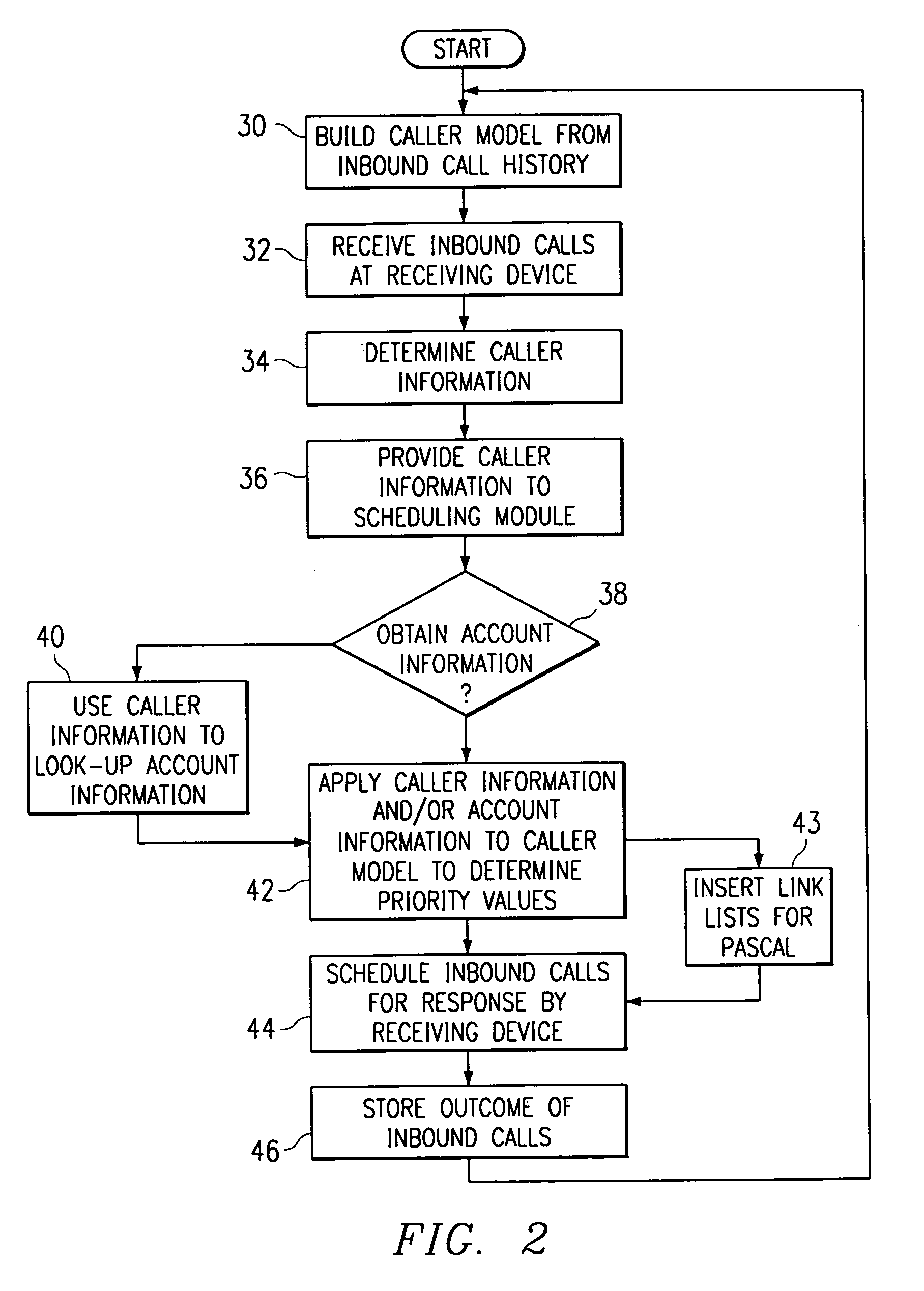

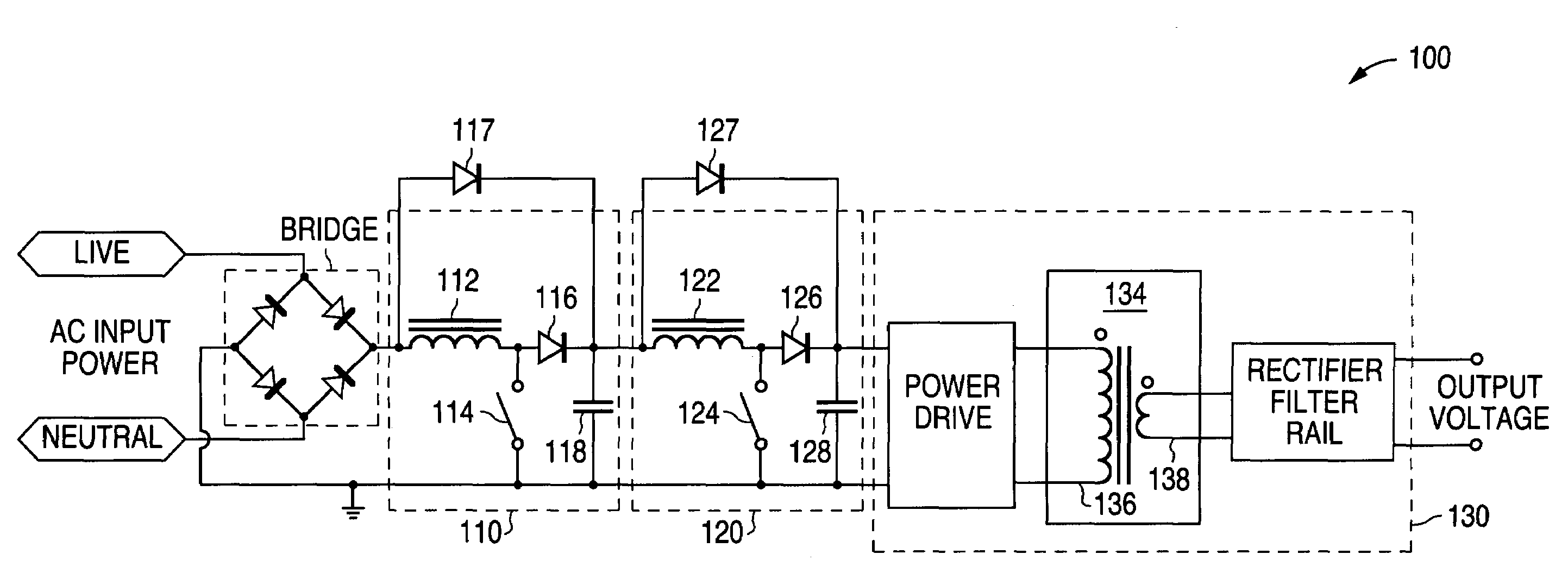

Circuit for maintaining hold-up time while reducing bulk capacitor size and improving efficiency in a power supply

InactiveUS7061212B2Improve efficiencyReduces peak current and voltage stressEfficient power electronics conversionApparatus with intermediate ac conversionCapacitanceDc dc converter

A circuit that utilizes most of the energy stored in the bulk capacitor of an AC to DC or DC to DC converter power supply by providing an intermediate converter between a first stage boost converter and a DC-DC converter. When the bulk voltage starts to fall during the hold-up time, the intermediate converter boosts the falling voltage to maintain the regulated DC input to the DC to DC converter while reducing the operating range and increasing the operating duty cycle, so as to increase efficiency, reduce peak current and voltage stresses. The circuit also reduces the size of the output filter components and reduces the size of the bulk capacitance by up to half.

Owner:ASTEC INT LTD

Method and device for clearing malicious power consumption applications, and user terminal

InactiveCN103324519APrecise positioningAccurate detectionMultiprogramming arrangementsPower supply for data processingEngineeringComputer terminal

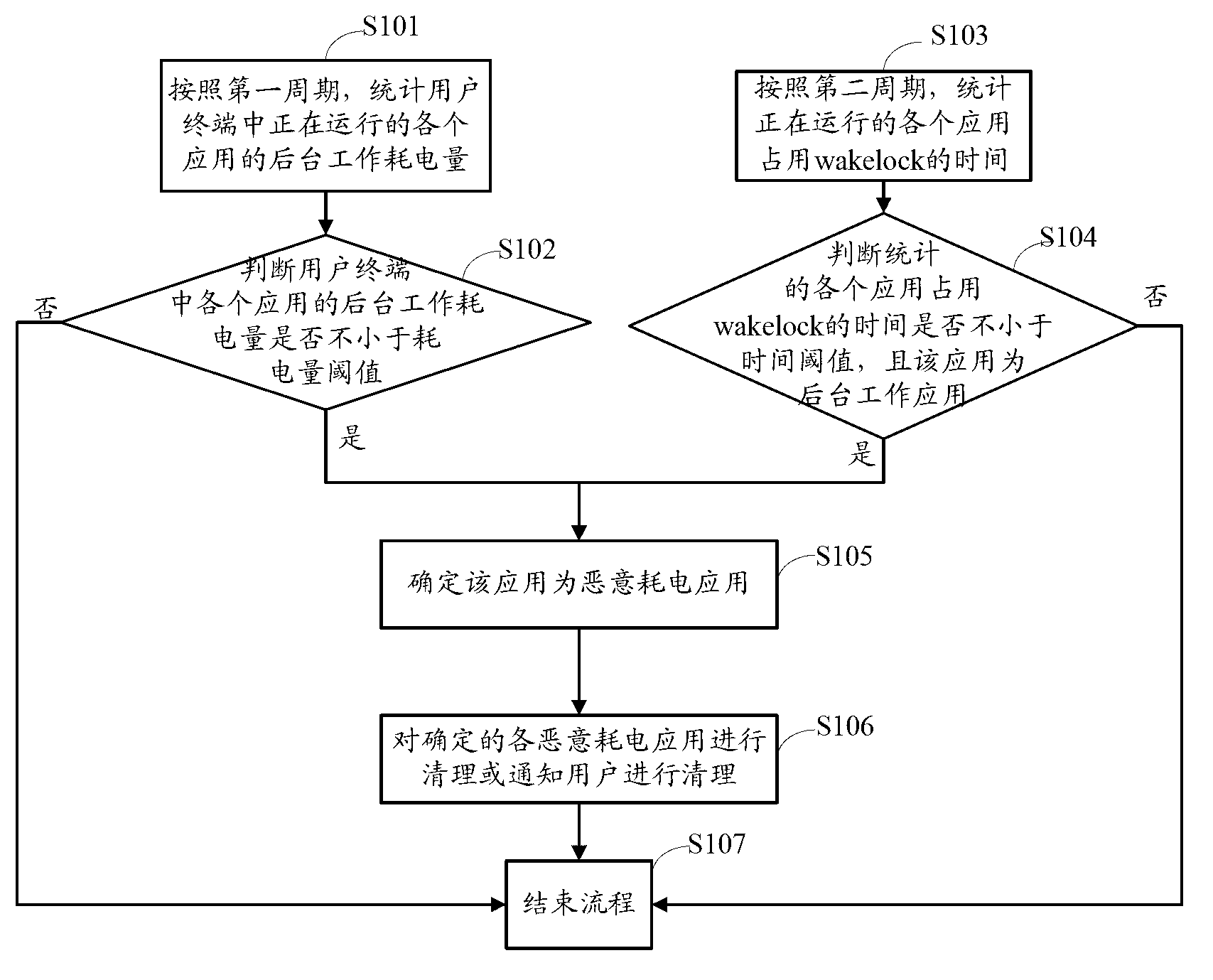

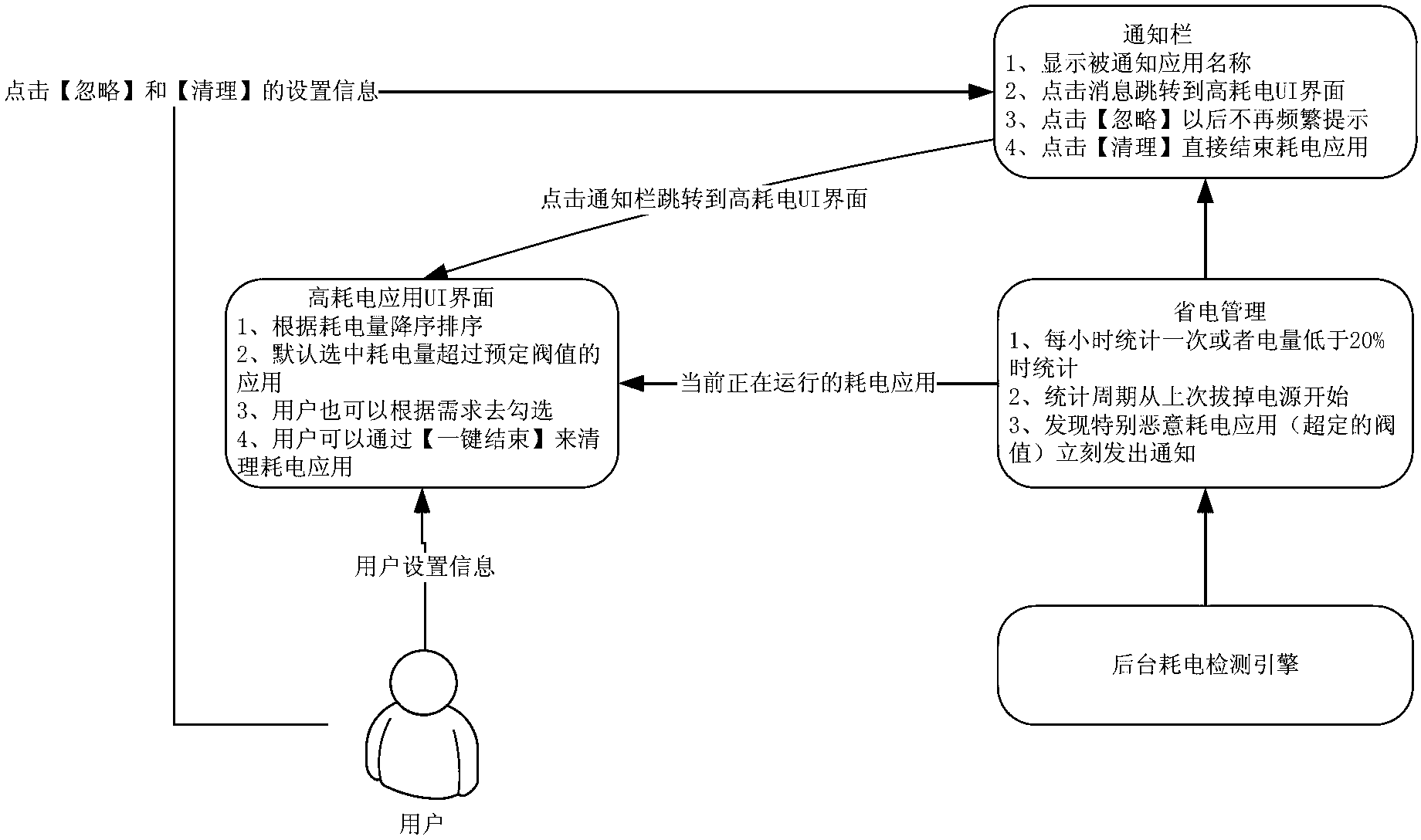

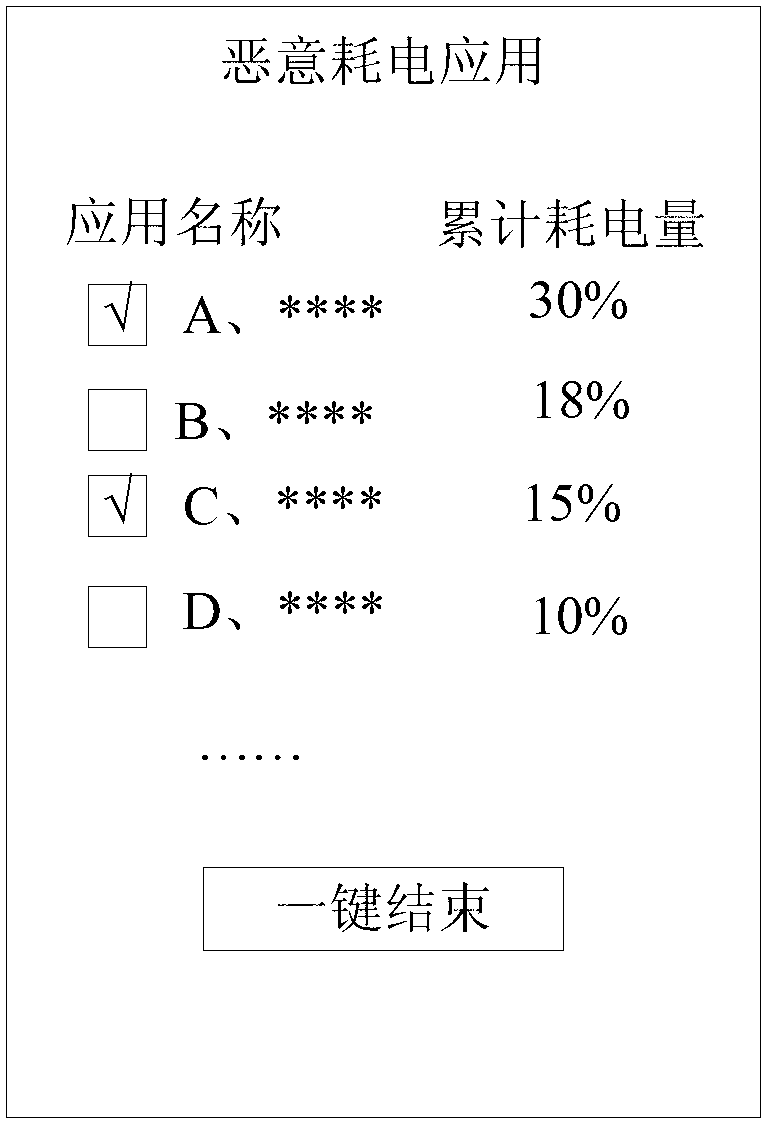

An embodiment of the invention provides a method and a device for clearing malicious power consumption applications, and a user terminal. Background work power consumption of applications running in the user terminal is periodically counted, the applications with the background work power consumption not lower than a power consumption threshold value are determined as the malicious power consumption applications, wake lock holding time of each application running in the user terminal with a screen closed is periodically counted, if a certain application with the holding time not shorter than a set time threshold value is a background work application, the application is determined as a malicious power consumption application unreasonably occupying resources in background, the applications with high power consumption but normally used by a user are not malicious power consumption applications, the malicious power consumption applications can be accurately positioned and detected, unnecessary power consumption of the user terminal is avoided while usage experience of the user is ensured, electric energy is saved, and the battery life of the user terminal is prolonged to a certain degree.

Owner:HUAWEI TECH CO LTD

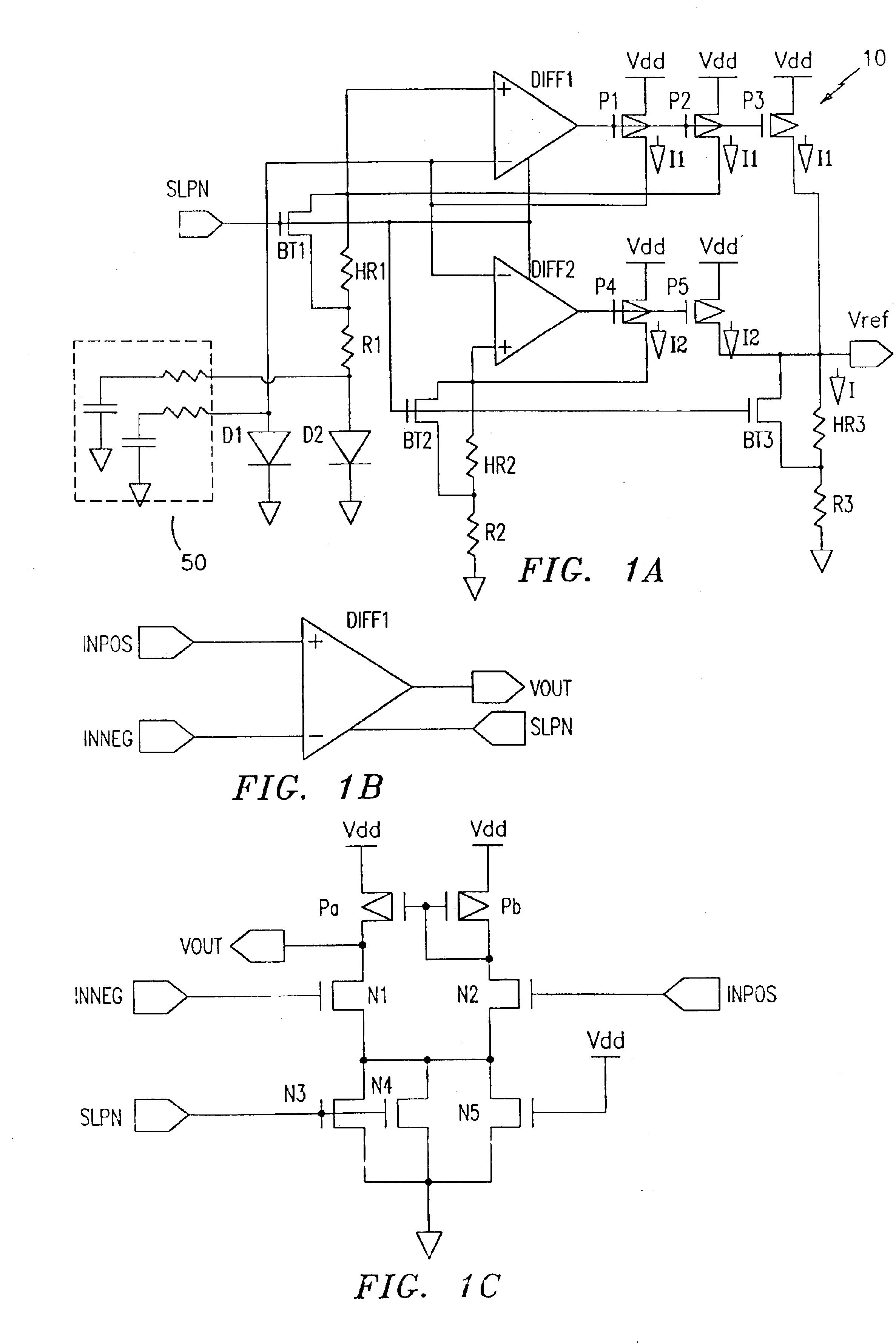

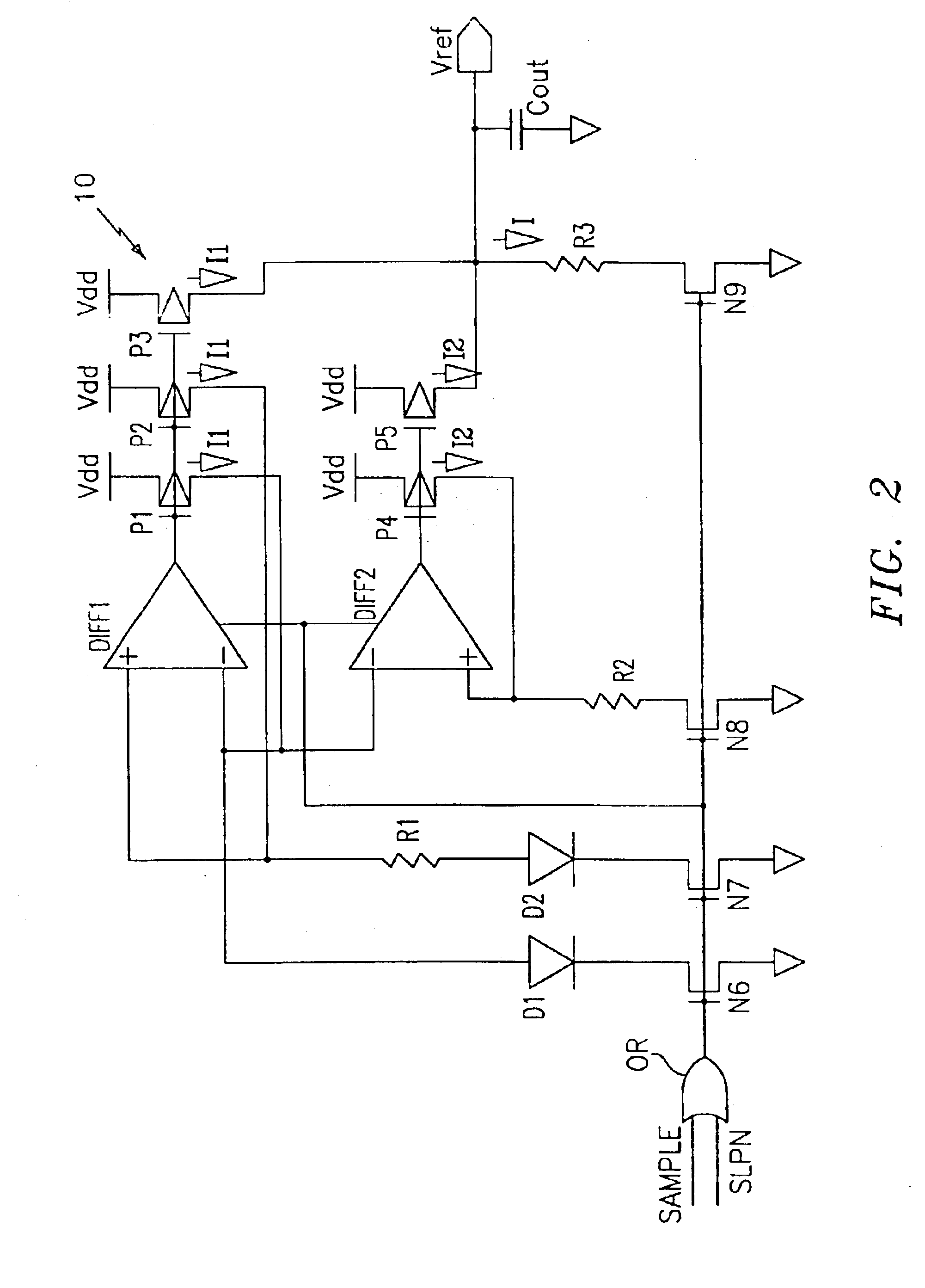

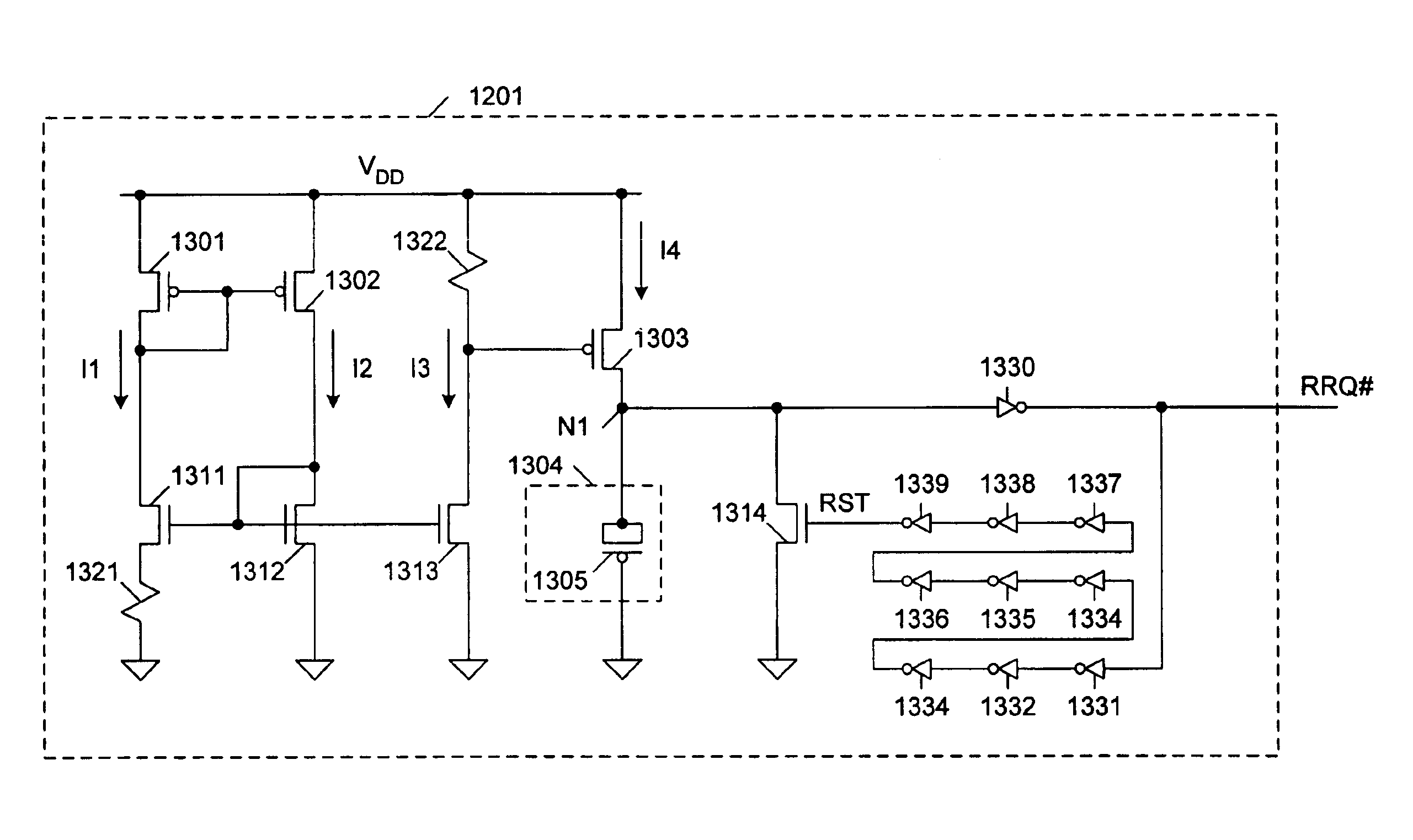

Low-power band-gap reference and temperature sensor circuit

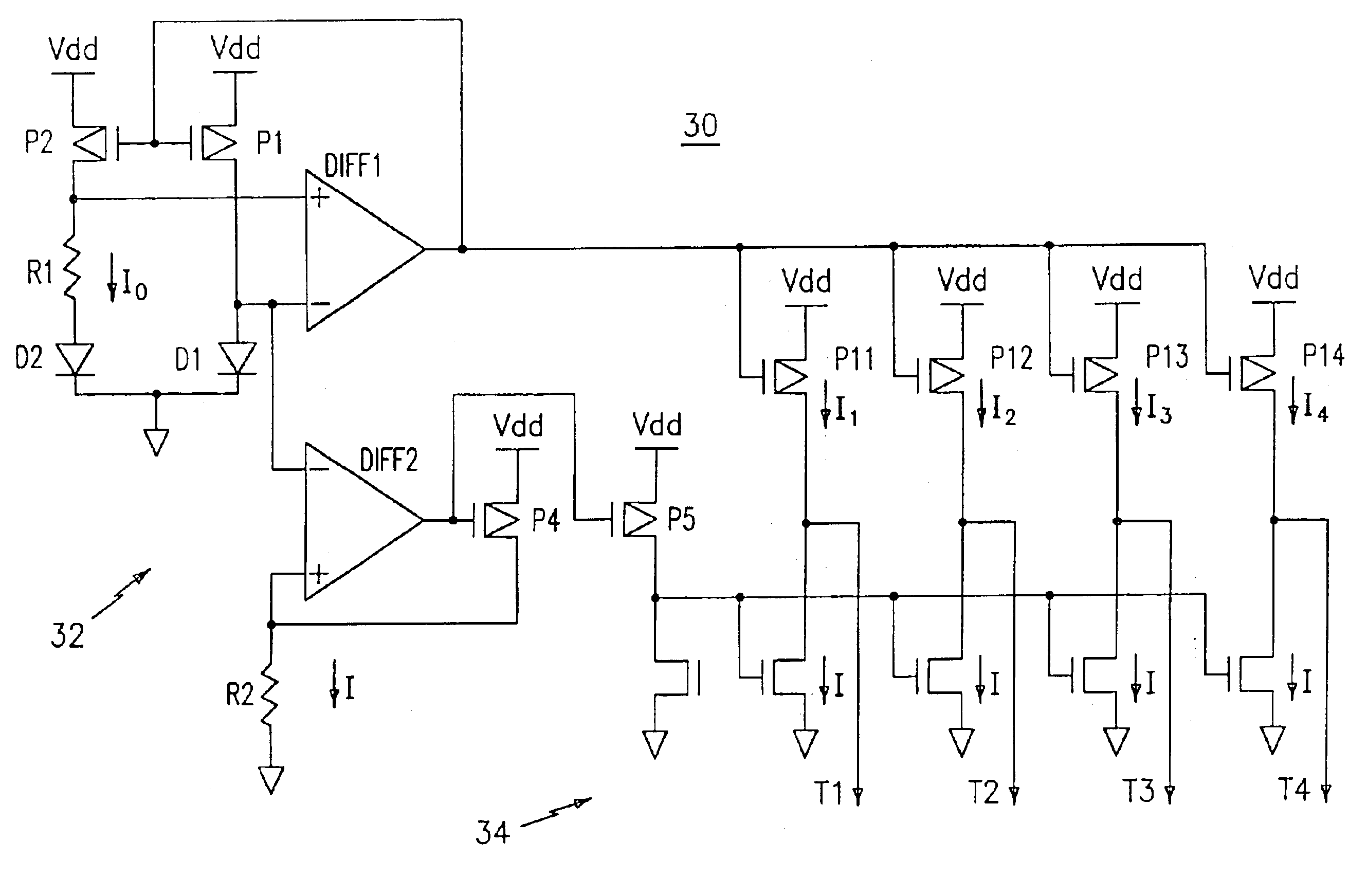

InactiveUS6876250B2Short refresh cycle timeIncrease temperatureSemiconductor/solid-state device detailsThermometers using electric/magnetic elementsLow voltageMicroprocessor

A combined low-voltage, low-power band-gap reference and temperature sensor circuit is provided for providing a band-gap reference parameter and for sensing the temperature of a chip, such as an eDRAM memory unit or CPU chip, using the band-gap reference parameter. The combined sensor circuit is insensitive to supply voltage and a variation in the chip temperature. The power consumption of both circuits, i.e., the band-gap reference and the temperature sensor circuits, encompassing the combined sensor circuit is less than one μW. The combined sensor circuit can be used to monitor local or global chip temperature. The result can be used to (1) regulate DRAM array refresh cycle time, e.g., the higher the temperature, the shorter the refresh cycle time, (2) to activate an on-chip or off-chip cooling or heating device to regulate the chip temperature, (3) to adjust internally generated voltage level, and (4) to adjust the CPU (or microprocessor) clock rate, i.e., frequency, so that the chip will not overheat. The combined band-gap reference and temperature sensor circuit of the present invention can be implemented within battery-operated devices having at least one memory unit. The low-power circuits of the sensor circuit extend battery lifetime and data retention time of the cells of the at least one memory unit.

Owner:GLOBALFOUNDRIES INC

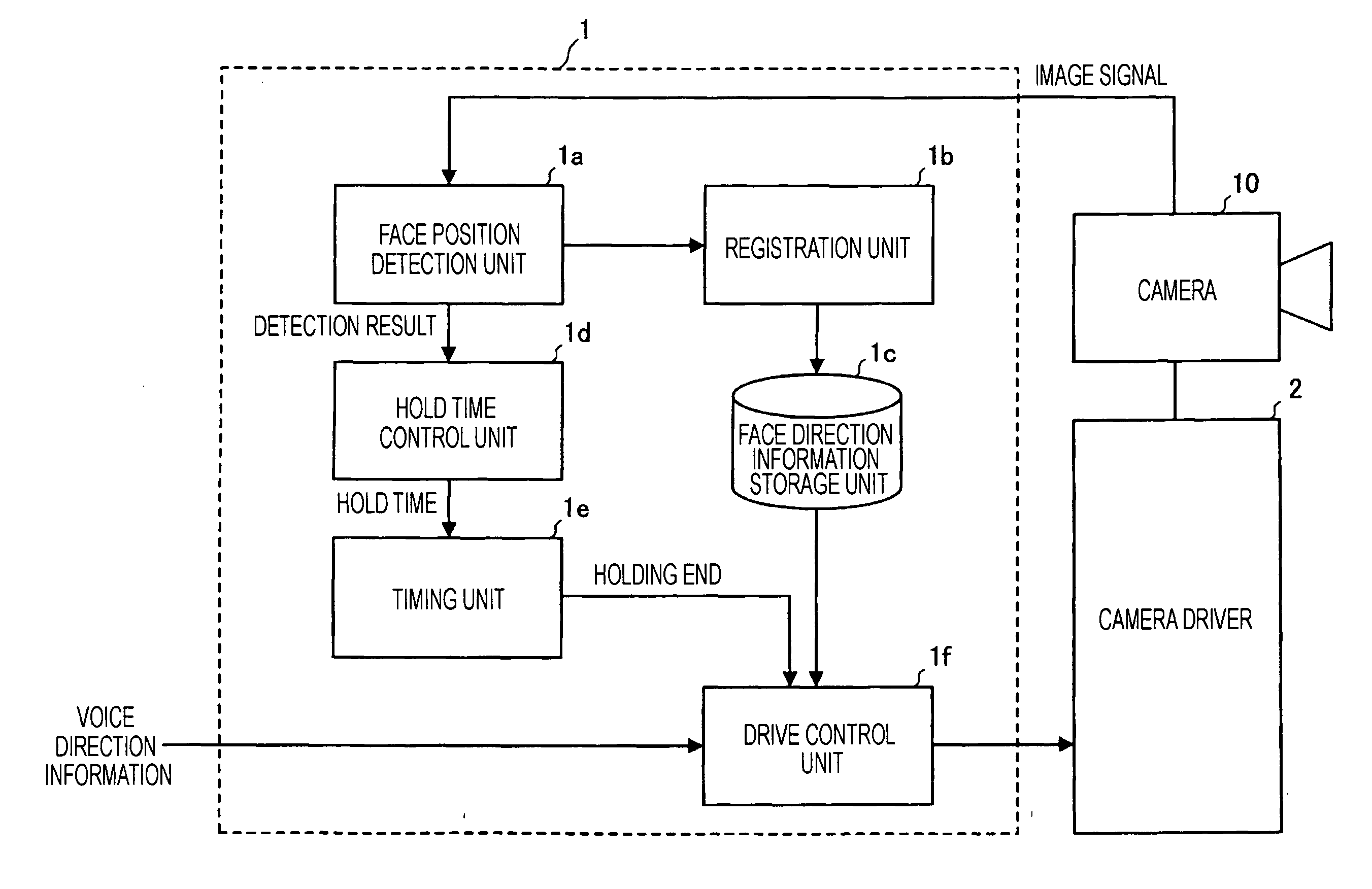

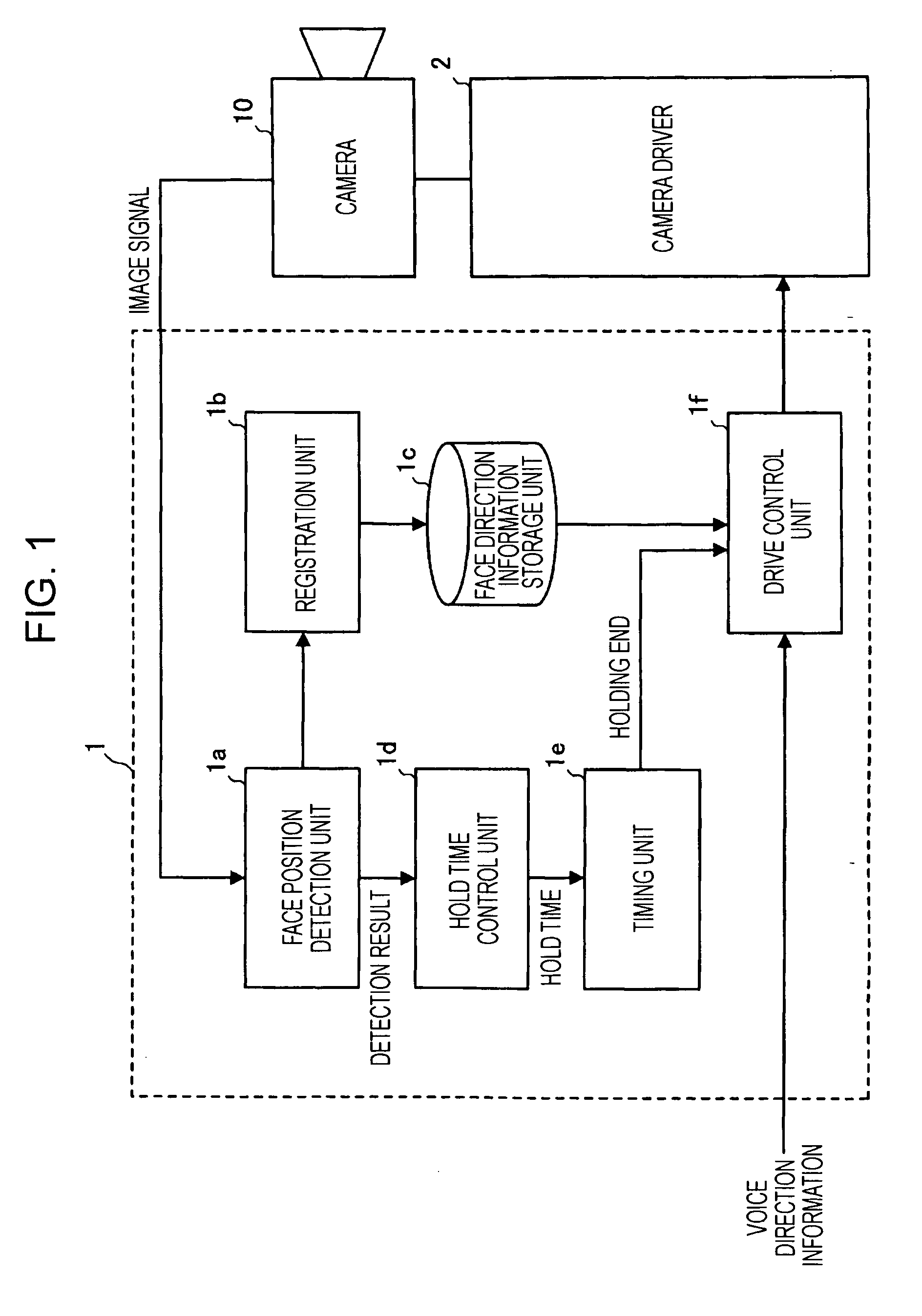

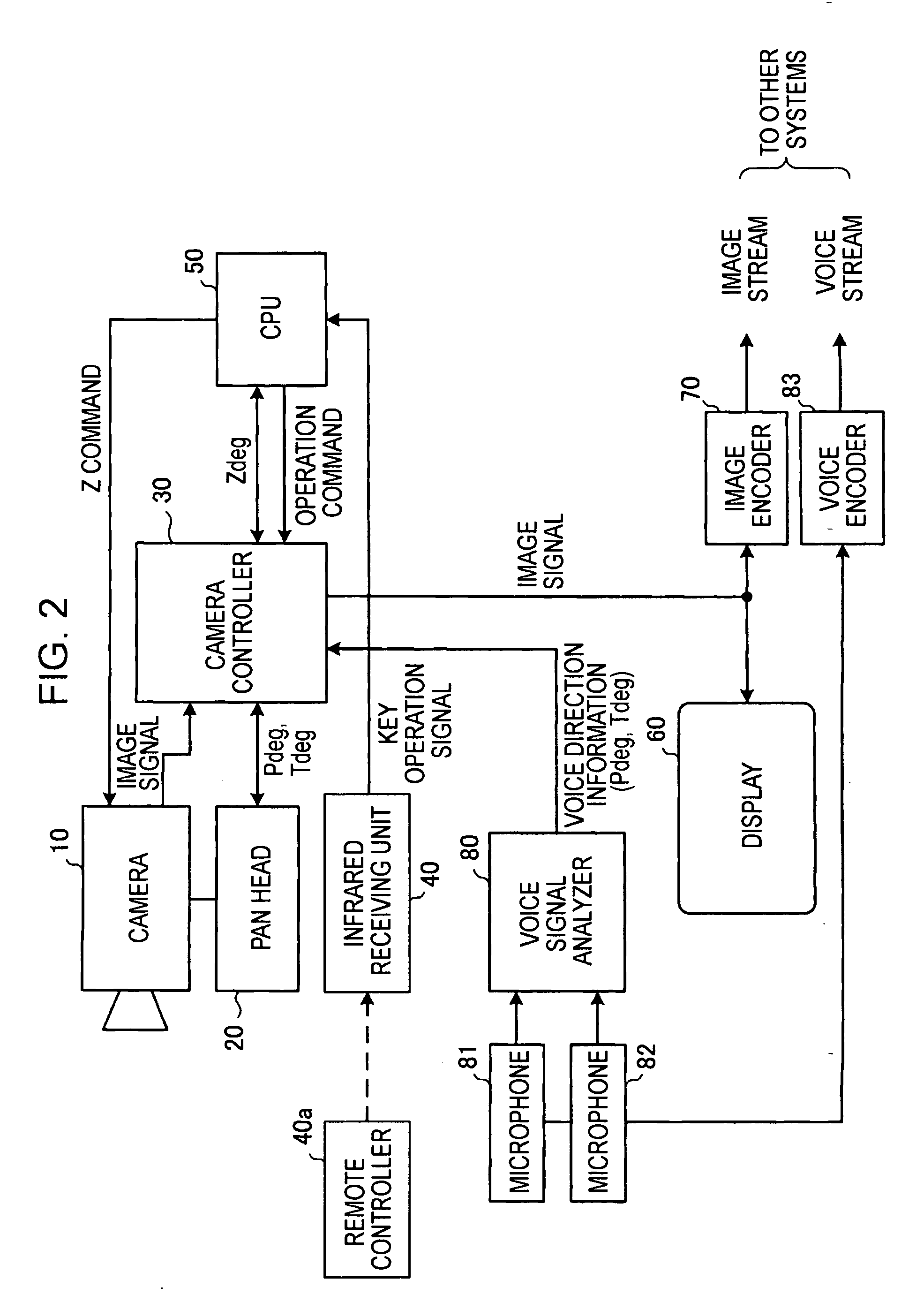

Camera controller and teleconferencing system

InactiveUS20070040903A1Move quicklyAccurately and stably imageTelevision conference systemsTwo-way working systemsCamera controlDriver/operator

Owner:SONY CORP

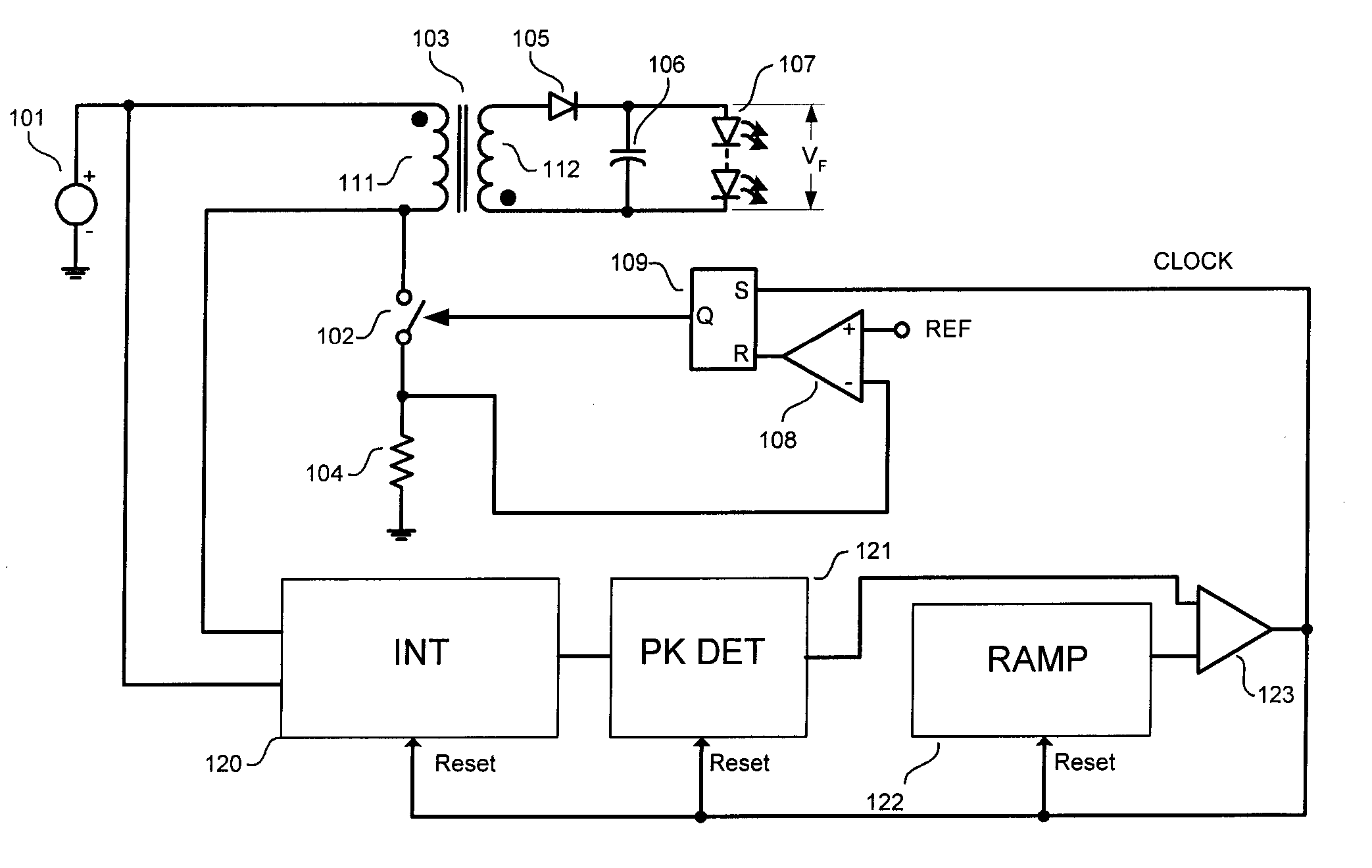

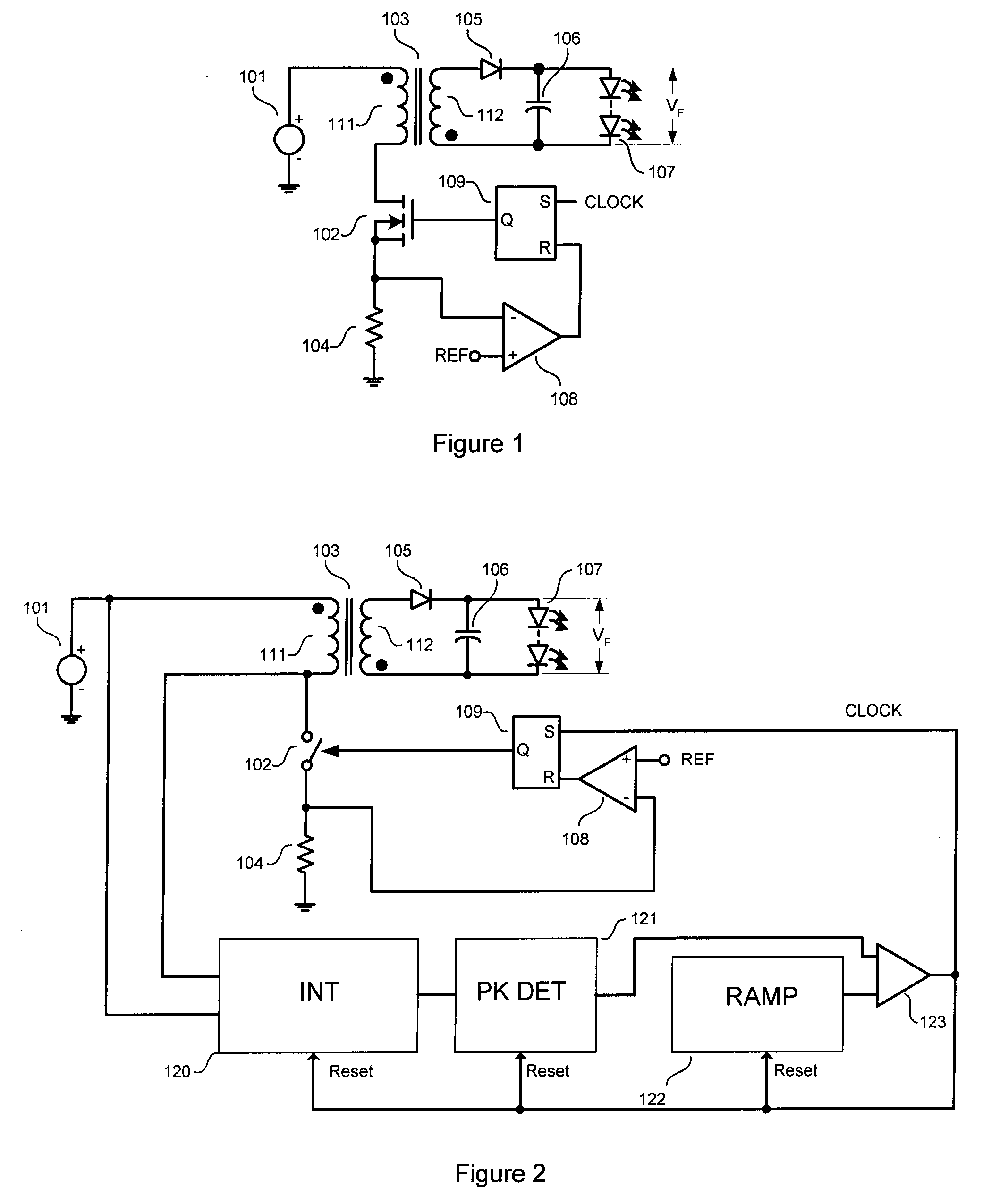

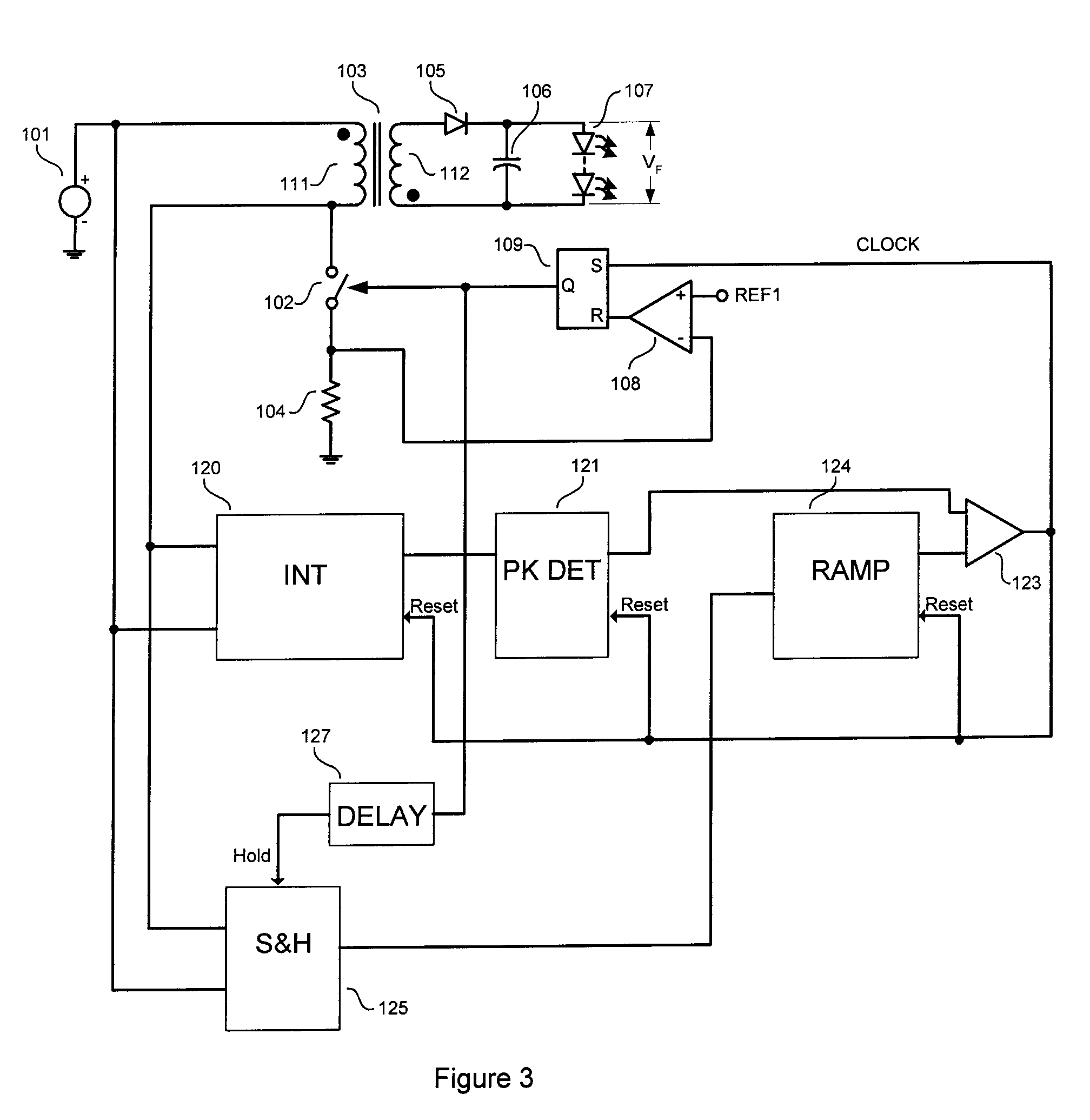

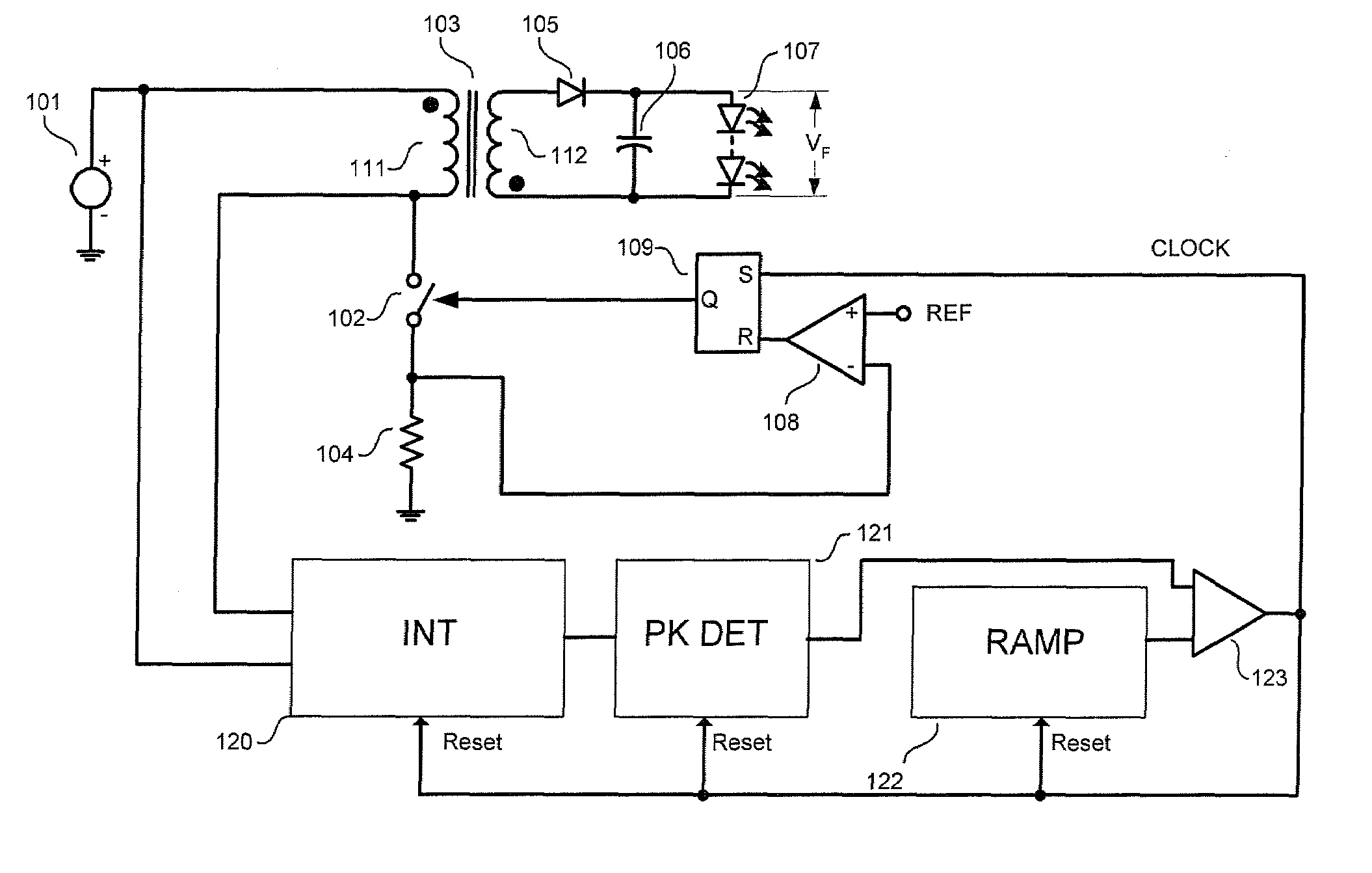

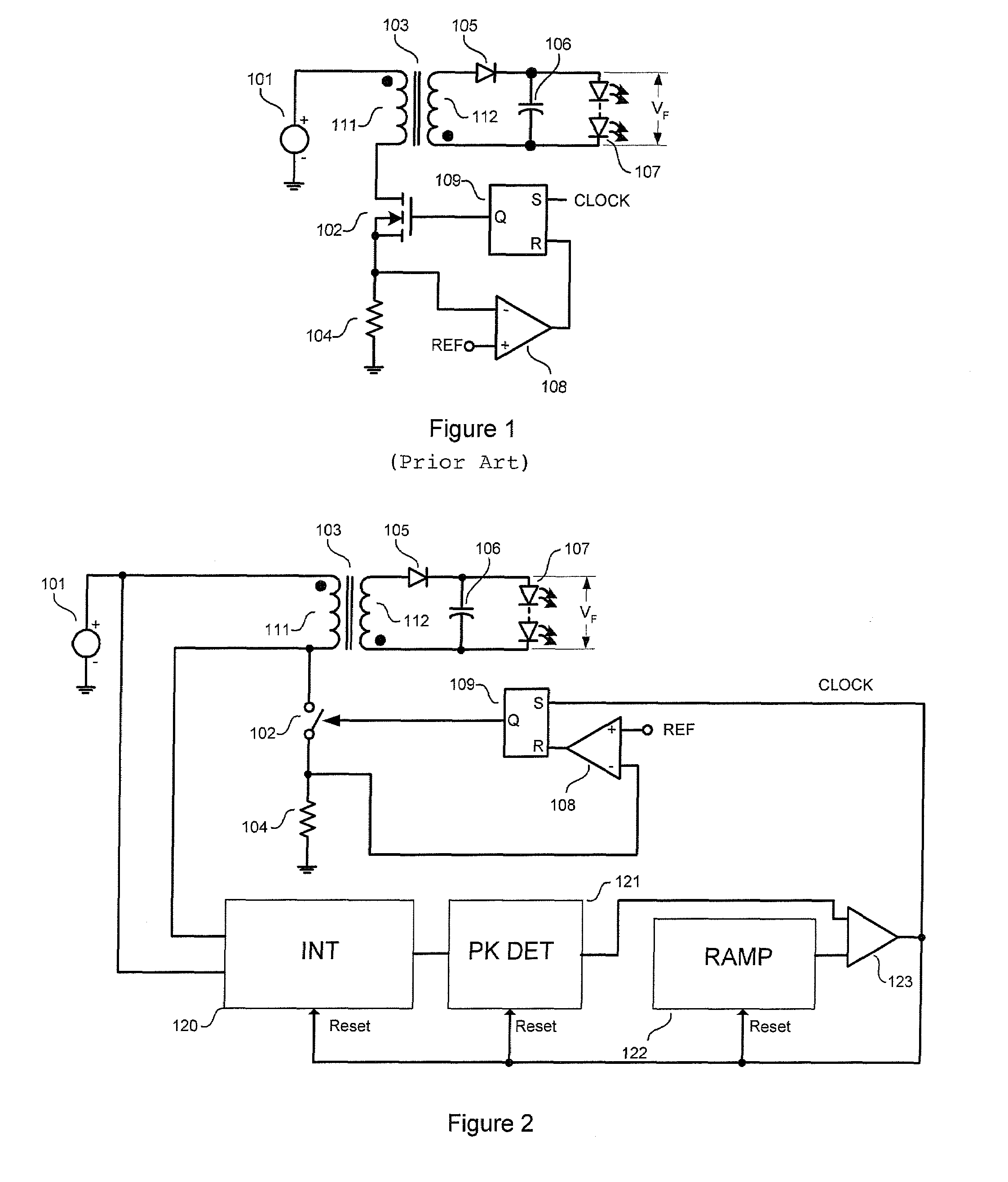

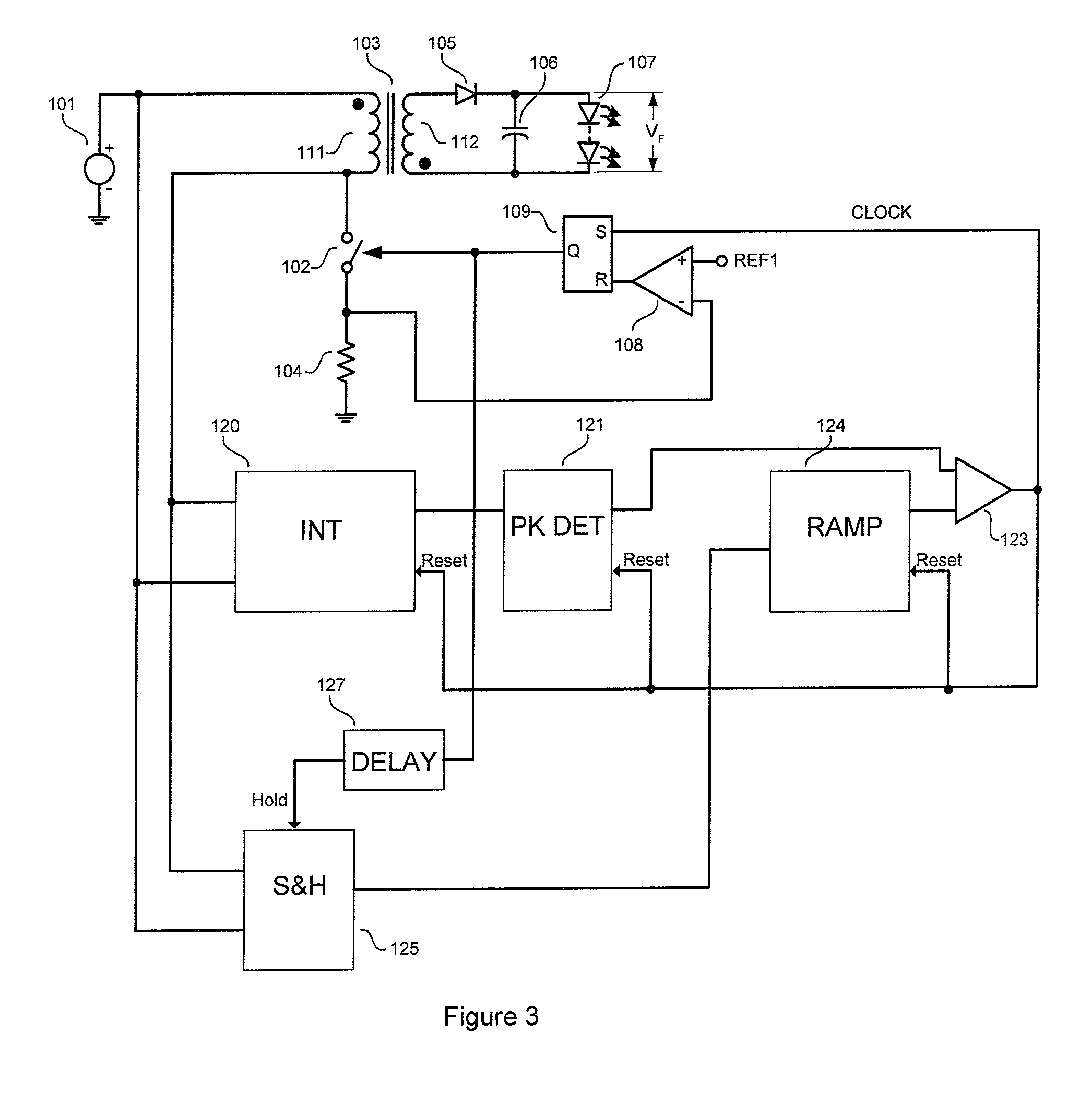

Transformer-isolated flyback converters and methods for regulating output current thereof

InactiveUS20070121349A1Conversion with intermediate conversion to dcDc-dc conversionIntegratorReference current

A system and method for delivering regulated power and current to an output load has a flyback transformer having a primary winding and a secondary winding. The secondary winding delivers stored energy to the output load. An oscillator circuit is provided for generating a periodical signal. A switching circuit is coupled to the flyback transformer and the oscillator circuit for energizing the primary winding to a reference current level each cycle of the oscillator circuit. The oscillator circuit has an integrator for deriving a time integral of a voltage at the primary winding. The oscillator circuit has a peak detector coupled to the integrator for holding a peak value of the time integral. The oscillator circuit further has a ramp generator for producing a ramp signal. A comparator is provided for comparing the peak value with the ramp signal and generating the periodical signal whenever the ramp signal exceeds the peak value.

Owner:MICROCHIP TECH INC

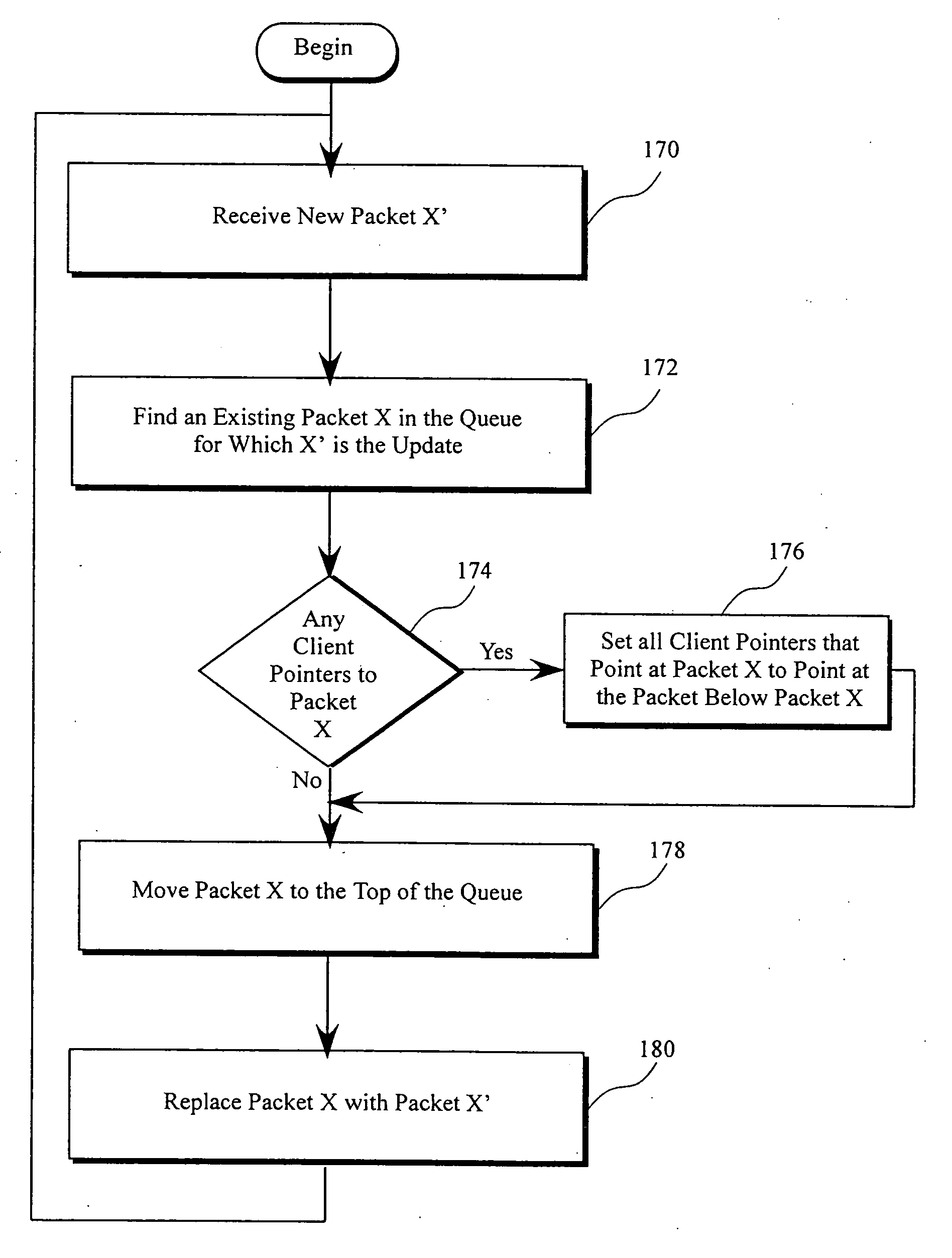

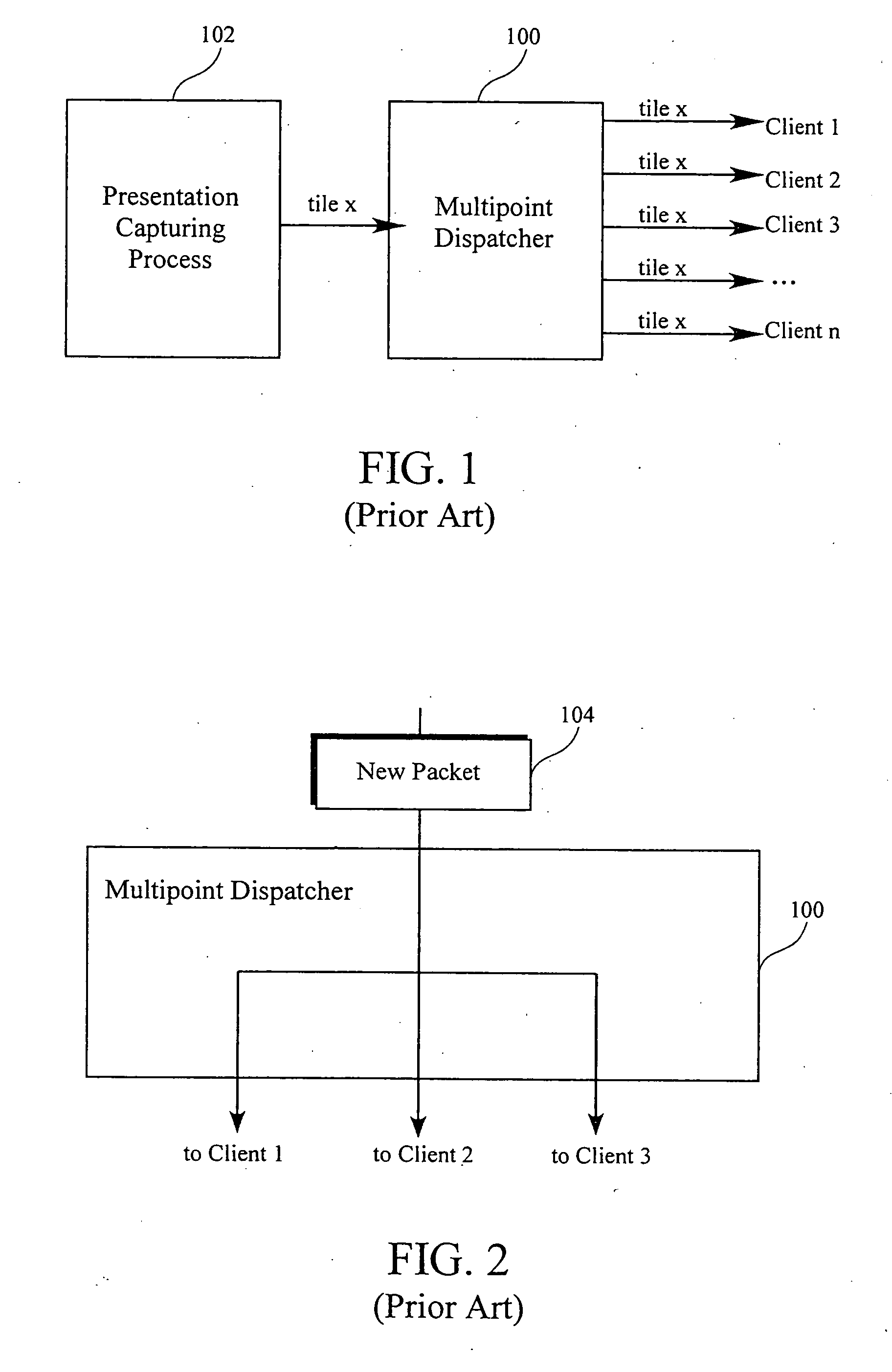

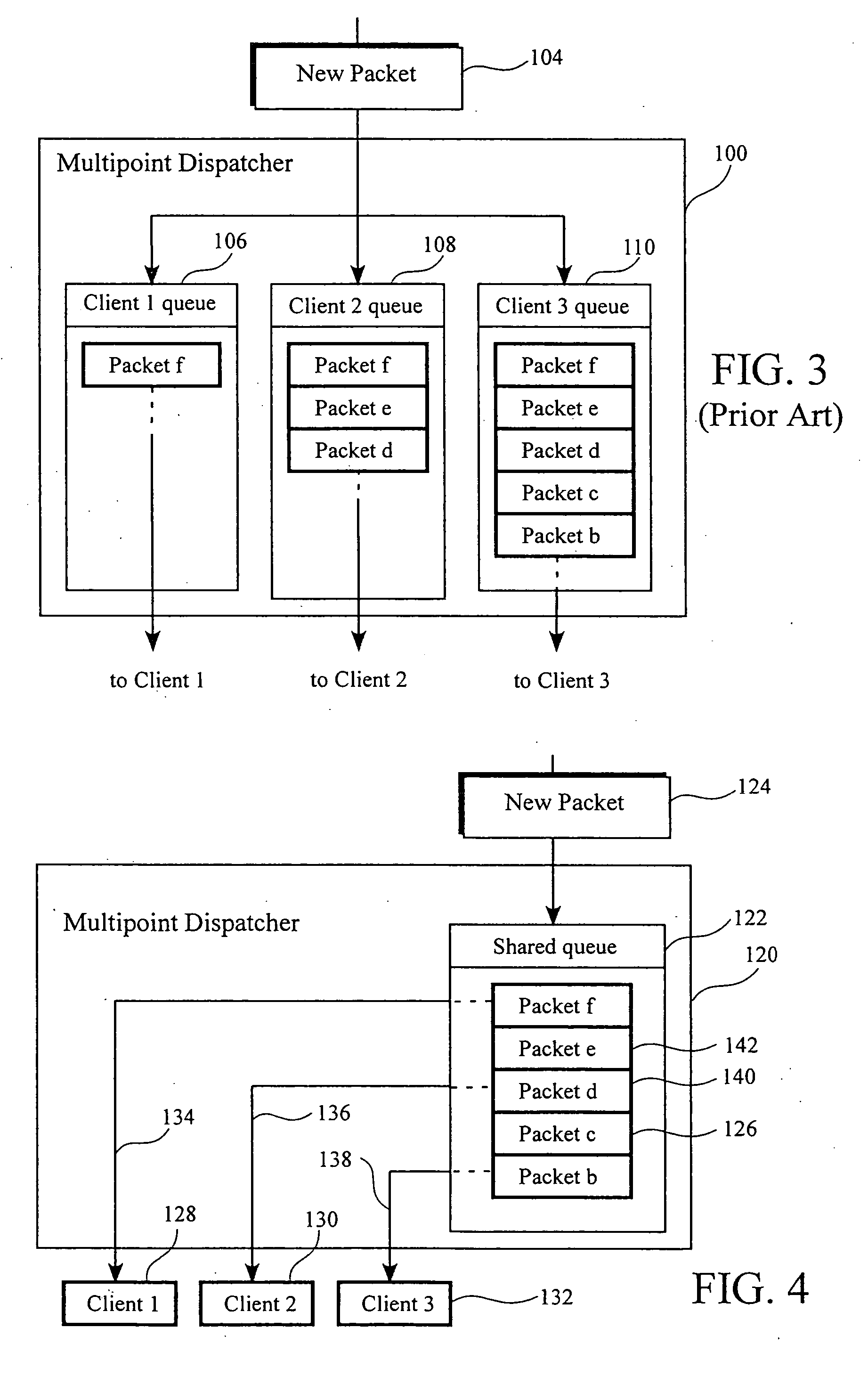

System for distributing objects to multiple clients

InactiveUS20060168302A1Television conference systemsMultiple digital computer combinationsDistributed objectSecond screen

A method for updating a set of presentation images through a single-buffered multipoint dispatcher over a network to multiple clients is provided. Each screen of a set of screens included in the presentation is divided into tiles. Packets respectively corresponding to the tiles of a first screen are stored in a single buffered multipoint dispatcher according to a time sorted hierarchy, a top packet having a most recent time value and a bottom packet having a least recent time value. Each tile of the first screen is compared with a corresponding tile of a second screen to identify any non-matching tile pairs. For each non-matching tile of the second screen, a packet corresponding to that non-matching tile is provided to the single buffered multipoint dispatcher. Then, non-matching tiles of the first screen are replaced with the respective non-matching tiles of the second screen, while maintaining the time sorted hierarchy. Such replacement supports clients with different connection speeds at different frame rates.

Owner:BOSKOVIC RONALD +2

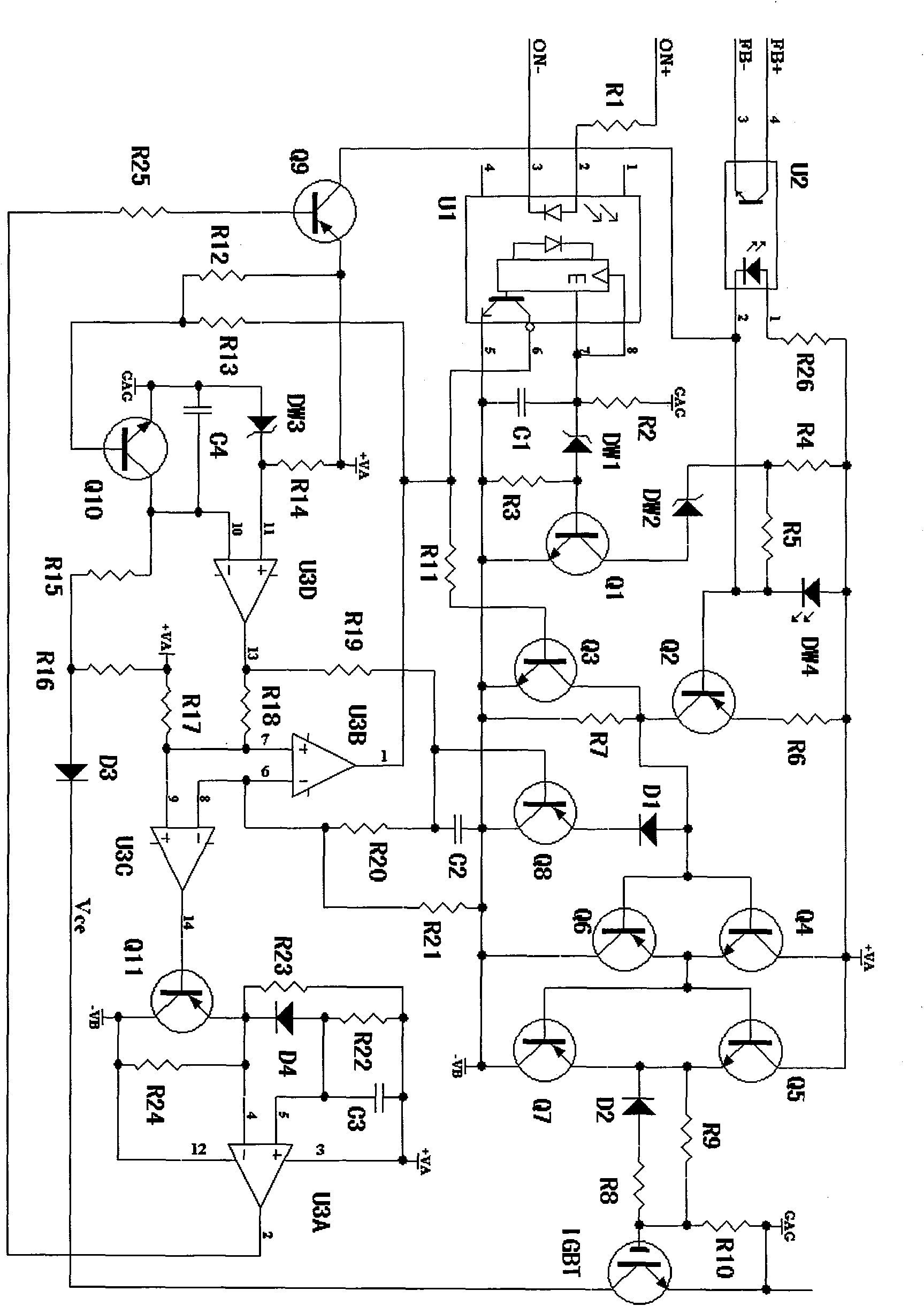

IGBT drive protection circuit

The invention discloses an IGBT drive protection circuit, which comprises positive and negative power supplies, a signal and feedback optical coupler, a signal amplification circuit, an undervoltage detection and indication circuit, an IGBT overcurrent detection and reset circuit, a soft turn-off circuit, a fault latch and retaining circuit and the like. The undervoltage detection circuit if the power supply at the receiving terminal of the signal optical coupler and the positive / negative power supply are undervoltage, and an LED is lighted if the power supply at the receiving terminal of thesignal optical coupler and the positive / negative power supply are not undervoltage to enable a drive circuit. The IGBT overcurrent detection circuit can sample a collector-emitter voltage drop duringthe period when the IGBT is turned on, detect time delay according to high-low dynamic adjustment of the collector-emitter voltage drop, start a soft turn-off process and perform self locking to ensure soft turn off when the collector-emitter voltage drop exceeds a preset threshold, retain the overcurrent fault state, keep the IGBT turned off during the retaining period, transmit the state to a control circuit and keep time set between millisecond and second.

Owner:SHENZHEN CLOU DRIVE TECH CO LTD

Transformer-isolated flyback converters and methods for regulating output current thereof

InactiveUS7561452B2Conversion with intermediate conversion to dcDc-dc conversionIntegratorReference current

A system and method for delivering regulated power and current to an output load has a flyback transformer having a primary winding and a secondary winding. The secondary winding delivers stored energy to the output load. An oscillator circuit is provided for generating a periodical signal. A switching circuit is coupled to the flyback transformer and the oscillator circuit for energizing the primary winding to a reference current level each cycle of the oscillator circuit. The oscillator circuit has an integrator for deriving a time integral of a voltage at the primary winding. The oscillator circuit has a peak detector coupled to the integrator for holding a peak value of the time integral. The oscillator circuit further has a ramp generator for producing a ramp signal. A comparator is provided for comparing the peak value with the ramp signal and generating the periodical signal whenever the ramp signal exceeds the peak value.

Owner:MICROCHIP TECH INC

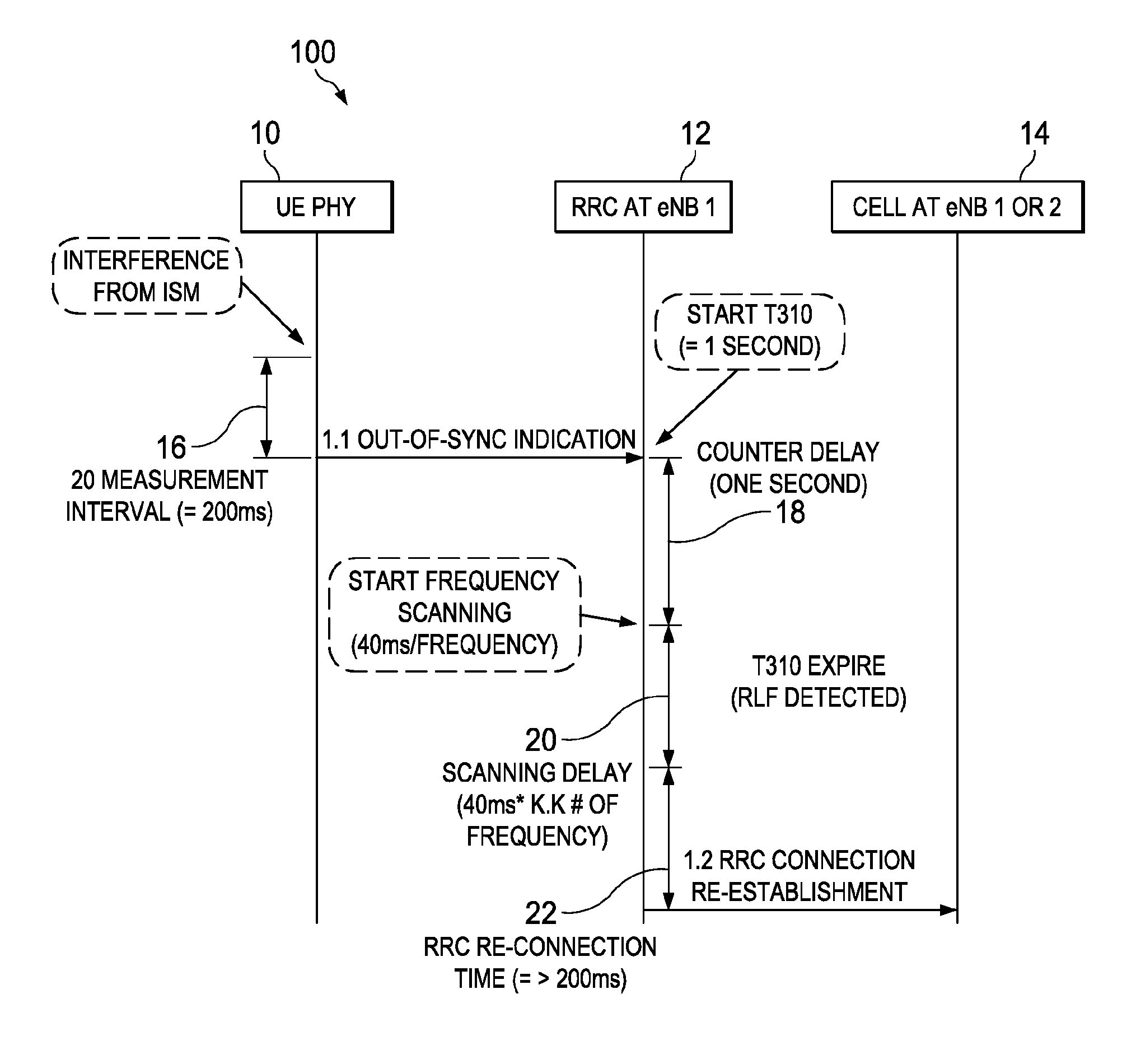

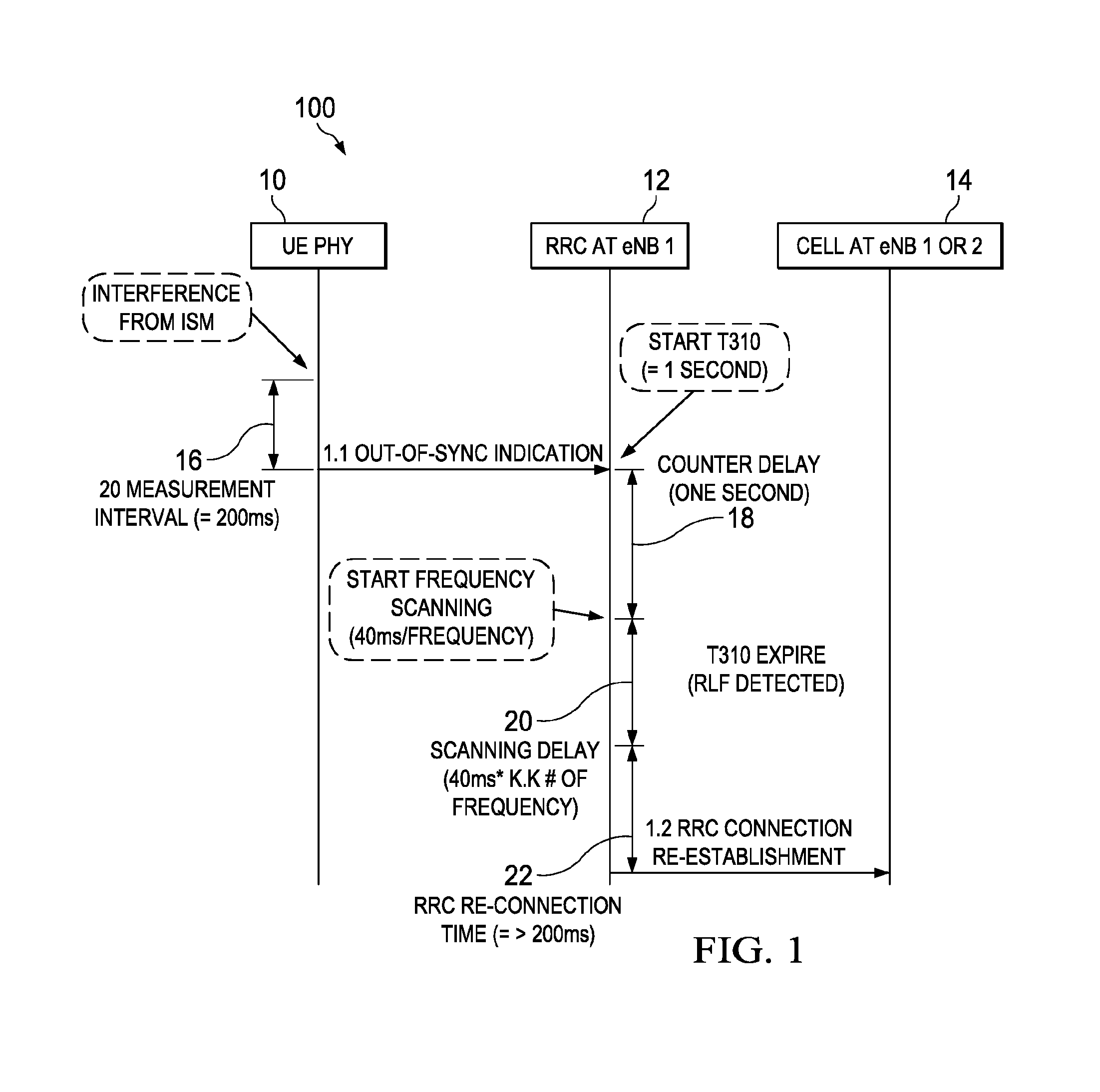

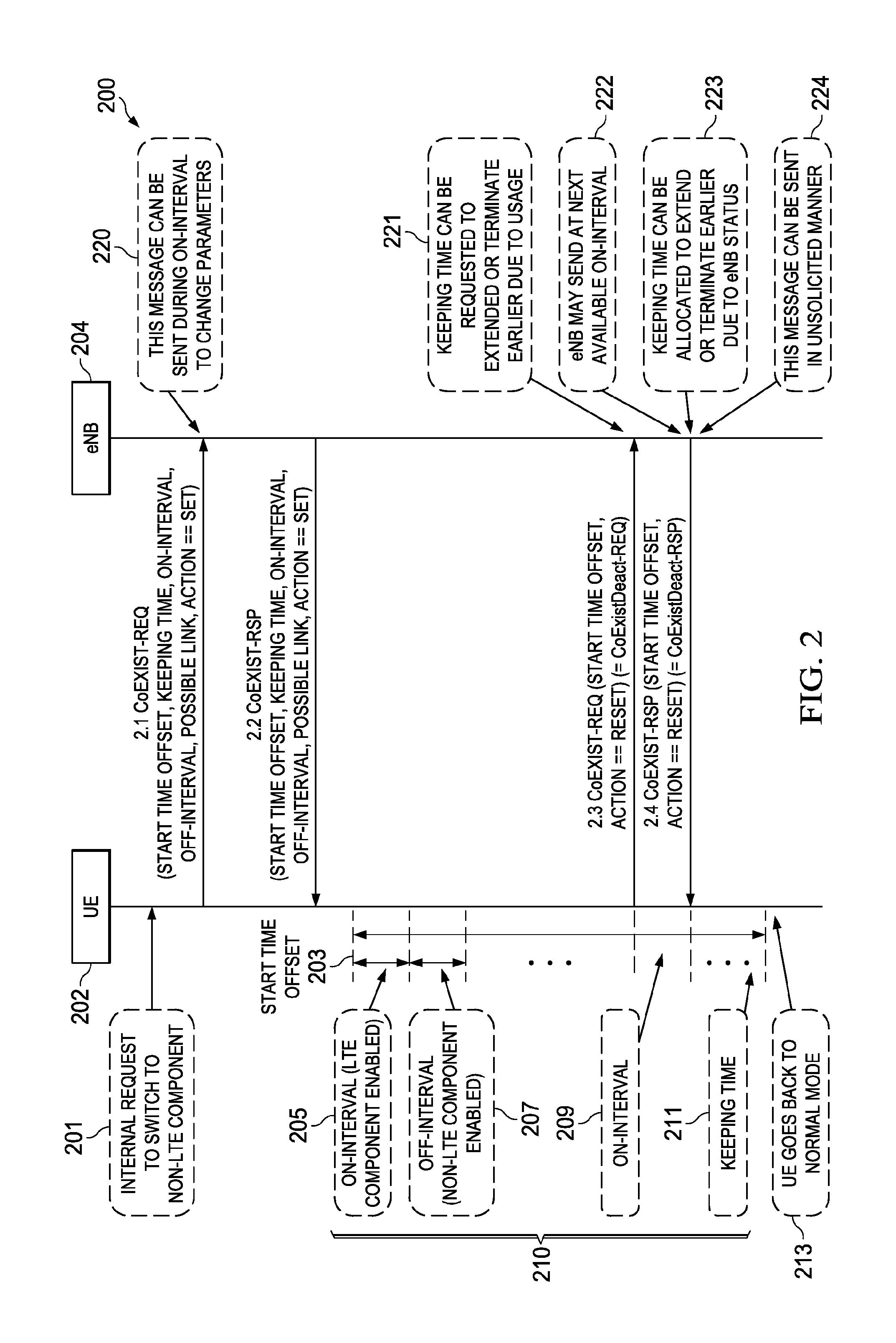

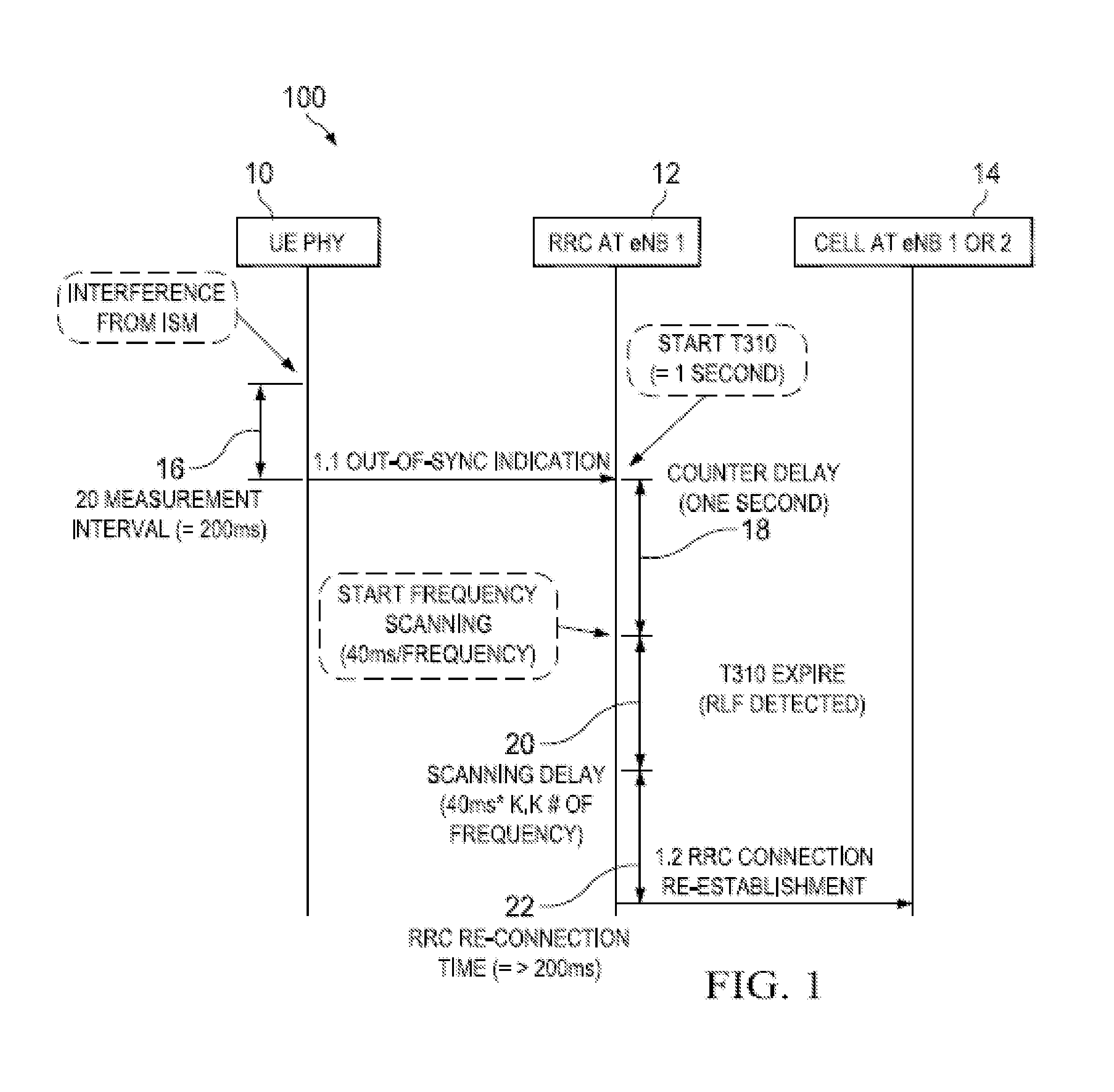

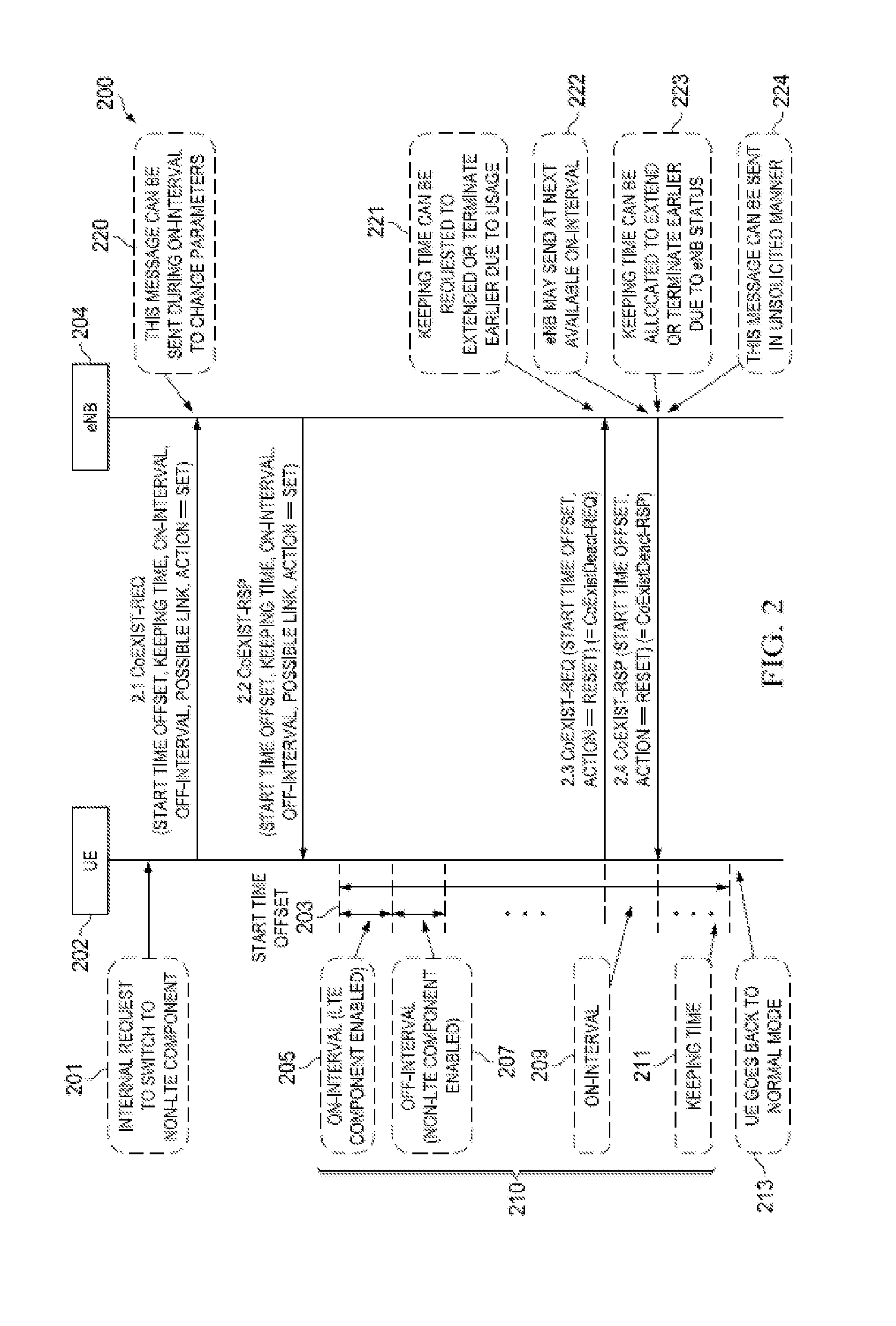

Method and Apparatus for Avoiding In-Device Coexistence Interference

A method, system and device are provided for avoiding in-device coexistence interference between different radio technologies deployed in adjacent bands on the same device by controlling and separating the LTE signaling and the non-LTE signaling using dedicated time intervals to separate LTE signaling from non-LTE signaling. In addition, coexistence mode handover procedures are provided which use threshold-based triggering events to avoid coexistence interference and to prevent ping-pong effects by establishing a “keeping time” parameter so that a non-interfering network node does not switch back to an interfering network node after handoff. Coexistence interference is also avoided by providing a hybrid automatic repeat request (HARQ) mechanism which accounts for coexistence interference by providing a fixed or variable on-interval parameter and an activity parameter indicating whether non-LTE activity is present to maximize a time interval for non-LTE devices without interference from LTE activity on the same device.

Owner:BLACKBERRY LTD

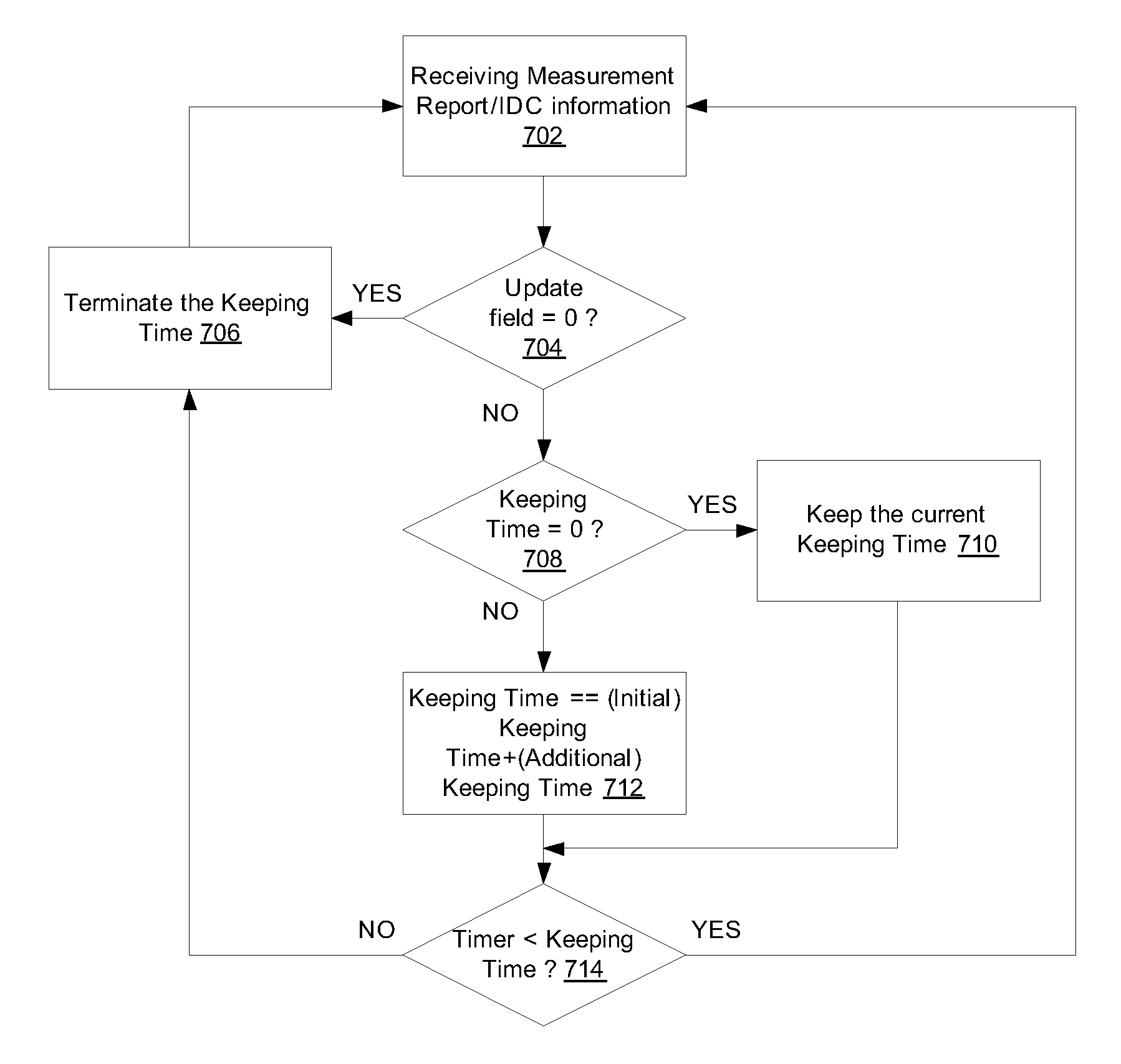

Method and Apparatus for Avoiding In-Device Coexistence Interference with Keeping Time Update for Handover

A method, system and device are provided for avoiding in-device coexistence interference between different radio technologies deployed in adjacent bands on the same device by providing coexistence mode handover procedures which establish an updateable “keeping time” parameter to prevent premature switch back or handover to an interfering network node after handoff.

Owner:MALIKIE INNOVATIONS LTD

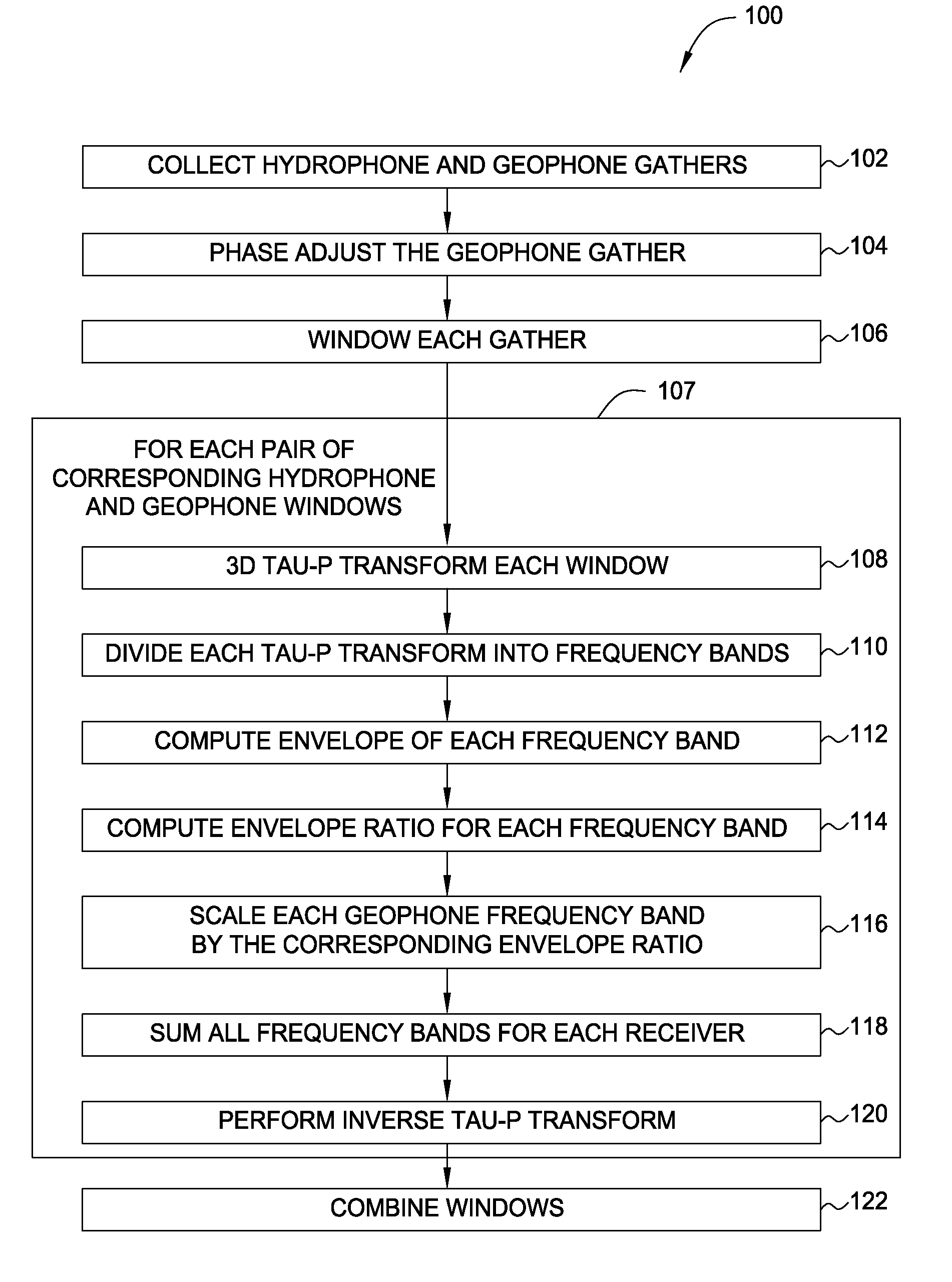

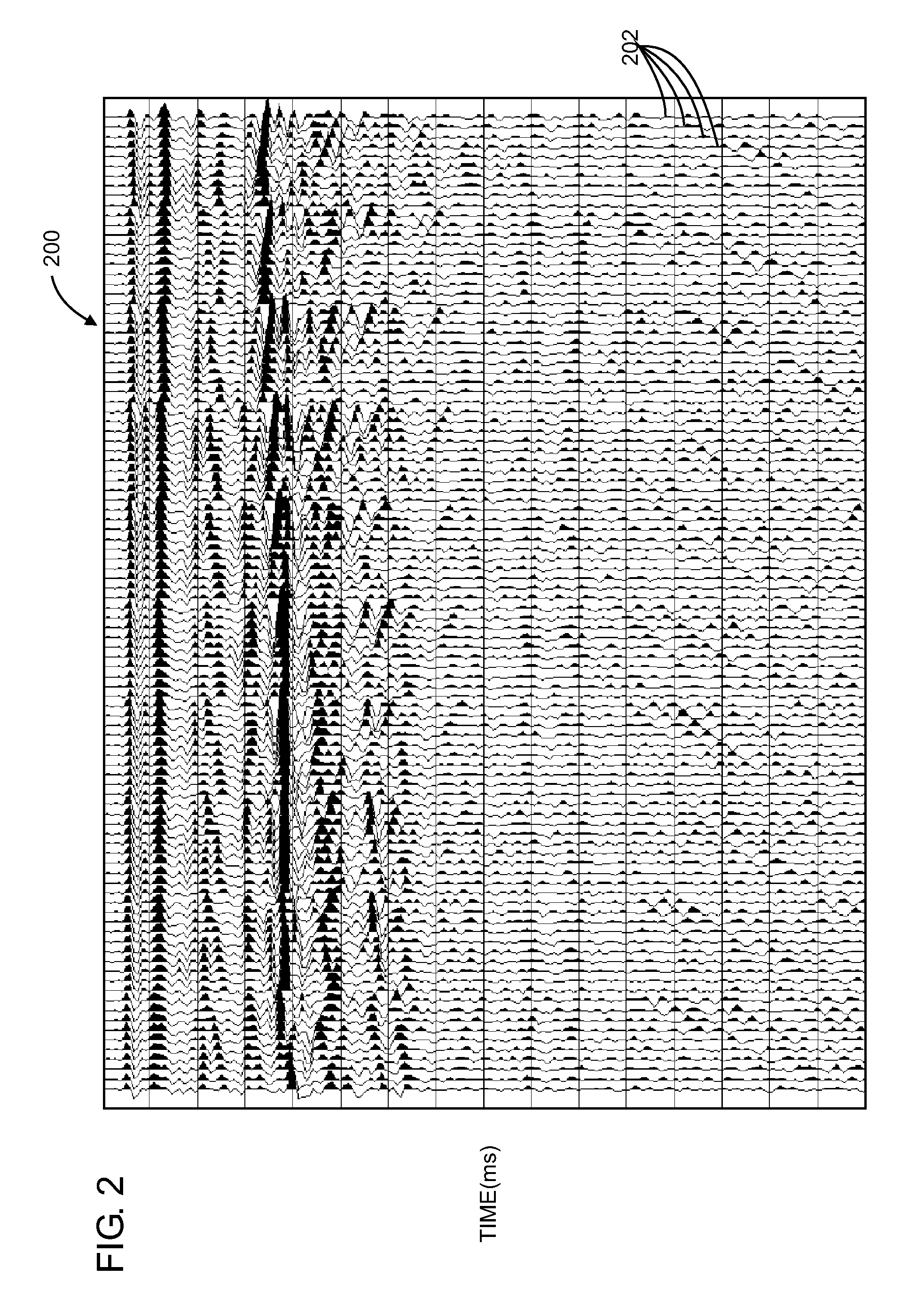

Geophone noise attenuation and wavefield separation using a multi-dimensional decomposition technique

ActiveUS20080221801A1Cancel noiseEasy to separateDigital variable/waveform displaySeismic signal processingGeophoneHydrophone

Methods and apparatus for processing dual sensor (e.g., hydrophone and vertical geophone) data that includes intrinsic removal of noise as well as enhancing the wavefield separation are provided. The methods disclosed herein are based on a decomposition of data simultaneously into dip and frequency while retaining temporal locality. The noise removed may be mainly coherent geophone noise from the vertical geophone, also known as V(z) noise.

Owner:FAIRFIELD INDUSTRIES INC

Ac to DC power converter with hold-up time function

InactiveUS20100014330A1Simple circuit configurationAc-dc conversion without reversalEfficient power electronics conversionTime functionEngineering

An AC to DC power converter with hold up time function has a charging switch and a mode switch. The charging switch is connected between an output capacitor of a PFC controlling circuit and an energy-storage capacitor. The mode switch is connected between the energy-storage capacitor and an input of the PFC controlling circuit. The charging and mode switches are controlled by a PFC controller. When AC power is normal, the charging switch turns on and mode switch turns off. Meanwhile, the energy-storage capacitor and the output capacitor are connected in parallel to store energy in the energy-storage capacitor. When the AC power source is interrupted, the charging switch turns off and mode switch turns on. Therefore, the energy-storage capacitor is disconnected from the output capacitor. The PFC circuit obtains power from the energy-storage capacitor and continuous to supply an output voltage for a while.

Owner:ACBEL POLYTECH INC

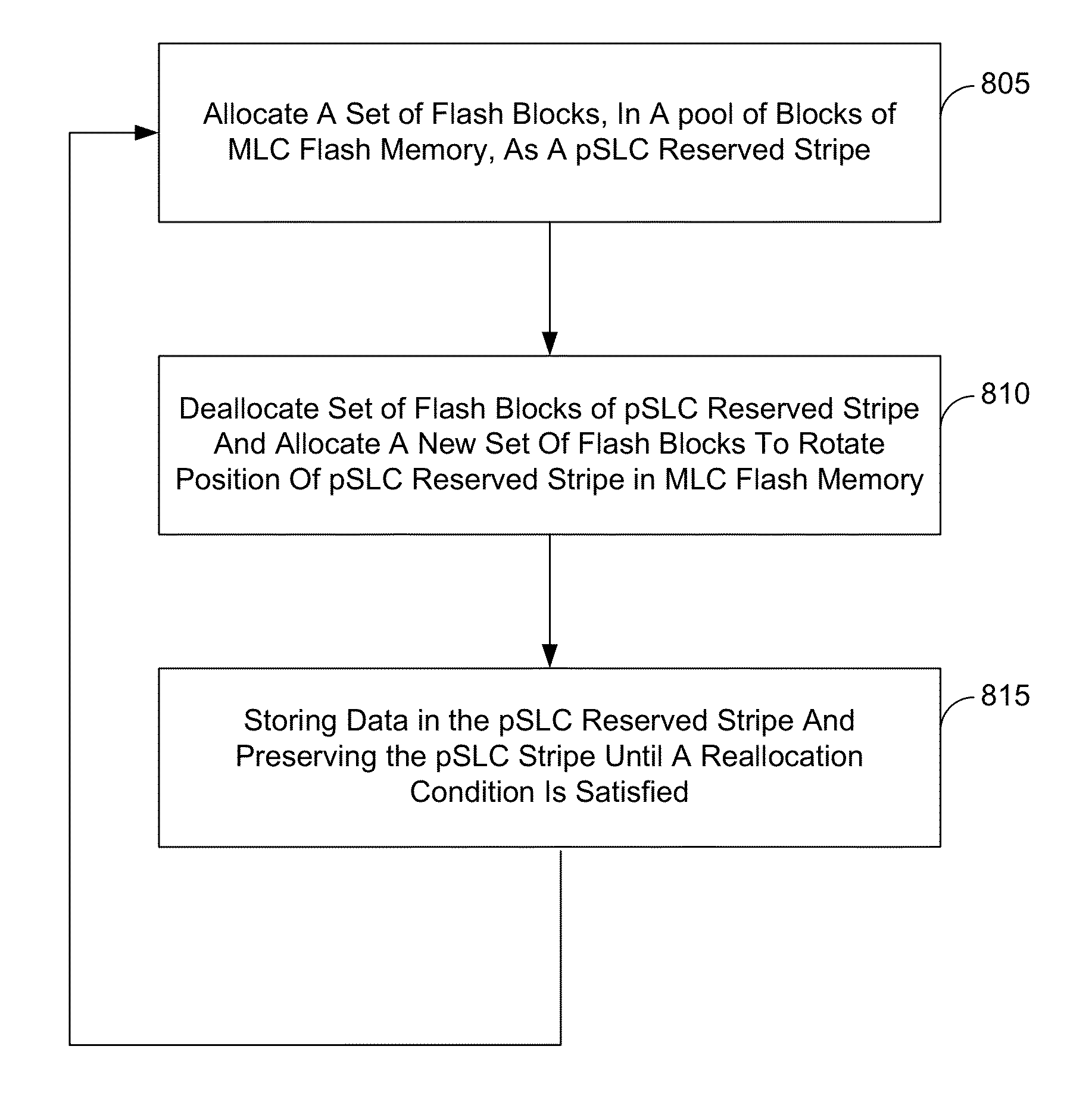

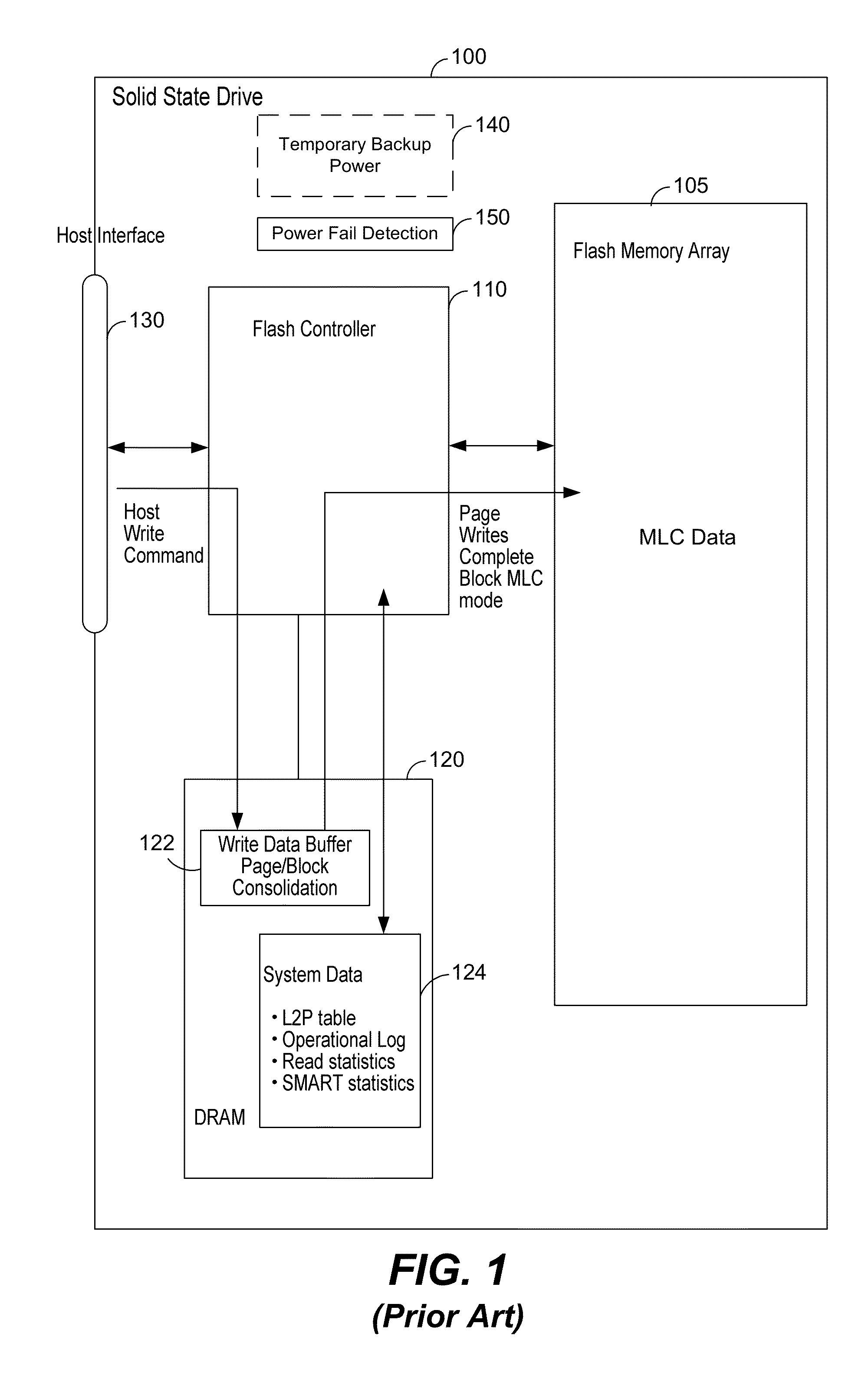

Power fail saving modes in solid state drive with mlc memory

ActiveUS20160268000A1Reduce dwell timePrevent corruptionRead-only memoriesDigital storageWrite bufferStandby power

A solid state drive has a power failure savings mode that permits a reduction in holdup time for a temporary backup power supply. The solid state drive stores data in a multi-level cell (MLC) mode. In a power fail saving mode system metadata is written in a pseudo Single Level Cell (pSLC) mode. In the normal operating mode page writes are performed in complete blocks. In the power fail save saving mode data from a write buffer is written and additional dummy pages written to reduce the total number of pages that must be written to below a complete block size with the dummy pages providing protection from data corruption.

Owner:KIOXIA CORP

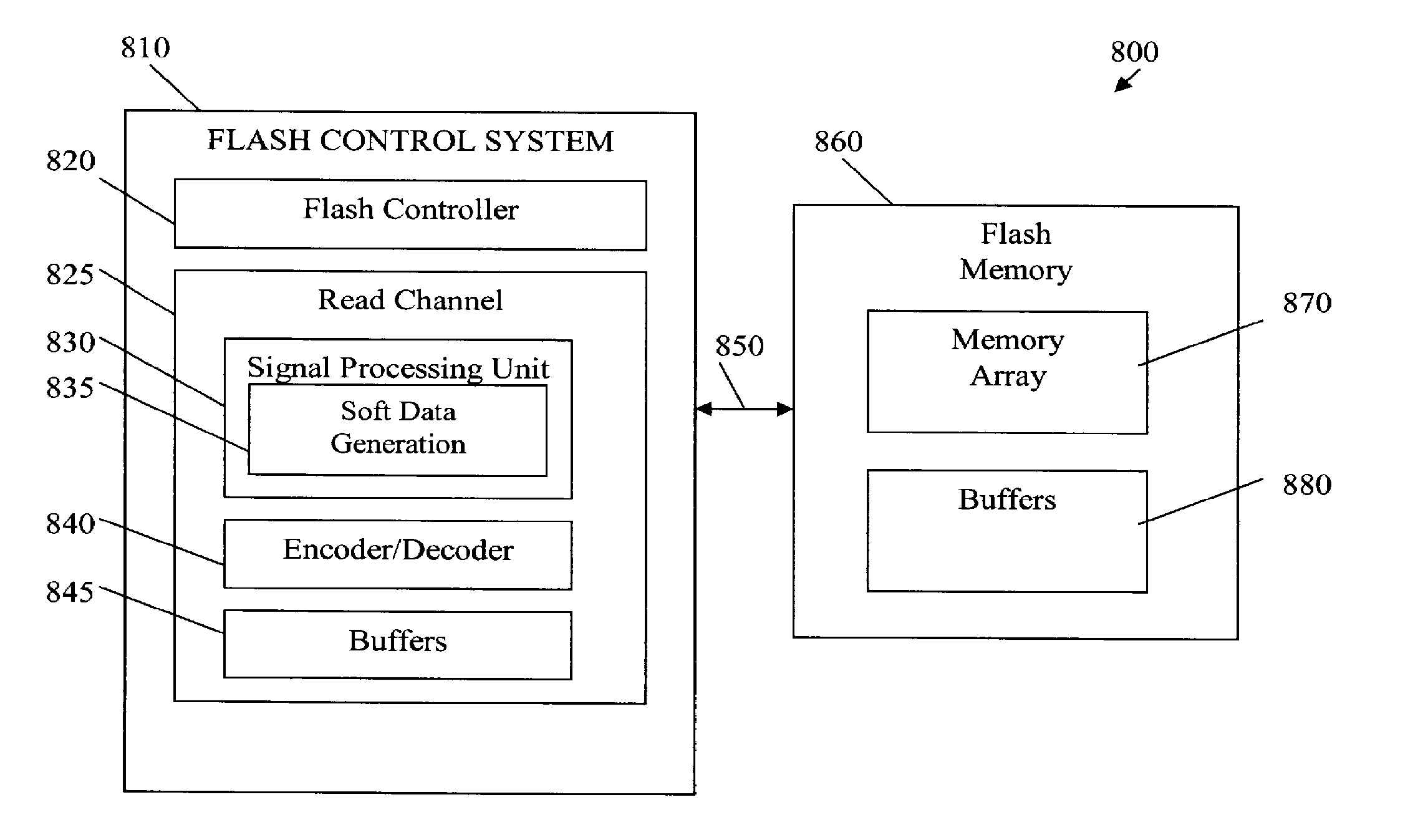

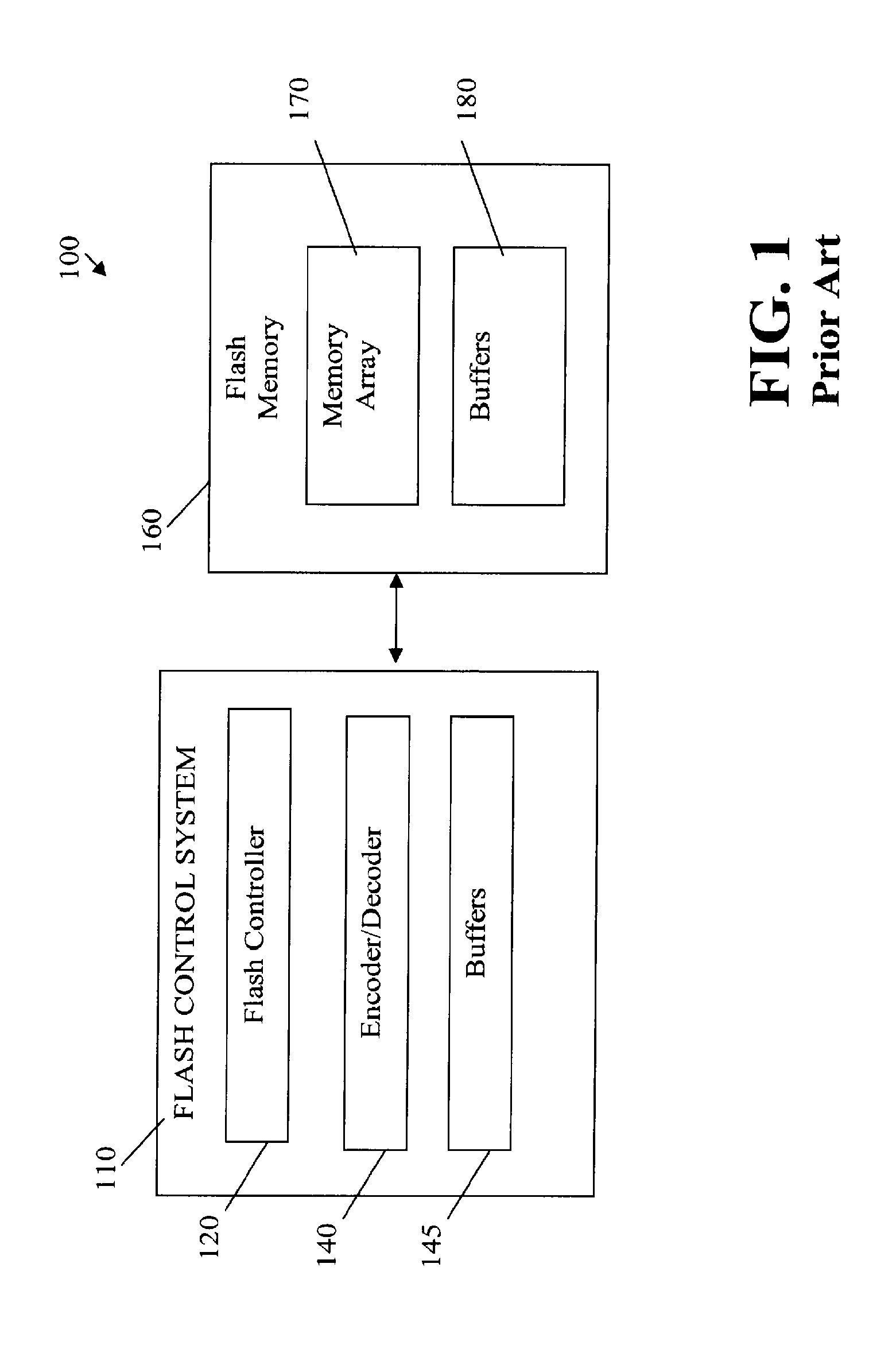

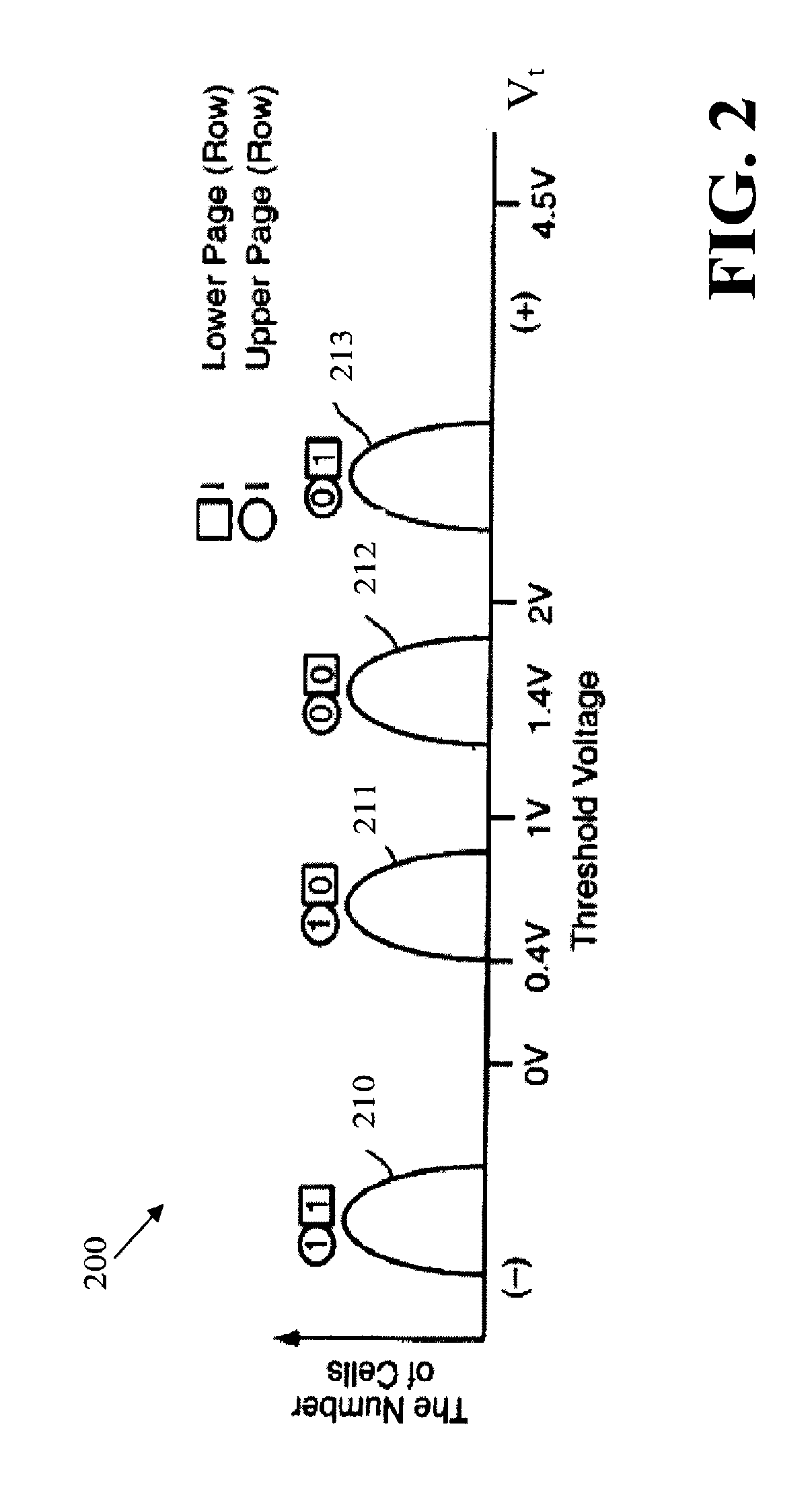

Methods and Apparatus for Soft Data Generation for Memory Devices Based on Performance Factor Adjustment

InactiveUS20110167305A1Memory architecture accessing/allocationError detection/correctionElectrical resistance and conductanceRetention time

Methods and apparatus are provided for soft data generation for memory devices based on a performance factor adjustment. At least one soft data value is generated for a memory device, by obtaining at least one read value; and generating the soft data value based on the obtained at least one read value and an adjustment based on one or more performance factors of the memory device. The read values may comprise, for example, data bits, voltage levels, current levels or resistance levels. The read values may be soft data or hard data. The possible performance factors include endurance, number of read cycles, retention time, temperature, process corner, inter-cell interference impact, location within the memory array and a pattern of aggressor cells. One or more pattern-dependent performance factors and / pr location-specific performance factors may also be considered. The generated soft data value may be a soft read value that is used to generate one or more log likelihood ratios, or may be the log likelihood ratios themselves.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

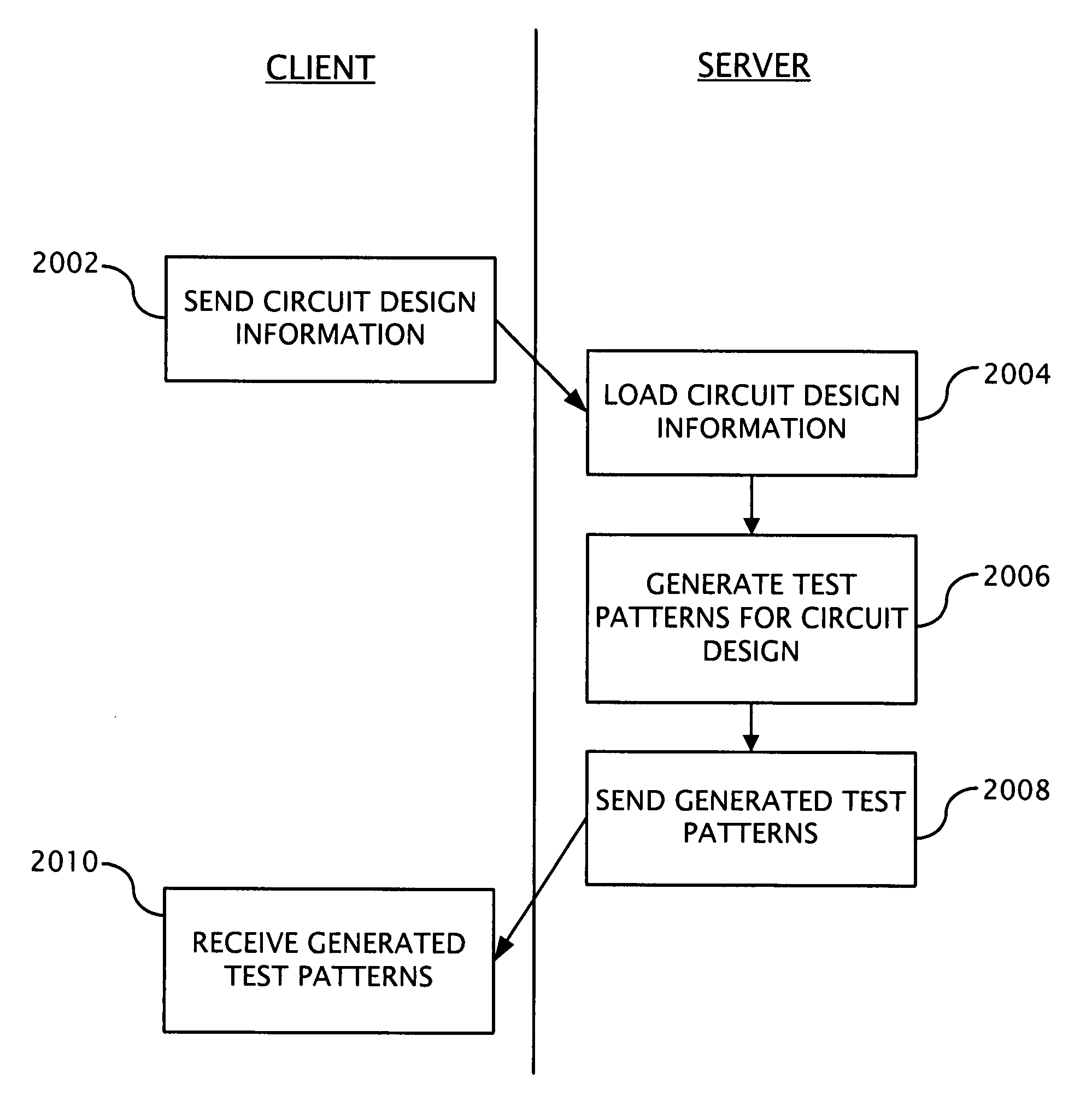

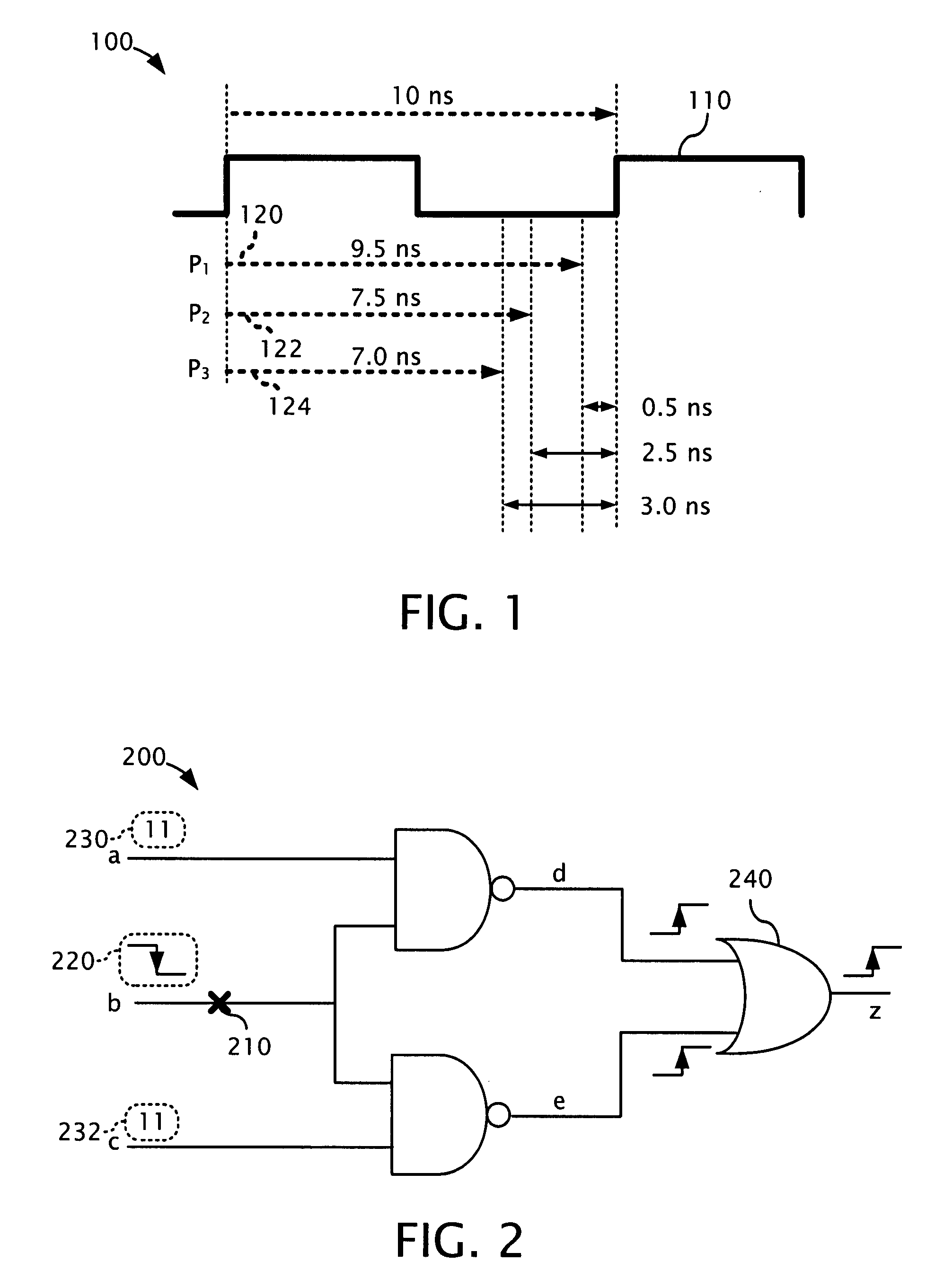

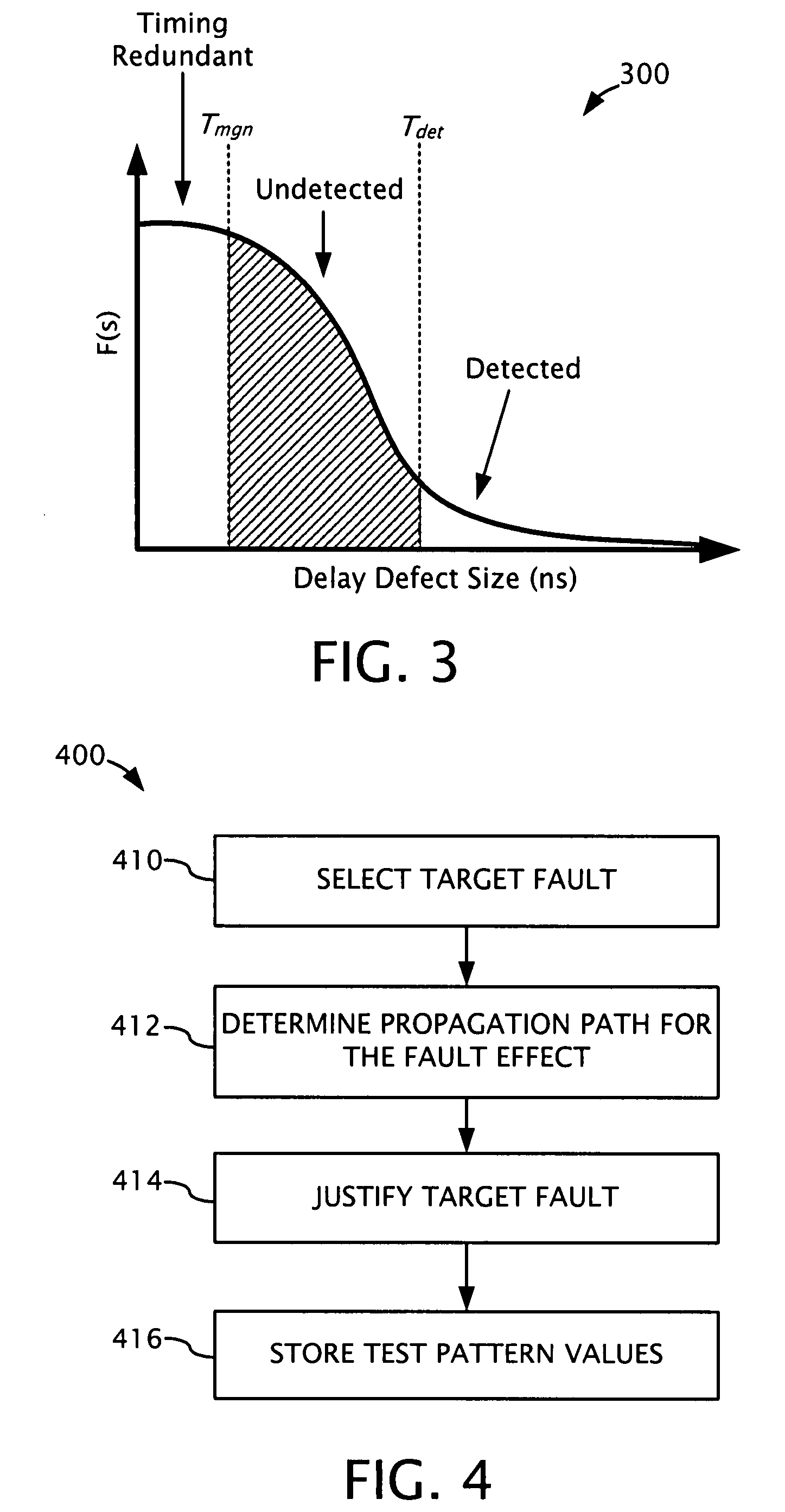

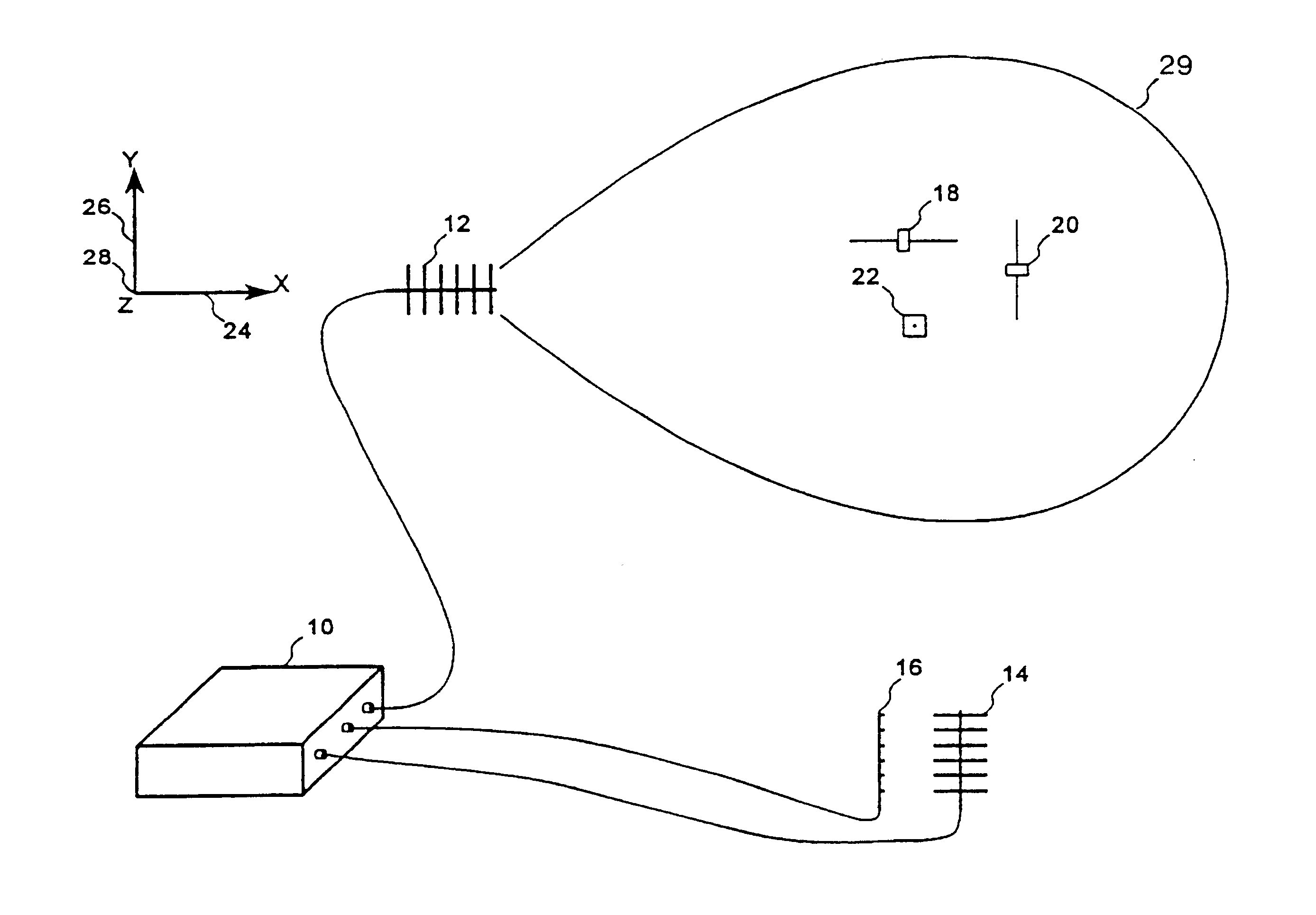

Timing-aware test generation and fault simulation

ActiveUS20070288822A1Quality improvementExpand coverageElectronic circuit testingError detection/correctionTime informationRandom method

Disclosed herein are exemplary methods, apparatus, and systems for performing timing-aware automatic test pattern generation (ATPG) that can be used, for example, to improve the quality of a test set generated for detecting delay defects or holding time defects. In certain embodiments, timing information derived from various sources (e.g. from Standard Delay Format (SDF) files) is integrated into an ATPG tool. The timing information can be used to guide the test generator to detect the faults through certain paths (e.g., paths having a selected length, or range of lengths, such as the longest or shortest paths). To avoid propagating the faults through similar paths repeatedly, a weighted random method can be used to improve the path coverage during test generation. Experimental results show that significant test quality improvement can be achieved when applying embodiments of timing-aware ATPG to industrial designs.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

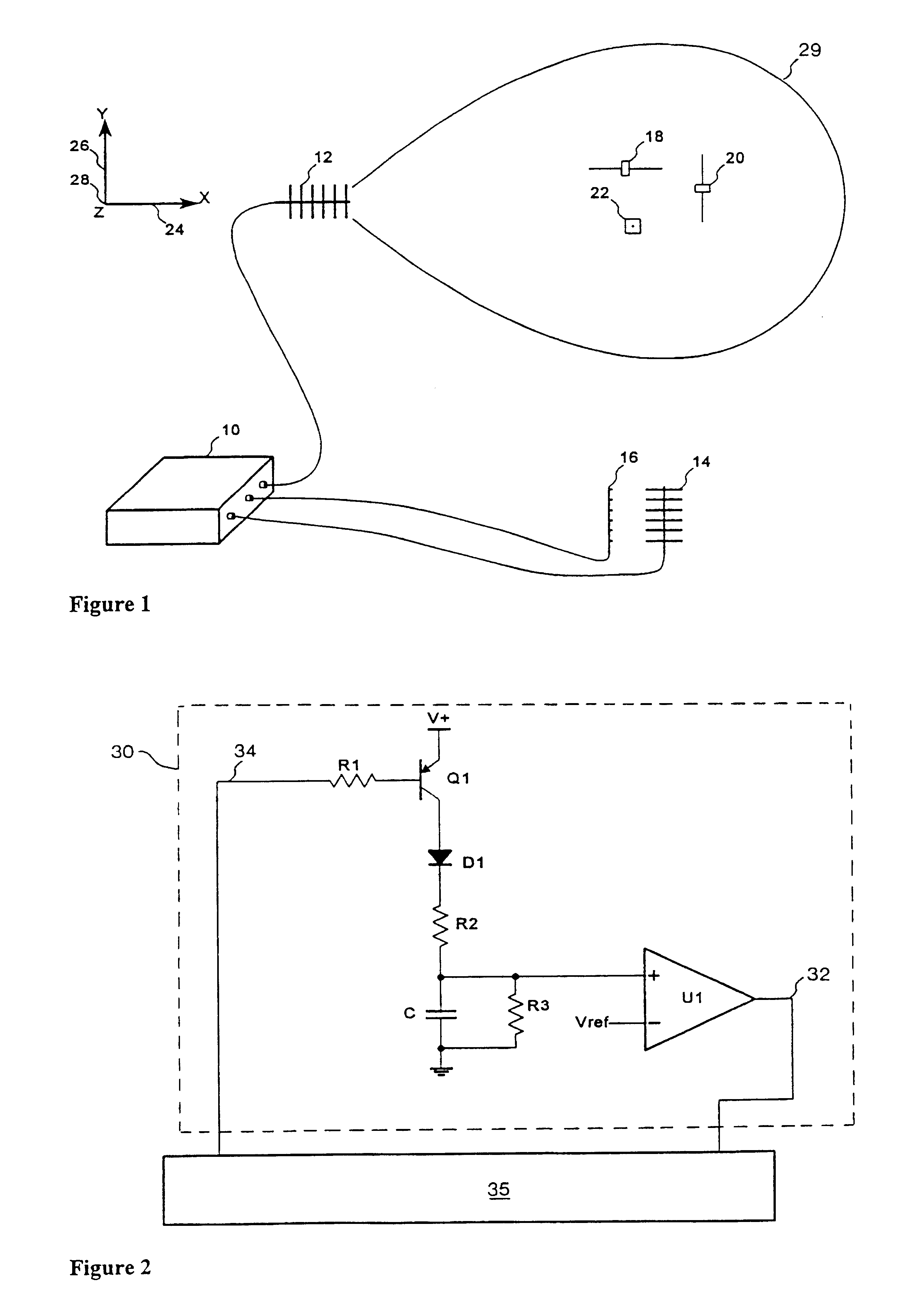

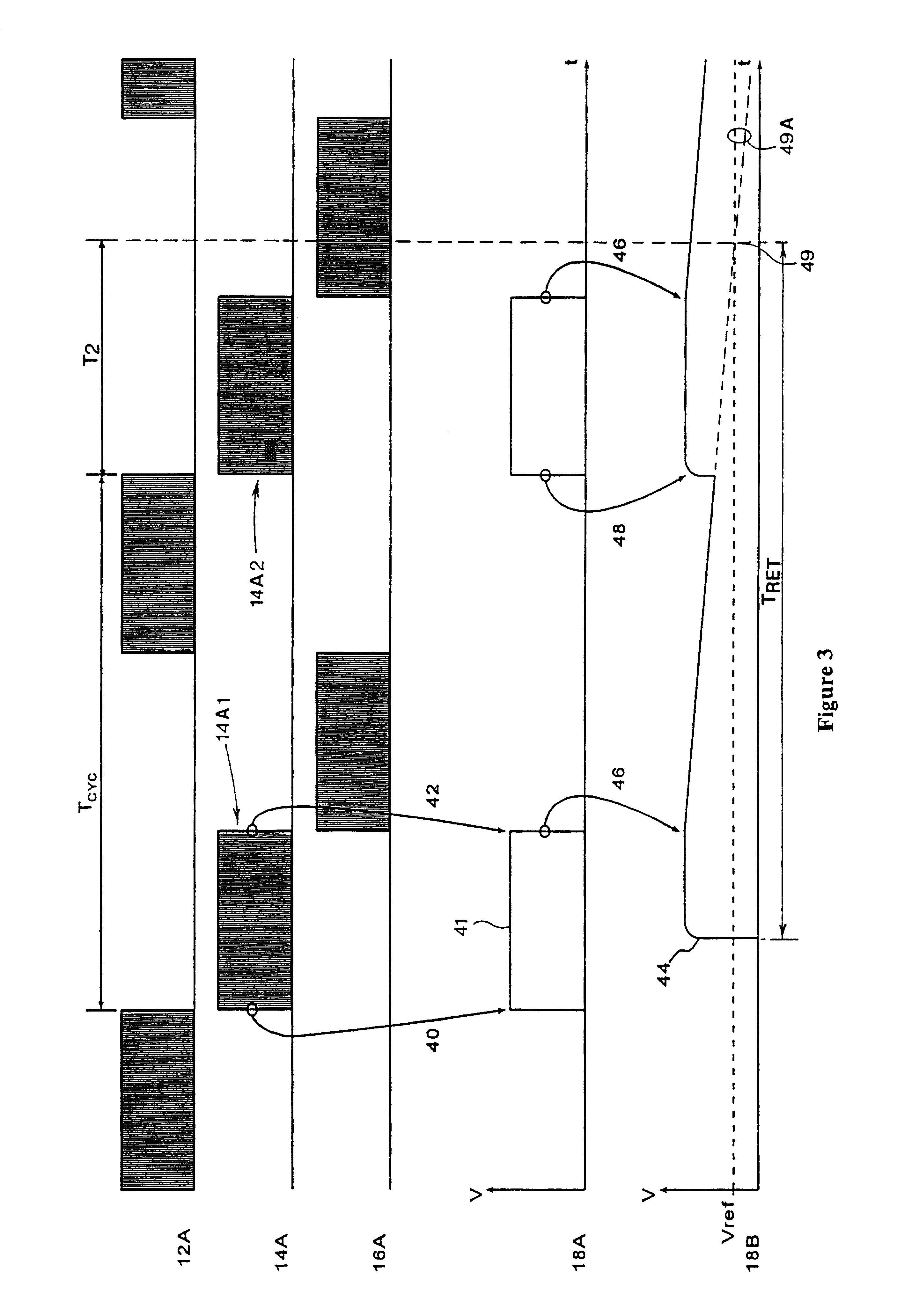

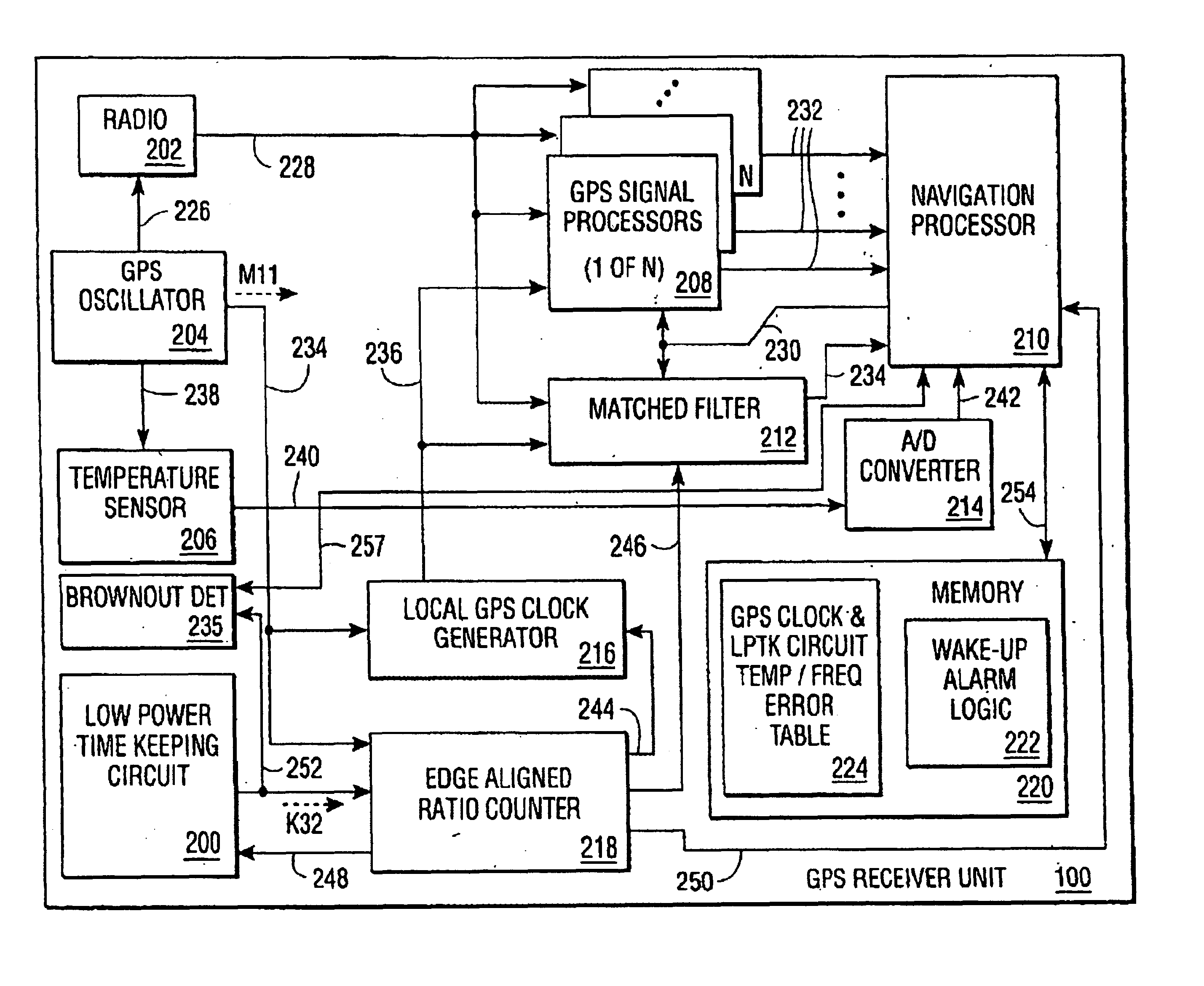

Multi-dimensional electronic identification of articles

InactiveUS6909366B1Avoid spreadingMemory record carrier reading problemsCo-operative working arrangementsMemory retentionObject based

An identification system is provided for identifying a plurality of randomly aligned object-based transponders (18, 20, 22) passing through a predetermined reading volume. A reader (10) includes multiple transmitting and receiving antenna arrays (12, 14, 16) which are arranged sequentially to transmit interrogating and energizing fields (29) into the reading volume, with each energizing field having a different polarisation. Each transponder (12, 14, 16) is arranged to be powered by at least one of the interrogating and energizing fields, and includes a short term memory module (30) which is arranged to record the successful transmission or otherwise of the identification signal of the transponder (20) and to retain the record in the absence of a power supply to the transponder. The short term memory module has a retention time longer than any predicted interruption of power supply to the transponder via one of the energizing fields within the reading volume. The minimum memory retention time is typically the time period taken for the sequential transmission of all but one of the interrogating and energizing fields (29) during an interrogation cycle.

Owner:TROLLEY SCAN

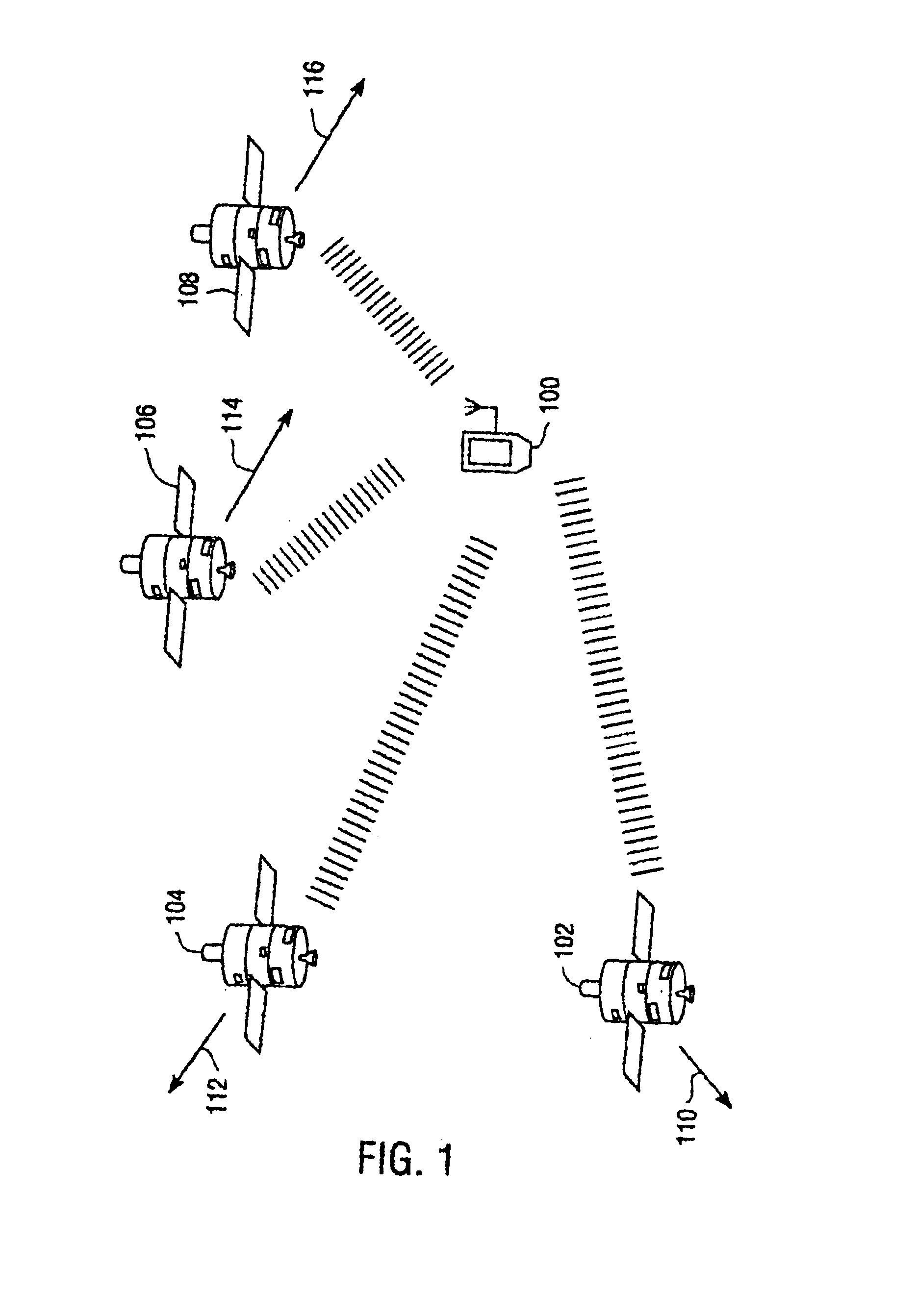

Method and apparatus for real time clock (RTC) brownout detection

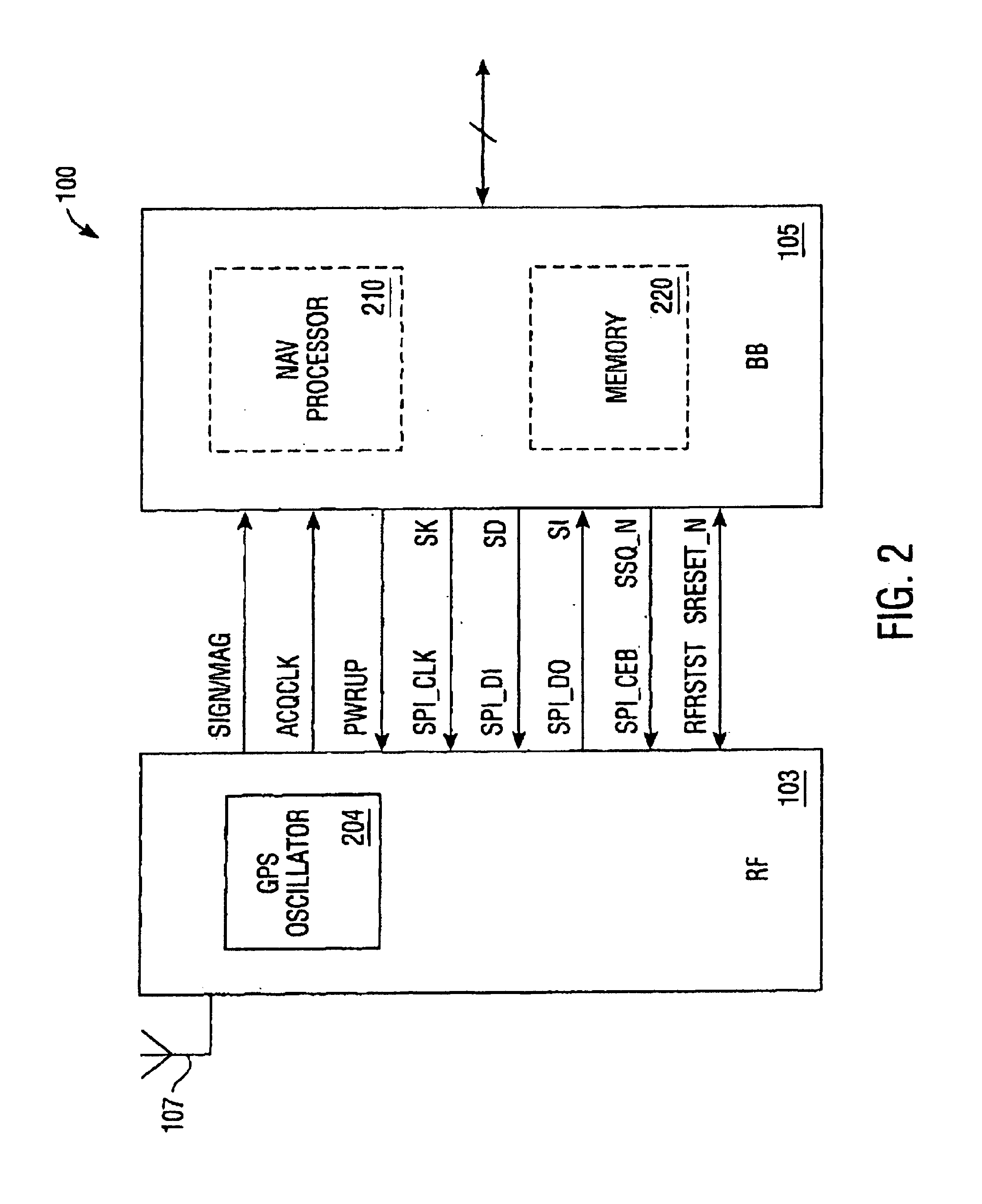

InactiveUS6985811B2Energy efficient ICTInstruments for road network navigationDetector circuitsReal-time clock

A method and apparatus for real time clock brownout detection. A low power real time clock (RTC) operates continuously to keep time in a global positioning system (GPS) receiver while some receiver components are powered down. In various embodiments, a brownout detector circuit detects a loss of RTC clock cycles. If a loss of RTC clock cycles exceeds a predetermined threshold such that the RTC is not reliable for GPS navigation, an RTC status signal so indicates.

Owner:SAMSUNG ELECTRONICS CO LTD

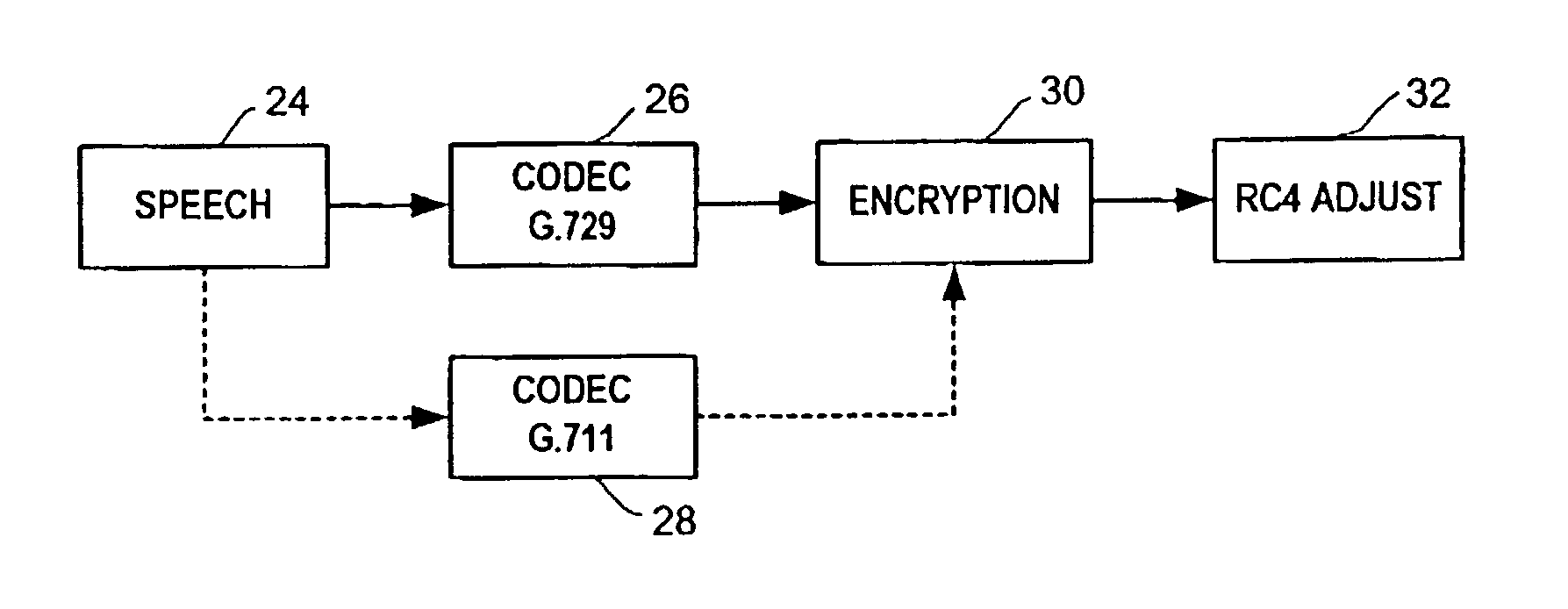

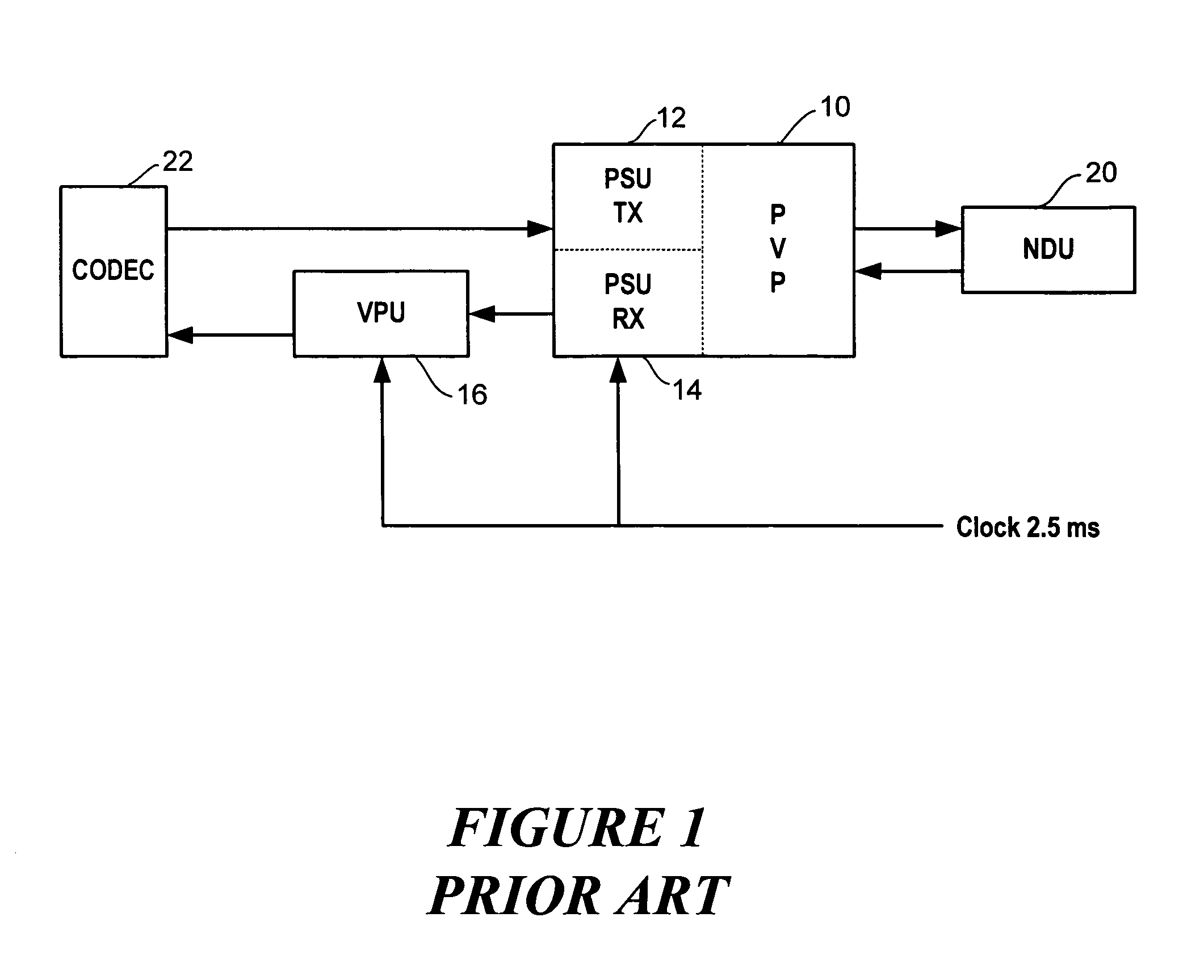

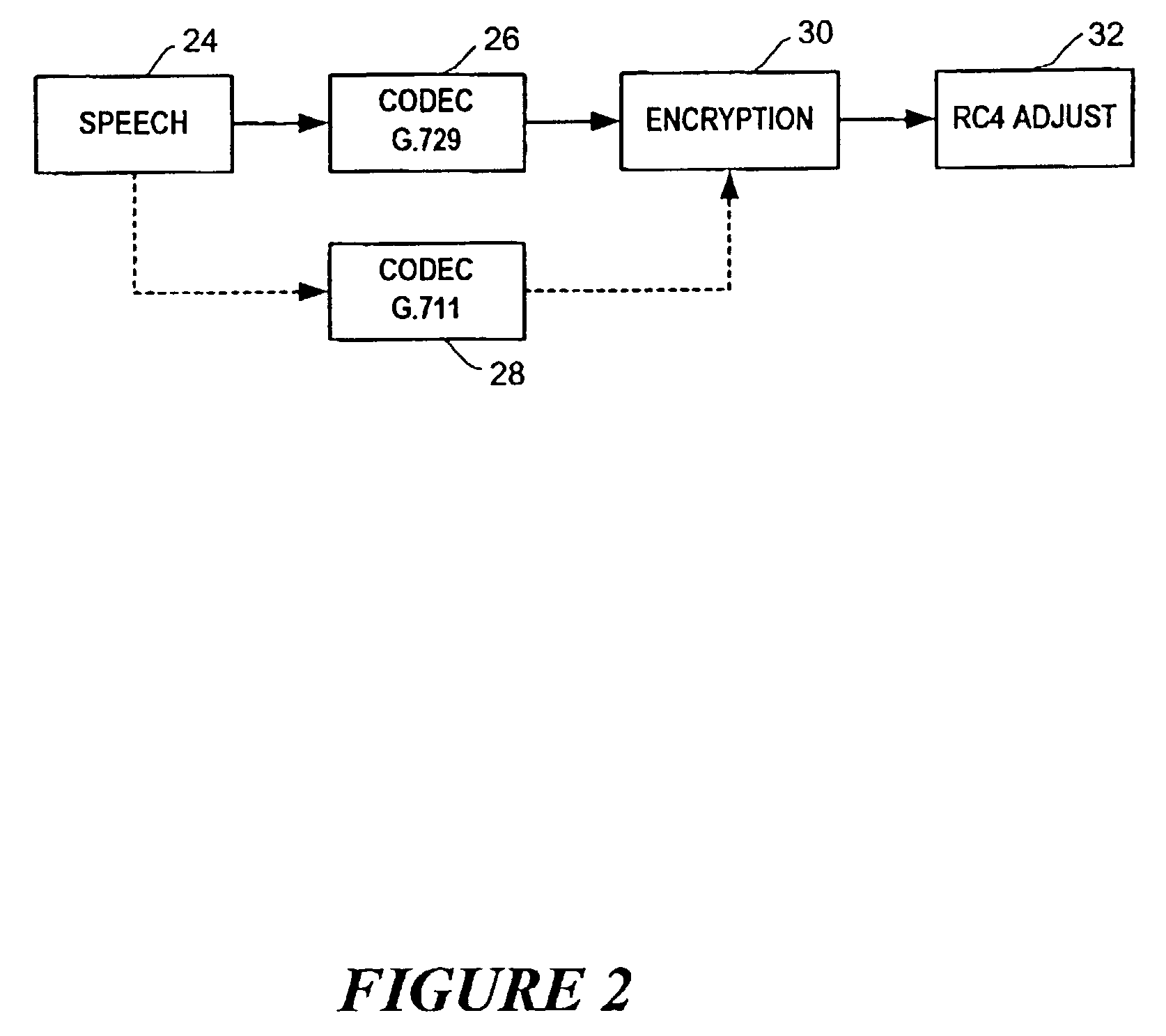

Changing a codec or MAC size without affecting the encryption key in PacketCable communication

ActiveUS7127604B2Synchronising transmission/receiving encryption devicesError detection/correctionComputer hardwareRC4

A technique is described to change the codec or MAC (message authentication code) size in a packet security unit for PacketCable communications during realtime voice transmissions is described. An algorithm that provides fast RC4 key advancing to prevent MIPS (millions of instruction cycles per second) overflow is used to perform codec or MAC size changes. The invention is performed without changing the keying material, where the sender and receiver must continue the RC4 encryption process from its state prior to the codec or MAC size change. A sender needs to preserve continuity of the timestamp across a codec change, since the timestamp reflects realtime. Changing the codec or MAC size is likely to change the frame parameters. To preserve continuity of the RC4 state and the timestamp across the codec / MAC size change, the sender TX and receiver RX generates a new frame number. The new frame number is applied to the first frame generated by the new codec or MAC size.

Owner:TELOGY NETWORKS

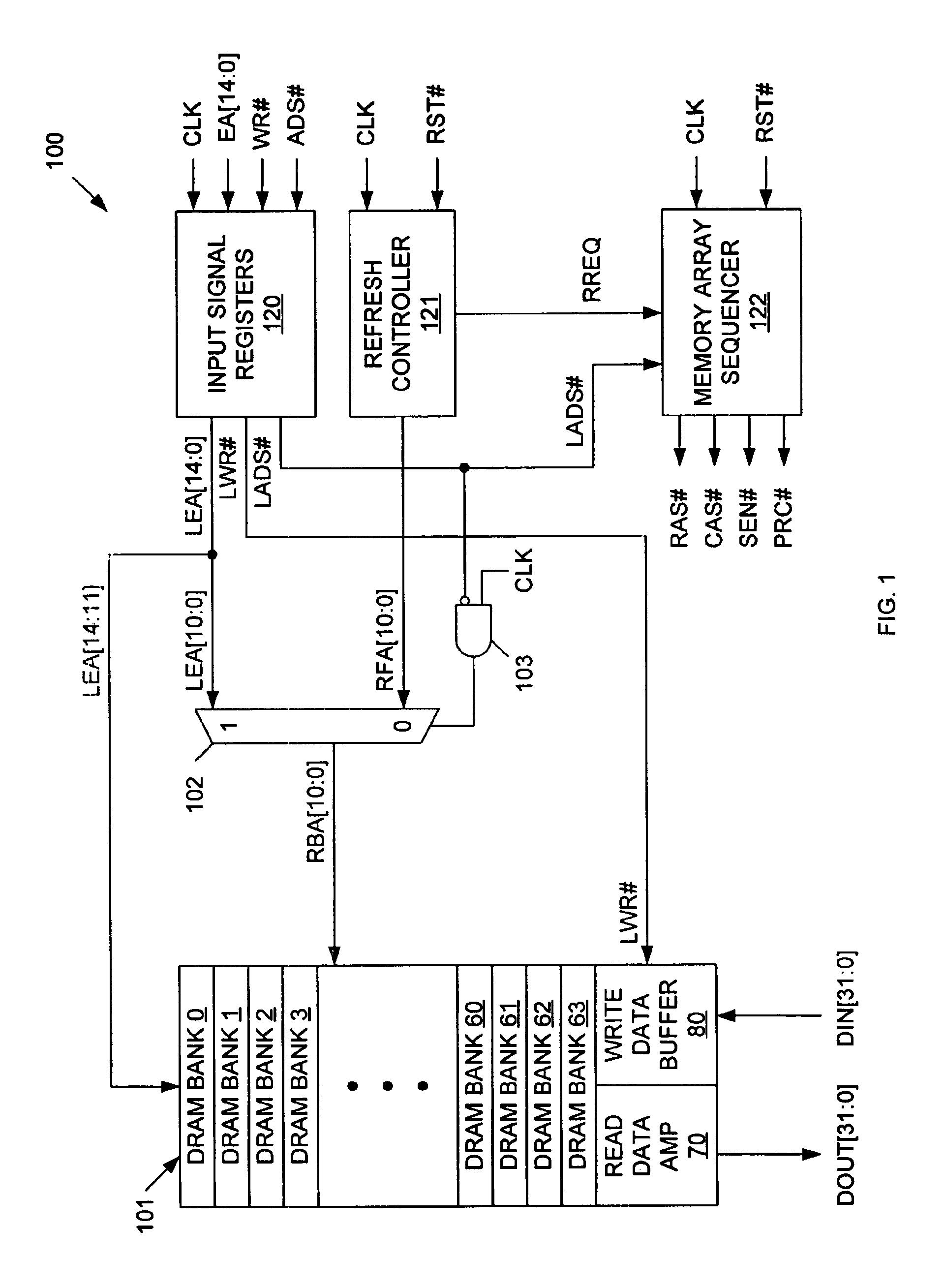

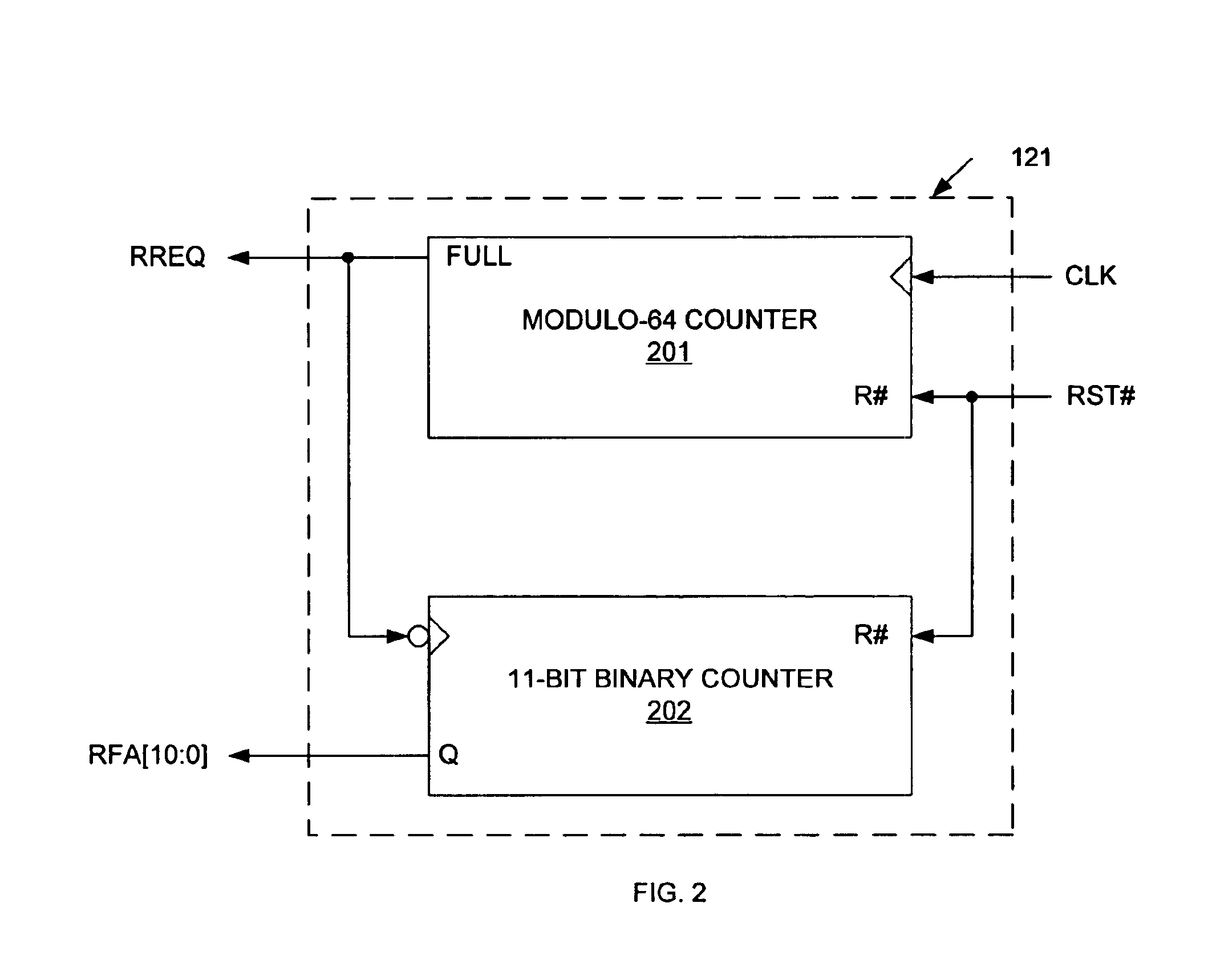

Method and apparatus for temperature adaptive refresh in 1T-SRAM compatible memory using the subthreshold characteristics of MOSFET transistors

A memory system is provided that includes an array of memory cells that require periodic refresh, and a temperature-adaptive refresh controller. Data retention time of the memory cells decreases exponentially as temperature increases. The temperature-adaptive refresh controller selects the refresh period of the memory cells in response to the subthreshold current of a reference transistor. The subthreshold current of the reference transistor increases exponentially as temperature increases As a result, the refresh period is empirically tied to the data retention time. Consequently, the power required for refresh operations decreases as temperature decreases. Power is therefore conserved in applications that operate predominantly at room temperature.

Owner:INVENSAS CORP

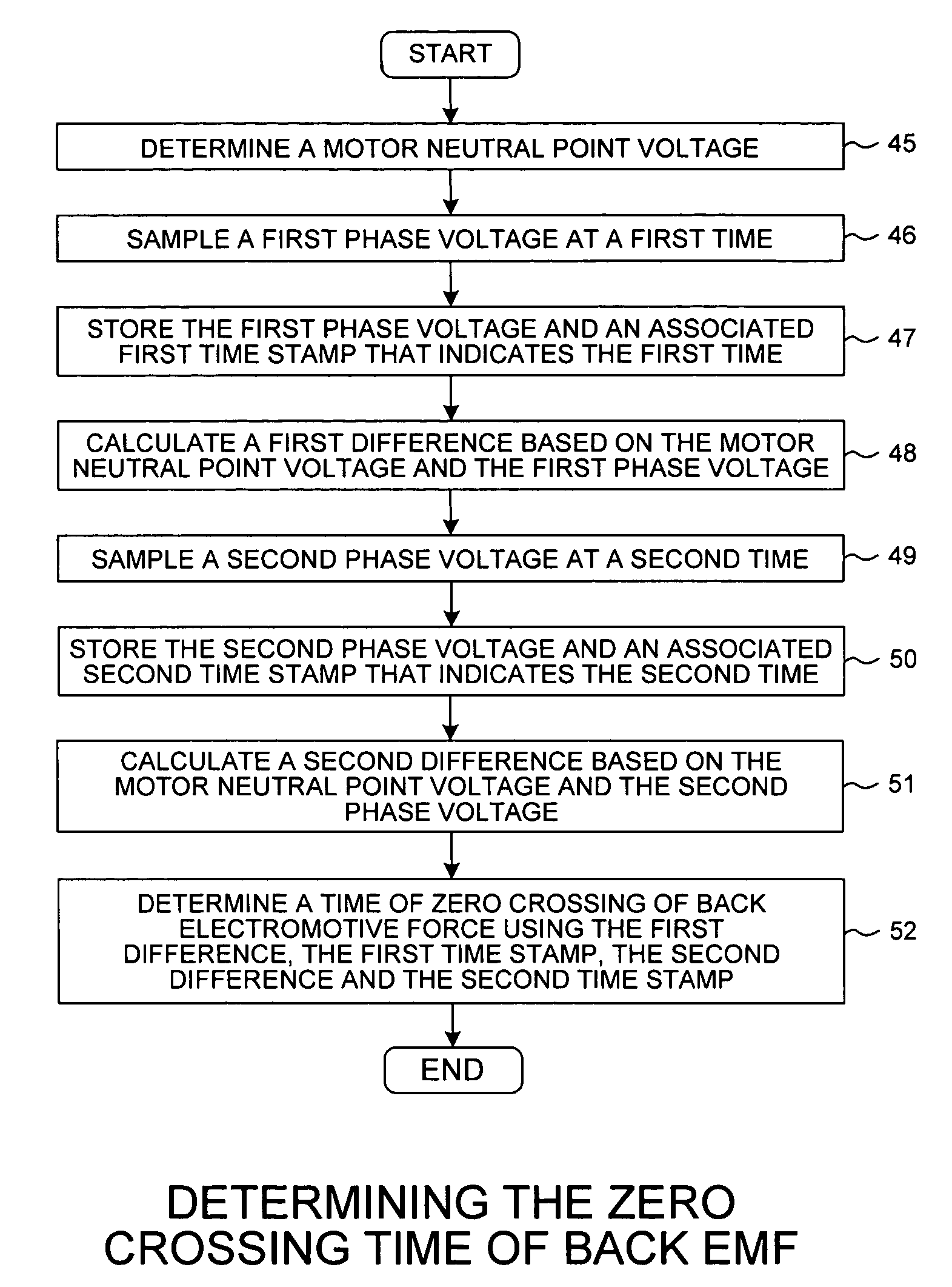

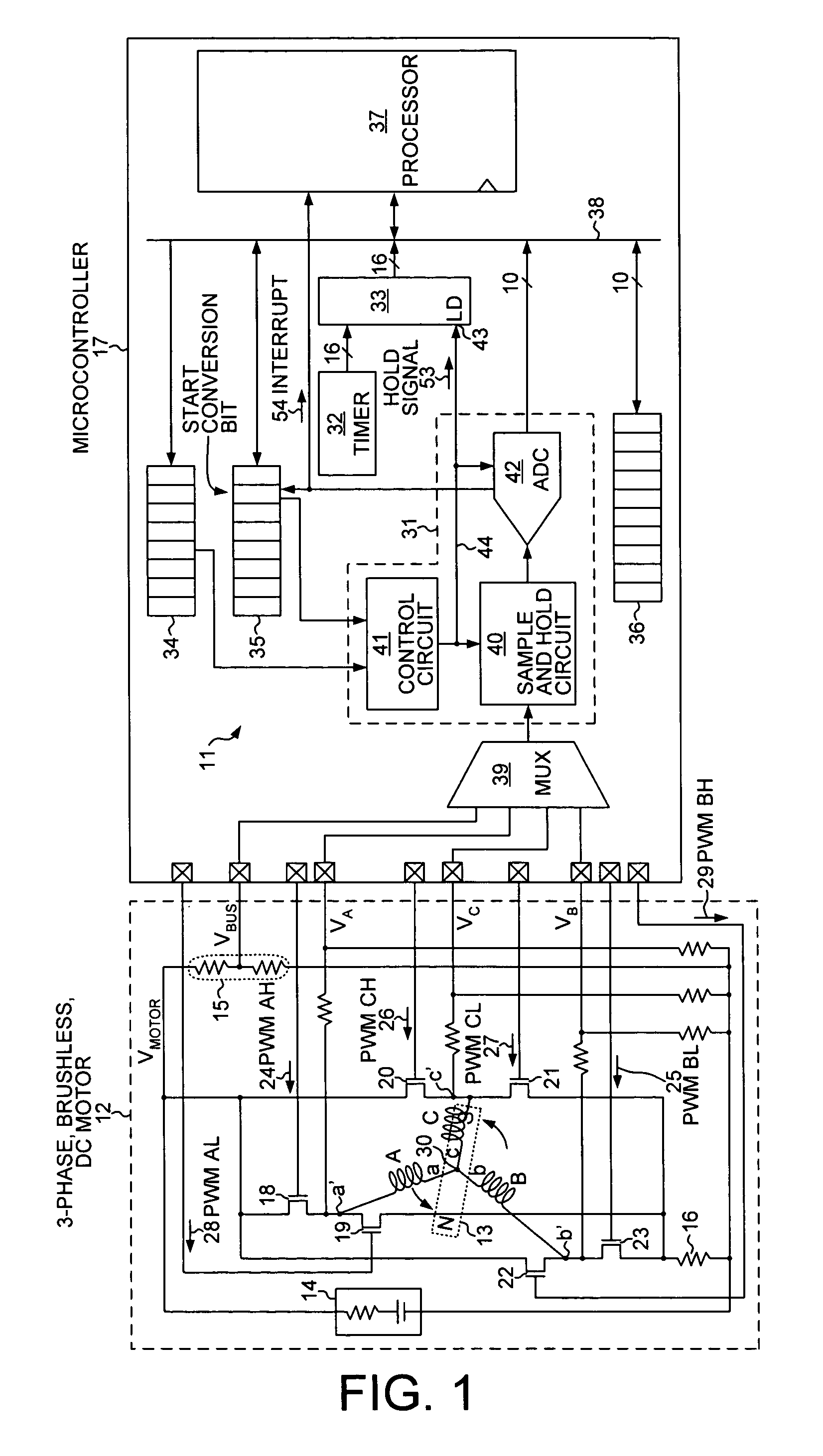

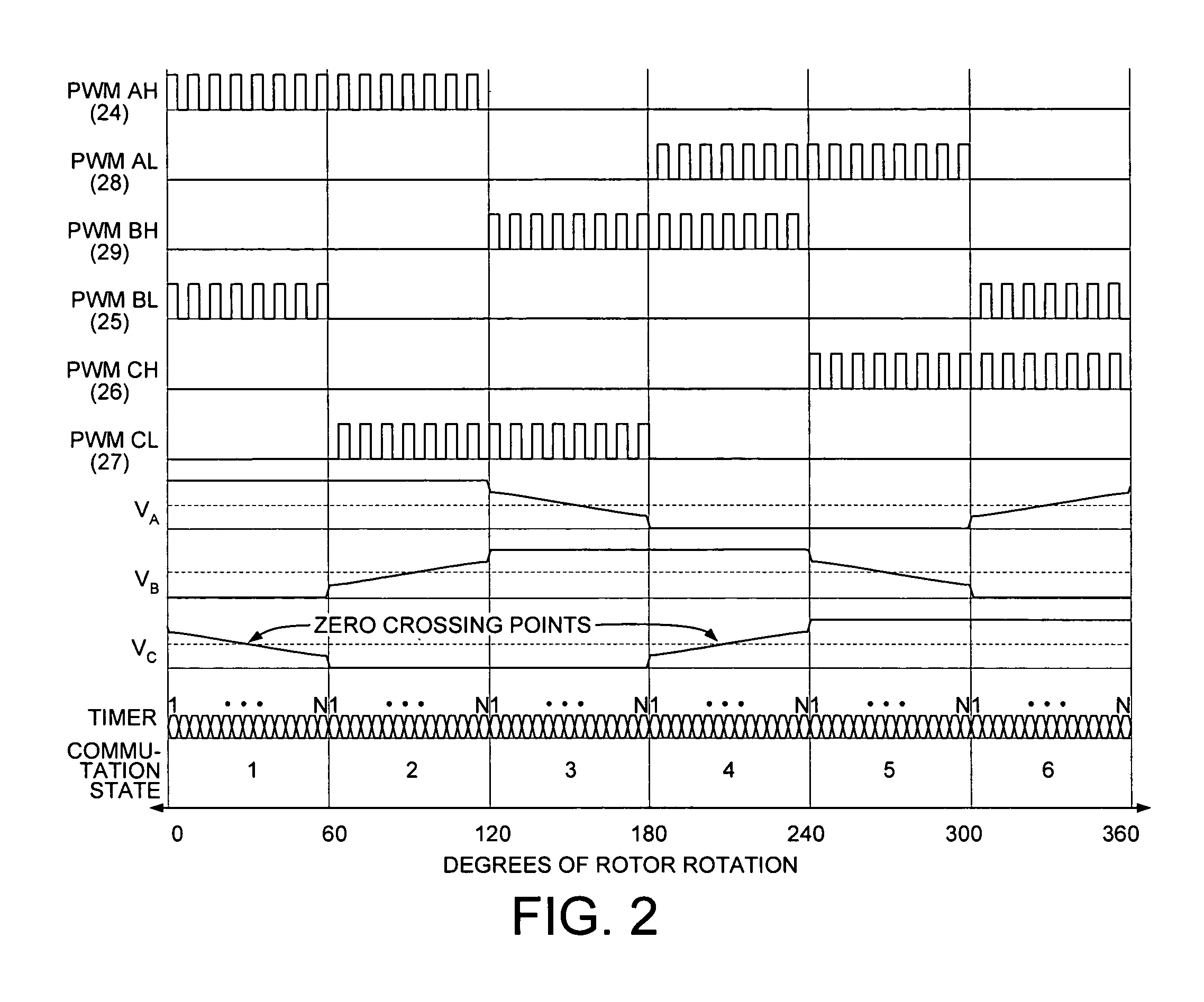

Sample and hold time stamp for sensing zero crossing of back electromotive force in 3-phase brushless DC motors

InactiveUS8030867B1Motor/generator/converter stoppersSynchronous motors startersMicrocontrollerEngineering

A microcontroller determines the position of the rotor of a brushless, direct-current motor by determining the time of zero crossing of back electromotive force (EMF) emanating from the non-driven phase winding. The zero crossing point is determined by interpolating voltage differentials that are time stamped. Each voltage differential is the difference between the phase voltage of the phase winding and the motor neutral point voltage. The time of zero crossing is determined without using a comparator and without interrupting the processor at each zero crossing point. The processor interpolates the time of zero crossing independently of when the zero crossing point occurs. A hold signal conductor is connected both to a sample and hold circuit and to the load input lead of a time stamp register. The microcontroller simultaneously captures a phase voltage in the sample and hold circuit and a timer count in the time stamp register.

Owner:IXYS INTL LTD

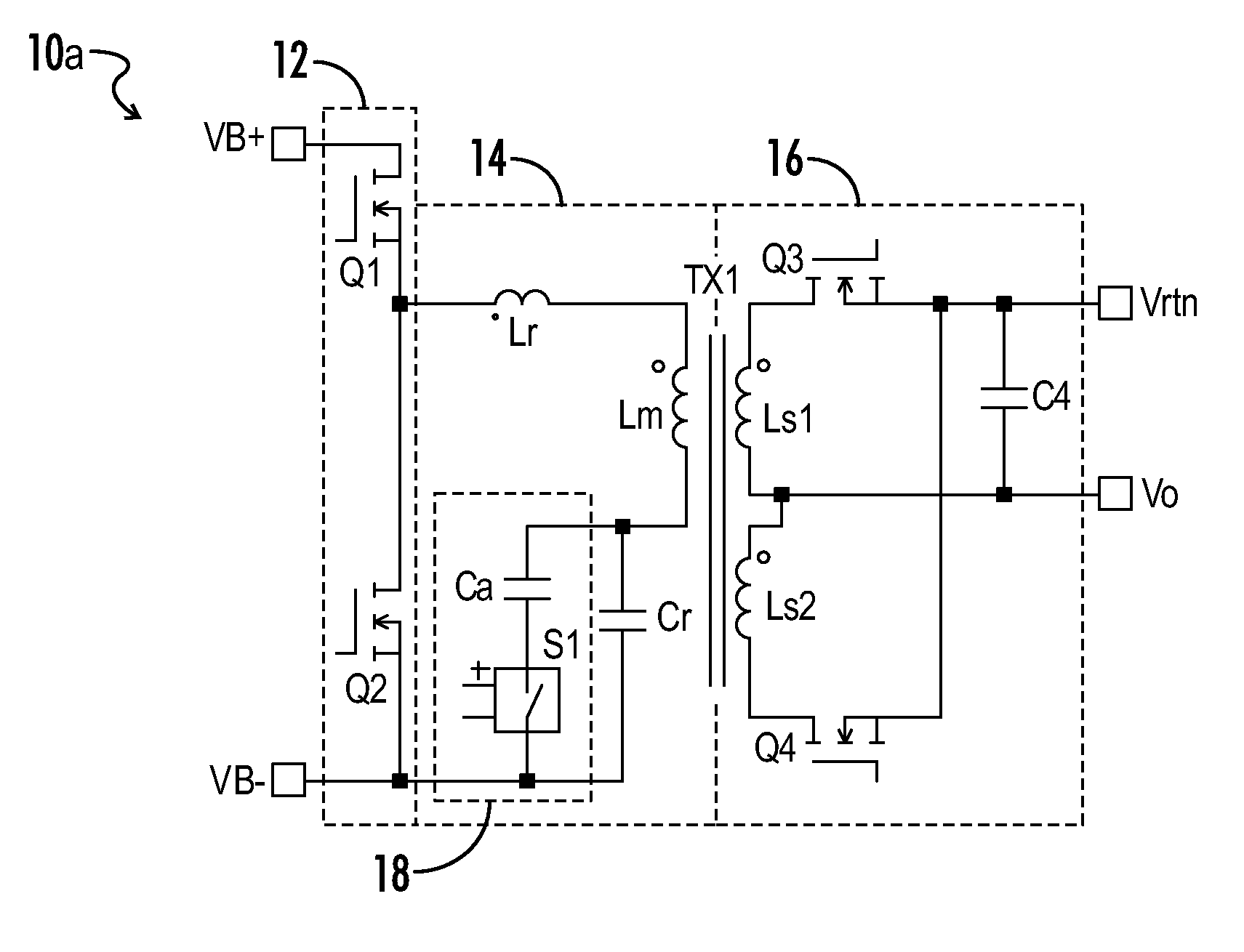

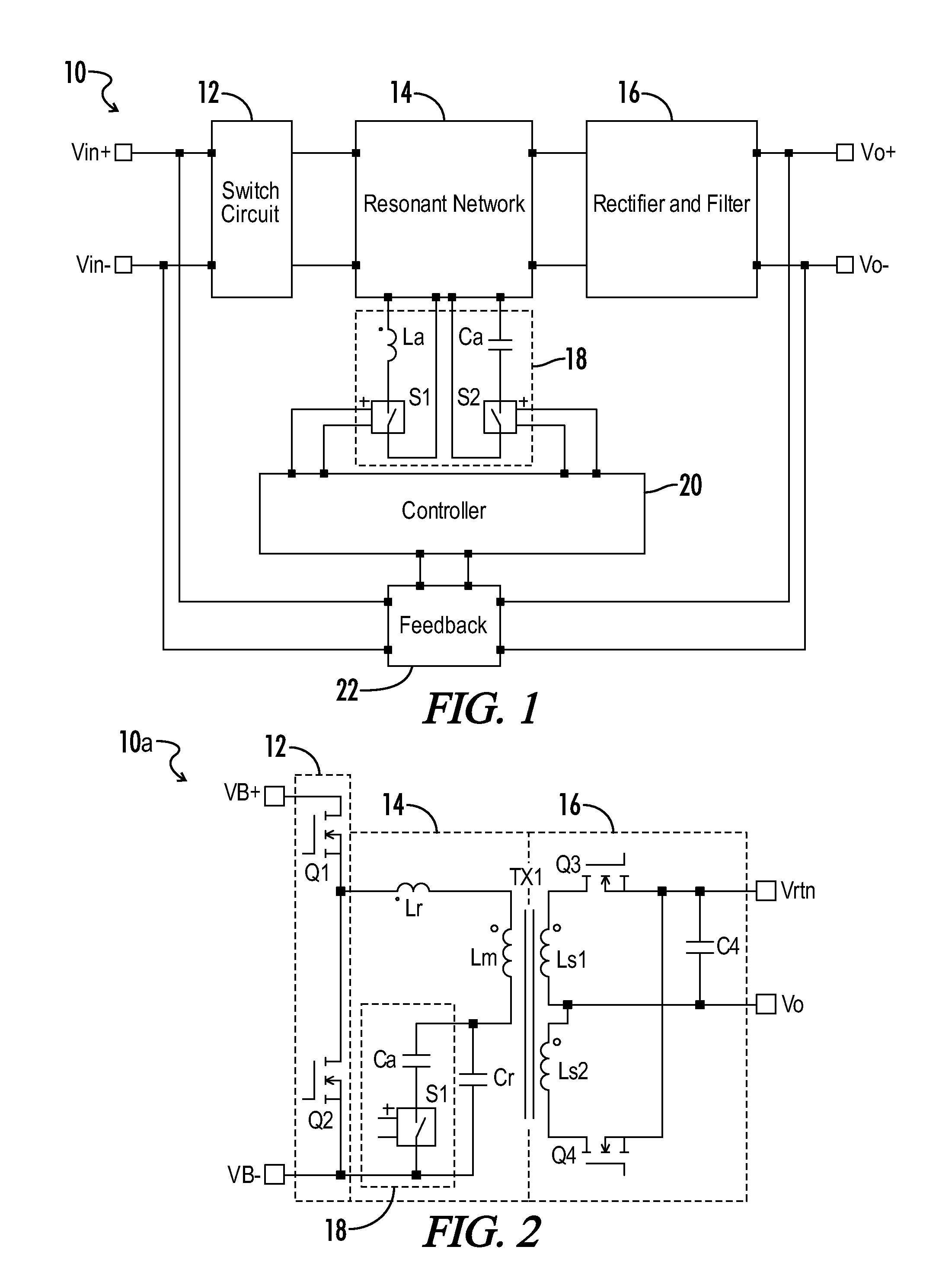

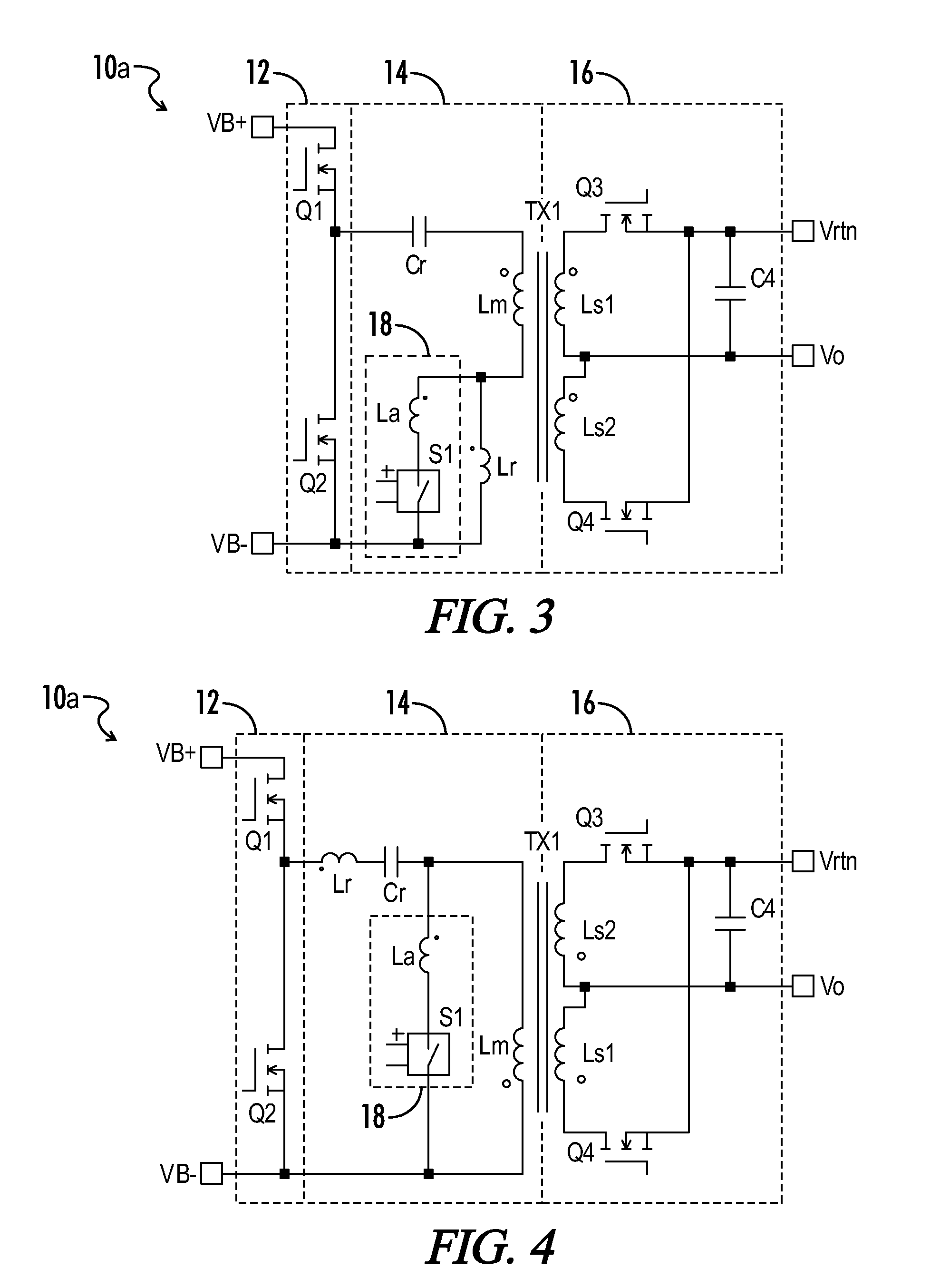

Resonant converter with auxiliary resonant components and holdup time control circuitry

InactiveUS20130194831A1Improve efficiencyLow efficiencyEfficient power electronics conversionDc-dc conversionResonant inverterCapacitance

A resonant power converter is provided with auxiliary circuit branches and control circuitry for switchably coupling the auxiliary branches to resonant circuit components during holdup times. Auxiliary branches are coupled in parallel with any one or more of a resonant inductor, a resonant capacitor, and a magnetizing inductive winding via respective switches. When a holdup time condition is detected in accordance with, for example, a drop in the mains line voltage, the switches are controlled to adjust the corresponding inductance or capacitance for the duration of the holdup time condition or otherwise for a predetermined duration. The power converter in normal operation is configured for high efficiency and in a holdup time operation is configured to produce sufficient holdup time.

Owner:BEL POWER SOLUTIONS INC

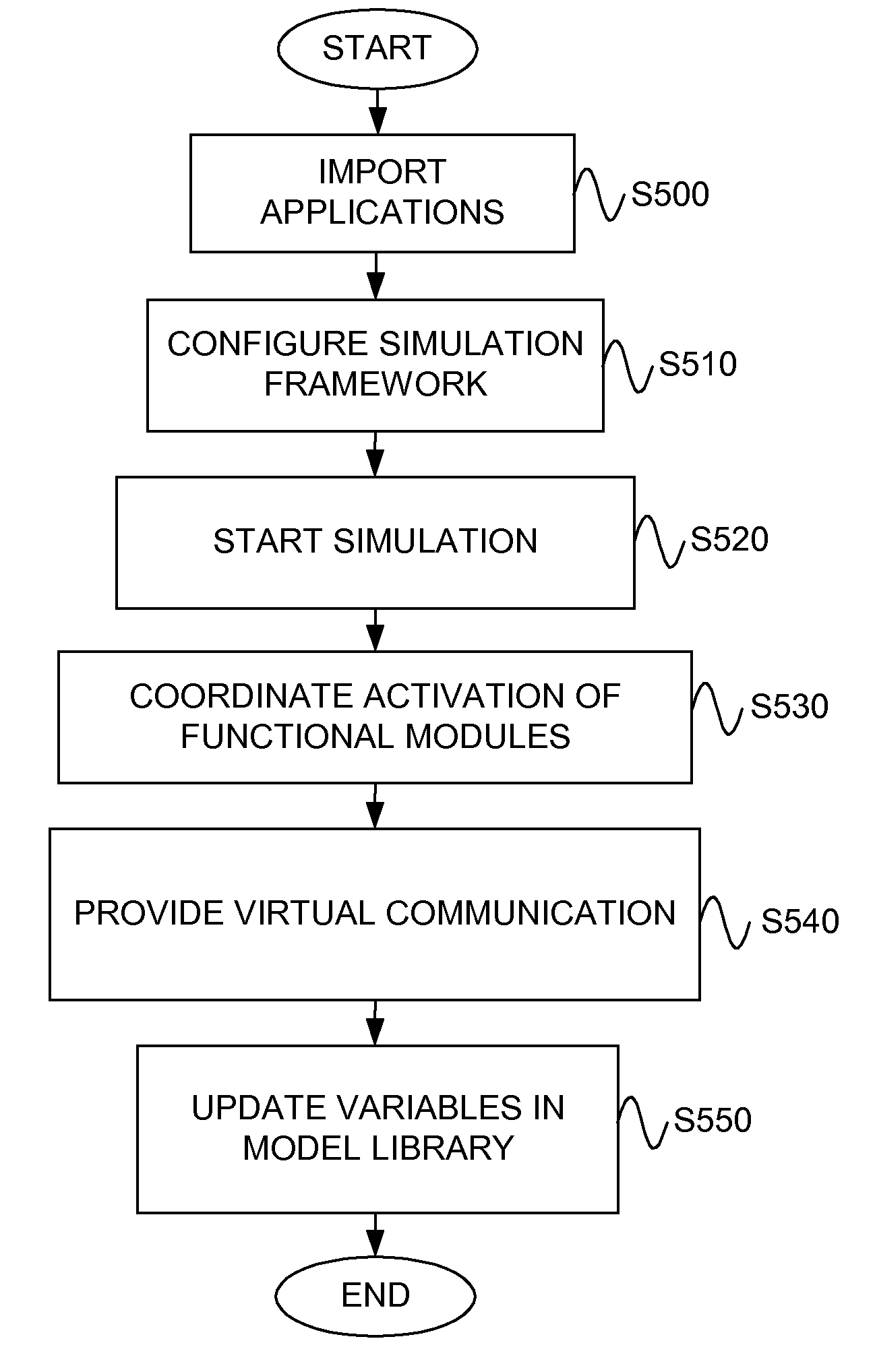

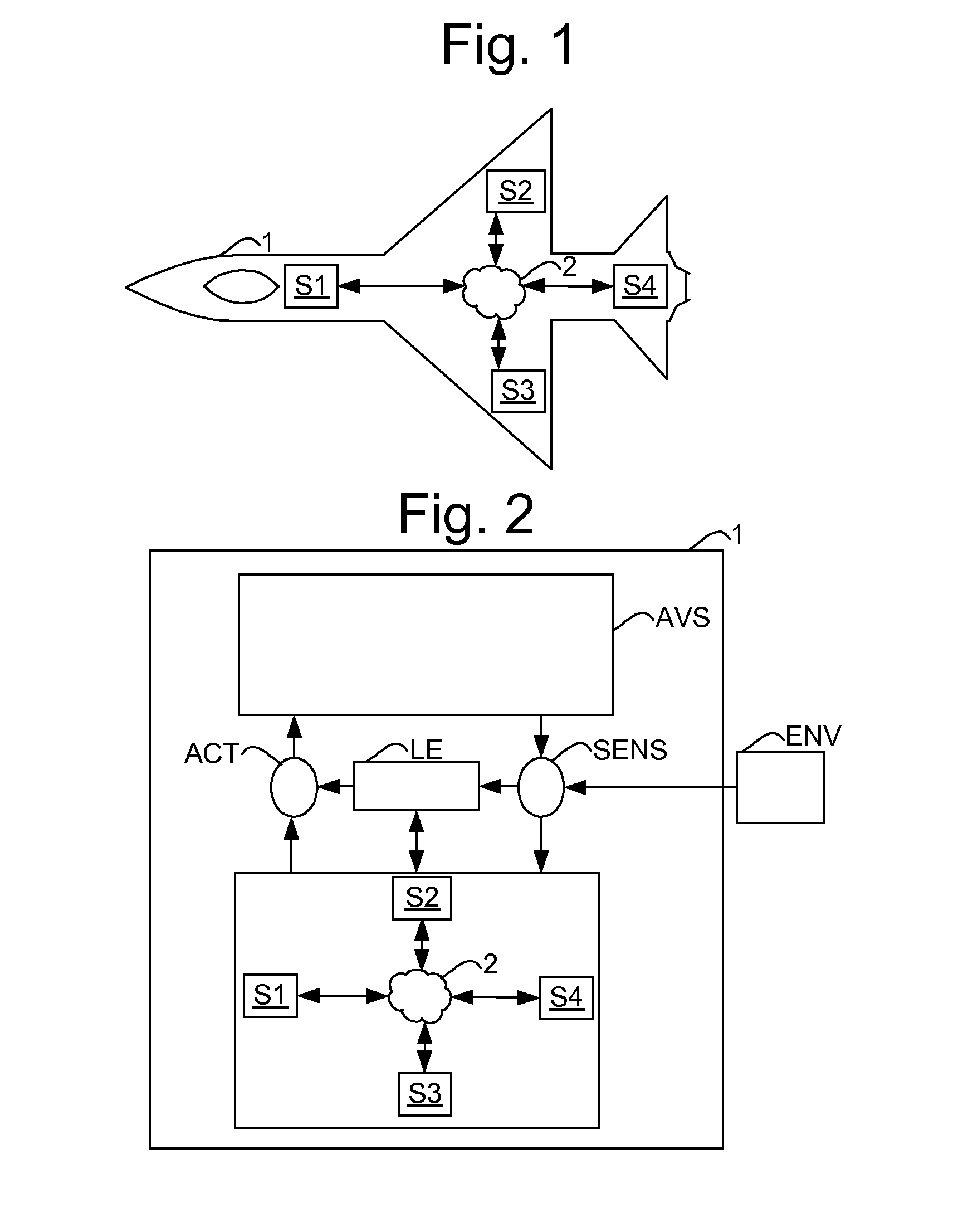

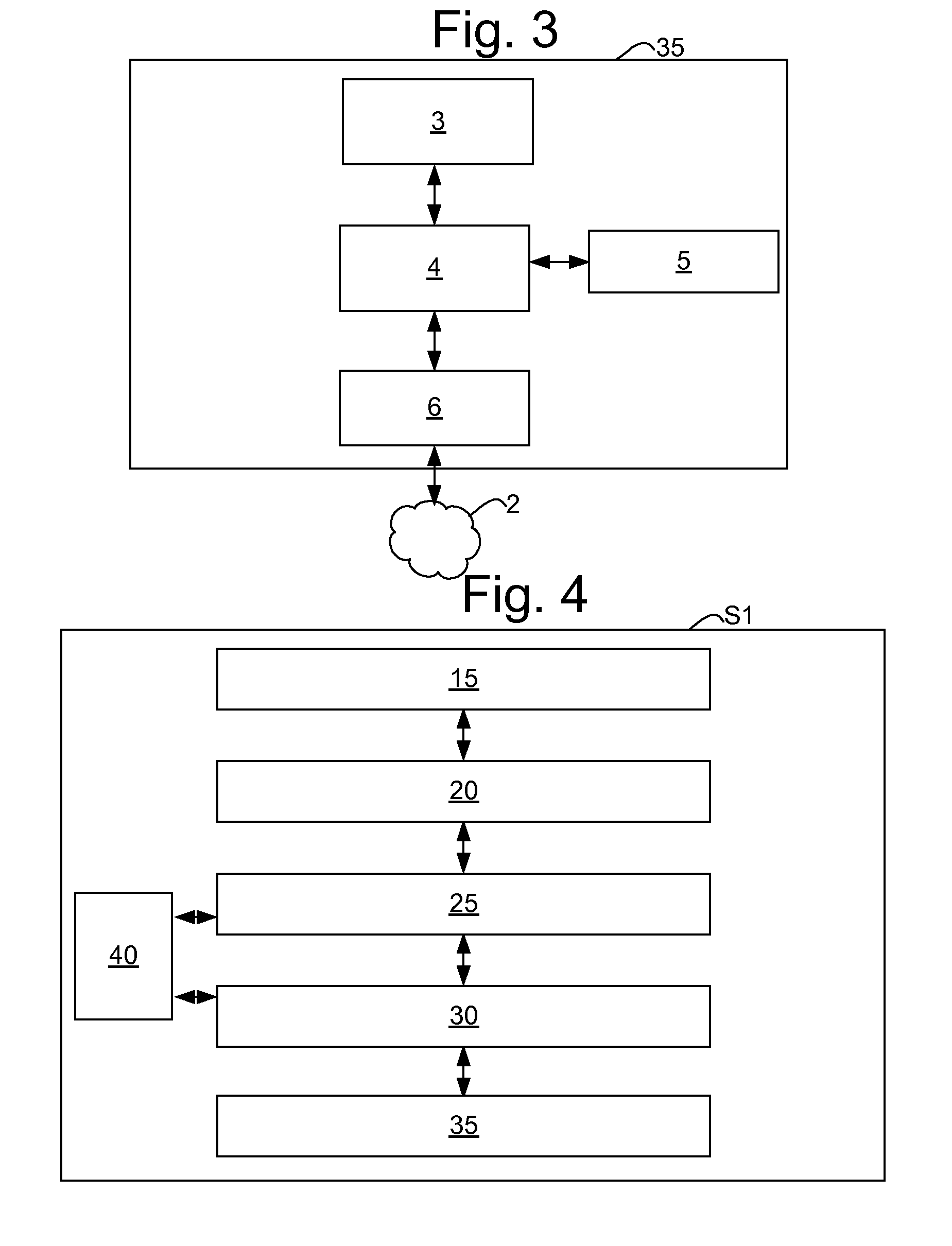

Simulating and testing avionics

InactiveUS20130166271A1High simulationEasy to testError detection/correctionDesign optimisation/simulationAviationControl system

An avionics application host system and method for simulating and / or testing a plurality of partitioned applications arranged to be periodically executed on a target system. The target system is a distributed avionics control system of an aerial vehicle. The host system includes a plurality of functional modules. The plurality of functional modules includes: an application module arranged to import the plurality of partitioned applications in un-modified form, a configuration module arranged to configure the operations of the host system, at least one communication module arranged to provide communication between the partitioned applications, a control module arranged to provide coordinated execution time to the functional modules, a service module associated to each imported partitioned application arranged to provide services to the imported partitioned applications so as to enable execution of the imported partitioned applications and to preserve the temporal order of events related to communication and execution.

Owner:SAAB AB

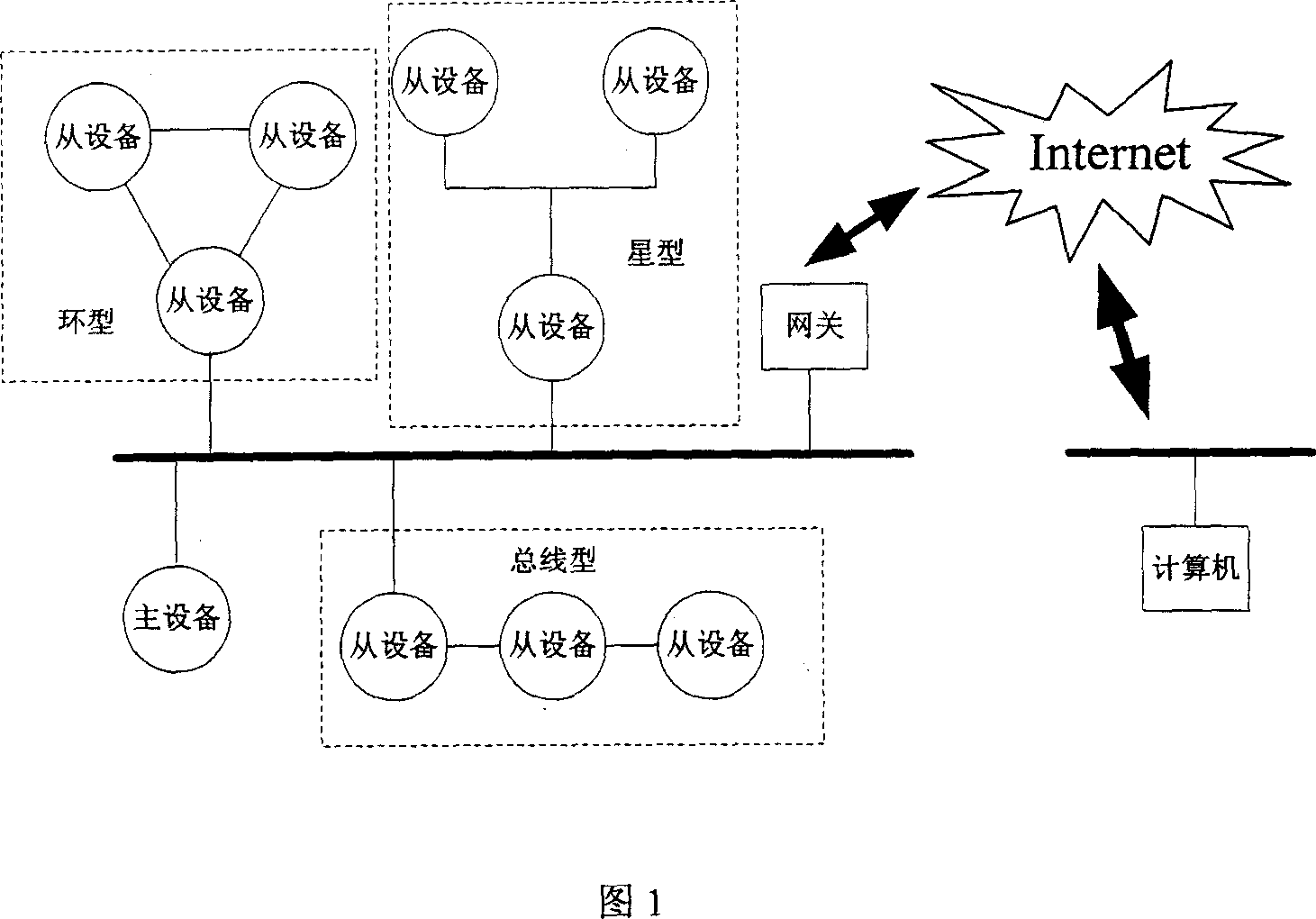

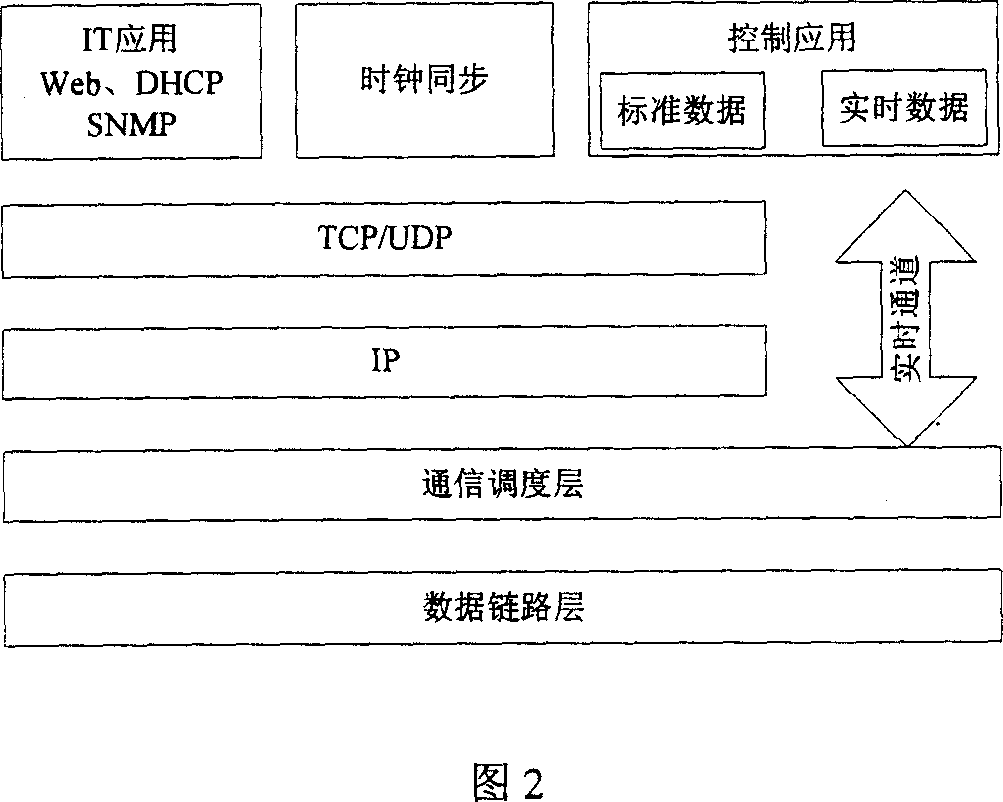

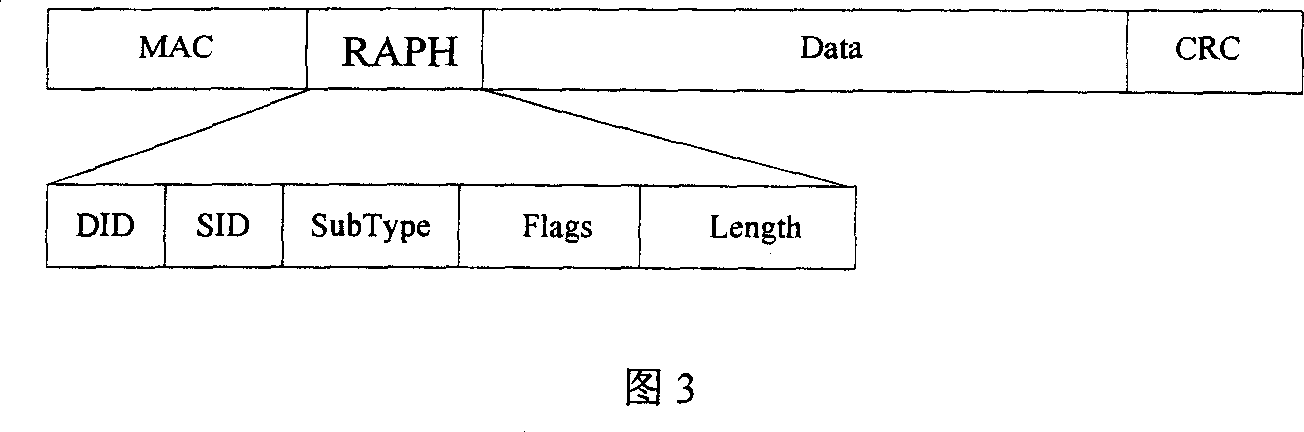

Method for determining realtime Ethernet tlecommunication

ActiveCN101075945ASatisfy real-timeFulfil requirementsData switching networksOriginal dataControl area

The method comprises: newly adding a communication scheduling layer into original data link layer of Ethernet; in relation to the standard channel using TCP / IP, newly adding a real time channel; according to the greatest common divisor of control cycle in the actual control area, using a three segmentation dividing principal to divide macro cycle into three time segmentations on time axis; the bus arbitration uses a approach of combining the distribution with the concentration, and uses a time slot distribution based scheduling approach to send the cyclic data relating to the realization of control function in the time segmentation, uses the centralized scheduling approach with priority controlling function to send the system data and non cyclic data in the time segmentation; all slave devices in the system keep the time consistence with the master device by using a clock synchronous algorithm; the logic addressing is made based on the device ID; realizing the real time Ethernet determinacy communication.

Owner:MICROCYBER CORP

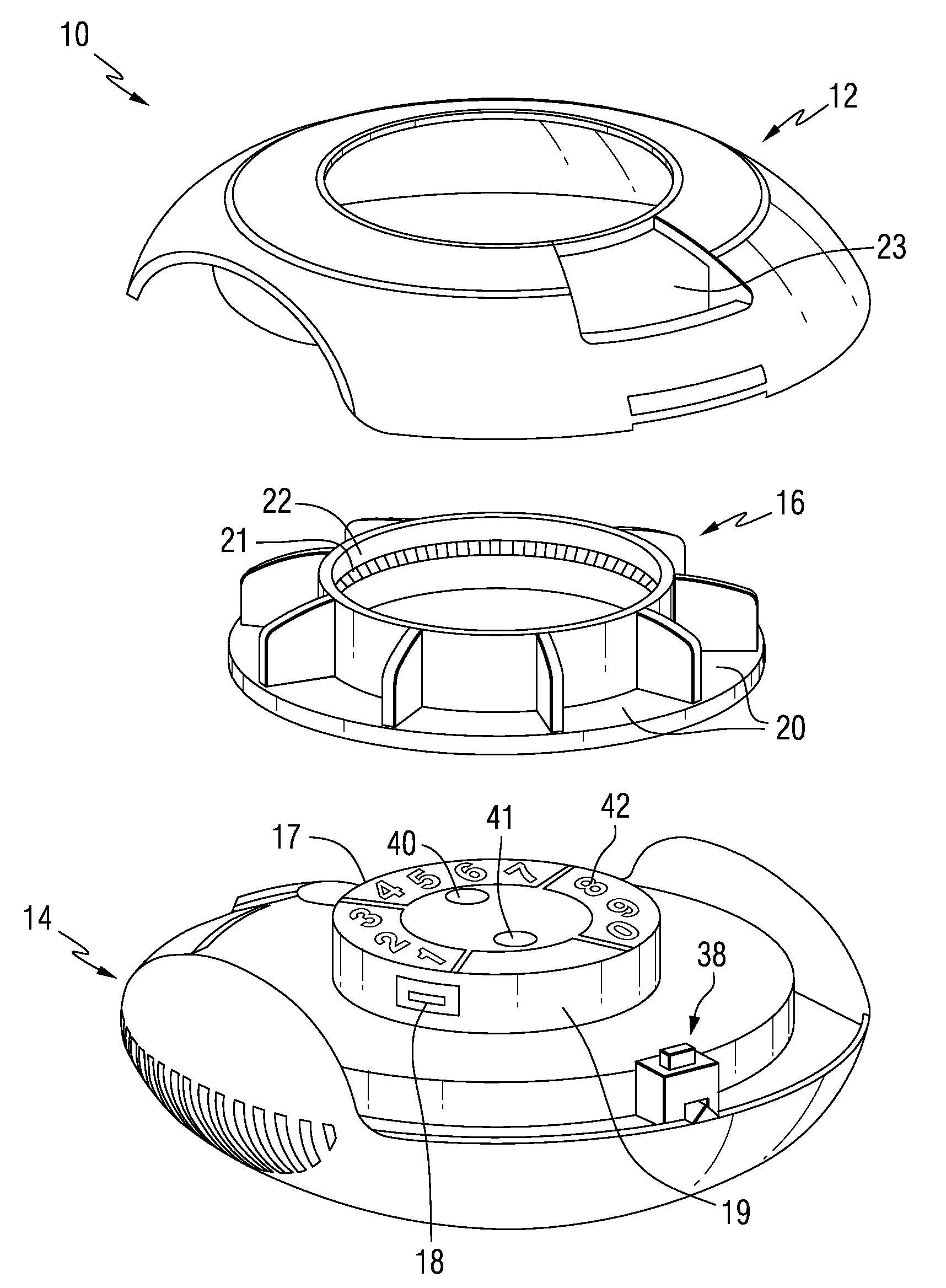

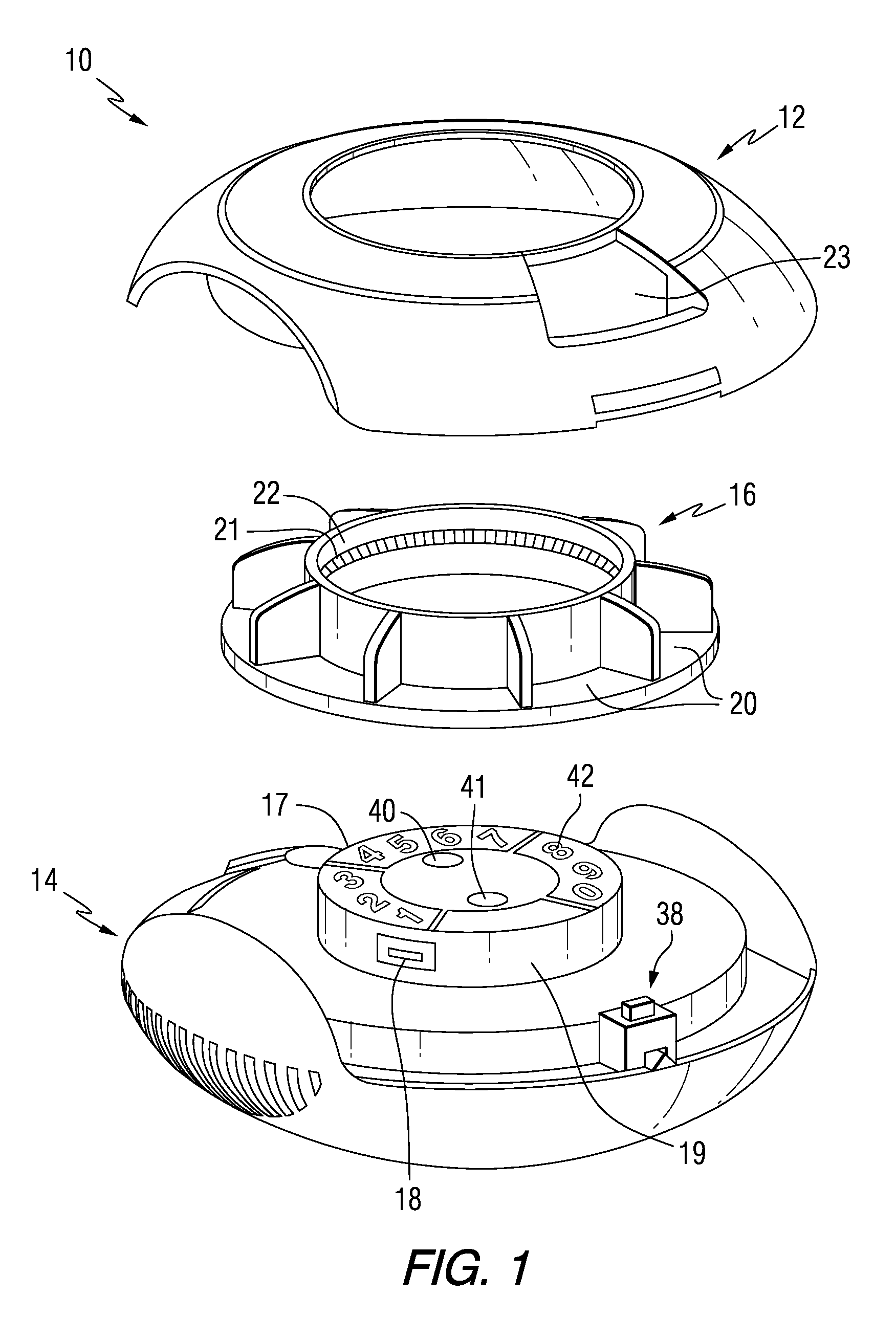

Patient Controlled Timed Medication Dispenser

InactiveUS20100305750A1Small article dispensingElectric signal transmission systemsMedication DispenserMedication dose

A medication dispenser for permitting administration of a medication dose to an authorized user only after a predetermined minimum-dosing interval has elapsed. The medication dispenser comprises: a medication tray having a substantially circular shape and comprising a plurality of compartments containing a medication dose, the compartments disposed about a circumference thereof; regions between two consecutive dose-carrying compartments comprising an empty compartment or a blank region; an enclosure for supporting the dispenser, the enclosure including an opening; and a controller for controlling the medication tray to align one of the plurality of compartments containing a medication dose with the opening after the minimum dosing interval has elapsed and after a person has been authenticated as an authorized user, thereby permitting the authorized user to access the medication dose through the opening, wherein the medication dispenser remains in a dose-accessible configuration for a predetermined hold period, after which the medication tray is controlled to align a next successive empty compartment or blank region with the opening.

Owner:CONLEY N SHARON

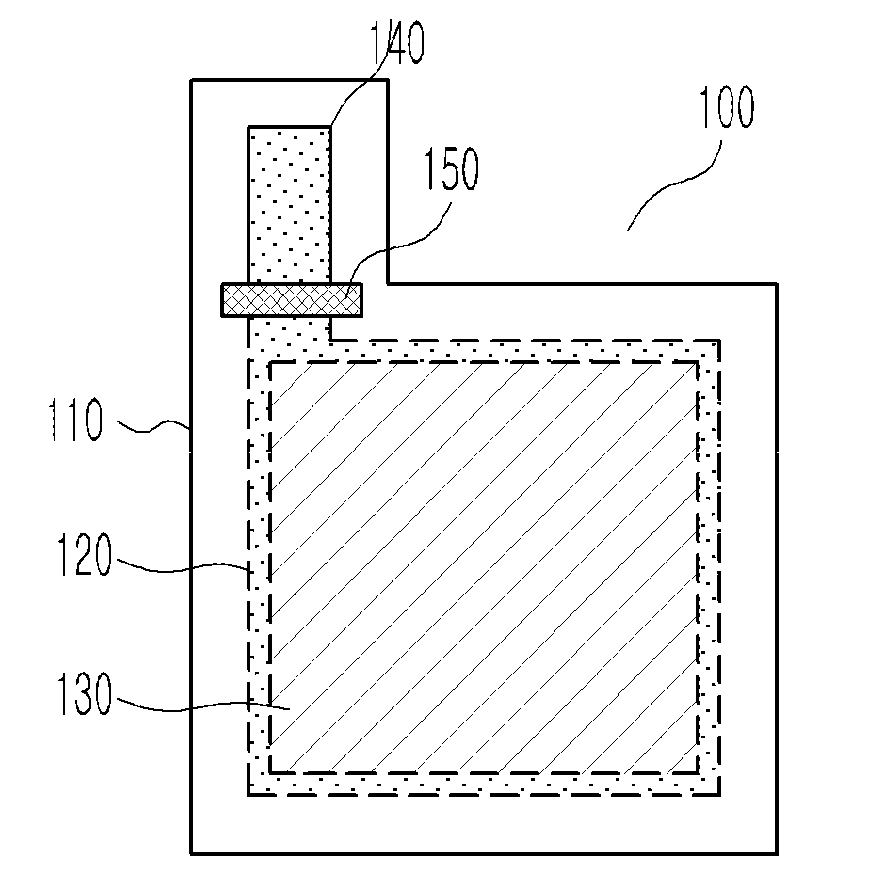

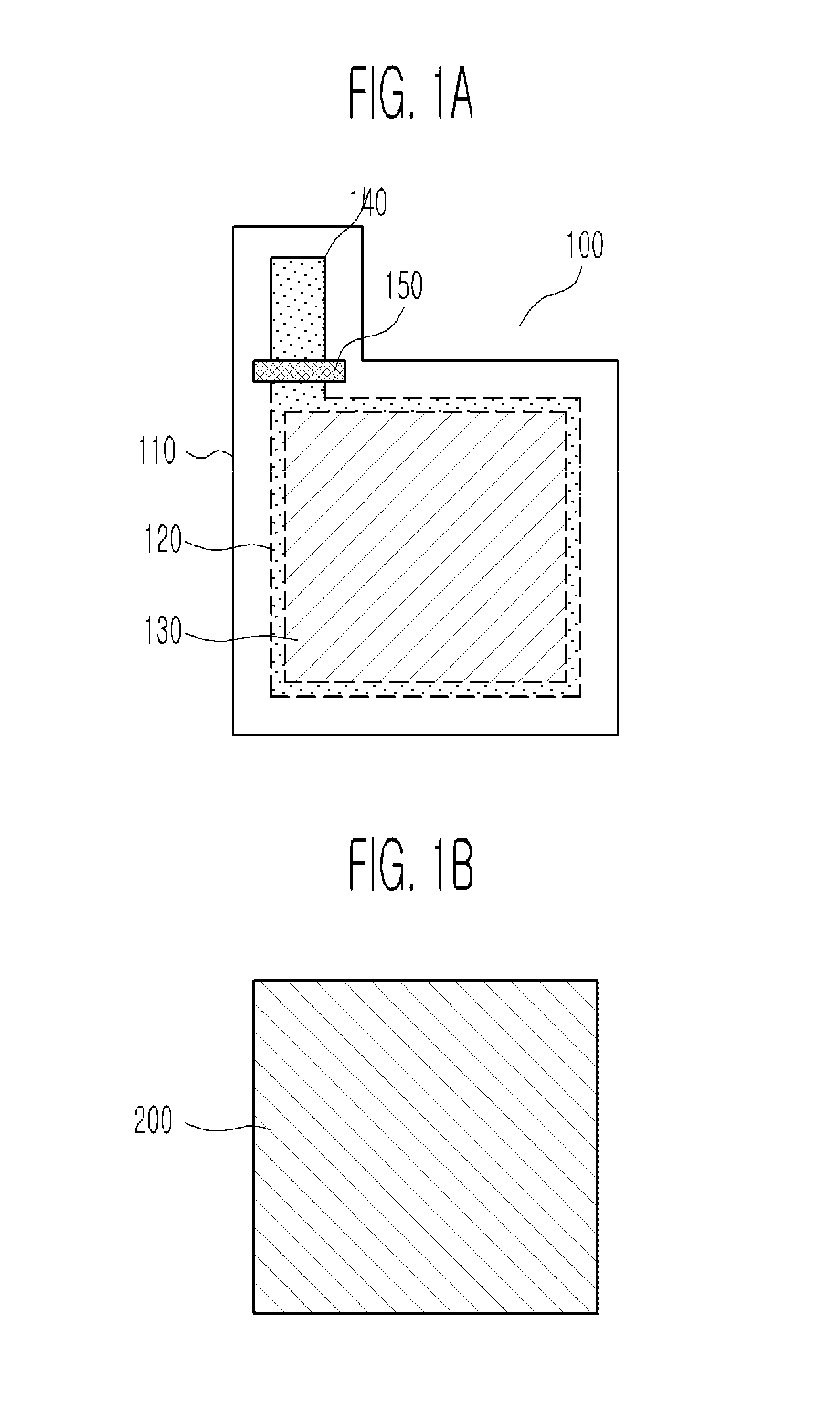

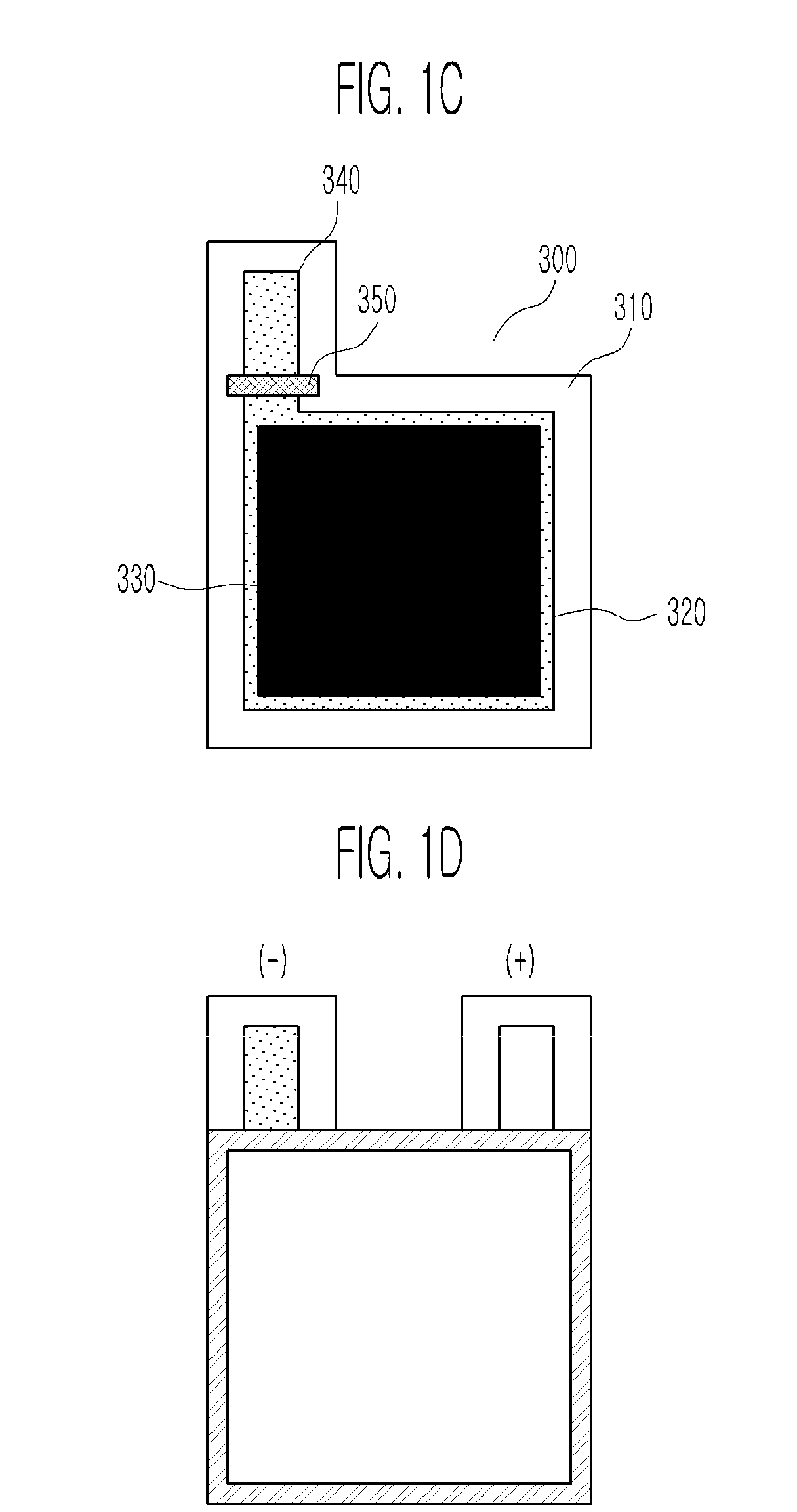

Vacuum-sealing-type flexible-film primary battery and method of manufacturing the same

ActiveUS20110045337A1Improve corrosion resistanceElectrode carriers/collectorsPrinted batteriesCarbon layerScreen printing

Provided are a vacuum-sealing-type flexible-film primary battery and a method of manufacturing the same. The primary battery includes a battery assembly comprising a positive electrode plate including a positive electrode collector having a first conductive carbon layer disposed on a surface-treated inner surface of a first pouch and a positive electrode layer disposed on the first conductive carbon layer of the positive electrode collector, a negative electrode plate including a negative electrode collector having a second conductive carbon layer disposed on a surface-treated inner surface of a second pouch and a negative electrode layer disposed on the second conductive carbon layer of the negative electrode collector, and an adhesion / post-injection polymer electrolyte layer interposed between the positive electrode plate and the negative electrode plate, wherein the battery assembly is completely sealed. The flexible-film primary battery may employ the pouch as a collector film to improve flexibility. Also, the flexible-film primary battery may be completely sealed using the pouch to improve a retention period and cell performance. Furthermore, the flexible-film primary battery may be manufactured using a screen printing technique, thereby facilitating a roll-to-roll sequential process.

Owner:ELECTRONICS & TELECOMM RES INST

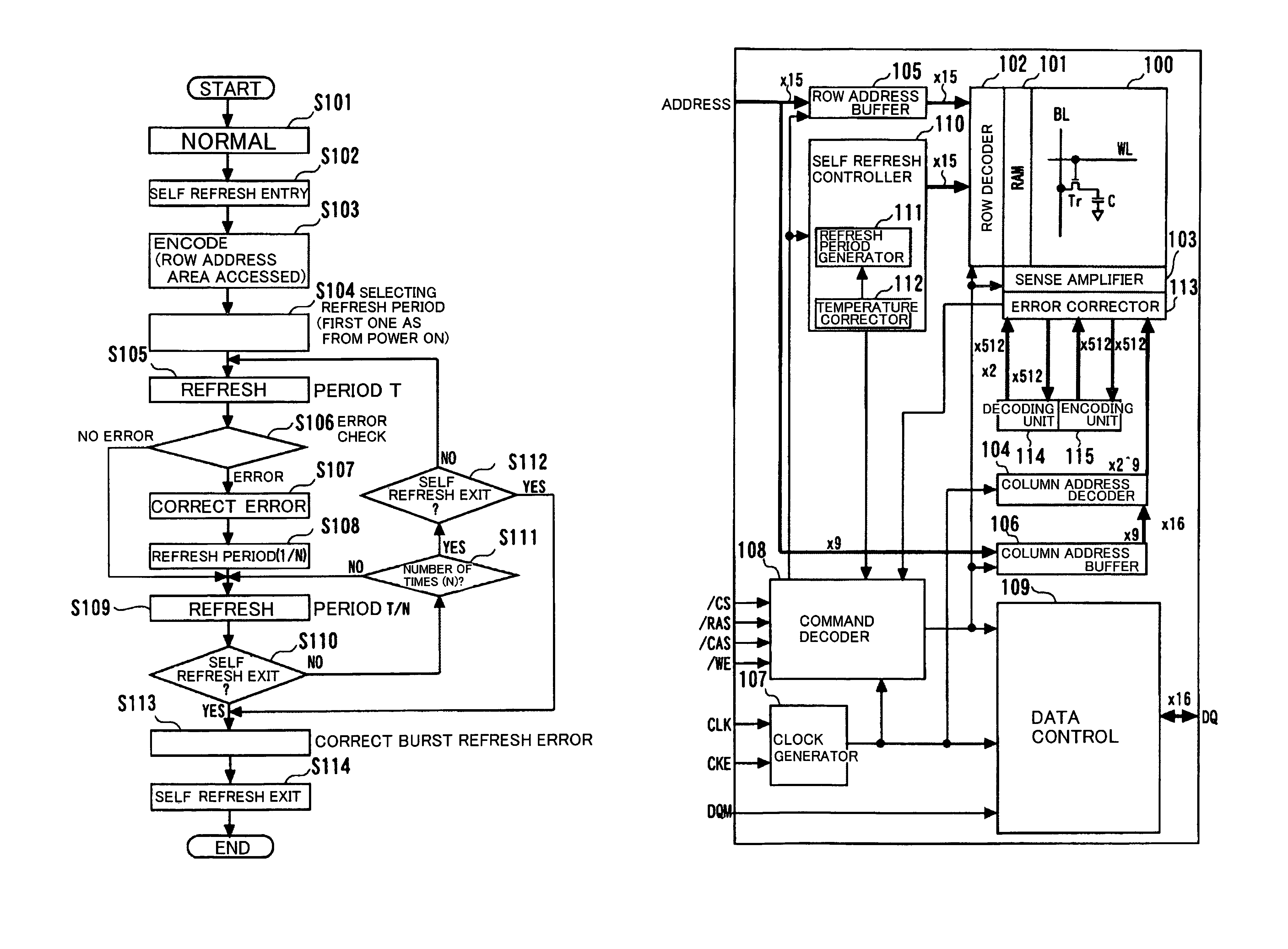

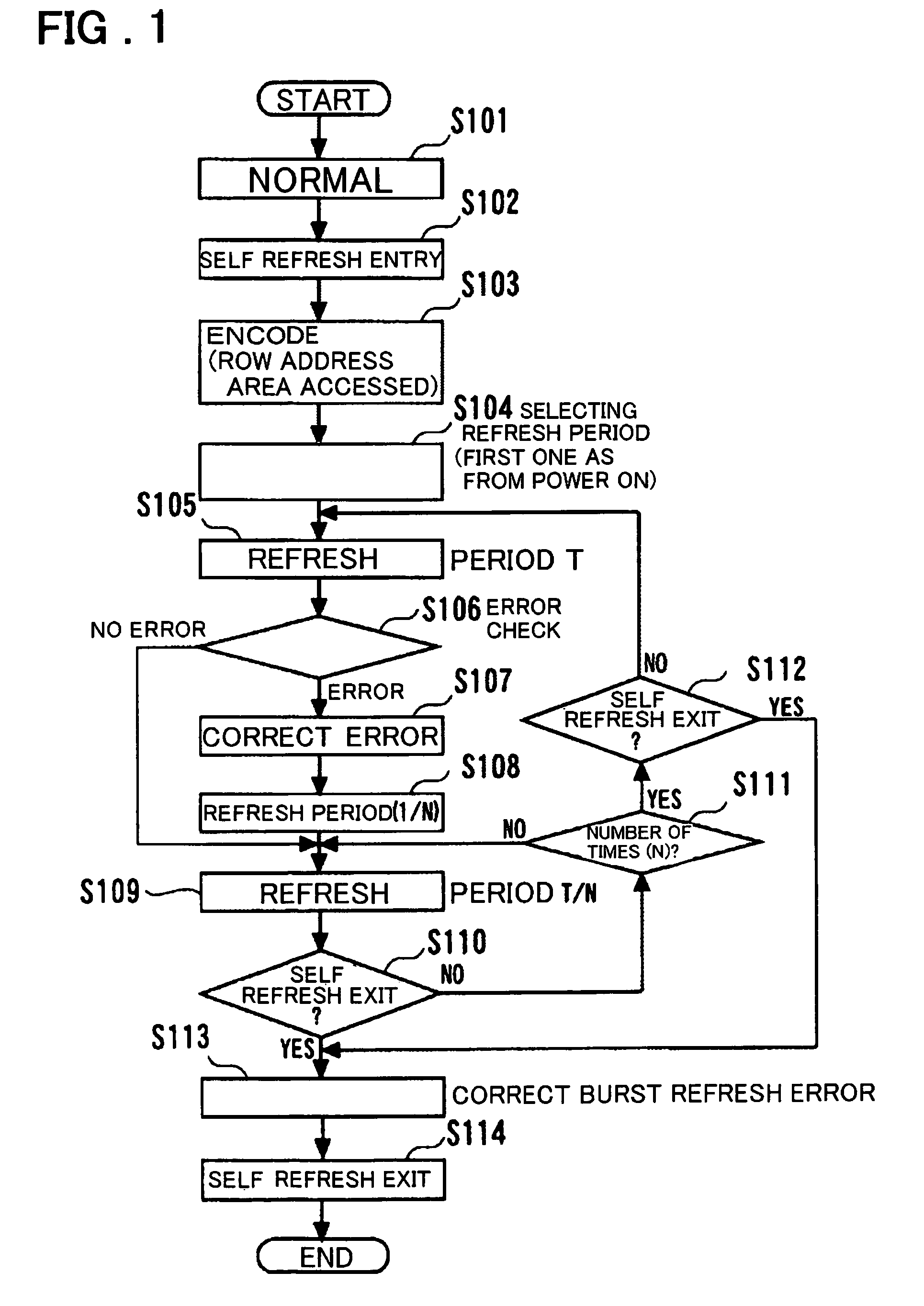

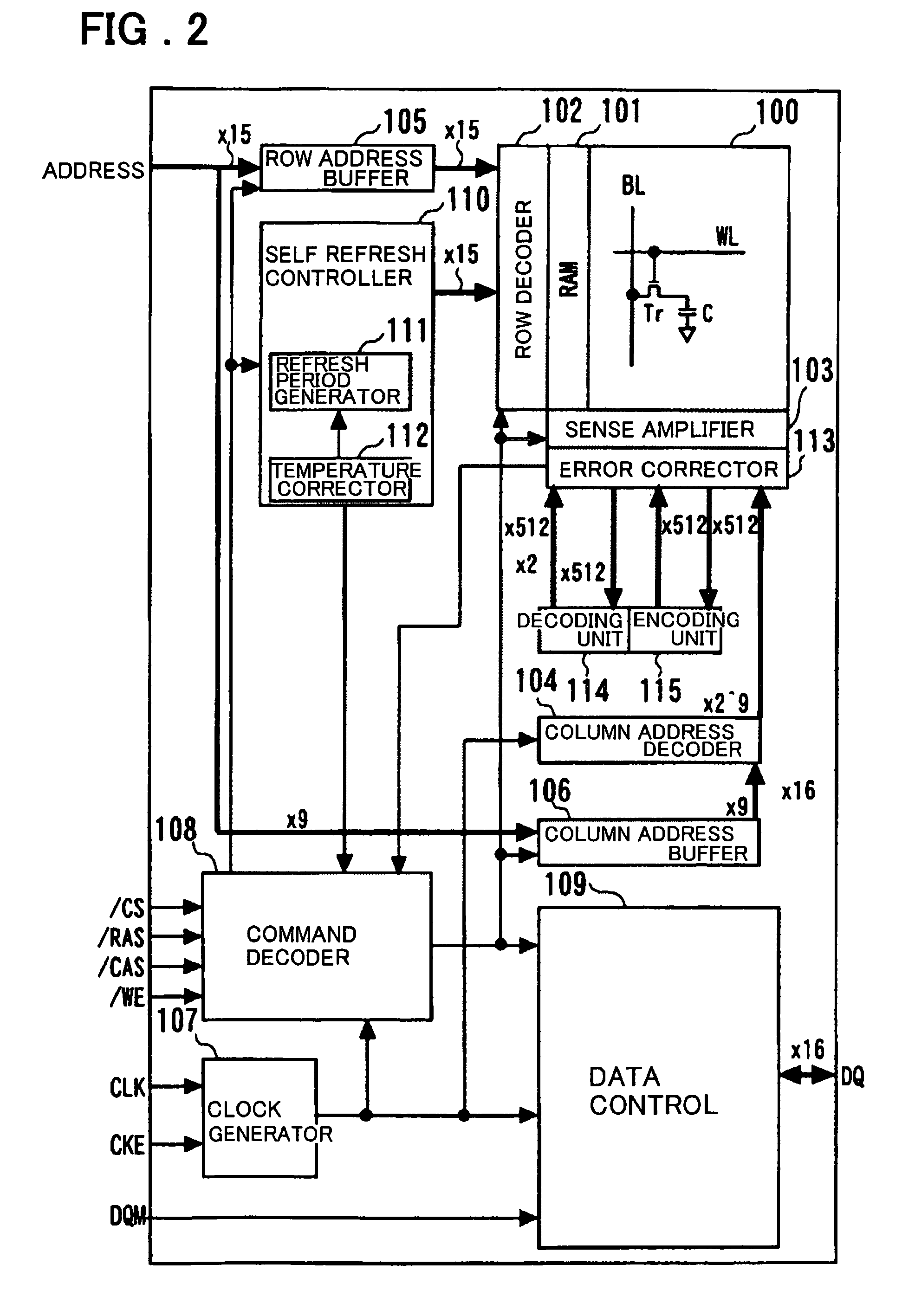

Semiconductor storage device and refresh control method therefor

InactiveUS7167403B2Reduce chip areaSimple structureDigital storageRedundant data error correctionError checkSemiconductor storage devices

A dynamic semiconductor storage device in which the power supply current during the standby time is diminished to decrease the power consumption and to suppress the chip area from increasing. During the normal operation, the information as to a word line associated with a row address accessed during the normal operation is stored in a RAM. In entering self refresh, data of memory cells connected to a word line associated with a row address accessed during the normal operation time is read out and check bits for the data are appended in an encoder and written in a check bit area. As an initializing operation for the first self refresh entry after power up sequence, the data retention time of the memory cells is inspected every word line. Based on the results of inspection, the setting value of the refresh period of the word line is determined and written in the RAM to set the word line based refresh period. During error check for the refresh operation, any error is corrected by an error correction circuit.

Owner:LONGITUDE SEMICON S A R L

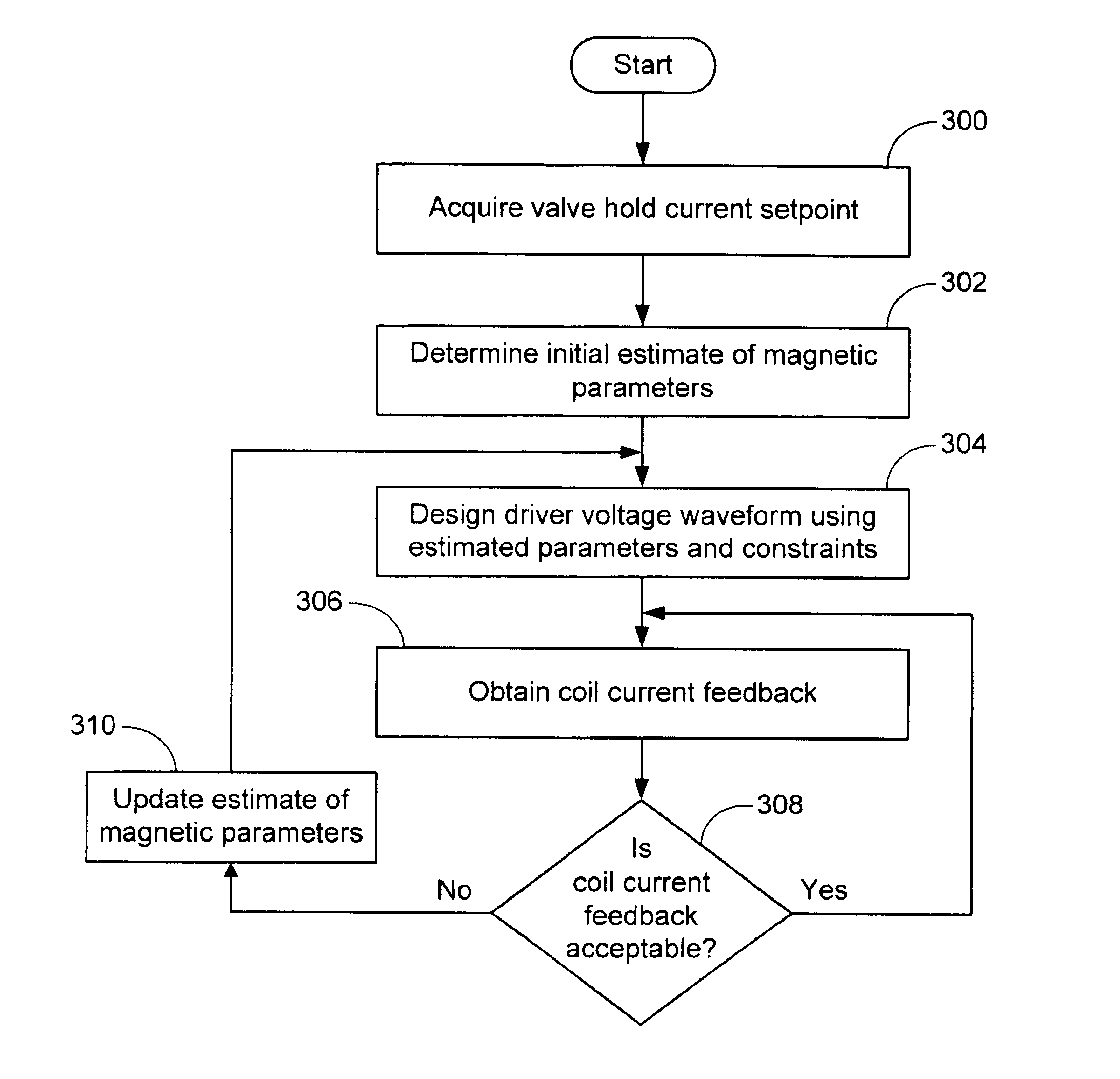

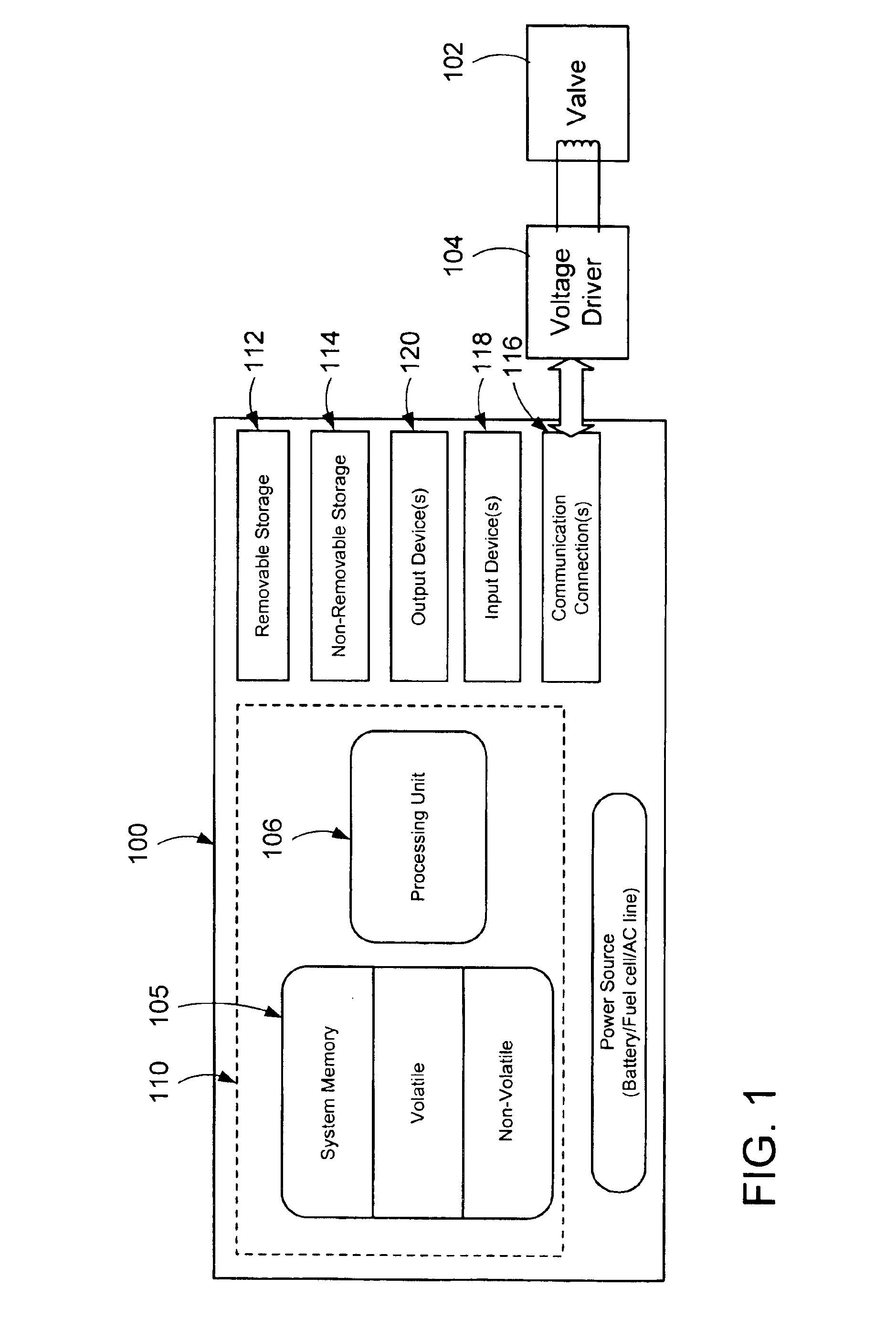

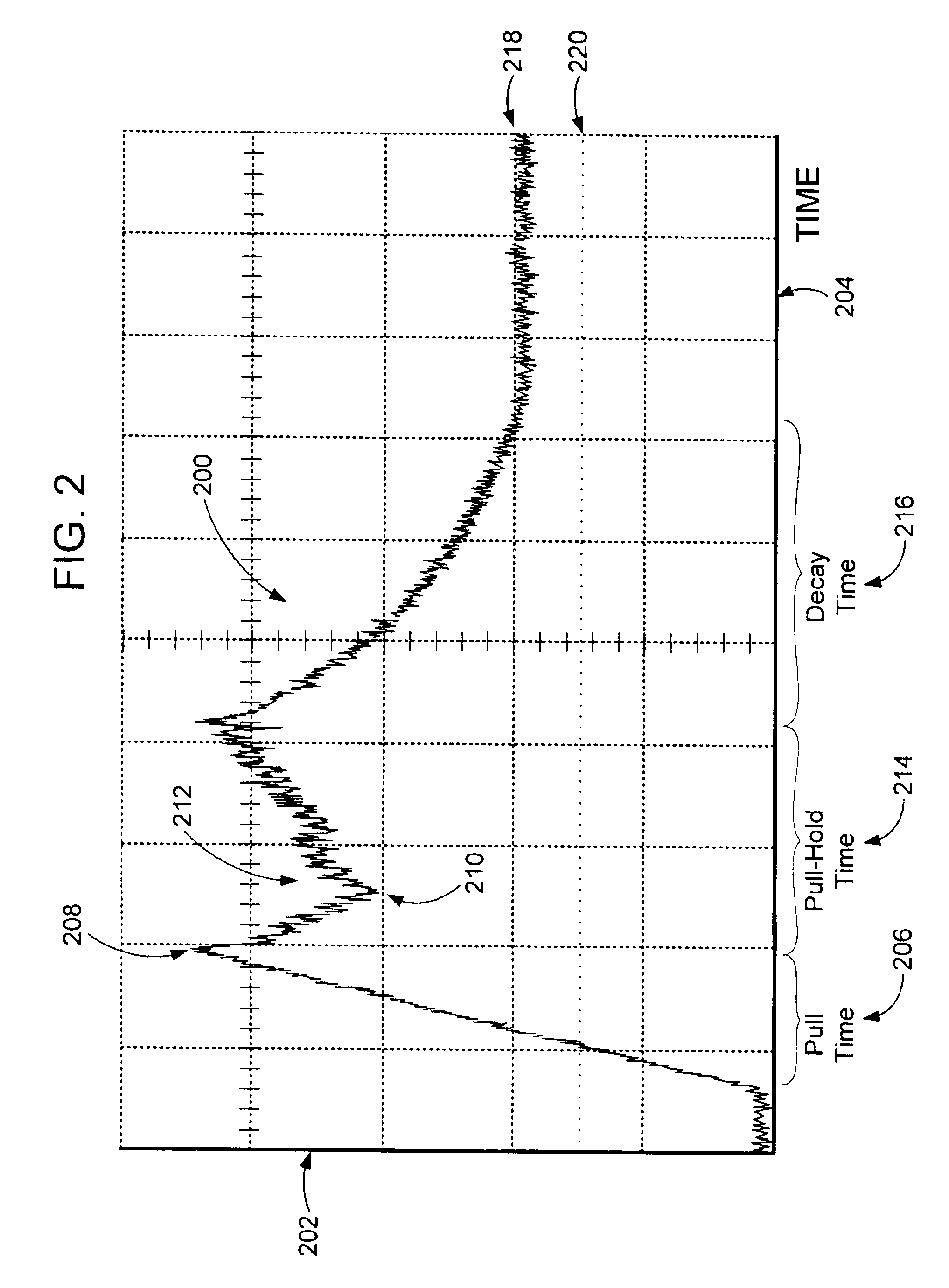

Method to adaptively control and derive the control voltage of solenoid operated valves based on the valve closure point

ActiveUS6889121B1Automate CalibrationOperating means/releasing devices for valvesMachines/enginesElectrical resistance and conductanceSolenoid valve

The invention provides a computer implemented method to automate the calibration of the drive voltage waveform of a solenoid operated valve. An initial estimate of valve electromagnetic parameters and valve closure point is derived and the drive voltage waveform is created based in part on circuit constraints and the parameters and valve closure point. The drive voltage waveform is applied to the valve coil and the coil current feedback is obtained and used to update the initial estimate. This process is repeated until the coil current feedback meets predetermined criteria. The electromagnetic parameters include the L / R ratio of the valve during the pull-in time and decay time, the valve back emf during the pull-hold time, and the average resistance during hold when current is steady. The closure point is used to anchor the drive voltage waveform and is adjusted at a slower rate than the other parameters.

Owner:WOODWARD GOVERNOR CO