Patents

Literature

81 results about "Memory retention" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

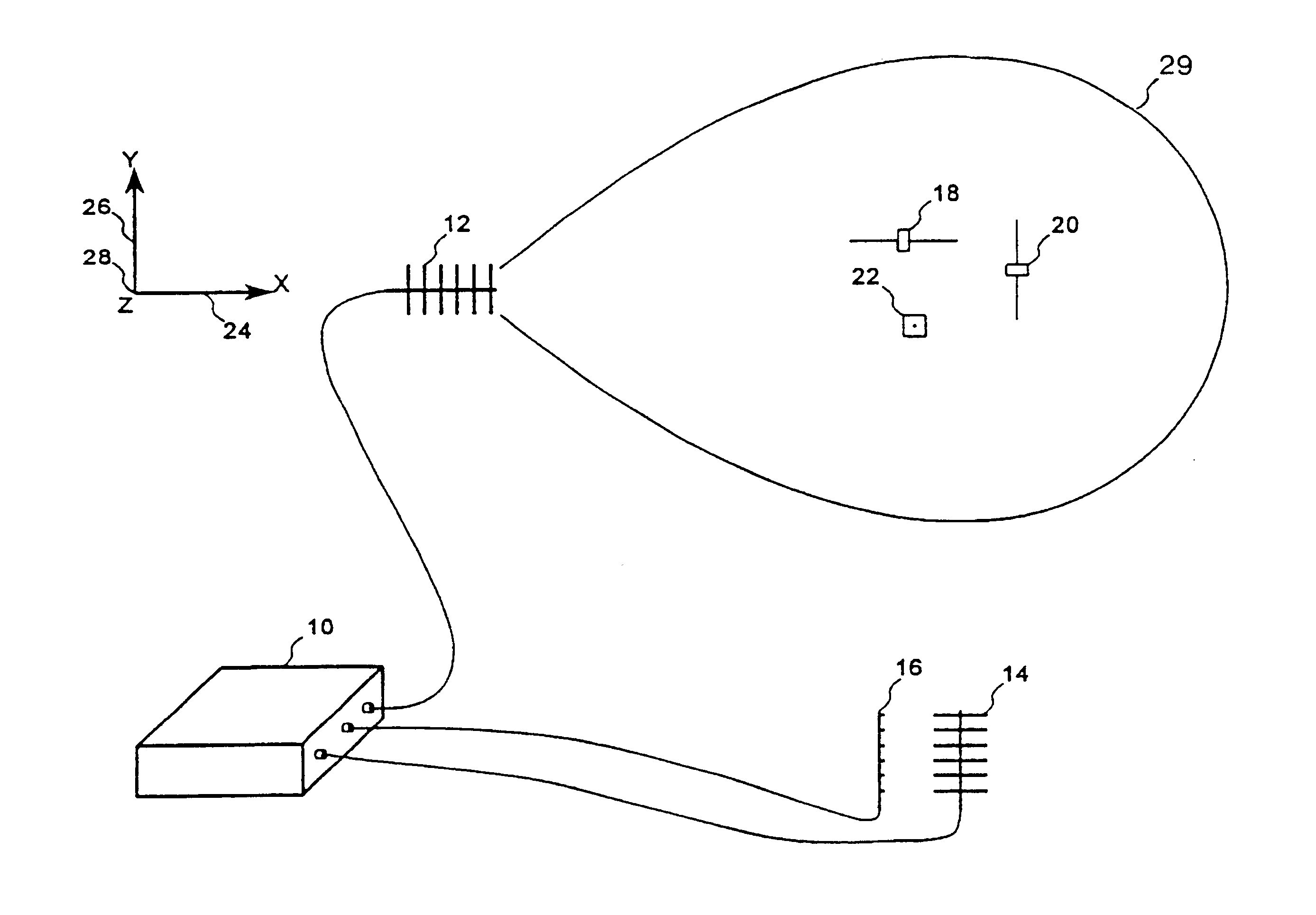

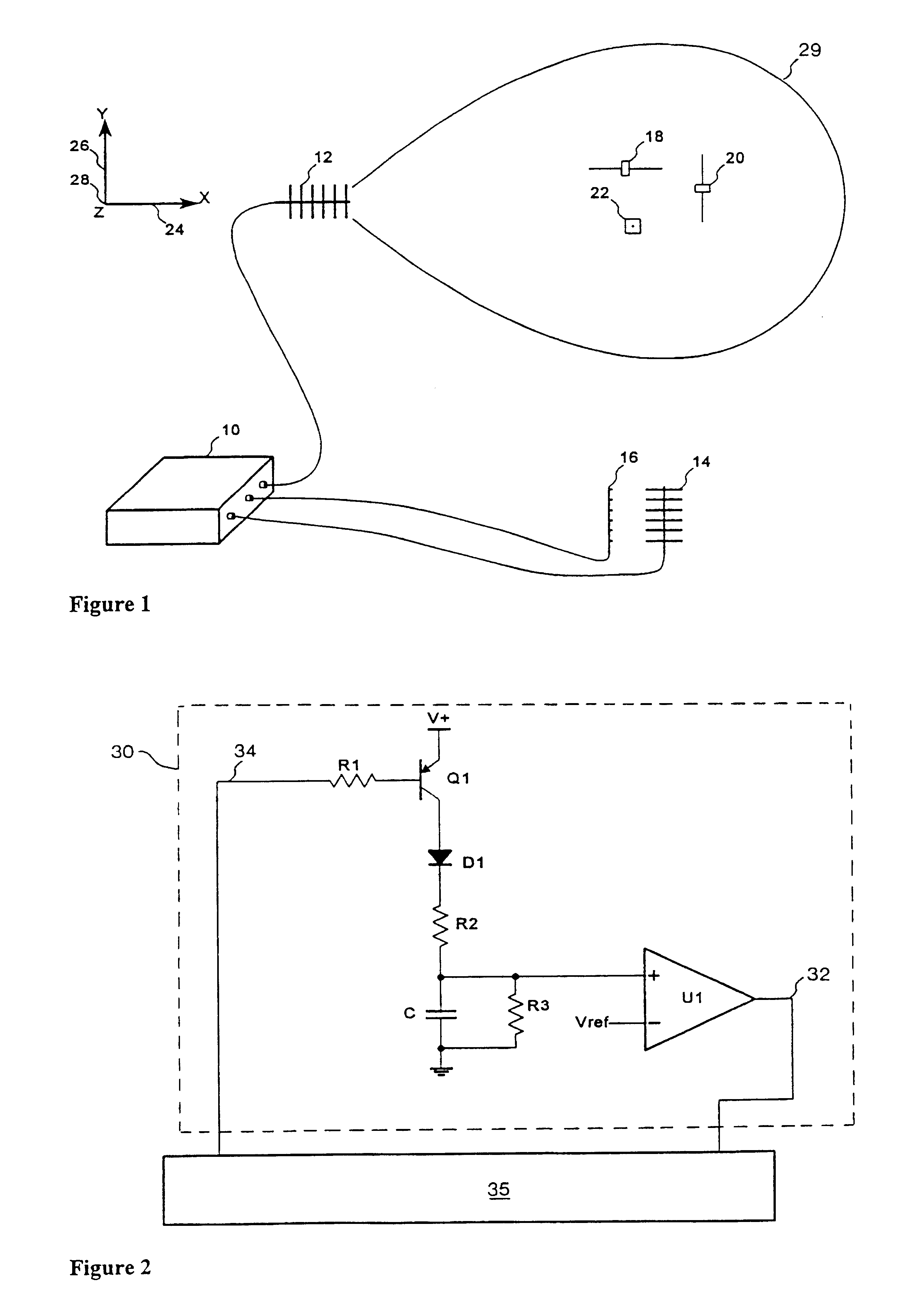

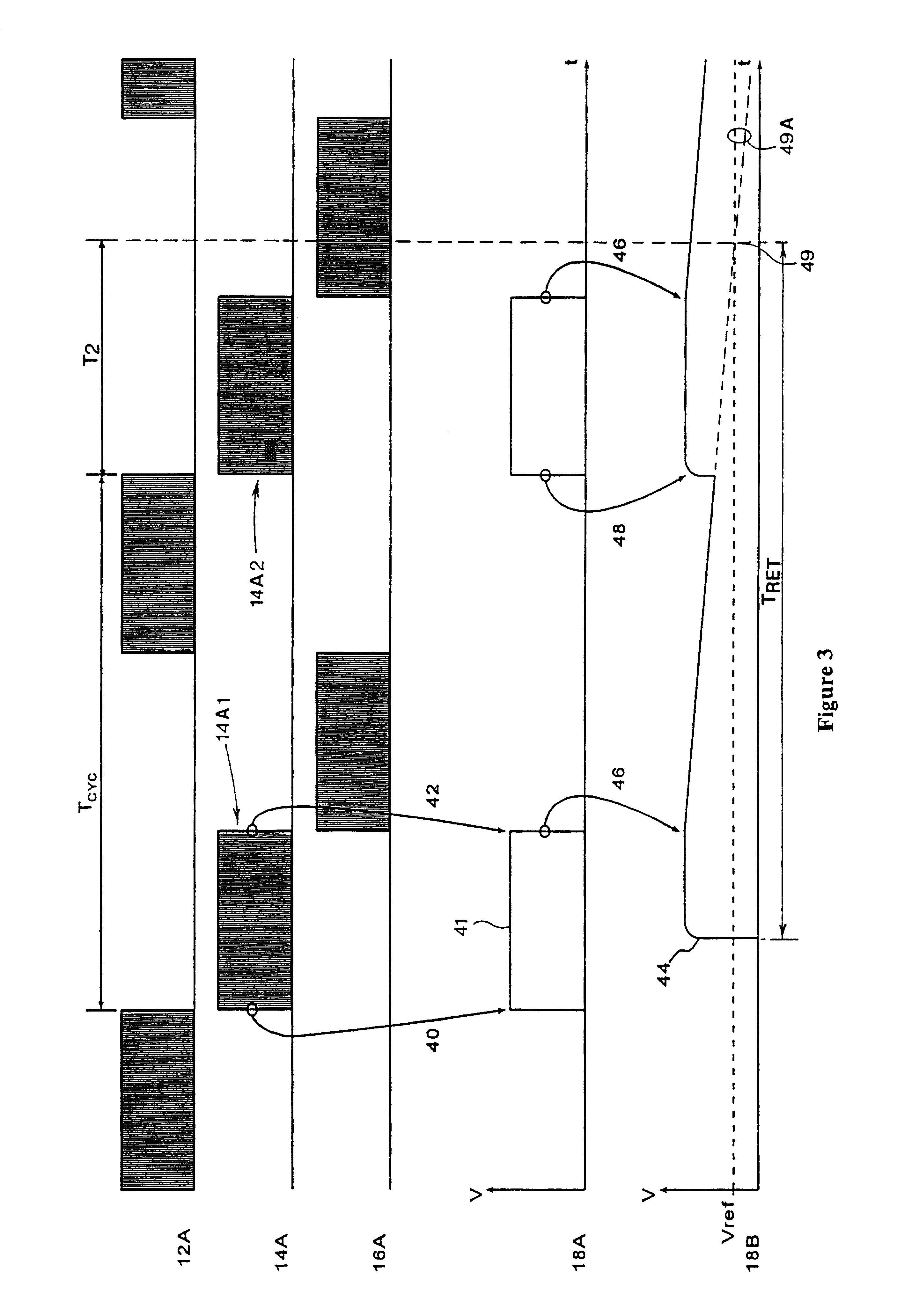

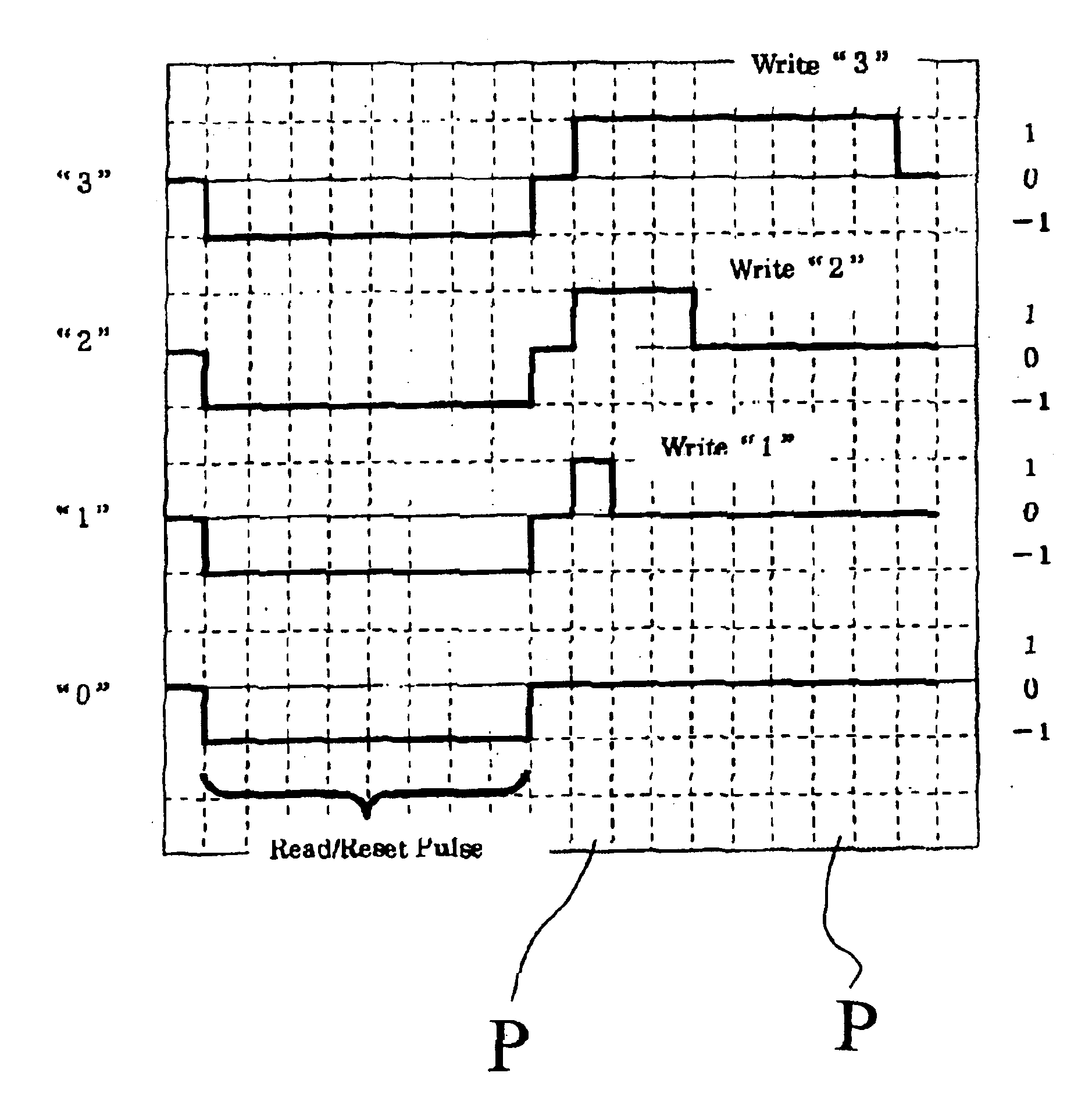

Multi-dimensional electronic identification of articles

InactiveUS6909366B1Avoid spreadingMemory record carrier reading problemsCo-operative working arrangementsMemory retentionObject based

An identification system is provided for identifying a plurality of randomly aligned object-based transponders (18, 20, 22) passing through a predetermined reading volume. A reader (10) includes multiple transmitting and receiving antenna arrays (12, 14, 16) which are arranged sequentially to transmit interrogating and energizing fields (29) into the reading volume, with each energizing field having a different polarisation. Each transponder (12, 14, 16) is arranged to be powered by at least one of the interrogating and energizing fields, and includes a short term memory module (30) which is arranged to record the successful transmission or otherwise of the identification signal of the transponder (20) and to retain the record in the absence of a power supply to the transponder. The short term memory module has a retention time longer than any predicted interruption of power supply to the transponder via one of the energizing fields within the reading volume. The minimum memory retention time is typically the time period taken for the sequential transmission of all but one of the interrogating and energizing fields (29) during an interrogation cycle.

Owner:TROLLEY SCAN

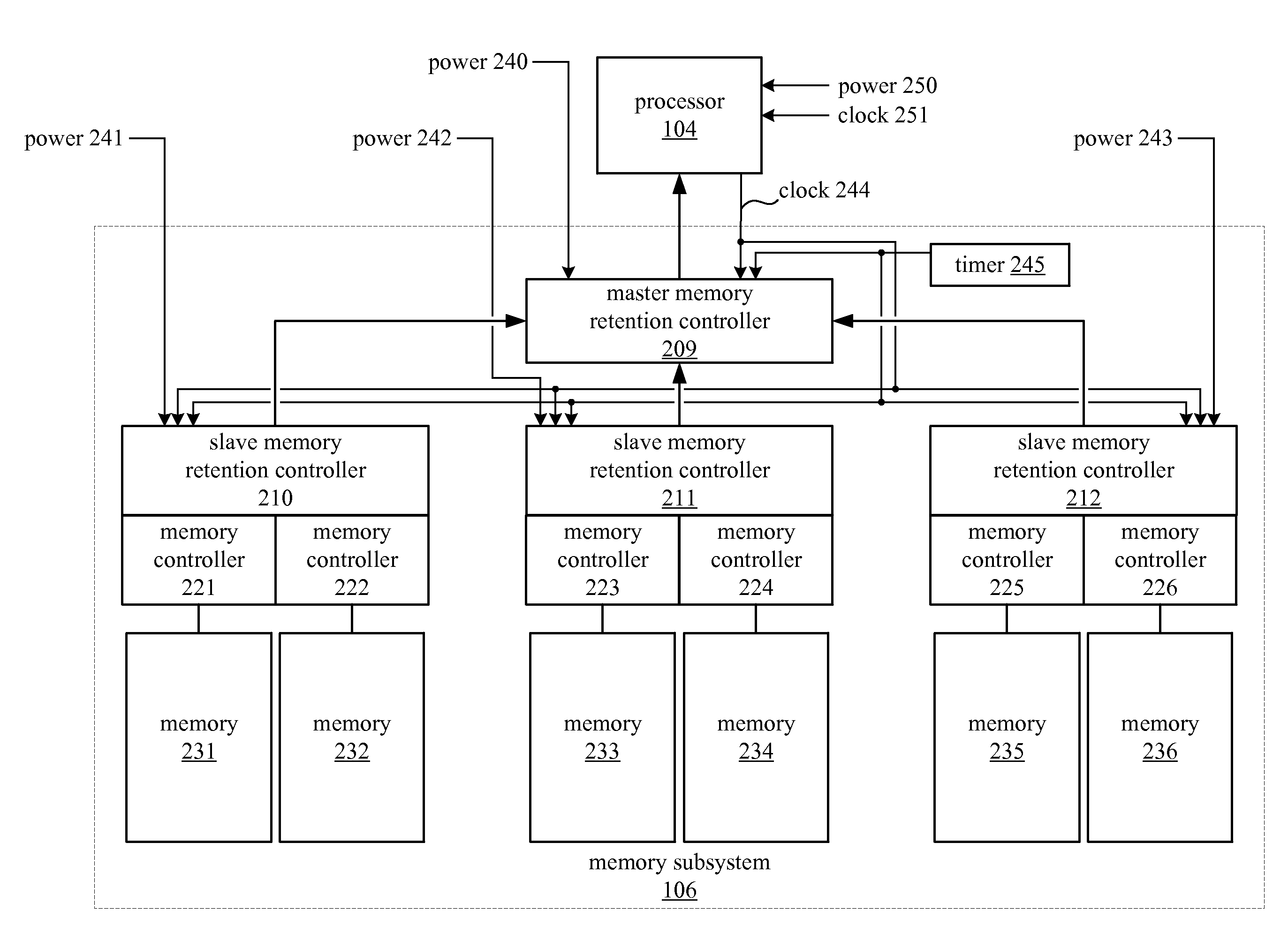

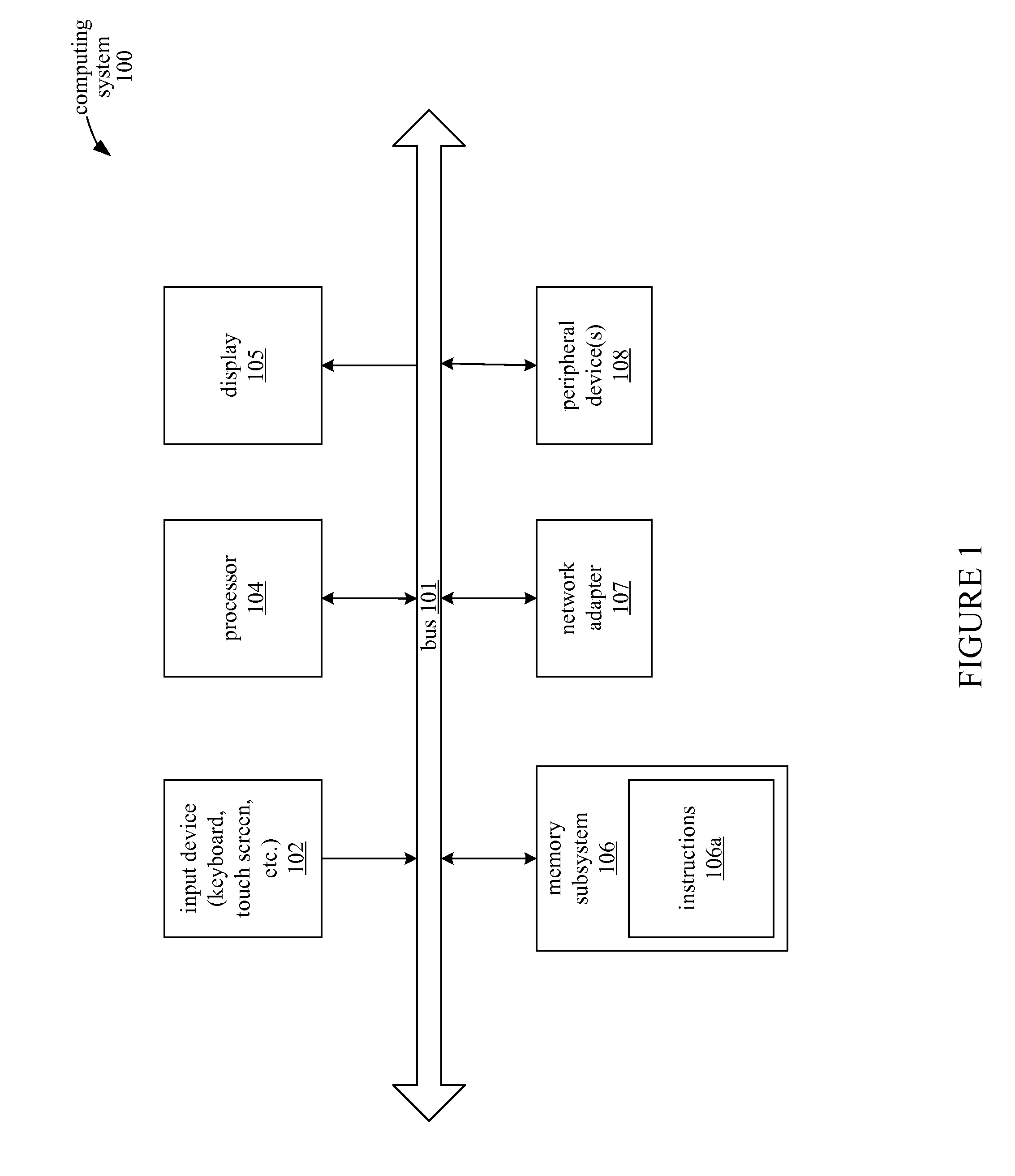

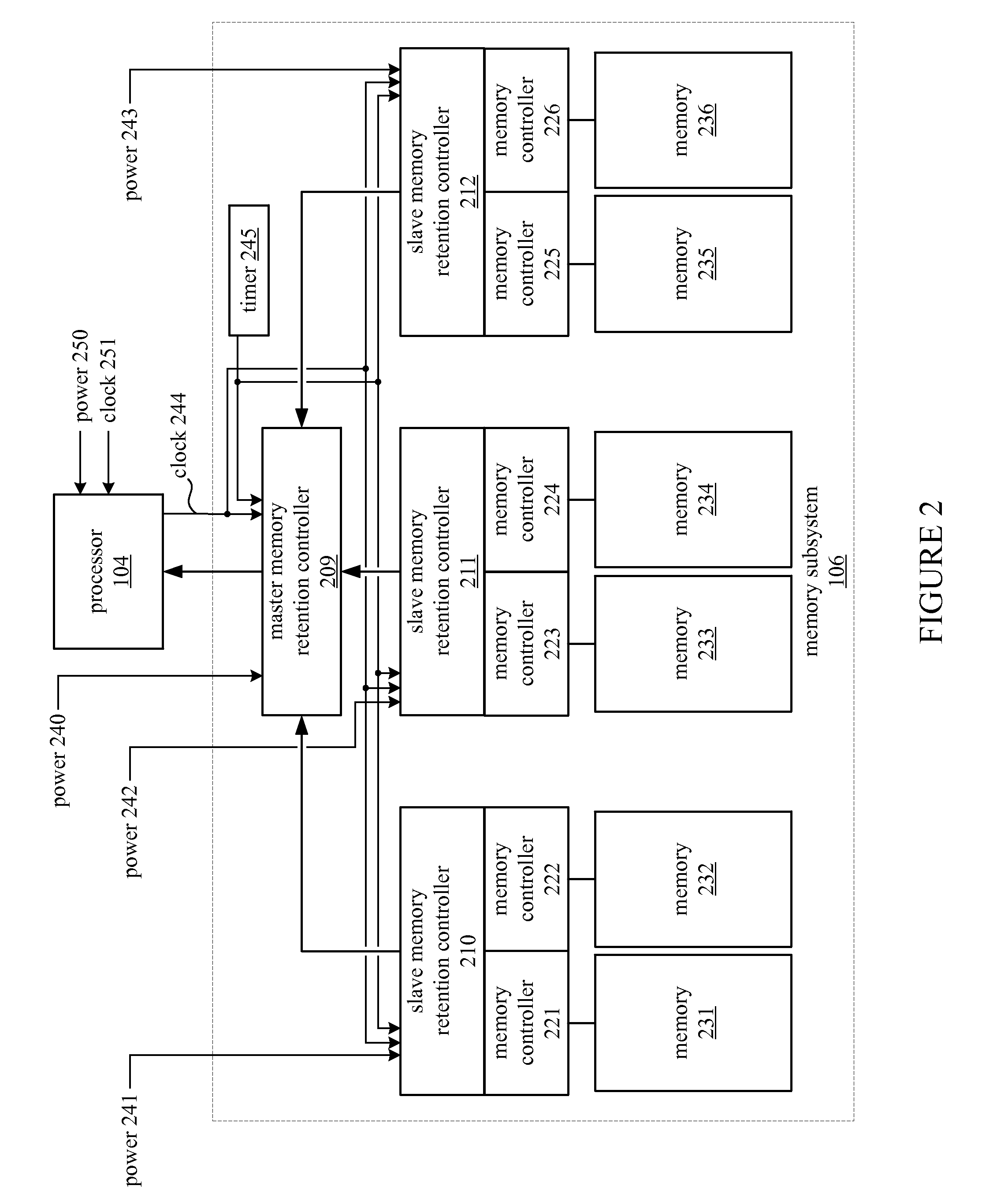

Memory persistence management control

A memory retention controller may include a data structure configured to store a memory refresh interval corresponding to a memory region in a memory subsystem and control logic coupled with the data structure. The control logic is configured to perform a first refresh of the memory region prior to a power off transition of a host processor coupled with the memory subsystem, and to perform a second refresh of the memory region after the power off transition of the host processor, based on the memory refresh interval corresponding to the memory region, and in response to an elapsed time since the first refresh of the memory region.

Owner:ADVANCED MICRO DEVICES INC

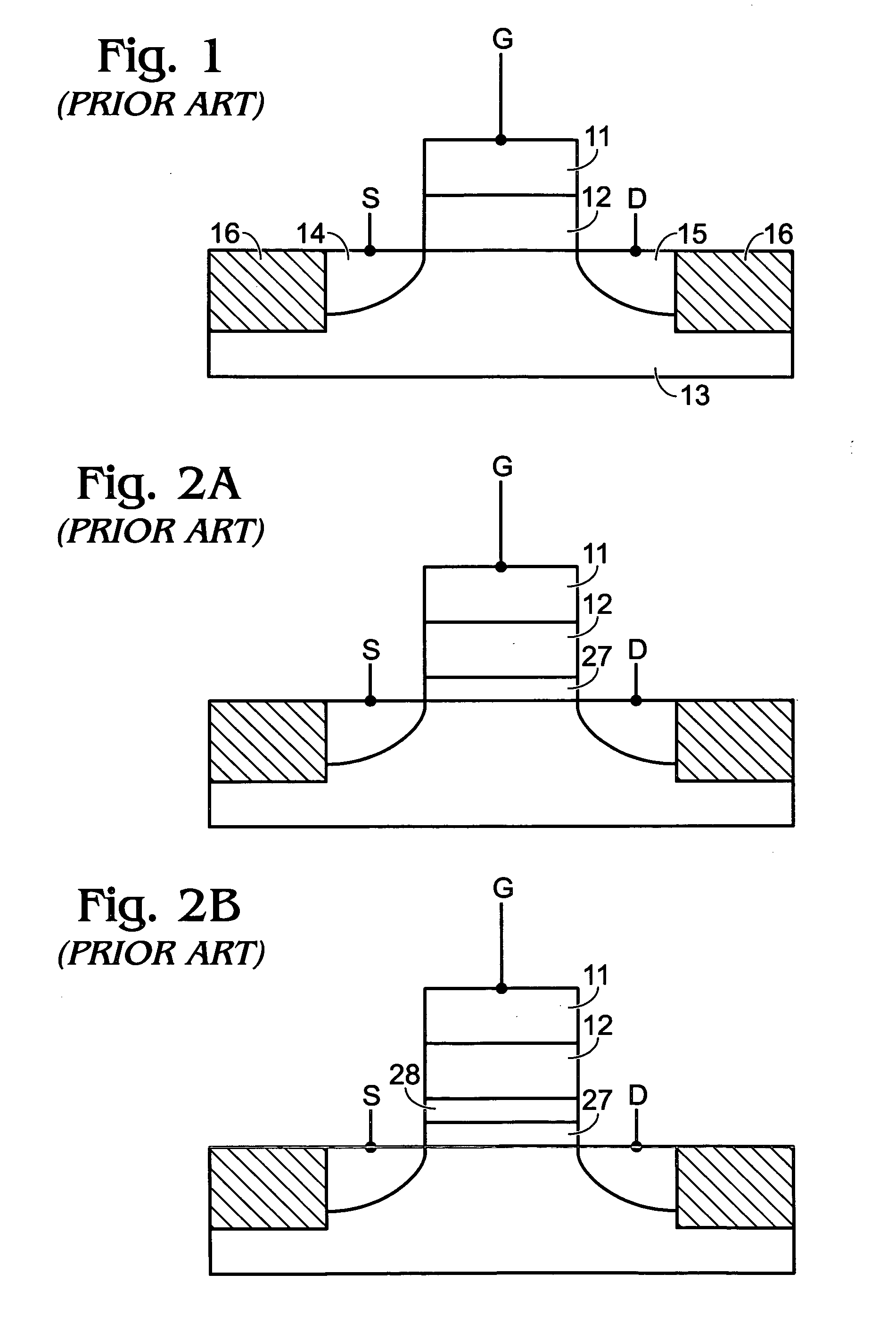

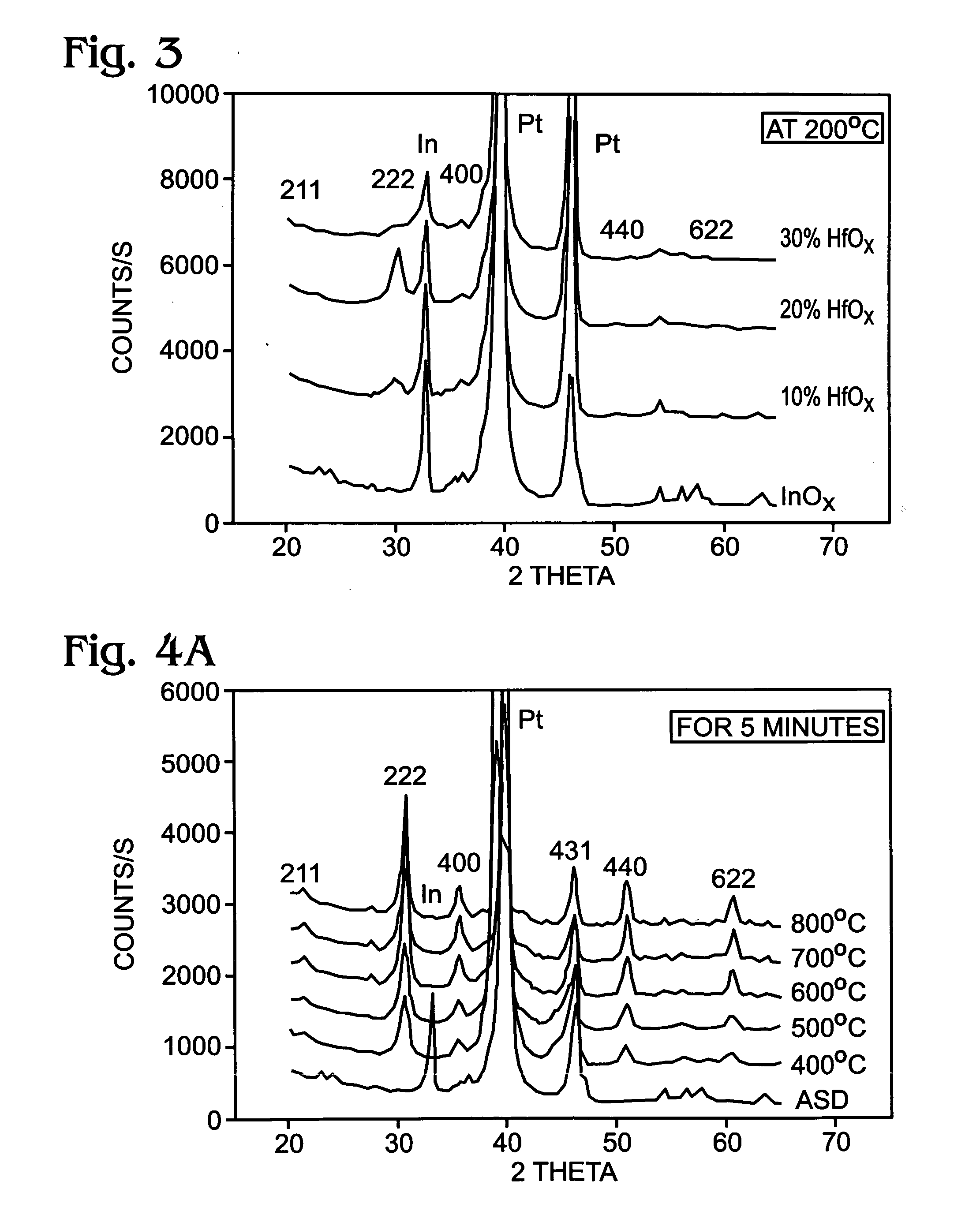

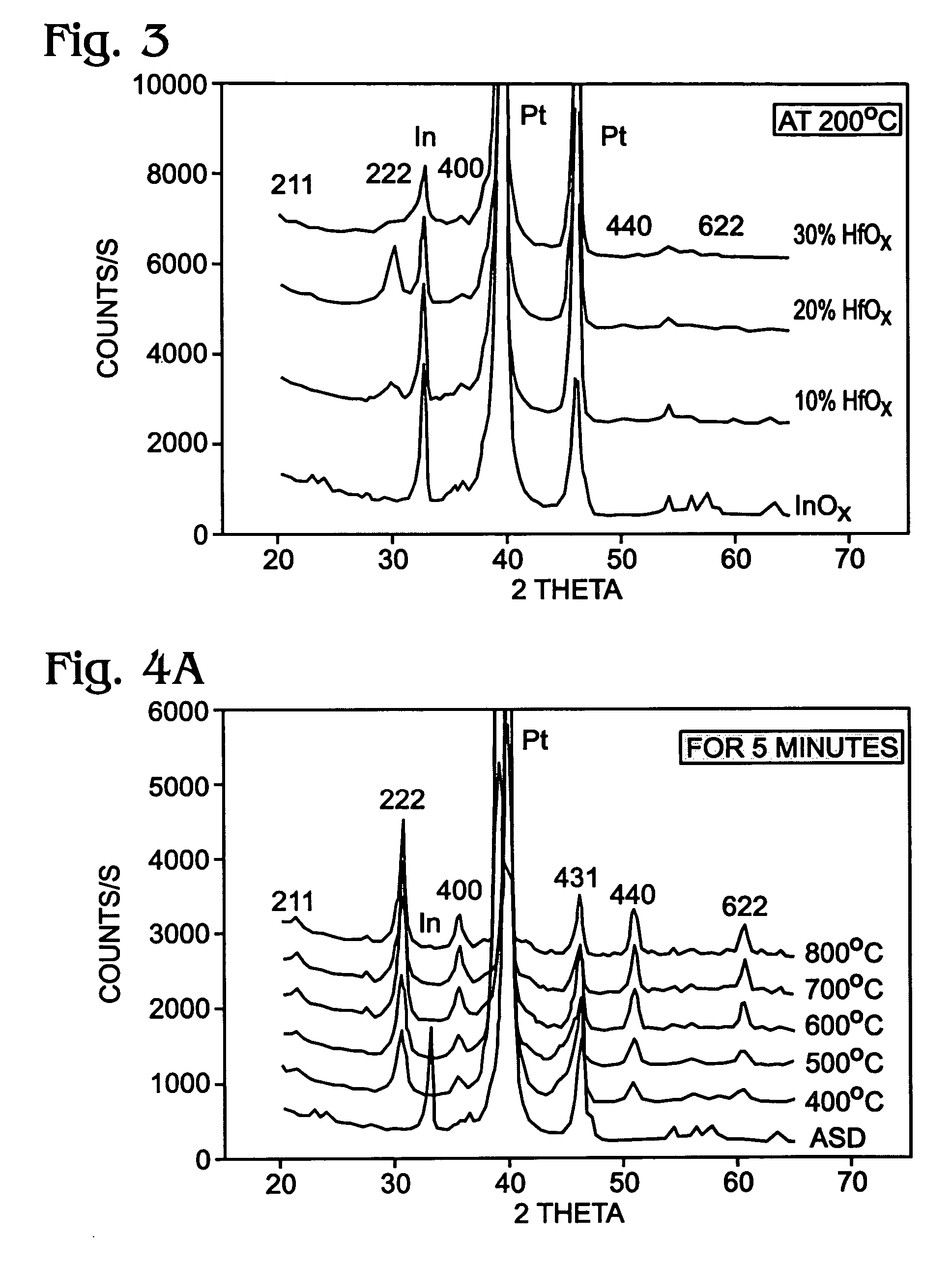

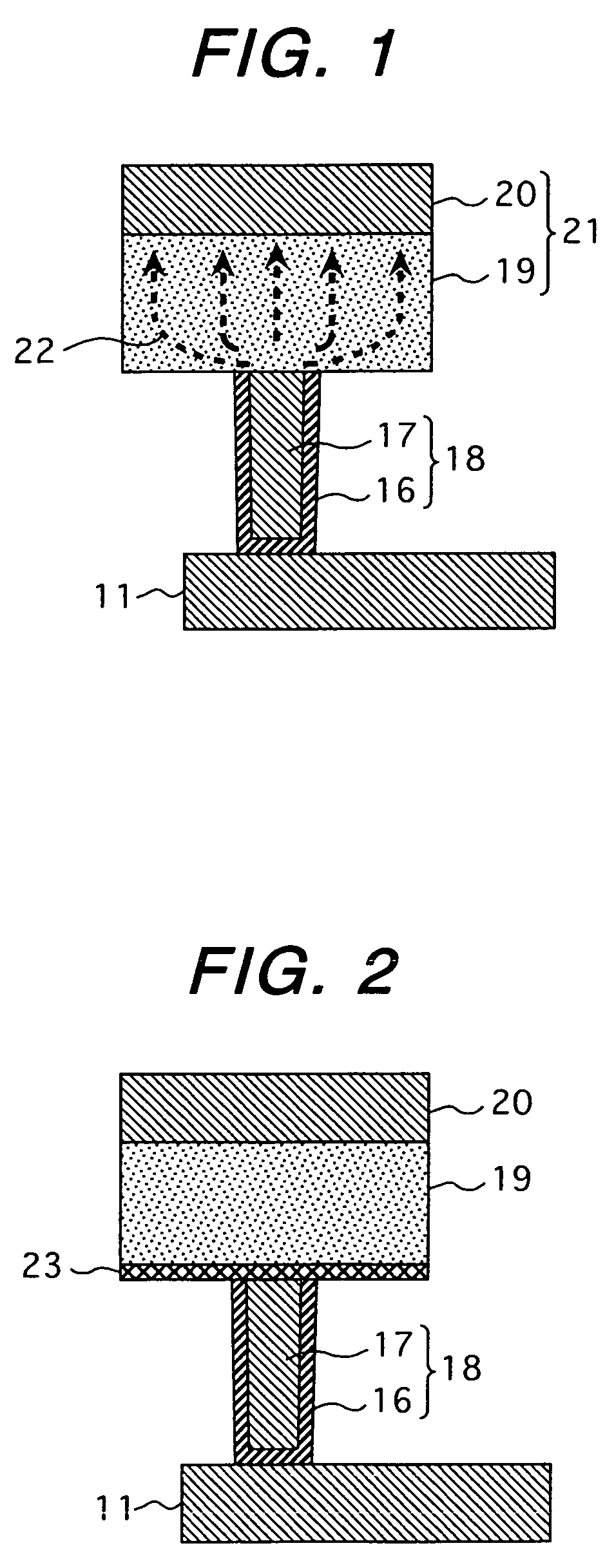

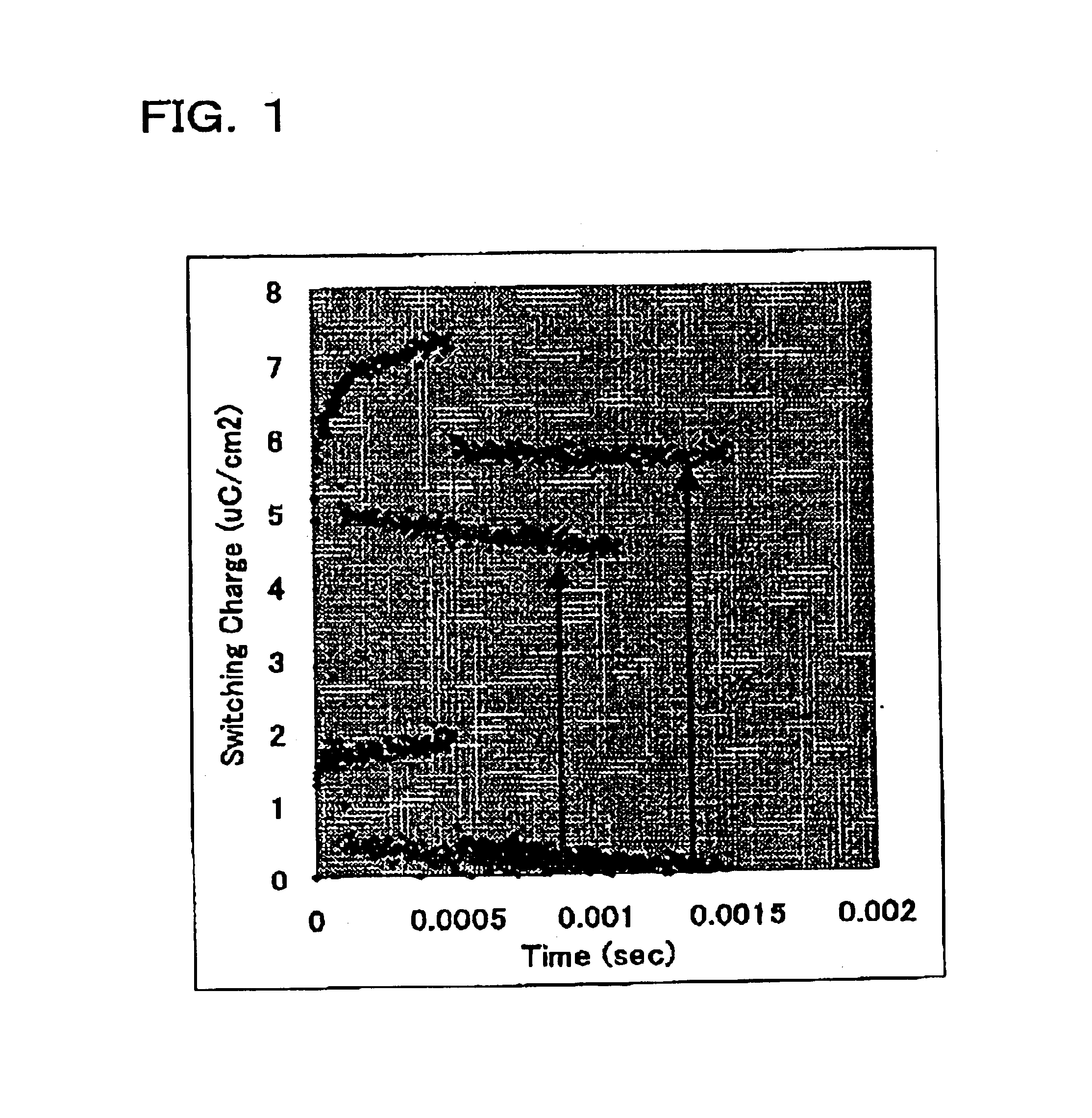

In2O3 thin film resistivity control by doping metal oxide insulator for MFMox device applications

ActiveUS20050151210A1Reduce chargeImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesMemory retentionFilm resistance

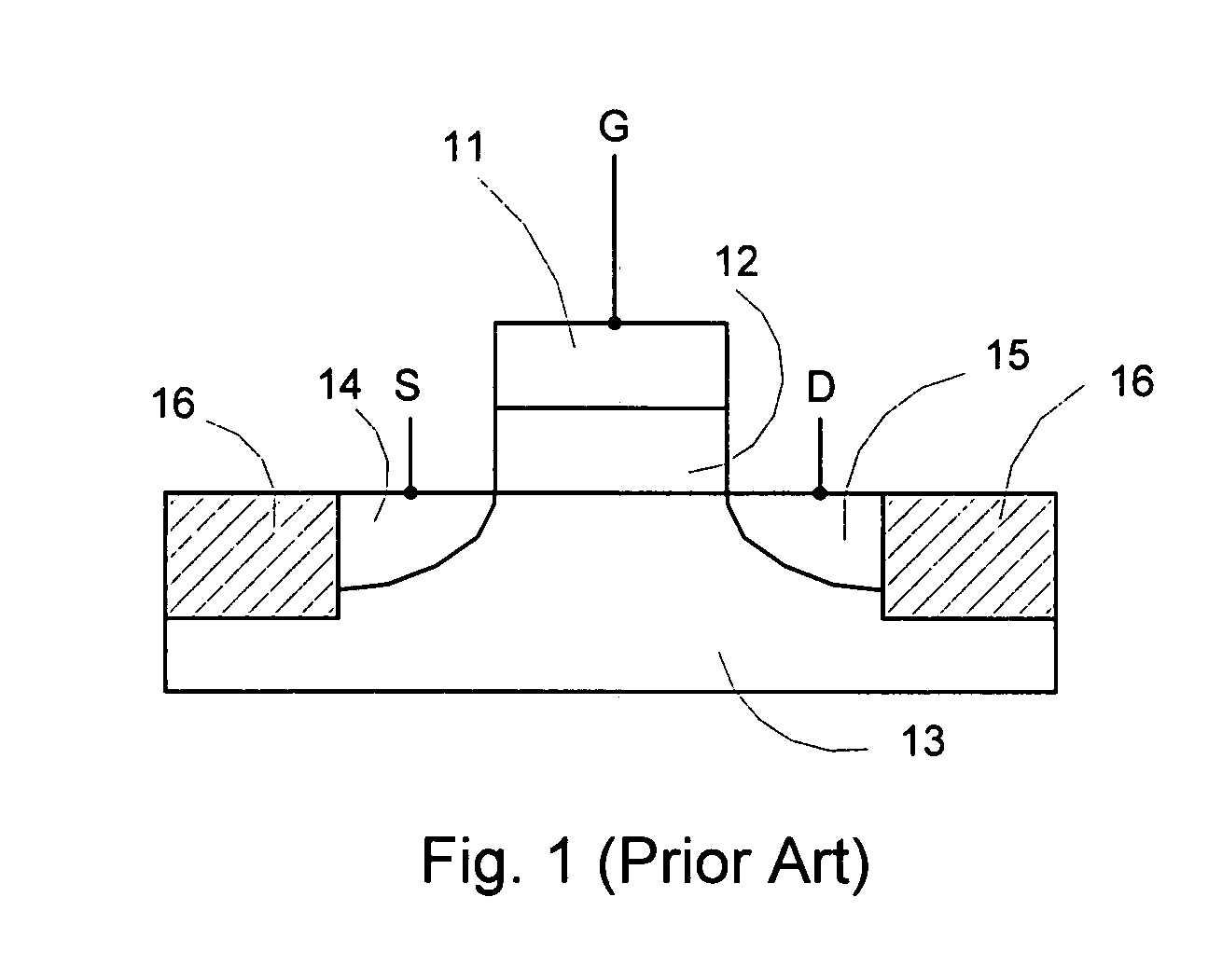

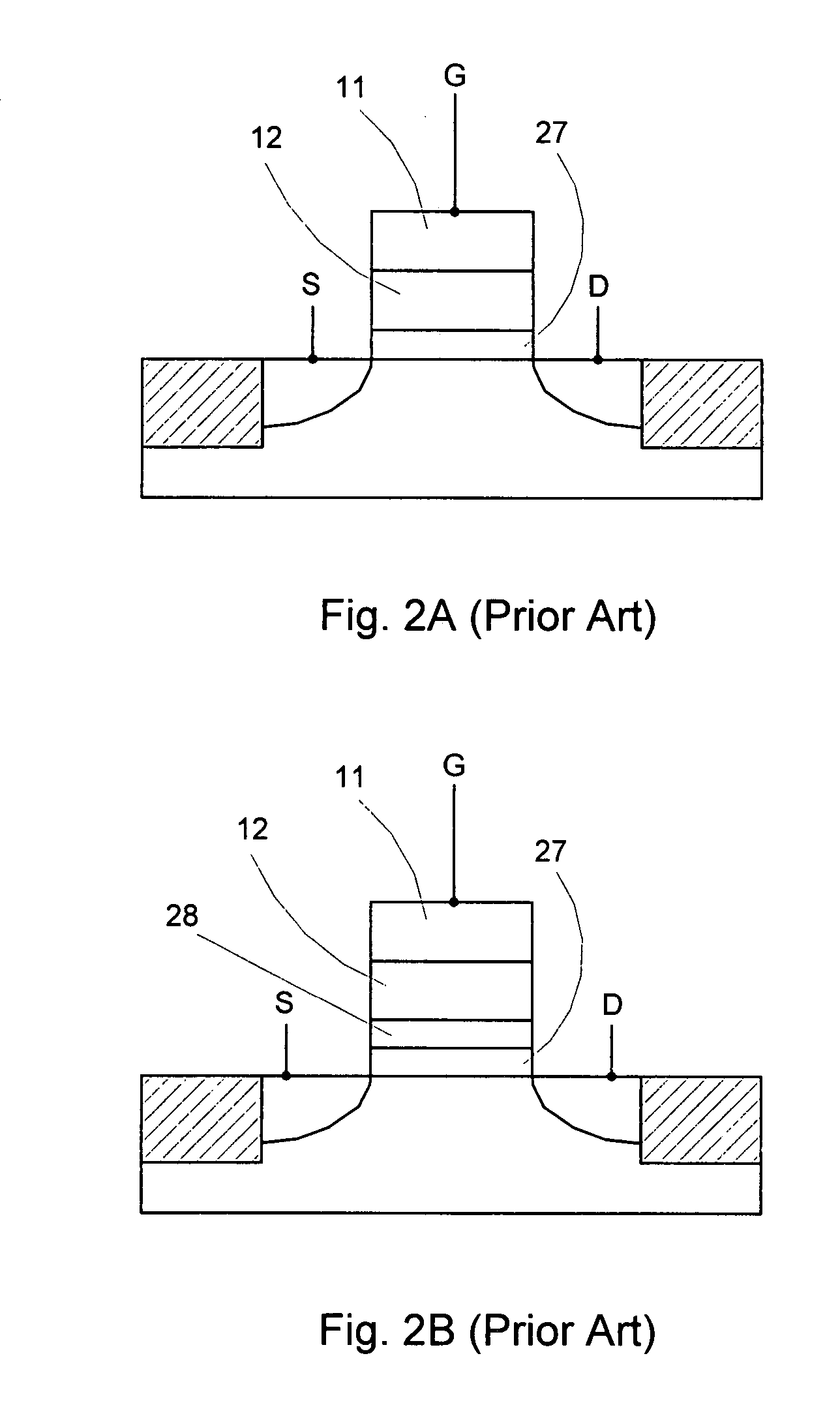

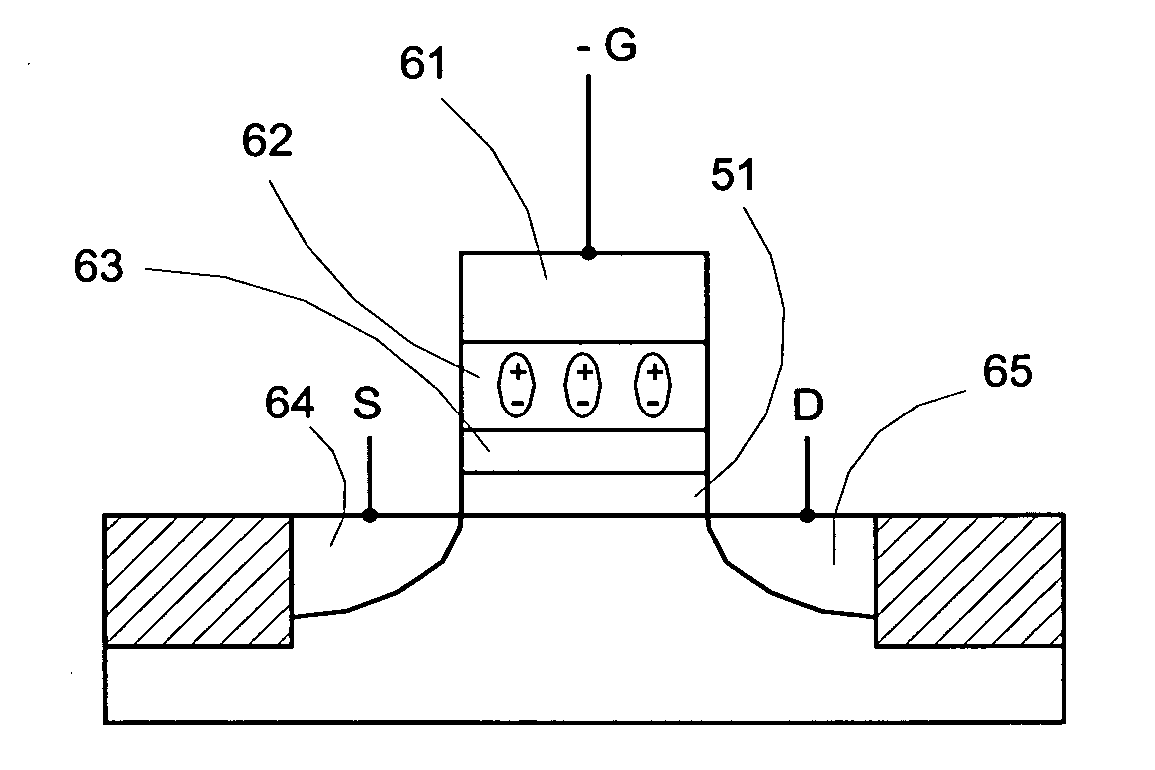

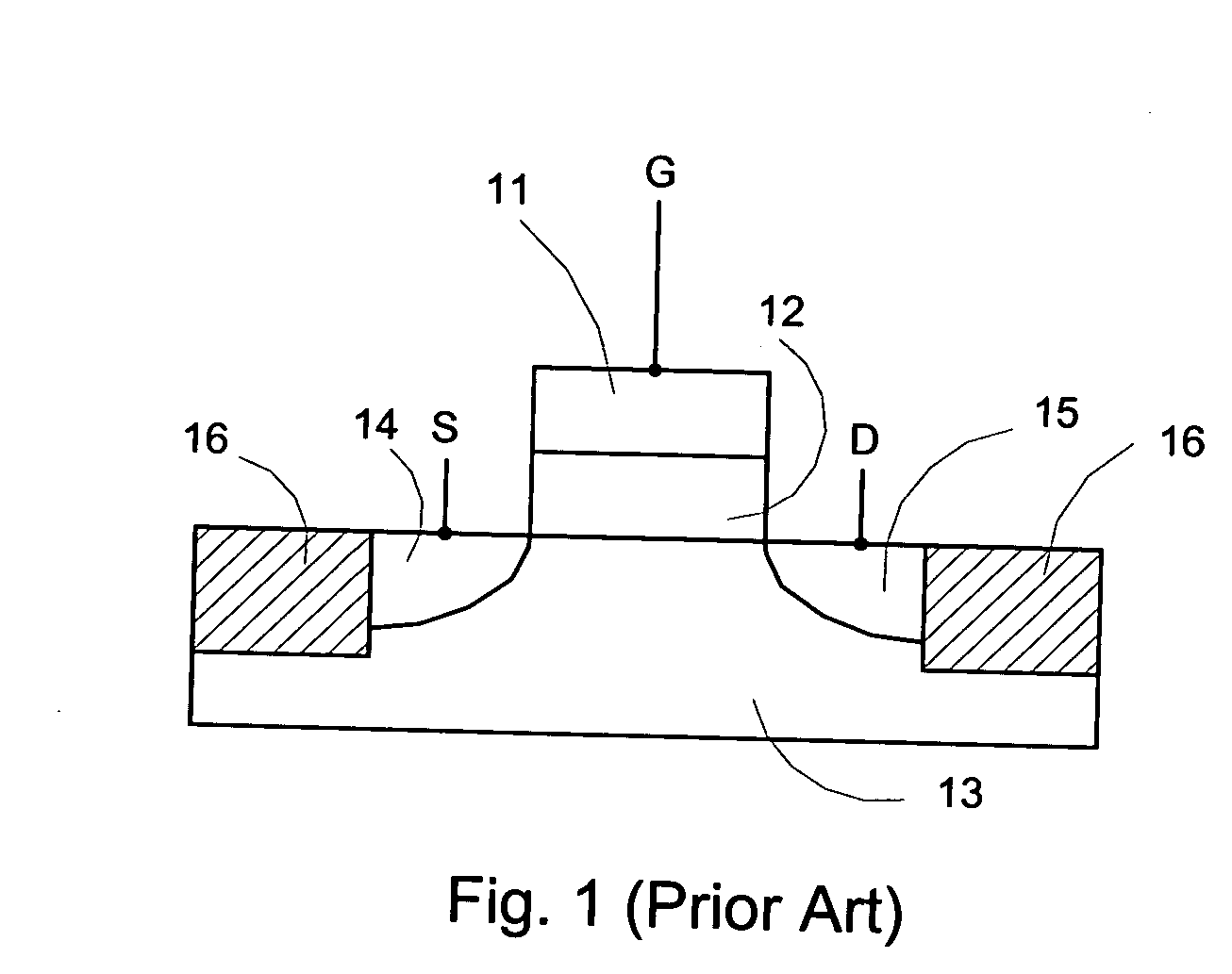

The present invention discloses a novel ferroelectric transistor design using a resistive oxide film in place of the gate dielectric. By replacing the gate dielectric with a resistive oxide film, and by optimizing the value of the film resistance, the bottom gate of the ferroelectric layer is electrically connected to the silicon substrate, eliminating the trapped charge effect and resulting in the improvement of the memory retention characteristics. The resistive oxide film is preferably a doped conductive oxide in which a conductive oxide is doped with an impurity species. The doped conductive oxide is most preferred to be In2O3 with the dopant species being hafnium oxide, zirconium oxide, lanthanum oxide, or aluminum oxide.

Owner:SHARP KK

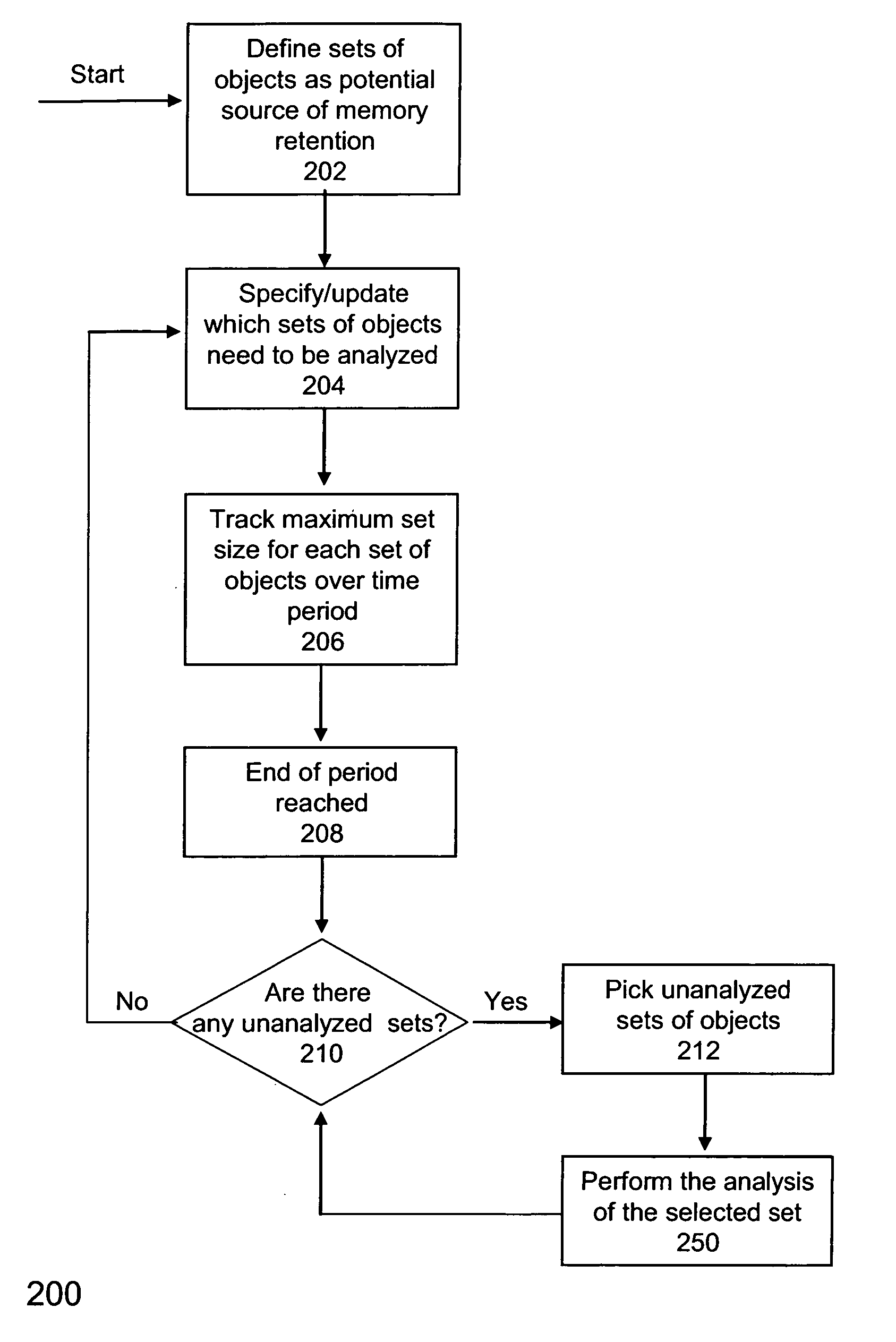

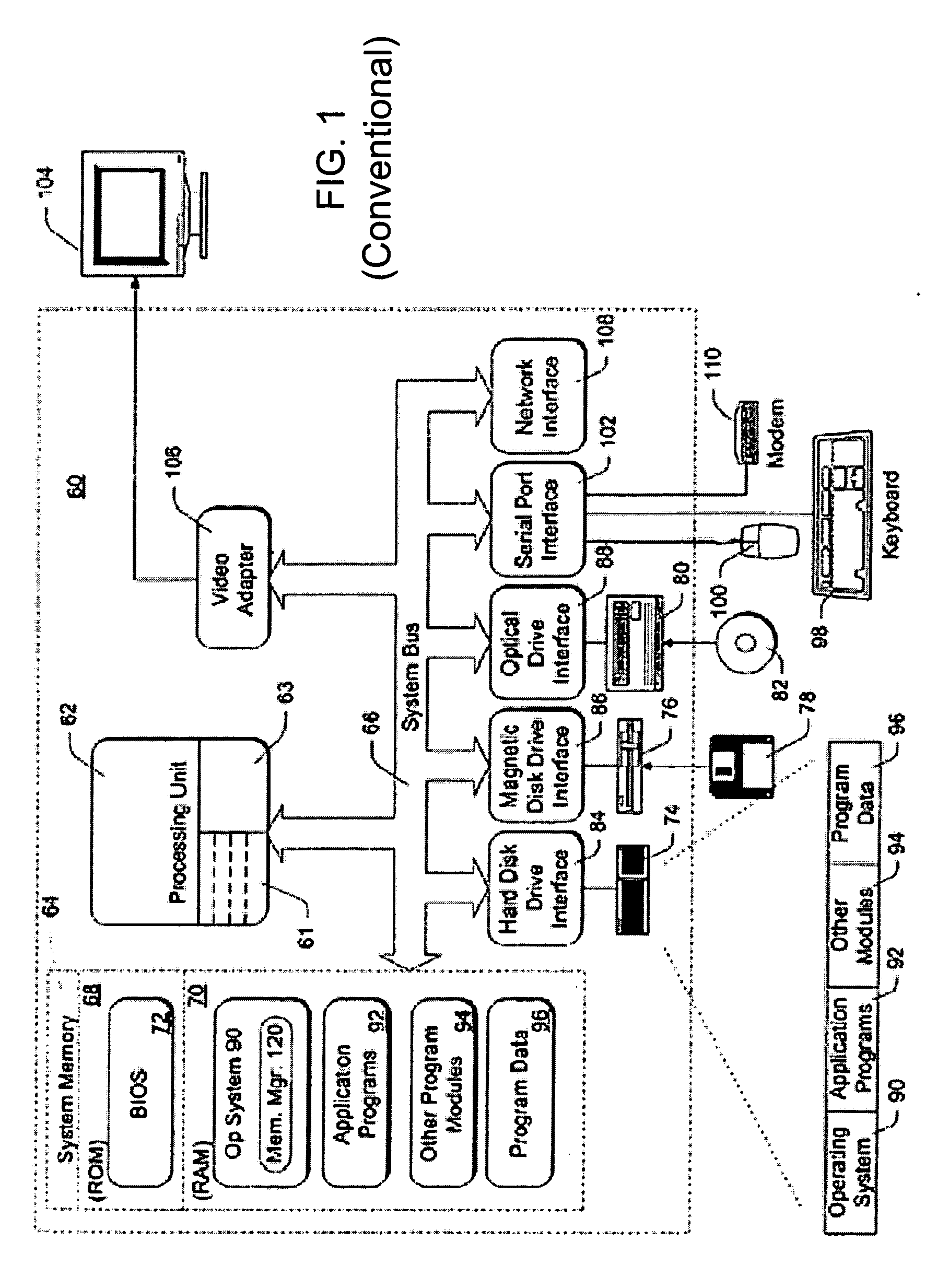

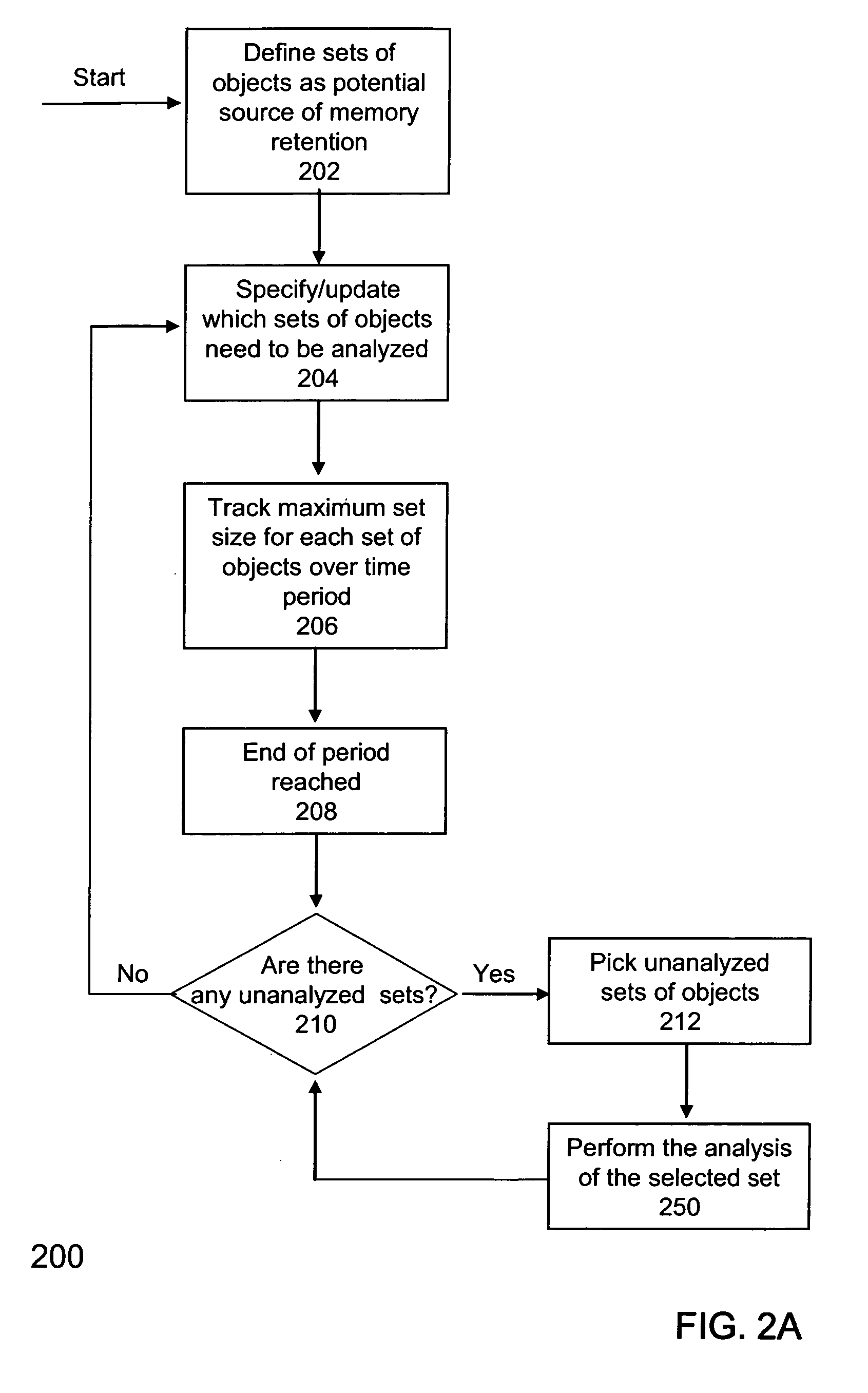

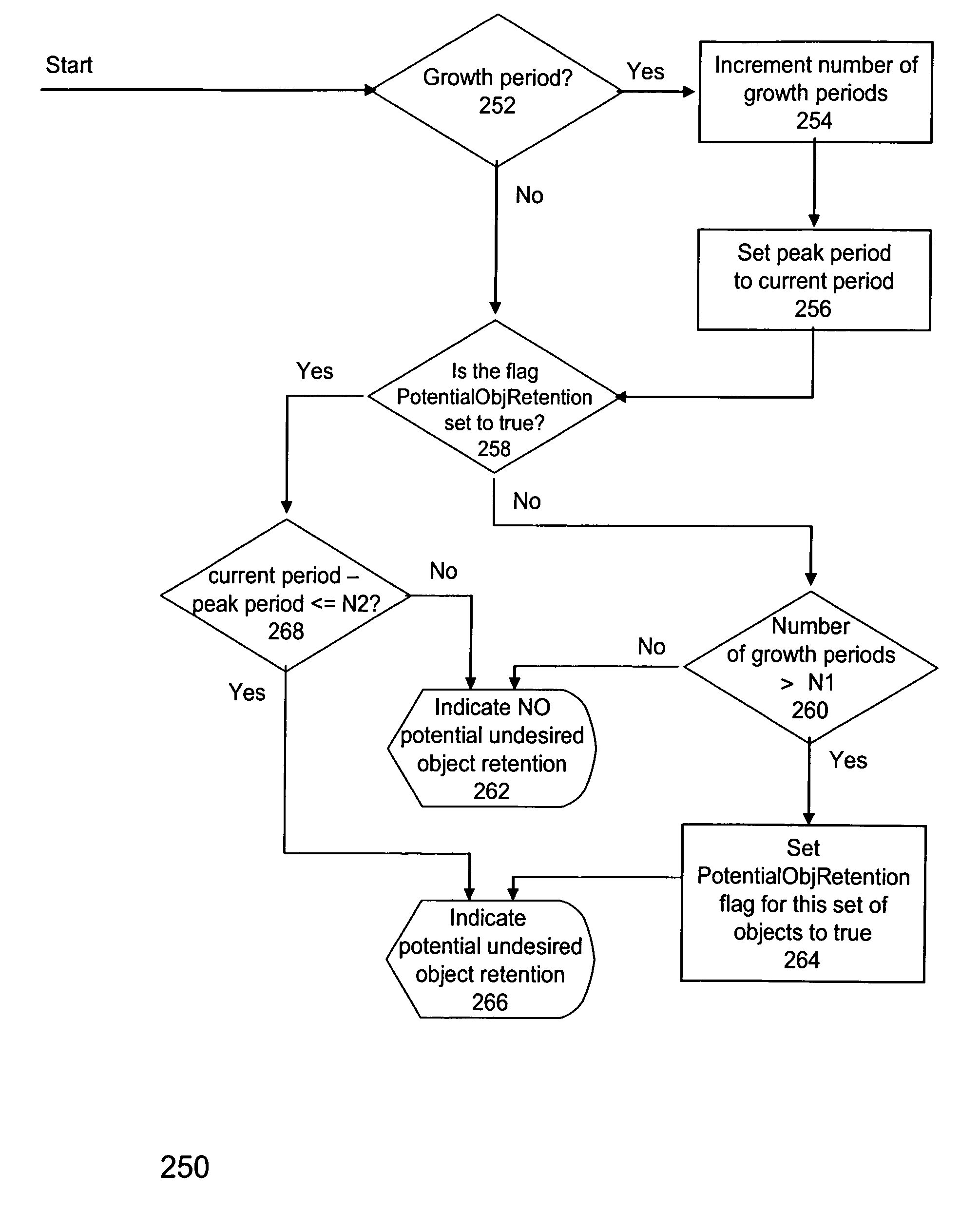

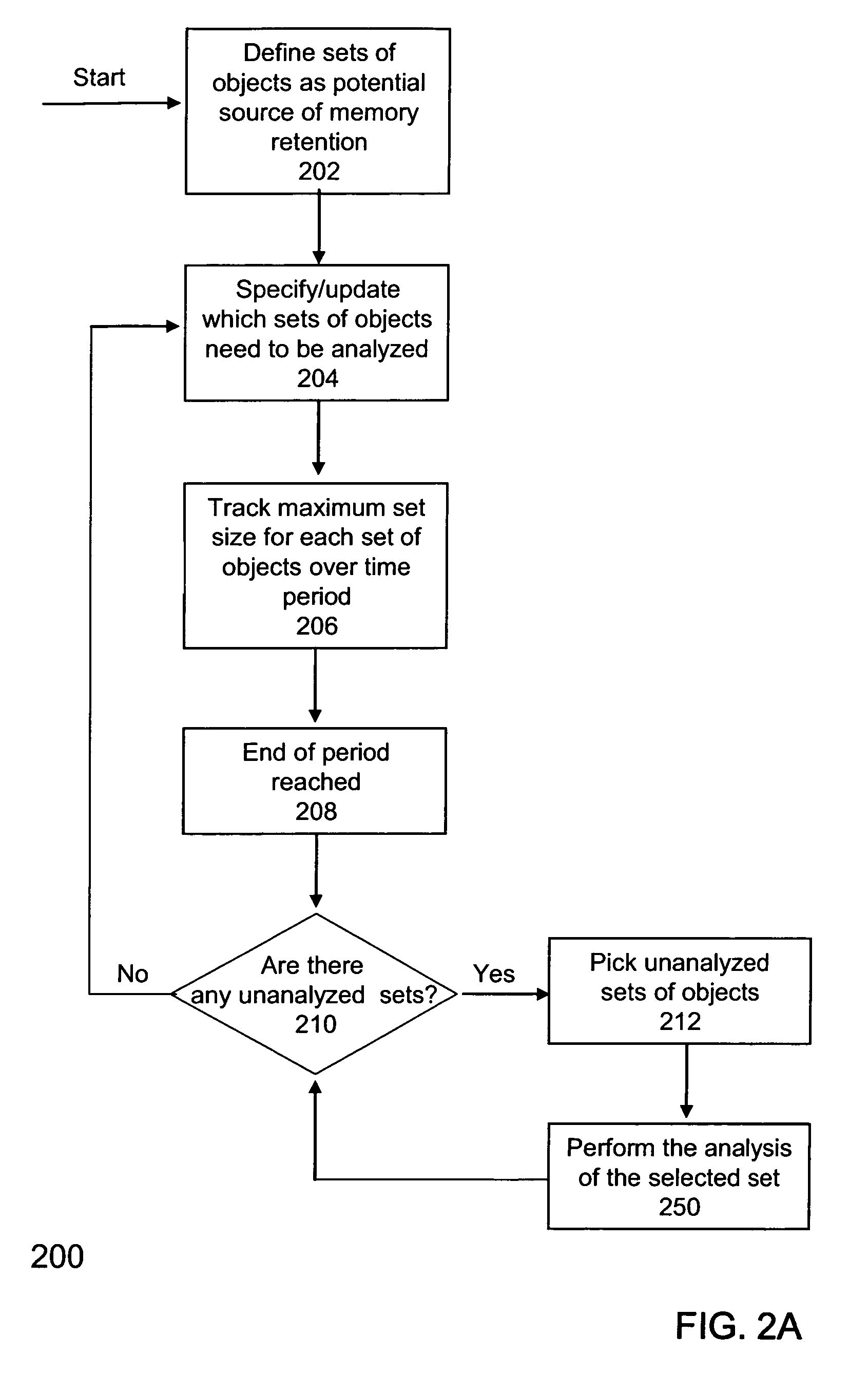

Identifying sources of memory retention

ActiveUS20070067758A1Reduce overheadMultiprogramming arrangementsNon-redundant fault processingMemory retentionParallel computing

One embodiment relates to a method for identifying sources of memory retention in an executing application. A size of a set of objects is tracked over multiple periods. A period is determined to be a growth period if the size for the set of objects increases above a previous maximum size, and the number of growth periods is counted. The set of objects is flagged as having potential undesired object retention (a memory leak) if the number of growth periods is greater than a threshold number. Other embodiments are also disclosed.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

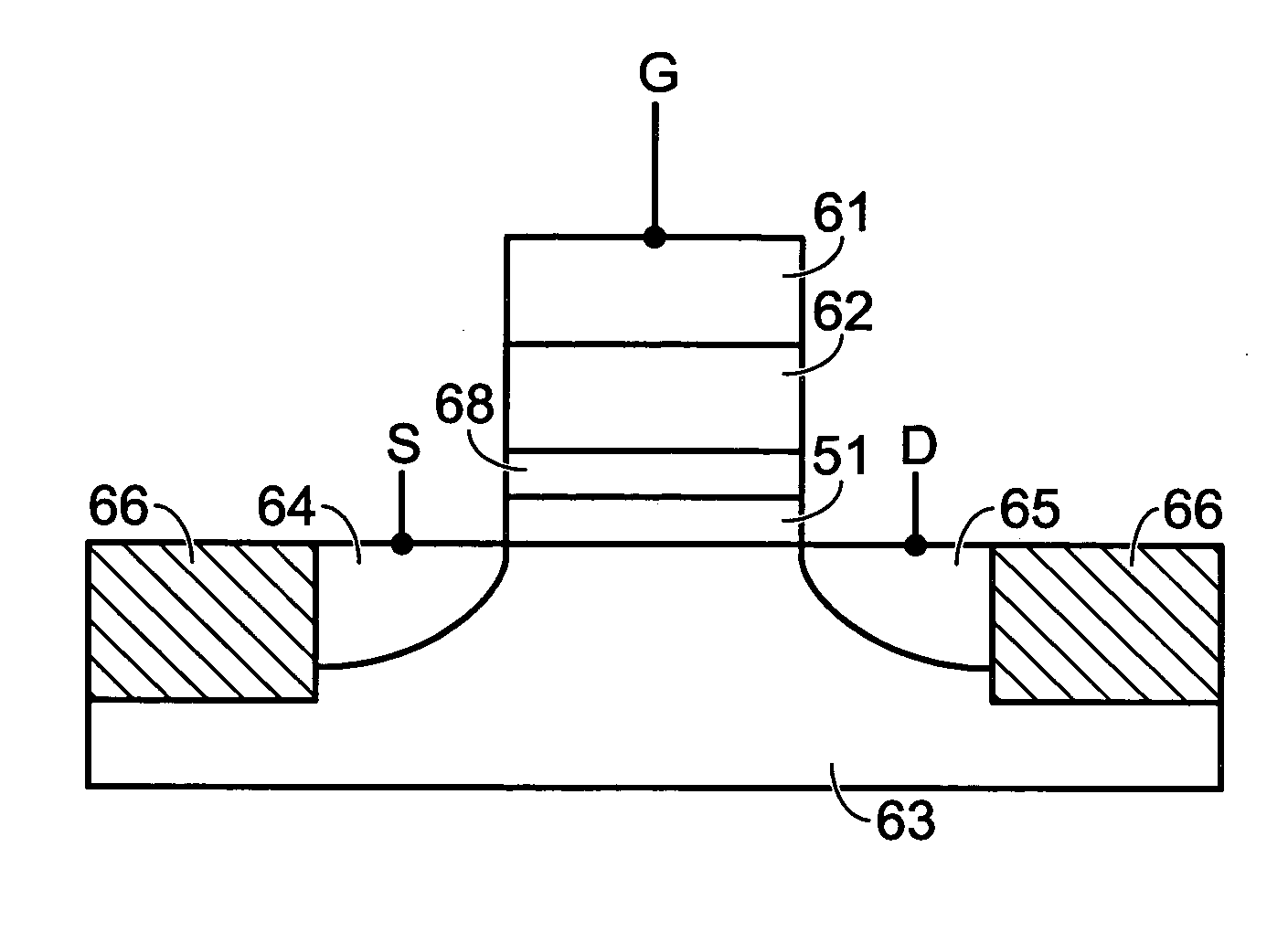

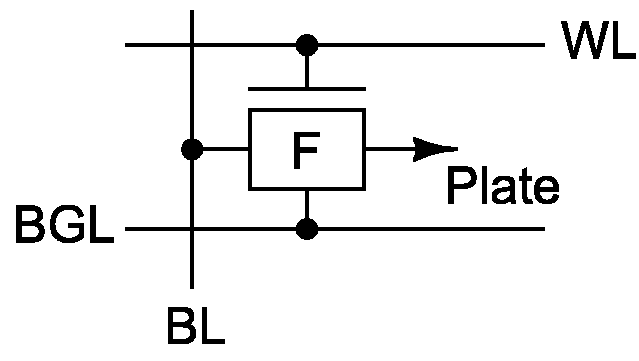

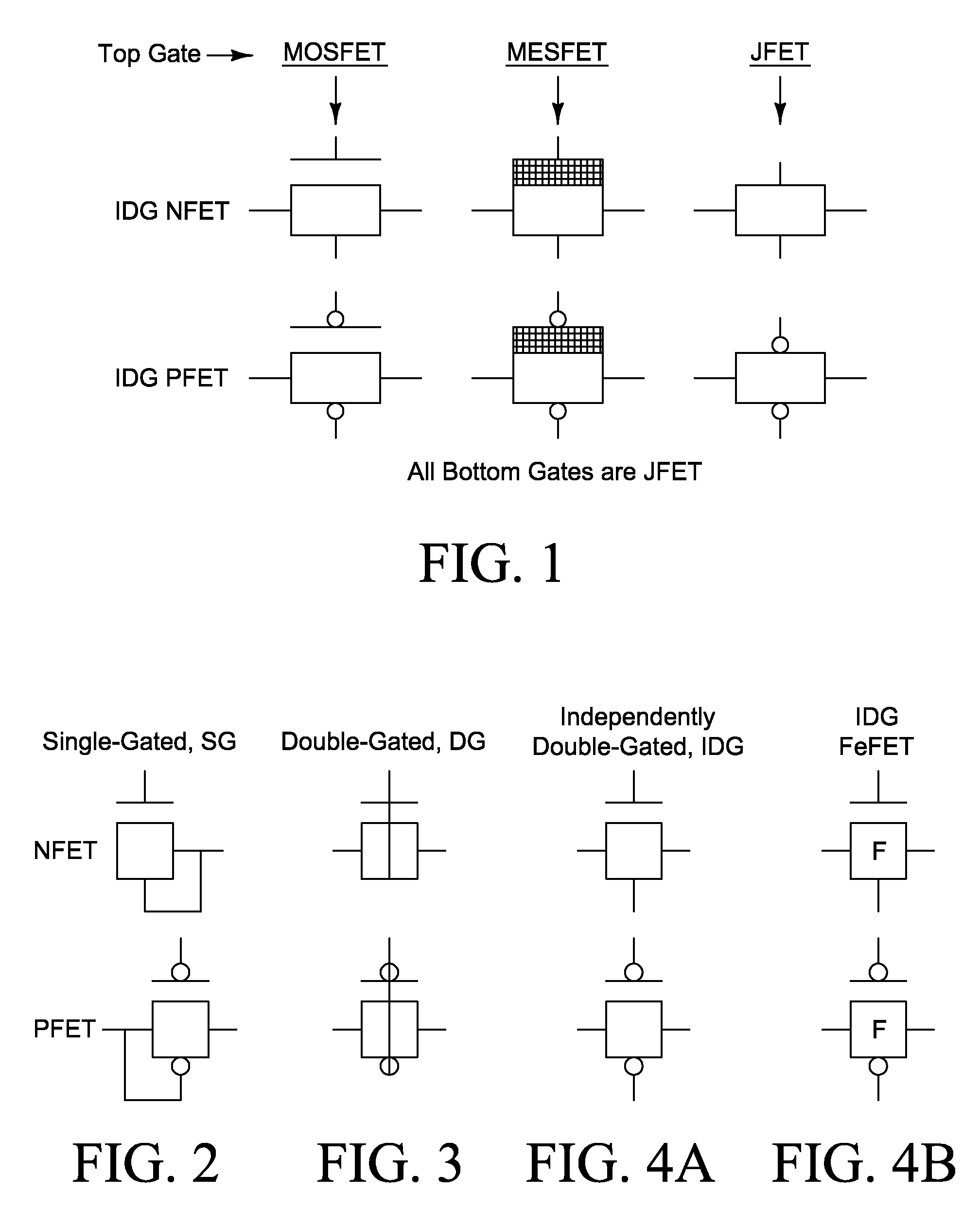

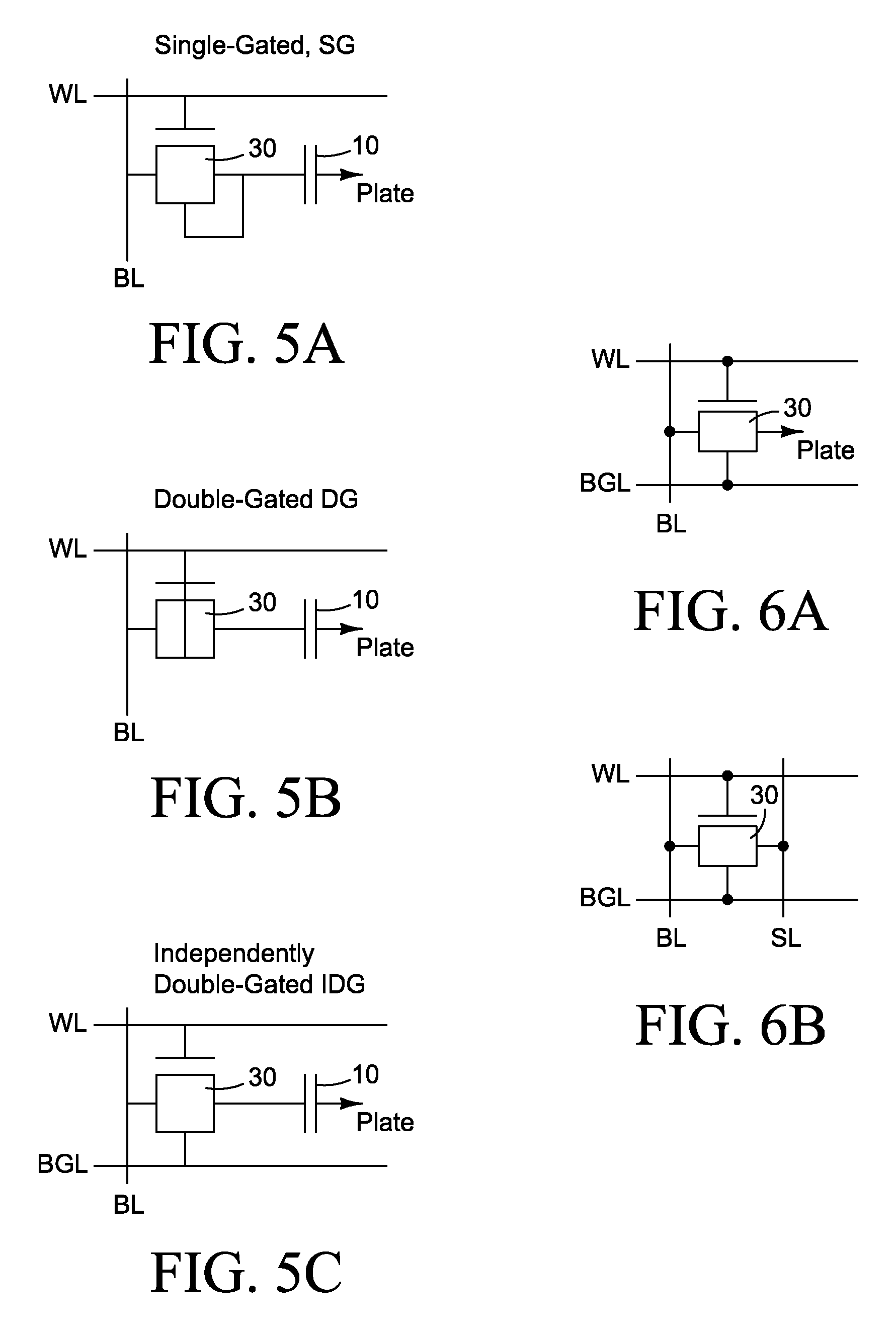

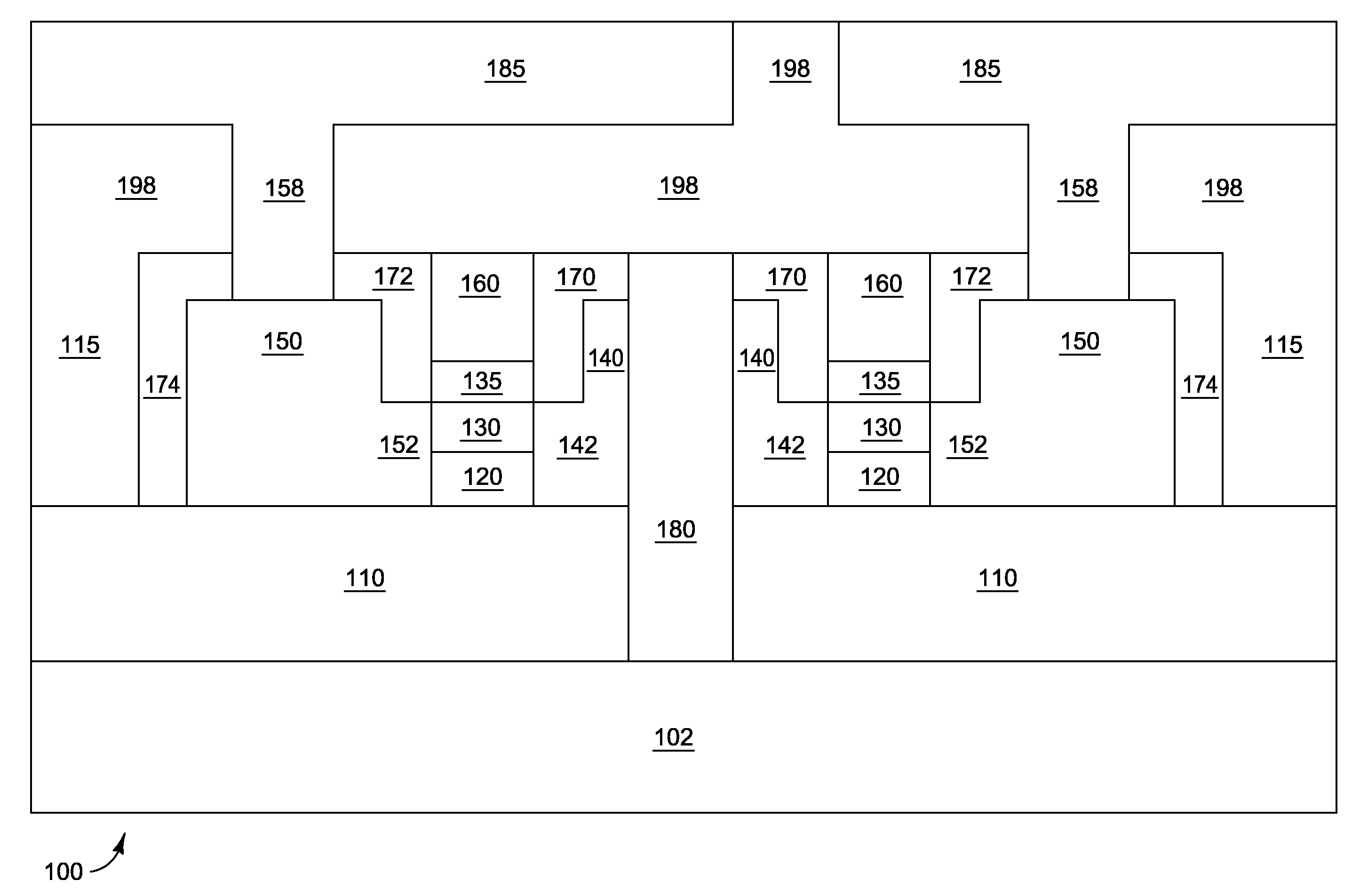

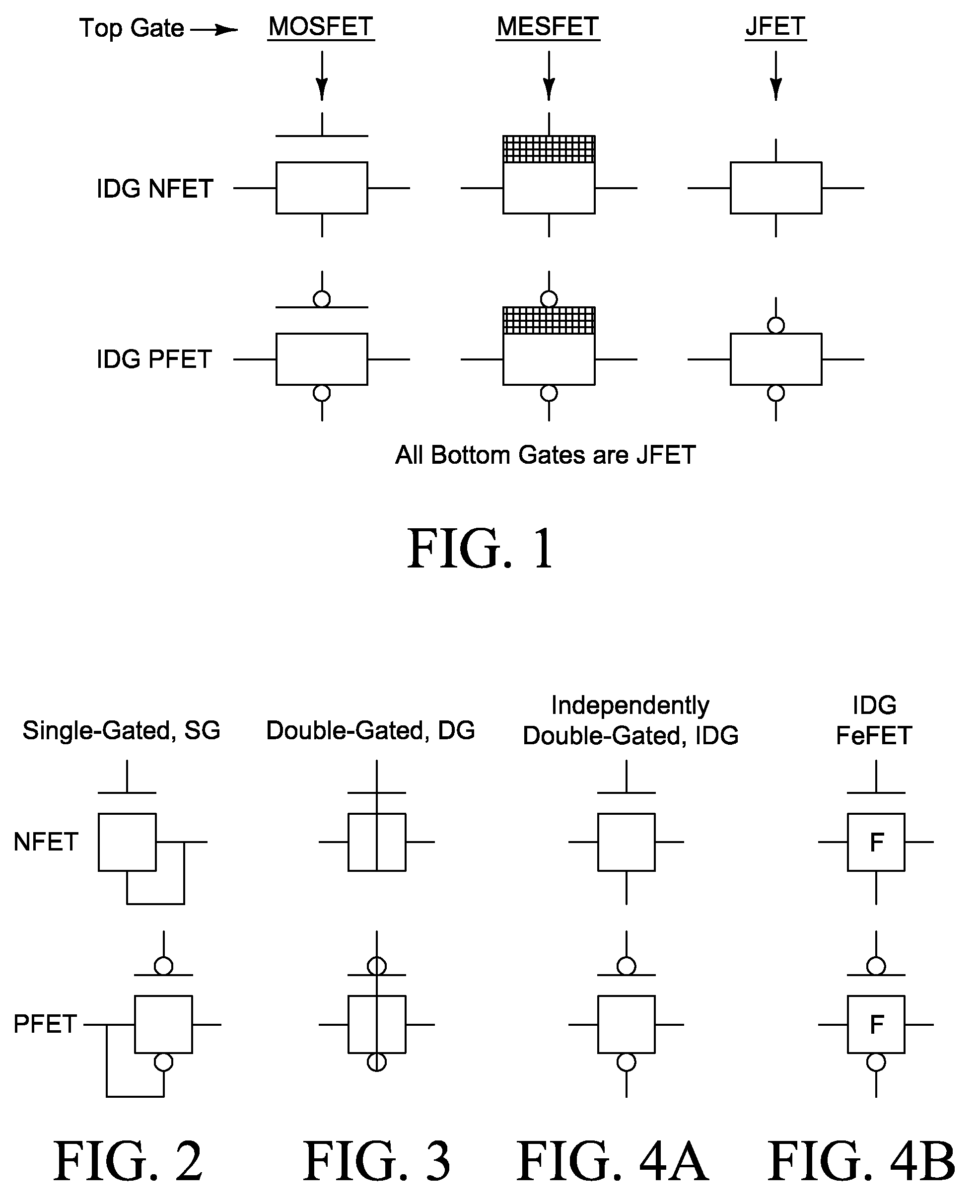

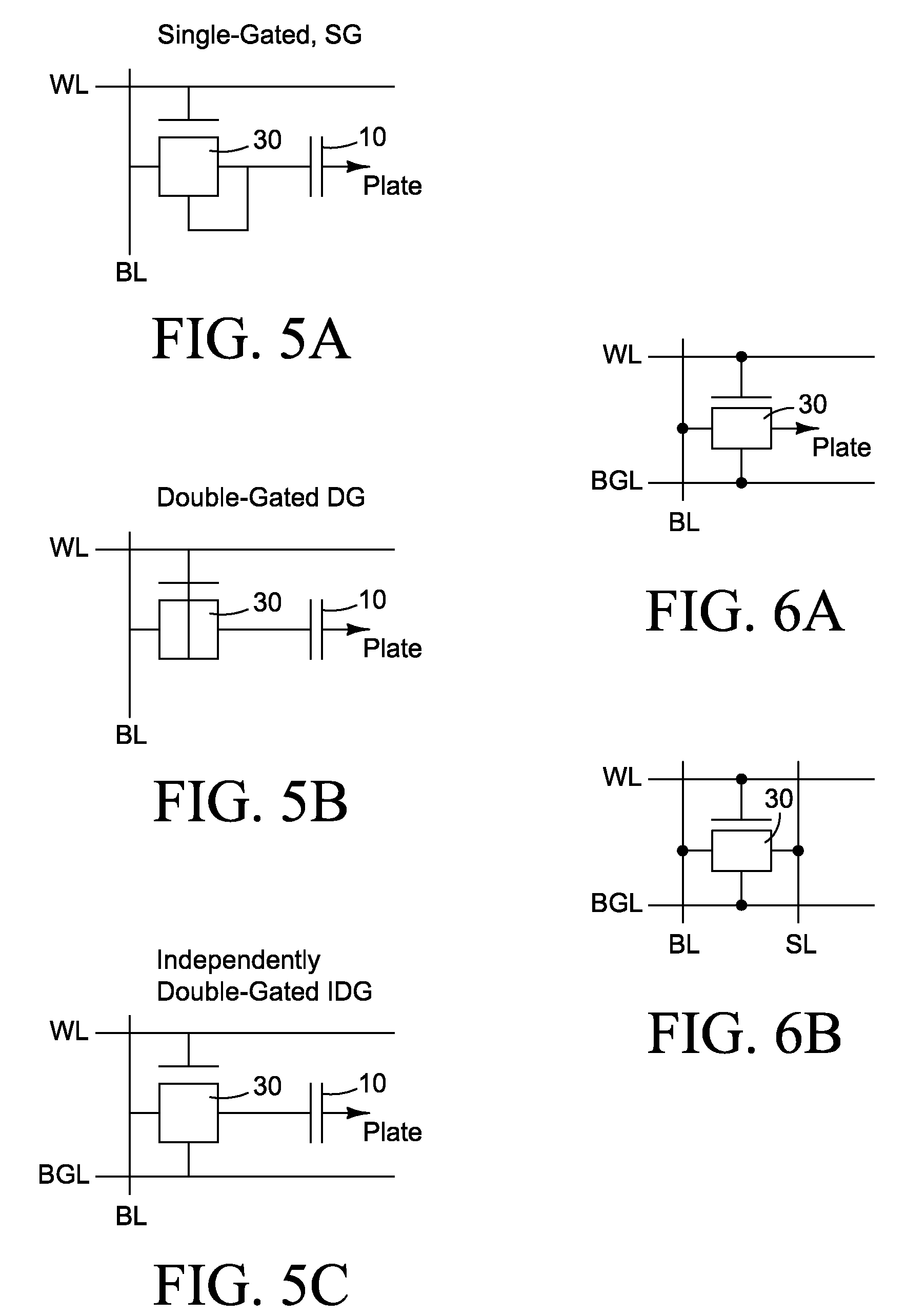

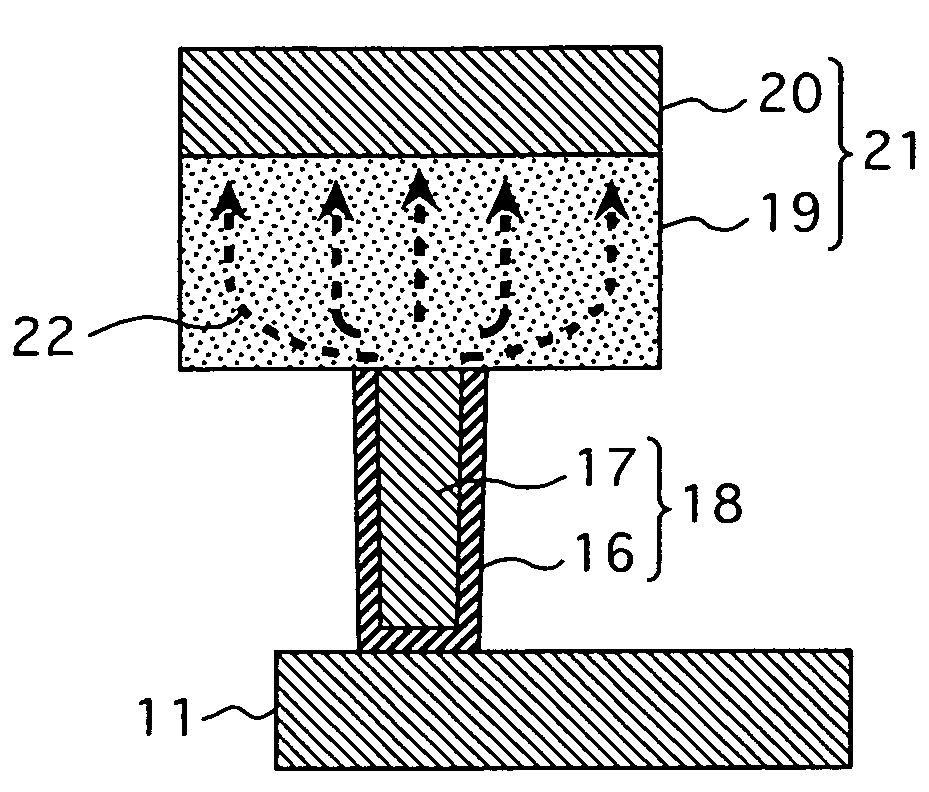

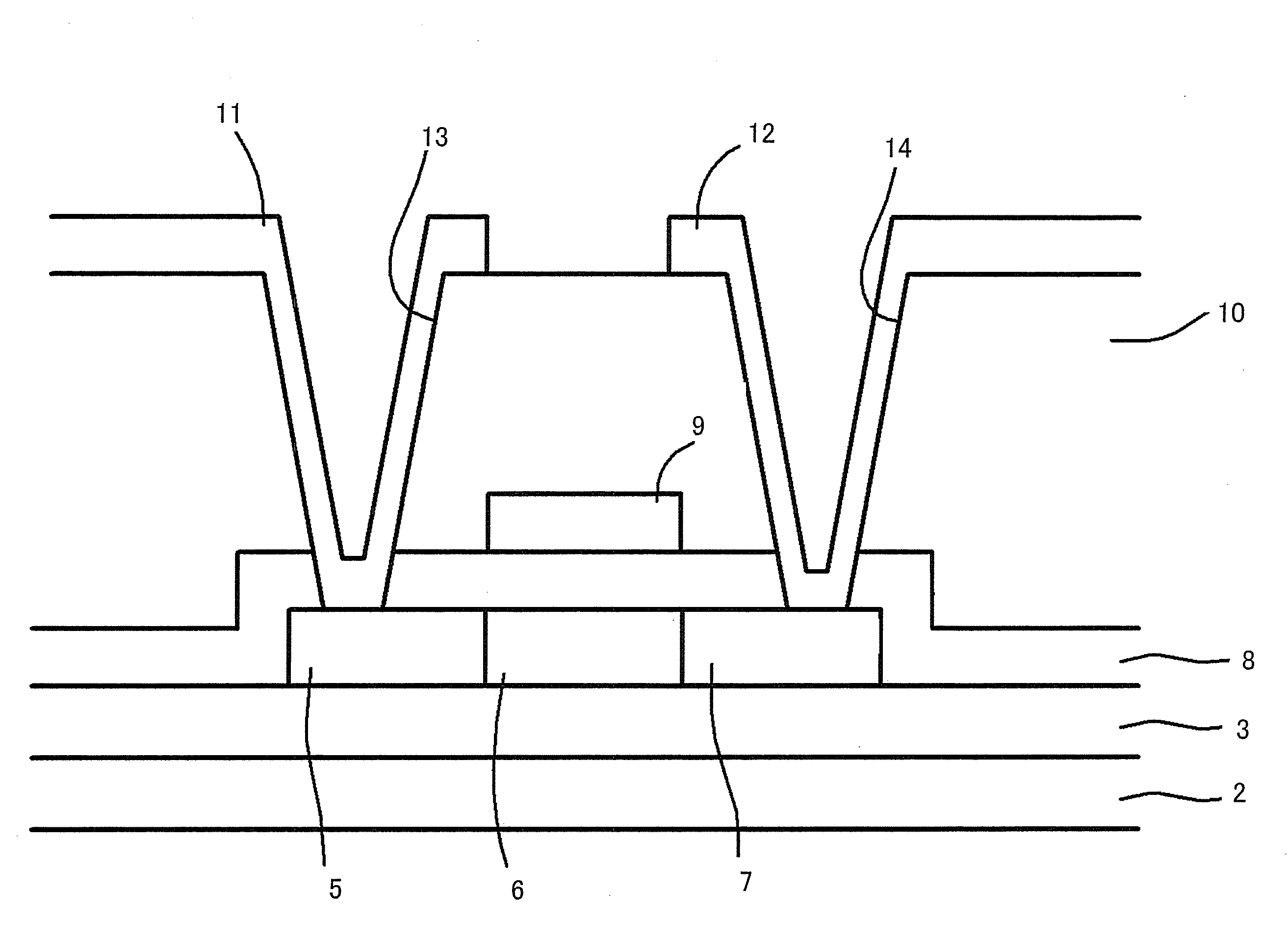

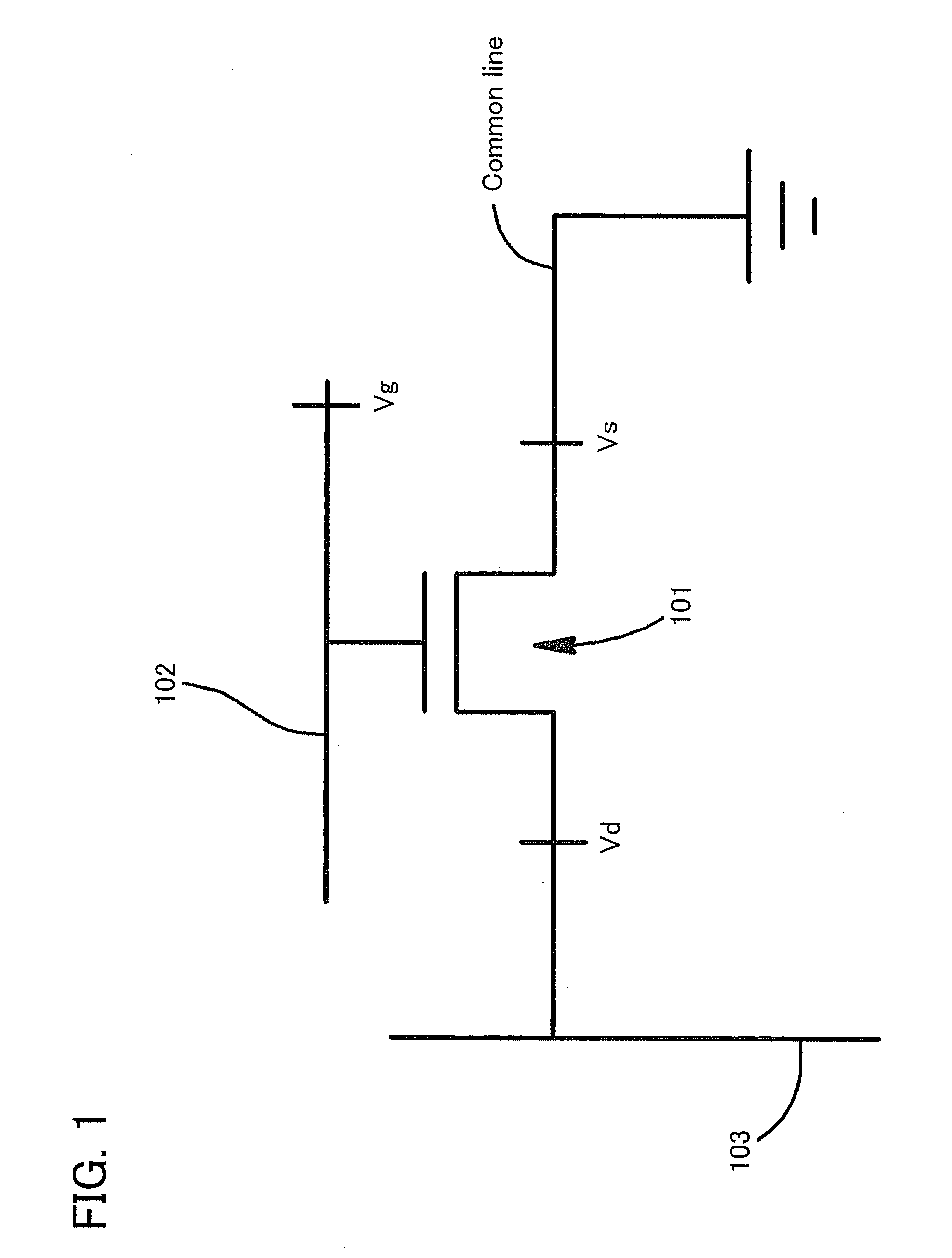

Independently-Double-Gated Transistor Memory (IDGM)

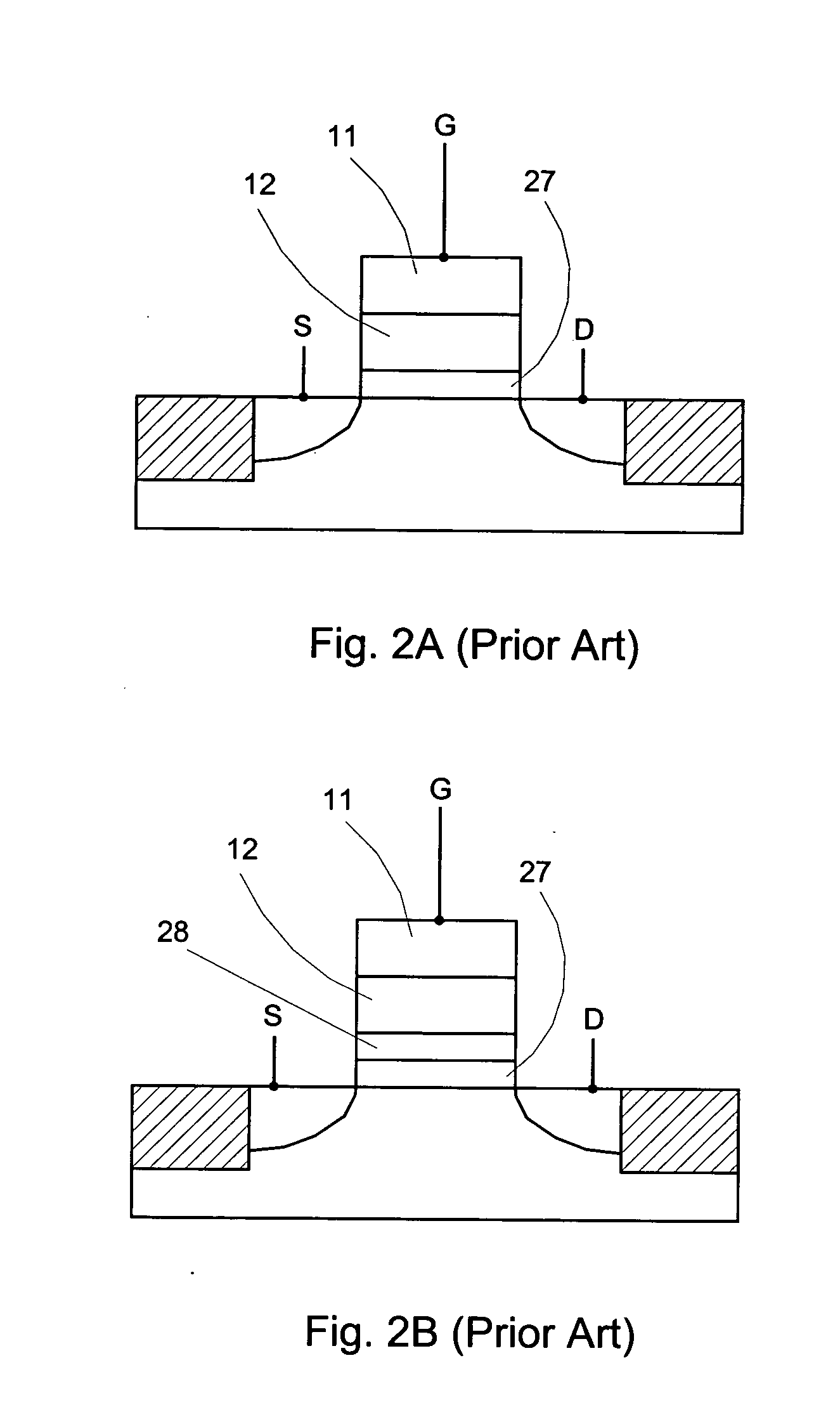

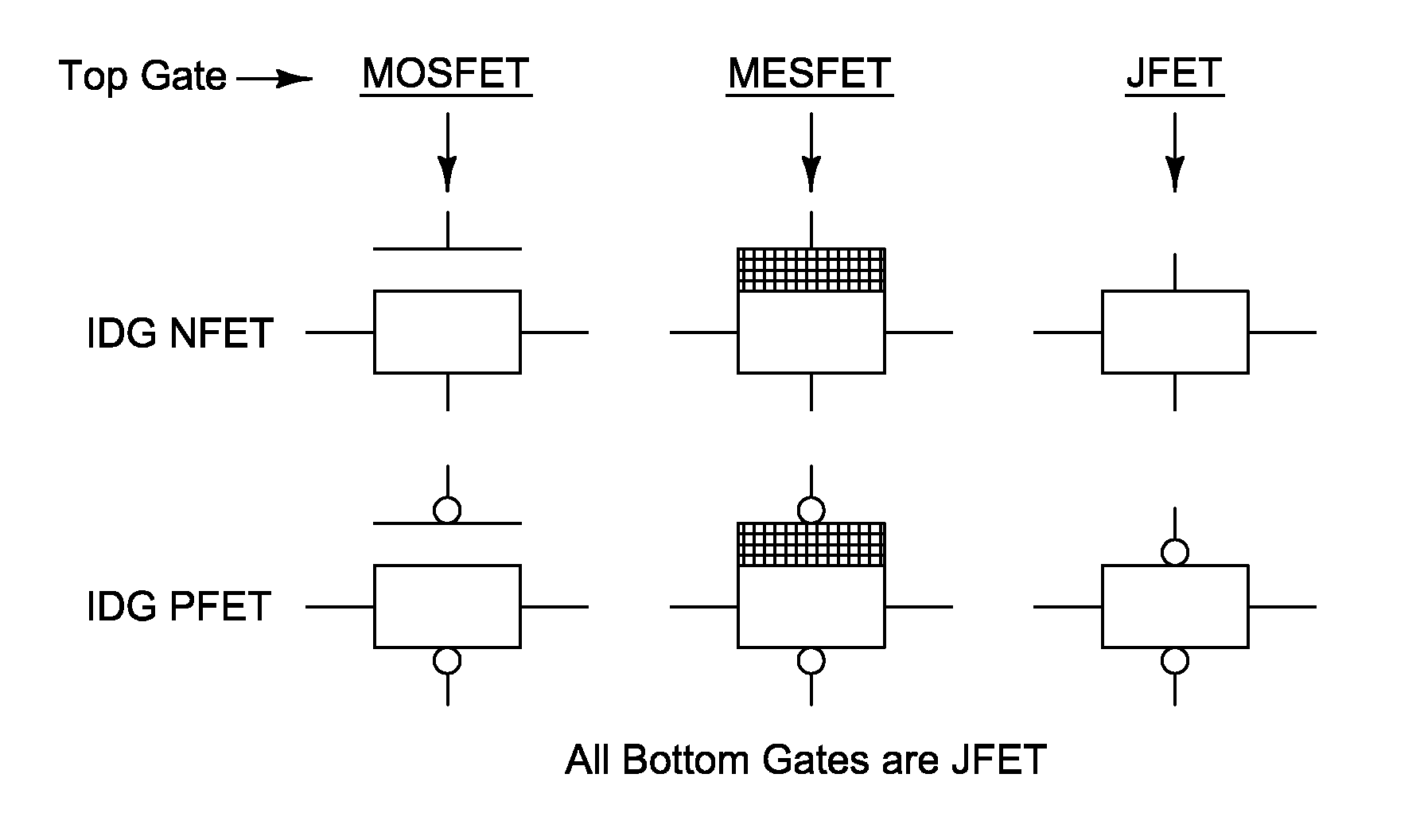

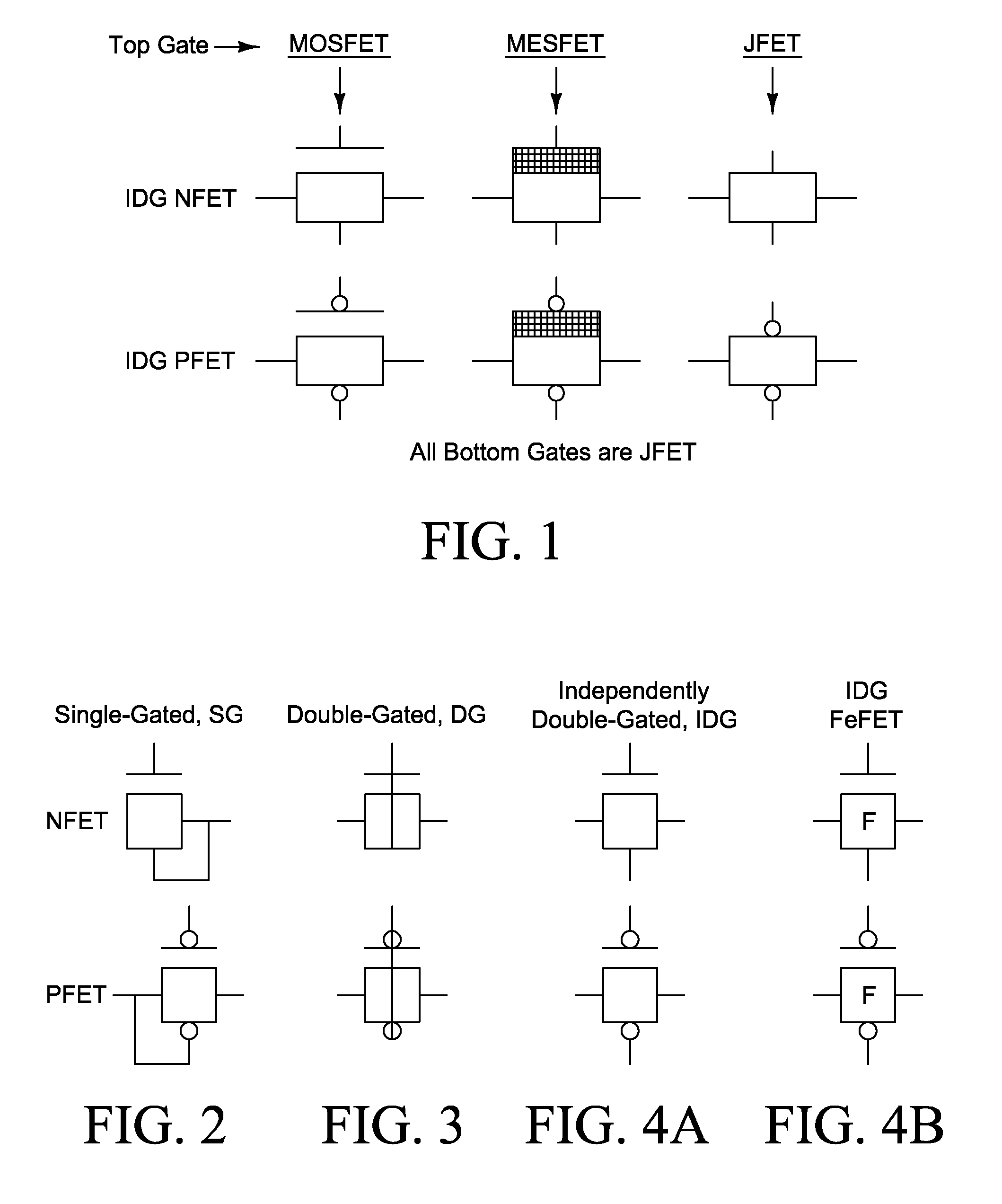

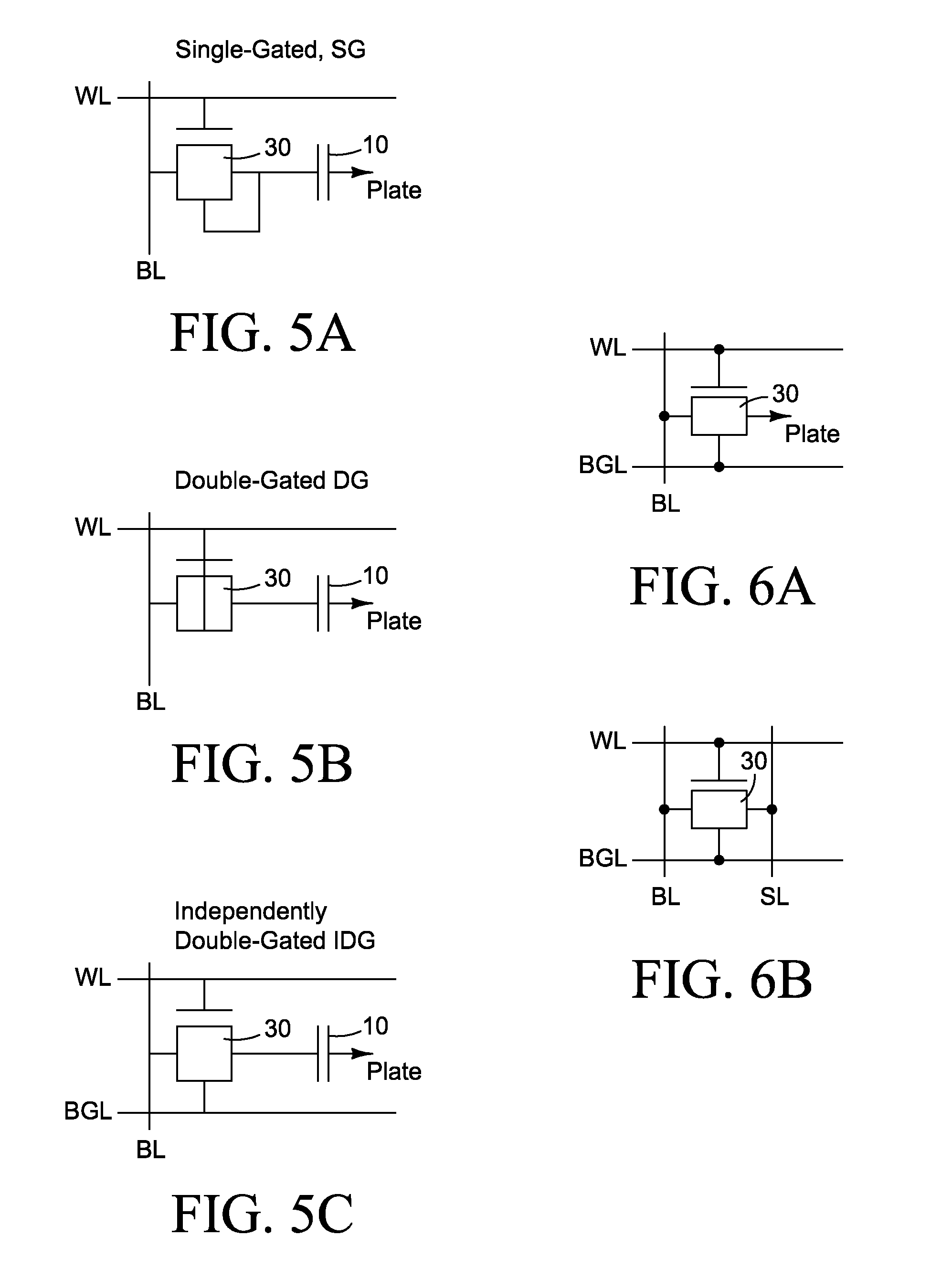

InactiveUS20080203443A1Function increaseSmall and efficientTransistorSolid-state devicesMemory retentionPower parameter

Memory cells are constructed from double-gated four terminal transistors having independent gate control. DRAM cells may use one, two or three transistors. Single transistor cells are constructed either with or without a bit storage capacitor, and both NAND- and NOR-type Non-Volatile NVRAM cells, as well as Ferroelectric FeRAM cells, are described. For all cells, top gates provide conventional access while independent bottom gates provide control to optimize memory retention for given speed and power parameters as well as to accommodate hardening against radiation. In a single transistor cell without a capacitor, use of the bottom gate allows packing to a density approaching 2 F2. Using a ferroelectric material as the gate insulator produces a single-transistor FeRAM cell that overcomes the industry-wide Write Disturb problem. The memory cells are compatible with SOI logic circuitry for use as embedded RAM in SOC applications.

Owner:AMERICAN SEMICON

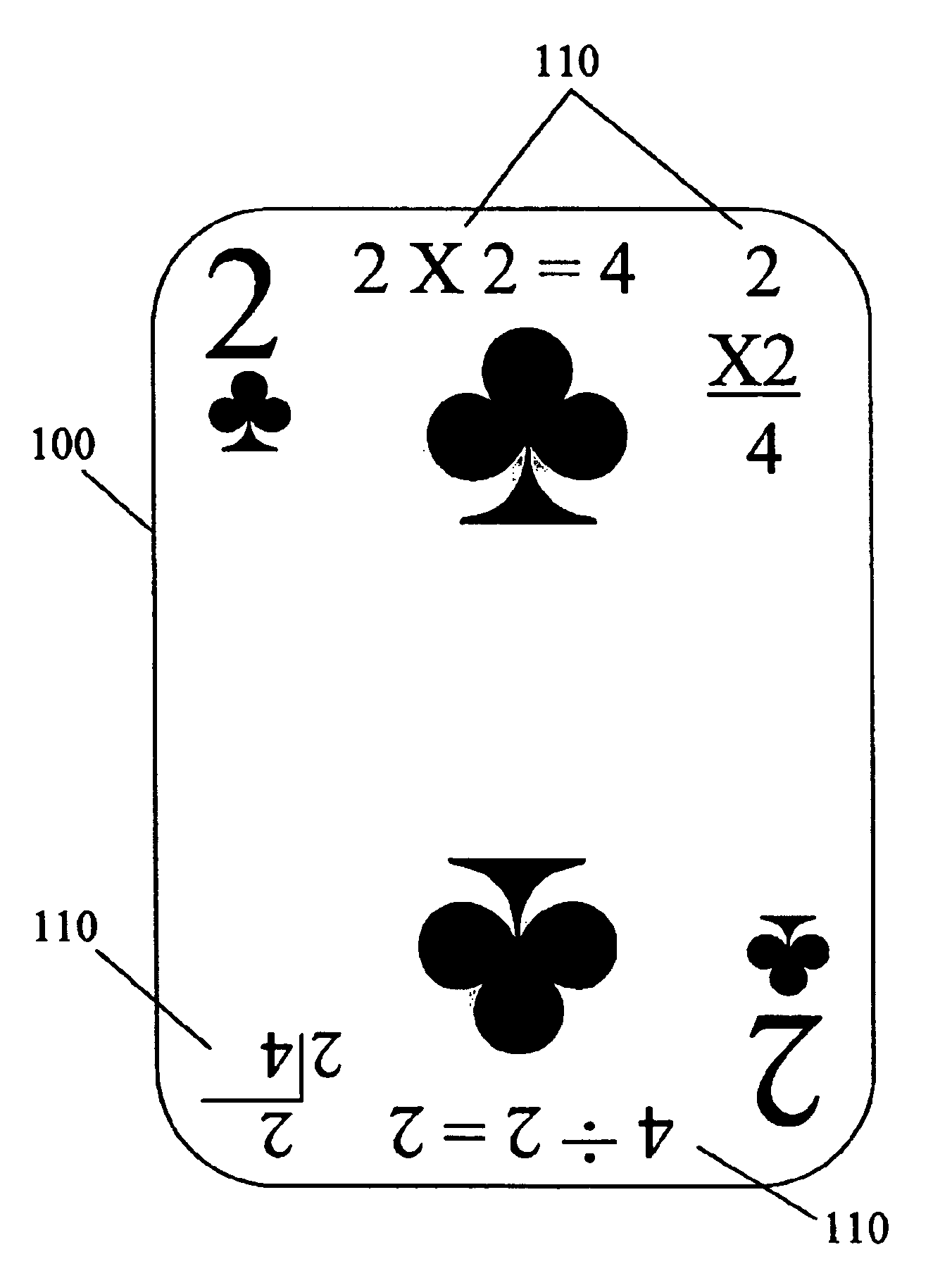

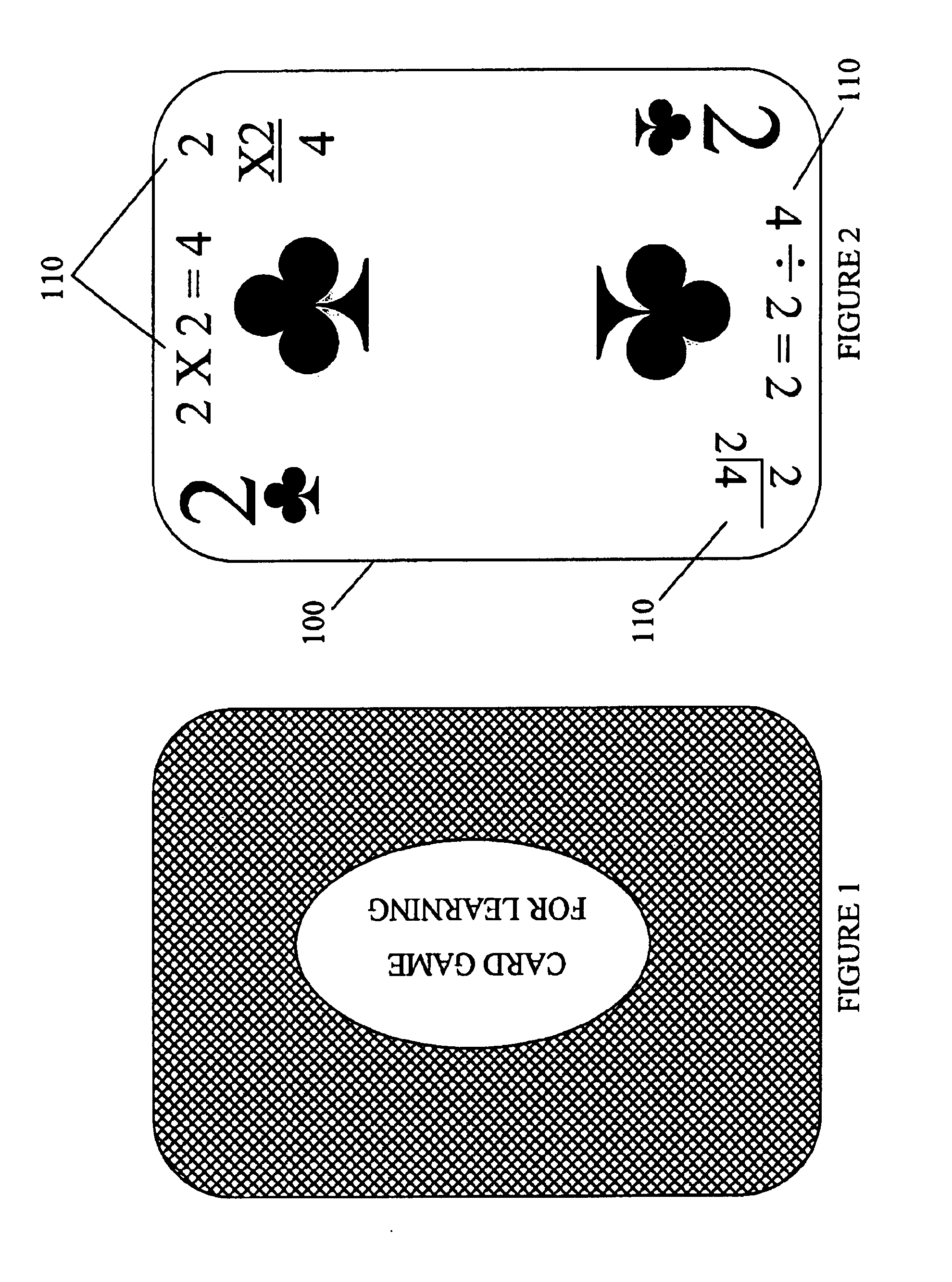

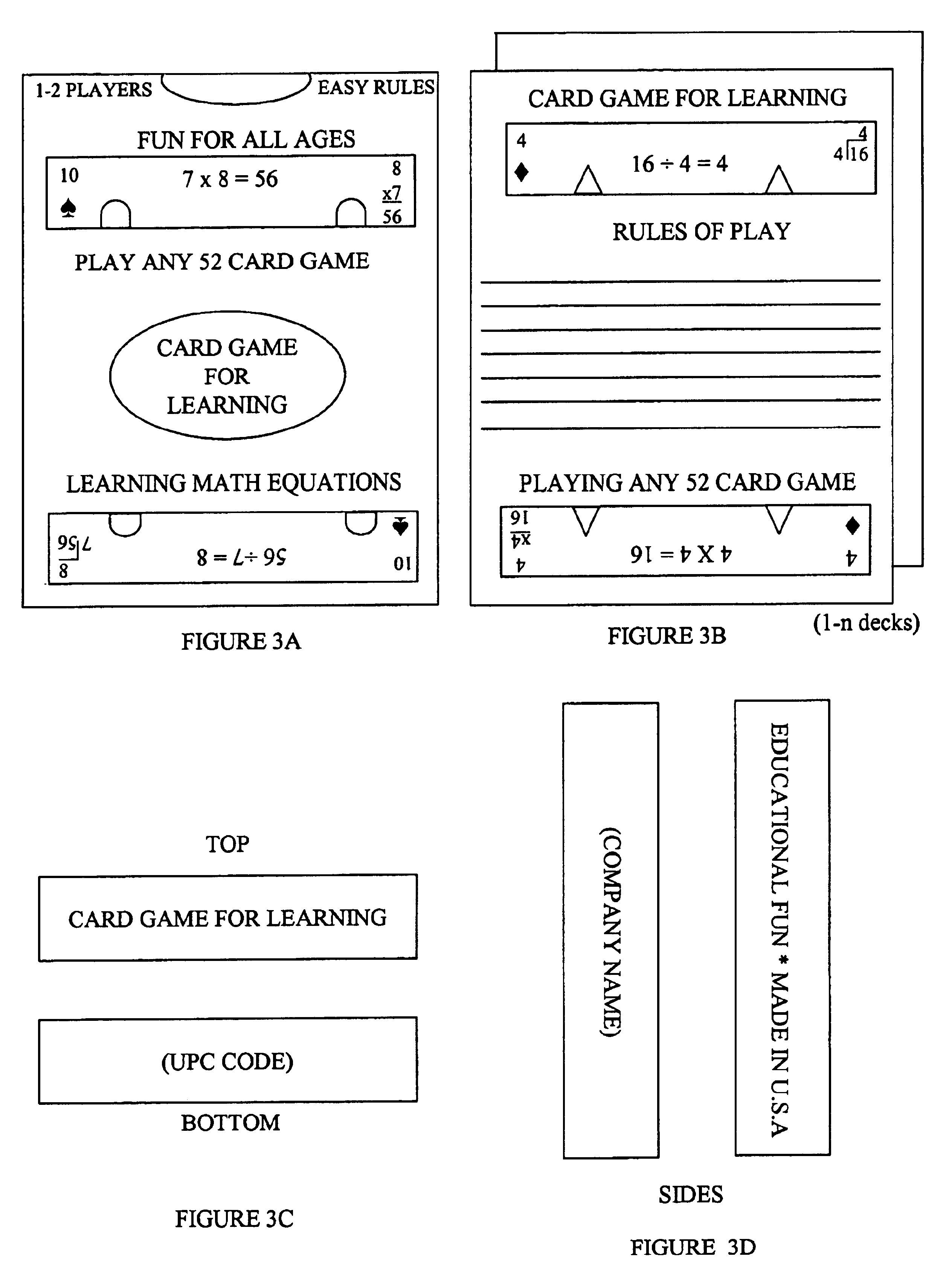

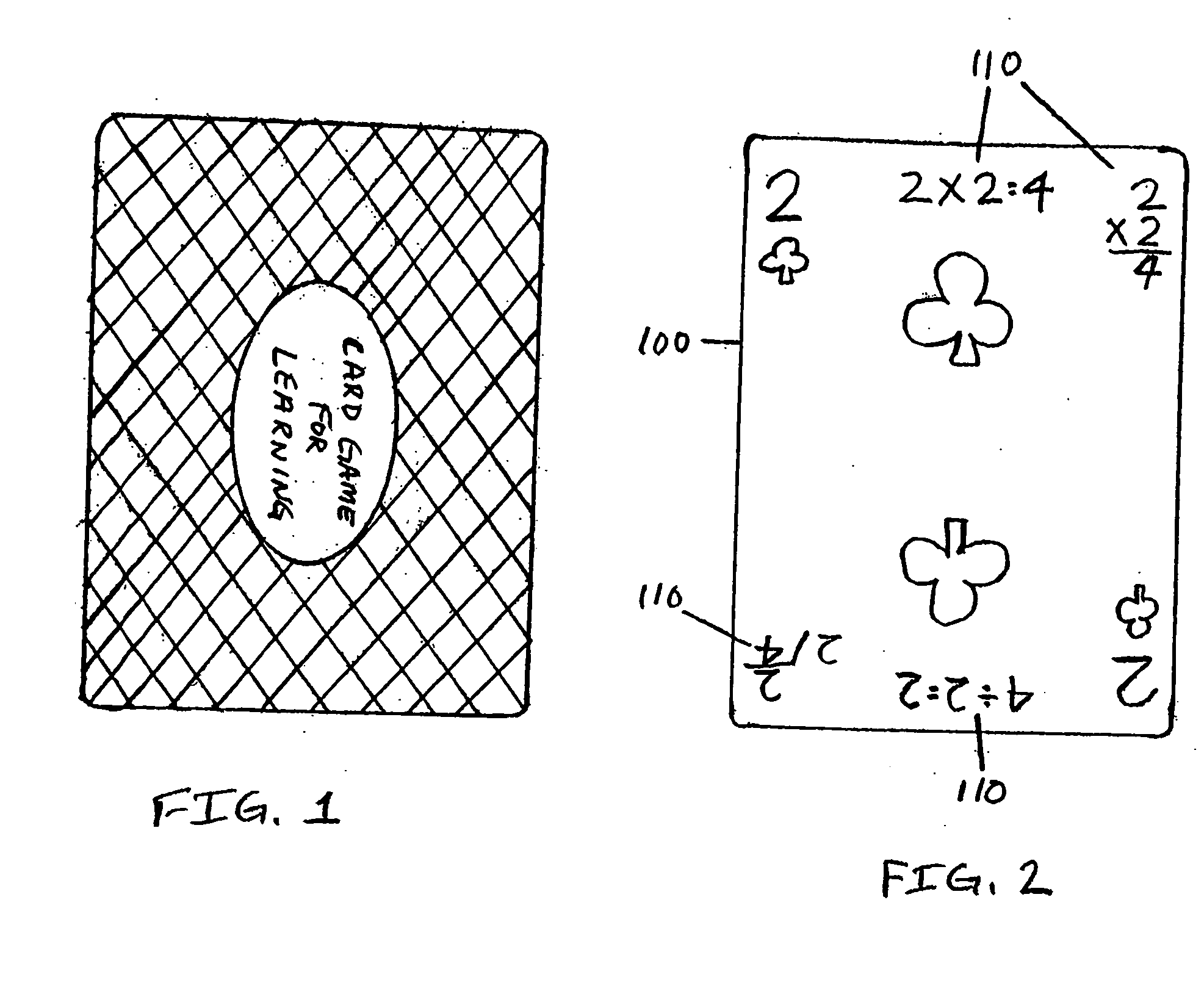

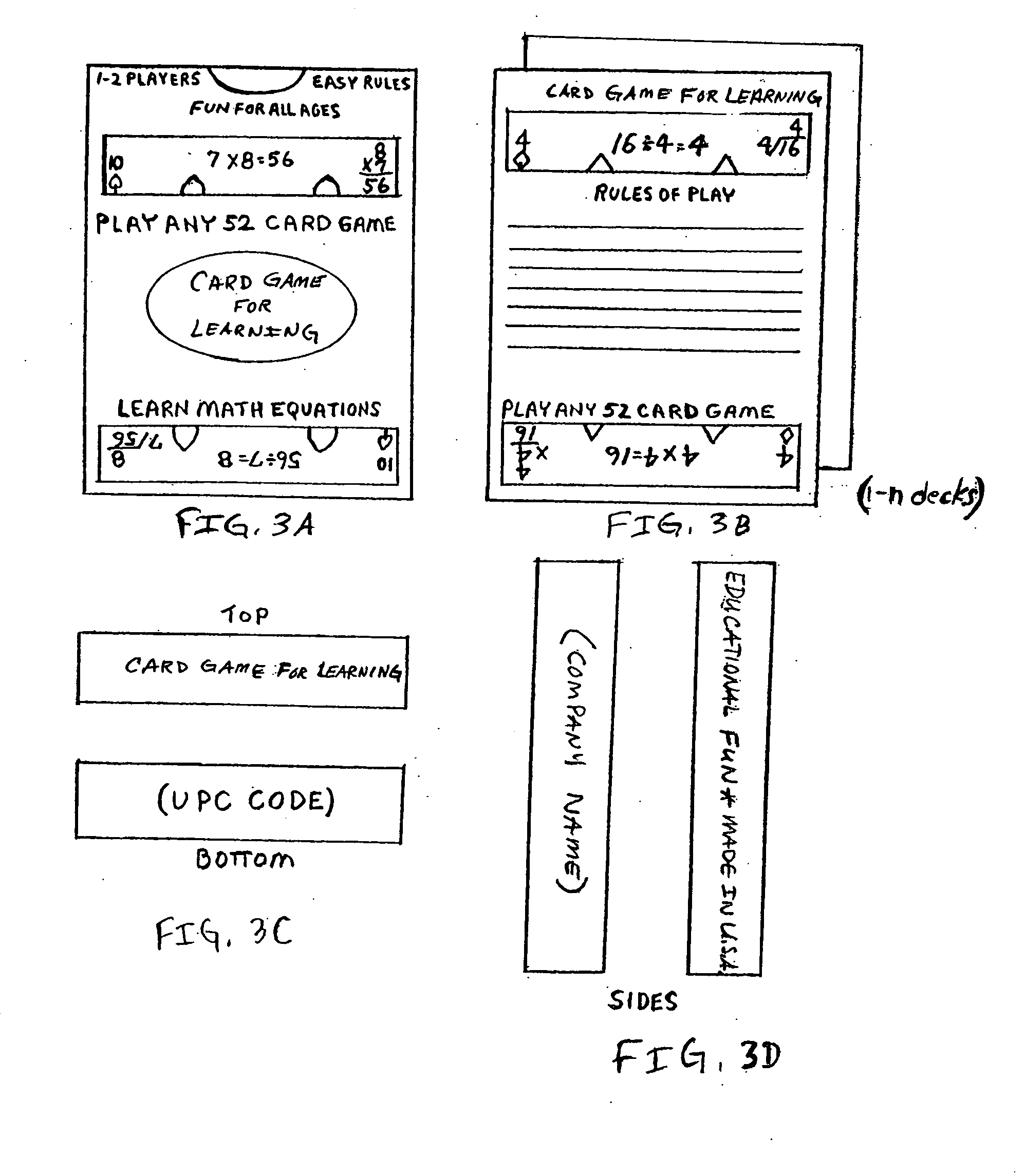

Card game for learning

A card game for learning entails competitive play between players. As the game proceeds, the winner of a match must recite out loud the facts of learning printed on the playing cards. The game repetitively exposes the players to facts in a given subject area such as math, history, science, geography, literature, etc. The learning experience may be geared to different age brackets by tailoring the subject facts to different age brackets. Audible and visual cues help players to associate information for memory retention. Different decks for different age brackets and subjects are provided.

Owner:FUNWAY GAMES

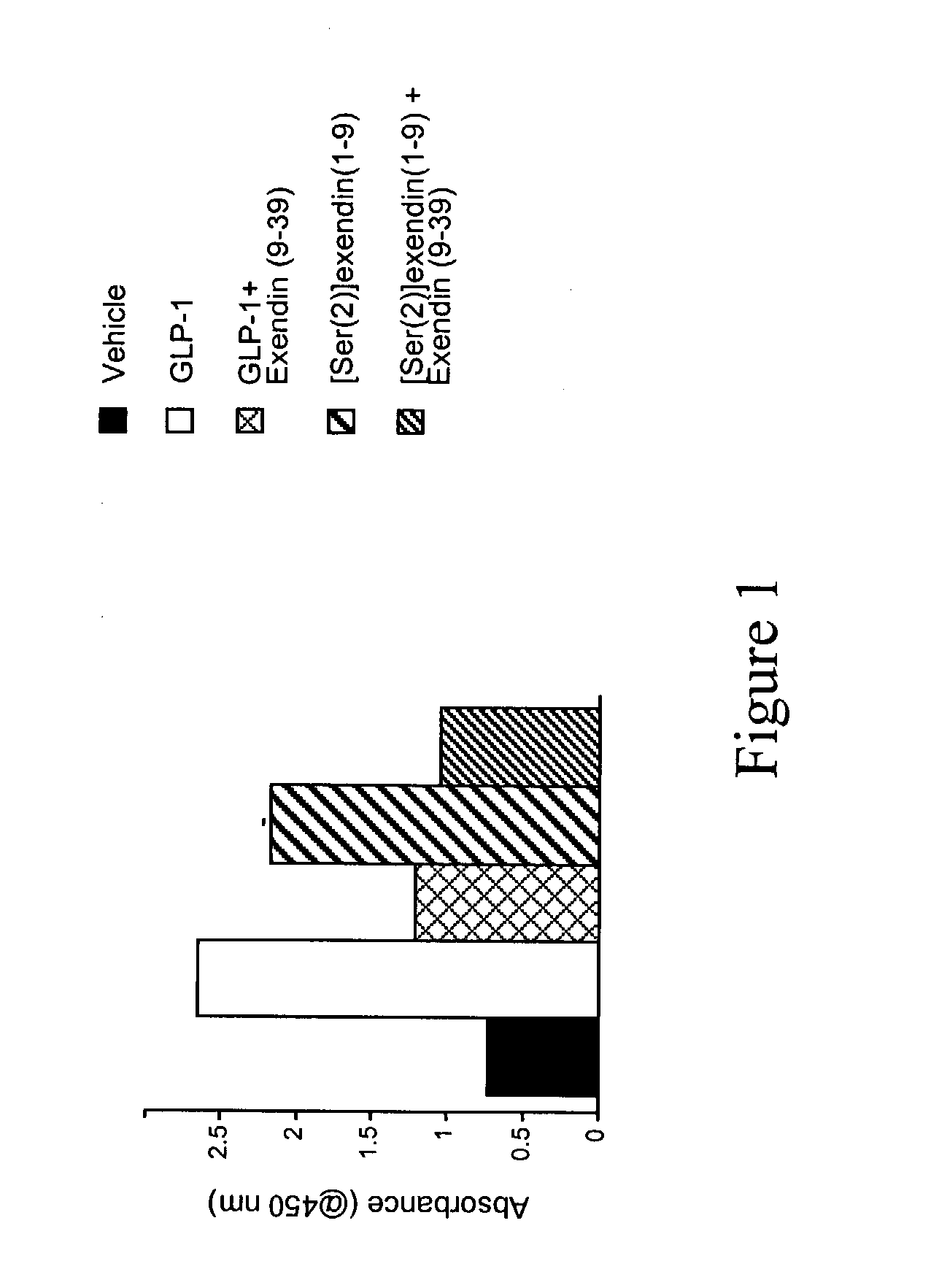

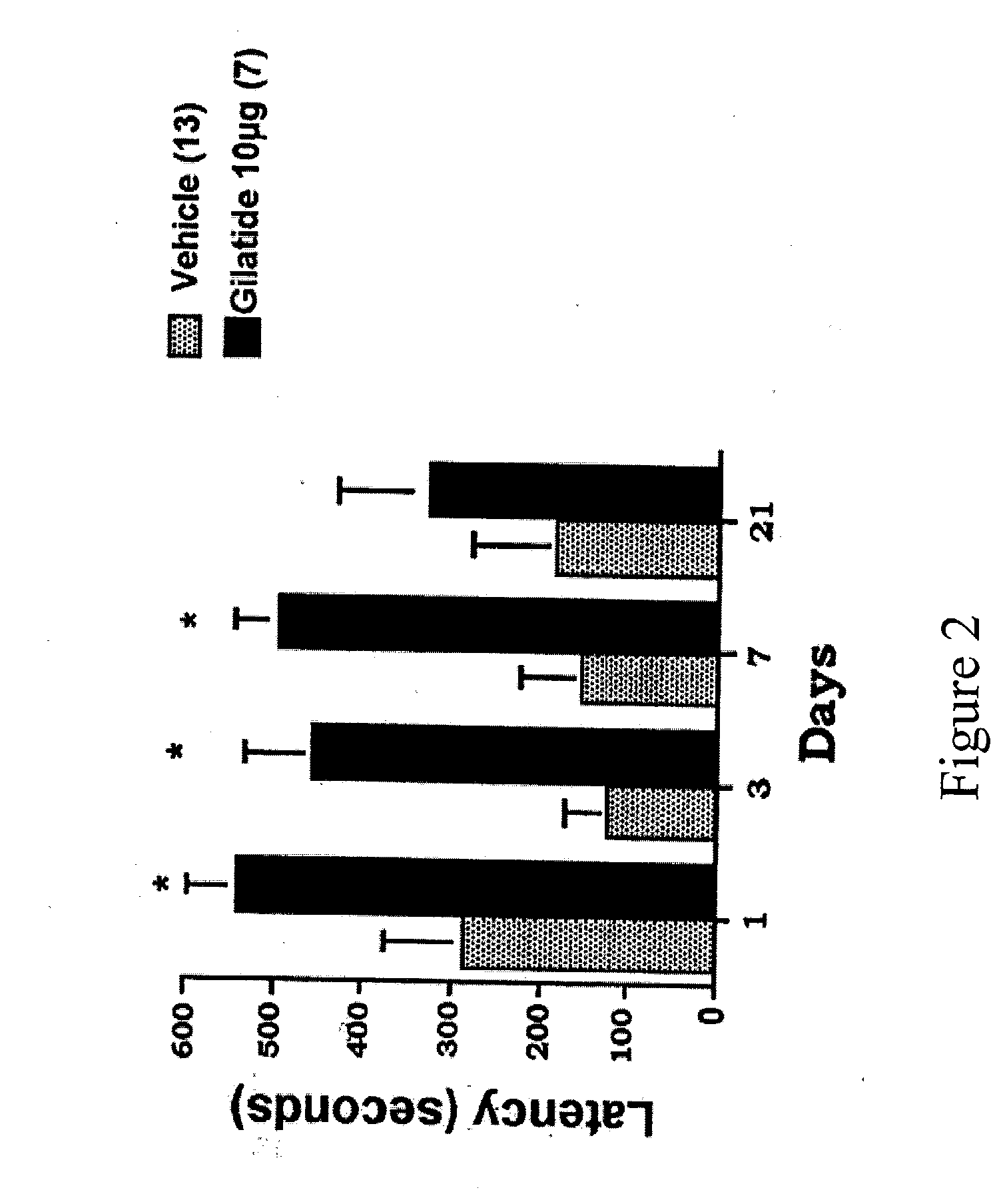

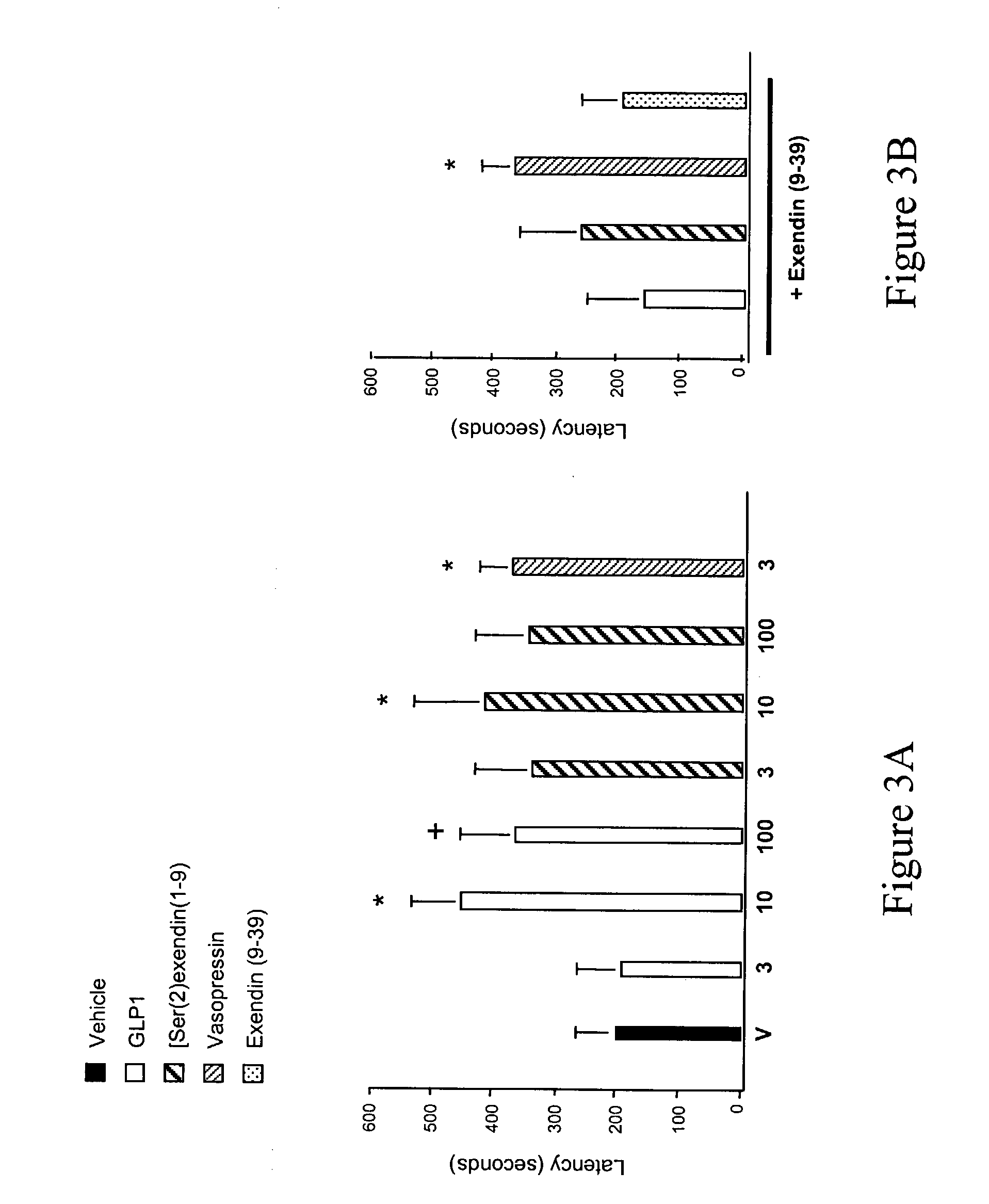

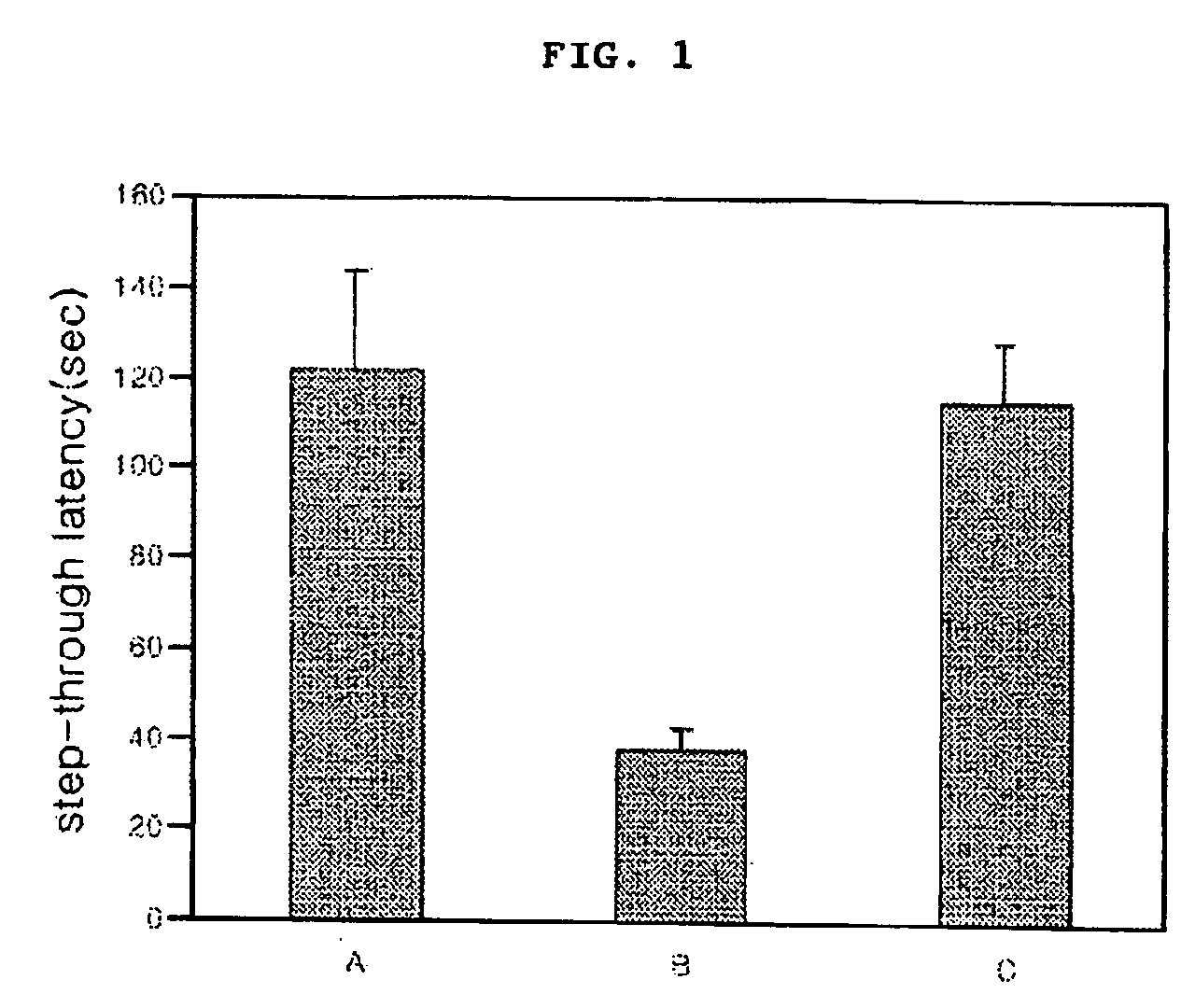

Peptide compositions with effects on blood glucose

InactiveUS20050222036A1Strengthen associationEnhance spatial learningPeptide/protein ingredientsMetabolism disorderDiseaseMemory retention

The present invention provides compositions and methods for ameliorating neurological or memory disorders and improving learning and cognition through the increase of cyclic AMP. Gilatides, peptides comprising the nine amino acid sequence (SEQ ID NO:1), and functional analogs thereof are disclosed to modulate neurological activity when administered to a subject. The methods of the invention can be used to prevent or treat neurological disorders as well as improve memory retention and acquisition. In addition, the invention can be used to modulate insulin levels and blood glucose. The invention includes pharmaceutical compositions comprising a therapeutically or prophylactically effective amount of a Gilatide peptide or a functional analog thereof.

Owner:THOMAS JEFFERSON UNIV

Independently-double-gated transistor memory (IDGM)

InactiveUS7898009B2Small and efficientMade small and moreTransistorSolid-state devicesMemory retentionPower parameter

Memory cells are constructed from double-gated four terminal transistors having independent gate control. DRAM cells may use one, two or three transistors. Single transistor cells are constructed either with or without a bit storage capacitor, and both NAND- and NOR-type Non-Volatile NVRAM cells, as well as Ferroelectric FeRAM cells, are described. For all cells, top gates provide conventional access while independent bottom gates provide control to optimize memory retention for given speed and power parameters as well as to accommodate hardening against radiation. In a single transistor cell without a capacitor, use of the bottom gate allows packing to a density approaching 2 F2. Using a ferroelectric material as the gate insulator produces a single-transistor FeRAM cell that overcomes the industry-wide Write Disturb problem. The memory cells are compatible with SOI logic circuitry for use as embedded RAM in SOC applications.

Owner:AMERICAN SEMICON

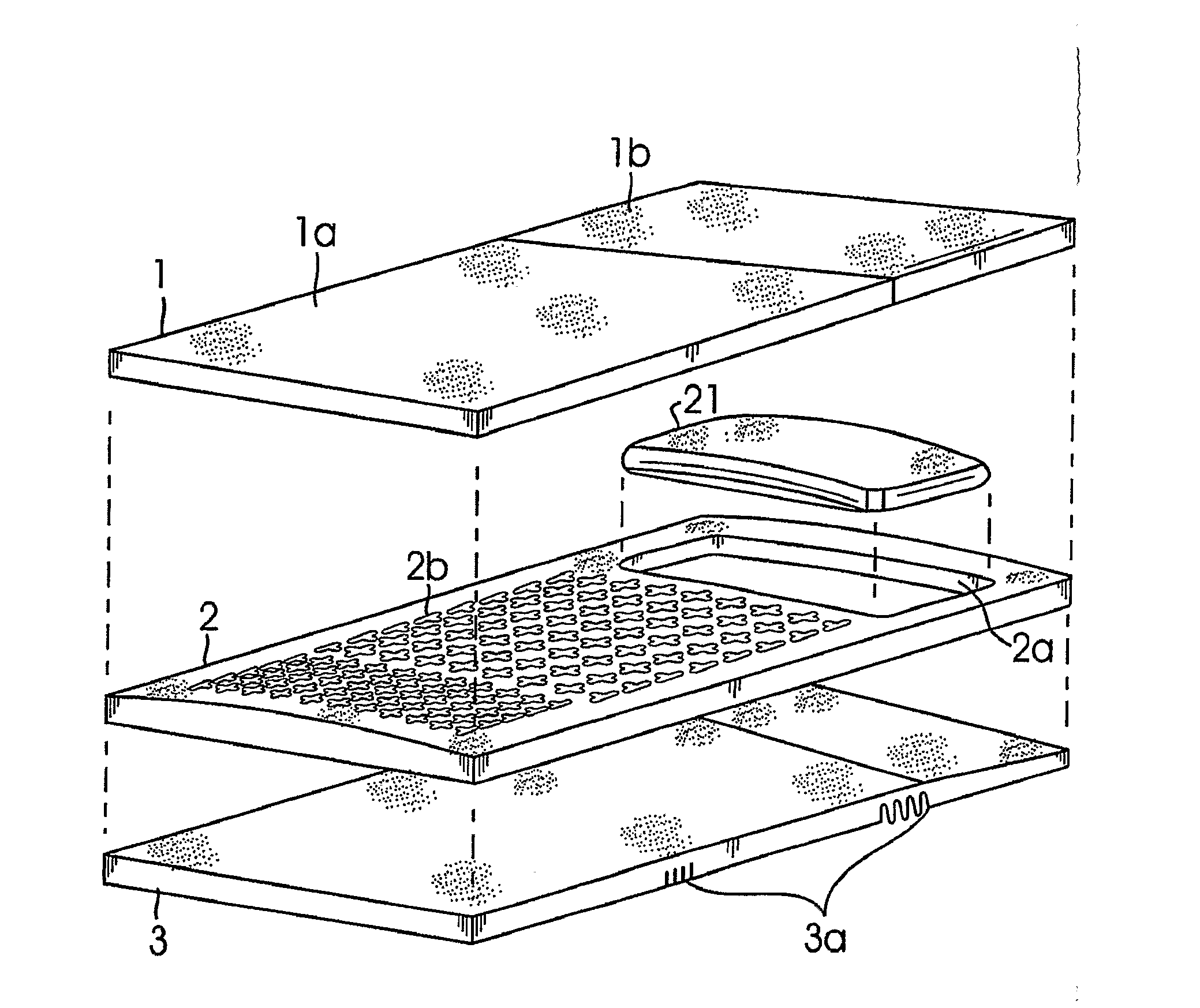

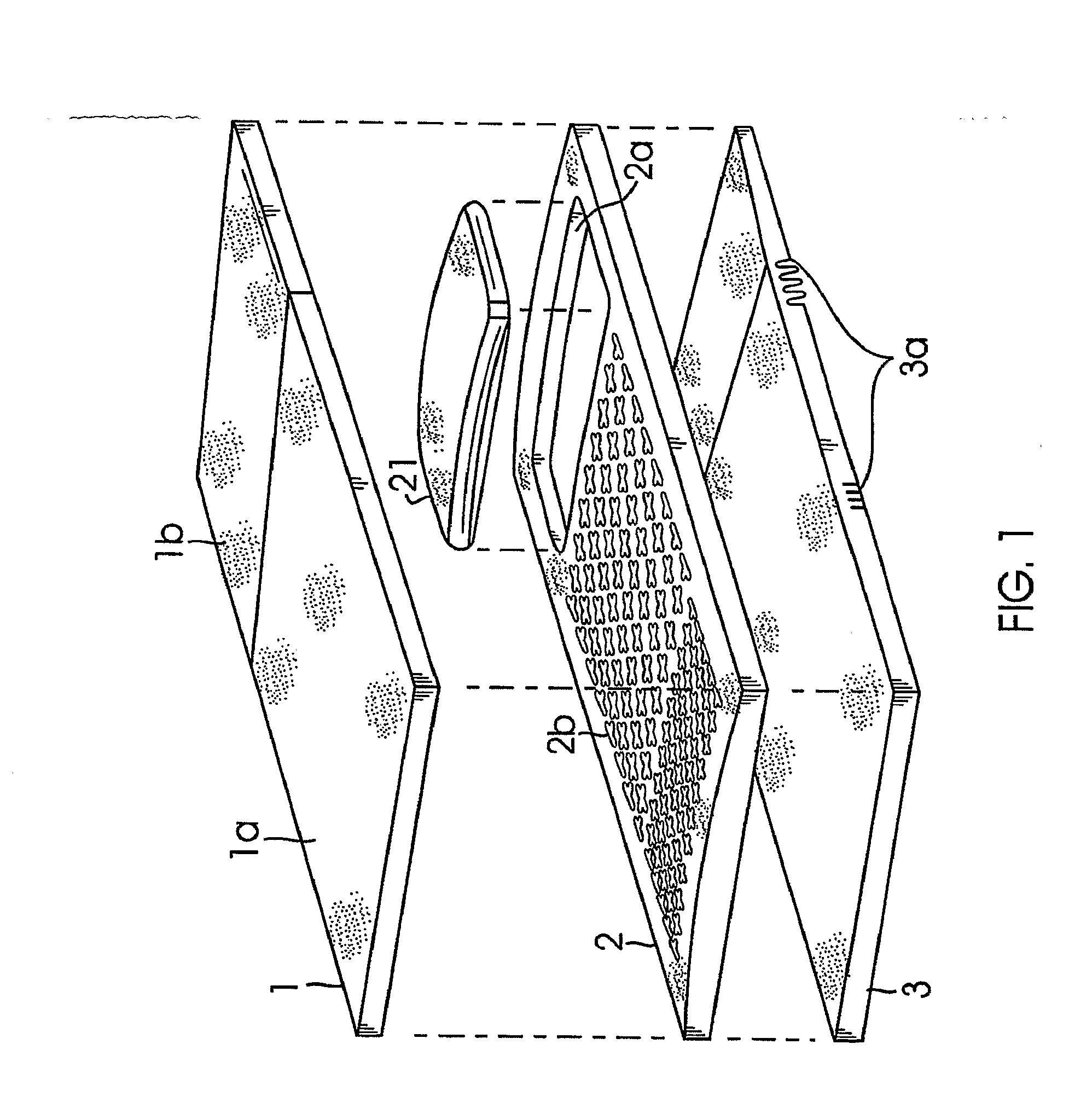

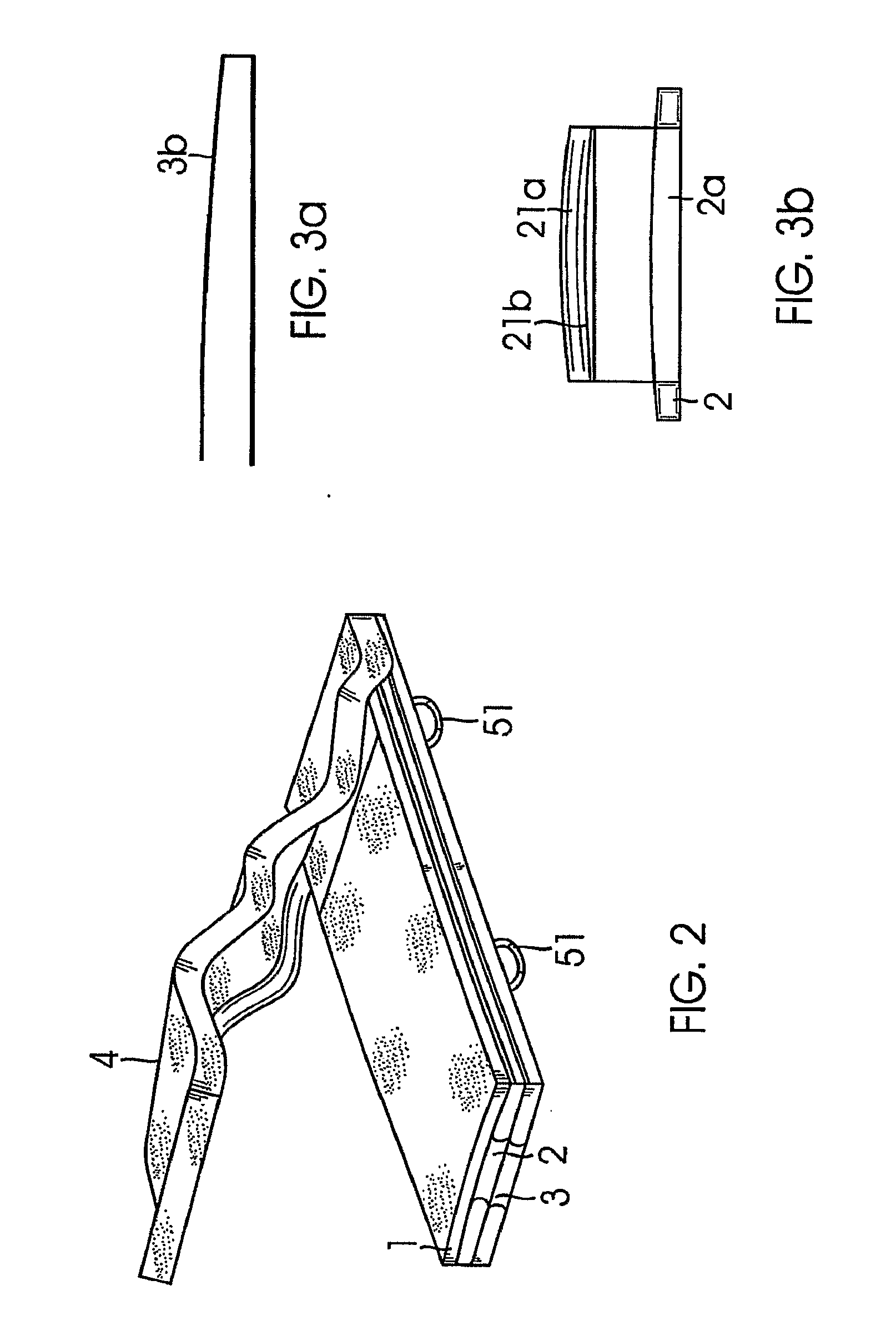

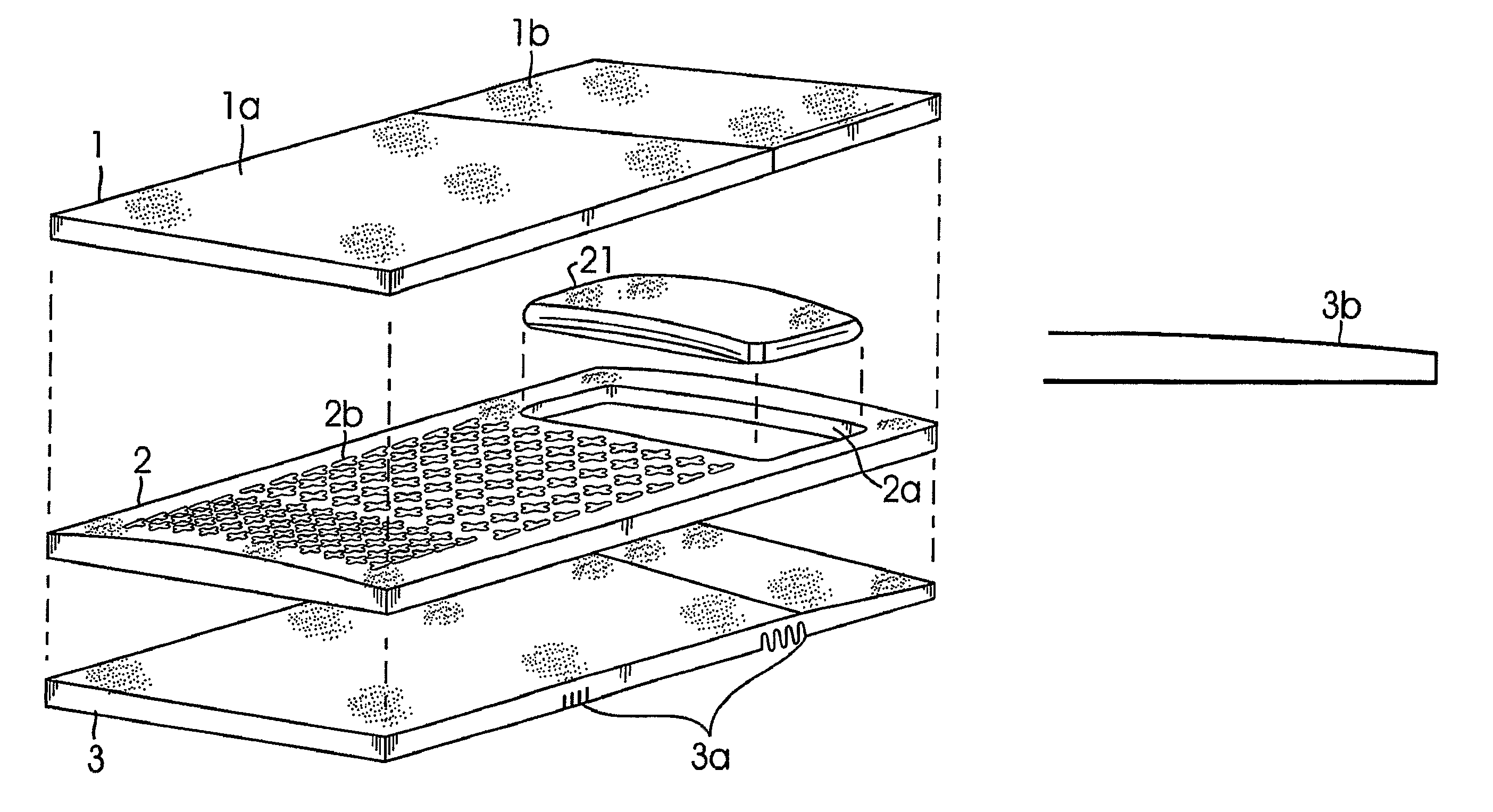

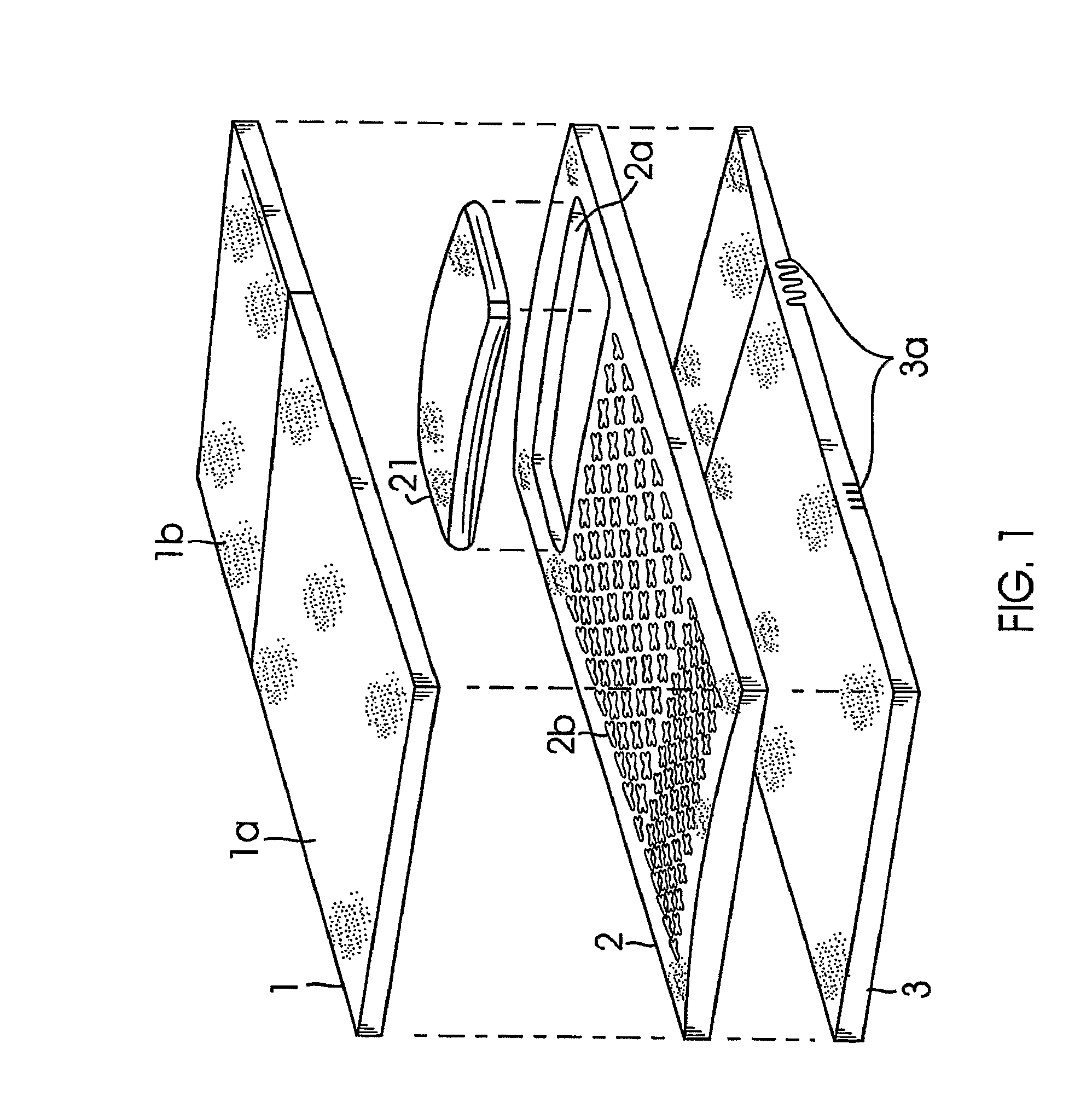

Pressure reduction healthcare mattress system

A foam core for a pressure reduction healthcare mattress is disclosed. It includes a top layer made of memory retention foam, a middle layer made of foam and having a convex shape that is higher along a longitudinal center line than along the two sides, and a lower support layer made of foam. The top layer is made of a torso piece and a softer foot / lower leg piece. The middle layer includes a heel pillow that fits into a heel pillow cavity in the foam, the heel pillow including layers of fiber material over a crown shaped foam insert. The lower support layer has a sloped portion in a lower leg section that slopes down toward a heel end of the foam core. Also disclosed is a pressure reduction healthcare mattress that includes the foam core and a cover.

Owner:HILL ROM SERVICES

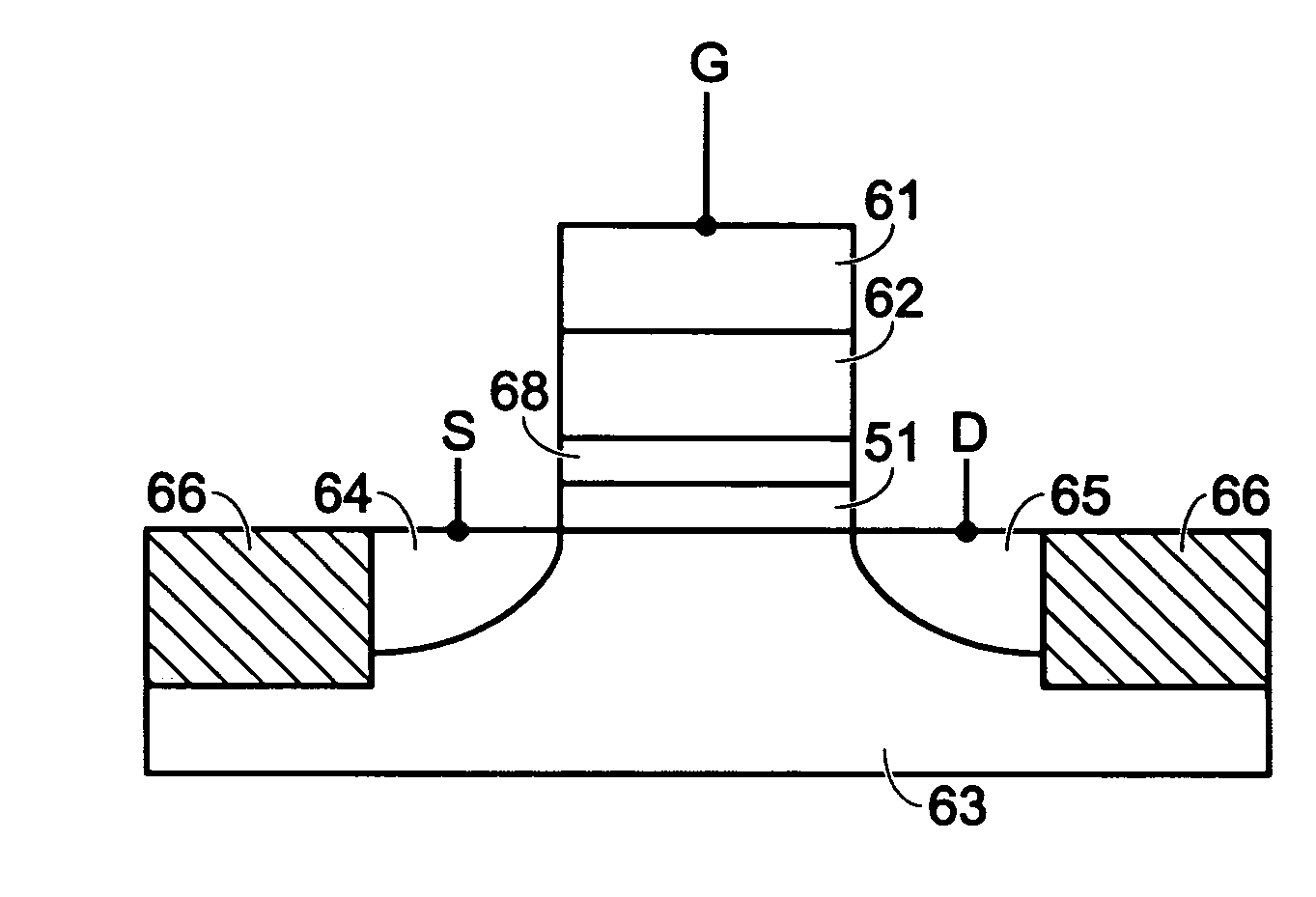

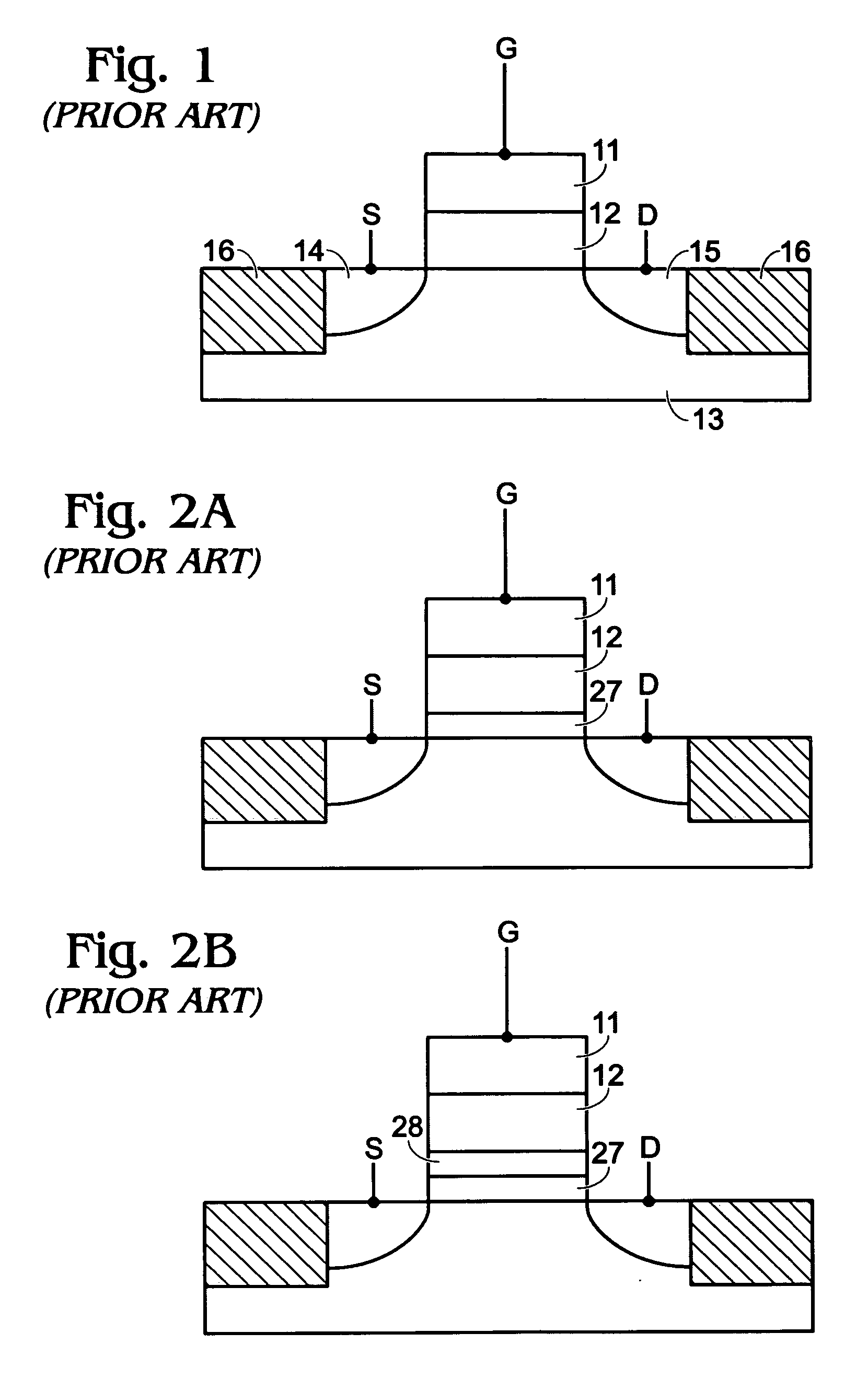

Ferroelectric memory transistor with conductive oxide gate structure

InactiveUS20070272960A1Reduce stepsLow working voltageSolid-state devicesSemiconductor/solid-state device manufacturingMemory retentionGate dielectric

The present invention discloses a ferroelectric transistor having a conductive oxide in the place of the gate dielectric. The conductive oxide gate ferroelectric transistor can have a three-layer metal / ferroelectric / metal or a two-layer metal / ferroelectric on top of the conductive oxide gate. By replacing the gate dielectric with a conductive oxide, the bottom gate of the ferroelectric layer is conductive through the conductive oxide to the silicon substrate, thus minimizing the floating gate effect. The memory retention degradation related to the leakage current associated with the charges trapped within the floating gate is eliminated. The fabrication of the ferroelectric transistor by a gate etching process or a replacement gate process is also disclosed.

Owner:SHARP LAB OF AMERICA INC

Conductive metal oxide gate ferroelectric memory transistor

InactiveUS20050054166A1Reduce stepsEliminate degradationSolid-state devicesSemiconductor/solid-state device manufacturingMemory retentionGate dielectric

The present invention discloses a ferroelectric transistor having a conductive oxide in the place of the gate dielectric. The conductive oxide gate ferroelectric transistor can have a three-layer metal / ferroelectric / metal or a two-layer metal / ferroelectric on top of the conductive oxide gate. By replacing the gate dielectric with a conductive oxide, the bottom gate of the ferroelectric layer is conductive through the conductive oxide to the silicon substrate, thus minimizing the floating gate effect. The memory retention degradation related to the leakage current associated with the charges trapped within the floating gate is eliminated. The fabrication of the ferroelectric transistor by a gate etching process or a replacement gate process is also disclosed.

Owner:SHARP KK

Double-Gated Transistor Memory

InactiveUS20110147806A1Small and efficientMade small and moreTransistorSolid-state devicesMemory retentionPower parameter

Memory cells are constructed from double-gated four terminal transistors having independent gate control. DRAM cells may use one, two or three transistors. Single transistor cells are constructed either with or without a bit storage capacitor, and both NAND- and NOR-type Non-Volatile NVRAM cells, as well as Ferroelectric FeRAM cells, are described. For all cells, top gates provide conventional access while independent bottom gates provide control to optimize memory retention for given speed and power parameters as well as to accommodate hardening against radiation. In a single transistor cell without a capacitor, use of the bottom gate allows packing to a density approaching 2 F2. The memory cells are compatible with SOI logic circuitry for use as embedded RAM in SOC applications.

Owner:AMERICAN SEMICON

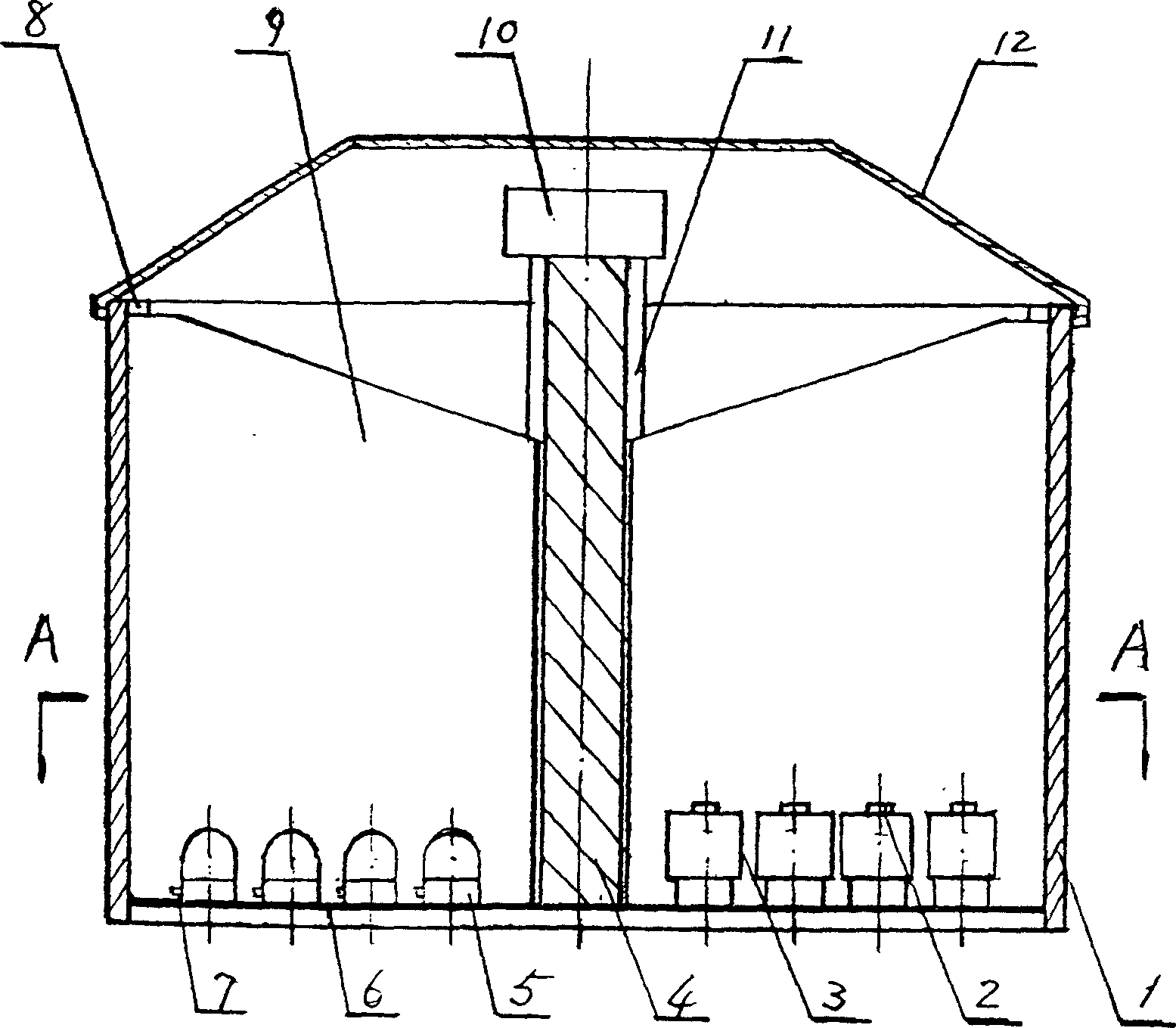

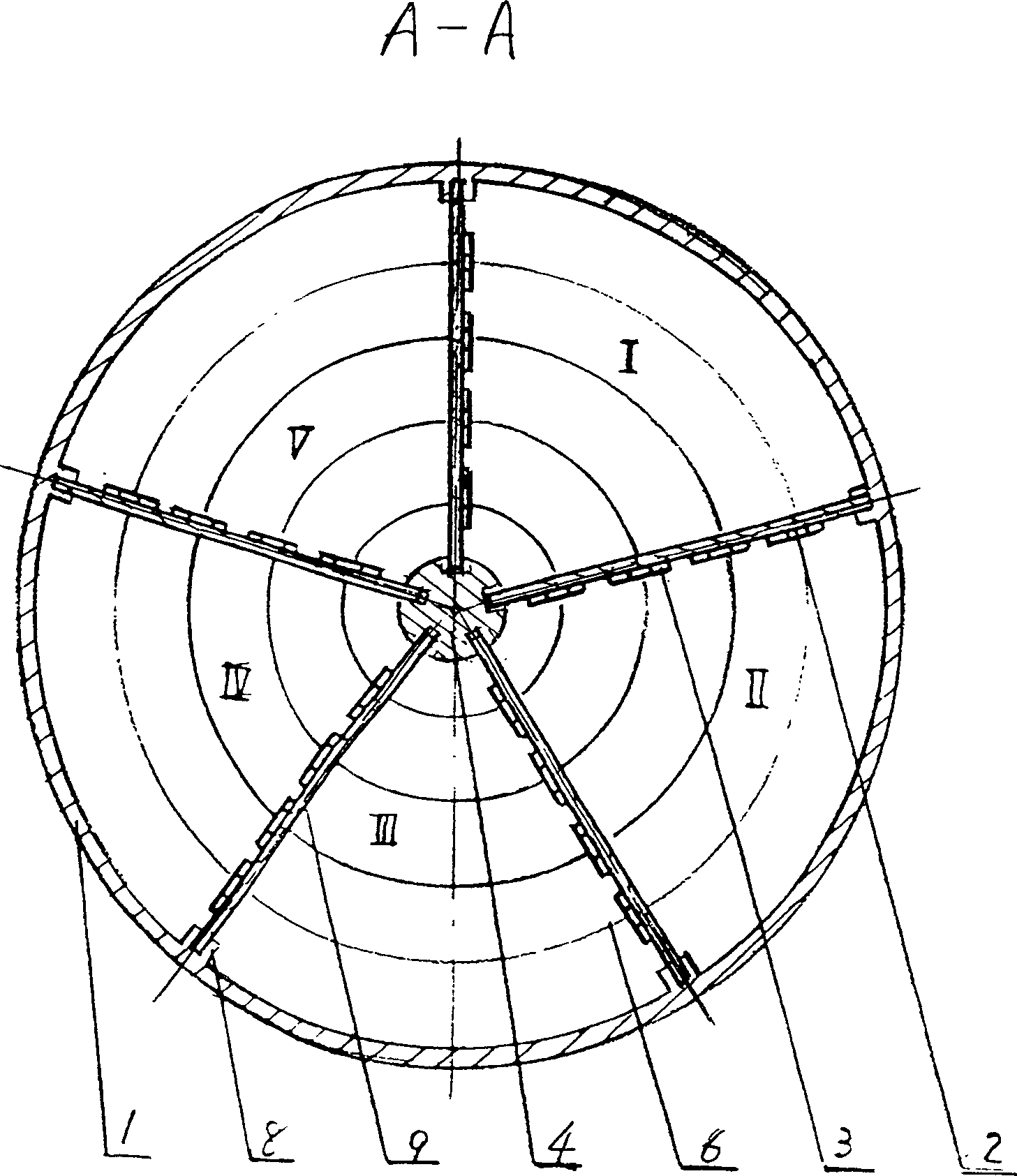

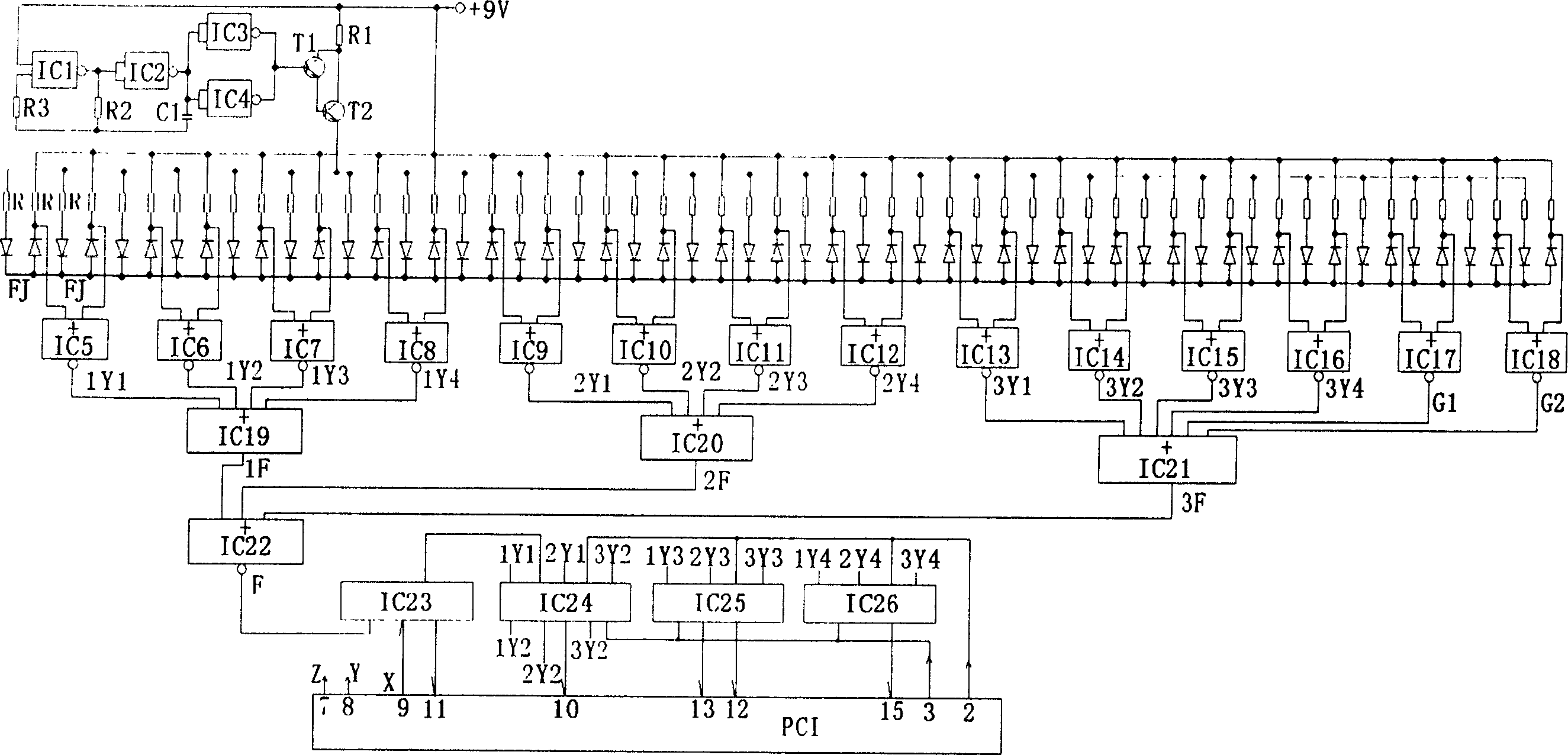

Mouse space memory retention model and intelligent action inspecting system

InactiveCN1817326AInconsistent dwell timeAccurate detectionEducational modelsVeterinary instrumentsMemory retentionData acquisition

A mouse's space memory holding model and its intelligent behavior detection system are disclosed. A circular dark box type labyrinth is used as the behavior data acquiring unit. The mouse to be tested passes through a tubular channel with adjustable one-way gates along a pointed path and closed loop for performing the cyclic training. The signals about the active movement and passive movement caused by electric shock are acquired and processed by the data processing control unit. Said signals are transmitted via PCI bus to the Access database in control system, and then processed by the statistical software package, so controlling and monitoring the behavior of mouse at any time.

Owner:SHENYANG MEDICAL COLLEGE

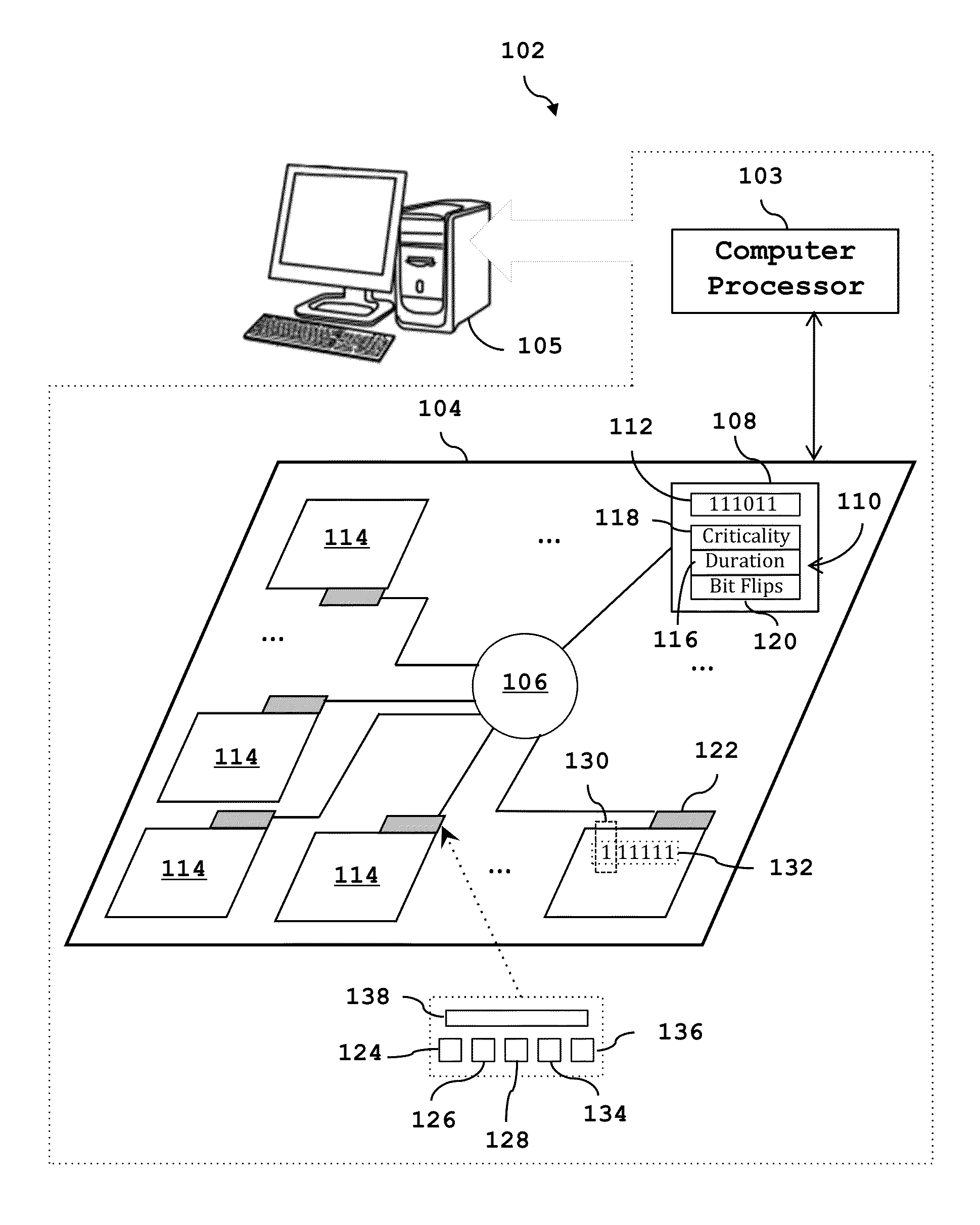

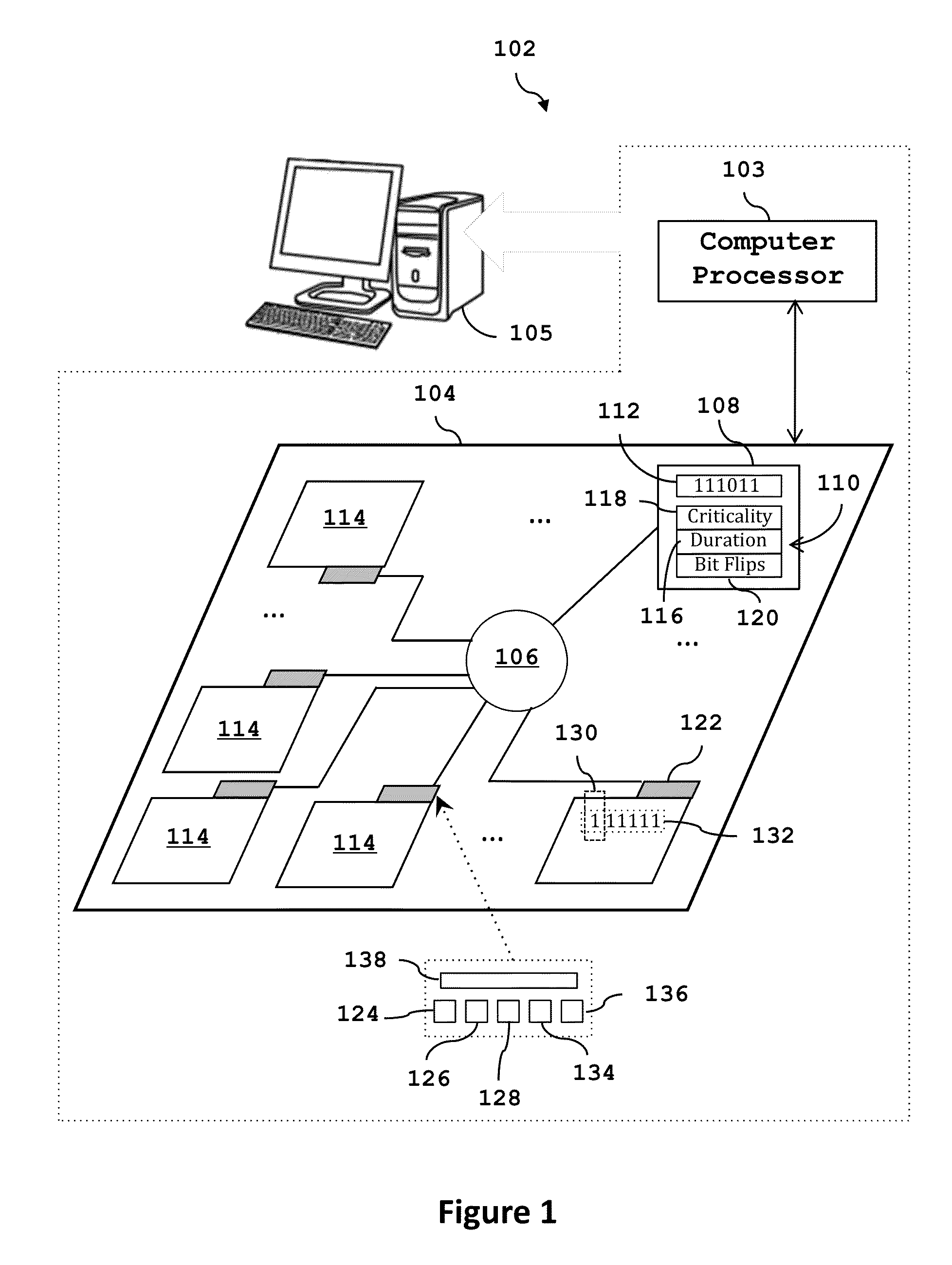

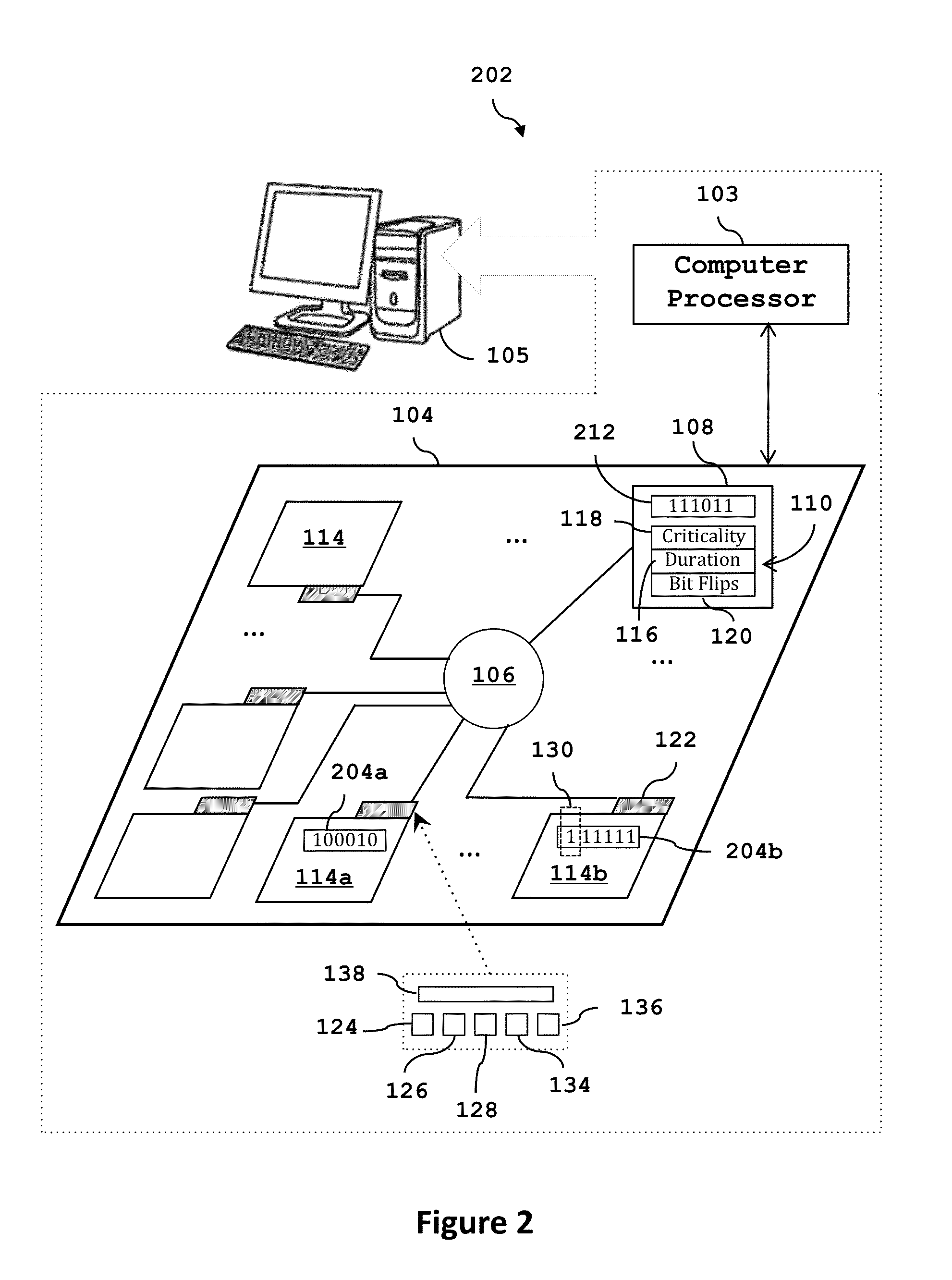

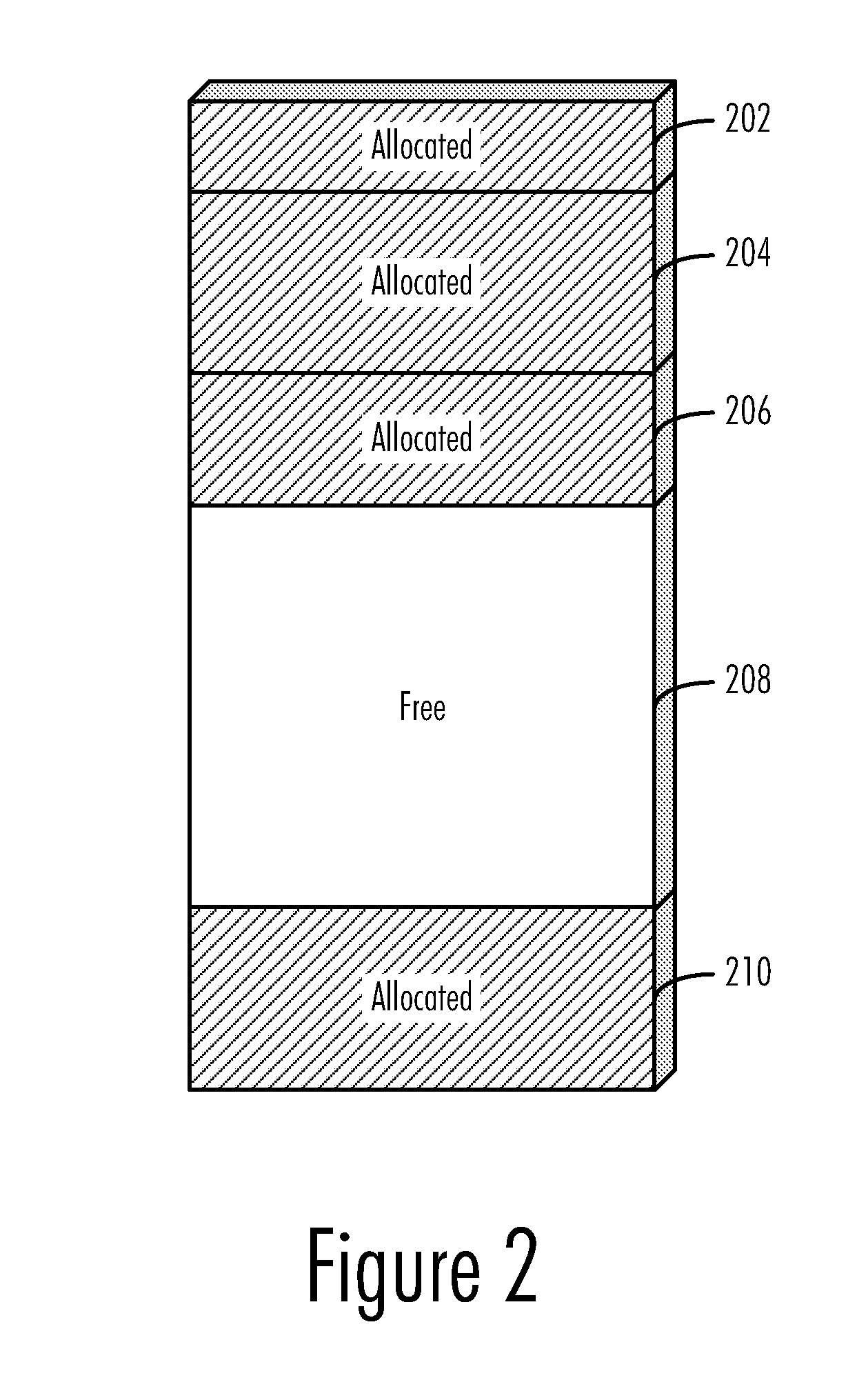

Retention management for phase change memory lifetime improvement through application and hardware profile matching

ActiveUS20130073785A1Minimized number of bitHigh wear out complicationMemory architecture accessing/allocationDigital storageMemory retentionPhase-change memory

Methods and systems for managing memory and stress to memory systems. A method for managing memory includes receiving from a software application memory retention requirements for application data. The memory retention requirements include storage duration length and / or criticality of data retention. The method also includes storing the application data in one of a plurality of memory regions in non-volatile memory based on the memory retention requirements and memory retention characteristics of the memory regions. Each memory region may have different memory retention characteristics.

Owner:IBM CORP

Identifying sources of memory retention

ActiveUS7765528B2Multiprogramming arrangementsNon-redundant fault processingMemory retentionParallel computing

One embodiment relates to a method for identifying sources of memory retention in an executing application. A size of a set of objects is tracked over multiple periods. A period is determined to be a growth period if the size for the set of objects increases above a previous maximum size, and the number of growth periods is counted. The set of objects is flagged as having potential undesired object retention (a memory leak) if the number of growth periods is greater than a threshold number. Other embodiments are also disclosed.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

Pressure reduction healthcare mattress system

Owner:HILL ROM SERVICES

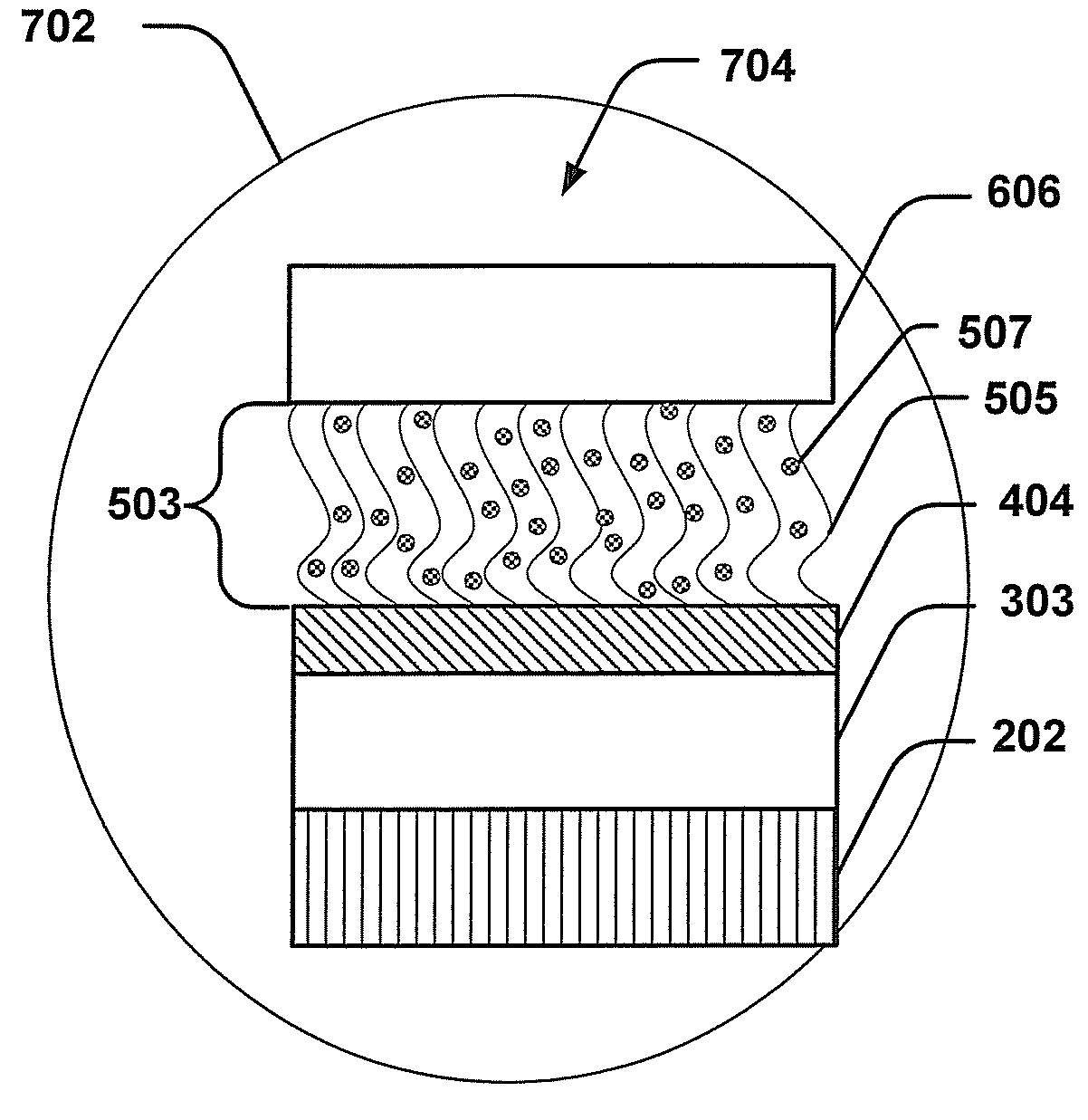

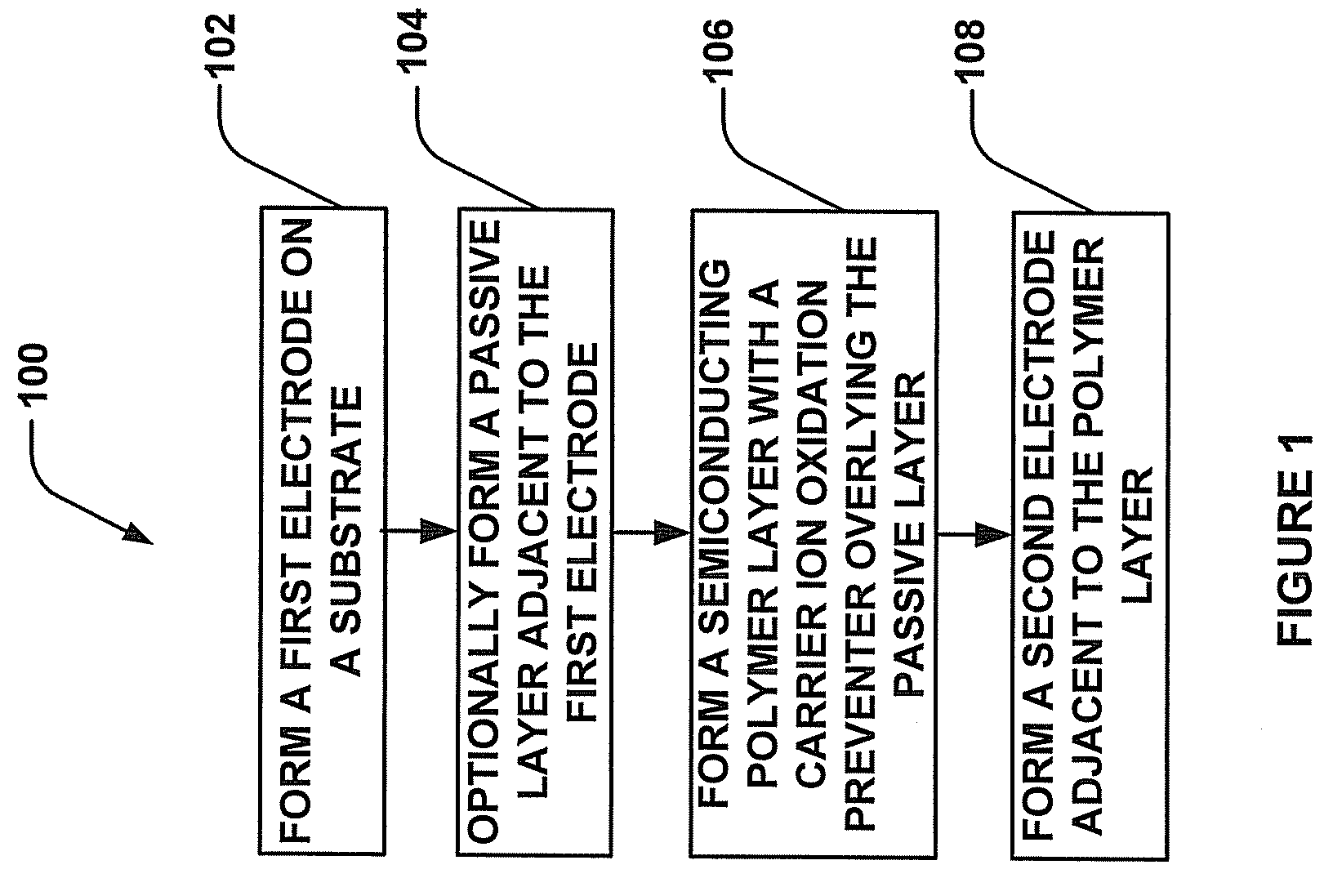

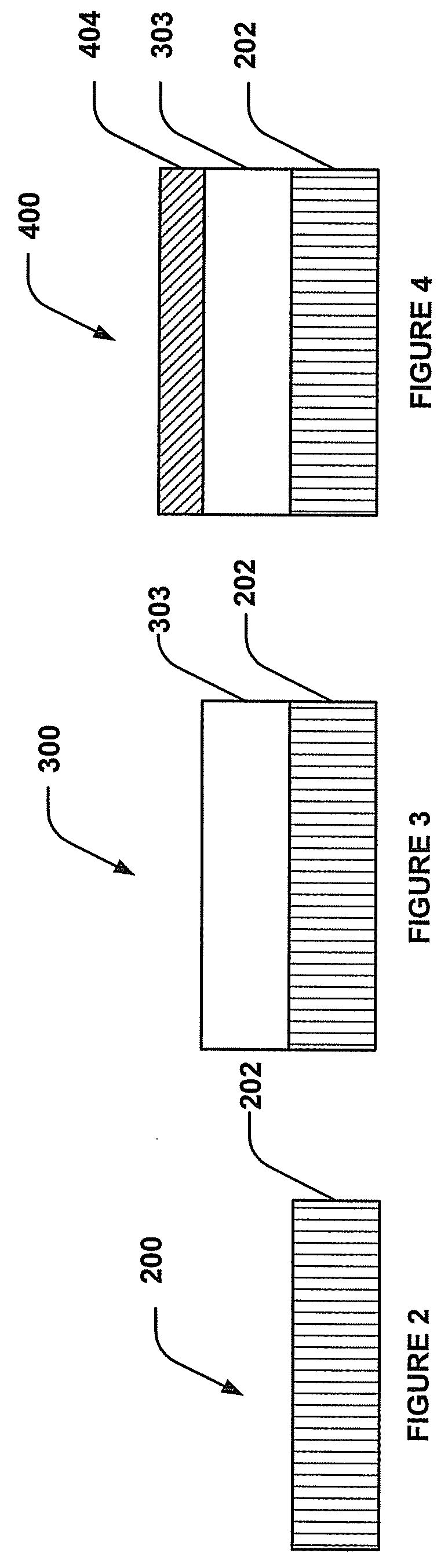

Prevention of oxidation of carrier ions to improve memory retention properties of polymer memory cell

ActiveUS20080135834A1Improve retentionImprove practicalitySolid-state devicesSemiconductor/solid-state device manufacturingMemory retentionMemory cell

Improving memory retention properties of a polymer memory cell are disclosed. The methods include providing a semiconducting polymer layer containing at least one organic semiconductor and at least one of a carrier ion oxidation preventer and an electrode oxidation preventer. The oxidation preventers may contain at least one of 1) an oxygen scavenger, 2) a polymer with oxidizable side-chain groups which can be preferentially oxidized over the carrier ions / electrodes, and 3) an oxidizable molecule that can be preferentially oxidized over the carrier ions / electrodes.

Owner:MONTEREY RES LLC

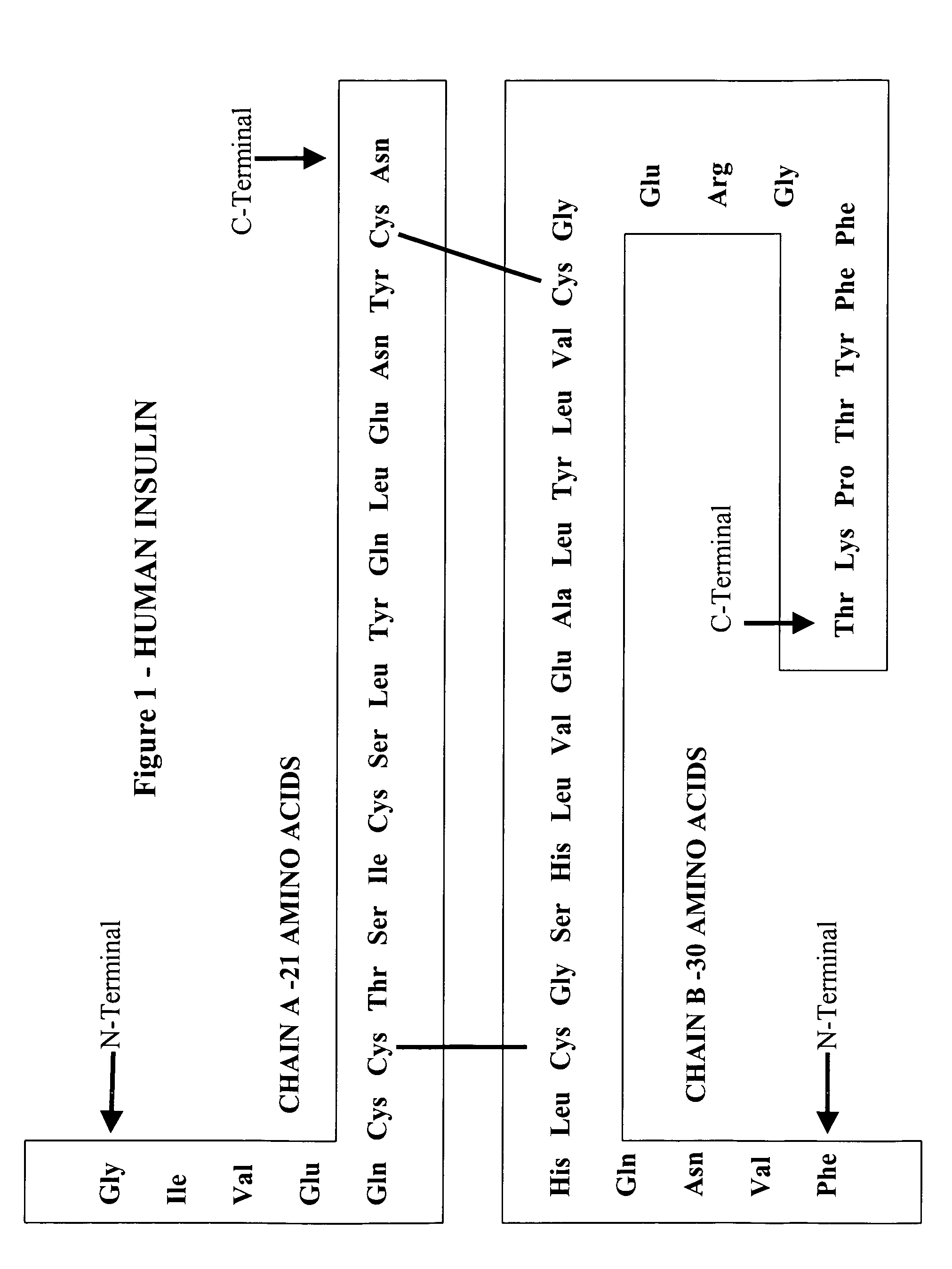

Insulin-associated peptides with effects on cerebral health

InactiveUS7655619B2Efficiently enter brainImprove performanceNervous disorderCell receptors/surface-antigens/surface-determinantsMemory retentionInsulin A Chain

The present invention provides compositions and methods for ameliorating neurological, attention, or memory disorders and improving learning and cognition through the delivery of insulin A-chain and analogs thereof to a subject. Insulin A-chain, peptides comprising the 21 amino acid sequence GIVEQ CCASV CSLYQ LENYC N (SEQ ID NO:1), and functional analogs thereof are disclosed to modulate neurological activity when administered to a subject. The methods of the invention can be used to prevent or treat neurological disorders as well as improve memory retention and acquisition. The invention includes pharmaceutical compositions comprising a therapeutically or prophylactically effective amount of insulin A-chain peptide or a functional analogs thereof.

Owner:THOMAS JEFFERSON UNIV

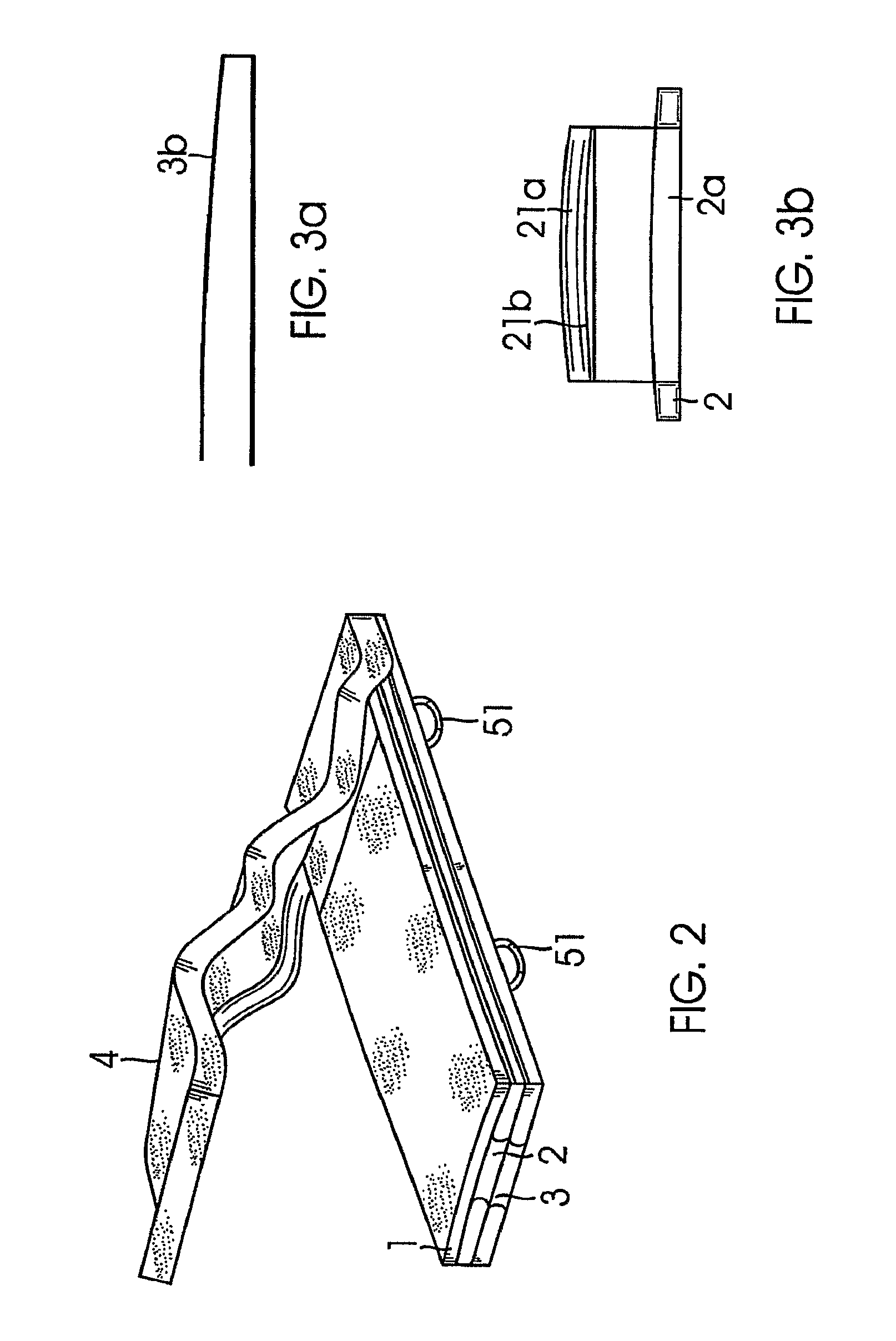

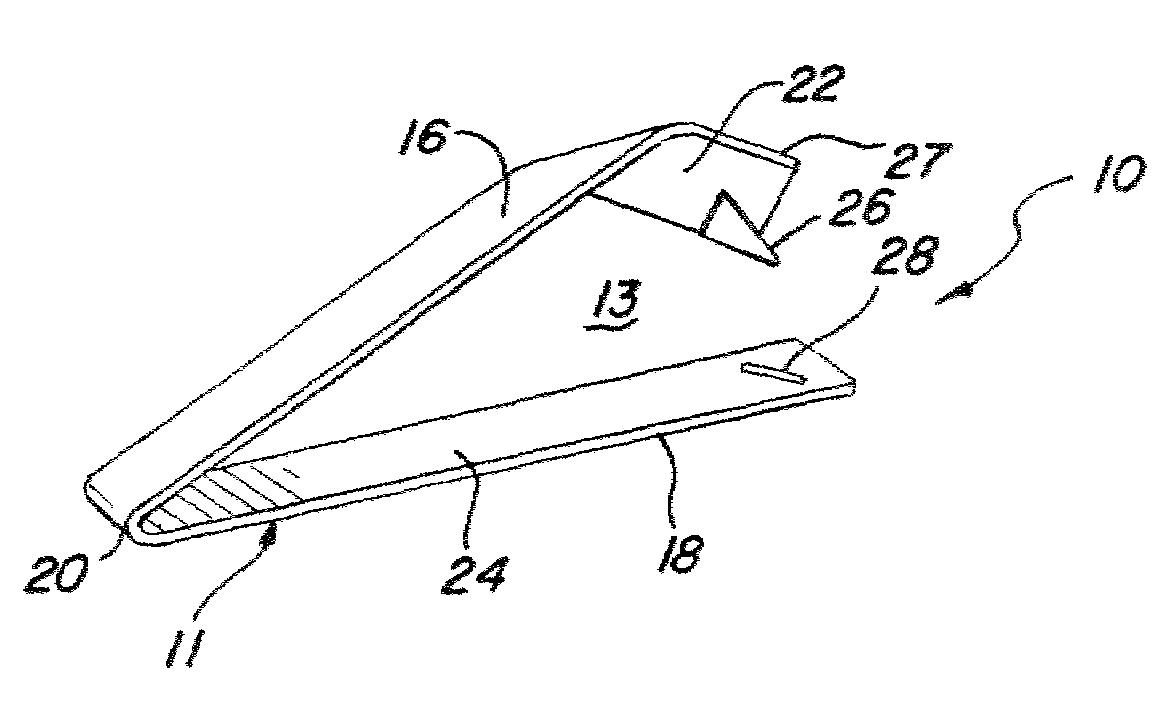

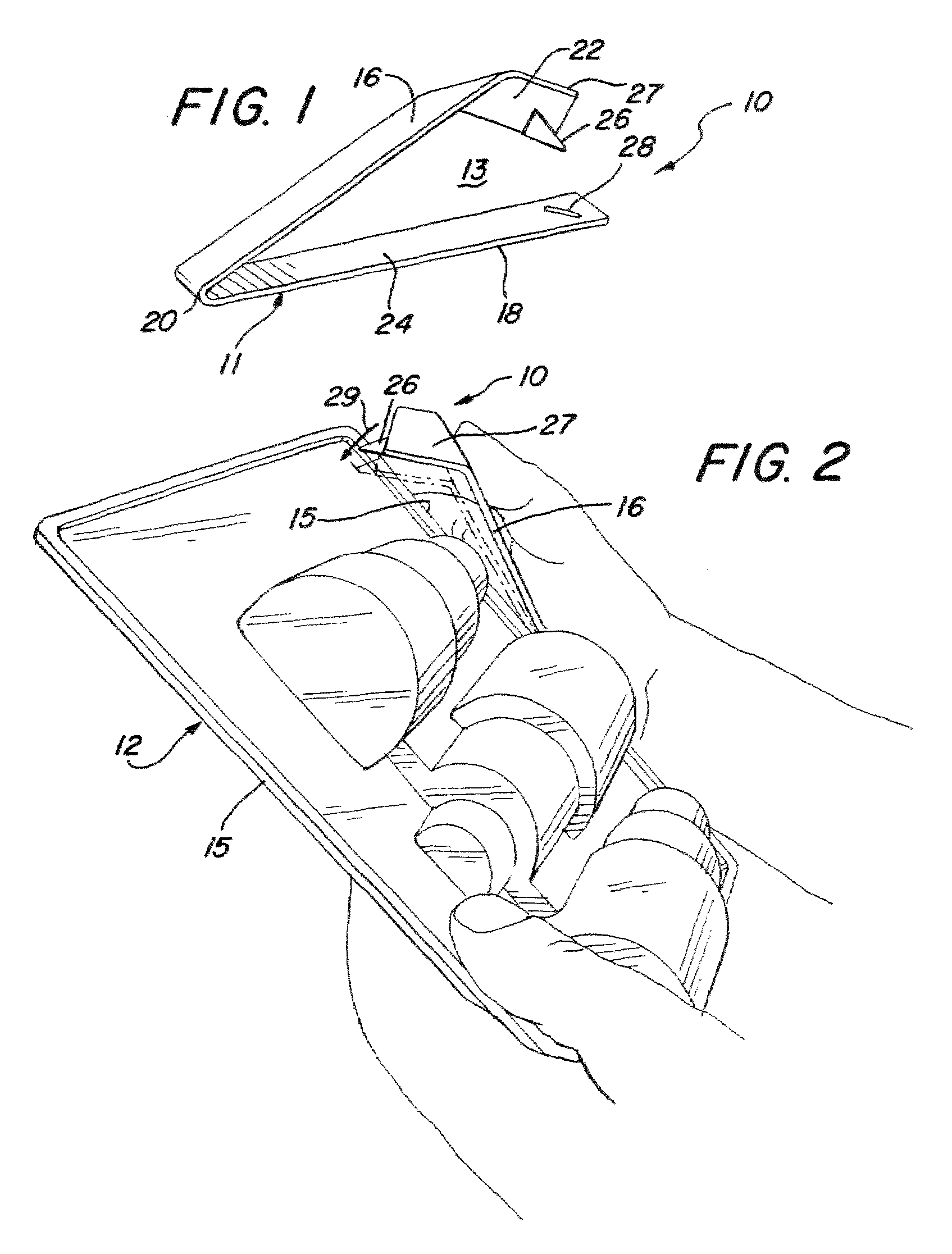

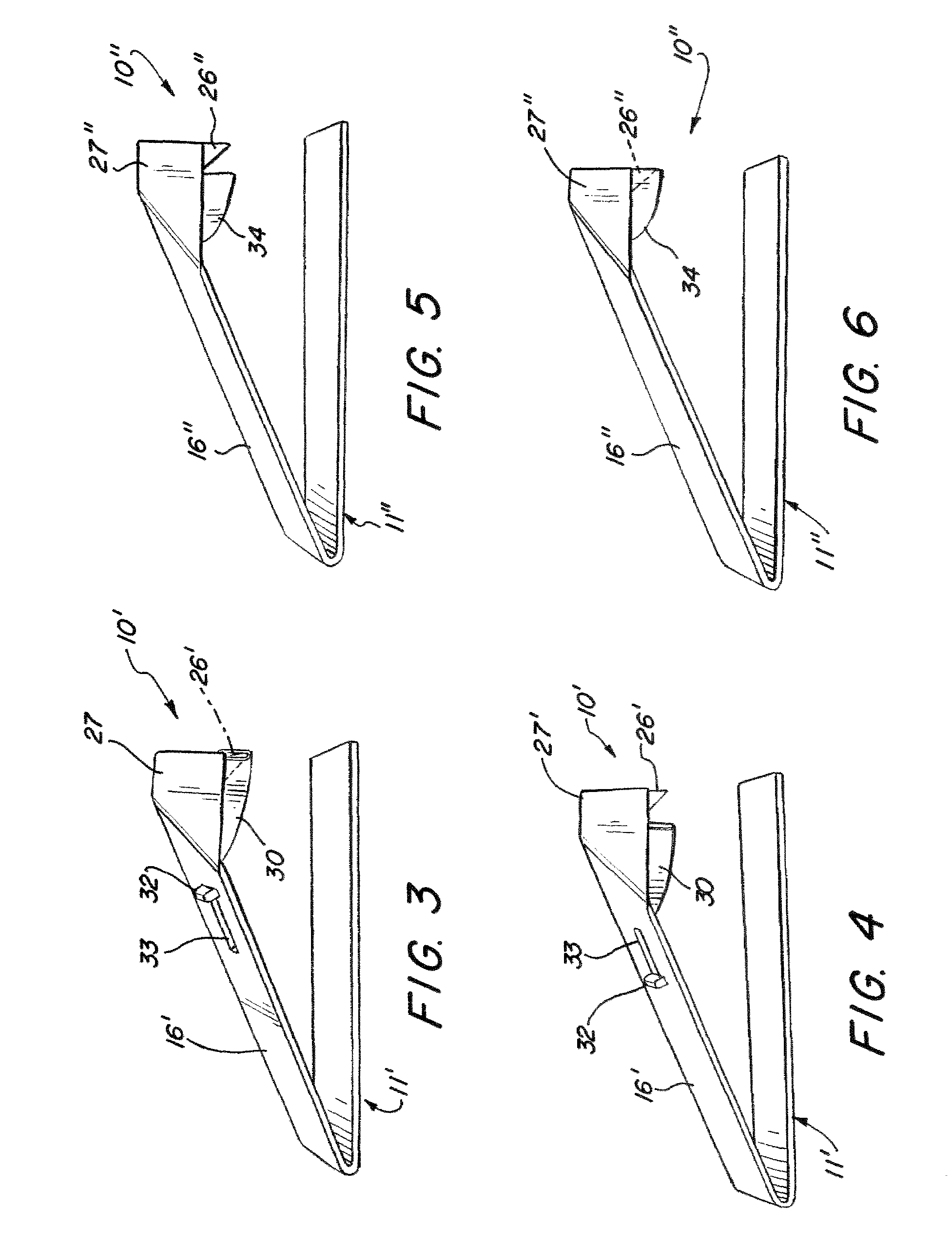

Plastic package opener

InactiveUS7730620B1Easy to operate manuallyEasily and safely openedOpening closed containersBottle/container closureMemory retentionPlastic packaging

A plastic package opener having a body with a generally “V” shaped configured is formed from a memory retention material, by angled first and second legs held together by a portion of material. A sharp edge or blade member is held to an interior surface of one of the legs at an angle to the terminal ends of the legs. A movable blade cover may be provided for safety. A plastic package to be opened is inserted between the open ends of the legs and the blade member brought against the plastic package by squeezing the two legs together and directed across the surface of the plastic package to sever the plastic package and open the same for removal of an item or items held therein.

Owner:ANASTASI CHRIS +1

Ferroelectric transistor gate stack with resistance-modified conductive oxide

InactiveUS20050269613A1Reduce chargeImprove performanceTransistorSolid-state devicesMemory retentionFilm resistance

The present invention discloses a novel ferroelectric transistor design using a resistive oxide film in place of the gate dielectric. By replacing the gate dielectric with a resistive oxide film, and by optimizing the value of the film resistance, the bottom gate of the ferroelectric layer is electrically connected to the silicon substrate, eliminating the trapped charge effect and resulting in the improvement of the memory retention characteristics. The resistive oxide film is preferably a doped conductive oxide in which a conductive oxide is doped with an impurity species. The doped conductive oxide is most preferred to be In2O3 with the dopant species being hafnium oxide, zirconium oxide, lanthanum oxide, or aluminum oxide.

Owner:SHARP KK

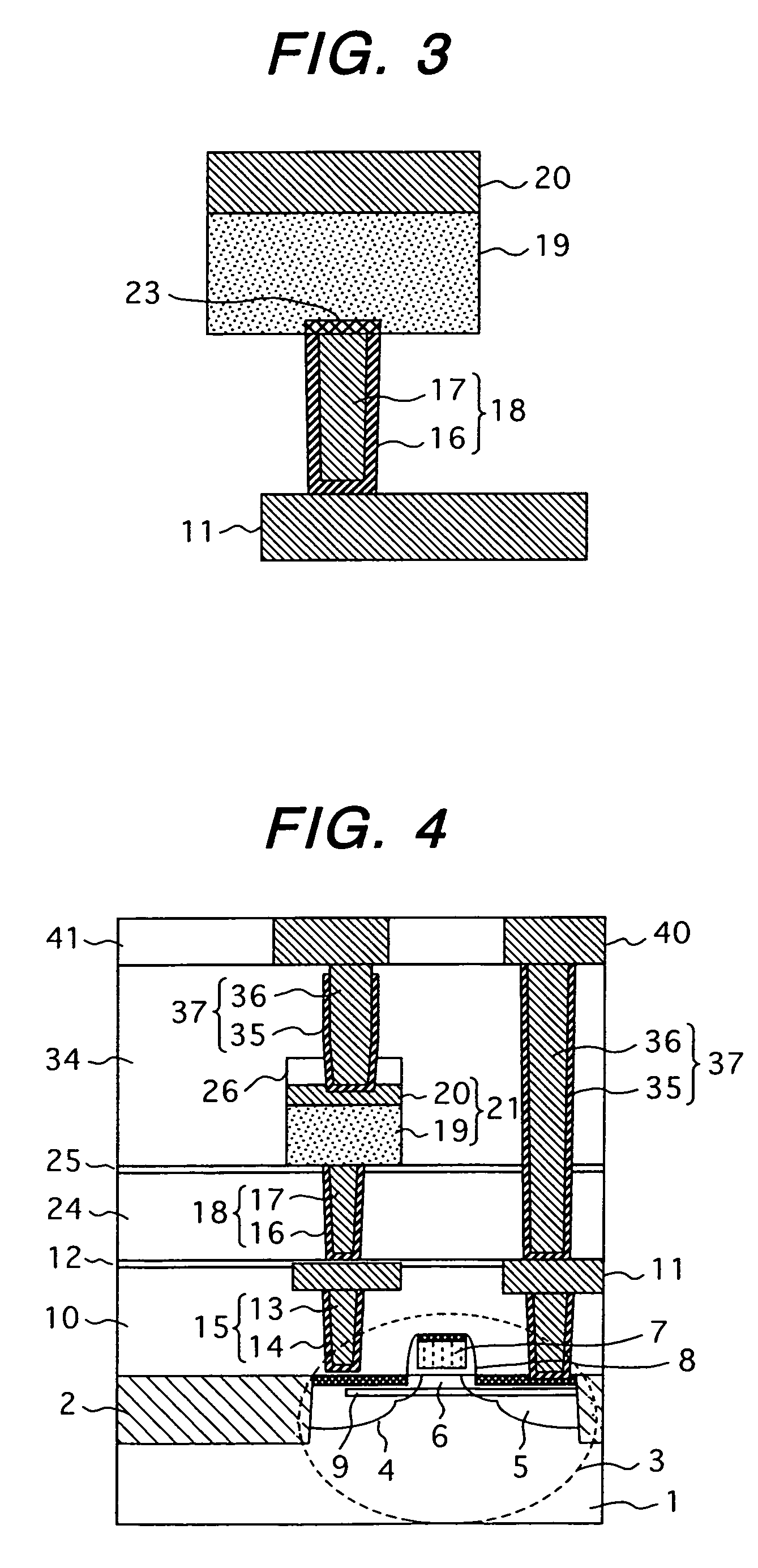

Semiconductor integrated circuit device and method of manufacturing the same

ActiveUS7667218B2Improve the immunityReduce power consumptionTransistorSemiconductor/solid-state device detailsMemory retentionPhase-change memory

Disclosed herein is a phase change memory semiconductor integrated circuit device using a chalcogenide film that solves a problem that the operation temperature capable of ensuring long time memory retention is low due to low phase change temperature is and, at the same time, a problem that power consumption of the device is high since a large current requires to rewrite memory information due to low resistance. A portion of constituent elements for a chalcogenide comprises nitride, oxide or carbide which are formed to the boundary between the chalcogenide film and a metal plug as an underlying electrode and to the grain boundary of chalcogenide crystals thereby increasing the phase change temperature and high Joule heat can be generated even by a small current by increasing the resistance of the film.

Owner:RENESAS ELECTRONICS CORP

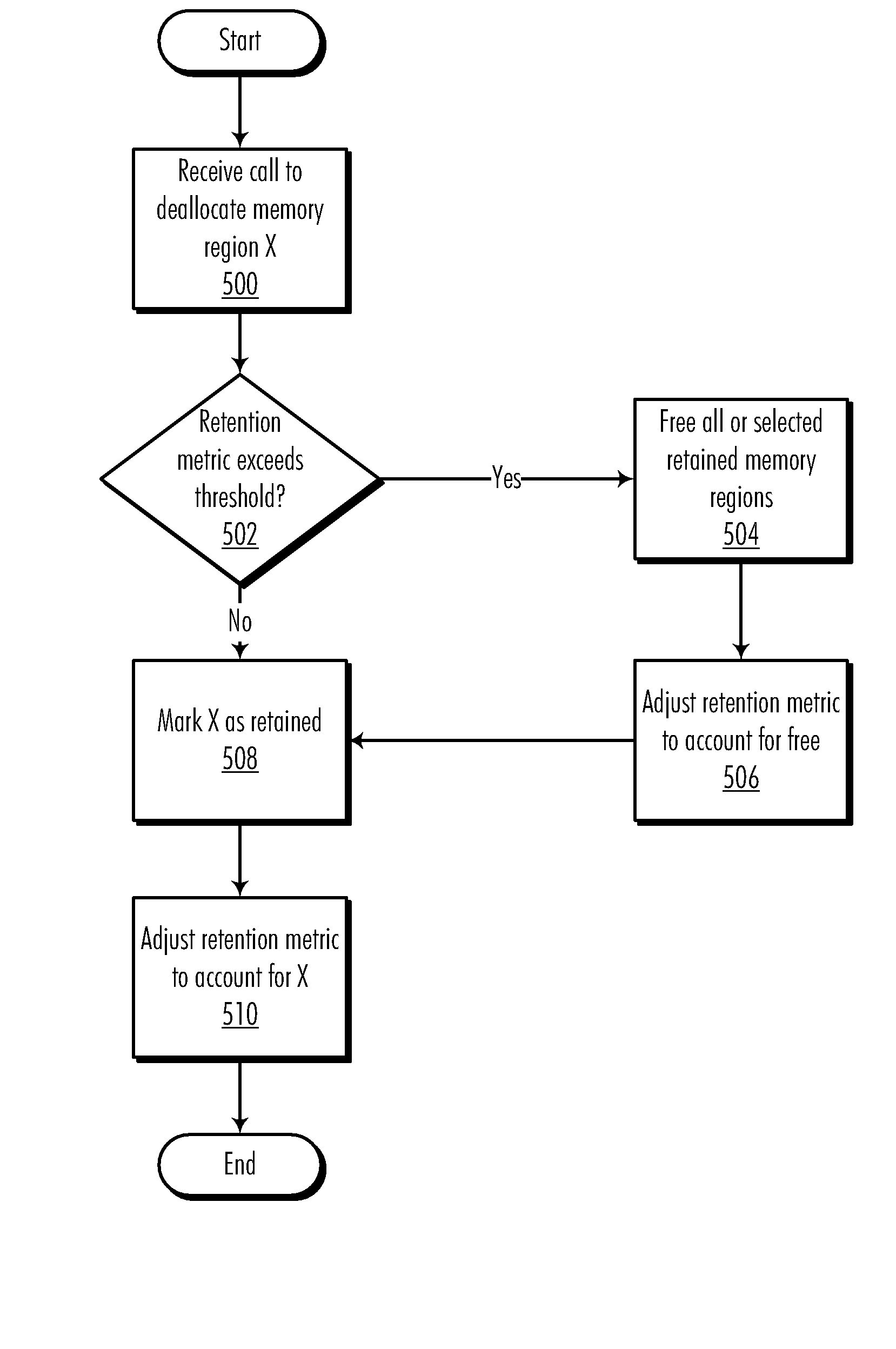

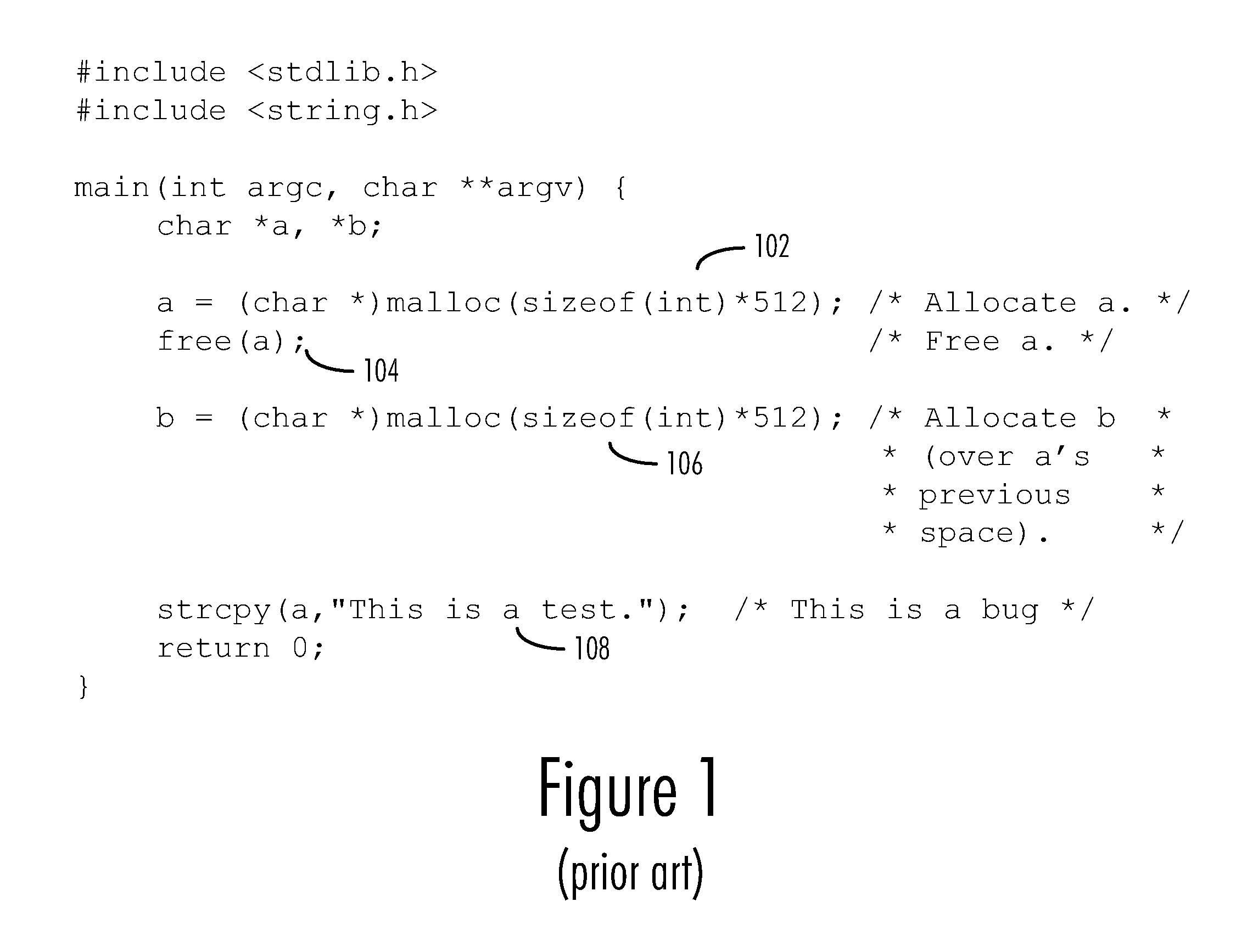

Detecting Illegal Reuse of Memory with Low Resource Impact

InactiveUS20080168112A1Avoid it happening againEasy to detectMemory systemsData processing systemMemory retention

A method, computer program product, and data processing system for preventing the occurrence of undetectable dangling pointers through memory reallocation are disclosed. Allocated memory regions that are no longer needed are deallocated but are not immediately freed for reallocation, being designated as “retained.” A memory retention metric is computed as a measure of an extent of the retained memory regions in the computer's memory space. Once the memory retention metric exceeds a pre-determined threshold, some or all of the retained memory regions are freed for reuse. In this manner, improper accesses to deallocated memory regions can be detected more easily, since reuse of those regions is delayed, while at the same time excessive resource usage and heap fragmentation is avoided by only retaining deallocated regions for a limited time (determined by the threshold and retention metric chosen).

Owner:IBM CORP

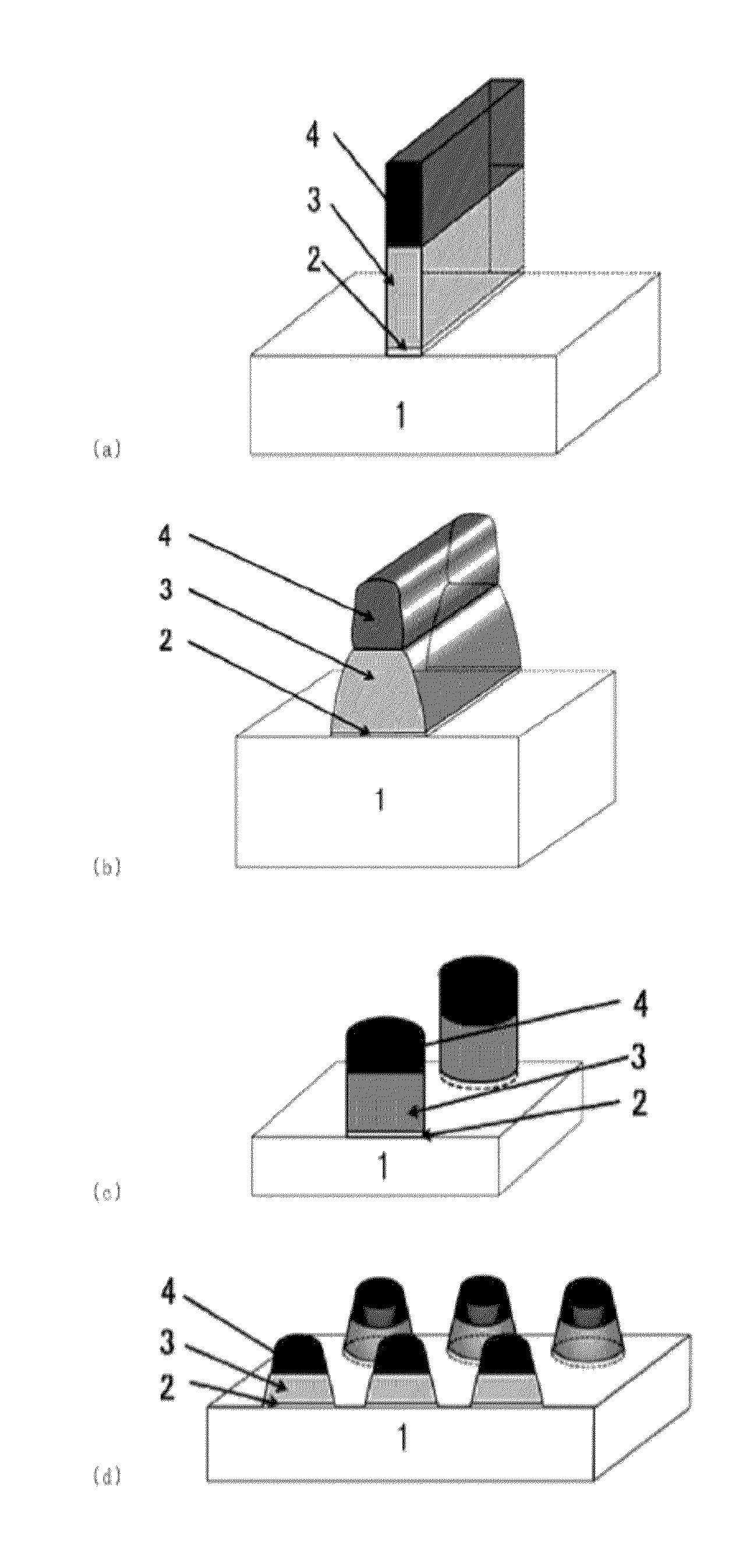

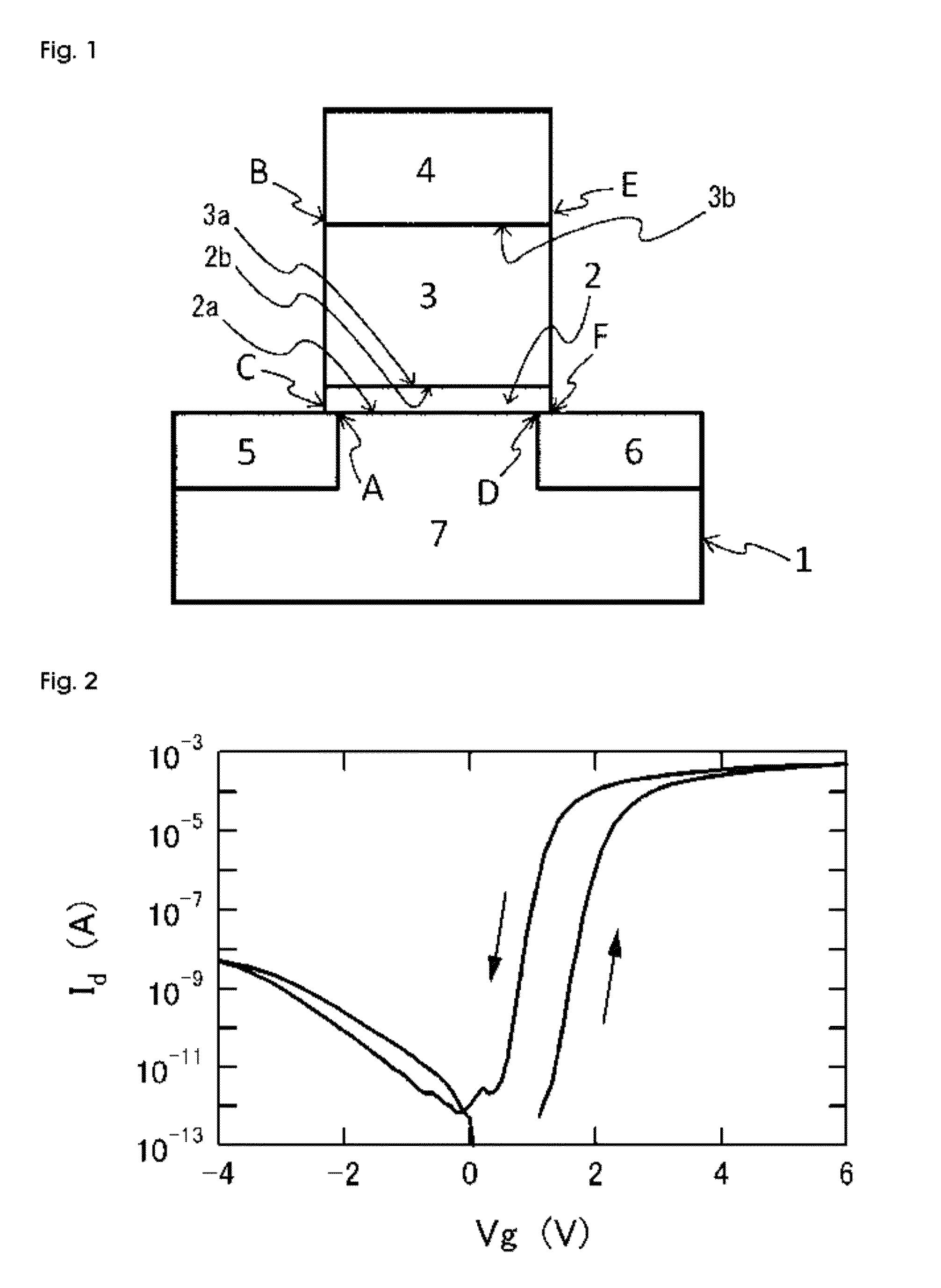

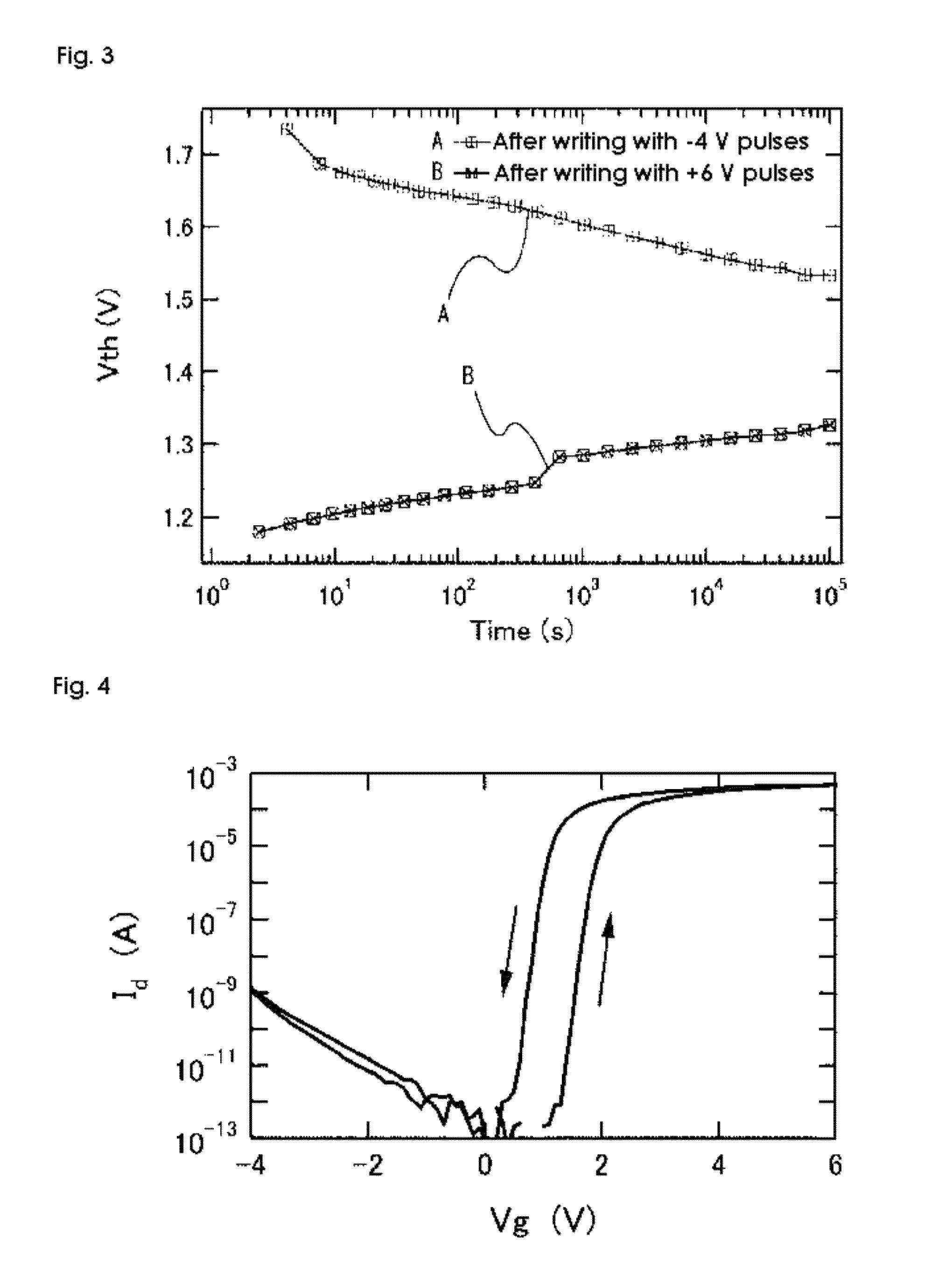

Ferroelectric device and meethod for manufacturing same

ActiveUS20160247932A1Wide memory windowSmall volumeSolid-state devicesSemiconductor/solid-state device manufacturingMemory retentionElectrical conductor

A ferroelectric device and a manufacturing method are provided. While holding a nonvolatile memory retention capability and a multiple rewriting endurance as the distinctive features of a ferroelectric device, the disclosed ferroelectric device is wider in memory window and more adaptively made microfiner than a conventional ferroelectric device that has used a ferroelectric mainly constituted of Sr—Bi—Ta—O as an oxide of strontium, bismuth and tantalum. Directly on or with intermediary of an insulator on a semiconductor there are layered a first ferroelectric and a conductor to form a gate stack, the first ferroelectric being mainly constituted of Sr—Ca—Bi—Ta—O as an oxide of strontium, calcium, bismuth and tantalum and being built up by a metal organic vapor deposition technique from a suitable film-forming raw material. The gate stack is heat-treated to cause the first ferroelectric to develop its ferroelectricity.

Owner:NAT INST OF ADVANCED IND SCI & TECH +1

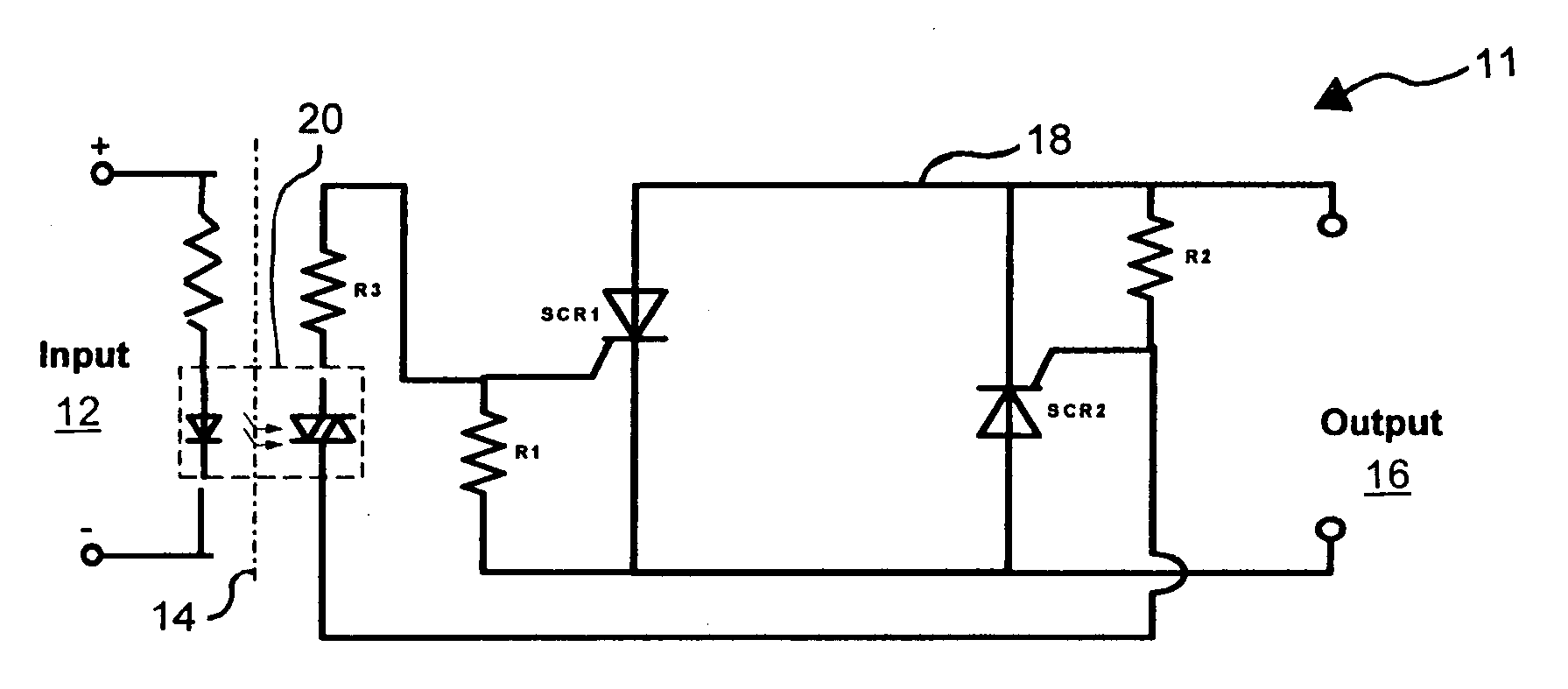

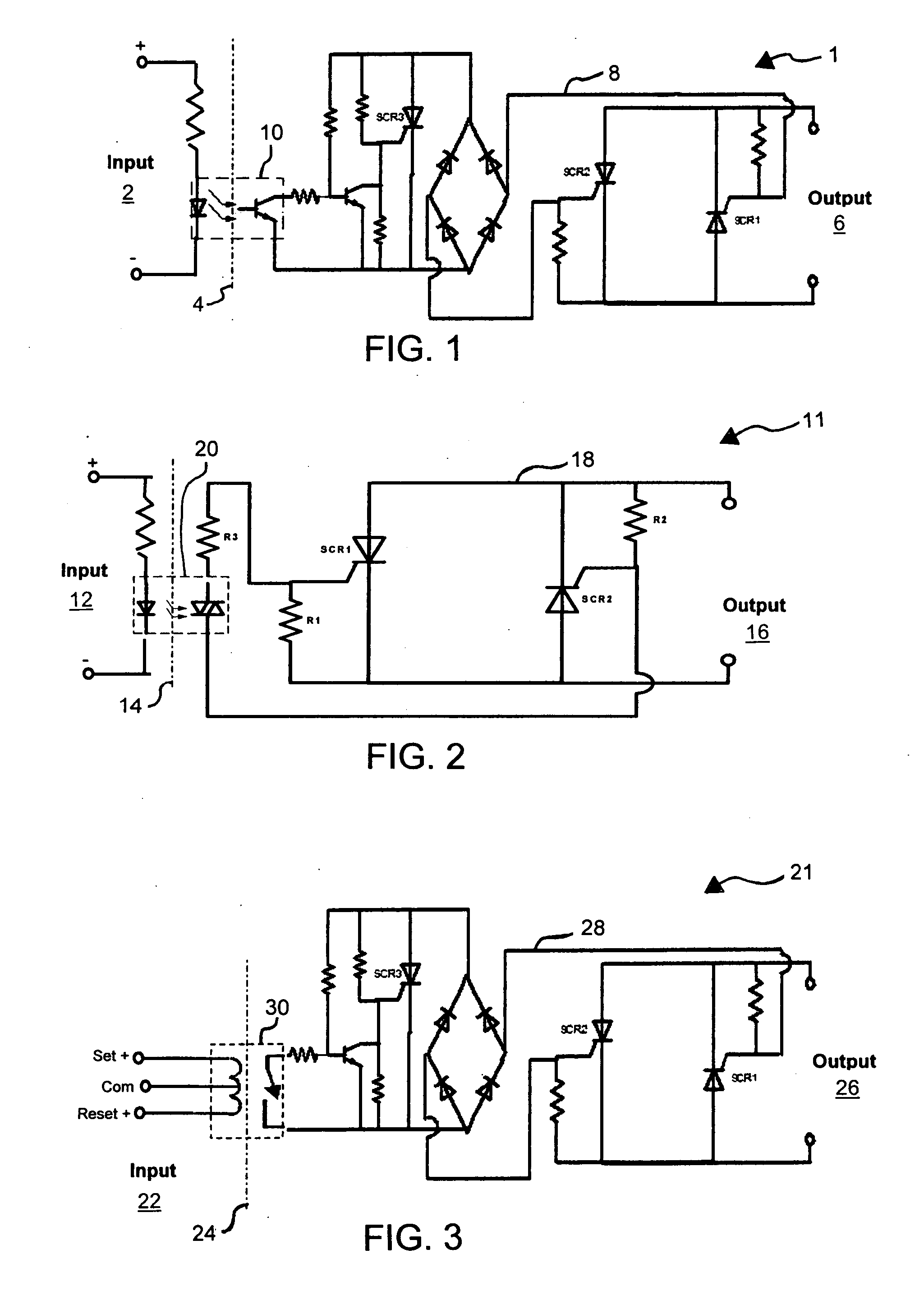

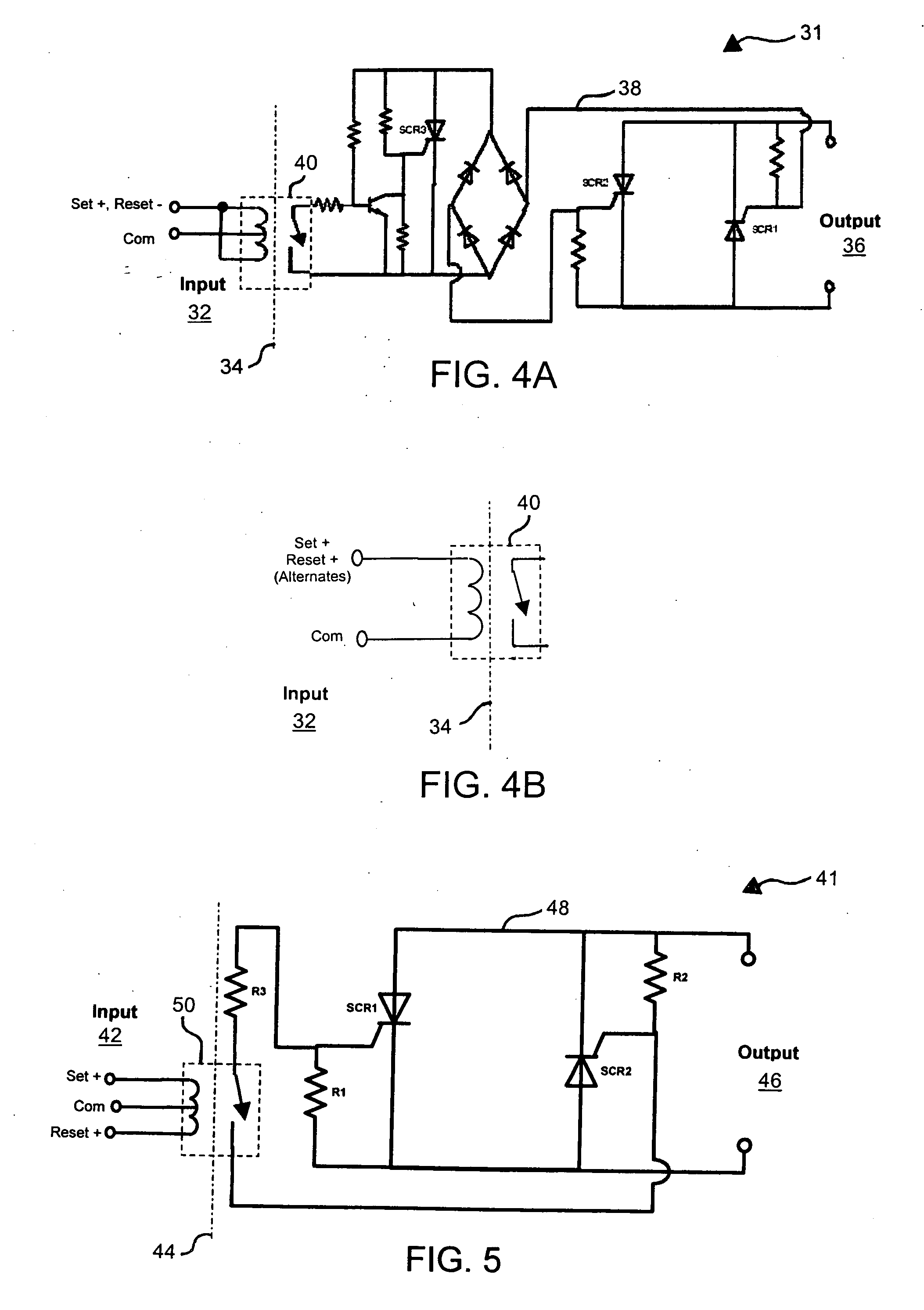

Latching solid state relay

InactiveUS20060245129A1Electric switchesEmergency protective arrangements for automatic disconnectionMemory retentionWave shape

A latching relay coupled SSR circuit provides a simple means of achieving a true latching solid-state relay in both two or three input terminal configurations, with two output terminals switched by standard solid-state relay devices. The circuit does not require any additional power sources, and has true indefinite memory retention of the last state the output was in when all power is disconnected. The latching relay coupled SSR circuit can be configured for a “zero-cross” mode of turn-on style to synchronize with the AC waveform powering the load that cannot be done with electromechanical latching relays, in addition to the purely “random” style of load switching. A latching relay is utilized. The isolation of the input side to the output side is provided by the physical separation of the coil and switch, utilizing the magnetic field of the coil to actuate the switch.

Owner:CRYDOM TECH

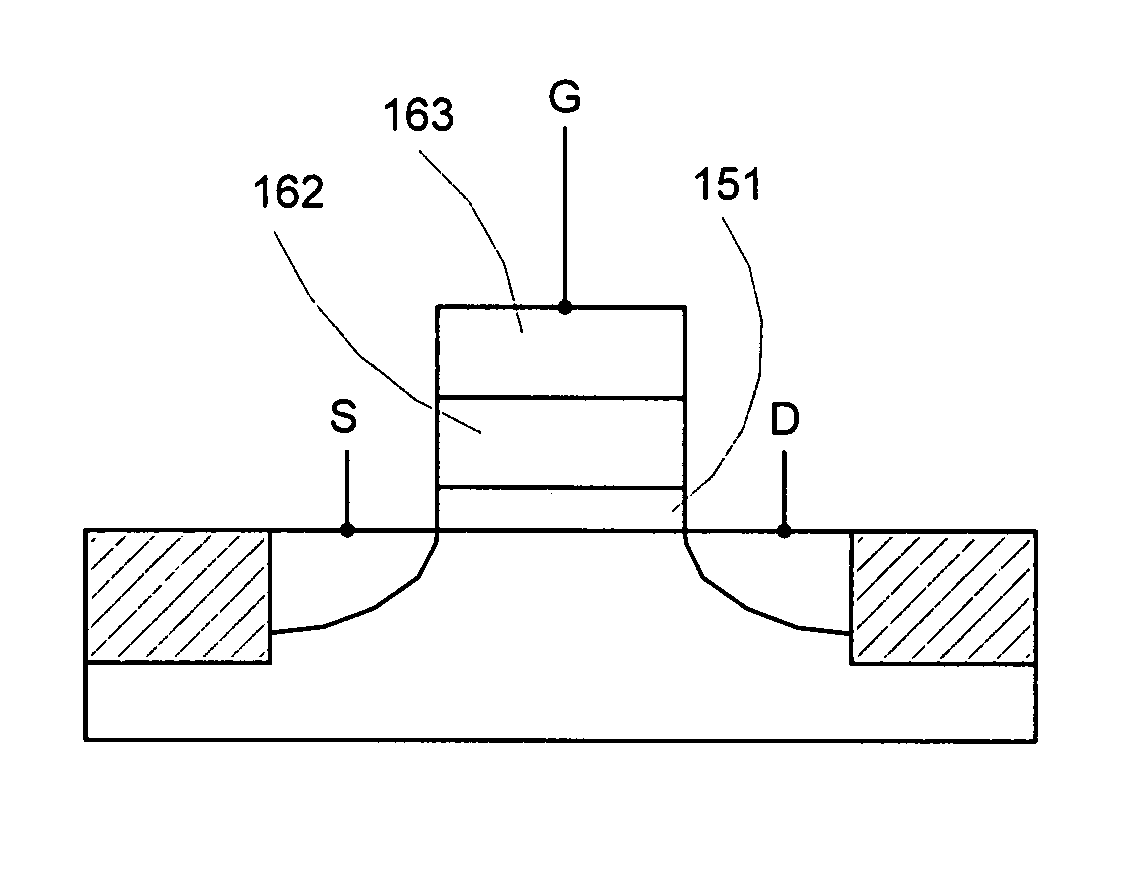

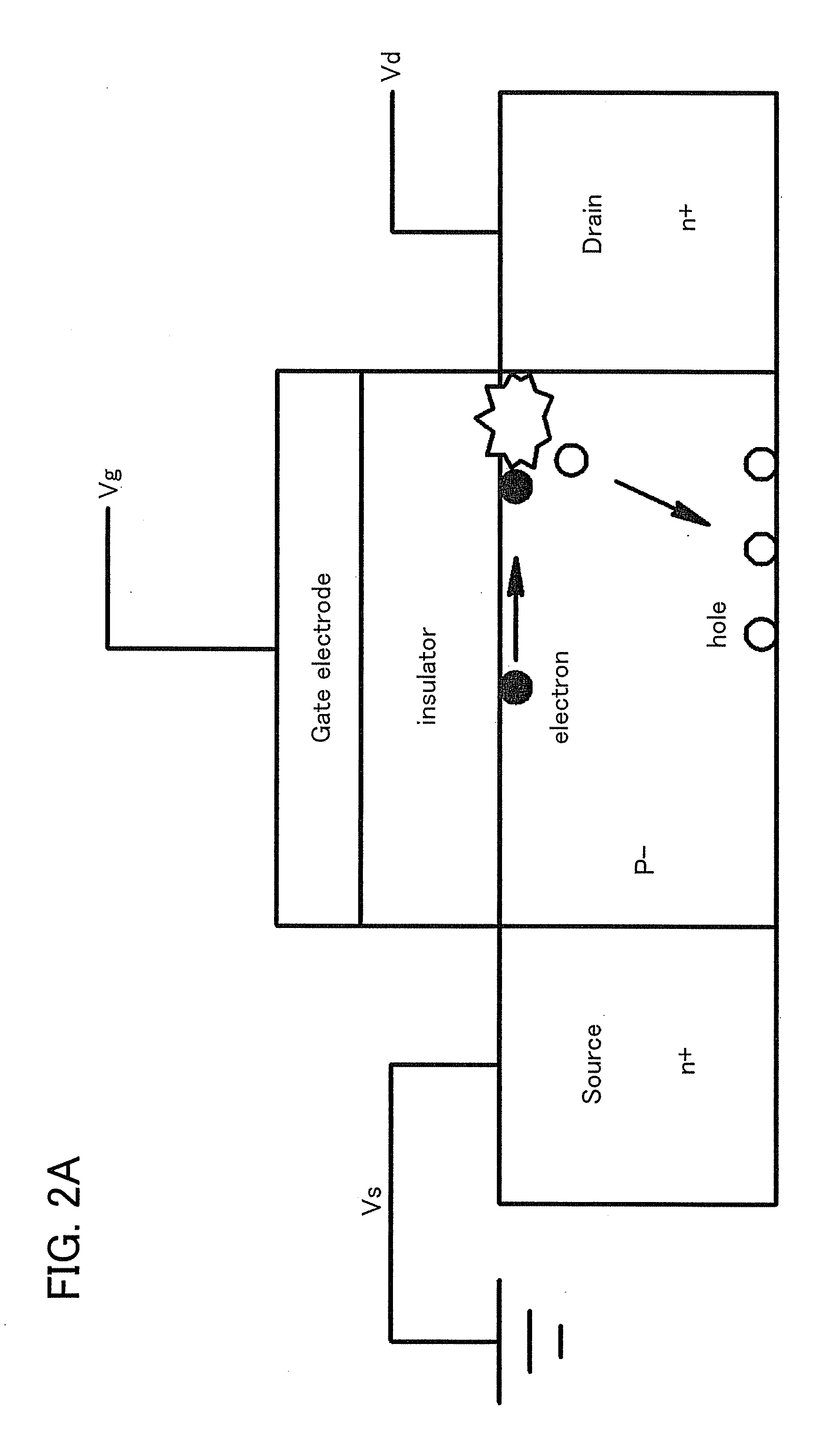

Capacitor-Less Memory

InactiveUS20080308802A1Reduce in quantitySimple structureTransistorSolid-state devicesCapacitanceMemory retention

It is an object of the present invention to provide a capacitor-less memory which can prevent a change of a threshold voltage due to flowing out of carriers and improve the memory retention property without a complicated structure. In the capacitor-less memory which uses a transistor, the transistor includes a source region, a drain region, an active layer region which is provided between the source region and the drain region, and a gate electrode which is adjacent to the active layer region with an insulating film interposed therebetween. The source region is formed of a semiconductor having a larger band gap than a band gap of a semiconductor of the active layer region and a band gap of a semiconductor of the drain region, and a heterojunction is formed at the interface between the source region and the active layer region.

Owner:SEMICON ENERGY LAB CO LTD

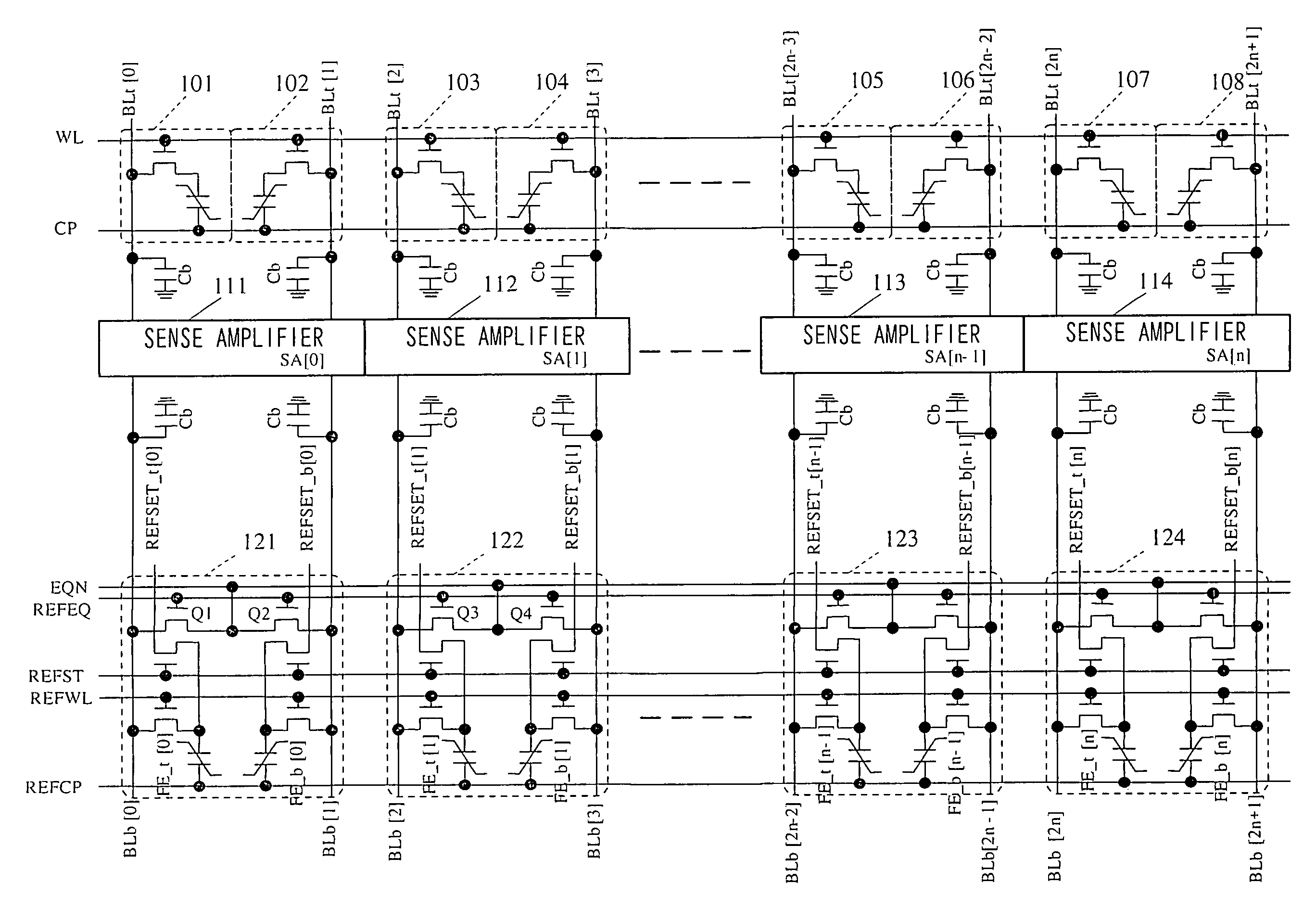

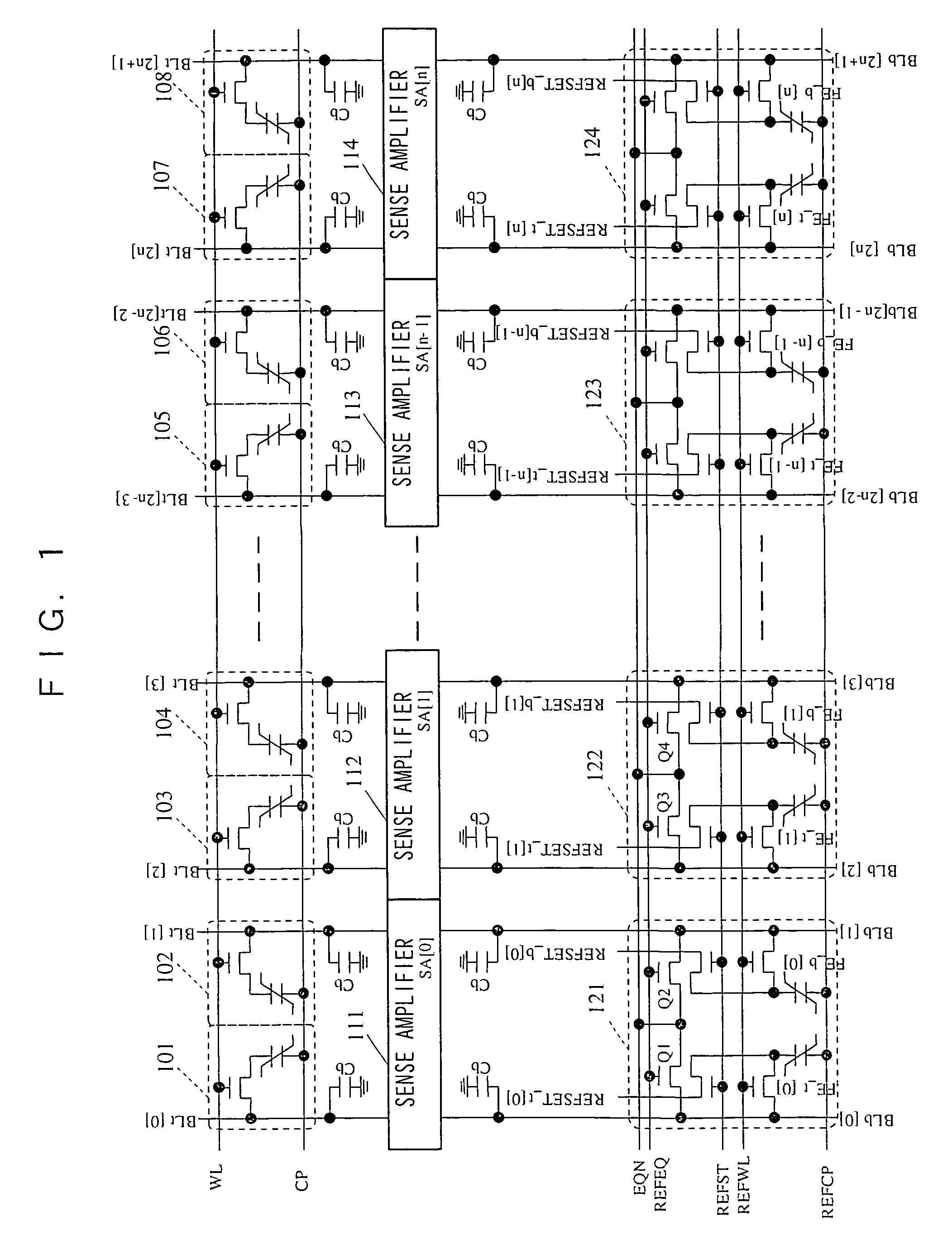

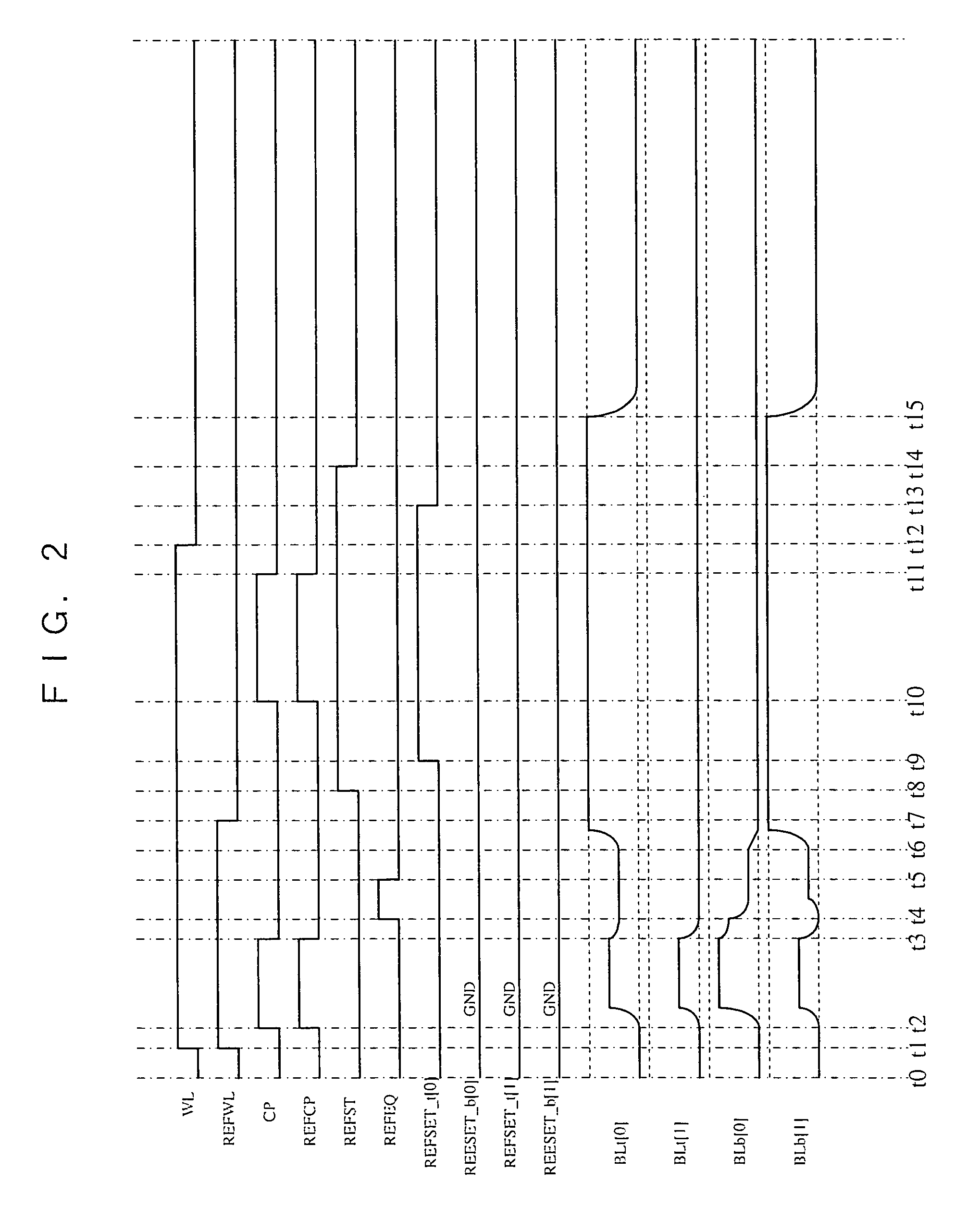

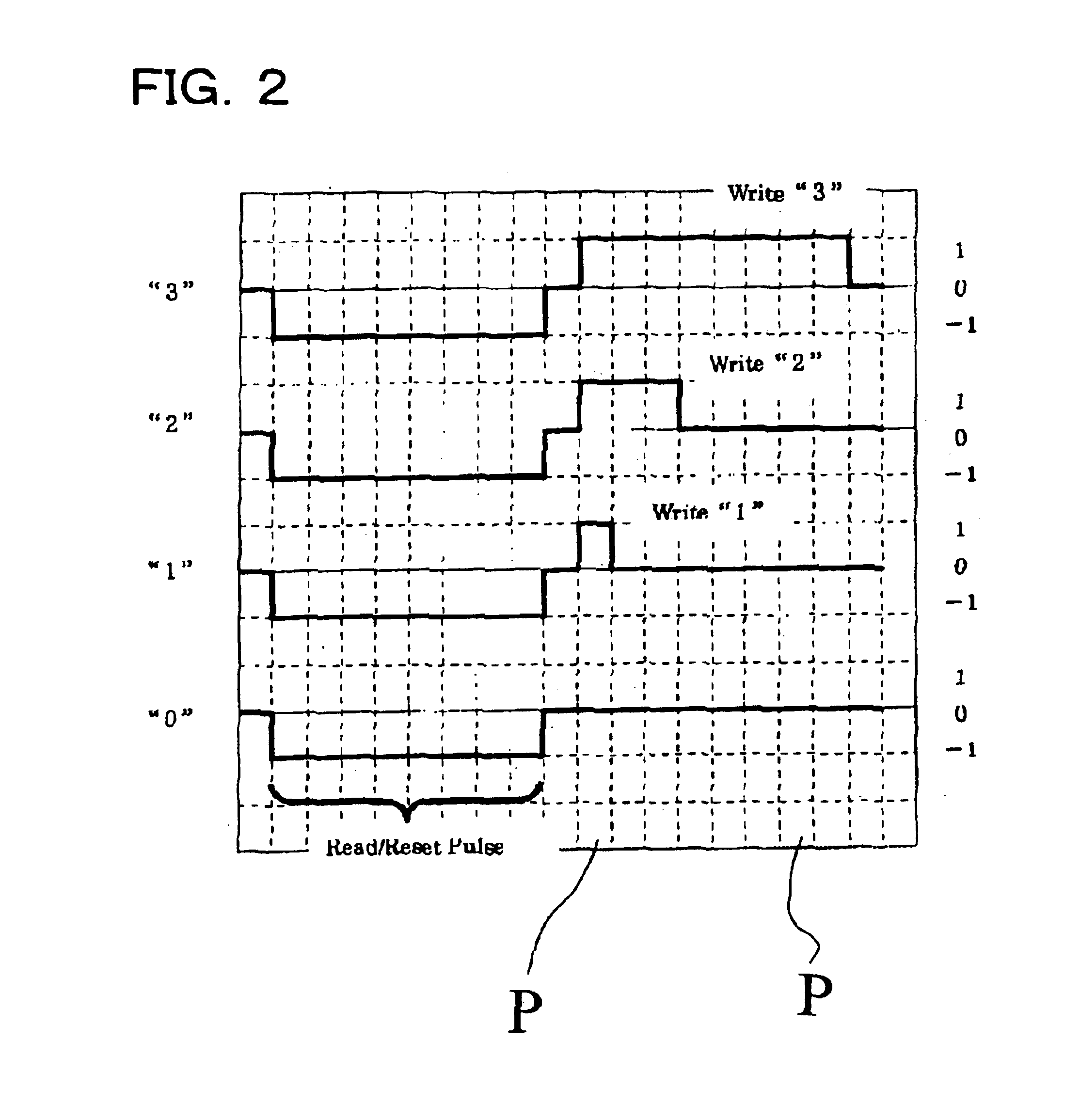

Semiconductor memory device with improved memory retention

A semiconductor memory device permitting the data “0” and the data “1” to be arbitrarily written to a reference cell capacitor for generating a reference potential, having a non-volatile capacitor for storing the data to be written. Fine adjustment of the reference potential is possible without a mask correction, which improves yield. The present invention also permits rewriting only the reference capacitors. As such, the dispersion of the reference potential can be controlled, and yield is improved.

Owner:PANASONIC CORP

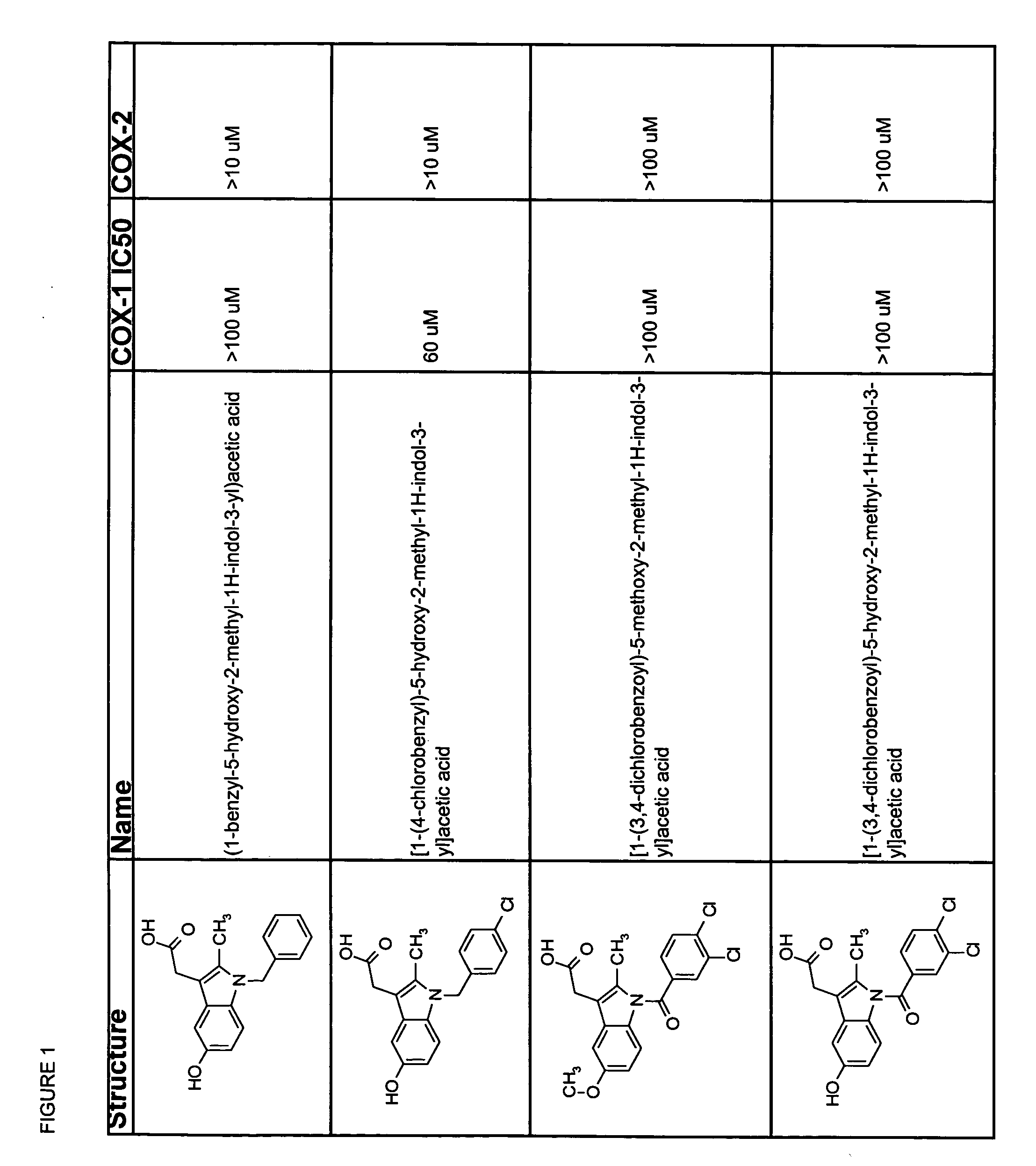

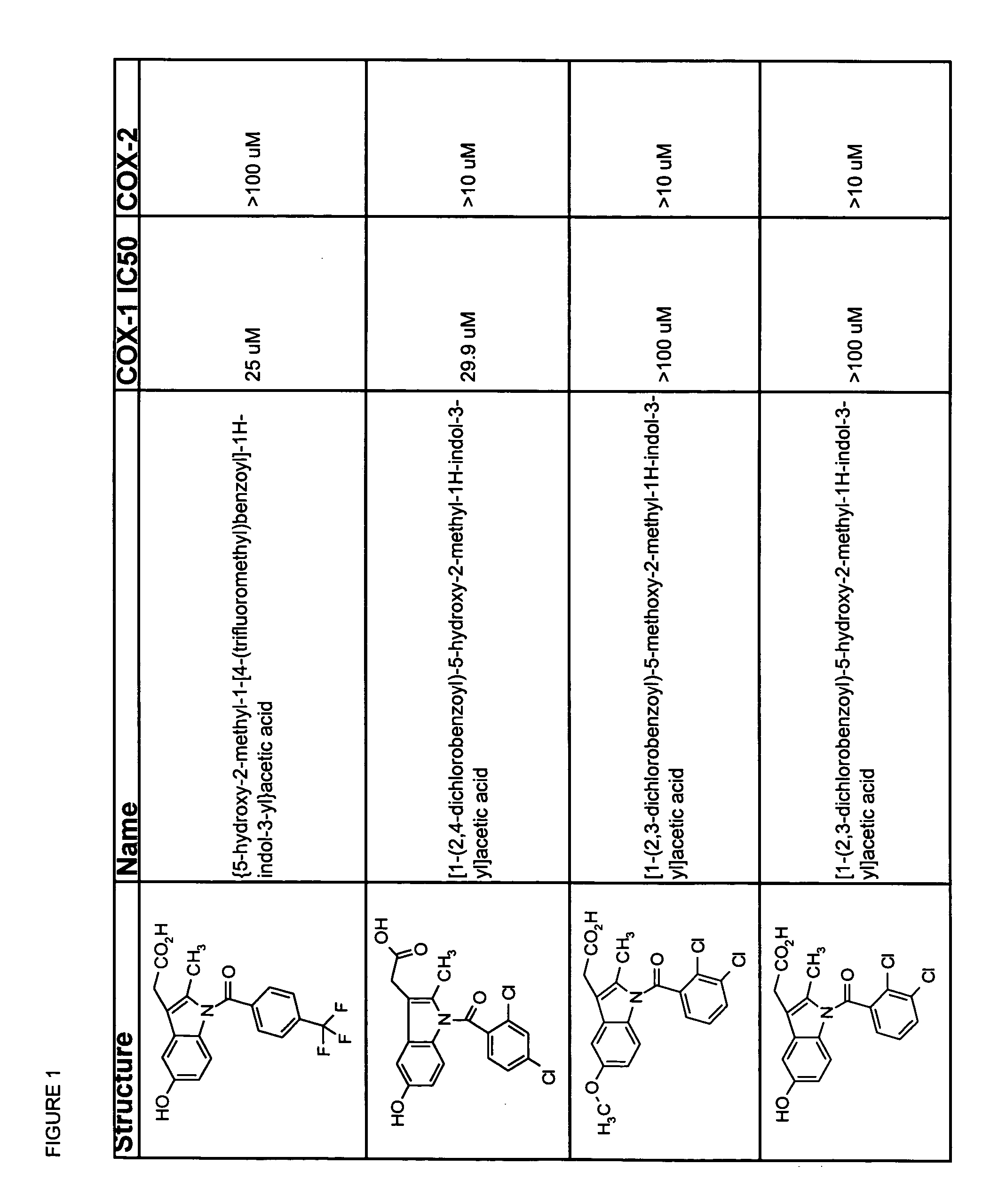

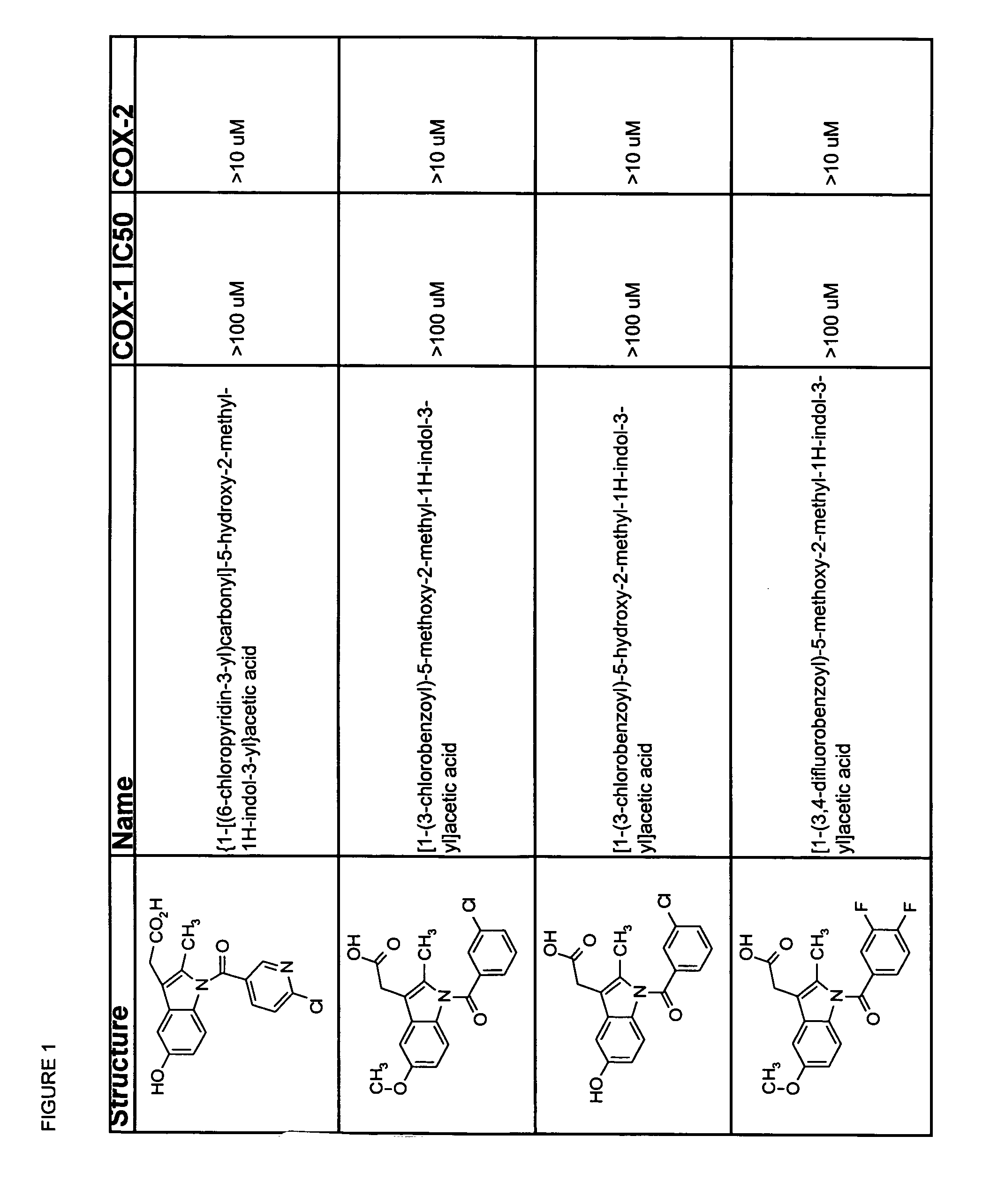

Methods for the protection of memory and cognition

InactiveUS20050004104A1Function increaseSlowing or reducing cognitive impairment or memory lossBiocideNervous disorderMemory retentionAmnesia

The invention features certain compounds useful in the treatment of memory disorders, i.e., they reduce or delay memory loss or they enhance memory retention. Because certain of the compounds do not substantially inhibit either COX-1 or COX-2 at therapeutically relevant doses, these compounds are far less likely to cause gastrointestinal ulceration than is indomethacin, which is known to inhibit both COX-1 and COX-2. Certain of the compounds inhibit the activity of DAO at therapeutically relevant doses. Among the memory disorders that can be treated are AD, mild cognitive impairment (MCI; a common precursor to AD), and memory loss or cognitive impairment associated with vascular dementias, amnesia, dementia, AIDS dementia, Huntington's Disease, hydrocephalus, depression, Pick's Disease, Creutzfeldt-Jakob Syndrome, electroconvulsive therapy, or Parkinson's Disease.

Owner:IRONWOOD PHARMA

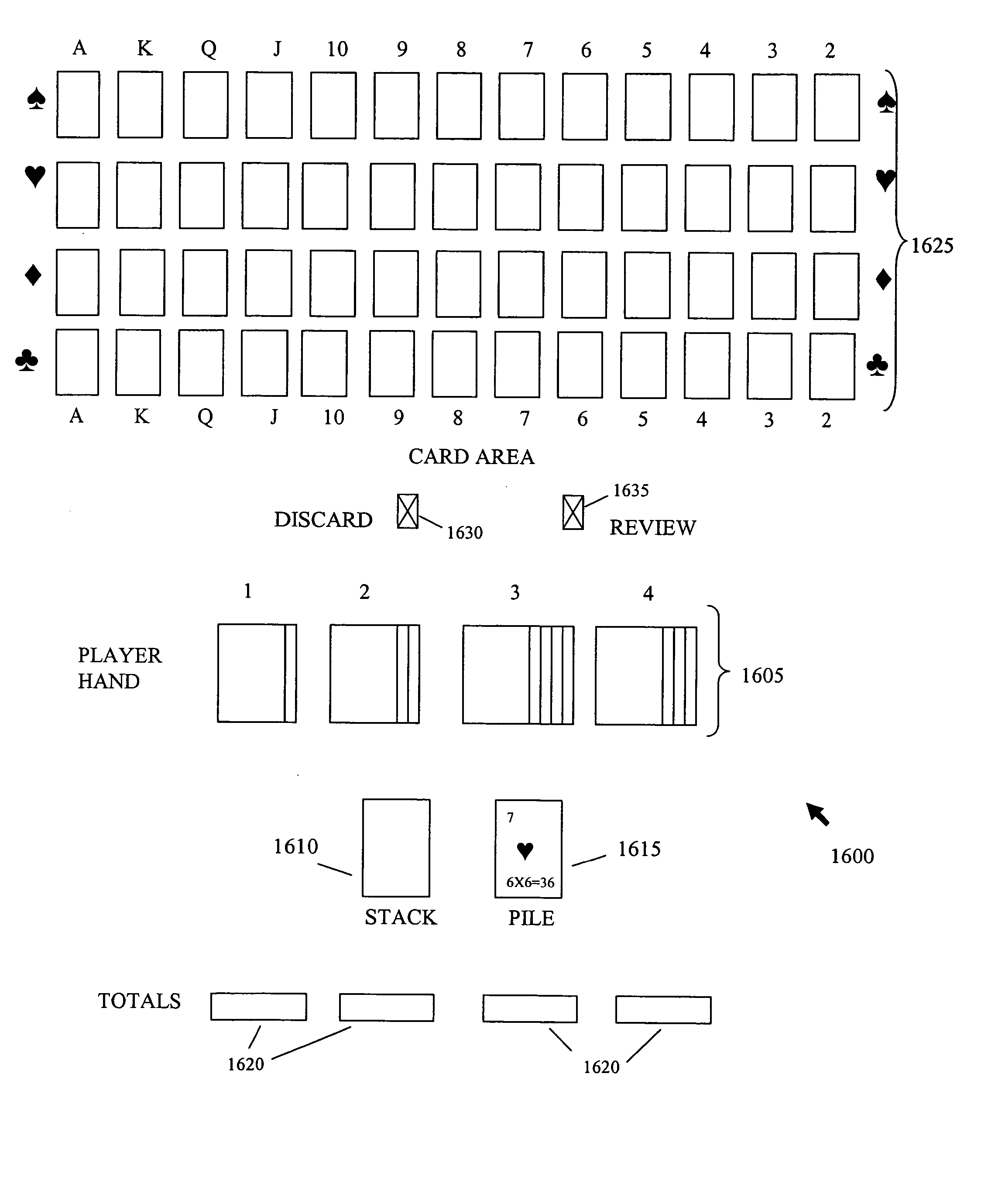

Card game for learning

A card game for learning entails competitive play between players. As the game proceeds, the winner of a match must recite out loud the facts of learning on the playing cards. The game repetitively exposes the players to facts in a given subject area such as math, history, science, geography, literature, etc. The learning experience may be geared to different age brackets by tailoring the subject facts to different age brackets. Audible and visual cues help players to associate information for memory retention. The game may be played electronically.

Owner:DILLHOFF RICHARD

Ferroelectric memory

InactiveUS6870753B2Easy to produceEasy to implementRead-only memoriesDigital storageMemory retentionComputer hardware

Owner:SEIKO EPSON CORP

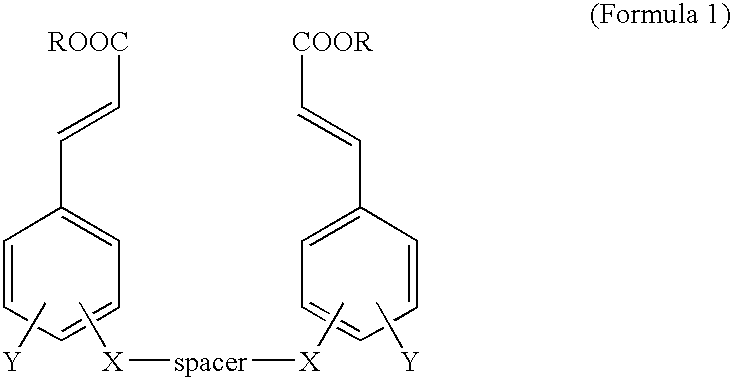

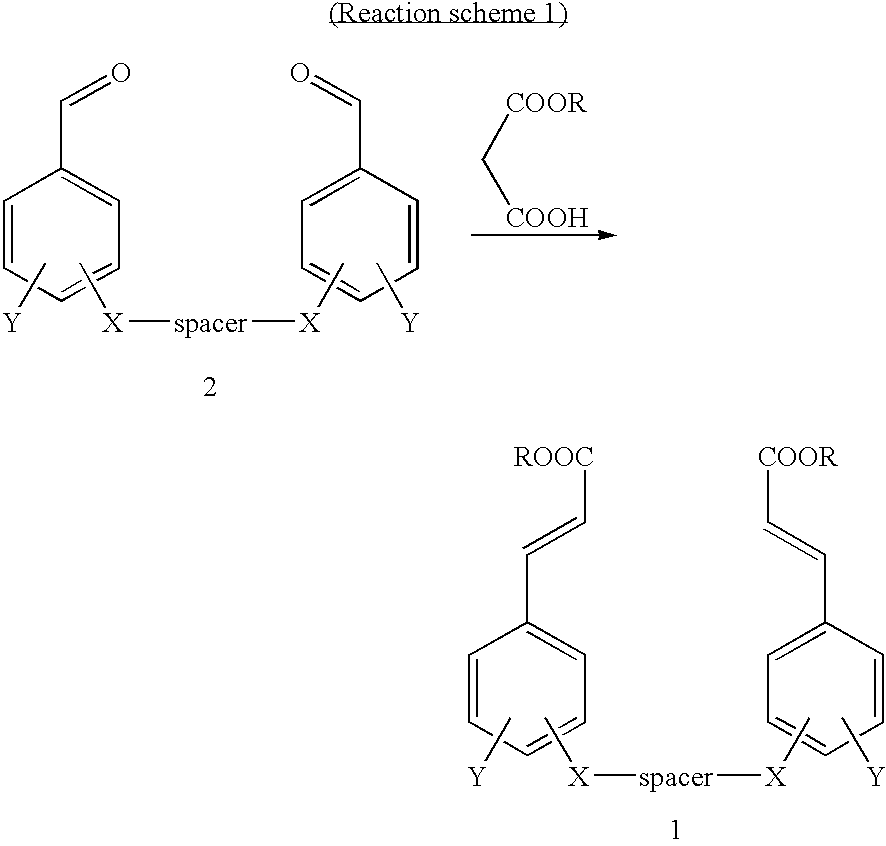

Cinnamic acid dimers, their preparation and the use thereof for treating neurodegenerative disease

InactiveUS20050203180A1Good treatment effectMinimizing side-effectsBiocideNervous disorderMemory retentionSide effect

The present invention relates to cinnamic acid dimers, their preparation and the use thereof for treating neurodegenerative disease, which have excellent effect on enhancing the learning and memory-retention ability in vivo and have fewer side-effects by showing no hormone properties, even when administered for a long period of time, and thus which can be used for neurodegenerative disease including dementia.

Owner:KOREA INST OF SCI & TECH +1